### LC89513K

# CD-ROM/CD-I Error Correction LSI for Integrated Host CPU Systems

### **Preliminary**

#### **Overview**

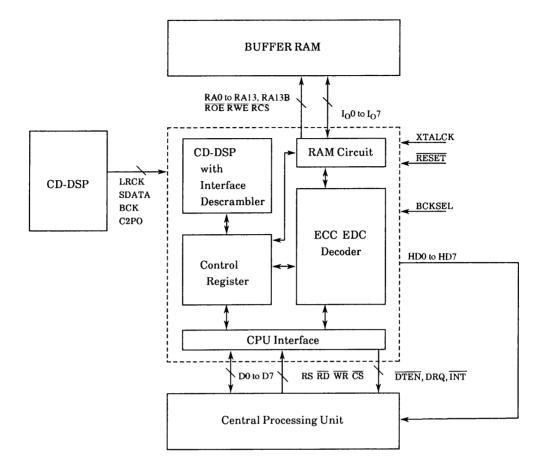

The LC89513K is an error correction LSI appropriate for systems in which a single CPU handles both system control and data readout. The LC89513K consists of the three major blocks described below.

• CD Player Interface/Data Input Block

The LC89513K supports three serial input formats, with the format used selected by setting internal register. That is, an application system can compensate for CD player serial data format differences by setting the LC89513K CDIF0 and CDIF1 registers.

The LC89513K uses an internal synchronization detection circuit to synchronize internal operations with the input data in block (sector) units. LC89513K synchronization uses not only input data pattern detection, but also uses a synchronization signal interpolation circuit for synchronization protection. These two synchronization systems can be turned on and off under program control. Input data is stored in buffer RAM in 8-bit units after being processed by a descrambling circuit. All of the 2,352 bytes of the input data, including the synchronization, header and parity data, is stored in RAM in the order received from the CD player without exception.

• Error Correction Block

This block corrects the errors in the CD-ROM data output from the CD player block.

CD-ROM data output from the CD player is temporarily stored in the LC89513K's external buffer RAM. After one sector is buffered, the LC89513K automatically performs error correction. (Error detection and correction are only performed once.) After the correction procedure completes, the LC89513K issues an interrupt to the control CPU, and the control CPU reads the data through the LC89513K.

Since the buffering, error correction, and data read operations are pipelined, as they are in the LC8951, these operations are performed in real time.

• CPU Interface Block

In the LC8951, the CPU interface was divided into a microcontroller interface block (the LC8951 control bus) and a host interface block (data output bus). However, in the LC89513K, these functions are combined in a single block so that a single CPU can both control the CD player and read data from the LC89513K. The LC89513K outputs CD-ROM data from a separate port (pin), as did the earlier LC8951. The LC89513K CPU interface uses the same indirect addressing scheme used in the LC8951 interface, and programs written for the LC8951 can be used without modification.

#### **Features**

- Supports both double- and quad-speed playback, selectable by internal register settings.

- Operating frequencies: double-speed: 16.9344 MHz, quad speed: 33.8688 MHz

- Can be operated at 3.5 V.

- In normal operation SRAM with an access time of 300 ns or shorter must be used.

- In double-speed operation SRAM with an access time of 120 ns or shorter must be used.

- Supports CD-ROM drive systems in which a single CPU performs both control and data readout functions.

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

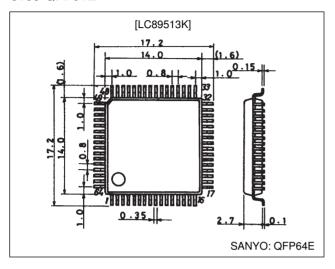

### **Package Dimensions**

unit: mm

#### 3159-QFP64E

### **Specifications**

### Absolute Maximum Ratings at $V_{SS}$ = 0 V

| Parameter                      | Symbol                        | Conditions | Ratings                       | Unit |

|--------------------------------|-------------------------------|------------|-------------------------------|------|

| Maximum supply voltage         | V <sub>DD</sub> max           | Ta = 25°C  | -0.3 to +7.0                  | V    |

| I/O voltages                   | V <sub>I</sub> V <sub>O</sub> | Ta = 25°C  | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Allowable power dissipation    | Pd max                        | Ta ≤ 70°C  | 350                           | mW   |

| Operating temperature          | Topr                          |            | −30 to +70                    | °C   |

| Storage temperature            | Tstg                          |            | -55 to +125                   | °C   |

| Soldering thermal stress limit |                               | 10 seconds | 260                           | °C   |

## Allowable Operating Ranges at Ta = –30 to +70 $^{\circ}C,\,V_{SS}$ = 0 V

| Parameter           | Symbol   | Conditions | min | typ | max      | Unit |

|---------------------|----------|------------|-----|-----|----------|------|

| Supply voltage      | $V_{DD}$ |            | 3.5 | 5.0 | 5.5      | V    |

| Input voltage range | $V_{IN}$ |            | 0   |     | $V_{DD}$ | V    |

### DC Characteristics at Ta = –30 to +70°C, $V_{SS}$ = 0 V, $V_{DD}$ = 3.5 to 5.5 V

| Parameter                 | Symbol            | Conditions                                                                                | min | typ | max | Unit |

|---------------------------|-------------------|-------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Input high level voltage  | V <sub>IH</sub> 1 | All input pins other than (1) and XTALCK                                                  | 2.2 |     |     | V    |

| Input low level voltage   | V <sub>IL</sub> 1 | All hiput pins other than (1) and XTALOK                                                  |     |     | 0.8 | V    |

| Input high level voltage  | V <sub>IH</sub> 2 | RS, CS, RD, WR, RESET, HRD and I <sub>O</sub> 0 to I <sub>O</sub> 7 (1)                   | 2.5 |     |     | V    |

| Input low level voltage   | V <sub>IL</sub> 2 | 1 NO, CO, ND, WN, NESET, FIND AND 10 10 10 10 10 10 10 10 10 10 10 10 10                  |     |     | 0.6 | V    |

| Output high level voltage | V <sub>OH</sub> 1 | I <sub>OH</sub> 1 = -3 mA: All output pins (including bus pins) other than (2) and XTALCK | 2.4 |     |     | V    |

| Output low level voltage  | V <sub>OL</sub> 1 | I <sub>OL</sub> 1 = 3 mA: All output pins (including bus pins) other than (2) and XTALCK  |     |     | 0.4 | V    |

| Output low level voltage  | V <sub>OL</sub> 2 | I <sub>OL</sub> 2 = 3 mA: <del>INT</del> (pull-up resistor open drain) (2)                |     |     | 0.4 | V    |

| Input leakage current     | IL                | V <sub>I</sub> = V <sub>SS</sub> , V <sub>DD</sub> : All input pins                       | -25 |     | +25 | μΑ   |

| Pull-up resistance        | R <sub>UP</sub>   | All bus pins and INT                                                                      | 10  | 20  | 40  | kΩ   |

#### **Block Diagram**

### LC89513K

#### **Pin Functions**

Type: I: Input pin, O: Output pin, B: Bidirectional pin, P: Power supply pin, NC: No connection pin

| Pin No. | Pin             | Туре | Type: I: Input pin, O: Output pin, B: Bidirectional pin, P: Power supply pin, NC: No connection pin  Function |  |  |

|---------|-----------------|------|---------------------------------------------------------------------------------------------------------------|--|--|

| 1       |                 | Р    | 1 unction                                                                                                     |  |  |

| 2       | V <sub>SS</sub> | 0    |                                                                                                               |  |  |

| 3       | RA1             | 0    |                                                                                                               |  |  |

| 4       | RA2             | 0    |                                                                                                               |  |  |

|         | RA3             | 0    | Data buffer RAM address signal outputs                                                                        |  |  |

| 5       | -               |      | Data buller RAM address signal outputs                                                                        |  |  |

| 6       | RA4             | 0    |                                                                                                               |  |  |

| 7       | RA5             | 0    |                                                                                                               |  |  |

| 8       | RA6             | 0    |                                                                                                               |  |  |

| 9       | V <sub>SS</sub> | P    |                                                                                                               |  |  |

| 10      | RA7             | 0    |                                                                                                               |  |  |

| 11      | RA8             | 0    |                                                                                                               |  |  |

| 12      | RA9             | 0    |                                                                                                               |  |  |

| 13      | RA10            | 0    | Data buffer RAM data signals                                                                                  |  |  |

| 14      | RA11            | 0    |                                                                                                               |  |  |

| 15      | RA12            | 0    |                                                                                                               |  |  |

| 16      | RA13            | 0    |                                                                                                               |  |  |

| 17      | V <sub>SS</sub> | P    |                                                                                                               |  |  |

| 18      | RA13B           | 0    | Data buffer RAM address signal output                                                                         |  |  |

| 19      | RCS             | 0    | RAM chip select                                                                                               |  |  |

| 20      | RWE             | 0    | RAM data write signal output                                                                                  |  |  |

| 21      | ROE             | 0    | RAM data write signal output                                                                                  |  |  |

| 22      | RESET           | 1    | Chip select signal input                                                                                      |  |  |

| 23      | XTALCK          | 1    | Crystal oscillator circuit input                                                                              |  |  |

| 24      | V <sub>DD</sub> | Р    |                                                                                                               |  |  |

| 25      | C2PO            | 1    | C2 pointer input                                                                                              |  |  |

| 26      | BCK             | 1    | Serial data input clock                                                                                       |  |  |

| 27      | SDATA           | 1    | Serial data input                                                                                             |  |  |

| 28      | LRCK            | 1    | 44.1 kHz strobe signal input                                                                                  |  |  |

| 29      | RS              | 1    | Register selection signal input                                                                               |  |  |

| 30      | RD              | 1    | CPU data read signal input                                                                                    |  |  |

| 31      | WR              | 1    | CPU data write signal input                                                                                   |  |  |

| 32      | CS              | ı    | Chip select signal input (from the CPU)                                                                       |  |  |

| 33      | V <sub>SS</sub> | Р    |                                                                                                               |  |  |

| 34      | D0              | В    |                                                                                                               |  |  |

| 35      | D1              | В    |                                                                                                               |  |  |

| 36      | D2              | В    |                                                                                                               |  |  |

| 37      | D3              | В    | CPU data signal pins                                                                                          |  |  |

| 38      | D4              | В    | These pins have built-in pull-up resistors.                                                                   |  |  |

| 39      | D5              | В    |                                                                                                               |  |  |

| 40      | D6              | В    |                                                                                                               |  |  |

| 41      | D7              | В    |                                                                                                               |  |  |

| 42      | GSRAM           | ı    | Pseudo-SRAM selection                                                                                         |  |  |

| 43      | INT             | 0    | CPU interrupt request signal output                                                                           |  |  |

| 44      | DRQ             | 0    | DRQ signal output                                                                                             |  |  |

| 45      | HD0             | 0    | Sind organic output                                                                                           |  |  |

| 46      | HD1             | 0    |                                                                                                               |  |  |

| 47      | HD2             | 0    | Data outputs to the CPU                                                                                       |  |  |

|         | HD3             | _    |                                                                                                               |  |  |

| 48      |                 | 0    |                                                                                                               |  |  |

| 49      | V <sub>SS</sub> | P    |                                                                                                               |  |  |

| 50      | HD4             | 0    |                                                                                                               |  |  |

| 51      | HD5             | 0    | Data outputs to the CPU                                                                                       |  |  |

| 52      | HD6             | 0    |                                                                                                               |  |  |

| 53      | HD7             | 0    |                                                                                                               |  |  |

Continued on next page.

#### LC89513K

Continued from preceding page.

Type: I: Input pin, O: Output pin, B: Bidirectional pin, P: Power supply pin, NC: No connection pin

| Pin No. | Pin              | Туре | Function                                    |

|---------|------------------|------|---------------------------------------------|

| 54      | HRD              | I    | Data read signal input                      |

| 55      | DTEN             | 0    | Data enable signal output                   |

| 56      | V <sub>DD</sub>  | Р    |                                             |

| 57      | I <sub>O</sub> 0 | В    |                                             |

| 58      | I <sub>O</sub> 1 | В    |                                             |

| 59      | I <sub>O</sub> 2 | В    |                                             |

| 60      | I <sub>O</sub> 3 | В    | Data buffer RAM data signals                |

| 61      | I <sub>O</sub> 4 | В    | These pins have built-in pull-up resistors. |

| 62      | I <sub>O</sub> 5 | В    |                                             |

| 63      | I <sub>O</sub> 6 | В    |                                             |

| 64      | I <sub>O</sub> 7 | В    |                                             |

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any and all SANYO products described or contained herein fall under strategic products (including services) controlled under the Foreign Exchange and Foreign Trade Control Law of Japan, such products must not be exported without obtaining export license from the Ministry of International Trade and Industry in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of August, 1998. Specifications and information herein are subject to change without notice.