# CMOS Programmable Logic (CPL™) Data Book

1988

# CMOS PROGRAMMABLE LOGIC (CPLTM)

Data Book

#### COPYRIGHT 1988 by Samsung Semiconductor

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photo copying, recording, or otherwise, without the prior written permission of Samsung Semiconductor Inc.

All information in these specifications is subject to change without notice, for product improvement. The information, circuits, and all other data included herein are believed to be accurate and reliable. However, no responsibility is assumed by Samsung Semiconductor for their use, nor for any infringements of patents or other rights belonging to third parties which may result from their use.

FIRST EDITION

CPL™ is a trademark of Samsung Semiconductor Inc.

1988 SAMSUNG SEMICONDUCTOR

## INTRODUCTION

Samsung's CMOS Programmable Logic (CPL™) family introduces the benefits of advanced CMOS technology into the field programmable logic area, allowing system designers to save significant amounts of power without compromising performance.

The first generation of CPL devices, as specified in this book, are CMOS implementations of the industry standard PAL<sup>®</sup> devices. The 1.2 micron CMOS EPROM technology allows CPL parts to achieve bipolar performance at a much lower power, resulting in reduced system costs and easier prototyping. The erasable EPROM cell also facilitates 100% functional and AC testing of every part before it is released to market, making possible 100% programming yields.

Programming CPL devices is done by using standard PLD programmers. Because of the architectural compatibility with bipolar PALs, all current software tools also support the CPL devices. Therefore, no modification in the code is necessary when replacing a bipolar PAL device with a CPL device.

PAL® is a registered trademark of Monolithic Memories Inc.

| Product Guide                             | 1 |

|-------------------------------------------|---|

| Technical Overview                        | 2 |

| Product Specifications                    | 3 |

| CPL Programming Electrical Specifications | 4 |

| CPL Programmer and Software Guide         | 5 |

| Definition of Terms                       | 6 |

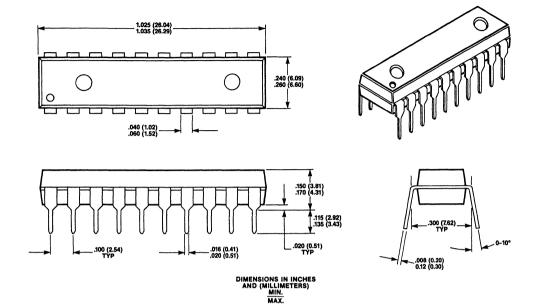

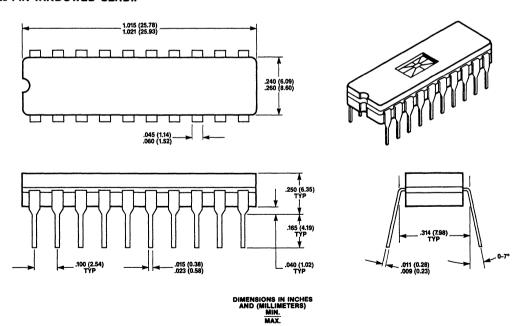

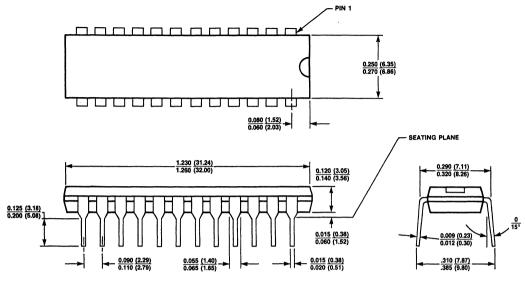

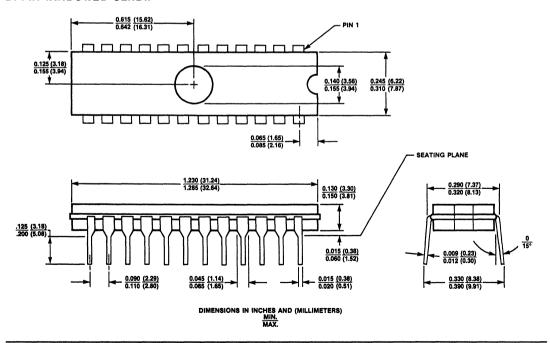

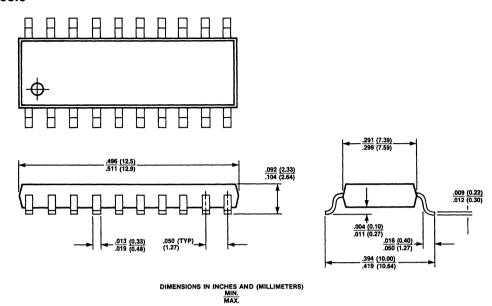

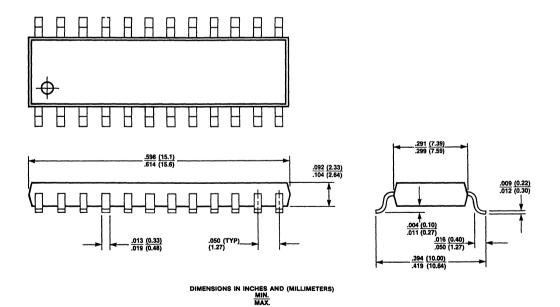

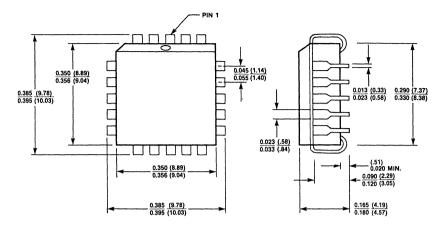

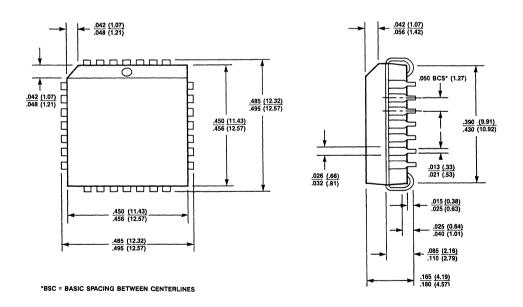

| Package Drawings                          | 7 |

| Sales Offices                             | 8 |

| Product Guide                             | 1 |

|-------------------------------------------|---|

| Technical Overview                        | 2 |

| Product Specifications                    | 3 |

| CPL Programming Electrical Specifications | 4 |

| CPL Programmer and Software Guide         | 5 |

| Definition of Terms                       | 6 |

| Package Drawings                          | 7 |

| Sales Offices                             | 8 |

## **PRODUCT INDEX**

| PRODUCT<br>DESIGNATION                                                                           | DESCRIPTION                                                                                                                                                                                                                                                                                                                           | PAGES                                              |

|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| CPL20                                                                                            |                                                                                                                                                                                                                                                                                                                                       |                                                    |

| CPL16L8L-25NC<br>CPL16L8L-25WC<br>CPL16L8-25NC<br>CPL16L8L-35NC<br>CPL16L8L-35WC<br>CPL16L8-35NC | OTP, Plastic 20-pin 1/4 Power, 25ns, CMOS PLD, Comm. 20-pin Windowed CERDIP, 1/4 Power, 25ns, CMOS PLD, Comm. OTP, Plastic 20-pin 1/2 Power, 25ns, CMOS PLD, Comm. OTP, Plastic 20-pin 1/4 Power, 35ns, CMOS PLD, Comm. 20-pin Windowed CERDIP, 1/4 Power, 35ns, CMOS PLD, Comm. OTP, Plastic 20-pin 1/2 Power, 35ns, CMOS PLD, Comm. | 21-29<br>21-29<br>21-29<br>21-29<br>21-29<br>21-29 |

| CPL16R4L-25NC<br>CPL16R4L-25WC<br>CPL16R4-25NC<br>CPL16R4L-35NC<br>CPL16R4L-35WC<br>CPL16R4-35NC | OTP, Plastic 20-pin 1/4 Power, 25ns, CMOS PLD, Comm. 20-pin Windowed CERDIP, 1/4 Power, 25ns, CMOS PLD, Comm. OTP, Plastic 20-pin 1/2 Power, 25ns, CMOS PLD, Comm. OTP, Plastic 20-pin 1/4 Power, 35ns, CMOS PLD, Comm. 20-pin Windowed CERDIP, 1/4 Power, 35ns, CMOS PLD, Comm. OTP, Plastic 20-pin 1/2 Power, 35ns, CMOS PLD, Comm. | 21-29<br>21-29<br>21-29<br>21-29<br>21-29<br>21-29 |

| CPL16R6L-25NC<br>CPL16R6L-25WC<br>CPL16R6-25NC<br>CPL16R6L-35NC<br>CPL16R6L-35WC<br>CPL16R6-35NC | OTP, Plastic 20-pin 1/4 Power, 25ns, CMOS PLD, Comm. 20-pin Windowed CERDIP, 1/4 Power, 25ns, CMOS PLD, Comm. OTP, Plastic 20-pin 1/2 Power, 25ns, CMOS PLD, Comm. OTP, Plastic 20-pin 1/4 Power, 35ns, CMOS PLD, Comm. 20-pin Windowed CERDIP, 1/4 Power, 35ns, CMOS PLD, Comm. OTP, Plastic 20-pin 1/2 Power, 35ns, CMOS PLD, Comm. | 21-29<br>21-29<br>21-29<br>21-29<br>21-29<br>21-29 |

| CPL16R8L-25NC<br>CPL16R8L-25WC<br>CPL16R8-25NC<br>CPL16R8L-35NC<br>CPL16R8L-35WC<br>CPL16R8-35NC | OTP, Plastic 20-pin 1/4 Power, 25ns, CMOS PLD, Comm. 20-pin Windowed CERDIP, 1/4 Power, 25ns, CMOS PLD, Comm. OTP, Plastic 20-pin 1/2 Power, 25ns, CMOS PLD, Comm. OTP, Plastic 20-pin 1/4 Power, 35ns, CMOS PLD, Comm. 20-pin Windowed CERDIP, 1/4 Power, 35ns, CMOS PLD, Comm. OTP, Plastic 20-pin 1/2 Power, 35ns, CMOS PLD, Comm. | 21-29<br>21-29<br>21-29<br>21-29<br>21-29<br>21-29 |

## **PRODUCT INDEX** (Continued)

| PRODUCT<br>DESIGNATION                                                                                 | DESCRIPTION                                                                                                                                                                                                                                                                                                                           | PAGES                                     |

|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| CPL24                                                                                                  |                                                                                                                                                                                                                                                                                                                                       |                                           |

| CPL20L8L-25NC<br>CPL20L8L-25WC<br>CPL20L8-25NC<br>CPL20L8L-35NC<br>CPL20L8L-35WC<br>CPL20L8-35NC       | OTP, Plastic 24-pin 1/4 Power, 25ns, CMOS PLD, Comm. 24-pin Windowed CERDIP, 1/4 Power, 25ns, CMOS PLD, Comm. OTP, Plastic 24-pin 1/2 Power, 25ns, CMOS PLD, Comm. OTP, Plastic 24-pin 1/4 Power, 35ns, CMOS PLD, Comm. 24-pin Windowed CERDIP, 1/4 Power, 35ns, CMOS PLD, Comm. OTP, Plastic 24-pin 1/2 Power, 35ns, CMOS PLD, Comm. | 33-43<br>33-43<br>33-43<br>33-43<br>33-43 |

| CPL20R4L-25NC<br>CPL20R4L-25WC<br>CPL20R4-25NC<br>CPL20R4L-35NC<br>CPL20R4L-35WC<br>CPL20R4-35NC       | OTP, Plastic 24-pin 1/4 Power, 25ns, CMOS PLD, Comm. 24-pin Windowed CERDIP, 1/4 Power, 25ns, CMOS PLD, Comm. OTP, Plastic 24-pin 1/2 Power, 25ns, CMOS PLD, Comm. OTP, Plastic 24-pin 1/4 Power, 35ns, CMOS PLD, Comm. 24-pin Windowed CERDIP, 1/4 Power, 35ns, CMOS PLD, Comm. OTP, Plastic 24-pin 1/2 Power, 35ns, CMOS PLD, Comm. | 33-43<br>33-43<br>33-43<br>33-43<br>33-43 |

| CPL20R6L-25NC<br>CPL20R6L-25WC<br>CPL20R6-25NC<br>CPL20R6L-35NC<br>CPL20R6L-35WC<br>CPL20R6-35NC       | OTP, Plastic 24-pin 1/4 Power, 25ns, CMOS PLD, Comm. 24-pin Windowed CERDIP, 1/4 Power, 25ns, CMOS PLD, Comm. OTP, Plastic 24-pin 1/2 Power, 25ns, CMOS PLD, Comm. OTP, Plastic 24-pin 1/4 Power, 35ns, CMOS PLD, Comm. 24-pin Windowed CERDIP, 1/4 Power, 35ns, CMOS PLD, Comm. OTP, Plastic 24-pin 1/2 Power, 35ns, CMOS PLD, Comm. | 33-43<br>33-43<br>33-43<br>33-43<br>33-43 |

| CPL20R8L-25NC<br>CPL20R8L-25WC<br>CPL20R8-25NC<br>CPL20R8L-35NC<br>CPL20R8L-35WC<br>CPL20R8-35NC       | OTP, Plastic 24-pin 1/4 Power, 25ns, CMOS PLD, Comm. 24-pin Windowed CERDIP, 1/4 Power, 25ns, CMOS PLD, Comm. OTP, Plastic 24-pin 1/2 Power, 25ns, CMOS PLD, Comm. OTP, Plastic 24-pin 1/4 Power, 35ns, CMOS PLD, Comm. 24-pin Windowed CERDIP, 1/4 Power, 35ns, CMOS PLD, Comm. OTP, Plastic 24-pin 1/2 Power, 35ns, CMOS PLD, Comm. | 33-43<br>33-43<br>33-43<br>33-43<br>33-43 |

| CPL20L10L-25NC<br>CPL20L10L-25WC<br>CPL20L10-25NC<br>CPL20L10L-35NC<br>CPL20L10L-35WC<br>CPL20L10-35NC | OTP, Plastic 24-pin 1/4 Power, 25ns, CMOS PLD, Comm. 24-pin Windowed CERDIP, 1/4 Power, 25ns, CMOS PLD, Comm. OTP, Plastic 24-pin 1/2 Power, 25ns, CMOS PLD, Comm. OTP, Plastic 24-pin 1/4 Power, 35ns, CMOS PLD, Comm. 24-pin Windowed CERDIP, 1/4 Power, 35ns, CMOS PLD, Comm. OTP, Plastic 24-pin 1/2 Power, 35ns, CMOS PLD, Comm. | 33-43<br>33-43<br>33-43<br>33-43<br>33-43 |

### **PRODUCT SELECTION GUIDE**

|          |      |                 | Dedi-           |       | O                    | utputs          |       | Max Sp                                  | need (ns) (1,2)                         | Max I        | c (mA)        | Available       |

|----------|------|-----------------|-----------------|-------|----------------------|-----------------|-------|-----------------------------------------|-----------------------------------------|--------------|---------------|-----------------|

| Part #   | Pins | Array<br>Inputs | cated<br>Inputs | I/O's | Combi-<br>natorial   | Regis-<br>tered | Total | -25                                     | -35                                     | Low<br>Power | Std.<br>Power | Packages<br>(3) |

| CPL16L8  | 20   | 16              | 10              | 6     | 8                    | 0               | 8     | t <sub>PD</sub> =25                     | t <sub>po</sub> =35                     | 45           | 70            | N, W            |

| CPL16R4  | 20   | 16              | 8               | 4     | 4                    | 4               | 8     |                                         | t <sub>PD</sub> /t <sub>co</sub> =35/25 | 45           | 70            | N, W            |

| CPL16R6  | 20   | 16              | 8               | 2     | 2                    | 6               | 8     |                                         | t <sub>PD</sub> /t <sub>co</sub> =35/25 | 45           | 70            | N, W            |

| CPL16R8  | 20   | 16              | 8               | 0     | 0                    | 8               |       | t <sub>co</sub> =15                     | t <sub>co</sub> =25                     | 45           | 70            | N, W            |

| CPL20L10 | 24   | 20              | 12              | 8     | 10                   | 0               | 10    | t <sub>PO</sub> =25                     | t <sub>eo</sub> =35                     | 45           | 70            | N, W            |

| CPL20L8  | 24   | 20              | 14              | 6     | 8                    | 0               |       | t <sub>pp</sub> =25                     | t <sub>e0</sub> =35                     | 45           | 70            | N, W            |

| CPL20R4  | 24   | 20              | 12              | 4     | 4                    | 4               | 8     | t <sub>pp</sub> /t <sub>co</sub> =25/15 | t <sub>PD</sub> /t <sub>co</sub> =35/25 | 45           | 70            | N, W            |

| CPL20R6  | 24   | 20              | 12              | 2     | 2                    | 6               | 8     | t <sub>pp</sub> /t <sub>co</sub> =25/15 | t <sub>pp</sub> /t <sub>co</sub> =35/25 | 45           | 70            | N, W            |

| CPL20R8  | 24   | 20              | 12              | 0     | 0                    | 8               | 8     | t <sub>co</sub> =15                     | t <sub>co</sub> =25                     | 45           | 70            | N, W            |

| CPL22V10 | 24   | 22              | 12              | 10    | Program:<br>Macrocel |                 | 10    | t <sub>p0</sub> /t <sub>co</sub> =25/15 | t <sub>po</sub> /t <sub>co</sub> =35/25 | 55           | 90            | N, W            |

| CPL16V8  | 20   | 16              | 10              | 8     | Program:<br>Macrocel |                 | 8     | t <sub>P0</sub> /t <sub>co</sub> =25/15 | t <sub>po</sub> /t <sub>co</sub> =35/25 | 55           | 90            | N, W            |

Package Codes: N = Plastic DIP, W = Windowed CERDIP

#### Notes:

- (1) The above specifications are for the commercial temperature range of 0 to 70°C. All Power supplies are  $V_{cc}$  = 5V  $\pm$  10%

- (2) Military product in the temperature ranges of -55°C to +125°C is also available. Speed and power selections may vary from those above. See data sheet.

- (3) PLCC and SOIC packages are available. Please contact factory.

## **CROSS REFERENCE**

| AMD                                     | SAMSUNG         | HARRIS        | SAMSUNG         |

|-----------------------------------------|-----------------|---------------|-----------------|

| PAL16L8AC                               | CPL16L8-25C     | HPL16LC8-5    | CPL16L8L-35C-   |

| PAL16L8ALC                              | CPL16L8-25C     | HPL16RC4-5    | CPL16R4L-35C-   |

| PAL16L8C                                | CPL16L8-35C     | HPL16RC6-5    | CPL16R6L-35C-   |

| PAL16L8LC                               | CPL16L8-35C     | HPL16RC8-5    | CPL16R8L-35C-   |

| PAL16L8QC                               | CPL16L8L-35C    | 111 E101108-5 | OI E101(6E-330) |

|                                         |                 | ММІ           | SAMSUNG         |

| PAL16R4ALC                              | CPL16R4-25C     |               |                 |

| PAL16R4LC                               | CPL16R4-35C     | PAL12L10C     | CPL20L10-35C*   |

| PAL16R4C                                | CPL16R4-35C     | PAL14L8C      | CPL20L8-35C*    |

| PAL16R4QÇ                               | CPL16R4L-35C    |               |                 |

| PAL16R6AC                               | CPL16R6-25C     | PAL16L6C      | CPL20L8-35C*    |

| PAL16R6C                                | CPL16R6-35C     | PAL16L8AC     | CPL16L8-25C     |

| PAL16R6LC                               | CPL16R6-35C     | PAL16L8A-2C   | CPL16L8-35C     |

| PAL16R6QC                               | CPL16R6L-35C    | PAL16L8A-4C   | CPL16L8L-35C    |

|                                         |                 | PAL16L8B-2C   | CPL16L8-25C     |

| PAL16R8AC                               | CPL16R8-25C     | PAL16L8B-4C   | CPL16L8L-35C    |

| PAL16R8ALC                              | CPL16R8-25C     | PAL16L8C      | CPL16L8-35C     |

| PAL16R8C                                | CPL16R8-35C     | PAL16L8D-4C   | CPL16L8L-25C    |

| PAL16R8LC                               | CPL16R8-35C     | I ALTOLOD-40  | O1 E10E0E-250   |

| PAL16R8QC                               | CPL16R8L-35C    | PAL16R4AC     | CPL16R4-25C     |

| PALITORIOGO                             |                 | PAL16R4A-2C   | CPL16R4-35C     |

| PAL22V10AC                              | CPL22V10-25C    | PAL16R4A-4C   | CPL16R4L-35C    |

| PAL22V10C                               | CPL22V10-35C    | PAL16R4B-2C   | CPL16R4-25C     |

|                                         |                 | PAL16R4B-4C   | CPL16R4L-35C    |

| CYPRESS                                 | SAMSUNG         | PAL16R4C      | CPL16R4-35C     |

| OTTTLOS                                 | JAMJONG         | PAL16R4D-4C   | CPL16R4-35C     |

| PALC16L8-25C                            | CPL16L8-25C     |               |                 |

| PALC16L8L-25C                           | CPL16L8L-25C    | PAL16R6A-4C   | CPL16R6L-35C    |

| PALC16L8-35C                            | CPL16L8-35C     | PAL16R6B-2C   | CPL16R6-25C     |

| PALC16L8L-35C                           | CPL16L8L-35C    | PAL16R6B-4C   | CPL16R6L-35C    |

| PALCIOLOL-33C                           | CFL10L0L-33C    | PAL16R6B-2C   | CPL16R6-25C     |

| PALC16R4-25C                            | CPL16R4-25C     | PAL16R6B-4C   | CPL16R6L-35C    |

| PALC16R4L-25C                           | CPL16R4L-25C    | PAL16R6C      | CPL16R6-35C     |

| PALC16R4-35C                            | CPL16R4-35C     | PAL16R6D-4C   | CPL16R6L-25C    |

| PALC16R4L-35C                           | CPL16R4L-35C    | PAL16R6AC     | CPL16R6-25C     |

|                                         |                 | PAL16R6A-2C   | CPL16R6-35C     |

| PALC16R6-25C                            | CPL16R6-25C     | I ALTOHOA-20  | OI E10110-050   |

| PALC16R6L-25C                           | CPL16R6L-25C    | PAL16R8AC     | CPL16R8-25C     |

| PALC16R6-35C                            | CPL16R6-35C     | PAL16R8A-2C   | CPL16R8-35C     |

| PALC16R6L-35C                           | CPL16R6L-35C    | PAL16R8A-4C   | CPL16R8L-35C    |

| D41.040D0.050                           | 001.4000.050    | PAL16R8B-2C   | CPL16R8-25C     |

| PALC16R8-25C                            | CPL16R8-25C     | PAL16R8B-4C   | CPL16R8L-35C    |

| PALC16R8L-25C                           | CPL16R8L-25C    | PAL16R8C      | CPL16R8-35C     |

| PALC16R8-35C                            | CPL16R8-35C     | PAL16R8D-4C   | CPL16R8L-25C    |

| PALC16R8L-35C                           | CPL16R8L-35C    | PALIBROD-4C   |                 |

| PALC22V10-25C                           | CPL22V10-25C    | MMI           | SAMSUNG         |

| PALC22V10-35C                           | CPL22V10-35C    |               |                 |

| . , , , , , , , , , , , , , , , , , , , | J. 222 V. O GOO |               |                 |

| FAIRCHILD                               | SAMSUNG         | PAL18L4C      | CPL20L8-35C*    |

|                                         |                 | PAL20L10AC    | CPL20L10-25C    |

| 16L8A                                   | CPL16L8-25C     | PAL20L10C     | CPL20L10-35C    |

| 16P8A                                   | CPL16L8-25C-    | 1             |                 |

| 16R4A                                   | CPL16R4-25C     | PAL20L8AC     | CPL20L8-25C     |

| 16R6A                                   | CPL16R6-25C     | PAL20L8A-2C   | CPL20L8-35C     |

| 16R8A                                   | CPL16R8-25C     | PAL20L8C      | CPL20L8-35C     |

|                                         | CPL16R4-25C-    | PAL20R4AC     | CPL20R4-25C     |

| 16RP4A                                  |                 | PAL20R4A-2C   | CPL2OR4-25C     |

| 16RP6A                                  | CPL16R6-25C-    |               | CPL20R4-35C     |

| 16RP8A                                  | CPL16R8-25C-    | PAL20R4C      | OF L2014-330    |

## **CROSS REFERENCE** (Continued)

| ммі                                                             | SAMSUNG                                                                  | NATIONAL                                                         | SAMSUNG                                                   |  |  |

|-----------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------|--|--|

| PAL20R6AC<br>PAL20R6A-2C                                        | CPL20R6-25C<br>CPL20R6-35C                                               | PAL20R4BC<br>PAL20R4C                                            | CPL20R4-25C<br>CPL20R4-35C                                |  |  |

| PAL20R6C<br>PAL20R8AC<br>PAL20R8A-2C                            | CPL20R6-35C<br>CPL20R8-25C<br>CPL20R8-35C                                | PAL20R6AC<br>PAL20R6BC                                           | CPL20R6-25C<br>CPL20R6-25C                                |  |  |

| PAL20R8AC<br>PAL20R8A-2C                                        | CPL20R8-25C<br>CPL20R8-35C                                               | PAL20R6C<br>PAL20R8AC                                            | CPL20R6-35C<br>CPL20R8-25C                                |  |  |

| PALC22V10H-25C                                                  | CPL20R8-35C<br>CPL22V10-25C                                              | PAL20R8BC<br>PAL20R8C                                            | CPL20R8-25C<br>CPL20R8-35C                                |  |  |

| PALC22V10H-35C<br>PALC16L8Q-25C                                 | CPL22V10-35C<br>CPL16L8L-25C                                             | ТІ                                                               | SAMSUNG                                                   |  |  |

| PALC16R4Q-25C<br>PALC16R6Q-25C<br>PALC16R8Q-25C                 | CPL16R4L-25C<br>CPL16R6L-25C<br>CPL16R8L-25C                             | PAL22V10AC<br>PAL16L8AC<br>PAL16L8A-2C<br>PAL16L8B-25C           | CPL22V10-25C<br>CPL16L8-25C<br>CPL16L8-35C<br>CPL16L8-25C |  |  |

| NATIONAL                                                        | SAMSUNG                                                                  | PAL16R4AC<br>PAL16R4A-2C<br>PAL16R4-25C                          | CPL16R4-25C<br>CPL16R4-35C<br>CPL16R4-25C                 |  |  |

| 12L10C<br>14L8C<br>16L6C<br>18L4C                               | CPL20L10-35C*<br>CPL20L8-35C*<br>CPL20L8-35C*<br>CPL20L8-35C*            | PAL16R6AC<br>PAL16R6A-2C<br>PAL16R6-25C                          | CPL16R6-25C<br>CPL16R6-35C<br>CPL16R6-25C                 |  |  |

| PAL16L8A2C<br>PAL16L8AC<br>PAL16L8B2C                           | CPL16L8-35C<br>CPL16L8-25C<br>CPL16L8-25C                                | PAL16R8AC<br>PAL16R8A-2C<br>PAL16R8-25C                          | CPL16R8-25C<br>CPL16R8-35C<br>CPL16R8-25C                 |  |  |

| PAL16L8B4C<br>PAL16L8C                                          | CPL16L8L-35C<br>CPL16L8-35C                                              | PAL20L10AC<br>PAL20L10A-2C                                       | CPL20L10-25C<br>CPL20L10-35C                              |  |  |

| PAL16R4A2C<br>PAL16R4AC<br>PAL16R4B2C                           | CPL16R4-35C<br>CPL16R4-25C<br>CPL16R4-25C                                | PAL20L8AC<br>PAL20L8A-2C                                         | CPL20L8-25C<br>CPL20L8-35C                                |  |  |

| PAL16R4B4C<br>PAL16R4C                                          | CPL16R4L-35C<br>CPL16R4-35C                                              | PAL20R4AC<br>PAL20R4A-2C                                         | CPL20R4-25C<br>CPL20R4-35C                                |  |  |

| PAL16R6A2C<br>PAL16R6AC<br>PAL16R6B2C                           | CPL16R6-35C<br>CPL16R6-25C<br>CPL16R6-25C                                | PAL20R6AC<br>PAL20R6A-2C                                         | CPL20R6-25C<br>CPL20R6-35C                                |  |  |

| PAL16R6B4C<br>PAL16R6C                                          | CPL16R6L-35C<br>CPL16R6-35C                                              | PAL20R8AC<br>PAL20R8A-2C                                         | CPL20R8-25C<br>CPL20R8-35C                                |  |  |

| PAL16R8A2C<br>PAL16R8AC<br>PAL16R8B2C<br>PAL16R8B4C<br>PAL16R8C | CPL16R8-35C<br>CPL16R8-25C<br>CPL16R8-25C<br>CPL16R8L-35C<br>CPL16R8-35C |                                                                  |                                                           |  |  |

| PAL20L10B2C<br>PAL20L10C                                        | CPL20L10-25C<br>CPL20L10-35C                                             |                                                                  |                                                           |  |  |

| PAL20L2C<br>PAL20L8AC                                           | CPL20L8-35C<br>CPL20L8-25C                                               | Unless otherwise noted                                           |                                                           |  |  |

| PAL20L8AC<br>PAL20L8BC<br>PAL20L8BC<br>PAL20L8C                 | CPL20L8-25C<br>CPL20L8-25C<br>CPL20L8-25C<br>CPL20L8-35C                 | power specs are met o product.                                   |                                                           |  |  |

| PAL20R4AC                                                       | CPL20R4-25C                                                              | (-) FUNCTIONALLY EQUIVALENT<br>(*) SUPERSET, DOWNWARD COMPATIBLE |                                                           |  |  |

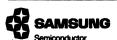

## **CPL™ ORDERING INFORMATION**

# Product Guide 1

| Technical Overview                        | 2 |

|-------------------------------------------|---|

| Product Specifications                    | 3 |

| CPL Programming Electrical Specifications | 4 |

| CPL Programmer and Software Guide         | 5 |

| Definition of Terms                       | 6 |

| Package Drawings                          | 7 |

| Sales Offices                             | 8 |

#### **TECHNICAL OVERVIEW**

#### Samsung CPL Family Features

Samsung's CPL (CMOS Programmable Logic) devices use a state-of-the-art CMOS EPROM technology which emphasizes complete testability. The 1.2 micron advanced CMOS process provides high performance, which was previously achieved only with bipolar processes, at a much lower power. Testability is inherent to the technology because it allows devices to be programmed and erased, thus facilitating 100% programming, AC, and functional testing.

The first generation of CPL devices are CMOS implementations of the industry standard PAL devices. The CPL devices offer significant advantages over TTL logic, some of which are listed below:

- · 100% user-programmability

- Design flexibility

- · Chip-count and pin-count reduction

- Pattern duplication prevention (Security Bit)

The CPL family also offers additional features and benefits which can be attributed to the CMOS EPROM technology:

- 100% programming, AC, and functional testing

- Increased reliability

- Easier, lower-cost prototyping with reprogrammable CPL devices (windowed, CERDIP)

- Lower power consumption over bipolar PALs with matched performance

The CPL EPROM cells are programmed by charging a floating gate with electrons and unprogrammed by irradiating the cells with ultraviolet (UV) light, making complete testing of all circuitry possible before shipping. On the other hand, bipolar devices which use fuse programmable cells, can be programmed only once, making 100% testing impossible. Special, on-chip test arrays also allow additional functional and AC testing without having to program the CPL devices.

CPL devices which are contained in windowed CERDIP packages may be programmed and erased, at the customer site. This allows the designer to develop, test, and fine-tune his/her logic without having to replace each programmed device.

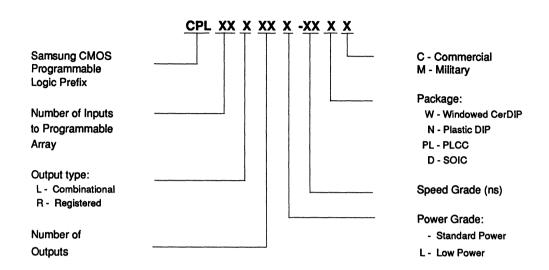

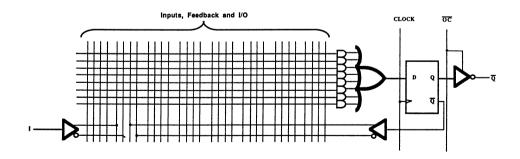

Figure 1. CPL-PAL Comparison

The CPL family offers the system designer a better alternative to the standard bipolar PLDs (Programmable Logic Devices). The devices are function and pinout compatible with their respective PAL predecessors. They may be designed into existing PAL sockets without changing the board layout or the PLD equations. The propagation delays of the CPL devices are 25 nsec or 35 nsec with 45mA or 70mA (max.) I<sub>CC</sub>. Thus, the CPL devices provide bipolar speeds at a fraction of the bipolar power consumption, reducing the system's power requirements and increasing its reliability.

#### **PLD Notation**

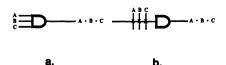

In describing CPL devices, an industry standard PLD notation is used. Figure 2a shows the conventional notation of a multiple-input AND gate. Figure 2b shows the adopted PLD notation of the same logic gate. An X on an intersection of an input term and the input line of an AND gate represents that the input term is connected

Figure 2. PLD Notation Example

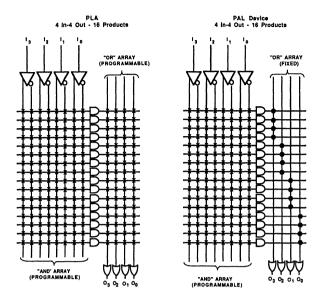

Figure 3. PLA and PAL AND-OR Structure

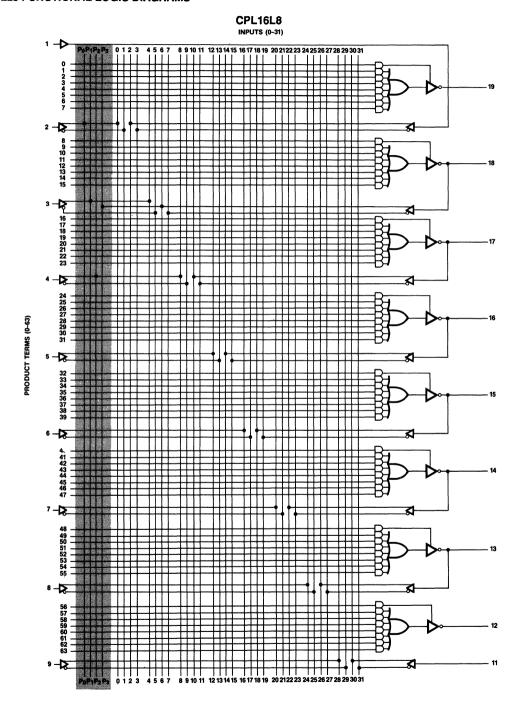

to one of the AND gate inputs. In a physical CPL device, an X represents an unprogrammed cell. (In an unprogrammed CPL device, all input terms are connected to all AND gates.) Each CPL device is illustrated by a logic diagram similar to the basic AND-OR structure diagram shown in Figure 3.

#### **CPL Architecture**

The CPL devices utilize the basic PLA (Programmable Logic Array) structure. This structure consists of an AND array followed by an OR array (see Figure 3). The

CPL devices, like the PAL devices which they may replace, have a programmable AND array followed by a non-programmable OR array. Such a structure offers PLA flexibility while decreasing silicon complexity. In comparison, an FPLA (Field Programmable Logic Array) structure has both arrays programmable but occupies more silicon area.

The CPL devices, which have a basic PLA structure, lend themselves to easy implementation of Boolean transfer functions. These functions are expressed in the

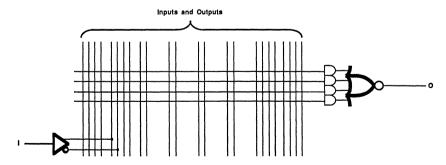

Figure 4. A Simple Combinatorial Output Structure

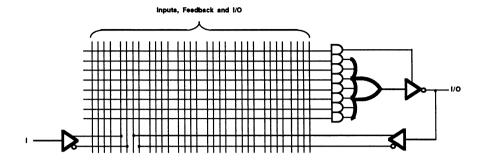

Figure 5. The Programmable Combinatorial Input/Output Structure

sum-of-products form. This allows quick and easy implementation of logic functions of varying complexity.

The CPL devices allow the designer to configure complex interconnections within the chip as opposed to configuring them on the PC board. The design, therefore, becomes more efficient and takes less time to complete. Furthermore, the interconnections, made by writing into EPROM cells, can be easily modified during prototype testing, saving lengthy and costly printed circuit board changes.

One CPL device can implement logic functions that require four or more conventional logic packages, reducing IC inventories while increasing board savings.

While all CPL devices are based on the PLA structure, they differ in their output structure combinations. The CPL devices feature a variety of output structures: combinatorial outputs, registered outputs, and programmable macro cells.

Figure 6. A Registered Output Structure with Feedback

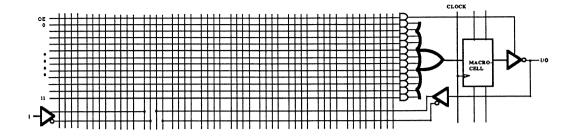

Figure 7. A Programmable Macro Cell Output Structure

#### Combinatorial Outputs

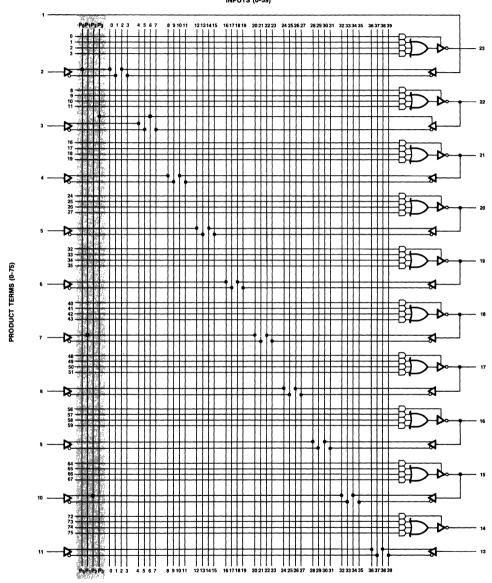

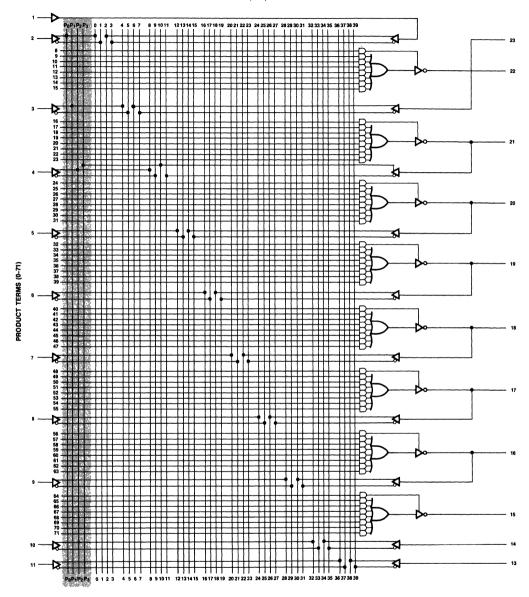

There are two types of combinatorial outputs. The simplest one is a combinatorial output without feedback (see Figure 4). It is used in the CPL16L8, CPL20L8, and CPL20L10 devices. This output sums several product terms (P-terms) into an active low signal. One additional P-term is used to individually enable/disable the output signal.

Another type of combinatorial output is the programmable combinatorial I/O (see Figure 5). When enabled, this output stage acts like the simple combinatorial output with the addition of a feedback path into the AND array. When disabled, the output stage allows the I/O pin to act as an input into the CPL AND array. This flexibility allows variable input/output ratios as well as bidirectional parts. The programmable combinatorial I/O output is used in all CPL20 and CPL24 devices with the exception of the CPL16R8 and CPL20R8.

#### Registered Outputs

This type of output features a data register with registered feedback. Each product term is summed into the data input of a D-type flip-flop. The flip-flop records the state of its input on the rising edge of the clock. The Q output of the flip-flop is gated to the output pin through a three-state buffer and is also fed back to the CPL AND array as an input term. This feature allows the CPL device to implement a state machine. The Clock and Output Enable/Disable signals are common to all registered outputs of a single device (See Figure 6). Registered outputs are used in all CPL20 and CPL24 devices with the exception of CPL16L8, CPL20L8, and CPL20L10.

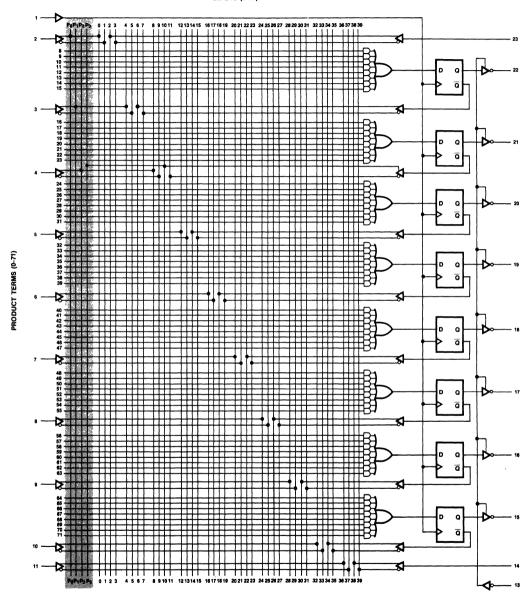

#### Programmable Macro Cell I/O

The programmable macro cell, illustrated in Figure 7, is a very flexible structure which allows the designer to individually define the architecture of each I/O. Each I/O structure may be configured to be a combinatorial or registered output. Each output features an individually programmable Output Enable/Disable function as well as an individually programmable polarity function. Common Clock, Reset, and Preset signals facilitate preload, power reset and state-machine operations. Programmable macro cells are used in the CPL16V8 and CPL22V10 devices.

#### Test Circuitry

A PLD is tested, like any other digital circuit, by applying known values to its inputs. A fault may be detected by comparing the device's outputs with desired values. In general, a non-programmed PLD does not lend itself to exhaustive fault testing. Furthermore, since some of the PLDs have registered outputs with internal feedback lines to the programmable array, these feedback lines must be controlled during testing as well. Applying known values at these inputs of the array requires the application of many vectors to the device's inputs. Therefore, the device must be cycled many times to arrive at a known state, and the testing of the device becomes long and impractical.

To solve this problem, Samsung's CPL incorporates register preload and test arrays onto the devices, making testing simple and complete.

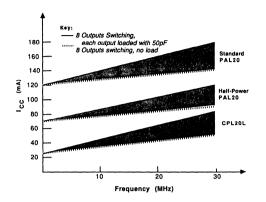

Figure 8. CPL and PAL Power Consumption as a Function of Frequency

#### Register Preload

The register preload feature allows the user, as well as the manufacturer, to load known values into the device's output registers. Known values are then applied to the array's feedback lines to help facilitate simple and complete device testing. The register preload operation is accomplished by applying a super-voltage pulse to a specified pin (see data sheets).

#### Test Array

The on-chip test array consists of additional input terms which may be accessed for AC and functional testing before and after packaging. The test array is not ac-

cessed during, and does not affect, normal device operation. During testing, the test array is activated and used to drive the device circuitry, bypassing the non-programmed programmable array. The test array is used during in-house final testing and may also be used by the customer for incoming inspection.

#### CPL Development Software

A variety of software packages are available to define and simulate CPL devices. All CPL devices are supported by industry-standard software packages such as Data I/O's ABEL, P-CAD's CUPL, and others. These software packages assemble CPL definition files in various formats, simulate the CPL devices, and create bit patterns conforming to a JEDEC standard format that may be transmitted to PLD programming systems.

The CPL devices can be programmed by all major PROM/PLD systems. Some PROM/PLD programmers may require a software update or a personality card/module to facilitate CPL programming. All programmers accept bit patterns which conform to JEDEC standard format.

More detailed information and a list of PLD software vendors and programmers is included in the CPL Programmer and Software Guide section of this book.

#### **Power Dissipation**

Low power consumption is one of the most important features of CMOS technology. With most of the power dissipating only during device switching, it is important to describe the power dissipation in terms which reflect its dependency on operating frequency.

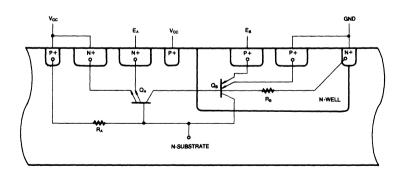

Figure 9. Simplified Cross Section of a CMOS Inverter

Figure 10. CMOS SCR Structure

A standard power dissipation model includes the device's quiescent current  $(I_Q)$ , the device's internal "power dissipation" capacitance  $(C_{pp})$ , the external load

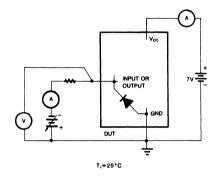

Figure 11. Test Setup for Measuring DC Latch-Up

capacitance (C,), and the output buffer capacitance (Co):

$$P_{D} = V_{CC}I_{Q} + C_{PD}V_{CC}^{2}f + (C_{L}+C_{O})V_{DS}^{2}f$$

The quiescent power is determined by the static current. The switching power consumption is determined by the internal power dissipation capacitance and by the operating frequency (f). The power consumed by driving the external load depends on the external load itself, the output buffer capacitance, the operating frequency (f), and the output low-to-high voltage swing (V<sub>DD</sub>).

The internal power capacitance as well as the static supply current vary from one CPL type to another. Moreover, they depend on the specific code which is programmed into the device. The typical  $\rm I_{\rm o}$  for CPL20 and CPL24 is 25mA, and the typical  $\rm C_{\rm PD}$  is 45pF. The load capacitance plays an even more important role in determining the power consumption of a CPL device. Since 8 outputs may toggle, each consisting of typically 10pF, and each driving a 50pF load, up to 2.4 mA per MHz may add to the device's static supply current.

The graph in Figure 8 illustrates CPL power consumption as a function of operating frequency in comparison with bipolar PAL power consumption. All unused inputs are assumed to be tied to ground or  $V_{\rm CC}$ , all active inputs are driven rail-to-rail, and the duty cycle is 50%. Measurements have shown that while the duty cycle does not greatly affect the CPL power consumption, up to 20% more power is consumed by the input buffers when the input voltage swings between 0.8V to 2.0V.

Figure 12. Input Protection Circuit

#### Latchup

In circuits fabricated using CMOS technology, a parasitic four- layer SCR structure appears between  $V_{\rm cc}$  and ground. This parasitic structure can short  $V_{\rm cc}$  to ground when voltages greater than  $V_{\rm cc}$  or lower than ground are applied to an input or an output pin. The phenomenon is called "latchup" and may result in a damaged device. When a device is in latchup mode, the power supply must be shut-off to release the device back to normal operating mode.

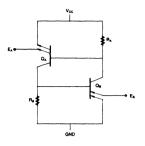

The parasitic SCR structure in CMOS is illustrated in the simplified cross section of an inverter shown in Figure 9. Figure 10 shows a schematic representation of the same structure. When EA is raised above V<sub>CC</sub>, current is injected from the emitter of QA and is swept to its collector. This current will increase the voltage at the gate of QB and once above 0.78V, it will turn QB on. QB will feed current back into RA and once a 0.7V voltage drop appears across RA, QA will turn on and inject more current into RB. Once both transistors are on and enough current is provided to sustain the SCR, it will stay on even after EA and EB return to within the rail voltages.

Because low RA and RB resistance values reduce the gain of QA and QB, Samsung's CPL devices are designed to have low RA and RB. In addition, large diodes are connected between each signal pin and the supply, to shunt out latchup trigger currents.

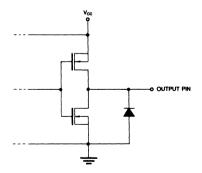

When a p-channel MOS transistor is used as a pull-up transistor on the output driver of an IC, another parasitic transistor is formed which worsens the latchup problem. The CPL devices use N- channel pull-up transistors which maintain TTL compatibility and improve latchup protection.

A substrate bias generator provides important additional latchup protection in CPL devices. It keeps the substrate at approximately -3V below ground level. The parasitic diode at an input pin will not turn on unless the voltage applied to that pin is more negative than -3V. The substrate bias also eliminates the substrate currents due to undershoot, thereby providing higher input noise tolerance.

Samsung's CPL devices are designed to withstand currents typically well above the specified minimum of 200 mA at 7V  $V_{\rm CC}$  and 125°C. This parameter is measured on a static basis (see Figure 11).

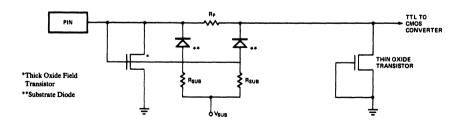

#### ESD Protection

ESD protection is accomplished by preventing a high voltage from reaching the internal transistors of the integrated circuit. The circuit of each input pin includes a thick-oxide transistor, a thin-oxide transistor and the line resistance, Rp, between the transistors (see Figure 12). The thick-oxide transistor turns on when a large positive voltage is applied to the input pin. When the voltage arriving at the thin-oxide transistor exceeds 13V. the transistor turns on and protects the internal circuitry by discharging the current to ground. This current is then limited by the line resistance, Rp. A high negative voltage applied to the input pin is similarly discharged by the network of the substrate diodes which start conducting when the applied negative voltage is below the substrate level. The ESD protection incorporated in the output structure is shown in Figure 13.

Figure 13. A typical output circuit of a CPL device.

| 1 | Product Guide                             |  |

|---|-------------------------------------------|--|

| 2 | Technical Overview                        |  |

| 3 | Product Specifications                    |  |

| 4 | CPL Programming Electrical Specifications |  |

| 5 | CPL Programmer and Software Guide         |  |

| 6 | Definition of Terms                       |  |

| 7 | Package Drawings                          |  |

| 8 | Sales Offices                             |  |

|   |                                           |  |

# CPL20

Features/Benefits

Description

Logic Symbols and Pinouts

Absolute Maximum Ratings

Recommended Operating Conditions

DC Electrical Characteristics

AC Electrical Characteristics

Switching Waveforms

#### **FEATURES/BENEFITS**

- High-speed CMOS equivalent to Bipolar PALs

- CMOS UV-erasable EPROM cell to allow reprogrammability

- Low power (45mA Max. I<sub>cc</sub>) and standard (70mA Max. I<sub>cc</sub>) versions

- Two speed grades (t<sub>PD</sub> = 25ns Max. and t<sub>PD</sub> = 35ns Max.)

- >2000V ESD input and output protection

- 100% functional and AC tested

- 100% programming tested

- Programmable security bit to prevent pattern duplication

- Register Preload for register configuration

- Programmable three-state outputs

#### DESCRIPTION

The CPL20 Series devices are high-speed, UV-erasable, electrically programmable CMOS logic replacements of the Bipolar PAL20 family. They utilize the familiar sum-of-products form (AND array followed by an OR array) allowing the user to customize logic to his/her needs.

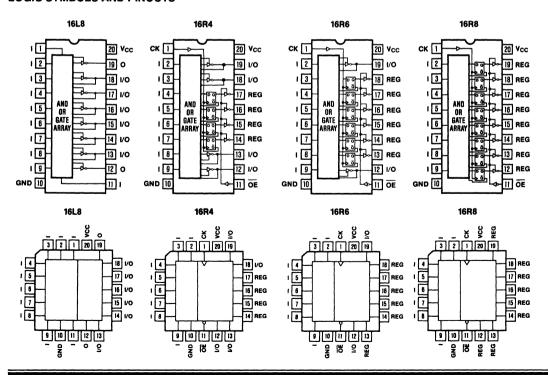

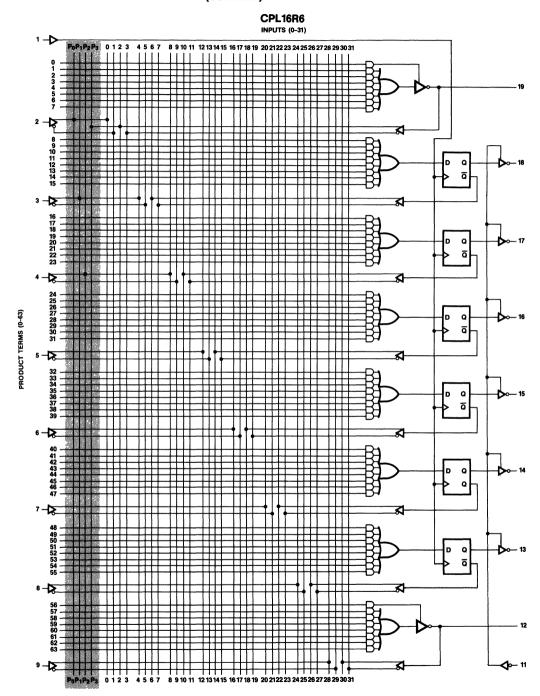

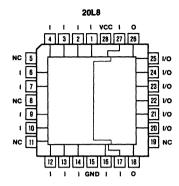

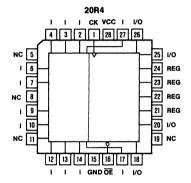

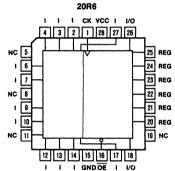

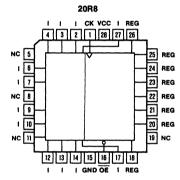

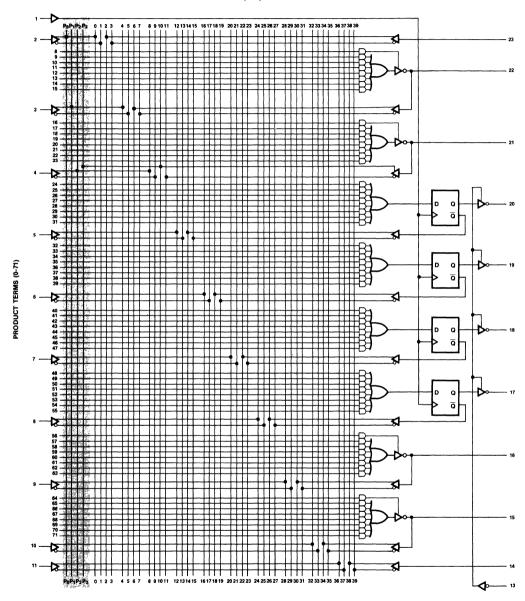

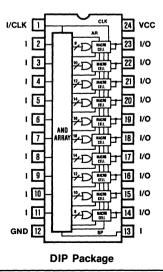

Four devices are offered in the CPL20 Series. They are: the CPL16L8, the CPL16R4, the CPL16R6, and the CPL16R8. Each of these devices has 16 array inputs and 8 outputs. All the outputs to the CPL16L8 are combinatorial, while all the outputs to the CPL16R8 are registered. In contrast, the CPL16R4 has 4 registered and 4 combinatorial outputs, and the CPL16R6 has 6 registered and 2 combinatorial outputs. Each combinatorial output in the CPL16R6 and CPL16R4 devices serves as an I/O pin. The CPL16L8 device has 6 I/O pins.

#### LOGIC SYMBOLS AND PINOUTS

#### **DESCRIPTION** (Continued)

The CPL devices are manufactured using a 1.2 micron EPROM technology which offers low power dissipation (45/70 mA maximum  $I_{\rm cc}$ ) combined with high performance (25ns maximum propagation delay). Because the CPL devices are erasable, they can be thoroughly tested for programming, functional and AC integrity, resulting in high-reliability and 100% programming yields.

The CPL20 devices are housed in 20-pin plastic DIP, PLCC, SOIC, and windowed CERDIP packages. The windowed CERDIP package allows the user to erase the CPL device using UV light, and later to reprogram it with a different pattern. The plastic DIP, PLCC, and SOIC devices are one-time-programmable (OTP) and may not be erased.

#### Register Preload

The register preload feature of the CPL20 Series allows output pins to be loaded with arbitrary states, making functional testing easier than ever.

#### Security Bit

All CPL20 devices feature a security bit. The security bit allows the user to protect his/her design against unauthorized duplication. When the security bit is set, the contents of the programmable-cell array may not be accessed in Read or Verify modes. Since the CPL devices do not have visible fuses, they offer enhanced security over what is available in bipolar PAL devices.

#### Test Array

Another feature of the devices in the CPL20 Series is the on-chip test array. It is programmed for final functional and AC testing of the devices after they have been packaged (even if the security bits have been programmed). In the normal operation of the device, the test arrays are not accessed. In the test mode of operation, only the input terms in the shaded portion of the functional block diagram are accessed. The test array facilitates high-reliability as well as simple and short testing.

#### **ERASURE (windowed-CERDIP only)**

The CPL devices will erase by light at wavelengths of under 4000 Angstroms. The window must be covered by an opaque label to prevent erasure by exposure to sunlight or fluorescent lighting.

Recommended dose of ultraviolet light for erasure:

Wavelength of 2537 Angstroms

(minimum dose -- 25 Wsec/cm²)

If an ultraviolet lamp with a 12mW/cm² power rating is used, 30 to 35 minutes of erasure time will suffice. The lamp must be closer than 1 inch from the window to guarantee optimal erasing conditions. Exposure to high intensity UV light for an extended period of time may cause permanent damage to the CPL devices. The maximum dosage recommended is 7250 Wsec/cm².

#### **CPL20 ABSOLUTE MAXIMUM RATINGS**

#### **ABSOLUTE MAXIMUM RATINGS (Note 1)**

| Item                          | Symbol                               | Rating                       | Unit |

|-------------------------------|--------------------------------------|------------------------------|------|

| Supply Voltage                | V <sub>CC</sub>                      | -0.5 to +7.0                 | ٧    |

| DC Input Voltage              | $V_{IN} ( I_{IN}  \le 20 \text{mA})$ | -3.0 to +7.0                 | ٧    |

| Off-State DC Output Voltage   | V <sub>o</sub>                       | -0.5 to V <sub>CC</sub> +0.5 | ٧    |

| DC Programming Voltage        |                                      | 14.0                         | ٧    |

| Storage Temperature           | T <sub>STG</sub>                     | -65 to +150                  | °C   |

| Power Dissipation per Package | P <sub>D</sub> (Note 2)              | 500                          | mW   |

Note 1: Absolute Maximum Ratings are those values beyond which permanent damage to the device may occur. These are stress ratings only, and functional operation of the device at or beyond them is not implied. Long exposure to these conditions may affect device reliability.

Note 2: Power dissipation temperature derating:

Plastic Package (N): -12mW/°C from 65°C to 85°C

Ceramic Package (J): -12mW/°C from 100°C to 125°C

#### RECOMMENDED OPERATING CONDITIONS

| Item                                     | Symbol                                    | Rating               | Unit |

|------------------------------------------|-------------------------------------------|----------------------|------|

| Supply Voltage                           | V <sub>CC</sub>                           | 4.5 to 5.5           | V    |

| DC Input and Output (Off-State) Voltages | V <sub>IN</sub> , V <sub>O</sub> (Note 3) | 0 to V <sub>CC</sub> | V    |

| Operating Temperature Range, Commercial  | TA                                        | 0 to +70             | °C   |

| Operating Temperature Range, Military    | T <sub>A</sub>                            | -55 to +125          | °C   |

Note 3: Unused inputs must always be tied to an appropriate logic voltage level (either V<sub>CC</sub> or GND).

#### DC ELECTRICAL CHARACTERISTICS

Over Recommended Operating Conditions

| Parameter                       | Symbol           | Test Conditions                                                               |                                                                      | Min | Max            | Unit           |

|---------------------------------|------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------|-----|----------------|----------------|

| Low Level Input Voltage         | V <sub>IL</sub>  | (Note 4)                                                                      | (Note 4)                                                             |     | 0.8            | ٧              |

| High Level Input Voltage        | V <sub>IH</sub>  | (Note 4)                                                                      |                                                                      | 2.0 |                | ٧              |

| Input Current                   | I <sub>IN</sub>  | $0 < V_{IN} < V_{CC}$                                                         |                                                                      | -10 | 10             | μΑ             |

| Low Level Output Voltage        | V <sub>OL</sub>  | V <sub>CC</sub> = Min<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | Military I <sub>OL</sub> =12mA<br>Commercial I <sub>OL</sub> =24mA   |     | 0.5            | ٧              |

| High Level Output Voltage       | V <sub>OH</sub>  | V <sub>CC</sub> = Min<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | Military I <sub>OH</sub> =-2mA<br>Commercial I <sub>OH</sub> =-3.2mA | 2.4 |                | ٧              |

| Off-State Output                | I <sub>OZL</sub> | V <sub>CC</sub> = Max,                                                        | V <sub>O</sub> = 0.4V                                                |     | -100           |                |

| Leakage Current                 | l <sub>ozh</sub> | V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub>                          | V <sub>O</sub> = 2.4V                                                |     | 100            | μΑ             |

| Output Short-Circuit<br>Current | los              | V <sub>CC</sub> = Max, V <sub>O</sub> = 0.5V (Note 5)                         |                                                                      |     | -300           | mA             |

| Power Supply Current            | Icc              | All inputs = GND<br>V <sub>CC</sub> = Max<br>I <sub>OUT</sub> = 0mA           | "L"<br>STD<br>MIL                                                    |     | 45<br>70<br>70 | mA<br>mA<br>mA |

Note 4: These are absolute values with respect to device ground. The applied voltage plus overshoots due to system and/or tester noise must not exceed these worst-case values.

Note 5: Only one output shorted at a time. Duration of the short circuit should not be more than one second. V<sub>O</sub> = 0.5V has been chosen to avoid test problems caused by tester ground degradation.

#### **CPL20 AC ELECTRICAL CHARACTERISTICS**

Over Recommended Operating Conditions (Note 6)

|                                                              | Commercial         |      |     |     | Military |     |     |      |     |      |

|--------------------------------------------------------------|--------------------|------|-----|-----|----------|-----|-----|------|-----|------|

|                                                              |                    | -    | 25  | -:  | 35       | -2  | 25  |      | 35  | 1    |

| Parameter                                                    | Symbol             | Min  | Max | Min | Max      | Min | Max | Min  | Max | Unit |

| Input or Feedback to Non-Registered Output, 16R6, 16R4, 16L8 | t <sub>PD</sub>    |      | 25  |     | 35       |     | 30  |      | 40  | ns   |

| Clock to Registered Output or Feedback, 16R8, 16R6, 16R4     | t <sub>co</sub>    |      | 15  |     | 25       |     | 20  |      | 25  | ns   |

| Pin 11 to Output Enable, 16R8, 16R6, 16R4                    | t <sub>PZX11</sub> |      | 20  |     | 25       |     | 25  |      | 25  | ns   |

| Pin 11 to Output Disable,<br>16R8, 16R6, 16R4                | t <sub>PXZ11</sub> |      | 20  |     | 25       |     | 25  |      | 25  | ns   |

| Input to Output Enable,<br>16R6, 16R4, 16L8                  | t <sub>PZX</sub>   |      | 25  |     | 35       |     | 30  |      | 40  | ns   |

| Input to Output Disable,<br>16R6, 16R4, 16L8                 | t <sub>PXZ</sub>   |      | 25  |     | 35       |     | 30  |      | 45  | ns   |

| Setup Time from Input or Feedback to Clock, 16R8, 16R6, 16R4 | t <sub>SU</sub>    | 20   |     | 30  |          | 25  |     | 35   |     | ns   |

| Hold Time, 16R8, 16R6, 16R4                                  | t <sub>H</sub>     | 0    |     | 0   |          | 0   |     | 0    |     | ns   |

| Clock Width (High or Low)                                    | t <sub>W</sub>     | 15   |     | 20  |          | 20  |     | 25   |     | ns   |

| Clock Period                                                 | tp                 | 35   |     | 55  |          | 45  |     | 60   |     | ns   |

| Maximum Frequency                                            | f <sub>MAX</sub>   | 28.5 |     | 18  |          | 22  |     | 16.5 |     | MHz  |

**Note 6:** Input rise and fall times (10% to 90% of  $V_{CC}$ ):  $t_r = t_f \le 6$ ns.

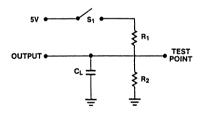

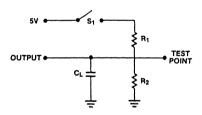

#### **AC Test Circuit**

#### Resistor Values (Ω)

|       | R1  | R2  |

|-------|-----|-----|

| COM'L | 200 | 390 |

| MIL   | 390 | 750 |

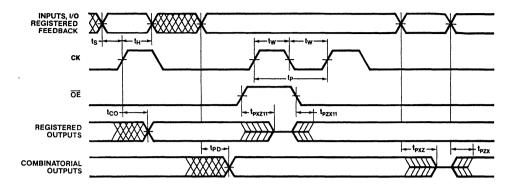

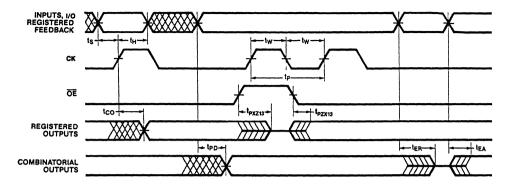

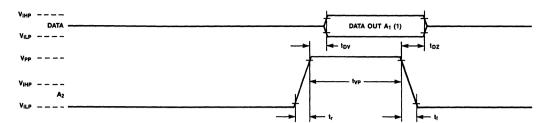

#### **CPL20 SWITCHING WAVEFORMS**

Note 7:  $C_L$  includes load and test jig capacitance.

Note 8:  $t_{PD}$  is tested with switch  $S_1$  closed and  $C_L = 50pF$ .

Note 9: For 3-State outputs, output enable times are tested with C<sub>L</sub> = 50pF to the 1.5V level; S<sub>1</sub> is open for high impedance to HIGH tests and closed for high impedance to LOW tests. Output disable times are tested with C<sub>L</sub> = 5pF. HIGH to high impedance tests are made to an output voltage of V<sub>OH</sub> - 0.5V with S<sub>1</sub> open; LOW to high impedance tests are made to the V<sub>OL</sub> = 0.5V level with S<sub>1</sub> closed.

#### **CPL20 FUNCTIONAL LOGIC DIAGRAMS**

#### **CPL20 FUNCTIONAL LOGIC DIAGRAMS (Continued)**

## CPL16R4 INPUTS (0-31) 1-0 0123 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 D Q ₫ 4-12 24 25 26 27 28 29 30 D Q ā PRODUCT TERMS 32 33 34 35 36 37 38 39 D Q ā Ø 40 41 42 43 44 45 46 D Q ā 13 56 57 58 59 60 61 62 63 12 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

#

# CPL20 FUNCTIONAL LOGIC DIAGRAMS (Continued)

# CPL24

Features/Benefits

Description

Logic Symbols and Pinouts

Absolute Maximum Ratings

Recommended Operating Conditions

DC Electrical Characteristics

AC Electrical Characteristics

Switching Waveforms

#### FEATURES/BENEFITS

- High-speed CMOS equivalent to Bipolar PALs

- CMOS UV-erasable EPROM cell to allow reprogrammability

- Low power (45 mA Max. I<sub>cc</sub>) and Standard (70 mA Max. I<sub>cc</sub>) versions

- Two speed grades (t<sub>PD</sub> = 25ns Max. and t<sub>PD</sub> = 35ns Max.)

- >2000V ESD input and output protection

- 100% functional and AC tested

- 100% programming tested

- Programmable security bit to prevent pattern duplication

- Register preload for register initialization

- Programmable three-state outputs

#### DESCRIPTION

The CPL24 Series devices are high-speed, UV-erasable, electrically programmable CMOS logic replacements of the Bipolar PAL24 family. They utilize the familiar sum-of-products form (AND array followed by an OR array) allowing the user to customize logic to his/her needs.

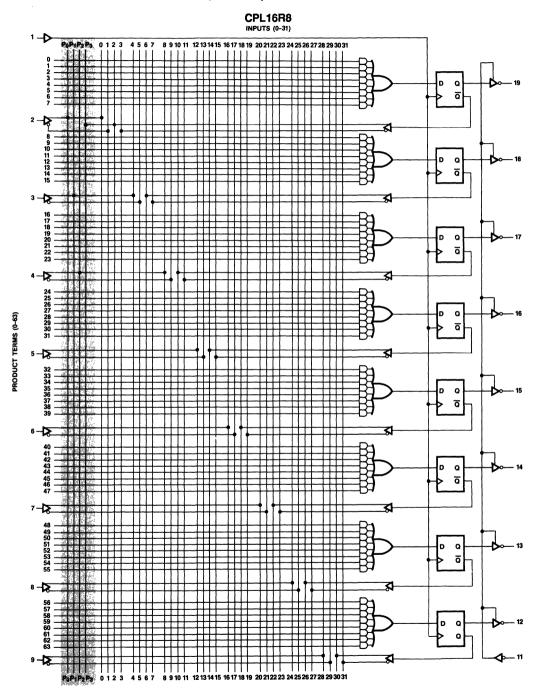

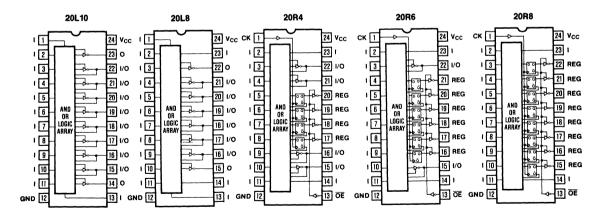

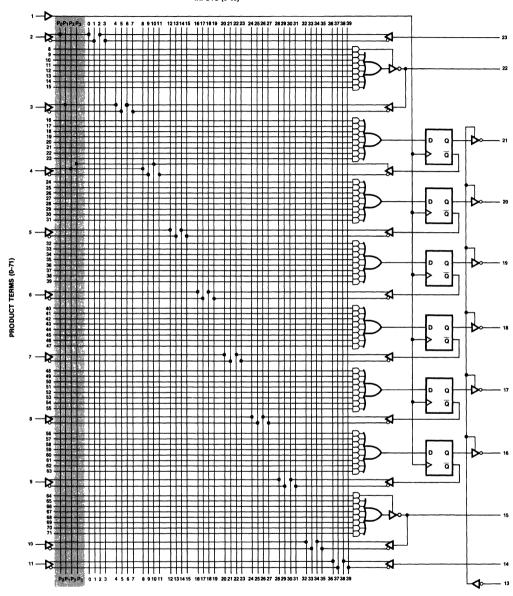

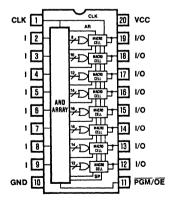

Five devices are offered in the CPL24 Series. They are: the CPL20L10, the CPL20L8, the CPL20R4, the CPL20R6, and the CPL20R8. Each of these devices has 20 array inputs. The CPL20L10 has 10 outputs and the others have 8 outputs. All the outputs to the CPL16L8 and CPL20L10 are combinatorial, while all outputs to the CPL20R8 are registered. In contrast, the CPL20R4 has 4 registered and 4 combinatorial outputs and the CPL20R6 has 6 registered and 2 combinatorial outputs. Each combinatorial output in the CPL20R6 and CPL20R4 devices serves as an I/O pin. The CPL20L10 device has 8 I/O pins, and the CPL20L8 device has 6 I/O pins.

#### LOGIC SYMBOLS AND PINOUTS

### **LOGIC SYMBOLS AND PINOUTS (Continued)**

#### **DESCRIPTION** (Continued)

The CPL devices are manufactured using a 1.2 micron EPROM technology which offers low power dissipation (45/70 mA maximum  $I_{\rm cc}$ ) combined with high performance (25ns maximum propagation delay). Because the CPL devices are erasable, they can be thoroughly tested for programming, functional and AC integrity, resulting in high-reliability and 100% programming yields.

The CPL24 devices are housed in 24-pin plastic DIP, SOIC, and windowed CERDIP packages, as well as a 28-pin PLCC package. The windowed CERDIP package allows the user to erase the CPL device using UV light, and later to reprogram it with a different pattern. The plastic DIP, PLCC, and SOIC devices are one-time-programmable (OTP) and may not be erased.

#### Reaister Preload

The register preload feature of the CPL24 Series allows output pins to be loaded with arbitrary states, making functional testing easier than ever.

# Security Bit

All CPL24 devices feature a security bit. The security bit allows the user to protect his/her design against unauthorized duplication. When the security bit is set, the contents of the programmable-cell array may not be accessed in Read or Verify modes. Since the CPL devices do not have visible fuses, they offer enhanced security over what is available in bipolar PAL devices.

#### Test Array

Another feature of the devices in the CPL24 Series is the on-chip test array. It is programmed for final functional and AC testing of the devices after they have been packaged (even if the security bits have been programmed). In the normal operation of the device, the test arrays are not accessed. In the test mode of operation, only the input terms in the shaded portion of the functional block diagram are accessed. The test array facilitates high-reliability as well as simple and short testing.

# **ERASURE** (windowed-CERDIP only)

The CPL devices will erase by light at wavelengths of under 4000 Angstroms. The window must be covered by an opaque label to prevent erasure by exposure to sunlight or fluorescent lighting.

Recommended dose of ultraviolet light for erasure:

Wavelength of 2537 Angstroms

(minimum dose -- 25 Wsec/cm²)

If an ultraviolet lamp with a 12mW/CM² power rating is used, 30 to 35 minutes of erasure time will suffice. The lamp must be closer than 1 inch from the window to guarantee optimal erasing conditions. Exposure to high intensity UV light for an extended period of time may cause permanent damage to the CPL devices. The maximum dosage recommended is 7250 Wsec/cm².

# CPL24 ABSOLUTE MAXIMUM RATINGS (Note 1)

| Item                          | Symbol                                | Rating                       | Unit |

|-------------------------------|---------------------------------------|------------------------------|------|

| Supply Voltage                | V <sub>CC</sub>                       | -0.5 to +7.0                 | ٧    |

| DC Input Voltage              | $V_{IN} ( I_{IN}  \leq 20 \text{mA})$ | -3.0 to +7.0                 | ٧    |

| Off-State DC Output Voltage   | Vo                                    | -0.5 to V <sub>CC</sub> +0.5 | V    |

| DC Programming Voltage        | V <sub>PP</sub>                       | 14.0                         | V    |

| Storage Temperature           | T <sub>STG</sub>                      | -65 to +150                  | °C   |

| Power Dissipation per Package | P <sub>D</sub> (Note 2)               | 500                          | mW   |

Note 1: Absolute Maximum Ratings are those values beyond which permanent damage to the device may occur.

These are stress ratings only, and functional operation of the device at or beyond them is not implied.

Long exposure to these conditions may affect device reliability.

Note 2: Power dissipation temperature derating:

Plastic Package (N): -12mW/°C from 65°C to 85°C Ceramic Package (J): -12mW/°C from 100°C to 125°C

#### RECOMMENDED OPERATING CONDITIONS

| Item                                     | Symbol                                    | Rating               | Unit |

|------------------------------------------|-------------------------------------------|----------------------|------|

| Supply Voltage                           | V <sub>CC</sub>                           | 4.5 to 5.5           | V    |

| DC Input and Output (Off-State) Voltages | V <sub>IN</sub> , V <sub>O</sub> (Note 3) | 0 to V <sub>CC</sub> | V    |

| Operating Temperature Range, Commercial  | T <sub>A</sub>                            | 0 to +70             | °C   |

| Operating Temperature Range, Military    | TA                                        | -55 to +125          | °C   |

Note 3: Unused inputs must always be tied to an appropriate logic voltage level (either V<sub>CC</sub> or GND).

# DC ELECTRICAL CHARACTERISTICS

Over Recommended Operating Conditions

| Parameter                       | Symbol           | Test Conditions                                                               |                                                                      | Min | Max            | Unit           |

|---------------------------------|------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------|-----|----------------|----------------|

| Low Level Input Voltage         | V <sub>IL</sub>  | (Note 4)                                                                      |                                                                      |     | 0.8            | V              |

| High Level Input Voltage        | V <sub>IH</sub>  | (Note 4)                                                                      |                                                                      | 2.0 |                | V              |

| Input Current                   | I <sub>IN</sub>  | 0 < V <sub>IN</sub> < V <sub>CC</sub>                                         |                                                                      | -10 | 10             | μΑ             |

| Low Level Output Voltage        | V <sub>OL</sub>  | V <sub>CC</sub> = Min<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | Military I <sub>OL</sub> =12mA<br>Commercial I <sub>OL</sub> =24mA   |     | 0.5            | V              |

| High Level Output Voltage       | V <sub>OH</sub>  | V <sub>CC</sub> = Min<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | Military I <sub>OH</sub> =-2mA<br>Commercial I <sub>OH</sub> =-3.2mA |     | 2.4            | V              |

| Off-State Output                | l <sub>OZL</sub> | V <sub>CC</sub> = Max,                                                        | V <sub>O</sub> = 0.4V                                                |     | -100           |                |

| Leakage Current                 | lozh             | V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub>                          | V <sub>O</sub> = 2.4V                                                |     | 100            | μΑ             |

| Output Short-Circuit<br>Current | los              | V <sub>CC</sub> = Max, V <sub>O</sub> = 0.5V (Note 5)                         |                                                                      |     | -300           | mA             |

| Power Supply Current            | Icc              | All inputs = GND<br>V <sub>CC</sub> = Max<br>I <sub>OUT</sub> = 0mA           | "L"<br>STD<br>MIL                                                    |     | 45<br>70<br>70 | mA<br>mA<br>mA |

Note 4: These are absolute values with respect to device ground. The applied voltage plus overshoots due to system and/or tester noise must not exceed these worst-case values.

Note 5: Only one output shorted at a time. Duration of the short circuit should not be more than one second. V<sub>O</sub> = 0.5V has been chosen to avoid test problems caused by tester ground degradation.

# **CPL 24 AC ELECTRICAL CHARACTERISTICS**

Over Recommended Operating Conditions (Note 6)

|                                                                     |                    |      | Commercial |     |     | Military |     |      |     |      |

|---------------------------------------------------------------------|--------------------|------|------------|-----|-----|----------|-----|------|-----|------|

|                                                                     |                    | -:   | -25 -35    |     | -25 |          | -35 |      |     |      |

| Parameter                                                           | Symbol             | Min  | Max        | Min | Max | Min      | Max | Min  | Max | Unit |

| Input or Feedback to Non-Registered Output, 20R6, 20R4, 20L8, 20L10 | t <sub>PD</sub>    |      | 25         |     | 35  |          | 30  |      | 40  | ns   |

| Clock to Registered Output or Feedback, 20R8, 20R6, 20R4            | t <sub>CO</sub>    |      | 15         |     | 25  |          | 20  |      | 25  | ns   |

| Pin 13 to Output Enable,<br>20R8, 20R6, 20R4                        | t <sub>PZX13</sub> |      | 20         |     | 25  |          | 25  |      | 25  | ns   |

| Pin 13 to Output Disable,<br>20R8, 20R6, 20R4                       | t <sub>PXZ13</sub> |      | 20         |     | 25  |          | 25  |      | 25  | ns   |

| Input to Output Enable,<br>20R6, 20R4, 20L8, 20L10                  | t <sub>PZX</sub>   |      | 25         |     | 35  |          | 30  |      | 40  | ns   |

| Input to Output Disable,<br>20R6, 20R4, 20L8, 20L10                 | t <sub>PXZ</sub>   |      | 25         |     | 35  |          | 30  |      | 45  | ns   |

| Setup Time from Input or Feedback to Clock, 20R8, 20R6, 20R4        | t <sub>SU</sub>    | 20   |            | 30  |     | 25       |     | 35   |     | ns   |

| Hold Time, 20R8, 20R6, 20R4                                         | t <sub>H</sub>     | 0    |            | 0   | -   | 0        |     | 0    |     | ns   |

| Clock Width (High or Low)                                           | t <sub>W</sub>     | 15   |            | 20  |     | 20       |     | 25   |     | ns   |

| Clock Period                                                        | t₽                 | 35   |            | 55  |     | 45       |     | 60   |     | ns   |

| Maximum Frequency                                                   | f <sub>MAX</sub>   | 28.5 |            | 18  |     | 22       |     | 16.5 |     | MHz  |

**Note 6:** Input rise and fall times (10% to 90% of  $V_{CC}$ ):  $t_r = t_f \le 6$ ns.

# **AC Test Circuit**

# Resistor Values (Ω)

|       | R1  | R2  |

|-------|-----|-----|

| COM'L | 200 | 390 |

| MIL   | 390 | 750 |

# **CPL24 WAVEFORMS**

Note 7: C<sub>L</sub> includes load and test jig capacitance.

Note 8:  $t_{PD}$  is tested with switch  $S_1$  closed and  $C_L = 50pF$ .

Note 9: For 3-State outputs, output enable times are tested with  $C_L$  = 50pF to the 1.5V level;  $S_1$  is open for high impedance to HIGH tests and closed for high impedance to LOW tests. Output disable times are tested with  $C_L$  = 5pF. HIGH to high impedance tests are made to an output voltage of  $V_{OH}$  - 0.5V with  $S_1$  open; LOW to high impedance tests are made to the  $V_{OL}$  = 0.5V level with  $S_1$  closed.

# **CPL24 FUNCTIONAL LOGIC DIAGRAMS**

CPL20L10 INPUTS (0-39)

# CPL20L8

#### CPL20R4

#### CPL20R6

#### CPL20R8

# **ADVANCE INFORMATION**

CPL22V10 CPL16V8

# **CPL22V10**

CMOS Programmable Logic Array With Output Macrocells (24-Pin) ADVANCE INFORMATION

#### **FEATURES/BENEFITS**

- High speed CMOS programmable alternative to bipolar 22V10 PLDs

- Two speed grades

t<sub>PD</sub>= 25ns max., t<sub>PD</sub>= 35ns max.

- Low power 90mA max.

- CMOS UV-erasable EPROM cell to allow reprogrammability

- 10 input/output macrocells for maximum flexibility

- Up to 22 inputs and 10 outputs

- Programmable output polarity

- Registered or combinatorial output selection

- Variable product term distribution

- From 8 to 16 product terms available per output

- Global synchronous preset and asychronous reset of all registers

- On power-up, registers reset

- Test array and preloadable output registers for testability

- 100% functional, AC, and programming tested

- >2000V ESD input protection

- Security bit to prevent CPL duplication

#### **DESCRIPTION**

The CPL22V10 is a high-speed CMOS UV-erasable, electrically programmable device with an advanced architecture. The device is manufactured using a 1.2 micron EPROM technology offering low power dissipation combined with high performance. The UV-erasability of the CPL devices allow 100% programming, functional, and AC testing, providing high reliability and 100% programming yields.

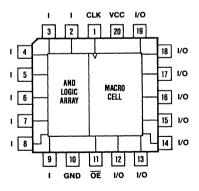

The CPL22V10 uses the standard programmable AND/ Fixed OR logic array structure, familiar to most programmable logic users, to implement complex logic functions. Each logic function consists of up to sixteen product terms per output and each product term consists of up to 22 inputs. Each output from the array feeds a programmable macro cell enabling it to be programmed as a combinatorial or registered, active high or low output.

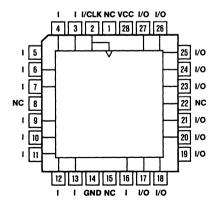

The 22V10 device is housed in a 24-pin plastic DIP, 28-pin PLCC, and a windowed 24-pin CERDIP package. The windowed-CERDIP package allows the user to erase the CPL device using UV light, and later to reprogram the device with a different pattern. The devices in plastic packages are OTP (One-Time-Programmable) devices and may not be erased

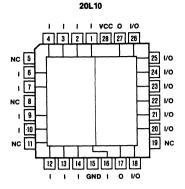

#### **PIN CONFIGURATIONS**

**Plastic Leaded Chip Carrier**

#### **FEATURES/BENEFITS**

- Equivalent to industry standard 16V8 architecture

- Two speed grades

$(t_{PD} = 25 \text{ns max.},$

$t_{pn} = 35$ ns max.)

- Low power 45mA active Max I<sub>cc</sub>

- CMOS UV-erasable EPROM cell to allow reprogrammability

- 8 input/output macrocells for maximum flexibility

- Up to 16 inputs and 8 outputs

- Programmable output polarity

- Registered or Combinatorial output selection

- Test Array and preloadable output registers for testability

- 100% functional, AC, and programming tested

- >2000V ESD input protection

- Programmable Security bit to prevent pattern duplication

#### DESCRIPTION

The CPL16V8 is a high-speed CMOS UV-erasable, electrically programmable device with an advanced architecture. The device is manufactured using a 1.2 micron EPROM technology offering low power dissipation combined with high performance. The UV-erasability of the CPL devices allow 100% programming, functional, and AC testing, providing high reliability and 100% programming yields.

The CPL16V8 uses the standard programmable AND/ Fixed OR logic array structure, familiar to most programmable logic users, to implement complex logic functions. Each logic function consists of up to eight product terms per output, and each product term consists of up to 16 inputs. Each output from the array feeds a programmable macro cell enabling it to be programmed as a combinatorial or registered, active high or low output.

The 16V8 device is housed in a 20-pin plastic DIP, 20-pin PLCC, and a windowed 20-pin CERDIP package. The windowed-CERDIP package allows the user to erase the CPL device using UV light, and later to reprogram the device with a different pattern. The devices in plastic packages are OTP (One-Time-Programmable) devices and may not be erased.

### **PIN CONFIGURATIONS**

**DIP Package**

**Plastic Leaded Chip Carrier**

| Product Guide                             | 1 |

|-------------------------------------------|---|

| Technical Overview                        | 2 |

| Product Specifications                    | 3 |

| CPL Programming Electrical Specifications | 4 |

| CPL Programmer and Software Guide         | 5 |

| Definition of Terms                       | 6 |

| Package Drawings                          | 7 |

| Sales Offices                             | 8 |

# **CPL PROGRAMMING ELECTRICAL SPECIFICATIONS**

# Programming Samsung's CMOS PLDs

Samsung's CPL (CMOS programmable logic) devices use an EPROM programming technology which emphasizes complete testability (100% programming, functional, and AC) and high performance. Testability is inherent to the technology because it allows devices to be programmed and reprogrammed many times. High performance is achieved using a two-transistor EPROM cell which optimizes the speed of both read and write transistors. This results in CPL devices being as fast as many of their bipolar counterparts, and since they are fully tested prior to delivery to the customer, they provide higher programming yields.

Samsung's CPL devices are programmed using high voltage pulses, from 100 microseconds to 10 milliseconds in duration, which produce about 50 mA of programming current. At one time, eight to ten EPROM cells are programmed, depending on the device.

CPL EPROM cells are programmed by charging a floating gate with electrons and unprogrammed by irradiating the cells with ultraviolet (UV) light, making complete testing of all circuitry possible before shipping. (Bipolar parts, which use fuse cells, on the other hand, can be programmed only once, making 100% AC testing impossible.) By using special on-chip test arrays, additional functional and AC testing of CPL devices can also be performed without having to program the devices. Also, if the devices are contained in windowed packages, they may be programmed and erased, at the customer site a number of times, allowing the designer to test, develop, and fine-tune his/her logic without having to replace each programmed device.

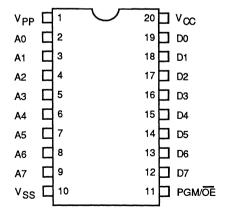

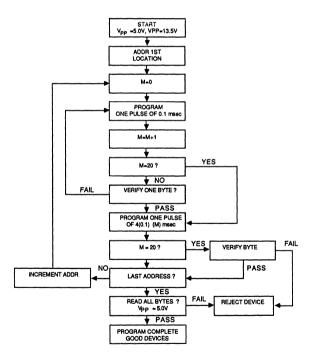

CPL 20 Series (CPL16L8, CPL16R4, CPL16R6, CPL16R8)

The critical AC and DC parameters for programming the CPL 20 series devices are listed in Tables 1 and 2. The minimum and maximum parameter values are given for an ambient temperature of 25°C.

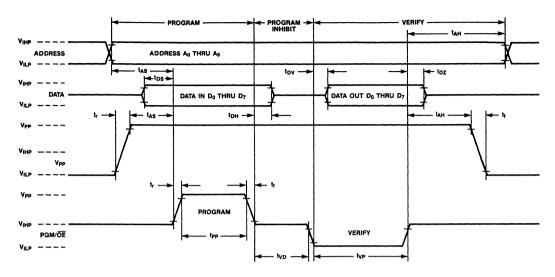

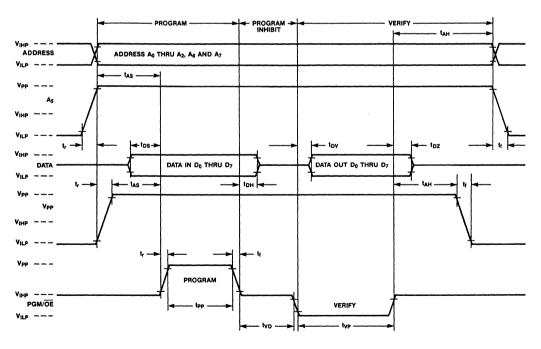

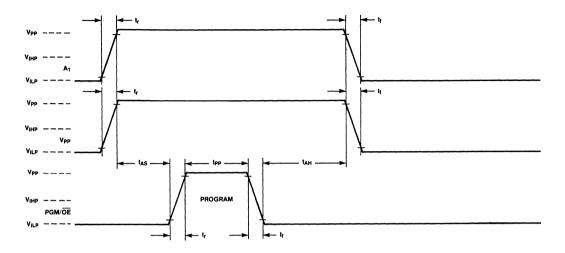

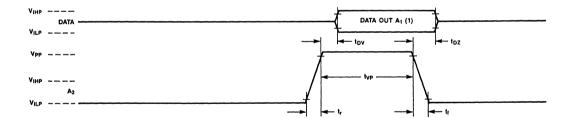

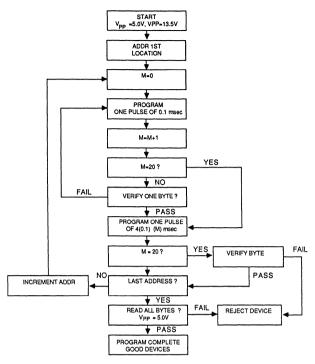

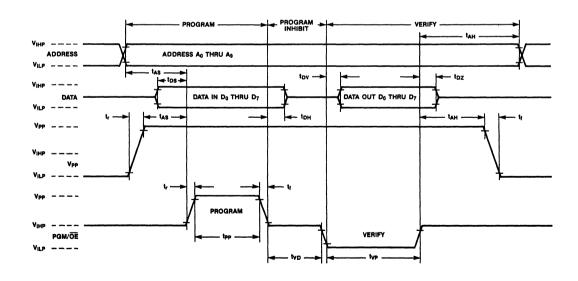

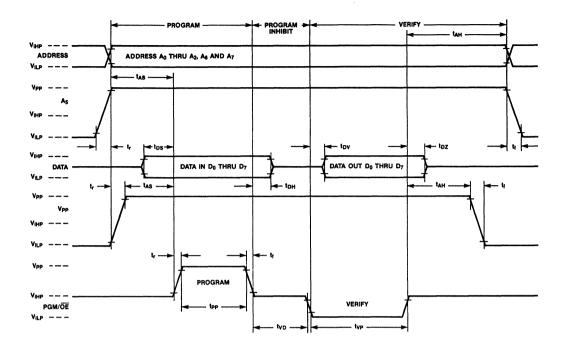

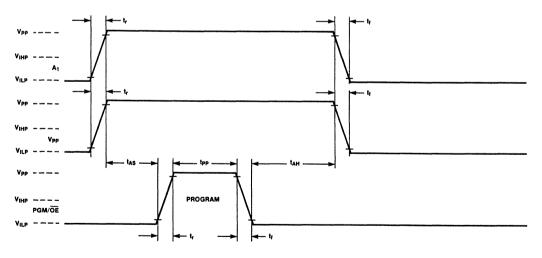

The pin configuration for programming the CPL 20 series parts is given in Figure 1. Notice that pin 1 is now called Vpp. It is raised to a programming voltage, Vpp, during programming (see Table 1). In this mode, pins 2 - 9 are used for addressing each location to be programmed and pins 12 - 19 are used for supplying data. Pin 11, the PGM/~OE pin, is the READ/WRITE pin in the programming mode. When it is raised to the programming voltage, Vpp, a write occurs and the data on the output pins is written into the addressed array locations. When it is switched to a logic LOW, a read occurs and the contents of the addressed locations can be checked or verified. When pin 11 is switched to a logic HIGH, the device is inhibited and the outputs go into a high impedance (Z) state.

The CPL devices are programmed one byte at a time for a total of 256 (32 input terms, 8 wide) bytes of memory. This memory can be addressed once the array is programmed. The addresses are selected via pins 2 - 9 (A0 - A7). Pins 2 - 4 select one of eight product terms (or outputs) as shown in Table 3, whereas pins 5 - 9 select one of 32 input terms according to Table 4. The test input terms can be selected, as in Table 5, by raising pin 7 to Vpp and entering the test programming mode of operation. Here, the duplicated memory cells of the test array are addressed at the same locations as the 0, 1, 2, and 3 product terms. (The test arrays, having 32 bytes of memory, are provided for the purpose of post-assembly testing and are disconnected in normal operation.)

| Parameter           | Description                       | Min. | Max. | Units |

|---------------------|-----------------------------------|------|------|-------|

| V <sub>PP</sub>     | Programming Voltage               | 13.0 | 14.0 | ٧     |

| Vcc                 | Supply Voltage During Programming | 4.75 | 5.25 | V     |

| V <sub>IH</sub>     | Programming Input High Voltage    | 3.0  |      | V     |

| VIL                 | Programming Input Low Voltage     |      | 0.4  | V     |

| V <sub>OH</sub> (1) | Output High Voltage               | 2.4  |      | V     |

| Vol(1)              | Output Low Voltage                |      | 0.4  | V     |