# Rocky 2 RT6224K

# hyperSPARC<sup>™</sup> CPU Module

### Features

- Based on ROSS' fourth-generation hyperSPARC<sup>™</sup> processor

- RT620C Central Processing Unit (CPU)

- RT625 Cache Controller, Memory Management, and Tag Unit (CMTU)

- Two RT628 Cache Data Units (CDUs)

- Intra-Module Bus incorporates low voltage logic to reduce power and increase speed

- Full multiprocessing implementation — Hardware support for symmetric,

- shared-memory multiprocessing — Level 2 MBus support for cache

- Level 2 MBus support for cache coherency

- SPARC compliant

- --- Conforms to SPARC Reference MMU Architecture

- Conforms to SPARC Level 2 MBus Module Specification (Revision 1.2)

- Dual-clock architecture

- CPU scaleable up to 125 MHz

- MBus scaleable up to 50 MHz

- Each hyperSPARC processor features

Superscalar SPARC CPU with integrated floating point unit and 8-Kbyte instruction cache

- Zero-wait-state, 256-Kbyte or 2ndlevel cache

- Demand-paged virtual memory management

- Module design

- Provides CPU upgrade path at module level

- Advanced packaging technology for a compact design

- High performance \*

- -120-154 SPECfp92

- \* in a 50MHz MBus system

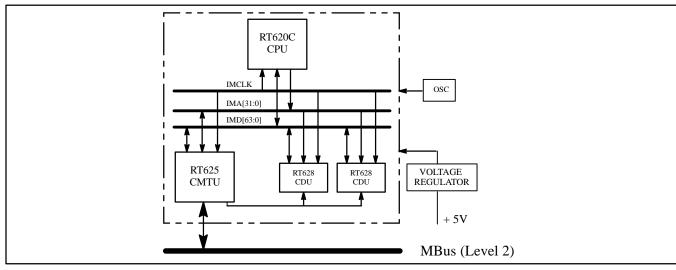

## Figure 1. Logic Block Diagram

## **Selection Guide**

| Part Number: RT6224K*                              | -90/256     | -100/256    | -125/256    |

|----------------------------------------------------|-------------|-------------|-------------|

| CPU Operating Frequency (MHz)                      | 90          | 100         | 125         |

| Typical Power Consumption (w)**                    | 15          | 17.5        | 21          |

| Second-level Cache Size                            | 256K        | 256K        | 256K        |

| SPECint92 / SPECfp92                               | 103 / 120   | 112 / 130   | 132 / 154   |

| SPECrateint92 / SPECratefp92<br>(single processor) | 2419 / 2849 | 2660 / 3091 | 3200 / 3661 |

| SPECrateint92 / SPECratefp92<br>(dual processor)   | 4568 / 5226 | 6185 / 7697 | 5857 / 6510 |

\*See Appendix B for hyperSPARC ordering information

\*\* Commercial

# Rocky 2 RT6224K

## **Functional Description**

The RT6224K hyperSPARC Module is a complete SPARC CPU, including on-board primary and secondary cache memories. It is packaged as a compact PCB and interfaces to the remainder of the system via a SPARC-standard MBus connector. The CPU on the RT6224K consists of a high-speed superscalar, highly pipelined processor with dual integer ALUs and an on-chip floating-point unit (RT620C), a Cache Controller, Memory Management, and Tag Unit (RT625), and two RT628 Cache Data Units. The RT6224K fits within the clearance envelope for MBus modules per the SPARC MBus Specification.

The RT6224K interfaces to the rest of the system via the SPARC MBus and conforms to the SPARC Reference MMU. This standardization allows the RT6224K to be interchangeable with other SPARC MBus-based CPU modules without having to modify any portion of the memory system or I/O. This CPU "building block" strategy not only decreases the user's time to market, but provides a mechanism for upgrading in the field.

## **Component Overview**

### Superscalar SPARC Processor (RT620C)

The RT620C Central Processing Unit is the heart of ROSS' fourth-generation of microprocessor. The RT620C CPU ar-

chitecture employs two advanced concepts for increasing computer system performance: superscalability and superpipelining.

The RT620C is a high performance full-custom CMOS implementation of integrated SPARC integer and floating-point logic, with an on-chip cache for instructions.

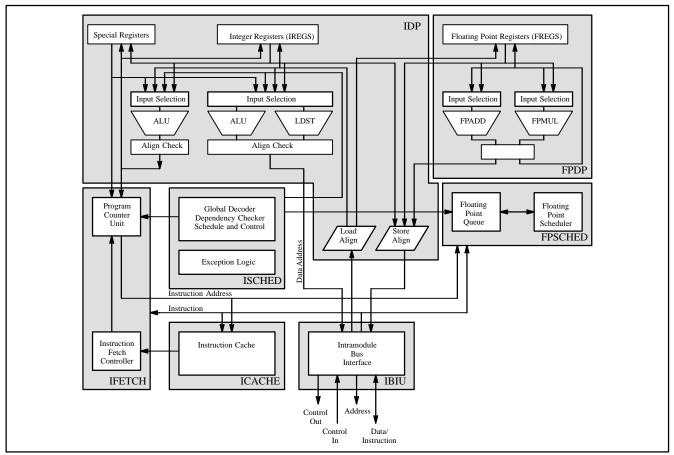

Advanced architecture and manufacturing technologies give the RT620C ultra high performance without requiring software recompilation. *Figure 2* is a logic block diagram of the RT620.

**IDP.** The Integer Data Path comprises several units. Two independent Arithmetic and Logic Units (ALUs) handle integer arithmetic, logical, and shift instructions. The Load/Store Unit (LSU) handles instructions that load and store data between memory and registers which includes the loading and storing of both integer and floating-point data. The Special Register Unit (SRU) handles instructions that read and write the SPARC Special Registers (SREGS). The Integer Register File (IREGS) is also contained in the IDP.

**FPDP.** The Floating-Point Data Path also comprises several units. These are the Floating-Point Queue (FPQ), the Floating-Point Arithmetic Unit (FAU), The Floating-Point Multiplier Unit (FMU), the Floating-Point Register File (FREGS),

PRELIMINARY

Figure 2. RT620C CPU Logic Block Diagram

and the Floating-Point Status Register (FSR). These floating-point units handle all SPARC floating-point instructions.

**ISCHED.** The Integer Scheduler performs key control functions. It provides global instruction decodes to identify which execution unit resources are required, and determines whether sequential or simultaneous execution is possible.

The ISCHED also determines whether data forwarding can be performed and whether instruction dispatches (also called "launches") need to be delayed due to data dependencies. The ISCHED initiates instruction launch and identifies and controls interrupt and trap handling.

**FPSCHED.** The Floating-Point Instruction Scheduler performs key control functions for the floating-point unit. When the Integer Unit detects floating-point instructions in the decode stage, it offloads these instructions to the floatingpoint functional units and continues processing. Therefore, functional blocks exist that perform necessary decode, scheduling, and control for the floating-point operations.

The FPSCHED performs floating-point instruction decoding, resolves floating-point data dependency and data-forwarding conditions, and provides the ISCHED with floating-point execution status. Delayed instructions are stored temporarily in the Floating-Point Instruction Queue (FPQ). Instructions are launched from the FPQ as data dependencies are resolved.

**IFETCH.** The Instruction Fetch Unit consists of two major functional blocks referred to as the Program Counter Unit (PCU) and the Instruction Fetch Controller (IFETCHC).

The PCU calculates the address of the next instruction to be fetched. It handles instructions that cause program control transfer, such as CALL and BRANCH. This unit handles both integer and floating-point branch instructions.

The IFETCHC fetches two instructions at a time, and in each clock cycle, the CPU attempts to launch both at once.

**ICACHE.** The on-chip instruction cache is organized as a two way set associative buffer. The ICACHE stores 8 Kbytes of instructions. Its inclusion follows the Harvard architecture approach, reducing bus contention during memory accesses. The ICACHE has a high-performance, one-wait-state cache miss penalty.

**IBIU.** The Intra-Module Bus Interface Unit provides the interface between the RT620 CPU and the external world. The IBIU samples incoming control signals and propagates controls to appropriate functional blocks. The IBIU is responsible for generating memory access control signals to the cache memory subsystem. Data and instructions are read from memory and data is written to memory, through the IBIU.

# Cache Control, Memory Management, and Tag Unit (RT625)

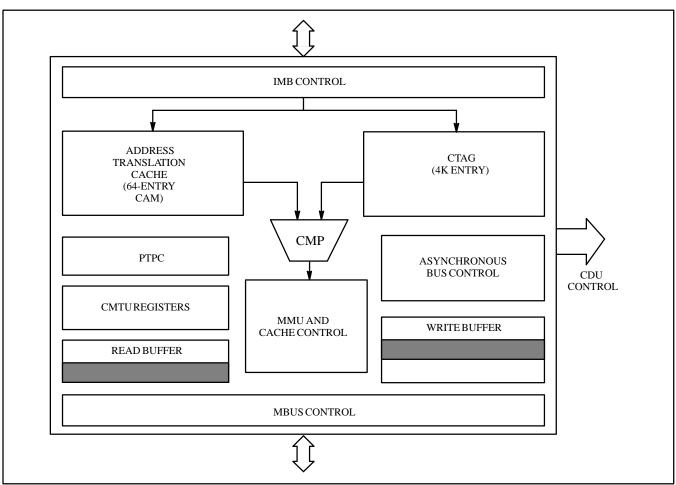

The CMTU (RT625) is a combined Cache Controller and Memory Management Unit optimized for multiprocessing systems. The CMTU is a high-speed CMOS implementation of the SPARC Reference MMU, combined with cache, a memory controller, and on-chip physical cache tag memory. The CMTU supports the SPARC MBus Level 2 protocol for multiprocessing systems. *Figure 3* depicts the CMTU block diagram.

The CMTU directly connects to the RT620C Central Processing Unit and RT628 Cache Data Units without any external circuitry. The RT625 CMTU controls two RT628 CDUs to realize 256 Kbytes of zero-wait-state, direct-mapped virtual cache memory.

**MMU.** The MMU portion of the CMTU provides translation from a 32-bit virtual address (4 gigabytes) to 36-bit physical address (64 gigabytes), as provided in the SPARC reference MMU specification. Virtual addresses are further extended with the use of a context register, which is used to identify up to 4096 contexts or tasks. The TLB entries contain context numbers to identify tasks or processes. This minimizes unnecessary TLB entry replacement during task switching.

The CMTU performs its address translation task by comparing a virtual address supplied by the RT620C through the Intra-Module Bus to the address tags in the TLB entries. If a "hit" occurs, the physical address stored in the TLB is used to translate the virtual-to-physical address. If the virtual address does not match any valid TLB entry, a "miss" occurs. This causes a table walk to be performed by the MMU. The table walk is a search performed by the MMU through the address translation tables stored in main memory. Upon finding the PTE, the MMU translates the address and selects a TLB entry for replacement.

**Cache Controller** The CMTU's cache controller supports two modes of caching: write-through with no write allocate and copy-back with write allocate. The cache is "virtually indexed" and "physically tagged."

The cache is organized as 4096 lines with two sub-blocks, each of which is 32 bytes. Intra-module address bits IMA[17:6] select the cache line, IMA[5] selects the subblock, and IMA[4:3] select the 64-bit word of the cache line.

The 4096 cache tag entries in the RT625 are virtual address indexed. From the processor side, the virtual address on the Intra-Module Bus is used to select a cache line entry and its corresponding cache tag entry. The translated physical address is then compared against the physical address in the selected cache tag entry to determine if the required data resides in the cache.

From the MBus side, the superset virtual address bits are concatenated with physical address bits [11:5] to select a cache line entry and its corresponding cache tag entry. The physical address on MBus is then compared against the physical address in the selected cache tag entry to determine if the required data resides in the cache.

A 64-byte write buffer and a 32-byte read buffer are provided in the RT625 to fully buffer the transfer of cache lines. This feature allows the CMTU to simultaneously read a cache line from main memory as it flushes a modified cache line from the cache.

**MBus.** The CMTU supports the SPARC MBus interface standard and the SPARC MBus Level 2 cache coherency protocol. It supports data transfers in transaction sizes of 1, 2, 4, 8,

# Rocky 2 RT6224K

## Figure 3. RT625 CMTU Block Diagram

or 32 bytes. These data transfers are performed in either burst or non-burst mode, depending upon the size. Data transactions larger than 8 bytes are transferred in burst mode. Bus mastership is granted and controlled by an external bus arbiter.

The CMTU also supports the MBus Module Identifier feature of the MBus, in which it accepts the Module Identifier input from the MBus and embeds it in the MBus address phase of all MBus transactions initiated by the CMTU.

## Cache Data Units (RT628)

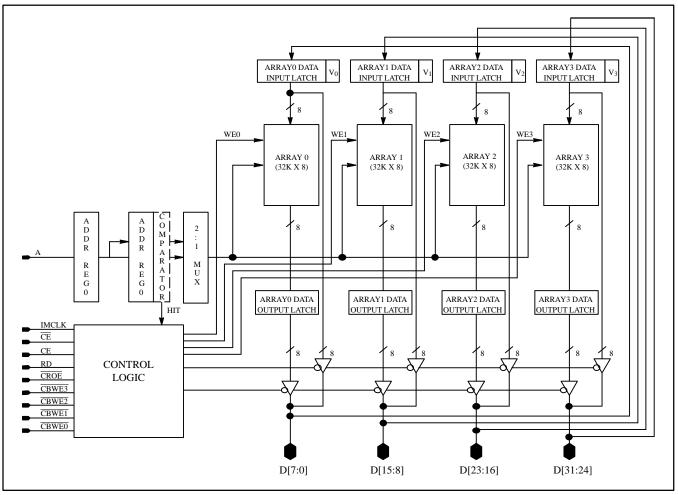

The RT628 is organized as four arrays of 32-Kbytes each. It contains a one-deep write buffer pipeline, byte write logic, registered inputs, data-in and data-out latches, and data forwarding logic for the write buffer.

Writing into the RAM core is delayed until the next write access. To allow data forwarding, the CDU incorporates a comparator to compare the address of the write-buffer to the incoming read address. If a match occurs, data is forwarded directly from the write-buffer to satisfy the current read cycle.

For a more complete description of the individual SPARC components used in the RT6224K, please refer to the *ROSS SPARC RISC User's Guide*.

## **Module Design**

### **Advanced Packaging Technology**

The RT6224K employs multi-die packaging (MDP) technology to facilitate higher clock frequencies and reliable operation. Each MDP component contains a complete hyper-SPARC CPU chipset. MDP technology improves electrical characteristics by reducing electrical parasitics, allowing multiple discrete chips to function as a single monolithic die.

## **Clock Distribution**

The RT6224K uses two MBus clock signals (MCLK[0] and MCLK[1]) as defined in the MBus Specification. In order to minimize clock skew, traces have been carefully routed. All clock lines are routed on inner layers of the module PCB, and their lengths and impedances are matched. The MBus clock lines have diode termination to reduce signal undershoot and

# Rocky 2 RT6224K

Figure 4. RT628 Block Diagram

overshoot, and all intramodule clock lines use a parallel resistive termination of  $60\Omega$ .

## **MBus Connector (Module)**

The RT6224K interface is via the 100-pin SPARC MBus connector, which is a two-row male connector with 0.050" spacing (AMP part number 121354-4 or Fujitsu part number FCN-264P100-G/C). The connector is a controlled impedance-type ( $50\Omega \pm 10\%$ ) based on a microstrip configuration that provides a controlled characteristic impedance plus very low inductance and capacitance. Separate power and ground blades are provided for isolation to prevent noise transference. *Table 1* details the RT6224K standard connector pinout. This MBus connector supports Level 2 MBus.

### Mating MBus Connector (System Interface Board)

The module connects to the system interface through the standard MBus female connector (vertical receptacle assembly, AMP part number 121340-4 or Fujitsu FCN-264J100-G/0).

### **Reset and Interrupt Signals**

A power-on reset signal is generated to the module from the MBus via the RSTIN signal. Level sensitive interrupts (15

max) are generated to the RT620C via the MIRL0[3:0] lines from the MBus. A value of 0000b means that there is no interrupt, while a value of 1111b means an NMI (Non-Maskable Interrupt) is being asserted. IRL values between 1 and 14 represent interrupt requests that can be masked by the processor.

### **MBus Request and Grant Signals**

One set of request and grant signals ( $\overline{MBR[0]}$  and  $\overline{MBG[0]}$ ) are generated to/from the RT6224K modules to arbitration logic on the motherboard.

### **MBus SCAN Test Feature**

The RT6224K module supports the Boundary SCAN test feature of the MBus. For more details on the SCAN test, please refer to the *ROSS SPARC RISC User's Guide* and *SPARC MBus Interface Specification*.

## MID Lines

MID[0] is tied to ground.

# Rocky 2 RT6224K

| Table 1. MBus Connector Pinout [1] |             |          |       |             |  |       |             |          |       |             |

|------------------------------------|-------------|----------|-------|-------------|--|-------|-------------|----------|-------|-------------|

| Pin #                              | Signal Name | Blade    | Pin # | Signal Name |  | Pin # | Signal Name | Blade    | Pin # | Signal Name |

| 1                                  | TDI         | Blade #1 | 2     | TMS         |  | 51    | MCLK[2]     | Ground   | 52    | MERR        |

| 3                                  | TDO         | Ground   | 4     | TRST        |  | 53    | MCLK[3]     |          | 54    | MAS         |

| 5                                  | TCLK        |          | 6     | MIRL0[1]    |  | 55    | RES         | Ground   | 56    | MBB         |

| 7                                  | MIRL0[0]    | Ground   | 8     | MIRL0[3]    |  | 57    | RES         |          | 58    | RSVD0       |

| 9                                  | MIRL0[2]    |          | 10    | RES         |  | 59    | MAD[32]     |          | 60    | MAD[33]     |

| 11                                 | MAD[0]      | Ground   | 12    | MAD[1]      |  | 61    | MAD[34]     | Blade #4 | 62    | MAD[35]     |

| 13                                 | MAD[2]      |          | 14    | MAD[3]      |  | 63    | MAD[36]     | +5V      | 64    | MAD[37]     |

| 15                                 | MAD[4]      | Ground   | 16    | MAD[5]      |  | 65    | MAD[38]     |          | 66    | MAD[39]     |

| 17                                 | MAD[6]      |          | 18    | MAD[7]      |  | 67    | MAD[40]     | +5V      | 68    | MAD[41]     |

| 19                                 | MAD[8]      |          | 20    | MAD[9]      |  | 69    | MAD[42]     |          | 70    | MAD[43]     |

| 21                                 | MAD[10]     | Blade #2 | 22    | MAD[11]     |  | 71    | MAD[44]     | +5V      | 72    | MAD[45]     |

| 23                                 | MAD[12]     | +5V      | 24    | MAD[13]     |  | 73    | MAD[46]     |          | 74    | MAD[47]     |

| 25                                 | MAD[14]     |          | 26    | MAD[15]     |  | 75    | MAD[48]     | +5V      | 76    | MAD[49]     |

| 27                                 | MAD[16]     | +5V      | 28    | MAD[17]     |  | 77    | MAD[50]     |          | 78    | MAD[51]     |

| 29                                 | MAD[18]     |          | 30    | MAD[19]     |  | 79    | MAD[52]     |          | 80    | MAD[53]     |

| 31                                 | MAD[20]     | +5V      | 32    | MAD[21]     |  | 81    | MAD[54]     | Blade #5 | 82    | MAD[55]     |

| 33                                 | MAD[22]     |          | 34    | MAD[23]     |  | 83    | MAD[56]     | Ground   | 84    | MAD[57]     |

| 35                                 | MAD[24]     | +5V      | 36    | MAD[25]     |  | 85    | MAD[58]     |          | 86    | MAD[59]     |

| 37                                 | MAD[26]     |          | 38    | MAD[27]     |  | 87    | MAD[60]     | Ground   | 88    | MAD[61]     |

| 39                                 | MAD[28]     |          | 40    | MAD[29]     |  | 89    | MAD[62]     |          | 90    | MAD[63]     |

| 41                                 | MAD[30]     | Blade #3 | 42    | MAD[31]     |  | 91    | RSVD1       | Ground   | 92    | RES         |

| 43                                 | MBR[0]      | Ground   | 44    | MSH         |  | 93    | RES         |          | 94    | RES         |

| 45                                 | MBG[0]      |          | 46    | MIH         |  | 95    | RES         | Ground   | 96    | AERR        |

| 47                                 | MCLK[0]     | Ground   | 48    | MRTY        |  | 97    | RSTIN       |          | 98    | MID[1]      |

| 49                                 | MCLK[1]     |          | 50    | MRDY        |  | 99    | MID[2]      |          | 100   | MID[3]      |

Notes:

1. RES and RSVD pins are not used in the RT6224K but reserved for other MBus module upgrades. See the System Design Considerations section

for the assignment of these reserved pins per the SPARC MBus Specification.

# Rocky 2 RT6224K

## Absolute Maximum Ratings <sup>[2]</sup> (Provided as guidelines; not tested.)

| Parameter         | Description                              |                                         | Rating       | Units |

|-------------------|------------------------------------------|-----------------------------------------|--------------|-------|

| V <sub>CC</sub>   | Supply Voltage Range                     |                                         | -0.5 to +7.0 | V     |

|                   |                                          | RT6224K-90/256                          | 18           | W     |

| P <sub>D</sub>    | Maximum Power Consumption                | RT6224K-100/256                         | 21           | W     |

|                   | RT6224K-125/256                          | 25                                      | W            |       |

|                   |                                          | RT6224K-90/256, $V_{CC} = 5.0V$         | 3.6          | W     |

| I <sub>CC</sub>   | Maximum Supply Current                   | RT6224K-100/256, V <sub>CC</sub> = 5.0V | 4.2          | W     |

|                   |                                          | RT6224K-125/256, V <sub>CC</sub> = 5.0V | 5.0          | W     |

| VI                | Input Voltage Range                      | •                                       | -0.3 to +7.0 | V     |

| T <sub>STG</sub>  | Storage Temperature                      |                                         | -20 to +75   | °C    |

| RH <sub>STG</sub> | Storage Relative Humidity <sup>[3]</sup> |                                         | 5 to 80      | %     |

## **Recommended Operating Conditions**<sup>[4]</sup>

| Parameter         | Description                                      |                                                  | Min. | Тур. | Max.            | Units |

|-------------------|--------------------------------------------------|--------------------------------------------------|------|------|-----------------|-------|

| V <sub>CC</sub>   | Supply Voltage                                   |                                                  | 4.75 | 5.00 | 5.25            | V     |

| V <sub>IH</sub>   | Input HIGH Voltage                               | 5V signals                                       | 2.0  |      | V <sub>CC</sub> | V     |

| V <sub>IL</sub>   | Input LOW Voltage                                | •                                                | -0.5 |      | 0.8             | V     |

| V <sub>OH</sub>   | Output HIGH Voltage                              | $V_{CC} = Min., I_{OH} = -2.0 \text{ mA}$        | 2.4  |      |                 | V     |

| V <sub>OL</sub>   | Output LOW Voltage                               | V <sub>CC</sub> = Min., I <sub>OL</sub> = 8.0 mA |      |      | 0.5             | V     |

| I <sub>IZ</sub>   | Input Leakage Current (non-clock pins)           | $V_{CC} = Max., V_{SS} \le V_{OUT} \le V_{CC}$   | -10  |      | +10             | μΑ    |

| I <sub>CLKZ</sub> | Input Leakage Current (clock pins)               | $V_{CC} = Max., V_{SS} \le V_{OUT} \le V_{CC}$   | -40  |      | +40             | μΑ    |

| I <sub>OZ</sub>   | Output Leakage Current                           | $V_{CC} = Max., V_{SS} \le V_{OUT} \le V_{CC}$   | -15  |      | +15             | μΑ    |

| I <sub>SC</sub>   | Output Short Circuit Current <sup>[5]</sup>      | $V_{CC} = Max., V_{OUT} = 0V$                    | - 30 |      | - 350           | mA    |

| T <sub>A</sub>    | Operating Ambient Air Temperature <sup>[6]</sup> |                                                  | 0    |      | 50              | °C    |

| RH <sub>OP</sub>  | Operating Relative Humidity <sup>[3]</sup>       |                                                  | 5    |      | 95              | %     |

# Capacitance<sup>[7]</sup>

| Parameter          | Description              |                                                     |    | Units |

|--------------------|--------------------------|-----------------------------------------------------|----|-------|

| C <sub>IN</sub>    | Input Capacitance        |                                                     | 18 | pF    |

| C <sub>OUT</sub>   | Output Capacitance       | $V_{CC} = 5.0V$<br>$T_A = 25^{\circ}C$<br>f = 1 MHz | 20 | pF    |

| C <sub>IO</sub>    | Input/Output Capacitance | f = 1  MHz                                          | 23 | pF    |

| C <sub>INCLK</sub> | Clock Input Capacitance  |                                                     | 28 | pF    |

### Notes:

- 2. All power and ground pins must be connected to other pins of the same type before any power is applied to the RT6224K. At least three clock cycles must be applied to set up the internal chip drivers properly.

- 3. Non-condensing. Maximum rate of change of 30% per hour.

- 4. Recommended use of this module does not include "hot-socketing" or "live-insertion" (i.e., it is not recommended that the RT6224K be placed in the MBus socket with the power supply on).

- 5. Not more than one output should be tested at one time. Duration of the short circuit should not be more than one second.

- 6. See Appendix A. hyperSPARC Module Thermal Specifications. This temperature should not be exceeded when the device is consuming maximum power with 300 linear feet per minute (LFM) of airflow at sea level.

- 7. Tested initially and after any design or process changes that may affect these parameters.

# Rocky 2 RT6224K

## AC Electrical Characteristics Over the Operating Range [8,9]

| Param                    | Description                                  | Min. | Max. | Unit             |  |

|--------------------------|----------------------------------------------|------|------|------------------|--|

| Synchronous signals [10] |                                              |      |      |                  |  |

| t <sub>CP</sub>          | MBus Clock period                            | 20   |      | ns               |  |

| t <sub>PWH</sub>         | MBus Clock High period                       | 9.2  |      | ns               |  |

| tPWL                     | MBus Clock Low period                        | 9.2  |      | ns               |  |

| t <sub>CSR</sub>         | MBus Clock Slew Rate (between 0.8V and 2.0V) | 0.8  |      | V/ <sub>ns</sub> |  |

| t <sub>SKU</sub>         | MBus Clock Skew <sup>[11]</sup>              |      | 1.0  | ns               |  |

| t <sub>MOD</sub>         | MAD(63:0) Output Delay                       |      | 13.5 | ns               |  |

| t <sub>MOH</sub>         | MAD(63:0) Output Valid                       | 4.0  |      | ns               |  |

| t <sub>MIS</sub>         | MAD(63:0) Input Set-Up                       | 3.5  |      | ns               |  |

| t <sub>MIH</sub>         | MAD(63:0) Input Hold                         | 2.0  |      | ns               |  |

| t <sub>COD</sub>         | MBus Bused Control Output Delay              |      | 13.5 | ns               |  |

| tCOH                     | MBus Bused Control Output Valid              | 4.0  |      | ns               |  |

| t <sub>CIS</sub>         | MBus Bused Control Input Set-Up              | 5.5  |      | ns               |  |

| t <sub>CIH</sub>         | MBus Bused Control Input Hold                | 2.0  |      | ns               |  |

| t <sub>POD</sub>         | MBus Point-to-Point Control Output Delay     |      | 13.5 | ns               |  |

| t <sub>POH</sub>         | MBus Point-to-Point Control Output Valid     | 4.0  |      | ns               |  |

| t <sub>PIS</sub>         | MBus Point-to-Point Control Input Set-Up     | 5.5  |      | ns               |  |

| t <sub>PIH</sub>         | PIH MBus Point-to-Point Control Input Hold   |      |      | ns               |  |

| Asynchr                  | onous Signals                                |      | •    | •                |  |

| t <sub>RST</sub>         | MBus Reset Duration <sup>[12]</sup>          | 100  |      | ms               |  |

### Notes:

- 8. Test conditions assume signal transition times of 3 ns or less, a timing reference level of 1.5V, input levels of 0 to 3.0V, and output loading of 80-pF capacitance, not including the module itself (with the exception of MBus point-to-point control signals, tested with an output loading of 40 pF).

- 9. All measurements made at MBus connector.

- All timing parameters are relative to one of the two processors (e.g., t<sub>MOD</sub> is guaranteed relative to MCLK[0]).

- 11. Measured between any two MCLK signals.

- 12. This is the minimum time for which RSTIN must be asserted after both high and low power supply voltages are stable.

### 830-0016-04 Rev A 10/9/96

**PRELIMINARY**

# Rocky 2 RT6224K

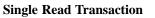

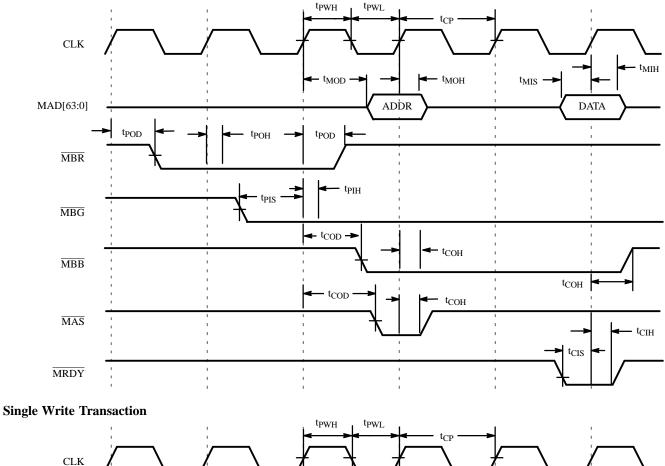

**MBus Timing Diagrams**

Rocky 2 RT6224K

## **System Design Considerations**

The RT6224K implements a subset of all possible MBus signals. Signals that are optional and/or specifically for multiprocessor modules may not be supported. The MBus connector, per the SPARC MBus Specification, defines the assignments listed in *Table 2* for pins reserved on the RT6224K. Although these signals are not used on the RT6224K, systems designers should be aware of these assignments to preserve compatibility with other MBus modules.

### Table 2. Pins Reserved on RT6224K

| Pin # | Signal Name |

|-------|-------------|

| 10    | INTOUT      |

| 51    | MCLK2       |

| 53    | MCLK3       |

| 55    | MBR[1]      |

| 57    | MBG[1]      |

| 58*   | RSVD0       |

| 91*   | RSVD1       |

| 92    | MIRL1[0]    |

| 93    | MIRL1[1]    |

| 94    | MIRL1[2]    |

| 95    | MIRL1[3]    |

\* Non-floating. Reserved for ROSS internal use only. These signals should not be driven. All MAD, bused control, and point to point control signals use 8-mA drivers. The MSH and AERR signals use opendrain drivers.

<u>10-Kohm pull up resistors are required on MAS, MRDY,</u> <u>MRTY, MERR, MBB, and MIH.</u> A 1.5-Kohm pull up resistor is recommended on <u>AERR</u>. A 619 ohm pull up resistor is recommended on <u>MSH</u>. MAD signals require holding amplifiers.

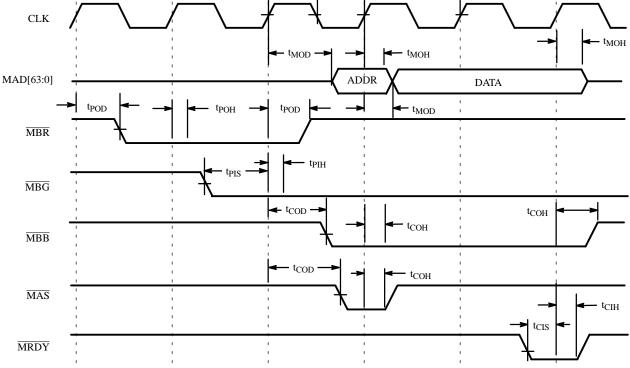

In order to assure that all module scan circuitry is initialized to the normal operating state on reset, the following is recommended for the MBus scan signals. TDI and TMS should be pulled up to 5V with  $10K\Omega$  resistors. TCLK must toggle at least 3 full cycles while TRST is asserted in order to reset all scan circuitry. RSTIN may be driven by the module when the module is in scan mode, so it should be buffered from the rest of the system. These requirements may be met by connecting each signal as shown in *Figure 5*. The RT6224K uses MCLK[0] to clock the processor and MCLK[1] for test.

As the frequency of operation increases, transmission line effects play a bigger role. Care must be taken to keep skew between any two clock signals at the MBus connector within the specifications given in the Synchronous Signals table in the AC Characteristics section. MBus signal lines must be routed carefully to minimize crosstalk and interference. A thorough SPICE analysis of the motherboard design is recommended.

Use of HH Smith #4387 (3/4" length by 1/4" OD) stand-offs or equivalent is recommended on the motherboard to support the module and prevent damage to the connector.

If mounting screws are used, nylon screws are recommended to prevent over-torquing and damage to the PCB.

PRELIMINARY

**Figure 5. Scan Pin Connections**

# Rocky 2 RT6224K

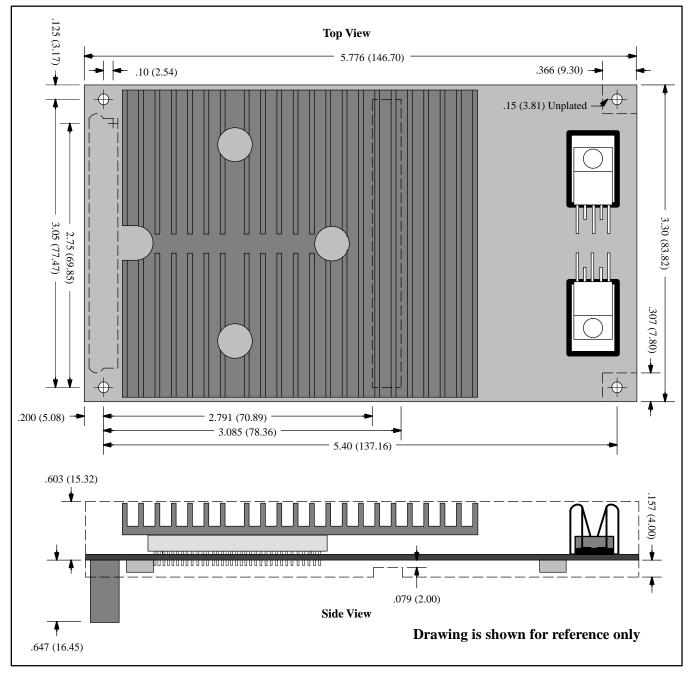

**RT6224K Mechanical Drawing**<sup>[13,14, 15]</sup>

## Figure 6. RT6224K Mechanical Dimensions

- Notes: 13. Drawing is for reference only. Appearance of module is subject to change without notice.

- 14. Drawing is not to scale. All dimensions are in inches (mm).

- To ensure compliance with all future MBus modules, systems developers should design to the MBus module envelope per the SPARC MBus Specification.

# Rocky 2 RT6224K

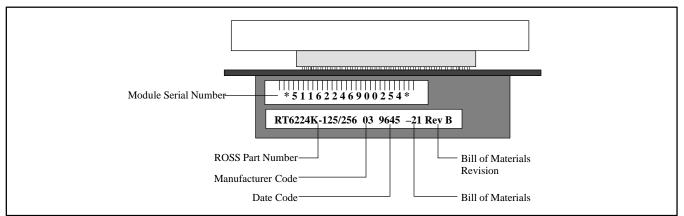

# **RT6224K Module Label Specification**

Figure 7. RT6224K Module Labeling

# Rocky 2 RT6224K

# Appendix A. hyperSPARC Module Thermal Specifications

### **Ambient Temperature**

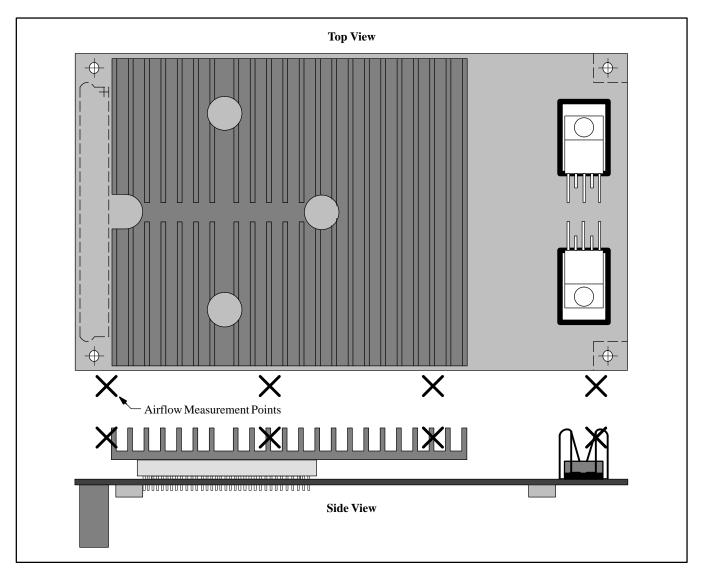

Ambient temperatures as high as  $50^{\circ}$ C are acceptable for the RT6224K provided airflow is 300 linear feet per minute (LFM) minimum through the heatsink fins at all locations indicated in *Figure 8*. In this context, ambient temperature is defined as the air temperature in immediate proximity to the module.

Module airflow measurements must be taken with the anemometer probe in front of the fins, approximately 1/2"

above the top of the PCB at the indicated locations. The airflow must meet the minimum requirements at all locations indicated in *Figure 8*. When taking airflow measurements the module should be installed in a system that is configured in the same fashion as the actual final production system (for example, all external covers and panels should be installed, and any internal ducting or baffling should also be installed).

Ambient temperature should be measured within the system, as it enters the fins of the heatsinks on the module.

Figure 8. RT6224K Airflow Measurement

# Rocky 2 RT6224K

## **Appendix B. hyperSPARC Ordering Information**

| Ordering Code   | CPU Clock<br>Frequency (MHz) | Second-level<br>Cache size |

|-----------------|------------------------------|----------------------------|

| RT6224K-90/256  | 90                           | 256K                       |

| RT6224K-100/256 | 100                          | 256K                       |

| RT6224K-125/256 | 125                          | 256K                       |

For up-to-date ordering and sales information contact:

| ROSS Technology, Inc.        | <b>ROSS Technology, Inc., Europe</b> |  |  |  |

|------------------------------|--------------------------------------|--|--|--|

| 5316 Hwy. 290 West           | Avenue Ernest Solvay, 80             |  |  |  |

| Austin, Texas 78735-8930 USA | 1310 La Hulpe                        |  |  |  |

| Telephone: (800) ROSS-YES    | Belgium                              |  |  |  |

| (512) 349-3108               | Telephone: +32 2 652 1014            |  |  |  |

| FAX: (512) 436-2471          | FAX: +32 2 652 1062                  |  |  |  |

This document contains preliminary information on a product under development at ROSS Technology, Inc. ROSS Technology reserves the right to change this information without notice.

SPARC is a registered trademark of SPARC International, Inc.

hyperSPARC is a trademark of SPARC International, Inc., used under permission by ROSS Technology, Inc.

© ROSS Technology, Inc., 1994. The information contained herein is subject to change without notice. ROSS Technology, Inc. assumes no responsibility for the use of any circuitry other than circuitry embodied in a ROSS Technology, Inc. product. Nor does it convey or imply any license under patent or other rights. ROSS Technology does not authorize its products for use as critical components in life-support systems where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user. The inclusion of ROSS Technology products in life-support systems applications implies that the manufacturer assumes all risk of such use and in so doing indemnifies ROSS Technology against all damages.