# SPARC USER'S GUIDE

NDerspance Edition

LUL

ECHNOLOGY, INC

FER

# **SPARC RISC USER'S GUIDE**

## **ROSS Technology, Inc.**

A Fujitsu Limited Company

ROSS Technology, Inc. • 5316 Hwy. 290 West • Austin, TX 78735 • PH 512-892-7802 • FAX 512-892-3036

#### Third Edition – September 1993

Products bearing the SPARC trademarks are based on an architecture developed by Sun Microsystems, Inc. SPARC is a registered trademark of SPARC International, Inc. hyperSPARC is a trademark of SPARC International, Inc. used under permission by ROSS Technology, Inc.

Numerous features of hyperSPARC technology are covered by US Patent No. 5,226,142 and other patents pending.

ROSS Technology, Inc. is a subsidiary of Fujitsu Limited

© ROSS Technology, Inc., 1993. The information contained herein is subject to change without notice. ROSS Technology, Inc. assumes no responsibility for the use of any circuitry other than circuitry embodied in a ROSS Technology, Inc. product. Nor does it convey or imply any license under patent or other rights. "ROSS Technology does not authorize its products for use as critical components in life support systems where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user. The inclusion of ROSS Technology products in life support systems applications implies that the manufacturer assumes all risk of such use and in so doing indemnifies ROSS Technology against all damages."

## Table of Contents

#### **Chapter 1: Introduction**

| 1.1 | SPARC Architecture Features1 |                                                                |  |

|-----|------------------------------|----------------------------------------------------------------|--|

|     | 1.1.1                        | Load/Store Architecture                                        |  |

|     | 1.1.2                        | Register Windows                                               |  |

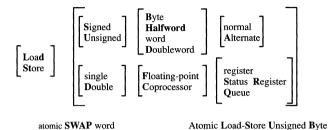

|     | 1.1.3                        | Instruction Set                                                |  |

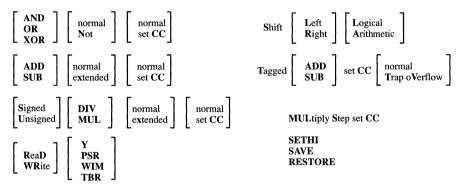

|     | 1.1.4                        | Arithmetic /Logical /Shift Instructions1-3                     |  |

|     | 1.1.5                        | Control Transfer Instructions1-3                               |  |

|     | 1.1.6                        | Read/Write Control Register Instructions1-3                    |  |

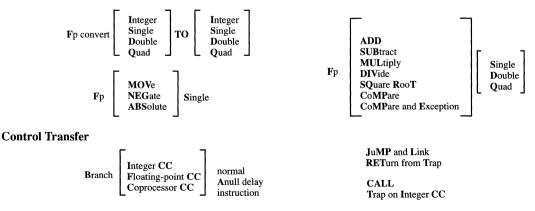

|     | 1.1.7                        | Floating-Point-Operate and Coprocessor-Operate Instructions1-3 |  |

| 1.2 | hyperS                       | PARC Overview                                                  |  |

|     | 1.2.1                        | hyperSPARC Design Features1-5                                  |  |

| 1.3 | CY7Ce                        | 500 Overview                                                   |  |

|     | 1.3.1                        | Partitioning                                                   |  |

#### **Chapter 2: SPARC Programming Environment**

| 2.1 | Progra | mming Model                             |

|-----|--------|-----------------------------------------|

|     | 2.1.1  | Supervisor/User Modes                   |

|     | 2.1.2  | Register Windows                        |

|     | 2.1.3  | Floating-Point Register File (FREGS)2-7 |

| 2.2 | SPARC  | C Control/Status Registers              |

|     | 2.2.1  | Integer Unit Control/Status Registers   |

|     | 2.2.2  | FPU Control/Status Registers            |

|     | 2.2.3  | Cache Controller/MMU Control2-14        |

| 2.3 | SPARC  | 2-14 Types                              |

|     | 2.3.1  | Data Organization In Registers2-14      |

|     | 2.3.2  | Data Organization In Memory2-16         |

|     | 2.3.3  | SPARC Floating-Point Data Types         |

| 2.4 | SPARC  | CInstruction Set                        |

|     | 2.4.1  | Instruction Formats                     |

|     | 2.4.2  | Addressing                              |

|     | 2.4.3  | Instruction Types                       |

|     | 2.4.4  | SPARC Instruction OP Codes              |

|     | 2.4.5  | SPARC Exception Model                   |

#### Chapter 3: RT620 hyperSPARC Central Processing Unit

| 3.1 | RT620 I  | hyperSPARC CPU                                                     |

|-----|----------|--------------------------------------------------------------------|

| 3.2 | Integer  | Data Path (IDP)                                                    |

|     | 3.2.1    | Arithmetic and Logical Unit (ALU)                                  |

|     | 3.2.2    | Load and Store Unit (LSU)                                          |

|     | 3.2.3    | Program Counter Unit (PCU)                                         |

|     | 3.2.4    | Special Register Unit (SRU)                                        |

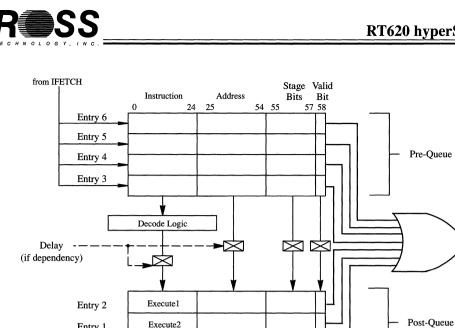

| 3.3 | Instruct | ion Fetch Unit (IFETCH)                                            |

| 3.4 | Instruct | ion Scheduler (ISCHED)                                             |

|     | 3.4.1    | Single Instruction Launch Group                                    |

|     | 3.4.2    | Multiple Instruction Launch Group                                  |

|     | 3.4.3    | Interlocks and Dependencies                                        |

|     | 3.4.4    | Special Features                                                   |

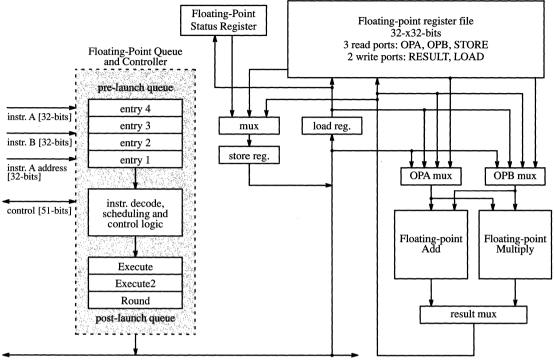

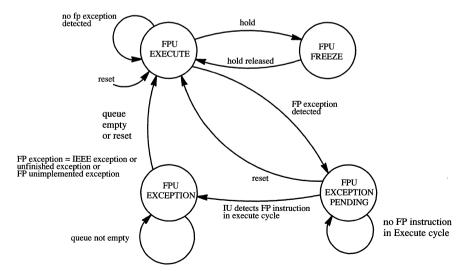

| 3.5 | Floating | g-Point Unit (FPU)                                                 |

|     | 3.5.1    | Floating-Point Instruction Decode-Schedule-and-Dispatch Controller |

|     |          | (FPSCHED)                                                          |

|     | 3.5.2    | Floating-Point Execution Units                                     |

| 3.6 | Instruct | tion Cache (ICACHE)                                                |

|     | 3.6.1    | Virtual Addresses                                                  |

|     | 3.6.2    | ICACHE Hits                                                        |

|     | 3.6.3    | Instruction Cache Control Register                                 |

|     | 3.6.4    | On-Chip Instruction Cache Read/Write Diagnostic Support            |

| 3.7 | hyperSI  | PARC Signal Descriptions                                           |

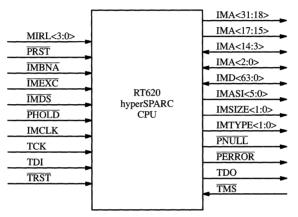

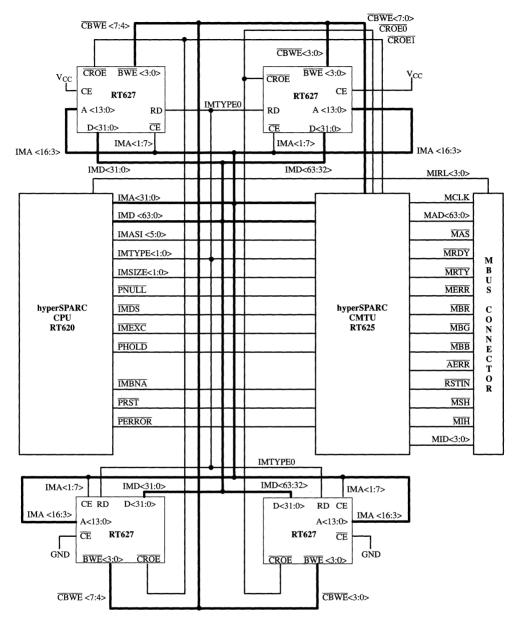

|     | 3.7.1    | hyperSPARC CPU Pinouts                                             |

|     | 3.7.2    | hyperSPARC Intra-Module Bus (IMB)                                  |

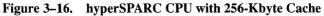

|     | 3.7.3    | hyperSPARC CPU Bus Timing Waveforms                                |

| 3.8 | Instruct | tion Pipelines                                                     |

|     | 3.8.1    | Instruction Fetch Timing                                           |

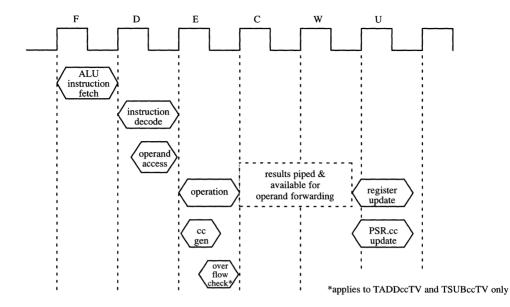

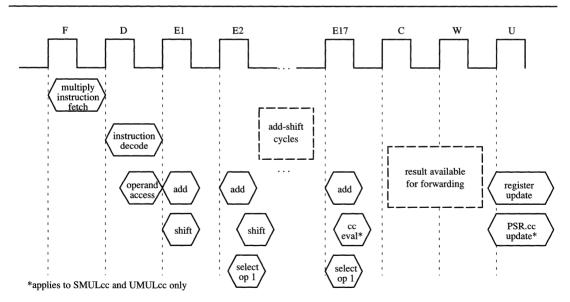

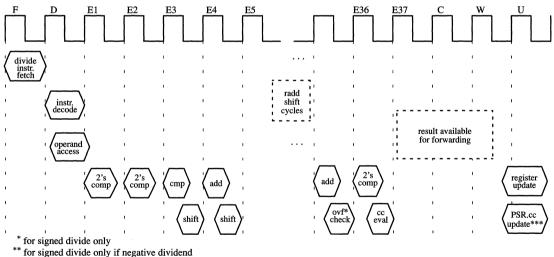

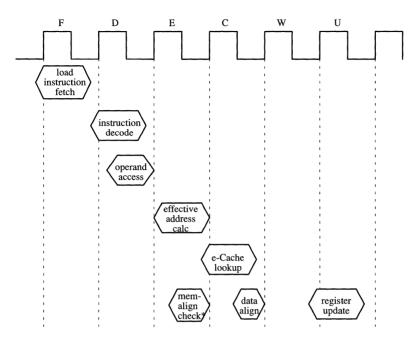

|     | 3.8.2    | Integer Instruction Pipeline                                       |

|     | 3.8.3    | ALU Instructions                                                   |

|     | 3.8.4    | Load Instructions                                                  |

|     | 3.8.5    | Store Instructions                                                 |

|     | 3.8.6    | Atomic Load-Store Instructions                                     |

|     | 3.8.7    | Branch Instructions                                                |

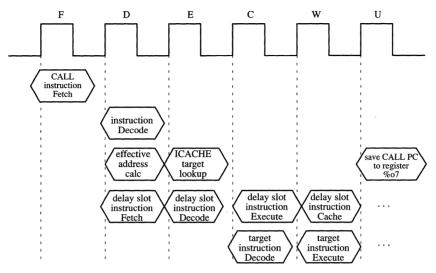

|     | 3.8.8    | CALL Instructions                                                  |

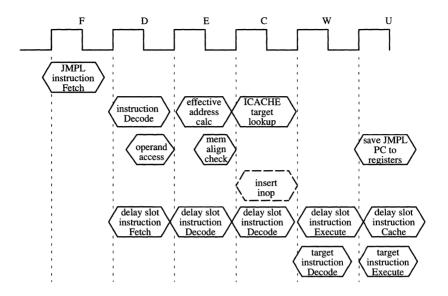

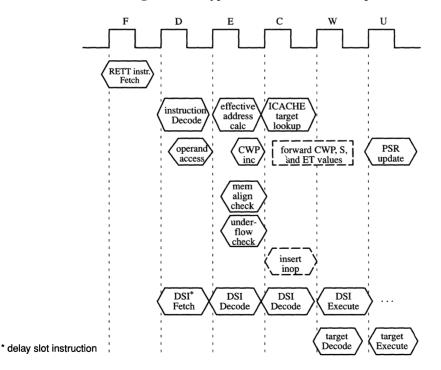

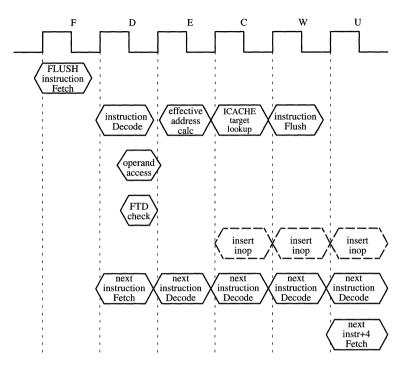

|     | 3.8.9    | JMPL/RETT/FLUSH Instructions                                       |

|     | 3.8.10   | Save/Restore Instructions                                          |

|     | 3.8.11   | Read/Write Special Register Instructions                           |

|     | 3.8.12   | Special Feature Pipelines                                          |

|     | 3.8.13   | Floating-Point Instruction Pipelines 3-75                          |

| 3.9 | -        | nd Interrupts                                                      |

|     | 3.9.1    | Machine State at Reset                                             |

|     | 3.9.2    | Exception Pipeline                                                 |

|     | 3.9.3    | Trap Operation                                                     |

|         | 3.9.4<br>3.9.5<br>3.9.6<br>3.9.7<br>3.9.8<br>3.9.9<br>3.9.10 | Error Mode3-79Trap Priorities3-80Precise Traps3-80Interrupting Traps (Asynchronous)3-81Floating-Point Unit Traps (Deferred Traps)3-82IU-FPU Exception Flush Logic3-100RT620 Method for Handling Traps and Error Mode3-100 |

|---------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter | r 4: RT62                                                    | 5 hyperSPARC Cache Controller, Memory Management, and Tag Unit                                                                                                                                                            |

| 4.1     |                                                              | hyperSPARC CMTU4-1                                                                                                                                                                                                        |

| 4.2     | <b>RT625</b>                                                 | Memory Management Unit 4-4                                                                                                                                                                                                |

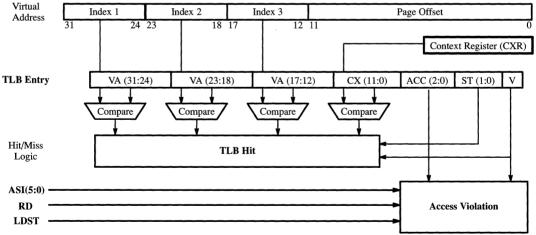

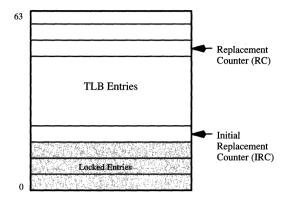

|         | 4.2.1                                                        | Translation Lookaside Buffer (TLB)                                                                                                                                                                                        |

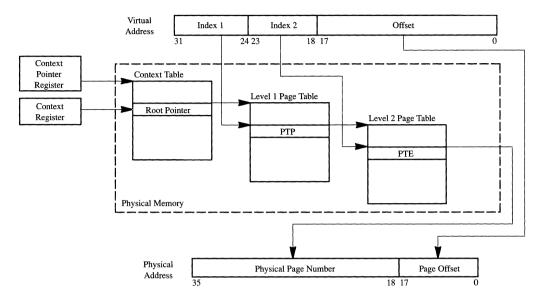

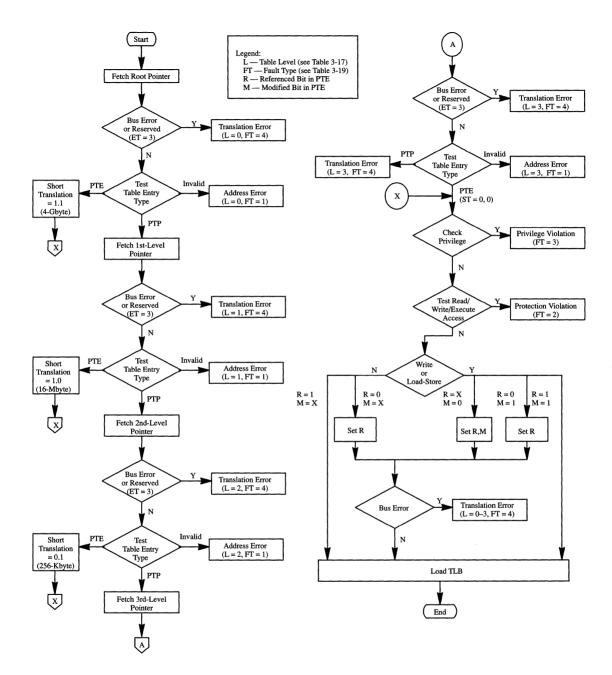

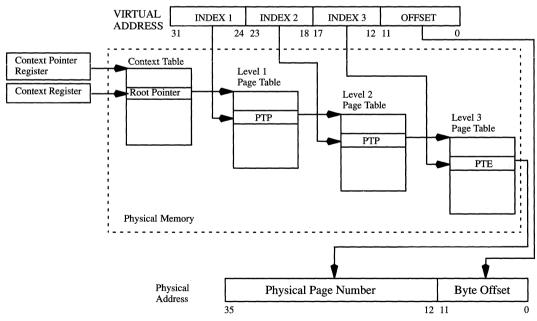

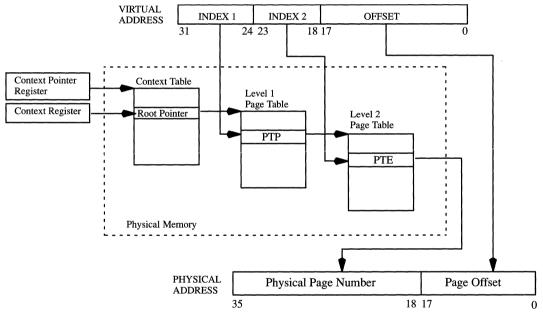

|         | 4.2.2                                                        | Table Walk   4-8                                                                                                                                                                                                          |

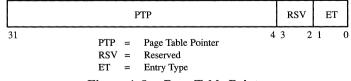

|         | 4.2.3                                                        | Page Table Pointer (PTP)                                                                                                                                                                                                  |

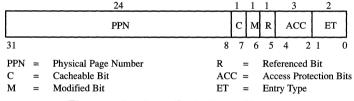

|         | 4.2.4                                                        | Page Table Entry (PTE)                                                                                                                                                                                                    |

|         | 4.2.5                                                        | Page Table Pointer Cache (PTPC)                                                                                                                                                                                           |

| 4.3     | RT625                                                        | MMU Operation Modes                                                                                                                                                                                                       |

|         | 4.3.1                                                        | MMU Invalidate and Probe Operations4-17                                                                                                                                                                                   |

| 4.4     | RT625                                                        | Cache Controller                                                                                                                                                                                                          |

|         | 4.4.1                                                        | RT625 Cache Modes                                                                                                                                                                                                         |

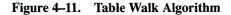

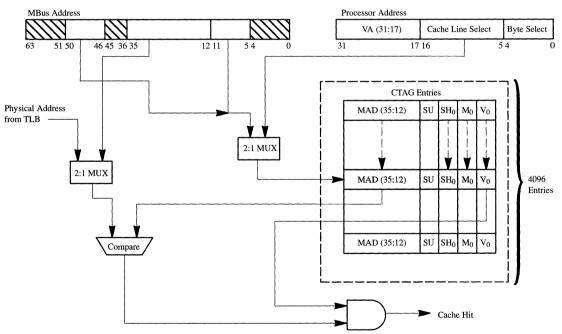

|         | 4.4.2                                                        | RT625 Cache Controller                                                                                                                                                                                                    |

|         | 4.4.3                                                        | RT625 Software Cache Flushing Operations                                                                                                                                                                                  |

|         | 4.4.4                                                        | RT625 Cacheable/Non-Cacheable Memory Accesses                                                                                                                                                                             |

|         | 4.4.5                                                        | RT625 MBus Cacheable (MC) Bit                                                                                                                                                                                             |

|         | 4.4.6                                                        | RT625 LDST (Atomic Load-Store Instruction) Cycles                                                                                                                                                                         |

|         | 4.4.7                                                        | RT625 Cache Byte Write Enables                                                                                                                                                                                            |

|         | 4.4.8                                                        | Cache Data Forwarding                                                                                                                                                                                                     |

| 4.5     | RT625                                                        | Registers                                                                                                                                                                                                                 |

|         | 4.5.1                                                        | RT625 System Control Register (SCR) 4-37                                                                                                                                                                                  |

|         | 4.5.2                                                        | RT625 Context Table Pointer Register (CTPR)                                                                                                                                                                               |

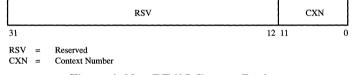

|         | 4.5.3                                                        | RT625 Context Register (CXR)                                                                                                                                                                                              |

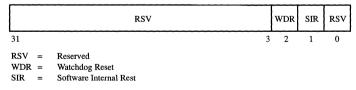

|         | 4.5.4                                                        | RT625 Reset Register (RR)                                                                                                                                                                                                 |

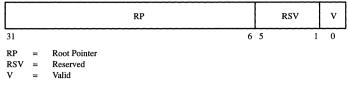

|         | 4.5.5                                                        | RT625 Root Pointer Register (RPR)                                                                                                                                                                                         |

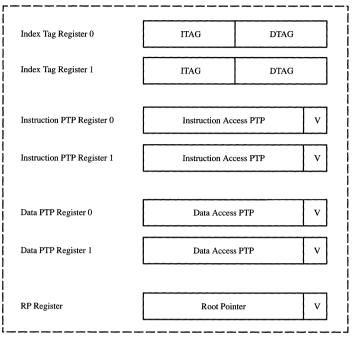

|         | 4.5.6                                                        | RT625 Instruction access PTPs (IPTP0, IPTP1)4-40                                                                                                                                                                          |

|         | 4.5.7                                                        | RT625 Data Access PTPs (DPTP0, DPTP1)                                                                                                                                                                                     |

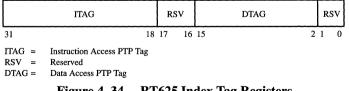

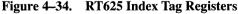

|         | 4.5.8                                                        | RT625 Index Tag Registers (ITR0, ITR1)                                                                                                                                                                                    |

|         | 4.5.9                                                        | RT625 TLB Replacement Control Register (TRCR)                                                                                                                                                                             |

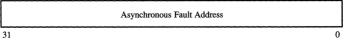

|         | 4.5.10                                                       | RT625 Synchronous Fault Status Register (SFSR)                                                                                                                                                                            |

|         | 4.5.11                                                       | RT625 Synchronous Fault Address Register (SFAR)                                                                                                                                                                           |

|         | 4.5.12<br>4.5.13                                             | RT625 Asynchronous Fault Status Register (AFSR)                                                                                                                                                                           |

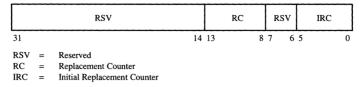

|         |                                                              | RT625 Asynchronous Fault Address Register (AFAR)                                                                                                                                                                          |

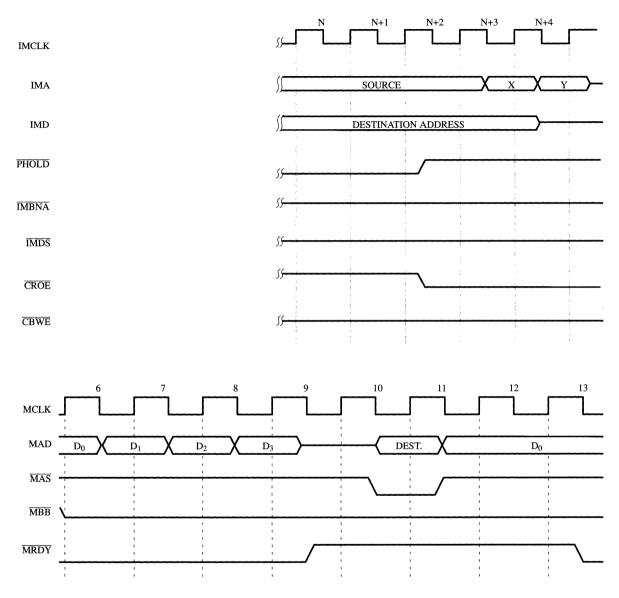

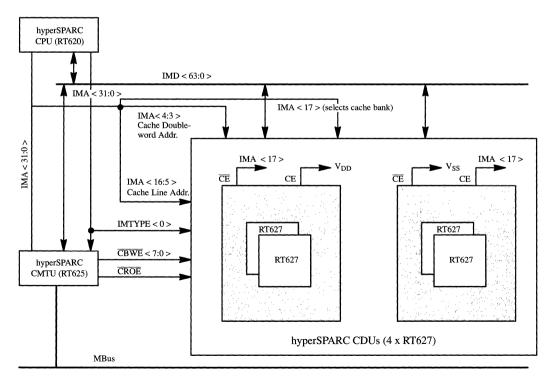

| 4.6     |                                                              | Block Copy and Block Fill 4-43                                                                                                                                                                                            |

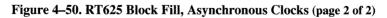

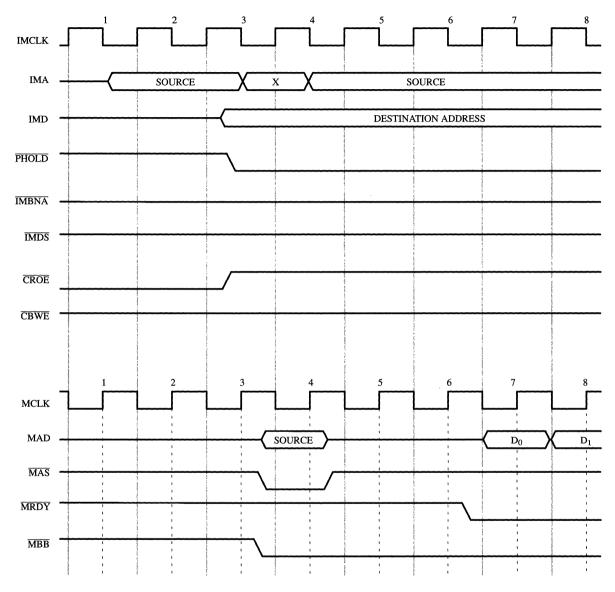

|         | 4.6.1                                                        | RT625 Block Copy                                                                                                                                                                                                          |

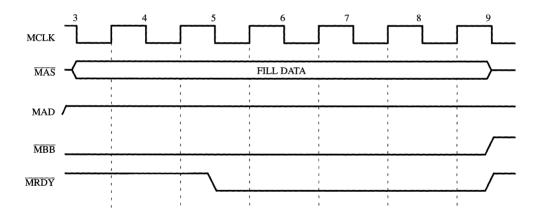

|         | 4.6.2                                                        | RT625 Block Fill                                                                                                                                                                                                          |

| 4.7     | RT625                                                        | Diagnostic Support                                                                                                                                                                                                        |

|         | 4.7.1                                                        | RT625 MMU TLB Entries                                                                                                                                                                                                     |

|         | 4.7.2                                                        | RT625 Cache Tag Entries                                                                                                                                                                                                   |

|         | 4.7.3                                                        | CDU Cache Data Entries                                                                                                                                                                                                    |

| 4.8     | RT625 I    | Reset                                        |

|---------|------------|----------------------------------------------|

|         | 4.8.1      | Power-On Reset (RSTIN)                       |

|         | 4.8.2      | Watchdog Reset (WDR)                         |

|         | 4.8.3      | Software Internal Reset (SIR)                |

|         |            |                                              |

| 4.9     | RT625 A    | ASI and Register Mapping 4-46                |

| 4.10    | e          | nous Faults                                  |

|         | 4.10.1     | Synchronous Fault Cases                      |

| 4.11    | RT625 H    | Pinouts                                      |

|         | 4.11.1     | Pin Description                              |

|         | 4.11.2     | Pin Virtual Bus (Intra-Module Bus) Operation |

| Chapter | • 5: RT62' | 7 hyperSPARC Cache Data Unit                 |

| 5.1     | RT627 F    | Pinouts                                      |

|         |            |                                              |

| 5.2     | RT627 A    | Access Waveforms                             |

| Chapter | : 6: CY7C  | 2601/611 Integer Unit                        |

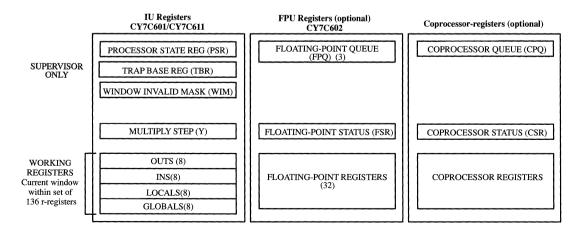

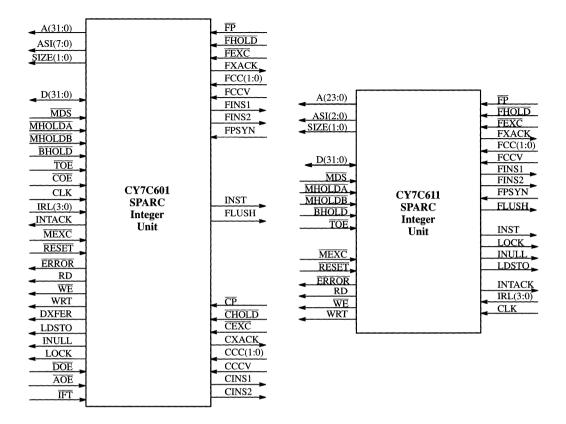

| 6.1     | CY7C60     | 01/CY7C611 Register Set6-2                   |

|         | 6.1        | CY7C601/CY7C611 Cycle Per Instruction (CPI)  |

| ( )     |            |                                              |

| 6.2     |            | Description                                  |

|         | 6.2.1      | Memory Subsystem Interface Signals           |

|         | 6.2.2      | Floating-Point/Coprocessor Interface Signals |

|         | 6.2.3      | Interrupt and Control Signals                |

|         | 6.2.4      | Power and Clock Signals                      |

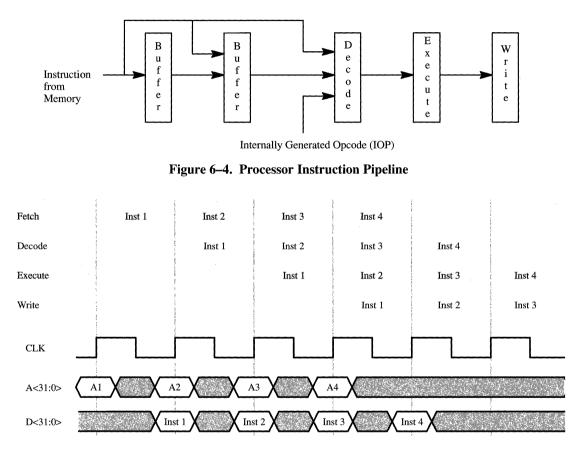

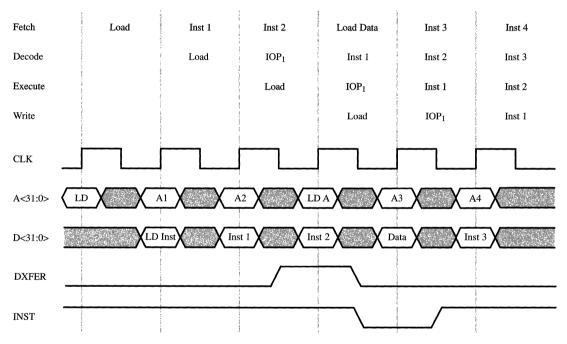

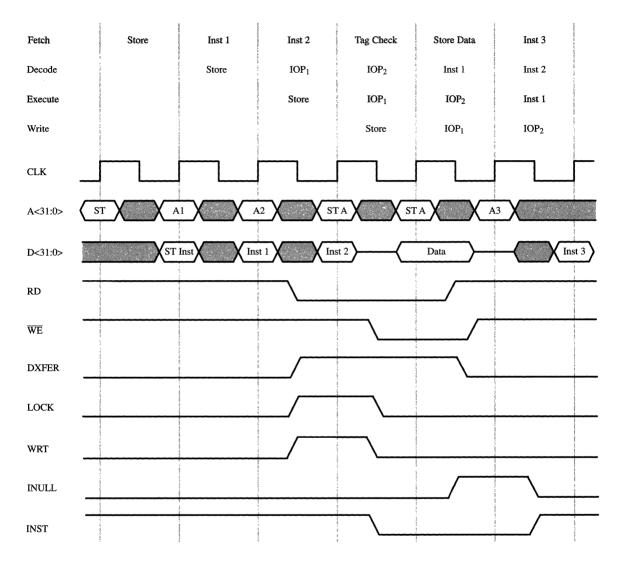

| 6.3     | Pipeline   | And Instruction Execution Timing             |

|         | 6.3.1      | Stages                                       |

|         | 6.3.2      | Multicycle Instructions                      |

|         | 6.3.3      | Pipeline Freezes                             |

|         | 6.3.4      | Traps                                        |

| 6.4     | Bus Ope    | eration And Timing                           |

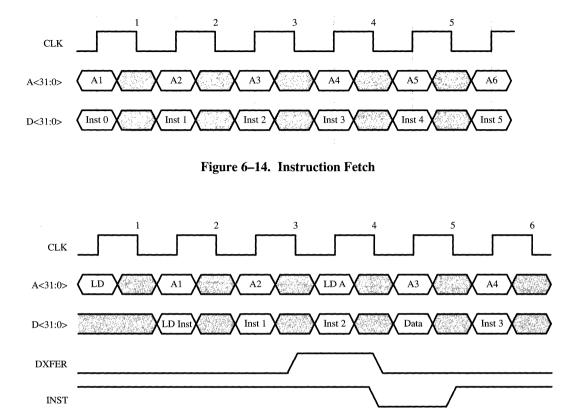

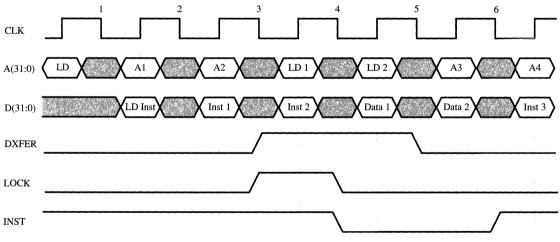

|         | 6.4.1      | Instruction Fetch                            |

|         | 6.4.2      | Load                                         |

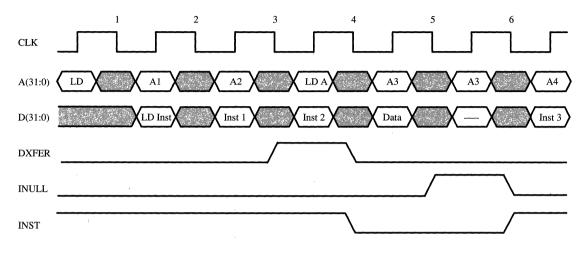

|         | 6.4.3      | Load with Interlock                          |

|         | 6.4.4      | Load Double                                  |

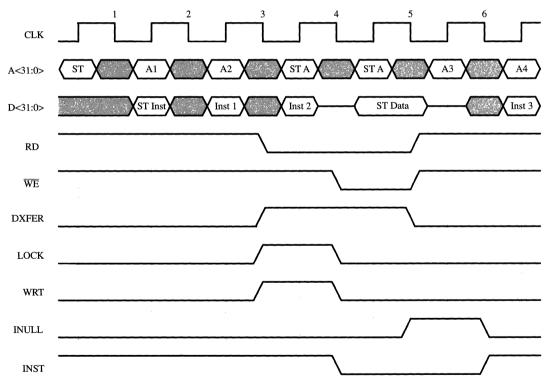

|         | 6.4.5      | Store                                        |

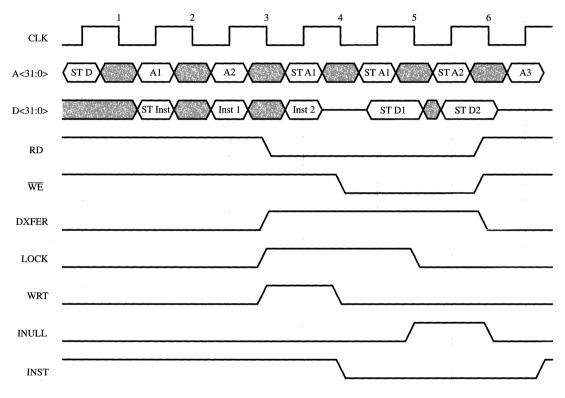

|         | 6.4.6      | Store Double                                 |

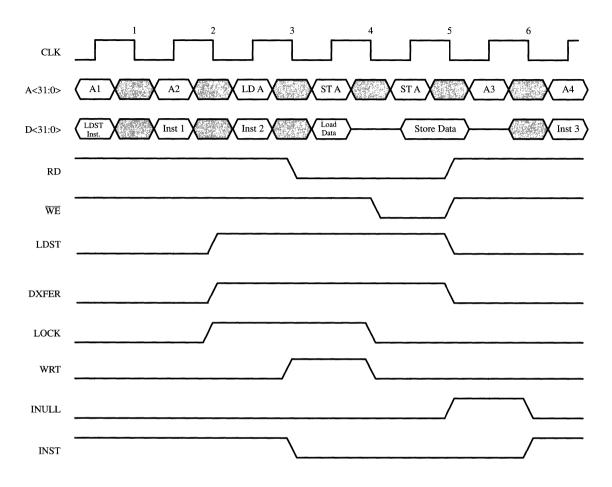

|         | 6.4.7      | Atomic Load-Store                            |

|         | 6.4.8      | Floating-Point Operations                    |

|         | 6.4.9      | Bus Arbitration                              |

|         | 6.4.10     | Load with Cache Miss                         |

|         | 6.4.11     | Store with Cache Miss                        |

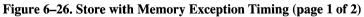

|         | 6.4.12     | Memory Exceptions                            |

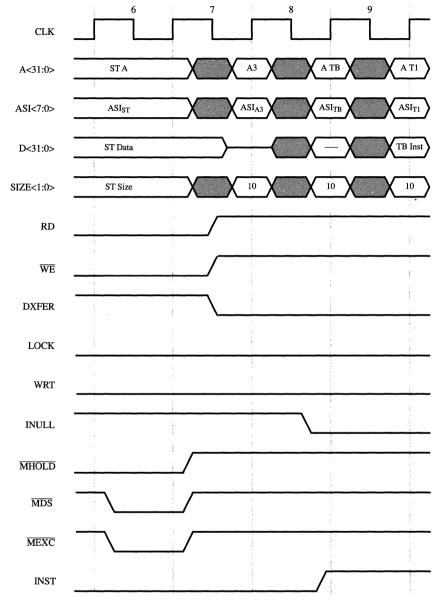

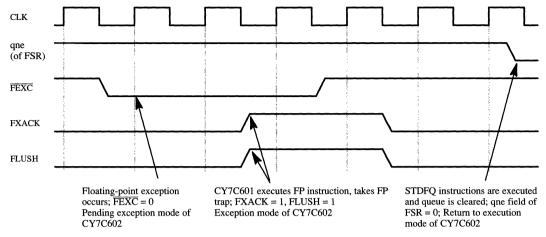

|         | 6.4.13     | Floating-Point Exceptions                    |

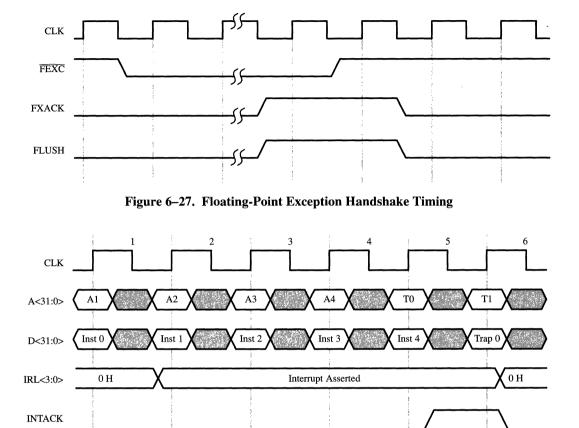

|         | 6.4.14     | Interrupts                                   |

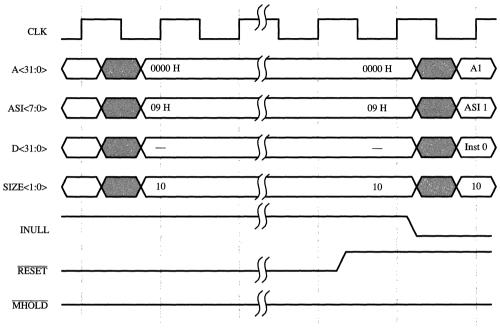

|         | 6.4.15     | Reset Condition                              |

|         | 6.4.16     | Error Condition                              |

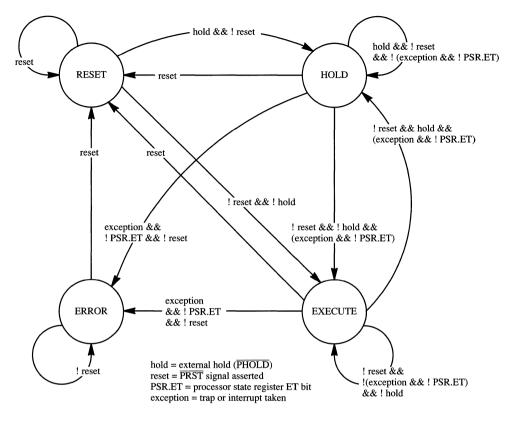

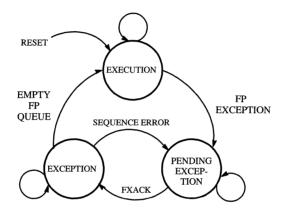

| 6.5    | Exceptio  | n Model                                                 |

|--------|-----------|---------------------------------------------------------|

|        | 6.5.1     | Reset                                                   |

|        | 6.5.2     | Synchronous Traps                                       |

|        | 6.5.3     | Interrupts (Asynchronous Traps)                         |

|        | 6.5.4     | Floating-Point/Coprocessor Traps                        |

|        | 6.5.5     | Trap Operation                                          |

| 6.6    | Coproce   | ssor Interface                                          |

|        | 6.6.1     | Protocol                                                |

|        | 6.6.2     | Register Model                                          |

|        | 6.6.3     | Exceptions                                              |

| 6.7    | CY7C61    | 1 Integer Unit for Embedded Control6-52                 |

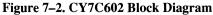

| Chapte | r 7: CY7C | 602 Floating-Point Unit                                 |

| 7.1    | CY7C60    | 2 Functional Description7-2                             |

| 7.2    | Floating  | -Point/Integer Unit Interface                           |

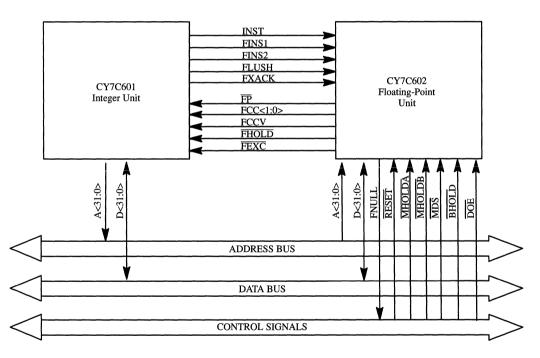

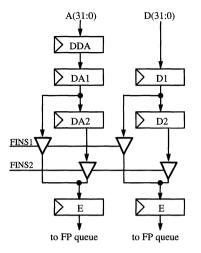

|        | 7.2.1     | CY7C602 Instruction Fetch and Execution                 |

|        | 7.2.2     | Instruction Pipeline Flush                              |

| 7.3    | CY7C60    | 2 Programming Model                                     |

|        | 7.3.1     | CY7C602 Registers                                       |

|        | 7.3.2     | CY7C602 Floating-Point Instructions7-18                 |

|        | 7.3.3     | CY7C602 Internal Operation                              |

|        | 7.3.4     | CY7C602 Exception Cases                                 |

| 7.4    | CY7C60    | 2 Signal Descriptions                                   |

|        | 7.4.1     | Integer Unit Interface Signals                          |

|        | 7.4.2     | Coprocessor Interface Signals                           |

|        | 7.4.3     | System/Memory Interface Signals                         |

| Chapte | r 8: CY7C | 604/CY7C605 Cache Controller and Memory Management Unit |

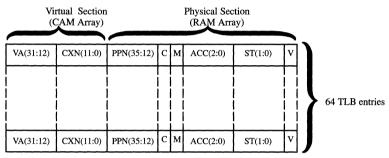

| 8.1    | Memory    | Management Unit                                         |

|        |           |                                                         |

| 8.1 | Memory | Management Unit                    | i-3 |

|-----|--------|------------------------------------|-----|

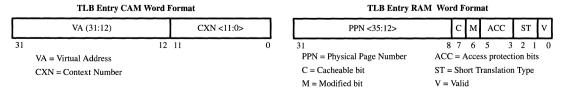

|     | 8.1.1  | Translation Lookaside Buffer (TLB) | 3-4 |

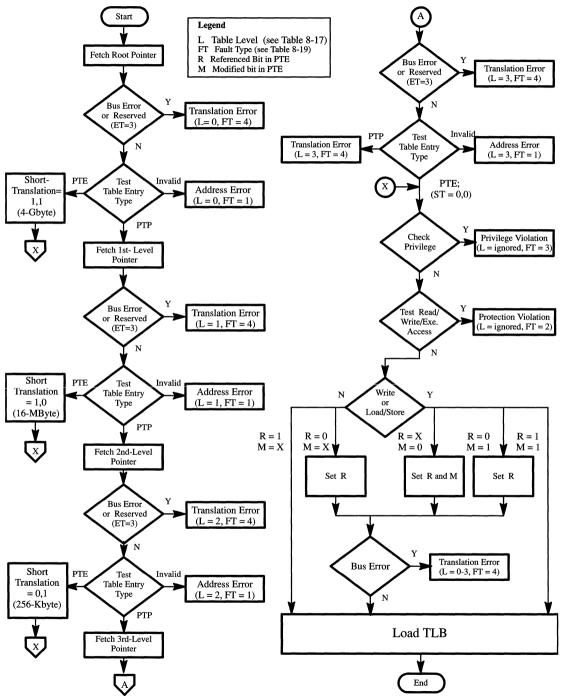

|     | 8.1.2  | Table Walk                         | 3-9 |

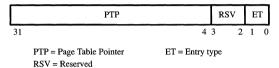

|     | 8.1.3  | Page Table Pointer (PTP)           | 10  |

|     | 8.1.4  | Page Table Entry (PTE)             | 11  |

|     | 8.1.5  | Page Table Pointer Cache (PTPC)8-  | 12  |

| 8.2 | MMU O  | peration Modes                     | 15  |

|     | 8.2.1  | MMU Flush and Probe Operations     | 16  |

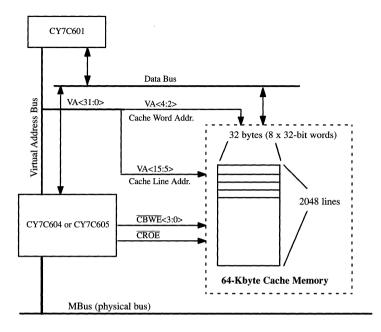

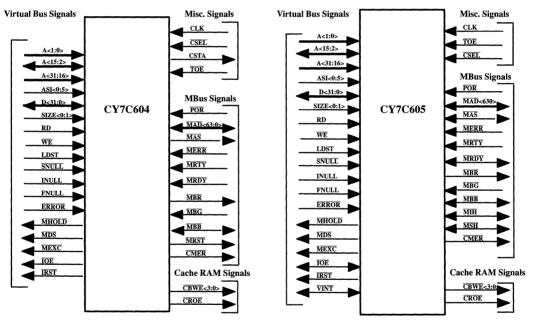

| 8.3 | CY7C6   | 04 / CY7C605 Cache Controllers8-17                        |

|-----|---------|-----------------------------------------------------------|

|     | 8.3.1   | CY7C604/605 Cache Modes                                   |

|     | 8.3.2   | CY7C604 Cache Controller                                  |

|     | 8.3.3   | CY7C605 Cache Controller                                  |

|     | 8.3.4   | CY7C604/CY7C605 Cache Control Signals                     |

|     | 8.3.5   | CY7C604/605 Write Buffer                                  |

|     | 8.3.6   | CY7C604/605 Read Buffer                                   |

|     | 8.3.7   | CY7C604/605 Cache Flushing Operations8-38                 |

|     | 8.3.8   | CY7C604/605 Cacheable/Non-Cacheable Memory Accesses       |

|     | 8.3.9   | CY7C604/605 MBus Cacheable (MC) Bit                       |

|     | 8.3.10  | CY7C604/605 LDST (Atomic Load-Store Instruction) cycles   |

|     | 8.3.11  | CY7C604/605 Cache Byte Write Enables                      |

| 8.4 | CY7C6   | 04 / CY7C605 Registers                                    |

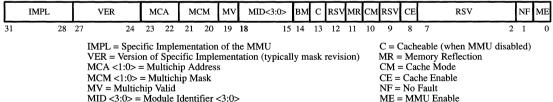

|     | 8.4.1   | CY7C604 System Control Register (SCR)8-41                 |

|     | 8.4.2   | CY7C605 System Control Register (SCR)                     |

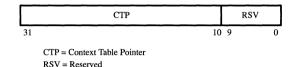

|     | 8.4.3   | CY7C604/605 Context Table Pointer Register (CTPR)         |

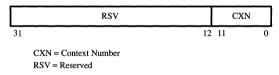

|     | 8.4.4   | CY7C604/605 Context Register (CXR)                        |

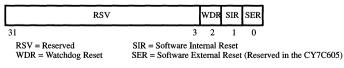

|     | 8.4.5   | CY7C604/605 Reset Register (RR)                           |

|     | 8.4.6   | CY7C604/605 Root Pointer Register (RPR)8-45               |

|     | 8.4.7   | CY7C604/605 Instruction access PTP (IPTP)                 |

|     | 8.4.8   | CY7C604/605 Data access PTP (DPTP)                        |

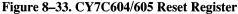

|     | 8.4.9   | CY7C604/605 Index Tag Register (ITR)8-45                  |

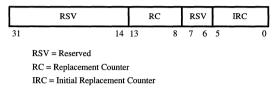

|     | 8.4.10  | CY7C604/605 TLB Replacement Control Register (TRCR)8-46   |

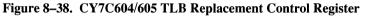

|     | 8.4.11  | CY7C604/605 Synchronous Fault Status Register (SFSR)      |

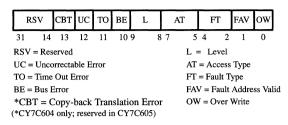

|     | 8.4.12  | CY7C604/605 Synchronous Fault Address Register (SFAR)8-47 |

|     | 8.4.13  | CY7C604/605 Asynchronous Fault Status Register (AFSR)8-47 |

|     | 8.4.14  | CY7C604/605 Asynchronous Fault Address Register (AFAR)    |

| 8.5 | CY7C6   | 04 / CY7C605 Multichip Configuration8-48                  |

|     | 8.5.1   | System Initialization                                     |

|     | 8.5.2   | Cache Configurations                                      |

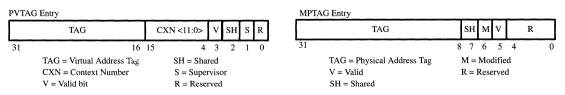

| 8.6 | CY7C6   | 04/605 Diagnostic Support                                 |

|     | 8.6.1   | CY7C604/605 MMU TLB Entries                               |

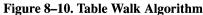

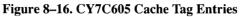

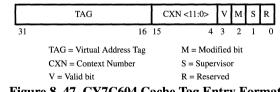

|     | 8.6.2   | CY7C604/605 Cache Tag Entries                             |

|     | 8.6.3   | CY7C604/605 Cache Data Entries                            |

| 8.7 | CY7C6   | 04/605 Reset                                              |

|     | 8.7.1   | Power-On Reset (POR)                                      |

|     | 8.7.2   | Watchdog Reset (WDR)                                      |

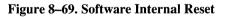

|     | 8.7.3   | Software Internal Reset (SIR)                             |

|     | 8.7.4   | Software External Reset (SER) (CY7C604 only)8-55          |

|     | 8.7.5   | CY7C604/605 Reset in Multichip Configuration              |

| 8.8 | CY7C6   | 04/605 ASI and Register Mapping                           |

| 8.9 | Synchro | onous Faults                                              |

|     | 8.9.1   | Synchronous Fault Cases                                   |

| 8.10            | CY7C60                                                                                                                                                                                                                                                                                                    | 14/605 Pin Definitions                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 8.11            | Virtual 3                                                                                                                                                                                                                                                                                                 | Virtual Bus Operation                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Chapter         | Chapter 9: CY7C157 Cache Storage Unit                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

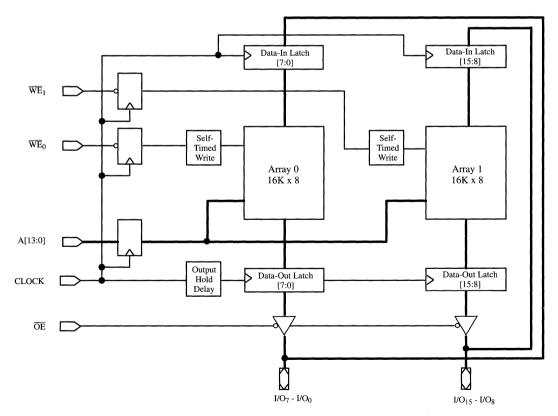

| 9.1             | Descript                                                                                                                                                                                                                                                                                                  | Description Of Part9-2                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 9.2             | Operatio                                                                                                                                                                                                                                                                                                  | Operation                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 9.3             | Signal D                                                                                                                                                                                                                                                                                                  | Descriptions                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Chapter         | 10: SPA                                                                                                                                                                                                                                                                                                   | RC MBus CPU Modules                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 10.1            | hyperSP<br>10.1.1<br>10.1.2<br>10.1.3                                                                                                                                                                                                                                                                     | ARC Modules10-1hyperSPARC Module Description10-2hyperSPARC Module Design10-2hyperSPARC System Design Considerations10-3                                                                                                                                                                                                                                                     |  |  |  |

| 10.2            | <b>CYM60</b><br>10.2.1<br>10.2.2                                                                                                                                                                                                                                                                          | <b>DX Modules</b> 10-4           CYM600X Module Design         10-5           System Design Considerations         10-5                                                                                                                                                                                                                                                     |  |  |  |

| 10.3            | <b>CYM61</b><br>10.3.1                                                                                                                                                                                                                                                                                    | 11 Multi-Die Package CPU       10-6         Multi-Die Packaging Technology       10-6                                                                                                                                                                                                                                                                                       |  |  |  |

|                 |                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Chapter         | 11: MBu                                                                                                                                                                                                                                                                                                   | is Operation                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| -               | MBus I                                                                                                                                                                                                                                                                                                    | -<br>Principles 11-1                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| -               | <b>MBus I</b><br>11.1.1                                                                                                                                                                                                                                                                                   | Principles         11-1           MBus Level 1 Overview         11-1                                                                                                                                                                                                                                                                                                        |  |  |  |

| -               | <b>MBus H</b><br>11.1.1<br>11.1.2                                                                                                                                                                                                                                                                         | Principles       11-1         MBus Level 1 Overview       11-1         MBus Level 2 Overview       11-2                                                                                                                                                                                                                                                                     |  |  |  |

| -               | <b>MBus H</b><br>11.1.1<br>11.1.2<br>11.1.3                                                                                                                                                                                                                                                               | Principles       11-1         MBus Level 1 Overview       11-1         MBus Level 2 Overview       11-2         MBus Physical Signal Summary       11-3                                                                                                                                                                                                                     |  |  |  |

| -               | <b>MBus H</b><br>11.1.1<br>11.1.2<br>11.1.3<br>11.1.4                                                                                                                                                                                                                                                     | Principles11-1MBus Level 1 Overview11-1MBus Level 2 Overview11-2MBus Physical Signal Summary11-3MBus Multiplexed Signal Summary11-7                                                                                                                                                                                                                                         |  |  |  |

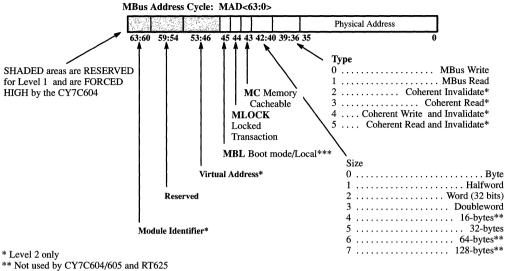

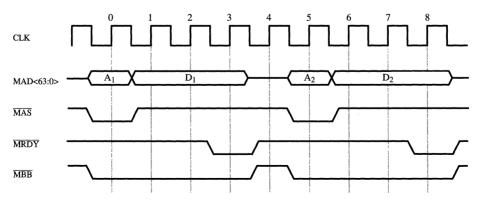

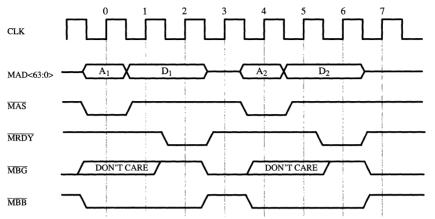

| -               | <b>MBus H</b><br>11.1.1<br>11.1.2<br>11.1.3<br>11.1.4<br>11.1.5                                                                                                                                                                                                                                           | Principles       11-1         MBus Level 1 Overview       11-1         MBus Level 2 Overview       11-2         MBus Physical Signal Summary       11-3         MBus Multiplexed Signal Summary       11-7         MBus Address Cycle       11-7                                                                                                                            |  |  |  |

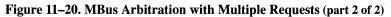

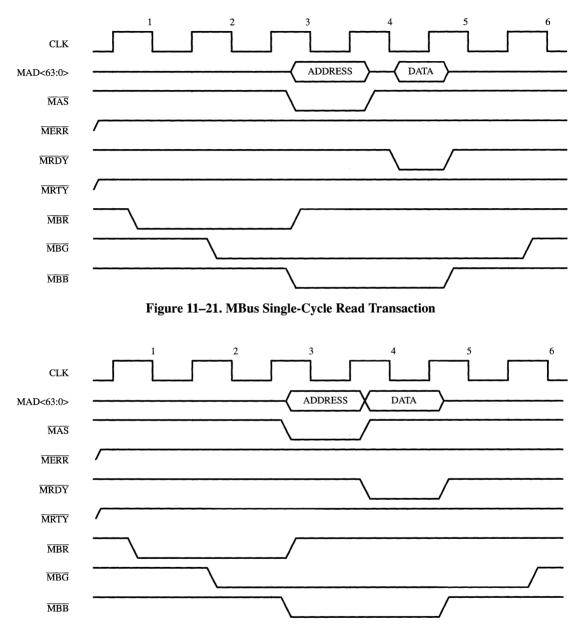

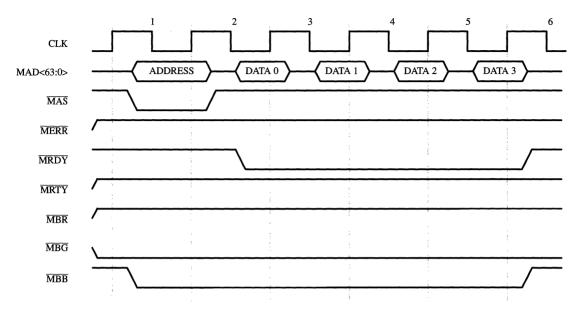

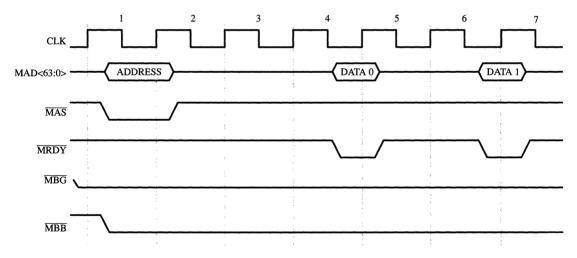

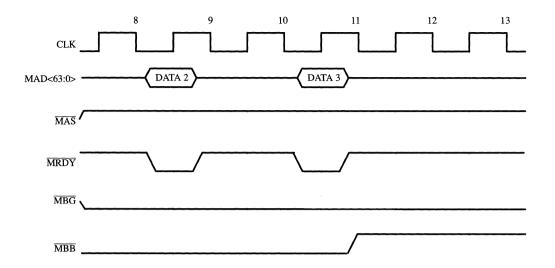

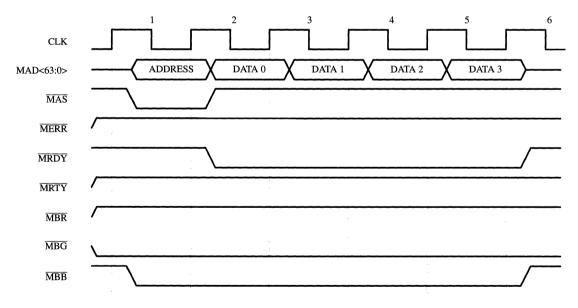

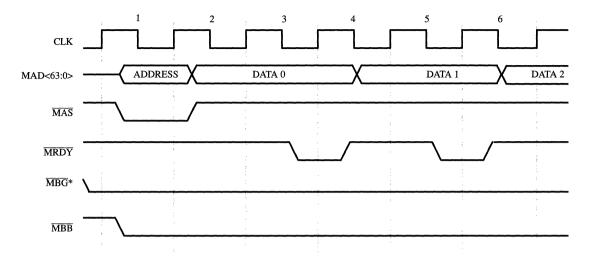

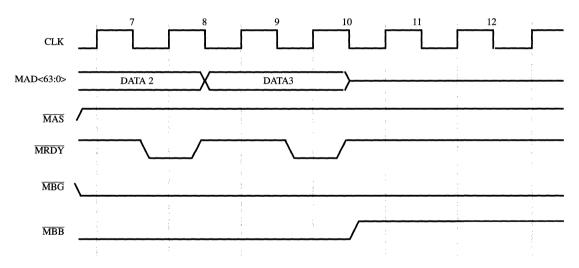

| -               | <b>MBus H</b><br>11.1.1<br>11.1.2<br>11.1.3<br>11.1.4<br>11.1.5<br>11.1.6                                                                                                                                                                                                                                 | Principles11-1MBus Level 1 Overview11-1MBus Level 2 Overview11-2MBus Physical Signal Summary11-3MBus Multiplexed Signal Summary11-7MBus Address Cycle11-7MBus Data Cycle11-10                                                                                                                                                                                               |  |  |  |

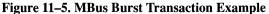

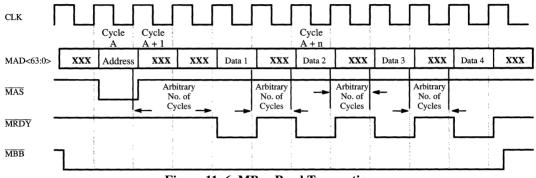

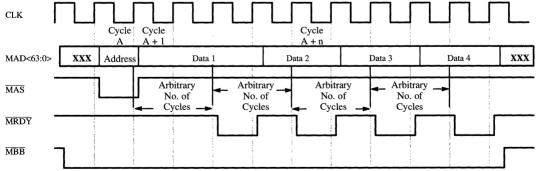

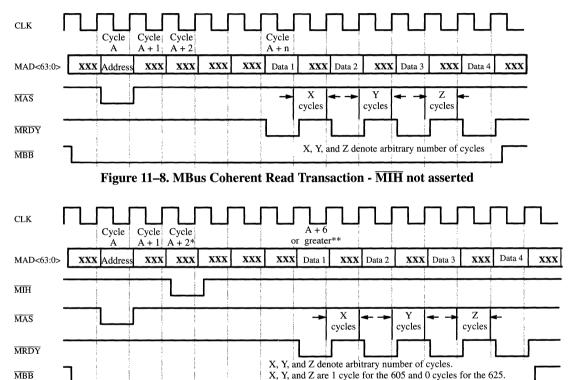

| -               | <b>MBus H</b><br>11.1.1<br>11.1.2<br>11.1.3<br>11.1.4<br>11.1.5                                                                                                                                                                                                                                           | Principles11-1MBus Level 1 Overview11-1MBus Level 2 Overview11-2MBus Physical Signal Summary11-3MBus Multiplexed Signal Summary11-7MBus Address Cycle11-7MBus Data Cycle11-10MBus Transactions11-11                                                                                                                                                                         |  |  |  |

| -               | <b>MBus H</b><br>11.1.1<br>11.1.2<br>11.1.3<br>11.1.4<br>11.1.5<br>11.1.6<br>11.1.7                                                                                                                                                                                                                       | Principles11-1MBus Level 1 Overview11-1MBus Level 2 Overview11-2MBus Physical Signal Summary11-3MBus Multiplexed Signal Summary11-7MBus Address Cycle11-7MBus Data Cycle11-10                                                                                                                                                                                               |  |  |  |

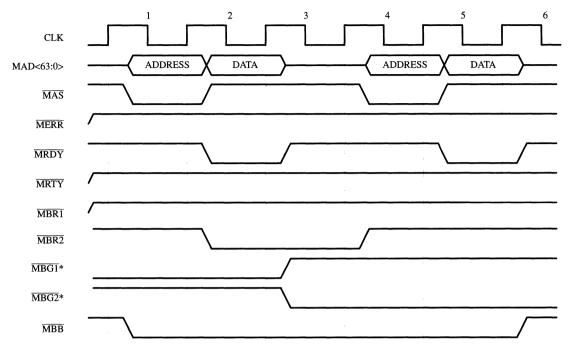

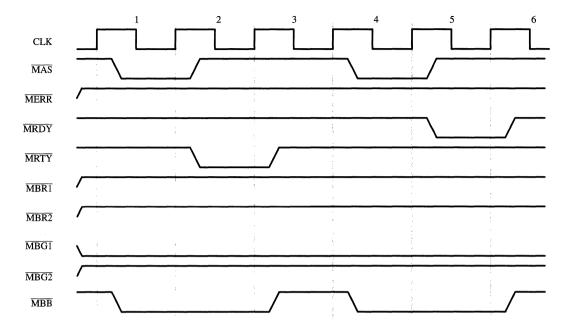

| -               | MBus         H           11.1.1         11.1.2           11.1.3         11.1.4           11.1.5         11.1.6           11.1.7         11.1.8                                                                                                                                                            | Principles11-1MBus Level 1 Overview11-1MBus Level 2 Overview11-2MBus Physical Signal Summary11-3MBus Multiplexed Signal Summary11-7MBus Address Cycle11-7MBus Data Cycle11-10MBus Transactions11-11MBus Acknowledgement Cycles11-19                                                                                                                                         |  |  |  |

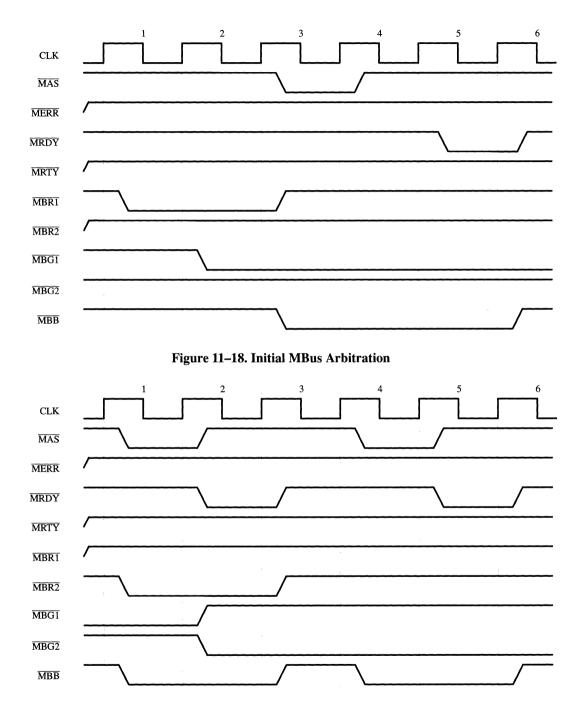

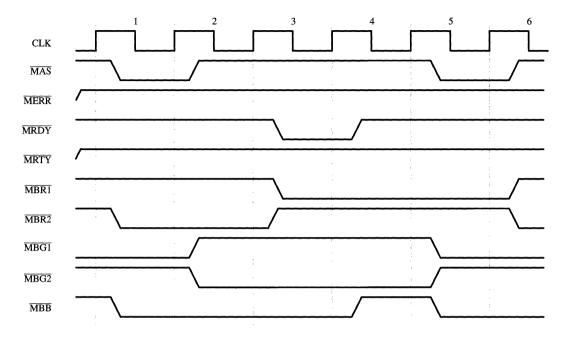

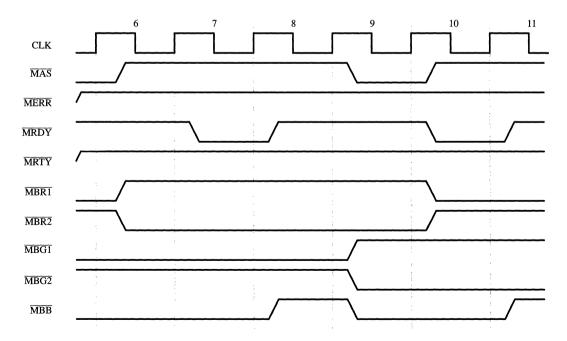

| -               | MBus         H           11.1.1         11.1.2           11.1.3         11.1.4           11.1.5         11.1.6           11.1.7         11.1.8           11.1.8         11.1.9                                                                                                                            | Principles11-1MBus Level 1 Overview11-1MBus Level 2 Overview11-2MBus Physical Signal Summary11-3MBus Multiplexed Signal Summary11-7MBus Address Cycle11-7MBus Data Cycle11-10MBus Transactions11-11MBus Acknowledgement Cycles11-19MBus Arbitration11-21                                                                                                                    |  |  |  |

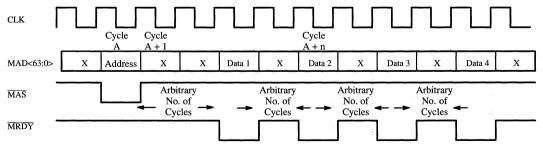

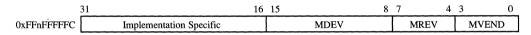

| 11.1            | MBus         H           11.1.1         11.1.2           11.1.3         11.1.4           11.1.5         11.1.6           11.1.7         11.1.8           11.1.9         11.1.10           11.1.11         11.1.10                                                                                         | Principles11-1MBus Level 1 Overview11-1MBus Level 2 Overview11-2MBus Physical Signal Summary11-3MBus Multiplexed Signal Summary11-7MBus Address Cycle11-7MBus Data Cycle11-10MBus Transactions11-11MBus Acknowledgement Cycles11-19MBus Arbitration11-21MBus Configuration Address Map11-22                                                                                 |  |  |  |

| 11.1<br>Chapter | MBus         H           11.1.1         11.1.2           11.1.3         11.1.4           11.1.5         11.1.6           11.1.7         11.1.8           11.1.9         11.1.10           11.1.11         11.1.10           11.1.11         11.1.10                                                       | Principles11-1MBus Level 1 Overview11-1MBus Level 2 Overview11-2MBus Physical Signal Summary11-3MBus Multiplexed Signal Summary11-7MBus Address Cycle11-7MBus Data Cycle11-7MBus Transactions11-11MBus Acknowledgement Cycles11-19MBus Arbitration11-21MBus Configuration Address Map11-22MBus Transaction Timing11-24RC Instruction Set12-1                                |  |  |  |

| 11.1<br>Chapter | MBus         H           11.1.1         11.1.2           11.1.3         11.1.4           11.1.5         11.1.6           11.1.7         11.1.8           11.1.9         11.1.10           11.1.11         11.2.11           Assemble         12.1.1                                                       | Principles11-1MBus Level 1 Overview11-1MBus Level 2 Overview11-2MBus Physical Signal Summary11-3MBus Multiplexed Signal Summary11-7MBus Address Cycle11-7MBus Data Cycle11-7MBus Transactions11-11MBus Acknowledgement Cycles11-19MBus Configuration Address Map11-22MBus Transaction Timing11-24RC Instruction Set12-1Register Names12-1                                   |  |  |  |

| 11.1<br>Chapter | MBus         H           11.1.1         11.1.2           11.1.3         11.1.4           11.1.5         11.1.6           11.1.7         11.1.8           11.1.9         11.1.10           11.1.11         11.1.11           H2: SPA           Assemble           12.1.1           12.1.2                  | Principles11-1MBus Level 1 Overview11-1MBus Level 2 Overview11-2MBus Physical Signal Summary11-3MBus Multiplexed Signal Summary11-7MBus Address Cycle11-7MBus Data Cycle11-10MBus Transactions11-11MBus Acknowledgement Cycles11-19MBus Configuration Address Map11-22MBus Transaction Timing11-24RC Instruction Set12-1Register Names12-1Special Symbol Names12-2          |  |  |  |

| 11.1<br>Chapter | MBus         H           11.1.1         11.1.2           11.1.3         11.1.4           11.1.5         11.1.6           11.1.7         11.1.8           11.1.9         11.1.10           11.1.11         11.1.11           12: SPA           Assemble           12.1.1           12.1.2           12.1.3 | Principles11-1MBus Level 1 Overview11-1MBus Level 2 Overview11-2MBus Physical Signal Summary11-3MBus Multiplexed Signal Summary11-7MBus Address Cycle11-7MBus Data Cycle11-7MBus Transactions11-11MBus Acknowledgement Cycles11-19MBus Configuration Address Map11-22MBus Transaction Timing11-24RC Instruction Set12-1Register Names12-1Special Symbol Names12-2Values12-2 |  |  |  |

| 11.1<br>Chapter | MBus         H           11.1.1         11.1.2           11.1.3         11.1.4           11.1.5         11.1.6           11.1.7         11.1.8           11.1.9         11.1.10           11.1.11         11.1.11           H2: SPA           Assemble           12.1.1           12.1.2                  | Principles11-1MBus Level 1 Overview11-1MBus Level 2 Overview11-2MBus Physical Signal Summary11-3MBus Multiplexed Signal Summary11-7MBus Address Cycle11-7MBus Data Cycle11-10MBus Transactions11-11MBus Acknowledgement Cycles11-19MBus Configuration Address Map11-22MBus Transaction Timing11-24RC Instruction Set12-1Register Names12-1Special Symbol Names12-2          |  |  |  |

| 12.2 | Definitions    |                                                                    |

|------|----------------|--------------------------------------------------------------------|

|      | ADD            | Add                                                                |

|      | ADDcc          | Add and modify icc                                                 |

|      | ADDX           | Add with Carry                                                     |

|      | ADDXcc         | Add with Carry and modify icc 12-11                                |

|      | AND            | And                                                                |

|      | ANDcc          | And and modify icc                                                 |

|      | ANDN           | And Not                                                            |

|      | ANDNcc         | And Not and modify icc 12-15                                       |

|      | Bicc           | Integer Conditional Branch 12-16                                   |

|      | CALL           | Call                                                               |

|      | CBccc          | Coprocessor Conditional Branch                                     |

|      | СРор           | Coprocessor Operate                                                |

|      | FABSs          | Absolute Value Single                                              |

|      | FADDd          | Add Double 12-23                                                   |

|      | FADDq          | Add Quad 12-24                                                     |

|      | FADDs          | Add Single 12-25                                                   |

|      | FBfcc          | Floating-Point Conditional Branch                                  |

|      | FCMPd          | Compare Double                                                     |

|      | FCMPEd         | Compare Double and Exception if Unordered                          |

|      | FCMPEq         | Compare Quad and Exception if Unordered                            |

|      | FCMPEs         | Compare Single and Exception if Unordered                          |

|      | FCMPq          | Compare Quad 12-32                                                 |

|      | FCMPs          | Compare Single 12-33                                               |

|      | FDIVd          | Divide Double                                                      |

|      | FDIVq          | Divide Quad                                                        |

|      | FDIVs          | Divide Single                                                      |

|      | FdMULq         | Multiply Double to Quad                                            |

|      | FdTOi          | Convert Double to Integer 12-38                                    |

|      | FdTOq          | Convert Double to Quad                                             |

|      | FdTOs          | Convert Double to Single                                           |

|      | FiTOd          | Convert Integer to Double                                          |

|      | FiTOq          | Convert Integer to Quad                                            |

|      | FiTOs          | Convert Integer to Single                                          |

|      | FLUSH<br>FMOVs | Instruction Cache Flush         12-44           Move         12-45 |

|      | FMULd          | Move                                                               |

|      | FMULq          | Multiply Quad                                                      |

|      | FMULs          | Multiply Single                                                    |

|      | FNEGs          | Negate                                                             |

|      | FqTOd          | Convert Quad to Double                                             |

|      | FqTOi          | Convert Quad to Double 12-50<br>Convert Quad to Integer            |

|      | FqTOs          | Convert Quad to Single                                             |

|      | FsMULd         | Multiply Single with Double                                        |

|      | FSQRTd         | Square Root Double                                                 |

|      | FSQRTq         | Square Root Quad                                                   |

|      | FSQRTs         | Square Root Single       12-56                                     |

|      | FsTOd          | Convert Single to Double                                           |

|      |                | $\mathbf{J}$                                                       |

| FsTOi      | Convert Single to Integer                                                    |

|------------|------------------------------------------------------------------------------|

| FsTOq      | Convert Single to Quad                                                       |

| FSUBd      | Subtract Double                                                              |

| FSUBa      | Subtract Quad                                                                |

| FSUB       |                                                                              |

|            | Subtract Single                                                              |

| JMPL       | Jump and Link                                                                |

| LD         | Load Word                                                                    |

| LDA        | Load Word from Alternate space                                               |

| LDC        | Load Coprocessor Register                                                    |

| LDCSR      | Load Coprocessor State Register 12-67                                        |

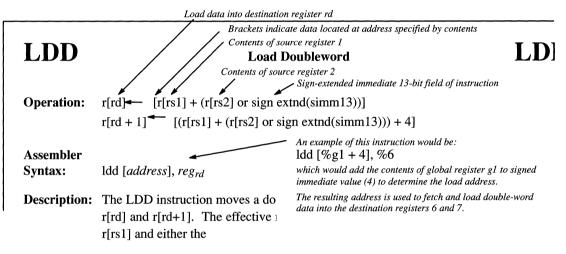

| LDD        | Load Doubleword                                                              |

| LDDA       | Load Doubleword from Alternate space                                         |

| LDDC       | Load Doubleword Coprocessor 12-70                                            |

| LDDF       | Load Doubleword Floating-Point                                               |

| LDF        | Load Floating-Point Register 12-72                                           |

| LDFSR      | Load Floating-Point State Register                                           |

| LDSB       | Load Signed Byte 12-74                                                       |

| LDSBA      | Load Signed Byte from Alternate space 12-75                                  |

| LDSH       | Load Signed Halfword 12-76                                                   |

| LDSHA      | Load Signed Halfword from Alternate space                                    |

| LDSTUB     | Atomic Load-Store Unsigned Byte 12-78                                        |

| LDSTUBA    | Atomic Load-Store Unsigned Byte in Alternate space 12-79                     |

| LDUB       | Load Unsigned Byte                                                           |

| LDUBA      | Load Unsigned Byte from Alternate space                                      |

| LDUH       | Load Unsigned Halfword 12-82                                                 |

| LDUHA      | Load Unsigned Halfword from Alternate space                                  |

| MULScc     | Multiply Step and modify icc                                                 |

| OR         | Inclusive-Or                                                                 |

| ORcc       | Inclusive-Or and modify icc                                                  |

| ORN        | Inclusive-Or Not                                                             |

| ORNcc      | Inclusive-Or Not and modify icc                                              |

| RDASR      | Read Ancillary State Register                                                |

| RDPSR      | Read Processor State Register                                                |

| RDTBR      | Read Trap Base Register                                                      |

| RDWIM      | Read Window Invalid Mask Register                                            |

| RDY        | Read Y Register                                                              |

| RESTORE    | Restore caller's window                                                      |

| RETT       | Return from Trap                                                             |

| SAVE       | Save caller's window                                                         |

| SDIV       | Signed Divide                                                                |

| SDIV       | Signed Divide (modify icc)                                                   |

| SETHI      | Set High 22 bits of r-Register                                               |

| SLL        | Set High 22 bits of 1-kegister                                               |

| SMUL       | Signed Multiply                                                              |

| SMUL       |                                                                              |

| SMULCC     | Signed Multiply (modify icc)                                                 |

| SRA<br>SRL | Shift Right Arithmetic       12-104         Shift Right Logical       12-105 |

|            |                                                                              |

| ST         | Store Word                                                                   |

| CIT A      |                                                |

|------------|------------------------------------------------|

| STA<br>STB | Store Word into Alternate space                |

| STBA       | Store Byte into Alternate space                |

| STC        | Store Coprocessor Register                     |

| STCSR      | Store Coprocessor State Register               |

| STCSK      | Store Doubleword                               |

| STDA       | Store Doubleword into Alternate space          |

| STDA       | Store Doubleword Coprocessor                   |

| STDC       | Store Doubleword Coprocessor Queue             |

| STDEQ      | Store Doubleword Floating-Point                |

|            | Store Doubleword Floating-Point                |

| STDFQ      |                                                |

| STF        | Store Floating-Point Register                  |

| STFSR      | Store Floating-Point State Register            |

| STH        | Store Halfword                                 |

| STHA       | Store Halfword into Alternate space            |

| SUB        | Subtract                                       |

| SUBcc      | Subtract and modify icc                        |

| SUBX       | Subtract with Carry                            |

| SUBXcc     | Subtract with Carry and modify icc             |

| SWAP       | Swap r-Register with memory 12-126             |

| SWAPA      | Swap r-Register with memory in Alternate space |

| TADDcc     | Tagged Add and modify icc 12-128               |

| TADDccTV   | Tagged Add (modify icc) Trap on Overflow       |

| Ticc       | Trap on integer condition codes 12-130         |

| TSUBcc     | Tagged Subtract and modify icc 12-132          |

| TSUBccTV   | Tagged Subtract (modify icc) Trap on Overflow  |

| UDIV       | Unsigned Divide                                |

| UDIVcc     | Unsigned Divide (modify icc)                   |

| UMUL       | Unsigned Multiply                              |

| UMULcc     | Unsigned Multiply (modify icc)                 |

| UNIMP      | Unimplemented instruction                      |

| WRASR      | Write Ancillary State Register                 |

| WRPSR      | Write Processor State Register                 |

| WRTBR      | Write Trap Base Register                       |

| WRWIM      | Write Window Invalid Mask Register             |

| WRY        | Write Y Register                               |

| XNOR       | Exclusive-Nor                                  |

| XNOR       | Exclusive-Nor and modify icc                   |

| XOR        | Exclusive-Ivol and mounty ice                  |

| XORcc      | Exclusive-Or and modify icc                    |

| AUNCC      | Exclusive-of and mounty ice                    |

#### Appendix A: hyperSPARC Software Notes

| A.1      | Reset C | onsiderations                     |

|----------|---------|-----------------------------------|

|          | A.1.1   | Miscellaneous Notes A-2           |

| A.2      | Compile | er Optimization Notes A-2         |

|          | A.2.1   | Software pipelining: A-2          |

|          | A.2.2   | Loop Unrolling: A-3               |

|          | A.2.3   | Inter-procedure Optimizations A-3 |

|          | A.2.4   | Operating Systems Notes           |

| Glossary | y       | G-1                               |

| Index    | •••••   |                                   |

.

# List of Tables

#### **Chapter 2: SPARC Programming Environment**

| Table 2–1.  | Register Addressing                                         | . 2-3 |

|-------------|-------------------------------------------------------------|-------|

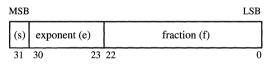

| Table 2–2.  | Single-Precision Floating-Point Format                      | 2-18  |

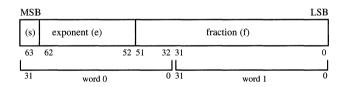

| Table 2–3.  | Double-Precision Floating-Point Format                      | 2-19  |

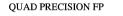

| Table 2–4.  | Quad-Precision Floating-Point Format                        | 2-20  |

| Table 2–5.  | op field Coding                                             | 2-22  |

| Table 2-6.  | op2 Field Coding                                            | 2-22  |

| Table 2–7.  | Standard SPARC ASI Assignments                              | 2-25  |

| Table 2-8.  | Load and Store Instructions                                 | 2-26  |

| Table 2–9.  | Arithmetic/Logical/Shift Instructions                       | 2-27  |

| Table 2–10. | Control Transfer Instructions                               | 2-29  |

| Table 2-11. | Control Transfer Instruction Characteristics                | 2-30  |

| Table 2–12. | Bicc and Ticc Condition Codes                               | 2-31  |

| Table 2–13. | FBfcc Condition Codes                                       | 2-31  |

| Table 2–14. | CBccc Condition Codes                                       | 2-31  |

| Table 2–15. | Delayed Control Transfer Instruction Example                | 2-32  |

| Table 2–16. | Effect of Annul Bit Reset (a=0)                             | 2-33  |

| Table 2–17. | Effect of Annul Bit Set (a=1)                               | 2-33  |

| Table 2–18. | Effect of Annul Bit on Delay Instruction                    | 2-34  |

| Table 2–19. | Delayed Control Transfer Couple Instruction Sequence        | 2-35  |

| Table 2–20. | Execution of Delayed Control Transfer Couples               | 2-35  |

| Table 2–21. | Read/Write Control Register Instructions                    | 2-37  |

| Table 2–22. | Floating-Point-Operate and Coprocessor-Operate Instructions | 2-37  |

| Table 2–23. | Miscellaneous Instructions                                  | 2-37  |

| Table 2–24. | Load and Store Instruction Opcodes                          | 2-39  |

| Table 2-25. | Arithmetic/Logical/Shift Instruction Opcodes                | 2-41  |

| Table 2–26. | Control Transfer Instruction Opcodes                        | 2-43  |

| Table 2–27. | Bicc and Ticc Condition Codes                               | 2-43  |

| Table 2–28. | FBcc Condition Codes                                        | 2-44  |

| Table 2–29. | CBccc Condition Codes                                       | 2-44  |

| Table 2-30. | Read/Write Control Register Instruction Opcodes             | 2-44  |

| Table 2-31. | Floating-Point /Coprocessor Instruction Opcodes             | 2-45  |

| Table 2-32. | Miscellaneous Instruction Opcodes                           | 2-46  |

| Table 2-33. | Instruction Opcode Numeric Listing                          | 2-46  |

#### Chapter 3: RT620 hyperSPARC Central Processing Unit

| Table 3–1. | Instruction Grouping                                         | . 3-9 |

|------------|--------------------------------------------------------------|-------|

| Table 3–2. | Instruction Combinations Eligible for Simultaneous Execution | 3-11  |

| Table 3–3. | CACHE Line Privilege Match                                   | 3-26  |

| Table 3-4. | FLUSH instructions                                           | 3-29  |

| Table 3–5. | Integer Unit Cycle Per Instruction (CPI)                     | 3-62  |

|    | Table 3-6.    | Typical FPU Instruction Cycle Times 3-77                        | 7 |

|----|---------------|-----------------------------------------------------------------|---|

|    | Table 3–7.    | RT620 Supported Exceptions 3-80                                 | С |

|    | Table 3-8.    | Pipeline Stage Exception Recognition 3-8                        | 1 |

|    | Table 3–9.    | FIT Field of FSR 3-82                                           | 2 |

|    | Table 3-10.   | FP Pipeline Stage Exception Recognition 3-82                    | 3 |

|    | Table 3-11.   | IU Actions Upon Reset, Trap, and Error Mode Events 3-10         | 1 |

|    | Table 3-12.   | FPU Actions Upon Reset, Trap, And Error Mode Events 3-10        | 1 |

|    |               |                                                                 |   |

| Ch | apter 4: RT62 | 25 hyperSPARC Cache Controller, Memory Management, and Tag Unit |   |

|    | Table 4–1.    | Short Translation Bits ST(1:0) 4-:                              |   |

|    | Table 4–2.    | Access-Level Protection Bits-ACC < 2:0 > 4-7                    |   |

|    | Table 4–3.    | Page Table Entry Type 4-12                                      | 2 |

|    | Table 4-4.    | MMU Operation Modes 4-10                                        | 6 |

|    | Table 4-5.    | TLB Entry Invalidation 4-18                                     | 8 |

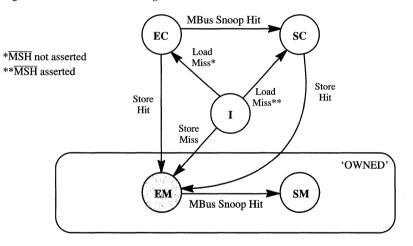

|    | Table 4-6.    | MBus Snooping Transactions 4-3                                  | 1 |

|    | Table 4–7.    | Cache Flush operations 4-34                                     | 4 |

|    | Table 4-8.    | Cacheable/Non-Cacheable Accesses 4-3:                           | 5 |

|    | Table 4-9.    | State Table for MC (Memory Cacheable) Bit 4-3:                  | 5 |

|    | Table 4-10.   | Cache Byte Write Enables 4-30                                   | 6 |

|    | Table 4-11.   | TLB Entry Address Mapping 4-44                                  | 4 |

|    | Table 4-12.   | Cache Tag Entry Address Mapping 4-4:                            | 5 |

|    | Table 4-13.   | Power-On Reset States 4-4                                       | 6 |

|    | Table 4-14.   | RT625 Register Address Mapping 4-4'                             | 7 |

|    | Table 4-15.   | Standard SPARC ASI Assignments 4-4'                             | 7 |

|    | Table 4-16.   | SPARC Fault Cases 4-44                                          | 8 |

|    | Table 4-17.   | OW Bit States                                                   | 9 |

|    | Table 4-18.   | Fault Register Level Field 4-4                                  | 9 |

|    | Table 4-19.   | Fault Register Access Type Field 4-4                            | 9 |

|    | Table 4-20.   | Fault Register Fault Type Field    4-50                         | D |

|    | Table 4-21.   | Fault Type (FT) for PTE[ET] = 2 4-50                            | 0 |

|    | Table 4-22.   | Fault Register Error Priorities    4-50                         | D |

|    | Table 4-23.   | Transaction Status Bit Encoding 4-60                            | D |

|    |               |                                                                 |   |

#### Chapter 6: CY7C601/611 Integer Unit

| Table 6–1. | CY7C601/CY7C611 Instruction CPI                  | 6-3  |

|------------|--------------------------------------------------|------|

| Table 6–2. | CY7C601 External Signal Summary                  | 6-6  |

| Table 6–3. | ASI Assignments                                  | 6-8  |

| Table 6-4. | SIZE Bit Encoding 6                              | j-11 |

| Table 6-5. | Internally Generated Opcodes 6                   | -17  |

| Table 66.  | Externally Generated Synchronous Exception Traps | -42  |

| Table 6–7. | Trap Type and Priority Assignments               | -48  |

| Table 6-8. | Signal Differences Between CY7C601 and CY7C611 6 | -52  |

| Table 6–9. | CY7C611 Signal Summary 6                         | -53  |

#### Chapter 7: CY7C602 Floating-Point Unit

| Table 7–1. | FPop execution             | 7-6 |

|------------|----------------------------|-----|

| Table 7–2. | Load instruction execution | 7-6 |

| Table 7–3.     | Store instruction execution                              |

|----------------|----------------------------------------------------------|

| Table 7-4.     | FHOLD Resource/Operand Dependency Cases                  |

| Table 7–5.     | Floating-Point Status Register Summary 7-17              |

| Table 7-6.     | Floating-Point Load and Store Instruction Cycle Count    |

| Table 7–7.     | Floating-Point Operate (FPops) Instruction Cycle Count   |

| Table 7–8.     | FCC(1:0) Condition Codes                                 |

| Chapter 8: CY7 | C604/CY7C605 Cache Controller and Memory Management Unit |

| Table 8-1.     | Short Translation Bits - ST(1:0)                         |

| Table 8-2.     | Access-Level Protection Bits—ACC(2:0)                    |

| Table 8-3.     | Page Table Entry Type         8-11                       |

| Table 8-4.     | MMU Operation Modes 8-15                                 |

| Table 8-5.     | TLB Entry Flushing                                       |

| Table 8-6.     | MBus Snooping Transactions 8-35                          |

| Table 8-7.     | Cache Flush Operations 8-38                              |

| Table 8-8.     | Cacheable / Non-Cacheable Accesses 8-39                  |

| Table 8-9.     | State Table for MC (Memory Cacheable) Bit 8-40           |

| Table 8-10.    | Byte Write Enables                                       |

| Table 8-11.    | TLB Entry Address Mapping 8-52                           |

| Table 8-12.    | Cache Tag Entry Address Mapping 8-53                     |

| Table 8-13.    | CY7C604/605 Power-On Reset States                        |

| Table 8-14.    | CY7C604/605 Register Address Mapping 8-55                |

| Table 8-15.    | Standard ASI Assignments 8-56                            |

| Table 8-16.    | OW Bit States                                            |

| Table 8-17.    | Fault Register Level Field    8-58                       |

| Table 8-18.    | Fault Register Access Type Field    8-58                 |

| Table 8-19.    | Fault Register Fault Type Field    8-58                  |

| Table 8-20.    | Fault Type (FT) for PTE [ET] = 2                         |

| Table 8-21.    | Fault Register Error Priorities    8-59                  |

| Chapter 11: MB | us Operation                                             |

| Table 11–1.    | MBus Signal Summary 11-3                                 |

| Table 11-2.    | Transaction Status Bit Encoding 11-5                     |

| Table 11-3.    | Multiplexed Signal Summary 11-7                          |

| Table 11-4.    | TYPE Encodings         11-8                              |

| Table 11-5.    | SIZE Encodings 11-9                                      |

#### Chapter 12: SPARC Instruction Set

| Table 12-1. | Instruction Description Notations | 12-4 |

|-------------|-----------------------------------|------|

|             | Instruction Set Summary           |      |

Table 11–6.

Bus Status Encoding

11-12

## List of Figures

#### **Chapter 1: Introduction**

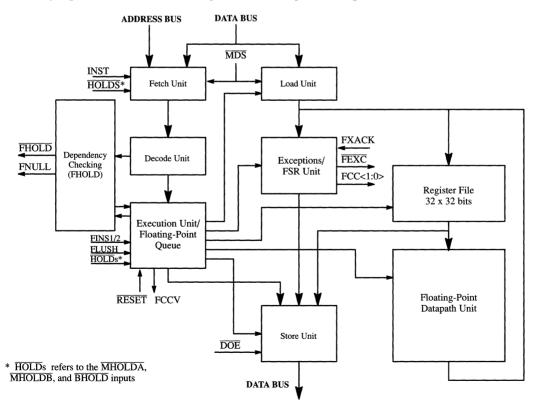

| Figure 1–1. | hyperSPARC CPU Block Diagram 1-                    | -4 |

|-------------|----------------------------------------------------|----|

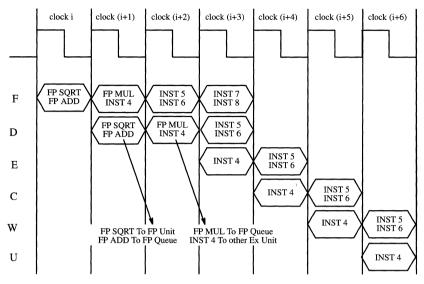

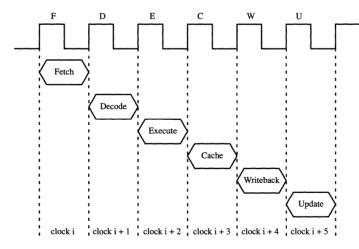

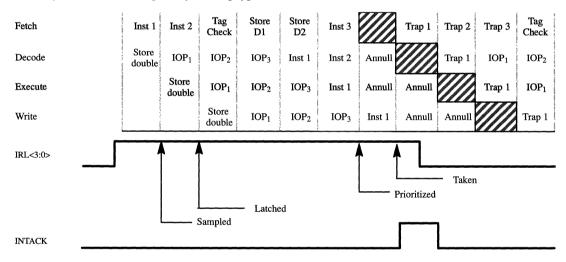

| Figure 1–2. | RT620 Instruction Pipeline Example 1-              | -7 |

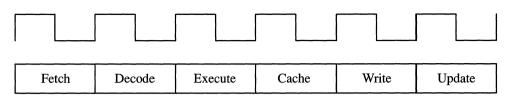

| Figure 1–3. | RT620 Pipeline Stages 1-                           | -8 |

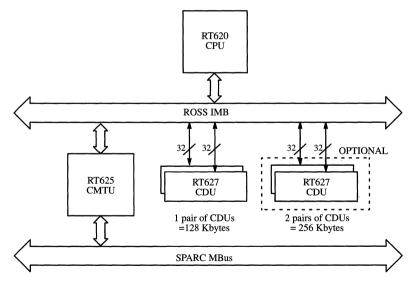

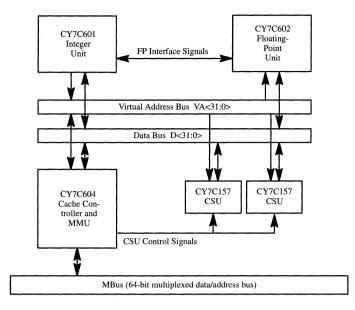

| Figure 1-4. | Architectural Partitioning—Uniprocessor System 1-1 | 0  |

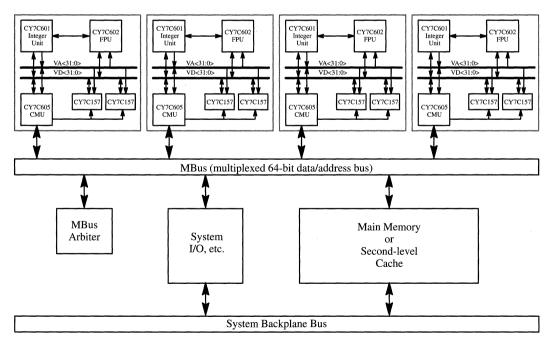

| Figure 1–5. | Architectural Partitioning-Multiprocessors 1-1     | 0  |

#### **Chapter 2: SPARC Programming Environment**

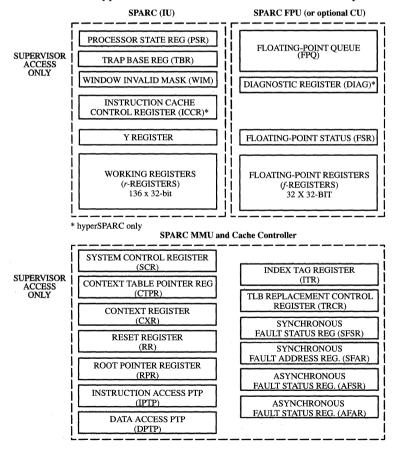

| Figure 2–1.  | SPARC Register Models                         | 2-1  |

|--------------|-----------------------------------------------|------|

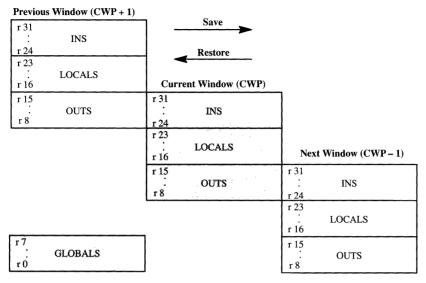

| Figure 2–2.  | Overlapping Windows                           | 2-3  |

| Figure 2–3.  | Registers as Seen by a Procedure              | 2-5  |

| Figure 2-4.  | FPU Register File                             | 2-7  |

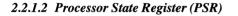

| Figure 2–5.  | Processor State Register                      | 2-8  |

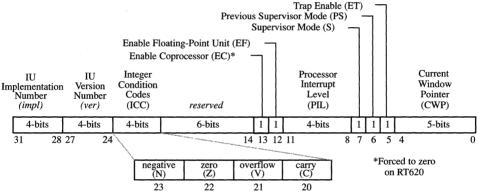

| Figure 2-6.  | Window Invalid Mask                           | 2-10 |

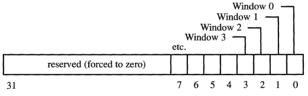

| Figure 2–7.  | Trap Base Register                            | 2-11 |

| Figure 2–8.  | Y Register                                    | 2-11 |

| Figure 2–9.  | ICCR Register                                 | 2-12 |

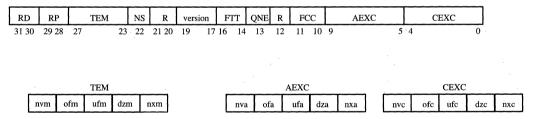

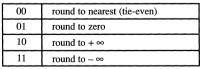

| Figure 2–10. | Floating-Point Status Register (FSR)          | 2-12 |

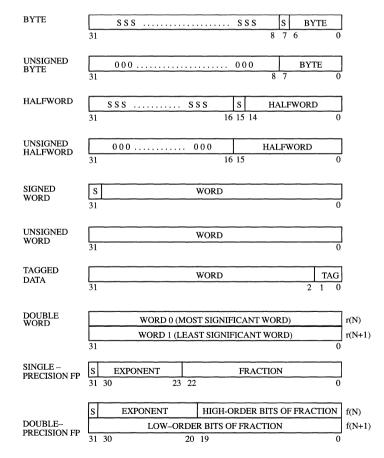

| Figure 2–11. | Processor Data Types                          | 2-15 |

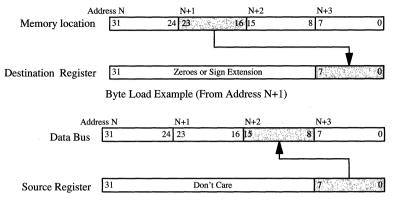

| Figure 2–12. | Byte Operand Load and Store                   | 2-16 |

| Figure 2–13. | Data Organization in Memory                   | 2-16 |

| Figure 2–14. | Single-Precision Floating-Point Format        | 2-18 |

| Figure 2–15. | Double-Precision Floating-Point Format        | 2-19 |

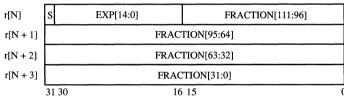

| Figure 2–16. | Quad-Precision Data Organization in Registers | 2-20 |

| Figure 2–17. | Quad-Precision Data Organization in Memory    | 2-20 |

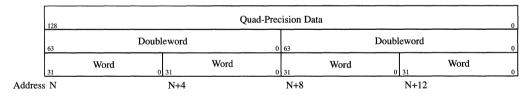

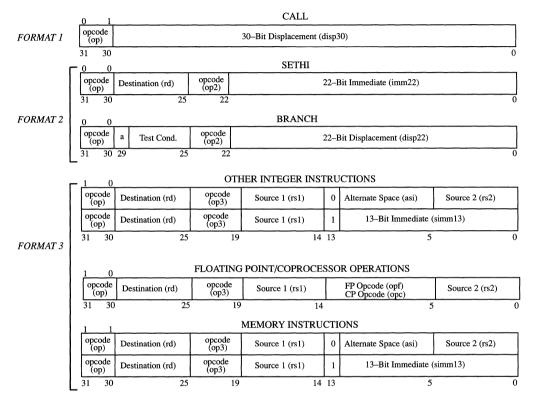

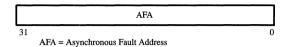

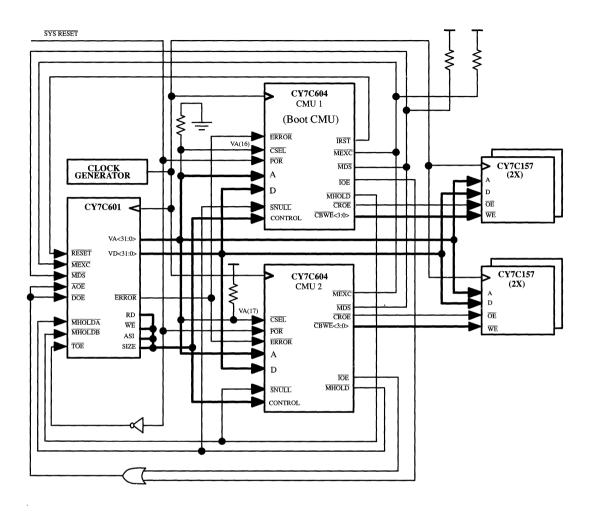

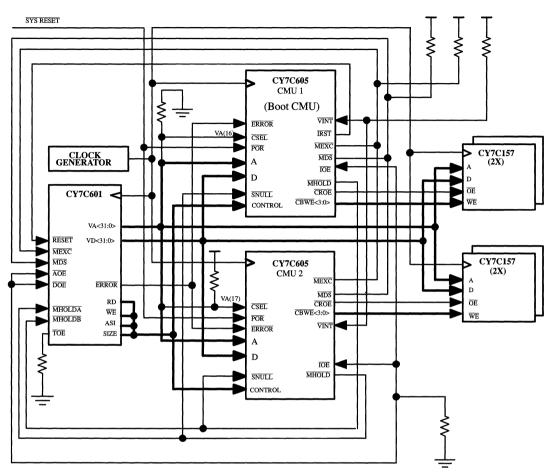

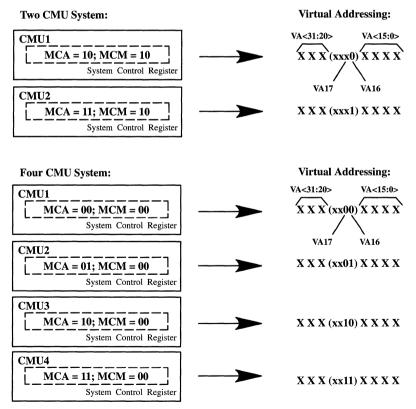

| Figure 2–18. | Instruction Format Summary                    | 2-21 |