FPGA DATA BOOK

1992

# VERY HIGH SPEED FPGAS

# 1992 Data Book

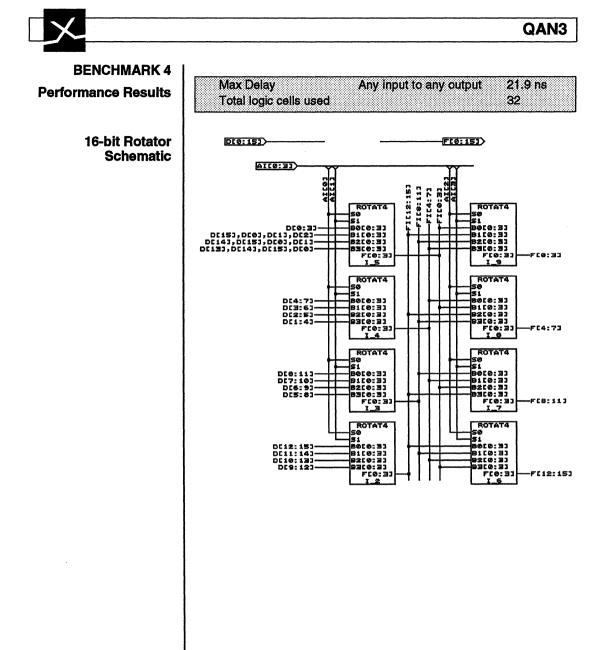

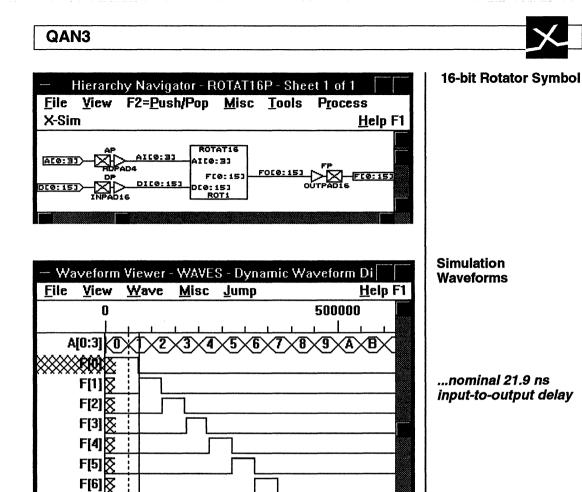

#

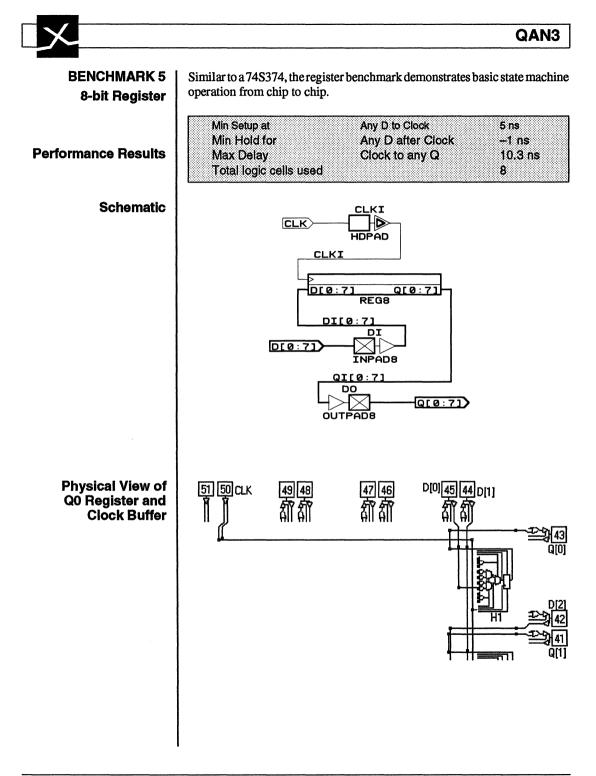

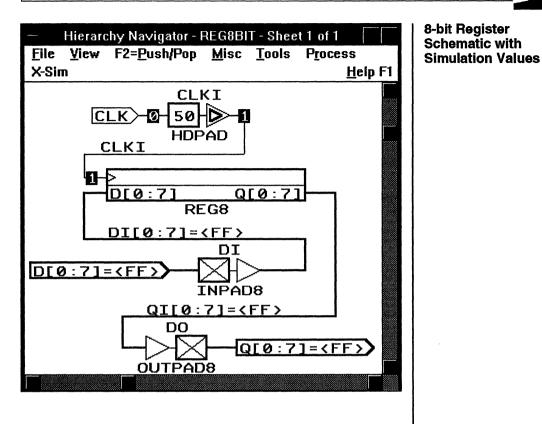

QUICKLOGIC PASIC QL8x12-2PL68C 2091 AAA

QUICK LOGIC pASIC QL8x12-2PL68C 3491 AAA

26

26

# **Very-High-Speed FPGAs**

## **General Information**

| Family Overview                 | . 1-1 |

|---------------------------------|-------|

| System Application Case Studies | 1-13  |

#### **FPGA Data Sheets**

| pASIC Fa | mily Data Sheet |  |

|----------|-----------------|--|

|          | 1000-gate FPGA  |  |

|          | 2000-gate FPGA  |  |

|          | 4000-gate FPGA  |  |

## **CAE Design Tools**

| pASIC Toolkit 3.0     | 3-1  |

|-----------------------|------|

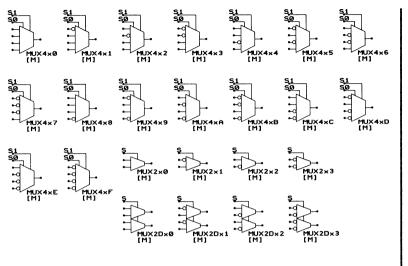

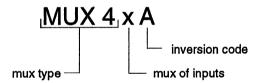

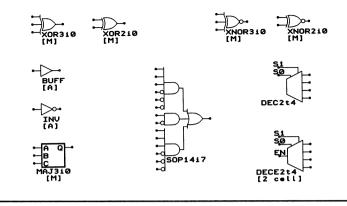

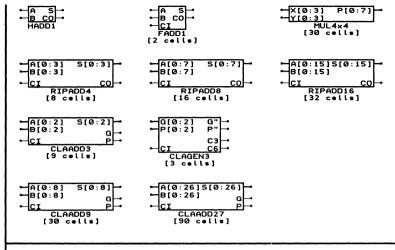

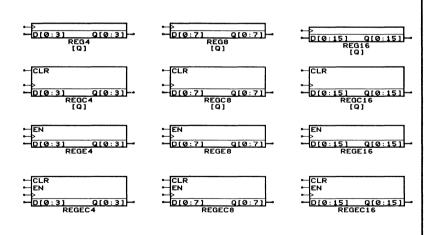

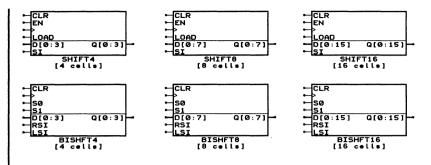

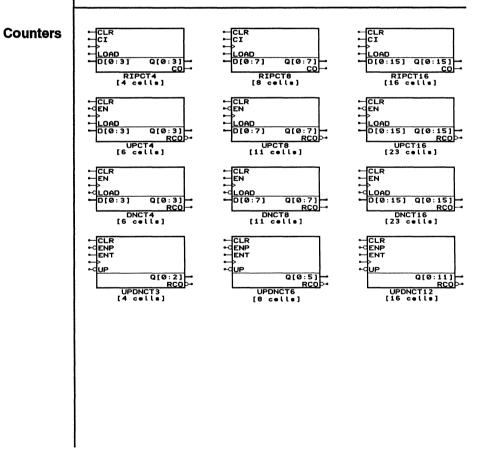

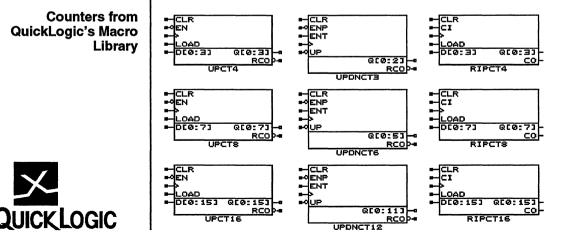

| Macro Libraries       |      |

| SpDE Tools            |      |

| Programmer and Tester | 3-31 |

## **Application Notes**

| Register QuickNote | QAN1 | 4-1 |

|--------------------|------|-----|

| Counter QuickNote  | QAN2 |     |

| JEDEC QuickNote    | QAN3 |     |

#### Quality, Reliability, and Packaging Information

| Quality Program              | 5-1  |

|------------------------------|------|

| pASIC Reliability Report     | 5-3  |

| Packaging/Thermal Data       |      |

| Ordering Information         | 5-25 |

| Third-party Design Support   |      |

| Power vs Operating Frequency | 5-29 |

### **Sales Representatives and Distributors**

| QuickLogic Corporation | General Information (408) 987-2000  |

|------------------------|-------------------------------------|

| 2933 Bunker Hill Lane  | Applications Hotline (408) 987-2037 |

| Santa Clara, CA 95054  | FAX: (408) 987-2012                 |

Copyright © 1992 QuickLogic Corporation

#### LIFE SUPPORT POLICY

QuickLogic's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and the President of QuickLogic.

- Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or affect its safety or effectiveness.

pASIC, SpDE, ViaLink, and QuickLogic are trademarks of QuickLogic Corp. All other trademarks are the property of their respective companies. QuickLogic does not assume any liability resulting from the application or use of any product described within. No circuit patent licenses are implied. QuickLogic Corporation reserves the right to make changes without notice to any product herein to improve reliability, function or design.

Products discussed in this literature are covered by U.S. and foreign patents pending.

QuickLogic Corporation 2933 Bunker Hill Lane Santa Clara, CA 95054 Tel: 408-987-2000 Fax: 408-987-2012

## USERS AGREE THAT QUICKLOGIC DELIVERS THE FASTEST FPGAs

"The entire industry has been waiting for an FPGA that delivers the speed QuickLogic claims. Plenty of start-ups have claimed to be fast, routable and predictable - and each one has disappointed me. But not this time. We've installed the QL8x12 in a real system, replacing several 7ns and 10ns PALs. The part works just as you would expect from the data sheet."

> Jack Regula Hardware Engineering Manager Force Computers Inc.

"There is little doubt that this is the fastest FPGA on the market. You don't need to invest lots of training hours to get great functionality and amazing speed - and you get this without having to waste valuable design time on tedious manual intervention."

> Michael Dini Design Consultant San Diego

"These people designed their tools as though they had to use them themselves....even the first time user has some fluency in navigating around the system. After some initial performance checking, I can see that the FPGAs will actually deliver the performance the company claims for itself."

> George Morrow VP Engineering Intelligent Access Corp.

"I have found the tools to be powerful, easy to use and efficient to design with. I have also found QuickLogic's pASIC architecture to readily accommodate a wide variety of designs with surprising performance characteristics."

> Roger C. Alford Author Programmable Logic Designer's Guide

"I did the entire design for four QuickLogic parts over a single weekend. We have other EPLD and FPGA tools in-house... the speed criteria eliminated most of the choices. QuickLogic is a great solution for people needing high speed and low power."

> Stewart J. Dunn VP Research and Development Datacube Inc.

"Even without programming logic into the other FPGAs, getting on and off the daughter cards took 45 - 50 ns. With QuickLogic, the I/O delay fell to 9 ns, and we could preserve all the performance of the (previous) design."

> John Thomas Director of Sales and Marketing Universal Computing

"QuickLogic offers a great way to implement very fast state machines in an easy-to-use part."

Brian Fenstermacher Design Engineer Performance Controls

# THIRD-PARTIES AGREE THAT QUICKLOGIC DELIVERS THE FASTEST FPGAs

| Device Performa  | nce Evaluati | ion      |        |

|------------------|--------------|----------|--------|

|                  |              |          |        |

| UART Design      |              |          |        |

| Architecture     | Area         | Speed    | Device |

| Actel Act2       | 160 logic    | 90 ns    | 1225   |

| QuickLogic pASIC | 122 "gates"  | 29 ns    | QL8x12 |

| Xilinx 4000      | 93 CLBs      | 6 levels | 4005   |

This data was presented by Exemplar Logic Inc. of Berkeley, CA for the 1992 PLD conference and shows that the QuickLogic QL8x12 is **3x** the speed of Actel's fastest ACT2 device. Xilinx will also be slow, but must be fully routed to generate precise results.

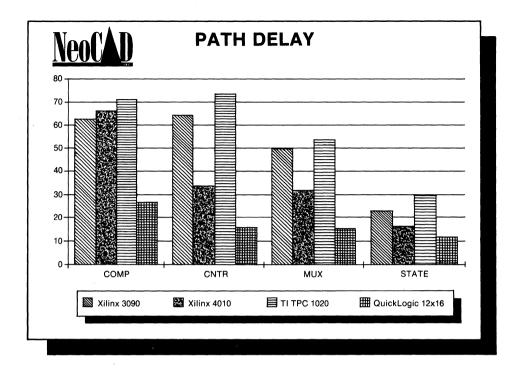

NeoCAD, Inc of Boulder, CO offers a generic FPGA place and route tool that supports QuickLogic, Actel, and Xilinx. NeoCAD showed the results of using their tool on 4 simple logic functions; comparator, counter, multiplexer, and state machine. The data was presented at the 1992 ASIC and EDA sponsored IDEA conference.

The QuickLogic QL8x12 - 1000 usable gate Very-High-Speed FPGA features 96 logic cells in an 8 by 12 matrix. It is equivalent in capacity to many so called 3000 gate EPLD and LCA<sup>™</sup> devices.

The QuickLogic QL12x16 - 2000 usable gate Very-High-Speed FPGA delivers "real-world" Operating Performance above 100 MHz.

## Very-High-Speed FPGAs Through Technology, Architecture, and Tools

QuickLogic Corporation provides very-high-speed programmable ASIC solutions for designers of high-performance systems who must get their products to market quickly.

The company was founded by the engineers who invented the PAL device and PALASM software. By offering the ability to create high-speed custom logic circuits with standard off-the-shelf products, their invention revolutionized the world of logic design. First-generation FPGAs extended these benefits to higher levels of density, but at much lower speeds. QuickLogic was formed to create a single solution combining the fast speed of PAL devices with the high density, low power and logic flexibility of FPGAs.

QuickLogic pASIC 1 Family FPGAs operate at two to three times the usable system speed of first-generation devices.

To achieve these goals, QuickLogic has created a CMOS antifuse technology, called the ViaLink<sup>TM</sup> element, which couples small size with high speed. It results in FPGAs operating two to three times faster than other technologies using the same process lithography. The small size also provides a technology migration path to 50,000 gates and beyond.

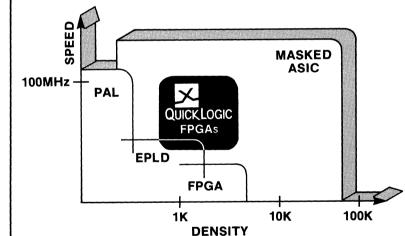

FIGURE 1 Comparative Speed/Density Chart

...FPGAs operating two to three times faster

...can be used in applications with 33, 40 and 50 MHz microprocessors The first product line from QuickLogic, the pASIC  $1^{TM}$  Family of Very-High-Speed CMOS FPGAs, delivers new levels of speed and density in an easy-to-use product. High-density programmable devices can now be used in data path applications with 33, 40 and 50 MHz microprocessors. And in designs with useful internal logic functions operating at over 100 MHz.

QuickLogic engineers achieve industry-leading performance by addressing the design task through the three aspects of Technology, Architecture, and Tools. In each area they combine a variety of techniques to yield the optimum solution.

#### Speed Through Technology

- ViaLink direct metal-to-metal antifuse

- Speed-critical links less than 50 ohms

- Standard high-speed CMOS logic process

These features yield both the smallest physical programming element size and fastest interconnect speed of all programmable technologies.

#### **Speed Through Architecture**

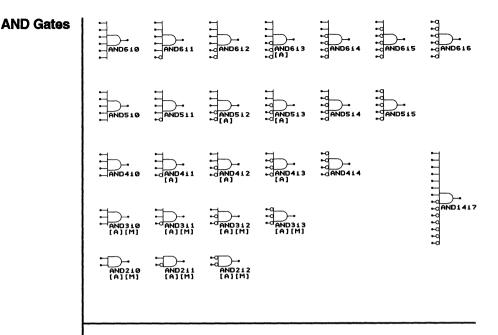

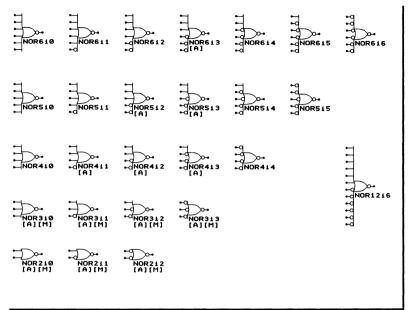

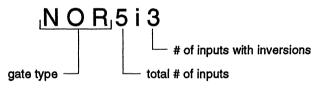

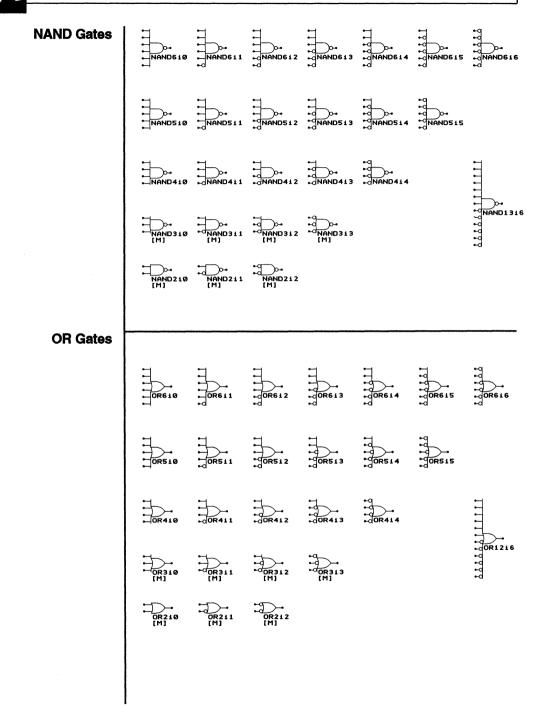

- Up to 14-input wide gates

- Highly tuned, dedicated register in every logic cell

- Regular and orthogonal interconnect wiring resources

These features provide an architecture optimized for a wide range of highspeed control, data path and general-purpose logic integration applications.

#### **Speed Through Tools**

- Architecture-optimized place and route tools

- Precise timing simulation using actual wire lengths, fanout, and loading

- · Rapid design iterations permit design optimization

Users achieve high speed and fast design implementation through 100% automatic place and route tools even on functions using up to 100% of the available logic cells.

...100% automatic place and route

At the heart of every programmable device is an electronic switch for user configuration of specific logic functions. It may be an active device, such as an EPROM cell or an SRAM bit. Or a passive fuse or antifuse element. Two basic electrical characteristics limit the maximum useful operating speed which can be achieved with each approach.

- The capacitance, C, of the programmable element in the OFF (OPEN) state. This determines the capacitive loading effect of unprogrammed elements on metal interconnect wires.

- The resistance, R, of the programmable element in the ON (CLOSED) state. This determines the series resistance of the programmed element when interconnecting wires and logic functions.

The technology with the lowest values of R and C delivers the fastest raw speed to the circuit designer.

Early CMOS programmable ASIC devices using EPROM and SRAM programming elements typically have high resistance values, above 1000 ohms, plus large physical size. Dielectric antifuses improve on both these factors but still cannot yield the performance demanded by today's systems.

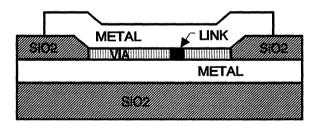

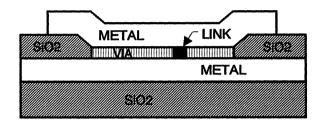

QuickLogic created the ViaLink antifuse to provide a low-resistance, lowcapacitance programmable connection directly from one metal layer to another. The ViaLink element is formed by depositing a very high resistance layer of programmable silicon into a via between the two metal layers of a standard high-volume CMOS gate array process.

The ViaLink element provides a direct metal-to-metal connection.

#### ViaLink Antifuses

FIGURE 2 ViaLink Cross Section

SPEED THROUGH TECHNOLOGY

Selected vias are addressed with a programming voltage. This creates a direct metal-to-metal link by permanently converting the silicon to a low resistance state. Typical resistance is less than 50 ohms.

In one micron process, the size of a ViaLink via is approximately one micron square; or orders of magnitude smaller than active elements. This, coupled with the high dielectric constant of the via material, ensures that unprogrammed ViaLink devices exhibit low capacitive loading (less than 1fF). As the size of the programmed link is physically much smaller than the via, the technology can potentially be scaled below 0.5 microns for future very-high-density applications.

A ViaLink antifuse is located at the intersection of every horizontal and vertical wire. Array density is limited by the process lithography, not by the programmable element size.

#### EPLD AND FPGA TECHNOLOGY COMPARISONS

| Programmable Element      | SRAM       | E/EEPROM  | Dielectric<br>Antifuse | ViaLink<br>Antifuse |

|---------------------------|------------|-----------|------------------------|---------------------|

| Typical ON Resistance R   | ~1000 ohm  | ~1000 ohm | ~500 ohm               | ~50 ohm             |

| Typical OFF Capacitance C | ~50 fF     | ~15 fF    | ~5 fF                  | ~1 fF               |

| Physical Size             | Very Large | Large     | Medium                 | Small               |

FIGURE 3 Photomicrograph of an Array of ViaLink Elements

The ViaLink element delivers the lowest ON resistance, lowest OFF capacitance and smallest physical size of any programmable technology. These characteristics open up a new spectrum of high-speed, high-density applications to programmable devices.

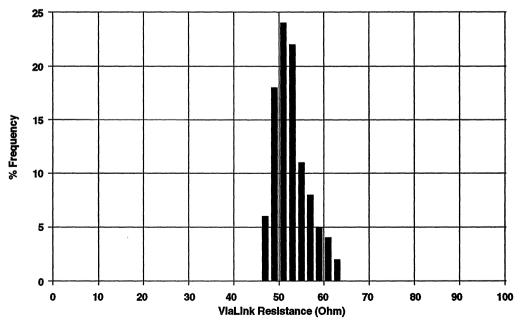

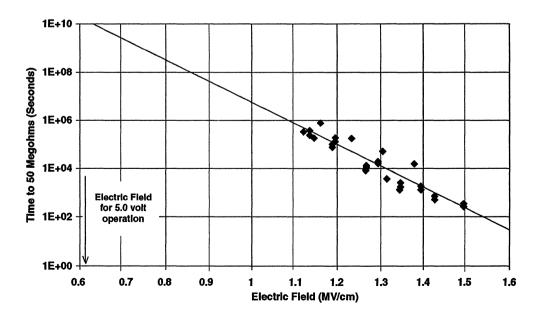

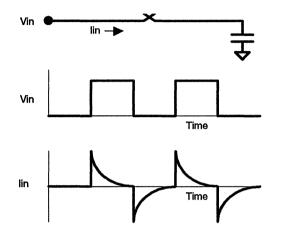

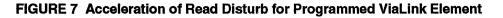

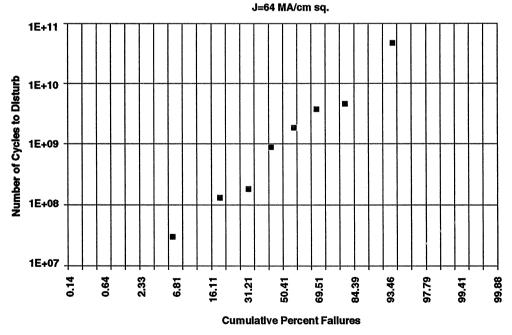

ViaLink elements have been subjected to accelerated stress testing in both programmed and unprogrammed states. Test results indicate that the ViaLink element has no measurable impact on the reliability of the underlying CMOS process. Product reliability levels in the system environment compare favorably with gate arrays and other FPGAs.

A simple interconnect architecture, a performance-oriented logic cell, and optimized I/O circuitry maximize the fundamental speed advantage of the ViaLink technology.

Early FPGAs employ a variety of wiring types to limit the number of highresistance connections in a net. For example, signals can be routed through a variety of short lines, long lines, switch boxes and other structures. These irregular routing resources cause unpredictable delay behavior and limit logic utilization.

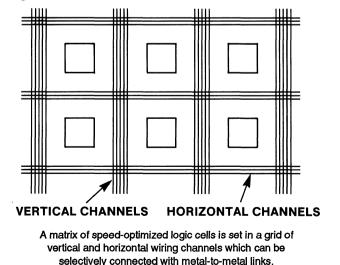

The low impedance of the ViaLink antifuse allows a regular and orthogonal architecture. The pASIC structure features a matrix of logic cells interconnected by vertical and horizontal routing channels. A ViaLink element located at every wire intersection allows direct, metal-to-metal links between signal lines.

#### **ViaLink Reliability**

#### SPEED THROUGH ARCHITECTURE

Fast, Yet Regular Routing

#### FIGURE 4 pASIC Architecture

According to users (*Computer Design*, 12/91, pg. 78), QuickLogic FPGAs are the closest to masked gate arrays both in predictability and in absolute levels of performance.

- Delays are "predictable no matter what the layout is."

- "Wire delays are shorter than logic delays."

- As net lengths increase, delays increase proportionally.

- Small design changes result only in small changes in speed.

All these characteristics allow rapid iteration towards the fastest possible solution.

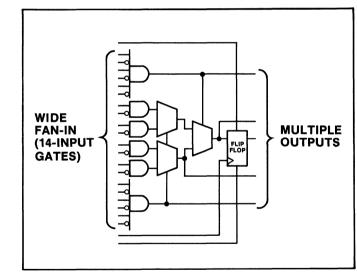

d The pASIC logic cell is optimized for high-speed applications. Gates up to 14 inputs wide, multiplexers, decoders and sum-of-products functions can be implemented in a single cell delay with worst case nominal t<sub>PD</sub> of under 4 ns. Many logic functions therefore incur just half the propagation delay of traditional, narrow fan-in, FPGA logic cell structures.

The wide fan-in and multiple outputs of the pASIC logic cell permit high-speed logic functions and efficient use of resources.

High-Speed Logic Cell

> FIGURE 5 pASIC Logic Cell

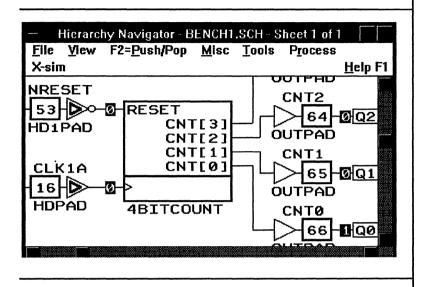

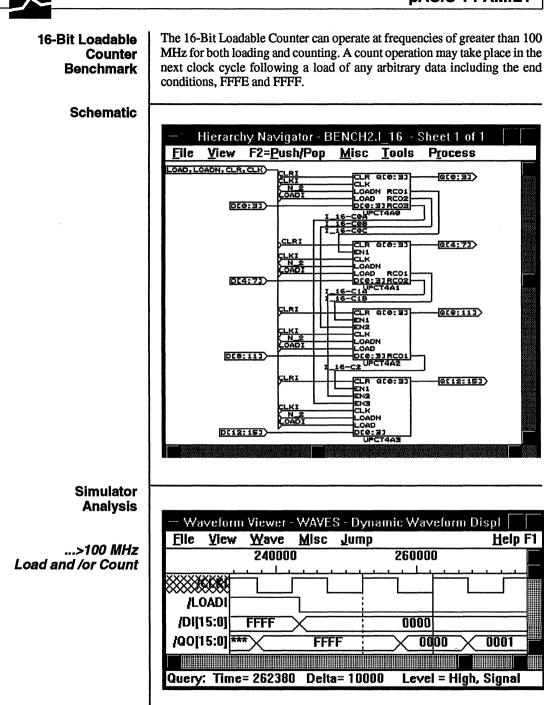

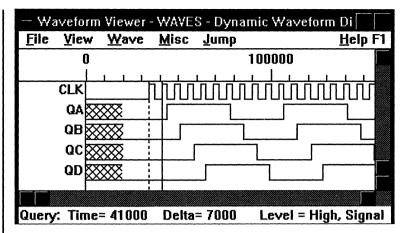

...16-bit loadable counters operate at over 100 MHz

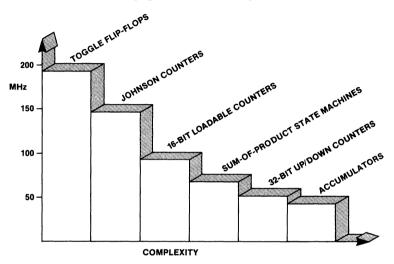

Each cell includes a dedicated, highly-tuned register element. Flip-flop toggle rates are close to 200 MHz; simple Johnson counters run at 150 MHz. 16-bit loadable counters, capable of doing useful work, require one logic cell delay and operate at over 100 MHz.

Fast sum-of-product state machines require just two cell delays. Complex arithmetic functions using up to four levels of logic run faster than 40 MHz.

FIGURE 6 Real World Operating Speeds of 50 to 75 MHz

Typical examples of speed versus logic function complexity.

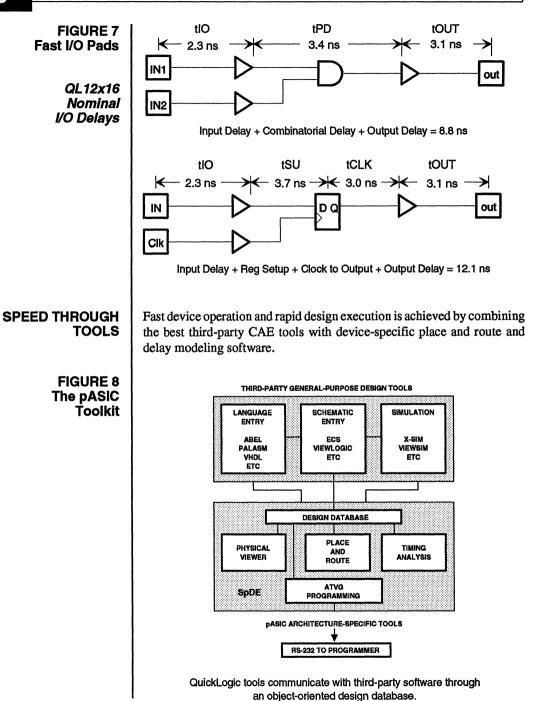

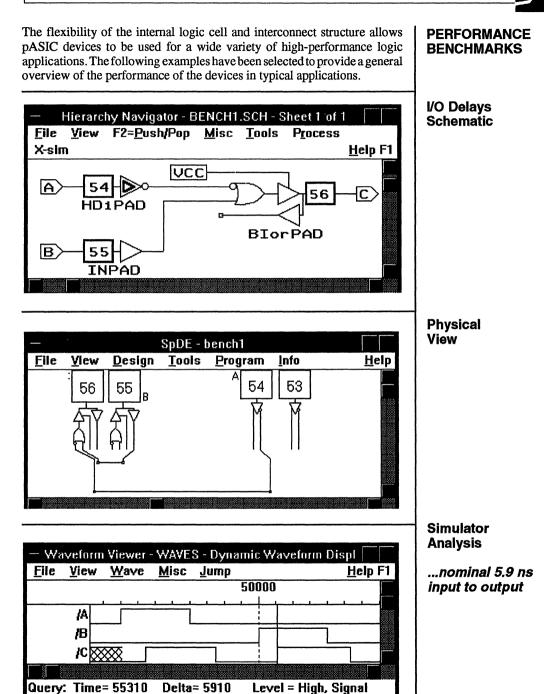

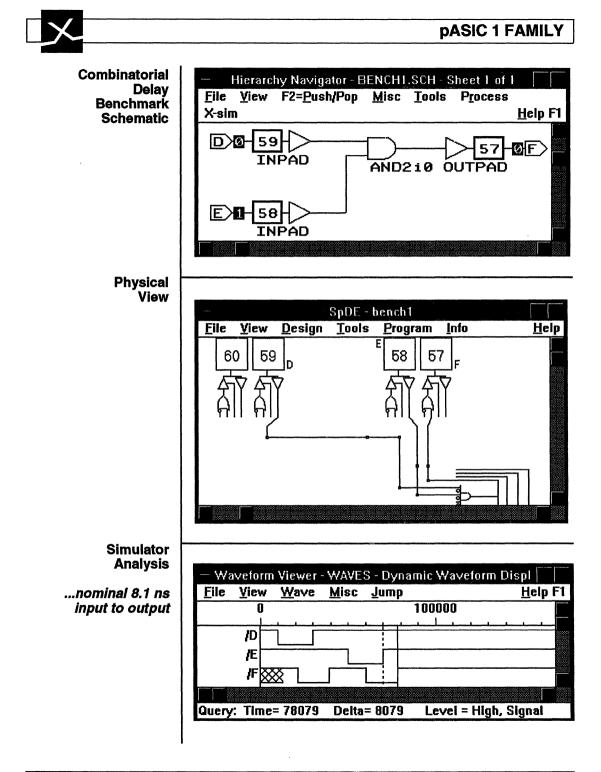

These impressive on-chip specs are matched by fast I/O performance. Worst case nominal input pad to output pad delay through a 14-input AND gate, or a 4-input MUX, for example, is less than 10 ns.

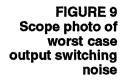

Fast I/O circuits allow logic functions in separate packages to operate together at over 60 MHz. This speed is achieved while preserving low output switching noise levels. Switching of up to 48 outputs simultaneously has been demonstrated with less than 1 volt of ground bounce.

Fast I/O

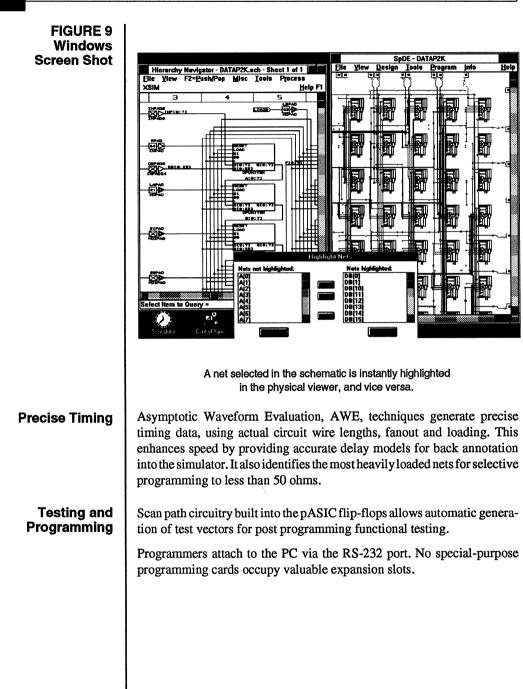

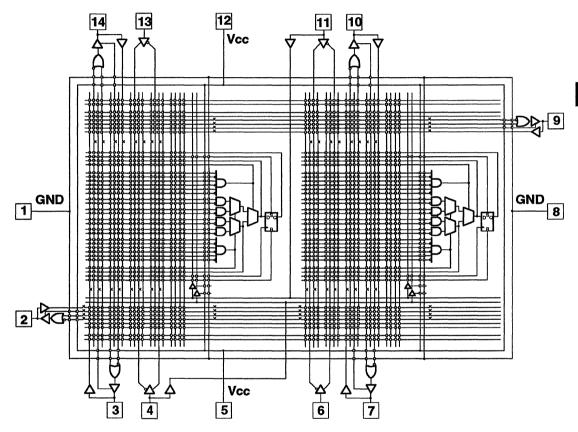

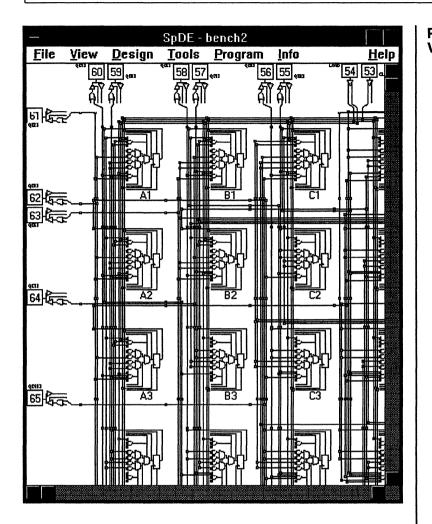

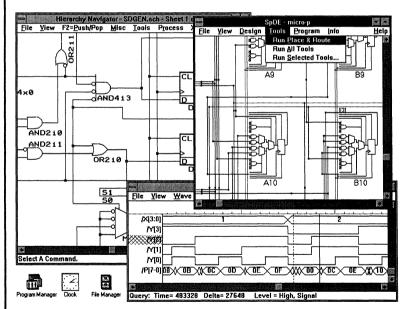

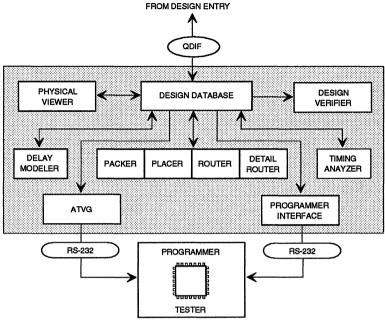

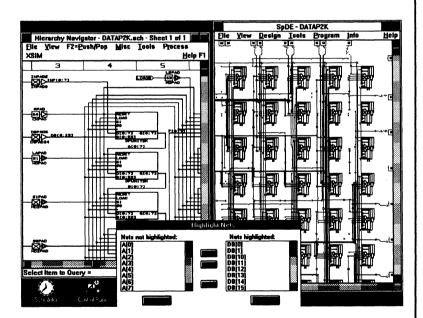

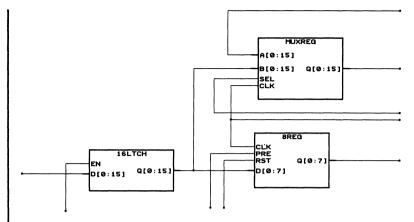

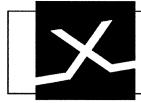

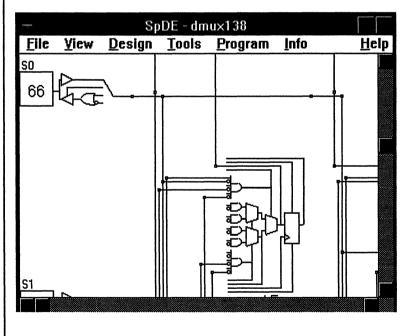

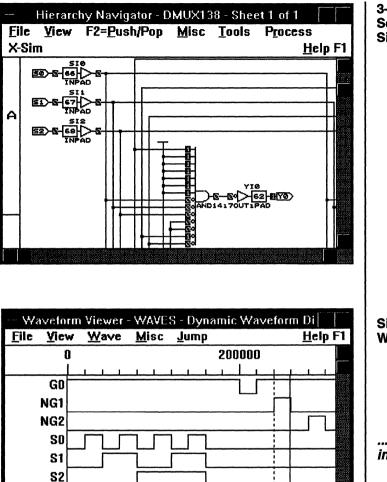

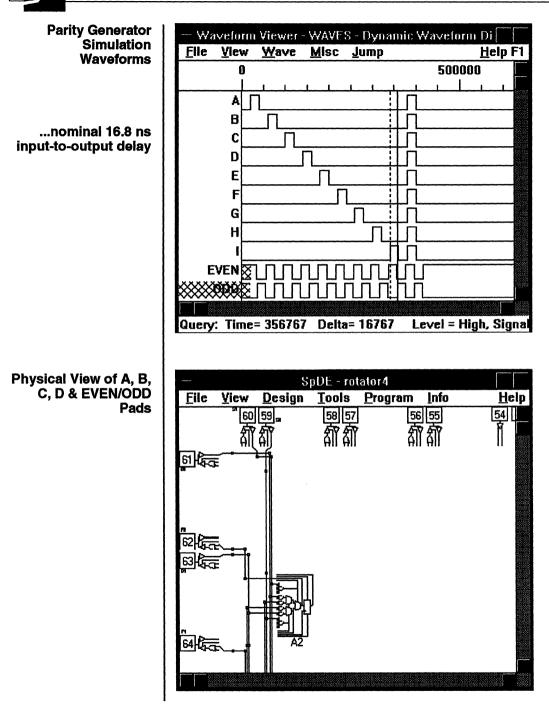

Designs are created using general-purpose schematic, language entry and simulation packages on PC and Sun workstation platforms. These tools interface to the QuickLogic Seamless pASIC Design Environment (SpDE — pronounced "Speedy") for place and route, delay modeling, and other tasks best served by architecture specific code.

VHDL, state machine, and Boolean (ABEL, CUPL, MINC, PALASM, etc.) language entry is available through Exemplar and other logic synthesis packages.

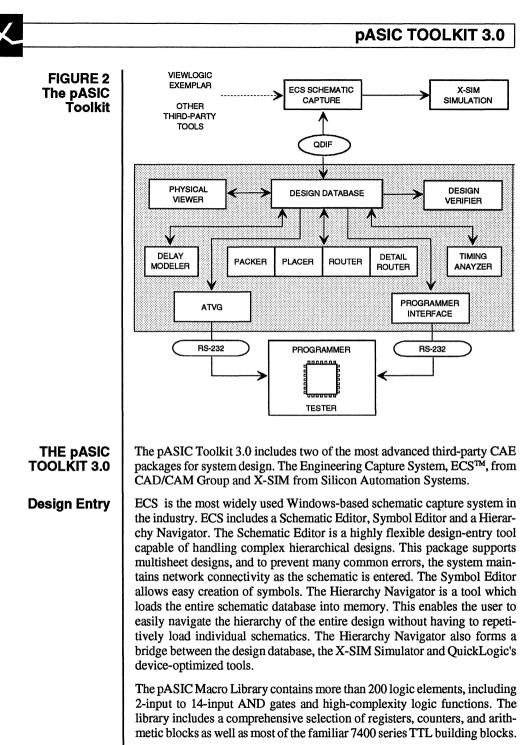

A low-cost, fully integrated design solution, operating under Microsoft Windows on the PC, is available as the pASIC Toolkit 3.0. This includes ECS schematic capture from the CAD/CAM Group, and X-SIM simulation from SAS, plus SpDE software and device programming hardware.

The regular gate array-like architecture, combined with ample wiring resources, enables 100% automatic placement and routing with high utilization. QL8x12 users report completing designs using 100% of the 96 logic cells, even with a large number of fixed pin locations.

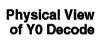

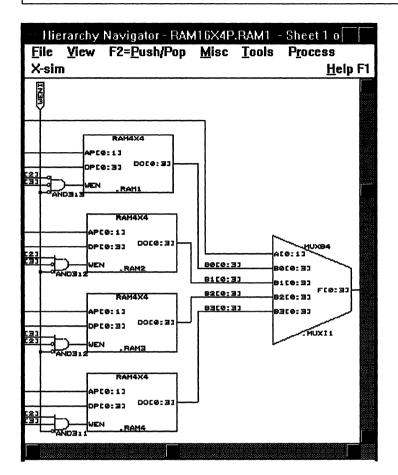

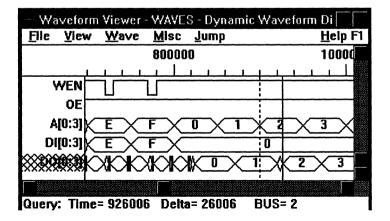

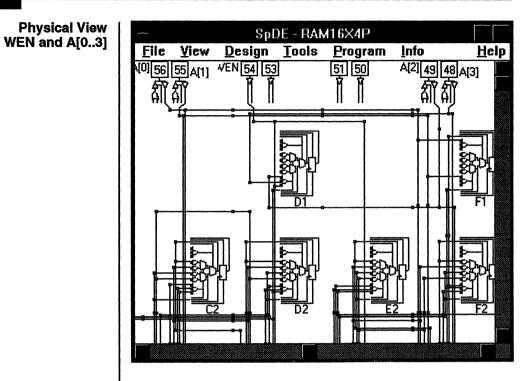

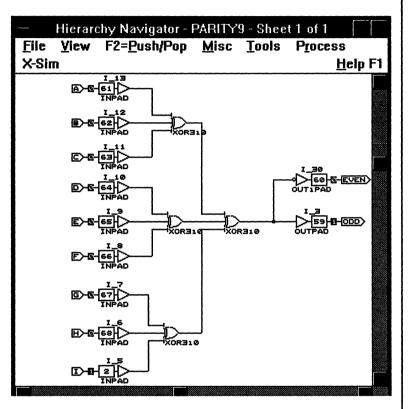

A physical viewer shows how the automatic tools fit logic functions into the silicon resources.

Cross probing between applications allows for easy analysis of designs and fast debugging of problems. Click on a net in the schematic and it is instantly highlighted in the physical layout. Or vice versa. Similar interactive links exist to the simulator.

#### Third-Party Design Entry

Optimized Place and Route

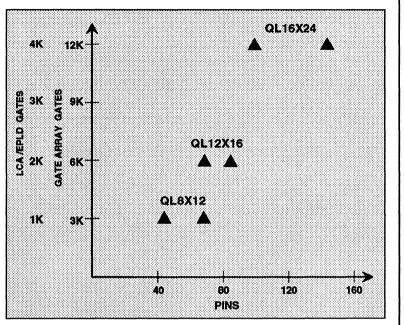

The pASIC 1 Family serves general-purpose, high-speed logic integration tasks in arithmetic, control, data path and RISC and CISC microprocessor support applications. Three basic devices cover a broad range of speed, package, density, and I/O options.

The pASIC 1 family includes density and I/O options meeting the needs of most high-speed, high-density programmable device applications.

Device part numbers describe the organization of logic cells. For example, the QL8x12 features 96 logic cells in an eight by twelve matrix. A fully utilized QL8x12 accommodates 800 to 1200 gates, for an average of ten gates per cell. QuickLogic describes this as a 1000 usable-gate FPGA. It is equivalent in capacity to many, so called "3000 to 4000 gate" EPLD and LCA devices.

**Family Features**

**VERY-HIGH-SPEED FPGAs**

FIGURE 10 The pASIC 1 Product Family Family Features As each logic cell contains a dedicated register function plus combinatorial logic sufficient to create two latches, the QL8x12 can contain up to 288 storage elements.

|                       | Part<br>Number                                              | Logic<br>Cells                        | Storage<br>Elements                     | Max I/O<br>Cells                      | Dedicated<br>Inputs                      | Package<br>Pins                    | Usable<br>Gates     | EPLD/LCA<br>Gates                                   |

|-----------------------|-------------------------------------------------------------|---------------------------------------|-----------------------------------------|---------------------------------------|------------------------------------------|------------------------------------|---------------------|-----------------------------------------------------|

|                       | QL8x12                                                      | 96                                    | 288                                     | 56                                    | 8                                        | 44, 68                             | 1000                | 3000                                                |

|                       | QL12x16                                                     | 192                                   | 576                                     | 68                                    | 8                                        | 68, 84                             | 2000                | 6000                                                |

|                       | QL16x24                                                     | 384                                   | 1152                                    | 104                                   | 8                                        | 100, 144                           | 4000                | 12000                                               |

| Product Features      | <ul><li>selections</li><li>Input</li><li>Multiput</li></ul> | s on each<br>buffer plu<br>ple-chip ( | device all<br>us logic co<br>operating  | low the u<br>ell plus or<br>frequenci | ser to trad<br>utput buff<br>les over 60 | le-off per<br>er delay (<br>) MHz. | formanc<br>of under | iple speed<br>e and cost.<br>10 ns.                 |

|                       | <ul> <li>Logic</li> </ul>                                   | function                              | delays, u                               | p to two I                            | evels dee                                | p, in unde                         | er 4 ns.            |                                                     |

|                       | • Usefu                                                     | l counter                             | speeds up                               | p to 100 N                            | MHz.                                     |                                    |                     |                                                     |

|                       |                                                             |                                       | itching no<br>ing simult                |                                       |                                          | lt of grou                         | ind bour            | nce with 48                                         |

|                       | • Worst                                                     | case clo                              | ck skew l                               | ess than 1                            | l ns.                                    |                                    |                     |                                                     |

|                       | • Input ments                                               |                                       | is provide                              | s high re                             | eliability :                             | in noisy                           | operatin            | g environ-                                          |

|                       | • Low (                                                     | CMOS po                               | ower cons                               | umption;                              | typically                                | 2 mA sta                           | ndby cu             | rrent.                                              |

| Future pASIC Families | offer FPC<br>masked g                                       | GA familing ate array<br>and ease     | ies with d<br>ys. ViaLin<br>e of use of | ensities ank techno                   | and I/O co<br>ology will                 | ounts con<br>also be               | nparable<br>used to | element to<br>to today's<br>extend the<br>grammable |

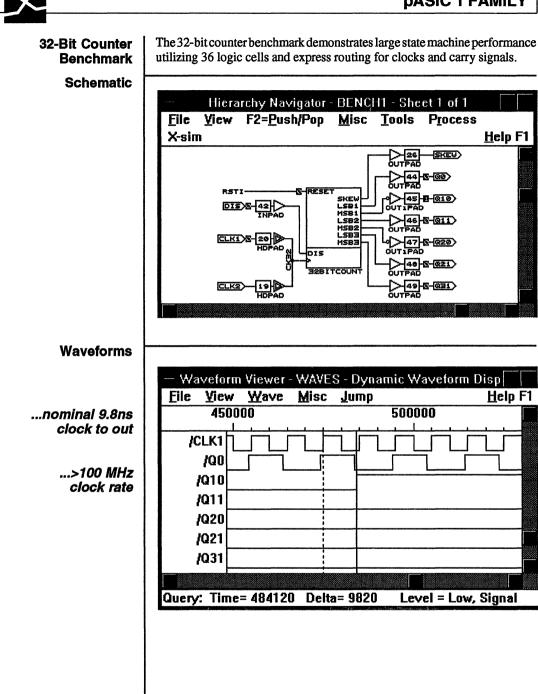

## pASIC 1 FAMILY System Application Case Studies

QuickLogic very-high-speed FPGAs are allowing users to extend the benefits of programmable solutions to new applications which could not be served before due to speed, density, power dissipation or time-to-market limitations of earlier products. The following five case studies demonstrate a variety of applications where pASIC<sup>TM</sup> 1 Family FPGAs offered significant advantages over alternative TTL, FPGA, PAL/GAL and gate array implementations.

#### Universal Computing San Diego, CA

Design Problem

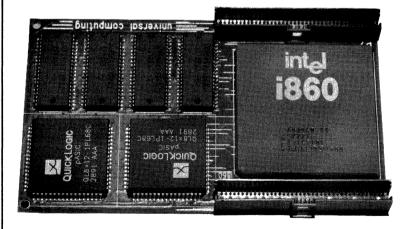

QuickLogic FPGAs help systems company to beat the competition to market with 40-MHz Intel i860-based small form factor multiprocessor system

Universal Computing designs and manufactures high-performance systems for a wide range of vertical market customers. One of Universal's designs is a multiprocessing VME board for signal processing applications in defense, medical imaging, seismology, image processing, molecular modeling and 3-D visualization. In addition to a motherboard supporting a VME bus and high-speed external interface, the system provides four "supercards," each containing a 40-MHz i860 XR microprocessor, up to 4 MB of high-speed DRAM, and high-speed interprocessor communications logic.

FIGURE 1 The MPi860 offers up to 320 MFLOPS of floating point performance in a single 6U VME slot

| to meet VME power<br>specifications, PALs<br>or EPLDs were out<br>of the question. | According to sales and marketing director John Thomas, several other companies offered similar products in the large 9-U VME form factor. However, the 9-U standard is considered by some potential customers to be unwieldy. The large form factor can create vibration problems, has loose power standards, and often suffers from inadequate cooling. While the 9-U product is a low-volume opportunity by nature, more compact 6-U products are far more popular and available. Thomas wanted Universal to become the first company on the market to offer such a powerful multiprocessing system in the 6-U form factor. The major challenge for Universal was redesigning each of the four supercards to create four highly compact daughtercards. In addition, while 9-U systems may use as much as 175W, Universal's 6-U system would need to draw less than 45W to meet VME power specifications. As a result, high-speed PALs or EPLDs were out of the question. A masked gate array could have been used, but the time needed to design and manufacture the part would shorten the period during which Universal would be the sole supplier of 6-U boards. |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design Solution                                                                    | Universal recognized FPGAs as the solution. The company had used FPGAs from other vendors in several previous designs and considered them for the new design, along with the new pASIC FPGAs from QuickLogic. According to Thomas, "Even without programming logic into the other FPGAs, getting on and off the daughtercards took 45-50 ns. The only way to make the design work would be to drop the performance of the system from 40 MHz to as low as 25 MHz. With QuickLogic, the I/O delay fell to 9 ns, and we could preserve all of the high performance of the 9-U design."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Design Process                                                                     | Universal used two QL8x12 FPGAs to provide the high-speed memory and<br>bus interface logic required by each of the 40-MHz i860 XR microprocessors.<br>Using the pASIC Toolkit development system, Universal's designers were<br>able to create their logic quickly using high-level schematics. The design<br>tools automatically routed the schematics into optimized gate-level designs<br>that made efficient use of the FPGA logic cells and preserved the high<br>performance needed. By cross probing between the schematic entry, timing<br>simulator and physical viewer, the designers were able to easily debug and<br>optimize the design to support the full potential of the i860 processors and the<br>high-speed memories.                                                                                                                                                                                                                                                                                                                                                                                                                            |

## **pASIC 1 FAMILY SYSTEM APPLICATION CASE STUDIES**

#### QuickLogic FPGA replaces Xilinx device on 88000-based VME board to boost system speed from 20 MHz to 33 MHz

Force Computers manufactures high-performance VME boards for its OEM customers worldwide. Engineering manager Jack Regula was responsible for the design of a VME board based on a 33 MHz version of the Motorola 88000 RISC microprocessor. Regula had chosen to implement the design with the help of programmable logic, selecting an LCA device from Xilinx. When the system design was complete, Regula realized that the system would not function properly beyond 20 MHz. A critical path in the design was a DRAM controller for the 88000 CPU, and although specified to run at high speeds, the SRAM-based FPGA proved too slow in the system. Regula sought a replacement solution that could provide the same pin functionality along with a 65 percent increase in speed.

Regula knew that QuickLogic's new pASIC FPGAs were designed to support high-speed RISC and CISC processors, but by this time, he was skeptical about vendor performance claims. "Each one of the FPGAs I've used has disappointed me," he stated. At the time, however, Force was a beta site for QuickLogic's pASIC Toolkit FPGA development system. Because the 68pin QL8x12 provided virtually identical pin functionality, Regula decided to find out whether QuickLogic could be used to boost the board's speed to 33 MHz with a minimal redesign effort.

Within days, Regula was able to reenter all of the design schematics into the easy-to-use QuickLogic environment. He programmed the QL8x12 to be virtually pin-compatible with the LCA device and easily achieved his 33 MHz speed objective. Regula decided that getting high performance from a Xilinx device requires more than just a synchronous design. "You have to tweak the design to fit the layout and to fit the board. How far apart the CLBs (configurable logic blocks) are affects the propagation delays between them. You don't know what the delay is 'til you route them."<sup>[1]</sup>

Regula found that QuickLogic delays are always larger than interconnect delays. "They're predictable, no matter what the layout is, very much like a masked gate array." According to Regula, "The entire industry has been waiting for an FPGA that delivers the speed needed to support high-performance designs. Plenty of start-ups have claimed to be fast, routable and predictable, but QuickLogic FPGAs are the first to actually work as you would expect from the data sheet."

<sup>[1]</sup> Source: *Computer Design*, December 1991

Design Problem

**Design Solution**

#### Design Process

"QuickLogic FPGAs are the first to work as you would expect from the data sheet."

| Datacube, Inc.<br>Dearborn, MA                                                                                                                   | QuickLogic FPGAs allow developer of powerful real-<br>time video processing systems to complete custom logic<br>design in one weekend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design Problem                                                                                                                                   | Datacube, Inc. develops extremely powerful computers designed to manipu-<br>late complex video data in real time. One Datacube product called the<br>MaxVideo 20 provides 3,500 MIPS for compute-intensive video processing<br>applications such as real-time correction of the geometric image distortion<br>caused by a wide-angle lens. Datacube is a sophisticated user of all kinds of<br>programmable logic, using 80 FPGAs and EPLDs in the MaxVideo 20<br>product to help integrate the functionality of 14 standard image processing<br>boards onto one double-VME board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                  | R&D vice president J. Dunn was responsible for developing a new system for real-time pipeline processing of video data. A custom logic design was needed for data formatting and routing, and a critical path existed where 12 memory modules output 96 video data signals at 40 MHz. Here, custom logic was needed to format the data as 192 signals at 20 MHz and then route the data to other system components according to various board and operating mode specifications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <b>Design Solution</b><br>"We have the Xilinx<br>and Actel tools<br>in-house, but I didn't<br>believe I could<br>make either go fast<br>enough." | A masked gate array would solve Dunn's custom logic requirements, but<br>time-to-market was a consideration, and the one masked gate array used on<br>the MaxVideo 20 product proved to be the longest-lead component in the<br>system. Dunn decided instead to evaluate all of the programmable logic<br>alternatives in packages ranging from 28 pins to 160 pins, looking for the right<br>high-speed partition for his 24-bit data path. Fast PALs or EPLDs might meet<br>the 40 MHz data rates, but according to Dunn, "EPLDs use substantial power<br>in the process — from 150 mA on up." FPGAs posed the ideal solution, but<br>in Dunn's experience, "The speed criteria eliminated most of the choices. We<br>have the Xilinx tools and the Actel tools in-house, but I didn't believe that I<br>could make either of the architectures go fast enough." Dunn instead chose<br>the 1,000-usable-gate QL8x12 from QuickLogic because the device easily<br>met the 40 MHz data rate and low power requirements. "The 68-pin package<br>was just right," Dunn added. |

| Design Process                                                                                                                                   | Dunn designed his logic on the pASIC Toolkit, which is designed to be easy<br>to learn and use, even for first-time customers. According to Dunn, "I did the<br>entire logic design for four QuickLogic parts over a single weekend." Added<br>Dunn, "QuickLogic is a great solution for people needing high speed and low<br>power. I hear other vendors trying to build excitement for their next-<br>generation products. QuickLogic is already there with devices that I can use<br>today."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

## **pASIC 1 FAMILY SYSTEM APPLICATION CASE STUDIES**

1

| QuickLogic FPGAs boost speed of servo control system to<br>40 MHz while integrating 25 TTL devices into a single<br>component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Performance Controls<br>Horsham, PA                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Performance Controls is a manufacturer of high-performance motion control systems. Digital design engineer Brian Fenstermacher was assigned to create a higher-speed implementation of an existing servo control system. The prior system logic implementation used about 25 TTL logic components, including LS-TTL, AS-TTL and F-TTL parts. Board space was an issue in the previous design and would be a problem in the redesign as well. More importantly, Fenstermacher predicted that the speed requirements of the redesign exceeded the capabilities of discrete logic parts. A new approach was inevitable.                                                                                                                                                                                                                                                                                                                                                                             | Design Problem                                                                |

| Fenstermacher decided to try to integrate the functionality of the TTL devices into a single, high-speed FPGA. He considered all of the available FPGA solutions, looking for the one that could best meet the high-speed logic requirements of the new product specification. Fenstermacher decided to use the first member of QuickLogic's pASIC 1 family of FPGAs, the 1,000-usable-gate QL8x12.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Design Solution                                                               |

| According to Fenstermacher, QuickLogic's Microsoft Windows-based pASIC<br>Toolkit was easy to learn and more intuitive than competing FPGA develop-<br>ment systems. He mastered the design tools in days, using schematic capture<br>for design entry. Fenstermacher took advantage of cross probing between the<br>schematic capture, simulation and physical viewer tools to quickly optimize<br>and debug the design. The simulator provided precise results, and the<br>programmed QL8x12 performed exactly as predicted. Within two weeks of<br>receiving the QuickLogic tools, the pASIC FPGAs were programmed and<br>ready for system installation. Fenstermacher was successful at integrating the<br>functionality of two dozen MSI and LSI parts into the QL8x12 while<br>comfortably meeting the 40 MHz speed requirements of the redesign.<br>According to Fenstermacher, "QuickLogic offers a great way to implement<br>very fast, complex state machines in an easy-to-use part." | Design Process<br>the programmed<br>QL8x12 performed<br>exactly as predicted. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                               |

## PASIC 1 FAMILY SYSTEM APPLICATION CASE STUDIES

| VLSI Technology<br>San Jose, CA                        | QuickLogic FPGAs enable 50-MHz memory controller<br>for RISC processor evaluation board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design Problem                                         | VLSI Technology is a manufacturer of CMOS ASICs and ASSPs as well as<br>the ARM family of RISC processors. When a new family of ARM6 proces-<br>sors was introduced last autumn, design engineer Art Sobel became respon-<br>sible for designing an evaluation board that would allow engineers to adapt<br>hardware and software to the new processors. Two functions were needed to<br>complete a minimal system design. One function was a memory controller<br>capable of driving DRAM, EPROM and I/O functions, and 50-MHz operat-<br>ing frequency was mandatory. The second function was a simple interrupt<br>controller.                                                                                                                                       |

|                                                        | The logic requirements of each element could be met with high-speed PALs,<br>but with much greater part count and some loss of flexibility. Moreover, a<br>masked gate array solution was not appropriate because of the long lead time,<br>and the possibility of design changes on the product.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Design Solution                                        | In response to these requirements, Sobel decided to use the QuickLogic QL8x12 for both logic functions. For memory control, the QL8x12 had the capability of operating with the 50-MHz clock needed to craft the DRAM waveforms while providing a high enough drive capability to drive the DRAM address pins and the ARM600 clock pins. The QL8x12 was also very well suited to the design requirements of the interrupt controller. In addition, the solution greatly reduced the number of parts that Sobel needed to procure. Both designs used all 56 I/O pins and several of the input-only pins on the QL8x12 and utilized about 60 percent of the available logic cells. In both designs, all of the I/O pins were preassigned to simplify the PC board design. |

| Design Process                                         | Sobel designed his logic using schematic capture, taking advantage of QuickLogic's macro library of more than 200 commonly used logic elements. The simulator was used to provide functional verification of the design even before the first pASIC device was programmed. Timing analysis ensured that the QL8x12 devices would meet the speed requirements of the RISC processor's                                                                                                                                                                                                                                                                                                                                                                                    |

| well on the board<br>at the 50 MHz<br>clock frequency. | me or interface, and both parts worked well on the board at the 50 MHz clock frequency. The memory controller function FPGA was revised once to correct for an unexpected logic signal and was fully functional once a second part was programmed. The interrupt controller FPGA was fully functional on the first attempt. According to Sobel, "Igot completely over the learning curve in just a couple of weeks. After designing only two chips, I would feel comfortable taking on any design challenge with QuickLogic."                                                                                                                                                                                                                                           |

## **PASIC 1 FAMILY SYSTEM APPLICATION CASE STUDIES**

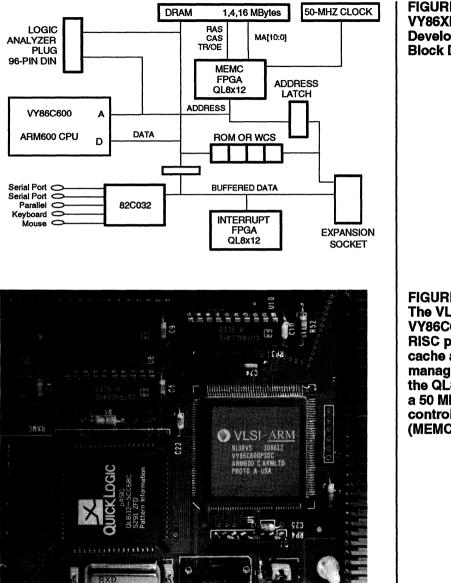

FIGURE 2 VY86XPID Development Board Block Diagram

FIGURE 3 The VLSI Technology VY86C600 - ARM60D RISC processor with cache and memory management plus the QL8x12 used as a 50 MHz memory controller (MEMC PGA)

## pASIC 1 FAMILY ViaLink Technology Very-High-Speed CMOS FPGAs

| FAMILY<br>HIGHLIGHTS          | X             | ant  | tifuse te                      | <b>h</b> Speed – ViaLink <sup><math>TM</math></sup> metal-to-metal, programmable-via chnology ensures useful internal logic function speeds over and logic cell delays of under 4 ns. |

|-------------------------------|---------------|------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                               | X             | 12   |                                | <b>ble Density</b> – Up to 4,000 "gate array" gates, equivalent to PLD or LCA Gates. Technology migration path to 20,000 above.                                                       |

| migration path                | X             |      |                                | er – Stand-by current typically 2 mA. A 16-bit counter at 100 MHz consumes 50 mA.                                                                                                     |

| to 20,000 gates               |               | eff  | icient, h                      | <b>FPGA Architecture</b> – The pASIC <sup>TM</sup> logic cell supports nigh-speed arithmetic, counter, data path, state machine and gic applications with up to 14-input wide gates.  |

|                               | X             | late | ed using                       | t, Easy-to-Use Design Tools – Designs entered and simu-<br>third-party CAE tools. Fast, fully automatic place and route<br>workstation platforms.                                     |

| FIGURE 1<br>pASIC 1<br>Family | 4             | ĸ    | 12K                            | QL16X24                                                                                                                                                                               |

|                               | CA/EPLD GATES | ĸ    | але аннат салез<br>9 – Уб<br>– | -                                                                                                                                                                                     |

|                               | CA /EPL(      | K    | 5<br>6<br>6<br>6<br>7          | QL12X16                                                                                                                                                                               |

|                               | FC            | ;    | Š                              | QL8X12                                                                                                                                                                                |

|                               | 1             | ĸ    | 3К −                           | - <b>Å Å</b>                                                                                                                                                                          |

| X                             |               |      |                                | <u>+</u> + + →<br>40 80 120 160                                                                                                                                                       |

|                               |               |      |                                | PINS                                                                                                                                                                                  |

#### FAMILY SUMMARY

The pASIC 1 Family of very-high-speed CMOS user-programmable ASIC (pASIC) devices is based on the first FPGA technology to combine high speed, high density and low power in a single architecture.

All pASIC 1 Family devices are based on an array of highly flexible logic cells which have been optimized for efficient implementation of high-speed arithmetic, counter, data path, state machine, random and glue logic functions. Logic cells are configured and interconnected by rows and columns of routing metal and ViaLink metal-to-metal programmable-via interconnect elements.

ViaLink technology provides a nonvolatile, permanently programmed custom logic function capable of operating at counter speeds of over 100 MHz. Internal logic cell nominal worst case delays are under 4 ns and total input to output combinatorial logic delays are under 10 ns. This permits high-density programmable devices to be used with today's fastest CISC and RISC microprocessors, while consuming a fraction of the power and board area of PAL, GAL and discrete logic solutions.

pASIC 1 Family devices range in density from 1000 "gate array" gates (3,000 EPLD/LCA gates) in a 44-pin package, to 4,000 (12,000) gates in high-pincount packages. All devices share a common architecture and CAE design software to allow easy transfer of designs from one product to another. The small size of the ViaLink programming element ensures a technology migration path to devices of 20,000 gates and above.

Designs are entered into the pASIC Family devices on PC or workstation platforms using third-party, general-purpose design-entry and simulation CAE packages, together with QuickLogic device-specific place and route and programming software, called SpDE tools. Sufficient on-chip routing channels are provided to allow fully automatic place and route of designs using up to 100% of the available logic cells.

All the necessary hardware and software, required to complete a design, from entering a schematic to programming a device are included in pASIC Toolkits available from QuickLogic. The pASIC Toolkit 3.0, includes the CAD/CAM  $ECS^{TM}$  Engineering Capture System together with a waveform-driven version of the X-SIM<sup>TM</sup> simulator from Silicon Automation Systems. All applications run on the PC under the Microsoft Windows 3.0 graphical user interface to ensure a highly productive and easy-to-use design environment. An open interface (QDIF) allows many other third-party tools (Exemplar, Viewlogic, etc.) to be used with QuickLogic software on both PC and workstation platforms.

Programmable devices implement customer-defined logic functions by interconnecting user-configurable logic cells through a variety of semiconductor switching elements. The maximum speed of operation is determined by the effective impedance of the switch in both programmed, ON, and unprogrammed, OFF, states.

In pASIC devices the switch is called a ViaLink element. The ViaLink element is an antifuse formed in a via between the two layers of metal of a standard CMOS gate array process. The direct metal-to-metal link created as a result of programming achieves a connection with resistance values below 50 ohms. This is less than 5 percent of the resistance of an EPROM or SRAM switch and 10 percent of that of a dielectric antifuse. The capacitance of an unprogrammed ViaLink site is also lower than these alternative approaches. The resulting low RC time constant provides speeds two to three times faster than older generation technologies.

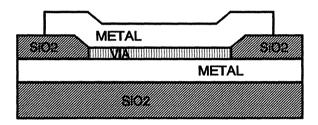

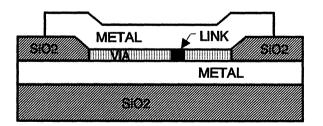

Figure 2a shows an unprogrammed ViaLink site. In a custom metal masked ASIC, such as a gate array, the top and bottom layers of metal make direct contact through the via. In a ViaLink programmable ASIC device the two layers of metal are initially separated by an insulating silicon layer with resistance in excess of 1 gigaohm.

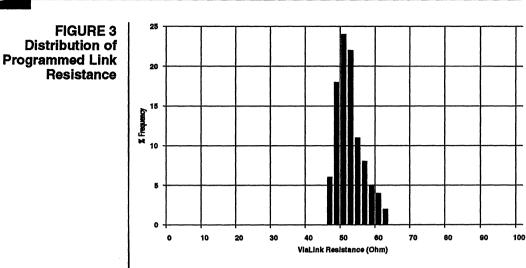

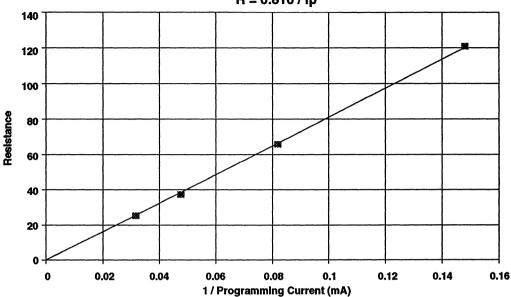

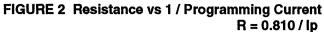

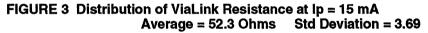

A programming pulse of 10 to 11 volts applied across the via forms a bidirectional conductive link connecting the top and bottom metal layers, Figure 2b. The tight distribution of link resistance is shown in Figure 3.

#### VIALINK PROGRAMMING ELEMENT

FIGURE 2a Unprogrammed ViaLink Element

FIGURE 2b Programmed ViaLink Element

#### STANDARD CMOS PROCESS

QuickLogic pASIC devices are the first FPGA devices to be fabricated on a conventional high-volume CMOS gate array process. The base technology is a 1 micron, n-well CMOS technology with a single polysilicon layer and two layers of metal interconnect. The only deviation from the standard process flow occurs when the ViaLink module is inserted between the metal deposition steps.

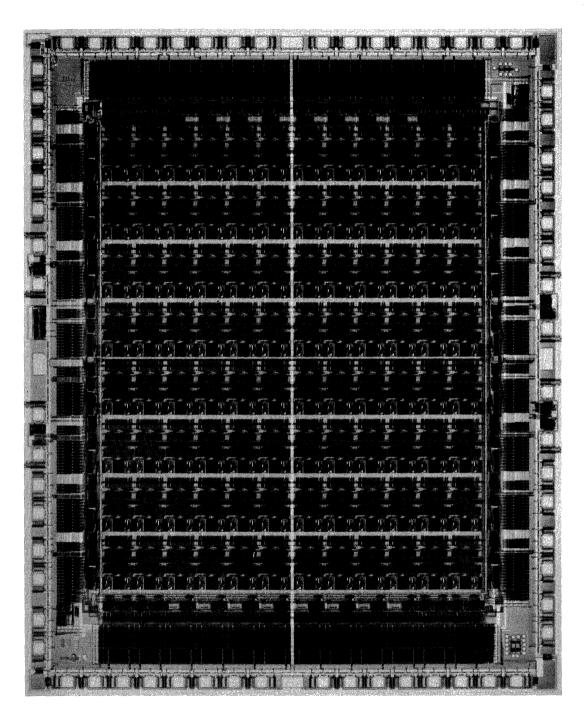

#### FIGURE 4 An Array of ViaLink Elements

As the size of a ViaLink via is identical to that of a standard metal interconnect via, programmable elements can be packed very densely. The microphotograph of Figure 4 shows an array of ViaLink elements. The density is limited only by the minimum dimensions of the metal-line to metal-line pitch. Migration of the gate array process to submicron dimensions will allow the development of pASIC devices with tens of thousands of usable gates.

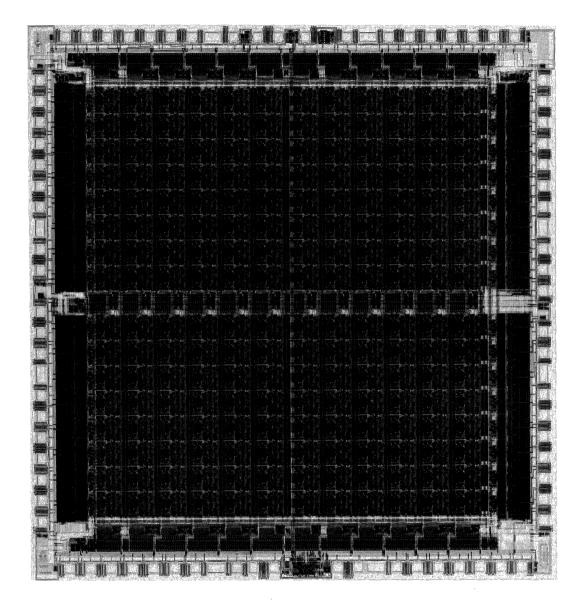

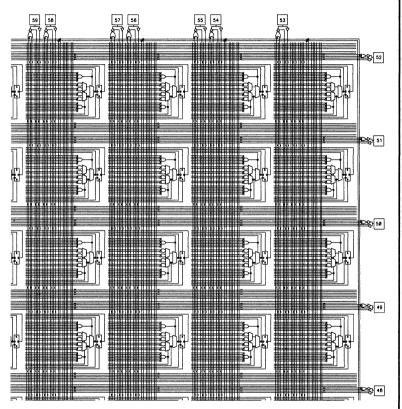

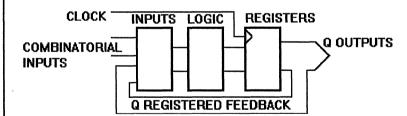

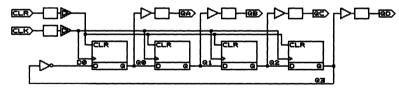

The pASIC device architecture consists of an array of user-configurable logic building blocks, called logic cells, set in a grid of metal wiring channels similar to those of a gate array. Figure 5 shows a section of a pASIC device containing internal logic cells, input/output cells and dual-layer vertical and horizontal metal routing channels. Through ViaLink elements located at the wire intersections, the output of any cell may be programmed to connect to the input of any other cell.

This regular and orthogonal interconnect, makes the pASIC architecture similar in structure and performance to a metal masked gate array. It also makes system operating speed far less sensitive to partitioning and placement decisions, as minor revisions to a logic design result only in small changes in performance.

Adequate wiring resources permit 100% automatic placement and routing of designs using up to 100% of the logic cells. This has been demonstrated on designs that include a high percentage of fixed pin placements.

#### PASIC FAMILY ARCHITECTURE

FIGURE 5 A Matrix of Logic Cells and Wiring Channels

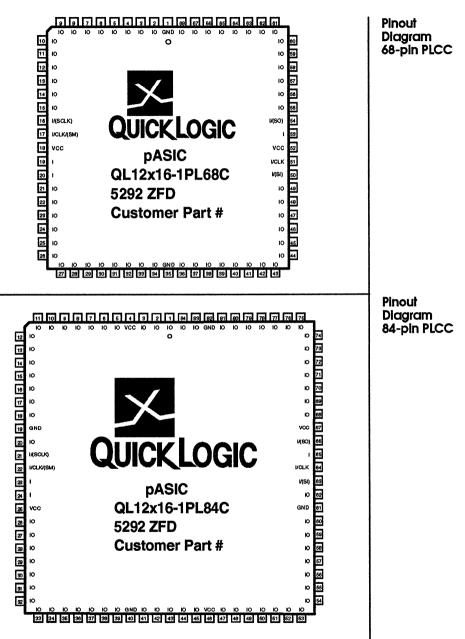

| ORGANIZATION | The pASIC 1 Family of very-high-speed FPGAs contains devices covering<br>a wide spectrum of I/O and density requirements. Three members ranging<br>from 1,000 gates in a 44-lead package to 4000 gates in a 144-lead package are<br>shown in Figure 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

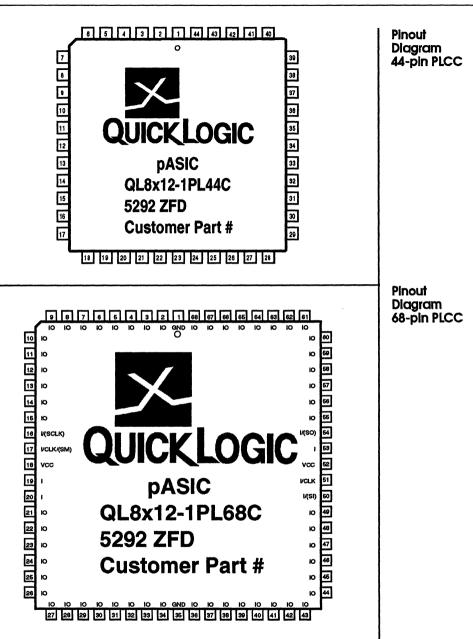

|              | Device part numbers are derived from the organization of internal logic cells.<br>For example, in Figure 6, the QL8x12 contains 96 logic cells in an 8-by-12<br>matrix. The single lines between logic cells represent channels containing up<br>to twenty-two wires. Each of the internal logic cells has the logic capacity of<br>up to 30 "gate array gates." As a typical application will use 10 to 12 gates<br>from each logic cell, the QL8x12 is described as a 1000-usable-gate device.<br>Based on the "available gate" gate counting approach of some programmable<br>logic vendors, it would be called a 3000-gate part. The QL8x12 is available<br>in a 68-lead package with 56 bidirectional I/O pins and 8 dedicated input/high<br>drive clock pins and a 44-lead package with 32 I/O pins. |

|              | The key features of these three pASIC devices are as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Device<br>Cells | Logic<br>Cells | Max I/O<br>Inputs | Dedicated<br>Pins | Package<br>Pins | Usable<br>Gates | EPLD/LCA<br>Gates |

|-----------------|----------------|-------------------|-------------------|-----------------|-----------------|-------------------|

| QL8x12          | 96             | 56                | 8                 | 44,68           | 1000            | 3000              |

| QL12x16         | 192            | 68                | 8                 | 68,84           | 2000            | 6000              |

| QL16x24         | 384            | 104               | 8                 | 100,144         | 4000            | 12000             |

See individual product data sheets for specific information on each device.

8x12

|   | • • |   | • | • |   | • |  | <br> |  |

|---|-----|---|---|---|---|---|--|------|--|

|   |     |   |   |   |   |   |  |      |  |

| - |     |   |   |   | • | 0 |  |      |  |

| - |     |   |   |   |   |   |  |      |  |

| - |     |   |   |   |   |   |  |      |  |

|   |     | ۵ |   |   |   |   |  |      |  |

|   |     |   |   |   |   |   |  |      |  |

|   |     |   |   |   |   |   |  |      |  |

| - |     |   |   |   |   |   |  |      |  |

| 1 |     |   |   |   |   |   |  | <br> |  |

12x16

|   |   |   |   |   |   | • |   |  |   |   |   |  |   |

|---|---|---|---|---|---|---|---|--|---|---|---|--|---|

|   |   |   |   |   |   |   |   |  |   | 0 |   |  |   |

| - |   |   |   |   |   | ۵ |   |  |   |   |   |  |   |

|   |   |   |   |   |   |   |   |  |   |   |   |  | : |

| - |   |   |   |   | ۵ |   |   |  |   |   |   |  |   |

| : |   |   |   |   |   |   |   |  |   |   |   |  | : |

|   |   | ۵ |   |   |   |   |   |  |   |   |   |  | : |

|   |   |   |   | 0 |   |   |   |  | ۵ |   | ۵ |  | : |

| : |   |   |   |   |   |   |   |  |   |   |   |  | : |

| - |   |   |   |   | ۵ |   | 0 |  |   |   |   |  | : |

| : |   |   | ۵ |   |   |   |   |  | ٥ |   |   |  | : |

| : |   |   |   |   | ۵ |   |   |  |   |   |   |  | : |

| _ | ۵ |   |   |   |   |   |   |  | ۵ |   |   |  |   |

|   |   |   |   |   |   |   |   |  |   |   |   |  |   |

16x24

|  |  |  |  |  |  |  |  |  |   | • |  |   |

|--|--|--|--|--|--|--|--|--|---|---|--|---|

|  |  |  |  |  |  |  |  |  |   |   |  |   |

|  |  |  |  |  |  |  |  |  |   |   |  |   |

|  |  |  |  |  |  |  |  |  |   |   |  |   |

|  |  |  |  |  |  |  |  |  |   |   |  |   |

|  |  |  |  |  |  |  |  |  |   |   |  |   |

|  |  |  |  |  |  |  |  |  |   |   |  |   |

|  |  |  |  |  |  |  |  |  | ۵ |   |  |   |

|  |  |  |  |  |  |  |  |  | 0 |   |  |   |

|  |  |  |  |  |  |  |  |  |   |   |  |   |

|  |  |  |  |  |  |  |  |  |   |   |  |   |

|  |  |  |  |  |  |  |  |  |   |   |  |   |

|  |  |  |  |  |  |  |  |  |   |   |  | ۵ |

|  |  |  |  |  |  |  |  |  |   |   |  |   |

|  |  |  |  |  |  |  |  |  |   |   |  |   |

|  |  |  |  |  |  |  |  |  |   |   |  |   |

|  |  |  |  |  |  |  |  |  | 0 |   |  |   |

= I/O /High-drive Input/ Clock Cells

- Logic Cells

+ = Interconnect Wiring Channels

#### PASIC INTERNAL LOGIC CELL

#### FIGURE 7 pASIC Internal Logic Cell

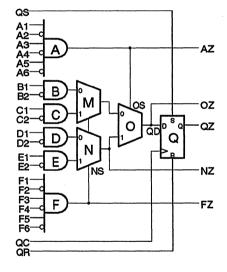

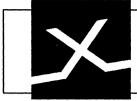

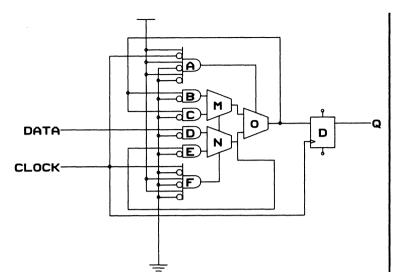

The pASIC internal logic cell, shown in Figure 7, is a general-purpose building block that can implement most TTL and gate array macro library functions. It has been optimized to maintain the inherent speed advantage of the ViaLink technology while ensuring maximum logic flexibility.

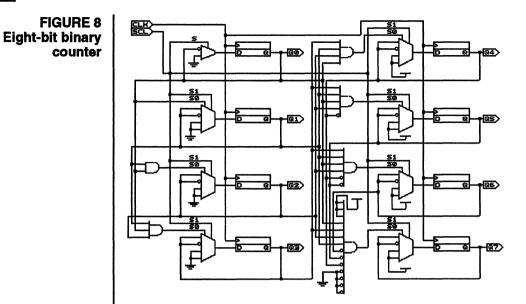

The logic cell consists of two 6-input AND gates, four 2-input AND gates, three 2to-1 multiplexers and a D flip-flop. In addition to the dedicated flip-flop, logic gates in each cell can be configured to provide two latches. As noted above, each cell represents approximately 30 gate-equivalents of logic capability. Multiple outputs from the logic cell allow the automatic place and route software to pack unrelated logic functions into a single cell to maximize silicon utilzation.

The pASIC logic cell is unique among FPGA architectures in that it offers up to 14-input-wide gating functions. This allows many logic functions to be accomplished in a single cell delay that require two or more delays with other architectures. It can implement all possible Boolean transfer functions of up to three variables as well as many functions of up to 14 variables.

Glitch-free switching of the multiplexer is ensured as the internal capacitance of the circuit maintains enough charge to hold the output in a steady state during input transitions. The multiplexer output feeds the D-type flip-flop which can also be configured to provide J-K, S-R, or T-type functions as well as count with carry-in. Two independent SET and RESET inputs can be used to asynchronously control the output condition. The combination of wide gating capability and a built-in sequential function makes the pASIC logic cell particularly well suited to the design of high-speed state machines, shift registers, encoders, decoders, arbitration and arithmetic logic, as well as a wide variety of counters.

The function of a logic cell is determined by the logic levels applied to the inputs of the AND gates. ViaLink sites located on signal wires tied to the gate inputs perform the dual role of configuring the logic function of a cell and establishing connections between cells.

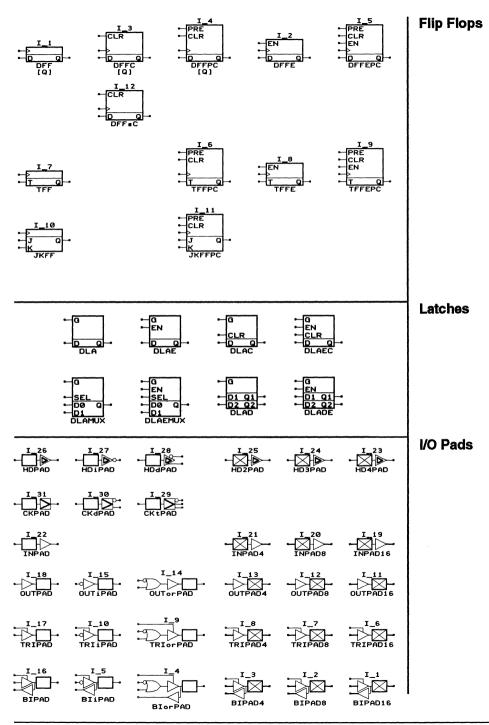

The pASIC macro library contains more than 200 of the most frequently used logic functions optimized to fit the logic cell architecture. A detailed understanding of the logic cell is therefore not necessary to successfully design with pASIC devices. CAE tools will automatically translate a conventional logic schematic into a device and provide excellent performance and utilization.

Many useful hints on how to achieve optimum results are provided in The pASIC Users Guide supplied with the pASIC Toolkit. Application Notes QAN 1 and QAN 2 provide more details for users who wish to add special-purpose counter or register macros to the library.

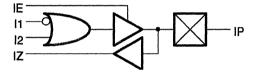

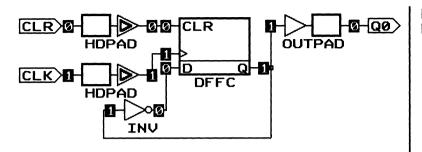

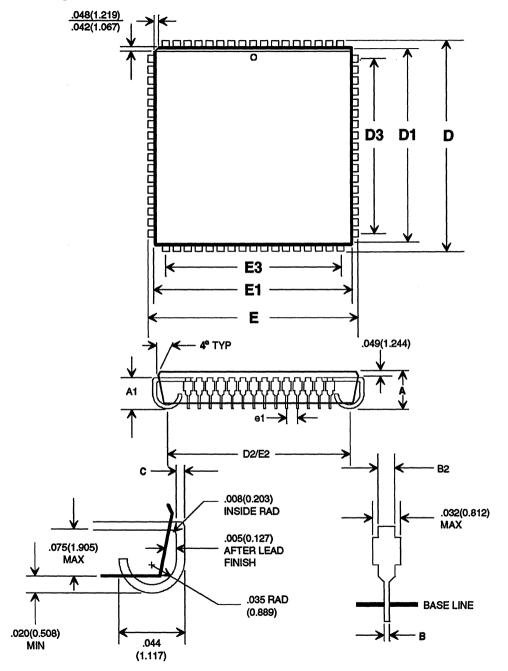

Three types of input and output structures are provided on pASIC devices to configure buffering functions at the external pads. They are the Bidirectional Input/Output (I/O) cell, the Dedicated Input (I) cell and the Clock Input cell (I/CLK).

The bidirectional I/O cell, shown in Figure 8, consists of a 2-input OR gate connected to a pin buffer driver. The buffer output is controlled by a three-state enable line to allow the pad to also act as an input. The output may be configured as active HIGH, active LOW, or as an open drain inverting buffer.

INPUT AND OUTPUT CELLS

FIGURE 8 Bidirectional I/O Cell

The output buffers (IOL/IOH of 8 mA) are designed to ensure quiet switching characteristics while maintaining high speed. Measured results show up to 48 outputs switching simultaneously into a 10 pF load with less than  $\pm 1$  volt of output switching noise.

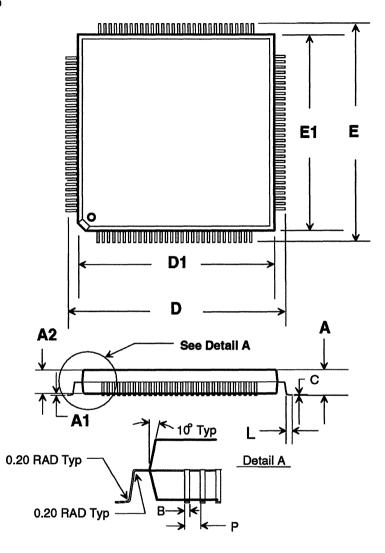

#### FIGURE10a Dedicated Input High-Drive Cell

FIGURE10b Clock Input Cell

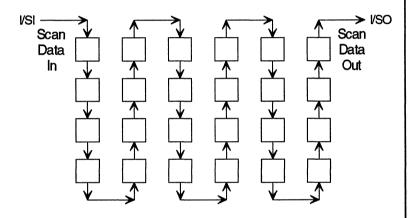

The Dedicated Input I cell, Figure 10a, conveys true and complement signals from the input pads into the array of logic cells. As these pads have nearly twice the current drive capability of the I/O pads, they are useful for distributing high fanout signals across the device. The Clock Input I/CLK cell (Figure 10b) drives a low-skew, fanout-independant clock tree that can connect to the clock, set, or reset inputs of the flip-flop. The QL12x16 device, for example, has 68 I/O cells, 6 I cells, and 2 I/CLK cells.

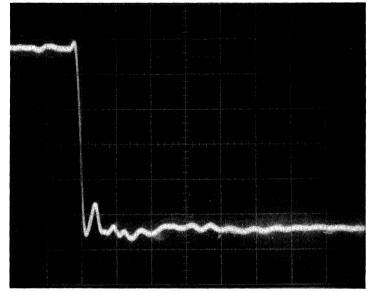

Multiple logic cells can be programmed to form a complex logic function by interconnection through the routing channels. To describe the organization of these routing channels, a hypothetical 14-pin function consisting of two logic cells is shown in Figure 11. This device contains the same architectural features as the members of the pASIC 1 family.

PASIC INTERCONNECT STRUCTURE

Active logic functions are performed by the internal logic cells, the I/O cells (pins 2, 3, 7, 9, 10 and 14) the I cells (pins 4, 6), and the I/CLK cells (pins 11 and 13). These cells are connected with vertical and horizontal wiring channels.

FIGURE 11 pASIC Device Features

2-11

|              | Three types of signal wires are employed; Segmented Wires, Express Wires, and Clock Wires. Segmented wires are predominantly used for local connections and have a ViaLink element, known as a Cross Link (denoted by the open box symbol) at every crossover point. They may also be connected to the segmented wires of cells above and below through ViaLink elements, called Pass Links (denoted by the X symbol). Express lines are similar to segmented wires except that they are not divided by pass links. Dedicated Clock wires are lightly loaded with only three links per cell to distribute high-speed clock edges to the flip-flop CLK, SET and RESET pins. Express wires may also be used to deliver clock signals into the multiplexer region of the cell for combinatorial gating. The automatic place and route software allocates signals to the appropriate wires to ensure the optimum speed/density combination. |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | Vertical VCC and GND wires are located close to the logic cell AND-gate inputs to allow any input that is not driven by the output of another cell to be automatically tied to either VCC or GND. All the vertical wires (segmented, express, clock and power) considered as a group are called vertical channels. These channels span the full height of the device and run to the left of each column of logic cells.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|              | Horizontal wiring channels, called rows, provide connections, via cross links, to other columns of logic cells and to the periphery of the chip. Appropriate programming of ViaLink elements allows electrical connection to be made from any logic cell output to the input of any other logic or I/O cell. Ample wires are provided in the channels to permit automatic place and route of many designs using up to 100 percent of the device logic cells. Designs can be completed automatically even with a high percentage of fixed user placement of internal cells and pin locations.                                                                                                                                                                                                                                                                                                                                            |

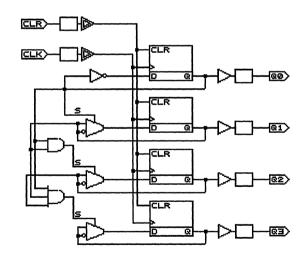

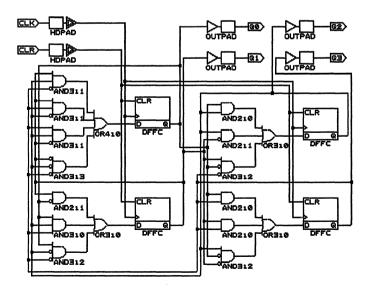

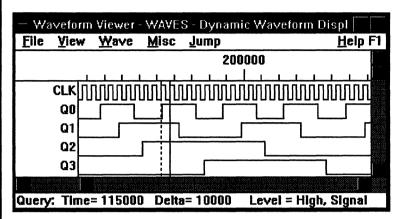

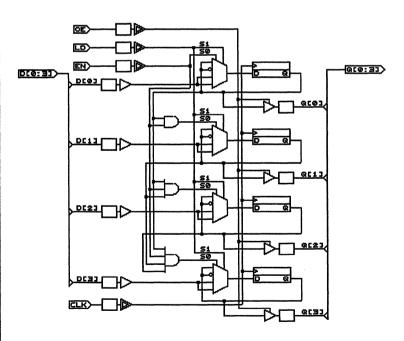

|              | This information is presented to provide the user with insight into how a logic function is implemented in pASIC devices. However it is not necessary to develop a detailed understanding of the architecture in order to achieve efficient designs. All routing tasks are fully automatic. No manual wire routing is necessary, nor is it permitted by the software. Fully automatic placement of logic fuctions is also offered. But if necessary to achieve a specific pin configuration or register alignment, for example, manual placement is supported.                                                                                                                                                                                                                                                                                                                                                                          |