# Radar & Radio Communications IC Handbook

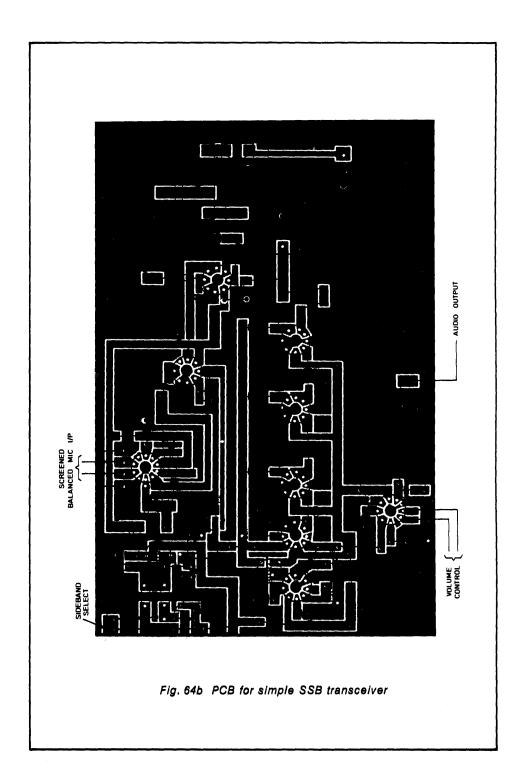

# RADAR & RADIO COMMUNICATIONS IC HANDBOOK

**JULY 1981**

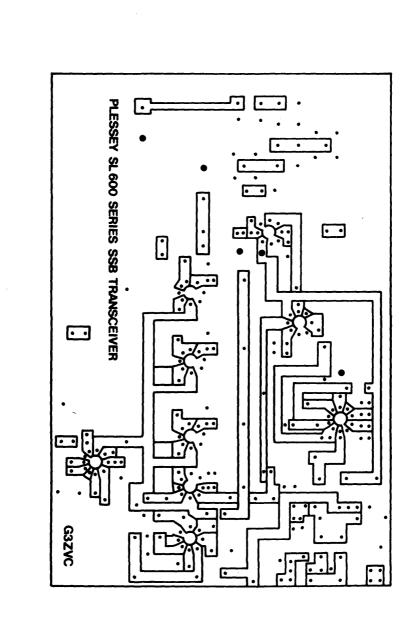

### \$4.00 PSI 1806

This publication is issued to provide outline information and (unless specifically agreed to the contrary by the Company in writing) is not to form part of any order or contract or be regarded as a representation relating to the products or services concerned. We reserve the right to alter without notice the specification, design, price or conditions of supply of any products.

# Contents

| PROI    | DUCT RANGE INFORMATION                      | 9     | - 32 |

|---------|---------------------------------------------|-------|------|

| RADI    | O APPLICATION NOTES                         |       |      |

| tion 1. | . SL600/1600 Circuit Description            | 33    | - 52 |

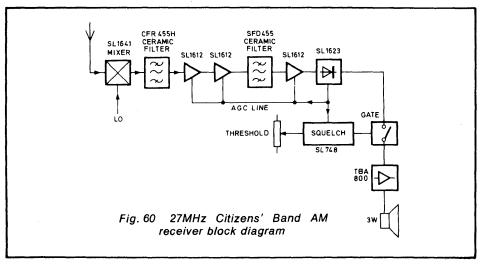

| 2.      | AM Receiver                                 | 53    | - 57 |

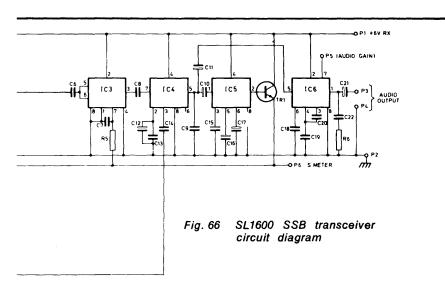

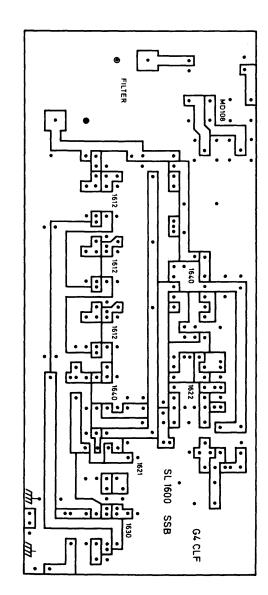

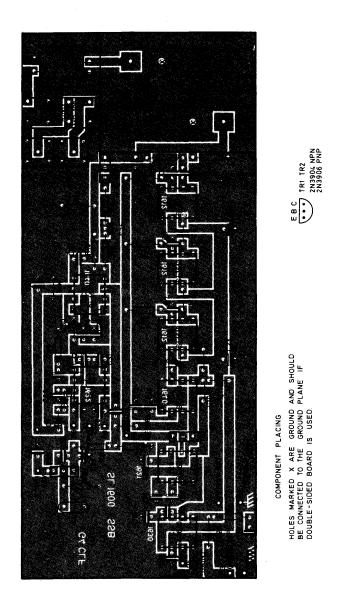

| 3.      | SSB Transceiver                             | 58    | - 69 |

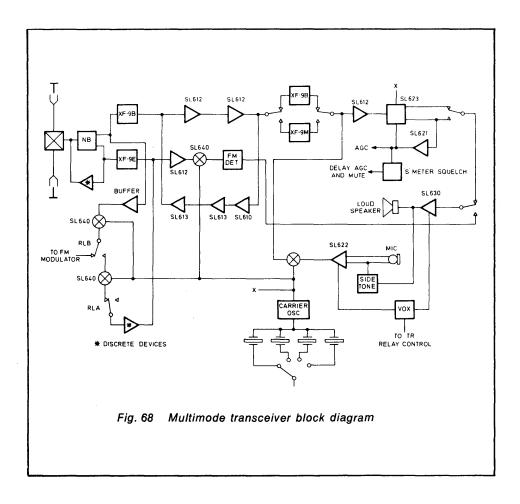

| 4.      | Multimode Transceiver                       | 70    | - 88 |

| 5.      | 27 MHz AM/SSB Transceiver                   | 89    | - 92 |

| 6.      | SL6000 Circuit Description and Applications | 93 -  | 108  |

| 7.      | High Speed Dividers and Characteristics     | 109 - | 124  |

| 8.      | Synthesiser System                          | 125 - | 142  |

| RADA    | AR APPLICATION NOTES                        |       |      |

| 1.      | Plessey ICs for radar IFs                   | 143 - | 148  |

| 2.      | A wide dynamic range preamplifier           | 149 - | 154  |

| 3.      | A 120MHz log using SL1521s                  | 155 - | 160  |

| 4.      | A swept Gain IF Strip and Detector          | 161 - | 166  |

| 5.      | Low noise Amplifier                         | 167 - | 170  |

| 6.      | Low Cost IF Strip                           | 171 - | 180  |

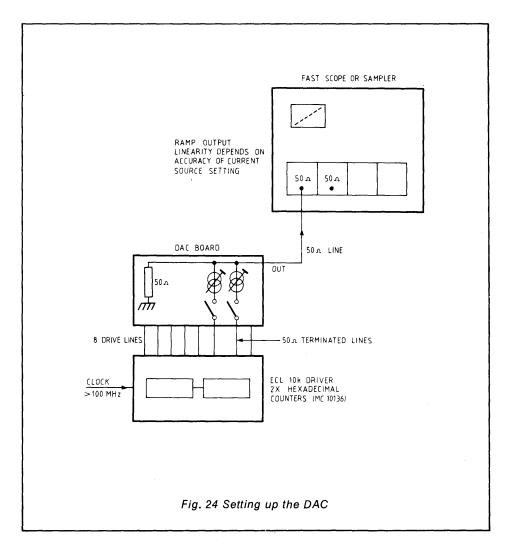

| 7.      | Digital Signal Processing Applications      | 181 - | 214  |

| CHNIC   | CAL DATA                                    | 215 - | 478  |

|         | ES                                          |       |      |

|         | SEMICONDUCTORS WORLD WIDE                   |       |      |

|         |                                             |       |      |

### RODUCT INDEX

| ODULATORS      | ,                                         |     |

|----------------|-------------------------------------------|-----|

| _355C          | 4 Transistor modulator/demodulator        | 225 |

| _1496C         | Double balanced modulator/demodulator     | 341 |

| _1596C         | Double balanced modulator/demodulator     | 341 |

| NEAR RF AMP    | PI IFIFR                                  |     |

| .501A & B      | Linear wideband amplifier                 | 235 |

| .502A & B      | Linear wideband amplifier                 |     |

| .503A & B      | Linear wideband amplifier                 |     |

| .510C          | DC-24MHz RF detector/video amplifier      |     |

| .511C          | DC-14MHz RF detector/video amplifier      |     |

| .541A & B      | High slew rate-operational amp            |     |

| .541C & D      | High speed video amplifier                |     |

| .550C & D      | Low noise amp. with external gain control |     |

| _560C          | 300MHz low noise amplifier                |     |

| .561C          | Low noise preamplifier                    |     |

| <b>-</b> 565   | 1GHz UHF amplifier                        |     |

| _1550C         | Low noise amp. with external gain control |     |

|                | LOOP CIRCUITS                             |     |

| .650B & C      | Modulator/PPL                             | 215 |

| .651B & C      | Modulator/PPL                             |     |

| _652C          | Modulator/PPL                             |     |

|                |                                           | 315 |

|                | BAND AMPLIFIERS                           |     |

| L521A,B & C    | Wideband log, amplifier                   |     |

| .523B,C & H    | Dual wideband log amplifier               |     |

| L525C          | Wideband log If strip amplifier           |     |

| L530C          | True log amplifier                        |     |

| _531C          | True log amplifier                        |     |

| .532C          | True log amplifier                        |     |

| _1521A,B,C     | 200MHz wideband amplifier                 |     |

| _1522C         | 200MHz wideband amplifier                 |     |

| L1523C         | 200MHz wideband amplifier                 |     |

| _1524<br>_1525 | 120MHz wideband amplifier                 |     |

| _1531          | Five stage - Log IF strip                 |     |

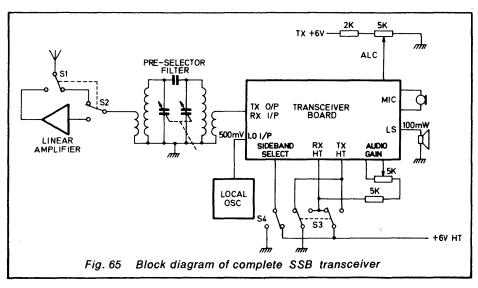

| _1532          | Five stage - Log IF strip                 |     |

|                |                                           | 201 |

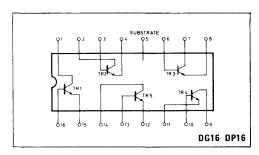

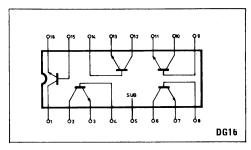

|                | TRANSISTORS & ARRAYS                      |     |

| .301K & L      | Dual NPN transistors                      |     |

| L303L          | Matched pair + tall transistor            |     |

| _360C          | 2.5GHz matched transistor pair            |     |

| .362C          | Low noise transistor pair                 |     |

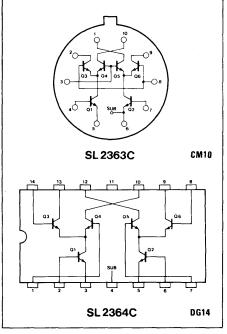

| _2363C         | High performance transistor array         |     |

| _2364C         | High performance transistor array         |     |

| .3045C         | General purpose transistor array          | 390 |

| SL30.46C       | General purpose transistor array               | 399 |

|----------------|------------------------------------------------|-----|

| SL3081D        | High current, common emitter array             | 403 |

| SL3082D        | High current, common collector array           | 403 |

| SL3085D        | High current, five transistor array            | 40  |

| SL3127C        | High frequency transistor array                | 40  |

| SL3145C        | 2.5GHz transistor array                        | 41  |

| SL3146A & C    | High voltage transistor                        | 41. |

| SL3183A & C    | High voltage transistor                        | 41  |

| RADIO COMMU    | UNICATION CIRCUITS                             |     |

| SL610C         | RF amplifier                                   | 29  |

| SL611C         | RF amplifier                                   | 29  |

| SL612C         | IF amplifier                                   | 29  |

| SL613C         | Limited wideband amplifier                     |     |

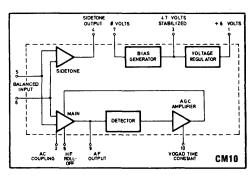

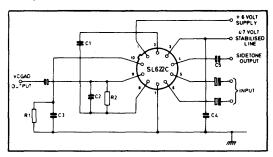

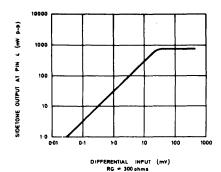

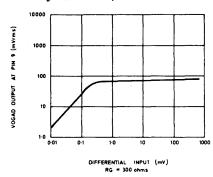

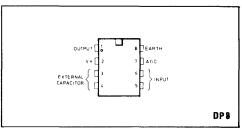

|                | VOGAD                                          |     |

|                | AGC generator                                  |     |

|                | AF amp./VOGAD/sidetone                         |     |

| SL623C         | AM det./AGC amp./SSB demodulator               |     |

| SL604C         | Mulitmode detector                             |     |

| SL624C         | Multimode detector                             |     |

| SL630C         | AF amplifier                                   |     |

| SL640C         | Double-balanced modulator                      |     |

| SL641C         | Receiver mixer                                 |     |

| SL1610C        | RF/IF amplifier                                |     |

| SL1611C        | RF/IF amplifier                                |     |

| SL1612C        | RF/IF amplifier                                |     |

| SL1613C        | Limiting amplifier/detector                    |     |

| SL1620C        | AGC generator                                  |     |

| SL1621C        | AGC generator                                  |     |

| SL1623C        | AM detector, AGC amplifier and SSB demod       |     |

| SL1625C        | AM detector & AGC amplifier                    |     |

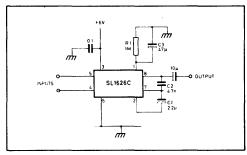

| SL1626C        | Audio amplifier and VOGAD                      |     |

| SL1630C        | Microphone/headphone amplifier                 |     |

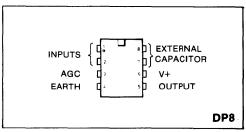

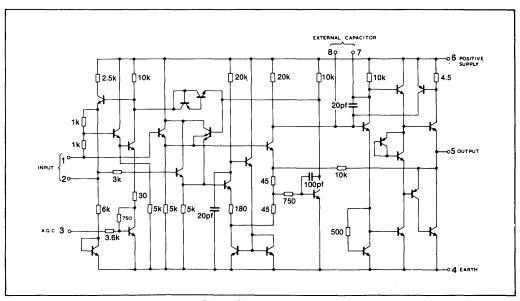

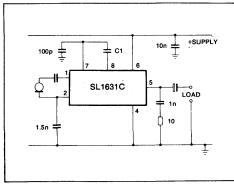

| SL1631C        | Microphone/headphone amplifier                 |     |

| SL1640C        | Double balanced modulator                      |     |

| SL1641C        | Double balanced modulator                      |     |

| SL6270C        | Gain control preamplifier                      |     |

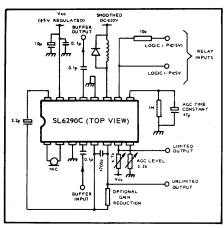

| SL6290C        | VOGAD transmit circuit                         |     |

| SL6310C        | Switchable audio amplifier                     |     |

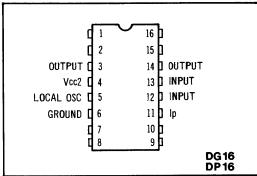

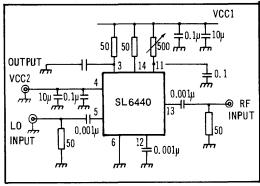

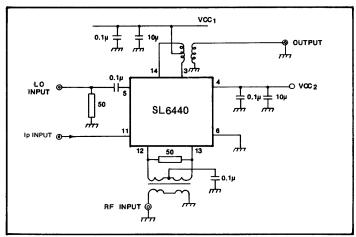

| SL6440C        | High level mixer                               |     |

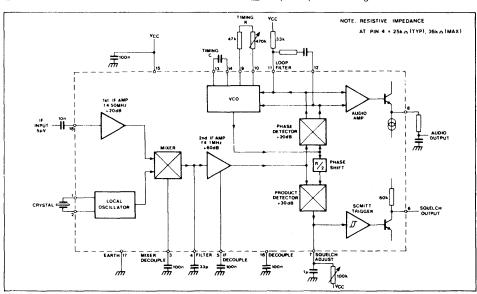

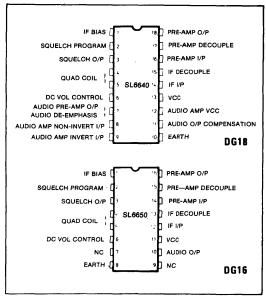

| SL6600C        | Low power IF/AF/PLL circuit for narrow band FM |     |

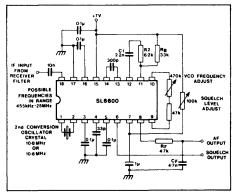

| SL6640C        | Low power IF/AF/ circuit for narrow band FM    |     |

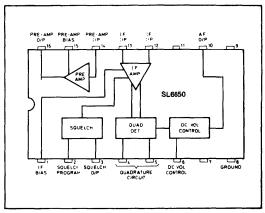

| SL6650C        | Low power IF/AF circuit for narrow band FM     |     |

| SL6700C        | IF amplifier and AM detector                   |     |

|                | ·                                              |     |

| SI 1020C       | OMMUNICATION CIRCUITS                          | 20  |

| STREET, STREET | CATHER AND A CONTRACTOR OF CONTRACTOR          |     |

| GING CIRCUITS                          |                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low noise preamplifier                 | 333                                                                                                                                                                                                                                                                                                             |

| Low noise preamplifier                 | 333                                                                                                                                                                                                                                                                                                             |

| Low noise preamplifier                 | 337                                                                                                                                                                                                                                                                                                             |

| TIONS                                  |                                                                                                                                                                                                                                                                                                                 |

| Crystal oscillator maintaining circuit | 323                                                                                                                                                                                                                                                                                                             |

| Crystal osillator maintaining circuit  | 323                                                                                                                                                                                                                                                                                                             |

| SION PRODUCTS                          |                                                                                                                                                                                                                                                                                                                 |

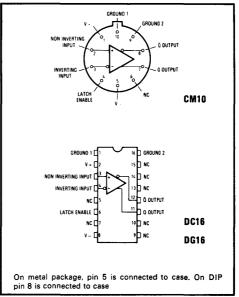

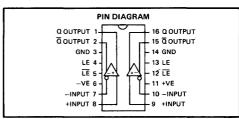

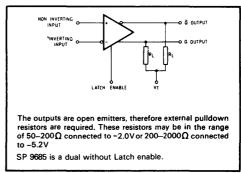

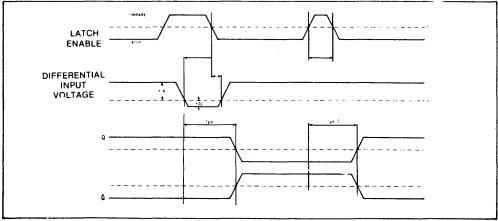

| Ultra fast comparator                  | 447                                                                                                                                                                                                                                                                                                             |

| Ultra fast comparator                  |                                                                                                                                                                                                                                                                                                                 |

| High speed comparator                  | 453                                                                                                                                                                                                                                                                                                             |

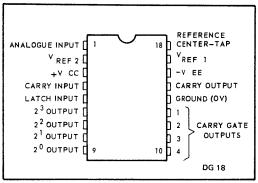

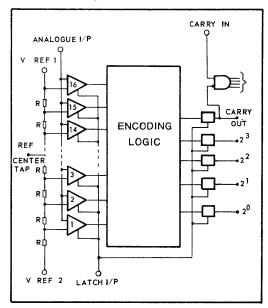

| Two-Bit expandable A & D converter     | 459                                                                                                                                                                                                                                                                                                             |

| Four-Bit expandable A & D converter    | 463                                                                                                                                                                                                                                                                                                             |

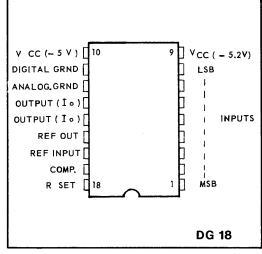

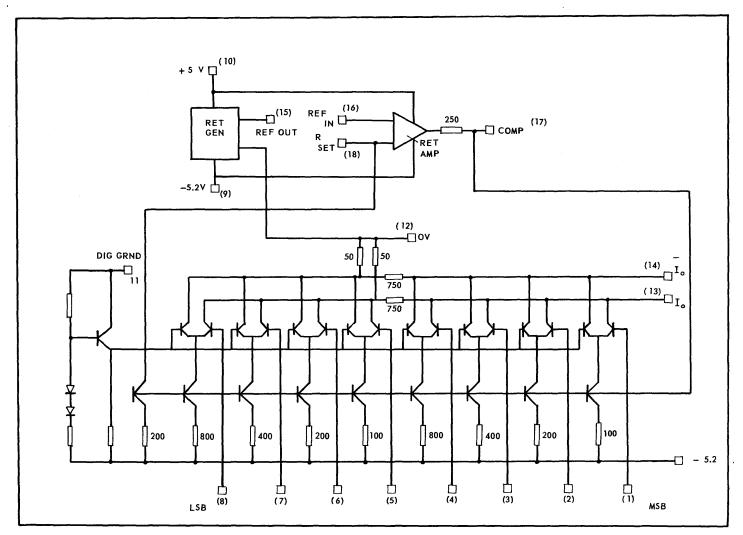

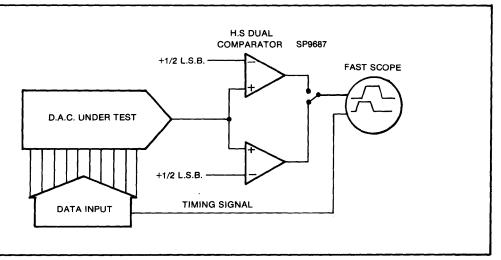

| Eight-Bit DAC converter                |                                                                                                                                                                                                                                                                                                                 |

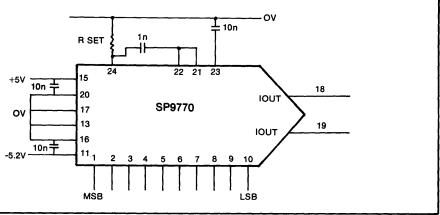

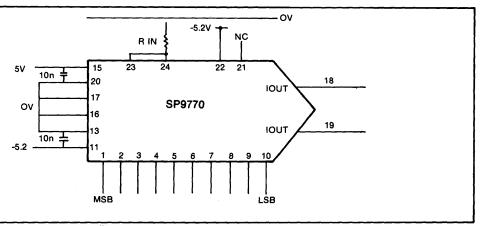

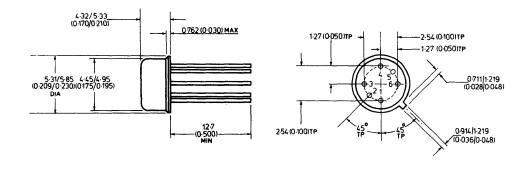

| Ten-Bit high speed D to A convrter     | 475                                                                                                                                                                                                                                                                                                             |

|                                        | Low noise preamplifier Low noise preamplifier Low noise preamplifier  FIONS Crystal oscillator maintaining circuit Crystal osillator maintaining circuit SION PRODUCTS Ultra fast comparator Ultra fast comparator Gwo-Bit expandable A& D converter Four-Bit expandable A& D converter Eight-Bit DAC converter |

# PRODUCT RANGE INFORMATION

# **Building Block IC's**

Plessey integrated circuits are on the leading edge of technology without pushing the ragged edge of capability.

We developed the first 2 GHz counter. And a family of prescalers and controllers for your TV, radio and instrumentation frequency synthesizers.

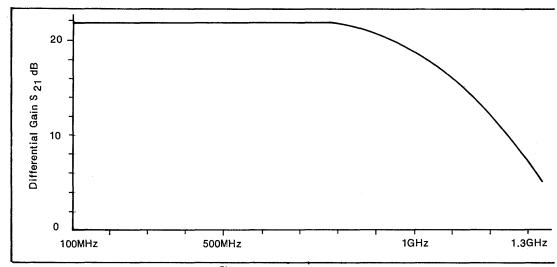

We have a monolithic 1 GHz amplifier. And a complete array of complex integrated function blocks for radar signal processing and radio communications.

We can supply data conversion devices with propagation delays of just 2½ nanoseconds.

And a range of MNOS logic that stores data for a year when you remove the power, yet uses only standard supplies and is fully TTL/CMOS-compatible.

To develop this edge, we developed our own processes, both bipolar and MOS. The processes were designed for quality and repeatability, then applied to our high volume lines. Most of our IC's are available screened to MIL-STD-883B, and our quality levels exceed the most stringent military, TV and automotive requirements.

Millions of Plessey complex function building block IC's are being used in TV sets and car radios; CATV, navigation and radar systems; frequency synthesizers and telecommunications equipment.

Our global scope of operations, our high volume manufacturing facilities, our proprietary processes ensure that we will continue to deliver state-of-the-art technology and reliability in IC devices at the appropriate prices and in the required volumes. Day after day. Week after

# **Plessey Semiconductors**

1641 Kaiser Avenue, Irvine, CA 92714. (714) 540-9979

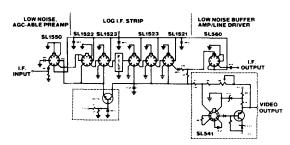

# **Radar Signal Processing**

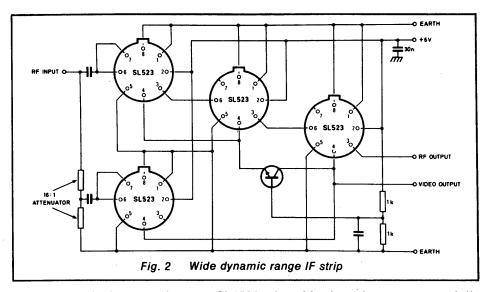

Since the performance of a radar receiver is critically dependent on the performance of its I.F. strip, we offer a range of "building block" IC's that can be used in systems with different performance requirements and configurations.

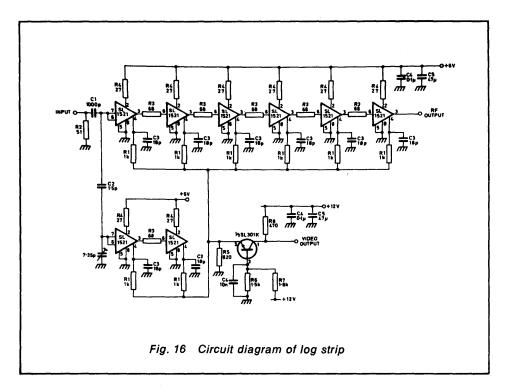

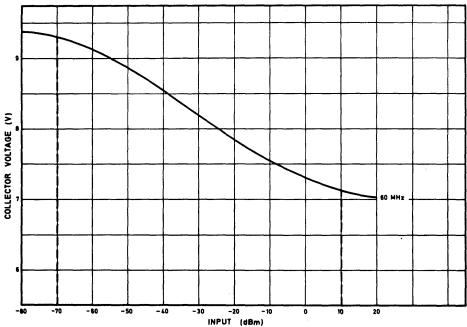

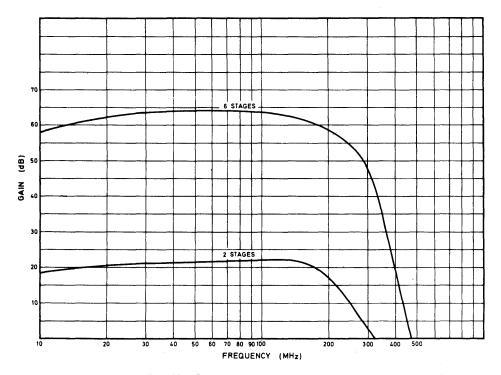

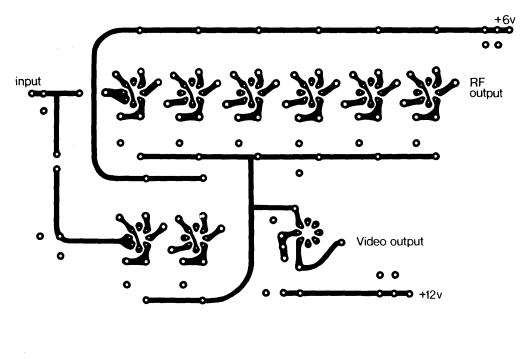

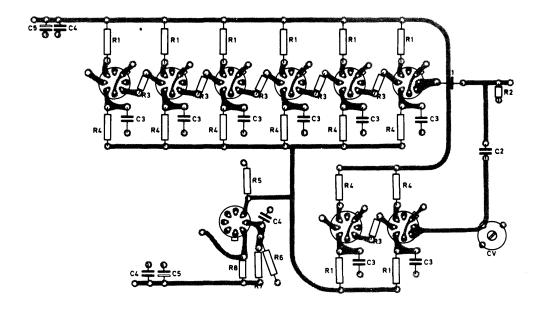

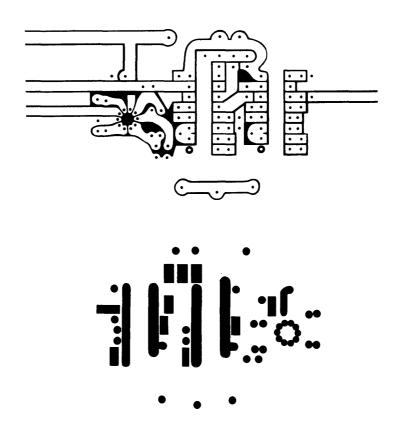

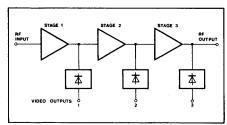

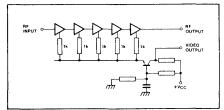

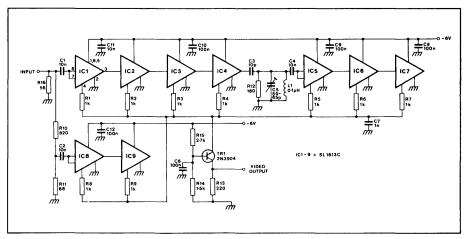

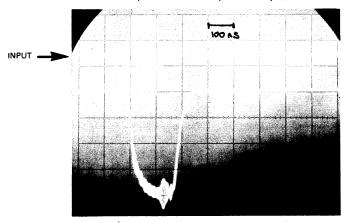

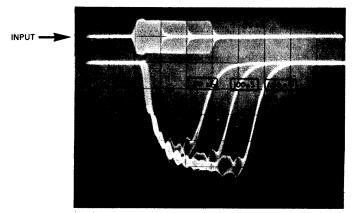

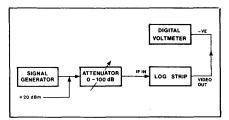

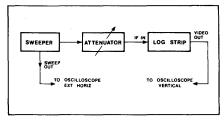

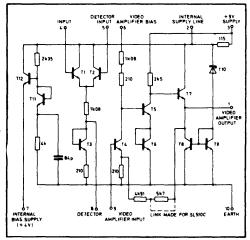

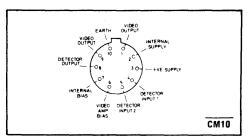

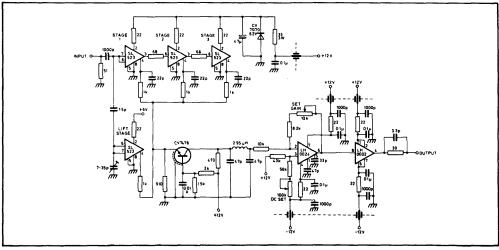

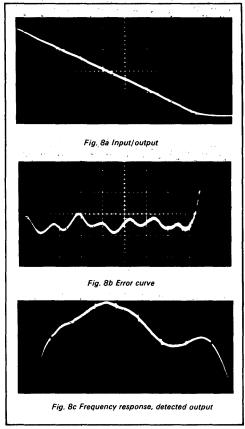

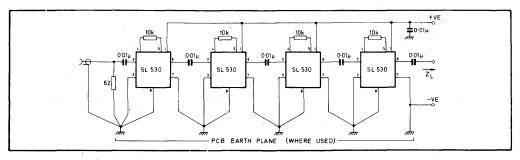

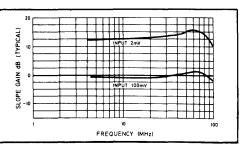

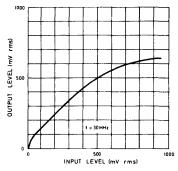

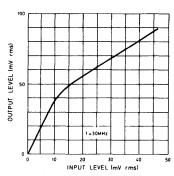

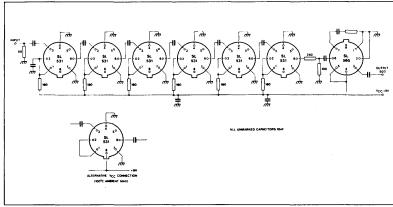

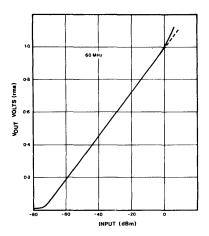

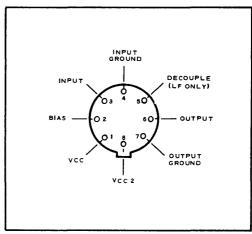

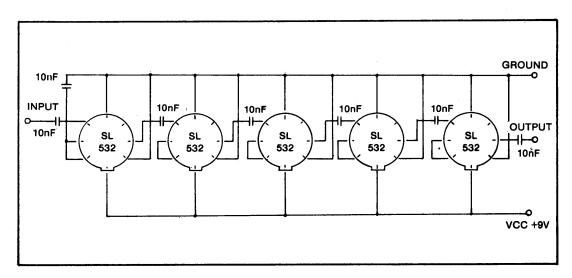

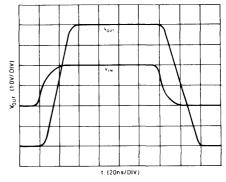

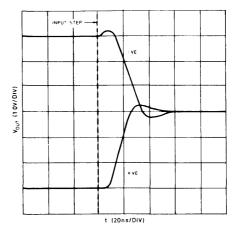

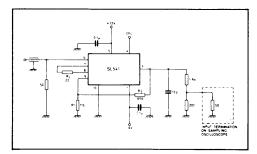

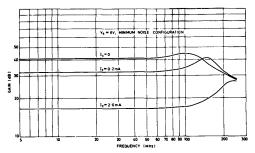

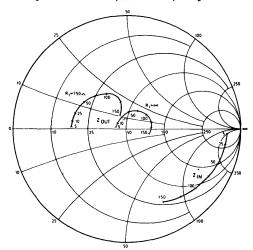

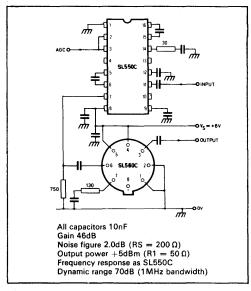

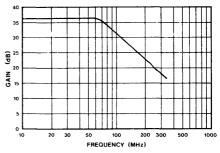

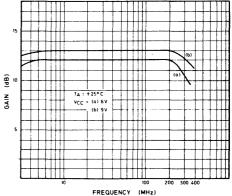

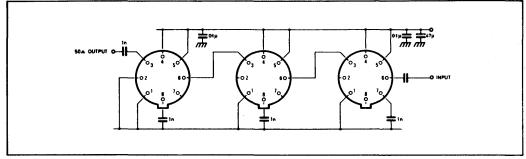

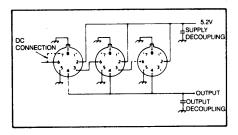

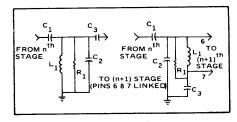

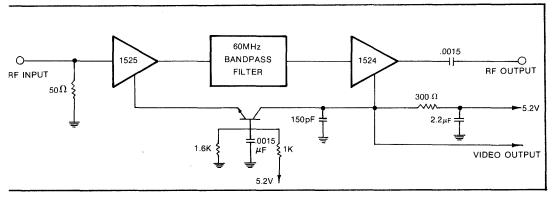

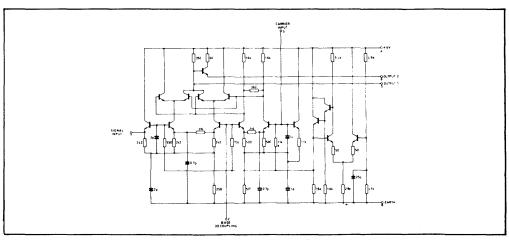

The logarithmic I.F. strip shown is an example of a low cost, high performance strip fabricated with Plessey IC's. It uses only five devices and a single interstage filter to achieve a logging range of 90 dB,  $\pm 1$  dB accuracy, -90 dBm tangential sensitivity and a video rise time of

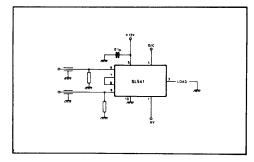

minimum of external components (one capacitor, one resistor per stage), yet has a band-width of 500 MHz, a dynamic range of 70 dB and has a phase shift of only  $\pm 3^{\circ}$  over its entire range. As with most of our other devices, it operates over the full MIL-temp range and is available screened to MIL-STD-883.

The chart summarizes our Radar Signal Processing IC's. Whether you're working with radar and ECM, weapons control or navigation and guidance systems, our IC's are a simpler, less expensive, more flex-

ible alternative to whatever you're using now for any I.F. strip up to 160 MHz.

For more details, please use the postage-paid reply card at the back of this book to order our RADAR AND RADIO COMMUNICATIONS IC HANDBOOK, or contact your nearest Plessey Semiconductors representative.

20 ns or less.

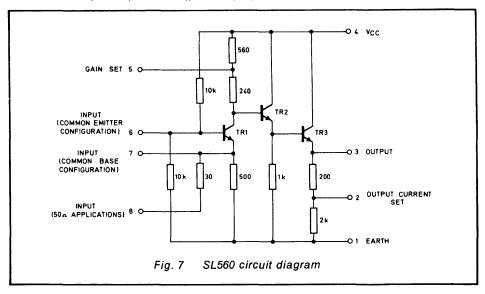

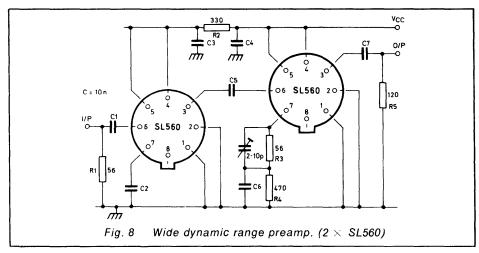

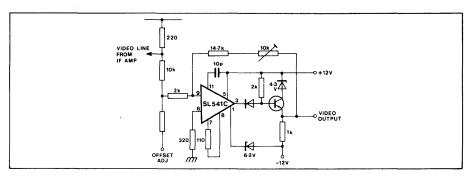

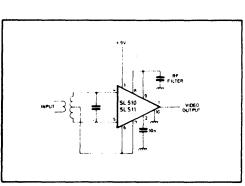

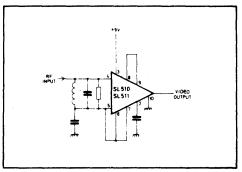

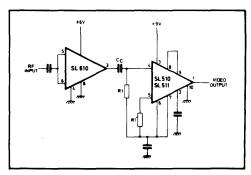

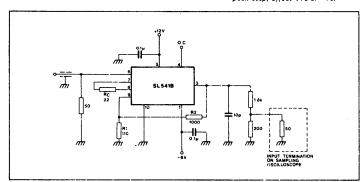

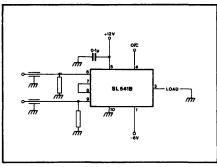

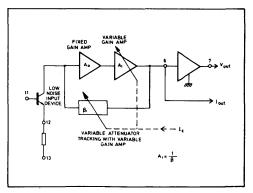

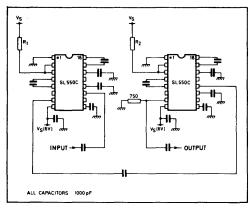

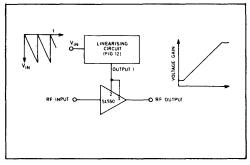

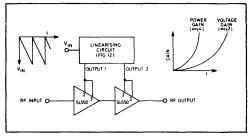

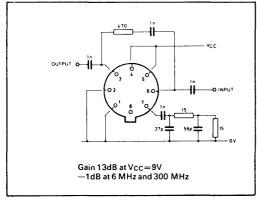

Three other Plessey IC's complete the system simply and economically. The AGC-able SL1550 on the front end improves noise figure, dynamic range and sensitivity. The SL541 lets you vary video output levels, with on-chip compensation making it easy to use. And the SL560 is a "gain block" that replaces your hybrid and discrete amplifiers, usually with no external components.

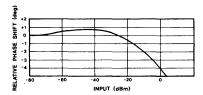

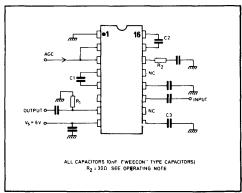

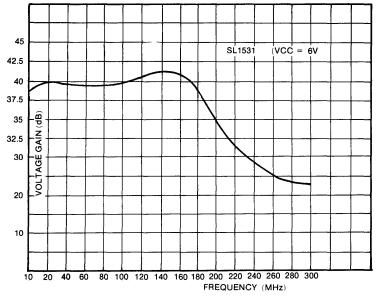

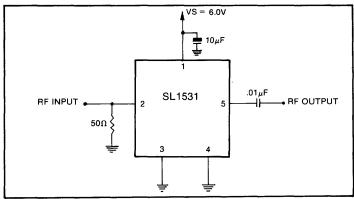

Another advanced system function block is the Plessey SL531 True Log Amplifier. A 6-stage log strip requires a

### PLESSEY IC'S FOR RADAR I.F.'S

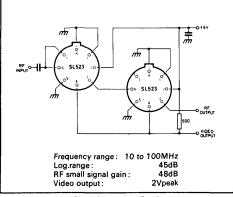

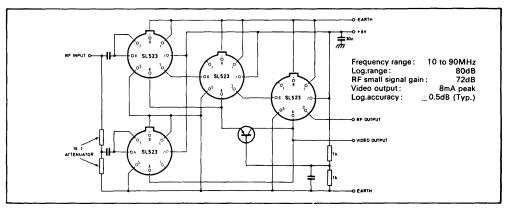

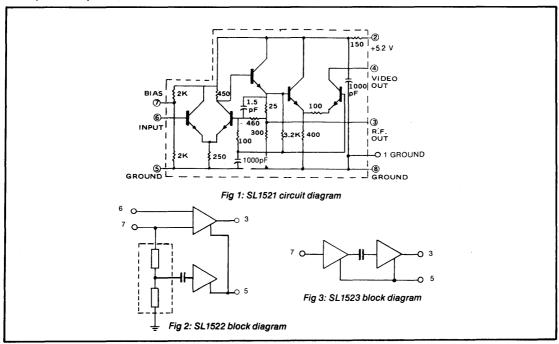

### Wideband Amplifiers for Successive Detection Log Strips

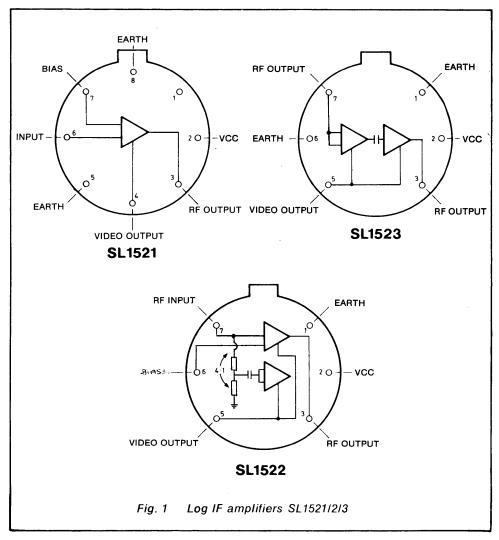

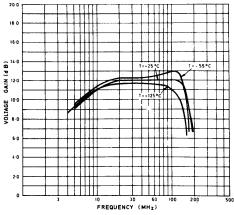

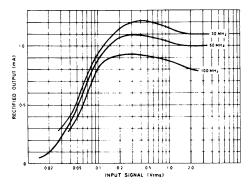

SL521 30 to 60 MHz center frequency, 12 dB gain.

\$L523 Dual \$L521 (series).

SL1521 60 to 120 MHz center frequency, 12 dB gain.

SL1522 Dual SL1521 (parallel). SL1523 Dual SL1521 (series).

### Low Phase Shift Amplifiers

SL531 True log I.F. amplifier, 10-200 MHz, ±0.5°/10 dB max phase shift.

SL532 400 MHz bandwidth limiting amplifier, 1° phase shift max, when overdriven 12 dB.

### Linear Amplifiers

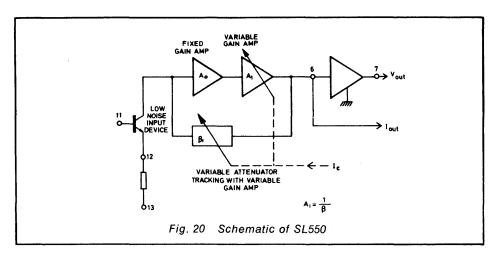

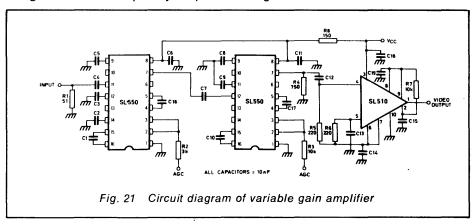

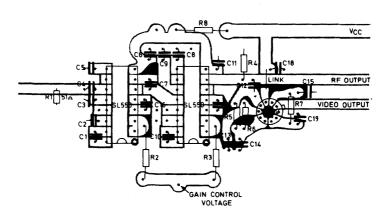

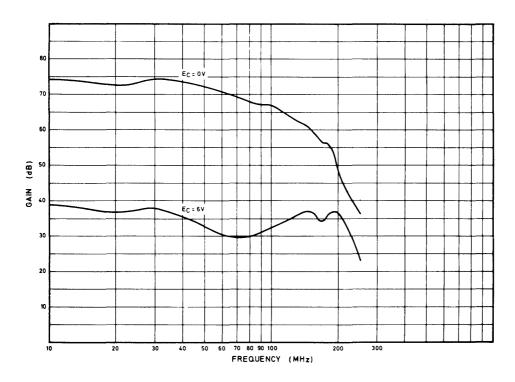

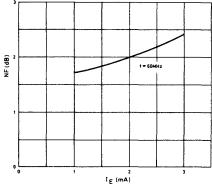

SL550 125 MHz bandwidth, 40 dB gain, 25 dB swept gain control range, 1.8 dB noise figure, interfaces to microwave mixers.

SL1550 320 MHz bandwidth version of SL550.

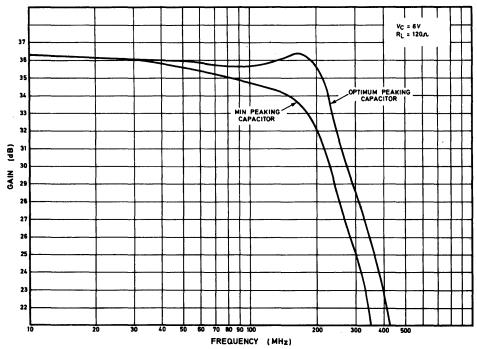

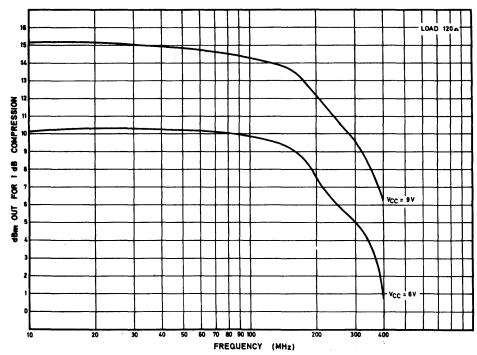

SL560 300 MHz bandwidth, 10 to 40 dB gain, 1.8 dB noise figure drives 50 ohm loads, low power consumption.

### Video Amplifiers and Detectors

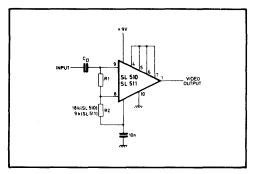

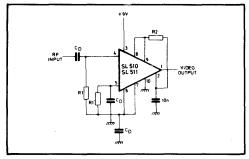

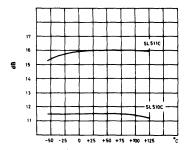

SL510 Detector (DC to 100 MHz) and video amplifier (DC to 24 MHz) may be used separately, 11 dB incremental gain 28 dB dynamic range.

SL511 Similar to SL510 with DC to 14 MHz video amplifier, 16 dB incremental gain.

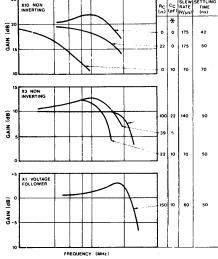

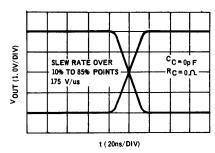

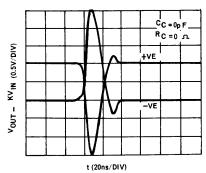

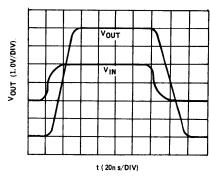

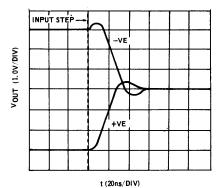

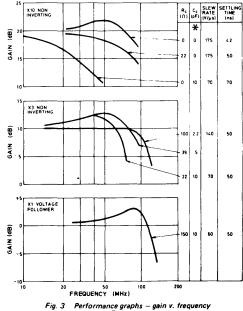

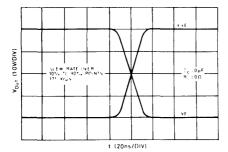

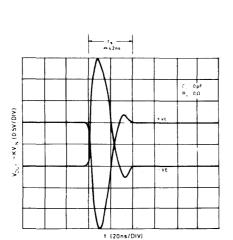

SL541 High speed op amp configuration, 175 V/µs slew rate 50 ns settling time, stable 70 dB gain, 50 ns recovery from overload.

# **Radio Communications**

-1161-

Our comprehensive line of radio system function blocks is cutting costs, increasing reliability and reducing the size of systems

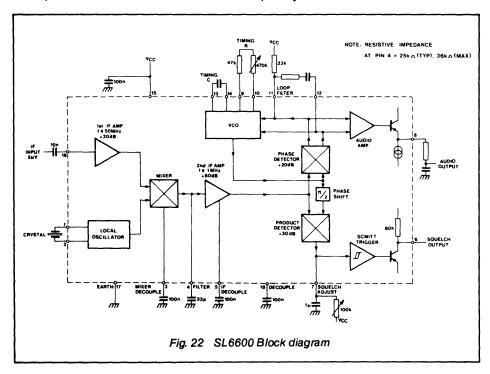

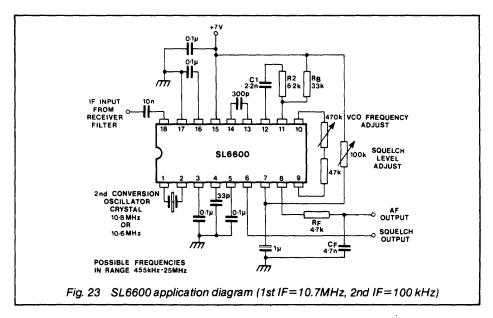

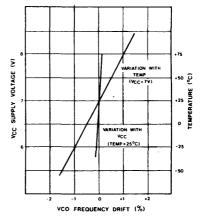

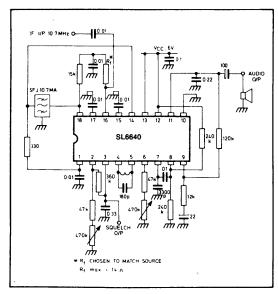

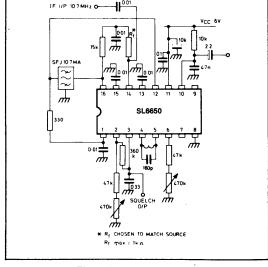

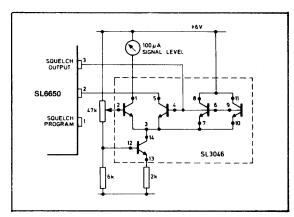

peak deviation. The SL6600 can be used at I.F. frequencies up to 50 MHz, with deviations up to 10 kHz.

If any of the Plessey devices appear interesting, use the postage-paid reply card at the back of this book to order our RADAR AND RADIO COMMUNICATIONS IC HANDBOOK. The Handbook includes full details on our integrated circuits, along with a number of applications circuits and design tips that will help you get the maximum system benefits from Plessey products.

Or if your need is more urgent, contact your nearest Plessey Semi-conductors representative.

in applications that range from commercial communications to military manpack radios.

Using our bipolar Process I, the Plessey SL600 Series (hermetic) and SL1600 Series (plastic DIP) feature a high degree of integration, low power consumption and exceptional system design flexibility for I.F.'s up to 10.7 MHz.

Our SL6000 Series uses our bipolar Process III to extend our building block concept even further. Devices all feature advanced circuit design techniques that permit higher levels of integration, lower power consumption and exceptional performance.

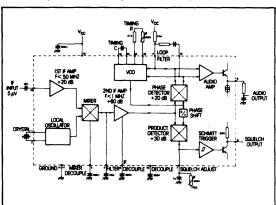

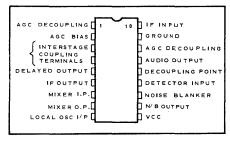

Typical is our SL6600, a monolithic IC that contains a complete IF amplifier, detector, phase locked loop and squelch control. Power consumption is a meager 1.5 mA at 6 V, S/N ratio is 50 dB, dynamic range is 120 dB and THD is just 1.3% for 5 kHz

### PLESSEY RADIO IC'S

| Amplific      | ers           |                                                                                             |

|---------------|---------------|---------------------------------------------------------------------------------------------|

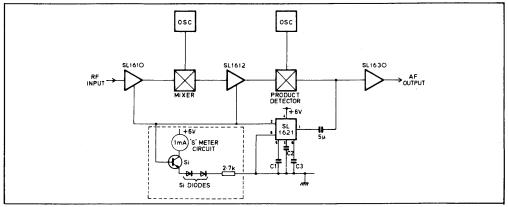

| SL610         | SL1610        | 140 MHz bandwidth, 20 dB gain, 50 dB AGC range, low 4 dB N.F., low distortion.              |

| SL611         | SL1611        | 100 MHz bandwidth, 26 dB gain, sim, to SL610.                                               |

| SL612         | SL1612        | 15 MHz bandwidth, 34 dB gain, 70 dB AGC                                                     |

|               |               | range, 20 mW power consumption.                                                             |

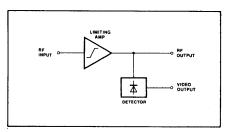

| SL613         |               | 145 MHz bandwidth, 12 dB gain, limiting amp/detector.                                       |

| Mixers        |               |                                                                                             |

| SL640         | SL1640        | Double balanced modulator eliminates diode rings up to 75 MHz, standby power 75 mW typical. |

| Detecto       | rs and A      | GC Generators                                                                               |

| <b>SL620</b>  | \$L1620       | AGC with VOGAD (Voice Operated Gain Adjusting Device).                                      |

| SL621         | SL1621        | AGC from detected audio.                                                                    |

| SL623         |               | AM SSB detector and AGC from carrier.                                                       |

|               | SL1625        | AM detector and AGC from carrier.                                                           |

| SL624         |               | AM/FM/SSB/CW detector with audio amplifier.                                                 |

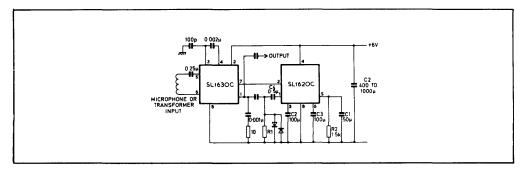

| Audio A       | mplifier      |                                                                                             |

| SL622         |               | Microphone amp. with VOGAD and sidetone amp.                                                |

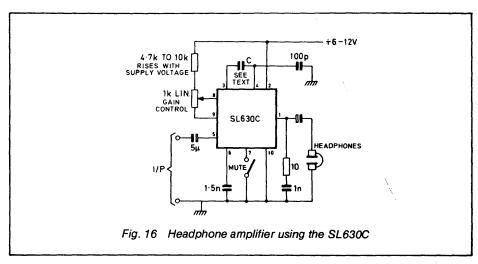

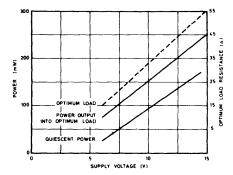

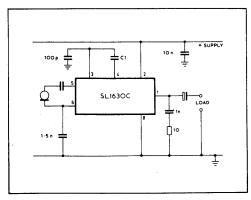

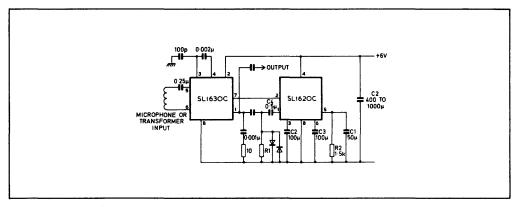

| SL630         | SL1630        | 250 mW microphone/headphone amplifier.                                                      |

| I.F. Amp      | olifiers/D    | etectors                                                                                    |

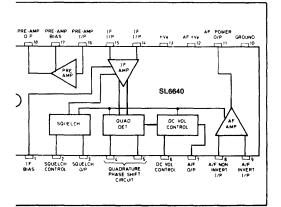

| SL6600        |               | FM double conversions with PLL detector.                                                    |

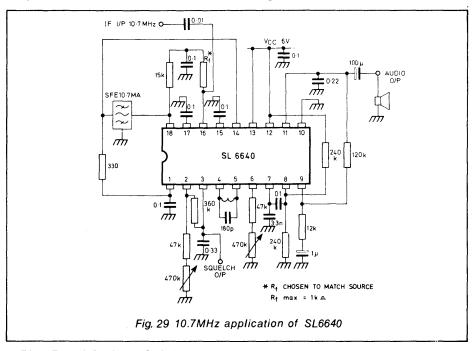

| <b>SL6640</b> |               | FM single conversion, audio stage (10.7 MHz).                                               |

| SL6650        |               | FM single conversion (10.7 MHz).                                                            |

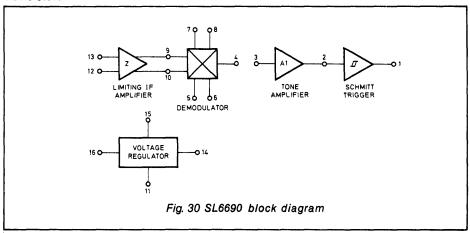

| SL6690        |               | FM single conversion, low power for pagers (455 kHz).                                       |

| <b>SL6700</b> |               | AM double conversion.                                                                       |

| Audio A       | mplifiers     |                                                                                             |

| SL6270        |               | Microphone amplifier with AGC.                                                              |

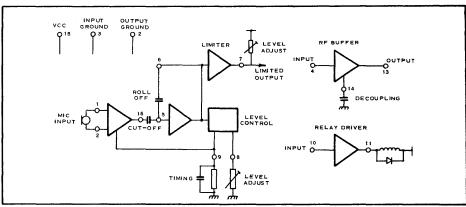

| SL6290        | <b>SL6270</b> | with speech clipper, buffer and relay driver.                                               |

| SL6310        |               | Switchable audio amplifier (400 mW/9V/8 ohms).                                              |

| SL6440        |               | High-level mixer.                                                                           |

|               |               |                                                                                             |

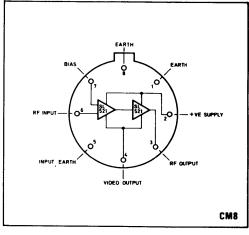

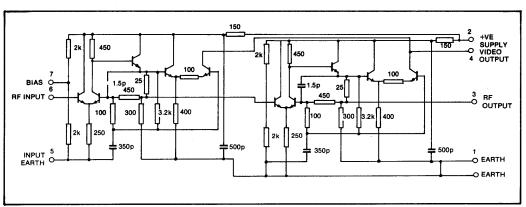

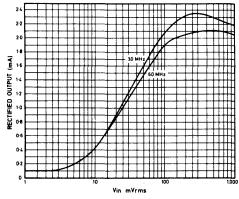

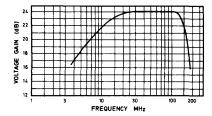

# R.F. Hybrids

To enhance your systems even further, we have established an R.F. hybrid manufacturing facility in our Irvine, California, U.S.A. headquarters.

For small production quantities or extremely complex functions, our hybrid capabilities can save you time and money while improving your system performance, reducing system size and increasing system reliability. We can help with your I.F. strips, instrumentation front ends, synthesizer subsystems, high speed A-to-D and D-to-A converters and other complex high-frequency functions.

They can be fabricated to MIL-STD-883 using thick and thin film techniques, using our own integrated circuits in combination with discrete transistors, diodes and other components.

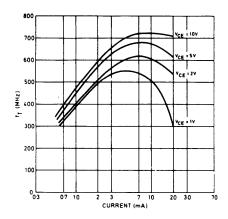

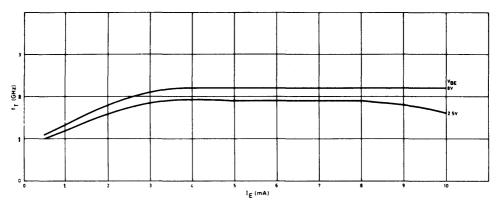

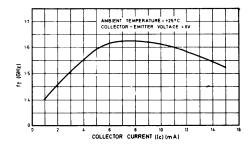

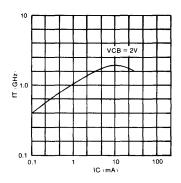

Our IC functions represent the state-of-the-art in high frequency integration, with  $f_t$ 's as high as 5 GHz. The chips are backed by an in-depth in-house systems knowledge that encompasses radar, radio communications, telecommunications analog and digital conversion, frequency synthesis and a broad range of applications experience.

We can work to your prints, or we can design a full system based on your "black box" specifications. For more information, please contact: Plessey Semiconductors, 1641 Kaiser Avenue, Irvine CA 92714, (714) 540-9979.

# **Frequency Synthesis**

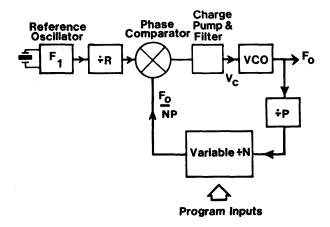

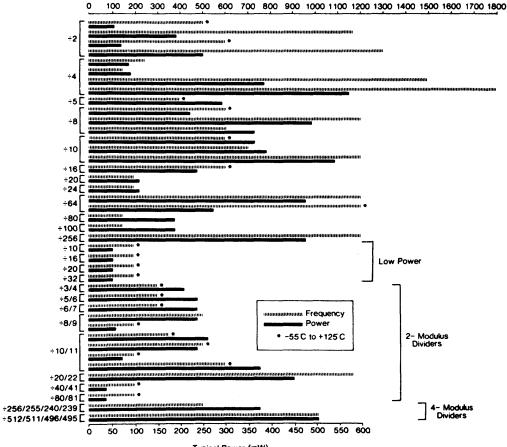

Plessey's IC's offer a quick and easy way to lower synthesizer costs while increasing loop response and channel spacing all the way from dc through the HF, VHF, UHF, TACAN and satellite communications bands.

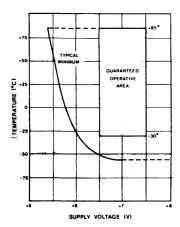

Our single-modulus prescalers operate at frequencies all the way up to 1.8 GHz. They feature self-biasing clock inputs, TTL/CMOS-compatibility and all guaranteed to operate to at least the frequencies shown, most of them over the temperature range from  $-55^{\circ}$ C to  $+125^{\circ}$ C.

Our 2-modulus and 4-modulus dividers expand your system flexibility and allow even tighter channel spacing. All of them provide low power consumption, low propagation delay and ECL compatibility.

gation delay and ECL-compatibility.

To simplify your systems even further, we also offer highly integrated control chips. Our NJ8811, for example, includes a crystal oscillator maintaining circuit, a programmable reference divider, a programmable divider to control the four-modulus prescaler and a high performance phase/frequency comparator so that you can phase lock your synthesizer to a crystal with none of the usual headaches and hassles.

We've put together a FREQUENCY SYNTHESIZER IC HANDBOOK that details all of the Plessey IC's and includes a number of applications circuits, practical examples of how Plessey integrated circuits can simplify your designs and improve system performance.

For your copy of the Handbook, please use the postagepaid reply card at the back of this book, or contact your nearest Plessey Semiconductors representative.

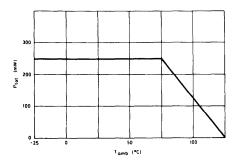

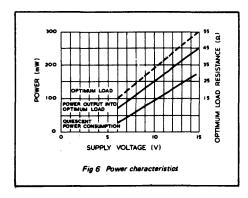

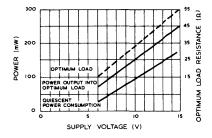

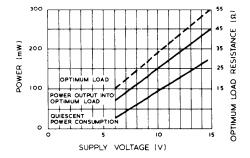

Typical Power (mW)

# **Telecommunications**

Plessey functional building block IC's are exceptionally versatile. Designed from a systems standpoint, they reduce complexity and lower costs while increasing the performance of telecommunications systems.

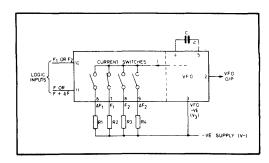

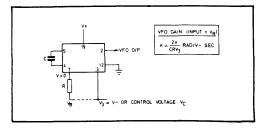

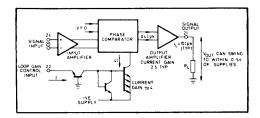

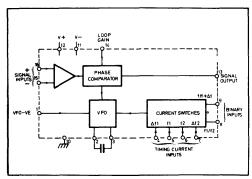

Our SL600 Modulator/Phase Locked Loops are used in waveform generators and in AM, PAM, FM, FSK, PSK, PWM, tone burst and Delta modulators.

Our SL1000 Series amplifiers meet the most stringent demands of telephone transmission equipment.

Our transistor arrays with up to five electrically and thermally matched transistors on a chip are ideal for discrete and hybrid amplifiers and mixers. In addition to standard second-source devices that plug directly into your designs, we have a number of devices designed for your low noise and ultrahigh frequency applications.

The Plessey TELECOMMUNICA-TIONS IC HANDBOOK contains complete information on all of these devices, as well as application notes, to help you get the most out of them. To get your copy, please use the postage-paid reply card at the back of this book or call your nearest Plessey Semiconductors representative.

### **Telecommunications Devices**

| M11440  | HDB3 encoder/decoder |

|---------|----------------------|

| WJ 1440 | nubs encoder/decoder |

MJ1444 PCM synchronizing word generator

MJ1445 PCM synchronizing word receiver MJ1471 HDB3/AMI encoder/decoder

Data Communications MOS

MP3812 32 x 8-bit FIFO memory, serial or parallel, up to 0.25 MHz data rates, easily stacked.

MJ2841 64 x 4-bit FIFO memory, 5 MHz clock rate.

### Modulator/Phase Locked Loops

SL650 Modulator/PLL for AM, PAM, SCAM, FM, FSK, PSK, tone-burst and Delta modulation:

VFO variable 100:1.

SL651 Similar to SL650 without auxiliary amplifier.

\$L652 Similar to \$L650, low cost.

### **Telephone Circuits**

SL1001 Modulator/demodulator, 50 dB carrier and signal suppression, -112 dBm noise level.

\$L1021 3 MHz channel amplifier, stable remote

gain control.

SL1025 FDM balanced modulator, 50 dB carrier and signal

suppression, 5 dB conversion gain.

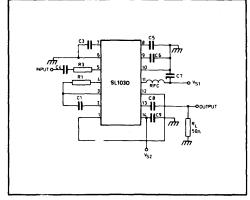

SL1030 200 MHz wideband amplifier, programmable gain, low noise.

### Transistor Arrays

| PLESSEY<br>PART NO. | 2ND-SOURCE<br>PART NO. | PLESSEY<br>PART NO. | 2ND-SOURCE<br>PART NO. |

|---------------------|------------------------|---------------------|------------------------|

| SL3081              | CA3081                 | SL3051              | CA3951                 |

| SL3082              | CA3082                 | SL355               | NONE                   |

| SL3083              | CA3083                 | TBA673              | TBA673                 |

| SL3183              | CA3183                 | SL1495              | CA1495L                |

| SL3146              | CA3146                 | SL1496              | MC1496G                |

| <b>SL</b> 3093      | CA3093                 | SL1496              | MC1496L                |

| SL3018              | CA3018                 | SL1595              | MC1595L                |

| \$L3018A            | CA3018A                | SL1596              | MC1596G                |

| SL3118A             | CA3118A                | SL1596              | MC1596L                |

| SL3118              | CA3118                 | SL3054              | CA3054                 |

| SL3050              | CA3050                 | SL3086              | CA3086                 |

\$L360 High frequency matched pair, ft=2.5 GHz. Low noise matched pair, ft=2.2 GHz.

\$L2363/4 5GHz dual long-tailed pair.

\$L3145 Five transistor array, ft=2.5 GHz.

# **Television IC's**

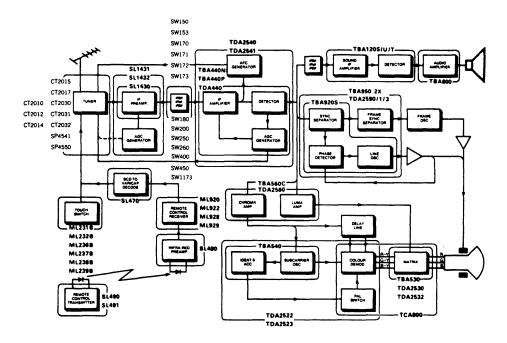

Plessey integrated circuits are in millions of homes, in television sets around the world.

Economical and reliable, our devices cover the range from remote controls to touch tuners to frequency synthesizers, as well as a range of second-source devices for the IF color processing and line oscillators.

For the 1980's, we have introduced the Plessey KEY System, designed for maximum flexibility, simplicity and ease of manufacture. The KEY System frequency synthesizer offers accurate, high stability frequency selection, channel and program identification, and the very finest digital fine tuning. It can be configured to

receive up to four completely different standards (PAL, SECAM, SECAMF, and NTSC) in a single TV set. It has 100 channel capability per standard, and includes a 32-program non-volatile memory that contains channel, fine tuning and standards information. And it can be interfaced to a Plessey or other microprocessor for games, Teletext or similar applications.

Complete data on all our television devices has been assembled in our TELE-VISION IC HANDBOOK, along with application notes to make them even easier to use. Please use the postage-paid reply card at the back of this book to order your copy, or simply contact your nearest Plessey Semiconductors representative.

ALL TBA, TCA, TDA DEVICES ARE SECOND-SOURCED.

# **ECL III Logic and Data Conversion**

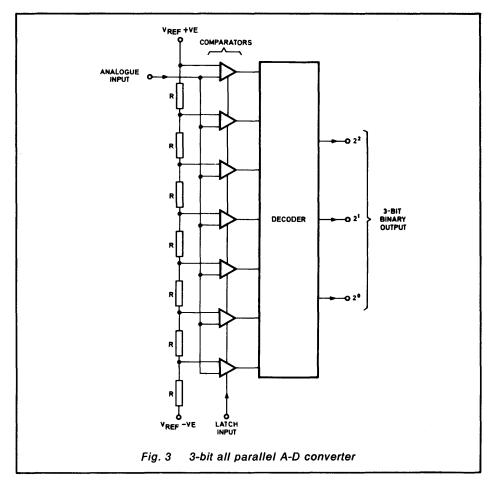

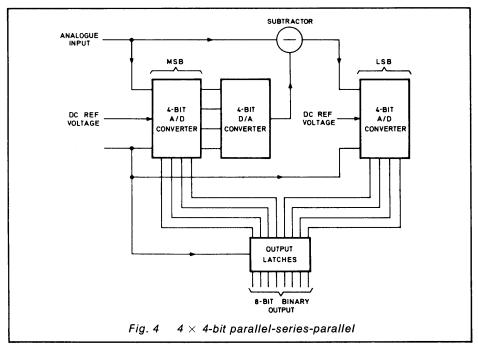

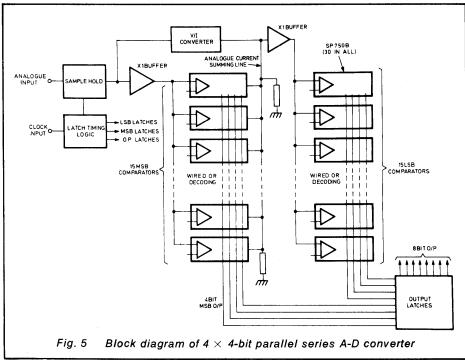

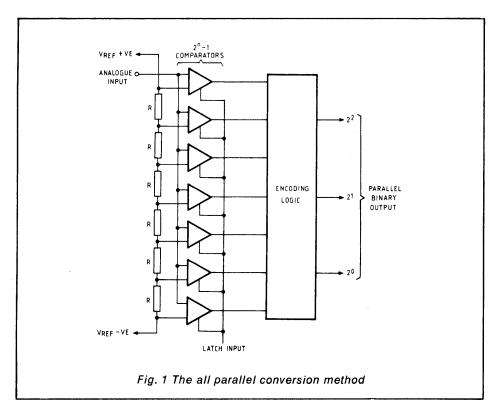

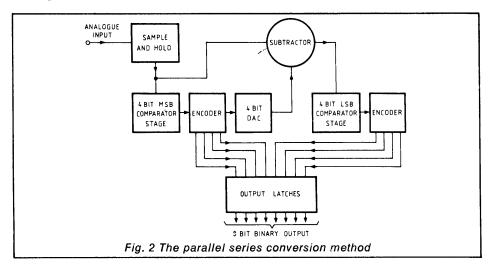

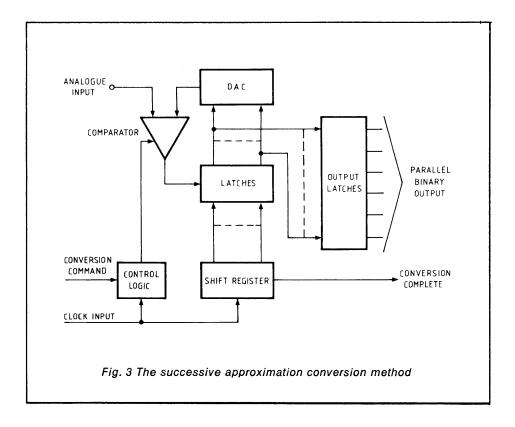

As radar and communications systems become faster and more complex, the need arises for digital processing. We have developed a family of functions with speeds unequalled anywhere.

Part of our family is a range of ECL III logic that is a direct plug-in replacement for MECL logic, including low impedance as well as high impedance devices. We extended the range by adding functions with lower delays and much higher operating speeds. Our SP16F60, for example, is the world's fastest dual 4-input OR/NOR gate, with a switching speed of just 500 picoseconds. Devices can also be selected for certain specifications (such as threshold voltage or slew rate on

our SP1650/1, toggle rates or delays on our SP1670) to handle your most demanding applications. We've also developed a family of high speed comparators and circuits for ultra-high

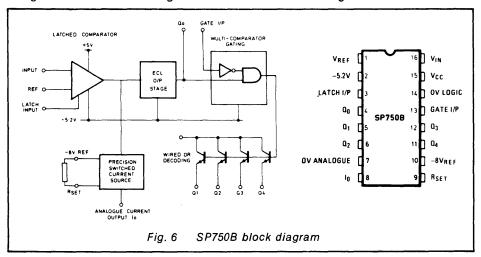

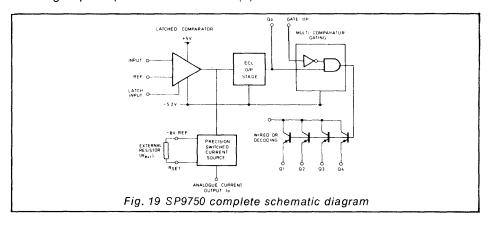

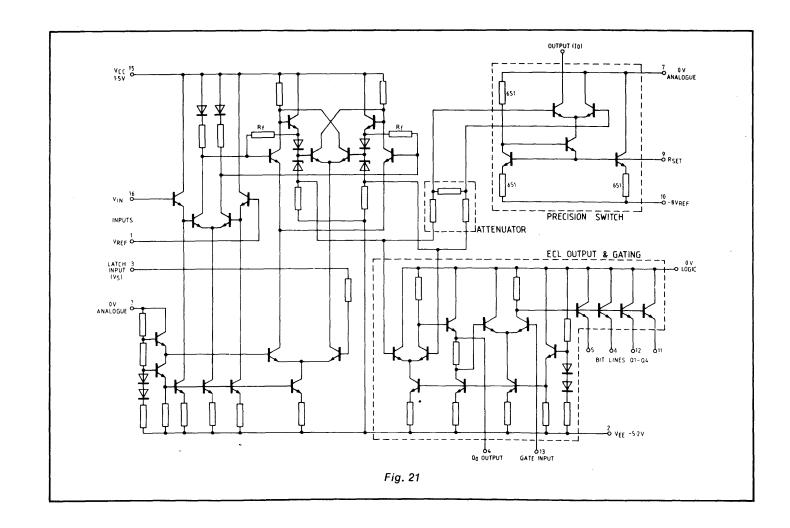

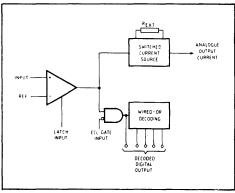

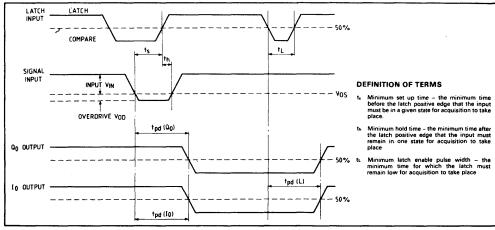

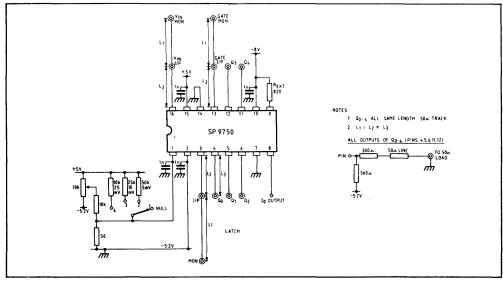

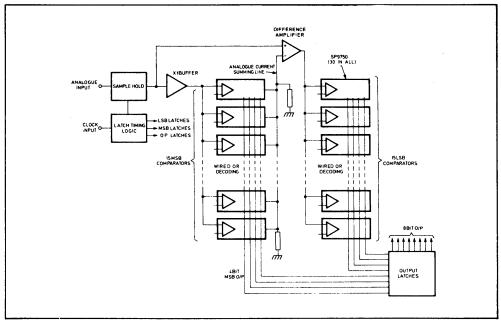

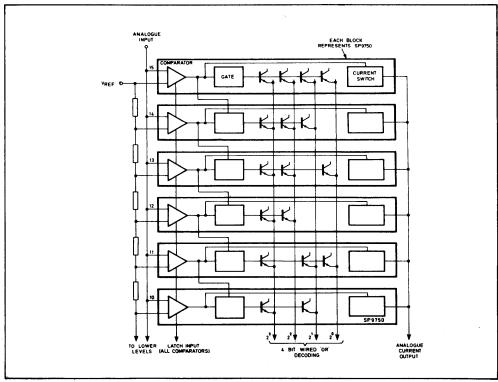

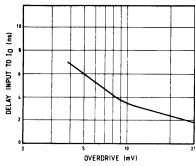

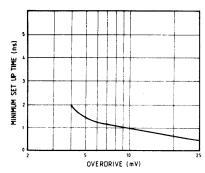

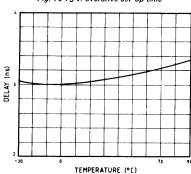

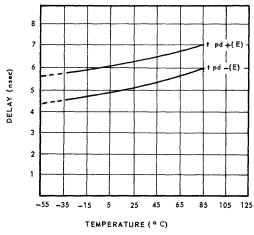

speed A-to-D converters. Our latching SP9750 high speed comparator features a maximum settling time of 2 ns, a propagation delay of 3.5 ns and is capable of operating at rates up to 100 million samples per second.

Currently, our devices are being used in radar and video processing, nucleonics systems, transient recorders and secure speech transmission systems. We have compiled a number of application notes and details on the devices in our ECL III LOGIC AND DATA CONVERSION IC HANDBOOK. To get your copy, please use the postage-paid reply card at the back of this book, or contact your nearest Plessey Semiconductors representative.

### HIGH SPEED ECL III LOGIC

| SP1648  | Voltage controlled oscillator         |

|---------|---------------------------------------|

| SP1650  | Dual A/D comparator, Hi-Z             |

| SP1651  | Dual A/D comparator, Lo-Z             |

| SP1658  | Voltage controlled multivibrator      |

| SP1660  | Dual 4-I/P OR/NOR gate, Hi-Z          |

| SP1661  | Dual 4-I/P OR/NOR gate, Lo-Z          |

| SP1662  | Quad 2-I/P NOR gate, Hi-Z             |

| SP1663  | Quad 2-I/P NOR gate, Lo-Z             |

| SP1664  | Quad 2-I/P OR gate, Hi-Z              |

| SP1665  | Quad 2-I/P OR gate, Lo-Z              |

| SP1666  | Dual clocked R-S Flip-Flop, Hi-Z      |

| SP1667  | Dual clocked R-S Flip-Flop, Lo-Z      |

| SP1668  | Dual clock latch, Hi-Z                |

| SP1669  | Dual clock latch, Lo-Z                |

| SP1670  | Master-slave D Flip-Flop, Hi-Z        |

| SP1671  | Master-slave D Flip-Flop, Hi-Z        |

| SP1672  | Triple 2-I/P exclusive-OR gate, Hi-Z  |

| SP1673  | Triple 2-I/P exclusive-OR gate, Lo-Z  |

| SP1674  | Triple 2-I/P exclusive-NOR gate, Hi-Z |

| SP1675  | Triple 2-I/P exclusive-NOR gate, Lo-Z |

| SP1692  | Quad line receiver                    |

| SP16F60 | Dual 4-I/P OR/NOR gate                |

### HIGH SPEED DATA CONVERSION PRODUCTS

| SP9680 | High speed latched comparator.                             |

|--------|------------------------------------------------------------|

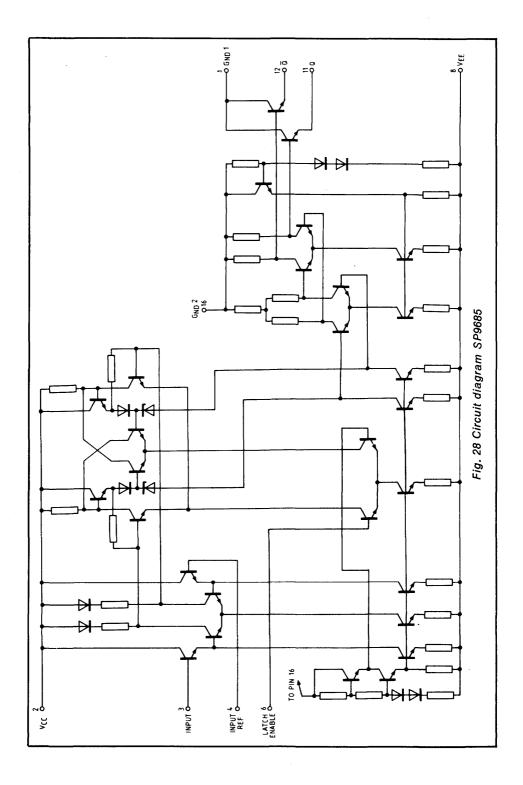

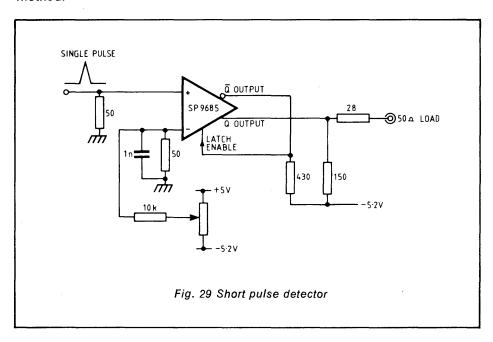

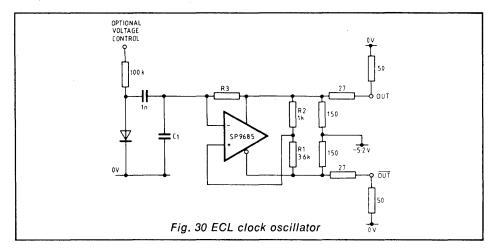

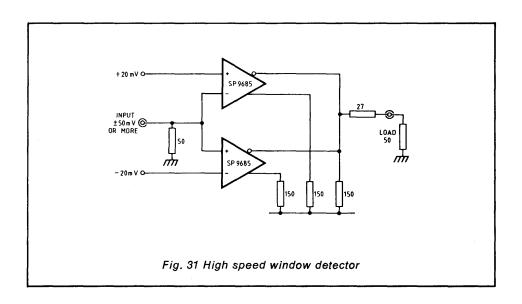

| SP9685 | Ultra-fast comparator; 0.5 ns typical set-up time; typical |

|        | 2.2 ns propagation delay; excellent CMR.                   |

SP9687 Dual SP 9685.

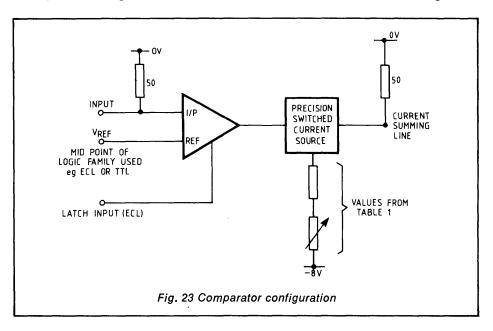

\$P9750 High speed latched comparator with precision current source, wired-OR decoding; 2 ns min. set-up time; 2.5 ns propagation delay.

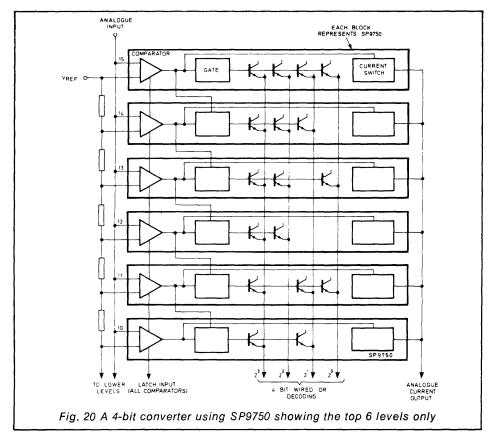

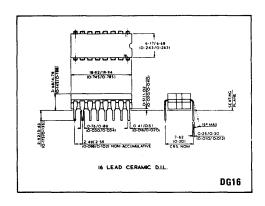

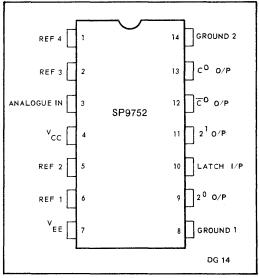

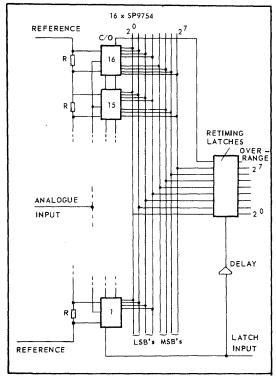

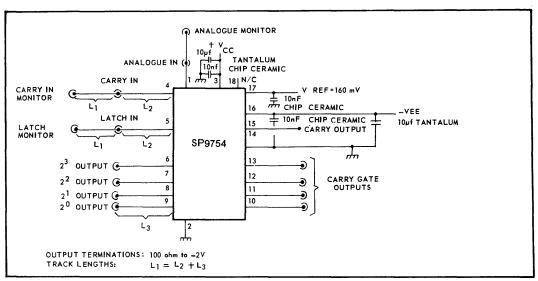

propagation delay. SP9752 2-bit ADC expandable to 6-bit ADC; very fast 125 MHz clock. SP9754 4-bit ADC expandable to 8-bit ADC; very fast 100 MHz clock.

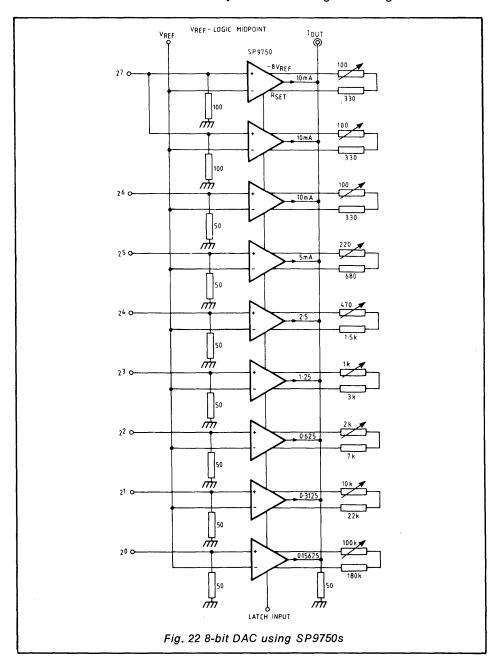

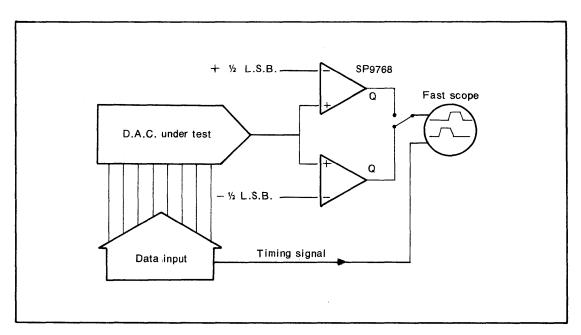

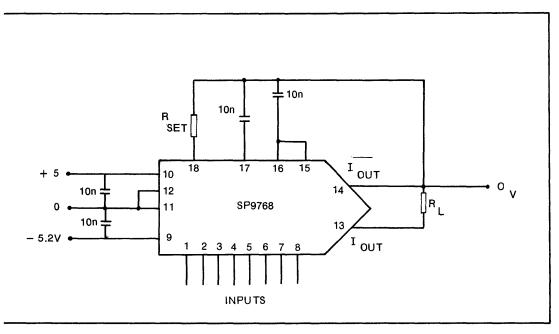

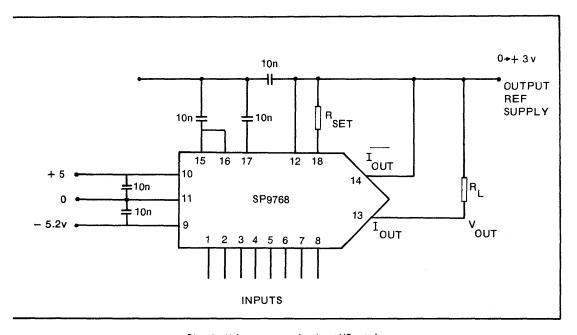

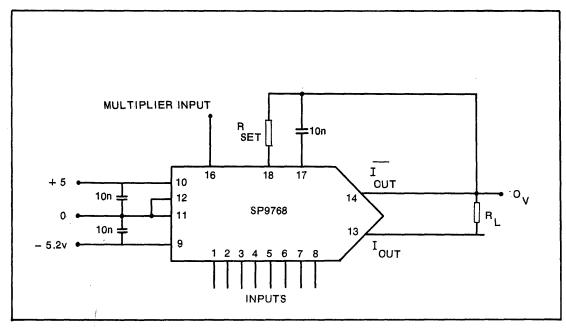

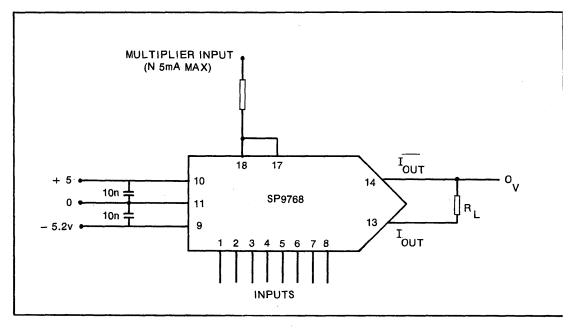

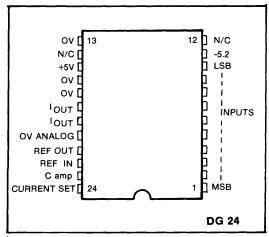

SP9768 8-bit DAC; extremely fast; available 3rd quarter 1980. SP9778 8-bit SAR; works with SP9768 to make a two-chip successive approximation ADC (20 MHz clock); available 4th quarter 1980.

# **MNOS Non-Volatile Logic**

As semiconductors become more pervasive in military and commercial applications, the need for non-volatile data retention becomes more and more critical.

Plessey NOVOL MNOS devices answer that need, and will retain their data for at least a year  $(-40^{\circ}\text{C to} + 70^{\circ}\text{C})$  in the event of "power down" or a system crash.

Our devices all operate from standard MOS supplies and are fully compatible with your TTL/CMOS designs. The high voltages normally associated with electrically-alterable memories are generated on-chip to make system interface simpler and less expensive.

Plessey NOVOL devices provide a reliable, sensible alternative to CMOS with battery back-up or mechanical, electro-mechanical and magnetic devices. Applications include metering, security code storage, microprocessor back-up, elapsed time indicators, counters, latching relays and a variety of commercial, industrial and military systems.

For more information, contact your nearest Plessey Semiconductors representative, or use the postage-paid reply card at the back of this brochure to order your copy of the Plessey NOVOL literature package.

### PLESSEY NOVOL MNOS

MN9102 4-bit Data Latch (+5V, -12V) MN9105 4-Decade Up/Down Counter (+5V, -12V) 6-Decade Up Counter (12V only) MN9106 MN9107 100-Hour Timer (12V only) MN9108 10,000-Hour Timer (12V only) MN9110 6-Decade Up Counter with Carry (12V only) 64 x 4-Bit Memory MN9210 8 x 4-Bit Memory 6-Decade Up/Down Counter, BCD Output 6-Decade Up/Down Counter with Preset BCD Output \* COMING SOON

### **Power Control**

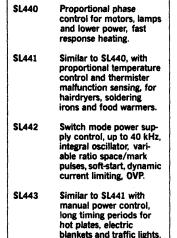

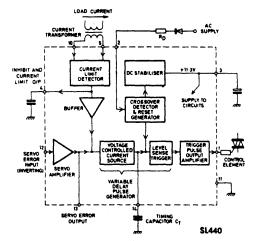

Plessey power control devices are highly integrated not just to solve the problems, but to solve them at a lower cost than any other available method.

For timing, our devices use a pulse integration technique that eliminates the need for expensive electrolytic capacitors, thus increasing accuracy and repeatability while reducing costs. An integral supply voltage sensing circuit inhibits triac gate drive circuitry if the supply is dangerously low to prevent half-wave

firing and firing without achieving complete bulk conduction. A zero-voltage

spike filter prevents misfiring on noise inputs. Symmetrical control prevents the introduction of dc components onto the power lines.

Devices have been tailored for specific applications as indicated in the chart. For more information, please use the postage-paid reply card at the back of this book to order our POWER CONTROL IC HANDBOOK, or contact your nearest Plessey Semiconductors representative.

SL444 Similar to SL441 for 240V permanent magnet motor with thermal trip, current limit detector.

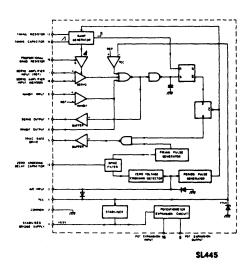

St.445 Proportional or On/Off control, temperature trip/inhibit circuitry, LED and alarm drive facilities, for ovens, heaters, industrial temperature controllers.

SL446 On/Off servo loop temperature controller, low external component count, for water and panel heaters, refrigerators. irons.

TBA1085 Motor speed control

# **Processes, Testing and Quality Control**

Just as we applied our systems knowledge to the partitioning of functions to make our IC's extremely flexible and cost effective, we also developed an internal system concept to ensure that we could deliver our state-of-the-art solutions year after year.

Our concept of standard processes and rigid design rules ensures that our devices are reproducible this year, next year and five years from now. Our continuing investment in research and development ensures that any new products we introduce will be on the leading edge of technology, yet with the same high performance and reliability that our customers have come to expect as the Plessey standard.

The result is that millions of Plessey devices have been built into TV sets and car radios; CATV, navigation and radar systems; frequency synthesizers and telecommunications equipment.

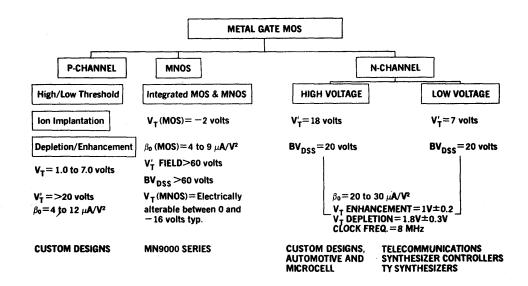

# **Plessey MOS Processes**

P-channel metal gate MOS has been in production for years and is used for both standard Plessey products and custom LSI. Using ion implantation to modify transistor and field threshold voltages, we can reproduce virtually any p-channel metal gate process, with or without depletion loads.

MNOS (non-volatile) is essentially a p-MOS process with variable threshold memory transistors fabricated alongside conventional MOS transistors. A modified oxide-nitride gate dielectric permits the injection and retention of charge to change the threshold voltage. Current Plessey products will retain an injected charge for at least a year, and include an on-chip high voltage generator so that

they may be used with standard supply voltages.

N-channel metal gate MOS uses an auto-registration co-planar process with layout similar to our p-MOS. Ion implantation is used to define the threshold voltage of the depletion and enhancement transistors. The constant-current-like characteristics of depletion load devices give the most effective driving capability. and enhancement-depletion technology simplifies design and increases packing density. The field threshold voltage is also controlled by an ion implant, allowing the use of a lightly doped substrate. This reduces both the body constant and the junction capacitance and results in faster switching speeds.

# Plessey Bipolar Processes

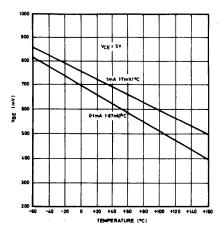

**Bipolar Process I** is a conventional buried +N layer diffusion process with  $f_t$ =600 MHz and other characteristics similar to industry-standard processes. Applications range from high reliability military devices to high volume consumer products.

| Process Variant         | A                  | B<br>Non            | G                   | D                               |

|-------------------------|--------------------|---------------------|---------------------|---------------------------------|

| Application             | General<br>Purpose | Saturating<br>Logic | Saturating<br>Logic | Linear<br>Consumer              |

| BVcB0 @ 10µA            | 20V min.           | 10 <b>V</b> min.    | 10 <b>V</b> min.    | 45 <b>V</b> min.                |

| BVEB0 @ 10µA            | 5.3V to<br>5.85V   | 5.15V min.          | 5.15V min.          | 6.8 <b>V</b> to<br>7.4 <b>V</b> |

| LVCEO                   | 12V min.           | 8V min.             | 8V min.             | 20V min.                        |

| VCE (SAT) @             |                    |                     |                     |                                 |

| lB=1mA.                 | 0.43 <b>V</b>      | 0.32 <b>V</b>       | 0.43 <b>V</b>       | 0.6 <b>V</b>                    |

| lc=10mÁ                 | max.               | max.                | max.                | max.                            |

| hFE @ IC=5mA,<br>VCE=5V | 40 to 200          | 50 min.             | 50 min.             | 50 to 200                       |

| ft @ lc=5mA,<br>VcE=5V  | 500<br>MHz         | 500<br>MHz min.     | 500<br>MHz min.     | 350<br>MHz min.                 |

Bipolar High Voltage (HV) Process is a variant of Process I that yields an  $LV_{ceo}$  greater than 45 volts. Doping levels can be controlled and an extra diffusion used to fabricate a buried avalanche diode with a 40 V breakdown for absorbing powerful noise transients without being destroyed.

| Process Variant     | CA               |

|---------------------|------------------|

| ВVсво @ 10µA        | 80V min.         |

| BVEB0 @ 10μA        | 7.2V to 8.0V     |

| LVCEO               | 45 <b>V</b> min. |

| VCE (SAT) @ IB=1mA, |                  |

| ic=10mA             | 0.4V max.        |

| hFE @ lc=5mA        |                  |

| VCE=5V,             | 80 to 300        |

| fT @ IC=5mA, VCE=5V | 250 MHz min.     |

Bipolar Process III uses very shallow diffusion and extremely narrow spacing for high frequency integrated circuits with unusually low power consumption and high packing densities. An  $f_t$  of 2.5 GHz allows us to routinely produce analog amplifiers with bandwidths as high as 300 MHz and low power dividers and prescalers that operate at frequencies up to 1.2 GHz. Process variants allow us to produce devices with an extended  $\beta$ , higher breakdown voltages and very small geometries.

| Process Variant      | WE           |

|----------------------|--------------|

| Application          | Digital      |

| BVcB0 @ 10μA         | 10V min.     |

| BVEBO @ 10μA         | 5.1V to 5.8V |

| LVCEO                | 7V min.      |

| VCE (SAT) @ IB=1mA,  |              |

| lc=10mÅ              | 0.5V max.    |

| hfe @ Ic=5mA, VcE=2V | 40 to 200    |

| fT @ IC=5mA, VCE=2V  | 1.8 GHz      |

Bipolar Process 3V is an extension of our Process III. Ion implantation and washed emitters have given the process an  $f_t$ =6.5 GHz, allowing us to produce dividers working at 2 GHz, logic gates with delays of less than 500 picoseconds and linear amplifiers at 1 GHz.

| Process Variant       | wv           |

|-----------------------|--------------|

| Application           | Digital      |

| BVcво @ 10µA          | 8V min.      |

| BVEBO @ 10µA          | 3.0V to 5.0V |

| LVCEO@ 5mA            | 6V min.      |

| VCE (SAT) @ IB=1mA,   |              |

| IC=10mA               | 0.5V max.    |

| hFE @ Ic=10mA, VCE=5V | 40 to 120    |

| fT @ IC=5mA, VCE=2V   | 6.5 GHz      |

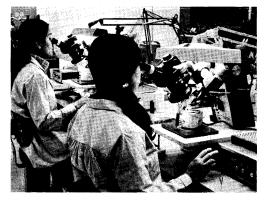

# Testing and Quality Control

A major thrust of our development work is to ensure that our processes will routinely produce reliable devices. Our Process III has a projected MTBF of 400,000 hours while our Process I is even better.

Our facilities include the latest test equipment (such as the Macrodata MD501, Teradyne J324 and Fairchild Sentry VII and Sentinel) to allow us to perform all the necessary functional and parametric testing in-house. We have an internal capability to provide specific applications-oriented

screening, and most Plessey IC's are available screened to MIL-STD-883 and other international specifications. Our quality levels exceed the most stringent military, TV and automotive requirements as a matter of course.

But the best proof of all these claims is our products themselves. After you've reviewed the products that could help you with your systems, use the postage-paid reply card or contact your nearest Plessey representative for complete details.

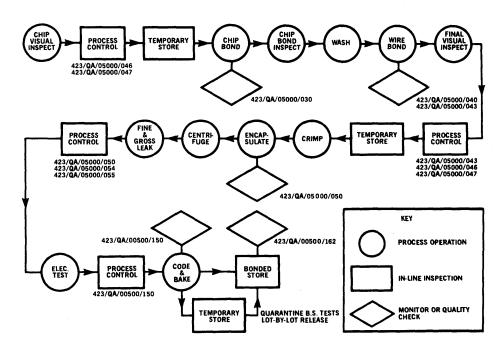

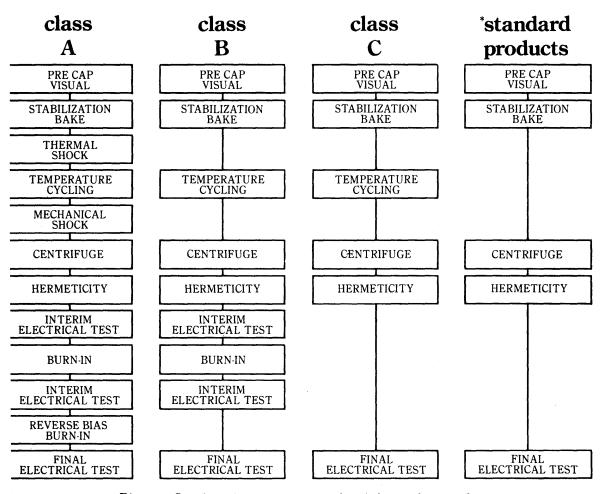

### ASSEMBLY OF INTEGRATED CIRCUITS QUALITY ASSURANCE

# I.C. Screening to MIL-STD-883

The following Screening Procedures are available from Plessey Semiconductors

Plessey Semiconductors reserve the right to change the Screening Procedure for Standard Products.

# Introducing Plessey CMOS

Plessey Semiconductors new range of high performance CMOS products form an important addition to its range of established Bipolar and metal gate MOS integrated circuits.

With the active co-operation of the Mitel Corporation of Canada - where CMOS products are in volume production - Plessey Semiconductors has chosen the ISO-CMOS® process, an isolated polysilicon gate process that results in low power, high packing densities and high speeds. In fact,ISO-CMOS products are among the fastest in the world.

The products and facilities listed in this shortform have been chosen to serve the four areas

of application for which CMOS is today one of the essential technologies:

Telecommunications, page 1.

EDP products pages 2 and 3.

Semi-Custom Design, page 3.

Full Custom Design - especially for Radio Communications - see pages 3 and 4 for full process details.

Over 25 Plessey Semiconductors CMOS types are available now, with a further 17 (including a high performance version of the popular 6802 microprocessor, a 16K ROM and a 4K static RAM) becoming available through 1981.

Full technical information on these products is available on request.

## Product list

### **Planned introduction**

| · · · · · · · · · · · · · · · · · · ·                                                |                                                                        |  |  |  |

|--------------------------------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|

| Available now                                                                        |                                                                        |  |  |  |

| MV4320, MV4322, MV4323,<br>MV4325, MV4326                                            | Family of loop disconnect push-button telephone circuits               |  |  |  |

| MV8820, MV8860, MV8865                                                               | Family of DTMF telephone dialling decoders and filters                 |  |  |  |

| MV41SC04                                                                             | Quad 5V to 12V level shifter                                           |  |  |  |

| MV4330, MV4331, MV4332                                                               | 30 and 32-bit static shift registers/<br>7-segment LCD display drivers |  |  |  |

| MV4311, MV4368, MV4511                                                               | 7-segment LED drivers                                                  |  |  |  |

| MV74SC137/138/139<br>MV74SC237/238/239<br>MV74SC240/241/244/540/541<br>MV74SC245/545 | Family of octal pin-for-pin replacements for 74LS series TTL           |  |  |  |

| Available Mid-1981                                                                   |                                                                        |  |  |  |

| MV5087, MV5089, MV5091,<br>MV5093                                                    | DTMF telephone tone generator circuits                                 |  |  |  |

| MV8862, MV8863                                                                       | Extensions to family of DTMF decoders                                  |  |  |  |

| MV74SC373/573, MV74SC533/563<br>MV74SC374/574, MV74SC534/564                         | Extensions to family of octal bus circuits equivalent to 74LS TTL      |  |  |  |

### Telecommunications

### Telephone dialling - loop disconnect

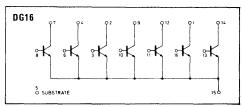

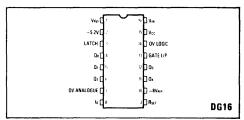

Each of the circuits in the MV43XX family of keypad pulse diallers contains all the logic necessary to interface a 2 of 7 keypad and convert this key information to control and mute pulses simulating a telephone rotary dial. The circuits all store up to 20 digits with redial option and feature wide supply voltage range, low power dissipation, and are available in standard 18-lead ceramic DIL (DG) packages.

### MV4320

### KEYPAD PULSE DIALLER

- Pin-for-pin replacement for DF320

- Selectable pulse mark/space ratio 2:1 or 3:2

- Selectable outpulsing rates of 10, 16, 20 or 932Hz

- M1 masking output

- Supply range: +2.5V to +5.5V

- Low power: 375µW at 3V

### MV4322 As MV4320 except M2 masking replaces M1

MV4323

As MV4320 except selectable interdigit pause (4T or 8T) with fixed 2:1 pulse mark/space ratio

### MV4325

### PROGRAMMABLE KEYPAD PULSE DIALLER

- 300Hz keytone output during valid key

- Pulse raté fixed at 10Hz

- Supply range: +2V to +7V

- Lower power: 300µW at 3V

- Programmable access pause

- M1 masking output

MV4326 As MV4325 except M2 masking replaces M1

### Telephone dialling - DTMF or MF4

Plessey Semiconductors offer a complete range of CMOS circuits for the generation, filtering and decoding of Dual Tone Multi-Frequency (DTMF) tones.

The MV88XX family of DTMF decoders are designed to operate in conjunction with a DTMF filter (for example the MV8865, accepting all 16 DTMF combinations (with excellent voice talk-off performance) and converting then to digital output codes which represent the number originated at the transmitting unit. The MV88XX family presents the system designer with a variety of output code formats and facilities from which to choose.

The range of decoders is complemented by the **MV8865** DTMF filter, which filters, separates and squares the dual-tone input to provide High Group and Low Group outputs.

The **MV5087/89** generates the high-accuracy tones required for DTMF transmission.

All these Plessey Semiconductors DTMF circuits feature wide supply range, low power dissipation, contain an on-chip clock oscillator which requires only an inexpensive 3.58MHz crystal and are available in standard DIL packages.

### MV8820

### DTMF DECODER

- +5V or +12V to +15V supply

- Low power: 1.5mW at 5V, 18mW at 12V, 30mW at 15V

- Selectable 2 of 8-bit binary or Hex. plus GI AY-5-9100 output codes

### **MV8860**

- +5V or +8V to +13V supply

- Low power: 6.5mW at 5V, 30mW at 12V

- 4-bit binary output

### MV8862/3

- +5V or +8V to +13V supply

- Low power: 6.5mW at 5V, 30mW at 12V

- Selectable 2 of 8-bit binary or Hex. output code formats

- MV8862 and MV8863 differ only in output code formats

MV8865

DTMF FILTER

- High and low group filtering

- 38dB intergroup attenuation

- ▶ +5V or +12V supply

- Logical power down facility

- Low operating power: 6mW at 5V, 60mW at 12V

- Very low standby power: 0.5mW at 5V, 1.5mW at 12V

### MV5087/MV5089

DTMF GENERATOR

- +3.5V to +10V supply

- Low standby power: 200µA at 10V supply

- High accuracy tones requiring no trimming

- On-chip regulation of tone amplitudes

- 2nd source MK 5087, 5089

# EDP products

### **CMOS Octal Family**

A family of 21 CMOS MSI devices, particularly suited to bus buffering, interfacing, decoding and selecting applications in high speed low power microprocessor and memory subsystems.

Features of this family include: •Improved noise margins with input hysteresis. •High speed (25ns typical tpd), •Low quiescent power (0.5mW typical), •High sink/source current capability (12mA typical), •16 and 20-pin 0.3 inch ceramic DIL (DG) packages, •Pin-for-pin compatible with 74LS series TTL counterparts, •Operating voltage range 3V to 7V.

### MV74SC137/8, 237/8, 139/239 DECODERS/DEMULTIPLEXERS

- One of eight with latched/unlatched inputs, inverted outputs (137/138)

- One of eight with latched/unlatched inputs, non-inverted outputs (237/238)

- Dual one of four with unlatched inputs, inverted/non-inverted outputs (139/239)

### MV74SC240/244, 241, 540/541

BUFFERS/LINE DRIVERS

- Bi-directional connections, inverting/non-inverting (240/244)

- Bi-directional connections, non-inverting, complementary enable (241)

- Uni-directional connections, inverting/non-inverting (540/541)

### MV74SC245/545

**TRANSCEIVERS**

Non-inverting/inverting

### MV74SC373/573, 533/563

TRANSPARENT LATCHES

- Bi-directional/uni-directional connections, non-inverted outputs (373,573)

- Bi-directional/uni-directional connections, inverted outputs (533/563)

### MV74SC374/574, 534/564

EDGE TRIGGERED D FLIP FLOPS

- Bi-directional/uni-directional connections, non-inverted outputs (374/574)

- Bi-directional/uni-directional connections, inverted outputs (534/564)

### **CMOS Interface and Display Driver Family**

### MV41SC04

QUAD 5V to 12V LEVEL SHIFTER

- High speed

- Latchup protected

- 3-state inverting and non-inverting outputs

- 16-pin ceramic DIL (DG) package

- 3V to 12V operation

### MV4330/4331

30-BIT STATIC SHIFT REGISTERS

- Cascadable static shift registers with true/complement outputs

- Will direct drive four 7-segment LCD displays

- Will direct drive two 16-segment alphanumeric LCD displays

- 40 pin plastic DIL (DP) package

- 3V to 18V operation

- Synchronous reset on MV4330

# MV4311/MV4368 LATCHED HEX TO 7-SEGMENT LED DRIVER MV4511 LATCHED BCD TO 7-SEGMENT LED DRIVER

- Bipolar NPN outputs guaranteed at 20mA for bright display

- Direct drive of common cathode LED display

- 16-pin plastic DIL (DP) package

- 3V to 18V operation

- MV4311/MV4511 have lamp test and blanking inputs

- MV4368 has ripple blanking for leading zero suppression in multidigit displays

# CMOS semi-custom design

Semi-custom techniques enable users to have circuits dedicated to their application without incurring the costs associated with a full custom design. This makes the techniques especially attractive to users with moderate size of production potential. Semi-custom falls into either the **ULA** (Uncommitted Logic Array) in which logic elements are pre-positioned and the design task is to interconnect those elements within the space allocated, or Cell-Based systems where a wider selection of cells is held in a computer library and called up, placed and interconnected by the designer.

Building upon considerable success with **Microcell**, Plessey Semiconductors' N-Channel MOS cell-based layout system, it is now planned to introduce semi-custom techniques in CMOS as follows:

Mid- 1981

A 1400-gate CMOS ULA with full design and characterisation

information, supporting simulation and checking software.

Fall 1981

**CMOS Microcell** with capability up to 2000 gates Also add further extensions to the ULA range

**Spring 1982** Add two-layer metal to the **ULA** programme.

# CMOS full custom design

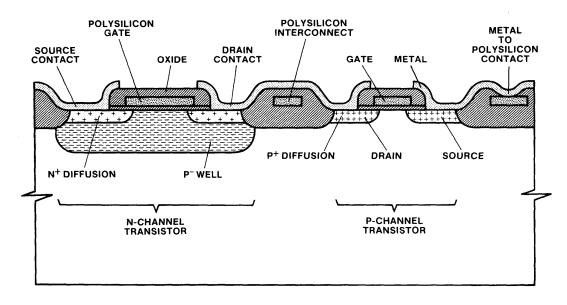

### **ISO-CMOS** technology

**ISOPLANAR**—using an oxide-nitride sandwich to define regions for local oxidation, which is recessed by etching away silicon

is recessed by etching away silicon. **REDUCED CAPACITANCE, INCREASED SPEED**The recessing technique reduces sidewall capacitance. The process is also self-aligned to reduce overlap capacitance. **ACCURATE CONTROL OF THRESHOLDS**Both P-channel and N-channel transistor thresholds are determined by implant levels for precise control.

### **Process electrical parameters**

| Parameter                         | P-channel  | N-channel  | Unit          | Conditions            |

|-----------------------------------|------------|------------|---------------|-----------------------|

| Threshold voltage,Vbo             | 0.4 to 0.9 | 0.4 to 0.9 | V             | Id=0,Vb=0             |

| Junction breakdown voltage, Vbds  | 10         | 10         | V             | ld=1µA,<br>Vg=Vs=Vb=0 |

| Diffusion resistivity             | 60 to 120  | 5 to 12    | $\Omega/\Box$ |                       |

| 1st polysilicon layer resistivity | 20 to 70   | 15 to 40   | $\Omega/\Box$ |                       |

| 2nd polysilicon layer resistivity | 30 to 80   | 30 to 80   | $\Omega/\Box$ |                       |

ISO-CMOS, simplified cross-section

# RADIO APPLICATION NOTES

### Radio Linear Circuits

### INTRODUCTION TO SL600 AND SL1600 SERIES

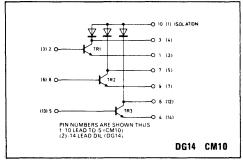

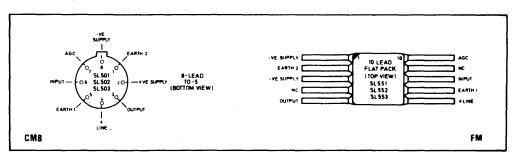

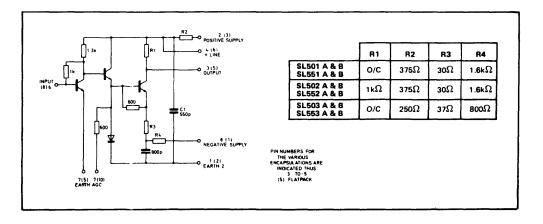

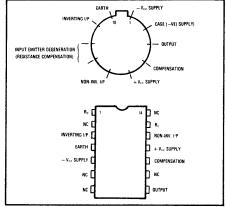

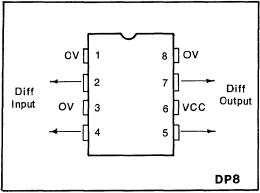

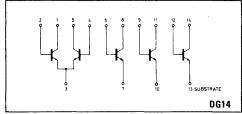

Plessey Semiconductors originally developed the SL600 series for use in military SSB systems. For such applications, hermetic packages and full-temperature operation are necessary: the SL600 series devices meet such specifications. As the range expanded, requirements arose for less expensive versions of SL600 devices and the SL1600 series was introduced. The SL1600 series consists of the same chips as are used in the SL600 series but packaged in plastic DIL packages (mostly 8-lead minidips) tested to less stringent specifications, and supplied with a  $-30^{\circ}\text{C}$  to  $+70^{\circ}\text{C}$  temperature specification. In a few cases some of the pins present in the SL600 devices are omitted in the SL1600 devices in order to allow a chip previously supplied in a 10-lead TO-5 to be encapsulated in an 3-lead minidip.

SL600 and SL1600 type numbers are used in section headings but to avoid tedious repetition, only the SL600 type numbers will be used in the text unless there are significant differences between the SL600 and SL1600 devices. Pin numbers generally refer to both types; in cases where pin numbers differ, the pin numbers for the SL1600 device is given in brackets, e.g. Pin 6(7).

| SL600/1600 PRODUCT RANGE              |                         |                            |                                     |  |

|---------------------------------------|-------------------------|----------------------------|-------------------------------------|--|

| AMPLIFIERS                            | SL610<br>SL611<br>SL612 | SL1610<br>SL1611<br>SL1612 | 100MHz, 26dB                        |  |

| MIXERS                                | SL640<br>SL 641         | SL1640<br>SL1641           |                                     |  |

| DETECTORS<br>AND<br>AGC<br>GENERATORS | SL621<br>SL623          | SL1621<br>SL1623<br>SL1625 | AMSSB detector and AGC from carrier |  |

| AUDIO                                 | SL630                   | SL1630                     | 200mW headphone amplifier           |  |

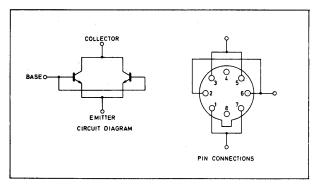

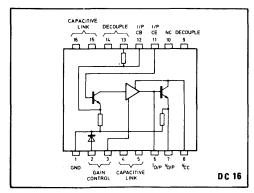

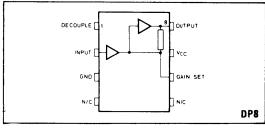

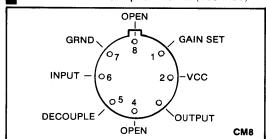

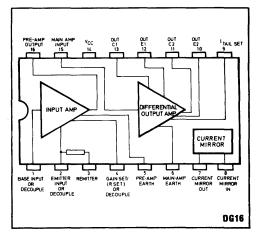

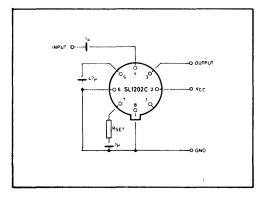

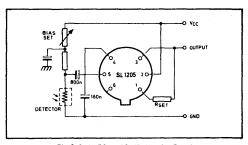

### SL610C, SL611C, SL612C, SL1610C, SL1611C & SL1612C

### RF/IF amplifiers

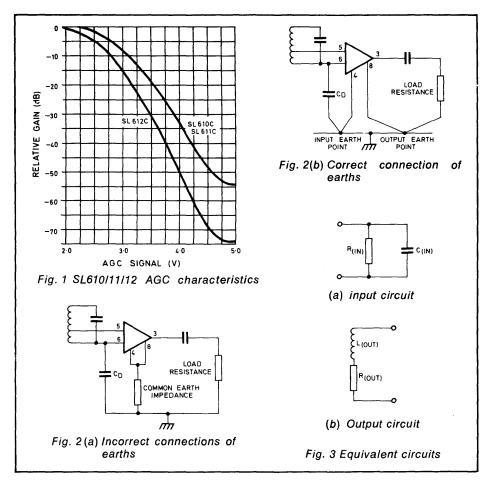

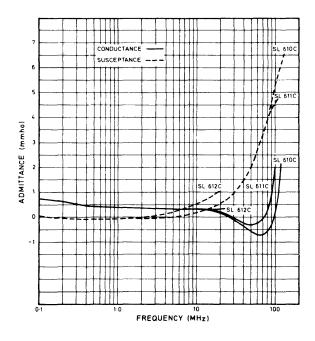

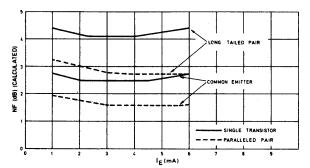

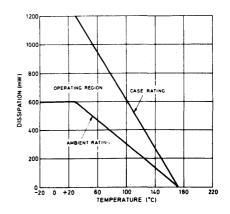

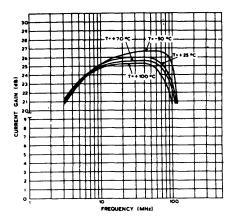

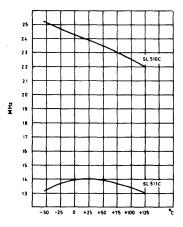

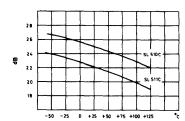

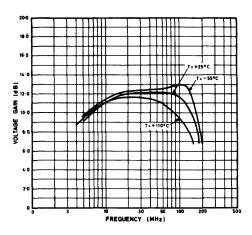

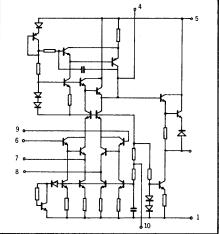

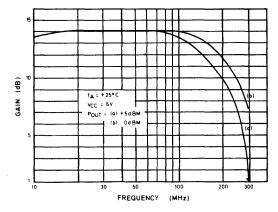

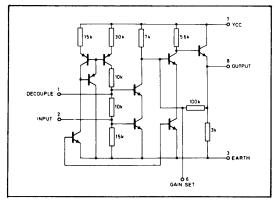

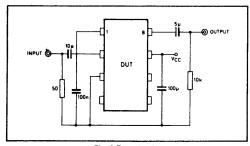

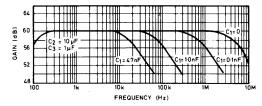

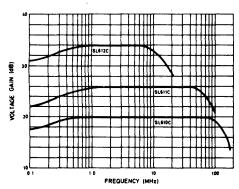

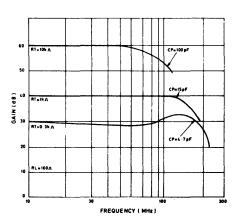

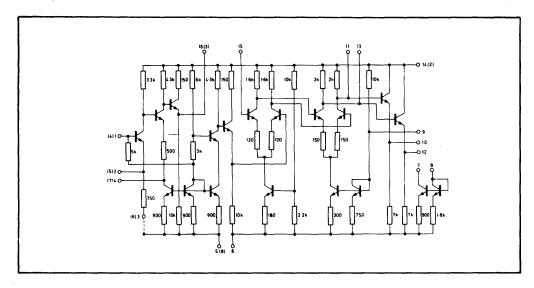

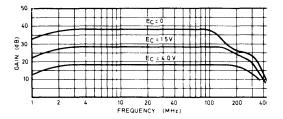

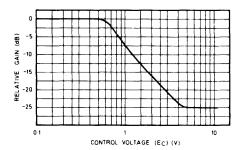

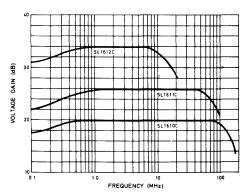

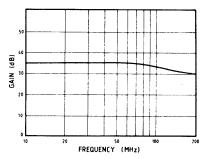

The SL610C, SL611C and SL612C integrated RF amplifiers are similar circuits, having typical voltage gains of 10, 20 and 50 and upper 3dB gain points at 140MHz, 100MHz and 15MHz respectively. The first two draw a supply current of about 15mA at 6V and have some 50dB AGC range while the SL612C draws 3.5mA and has 70dB of AGC. All three are intended to use with  $\pm$ 6V supplies and have internal decoupling. They will drive an output signal of about 1V rms.

The cross-modulation of the circuits is 40dB down on signal at 1V rms output with no AGC, and at 250mV rms input with full AGC. The input and output admittances of the circuits are not greatly affected by AGC level.

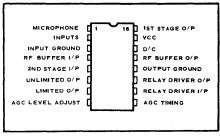

### CIRCUIT APPLICATIONS

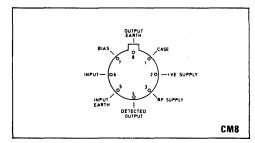

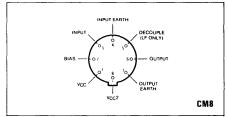

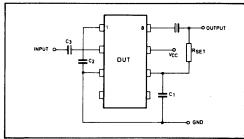

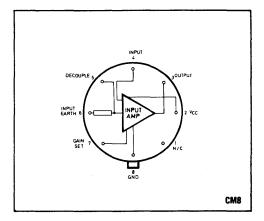

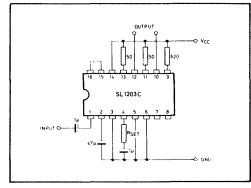

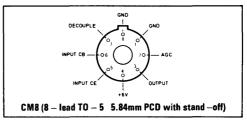

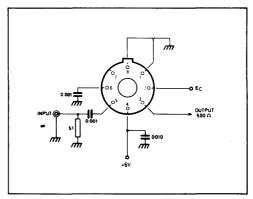

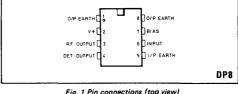

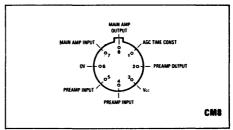

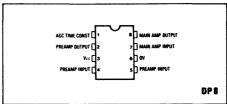

There are seven connections to each circuit: an input, an input bias point, an AGC input, the output, the positive supply pin and two earths — for input and output respectively.

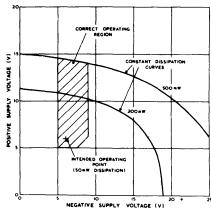

The positive supply should be 6V, but the devices will function at supplies of up to 9V. Since internal HF supply decoupling is incorporated a certain amount of HF ripple can be tolerated in the supply. LF ripple should be kept down as it can cause intermodulation — especially at large HF signal levels — and 10mV rms of LF ripple should be considered a maximum.

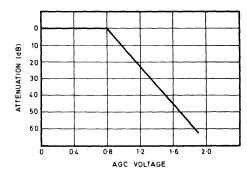

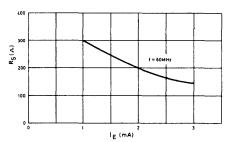

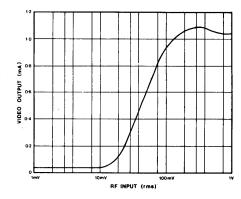

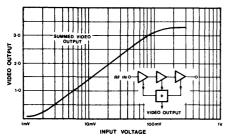

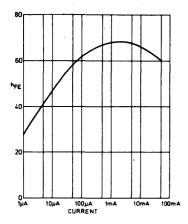

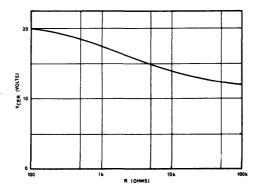

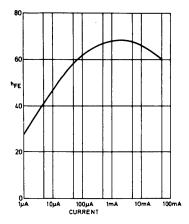

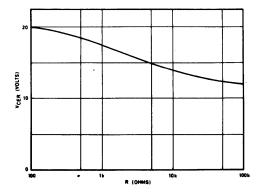

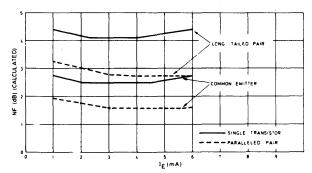

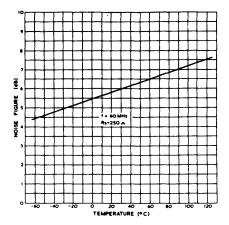

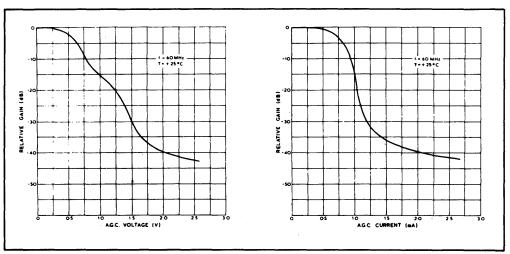

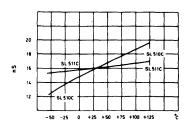

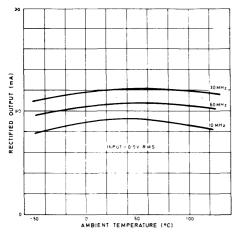

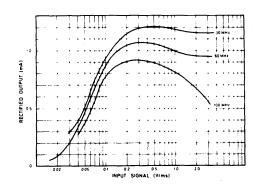

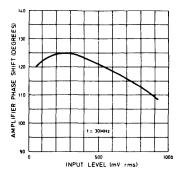

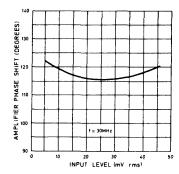

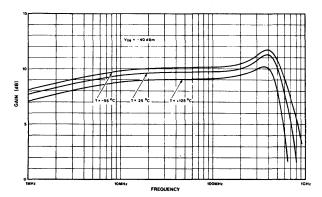

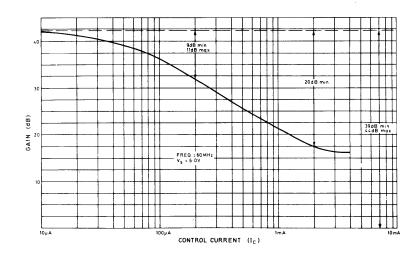

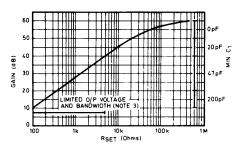

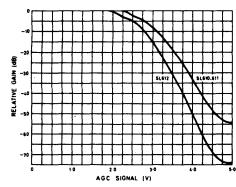

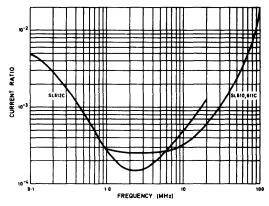

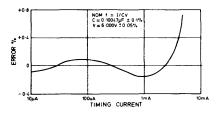

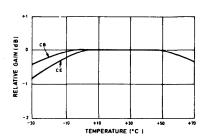

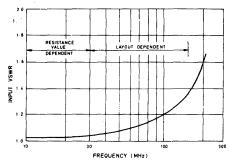

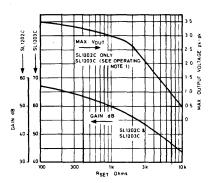

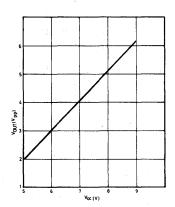

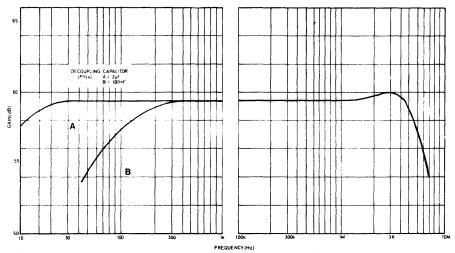

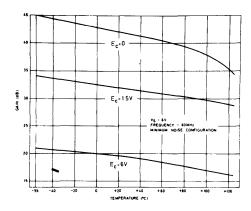

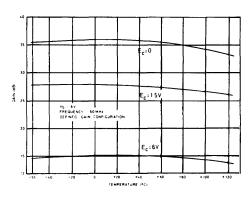

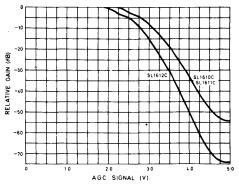

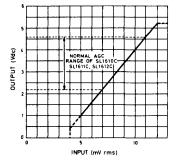

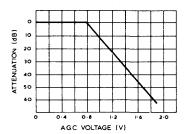

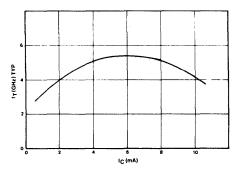

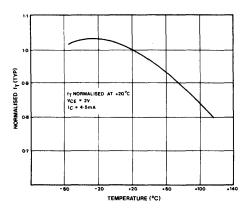

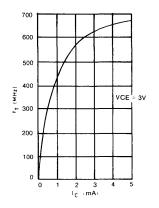

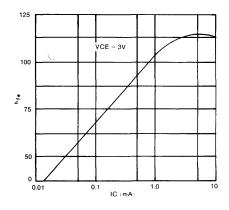

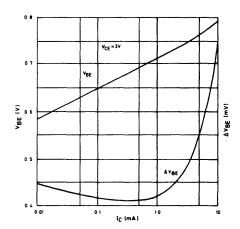

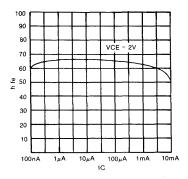

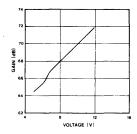

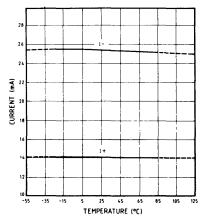

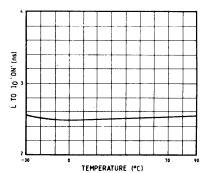

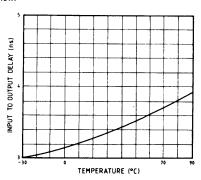

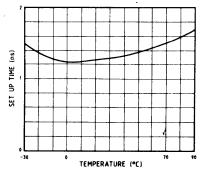

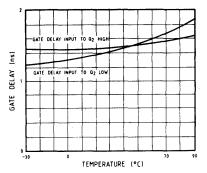

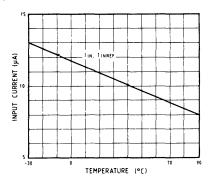

The AGC characteristic is shown in Fig. 1. It is temperature dependent, so that while a potentiometer may be used to provide a gain control voltage the gain so defined will not be temperature stable to better than  $\pm$  2dB. The AGC terminal will normally draw about 200 microamps at 5V — in some SL610C and SL611C devices this may be as high as 600 microamps.

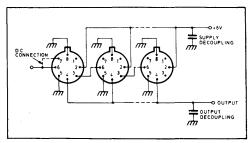

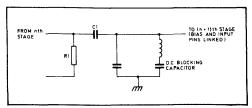

There are two earth connections: pin 4 is the input earth and pin 8 the output earth. When several devices are cascaded pin 8 of one stage and pin 4 of the next should have a common earth point — also high common earth impedances to pin 4 and pin 8 of the same device should be avoided. Fig. 2a shows a circuit where common earth impedance could cause instability and Fig. 2b shows one where the input and output signals have correct point earthing. If extra supply decoupling is used the capacitor should ground to the output earth point. The can should be separately earthed in applications at VHF or in the presence of a large RF field.

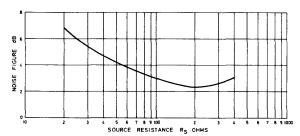

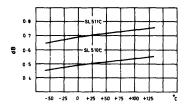

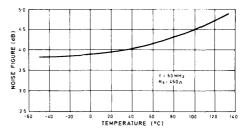

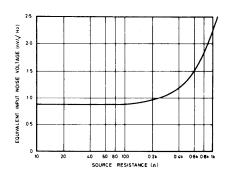

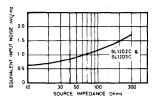

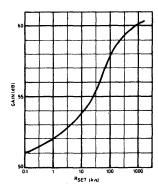

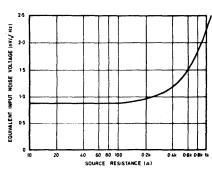

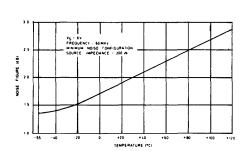

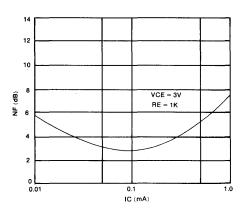

The input bias point (pin 6) is normally connected directly to the input (pin 5) and the signal applied through a capacitor but occasionally, when the signal is obtained from a tap on a coil, the arrangement in Fig. 2b may be used to give slightly improved noise performance.  $C_D$  is a decoupling capacitor. The SL610/611 noise figure is approximately 4dB at 300 ohms source impedance and 6dB at 50 ohms and at 2.5 kilohms the noise figure for the SL612 is 3dB at 800 ohms source impedance.

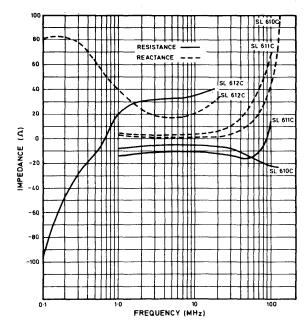

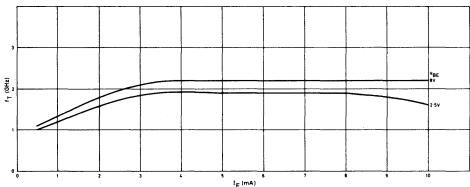

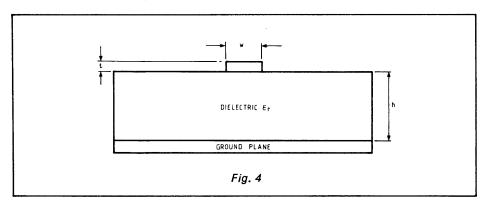

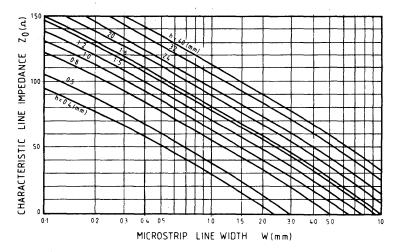

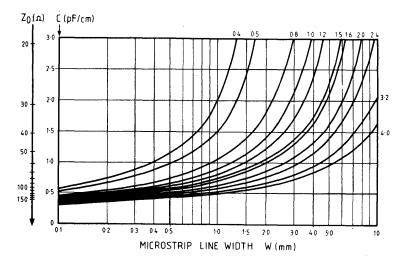

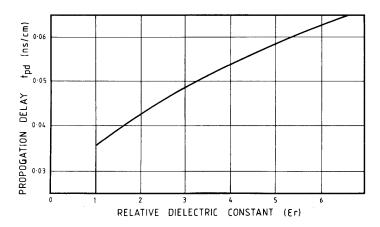

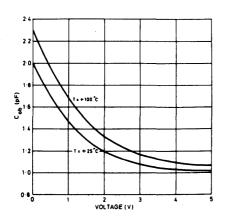

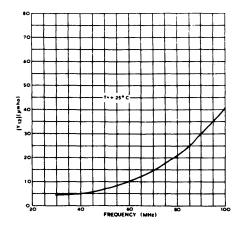

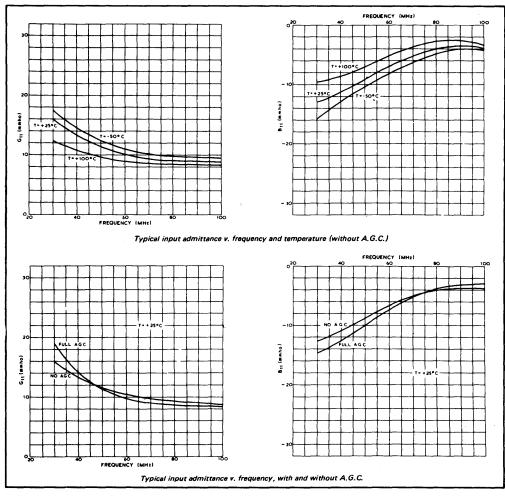

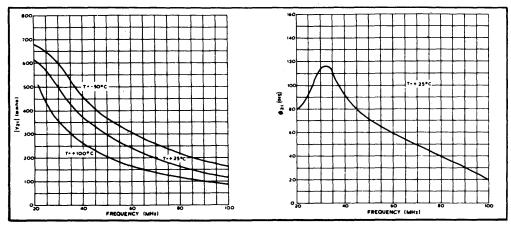

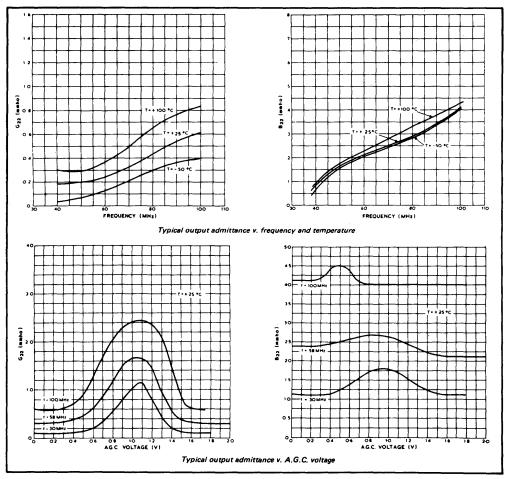

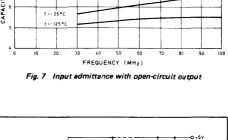

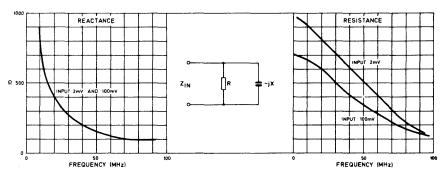

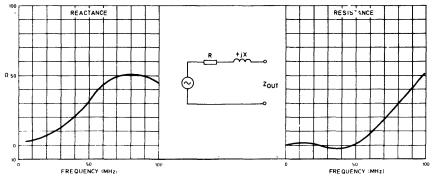

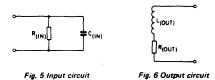

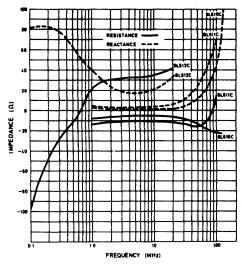

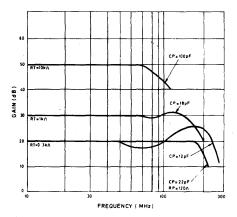

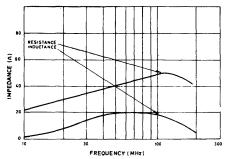

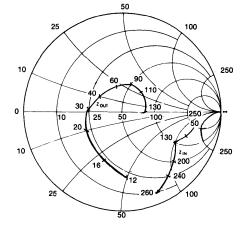

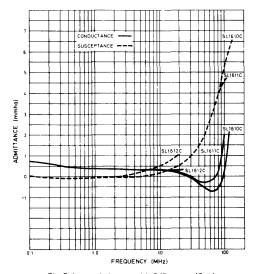

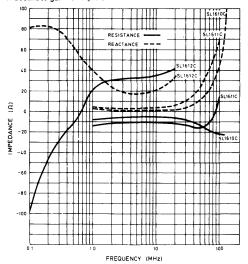

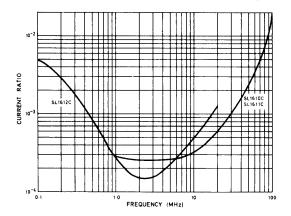

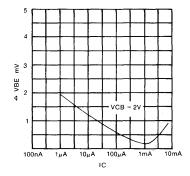

Both the input admittance  $G_{11}$  and the output impedance  $G_{22}$  have negative real parts at certain frequencies. The equivalent circuits of input and output respectively are shown in Figs. 3a and 3b and the values of  $R_{in}$ ,  $R_{out}$ ,  $C_{in}$  and  $L_{out}$  may be determined for any particular frequency from the graphs Figs. 4 and 5. It will be seen that for the SL610C and the SL611C,  $R_{in}$  is negative between 30 and 100MHz, and  $R_{out}$  is negative over the whole operating frequency range. For the SL612C,  $R_{in}$  is not negative and  $R_{out}$  is negative only below 700kHz.

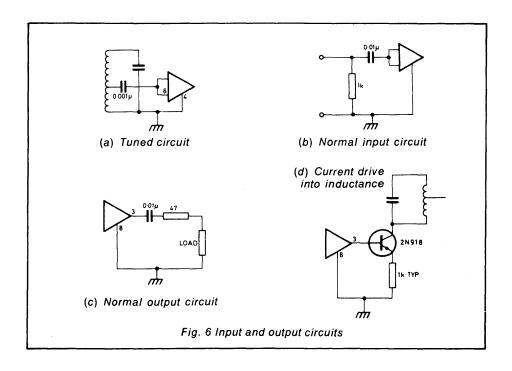

If an inductive element having inductance L1 and parallel resistance R1 is connected across the input, oscillation will occur if  $R_{\rm in}$  is negative at the resonant frequency of  $C_{\rm in}$  and L1, and if R1 is higher than  $R_{\rm in}$ . Similarly, if a capacitor C1 in series with a resistance R2 is connected across the output oscillation will occur if, at the resonant frequency of  $L_{\rm out}$  and C1,  $R_{\rm out}$  has a negative resistance greater than the positive resistance R2. Where the input is inductive, therefore, it may be shunted by a 1k resistor; where the load is capacitive, 47 ohms should be placed in series with the output.

Suitable input arrangements for the amplifiers are shown in Fig. 2b and Fig. 6. The method shown in Fig. 6a is representative of all inputs — the input and bias points are directly-connected and the signal is coupled via a capacitor. If the input is inductive the 1k resistor shown in Fig. 6b may be required, although usually it can be omitted. If a crystal filter is used it should be correctly terminated, allowing for the impedance of the IC, and coupling made via a capacitor.

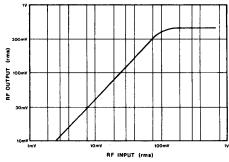

Fig. 4 Input admittance with o/c output (G11)

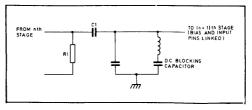

The output is a voltage source, with the impedance characteristics mentioned above. Output coupling is via a capacitor, with a series resistor if necessary to preserve stability (Fig. 6c). If a current output to a tuned circuit is required the arrangement in Fig. 6d is suitable, using almost any small signal NPN transistor with an  $f_T$  of over 300MHz and low  $C_{OB}$ . To drive particularly low impedances, e.g. a 50 ohm coaxial cable, this impedance should be increased somewhat by a series output resistor (say, 100 ohms) as, if the output is loaded directly by low impedance, most of the negative feedback will be removed — with consequently poor linearity and constancy of gain. Examples of the use of these amplifiers are shown in Fig. 7.

Fig. 5 Output impedance with s/c input (G22)

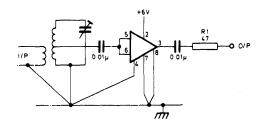

(a) RF preamplifier. Use SL610C up to 140MHz, SL611C up to 70MHz, SL612C up to 12MHz. R1 may be omitted if the load is neither capacitive nor very low impedance.

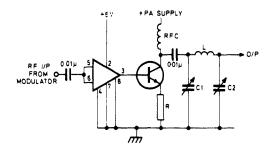

(b) Linear power amplifier for low power SSB transceivers. L, C1 and C2 form the output π tank circuit. The values of PA supply and R should be chosen to suit the transistor used. Cob should be as low as possible.

(c) Constant level RF amplifier stabilising at approximately 500mV rms output over a range of inputs greater than 20dB. SL610C, 611C or 612C may be used. With tuned feedback, this circuit makes an excellent constant level oscillator.

Fig. 7 SL610/11/12

## SL640C, SL641C, SL1640C & SL1641C

## Double balanced modulators

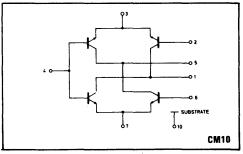

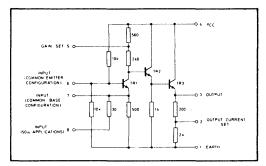

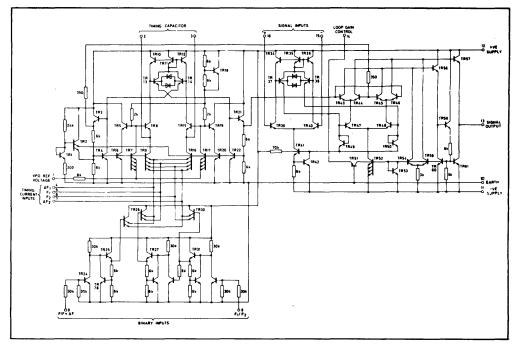

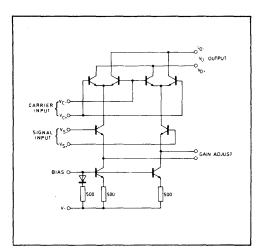

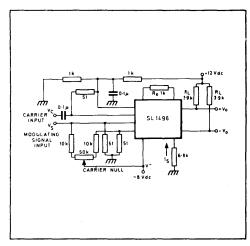

### PRINCIPLES OF OPERATION

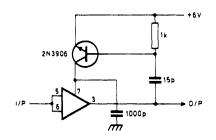

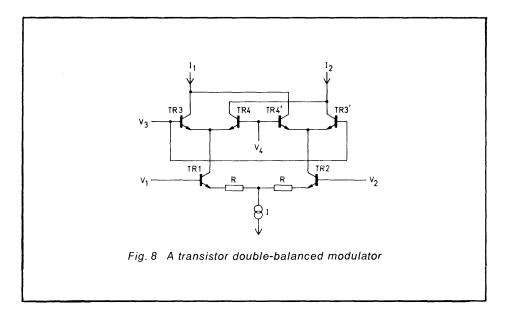

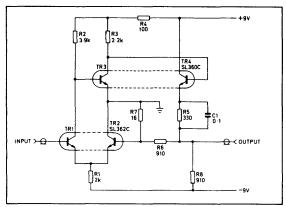

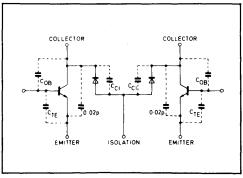

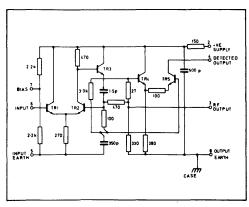

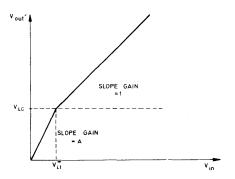

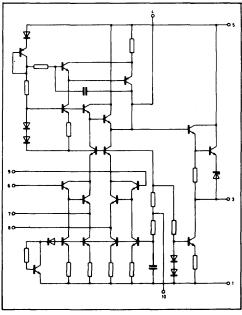

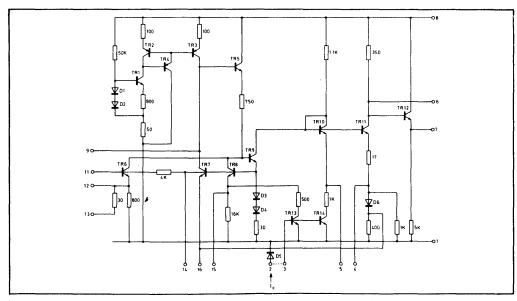

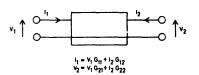

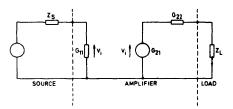

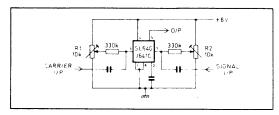

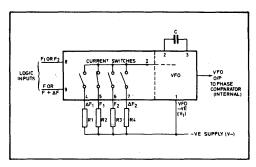

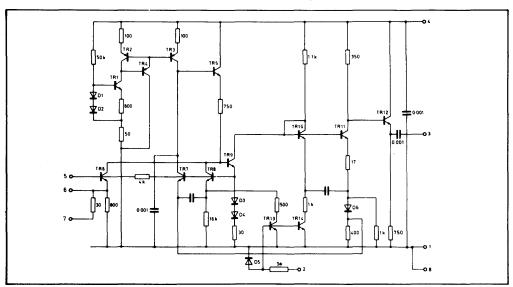

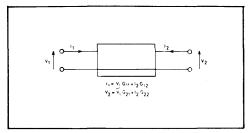

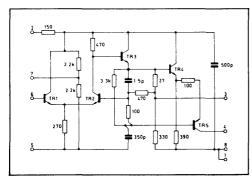

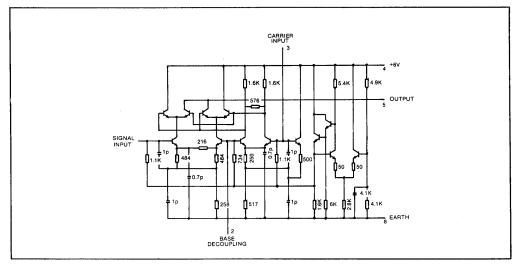

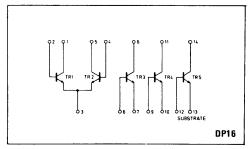

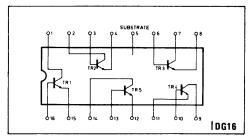

A simple double-balanced modulator is shown in Fig. 8 . It is evident that the sum of the two output currents equals the tail current and that, from considerations of symmetry, if either V1=V2 or V3=V4 then I1=I2. Also if R is much greater than  $R_e$  the collector currents of TR1 and TR2 will differ by an amount proportional to the difference between V1 and V2. If, therefore, a small input at frequency  $f_1$  is applied between V1 and V2 and a large signal at  $f_2$  is applied between V3 and V4, sufficient to turn the transistors TR3, TR3, and TR4, and TR4, fully on and off, it is evident that switching modulation, similar to that of a diode ring will occur and frequencies If1  $\pm f_2$  I will occur at the output as will sums and differences of  $f_1$  and the odd harmonics of  $f_2$  i.e. If1  $\pm 3f_2$  I, If1  $\pm 5f_2$  I, etc.

### CIRCUIT DESCRIPTION AND APPLICATIONS

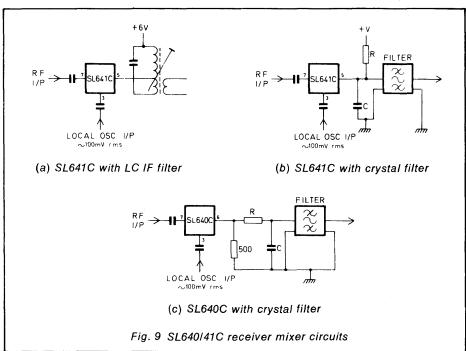

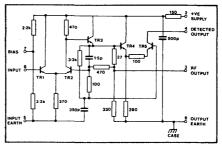

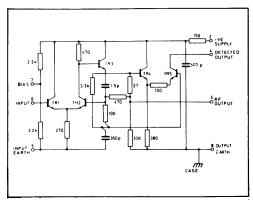

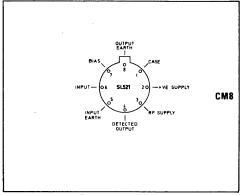

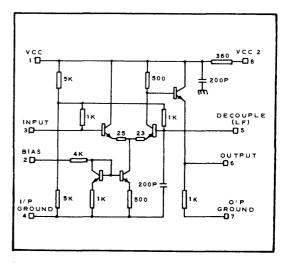

The circuits of the SL640C and SL641C are very similar but have different signal input and output configurations — these are fully discussed below.

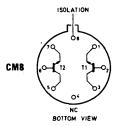

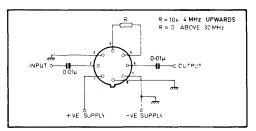

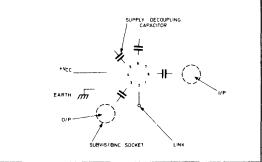

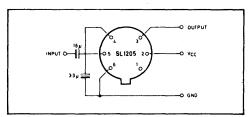

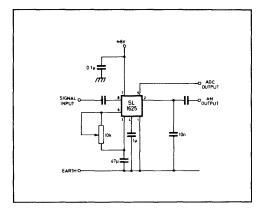

The circuits require a single, well-decoupled positive supply of between 6 and 9 volts and consume about 12mA. Pin 2, an internal bias point, must also be decoupled by a low-leakage (less than 100nA) capacitor having a low reactance at the lowest signal or carrier input frequency.

Pin 1, which is connected to the can, should be earthed to prevent HF pickup.

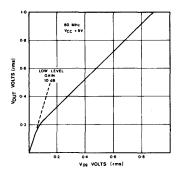

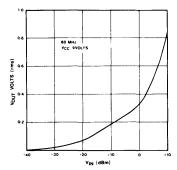

The input and carrier signals, which should not exceed 200mV rms, are applied to pins 7 and 3 respectively. Both the SL640C and the SL641C have a carrier input impedance of 1 kilohm and 4pF and the SL641C has a similar signal input impedance. The signal input impedance of the SL640C is 500 ohms and 5pF. The input coupling capacitors should have a leakage of less than 100nA and an impedance of less than 100 ohms at the lowest frequency they will carry. This should be reduced to less than 10 ohms above 10MHz.

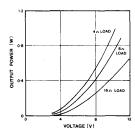

The output of the SL641C is intended as a current drive to a tuned circuit. If both sidebands are developed across this load its dynamic impedance must be less than 800 ohms. If only one sideband is significant this may be raised to 1600 ohms and it may be further raised if the maximum input swing of 200mV rms is not used. The DC resistance of the load should not exceed 800 ohms. If the circuit is connected to a  $+6\mathrm{V}$  supply and the load impedance to  $+9\mathrm{V}$ , the load may be increased to 1.8 kilohms at AC or DC. This, of course, increases the gain of the circuit.

There are two outputs from the SL640C; one is a voltage source of output impedance 350 ohms and 8pF and the other is the emitter of an emitter follower connected to the first output, which requires a discrete load resistor of not less than 560 ohms. The emitter follower output should not be used to drive capacitive loads as emitter followers act as detectors under such circumstances with resultant distortion and harmonic generation. Frequency-shaping components may be connected to the voltage output and the shaped signal taken from the emitter follower.

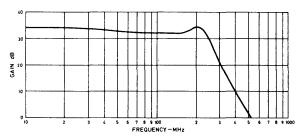

The circuits will operate with input frequencies between 1Hz and 70MHz with the specified performance; the SL641C will operate at up to about

150MHz with reduced performance. To use them at frequencies below 100Hz precautions must be taken to prevent leakage in the input coupling capacitor from altering the device bias.

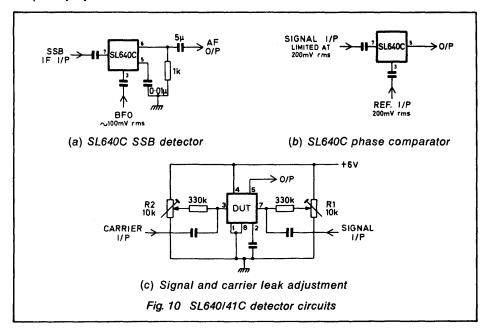

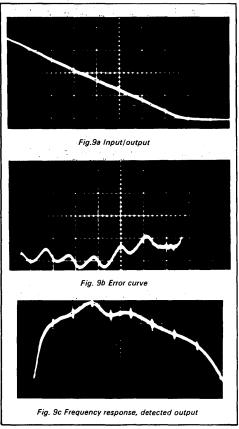

Some applications of the SL640C and SL641C are shown in Figs. 9 and 10 Power, decoupling, and earth connections are not shown.

Fig. 9a shows the SL641C used as a receiver mixer driving a wound IF coil. Fig. 9b shows it driving a crystal filter. R and C must be selected to match the filter. If R is less than 800 ohms it may be connected to the +6V line supplying power to the SL641C; if it is between 800 ohms and 1.8 kilohms it should be connected to +9V (while the SL641C supply must remain at +6V). If R is greater than 1.8 kilohms the circuit in Fig. 9 b is unsuitable and the SL640C circuit illustrated in Fig. 9 c should be used.

The SL640C and SL641C have a noise figure of about 10dB at 100 ohms source impedance. When used as receiver mixers they have better than —40dB intermodulation products so long as unwanted signals do not exceed 30mV rms. Thus, either can be used as a receiver mixer at HF without an RF amplifier since atmospheric noise will far exceed device noise at these frequencies if the antenna is reasonably good. If an SL610C RF amplifier is used the intermodulation threshold will be reduced to 3mV rms (since the SL610C has a gain of 10). The SL640/41 is then less attractive as a mixer and a diode ring mixer should be used.

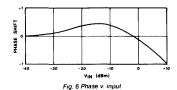

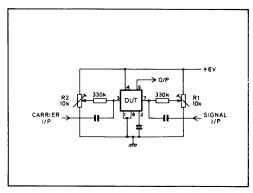

Fig. 10 a shows the SL640C used as an SSB detector. The capacitor connected to output pin 5 decouples the sum frequency If1 +f2l, while the audio difference frequency If1 -f2l is taken from pin 6. The phase comparator shown in Fig. 10b is more useful — it may be used as a detector for phase modulated signals or as a comparator in phase-locking systems such as frequency synthesisers.

Signal and carrier leak may be reduced by altering the bias on the carrier and signal input pins, as shown in Fig. 10 c. With carrier but no signal R1 is adjusted for minimum carrier leak. A similar network is connected to the carrier input and with signal and carrier present, signal leak is minimised by means of R2.

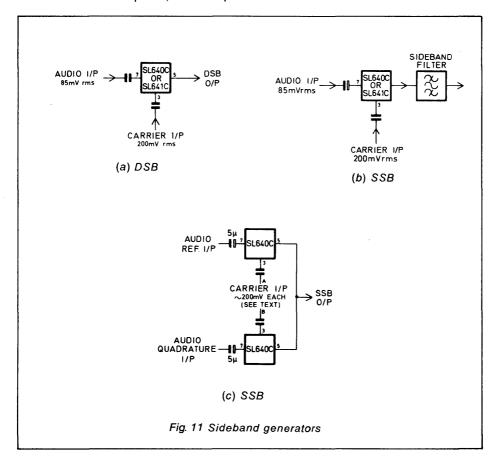

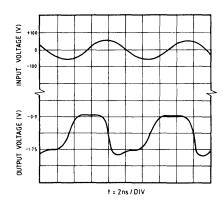

Fig. 11a shows the SL640C or SL641C used as a sideband generator. Both sidebands are produced so that if a single sideband is required it must be obtained by subsequent filtering (Fig. 11b). If pin 2 is earthed by a resistor of about 15 kilohms (its actual value may need to be selected) the device's carrier leak is increased to a point where the DSB signal becomes AM. This is useful where it is desired to select sideband or AM. In the circuit shown in Fig. 11c a single sideband only is produced. It is important that both the audio and carrier reference and quadrature signals should be accurately 90 degrees out of phase. The amplitude of one phase of audio should be adjusted to obtain maximum second sideband rejection.

If the carrier reference is connected to input A, and the carrier quadrature to input B, LSB output results. If the carrier quadrature is connected to input A, and reference to input B, USB output results.

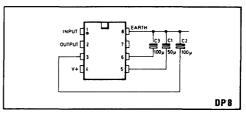

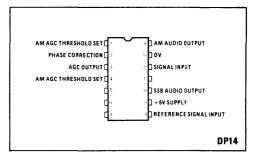

## SI 621C & SI 1621C

## **AGC** generators

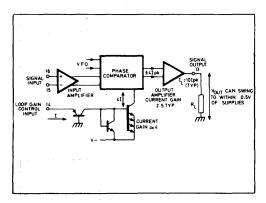

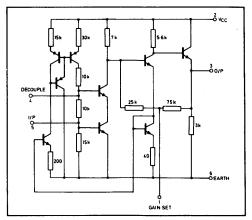

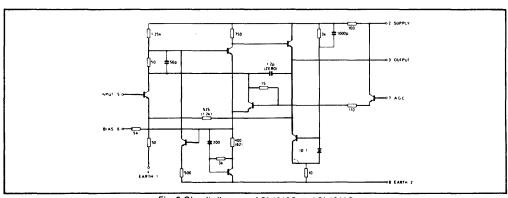

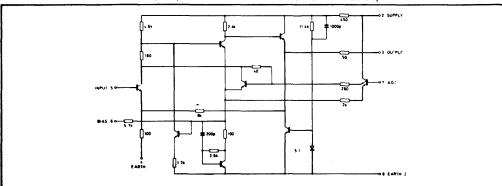

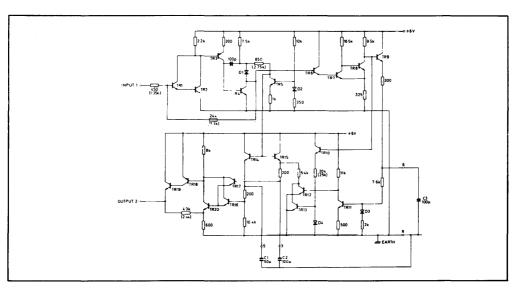

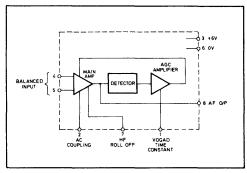

The SL621C is an audio-operated AGC generator designed for use with the SL610/11/12 RF amplifiers in SSB receivers.

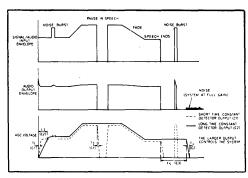

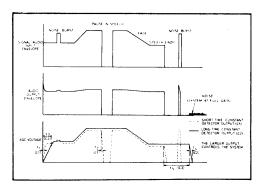

An ideal single sideband AGC generator must set the AGC rapidly when a new signal appears and follow a rising or fading signal but, if the signal disappears altogether (as in pauses in speech), retain the AGC level until the signal recommences. If the signal remains absent for more than a preset time, however, the system should rapidly revert to full gain. The SL621C will perform these functions and will also produce short-lived pulses of AGC to suppress noise bursts.

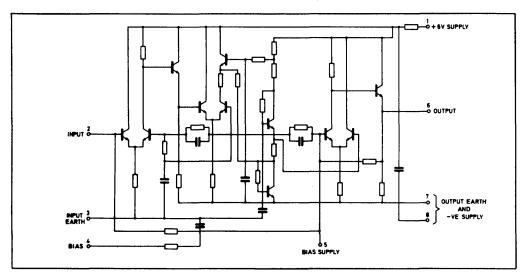

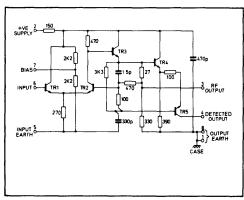

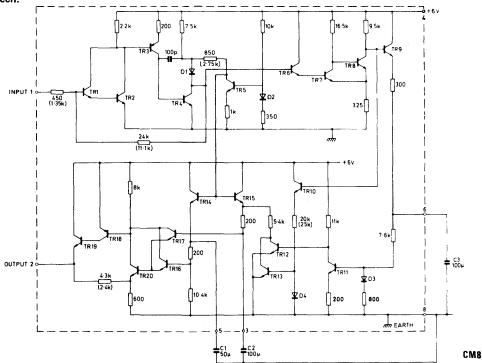

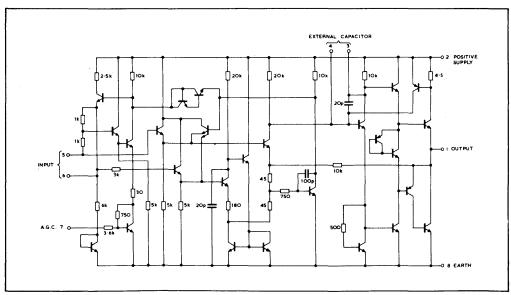

### CIRCUIT DESCRIPTION

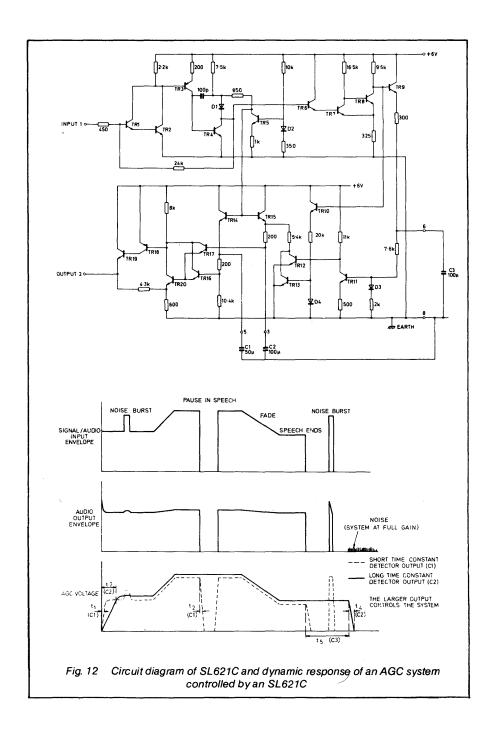

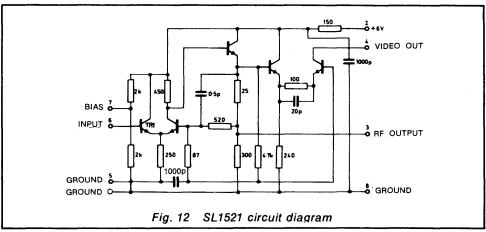

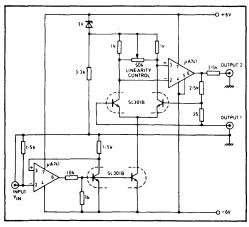

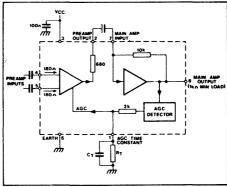

The operation of the circuit is described with reference to Fig. 12, which also illustrates the dynamic response of a system controlled by an SL621C AGC generator.

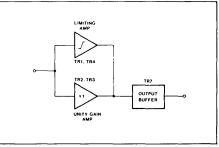

The SL621C consists of an input AF amplifier, TR1-TR4, coupled to a DC output amplifier, TR16-TR19, by means of a voltage back-off circuit, TR5, and two detectors, TR14 and TR15, having short and long rise and fall time constants respectively.

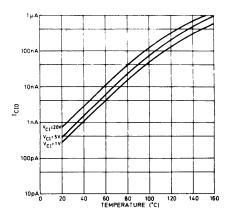

An audio signal applied to the input rapidly establishes an AGC level, via TR14, in time  $t_1$ . Meanwhile the long time constant detector output (TR15) will rise and after  $t_3$  will control the output because this detector is the more sensitive. If the signals at the SL621C input are greater than approximately 4mV rms they will actuated the trigger circuits TR6-TR8 whose output pulses will provide a discharge current for C2 via TR10, TR13.

By this means the voltage on C2 can decay at a maximum rate which corresponds to a rise in receiver gain of 20dB/sec. Therefore the AGC system will smoothly follow signals which are fading at this rate or slower. However, should the receiver input signals fade faster than this, or disappear completely as in pauses in speech, then the input to the AGC generator will drop below the 4mV rms threshold and the trigger will cease to operate. As C2 then has no discharge path, it will hold its charge (and hence the output AGC level) at the last attained value. The output of the short time constant detector (TR14) falls to zero in time  $t_2$  after the disappearance of the signal.

The trigger pulses also charge C3 via TR9, thus holding off TR12 via TR11. When the pulses cease, C3 discharges and after  $t_5$  turns on TR12, rapidly discharging C2 (in time  $t_4$ ) thus restoring full receiver gain. The hold time,  $t_5$ , is approximately one second with C3=100 microfarads. If signals reappear during  $t_5$ , then C3 will re-charge and normal operation will continue. The C3 re-charge time is made long enough to prevent prolongation of the hold time by noise pulses. Fig. 12 also shows how a noise burst superimposed on speech will initiate rapid AGC action via the short time constant detector while the long time constant detector effectively remembers the pre-noise AGC level.

The various time constants quoted are for C1=50 microfarads and C2=C3=100 microfarads. These time constants may be altered by varying the appropriate capacitors.

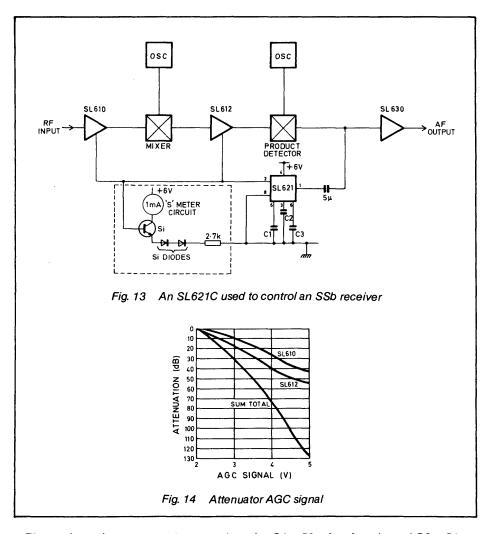

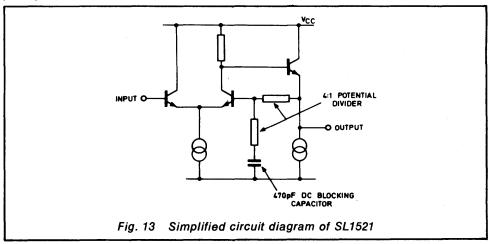

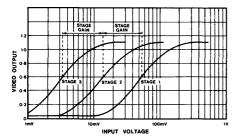

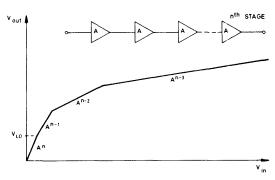

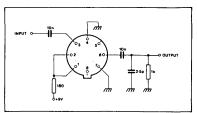

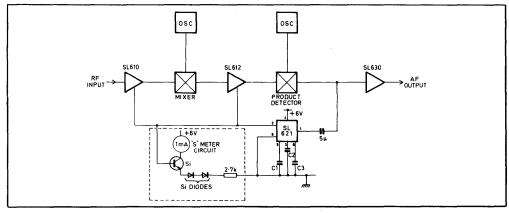

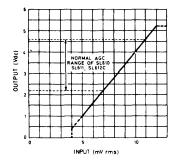

### CIRCUIT APPLICATIONS

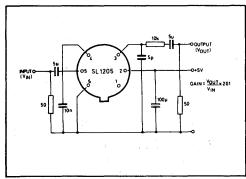

The SL621 is used in an SSB receiver as shown in Fig. 13. AGC need only be applied to two of the gain stages even if there are more than two such stages in the receiver since AGC applied to two stages only will result in over 120dB AGC range. It is usual to apply AGC to the first RF stage and the first IF stage and it will be seen from Fig. 14 that an SL612 IF amplifier reacts earlier to an increasing AGC voltage than an SL610C RF amplifier. This has the effect of delaying the AGC to the input stage, thus improving the receiver signal to noise ratio at low AGC levels.