# Frequency Synthesis IC Handbook

Plessey Semiconductors

PLESSEY Semiconductors

### FREQUENCY SYNTHESIS IC HANDBOOK

**SEPTEMBER 1980**

1641 Kaiser Avenue, Irvine, CA. 92714

This publication is issued to provide outline information only and (unless specifically agreed to the contrary by the Company in writing) is not to form part of any order or contract or be regarded as a representation relating to the products or services concerned. We reserve the right to alter without notice the specification, design, price or conditions of supply of any product or service.

#### Contents

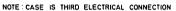

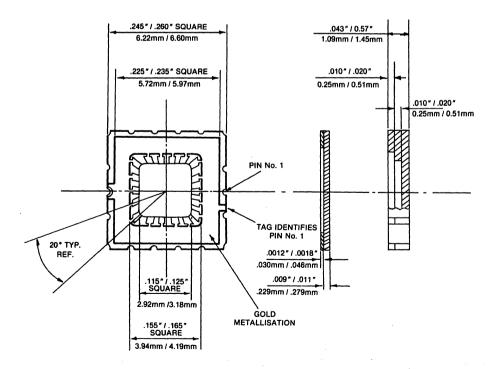

(

| 1 · PRODUCT INFORMATION                                                         | 9-26    |

|---------------------------------------------------------------------------------|---------|

| 2 · THE DESIGN OF PROGRAMMABLE DEVICES FOR UHF<br>AND VHF SYNTHESISERS          | 27-48   |

| 3 - THE DESIGN OF UHF AND VHF PHASE LOCKED<br>LOOPS USING FOUR MODULUS DIVIDERS | 49-64   |

| 4 - PRACTICAL SOLUTIONS TO VHF SYNTHESIS                                        | 65-72   |

| 5 • CITIZEN AND AMATEUR BAND 2 CHIP SYNTHESISER                                 | 73-86   |

| 6 - CHARACTERISTICS AND INTERFACING FOR THE SP8000 SERIES                       | 87-106  |

| 7 • TECHNICAL DATA                                                              | 107-250 |

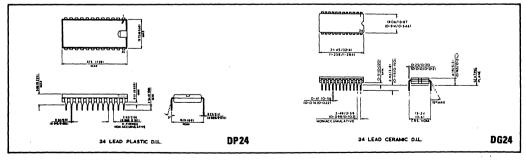

| 8 · PACKAGES                                                                    | 251-260 |

| 9 • PLESSEY SEMICONDUCTORS WORLD WIDE                                           | 261-268 |

ې. ۲

jan terretari i

а а а а а а а а а а а а а а

4

# product index DEVICE TYPE

| NJ8000 SERI                                 | ES SYNTHESISER CONTROLLERS                          |     |

|---------------------------------------------|-----------------------------------------------------|-----|

| NJ8811 Controller for frequency synthesiser |                                                     | 10  |

| NJ8812                                      | NJ8812         Controller for frequency synthesiser |     |

| SP4000 SERI                                 | ES HIGH SPEED DIVIDERS                              |     |

| Prescalers                                  |                                                     |     |

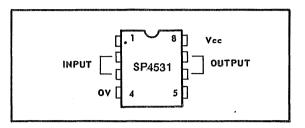

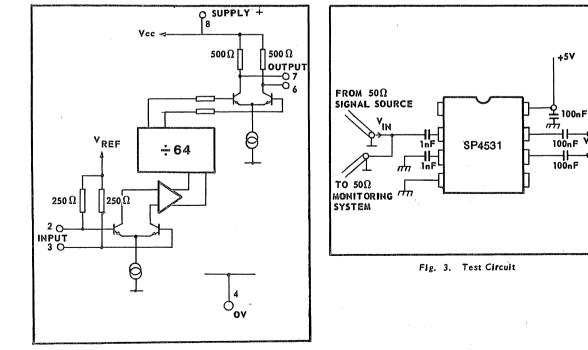

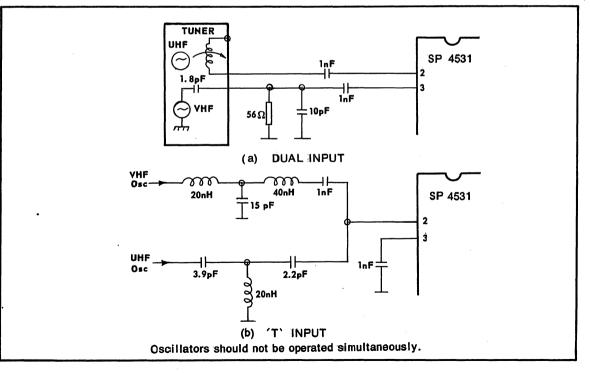

| SP4531                                      | 950MHz VHF/UHF ÷ 64                                 | 117 |

| SP4541                                      | 950MHz ÷ 256                                        | 119 |

| SP4550                                      | P4550 950MHz VHF/UHF ÷ 256                          |     |

| NOVOL                                       |                                                     |     |

| NON-Volatile                                | Logic                                               |     |

| MN9102                                      | Non Volatile Quad Latch                             | 237 |

| MN9105                                      | Quad Up/Down Counter                                | 240 |

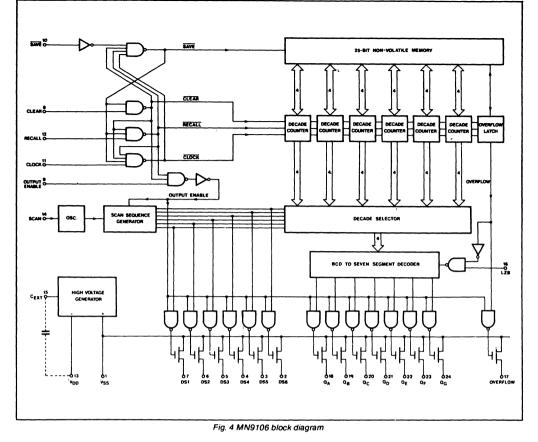

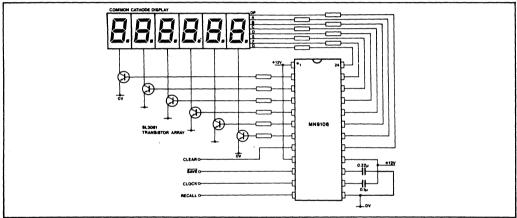

| MN9106                                      | Six Decade Up Counter                               | 242 |

| MN9107                                      | Six Decade Up Counter                               | 242 |

| MN9108                                      | Six Decade Up Counter                               | 242 |

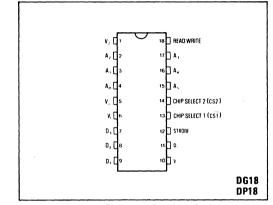

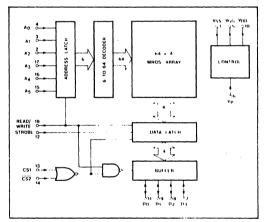

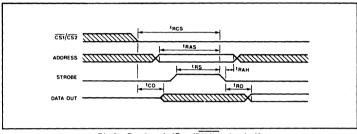

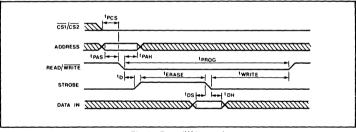

| MN9210                                      | 256 Bit Earom                                       | 246 |

1.4

•

|             | S HIGH SPEED DIVIDERS        |     |

|-------------|------------------------------|-----|

| Prescalers  |                              |     |

| SP8600A, B  | 250MHz ÷ 4                   | 123 |

| SP8601A, B  | 150MHz ÷ 4                   | 127 |

| SP8602A, B  | 500MHz ÷ 2                   | 130 |

| SP8605B & M | 1.0GHz ÷ 2                   | 133 |

| SP8606B & M | 1.3GHz ÷ 2                   | 133 |

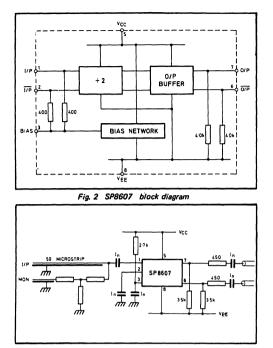

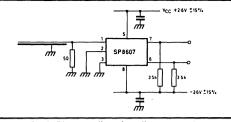

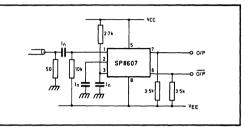

| SP8607A, B  | 600MHz ÷ 2                   | 136 |

| SP8610B & M | 1.0GHz ÷ 4                   | 138 |

| SP8611B & M | 1.5GHz ÷ 4                   | 138 |

| SP8617B & M | 1.3GHz ÷ 4                   | 141 |

| SP8619B & M | 1.5GHz ÷ 4                   | 141 |

| SP8620A, B  | 400MHz ÷ 5                   | 144 |

| SP8627      | 150MHz ÷ 80                  | 146 |

| SP8628      | 150MHz ÷ 100                 | 146 |

| SP8629      | 150MHz ÷ 100                 | 146 |

| SP8630A, B  | 600MHz ÷ 10                  | 149 |

| SP8634B     | 700MHz ÷ 10 (BCD O/P)        | 152 |

| SP8650A, B  | 600MHz ÷ 16                  | 160 |

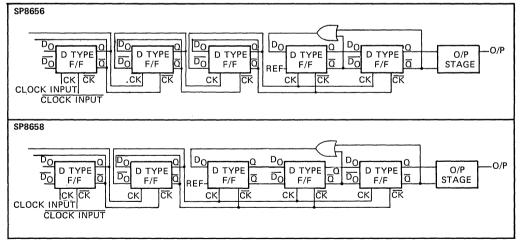

| SP8656      | 200MHz ÷ 24                  | 165 |

| SP8658      | 200MHz ÷ 20                  | 165 |

| SP8655A, B  | 200MHz ÷ 32 Low power (50mW) | 163 |

| SP8657A, B  | 200MHz ÷ 20 Low Power (50mW) | 163 |

| SP8659A, B  | 200MHz ÷ 16 Low power (50mW) | 163 |

| SP8660A, B  | 200MHz ÷ 10 Low power (50mW) | 167 |

| SP8665B     | 1GHz ÷ 10                    | 169 |

| SP8667B     | 1.2GHz ÷ 10                  | 169 |

| SP8670A, B  | 600MHz ÷ 8                   | 171 |

| SP8675B & M | 1GHz ÷ 8                     | 174 |

| SP8677B & M | 1.2GHz ÷ 8                   | 174 |

| SP8735B     | 600MHz ÷ 8 with binary O/Ps  | 194 |

| SP8755A, B  | 1200MHz ÷ 64                 | 206 |

| SP8775B     | 1.2GHz ÷ 256                 | 211 |

|             |                              |     |

| Two modulus P  | rogrammable Dividers                                          |     |

|----------------|---------------------------------------------------------------|-----|

| SP8643A, B     | 350MHz ÷ 10/11 (ECL O/P)                                      | 156 |

| SP8647A, B     | 250MHz ÷ 10/11 (TTL O/P)                                      | 156 |

| SP8680A, B     | $600MHz \div 10/11$ (ECL TTL O/P)                             | 176 |

| SP8685A        | $500MHz \div 10/11 (ECL)$                                     | 180 |

| SP8690A, B     | $200 \text{MHz} \div 10/11 \text{ Low power TTL O/P (70 mW)}$ | 182 |

| 0. 00001., 2   | AC coupled I/P                                                |     |

| SP8691A, B     | 200MHz ÷ 8/9 Low power TTL O/P 70mW                           | 185 |

| ,              | AC coupled I/P                                                |     |

| SP8695A, B     | 200MHz ÷ 10/11 Low power TTL O/P (70mW)                       | 188 |

|                | DC coupled I/P                                                |     |

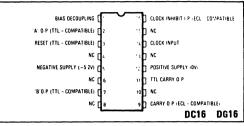

| SP8720A, B     | 300MHz ÷ 3/4                                                  | 191 |

| SP8740A, B     | 300MHz ÷ 5/6 AC coupled I/P                                   | 197 |

| SP8741A, B     | 300MHz ÷ 6/7 AC coupled I/P                                   | 200 |

| SP8743B & M    | 500MHz ÷ 8/ <sup>9</sup> AC coupled I/P                       | 203 |

| SP8785B & M    | 1.0GHz ÷ 20/22                                                | 213 |

| SP8786B & M    | 1.3GHz ÷ 20/22                                                | 213 |

| SP8792         | 200MHz ÷ 80/81 Low power                                      | 220 |

| SP8793         | 200MHz ÷ 40/41 Low power                                      | 220 |

| Four-modulus F | Programmable Dividers                                         |     |

| SP8901         | 1GHz ÷ 512/510/480/478                                        | 225 |

| SP8906         | 500MHz ÷ 256/255/240/239                                      | 227 |

| Modulus Exten  | ders                                                          |     |

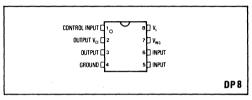

| SP8790A, B     | LP ÷ 4 control for all programmable devices (40mW)            | 217 |

| SP8794A, B     | LP ÷ 8 control for all programmable devices (40mW)            | 222 |

| SP8760B & M    | General purpose synthesiser circuit                           | 208 |

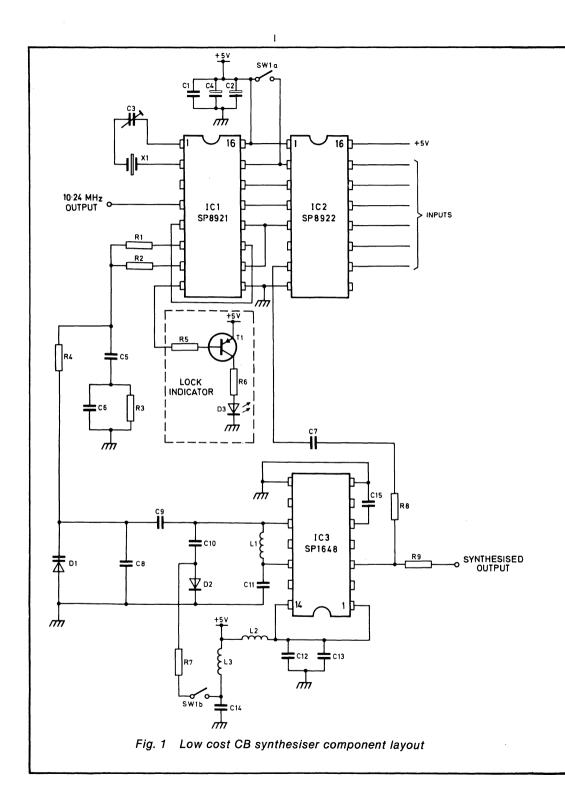

| CB Circuits    |                                                               |     |

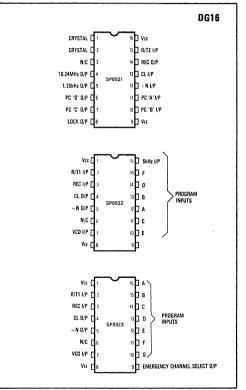

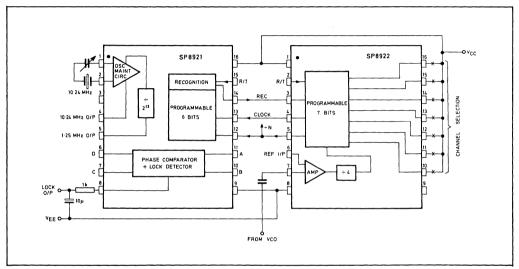

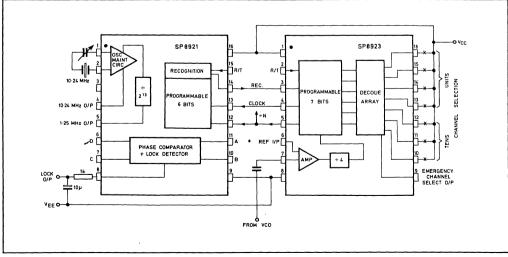

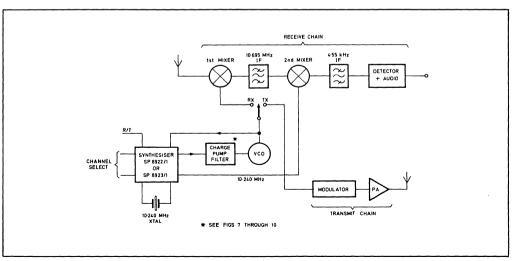

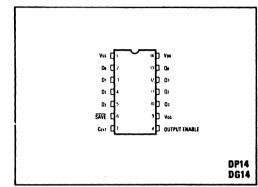

| SP8922         | 40 Channel CB Synthesiser IC Set                              | 229 |

| SP8921         | 40 Channel CB Synthesiser IC Set                              | 229 |

| SP8923         | 40 Channel CB Synthesiser IC Set                              | 229 |

•

7

#### 1. Product Information.

• • •

10

•

# **Building Block IC's**

Plessey integrated circuits are on the leading edge of technology without pushing the ragged edge of capability.

We developed the first 2 GHz counter. And a family of prescalers and controllers for your TV, radio and instrumentation frequency synthesizers.

We have a monolithic 1 GHz amplifier. And a complete array of complex integrated function blocks for radar signal processing and radio communications.

We can supply data conversion devices with propagation delays of just  $2\frac{1}{2}$  nanoseconds.

And a range of MNOS logic that stores data for a year when you remove the power, yet uses only standard supplies and is fully TTL/CMOS-compatible.

To develop this edge, we developed our own processes, both bipolar and MOS. The processes were designed for quality and repeatability, then applied to our high volume lines. Most of our IC's are available screened to MIL-STD-883B, and our quality levels exceed the most stringent military, TV and automotive requirements.

Millions of Plessey complex function building block IC's are being used in TV sets and car radios; CATV, navigation and radar systems; frequency synthesizers and telecommunications equipment.

Our global scope of operations, our high volume manufacturing facilities, our proprietary processes ensure that we will continue to deliver state-of-the-art technology and reliability in IC devices at the appropriate prices and in the required volumes. Day after day. Week after

week. Year after year.

#### **Plessey Semiconductors**

1641 Kaiser Avenue, Irvine, CA 92714. (714) 540-9979

# **Radar Signal Processing**

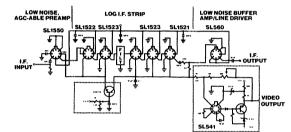

Since the performance of a radar receiver is critically dependent on the performance of its I.F. strip, we offer a range of "building block" IC's that can be used in systems with different performance requirements and configurations.

The logarithmic I.F. strip shown is an example of a low cost, high performance strip fabricated with Plessey IC's. It uses only five devices and a single interstage filter to achieve a logging range of 90 dB,  $\pm 1$  dB accuracy, -90 dBm tangential sensitivity and a video rise time of

20 ns or less.

Three other Plessey IC's complete the system simply and economically. The AGCable SL1550 on the front end improves noise figure, dynamic range and sensitivity. The SL541 lets you vary video output levels, with on-chip compensation making it easy to use. And the SL560 is a "gain block" that replaces your hybrid and discrete amplifiers, usually with no external components.

Another advanced system function block is the Plessey SL531 True Log Amplifier. A 6-stage log strip requires a minimum of external components (one capacitor, one resistor per stage), yet has a band-width of 500 MHz, a dynamic range of 70 dB and has a phase shift of only  $\pm 3^{\circ}$  over its entire range. As with most of our other devices, it operates over the full MIL-temp range and is available screened to MIL-STD-883.

The chart summarizes our Radar Signal Processing IC's. Whether you're working with radar and ECM, weapons control or navigation and guidance systems, our IC's are a simpler, less expensive, more flex-

> ible alternative to whatever you're using now for any I.F. strip up to 160 MHz.

For more details, please use the postage-paid reply card at the back of this book to order our RADAR AND RADIO COMMUNICA-TIONS IC HANDBOOK, or contact your nearest Plessey Semiconductors representative.

#### PLESSEY IC'S FOR RADAR I.F.'S

#### Wideband Amplifiers for Successive Detection Log Strips

- SL521 30 to 60 MHz center frequency, 12 dB gain.

- SL523 Dual SL521 (series).

- SL1521 60 to 120 MHz center frequency, 12 dB gain.

- SL1522 Dual SL1521 (parallel).

- SL1523 Dual SL1521 (series).

- Low Phase Shift Amplifiers

- SL531 True log I.F. amplifier, 10-200 MHz,  $\pm 0.5^{\circ}/10 \text{ dB}$  max phase shift.

- SL532 400 MHz bandwidth limiting amplifier, 1° phase shift max. when overdriven 12 dB.

#### Linear Amplifiers

- SL550 125 MHz bandwidth, 40 dB gain, 25 dB swept gain control range, 1.8 dB noise figure, interfaces to microwave mixers.

- SL1550 320 MHz bandwidth version of SL550.

- SL560 300 MHz bandwidth, 10 to 40 dB gain, 1.8 dB noise figure drives 50 ohm loads, low power consumption.

**Video Amplifiers and Detectors**

- SL510 Detector (DC to 100 MHz) and video amplifier (DC to 24 MHz) may be used separately, 11 dB incremental gain 28 dB dynamic range.

- SL511 Similar to SL510 with DC to 14 MHz video amplifier, 16 dB incremental gain.

- SL541 High speed op amp configuration, 175 V/µs slew rate 50 ns settling time, stable 70 dB gain, 50 ns recovery from overload.

~

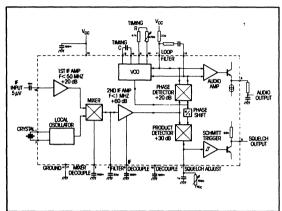

# **Radio Communications**

Our comprehensive line of radio system function blocks is cutting costs, increasing reliability and reducing the size of systems

peak deviation. The SL6600 can be used at I.F. frequencies up to 50 MHz, with deviations up to 10 kHz.

> If any of the Plessey devices appear interesting, use the postagepaid reply card at the back of this book to order our RADAR AND RADIO COMMUNICATIONS IC HANDBOOK. The Handbook includes full details on our integrated circuits, along with a number of applications circuits and design tips that will help you get the maximum system benefits from Plessey products.

> Or if your need is more urgent, contact your nearest Plessey Semiconductors representative.

in applications that range from commercial communications to military manpack radios.

Using our bipolar Process I, the Plessey SL600 Series (hermetic) and SL1600 Series (plastic DIP) feature a high degree of integration, low power consumption and exceptional system design flexibility for I.F.'s up to 10.7 MHz.

Our SL6000 Series uses our bipolar Process III to extend our building block concept even further. Devices all feature advanced circuit design techniques that permit higher levels of integration, lower power consumption and exceptional performance.

Typical is our SL6600, a monolithic IC that contains a complete IF amplifier, detector, phase locked loop and squelch control. Power consumption is a meager 1.5 mA at 6 V, S/N ratio is 50 dB, dynamic range is 120 dB and THD is just 1.3% for 5 kHz

|          |           | PLESSEY RADIO IC'S                                                                        |

|----------|-----------|-------------------------------------------------------------------------------------------|

| Amplifie | ers       |                                                                                           |

| SL610    | SL1610    | 140 MHz bandwidth, 20 dB gain, 50 dB AGC range, low 4 dB N.F., low distortion.            |

| SL611    | SL1611    | 100 MHz bandwidth, 26 dB gain, sim. to SL610.                                             |

| SL612    | SL1612    | 15 MHz bandwidth, 34 dB gain, 70 dB AGC range, 20 mW power consumption.                   |

| SL613    |           | 145 MHz bandwidth, 12 dB gain, limiting amp/detector.                                     |

| Mixers   |           |                                                                                           |

| SL640    | SL1640    | Double balanced modulator eliminates diode rings up to 75 MHz, standby power 75 mW typica |

| Detecto  | rs and A  | GC Generators                                                                             |

| SL620    | SL1620    | AGC with VOGAD (Voice Operated Gain<br>Adjusting Device).                                 |

| SL621    | SL1621    | AGC from detected audio.                                                                  |

| SL623    |           | AM SSB detector and AGC from carrier.                                                     |

|          | SL1625    | AM detector and AGC from carrier.                                                         |

| SL624    |           | AM/FM/SSB/CW detector with audio amplifier.                                               |

| Audio A  | mplifiers |                                                                                           |

| SL622    |           | Microphone amp. with VOGAD and sidetone amp                                               |

| SL630    | SL1630    | 250 mW microphone/headphone amplifier.                                                    |

| I.F. Amp | lifiers/D | etectors                                                                                  |

| SL6600   |           | FM double conversions with PLL detector.                                                  |

| SL6640   |           | FM single conversion, audio stage (10.7 MHz).                                             |

| SL6650   |           | FM single conversion (10.7 MHz).                                                          |

| SL6690   |           | FM single conversion, low power for pagers                                                |

|          |           | (455 kHz).                                                                                |

| SL6700   |           | AM double conversion.                                                                     |

| Audio A  | mplifiers | i                                                                                         |

| SL6270   |           | Microphone amplifier with AGC.                                                            |

|          | SL6270    | with speech clipper, buffer and relay driver.                                             |

| SL6310   |           | Switchable audio amplifier (400 mW/9V/8 ohms)                                             |

| SL6440   |           | High-level mixer.                                                                         |

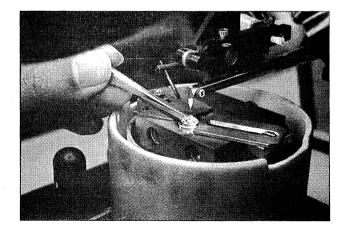

# **R.F.Hybrids**

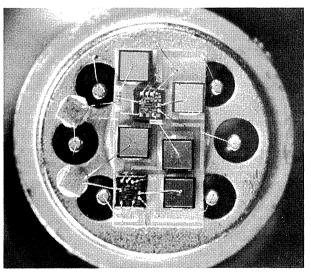

To enhance your systems even further, we have established an R.F. hybrid manufacturing facility in our Irvine, California, U.S.A. headquarters.

For small production quantities or extremely complex functions, our hybrid capabilities can save you time and money while improving your system performance, reducing system size and increasing system reliability. We can help with your I.F. strips, instrumentation front ends, synthesizer subsystems, high speed A-to-D and D-to-A converters and other complex high-frequency functions.

They can be fabricated to MIL-STD-883 using thick and thin film techniques, using our own integrated circuits in combination with discrete transistors, diodes and other components.

Our IC functions represent the state-of-the-art in high frequency integration, with  $f_t$ 's as high as 5 GHz. The chips are backed by an in-depth in-house systems knowledge that encompasses radar, radio communications, tele-communications analog and digital conversion, frequency synthesis and a broad range of applications experience.

We can work to your prints, or we can design a full system based on your "black box" specifications. For more information, please contact: Plessey Semiconductors, 1641 Kaiser Avenue, Irvine CA 92714, (714) 540-9979.

# **Frequency Synthesis**

Plessey's IC's offer a quick and easy way to lower synthesizer costs while increasing loop response and channel spacing all the way from dc through the HF, VHF, UHF, TACAN and satellite communications bands.

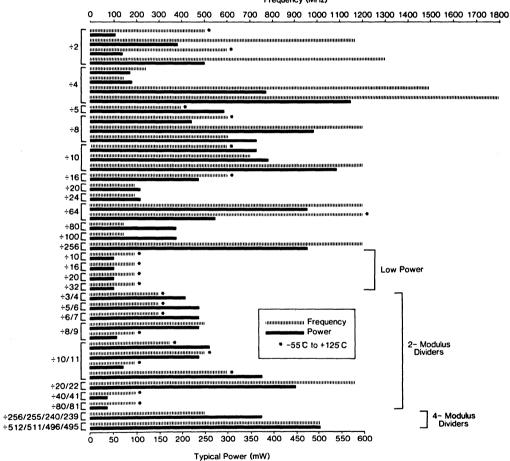

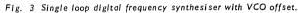

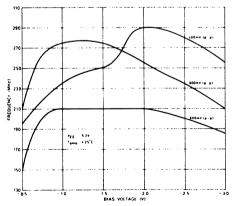

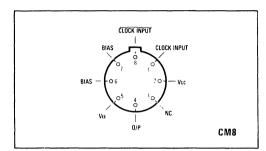

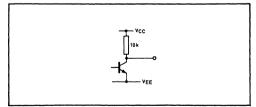

Our single-modulus prescalers operate at frequencies all the way up to 1.8 GHz. They feature self-biasing clock inputs, TTL/CMOS-compatibility and all guaranteed to operate to at least the frequencies shown, most of them over the temperature range from  $-55^{\circ}$ C to  $+125^{\circ}$ C.

Our 2-modulus and 4-modulus dividers expand your system flexibility and allow even tighter channel spacing. All of them provide low power consumption, low propagation delay and ECL-compatibility.

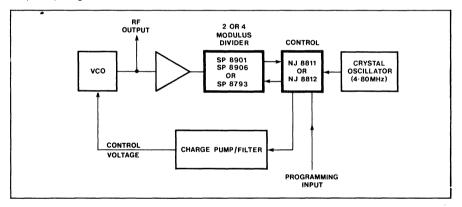

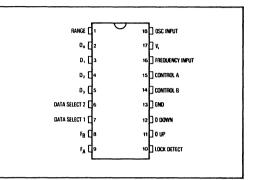

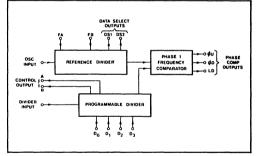

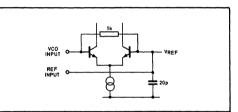

To simplify your systems even further, we also offer highly integrated control chips. Our NJ8811, for example, includes a crystal oscillator maintaining circuit, a programmable reference divider, a programmable divider to control the four-modulus prescaler and a high performance phase/frequency comparator so that you can phase lock your synthesizer to a crystal with none of the usual headaches and hassles.

We've put together a FREQUENCY SYNTHESIZER IC HANDBOOK that details all of the Plessey IC's and includes a number of applications circuits, practical examples of how Plessey integrated circuits can simplify your designs and improve system performance.

For your copy of the Handbook, please use the postagepaid reply card at the back of this book, or contact your nearest Plessey Semiconductors representative.

16

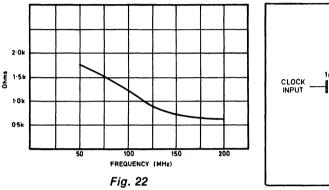

Frequency (MHz)

### **Telecommunications**

Plessey functional building block IC's are exceptionally versatile. Designed from a systems standpoint, they reduce complexity and lower costs while increasing the performance of telecommunications systems.

Our SL600 Modulator/Phase Locked Loops are used in waveform generators and in AM, PAM, FM, FSK, PSK, PWM, tone burst and Delta modulators.

Our SL1000 Series amplifiers meet the most stringent demands of telephone transmission equipment.

Our transistor arrays with up to five electrically and thermally matched transistors on a chip are ideal for discrete and hybrid amplifiers and mixers. In addition to standard second-source devices that plug directly into your designs, we have a number of devices designed for your low noise and ultrahigh frequency applications.

The Plessey TELECOMMUNICA-TIONS IC HANDBOOK contains complete information on all of these devices, as well as application notes, to help you get the most out of them. To get your copy, please use the postage-paid reply card at the back of this book or call your nearest Plessey Semiconductors representative.

| Telecommunications Devices                       |                                           |                                                                                      |                     |                        |

|--------------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------|---------------------|------------------------|

| MJ1440<br>MJ1444<br>MJ1445<br>MJ1471<br>Data Com |                                           |                                                                                      |                     |                        |

| MP3812                                           |                                           | it FIFO memory, si<br>z data rates, easil                                            |                     | l, up to               |

| MJ2841                                           |                                           | it FIFO memory, 5                                                                    |                     | e.                     |

| Modulato                                         |                                           | ocked Loops                                                                          |                     |                        |

| SL650                                            | PSK, ton                                  | or/PLL for AM, PA<br>e-burst and Delta<br>able 100:1.                                |                     | FSK,                   |

| SL651                                            |                                           | o SL650 without a                                                                    | uxiliary amplif     | ier.                   |

| SL652                                            |                                           | o SL650, low cost                                                                    |                     |                        |

| Telephon                                         | e Circuits                                |                                                                                      |                     |                        |

| SL1001                                           |                                           | or/demodulator, 5                                                                    |                     | nd signal              |

| <b>SL</b> 1021                                   |                                           | sion, —112 dBm n<br>hannel amplifier, s                                              |                     |                        |

| JLIUZI                                           | gain con                                  |                                                                                      | lable remote        |                        |

| SL1025                                           |                                           | anced modulator,                                                                     | 50 dB carrier       | and signal             |

| <b>SL</b> 1030                                   | suppress<br>200 MH:<br>low nois           | suppression, 5 dB conversion gain.<br>200 MHz wideband amplifier, programmable gain, |                     |                        |

| Transisto                                        |                                           | с.                                                                                   |                     |                        |

|                                                  | ESSEY                                     | 2ND-SOURCE<br>PART NO.                                                               | PLESSEY<br>PART NO. | 2ND-SOURCE<br>PART NO. |

| SL                                               | .3081                                     | CA3081                                                                               | SL3051              | CA3951                 |

|                                                  | .3082                                     | CA3082                                                                               | SL355               | NONE                   |

|                                                  | .3083                                     | CA3083                                                                               | TBA673              | TBA673                 |

|                                                  | .3183                                     | CA3183                                                                               | SL1495              | CA1495L                |

|                                                  | .3146                                     | CA3146<br>CA3093                                                                     | SL1496<br>SL1496    | MC1496G<br>MC1496L     |

| SL3093<br>SL3018                                 |                                           | CA3018                                                                               | SL1496<br>SL1595    | MC1496L<br>MC1595L     |

| SL3018<br>SL3018A                                |                                           | CA3018A                                                                              | SL1595              | MC1596G                |

|                                                  | .3118A                                    | CA3118A                                                                              | SL1596              | MC1596L                |

|                                                  | .3118                                     | CA3118                                                                               | SL3054              | CA3054                 |

| SL3050                                           |                                           | CA3050                                                                               | SL3086              | CA3086                 |

| SL360                                            | High f                                    | requency matched                                                                     | l pair, ft=2.5 G    | Hz.                    |

| SL363                                            |                                           |                                                                                      |                     |                        |

|                                                  | L2363/4 5GHz dual long-tailed pair.       |                                                                                      |                     |                        |

| <b>SL</b> 3145                                   | SL3145 Five transistor array, ft=2.5 GHz. |                                                                                      |                     |                        |

|                                                  |                                           |                                                                                      |                     |                        |

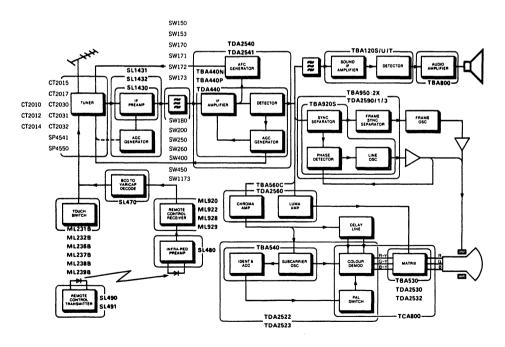

### **Television IC's**

Plessey integrated circuits are in millions of homes, in television sets around the world.

Economical and reliable, our devices cover the range from remote controls to touch tuners to frequency synthesizers, as well as a range of second-source devices for the IF color processing and line oscillators.

For the 1980's, we have introduced the Plessey KEY System, designed for maximum flexibility, simplicity and ease of manufacture. The KEY System frequency synthesizer offers accurate, high stability frequency selection, channel and program identification, and the very finest digital fine tuning. It can be configured to receive up to four completely different standards (PAL, SECAM, SECAMF, and NTSC) in a single TV set. It has 100 channel capability per standard, and includes a 32-program non-volatile memory that contains channel, fine tuning and standards information. And it can be interfaced to a Plessey or other microprocessor for games, Teletext or similar applications.

Complete data on all our television devices has been assembled in our TELE-VISION IC HANDBOOK, along with application notes to make them even easier to use. Please use the postage-paid reply card at the back of this book to order your copy, or simply contact your nearest Plessey Semiconductors representative.

ALL TBA, TCA, TDA DEVICES ARE SECOND-SOURCED.

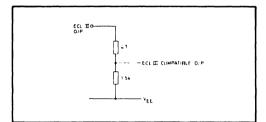

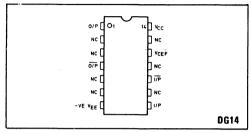

### **ECL III Logic and Data Conversion**

As radar and communications systems become faster and more complex, the need arises for digital processing. We have developed a family of functions with speeds unequalled anywhere.

Part of our family is a range of ECL III logic that is a direct plug-in replacement for MECL logic, including low impedance as well as high impedance devices. We extended the range by adding functions with lower delays and much higher operating speeds. Our SP16F60, for example, is the world's fastest dual 4-input OR/NOR gate, with a switching speed of just 500 picoseconds. Devices can also be selected for certain specifications (such as threshold voltage or slew rate on

our SP1650/1, toggle rates or delays on our SP1670) to handle your most demanding applications. We've also developed a family of high speed comparators and circuits for ultra-high speed A-to-D converters. Our latching SP9750 high speed comparator features a maximum settling time of 2 ns, a propagation delay of 3.5 ns and is capable of operating at rates up to 100 million samples per second.

Currently, our devices are being used in radar and video processing, nucleonics systems, transient recorders and secure speech transmission systems. We have compiled a number of application notes and details on the devices in our ECL III L'OGIC AND DATA CONVERSION IC HANDBOOK. To get your copy, please use the postage-paid reply card at the back of this book, or contact your nearest Plessey Semiconductors representative.

#### HIGH SPEED ECL III LOGIC

| SP1648  | Voltage controlled oscillator         |

|---------|---------------------------------------|

| SP1650  | Dual A/D comparator, Hi-Z             |

| SP1651  | Dual A/D comparator, Lo-Z             |

| SP1658  | Voltage controlled multivibrator      |

| SP1660  | Dual 4-I/P OR/NOR gate, Hi-Z          |

| SP1661  | Dual 4-I/P OR/NOR gate, Lo-Z          |

| SP1662  | Quad 2-I/P NOR gate, Hi-Z             |

| SP1663  | Quad 2-I/P NOR gate, Lo-Z             |

| SP1664  | Quad 2-I/P OR gate, Hi-Z              |

| SP1665  | Quad 2-I/P OR gate, Lo-Z              |

| SP1666  | Dual clocked R-S Flip-Flop, Hi-Z      |

| SP1667  | Dual clocked R-S Flip-Flop, Lo-Z      |

| SP1668  | Dual clock latch, Hi-Z                |

| SP1669  | Dual clock latch, Lo-Z                |

| SP1670  | Master-slave D Flip-Flop, Hi-Z        |

| SP1671  | Master-slave D Flip-Flop, Hi-Z        |

| SP1672  | Triple 2-I/P exclusive-OR gate, Hi-Z  |

| SP1673  | Triple 2-I/P exclusive-OR gate, Lo-Z  |

| SP1674  | Triple 2-1/P exclusive-NOR gate, Hi-Z |

| SP1675  | Triple 2-I/P exclusive-NOR gate, Lo-Z |

| SP1692  | Quad line receiver                    |

| SP16F60 | Dual 4-I/P OR/NOR gate                |

#### HIGH SPEED DATA CONVERSION PRODUCTS

| SP9680   | High speed latched comparator.                                                                                  |

|----------|-----------------------------------------------------------------------------------------------------------------|

| SP9685 1 | Ultra-fast comparator; 0.5 ns typical set-up time; typical                                                      |

| 2        | 2.2 ns propagation delay; excellent CMR.                                                                        |

| SP9687   | Dual SP 9685.                                                                                                   |

| SP9750 H | High speed latched comparator with precision current                                                            |

|          | source, wired-OR decoding; 2 ns min. set-up time; 2.5 ns propagation delay.                                     |

| SP9752   | 2-bit ADC expandable to 6-bit ADC; very fast 125 MHz clock.                                                     |

| SP9754 4 | 4-bit ADC expandable to 8-bit ADC; very fast 100 MHz clock.                                                     |

| SP9768 8 | 8-bit DAC; extremely fast; available 3rd quarter 1980.                                                          |

| SP9778 8 | 8-bit SAR; works with SP9768 to make a two-chip succes-<br>sive approximation ADC (20 MHz clock); available 4th |

| 9        |                                                                                                                 |

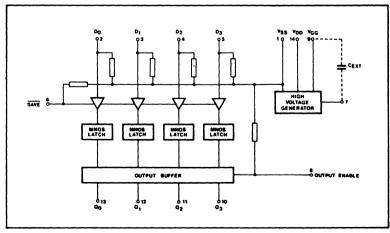

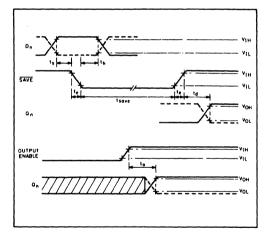

### **MNOS Non-Volatile Logic**

As semiconductors become more pervasive in military and commercial applications, the need for non-volatile data retention becomes more and more critical.

ź

Plessey NOVOL MNOS devices answer that need, and will retain their data for at least a year  $(-40^{\circ}C \text{ to } +70^{\circ}C)$  in the event of "power down" or a system crash.

Our devices all operate from standard MOS supplies and are fully compatible with your TTL/CMOS designs. The high voltages normally associated with electricallyalterable memories are generated on-chip to make system interface simpler and less expensive.

Plessey NOVOL devices provide a reliable, sensible alternative to CMOS with battery back-up or mechanical, electro-mechanical and magnetic devices. Applications include metering, security code storage, microprocessor back-up, elapsed time indicators, counters, latching relays and a variety of commercial, industrial and military systems.

For more information, contact your nearest Plessey Semiconductors representative, or use the postage-paid reply card at the back of this brochure to order your copy of the Plessey NOVOL literature package.

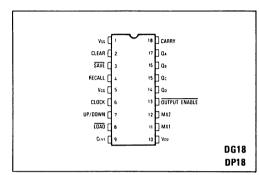

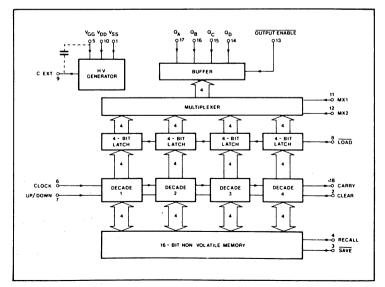

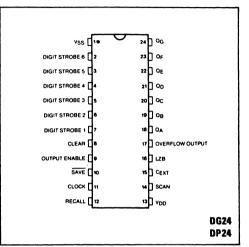

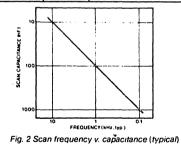

| PLESSEY NOVOL MNOS |                                                 |  |  |

|--------------------|-------------------------------------------------|--|--|

| MN9102             | 4-bit Data Latch (+5V, -12V)                    |  |  |

| MN9105             | 4-Decade Up/Down Counter (+5V, -12V)            |  |  |

| MN9106             | 6-Decade Up Counter (12V only)                  |  |  |

| MN9107             | 100-Hour Timer (12V only)                       |  |  |

| MN9108             | 10,000-Hour Timer (12V only)                    |  |  |

| MN9110             | 6-Decade Up Counter with Carry (12V only)       |  |  |

| MN9210             | 64 x 4-Bit Memory                               |  |  |

| *                  | 8 x 4-Bit Memory                                |  |  |

| *                  | 6-Decade Up/Down Counter, BCD Output            |  |  |

| *                  | 6-Decade Up/Down Counter with Preset BCD Output |  |  |

|                    |                                                 |  |  |

COMING SOON

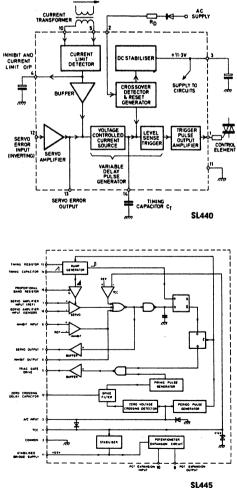

### **Power Control**

Plessey power control devices are highly integrated not just to solve the problems, but to solve them at a lower cost than any other available method.

For timing, our devices use a pulse integration technique that eliminates the need for expensive electrolytic capacitors, thus increasing accuracy and repeatability while reducing costs. An integral supply voltage sensing circuit inhibits triac gate drive circuitry if the supply is dangerously low to prevent half-wave firing and firing without achieving complete bulk spike filter prevents misfiring on noise inputs. Symmetrical control prevents the introduction of dc components onto the power lines.

Devices have been tailored for specific applications as indicated in the chart. For more information, please use the postage-paid reply card at the back of this book to order our POWER CONTROL IC HANDBOOK, or contact your nearest Plessey Semiconductors representative.

LOAD CURRENT

|         | _                                                                                                                                                                           |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SL440   | Proportional phase<br>control for motors, lamps<br>and lower power, fast<br>response heating.                                                                               |

| SL441   | Similar to SL440, with<br>proportional temperature<br>control and thermister<br>malfunction sensing, for<br>hairdryers, soldering<br>irons and food warmers.                |

| SL442   | Switch mode power sup-<br>ply control, up to 40 kHz,<br>integral oscillator, vari-<br>able ratio space/mark<br>pulses, soft-start, dynamic<br>current limiting, OVP.        |

| SL443   | Similar to SL441 with<br>manual power control,<br>long timing periods for<br>hot plates, electric<br>blankets and traffic lights.                                           |

| SL444   | Similar to SL441 for 240V<br>permanent magnet motor<br>with thermal trip,<br>current limit detector.                                                                        |

| SL445   | Proportional or On/Off<br>control, temperature trip/<br>inhibit circuitry, LED and<br>alarm drive facilities, for<br>ovens, heaters, industrial<br>temperature controllers. |

| SL446   | On/Off servo loop temper-<br>ature controller, low exter-<br>nal component count, for<br>water and panel heaters,<br>refrigerators, irons.                                  |

| TBA1085 | Motor speed control                                                                                                                                                         |

conduction. A zero-voltage

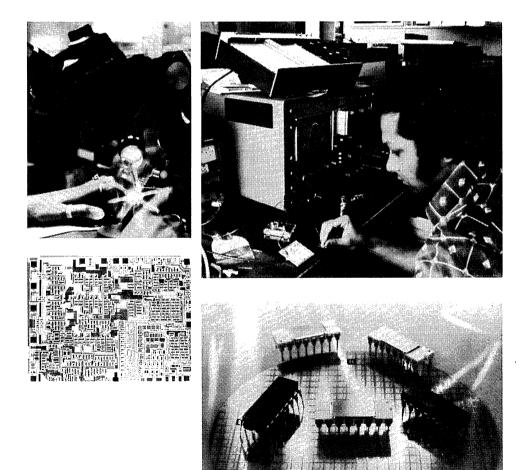

### **Processes, Testing and Quality Control**

Just as we applied our systems knowledge to the partitioning of functions to make our IC's extremely flexible and cost effective, we also developed an internal system concept to ensure that we could deliver our state-of-the-art solutions year after year.

Our concept of standard processes and rigid design rules ensures that our devices are reproducible this year, next year and five years from now. Our continuing investment in research and development ensures that any new products we introduce will be on the leading edge of technology, yet with the same high performance and reliability that our customers have come to expect as the Plessey standard.

The result is that millions of Plessey devices have been built into TV sets and car radios; CATV, navigation and radar systems; frequency synthesizers and telecommunications equipment.

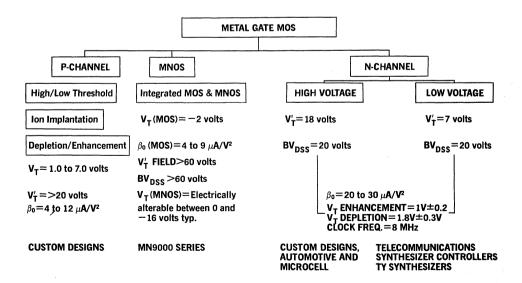

### **Plessey MOS Processes**

P-channel metal gate MOS has been in production for years and is used for both standard Plessey products and custom LSI. Using ion implantation to modify transistor and field threshold voltages, we can reproduce virtually any p-channel metal gate process, with or without depletion loads.

**MNOS (non-volatile)** is essentially a p-MOS process with variable threshold memory transistors fabricated alongside conventional MOS transistors. A modified oxide-nitride gate dielectric permits the injection and retention of charge to change the threshold voltage. Current Plessey products will retain an injected charge for at least a year, and include an on-chip high voltage generator so that

they may be used with standard supply voltages.

N-channel metal gate MOS uses an auto-registration co-planar process with layout similar to our p-MOS. Ion implantation is used to define the threshold voltage of the depletion and enhancement transistors. The constant-current-like characteristics of depletion load devices give the most effective driving capability. and enhancement-depletion technology simplifies design and increases packing density. The field threshold voltage is also controlled by an ion implant, allowing the use of a lightly doped substrate. This reduces both the body constant and the junction capacitance and results in faster switching speeds.

### **Plessey Bipolar Processes**

**Bipolar Process I** is a conventional buried +N layer diffusion process with  $f_t$ =600 MHz and other characteristics similar to industry-standard processes. Applications range from high reliability military devices to high volume consumer products.

| Process Variant         | Α                  | B<br>Non            | G                   | D                  |

|-------------------------|--------------------|---------------------|---------------------|--------------------|

| Application             | General<br>Purpose | Saturating<br>Logic | Saturating<br>Logic | Linear<br>Consumer |

| <b>ВVсво</b> @ 10µА     | 20V min.           | 10V min.            | 10V min.            | 45 <b>V</b> min.   |

| ВVЕВО @ 10µА            | 5.3V to<br>5.85V   | 5.15V min.          | 5.15V min.          | 6.8V to<br>7.4V    |

| LVCEO                   | 12V min.           | 8V min.             | 8V min.             | 20V min.           |

| VCE (SAT) @             |                    |                     |                     |                    |

| IB=1mA,                 | 0.43V              | 0.32V               | 0.43V               | 0.6V               |

| IC=10mÅ                 | max.               | max.                | max.                | max.               |

| hFE @ IC=5mA,<br>VCE=5V | 40 to 200          | 50 min.             | 50 min.             | 50 to 200          |

| ft @ IC=5mA,<br>VCE=5V  | 500<br>MHz         | 500<br>MHz min.     | 500<br>MHz min.     | 350<br>MHz min.    |

**Bipolar High Voltage (HV) Process** is a variant of Process I that yields an  $LV_{ceo}$ greater than 45 volts. Doping levels can be controlled and an extra diffusion used to fabricate a buried avalanche diode with a 40 V breakdown for absorbing powerful noise transients without being destroyed.

| Process Variant     | CA           |

|---------------------|--------------|

| BVCB0 @ 10μA        | 80V min.     |

| BVEB0 @ 10µA        | 7.2V to 8.0V |

| LVCEO               | 45V min.     |

| VCE (SAT) @ IB=1mA, |              |

| IC=10mÅ             | 0.4V max.    |

| hFE @ IC=5mA        |              |

| VCE=5V,             | 80 to 300    |

| ft @ IC=5mA, VCE=5V | 250 MHz min. |

|                     |              |

**Bipolar Process III** uses very shallow diffusion and extremely narrow spacing for high frequency integrated circuits with unusually low power consumption and high packing densities. An f<sub>t</sub> of 2.5 GHz allows us to routinely produce analog amplifiers with bandwidths as high as 300 MHz and low power dividers and prescalers that operate at frequencies up to 1.2 GHz. Process variants allow us to produce devices with an extended  $\beta$ , higher breakdown voltages and very small geometries.

| Process Variant      | WE           |

|----------------------|--------------|

| Application          | Digital      |

| ВVсво @ 10µА         | 10V min.     |

| ВVево @ 10µА         | 5.1V to 5.8V |

| LVCEO                | 7V min.      |

| VCE (SAT) @ IB=1mA,  |              |

| IC=10mÅ              | 0.5V max.    |

| hFE @ IC=5mA, VCE=2V | 40 to 200    |

| ft @ IC=5mA, VCE=2V  | 1.8 GHz      |

**Bipolar Process 3V** is an extension of our Process III. Ion implantation and washed emitters have given the process an  $f_t=6.5$  GHz, allowing us to produce dividers working at 2 GHz, logic gates with delays of less than 500 picoseconds and linear amplifiers at 1 GHz.

| Process Variant       | wv           |

|-----------------------|--------------|

| Application           | Digital      |

| <b>ВVсво @ 10µA</b>   | 8V min.      |

| BVEBO @ 10µA          | 3.0V to 5.0V |

| LVCEO@ 5mÅ            | 6V min.      |

| VCE (SAT) @ IB=1mA,   |              |

| IC=10mA               | 0.5V max.    |

| hFE @ IC=10mA, VCE=5V | 40 to 120    |

| ft @ IC=5mA, VCE=2V   | 6.5 GHz      |

|                       |              |

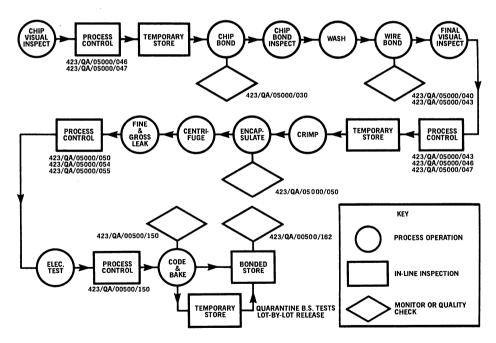

# **Testing and Quality Control**

A major thrust of our development work is to ensure that our processes will routinely produce reliable devices. Our Process III has a projected MTBF of 400,000 hours while our Process I is even better.

Our facilities include the latest test equipment (such as the Macrodata MD501, Teradyne J324 and Fairchild Sentry VII and Sentinel) to allow us to perform all the necessary functional and parametric testing in-house. We have an internal capability to provide specific applications-oriented screening, and most Plessey IC's are available screened to MIL-STD-883 and other international specifications. Our quality levels exceed the most stringent military, TV and automotive requirements as a matter of course.

But the best proof of all these claims is our products themselves. After you've reviewed the products that could help you with your systems, use the postage-paid reply card or contact your nearest Plessey representative for complete details.

#### ASSEMBLY OF INTEGRATED CIRCUITS QUALITY ASSURANCE

2. The Design of Programmable Devices for UHF and VHF Synthesisers.

. •

.

. .

.

Si a

#### INTRODUCTION

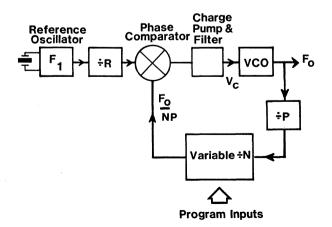

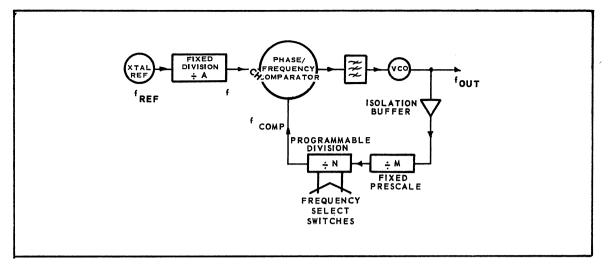

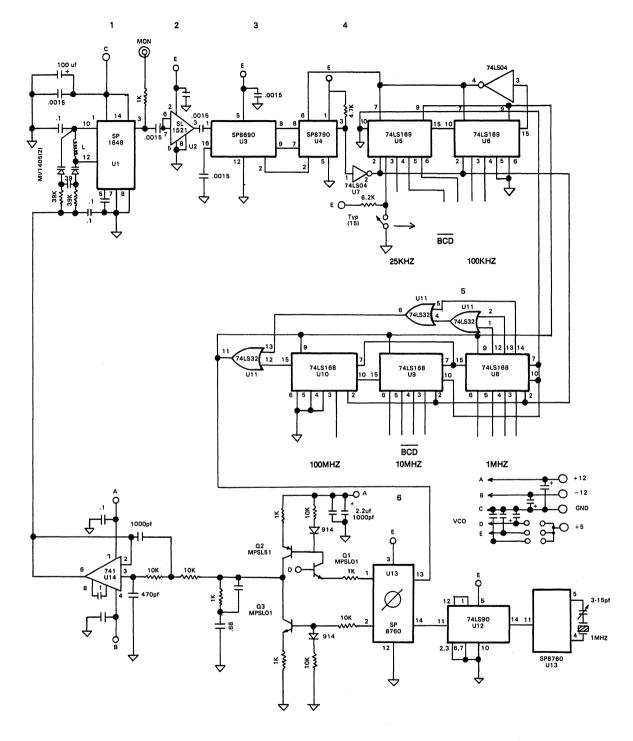

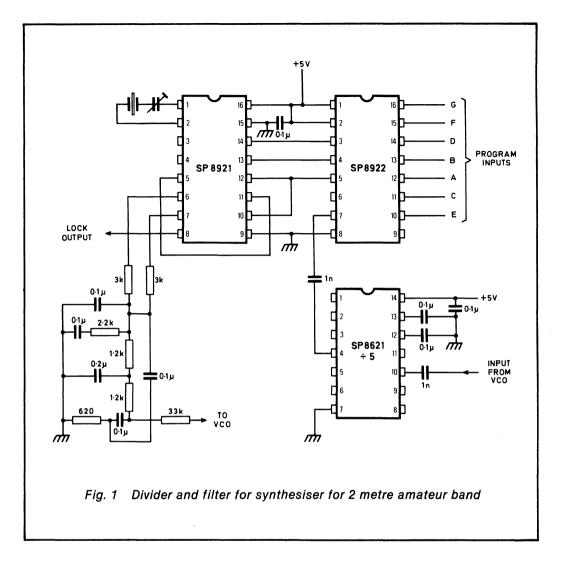

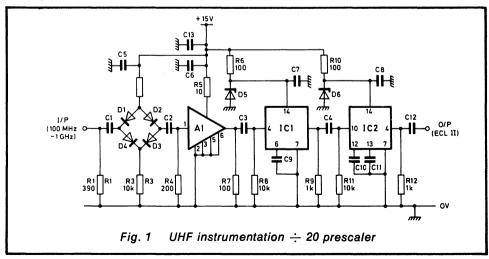

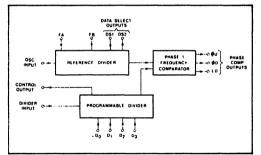

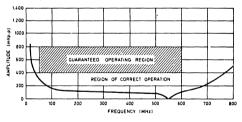

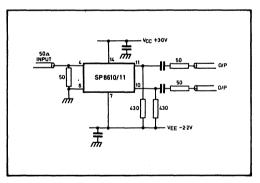

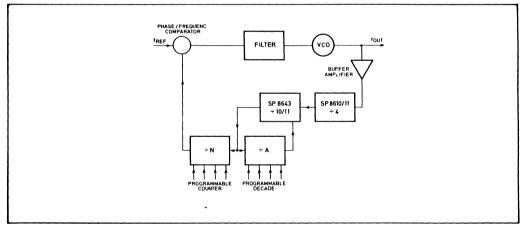

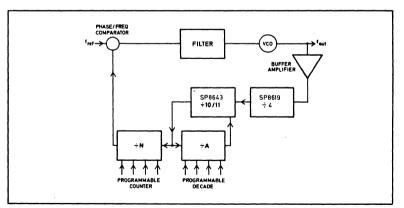

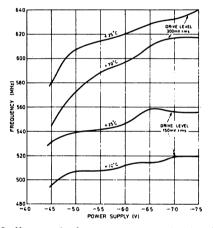

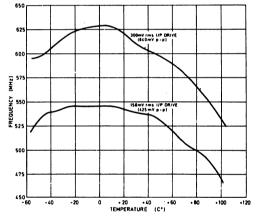

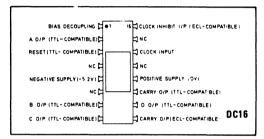

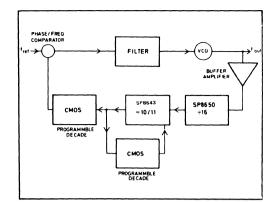

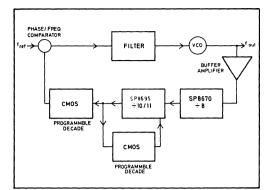

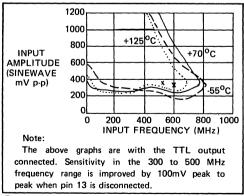

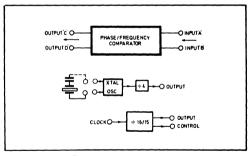

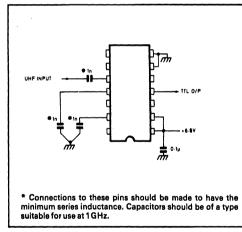

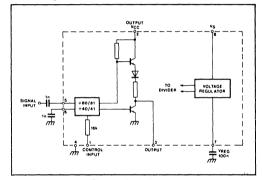

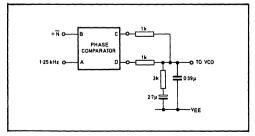

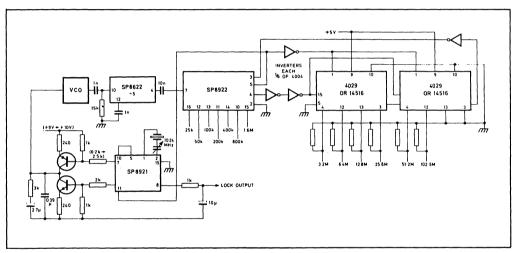

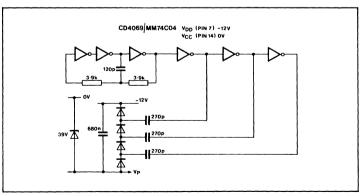

As communications traffic in the VHF and UHF radio bands increases, users of communications equipment are demanding more stringent specifications. These include a much greater number of channels available in an equipment, closer channel spacing, improved frequency stability, for both receiver local oscillators and transmitter drivers, and high speed channel selection of tuning. These pressures have led to the adoption of frequency synthesis to replace local oscillators in an increasing number of equipments. This move to synthesis gives an equipment virtually unlimited channel selection capability and a long term frequency stability derived from one reference source (typically an ovened crystal oscillator). Other require – ments such as high tuning speed and good short term frequency stability are achieved by careful synthesiser loop design once a maximum comparison frequency (see Fig. 1) has been established.

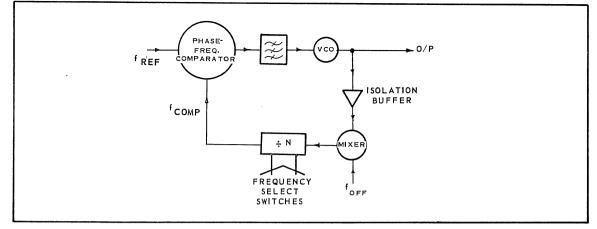

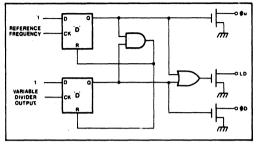

If we look at a single loop synthesiser as shown in Fig. 1 we can see from the amount of programmable division required (typically 4000-16000 for a VHF-UHF avionics equipment) that a high proportion of any synthesiser's hardware will be devoted to this function. Clearly any economies that can be achieved in this area, in both total package count and in total power consumption will add appreciably to the final equipment's technical and economic viability. This area, in the feedback path between the Voltage Controlled Oscillator (VCP (VCO) and the phase/frequency comparator, is the particular concern of this application note.

#### General Requirements of the Programmable Divider

The Phase lock loop of a frequency synthesiser acts to keep (see Fig. 1.):

$$f_{ch} = f_{comp}$$

since fcomp = fout  $(N \times M)$

the output frequency fout is related to fch by:

$$\frac{fout}{N \times M} = f_{ch}$$

The factors M and N in equation 2 are the division ratios of the fixed and programmable parts of the feedback divider. N, the division ratio of the programmable divider is normally set in integer steps and consequently fout can only be altered in steps of M. f<sub>ch</sub>. This figure, M. f<sub>ch</sub>, is the minimum channel spacing attainable in a single loop synthesiser. A study of the dynamics of the loop (see refs) shows clearly that the reference frequency, fref, imposes an upper limit to the loop. This limitation in turn re-stricts the tuning time of the loop and also limits the short term stability which is attainable in the VCO. Consequently to achieve a given channel spacing on fout, without compromising the reference frequency fch, the value of fixed prescale M should be as small as possible.

At this point we should investigate the reasons for inserting M in the first place. Economical programmable division can only be achieved by using standard decades fabricated in one of the established technologies such as cosmos or TTL, or in extreme cases ECL 10K and the operational speed of these standard decades is restricted to a figure well below the VHF and UHF frequencies required (100MHz-500MHz) as output from the VCO.

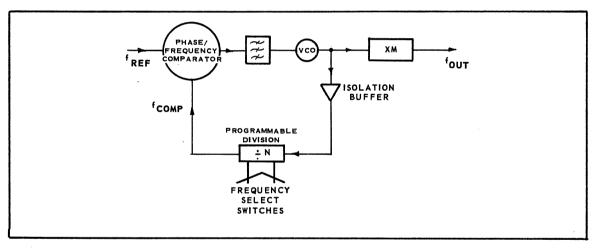

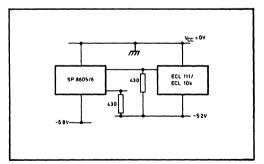

Clearly, some means of reducing the VCO output frequency to an area where programmable division is possible is required. Until the advent of high speed ECL dividers such as the Plessey SP8000 series, linear techniques were adopted for this function. One of these techniques was to operate the VCO at a frequency sufficiently low to allow direct programmable division. The required output frequency was produced by frequency multiplication of the VCO output (see Fig. 2). With this technique it was difficult to produce a spectrally pure output. Additionally the minimum channel spacing was M. fref, limiting the loop performance for given channel spacing.

1

Fig. 1 Single loop digital frequency synthesiser with prescaled division.

Fig. 2 Single loop digital frequency synthesiser with frequency multiplier output.

4

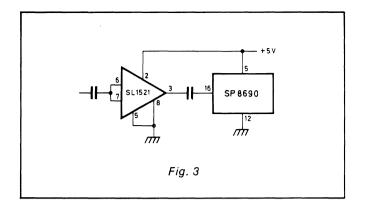

Another technique often adopted was to offset the VCO output in a mixer, shown in Fig. 3. The effect of the offset frequency, f off, on f comp is shown in equation 4.

$$fcomp = \underbrace{\frac{f_{out} - f_{off}}{N}}_{N}$$

i.e. fout =  $N \cdot f_{comp} + f_{off}$

It is clear from equation 4 that this technique gives a reference frequency which is equal to the required channel spacing, so that loop performance is not compromised. However the addition of the offset frequency automatically reduces the achievable frequency stability of the VCO output. In addition the VCO 30

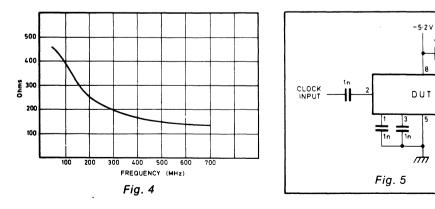

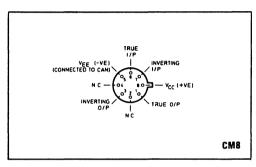

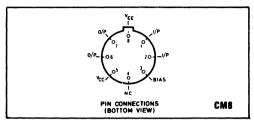

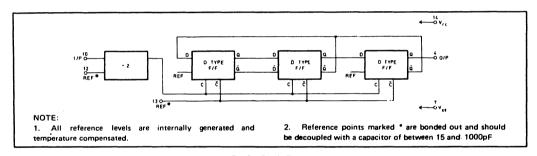

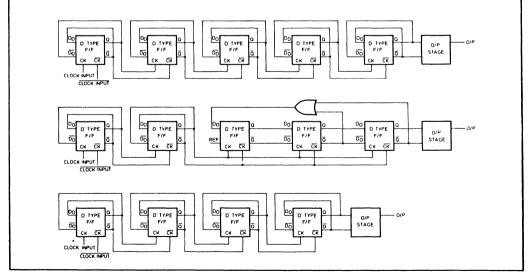

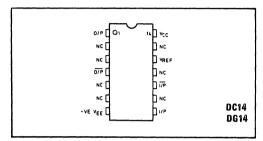

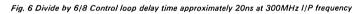

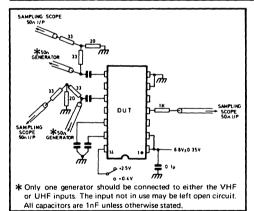

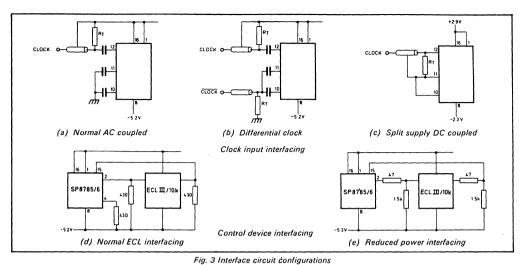

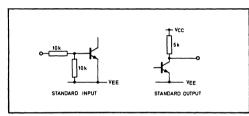

Fig. 4 The SP8000 range of fixed-modulus dividers.

output will be contaminated by sidebands introduced from f<sub>off</sub> via the offset mixer.

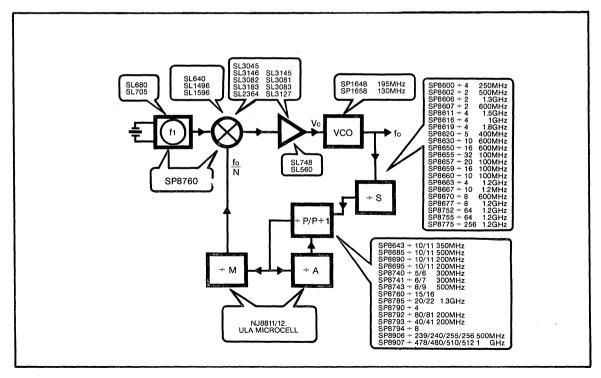

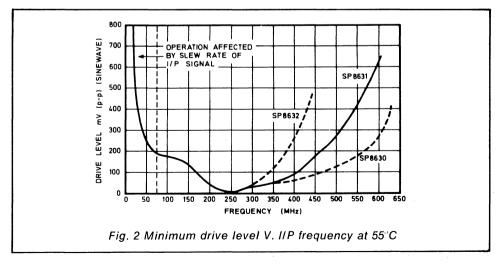

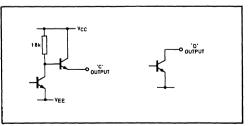

As I previously mentioned, these techniques became obsolete with the introduction of the Plessey SP8000 range of high speed dividers.

This range, illustrated in Fig. 4, has a comprehensive selection of division ratios, frequency perform ance and power consumption which can suit almost all requirements where fixed prescaling is appropriate.

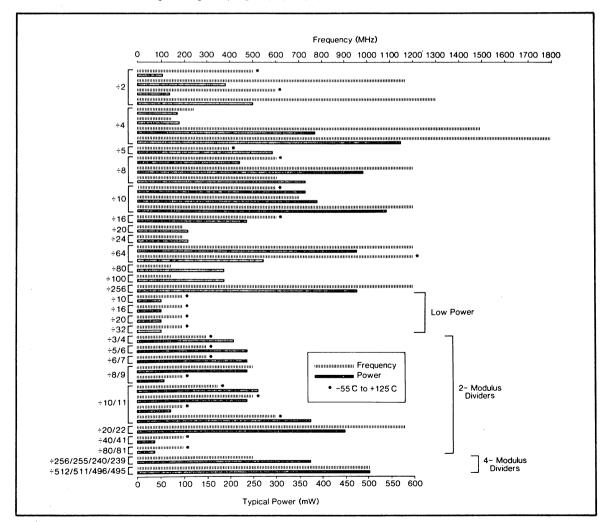

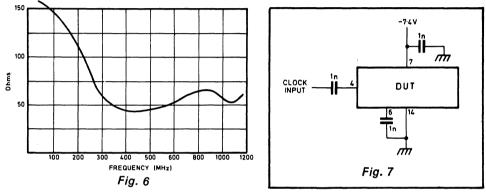

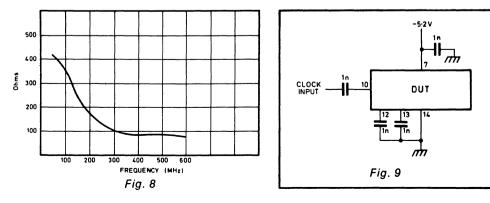

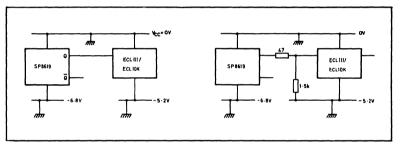

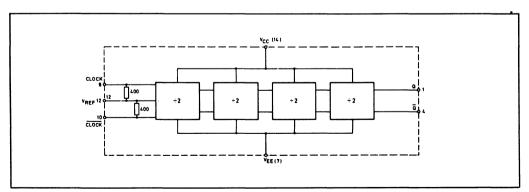

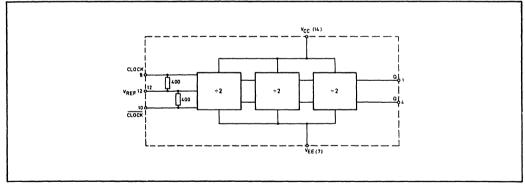

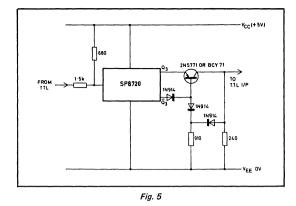

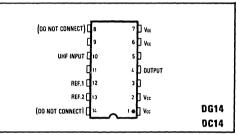

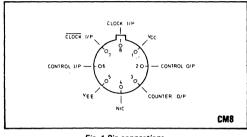

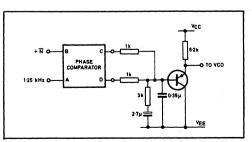

Fig. 5 The SP8000 series (Two modulus prescalers).

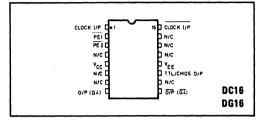

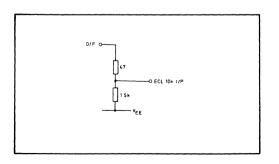

#### Fixed or Variable Prescaling?

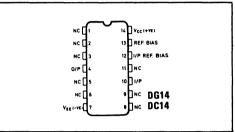

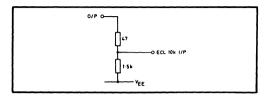

If we return to the effect of fixed prescaling on loop response times it is clear that as the VCO frequency extends upwards in the UHF band the amount of prescaling required to reduce it to a suitable value for programmable division becomes excessive. Fortunately help is at hand. If a prescaler is available whose division radix can be switched between two or more values then it is possible to have effective programmable division at the prescaler input frequency, with the actual programmable dividers operating at the output frequency of the prescaler. Fortunately such devices are available as  $\div$  10/11 in several forms in the Plessey SP8000 series. The available versions of  $\div$  10/11 circuits are shown in Fig. 5 which illustrates the wide range of speed/power option in the SP8000 series. Also available are alternative division ratios of  $\div$  3/4, 5/6, 6/7, 8/9, 20/22, 40/41 and 80/81.

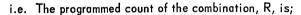

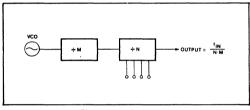

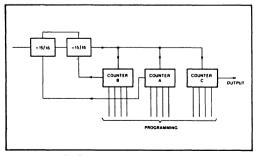

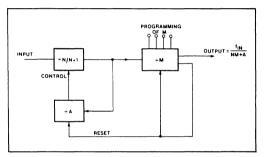

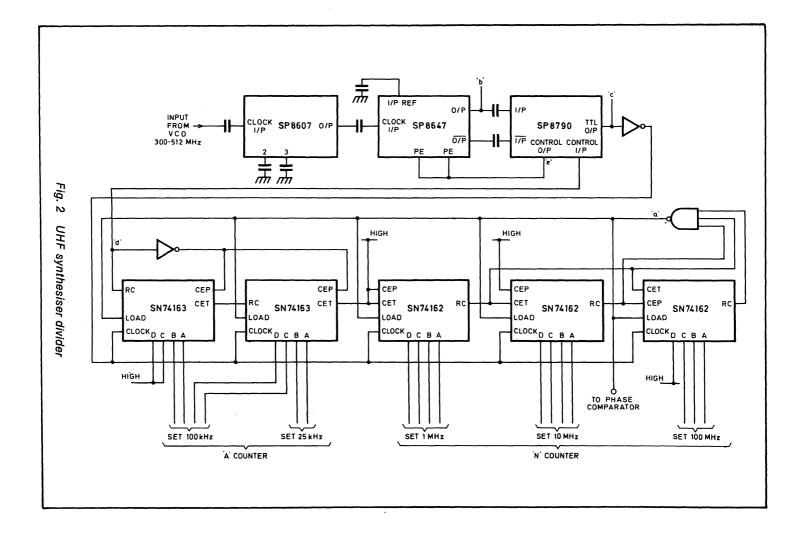

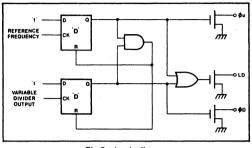

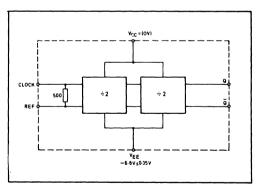

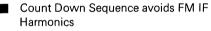

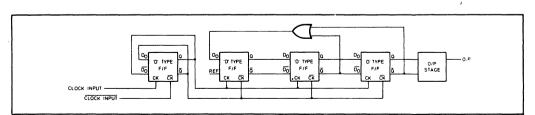

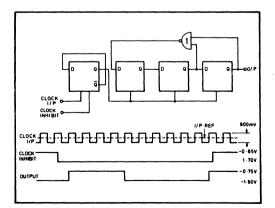

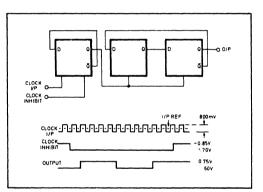

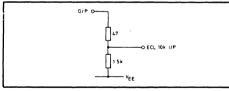

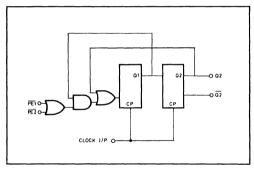

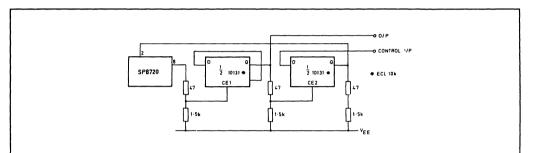

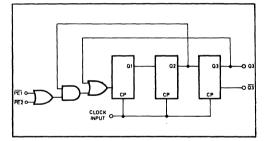

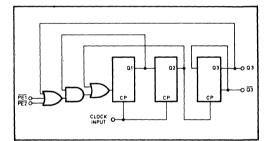

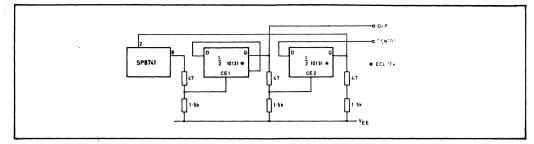

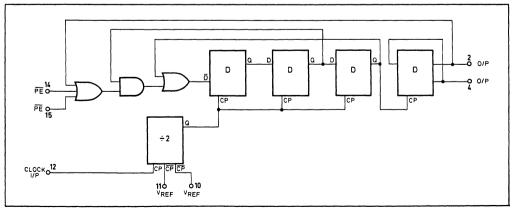

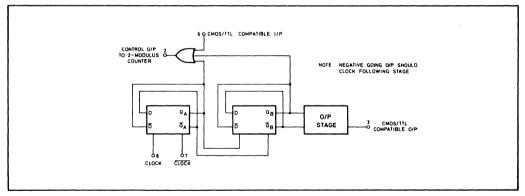

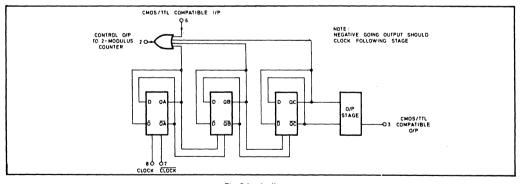

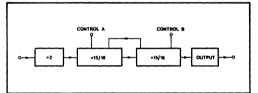

In order to illustrate how a two modulus divider operates we should look at Fig. 6 which shows, in block diagram form, how a two modulus divider system is organised. In Fig. 6 the output of the prescaler, (which can divide by 'P' and(P + Q), drives two programmable dividers in parallel. These two dividers are programmed to 'A' and 'N'. The 'A' counter and the prescaler are interconnected in such a way that in a complete count cycle the prescaler divides by (P + Q) until the A counter reaches zero and then reverts to a division ratio of 'P'. The 'A' counter is connected to the 'N' counter such that when the 'N' counter reaches its programmed state both the 'N' and 'A' counters reset. Consequently the prescaler divides by '(P + Q)' for '(N + A)'.

$$R = (N - A) P + A (P + Q)$$

i.e.

$$R = NP + AQ$$

Fig. 6 A two modulus division system.

5 6

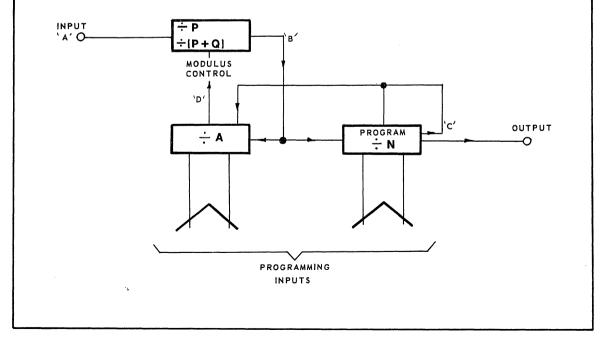

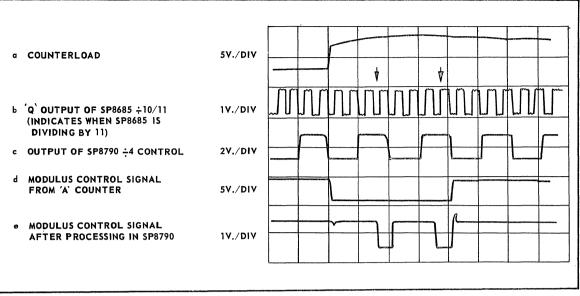

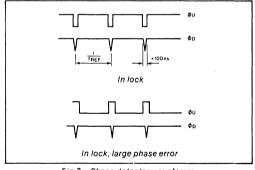

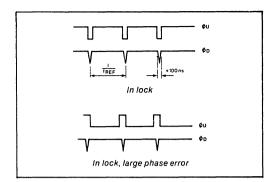

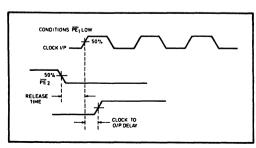

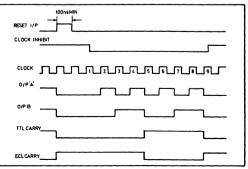

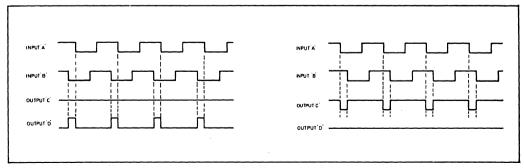

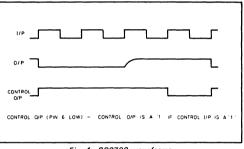

Fig. 7 Typical two-modulus waveforms.

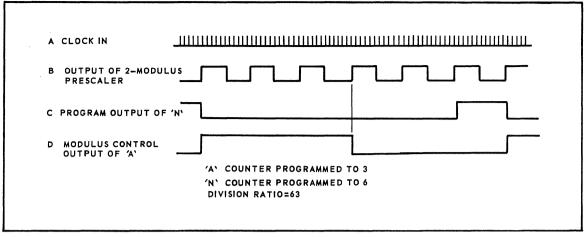

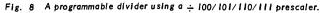

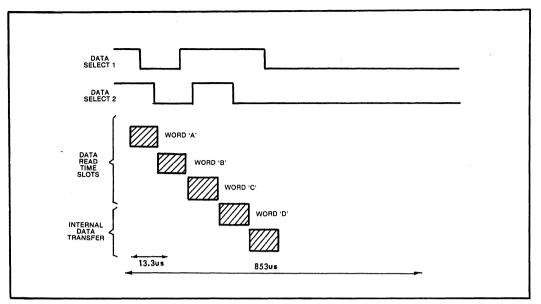

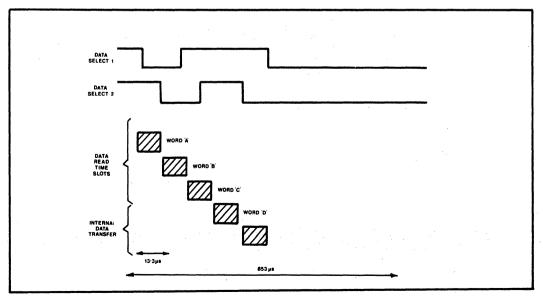

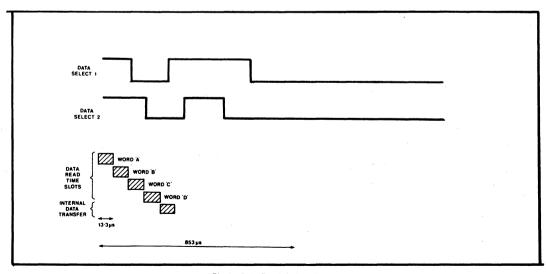

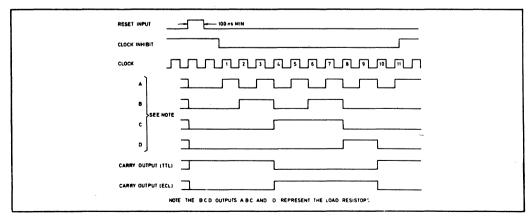

Fig. 9 Waveforms for four-modulus prescaler.

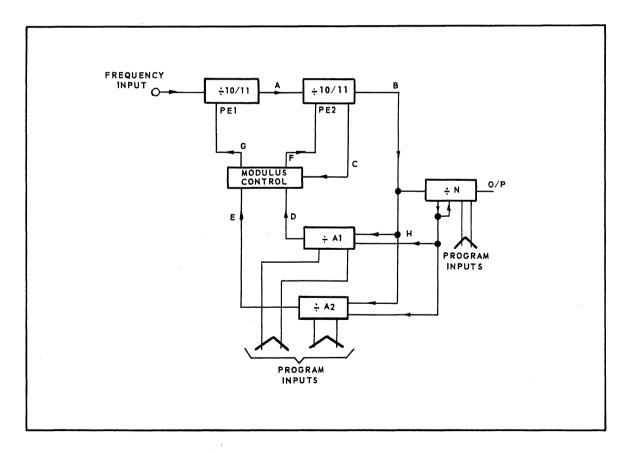

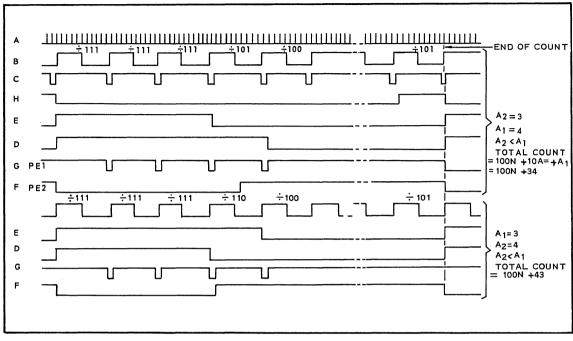

Fig 10 Generalised divider.

clearly if P=10, Q=1 then for a complete divider 'A' will give the least significant digit and 'N' will cover the rest of the required digits. Clearly, the minimum range of 'A' which can be tolerated for continuous programming is 'P' (10 in this case). The only restriction on the programmed division ratio attainable with this scheme is that

7

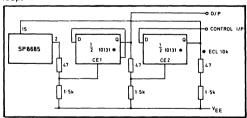

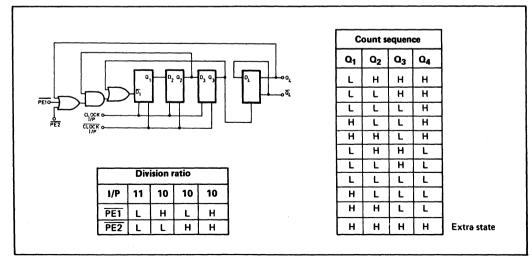

consequently, in the particular example given above of  $a \div 10/11$ ,

N > A $A_{max} = P$  gives a minimum division ratio; R = 100

This minimum count of 100 would not normally cause any problems in a system. However in a practical system, i.e. a VHF synthesiser covering the band 85MHz to 130MHz in 10kHz steps, a two modulus prescaler with moduli of 100 and 101 would be required to reduce the VCO output to a level at which cmos decades can be used. This gives a minimum count 10000 and consequently the minimum frequency that could be programmed would be 100MHz. Clearly a large part of the required frequency spectrum is not covered. To overcome this restriction it is possible using a basic 10/11 prescaler, to construct a prescaler with three or four moduli and this will be described in more detail below. In this particular VHF synthesiser we would use a four modulus prescaler with moduli of 100/010/110/111, and these would be controlled by two `A´ counters in parallel as shown in Fig. 8, with operational waveforms illustrated in Fig. 9. Counter `A2' controls the addition of 10 to the basic modulus of 100 and consequently 'A2' should be programmable from 0–9. Counter `A1´ controls the addition of 1 to the basic modulus (100) and should also be programmable from 0-9. For programming, `A1'and`A2' may be visualised as setting the least significant digits respectively. By putting `A1' and `A2' in parallel we have reduced the minimum count of `N' to the greater of 'A1' and 'A2', 10 in this case, consequently the overall minimum count is 1000 (= N<sub>MIN</sub> x P) and the minimum programmable freugency is now 10MHz. Various changes can be rung with this technique. For example, if a three modulus prescaler, 100/101/110, is used for this VHF synthesiser, two `A´ counters are still required but they now operate in series, `A]´which controls the addition of 1 to the modulus, is now required to be programmable from 10-19, while A2, which controls the addition of 10 to the modulus is still only required to be programmed from 0–9. However the minimum count of `N´ is now 20 and consequently the overall minimum count of the counter is 2000, giving a minimum output frequency of 20MHz. In this case, then, we have traded minimum count for prescaler complexity. An example of this type is given below.

When deciding whether to use fixed or variable prescaling in a synthesiser divider, the designer will have to consider the cost of improving performance. In most situations the minimal extra cost of incorporating a variable modulus prescaler with its more complex programmable divider will be more than offset by the performance improvements achieved by increasing the reference frequency.

# **Division Radix Requirements**

Regardless of whether fixed or variable prescaling is adopted in any synthesiser divider, a consider able amount of programmable division is required. There exsist in the semiconductor market today standard building blocks from which programmable dividers can be fabricated. These blocks are are available, usually, in decades although the basic division radix can be reduced if necessary. Nowadays the output frequency of a synthesiser is most often set from thumbwheel or rotary switches located on the equipment front panel. 36 It would obviously be a considerable advantage to be able to control each block of programmable division from its own switch. Where channel frequency spacings are decadic switch programming corresponds to division programming in a direct manner, but to see what general requirements are put on the division radices of a programmable divider we should consider a generalised divider as shown in Fig. 10.

Fig. 10 represents a variable divider of `K´ stages where each stage has a division radix of  $R_k$  and is programmed to  $D_k$  where 1 k (. The total division ratio `N´ is:

$$N = D_{\kappa} (R_{1} \times R_{2} ... R_{\kappa-1}) + D_{\kappa-1} (R_{1} \times R_{2} ... R_{\kappa-2}) + D_{3} (R_{1} \times R_{2}) + D_{2} \times R_{1} + D_{1}$$

and from equation 2

$$fout = fch.N$$

$$fout = fch \ D_{\kappa} (R_1 \times R_2 ... R_{\kappa-1}) + D_{\kappa-1} (R_1 \times R_2 ... R_{\kappa-2})$$

$$+ D_3 (R_1 \times R_2) D_2 \times R_1 D_1$$

$$fout = fch R_1 \ D_{\kappa} (R_2 \times R_2 ... R_{\kappa-1}) + D_{\kappa-1} (R_2 \times R_3 ... R_{\kappa-2})$$

or

$$+ D_{2} \times R_{2} + D_{2} / R_{1}$$

10

i.e. for R<sub>2</sub>...R  $_{\kappa-1}$  to be decades and for a direct relationship between the programmed digits, D  $\kappa$  , and fout:

fch x R<sub>1</sub>  $10^{P}$  where P is an integer

A typical non decadic channel spacing would be 25kHz and this would require R<sub>1 MIN</sub> = 4.

This argument also applies to variable modulus prescalers. The basic modulus (or radix) of the prescaler must obey equation 11 for R<sub>1</sub> if the 'N` counter is to be directly programmed. The prescaler is usually given a basic modulus larger than the minimum required by equation 11 for two reasons:

- (1) Variable modulus prescalers are normally specified where a large amount of fixed prescaling would be the alternative. The VCO frequency still has to be reduced to a value suitable for standard logic families.

- (2) The most common base unit for variable modulus prescalers is ÷10/11 and other moduli are produced by cascading this with fixed dividers, for example, a ÷4 or ÷8 to give prescalers od ÷40/41 or ÷80/81.

In the example used above with 25kHz spacing, a two modulus prescaler, with moduli of 40 and 41 would be required to give a directly programmable 'N' counter. The 'A' counter would also have to obey equation 11 on these lines i.e. it would consist of a ÷4 followed by a decade.

# The Programmable Divider

There are several integrated circuit technologies which are suitable for use in the programmable divider These can be divided into two groups; those with standard building blocks and those which are useful for custom designed dividers.

- (a) Standard Building Blocks

- (1) Plessey SP8200 series of RTL programmable dividers with switchable offset.

- (2) Plessey NJ8000 series of N channel programmable dividers.

- (3) Standard TTL programmable decades.

- (4) Standard CMOS programmable decades.

11

# (b) Custom Technologies

- (1) NMOS arrays (available from Plessey Semiconductors).

- (2) I<sup>2</sup> L arrays (available from Plessey Semiconductors).

- (3) CMOS arrays (available from Plessey Semiconductors).

This list is not exhaustive but covers the commonly used technologies. Plessey Semiconductors has competence in all groups.

This note will note attempt to explore the area of custom solutions to the programmable divider but will concentrate on designs using standard building blocks of the types listed in group (a) and more particularly those of sub groups '2' and '3'.

To illustrate how the techniques of variable modulus prescaling and programmable division which have been described above can be applied to practical systems; two divider chain requirements will be disscussed. The first will be for a VHF-UHF avionics synthesiser covering the bands 117.5MHz-136MHz and 225MHz-399.9MHz with 25kHz channel spacing, the divider for this will be designed using TTL parts. The second illustration will be for a low power VHF synthesiser with 10kHz channel spacing, using standard CMOS parts for the programmable f divider.

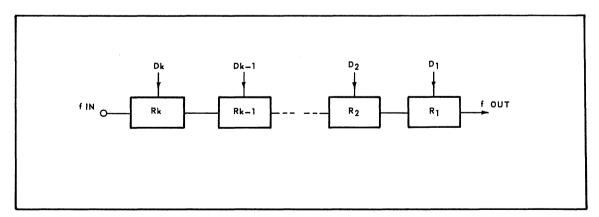

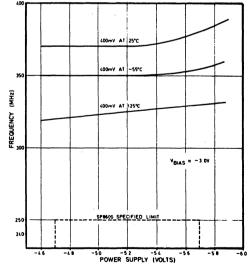

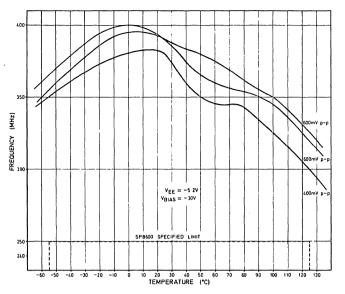

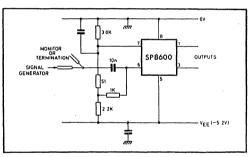

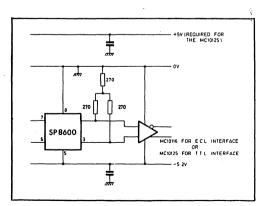

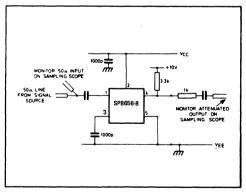

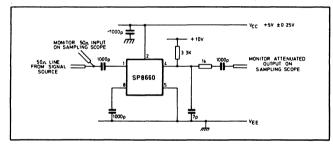

# <u>A PROGRAMMABLE DIVIDER SUITABLE FOR A VHF-UHF AVIONICS TRANSCEIVER SYNTHESISER</u> USING PLESSEY SP8600 AND STANDARD TTL DEVICES

The frequency specification for the synthesiser is as follows:

| Frequency Coverage: | 117.5MHz-136MHz<br>225MHz-399MHz |

|---------------------|----------------------------------|

| Channel spacing     | 25kHz                            |

| IF offset           | +21MHz                           |

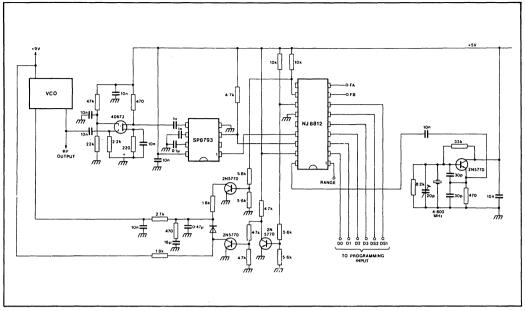

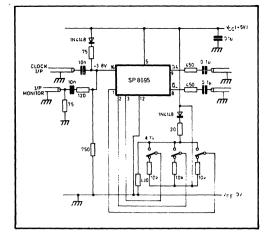

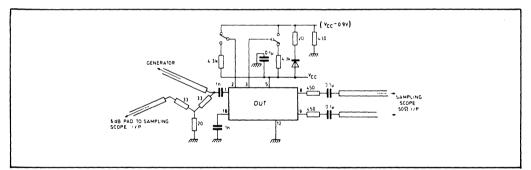

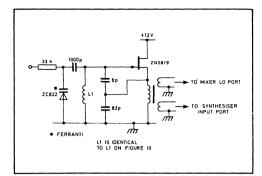

Other performance requirements such as lock range, loop response times and so on, although important will not considered in the design of the programmable divider. The emphasis in this design will be on a high performance divider providing a high frequency. The final Design is shown in Fig. 11. In order to achieve a high reference frequency it is necessary to restrict the amount of fixed prescaling to a minimum. Consequently a two-modulus prescaler system has been adopted. Referring back to the section on radixes we note that equation 11 gives:

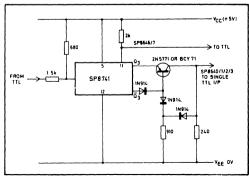

fch .  $R_{\oplus} = 10^{p}$

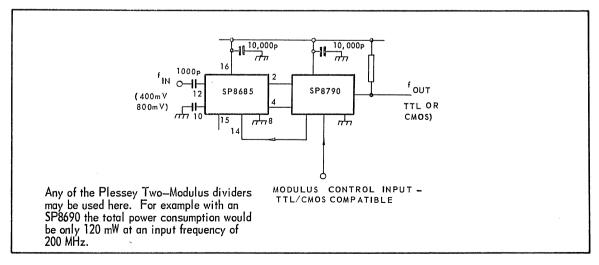

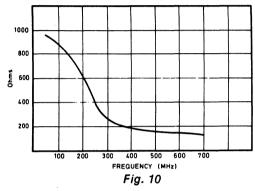

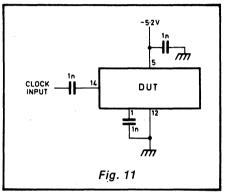

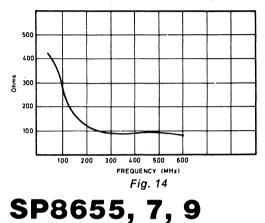

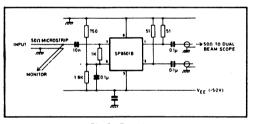

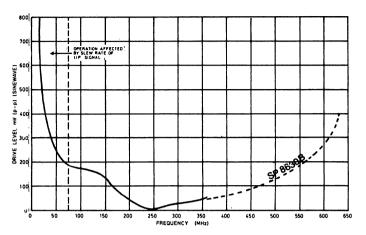

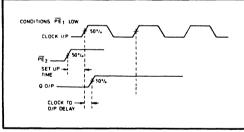

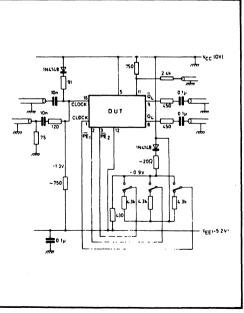

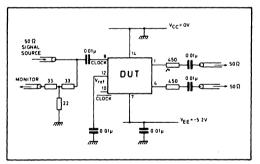

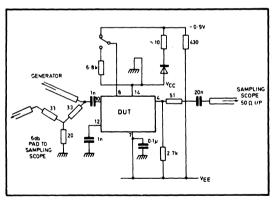

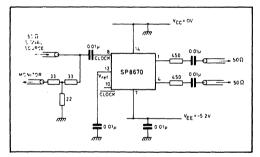

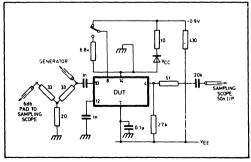

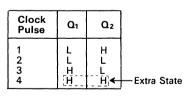

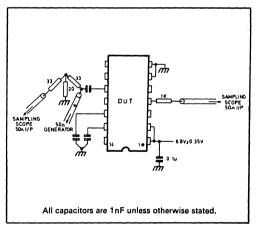

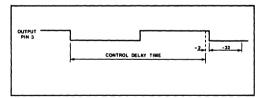

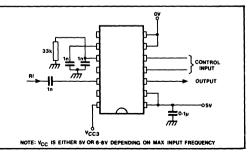

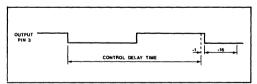

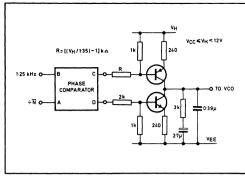

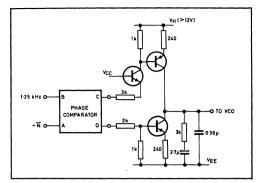

fch=25kHz and consequently R  $_{\oplus}$  min =4. This value of 'R'  $_{\oplus}$ , as a base modulus for the prescaler would give a frequency for programmable division at the high end of the required band of 100MHz. This would be extremely difficult to achieve. Increasing 'R  $_{\oplus}$ ' by a factor of 10 gives the prescaler a base modulus of 40 and reduces the frequency at which true programmable division is required to 10 MHz, well within the capabilities of TTL, and a suitable combination of devices for this  $\div 40/41$  is the SP8685 500MHz  $\div 10/11$ followed by the SP8790 low power  $\div 4$  control circuit, as shown in Fig. 12. A more stringent performance requirement for the programmable divider is its clock to carry delay, as this determines the overall speed of the two modulus prescaler programmable divider combination. To understand this we should look at Fig. 13. Assuming that the modulus control signal for the prescaler is required immediately prior to its output clocking edge then the 'clock to carry' delay for the controlling counters must be less than one complete 'clock out' period. In this case the 'clock to carry' propagation delay should be less than 100nsecs at 400 MHz input frequency. In practice not all of the 'clock out' period available to the programmable divider as there is a clock in to clock out delay for the prescaler combination, an interface delay from the 'programmable divider carry out' to'modulus control' and a set up time for the modulus control. These can easily total 30nsecs and start to put pressure on the slow programmable divider chain. This will be covered in more detail below.

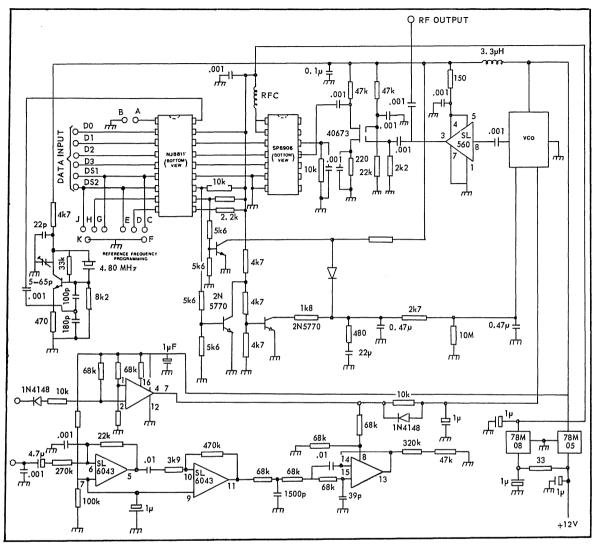

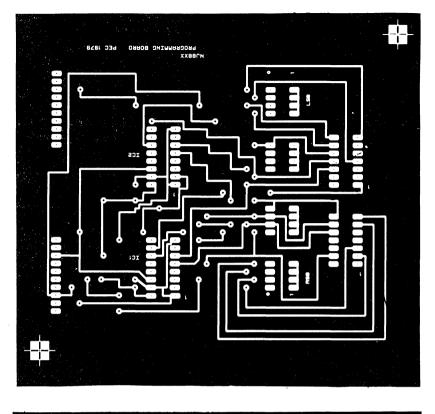

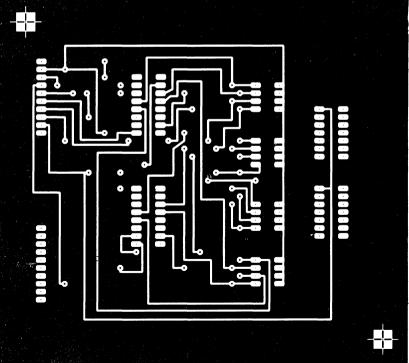

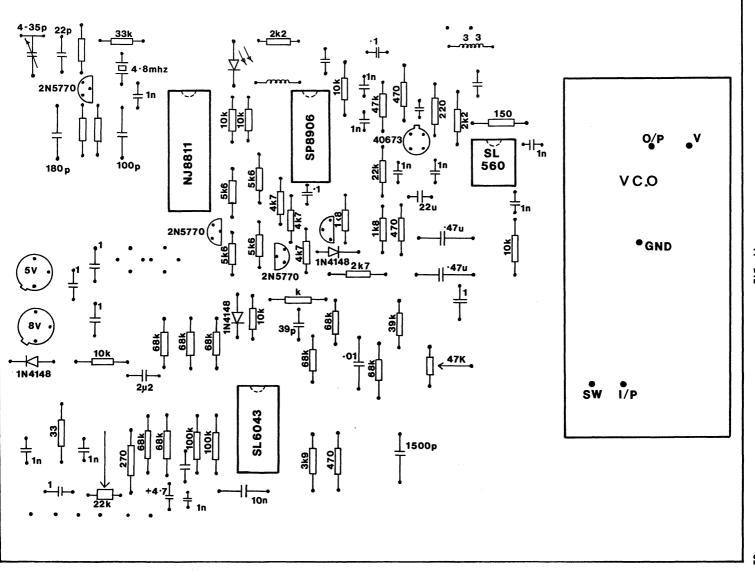

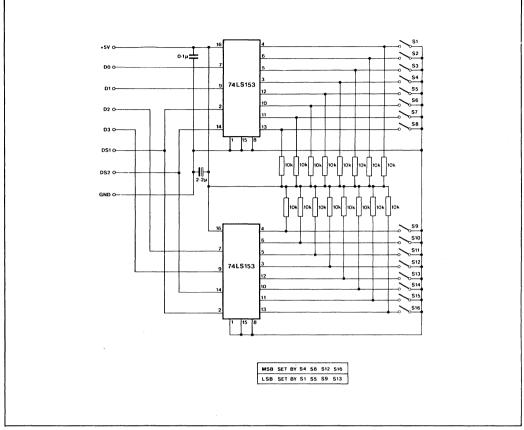

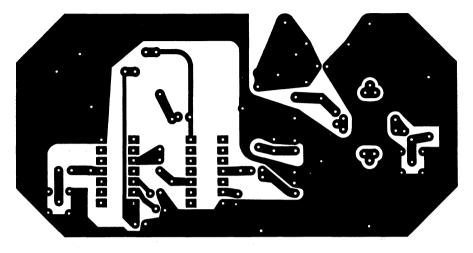

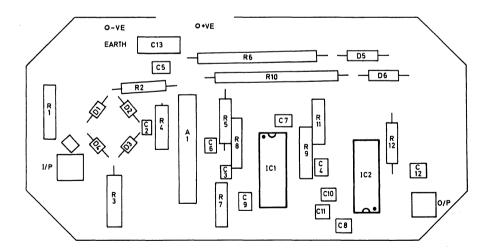

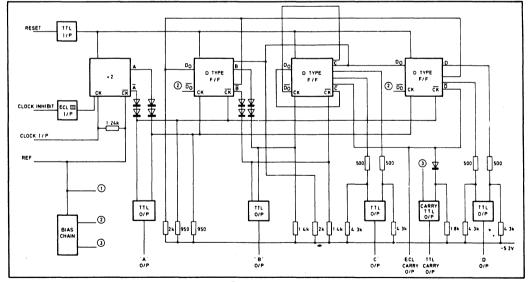

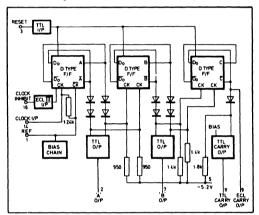

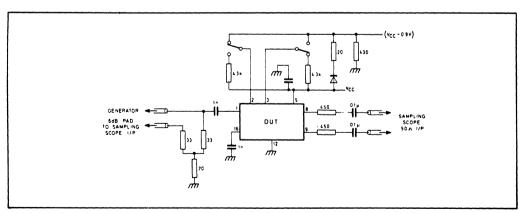

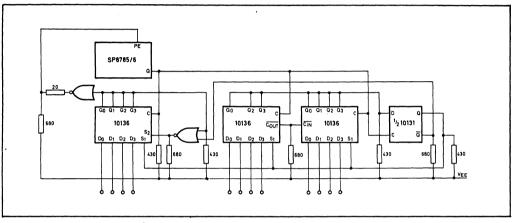

Fig. 11 Complete UHF|VHF synthesiser divider.

Fig. 12 A 500 MHz two-modulus (40/41) prescaler.

Fig. 13 Critical timing of -40/41.

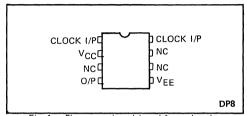

Fig. 14 Logic diagram of SP8685 two-modulus (÷10/11) divider.

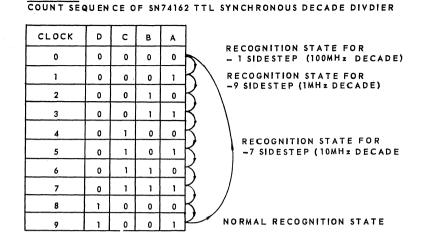

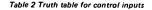

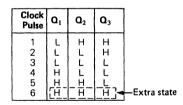

TABLE 1 COUNT SEQUENCE OF PLESSEY +10/11 TWO MODULUS - DIVIDERS

# The ÷40/41 Prescaler

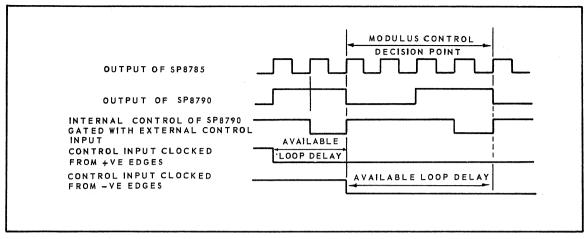

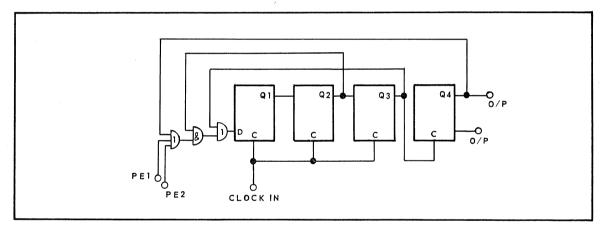

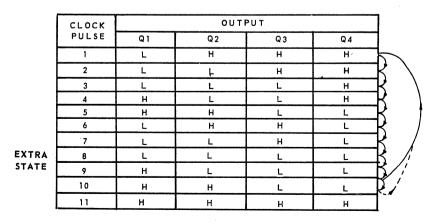

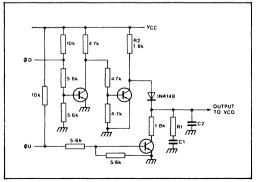

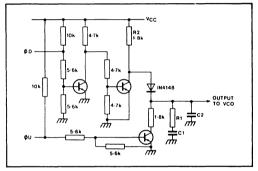

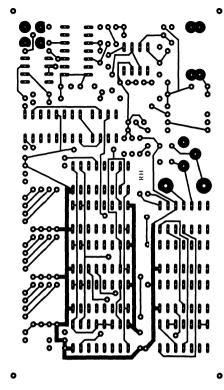

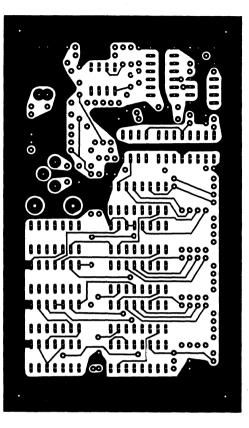

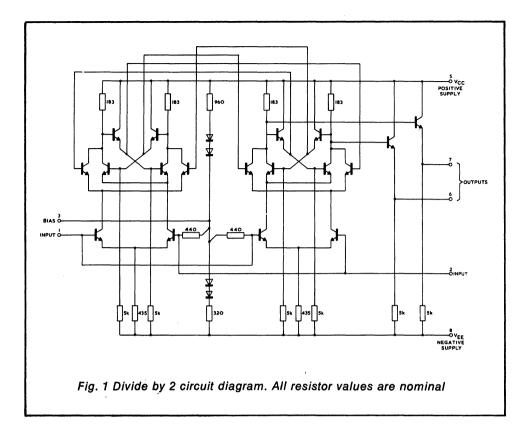

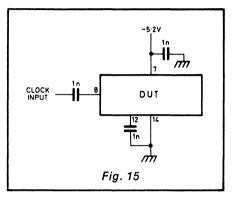

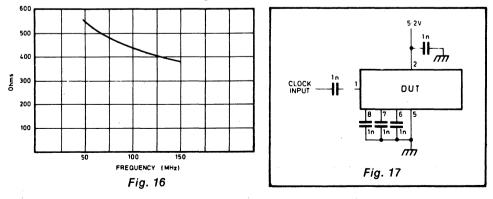

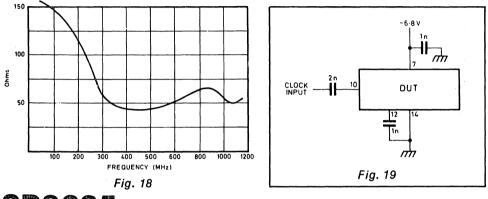

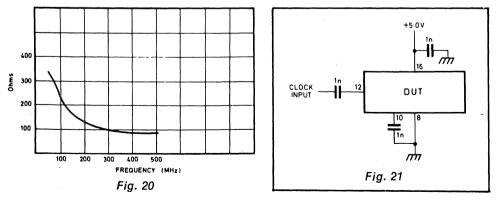

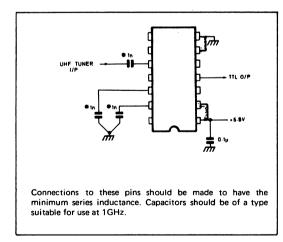

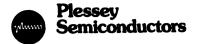

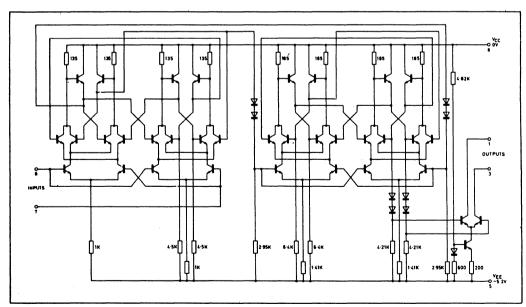

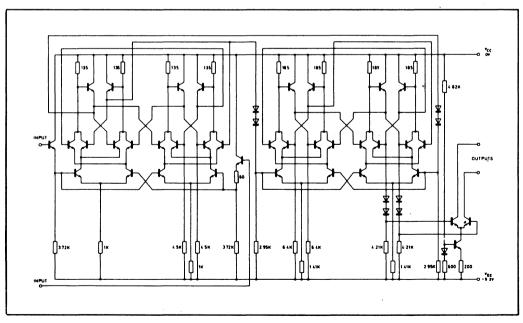

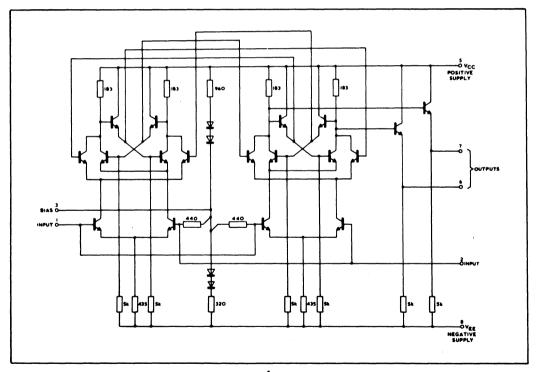

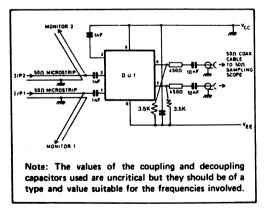

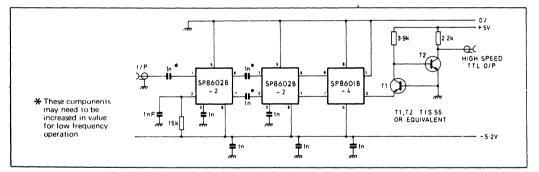

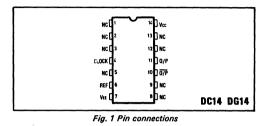

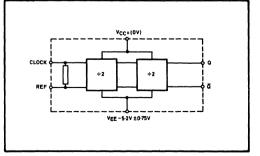

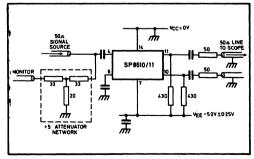

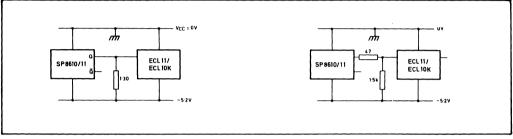

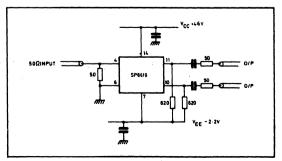

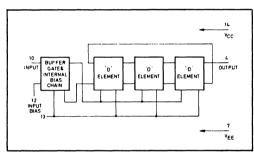

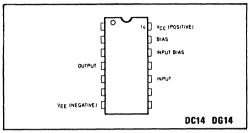

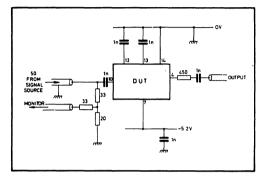

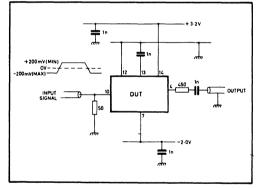

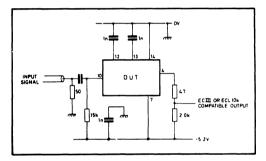

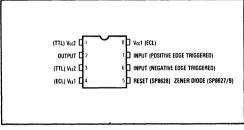

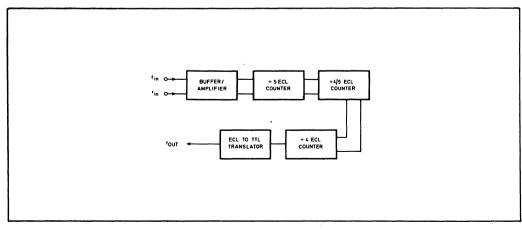

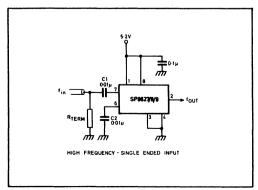

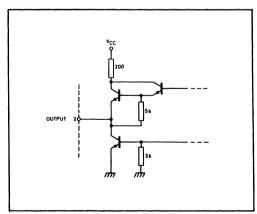

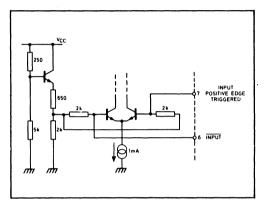

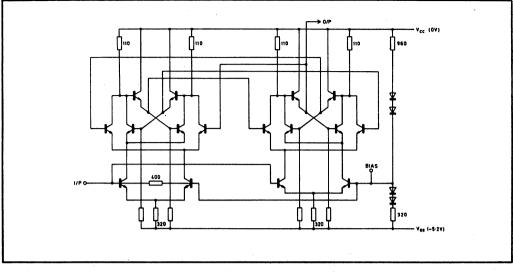

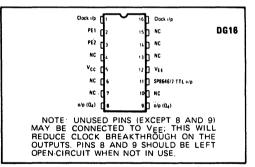

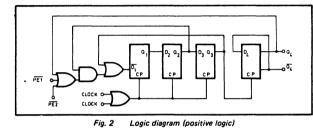

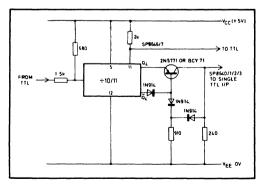

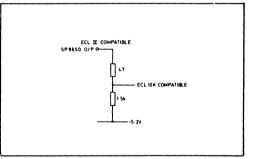

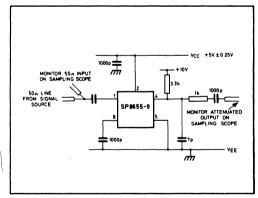

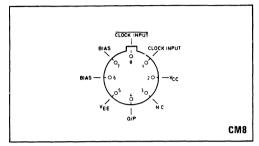

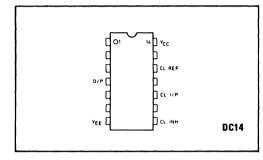

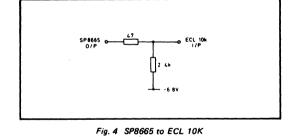

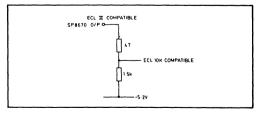

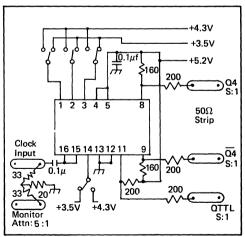

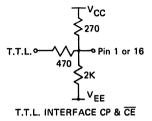

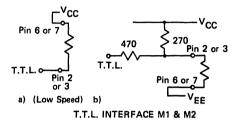

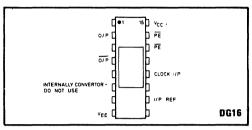

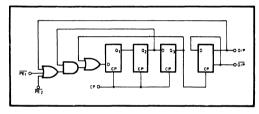

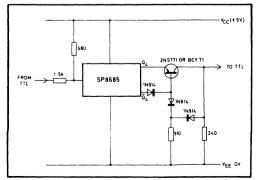

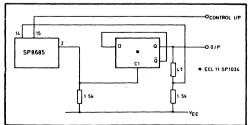

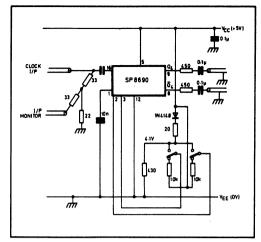

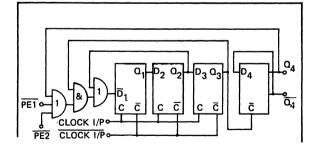

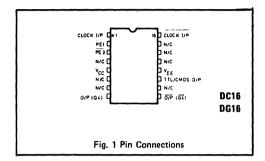

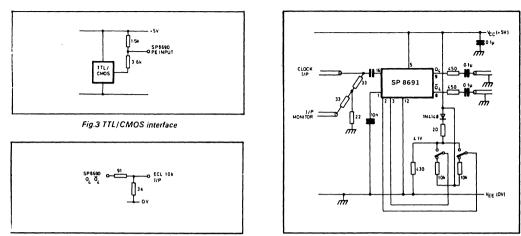

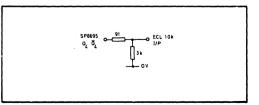

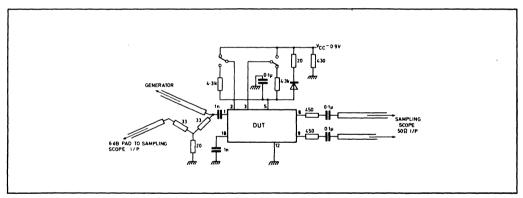

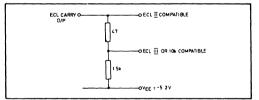

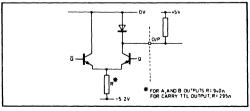

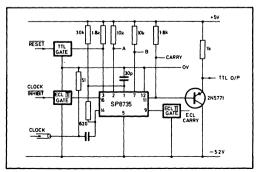

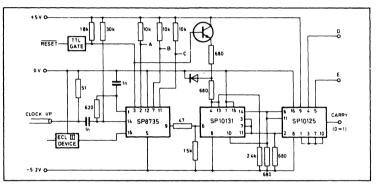

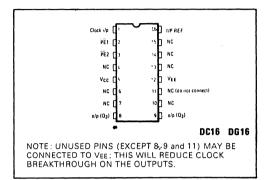

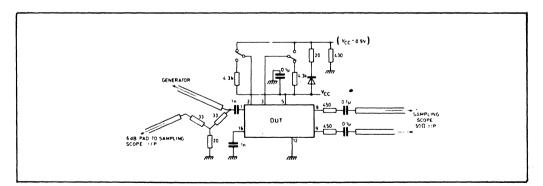

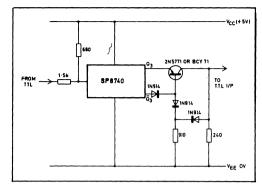

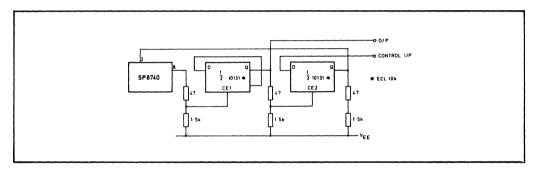

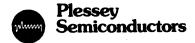

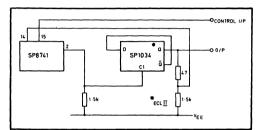

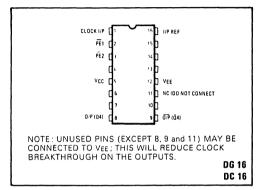

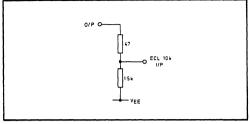

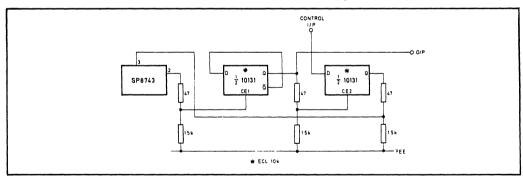

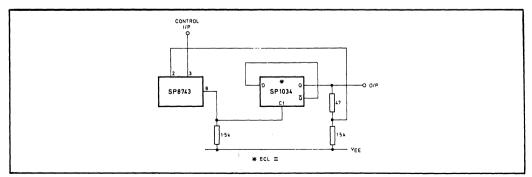

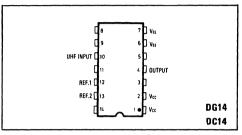

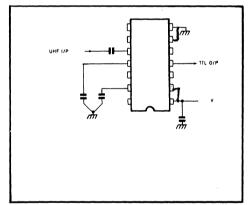

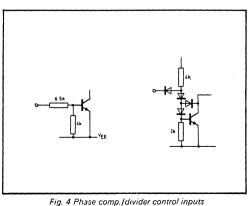

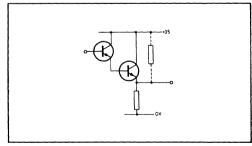

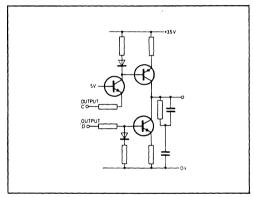

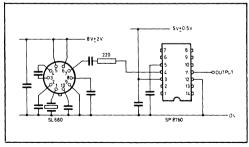

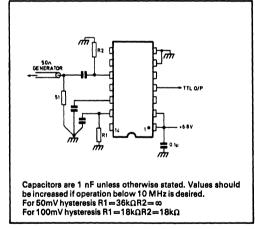

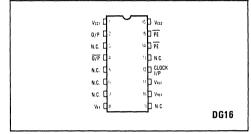

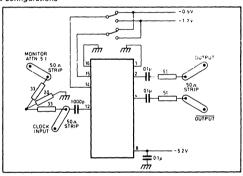

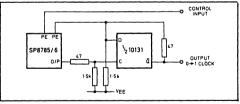

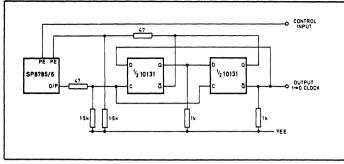

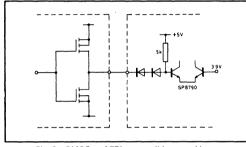

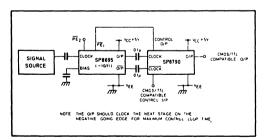

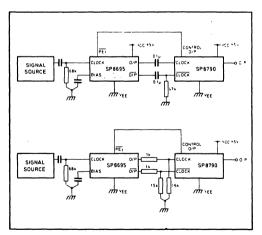

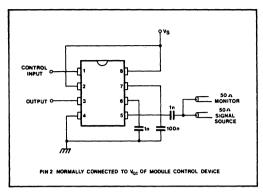

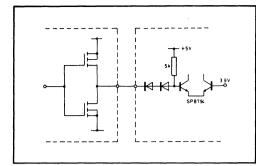

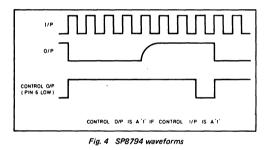

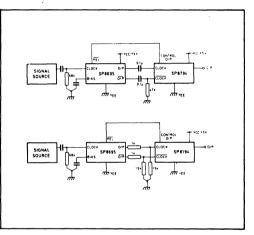

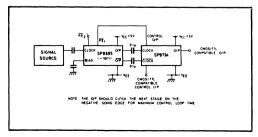

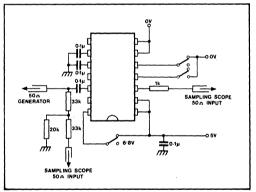

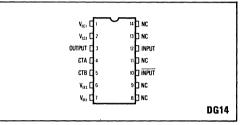

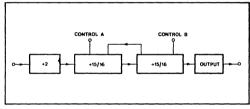

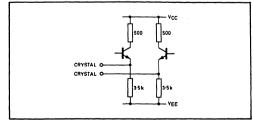

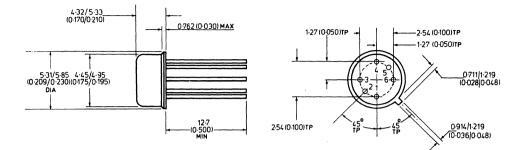

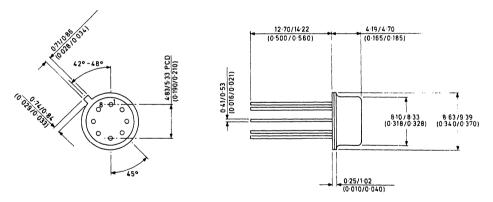

Two modulus prescalers can be constructed in a variety of ways. One approach is to use standard ECL 10k dual J-K flip-flops to perform the counting function with additional peripheral gating to accomplish the the modulus changing and interface requirements. However this would be limited to a maximum count frequency of about 100MHz. In order to produce the  $\div 40/41$  function economically with performance adequate for the stated specification we must turn to a combination of two Plessey Semiconductor parts. These are the SP8685, a UHF two modulus ( $\div 10/11$ ) divider specified to operate at frequencies up to 500MHz, and the SP8790, a  $\div 4$  control circuit designed to follow any of the Plessey two modulus dividers, which includes the necessary interfaces between the ECL levels in the prescaler and the TTL (or CMOS) levels of the following fully programmable divider. This combination, which given the  $\div 40/41$  function, is illustrated in Fig. 11. Fig. 15 gives the expected waveforms and some timing information.

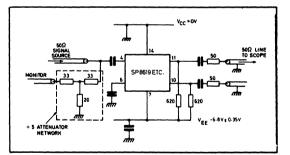

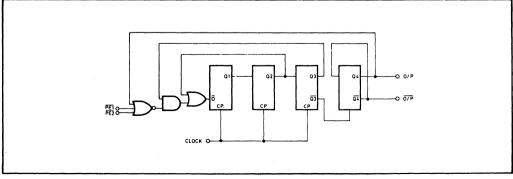

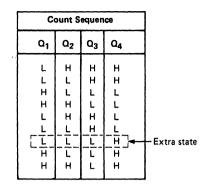

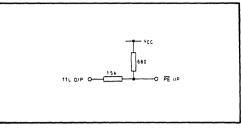

The Plessey SP8685 two modulus prescaler consists of a synchronously clocked decade as shown in Fig. 14 with additional gating to add an extra state, converting the decade to ÷11, when required. The counting sequence is shown in Table 1. This extra state is added immediately prior to Q4 going high and consequently the following stages must all be synchronous with this positive going edge to achieve the maximum available loop delay as shown in Fig. 13. The SP8790 clocks on positive going edges and following stages should clock on -ve going edges of its output. Since following TTL dividers usually clock on +ve going edges this would appear to be an embarassment. However the following stages are usually arranged to be synchronously clocked to reduce sources of VCO output phase jitter. Since the open collector output of the SP8790 has a limited fan out some form of buffer will be required, and an inverting TTL buffer, having shorter propagation delays than non-inverting buffers, represent the optimum choice here.

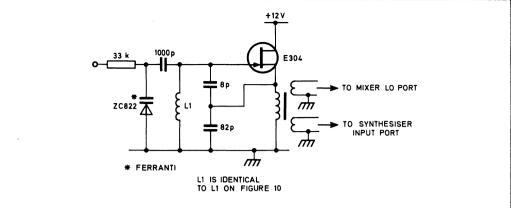

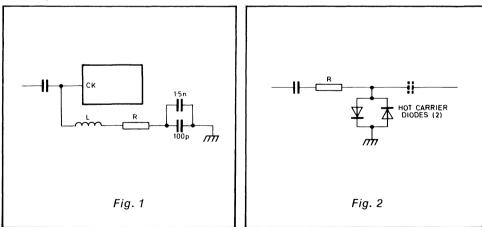

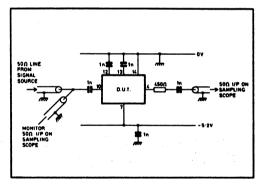

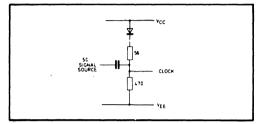

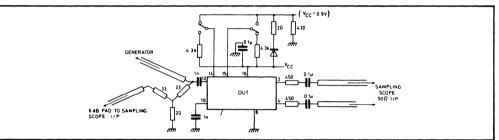

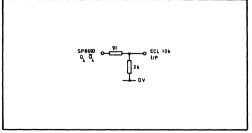

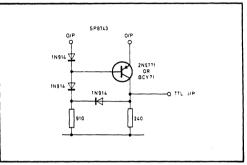

It can be seen from Fig. 9 that the input of the prescaler is buffered. If we examine the input circuitry of the prescaler we can see that it presents a non-linear impedance. Since this is driven by a Voltage Controlled Oscillator which is also intended to provide a spectrally pure signal for use elsewhere, (i.e. in a communications receiver) it is important to isolate the VCO from the divider input impedance so that the VCO output is not degraded. The buffer is intended to provide this function. A target for the amount of isolation between the divider input port and the VCO output port is typically 60dB although many systems will tolerate lower values. There are many commerically available microwave integrated circuits (MICs) available (i.e. Avantek GPD401) which give upwards of 20dB isolation and similar amounts of `tame' gain, if one of these is coupled with an attenuator, adequate amounts of isolation can be provided economically.

# The TTL Programmable Divider

Essential functional features of the TTL programmable dividers are:

- (1) Clock speed, including programming, exceeding 10MHz.

- (2) Low propagation delay from clock to carry for a complete divider (< 70nsecs).

- (3) Synchronous clocking for minimum phase jitter.

- (4) Ability to add fixed offsets to the programmed count easily.

There are several different ways of assembling programmable dividers but one of the faster and more flexible dividers to use are those in the SN74160 series. These are decade and binary programmable up counters with synchronous load and synchronous or asynchronous clear, together with internal logic to give a modified carry look ahead system. (A detailed description of the operation and interconnection of these devices can be found in TI's Semiconductors Circuit Design Vol 11.)

The programmable divider as previouly described and illustrated in Fig. 6 is split into two parts: the A counter and the 'N' counter. The total division ratio achieved by this combination is given by equation 6 and the required range of division ratios can be calculated from

$$N_{T} = \frac{f \text{ out}}{f \text{ ch}}$$

$$N_{Tmax} = \frac{f \text{ out max}}{f \text{ ch}} = \frac{400 \times 10.6}{25 \times 10.6} + 21 \times 10^{6}$$

13

$$N_{Tmax} = 16840$$

and  $N_{Tmin} = \frac{117.5 \times 10.6}{25 \times 10.6} = 4700$

41

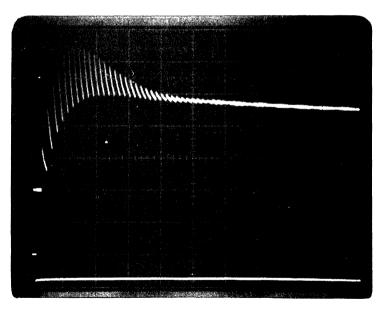

Fig. 15 Waveforms of ÷40/41 programmable divider with 'A' counter programmed to 50 Khz.

# The A Counter

For correct operation it is clear from equation 6 that the 'A' counter must interpolate within the steps caused by the prescaler's base modulus, 40 in this case; consequently the 'A' counter must be programmable between '0' and '39'. Furthermore the 'A' counter must be split into a radix 4 first stage for programming 25kHz steps, followed by however many decades are required to make the desired maximum count.

In this example where 'A' max = 39, the next stage is the most significant stage of the 'A' counter and as such does not have a fixed radix but counts down from its programmed number, in the range '0-9', to zero. Consequently a 6 bit binary divider can be used for the 'A' counter. This is formed from two cascaded 4 bit binary counters connected the programmed as shown in Fig. 11.

# The 'N' Counter

The ´N` counter should be programmable from 117 to 421, and is formed in a straightforward way from 3 standard cascaded decades, shown in Fig. 11.

# Sidestep

Extra gating has been added to the basic divider so that the fixed sidestep of+21MHz can be added. The counters are such that it is, in general, difficult to arrange for a positive sidestep, to get around this we split the sidestep into a positive sidestep of one on the most significant stage, which is relatively easy, and a negative sidestep on the preceding decades so that the sum of the two equals the required sidestep.

Since the most significant stage has a limited programming range (1-3) it is a simple matter to arrange to recognise one count further on in the counter cycle than its normal recognition state of all '1s' without interfacing with programming. This is shown in Table 2. This gives an overall sidestep of +100. To achieve the required+21 we must subtract 79 from the two preceding stage and this is done by recognising the requisite counter states, rather than the normal all '1s'. This combined recognition (Fig. 11, 'f) is selected as the counter load signal ('a') whenever the sidestep is required. Clearly this scheme is applicable to positive sidesteps of up to several hundred megahertz. Negative sidesteps which do not exceed the programmed count can be equally easily inserted on the two least significant stages of the count.

## Operation

To understand the operation of the two combined counters we will follow the operation of the counter from the instant when it is programmed. Looking at Fig.11 the complete circuit diagram and Fig. 15, the photo of some of the internal waveforms, the two counters 'A' and 'N' are programmed on the first -ve going edge of 'c' following the load 'a' going low, 'A' and 'N' start to count up from their programmed values at this instant. 'd'(Fig. 11) is set low and its inverse is used to drive the 'CEP' inputs of the 'A' counter. 'd' is used directly to control the  $\div 40/41$  via the SP8790. Consequently, for the whole of the period that 'A' is counting down the prescaler is dividing by 41. This is illustrated in Fig. 15, if traces 'b', d' and 'e' are compared we can see that'e' goes low for a quarter of the period of 'c' while d' is low. If 'e' and 'b' are correlated we can see that the high period of 'b is slightly longer when'e' is low (marked with arrow). This corresponds to the two modulus divider dividing by 11 rather than 10. As soon as the 'A' counter reaches its recognition state d'goes high and the prescaler reverts to  $\div 40$ . CEP goes low, preventing further incrementing of the 'A' counter, hence'd'remain high. When the 'N' counter reaches it recognition state, either direct or sidestepped, a goes low for 1 complete period of 'c' and both dividers are synchronously loaded with the frequency setting data, 'd'goes low and the count cycle repeats.

# **Operating Speed**

The maximum operating speed is determined by the loop delay from clock in to modulus control. For the loop to operate correctly this delay must be less than the output period of the prescaler, in this case equal to 1

| 400 | x  | 106 |

|-----|----|-----|

|     | 40 |     |

or 100nsec. This delay is made up of two parts, the clock propagation delay through the prescaler and the return propagation delay of the modulus control through the SP8790, which is <20nsec in total, and the delay through the programmable divider.

The delay through the programmable divider consists of 1 gate delay in the clock buffer plus the clock to carry delay for 1 counter stage. This is less than 40nsec for both edges. There is however an additional factor to be considered. This is the delay from clock to load for the divider. This has different values depending on whether sidestep is in use or not.

|                    | Delay (nsec)        |                  |  |

|--------------------|---------------------|------------------|--|

|                    | without<br>sidestep | with<br>sidestep |  |

| Clock buffer       | 4.5                 | 4.5              |  |

| Clock to RC        | 35                  |                  |  |

| Clock to Q         |                     | 20               |  |

| Recognition gate   | 4.5                 | 9.0              |  |

| Recognition select | 9.0                 | 9.0              |  |

| Load set up time   | 25                  | 25               |  |

| Total              | 78nsec              | 67. 5nsec        |  |

Clearly this scheme is capable of operating well beyond the required limit of 400+21MHz, in fact a prototype of this system operated satisfactorily to beyond 500MHz at room temperature. This solution, although representing the ultimate in a divider for a single loop synthesiser, is clearly economical in packages and in power consumption, thanks mainly to the functional specifications of the Plessey SP8685 and SP8790 combination.

# A PROGRAMMABLE DIVIDER SUITABLE FOR A PORTABLE VHF SIGNAL SOURCE USING PLESSEY SP8600 DEVICES AND STANDARD COSMOS INTEGRATED CIRCUITS

The specification for the synthesiser is as follows:

| Frequency coverage | 85MHz - 130MHz |

|--------------------|----------------|

| Channel spacing    | 10kHz          |

| IF offset          | 0              |

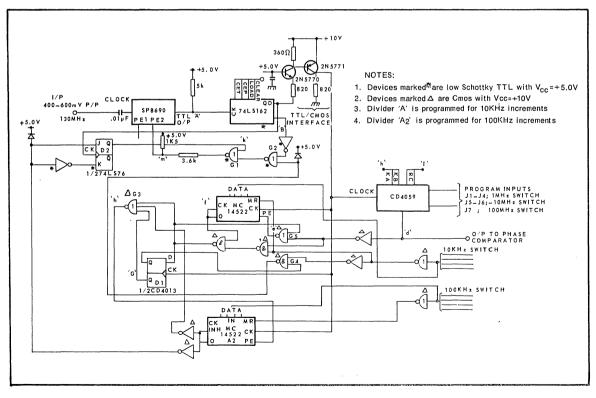

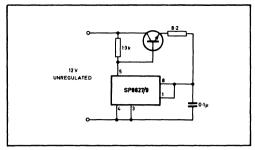

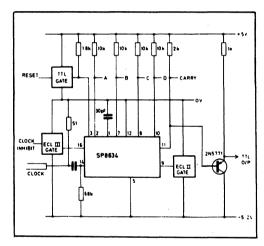

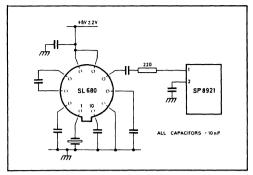

The other performance specification of concern is the requirement for portability. This predicates a low power approach to the design of the prescaler and variable divider. For this reason the prescaler is made of low power devices from the SP8600 series driving CMOS programmable divider chains.

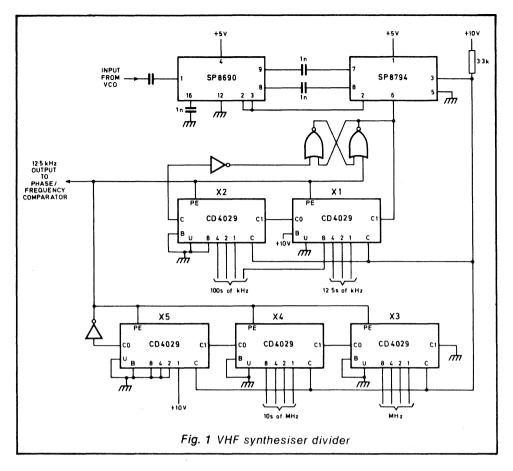

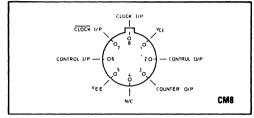

#### The Prescaler

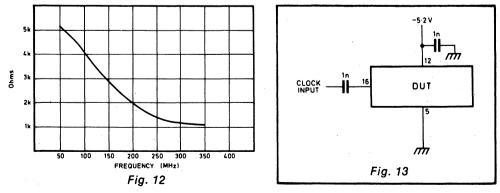

The use of CMOS programmable dividers for the 'A' and 'N' dividers means that there must be a large amount of prescaling used to reduce the input frequency of 130MHz maximum to the 1-2MHz suite-able for CMOS.

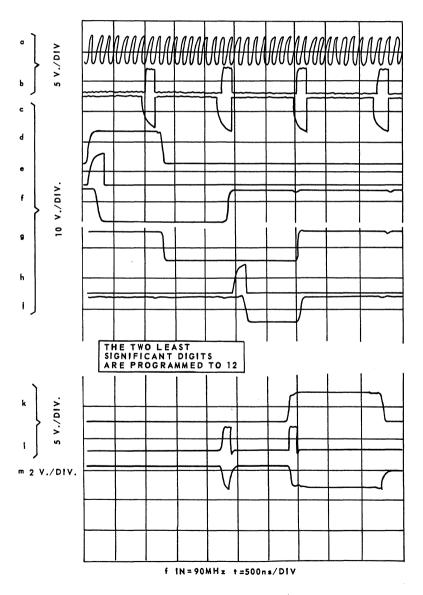

In order to keep the phase comparison frequency (fcomp in Fig. 1) as high as possible it is desirable to use a two (or more) modulus prescaler. To maintain direct decadic frequency programming with the required 10kHz frequency incf increment (or channel spacing) the base modulus of the prescaler must be a power of 10. Clearly a straight ÷10/11 prescaler would not interface with CMOS as its output frequency would be 13MHz. The next available step would be to use a ÷100/101 prescaler which satisfies the CMOS requirement. The large base modulus of the prescaler brings us up against a problem mentioned previously, that of minimum count. The minimum count which could be achieved with a ÷100/101 prescaler is 10,000, see equations 6 and 7. The minimum count required by the synthesiser, Q min 65:-

$$Q_{\min} = \frac{85 \times 106}{103} = 8,500$$