Integrated Circuit Databook

# digital integrated circuits

**NOVEMBER 1979**

This publication is issued to provide outline information only and (unless specifically agreed to the contrary by the Company in writing) is not to form part of any order or contract or be regarded as a representation relating to the products or services concerned. We reserve the right to alter without notice the specification, design, price or conditions of supply of any product or service.

## contents

|                                        | Page      |

|----------------------------------------|-----------|

| Product Index                          | 7 - 10    |

| Technical Data                         |           |

| ECL III                                | 13 - 71   |

| Sub-nanosecond logic                   | 74        |

| SP8000 series high speed dividers      | 87 - 214  |

| SP4000 series high speed dividers      | 77 - 85   |

| NOV0L Non volatile logic               | 233 - 238 |

| SP9000 series data conversion products | 221 - 232 |

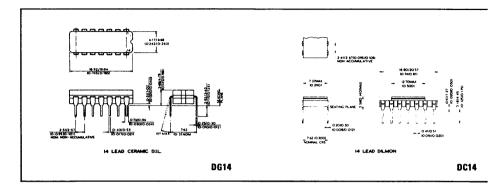

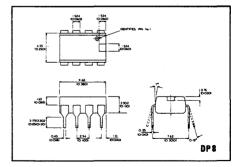

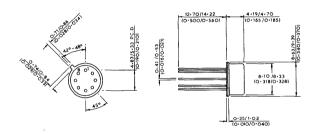

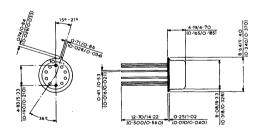

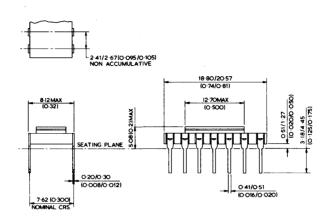

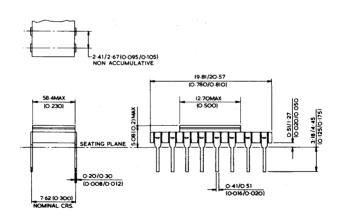

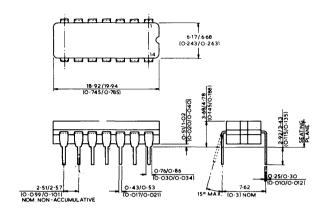

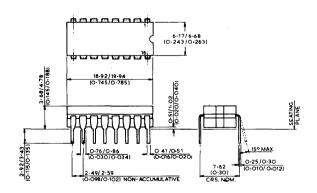

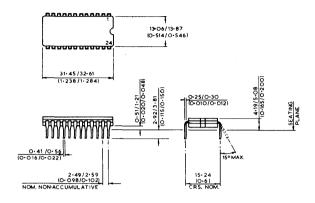

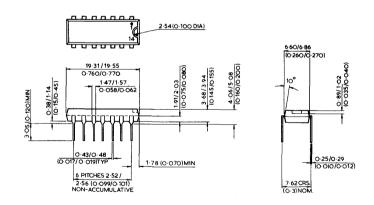

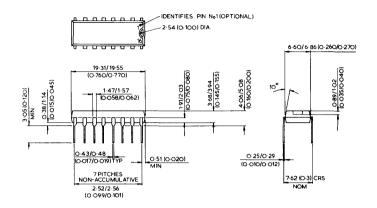

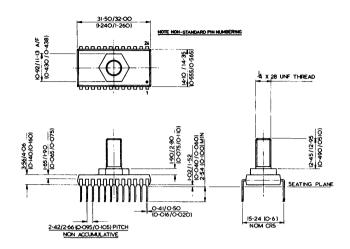

| Package Outlines                       | 242 - 248 |

| Ordering Information                   | 249       |

| Plessey Semiconductors U.S.A.          | 252       |

| Plessey Semiconductors World-Wide      | 254       |

| Sales offices                          |           |

| Agents                                 | 255       |

| Distributors                           | 256       |

### product index

#### DEVICE TYPE

| ECLIII PRODI | UCT INDEX                            |    |

|--------------|--------------------------------------|----|

| SP1648B      | Voltage controlled oscillator        | 13 |

| SP1650B      | Dual A/D comparator                  | 21 |

| SP1651B      | Dual A/D comparator                  | 21 |

| SP1658B      | Voltage controlled multivibrator     | 32 |

| SP1660B      | Dual 4-I/P OR/NOR gate Hi-Z          | 36 |

| SP1662B      | Quad 2-I/P NOR gate Hi-Z             | 39 |

| SP1664B      | Quad 2-I/P OR gate Hi-Z              | 42 |

| SP1666B      | Dual clocked R-S Flip-Flop Hi-Z      | 45 |

| SP1668B      | Dual clock latch Hi-Z                | 49 |

| SP1670B      | Master-slave D Flip-Flop Hi-Z        | 53 |

| SP1672B      | Triple 2-I/P exclusive OR gate Hi-Z  | 60 |

| SP1674B      | Triple 2-I/P exclusive NOR gate Hi-Z | 63 |

| SP1690B      | UHF prescaler type D Flip-Flop       | 66 |

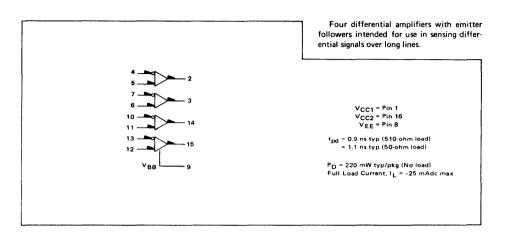

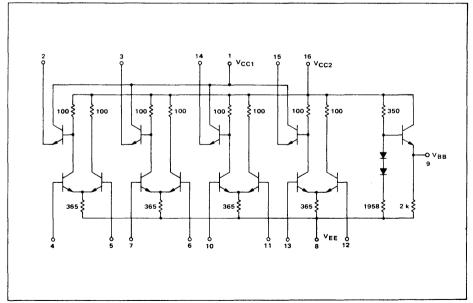

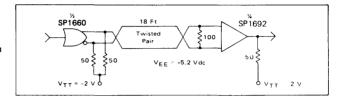

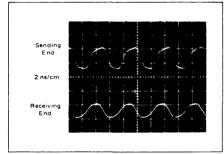

| SP1692B      | Quad line receiver                   | 71 |

| SUB-NANOSI   | ECOND LOGIC                          |    |

| SP 16 F60    | Dual 4-I/P OR/NOR Gate               | 74 |

|              |                                      |    |

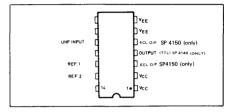

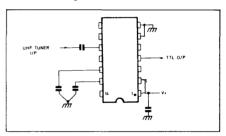

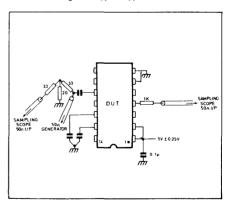

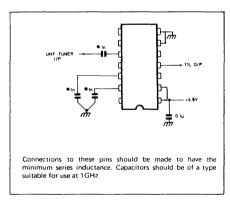

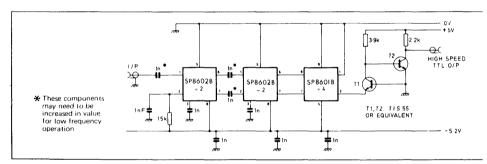

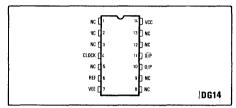

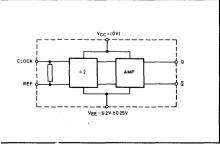

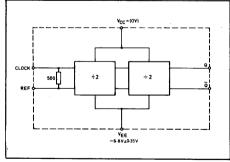

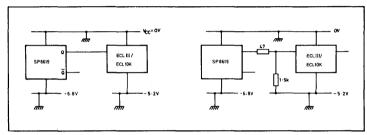

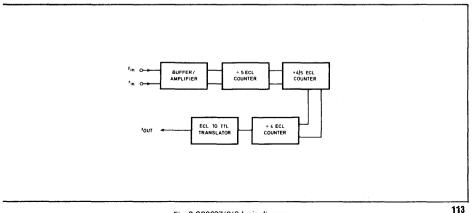

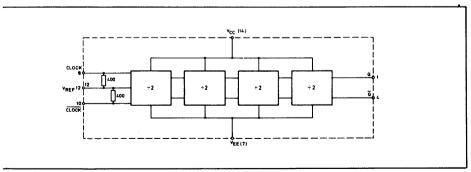

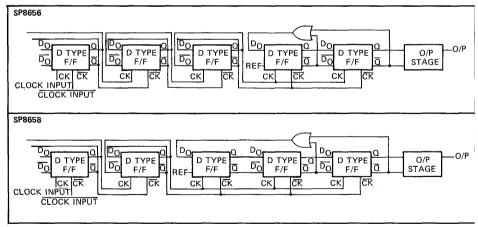

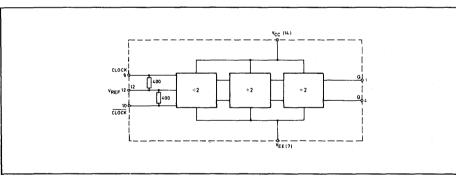

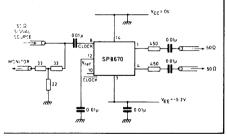

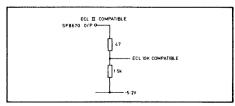

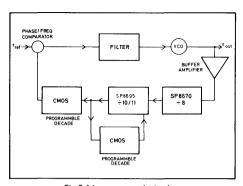

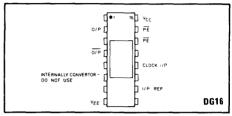

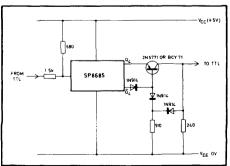

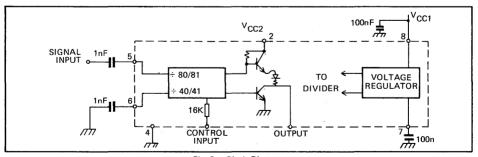

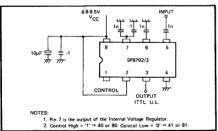

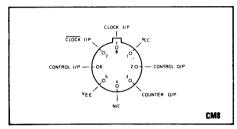

#### SP8000 SERIES HIGH SPEED DIVIDERS **Prescalers** SP8600A. B 250MHz ÷ 4 87 SP8601A, B 150HMz ÷ 4 91 SP8602A. B 500MHz ÷ 2 94 SP8605B & M 1.0GHz ÷ 2 97 SP8606B & M $1.3GHz \div 2$ 97 SP8607A. B $600MHz \div 2$ 100 SP8608B & M 1.0GHz ÷ 2 102 SP8609B & M 1.3GHz ÷ 2 102 SP8610B & M 1.0GHz ÷ 4 105 SP8611B & M 1.5GHz ÷ 4 105 SP8617B & M 1.3GHz ÷ 4 108 SP8619B & M 1.5GHz ÷ 4 108 SP8620A, B 400MHz ÷ 5 111 SP8627 150MHz ÷ 80 113 SP8628 150MHz ÷ 100 113 SP8629 150MHz ÷ 100 113 SP8630A. B 600MHz ÷ 10 116 SP8634B $700MHz \div 10 (BCD O/P)$ 119 SP8650A, B 600MHz ÷ 16 127 SP8656 200MHz ÷ 24 132 SP8658 200MHz ÷ 20 132 200MHz ÷ 32 Low power (50mW) SP8655A. B 130 SP8657A. B 200MHz ÷ 20 Low power (50mW) 130 SP8659A, B 200MHz ÷ 16 Low power (50mW) 130 SP8660A. B 200MHz ÷ 10 Low power (50mW) 134 SP8665B 1GHz ÷ 10 136 SP8667B 1.2GHz ÷ 10 136 SP8670A. B 600MHz ÷ 8 138 SP8675B & M 1GHz ÷ 8 141 SP8677B & M 1.2GHz ÷ 8 141 SP8680A. B $600MHz \div 10/11$ 143 Two Modulus SP8691A, B 200MHz ÷ 8/9 152 SP8735B 600MHz ÷ 8 with binary O/Ps 165 SP8750B & M 1GHz ÷ 64 185 SP8752B 1.2GHz ÷ 64 185 SP8755A, B 1200MHz ÷ 64 188 SP8770B 1 GHz ÷ 256 190 SP8772B 1.2GHz ÷ 256 190 SP8792 200MHz ÷ 80/81 Low power ) 203 Two Modulus SP8793 200MHz ÷ 40/41 Low power 203 SP8901 1GHz ÷ 512 208 Four Modulus SP8906 500MHz ÷ 256 211

| SP4000 SERIES<br>Prescalers | HIGH SPEED DIVIDERS                                |     |

|-----------------------------|----------------------------------------------------|-----|

|                             | \(\I\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\             | 77  |

| SP4020                      | VHF/UHF ÷ 64                                       |     |

| SP4021                      | 950MHz ÷ 64                                        | 79  |

| SP4040                      | VHF/UHF ÷ 256                                      | 81  |

| SP4041                      | 950MHz ÷ 265                                       | 83  |

| SP4140                      | 950MHz ÷ 265                                       | 85  |

| SP4150                      | 950MHz ÷ 265                                       | 85  |

| NOVOL                       |                                                    |     |

| Non-Volatile Log            | ic                                                 |     |

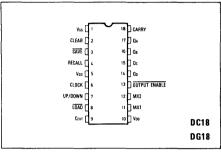

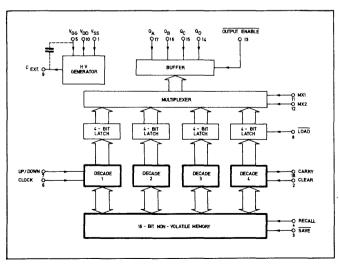

| MN9102                      | Non Volatile Quad Latch                            | 233 |

| MN9105                      | Quad Up/Down Counter                               | 235 |

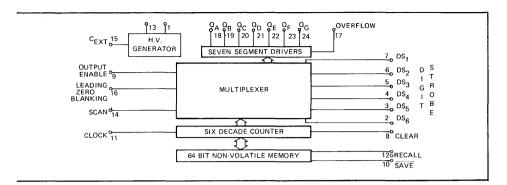

| MN9106                      | Six Decade Up Counter                              | 238 |

| Two-modulus Pr              | ogrammable Dividers                                |     |

| SP8643A, B                  | 350MHz ÷ 10/11 (ECL O/P)                           | 123 |

| SP8647A, B                  | 250MHz ÷ 10/11 (TTL O/P)                           | 123 |

| SP8685A                     | 500MHz ÷ 10/11 (ECL)                               | 147 |

| SP8690A, B                  | 200MHz ÷ 10/11 Low power TTL O/P (70mW)            | 149 |

| OI 0030A, D                 | AC coupled I/P                                     |     |

| SP8695A, B                  | 200MHz ÷ 10/11 Low power TTL O/P (70mW)            | 155 |

| OI 0035A, D                 | DC coupled I/P                                     | 100 |

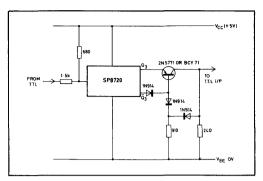

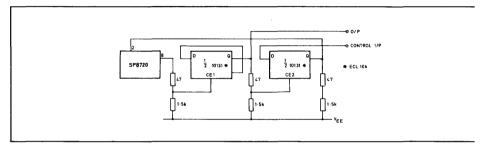

| SP8720A, B                  | 300MHz ÷ 3/4                                       | 158 |

| SP8725A, B                  | 300MHz ÷ 3/4                                       | 161 |

|                             |                                                    |     |

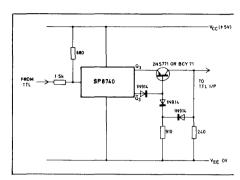

| SP8740A, B                  | 300MHz ÷ 5/6 AC coupled I/P                        | 168 |

| SP8741A, B                  | 300MHz ÷ 6/7 AC coupled I/P                        | 171 |

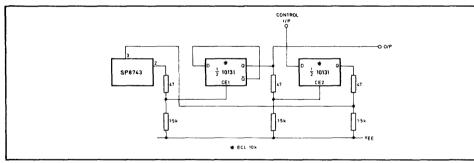

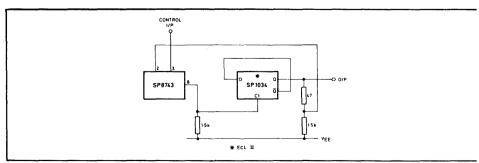

| SP8743B & M                 | 500MHz ÷ 8/9 AC coupled I/P                        | 174 |

| SP8745A, B                  | 300MHz ÷ 5/6 DC coupled I/P                        | 177 |

| SP8746A, B                  | 300MHz ÷ 6/7 DC coupled I/P                        | 181 |

| SP8785, B & M               | 1.0GHz ÷ 20/22                                     | 196 |

| SP8786, B & M               | 1.3GHz ÷ 20/22                                     | 196 |

| Modulus Extend              | ers                                                |     |

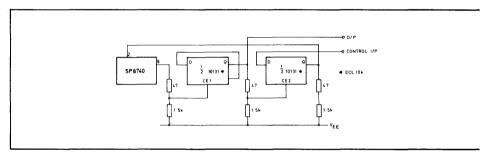

| SP8790A, B                  | LP ÷ 4 control for all programmable devices (40mW) | 200 |

| SP8794A, B                  | LP ÷ 8 control for all programmable devices (40mW) | 205 |

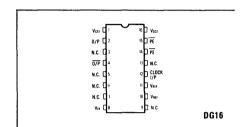

| SP8760B & M                 | General purpose synthesiser circuit                | 193 |

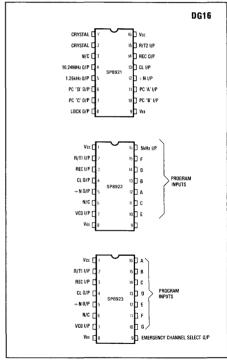

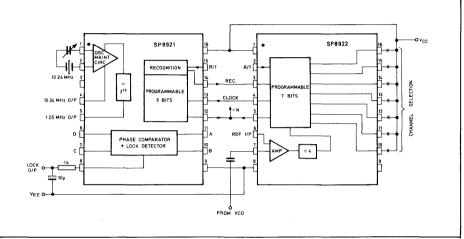

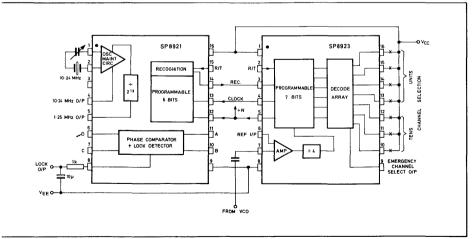

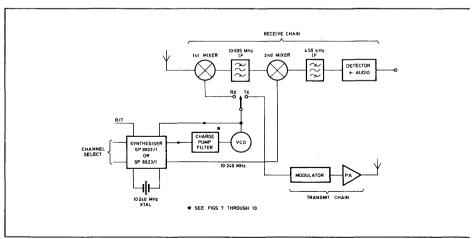

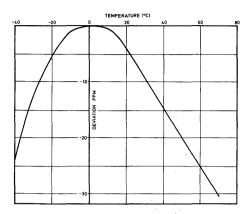

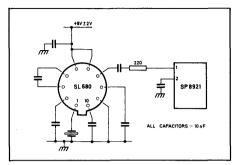

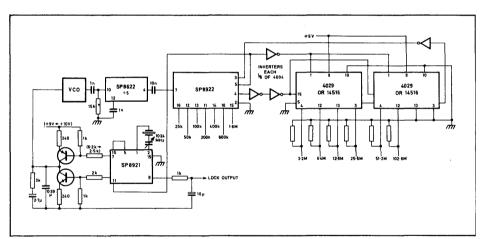

| SP8922                      | 40 Channel CB Synthesiser IC Set                   | 214 |

| SP8921                      | 40 Channel CB Synthesiser IC Set                   | 214 |

| SP8923                      | 40 Channel CB Synthesiser IC Set                   | 214 |

|                             |                                                    |     |

| SP9000 SERIES         | DATA CONVERSION PRODUCTS   |     |

|-----------------------|----------------------------|-----|

| <b>High Speed Com</b> | parators                   |     |

| SP9685                | Ultra Fast Comparator      | 221 |

| SP9687                | Ultra Fast Dual Comparator | 221 |

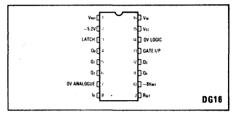

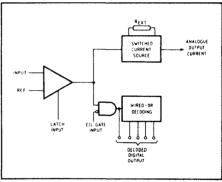

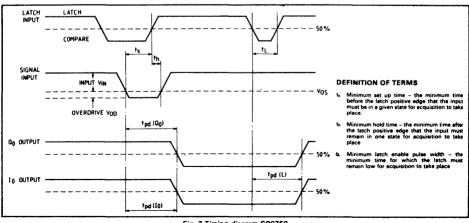

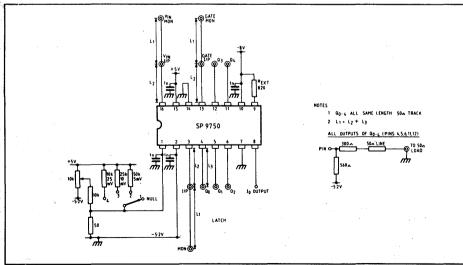

| SP9750                | High Speed Comparator      | 227 |

# technical data

#### VOLTAGE-CONTROLLED OSCILLATOR

#### SP1648

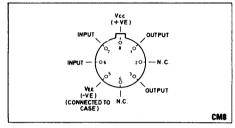

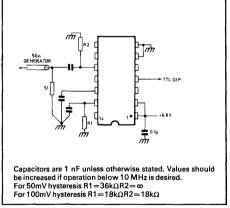

Input Capacitance = 6 pF typ Maximum Series Resistance for L (External Inductance) = 50  $\Omega$  typ Power Dissipation = 150 mW typ/pkg (+5.0 Vdc Supply) Maximum Output Frequency = 225 MHz typ

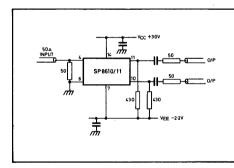

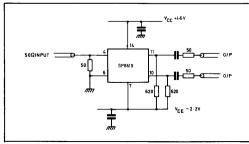

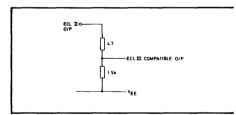

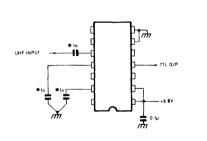

The SP1648 is an emitter-coupled oscillator, constructed on a single monolithic silcon chip. Output levels are compatible with PECL III logic levels. The oscillator requires an external parallel tank circuit consisting of the inductor (L) and capacitor (C).

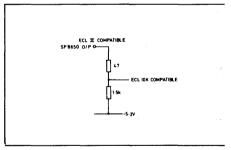

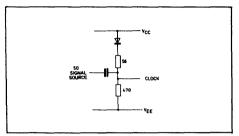

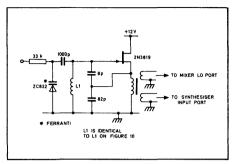

A varactor diode may be incorporated into the tank circuit to provide a voltage variable input for the oscillator (VCO). The SP1648 is used in the Phase-Locked Loop shown in Figure 9. This device may be used in many applications requiring a fixed or variable frequency clock source of high spectral purity (See figure 2).

The SP1648 may be operated from a +5.0 Vdc supply or a -5.2 Vdc supply, depending upon system requirements.

| SUPPLY VOLTAGE | GND PINS | SUPPLY PINS |

|----------------|----------|-------------|

| +5.0 Vdc       | 7, 8     | 1, 14       |

| -5.2 Vdc       | 1, 14    | 7, 8        |

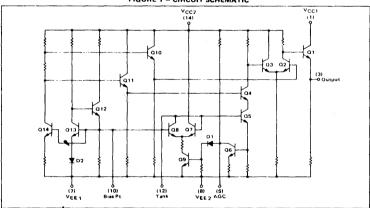

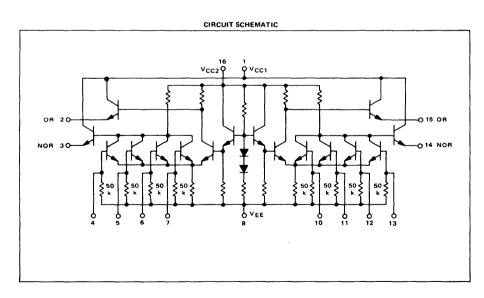

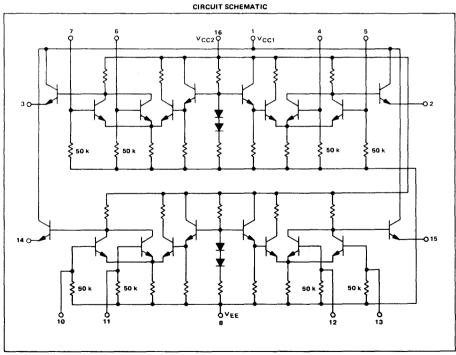

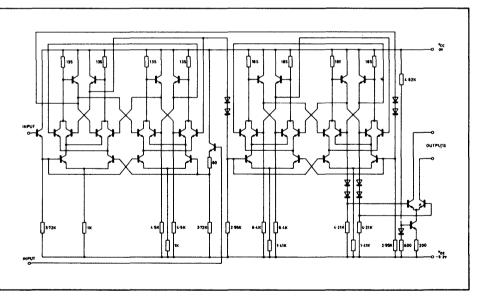

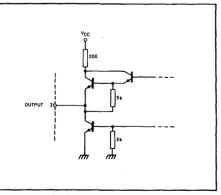

FIGURE 1 - CIRCUIT SCHEMATIC

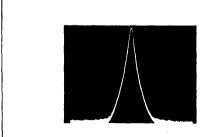

FIGURE 2 - SPECTRAL PURITY OF SIGNAL AT OUTPUT

B.W. = 10 kHz Scan Width - 50 kHz/div Center Frequency = 100 MHz Vertical Scale = 10 dB/div

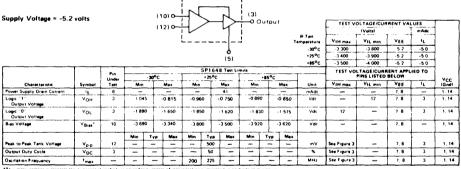

#### **ELECTRICAL CHARACTERISTICS**

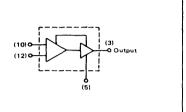

| Supply Voltage = +5.       | 0 volts |      |      |       | 10) <b>0-</b><br>12) <b>0-</b> | 1    | 5     | 3         | (3)   | Outp  | ut   |                       | TEST V       | OL TAGE/CUI | RRENT VA | LUES  | r            |

|----------------------------|---------|------|------|-------|--------------------------------|------|-------|-----------|-------|-------|------|-----------------------|--------------|-------------|----------|-------|--------------|

|                            |         |      |      |       |                                | !レ   |       | -         | ĺ     |       |      |                       |              | (Volts)     |          | mAde  | 1            |

|                            |         |      |      |       |                                |      |       | -         | ٤.    |       |      | P Tost<br>Temperature | VIH max      | VIL mm      | Vcc      | 16    | ]            |

|                            |         |      |      |       |                                |      |       | ٥         |       |       |      | -30°C                 | +1 960       | +1.410      | 5.0      | -50   | 1            |

|                            |         |      |      |       |                                |      |       | (5)       |       |       |      | +25°C                 | -1 800       | +1 300      | 5.0      | -50   | 1            |

|                            |         |      |      |       |                                |      |       |           |       |       | _    | +85°C                 | -1 680       | •1 180      | 5.0      | -50   | 1            |

|                            |         | Pin  |      | -30°C |                                | r    | SP164 | 48 Test L | mits  | +85°C |      |                       |              | TAGE/CURP   |          | ED TO | l            |

| Characteristic             | Symbol  | Test | Min  |       | Max                            | Men  |       | Mex       | Min   |       | Max  | Unit                  | VIH max      | VIL min     | Vcc      | 1     | VEE<br>(Gnd) |

| Power Supply Drain Current | ¹E      | 8    | _    |       |                                |      |       | 40        | _     |       |      | mAdu                  |              |             | 1 14     |       | 7.8          |

| Cogic "f Output Voltage    | VO:4    | 3    | 3 94 |       | 4 18                           | 4 04 |       | 4 25      | 411   |       | 4 36 | Vdc                   | T            | 17          | 1 14     | 3     | 7.8          |

| Logic '0' Output Voltage   | VOL     | 3    | 3 16 |       | 3 40                           | 3 20 | ,     | 3 43      | 3 23  | 7     | 3 46 | Vdc                   | - 12         | -           | 1, 14    | 3     | 7.8          |

| Bias Voltage               | VB.as   | 10   | 1 51 |       | 1 86                           | 1 40 | 5     | 1 70      | 1 28  |       | 1 58 | Vdc                   |              |             | 1 14     |       | 7.8          |

|                            | 1       | •    | Min  | Typ   | Mex                            | Min  | Typ   | Max       | Min   | Typ   | Mex  | 1                     | t            |             | t        |       |              |

| Peak to Peak Tank Voltage  | Vp-p    | 12   | -    | _     | ) <u>-</u> -                   | -    | 500   | 7         | - 1   | _     | -    | - nv                  | See Figure 3 | i -         | 1 14     | 3     | 7.8          |

| Output Duty Cycle          | VDC     | 3    | -    | _     | T =                            | -    | 50    | T         | 1 - 1 | -     | -    | 1                     | See Figure 3 |             | 1.14     | 3     | 7.8          |

| Oscillation Frequency      | Imex    | _    | _    | _     | _                              | 200  | 225   | T-        | - 1   |       | T =  | MH,                   | See Figure 3 | _           | 1 14     | 3     | 7 8          |

<sup>&</sup>quot;This measurement guarantees theidc potential at the bias point for ourposes of incorporating a varactor funing those at this point

#### **ELECTRICAL CHARACTERISTICS**

This measurement guarantees the do potential at the bias point for purposes of incorporating a varactor tuning diode at this point

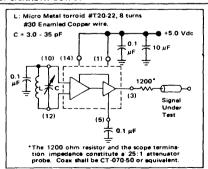

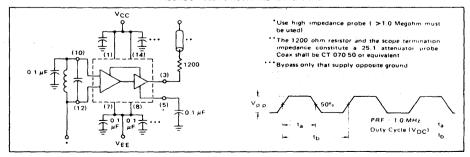

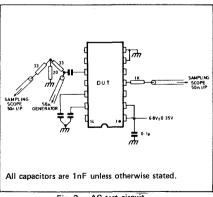

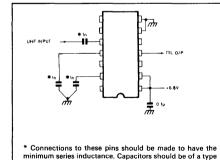

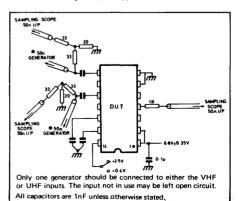

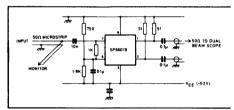

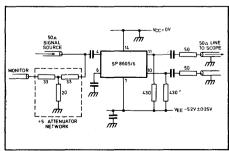

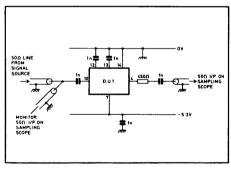

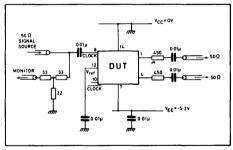

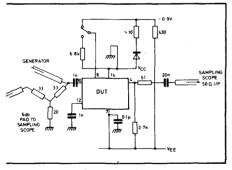

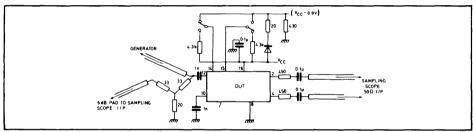

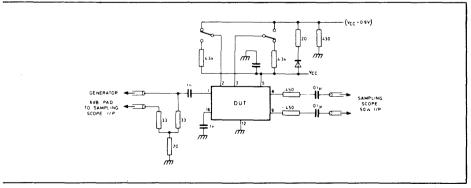

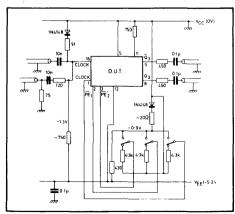

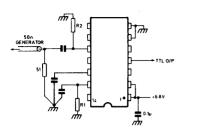

#### FIGURE 3 - TEST CIRCUIT AND WAVEFORMS

#### OPERATING CHARACTERISTICS

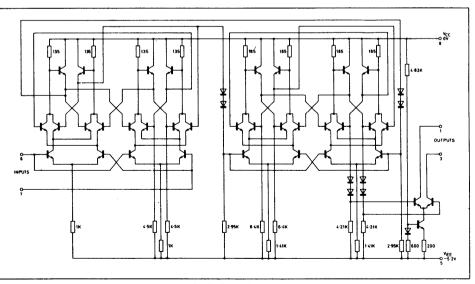

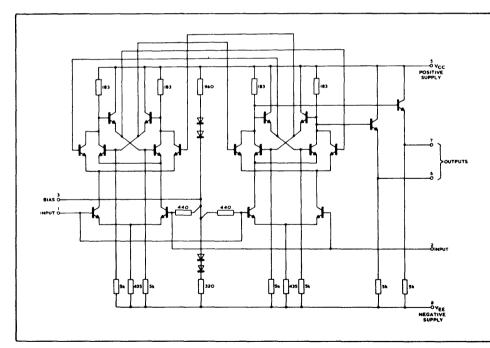

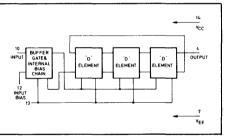

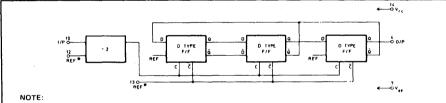

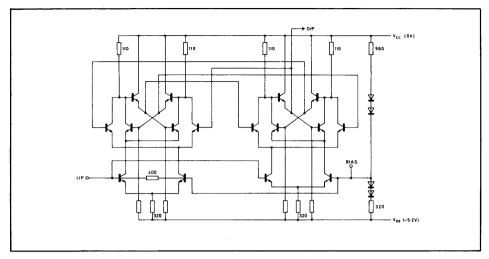

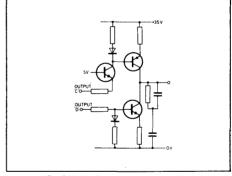

Figure 1 illustrates the circuit schematic for f. 2 SP1648. The oscillator incorporates positive feedback by coupling the base of transistor Q7 to the collector of Q8. An automatic gain control (AGC) is incorporated to limit the current through the emitter-coupled pair of transistors (Q7 and Q8) and allow optimum frequency response of the oscillator.

In order to maintain the high Q of the oscillator, and provide high spectral purity at the output, a cascode transistor (Q4) is used to translate from the emitter follower (Q5) to the output differential pair Q2 and Q3. Q2 and Q3, in conjunction with output transistor Q1, provide a highly buffered output which produces a square wave. Transistors Q10 thru Q14 provide the bias drive for the oscillator and output buffer. Figure 2 indicates the high spectral purity of the oscillator output (pin 3).

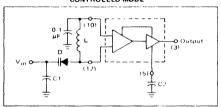

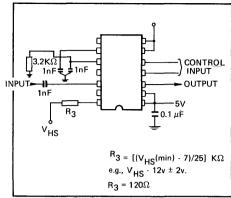

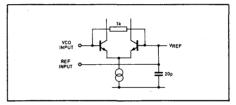

When operating the oscillator in the voltage controlled mode (Figure 4), it should be noted that the cathode of the varactor diode (D) should be biased at least 2 VBE above VEE ( $\approx$  1.4 V for positive supply operation).

FIGURE 4 – THE SP1648 OPERATING IN THE VOLTAGE CONTROLLED MODE

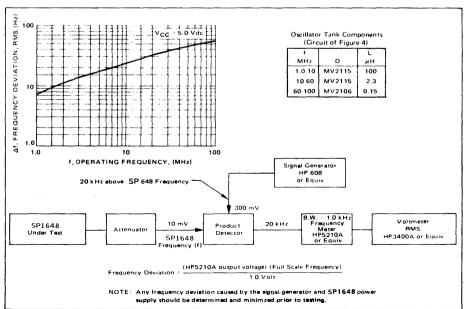

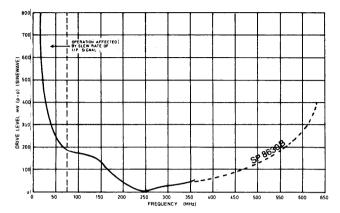

When the SP1648 is used with a constant do voltage to the variactor diode, the output frequency will vary slightly because of internal noise. This variation is plotted versus operating frequency in Figure 5.

FIGURE 5 - NOISE DEVIATION TEST CIRCUIT AND WAVEFORM

four, OUTPUT FREQUENCY (MHz)

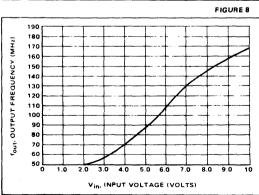

#### TRANSFER CHARACTERISTICS IN THE VOLTAGE CONTROLLED MODE USING EXTERNAL VARACTOR DIODE AND COIL. TA = 25°C

#### FIGURE 6 60 56 52 48 44 40 36 32 28 24 20 16 12 2.0 3.0 4.0 5.0 6.0 7.0 8.0 9.0

VID. INPUT VOLTAGE (VOLTS)

#### FIGURE 7 fout, OUTPUT FREQUENCY (MHz) 16 15 14 13 10 9 0 8.0 1.0 2.0 3.0 5.0 7.0 8.0 10 Vin. INPUT VOLTAGE (VOLTS)

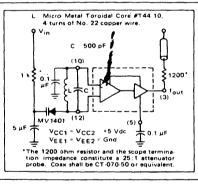

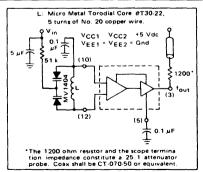

Typical transfer characteristics for the oscillator in the voltage controlled mode are shown in Figures 6, 7 and 8. Figures 6 and 8 show transfer characteristics employing only the capacitance of the varactor diode (pluse the input capacitance of the oscillator, 6 pF typical). Figure 7 illustrates the oscillator operating in a voltage controlled mode with the output frequency range limited. This is achieved by adding a capacitor in parallel with the tank circuit as shown. The 1 k $\Omega$  resistor in Figures 6 and 7 is used to protect the varactor diode during testing. It is not necessary as long as the dc input voltage does not cause the diode to become forward biased. The larger-valued resistor (51 k $\Omega$ ) in Figure 8 is required to provide isolation for the high-impedance junctions of the two varactor diodes.

The tuning range of the oscillator in the voltage controlled mode may be calculated as:

$$\frac{f_{max}}{f_{min}} = \frac{\sqrt{C_D (max) + C_S}}{\sqrt{C_D (min) + C_S}}$$

where

$$f_{min} = \frac{1}{2\pi \sqrt{L (C_D (max) + C_S)}}$$

CS = shunt capacitance (input plus external capacitance):

CD = varactor capacitance as a function of bias voltage. Good RF and low-frequency bypassing is necessary on the power supply pins (see Figure 2).

Capacitors (C1 and C2 of Figure 4) should be used to bypass the AGC point and the VCO input (varactor diode), guaranteeing only dc levels at these points.

For output frequency operation between 1 MHz and 50 MHz a  $0.1~\mu F$  capacitor is sufficient for C1 and C2. At higher frequencies, smaller values of capacitance should be used; at lower frequencies, larger values of capacitance. At higher frequencies the value of bypass capacitors depends directly upon the physical layout of the system. All bypassing should be as close to the package pins as possible to minimize unwanted lead inductance.

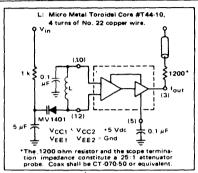

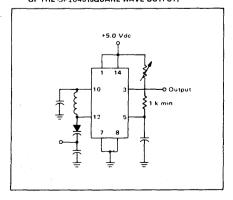

The peak-to-peak swing of the tank circuit is set internally by the AGC circuitry. Since voltage swing of the tank circuit provides the drive for the output buffer, the AGC potential directly affects the output waveform. If it is desired to have a sine wave at the output of the SP1648, a series resistor is tied from the AGC point to the most negative power potential (ground if +5.0 volt supply is used, -5.2 volts if a negative supply is used) as shown in Figure 10.

At frequencies above 100 MHz typ, it may be necessary to increase the tank circuit peak-to-peak voltage in order to maintain a square wave at the output of the SP1648. This is accomplished by tying a series resistor (1 k $\Omega$  minimum) from the AGC to the most positive power potential (+5.0 volts if a +5.0 volt supply is used, ground if a -5.2 volt supply is used). Figure 11 illustrates this principle.

#### **APPLICATIONS INFORMATION**

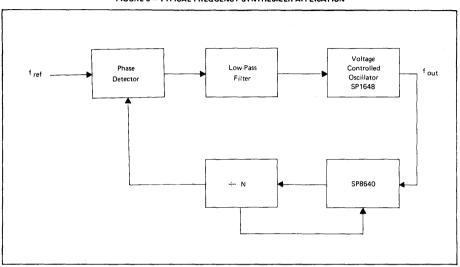

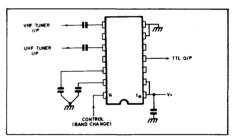

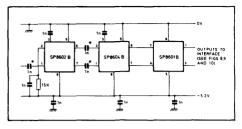

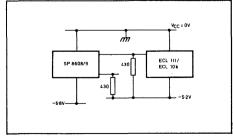

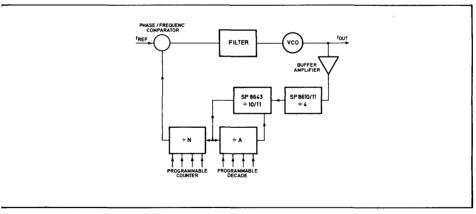

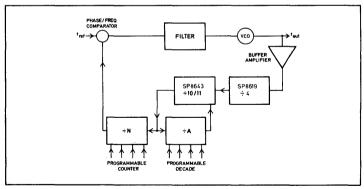

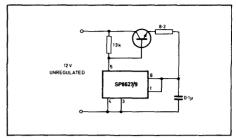

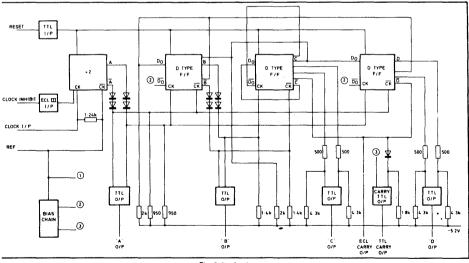

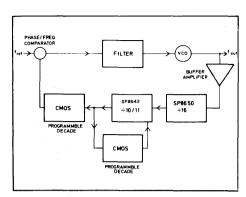

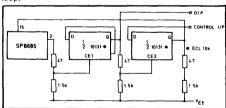

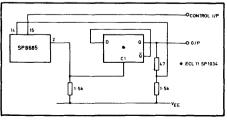

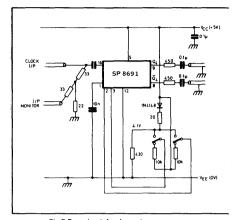

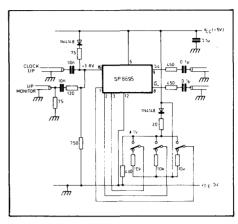

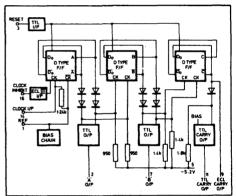

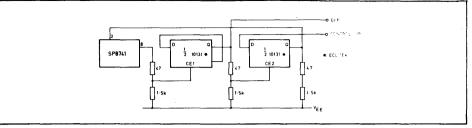

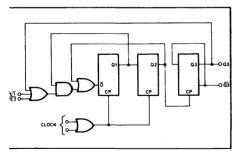

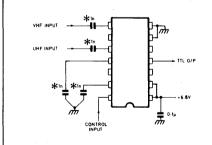

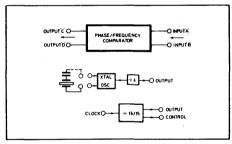

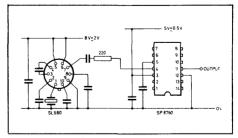

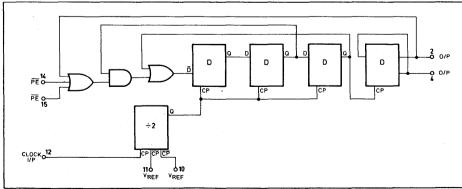

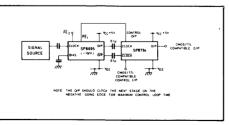

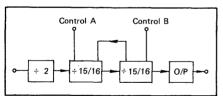

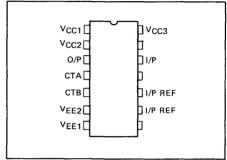

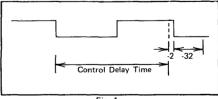

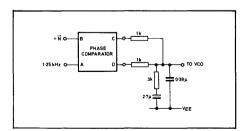

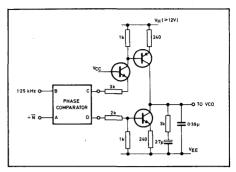

The phase locked loop shown in Figure 9 illustrates the use of the SP1648 as a voltage controlled oscillator. The figure illustrates a frequency synthesizer useful in tuners for FM broadcast, general aviation, maritime and landmobile communications, amateur and CB receivers. The system operates from a single +5.0 Vdc supply, and requires no internal translation, since all components are compatible.

Frequency generation of this type offers the advantages of single crystal operation, simple channel selection, and elimination of special circuitry to prevent harmonic lock-up. Additional features include dc digital switching (pref-

erable over RF switching with a multiple crystal system), and a broad range of tuning (up to 150 MHz, the range being set by the varactor diode).

The output frequency of the synthesizer loop is determined by the reference frequency and the number programmed at the programmable counter;  $f_{out} = Nf_{ref}$ . The channel spacing is equal to frequency  $(f_{ref})$ .

FIGURE 9 - TYPICAL FREQUENCY SYNTHESIZER APPLICATION

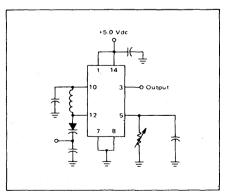

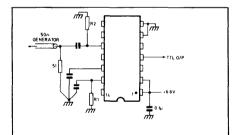

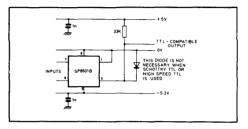

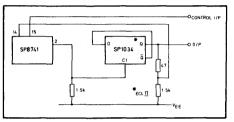

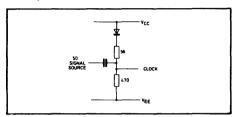

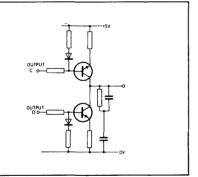

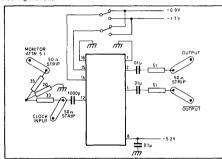

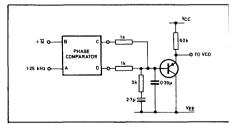

Figure 10 shows the SP1648 in the variable frequency mode operating from a +5.0 Vdc supply. To obtain a sine wave at the output, a resistor is added from the AGC circuit (pin 5) to VEE.

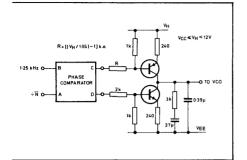

Figure 11 shows the SP1648 in the variable frequency mode operating from a +5.0 Vdc supply. To extend the useful range of the device (maintain a square wave output above 175 MHz), a resistor is added to the AGC circuit at pin 5 (1 k-ohm minimum).

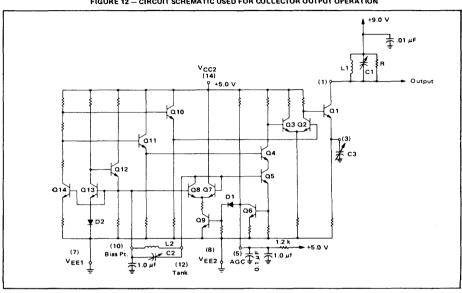

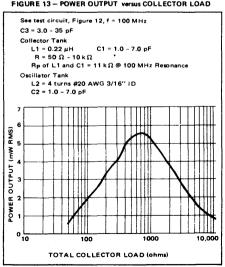

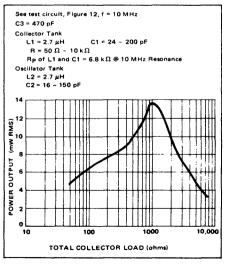

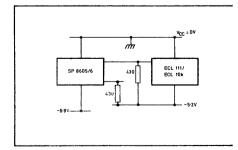

FIGURE 10 - METHOD OF OBTAINING A SINE-WAVE OUTPUT

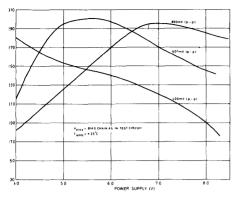

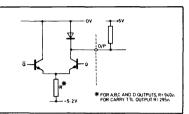

Figure 12 shows the SP1648 operating from +5.0 Vdc and +9.0 Vdc power supplies. This permits a higher voltage swing and higher output power than is possible from the PECL output (pin 3). Plots of output power versus total collector load resistance at pin 1 are given in Figures 13 and 14 for 100 MHz and 10 MHz operation. The total collector load includes R in parallel with Rp of L1 and C1 at resonance. The optimum value for R at 100 MHz is approximately 850 ohms.

FIGURE 11 - METHOD OF EXTENDING THE USEFUL RANGE OF THE ISP1648 (SQUARE WAVE OUTPUT)

FIGURE 12 - CIRCUIT SCHEMATIC USED FOR COLLECTOR OUTPUT OPERATION

FIGURE 14 - POWER OUTPUT versus COLLECTOR LOAD

#### DUAL A/D COMPARATOR

#### SP1650 • SP1651

- PD = 330 mW typ/pkg (No Load)

- t<sub>pd</sub> = 3.5 ns typ (SP1650)

- = 3.0 ns typ (SP1651)

- input Siew Rate = 350 V/µs (SP1 650) = 500 V/us (SP1651)

- Differential Input Voltage: -5.0 V to +5.0 V (-30°C to +85°C)

- Common Mode Range:

- -3.0 V to +2.5 V (-30°C to +85°C) (SP1650) -2.5 V to +3.0 V (-30°C to +85°C) (SP1651)

- Resolution:  $\leq$  20 mV (-30°C to +85°C)

- Drives 50  $\Omega$  lines

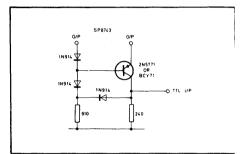

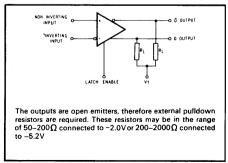

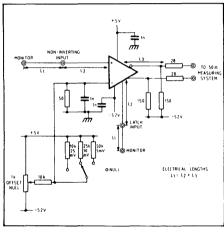

The SP1650 and the SP1651 are very high speed comparators utilizing differential amplifier inputs to sense analog signals above or below a reference level. An output latch provides a unique sample-hold feature. The SP1 650 provides high impedance Darlington inputs, while the SP-1651 is a lower impedance option, with higher input slew rate and higher speed capability.

Complementary outputs permit maximum utility for applications in high speed test equipment, frequency measurement, sample and hold, peak voltage detection, transmitters, receivers, memory translation, sense amplifiers and more.

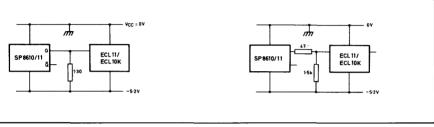

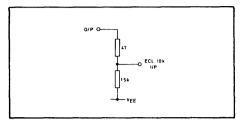

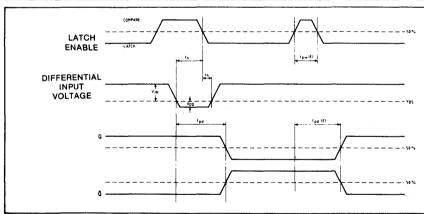

The clock inputs ( $\overline{C}_a$  and  $\overline{C}_b$ ) operate from PECL III or PECL 10,000 digital levels. When Ca is at a logic high level, Q0 will be at a logic high level provided that V1> V2 (V1 is more positive than V2). Q0 is the logic complement of Q0. When the clock input goes to a low logic level, the outputs are latched in their present state.

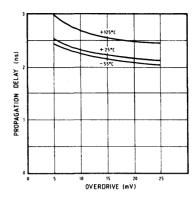

Assessment of the performance differences between the SP1650 and the SP1651 may be based upon the relative behaviors shown in Figures 3 and 6.

|   | TRUTH TA                        | BLE               |                   |

|---|---------------------------------|-------------------|-------------------|

| Ē | v <sub>1</sub> , v <sub>2</sub> | Ω0 <sub>n+1</sub> | ā0 <sub>n+1</sub> |

| н | V <sub>1</sub> >V <sub>2</sub>  | Н                 | L                 |

| н | V1 < V2                         | L                 | н                 |

| L | φ φ                             | 00 <sub>n</sub>   | āo <sub>n</sub>   |

φ = Don't Care

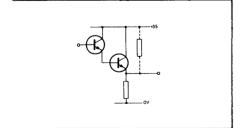

CIRCUIT SCHEMATIC SP1650 Inputs 1/2 of Device Shown (Both Devices) Vсс Gnd Gnd 7,10 9 16 02 O - ദെ റ് SP1651 Inputs V2

#### **ELECTRICAL CHARACTERISTICS**

This PECL III circuit has been designed to meet the dc specifications shown in the test table after thermal equilibrium has been established. The package should be housed in a suitable heat sink (IERC-LIC-214A2WCB or equivalent) or a transverse air flow greater than 500 linear fpm should be maintained while the circuit is either in a test socket or is mounted on a printed circuit board. Test procedures are shown for selected inputs and selected outputs. The other inputs and outputs are tested in a similar manner. Outputs are tested with a 50-ohm resistor to -2.0 Vdc. See general information section for complete thermal data

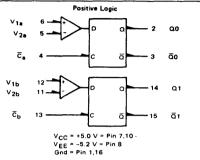

# POSITIVE LOGIC V1a 6 V2a 5 D Q 2 Q0 Ca 3 \(\tilde{Q}\) V1b 12 V2b 11 Cb 13 C \(\tilde{Q}\) The Q 14 Q1

CERAMIC PACKAGE E

|                       |        | TEST VOLTAGE VALUES |         |         |        |        |     |       |                 |     |                   |       |  |  |  |  |

|-----------------------|--------|---------------------|---------|---------|--------|--------|-----|-------|-----------------|-----|-------------------|-------|--|--|--|--|

|                       |        | (Volts)             |         |         |        |        |     |       |                 |     |                   |       |  |  |  |  |

| @ Test<br>Temperature | ViHmax | ViLmin              | VIHAmin | VILAmax | VA1    | VA2    | VA3 | VA4   | V <sub>A5</sub> | VA6 | v <sub>cc</sub> 3 | vee 4 |  |  |  |  |

| -30°C                 | -0 875 | -1.890              | -1 180  | -1.515  | +0 020 | -0.020 |     |       |                 |     | +5.0              | -5.2  |  |  |  |  |

| +25°C                 | -0810  | -1.850              | -1.095  | -1.485  | +0.020 | -0.020 |     | See A | lote 🕙          |     | +5.0              | -5.2  |  |  |  |  |

| +85°C                 | -0 700 | -1 830              | -1 025  | -1 440  | +0.020 | -0 020 |     |       |                 |     | +5.0              | -5.2  |  |  |  |  |

|                                                    |                   | 1.                                                                                               | SF              | P1656  | SP169  | Test             | Limits | 1              |              |         |           |                  | 7557 110 |              | PPLIED T    |                                             |                                                            |                 |                                         |                   | •     | ĺ                                                                             |

|----------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------|-----------------|--------|--------|------------------|--------|----------------|--------------|---------|-----------|------------------|----------|--------------|-------------|---------------------------------------------|------------------------------------------------------------|-----------------|-----------------------------------------|-------------------|-------|-------------------------------------------------------------------------------|

|                                                    |                   | Pin                                                                                              | -3              | 0°C    | +2     | 5°C              | +8     | 5°C            |              | <b></b> |           |                  |          |              |             |                                             |                                                            |                 |                                         |                   | T @   | ĺ                                                                             |

| Characteristic                                     | Symbol            | Test                                                                                             | Min             | Max    | Min    | Max              | Min    | Max            | Unit         | ViHmax  | VILmin    | VIHAmin          | VILAmax  | VAI          | VA2         | VA3                                         | VA4                                                        | V <sub>A5</sub> | VA6                                     | v <sub>cc</sub> 3 | VEE 3 | Gnd                                                                           |

| Power Supply Drain Current<br>Positive<br>Negative | ¹CC               | 7,10<br>8                                                                                        | -               |        | -      | 25°              | -      | -              | mAdc<br>mAdc | 4.13    | 4,13<br>- | -                | -        | 6,12<br>6,12 | -           | -                                           | -                                                          | -               | -                                       | 7,10<br>7,10      | 8 8   | 1,5,11,16<br>1,5,11,16                                                        |

| Input Current<br>SP1650<br>SP1651                  | 1 <sub>in</sub>   | 6                                                                                                | -               | -      | -      | 10<br>40         | -      |                | µAdc<br>µAdc | 4       | 13<br>13  | -                | -        | 12<br>12     | -           | 6                                           | -                                                          | -               | -                                       | 7.10<br>7.10      | 8     | 1,5,11,16<br>1,5,11,16                                                        |

| Input Leakage Current<br>SP1650<br>SP1651          | <sup>1</sup> R    | 6                                                                                                | -               | _      | -      | 7                | -      | -              | μAdc<br>μΑdc | 4       | 13<br>13  |                  | ~        | 12           | -           |                                             | -                                                          | 6               | =                                       | 7,10<br>7,10      | 8 8   | 1,5,11,16<br>1,5,11,16                                                        |

| Input Clock Current                                | LinH              | 4                                                                                                | -               | -      | -      | 350              |        |                | μAdc         | 4       | 13        | -                |          | 6.12         | -           | -                                           | -                                                          | -               | -                                       | 7,10              | 8     | 1,5,11,16                                                                     |

|                                                    | I <sub>in</sub> L | 4                                                                                                | Ξ               | -      | 0.5    |                  | -      | -              | μAdc         |         | 13        | -                |          | 6,12         |             | -                                           | -                                                          | -               |                                         | 7,10              | 4,8   | 1,5,11,16                                                                     |

| Logic "1" Output Voltage                           | VOL               | 2<br>2<br>2<br>2<br>3<br>3<br>3<br>3<br>2<br>2<br>2<br>2<br>2<br>3<br>3<br>3<br>3<br>3<br>3<br>3 |                 | -1650  | -1850  |                  | -1830  |                |              | 4,13    |           |                  | -        | 5.11         | 5,11<br>    | 5,11<br>-<br>5,11<br>-<br>5,11<br>-<br>6,12 | 5,11<br>-<br>-<br>6,12<br>-<br>-<br>6,12<br>-<br>-<br>5,11 | 5,11<br>        | 6.12<br>                                | 7,10              | 8     | 1,5,11,16<br>1,6,12,16<br>1,16<br>1,5,11,16<br>1,5,11,16<br>1,16<br>1,16<br>1 |

| Logic "1" Threshold Voltage (1<br>2)   3<br>  4    | Vона              | 2<br>2<br>3<br>3                                                                                 | -1.065<br> <br> | -      | -0.980 | -<br>-<br>-<br>- | -0910  | -              | Vdc          |         | 13        | 4                | 4        | 6            | -<br>6<br>6 | -<br>-<br>-                                 | =                                                          | =               | = = = = = = = = = = = = = = = = = = = = | 7,10              | 8     | 1,5,16                                                                        |

| Lagra "0" Threshold Voltage (1<br>2)<br>3<br>4     | VOLA              | 3<br>3<br>2<br>2                                                                                 |                 | -1.630 | -<br>- | -1.600           | -      | -1555<br> <br> | Vdc          | -       | 13        | 4<br>-<br>4<br>- | 4        | 6            | 6<br>6<br>- | -                                           | -                                                          | -               | -                                       | 7,10              | i     | 1,5,16                                                                        |

| HOTES | 0 | All data is for % SP1650 or SP1651, except data marked (*) which refers to the entire package. |

|-------|---|------------------------------------------------------------------------------------------------|

|       | @ | These tests done in order indicated. See Figure 4.                                             |

இ Maximum ?oxcr Supply Voltages (beyond which device life may be impaired) | vps + ்்ரி ≨ 12 Vdc.

| ④ | All Temperatures | V <sub>A3</sub> | VA4    | VA5    | V <sub>A6</sub> |

|---|------------------|-----------------|--------|--------|-----------------|

|   | SP1650           | +3.000          | +2.980 | -2.500 | -2.480          |

|   | SP1651           | +2.500          | +2.480 | -3.000 | -2.980          |

#### CERAMIC PACKAGE E

POSITIVE LOGIC

V1a 6

V2a 5

D Q 2 Q0

Ca 4

C Q 3 Q0

V1b 12

V2b 11

C Q 115 Q1

C Q 15 Q1

9 Test Temperature -30°C +25°C

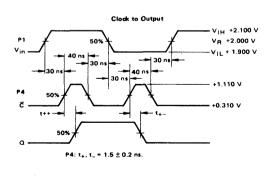

TEST VOLTAGE VALUES (Volts) vcc 0 VEE O V<sub>R3</sub> ٧x VR1 V<sub>R2</sub> V<sub>XX</sub> +1.040 +2.000 +2.00 +7.00 -3.20 +2.000 See Note 4 +1.110 +2.00 +7.00 -3.20 +2.000 +1.190 +2.00 +7.00 -3.20

See Figure 2

|                       |                   | Pin   |     | SP1 | 650/ | 1651 T | est L | imits |      | -               |                 |                 |         |                 |                   |      |          |     |     |     |

|-----------------------|-------------------|-------|-----|-----|------|--------|-------|-------|------|-----------------|-----------------|-----------------|---------|-----------------|-------------------|------|----------|-----|-----|-----|

|                       |                   | Under | -30 | o°C | +2   | 5°C    | +80   | 5°C   | Unit | - '6            | SO VULI         | AUE AFF         | LIED IO | PINS LIST       |                   |      | <b>├</b> |     |     | _   |

| Cheracteristic        | Symbol            | Test  | Min | Max | Min  | Max    | Min   | Mex   |      | V <sub>R1</sub> | V <sub>R2</sub> | V <sub>R3</sub> | ٧x      | V <sub>XX</sub> | v <sub>cc</sub> O | AEEQ | P1       | P2  | Р3  | P4  |

| Switching Times       | t6+2+             | 2     | 2.0 | 5.0 | 2.0  | 5.0    | 2.0   | 5.7   | ns   | 5               | _               | -               | 4       | 1,11,16         | 7,10              | 8    | 6        | -   | _   | Τ-  |

| Propagation Delay     | t6+2+             | 2     | 1 1 | 1 i | 1 1  | ۱,     | [ ]   | ۱.    | 11   | -               | 5               | _               |         | 1 1             | 1                 | 1 1  | 1 - 3    | 6   | -   | -   |

| (50% to 50%)          | t6+2+             | 2     | 1 1 | 11  | 1 1  | 1      | 1     |       | 1    | -               | -               | 5               | 1 1     | 1 1             | 1 1               | 1 1  | -        | _   | 6   | -   |

| V-Input to Output     | t6+3-             | 3     | 1 1 | l i | 11   | 1      |       |       | 1    | 5               | -               | -               |         |                 | 1 1               | 1 1  | 6        | -   | -   | 1 - |

|                       | t6+3-             | 3     |     | l i |      | 11     | 1 1   |       |      | -               | 5               | - 1             | 1 1     | 1 1             | 1 1               | 11   | -        | 6   | -   | 1 - |

|                       | t6+3-             | 3     | 1 1 | 11  |      | 1 1    |       |       | 11   | ~               | - 1             | 5               |         | l i             | 1                 | l I  | - :      | -   | 6   | -   |

|                       | t6-2-             | 2     | 1 1 | 1 1 | l l  | 11     | 11    | 1 1   | 1 1  | 5               | I –             | -               | 1 1     | 1               | 1 1               | 1 1  | 6        | _   | - 1 | -   |

|                       | t6-2-             | 2     | 1 1 | 1 1 |      | 1 1    |       | li    | 11   | -               | 5               | -               | 1 1     | 1 1             | 1 1               | 1 1  | 1 -      | 6   | -   | 1 - |

|                       | <sup>1</sup> 6-2- | 2     | 1 1 | 11  | 1 1  |        | 1 1   | 1 1   | 1 1  | -               | - 1             | 5               | 11      | 1 1             | 1 1               | 1 1  | -        | _   | 6   | -   |

|                       | t6-3+             | 3     | 1 1 | 1 1 | 1 1  | 11     | 11    |       | 11   | 5               | i –             |                 | 1 1     | 1 1             | 1 1               |      | 6        | -   | -   | -   |

|                       | t6-3+             | 3     | 1 4 | ۱ ∔ | 1    | ۱ ∔    | ۱ .   |       | ١.   | l –             | 5               | -               | 1 4     | 1 1             | 1 4               | 1 1  | -        | 6   | -   | -   |

|                       | t6-3+             | 3     |     | _ • |      | 7      |       |       |      | -               | _               | 5               |         |                 |                   | ,    | -        | _   | 6   | 1 = |

| Clock to Output ②     | t4+2+             | 2     | 2.0 | 4.7 | 2.0  | 4.7    | 2.0   | 5.2   | ns   | 5               | -               | _               | -       | 1,11,16         | 7,10              | - 8  | 6        | -   | -   | 4   |

|                       | 14+2-             | 2     | 1   | 1 1 | 1 1  | 1 1    | 1     | lı    | 1 1  | 6               | -               | -               | - 1     | 1 1             | 1 1               | 1    | 5        | - 1 | _   | 1.1 |

|                       | 14+3+             | 3     | 1 1 | 1 1 | 1 1  | ΙI     | l I   | 1 1   | 11   | 6               | ! -             | -               | - 1     | 1 1             | 1 1               | 1 1  | 5        | -   | -   | 1.1 |

|                       | t4+3-             | 3     | 1   | 1   | ₹    | . 7    |       | 1     |      | 5               | -               | -               | 1 –     | 1               | 1                 | 1    | 6        | - 1 | -   | 1 7 |

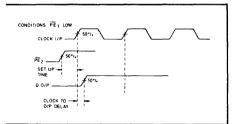

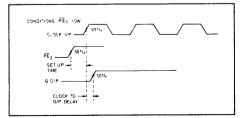

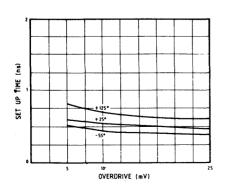

| Clock Enable Time 3   | tsetup            | 6     | -   | -   | 2.5  | -      | -     | -     | ns   | 5               | T -             | -               | -       | 1,11,16         | 7,10              | 8    | 6        | -   | -   | 4   |

| Clock Aperture Time 3 | tap               | 6     | -   | -   | 1.5  |        | -     | -     | ns   | 5               | -               | -               | -       | 1,11,16         | 7,10              | 8    | 6        | -   | -   | 4   |

| Rise Time             | t <sub>2+</sub>   | 2     | 1.0 | 3.5 | 1.0  | 3.5    | 1.0   | 3.8   | ns   | 5               | -               | -               | 4       | 1,11,16         | 7,10              | 8    | 6        | -   | -   | ΤΞ  |

| (10% to 90%)          | t3+               | 3     | 1.0 | 3.5 | 1.0  | 3.5    | 1.0   | 3.8   | ns   | 5               | -               | -               | 4       | 1,11,16         | 7,10              | 8    | 6        | -   | -   | -   |

| Fell Time             | t2-               | 2     | 1.0 | 3.0 | 1.0  | 3.0    | 1.0   | 3.3   | ns   | 5               | T -             | T -             | 4       | 1,11,16         | 7,10              | 8    | 6        | _   | -   | 1 - |

| (10% to 90%)          | 12_               | 3     | 1.0 | 3.0 | 1.0  | 3.0    | 1.0   | 3.3   | ns   | 5               | I -             | _               | 4       | 1.11.16         | 7.10              | 8    | 6        | -   | -   | 1 - |

NOTES: ① Meximum Power Supply Voltages (beyond which device life may be impaired: |VCC| + |VEE| ≤ 12 Vdc.

2 Unused clock inputs may be tied to ground.

3 See Figure 8.

| <b>④</b> | All Temperatures | VR2    | V <sub>R3</sub> |  |  |  |

|----------|------------------|--------|-----------------|--|--|--|

|          | SP1650           | +4.900 | -0.400          |  |  |  |

|          | SP1651           | +4.400 | -0.900          |  |  |  |

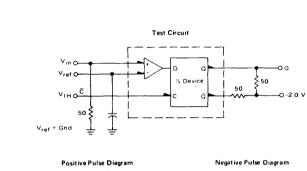

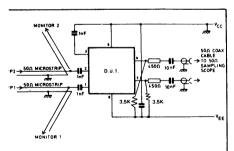

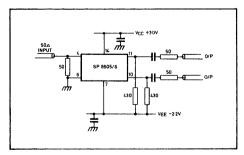

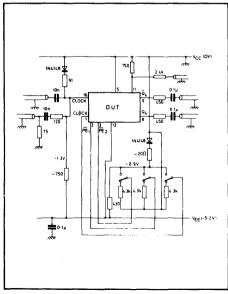

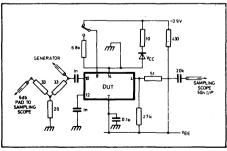

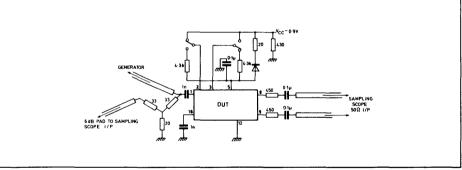

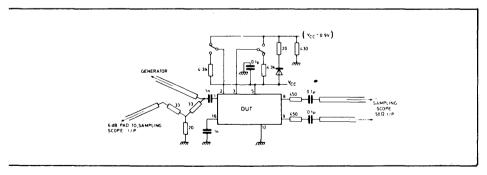

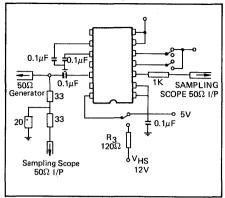

FIGURE 1 - SWITCHING TIME TEST CIRCUIT @ 25°C \*Vout to Vin to Channel A V<sub>XX</sub> = 9 +2.0 vdc VCC # +7.0 Vdc 9 CC Gnd ā V<sub>X</sub> o VEE = -3.2 Vdc 50-ohm termination to ground located in each scope channel input All input and output cables to the scope are equal lengths of 50-ohm coaxiel cable. \*Complement of output under test should always be loaded with 50-ohms to ground.

24

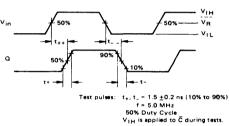

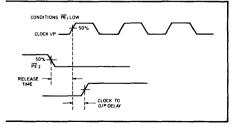

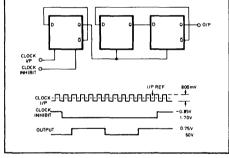

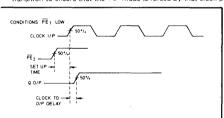

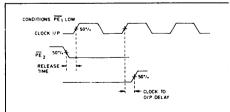

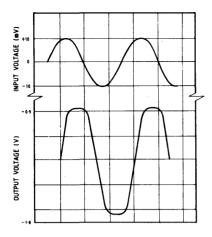

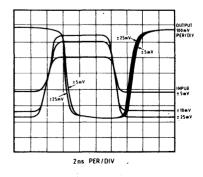

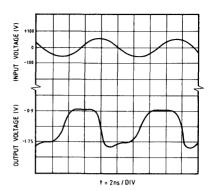

FIGURE 2 - SWITCHING AND PROPAGATION WAVEFORMS @ 25°C

The pulse levels shown are used to check ac parameters over the full common-mode range.

#### V - Input to Output

#### TEST PULSE LEVELS

|     | Pul      | se 1     | Pul      | se 2     | Pulse 3  |          |  |  |  |

|-----|----------|----------|----------|----------|----------|----------|--|--|--|

|     | SP1650   | SP1651   | SP1650   | SP1651   | SP1650   | SP1651   |  |  |  |

| ViH | +2.100 V | +2.100 V | +5.000 V | +4.500 V | -0.300 V | -0.800 ∨ |  |  |  |

| ٧R  | +2.000 V | +2.000 V | +4.900 V | +4.400 V | -0.400 V | -0.900 V |  |  |  |

| VIL | +1.900 V | +1.900 V | +4.800 V | +4.300 V | -0.500 V | -1.000 V |  |  |  |

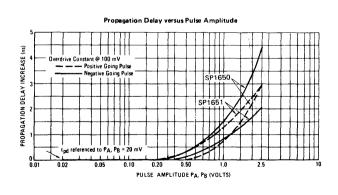

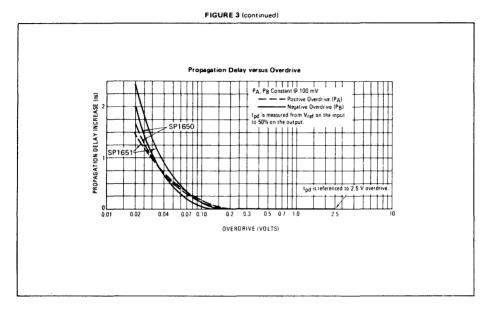

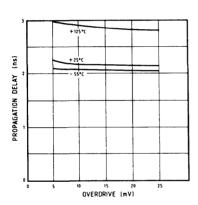

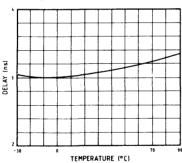

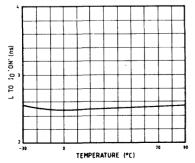

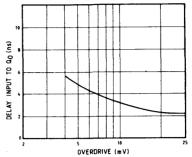

FIGURE 3 – PROPAGATION DELAY  $(\tau_{\mathbf{pd}})$  versus INPUT PULSE AMPLITUDE AND CONSTANT OVERDRIVE

at 1.5 ns (10% to 90%).

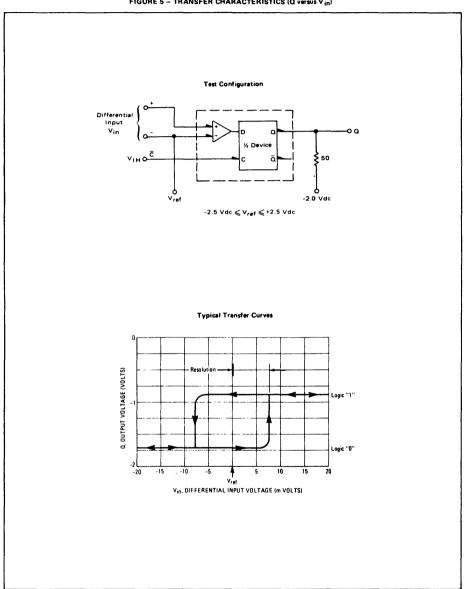

FIGURE 5 - TRANSFER CHARACTERISTICS (Q versus V in)

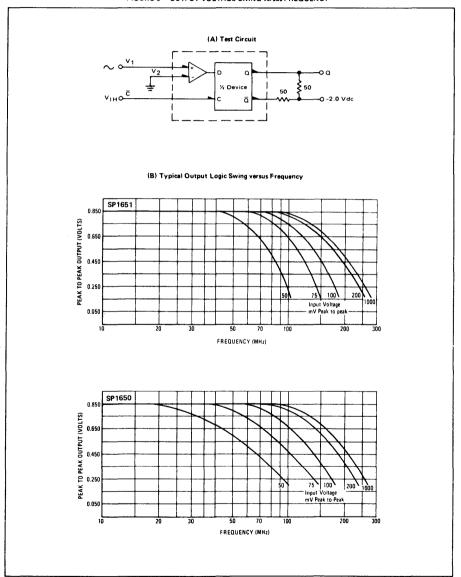

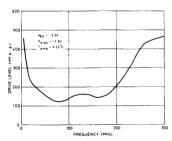

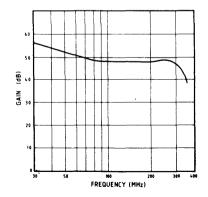

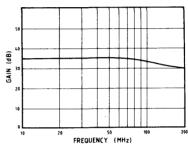

FIGURE 6 - OUTPUT VOLTAGE SWING Versus FREQUENCY

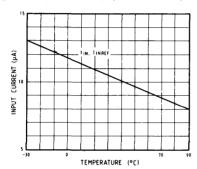

FIGURE 7 - INPUT CURRENT versus INPUT VOLTAGE TEST CIRCUIT νcc Vсс 50 0 -2.0 Vdc 50 Typical SP1650 (Complementary Input Grounded) Typical SP1651 (Complementary Input Grounded) lin. INPUT CURRENT (#A) In. INPUT CURRENT (MA) Vin. INPUT VOLTAGE (VOLTS) Vin. INPUT VOLTAGE (VOLTS)

FIGURE 8 - CLOCK ENABLE AND APERTURE TIME TEST CIRCUIT AND WAVEFORMS @ 25°C Vin to Channel A Vout to Channel B V<sub>CC</sub> = +7.0 Vdc Q V<sub>XX</sub> = +2.0 Q Vdc 0.1 Gnd V<sub>in O</sub> Q VRO č٥ ã a VEE -0 VEE = -3.2 Vdc 0.1 µF 50-ohm termination to ground located in each scope channel input. All input and output cables to the scope are equal lengths of 50-ohm coaxial cable. Analog Signal Positive and Negative Slew Case -VR + 100 mV = +2.100 V Vin Negative -V<sub>R</sub> = 2.000 V Clock Enable V<sub>B</sub> - 100 mV = +1.900 V Time Vin Positive VIH = +1.110 V ō -VIL = +0.310 V Clock Aperture 50% Q Positive -Q Negative -50% Clock enable time = minimum time between analog and clock signal such that output switches, and  $t_{\mbox{\scriptsize pd}}$  (analog to Q) is not degraded by more than 200 ps. ---- Clock aperture time = time difference between clock enable time and time that output does not switch and V is less than 150 mV.

#### VOLTAGE CONTROLLED MULTIVIBRATOR

#### SP1658

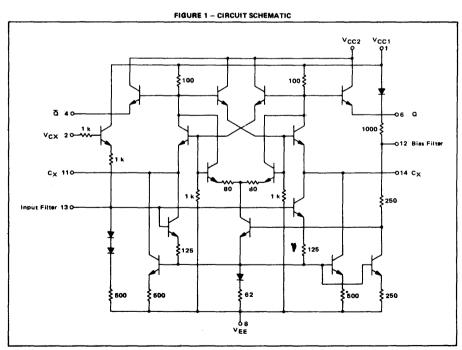

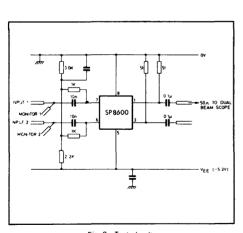

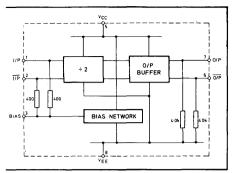

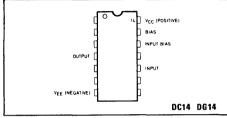

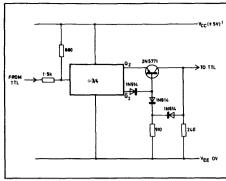

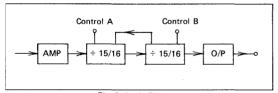

The SP1658 is a voltage-controlled multivibrator which provides appropriate level shifting to produce an output compatible with PECL. III and PECL. 10,000 logic levels. Frequency control is accomplished through the use of voltage-variable current sources which control the slew rate of a single external capacitor.

The bias filter may be used to help eliminate ripple on the output voltage levels at high frequencies and the input filter may be used to decouple noise from the analog input signal.

The 'SP1658i is useful in phase-locked loops, frequency synthesizer and clock signal generation applications for instrumentation, communication, and computer systems.

32

#### **ELECTRICAL CHARACTERISTICS**

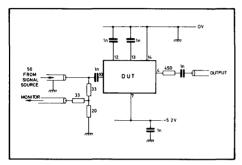

This PECL III circuit has been designed to meet the dc specifications shown in the test table, after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse air flow greater than 500 linear fpm is maintained. Outputs are terminated through a 50-ohm resistor to -2.0 volts.

#### CERAMIC PACKAGE E

|             | TEST VOLTAGE VALUES |      |                |      |      |  |  |  |  |  |  |  |  |

|-------------|---------------------|------|----------------|------|------|--|--|--|--|--|--|--|--|

|             | Vdc ±1%             |      |                |      |      |  |  |  |  |  |  |  |  |

| @ Test      |                     |      |                |      | T    |  |  |  |  |  |  |  |  |

| Temperature | VIH                 | VIL  | v <sub>3</sub> | VIHA | VEE  |  |  |  |  |  |  |  |  |

| -30°C       | 0.0                 | -2.0 | -1.0           | +2.0 | -5.2 |  |  |  |  |  |  |  |  |

| +25°C       | 0.0                 | -2.0 | -1.0           | +2.0 | -5.2 |  |  |  |  |  |  |  |  |

| +85°C       | 0.0                 | -2.0 | -1.0           | +2.0 | -5.2 |  |  |  |  |  |  |  |  |

|                                                                | 1        | Pin      | SP 1658 Test Limits |                  |                  |            |                  |                  |                  |              |                                    | VOLTAGE APPLIED TO PINS LISTED BELOW: |     |      |               |                           |

|----------------------------------------------------------------|----------|----------|---------------------|------------------|------------------|------------|------------------|------------------|------------------|--------------|------------------------------------|---------------------------------------|-----|------|---------------|---------------------------|

|                                                                | 1        | Under    | -30°C               |                  | +25°C            |            |                  | +85°C            |                  |              | TOURSE AFFEIGN TO THIS EIGHT DECOM |                                       |     |      |               | (Vcc)                     |

| Characteristic                                                 | Symbol   | Test     | Min                 | Max              | Min              | Тур        | Max              | Min              | Max              | Unit         | VIH                                | V <sub>IL</sub>                       | V3  | VIHA | VEE           | Gnd                       |

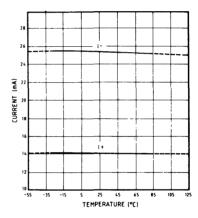

| Power Supply Drain Current                                     | ¹E       | 8.       |                     | -                | -                | -          | 32<br>32         | -                | -                | mAdc<br>mAdc | 2 2                                | -                                     | -   | =    | 8<br>8        | 1,5<br>1,5                |

| Input Current                                                  | linH     | 2*       | -                   | -                | -                | -          | 350              | -                | -                | μAdc         | 2                                  | -                                     | -   |      | 8             | 1,5                       |

| Input Leakage Current                                          | linL     | 2*       | -                   | -                | 0.5              | -          |                  | -                | -                | μAdc         | -                                  | 2                                     | - 1 |      | 8             | 1,5                       |

| ''Q'' High<br>Output Voltage                                   | ∨он      | 4°<br>6° | -1.045<br>-1.045    | -0.875<br>-0.875 | -0.960<br>-0.960 | -          | -0.810<br>-0.810 | -0.890<br>-0.890 | -0.700<br>-0.700 | Vdc<br>Vdc   | -                                  | -                                     | 2 2 | =    | 8             | 1,5<br>1,5                |

| "Q" Low<br>Output Voltage                                      | VOL      | 4.       | -1.890<br>-1.890    | -1.650<br>-1.650 | -1.850<br>-1.850 | -          | -1.620<br>-1.620 | -1.830<br>-1.830 | -1.575<br>-1.575 | Vdc<br>Vdc   | -                                  | -                                     | 2 2 |      | 8             | 1,5<br>1,5                |

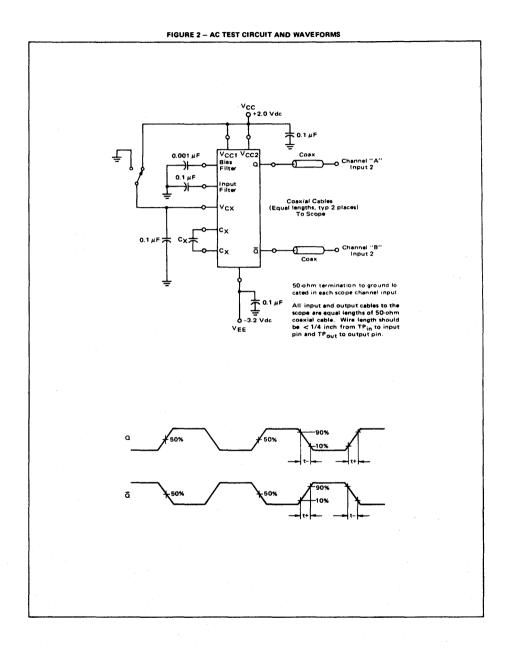

| AC Characteristics (Figure 2) (Tests shown for one output, but |          |          |                     |                  |                  |            |                  |                  |                  |              | CX1                                | C <sub>X2</sub>                       | Gnd |      | VEE<br>-3.2 V | V <sub>CC</sub><br>+2.0 V |

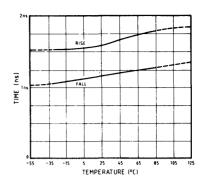

| checked on both) Rise Time (10% to 90%) Fall Time (10% to 90%) | t+<br>t- | 6<br>6   | -<br>-              | 2.7<br>2.7       | -                | 1.6<br>1.4 | 2.7<br>2.7       | -                | 3.0<br>3.0       | ns<br>ns     | -                                  | 11,14<br>11,14                        | -   | 2 2  | 8<br>2        | 1,5<br>1,5                |

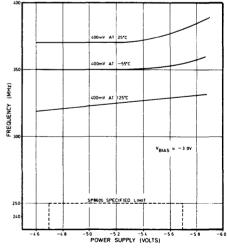

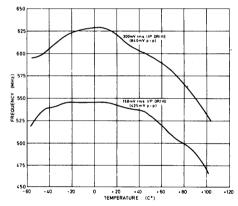

| Oscillator Frequency                                           | fosc1    | -        | 130                 |                  | 130              | 155        | 175              | 110              | -                | MHz          | -                                  | 11,14                                 | -   |      | 8             | 1,5                       |

|                                                                | fosc2    | -        | -                   |                  | 78               | 90         | 100              | _                |                  | MHz          | 11,14                              | -                                     | - 1 |      | 8             | 1,5                       |

| Tuning Ratio Test 1                                            | TR       | -        |                     | -                | 3.1              | 4.5        |                  | _                | -                |              | 11,14                              | -                                     | -   |      | 8             | 1,5                       |

<sup>\*</sup>Germanium diode (0.4 drop) forward biased from 11 to 14 (11 14).

\*Germanium diode (0.4 drop) forward biased from 14 to 11 (11 14).

<sup>†</sup>TR = Output frequency at V<sub>CX</sub> = Gnd

Output frequency at V<sub>CX</sub> = -2.0 V

C1 = 0.01 µF connected from pin 12 to Gnd.

C2 = 0.001 µF connected from pin 13 to Gnd.

CX1 = 10 pF connected from pin 11 to pin 14.

CX2 = 5 pF connected from pin 11 to pin 14.

34

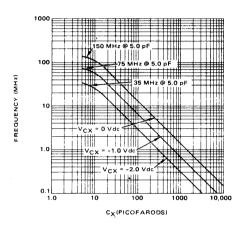

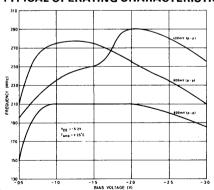

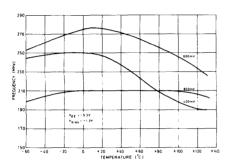

FIGURE 3 — OUTPUT FREQUENCY versus CAPACITANCE FOR VARIOUS VALUES OF INPUT VOLTAGE

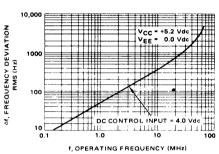

FIGURE 4 – RMS NOISE DEVIATION versus OPERATING FREQUENCY

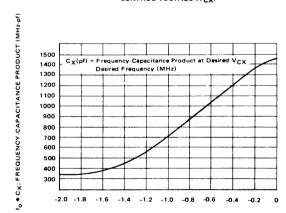

FIGURE 5 – FREQUENCY-CAPACITANCE PRODUCT versus

CONTROL VOLTAGE (VCX)

VCX, INPUT VOLTAGE (Vdc)

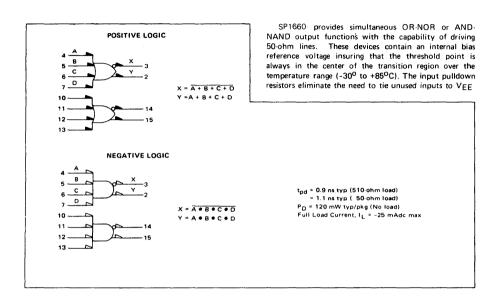

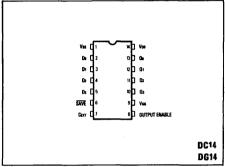

#### **DUAL 4-INPUT GATE**

#### SP1660

#### **ELECTRICAL CHARACTERISTICS**

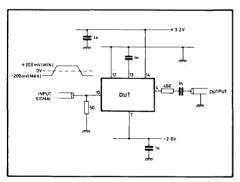

This PECL III circuit has been designed to meet the dc specifications shown in the test table, after thermal equilibrium has been established. The package should be housed in a suitable heat sink (LIO21 4A2WCB or equivalent) or a transverse air flow greater than 500 linear fpm should be maintained while the circuit is either in a test socket or is mounted on a printed circuit board. Test procedures are shown for only one input and one output. The other inputs and outputs are tested in a similar manner. Outputs are tested with a 50-ohm resistor to -2.0 Vdc. See general information section for complete thermal data

CERAMIC PACKAGE E

TEST VOLTAGE VALUES (Volts) V<sub>IHmax</sub> V<sub>ILmin</sub> V<sub>IHAmin</sub> V<sub>ILAmax</sub> V<sub>EE</sub>

-0.875 -1.890 -1.180 -1.515 -5.2 -0.810 -1.850 -1.095 -1.485 -5.2

|                                    |                    |                    |          |                  |        |              |            |          | +85°C    | -0.700                  | -1.830      | -1.025        | -1.440  | -5.2   | J        |

|------------------------------------|--------------------|--------------------|----------|------------------|--------|--------------|------------|----------|----------|-------------------------|-------------|---------------|---------|--------|----------|

|                                    | Pin                | SP1660 Test Limits |          |                  |        |              |            |          |          | TEST VOLTAGE APPLIED TO |             |               |         |        |          |

|                                    | ł                  | Under              | -30°C    |                  |        | +25°C        |            | 5°C      | 1        | ļ                       |             | LISTED BELOW: |         |        | (Vcc)    |

| Characteristic                     | Symbol             | Test               | Min      | Max              | Min    | Mex          | Min        | Max      | Unit     | ViHmex                  | VILmin      | VIHAmin       | VILAmex | VEE    | Gnd      |

| Power Supply Drain Current         | IE.                | 8                  |          |                  |        | 28           | <u> </u>   | 1 -      | mAdc     | -                       |             |               | -       | 8      | 1,16     |

| Input Current                      | linH               |                    | -        | -                | -      | 350          | -          | -        | μAdc     |                         | ~           | -             | -       | 8      | 1,16     |

|                                    | linL               |                    | _        | 1 -              | 0.5    | -            | -          | <u> </u> | μAdc     | -                       |             | -             |         | 8      | 1,16     |

| NOR Logic "1" Output Voltage       | VOH ♥              | 3                  | -1.045   | -0.875           | -0.960 | -0.810       | -0.890     | -0.700   | Vdc      | _                       | 4           | _             | _       | 8      | 1,16     |

|                                    | 1                  | 1 1                | 11       | 1 1              | 1 1    |              |            | 1 1      |          | 1 -                     | 5<br>6      | 1 -           | 1 =     |        | 1 1      |

|                                    | <u> </u>           | •                  | •        |                  |        | •            | •          |          |          | -                       |             | -             | -       |        | ,        |

| NOR Logic "0" Output Voltage       | VOL #              | 3                  | -1.890   | -1.650           | -1.850 | -1.620       | -1.830     | -1.575   | Vdc      | 4                       | -           | -             | -       | 8      | 1,16     |

|                                    |                    |                    |          | 1 1              | 1 1    | ] [          |            | 11       | 1 1      | 5                       | -           | -             | -       | 11     |          |

|                                    | l                  | •                  |          | +                |        | ♦            | <b>!</b> • | ! •      | 1 1      |                         | <u>-</u>    | -             | _       | . +    | +        |

| OR Logic "1" Output Voltage        | V <sub>OH</sub> Ø  | 2                  | -1.045   | -0.875           | -0.960 | -0.810       | -0.890     | -0.700   | 'Vdc     | 4                       | -           | -             |         | 8      | 1,16     |

|                                    |                    | 1 1                | 1 1      | 1 1              |        |              | 1 1        | 1 1      | 1 1      | 5                       | -           | -             | -       | 1 1    | 1        |

|                                    | l                  | l .                | 1 1      | ١ ا              | 1 1    | 1            | ١ ٠        | 1 4      | ١ .      | 6 7                     | _           |               | _       | ↓      |          |

| OR Logic "0" Output Voltage        | VOL Ø              | 2                  | -1.890   | -1.650           | -1.850 | -1.620       | -1.830     | -1.575   | Vdc      | <u> </u>                | 4           | _             |         | 8      | 1,16     |

|                                    | "                  | ìī                 | 1 1      | 1                |        | 1 7          | 1          | 1        | 1 1      | - :                     | 5           | - 1           | -       | li     | 1        |

|                                    |                    | 1 1                | i i      | 1 1              | 1      |              | ↓          |          | ↓        | - 1                     | 6 7         | -             | -       | ١.     |          |

| NOR Logic "1"                      | V <sub>OHA</sub> ø | 3                  | -1.065   | <del>  '</del> - | -0.980 | <del>-</del> | -0.910     |          | Vdc      | -                       | <del></del> |               | -       | +      | 1,16     |

| Threshold Voltage                  | VOHA W             | l i                | -1.065   | _                | 20.360 | -            | 1 1        | 1 -      | 1        | -                       | _           |               | 5       | l i    | 170      |

| -                                  | l                  | 1 1                | 1 1      | -                |        | -            | 1          | -        |          | -                       | -           | -             | 6       | 1 1    | 1 1      |

|                                    |                    | <u>'</u>           | <u>'</u> | -                | '      | <u> </u>     | - · ·      |          | <u> </u> |                         | <u> </u>    |               | 7       |        | <u>'</u> |

| NOR Logic "0"<br>Threshold Voltage | VOLA P             | 3                  | -        | -1.630           | _      | -1.600       | 1 :        | -1.555   | Vdc      | _                       | _           | 5             |         | 8      | 1,16     |

| This ariono vortage                |                    |                    | -        | ll               | -      |              | 1 -        | 1 1      | 1 1      | -                       | _           | 6             | -       | ll     |          |

|                                    |                    | ,                  | -        | •                |        | 1            |            | '        | 1        | -                       |             | 7             | -       |        |          |

| OR Logic "1" Threshold Voltage     | VOHA Ø             | 2                  | -1.065   | ] [              | -0.980 |              | -0.910     | -        | Vdc      | _                       | -           | 4 5           | -       | 8      | 1,16     |

|                                    |                    |                    |          | -                |        | -            |            | _        |          | _                       | _           | 6             | -       |        |          |

|                                    |                    | •                  | 1        | -                | ,      |              |            | -        | 1        |                         | -           | 7             | -       | •      | '        |

| OR Logic "O" Threshold Voltage     | VOLA P             | 2                  | -        | -1.630           | -      | -1.600       | -          | -1.555   | Vdc      | -                       | -           | -             | 4       | 8      | 1,16     |

|                                    |                    | 11                 | -        |                  |        |              | -          | !        | -        |                         | _           | _             | 5<br>6  | I      | 1 1      |

|                                    |                    | +                  | _        |                  | -      |              | -          | +        | †        | _                       | _           | _             | 7       |        | <u> </u> |

| Switching Times (50 Ω Load)        |                    |                    |          |                  |        |              |            |          |          | Pulse In                | Pulse Out   |               |         | -3.2 V | +2.0 V   |

| Propagation Delay                  | t4+3-              | 3                  | -        | 1.8              | -      | 1.7          | -          | 1.9      | ns       | 4                       | 3           | 1 - 1         | -       | 8      | 1,16     |

|                                    | 14-2-              | 2 2                | _        | 1.8              |        | 1.7          | _          | 1.9      | 11       |                         | 2 2         | 1 - 1         | -       |        |          |

|                                    | 14+2+<br>14-3+     | 3                  | -        | 1.6              | =      | 1.5          | ] -        | 1.7      | +        | †                       | 3           | - 1           | -       |        |          |

| Rise Time                          | 13+                | 3                  | -        | 2.2              | -      | 2.1          | -          | 2.3      | ns       | 4                       | 3           | -             |         | 8      | 1,16     |

|                                    | 12+                | 2                  | -        | 2.2              | -      | 2.1          |            | 2.3      | ns       | 4                       | 2           |               | -       | 8      | 1,16     |

| Fall Time                          | t3-                | 3                  |          | -2.2             | -      | 2.1          | -          | 2.3      | ns       | 4                       | 3           | -             | -       | 8      | 1,16     |

|                                    | 12-                | 1 2                | -        | 2.2              | -      | 2.1          |            | 2.3      | ns '     | 14                      | 2           | - 1           | -       | 8      | 1,16     |

vidually test each input applying VIH or VIL to the input under test.

• NOTES

The electrical specifications shown above apply to the SP1660 under the following conditions:

1. The package is housed in a suitable heat sink.†

- Air is blown transversely over the package. See general information section for more details.

TA suitable heat sink is an IERC LICZIAAZWCs or equivalent

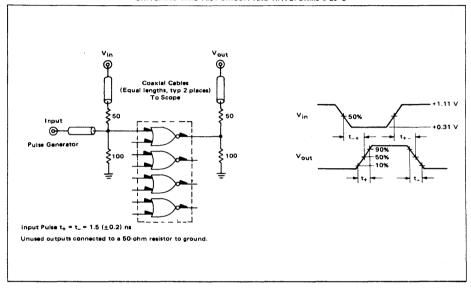

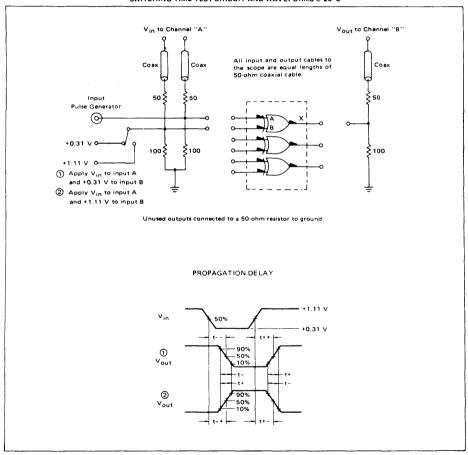

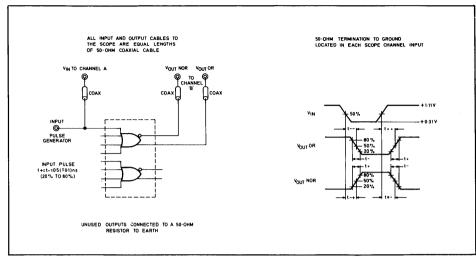

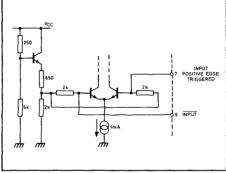

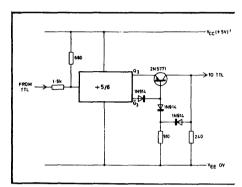

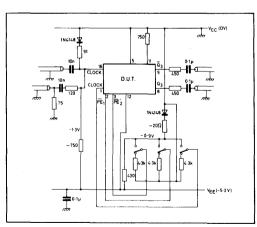

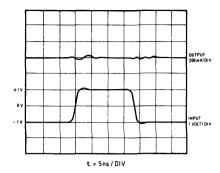

### SWITCHING TIME TEST CIRCUIT AND WAVEFORMS @ 25°C

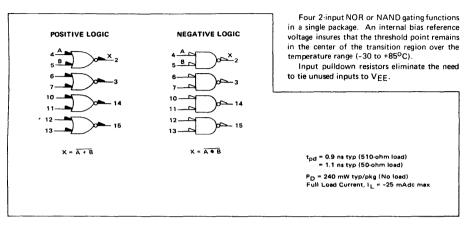

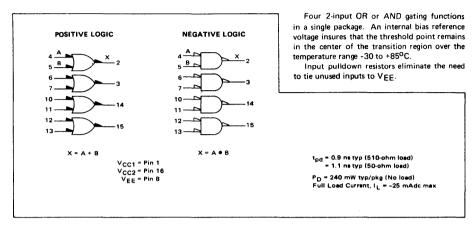

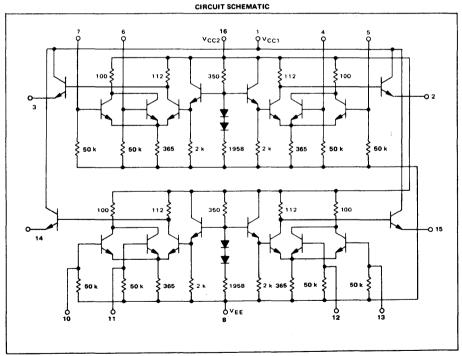

# SP1662

This PECL III circuit has been designed to meet the dc specifications shown in the test table, after thermal equilibrium has been established. The package should be housed in a suitable heat sink(IERC-21 4 A2WCB or equivalent) or a transverse air flow greater than 500 linear fpm should be maintained while the circuit is either in a test socket or is mounted on a printed circuit board. Test procedures are shown for only one input and one output. The other inputs and outputs are tested in a similar manner. Outputs are tested with a 50-ohm resistor to -2.0 Vdc. See general information section for complete thermal data.

CERAMIC PACKAGE E

|                       |                     | TEST    | VOLTAGE VAL | UES      |      |

|-----------------------|---------------------|---------|-------------|----------|------|

|                       |                     |         | (Valts)     |          |      |

| @ Test<br>Temperature | V <sub>IH max</sub> | VIL min | VIHA min    | VILA max | VEE  |

| -30°C                 | -0.875              | -1.890  | -1.180      | -1.515   | -5.2 |

| +25°C                 | -0.810              | -1.850  | -1.095      | -1.485   | -5.2 |

| +85°C                 | -0.700              | -1.830  | -1.025      | -1.440   | -5.2 |

| ·                              |                   | Pin    |                  |                  | SP1662           | Test Limits      |                  |                  |            | TEST VOLTAGE APPLIED TO PINS LISTED BELOW: |            |               |               |        | i            |

|--------------------------------|-------------------|--------|------------------|------------------|------------------|------------------|------------------|------------------|------------|--------------------------------------------|------------|---------------|---------------|--------|--------------|

|                                |                   | Under  | -30              | PC               | +2               | 5°C              | +8               | 5°C              |            | 1231                                       | VOLINGE AF | PERED TO PING | LISTED BELOW  | '.     | i            |

| Characteristic                 | Symbol            | Test   | Min              | Max              | Min              | Max              | Min              | Max              | Unit       | VIH max                                    | VIL min    | VIHA min      | VILA max      | VEE    | Gnd          |

| Power Supply Drain Current     | 1E                | 8      | -                |                  | -                | 56               | -                | _                | mAdc       | _                                          | -          | -             | _             | 8      | 1,16         |

| Input Current                  | <sup>1</sup> in H |        | -                | _                | -                | 350              | -                | -                | μAdc       | •                                          |            | -             | _             | 8      | 1,16         |

|                                | lin L             | •      | -                | -                | 0.5              | -                | -                | -                | μAdc       | -                                          | •          | -             | _             | 8      | 1,16         |

| Logic "1"<br>Output Voltage    | Voн               | 2      | -1.045<br>-1.045 | -0.875<br>-0.875 | -0.960<br>-0.960 | -0.810<br>-0.810 | -0.890<br>-0.890 | ~0.700<br>~0.700 | Vdc<br>Vdc | -                                          | 4 5        | -             | =             | 8      | 1,16<br>1,16 |

| Logic "0" Output Voltage       | VOL               | 2 2    | -1.890<br>-1.890 | -1.650<br>-1.650 | -1.850<br>-1.850 | -1.620<br>-1.620 | -1.830<br>-1.830 | -1.575<br>-1.575 | Vdc<br>Vdc | 4 5                                        | =          | =             | =             | 8 8    | 1,16<br>1,16 |

| Logic "1" Threshold Voltage    | VOHA              | 2 2    | -1.065<br>-1.065 | =                | -0.980<br>-0.980 | -                | -0.910<br>-0.910 | -                | Vdc<br>Vdc | -                                          | -          | =             | <b>4</b><br>5 | 8 8    | 1,16<br>1,16 |

| Logic "0"<br>Threshold Voltage | VOLA              | 2 2    | =                | -1.630<br>-1.630 | -                | -1.600<br>-1.600 | -                | -1.555<br>-1.555 | Vdc<br>Vdc | -                                          | -          | 4<br>5        | -             | 8 8    | 1,16<br>1,16 |

| Switching Times (50 Ω Load)    |                   |        |                  |                  |                  |                  |                  |                  |            | Pulse in                                   | Pulse Out  |               |               | -3.2 V | +2.0 V       |

| Propagation Delay              | t4+2+<br>t4-2-    | 2<br>2 |                  | 1.6<br>1.8       | 1.0<br>1.1       | 1.5<br>1.7       |                  | 1.7<br>1.9       | ns<br>ns   | 4                                          | 2 2        | -             | -             | 8      | 1,16<br>1,16 |

| Rise Time                      | 12+               | 2      | -                | 2.2              | 1.4              | 2.1              |                  | 2.3              | ns         | 4                                          | 2          | -             | -             | 8      | 1,16         |

| Fall Time                      | 12-               | 2      | -                | 2.2              | 1.2              | 2.1              | -                | 2.3              | ns         | 4                                          | 2          | - 1           |               | 8      | 1,16         |

<sup>\*</sup>Individually test each input applying VIH or VIL to input under test.

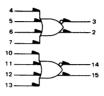

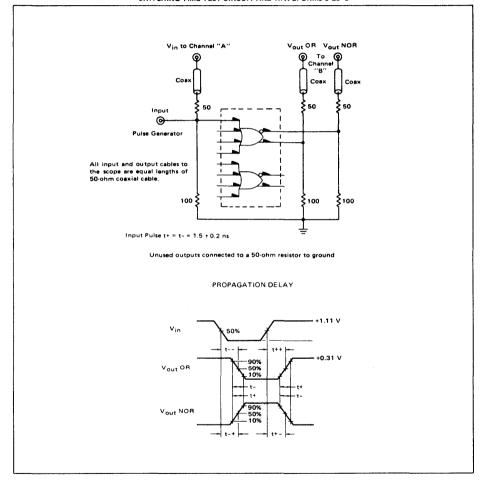

### SWITCHING TIME TEST CIRCUIT AND WAVEFORMS @ 25°C

# SP1664

This PECL III circuit has been designed to meet the dc specifications shown in the test table, after thermal equilibrium has been established. The package should be housed in a suitable heat sink(IERC-21 4 A2WCB or equivalent) or a transverse air flow greater than 500 linear fpm should be maintained while the circuit is either in a test socket or is mounted on a printed circuit board. Test procedures are shown for only one input and one output. The other inputs and outputs are tested in a similar manner. Outputs are tested with a 50-ohm resistor to -2.0 Vdc. See general information section for complete thermal deta.

CERAMIC PACKAGE E

| [                     |         | TEST    | VOLTAGE VAL | .UES     |      |

|-----------------------|---------|---------|-------------|----------|------|

| [                     |         |         | (Volts)     |          |      |

| @ Test<br>Temperature | VIH max | VIL min | VIHA min    | VILA mex | VEE  |

| -30°C                 | -0.875  | -1.890  | -1.180      | -1.515   | -5.2 |

| +25°C                 | ~0.810  | -1.850  | -1.095      | -1.485   | -5.2 |

| +85°C                 | -0.700  | -1.830  | -1.026      | -1.440   | -5.2 |

|                                    |                 |              |                  |                  | SP16             | 64 Test Lin      | nits             |                  |            | TEST VOLTAGE APPLIED TO PINS LISTED BELOW: |            |              |              |        |              |

|------------------------------------|-----------------|--------------|------------------|------------------|------------------|------------------|------------------|------------------|------------|--------------------------------------------|------------|--------------|--------------|--------|--------------|

|                                    | 1               | Pin<br>Under | -30              | °C               | +2               | 5°C              | +85              | 5°C              |            | 1 1 2 3 1                                  | VOLTAGE AF | PLIED IOPINS | LISTED BELOW |        | 1            |

| Characteristic                     | Symbol          | Test         | Min              | Max              | Min              | Max              | Min              | Max              | Unit       | VIH mex                                    | VIL min    | VIHA min     | VILA max     | VEE    | Gnel         |

| Power Supply Drain Current         | ¹E              | 8            | -                | - "              | -                | 56               |                  | -                | mAdc       | -                                          | _          | -            |              | 8      | 1,16         |

| Input Current                      | lin H           | •            | T -              | _                | -                | 350              | -                | -                | μAdc       | •                                          |            | -            | _            | 8      | 1,16         |

|                                    | lin L           | •            | T -              | -                | 0.5              | -                | -                | -                | μAdc       | _                                          | •          | -            | _            | 8      | 1,16         |

| Logic "1"<br>Output Voltage        | ∨он             | 2 2          | -1.045<br>-1.045 | -0.875<br>-0.875 | -0.960<br>-0.960 | -0.810<br>-0.810 | -0.890<br>-0.890 | -0.700<br>-0.700 | Vdc<br>Vdc | 4<br>5                                     | -          | -            | _            | 8      | 1,16<br>1,16 |

| Logic "0"<br>Output Voltage        | VOL             | 2 2          | -1.890<br>-1.890 | -1.650<br>-1.650 | -1.850<br>-1.850 | -1.620<br>-1.620 | -1.830<br>-1.830 | -1.575<br>-1.575 | Vdc<br>Vdc | -                                          | 4<br>5     | -            | = -          | 8      | 1,16<br>1,16 |

| Logic "1" Threshold Voltage        | VOHA            | 2 2          | -1.065<br>-1.065 | -                | -0.980<br>-0.980 | =                | -0.910<br>-0.910 | =                | Vdc<br>Vdc | -                                          | -          | 4<br>5       | =            | 8      | 1,16<br>1,16 |

| Logic "0" Threshold Voltage        | VOLA            | 2 2          | -                | -1.630<br>-1.630 | -                | -1.600<br>-1.600 | -                | -1.555<br>-1.555 | Vdc<br>Vdc | -                                          | <u>-</u> , | -            | 4 5          | 8      | 1,16<br>1,16 |

| Switching Times (50 $\Omega$ Load) |                 |              |                  |                  |                  |                  |                  |                  |            | Pulse In                                   | Pulse Out  |              |              | -3.2 V | +2.0 V       |

| Propagation Delay                  | 14+2+<br>14-2-  | 2 2          | -                | 1.6<br>1.8       | -                | 1.5              | -                | 1.7<br>1.9       | ns<br>ns   | 4 4                                        | 2 2        | _            | =            | 8      | 1,16<br>1,16 |

| Rise Time                          | t <sub>2+</sub> | 2            | -                | 2.2              |                  | 2.1              | -                | 2.3              | ns         | 4                                          | 2          | -            | -            | 8      | 1,16         |

| Fall Time                          | 12-             | 2            | -                | 2.2              |                  | 2.1              |                  | 2.3              | ns         | 4                                          | 2          |              |              | 8      | 1,16         |

<sup>\*</sup>Individually test each input applying VIH or VIL to input under test.

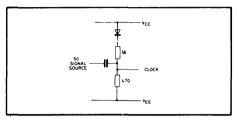

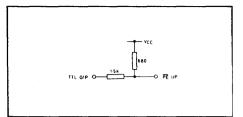

# V<sub>In</sub> to Channel "A" Vout to Channel "B" Coax Coax Coax Vin Fulse Generator All input and output cables to the scope are equal lengths of 50-ohm coaxial cable. Unused outputs connected to a 50-ohm resistor to ground.

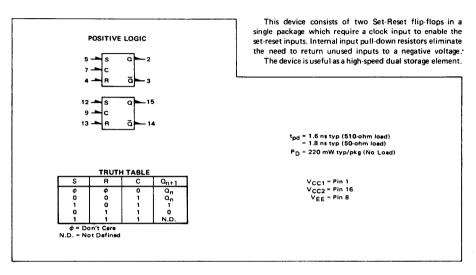

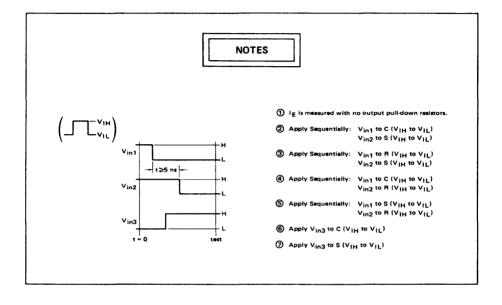

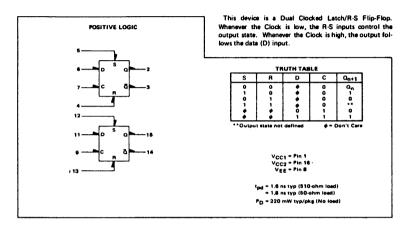

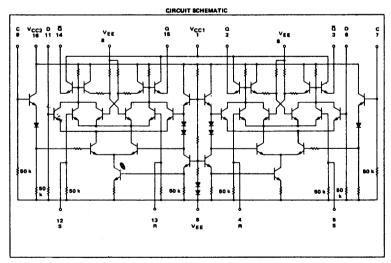

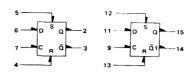

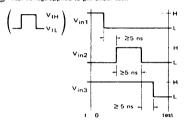

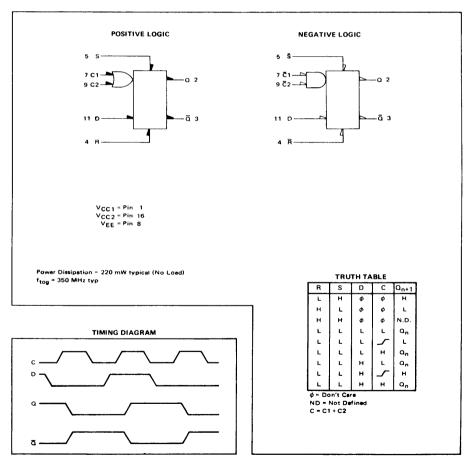

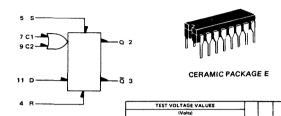

### **DUAL CLOCKED R-S FLIP-FLOP**

# SP1666

# C V<sub>CC2</sub> s ā Q R V<sub>CC1</sub> R Q ā s c 9 16 12 14 VEE 15 13 1 4 2 VEE 3 5 7 50 k Numbers at ends of terminals denote pin numbers for L package (Case 620). Numbers in parenthesis denote pin numbers for F package (Case 620).

This PECL III circuit has been designed to meet the dc apscifications shown in the test table, after thermal equilibrium has been established. The package should be housed in a suitable heat sinkIERC21 4A2WCBor equivalent) or a transverse air flow greater than 500 linear fpm should be maintained while the circuit is either in a test socket or is mounted on a printed circuit board. Test procedures are shown for only one input and one output. The other inputs and outputs are tested in a similar menner. Outputs are tested with a 50-ohm resistor to -2.0 Vdc. See general information section for complete thermal data.

@ Test

Temperature

TEST VOLTAGE VALUES

(Volts)

VIHMAX VILMIN VIHAMIN VILAMAX

CERAMIC PACKAGE E

| 0-ohm resistor to -2.0 Vdc.               |                    |              |                  |                  |                                 |                  |                  |                  | -30°C        | -0 875   | -1 890    | -1.180   | -1 515       | -5.2   | 1      |

|-------------------------------------------|--------------------|--------------|------------------|------------------|---------------------------------|------------------|------------------|------------------|--------------|----------|-----------|----------|--------------|--------|--------|

| formation section for comp<br>its.        | Hete therm         | 181          |                  |                  |                                 |                  |                  |                  | +25°C        | -0.810   | -1 850    | -1 095   | -1 485       | -52    | į      |

| ite.                                      |                    |              |                  |                  |                                 |                  |                  |                  | +85°C        | -0 700   | -1 830    | -1 025   | 1.440        | -5.2   | l      |

|                                           |                    | Pin          |                  |                  |                                 | 66 Test I        | umits            |                  |              | 1        |           |          | PLIED TO     |        | 1      |

|                                           | 1                  | Under        | -30              | °C               | +2                              | 5°C              | +8               | 5                | ]            |          |           | LISTED B |              |        | (Vcc)  |

| Characteristic                            | Symbol             | Test         | Min              | Max              | Min                             | Max              | Min              | Max              | Unit         | VIHmax   | VILmin    | VIHAmin  | VILAmax      | VEE    | Gnd    |