# '94 Data Book for VOICE SYNTHESIS LSI

## OKI VOICE SYNTHESIS LSI DATA BOOK 1994

INTRODUCTION

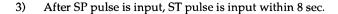

DATA SHEETS

## CONTENTS

### INTRODUCTION

| 1. | VOICE SYNTHESIS LSI PRODUCTS                           | 3  |

|----|--------------------------------------------------------|----|

| 2. | PRODUCTS AND TYPICAL CHARACTERISTICS                   | 4  |

| 3. | FLOWCHART FOR BUILT-IN ROM VOICE SYNTHESIS DEVELOPMENT | 13 |

| 4. | USER ANALYSIS SUPPORT TOOLS                            | 14 |

| 5. | PACKAGING                                              | 22 |

| 6. | RELIABILITY                                            | 31 |

#### DATA SHEETS

| 1 | VOICE SYNTHESIS                                 |     |

|---|-------------------------------------------------|-----|

|   | MSM5205                                         | 37  |

|   | MSM6585                                         | 49  |

|   | MSM6295                                         | 59  |

|   | MSM6372-XXX/6373-XXX/6374-XXX/6375-XXX          | 75  |

|   | MSM63P74-XX                                     | 119 |

|   | MSM6376                                         | 143 |

|   | MSM6378A/6379                                   | 169 |

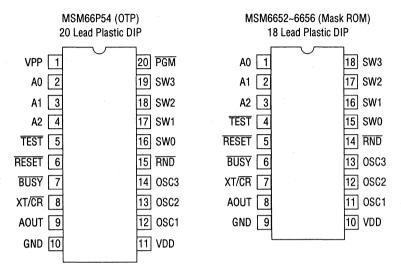

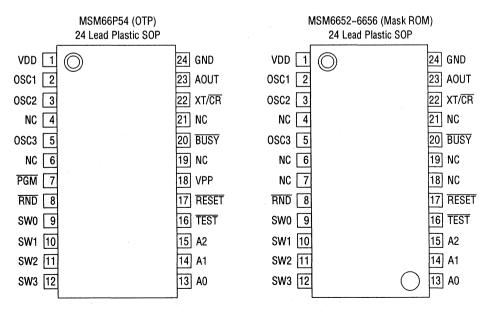

|   | MSM6652-XXX/6653-XXX/6654-XXX/6655-XXX/6656-XXX | 183 |

|   | MSM66P54-XX                                     | 285 |

|   | MSM6650                                         | 309 |

| 2 | VOICE RECORDER                                  |     |

|   | MSM5218                                         | 415 |

|   | MSM6258/MSM6258V                                | 433 |

|   | MSM6310                                         | 491 |

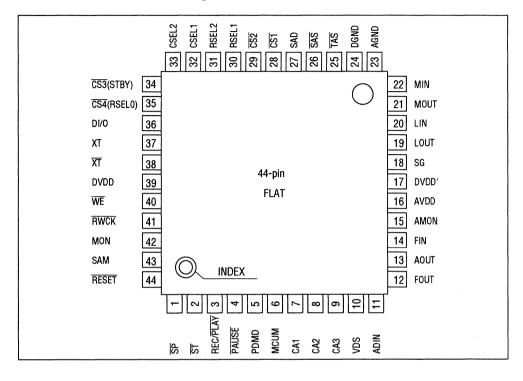

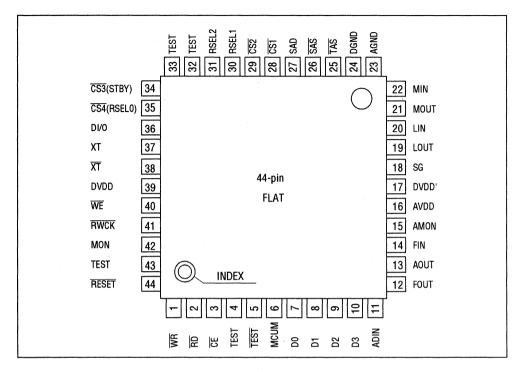

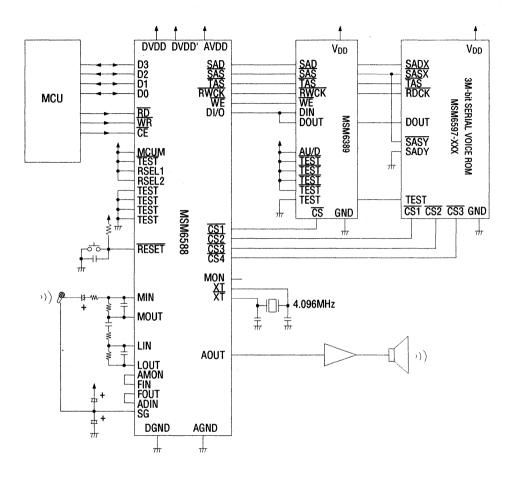

|   | MSM6388                                         | 509 |

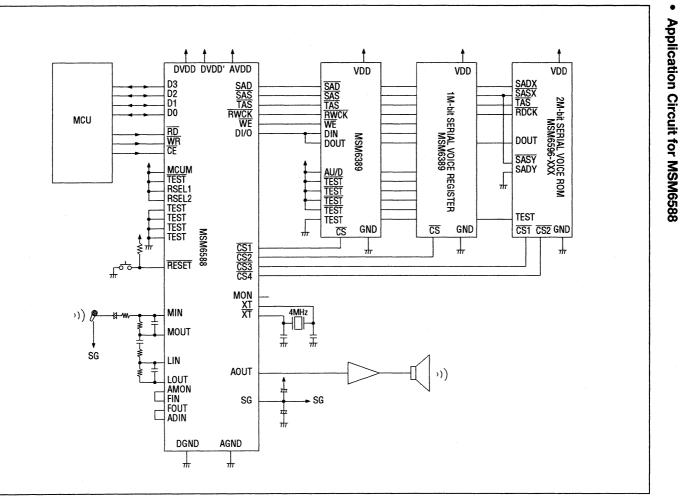

|   | MSM6588                                         | 565 |

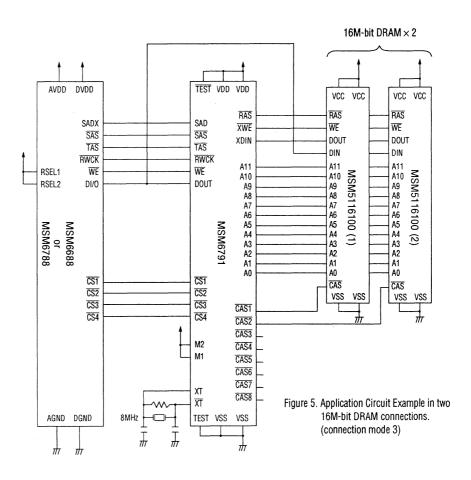

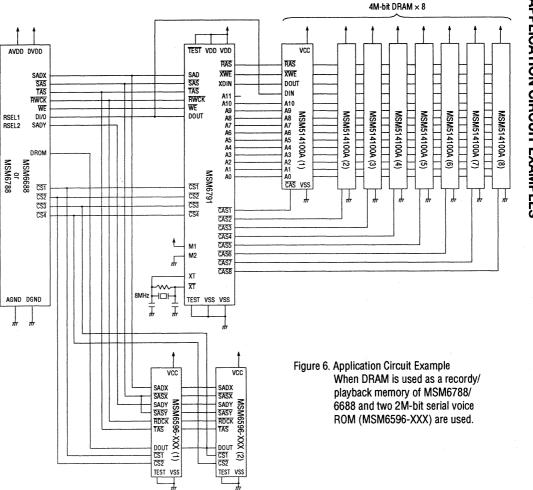

|   | MSM6688                                         | 663 |

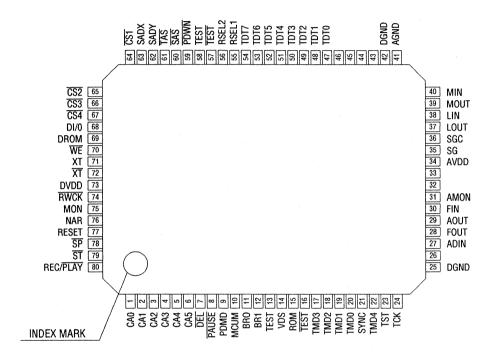

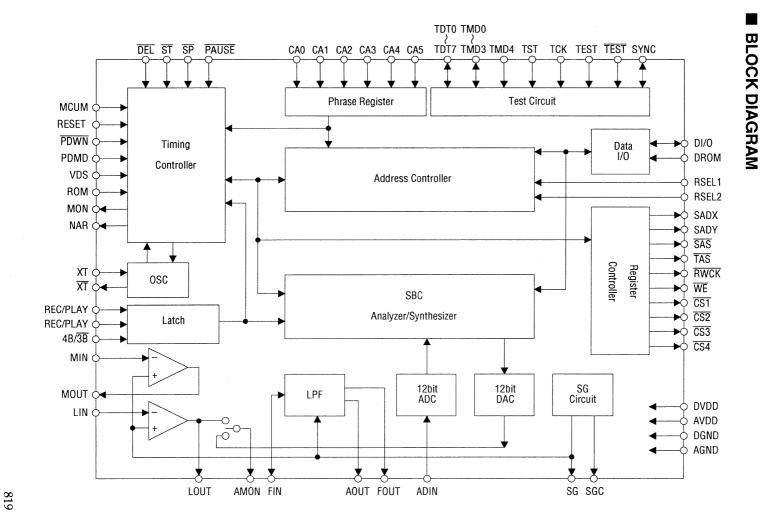

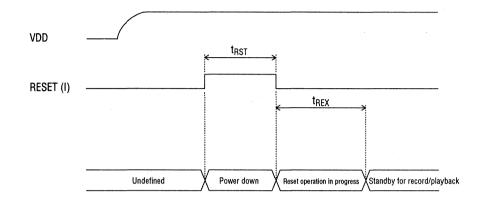

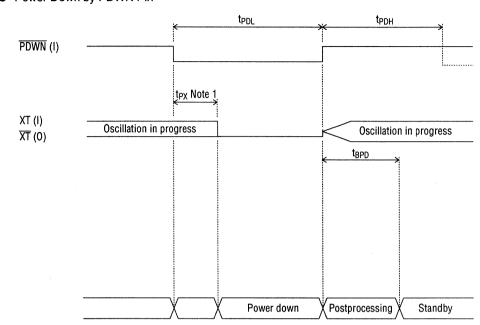

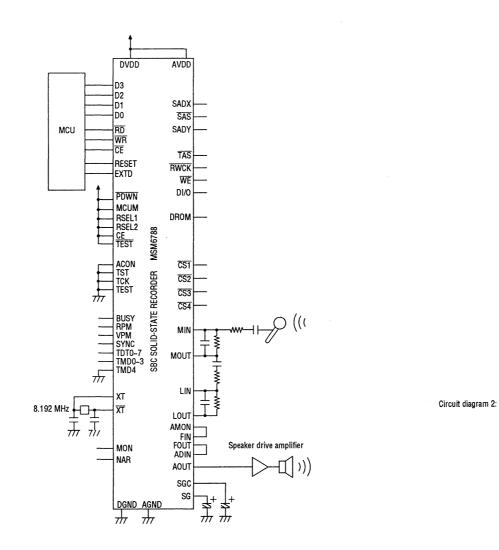

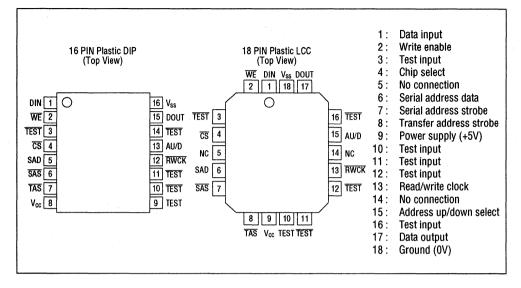

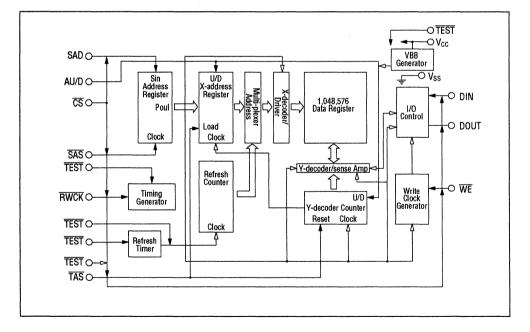

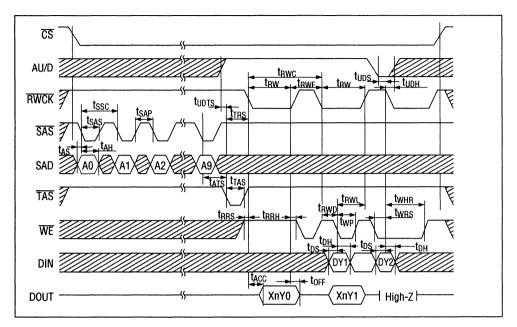

|   | MSM6788                                         | 815 |

| 3 | VOICE REGISTER/ROM                              |     |

|   | MSM6389                                         | 955 |

|   | MSM6587                                         | 961 |

|   | MSM6586                                         | 967 |

|   | MSM6595-XXX                                     | 973 |

|   | MSM6596-XXX                                     | 981 |

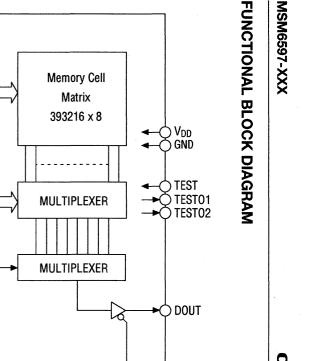

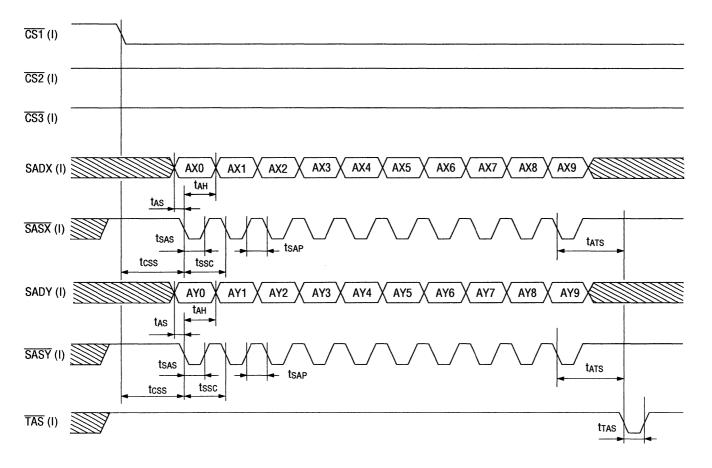

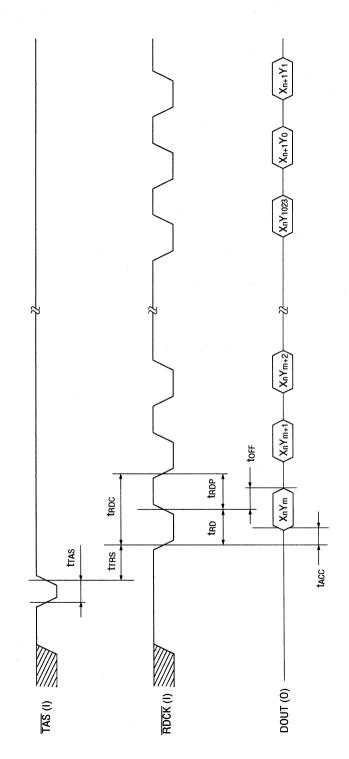

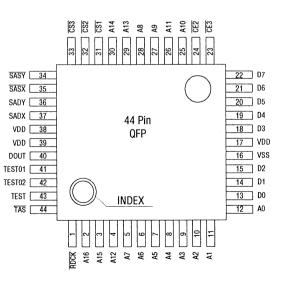

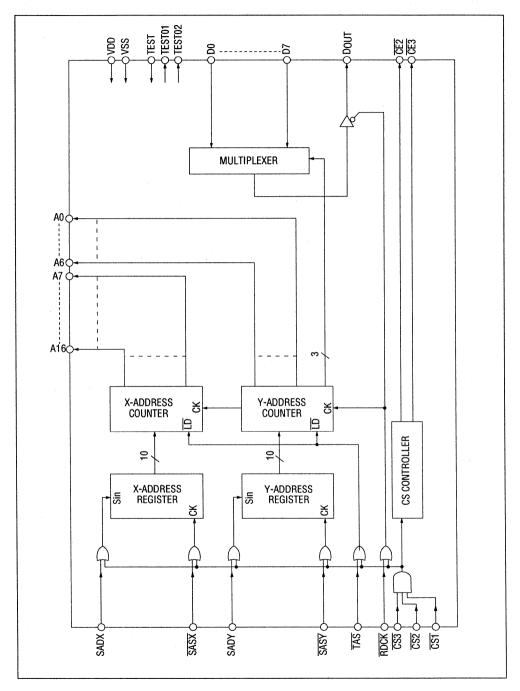

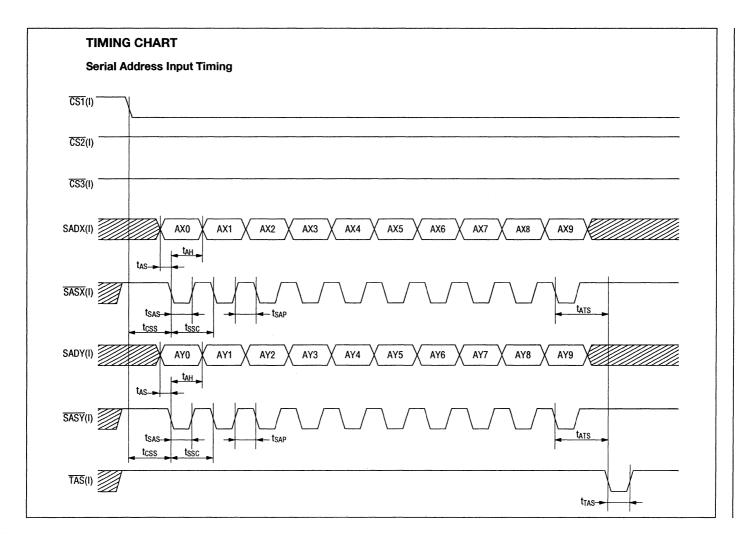

| MSM6597-XXX         |         |

|---------------------|---------|

| INTERFACE LSI       |         |

| MSM6690             |         |

| MSM6691             |         |

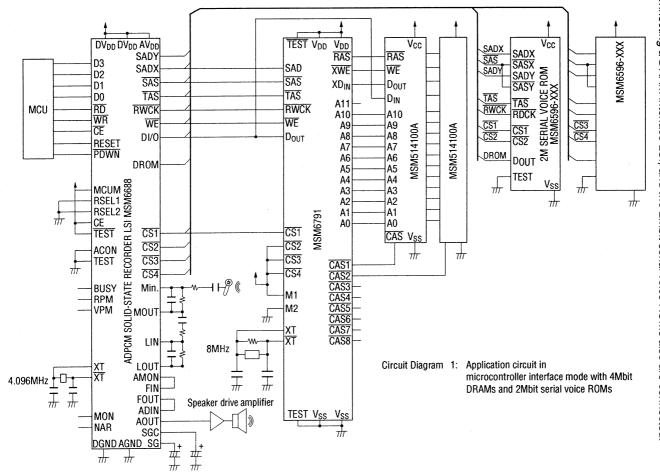

| MSM6791             |         |

| PITCH CONTROL       |         |

| MSM6322             |         |

| MSM6722             |         |

| SPEAKER AMPLIFIER   |         |

| MSC1191/1192        |         |

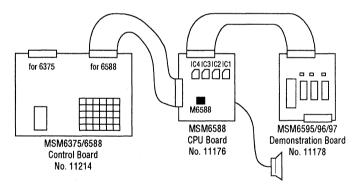

| DEMONSTRATION BOARD |         |

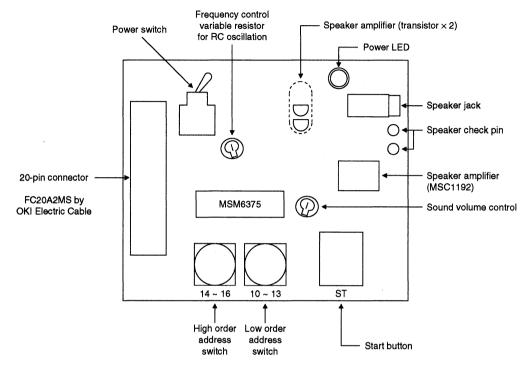

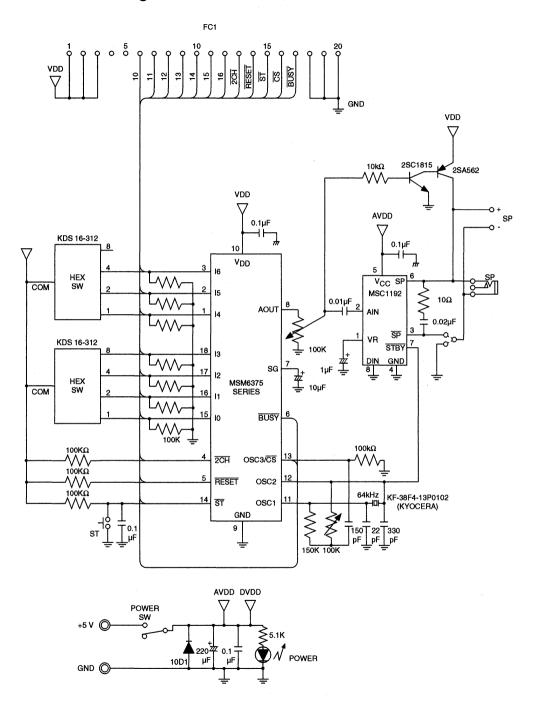

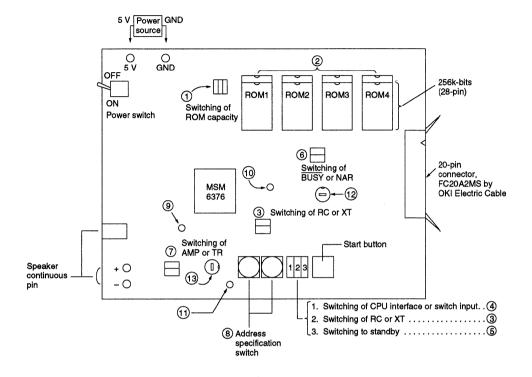

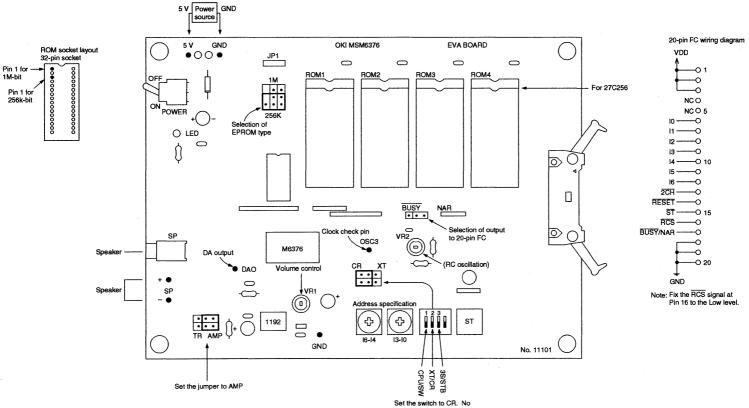

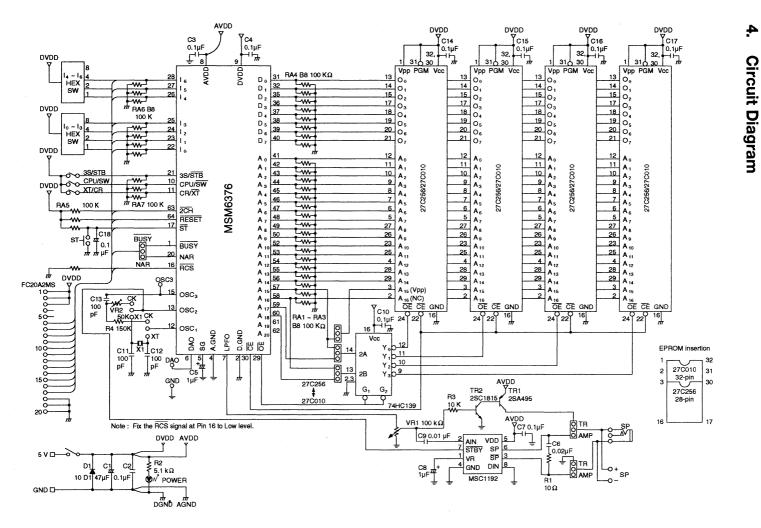

| MSM6375             |         |

| MSM6376             |         |

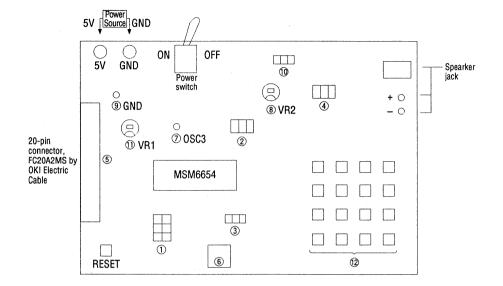

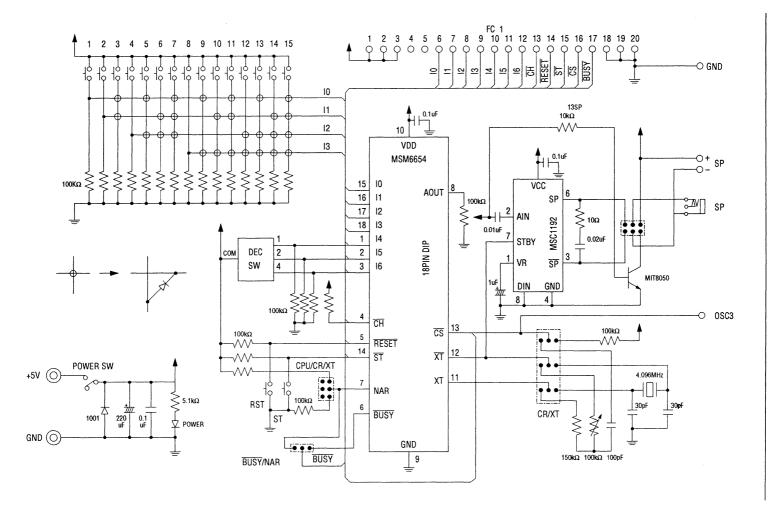

| MSM6654             |         |

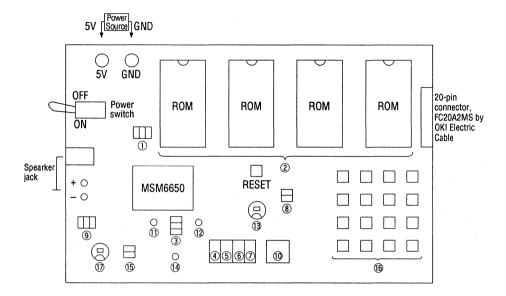

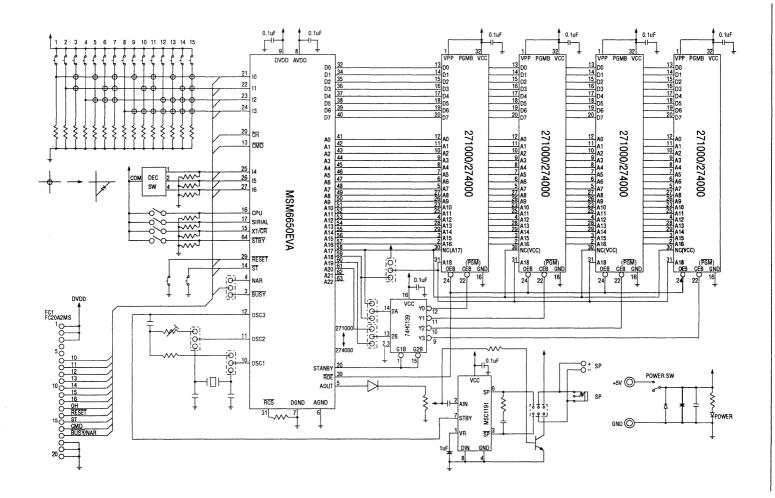

| MSM6650             |         |

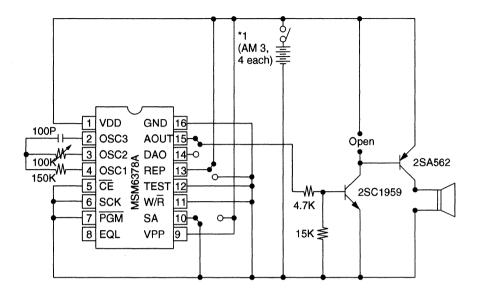

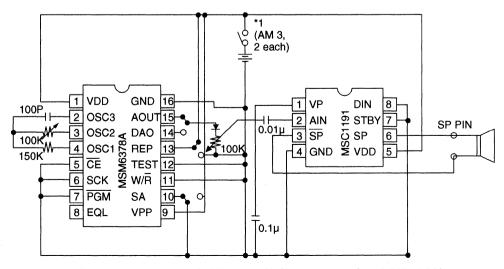

| MSM6378A            |         |

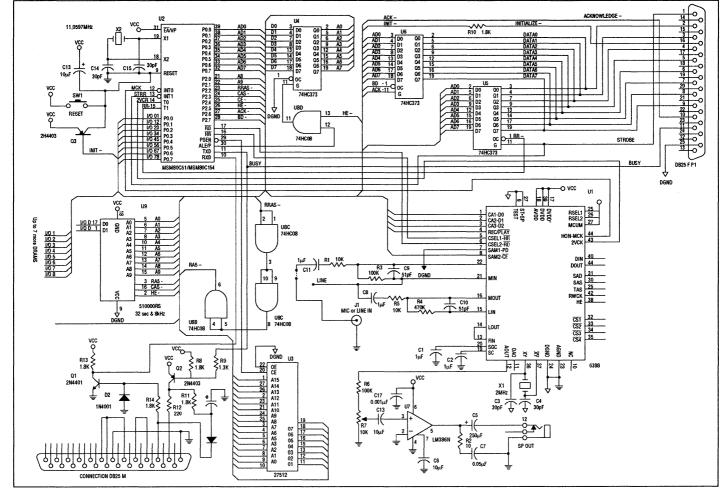

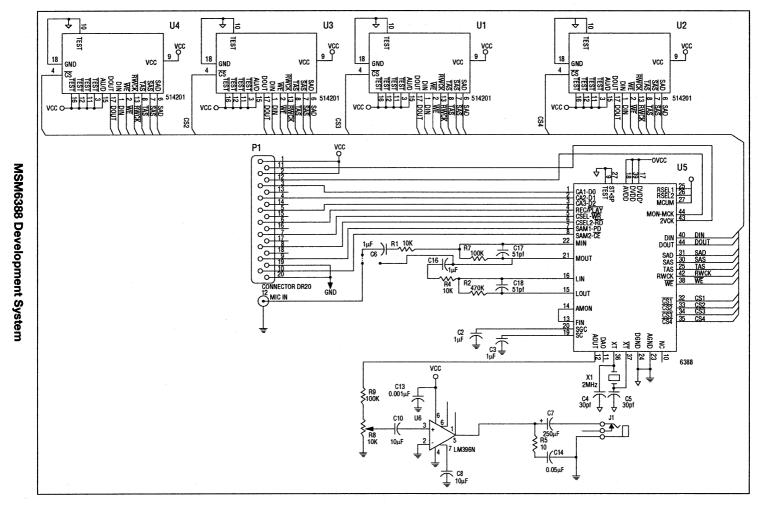

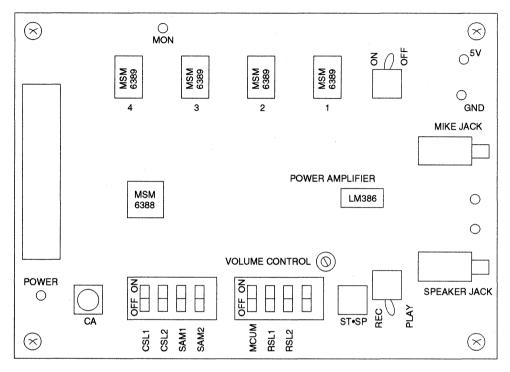

| MSM6388             |         |

| MSM6588             |         |

| MSM6596             |         |

| MSM6322             |         |

|                     | MSM6690 |

## INTRODUCTION -----

## **1. VOICE SYNTHESIS LSI PRODUCTS**

### **OKI SPEECH LSI PRODUCTS**

| SYNTHESI                           | ZER                        | г                             |                                     |            |                            |                                                |

|------------------------------------|----------------------------|-------------------------------|-------------------------------------|------------|----------------------------|------------------------------------------------|

| Internal Mask-RON<br>-MSM6375 FAMI |                            | 256Kbit                       | nternal Mask-RC<br>-MSM6650 FAN     |            | 3653 5<br>3654 1<br>3655 1 | 88Kbit<br>44Kbit<br>.0Mbit<br>.5Mbit<br>.0Mbit |

| Internal OTP                       | MSM63F<br>MSM66F<br>MSM637 | • •                           | 6375 Fa<br>6650 Fa<br>378A for Void | mily       |                            |                                                |

| External ROM                       | İ                          | VSM6376<br>VSM6650<br>VSM6295 |                                     |            |                            |                                                |

| Prototype                          | •                          | ASM5205<br>ASM6585            |                                     |            |                            |                                                |

|                                    |                            |                               |                                     |            |                            |                                                |

| <b>·RECORDE</b>                    |                            |                               |                                     |            |                            |                                                |

| Special memory T                   |                            | ASM6388                       |                                     | it ADPCM   |                            |                                                |

|                                    |                            | ASM6588                       | •••                                 | 4bit ADPCN | •                          |                                                |

|                                    |                            | ASM6688                       | 3 or 4                              | 4bit ADPCN | 1                          |                                                |

|                                    |                            | ASM6788                       |                                     | SBC        |                            |                                                |

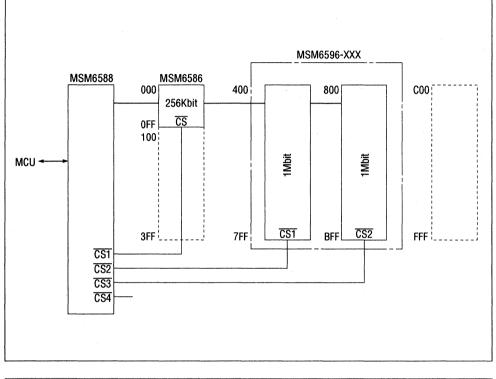

| Spe                                | Serial Memory fo           |                               | 88, MSM6588,<br>MSM6586             |            | , MSM6<br>256Kbit          |                                                |

|                                    | Serial Voice R             | egister                       | MSM6587                             |            | 512Kbit                    |                                                |

|                                    |                            |                               | MSM6389                             |            | 1Mbit                      |                                                |

|                                    |                            |                               | MSM6684                             |            | 4Mbit                      |                                                |

|                                    |                            |                               | MSM6685                             |            | 8Mbit                      |                                                |

|                                    | Serial Voice R             | MC                            | MSM6595                             |            | 1 Mbi                      |                                                |

|                                    |                            |                               | MSM6596                             |            | 2Mbi                       | :                                              |

|                                    |                            |                               | MSM6597                             |            | 3Mbi                       |                                                |

| Standard memory                    |                            | ASM6258<br>ASM6310            |                                     |            |                            |                                                |

| Prototype                          | Ν                          | /SM5218                       |                                     |            |                            |                                                |

| ·                                  |                            |                               |                                     |            |                            |                                                |

**•PITCH CONTROL** MSM6322

MSM6722

·SPEAKER AMP

MSC1191 MSC1192

| nalysis/Editing Tool   | AR761<br>AR76-202                      | Working on PC9801 Japanese<br>Working on IBM-PC English |

|------------------------|----------------------------------------|---------------------------------------------------------|

| upport Tool for M6378A | Anawriter<br>Buckup Unit<br>Parawriter |                                                         |

## 2. PRODUCTS AND TYPICAL CHARACTERISTICS

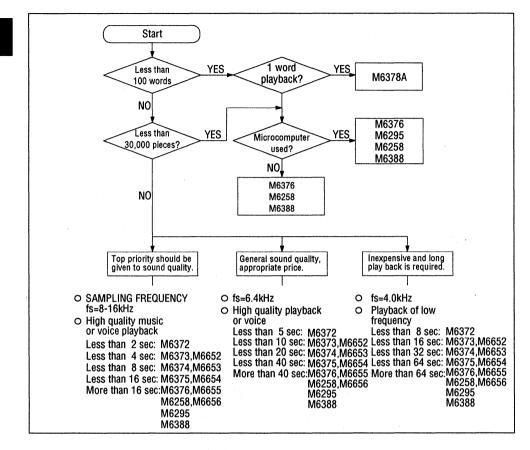

#### 2-1) VOICE SYNTHESIS LSI PRODUCTS (Fixed message type)

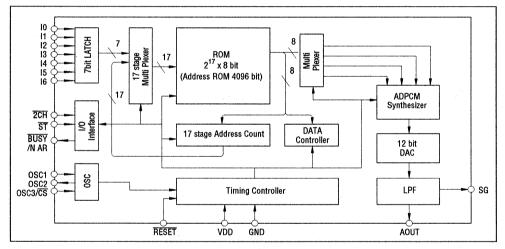

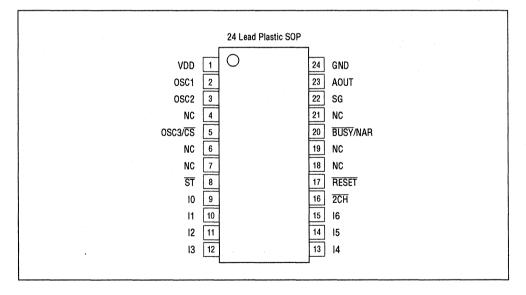

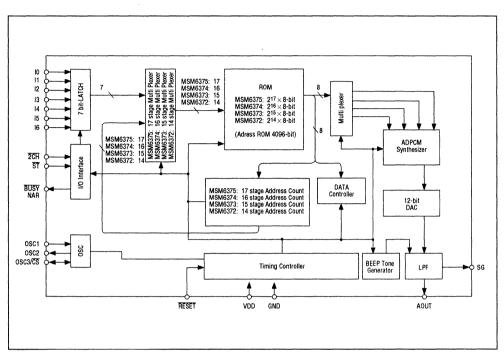

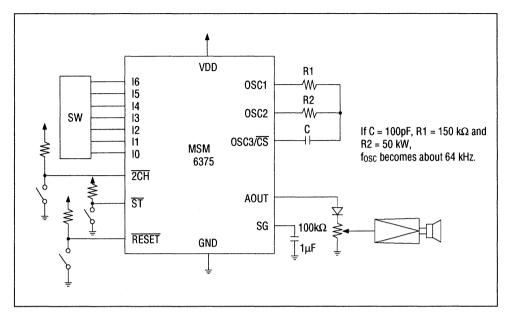

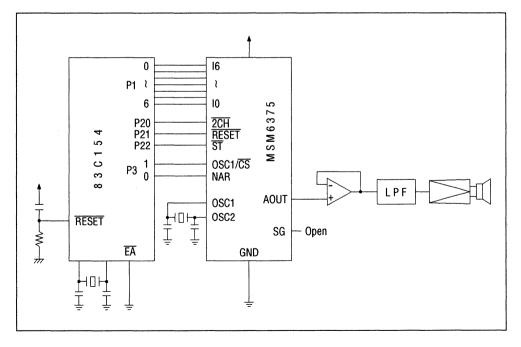

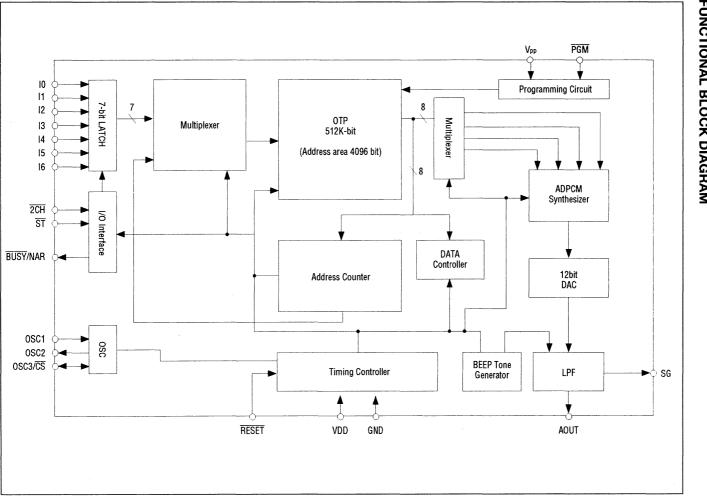

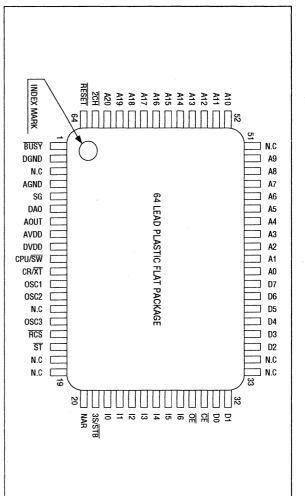

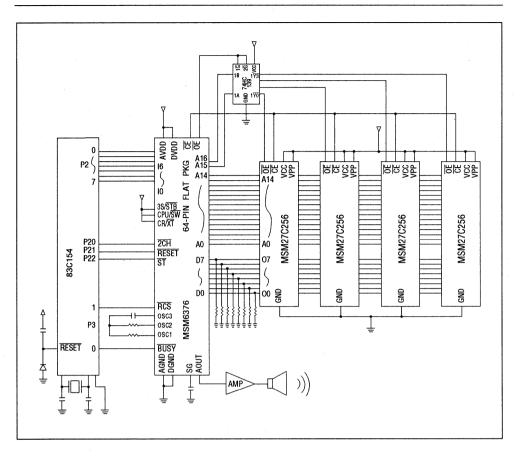

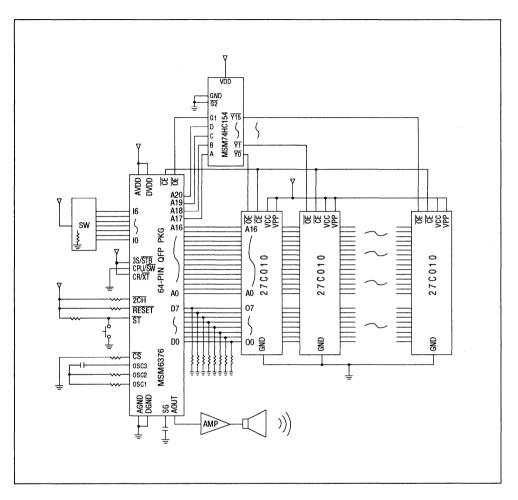

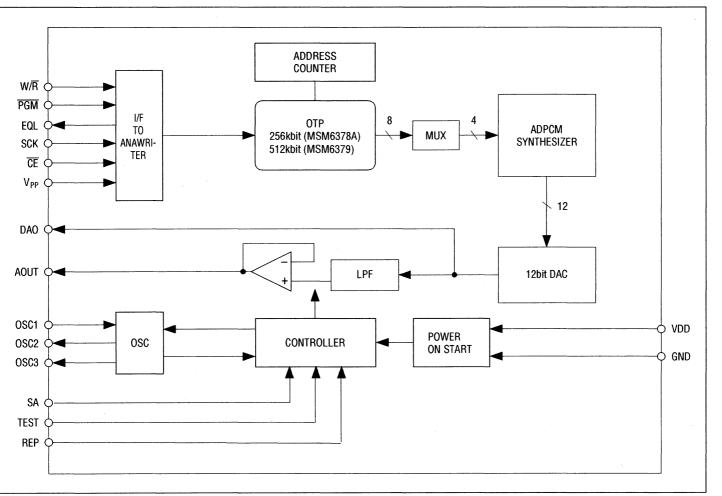

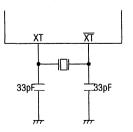

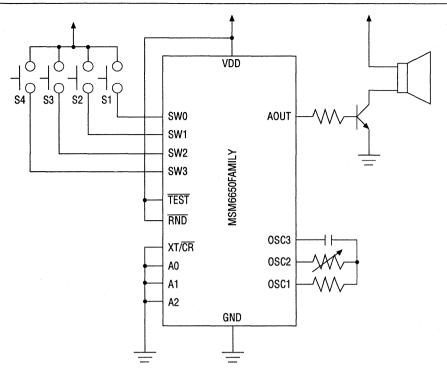

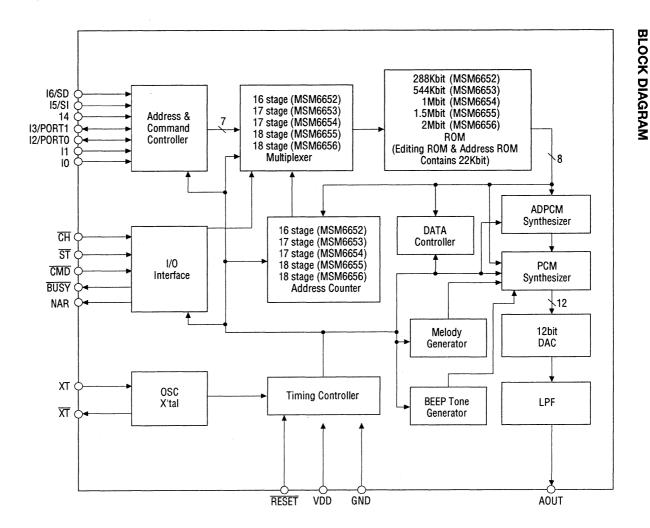

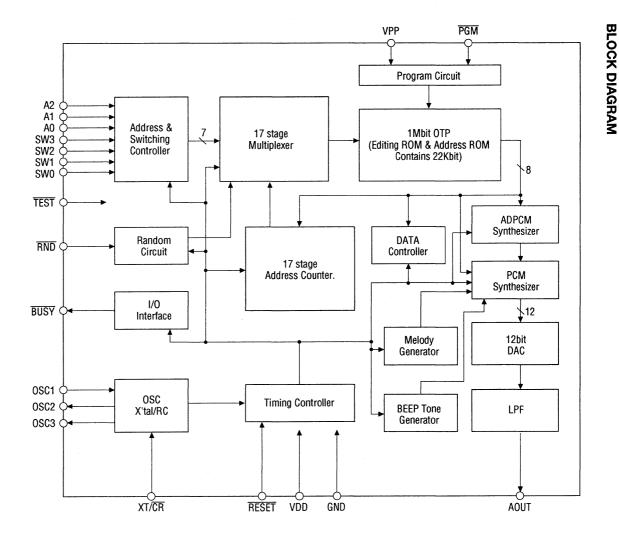

There are various types of voice synthesizer's suitable for a large number of applications, such as: A) Built-in ROM synthesizers tailored for mass production of "fixed messages". B) An OTP(One Time Programmable) device which adds versatility in applications where low volume, multiple messages, and field programmability are needed. C) Voice synthesizers using external memory for extended playback requirements.

Oki's voice synthesizers have many common characteristics, such as the ADPCM method, internal D/A converters, a wide range of sampling rates to choose from, and excellent sound fidelity.

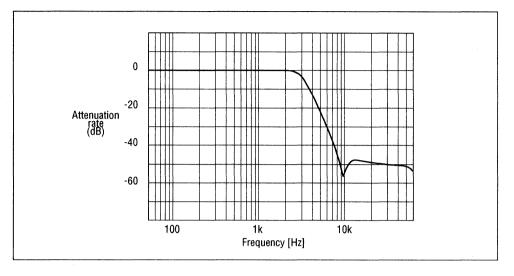

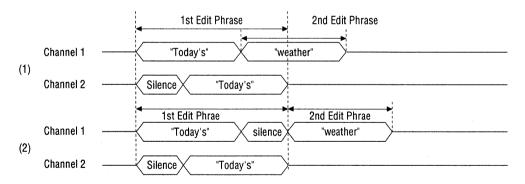

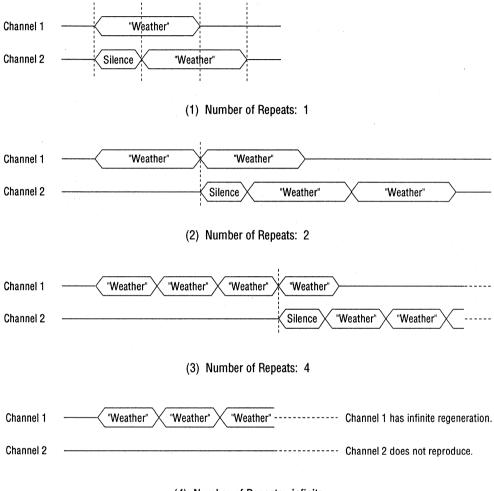

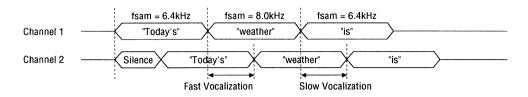

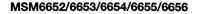

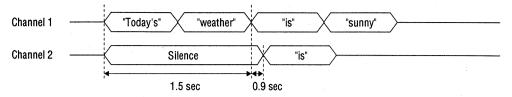

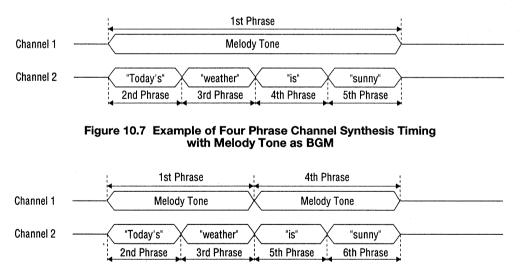

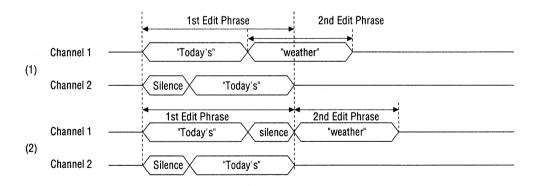

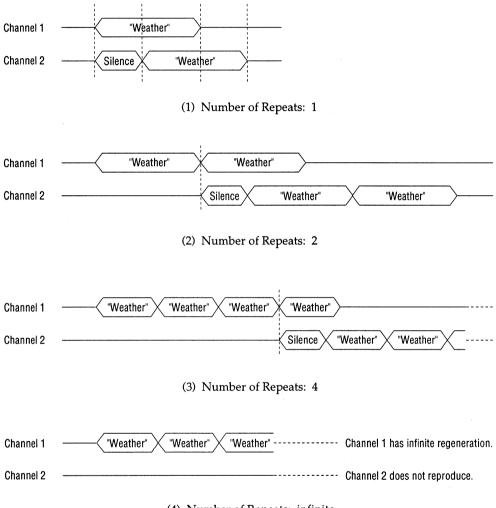

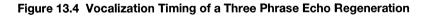

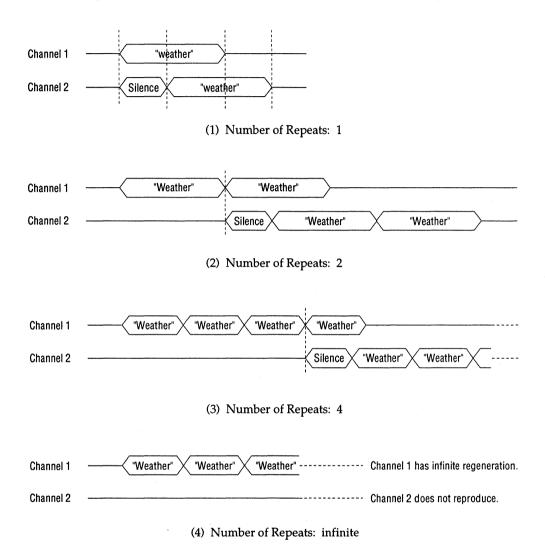

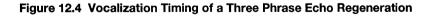

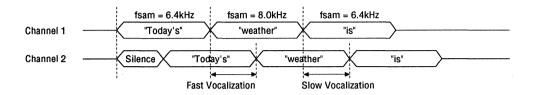

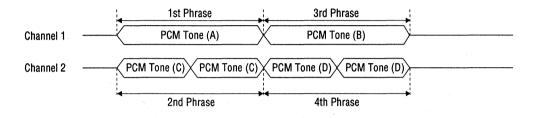

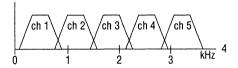

Furthermore, the mask ROM synthesizers contain a LPF (Low Pass Filter), 2-channel mixing capability, echo reproduction, and variable Beep Tone functions.

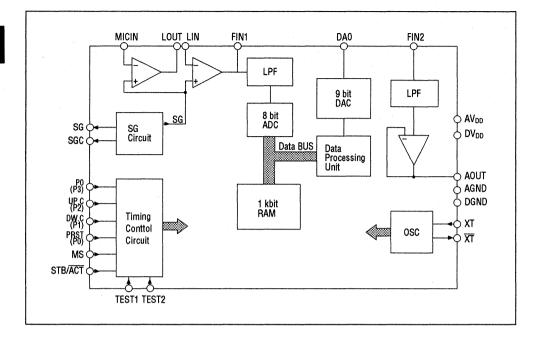

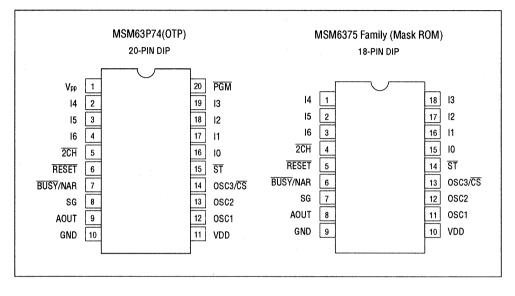

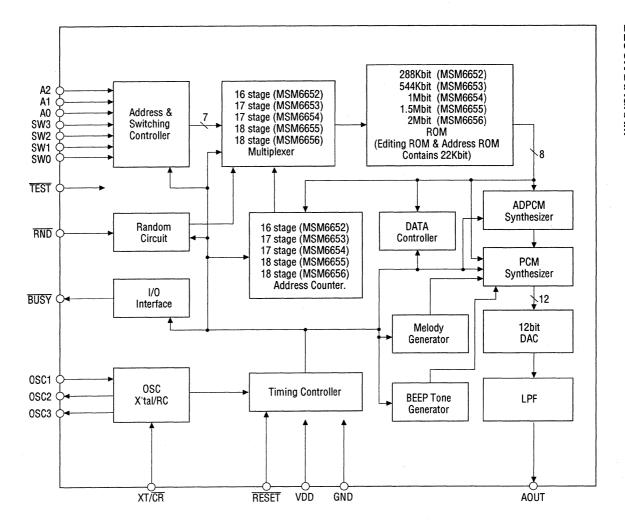

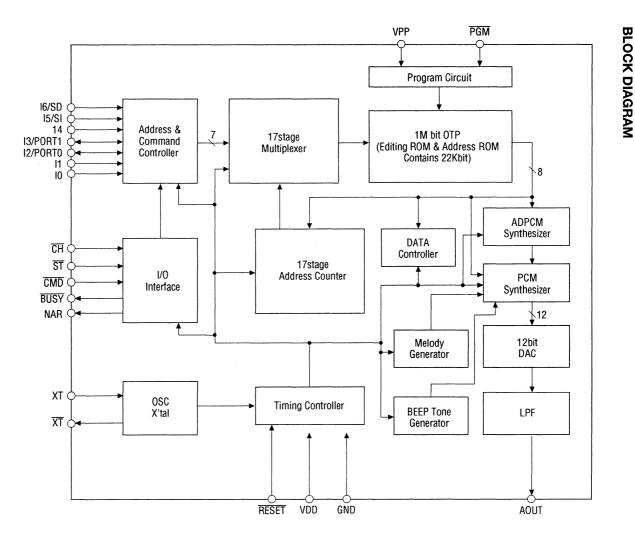

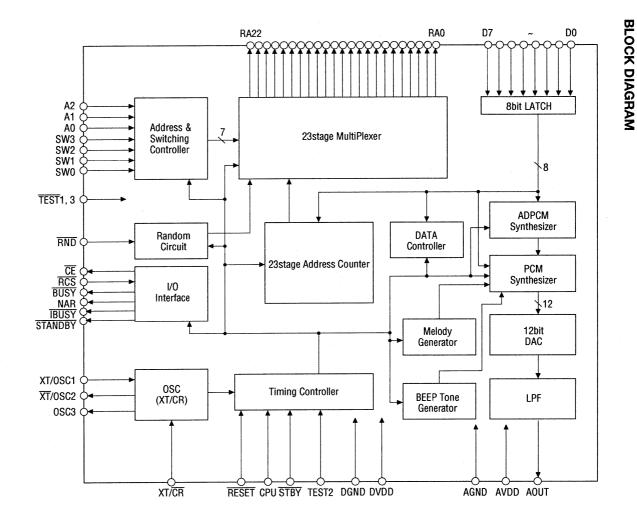

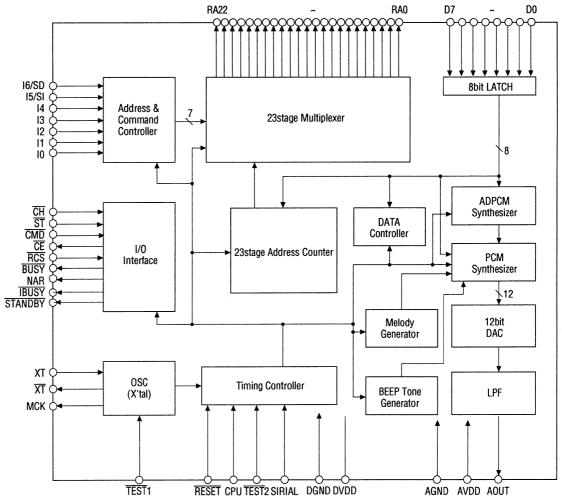

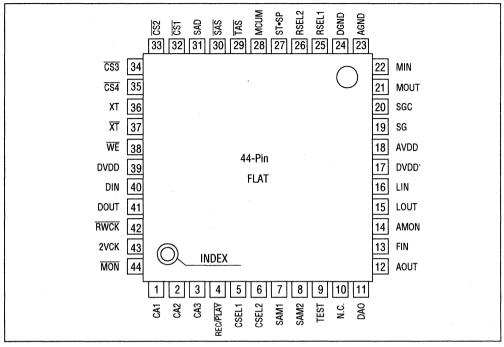

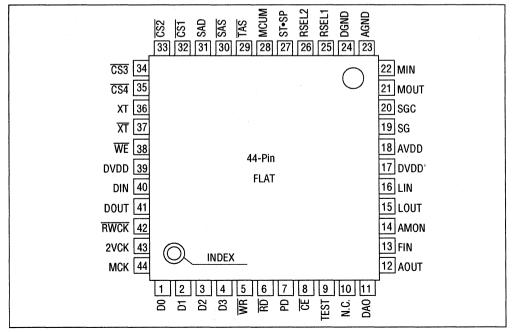

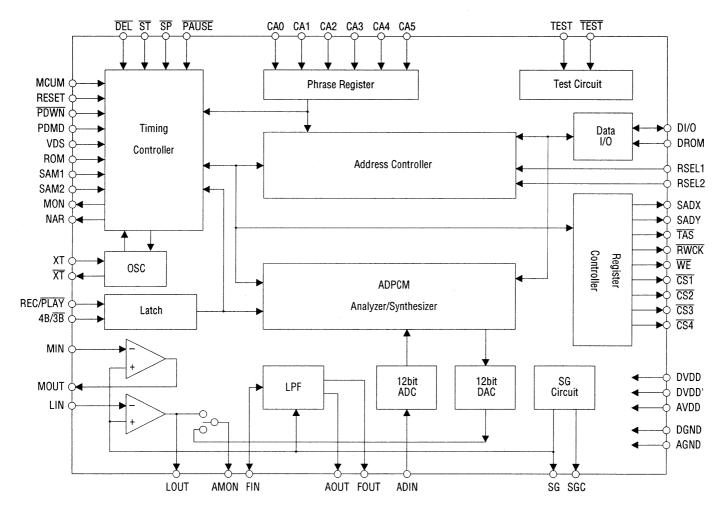

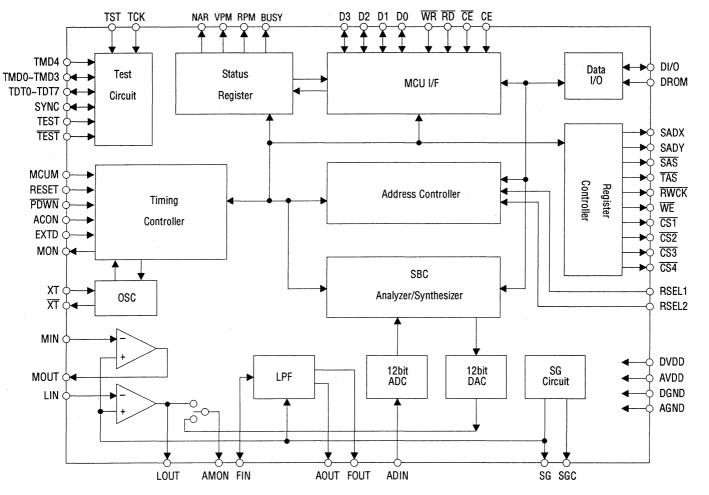

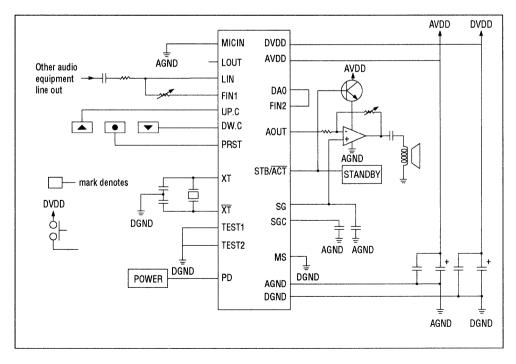

#### MSM6375 Block Diagram

#### **PRODUCT CONFIGURATION**

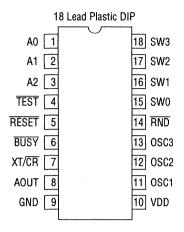

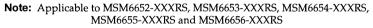

| Product name                             | MSM6372                                                                                      | MSM6373                                           | MSM6374                                           | MSM6375                                            | MSM63P74                                          | MSM6378A                                       | MSM6376                                             | MSM6295                               | MSM5205             | MSM6585                   |

|------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------|---------------------------------------------------|----------------------------------------------------|---------------------------------------------------|------------------------------------------------|-----------------------------------------------------|---------------------------------------|---------------------|---------------------------|

| Coding                                   |                                                                                              | ••••••••••••••••••••••••••••••••••••••            |                                                   | 4-bit ADP(                                         | CM method                                         |                                                |                                                     |                                       | 3/4-bit ADPCM       | 4-bit ADPCM               |

| ROM type                                 |                                                                                              | Mask RO                                           | M built-in                                        |                                                    | Built-in OPT                                      |                                                | Exte                                                | External                              |                     |                           |

| ROM capacity                             | 128K bits                                                                                    | 256K bits                                         | 512K bits                                         | 1M bits                                            | 512K bits                                         | 256K bits                                      | Up to<br>16M bits                                   | Up to<br>2M bits                      |                     | -                         |

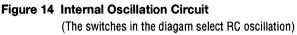

| Synthesis time<br>(sampling<br>frequeny) | 8 sec (4kHz)<br>5sec (6.4kHz)<br>2 sec (16kHz)                                               | 16 sec (4kHz)<br>10 sec (6.4kHz)<br>4 sec (16kHz) | 32 sec (4kHz)<br>20 sec (6.4kHz)<br>8 sec (16kHz) | 64 sec (4kHz)<br>40 sec (6.4kHz)<br>16 sec (16kHz) | 32 sec (4kHz)<br>20 sec (6.4kHz)<br>8 sec (16kHz) | 16 sec (4kHz)<br>8 sec (8kHz)<br>4 sec (16kHz) | 17 min (4kHz)<br>10 min (6.4kHz)<br>256 sec (16kHz) | 128 sec (4kHz)<br>16 sec (32kHz)      |                     | dernal<br>cuit            |

| Sampling<br>frequency                    | 4.0, 6.4, 8.0kHz (f <sub>OSC</sub> = 64kHz)<br>8.0, 12.8, 16.0kHz(f <sub>OSC</sub> = 128kHz) |                                                   |                                                   |                                                    | <u> </u>                                          | 4.0kHz ~<br>16.0 kHz                           | 4.0kHz ~<br>32.0 kHz                                | 8.0kHz ~<br>32.0 kHz                  | 4.0, 6.0<br>8.0 kHz | 4.0, 8.0<br>16.0, 32.0kHz |

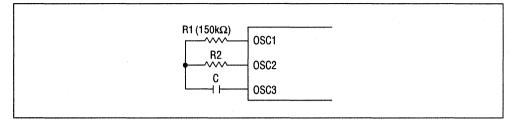

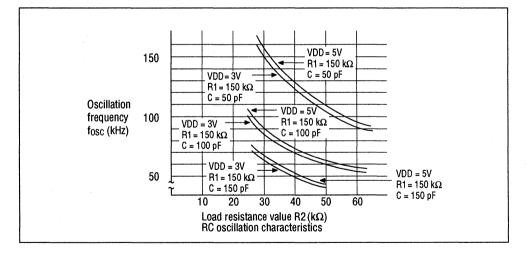

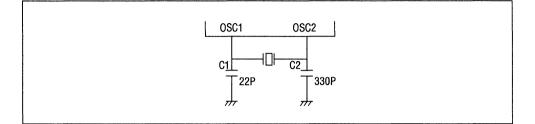

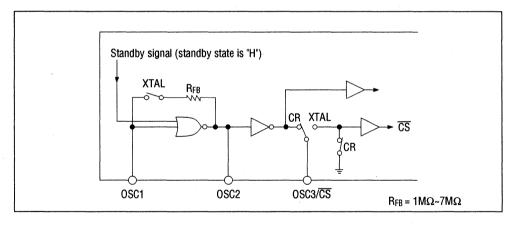

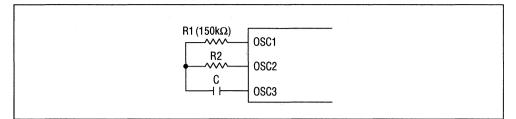

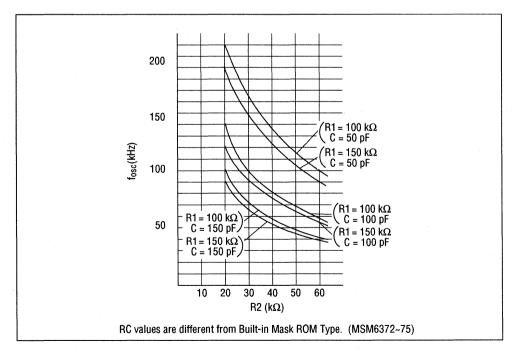

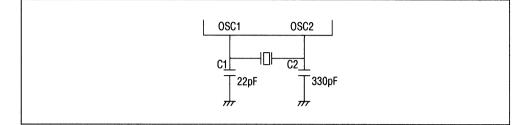

| Clock<br>frequency                       | 64 ~ 128kHz (LPF selected)<br>64 ~ 256kHz (DAC selected)                                     |                                                   |                                                   |                                                    |                                                   | 64 ~ 256kHz<br>(RC oscillation)                | 64 ~ 128kHz                                         | 1 ~ 4MHz                              | 384kHz              | 640kHz                    |

| D-A converter                            |                                                                                              |                                                   |                                                   | 12                                                 | -bit                                              |                                                |                                                     |                                       | 10-bit              | 12-bit                    |

| Low-pass filter                          | -24dB/oct                                                                                    |                                                   |                                                   |                                                    |                                                   |                                                |                                                     | None                                  | None                | -40dB/oct                 |

| Supply voltage                           | 2.4 ~ 5.5V (DAC selected)<br>2.7 ~ 5.5V (LPF selected, fosc = 64kHZ)                         |                                                   |                                                   |                                                    | 2.7 ~ 5.5V                                        | 2.4 ~ 5.5V                                     | 4.5 ~                                               | · 5.5V                                | 3.0 ~ 6.0V          | 4.5 ~ 5.5V                |

| Operating current                        | 10mA                                                                                         |                                                   |                                                   |                                                    | 20                                                | 20mA 10mA                                      |                                                     | 4mA                                   | 10mA                |                           |

| Standby current                          | 10μΑ                                                                                         |                                                   |                                                   | 100µA                                              | 10                                                | μA                                             |                                                     | -                                     |                     |                           |

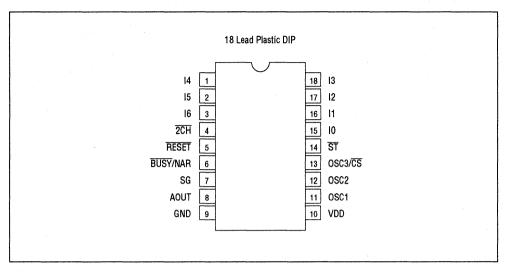

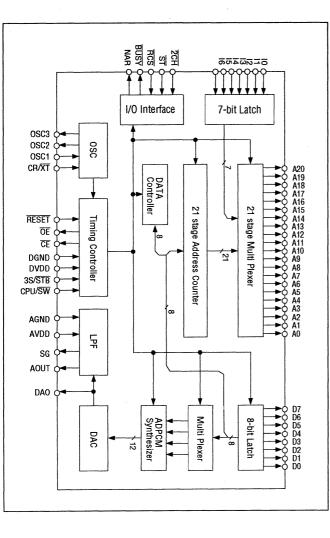

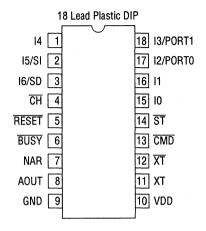

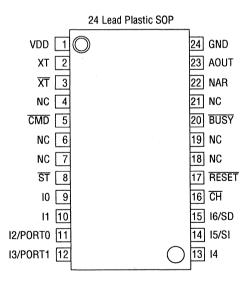

| Package                                  | Chip, 18-pin DIP<br>24-pin SOP                                                               |                                                   |                                                   |                                                    | 20-pin DIP                                        | 16-pin DIP                                     | 64-pin QFP                                          | 44-pin QFP<br>40-pin DIP              | 18-pi               | in DIP                    |

| Voice analysis<br>tool                   | AR76-202                                                                                     |                                                   |                                                   |                                                    | <u> </u>                                          | ANA WRITER<br>AR76-202                         | AR76-202                                            |                                       |                     |                           |

| Other<br>characteristics                 |                                                                                              | Channel 2                                         | 2 mixing, echo<br>beep tones                      | playback                                           |                                                   | Power ON<br>start                              | MSM6373/74/<br>75 evaluation                        | 4 Channel<br>mixing,<br>echo playback | _                   | _                         |

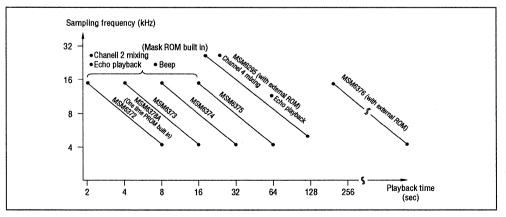

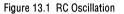

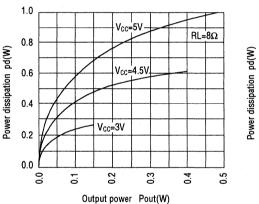

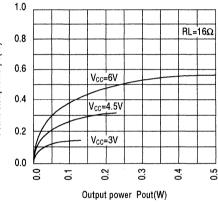

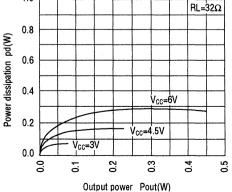

**TYPICAL CHARACTERISTICS**

#### SELECTION GUIDE

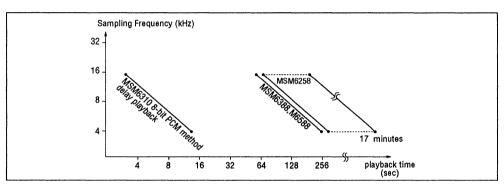

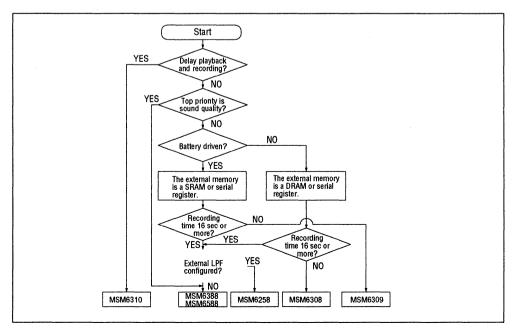

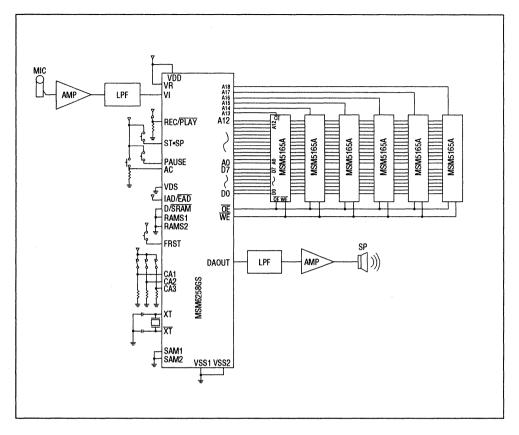

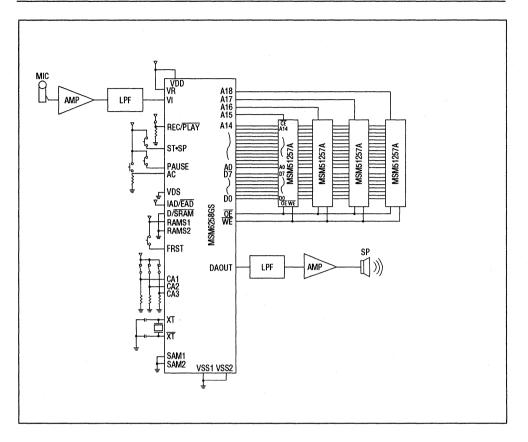

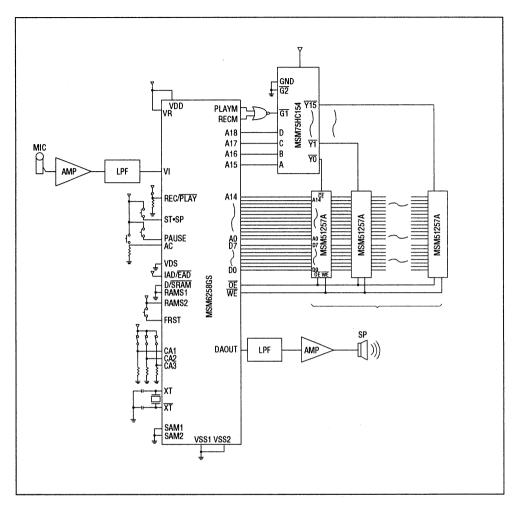

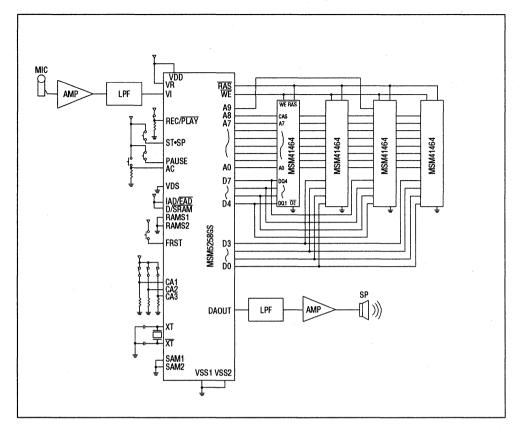

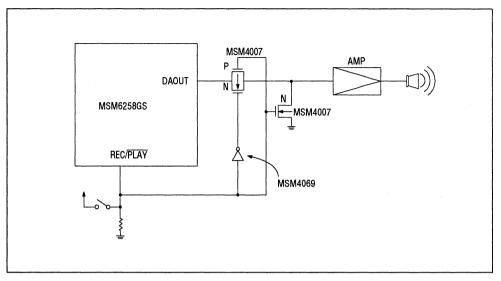

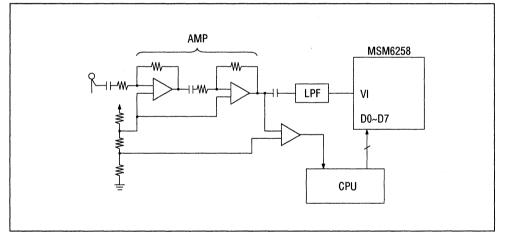

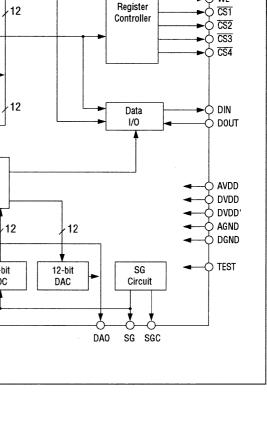

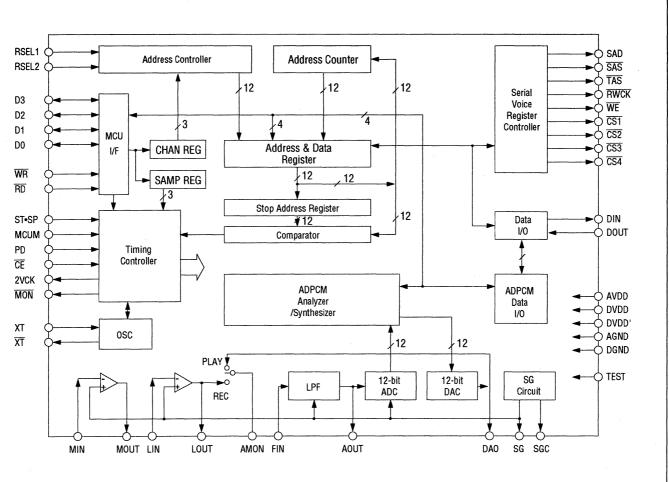

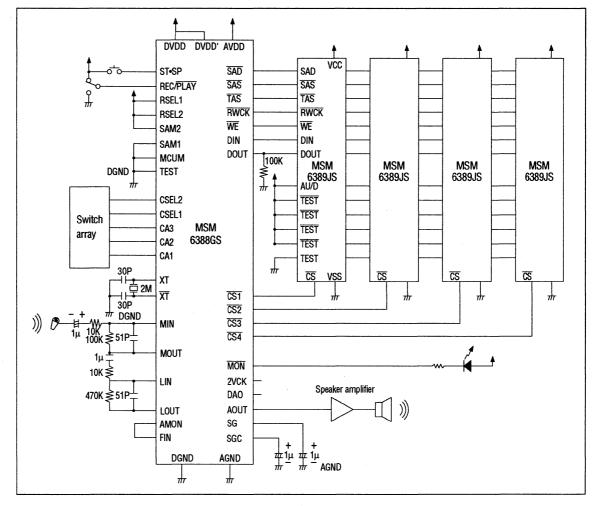

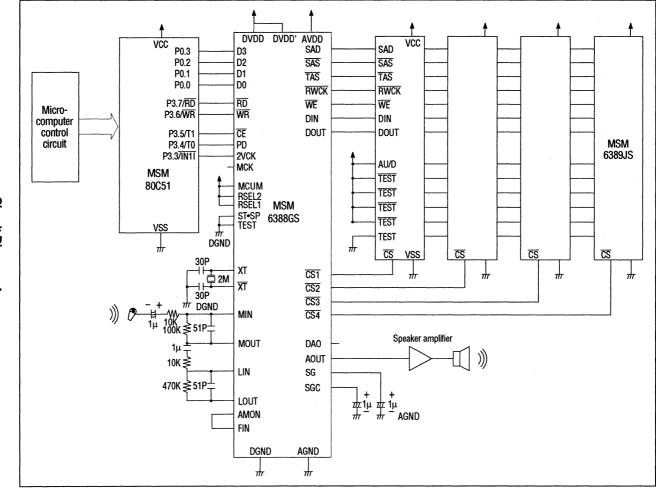

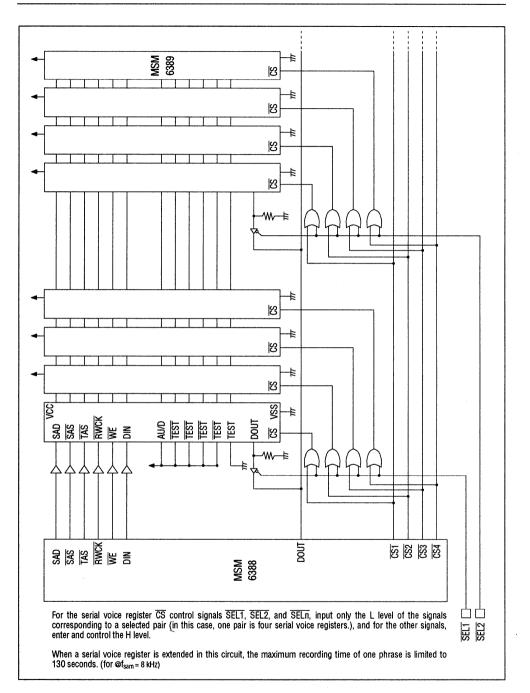

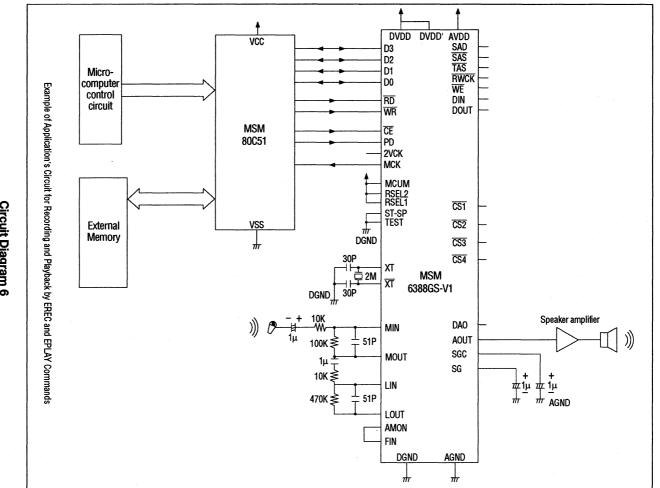

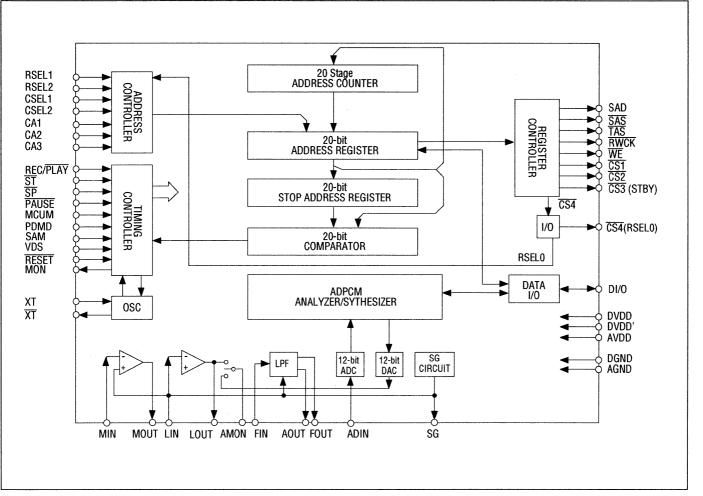

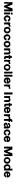

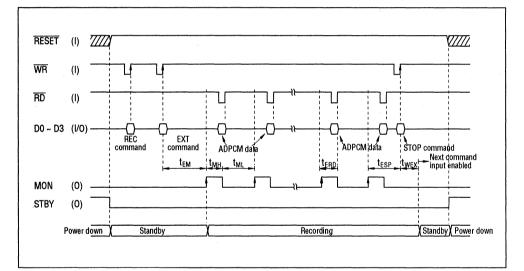

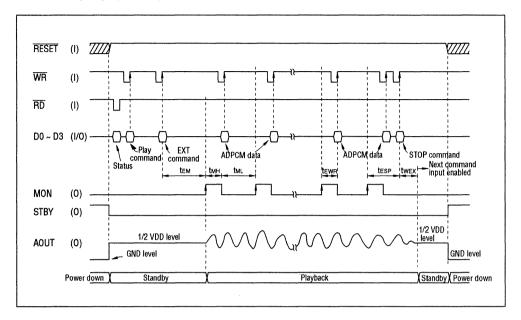

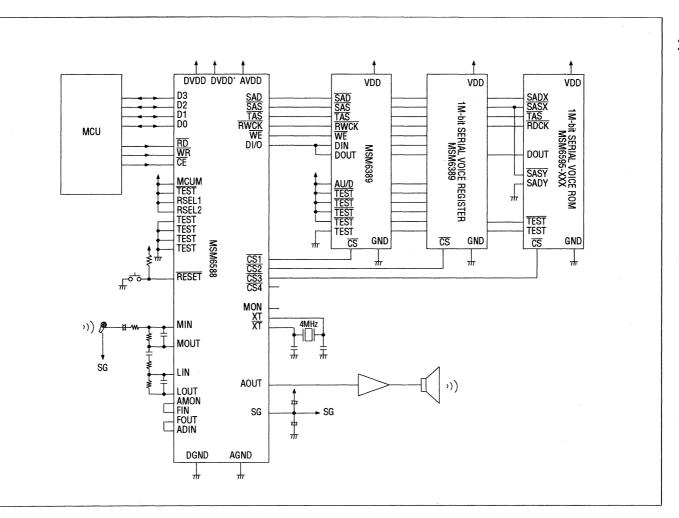

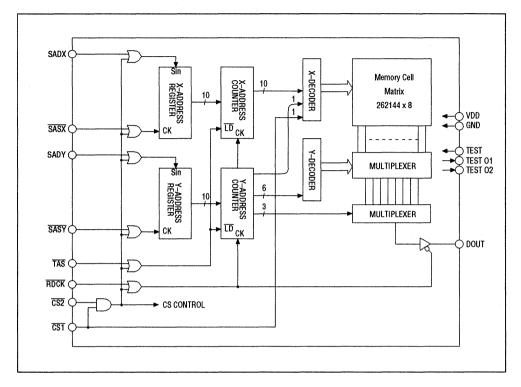

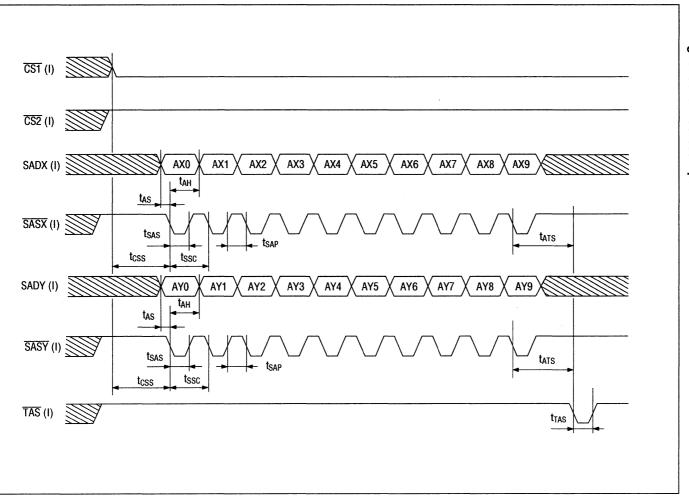

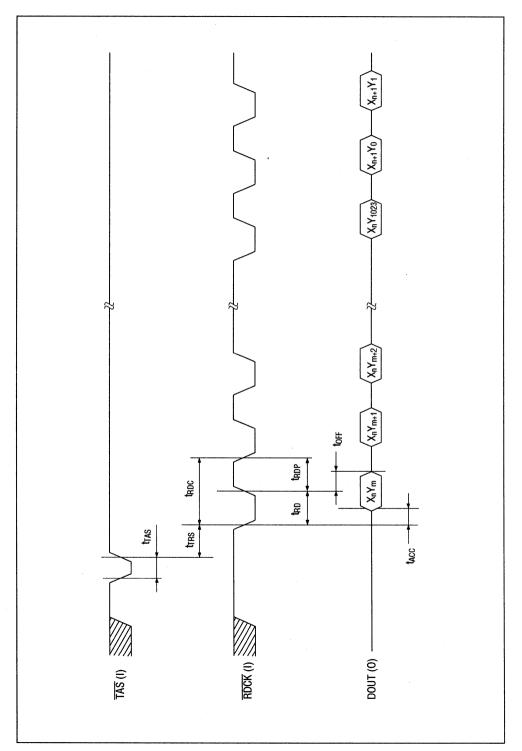

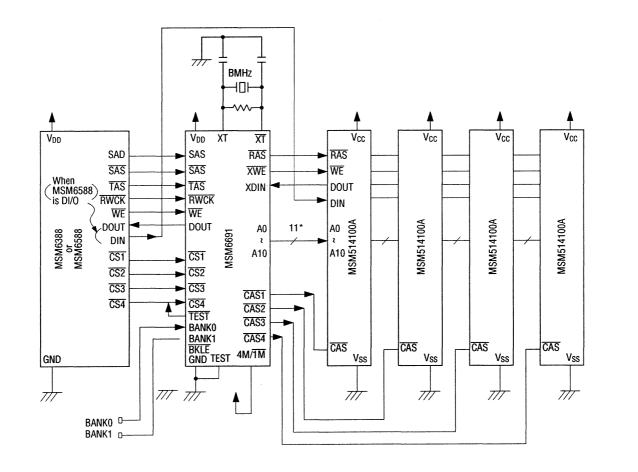

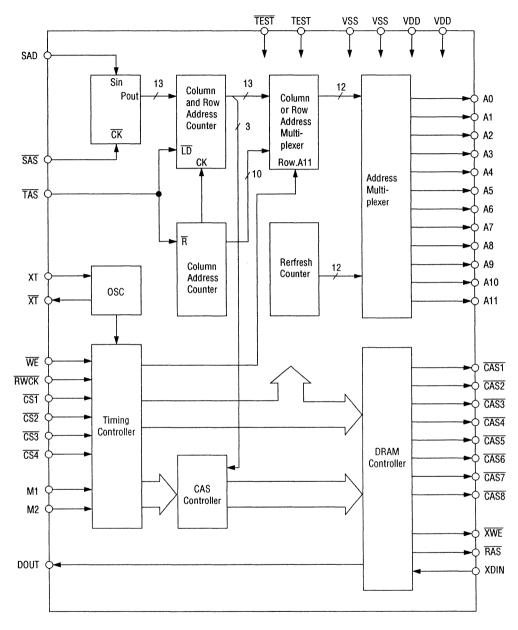

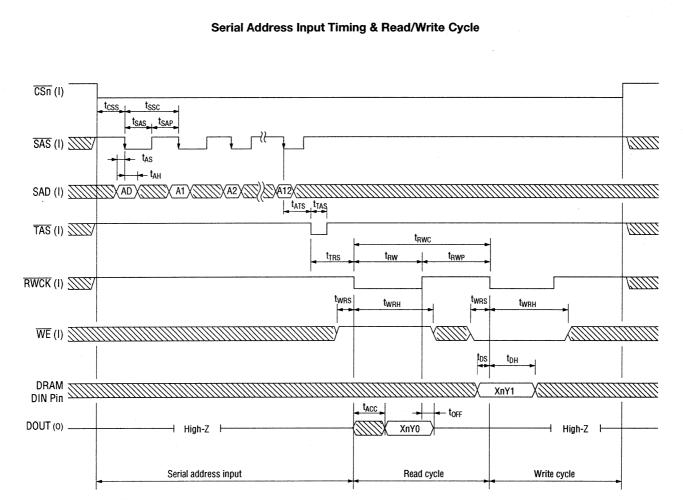

#### 2-2) RECORDING AND PLAYBACK LSI LINE-UP

#### **GENERAL DESCRIPTION**

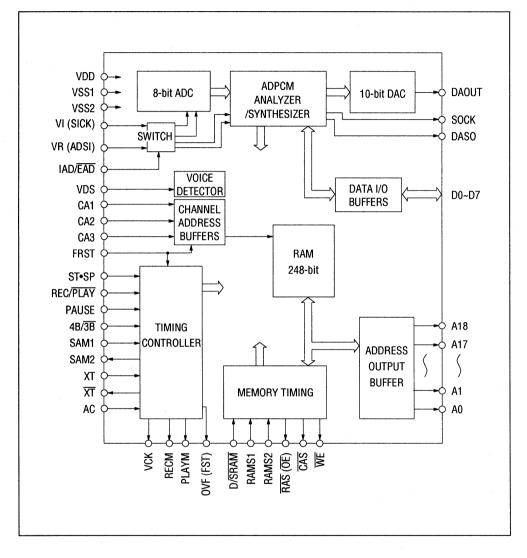

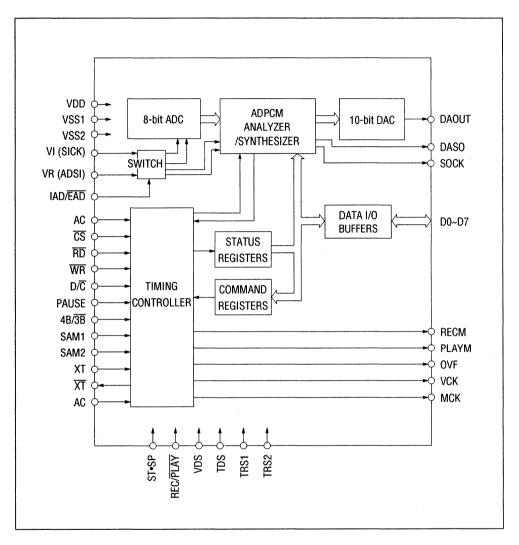

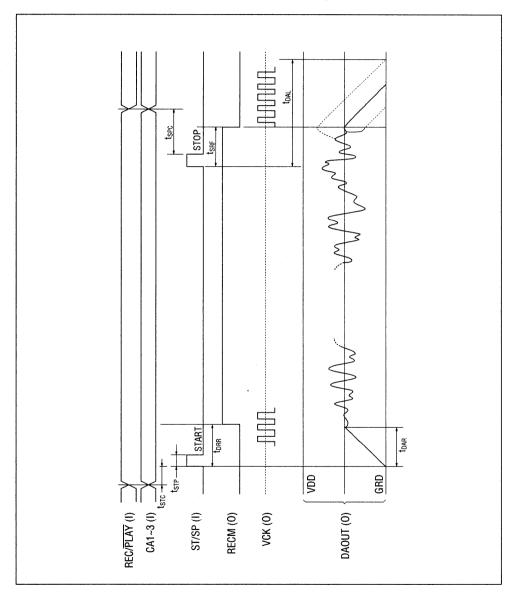

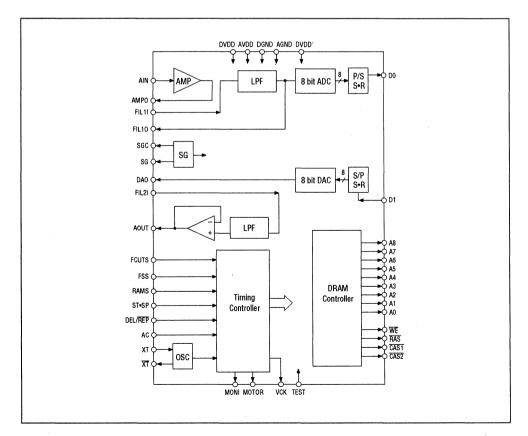

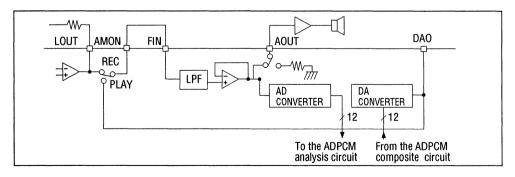

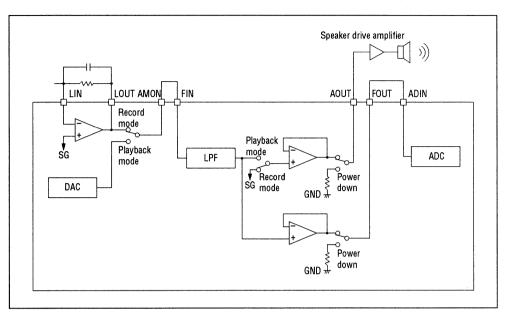

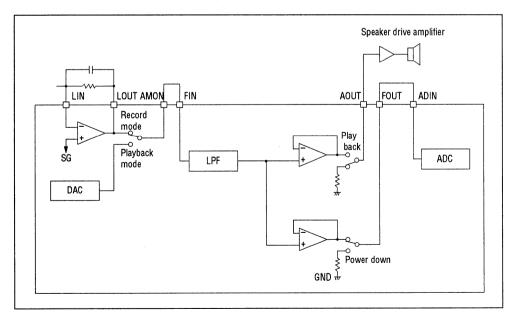

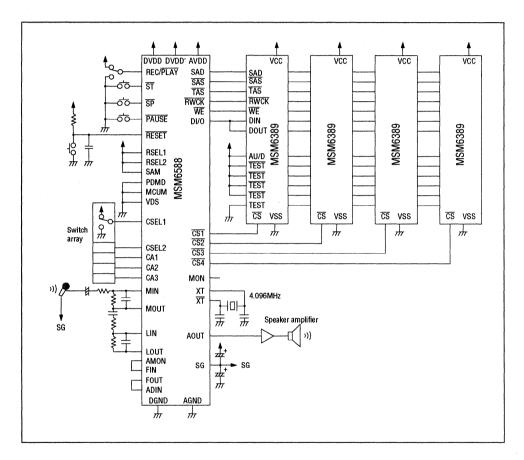

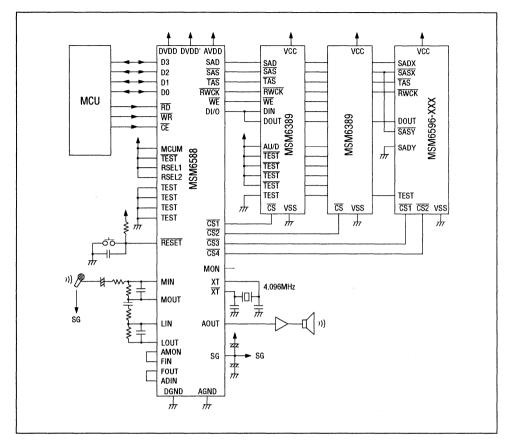

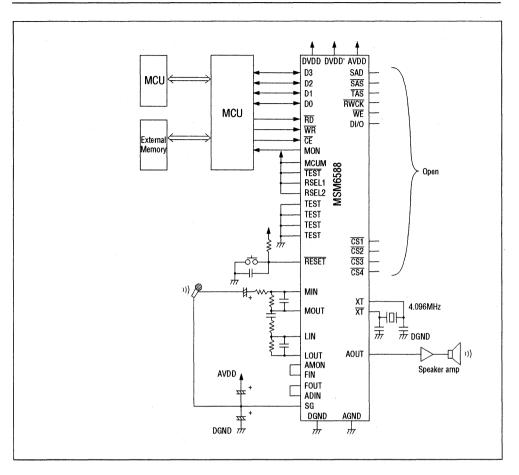

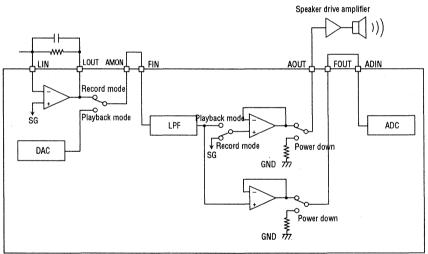

There are two basic types of record/playback devices which use external memory for data storage, LSI's using ADPCM processing, and LSI's using PCM processing.

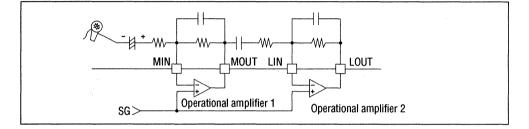

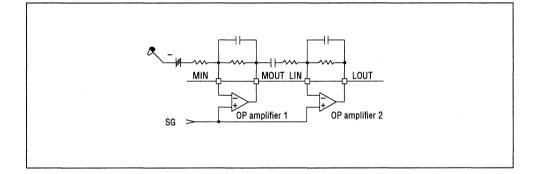

The ADPCM processors incorporate an A/ D and D/A of up to 12-bits, LPF (Low Pass Filter) up to -40dB/octave (outband attenuator) for input and output, and microphone and line amplification. These devices directly address from 256-bits to 16Mega bits of external memory. Under processor control and with additional external circuitry, almost any external memory requirement can be met.

#### **PRODUCT CONFIGURATION**

#### **SELECTION GUIDE**

#### **TYPICAL CHARACTERISTICS**

|                                                   | and the second |                                                                                |               |                               |                                       |      |            |      |  |  |     |

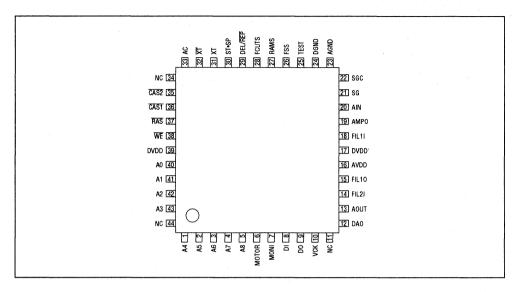

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------|-------------------------------|---------------------------------------|------|------------|------|--|--|-----|

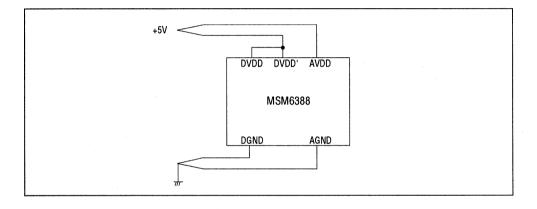

| Product name                                      | MSM6258 (V)                                                                                                      | MSM6388                                                                        | MSM6588       | MSM6310                       | MSM5218                               |      |            |      |  |  |     |

| Coding                                            | 3/4-bit ADPCM                                                                                                    | 4-bit ADPCM<br>method                                                          | 3/4-bit ADPCM | 8-bit PCM                     | 3/4-bit ADPCN                         |      |            |      |  |  |     |

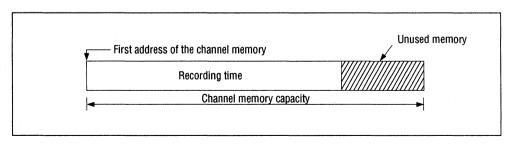

| Memory type to be connected (capacity)            | DRAM (16Mb)<br>SRAM (4Mb)                                                                                        | Serial Voice register DR<br>Serial Voice ROM (4Mb)                             |               | DRAM (512Kb)                  | л.<br>П                               |      |            |      |  |  |     |

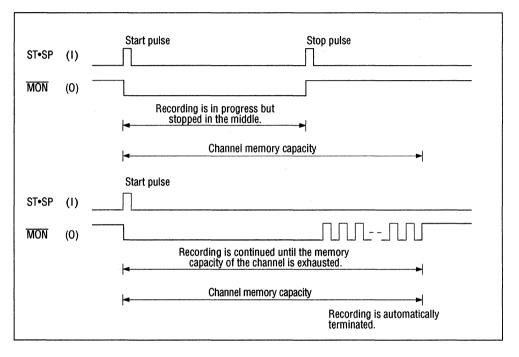

| Maximum recording<br>time<br>(sampling frequency) | SRAM 256 sec (4kHz)                                                                                              | 256 sec (4kHz) 256 sec (5.3kHz x 3bit)<br>128 sec (8kHz) 170 sec (8kHz x 3bit) |               | 16 sec (4kHz)<br>8 sec (8kHz) | By external<br>circuit                |      |            |      |  |  |     |

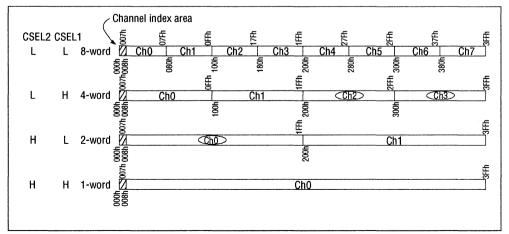

| Number of<br>words/phrases                        | 7 words *1                                                                                                       | 8 w                                                                            | 8 words *1    |                               | Determined<br>by external<br>circuity |      |            |      |  |  |     |

| Sampling<br>frequency                             | 4.0kHz ~<br>15.6kHz                                                                                              | 4.0kHz ~ 4.0kHz ~<br>16.0kHz 16.0kHz                                           |               |                               | 4.0, 6.0<br>8.0kHz                    |      |            |      |  |  |     |

| Clock frequency                                   | 4MHz ~ 8MHz                                                                                                      | 1.5MHz ~ 4MHz ~<br>4MHz 8.192MHz                                               |               | 4MHz ~<br>8.2MHz              | 384kHz                                |      |            |      |  |  |     |

| Microphone/line<br>amplifier                      | External                                                                                                         | Built-in                                                                       |               | Built in Line<br>amplifier    | None                                  |      |            |      |  |  |     |

| A-D converter                                     | 8 bits                                                                                                           | 12 bits                                                                        |               | 8 bits                        | None                                  |      |            |      |  |  |     |

| D-A converter                                     | 10 bits                                                                                                          | 12 bits                                                                        |               | 8 bits                        | 10 bits                               |      |            |      |  |  |     |

| Low-pass filter                                   | None                                                                                                             | -40                                                                            | dB/oct        | -24dB/oct                     | None                                  |      |            |      |  |  |     |

| Supply voltage                                    | 3.5 ~ 6.0V                                                                                                       | 3.5 ~ 5.5V                                                                     |               | 4.5 ~ 5.5V                    | 3.0 ~ 6.0V                            |      |            |      |  |  |     |

| Operating current                                 | 4mA                                                                                                              | 10mA                                                                           |               | 10mA                          |                                       | 10mA |            | 10mA |  |  | 6mA |

| Standby current                                   | 10µA                                                                                                             | 10µA                                                                           |               | 10μΑ                          |                                       |      | -          |      |  |  |     |

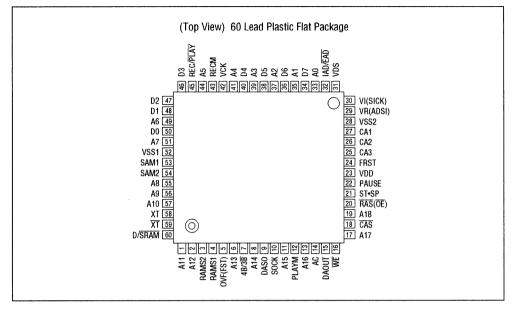

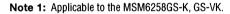

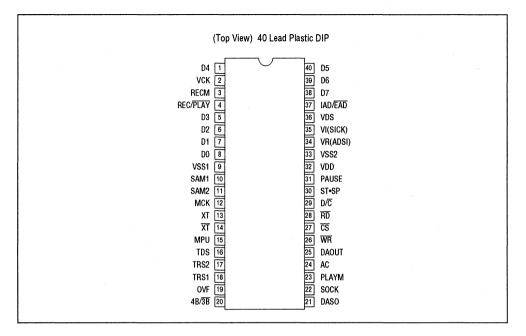

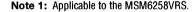

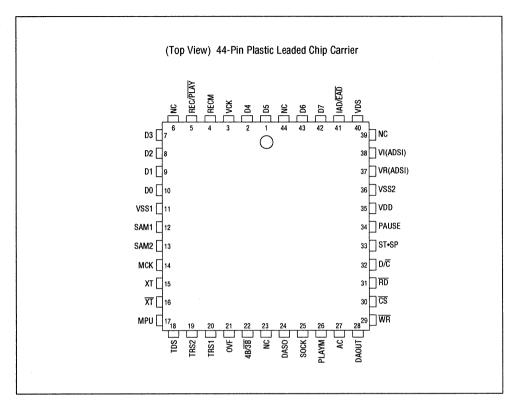

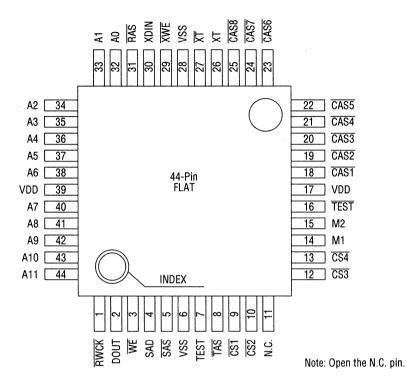

| Package                                           | 40-pin DIP<br>44-pin QFP<br>60-pin QFP<br>44-pin PLCC<br>68-pin PLCC                                             | 44-pin QFP                                                                     |               | 44-pin QFP                    |                                       |      | 24-pin DIP |      |  |  |     |

\*1 During MCU or microprocessor control, the number of words depends on the MCU and its associated circuity driving the speech chip.

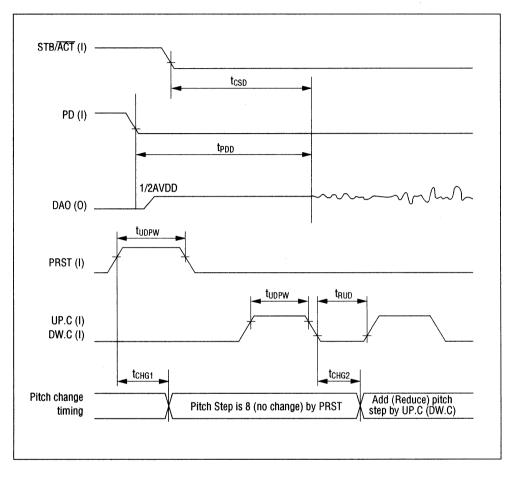

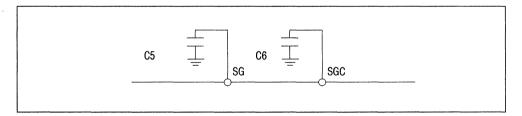

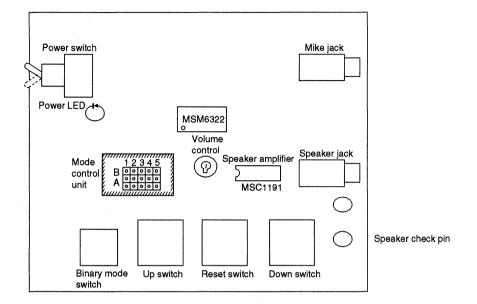

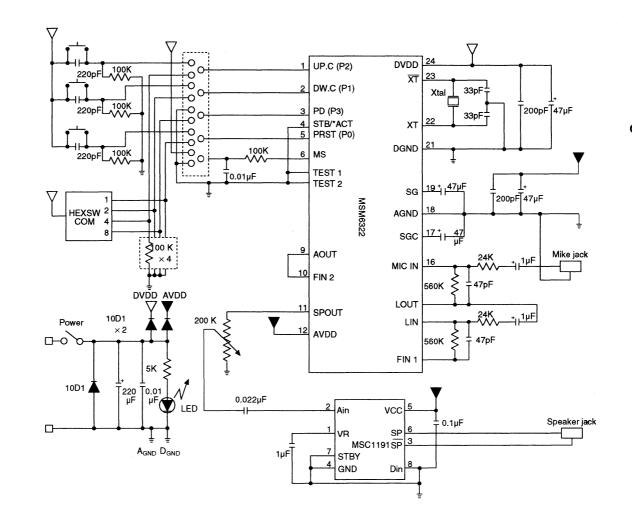

## 2-3) VOICE PITCH CONTROL LSI

#### **GENERAL DESCRIPTION**

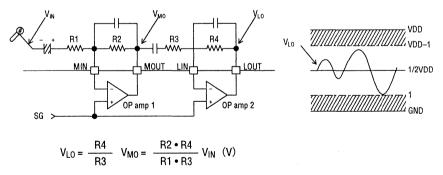

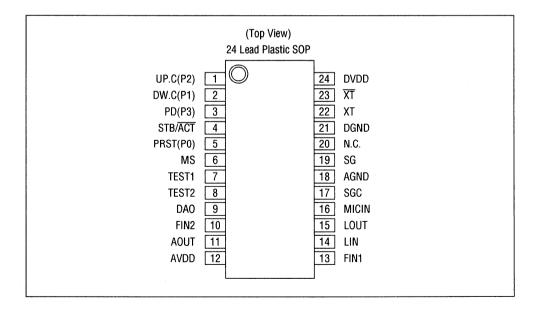

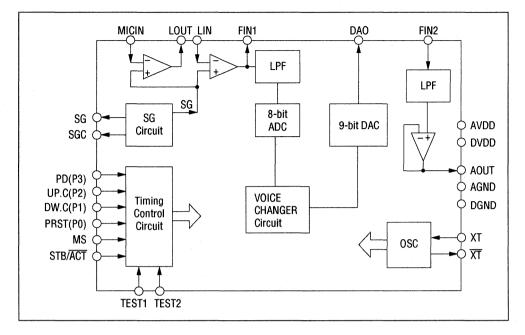

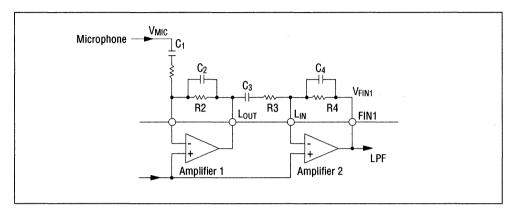

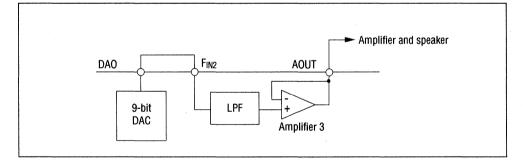

MSM6322 is a voice pitch control LSI providing a voice pitch changer function. This LSI provides a 17-step voice pitch conversion function using the PCM method. This single chip solution contains all necessary

#### FEATURES

- 17-step voice pitch conversion using the 8-bit PCM method

- Sampling frequency: Input 8 kHz, output 4 to 16 kHz

functions to realize a voice changer, such as A-D conversion, D-A conversion, LPF, microphone amplification, and line amplification.

- 8-bit A-D converter, 9-bit D-A converter, LPF, microphone amplifier, and line amplifier built-in

- 24-pin flat package

| Product name            | MSM6322                                                                                |  |  |

|-------------------------|----------------------------------------------------------------------------------------|--|--|

| Function                | 17-step voice pitch conversion                                                         |  |  |

| Coding method           | 8-bit PCM method                                                                       |  |  |

| Sampling frequency      | Input 8kHz, Output 4k~16kHz                                                            |  |  |

| Clock frequency         | 4MHz                                                                                   |  |  |

| Built-in analog circuit | 8-bit A-D converter, 9-bit D-A converter, LPF,<br>microphone amplifier, line amplifier |  |  |

| Supply voltage          | 4.0-6.0V                                                                               |  |  |

| Operating current       | 10mA                                                                                   |  |  |

| Standby current         | 10µA                                                                                   |  |  |

| Package                 | 24-pin flat                                                                            |  |  |

#### **VOICE PITCH CONTROL LSI**

#### MSM6322 BLOCK DIAGRAM

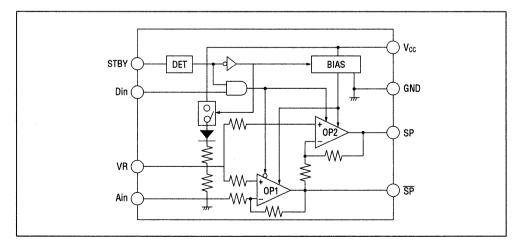

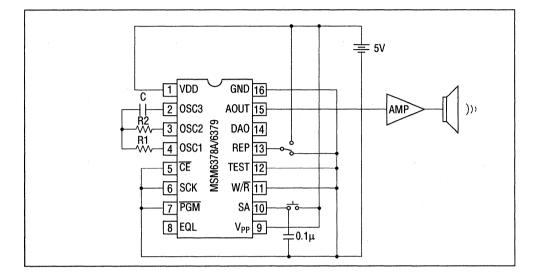

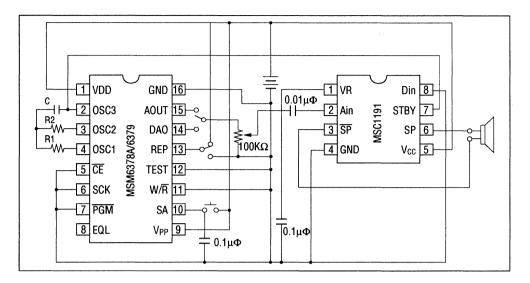

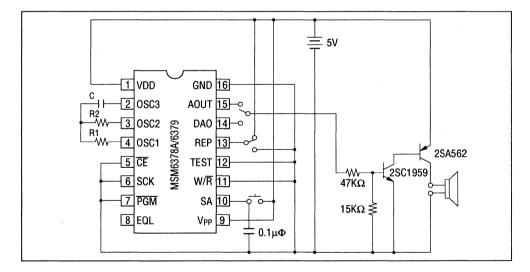

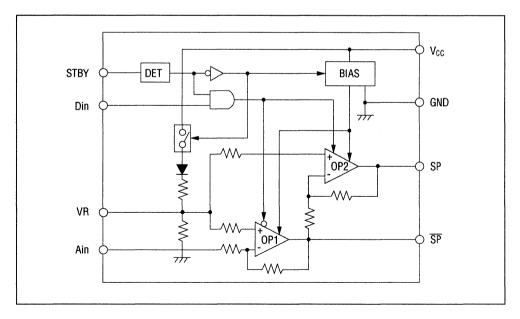

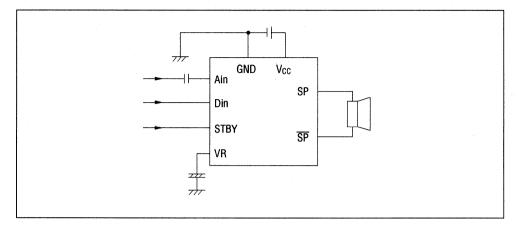

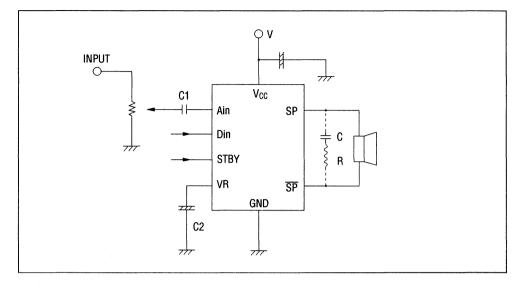

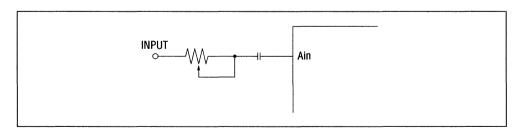

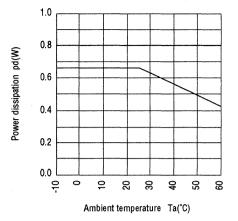

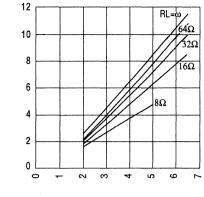

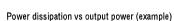

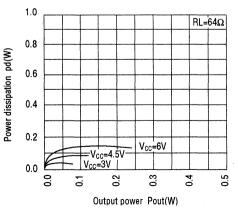

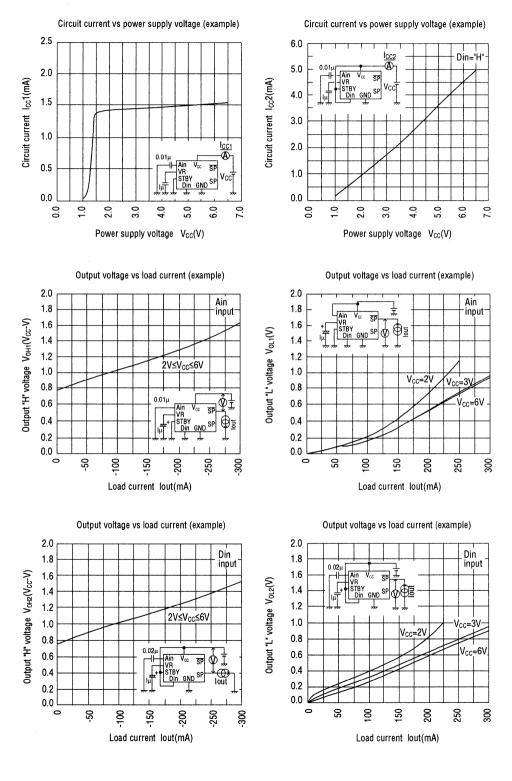

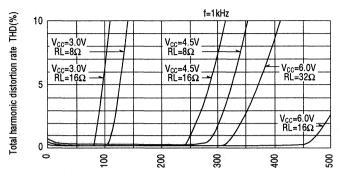

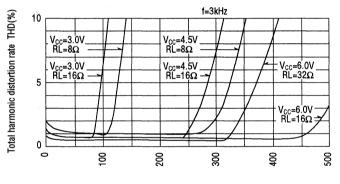

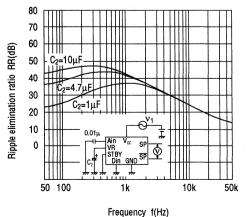

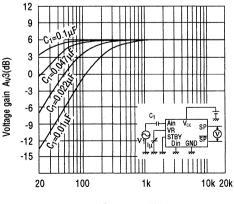

#### 2-4) DIRECT DRIVE SPEAKER AMPLIFIER

#### **GENERAL DESCRIPTION**

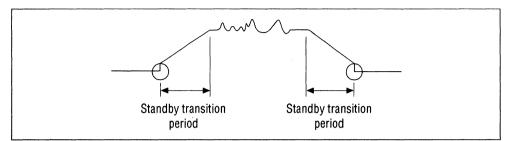

MSC 1191/1192 is a speaker drive amplifier IC for Oki's voice LSIs. This is a power amplifier with low consumption at a low

#### FEATURES

- Operating at a low voltage

- A voice analog signal input pin and a digital signal input pin such as an alarm signal is provided

#### DIRECT DRIVE SPEAKER AMPLIFIER

voltage, and directly drives a speaker without a coupling capacitor.

- The speaker can be directly connected between the differential output pins.

- Standby function provided

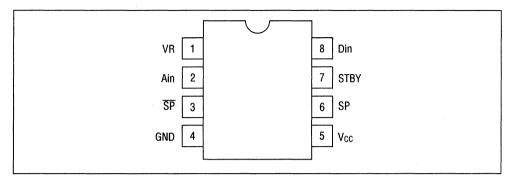

| Product name              | MSC1191/MSC1192 Speaker drive amplifier |  |  |

|---------------------------|-----------------------------------------|--|--|

| Function                  |                                         |  |  |

| Supply voltage            | 2.0 ~ 6.0V                              |  |  |

| Maximum output current    | 250mA                                   |  |  |

| No-load operating current | 1.5mA (TYP)                             |  |  |

| Standby current           | 1mA (MAX)                               |  |  |

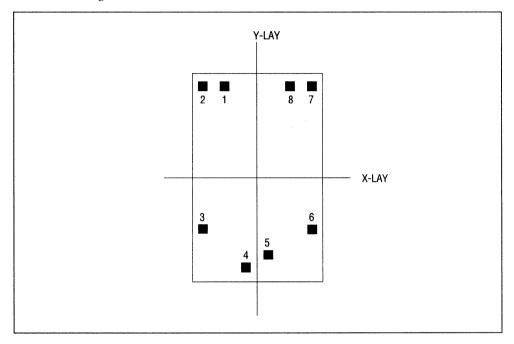

| Package                   | Chip, 8-pin DIP, 8-pin SOP              |  |  |

#### MSC1191/1192 BLOCK DIAGRAM

Note: MSC1191: Standby mode is activated by "H" level to the input STBY MSC1192: Standby mode is activated by "L" level to the input STBY

#### Features of Oki Voice Synthesis LSIs

The major features of Oki voice synthesis LSIs are summarized below.

- (1) Quality of Synthesis

- (i) Good quality sound with a high degree of naturalness.

- (ii) Synthesis of sound effects, musical instruments, and animal sounds also possible.

- (2) Hardware

- Easy to handle (built-in ROM) SINGLE-chip devices ready for simple application.

- (ii) A range of voice synthesis LSIs with various built-in ROM sizes to meet diversified market needs.

- (iii) Low power requirements due to CMOS with low fundamental oscillating frequency-ideal also for battery operated applications.

#### (3) Software

(i) Simple and precise analysis for any customized sound/voice.

Because of the fine sound quality achieved for a wide range of applications, Oki voice synthesis LSIs are used worldwide by a large number of client in numerous applications.

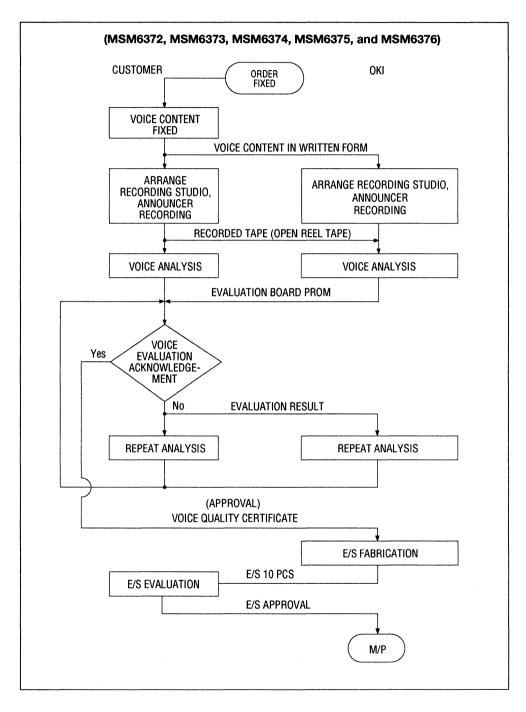

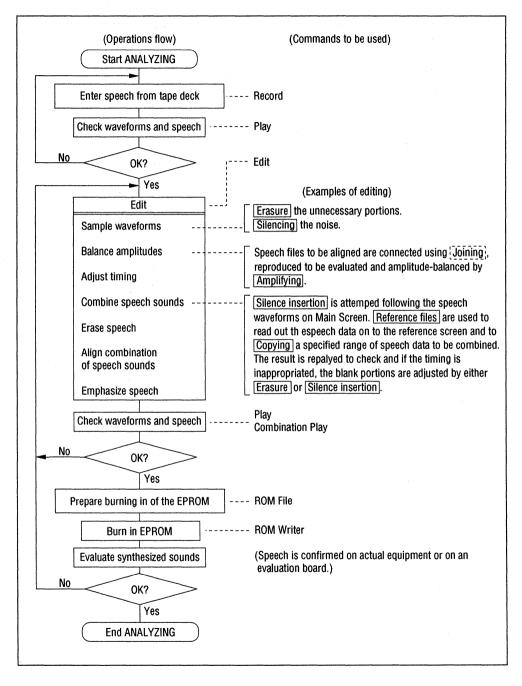

## 3. FLOWCHART FOR BUILT-IN ROM VOICE SYNTHESIS DEVEL-OPMENT

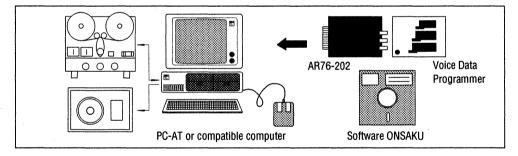

## 4. USER ANALYSIS SUPPORT TOOLS

#### 4-1) SPEECH DEVELOPMENT SYSTEM

#### **OUTLINE OF AR76-202**

AR76-202 is fully PC supported. Included with the shipment is a standard 16-bit PC slot card, an EPROM programmer, a software driver and an English manual.

The host environment should consist of a PC-AT<sup>®</sup> or 100% compatible machine equipped with a harddisk, VGA<sup>®</sup> graphic adaptor and serial mouse. A printer is useful but not essential. The driver software

runs under DOS 3.2 and higher on a 640K machine. However, for speech phrases of more than 15 seconds, EMS expansions are strongly recommended in order to record long phrases in one piece without concatenations. A tape deck or cassette player is needed as an analog source which can be connected directly to the installed board as well as a loudspeaker.

#### **TARGET LSIs**

MSM6372/73/74/75 MSM6585 MSM6376 MSM6295 MSM63P74 MSM6258

#### SYSTEM CONFIGURATION

MSM6378A MSM5205 MSM6595 MSM6596

#### PERFORMANCE

What AR76-202 does for you comprises all essentially demanded functions from recording all the way up to EPROM programming, plus a few extras. In detail:

- Recording into host memory through an audio line input

- Playback of a recording from host memory via speaker

- Editing of a recorded voice file, including -Amplitude manipulation

-Silencing/Silence insertion -Fading/Cut/Copy/Paste

- HEX-file or BIN-file generation

- EPROM/OTP programming

- EPROM duplication

- Random access playback of speech files

- Covers all OKI speech LSIs, including OTP synthesizers

- Makes full use of Expanded Memory System

## HARDWARE

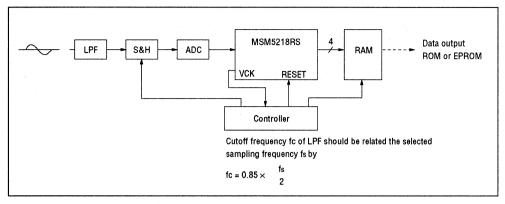

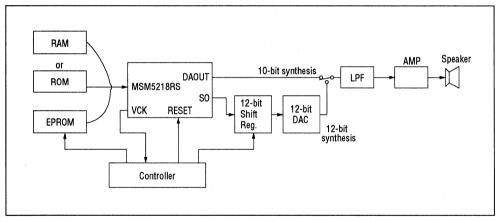

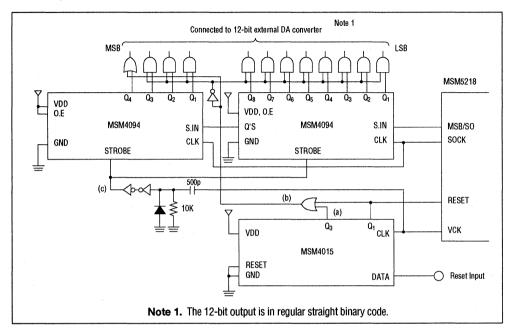

Measuring approximately 284(L) x 107(W) mm, the slot card is designed around OKI Electric's MSM5218 speech recorder LSI in connection with external 12-bit converters plus low pass filter featuring –48dB attenuation per octave. Both analog and digital

#### SOFTWARE

The software driver, "ONSAKU", is fully graphics oriented and operable with keys or preferably with a mouse. The primary application of the software is for editing raw speech recordings. This includes amplitude amplification and attenuation, cutting, copying and insertion of selected excerpts. Additionally, the auto-face in/fade out function helps to save time. Using this software is like circuits are provided through to analog inputs and outputs for direct connection of a tape deck and a speaker. Likewise, the external EPROM/OTP writer is linked to the card's interface.

using a modern wordprocessor. A recorded waveform is displayed on the graphic screen in three scales allowing for precise editing at any point.

"ONSAKU" can be started with a variety of option switches in order to adjust operating parameters for more convenience and easier further processing.

#### INTRODUCTION

#### **GENERAL FLOW OF OPERATIONS**

16

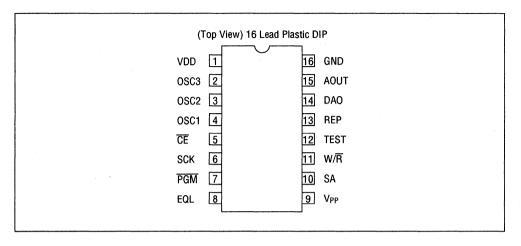

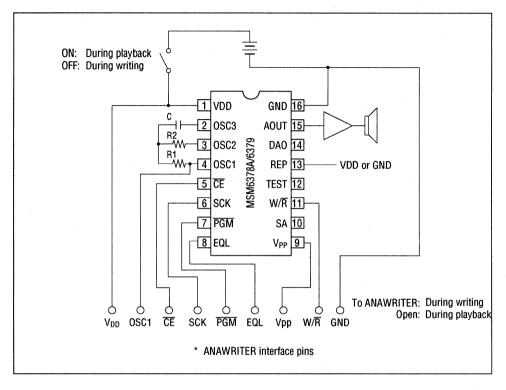

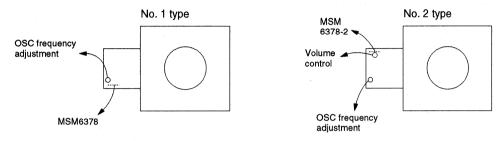

#### 4-2) ANAWRITER, PARAWRITER, BACK-UP SYSTEM (FOR MSM6378A)

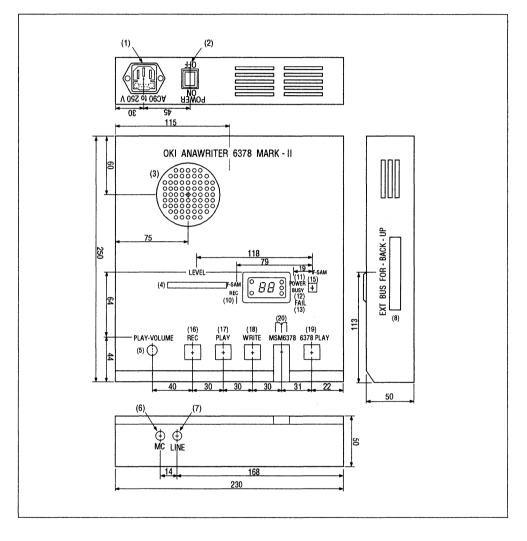

#### ANAWRITER 6378 MARK II

#### **GENERAL DESCRIPTION**

The ANAWRITER 6378 MARK II is a tool dedicated to voice analysis for the Oki MSM6378A 256 Kbit OTP (one-time programmable device.)

It can run on 90 to 250 V AC. Therefore, it can be used in any country without voltage modifications.

It has two input jacks: microphone input (with built-in ALC) and line input jacks.

#### **FEATURES**

- Voice analysis: Oki ADPCM MSM6378A

- Microphone input:  $600 \Omega$ , with built-in ALC

- Line input: 10KΩ, -10dB

- Recording monitor:

Input level is displayed on a bar

graph LED

• Play monitor: Reproduced sound can be heard from a built-in speaker

Programming time in a MSM6378A is 8 seconds, including time for verify.

A ROM (EPROM) master can be made by preparing a backup using an external I/F. If a PARAWRITER is used with the master ROM, write and verify for ten MSM6378A can be simultaneously completed within 11 seconds.

- Functions:

- Options:

- PLAYBACK FROM PROGRAMMED MSM6378A Backup (master ROM generation tool), PARAWRITER (ten-ROM parallel writing tool)

REC, PLAY, WRITE,

- Supply voltage: 90 ~ 250V AC

- Write and verify time:

8.0 seconds for one device, 11.0 seconds (PARAWRITER) for ten devices.

#### **RECORDING TIME**

| Sampling<br>frequency (kHz) | Recording time<br>(sec) |

|-----------------------------|-------------------------|

| 4                           | 15.6                    |

| 6                           | 10.4                    |

| 8                           | 7.8                     |

| 10                          | 6.2                     |

| 12                          | 5.2                     |

| 14                          | 4.5                     |

| 16                          | 3.9                     |

#### INTRODUCTION

#### OPERATION

a. Power-on

Connect the AC power supply (1), and turn on the power switch (2).

- The power lamp (11) is lit up.

- "88" is displayed on the indicator (14). Then, it is changed to "4".

- The sampling lamp (9) is lit.

- b. Switching of sampling frequency

- Pressing the sampling frequency selector switch (15) selects another sampling frequency.

- The indicator (14) shows the selected sampling frequency.

- Each time the sampling frequency switch (15) is pressed, the sampling frequency changes as follows:

$$\rightarrow 4 \rightarrow 6 \rightarrow 8 \rightarrow 10 \rightarrow 12 \rightarrow 14 \rightarrow 16$$

- While a sampling frequency is indicated on the sampling indicator (14), the sampling lamp remains on.

- c. Recording

Insert the microphone connector into the microphone input jack (6), or set a sound source to the input jack (7). When sound is entered, the level meter (4) works.

Pressing the record switch (16) starts recording.

At the same time, ADPCM analysis is performed.

- The lamp for the record switch (16) is lit.

- During recording, the lamp (10) remains on.

- The indicator (14) shows the residual recording time.

When recording is complete, the indicator (14) shows a sampling frequency again.

d. Play (checking of recorded voice)

Pressing the switch (17) begins voice reproduction. Sound volume can be adjusted using the monitor control (5). During play, the lamp for the play switch (17) is lit.

e. Writing to 6378

Check the direction of 6378 with the lever of TEXTOOL<sup>®</sup> (20) raised. Place the 6378 in TEXTOOL<sup>®</sup> socket, and lower the lever.

Make sure that 6378 is placed horizontally.

Pressing the 6378 write switch starts writing.

During writing, the 6378 busy lamp (12), and write lamp (18) are lit. In eight seconds, write and verify are completed.

If the error lamp (13) comes on when writing is over, it means writing has not been done normally.

In this case, the indicator (14) shows an error code.

- E0: 6378 is not in the TEXTOOL<sup>®</sup> socket, or is not in the socket correctly.

- E3: An error occurred during writing. So, writing was aborted.

Any other error :

May mean a failure has occurred with the ANAWRITER.

If any key is pressed when the indicator (14) is displaying an error, the display is changed to a sampling frequency.

f. Reproduction from 6378

Check the direction of the 6378 with the lever of TEXTOOL<sup>®</sup>(20) raised. Placeitin TEXTOOL<sup>®</sup> socket, and lower the lever to fix it.

Sound volume can be adjusted using the monitor control (5) in play.

During voice reproduction, the lamp for the 6378 play switch (19) and the 6378 busy lamp (12) are lit.

## **MECHANICAL DIMENSION**

#### PARAWRITER

#### **GENERAL DESCRIPTION**

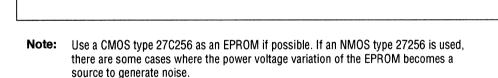

The PARAWRITER writes data for up to ten MSM6378As at a time using a master EPROM (27256), which is prepared with the EPROM BACKUP writer.

#### SPECIFICATIONS

| Master ROM             | : 27C256 or 27256                |                                      |

|------------------------|----------------------------------|--------------------------------------|

| Programmable<br>device | : MSM6378A                       |                                      |

| Writing time           | : 11 seconds (with data writ     | ten to ten MSM6378As simultaneously) |

| Function keys          | : LOAD Reads data from EI        | PROM.                                |

|                        | WRITE Writes data to MSN         | M6378A                               |

|                        | <b>RESET Resets an error lam</b> | p.                                   |

| Buzzer                 | : Write error                    | Beep                                 |

|                        | Normal end of writing            | Веер                                 |

|                        | Upon loading                     | Beep                                 |

|                        | Upon resetting                   | Веер                                 |

|                        |                                  |                                      |

#### **FUNCTION KEYS**

| LOAD key  | Loads data from a master EPROM (27256) to PARAWRITER. |

|-----------|-------------------------------------------------------|

| WRITE key | Writes data to up to ten MSM6378As simultaneously.    |

| RESET key | Resets any error lamp 1 through 10.                   |

#### **FUNCTION LAMP**

BUSY lamp Lit during loading/writing.

#### LAMPS 1 THROUGH 10

Any of the lamps 1 through 10 is lit if in MSM6378A is not placed in the 16-pin TEXTOOL socket, or if a write error occurs. More precisely, a lamp for the position where the MSM6378A is not placed is lit upon completion of writing.

If an error occurs during writing to the MSM6378A, the lamp for the position where the error has occurred is lit. Pressing the RESET switch turns off the lamp.

#### **BACK-UP UNIT**

#### **GENERAL DESCRIPTION**

BACKUP is an EPROM writer for a 27256 EPROM. It loads the EPROM with voice and other data, which are generated using the ANAWRITER 6378 MARK II. BACKUP is connected to the 6378 ANAWRITER through a 40-pin flat cable.

#### FEATURES

- Applicable EPROMs: 27C256 or 27256

- Functions switches : LOAD PLAY BLANK Blank check WRITE EPROM write VERIFY EPROM verify

Function lamps : BUSY

- Function lamps : BUSY FAIL

#### FUNCTION SWITCHES CONTINUED

- LOAD Loads data from EPROM to 6378 ANAWRITER.

- PLAY Reproduces voice data loaded into 6378 ANAWRITER. The switch has the same function as the 6378 play switch.

- BLANK Used for blank check of EPROM (27256).

- WRITE Write voice data generated in 6378 to EPROM (27256). This switch invokes three modes: blank, write, and verify modes.

- VERIFY Compares data in 6378 ANAWRITER with those in EPROM for verification.

#### FUNCTION LAMPS CONTINUED

BUSY lamp : It is lit during LOAD, BLANK, WRITE, and VERIFY. It is not lit during PLAY.

- FAIL lamp : If this lamp is lit, an error lamp is also lit.

- Upon blank check, the data in the EPROM was found not to be blank.

- A write error occurred during writing.

- A verify error occurred during verify.

## 5. PACKAGING

| Product<br>name | No. of<br>Pins | Die<br>Form | DIP<br>RS | SOP/QFP |      |          |          | QFJ(PLCC) |

|-----------------|----------------|-------------|-----------|---------|------|----------|----------|-----------|

|                 |                |             |           | MS-K    | GS-K | GS-VK    | GS-V1K   | JS        |

| MSM5205         | 18             |             | 0         |         |      |          |          |           |

| MSM6585         | 18             |             | 0         |         |      |          |          |           |

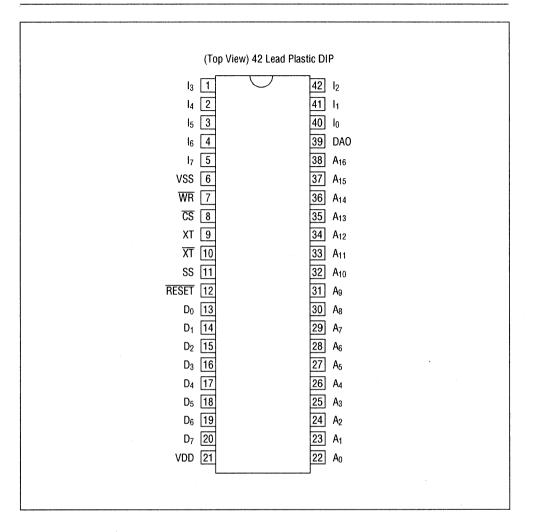

| MSM6295         | 42             |             | 0         |         |      |          |          |           |

|                 | 44             |             |           |         | 0    |          | 0        |           |

| MSM6376         | 64             |             |           |         |      |          | 0        |           |

| MSM6372         | 18             |             | 0         |         |      |          |          |           |

|                 | 24             |             |           |         |      | 0        |          |           |

| MSM6373         | 18             |             | 0         |         |      |          |          |           |

|                 | 24             |             |           |         |      | 0        |          |           |

| MSM6374         | 18             |             | 0         |         |      | 1        |          |           |

|                 | 24             |             |           |         |      | 0        |          |           |

| MSM6375         | 18             |             | 0         | 1       |      |          |          |           |

|                 | 24             |             |           |         |      | 0        |          |           |

| MSM63P74        | 20             |             | 0         |         |      |          |          | 1         |

| MSM6378A        | 16             |             | 0         | 1       |      |          |          |           |

| MSM6379         | 16             |             | 0         |         |      |          |          |           |

| MSM6652         | 18             |             | 0         |         |      |          |          |           |

|                 | 24             |             | <u> </u>  |         |      | 0        |          |           |

| MSM6653         | 18             |             | 0         |         |      |          |          |           |

|                 | 24             |             | ļ         |         |      | 0        |          |           |

| MSM6654         | 18             |             | 0         |         |      | -        |          |           |

|                 | 24             |             |           |         |      | 0        |          |           |

| MSM6655         | 18             |             | 0         |         |      |          |          |           |

|                 | 24             |             |           |         |      | 0        |          |           |

| MSM6656         | 18             |             | 0         |         |      |          |          |           |

| memocoo         | 24             |             |           | +       |      | 0        |          |           |

| MSM66P54        | 20             |             | 0         |         |      |          |          |           |

| 1000000         | 20             |             |           |         |      | 0        |          |           |

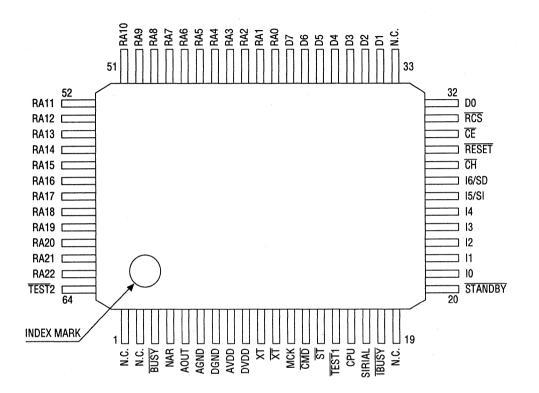

| MSM6650         | 64             |             |           |         |      | $\vdash$ | 0        | -         |

| MSM5050         | 24             |             |           | +       |      |          | $\vdash$ |           |

|                 | 60             |             | 0         |         |      | $\vdash$ | +        |           |

| MSM6258         |                |             |           | -       | 0    | 0        | -        |           |

| MCMCOEDU        | 68             |             |           | -       |      | ļ        |          | 0         |

| MSM6258V        | 40             |             | 0         |         |      |          | ļ        | <u> </u>  |

|                 | 44             |             |           |         | 0    |          | 0        | 0         |

| Product name | No. of<br>Pins | Die<br>Form | DIP |      | QFJ(PLCC) |       |        |    |

|--------------|----------------|-------------|-----|------|-----------|-------|--------|----|

|              |                |             | RS  | MS-K | GS-K      | GS-VK | GS-V1K | JS |

| MSM6310      | 44             |             |     |      |           |       |        |    |

| MSM6388      | 44             |             |     |      |           |       | 0      |    |

| MSM6588      | 44             |             |     |      |           |       | 0      |    |

| MSM6688      | 56             |             |     |      |           |       | 0      |    |

| MSM6788      | 80             |             |     |      |           |       | 0      |    |

| MSM6389      | 16             |             | 0   |      |           |       |        |    |

|              | 18             |             |     |      |           |       |        | 0  |

| MSM6586      | 18             |             |     |      |           |       |        | 0  |

| MSM6587      | 18             |             |     |      |           |       |        | 0  |

| MSM6595      | 18             |             | 0   |      |           |       |        | 0  |

|              | 24             |             |     |      |           | 0     |        |    |

| MSM6596      | 18             |             | 0   |      |           |       |        | 0  |

|              | 24             |             |     |      |           | 0     |        |    |

| MSM6597      | 24             |             |     |      |           | 0     |        |    |

| MSM6690      | 42             |             | 0   |      |           |       |        |    |

|              | 44             |             |     |      |           | 0     |        |    |

| MSM6691      | 44             |             |     |      |           | 0     |        |    |

| MSM6791      | 44             |             |     |      |           | 0     |        |    |

| MSM6322      | 24             |             |     |      | 0         |       |        |    |

| MSM6722      | 24             |             |     |      |           | 0     |        |    |

| MSC1191      | 8              | 0           | 0   | 0    |           |       |        |    |

| MSC1192      | 8              | 0           | 0   | 0    |           | 1     |        |    |

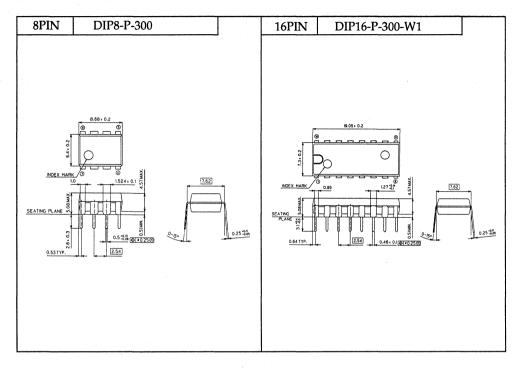

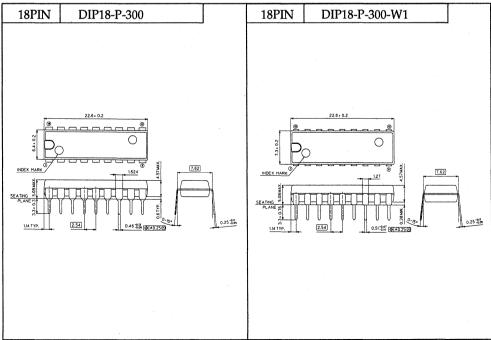

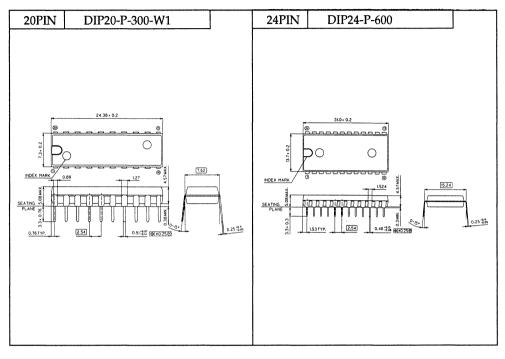

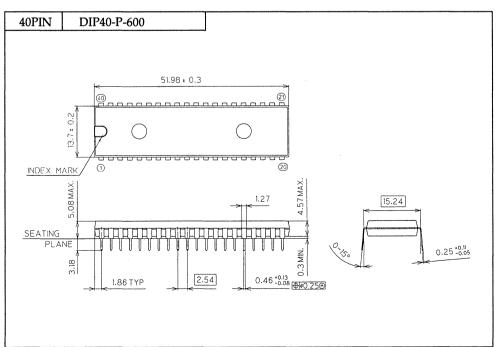

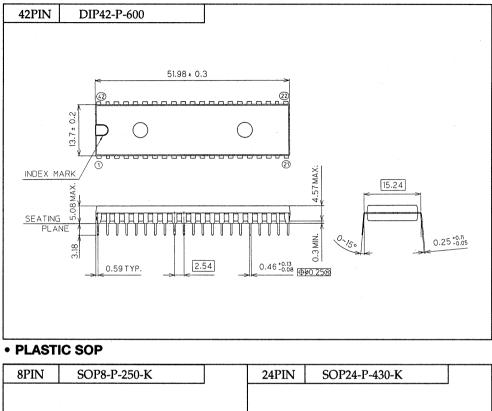

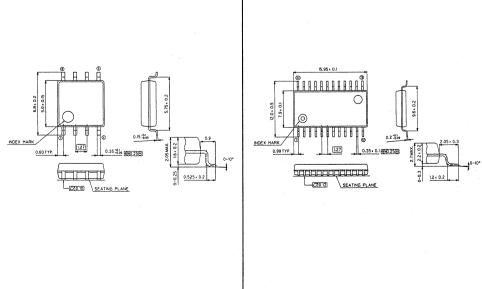

## PACKAGE OUTLINES AND DIMENSIONS

#### • PLASTIC STANDARD DIP

#### • PLASTIC STANDARD DIP

#### INTRODUCTION

#### PLASTIC STANDARD DIP

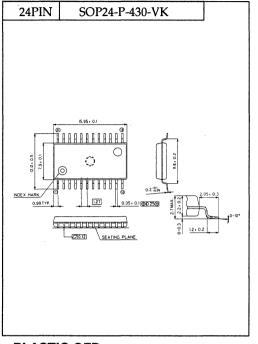

## PLASTIC SOP

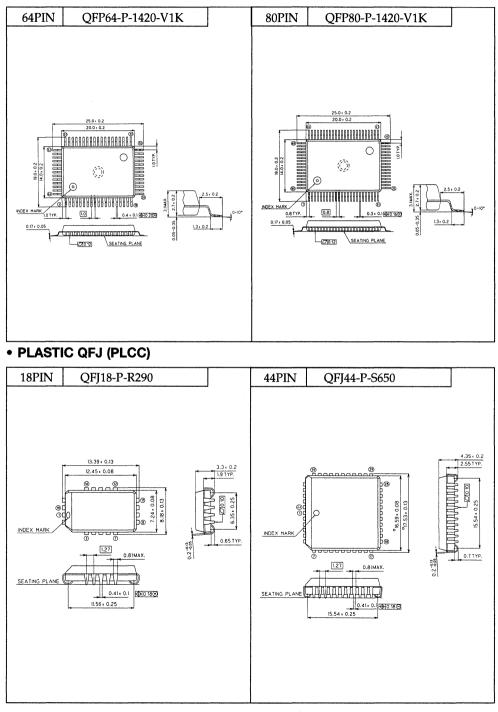

#### PLASTIC QFP

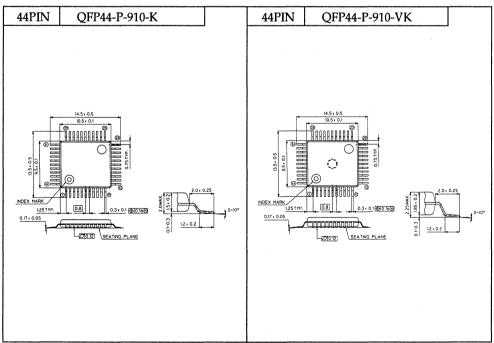

#### • PLASTIC QFP

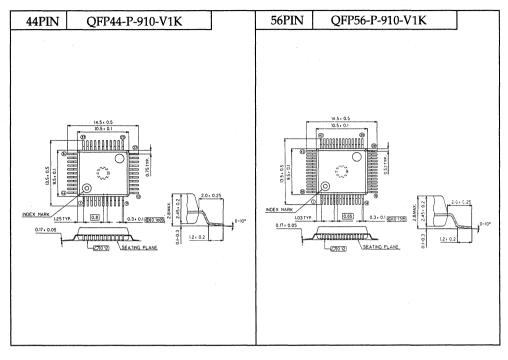

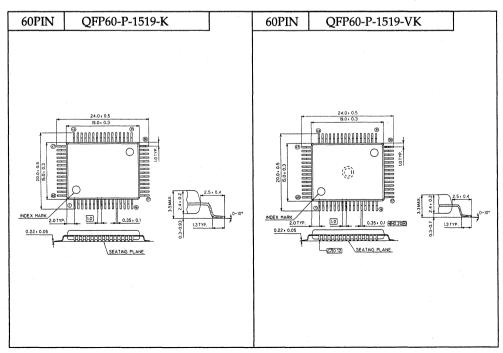

#### PLASTIC QFP

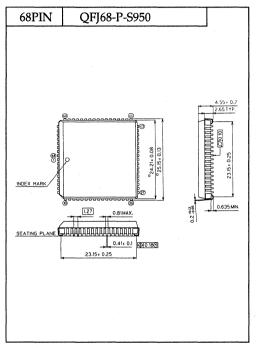

## • PLASTIC QFJ (PLCC)

~-

## 6. RELIABILITY

## 1. GENERAL DESCRIPTIONS FOR RELIABILITY

Refer to "QUALITY/RELIABILITY HAND-BOOK FOR INTEGRATED CIRCUITS" on the General Descriptions of Reliability Information.

# DATA SHEETS

# Voice Synthesis

# OKI Semiconductor MSM5205

# ADPCM SPEECH SYNTHESIS LSI

# TO CUSTOMERS FOR NEW CIRCUIT DESIGN

For a new circuit design, it is recommended to use the MSM6585 as described later. The MSM5205 has a 10-bit DA converter and does not have a built-in low-pass filter. On the other hand, the MSM6585 has a 12-bit DA

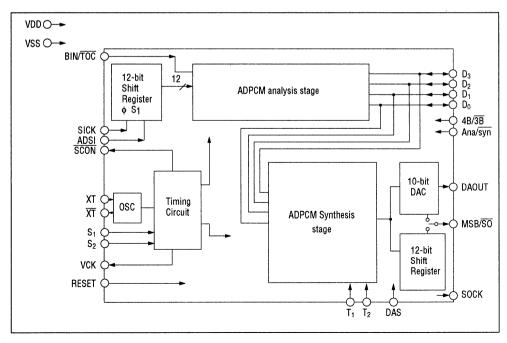

## **GENERAL DESCRIPTION**

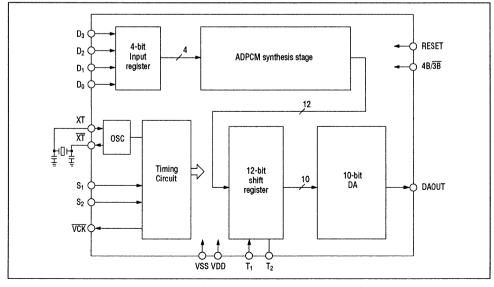

The MSM5205 is a speech synthesis integrated circuit which accepts Adaptive Differential Pulse Code Modulation (ADPCM) data. The circuit consists of synthesis stage which expands the 3- or 4-bit ADPCM data to 12-bit Pulse Code Modulation (PCM) data and a D/ A stage which reproduces analog signals from the PCM data. converter and includes a -40dB/oct low-pass filter. The sampling frequency can also be selected up to 32kHz. Therefore, the MSM6585 can realize a high quality voice.

The MSM5205 is fabricated using Oki's advanced CMOS process which enables lowpower consumption. The single power supply requirement and its availability in 18-pin molded DIP allow the MSM5205 to be ideally suited for various applications.

# FEATURES

- 3 or 4-bit ADPCM system

- On-chip 10-bit D/A converter

- Low power consumption (10 mW typical)

- Single +5V supply

#### Wide operating temperature (Ta = -30°C ~ +70°C) 18-pin Plastic DIP

• 18-pin Plastic DIP (DIP 18-P-300)

# **BLOCK DIAGRAM**

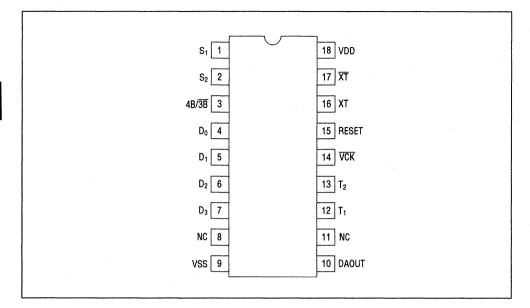

# **PIN CINFIGURATION**

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter            | Symbol           | Conditions            | Ratings     | Unit |

|----------------------|------------------|-----------------------|-------------|------|

| Power supply voltage | VDD              | T <sub>a</sub> = 25°C | -0.3 ~ +7.0 | v    |

| Input voltage        | VIN              | T <sub>a</sub> = 25°C | -0.3 ~ VDD  | v    |

| Power dissipation    | PD               | T <sub>a</sub> = 25°C | 200 max     | mW   |

| Storage temperature  | T <sub>stg</sub> |                       | -55 ~ + 150 | °C   |

Note: Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **OPERATING CONDITIONS**

| Parameter             | Symbol | Conditions           | Ratings   | Unit       |

|-----------------------|--------|----------------------|-----------|------------|

| Power supply voltage  | VDD    | -                    | +3 ~ +6   | V          |

| Operating temperature | Тор    | -                    | -30 ~ +70 | <b>°</b> C |

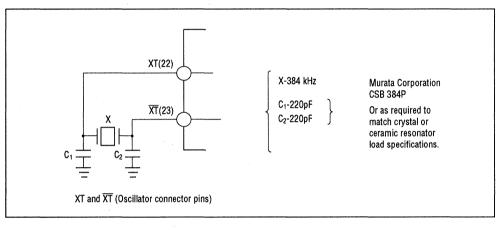

| Oscillator Frequency  | fosc   | Specified Oscillator | 384 ~ 768 | kHz        |

# D.C./A.C. CHARACTERISTICS

(VDD = 5V $\pm$ 5%; Ta = -30°C ~ +70°C, unless otherwise noted)

| Parameter                             | Symbol          | Conditions                                         | Min.                 | Тур. | Max.    | Unit |

|---------------------------------------|-----------------|----------------------------------------------------|----------------------|------|---------|------|

| Input High Voltage                    | ViH             | All inputs except $T_1$ , $T_2$                    | 4.2                  | -    | VDD+0.3 | v    |

| Input Low Voltage                     | VIL             | All inputs except $T_1$ , $T_2$                    | V <sub>SS</sub> -0.3 | -    | 0.8     | v    |

| Input High Current                    | Ін              | V <sub>IN</sub> = VDD                              | -                    | -    | 1       | μA   |

| Input Low Current                     | IIL             | V <sub>IN</sub> = 0V                               | -                    | -    | -1      | μA   |

| Output High Current                   | I <sub>он</sub> | $\overline{\text{VCK}}$ pin: V <sub>0</sub> = 4.2V | -50                  | -    | _       | μA   |

| Output Low Current                    | IoL             | $\overline{VCK}$ pin: V <sub>0</sub> = 0.4V        | +50                  | -    | -       | μA   |

| Operating Current                     | I <sub>DD</sub> | f <sub>osc</sub> = 384 kHz<br>VDD = 5V             | _                    | 2    | 4       | mA   |

| D/A Accuracy<br>(Internal 10-bit D/A) | VE              | Full Scale; VDD = 5V                               | -                    | ±4   | _       | LSB  |

| DAOUT<br>Output Impedance             | V <sub>OR</sub> | _                                                  | -                    | 100  | _       | kΩ   |

# **PIN DESCRIPTION**

| Pin Name                                    | Terminal Number                                 | I/O                                                 |

|---------------------------------------------|-------------------------------------------------|-----------------------------------------------------|

| S1                                          | 1                                               | 1                                                   |

| S2                                          | 2                                               | I                                                   |

| These inputs select the sam                 | pling data according to Figure 1.               |                                                     |

| 4B/3B                                       | 3                                               |                                                     |

| Specifies whether 3-bit or 4 bit (ADPCM).   | I-bit ADPCM data is to be processed. "H" leve   | el input is 4-bit (ADPCM). "L" level input is 3-    |

| D <sub>0</sub>                              | 4                                               |                                                     |

| D <sub>1</sub>                              | 5                                               | I                                                   |

| D <sub>2</sub>                              | 6                                               | · · · · · · · · · · · · · · · · · · ·               |

| D3                                          | 7                                               | <u> </u>                                            |

| ADPCM data inputs. For 3-                   | bit ADPCM data, $D_0$ input is not used and sho | ould be connected to ground.                        |

| VSS                                         | 9                                               |                                                     |

| Ground (0 V)                                |                                                 |                                                     |

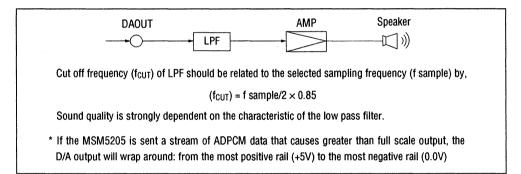

| DAOUT                                       | 10                                              | 0                                                   |

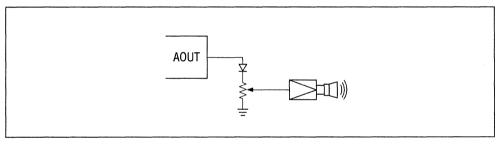

| Output for synthesized anal shown Figure 2. | log signal. Peak-to-peak swing is proportior    | nal to VDD. Typical method of connection is         |

| T <sub>1</sub>                              | 12                                              | 1                                                   |

| T <sub>2</sub>                              | 13                                              | 1                                                   |

| IC test pins used at the fac<br>open.       | tory for testing purposes only. During norr     | nal operations, $T_1$ is grounded and $T_2$ is left |

| VCK                                         | 14                                              | 0                                                   |

| This pin outputs a signal w figure1.        | hose frequency is equal to the sampling freq    | uency selected by the $S_1$ , $S_2$ inputs. See the |

# **PIN DESCRIPTION (continued)**

| Pin Name                    | Terminal Number                                                                             | I/O                                                       |

|-----------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| RESET                       | 15                                                                                          | l                                                         |

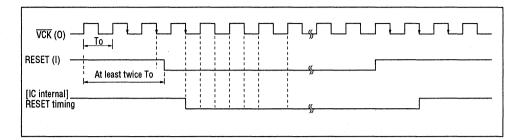

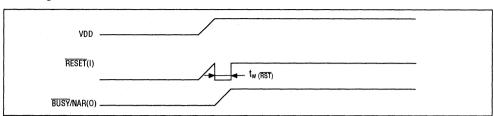

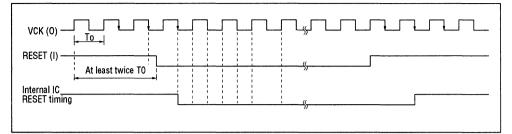

| • •                         | n initializes the internal circuitry. Internally, nust be true for at least twice VCK time. | the reset pulse is synchronized with the $\overline{VCK}$ |

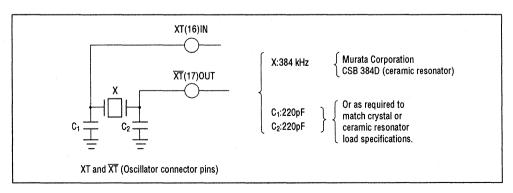

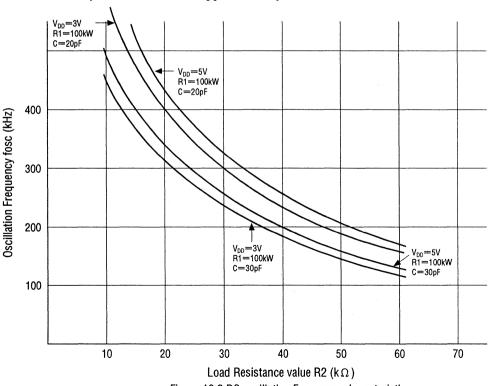

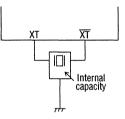

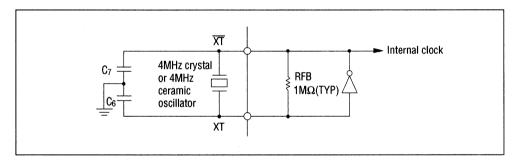

| XT                          | 16                                                                                          | I                                                         |

| XT                          | 17                                                                                          | 0                                                         |

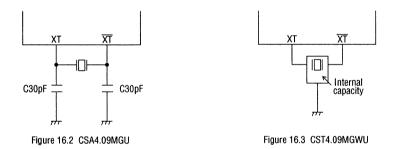

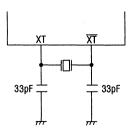

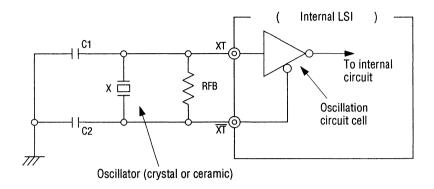

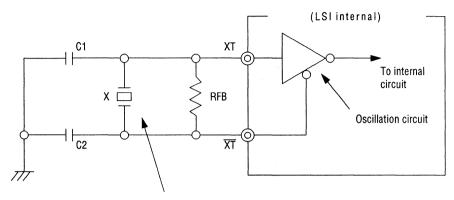

| Oscillator input and output | for a crystal or ceramic resonator (Figure 3).                                              |                                                           |

| VDD                         | 18                                                                                          |                                                           |

Power supply pin (Typical +5V)

| S1 | S2 | Sampling Frequency (fosc=384kHz) |                                          |

|----|----|----------------------------------|------------------------------------------|

| L  | L  | 4 kHz (f <sub>OSC</sub> /96)     | Note: *1 A 384kHz oscillator can be used |

| L  | Н  | 6 kHz (f <sub>OSC</sub> /64)     | to select 4kHz, 6kHz or 8kHz.            |

| Н  | L  | 8 kHz (f <sub>OSC</sub> /48)     | A 768kHz oscillator can be used          |

| Н  | н  | Prohibited See Note *1           | to select 8kHz, 12kHz or 16kHz.          |

40

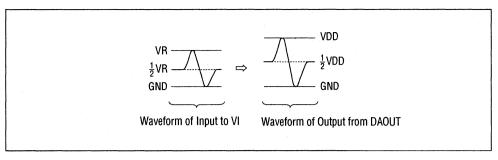

# DA converter SN ratio improvement method

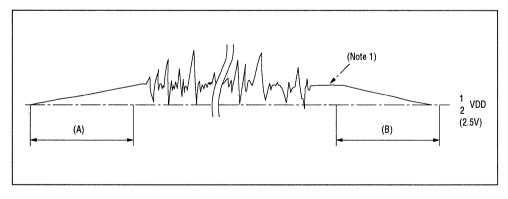

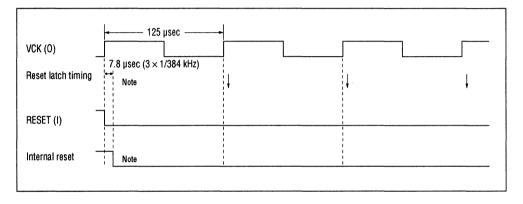

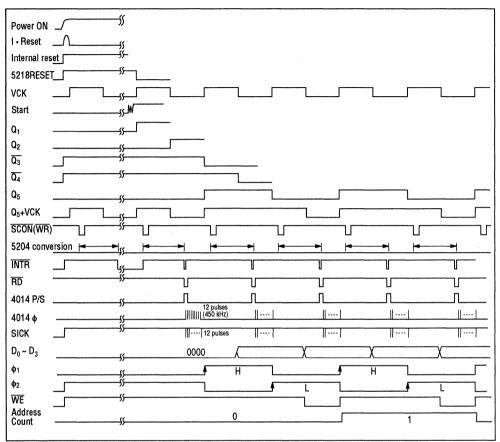

The accuracy near center of the voice waveform of this LSI may be worse due to the configuration of the DA converter. Therefore, the SN ratio can be improved by shifting the waveform center up or down. This is an extremely effective method for improving the SN ratio of a small signal or improving residual noise during silence (between 2 speech patterns.)

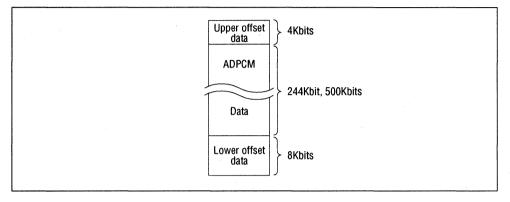

To put it concretely, by adding data before or after the current ADPCM data (voice data), the waveform center can be shifted as shown in Figure 4.

Adding data is as follows:

| (A | .) se | ctio | n |  | (B | ) se | ctio | n |          |

|----|-------|------|---|--|----|------|------|---|----------|

| 0  | 0     | 0    | 0 |  | 1  | 0    | 0    | 0 |          |

| 0  | 0     | 0    | 0 |  | 1  | 0    | 0    | 0 | 100 data |

|    |       |      |   |  |    |      |      |   |          |

(The ADPCM bit length is 4-bit.)

Since an offset of about 5 mV can be obtained for each 2 samples of data, it is recommended that about 100 samples of data be entered to shift the waveform center about 250 mV.

For 3-bit data, an offset of about 5 mV can be obtained for each data. Therefore, about 50 samples of data is required to be entered to shift the waveform center about 250 mV.

In the (A) section, the waveform center should be shifted up. In the (B) section, the waveform center should be shifted down. The number of data in the (A) section should be the same as that in the (B) section.

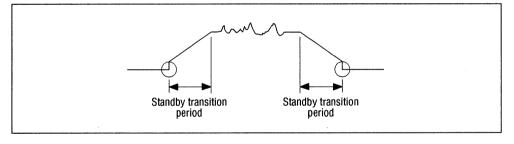

When (A) is added before voice data and (B) is added after the voice data, the output waveform is as shown in Figure 4.

Since the dynamic range is narrowed by the shifted area, some data may overflow, causing the voice to be distorted.

If this occurs, decrease the sound level about 20% and analyze the data once again. (For an overflow, see the precautions for ADPCM data creation on the next page.)

# Figure 4 Waveform the DA Converter

Note 2: Voice data should be sufficiently small just prior to (B). For voice editing, insert a silence of about 10msec.

#### Precaution for ADPCM data creation

When voice is synthesized by the MSM5205 using ADPCM data analyzed by the MSM5218, noise may be generated in the synthesized voice.

The MSM5205 is not equipped with an overflow protection unit in the internal operation circuit even though the MSM5218 is. Therefore, although the MSM5218 produces normal voice, the MSM5205 may cause noise in the composite voice due to an overflow in

the data. If this occurs, analyze and create the ADPCM data once again.

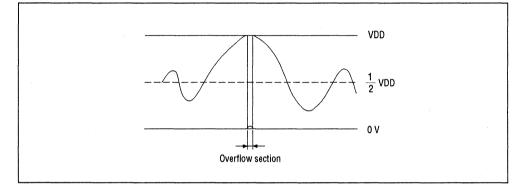

An example of a waveform when an overflow occurs and the overflow protection method is as follows :

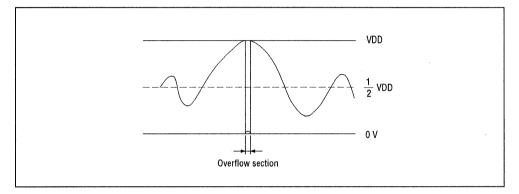

(1) Waveform when an overflow occcurs

The observation of the output waveform from the DA converter of the MSM5205 on an oscilloscope shows that an overflowed waveform is looped as shown in Figure 5.

#### Figure 5 Output Waveform When an Overflow Occurs

(2) Overflow protection method

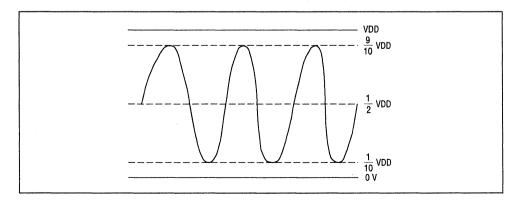

Even if an input waveform is not beyond the dynamic range when the ADPCM data is analyzed by the MSM5218, the output waveform may overflow due to an internal operation error. Therefore, if the maximum amplitude level of the input waveform when the ADPCM data is analyzed by the MSM5218, is controlled to about 80% of the dynamic range or less (see Figure 6), the output waveform of the MSM5205 will not overflow, causing no noise in the composite voice.

Figure 6 Waveform When the Maximum Amplitude Level of the Input Waveform is about 80% of the Dynamic Range.

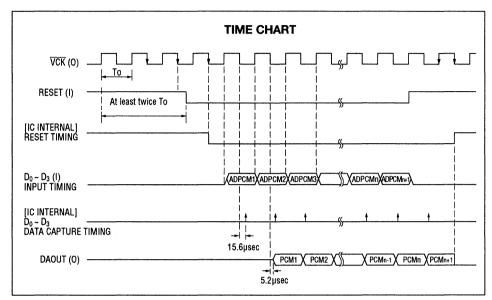

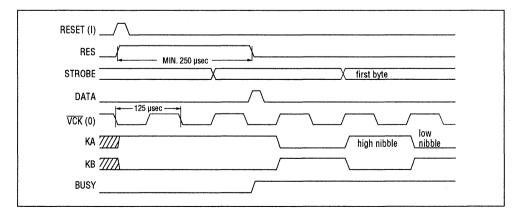

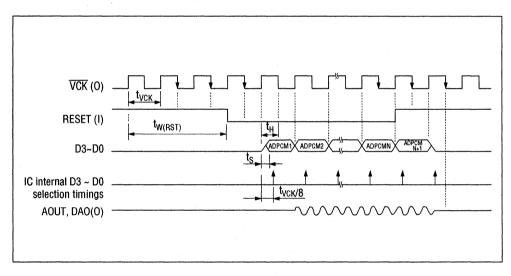

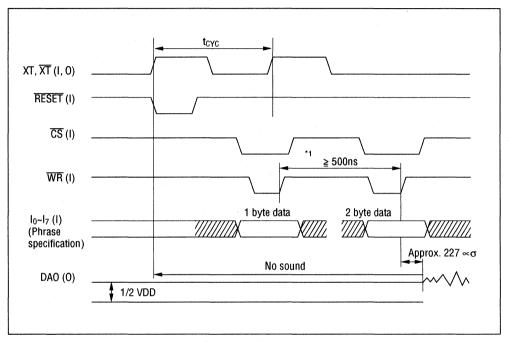

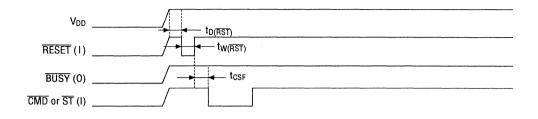

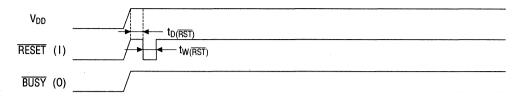

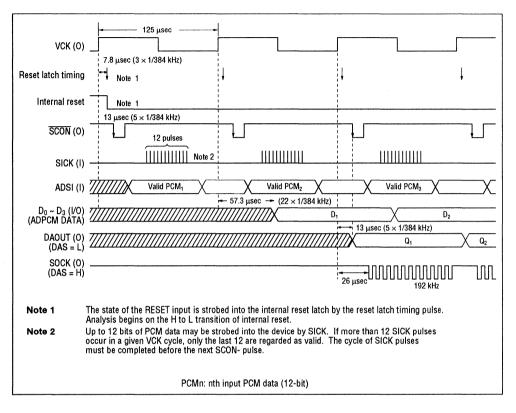

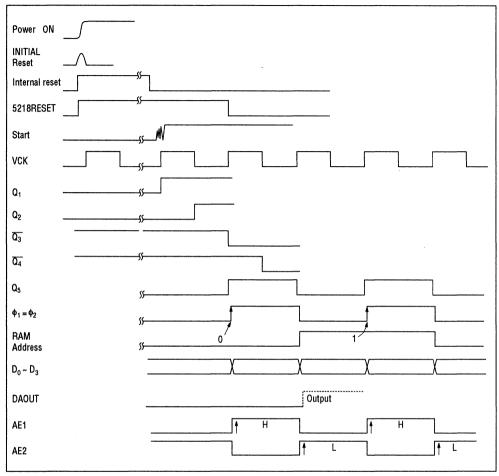

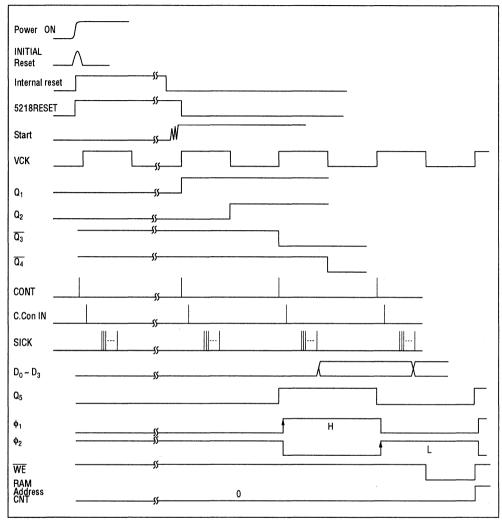

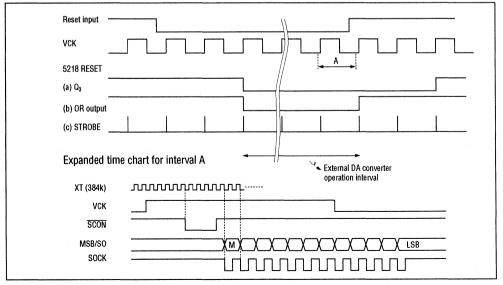

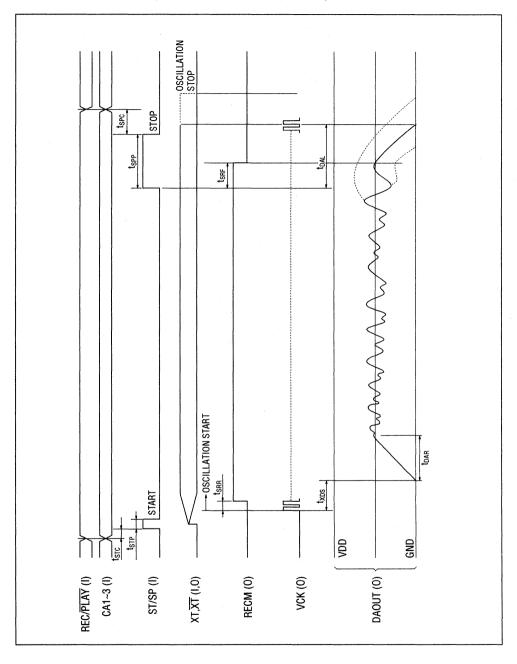

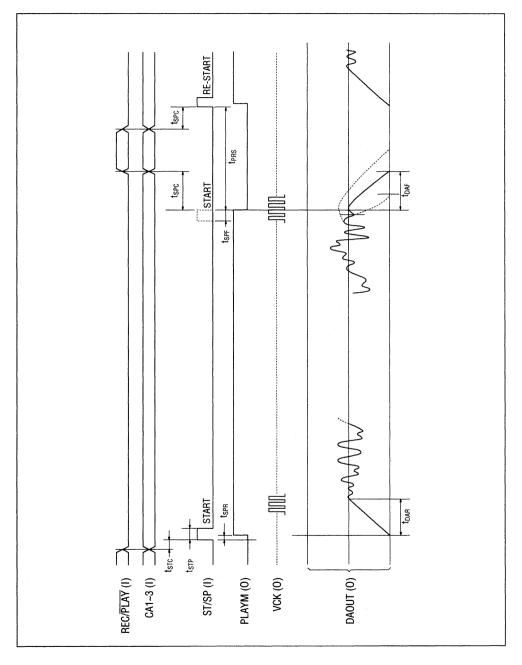

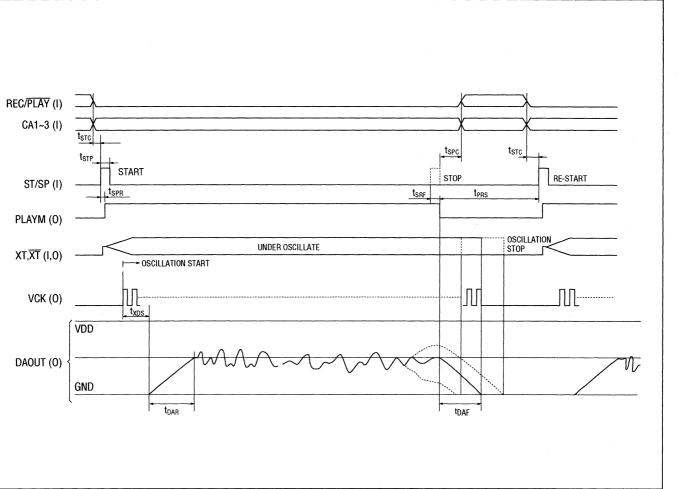

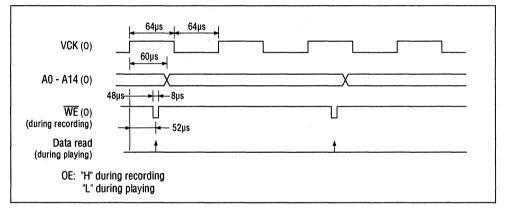

Figure 7 shows the time chart for MSM5205.

Note 3: See the RESET pin description about RESET timing of the IC internal.

Figure 7

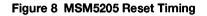

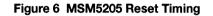

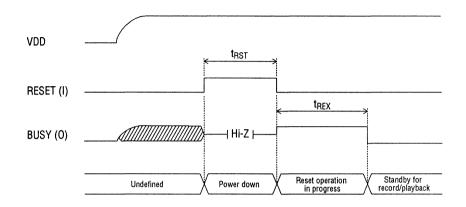

## THE FOLLOWING TIMING SHOWS HOW TO APPLY THE RESET

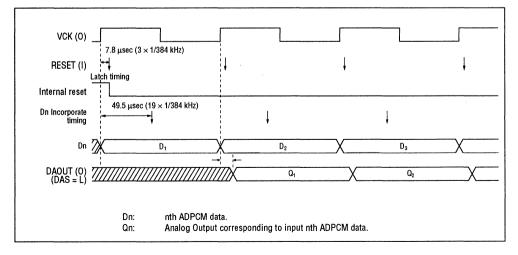

#### Figure 9 MSM5218 Reset Timing (8 kHz Sampling Example)

Note 4: The reset signal is latched within the LSI by the reset latch timing. Analysis is commenced by switching the external reset signal from H to L before this timing. Switching is probably best achieved by the leading edge of the VCK signal.

#### DISTINCTION BETWEEN MSM5218 AND MSM5205

Both Synthesis stages (MSM5218 and MSM5205) work with the same method, however, with the exception that MSM5218 is equipped with an overflow protection.

In other words, when all 12-bit PCM become '1' any further exceeding analog input would cause a data overflow which is caught and re-routed as the MSB in case of MSM5218.

MSM5205 returns to 'all bits zero' when a data overflow occurs.

Therefore, the DA output of MSM5205 is distorted badly.

When MSM5218 is being used to generate ADPCM data for playback on MSM5205, the peak to peak input level to the AD converter should be limited to 80% of the converters maximum input range.

The use of an automatic gain control (AGC) amplifier or a hard limiter is recommended.

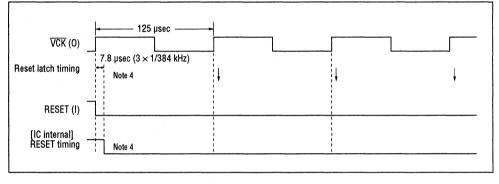

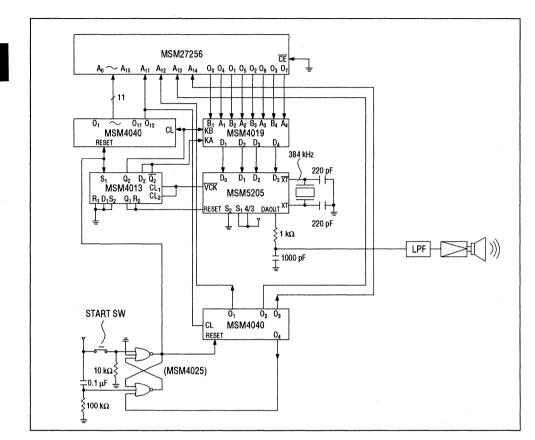

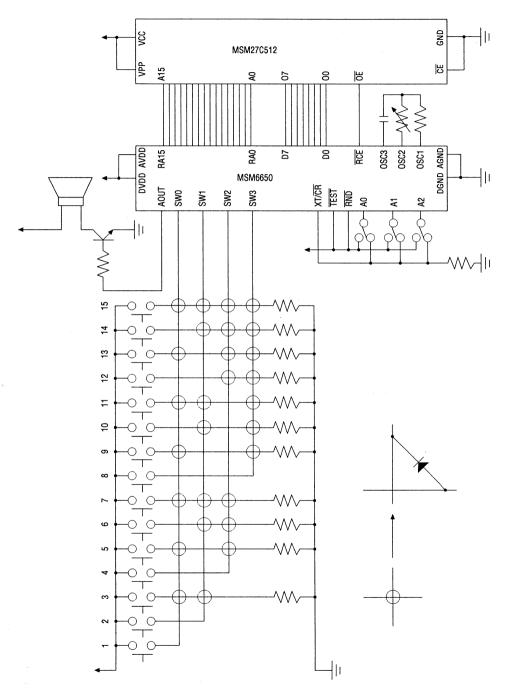

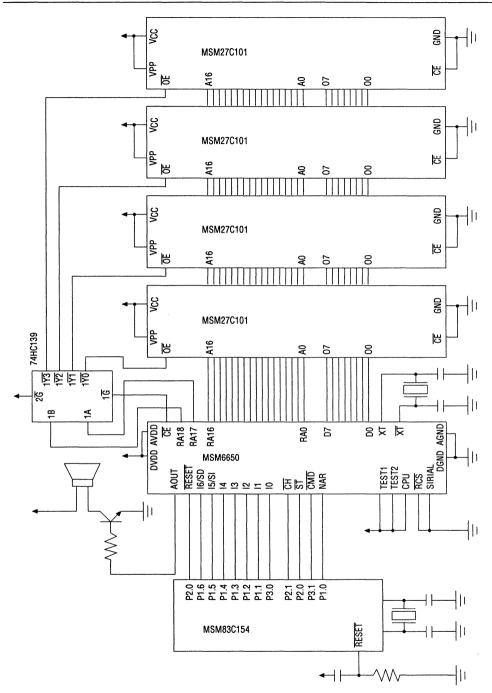

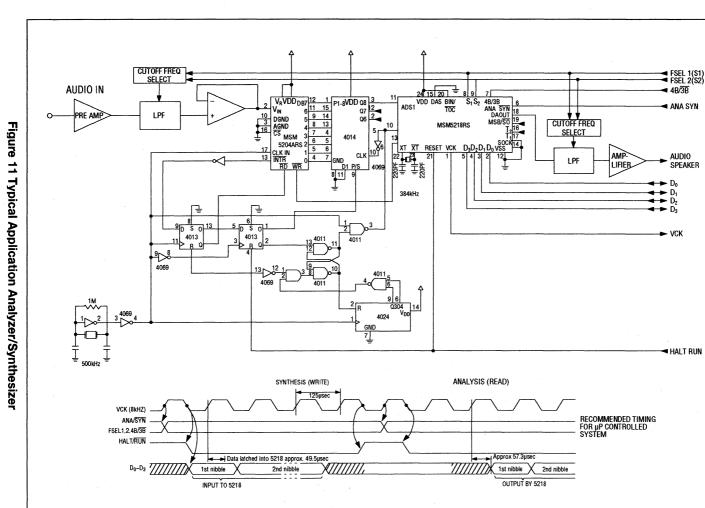

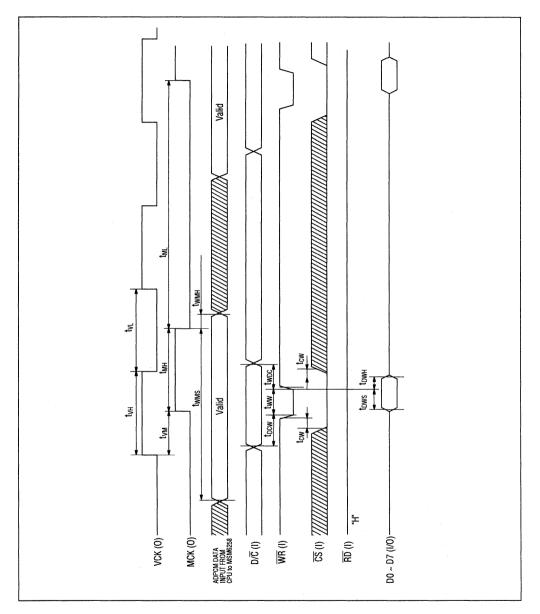

## TYPICAL APPLICATION MSM5205 TO CENTRONICS INTERFFACE CIRCUITS (fsam = 8kHz)

Figure 10 shows the MSM5205 to centronics interface circuit ( $f_{SAM} = 8kHz$ ), and Figure 11

shows that timing chart.

#### MSM5205 to Centronics Timing Diagram

Figure 11

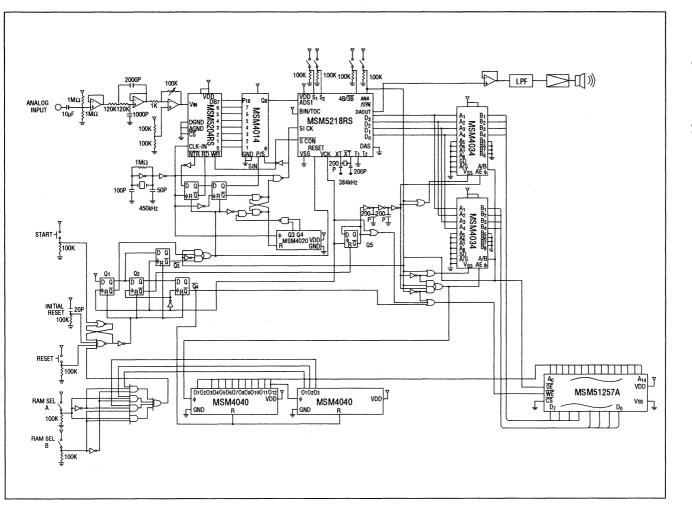

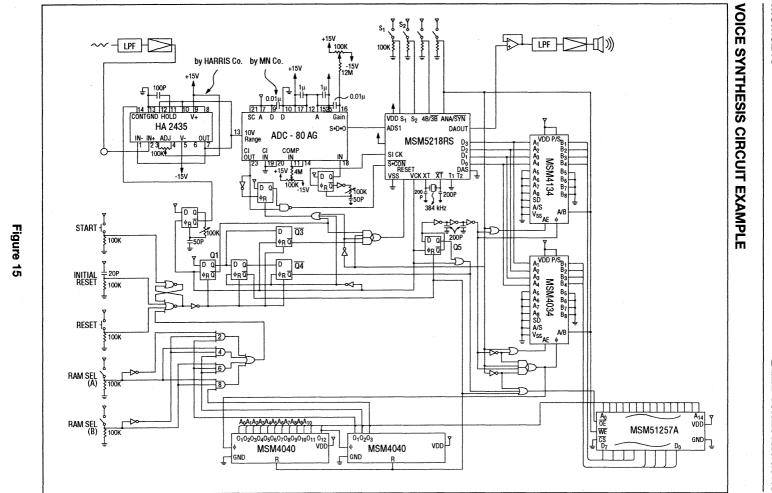

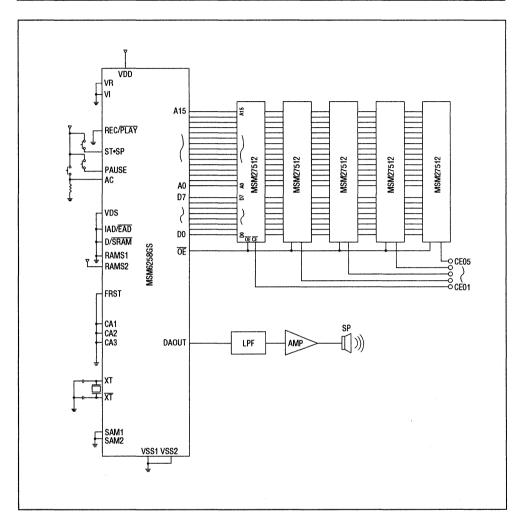

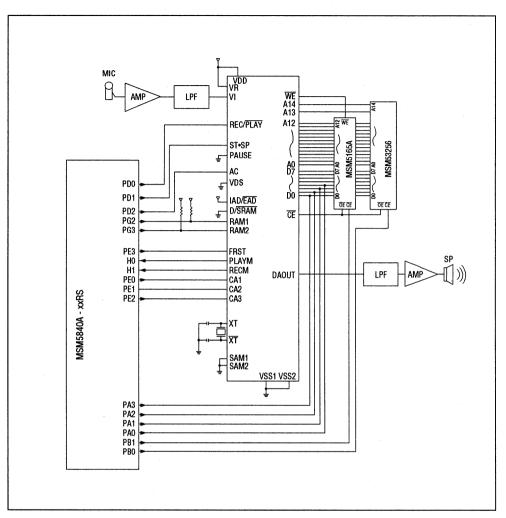

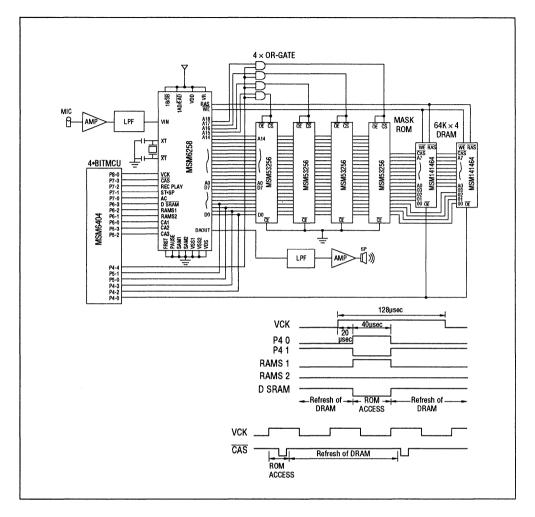

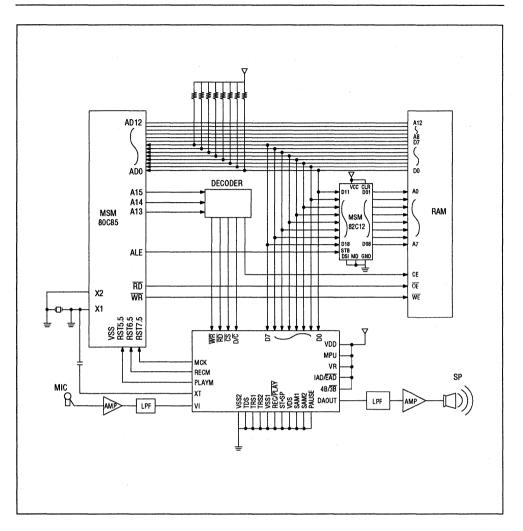

#### MSM5205 VOICE SYNTHESIS CIRCUIT EXAMPLE

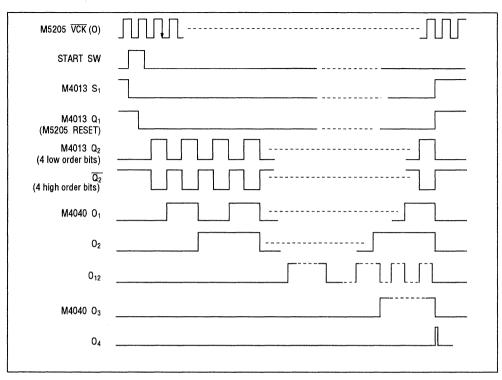

linked together is shown in Figure 12. The timing chart for this example is provided in Figure 13.

An example where 256k-bit EPROM are used

Figure 12

Figure 13

# **OKI** Semiconductor

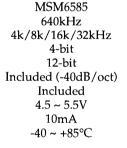

# **MSM6585**

# ADPCM SPEECH SYNTHESIS LSI

# **GENERAL DESCRIPTION**

The MSM6585 is an upversion product of the MSM5205 voice synthesis LSI. Mainly improved points are improvement for the precision of an internal DA converter, a built-in low-pass filter, and expansion on the sampling frequency. The MSM6585 does not in-

clude a control circuit to drive an external memory similar to the MSM5205. Therefore, the MSM6585 can be connected with not only semiconductor memories, but other memory media (CD-ROM, etc.) by the control of CPU.

# FEATURES

- 4-bit ADPCM system

- Built-in 12-bit DA converter

- Built-in LPF (-40dB/oct)

- Sampling frequencies: 4k/8k/16k/32kHz

- Original oscillation frequency (ceramic oscillator): 640kHz

- Package: 18-pin DIP (DIP 18-P-300)

- Voice data synthesis :

- Support by voice analysis editing tool AR76-202

# DEFFERENCES BETWEEN MSM6585 AND MSM5205

- Original oscillation frequency:

- Sampling frequency:

- ADPCM bit length:

- DA Converter:

- Low pass filter:

- Overflow preventing circuit:

- Power supply voltage:

- Operating current consumption:

- Operating temperature:

- D3 to D0 input timing

## **PIN CONFIGURATION**

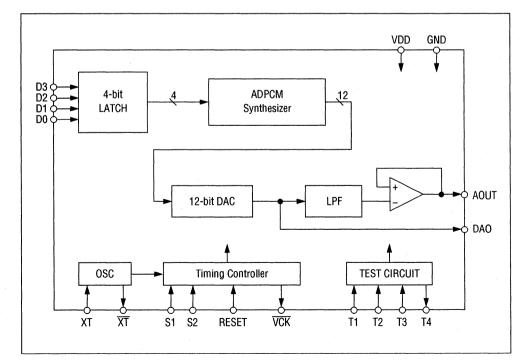

# **BLOCK DIAGRAM**

# **ELECTRIC CHARACTERISTICS**

# Absolute Maximum Ratings

|                      |        |            |                | (GND = 0V) |

|----------------------|--------|------------|----------------|------------|

| Parameter            | Symbol | Conditions | Ratings        | Unit       |

| Power supply voltage | VDD    | Ta = 25°C  | -0.3 ~ +7.0    | V          |

| Input voltage        | VIN    | Ta = 25°C  | 0.3 ~ VDD +0.3 | V          |

| Storage temperature  | Tstg   |            | -55~ +150      | °C         |

## **Operating Conditions**

(GND = 0V)

| Parameter            | Symbol | Conditions            | Ratings     | Unit |

|----------------------|--------|-----------------------|-------------|------|

| Power supply voltage | VDD    |                       | +4.5 ~ +5.5 | V    |

| Operating temperture | Тор    |                       | -40 ~ +85   | °C   |

| Original oscillation | f      |                       | 0.40        | kHz  |

| frequency            | fosc   | oscillator connection | 640         | KFIZ |

#### **DC** Chracteristics

(VDD= 4.5 ~ 5.5V, GND = 0V, Ta = -40 ~ +85°C)

| Parameter                | Symbol           | Conditions                              | Min.    | Тур. | Max.    | Unit |

|--------------------------|------------------|-----------------------------------------|---------|------|---------|------|

| "H" input voltage        | Vih              |                                         | 0.8×VDD |      | VDD+0.1 | ٧    |

| "L" input voltage        | VIL              |                                         | -0.1    |      | 0.2×VDD | V    |

| "H" output voltage       | Vон              | VCK: I <sub>OH</sub> = -40µA            | VDD0.4  |      | _       | V    |

| "L" output voltage       | Vol              | VCK: I <sub>OL</sub> = 40µA             |         |      | 0.4     | ۷    |

| "H" input current        | Іінт             | T1, T2, RESET: VIH = VDD                | 20      | 150  | 400     | μA   |

| "H" input current        | I <sub>IH2</sub> | S1,S2, D0~D3, T3: V <sub>IH</sub> = VDD |         |      | 10      | μA   |

| "H" input current        | Іінз             | XT: V <sub>IH</sub> = VDD               |         |      | 20      | μA   |

| "L" input current        | liL1             | T3: V <sub>IL</sub> = 0V                | -400    | -120 | -20     | μA   |

| "L" input current        | l <sub>IL2</sub> | S1,S2, D0~D3, T1, T2,                   | 10      |      |         | μA   |

|                          | 412              | RESET: V <sub>IL</sub> = 0V             | -10     |      | -       | μΛ   |

| "L" input current        | I <sub>IL3</sub> | XT: V <sub>IL</sub> = 0V                | -20     |      | —       | μA   |

| Current consumption      | I <sub>DD</sub>  | f <sub>OSC</sub> = 640kHz, No load      |         | 5    | 10      | mA   |

| DA output relative error | Vdae             | No load                                 | _       |      | 40      | mV   |

| DA output impedance      | R <sub>DAO</sub> |                                         | 10      |      | 40      | kΩ   |

| LPF load resistance      | RAOUT            |                                         | 50      |      |         | kΩ   |

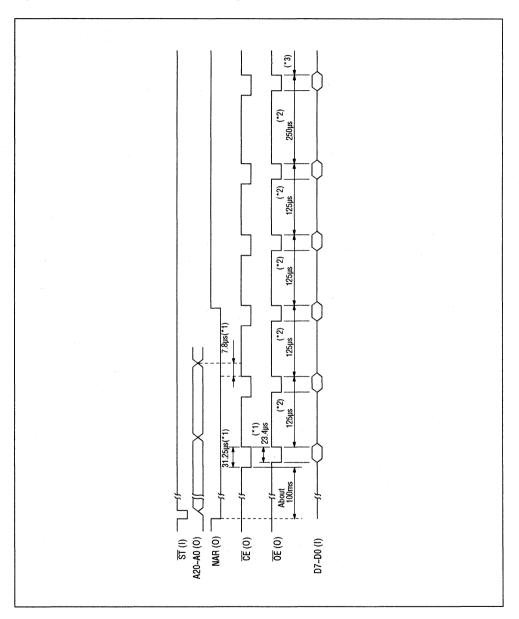

#### **AC Characteristics**

| Prameter                           | Symbol              | Conditions                               | Min.   | Тур. | Max. | Unit |

|------------------------------------|---------------------|------------------------------------------|--------|------|------|------|

| Original oscillation<br>duty cycle | fduty               |                                          | 40     | 50   | 60   | %    |

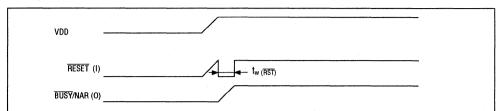

| RESET input pulse width            | t <sub>W(RST)</sub> | fsam = 4kHz tvck = 250µs                 | 2×tvcк |      |      | μs   |

| Data setup time                    | ts                  | = 8kHz ··· = 125µs<br>=16kHz··· = 62.5µs |        |      | 3    | μs   |

| Data hold time                     | t <sub>H</sub>      | =32kHz··· = 31.25µs                      | tvcк/2 |      |      | μs   |

When the MSM5205 and data are commonly used, note that the D3 to D0 selection timings of the MSM6585 and MSM5205 are different. (Refer to DEFFERENCES BETWEEN MSM6585 AND MSM5205.)

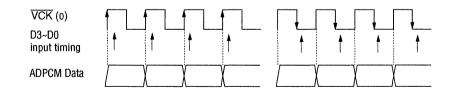

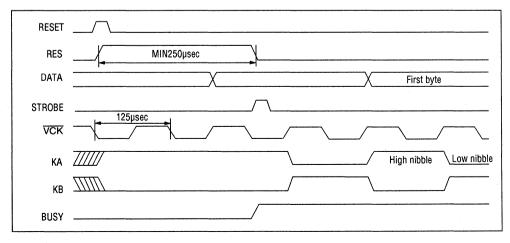

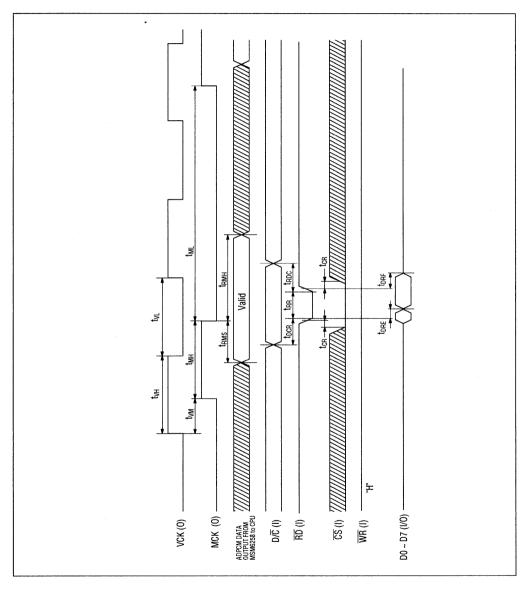

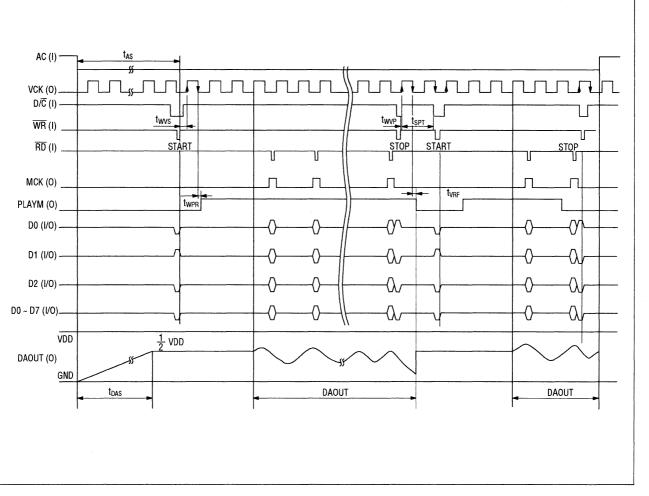

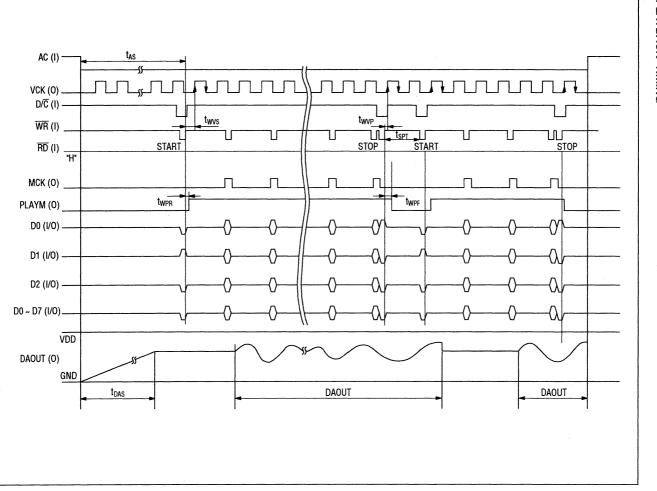

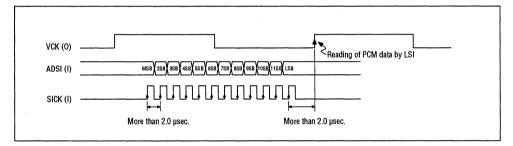

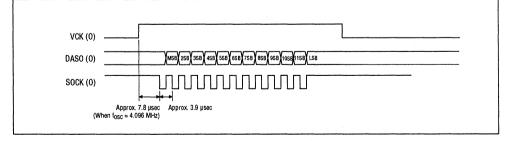

#### **TIMING CHART**

52

# **PIN DESCRIPTION**

| Pin Name | I/O                                   | Function                                                                                            |

|----------|---------------------------------------|-----------------------------------------------------------------------------------------------------|

| S1, S2   | ł                                     | Pins to determine the sampling frequency.                                                           |

|          |                                       | The sampling frequencies of 32k, 16k, 8k, and 4kHz can be selected by                               |

|          |                                       | combinations. (See the sampling frequencies of the functional description                           |

|          |                                       | on the selection of combinations.)                                                                  |

| ТЗ       | l                                     | Pin to test the internal circuit. Set this pin to a high level or make it open                      |

|          |                                       | because it has a built-in pull-up resistor.                                                         |

| D0~D3    | 1                                     | Input pin for ADPCM data.                                                                           |

| T4       | 0                                     | Pin to test the internal circuit. Make this pin open.                                               |

| GND      |                                       | Ground pin                                                                                          |

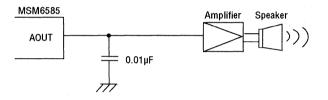

| AOUT     | 0                                     | Pin to output the analog voice from the low-pass filter. Connect a 0.01 $\mu F$                     |

|          |                                       | capacitor to this pin. (See the AOUT connecting circuit of the functional                           |

|          |                                       | description on the connecting circuit.)                                                             |

| DAO      | 0                                     | Pin to output the analog voice form the DA converter.                                               |

| T1, T2   | l                                     | Pins to test the internal circuit. Set these pins to a low level or make them                       |

|          | i i i i i i i i i i i i i i i i i i i | open because pull-down resistors are included.                                                      |

| VCK      | 0                                     | This pin outputs the sampling frequency selected by the combinations of                             |

|          |                                       | S1 and S2.                                                                                          |

|          |                                       | The voice synthesis starts or stops by synchronizing with $\overline{\text{VCK}}$ .                 |

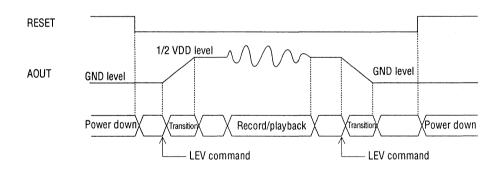

| RESET    | I                                     | Reset pin. The voice synthesis circuit is initialized by synchronizing with                         |

|          |                                       | $\overline{\text{VCK}}$ . If this pin is set to a high level, the D0 to D3 data inputs are disabled |

|          |                                       | by synchronizing with $\overline{\text{VCK}}$ . The AOUT and DA0 pins output 1/2 VDD and            |

|          |                                       | become the state of no voice.                                                                       |

| XT       | 1                                     | Pin to connect an oscillator. When the external clock is used, input it                             |

|          |                                       | from this pin.                                                                                      |

| XT       | 0                                     | Pin to connect an oscillator.                                                                       |

|          |                                       | When the external clock is used, make this pin open.                                                |

| VDD      | _                                     | Power supply pin.                                                                                   |

#### FUNCTIONAL DESCRIPTION

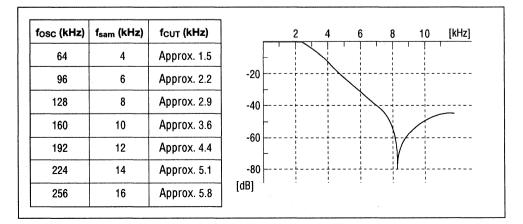

1. Sampling Frequency

The relationship of the sampling frequencies on S1 and S2, and the cutoff frequencies are listed below.

| S1 | S2 | Sampling frequency (f <sub>SAM</sub> ) | Cutoff frequency (f <sub>CUT</sub> ) |

|----|----|----------------------------------------|--------------------------------------|

| L  | L  | 4 kHz                                  | 1.6 kHz                              |

| Н  | L  | 8 kHz                                  | 3.2 kHz                              |

| L  | Н  | 16 kHz                                 | 6.4 kHz                              |

| Н  | Н  | 32 kHz                                 | 12.8 kHz                             |

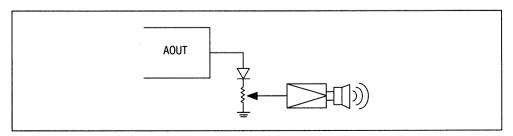

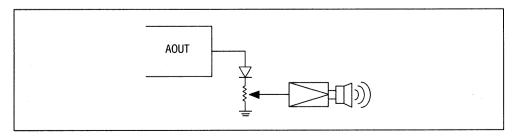

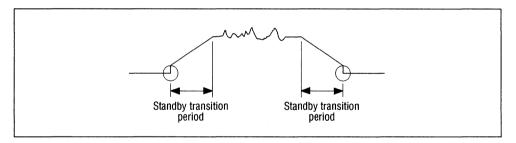

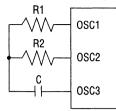

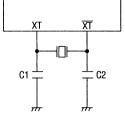

#### 2. AOUT Connecting Circuit

Connect a 0.01uF capacitor to the AOUT pin. The circuit diagram is as shown below.

Even when the DAO pin is used, connect a  $0.01\mu$ F capacitor to the AOUT pin. This capacitor is used for the improvement of a voice quality.

3. Voice Output

The MSM6585 has two voice output pins. The DAO is direct output pin from the internal DA converter. The AOUT is a pin to output a voice after which the DAO output passed a built-in LPF.

#### 3-1. DA Converter Output Waveform

The output amplitude from the DA converter is max.  $(4095/4096) \times VDD$  and becomes a stair step waveform synchronized with the sampling frequency. The DAO output impedance varies in the ranges from  $10k\Omega$  to  $40k\Omega$ . Therefore, determine the filter constant so that the resistor variation does not have influence on the cutoff frequency of the filter.

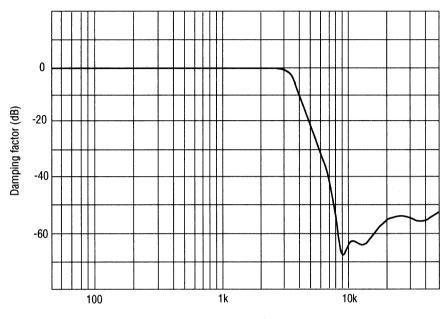

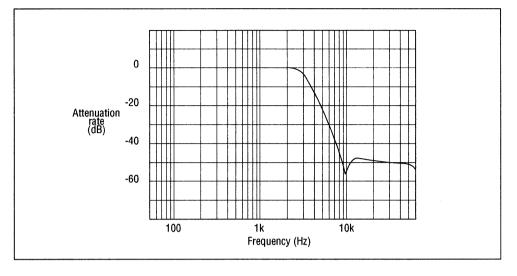

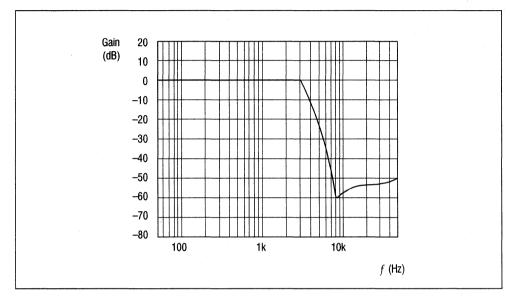

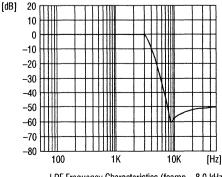

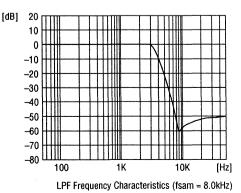

#### 3-2. Low-pass Filter Output

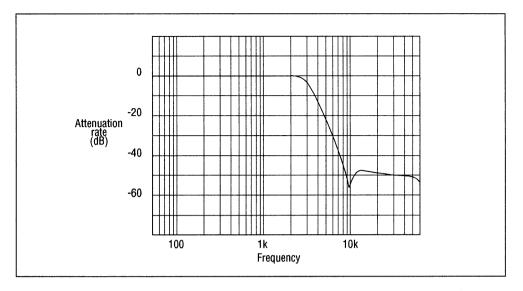

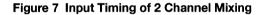

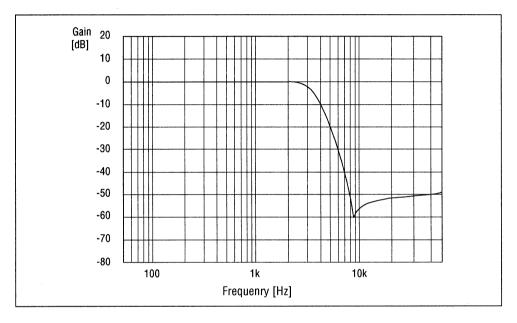

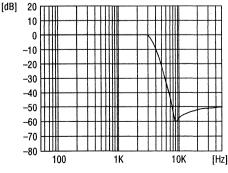

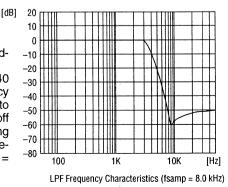

The cutoff frequency of the low-pass filter varies in proportion to the sampling frequency. The following figure shows the low-pass filter characteristics in the sampling frequency 8kHz.

Frequency (Hz)

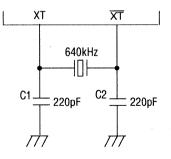

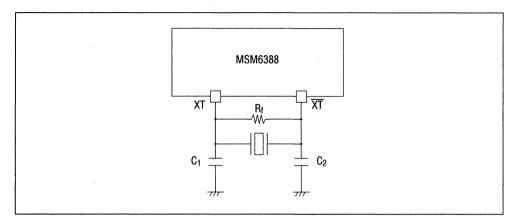

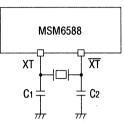

#### 4. Oscillation

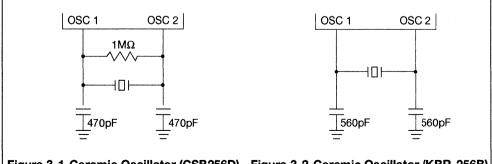

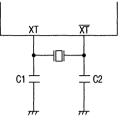

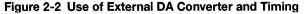

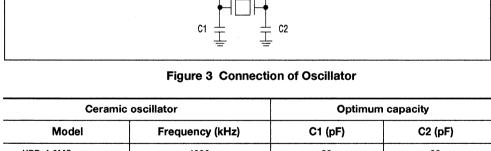

The external circuit that used a ceramic oscillator KBR-640B (640kHz) of Kyosera, manufacture is as shown below.

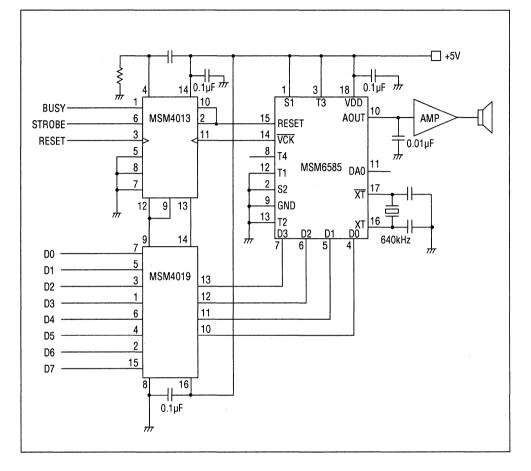

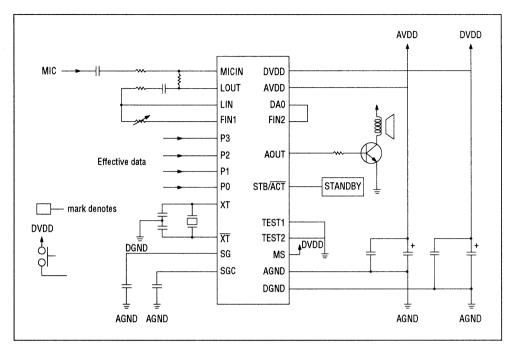

# TYPICAL APPLICATION DIAGRAM

Centronics Interface Circuit (sampling frequency 8kHz)

#### **Centronics Timing Chart**

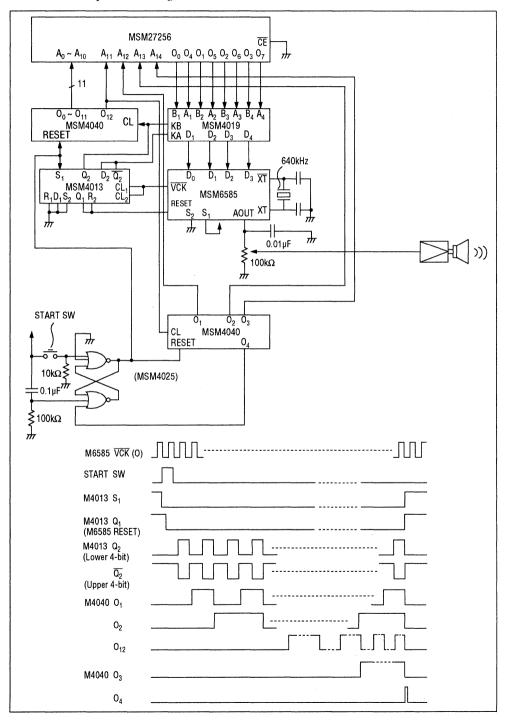

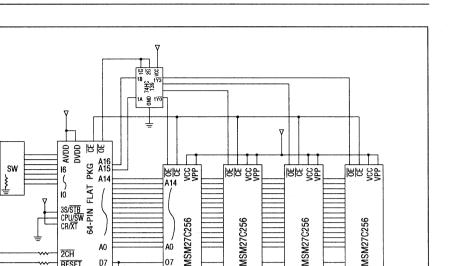

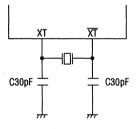

#### Example of Interface Circuit with 256Kbit EPROM

The circuit example and timing chart that used the 256K-bit EPROM are shown below.

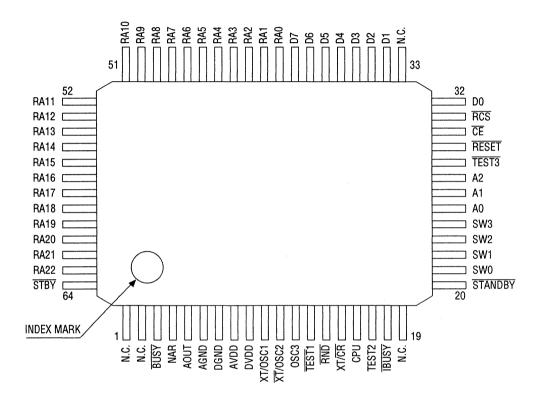

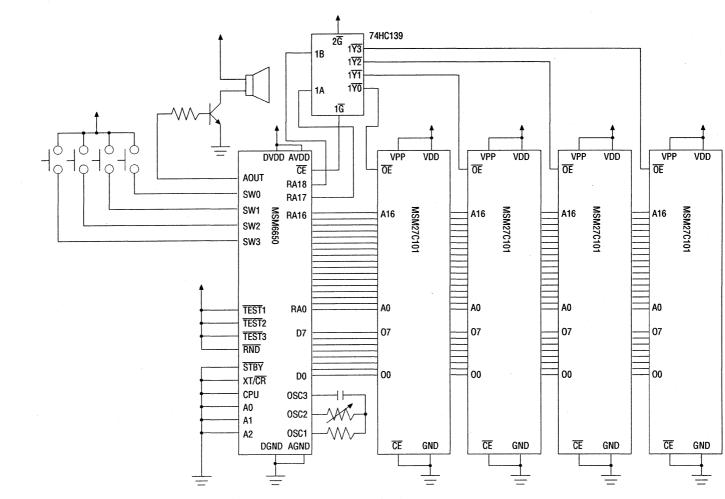

# OKI Semiconductor MSM6295

#### 4-CHANNEL MIXING ADPCM VOICE SYNTEHSIS LSI

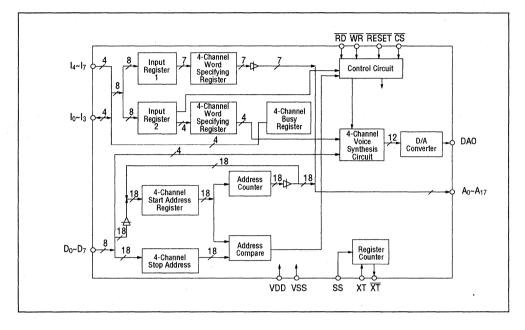

#### **GENERAL DESCRIPTION**

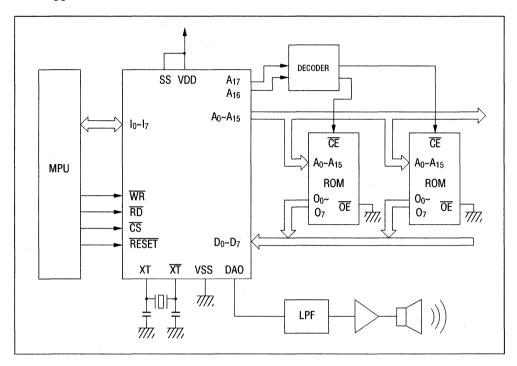

The Oki MSM6295 is a 4-channel mixing ADPCM voice synthesis LSI which is fabricated using Oki's low power CMOS silicon gate technology.

The MSM6295 can access an external ROM, where speech or sound effects data is stored. The maximum external ROM size is 256K

# FEATURES

- Oki straight ADPCM algorithm

- Number of bits/sample: 4

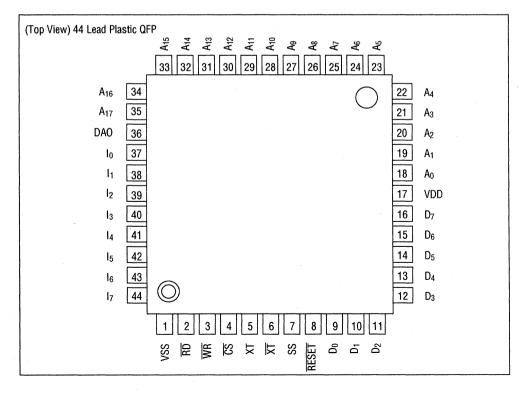

- 18 address lines for external ROM

- 8-bit control bus for mode setting

- External memory capacity 2Mbit

- Interface with common CPU and MPU

- Clock frequency: 1 MHz to 5 MHz

- Sampling frequency:

6.5 kHz and 8 kHz (@1.056 MHz clock) 25.6 kHz and 32 kHz (@4.224 MHz clock) bytes.