DATABOOK

## MOS

1980

MOS DATABOOK

## NATIONAL SEMICONDUCTOR

#### Introduction:

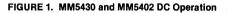

This is the MOS Data Book from National Semiconductor. It contains information on products fabricated from all the MOS processes in high volume production today; NMOS, CMOS, and PMOS. These products are unique functions in electronic systems. Their common denominator is providing the most cost-effective solution to a system need.

To minimize system costs, many of these products have customized features, such as the COPS<sup>™</sup> family of single chip micro-controllers, MAXI-ROMS<sup>™</sup> and Custom Circuits. Each of these has minimum order quantities to maintain production efficiencies.

A large part of this book is Standard Circuits which, due to large scale integration, have incorporated features which make many of them unique and cost effective in specific applications and/or markets. The organization of this book highlights those areas. The Standards have no minimum quantities.

Of concern to everyone who uses LSI products is the quality and reliability levels of the product. National is careful not to cut corners in this respect, designing in both quality and reliability from the ground up. From quality control of the raw materials through design engineering, wafer fab, test and assembly, the emphasis is uniformly there and we are proud of the results. Additional information may be obtained through your local National Semiconductor Sales Office.

Other large scale integration MOS product lines not included in this book are RAM and PROM memories and Microprocessors, which are covered in other National Semiconductor Data Books

COPS<sup>TM</sup> and MAXI-ROM<sup>TM</sup> are trademarks of National Semiconductor Corporation.

Information contained herein is intended to be a general product description and is subject to change.

National does not assume any responsibility for use of any circuitry described; no circuit patent licenses are implied; and National reserves the right, at any time without notice, to change said circuitry.

## MOS DATABOOK

## **Table of Contents**

| Se | ection 1 COP             | S Devices                                                            |       |

|----|--------------------------|----------------------------------------------------------------------|-------|

|    | COPS <sup>™</sup> Select | tion Guide                                                           | 1-3   |

|    | COP402/COP4              | 02M ROMIess N-Channel Microcontrollers                               | 1-5   |

|    | COP404L ROI              | Mless N-Channel Microcontroller                                      | 1-24  |

|    |                          | 2411L Single-Chip N-Channel Microcontrollers                         |       |

|    |                          | 21 and COP320/COP321 Single-Chip N-Channel Microcontrollers          |       |

|    |                          | P421C and COP320C/COP321C Single-Chip CMOS Microcontrollers          |       |

|    |                          | 2421L Single-Chip N-Channel Microcontrollers                         |       |

|    |                          | 2445L Single-Chip N-Channel Microcontrollers                         |       |

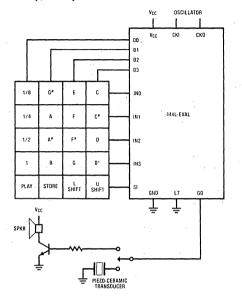

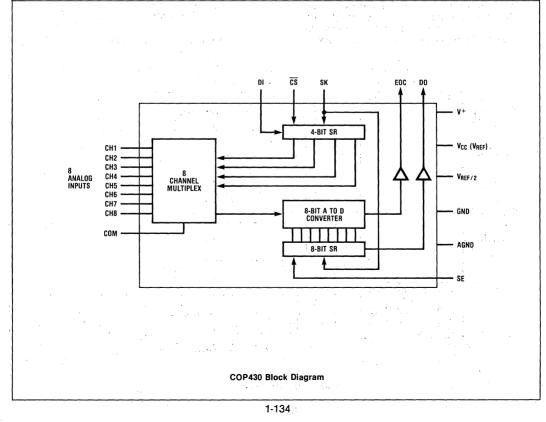

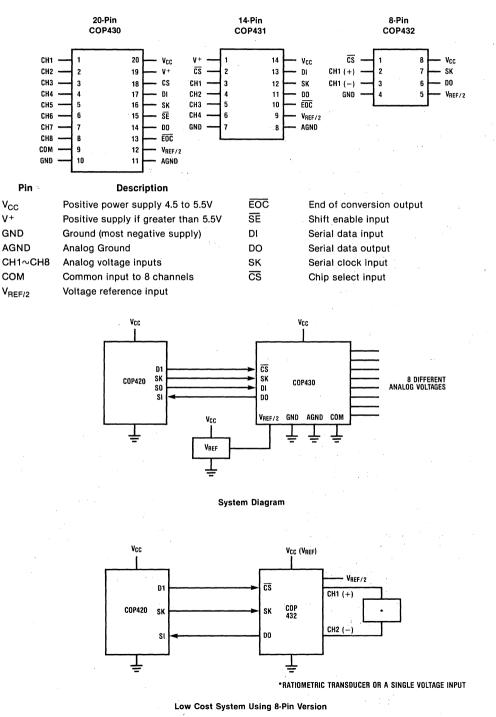

|    |                          | 31/COP432 A to D Converters                                          |       |

|    |                          | 51 PROM-RAM Interface Chip                                           |       |

|    |                          | uency/Counter Peripheral                                             |       |

|    |                          | Display Driver                                                       |       |

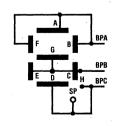

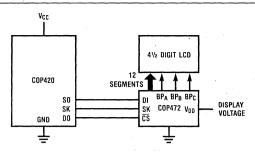

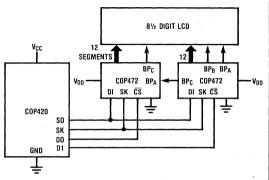

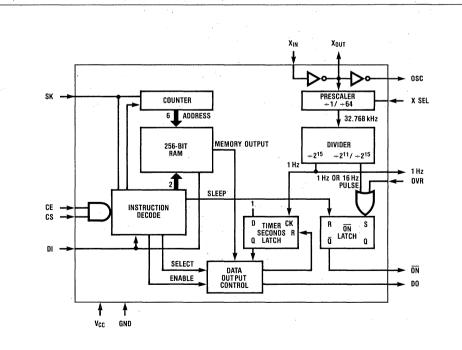

|    |                          | d Crystal Display Controller                                         |       |

|    |                          | Power CMOS RAM and Timer                                             |       |

|    |                          | Power CMOS Memory                                                    |       |

|    |                          | -                                                                    |       |

| Se | ection 2 COP             | S Application Information                                            |       |

|    |                          | S™Family User's Guide                                                | 2-3   |

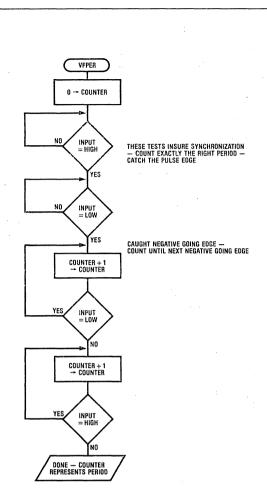

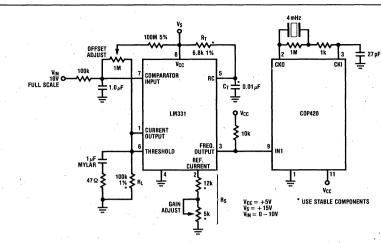

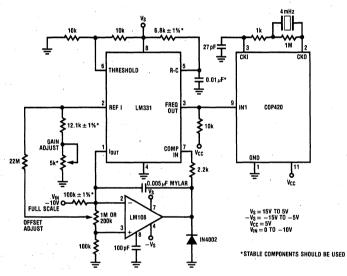

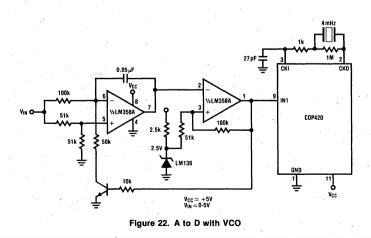

|    | COP Note 1               | Analog to Digital Conversion Techniques with COPs Family             |       |

|    |                          | Microcontrollers                                                     | 2-84  |

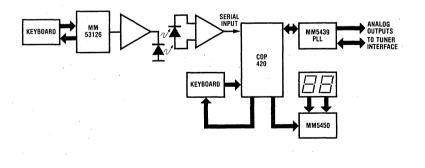

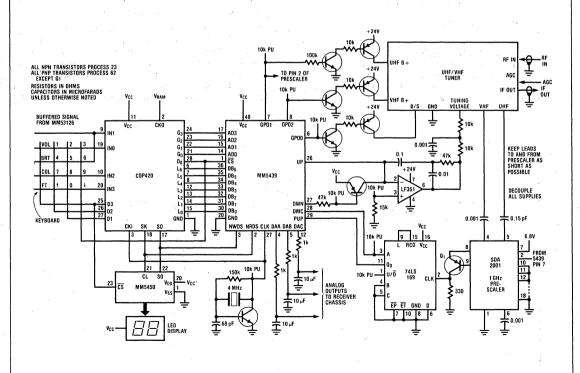

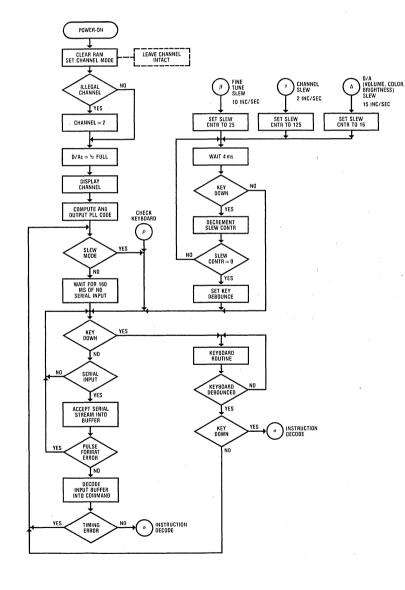

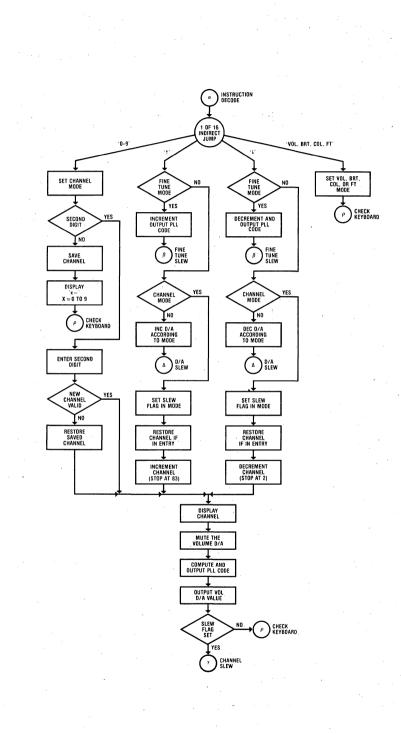

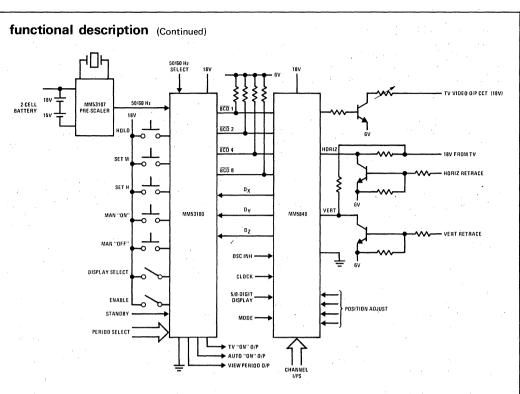

|    | COP Note 2               | COP Television Controller                                            | 2-119 |

|    | COP Brief 1              | SIO Input/Output Register Description                                |       |

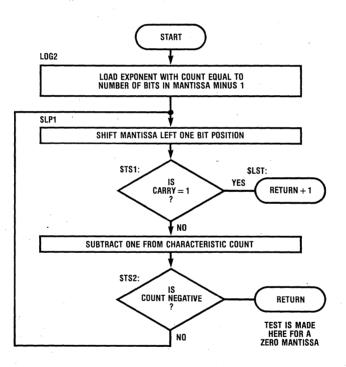

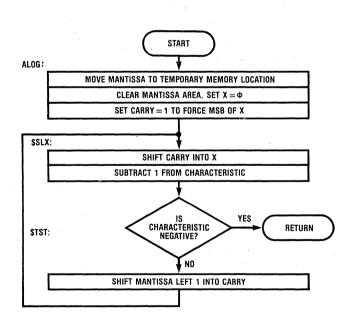

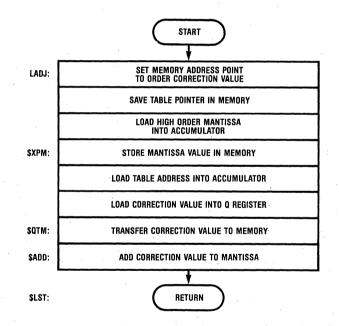

|    | COP Brief 2              | Easy Logarithms for COP400                                           |       |

|    | COP Brief 3              | Use of Macro-Assembled Code                                          |       |

|    | COP Brief 4              | L-Bus Considerations                                                 |       |

|    | COP Brief 5              | Software and Opcode Differences in the COP444L Instruction Set       |       |

|    | COP Brief 6              | RAM Keep-Alive                                                       |       |

|    | COP Brief 7              | Microbus Programming Considerations                                  | 2-142 |

|    | COP Brief 8              | COPS Peripheral Chips                                                |       |

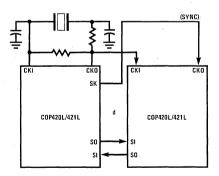

|    | COP Brief 9              | Serial Interface Between COPS Microcontrollers and Peripheral Chips. |       |

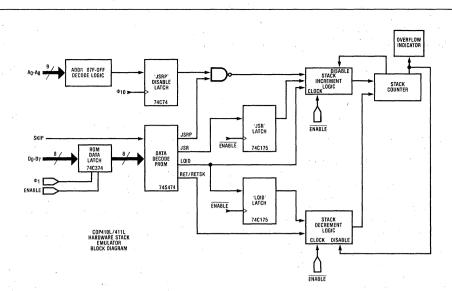

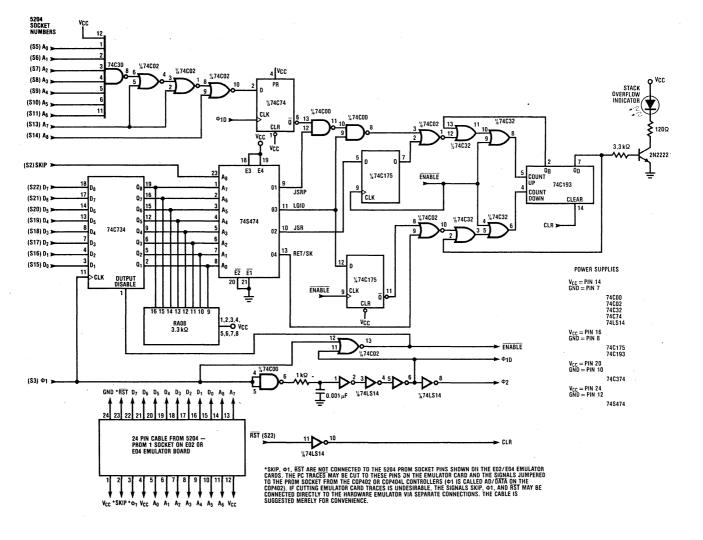

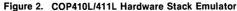

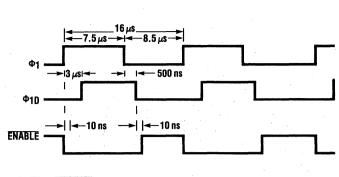

|    | COP Brief 10             | COP410L/COP411L Hardware Subroutine Stack Emulator                   |       |

|    | COP Brief 11             |                                                                      |       |

|    |                          | An Automotive Diagnostics Display                                    |       |

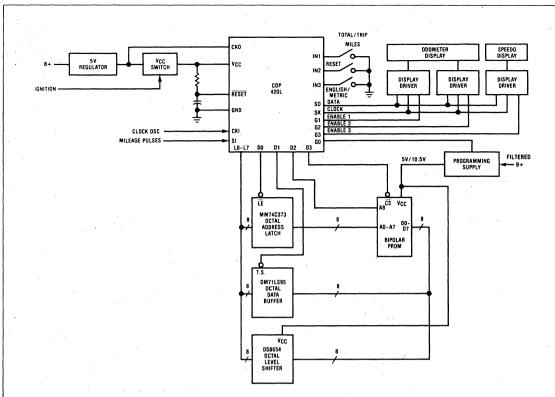

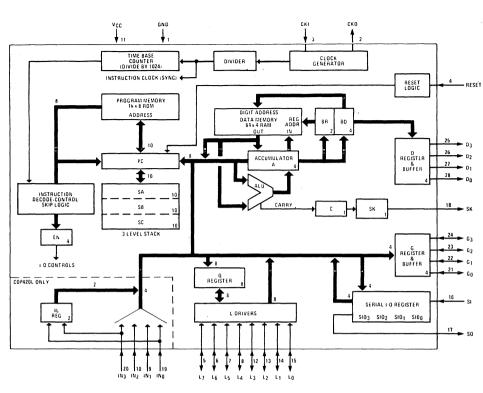

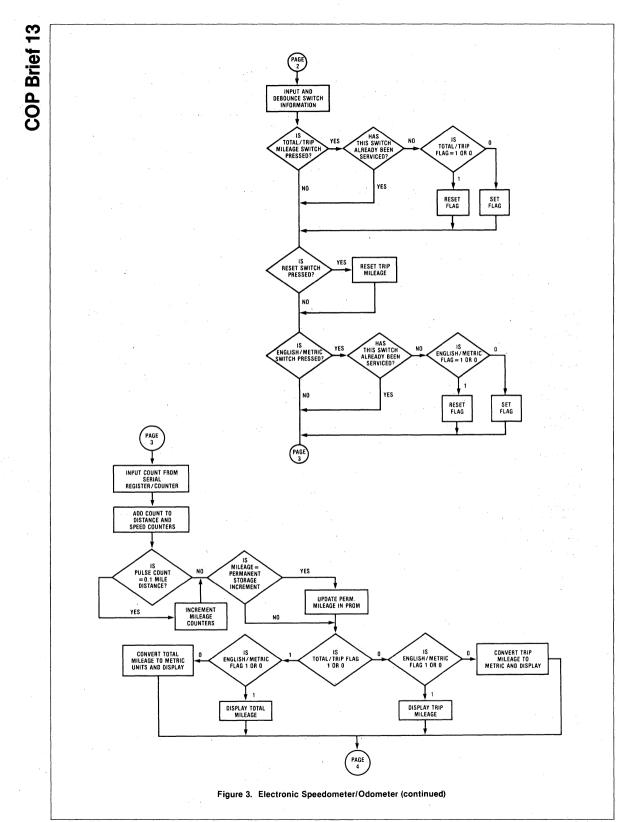

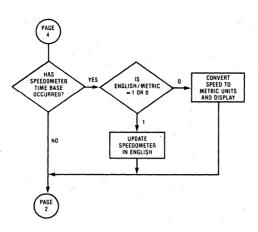

|    | COP Brief 13             | An Electronic Speedometer and Odometer with Permanent                |       |

|    | OUP blief 15             | Mileage Accumulation                                                 | 2.157 |

|    |                          |                                                                      |       |

| Se | ction 3 MOS              | S/ROMs                                                               |       |

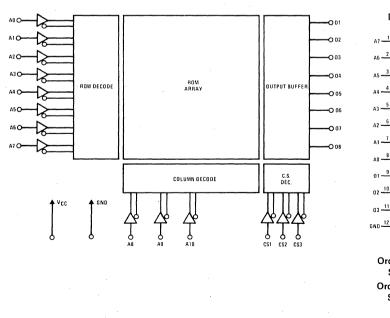

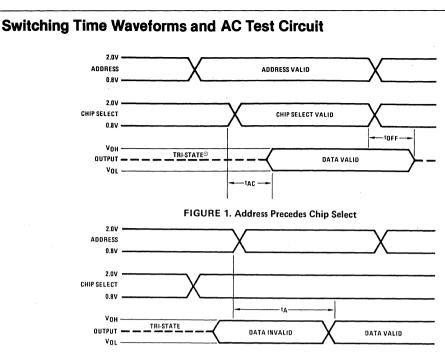

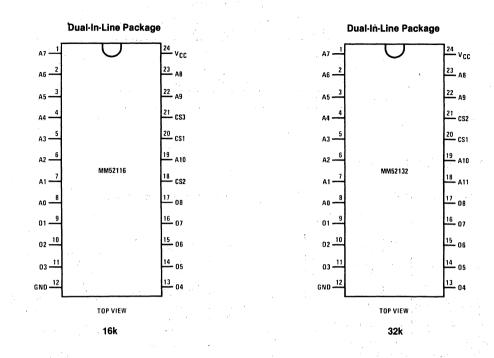

|    | MM52116(2316             | 6E) 16,384-Bit (2048 × 8) Read Only Memory                           | 3-3   |

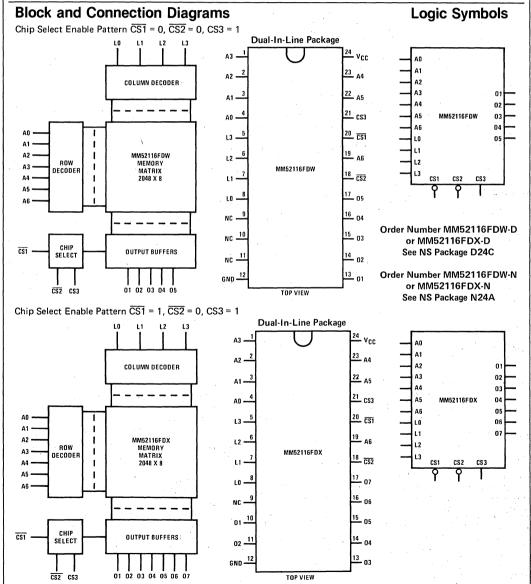

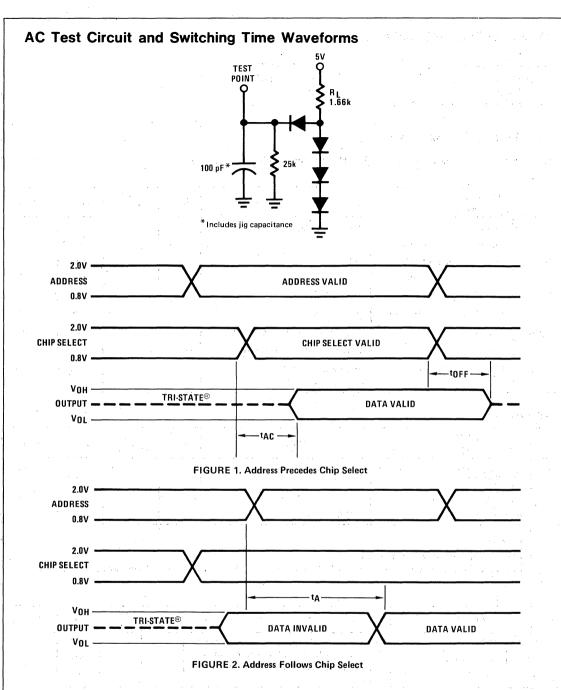

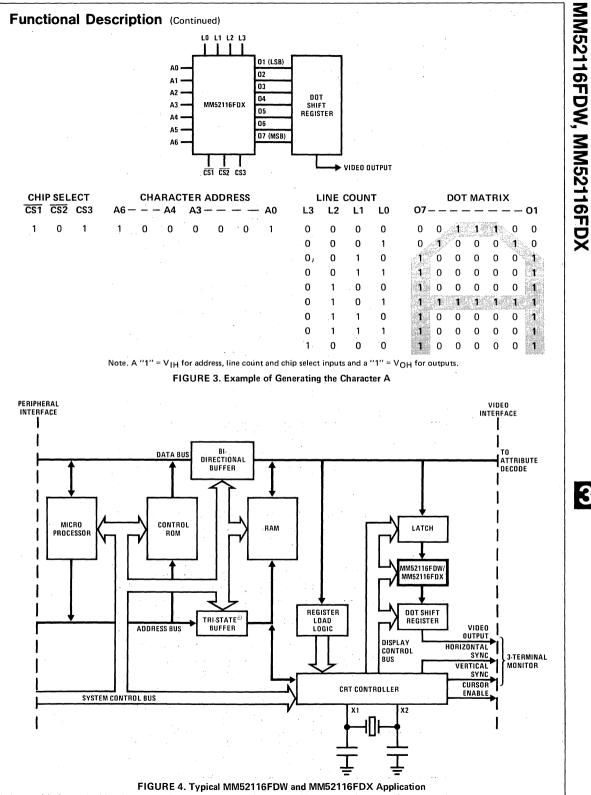

| .' | MM52116FDW               | /, MM52116FDX Character Generators                                   | 3-6   |

|    |                          |                                                                      |       |

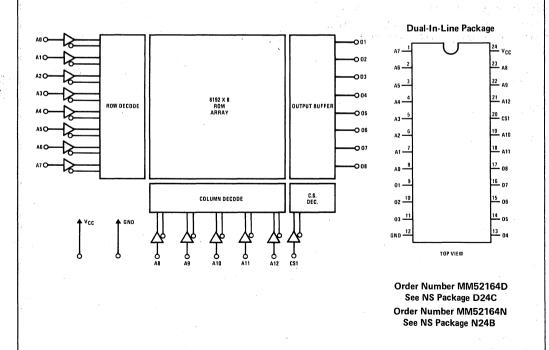

|    | MM52164 65.5             | 768-Bit (4096 x 8) MAXI-ROM <sup>™</sup>                             | 3-16  |

|    | MM52264 65 P             | 536-Bit (8192 × 8) Clocked MAXI-ROM <sup>™</sup>                     | 3-19  |

|    |                          |                                                                      |       |

| Se | ection 4 Spee            | ech Synthesis                                                        |       |

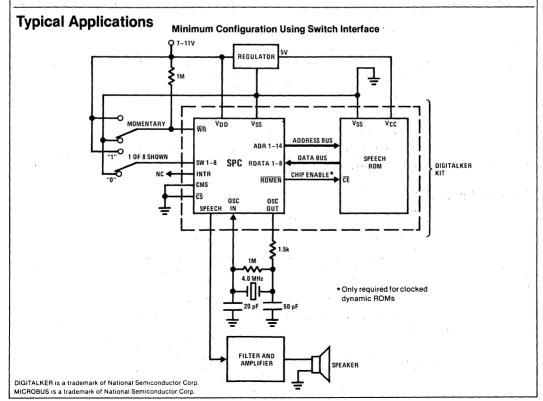

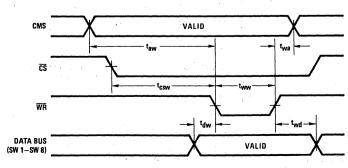

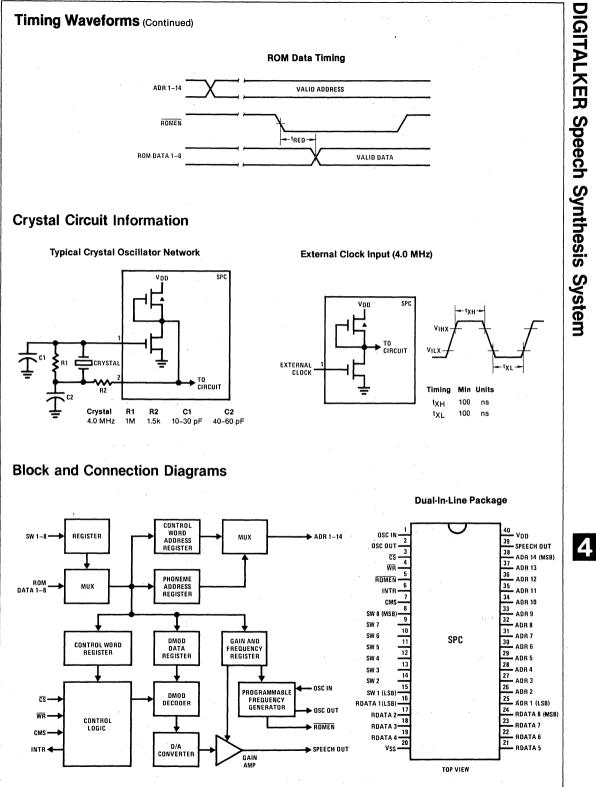

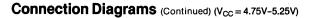

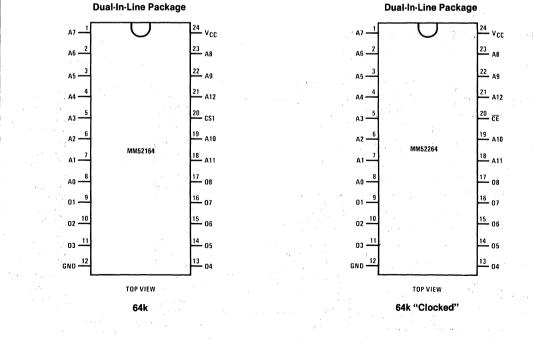

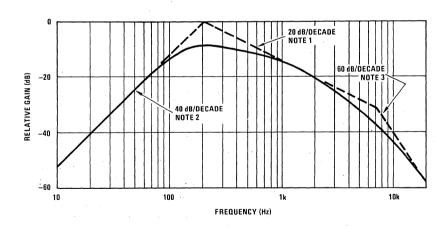

|    |                          | <sup>4</sup> Speech Synthesis System                                 | 4-3   |

|    |                          |                                                                      |       |

## Table of Contents (continued)

| Section 5 STANDARD MOS/LSI                                            |       |

|-----------------------------------------------------------------------|-------|

| Digital Clock Product Selection Guide                                 | 5-3   |

| Television/Radio Product Selection Guide                              |       |

| Games/Calculators Product Selection Guide                             | 5-5   |

| Telecommunication Device Product Selection Guide                      |       |

| Display Driver Product Selection Guide                                |       |

| Oscillator/Divider Product Selection Guide                            |       |

| Electronic Data Processing Product Selection Guide                    |       |

|                                                                       |       |

| Digital Clocks                                                        | 4. •  |

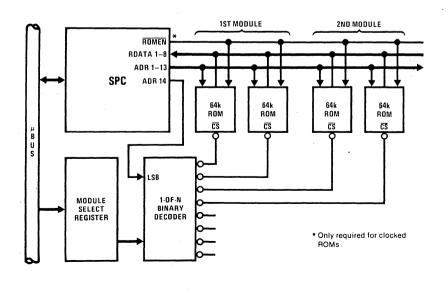

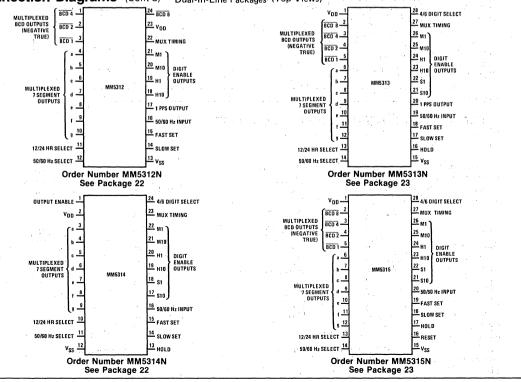

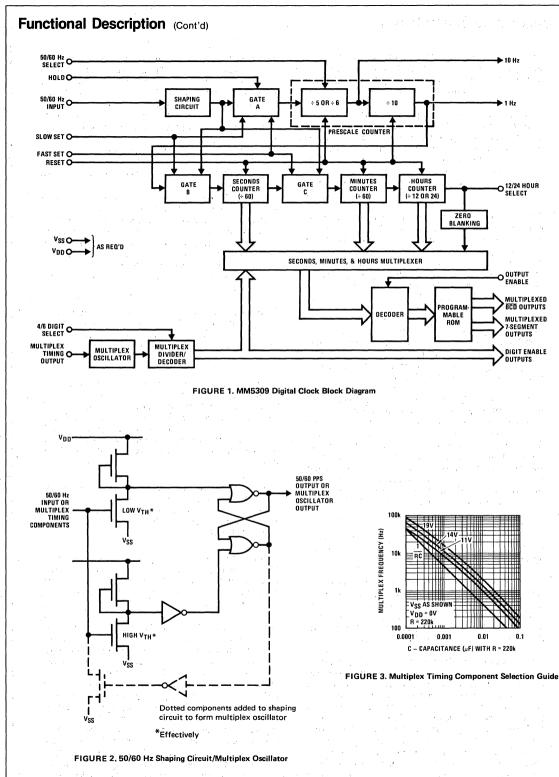

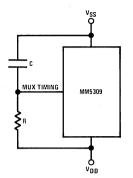

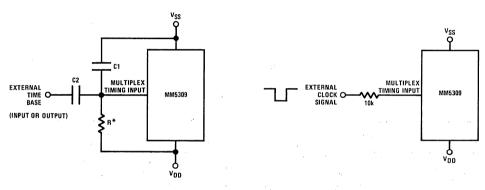

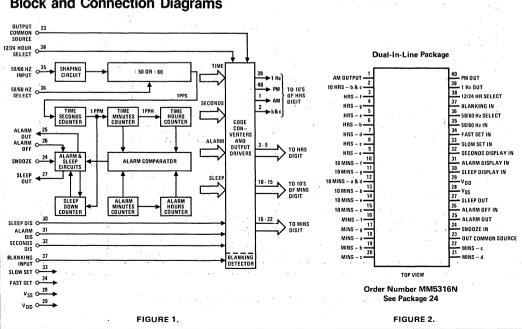

| MM5309, MM5311, MM5312, MM5313, MM5314, MM5315 Digital Clocks         |       |

| MM5316 Digital Alarm Clocks                                           |       |

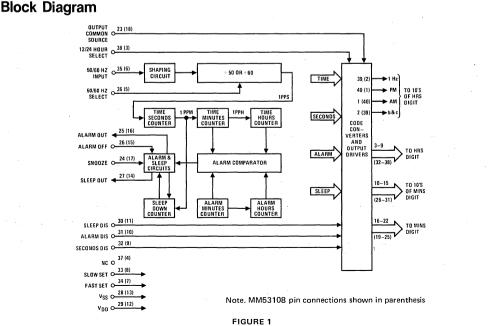

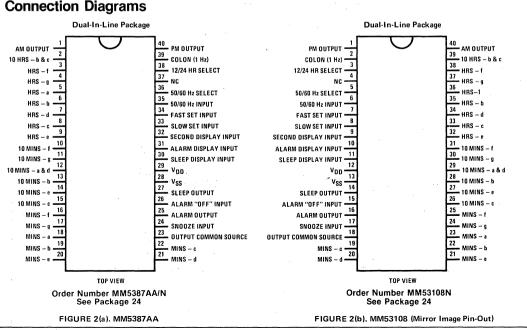

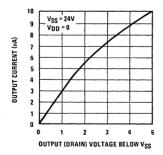

| MM5387AA, MM53108 Digital Alarm Clocks                                |       |

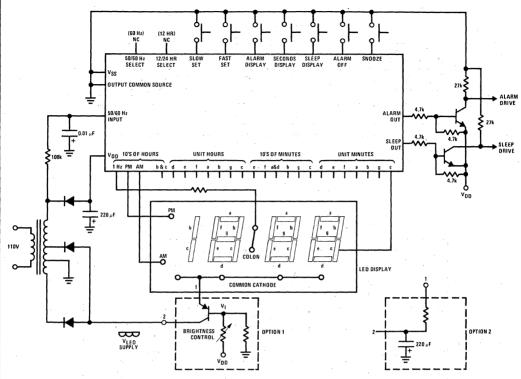

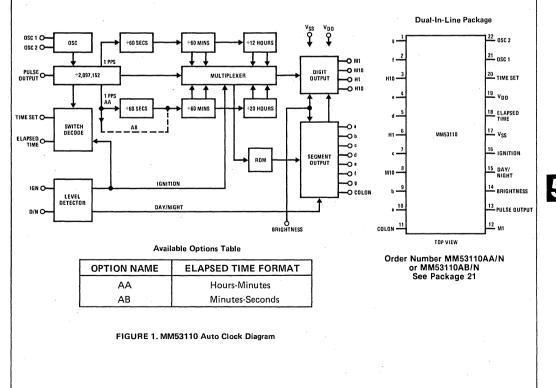

| MM53110 Series Auto Clock and Elapsed Timer                           |       |

| MM53113 Digital Alarm Clock                                           |       |

| MM53124 Automobile Clock and Elapsed Timer                            |       |

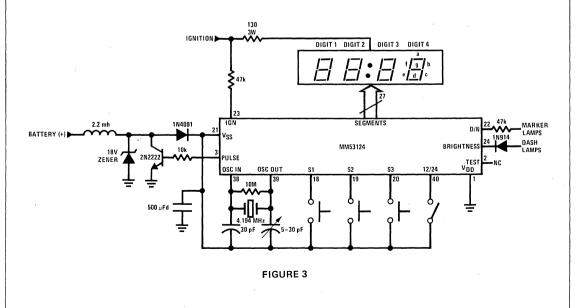

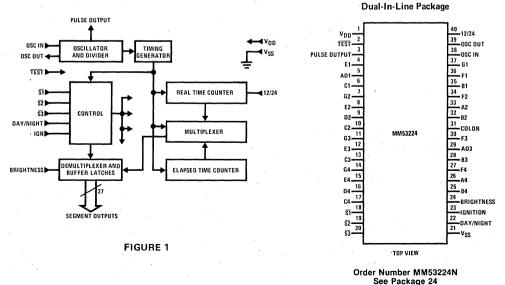

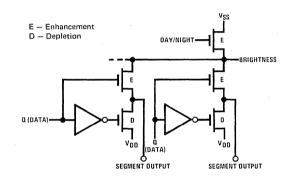

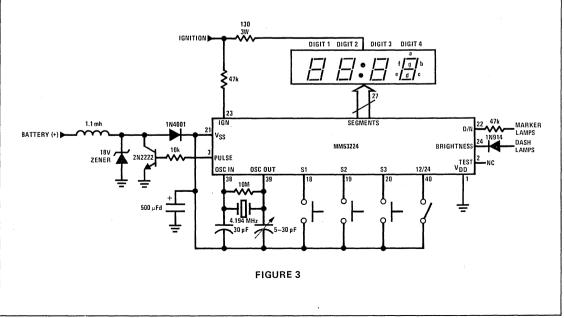

| MM53224 Automobile Clock and Elapsed Timer                            |       |

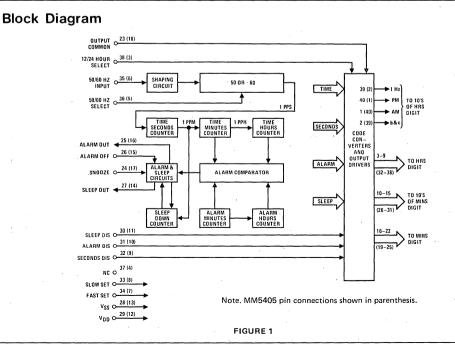

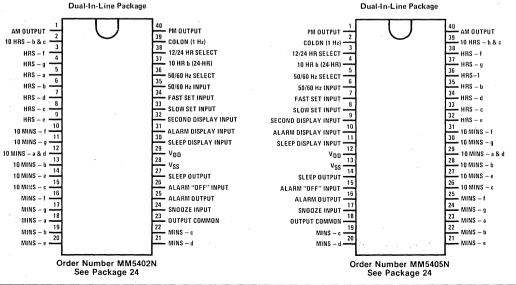

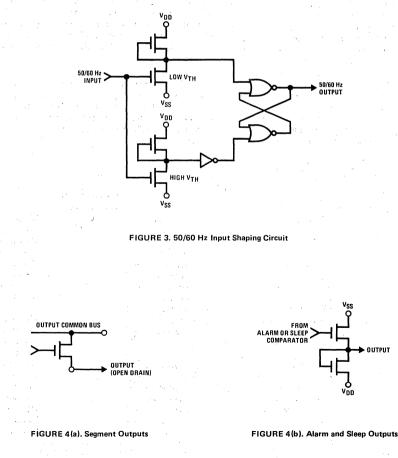

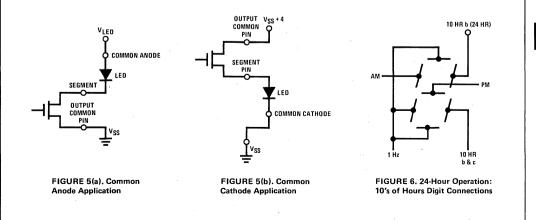

| MM5402, MM5405 Digital Alarm Clocks                                   |       |

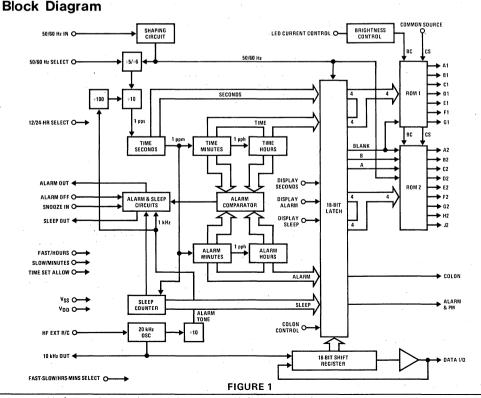

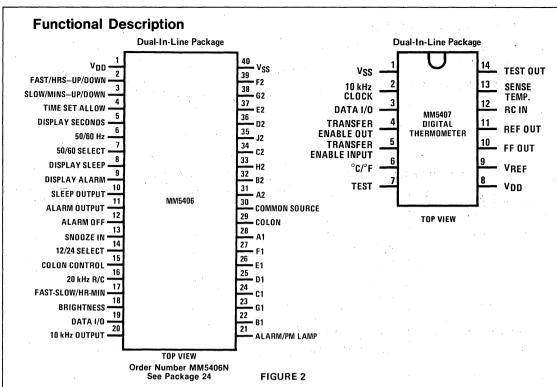

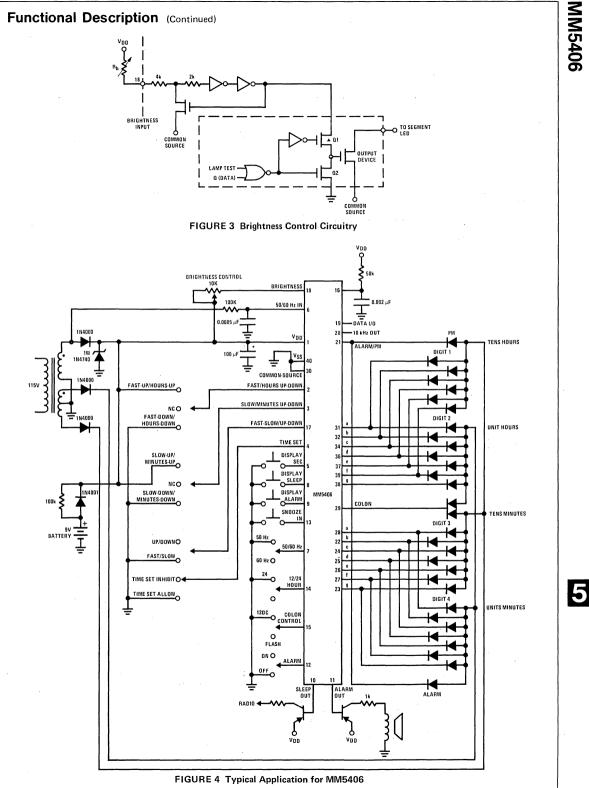

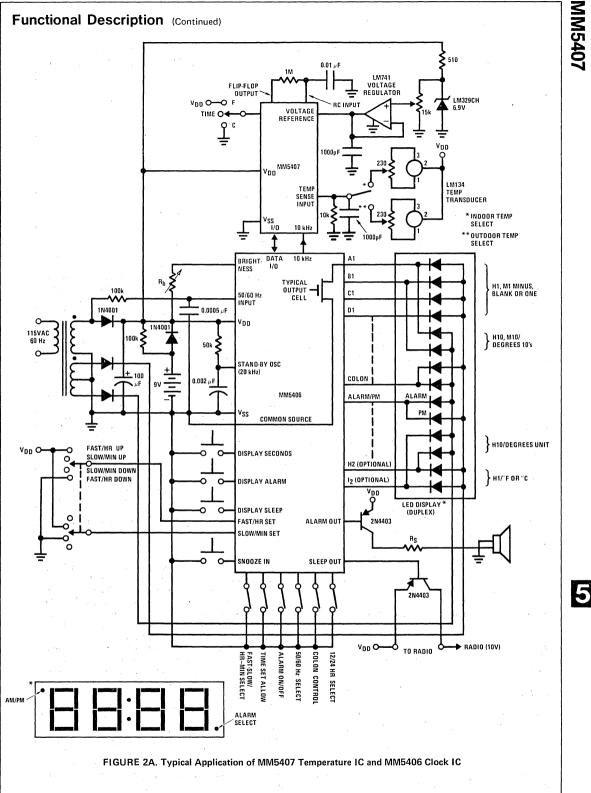

| MM5406 Delux Display and Clock Radio                                  |       |

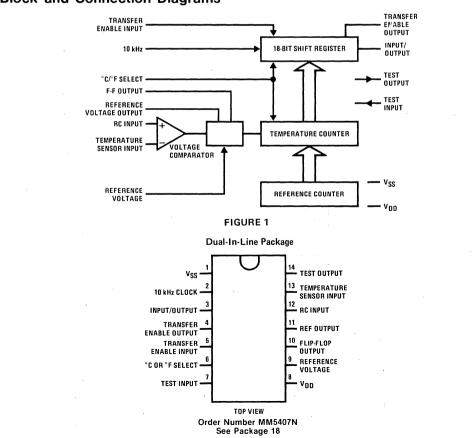

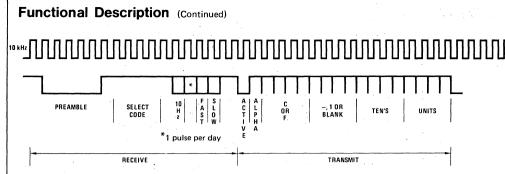

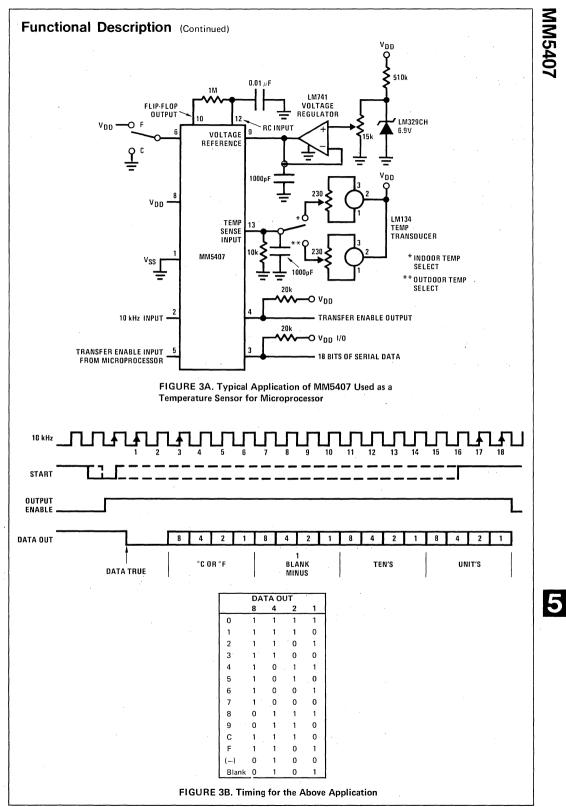

| MM5407 Digital Thermometer                                            |       |

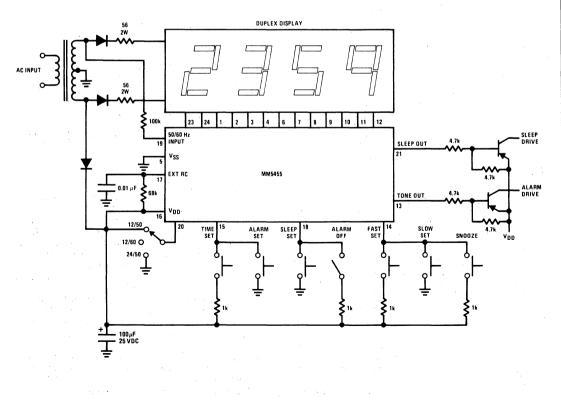

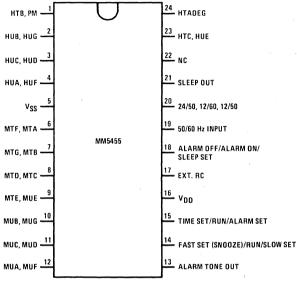

| MM5455 Digital Alarm Clock                                            |       |

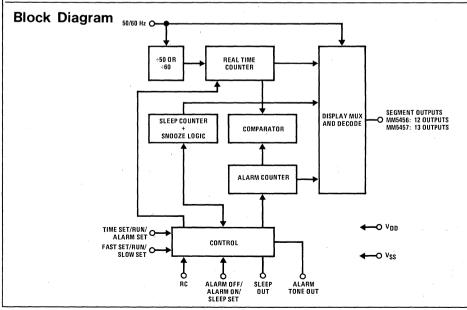

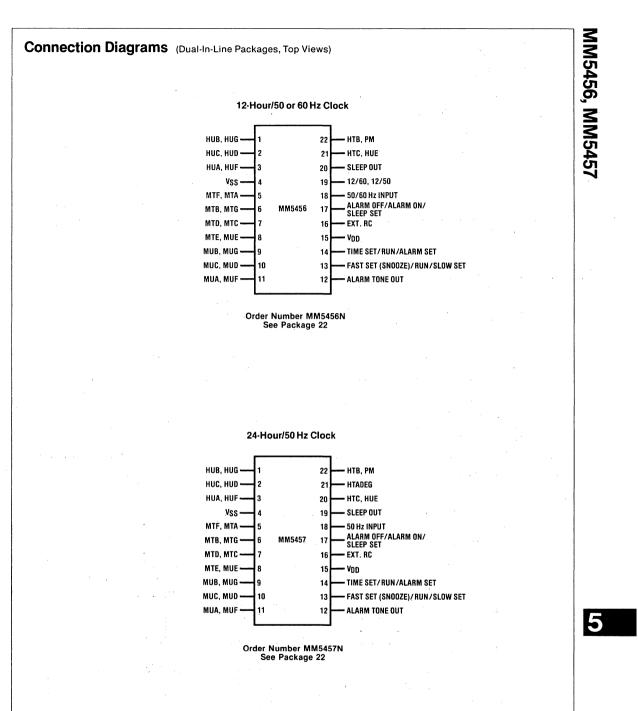

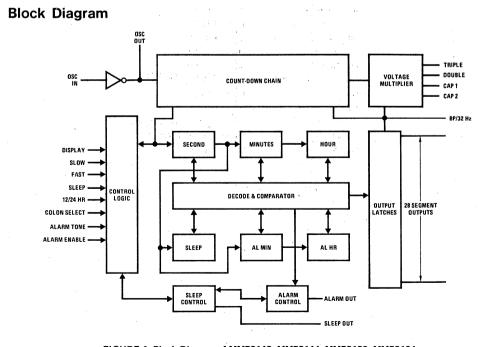

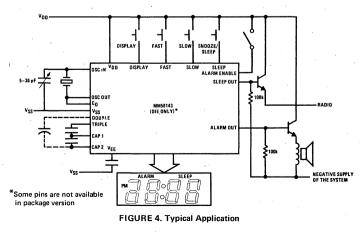

| MM5456, MM5457 Digital Alarm Clocks                                   |       |

| MM58143, MM58144, MM58183, MM58184 LCD Alarm Clock Circuits           |       |

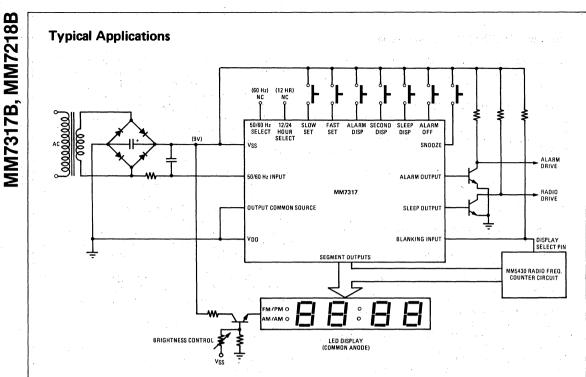

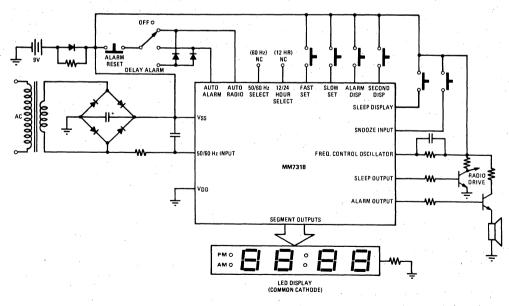

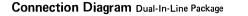

| MM7317B, MM7318B Alarm Clock Calendar                                 |       |

|                                                                       |       |

| Television/Radio                                                      |       |

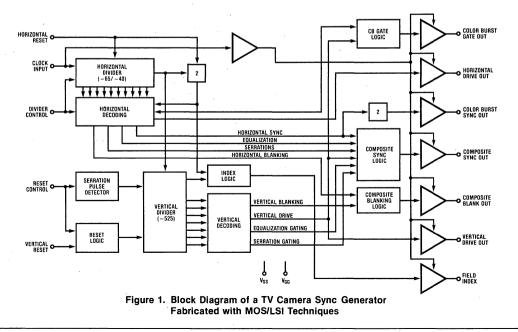

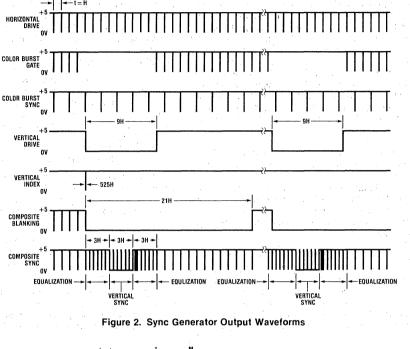

| MM5321 TV Camera Sync Generator                                       |       |

| MM5322 Color Bar Generator Chip                                       |       |

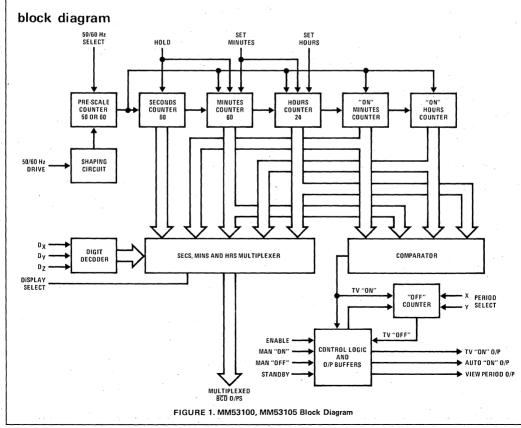

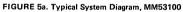

| MM53100, MM53105 Programmable TV Timers                               |       |

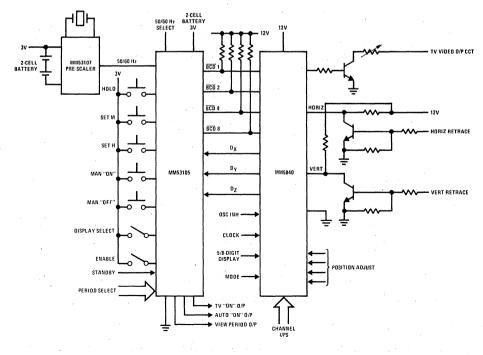

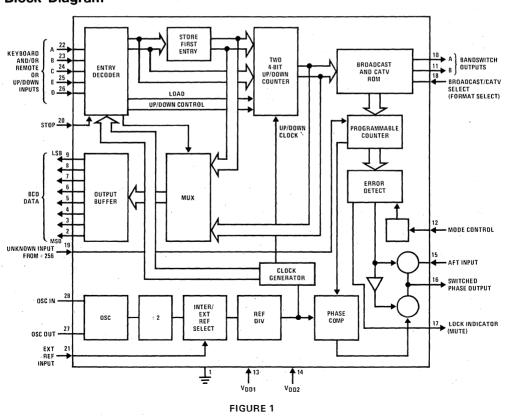

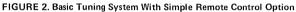

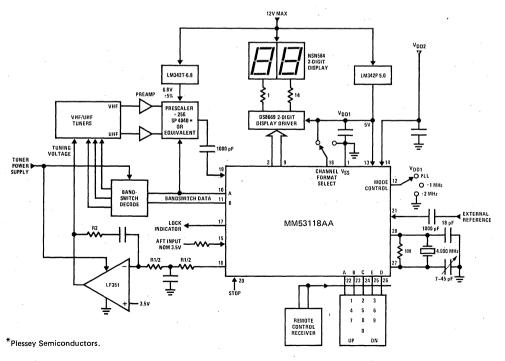

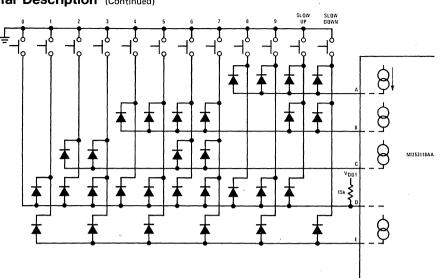

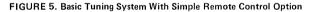

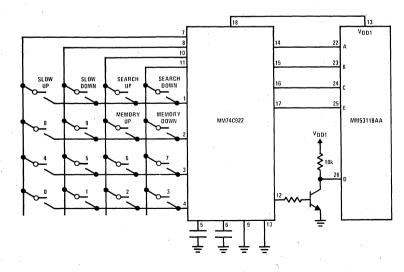

| MM53118AA TV Digital Tuning                                           |       |

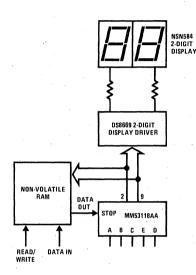

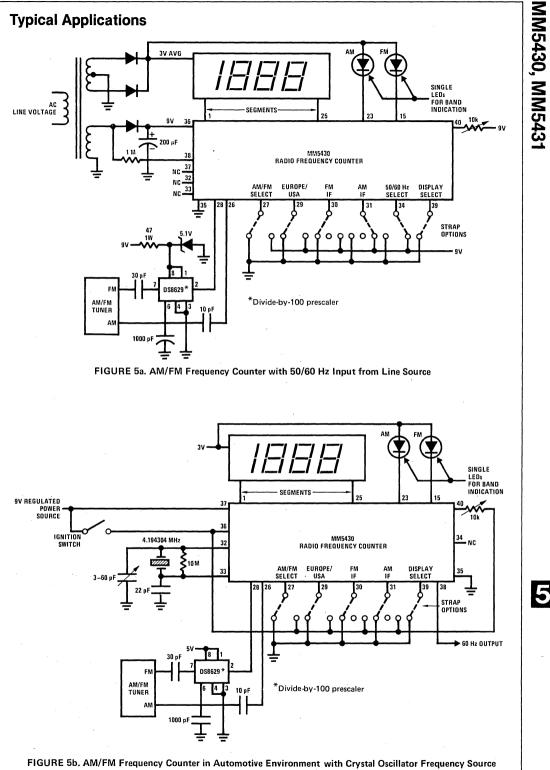

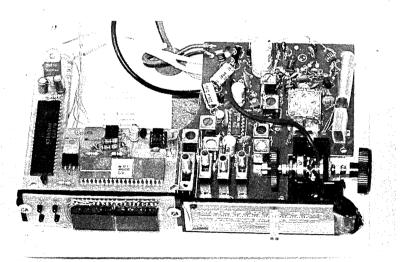

| MM5430, MM5431 AM/FM Radio Frequency Display                          | 5-115 |

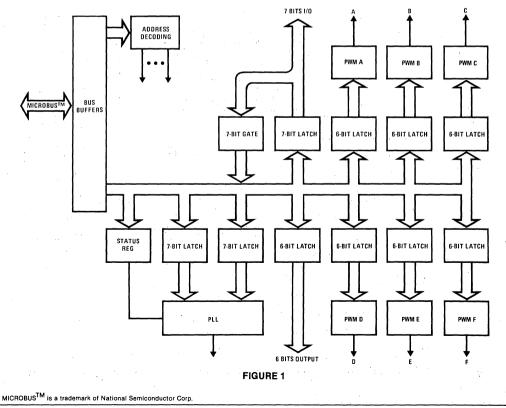

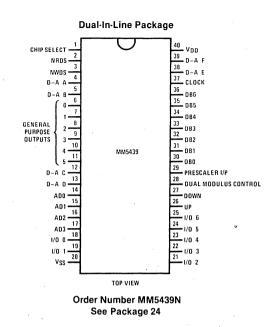

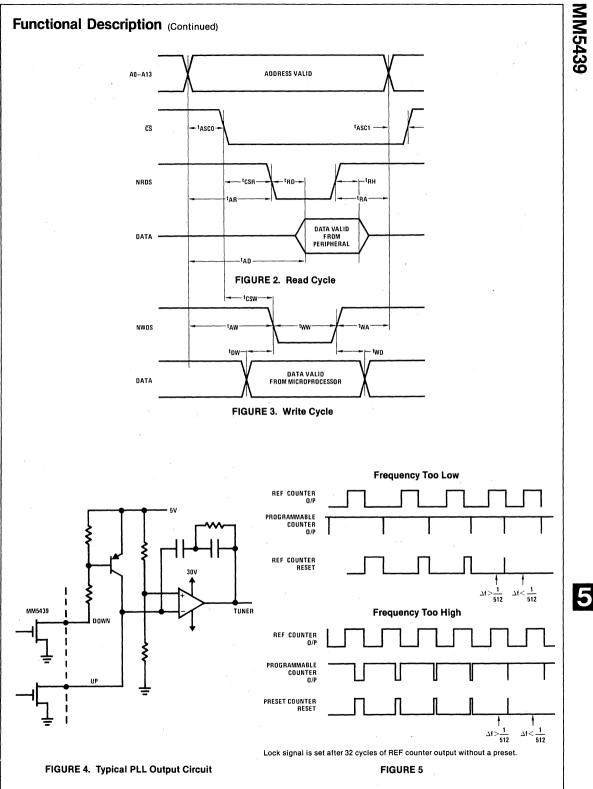

| MM5439 Microprocessor Compatible Phase Lock Loop (PLL)                |       |

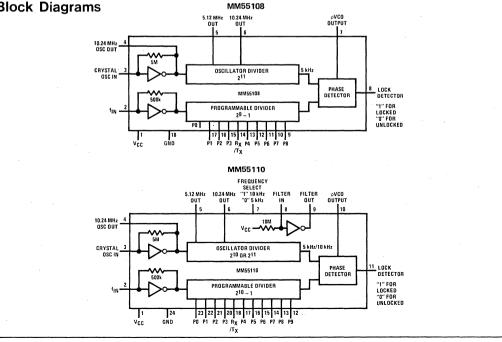

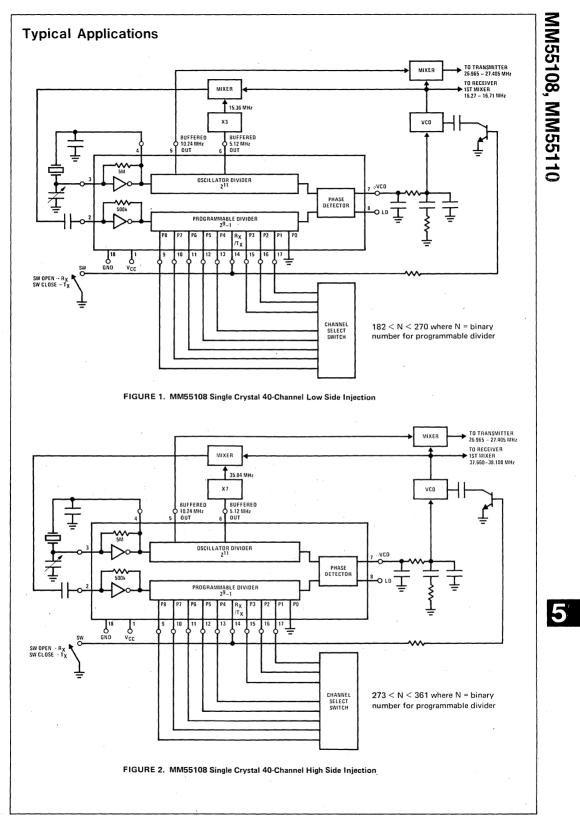

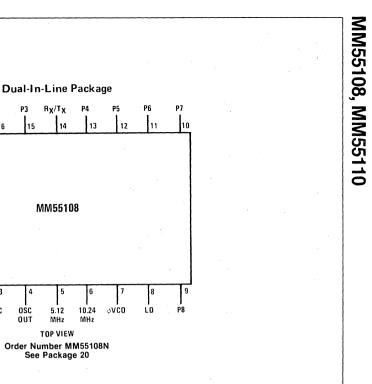

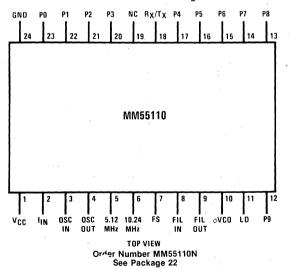

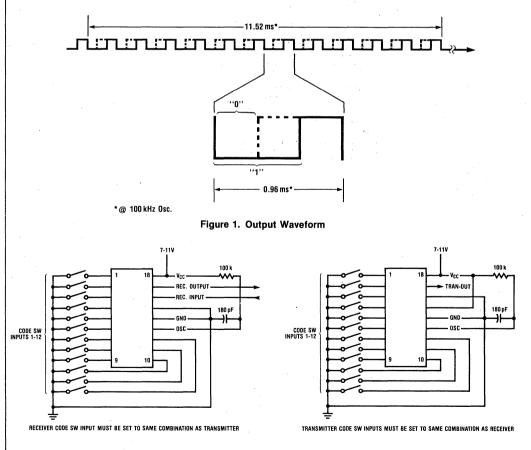

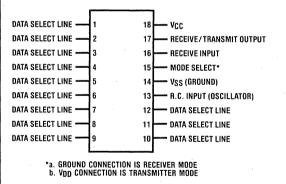

| MM55108, MM55110 PLL Frequency Synthesizer with Receive/Transmit Mode | 5-127 |

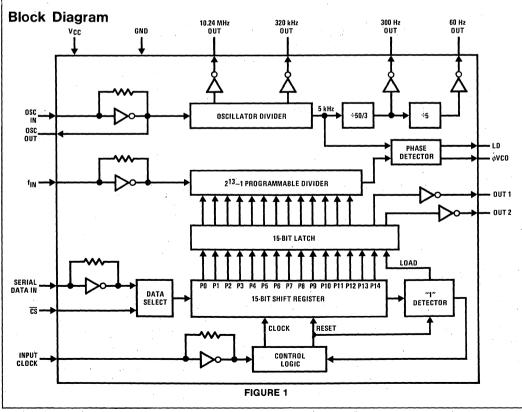

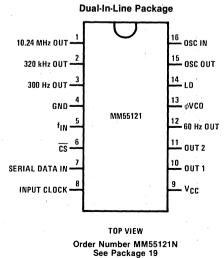

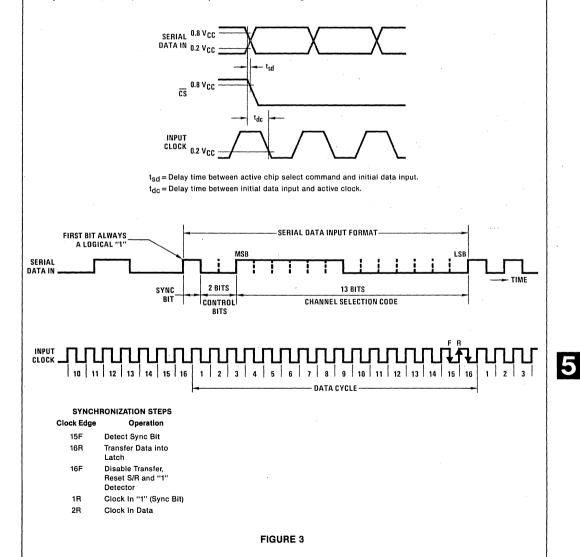

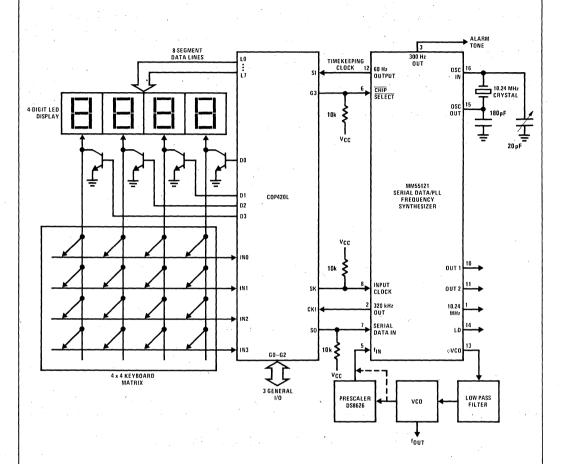

| MM55121 Serial Data/PLL Frequency Synthesizer                         | 5-132 |

| MM55122 Serial Data/PLL Frequency Synthesizer                         |       |

| MM55123 Serial Data/PLL Frequency Synthesizer                         |       |

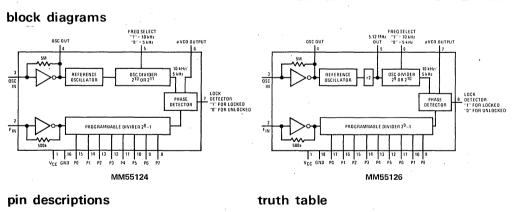

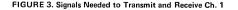

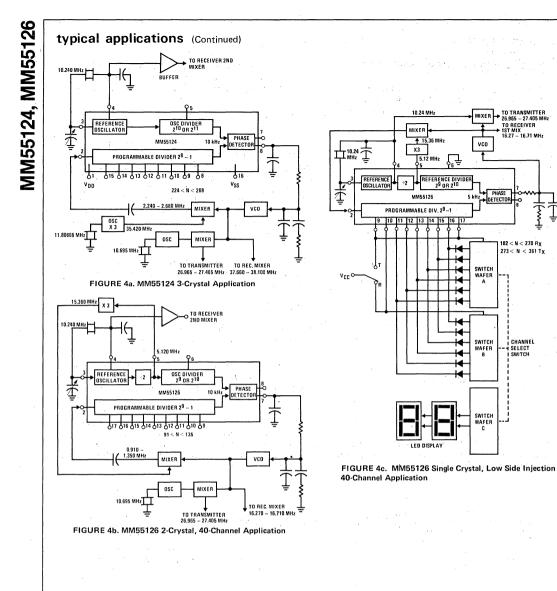

| MM55124, MM55126 PLL Frequency Synthesizer                            |       |

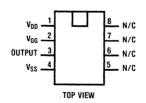

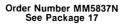

| MM5837 Digital Noise Source                                           |       |

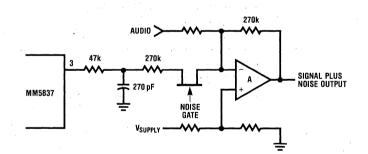

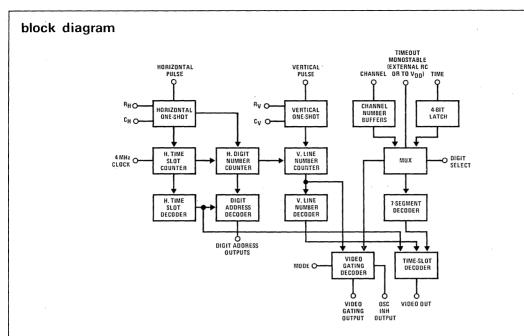

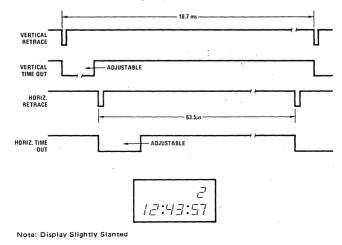

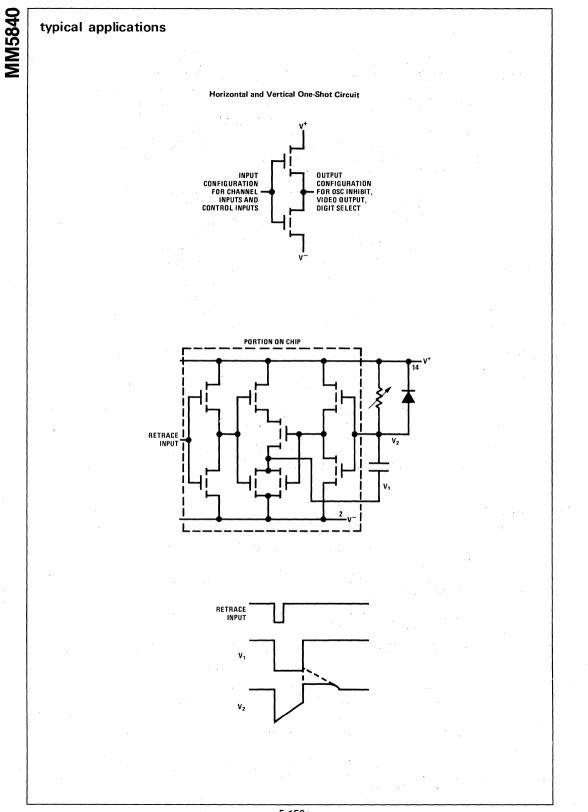

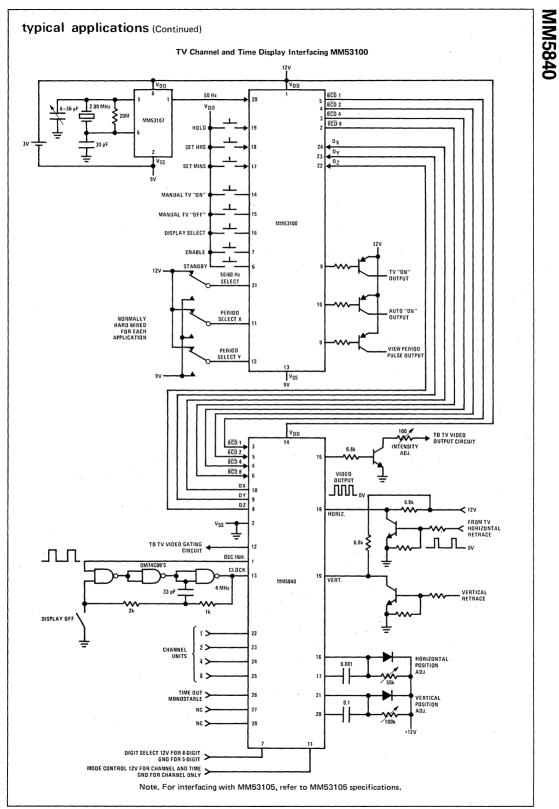

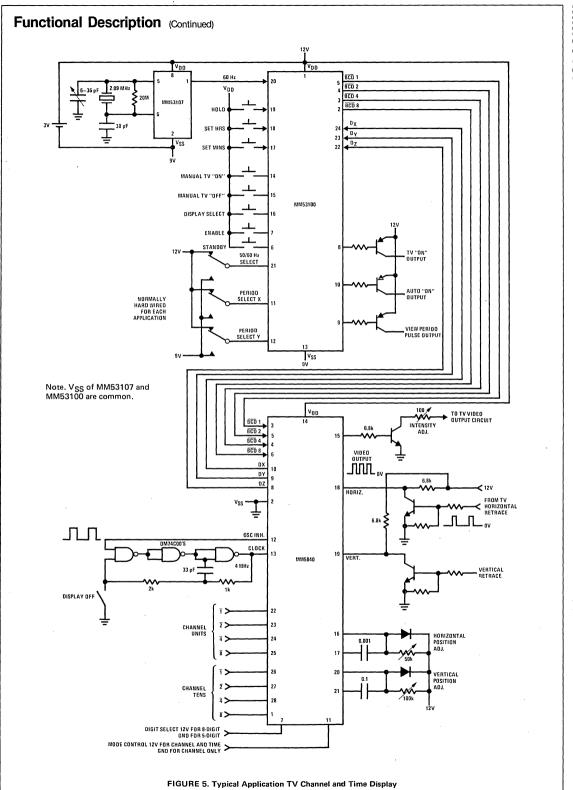

| MM5840 TV Channel Number (16-Channel) and Time Display Circuit        |       |

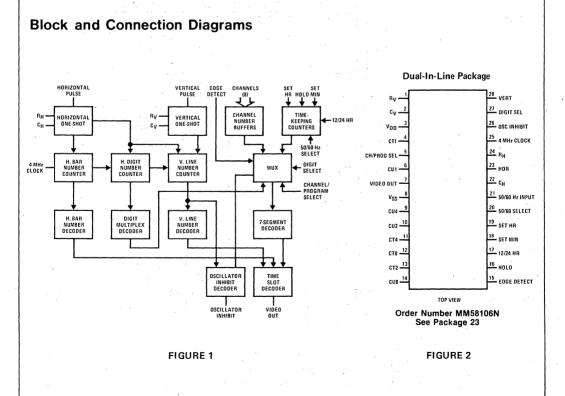

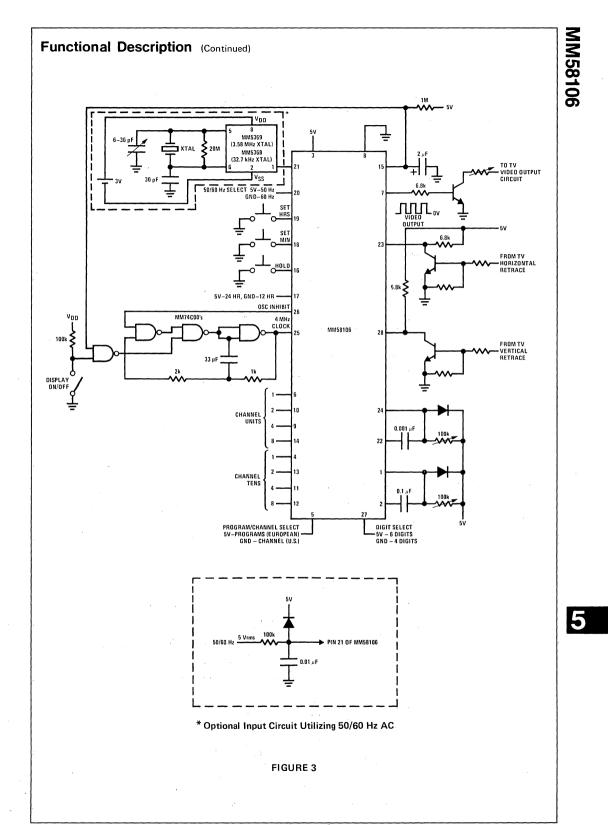

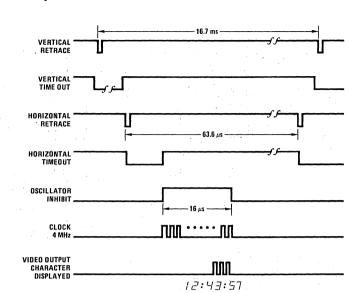

| MM58106 Digital Clock and TV Display Circuit                          |       |

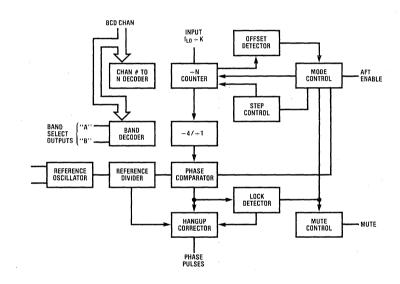

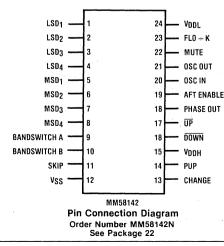

| MM58142 TV Synthesizer                                                |       |

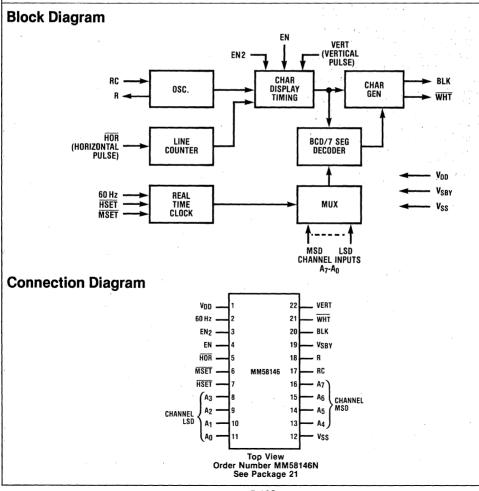

| MM58146 TV Clock and Channel Display                                  |       |

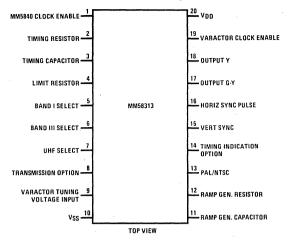

| MM58313 Varactor Tuner Display Circuit                                |       |

## Table of Contents (continued)

Section 5 STANDARD MOS/LSI (continued)

| Games/Calculators                                                  |       |

|--------------------------------------------------------------------|-------|

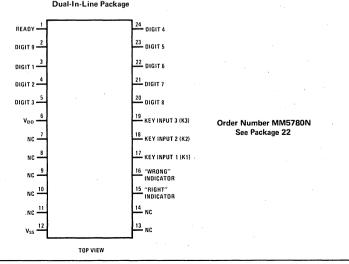

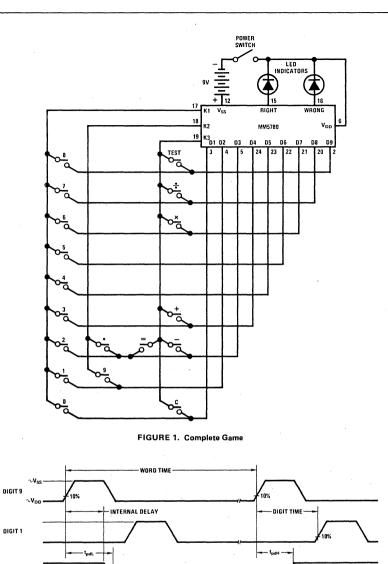

| MM5780 Educational Arithmetic Game                                 | 5-181 |

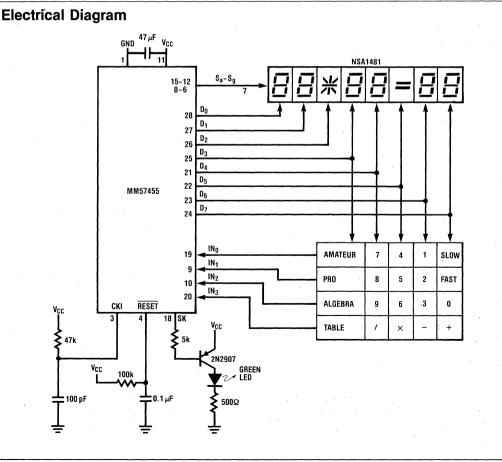

| MM57455 Advanced Educational Arithmetic Game                       | 5-187 |

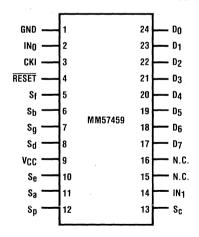

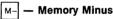

| MM57459 8-Digit LED Direct-Drive Memory Calculator                 | 5-190 |

| Telecommunications                                                 | •     |

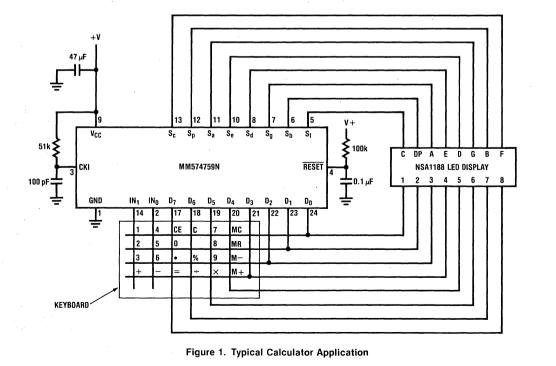

| MM5393, MM5394, MM53143, MM53144 Push Button Pulse Dialer Circuits |       |

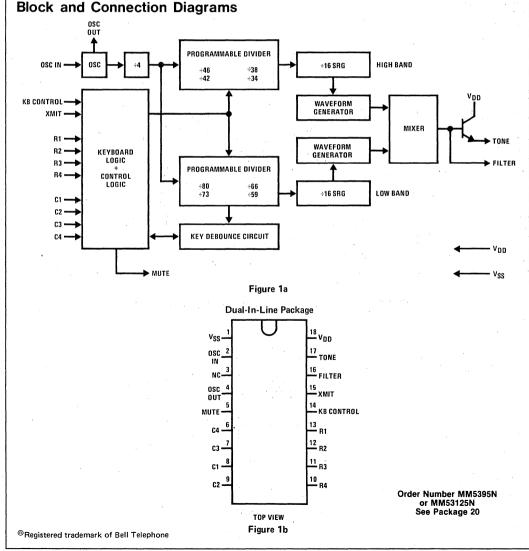

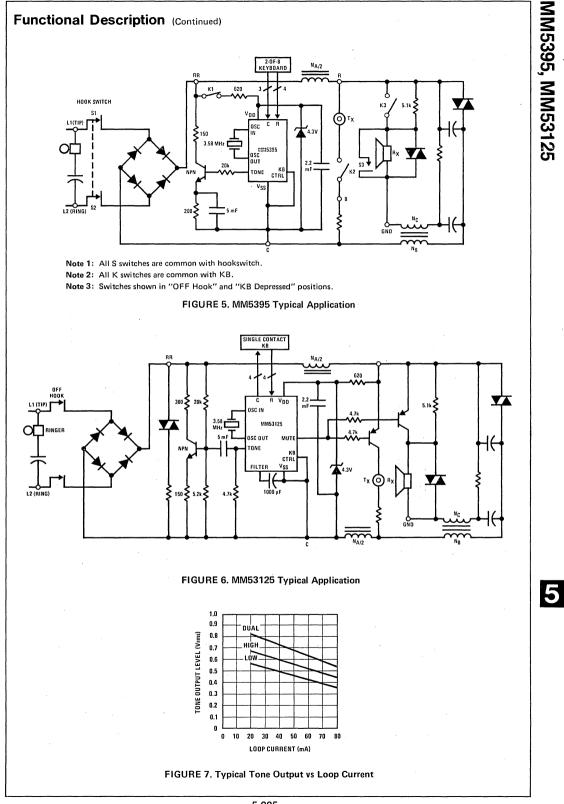

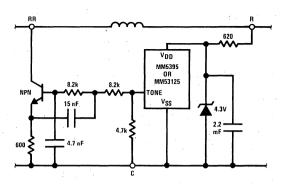

| MM5395, MM53125 DTMF (Touch Tone <sup>®</sup> ) Generators         |       |

| MM53130 DTMF (Touch Tone <sup>®</sup> ) Generator                  |       |

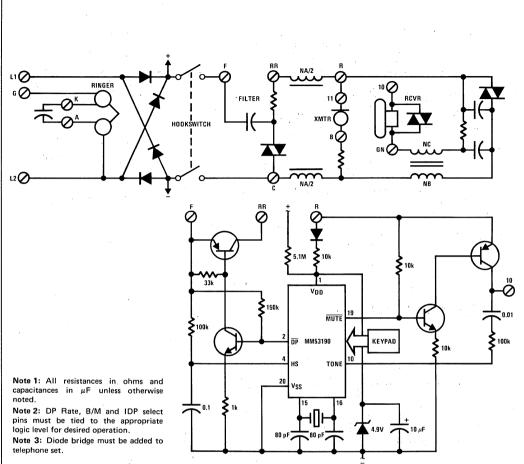

| MM53190 Push-Button Pulse Dialer                                   | 5-212 |

| ,                                                                  |       |

#### **Display Drivers**

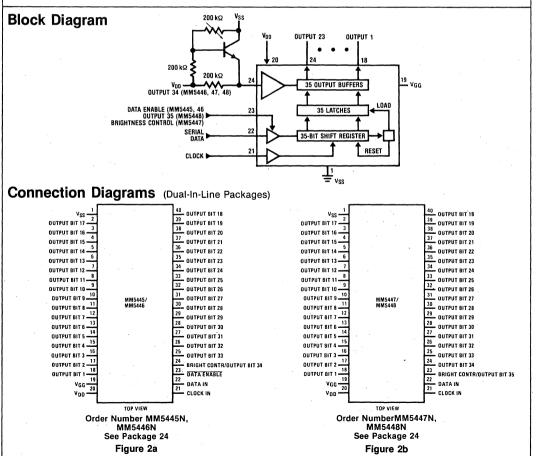

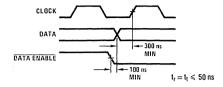

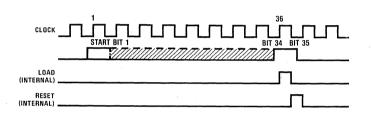

| MM5445, MM5446, MM5447, MM5448 VF Display Drivers |       |

|---------------------------------------------------|-------|

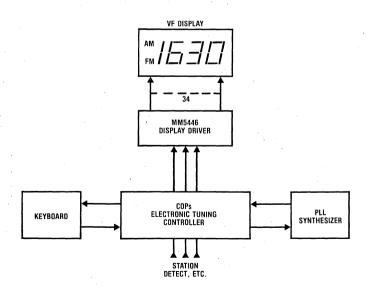

| MM5450, MM5451 LED Display Drivers                | 5-222 |

| MM5452, MM5453 Liquid Crystal Display Drivers     |       |

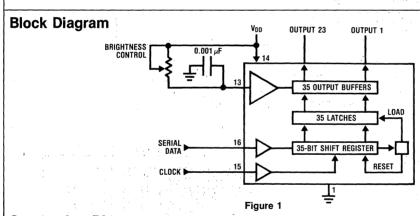

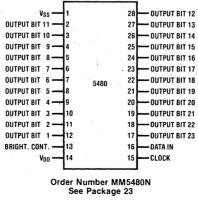

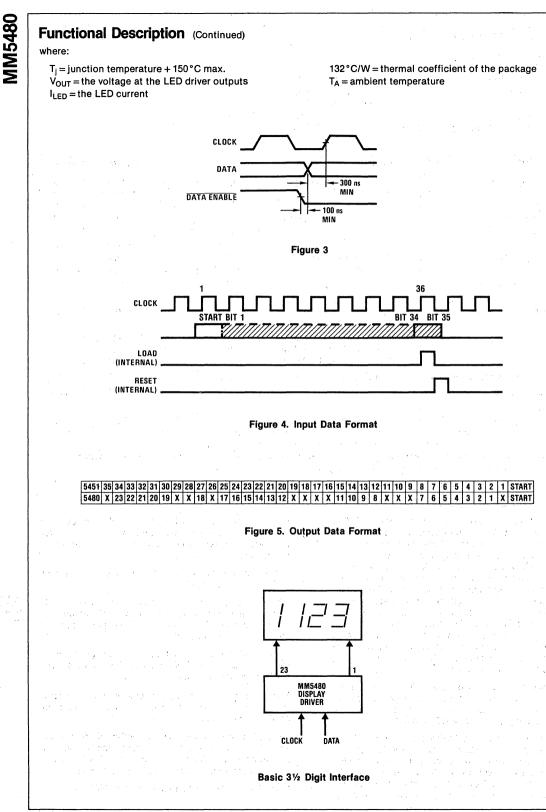

| MM5480 LED Display Driver                         |       |

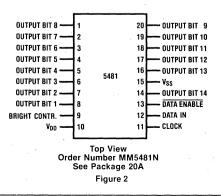

| MM5481 LED Display Driver                         | 5-235 |

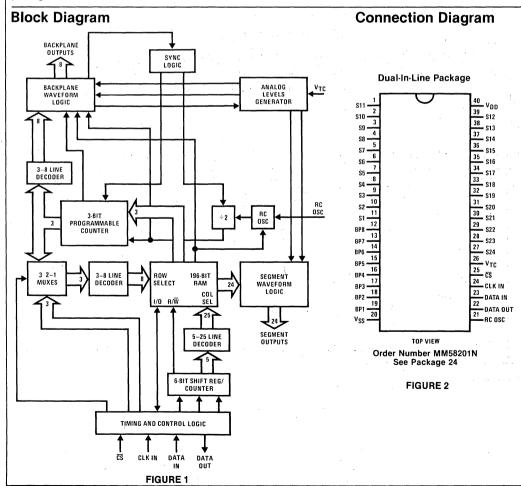

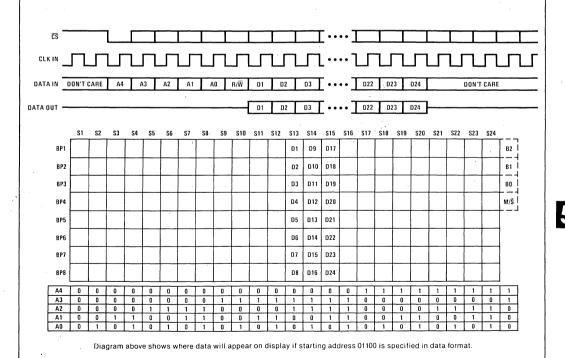

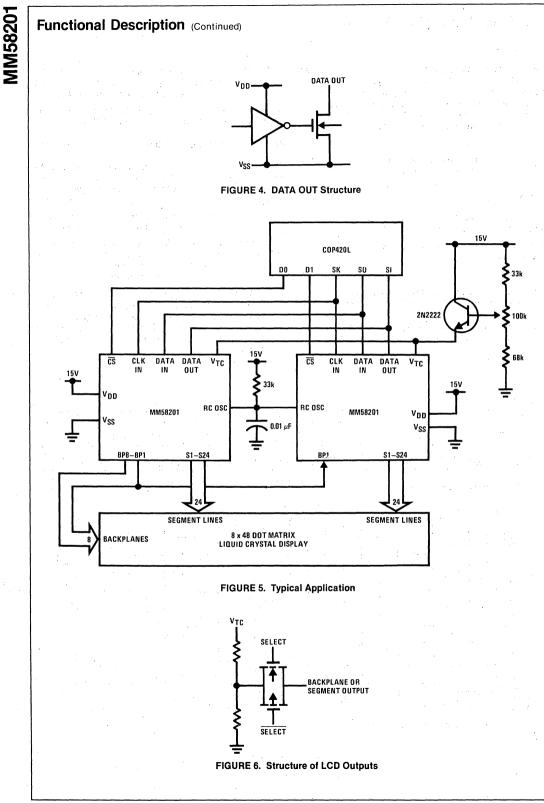

| MM58201 Multiplexed LCD Driver                    |       |

|                                                   |       |

#### Oscillators

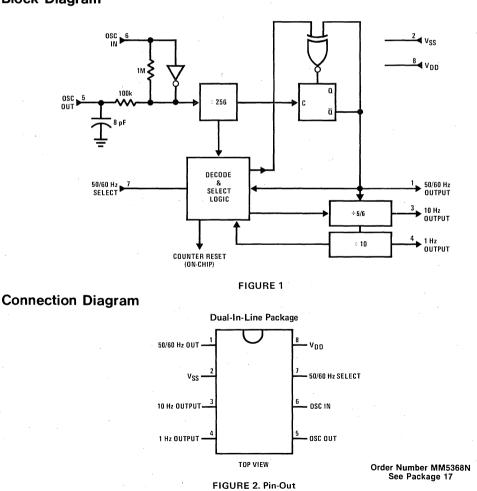

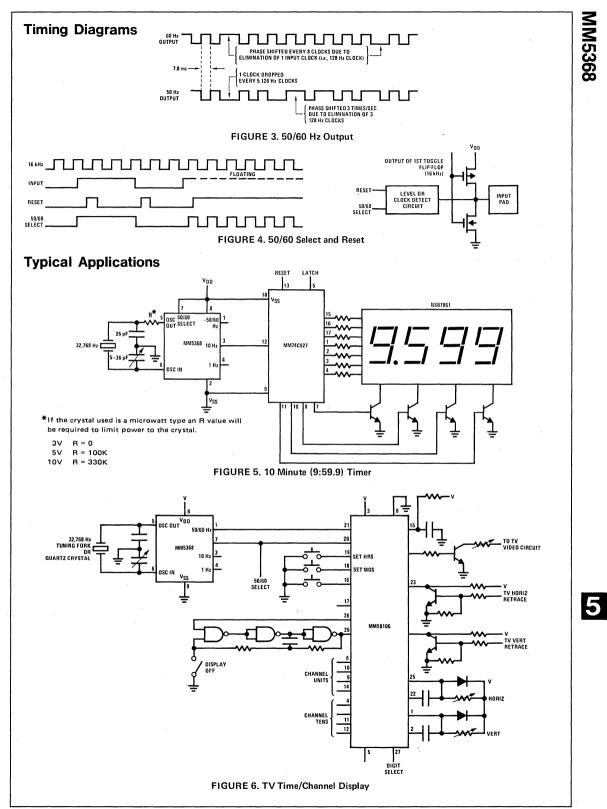

| MM5368 CMOS Oscillator Divider Circuit                      | 5-245 |

|-------------------------------------------------------------|-------|

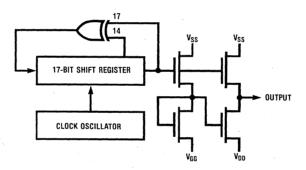

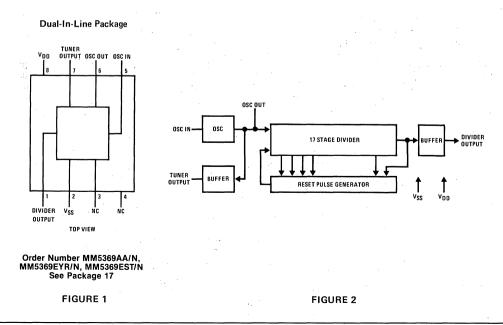

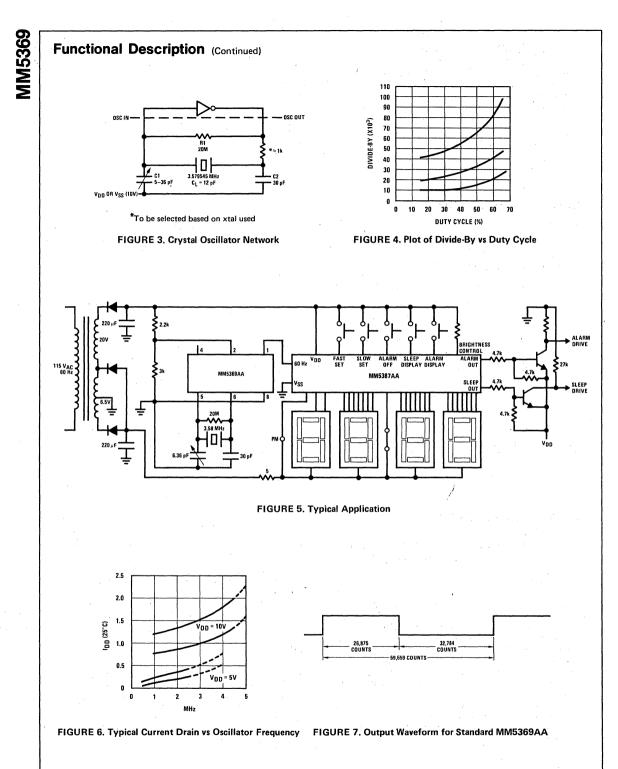

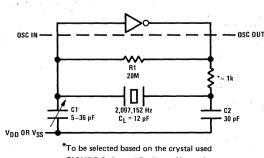

| MM5369 Series 17 Stage Mask Programmable Oscillator/Divider | 5-248 |

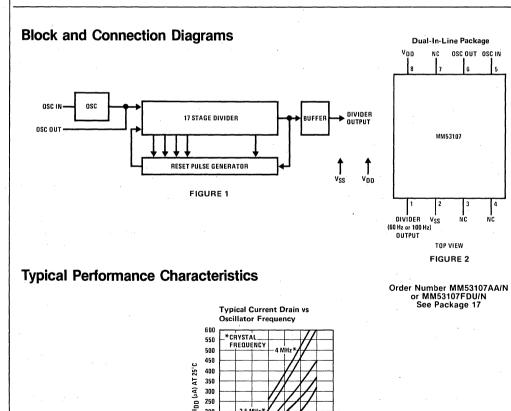

| MM53107 Series 17-Stage Oscillator/Divider                  | 5-251 |

#### Electronic Data Processing

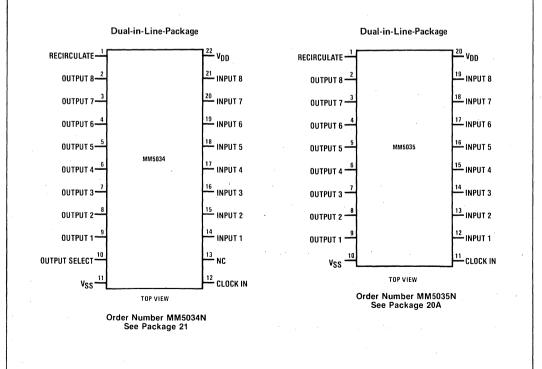

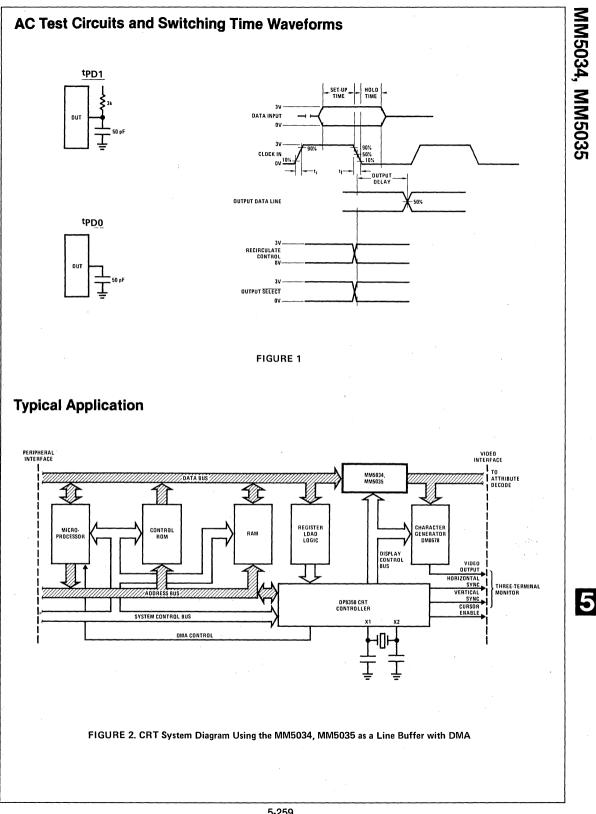

| MM5034, MM5035 Octal 80-Bit Static Shift Register           |       |

|-------------------------------------------------------------|-------|

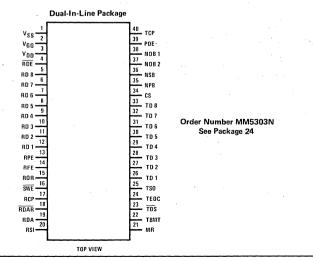

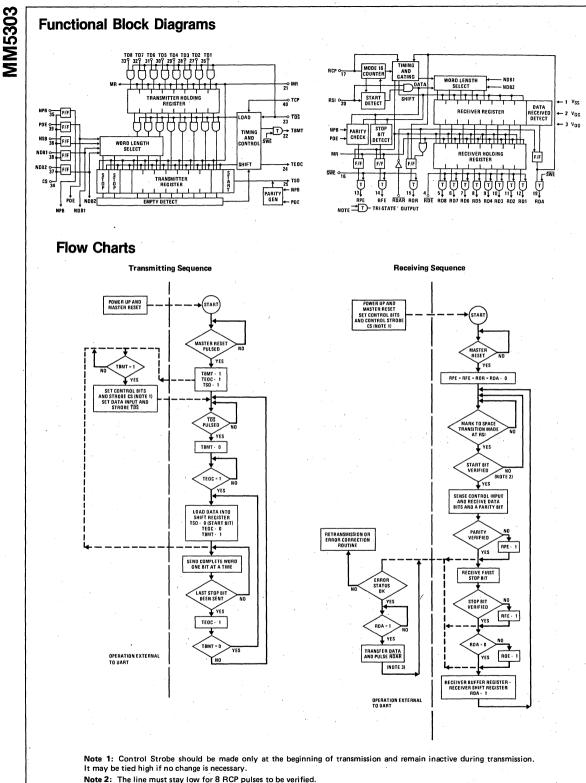

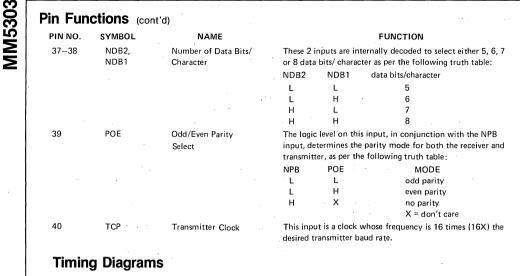

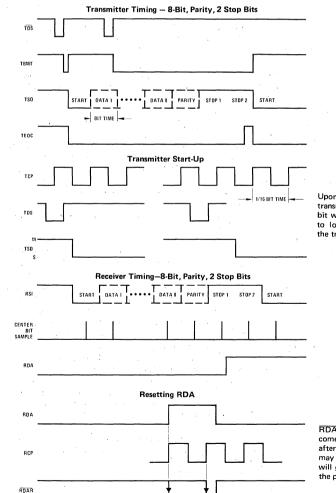

| MM5303 Universal Fully Asynchronous Receiver/Transmitter    | 5-260 |

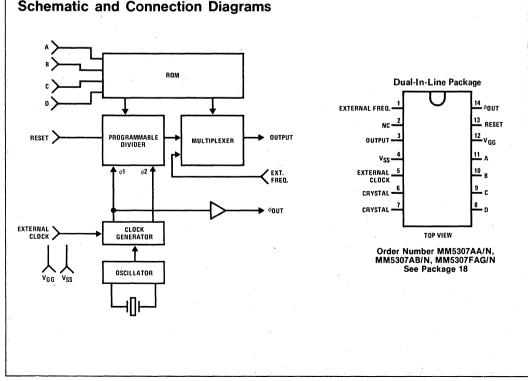

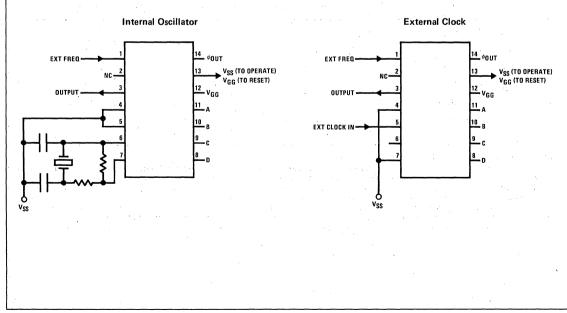

| MM5307 Baud Rate Generator/Programmable Divider             | 5-266 |

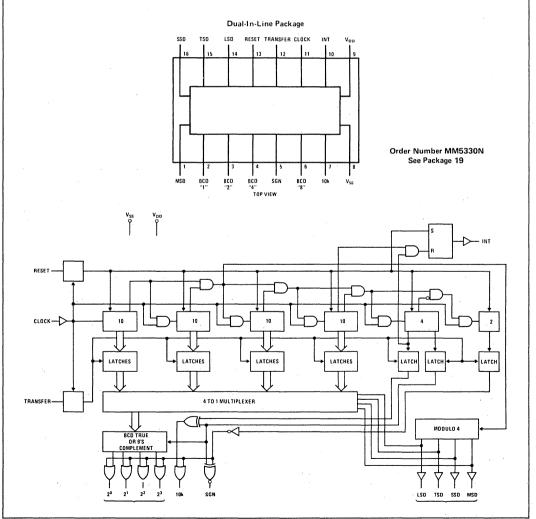

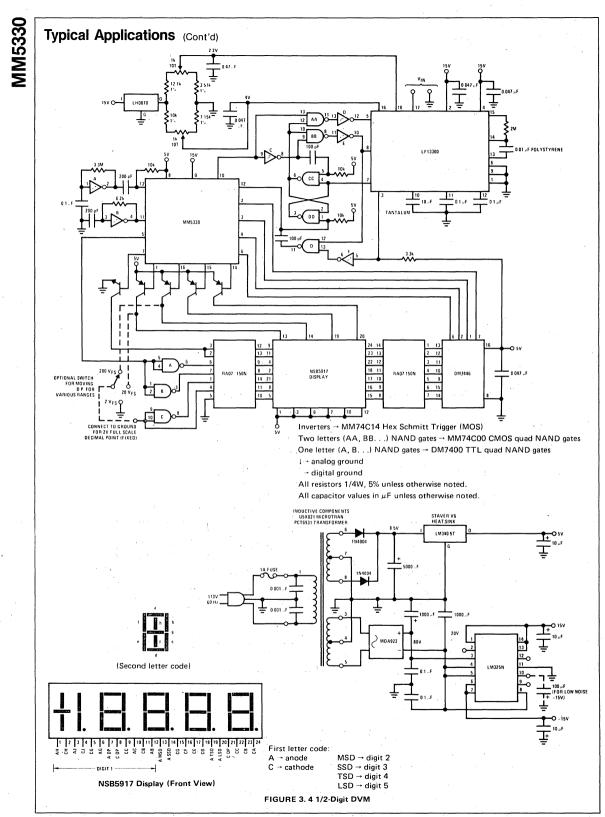

| MM5330 41/2-Digit Panel Meter Logic Block                   | 5-271 |

| MM53200 Encode/Decoder                                      | 5-278 |

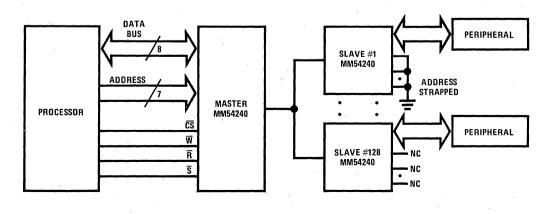

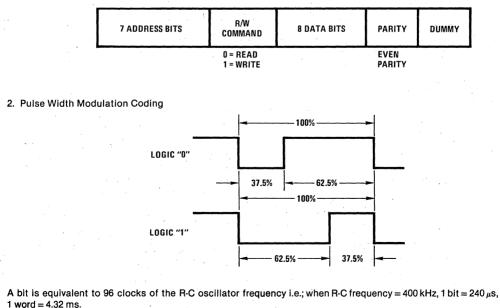

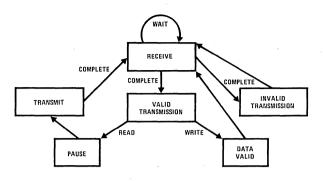

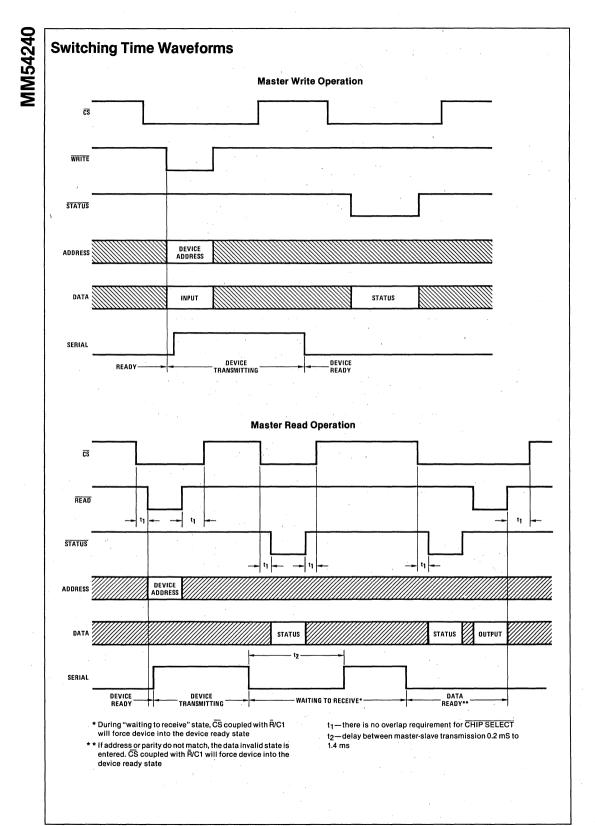

| MM54240 Asynchronous Receiver/Transmitter Remote Controller |       |

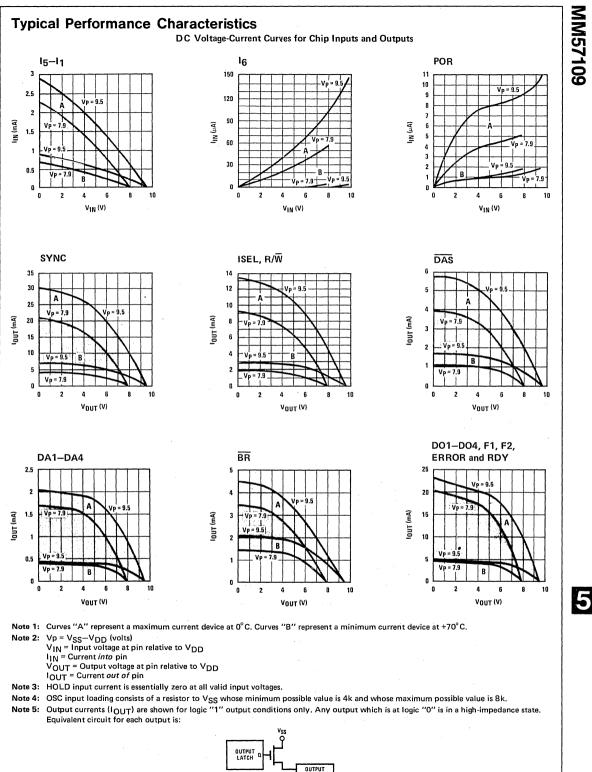

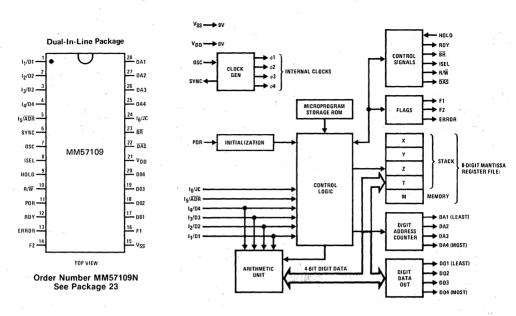

| MM57109 MOS/LSI Number-Oriented Processor                   | 5-284 |

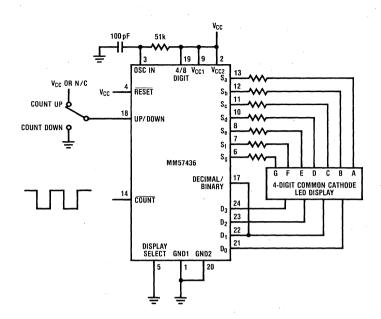

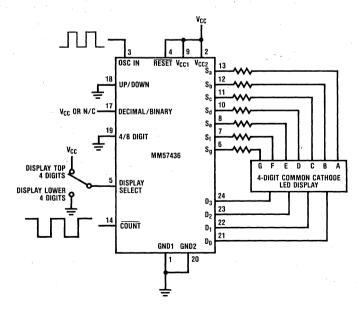

| MM57436 Decimal/Binary Up/Down Counter                      | 5-309 |

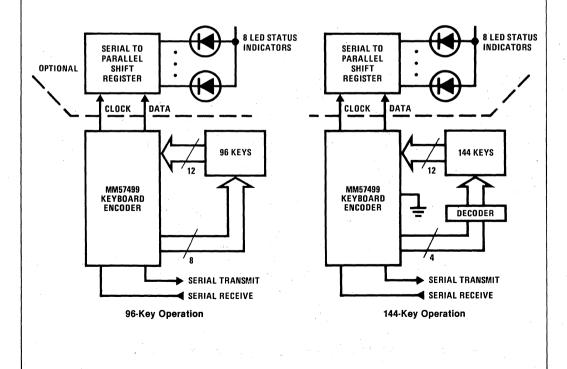

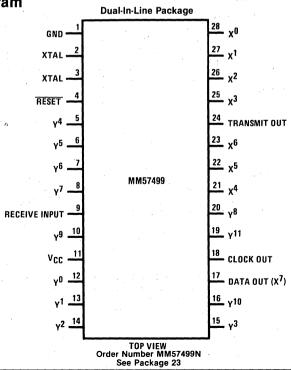

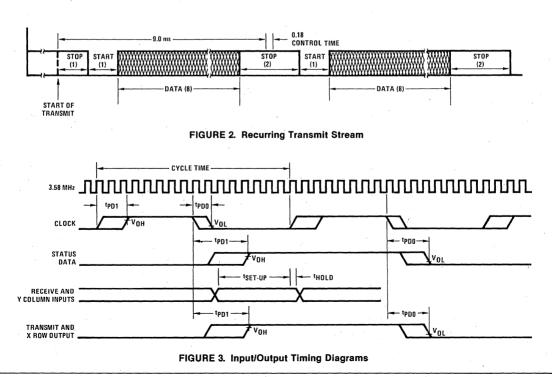

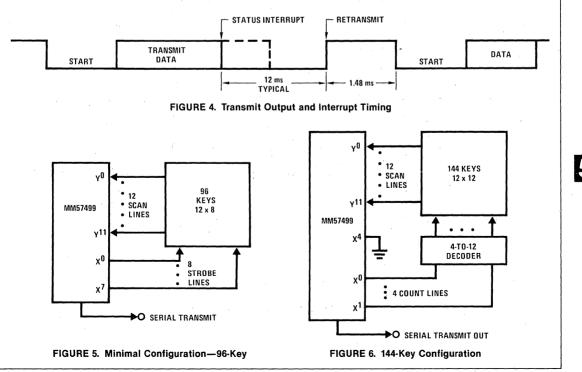

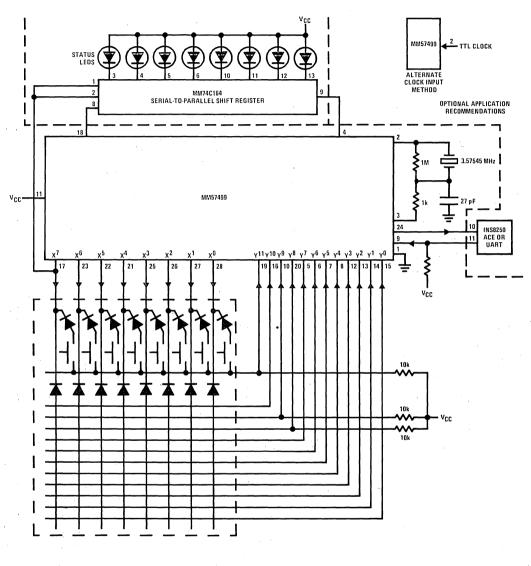

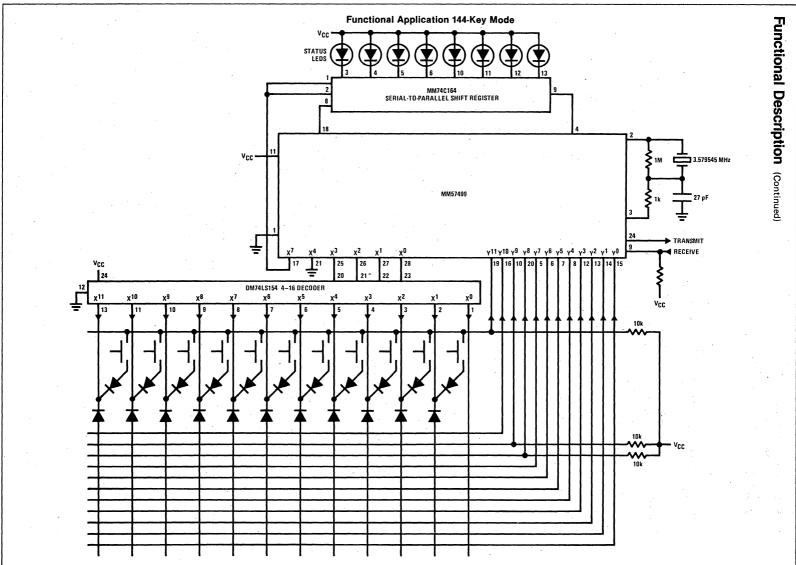

| MM57499 96- or 144-Key Serial Keyboard Interface (SKI)      | 5-316 |

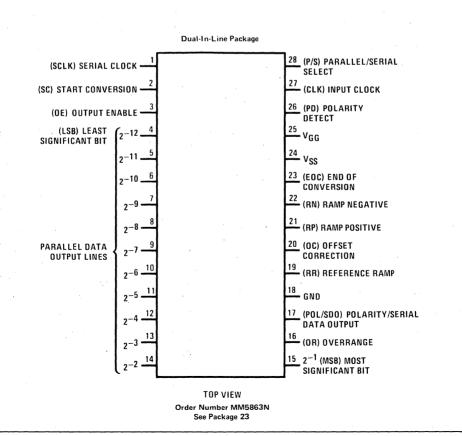

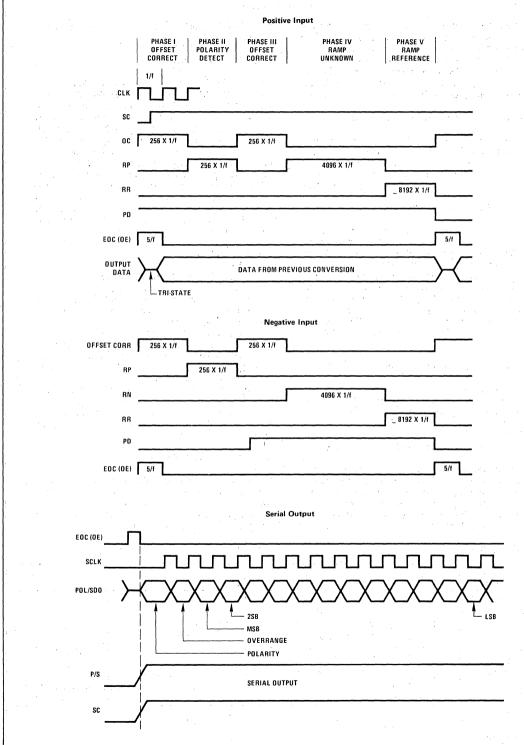

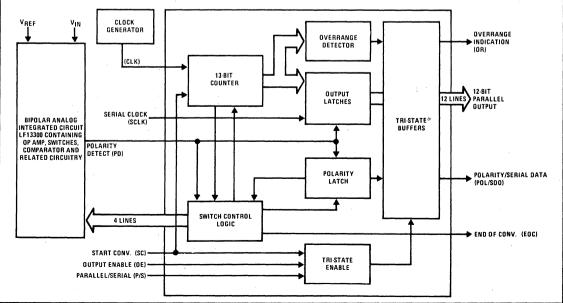

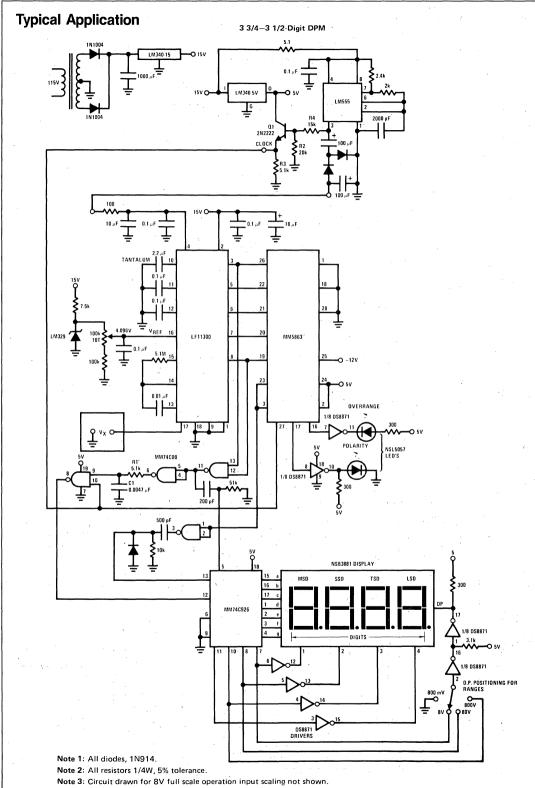

| MM5863 12-Bit Binary A/D Building Block                     | 5-331 |

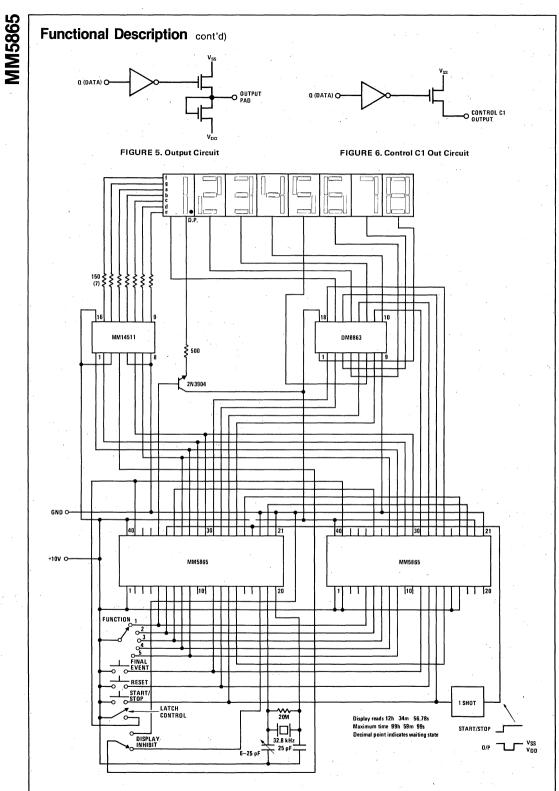

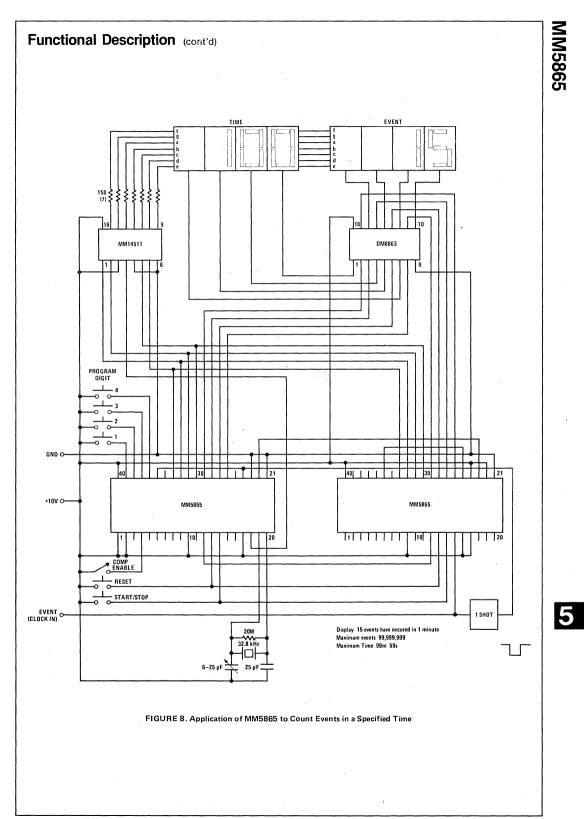

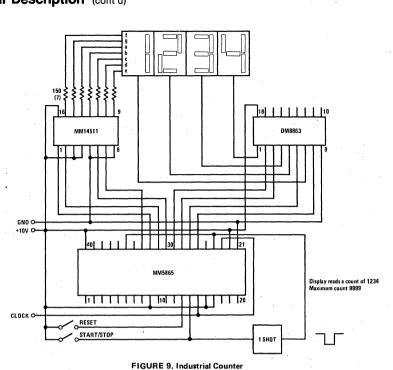

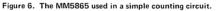

| MM5865 Universal Timer                                      | 5-337 |

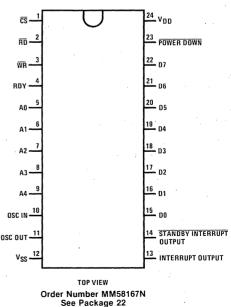

| MM58167 Microprocessor Compatible Real Time Clock           | 5-347 |

| MM58174 Microprocessor-Compatible Real Time Clock           | 5-353 |

Touch Tone<sup>®</sup> is a Registered Trademark of Bell Telephone

## Table of Contents (continued)

| Section 6 | Application Notes                                                  |      |

|-----------|--------------------------------------------------------------------|------|

| AN143     | Using National Clock Integrated Circuit in Timer Applications      |      |

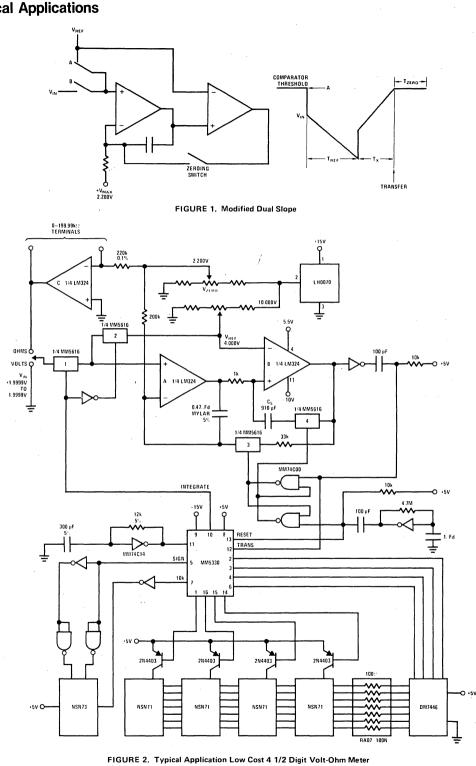

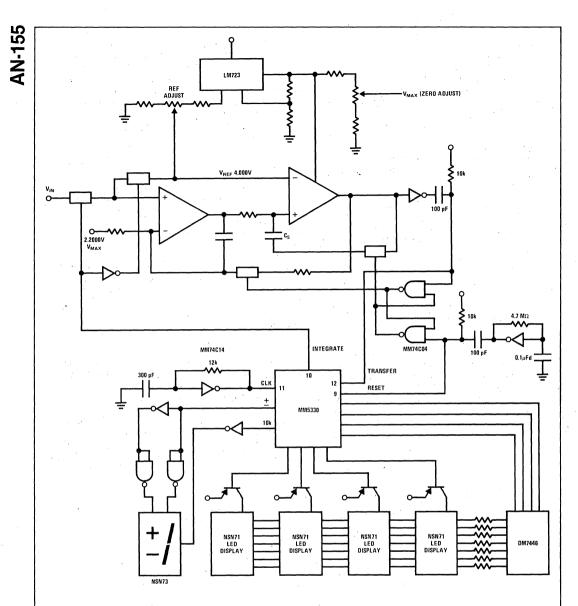

| AN155     | Digital Voltmeters and the MM5330                                  |      |

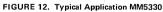

| AN156     | Specifying A/D and D/A Converters                                  | 6-15 |

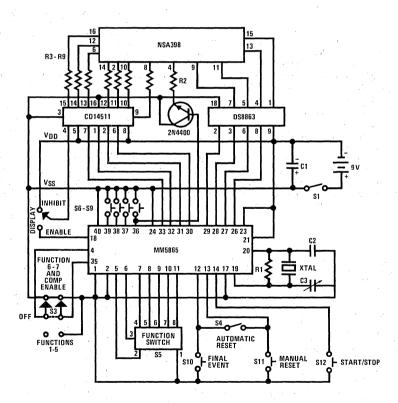

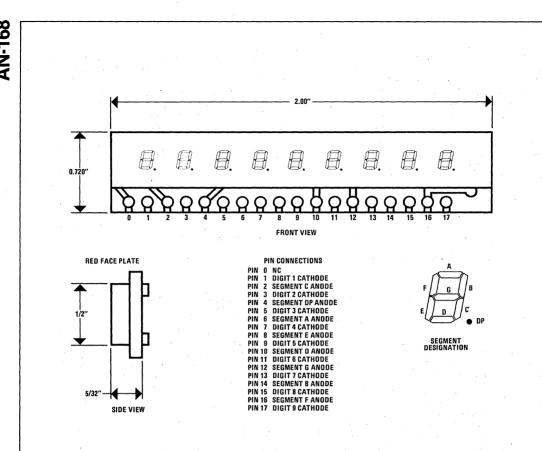

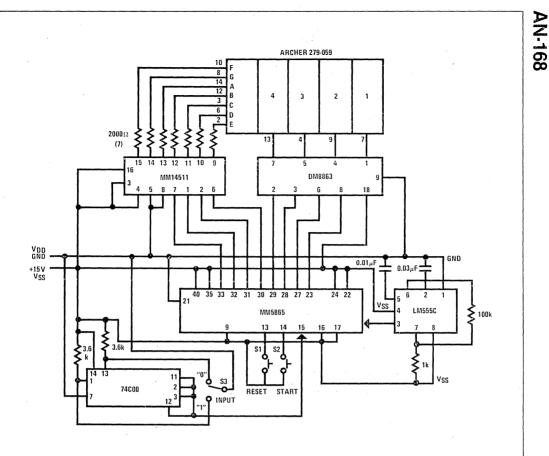

| AN168     | MM5865 Universal Timer Applications                                | 6-21 |

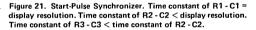

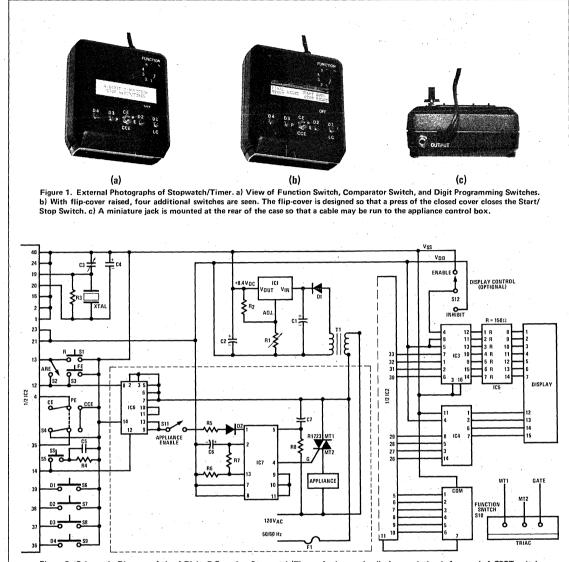

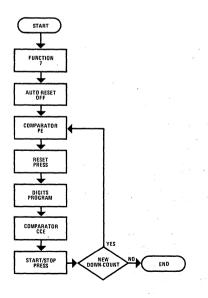

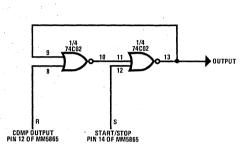

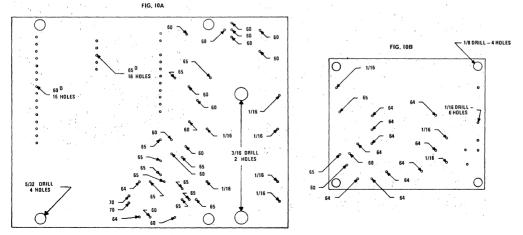

| AN169     | A 4-Digit, 7-Function Stop Watch/Timer                             | 6-31 |

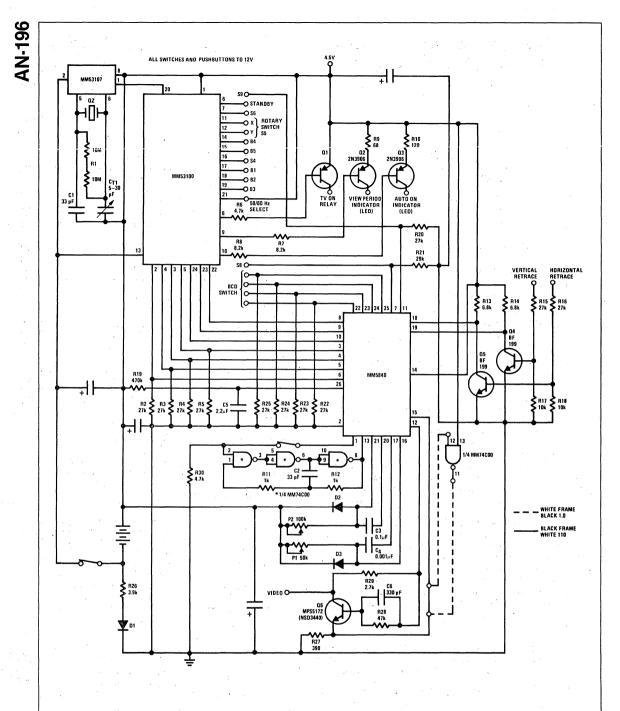

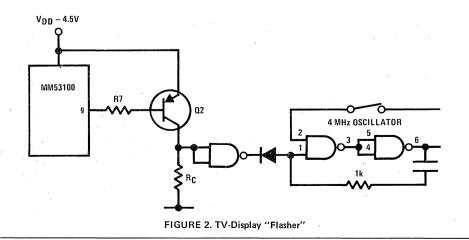

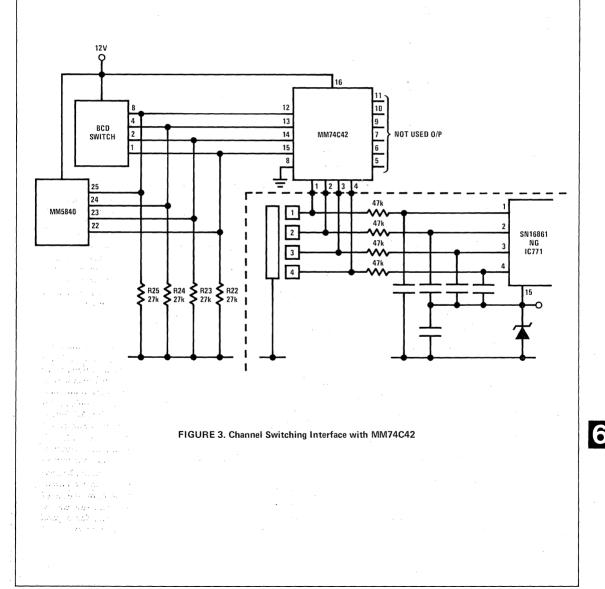

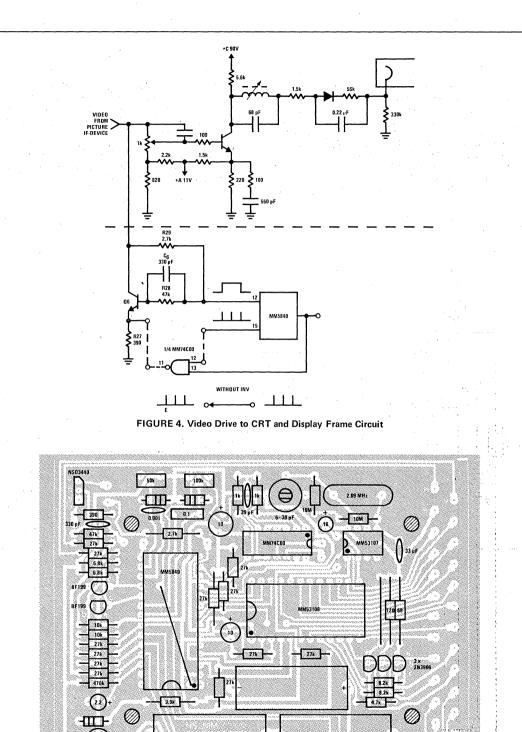

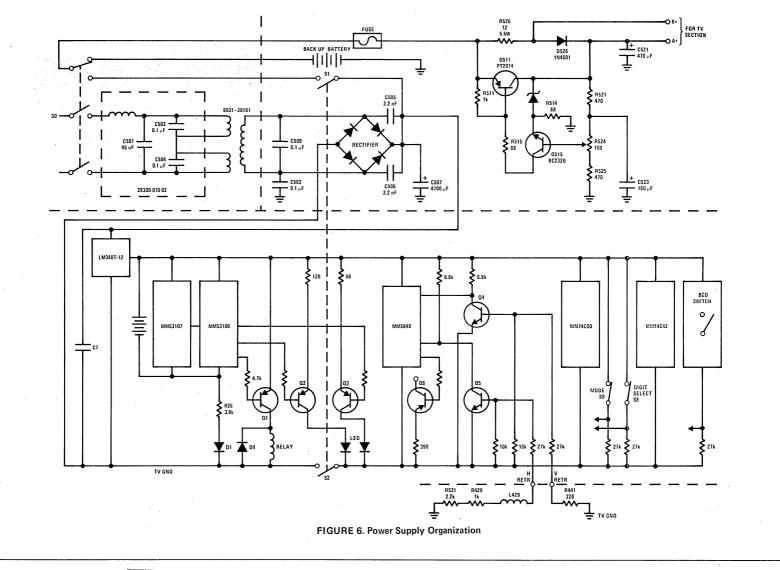

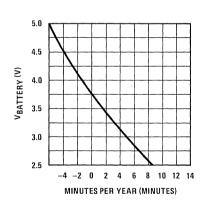

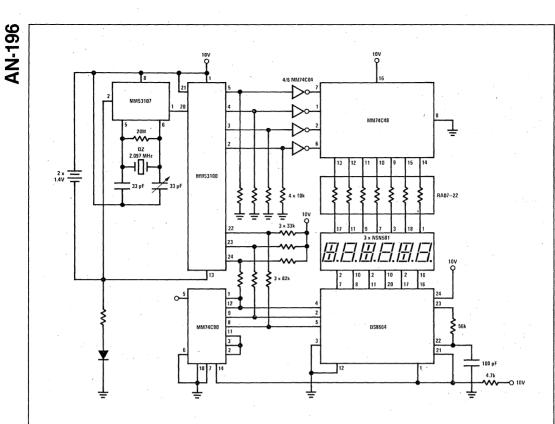

| AN196     | Programmable TV Timer/Time-Channel Display                         | 6-45 |

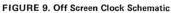

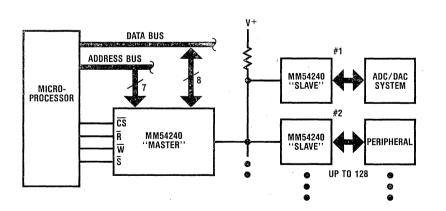

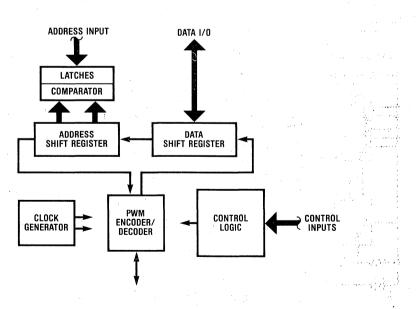

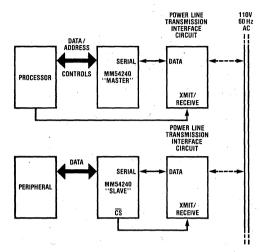

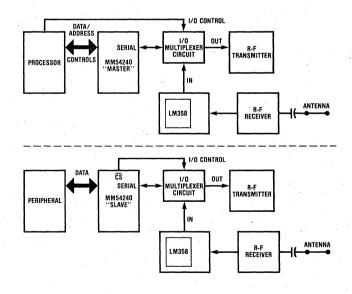

| AN249     | MM54240 Asynchronous Receiver/Transmitter Remote Controller        |      |

|           | Applications                                                       |      |

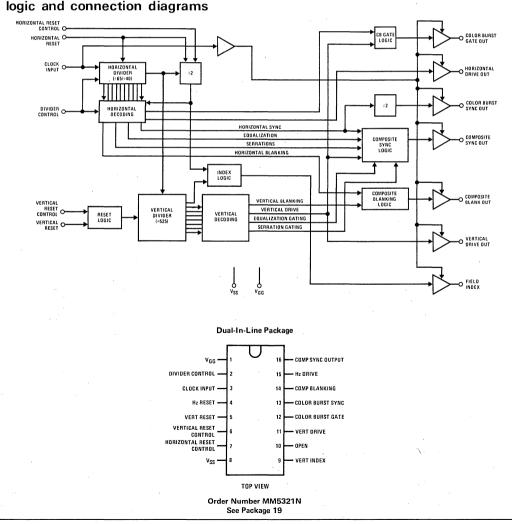

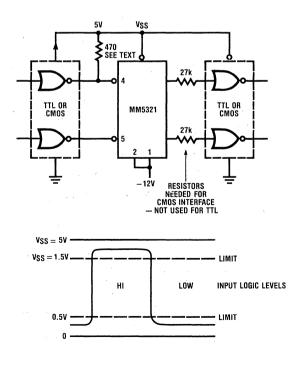

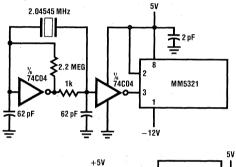

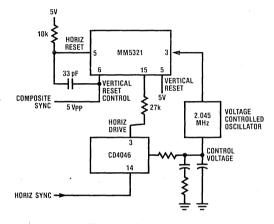

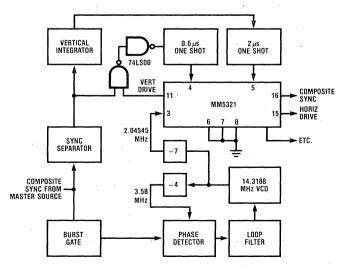

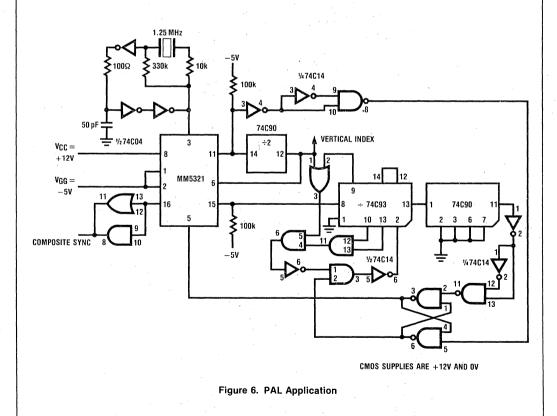

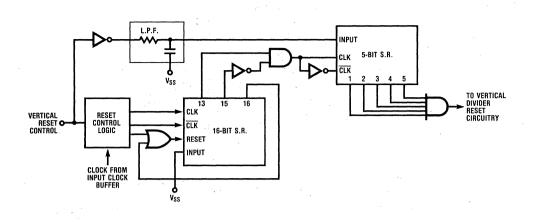

| AN250     | Applications and Uses of the MM5321 TV Camera Sync Generator       | 6-59 |

| AN251     | A Broadcast Quality TV Sync Generator Made Economical through LSI. |      |

| MOS Br    |                                                                    |      |

|           | with Digital Clock for Radios                                      | 6-69 |

| Section 7 | Custom MOS/LSI                                                     |      |

| Your Cho  | oice for Custom MOS/LSI Circuits                                   | 7-3  |

|           | Together to Get the Job Done with Custom MOS/LSI                   |      |

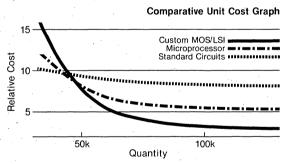

| The Cus   | tom MOS/LSI Development Cycle                                      | 7-5  |

| A Worki   | ng Partnership                                                     | 7-6  |

|           |                                                                    |      |

| Section 8 |                                                                    |      |

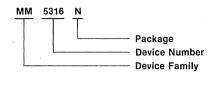

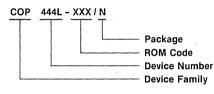

| Ordering  | Information                                                        |      |

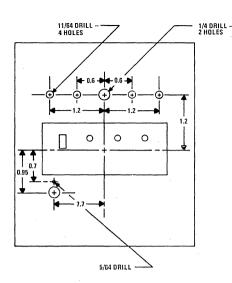

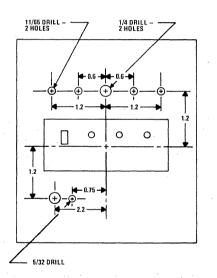

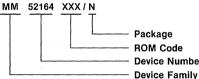

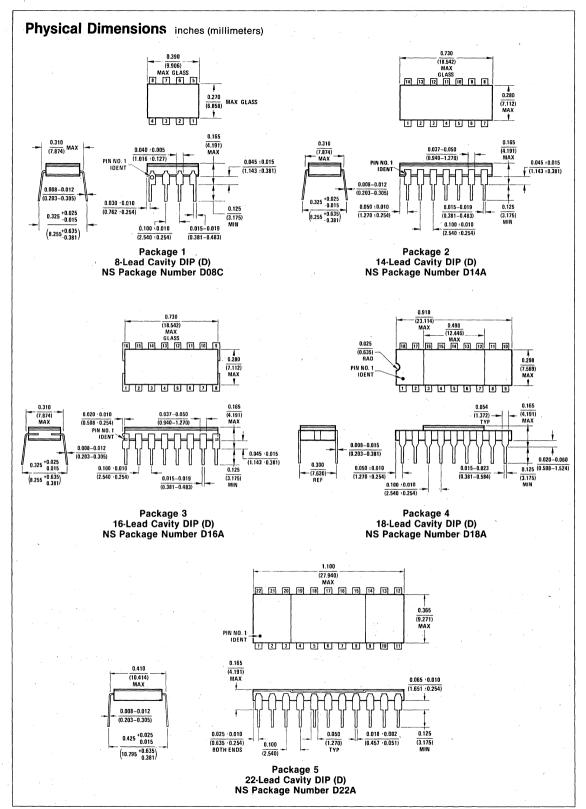

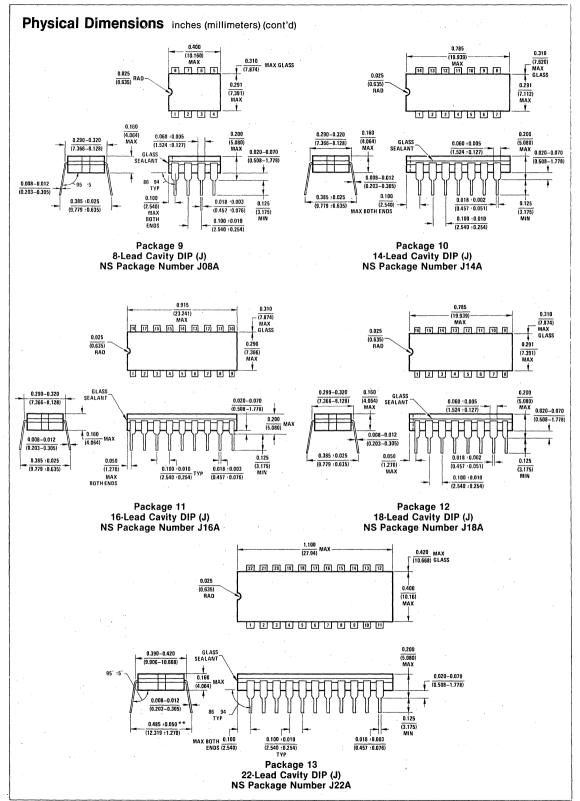

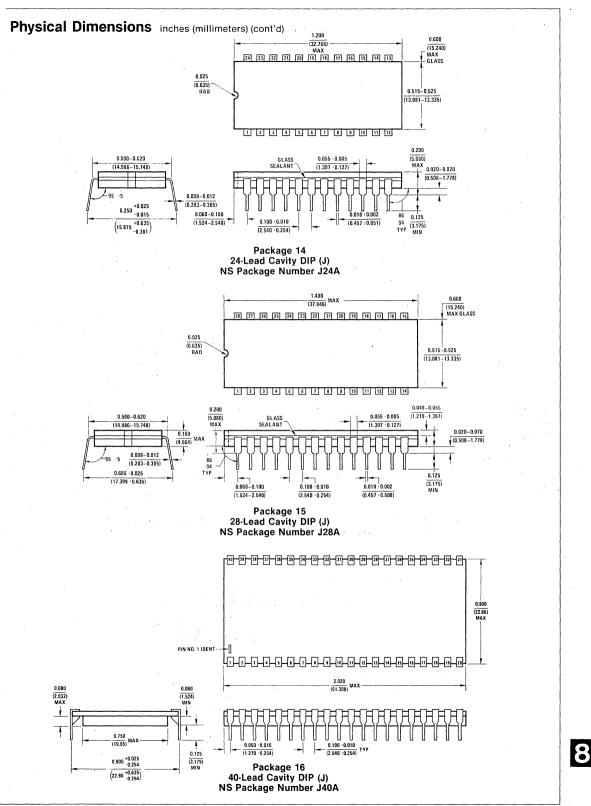

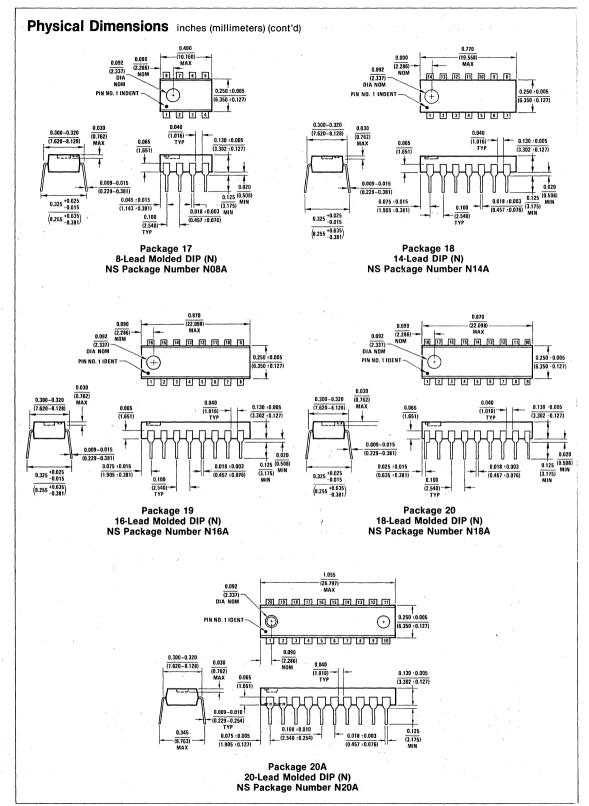

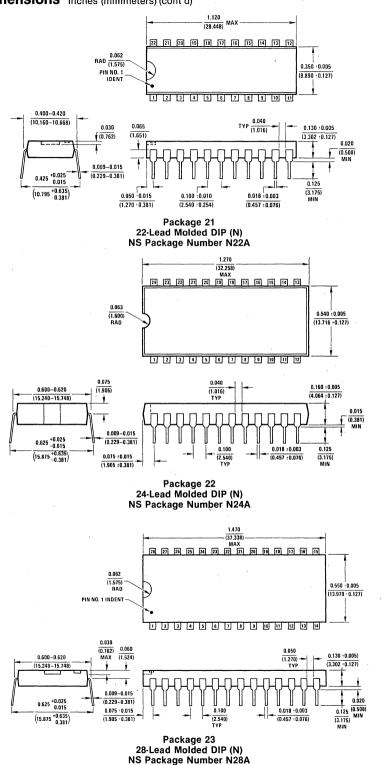

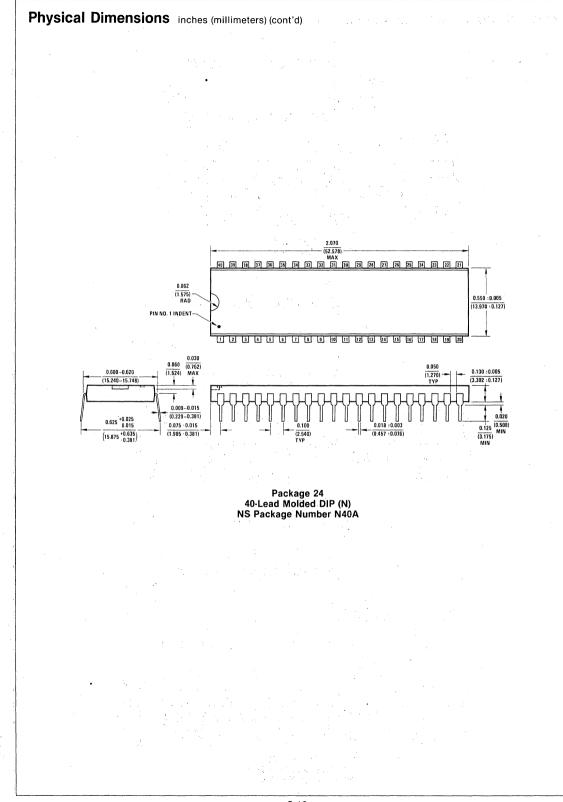

| Physica   | l Dimensions                                                       | 8-4  |

|           |                                                                    |      |

## Alpha-Numerical Index

| COP320 Single-Chip N-Channel Microcontroller                | 1-56  |

|-------------------------------------------------------------|-------|

| COP320C Single-Chip CMOS Microcontroller                    | 1-79  |

| COP321 Single-Chip N-Channel Microcontroller                | 1-56  |

| COP321C Single-Chip CMOS Microcontroller                    | 1-79  |

| COP400 COPS <sup>™</sup> Family User's Guide                | 2-3   |

| COP402 ROMless N-Channel Microcontroller                    | 1-5   |

| COP402M ROMIess N-Channel Microcontroller                   |       |

| COP404L ROMIess N-Channel Microcontroller                   |       |

| COP410L Single-Chip N-Channel Microcontroller               |       |

| COP411L Single-Chip N-Channel Microcontroller               |       |

| COP420 Single-Chip N-Channel Microcontroller                |       |

| COP420C Single-Chip CMOS Microcontroller                    |       |

| COP420L Single-Chip N-Channel Microcontroller               | 1-96  |

| COP421 Single-Chip N-Channel Microcontroller                | 1-56  |

| COP421C Single-Chip CMOS Microcontroller                    | 1-79  |

| COP421L Single-Chip N-Channel Microcontroller               |       |

| COP430 A to D Converter                                     |       |

| COP431 A to D Converter                                     |       |

| COP432 A to D Converter                                     |       |

| COP444L Single-Chip N-Channel Microcontroller               |       |

| COP445L Single-Chip N-Channel Microcontroller               | 1-115 |

| COP450 PROM-RAM Interface Chip                              | 1-136 |

| COP451 PROM-RAM Interface Chip                              |       |

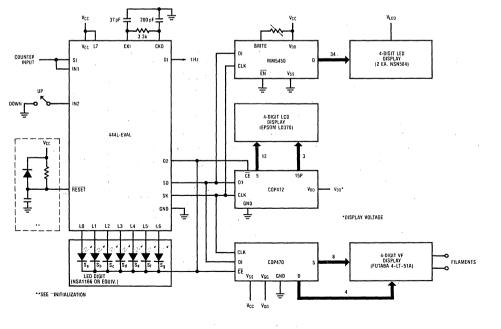

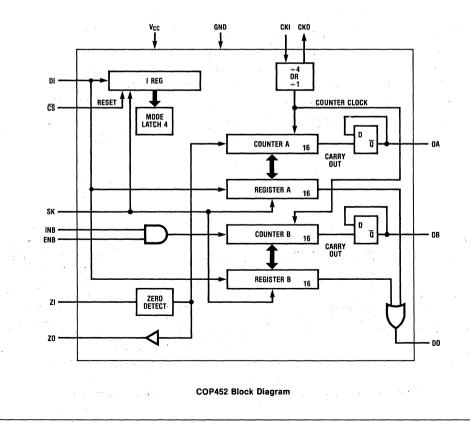

| COP452 Frequency/Counter Peripheral                         | 1-138 |

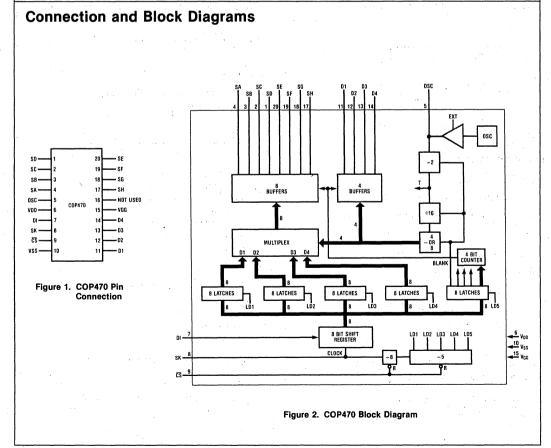

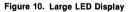

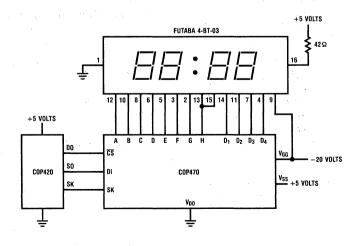

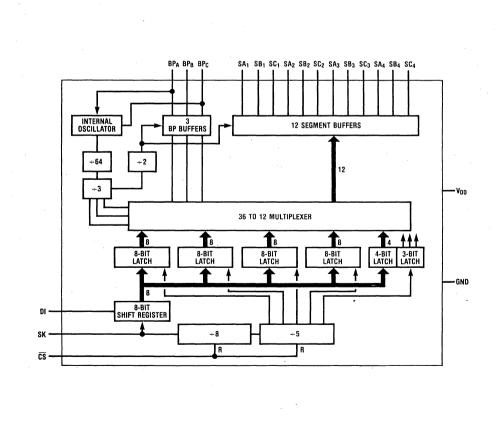

| COP470 V.F. Display Driver                                  | 1-140 |

| COP472 Liquid Crystal Display Controller                    | 1-147 |

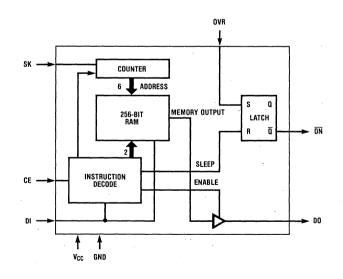

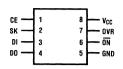

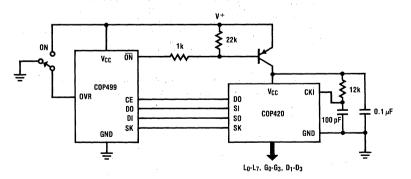

| COP498 Low Power CMOS RAM and Timer                         | 1-153 |

| COP499 Low Power CMOS Memory                                | 1-155 |

| MM5034 Octal 80-Bit Static Shift Register                   | 5-257 |

| MM5035 Octal 80-Bit Static Shift Register                   |       |

| MM5303 Universal Fully Asynchronous Receiver/Transmitter    |       |

| MM5307 Baud Rate Generator/Programmable Divider             |       |

| MM5309 Digital Clock                                        |       |

| MM5311 Digital Clock                                        |       |

| MM5312 Digital Clock                                        |       |

| MM5313 Digital Clock                                        |       |

| MM5314 Digital Clock                                        | 5-13  |

| MM5315 Digital Clock                                        |       |

| MM5316 Digital Alarm ClockClock                             | 5-20  |

| MM5321 TV Camera Sync Generator                             |       |

| MM5322 Color Bar Generator Chip                             |       |

| MM5330 41/2-Digit Panel Meter Logic Block                   |       |

| MM5368 CMOS Oscillator Divider Circuit                      |       |

| MM5369 Series 17 Stage Mask Programmable Oscillator/Divider |       |

| MM5387AA Digital Alarm Clock                                | 5-25  |

## Alpha-Numerical Index (Continued)

|         | Push Button Pulse Dialer Circuit                        |        |

|---------|---------------------------------------------------------|--------|

| MM5394  | Push Button Pulse Dialer Circuit                        | 5-197  |

| MM5395  | DTMF (Touch Tone®) Generator                            | .5-202 |

|         | Digital Alarm Clock                                     |        |

| MM5405  | Digital Alarm Clock                                     | 5-49   |

|         | Deluxe Display and Clock Radio                          |        |

| MM5407  | Digital Thermometer                                     | 5-61   |

|         | AM/FM Radio Frequency Display                           |        |

|         | AM/FM Radio Frequency Display                           |        |

| MM5439  | Microprocessor Compatible Phase Lock Loop (PLL)         | .5-120 |

|         | VF Display Driver                                       |        |

| MM5446  | VF Display Driver                                       | .5-219 |

| MM5447  | VF Display Driver                                       | .5-219 |

|         | VF Display Driver                                       |        |

| MM5450  | LED Display Driver                                      | .5-222 |

| MM5451  | LED Display Driver                                      | .5-222 |

| MM5452  | Liquid Crystal Display Driver                           | .5-227 |

| MM5453  | Liquid Crystal Display Driver                           | .5-227 |

|         | Digital Alarm Clock                                     |        |

| MM5456  | Digital Alarm Clock                                     | 5-70   |

| MM5457  | Digital Alarm Clock                                     |        |

| MM5480  | LED Display Driver                                      | .5-232 |

| MM5481  | LED Display Driver                                      | .5-235 |

| MM5780  | Educational Arithmetic Game                             | .5-181 |

| MM5837  | Digital Noise Source                                    | .5-151 |

| MM5840  | TV Channel Number (16-Channel) and Time Display Circuit | 5-153  |

| MM5863  | 12-Bit Binary A/D Building Block                        | .5-331 |

| MM5865  | Universal Timer                                         | .5-337 |

| MM7317  | B Alarm Clock Calendar                                  |        |

|         | B Alarm Clock Calendar                                  |        |

| MM52116 | 6(2316E) 16,384-Bit (2048 × 8) Read Only Memory         | 3-3    |

| MM52116 | 3FDW Character Generator                                | 3-6    |

| MM52116 | 6FDX Character Generator                                |        |

| MM52132 | 2 32,768-Bit (4096 x 8) MAXI-ROM <sup>™</sup>           | 3-13   |

|         | 4 65,536-Bit (8192 x 8) MAXI-ROM                        |        |

|         | 4 65,536-Bit (8192 × 8) Clocked MAXI-ROM                |        |

| MM5310  | 0 Programmable TV Timer                                 | .5-102 |

| MM5310  | 5 Programmable TV Timer                                 | .5-102 |

|         | 7 Series 17-Stage Oscillator/Divider                    |        |

|         | B Digital Alarm Clock                                   |        |

|         | D Series Auto Clock and Elapsed Timer                   |        |

|         | 3 Digital Alarm Clock                                   |        |

|         | BAA TV Digital Tuning                                   |        |

|         | 4 Automobile Clock and Elapsed Timer                    |        |

|         |                                                         |        |

MAXI-ROMTM is a Trademark of National Semiconductor Corp., Touch Tone® is a Registered Trademark of Bell Telephone

## Alpha-Numerical Index (Continued)

| MM53125 | DTMF (Touch Tone®) Generator                         |       |

|---------|------------------------------------------------------|-------|

| MM53130 | DTMF (Touch Tone®) Generator                         |       |

| MM53143 | Push Button Pulse Dialer Circuit                     |       |

| MM53144 | Push Button Pulse Dialer Circuit                     | 5-197 |

| MM53190 | Push Button Pulse Dialer                             |       |

|         | Encode/Decoder                                       |       |

| MM53224 | Automobile Clock and Elapsed Timer                   | 5-45  |

| MM54240 | Asynchronous Receiver/Transmitter Remote Controller  |       |

| MM55108 | PLL Frequency Synthesizer with Receive/Transmit Mode | 5-127 |

| MM55110 | PLL Frequency Synthesizer with Receive/Transmit Mode |       |

| MM55121 | Serial Data/PLL Frequency Synthesizer                | 5-132 |

| MM55122 | Serial Data/PLL Frequency Synthesizer                | 5-137 |

| MM55123 | Serial Data/PLL Frequency Synthesizer                | 5-142 |

| MM55124 | PLL Frequency Synthesizer                            | 5-147 |

| MM55126 | PLL Frequency Synthesizer                            | 5-147 |

|         | MOS/LSI Number-Oriented Processor                    |       |

| MM57436 | Decimal/Binary Up/Down Counter                       | 5-309 |

|         | Advanced Educational Arithmetic Game                 |       |

| MM57459 | 8-Digit LED Direct-Drive Memory Calculator           | 5-190 |

|         | 96- or 144-Key Serial Keyboard Interface (SKI)       |       |

| MM58106 | Digital Clock and TV Display Circuit                 |       |

|         | TV Synthesizer                                       |       |

|         | LCD Alarm Clock Circuit                              |       |

|         | LCD Alarm Clock Circuit                              |       |

|         | TV Clock and Channel Display                         |       |

|         | Microprocessor-Compatible Real Time Clock            |       |

|         | Microprocessor-Compatible Real Time Clock            |       |

|         | LCD Alarm Clock Circuit                              |       |

|         | LCD Alarm Clock Circuit                              |       |

|         | Multiplexed LCD Driver                               |       |

| MM58313 | Varactor Tuner Display Circuit                       | 5-173 |

Touch Tone® is a Registered Trademark of Bell Telephone

Introduction to COPS<sup>™</sup>

COPS Single Chip Microcontroller and Peripherals • 1 ·

#### COPS<sup>™</sup> Family Introduction:

Computer on a Chip

National Semiconductor manufactures a wide-ranging and sophisticated family of single-chip microcomputers to meet the total needs of the microcontroller marketplace.

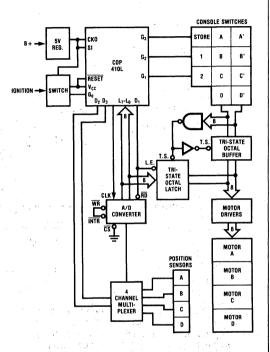

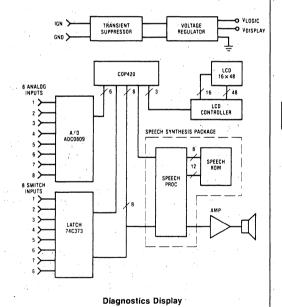

Each member of the COP400 series of single-chip microcontrollers is a complete "computer-on-a-chip," containing all system timing, internal logic, ROM, RAM, and I/O necessary to implement dedicated control functions in a wide variety of applications. The COP400 family of devices feature instruction sets, internal architectures and I/O schemes designed to ease keyboard input/display output and efficient binary and BCD data manipulation. On-chip ROM sizes range from  $512 \times 8$  to  $2,048 \times 8$  bits, RAM from  $32 \times 4$  to  $128 \times 4$  bits, instruction sets from 43 to 57 commands, I/O lines from 16 to 36, and instruction cycle execution times ranging from 4 to 16 microseconds. The family is fabricated using three processes: an advanced, high speed N-channel MOS; a low power NMOS; and an even lower power complementary MOS.

To ease program development on the new COP400 series a specially designed COPS Product Development System (PDS), has been introduced.

#### Programmable Features

The range of the microcontrollers available in the COP400 family allow the user to specify the optimum device for use in a particular application. Not only can the user pick a part with RAM, ROM, I/O and speed optimized for specific tasks, but the family also offers a choice of ports with differing electrical characteristics. Each part contains a number of clock, I/O and other options, mask programmed into the device at the same time the ROM is coded with the user's dedicated program. This allows great flexibility in matching particular COP400 microcontrollers to the user need.

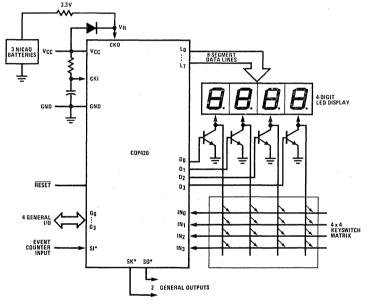

All COP400 devices feature single supply operation and fast standardized test procedures that verify the internal logic and user program. The flexible I/O configuration of the COP400 microcontrollers allow them to interface and drive a wide range of devices using a minimal amount of external parts. Typical interfaced devices include: keyboards and displays (direct segment and direct digit drive), external data memories, printers, other COP devices, A/D and D/A converters, power control devices such as SCRs and TRIACs, mechanical actuators, general purpose microprocessors, shift registers and external ROM storage devices.

#### Applications

The COP400 devices are aimed at such high volume applications as clocks, timers, laboratory instruments, radio controllers, applicance controllers, programmable sequencers, scales, cash registers, calculators, microcontroller computational elements, toys, games, and automotive computers.

#### Performance

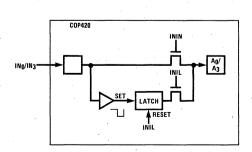

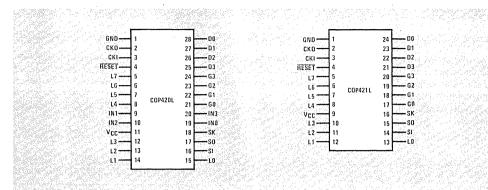

The COP420/420L/420C devices constitute the center-piece configurations of the family, with 1k × 8 ROM, 64 × 4 RAM, true vectored interrupt plus restart, three level subroutine stack, 23 I/O lines, 57 command instruction set, internal time base counter for real time processing, internal binary counter register with serial I/O capability, general purpose and TRI-STATE outputs, LED direct drive, and software/hardware compatibility with the rest of the COP400 family — all within a 28-pin dual-in-line package. The NMOS COP420 operates over a 4.5 to 6.3 volt single supply range and has a 4 microsecond instruction cycle execution time. Operating supply current is 20 milliamperes at 5 volts. The low power (40 mW, max.) NMOS COP420L differs from the COP420 in that it has a 4.5 to 9.5 volt supply range, a 16 $\mu$ s instruction cycle execution time, a divide by 32 crystal clock option and direct LED digit drive capability. The COP420C is the CMOS version with a 2.4 to 6.0 volt operating supply range and a dual clock mode option for operation at low speed (244 $\mu$ s) with low power consumption or high speed (16 $\mu$ s) when necessary to perform internal data computations at a faster rate. The COP420C also provides the user with a sleep (timed pause) mode entered under program control with very low power consumption (15 $\mu$ A).

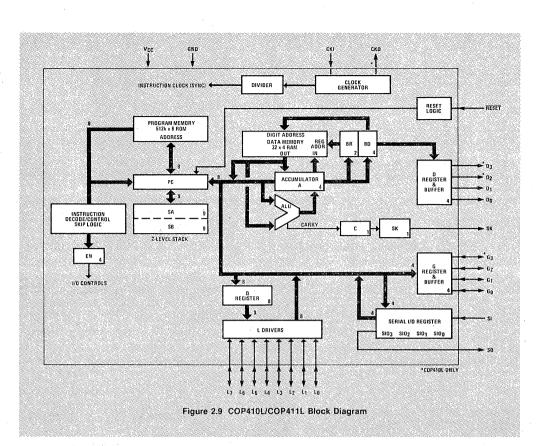

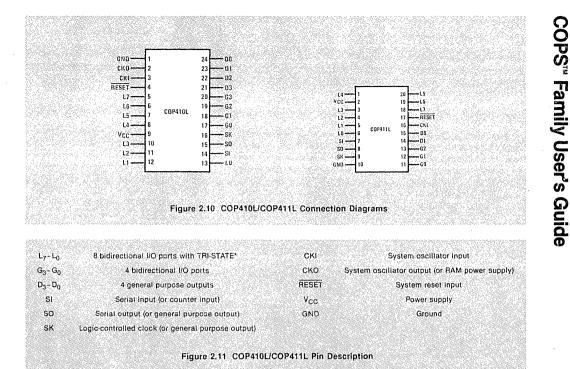

The 24-pin COP421/421L devices are identical to the COP420/420L versions except that they have 19 I/O lines instead of 23, and no interrupt capability. The COP410L/411L have the same electrical specifications as the COP420L/421L but half the program storage ( $512 \times 8$  ROM), half the data storage ( $32 \times 4$  RAM), only 43 instructions, two instead of three stack levels, no interrupt capability, 19 and 16 I/O lines respectively. They are in 24-pin and 20-pin packages, respectively.

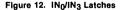

The COP440/444L are expanded versions of the COP420/420L devices, with the same instruction set but double the memory (2,048  $\times$  8 ROM and 128  $\times$  4 RAM). The 28-pin COP444L has 24 I/O lines and the 40-pin COP440 (future product) has 36 lines of I/O. The 40-pin COP402 and COP404L are ROM-less version of the COP420 and COP404L, respectively, available for prototyping, or in quantity for small volume applications using up to 1024  $\times$  8 and 2048  $\times$  8 bits of external ROM.

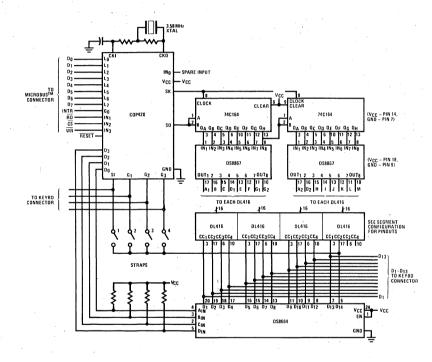

#### **Bus Compatibility**

A key feature of the COP420 and COP 420C is that they are MICROBUS<sup>™</sup> compatible, an option that allows it to be used as a peripheral microprocessor device, inputting and outputting data from and to any host microprocessor in National's MICROBUS-compatible family of 8-and 16-bit microprocessors. MICROBUS is a standard interconnect system for 8-bit parallel data transfer between MOS/LSI CPUs and interface devices. The COP402M is the ROM-less MICROBUS-compatible version of the COP402. It is intended for use in prototyping systems in low volume applications which use the COP420 as a host CPU peripheral component.

#### **Development Systems**

To aid in the efficient and speedy programming of the COP400 series microcontrollers National has developed the COP Product Development System (PDS), built around a 16-bit microcomputer, 32k bytes of R/W memory and 12k bytes of PROM firmware. The disk-based system features an editor and assembler for handling source code entry, conversion to object code and maintaining documentation. An in-circuit emulator card attachment allows object code to be executed under the careful control of a COP Monitor de-bug utility. The PDS also features a circuit fixture for incoming inspection of COP400 devices.

National is continually expanding the COP400 family. Future members will include expanded software and hardware capabilities, alternative electrical specification devices, and smaller devices suitable for use in less demanding applications.

#### Schools

A COPS<sup>™</sup> training course is available for instruction in programming, interfacing, and applications. For further information on the course, contact your local National Semiconductor Sales Office.

Section 1

#### **COPS Devices**

#### NATIONAL SEMICONDUCTOR COP400 MICROCONTROLLER FAMILY GUIDE

|                  | Specifications COP:                                  | RON<br>402      | Alless Dev<br>402M                          | vices<br>404L | 410L | 411L    | 420     |            | Chip Mi<br>420C | crocont<br>421 | rollers<br>421L | 421C    | 444L | 445L       |

|------------------|------------------------------------------------------|-----------------|---------------------------------------------|---------------|------|---------|---------|------------|-----------------|----------------|-----------------|---------|------|------------|

| M<br>E<br>M      | ROM × 8                                              |                 | up to<br>1024 ext.<br>up to<br>2048<br>ext. |               | 512  |         | 1024    |            | 1024            |                |                 | 2048    |      |            |

| O<br>R<br>Y      | RAM × 4                                              | 64              |                                             | 128           | 32.  |         | 64*     |            | 64*             |                |                 | 128*    |      |            |

| IN               | Inputs                                               | 4               |                                             |               | 0    |         | 4       |            | 0               |                |                 | 4       | 0    |            |

| U<br>U<br>T<br>e | N Hypers<br>P<br>U Bidirectional TRI-STATE™ I/O<br>S |                 | 8                                           |               | 8    |         | 8       |            | 8               |                |                 | 8       |      |            |

|                  | Bidirectional I/O                                    | 4               |                                             | 4             | 3    | 4       |         | 4          |                 |                | 4               |         |      |            |

| OUTPUT           | Outputs                                              |                 | 4                                           |               | 4    | 2       |         | 4          |                 | 4 .            |                 | 4       |      |            |

| T<br>S           | Serial I/O and External Event Counter                | Yes             |                                             |               | Y    | es      | Yes SIO |            | Yes SIO         |                | Yes             |         |      |            |

|                  | Interrupt                                            | Yes             | No                                          | Yes           | ٨    | 40      |         | Yes        |                 |                | No              |         | Yes  | No         |

| GENERA           | Stack Levels                                         |                 | 3                                           |               |      | 2       |         | 3          |                 |                | 3               |         |      | 3          |

| Ř                | MICROBUS™ Option                                     | No              | Yes                                         | No            | Ν    | 10      | Yes     | No         | Yes             |                | No              |         |      | No         |

| -                | Instruction Cycle (µs)                               |                 | 4                                           | 16            | 1    | 16      | 4       | 16         | 6               | 4              | 10              | 3       |      | 16         |

| POW              | Supply Voltage                                       | 4.5-6.3 4.5-9.5 |                                             | 4.5-9.5       | 4.5  | -6.3*** | 4.5-6.3 | 4.5-6.3*** | 2.4-6.0         | 4.5-6.3        | 4.5-6.3***      | 2.4.6.0 | -    | 1.5-6.3*** |

| O₩ER             | Supply Current (mA)                                  | 30 15           |                                             | 15            |      | 5       | 30      | 8          |                 | 30             | 8               |         |      | 11         |

| PKG              | Package Size (pins)                                  |                 | 40                                          |               | 24   | 20      |         | 28         |                 |                | 24              |         | 28   | 24         |

\*RAM keep-alive option (except 420C/421C). \*\*Fast: 800 µA, Slow: 35 µA, Sleep: 15 µA. \*\*\*4.5-9.5V optionally available

### National Semiconductor

### **COP402/COP402M ROMIess N-Channel Microcontrollers**

#### **General Description**

The COP402 and COP402M ROMless Microcontrollers are members of the COPS<sup>™</sup> family, fabricated using N-channel silicon gate MOS technology. Each part contains CPU, RAM and I/O, and is identical to a COP420 device, except the ROM has been removed; pins have been added to output the ROM address and to input ROM data. In a system, the COP402 or 402M will perform exactly as the COP420; this important benefit facilitates development and debug of a COP420 program prior to masking the final part. These devices are also appropriate in low volume applications, or when the program may require changing. The COP402M is identical to the COP402, except the MICROBUS<sup>™</sup> interface option has been implemented.

The COP402 may also be used to emulate the COP410L, 411L, 420L or 420C by appropriately reducing the clock frequency.

#### **Features**

- Low cost

- Exact circuit equivalent of COP420

- Standard 40-pin dual-in-line package

- Interfaces with standard PROM or ROM

- 64×4 RAM, addresses up to 1k×8 ROM

- MICROBUS<sup>TM</sup> compatible (COP402M)

- Powerful instruction set

- True vectored interrupt, plus restart

- Three-level subroutine stack

- 4.0µs instruction time

- Single supply operation (4.5V to 6.3V)

- Internal time-base counter for real-time processing

- Internal binary counter register with serial I/O capability

- Software/hardware compatible with other members of COP400 family

#### **Absolute Maximum Ratings**

Voltage at Any Pin Relative to GND Ambient Operating Temperature Ambient Storage Temperature Lead Temperature (Soldering, 10 seconds) Power Dissipation - 0.5V to + 7V 0°C to + 70°C - 65°C to + 150°C 300°C 0.75 Watt at 25°C 0.4 Watt at 70°C

Absolute maximum ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications are not ensured when operating the device at absolute maximum ratings.

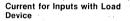

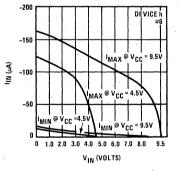

#### DC Electrical Characteristics $0^{\circ}C \le T_A \le +70^{\circ}C$ , $4.5V \le V_{CC} \le 6.3V$ unless otherwise noted.

| Parameter                                         | Conditions                                                            | Min                         | Max                                   | Units |

|---------------------------------------------------|-----------------------------------------------------------------------|-----------------------------|---------------------------------------|-------|

| Operating Voltage (V <sub>CC</sub> )              |                                                                       | 4.5                         | 6.3                                   | V     |

| Operating Supply Current                          | $V_{CC} = 5V$ , $T_A = 25 \degree C$<br>(all inputs and outputs open) |                             | 30                                    | mA    |

|                                                   |                                                                       |                             |                                       |       |

| Input Voltage Levels                              |                                                                       |                             |                                       |       |

| CKI Input Levels<br>Logic High (V <sub>IH</sub> ) |                                                                       | 2.0                         |                                       |       |

| Logic Low (V <sub>IL</sub> )                      | · · · ·                                                               |                             | 0.4                                   | V A   |

| RESET Input Levels<br>Logic High                  |                                                                       | 0.7 V <sub>CC</sub>         |                                       | v     |

| Logic Low                                         |                                                                       |                             | 0.6                                   | V .   |

| RESET Hysteresis                                  |                                                                       | 1.0                         |                                       | V     |

| SO Input Level (Test mode)                        |                                                                       | 2.0                         | 3.0                                   | V     |

| Input Levels                                      |                                                                       |                             |                                       |       |

| Logic High                                        | V <sub>CC</sub> = max                                                 | 3.0                         | 1. T. P.                              | V     |

| Logic High<br>Logic Low                           | $V_{\rm CC} = 5V \pm 5\%$                                             | 2.0<br>0.3                  | 0.8                                   |       |

| Logic Low (IN <sub>0:3</sub> with Load)           |                                                                       | -0.3                        | 0.5                                   | v     |

| Output Voltage Levels (Note 2)                    |                                                                       |                             | · · · · · · · · · · · · · · · · · · · |       |

| TTL Operation                                     | $V_{CC} = 5V \pm 5\%$                                                 |                             |                                       |       |

| Logic High (V <sub>OH</sub> )                     | $I_{OH} = -100 \mu A$                                                 | 2.4                         |                                       | V ,   |

| Logic Low (V <sub>OL</sub> )                      | $I_{OL} = +1.6 \text{mA}^2$                                           | -0.3                        | 0.4                                   | V     |

| CMOS Operation                                    |                                                                       |                             | •<br>                                 |       |

| Logic High (V <sub>OH</sub> )                     | $I_{OH} = -10 \mu A$                                                  | V <sub>CC</sub> – 1<br>–0.3 | 0.2                                   | V     |

| Logic Low (V <sub>OL</sub> )                      | $I_{OL} = +10\mu A$                                                   | -0.3                        | 0.2                                   | V     |

| Output Current Levels                             |                                                                       |                             |                                       |       |

| LED Direct Drive Output                           | $V_{CC} = 6V$                                                         |                             |                                       |       |

| Logic High (I <sub>OH</sub> )                     | $V_{OH} = 2.0V$                                                       | 2.5                         | 14                                    | mA    |

| TRI-STATE® Output                                 |                                                                       | <b>— 10</b>                 | + 10                                  | μA    |

| Leakage Current                                   |                                                                       |                             | · · ·                                 |       |

| IP7 $\sim$ IP0 Output Voltage Levels              |                                                                       |                             |                                       |       |

| v <sub>он</sub>                                   | $I_{OH} = -50 \mu A$                                                  | 2.7                         |                                       | v     |

| V <sub>OL</sub>                                   | $I_{OL} = +360 \mu A$                                                 | -0.3                        | 0.4                                   | l v   |

1-6

1

| Parameter                                                                                         | Conditions                                                              | Min | Мах        | Units<br>μs |  |

|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----|------------|-------------|--|

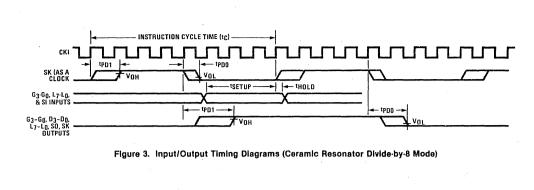

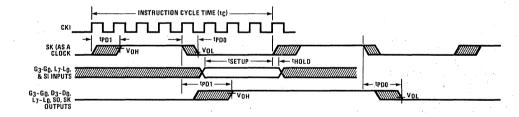

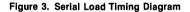

| nstruction Cycle Time — t <sub>C</sub>                                                            | figure 3                                                                | 4   | 10         |             |  |

| CKI Using Crystal (figure 8)                                                                      |                                                                         |     |            |             |  |

| Input Frequency — f <sub>l</sub>                                                                  | ÷16 mode                                                                | 1.6 | 4          | MHz         |  |

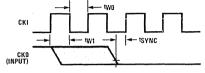

| Duty Cycle (Note 2)                                                                               | figure 3a                                                               | 30  | 55         | %           |  |

| NPUTS: (figure 3a)                                                                                |                                                                         |     |            |             |  |

| N <sub>3</sub> -IN <sub>0</sub> , G <sub>3</sub> -G <sub>0</sub> , L <sub>7</sub> -L <sub>0</sub> |                                                                         |     |            |             |  |

|                                                                                                   |                                                                         | 1.7 |            | μs          |  |

| t <sub>HOLD</sub>                                                                                 |                                                                         | 312 |            | ns          |  |

| SI, IP <sub>7</sub> -IP <sub>0</sub>                                                              |                                                                         |     |            |             |  |

| tSETUP                                                                                            |                                                                         | 0.3 |            | μs          |  |

| t <sub>HOLD</sub>                                                                                 |                                                                         | 250 |            | ns          |  |

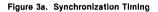

| OUTPUTS:                                                                                          |                                                                         |     |            |             |  |

| COP TO CMOS PROPAGATION                                                                           | $4.5V \leq V_{CC} \leq 6.3V, C_{L} = 50 pF,$                            |     |            |             |  |

| DELAY                                                                                             | $V_{OH} = 0.7 V_{CC}, V_{OL} = 0.3 V_{CC}$                              |     |            |             |  |

| SK as a Logic-Controlled Clock                                                                    |                                                                         |     |            |             |  |

| t <sub>PD1</sub>                                                                                  |                                                                         |     | 1.1        | μs          |  |

| t <sub>PD0</sub>                                                                                  |                                                                         |     | 0.3        | μs          |  |

| SO, SK as a Data Output                                                                           |                                                                         |     |            |             |  |

| t <sub>PD1</sub>                                                                                  |                                                                         |     | 1.4        | μs          |  |

| t <sub>PD0</sub>                                                                                  | $V_{OH} = 2V$                                                           |     | 0.3<br>0.7 | μs          |  |

|                                                                                                   | •OH - 2•                                                                |     | 0.7        | μs          |  |

| $D_3 - D_0, G_3 - G_0$                                                                            |                                                                         |     | 16         |             |  |

| t <sub>PD1</sub><br>t <sub>PD0</sub>                                                              |                                                                         |     | 1.6<br>0.6 | μs<br>μs    |  |

| -7-L0 (LED Direct Drive)                                                                          |                                                                         |     | 0.0        | μο          |  |

|                                                                                                   | $V_{OH} = 2V$                                                           |     | 2.4        | μS          |  |

| t <sub>PD0</sub>                                                                                  | - UH                                                                    |     | 0.4        | μs<br>μs    |  |

|                                                                                                   |                                                                         |     |            |             |  |

| COP TO TTL PROPAGATION                                                                            | fanout = 1 Standard TTL Load                                            |     |            |             |  |

|                                                                                                   | $V_{CC} = 5V \pm 5\%, C_{L} = 50 pF,$<br>$V_{OH} = 2.4V, V_{OL} = 0.4V$ |     |            |             |  |

|                                                                                                   | -0H = 2.77, VOL = 0.47                                                  |     |            |             |  |

| t <sub>PD1</sub>                                                                                  |                                                                         |     | 0.5        | μs          |  |

| t <sub>PD0</sub>                                                                                  |                                                                         |     | 0.5        | μs          |  |

| SKIP                                                                                              |                                                                         |     |            |             |  |

| t <sub>PD1</sub>                                                                                  |                                                                         |     | 0.6        | μs          |  |

| t <sub>PD0</sub>                                                                                  |                                                                         |     | 0.6        | μS          |  |

1

### AC Electrical Characteristics (continued) $0^{\circ}C \le T_A \le +70^{\circ}C$ , $4.5V \le V_{CC} \le 6.3V$ unless otherwise noted.

| Parameter                                                          | Conditions                             | Min | Max        | Units |  |

|--------------------------------------------------------------------|----------------------------------------|-----|------------|-------|--|

| OUTPUTS (cont.):                                                   |                                        |     |            |       |  |

| SK as a Logic-Controlled Clock                                     |                                        |     |            |       |  |

| t <sub>PD1</sub>                                                   |                                        |     | 0.8        | μS    |  |

| t <sub>PD0</sub>                                                   |                                        |     | 0.8        | μs    |  |

| SK as a Data Output, SO                                            |                                        |     |            |       |  |

| t <sub>PD1</sub>                                                   |                                        | ·   | 1.0        | μs    |  |

| t <sub>PD0</sub>                                                   |                                        |     | 1.0        | μs    |  |

| D <sub>3</sub> -D <sub>0</sub> , G <sub>3</sub> -G <sub>0</sub>    |                                        |     |            |       |  |

| t <sub>PD1</sub>                                                   |                                        |     | 1.3        | μs    |  |

| t <sub>PD0</sub>                                                   |                                        |     | 1.3        | μs    |  |

| L7-L0                                                              |                                        |     |            |       |  |

| t <sub>PD1</sub>                                                   |                                        |     | 1.4        | μs    |  |

| t <sub>PD0</sub>                                                   |                                        |     | 0.4        | μs    |  |

| IP <sub>7</sub> -IP <sub>0</sub> , P <sub>9</sub> , P <sub>8</sub> |                                        |     |            |       |  |

| t <sub>PD1</sub>                                                   |                                        |     | 1.5        | μs    |  |

| t <sub>PD0</sub>                                                   |                                        |     | 1.5        | μs    |  |

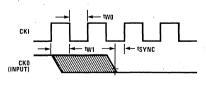

| CKO (figure 3a)                                                    |                                        |     |            |       |  |

| t <sub>PD1</sub>                                                   |                                        | -   | 0.2<br>0.2 | μs    |  |

| t <sub>PD0</sub>                                                   |                                        |     | 0.2        | μS    |  |

| MICROBUS™ TIMING<br>(COP402M)                                      | $C_{L} = 50  pF,  V_{CC} = 5V \pm 5\%$ |     |            |       |  |

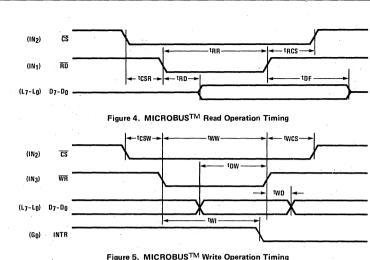

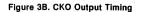

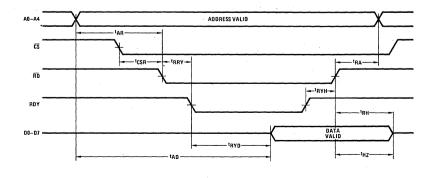

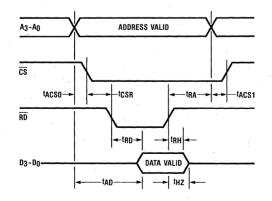

| A. Read Operation (figure 4)                                       |                                        |     |            |       |  |

| Chip Select Stable before                                          | •                                      | 50  |            | ns    |  |

| RD — t <sub>CSR</sub>                                              |                                        | -   |            |       |  |

| Chip Select Hold Time for<br>RD — t <sub>RCS</sub>                 |                                        | 5   |            | ns    |  |

| RD Pulse Width — t <sub>BR</sub>                                   |                                        | 300 |            | ns    |  |

| Data Delay from RD — t <sub>RD</sub>                               |                                        |     | 250        | ns    |  |

| RD to Data Floating - t <sub>DF</sub>                              |                                        |     | 200        | ns    |  |

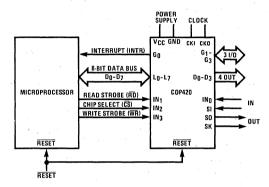

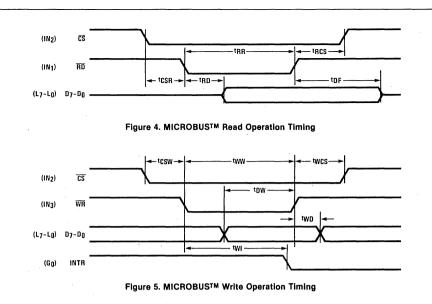

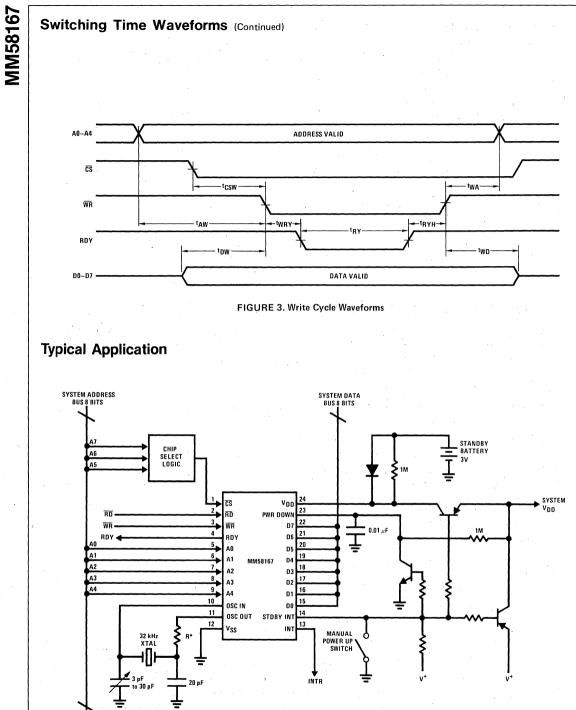

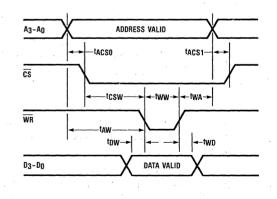

| B. Write Operation (figure 5)                                      |                                        |     |            |       |  |

| Chip Select Stable before                                          |                                        | 20  |            | ns    |  |

| WR — t <sub>CSW</sub><br>Chip Select Hold Time for                 |                                        | 20  |            | ns    |  |

| WR - twcs                                                          |                                        | 20  |            | 115   |  |

| WR Pulse Width - tww                                               |                                        | 300 | А.         | ns    |  |

| <u>Data</u> Setup Time for<br>WR — t <sub>DW</sub>                 |                                        | 200 |            | ns    |  |

| Data Hold Time for<br>WR — t <sub>WD</sub>                         |                                        | 40  |            | ns    |  |

| INTR Transition Time from                                          |                                        |     | 700        | ns    |  |

| $\overline{WR} - t_{WI}$                                           |                                        |     |            |       |  |

Note 1: Duty Cycle =  $t_{WI}/(t_{WI} + t_{WO})$ .

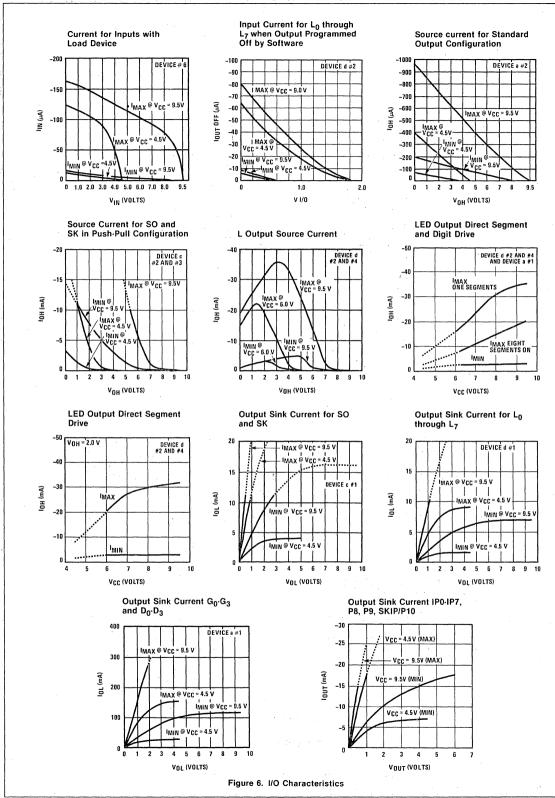

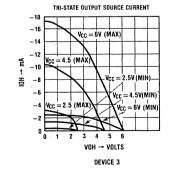

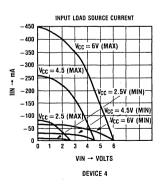

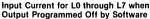

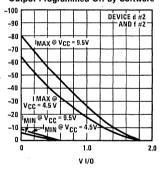

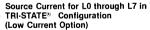

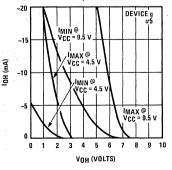

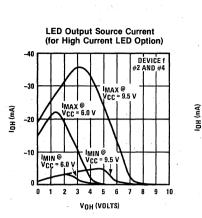

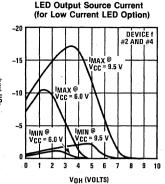

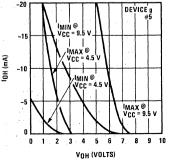

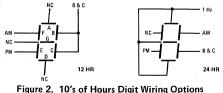

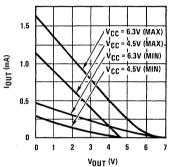

Note 2: See figure 11 for additional I/O characteristics.

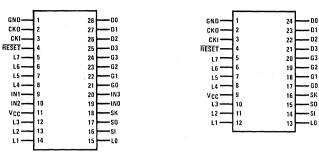

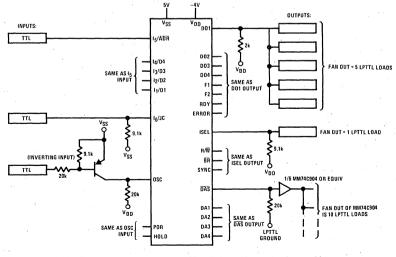

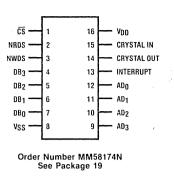

Figure 2. Connection Diagram

| Pin                            | Description                                           | Pin             | Description                                   |

|--------------------------------|-------------------------------------------------------|-----------------|-----------------------------------------------|

| L7-L0                          | 8 bidirectional I/O ports with                        | SKIP            | Instruction skip output                       |

| TRI-STA                        | TRI-STATE®                                            | СКІ             | System oscillator input                       |

| $G_3 - G_0$                    | 4 bidirectional I/O ports                             | ско             | System oscillator output                      |

| D <sub>3</sub> -D <sub>0</sub> | 4 general purpose outputs                             | RESET           | System reset input                            |

| $IN_3 - IN_0$                  | 4 general purpose inputs                              | V <sub>CC</sub> | Power supply                                  |

| SI                             | Serial input (or counter input)                       | GND             | Ground                                        |

| so                             | Serial output (or general purpose                     |                 |                                               |

|                                | output)                                               | IP7-IP0         | 8 bidirectional ROM address and data<br>ports |

| SK                             | Logic-controlled clock (or general<br>purpose output) | P8, P9          | 2 ROM address outputs                         |

| AD/DATA                        | Address out/data in flag                              | •               |                                               |

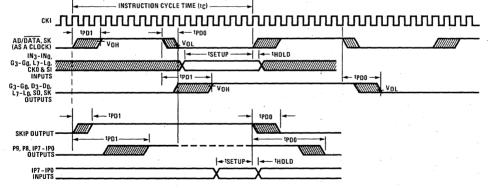

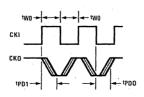

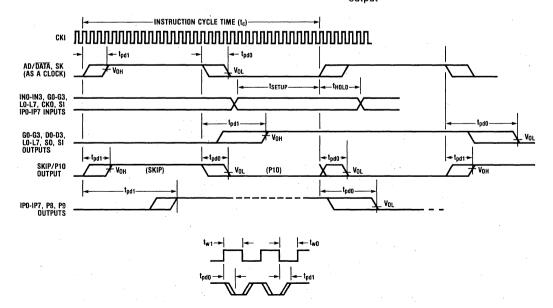

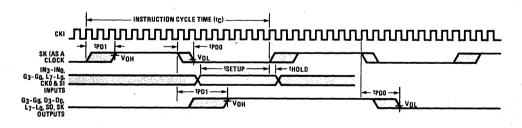

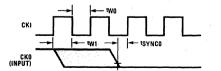

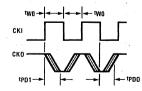

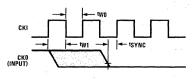

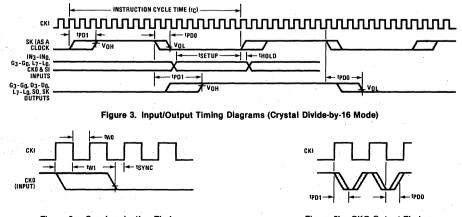

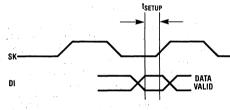

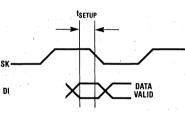

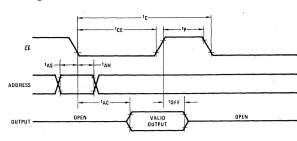

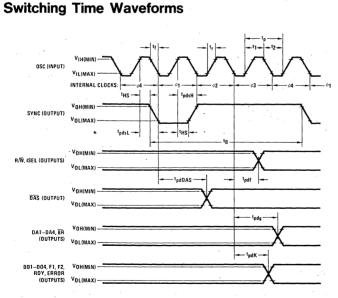

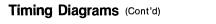

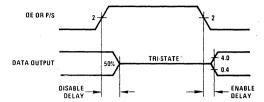

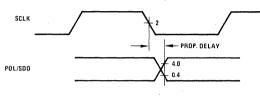

Figure 3a. Input/Output Timing Diagrams (Crystal + 16 Mode)

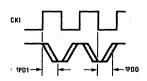

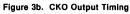

Figure 3b. CKO Output Timing

Figure 5. MICROBUS<sup>™</sup> Write Operation Timing

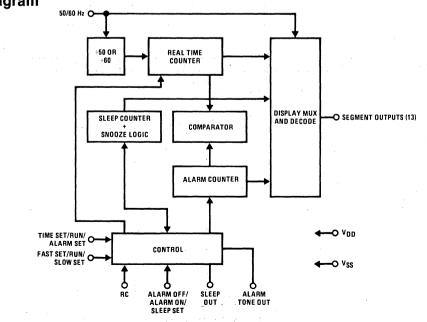

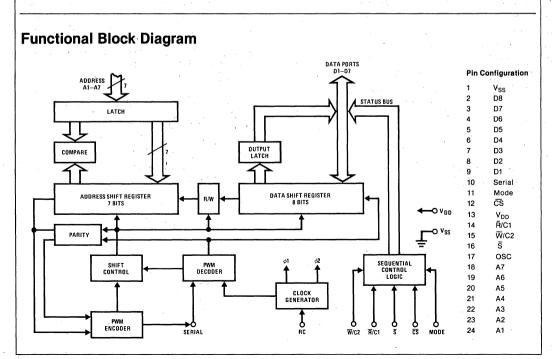

#### FUNCTIONAL DESCRIPTION

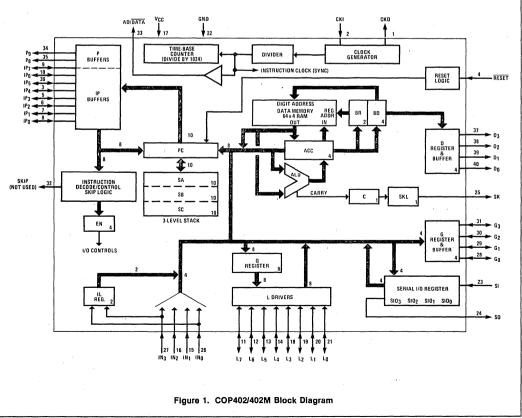

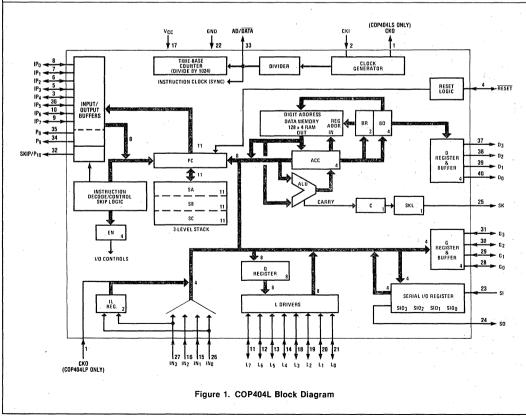

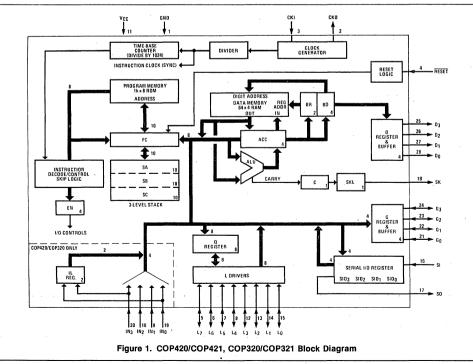

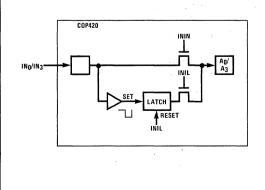

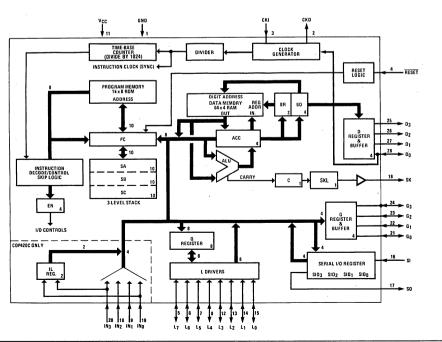

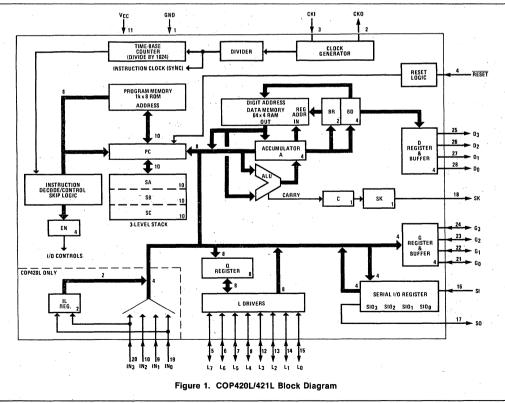

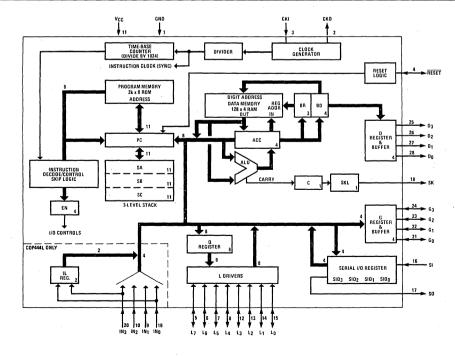

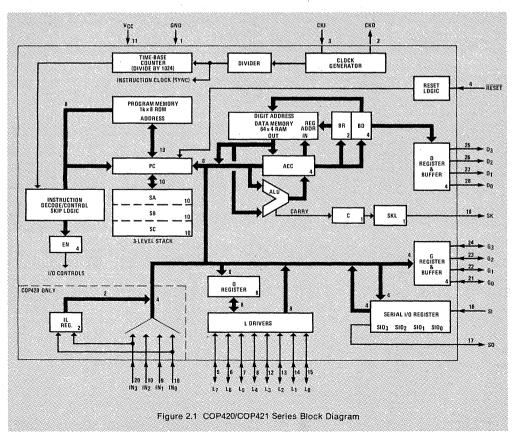

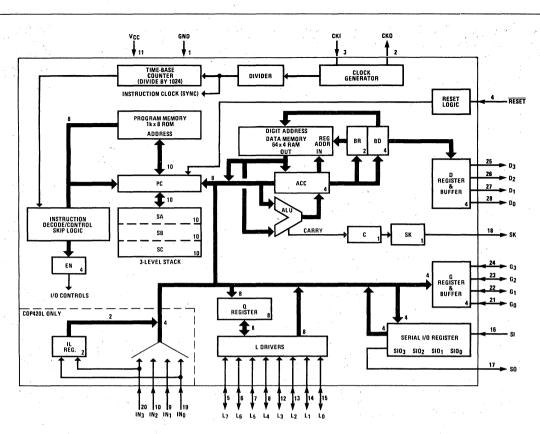

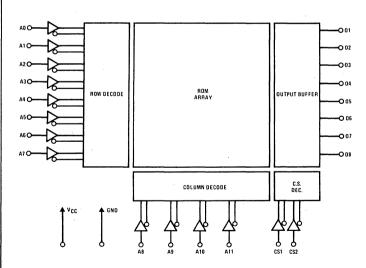

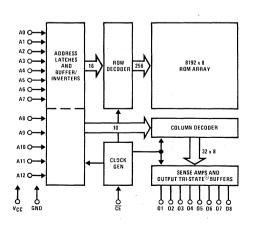

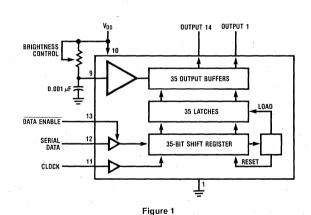

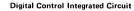

A block diagram of the COP402 is given in figure 1. Data paths are illustrated in simplified form to depict how the various logic elements communicate with each other in implementing the instruction set of the device. Positive logic is used. When a bit is set, it is a logic "1" (greater than 2 volts). When a bit is reset, it is a logic "0" (less than 0.8 volts).

#### **Program Memory**

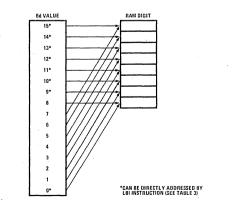

Program Memory consists of a 1,024-byte external memory (typically PROM). Words of this memory may be program instructions, program data or ROM addressing data. Because of the special characteristics associated with the JP, JSRP, JID and LQID instructions, ROM must often be thought of as being organized into 16 pages of 64 words each.

ROM addressing is accomplished by a 10-bit PC register. Its binary value selects one of the 1,024 8-bit words contained in ROM. A new address is loaded into the PC register during each instruction cycle. Unless the instruction is a transfer of control instruction, the PC register is loaded with the next sequential **10-bit binary count** value. Three levels of subroutine nesting are implemented by the 10-bit subroutine save registers, SA, SB and SC, providing a last-in, first-out (LIFO) hardware subroutine stack.

ROM instruction words are fetched, decoded and executed by the Instruction Decode, Control and Skip Logic circuitry.

#### **Data Memory**

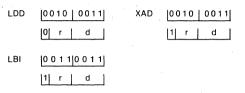

Data memory consists of a 256-bit RAM, organized as 4 data registers of 16 4-bit digits. RAM addressing is implemented by a 6-bit B register whose upper 2 bits (Br) select 1 of 4 data registers and lower 4 bits (Bd) select 1 of 16 4-bit digits in the selected data register. While the 4-bit contents of the selected RAM digit (M) is usually loaded into or from, or exchanged with, the A register (accumulator), it may also be loaded into or from the Q latches or loaded from the L ports. RAM addressing may also be performed directly by the LDD and XAD instructions based upon the 6-bit contents of the operand field of these instructions. The Bd register also serves as a source register for 4-bit data sent directly to the D outputs.

#### Internal Logic

The 4-bit **A register** (accumulator) is the source and destination register for most I/O, arithmetic, logic and data memory access operations. It can also be used to load the Br and Bd portions of the B register, to load and input 4 bits of the 8-bit Q latch data, to input 4 bits of the 8-bit L I/O port data and to perform data exchanges with the SIO register.

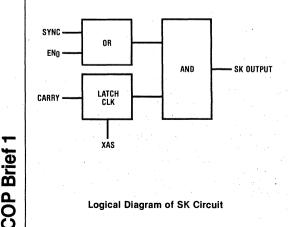

A 4-bit adder performs the arithmetic and logic functions of the COP402/402M, storing its results in A. It also outputs a carry bit to the 1-bit **C register**, most often employed to indicate arithmetic overflow. The C register, in conjunction with the XAS instruction and the EN register, also serves to control the SK output. C can be outputted directly to SK or can enable SK to be a sync clock each instruction cycle time. (See XAS instruction and EN register description, below.)

Four general-purpose inputs,  $IN_3 - IN_0$ , are provided;  $IN_1$ ,  $IN_2$  and  $IN_3$  may be selected, by a mask-programmable option, as Read Strobe, Chip Select and Write Strobe inputs, respectively, for use in MICROBUS<sup>TM</sup> applications.

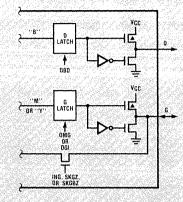

The **D** register provides 4 general-purpose outputs and is used as the destination register for the 4-bit contents of Bd.

The **G** register contents are outputs to 4 generalpurpose bidirectional I/O ports.  $G_0$  may be maskprogrammed as a "ready" output for MICROBUS<sup>TM</sup> applications. The **Q** register is an internal, latched, 8-bit register, used to hold data loaded to or from M and A, as well as 8-bit data from ROM. Its contents are output to the L I/O ports when the L drivers are enabled under program control. (See LEI instruction.) With the MICROBUS<sup>TM</sup> option selected, Q can also be loaded with the 8-bit contents of the L I/O ports upon the occurrence of a write strobe from the host CPU.

The **8 L drivers**, when enabled, output the contents of latched Q data to the L I/O ports. Also, the contents of L may be read directly into A and M. As explained above, the MICROBUS<sup>TM</sup> option allows L I/O port data to be latched into the Q register. L I/O ports can be directly connected to the segments of a multiplexed LED display (using the LED Direct Drive output configuration option) with Q data being outputted to the Sa-Sg and decimal point segments of the display.

The **SIO register** functions as a 4-bit serial-in/serialout shift register or as a binary counter depending on the contents of the EN register. (See EN register description, below.) its contents can be exchanged with A, allowing it to input or output a continuous serial data stream. SIO may also be used to provide additional parallel I/O by connecting SO to external serial-in/parallel-out shift registers.

The XAS instruction copies C into the SKL latch. In the counter mode, SK is the output of SKL. In the shift register mode, SK outputs SKL ANDed with internal instruction cycle clock.

The **EN register** is an internal 4-bit register loaded under program control by the LEI instruction. The state of each bit of this register selects or deselects the particular feature associated with each bit of the EN register ( $EN_3 - EN_0$ ).

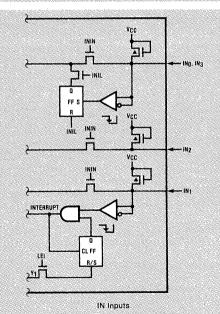

1. The least significant bit of the enable register, EN<sub>0</sub>, selects the SIO register as either a 4-bit shift register or a 4-bit binary counter. With EN<sub>0</sub> set, SIO is an asynchronous binary counter, *decrementing* its value by one upon each low-going pulse ("1" to "0") occurring on the SI input. Each pulse must be at least two instruction cycles wide. SK outputs the value of SKL. The SO output is equal to the value of EN<sub>3</sub>. With EN<sub>0</sub> reset, SIO is a serial shift register shifting left each instruction cycle time. The data present at SI goes into the least significant bit of SIO. SO can be enabled to output the most significant bit of SIO each cycle time. (See 4 below.) The SK output becomes a logiccontrolled clock.

- With EN<sub>1</sub> set the IN<sub>1</sub> input is enabled as an interrupt input. Immediately following an interrupt, EN<sub>1</sub> is reset to disable further interrupts.

- 3. With EN<sub>2</sub> set, the L drivers are enabled to output the data in Q to the L I/O ports. Resetting EN<sub>2</sub> disables the L drivers, placing the L I/O ports in a high-impedance input state. If the MICROBUS<sup>™</sup> option is being used, EN<sub>2</sub> does not affect the L drivers.

- 4. EN<sub>3</sub>, in conjunction with EN<sub>0</sub>, affects the SO output. With EN<sub>0</sub> set (binary counter option selected) SO will output the value loaded into EN<sub>3</sub>. With EN<sub>0</sub> reset (serial shift register option selected), setting EN<sub>3</sub> enables SO as the output of the SIO shift register, outputting serial shifted data each instruction time. Resetting EN<sub>3</sub> with the serial shift register option selected disables SO as the shift register output; data continues to be shifted through SIO and can be exchanged with A via an XAS instruction but SO remains reset to "0." The table below provides a summary of the modes associated with EN<sub>3</sub> and EN<sub>0</sub>.

#### Interrupt

The following features are associated with the  $IN_1$  interrupt procedure and protocol and must be considered by the programmer when utilizing intertupts.

a. The interrupt, once acknowledged as explained below, pushes the next sequential program counter address (PC + 1) onto the stack, pushing in turn the contents of the other subroutine-save registers to the next lower level (PC + 1  $\rightarrow$  SA  $\rightarrow$  SB  $\rightarrow$  SC). Any previous contents of SC are lost. The program counter is set to hex address OFF (the last word of page 3) and EN<sub>1</sub> is reset.

| $EN_3$ | EN <sub>0</sub> | SIO            | SI                      | SÓ         | SK                                          |

|--------|-----------------|----------------|-------------------------|------------|---------------------------------------------|

| 0      | 0               | Shift Register | Input to Shift Register | 0          | If SKL = 1, SK = SYNC<br>If SKL = 0, SK = 0 |

| 1      | 0               | Shift Register | Input to Shift Register | Serial Out | If SKL = 1, SK = SYNC<br>If SKL = 0, SK = 0 |

| 0      | 1               | Binary Counter | Input to Binary Counter | 0          | If SKL = 1, Sk = 1<br>If SKL = 0, SK = 0    |

| 1      | 1               | Binary Counter | Input to Binary Counter | 1          | If SKL = 1, SK = 1<br>If SKL = 0, SK = 0    |

- b. An interrupt will be acknowledged only after the following conditions are met:

- 1. EN<sub>1</sub> has been set.

- 2. A low-going pulse ("1" to "0") at least two instruction cycles wide occurs on the IN1 input.

- 3. A currently executing instruction has been completed.

- 4. All successive transfer of control instructions and successive LBIs have been completed (e.g., if the main program is executing a JP instruction which transfers program control to another JP instruction, the interrupt will not be acknowledged until the second JP instruction has been executed.

- c. Upon acknowledgement of an interrupt, the skip logic status is saved and later restored upon the popping of the stack. For example, if an interrupt occurs during the execution of ASC (Add with Carry, Skip on Carry) instruction which results in carry, the skip logic status is saved and program control is transferred to the interrupt servicing routine at hex address OFF. At the end of the interrupt routine, a RET instruction is executed to "pop" the stack and return program control to the instruction following the original ASC. At this time, the skip logic is enabled and skips this instruction because of the previous ASC carry. Subroutines and the LQID instruction should not be nested within the interrupt servicing routine since their popping of the stack enables any previously saved main program skips, interfering with the orderly execution of the interrupt routine.

- d. The first instruction of the interrupt routine at hex address 0FF must be a NOP.

- e. A LEI instruction can be put immediately before the RET to re-enable interrupts.

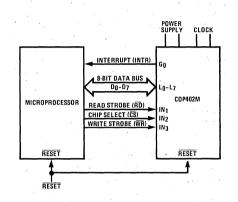

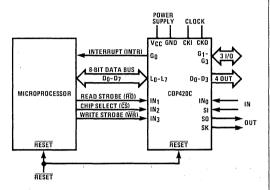

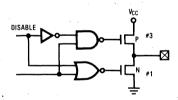

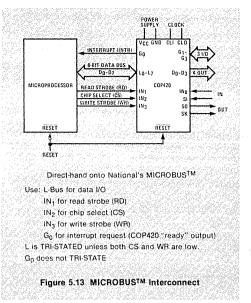

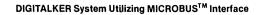

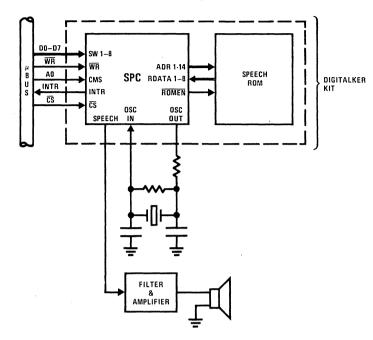

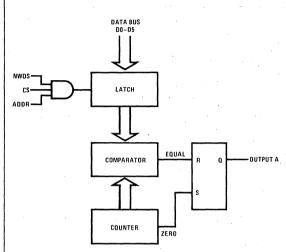

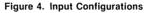

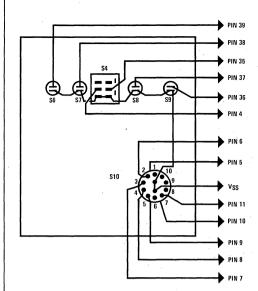

#### **MICROBUS™** Interface

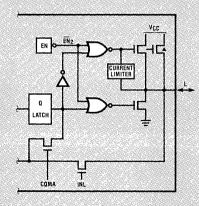

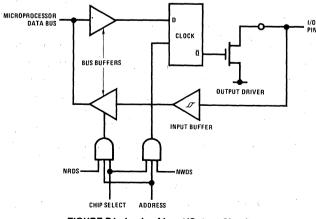

The COP402M can be used as a peripheral microprocessor device, inputting and outputting data from and to a host microprocessor (µP). IN1, IN2, and IN3 general purpose inputs become MICROBUS™ compatible read-strobe, chip-select, and write-strobe lines, respectively.  $IN_1$  becomes  $\overline{RD}$  — a logic "0" on this input will cause Q latch data to be enabled to the L ports for input to the  $\mu$ P. IN<sub>2</sub> becomes  $\overline{CS}$  — a logic "0" on this line selects the COP402M as the  $\mu$ P peripheral device by enabling the operation of the RD and WR lines and allows for the selection of one of several peripheral components. IN<sub>3</sub> becomes WR a logic "0" on this line will write bus data from the L ports to the Q latches for input to the COP402M, Go becomes INTR, a "ready" output reset by a write pulse from the  $\mu P$  on the WR line, providing the "handshaking" capability necessary for asynchronous data transfer between the host CPU and the COP402M.

This option has been designed for compatibility with National's MICROBUS<sup>™</sup> — a standard interconnect

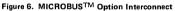

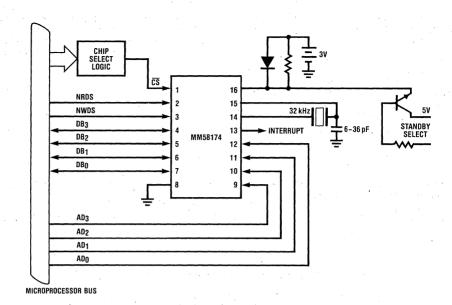

system for 8-bit parallel data transfer between MOS/LSI CPUs and interfacing devices. (See MICROBUS<sup>™</sup>, National Publication.) The functioning and timing relationships between the COP402M signal lines affected by this option are as specified for the MICROBUS<sup>™</sup> interface, and are given in the AC electrical characteristics and shown in the timing diagrams (figures 4 and 5). Connection to the MICROBUS<sup>™</sup> is shown in figure 6.

#### Figure 6. MICROBUS™ Option Interconnect

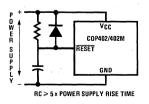

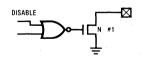

#### Initialization

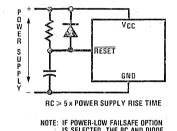

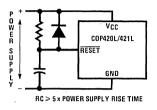

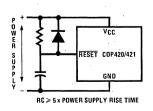

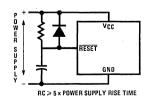

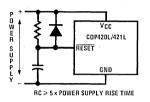

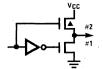

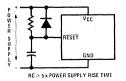

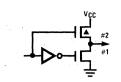

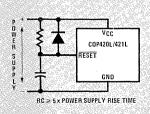

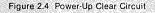

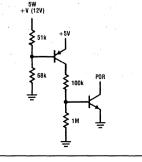

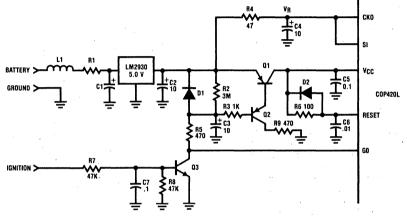

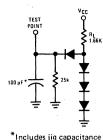

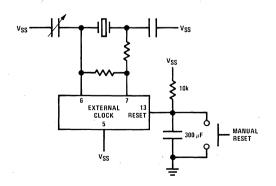

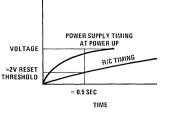

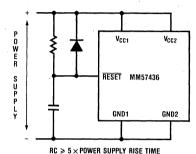

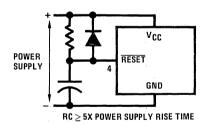

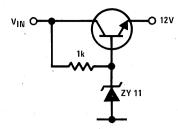

The Reset Logic will initialize (clear) the device upon power-up if the power supply rise time is less than 1ms and greater than 1 $\mu$ s. If the power supply rise time is greater than 1ms, the user must provide an external RC network and diode to the RESET pin as shown below. The RESET pin is configured as a Schmitt trigger input. If not used it should be connected to V<sub>CC</sub>. Initialization will occur whenever a logic "0" is applied to the RESET input, provided it stays low for at least two instruction cycle times.

Upon initialization, the PC register is cleared to 0 (ROM address 0) and the A, B, C, D, EN, G, and SO are cleared. The SK output is enabled as a SYNC output, providing a pulse each instruction cycle time. Data Memory (RAM) must be cleared by the user's program. The first instruction at address 0 must be a CLRA.

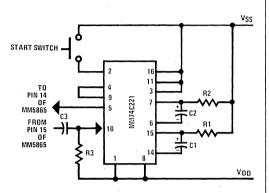

Figure 7. Power-Up Clear Circuit

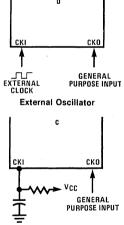

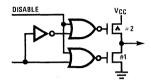

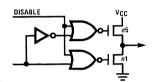

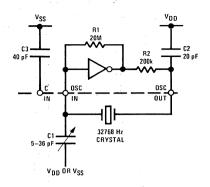

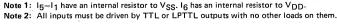

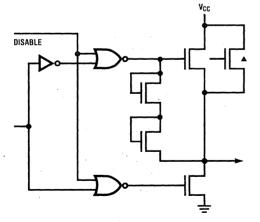

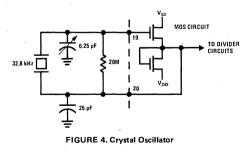

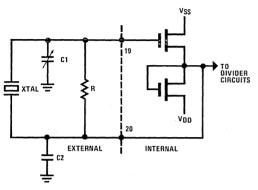

#### Oscillator

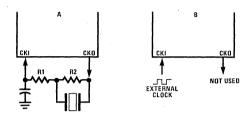

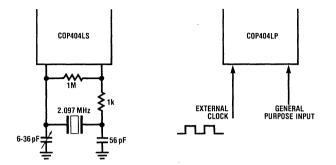

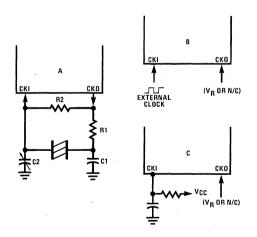

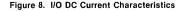

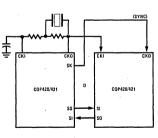

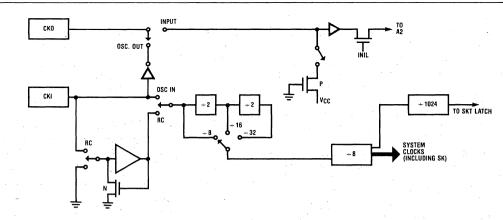

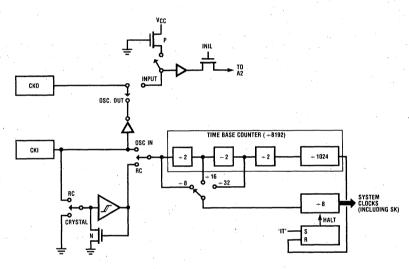

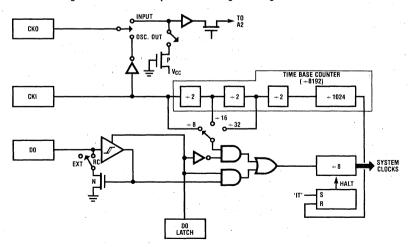

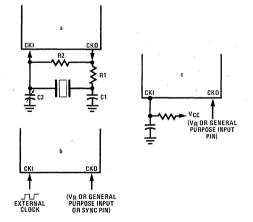

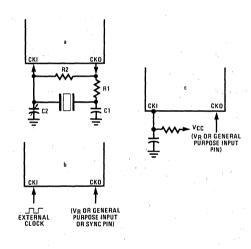

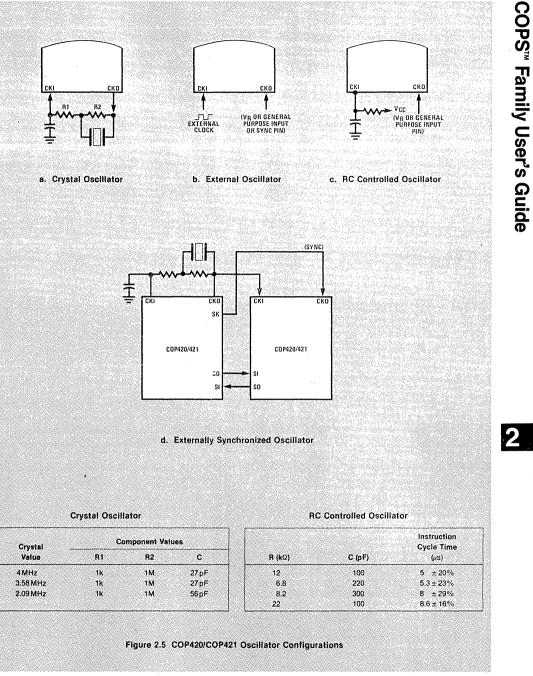

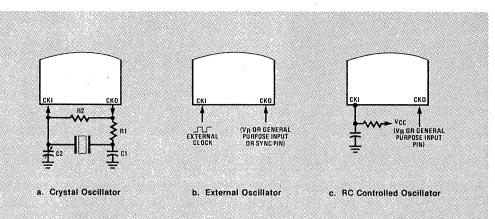

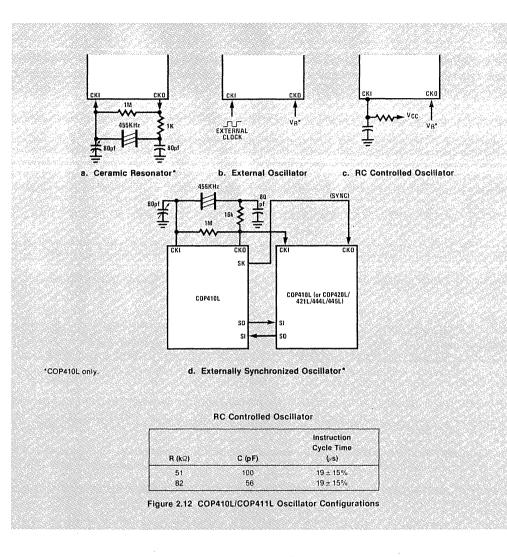

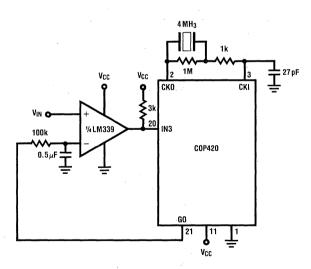

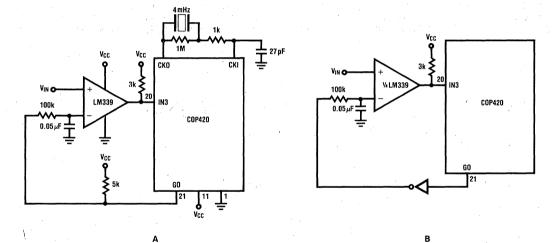

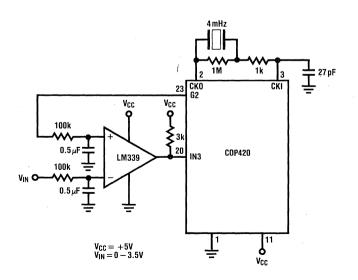

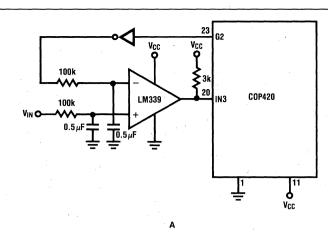

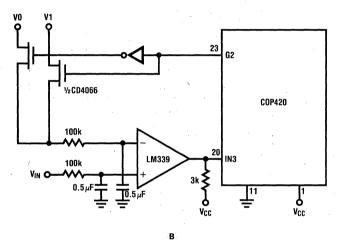

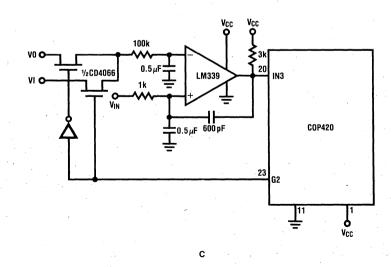

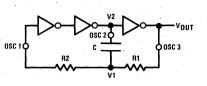

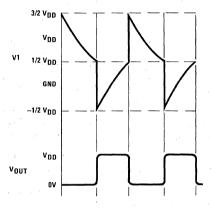

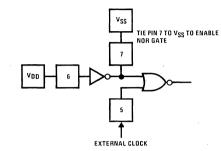

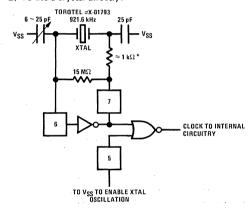

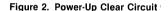

There are two basic clock oscillator configurations available as shown by figure 8.

- a. Crystal Controlled Oscillator. CKI and CKO are connected to an external crystal. The instruction cycle time equals the crystal frequency divided by 16.

- **b. External Oscillator.** CKI is driven by an external clock signal. The instruction cycle time is the clock frequency divided by 16.

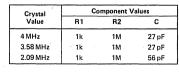

| Crystal | Component Values |    |        |  |  |

|---------|------------------|----|--------|--|--|

| Value   | R1               | R2 | С      |  |  |

| 4MHz    | 1k               | 1M | 27 p F |  |  |

| 3.58MHz | 1k               | 1M | 27 p F |  |  |

| 2.09MHz | 1k               | 1M | 56pF   |  |  |

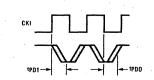

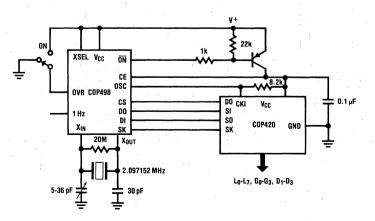

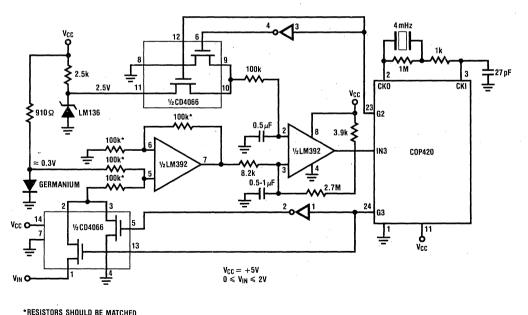

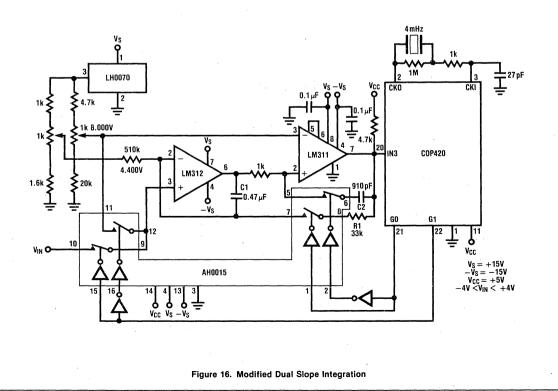

#### Figure 8. COP402/402M Oscillator

#### **External Memory Interface**

The COP402 and COP402M are designed for use with an external Program Memory. This memory may be implemented using any devices having the following characteristics:

- 1. random addressing

- 2. TTL-compatible TRI-STATE® outputs

- TTL-compatible inputs

- 4. access time =  $1.7\mu$ s, max

Typically these requirements are met using bipolar or MOS PROMs.

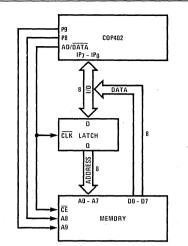

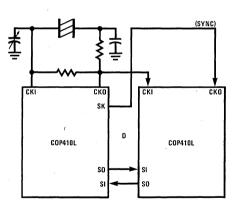

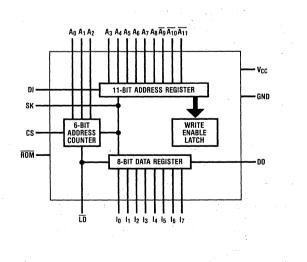

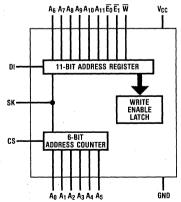

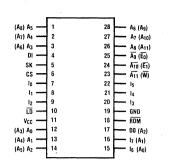

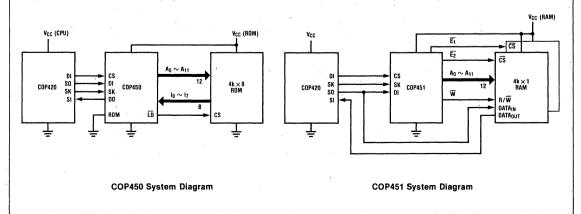

During operation, the address of the next instruction is sent out on P9, P8, and IP7 through IP0 during the time that AD/DATA is high (logic "1" = address mode). Address data on the IP lines is stored into an external latch on the high-to-low transition of the AD/DATA line; P9 and P8 are dedicated address outputs, and do not need to be latched. When AD/DATA is low (logic "0" = data mode), the output of the memory is gated onto IP7 through IP0, forming the input bus. Note that the AD/DATA output has a period of one instruction time, a duty cycle of approximately 50%, and specifies whether the IP lines are used for address output or instruction input. A simplified block diagram of the external memory interface is shown in figure 9.

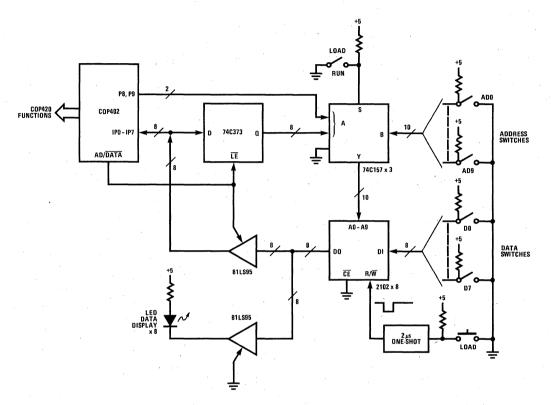

Figure 9. External Memory Interface to COP402

#### Input/Output

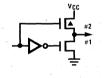

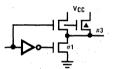

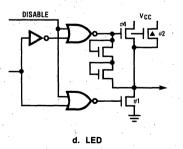

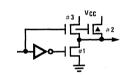

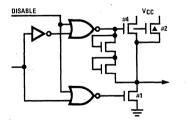

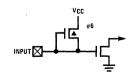

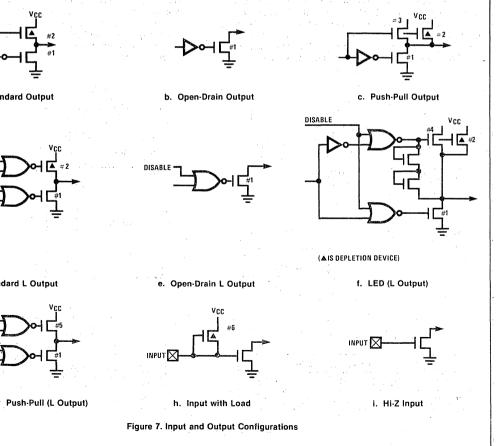

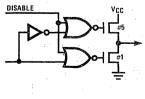

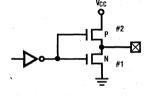

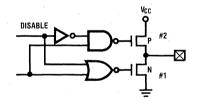

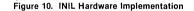

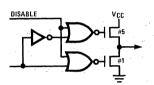

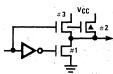

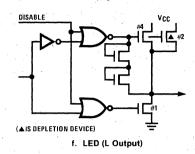

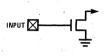

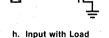

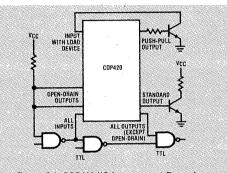

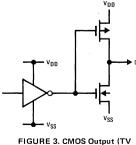

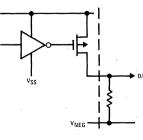

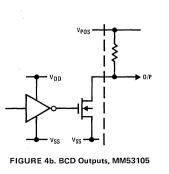

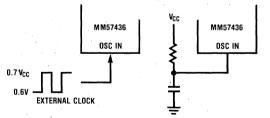

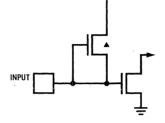

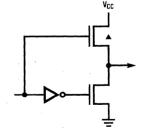

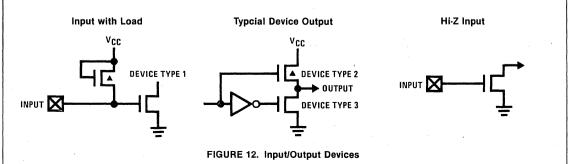

COP402 outputs have the following configurations, illustrated in figure 10:

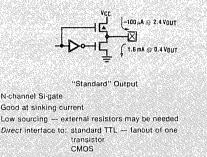

- a. Standard an enhancement-mode device to ground in conjunction with a depletion-mode device to  $V_{CC}$ , compatible with TTL and CMOS input requirements.

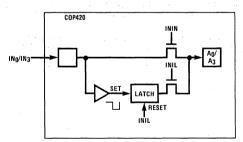

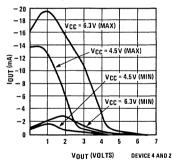

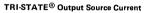

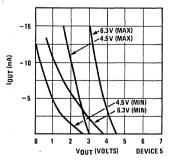

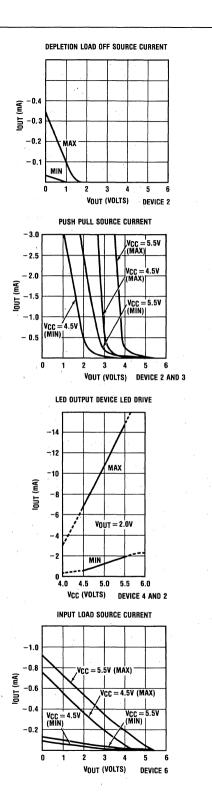

- **b. High Drive** same as a. except greater current sourcing capability.