# MEMORY APPLICATIONS HANDBOOK

# NATIONAL SEMICONDUCTOR

# MEMORY APPLICATIONS HANDBOOK

Edited by

Charles B. Mitchell Manager, Memory Components Applications and William C. Johnston

Senior Memory Applications Engineer

© National Semiconductor Corporation 2900 Semiconductor Drive Santa Clara, California 95051

National does not assume any responsibility for use of any circuitry described; no circuit patent licenses are implied; and National reserves the right, at any time without notice, to change said circuitry.

# MEMORY APPLICATIONS HANDBOOK

Introduction

**Dynamic Read/Write Memory**

Static Read/Write Memory

**Read Only Memory**

**PROMs and EPROMs**

**CRT Display Applications**

**Charge Coupled Devices**

**Memory Support Components**

**Microprocessor Guide**

**Systems Applications**

Reliability

**Definitions and Standards**

National's Literature Index

Memory Databook Referral Index

# **Table of Contents**

8

| Section 1-Introduction                                                   |

|--------------------------------------------------------------------------|

| President's Message                                                      |

| Preface                                                                  |

| Future Memory Technology Development 1-3                                 |

| Static or Dynamic – The Selection Process for a Memory System            |

| Section 2-Dynamic Read/Write Memory                                      |

| Dynamic RAM Board Design Made Easy 2-1                                   |

| A Memory Design for an 8080A-Based Microprocessor System                 |

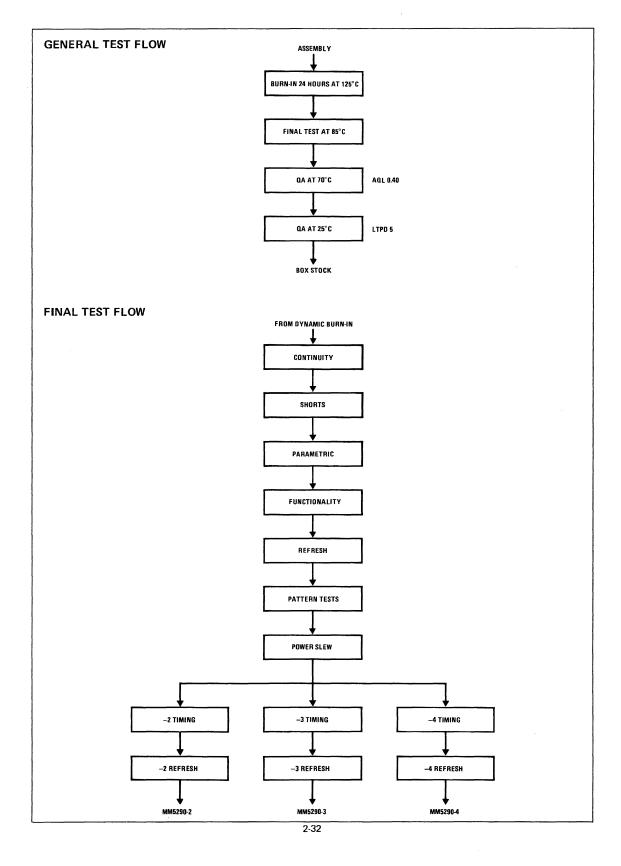

| MM5290 16k RAM Functional Description                                    |

| Trouble Shooting Check List for Memory Systems Using the MM5290          |

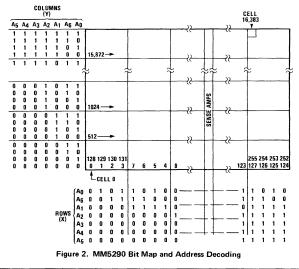

| MM5290 Bit Map and Address Decoding                                      |

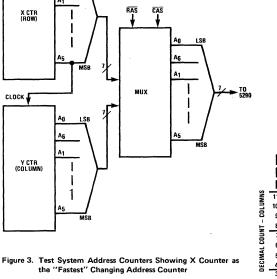

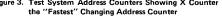

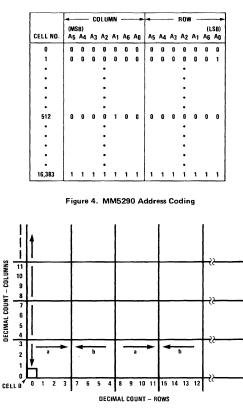

| MM5290 RAM Test Description                                              |

| Trouble Shooting Check List for Memory Systems Using the MM5280          |

| Section 3-Static Read/Write Memory                                       |

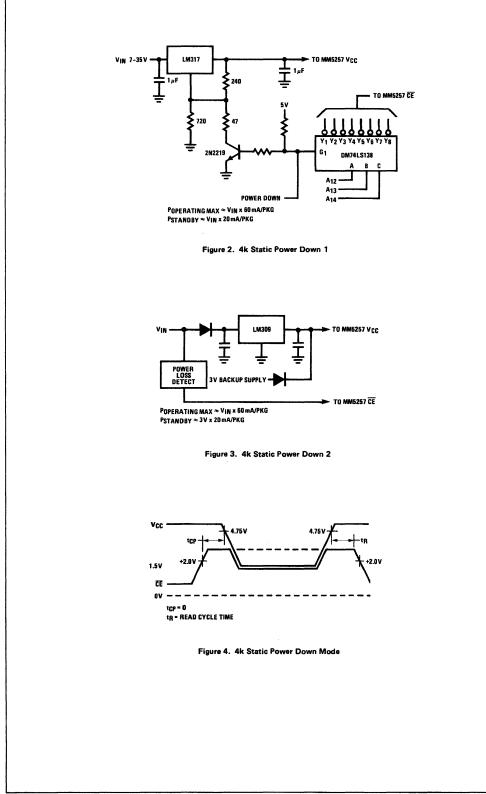

| Static RAM Applications                                                  |

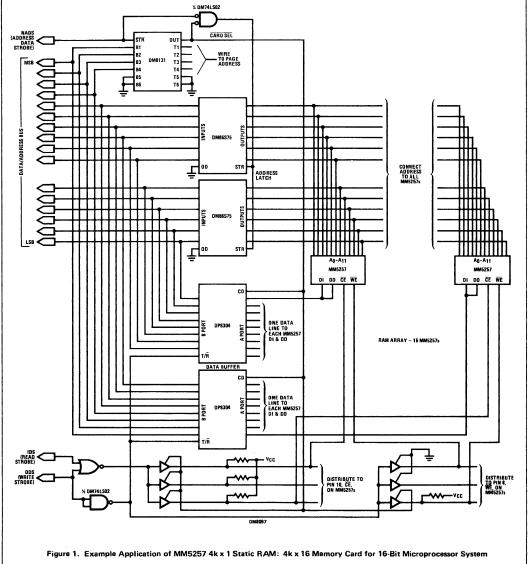

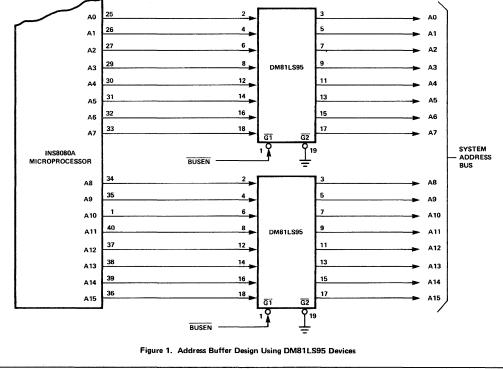

| Interfacing Static Read/Write Memories to the 8080 3-3                   |

| Interfacing the 6800 Microprocessor to National CMOS MM74C910 Memory 3-7 |

| 1k CMOS RAMs                                                             |

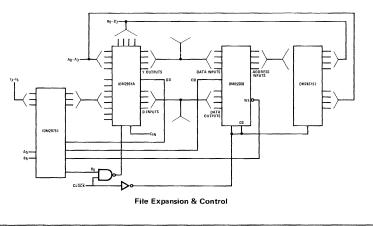

| IDM2901A File Expansion Using the DM85S68                                |

### Static RAM Applications ..... Interfacing Static Read/Write Memories to the

| Interfacing the 6800 Microprocessor to National CMOS MM74C910 Memory | . 3-7  |

|----------------------------------------------------------------------|--------|

| 1k CMOS RAMs                                                         | . 3-9  |

| IDM2901A File Expansion Using the DM85S68                            | . 3-22 |

## Section 4-Read Only Memory

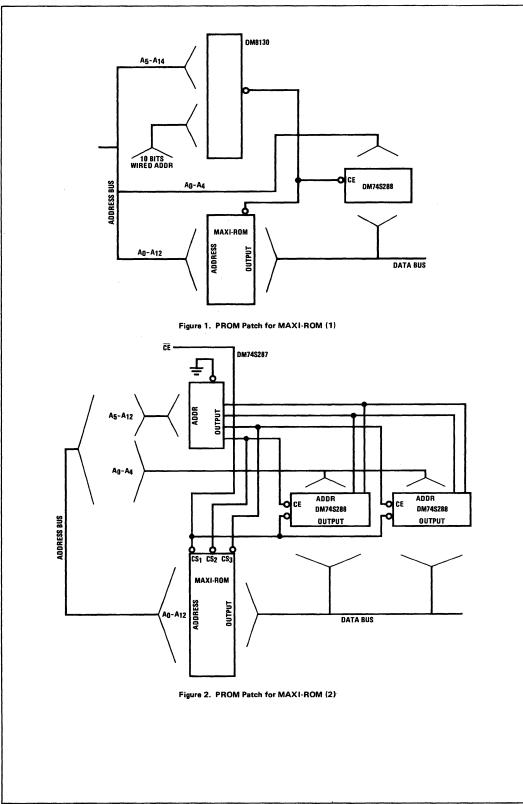

| PROM Patches for the MAXI-ROM                | 4-1  |

|----------------------------------------------|------|

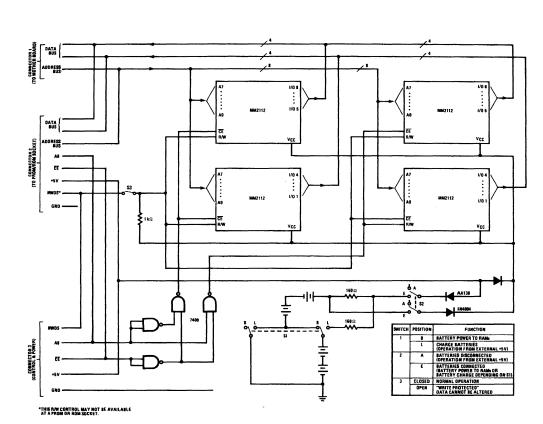

| ROM Emulator Using a Non-Volatile RAM        | 4-3  |

| Custom ROM Programming                       | 4-6  |

| How to Design with Programmable Logic Arrays | 4-14 |

### Section 5-PROMs and EPROMs

| A Guide to Implementing Logic Functions Using PROMs            | 5-1 |

|----------------------------------------------------------------|-----|

| MOS Encoder Plus PROM Yields Quick Turnaround Keyboard Systems | 5-5 |

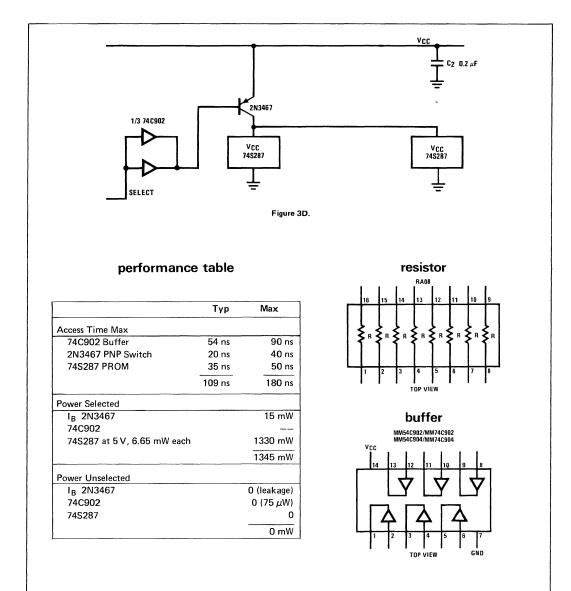

| PROM Power-Down Circuits                                       | 5-9 |

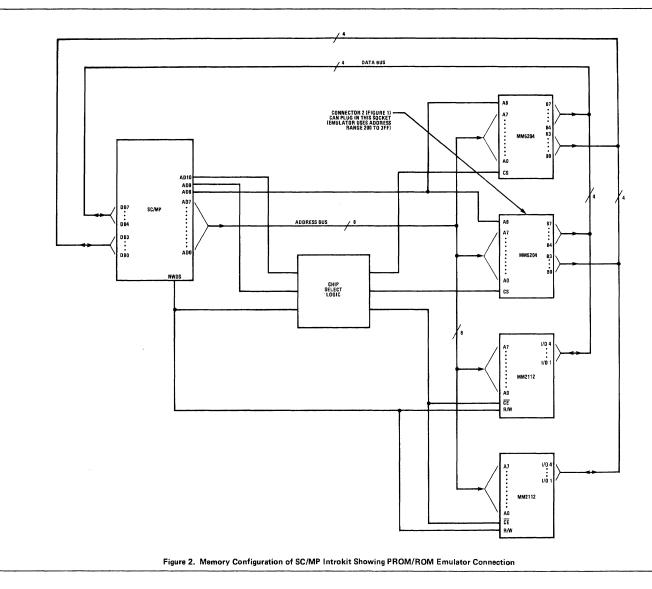

| A PROM Programmer for the SC/MP LCDS                           | 13  |

| Bipolar PROM Programming Procedure                             | 36  |

| Programming Equipment for National PROMs 5-                    | 38  |

| EPROM Notes                                                    | 39  |

# **DESIGN AID**

## **APPLICATION NOTE**

**BACKGROUND INFORMATION**

### **TECHNICAL DESCRIPTION**

# **Table of Contents**

# Section 6-CRT Display Applications

| 6-1 |

|-----|

| -10 |

| -22 |

| -26 |

| -28 |

|     |

### Section 7-Charge Coupled Devices

| _                              |                                                  |     |  |

|--------------------------------|--------------------------------------------------|-----|--|

| The MM2464: A Practical Charge | e Coupled Device for Digital Memory Applications | 7-1 |  |

### Section 8-Memory Support Components

| Memory Support Circuits                                     | 8-1  |

|-------------------------------------------------------------|------|

| Improving Power Supply Reliability with IC Power Regulators | 8-5  |

| A Cheap and Easy DC-DC Converter                            | 8-8  |

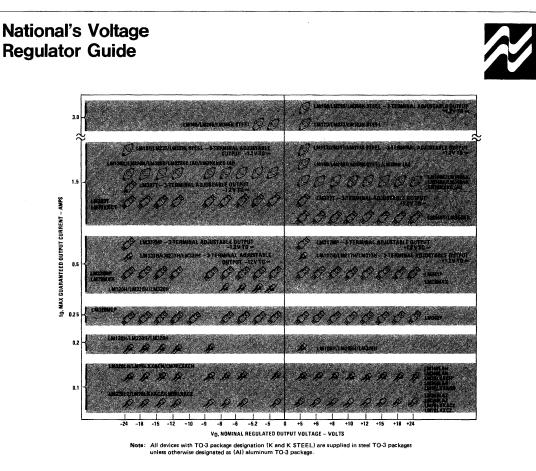

| National's Voltage Regulator Guide                          | 8-12 |

### Section 9-Microprocessor Guide

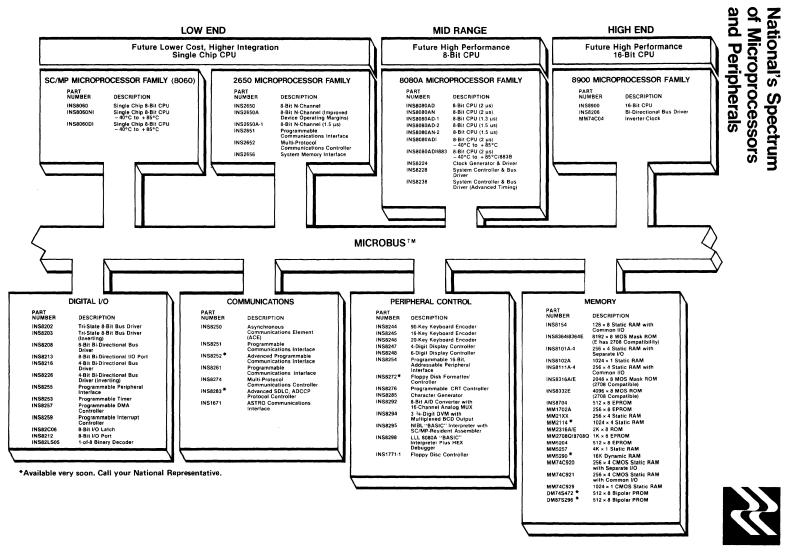

| National's Full Spectrum of Microprocessors             | 9-1 |

|---------------------------------------------------------|-----|

| National's Fast IDM2900 Bit-Slice Microprocessor Family | 9-2 |

| National's Spectrum of Microprocessors and Peripherals  | 9-3 |

### Section 10-Systems Applications

| Systems Application of MM5270 4k Dynamic RAM   | . 10-1 |

|------------------------------------------------|--------|

| Systems Application of MM5290 16k Dynamic RAM. | . 10-6 |

| Systems Application of MM74C929 CMOS RAM       | 10-10  |

### Section 11—Reliability

| National's Reliability Programs                                                         | 11-1 |

|-----------------------------------------------------------------------------------------|------|

| Section 12–Definitions and Standards                                                    |      |

| Definitions of Frequently-Used Acronyms                                                 | 12-1 |

| Excerpts from the Proposed IEEE Standard for Semiconductor Memory Data Sheet Generation | 12-2 |

# Section 13-National's Literature Index

| Databooks Available | from National | <br> | <br> | 13-1 |

|---------------------|---------------|------|------|------|

# Section 14—Memory Databook Referral Index

### **DESIGN AID**

### APPLICATION NOTE

BACKGROUND INFORMATION

### **TECHNICAL DESCRIPTION**

# Page Index of Devices Discussed

| Page      |

|-----------|

| Index     |

| 옃         |

| Devices   |

| Discussed |

| Device          | Page                               |

|-----------------|------------------------------------|

| IDM2900         |                                    |

| IDM2901A        |                                    |

| INS2650         |                                    |

| INS4004         |                                    |

| INS8060 (SC/MP) |                                    |

|                 | 2-9, 3-3, 9-1, 9-3                 |

|                 | 3-1, 9-1, 9-3                      |

|                 |                                    |

| DM74S188        |                                    |

| DM74S287        | . 4-1, 4-11, 5-9, 5-36, 5-38, 11-3 |

| DM74S288        |                                    |

| DM74S387        |                                    |

| DM74S570        |                                    |

| DM74S571        |                                    |

| DM74S572/573    |                                    |

| DM74S574        |                                    |

| DM85S68         |                                    |

| DM8575/6        |                                    |

| DM8678          | 6-12, 6-22, 6-26, 6-28             |

| DM87S295/296    |                                    |

| DP8350          |                                    |

|                 |                                    |

| MM2102A         |                                    |

| MM2111A         |                                    |

|                 |                                    |

|                 |                                    |

| MM2464          |                                    |

|                 | 4-11, 4-12, 5-38, 5-39, 11-3       |

|                 |                                    |

| MM5204Q         | 4-3, 5-7, 5-13, 5-38, 5-39         |

| MM5235          |                                    |

| MM5257          |                                    |

|                 |                                    |

|                 |                                    |

| MM5290          | 2-9, 2-17, 2-25, 2-26, 2-29, 10-6  |

| MM52157         |                                    |

| MM52179         |                                    |

| MM5740          |                                    |

| MM74C910        |                                    |

|                 |                                    |

|                 |                                    |

|                 |                                    |

| MM74C930        |                                    |

|                 |                                    |

Section 1

# Introduction

# **President's Message**

Dear Customer:

The exciting future of memory applications is limited only by our collective abilities to make use of the continuing stream of rapid technological advances. Annual consumption of semiconductor memory components has already surpassed a half billion dollars per year and will cross the one billion dollar level within the next three years. Years ago National established the reputation as a high volume supplier of high quality, cost-effective components for the complete range of discretes, linears, optoelectronics, transducers, A/D and D/A, hybrids and large scale integrated memory, microprocessor, and logic arrays. We are pleased to continue our expansion of this broad product line to include the memories you will require in the future. Our world-wide network of factory representatives, local stocking distributors, and field applications engineers is at your service to help meet your needs - just give any of them a call.

We appreciate your interest in National's products and services, and look forward to supplying your present and future requirements.

National Semiconductor Corporation

Charles E. Sporck President

# Preface

The application of today's memory components can present either another day-to-day engineering problem or an immense task involving a full team of design and components specialists. This does not mean that designing an add-on memory for a large mainframe computer is more difficult than producing a memory system based on a two-chip microprocessor (it most likely is not). The difference in complexity may well depend on how your organization is structured. In some organizations the memory designer concerns himself strictly with memory proper. In other organizations, a given engineer may be directly involved in designing the entire system, from the screws that hold the enclosure together to the choice of memory components. But whether your interest in this book is solely to obtain the MM5290 bit map or because you want help with your first dynamic RAM design, we hope the end result will be the same: optimization of your design engineering effort.

It would be impossible to make a memory applications handbook comprehensive. However, we have tried to make the scope of this book broad with respect to application as well as product type (made possible by the broad range of product National produces). In order to relate to the real-life problems of the design engineer, we have attempted to present actual systems as examples. To do this we have enlisted the aid of National's systems' divisions and their personnel. To provide full credit to these contributors, we have included their names with the applications; but we ask that, should questions arise, you do not initially contact these perple directly. We ask instead that you contact your local National sales representative or this Memory Applications group.

If you find any errors or omissions or have other contributions to make, please contact us. We welcome your suggestions and will try to include them in future editions. We would like to express our appreciation to the authors of the applications and support material whose names are listed at the head of their work. We also express our appreciation to the people listed below who helped in data gathering and preparation.

| J. Bizjak    | T. Fredriksen | M. Rampleburg     |

|--------------|---------------|-------------------|

| E. Bohn      | M. Frie       | G. Rice           |

| C. Boettcher | W. Fowler     | N. Sevastopoulous |

| D. Brown     | P. Hillen     | A. Shultz         |

| C. Carinalli | H. Holt       | F. Smith          |

| P. Clemo     | H. Marks      | J. Sutherland     |

| D. Cole      | G. Miles      | D. Whetstone      |

| W. Curtis    | R. Pease      | F. Wickersham     |

In addition we would like to thank all those who helped in proofreading and typing.

Memory Component Applications National Semiconductor Corporation Santa Clara, California

#### THE FINE PRINT

The circuit diagrams and schematics contained in this handbook are presented as a means of illustrating typical memory component applications. Unless otherwise stated, they have been checked and breadboarded and in some cases are in production. However, complete information for circuit construction is not presented, as these circuit diagrams are intended only as representative examples. National Semiconductor cannot assume any responsibility for errors, oversights, or other examples of human frailty.

P.S.: You don't get the patent rights, either.

### Future Memory Technology Development

ABSTRACT: Semiconductor integrated circuit based memory devices became the dominant Random Access Memory technology in less than 8 years. They were able to achieve this because their batch manufacturing process allowed a very rapid reduction of cost per bit of storage through technological changes to increase batch density. Continued progress in density improvement at essentially unchanged rates is still feasible. It will, however, require major changes in manufacturing, device and material technology.

Since the beginning of the 70's, semiconductor integrated circuits used as digital storage elements have become a very significant factor in the total spectrum of information storage technology. They became the dominant technology for random access memories and are beginning to make inroads into the slower serial access memory market, presently dominated by magnetic discs and drums.

The ability of integrated circuit technology to continue to offer digital data storage at very rapidly decreasing cost per bit of storage is a consequence of the batch manufacturing process. It allows introductions of new products which are cost effective even at very low manufacturing efficiency level, obtain very steep cost reduction during product life by rapid increase of manufacturing efficiency and continue to stay on the steep cost reduction curve by going to a higher level of integration when cost improvements through improved manufacturing efficiencies are starting to flatten out.

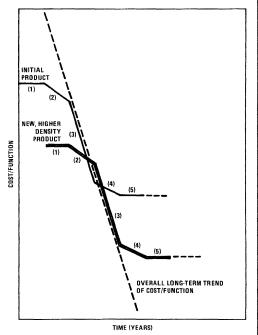

However, to go to a higher level of integration, which in case of Random Access Memory circuits, usually means a four-fold increase in number of bits on the chip, a significant improvement in batch density is required, otherwise no benefit is derived (*Figure 1*).

This batch density (i.e., number of potentially good storage elements processed together as a single unit (i.e., a silicon wafer) has shown an even higher rate of growth than the much more visible increase in the number storage bits/memory circuit.

During the past eight years the number of potentially good storage elements contained on a single silicon wafer has risen from about 50,000 to over 6 million, with the cost of processing a wafer rising only very slowly and manufacturing efficiency expressed as the percentage of good units staying level or improving slightly.

Future progress in memory technology can be examined in terms of this single variable common to all present and future solid state memory technologies.

There are several technological trends that are unfolding right now which are likely to impact future memory technology developments.

\*Refer to Introduction. This paper presented at COMPCON 1977

National Semiconductor Thomas Klein\* January 1978

These trends can be classified under the following categories:

a. Continued evolutionary process of memory cost reduction through more advanced circuit and device design techniques and improved process and manufacturing efficiencies.

b. A significant change in device and circuit sizes through major changes in pattern definition technology and an electrical scaling of devices to take advantage of the size reduction.

c. Charge Coupled Device and Magnetic Bubble Domain device based memory technologies.

#### NOTES:

(1) Product is introduced, very little or no competition.

- (2) Product is multiple sourced but prices still hold up as production is limited.

- (3) Production expands dramatically as yields improve, competition is fierce, prices tumble, marginal suppliers are beginning to drop out.

- (4) Significant yield improvements are no longer available, new product is beginning to compete for the same market, competition is still intense, suppliers still drop out.

- (5) Major market share is taken by new generation of product, market shrinks but prices hold up as competition is minimal.

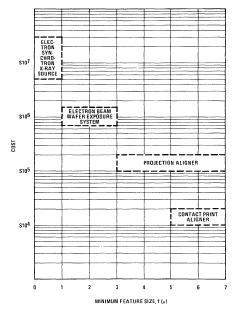

FIGURE 1. Typical Decrease of Memory Products' Prices/Costs During Product Life

#### a. EVOLUTIONARY PROCESS

This approach has so far been the most successful and continued improvements may still be expected. In fact, as long as this is a viable path for future development, it is likely to be the most vigorously pursued approach.

In terms of its future potential, we might examine past contributions to batch density improvements.

The total batch density improvement of 120-fold in eight years was contributed by:

- 1. Higher bit density through design and process innovation: 13.5x

- 2. Larger wafer area: 4x

- 3. Smaller feature sizes and tighter alignment tolerances:  $2.2 \ensuremath{x}$

Continued improvement based on comparable contributions from the same sources is no longer feasible for the following reasons:

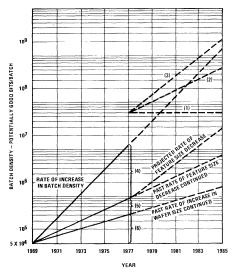

Design and process improvements, the most profitable source of past batch density improvement, is getting sufficiently close to its theoretical limits so that progress in it is likely to slow down (*Figure 2*). It is clear that regardless of whatever technique we use to design or build a memory cell, it must have at least 2 features in both x and y directions, one to store the information and one to separate it from the adjacent cell. This

#### NOTES:

- (1) Theoretical limit, current wafer and feature sizes.

- (2) Theoretical limit, assuming continued improvements in wafer size increase and feature size reduction.

- (3) Theoretical limit, assuming constant rate of wafer size increase and an *increasing* rate of feature size reduction.

- (4) Increase due to design and process innovations.

- (5) Increase due to feature size improvement.

- (6) Increase due to wafer size.

FIGURE 2. Past and Projected Contributions to Batch Density Improvements defines a theoretical minimum cell size of 4  $f^2$  where f is the minimum feature size determined by the limits of pattern definition technology.

Cell size eight years ago was a rich 200 f<sup>2</sup> leaving plenty of room for improvement. Today's cell size of 20 f<sup>2</sup> or less is sufficiently close to the theoretical limit of 4 f<sup>2</sup> that we can no longer project a rate of improvement comparable to past norms. We will do extremely well if we can extract a further 3-fold improvement.

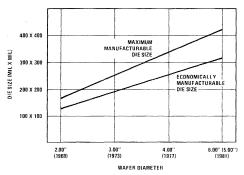

Wafer size improvement will continue at an essentially constant rate. Wafer size increases are important not only for increased productivity, but wafer size is strongly correlated to maximum economically manufacturable die size (*Figure 3*). Wafer diameter has been increasing at a rate of about 1.4 times every four years. This rate of increase is tied not only to the rate at which equipment manufacturers can develop new tooling to handle the larger wafer size, but also to the rate at which capital is invested in the semiconductor industry.

FIGURE 3. Maximum and Economic Die Size as a Function of Wafer Diameter (Time)

Feature size reduction. While we expect significant progress in this area, little of it can be considered evolutionary. In the past, progress in this area was completely evolutionary; contributing relatively little to density improvement. In the next 5 to 10 years we expect major changes in the technology and we will discuss those changes in detail later.

We also expect that manufacturing yields will increase in the next 5 to 10 years. This will be a factor in cost reduction but not in density.

The reason for yield improvement is the expected reduction in the rate of density improvement due to design and process improvements. Present manufacturing yields which include losses in wafer manufacturing, die sort, assembly and final test vary from under 5% for a leading edge product to about 25% for a mature product.

In the past, as long as significant density improvements were available from design and process innovations, engineering effort and talent was better utilized in trying to improve a new high density product's yield from 5% to 25%. Trying to extract the yield improvement available between 25% and 50%-60% which is

probably the practical upper limit for any semiconductor product, was both harder and less rewarding. With less potential improvement available from design and process innovations, we can probably expect higher overall yields for mature products.

In summary, the evolutionary trend, while it will still contribute significantly to future cost reductions, its contribution will be proportionately less than it has been in the past.

#### **b. FEATURE SIZE IMPROVEMENT**

Minimum feature size has been remarkably stable over the past 20 years of integrated circuit technology development. This was probably due to the fact that there was very little change in pattern definition technology. Up to 1975 the pattern definition technology, at least at wafer level, was basically unchanged from what it was in the late 50's and progress was obtained by better engineering, controlling and understanding the process and using improved photochemical materials.

Maskmaking technology made much more consistent progress, converting from an essentially manual drafting to a completely computerized pattern definition process.

Since the mid-70's, very significant changes are beginning to occur at wafer level too. Availability and acceptance of *projection aligners* is the first and probably the most significant of these changes.

Their introduction did not lead to an immediate reduction in feature size, but the control, reproducibility and accuracy of mask dimensions that they allow, makes feature size reduction a much more realistic task.

Improved high resolution photoresists are also becoming available.

*Dry etching techniques* are important technological achievements and will also be contributing to feature size reduction.

*Electron beam and X-ray lithography* are the most frequently mentioned technologies to achieve significant reductions in feature size.

There is undoubtedly significant progress being made in these areas and some of the results are impressive. However, they have to overcome some very significant technical and economic hurdles before they can make an impact on memory technology (*Figure 4*).

Electron beam writing techniques are already available for maskmaking purposes where they offer some very real advantages. For direct writing on wafers, however, they still have to improve significantly and come down in price before they can make an impact on memory technology. Presently, projected machine costs and throughput times are such that processing wafers with electron beam writing instead of conventional masking assuming no other technical problems—would raise wafer processing cost by a factor of 5. This cost increase would take care of all cost reduction achieved by the smaller feature size at *equal yield*. Since the smaller feature size means more densely built circuits sensitive to much smaller defect sizes the most immediate consequence of feature size reduction is yield reduction.

FIGURE 4. Cost of Key Equipment for Various Pattern Definition Technologies and Minimum Feature Sizes

X-ray lithography techniques have still to resolve three basic problems.

- a. Maskmaking technology

- b. Sufficiently intensive X-ray sources

- c. Pattern registration

If they can solve these problems, they can be potentially very powerful as they can use a fixed mask and do not have to regenerate the entire pattern at every exposure.

Summarizing present status of pattern definition technologies, we can project improvements in optical pattern definition technology to yield a 5 to 8-fold increase in batch density over the next 5 to 8 years. This will represent a 2.5 to 4-fold increase in the rate of progress compared to past experience. Even higher rates of progress are possible if electron beam and/or X-ray lithography matures sufficiently to become cost effective, over the next 5 to 8 years.

#### **Electrical Scaling of Devices**

In the previous discussion, we have made the implicit assumption that feature size reduction is equivalent to circuit area reduction.

This is most certainly not the case. Feature size reduction will merely define limits to circuit size reduction. The actual reduction available will be determined by how closely the electrical device and circuit characteristics allow us to approach the limits imposed by pattern definition technology. All three presently used major memory technologies (i.e., MOS dynamic, MOS static and bipolar static) are more limited by device and circuit design considerations, rather than optical pattern resolution.

In case of MOS devices, their performance is a function of the operating voltages and their ability to handle high operating voltages decreases very rapidly with reduced device sizes. Consequently, if denser memory circuits were to be built by taking advantage of feature size reduction, the operating voltages will have to be reduced. The resulting device and circuit performance reduction can be regained by re-engineering the entire device, reducing oxide thickness, junction depth and increasing substrate doping to make the device deliver an equivalent performance at lower operating voltages.

This total re-engineering of device structure, processing and manufacturing technology is called "scaling" and it is obviously a major engineering and manufacturing task, involving all aspects of wafer technology.

Bipolar memory circuits do not appear to suffer from this limitation; their's is, however, a different one. Device sizes can be reduced but their density cannot be significantly increased, because current drain of a bipolar device does not scale with size. Consequently, any attempt to take advantage of reduced device size by increasing number of bits/chip will run into severe power dissipation limits. Again the problem is technically solvable at an expense of major circuit design/process re-engineering efforts to "current scale" bipolar device/ process technology.

I<sup>2</sup>L technology appears technically attractive from this point of view (i.e., it would be able to take advantage of feature size reduction with the least amount of device and/or process engineering changes). Its problem is that it has so far not been able to establish a sufficiently attractive price/performance combination to gain a significant position in the memory market.

Feature size reduction and the required electrical scaling of devices will have some very important consequences in terms of relative impact on various memory technologies. When we scale devices, we adjust some basic device parameters and operating voltages so as to obtain as nearly identical device and circuit characteristics as possible. This can be achieved quite successfully for the type of circuits whose design is by and large based on the device characteristics that we have scaled (i.e., MOS static devices). For these devices, reduction of supply voltage also brings about a reduction in power dissipation, so one limitation to higher density, characteristic

MOS dynamic circuits which have traditionally enjoyed a 4:1 density advantage over static devices, rely more on second order effects like leakage currents, subthreshold conduction and signal to noise ratio in their sense amplifier designs, do not benefit quite as readily from scaling.

Leakage current, whose relation to stored charge is vitally important to the successful operation of MOS dynamic random access memory circuits, does not scale proportionately with voltage, due the point defect

nature of the leakage current. Typically any junction's leakage current represents a spatial averaging over a relatively large number of defects. Reducing junction area will increase fluctuation in number of defect sites from one storage area to the next. Since dynamic RAM design imposes requirement that all storage areas have less than certain pre-determined amount of leakage current, scaling will typically reduce ratio of stored charge to leakage current. Since the signal available is already reduced by both scaling and the resulting increase in density, designers of future generation of dynamic RAM's face some formidable challenges. It is possible that the only way they will be able to overcome these challenges is to impose very strict environmental limitations on the finished product, namely cooling or even refrigeration of memory systems.

Feature size reduction and electrical scaling will impose some very stringent demands on process engineering in terms of both control and the degree of perfection required for good yields from the scaled structures. We are assuming that these problems are solvable by evolutionary improvements in processing techniques. We should not be surprised, however, if progress in those areas from time to time fails to keep up with the more visible improvements available from pattern definition technology.

#### c. NEW TECHNOLOGIES

Success in semiconductor integrated circuit based random access memory technology prompted considerable interest in solid state replacements for serial memories. The two most often considered candidates are Charge Coupled Devices and Bubble Domain Memory devices.

Charge Coupled Devices represent the densest silicon based technology we know. However, their speed and ease of use is considerably inferior to random access memories and as long as random access memories can be made with comparable circuit density, C.C.D. is hard pressed to carve out a market position. Typically, for a C.C.D. circuit to be competitive with RAMs, it has to offer a 4:1 density advantage over a comparably sized RAM circuit. So far it has not been able to do it, partly because RAM technology very quickly adopted all process improvements made for C.C.D. circuits and used them to make competitively sized RAMs.

However, C.C.D. technology is expected to establish a 4:1 density advantage over RAMs in the reasonably near future because its technology and organization permits:

a. Approaching the theoretical minimum storage area of 4  $f^2$  both more easily and more closely than RAMs.

b. Meeting the challenges of feature size reduction and device scaling more easily than dynamic RAM's.

Several features of C.C.D. technology contribute to these advantages. Absence of P-N junctions allows storage and transfer functions to be very similar structurally and either very closely spaced, or used interchangeably for both functions.

Although charge is stored dynamically, it is not held at any location for longer than a clock cycle so effect of defect density fluctuation is averaged out over a large area. Signal strength is comparable to RAM's but there is more flexibility in sense amplifier design. Absence of contacts and P-N junctions allows more efficient layout and easier scaling of devices.

#### **Bubble Memory Technology**

Although both its device and material technology is significantly different from silicon integrated circuits, it is also based on a batch manufacturing process with the cost of a function very strongly dependent of the functional density per batch and manufacturing yields.

Examined from this point of view, it has some very major disadvantages coupled with some even greater potential long-term benefits.

First of all, as a device it is very well suited to serial storage of data. Although it is slower than any silicon I.C. based storage circuit, it is non-volatile—or at least it can be designed to be—and it can also be used to perform very simple logic functions which allow data to be stored and retrieved efficiently. Also, it can be used to pre-amplify the otherwise very small signal magnetically so it can be used to design a reasonably self-contained memory chip.

Its known major disadvantages are:

1. Very high material cost, caused by both very high initial substrate cost and a very costly, difficult and low productivity liquid phase epitaxy deposition process. Material cost is 30-50 times higher than silicon.

2. Very high packaging cost. Every circuit has to have an individually adjusted bias field and a rotating magnetic field built into the package.

3. A batch density which is presently not significantly higher than what is achievable with silicon.

Set against these disadvantages we can consider the potential long-term benefits which motivate the ever increasing activity in the field:

1. Processing typically requires only 3 masking steps, only one of which is critical, compared to 6+ for silicon.

2. Although present bit density is not impressive, it is based on a relatively simple design with bit area being in the 200 f<sup>2</sup> region for a T bar configuration, indicating very much room for improvement, some of which has already been implemented experimentally.

3. Because it has only one critical masking step and no critical alignment requirements, it is the technology best positioned to take advantage of improvements in pattern definition techniques.

It is difficult today to determine the point both in time and in level of complexity at which Bubble Memory Devices will be able to enter the market and compete successfully. But once they do, they will enjoy a very rapid growth comparable to silicon integrated circuit based memory circuits for exactly the same reasons.

Summarizing these trends, there is sufficient visibility for the continued technical progress of memory technology at essentially unchanged rates for the next 5 to 8 years.

One word of caution, however, is worth mentioning here. The key to past success and the continued objective of memory technology development is *cost reduction*.

Technical developments to continue to increase density of memory circuits are worthwhile only if they can make a significant contribution to this overall objective. They cannot do it if the cost of improvement is so high that it swallows up all future cost benefits.

Even if their cost is less than potential cost reduction benefit, they still represent a very significant investment in design, process development, production and testing facilities and product start-up costs for the component manufacturer.

Such an investment will only be economically attractive if the market for memory products continues to expand at a fast rate.

### Static or Dynamic – The Selection Process for a Memory System

#### INTRODUCTION

Today's memory system designer is faced with a bewildering number of technology choices for his memory devices. He is offered overlapping performances from different technologies, different cell structures, and different packages. In addition, he is told of new developments daily that will obsolete all of the information he has already gathered. He is placed in the position where he must choose a technology, not on today's price, but on a projected price based on estimated minimum costs from vendors who are not yet in production with the devices they are offering.

There are many charts available showing the relationship between cost per bit, and learning experience, and the relationship between die size, and cost, on devices sharing the same learning experience; yet the driving reasons behind the costs are not always discussed. In addition, the device costs given do not reflect any additional expense that the user must incur in additional test costs. This additional testing can require significant capital expenditure and additional processing cost if the memory system is to achieve the reliability levels possible from semiconductor memories.

In an attempt to identify these costs more clearly, this paper will outline the decision processes and qualification testing to be followed by a design team choosing devices to be used in a line of standard memory systems that are to be competitive with existing core systems.

The systems were required to be single-card products utilizing power available in the user's system. They cover memory ranges from 16k x 18 to 128k x 18, in increments of 16k. The fact that the systems are to compete directly with well-established core modules, places a high emphasis on low cost and reliability. In addition, it dictates that static memory devices have to be seriously considered for potential applications where dynamic memories can not meet existing interface restrictions. In order to be cost effective with core systems, a volume selling price goal of 0.3¢/bit for the lowest density system, dropping to 0.18¢/bit at the highest density, was required. An analysis of the manufacturing costs of a wide range of semiconductor memory systems currently in production provided a set of non-storage cost constants. These constants define price goals for the memory devices. The systems analyzed had complexities ranging from cards with transparent error correction and powerdown modes for battery back-up operation, to those offering high-storage densities with minimal overhead logic.

Figure 1 shows total non-storage costs in cents per bit of memory system versus memory system size. Although this data was compiled from dynamic memories, static figures were obtained by deducting the cost of all elements whose sole purpose is to support the need to refresh the system. Using the numbers shown in the table, one is able to establish maximum prices for memory devices that allow the design of semiconductor National Semiconductor Memory Systems Division J.C. Blackie<sup>†</sup> November 1977

systems that are cost effective against core modules. Using a composite of predicted pricing from many vendors, the lowest cost per bit anticipated in mid-1978 for dynamic memory is 0.06 e/bit for both a 4k x 1 configuration and a 16k x 1 configuration. The lowest cost per bit anticipated for static devices is 0.15 e/bit for a 1k x 1 configuration or a 4k x 1 configuration. In each type, pricing per bit of the higher density configurations are projected to be on a significant downward trend while the lower densities are flat. Another fact that emerges is that static devices can be cost effective with core at low densities, but do not yield the lowest cost per bit solution in applications that can accept dynamic devices. Static devices greatest application appears to lie in areas where:

- a. System performance is severely impacted by cycle stealing for refresh of dynamic memory.

- b. Board space limitations do not allow space for additional logic required for dynamic interface

- c. Memory requirements are small and can share a board with other system components.

As the system design goal is to replace core systems, there are many situations where the requirement to interrupt system usage for refresh cycles is impractical, thus there is a requirement for static versions of all modules.

Figure 1 shows that even with devices currently in production (1k x 1 static and 4k x 1 dynamic) semiconductor memory can be cost effective up to 32k x 18; the choice becomes marginal at 128k x 18. However, with the advent of the higher density devices in 1978 (16k x 1 dynamic), semiconductor systems establish a clear price advantage over the entire range (16k - 128k). Having established that cost effective devices are available, the designer is now faced with the task of choosing which device and which vendor should be selected. Since the goal is core replacement, the designer can restrict his choices to MOS devices that provide access times in the 150 ns to 200 ns range. These speeds allow him to provide systems to match or exceed typical core performance, even if a transparent ECC scheme is used to enhance reliability.

| MEMORY SYSTEM | *TYPICAL NON-STORAGE<br>COST TO BUILD/BIT |        |  |  |  |

|---------------|-------------------------------------------|--------|--|--|--|

| CAPACITY      | DYNAMIC                                   | STATIC |  |  |  |

| 16k x 18      | 0.046¢                                    | 0.032¢ |  |  |  |

| 32k x 18      | 0.04¢                                     | 0.027¢ |  |  |  |

| 64k x 18      | 0.039¢                                    | 0.027¢ |  |  |  |

| 128k x 18     | 0.039¢                                    | **     |  |  |  |

\*Includes PC board, peripheral circuitry and assembly \*\*Single card product not available

FIGURE 1

<sup>†</sup>Refer to Introduction. This paper presented at COMPCON 1977

Because it is uncertain when the higher density parts will be available at a lower cost per bit than established product, careful consideration should be given to a design approach that will allow a single board to use both high and low density devices. However, this approach should only be followed if an analysis of the devices and vendors shows that the compatible devices offered meet all of the performance and cost goals. The cost of designing a card for each type is not great enough to warrant compromising performance or reliability with a single card design. Thus, the designer should feel free to make an unbiased choice of device for high and low density products as he starts the device selection phase of his design.

#### DEVICE SELECTION

A survey of product available shows several choices of  $4k \times 1$  dynamic configurations, an  $8k \times 1$  dynamic device, and a couple of  $16k \times 1$  dynamic configurations. In addition, there are several choices of  $4k \times 1$  static configurations. (In order to reduce the choices to a more manageable number, the designer must compile a list of factors that will impact the potential cost of a device).

The first and major factor is pressure of competition. The availability of several qualified vendors committing to volume production ensures a long-lived product with an industry-wide commitment to maximize yields. Because volume production commitments from several vendors is dependent on large users choosing a particular configuration, a knowledge of who is committing to use the device types selected, and when, is significant in the selection of a device.

The second factor is die size. This is more difficult to evaluate because the smallest die sizes might be obtained with special processing technology that has not been optimized and therefore will take longer to reach an optimum yield. This would have a serious impact on a product that must be introduced into an established market place as soon as possible. It is necessary to weigh projected die cost by a process learning factor. (Learning experience on a product typically leads to a 3:1 improvement in yield over a one-year period of volume production). Thus, the means employed to reach a small die size is more important than the actual size. A small die achieved by unique chip design without resorting to especially tight masking tolerances or critical processing techniques certainly would give a vendor a definite cost advantage which would be available to a system designer. The variation in die size offered by the vendors who scored high on the other factors outlined in this paper was not significant enough to influence the potential die cost.

The third factor is the type of package that will be offered. Several considerations can create package limitations that may not be obvious from the initial evaluation samples which are usually supplied in a hermetic side-brazed ceramic package which, although expensive, places the fewest restrictions on the device's performance. The lowest cost product will be one that can be packaged in CERDIP and plastic. CERDIP can put a restraint on the die size, and plastic can restrict its operating speed. Thus, the choice of a high-performance part with a wide die may be a poor choice from a lowcost standpoint, because its die may not fit in CERDIP and a high performance device may suffer degraded performance in plastic.

The fourth factor really concerns the choice of vendor rather than a specific product or process, but it is a key consideration from a cost viewpoint. An evaluation of the component supplier's process control program and his level of quality and reliability activity is important. Absence of a meaningful program will affect the level of yield improvement that can be expected within a certain time frame, and will raise the cost of administering product through the system designer's facility. Troublesome vendors with marginal product create extra costs.

Application of the above factors to the devices, in our case, allowed the device selection to be narrowed down to a 16k x 1 RAM from 4 viable vendors, and a 4k x 1 static from 4 viable vendors. These 2 parts offered the lowest potential cost per bit through 1979. This choice did not take into account the high performance static product announced at the Solid State Conference in Philadelphia in February 1977 because that level of performance was not needed. In addition, the technologies outlined, although very significant in terms of superior performance at a lower bit cost, will not be cost effective in lower performance applications in the near future.

Having chosen the devices and vendors, the designer must develop a detailed specification for the parts he needs to procure. This leads him to the next phase of his device selection.

#### CHARACTERIZATION

The error-free performance of any memory device is a function of the stability of the memory element and its ability to function correctly in the presence of electrical noise and temperature variation. In order to ensure that a system design does not exceed the tolerance of the memory device, a designer must have these limitations defined so he can structure his design correctly. The purpose of the characterization phase of the system design is to define these optimum operating conditions.

Each potential vendor chosen during the device selection stage submitted a small quantity of his devices for initial evaluation. This evaluation merely allows one to gain a familiarity with the device and is used as a vehicle to set up a characterization program. Any potential problems that would eliminate further consideration are noted, but this sample cannot be considered as suitable for final characterization. This device characterization must be performed on a group of devices comprised of samples from each speed range offered by the vendor. Each vendor's composite group is split into 2 groups. One is scheduled for a 1000-hour life test and the other for board characterization. This characterization and life test evaluation is the first and most critical phase of any memory system design. It must establish, as much as possible, each vendor's distribution. This will allow the designer to optimize his system around the chip design. Observing parts from the entire distribution allows him to identify operating region limitations with temperature, patterns, and voltage levels without regard to specific data sheets. Potential pattern problems can often be identified by investigating anomalies in the device operating regions that are far outside the range specified in the data sheet using fairly simple test patterns. Once identified, these same anomolies can often be seen to move within the specified operating range when subjected to more complex patterns.

During the earlier selection phase every vendor supplies some level of characterization and life test data. Unfortunately in the early stages of new devices, the vendor has very little to offer. The most meaningful data is generated by device users and is not available for review. This is especially true for life test evaluations where it is very difficult to measure the need for extended burn-in from vendor's data. Most vendors offer some level of burn-in as part of their standard process flow, but do not define the level of infant mortality that might remain in the product shipped. This criteria is very critical to systems planned for high reliability. Therefore, the system designer must structure a life test evaluation that monitors infant mortality as well as long-term shifts in operating parameters. Infant mortality problems in semiconductor devices are shipping-lot dependent, thus lots should be continuously sampled for evidence of infant mortality problems remaining after the vendor's standard burn-in. This problem can be avoided by providing 100% extended burn-in, but this is prohibitively expensive for a low-cost product. An incoming program that required a sample burn-in of all lots can effectively identify lots requiring extended burn-in. In addition, it gives valuable information on the control levels implemented by each vendor. So armed with the data collected from the characterization phase the system designer can proceed to the design of his peripheral logic, and the structuring of his system. He can weigh the impact of interface logic design against chip performance and arrive at the most cost effective and reliable memory system. His system test plan can be designed to effectively catch marginal devices that could create field problems, and achieve the highest levels of reliable operation.

#### CONCLUSIONS

The rapid development of the semiconductor memory market has made available a wide range of products, offering potential performance and cost advantages. However, the market place is limited and not all of the devices offered will reach their cost goals. Thus, the system designer's task is to first select a device that has wide acceptance, and has several viable vendors. Device performance must be obtained without resorting to stateof-the-art technologies. He must then accept the fact that to obtain the optimum cost device it is necessary to precisely specify the performance needed and he must assure himself that each vendor's device comfortably meets that performance. He must accept the fact that he will be required to perform a significant amount of device characterization so that his design can be optimized to meet the twin goals of low cost and high reliability. Finally, his system test plan must be structured to thoroughly exercise all discovered pattern sensitivities in the basic devices. The choice of static or dynamic is one of system interfacing and not cost, and the use of static devices does not eliminate the need for careful device evaluation.

With the advent of the 16k x 1 dynamic device, the semiconductor industry is moving toward a standard configuration which will remove a significant amount of the present confusion of choice. The industry is also starting to extend the life of MOS products with cost reductions obtained by optimizing and shrinking existing designs. This will further simplify the designer's choice, as cell designs and chip structures will remain the same. However, it appears that the user of memory devices will still be faced with a need to carefully evaluate the devices he intends to use and perform some device screening if semiconductor memory systems are to reach the highest levels of reliability.

Section 2

# Dynamic Read/Write Memory

Worldwide consumption of dynamic MOS read/write memory today exceeds that of any other type of semiconductor memory component. This has resulted in volume costs of devices such as the 4kx1 at under 50 millicents (\$0.0005) per bit. Despite the low cost and extreme widespread usage, there still exists some concern and even mistrust regarding dynamic memory even among professionals. This is usually reflected in an effort to "avoid the hassle" at resulting higher costs. If you have experienced doubts regarding the application of dynamic RAM to your needs, this section should prove helpful. It is intended to reduce "problem pollution" and to eliminate the "hassle." .

.

.

## Dynamic RAM Board Design Made Easy

National Semiconductor Memory Application Stephen Calebotta\* November 1977

#### INTRODUCTION

Many new memory system designs are being done with dynamic RAMs. This is especially true as the new 16k RAM chips become more readily available. This application note is aimed at those engineers who are doing their first dynamic RAM designs. Its intent is to give some direction in how to design a RAM board so that it will give the greatest production yield with the least amount of difficulty.

We shall not talk about specific RAMs or interface to a specific processor. Most engineers can design control and interface logic for RAMs and most board designers can lay out a PC board for that design. However, the quality of that design will become apparent only after the RAM board is built and phased into production. Does it come up easily? Does it go through testing with little or no RAM chip fallout? Is it reliable in the field?

The key to success in a dynamic RAM system, or any other system for that matter, is margin. A system designed to maximize power supply and timing margins will be reliable and easy to manufacture. One that doesn't will be a manufacturing and field service nightmare.

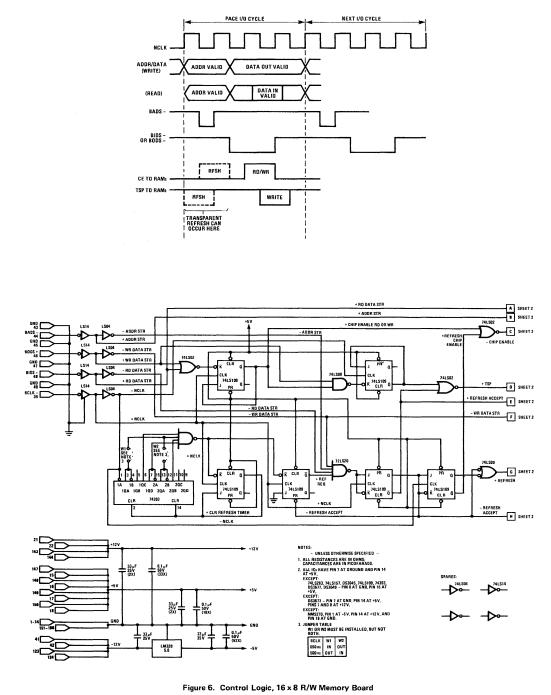

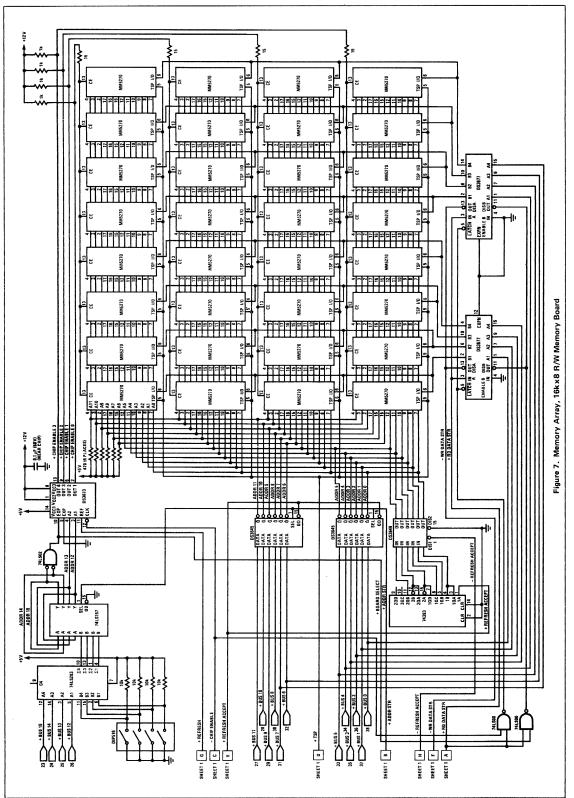

In this application note we shall discuss RAM chip characteristics, power supply and control signal distribution on PC boards, and control logic implementation suggestions. As successful examples, in the appendix we shall provide the schematics and foils for some memory boards that are in production.

#### RAM CHIP CHARACTERISTICS

For reference we shall compare dynamic and static RAMs at the chip level. Then we shall describe the unique characteristics of dynamic RAMs which must be considered in a memory system design.

#### Dynamic RAMs versus Static RAMs

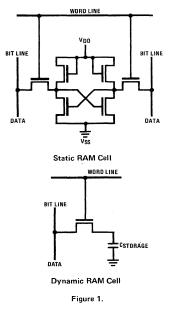

The basic difference between dynamic and static RAMs is the way they store data. The static RAM uses a flipflop to store a bit, while the dynamic RAM uses a capacitor to store a bit. (See figure 1.)

It is their respective cell designs that give each RAM its advantages over the other. Let's compare the RAMs for ease of use, power dissipation, die size, and price.

Ease of Use: The static RAM is easier to use because no refresh logic is required. In addition, static RAM control signals tend to be easier to generate because cycling is usually unnecessary.

**Power Dissipation:** The dynamic RAM draws less power. The static RAM draws power continuously to sustain its flip-flops, while the dynamic RAM draws minimal power (1 to 2mA) between cycles. With continuous cycling, the dynamic RAM draws about as much power as the static. However, in a large memory system, dynamic RAMs save total system power since only one bank of RAMs is ever accessed during a memory cycle. All other banks draw minimal current except during refresh cycles. The duty cycle for refresh is approximately 1% to 3%.

Die Size: Dynamic RAMs tend to be smaller. Due to the difference in cell designs, the die size of the dynamic RAM is often at least 20% smaller than that of a comparable static RAM from the same manufacturer.

**Price:** Because of smaller die sizes and much larger production runs, dynamic RAMs should always remain considerably cheaper than comparable static RAMs. In addition, dynamic RAMs save money in larger systems. Less chip power means smaller and cheaper power supplies. Smaller supplies mean a further saving in reduced cooling requirements. In general, the larger the memory system, the greater the savings by using dynamics.

#### Dynamic RAMs

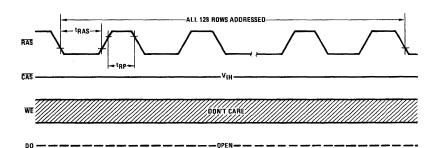

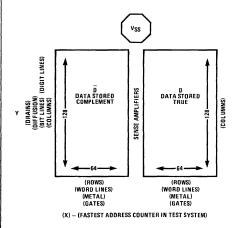

**Refresh:** Since charge leaks off the storage capacitors, it must be replenished periodically in order for a dynamic RAM chip to retain its data. The charge in any one cell is replenished, or refreshed, every time that cell is accessed for a read or a write, At the same time, all the other cells in the same row are also refreshed. For that reason the entire RAM chip can be refreshed by doing only 64 cycles (for 4k RAM; a 16k RAM needs 128

cycles) in 2 ms while sequencing through all the row addresses. The bit pattern presented to the column addresses does not matter. However, the setup and hold times must still be met. Unstable column addresses during refresh will cause data loss.

The hardware required for refresh amounts to a 6or 7-bit counter for the refresh addresses, some way to multiplex the counter onto the RAM row address lines, a timer to signal when a refresh should be done, and the miscellaneous gating needed to couple into the usual read/write logic.

In some systems no extra refresh logic is needed. For example, in CRT systems normal operation sequences through all the row addresses in less than a 2 ms refresh period. This will be true only if the row address bits on the RAM chip are driven from the least significant address bits of the system. As a rule, this is good practice in all systems. By placing the most active system address bits on the RAM row addresses, normal system operation will automatically refresh the bulk of the RAM.

Cycling: One of the key functional differences between static and dynamic RAMs is the fact that dynamic RAMs must run through a cycle in order to read or write. Aborting the cycle by removing the chip enable too early or by trying to start a second cycle too soon after the first will probably cause data loss. Minimum chip enable on and off times must be observed.

#### Summary

Static RAMs are easier to use. Dynamic RAMs are cheaper, use less power, must be refreshed, and must be cycled.

#### MEMORY SUBSYSTEM DESIGN CONSIDERATIONS

Some memory board designs are easy to manufacture, while others, functionally identical, have low manufacturing yields seemingly due to the many "bad" chips. The difference between them is usually the amount of margin designed into each system. Power supply and timing margins are both critical, and as the margins go to zero or negative, the amount of "soft" errors goes up. (A chip has a "hard" error if a location consistently cannot be written and read back properly. It has a "soft" error if it only occasionally fails.)

On careful analysis, "soft" errors usually occur during a memory cycle in which some system parameter has gone out of spec. Since the RAM chips themselves have variations in their margins, replacing the offending RAM with one that has a greater margin in the out-of-spec parameter seems to cure the problem. This results in a large pile of "bad" RAMs. However, the real solution to this type of problem is in a careful system design and board layout in the beginning.

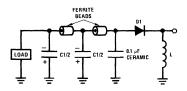

#### **Power Distribution**

By far the single most important aspect of a successful RAM system is good power distribution consisting of carefully designed decoupling and power gridding. The importance of good power distribution cannot be over-emphasized.

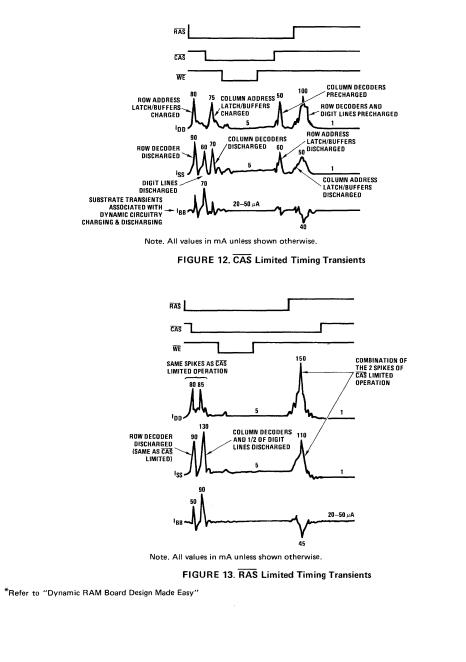

Let's examine the problem. All dynamic RAMs have at least two supplies ( $V_{DD}$  and  $V_{BB}$ ;  $V_{SS}$  is the RAM internal ground). Most also have a third called  $V_{CC}$ .

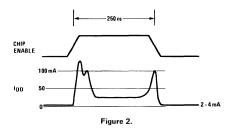

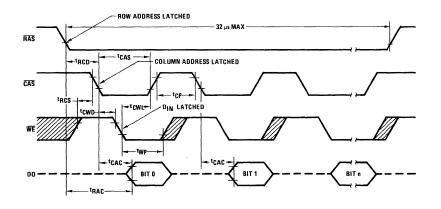

We will discuss only V<sub>DD</sub> since the other supplies have similar characteristics. Figure 2 shows the I<sub>DD</sub> current waveform for a typical dynamic RAM chip during a memory cycle.

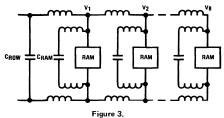

At the beginning and end of chip enable, each RAM chip draws 50 to 100 mA current spikes with rise times of 20 ns. In addition, each RAM package draws a 20 to 40 mA DC current lasting for the duration of chip enable. The power distribution system must supply these currents while the voltages at the RAMs remain constant. Figure 3 is a schematic of the V<sub>DD</sub> supply for a row of eight RAMs. The inductors are due to PC trace inductance which is about 10 nH per inch for a 13 mil trace. If the RAMs are on ½-inch centers there is 10 nH total between RAMs.

If there is only one capacitor per row, and if that row capacitor,  $C_{row}$ , were infinite, the voltage spikes at the first, second, and last RAMs would be:

$$V_1$$

spike = L x  $8\frac{di}{dt}$  = 10 nH x 8 x  $\frac{100 \text{ mA}}{20 \text{ ns}}$

= 400 mV

$$V_2$$

spike = L x  $15\frac{di}{dt}$  = 750 mV

V8 spike =

$$L \times 36 \frac{di}{dt} = 1800 \text{ mV}$$

These spikes, especially the last two, are unacceptable.

If each RAM had its own decoupling capacitor,  $C_{RAM}$ , in series with 10 nH of trace inductance, the voltage spikes would be:

$$V_{spike} = L \frac{di}{dt} = 10 \text{ nH x} \frac{100 \text{ mA}}{20 \text{ ns}} = 50 \text{ mV}$$

which is very good. Local decoupling should be used to overcome the spiking problem.

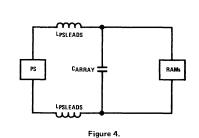

The ability of the power distribution system to supply the 20 to 40mA per chip during a RAM cycle is also a function of the series inductance. For example, see figure 4.

Let the total power supply lead inductance be 50 nH. (We are ignoring the PC trace inductance within the RAM array itself.) What would the voltage step have to be at the RAMs to get  $40 \text{ mA} \times 8$  flowing in 20 ns? The equation is:

$$E = L \frac{di}{dt} = 50 \text{ nH x 8 x} \frac{40 \text{ mA}}{20 \text{ ns}} = 800 \text{ mV}$$

which is a large step which should not occur with adequately designed decoupling. Therefore, the bulk of the DC current for cycling the RAMs comes from decoupling caps themselves, and therefore they should be large enough to supply these currents with little droop. They should also be close enough to the RAMs to minimize the effect of the spikes. If we use a  $0.1\,\mu\text{F}$  cap, the droop for a 250 ns cycle would be:

$$V_{droop} = V = \frac{I}{C}t = \frac{40 \text{ mA}}{0.1 \,\mu\text{F}} \times 250 \text{ ns} = 100 \text{ mV}$$

which is acceptable. Obviously, a larger capacitor will do an even better job of handling the droop. In addition, to help keep the droop to a minimum, the board should have about 50 to  $200\,\mu\text{F}$  of bulk decoupling on the +12 V supply. The other supplies can have less. Half should be placed near the point where the supplies enter the board. The other half should be placed at the far side of the RAMs so that the array lies between the bulk decoupling capacitors.

Alternatively, half of the bulk capacitors can be spread throughout the array. If this is done, use approximately 5 to  $10\mu$ F per eight RAM chips for V<sub>DD</sub> and V<sub>BB</sub>. For V<sub>CC</sub>, 5 to  $10\mu$ F for 32 chips should be adequate.

Intuitively, this second approach seems better. However, the first technique works fine and is probably more cost effective.

The choice of capacitor types is very important. In all of the above decoupling calculations we have ignored the effective series resistance (ESR) of the capacitors. The effect of the ESR of real capacitors is probably at least as large as the effect of PC trace inductance and is a function of the capacitor type.

For best results, use ceramic capacitors for the local decoupling. The Memory Systems Group at National Semiconductor has had good results with ceramic capacitors of Z5U material from AVX and Sprague. To illustrate how important the Memory Systems Group feels these capacitors are to good memory board performance, every lot is subjected to an incoming inspection which includes, among other things, a transient response test.

For bulk decoupling, solid tantalum capacitors are recommended. They have better transient response than most other large value capacitors and they put a lot of capacitance into a small package which simplifies board layout.

A word about power gridding. If there are a number of rows of RAMs, all power supply traces to all RAMs should be run both vertically and horizontally throughout the array. Providing multiple paths through the array reduces the effective inductance of the power distribution system.

To summarize power distribution, we can say the following:

- 1. It is the single most important aspect of a good RAM board layout.

- 2. Use plenty of decoupling. The decoupling caps not only reduce voltage spikes, but also provide most of the RAM power during the cycling. Lay out the board for a  $0.1 \mu$ F capacitor per power supply per RAM chip (up to three capacitors per chip). As production history accumulates, it may be possible to omit half the capacitors. However, lay out the board for one per supply per chip. Use 50 to  $200 \mu$ F of bulk decoupling on +12 V. On +5 V and -5 V use 25 to  $100 \mu$ F.

- The decoupling capacitors should have the shortest possible traces back to their respective RAM power supply and ground pins. To reduce inductance further, these traces should be as wide as room will allow.

- 4. Traces running the power supply voltages throughout the array should be as wide as possible. However, with good decoupling design, even minimum trace widths will probably be acceptable. If some power supply traces can be wider than others, make VSS (Ground) wider first, VDD next, VBB next, and finally VCC. Ground is the key. Grid the supplies even if the traces are heavy in one direction and light in the other.

- 5. We have purposely omitted any discussion of multilayer boards. They tend to simplify power distribution problems, but the types of problems that must be solved are the same. Only the magnitudes have been somewhat reduced. Almost everything that has been said up to now is still applicable to multilayer boards.

#### **Data and Control Signal Distribution**

The second most important aspect of the successful RAM system is address, data, and control signal distribution.

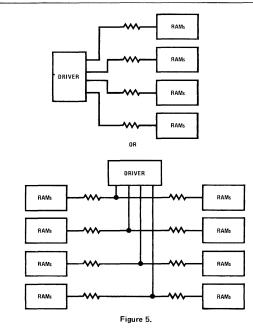

Let's discuss the chip enables first. This is the most important signal to the RAM and all timing is referenced to it. There are two types of chip enables in common use today: 12 volt and TTL level swings. Running chip enable lines through an array tends to be less of a problem than one would think. There are only two things to keep in mind. First, place the actual driver chip near the RAM array it is driving, making the chip enable run short and direct. Second, put a damping resistor near the driver. Do this for either TTL level or 12 volt chip enables. Select the value of this resistor to

give the best clock waveform at the RAM chips. Its value will probably be between 10 and 51  $\Omega$ . Figure 5 shows the commonly used arrangements.

The reasons for these two recommendations stem from the fact that, at the frequencies encountered here, the clock lines are, in fact, transmission lines. The impedance of the line is determined by:

$$Z_0 = \sqrt{L/C}$$

where the impedance of the clock line within the array of chips is in the range of 10 to 15  $\Omega$  while the unloaded line between the clock driver and the chip array is in the range of 30 to 50  $\Omega$ .

In order to drive the clock line cleanly, some attempt must be made to match the clock driver's output impedance to that of the line. The actual output impedance of most monolithic clock drivers varies as much as 3 to 1 and so we choose a fast clock driver with low output impedance and put a damping resistor in series to empirically set the effective output impedance to match the line (with only about 10% variation).

Long clock lines or long lengths of unloaded clock lines can cause problems. In the case of the long clock line, the open circuit at the far end of the line causes the reflection from the end of the line to return to the driver after the end of the rise time, resulting in ringing. In the case of the long unloaded length of line, the reflection from the junction of the unloaded and loaded sections of the line (due to the mismatch) causes glitches in the clock transitions.

To minimize crosstalk from chip enable to other signals, try to run chip enable at  $90^{\circ}$  to other signals. This is usually hard to do in an actual layout. As an alternative, leave as much room as possible between chip enable and adjacent traces as it runs through the array. Typically, signals in the array are on 50 mil centers. Moving the two adjacent signals more than 50 mils away from chip enable will help some in reducing crosstalk. However, as stated earlier, there seem to be very few problems associated with chip enable. Neither CE itself nor crosstalk to other signals will be troublesome if the above guidelines are observed.

Address, data, and control signals such as read/write (or equivalent) should be run as directly as possible. Their layouts tend to be non-critical. The critical thing is timing. The control logic should be designed to maximize setup and hold times with respect to chip enable. Again, high production yield is related to margins. As an example, consider a RAM board that was built for an 8080 system. The chip used was MM5271 4k RAM which has a low true TTL level clock input. The signal that controls read, write, and refresh is called TSP. The MM5271 data sheet says that the setup time for TSP is zero ns with respect to the leading edge of chip enable. When doing a refresh, TSP must be low at the beginning of chip enable. The original timing brought TSP down at the same time as chip enable. The system seemed to work. However, it would make an error once every half hour or so. With an oscilloscope everything appeared to be within specification. When TSP and chip enable were superimposed on the scope, their leading edges were absolutely coincident in both time and waveshape. The TSP/chip enable relationship was examined very, very carefully and pronounced okay. Finally, in an attempt to cure the problem, the TSP timing was changed to give about 50 ns of setup time and the problem disappeared.

The point was that the original design was done to the limit of the memory data sheet even though there was no need to do so. The success of the operation depended on the shape of the two waveforms to keep the system in spec. Once margin was designed in, with no hardship at all in the design, the system operated flawlessly.

In high-speed systems where it is hard to design in extra margin, use damping resistors in address, data, and control lines to help control their waveshapes. A resistor in every address, data, and control line allows these waveforms to be optimized, which gives the system improved margin over an undamped design. Use damping resistors only where necessary. Leave them out of signals that have time to settle down before they are needed.

Summarizing the use of damping resistors: always put them in chip enable lines, whether they are TTL levels or 12 V levels. Use them as necessary in those address, data, and control lines whose timings are approaching the limits of the RAM chip data sheet. Design in margin first. Tune it in when it can't be designed in.

#### LOGIC CONSIDERATIONS

These also affect yield. For example, a RAM cycle must never be aborted before its normal completion. The control logic must be designed to never permit a shortened cycle. At this point we shall briefly discuss some techniques for timing and control.

#### **Timing Generation**

The actual phasing of control signals can be done a number of ways. Existing system level control signals can be used. This is easy in some 8080 and PACE systems. When the available system control signals aren't quite up to the job, another technique that works

quite well is to use a high frequency oscillator and a shift register connected as a Johnson counter. Any timing signal that is necessary can be generated from a Johnson counter using a 2 input gate. This technique has a minor drawback if the high frequency oscillator is asynchronous with respect to the main system timing. The RAM cycle timing will always have a finite uncertainty with respect to the system cycle timing. This uncertainty is equal to the clock period of the high frequency oscillator. To apply the same technique but to avoid the timing uncertainty, use a gated delay line oscillator instead of a crystal or RC oscillator. Delay line oscillators can be started and stopped reliably. Crystal and RC oscillators take a few cycles to settle down and therefore are not reliable in a start-stop mode. How about one-shots? Do not, under any circumstances, use one-shots in critical timing applications!

#### **Refresh Timeouts**

A counter and oscillator are best. An astable oscillator is acceptable but must be carefully designed for worst case minimum frequency with respect to temperature to ensure the RAM gets refreshed often enough. At the end of the timeout a flip-flop should be set. When the refresh cycle is finally completed, that flip-flop should be reset. The timing should be such that it doesn't matter when the RAM gets refreshed within the refresh timer period.

#### Transparent versus Non-Transparent Refresh

Most microprocessors have predictable periods of time when they will not access the RAM board. Usually it takes little effort to insert refresh cycles in these times, thereby making refresh transparent to the CPU. When the CPU is very fast and is using the bus almost continuously, the refresh will have to hold up the processor. Even then, some clever design will minimize the time spent doing non-transparent refresh.

#### Single Step

Some systems need the capability of single stepping through programs. Since dynamic RAMs must be refreshed continuously, the output data from RAM should be latched. This permits single stepping because every time the address changes, the RAM is read and the data is latched. Then the refresh proceeds behind the latches, never disturbing the data. The RAM appears static.

#### DMA

DMA should be little different from normal cycles. One thing that must be considered is how to handle refresh. Three techniques immediately come to mind. First, have the DMAing device permit refresh periodically. Second, limit the DMA frequency. Make the period between DMA cycles equal to a normal RAM cycle plus a refresh cycle. This way the refresh can be handled transparently to the DMA. The third technique would be to limit the DMA time to something under 2 ms and at the end of the DMA do a burst refresh of the entire memory. There are a number of other ways to handle refresh and DMA. Performance of the system will determine which technique is most appropriate.

From a system standpoint, the most important aspect of DMA and dynamic RAMs is the polarity of the system level control signals. In a TTL system where bus control can change hands, the control signals must be low true. The reason for this is that, as control transfers from the CPU to the DMA device and back again, there will be short periods of time when the control lines are floating since neither device is driving the lines. In a TTL system, floating lines look high. If control signals have been defined as high true, then as the lines momentarily float, devices such as our RAM board will think that a command has been issued and will start an unintended cycle. Then the problem gets compounded. During the unintended cycle comes the command for a real cycle. Either the unintended cycle will be aborted, which destroys some RAM contents, or the intended cycle will start too late, causing other problems in the external system. An example of a bus with this problem is the S100, or hobby standard bus. It mixes signal polarities and, therefore, makes dynamic RAM control logic unnecessarily complex. If there is only one controlling device, signal polarities are academic. But if control can transfer, make the control lines low true.

#### SUMMARY

Refresh requirements make dynamic RAMs slightly harder to use than static RAMs. However, they pay the designer back for his efforts by reducing overall system cost in three ways. First, dynamic RAMs tend to be cheaper than static RAMs of the same size. This is primarily due to smaller chip sizes and higher production volumes than comparable static RAMs. Second, dynamic RAMs use less power. When a dynamic RAM is not being accessed it draws much less current than a static RAM. During access, dynamic and static RAMs draw similar amounts of power. However, in a large array, only that bank being accessed draws full power. All others still draw standby currents so that the total system power is lower than for a comparable static system. Because of the reduced power requirements, power supplies are cheaper. And, third, due to lower power dissipation, cooling requirements are reduced, allowing a further saving.