BR1333/D REV 6

# **TIMING SOLUTIONS**

# **Over 10 Newly Released Parts!**

- Low Skew Fanout Buffers

- Low Voltage, Low Skew Fanout Buffers

- PC Clock Generators

- PLL Clock Drivers

- Low Voltage PLL Clock Drivers

- Clock Generation Circuits

Q1/97 BR1333 REV 6

# **Timing Solutions**

This brochure contains device information on Motorola's family of timing solution products. The brochure includes datasheets on both PLL and fanout buffer based products both at 5.0V and 3.3V V<sub>CC</sub>'s. The timing solutions family will continue to grow rapidly. For datasheets designated "Advance Information" or "Product Preview", as well as new products, please contact your Motorola representative.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use. even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

© Motorola, Inc. 1997 Previous Edition © August 1995 "All Rights Reserved"

Printed in U.S.A.

Mfax, ECLinPS, ECLinPS Lite, MECL 10H, Yield Surface Modeling and YSM are trademarks of Motorola, Inc. The brands or product names mentioned are trademarks or registered trademarks of their respective holders.

### **Table of Contents**

#### Introduction

| Selector Guide 1                                |

|-------------------------------------------------|

| System Design Considerations (AN1091) 3         |

| Clock Distribution Techniques (AN1405) 10       |

| Designing With PECL (AN1406) 17                 |

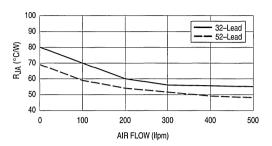

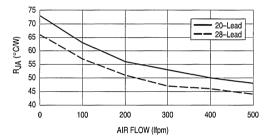

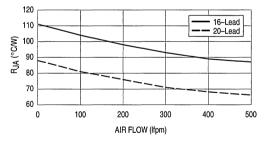

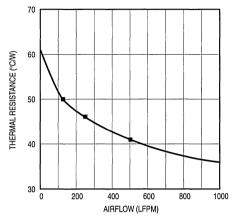

| Thermal Data for<br>MPC Clock Drivers* (AN1545) |

#### **Data Sheets**

#### Low Skew Fanout Buffers

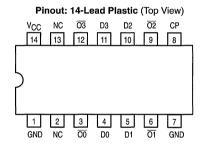

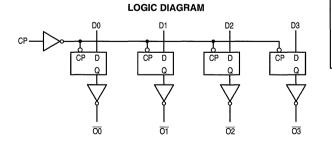

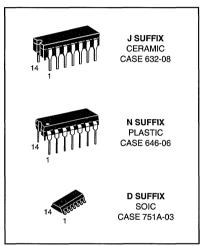

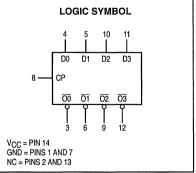

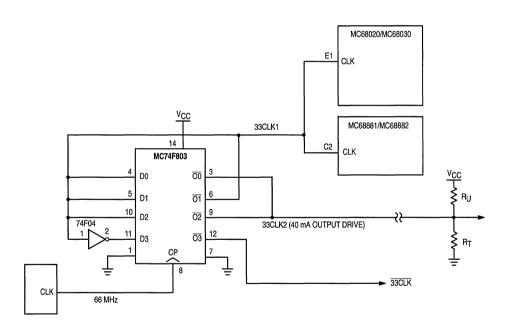

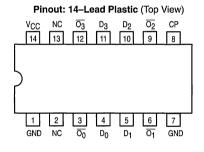

| MC74F803 32            |

|------------------------|

| MC74F1803 35           |

| MC88913 38             |

| MC88914 41             |

| MC10H640, MC100H640 44 |

| MC10H641, MC100H641 50 |

| MC10H642, MC100H642 56 |

| MC10H643, MC100H643 63 |

| MC10H644, MC100H644 66 |

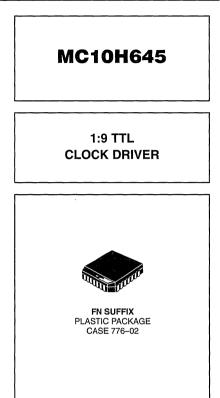

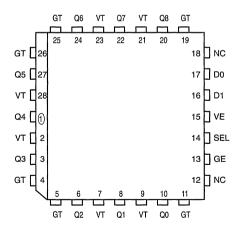

| MC10H645 69            |

| MC10H646, MC100H646 72 |

| MC10EL11, MC100EL11    |

| MC100EL13 94           |

| MC100EL14 96           |

| MC10EL15, MC100EL15 80 |

| MC10E111, MC100E111 83 |

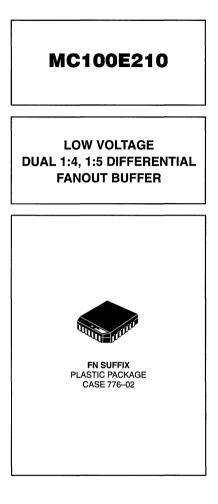

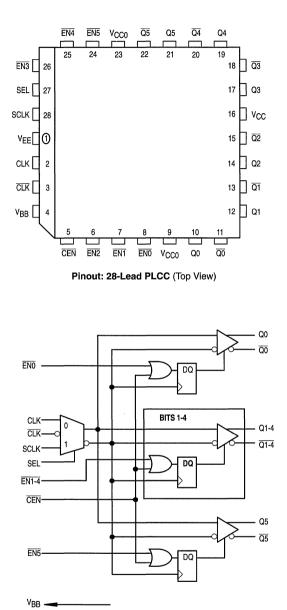

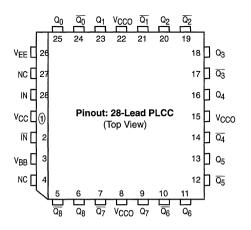

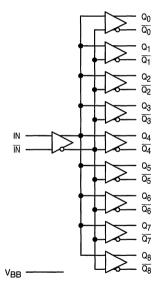

| MC100E210 102          |

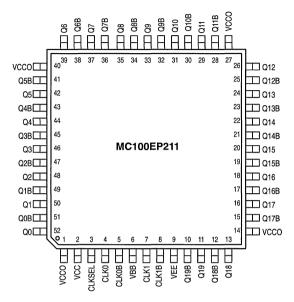

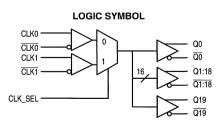

| MC10E211, MC100E211 87 |

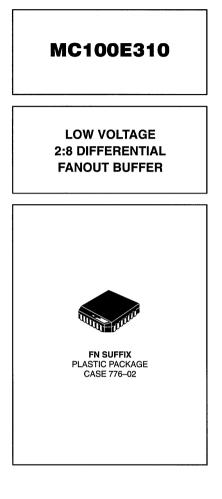

| MC100E310 110          |

|                        |

#### Low Voltage, Low Skew Fanout Buffers

| MC100LVEL13 . | <br>            | <br>    |

|---------------|-----------------|---------|

| MC100LVEL14 . | <br>            | <br>    |

| MC100LVE111 . | <br>            | <br>    |

| MC100LVE210 . | <br>            | <br>102 |

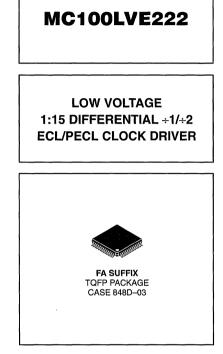

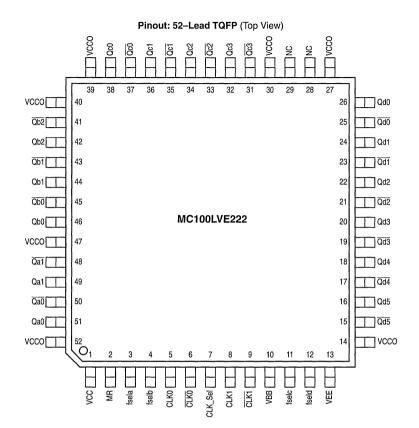

| MC100LVE222 . | <br>            | <br>106 |

| MC100LVE310 . | <br>            | <br>110 |

| MC100EP111* . | <br>• • • • • • | <br>114 |

| MC100EP221* . | <br>            | <br>117 |

|               |                 |         |

| MPC903, MPC904, MPC905*       1         MPC911       1         MPC940*       1         MPC941*       1         MPC946       1         MPC947       1         MPC948       1         MPC949       1                | 25<br>28<br>31<br>34<br>38<br>42                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| PC Clock Generators<br>MPC9108* 1                                                                                                                                                                                 | 51                                                       |

| PLL Clock Drivers           MC88915         1           MC88915TFN55, 70, 100, 133, 160         1           MC88916         1           MC88920         1           MC88921         2           MC88921         2 | 67<br>85<br>93<br>02                                     |

| Low Voltage PLL Clock Drivers<br>MC88LV915T                                                                                                                                                                       | 30<br>39<br>51<br>57<br>68<br>73<br>87<br>98<br>05<br>09 |

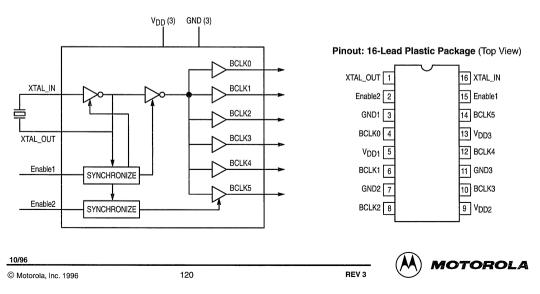

| Clock Generation Circuits<br>MC12429                                                                                                                                                                              | 32                                                       |

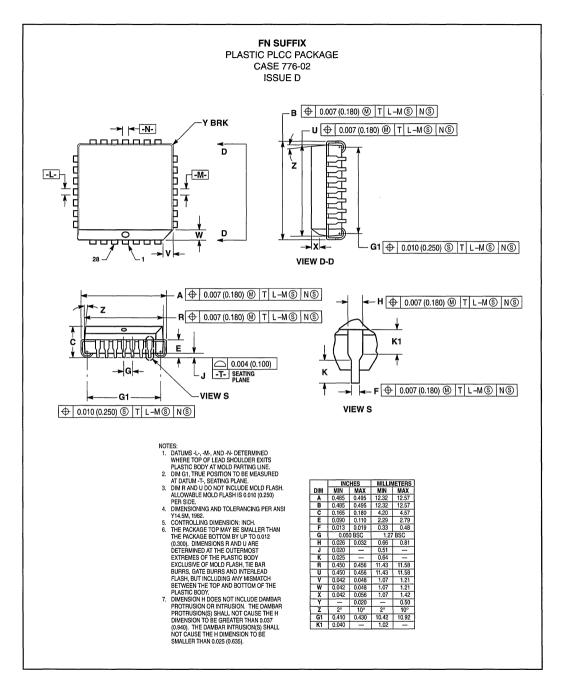

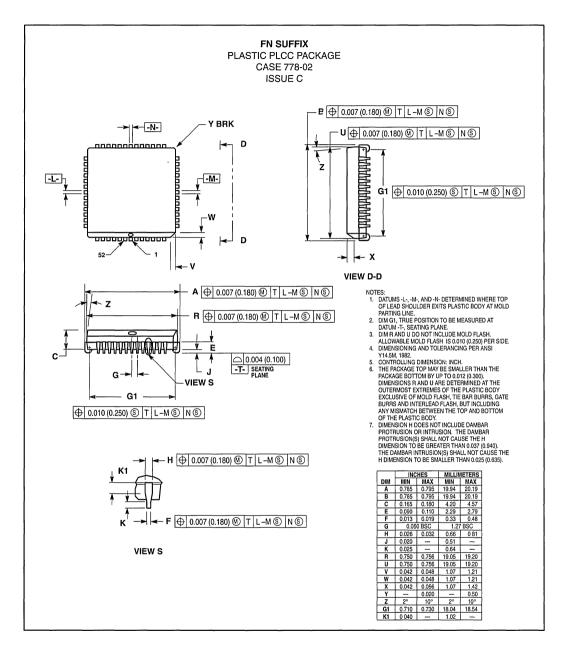

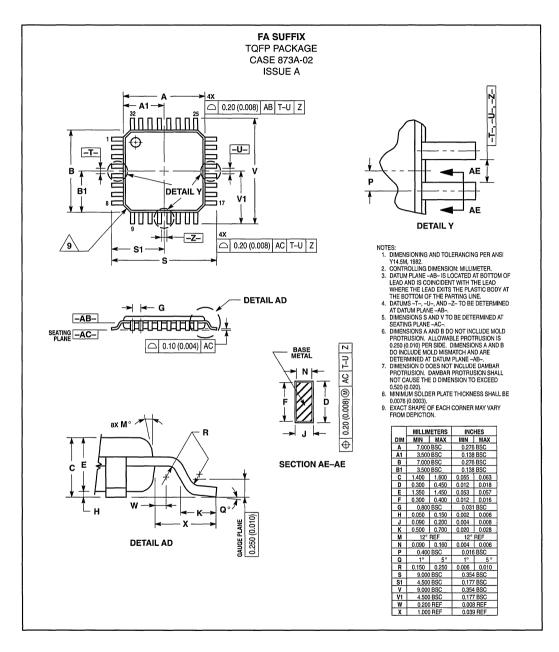

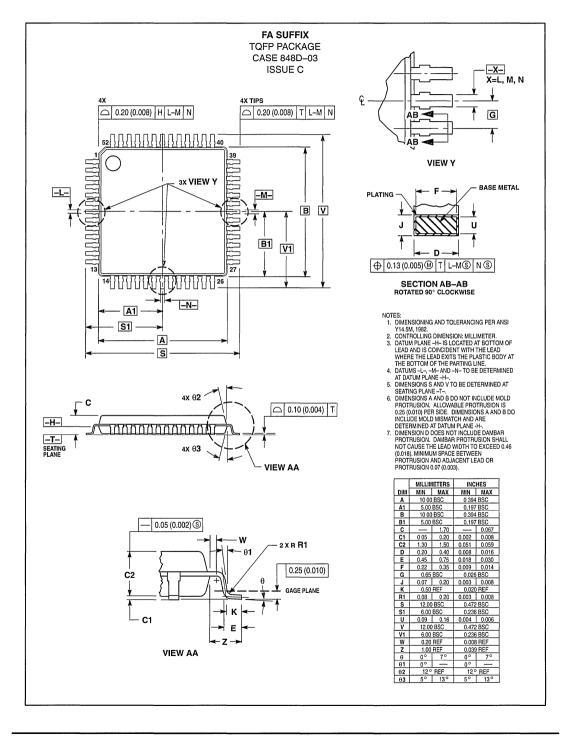

| Case Outlines 3                                                                                                                                                                                                   | 51                                                       |

| How to Reach Us 3                                                                                                                                                                                                 | 58                                                       |

| Motorola Distributors and Worldwide<br>Sales Offices                                                                                                                                                              | 59                                                       |

\* = Represents information that has not appeared in previous issues of this publication.

Italics represent documents that have been revised since the last issue of this publication.

## MOTOROLA'S LOW SKEW CLOCK DRIVERS

| Part<br>Number   | Output<br>Level | Max Out-to-Out<br>Skew (ns) (Note 1.) | Max Output<br>Freq. (MHz) | Number of<br>Q Outputs | Q′<br>Outputs | Package<br>Types    | Other Features               |

|------------------|-----------------|---------------------------------------|---------------------------|------------------------|---------------|---------------------|------------------------------|

| MC74F803         | ΠL              | 1.0                                   | 35                        |                        | 4             | 14 DIP/SOIC         | TTL Inputs                   |

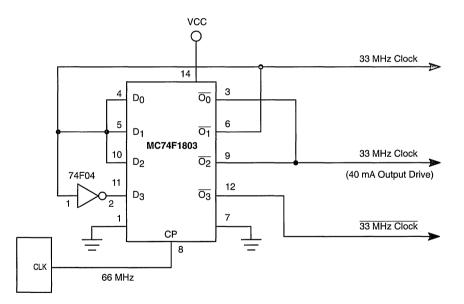

| MC74F1803        | TTL             | 2.0                                   | 35                        |                        | 4             | 14 DIP/SOIC         | TTL Inputs                   |

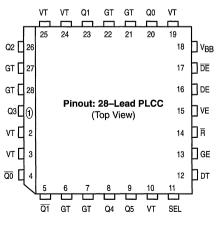

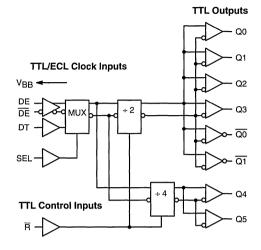

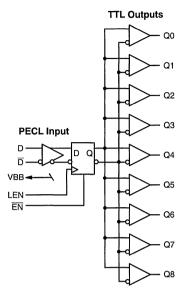

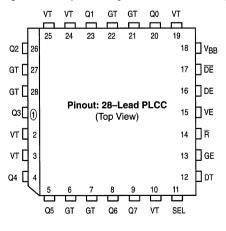

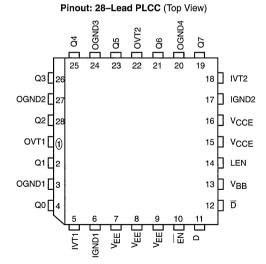

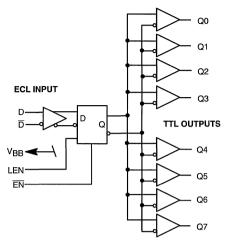

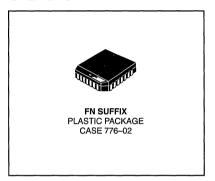

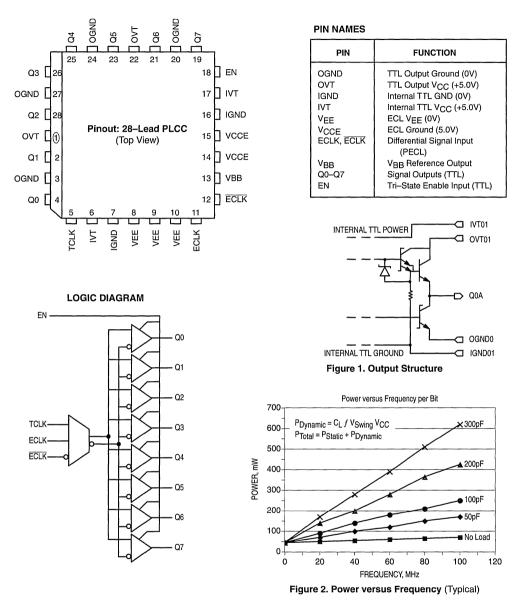

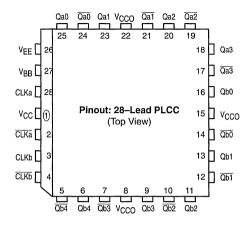

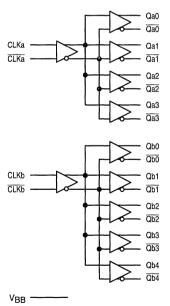

| MC10/100H640     | TTL             | 0.5                                   | 33 & 66                   | 6                      | 2             | 28 PLCC             | PECL or TTL Inputs (Note 2.) |

| MC10/100H641     | TTL             | 0.5                                   | 65                        | 9                      |               | 28 PLCC             | PECL Inputs (Note 2.)        |

| MC10/100H642     | TTL             | 0.5                                   | 33 & 66                   | 8                      |               | 28 PLCC             | PECL or TTL Inputs (Note 2.) |

| MC10/100H643     | TTL             | 0.5                                   | 65                        | 9                      |               | 28 PLCC             | ECL Inputs                   |

| MC10/100H644     | ΠL              | 0.5                                   | 33 & 66                   | 4                      | 2             | 20 PLCC             | PECL or TTL Inputs (Note 2.) |

| MC10/100H645     | TTL             | 0.65                                  | 66                        | 9                      |               | 28 PLCC             | TTL Inputs                   |

| MC10/100H646     | TTL             | 0.5                                   | 100                       | 8                      |               | 28 PLCC             | PECL or TTL Inputs (Note 2.) |

| MC88913          | CMOS            | 1.0                                   | 55                        | 4                      | 2             | 14 DIP/SOIC         |                              |

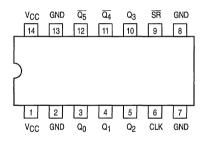

| MC88914          | CMOS            | 1.0                                   | 55                        | 4                      | 2             | 14 DIP/SOIC         | Pwr-On & Ext Resets          |

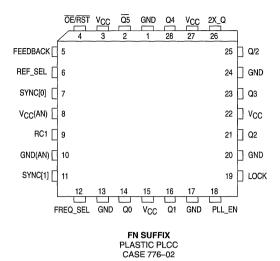

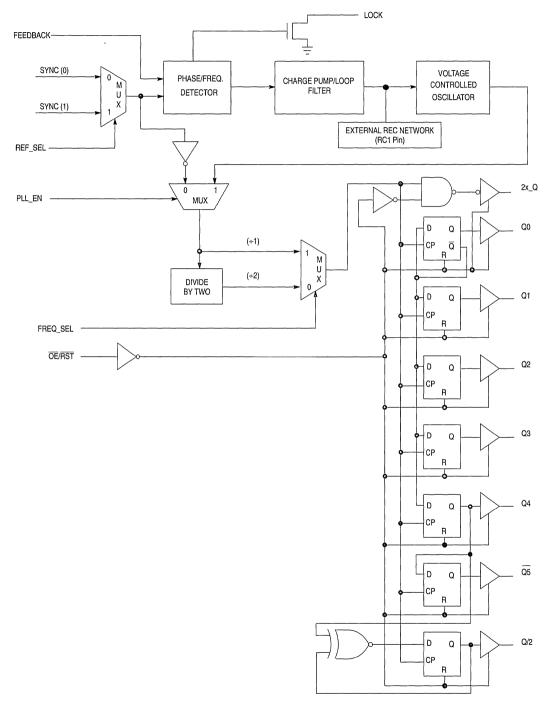

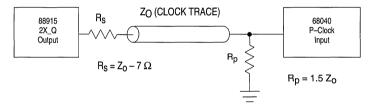

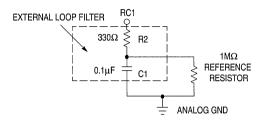

| MC88915          | CMOS            | 0.5                                   | 55, 70                    | 7                      | 1             | 28 PLCC             | Phase-Locked Loop            |

| MC88915T         | CMOS            | 0.5                                   | 133, 160                  | 7                      | 1             | 28 PLCC             | Phase-Locked Loop            |

| MC88916          | CMOS            | 0.5                                   | 20, 40, 80                | 5                      | 1             | 20 SOIC             | Phase-Locked Loop            |

| MC88920          | CMOS            | 0.5                                   | 12.5, 25, 50              | 5                      | 1             | 20 SOIC             | Phase-Locked Loop            |

| MC88921          | CMOS            | 0.5                                   | 80                        | 2                      | 1             | 20 SOIC             | Phase-Locked Loop            |

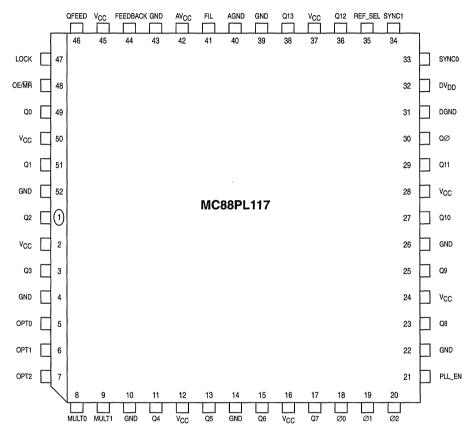

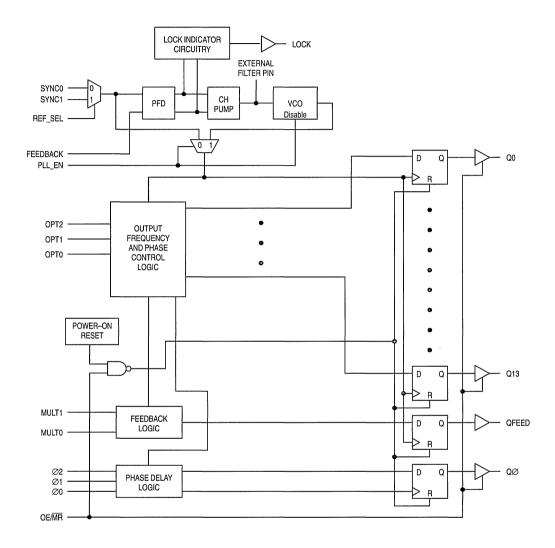

| MC88PL117        | CMOS            | 0.35                                  | 133, 160                  | 16                     |               | 52 PLCC             | Phase-Locked Loop            |

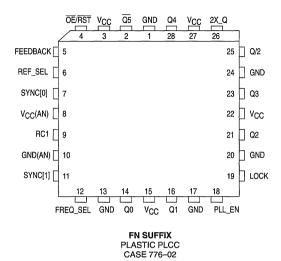

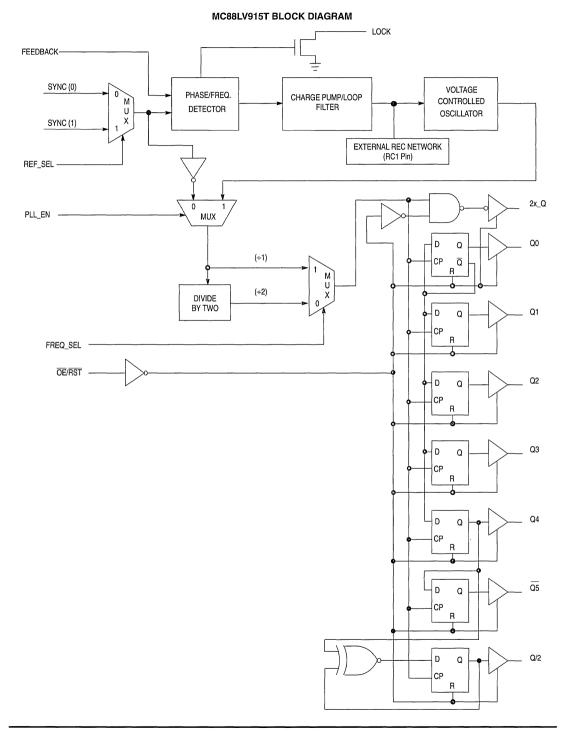

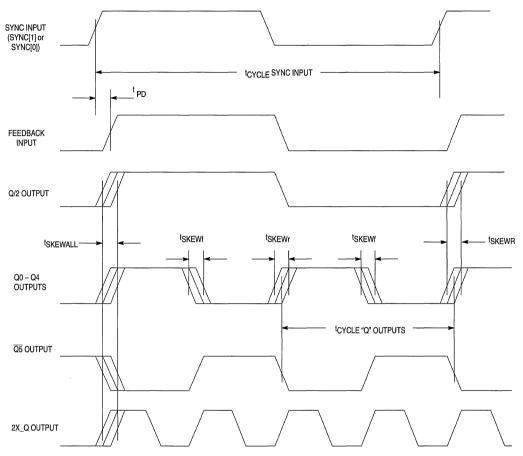

| MC88LV915T       | LVCMOS          | 0.5                                   | 100                       | 7                      | 1             | 28 PLCC             | 3.3V PLL                     |

| MC88LV926        | LVCMOS          | 0.5                                   | 66                        | 4                      | 1             | 20 F LOC<br>20 SOIC | 3.3V PLL                     |

| MPC903/904/905   | LVCMOS          | 0.4                                   | 66                        | 6                      |               | 16 SOIC             | 3.3V Osc/Buffer              |

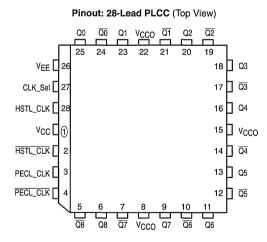

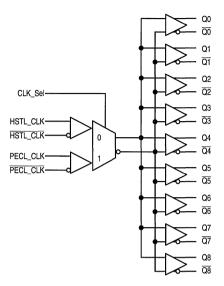

| MPC911           | HSTL            | 0.05                                  | 200                       | 9                      |               | 28 PLCC             | 3.3V Fanout Buffer           |

| MPC930/931       | LVCMOS          | 0.3                                   | 125                       | 5                      |               | 32 TQFP             | 3.3V PLL                     |

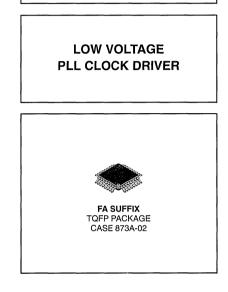

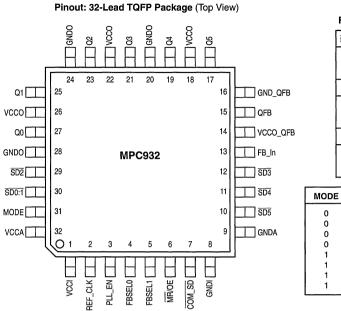

| MPC932           | LVCMOS          | 0.35                                  | 125                       | 5                      |               | 32 TQFP<br>32 TQFP  | 3.3V PLL                     |

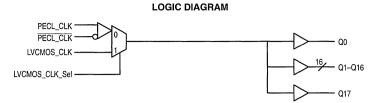

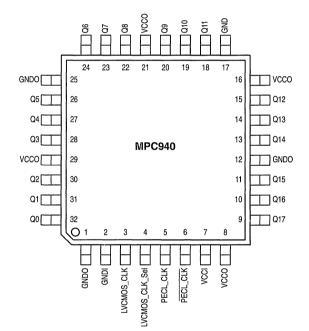

| MPC940           | LVCMOS          | 0.35                                  | 200                       | 18                     |               | 32 TQFP<br>32 TQFP  | 1:18 Fanout Buffer           |

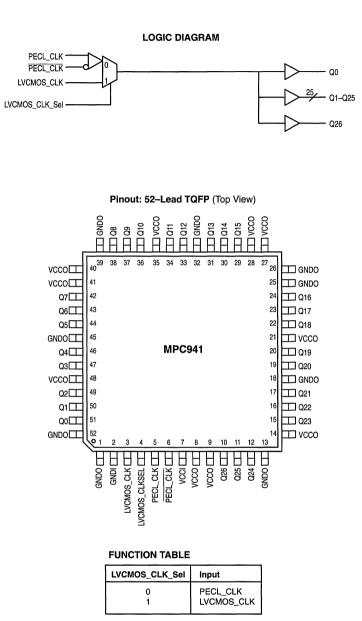

| MPC940<br>MPC941 | LVCMOS          |                                       | 200                       | 27                     |               |                     |                              |

|                  |                 | 0.25                                  |                           |                        |               | 52 TQFP             | 1:27 Fanout Buffer           |

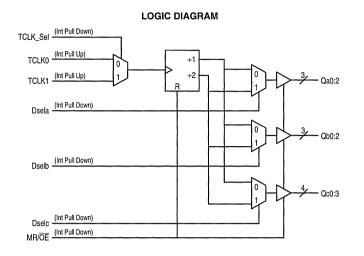

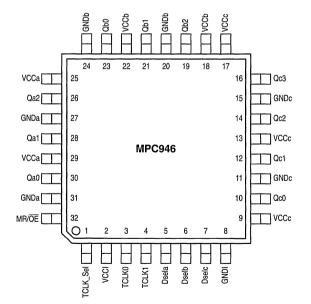

| MPC946           | LVCMOS          | 0.35                                  | 150                       | 10                     |               | 32 TQFP             | 3.3V +1,+2 Outputs           |

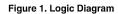

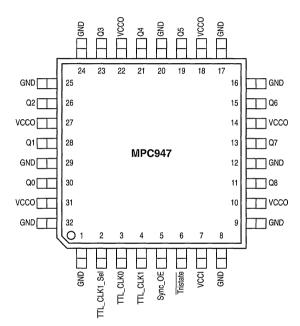

| MPC947           | LVCMOS          | 0.5                                   | 100                       | 9                      |               | 32 TQFP             | 3.3V Fanout Buffer           |

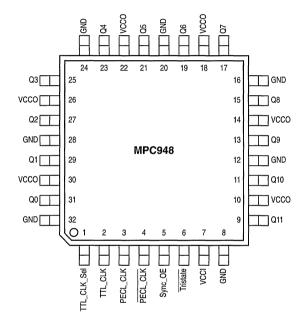

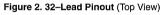

| MPC948           | LVCMOS          | 0.35                                  | 150                       | 12                     |               | 32 TQFP             | 3.3V Fanout Buffer           |

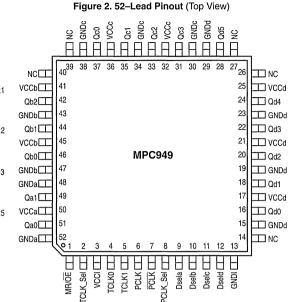

| MPC949           | LVCMOS          | 0.35                                  | 150                       | 15                     |               | 52 TQFP             | 3.3V +1,+2 Outputs           |

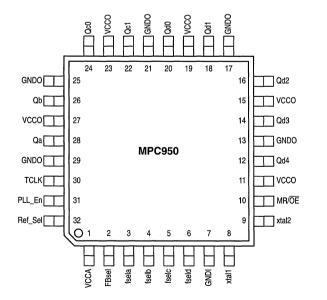

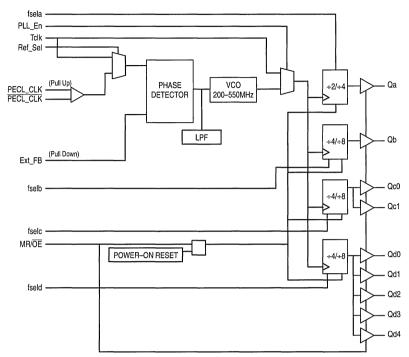

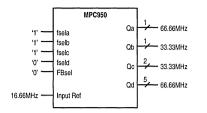

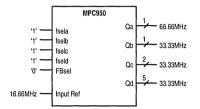

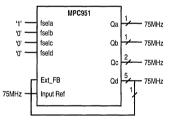

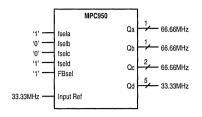

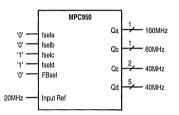

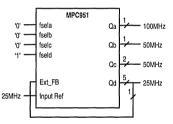

| MPC950/951       | LVCMOS          | 0.35                                  | 200                       | 9                      |               | 32 TQFP             | 3.3V PLL                     |

| MPC952           | LVCMOS          | 0.35                                  | 180                       | 11                     |               | 32 TQFP             | 3.3V PLL                     |

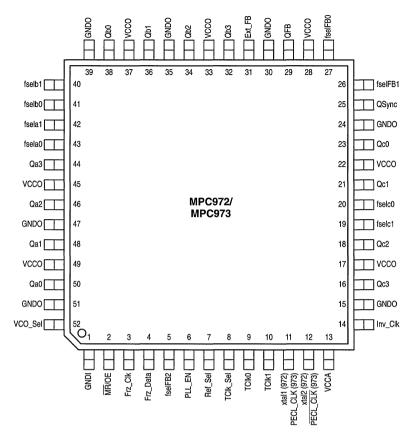

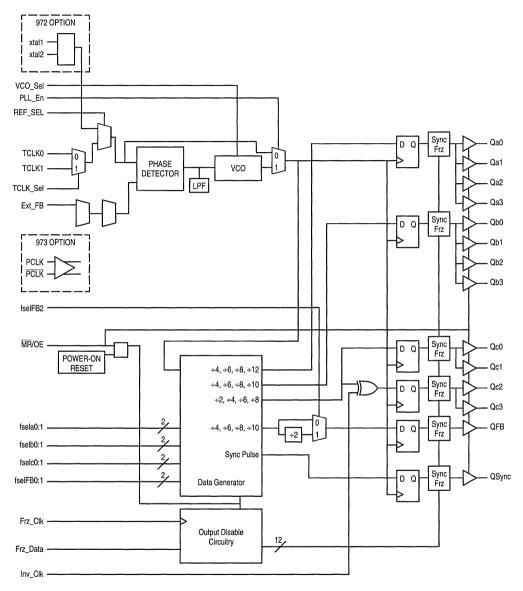

| MPC970/971       | LVCMOS          | 0.35                                  | 250                       | 13                     |               | 52 TQFP             | 3.3V PLL                     |

| MPC972/973       | LVCMOS          | 0.35                                  | 180                       | 14                     |               | 52 TQFP             | 3.3V PLL                     |

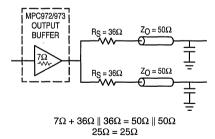

| MPC974           | LVCMOS          | 0.35                                  | 125                       | 15                     |               | 52 TQFP             | 3.3V PLL                     |

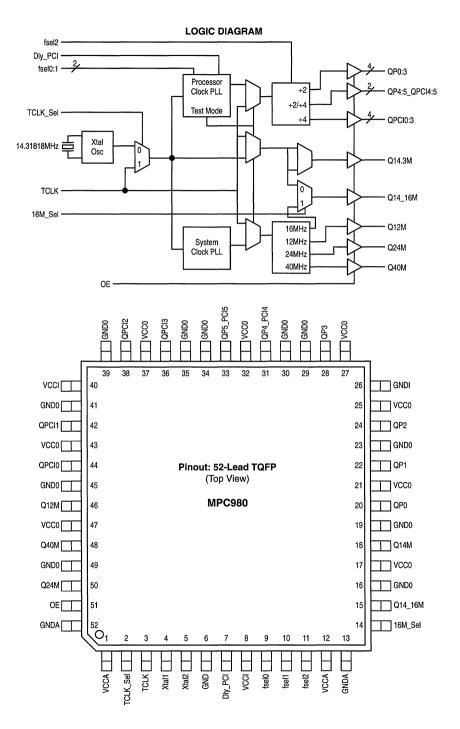

| MPC980           | LVCMOS          | 0.5                                   | 66                        | 10                     |               | 52 TQFP             | 3.3V Dual PLL                |

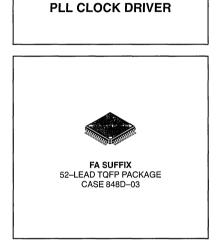

| MPC990/991       | LVECL/LVPECL    | 0.1                                   | 400                       | diff 14/pairs          |               | 52 TQFP             | 3.3V PLL                     |

| MPC992           | LVECL/LVPECL    | 0.1                                   | 100                       | diff 7/pairs           |               | 32 TQFP             | 3.3V PLL                     |

| MPC9108          | CMOS            | N/A                                   | 50                        | 1                      |               | 8 SOIC              | 5V Clock Gen                 |

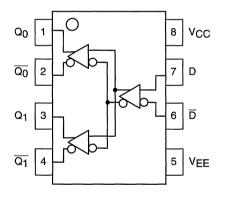

| MC10/100EL11     | ECL             | 0.02                                  | 1000                      | diff 2/pairs           |               | 8 SOIC              | PECL/ECL Inputs (Note 2.)    |

| MC10/100EL15     | ECL             | 0.05                                  | 600                       | diff 4/pairs           |               | 16 SOIC             | MUXed Test CLK Input         |

| MC10/100E111     | ECL             | 0.05                                  | 600                       | diff 9/pairs           |               | 28 PLCC             | PECL/ECL Inputs (Note 2.)    |

| MC10/100E211     | ECL             | 0.075                                 | 1000                      | diff 6/pairs           |               | 28 PLCC             | Indiv. Sync Enable           |

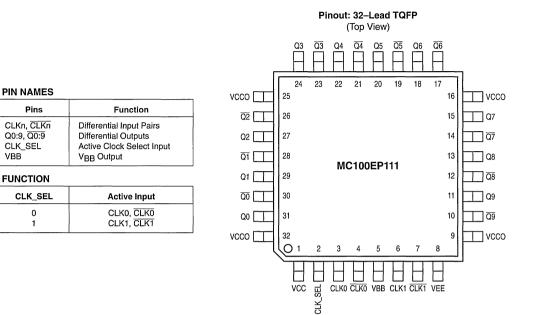

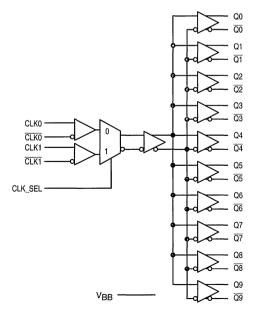

| MC100EP111       | LVECL           | 0.035                                 | 1500                      | diff 10/pairs          |               | 32 TQFP             | 1:10 Fanout Buffer           |

| MC100EP221       | LVECL           | 0.050                                 | 1500                      | diff 20/pairs          |               | 52TQFP              | 1:20 Fanout Buffer           |

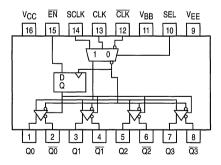

| MC100LVEL/EL13   | LVECL           | 0.05                                  | 600                       | diff 6/pairs           |               | 20 SOIC             | 3.3V Dual 1:3 Fanout         |

| MC100LVEL/EL14   | LVECL           | 0.05                                  | 600                       | diff 10/pairs          |               | 20 SOIC             | 3.3V 1:5 Fanout              |

| MC100LVE111      | LVECL           | 0.05                                  | 600                       | diff 9/pairs           |               | 28 PLCC             | 3.3V PECL/ECL                |

| MC100LVE/E210    | LVECL           | 0.05                                  | 600                       | diff 9/pairs           |               | 28 PLCC             | 3.3V Dual 1:4,1:5 Fanout     |

| MC100LVE222      | LVECL           | 0.05                                  | 600                       | diff 15/pairs          |               | 52 TQFP             | 3.3V Dual 1:15,+1, +2 Fanout |

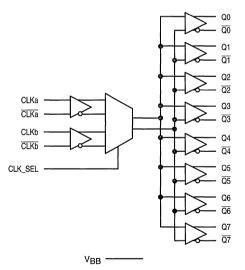

| MC100LVE/E310    | LVECL           | 0.05                                  | 600                       | diff 8/pairs           |               | 28 PLCC             | 3.3V 2:8 Fanout              |

| MC12429          | LVPECL          |                                       | 400                       | diff 1/pair            |               | 28 PLCC             | Clock Generator              |

| MC12430          | LVPECL          |                                       | 800                       | diff 1/pair            |               | 28 PLCC             | Clock Generator              |

| MC12439          | LVPECL          |                                       | 800                       | diff 1/pair            |               | 28 PLCC             | Clock Generator              |

|                  |                 |                                       |                           |                        | L             |                     |                              |

1. Within device skew.

2. PECL = Positive ECL (ECL levels referenced to +5.0V).

# Low Skew Clock Drivers and Their System Design Considerations

Prepared by Chris Hanke CMOS Design Engineering Gary Tharalson CMOS/ITTL Product Planning Management

This application note addresses various system design issues to help ensure that Motorola's low skew clock drivers are used effectively in a system environment.

### Low Skew Clock Drivers and Their System Design Considerations

#### ABSTRACT

Several varieties of clock drivers with 1ns or less skew from output-to-output are available from Motorola. Microprocessor-based systems are now running at 33MHz and beyond, and system clock distribution at these frequencies mandate the use of low skew clock drivers. Unfortunately, just plugging a high performance clock driver into a system does not guarantee trouble free operation. Only careful board layout and consideration of system noise issues can guarantee reliable clock distribution. This application note addresses these system design issues to help ensure that Motorola's low skew clock drivers are used effectively in a system environment.

#### INTRODUCTION

With frequencies regularly reaching 33MHz and approaching 40-50MHz in today's CISC and RISC microprocessor systems, well controlled and precise clock signals are required to maintain a synchronous system. Many microprocessors also require input clock duty cycles very close to 50%. These stringent timing requirements mandate the use of specially designed, low skew clock distribution circuits or 'clock drivers.' However, just plugging one of these parts into your board does not ensure a trouble free system. Careful system and board design techniques must be used in conjunction with a low skew clock driver to meet system timing requirements and provide clean clock signals.

#### Why are Low Skew Clock Drivers Necessary

An MPU system designer wants to utilize as much of a clock cycle as possible without adding unnecessary timing guardbands. Propagation delays of peripheral logic do not scale with frequency. Therefore, as the clock period decreases, the system designer has less time but the same logic delays to accomplish the function. How can he get more time? A viable option is to use a special clock source that minimizes clock 'uncertainty.'

A simple example illustrates this concept. At 33MHz, T<sub>Cycle</sub> = 30ns. An FCT240A, for example, has a High-Low uncertainty of the min/max spread of tp<sub>LH</sub> to tp<sub>HL</sub> of approximately 3.3ns. If 1.7ns of pin-to-pin skew due to the actual part and PCB trace delays is also considered, then only 25ns of the clock period is still available. The worst case tp of clock-to-data valid on the 88200 M-Bus is 12ns, which leaves only 13ns to accomplish additional functions. In this case 17% of a cycle is required for clock distribution or clock 'uncertainty,' which is an unacceptable penalty from a system designer's point of view. At 50MHz this penalty becomes 25%. A maximum of 10% of the period allotted for clock distribution is an acceptable standard.

If multiple levels of clock distribution (one clock driver's output feeding the inputs of several other clock drivers) are

necessary due to large clock fan-outs, the additional part-to-part skew variations add even more to the clock uncertainty. Standard logic has always been specified with a large (and conservative) delta between the minimum and maximum propagation delays. This delta creates the excessive amount of clock 'uncertainty' which the system designer has been forced to design into his system, even though it is not realistic. When system frequencies were below 16MHz this large clock penalty could be tolerated, but as the above example points out, not anymore. A clock driver's specs *guarantee* this min/max delta to be a specific, small value. To reduce the clock overhead to manageable levels, a clock driver with minimal variation (<5%) from a 50% duty cycle and guaranteed low output-to-output and part-to-part skew must be used.

#### DEFINITIONS

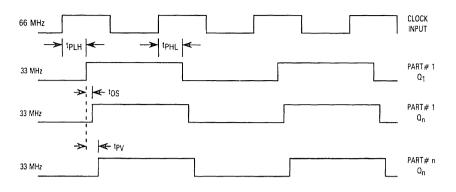

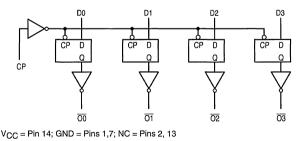

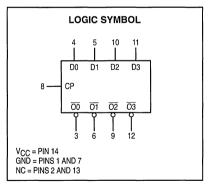

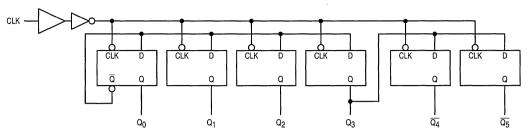

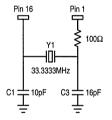

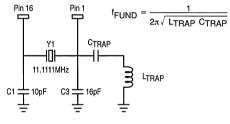

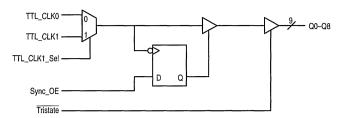

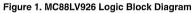

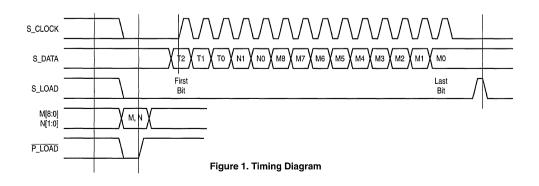

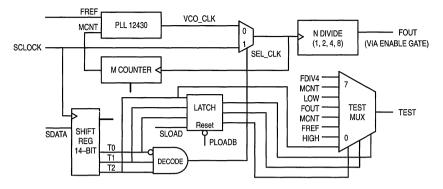

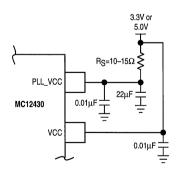

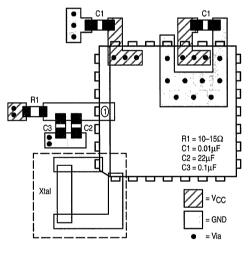

A typical clock driver has a single input which is usually driven by a crystal oscillator. The clock driver can have any number of outputs which have a certain frequency relationship to the clock input. Clock driver skew is typically defined by three different specs. These specs are graphically illustrated in Figure 1.

The first spec,  $t_{OS}$ , measures the difference between the fastest and slowest propagation delays (any transition) between the outputs of a single part. This number must be 1ns or less for high-end systems.

The second, tpS, measures the difference between the high-to-low and low-to-high transition for a single output (pin). This spec defines how close to a 50% duty cycle the outputs of the clock driver will be. For example, if this spec is 1ns ( $\pm 0.5ns$ ), at 33MHz the output duty cycle is 50%  $\pm 3.5\%$ . A clock driver which only buffers the crystal input, creating a 1:1 input to output frequency relationship, can be a problem if a very tight tolerance to a 50% duty cycle is required. In this situation the output duty cycle is directly dependent on the input duty cycle, which is not well controlled in most crystal oscillators. The clock driver's outputs switching at half the input frequency (+2) is a common relationship, which means that the outputs switch on only one edge of the oscillator, eliminating the output's dependence on the duty cycle of the input (crystal oscillator frequency is very stable).

The third spec, tpy, measures the maximum propagation delay delta between any given pin on any part. This spec defines the part to part variation between any clock driver (of the same device type) which is ever shipped. This number reflects the process variation inherent in any technology. For CMOS, this spec is usually 3ns or less. High performance ECL technologies can bring this number down into the 1-2ns range. Another way to minimize the part-to-part variation is to use a phase-locked loop clock driver, which are just now becoming available.

tpv measures the maximum difference between any tpHL or tpLH between any output on any part.

An important consideration when designing a clock driver into a system is that the skew specs described above are usually specified at a fixed, lumped capacitive load. In a real system environment the clock lines usually have various loads distributed over several inches of PCB trace which can contribute additional delay and sometimes act like transmission lines, so the system designer must use careful board layout techniques to minimize the total system skew. In other words, just plugging a low skew clock driver into a board will not solve all your timing problems.

#### **DESIGN CONSIDERATIONS**

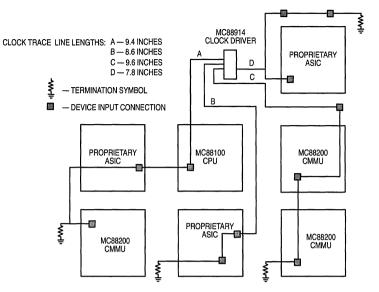

Figure 2 is a scale replication of a section of an actual 88000 RISC system board layout. The section shown in the figure includes the MC88100 MPU and the MC88200 CMMU devices and the MC88914 CMOS clock driver. The only PCB traces shown are the clock output traces from the MC88914 to the various loads. For this clock driver the output-to-output skew ( $t_{OS}$ ) is guaranteed to be less than 1ns at any given temperature, supply voltage, and fixed load up to 50 pF.

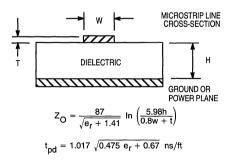

In calculating the total system skew, the difference in clock PCB trace length and loading must be taken into account. For an unloaded PCB trace, the signal delay per unit length, tpp, is dependent only on the dielectric constant,  $e_r$ . of the board material. The characteristic impedance, Z<sub>O</sub>, of the line is dependent upon  $e_r$  and the geometry of the trace. These relationships are depicted in Figure 3 for a microstrip line. 1 The formulas for tpp and Z<sub>O</sub> are slightly different for other types of strip lines, but for simplicity's sake all calculations in this article will assume a microstrip line.

The equations in Figure 3 are valid only for an unloaded trace; loading down a line will increase its delay and lower its impedance. The signal propagation delay (tpD') and characteristic impedance (ZO') due to a loaded trace are calculated by the following formulas:

$$t_{PD}' = t_{PD} \sqrt{1 + \frac{C_d}{C_O}}$$

$$Z_O' = \frac{Z_O}{\sqrt{1 + \frac{C_d}{C_O}}}$$

$C_d$  is the distributed load capacitance per unit length, which is the total input capacitance of the receiving devices divided by the length of the trace.  $C_O$  is the intrinsic capacitance of the trace, which is defined as:

$$C_{O} = \frac{t_{PD}}{Z_{O}}$$

Assuming typical microstrip dimensions and characteristics as w = 0.01 in, t = 0.002in, h = 0.012in, and  $e_r$  = 4.7, the equations of Figure 3 yield  $Z_O$  = 69.4 $\Omega$  and tpD = 0.144ns/in CO is then calculated as 2.075pF/in. If it is assumed that an MC88100 or 88200 clock input load is 15pF, and that two of these loads, in addition to a 7pF FAST TTL load, are distributed along a 9.6in clock trace,

$$C_d = (2 \times 15 + 7)pF/9.6in = pF/in.$$

The loaded trace propagation delay and characteristic impedance are then calculated as

$$t_{PD}$$

= 0.243ns/in and  $Z_{O}$  = 41 $\Omega$ .

Looking at trace C in Figure 2, the two MC88200's are approximately 3 inches apart. Using the calculated value of tpD', the clock signal skew due to the trace is about 0.7ns. Since these two devices are on the same trace, this is the total clock skew between these devices. Upon careful inspection of all the clock traces, it can be seen that clock signal skew was accounted for and minimized on this board layout. The longest

Figure 2. Scale Representation of an Actual 88000 System PCB Layout (Only sections of the board related to the clock driver outputs are shown.)

distance between any 88K devices on a single clock trace is about 4.5 inches, which translates to approximately 1.1ns of skew. The two 88K devices farthest away from the clock driver (traces a and c), are located at almost exactly the same distance along their respective traces, making the clock skew between them the 1ns guaranteed from output to output of the clock driver. This means that the worst case clock skew between any two devices on this board is approximately 2.1ns, which at 33MHz is 7% of the period. Without careful attention to matching the clock traces on the board, this number could easily exceed 3ns and the 10% cut-off point, even if a low skew clock driver is used.

#### WHERE:

$e_r$  = Relative Dielectric Constant of the Board Material w, h, t = Dimensions Indicated in a Microstrip Diagram

Figure 3. Formulas for the Characteristic Impedance and Propagation Delay of a Microstrip Line (Ref 1)

#### **CLOCK SIGNAL TERMINATIONS**

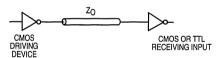

Transmission line effects occur when a large mismatch is present between the characteristic impedance of the line and the input or output impedances of the receiving or driving device. The basic guidelines used to determine if a PCB trace needs to be examined for transmission line effects is that if the smaller of the driving device's rise or fall time is less than three times the propagation delay of a switching wave through a trace, the transmission line effects will be present.<sup>2</sup> This relationship can be stated in equation form as:<sup>3</sup>

#### 3 X tpD' X trace length ≤ tRISE or tFALL

For the MC88914 CMOS clock driver described in this article, rise and fall times are typically 1.5ns or less (from 20% to 80% of V<sub>CC</sub>). Analyzing the clock trace characteristics presented earlier for transmission line effects,  $3 \times 0.243$ ns/in x trace length  $\leq 1$ ns (1ns is used as 'fastest' rise or fall time). Therefore the trace length must be less than 1.5 inches for the transmission line effects to be masked by the rise and fall times.

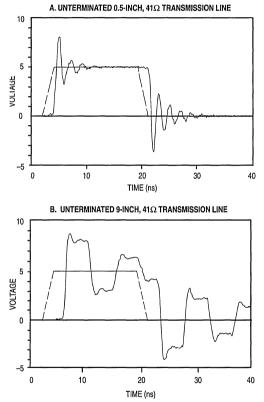

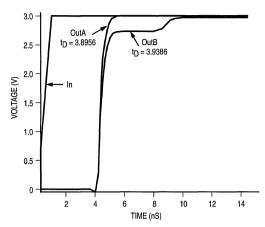

Figure 4 shows the clock signal waveform seen at the receiver end of an unterminated 0.5 inch trace and an unterminated 9 inch trace. These results were obtained using SPICE simulations. which may not be exact, but are adequate to predict trends and for comparison purposes. The 9 inch trace, which is well beyond the 1.5 inch limit where transmission line effects come into play, exhibits unacceptable switching characteristics caused by reflections going back and forth on the trace. Even the 0.5 inch line exhibits substantial overshoot and undershoot. Any unterminated line will exhibit some overshoot and undershoot at these edge rates.

Clock lines shorter than 1-1.5 inches are unrealistic on a practical board layout, therefore it is recommended that CMOS clock lines be terminated if the driver has 1-2ns edge rates. Termination, which is used to more closely match the line to the load or source impedances, has been a fact of life in the ECL world for many years (reference 1 is an excellent source for transmission line theory and practice in ECL systems), but CMOS and TTL devices have only recently reached the speeds and edge rates which require termination. CMOS outputs further complicate the issue by driving from rail to rail (5 V), with slew rates exceeding those of high performance ECL devices.

Figure 4. SPICE Simulation Results of 'Short' and 'Long' Transmission Lines. Simulations Were Run with Typical Parameters @  $25^{\circ}$ C and V<sub>CC</sub> = 5.0V

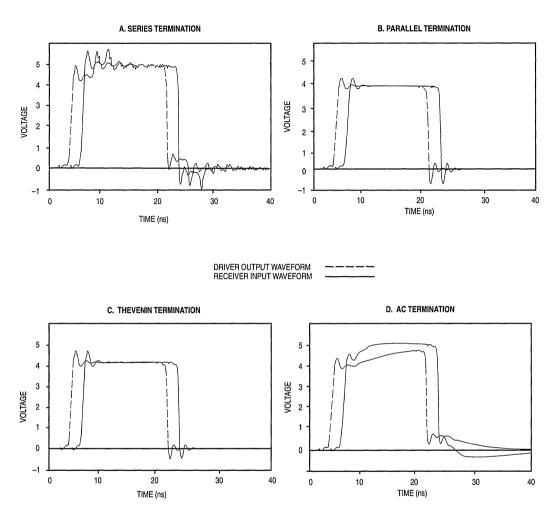

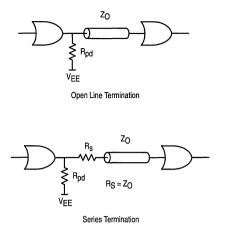

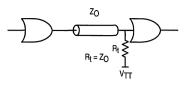

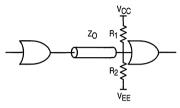

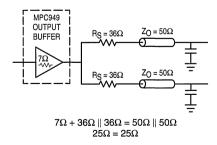

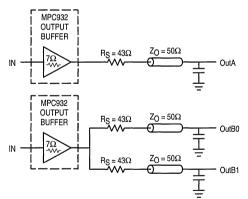

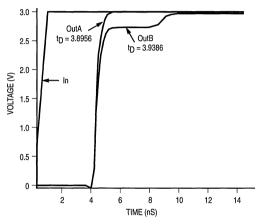

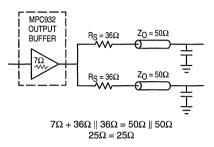

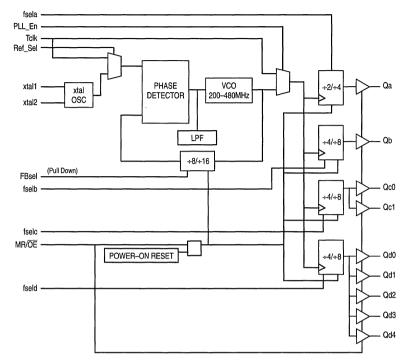

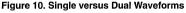

Since clock lines are only driven from a single location, they lend themselves to termination more easily than bus lines which are commonly driven from multiple locations. Termination of bus lines with multiple drivers is a complicated manner which will not be addressed in this article. The most common types of termination in digital systems are shown in Figure 5. Since no single termination scheme is optimal in all cases, the tradeoffs involving the use of each will be discussed, and recommendations specific to clock drivers will be made. Reference 2 is a comprehensive and practical treatment of transmission line theory and analysis of CMOS signals, and is recommended reading for those who want to gain a better understanding of transmission lines. Figure 6 shows SPICE simulated waveforms of the different termination schemes to be discussed. The driving device in the simulations was the MC88914 output buffer; in all simulations it drove a 9 inch 41 $\Omega$  transmission line. The simulations were run using typical model parameters at 25°C and V<sub>CC</sub> = 5V.

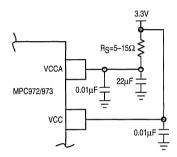

Series termination, depicted in Figure 5b, is recommended if the load is lumped at the end of the trace and the output impedance of the driving device is less than the loaded characteristic impedance of the trace, or when a minimum number of components is required. The main problem with series termination occurs when the driving device has different output impedance values in the low and high states. which is a problem in TTL and some CMOS devices. A well designed CMOS clock driver should have nearly equal output impedances in the high and low states, avoiding this problem. An additional advantage is that series termination does not create a DC current path, thus the VOL and VOH levels are not degraded. The SPICE generated waveforms of series termination in Figure 6a show that series termination effectively masks the transmission line effects exhibited in Figure 4. If each clock output is driving only one device, series termination would be recommended, but this is not a realistic case in most systems, so series termination is not generally recommended for termination of clock lines.

Parallel termination utilizes a single resistor tied to ground or V<sub>CC</sub> whose value is equal to the characteristic impedance of the line. Its major disadvantage is the DC current path it creates when the driver is in the high state (if the resistor is tied to ground). This causes excessive power dissipation and V<sub>OH</sub> level degradation. Since a clock driver output is always switching, the DC current draw argument loses some credibility at higher frequencies because the AC switching current becomes a major component of the overall current. Therefore the main consideration in parallel termination is how much V<sub>OH</sub> degradation can be tolerated by the receiving devices. Figure 6b demonstrates that this termination technique is effective in minimizing the switching noise, but Thevenin termination has some advantages over parallel termination.

Thevenin termination utilizes one resistor tied to ground and a second tied to V<sub>CC</sub>. An important consideration when using this type of termination is choosing the resistor values to avoid settling of the voltage between the high and low logic levels of the receiving device.2 TTL designers commonly use a 220/330 resistor value ratio, but CMOS is a little tricky because the switch point is at V<sub>CC</sub>/2. With a 1:1 resistor ratio a failure at the driver output would cause the line to settle at 2.5V, causing system debug problems and also potential damage to the receiving devices.

In Thevenin termination, the parallel equivalent value of the two resistors should be equal to the characteristic impedance of the line. A DC path does exist in both the high and low states, but it is not as bad as parallel termination because the resistance in the Thevenin DC path is at least 2 times greater.

#### AN1091

Figure 6c shows the termination waveforms, which exhibit characteristics similar to parallel termination, but with less  $V_{OH}$  degradation. The only real advantage of parallel over Thevenin is less resistors (1/2 as many) and less space taken up on the board by the resistors. If this is not a factor, Thevenin termination is recommended over parallel.

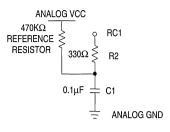

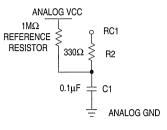

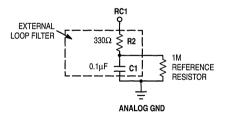

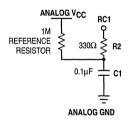

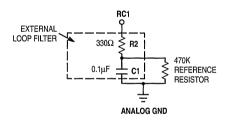

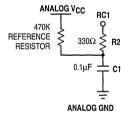

AC termination, shown in Figure 5e, normally utilizes a resistor and capacitor in series to ground. The capacitor blocks DC current flow, but allows the AC signal to flow to ground during switching. The RC time constant of the resistor and capacitor must be greater than twice the loaded line delay. AC termination is recommended because of its low power dissipation and also because of the availability of the resistor and capacitor in single-in-line packages (SIP). A pullup resistor to V<sub>CC</sub> is sometimes added to set the DC level at a certain point because of the failure condition described in regards to Thevenin termination. As discussed earlier, the argument of lower DC current is less convincing at high frequencies. The AC terminated waveform walks out slightly toward the end of a high-to-low or low-to-high transition as seen in Figure 6d, making it slightly less desirable than Thevenin termination.

Thevenin and AC termination are the two recommended termination schemes for clock lines, but it depends on what frequency the clock is running at when making a decision between these types of termination. Although hard data is not provided to back this statement up, it is a safe assumption that at frequencies of 25 MHz and below AC is the best choice. If the system frequency could reach 40 MHz and beyond, Thevenin becomes the better choice.

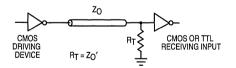

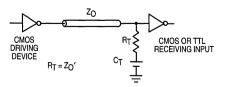

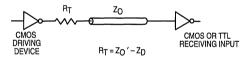

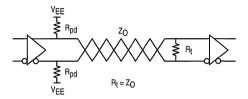

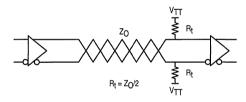

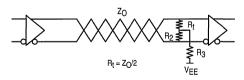

A. TRANSMISSION LINE WITH NO TERMINATION

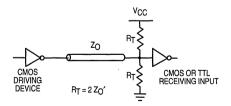

C. TRANSMISSION LINE WITH PARALLEL TERMINATION

E. TRANSMISSION LINE WITH AC TERMINATION

#### ADDITIONAL CONSIDERATIONS WHEN TERMINATING CLOCK LINES

The results presented might imply that terminating the clock lines will completely solve noise problems, but termination can cause secondary problems with some logic devices. Termination acts to reduce the noise seen at the receiver, but that noise actually is seen as additional current and noise at the output of the driving device. If the internal and input logic on the source device is not sufficiently decoupled on chip from the high current outputs, internal threshold problems can occur. This phenomenon is commonly known as 'dynamic threshold.' It is usually evidenced by glitches appearing on the outputs of a fast, high current drive logic device as it switches high or low. This is most severe on 'ACT' devices which have high current and high slew rate CMOS outputs along with TTL inputs which have low noise immunity. This problem can be minimized by decoupling the internal ground and V<sub>CC</sub> supplies on-chip and in the package. This decoupling is accomplished by having separate 'quiet' ground and V<sub>CC</sub> pads on chip which supply the input circuitry's ground and VCC references. These pads are then tied to extra 'quiet' ground and 'quiet' VCC pins on the package, or to special 'split leads' which resemble a tuning fork and utilize the leadframe inductance to accomplish the decoupling. When choosing a clock source, make sure that the part has one of these decoupling schemes.

#### References

- Blood, William R., MECL System Design Handbook, Motorola Inc., 1983.

- Application Note AN1051, Transmission Line Effects in PCB Applications, Motorola Inc., 1990.

- 3. Motorola FACT Data Book DL138, Motorola Inc., 1990.

WHERE, ZD = DRIVING DEVICE OUTPUT IMPEDANCE

B. TRANSMISSION LINE WITH SERIES TERMINATION

D. TRANSMISSION LINE WITH THEVENIN TERMINATION

#### Figure 5. Schematic Representation of Common Termination Techniques

Figure 6. SPICE Simulation Results for Various Terminations of a 9-Inch 41 $\Omega$  Transmission Line. Simulations Were Run with Typical Model Parameters @ 25°C and V<sub>CC</sub> = 5.0V

9

# **ECL Clock Distribution Techniques**

Prepared by Todd Pearson ECL Applications Engineering

This application note provides information on system design using ECL logic technologies for reducing system clock skew over the alternative CMOS and TTL technologies.

### **ECL Clock Distribution Techniques**

#### INTRODUCTION

The ever increasing performance requirements of today's systems has placed an even greater emphasis on the design of low skew clock generation and distribution networks. Clock skew, the difference in time between "simultaneous" clock transitions within a system, is a major component of the constraints which form the upper bound for the system clock frequency. Reductions in system clock skew allow designers to increase the performance of their designs without having to resort to more complicated architectures or more costly, faster logic. ECL logic technologies offer a number of advantages for reducing system clock skew over the alternative CMOS and TTL technologies.

#### SKEW DEFINITIONS

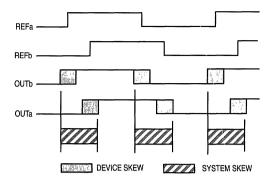

The skew introduced by logic devices can be divided into three parts: duty cycle skew, output-to-output skew and part-to-part skew. Depending on the specific application, each of the three components can be of equal or overriding importance.

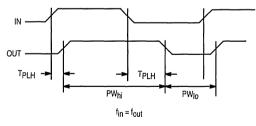

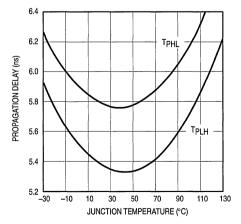

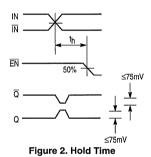

#### **Duty Cycle Skew**

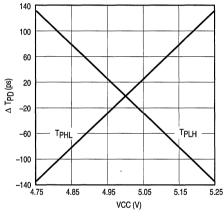

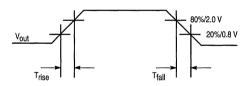

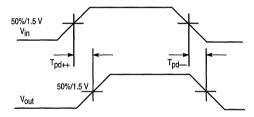

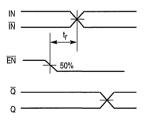

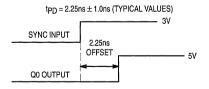

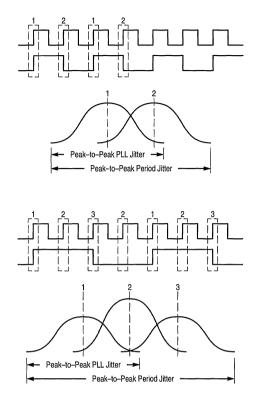

The duty cycle skew is a measure of the difference between the TPLH and TPHL propagation delays (Figure 1). Because differences in TPLH and TPHL will result in pulse width distortion the duty cycle skew is sometimes referred to as pulse skew. Duty cycle skew is important in applications where timing operations occur on both edges or when the duty cycle of the clock signal is critical. The later is a common requirement when driving the clock inputs of advanced microprocessors.

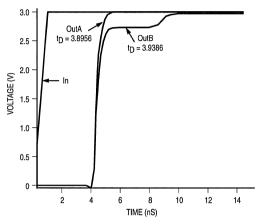

Figure 1. Duty Cycle Skew

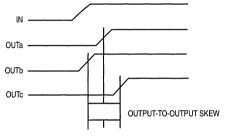

#### **Output-to-Output Skew**

Output-to-output skew is defined as the difference between the propagation delays of all the outputs of a device. A key constraint on this measurement is the requirement that the output transitions are identical, therefore if the skew between all edges produced by a device is important the output-to-output skew would need to be added to the duty cycle skew to get the total system skew. Typically the output-to-output skew will be smaller than the duty cycle skew for TTL and CMOS devices. Because of the near zero duty cycle skew of a differential ECL device the output-to-output skew will generally be larger. The output-to-output skew is important in systems where either a single device can provide all of the necessary clocks or for the first level device of a nested clock distribution tree. In these two situations the only parameter of importance will be the relative position of each output with respect to the other outputs on that die. Since these outputs will all see the same environmental and process conditions the skew will be significantly less than the propagation delay windows specified in the standard device data sheet.

Figure 2. Output-to-Output Skew

#### Part-to-Part Skew

The part-to-part skew specification is by far the most difficult performance aspect of a device to minimize. Because the part-to-part skew is dependent on both process variations and variations in the environment the resultant specification is significantly larger than for the other two components of skew. Many times a vendor will provide subsets of part-to-part skew specifications based on non-varying environmental conditions. Care should be taken in reading data sheets to fully understand the conditions under which the specified limits are guaranteed. If the part-to-part skew is specified and is different than the specified propagation delay window for the device one can be assured there are constraints on the part-to-part skew specification.

Power supply and temperature variations are major contributors to variations in propagation delays of silicon devices. Constraints on these two parameters are commonly seen in part-to-part skew specifications. Although there are situations where the power supply variations could be ignored, it is difficult for this author to perceive of a realistic system whose devices are all under identical thermal conditions. Hot spots on boards or cabinets, interruption in air flow and variations in IC density of a board all lead to thermal gradients within a system. These thermal gradients will guarantee that devices in various parts of the system are under different junction temperature conditions. Although it is unlikely that a designer will need the entire commercial temperature range, a portion of this range will need to be considered. Therefore, a part-to-part skew specified for a single temperature is of little use, especially if the temperature coefficient of the propagation delay is relatively large.

For designs whose clock distribution networks lie on a single board which utilizes power and ground planes an assumption of non-varying power supplies would be a valid assumption and a specification limit for a single power supply would be valuable. If, however, various pieces of the total distribution tree will be on different boards within a system there is a very real possibility that each device will see different power supply levels. In this case a specification limit for a fixed V<sub>CC</sub> will be inadequate for the design of the system. Ideally the data sheets for clock distribution devices should include information which will allow designers to tailor the skew specifications of the device to their application environment.

#### SYSTEM ADVANTAGES OF ECL

#### Skew Reductions

ECL devices provide superior performance in all three areas of skew over their TTL or CMOS competitors. A skew reducing mechanism common to all skew parameters is the faster propagation delays of ECL devices. Since, to some extent, all skew represent a percentage of the typical delays faster delays will usually mean smaller skews. ECL devices, especially clock distribution devices, can be operated in either single-ended or differential modes. To minimize the skew of these devices the differential mode of operation should be used, however even in the single-ended mode the skew performance will be significantly better than for CMOS or TTL drivers.

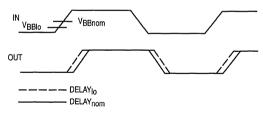

Figure 3. VBB Induced Duty Cycle Skew

ECL output buffers inherently show very little difference between TPLH and TPHL delays. What differences one does see are due mainly to switching reference levels which are not ideally centered in the input swing (see Figure 3). For worst case switching reference levels the pulse skew of an ECL device will still be less than 300ps. If the ECL device is used differentially the variation in the switching reference will not impact the duty cycle skew as it is not used. In this case the pulse skew will be less than 50ps and can generally be ignored in all but the highest performance designs. The problem of generating clocks which are capable of meeting the duty cycle requirements of the most advanced microprocessors, would be a trivial task if differential ECL compatible clock inputs were used. TTL and CMOS clock drivers on the other hand have inherent differences between the TPLH and TPHL delays in addition to the problems with non-centered switching thresholds. In devices specifically designed to minimize this parameter it generally cannot be guaranteed to anything less than 1ns.

The major contributors to output-to-output skew is IC layout and package choice. Differences in internal paths and paths through the package generally can be minimized regardless of the silicon technology utilized at the die level, therefore ECL devices offer less of an advantage in this area than for other skew parameters. CMOS and TTL output performance is tied closely to the power supply levels and the stability of the power busses within the chip. Clock distribution trees by definition always switch simultaneously, thus creating significant disturbances on the internal power busses. To alleviate this problem multiple power and ground pins are utilized on TTL and CMOS clock distribution devices. However even with this strategy TTL and CMOS clock distribution devices are limited to 500ps - 700ps output-to-output skew guarantees. With differential ECL outputs very little if any noise is generated and coupled onto the internal power supplies. This coupled with the faster propagation delays of the output buffers produces output-to-output skews on ECL clock chips as low as 50ps.

Two aspects of ECL clock devices will lead to significantly smaller part-to-part skews than their CMOS and TTL competitors: faster propagation delays and delay insensitivity to environmental variations. Variations in propagation delays with process are typically going to be based on a percentage of the typical delay of the device. Assuming this percentage is going to be approximately equivalent between ECL, TTL and CMOS processes, the faster the device the smaller the delay variations. Because state-of-the-art ECL devices are at least5 times faster than TTL and CMOS devices, the expected delay variation would be one fifth those of CMOS and TTL devices.

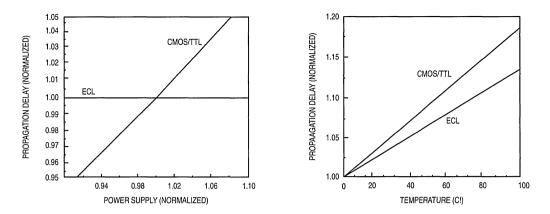

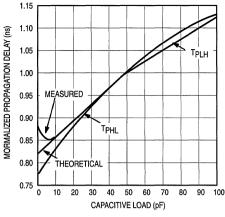

The propagation delays of an ECL device are insensitive to variations in power supply while CMOS and TTL device propagation delays vary significantly with changes in this parameter. Across temperature the percentage variation for all technologies is comparable, however, again the faster propagation delays of ECL will reduce the magnitude of the variation. Figure 4 on the following page represents normalized propagation delay versus temperature and power supply for the three technologies.

#### Low Impedance Line Driving

The clock requirements of today's systems necessitate an almost exclusive use of controlled impedance interconnect. In the past this requirement was unique to the performance levels associated with ECL technologies, and in fact precluded its use in all but the highest performance systems. However the high performance CMOS and TTL clock distribution chips now require care in the design and layout of PC boards to optimize their performance, with this criteria established the migration from these technologies to ECL is simplified. In fact, the difficulties involved in designing with these "slower" technologies in a controlled impedance environment may even enhance the potential of using ECL devices as they are ideally suited to the task.

Figure 4. TPD vs Environmental Condition Comparison

The low impedance outputs and high impedance inputs of an ECL device are ideal for driving 50 $\Omega$  to 130 $\Omega$  controlled impedance transmission lines. The specified driving impedance of ECL is 50 $\Omega$ , however this value is used only for convenience sake due to the 50 $\Omega$  impedance of most commonly used measurement equipment. Utilizing higher impedance lines will reduce the power dissipated by the termination resistors and thus should be considered in power sensitive designs. The major drawback of higher impedance lines (delays more dependent on capacitive loading) may not be an issue in the point to point interconnect scheme generally used in low skew clock distribution designs.

#### **Differential Interconnect**

The device skew minimization aspects of differential ECL have already been discussed however there are other system level advantages that should be mentioned. Whenever clock lines are distributed over long distances the losses in the line and the variations in power supply upset the ideal relationship between input voltages and switching thresholds. Because differential interconnect "carries" the switching threshold information from the source to the load the relationship between the two is less likely to be changed. In addition for long lines the smaller swings of an ECL device produce much lower levels of cross-talk between adjacent lines and minimizes EMI radiation from the PC board.

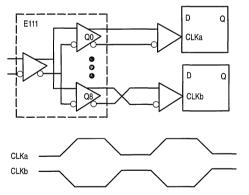

There is a cost associated with fully differential ECL, more pins for equivalent functions and more interconnect to be laid on a typically already crowded PC board. The first issue is really a non-issue for clock distribution devices. The output-to-output and duty cycle skew are very much dependent on quiet internal power supplies. Therefore the pins sacrificed for the complimentary outputs would otherwise have to be used as power supply pins, thus functionality is actually gained for an equivalent pin count as the inversion function is also available on a differential device. The presence of the inverted signal could be invaluable for a design which clocks both off the positive and negative edges. Figure 5 shows a method of obtaining very low skew (<50ps) 180° shifted two phase clocks.

It is true that differential interconnect requires more signals to be routed on the PC board. Fortunately with the wide data and address buses of today's designs the clock lines represent a small fraction of the total interconnect. The final choice as to whether or not to use differential interconnect lies in the level of skew performance necessary for the design. It should be noted that although single-ended ECL provides less attractive skew performance than differential ECL, it does provide significantly better performance than equivalent CMOS and TTL functions.

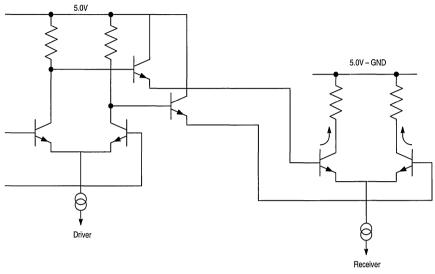

Figure 5. 180° Shifted Two Phase Clocks

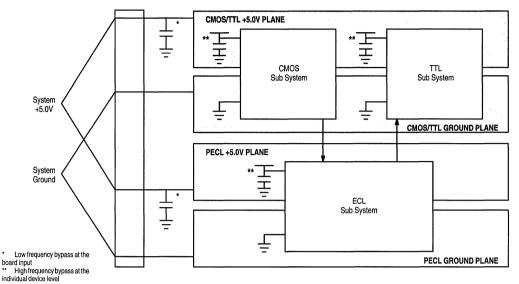

#### USING ECL WITH POSITIVE SUPPLIES

It is hard to argue with the clock distribution advantages of ECL presented thus far, but it may be argued that except for all ECL designs it is too costly to include ECL devices in the distribution tree. This claim is based on the assumption that at least two extra power supplies are required; the negative VEE supply and the negative VTT termination voltage. Fortunately both these assumptions are false. PECL (Positive ECL) is an acronym which describes using ECL devices with a positive

#### AN1405

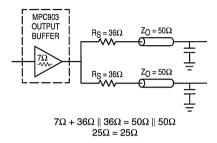

rather than negative power supply. It is important to understand that all ECL devices are also PECL devices. By using ECL devices as PECL devices on a +5 volt supply and incorporating termination techniques which do not require a separate termination voltage (series termination, thevenin equivalent) ECL can be incorporated in a CMOS or TTL design with no added cost.

The reason for the choice of negative power supplies as standard for ECL is due to the fact that all of the output levels and internal switching bias levels are referenced to the V<sub>CC</sub> rail. It is generally easier to keep the grounds quieter and equal potential throughout a system than it is with a power supply. Because the DC parameters are referenced to the V<sub>CC</sub> rail any disturbances or voltage drops seen on V<sub>CC</sub> will translate 1:1 to the output and internal reference levels. For this reason when communicating with PECL between two boards it is recommended that only differential interconnect be used. By using differential interconnect V<sub>CC</sub> variations within the specified range will not in any way affect the performance of the device.

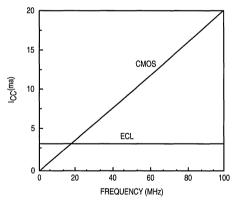

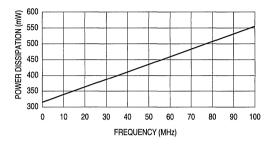

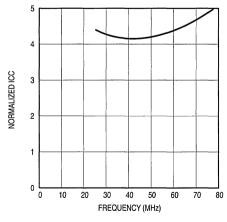

Finally mentioning ECL to a CMOS designer invariably conjures up visions of space heaters as their perception of ECL is high power. Although it is true that the static power of ECL is higher than for CMOS the dynamic power differences between the technologies narrows as the frequency increases. As can be seen in Figure 6 at frequencies as low as 20MHz the per gate power of ECL is actually less than for CMOS. Since clock distribution devices are never static it does not make sense to compare the power dissipation of the two technologies in a static environment.

Figure 6. ICC/Gate vs Frequency Comparison

#### MIXED SIGNAL CLOCK DISTRIBUTION

#### **ECL Clock Distribution Networks**

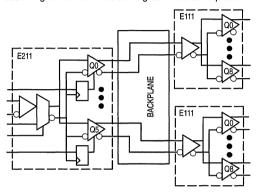

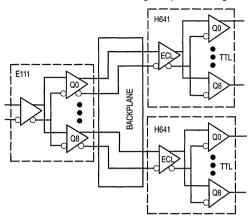

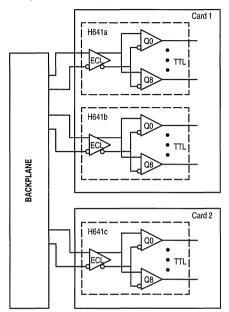

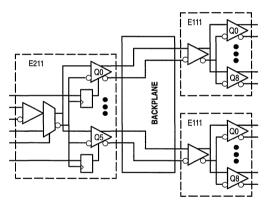

Clock distribution in a ECL system is a relatively trivial matter. Figure 7 illustrates a two level clock distribution tree which produces nine differential ECL clocks on six different cards. The ECLinPS E211 device gives the flexibility of disabling each of the cards individually. In addition the

synchronous registered enables will disable the device only when the clock is already in the LOW state, thus avoiding the problem of generating runt pulses when an asynchronous disable is used. The device also provides a muxed clock input for incorporating a high speed system clock and a lower speed test or scan clock within the same distribution tree. The ECLinPS E111 device is used to receive the signals from the backplane and distribute it on the card. The worst case skew between all 54 clocks in this situation would be 275ps assuming that all the loads and signal traces are equalized.

Figure 7. ECL Clock Distribution Tree

#### **Mixed Technology Distribution Networks**

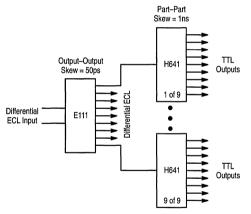

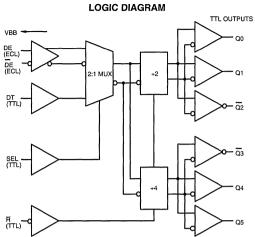

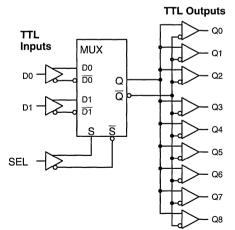

Building clock networks in TTL and CMOS systems can be a little more complicated as there are more alternatives available. For simple one level distribution trees fanout devices like the MECL 10H645 1:9 TTL to TTL fanout tree can be used. However as the number of levels of fanout increases. the addition of ECL devices in an other wise TTL or CMOS system becomes attractive. In Figure 8 on the next page an E111 device is combined with a MECL H641 device to produce 81 TTL level clocks. Analyzing the skew between the 81 clocks yields a worst case skew, allowing for the full temperature and V<sub>CC</sub> range variation, of 1.25ns. Under ideal situations, no variation in temperature or VCC supply, the skew would be only 750ps. When compared with distribution trees utilizing only TTL or CMOS technologies these numbers represent ~50% improvement, more if the environmental conditions vary to any degree. For a 50MHz clock the total skew between the 81 TTL clocks is less than 6.5% of the clock period, thus providing the designer extra margin for layout induced skew to meet the overall skew budget of the design.

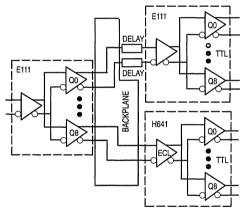

Many designers have already realized the benefits of ECL clock distribution trees and thus are implementing them in their designs. Furthermore where they have the capability, i.e. ASICs, they are building their VLSI circuits with ECL compatible clock inputs. Unfortunately other standard VLSI circuits such as microprocessors, microprocessor support chips and memory still cling to TTL or CMOS clock inputs. As a result many systems need both ECL and TTL clocks within the same system. Unlike the situation outlined in Figure 8 the ECL levels are not merely intermediate signals but rather are

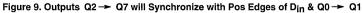

driving the clock inputs of the logic. As a result the ECL edges need to be matched with the TTL edges as pictured in Figure 9.

Figure 8. ECL to TTL Clock Distribution

Figure 9. Mixed ECL and TTL Distribution

An ECL clock driver will be significantly faster than a TTL or CMOS equivalent function. Therefore to de-skew the ECL and TTL signals of Figure 9 a delay needs to be added to the input of the ECL device. Because a dynamic delay adjust would not lend itself to most production machines a static delay would be used. The value of the delay element would be a best guess estimate of the differences in the two propagation delays. It is highly unlikely that the temperature coefficients of the propagation delays of the ECL devices, TTL devices and delay devices would be equal. Although these problems will add skew to the system, the resultant total skew of the distribution network will be less than if no ECL chips were used.

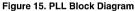

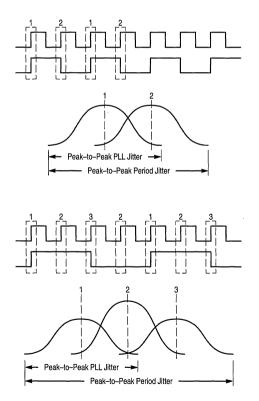

#### PLL Based Clock Drivers

A potential solution for the problem outlined in Figure 9 is in the use of phase locked loop based clock distribution chips. Because these devices feedback an output and lock it to a reference clock input the delay differences between the various technology output buffers will be eliminated. One might believe that with all of the euphoria surrounding the performance of PLL based clock distribution devices that the need for any ECL in the distribution tree will be eliminated. However when analyzed further the opposite appears to be the case.

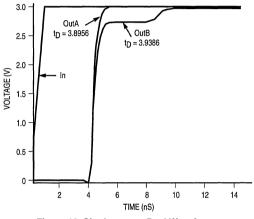

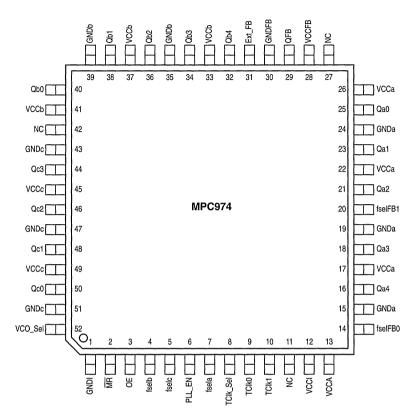

For a single board design with a one level distribution system there obviously is no need for ECL. When, however, a multiple board system is required where nested levels of devices are needed ECL once again becomes useful. One major aspect of part-to-part skew for PLL based clock chips often overlooked is the dependence on the skew of the various reference clocks being locked to. As can be seen in Figure 10 the specified part-to-part skew of the device would necessarily need to be added to the reference clock skew to get the overall skew of the clock tree. From the arguments presented earlier this skew will be minimized if the reference clock is distributed in ECL. It has not been shown as of vet where a PLL based ECL clock distribution chip can provide the skew performance of the simple fanout buffer. From a system standpoint the buffer type circuits are much easier to design with and thus given equivalent performance would represent the best alternative. The extra features provided by PLL based chips could all be realized if they were used in only the final stage of the distribution tree.

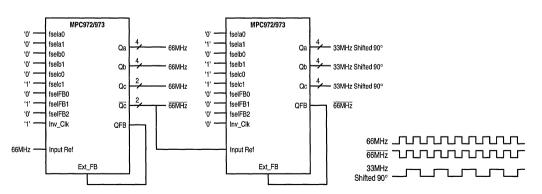

The MPC973 is a PLL based clock driver which features differential PECL reference clock inputs. When combined with the very low skew MC10E111 fanout buffer, very low skew clock trees can be realized for multiprocessor MPP designs. There will be a family of devices featuring various technology compatible inputs and outputs to allow for the building of precisely aligned clock trees based on either ECL, TTL, CMOS or differential GTL (or a mixture of all four) compatible levels.

Figure 10. System Skew For PLL Clock Distribution

#### Conclusion

The best way to maximize the performance of any synchronous system is to spend the entire clock period performing value added operations. Obviously any portion of the clock period spent idle due to clock skew limits the potential performance of the system. Using ECL technology devices in clock distribution networks will minimize all aspects of skew and thus maximize the performance of a system. Unfortunately the VLSI world is not yet ECL clock based so that the benefits of a totally ECL based distribution tree cannot be realized for many systems. However there are methods of incorporating ECL into the intermediate levels of the tree to significantly reduce the overall skew. In addition the system designers can utilize their new found knowledge to incorporate ECL compatible clocks on those VLSI chips of which they have control while at the same time pressuring other VLSI vendors in doing the same so that future designs can enjoy fully the advantages of distributing clocks with ECL.

# **Designing With PECL** (ECL at +5.0V)

Prepared by Cleon Petty Todd Pearson ECL Applications Engineering

This application note provides detailed information on designing with Positive Emitter Coupled Logic (PECL) devices.

9/92

### **Designing With PECL (ECL at +5.0V)** The High Speed Solution for the CMOS/TTL Designer

#### Introduction

PECL, or Positive Emitter Coupled Logic, is nothing more than standard ECL devices run off of a positive power supply. Because ECL, and therefore PECL, has long been the "black magic" of the logic world many misconceptions and falsehoods have arisen concerning its use. However, many system problems which are difficult to address with TTL or CMOS technologies are ideally suited to the strengths of ECL. By breaking through the wall of misinformation concerning the use of ECL, the TTL and CMOS designers can arm themselves with a powerful weapon to attack the most difficult of high speed problems.

It has long been accepted that ECL devices provide the ultimate in logic speed; it is equally well known that the price for this speed is a greater need for attention to detail in the design and layout of the system PC boards. Because this requirement stems only from the speed performance aspect of ECL devices, as the speed performance of any logic technology increases these same requirements will hold. As can be seen in Table 1 the current state-of-the-art TTL and CMOS logic families have attained performance levels which require controlled impedance interconnect for even relatively short distances between source and load. As a result system designers who are using state-of-the-art TTL or CMOS logic are already forced to deal with the special requirements of high speed logic: thus it is a relatively small step to extend their thinking from a TTL and CMOS bias to include ECL devices where their special characteristics will simplify the design task.

| Logic<br>Family | Typical Output<br>Rise/Fall | Maximum Open Line<br>Length (L <sub>max</sub> )* |

|-----------------|-----------------------------|--------------------------------------------------|

| 10KH            | 1.0ns                       | 3"                                               |

| ECLinPS         | 400ps                       | 1"                                               |

| FAST            | 2.0ns                       | 6"                                               |

| FACT            | 1.5ns                       | 4"                                               |

| Table | 1. | Relative | Logic | Speeds |

|-------|----|----------|-------|--------|

|-------|----|----------|-------|--------|

\* Approximate for stripline interconnect ( $L_{max} = T_{f}/2T_{pd}$ )

#### System Advantages of ECL

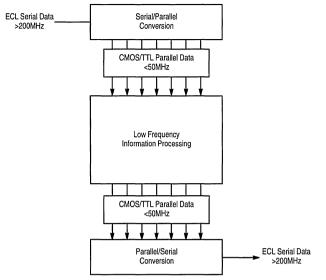

The most obvious area to incorporate ECL into an otherwise CMOS/TTL design would be for a subsystem which requires very fast data or signal processing. Although this is the most obvious it may also be the least common. Because of the need for translation between ECL and CMOS/TTL technologies the performance gain must be greater than the overhead required to translate back and forth between technologies. With typical delays of six to seven nanoseconds

for translating between technologies, a significant portion of the logic would need to be realized using ECL for the overall system performance to improve. However, for very high speed subsystem requirements ECL may very well provide the best system solution.

#### **Transmission Line Driving**

Many of the inherent features of an ECL device make it ideal for driving long, controlled impedance lines. The low impedance of the open emitter outputs and high input impedance of any standard ECL device make it ideally suited for driving controlled impedance lines. Although designed to drive  $50\Omega$  lines an ECL device is equally adept at driving lines of impedances of up to  $130\Omega$  without significant changes in the AC characteristics of the device. Although some of the newer CMOS/TTL families have the ability to drive 50Ω lines many require special driver circuits to supply the necessary currents to drive low impedance transmission interconnect. In addition the large output swings and relatively fast output slew rates of today's high performance CMOS/TTL devices exacerbate the problems of crosstalk and EMI radiation. The problems of crosstalk and EMI radiation, along with common mode noise and signal amplitude losses, can be alleviated to a great degree with the use of differential interconnect. Because of their architectures, neither CMOS nor TTL devices are capable of differential communication. The differential amplifier input structure and complimentary outputs of ECL devices make them perfectly suited for differential applications. As a result, for systems requiring signal transmission between several boards, across relatively large distances, ECL devices provide the CMOS/TTL designer a means of ensuring reliable transmission while minimizing EMI radiation and crosstalk.

Figure 1 shows a typical application in which the long line driving, high bandwidth capabilities of ECL can be utilized. The majority of the data processing is done on wide bit width words with a clock cycle commensurate with the bandwidth capabilities of CMOS and TTL logic. The parallel data is then serialized into a high bandwidth data stream, a bandwidth which requires ECL technologies, for transmission across a long line to another box or machine. The signal is received differentially and converted back to relatively low speed parallel data where it can be processed further in CMOS/TTL. logic. By taking advantage of the bandwidth and line driving capabilities of ECL the system minimizes the number of lines required for interconnecting the subsystems without sacrificing the overall performance. Furthermore by taking advantage of PECL this application can be realized with a single five volt power supply. The configuration of Figure 1 illustrates a situation where the mixing of logic technologies can produce a design which maximizes the overall performance while managing power dissipation and minimizing cost.

Figure 1. Typical Use of ECL's High Bandwidth, Line Driving Capabilities

#### **Clock Distribution**

Perhaps the most attractive area for ECL in CMOS/ TTL designs is in clock distribution. The ever increasing performance capabilities of today's designs has placed an even greater emphasis on the design of low skew clock generation and distribution networks. Clock skew, the difference in time between "simultaneous" clock transitions throughout an entire system, is a major component of the constraints which form the upper bound for the system clock frequency. Reductions in system clock skew allow designers to increase the performance of their designs without having to resort to more complicated architectures or costly, faster logic. BCL logic has the capability of significantly reducing the clock skew of a system over an equivalent design utilizing CMOS or TTL technologies.

The skew introduced by a logic device can be broken up into three areas; the part-to-part skew, the within-part skew and the rise-to-fall skew. The part-to-part skew is defined as the differences in propagation delays between any two devices while the within-device skew is the difference between the propagation delays of similar paths for a single device. The final portion of the device skew is the rise-to-fall skew or simply the differences in propagation delay between a rising input and a failing input on the same gate. The within-device skew and the rise-to-fall skew combine with delay variations due to environmental conditions and processing to comprise the part-to-part skew. The part-to-part skew is defined by the propagation delay window described in the device data sheets.

Careful attention to die layout and package choice will minimize within-device skew. Although this minimization is independent of technology, there are other characteristics of ECL which will further reduce the skew of a device. Unlike their CMOS/TTL counterparts, ECL devices are relatively insensitive to variations in supply voltage and temperature. Propagation delay variations with environmental conditions must be accounted for in the specification windows of a device. As a result because of ECLs AC stability the delay windows for a device will inherently be smaller than similar CMOS or TTL functions.

The virtues of differential interconnect in line driving have already been addressed, however the benefits of differential interconnect are even more pronounced in clock distribution. The propagation delay of a signal through a device is intimately tied to the switching threshold of that device. Any deviations of the threshold from the center of the input voltage swing will increase or decrease the delay of the signal through the device. This difference will manifest itself as rise-to-fall skew in the device. The threshold levels for both CMOS and TTL devices are a function of processing, layout, temperature and other factors which are beyond the control of the system level designer. Because of the variability of these switching references, specification limits must be relaxed to guarantee acceptable manufacturing yields. The level of relaxation of these specifications increases with increasing logic depth. As the depth of the logic within a device increases the input signal will switch against an increasing number of reference levels: each encounter will add skew when the reference level is not perfectly centered. These relaxed timing windows add directly to the overall system skew. Differential ECL, both internal and external to the die, alleviates this threshold sensitivity as a DC switching reference is no longer required. Without the need for a switching reference the delay windows, and thus system skew, can be significantly reduced while maintaining acceptable manufacturing yields.

What does this mean to the CMOS/TTL designer? It means that CMOS/TTL designers can build their clock generation card and backplane clock distribution using ECL. Designers will not only realize the benefits of driving long lines with ECL but will also be able to realize clock distribution networks with skew specs unheard of in the CMOS/TTL world. Many

specialized functions for clock distribution are available from Motorola (MC10/100E111, MC10/100E211, MC10/100EL11). Care must be taken that all of the skew gained using ECL for clock distribution is not lost in the process of translating into CMOS/TTL levels. To alleviate this problem the MC10/100H646 can be used to translate and fanout a differential ECL input signal into TTL levels. In this way all of the fanout on the backplane can be done in ECL while the fanout on each card can be done in the CMOS/TTL levels necessary to drive the logic.

Figure 2 illustrates the use of specialized fanout buffers to design a CMOS/TTL clock distribution network with minimal skew. With 50ps output-to-output skew of the MC10/100H646 or MC10/100H641, a total of 72 or 81 TTL clocks, respectively, can be generated with a worst case skew between all outputs of only 1.05ns. A similar distribution tree using octal CMOS or TTL buffers would result in worst case skews of more than 6ns. This 5ns improvement in skew equates to about 50% of the up/down time of a 50MHz clock cycle. It is not difficult to imagine situations where an extra 50% of time to perform necessary operations would be either beneficial or even a life saver. For more information about using ECL for clock distribution, refer to application note AN1405/D – ECL Clock Distribution Techniques.

Figure 2. Low Skew Clock Fanout Tree

#### PECL versus ECL

Nobody will argue that the benefits presented thus far are not attractive, however the argument will be made that the benefits are not enough to justify the requirements of including ECL devices in a predominantly CMOS/TTL design. After all the inclusion of ECL requires two additional negative voltage supplies; VEE and the terminating voltage VTT. Fortunately this is where the advantages of PECL come into play. By using ECL devices on a positive five volt CMOS/TTL power supply and using specialized termination techniques ECL logic can be incorporated into CMOS/TTL designs without the need for additional power supplies. What about power dissipation you

ask, although it is true that in a DC state ECL will typically dissipate more power than a CMOS/TTL counterpart, in applications which operate continually at frequency, i.e.. clock distribution, the disparity between ECL and CMOS/TTL power dissipation is reduced. The power dissipation of an ECL device remains constant with frequency while the power of a CMOS/TTL device will increase with frequency. As frequencies approach 50MHz the difference between the power dissipation of a CMOS or TTL gate and an ECL gate will be minimal. 50MHz clock speeds are becoming fairly common in CMOS/TTL based designs as today's high performance MPUs are fast approaching these speeds. In addition, because ECL output swings are significantly less than those of CMOS and TTL the power dissipated in the load will be significantly less under continuous AC conditions.

It is clear that PECL can be a powerful design tool for CMOS/TTL designers, but where can one get these PECL devices. Perhaps the most confusing aspect of PECL is the misconception that a PECL device is a special adaptation of an ECL device. In reality every ECL device is also a PECL device; there is nothing magical about the negative voltage supply used for ECL devices. The only real requirement of the power supplies is that the potential difference described in the device data sheets appears across the upper and lower power supply rails (V<sub>CC</sub> and V<sub>EE</sub> respectively). A potential stumbling block arises in the specified VFF levels for the various ECL families. The 10H and 100K families specify parametric values for potential differences between VCC and VEE of 4.94V to 5.46V and 4.2V to 4.8V respectively; this poses a problem for the CMOS/TTL designer who works with a typical VCC of 5.0V ±5%. However, because both of these ECL standards are voltage compensated both families will operate perfectly fine and meet all of the performance specifications when operated on standard CMOS/TTL power supplies. In fact, Motorola is extending the VFF specification ranges of many of their ECL families to be compatible with standard CMOS/TTL power supplies. Unfortunately earlier ECL families such as MECL 10K<sup>™</sup> are not voltage compensated and therefore any reduction in the potential difference between the two supplies will result in an increase in the  $V_{\mbox{OL}}$  level, and thus a decreased noise margin. For the typical CMOS/TTL power supplies a 10K device will experience an ≈50mV increase in the VOI level. Designers should analyze whether this loss of noise margin could jeopardize their designs before implementing PECL formatted 10K using 5.0V ± 5% power supplies.

The traditional choice of a negative power supply for ECL is the result of the upper supply rail being used as the reference for the I/O and internal switching bias levels of the technology. Since these critical parameters are referenced to the upper rail any noise on this rail will couple 1:1 onto them; the result will be reduced noise margins in the design. Because, in general, it is a simpler task to keep a ground rail as this reference. However when careful attention is paid to the power supply design, PECL can be used to optimize system performance. Once again the use of differential PECL will simplify the designer's task as the noise margins of the system will be doubled and any noise riding on the upper V<sub>CC</sub> rail will appear as common mode noise; common mode noise will be rejected by the differential receiver.

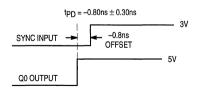

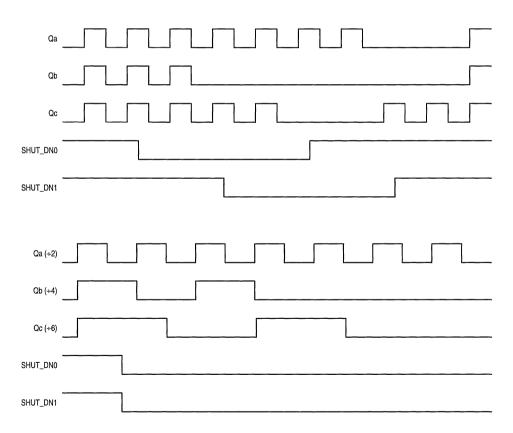

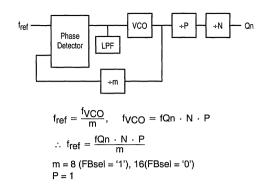

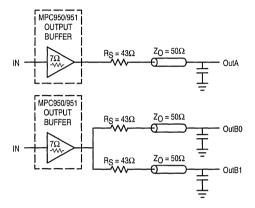

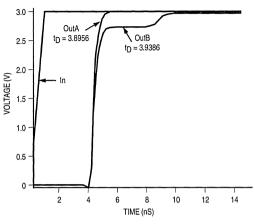

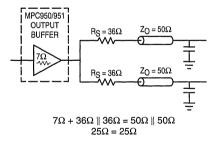

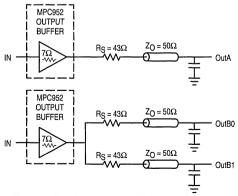

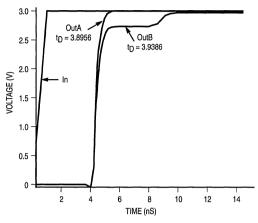

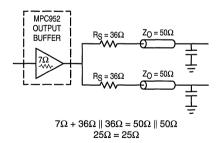

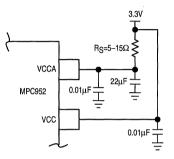

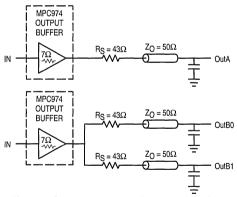

#### **MECL to PECL DC Level Conversion**