# OPTIMIZING POVERPC CODE

Programming the PowerPC Chip in Assembly Language

Gary Kacmarcik

# Optimizing PowerPC<sup>™</sup> Code

# Programming the PowerPC Chip in Assembly Language

# Gary Kacmarcik

# \*

#### Addison-Wesley Publishing Company

Reading, Massachusetts • Menlo Park, California • New York Don Mills, Ontario • Wokingham, England • Amsterdam Bonn • Sydney • Singapore • Tokyo • Madrid • San Juan Paris • Seoul • Milan • Mexico City • Taipei Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trademarks. Where those designations appear in the book, and Addison-Wesley was aware of a trademark claim, the designations have been printed in initial capital letters or all capital letters.

The authors and publishers have taken care in preparation of this book, but make no expressed or implied warranty of any kind and assume no responsibility for errors or omissions. No liability is assumed for incidental or consequential damages in connection with or arising out of the use of the information or programs contained herein.

#### Library of Congress Cataloging-in-Publication Data

Kacmarcik, Gary. Optimizing PowerPC code / Gary Kacmarcik. p. cm. Includes index. ISBN 0-201-40839-2 1. PowerPC microprocessors. I. Title. QA76.8.P67K33 1995 005.265—dc20

94-10489 CIP

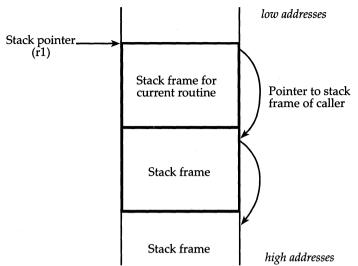

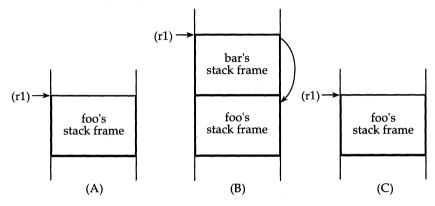

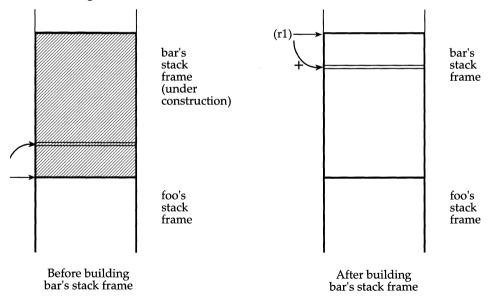

Copyright © 1995 by Gary Kacmarcik

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher. Printed in the United States of America. Published simultaneously in Canada.

Sponsoring Editor: Martha Steffen Project Manager: Eleanor McCarthy Production Coordinator: Deborah McKenna Cover design: Barbara T. Atkinson Cover art © Michael D. Coe Set in 10 point Palatino by Michael D. Wile

1 2 3 4 5 6 7 8 9-MA-9998979695 First printing, April 1995

Addison-Wesley books are available for bulk purchases by corporations, institutions, and other organizations. For more information please contact the Corporate, Government, and Special Sales Department at (800) 238-9682. Tous mes remerciements à ma femme Sylvie Giral, car sans son assistance et sa présence, ce livre aurait été bien difficile à accomplir. Aussi, toute ma gratitude à mes parents pour leur soutien et encouragements continuels: "J'espère qu'ils conserveront ton cerveau au vinaigre après avoir autant investi dans ton éducation."

Thanks are also in order to Tom Pittman of Itty-Bitty Computers for suffering through an earlier draft of this manuscript and suggesting numerous improvements and identifying areas that needed additional clarification.

Special thanks to 鮎川まどか and 音無響子 for providing much needed distractions and helping me maintain my sanity during the creation of this manuscript.

# Contents

#### Chapter 1 Introduction 1

Purpose of Book 1 Intended Audience 1 Why Assembly Language on a RISC Processor? 2 PowerPC as a RISC ISA 5 Overview of this Book 7

#### Chapter 2 PowerPC Architecture Overview 9

Data Organization 9 Functional Units 12 Processor Registers 13 32- versus 64-bit Implementations 23

#### Chapter 3 Instruction Set Overview 27

Instruction Groups 27 Instruction Suffixes 28 Extended Instruction Forms 29 Obsolete Instructions 29 Optional Instructions 29 Notation 30

#### Chapter 4 Branch and Trap Instructions 35

Branch Instructions 35 Branch Prediction 47 Trap Instructions 50 System Linkage Instructions 54

#### Chapter 5 Load and Store Instructions 57

Loads and Stores 57 Load and Store Byte 59 Load and Store Halfword 60 Load and Store Word 61 Load and Store Doubleword 63 Load and Store Byte-Reversed Data 64 Load and Store Floating-Point Double-Precision 65 Load and Store Floating-Point Single-Precision 65 Load and Store Multiple 66 Load and Store String 68 Load and Store Synchronization 71 Obsolete Load String 72

#### Chapter 6 Integer Instructions 75

Addition 75 Subtraction 78 Multiplication 80 Division 81 Miscellaneous Arithmetic Instructions 83 Comparison Instructions 84 Logical (Boolean) Instructions 86 Obsolete Arithmetic Instructions 88

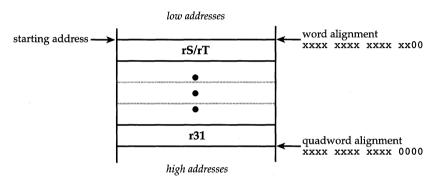

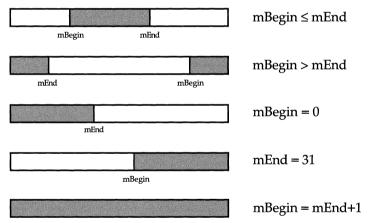

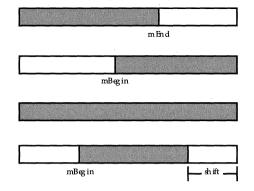

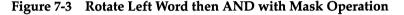

#### Chapter 7 Rotate and Shift Instructions 93

Rotation Masks 93 How Rotates and Shifts Update the CR 96 Rotate Instructions 97 Shift Instructions 102 Extended Rotate Instruction Forms 107 Multiple-Precision Shifts 115 Obsolete Rotate and Shift Instructions 129

#### Chapter 8 Floating-Point Instructions 135

Floating-Point Data Representation 135 Floating-Point Operation 142 Floating-Point Instructions 148 Floating-Point Conversions 155

vi Contents

#### Chapter 9 System Register Instructions 159

CR Instructions 159 FPSCR Instructions 162 MSR Instructions 163 SPR Instructions 164 User-Level SPR Extended Forms 164 Supervisor-Level SPR Extended Forms 166 Time Base Register Instructions 170 Segment Register Instructions 171

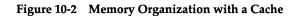

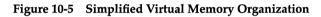

#### Chapter 10 Memory and Caches 173

Introduction 173 Memory and Cache Overview 174 Cache Architecture 176 PowerPC Cache Geometry 184 PowerPC Cache Coherency 185 PowerPC Storage Control Instructions 185 Virtual Memory 188 PowerPC Memory Management 192 PowerPC Memory Access Modes 196 PowerPC Lookaside Buffer Instructions 198

#### Chapter 11 Pipelining 201

What is a Pipeline? 201 Basic Pipeline Functions 202 PowerPC 601 Pipeline Description 205

#### Chapter 12 PowerPC 601 Instruction Timing 215

Reading the Timing Tables 215 Instruction Dispatch Timing 216 Fixed-Point Instruction Timings 219 Floating-Point Instruction Timings 225 Branch Instruction Timings 228 Cache Access Timings 238 Pipeline Synchronization 240 Abnormal Integer Conditions 243 Abnormal Floating-Point Conditions 245 Timing Pitfalls 248

#### Chapter 13 Programming Model 251

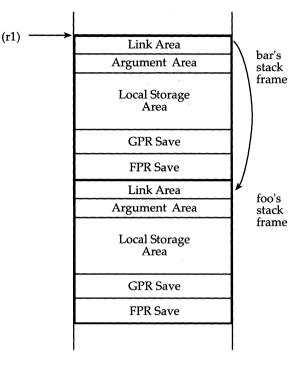

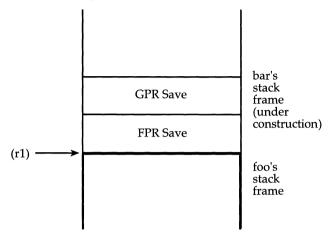

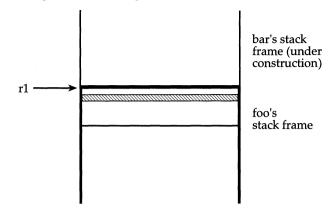

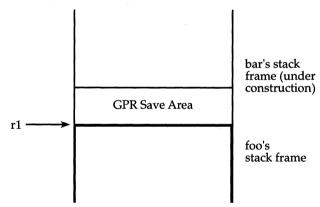

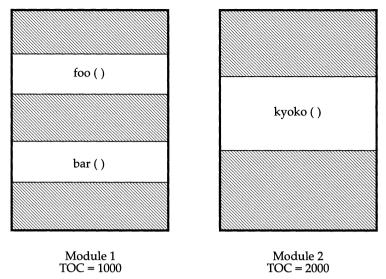

Register Usage Conventions 251 Table of Contents (TOC) 254 The Stack Pointer 255 Brief Interlude: Naming Conventions 261 Subroutine Calling Conventions 261 A Simple Subroutine Call 262 An Even Simpler Subroutine Call 268 Saving Registers on the Stack 270 Stack Frames 278 Passing Arguments to Routines 281 Retrieving Results from Routines 286 Stack Frames and alloca() 287 Linking with Global Routines 288

#### Chapter 14 Introduction to Optimizing 295

When to Optimize 295 Examining Compiled Code 297 Standard Optimizations 300

#### Chapter 15 Resource Scheduling 305

Types of Processor Resources305Pipeline Conflicts306Register Usage Dependencies314Memory Dependencies334

#### Chapter 16 More Optimization Techniques 341

Keeping the Processor Busy 341 Increasing Scheduling Opportunities 344 Strength Reduction 346 Load/Store Ordering 350 Software Pipelining 351

Appendix A Instruction Set Summary 353

Appendix B Complete List of Mnemonics 643

Appendix C Register Bit Definitions 669

Appendix D Optimization Summary 677

Appendix E References & Further Reading 679

Index 681

# Introduction

# 1.1 Purpose of Book

The purpose of this book is simple: to introduce programmers to the concepts of assembly language programming for PowerPC processors. Beyond simply presenting the information required to write functional code, this book presents the information necessary to write *efficient* code, and it also discusses the tricks that compilers use to produce fast code.

The vast majority of people reading this book may have little need to write a significant amount of code in assembly language. But the techniques presented here will be useful to the high-level programmer who needs to read compiler-generated code as part of the debugging process.

# **1.2 Intended Audience**

This book is intended for programmers who have had some sort of experience with high-level languages such as C or Pascal, or with assembly language for another processor.

This book will not spend time defining basic concepts such as hexadecimal notation nor expounding the virtues of null-terminated over length-encoded strings. It will, however, present definitions for any term that is used. For example, concepts like *latency* and *throughput* will be defined before being used.

## **1.3 Why Assembly Language on a RISC Processor?**

The first question that many people ask is something like: "Why would any sane person be interested in learning assembly language for a RISC processor?" The reasoning behind this question is the belief that properly written RISC assembly language routines are significantly more difficult to write than similar CISC assembly routines, and that today's compilers produce far better code than code generated by hand, so why bother?

The question is also valid because the computer industry has been moving away from programming in low-level languages and emphasizing languages that promise robustness, easy verification of correctness, and so on. Assembly language can promise none of those things. So, again, why bother?

The truth of the matter is that there are two major reasons for wanting to be familiar with assembly language for any processor (RISC or not). The first is that you need complete control of all processor resources to make the code as fast or small as possible. The second reason is that you need to debug your code (or someone else's) and see what's really going on. A source-level debugger may not be sufficient (or even available).

The first reason may sound like it's only for anal-retentive speed freaks, but there are reasons for normal human beings to want to hand-code assembly. It is a sad fact that many of the commercially available compilers do not generate highly optimized code. The best-selling compilers are typically those with the fastest *edit-compile-run* times, and a proper optimizer takes a bit of time to run. Thus, while it's true that a *properly written* optimizing compiler *can* generate code that is better than the code an average assembly language programmer would produce, many compilers are not properly written and thus, do not produce properly optimized code.

In addition, a compiler is limited by the source language. As a programmer in assembly language, you know exactly what you need and when you need it (and when you no longer need it). The compiler must try to figure out as much about the program as it can from the source, and when it's in doubt, it must play it safe and produce less efficient code. In the C programming language, the programmer is given such flexibility with addresses and pointers that it becomes extremely difficult for the compiler to determine if a range of memory can be modified by a section of code. Because of the compiler's inability to guarantee that the memory won't be modified, it may not be able to risk applying certain optimizations.

Debugging is another situation that causes programmers to drop down into assembly. Sometimes (one hopes rarely), compilers do not produce correct code. More commonly, you may find that your program works fine in some circumstances, but dies a horrible death when it interacts with other programs. Lacking the source code to the other program, assembly may be the only course of action available.

Of course, there's a reason high-level languages exist. The vast majority of your coding and debugging will be done in some sort of high-level language. You should need to use assembly only when you have a routine that needs to be as fast as possible.

To correctly respond to whether RISC assembly is more difficult than CISC assembly, the terms RISC and CISC must first be discussed in more detail.

#### **CISC versus RISC**

There is a lot of confusion surrounding the differences between a RISC and a CISC architecture arising from misuse of the terms and from various marketing departments propagating the "RISC is *always* faster/better than CISC" myth. Unfortunately, part of the confusion also comes from the fact that there is no clear line between the two design philosophies: some architectures are clearly RISC, others are clearly CISC, while still others fall somewhere in between.

The most important thing to note is that RISC ("Reduced Instruction Set Computer") and CISC ("Complex Instruction Set Computer") are terms that are properly applied to an Instruction Set Architecture (ISA) and not to a particular implementation of an ISA. Common usage allows a processor to be called a "RISC processor," but what is really meant is that the processor is an implementation of a RISC architecture.

This difference between an ISA and a hardware implemention of that ISA is fundamental to understanding RISC and CISC.

#### What RISC Is

The following is a list of features that are commonly associated with RISC ISA's:

- A large uniform register set

- A load / store architecture

- A minimal number of addressing modes

- A simple fixed-length instruction encoding

- No/minimal support for misaligned accesses

This set of "rules" is designed to make fast processors easier to implement. Notice that the list contains no requirements as to the number of instructions, nor does it indicate how the processor should be implemented. These are issues that are commonly mistaken as features required for a RISC processor. A processor implementing a RISC ISA is not necessarily a fast processor—performance is dependent on how the processor is implemented. However, because the features listed were designed to make it easier to implement fast processors, one can infer that a RISC processor is likely to be faster than a CISC processor of equivalent technology.

As an example to drive this point home, one can imagine two implementations of a particular RISC ISA: one that doesn't use pipelines or superscalar dispatch (these concepts are discussed later in this book); and another one that does. The first processor would perform very poorly when compared to the other processor, and it might even perform worse than many currently available CISC processors. However, just because this processor performs poorly does not mean that it is not a RISC processor.

If you think of RISC as standing for "Reduced Instruction Set Complexity," then you may be less likely to be confused by the term.

# What CISC Is

Given the definition of RISC, the original definition of CISC is trivially easy to define: CISC is anything that is not RISC.

When the designers of the first RISC architectures devised the term "RISC," they meant to differentiate their simpler, reduced processor from the current crop of complex processors. Thus, "CISC" was used as a pejorative term that meant non-RISC architectures.

This lack of a real definition has contributed to some of the confusion surrounding RISC and CISC. Today, a CISC architecture typically has:

- Many instruction types that access memory directly

- A large number of addressing modes

- Variable-length instruction encoding

- Support for misaligned accesses,

although architectures vary widely.

# What RISC/CISC Are Not

Note that the above lists do not require:

- An instruction pipeline.

- A superscalar instruction dispatch.

- Hardwired or microcoded instructions.

These are all implementation issues that any processor may make use of, regardless of its ISA. RISC processors have become associated with these features because RISC ISAs are designed to facilitate the implementation of these features. However, the presence of these features does not indicate that the processor in question is an implementation of a RISC ISA.

As an example, Intel's Pentium<sup>™</sup> processor has an instruction pipeline with a superscalar dispatch. These implementation issues do not change the fact that the Pentium is just another (albeit fast) implementation of a CISC instruction set architecture.

# Is RISC Assembly More Difficult than CISC Assembly?

So this brings us back to the original question: Is a RISC processor more difficult to program than a CISC processor? The answer to this question lies somewhere between "There's no way to tell" and "That's a silly question."

It's difficult to answer the question because the programming challenges depend more on the specific processor architecture (that is, 68K, i86, PowerPC) than on the general category (that is, RISC or CISC) of the processor architecture.

An easy way to make this clear is to compare the 68K and the i86 processor families. They are both CISC architectures, but the 68K is widely regarded as being much easier to program in assembly, mostly because of its large store of general purpose registers and flexible addressing modes. The same comparison can be made for RISC architectures: some RISC processor families will be easy to program while others will be more difficult.

In fact, an argument can be made that RISC assembly language programming is *easier* than CISC assembly. The large register store and the fact that most instructions have one cycle throughput reduces some of the complexity of assembly language programming.

For today's processors, the most complicated aspect of programming in assembly language is the instruction scheduling that is necessary on pipelined implementations. Because pipelines can exist on either RISC or CISC processors, this scheduling problem exists on processors of both architecture types. Since RISC simplifies the other aspects of programming, this becomes more manageable.

# 1.4 PowerPC as a RISC ISA

The preceding sections have spoken in general terms of RISC processors and how they fit into the general scheme of things. This section talks about how the PowerPC fits into the RISC category. As mentioned earlier, five basic features are commonly found on RISC processors. We'll touch on each one and discuss how the PowerPC fits.

# A Large, Uniform Register Set

The PowerPC architecture defines 32 general purpose registers and 32 floatingpoint registers. All of these registers are general purpose in that any of the registers can be used as arguments to any of the instructions.

The only exception to this is GPR r0. Some instructions (like the non-Update *Load* and *Store* instructions) use a register specification of 0 as a special case to indicate that no register should be used in the calculation.

# A Load/Store Architecture

The only instructions that access memory are the *Load* and *Store* instructions. Thus, the PowerPC ISA qualifies as a Load/Store architecture.

# A Minimal Number of Addressing Modes

Only two classes of instructions require addressing modes: the load/store instructions and the branch instructions. All other instructions operate on registers or immediate values.

The load/store instructions allow three addressing modes (register indirect, register indirect with register index, or register indirect with immediate index); and the branch instructions allow three modes (absolute, PC relative, or SPR indirect).

Contrast this with the 68000 (a CISC processor), which has a seemingly infinite number of addressing modes, with more coming out with each generation of the processor family.

# A Simple Fixed-length Instruction Encoding

Every PowerPC instruction is encoded in 32 bits. There are no exceptions to this rule. Instruction encodings that do not require the full 32 bits are padded with 0 bits so that they fill all 32 bits.

# **No/Minimal Support for Misaligned Accesses**

This is where the PowerPC architecture deviates from the standard RISC design principles. Following the RISC philosophy, misaligned accesses should never occur, so support for them needlessly complicates the implementation. However, one of the design considerations of the original POWER architecture (the PowerPC's parent) was that it be able to emulate other processors efficiently. Because many of the processors that were likely to be emulated allowed misaligned accesses, it made sense to include support for misaligned accesses in the POWER/PowerPC architecture.

# **1.5 Overview of this Book**

The book is divided conceptually into four parts: an architecture and instruction set description (Chapters 2 through 12), a basic programming section (Chapter 13), an advanced programming section (Chapters 14 through 16), and an instruction set summary (Appendices A and B).

Chapter 2 begins with a basic overview of the PowerPC architecture: the standard data types and the functional units of the processor; and introduces the differences between the 32-bit and 64-bit PowerPC implementations.

Chapter 3 contains a brief summary of the notation used in the remaining instruction set chapters. The following chapters (4 through 9) focus on a specific instruction type, such as floating-point or branch instructions. These are useful chapters to read through at least once, because they give a feel for which operations the PowerPC instruction set provides.

Chapters 10 through 12 provide basic information about memory hierarchies and pipelines.

Chapter 11 describes the standard function-calling mechanism that most PowerPC based systems will use. Note that the information provided in this chapter is not in any way enforced by the processor. It's just a set of conventions that allow routines generated by different compilers to interface consistently. This chapter will be of interest to programmers who need to debug high-level code at the assembly level.

The remaining chapters define more advanced architectural concepts and describe some implementation details for the PowerPC 601 processor. This information is then used in discussions that describe techniques for optimizing code sequences so that they use the processor resources efficiently.

The instruction set summaries in Appendices A and B provide easy-to-use instruction references, alphabetically organized by mnemonic. Appendix A devotes a page to each PowerPC instruction and includes the obsolete POWER instructions found on the 601. Appendix B lists every POWER and PowerPC instruction and all the extended mnemonics, and also gives the mapping of each extended mnemonic into standard instructions. Appendix B is quite useful for reading code that uses the extended mnemonics, because it isn't always apparent from which base instruction the extended form was derived.

# PowerPC Architecture Overview

Before the instruction set can be discussed, the basic architecture of the processor must first be defined. This chapter describes the data types and functional units of the PowerPC architecture.

# 2.1 Data Organization

An understanding of how data is organized is the best place to begin, because everything else in this book assumes you know this. If you are familiar with assembly language for another processor, then nothing in this section should surprise you, and you should be able to quickly skim the information presented here. This section is included for the sake of completeness and to give people completely new to assembly language a good starting point.

# **Basic Data Types**

The PowerPC provides six basic data types: byte, halfword, word, doubleword, and single- and double-precision floating-point. In addition, there is a quadword data type that is useful because quadword alignment is desirable in some circumstances. Table 2-1 summarizes these data types.

| Data Type                                                      | Data Size                        | Lower 8 Bits<br>of Address <sup>a</sup><br>(if aligned to this type) |

|----------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------|

| Byte                                                           | 8-bit                            |                                                                      |

| Halfword                                                       | 16-bit                           | 0                                                                    |

| Word                                                           | 32-bit                           | 00                                                                   |

| Doubleword <sup>b</sup>                                        | 64-bit                           | 000                                                                  |

| Quadword <sup>c</sup>                                          | 128-bit                          | 0000                                                                 |

| Floating-point single                                          | 32-bit                           | 00                                                                   |

| Floating-point double                                          | 64-bit                           | 000                                                                  |

| a. $A'-'$ in the address indicates that t                      | the bit may be either a 0 or a 1 | ·                                                                    |

| b. Fixed-point instructions that oper<br>implementations only. | ate directly on doublewords      | are found on 64-bit PowerP                                           |

| c. Other than cache instructions, no i                         | nstructions operate directly o   | n quadwords.                                                         |

Table 2-1 Standard PowerPC Data Types

Of these data types, the byte, halfword, word, and the two floating-point types are the most commonly used. The doubleword data type is available only on 64bit PowerPC implementations. The quadword data type is included for completeness.

# Data Alignment

*Alignment* refers to the placement of a data type in memory. Most processors are designed to operate more efficiently when data is aligned properly, so it is important to be aware of this concept. A data type is considered to be aligned if its address is an integral multiple of the data type size.

Thus, the address of an aligned word value must be a multiple of four. Halfword and doubleword values must have addresses that are multiples of two and eight, respectively, for proper alignment. Because bytes are one byte wide, they are always considered to be aligned.

When the addresses are viewed in binary, it is relatively easy to determine if the quantity is aligned. A multiple of 2 (halfword) always has a low order bit of b0; a multiple of four (word) has b00 for the low order bits; and a multiple of eight (doubleword) has b000.

# **Byte Ordering**

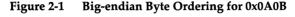

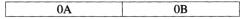

When storing values that require more than one byte, some convention for the order of the bytes must be agreed upon or else the data could potentially be misinterpreted. Figures 2-1 and 2-2 show the two possible organizations for the halfword (2-byte) value 0x0A0B.

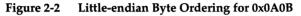

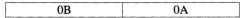

For the four-byte word 0x0A0B0C0D, there are 24 (4! = 24) possible combinations of bytes, but only the two shown in Figures 2-3 and 2-4 make sense.

| Figure 2-3 | <b>Big-endian</b> | <b>Byte Ordering</b> | for 0x0A0B0C0D |

|------------|-------------------|----------------------|----------------|

|            |                   | - ,                  |                |

| 0A | 0B | 0C | 0D |

|----|----|----|----|

|    |    |    |    |

Figure 2-4 Little-endian Byte Ordering for 0x0A0B0C0D

| 0D | 0C | 0B | 0A |

|----|----|----|----|

|    |    |    |    |

In both of these figures, the first encoding method stores the most significant byte, or *big*-end, first, and the second encoding stores the least significant byte, or *little*-end, first. Hence, the first method is referred to as *big-endian* and the second is referred to as *little-endian*.

By default, the PowerPC processors operate in big-endian mode, but there are switches to allow user-level or interrupt operations to occur in little-endian mode.

#### **Bit Numbering**

Just as the bytes within words are organized using a big-endian scheme, the bits within each byte or word are numbered using a big-endian numbering scheme. Thus, as Figure 2-5 shows, the most significant bit (*msb*) is bit #0 and the least significant bit (*lsb*) is bit #31.

| Figure 2-5 | Little-endian | <b>Bit Numbering</b> | for a 32-bit Register |

|------------|---------------|----------------------|-----------------------|

|            |               |                      |                       |

| 0   | 1 | 2 | 3 | s | · | 28 | 29 | 30 | 31  |

|-----|---|---|---|---|---|----|----|----|-----|

|     |   |   |   |   |   |    |    |    |     |

| msł | , |   |   |   |   |    |    |    | lsb |

When representing data in registers, the *msb* will always be on the left and the *lsb* will always be on the right so that the displayed data is intelligible.

In general, it doesn't matter how the bits are ordered or numbered within a register, because one typically uses the entire register at a time. However, with the PowerPC, there are instructions that require a starting or ending bit, and for these instructions it is important to be aware of the numbering scheme.

# 2.2 Functional Units

It is convenient to divide a PowerPC processor into five conceptional units: the Fixed-Point or Integer Unit (IU), the Floating-Point Unit (FPU), the Branch Processor Unit (BPU), the System Register Unit (SRU), and the Load/Store Unit (LSU).

It is important to note that these are conceptual functional units. Although these units will be present in some form on each PowerPC implementation, they will not necessarily be these five particular units. Some units may be combined, or there may be multiple units of the same type. For example, the 601 combines the IU, LSU, and SRU into a unified Integer Unit. Future PowerPC processors will offer multiple IUs to increase integer performance.

# Integer Unit (IU)

The Integer Unit performs all of the integer instructions. These instructions include the arithmetic, logical, and shift/rotate instructions.

The IU has a store of General Purpose Registers (GPRs) that are used to perform the calculations. In addition, there is a Fixed-Point Exception Register (XER) that contains status information.

The IU is sometimes called the Fixed-Point Unit (FXU).

# **Floating-Point Unit (FPU)**

The Floating-Point Unit performs all of the floating-point operations that the PowerPC supports. These operations conform to the IEEE 754 floating-point standard for floating-point arithmetic and include all of the required data types (normalized, denormalized, NotANumbers, and others).

The FPU also includes a Floating-Point Status and Control Register (FPSCR) that controls how floating-point operations are performed and provides status information.

# **Branch Processor Unit (BPU)**

The Branch Processor Unit handles all of the predictions and resolutions for the branch instructions. When a branch cannot be completely resolved, the BPU predicts whether or not the branch will be taken and fetches the appropriate instructions.

There are three SPRs associated with the BPU: the Link Register (LR), the Count Register (CTR), and the Condition Register (CR). Both the LR and the CTR can be used to hold target addresses for branching, although this is a secondary function for the CTR. The CR and CTR are used by the conditional branch instructions to hold the conditions that the branch depends on. The CR holds the relational information (*less than, greater than,* or *equal*) that is calculated by one of the compare instructions, and the CTR holds a count that can be automatically decremented to facilitate the coding of loop structures.

# Load/Store Unit (LSU)

The Load/Store Unit handles all of the load and store instructions executed by the processor. Because these instructions are the only interface between the processor registers and the memory subsystem, the LSU can be considered the data interface for the processor.

# System Register Unit (SRU)

The System Register Unit provides access to the various Special Purpose Registers (SPRs) that the PowerPC provides. This unit also implements the various Condition Register logical operations.

# 2.3 Processor Registers

This section provides an overview of both the user- and supervisor-level registers that the PowerPC specifies. In general, only the user-level registers will be useful to the programmer, but the supervisor-level registers are defined here to give a complete summary.

Remember that bits within registers are numbered using the *big-endian* scheme. That is, the left-most or *most-significant bit* is bit 0, and the right-most or *least significant bit* is bit 31 (or 63). Because some registers can be different widths on different implementations, this can cause some confusion about bit numbering. See §2.4, "32- versus 64-bit Implementations," for more information.

# **User-Level Registers**

The user-level registers are the only registers that most programs are likely to need.

#### **General Purpose Registers (GPRs)**

#### Figure 2-6 General Purpose Register

| 0 [63] |  |

|--------|--|

| GPR    |  |

|        |  |

There are 32 general purpose registers. These registers are referred to as GPR0 - GPR31, or simply r0 - r31. The size of these registers depends on the PowerPC implementation: they are 32-bits wide on 32-bit implementations and 64-bits wide on 64-bit implementations.

When instructions that operate on 32-bit data are executed on a 64-bit PowerPC implementation, only the lower (right-most) 32 bits are used.

#### **Floating-Point Registers (FPRs)**

#### Figure 2-7 Floating-Point Register

| 0 |     | 63 |

|---|-----|----|

|   | FPR |    |

There are 32 floating-point registers. These registers are referred to as FPR0 - FPR31, or simply fr0 - fr31. The floating-point registers are always 64 bits in width and always contain double-precision floating-point values.

#### **Condition Register (CR)**

|   |     |   |   |     |   |   | Fi  | igu | re | 2-8 | C  | ono | lition | K  | egi | ster |    |    |     |    |    |     |    |

|---|-----|---|---|-----|---|---|-----|-----|----|-----|----|-----|--------|----|-----|------|----|----|-----|----|----|-----|----|

| 0 |     | 3 | 4 |     | 7 | 8 |     | 11  | 12 | 1   | 15 | 16  |        | 19 | 20  |      | 23 | 24 |     | 27 | 28 |     | 31 |

|   | CR0 |   |   | CR1 |   |   | CR2 |     |    | CR3 |    |     | CR4    |    |     | CR5  |    |    | CR6 |    |    | CR7 |    |

The Condition Register is a 32-bit-wide register that contains eight 4-bit wide condition fields. These eight fields can be specified as the destination for the result of the comparison operations or as the source for the conditional branch operations.

These eight fields are referred to as crf0 - crf7, or  $CR{0} - CR{7}$ . As with the bit numbering, the fields are numbered from left to right. Thus, crf0 corresponds to CR[0:3], crf1 = CR[4:7], ..., and crf7 = CR[28:31].

How the four bits in each field are interpreted depends on the instruction that was used to set the field. Figure 2-9 shows how the bits of the field are set for fixed-point compare operations. In the figure, 0, 1, 2, and 3 specify the corresponding bit within the given CR field.

#### Figure 2-9 CR Field Bits Resulting from Fixed-Point Compare Operations

| LT GT | EQ | so |

|-------|----|----|

|-------|----|----|

- 0 LT Less Than

- 1 GT Greater Than

- 2 EQ Equal

- 3 SO Summary Overflow

Figure 2-10 shows how the bits are set for floating-point compare operations.

#### Figure 2-10 CR Field Bits Resulting from Floating-Point Compare Operations

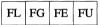

- 0 FL FP Less Than

- 1 FG FP Greater Than

- 2 FE FP Equal

- 3 FU FP Unordered

CR field 0 is implicitly set by fixed-point instructions and CR field 1 is implicitly set by floating-point instructions that have their Record bit set. Fixed-point instructions with the Record bit set update the CR field 0 as Figure 2-11 shows. In this figure, 0, 1, 2, and 3 are the bits within CR field 0, that is, CR[0:3].

#### Figure 2-11 CR Field Bits Resulting from Fixed-Point Operations with Record Bit

| LT GT E | Q SO |

|---------|------|

|---------|------|

- 0 LT Negative (Less Than Zero)

- 1 GT Positive (Greater Than Zero)

- 2 EQ Zero (Equal to Zero)

- 3 SO Summary Overflow

Figure 2-12 shows the interpretation of the bits of CR field 1 after a floating-point instruction with the Record bit set has been executed. In this figure, 0, 1, 2, and 3 are the bits within CR field 1, that is, CR[4:7].

#### Figure 2-12 CR Field Bits Resulting from FP Operations with Record Bit

| FX FEX VX | ЭΧ |

|-----------|----|

|-----------|----|

- 0 FX FP Exception Summary

- 1 FEX FP Enabled Exception Summary

- 2 VX FP Invalid Operation Exception Summary

- 3 OX FP Overflow Exception

#### **Fixed-Point Exception Register (XER)**

|                    | Figure 2-13 | Fixed-Point Exception Regi | ister        |

|--------------------|-------------|----------------------------|--------------|

| 0 1 2 3            |             |                            | 23 24 25 31  |

| SO OV CA 0 0 0 0 0 | 0 0 0 0 0   | 0 0 0 Byte compare value   | 0 Byte count |

The XER (see Figure 2-13) contains information about the operation of integer instructions, such as the Carry bit, the Overflow bit, and a Summary Overflow bit. The XER also contains special-purpose fields that are used by some instructions.

The Summary Overflow (SO) bit is the same as the Overflow (OV) bit except that it is *sticky*. A bit that is sticky is one that will remain set once it has been set—it must be explicitly cleared by using the mtxer or mcrxr instructions. This is contrasted with the OV bit, which will be updated (cleared or set) by the next instruction that provides overflow information. The SO bit can be used to check if any of a sequence of instructions has caused an overflow, thus eliminating the need to explicitly check after each instruction that could cause an overflow.

The "Byte compare value" and "Byte count" fields of the XER are used by some of the *Load String* and *Store String* instructions. The "Byte compare value" is used only on the 601 to support the obsolete POWER instruction lscbx.

A full definition of the XER bits is given in Appendix C.

#### Floating-Point Status and Control Register (FPSCR)

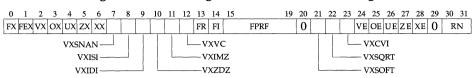

The FPSCR is a 32-bit register that contains the control and status bits for the FPU (see Figure 2-14). The control bits include enable bits for the various floating-point exceptions and rounding bits for controlling how the FPU performs rounding operations. The status bits record any floating-point exceptions that may have occurred.

#### Figure 2-14 Floating-Point Status and Control Register

A full definition of the FPSCR bits is given in Appendix C.

#### Link Register (LR)

The Link Register (see Figure 2-15) is used to hold the target address for a branch. Certain forms of the branch instruction will automatically update the LR with the address of the instruction immediately following the branch. This latter use is well suited for performing subroutine calls: when the branch is taken (that is, the subroutine is called), the LR contains the return address and the subroutine can return to the caller with a simple *Branch to LR* instruction.

#### Figure 2-15 Link Register

| 0 |    |

|---|----|

|   | LR |

#### **Counter Register (CTR)**

The primary function of the Count Register (see Figure 2-16) is to provide a counter that can be set to specify the number of iterations for a loop. Some forms of the conditional branch instructions automatically decrement this counter and use the new counter value as part of the expression to determine if the branch should be taken or not.

#### Figure 2-16 Count Register

| 0 |     |

|---|-----|

|   | CTR |

The CTR can also be used to hold branch addresses. By using the CTR, the target address can be calculated and branched to without affecting the contents of the Link Register. It is mostly operating system (OS) glue routines that take advantage of this use of the CTR, although user programs can safely do the same thing.

#### **Supervisor-Level Registers**

The supervisor-level registers are registers that contain information that is critical to the proper operation of the system. To help prevent programs from inad-

#### §2.3 Processor Registers

vertently accessing one of these registers and causing damage, access to all of these registers is privileged. This means that the program must be running in supervisor mode or a privilege exception will occur.

Fortunately, there is rarely any need to access these registers.

#### **Machine State Register (MSR)**

The MSR is a  $\left[\frac{32}{64}\right]$  bit register that contains the status bits that define the current state of the processor (see Figure 2-17). This includes the bits to indicate if the processor is in 32- or 64-bit mode, if certain interrupts are enabled, if the processor is in big- or little-endian mode, and other bits.

On 32-bit PowerPC implementations, the bits are arranged as shown in Figure 2-17.

#### Figure 2-17 Machine State Register for 32-bit PowerPC Implementations

| 0 1   | 4   | 5 |   |   |   | 9 | 10 |   | 12 | 13  | 14 | 15  | 16 | 17 | 18 | 19 | 20  | 21 | 22 | 23  | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

|-------|-----|---|---|---|---|---|----|---|----|-----|----|-----|----|----|----|----|-----|----|----|-----|----|----|----|----|----|----|----|----|

| 0 0 0 | 0 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0 | 0  | POW | 0  | ILE | EE | PR | FP | ME | FE0 | SE | BE | FE1 | 0  | IP | IŔ | DR | 0  | 0  | RI | LE |

On 64-bit PowerPC Implementations, there are an additional 32 bits that are part of the MSR, as shown in Figure 2-18. The bits of the 32-bit MSR are mapped into the low-order 32 bits (bits 32 to 63) of the 64-bit MSR. Currently, there is only one bit defined in the upper 32-bits of the 64-bit MSR: the processor mode bit (SF). This bit indicates whether the processor is in 32-bit or 64-bit mode.

|    |    | F | ig | ure | 2-: | 18 |   | Ma | ach | ine | e S | tat | e R | eg | iste | er f | for | 64 | -bi | t P | ów | erl | PC  | Im | pl | em | en | tati | ior | IS |    |

|----|----|---|----|-----|-----|----|---|----|-----|-----|-----|-----|-----|----|------|------|-----|----|-----|-----|----|-----|-----|----|----|----|----|------|-----|----|----|

| 0  | 1  |   |    |     |     |    |   |    |     |     |     |     |     |    |      |      |     |    |     |     |    |     |     |    |    |    |    |      |     |    | 31 |

| SF | 0  | 0 | 0  | 0   | 0   | 0  | 0 | 0  | 0   | 0   | 0   | 0   | 0   | 0  | 0    | 0    | 0   | 0  | 0   | 0   | 0  | 0   | 0   | 0  | 0  | 0  | 0  | 0    | 0   | 0  | 0  |

| 32 | 33 |   |    | 36  | 37  | 1  |   |    |     | 42  |     |     | 45  |    |      |      |     |    |     |     |    |     |     |    |    |    |    |      |     |    |    |

| 0  | 0  | 0 | 0  | 0   | 0   | 0  | 0 | 0  | 0   | 0   | 0   | 0   | POW | 0  | ILE  | EE   | PR  | FP | ME  | FE0 | SE | BE  | FE1 | 0  | IP | IR | DR | 0    | 0   | RI | LE |

A full definition of the MSR bits is given in Appendix C.

#### Save/Restore Registers (SRR0, SRR1)

The two Save and Restore Registers are used to save the machine status when an interrupt occurs and then to restore the original state when the interrupt has been serviced. These two registers are shown in Figure 2-19.

| 0                                         |                                       | [ <sup>31</sup> ] |

|-------------------------------------------|---------------------------------------|-------------------|

|                                           | SRR0                                  |                   |

|                                           |                                       |                   |

| 0                                         |                                       | [ <sup>31</sup> ] |

| 1. A. | SRR1                                  |                   |

|                                           | · · · · · · · · · · · · · · · · · · · |                   |

| Figure 2-19 | Save and Restore Registers |

|-------------|----------------------------|

|-------------|----------------------------|

F217

SRR0 records the next instruction to be executed after the interrupt has been serviced. SRR1 records the original state of the MSR. When an interrupt occurs, the bits  $\begin{bmatrix} 0\\0.32 \end{bmatrix}$ ,  $\begin{bmatrix} 5:9\\37/41 \end{bmatrix}$ , and  $\begin{bmatrix} 16:31\\48:63 \end{bmatrix}$  are copied from the MSR and placed in the corresponding bit positions of SRR1.

#### **Processor Version Register (PVR)**

The PVR is a read-only 32-bit register that provides a processor ID and revision level (see Figure 2-20). The upper 16 bits define the processor (for example, 0x0001 = 601; 0x0003 = 603), and the lower 16 bits define the engineering revision level.

#### Figure 2-20 Processor Version Register

| 0 | 15      | 16 31    |

|---|---------|----------|

|   | Version | Revision |

#### **Data Address Register (DAR)**

When a Data Storage Interrupt occurs, the DAR is loaded with the effective address of the storage element that caused the access interrupt. Figure 2-21 shows the DAR.

#### Figure 2-21 Data Address Register

| 0   | 63 |

|-----|----|

|     |    |

| DAR |    |

| DAK | 1  |

|     |    |

#### Data Storage Interrupt Status Register (DSISR)

The DSISR is a 32-bit register that defines the cause of Data Storage and Alignment interrupts (see Figure 2-22).

#### Figure 2-22 Data Storage Interrupt Status Register

| 0     | 31 |

|-------|----|

| DSISR |    |

This register is sometimes referred to as the DAE/Source Instruction Service Register.

#### Instruction and Data Block Address Translation Registers (IBAT, DBAT)

The Block Address Translation registers (BATs) are used by the BAT mechanism to record information about the range of memory pages that are considered to be grouped together as a block.

|    | Upper BA                                                                      | AT Register                                                                 |    |                                                                                                                     |

|----|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----|---------------------------------------------------------------------------------------------------------------------|

| 0  | $\begin{bmatrix} 14\\ 46 \end{bmatrix} \begin{bmatrix} 15\\ 47 \end{bmatrix}$ | $\begin{bmatrix} 18\\50 \end{bmatrix} \begin{bmatrix} 19\\51 \end{bmatrix}$ |    | $\begin{bmatrix} 29\\ 61 \end{bmatrix} \begin{bmatrix} 30\\ 62 \end{bmatrix} \begin{bmatrix} 31\\ 63 \end{bmatrix}$ |

| BE | PI 0                                                                          | 0 0 0                                                                       | BL | Vs Vp                                                                                                               |

| Figure 2-23 | Block Address | <b>Translation Registers</b> |

|-------------|---------------|------------------------------|

|-------------|---------------|------------------------------|

|   |      | Lower BA                                                                      | \T I | Reg | iste | er |   |   |   |   |                                          |                          |                                         |                                                                                 |

|---|------|-------------------------------------------------------------------------------|------|-----|------|----|---|---|---|---|------------------------------------------|--------------------------|-----------------------------------------|---------------------------------------------------------------------------------|

| 0 |      | $\begin{bmatrix} 14\\ 46 \end{bmatrix} \begin{bmatrix} 15\\ 47 \end{bmatrix}$ | ]    |     |      |    |   |   |   |   | $\begin{bmatrix} 24 \\ 56 \end{bmatrix}$ | [25]<br>[57] [28<br>[60] | $\begin{bmatrix} 29\\ 61 \end{bmatrix}$ | $\begin{bmatrix} 30 \\ 62 \end{bmatrix} \begin{bmatrix} 31 \\ 63 \end{bmatrix}$ |

|   | BRPN | 0                                                                             | 0    | 0   | 0    | 0  | 0 | 0 | 0 | 0 | 0                                        | WIMG                     | 0                                       | PP                                                                              |

There are four pairs of IBATs and four pairs of DBATs (see Figure 2-23). There are two sets of BAT registers because instruction and data references are handled separately. On PowerPC implementation with unified caches (like the 601), only the IBATs will be implemented.

#### General SPRs (SPRG0-SPRG3)

The four General SPRs are provided to give the operating system extra registers to store whatever information it needs without tying up GPRs. These registers are 32 bits on 32-bit implementations, and 64 bits on 64-bit implementations. Figure 2-24 shows the format of these four registers.

#### Figure 2-24 General SPRs

| 0 [31]        |    |

|---------------|----|

|               |    |

| SPRG <i>n</i> | İ. |

|               |    |

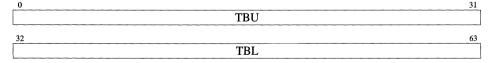

#### Time Base Register (TBU, TBL)

The Time Base Register is a 64-bit register that maintains a counter. The frequency of the counter is system-dependent—to convert the TBR value to calendar values requires the update frequency value that the OS needs to maintain. The two halves of the TBR are shown in Figure 2-25.

The TBR can be accessed as if it were two 32-bit registers by specifying either the upper or lower portion of the register. Read access to the TBR is user-level; write access is supervisor-level.

This register is not defined on the 601.

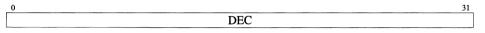

#### **Decrementer (DEC)**

The DEC register is a 32-bit register (see Figure 2-26) that counts down (at the same frequency as the Time Base Register) and generates a Decrementer interrupt when the counter passes 0.

#### Figure 2-26 Decrementer

Because the 601 doesn't have a Time Base Register, the frequency of the DEC on the 601 is the same as for the Real-Time Clock (RTC) defined in the next section.

For compatibility with the POWER architecture, the 601 also provides user-level read access to the DEC by using 6 instead of 22 as the SPR ID with the mfspr instruction.

#### **External Access Register (EAR)**

The EAR is an optional 32-bit SPR that is used to specify the (system specific) resource ID of the target external device that the eciwx and ecowx instructions can communicate with. The fields of the EAR are given in Figure 2-27.

#### Figure 2-27 External Access Register

| 0 | 1 |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 25 | 26  | 31 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----|-----|----|

| Ε | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | RID |    |

#### **Segment Registers (SRs)**

The sixteen 32-bit SRs are used to calculate the virtual address from the 32-bit effective address. These registers are defined for 32-bit implementations only.

The format of the Segment Registers is different depending on if the SR specified an ordinary or a direct-store segment (see Chapter 10, "Memory & Caches," for more information about segments). For ordinary segments, the SR is arranged as shown in Figure 2-28.

#### Figure 2-28 Segment Register for Ordinary Segments

| 0 1 2 3 7         | 8 31 |

|-------------------|------|

| T Ks Kp 0 0 0 0 0 | VSID |

For direct-store segments, the SR is arranged differently, as shown in Figure 2-29.

| Figure 2-29 | Segment | Register | for Direct-store | Segments |

|-------------|---------|----------|------------------|----------|

|             |         |          |                  |          |

| 0 | 1  | 2  | 3 | 11   | 12 31               |

|---|----|----|---|------|---------------------|

| Т | Ks | Кр |   | BUID | controller specific |

#### **Address Space Register (ASR)**

The ASR (Figure 2-30) is a 64-bit SPR that holds the address of the Segment Table. It is defined only for 64-bit implementations.

| Figure 2-30 | Address Space Register |

|-------------|------------------------|

|-------------|------------------------|

| 0 |                               | 51 | 52     | 63 |

|---|-------------------------------|----|--------|----|

|   | Real Address of Segment Table |    | unused |    |

#### **Storage Description Register 1 (SDR1)**

The SDR1 contains the encoded size and the address of the Page Table. This register is 32 bits wide on 32-bit implementations and 64 bits wide on 64-bit implementations, as shown in Figure 2-31.

| Figure 2-31 | Storage | Descriptio | n Register |

|-------------|---------|------------|------------|

|             |         | r          |            |

| 0       | 45 | 46 |        | 58 | 59    | 63   |

|---------|----|----|--------|----|-------|------|

| HTABORG |    |    | unused |    | HTABS | SIZE |

This register is also referred to as the Page Table Search Description Register or simply the Table Search Description Register.

### **Processor Specific Registers**

This section discusses the registers that are not part of the PowerPC specification but are defined by some implementation. These registers are provided by the 601 for POWER compatibility.

#### Multiply-Quotient Register (MQ)

The MQ register (Figure 2-32) is used to emulate the MQ register defined on POWER processors. Certain (non-PowerPC) instructions use this register.

| Figure 2-32 | Multiply-Quotient Register |

|-------------|----------------------------|

|-------------|----------------------------|

| 0  | 31 |

|----|----|

| MQ |    |

This register is defined on the 601 only.

#### Real-Time Clock Registers (RTCU, RTCL)

The RTC registers provide access to the POWER architecture's Real-Time Clock. The upper register (RTCU) keeps track of the number of seconds and the lower register (RTCL) keeps track of the number of nanoseconds since the beginning of the current second. Both halves of this register are shown in Figure 2-33.

| Figure 2-33 | Real-Time | Clock Register |

|-------------|-----------|----------------|

|-------------|-----------|----------------|

|   |        | 3             | 31 |

|---|--------|---------------|----|

|   | R      | rcu           |    |

|   |        |               |    |

| 1 | 2      | 24_253        | 31 |

| 0 | RTCL   | 0 0 0 0 0 0 0 | 0  |

|   | 1<br>0 | 1_2           |    |

This register is defined on the 601 only.

#### 2.4 32- versus 64-bit Implementations

This book describes both the 32-bit and 64-bit versions of the PowerPC architecture. For the most part, the programming model is the same for both versions, but there are some basic differences.

To avoid confusion, it is worth pointing out that the term "64-bit instruction" is used in this section to refer to an instruction that is available on 64-bit implementations only. All of the PowerPC floating-point instructions operate on 64-bit quantities, but are considered 32-bit instructions because they are available on 32-bit PowerPC implementations.

#### 32/64-bit Operating Modes

There are some subtle differences between the 32-bit and 64-bit operating modes for the PowerPC. In general, these differences affect only the instructions that are available for use and the method by which effective addresses are calculated, but in some instances instructions behave differently based on the operating mode.

#### **32-bit Mode on 32-bit Implementations**

All 32-bit instructions are available. No 64-bit instructions are available.

#### 64-bit Mode on 32-bit Implementations

Is not allowed. Any attempt to execute a 64-bit instruction on a 32-bit implementation will result in an Illegal Instruction exception.

#### 32-bit Mode on 64-bit Implementations

This compatibility mode for 32-bit implementations behaves just like the 32-bit mode on 32-bit implementations with these exceptions:

- Instructions defined only for 32-bit implementations (for example, mfsr, mtsr) are not available and will cause an Illegal Instruction exception.

- All effective address calculations are performed using all 64 bits of the source registers. However, the upper 32 bits are set to 0 before accessing data or fetching instructions.

- Instructions that always return a 64-bit result (for example, mulhd) will work properly (that is, they will return a 64-bit result as expected) in 32-bit mode.

#### 64-bit Mode on 64-bit Implementations

All instructions operate on all 64 bits of the source registers and produce 64-bit results.

### 32/64-bit Registers

The most significant difference between 32- and 64-bit implementations is the width of many of the processor registers. These differences are summarized in this section.

#### GPRs

All of the GPRs are 32 bits wide for 32-bit implementations and 64 bits wide for 64-bit implementations. For 64-bit implementations, all 64 bits of the register are affected, except when executing in 32-bit mode.

#### **Counter Register**

The Counter Register (CTR) is 32 or 64 bits wide, depending on the PowerPC implementation. To insure that 64-bit implementations executing in 32-bit mode operate the same as 32-bit implementations, only the low-order 32 bits of the CTR are used when the processor is in 32-bit mode.

#### **Machine State Register**

The MSR is 32 bits wide on 32-bit implementations and 64 bits wide on 64-bit implementations. The 32 additional bits for the 64-bit version are used to store the current mode (32- or 64-bit), and to extend the reserved field from the 32-bit MSR.

#### Save/Restore Registers

These registers (SSR0 and SSR1) are 32 bits on 32-bit implementations and 64 bits on 64-bit implementations. If an interrupt occurs on a 64-bit implementation executing in 32-bit mode, the upper 32 bits of SSR0 (the register that stores the *next instruction address*) are set to 0 because the lower 32 bits are enough to hold the address.

#### **Segment Registers**

The sixteen 32-bit SRs are present only on 32-bit implementations. The instructions to access the Segment Registers (mfsr, mfsrin, mtsr, and mtsrin) do not exist on 64-bit implementations (not even in 32-bit mode). Trying to execute them will result in an Illegal Instruction exception.

#### **Address Space Register**

The ASR is defined only for 64-bit implementations, and thus, does not exist on any 32-bit PowerPC implementation.

#### **Storage Description Register 1**

The SDR1 is 32 bits wide on 32-bit implementations and 64 bits wide on 64-bit implementations. Although the SDR1 always contains Page Table information, the format of the information is different for 32- and 64-bit implementations.

# Instruction Set Overview

The next few chapters contain an overview of all the instructions and extended instruction forms for the PowerPC ISA. The instructions are grouped according to function under the following headings: Branch and Trap, Load and Store, Integer, Rotate and Shift, Floating-Point, and System Register.

This chapter acts as an introduction to the following chapters. It describes the basic instruction structures and provides a summary of the notation used to describe the instructions and extended forms.

# 3.1 Instruction Groups

The instructions are grouped according to function within each of the major headings. For example, in Chapter 6, "Integer Instructions," there are subheadings for Addition, Subtraction, Multiplication, and Division. Within these subsections, all relevant instructions are presented along with a short textual description of the instruction operation.

Each section also includes many tables that summarize the operations and the syntax for each instruction form. These tables are meant to make it easy to see the (sometimes subtle) differences between the various instructions of the same type.

# 3.2 Instruction Suffixes

Many instructions allow standard suffixes to be specified to tell the processor to perform operations in addition to the basic instruction. For each instruction that allows suffixes, each valid suffix for the instruction is enclosed in square brackets ('[' and ']') immediately following the base mnemonic. If there are multiple suffixes for an instruction, they will each be enclosed in a separate set of brackets.

## Integer Suffixes: 'o' and '.'

For integer instructions, valid suffixes are 'o' and '.'. Appending an 'o' tells the instruction to update the Fixed-Point Exception Register (XER) to reflect the Overflow (XER[OV]) and Summary Overflow (XER[SO]) information from the instruction's operation. Without this option, integer instructions do not supply the overflow information as part of the result.

When the '.' suffix is appended to integer instructions, it indicates that the condition information should be recorded in field 0 of the Condition Register (CR{0}). This condition information records whether the result is less than zero, greater than zero, or equal to zero, and it contains a shadow copy of the Summary Overflow bit in the XER (XER[SO]).

## Floating-Point Suffixes: 's' and '.'

Most floating-point instructions allow two types of suffixes to be specified: 's' and '.'. The 's' suffix indicates that the operation should be performed by interpreting the registers as if they contained single-precision data. If the operand registers do not truly contain single-precision values, then the result of instructions executed with the 's' option is undefined.

All arithmetic floating-point instructions allow the ' $\cdot$ ' suffix to be specified. This suffix tells the instruction to record the condition information in field 1 of the Condition Register (CR{1}). This keeps track of any floating-point exceptions that may be caused by the instruction. Floating-point is discussed in detail in Chapter 8.

## Branch Suffixes: 'l' and 'a'

All branch instructions allow an '1' suffix and some forms also allow an 'a' suffix. The '1' suffix indicates that the address of the following instruction should be recorded in the Link Register as part of the instruction operation, and the 'a' suffix indicates that the specified address is an absolute (instead of a program counter relative) value. These suffixes are described in greater detail in §4.1, "Branch Instructions."

## 3.3 Extended Instruction Forms

Extended instruction forms are extra mnemonics that the assembler accepts and converts into valid instruction forms. These forms are not instructions themselves but are special cases of valid instruction forms. Extended forms are useful when the base form of an instruction is very general, as is the case with the branch and rotate instructions. The special cases provided by the extended forms can render an instruction that is complex and unwieldy (for example, *Rotate Left Word Immediate then AND with Mask*) into something more understandable (for example, *Shift Left Immediate*).

The following chapters present both the standard instruction forms and the extended forms. When an extended form is presented, the base mnemonic from which the form is derived is given, along with a description of how the extended form maps into the base instruction.

# 3.4 Obsolete Instructions

Obsolete instructions are instructions that were part of the POWER architecture specification but were not included in the PowerPC ISA in an effort to streamline the architecture. All obsolete instructions are clearly marked as being obsolete to eliminate any confusion that might arise from the inclusion of these instructions.

The obsolete instructions listed in the next few chapters are implemented only on the 601, for the purposes of backward compatibility only. New programs should *not* make use of these instructions. No future PowerPC implementation will support these instructions (although a computer system built using a PowerPC processor may trap and emulate them in software).

Wherever possible, a brief explanation is given of why the instruction was removed for the PowerPC architecture. In most cases, the instructions were removed to eliminate bottlenecks caused by seldom-used functionality or to reduce the complexity of PowerPC implementations.

## 3.5 Optional Instructions

The PowerPC ISA specification defines some instructions to be optional. These instructions may or may not be present on a particular PowerPC implementation. In these chapters, all optional instructions are clearly noted as being optional.

Before using these instructions, the programmer must first verify that the program is running on an implementation that supports the given instruction. To determine which PowerPC processors implement a particular instruction, instructions can be referenced in Appendix A, which contains an alphabetical list of all instructions.

Most of the optional instructions are defined as belonging to one of a variety of instruction groups, for example, the Graphical Group. A processor may implement any or all of the instructions in any of the groups, but if a processor claims to support a given group, it must implement all of the instructions in the given group.

At the moment, there are only two groups of optional instructions defined: the General Purpose Group and the Graphical Group. The General Purpose Group contains the fsqrt and fsqrts instructions, and the Graphical Group contains stfiwx, fres, frsqrte, and fsel.

An optional instruction need not belong to any of the optional groups. For example, eciwx and ecowx are both optional instructions, but they are not associated with any group.

## 3.6 Notation

Because of the complexity of most of the instructions, a special notation is needed to properly describe an instruction's operation.

The following notation is used throughout this chapter to describe the operation of instructions.

- rT Specifies any of the 32 General Purpose Registers (GPRs) that are part of the Integer Unit. These registers may be 32 or 64 bits wide, depending on the PowerPC implementation: 32 bits wide on 32-bit implementations and 64 bits wide on 64-bit implementations. For example, **r** 3 specifies GPR 3.

- frT Specifies any of the 32 64-bit Floating-Point Registers (FPRs) that are part of the Floating-Point Unit. For example, **fr13** specifies FPR 13.

- MQ Specifies the Multiply-Quotient Register. This register exists only on POWER implementations and is used for multiply, divide and extended shift and rotate operations.

- CR Specifies the Condition Register. This register is commonly divided into eight fields that are specified using CR{0} through CR{7}.

- CIP Current Instruction Pointer. This is not a user-visible register on the PowerPC, but the CIP notation is convenient when describing how an instruction affects the flow of control. For example, CIP  $\leftarrow$  LR indicates that the next instruction to be executed is at the address contained in the Link Register.

- (rT) Specifies the contents of the given register. The specified register may be any GPR, FPR, or Special Purpose Register. For example, (r2) specifies the contents of GPR 2; (fr4), which specifies the contents of FPR 4.

- (*x*) Groups the expressions in *x* so that they are executed before expressions outside of the parentheses.

- $\begin{bmatrix} \frac{x1}{x2} \end{bmatrix}$  Specifies a number *x*. Two values of *x* are given: the top value (*x*1) is the number for 32-bit PowerPC implementations, and the bottom value (*x*2) is the number for 64-bit PowerPC implementations. This notation is used when referring to bits in registers, since the bit numbering is slightly different between the two implementation types.

- rT[x] Specifies the bit x in the given register. The specified register may be any GPR, FPR, or Special Purpose Register. Note that bits are numbered using the big-endian notation, thus bit 0 is the *high-order* or *most-significant bit*, and bit 31 (or 63 for 64-bit implementation) is the *low-order* or *least-significant bit*. For example, r2[4] refers to bit 4 of GPR 2.

- rT  $\begin{bmatrix} x^1 \\ x^2 \end{bmatrix}$  Specifies the bit *x* in the given register. Two values for *x* are given: the top value (*x*1) specifies the bit for 32-bit PowerPC implementations, and the lower value (*x*2) specifies the bit for 64-bit PowerPC implementations. This is typically used only for GPRs since most other registers are the same size on both implementation types. For example, **r3**  $\begin{bmatrix} 0 \\ 32 \end{bmatrix}$  refers to the sign bit of the (low-order) word in GPR 3.

- rT[x:y] Specifies the range of bits from x to y in the given register. The specified register may be any GPR, FPR, or Special Purpose Register. For example, r1[0:7] refers to bits 0 through 7 in GPR 1.

- rT  $\begin{bmatrix} \frac{x1+y1}{x2+y2} \end{bmatrix}$  Specifies the range of bits from *x* to *y* in the given register. Two ranges of *x* and *y* are given: the upper range (*x*1:*y*1) for 32-bit PowerPC implementations and the lower range (*x*2:*y*2) for 64-bit implementations. This is typically used only for GPRs since most other registers are the same size on both implementation types. For example, r3  $\begin{bmatrix} 24\cdot31\\ 56\cdot63 \end{bmatrix}$  refers to the least significant byte of GPR 3.

- $rT{x}$  Specifies the range of bits corresponding to field *x* in the given register. The bits for a field *n* range from bit *n*×4 to bit *n*×4+3, thus, this notation is equivalent to  $rT[(x \times 4):(x \times 4) + 3]$ . The specified register may be any GPR, FPR, or Special Purpose Register. For example, CR{0} refers to field 0 (bits 0:3) of the Condition Register.

- *X* Where *X* is any number of digits 0-9, specifies a decimal constant, for example, 24.

- bX Where X is any number of digits 0-1, specifies a binary constant, for example, b0110.

#### §3.6 Notation

- **0x***X* Where *X* is any number of digits **0-9** or letters **A-F**, specifies a hexadecimal constant. Hexadecimal constants will always be specified using uppercase alphabetic characters, for example, **0xBABE**.

- $x \leftarrow y$  Loads x with the value y. This is used to identify the value that gets assigned to the instruction's target register. For example,  $rT \leftarrow 0$  means that register rT gets assigned a value of 0.

- x := y Loads the temporary variable x with the value y. Temporary variables are used when the instruction operation is too complex to express in a single expression. This separate assignment notation for temporary variables is used to emphasize the fact that the variable x is not a processor resource that is being updated. For example, m := (r2) means that the temporary variable m is set equal to the contents of register r2.

- x = y Returns true if x is equal to y, false otherwise.

- $x \neq y$  Returns true if x is not equal to y, false otherwise.

- x > y Returns true if x is greater than y, false otherwise.

- x < y Returns true if x is less than y, false otherwise.

- $x \ge y$  Returns true if x is greater than or equal to y, false otherwise.

- $x \le y$  Returns true if x is less than or equal to y, false otherwise.

- ≈*x* Returns a value that is approximately equal to *x*, for example,  $rT \Leftarrow \approx \sqrt{2}$  assigns *rT* with a value that is close to, but not necessarily equal to, the square root of *x*.

- |x| Calculates the absolute value of *x*.

- $\sim x$  Calculates the one's complement of x. A one's complement operation converts all binary '1's in the source value to binary '0's in the destination value and vice versa. For example,  $\sim$ b01101010 becomes b10010101.

- -*x* Negates *x*. This is the same as performing the two's complement of *x*. The two's complement of a value is equal to the one's complement plus 1. For example, -b0110 becomes b1010.

- `x Sign-extends the value x as appropriate. Sign-extension means that the most significant bit of x (also called the *sign bit*) is replicated to the left to fill all available bit positions. For example, `0x0042 sign-extends to 0x0000000 00000042 on 64-bit implementations; and `0xFADE sign-extends to 0xFFFFFADE on 32-bit implementations.

- °x Zero-extends the value x as appropriate. Zero-extension means that 0 bits are used to the left of x to fill all available bit positions. For example, °0xDEADF00D zero-extends to 0xDEADF00D on 32-bit implementations and to 0x00000000 DEADF00D on 64-bit implementations.

- x + y Adds x to y.

- 32 Chapter 3

- x y Subtracts y from x.

- $x \times y$  Multiplies *x* by *y*.

- $x \div y$  Divides x by y.

- x % y Calculates the remainder of *x* divided by *y*.

- $x \perp y$  Concatenates x with y. For example,  $0x5CAB \perp 0xFACE$  becomes 0x5CABFACE.

- x & y Logically ANDs x and y. For example, b0110 & b1010 becomes b0010.

- $x \mid y$  Logically ORs x and y. For example, **b0110** | **b1010** becomes **b1110**.

- $x \oplus y$  Logically XORs *x* and *y*. For example, **b0110**  $\oplus$  **b1010** becomes **b1100**.

- $x \equiv y$  Calculates the equivalence of x and y. The result of the equivalence is 1 wherever the bits of x and y are the same and 0 wherever they differ. For example, b0110 = b1010 becomes b0011.

- $x \ll y$  Shifts x left by y bits. For example, b10101111 « 2 becomes b10111100.

- x » y Shifts x right by y bits. For example, b10101111 » 2 becomes b00101011.

- x \* y

Shifts x right algebraically by y bits. An algebraic shift duplicates the most significant bit (bit 0 or the *sign* bit) as it shifts the data. For example, b10101010 \* 4 becomes b11111010; b01110101 \* 4 becomes b00000111.

- $x \bigcirc y$  Rotates x left by y bits. For example, b11110000  $\bigcirc$  2 becomes b11000011.

- $x \heartsuit y$  Rotates x right by y bits. For example, b00001111  $\heartsuit 2$  becomes b11000011.

- x ? y : z Returns either y or z depending on the value of x, where x is a Boolean expression. If x is true, then y is returned, otherwise z is returned. For example,  $rT \leftarrow (rA[26]=0) ? 0 : (rB)$  means that if bit rA[26] is 0, rT is set equal to 0, otherwise it is set equal to the contents of rB.

# Branch and Trap Instructions

The Branch, Trap, and System Call instructions are the only instructions that change the flow of control of the processor. Since this potential change of control can disrupt the smooth operation of the pipeline, these instructions are handled by a separate branch processor that does its best to remove these instructions from the instruction stream before passing the instructions on to the other execution units.

# 4.1 Branch Instructions

There are four basic types of branch instructions: *Branch, Branch Conditional,* and *Branch Conditional to* either the *Link Register* or the *Counter Register* (see Table 4.1). The first two of these instructions expect the target address to be encoded in the branch instruction, while the second two branch instructions get the target address from one of the processor's Special Purpose Registers.

All four of the branch instructions allow an optional '1' suffix to indicate that the address of the instruction following the branch should be stored in the Link Register (LR) as part of the branch operation. This provides a simple way of implementing subroutines, since the return address can be saved in the LR using the '1' option, and the subroutine can return to the caller by using a *Branch to Link Register* (blr) instruction.

The *Branch* (b) and *Branch Conditional* (bc) instructions have an additional option 'a' that allows the target address to be specified as an absolute value. Usually, the target address is specified relative to the current location counter,

| b[1][a] <i>addr</i><br>Branch                                  | $if(l = 1)$ $LR \Leftarrow CIP + 4$ $if(a = 1)$ $CIP \Leftarrow `addr$ else $CIP \Leftarrow CIP + `addr$               |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| bc[1][a] <i>BO, BI, addr</i><br>Branch Conditional             | $if(l = 1)$ $LR \leftarrow CIP + 4$ $if(condition)$ $if(a)$ $CIP \leftarrow `addr$ $else$ $CIP \leftarrow CIP + `addr$ |

| bcctr[1] <i>BO, BI</i><br>Branch Conditional to Count Register | $if(l = 1)$ $LR \Leftarrow CIP + 4$ $if(condition)$ $CIP \Leftarrow CTR$                                               |

| bclr[1] <i>BO, BI</i><br>Branch Conditional to Link Register   | oldLR := LR<br>if(l = 1)<br>$LR \Leftarrow CIP + 4$<br>if(condition)<br>$CIP \Leftarrow oldLR$                         |

#### Table 4-1 Basic Branch Instructions

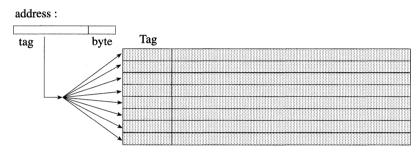

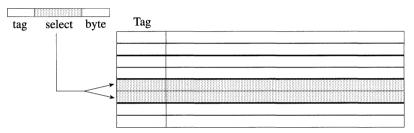

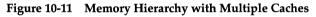

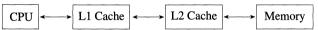

that is, as a positive or negative offset from the address of the branch instruction. If the "Absolute Address" option is set by using the 'a' option, then the target address is taken directly from the branch instruction, without adjusting for the current location counter.