# MITSUBISHI 1991 SEMICONDUCTORS

SINGLE-CHIP 16-BIT MICROCOMPUTERS

Enlarged edition

# MITSUBISHI 1991 SEMICONDUCTORS

SINGLE-CHIP 16-BIT MICROCOMPUTERS

**Enlarged** edition

All values shown in this catalogue are subject to change for product improvement.

The information, diagrams and all other data included herein are believed to be correct and reliable. However, no responsibility is assumed by Mitsubishi Electric Corporation for their use, nor for any infringements of patents or other rights belonging to third parties which may result from their use.

| 1 | GUIDANCE                         |

|---|----------------------------------|

| 2 | MELPS 7700 16-BIT MICROCOMPUTERS |

| 3 | PROGRAMMABLE ROM MICROCOMPUTERS  |

APPENDICES 4

## MITSUBISHI MICROCOMPUTERS INDEX

| 1 GUID  | ANCE                           |                                                      | PAGE          |

|---------|--------------------------------|------------------------------------------------------|---------------|

|         |                                |                                                      |               |

|         |                                |                                                      |               |

| Orderi  | ng Information······           |                                                      | 1—8           |

|         |                                |                                                      |               |

|         |                                | ters                                                 |               |

| Symbo   | logy                           |                                                      | 1—15          |

|         |                                |                                                      |               |

|         |                                |                                                      |               |

| 2 MELF  | PS 7700 16-BIT MICROCOM        | MPUTERS                                              |               |

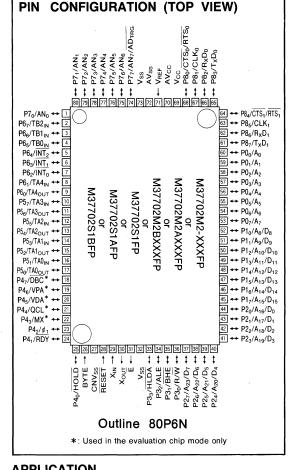

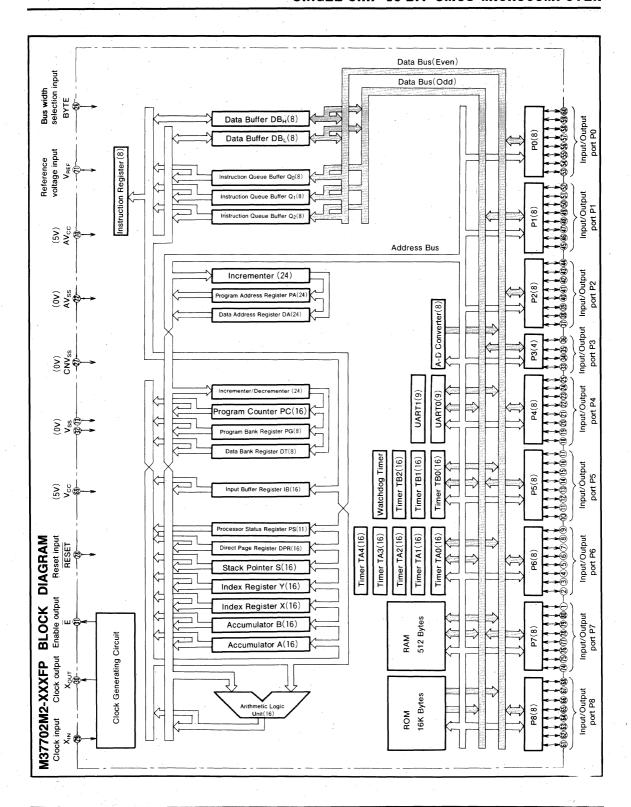

|         |                                | M37702M2BXXXFP, M37702S1FP, M37702S1AFP, M37         | 702S1BFP      |

|         | ,                              | Single-Chip 16-Bit CMOS Microcomputer ·····          |               |

| M3770   | 2M4-XXXFP M37702M4AXXXFP       | M37702M4BXXXFP, M37702S4FP, M37702S4AFP, M37         |               |

| 14.0770 | ENIA XXXIII, MOTTOEMAXXXXIII,  | Single-Chip 16-Bit CMOS Microcomputer ······         |               |

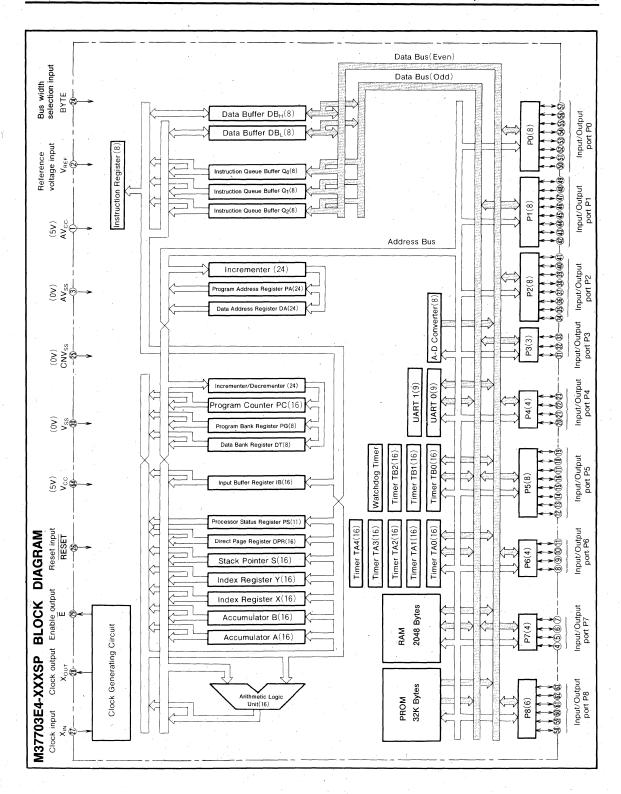

| M3770   | ISM2-XXXSP M37703M2AXXXSP      | , M37703M2BXXXSP, M37703S1SP, M37703S1ASP, M37       |               |

| 14.0770 | ome xxxxxx, morrouner, xxxxxx  | Single-Chip 16-Bit CMOS Microcomputer ·····          |               |

| M3770   | ISMA_YYYSP M37703M4AYYYSP      | , M37703M4BXXXSP, M37703S4SP, M37703S4ASP, M37       |               |

| 1410770 | OMIT-XXXXII, MOTTOOMITAXXXXII, | Single-Chip 16-Bit CMOS Microcomputer ·····          |               |

| M2772   | 0S1FP, M37720S1AFP             | 16-Bit CMOS Microcomputer                            |               |

|         | •                              | BFP, M37730S2SP, M37730S2ASP, M37730S2BSP            | 2 00          |

| W3773   | 032FF, M3773032AFF, M3773032   | 16-Bit CMOS Microcomputer······                      | 2—170         |

| 140770  | 0004ED M0770004AED M0770004    |                                                      | 2-179         |

| MS//S   | 32S4FP, M37732S4AFP, M37732S4  | 16-Bit CMOS Microcomputer·····                       | 2_227         |

| MELD    | 0.7700 Addus asing Mades       | 16-Bit CMOS Microcomputer                            |               |

|         |                                |                                                      |               |

|         |                                |                                                      |               |

| MELP    | 3 7700 Machine Instructions    |                                                      | 2—344         |

| 2       |                                | \$                                                   |               |

| PROC    | GRAMMABLE ROM MICRO            | COMPUTERS                                            |               |

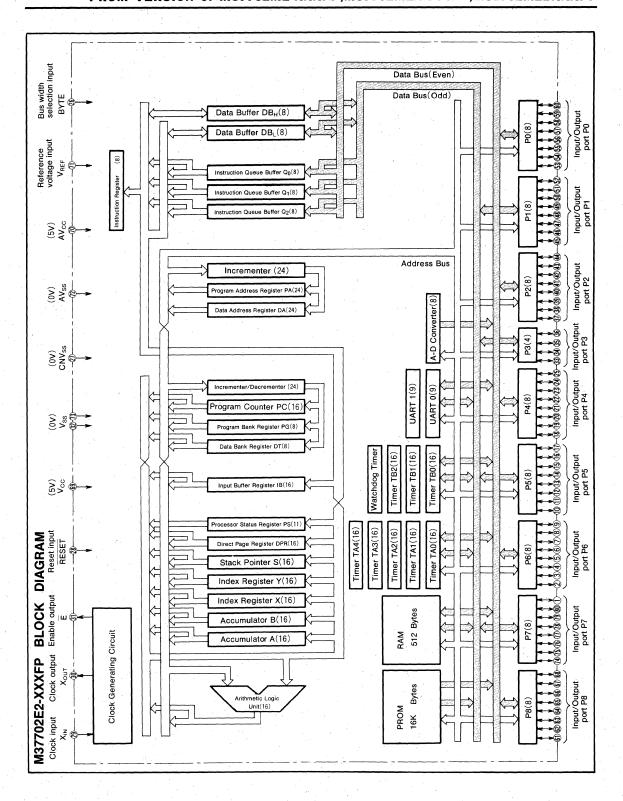

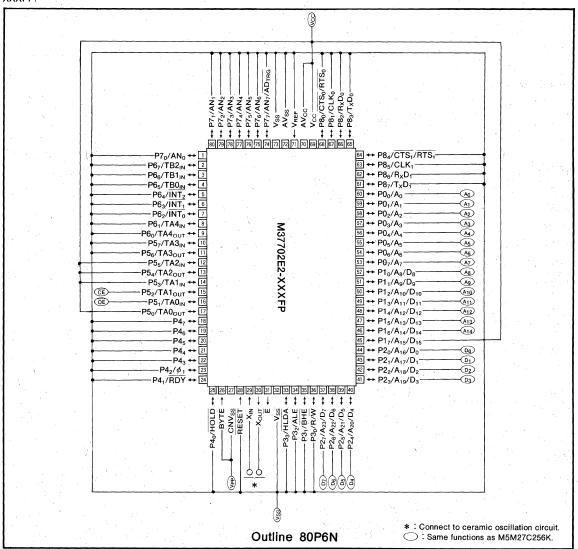

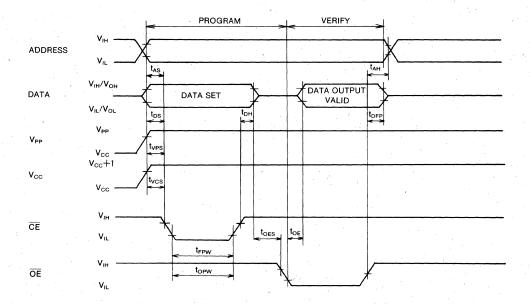

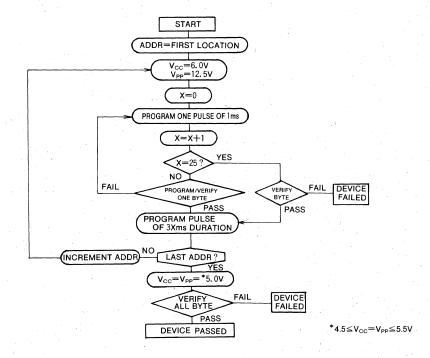

|         |                                | M37702E2BXXXFP, M37702E2FS, M37702E2AFS, M3770       | D2E2BFS       |

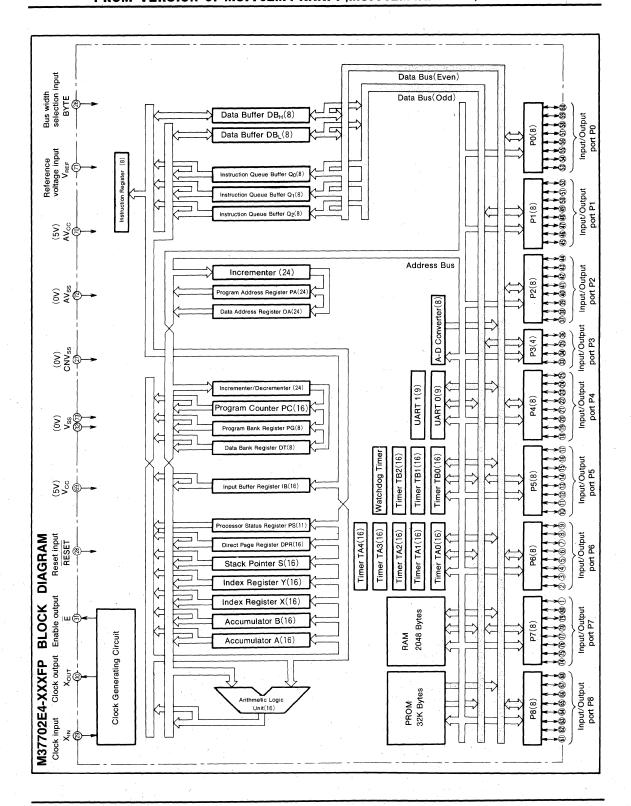

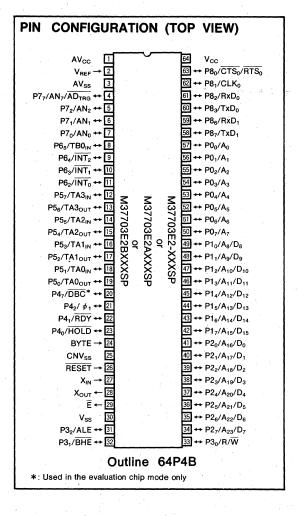

|         | PROM Ve                        | ersion of M37702M2-XXXFP, M37702M2AXXXFP, M37702M2BX | xxfp3—3       |

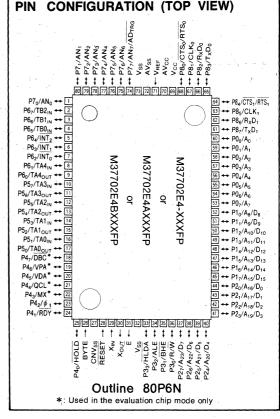

| M3770   | J2E4-XXXFP, M37702E4AXXXFP,    | M37702E4BXXXFP, M37702E4FS, M37702E4AFS, M3770       | 02E4BFS       |

|         |                                | ersion of M37702M4-XXXFP, M37702M4AXXXFP, M37702M4BX |               |

| M3770   | 3E2-XXXSP, M37703E2AXXXSP,     | M37703E2BXXXSP                                       |               |

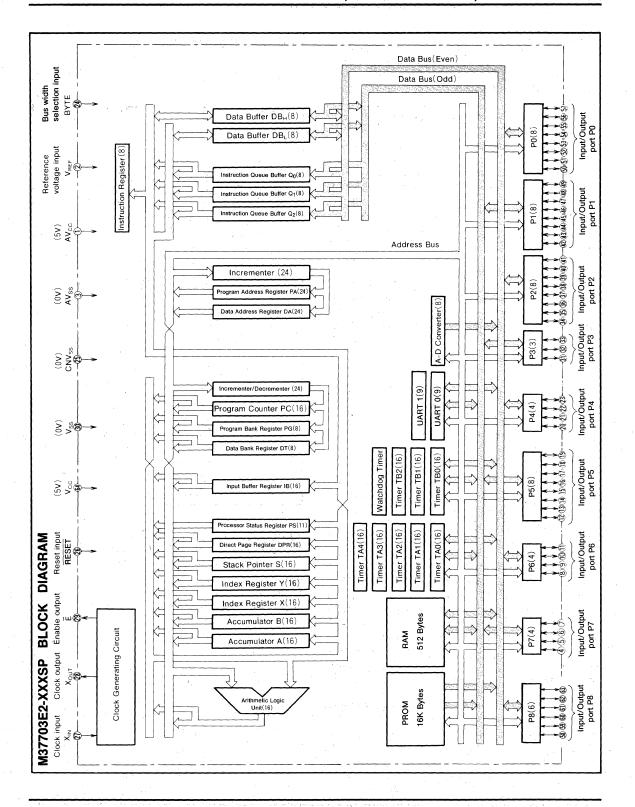

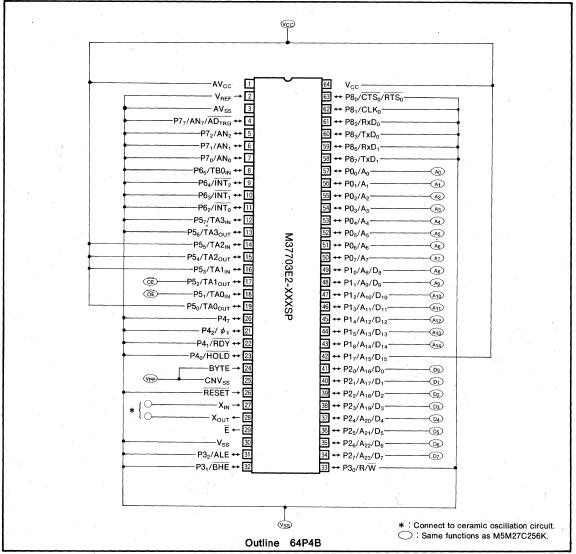

|         |                                | ersion of M37703M2-XXXSP, M37703M2AXXXSP, M37703M2BX | XXSP·····3—28 |

| M3770   | 3E4-XXXSP, M37703E4AXXXSP,     |                                                      |               |

|         |                                | ersion of M37703M4-XXXSP, M37703M4AXXXSP, M37703M4BX | xxsp3—51      |

| 4 APPE  | INDICES                        |                                                      |               |

| AFFE    |                                | od                                                   |               |

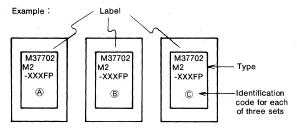

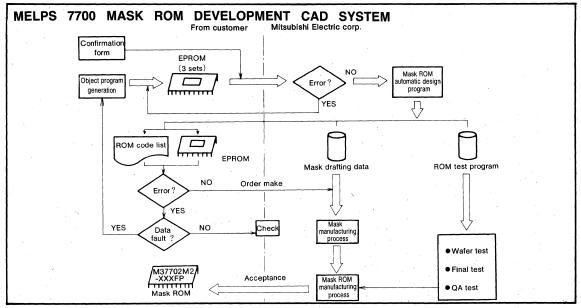

| MELP    | 5 7700 Mask ROM Ordering Metho | oa                                                   | 4 10          |

| MELP    | S //UU PROM Ordering Method    | ······································               | 4 00          |

| Mark S  | specification Form             |                                                      | 4—29          |

**Contact Addresses for Further Information**

## GUIDANCE 1

## MITSUBISHI MICROCOMPUTERS

## INDEX BY FUNCTION

## ■MELPS 7700 16-BIT MICROCOMPUTERS

|                |                                                                                               |           |                          |                                      | al charac |                                 |         |      |

|----------------|-----------------------------------------------------------------------------------------------|-----------|--------------------------|--------------------------------------|-----------|---------------------------------|---------|------|

| Туре           | Circuit function and organization                                                             | Structure | Supply<br>voltage<br>(V) | Typ.<br>power<br>dissipation<br>(mW) |           | Max.<br>fre-<br>quency<br>(MHz) | Package | Page |

| M37702M2-XXXFP | 16K-Byte Mask-Prog. ROM, 512-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O  | C, Si     | 5±10%                    | 30                                   | 500       | 8                               | 80P6N   |      |

| M37702M2AXXXFP | 16K-Byte Mask-Prog. ROM, 512-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O  | C, Si     | 5±10%                    | 60                                   | 250       | 16                              | 80P6N   |      |

| M37702M2BXXXFP | 16K-Byte Mask-Prog. ROM, 512-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O  | C, Si     | 5±10%                    | 95                                   | 160       | 25                              | 80P6N   | 2-3  |

| M37702S1FP     | External ROM, 512-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O             | C, Si     | 5±10%                    | 30                                   | 500       | 8                               | 80P6N   | 2-3  |

| M37702S1AFP    | External ROM, 512-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O             | C, Si     | 5±10%                    | 60                                   | 250       | 16                              | 80P6N   |      |

| M37702S1BFP    | External ROM, 512-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O             | C, Si     | ,5±10%                   | 95                                   | 160       | 25                              | 80P6N   |      |

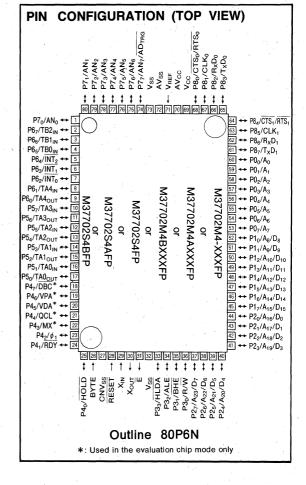

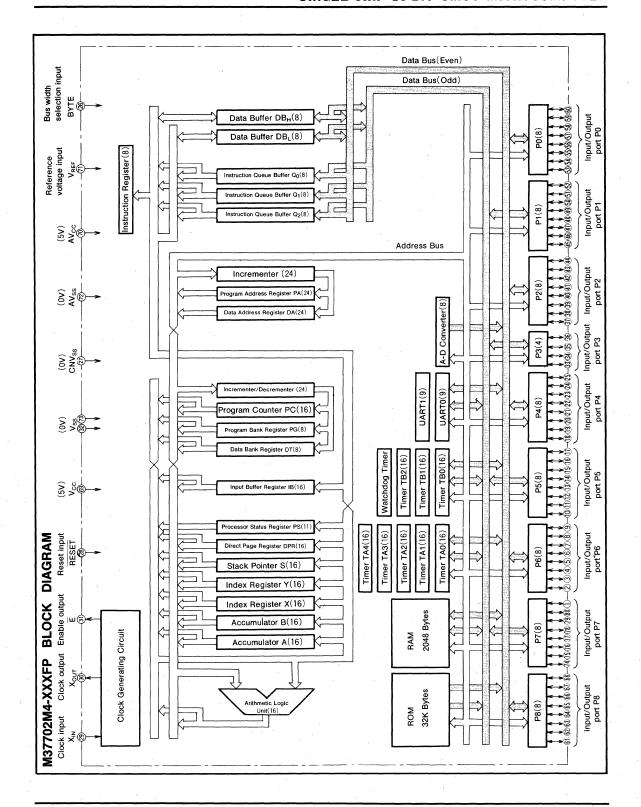

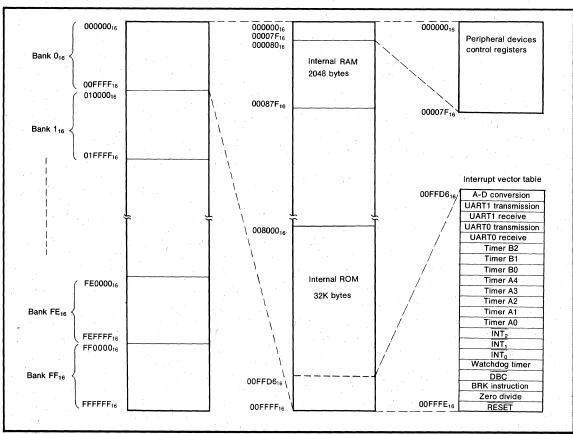

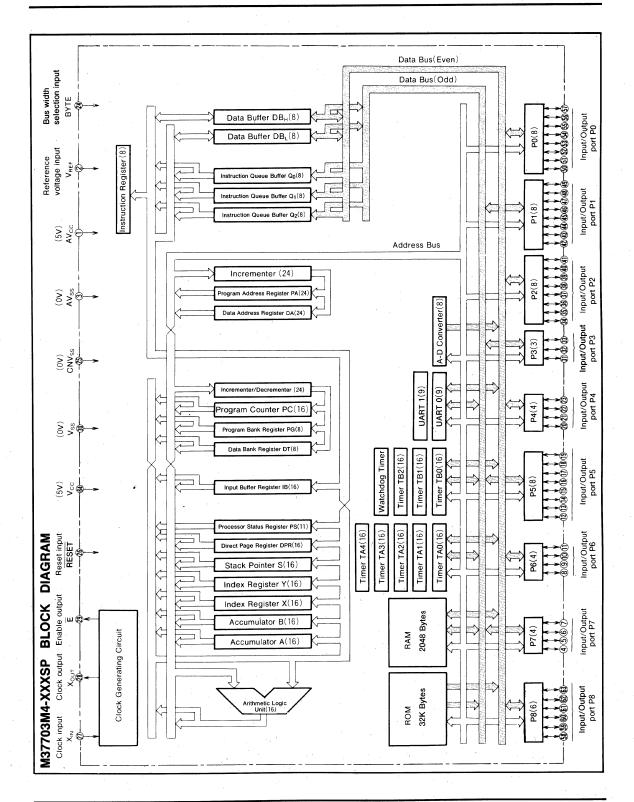

| M37702M4-XXXFP | 32K-Byte Mask-Prog. ROM, 2048-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O | C, Si     | 5±10%                    | 30                                   | 500       | 8                               | 80P6N   |      |

| M37702M4AXXXFP | 32K-Byte Mask-Prog. ROM, 2048-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O | C, Si     | 5±10%                    | 60                                   | 250       | 16                              | 80P6N   | 2-62 |

| M37702M4BXXXFP | 32K-Byte Mask-Prog. ROM, 2048-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O | C, Si     | 5±10%                    | 95                                   | 160       | 25                              | 80P6N   |      |

| M37702S4FP     | External ROM, 2048-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O            | C, Si     | 5±10%                    | 30                                   | 500       | 8                               | 80P6N   |      |

| M37702S4AFP    | External ROM, 2048-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O            | C, Si     | 5±10%                    | 60                                   | 250       | 16                              | 80P6N   |      |

| M37702S4BFP    | External ROM, 2048-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O            | C, Si     | 5±10%                    | 95                                   | 160       | 25                              | 80P6N   |      |

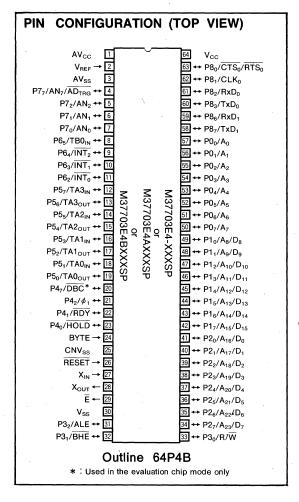

| M37703M2-XXXSP | 16K-Byte Mask-Prog. ROM, 512-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O  | C, Si     | 5±10%                    | 30                                   | 500       | 8                               | 64P4B   |      |

| M37703M2AXXXSP | 16K-Byte Mask-Prog. ROM, 512-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O  | C, Si     | 5±10%                    | 60                                   | 250       | 16                              | 64P4B   |      |

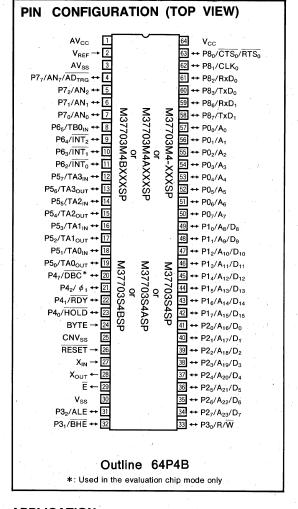

| M37703M2BXXXSP | 16K-Byte Mask-Prog. ROM, 512-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O  | C, Si     | 5±10%                    | 95                                   | 160       | 25                              | 64P4B   | 2-65 |

| M37703S1SP     | External ROM, 512-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O             | C, Si     | 5±10%                    | 30                                   | 500       | 8                               | 64P4B   |      |

| M37703S1ASP    | External ROM, 512-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O             | C, Si     | 5±10%                    | 60                                   | 250       | 16                              | 64P4B   |      |

| M37703S1BSP    | External ROM, 512-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O             | C, Si     | 5±10%                    | 95                                   | 160       | 25                              | 64P4B   |      |

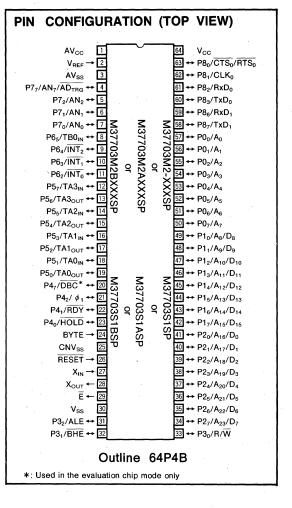

| M37703M4-XXXSP | 32K-Byte Mask-Prog. ROM, 2048-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O | C, Si     | 5±10%                    | 30                                   | 500       | 8                               | 64P4B   |      |

| M37703M4AXXXSP | 32K-Byte Mask-Prog. ROM, 2048-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O | C, Si     | 5±10%                    | 60                                   | 250       | 16                              | 64P4B   | 2—84 |

| M37703M4BXXXSP | 32K-Byte Mask-Prog. ROM, 2048-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O | C, Si     | 5±10%                    | 95                                   | 160       | 25                              | 64P4B   | 2-84 |

| M37703S4SP     | External ROM, 2048-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O            | C, Si     | 5±10%                    | 30                                   | 500       | 8                               | 64P4B   | 1    |

■MELPS 7700 16-BIT MICROCOMPUTERS (Continue)

|             | *                                                                                                      |           |       | Electric                             | al charac | teristics                       |         |       |

|-------------|--------------------------------------------------------------------------------------------------------|-----------|-------|--------------------------------------|-----------|---------------------------------|---------|-------|

| Туре        | Circuit function and organization                                                                      | Structure |       | Typ.<br>power<br>dissipation<br>(mW) |           | Max.<br>fre-<br>quency<br>(MHz) | Package | Page  |

| M37703S4ASP | External ROM, 2048-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O                     | C, Si     | 5±10% | 60                                   | 250       | 16                              | 64P4B   | 2-84  |

| M37703S4BSP | External ROM, 2048-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O                     | C, Si     | 5±10% | 95                                   | 160       | 25                              | 64P4B   | 2-04  |

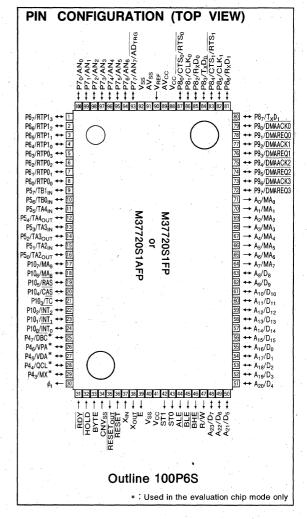

| M37720S1FP  | External ROM, 512-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O, DMA/DRAM Controller | C, Si     | 5±10% | 30                                   | 500       | 8                               | 100P6S  | 0.00  |

| M37720S1AFP | External ROM, 512-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O, DMA/DRAM Controller | C, Si     | 5±10% | 60                                   | 250       | 16                              | 100P6S  | 2—86  |

| M37730S2FP  | External ROM, 1024-Byte RAM<br>16-Bit Timer, Serial I/O                                                | C, Si     | 5±10% | 30                                   | 500       | 8                               | 64P6N   |       |

| M37730S2AFP | External ROM, 1024-Byte RAM<br>16-Bit Timer, Serial I/O                                                | C, Si     | 5±10% | 60                                   | 250       | 16                              | 64P6N   |       |

| M37730S2BFP | External ROM, 1024-Byte RAM<br>16-Bit Timer, Serial I/O                                                | C, Si     | 5±10% | 95                                   | 160       | 25                              | 64P6N   | 2-179 |

| M37730S2SP  | External ROM, 1024-Byte RAM<br>16-Bit Timer, Serial I/O                                                | C, Si     | 5±10% | 30                                   | 500       | 8                               | 64P4B   | 2-178 |

| M37730S2ASP | External ROM, 1024-Byte RAM<br>16-Bit Timer, Serial I/O                                                | C, Si     | 5±10% | 60                                   | 250       | 16                              | 64P4B   |       |

| M37730S2BSP | External ROM, 1024-Byte RAM<br>16-Bit Timer, Serial I/O                                                | C, Si     | 5±10% | 95                                   | 160       | 25                              | 64P4B   |       |

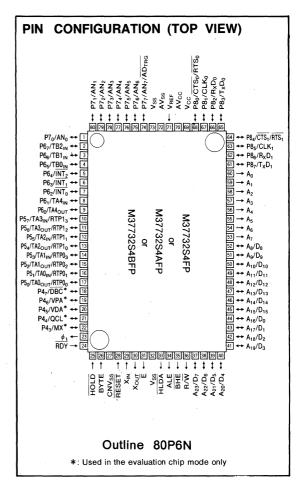

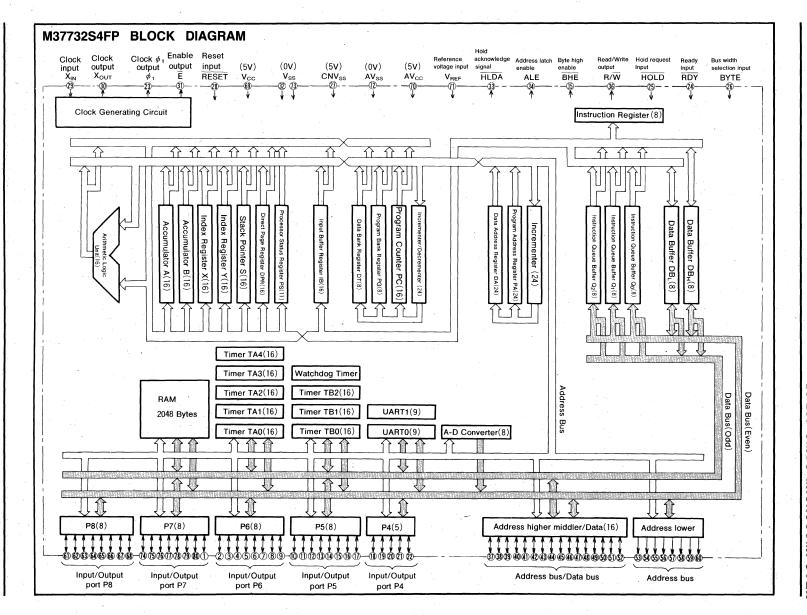

| M37732S4FP  | External ROM, 2048-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O                     | C, Şi     | 5±10% | 30                                   | 500       | 8                               | 80P6N   |       |

| M37732S4AFP | External ROM, 2048-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O                     | C, Si     | 5±10% | 60                                   | 250       | 16                              | 80P6N   | 2—237 |

| M37732S4BFP | External ROM, 2048-Byte RAM<br>16-Bit Timer, 8-Bit A-D Converter<br>Two Serial I/O                     | C, Si     | 5±10% | 95                                   | 160       | 25                              | 80P6N   |       |

## MITSUBISHI MICROCOMPUTERS INDEX BY FUNCTION

## **■PROGRAMMABLE ROM MICROCOMPUTERS**

|                | LE HOM MICHOCOMY CTERS                                                  |           |                          | Electric | al charac        | teristics |         |       |

|----------------|-------------------------------------------------------------------------|-----------|--------------------------|----------|------------------|-----------|---------|-------|

| Туре           | Circuit function and organization                                       | Structure | Supply<br>voltage<br>(V) | Тур.     | Min.<br>cycle    | Max.      | Package | Page  |

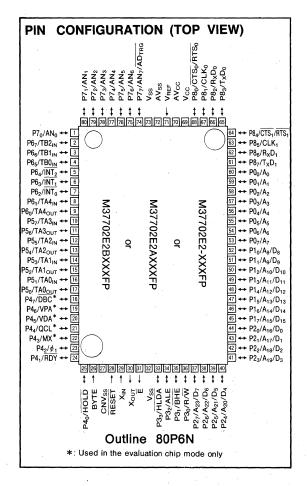

| M37702E2-XXXFP | One time PROM Version of M37702M2-XXXFP<br>16K-Byte PROM, 512-Byte RAM  | C, Si     | 5±10%                    | 30       | 500              | 8         | 80P6N   |       |

| M37702E2AXXXFP | One time PROM Version of M37702M2AXXXFP<br>16K-Byte PROM, 512-Byte RAM  | C, Si     | 5±10%                    | 60       | 250              | 16        | 80P6N   |       |

| M37702E2BXXXFP | One time PROM Version of M37702M2BXXXFP<br>16K-Byte PROM, 512-Byte RAM  | C, Si     | 5±10%                    | 95       | 160              | 25        | 80P6N   | 3-3   |

| M37702E2FS     | EPROM Version of M37702M2-XXXFP<br>16K-Byte EPROM, 512-Byte RAM         | C, Si     | 5±10%                    | 30       | 500              | 8         | 80D0    | ] 3—3 |

| M37702E2AFS    | EPROM Version of M37702M2AXXXFP<br>16K-Byte EPROM, 512-Byte RAM         | C, Si     | 5±10%                    | 60       | 250              | 16        | 80D0    |       |

| M37702E2BFS    | EPROM Version of M37702M2BXXXFP<br>16K-Byte EPROM, 512-Byte RAM         | C, Si     | 5±10%                    | 95       | 160              | 25        | 80D0    |       |

| M37702E4-XXXFP | One time PROM Version of M37702M4-XXXFP 32K-Byte PROM, 2048-Byte RAM    | C, Si     | 5±10%                    | 30       | 500              | 8         | 80P6N   |       |

| M37702E4AXXXFP | One time PROM Version of M37702M4AXXXFP 32K-Byte PROM, 2048-Byte RAM    | C, Si     | 5±10%                    | 60       | 250              | 16        | 80P6N   |       |

| M37702E4BXXXFP | One time PROM Version of M37702M4BXXXFP 32K-Byte PROM, 2048-Byte RAM    | C, Si     | 5±10%                    | 95       | 160              | 25        | 80P6N   | 3-26  |

| M37702E4FS     | EPROM Version of M37702M4-XXXFP<br>32K-Byte EPROM, 2048-Byte RAM        | C, Si     | 5±10%                    | 30       | 500              | 8         | 80D0    | 3-26  |

| M37702E4AFS    | EPROM Version of M37702M4AXXXFP<br>32K-Byte EPROM, 2048-Byte RAM        | C, Si     | 5±10%                    | 60       | 250              | 16        | 80D0    |       |

| M37702E4BFS    | EPROM Version of M37702M4BXXXFP<br>32K-Byte EPROM, 2048-Byte RAM        | C, Si     | 5±10%                    | 95       | 160              | 25        | 80D0    |       |

| M37703E2-XXXSP | One time PROM Version of M37703M2-XXXSP<br>16K-Byte PROM, 512-Byte RAM  | C, Si     | 5±10%                    | 30       | 500 <sup>-</sup> | 8         | 64P4B   |       |

| M37703E2AXXXSP | One time PROM Version of M37703M2AXXXSP<br>16K-Byte PROM, 512-Byte RAM  | C, Si     | 5±10%                    | 60       | 250              | 16        | 64P4B   | 3-28  |

| M37703E2BXXXSP | One time PROM Version of M37703M2BXXXSP<br>16K-Byte PROM, 512-Byte RAM  | C, Si     | 5±10%                    | 95       | 160              | 25        | 64P4B   |       |

| M37703E4-XXXSP | One time PROM Version of M37703M4-XXXSP<br>32K-Byte PROM, 2048-Byte RAM | C, Si     | 5±10%                    | 30       | 500              | 8         | 64P4B   |       |

| M37703E4AXXXSP | One time PROM Version of M37703M4AXXXSP<br>32K-Byte PROM, 2048-Byte RAM | C, Si     | 5±10%                    | 60       | 250              | 16        | 64P4B   | 3-51  |

| M37703E4BXXXSP | One time PROM Version of M37703M4BXXXSP<br>32K-Byte PROM, 2048-Byte RAM | C, Si     | 5±10%                    | 95       | 160              | 25        | 64P4B   |       |

## **DEVELOPMENT SUPPORT SYSTEMS**

## **Development support systems for MELPS 7700**

| MELPS 7700<br>type name | Assembler | Emulation pod                                                | For evaluate   |

|-------------------------|-----------|--------------------------------------------------------------|----------------|

| M37702M2-XXXFP          |           |                                                              |                |

| M37702M2AXXXFP          |           |                                                              |                |

| M37702S1FP              |           |                                                              |                |

| M37702S1AFP             |           |                                                              |                |

| M37702E2-XXXFP          |           | M37702T-HPD                                                  |                |

| M37702E2AXXXFP          |           |                                                              |                |

| M37702E2FS              |           |                                                              |                |

| M37702E2AFS             | •         |                                                              |                |

| M37702M4-XXXFP          |           |                                                              |                |

| M37702M4AXXXFP          |           |                                                              | M37702E2FS     |

| M37702S4FP              |           |                                                              | M37702E2AFS    |

| M37702S4AFP             |           | M37702T-HPD                                                  | M37702E2BFS    |

| M37702E4-XXXFP          |           | (Exchange MCU for M37702S4AFP)                               | M37702E4FS     |

| M37702E4AXXXFP          |           | ,,                                                           | M37702E4AFS    |

| M37702E4FS              | ,         |                                                              | M37702E4BFS    |

| M37702E4AFS             |           |                                                              |                |

| M37702M2BXXXFP          |           |                                                              |                |

| M37702S1BFP             | ,         |                                                              |                |

| M37702E2BXXXFP          |           | M37702TB-HPD**                                               |                |

| M37702E2BFS             |           |                                                              |                |

| M37702M4BXXXFP          |           |                                                              |                |

| M37702S4BFP             |           | M37702TB-HPD**                                               | ,              |

| M37702E4BXXXFP          |           | (Exchange MCU for M37702S4BFP)                               |                |

| M37702E4BFS             | -         | (Zamange mee var mee var |                |

| M37703M2-XXXSP          |           |                                                              |                |

| M37703M2AXXXSP          | RASM77    |                                                              |                |

| M37703S1SP              |           |                                                              |                |

| M37703S1ASP             | ·         | M37702T-HPD                                                  |                |

| M37703E2-XXXSP          |           |                                                              |                |

| M37703E2AXXXSP          |           |                                                              |                |

| M37703M4-XXXSP          |           |                                                              | M37703E2-XXXSP |

| M37703M4AXXXSP          |           |                                                              | M37703E2AXXXSP |

| M37703S4SP              |           | M37702T-HPD                                                  | M37703E2BXXXSP |

| M37703S4ASP             |           | (Exchange MCU for M37702S4AFP)                               | M37703E4-XXXSP |

| M37703E4-XXXSP          |           | (                                                            | M37703E4AXXXSP |

| M37703E4AXXXSP          |           |                                                              | M37703E4BXXXSP |

| M37703M2BXXXSP          |           |                                                              |                |

| M37703S1BSP             |           | M37702TB-HPD**                                               |                |

| M37703E2BXXXSP          |           |                                                              |                |

| M37703M4BXXXSP          |           |                                                              |                |

| M37703S4BSP             |           | M37702TB-HPD**                                               |                |

| M37703E4BXXXSP          |           | (Exchange MCU for M37702S4BFP)                               |                |

| M37720S1FP              |           |                                                              |                |

| M37720S1AFP             |           | M37720T-HPD**                                                |                |

| M37730S2FP              | 1         | · · · · · · · · · · · · · · · · · · ·                        |                |

| M37730S2AFP             |           |                                                              |                |

| M37730S2SP              |           | M37730T-HPD**                                                |                |

| M37730S2ASP             |           |                                                              | _              |

| M37730S2BFP             |           |                                                              |                |

| M37730S2BSP             |           | M37730TB-HPD**                                               |                |

| M37732S4FP              |           |                                                              |                |

|                         |           | M37732T-HPD**                                                | ~              |

| M37732S4AFP             |           |                                                              |                |

★★ Under development

## MITSUBISHI MICROCOMPUTERS

## **DEVELOPMENT SUPPORT SYSTEMS**

## Program writing adapter for built-in PROM type microcomputers of MELPS 7700

| Built-in PROM type       | Program writing adapter |

|--------------------------|-------------------------|

| microcomputers type name | . rogram many adaptor   |

| M37702E2-XXXFP           |                         |

| M37702E2AXXXFP           | PCA4774                 |

| M37702E2BXXXFP           |                         |

| M37702E2FS               |                         |

| M37702E2AFS              | PCA4708                 |

| M37702E2BFS              |                         |

| M37702E4-XXXFP           |                         |

| M37702E4AXXXFP           | PCA4774                 |

| M37702E4BXXXFP           |                         |

| M37702E4FS               | -                       |

| M37702E4AFS              | PCA4708                 |

| M37702E4BFS              |                         |

| M37703E2-XXXSP           |                         |

| M37703E2AXXXSP           |                         |

| M37703E2BXXXSP           | PCA4709                 |

| M37703E4-XXXSP           | PCA4709                 |

| M37703E4AXXXSP           |                         |

| M37703E4BXXXSP           |                         |

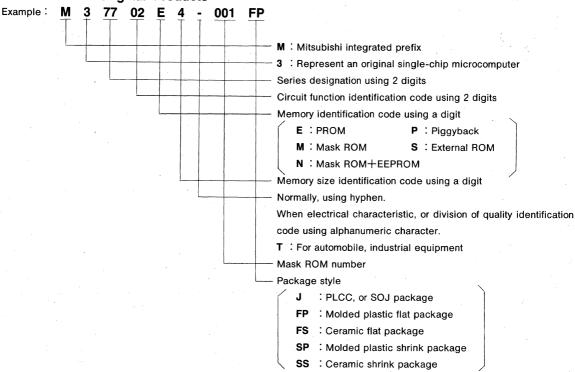

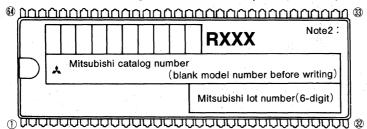

## **ORDERING INFORMATION**

#### **FUNCTION CODE**

Mitsubishi integrated circuit may be ordered using the following simplified alphanumeric type-codes which define the function of the IC/LSIs and the package style.

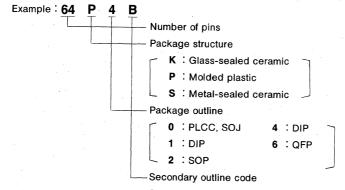

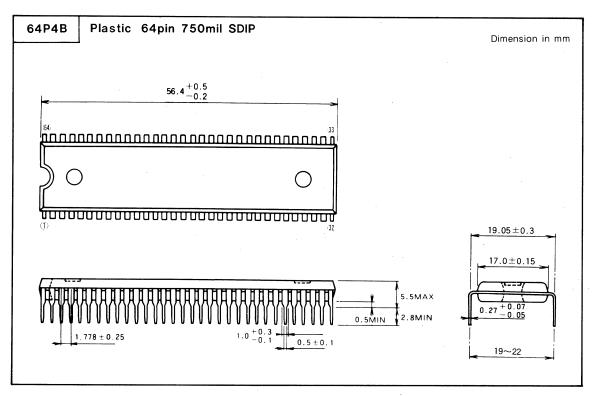

### PACKAGE CODE

Package style may be specified by using the following simplified alphanumeric code.

Special-purpose secondary codes describing outline are included as necessary. For details, contact your sales representative.

## MITSUBISHI MICROCOMPUTERS

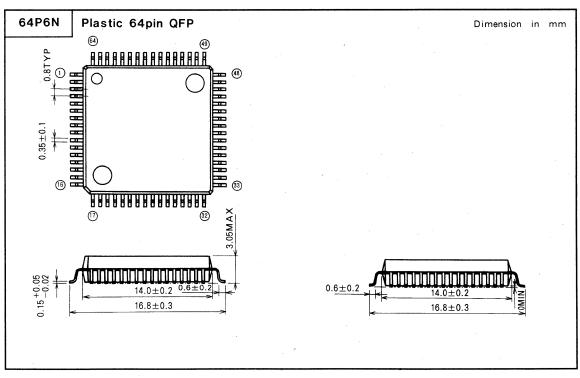

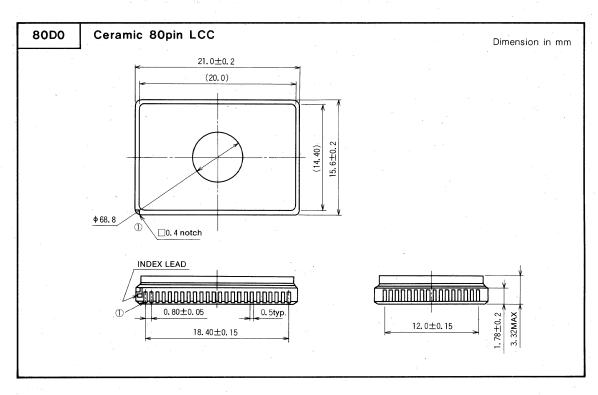

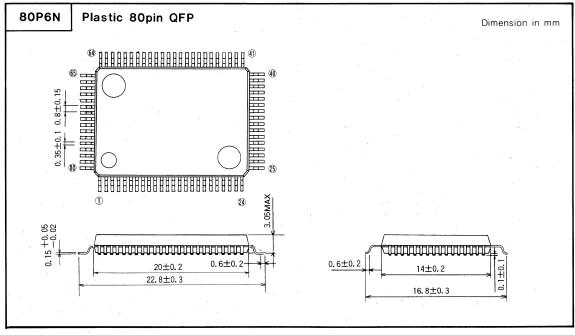

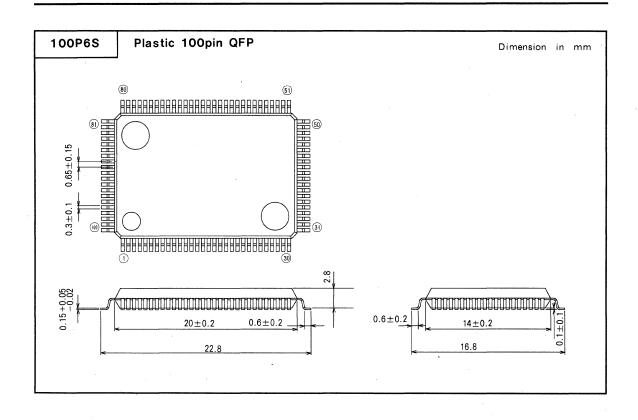

## PACKAGE OUTLINES

## MITSUBISHI MICROCOMPUTERS PACKAGE OUTLINES

## LETTER SYMBOLS FOR THE DYNAMIC PARAMETERS

#### 1. INTRODUCTION

A system of letter symbols to be used to represent the dynamic parameters of intergrated circuit memories and other sequential circuits especially for single-chip microcomputers, microprocessors and LSIs for peripheral circuits has been discussed internationally in the TC47 of the International Electrotechnical Committee (IEC). Finally the IEC has decided on the meeting of TC47 in February 1980 that this system of letter symbols will be a Central Office document and circulated to all countries to vote which means this system of letter symbols will be a international standard.

The system is applied in this LSI data book for the new products only. Future editions of this data book will be applied this system. The IEC document which describes "Letter symbols for dynamic parameters of sequential integrated circuits, including memories" is introduced below. In this data book, the dynamic parameters in the IEC document are applied to timing requirements and switching characteristics.

#### 2. LETTER SYMBOLS

The system of letter symbols outlined in this document enables symbols to be generated for the dynamic parameters of complex sequential circuits, including memories, and also allows these symbols to be abbreviated to simple mnemonic symbols when no ambiguity is likely to arise.

#### 2.1. General Form

The dynamic parameters are represented by the general symbol of the form:-

where:

Subscript A indicates the type of dynamic parameter being represented, for example; cycle time, setup time, enable time, etc.

Subscript B indicates the name of the signal or terminal for which a change of state or level (or establishment of a state or level) constitutes a signal event assumed to occur first, that is, at the beginning of the time interval. If this event actually occurs last, that is, at the end of the time interval, the value of the time interval is negative.

Subscript C indicates the direction of the transition and/or the final state or level of the signal represented by B. When two letters are used, the initial state or level is also indicated.

Subscript D indicates the name of the signal or terminal for which a change of state or level (or establishment of a state or level) constitutes a signal event assumed to occur last, that is, at the end of the time interval. If this event actually occurs first, that is, at the beginning of the time interval, the value of the time interval is negative.

Subscript E indicates the direction of the transition and/or the final state or level of the signal represented by D. When two letters are used, the initial state or level is also indicated.

Subscript F indicates additional information such as mode of operation, test conditions, etc.

Note 1: Subscripts A to F may each consists of one or more letters.

2: Subscripts D and E are not used for transition times.

3: The "-" in the symbol (1) above is used to indicate "to", hence the symbol represents the time interval from signal event B occurring to signal event D occurring, and it is important to note that this convention is used for all dynamic parameters including hold times. Where no misunderstanding can occur the hyphen may be omitted.

### 2.2. Abbreviated Form

The general symbol given above may be abbreviated when no misunderstanding is likely to arise. For example to:

$t_{A(B-D)}$

or tA(B)

or t<sub>A(D)</sub> - often used for hold times

or taf - no brackets are used in this case

or t<sub>A</sub>

or  $t_{BC-DE}$  — often used for unclassified time intervals

#### 2.3. Allocation of Subscripts

In allocating letter symbols for the subscripts, the most commonly used subscripts are given single letters where practicable and those less commonly used are designated by up to three letters. As far as possible, some form of mnemonic representation is used. Longer letter symbols may be used for specialised signals or terminals if this aids understanding.

## SUBSCRIPT A (For Type of Dynamic Parameter)

The subscript A represents the type of dynamic parameter to be designated by the symbol and, for memories, the parameters may be divided into two classes:

a) those that are timing requirements for the memory and

## LETTER SYMBOLS FOR THE DYNAMIC PARAMETERS

b) those that are characteristics of the memory. The letter symbols so far proposed for memory circuits are listed in sub-clauses 3.1 and 3.2 below.

All subscripts A should be in lower-case.

### 3.1. Timing Requirements

The letter symbols for the timing requirements of semiconductor memories are as follows:

| Term                                    | Subscript |

|-----------------------------------------|-----------|

| Cycle time                              | С         |

| Time interval between two signal events | d         |

| Fall time                               | f         |

| Hold time                               | h         |

| Precharging time                        | рс        |

| Rise time                               | r         |

| Recovery time                           | rec       |

| Refresh time interval                   | rf        |

| Setup time .                            | su        |

| Transition time                         | t         |

| Pulse duration (width)                  | w         |

#### 3.2. Characteristics

The letter symbols for the dynamic characteristics of semiconductor memories are as follows:

| Characteristic   | Subscript |

|------------------|-----------|

| Access time      | a         |

| Disable time     | dis       |

| Enable time      | en        |

| Propagation time | P         |

| Recovery time    | rec       |

| Transition time  | т         |

| Valid time       | v         |

Note: Recovery time for use as a characteristic is limited to sense recovery time.

## 4. SUBSCRIPTS B AND D (For Signal Name or Terminal Name)

The letter symbols for the signal name or the name of the terminal are as given below.

All subscripts B and D should be in upper-case.

| Signal or terminal    | Subscript  |

|-----------------------|------------|

| Address               | Α .        |

| Clock                 | C          |

| Column address        | CA         |

| Column address strobe | CAS        |

| Data input            | , <b>D</b> |

| Data input/output     | DQ         |

| Chip enable           | E          |

|                       |            |

| Erasure              | ER  |

|----------------------|-----|

| Output enable        | · G |

| Program              | PR  |

| Data output          | Q   |

| Read                 | R   |

| Row address          | RA  |

| Row address strobe   | RAS |

| Refresh              | RF  |

| Read/Write           | RW  |

| Chip select          | S   |

| Write (write enable) | W   |

Note 1: In the letter symbols for time intervals, bars over the subscripts, for example CAS, should not be used.

- 2. It should be noted, when further letter symbols are chosen, that the subscript should not end with H, K, V, X, or Z. (See clause 5)

- 3: If the same terminal, or signal, can be used for two functions (for example Data input/output, Read/Write) the waveform should be labelled with the dual function, if appropriate, but the symbols for the dynamic parameters should include only that part of the subscript relevant to the parameter.

## 5. SUBSCRIPTS C AND E (For Transition of Signal)

The following symbols are used to represent the level or state of a signal:

| Transition of signal                          | Subscript |

|-----------------------------------------------|-----------|

| High logic level                              | Н         |

| Low logic level                               | L         |

| Valid steady-state level (either low or high) | V         |

| Unknown, changing, or 'don't care' level      | X         |

| High-impedance state of three-state output    | Z         |

The direction of transition is expressed by two letters, the direction being from the state represented by the first letter to that represented by the second letter, with the letters being as given above.

When no misunderstanding can occur, the first letter may be omitted to give an abbreviated symbol for subscripts C and E as indicated below.

All subscripts C and E should be in upper-case.

|  | _  |     |      |  |

|--|----|-----|------|--|

|  | Su | her | rint |  |

| Examples                                                    | Full | Abbreviated |

|-------------------------------------------------------------|------|-------------|

| Transition from high level to low level                     | HL   | L           |

| Transition from low level to high level                     | LH   | н           |

| Transition from unknown or changing state to valid state    | XV   | V           |

| Transition from valid state to<br>unknown or changing state | vx   | X           |

| Transition from high-impedance state to valid state         | ZV   | <b>V</b>    |

Note: Since subscripts C and E may be abbreviated, and since subscripts B and D may contain an indeterminate number of letters, it is necessary to put the restriction on the subscripts B and D that they should not end with H, L, V, X, or Z, so as to avoid possible confusion.

## LETTER SYMBOLS FOR THE DYNAMIC PARAMETERS

## 6. SUBSCRIPT F (For Additional Information)

If necessary, subscript F is used to represent any additional qualification of the parameter such as mode of operation, test conditions, etc. The letter symbols for subscript F are given below.

Subscript F should be in upper-case.

| Modes of operation | Subscript  |

|--------------------|------------|

| Power-down         | PD         |

| Page-mode read     | PGR        |

| Page-mode write    | PGW        |

| Read               | . <b>R</b> |

| Refresh            | RF         |

| Read-modify-write  | RMW        |

| Read-write         | RW         |

| Write              | W          |

## FOR DIGITAL INTEGRATED CIRCUITS

| New symbol              | Former symbol       | Parameter—definition                                                                                                                                                               |

|-------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cı                      |                     | Input capacitance                                                                                                                                                                  |

| Co                      |                     | Output capacitance                                                                                                                                                                 |

| Cio                     |                     | Input/output terminal capacitance                                                                                                                                                  |

| C <sub>I(\$\phi)</sub>  |                     | Input capacitance of clock input                                                                                                                                                   |

| f                       |                     | Frequency                                                                                                                                                                          |

| f <sub>(\$\phi\$)</sub> |                     | Clock frequency                                                                                                                                                                    |

| 1                       |                     | Current—the current into an integrated circuit terminal is defined as a positive value and the current out of a terminal is defined as a negative value                            |

| l <sub>BB</sub>         |                     | Supply current from V <sub>BB</sub>                                                                                                                                                |

| I <sub>BB(AV)</sub>     |                     | Average supply current from V <sub>BB</sub>                                                                                                                                        |

| I <sub>CC</sub>         |                     | Supply current from V <sub>CC</sub>                                                                                                                                                |

| I <sub>GC(AV)</sub>     |                     | Avarage supply current from V <sub>CC</sub>                                                                                                                                        |

| I <sub>CC(PD)</sub>     |                     | Power-down supply current from V <sub>CC</sub>                                                                                                                                     |

| I <sub>DD</sub>         |                     | Supply current from V <sub>DD</sub>                                                                                                                                                |

| I <sub>DD(AV)</sub>     |                     | Average supply current from V <sub>DD</sub>                                                                                                                                        |

| ١.                      |                     | Supply current from V <sub>GG</sub>                                                                                                                                                |

| lgg<br>Lagran           |                     | Average supply current from V <sub>GG</sub>                                                                                                                                        |

| IGG(AV)                 |                     | Input current                                                                                                                                                                      |

| 14                      |                     | High-level input current—the value of the input current when V <sub>OH</sub> is applied to the input considered                                                                    |

| I <sub>I</sub> H        |                     |                                                                                                                                                                                    |

| l₁⊾                     |                     | Low-level input current—the value of the input current when V <sub>OL</sub> is applied to the input considered                                                                     |

| I <sub>OH</sub>         |                     | High-level output current—the value of the output current when V <sub>OH</sub> is applied to the output considered                                                                 |

| I <sub>OL</sub>         |                     | Low-level output current—the value of the output current when V <sub>OL</sub> is applied to the output considered                                                                  |

| loz                     |                     | Off-state(high-impedance state) output current—the current into an output having a three-state capability with input condition so applied that                                     |

| ١.                      |                     | it will establish according to the product specification, the off(high-impedance)state at the output                                                                               |

| Гохн                    |                     | Off-state(high-impedance state)output current, with high-level voltage applied to the output                                                                                       |

| lozL                    |                     | Off-state(high-impedance state) output current, with low-level voltage applied to the output                                                                                       |

| los                     |                     | Short-circuit output current                                                                                                                                                       |

| l <sub>ss</sub>         |                     | Supply current from V <sub>SS</sub>                                                                                                                                                |

| Pd                      |                     | Power dissipation                                                                                                                                                                  |

| N <sub>EW</sub>         |                     | Number of erase/write cycles                                                                                                                                                       |

| N <sub>RA</sub>         |                     | Number of read access unrefreshed                                                                                                                                                  |

| R <sub>I</sub>          |                     | Input resistance                                                                                                                                                                   |

| R <sub>L</sub>          |                     | External load resistance                                                                                                                                                           |

| R <sub>OFF</sub>        |                     | Off-state output resistance                                                                                                                                                        |

| R <sub>ON</sub>         |                     | On-state output resistance                                                                                                                                                         |

| ta.                     |                     | Access time—the time interval between the application of a specified input pulse during a read cycle and the availability of valid data signal at an output                        |

| ta(A)                   | ta(AD)              | Address access time—the time interval between the application of an address input pulse and the availability of valid data signals at an output  Column address strobe access time |

| ta(cas)                 | taran               |                                                                                                                                                                                    |

| ta(E)                   | ta(CE)              | Chip enable access time                                                                                                                                                            |

| ta(G)                   | ta(OE)              | Output enable access time                                                                                                                                                          |

| ta(PR)                  |                     | Data access time after program  Row address strope access time                                                                                                                     |

| ta(RAS)                 | <b>t</b> -()        | Row address strobe access time                                                                                                                                                     |

| <sup>t</sup> a(s)       | ta(cs)              | Chip select access time  Cycle time                                                                                                                                                |

| t <sub>C</sub>          | • • • • •           | Read cycle time—the time interval between the start of a read cylce and the start of the next cycle                                                                                |

| t <sub>CR</sub>         | t <sub>C(RD)</sub>  | •                                                                                                                                                                                  |

| t <sub>CRF</sub>        | t <sub>C(REF)</sub> | Refresh cycle time—the time interval between successive signals that are intended to restore the level in a dynamic memory cell to its original level                              |

| t <sub>CPG</sub>        | t <sub>C</sub> (PG) | Page-mode cycle time  Read-modify-write cycle time—the time interval between the start of a cycle in which the memory is read and now data is extered, and the effect of           |

| t <sub>CRMW</sub>       | t <sub>C(RMW)</sub> | Read-modify-write cycle time—the time interval between the start of a cycle in which the memory is read and new data is entered, and the start of                                  |

| <b>.</b>                | <br>                | the next cycle  Write cycle time, the time interval between the start of a write cycle and the start of the next cycle.                                                            |

| tcw                     | t <sub>C(WR)</sub>  | Write cycle time—the time interval between the start of a write cycle and the start of the next cycle                                                                              |

|                        | ,                       |                                                                                                                                                                                                                                                 |

|------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| New symbol             | Former symbol           | Parameter—definition .                                                                                                                                                                                                                          |

| t <sub>d</sub>         |                         | Delay time—the time between the specified reference points on two pulses                                                                                                                                                                        |

| $t_{\mathbf{d}(\phi)}$ |                         | Delay time between clock pulses—e.g., symbology, delay time, clock 1 to clock 2 or clock 2 to clock 1                                                                                                                                           |

| td(CAS-RAS)            |                         | Delay time, column address strobe to row address strobe                                                                                                                                                                                         |

| td(cas-w)              | td(CAS WR)              | Delay time, column address strobe to write                                                                                                                                                                                                      |

| td(RAS-CAS)            |                         | Delay time, row address strobe to column address strobe                                                                                                                                                                                         |

| t <sub>d(RAS-w)</sub>  | td(RAS-WR)              | Delay time, row address strobe to write                                                                                                                                                                                                         |

| t <sub>dis(R-O)</sub>  | tdis(R-DA)              | Output disable time after read                                                                                                                                                                                                                  |

| t <sub>dis(s)</sub>    | t <sub>PXZ(CS)</sub>    | Output disable time after chip select                                                                                                                                                                                                           |

| t <sub>dis(w)</sub>    | t <sub>PXZ(WR)</sub>    | Output disable time after write                                                                                                                                                                                                                 |

| t <sub>DHL</sub>       |                         | High-level to low-level delay time the time interval between specified reference points on the input and on the output pulses when the output is                                                                                                |

| t <sub>DLH</sub>       |                         | Low-level to high-level delay time going to the low (high)level and when the device is driven with a specified loading networks                                                                                                                 |

| t <sub>en(A-Q)</sub>   | t <sub>PZV(A-DQ)</sub>  | Output enable time after address                                                                                                                                                                                                                |

| t <sub>en(R-Q)</sub>   | t <sub>PZV(R-DQ)</sub>  | Output enable time after read                                                                                                                                                                                                                   |

| t <sub>en(s-q)</sub>   | t <sub>PZX(CS*DQ)</sub> | Output enable time after chip select                                                                                                                                                                                                            |

| tf                     |                         | Fall time                                                                                                                                                                                                                                       |

| th                     |                         | Hold time—the interval of time during which a signal at a specified input terminal appears after an active transition occurs at another specified input terminal                                                                                |

| th(A)                  | th(AD)                  | Address hold time                                                                                                                                                                                                                               |

| th(A-E)                | th(AD-CE)               | Chip enable hold time after address                                                                                                                                                                                                             |

| th(A-PR)               | th(AD-PRO)              | Program hold time after address                                                                                                                                                                                                                 |

| th(CAS-CA)             |                         | Column address hold time after column address strobe                                                                                                                                                                                            |

| th(cas-d)              | th(CAS-DA)              | Data-in hold time after column address strobe                                                                                                                                                                                                   |

| th(cas-q)              | th(CAS-OUT)             | Data-out hold time after column address strobe                                                                                                                                                                                                  |

| th(CAS-RAS)            |                         | Row address strobe hold time after column address strobe                                                                                                                                                                                        |

| th(cas-w)              | th(CAS-WR)              | Write hold time after column address strobe                                                                                                                                                                                                     |

| t <sub>h(D)</sub>      | th(DA)                  | Data-in hold time                                                                                                                                                                                                                               |

| t <sub>h(D—PR)</sub>   | th(DA-PRO)              | Program hold time after data-in                                                                                                                                                                                                                 |

| t <sub>h(E)</sub>      | t <sub>h(CE)</sub>      | Chip enable hold time                                                                                                                                                                                                                           |

| t <sub>h(E-D)</sub>    | th(CE-DA)               | Data-in hold time after chip enable                                                                                                                                                                                                             |

| t <sub>h(E-G)</sub>    | th(CE-OE)               | Output enable hold time after chip enable                                                                                                                                                                                                       |

| t <sub>h(R)</sub>      | t <sub>h(RD)</sub>      | Read hold time                                                                                                                                                                                                                                  |

| th(RAS-CA)             |                         | Column address hold time after row address strobe                                                                                                                                                                                               |

| th(RAS-CAS)            |                         | Column address strobe hold time after row address strobe                                                                                                                                                                                        |

| th(RAS-D)              | th(RAS-DA)              | Data-in hold time after row address strobe                                                                                                                                                                                                      |

| th(RAS-W)              | th(RAS-WR)              | Write hold time after row address strobe                                                                                                                                                                                                        |

| t <sub>h(s)</sub>      | t <sub>h(CS)</sub>      | Chip select hold time                                                                                                                                                                                                                           |

| t <sub>h(w)</sub>      | t <sub>h(wn)</sub>      | Write hold time                                                                                                                                                                                                                                 |

| th(w-cas)              | th(WR-CAS)              | Column address strobe hold time after write                                                                                                                                                                                                     |

| t <sub>h(w-D)</sub>    | th(wR-DA)               | Data-in hold time after write                                                                                                                                                                                                                   |

| th(w-RAS)              | th(WR-RAS)              | Row address hold time after write                                                                                                                                                                                                               |

| t <sub>PHL</sub>       |                         | High-level to low-level propagation time the time interval between specified reference points on the input and on the output pulses when the output is going to the low (high)level and when the device is driven and loaded by typical devices |

| t <sub>PLH</sub>       |                         | Low-level to high-level propagation time of stated type                                                                                                                                                                                         |

| t <sub>r</sub>         |                         | Rise time                                                                                                                                                                                                                                       |

| t <sub>rec(w)</sub>    | twr                     | Write recovery time—the time interval between the termination of a write pulse and the initiation of a new cycle                                                                                                                                |

| t <sub>rec(PD)</sub>   | t <sub>R(PD)</sub>      | Power-down recovery time                                                                                                                                                                                                                        |

| t <sub>su</sub>        |                         | Setup time—the time interval between the application of a signal which is maintained at a specified input terminal and a consecutive active                                                                                                     |

|                        |                         | tarnsition at another specified input terminal                                                                                                                                                                                                  |

| t <sub>Su(A)</sub>     | t <sub>SU(AD)</sub>     | Address setup time                                                                                                                                                                                                                              |

| tsu(A-E)               | t <sub>SU(AD-CE)</sub>  | Chip enable setup time before address                                                                                                                                                                                                           |

| t <sub>SU(A-W)</sub>   | t <sub>Su(AD-WR)</sub>  | Write setup time before address                                                                                                                                                                                                                 |

| tsu(CA-RAS)            |                         | Row address strobe setup time before column address                                                                                                                                                                                             |

|                        | <u> </u>                |                                                                                                                                                                                                                                                 |

## MITSUBISHI MICROCOMPUTERS SYMBOLOGY

| New symbol              | Former symbol           | Parameter—definition                                                                                                                                                                                                                                                                                   |

|-------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>su(D)</sub>      | t <sub>SU(DA)</sub>     | Data-in setup time                                                                                                                                                                                                                                                                                     |

| t <sub>su(D-E)</sub>    | t <sub>SU(DA-CE)</sub>  | Chip enable setup time before data-in                                                                                                                                                                                                                                                                  |

| t <sub>su(D-w)</sub>    | t <sub>su(DA-WR)</sub>  | Write setup time before data-in                                                                                                                                                                                                                                                                        |

| t <sub>su(E)</sub>      | t <sub>su(CE)</sub>     | Chip enable setup time                                                                                                                                                                                                                                                                                 |

| t <sub>su(E-P)</sub>    | t <sub>SU(CE-P)</sub>   | Precharge setup time before chip enable                                                                                                                                                                                                                                                                |

| t <sub>su(G-E)</sub>    | t <sub>su(OE-CE)</sub>  | Chip enable setup time before output enable                                                                                                                                                                                                                                                            |

| t <sub>SU(P-E)</sub>    | t <sub>su(P-CE)</sub>   | Chip enable setup time before precharge                                                                                                                                                                                                                                                                |

| t <sub>SU(PD)</sub>     | -Su(F-CE)               | Power-down setup time                                                                                                                                                                                                                                                                                  |

| t <sub>su(R)</sub>      | t <sub>Su(RD)</sub>     | Read setup time                                                                                                                                                                                                                                                                                        |

| t <sub>SU(R-CAS)</sub>  | t <sub>su(RA-CAS)</sub> | Column address strobe setup time before read                                                                                                                                                                                                                                                           |

| t <sub>SU(RA-CAS)</sub> | 'SU(HA-CAS)             | Cloumn address strobe setup time before row address                                                                                                                                                                                                                                                    |

|                         | tou(oo)                 | Chip select setup time                                                                                                                                                                                                                                                                                 |

| <sup>t</sup> su(s)      | t <sub>su(cs)</sub>     | Write setup time before chip select                                                                                                                                                                                                                                                                    |

| tsu(s-w)                | tsu(cs-wr)              | Write setup time                                                                                                                                                                                                                                                                                       |

| t <sub>Su(w)</sub>      | t <sub>Su(WR)</sub>     |                                                                                                                                                                                                                                                                                                        |

| t <sub>THL</sub>        |                         | High-level to low-level transition time time interval between specified reference points on the edge of the output pulse when the output is going to the low(high)level and when a specified input signal is applied through a specified network and the output is loaded by another specified network |

| t <sub>TLH</sub>        | tal                     | Data valid time after address                                                                                                                                                                                                                                                                          |

| t <sub>V(A)</sub>       | tdv(AD)                 |                                                                                                                                                                                                                                                                                                        |

| t <sub>V(E)</sub>       | tdv(ce)                 | Data valid time after chip enable                                                                                                                                                                                                                                                                      |

| t <sub>V(E)PR</sub>     | t <sub>V(CE)PR</sub>    | Data valid time after chip enable in program mode                                                                                                                                                                                                                                                      |

| t <sub>V(G)</sub>       | t <sub>V(OE)</sub>      | Data valid time after output enable                                                                                                                                                                                                                                                                    |

| t <sub>V(PR)</sub>      |                         | Data valid time after program                                                                                                                                                                                                                                                                          |

| t <sub>V(S)</sub>       | t <sub>v(cs)</sub>      | Data valid time after chip select                                                                                                                                                                                                                                                                      |

| t <sub>w</sub>          |                         | Pulse width (pulse duration) the time interval between specified reference points on the leading and training edges of the waveforms                                                                                                                                                                   |

| t <sub>W(E)</sub>       | t <sub>w(CE)</sub>      | Chip enable pulse width                                                                                                                                                                                                                                                                                |

| t <sub>W(EH)</sub>      | tw(CEH)                 | Chip enable high pulse width                                                                                                                                                                                                                                                                           |

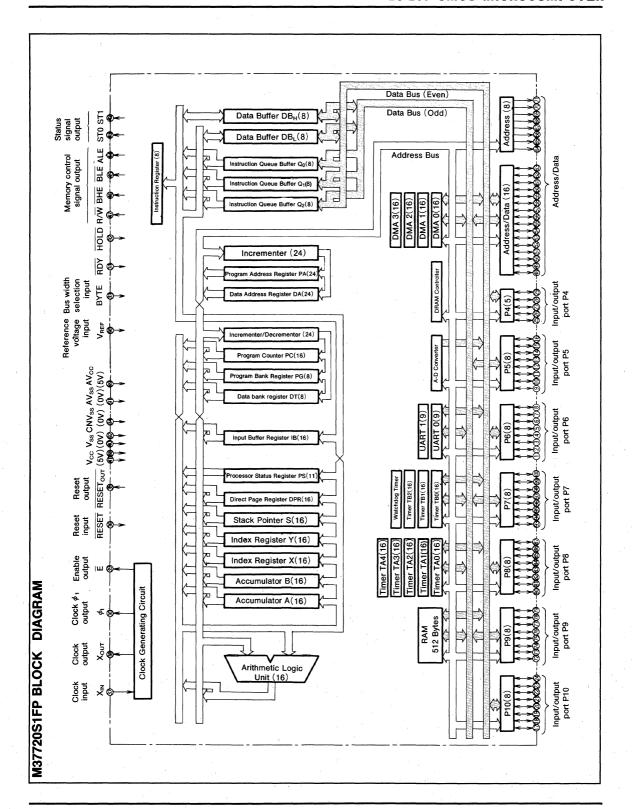

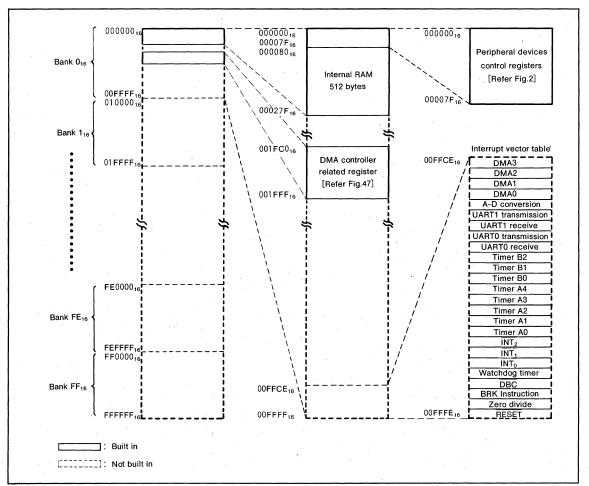

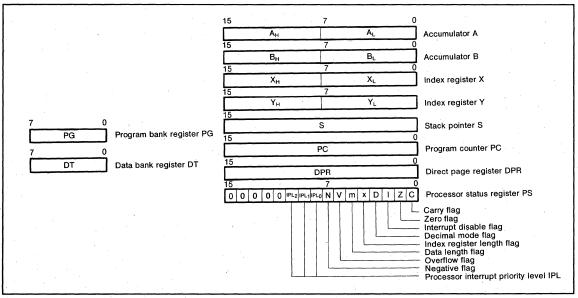

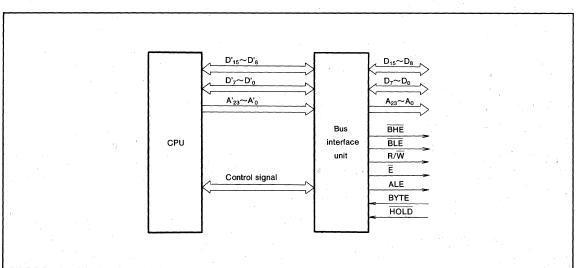

| t <sub>W(EL)</sub>      | t <sub>W(EL)</sub>      | Chip enable low pulse width                                                                                                                                                                                                                                                                            |