MITSUBISHI SEMICONDUCTORS

# M37702 Group M37703 Group USER'S MANUAL

Preface

# **Preface**

This manual describes the hardware of the Mitsubishi CNOS 16-bit microcomputer M37702 group. After reading this manual, the user should be able to fully utilize the functions of the microcomputers of M37702 group and M37703 group.

For details concerning the softwares for the M37702 group and M37703 group, refer to the MELPS 7700 SOFTWARE MANUAL. For details concerning the development support tools (assembler, option boards), refer to the respective operation manuals.

# **Table of contents**

| CHAPTER 1. DESCRIPTION                                        |    |

|---------------------------------------------------------------|----|

| 1.1 M37702 group                                              |    |

| 1.2 Performance overview                                      |    |

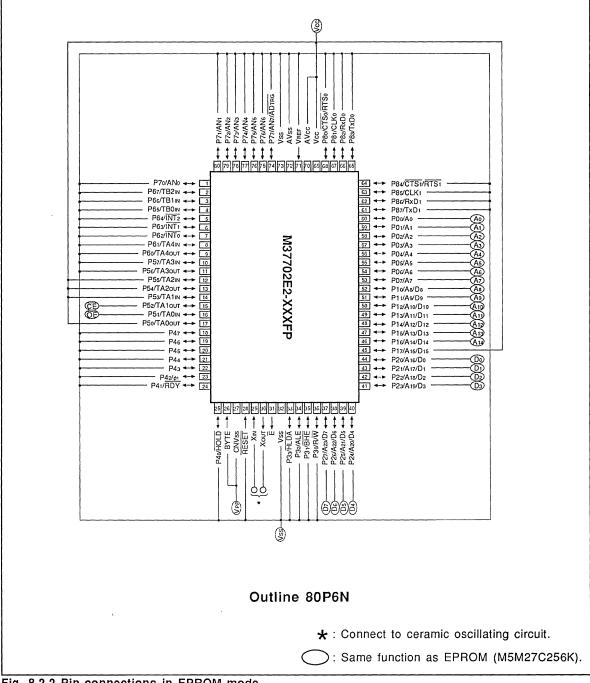

| <sup>*</sup> 1.3 Pin configuration                            |    |

| 1.4 Pin description                                           |    |

| 1.5 Block diagram                                             | 8  |

| CHAPTER 2. FUNCTIONAL DESCRIPTION                             |    |

| 2.1 Central processing unit (CPU)                             | 10 |

| 2.1.1 Accumulator (Acc)                                       |    |

| 2.1.2 Index register X (X)                                    |    |

| 2.1.3 Index register Y                                        |    |

| 2.1.4 Stack pointer (S)                                       |    |

| 2.1.5 Program counter (PC)                                    | 13 |

| 2.1.6 Program bank register (PG)                              |    |

| 2.1.7 Data bank register (DT)                                 |    |

| 2.1.8 Direct page register (DPR)                              |    |

| 2.1.9 Processor status register (PS)                          |    |

| 2.2 Internal bus interface                                    |    |

| 2.2.1 Internal bus interface overview                         |    |

| 2.2.2 Bus interface unit functions                            |    |

| 2.2.3 Bus interface unit operations                           |    |

| 2.2.4 Data read/write operations                              |    |

| 2.3 Addressable memory space                                  |    |

| 2.3.1 Banks                                                   |    |

| 2.3.2 Direct page                                             |    |

| 2.4 Memory allocation                                         |    |

| 2.4.1 Internal memory and peripheral device memory allocation | 23 |

| 2.4.2 Processor modes                                         |    |

| 2.4.3 External memory area bus control                        | 29 |

| 2.5 Input/Output pins                                         | 31 |

| 2.5.1 Programmable I/O ports                                  |    |

| 2.5.2 Pin functions                                           |    |

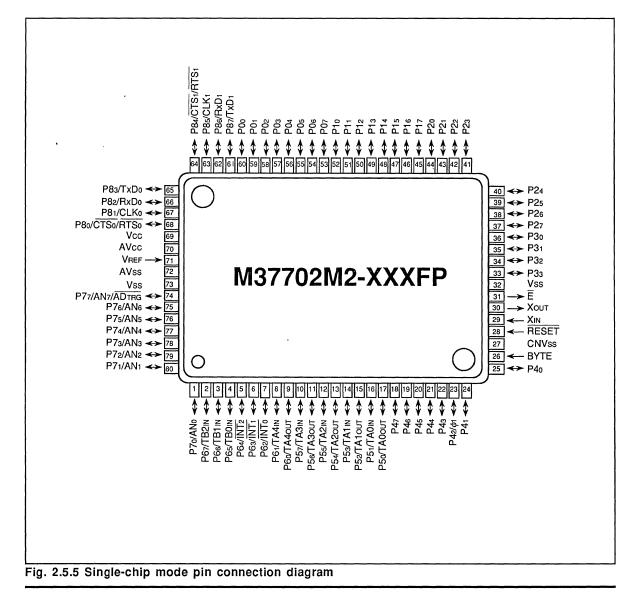

| 2.5.3 Single-chip mode pin functions                          |    |

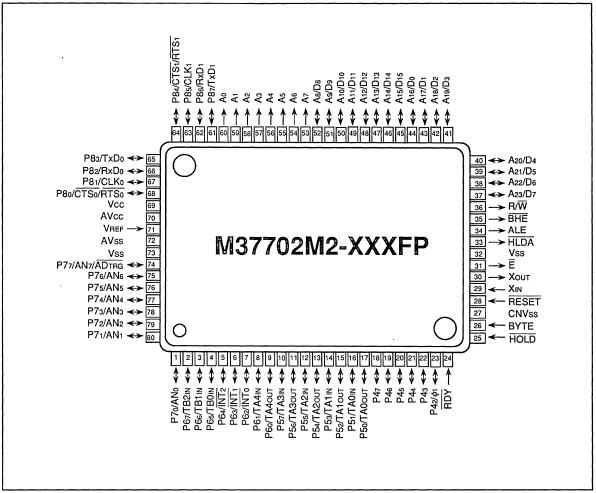

| 2.5.4 Memory expansion and microprocessor mode pin functions  | 40 |

| 2.6 Interrupts                                                |    |

| 2.6.1 Interrupt functions                                     | 45 |

| 2.6.2 Sources of interrupts                                   |    |

| 2.6.3 Interrupt control                                       |    |

| 2.6.4 Interrupt priority level                                |    |

| 2.6.5 Interrupt priority level detection circuit              | 53 |

| 2.6.6 Interrupt priority level detection time                 |    |

| 2.6.7 Interrupt processing sequence                           |    |

| 2.6.8 Returning from an interrupt service routine             | 60 |

| 2.6.9 Multiple interrupts                                     | 60 |

| 2.6.10 Interrupt response time and interrupt delay time       | 61 |

| 2.7 Timer A                                                        | 64  |

|--------------------------------------------------------------------|-----|

| 2.7.1 Timer A description                                          |     |

| 2.7.2 Block description                                            |     |

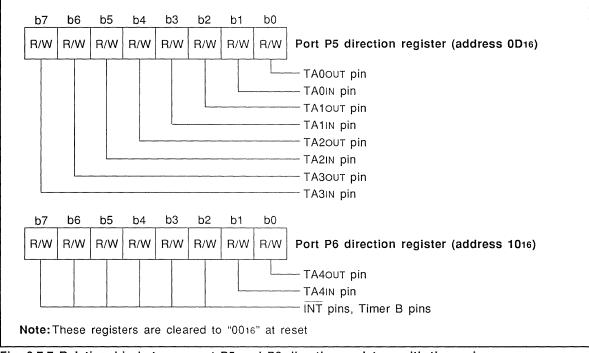

| 2.7.3 Timer mode                                                   |     |

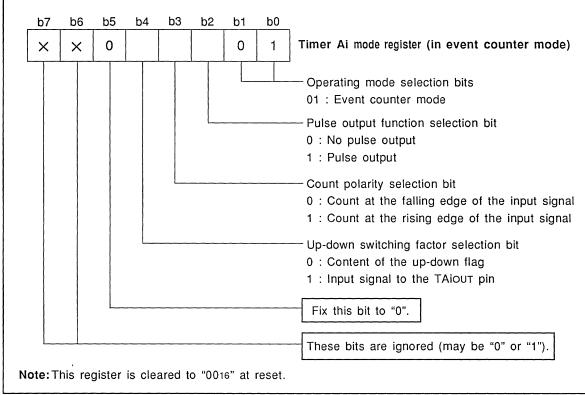

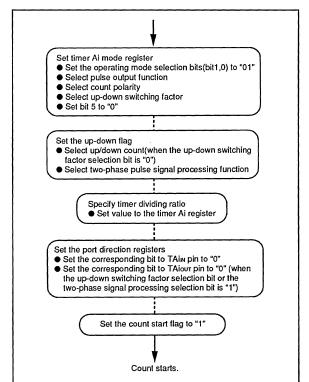

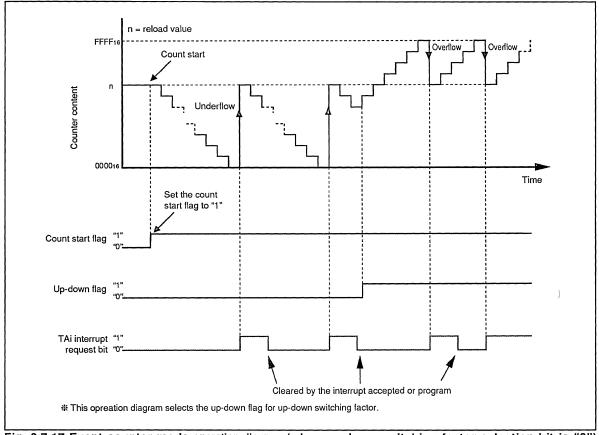

| 2.7.4 Event counter mode                                           |     |

| 2.7.5 One-shot pulse mode                                          |     |

| 2.7.6 Pulse width modulation (PWM) mode                            |     |

| 2.8 Timer B                                                        |     |

| 2.8.1 Timer B description                                          |     |

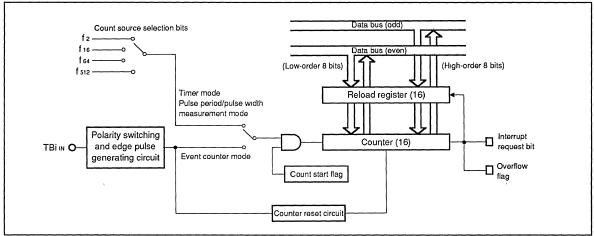

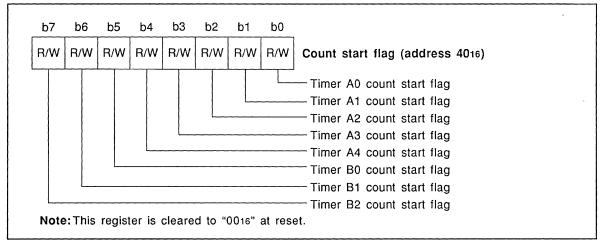

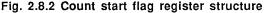

| 2.8.2 Block diagram                                                |     |

| 2.8.3 Timer mode                                                   |     |

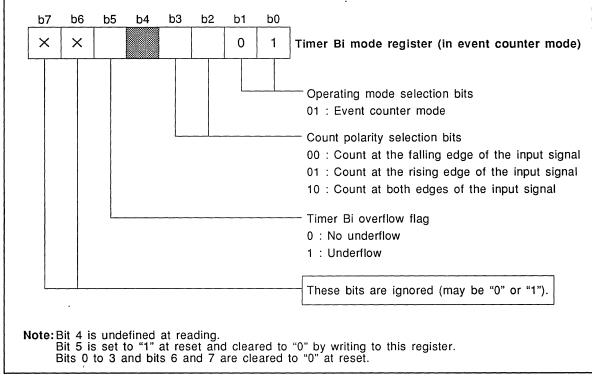

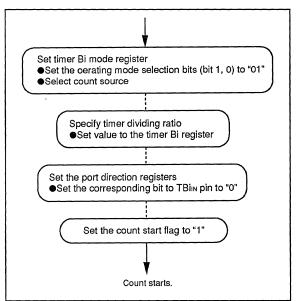

| 2.8.4 Event counter mode                                           |     |

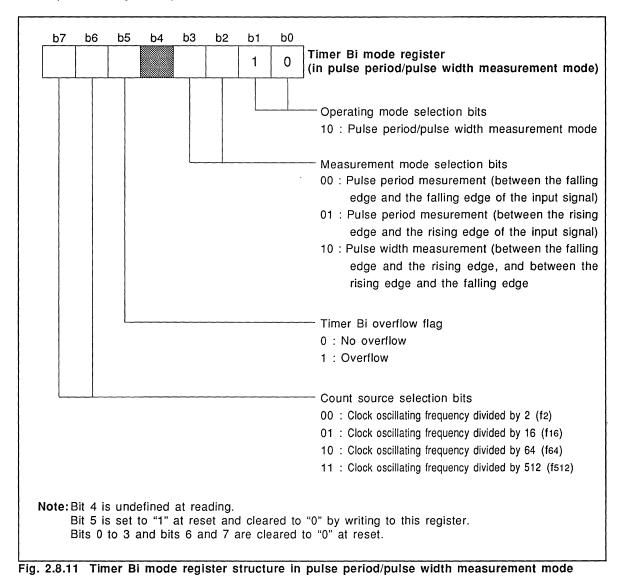

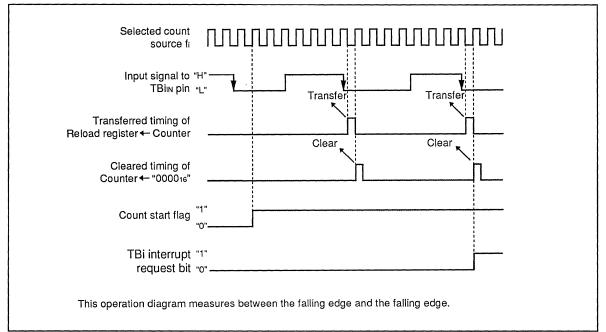

| 2.8.5 Pulse period/pulse width measurement mode                    |     |

|                                                                    |     |

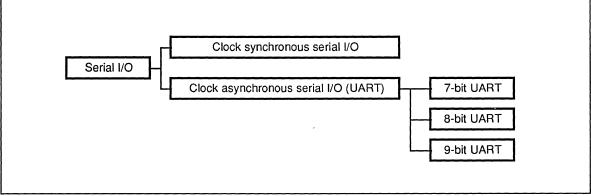

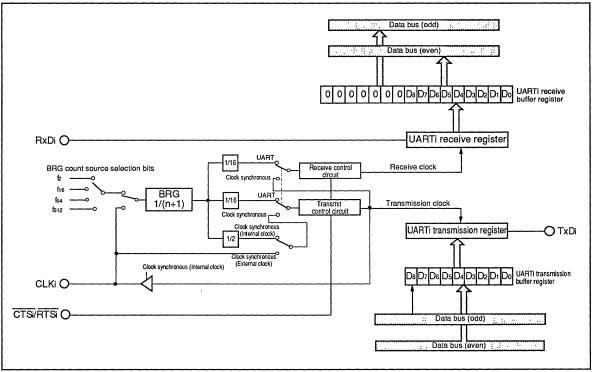

| 2.9 Serial I/O                                                     |     |

| 2.9.1 Serial I/O description                                       |     |

| 2.9.2 Block description                                            |     |

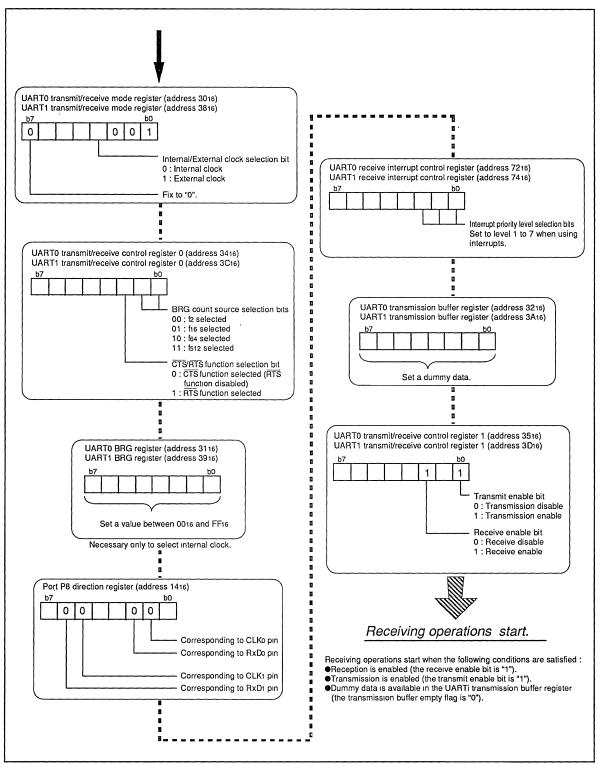

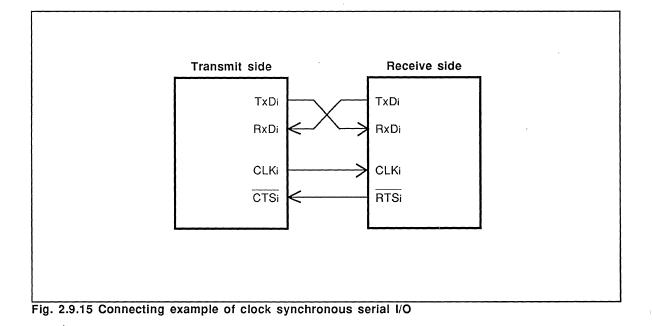

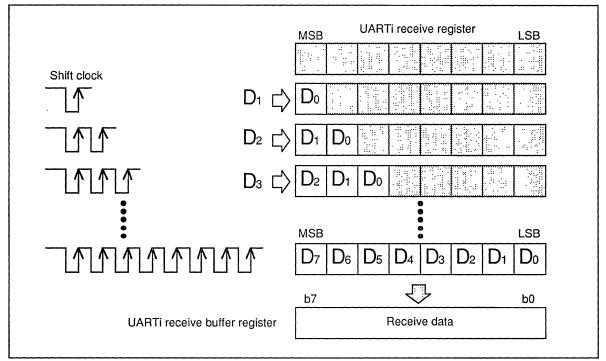

| 2.9.3 Clock synchronous serial I/O                                 |     |

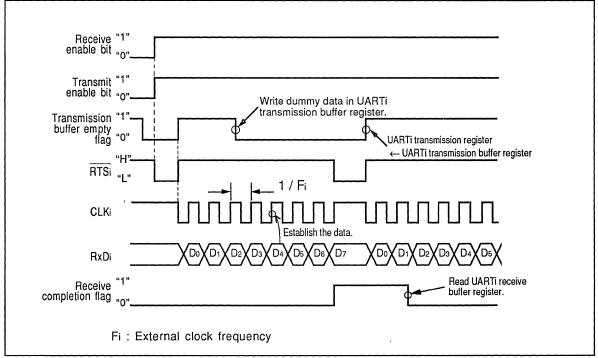

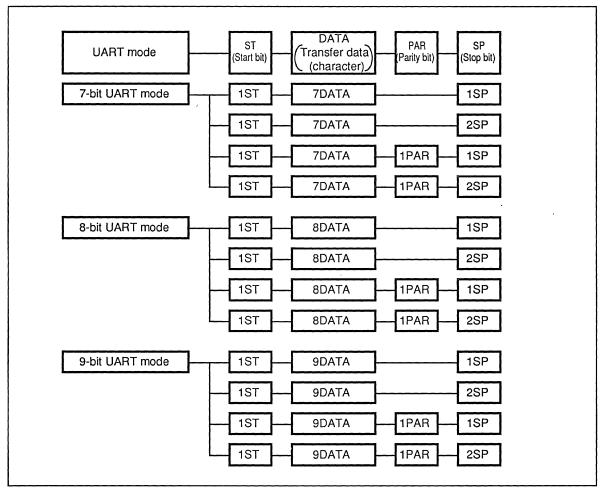

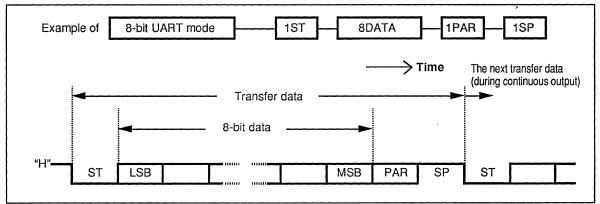

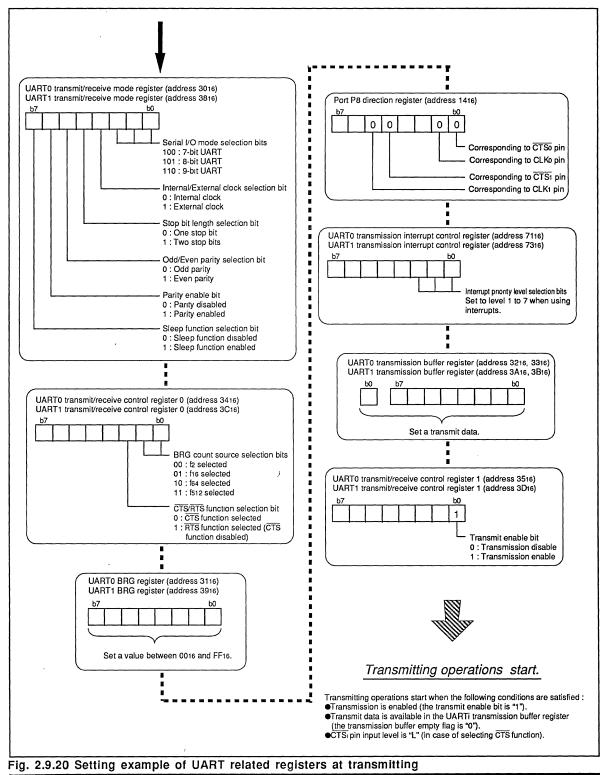

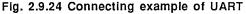

| 2.9.4 Clock asynchronous serial I/O (UART)                         |     |

| 2.9.5 Sleep mode                                                   |     |

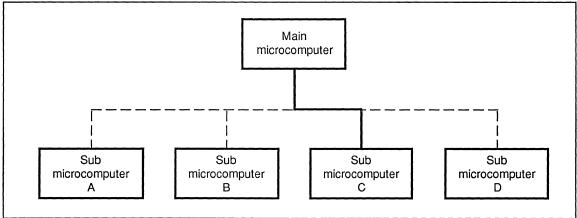

| 2.10 A-D converter                                                 |     |

| 2.10.1 A-D converter overview                                      |     |

| 2.10.2 Block description                                           |     |

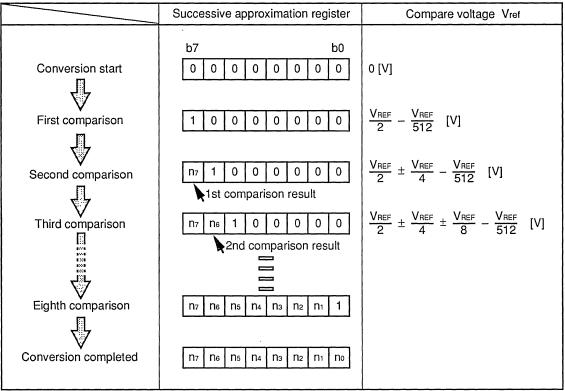

| 2.10.3 Successive approximation conversion                         |     |

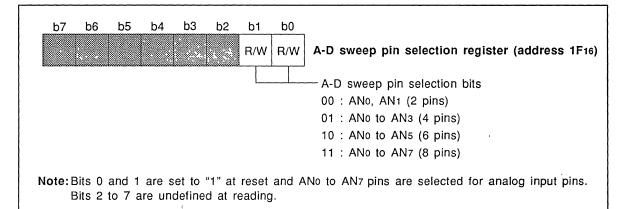

| 2.10.4 A-D conversion mode                                         |     |

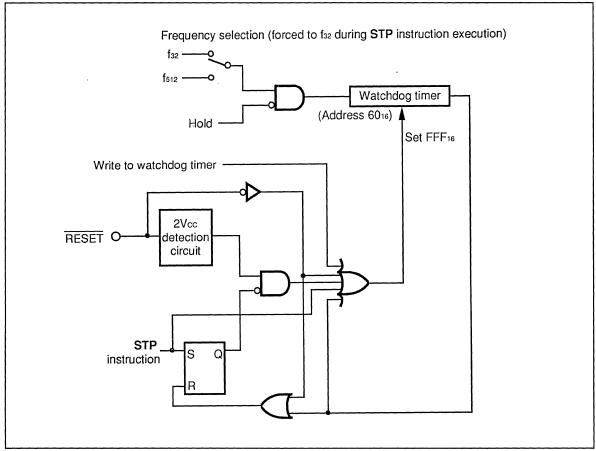

| 2.11 Watchdog timer                                                | 158 |

| 2.11.1 Operation description                                       |     |

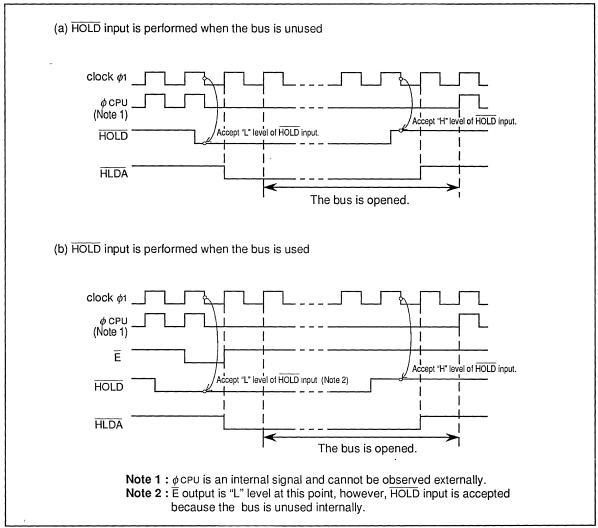

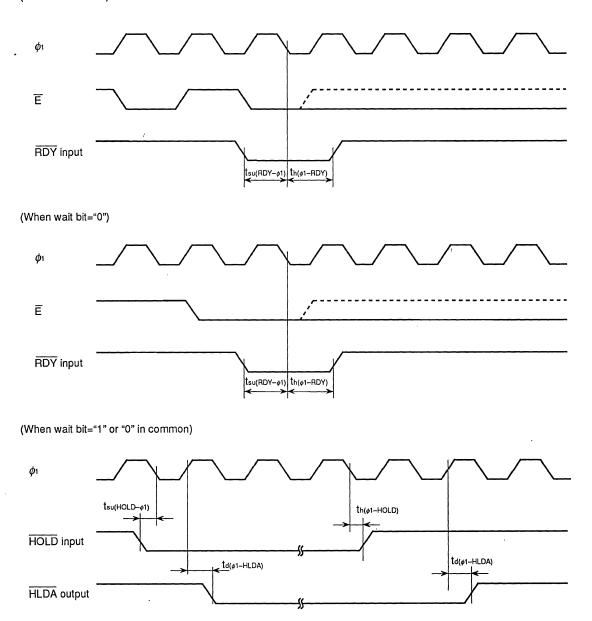

| 2.12 Hold function                                                 |     |

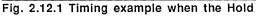

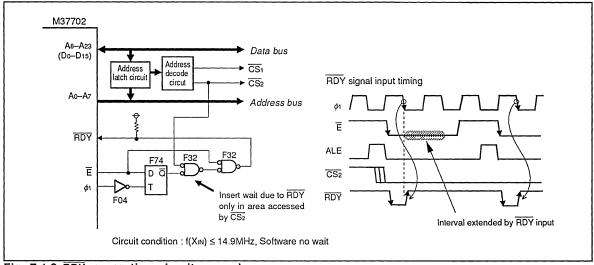

| 2.13 Ready function                                                |     |

|                                                                    |     |

| CHAPTER 3. RESET                                                   |     |

| 3.1 Reset                                                          | 164 |

| 3.1.1 Reset operation                                              | 164 |

| 3.1.2 Internal status at reset                                     | 165 |

| 3.1.3 Bus state during reset in microprocessor mode                |     |

| 3.2 Reset circuit                                                  |     |

| 3.3 Software reset                                                 |     |

|                                                                    |     |

| CHAPTER 4. OSCILLATING CIRCUIT                                     |     |

| 4.1 Oscillating circuit                                            |     |

| 4.1.1 Circuit using a ceramic resonator or a crystal resonator     |     |

| 4.1.2 External clock input circuit                                 |     |

| 4.2 Clock generator                                                |     |

| · · · · · · · · · · · · · · · · · · ·                              |     |

| CHAPTER 5. ELECTRICAL CHARACTERISTICS                              |     |

| 5.1 Electrical characteristics                                     |     |

| 5.1.1 Absolute maximum ratings                                     |     |

| 5.1.2 Recommended operating conditions                             |     |

| 5.1.3 Electrical characteristics and A-D converter characteristics |     |

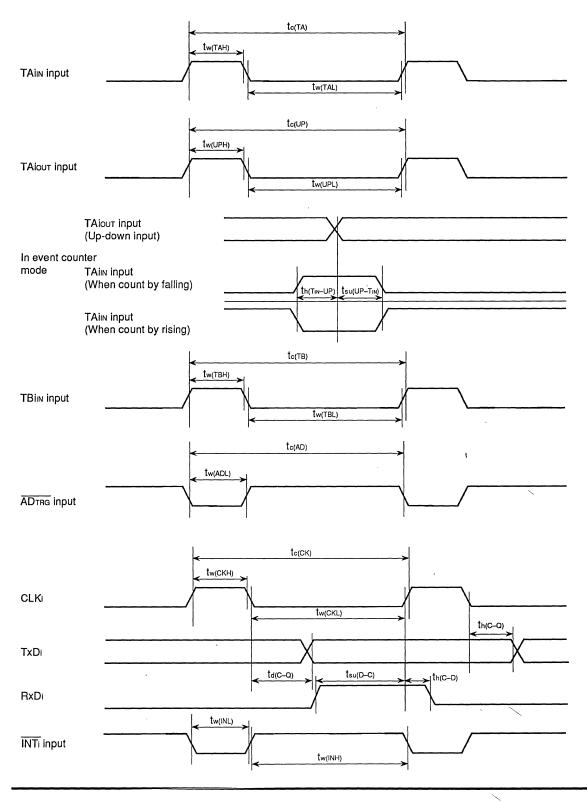

| 5.1.4 Timing requirements                                          |     |

|                                                                    |     |

|                                                                    |     |

| 5.1.5 Switching characteristics                                    |     |

|                                                                    |     |

| CHAPTER 6. STANDARD CHARACTERISTICS                                             |                    |

|---------------------------------------------------------------------------------|--------------------|

| 6.1 Standard characteristics                                                    |                    |

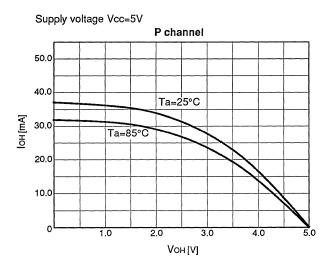

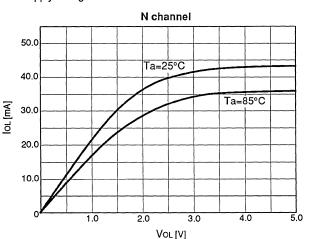

| 6.1.1 Standard port characteristics                                             |                    |

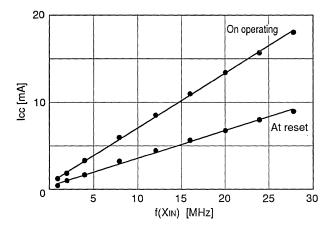

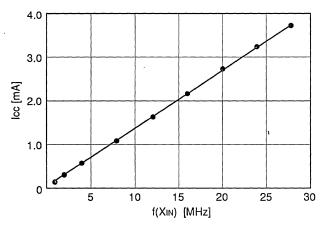

| 6.1.2 lcc-f(XIN) standard characteristics                                       |                    |

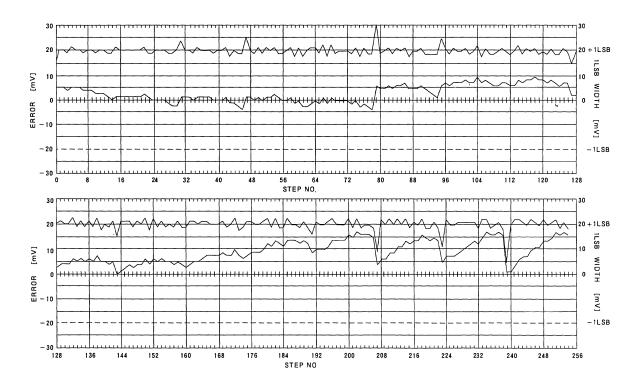

| 6.1.3 A-D converter standard characteristics                                    |                    |

| CHAPTER 7. APPLICATION                                                          |                    |

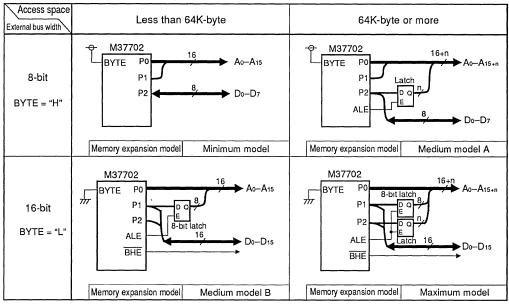

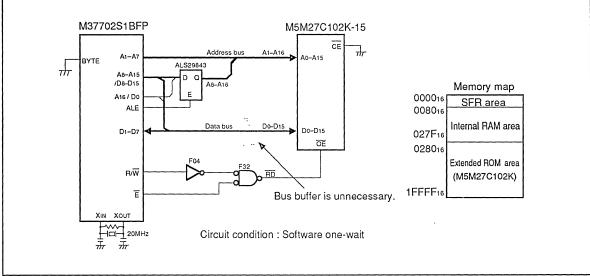

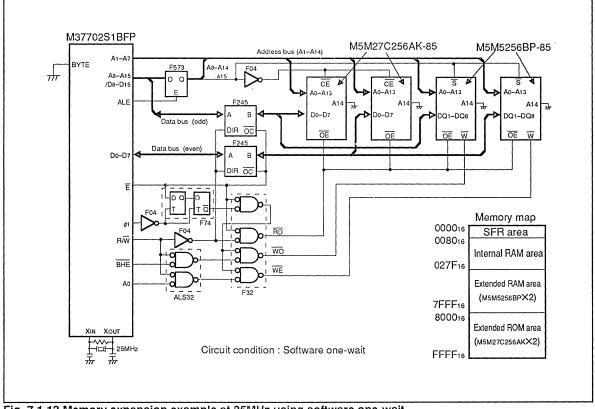

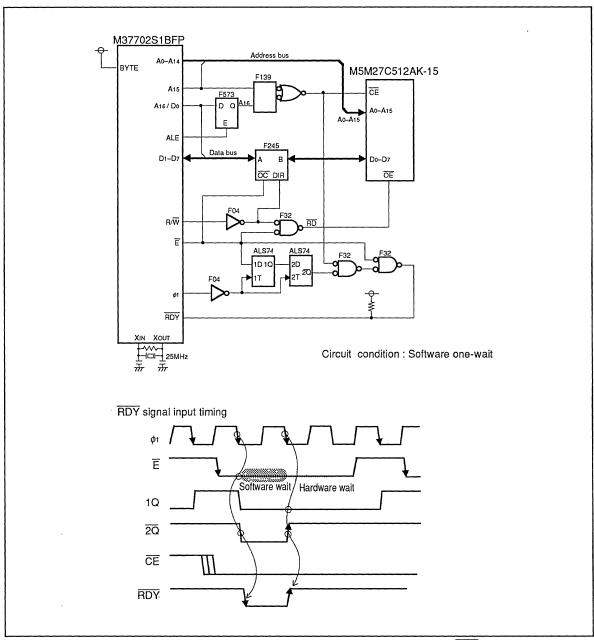

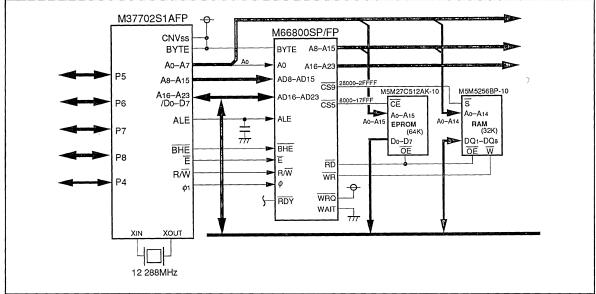

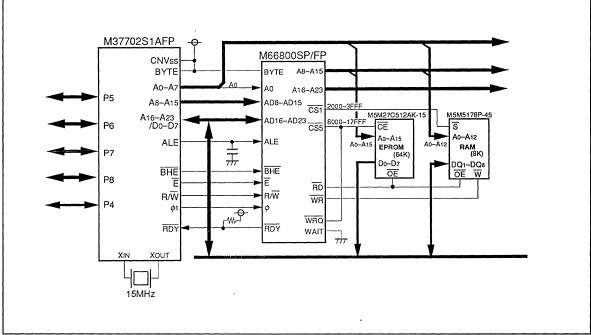

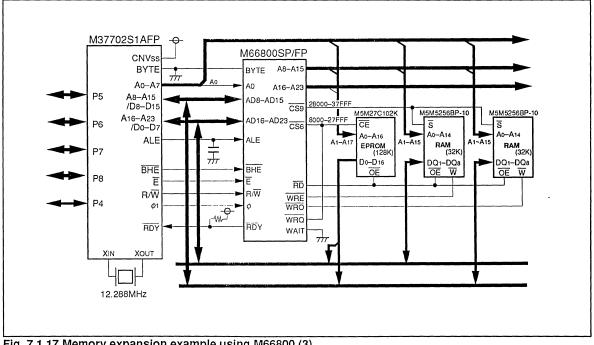

| 7.1 Memory expansion                                                            |                    |

| 7.1.1 Memory expansion model                                                    |                    |

| 7.1.2 Memory access time calculation                                            |                    |

| 7.1.3 Memory expansion precautions                                              |                    |

| 7.1.4 Connection to devices that request long access time                       |                    |

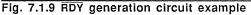

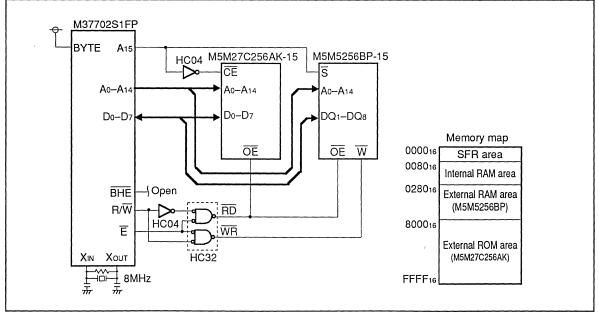

| 7.1.5 Memory expansion example                                                  |                    |

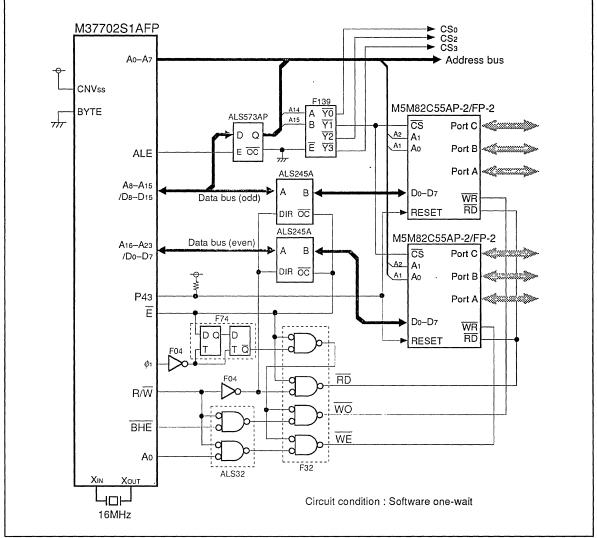

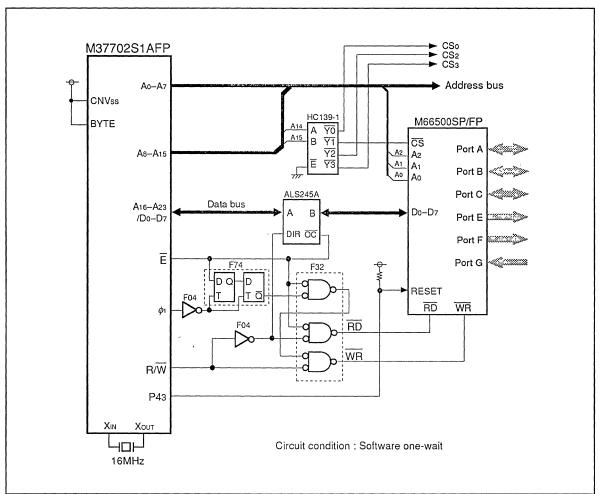

| 7.2 I/O expansion                                                               |                    |

| 7.2.1 I/O expansion model                                                       |                    |

| 7.2.2 I/O expansion examples                                                    |                    |

| 7.3 Program examples                                                            |                    |

| 7.3.1 Hardware definition                                                       |                    |

| 7.3.2 Initialization examples                                                   |                    |

| 7.3.3 Timer modes setting examples                                              |                    |

| 7.3.4 Serial I/O modes setting examples                                         |                    |

| 7.3.5 A-D conversion modes setting examples                                     |                    |

| 7.3.6 Interrupt processing examples                                             |                    |

| 7.3.7 Watchdog timer setting examples                                           |                    |

| 7.3.8 Software timer setting examples                                           |                    |

| 7.3.9 Interrupt vector table setting example                                    |                    |

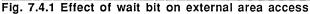

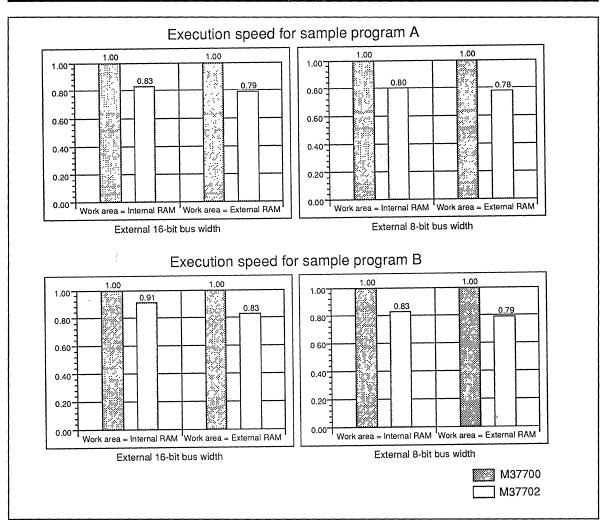

| 7.4 M37702 group execution performance                                          |                    |

| 7.4.1 Comparing the execution speed of M37702 and M37700.                       |                    |

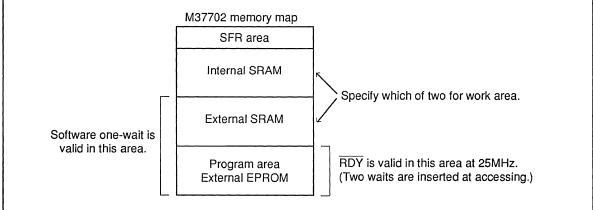

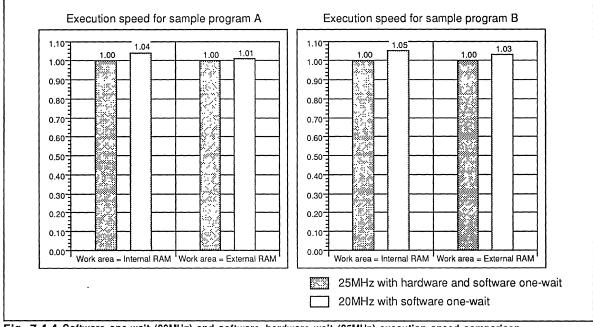

| 7.4.2 Software one-wait (20MHz) and software+hardware wait (25MHz) execution sp | eed comparison 252 |

| CHAPTER 8. PROM VERSION                                                         |                    |

| 8.1 Product expansion                                                           |                    |

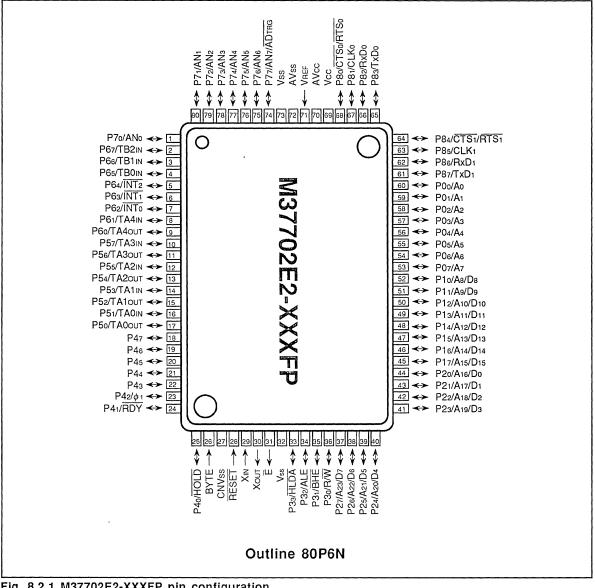

| 8.2 M37702E2-XXXFP                                                              |                    |

| 8.2.1 Description                                                               |                    |

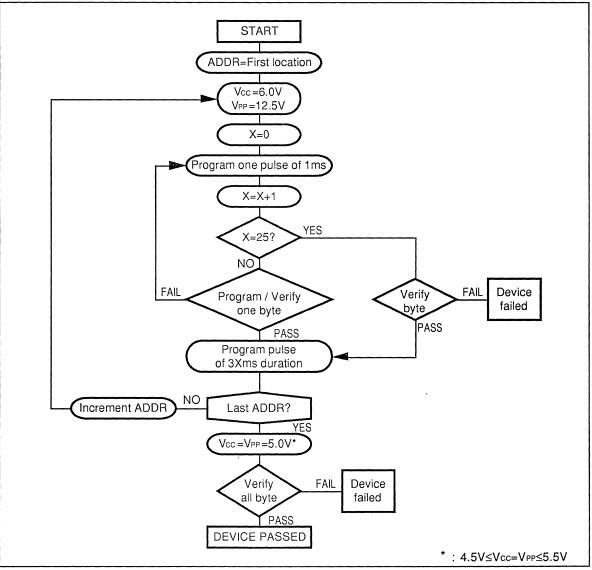

| 8.2.2 Functional description                                                    |                    |

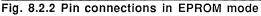

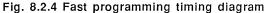

| 8.2.3 Fast programming algorithm                                                |                    |

9.1 Product expansion

266

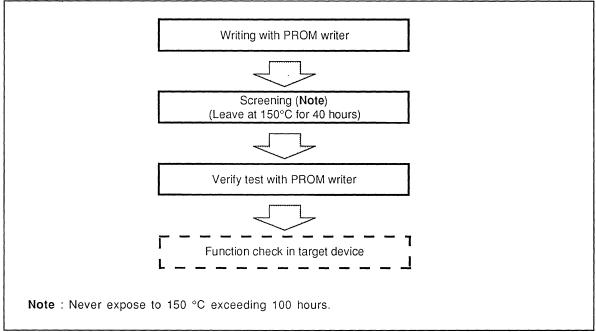

9.1.1 M37703M2-XXXSP characterictics

266

9.2 M37703M2-XXXSP

267

9.2.1 Description

267

9.2.2 Performance overview

268

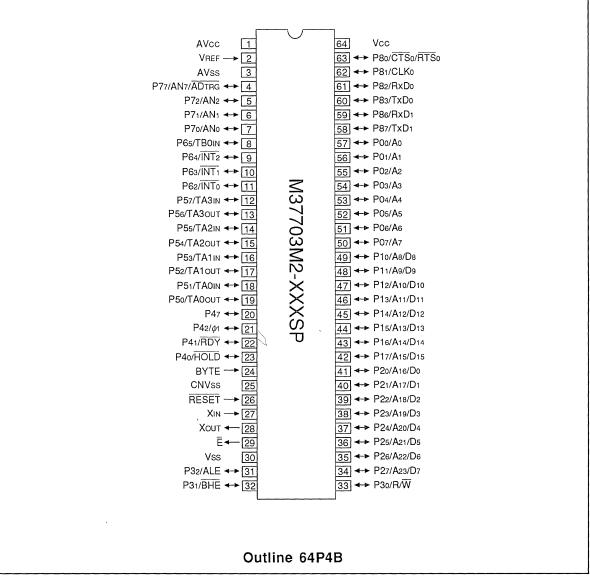

9.2.3 Differences between M37703M2-XXXSP and M37702M2-XXXFP

269

9.2.4 Functional description

270

CHAPTER 9. M37703 GROUP

#### iii

## Table of contents

.

| APPENDIX                                            |  |

|-----------------------------------------------------|--|

| Appendix 1. M37702 group memory map                 |  |

| Appendix 2. SFR area memory map                     |  |

| Appendix 3. Control registers                       |  |

| Appendix 4. Stop, wait, one-wait, Ready, Hold state |  |

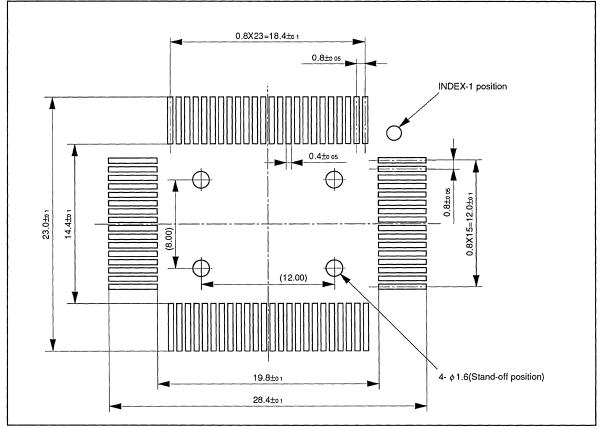

| Appendix 5. Package outlines                        |  |

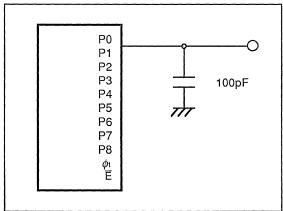

| Appendix 6. Setting of unused pins                  |  |

| Appendix 7. ROM ordering method                     |  |

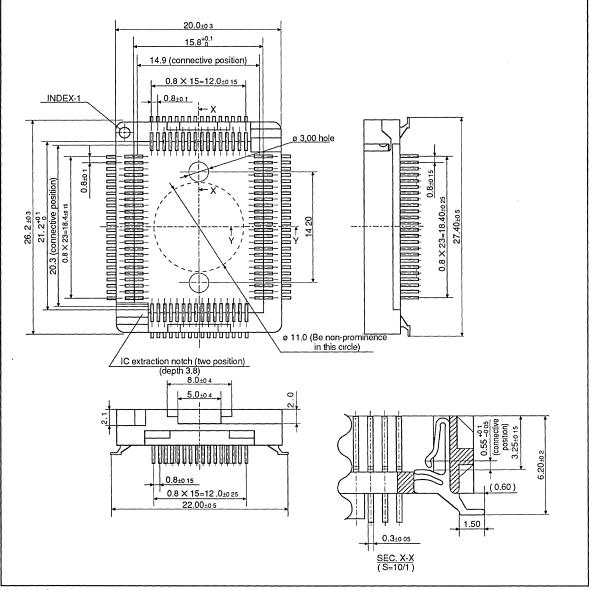

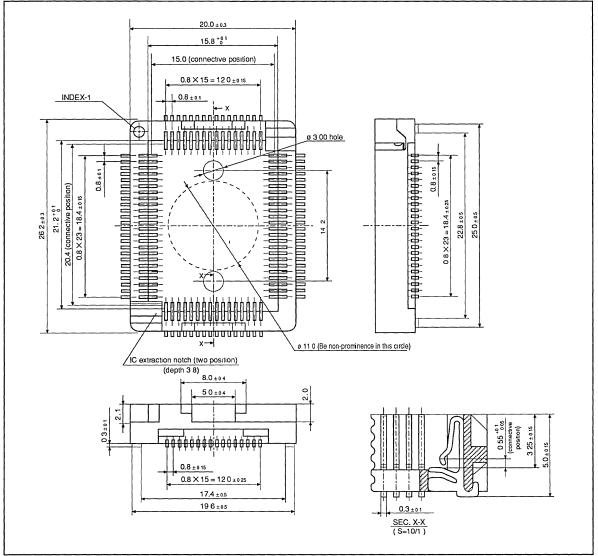

| Appendix 8. IC sockets                              |  |

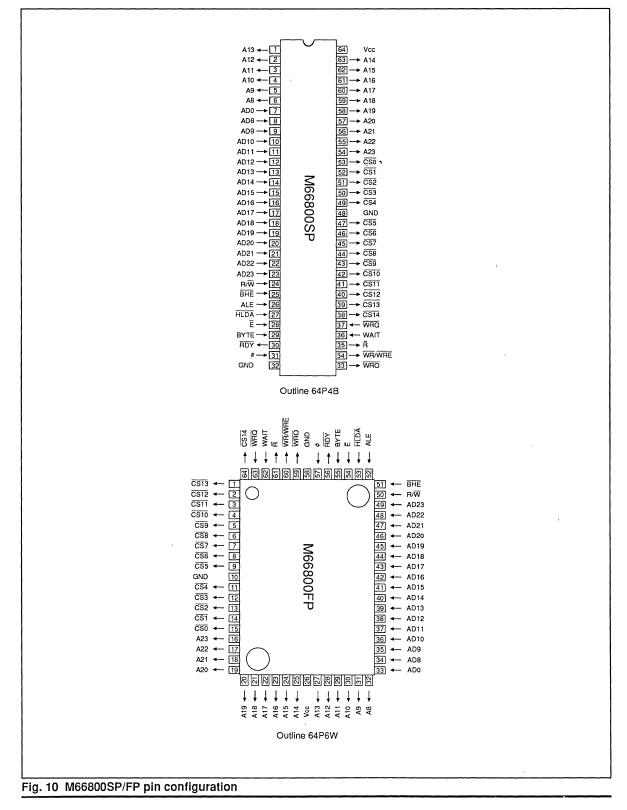

| Appendix 9. M66800SP/FP                             |  |

| Appendix 10. Instruction code table                 |  |

| Appendix 11. Machine instructions                   |  |

¢

| For using this manual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| This manual defines following items.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

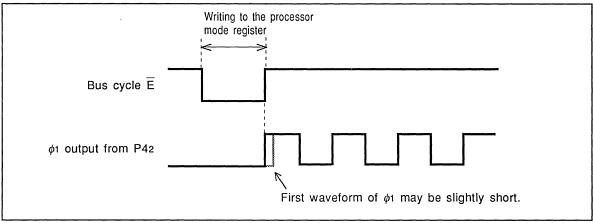

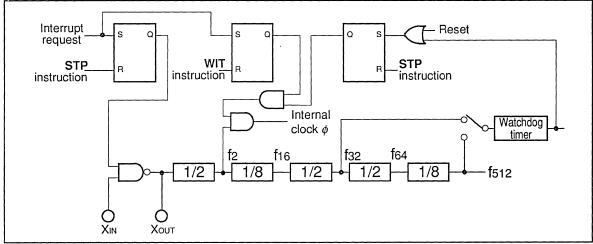

| <ul> <li>•f(XIN)</li> <li>f(XIN) means oscillating clock frequency.</li> <li>•Internal clock φ</li> <li>Internal clock φ means operating clock of this microcomputer. It is obtained by dividing the input clock to XIN pin by 2 ( = f(XIN)/2).</li> <li>•Clock φ1</li> <li>Clock φ1 means the internal clock φ output from P42 pin.</li> <li>•Bit attribute</li> <li>Bit attributes are described in the figure of register structure.</li> <li>The following abbreviations are used to indicate the attributes.</li> </ul> |  |  |  |  |  |  |  |

| b7 b6 b5 b4 b3 b2 b1 b0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| R/W : Possible to read and write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| W : Possible only to write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| R : Possible only to read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Nothing allocated, undefined at reading                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

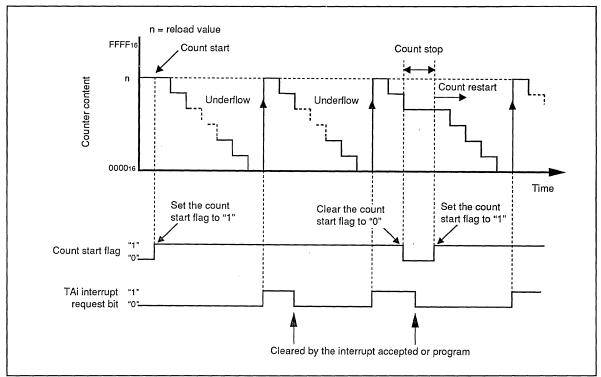

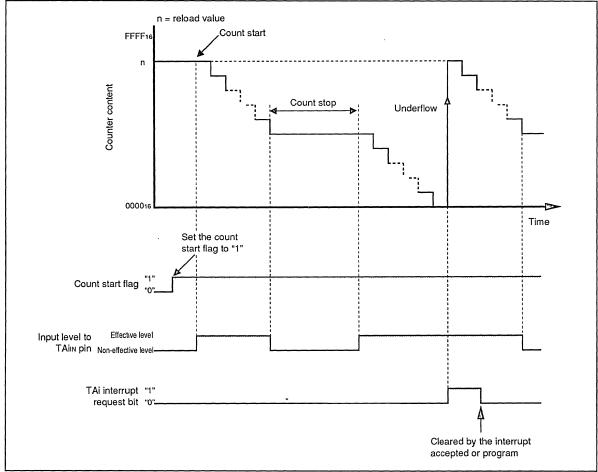

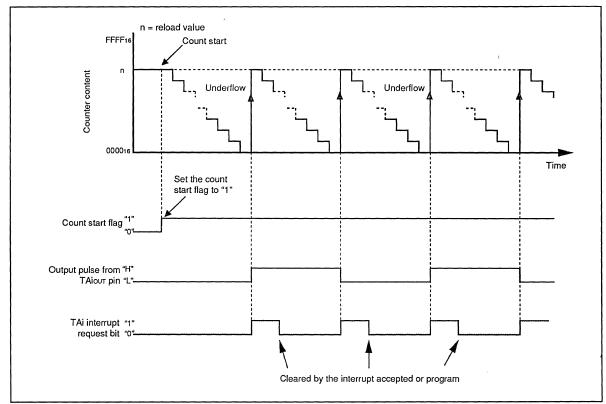

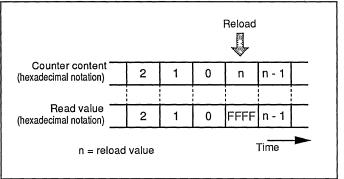

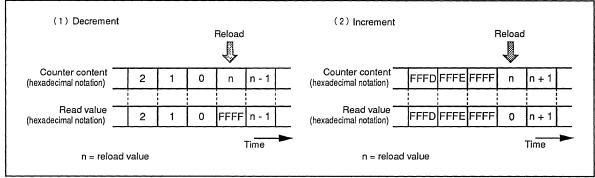

| •Overflow and Underflow of timers<br>Overflow of the timer means that the counter content reaches FFFF16 $\rightarrow$ reload value "n".<br>Underflow of the timer means that the counter content reaches 000016 $\rightarrow$ reload value "n".<br>"n" : Value set in reload register                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

•

•

# CHAPTER 1 DESCRIPTION

- 1.1 M37702 group

- 1.2 Performance overview

- 1.3 Pin configuration

- 1.4 Pin description

- 1.5 Block diagram

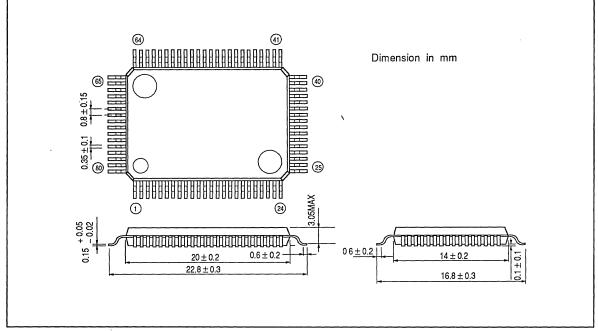

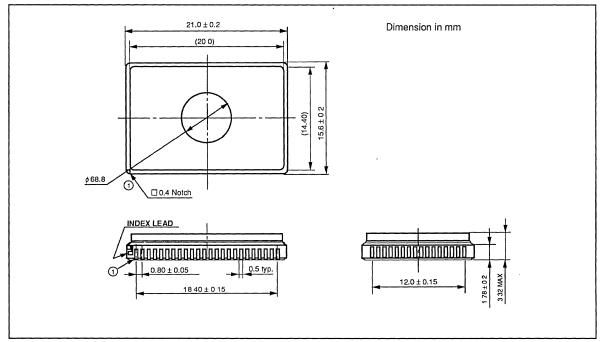

The M37702M2-XXXFP is a 16-bit single-chip microcomputer designed with high-performance CMOS silicon gate technology. It is housed in an 80-pin plastic molded flat package.

This single-chip microcomputer has a large 16M bytes address space, three instruction queue buffers, and two data buffers for high-speed instruction execution. The CPU is a 16-bit parallel processor that can also be switched to perform 8-bit parallel processing. This microcomputer is suitable for office, business, and industrial equipment controllers that require high-speed processing of large amounts of data.

Photo of M37702M2-XXXFP Chip

#### 1.1 M37702 group

The M37702 group consists of chips shown in Table 1.1.1 with the M37702M2-XXXFP as the base chip. These chips are all pin compatible and provide a variety of memory characteristics, memory size, and operating clock frequencies to enable the user to select the chip best suited for his system. Hereafter, the M37702 group microcomputers will be referred to simply as the M37702 unless there is a specific difference by version.

#### Table 1.1.1 M37702 group

|                | ROM                 | RAM     | Clock     | · · · · · · · · · · · · · · · · · · ·      |

|----------------|---------------------|---------|-----------|--------------------------------------------|

| Type name      | size                | size    | frequency | Remarks                                    |

| ·              | (bytes)             | (bytes) | (MHz)     |                                            |

| M37702M2-XXXFP |                     |         | 8         |                                            |

| M37702M2AXXXFP | 16K (Mask ROM)      |         | 16        | High-speed version of M37702M2-XXXFP       |

| M37702M2BXXXFP |                     |         | 25        | Super high-speed version of M37702M2-XXXFP |

| M37702S1FP     |                     |         | 8         | External ROM version of M37702M2-XXXFP     |

| M37702S1AFP    |                     |         | 16        | External ROM version of M37702M2AXXXFP     |

| M37702S1BFP    |                     | 540     | 25        | External ROM version of M37702M2BXXXFP     |

| M37702E2-XXXFP |                     | 512     | 8         | One time PROM version of M37702M2-XXXFP    |

| M37702E2AXXXFP | 16K (One time PROM) |         | 16        | One time PROM version of M37702M2AXXXFP    |

| M37702E2BXXXFP |                     |         | 25        | One time PROM version of M37702M2BXXXFP    |

| M37702E2FS     |                     |         | 8         | EPROM version of M37702M2-XXXFP            |

| M37702E2AFS    | 16K (EPROM)         |         | 16        | EPROM version of M37702M2AXXXFP            |

| M37702E2BFS    |                     |         | 25        | EPROM version of M37702M2BXXXFP            |

| M37702M4-XXXFP |                     |         | 8         | Memory expansion version of M37702M2-XXXFP |

| M37702M4AXXXFP | 32K (Mask ROM)      |         | 16        | Memory expansion version of M37702M2AXXXFP |

| M37702M4BXXXFP |                     |         | 25        | Memory expansion version of M37702M2BXXXFP |

| M37702S4FP     |                     |         | 8         | External ROM version of M37702M4-XXXFP     |

| M37702S4AFP    | ]                   |         | 16        | External ROM version of M37702M4AXXXFP     |

| M37702S4BFP    |                     | 2048    | 25        | External ROM version of M37702M4BXXXFP     |

| M37702E4-XXXFP |                     | 2048    | 8         | One time PROM version of M37702M4-XXXFP    |

| M37702E4AXXXFP | 32K (One time PROM) |         | 16        | One time PROM version of M37702M4AXXXFP    |

| M37702E4BXXXFP |                     |         | 25        | One time PROM version of M37702M4BXXXFP    |

| M37702E4FS     |                     |         | 8         | EPROM version of M37702M4-XXXFP            |

| M37702E4AFS    | 32K (EPROM)         |         | 16        | EPROM version of M37702M4AXXXFP            |

| M37702E4BFS    | 1_ <u></u>          |         | 25        | EPROM version of M37702M4BXXXFP            |

#### **1.2 Performance overview**

#### **1.2 Performance overview**

Table 1.2.1 shows the performance overview of the M37702M2-XXXFP/ M37702M2AXXXFP/ M37702M2BXXXFP.

|--|

| Paramete                     | ers                     | Functions                                           |  |  |  |  |  |

|------------------------------|-------------------------|-----------------------------------------------------|--|--|--|--|--|

| Number of basic instructions |                         | 103                                                 |  |  |  |  |  |

| Instruction execution time   | M37702M2-XXXFP          | 500ns (the fastest instruction at 8MHz frequency)   |  |  |  |  |  |

|                              | M37702M2AXXXFP          | 250ns (the fastest instruction at 16MHz frequency)  |  |  |  |  |  |

|                              | M37702M2BXXXFP          | 160ns (the fastest instruction at 25MHz frequency)  |  |  |  |  |  |

| Clock frequency              | M37702M2-XXXFP          | 8MHz (maximum)                                      |  |  |  |  |  |

|                              | M37702M2AXXXFP          | 16MHz (maximum)                                     |  |  |  |  |  |

|                              | M37702M2BXXXFP          | 25MHz (maximum)                                     |  |  |  |  |  |

| Memory size                  | ROM                     | 16384 bytes                                         |  |  |  |  |  |

|                              | RAM                     | 512 bytes                                           |  |  |  |  |  |

| Input/Output ports           | Ports P0-P2, P4-P8      | 8 bits $\times$ 8                                   |  |  |  |  |  |

|                              | Port P3                 | 4 bits $\times$ 1                                   |  |  |  |  |  |

| Multi-function timers        | TA0, TA1, TA2, TA3, TA4 | 16 bits $\times$ 5                                  |  |  |  |  |  |

|                              | TB0, TB1, TB2           | 16 bits × 3                                         |  |  |  |  |  |

| Serial I/O                   |                         | (UART or clock synchronous serial I/O) $\times$ 2   |  |  |  |  |  |

| A-D converter                |                         | 8 bits $\times$ 1 (8 channels)                      |  |  |  |  |  |

| Watchdog timer               |                         | 12 bits × 1                                         |  |  |  |  |  |

| Interrupts                   |                         | 3 external, 16 internal (priority levels 0 to 7 can |  |  |  |  |  |

|                              |                         | be set for each interrupt with software)            |  |  |  |  |  |

| Clock generating circuit     |                         | Built-in (externally connected to a ceramic         |  |  |  |  |  |

|                              |                         | resonator or quartz crystal oscillator)             |  |  |  |  |  |

| Supply voltage               |                         | 5V±10%                                              |  |  |  |  |  |

| Power dissipation            |                         | 30mW (at external 8MHz frequency)                   |  |  |  |  |  |

| Input/Output characteristics | Input/Output voltage    | 5V                                                  |  |  |  |  |  |

|                              | Output current          | 5mA                                                 |  |  |  |  |  |

| Memory expansion             |                         | Maximum 16M bytes                                   |  |  |  |  |  |

| Operating temperature range  | 9                       | –20 to 85°C                                         |  |  |  |  |  |

| Device structure             |                         | CMOS high-performance silicon gate process          |  |  |  |  |  |

| Package                      |                         | 80-pin plastic molded QFP                           |  |  |  |  |  |

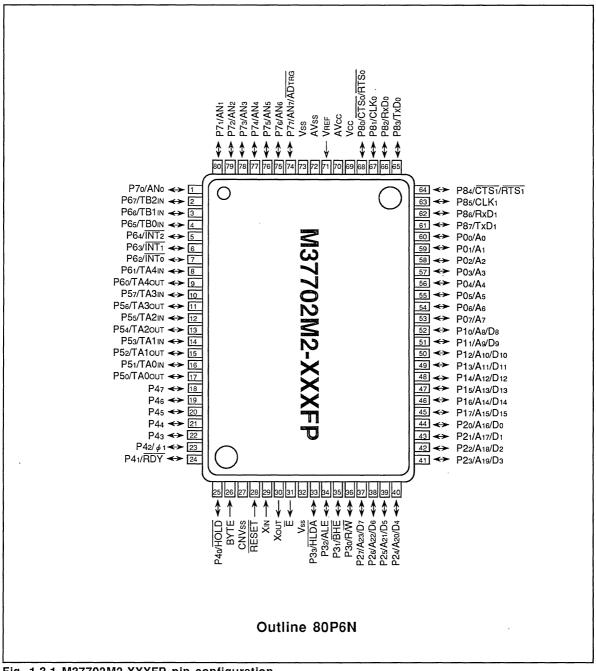

#### 1.3 Pin configuration

Figure 1.3.1 shows the M37702M2-XXXFP pin configuration.

**1.4 Pin description** Table 1.4.1 shows the pin description.

#### Table 1.4.1 Pin description (1)

| Pin        | Name                      | Input/Output | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|---------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcc, Vss   | Power supply              |              | Supply 5V±10% to Vcc and 0V to Vss.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

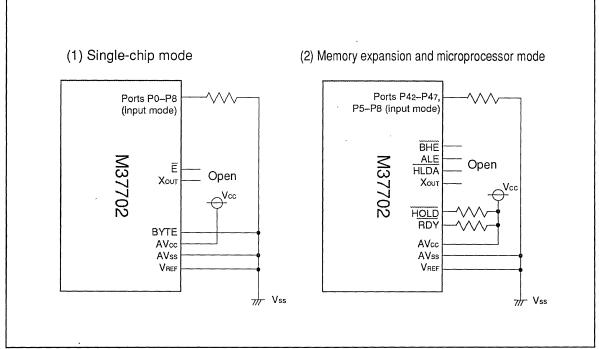

| CNVss      | CNVss input               | Input        | This pin controls the processor mode. Connect to Vss for<br>single-chip mode. It must be connected to Vcc for exter-<br>nal ROM types.                                                                                                                                                                                                                                                                                                                                             |

| RESET      | Reset input               | Input        | The microcomputer is reset when this pin is set to "L' level.                                                                                                                                                                                                                                                                                                                                                                                                                      |

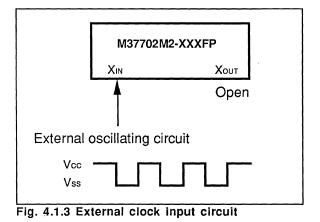

| Xin        | Clock input               | Input        | These are the I/O pins of the internal clock generating<br>circuit. Connect a ceramic or quartz crystal resonator                                                                                                                                                                                                                                                                                                                                                                  |

| Хоит       | Clock output              | Output       | between XIN and XOUT. When an external clock is used,<br>the clock source should be connected to the XIN pin and<br>the XOUT pin should be left open.                                                                                                                                                                                                                                                                                                                              |

| Ē          | Enable output             | Output       | Data or instruction read and data write are performed<br>when output from this pin is "L" level.                                                                                                                                                                                                                                                                                                                                                                                   |

| BYTE       | Bus width selection input | Input        | When in memory expansion mode or microprocesson<br>mode, this pin determines whether the external data bus<br>is 8-bit width or 16-bit width. The width is 16 bits when the<br>signal level is "L" and 8 bits when the signal level is "H".                                                                                                                                                                                                                                        |

| AVcc, AVss | Analog supply input       |              | Power supply for the A-D converter. Externally connect<br>AVcc to Vcc and AVss to Vss.                                                                                                                                                                                                                                                                                                                                                                                             |

| VREF       | Reference voltage input   | Input        | This is a reference voltage input pin for the A-D con-<br>verter.                                                                                                                                                                                                                                                                                                                                                                                                                  |

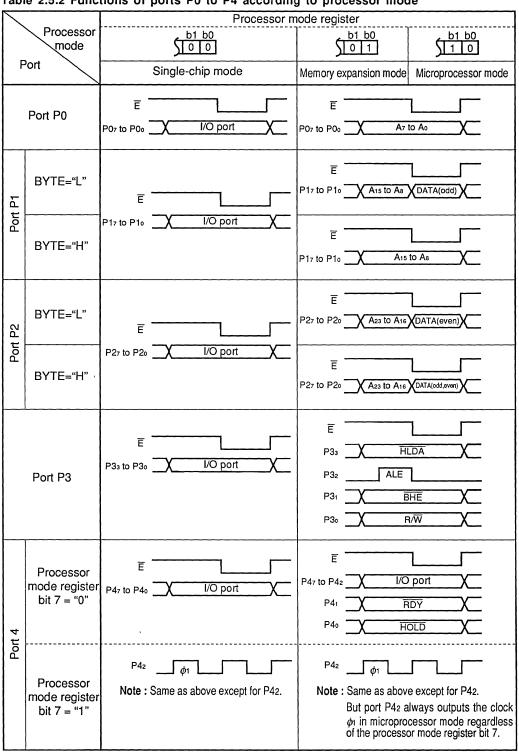

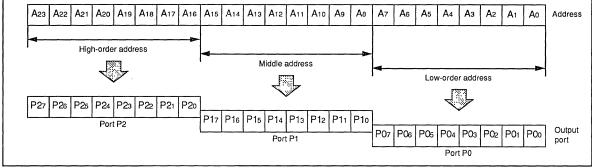

| P00–P07    | I/O port P0               | 1/0          | This port is a CMOS I/O port. An I/O direction register is<br>available so that each pin can be programmed for input<br>or output. Address (A <sub>0</sub> –A <sub>7</sub> ) is output in memory expan-<br>sion mode or microprocessor mode.                                                                                                                                                                                                                                       |

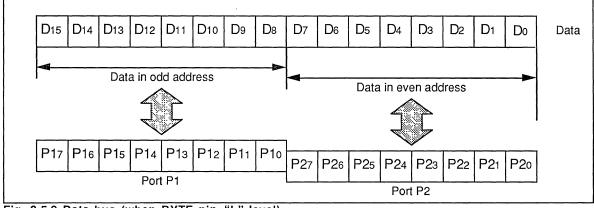

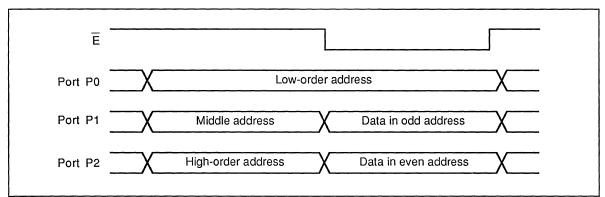

| P10-P17    | I/O port P1               | I/O          | This port is an 8-bit I/O port with the same function as P0.<br>When the BYTE pin is set to "H" level in memory expan-<br>sion mode or microprocessor mode, address (A <sub>8</sub> -A <sub>15</sub> ) is<br>output. In case the BYTE pin is set to "L" level, an address<br>(A <sub>8</sub> -A <sub>15</sub> ) is output when $\overline{E}$ pin level is "H", and high-order<br>data (D <sub>8</sub> -D <sub>15</sub> ) is input or output when $\overline{E}$ pin level is "L". |

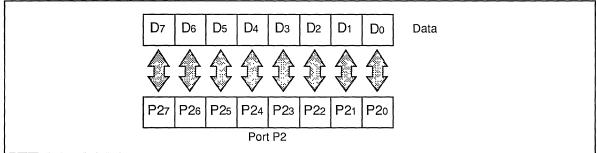

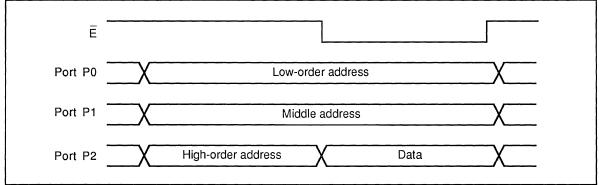

| P20-P27    | I/O port P2               | I/O          | This port is an 8-bit I/O port with the same function as P0<br>In memory expansion mode or microprocessor mode, ar<br>address (A <sub>16</sub> –A <sub>23</sub> ) is output when $\overline{E}$ pin level is "H", and<br>low-order data (D <sub>0</sub> –D <sub>7</sub> ) is input or output when $\overline{E}$ pin leve<br>is "L".                                                                                                                                               |

| P3₀–P3₃    | I/O port P3               | I/O          | This port is a 4-bit I/O port with the same function as P0<br>In memory expansion mode or microprocessor mode<br>P3o-P33 output R/W, BHE, ALE, and HLDA signals re-<br>spectively.                                                                                                                                                                                                                                                                                                 |

| P40–P47    | I/O port P4               | I/O          | This port is an 8-bit I/O port with the same function as P0<br>In memory expansion mode or microprocessor mode<br>P4 <sub>0</sub> and P4 <sub>1</sub> become HOLD and RDY input pin respec-<br>tively. P4 <sub>2</sub> can be programmed for a $\phi_1$ output pin.<br>In microprocessor mode, P4 <sub>2</sub> always outputs the clock $\phi_1$                                                                                                                                   |

,

Table 1.4.1 Pin description (2)

| Pin     | Name        | Input/Output | Functions                                                                                                                                                                                                                                    |

|---------|-------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P50-P57 | I/O port P5 | I/O          | This port is an 8-bit I/O port with the same function as P0. These pins can be programmed as I/O pins for timers A0–A3.                                                                                                                      |

| P60–P67 | I/O port P6 | 1/0          | This port is an 8-bit I/O port with the same function as P0. These pins can be programmed as I/O pins for timer A4, external interrupt input pins for INTo-INT2, and input pins for timers B0-B2.                                            |

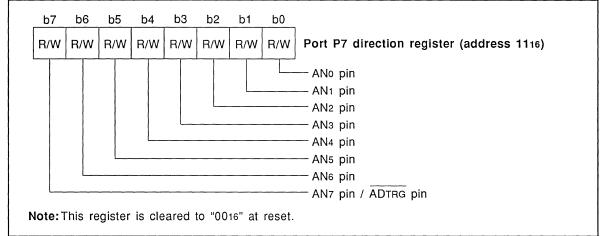

| P70–P77 | I/O port P7 | 1/0          | This port is an 8-bit I/O port with the same function as P0. These pins can be programmed as analog input pins AN <sub>0</sub> -AN <sub>7</sub> . P7 <sub>7</sub> also functions as the AD <sub>TRG</sub> pin for an A-D conversion trigger. |

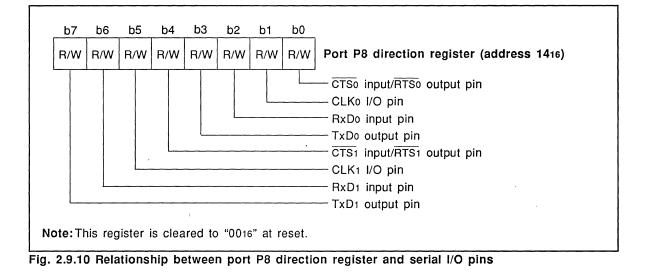

| P80-P87 | I/O port P8 | 1/0          | This port is an 8-bit I/O port with the same function as P0. These pins can be programmed as CTS/RTS, CLK, RxD, TxD pins for UART0 and UART1.                                                                                                |

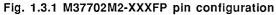

#### 1.5 Block diagram

Figure 1.5.1 shows the M37702M2-XXXFP block diagram

# CHAPTER 2 FUNCTIONAL DESCRIPTION

- 2.1 Central processing unit (CPU)

- 2.2 Internal bus interface

- 2.3 Addressable memory space

- 2.4 Memory allocation

- 2.5 Input/Output pins

- 2.6 Interrupts

- 2.7 Timer A

- 2.8 Timer B

- 2.9 Serial I/O

- 2.10 A-D converter

- 2.11 Watchdog timer

- 2.12 Hold function

- 2.13 Ready function

#### 2.1 Central processing unit (CPU)

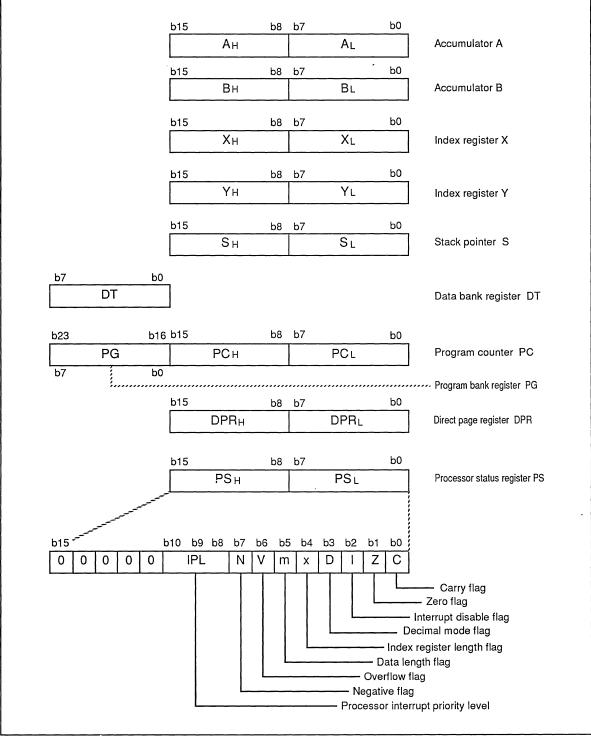

The MELPS 7700 CPU has ten registers as shown in Figure 2.1.1. Each of these registers is described below.

#### 2.1.1 Accumulator (Acc)

Accumulators A and B are available and each can be used as 8-bit or 16-bit register as necessary.

#### (1) Accumulator A (A)

Accumulator A is the main register of the microcomputer. Data operations such as calculations, data transfer, and input/output are executed mainly through accumulator A. It consists of 16 bits and the low-order 8 bits can be used separately. The data length flag (m) determines whether the register is used as a 16-bit register or as an 8-bit register. It is used as a 16-bit register when flag m is "0" and as an 8-bit register when flag m is "1". Flag m is a part of the processor status register (PS) which is described later. When an 8-bit register is selected, the low-order 8 bits of the accumulator A are used and the contents of the high-order 8 bits are unchanged.

#### (2) Accumulator B (B)

Accumulator B has the same functions as accumulator A. The MELPS 7700 instructions can use accumulator B instead of accumulator A, but the use of accumulator B requires more instruction bytes and execution cycles than accumulator A. Accumulator B is also controlled by the data length flag m.

#### 2.1.2 Index register X (X)

Index register X consists of 16 bits and the lower 8 bits can be used separately. The index register length flag (x) determines whether the register is used as a 16-bit register or as an 8-bit register. It is used as a 16-bit register when flag x is "0" and as an 8-bit register when flag x is "1". Flag x is a part of the processor status register (PS) which is described later. When an 8-bit register is selected, the low-order 8 bits of the index register X are used and the contents of the high-order 8 bits are unchanged.

In index addressing mode, register X is used as the index register and the contents of this address is added to obtain the real address.

Also, when executing a block transfer instruction MVP or MVN, the contents of the index register X indicate the low-order 16 bits of the source data address. The third byte of the MVP or MVN is the high-order 8 bits of the source data address.

#### 2.1.3 Index register Y

Index register Y is a 16-bit register with the same function as index register X. As with index register X, the index register length flag (x) determines whether this register is used as a 16-bit register or as an 8-bit register. Also, when executing a block transfer instruction **MVP** or **MVN**, the content of index register Y indicates the low-order 16 bits of the destination data address. The second byte of the **MVP** or **MVN** is the high-order 8 bits of the destination data address.

## FUNCTIONAL DESCRIPTION

#### 2.1 Central processing unit

Fig. 2.1.1 CPU registers structure

#### 2.1.4 Stack pointer (S)

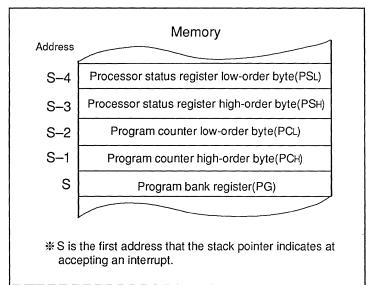

Stack pointer S is a 16-bit register. It is used during a subroutine call or interrupt. It is also used during addressing modes using the stack. The contents of the stack pointer S indicates the address (stack area) for storing registers during subroutine calls and interrupts. The bank 0 must be designated for the stack area (reffer to section " 2.3 Addressable memory space"). Normally, the stack area is reserved in internal RAM.

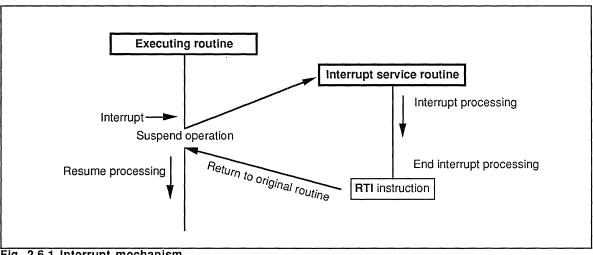

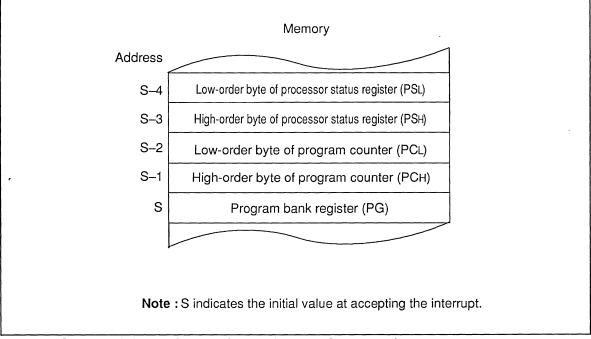

When an interrupt is accepted, the contents of the program bank register PG is stored at the address indicated by the content of the stack pointer S, and the content of the stack pointer S is decremented by 1. Then the contents of the program counter PC and the processor status register PS are stored with the high-order bytes followed by the low-order bytes (PCH, PCL, PSH, PSL). The contents of the stack pointer S after accepting an interrupt is equal to the content before the interrupt decremented by 5. Figure 2.1.2 shows the stored registers when an interrupt is accepted.

When returning to the original routine after processing the interrupt, the registers stored in the stack area are restored to the original registers in the reverse sequence and the content of the stack pointer is returned to the status before the interrupt. The same operation is performed during a subroutine call, but the content of the processor status register PS is not stored (the content of the program bank register PG may not be stored either depending on the addressing mode).

The user is responsible for storing registers other than those described above during interrupts or subroutine calls. In addition, the stack pointer S must be initialized at the beginning of the program because its content is undefined at reset. Normally, the stack pointer is initialized with the highest address of the internal RAM. The contents of the stack area changes when subroutines are nested or when multiple interrupts are accepted. Therefore, make sure necessary data in the internal RAM are not destroyed when nesting subroutines.

Fig. 2.1.2 Stored registers when an interrupt is accepted

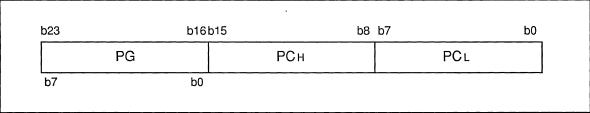

#### 2.1.5 Program counter (PC)

Program counter PC is a 16-bit counter that indicates the low-order 16 bits of the next program memory address to be executed. The content of the high-order program counter(PCH) becomes "FF16", and the low-order program counter(PCL) becomes "FE16" at reset. The content of the program counter PC becomes the content of the reset vector address(address FFFE16, FFF16) after removing reset state. Figure 2.1.3 shows the program counter PC and the program bank register.

#### Fig. 2.1.3 Program counter and program bank register

#### 2.1.6 Program bank register (PG)

Program bank register PG is an 8-bit register that indicates the high-order 8 bits (bank) of the next program memory address to be executed. When a carry occurs after incrementing the content of the program counter PC, the content of the program bank register PG is incremented by 1. Also, when a carry or borrow occurs after adding or subtracting the content of the program counter PC, the content of the program bank register PG is incremented by 1. Also, when a carry or borrow occurs after adding or subtracting the content of the program counter PC, the content of the program bank register PG is incremented or decremented by 1 so that programs can be written without considering bank boundaries, usually.

In single-chip mode, set the value "0016" because only address between 000016 and FFFF16 can be accessed.

This register is cleared to "0016" at reset.

#### 2.1.7 Data bank register (DT)

Data bank register DT is an 8-bit register. With some addressing modes using the data bank registerDT, the content of this register is used as the high-order 8 bits of a 24-bit address. In single-chip mode, set the value " $00_{16}$ " because only address between  $000_{16}$  and FFFF<sub>16</sub> can be accessed.

Use the LDT instruction to set the value in this register. This register is cleared to "0016" at reset.

\*Refer to "MEPS 7700 SOFTWARE MANUAL" for the addressing modes.

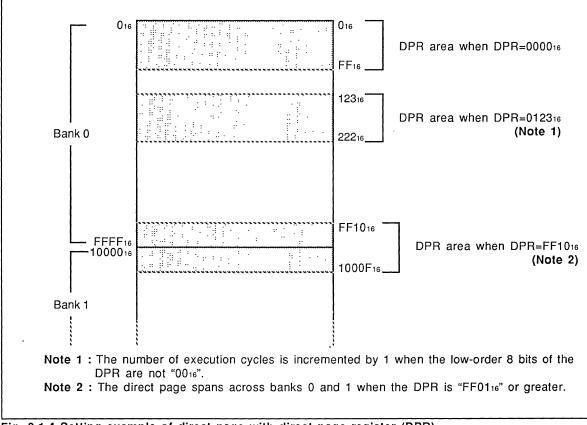

#### 2.1.8 Direct page register (DPR)

Direct page register DPR is a 16-bit register. The content of this register indicates whether the direct page area is allocated in bank 0 or spans across bank 0 and 1. This area can be accessed with two bytes by using the direct page addressing mode.

The content of the DPR is the base address (lowermost address) of the direct page area which extends 256 bytes above this address. The DPR can contain a value from 0000<sub>16</sub> to FFFF<sub>16</sub>. If it contains a value equal to or greater than "FF01<sub>16</sub>", the direct page area spans across banks 0 and 1. If the low-order 8 bits of the DPR is "00<sub>16</sub>", the number of cycles required to generate an address is minimized. Therefore, the low-order 8 bits of the DPR should normally be set to "00<sub>16</sub>".

This register is cleared to "000016" at reset. Figure 2.1.4 shows the setting example of the direct page with the direct page register(DPR).

Fig. 2.1.4 Setting example of direct page with direct page register (DPR)

#### 2.1 Central processing unit

#### 2.1.9 Processor status register (PS)

Processor status register is an 11-bit register. It consists of flags to indicate the result of operation and CPU interrupt levels. The flags C, Z, V, and N are tested by branch instructions.

Figure 2.1.5 shows the register structure of the processor status register.

The details of the processor status register bits are described below.

| b15 | b14 | b13 | b12 | b11 | b10 | b9  | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|

| 0   | 0   | 0   | 0   | 0   |     | IPL |    | N  | V  | m  | x  | D  | 1  | Z  | С  |

Note : Bits 11 to 15 always are "0" when the contents of the processor status register are read.

#### Fig. 2.1.5 Processor status register structure

#### (1) Carry flag (C)

The carry flag is assigned to bit 0 of the processor status register. It contains the carry or borrow bit from the arithmetic and logic unit (ALU) after an arithmetic operation. This flag is also affected by shift and rotate instructions. This flag can be set with the SEC or SEP instruction and cleared with the CLC or CLP instruction.

#### (2) Zero flag (Z)

The zero flag is assigned to bit 1 of the processor status register. It is set to "1" if the result of an arithmetic operation or data transfer is zero, and cleared to "0" if otherwise. This flag can be set with the SEP instruction and cleared with the CLP instruction directly.

Note : The content of this flag has no meaning during decimal mode addition (ADC instruction).

#### (3) Interrupt disable flag (I)

The interrupt disable flag is assigned to bit 2 of the processor status register. It disables all maskable interrupts (interrupts other than watchdog timer, **BRK** instruction, and zero divide). Interrupts are disabled when this flag is "1". When an interrupt is accepted, it is set to "1" automatically to prevent multiple interrupts. This flag can be set with the **SEI** or **SEP** instruction and cleared with the **CLI** or **CLP** instruction. This flag is set to "1" at reset.

#### (4) Decimal mode flag (D)

The decimal mode flag is assigned to bit 3 of the processor status register. It determines whether addition and subtraction are performed in binary or decimal. Binary arithmetic is performed when this flag is "0". If it is "1", decimal arithmetic is performed with each word treated as two or four digit decimal (determined by the data length flag m). Decimal adjust is performed automatically. Decimal operation is possible only with the ADC and SBC instructions. This flag can be set with the SEP instruction and cleared with the CLP instruction. This flag is cleared to "0" at reset.

#### (5) Index register length flag (x)

The index register length flag is assigned to bit 4 of the processor status register. It determines whether the index register X or index register Y is used as a 16-bit register or an 8-bit register. The register is used as a 16-bit register when flag x is "0" and as an 8-bit register when it is "1". This flag can be set with the **SEP** instruction and cleared with the **CLP** instruction. This flag is cleared to "0" at reset.

#### (6) Data length flag (m)

The data length flag is assigned to bit 5 of the program status register. It determines whether to treat data as 16-bit or as 8-bit. A data is treated as 16-bit when flag m is "0" and as 8-bit when it is "1". This flag can be set with the SEM or SEP instruction and cleared with the CLM or CLP instruction. This flag is cleared to "0" at reset.

#### (7) Overflow flag (V)

The overflow flag is assigned to bit 6 of the processor status register. It is used when adding or subtracting a word as signed binary. In case the data length flag m is "0", the overflow flag is set to "1" when the result of addition or subtraction is outside the range between -32768 and +32767, and cleared to "0" in all other cases. In case the data length flag m is "1", the overflow flag is set to "1" when the result of addition or subtraction is outside the range between -128 and +127, and cleared to "0" in all other cases. The overflow flag can also be set and cleared directly with the SEP, CLV, and CLP instructions.

Note : This flag has no meaning in decimal mode.

#### (8) Negative flag (N)

The negative flag is assigned to bit 7 of the processor status register. It is set when the result of arithmetic operation or data transfer is negative (Data bit 15 is 1 when data length flag m is "0", or data bit 7 is 1 when data length flag m is "1".). It is cleared in all other cases. It can also be set with the **SEP** instruction and cleared with the **CLP** instruction. **Note** : This flag has no meaning in decimal mode.

#### (9) Processor interrupt priority level (IPL)

The processor interrupt priority level (IPL) is assigned to bits 8, 9, and 10 of the processor status register. These three bits determine the priority level of processor interrupts from level 0 to level 7. Interrupt is enabled when the interrupt priority level of the requested interrupt (set with the interrupt control register) is higher than the processor interrupt priority. When an interrupt is accepted, the IPL is stored in the stack and the processor interrupt priority is replaced by the interrupt priority of the accepted interrupt. This simplifies control of multiple interrupts.

There are no instructions to directly set or clear the IPL. It can be changed by placing the new IPL on the stack and updating the processor status register with the **PUL** or **PLP** instruction. The content of the IPL is cleared to "000" at reset.

#### 2.2 Internal bus interface

#### 2.2.1 Internal bus interface overview

A bus interface unit (BIU) is provided between the CPU and the internal bus. Transfer of data between the CPU and memory or I/O device is always performed through the BIU. When the CPU reads data from memory or I/O device, it sends the address to be read to the BIU. The BIU reads the data from the specified address and the CPU receives the data from the BIU. Similarly, the CPU sends the address to be written to the BIU when writing data. Thus the BIU controls the transfer of data between the CPU and bus.

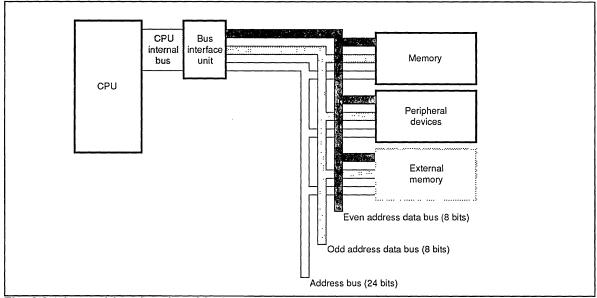

Figure 2.2.1 shows the block diagram of the bus interface unit.

Fig. 2.2.1 Internal bus interface block

#### 2.2.2 Bus interface unit functions

The M37702 group uses the clock  $\phi$  (=f(XIN)/2) as the clock. The CPU also uses clock  $\phi$  as the clock. However, since the CPU clock may be extended due to CPU wait under certain conditions, it is referred to as  $\phi_{CPU}$  to distinguish it from clock  $\phi$ .

The M37702 group internal bus (address bus and data bus) operates at timing  $\overline{E}$  which is slower than clock  $\phi$ . The operating clock of the CPU is different from the bus cycle because timing  $\overline{E}$  is normally  $f(X_{N})/4$ . Therefore, the BIU is provided between the CPU and bus to synchronize the transfer of data to and from memory and I/O device. The BIU enables the CPU to transfer data to and from memory through the bus without decreasing the instruction execution speed.

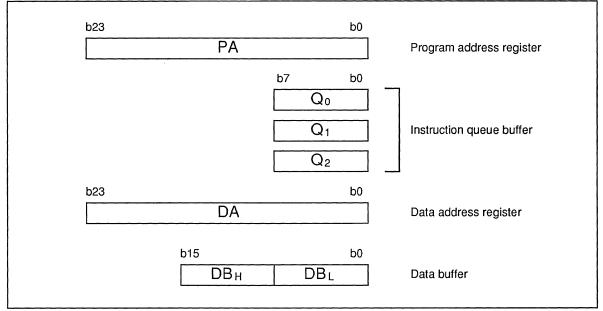

The BIU consists of four registers as shown in Figure 2.2.2. Table 2.2.1 shows the functions of each register and buffer.

| Name                     | Function                                                                        |

|--------------------------|---------------------------------------------------------------------------------|

| Program address register | Indicates the address of the program.                                           |

| Instruction queue buffer | A three-byte buffer for temporarily holding instruction prefetched from memory. |

| Data address register    | Indicates the address to be read from or to be written to memory or I/O.        |

| Data buffer              | A two-byte buffer for temporarily holding data read from memory or I/O device   |

|                          | by the BIU or data written to memory or I/O device by the CPU.                  |

Table 2.2.1 Functions of BIU registers and buffers

## FUNCTIONAL DESCRIPTION

#### 2.2 Internal bus interface

#### Fig. 2.2.2 Bus interface unit registers

The BIU performs the following operations.

## 1.Prefetches an instruction code from the program memory (area where the program is stored) and stores it in the instruction queue buffer.

Normally, a program is executed sequentially in ascending order of address. Therefore, if the next instruction code is prefetched in the instruction queue buffer, the CPU can execute instructions simply by obtaining the instruction code from the instruction queue buffer. This will eliminate the time needed by the CPU to access the memory.

When the CPU is not using the bus (for example when performing register to register operation), the BIU reads an instruction code from the program memory (area where the program is stored) and stores it in the instruction queue buffer. Data up to three bytes can be prefetched because the instruction queue buffer is three bytes long. Refer to Section "2.2.4 Data read/write operations" for more information concerning instruction code prefetch.

# 2.Reads data at the specified address into the BIU when the CPU requests data in memory and transfers it to the CPU.

When executing instructions that processes data in memory or I/O device, the CPU must access the address assigned to the memory or I/O device and read the data. Because the operating clock of the CPU and bus are different, the CPU reads the data through the data buffer of the BIU.

#### 3.Writes the data obtained from the CPU to the specified address in memory.

When writing data to a specific address, the CPU sends the address and data to the BIU. And after that, the CPU continues to execute the next instruction extracting from the instruction queue buffer, because actual writing to memory or I/O device is performed by the BIU.

# 4.Controls read of word data from odd number address and outputs the control signals required to access external memory in byte unit.

The transfer of data between the CPU and BIU is always performed through a 24-bit address bus and 16-bit data bus. This is also true between the BIU and internal memory or I/O device. The wait bit and BYTE pin (external bus width selection input pin) determine the data width only when an external memory is accessed.

#### 2.2.3 Bus interface unit operations

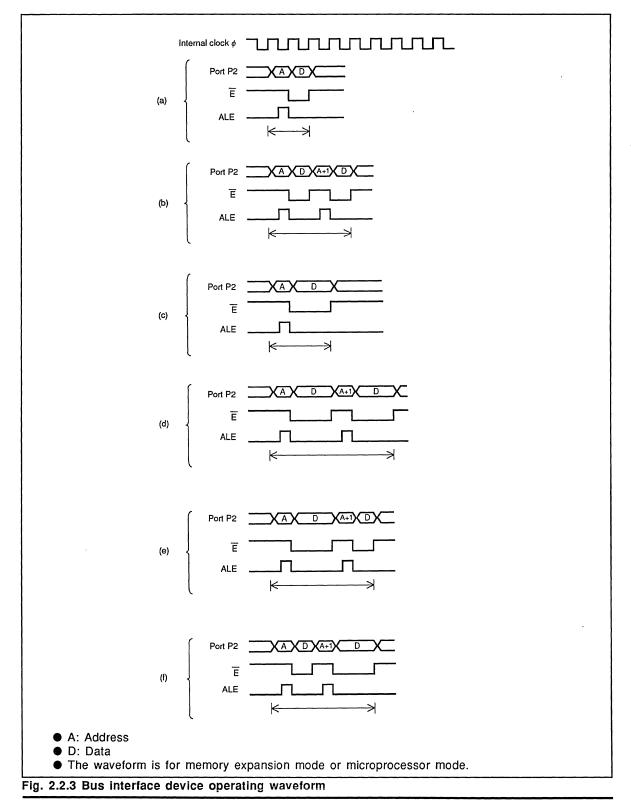

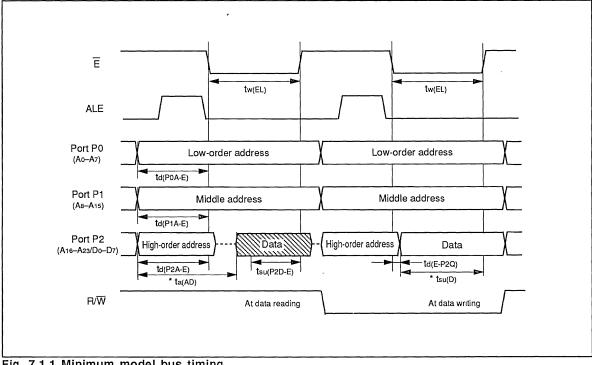

Figure 2.2.3 shows the operating waveforms of the bus interface unit in memory expansion mode or microprocessor mode. The M37702 group BIU always operates at one of the waveforms shown in Figure 2.2.3.

The meaning of signals ALE and  $\overline{E}$  in Figure 2.2.3 are as follows:

• ALE (Address Latch Enable)

Signal used to latch only address signals from multiplexed signals containing data and address.

θĒ

Signal set to "L" level when the bus interface unit reads instruction code or data from memory or when it writes data to memory. Table 2.2.2 shows the bus status according to  $\overline{E}$  and  $R/\overline{W}$  signals.

| Table 2.2.2 Bus | status according | to $\overline{E}$ and $R/\overline{W}$ |

|-----------------|------------------|----------------------------------------|

|                 | Status according |                                        |

| E | R/W | Bus Status |

|---|-----|------------|

| H | Н   | Not used   |

| Н | L   | Not used   |

| L | Н   | Read       |

| L | L   | Write      |

#### (1) Basic operation

Waveform (a) is the bus interface operating waveform under the following conditions:

- When a one byte internal/external memory is accessed.

- When two bytes in internal memory are accessed together (starting on an even address).

- When two bytes in external memory are accessed together (starting on an even address when the BYTE pin is at "L" level).

- When the instruction code is obtained from memory into the instruction queue buffer.

Waveform (b) is the bus interface operating waveform when accessing in byte unit under the following conditions:

- When two bytes in internal/external memory are accessed together (starting on an odd address).

- When two bytes in external memory are accessed together with the BYTE pin at "H" level.

Waveforms (a) and (b) are the basic operating waveforms of the BIU. Waveform (a) or (b) is always used when accessing the internal memory. However, signals other than  $\overline{E}$  cannot be observed in single-chip mode because the port P3 is used as a programmable I/O port.

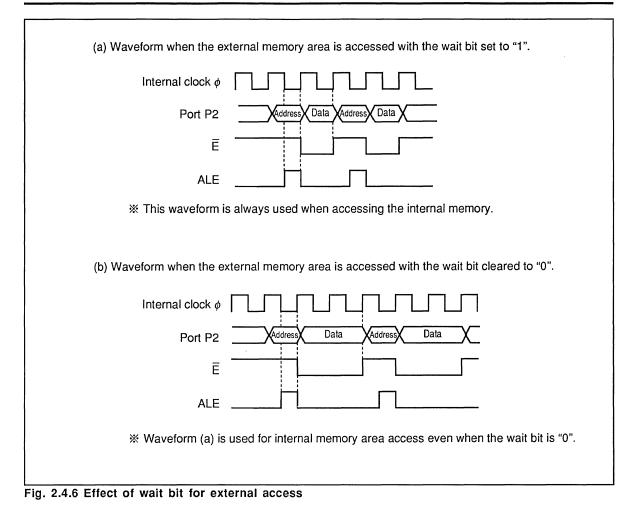

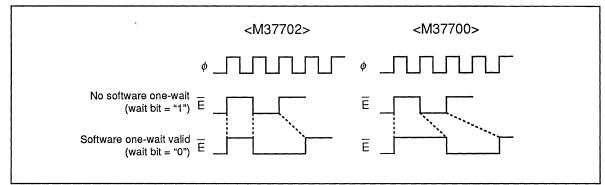

#### (2) Effect of the wait bit

When accessing the external memory area, the BIU operating waveform changes according to the wait bit.

With the M37702 group, the external memory access time can be 1.5 times as long (the "L" level width of  $\overline{E}$  signal becomes twice) by clearing the wait bit (bit 2) to "0" in the processor mode register (address 005E<sub>16</sub>). This enables external expansion of slow memories and peripheral LSIs. **Note** : Internal memory access is not affected by the wait bit.

Figure 2.2.3 (c) to (f) show the effect of the wait bit on waveforms (a) and (b). Waveform (c) is the waveform when an external memory area is accessed under the conditions for waveform (a) with the wait bit cleared to "0".

Waveforms (d) to (f) are the waveforms when an external memory area is accessed under the conditions for waveform (b) with the wait bit cleared to "0". The entire waveform is affected by the wait bit for waveform (d) and the first half or the last half is affected respectively for waveforms (e) and (f).

## FUNCTIONAL DESCRIPTION

#### 2.2 Internal bus interface

#### 2.2.4 Data read/write operations

#### (1) Instruction code read

The CPU reads instructions codes from the instruction queue buffer of the BIU and executes them. The CPU notifies the BIU that an instruction code is needed during the instruction code<sup>\*</sup> fetch cycle. At this point, the operation depends on whether the instruction queue buffer contains an instruction code or not. If there is an instruction code in the instruction queue buffer, it is passed to the CPU. If there is no instruction code in the instruction queue buffer, or if the amount of data in the instruction queue buffer is less than the necessary instruction code, the BIU halts the CPU until a sufficient amount of instruction codes is stored in the instruction queue buffer.

Even when there is no request for instruction code from the CPU, if the instruction queue buffer is empty or if there is only one instruction code and the bus is available at the next cycle (the CPU does not use the bus at the next cycle), the BIU reads instruction codes from memory and stores them in the instruction queue buffer (instruction prefetch). During instruction prefetch, if the first address accessed when reading an instruction code from memory is even, then the data at the next odd number address is also read and stored in the instruction queue buffer. If the first accessed address is only one byte is read and stored in the instruction queue buffer. However, if the instruction code is read from external memory with the BYTE pin at "H" level (external bus width 8-bit) in memory expansion or microprocessor mode, only one byte is read regardless of the accessed address.

Instruction code read is performed with operation (a) or (c) shown in Figure 2.2.3. When a branch or a jump or subroutine call instruction or an interrupt is executed, the content of the instruction queue buffer is cleared and a new instruction code is read from the new address.

#### (2) Data read/write

The CPU reads and writes data from/to the BIU data buffer. The CPU issues a request to BIU when it attempts to read or write data. At this point, if the BIU is using the bus or if there is a higher priority request, the CPU is made to wait until the BIU becomes ready. When the bus is available for data read or write, the BIU operates at one of the waveforms (a) to (f) shown in Figure 2.2.3.

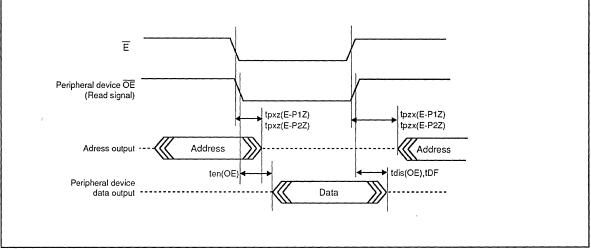

O Data read

When the CPU requests data from the BIU, it waits until the data becomes complete data in the data buffer. The BIU sends the address received from the CPU on the address bus, reads the content of memory when  $\bar{E}$  signal is "L" level, and stores it in the data buffer.

#### O Data write

The CPU sends address (address at which the data is written) and data to BIU.

The address is written in the BIU data address register and the data is written in the data buffer. The actual writing in memory is performed by BIU and the CPU can proceed to the next step without waiting for the BIU to complete writing data in memory. The BIU sends the address received from the CPU to the address bus, sends the contents of the data buffer to the data bus, and writes it in memory when  $\bar{E}$  signal is "L" level.

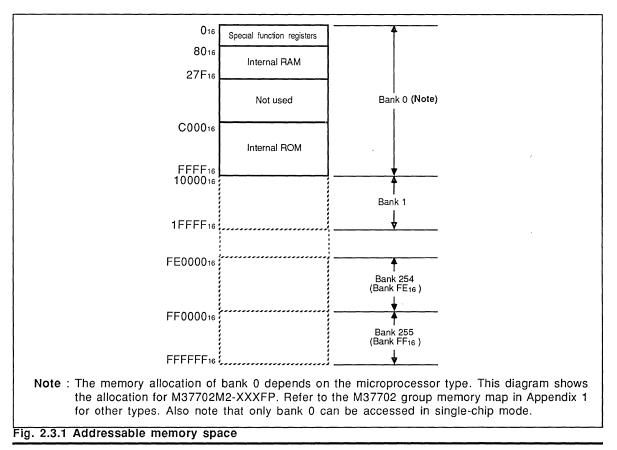

#### 2.3 Addressable memory space

The M37702 group allocates all ROM, RAM, I/O, and various control registers in the same memory space. Therefore, data transfer and operation can be performed with the same instruction without distinguishing memory and I/O area.

The M37702 group program counter (PC) consists of 16 bits. It is used together with an 8-bit program bank register (PG) to directly access a 16M-byte address space from 016 to FFFFF16.

#### 2.3.1 Banks

The M37702 group address space is divided into 64K-byte blocks called banks. The M37702 group can access 256 banks from bank 0 to bank 255 (FF<sub>16</sub>) in memory expansion or microprocessor mode.

The high-order 8 bits of the 24-bit address indicate the bank and the content of the program bank register (PG) or the data bank register (DT) indicates the bank to be used.

If the program counter overflows at a bank boundary, the content of the program bank register is incremented by 1. If a borrow occurs in the program counter register, the content of the program bank register is decremented by 1. Therefore, programs can be written without considering the bank boundaries, usually. The banks can be accessed efficiently by using an addressing mode that uses the data bank register.

Bank 0 (address 016 to FFFF16) contains the internal ROM, internal RAM, and internal I/O control registers. **Note** : In single-chip mode, only bank 0 can be accessed.

#### 2.3.2 Direct page

By using the direct page register (DPR), bank 0 or a 256-byte space spanning across bank 0 and bank 1 can be accessed with fewer instruction cycles by using direct page addressing mode. This area is referred to as the direct page and is normally used for frequently accessed information. The direct page area can be specified by setting the lowermost address of the required area in the direct page register (see section "2.1.8 Direct page register").

#### 2.4 Memory allocation

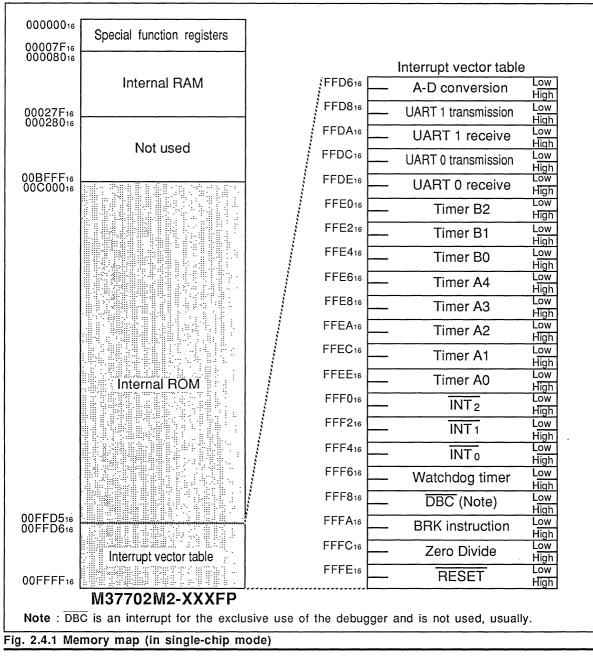

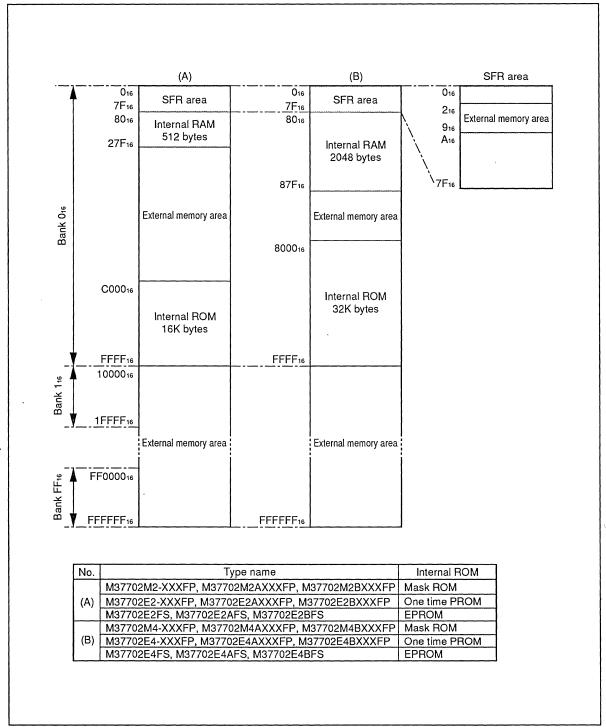

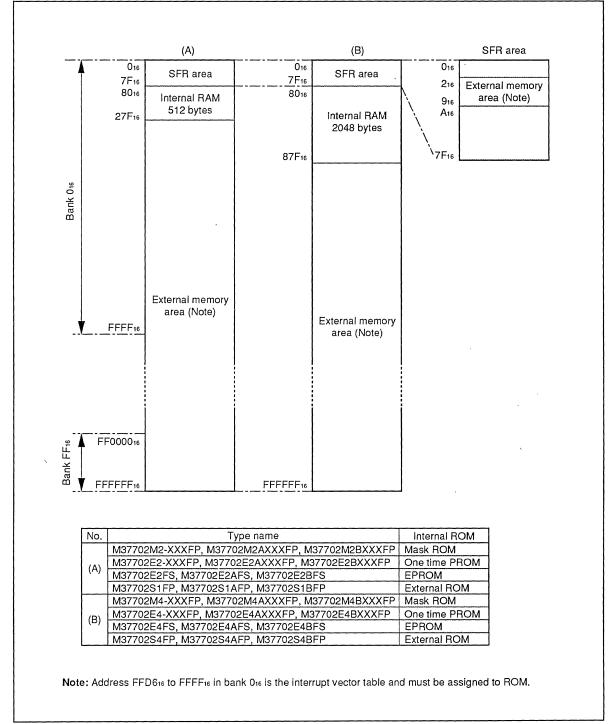

Figure 2.4.1 shows the memory map in single-chip mode. The allocated memory and I/O are described below.

### 2.4.1 Internal memory and peripheral device memory allocation

#### (1) SFR (Special Function Register) area

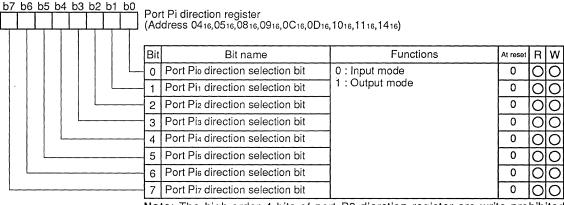

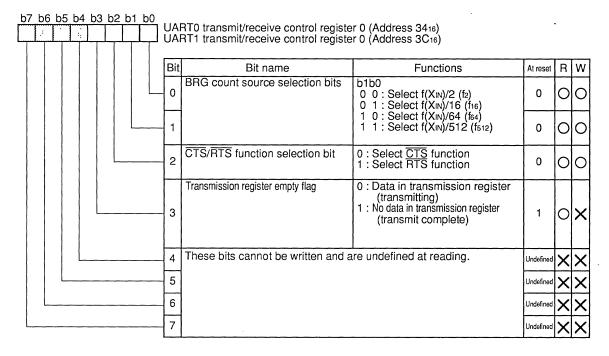

Address 000016 to 007F16 of bank 0 are the SFR (Special Function Register) area. This area contains the control registers of internal peripheral devices, I/O ports, timers, and so on. Internal peripheral devices can be accessed through these registers. Figure 2.4.2 shows the memory map of the SFR area.

## FUNCTIONAL DESCRIPTION

#### 2.4 Memory allocation

#### Address (Hexadecimal notation)

|                  | adecimal notation)                         |

|------------------|--------------------------------------------|

| 000000           |                                            |

| 000001           |                                            |

| 000002           | Port P0 register                           |

| 000002           | Port P1 register                           |

| 000003           | Port P0 direction register                 |

| 000004           |                                            |

|                  | Port P1 direction register                 |

| 000006           | Port P2 register                           |

| 000007           | Port P3 register                           |

| 000008           | Port P2 direction register                 |

| 000009           | Port P3 direction register                 |

| 00000A           | Port P4 register                           |

| 00000B           | Port P5 register                           |

| 00000C           | Port P4 direction register                 |

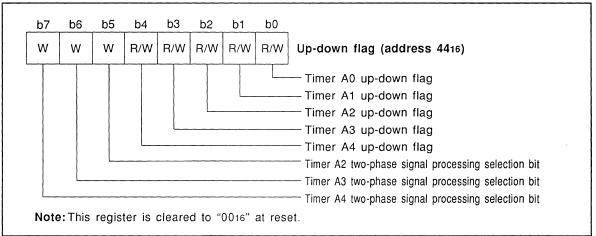

| 00000D           | Port P5 direction register                 |

| 00000E           | Port P6 register                           |

| 00000F           | Port P7 register                           |

| 000010           | Port P6 direction register                 |

| 000011           | Port P7 direction register                 |

| 000012           |                                            |

|                  | Port P8 register                           |

| 000013           | David DO dive sile a ve sileter            |

| 000014           | Port P8 direction register                 |

| 000015           |                                            |

| 000016           |                                            |

| 000017           |                                            |

| 000018           |                                            |

| 000019           |                                            |

| 00001A           |                                            |

| 00001B           |                                            |

| 00001C           |                                            |

| 00001D           |                                            |

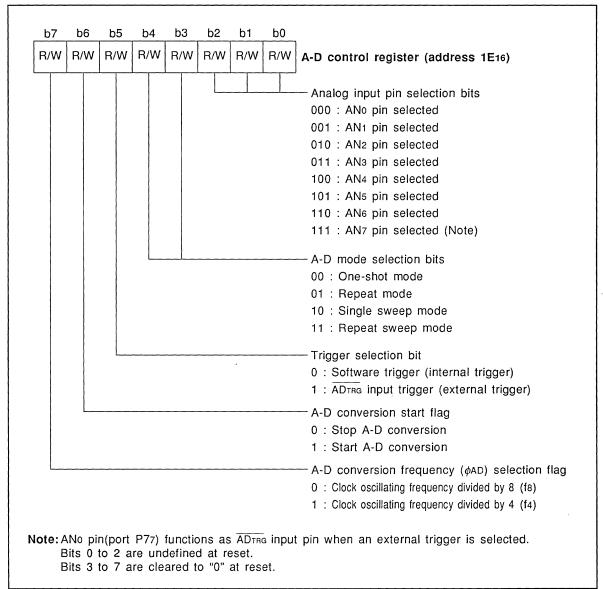

| 00001E           | A-D control register                       |

|                  |                                            |

| 00001F           | A-D sweep pin selection register           |

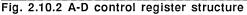

| 000020           | A-D register 0                             |

| 000021           |                                            |

| 000022           | A-D register 1                             |

| 000023           |                                            |

| 000024           | A-D register 2                             |

| 000025           |                                            |

| 000026           | A-D register 3                             |

| 000027           | ¥                                          |

| 000028           | A-D register 4                             |

| 000029           |                                            |

| 000023<br>00002A | A-D register 5                             |

|                  | A-D legislei 5                             |

| 00002B           | A D register C                             |

| 00002C           | A-D register 6                             |

| 00002D           |                                            |

| 00002E           | A-D register 7                             |

| 00002F           |                                            |

| 000030           | UART 0 transmit/receive mode register      |

| 000031           | UART 0 baud rate generator                 |

| 000032           |                                            |

| 000033           | UART 0 transmission buffer register        |

| 000034           | UART 0 transmit/receive control register 0 |

| 000035           |                                            |

|                  | UART 0 transmit/receive control register 1 |

| 000036           | UART 0 receive buffer register             |

| 000037           |                                            |

| 000038           | UART 1 transmit/receive mode register      |

| 000039           | UART 1 baud rate generator                 |

| 00003A           | UART 1 transmission buffer register        |

| 00003B           |                                            |

| 00003C           | UART 1 transmit/receive control register 0 |

| 00003D           | UART 1 transmit/receive control register 1 |

|                  |                                            |

| 00003E           | LIADT 1 reasing huffer reading             |

| 00003E<br>00003F | UART 1 receive buffer register             |

| Address (Hey             | adecimal notation)                                                                          |

|--------------------------|---------------------------------------------------------------------------------------------|

| 000040                   | Count start flag                                                                            |

| 000041                   |                                                                                             |

| 000042                   | One-shot start flag                                                                         |

| 000043                   |                                                                                             |

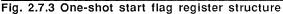

| 000044                   | Up-down flag                                                                                |

| 000045                   |                                                                                             |

| 000046                   | Timer A0 register                                                                           |

| 000047                   |                                                                                             |

| 000048<br>000049         | Timer A1 register                                                                           |

| 00004 <b>A</b><br>00004B | Timer A2 register                                                                           |

| 00004C<br>00004D         | Timer A3 register                                                                           |

| 00004E<br>00004F         | Timer A4 register                                                                           |

| 000050                   | Timer B0 register                                                                           |

| 000052                   | Timer B1 register                                                                           |

| 000053<br>000054         | Timer B2 register                                                                           |

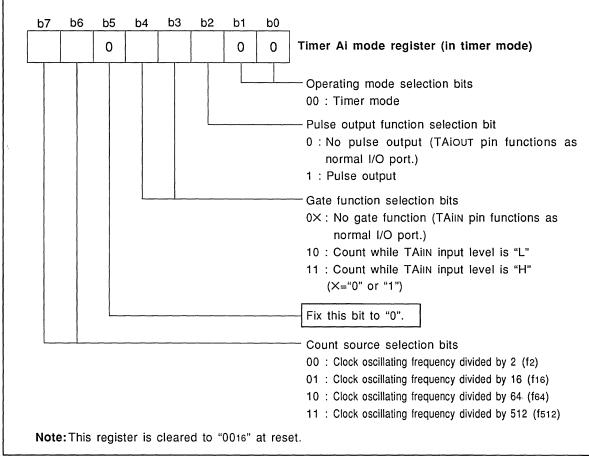

| 000055<br>000056         | Timer A0 mode register                                                                      |

| 000057                   | Timer A1 mode register                                                                      |

| 000018                   | Timer A2 mode register                                                                      |

| 000059                   | Timer A3 mode register                                                                      |

| 00005A                   | Timer A4 mode register                                                                      |

| 00005B                   | Timer B0 mode register                                                                      |

| 00005C                   | Timer B1 mode register                                                                      |

| 00005D                   | Timer B2 mode register                                                                      |

| 00005E                   | Processor mode register                                                                     |

| 00005F                   |                                                                                             |

| 000060                   | Watchdog timer                                                                              |

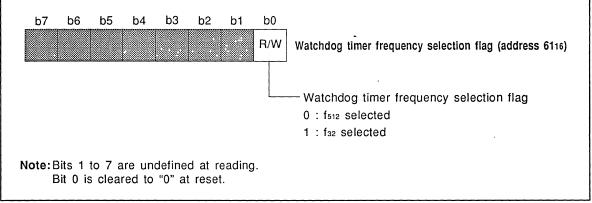

| 000061                   | Watchdog timer frequency selection flag                                                     |

| 000062                   |                                                                                             |

| 000063                   |                                                                                             |

| 000064                   |                                                                                             |

| 000065                   |                                                                                             |

| 000066                   |                                                                                             |

| 000067                   |                                                                                             |

| 000068                   |                                                                                             |

| 000069                   |                                                                                             |

| 00006A                   |                                                                                             |

| 00006B                   |                                                                                             |

| 00006C                   |                                                                                             |

| 00006D                   |                                                                                             |

| 00006E<br>00006F         |                                                                                             |

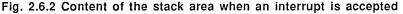

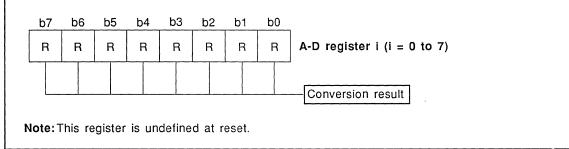

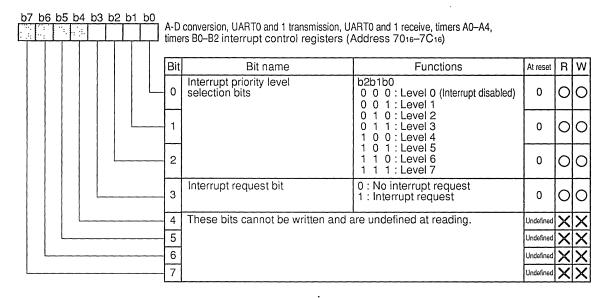

| 00006                    | A-D conversion interrupt control register                                                   |

| 000070                   | A-D conversion interrupt control register<br>UART 0 transmission interrupt control register |

| 000071                   | UART 0 receive interrupt control register                                                   |

| 000070                   |                                                                                             |

| 000073                   | UART 1 transmission interrupt control register                                              |

| 000075                   | Timer A0 interrupt control register                                                         |

| 000076                   | Timer A1 interrupt control register                                                         |

| 000077                   | Timer A2 interrupt control register                                                         |

| 000078                   | Timer A3 interrupt control register                                                         |

| 000079                   | Timer A4 interrupt control register                                                         |

| 00007A                   | Timer B0 interrupt control register                                                         |

| 00007B                   | Timer B1 interrupt control register                                                         |

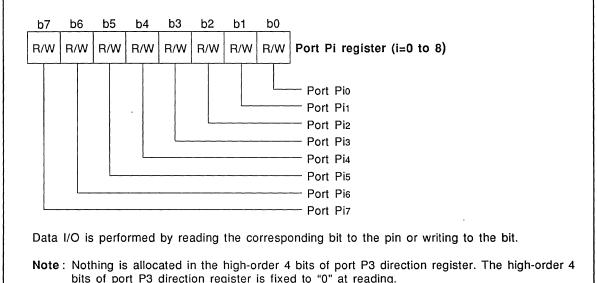

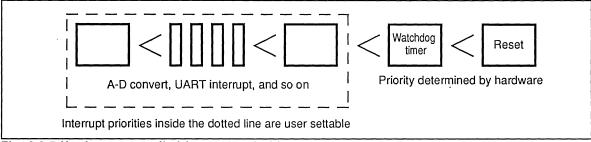

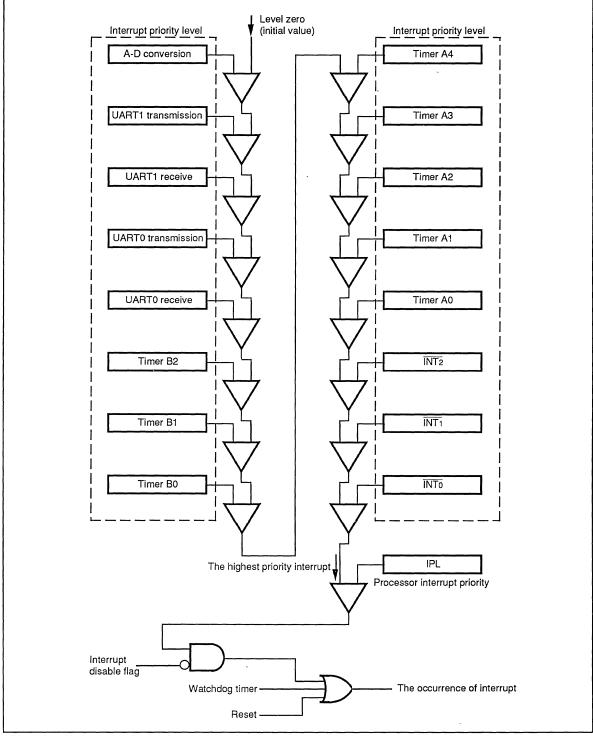

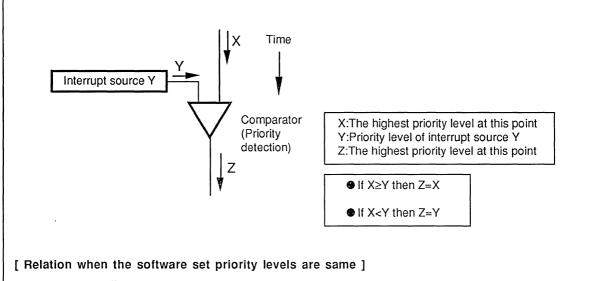

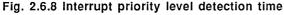

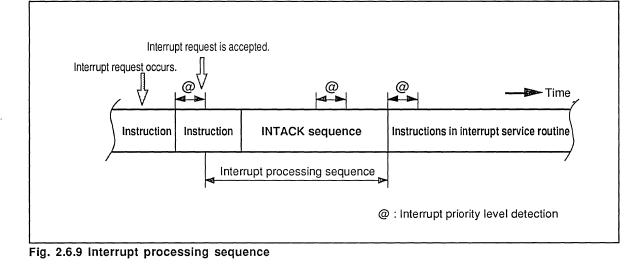

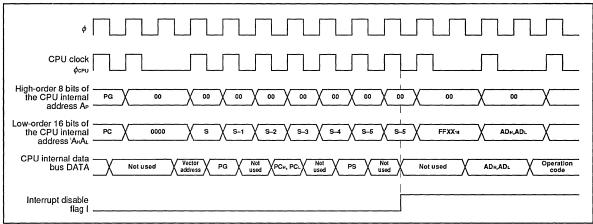

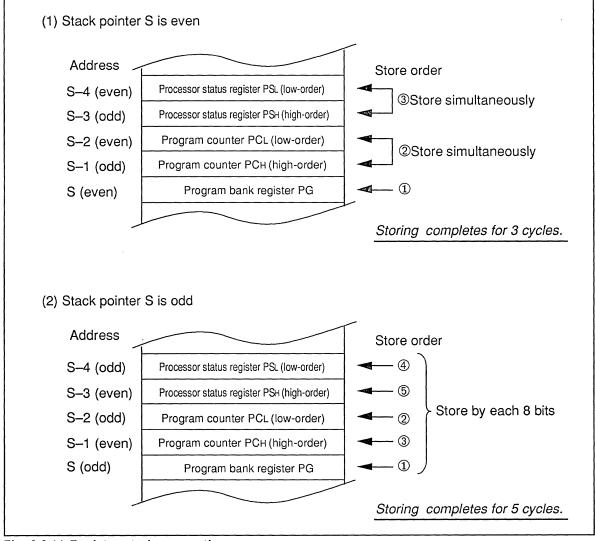

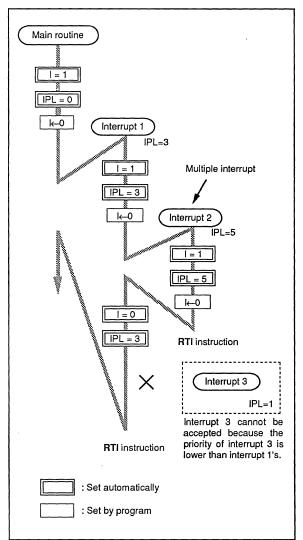

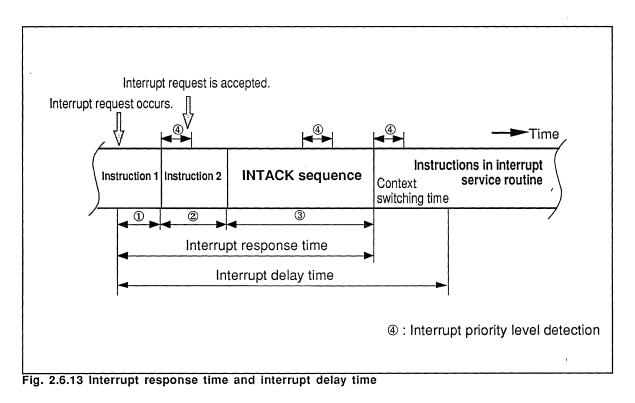

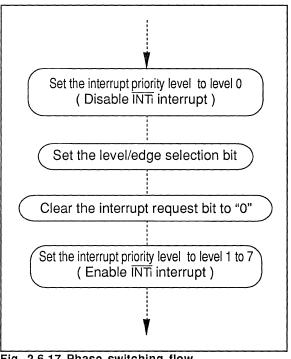

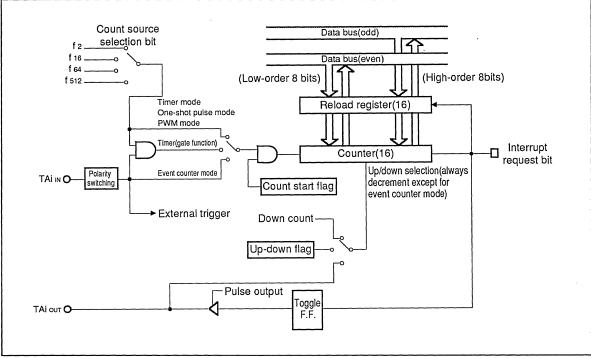

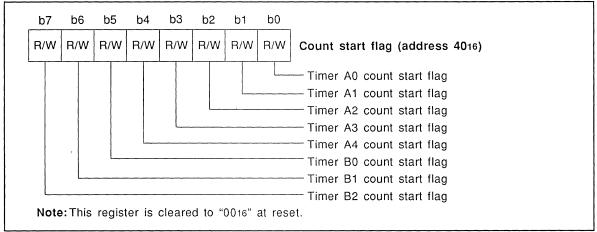

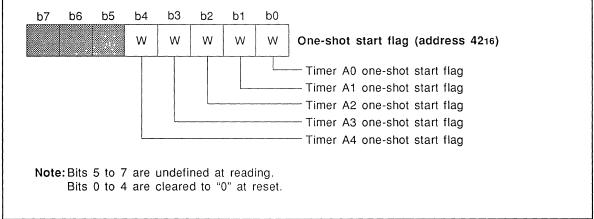

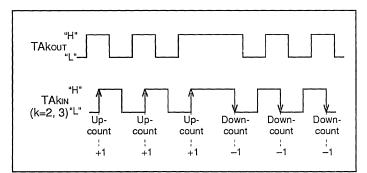

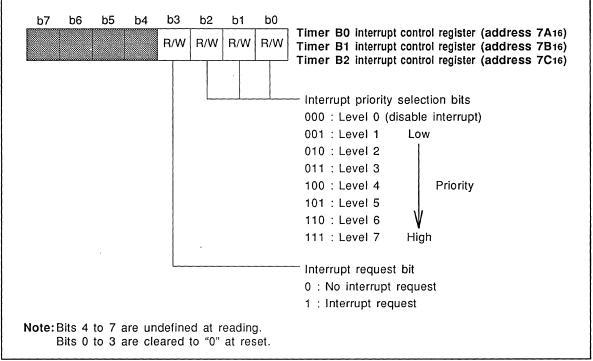

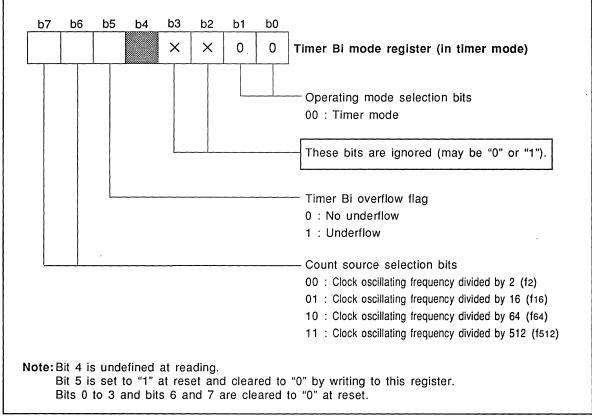

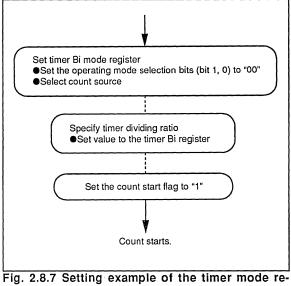

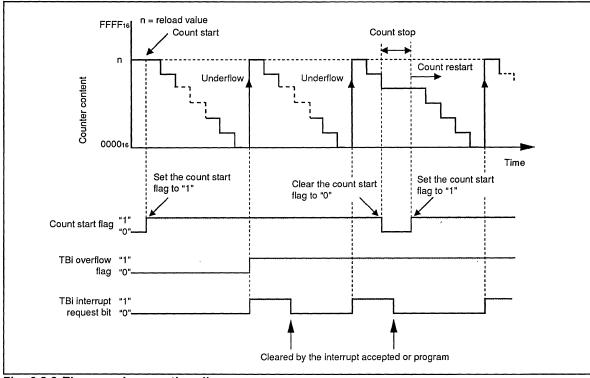

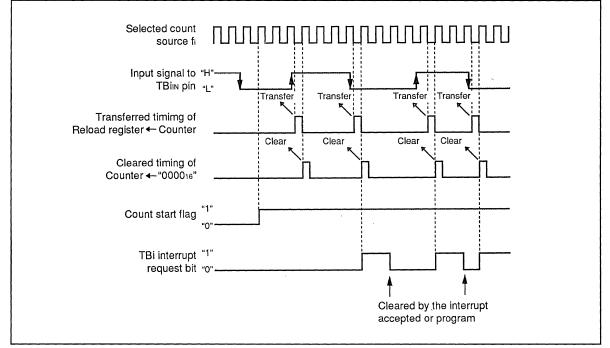

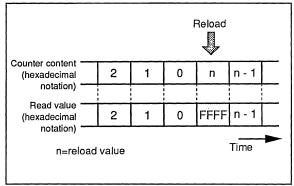

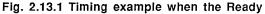

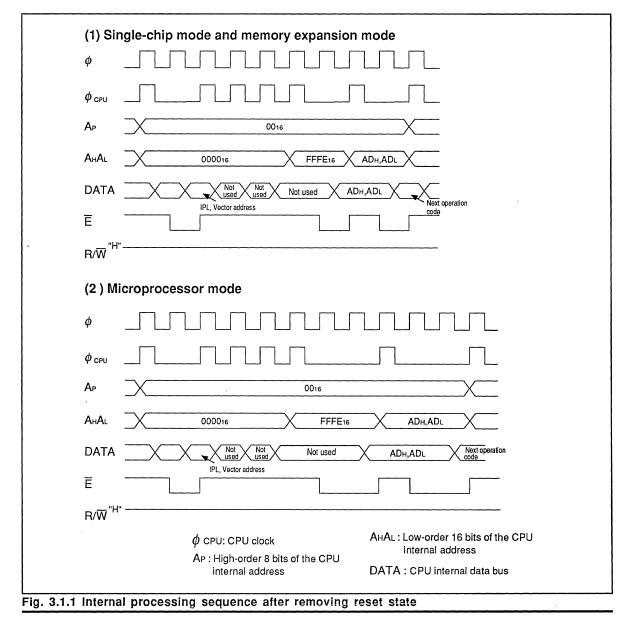

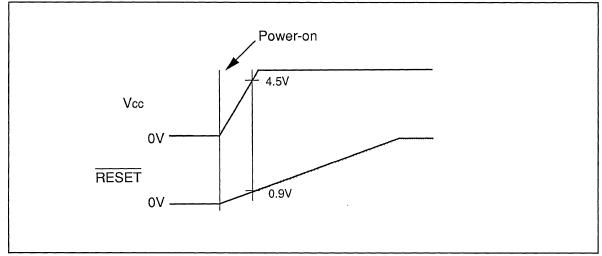

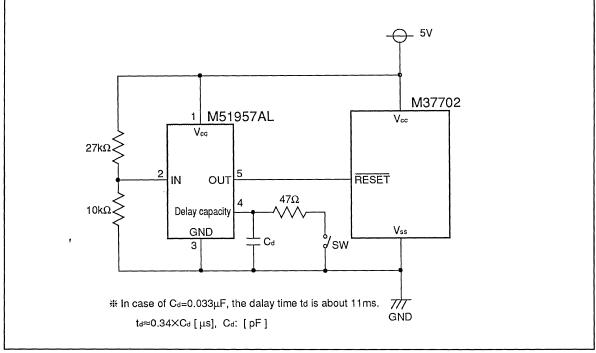

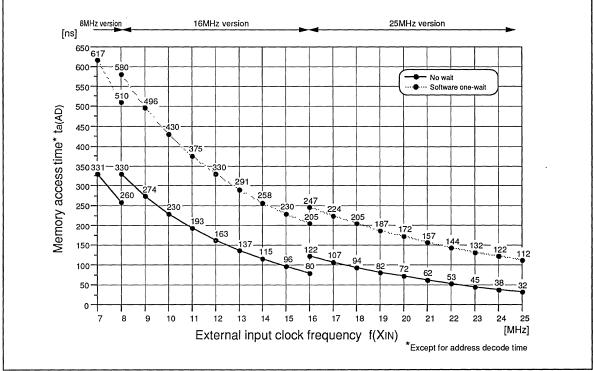

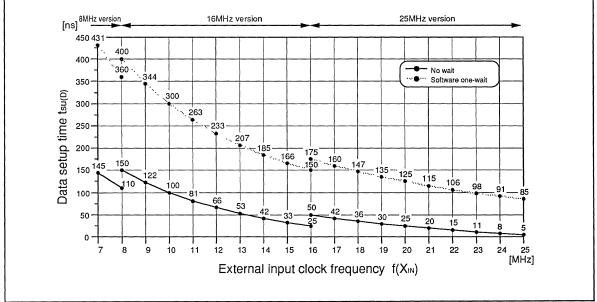

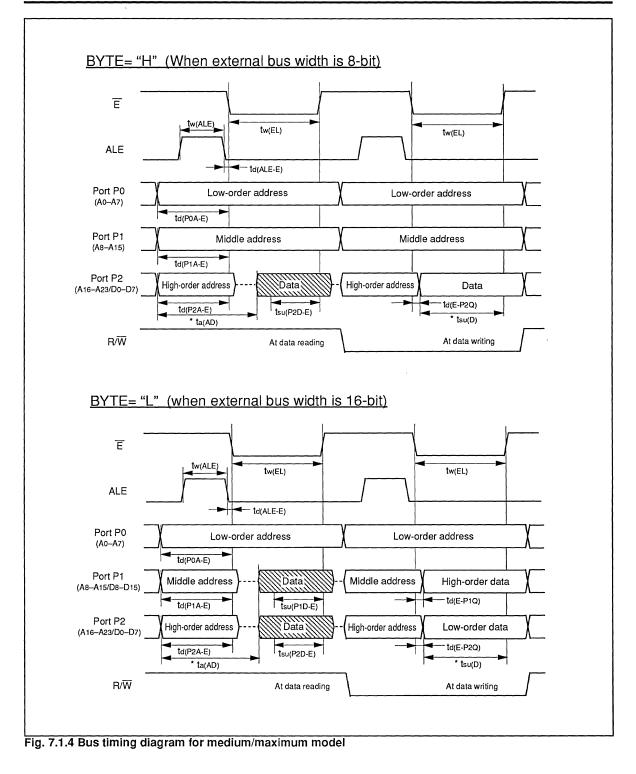

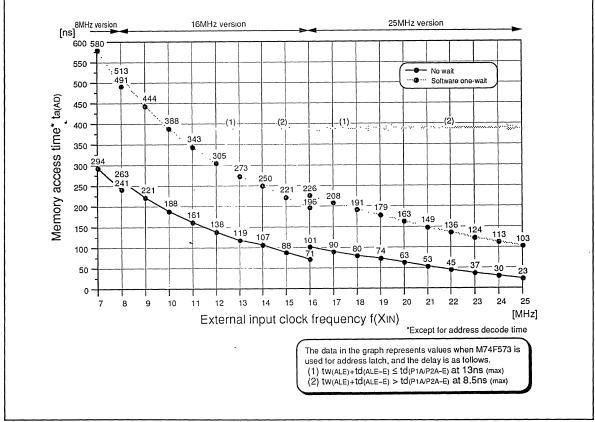

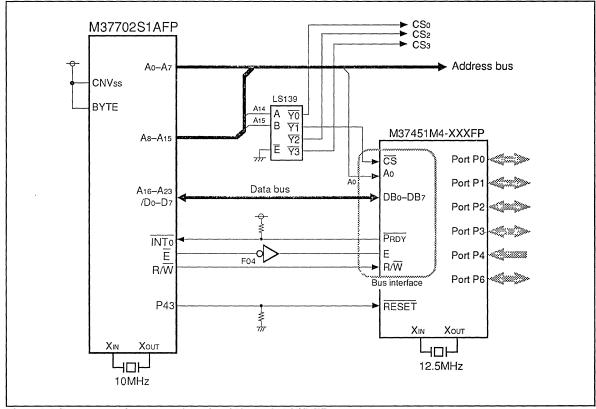

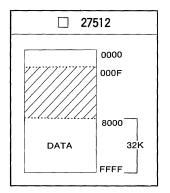

| 00007C                   | Timer B2 interrupt control register                                                         |