USER'S MANUAL

# M37700M2-XXFP M37700M2AXXFP USER'S MANUAL

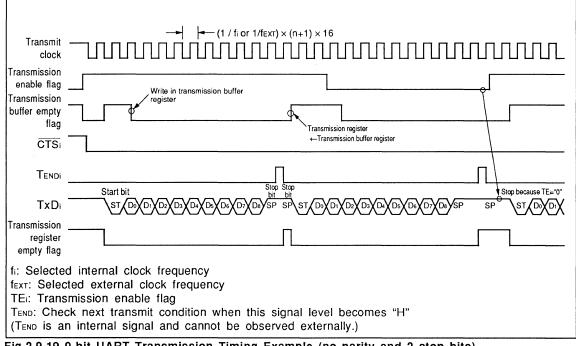

**MITSUBISHI SEMICONDUCTORS**

# Difference between Original M37700 and Revised Version (Version –A)

## Difference between Original M37700 and Revised Version (Version -A)

For the M37700/M37701 series, original version and -A version are available for the following 14 product types:

M37700SFP/M37700SAFP M37700E2FP/M37700E2AFP M37700E2FS/M37700E2AFS M37700S4FP/M37700S4AFP M37700E4FP/M37700E4AFP M37700E4FS/M37700E4AFS M37701E2SP/M37701E2ASP

The -A version are indicated by the suffix "-A" following the product type.

|         | Original product | –A version   |

|---------|------------------|--------------|

| Product | AM37700SFP       | AM37700SFP–A |

| type    | XXXXXX           | XXXXXX       |

The differences between the original version and the -A version are as follows:

#### (1)HOLD function

#### Original product

The HOLD function does not work properly. Therefore, in memory expansion mode and microprocessor mode, the P4<sub>0</sub>/HOLD pin must be held at "H" level to prevent the use of the HOLD function. In single-chip mode, this pin can be a normal port P4<sub>0</sub>.

#### ●–A version

The HOLD function can be used properly.

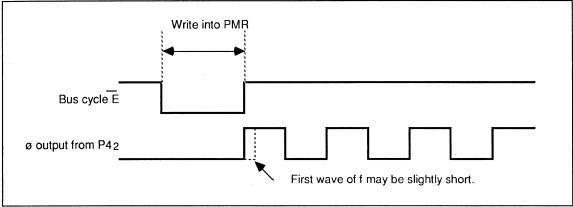

#### (2)P4<sub>2</sub>/ø function

#### Original product

When ø output is selected from the P4<sub>2</sub>/ø pin in memory expansion mode and microprocessor mode, the ø output stops at "L" level when the P4<sub>1</sub>/RDY pin is pulled to "L" level.

#### A version

When ø output is selected from the P4<sub>2</sub>/ø pin in memory expansion mode and microprocessor mode, the ø output does not stop at "L" level when the P4<sub>1</sub>/RDY pin is pulled to "L" level.

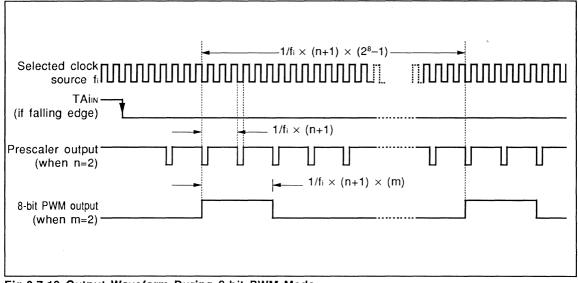

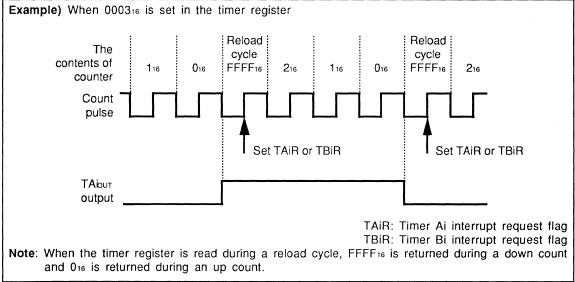

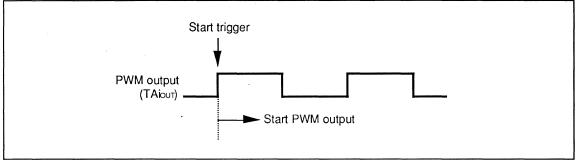

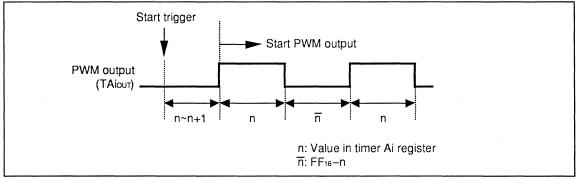

#### (3)PWM output function of the timer A

#### Original product

Pulse width must be changed while the PWM output is at "L". If write is performed while the PWM output as "H", the PWM output frequency temporarily changes.

#### A version

Pulse width can be changed at any time. The PWM output frequency does not change when write is performed while the PWM output is "H". However, the "L" interval (width) of the PWM output must be at least two timer clock source cycles. In other words, the value that can be set in the timer is 0016 to FD16 for 8-bit PWM mode and 000016 to FFFD16 in 16-bit PWM mode.

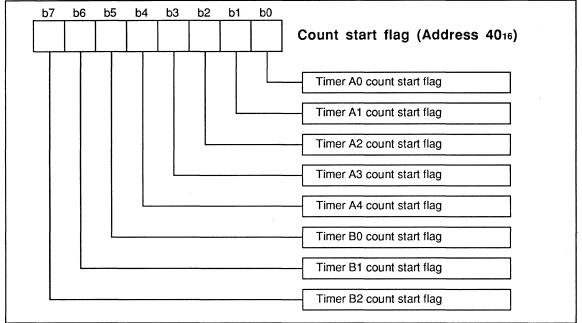

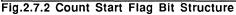

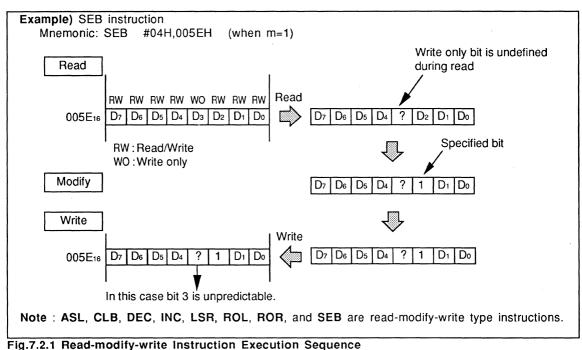

#### (4)Reading from processor mode register (5E<sub>16</sub>) and one-shot start flag (42<sub>16</sub>)

#### Original product

The software reset bit in the processor mode register and the bits corresponding to timers A0 to A4 in the oneshot start flag are unpredictable when read. Therefore, read-modify-write type instructions cannot used for these addresses.

#### A version

The software reset bit in the processor mode register and the bits corresponding to timers A0 to A4 in the oneshot start flag returns a "0" when read. Therefore, read-modify-write type instructions can be used for the addresses.

# Preface

This manual describes the hardware of the Mitsubishi CNOS 16-bit microcomputer M37700M2-XXXFP. After reading this manual, the user should be able to fully utilize the functions of the M37700 family of microcomputers.

For details concerning the softwares for the M37700 family, refer to the MELPS 7700 software manual. For details concerning the development support tools (assembler, option boards), refer to the respective operation manuals.

# **Table of Contents**

| CHAPTER 1. DESCRIPTION                                        |    |

|---------------------------------------------------------------|----|

| 1.1 Description                                               | 2  |

| 1.2 M37700 Family                                             |    |

| 1.2.1 M37700 family                                           |    |

| 1.2.2 Difference between types                                |    |

| 1.2.3 Meaning of type name                                    | 5  |

| 1.3 Performance Overview                                      |    |

| 1.4 Pin Configuration                                         |    |

| 1.5 Pin Description                                           | 8  |

| 1.6 Block Diagram                                             |    |

| CHAPTER 2. FUNCTIONAL DESCRIPTION                             |    |

| 2.1 Central Processing Unit (CPU)                             |    |

| 2.1.1 Accumulator (Acc)                                       |    |

| 2.1.2 Index register X                                        |    |

| 2.1.3 Index register Y                                        |    |

| 2.1.4 Stack pointer (S)                                       |    |

| 2.1.5 Program counter (PC)                                    | 14 |

| 2.1.6 Program bank register (PG)                              | 14 |

| 2.1.7 Data bank register (DT)                                 | 14 |

| 2.1.8 Direct page register (DPR)                              |    |

| 2.1.9 Processing status register (PS)                         |    |

| 2.2 Internal Bus Interface                                    |    |

| 2.2.1 Internal bus interface overview                         |    |

| 2.2.2 Bus interface unit functions                            |    |

| 2.2.3 Bus interface unit operations                           |    |

| 2.2.4 Data read/write operations                              |    |

| 2.3 Addressable memory space                                  |    |

| 2.3.1 Banks                                                   |    |

| 2.3.2 Direct page                                             |    |

| 2.4 Memory Allocation                                         |    |

| 2.4.1 Internal memory and peripheral device memory allocation |    |

| 2.4.2 Processor modes                                         |    |

| 2.4.3 External memory area bus control                        |    |

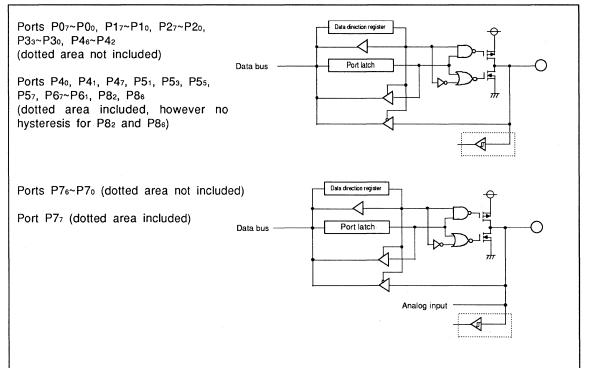

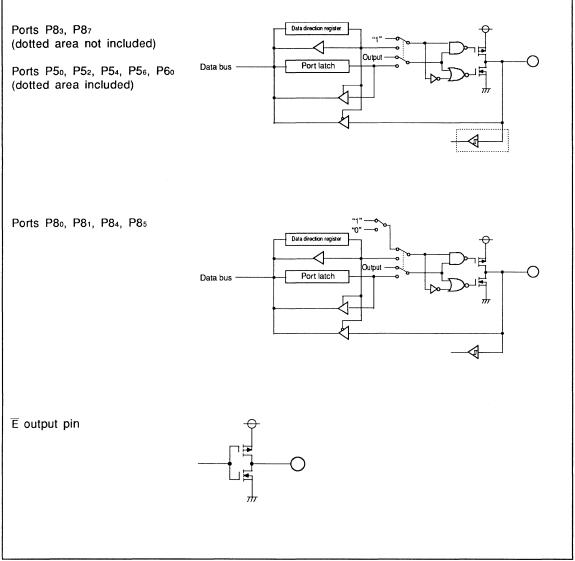

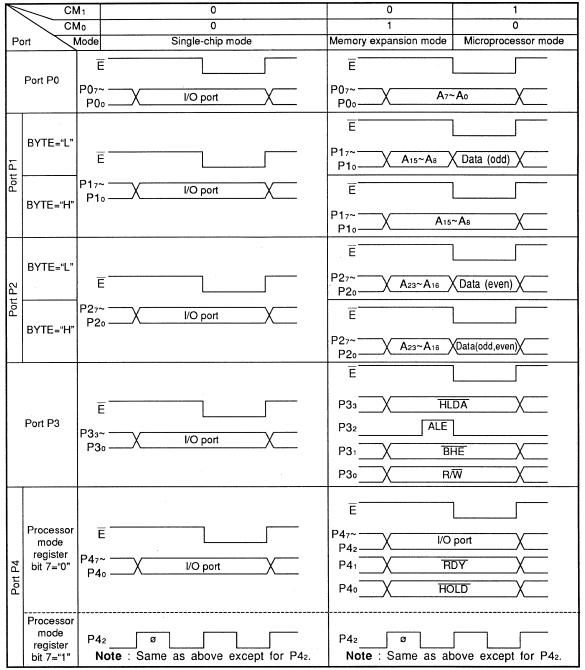

| 2.5 Input/Output Pins                                         | 4  |

| 2.5.1 Programmable I/O ports                                  |    |

| 2.5.2 Pin functions                                           |    |

| 2.5.3 Single-chip mode pin functions                          |    |

| 2.5.4 Memory expansion and microprocessor mode pin functior   |    |

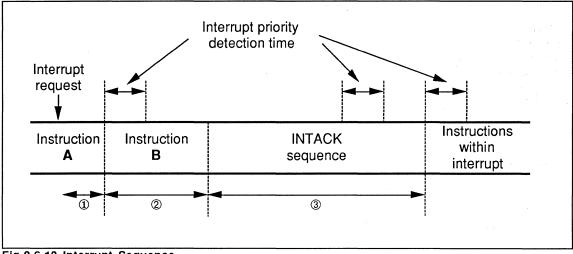

| 2.6 Interrupts                                                |    |

| 2.6.1 Interrupt functions                                     |    |

| 2.6.2 Source of interrupts                                    |    |

| 2.6.3 Interrupt control                                       |    |

| 2.6.4 Interrupt order                                         |    |

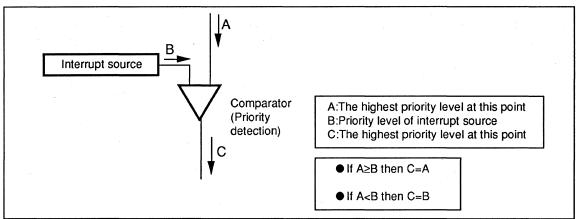

| 2.6.5 Interrupt priority detection circuit                    |    |

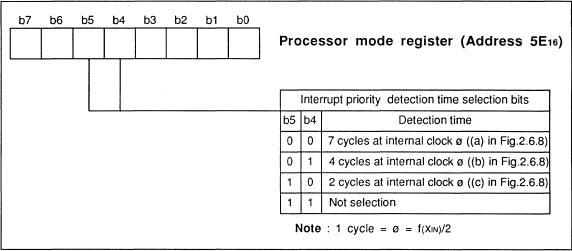

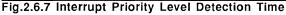

| 2.6.6 Interrupt priority detection time                       |    |

| 2.6.7 Interrupt processing sequence                           |    |

| 2.6.8 Interrupt service routine                               |    |

| 2.6.9 Returning from an interrupt service routine             |    |

| 2.6.10 Interrupt response time                                |    |

|                                                               |    |

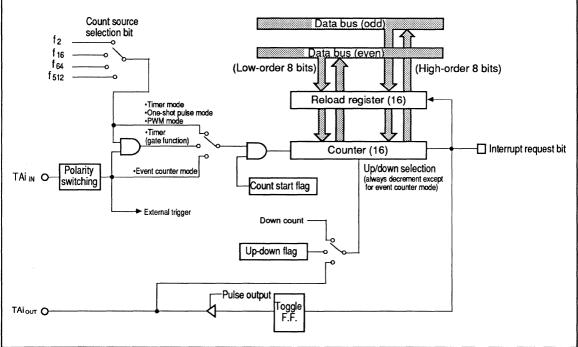

| 2.7 Timer A                                    |     |

|------------------------------------------------|-----|

| 2.7.1 Timer A description                      |     |

| 2.7.2 Block description                        | 57  |

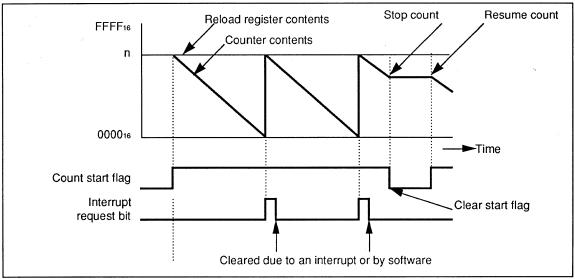

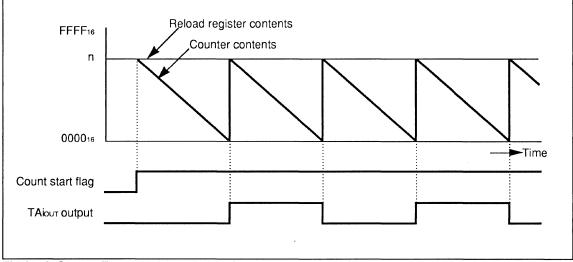

| 2.7.3 Timer mode                               | 62  |

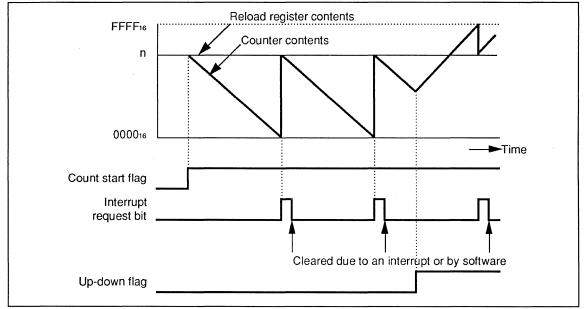

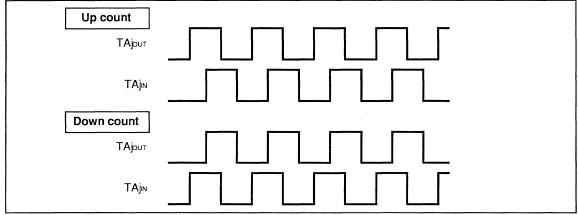

| 2.7.4 Event counter mode                       | 66  |

| 2.7.5 One-shot pulse mode                      | 70  |

| 2.7.6 PWM (Pulse Width Modulation) mode        | 74  |

| 2.8 Timer B                                    |     |

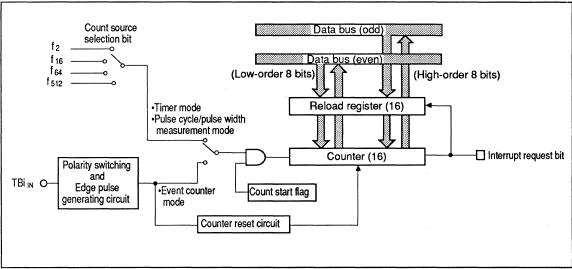

| 2.8.1 Timer B description                      |     |

| 2.8.2 Block diagram                            |     |

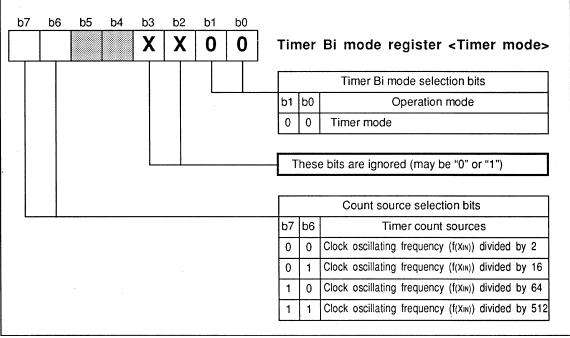

| 2.8.3 Timer mode                               | 82  |

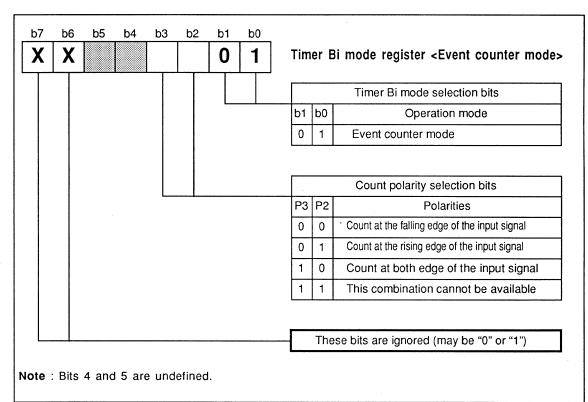

| 2.8.4 Event counter mode                       |     |

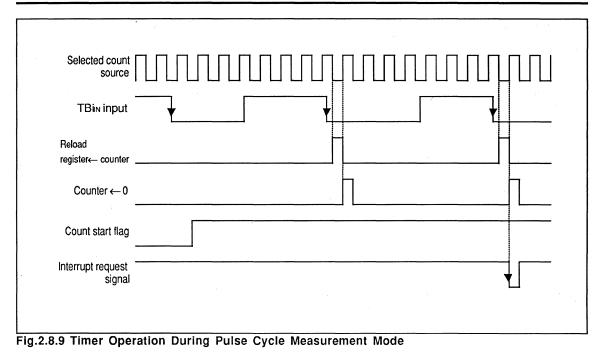

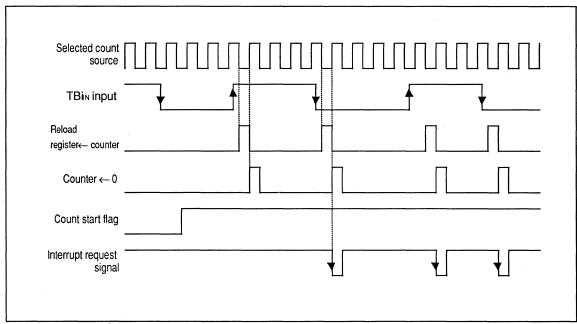

| 2.8.5 Pulse cycle/pulse width measurement mode |     |

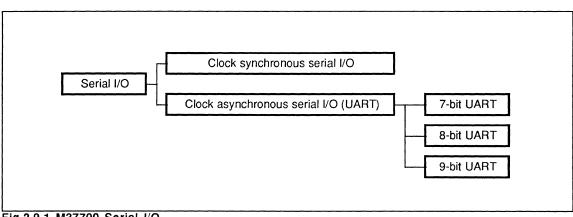

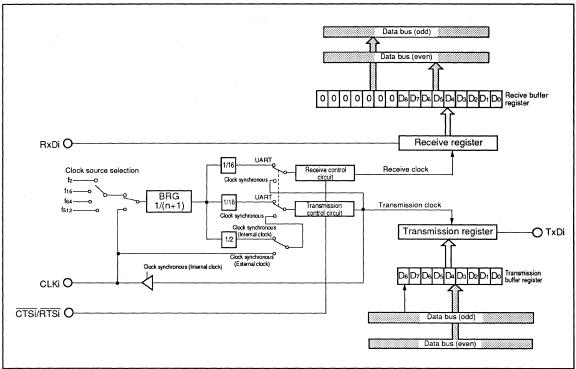

| 2.9 Serial I/O                                 |     |

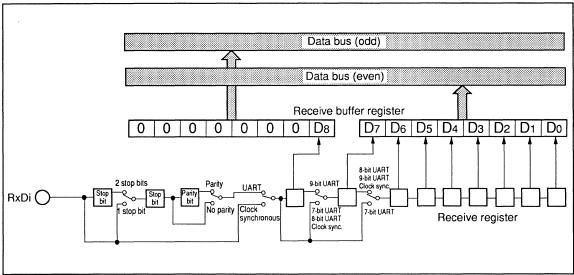

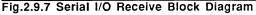

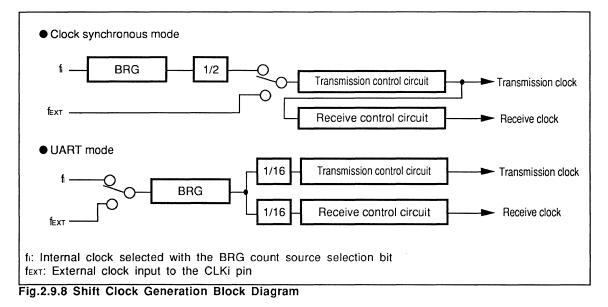

| 2.9.1 Serial I/O description                   |     |

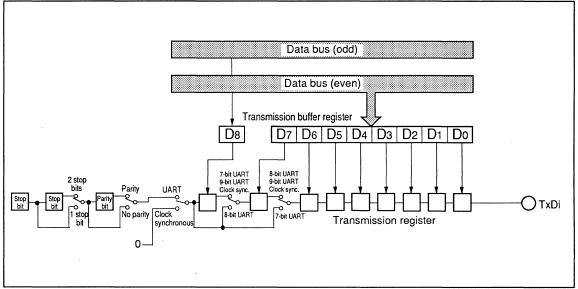

| 2.9.2 Block description                        | 90  |

| 2.9.3 Serial I/O operation mode selection      |     |

| 2.9.4 Clock synchronous serial I/O             |     |

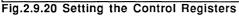

| 2.9.5 Clock asynchronous serial I/O (UART)     |     |

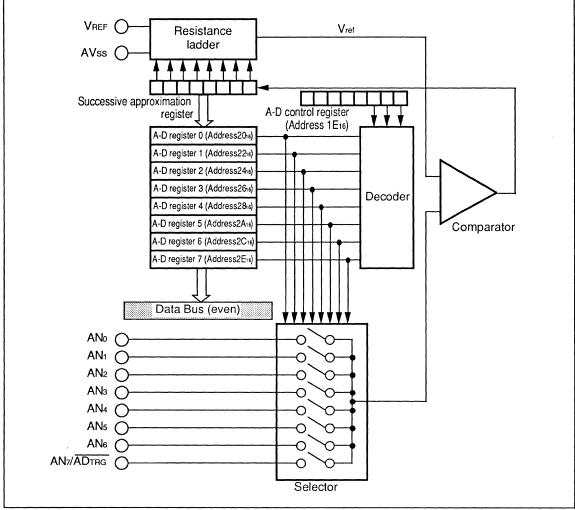

| 2.10 A-D Converter                             |     |

| 2.10.1 A-D converter description               |     |

| 2.10.2 Block description                       |     |

| 2.10.3 A-D conversion mode operation           |     |

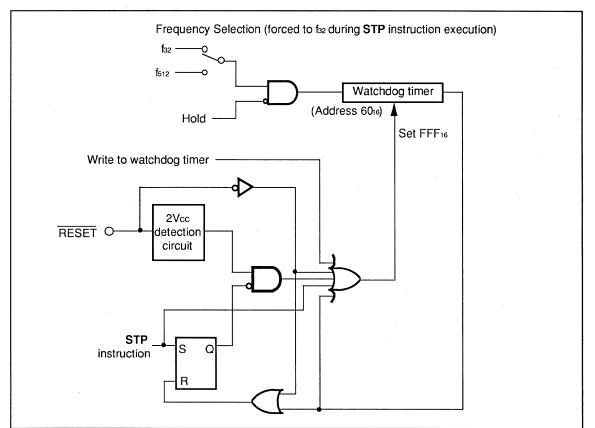

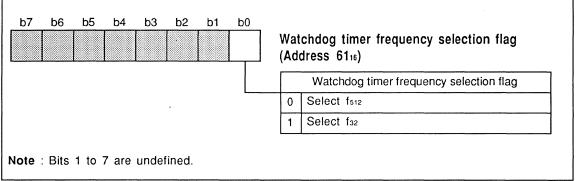

| 2.11 Watchdog Timer                            |     |

| 2.11.1 Watchdog timer description              |     |

| 2.11.2 Operation description                   | 127 |

| 2.11.3 Watchdog timer usage                    | 127 |

| CHAPTER 3. RESET                               |     |

| 3.1 Reset                                      |     |

| 3.1.1 Reset operation                          |     |

| 3.1.2 Internal states at reset                 |     |

| 3.2 Reset circuit                              |     |

| 3.3 Software reset                             |     |

|                                                |     |

# CHAPTER 4. OSCILLATING CIRCUIT

| CHAFTER 4. USCILLATING CINCOTT                                   |     |

|------------------------------------------------------------------|-----|

| 4.1 Oscillating Circuit                                          |     |

| 4.1.1 Circuit using a ceramic oscillator or a crystal oscillator |     |

| 4.1.2 External clock input circuit                               |     |

| 4.2 Clock Generation Circuit                                     |     |

| CHAPTER 5. ELECTRICAL CHARACTERISTICS                            |     |

| 5.1 Absolute Maximum Ratings                                     |     |

| 5.2 Recommended Operating Conditions                             |     |

| 5.3 M37700M2-XXXEP DC/AC Characteristics                         |     |

| 5.3.1 Electrical characteristics                                 |     |

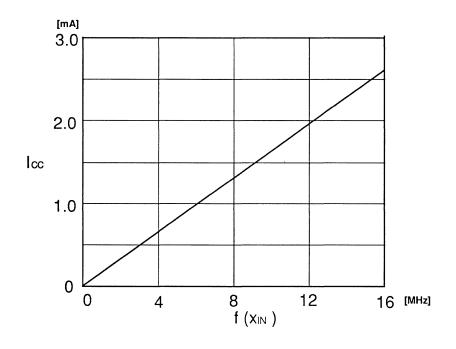

| 5.3.2 A-D converter characteristics                              |     |

| 5.3.3 Timing requirements                                        |     |

| 5.3.3 Timing requirements<br>5.3.4 Switching characteristics     |     |

| 5.4 M37700M2AXXXFP DC/AC Characteristics                         |     |

| 5.4.1 Electrical characteristics                                 |     |

| 5.4.2 A-D converter characteristics                              |     |

| 5.4.3 Timing requirements                                        |     |

| 5.4.4 Switching characteristics                                  | 154 |

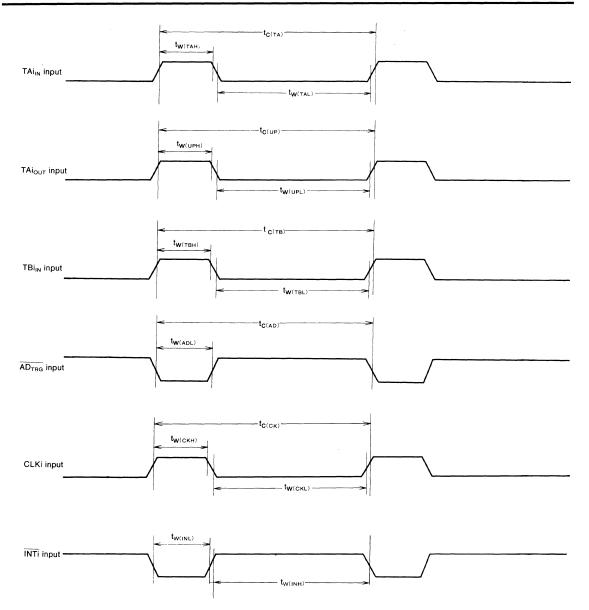

| 5.5 Timing Diagrams                                              |     |

|                                                                  |     |

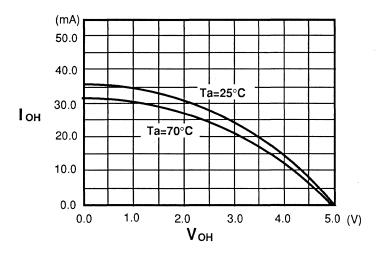

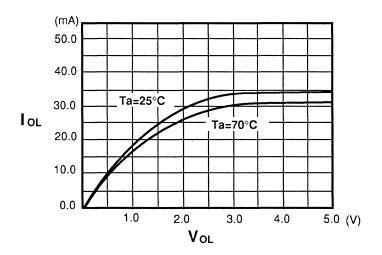

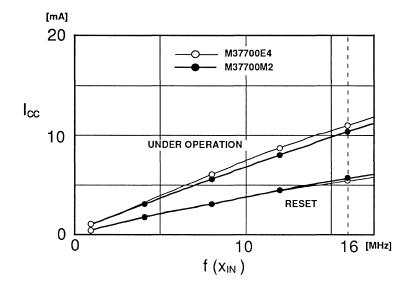

| CHAPTER 6. STANDARD CHARACTERISTICS                                           |     |

|-------------------------------------------------------------------------------|-----|

| 6.1 Standard Port Characteristics                                             |     |

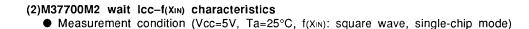

| 6.2 Icc-f(XIN) Standard Characteristics                                       |     |

| 6.3 A-D Converter Standard Characteristics                                    | 164 |

| CHAPTER 7. USAGE PRECAUTIONS                                                  |     |

| 7.1 Software                                                                  |     |

| 7.1.1 Stack pointer (S)                                                       |     |

| 7.1.2 Program bank register (PG) and data bank register (DT)                  |     |

| 7.1.3 Direct page register (DPR)                                              |     |

| 7.1.4 Processor status register (PS)                                          |     |

| 7.1.5 Register save and restore instructions                                  |     |

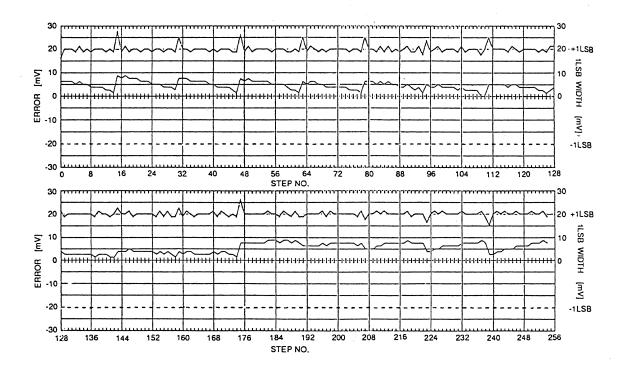

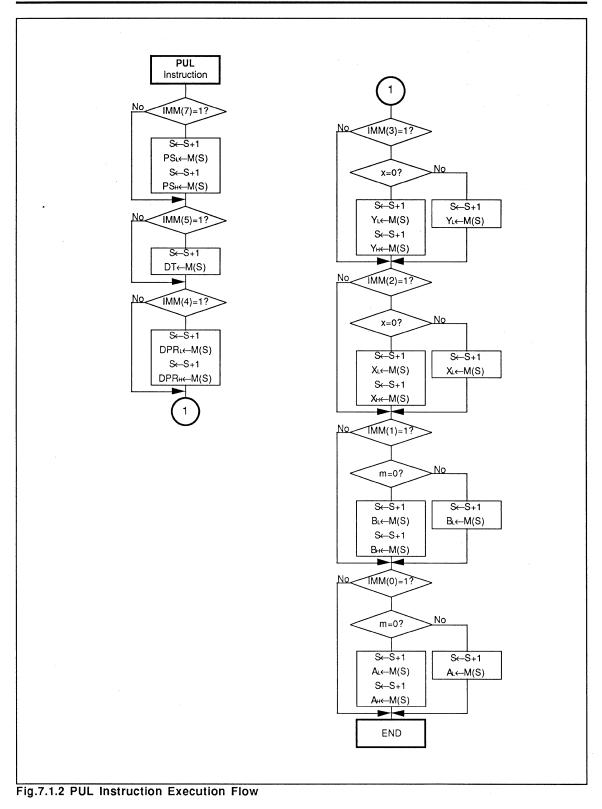

| 7.1.6 PSH instruction                                                         | 169 |

| 7.1.7 BRK instruction                                                         | 169 |

| 7.1.8 BRA instruction                                                         |     |

| 7.1.9 Instruction execution time (instruction execution cycle)                |     |

| 7.2 Hardware                                                                  |     |

| 7.2.1 Memory related features                                                 | 170 |

| 7.2.2 Input/output pin related features                                       | 170 |

| 7.2.3 Interrupts                                                              | 171 |

| 7.2.4 Timers related features                                                 |     |

| 7.2.5 Serial I/O                                                              |     |

| 7.2.6 A-D conversion                                                          | 176 |

| 7.2.7 Watchdog timer                                                          |     |

| 7.2.8 Reset related features                                                  |     |

| 7.2.9 Microprocessor status during stop, wait, one-shot wait, ready, and hold |     |

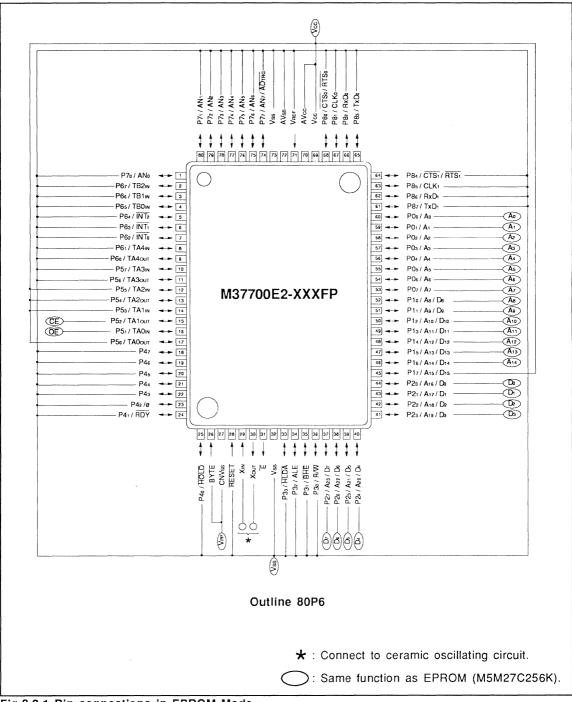

## CHAPTER 8.TREATMENT OF INTERNAL PROM TYPE

| 8.1 Description                       |  |

|---------------------------------------|--|

| 8.2 Functional Description            |  |

| 8.3 EPROM Mode                        |  |

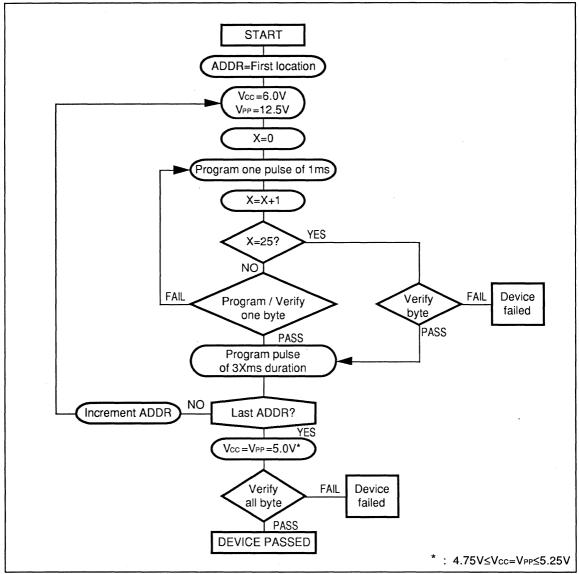

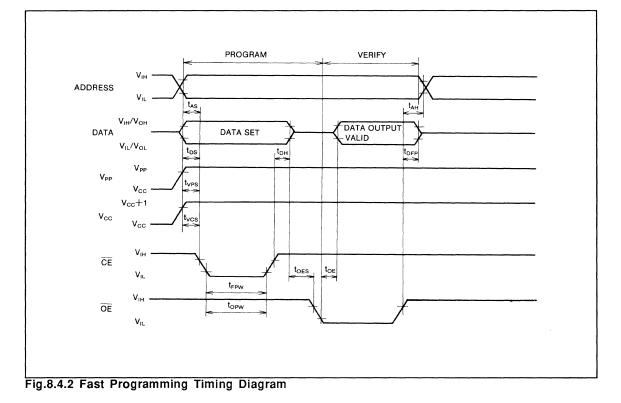

| 8.4 Fast Programming Algorithm        |  |

| 8.5 Notes                             |  |

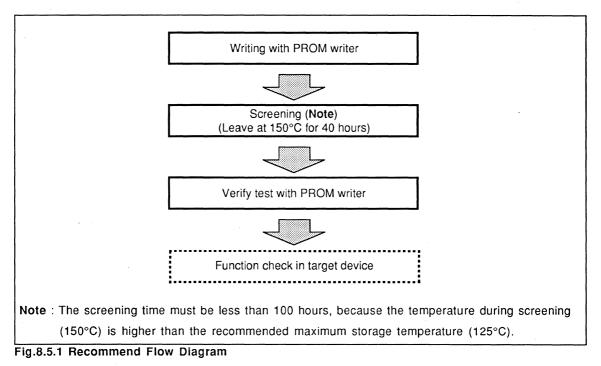

| 8.5.1 Notes on an built-in PROM types |  |

| 8.5.2 Notes on one-time PROM type     |  |

| 8.5.3 Notes on EPROM type             |  |

| 2                                     |  |

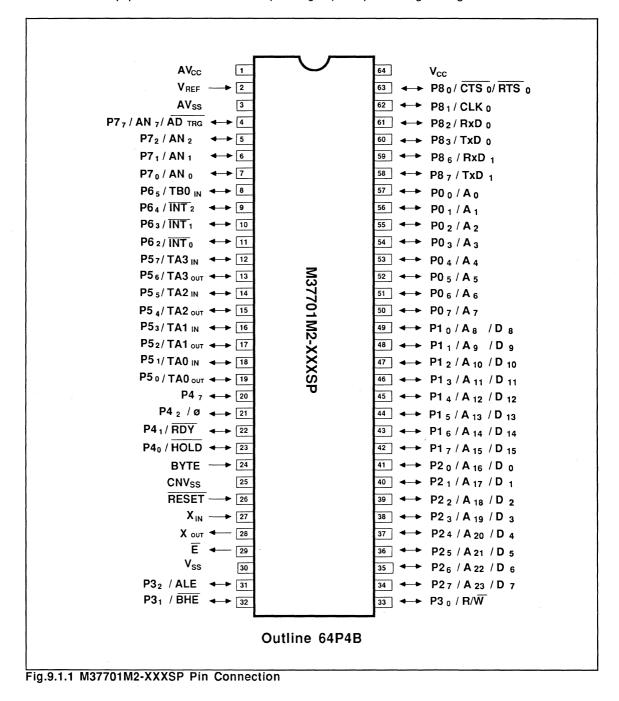

## CHAPTER 9.M37701M2-XXXSP

| 9.1 Description                                          |  |

|----------------------------------------------------------|--|

| 9.2 M37701 Family                                        |  |

| 9.3 M37701M2-XXXSP Characterictics                       |  |

| 9.4 M37701M2-XXXSP Performance Overview                  |  |

| 9.5 Diferences Between M37701M2-XXXSP and M37700M2-XXXFP |  |

| 9.6 M37701 Functional Description                        |  |

| 9.6.1 A-D converter                                      |  |

| 9.6.2 Timers                                             |  |

| 9.6.3 Serial I/O                                         |  |

| 9.6.4 Ports                                              |  |

|                                                          |  |

# TABLE OF CONTENTS

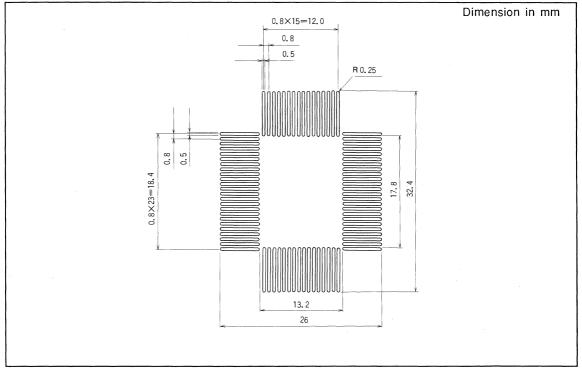

| APPENDIX 1. OUTLINE DRAWING                                                        |                                        |

|------------------------------------------------------------------------------------|----------------------------------------|

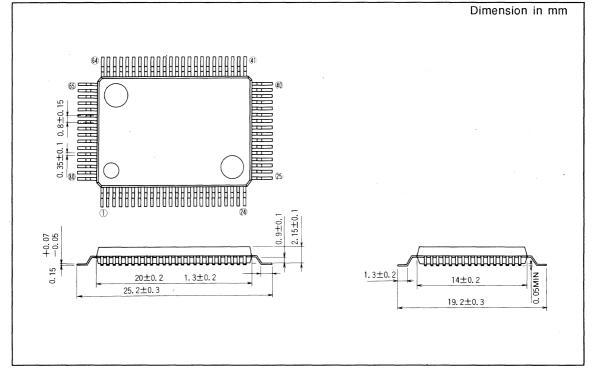

| 1.80-pin plastic molded QFP (80P6)                                                 |                                        |

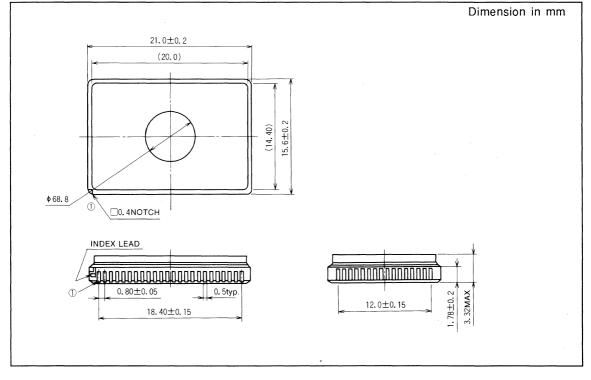

| 2.80-pin ceramic LCC (80D0O)                                                       |                                        |

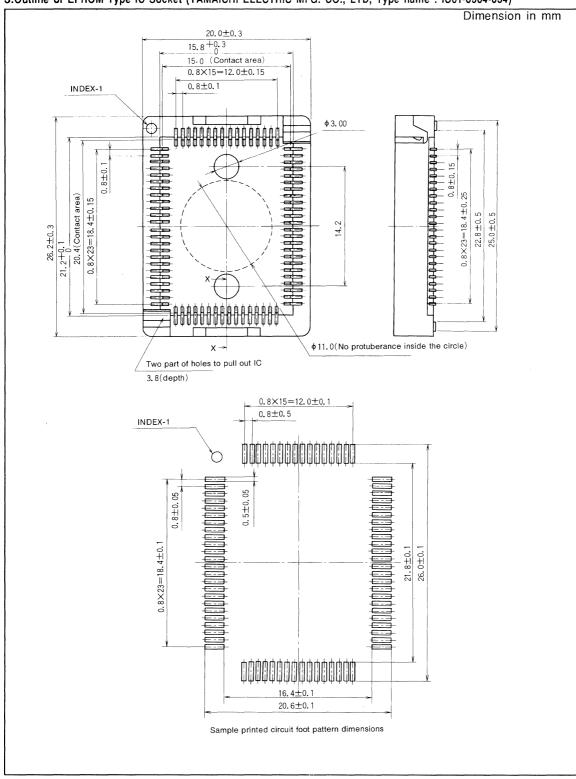

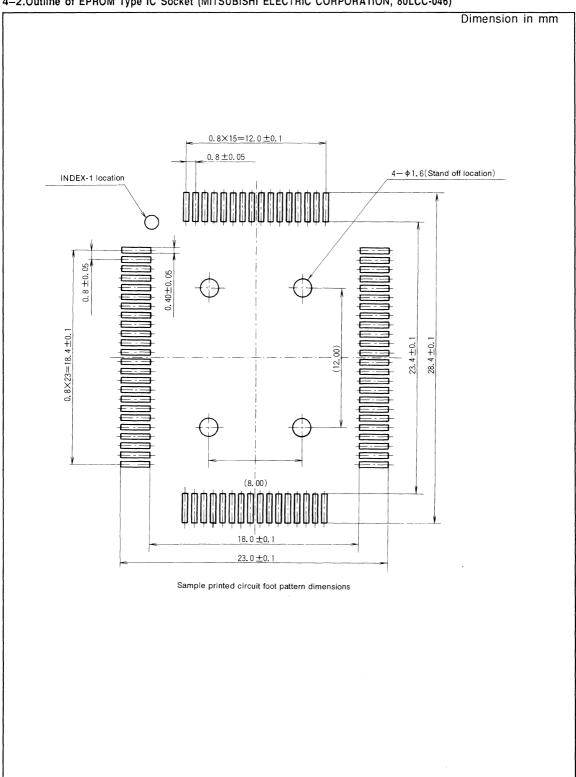

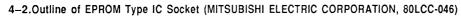

| 3.Outline of EPROM Type IC Socket                                                  |                                        |

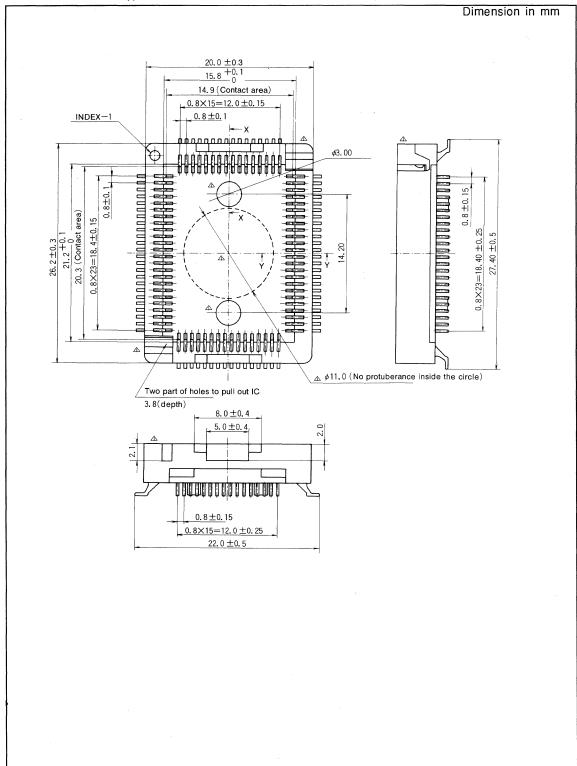

| 4.Outline of EPROM Type IC Socket                                                  |                                        |

| 5.Outline of One-time PROM Type IC Socket                                          |                                        |

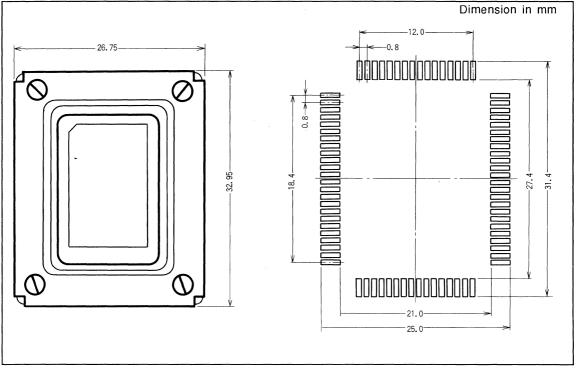

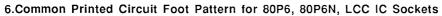

| 6.Common Printed Circuit Foot Pattern for 80P6, 80P6N, LCC IC Sockets              |                                        |

|                                                                                    |                                        |

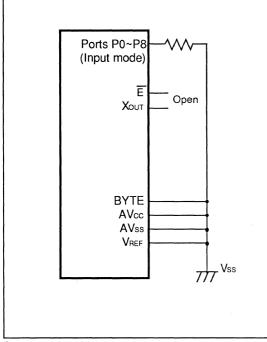

| APPENDIX 2. SETTING OF UNUSED PINS<br>1.Setting of unused pins in single-chip mode | 000                                    |

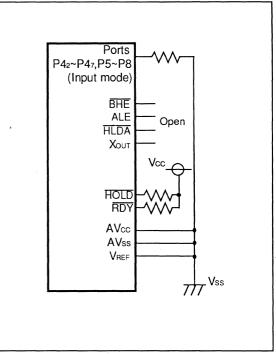

| 2.Setting of unused pins in memory expansion and microprocessor mode               | 200                                    |

| 2.Setting of unused pins in memory expansion and microprocessor mode               | 200                                    |

| APPENDIX 3. M37700 FAMILY PERFORMANCE OVERVIEW                                     |                                        |

| 1.M37700 family common performance                                                 |                                        |

| 2. Difference in external clock input frequency by type                            |                                        |

| 3.Memory characteristics and size by type                                          |                                        |

| 4.External ROM types                                                               |                                        |

| 5.Package                                                                          |                                        |

|                                                                                    |                                        |

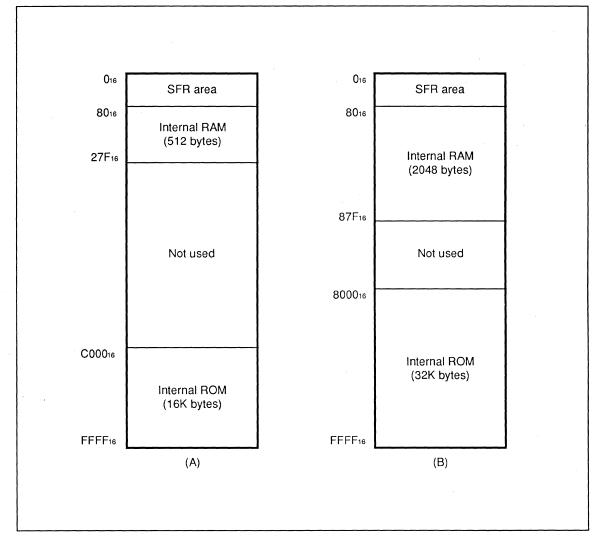

| APPENDIX 4. M37700 FAMILY MEMORY MAP                                               |                                        |

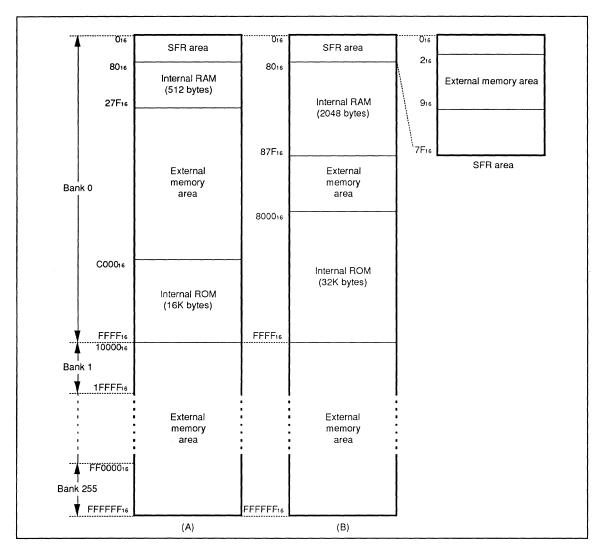

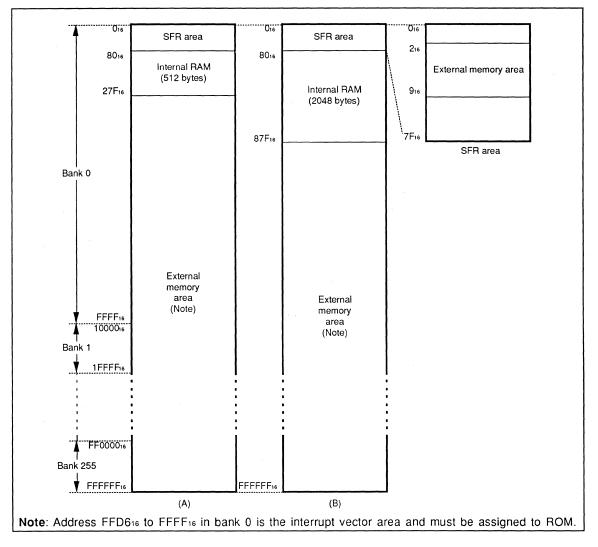

| 1.Memory map in single-chip mode                                                   |                                        |

| 2.Memory map in memory expansion mode                                              |                                        |

| 3.Memory map in microprocessor mode (and external ROM type)                        |                                        |

| APPENDIX 5. SFR AREA MEMORY MAP                                                    |                                        |

|                                                                                    |                                        |

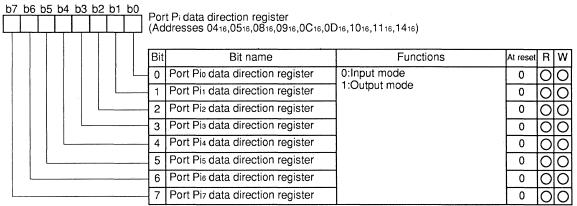

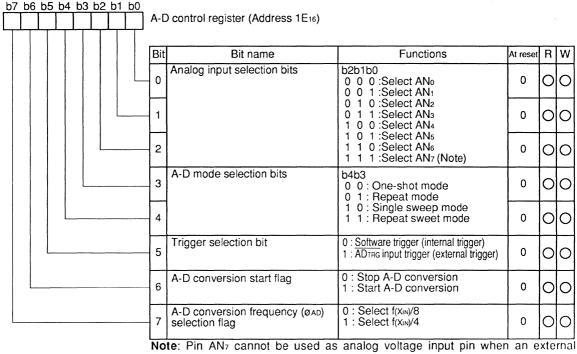

| APPENDIX 6. CONTROL REGISTERS                                                      | 014                                    |

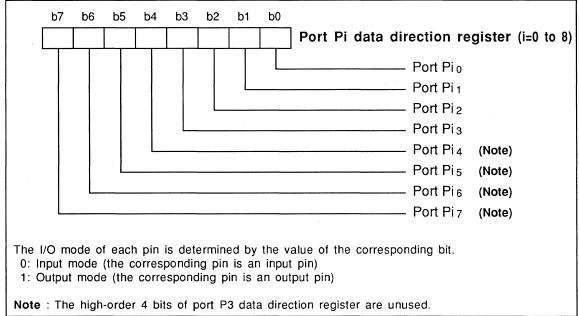

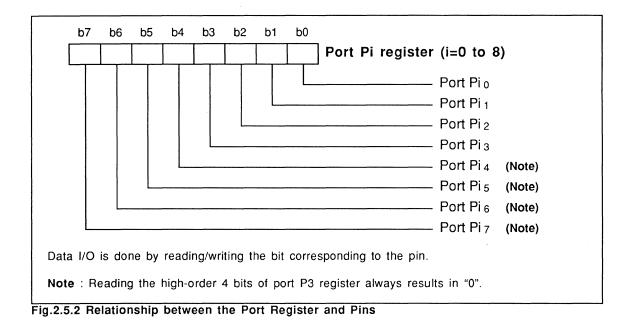

| 1.Port Pi data direction registers (i=0~8)<br>2.A-D control register               |                                        |

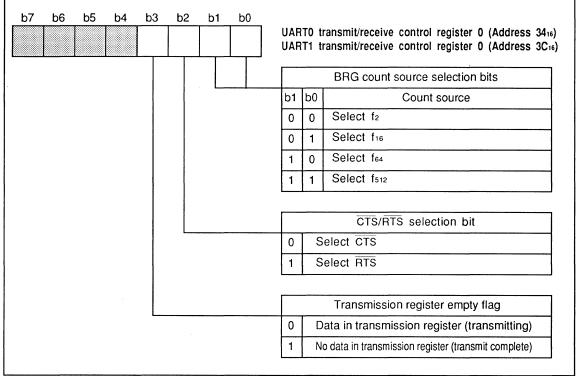

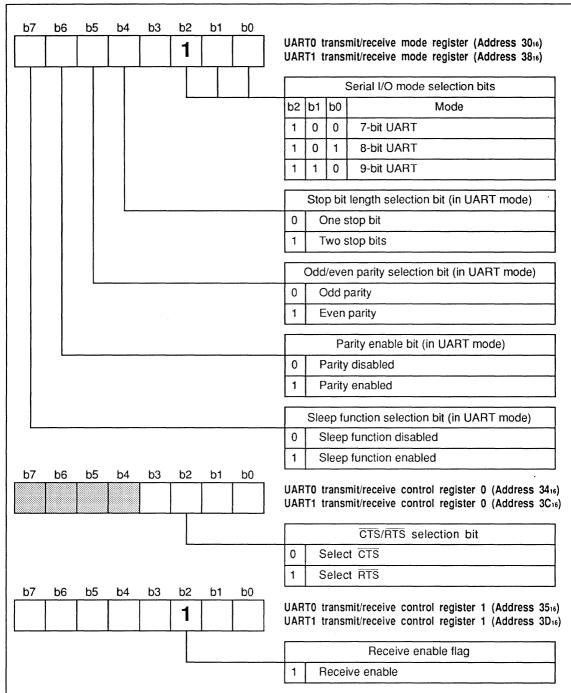

| 3.UARTi transmit/receive mode registers (i=0, 1)                                   |                                        |

| 4.UARTi transmit/receive control register 0 (i=0, 1)                               |                                        |

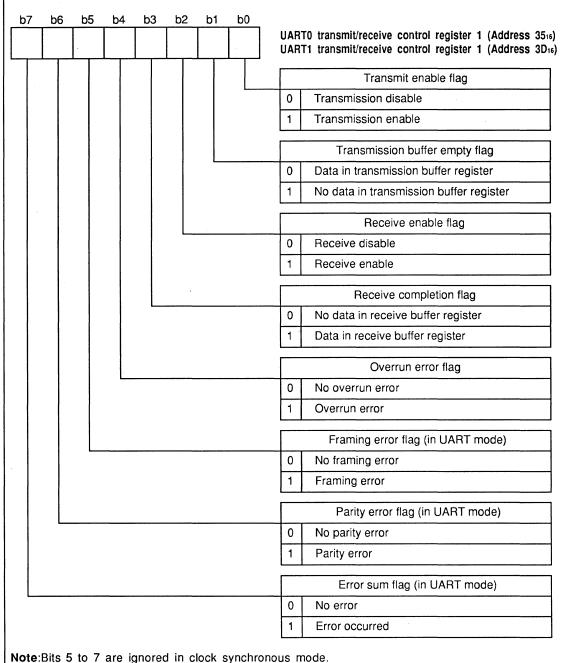

| 5.UARTi transmit/receive control register 0 (i=0, 1)                               |                                        |

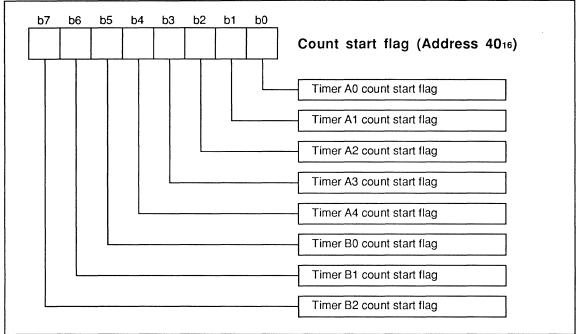

| 6.Count start flag                                                                 |                                        |

| 7.One-shot start flag                                                              |                                        |

| 8.Up-down flag                                                                     |                                        |

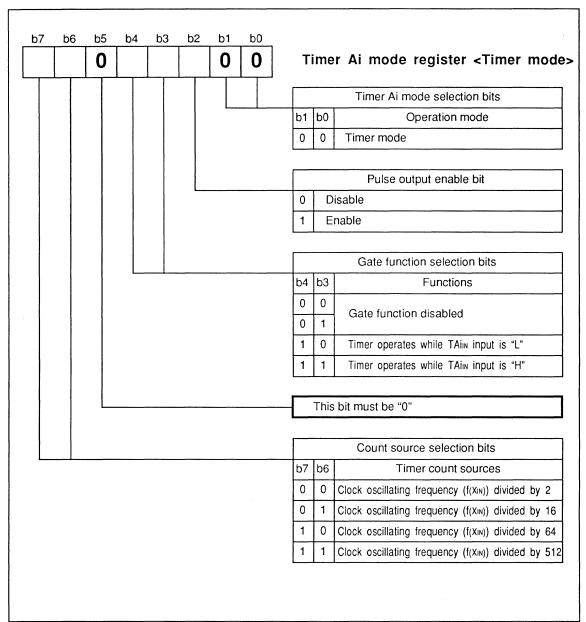

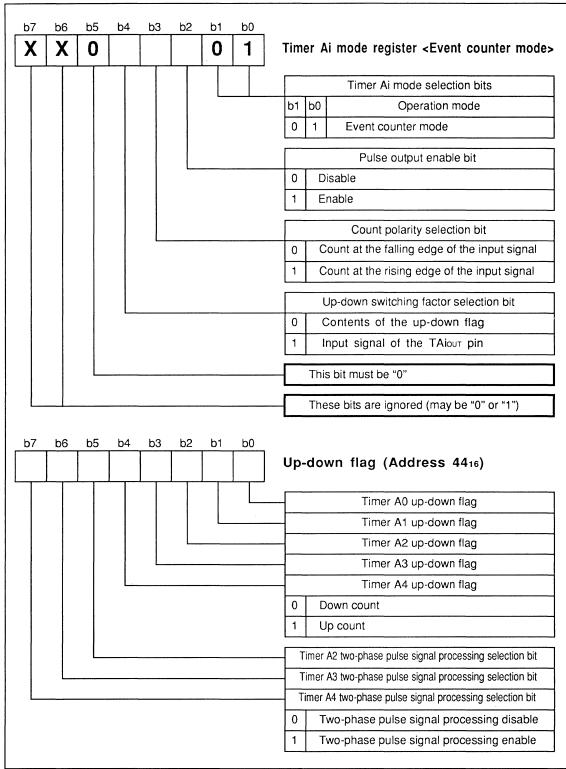

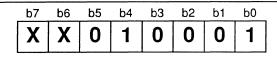

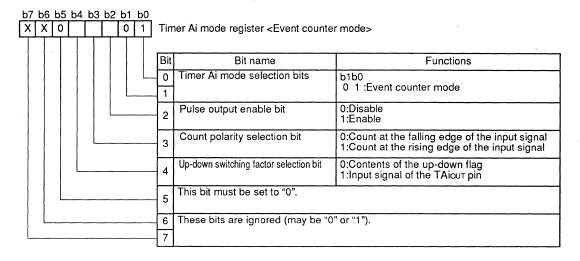

| 9.Timer Ai mode registers (i=0~4)                                                  | ······································ |

| (1) Timer mode                                                                     | - 219                                  |

| (2) Event counter mode                                                             |                                        |

| (3) One-shot pulse mode                                                            |                                        |

| (4) PWM mode                                                                       |                                        |

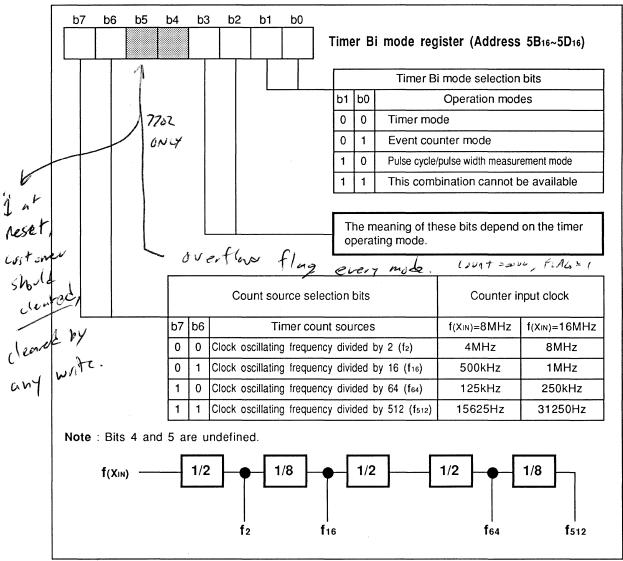

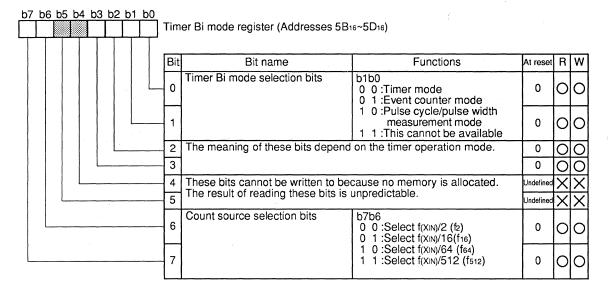

| 10.Timer Bi mode registers (i=0~2)                                                 |                                        |

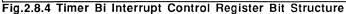

| (1) Timer mode                                                                     |                                        |

| (2) Event counter mode                                                             |                                        |

| (3) Pulse cycle/pulse width measurement mode                                       |                                        |

| 11.Processor mode register                                                         |                                        |

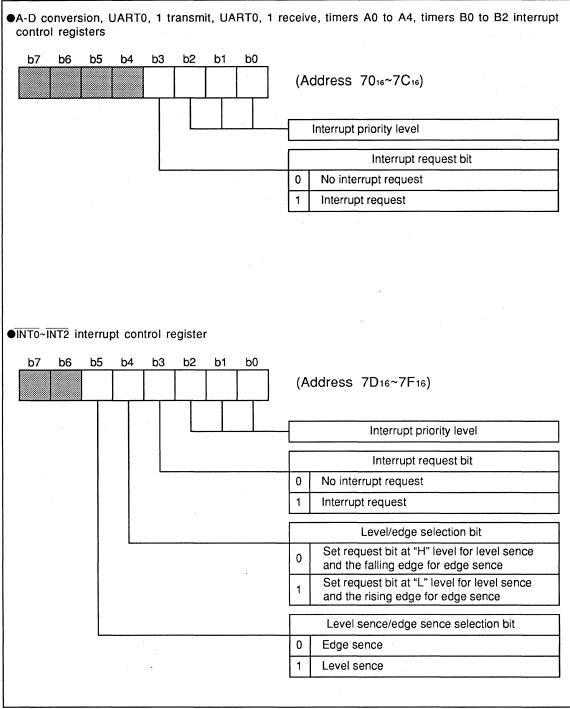

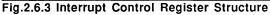

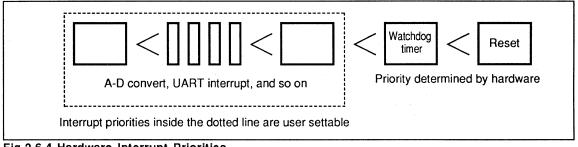

| 12.Interrupt control registers                                                     |                                        |

| A-D conversion                                                                     |                                        |

| UART0/1 transmission                                                               |                                        |

| UART0/1 receive                                                                    |                                        |

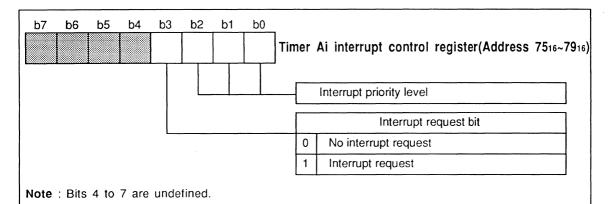

| timers A0~A4                                                                       |                                        |

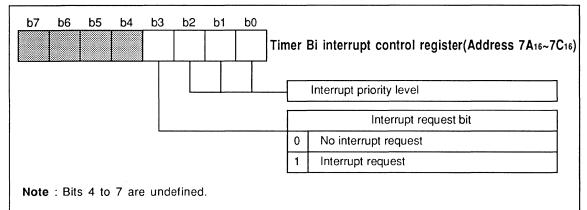

| timers B0~B2                                                                       |                                        |

| 13.INT0~INT2 interrupt control registers                                           |                                        |

| APPENDIX 7.INSTRUCTION CODE TABLE                                                  |                                        |

|                                                                                    |                                        |

| APPENDIX 8.MACHINE INSTRUCTIONS                                                    |                                        |

| APPENDIX 9.MASK ROM ORDERING METHOD                                                | 2/8                                    |

|                                                                                    |                                        |

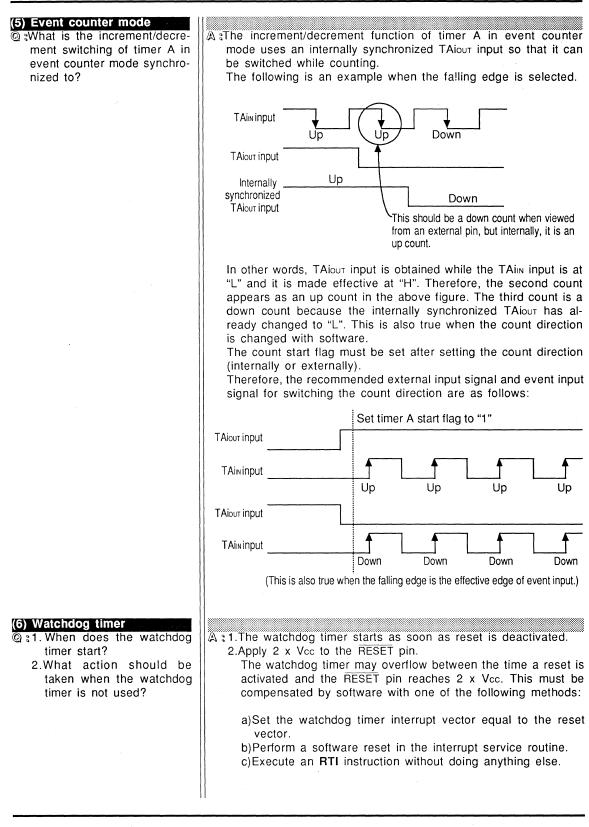

| APPENDIX 10.Q & A                                                                  |                                        |

# CHAPTER 1 DESCRIPTION

## CHAPTER 1.DESCRIPTION

#### 1.1 Description

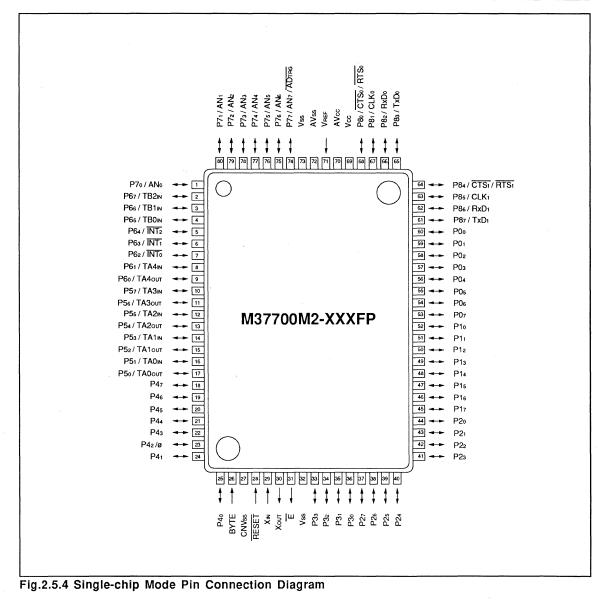

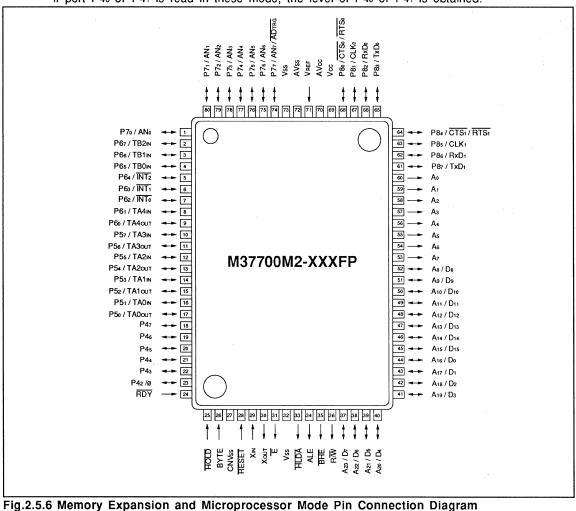

The M37700M2-XXXFP is a 16-bit single-chip microcomputer designed with high-performance CMOS silicon gate technology. It is housed in an 80-pin plastic molded flat package.

This single-chip microcomputer has a large 16M bytes address space, three instruction queue buffers, and two data buffers for high-speed instruction execution. The CPU is a 16-bit parallel processor that can also be switched to perform 8-bit parallel processing. This microcomputer is suitable for office, business, and industrial equipment controllers that require high-speed processing of large amounts of data.

Photo of M37700M2-XXXFP Chip

#### 1.2 M37700 Family

#### 1.2.1 M37700 family

The M37700 family consists of chips shown in Table 1.2.1 with the M37700M2-XXXFP as the base chip. These chips are all pin compatible and provide a variety of memory characteristics, memory size, and operating clock frequencies to enable the user to select the chip best suited for his system. Hereafter, the M37700 family microcomputers will be referred to simply as the M37700 unless there is a specific difference by type.

| Type name      | ROM<br>size<br>(bytes) | RAM<br>size<br>(bytes) | Clock<br>frequency<br>(MHz) | Remarks                                 |

|----------------|------------------------|------------------------|-----------------------------|-----------------------------------------|

| M37700M2-XXXFP | 16K (Mask ROM)         | 512                    | 8                           |                                         |

| M37700M2AXXXFP | 16K (Mask ROM)         | 512                    | 16                          | High-speed type of M37700M2-XXXFP       |

| M37700SFP      |                        | 512                    | 8                           | External ROM type of M37700M2-XXXFP     |

| M37700SAFP     |                        | 512                    | 16                          | External ROM type of M37700M2AXXXFP     |

| M37700E2-XXXFP | 16K (One-time PROM)    | 512                    | 8                           | One-time PROM type of M37700M2-XXXFP    |

| M37700E2AXXXFP | 16K (One-time PROM)    | 512                    | 16                          | One-time PROM type of M37700M2AXXXFP    |

| M37700E2FS     | 16K (EPROM)            | 512                    | 8                           | EPROM type of M37700M2-XXXFP            |

| M37700E2AFS    | 16K (EPROM)            | 512                    | 16                          | EPROM type of M37700M2AXXXFP            |

| M37700M4-XXXFP | 32K (Mask ROM)         | 2048                   | 8                           | Memory expansion type of M37700M2-XXXFP |

| M37700M4AXXXFP | 32K (Mask ROM)         | 2048                   | 16                          | Memory expansion type of M37700M2AXXXFP |

| M37700S4FP     |                        | 2048                   | 8                           | External ROM type of M37700M4-XXXFP     |

| M37700S4AFP    |                        | 2048                   | 16                          | External ROM type of M37700M4AXXXFP     |

| M37700E4-XXXFP | 32K (One-time PROM)    | 2048                   | 8                           | One-time PROM type of M37700M4-XXXFP    |

| M37700E4AXXXFP | 32K (One-time PROM)    | 2048                   | 16                          | One-time PROM type of M37700M4AXXXFP    |

| M37700E4FS     | 32K (EPROM)            | 2048                   | 8                           | EPROM type of M37700M4-XXXFP            |

| M37700E4AFS    | 32K (EPROM)            | 2048                   | 16                          | EPROM type of M37700M4AXXXFP            |

#### Table 1.2.1 M37700 Family

#### CHAPTER 1.DESCRIPTION

#### 1.2.2 Differences between types

- Mask ROM type microcomputer This type of microcomputers has programs printed using a mask during the manufacturing process.

- Applicable types: M37700M2-XXXFP/M37700M2AXXXFP M37700M4-XXXFP/M37700M4AXXXFP

- ② External ROM type microcomputer This type of microcomputers has no internal ROM. External ROMs must be provided. The function is identical with the mask ROM version microcomputer when it is operating in microprocessor mode.

- Applicable types: M37700SFP/M37700SAFP M37700S4FP/M37700S4AFP

- ③ One-time PROM type microcomputer This type of microcomputer is equipped with one-time PROM (Programmable ROM). Programs can be written using commercially available PROM writers. However, programs can be written only once and the written program cannot be erased.

- Applicable types: M37700E2-XXXFP/M37700E2AXXXFP M37700E4-XXXFP/M37700E4AXXXFP

#### ④ EPROM type microcomputer

This type of microcomputer is equipped with EPROM and programs can be written using commercially available PROM writers. Furthermore, programs can be re-written by exposing the window on top of the package to an ultraviolet rays.

Applicable types: M37700E2FS/M37700E2AFS M37700E4FS/M37700E4AFS

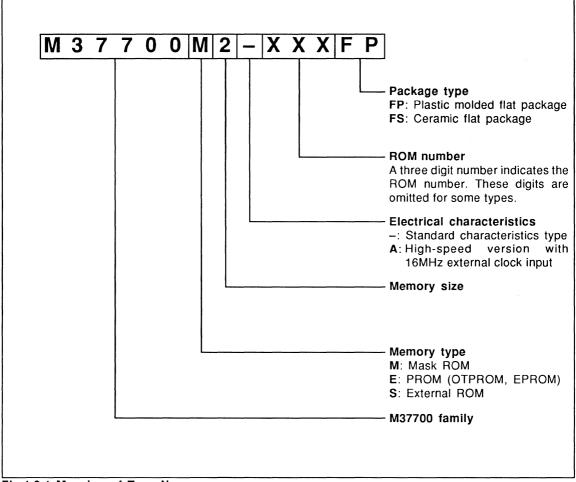

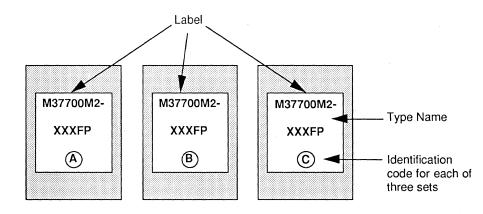

#### 1.2.3 Meaning of type name

The names of the Mitsubishi Single-chip microcomputers indicate the differences in functions and characteristics. The name of the M37700 family has the following meaning:

Fig.1.2.1 Meaning of Type Name

# **CHAPTER 1.DESCRIPTION**

#### **1.3 Performance Overview**

Table 1.3.1 shows the performance overview of the M37700M2-XXXFP/ M37700M2AXXXFP. Refer to "Appendix 3. M37700 Family Performance Overview" for the performance of other types.

| Parameters                   |                         | Functions                                           |

|------------------------------|-------------------------|-----------------------------------------------------|

| Number of basic instructions |                         | 103                                                 |

| Instruction execution time   | M37700M2-XXXFP          | 500ns (shortest instruction at 8MHz frequency)      |

|                              | M37700M2AXXXFP          | 250ns (shortest instruction at 16MHz frequency)     |

| Clock frequency              | M37700M2-XXXFP          | 8MHz (maximum)                                      |

|                              | M37700M2AXXXFP          | 16MHz (maximum)                                     |

| Memory size                  | ROM                     | 16384 bytes                                         |

|                              | RAM                     | 512 bytes                                           |

| Input/Output ports           | Ports P0~P2, P4~P8      | 8 bits x 8                                          |

|                              | Port P3                 | 4 bits x 1                                          |

| Multi-function timers        | TA0, TA1, TA2, TA3, TA4 | 16 bits x 5                                         |

|                              | TB0, TB1, TB2           | 16 bits x 3                                         |

| Serial I/O                   |                         | (UART or clock synchronous serial I/O) x 2          |

| A-D converter                |                         | 8 bits x 1 (8 channels)                             |

| Watchdog timer               |                         | 12 bits x 1                                         |

| Interrupts                   |                         | 3 external, 16 internal (priority levels 0 to 7 can |

|                              |                         | be set for each interrupt with software)            |

| Clock generating circuit     |                         | Built-in (externally connected to a ceramic         |

|                              |                         | resonator or quartz crystal oscillator)             |

| Supply voltage               |                         | 5V±10%                                              |

| Power dissipation            |                         | 30mW (at external 8MHz frequency)                   |

| Input/Output characteristics | Input/Output voltage    | 5V                                                  |

|                              | Output current          | 5mA                                                 |

| Memory expansion             |                         | Maximum 16M bytes                                   |

| Operating temperature range  | }                       | –10 to 70°C                                         |

| Device structure             |                         | CMOS high-performance silicon gate process          |

| Package                      |                         | 80-pin plastic molded QFP                           |

| Table 1.3.1 | M37700M2-XXXFP/M37700M2AXXXFP | Performance Overview |

|-------------|-------------------------------|----------------------|

|-------------|-------------------------------|----------------------|

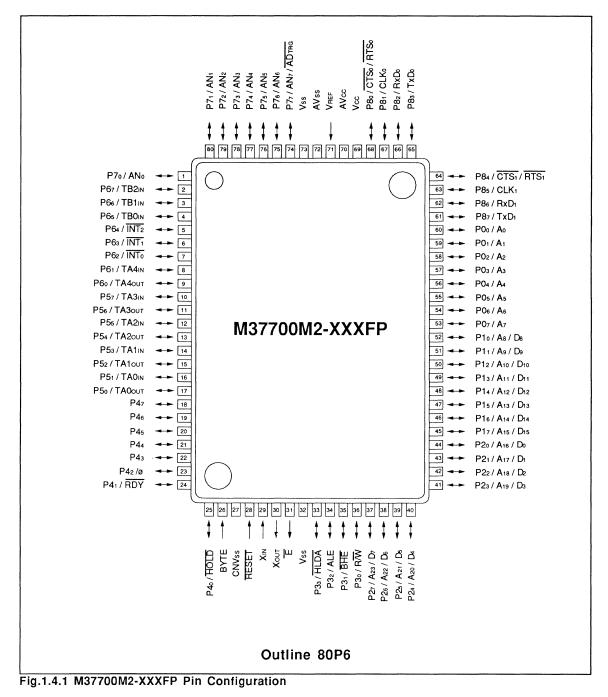

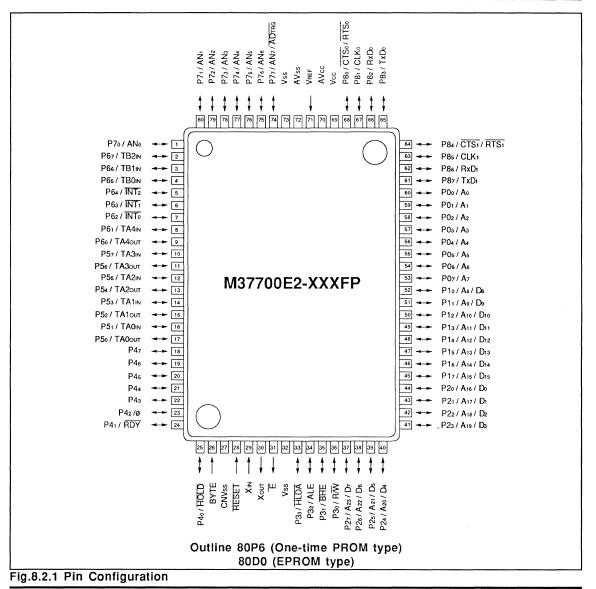

# **1.4 Pin Configuration**

#### 1.4 Pin Configuration

7

# **CHAPTER 1.DESCRIPTION**

# 1.5 Pin Description

## Table 1.5.1 Pin Description (a)

| Pin        | Name                      | Input/Output | Functions                                                                            |

|------------|---------------------------|--------------|--------------------------------------------------------------------------------------|

| Vcc, Vss   | Power supply              |              | Supply 5V±10% to Vcc and 0V to Vss.                                                  |

| CNVss      | CNVss input               | Input        | This pin controls the processor mode. Connect to Vss                                 |

|            |                           |              | for single-chip mode. It must be connected to Vcc for                                |

|            |                           |              | external ROM types.                                                                  |

| RESET      | Reset input               | Input        | The microcomputer is reset when this pin is set to "L'                               |

|            |                           |              | level.                                                                               |

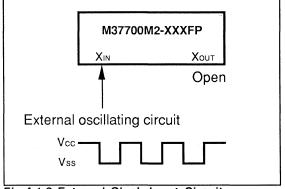

| XIN        | Clock input               | Input        | These are the I/O pins of the internal clock generating                              |

|            |                           |              | circuit. Connect a ceramic or quartz crystal resonator                               |

| Хоџт       | Clock output              | Output       | between XIN and XOUT. When an external clock is used                                 |

|            |                           |              | the clock source should be connected to the XIN pin and                              |

|            |                           |              | the Xour pin should be left open.                                                    |

| Ē          | Enable output             | Output       | Data or instruction read and data write are performed                                |

|            |                           |              | when output from this pin is "L".                                                    |

| BYTE       | Bus width selection input | Input        | When in memory expansion mode or microprocessor                                      |

|            |                           |              | mode, this pin determines whether the external data                                  |

|            |                           | i.           | bus is 8-bit width or 16-bit width. The width is 16 bits                             |

|            | · · · · ·                 |              | when the signal level is "L" and 8 bits when the signa                               |

|            |                           |              | level is "H".                                                                        |

| AVcc, AVss | Analog supply input       |              | Power supply for the A-D converter. Externally connect                               |

|            |                           |              | AVcc to Vcc and AVss to Vss.                                                         |

| VREF       | Reference voltage input   | Input        | This is a reference voltage input pin for the A-D con-                               |

|            |                           |              | verter.                                                                              |

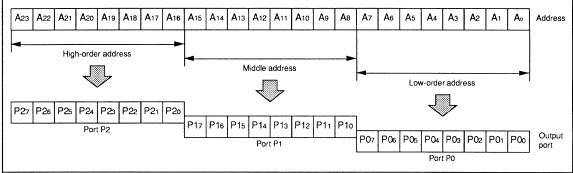

| P00~P07    | I/O port P0               | I/O          | This port is a CMOS I/O port. An I/O direction register is                           |

|            |                           |              | available so that each pin can be programmed for input                               |

|            |                           |              | or output. Address (Ao~A7) is output in memory expan-                                |

|            |                           |              | sion mode or microprocessor mode.                                                    |

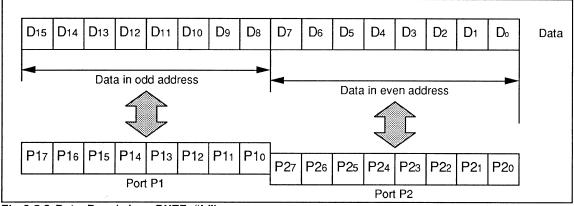

| P10~P17    | I/O port P1               | I/O          | This port is an 8-bit I/O port with the same function as                             |

|            |                           |              | P0. When the BYTE pin is set to "H" in memory expan-                                 |

|            |                           |              | sion mode or microprocessor mode, address (A8~A15) is                                |

|            |                           |              | output. When the BYTE pin is set to "L", an address                                  |

|            |                           |              | $(A_8 \sim A_{15})$ is output when $\overline{E}$ pin level is "H" and high-order    |

|            |                           |              | data (D <sub>8</sub> ~D <sub>15</sub> ) is input or output when E pin level is "L"   |

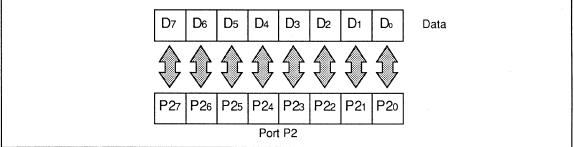

| P20~P27    | I/O port P2               | I/O          | This port is an 8-bit I/O port with the same function as                             |

|            |                           |              | P0. In memory expansion mode or microprocesso                                        |

|            |                           |              | mode, an address ( $A_{16} \sim A_{23}$ ) is output when $\overline{E}$ pin level is |

|            |                           |              | "H" and low-order data (Do~D7) is input or output wher                               |

|            |                           |              | E pin output is "L".                                                                 |

| P30~P33    | I/O port P3               | I/O          | This port is a 4-bit I/O port with the same function as P0                           |

|            |                           |              | In memory expansion mode or microprocessor mode                                      |

|            |                           |              | P30~P33 become R/W, BHE, ALE, and HLDA signals are                                   |

|            |                           |              | output respectively.                                                                 |

| P40~P47    | I/O port P4               | I/O          | This port is an 8-bit I/O port with the same function as                             |

|            |                           |              | P0. P4 <sub>2</sub> can be programmed as a $\emptyset$ output pin. In mem-           |

|            |                           |              | ory expansion mode or microprocessor mode, P4 <sub>0</sub> and                       |

|            |                           |              | P41 become HOLD and RDY input pin respectively.                                      |

| Pin     | Name        | Input/Output | Functions                                                                                                                                                                                                                        |

|---------|-------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P50~P57 | I/O port P5 | 1/0          | This port is an 8-bit I/O port with the same function as P0. These pins can also be programmed as I/O pins for timers A0~A3.                                                                                                     |

| P60~P67 | I/O port P6 | I/O          | This port is an 8-bit I/O port with the same function as P0. These pins can be programmed as I/O pins for timer A4, external interrupt input pins for $\overline{INT_0}$ - $\overline{INT_2}$ , and input pins for timers B0~B2. |

| P70~P77 | I/O port P7 | I/O          | This port is an 8-bit I/O port with the same function as P0. These pins can be programmed as analog input pins AN <sub>0</sub> ~AN <sub>7</sub> . P7 <sub>7</sub> also has an A-D conversion trigger input function.             |

| P80~P87 | I/O port P8 | I/O          | This port is an 8-bit I/O port with the same function as P0. These pins can be programmed as CTS/RTS, CLK, RxD, TxD pins for UART0 and UART1.                                                                                    |

Table 1.5.1 Pin Description (b)

.

# **CHAPTER 1.DESCRIPTION**

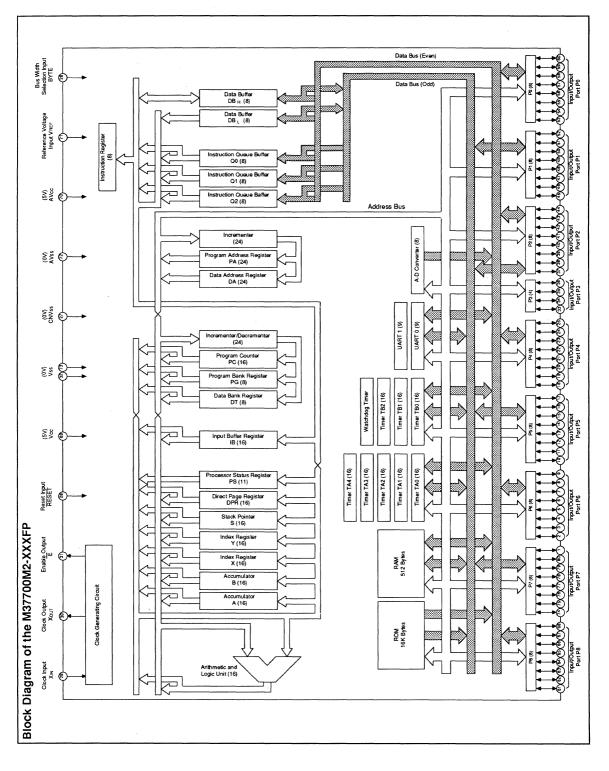

#### 1.6 Block Diagram

10

# CHAPTER 2 FUNCTIONAL DESCRIPTION

#### 2.1 Central Processing Unit (CPU)

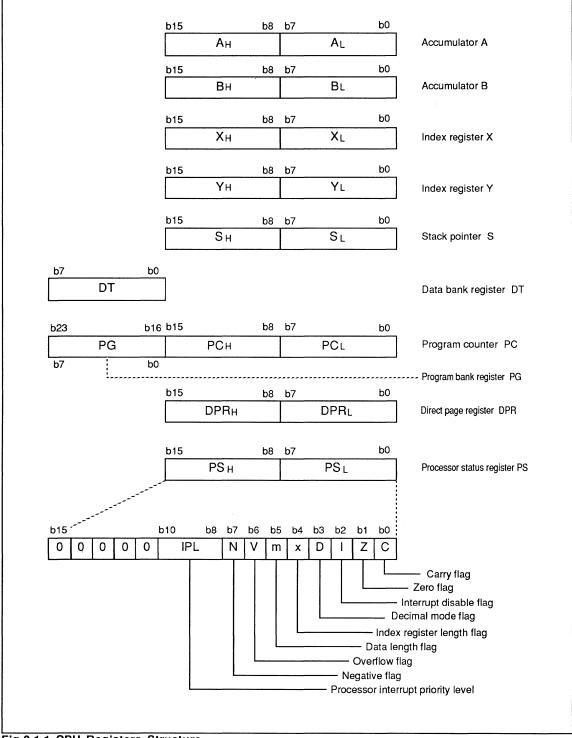

The MELPS 7700 Series CPU has ten registers as shown in Figure 2.1.1. Each of these registers is described below.

#### 2.1.1 Accumulator (Acc)

Accumulators A and B are available and each can be used as 8-bit or 16-bit register as necessary.

#### (1) Accumulator A (A)

Accumulator A is the main register of the microcomputer. Data operations such as calculations, data transfer, and input/output are executed mainly through accumulator A. It consists of 16 bits and the lower 8 bits can be used separately. The data length flag (m) determines whether the register is used as a 16-bit register or as an 8-bit register. It is used as a 16-bit register when flag m is "0" and as an 8-bit register when flag m is "1". Flag m is a part of the processor status register (PS) which is described later.

#### (2) Accumulator B (B)

Accumulator B has the same functions as accumulator A. The series MELPS 7700 instructions can use accumulator B instead of accumulator A, but the use of accumulator B requires more instruction bytes and execution cycles than accumulator A. Accumulator B is also controlled by the data length flag m.

#### 2.1.2 Index register X

Index register X consists of 16 bits and the lower 8 bits can be used separately. The index register length flag (x) determines whether the register is used as a 16-bit register or as an 8-bit register. It is used as a 16-bit register when flag x is "0" and as an 8-bit register when flag x is "1". Flag x is a part of the processor status register (PS) which is described later.

In index addressing mode, register X is used as the index register and the contents of this address is added to obtain the real address.

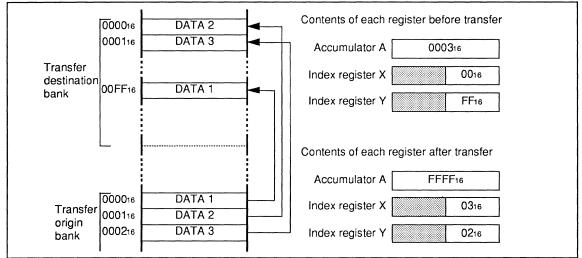

Also, when executing a block transfer instruction MVP or MVN, the contents of the index register X indicates the low-order 16 bits of the source data address. The third byte of the MVP and MVN is the high-order 8 bits of the source data address.

#### 2.1.3 Index register Y

Index register Y is a 16-bit register with the same function as index register X. As with index register X, the index register length flag (x) determines whether this register is used as a 16-bit register or as an 8-bit register. Also, when executing a block transfer instruction MVP or MVN, the content of index register Y indicates the low order 16 bits of the destination data address. The second byte of the MVP and MVN is the high-order 8 bits of the destination data address.

# 2.1 Central Processing Unit

Fig.2.1.1 CPU Registers Structure

#### 2.1.4 Stack pointer (S)

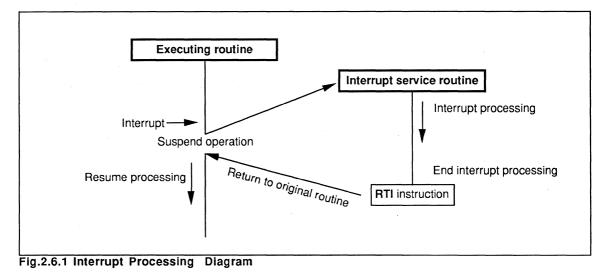

Stack pointer S is a 16-bit register. It is used during a subroutine call or interrupt. It is also used during addressing modes using the stack. The contents of the stack pointer S indicates the address (stack area) for saving registers during subroutine calls and interrupts. Normally, the stack area is reserved in internal RAM.

When an interrupt occurs, the contents of the program bank register PG is saved at the address indicated by the content of the stack pointer S and the content of the stack pointer is decremented by 1. Then the contents of the program counter PC and the processor status register PS are saved with the high-order bytes followed by the low-order bytes (PCH, PCL, PSH, PSL). The contents of the stack pointer S after an interrupt is equal to the content before the interrupt -5. When returning to the original routine after processing the interrupt, the registers saved in the stack area are restored to the original registers in the reverse sequence and the content of the stack pointer is returned to the status before the interrupt. The same operation is performed during a subroutine call, but the content of the processor status register PS is not saved (the content of the program bank register PG may not be saved either depending on the addressing mode).

The user is responsible for saving registers other than those described above during interrupts or subroutine calls. In addition, the stack pointer S must be initialized at the beginning of the program because its content is unpredictable after a reset. Normally, the stack pointer is initialized with the highest address of the internal RAM. The contents of the stack area changes when subroutines are nested or when multiple interrupts occur. Therefore, make sure necessary data in the internal RAM are not destroyed when nesting subroutines.

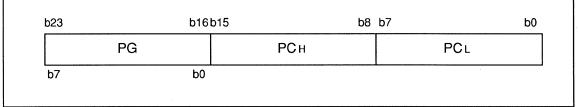

#### 2.1.5 Program counter (PC)

Program counter PC is a 16-bit counter that indicates the low-order 16 bits of the next program memory address to be executed.

#### 2.1.6 Program bank register (PG)

Program bank register PG is an 8-bit register that indicates the high-order 8 bits (bank) of the next program memory address to be executed. When a carry occurs after incrementing the content of the program counter, the content of the program bank register PG is incremented by 1. Also, when a carry or borrow occurs after adding or subtracting the content of the program counter PC, the content of the program bank register PG is incremented by 1 so that programs can be written without considering bank boundaries.

In single-chip mode, do not store values other than " $00_{16}$ " because only address between  $0000_{16}$  and FFFF<sub>16</sub> can be accessed.

#### Fig.2.1.2 Program Counter and Program Bank Register

#### 2.1.7 Data bank register (DT)

Data bank register DT is an 8-bit register. With some addressing modes, the content of this register is used as the high-order 8 bits of a 24-bit address. In single-chip mode, do not store values other than "0016" because only address between 000016 and FFFF16 can be accessed.

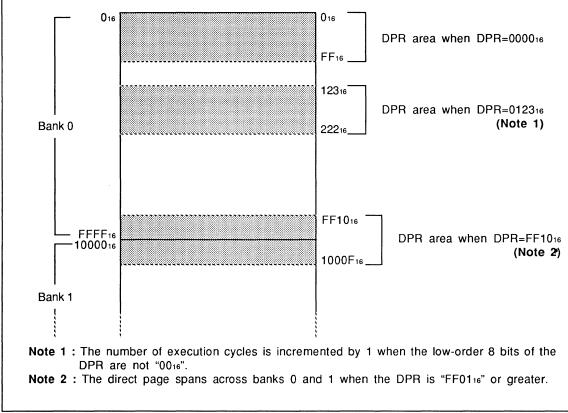

#### 2.1.8 Direct page register (DPR)

Direct page register DPR is a 16-bit register. The content of this register indicates whether the direct page area is allocated in bank 0 or spans across bank 0 and 1. This area can be accessed with two bytes by using the direct page addressing mode.

The content of the DPR is the base address (lowermost address) of the direct page area which extends 256 bytes above this address. The DPR can contain a value from 000016 to FFFF16. If it contains a value equal to or greater than "FF0116", the direct page area spans across banks 0 and 1. If the low-order 8 bits of the DPR is "0016", the number of cycles required to generate an address is minimized. Therefore, the low-order 8-bits of the DPR should normally be set to "0016".

# **CHAPTER 2.FUNCTIONAL DESCRIPTION**

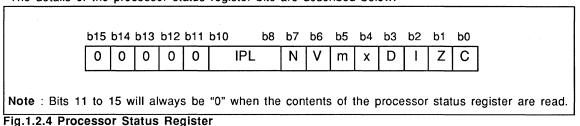

#### 2.1.9 Processor status register (PS)

Processor status register is an 11-bit register. It consists of flags to indicate the result of operation and CPU interrupt levels. The flags C, Z, V, and N are tested by branch instructions. The details of the processor status register bits are described below.

#### (1)Carry flag (C)

The carry flag is assigned to bit 0 of the processor status register. It contains the carry or borrow bit from the arithmetic and logic unit (ALU) after an arithmetic operation. This flag is also affected by shift and rotate instructions. This flag can be set with the SEC or SEP instruction and cleared with the CLC or CLP instruction.

#### (2)Zero flag (Z)

The zero flag is assigned to bit 1 of the processor status register. It is set if the result of an arithmetic operation or data transfer is zero and cleared if otherwise. This flag can be set and cleared directly with the SEP and CLP instructions.

Note : The content of this flag has no meaning during decimal mode addition (ADC instruction).

#### (3)Interrupt disable flag (I)

The interrupt disable flag is assigned to bit 2 of the processor status register. It disables all maskable interrupts (interrupts other than watchdog timer, **BRK** instruction, and zero divide). Interrupts are disabled when this flag is "1". When there is an interrupt, it is set automatically to prevent multiple interrupts. This flag can be set with the **SEI** or **SEP** instruction and cleared with the **CLI** or **CLP** instruction. This flag is set during reset.

#### (4)Decimal mode flag (D)

The decimal mode flag is assigned to bit 3 of the processor status register. It determines whether addition and subtraction are performed in binary or decimal. Binary arithmetic is performed when this flag is "0". If it is "1", decimal arithmetic is performed with each word treated as two or four digit decimal (determined by the data length flag m). Decimal adjust is performed automatically (Decimal operation is possible only with the **ADC** and **SBC** instructions.) This flag can be set and cleared with the **SEP** and **CLP** instructions. This flag is cleared during reset.

#### (5) Index register length flag (x)

The index register length flag is assigned to bit 4 of the processor status register. It determines whether the index register X or index register Y is used as a 16-bit register or an 8-bit register. The register is used as a 16-bit register when flag x is "0" and as an 8-bit register when it is "1". This flag can be set and cleared with the SEP and CLP instructions. This flag is cleared during reset.

#### (6) Data length flag (m)

The data length flag is assigned to bit 5 of the program status register. It determines whether to treat data as 16-bit or as 8-bit. A data is treated as 16-bit when flag m is "0" and as 8-bit when it is "1". This flag can be set with the **SEM** or **SEP** instruction and cleared with the **CLM** or **CLP** instruction. This flag is cleared during reset.

#### (7)Overflow flag (V)

The overflow flag is assigned to bit 6 of the processor status register. It is used when adding or subtracting a word as signed binary. When the data length flag m is "0", the overflow flag is set when the result of addition or subtraction is outside the range between -32768 and +32767. When the data length flag m is "1", the overflow flag is set when the result of addition or subtraction is outside the range between -128 and +127. It is cleared in all other cases. The overflow flag can also be set and cleared directly with the SEP, CLV, and CLP instructions. Note : This flag no meaning in decimal mode.

#### (8)Negative flag (N)

The negative flag is assigned to bit 7 of the processor status register. It is set when the result of arithmetic operation or data transfer is negative (Data bit 15 is 1 when data length flag m is "0" or data bit 7 is 1, when data length flag m is "1".). It is cleared in all other cases. It can also be set and cleared with the SEP and CLP instructions.

Note : This flag has no meaning in decimal mode.

#### (9)Processor interrupt priority level (IPL)

The processor interrupt priority level (IPL) is assigned to bits 8, 9, and 10 of the processor status register. These three bits determine the priority level of processor interrupts from level 0 to level 7. Interrupt is enabled when the interrupt priority level of the requested interrupt (set with the interrupt control register) is higher than the processor interrupt priority. When an interrupt occurs, the IPL is saved in the stack and the processor interrupt priority is replaced by the interrupt priority of the accepted interrupt. This simplifies control of multiple interrupts.

There are no instructions to directly set or clear the IPL. It can be changed by placing the new IPL on the stack and updating the processor status register with a **PUL** or **PLP** instruction.

#### 2.2 Internal Bus Interface

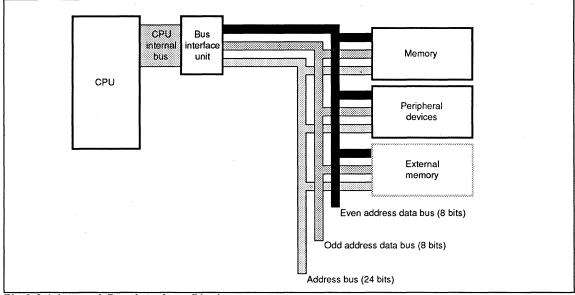

#### 2.2.1 Internal bus interface overview

A bus interface unit (BIU) is provided between the CPU and the internal bus. Transfer of data between the CPU and memory or I/O device is always performed through the BIU. When the CPU reads data from memory or an I/O device, it sends the address to be read to the BIU. The BIU reads the data from the specified address and the CPU receives the data from the BIU. Similarly, the CPU sends the address to be written to the BIU when writing data. Thus the BIU controls the transfer of data between the CPU and bus.

Figure 2.2.1 shows a block diagram of the bus interface unit.

Fig.2.2.1 Internal Bus Interface Block

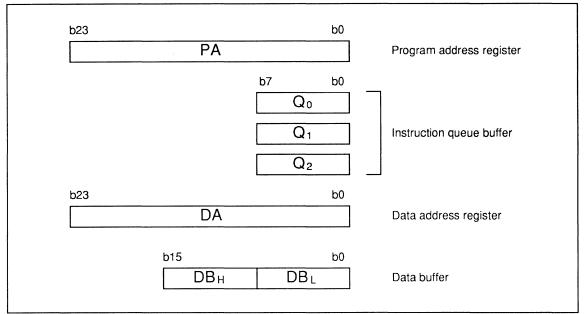

#### 2.2.2 Bus Interface unit functions

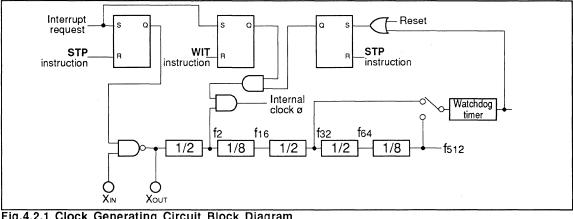

The M37700 uses the clock  $\emptyset$  (=f(X|N)/2) as the clock. The CPU also uses clock  $\emptyset$  as the clock. However, since the CPU clock may be extended due to CPU wait under certain conditions, it is referred to as  $\emptyset_{CPU}$  to distinguish it from clock  $\emptyset$ .

The M37700 internal bus (address bus and data bus) operate at timing  $\overline{E}$  which is slower than clock  $\emptyset$ The operating clock of the CPU is different from the bus cycle because timing  $\overline{E}$  is normally f(XIN)/4. Therefore, a BIU is provided between the CPU and bus to synchronize the transfer of data to and from memory and I/O device. The BIU enables the CPU to transfer data to and from memory through the bus without decreasing the instruction execution speed.

The BIU consists of four registers as shown in Figure 2.2.2. Table 2.2.1 summarizes the functions of each register and buffer.

| Name                     | Function                                                                                                                                      |  |  |  |  |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Program address register | Indicates the address of the program.                                                                                                         |  |  |  |  |  |

| Instruction queue buffer | A three bytes buffer for temporarily holding instruction prefetched from memory.                                                              |  |  |  |  |  |

| Data address register    | Indicates the address to be read from or to be written to memory or I/O.                                                                      |  |  |  |  |  |

| Data buffer              | A two bytes buffer for temporarily holding data read from memory or I/O device by the BIU or data written to memory or I/O device by the CPU. |  |  |  |  |  |

Table 2.2.1 Functions of BIU Registers and Buffers

Fig.2.2.2 Bus Interface Unit Registers

The BIU performs the following operations.

1.Prefetches an instruction code from the program memory (area where the program is stored) and stores it in the instruction queue buffer.

Normally, a program is executed sequentially in ascending order of addresses. Therefore, if the next instruction code is prefetched in the instruction queue buffer, the CPU can execute instructions simply by obtaining the instruction code from the instruction queue buffer. This will eliminate the time needed by the CPU to access the memory.

When the CPU is not using the bus (for example when performing register to register operation), the BIU reads an instruction code from the program memory (area where the program is stored) and stores it in the instruction queue buffer. Data up to three bytes can be prefetched because the instruction queue buffer is three bytes long. Refer to "Section 2.2.4" for more information concerning instruction code prefetch.

# 2.Reads data at the specified address into the BIU when the CPU requests data in memory and transfers it to the CPU.

When executing instructions that processes data in memory or I/O device, the CPU must access the address assigned to the memory or I/O device and read the data. Because the operating clock of the CPU and bus are different, the CPU reads the data through the data buffer of the BIU.

#### 3.Writes the data obtained from the CPU to the specified address in memory.

When writing data to a specific address, the CPU sends the address and data to the BIU. And after that, the CPU continue to execute the next instruction extracting from the instruction queue buffer, because actual writing to memory or I/O device is performed by the BIU.

# 4.Controls read of word data from odd number address and outputs the control signals required to access external memory in byte unit.

The transfer of data between the CPU and BIU is always performed through a 24-bit address bus and 16-bit data bus. This is also true between the BIU and internal memory or I/O device. The wait bit and BYTE pin (external bus width selection input pin) determine the data width only when an external memory is accessed.

## CHAPTER 2.FUNCTIONAL DESCRIPTION

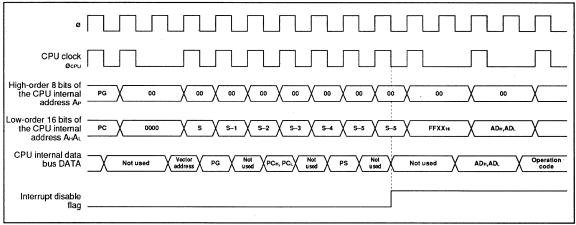

#### 2.2.3 Bus Interface unit operations

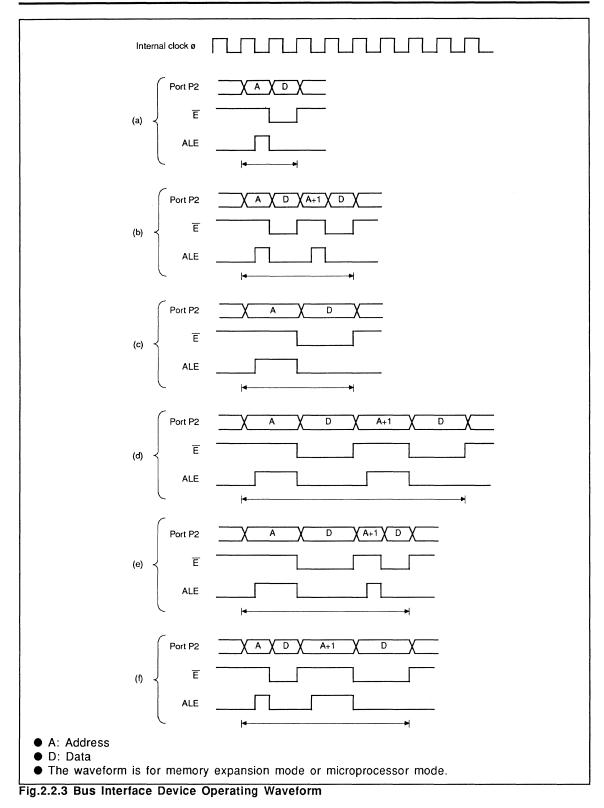

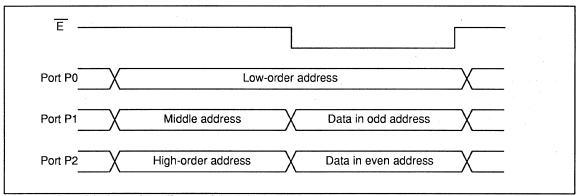

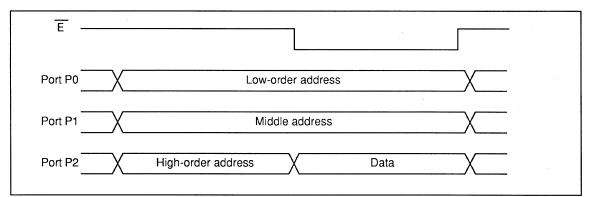

Figure 2.2.3 shows the operating waveforms of the bus interface unit in memory expansion mode or microprocessor mode. The M37700 BIU always operates at one of the waveforms shown in Figure 2.2.3. The meaning of signals ALE and  $\overline{E}$  in Figure 2.2.3 are as follows:

• ALE (Address Latch Enable)

Signal used to latch only address signals from multiplexed signals containing data and address.

• E

Signal set to "L" level when the bus interface unit reads instruction code or data from memory or when it writes data to memory. Table 2.2.2 shows the bus status according to  $\overline{\mathsf{E}}$  and  $\mathsf{R}/\overline{\mathsf{W}}$  signals.

| Table : | 2.2.2 | Bus | Status | According | to | E and | R/W |

|---------|-------|-----|--------|-----------|----|-------|-----|

|---------|-------|-----|--------|-----------|----|-------|-----|

| Ē | R/W | Bus Status |

|---|-----|------------|

| Н | Н   | Not used   |

| Н | L   | Not used   |

| L | Н   | Read       |

| L | L   | Write      |

#### (1)Basic operation

Waveform (a) is the bus interface operating waveform under the following conditions:

- When a one byte internal/external memory is accessed.

- When two bytes in internal memory are accessed together (starting on an even address).

- When two bytes in external memory are accessed together (starting on an even address when the BYTE pin is at "L" level).

Waveform (b) is the bus interface operating waveform when accessing in byte unit under the following conditions:

When two bytes in internal/external memory are accessed together (starting on an odd address).

• When two bytes in external memory are accessed together with the BYTE pin at "H" level.

As obtaining the instruction code from memory into the instruction queue buffer, waveform (a) is only used.

Waveforms (a) and (b) are the basic operating waveforms of the BIU. Waveform (a) or (b) is always used when accessing the internal memory. However, signals other than  $\overline{E}$  cannot be observed in single-chip mode because the port P3 is used as a programmable I/O port.

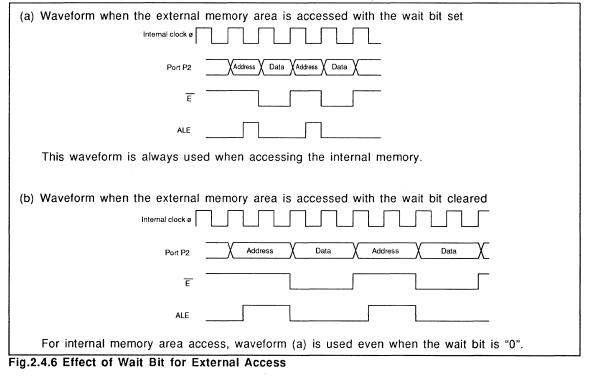

#### (2)Effect of the wait bit

When accessing the external memory area, the BIU operating waveform changes according to the wait bit.

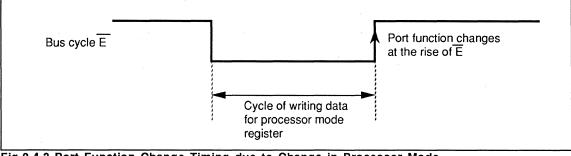

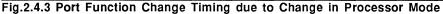

With the M37700, the external memory access time can be doubled (signal  $\overline{E}$  is doubled) by clearing the wait bit (bit 2) in the processor mode register (005E<sub>16</sub>). This enables external expansion of slow memories and peripheral LSIs.

Note : Internal memory access is not affected by the wait bit.

Figure 2.2.3 (c) to (f) show the effect of the wait bit on waveforms (a) and (b). Waveform (c) is the waveform when an external memory area is accessed under the conditions for waveform (a) with the wait bit cleared.

Waveforms (d) to (f) are the waveforms when an external memory area is accessed under the conditions for waveform (b) with the wait bit cleared. The entire waveform is affected by the wait bit for waveform (d) and the first half or the last half is affected respectively for waveforms (e) and (f).

#### 2.2.4 Data read/write operations

#### (1)Instruction code read

The CPU reads instructions codes from the instruction queue buffer of the BIU and executes them. The CPU notifies the BIU that an instruction code is needed during the instruction code fetch cycle. At this point, the operation depends on whether the instruction queue buffer contains an instruction code or not. If there is an instruction code in the instruction queue buffer, it is passed to the CPU. If there is no instruction code in the instruction queue buffer, or if the amount of data in the instruction queue buffer is less than the necessary instruction code, the BIU halts the CPU until a sufficient amount of instruction codes is stored in the instruction queue buffer.

Even when there is no request for instruction code from the CPU, if the instruction queue buffer is empty or if there is only one instruction code and the bus is available at the next cycle (the CPU does not use the bus at the next cycle), the BIU reads instruction codes from memory and stores them in the instruction queue buffer (instruction prefetch). During instruction prefetch, if the first address accessed when reading an instruction code from memory is even, then the data at the next odd number address is also read and stored in the instruction queue buffer. If the first accessed address is odd, only one byte is read and stored in the instruction queue buffer. However, if the instruction code is read from external memory with the BYTE pin at "H" (external bus width 8-bits) in memory expansion or microprocessor mode, only one byte is read regardless of the accessed address.

Instruction code read is performed with operation (a) or (c) shown in Figure 2.2.3. When a branch or a jump or subroutine call instruction or an interrupt is executed, the content of the instruction queue buffer is cleared and a new instruction code is read from the new address.

#### (2)Data read/write

The CPU reads and writes data from/to the BIU data buffer. The CPU issues a request to BIU when it attempts to read or write data. At this point, if the BIU is using the bus or if there is a higher priority request, the CPU is made to wait until the BIU becomes ready. When the bus is available for data read or write, the BIU operates at one of the waveforms (a) to (f) shown in Figure 2.2.3.

Data Read

When the CPU requests data from the BIU, it waits until the data is became complete data in the data buffer. The BIU sends the address received from the CPU on the address bus, reads the content of memory when  $\overline{E}$  is "L", and stores it in the data buffer.

#### Data Write

The CPU sends address data (address at which the data is written) and data to BIU.

The address data is written in the BIU data address register and the data is written in the data buffer. The actual writing in memory is performed by BIU and the CPU can proceed to the next step without waiting for the BIU to complete writing data in memory. The BIU sends the address data it received from the CPU to the address bus, sends the contents of the data buffer to the data bus, and writes it to memory when  $\overline{E}$  is "L".

#### 2.3 Addressable memory space

The M37700 allocates all ROM, RAM, I/O, and various control registers in the same memory space. Therefore, data transfer and operation can be performed with the same instruction without distinguishing memory and I/O area.

The M37700 program counter (PC) consists of 16 bits. It is used together with an 8-bit program bank register (PG) to directly address a 16M-byte address space from 016 to FFFFF16.

#### 2.3.1 Banks

The M37700 address space is divided into 64K byte blocks called banks. The Series MELPS 7700 can access 256 banks from bank 0 to bank 255 (FF16) in memory expansion or microprocessor mode.

The high order 8 bits of the 24-bit address indicate the bank and the content of the program bank register (PG) or the data bank register (DT) indicates the bank to be used.

If the program counter overflows at a bank boundary, the content of the program bank register is incremented by 1. If a borrow occurs in the program counter register, the content of the program bank register is decremented by 1. Therefore, programs can be written without considering the bank boundaries. The banks can be accessed efficiently by using an addressing mode that uses the data bank register.

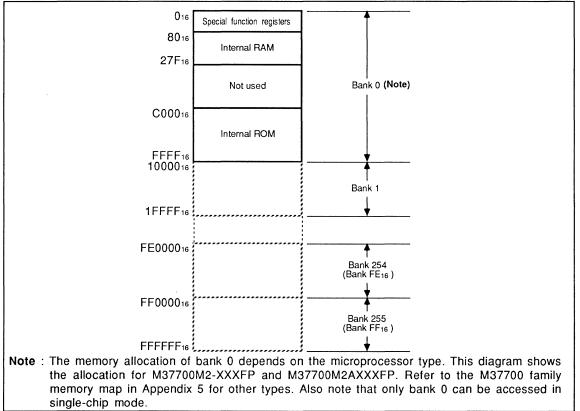

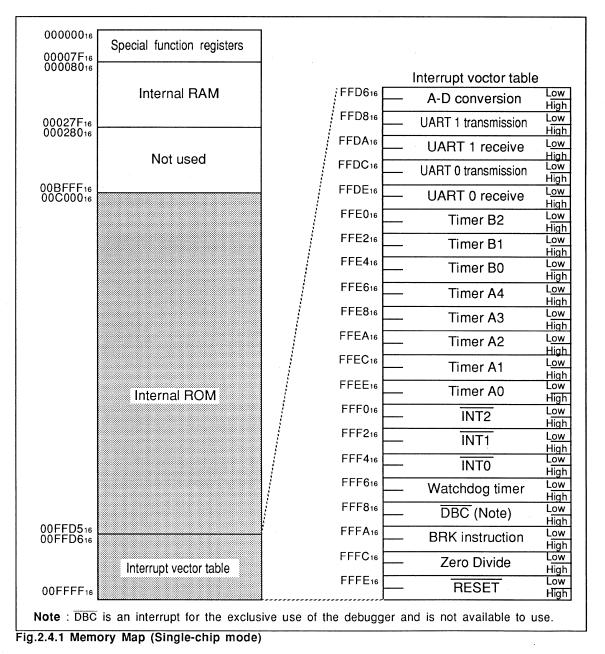

Bank 0 (addresses 0<sub>16</sub> to FFF<sub>16</sub>) contains the internal ROM, internal RAM, and internal I/O control registers.

Note : In single-chip mode, only bank 0 can be accessed.

#### 2.3.2 Direct Page

By using the direct page register (DPR), bank 0 or a 256-byte space spanning across bank 0 and bank 1 can be accessed with fewer instruction cycles in direct page addressing mode. This area is referred to as the direct page and is normally used for frequently accessed information (see "Section 2.1.8 Direct Page Register").

#### Fig.2.3.1 Addressable Memory Space

# **CHAPTER 2.FUNCTIONAL DESCRIPTION**

#### 2.4 Memory Allocation

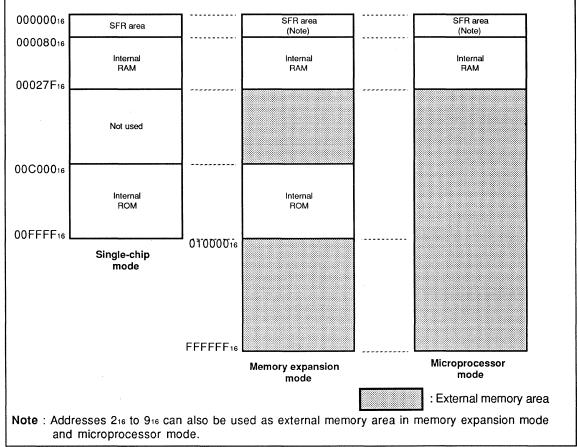

Figure 2.4.1 shows the memory map in single-chip mode. The allocated memory and I/O are described below.

#### 2.4.1 Internal memory and peripheral device memory allocation

#### (1)SFR area

Addresses 000016 to 007F16 of bank 0 are the SFR (Special Function Register) area. This area contains the control registers of internal peripheral devices, I/O ports, timers, and so on. Internal peripheral devices can be accessed through these registers. Figure 2.4.2 shows the memory map of the SFR area.

# 2.4 Memory Allocation

Address (Hexadecimal notation)

| aaress (He)                                                                                      | ,                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000000                                                                                           |                                                                                                                                                                                                                                                                                                                                                                               |

| 000001                                                                                           |                                                                                                                                                                                                                                                                                                                                                                               |

| 000002                                                                                           | Port P0 register                                                                                                                                                                                                                                                                                                                                                              |

| 000003                                                                                           | Port P1 register                                                                                                                                                                                                                                                                                                                                                              |

| 000004                                                                                           | Port P0 data direction register                                                                                                                                                                                                                                                                                                                                               |

| 000005                                                                                           | Port P1 data direction register                                                                                                                                                                                                                                                                                                                                               |

| 000006                                                                                           | Port P2 register                                                                                                                                                                                                                                                                                                                                                              |

| 000007                                                                                           | Port P3 register                                                                                                                                                                                                                                                                                                                                                              |

| 000008                                                                                           | Port P2 data direction register                                                                                                                                                                                                                                                                                                                                               |

| 000009                                                                                           | Port P3 data direction register                                                                                                                                                                                                                                                                                                                                               |

| 000003<br>00000A                                                                                 | Port P4 register                                                                                                                                                                                                                                                                                                                                                              |

| 00000A                                                                                           | Port P5 register                                                                                                                                                                                                                                                                                                                                                              |

| 00000B                                                                                           | Port P4 data direction register                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                  | Port P5 data direction register                                                                                                                                                                                                                                                                                                                                               |

| 00000D                                                                                           |                                                                                                                                                                                                                                                                                                                                                                               |

| 00000E                                                                                           | Port P6 register                                                                                                                                                                                                                                                                                                                                                              |

| 00000F                                                                                           | Port P7 register                                                                                                                                                                                                                                                                                                                                                              |

| 000010                                                                                           | Port P6 data direction register                                                                                                                                                                                                                                                                                                                                               |

| 000011                                                                                           | Port P7 data direction register                                                                                                                                                                                                                                                                                                                                               |

| 000012                                                                                           | Port P8 register                                                                                                                                                                                                                                                                                                                                                              |

| 000013                                                                                           |                                                                                                                                                                                                                                                                                                                                                                               |

| 000014                                                                                           | Port P8 data direction register                                                                                                                                                                                                                                                                                                                                               |

| 000015                                                                                           |                                                                                                                                                                                                                                                                                                                                                                               |

| 000016                                                                                           |                                                                                                                                                                                                                                                                                                                                                                               |

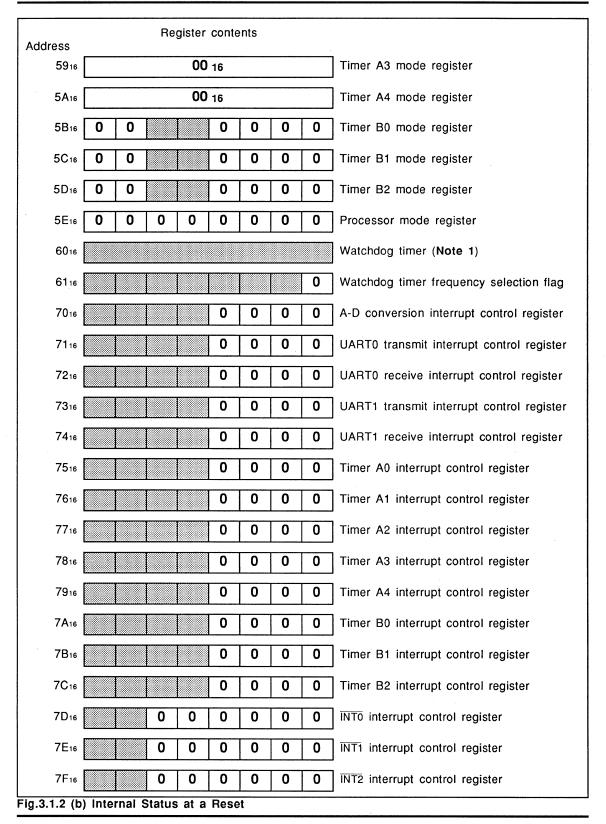

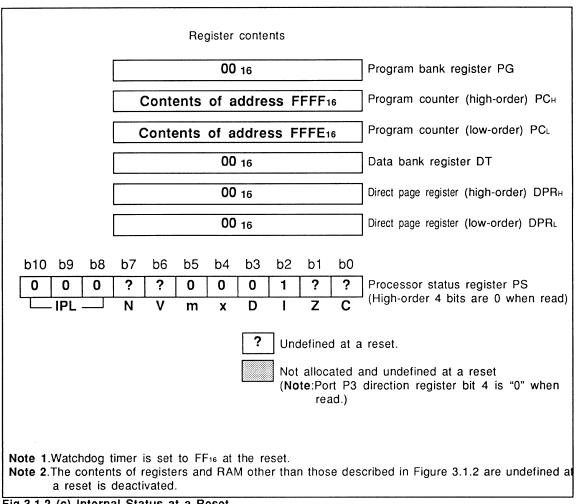

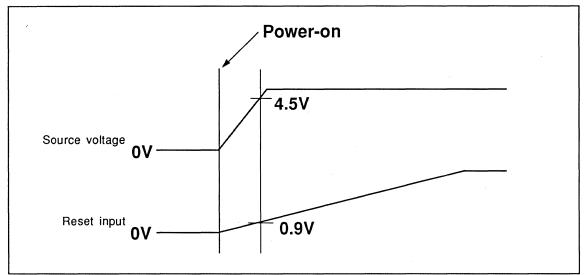

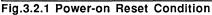

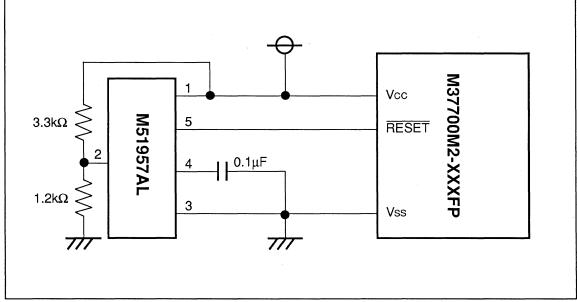

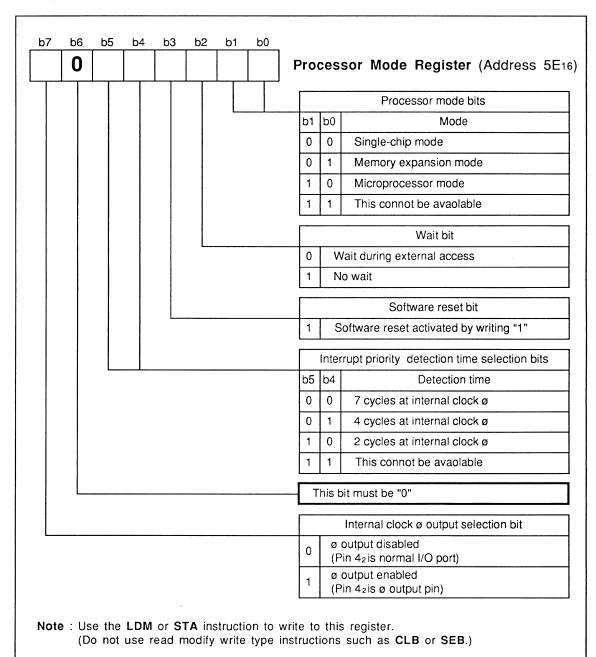

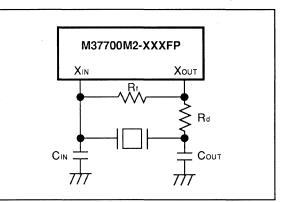

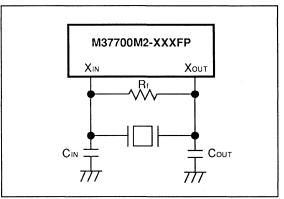

| 000017                                                                                           |                                                                                                                                                                                                                                                                                                                                                                               |