# Micro Linear

# **Applications Handbook**

#### **INTRODUCTION**

Micro Linear Corporation, headquartered in San Jose, California, designs, develops and markets high performance analog and mixed signal integrated circuits for a broad range of applications within the communications, computer and industrial markets. By combining its analog expertise with a unique development methodology, Micro Linear offers to its customers highly-integrated system-level solutions that add value and reduce systems costs.

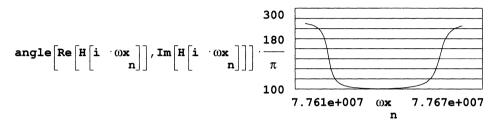

This applications handbook contains application notes and briefs based on standard products which are focused on the following application areas:

> Local Area Networks Telecommunications Hard Disk Drives Magnetic Tape Drives Magneto-Optical Drives Motor Controls Switch Mode Power Supplies DC to DC Converters Fluorescent Lamp Ballasts Data Acquisition Systems Bus Products pplication notes found in this b

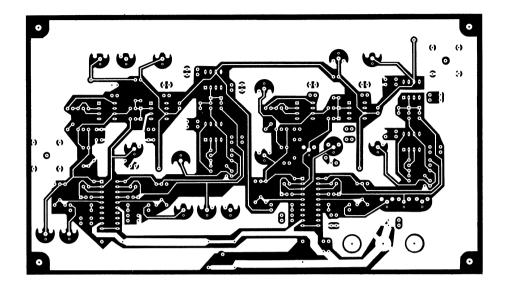

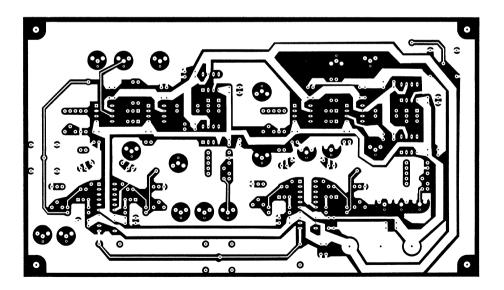

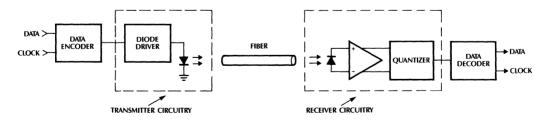

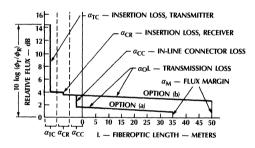

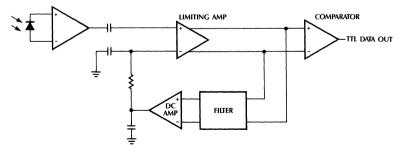

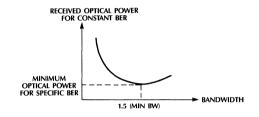

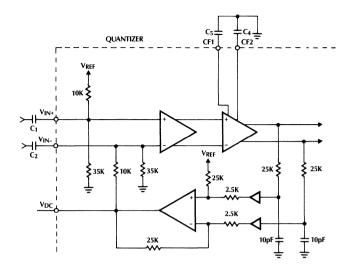

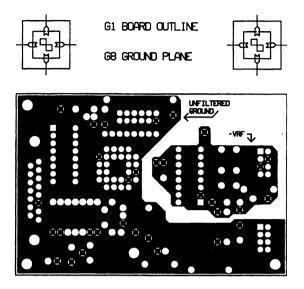

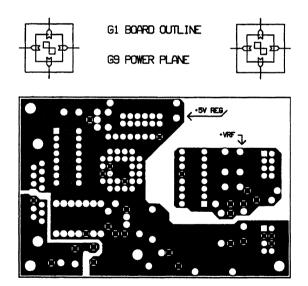

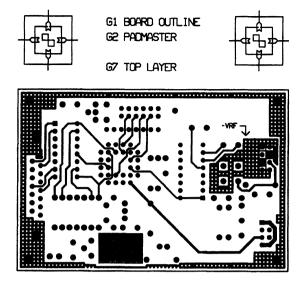

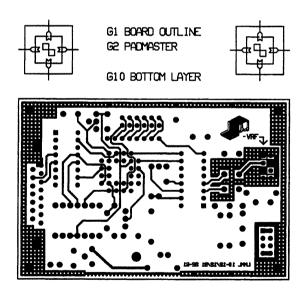

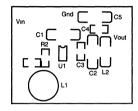

Most of the application notes found in this book are based on actual designs. These designs originated as evaluation kits for the specific parts. Micro Linear Corporation provides evaluation kits for most new devices to demonstrate the features of the part and speed up the evaluation of the part by customers. The kit includes a fully assembled PC board with all the necessary components, as well as a copy of the application note, parts list, and user guide with instructions on how to set up, use, and test the board. Gerber files are also included for guidance on the board layout to insure good performance of the circuit.

Kit descriptions are included in the data book as an "MLXXXXEVAL" part number. For example, the ML2223EVAL is an evaluation kit for the ML2223 12-bit plus sign serial A/D converter. A one page description of the evaluation kit can be found in the Micro Linear data book under the heading of ML2223EVAL in the table of contents. The kits are available directly from the factory or from a distributor for a nominal charge to our customers.

## Micro Linear Corporation Applications Handbook

Copyright © 1995

Micro Linear is a registered trademark of Micro Linear Corporation

#### LIFE SUPPORT POLICY

MICRO LINEAR'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF MICRO LINEAR CORPORATION. As used herein:

Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user. 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Micro Linear reserves the right to make changes at any time, without notice, to any of its products, specifications, processes, and suppliers. The application notes, schematic diagrams, printed circuit layouts and other information contained herein is provided as application aids only and are therefore provided "AS IS." MICRO LINEAR MAKES NO WARRANTIES WITH RESPECT TO THE INFORMATION CONTAINED HEREIN, EXPRESS, IMPLIED, STATUTORY OR OTHERWISE, AND MICRO LINEAR EXPRESSLY DISCLAIMS ANY IMPLIED WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS AND FITNESS FOR A PARTICULAR PURPOSE.

Micro Linear

## **Table of Contents**

#### PAGE

| Application Note 1 — FB3600 Digital Logic Design                                                                     | 1   |

|----------------------------------------------------------------------------------------------------------------------|-----|

| Application Note 2 — Trimming Analog Bipolar Arrays                                                                  | 8   |

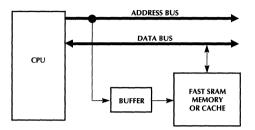

| Application Note 3 — Design Techniques for Low Input Bias Current                                                    | 11  |

| Application Note 4 — High Frequency Complex Filter Design Using the ML2111                                           | 13  |

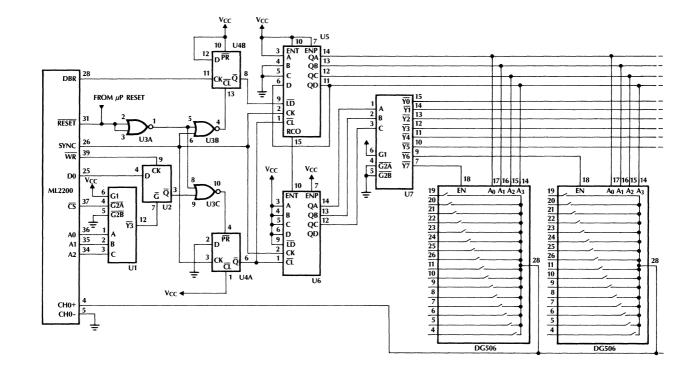

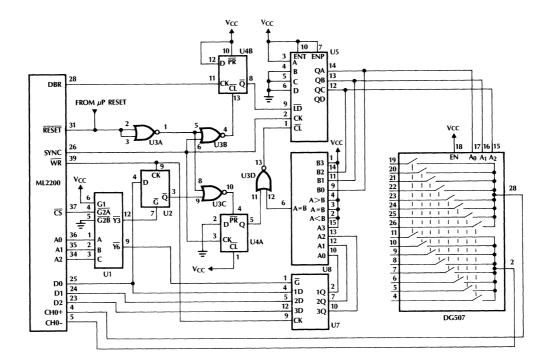

| Application Note 5 — ML2200, ML2208 Software Driver                                                                  | 33  |

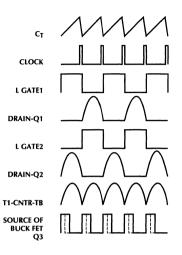

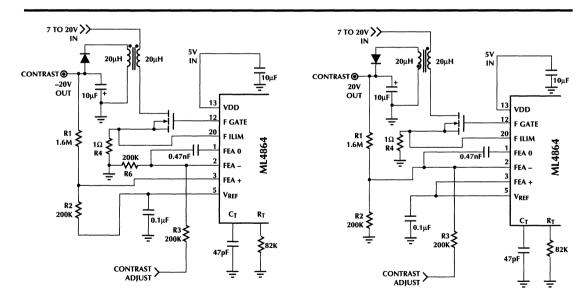

| Application Note 6 — Fiberoptics                                                                                     | 37  |

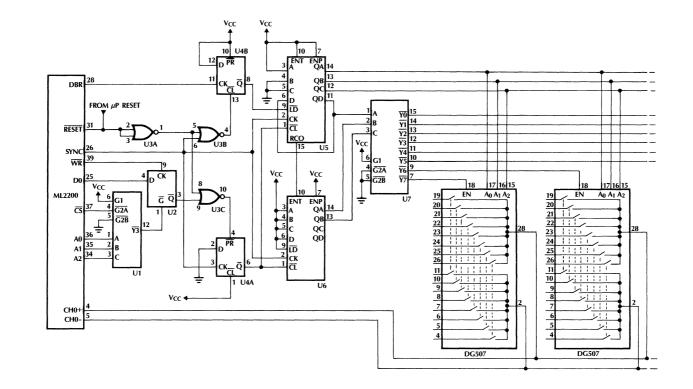

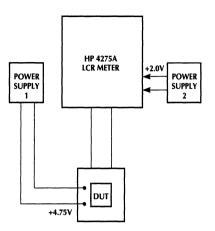

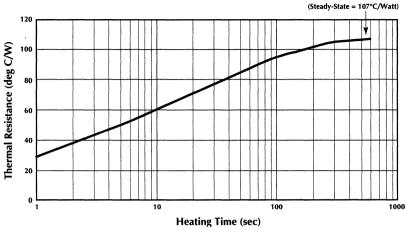

| Application Note 7 — Expanding the ML2200 Input Multiplexer                                                          | 47  |

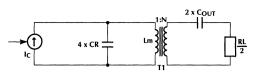

| Application Note 8 — Micro Linear's One Pin Crystal Ocillators                                                       | 52  |

| Application Note 10 — An Improved Method of Load Fault Detection                                                     | 75  |

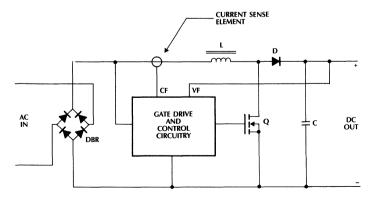

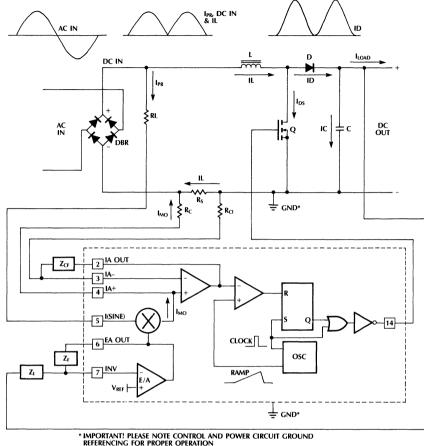

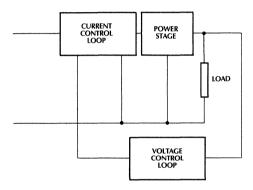

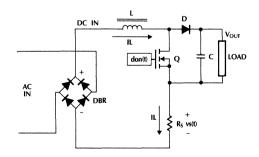

| Application Note 11 — Power Factor Enhancement Circuit                                                               | 77  |

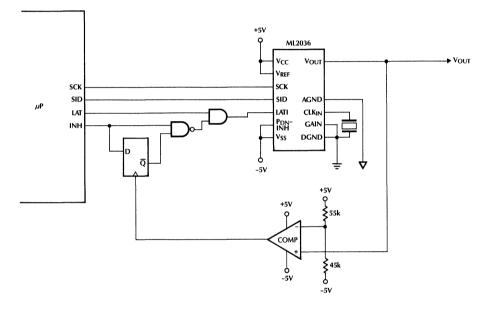

| Application Note 12 — Generating Phase Controlled Sinewaves with ML2036                                              | 79  |

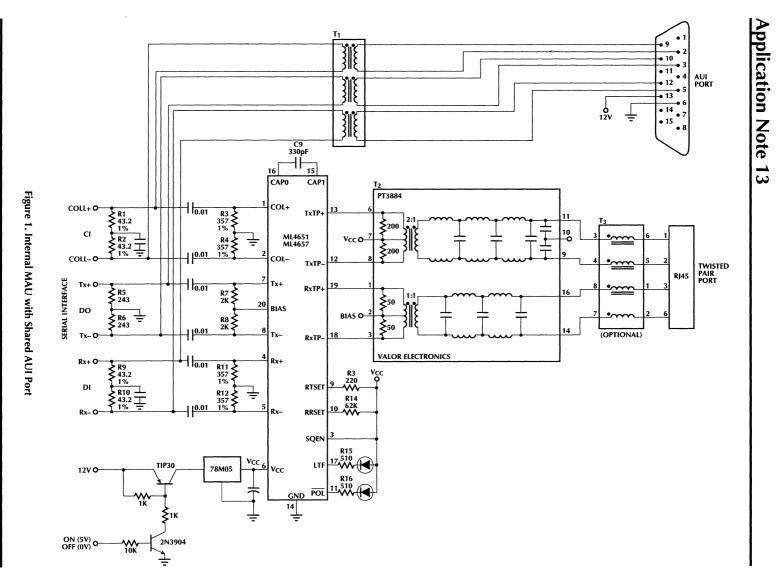

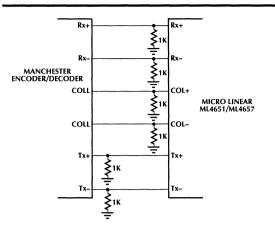

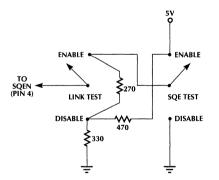

| Application Note 13 — Designing with 10BASE-T Transceivers                                                           | 81  |

| Application Note 14 — Generating Fixed Frequency Sinewaves with ML2035                                               | 84  |

| Application Note 15 — Designing an IEEE 802.3 10BASE-FL Transceiver                                                  | 86  |

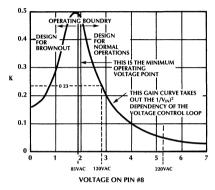

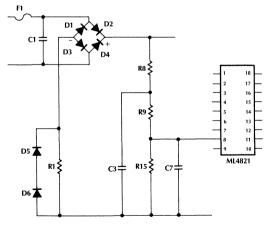

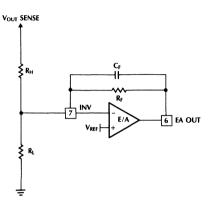

| Application Note 16 — Theory & Application of the ML4821                                                             | 102 |

| Application Note 17 — A Power Controller for Battery Powered Systems                                                 | 120 |

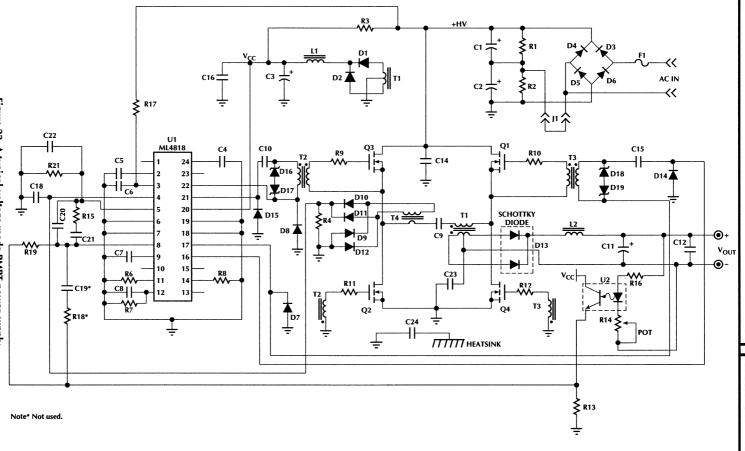

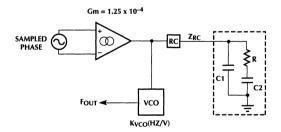

| Application Note 19 — Phase Modulated PWM Topology with the ML4818                                                   | 133 |

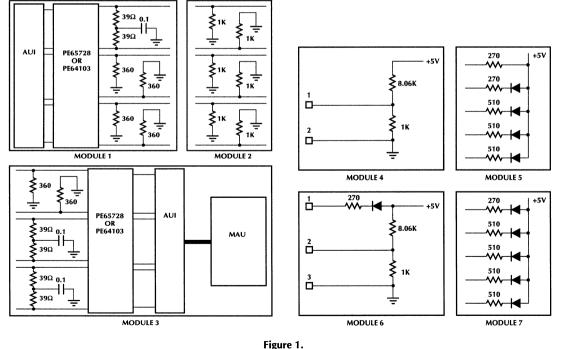

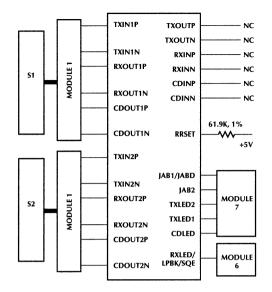

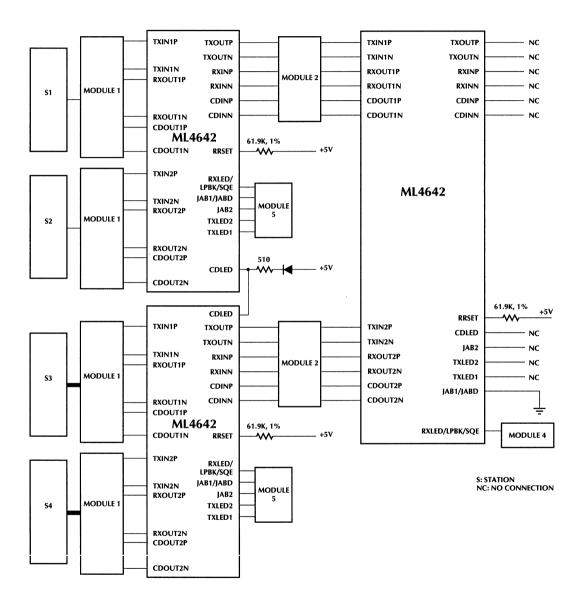

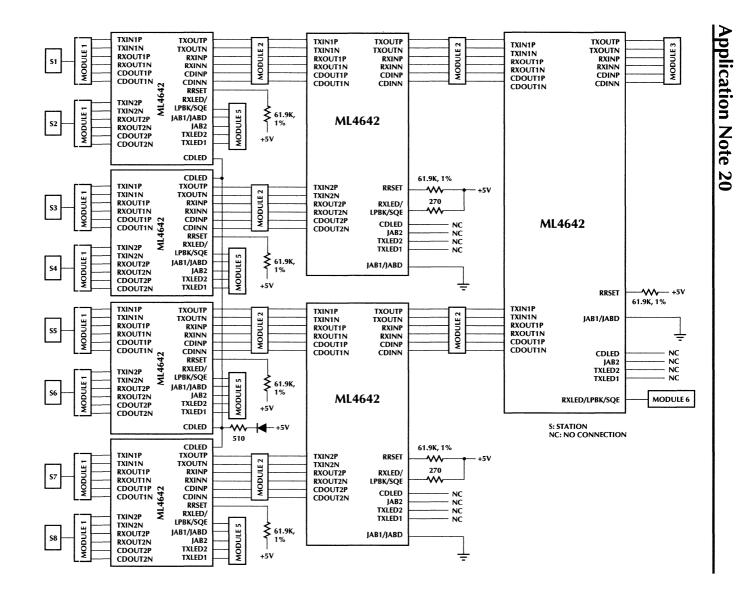

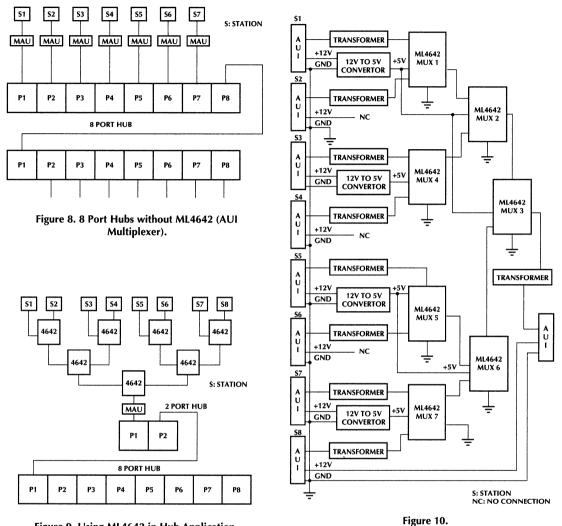

| Application Note 20 — ML4642 AUI Multiplexer                                                                         | 148 |

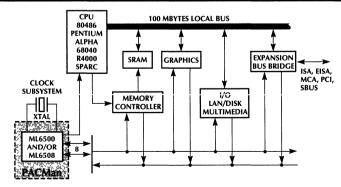

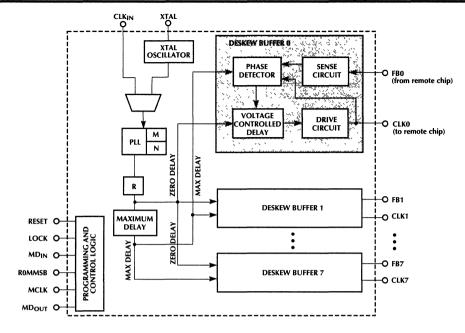

| Application Note 21 — High-Speed System Design with the ML6500 PACMan <sup>™</sup>                                   | 156 |

| Application Note 24 — Theory and Application of the ML4864 Backlight and<br>Contrast Controller IC                   | 170 |

| Application Note 25 — Active SCSI Terminator — Important Issues                                                      |     |

| Capacitance & Power Dissipation                                                                                      | 176 |

| Application Note 26 — Power Conversion Efficiencies for Miniature Fluorescent Lamp                                   | 180 |

| Application Note 27 — Active SCSI Termination for Higher Reliability<br>of Operation in Fast SCSI-2 and SCSI-3 Buses | 186 |

| Application Note 28 — Designing a 100MbP/s UTP Transceiver for Local Area Network                                    | 193 |

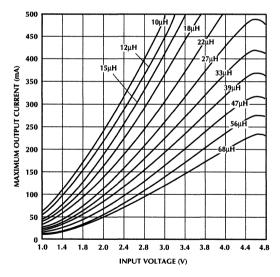

| Application Note 29 — Choosing an Inductor for your ML4861 Application                                               | 200 |

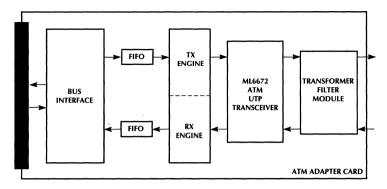

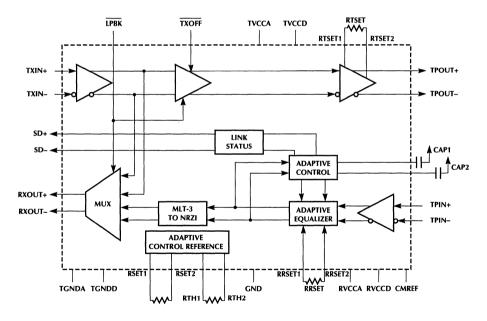

| Application Note 30 — ATM Applications Using the ML6672                                                              | 210 |

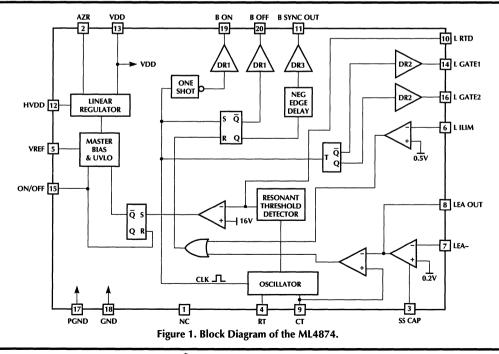

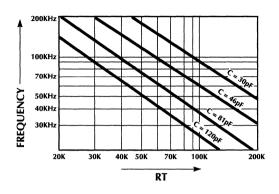

| Application Note 32 — Theory and Application of the ML4874<br>and ML4876 LCD Backlight Controller ICs                | 215 |

| Application Note 33 — ML4824 Combo Controller Applications                                                           | 226 |

| Application Note 34 — ML4824, A Novel Method for an Off-Line PFC-PWM<br>Combo Controller                             | 235 |

| Application Note 35 — Using the ML4411 BLDC Motor Controller                                                         |     |

|                                                                                                                      |     |

#### PAGE

| Application Note 37 — A Design Guide for the ML4873                                            | 260 |

|------------------------------------------------------------------------------------------------|-----|

| Application Note 38 — Applications Considerations and Circuits for the ML4861                  | 271 |

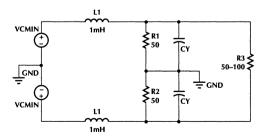

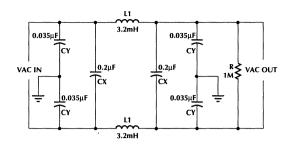

| Application Note 39 — Safety, EMI and RFI Considerations                                       | 276 |

| Application Note 40 — Low Cost Electronic Ballast System Design                                | 281 |

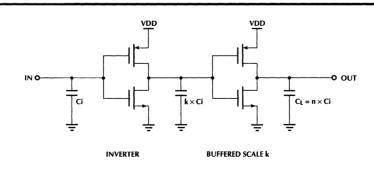

| Application Note 41 — 12-Bit Plus Sign A/D Converter with PC Compatible<br>Serial Interface    | 291 |

| Application Note 42 — ML6544, ML6545 and ML65541 Ultra Fast<br>Octal Buffer/Transceiver Family | 310 |

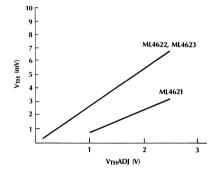

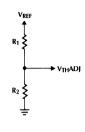

| Application Brief 1 — How to Set the Sensitivity of the ML4621, ML4622, ML4624                 | 325 |

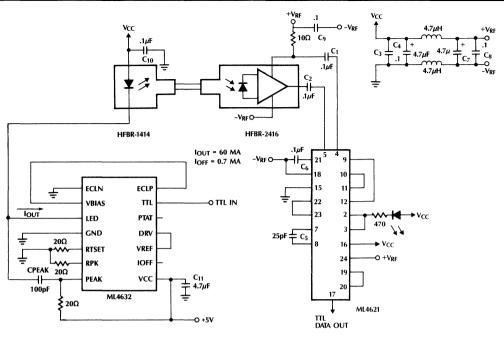

| Application Brief 2 — ML4632 Versus a Voltage Driven Output                                    | 327 |

## **Application Note 1**

FB3600 Digital Logic Design

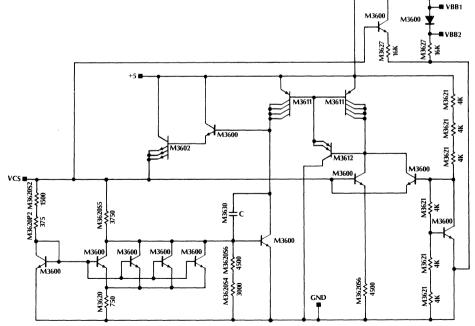

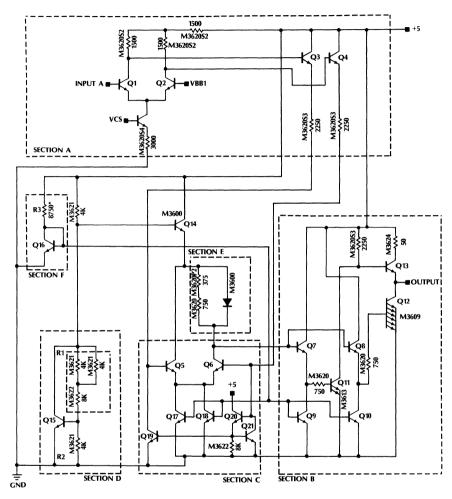

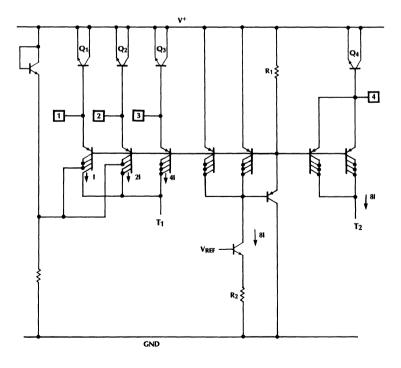

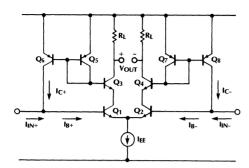

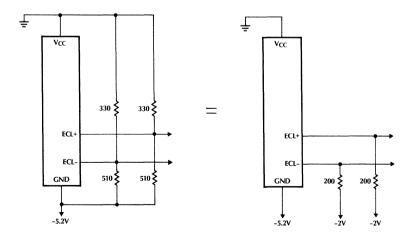

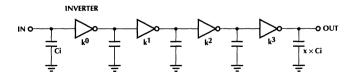

Micro Linear's Bipolar ASIC Technology allows the mixture of both analog and digital circuitry on an integrated circuit. Micro Linear has combined the advantages of TTL, and ECL logic on our FB3600 family of bipolar tile arrays. Our +5 volt version of ECL can interface to the outside world at standard TTL, CMOS or 10K ECL levels. It requires the use of only a standard +5 volt power supply. On-chip, gate propagation delay times as low as 2 nanoseconds are possible. High density ECL digital components occupy fifty percent of Micro Linear's FB3635 tile array. In addition, a certain amount of digital logic can be implemented on all of the FB3600 tile arrays.

Traditionally, 10K ECL logic uses -5.2 volts supply. This additional supply is only needed for applications requiring an external ECL logic interface. Our FB3635 and FB3621 tile arrays contain schottky components. These components are often useful for implementing high speed TTL & CMOS output drivers. On-chip ECL Logic requires a voltage reference which changes over temperature. Normally, on-chip voltage references are designed to be stable over variations in temperature. The schematic diagram for this circuit has been provided.

This application note has been designed to aid a design engineer using a workstation with Micro Linear's analog ASIC design libraries. The circuits provide basic building blocks which can be integrated on our FB3600 family of tile arrays. The circuitry and discussion provided in this application note provide a starting point for the design engineer's own workstation circuit design and simulations.

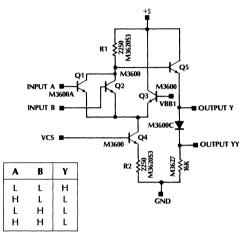

#### **Two Input ECL NOR Gate**

One of the major advantages of ECL logic is that the transistors never saturate. This plus the small signal swings reduce the propagation delay time through the gate. The propagation delay can be adjusted by changing the current level used by the circuit. The gate propagation delay decreases as the operating current level increases.

The ECL NOR gate, shown in figure 1, is designed for conventional +5 volt power supply operation. VCS is a preset bias voltage of 1.35 volts. This develops a voltage drop of 750mV across R2. The two ECL inputs (Input A & Input B) have a logic high (true) value of 4.25 volts and a logic low (false) value of 3.50 volts. VBB1 is a preset bias voltage which is about half way between the logic high and logic low voltages.

Micro Linear's single +5V operation is different from traditional 10K ECL logic which uses a single -5.2 volt supply. This establishes the 10K ECL logic high level in between -.810 and -.960 volts and a logic low level is in between -1.650 and -1.850 volts.

The NOR gate operates on the current flow from Q4. All the current from Q4 will be steered through either the Q3 leg or the Q1/Q2 leg of the circuit. If either Input A

Figure 1. NOR Gate

or Input B logic voltage is high, all the current will flow up the Q1/Q2 leg of the circuit. This occurs because either or both transistors (Q1, Q2) have an input voltage which is above Q3 input voltage. Current flowing up the Q1/Q2 leg will cause a 750mV voltage drop to occur across R1 (same resistance as R2). This also results in Output Y being set at 5 volts minus 750mV minus 750mV (Q5 base to emitter voltage drop). Thus, Output Y is set at a logic low level (3.05 volts).

Both inputs need to be logic low for Output Y to have a logic high result (4.4 volts). In this case, the voltages on both Q1 and Q2 bases are less than the voltage on the base of Q3. This will cause all the current from Q4 to flow up the Q3 leg. The base of Q5 will be about 5 volts since the voltage drop across R1 is close to zero.

It is important to note that R1 always equals R2 and that the voltage drops (typically 750mV) across the base emitter will change with temperature. Since all the transistors on this IC are about the same temperature, they and the ECL voltage references will all track together with temperature. Thus the ECL logic works well over variations in temperature. The absolute values of the voltages stated above will change slightly with temperature. The values of resistors R1, R2, and R3 are adjusted for the desired speed vs power tradeoffs. The values shown in the NOR gate (figure 1) are typical values.

Figure 1 also shows an Output YY terminal. Some ECL logic gates need to have an extra diode voltage drop for its output. We will call this the "bias level B" output/input. The Output Y terminal does not have this extra diode voltage drop. Thus, we will call this the "bias level A" output/input.

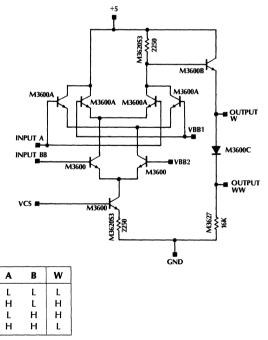

#### Two Input ECL NAND/AND Gate

The basic operation of this gate's differential pair and the two output stages is very similar to the NOR gate discussion. The NAND/AND gates input stage requires Input A to be a "bias level A" input and Input B to be a "bias level B" input. A "bias level A" input needs to be driven by a "bias level A" output. Similarly, a "bias level B" input needs to be driven by a "bias level B" output.

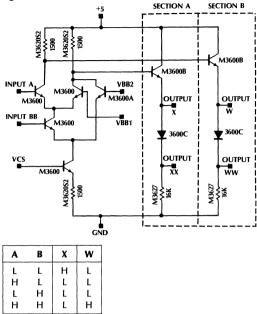

The NAND/AND gate shown in figure 2 has two output sections. The NAND output uses section A output stage. The AND output uses section B output stage. This gate can have either output stages omitted.

The NAND gate has its "bias level A" result on Output X and its "bias level B" output on Output XX. Similarly, the AND gate has its "bias level A" result on Output W and "bias level B" output on Output WW.

#### Two Input ECL XOR Gate

The basic operation of this gate's two differential pair and the output stages is very similar to the NAND/AND gate discussion. Figure 3 contains a circuit diagram for this gate. It uses one "bias level A" (Input A) input and one "bias level B" input (Input BB). The gates output is available as "bias level A" (Output W) and as "bias level B" (Output WW).

#### Figure 3. XOR Gate

#### Figure 2. NAND/AND Gate

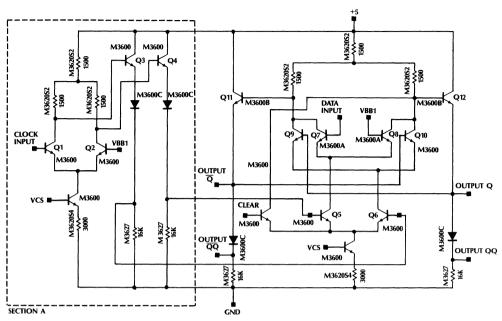

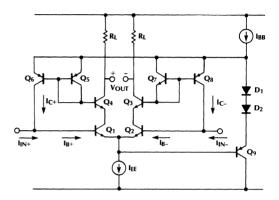

#### ECL Data Latch

The circuit diagram for a single bit ECL data latch is shown in figure 4. As long as the Clock Input is logic high, the data latch will pass the data from the Data Input through to the output. If the input data changes, the output will track the change. This is called the pass through mode of operation. The pass through mode will end as soon as the Clock Input signal changes to logic low. When this transition occurs, the current value of input data will latch. The data latch will remain fixed as long as the clock remains low. Should the Clock Input return to the high state, the data latch will return to the pass through mode of operation. The data latch is level triggered instead of edged triggered.

Both the Clock Input and the Data Input are "bias level A" inputs. The "bias level A" outputs are Q and  $\overline{Q}$ . The "bias level B" outputs are QQ and  $\overline{QQ}$ .

When the Clock Input is high, the current value of the Data Input will be present at the Q and QQ outputs. An inverted version of Data Input will be present at the  $\overline{Q}$  and  $\overline{QQ}$  outputs. When the Clock Input is low, the latched value of the previous Data Input will be present at the Q and QQ outputs.

The data latch circuit contains circuitry to adjust the Clock Input signal. The circuitry shown in section A contains a circuit for converting a "bias level A" logic input into two "bias level B" output signals. The two output signals reflect the input signal and a complement of the input signal.

The "bias level A" clock input signal drives the base of Q1. Transistor Q1 and Q2 form a different pair. The base of Q2 is driven by a reference voltage which is midway between logic high and logic low. When the Q1 input signal is high, the current will flow only through the Q1 leg of the differential pair. This will cause the collector of Q1 to have a voltage of about 4.25 volts and the collector of Q2 to have a voltage of about 5 volts. Substantial current will now flow through Q3. Thus, a "bias level A" logic low is present at the emitter of Q3. The diode in series with Q3 emitter shifts the output voltage to a "bias level B" output. This "bias level B" output will have a logic low value. Note that the Q3 outputs represent the complement of the Clock Input signal. Thus, a low Clock Input signal will result in a logic high output at the emitter of Q3.

A buffered version of the Clock Input signal is provided. This output will have the same logic level as the Clock Input signal. A "bias level A" version of the Clock Input signal is available at the emitter of Q4. The diode in series with Q4 emitter shifts the output voltage to a "bias level B" output.

The buffered Clock Input signal and its buffered complement will drive the bases of Q5 and Q6, respectively. When the data latch is in the data pass through mode (Clock Input high), transistor Q5 is turned on and transistor Q6 is turned off. If the Data Input is logic high, all of the current in the differential pair (Q7 & Q8) will flow in the Q7 leg. The current flow through the resistor in the Q7 leg will produce a 750mV drop. This sets the collector of Q7 at 4.25 volts. This will cause Q11 emitter to be at "bias level A" logic low (output  $\overline{Q}$ ). Output  $\overline{QQ}$  will be "bias level B" logic low. The lack of current flow in the Q8 leg will cause the collector of Q8 to be at about 5 volts. This will cause the emitter of Q12 to be logic high ("bias level A"). Output QQ will be at "bias level B" logic high.

When the Data Input is logic low, then all of the current will flow through the Q8 leg. Transistor Q11 emitter will now be at logic high. Output  $\overline{QQ}$  will be at "bias level B" logic high. Transistor Q12 emitter will now be at logic low and the output QQ will be at logic low.

The data latch will store the current state of the output when the Clock Input signal changes to logic low. This will cause transistor Q5 to turn off and transistor Q6 to turn on. The base of Q9 gets its input from output Q. The base of Q10 gets it's input from the output  $\overline{Q}$ . Since it takes a few nanoseconds for Q11 and Q12 to change state after the input data changes, the data latch is now getting its input data from the previous output data. This feedback loop causes the data latches output to remain fixed.

The data latch also contains a CLEAR input. This input should normally be logic low ("bias level B"). A logic high will reset the data latch to logic low. As long as the CLEAR input is logic high, the data latch will remain reset.

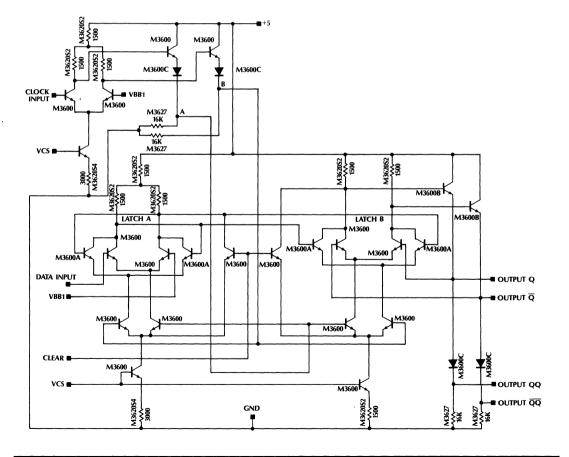

#### One Bit ECL Register or Flip Flop

The circuit shown in figure 5 can be used as a single bit positive edge triggered register or as a flip flop. We shall first review its operation as a one bit register. This circuit latches the Input Data upon the Clock Input changing from logic low to logic high. The data will remain latched until the next time the Clock Input changes from logic low to logic high. Similar to the data latch circuit, the Clock Input and Data Input signal are both "bias level A" inputs. The register has four outputs. The outputs are available in both "bias level A" (Q and  $\overline{Q}$ ) and "bias level B" (QQ and  $\overline{QQ}$ ). The register's stored value (Q and QQ) and its complement value ( $\overline{Q}$  and  $\overline{QQ}$ ) are also provided.

This circuit is simply two data latches in series. Both data latches use a common clock. When one latch is in the data pass through mode, the other latch is latched. When the Clock Input signal is high, data latch A is latched and data latch B is in the pass through mode. When the Clock Input signal is low, data latch A is in the data pass through mode and data latch B is latched. If the Clock Input signal

Figure 5. Register or Flip Flop

changes from low to high, latch A will latch its current input data and data latch B will pass data latch A output values directly to its output. This can change the data register's output. If the Clock Input signal changes from high to low, the output data will not change since latch B will latch itself using data provided by latch A previous outputs. Note that a flip flop can be implemented by connecting the register's Q output to the register's Data Input.

The register also contains a CLEAR input. This input should normally be logic low ("bias level B"). A logic high will reset the register to logic low. As long as the CLEAR input is logic high, the register will remain reset.

The Clock Input circuit has two "bias level B" outputs (point A and B). If these output connections are switched, the register will latch upon a logic high to low transition. This will cause it to be in pass through mode whenever the Clock Input is low. The data register will latch its data whenever the Clock Input is high.

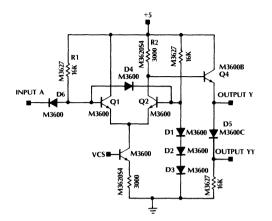

#### **TTL and CMOS Input Interface Circuit**

This circuit, shown in figure 6, converts a TTL or CMOS logic level input into an on-chip ECL level input. Output Y is a "bias level A" version of Input A. Output YY is a "bias level B" version of Input A. Transistors Q1 and Q2 forms a differential pair. The string of three diodes (D1, D2, and D3) sets the base of transistor Q2 at 2.25 volts. Given a high TTL/CMOS logic level drive at Input A, resistor R1 will bias the base of Q1 to be above the base Q2. This will cause all of the current to flow through the Q1 leg of the differential pair. Since the voltage drop across R2 will be about zero, the base of Q4 will be at 5 volts. The emitter of Q4 will be "bias level A" logic high. A "bias level B" version of this output will be produced at Output YY.

When Input A is driven by a TTL/CMOS low logic level, the base of Q1 will be biased below the base of Q2. Now all of the current will flow through the Q2 leg of the differential pair. The current flow will causes a 750mV voltage drop to occur across R2. The emitter of Q4 (Output Y) is now set at a "bias level A" logic low. Diode D5 produces a "bias level B" version of this output.

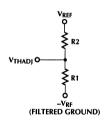

#### Voltage Reference for FB3600 ECL Logic

The circuit shown in figure 8 supplies the necessary reference voltages for our ECL logic. It has been designed to vary the output voltage with temperature. This block has been designed by Mirco Linear's engineering department as a standard function block to be included on all ECL logic designs.

#### Figure 8.

Figure 6. Input Interface

Micro Linear

#### **On-chip ECL to TTL or CMOS Output Interface**

The circuit shown in figure 7 takes an on-chip "bias level A" ECL input and produces a TTL/CMOS compatible output. If the input is logic high (true) then the output will be logic high (true). The circuit simply buffers and shifts the logic voltage level from on-chip ECL voltage levels to TTL/CMOS voltage levels.

Section A contains circuitry similar to the CLOCK input for the data latch circuit. It converts the input into two signals (buffered version and a complement buffered version). If the input is driven by a high logic level, Q1 will be turned on and Q2 will be turned off. This causes the base of Q3 to be 4.25 volts and the base of Q4 to be 5 volts. Transistors Q3 and Q4 drives the bases of Q5 and Q6 respectively. Since the base voltage of Q4 is greater than the base voltage of Q3, the base voltage of Q6 will be greater than the base voltage of Q5. This will cause all of the current in the Q5 & Q6 differential pair to flow in the Q6 leg. If Input A is driven by a logic low level, all of the Q5 leg.

The collector of Q6 drives the final output circuitry in section B. When Input A is at logic high, the collector of Q6 will be at .9 volts. The voltage drop across the base and emitter (.75 volts) of Q7 and Q8 will result in the bases of Q11 and Q12 being driven by less than .2 volts. Transistors Q11 and Q12 will be switched off. Since Q11 is off, the base of Q13 will be close to 5 volts. This turns Q13 on and results in a voltage of about 4.2 volts at the Output.

If Input A is at logic low, the collector of Q6 will be at 1.5 volts. The voltage drop across the base and emitter of Q7 and Q8 will result in the bases of Q11 and Q12 being driven by about .9 volts. This will turn on Q11 and Q12. With Q11 turned on, Q13 will be turned off and Q12 will be switched on. The output voltage will be about .75 volts.

We have just reviewed how section A circuitry drives the differential pair of Q5 & Q6. We have also reviewed how the collector of Q6 drives the output drive circuitry contained in section B. Next, we will examine how the Q5 & Q6 differential pair have been biased.

Section D contains a circuit known as a base emitter voltage multiplier. The voltage at the collector of Q15 will be determined by the following equation,

Voltage at collector of Q15 =  $[1 + (R1/R2)] \times .75$

The value of R1 and R2 is  $10K\Omega$  and  $4K\Omega$  respectively. The .75 represents the typical voltage drop across a transistors base to emitter. This sets voltage at the collector of Q15 at 2.6 volts. The voltage drop across the base and emitter of Q14 will set the collector voltage of Q5 at 2.6 - .75 = 1.85 volts.

When all of the current flows in the Q5 leg of the differential pair (Q5 & Q6), there will not be a voltage drop across the circuitry in section E (no current flow). The collector of Q6 is now set at 1.85 volts. If all of the current flows in the Q6 leg of the differential pair, there will be a .75 voltage drop across the diode. This sets the collector of Q6 at 1.1 volts.

The circuitry in section F provides a bias current for a current mirror. Resistor R3 value was chosen for a .5mA current flow with a 4.4 voltage drop across it. This input bias current generates the base to emitter voltage for Q16 which drives the bases of Q17, Q18, Q9 and Q10. Each of these transistors will sink .5mA.

Transistors Q19, Q21 and Q20 also form a current mirror. Transistor Q20 and its 8K emitter resistor have been added for stability. The purpose of the current mirror is to keep the curent flowing through Q3 and Q4 approximately equal.

Transistors Q11 and Q12 are schottky clamped transistors. They consist of a npn transistor with a schottky diode connected between the base and the collector. The function of this diode is to limit the current flowing into the base. This prevents the transistor from saturating. The schottky diode sends the excess base current into the collector. This limits the voltage drop across the collector and the emitter to about 200mV. The typical base emitter voltage drop is .75 volts. These devices can be replaced with regular npn transistors if the logic's switching rates are low (a few MHz). Saturated transistors have much slower switching times than non saturated transistors.

#### Voltage Reference for FB3600 ECL Logic

The circuit shown in figure 8 supplies the necessary reference voltages for our ECL logic. It has been designed to vary the output voltage with temperature. This block has been designed by Mirco Linear's engineering department as a standard function block to be included on all ECL logic designs.

#### Figure 7. Output Interface

\* BUILD UP OUT OF M3620s

Micro Linear

## Micro Linear

## **Application Note 2**

## **Trimming Analog Bipolar Arrays**

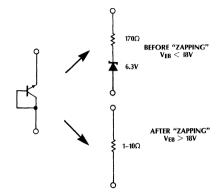

High performance analog integrated circuits are becoming a necessity in the design of state of the art analog/digital systems. With standard analog IC's this requires the designer to specify premium performance parts. These same premium performance circuit functions are not typically available in semicustom arrays. By utilizing trimming techniques, though, improved performance can still be obtained. Trimming analog bipolar arrays is a very viable, cost effective approach for improving the key parameters of a circuit.

If tighter specifications are required than can be obtained using good design techniques the circuit may be trimmed at the wafer level by a technique of selectively shorting zener diodes. This is known commonly as zener zapping. This technique can be used to trim the input offset voltage of an op amp or the output voltage of a precision reference. For example, the offset voltage of our MLC350<sup>(1)</sup> operational amplifier can be trimmed from a maximum of 7mV to less than 1mV. The MLC340 voltage reference can be trimmed to an accuracy of better than 1%. Many types of parameters may be trimmed within the limitations of the technique as described below.

Although there are other ways in which a bipolar integrated circuit may be trimmed, zener zapping has become well established because it does not require extra processing steps and can be implemented at the wafer level. Unlike laser trimming, the technique is not limited to altering a resistive element, and does not require a large capital investment. Fusible links, another wellestablished method, requires currents in the ampere range in order to blow the standard 1 micron thick aluminum, resulting in a questionable blown connection. A thinner link would require additional wafer processing steps.

#### The Zener Zapping Technique

This process is called zener zapping because the emitterbase diode of a bipolar transistor is permanently shorted by passing a relatively large current through it while in the reverse breakdown avalanche mode. It produces a reliable 1-10 ohm link between the emitter and base pads. (See Fig. 1) This is a very reliable connection because of the double short which actually occurs. The first short is caused by the destruction of the pn junction. In addition, the presence of a large electric field during thermal runaway causes metal to migrate across the silicon surface beneath the oxide layer, producing a second short.

This set of events occurs when the voltage across the emitter-base junction is increased beyond the 6.3V

Figure 1.

avalanche breakdown point, to above 18V. At about 18V the instantaneous power dissipation exceeds 1.2W (figure 2) and an oscillatory, thermal runaway condition occurs. In less than a second the junction is destroyed leaving a 1-10 ohm short. The current required is less than 300mA, so remote probe pads (the bonding pads) can be used without damage to the pads or traces.

Power Dissipation = iV = (69mA)(18V) = 1.24W

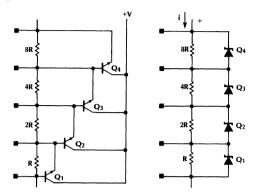

The circuit in figure 3 illustrates a simple implementation of this technique to alter the total resistance of a circuit path. Before any of the zeners are blown the total resistance equals 15R. This value can be altered to equal any integer multiple of R from 1R to 15R by selectively blowing only four zeners in a binary fashion. This is possible due to the binary arrangement of the resistor values. For example, to obtain a resistance of 5R, Q<sub>2</sub> and Q<sub>4</sub> should be shorted resulting in 4R + 1R = 5R. Note that 5 equals 0101 in binary which is represented by Q<sub>4</sub>, Q<sub>3</sub>, Q<sub>2</sub>, Q<sub>1</sub> with shorts being 0's and opens being 1's. Figure 3.

This type of circuit arrangement has two restrictions of which the designer should be aware. During normal operation of the circuit, the current through the resistor string should not be allowed to flow opposite to the direction indicated in the drawing. This would forward bias the base-emitter junction of the transistors, and effectively short out a resistor intended to be used. In

#### Figure 4a.

addition, the forward voltage drop across each of the resistors should not exceed the zener breakdown voltage, about 6.3V. This would allow current to flow out of the resistor string and through the zener, altering the intended operation of the circuit.

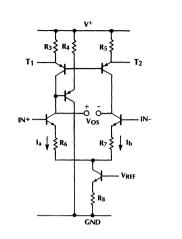

The preceding example illustrates the use of zener zapping to alter a resistive element in a circuit. In many cases modifying a current source is a more useful way of trimming a design. Figure 4a shows trimmable current sources used to reduce the input offset voltage of an op amp.

In this example the balance of current in two circuit paths is altered using zener zapping. This technique is particularly useful for reducing the input offset voltage of an operational amplifier which has added emitter degeneration in the input stage in order to improve slew rate (figure 4b). The emitter resistors used in this circuit, R<sub>6</sub> and R<sub>7</sub>, will contribute significantly to the offset voltage of the input stage. By modifying the balance of current between  $I_A$  and  $I_B$  the increased offset voltage VOS can be compensated. In this example there are again 4 bits of trimming resolution with the 3 least significant bits controlling one current path and the most significant bit controlling the other. With this configuration the balance of current can be altered in either direction. In other words, the current in T1 can be increased or decreased relative to T<sub>2</sub>.

Figure 4b.

١

To increase the current through  $T_1$  relative to  $T_2$  you simply short  $Q_1$ ,  $Q_2$ , and  $Q_3$  in a binary fashion to get increments of 1 from 11 to 71. To increase the current through  $T_2$  relative to  $T_1$  you short  $Q_4$  which increase the current through  $T_2$  by 81. Then if you want less current, short  $Q_1$ ,  $Q_2$ , and  $Q_3$  in a binary fashion to offset the increase in  $T_2$  by increments of 1 down to 11.

The source of current in the trim circuit should be of the same type as the circuit to be trimmed so their temperature coefficients will match. In this case the V<sub>RFF</sub> in both circuits should be the same, and resistors R<sub>2</sub> and R<sub>8</sub> should be of the same type.

Shorting zeners is an irreversible process. Thus, it is important to check the results of a trim bit pattern before actually destroying the junctions. This is done by shorting the probe pads externally in the desired pattern through relays. In this way all combinations can be tried and the best results can be chosen and implemented.

Although these two examples both use 4 bits (4 zeners) to trim a circuit, any number can be used to get more or less resolution. The designer should be aware though of the practical limitations of each circuit to be trimmed. Other error terms like temperature coefficients will eventually become significant, and additional trimming beyond this point would be fruitless. In addition, the more zeners you use, the more probe pads are required. In a full custom circuit where minimum die size is the ultimate goal, the additional die area required for the diodes, pads and trim circuitry may become significant. An array, however, typically has unused components available for the trim circuitry, and you only have to be concerned with the number of bonding pads available. If all of the pads are already being used for pinouts then a larger array would be required.

These examples illustrate the usefulness and flexibility of zener zapping. There are many other potential applications for this technique though, and with a good understanding of the basic diode shorting process the design engineer can be creative in its application.

<sup>&</sup>lt;sup>(1)</sup> The MLC350 is one of the circuits in Micro Linear's library of macrocells. Performance details of this circuit and other macrocells can be found in the FB300 Macrocell and Component Library booklet.

## Micro Linear

## **Application Note 3**

### **Design Techniques for Low Input Bias Current**

Analog systems often require high impedance inputs to accommodate the demand for higher accuracy. Measurement systems which interface to photodetectors or high impedance transducers require devices with low offset voltage and low input bias current. This is necessary to receive and amplify the signal without introducing any significant errors. Under this constraint, the designer will often select a FET as the primary input device. Although a FET input stage may be appropriate in a discrete circuit design, there are other all bipolar techniques which are just as effective and better suited to an analog array. In some cases, these techniques will out perform the FET alternative.

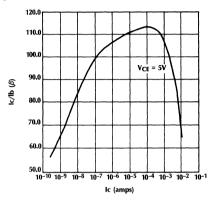

This application note describes three alternatives for obtaining low input bias currents. The design techniques described can be applied to many different types of circuits from simple emitter followers to complex amplifiers. For example, a typical all bipolar operational amplifier can achieve input bias currents of about 100nA with an offset voltages of about 1mV<sup>(1)</sup>. Unfortunately these characteristics are still not good enough for many of the applications previously mentioned. The input bias current can be minimized by using one of the following design techniques, 1) reducing the collector current 2) using a Darlington configuration 3) employing current cancellation techniques. This document will briefly describe the first two methods but will provide a detailed analysis of the cancellation technique as it provides the best performance trade-off and is the most involved.

#### **Reducing the Collector Current**

The simplest approach to achieve low input bias current is to reduce the collector current of the input transistors. Since the base current tracks the collector current by a factor of beta, reducing the collector current of the input transistors will reduce the input bias current into the bases. Beta will degrade at lower collector currents (figure 1), however, setting a practical limitation on this technique at about 50pA base current. If the circuit does not require a high slew rate or high gain bandwidth, this may be an acceptable method.

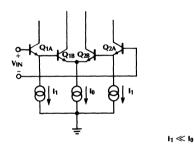

#### The Darlington Configuration

Figure 2 shows a differential Darlington configuration which will reduce the input bias requirements by a factor of beta. It will also double the offset voltage and reduce the voltage gain by 2. The offset voltage doubles due to the additional mismatching of the added devices, while the voltage gain suffers because only one-half of the input signal appears across the inner pair of transistors. A higher slew rate and gain bandwidth, though, can be achieved with this technique, over simply reducing the collector current, but it requires more components.

#### Figure 1. Current Gain vs. Collector Current

Figure 2.

#### The Cancellation Technique

An all bipolar solution to low input bias current with low offset voltage while maintaining high collector currents for noise, slew rate or bandwidth reasons requires a technique called Input Bias Current Cancellation.

Input bias current cancellation is a circuit design technique which measures the input current and forces an equivalent amount back into the input nodes (figure 3). Ideally, this results in perfect cancellation of the input current. In the circuit in figure 3, the base currents into  $Q_3$  and  $Q_4$  duplicate the base currents into  $Q_1$  and  $Q_2$ . These currents are then sensed by  $Q_5$  and  $Q_7$  and equivalent currents are fed back, via  $Q_6$  and  $Q_8$ , into the input nodes. The total current at each input is thus,

$I_{IN} = I_B - I_C$

Figure 3.

Assuming all PNP betas ( $\beta_P$ ) are equal, all NPN betas ( $\beta_N$ ) and all base-emitter voltage drops are equal,

$$I_{\rm C} = I_{\rm B} \frac{\beta_{\rm N}}{(1+\beta_{\rm N})} \frac{\beta_{\rm P}}{(2+\beta_{\rm P})}$$

$$I_{\rm IN} = I_{\rm B} \left(1 - \frac{\beta_{\rm N}}{(1+\beta_{\rm N})} \frac{\beta_{\rm P}}{(2+\beta_{\rm P})}\right)$$

If all betas are very high,

$$I_{\rm C} = I_{\rm B}$$

so

$I_{\rm IN} = 0$

The main contributor to cancellation errors in this circuit is the low beta of the PNP devices. This sets a practical limitation on this technique at about 5–10% of the uncanceled current, as shown by the following example.

Assumptions:  $\beta_N = 100$ ,  $\beta_P = 30$ ,  $I_B = 70$  nA

$$I_{IN} = 70 \left(1 - \frac{100}{1 + 100} \frac{30}{2 + 30}\right)$$

$$I_{IN} = 70 (.0718)$$

$$I_{IN} = 5nA$$

This technique does not reduce the input offset current. In fact, the additional circuitry, with its additional mismatches, increases the offset current by a factor of about 3. The input bias current can be reduced to about the same value as the offset current, setting the limitation on this technique at about 1–10nA.

In the equations above, the betas of PNPs in the current mirror were assumed to be equal. To enhance the viability of this assumption, the V<sub>CE</sub> of each PNP should be kept equal. With the cancellation circuitry tied to the positive supply the V<sub>CE</sub> of Q<sub>6</sub> and Q<sub>8</sub> will change with the input voltage, while the V<sub>CE</sub> of Q<sub>5</sub> and Q<sub>7</sub> will remain constant. This further aggravates any beta mismatch which already exists. To reduce this effect the circuit can be self-biased using current source I<sub>BB</sub>, diodes D<sub>1</sub> and D<sub>2</sub>, and transistor Q<sub>9</sub>, as shown in figure 4.

This circuit keeps the voltage across the cancellation circuitry fixed as the input common mode voltage changes, which in turn keeps the beta of each device constant.

These techniques for reducing input bias current demonstrate the reality of achieving levels sometimes thought only possible with JFETs or MOSFETs. Circuits being considered for analog array integration which contain discrete FETs or FET input op amps should not be categorized as not possible. Rather, each individual circuit should be analyzed for its critical parameters, keeping in mind the trade-offs described above. If none of the bipolar solutions is adequate an external FET can always be used as an input buffer.

<sup>&</sup>lt;sup>(1)</sup> The offset voltage can be reduced by making use of wafer trimming techniques. At Micro Linear a process called zener zapping is used. For more information about this process see the application note titled "Trimming Bipolar Arrays".

### **Application Note 4**

### **High Frequency Complex Filter Design** Using the ML2111

Charles Yager Carlos Laber

#### 1.0 Introduction

Switched capacitor filters have been growing in popularity because of their advantages over active filters. Switched capacitor filters don't require external precision capacitors like active filters. Their cutoff frequencies have a typical accuracy of  $\pm 0.3\%$ , and they are less sensitive to temperature changes. This allows consistent, repeatable filter designs. Another distinct advantage of switched capacitor filters is that their cutoff frequency can be adjusted by changing the clock frequency. Switched capacitor filters offer higher integration at a lower system cost.

Until the introduction of the ML2111, commercially available switched capacitor filters were limited to about 20 KHz center frequencies. The ML2111 uses the versatile architecture of the MF10 with enhanced performance to reach center frequencies of up to 150 KHz with Q values up to 20.

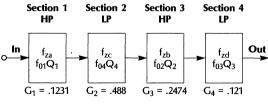

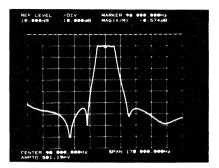

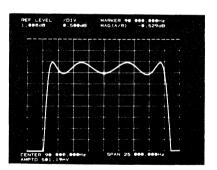

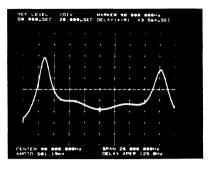

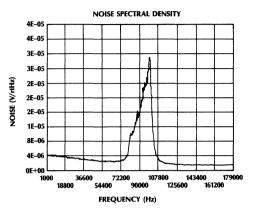

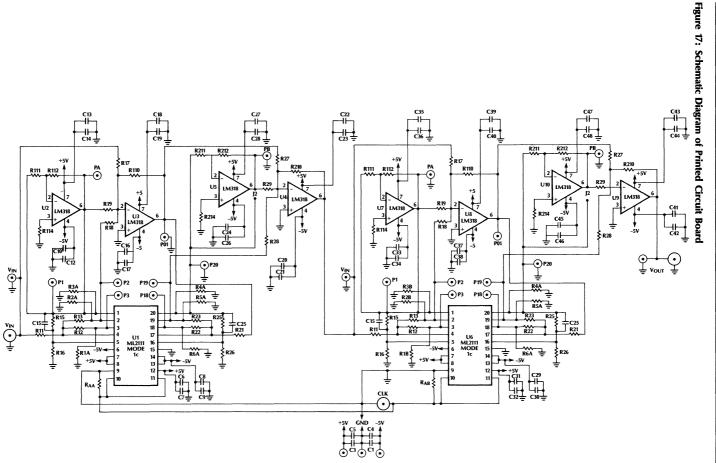

Designing high frequency, high order filters using the ML2111 is the main topic of this application note. Particular attention is focused on mode 1c, which has the advantage of operating at high frequencies while allowing the center frequency to clock ratio to vary based on external resistors. A flexible building block is introduced which implements all the necessary types of bi-quads to realize high order complex filters. Finally an example is given which illustrates the design of an eighth order Elliptic bandpass filter with a center frequency of 90 KHz and a passband from 81 KHz to 100 KHz.

The first part of the application note covers a variety of issues: layout, how fast the system clock can be changed for sweeping filters, and some differences between continuous and sampled data filters. For the reader who is already familiar with sampled data filters, section 2 on Effects of Sampling, Aperature, Aliasing, and Signal Reconstruction may be skipped.

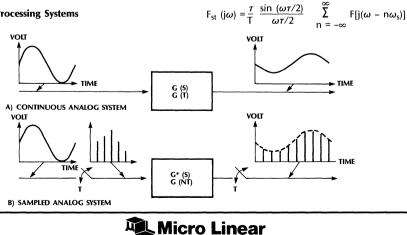

#### 2.0 Effects of Sampling

Since the ML2111 is a switched capacitor filter, it behaves as a sampled data system. Switched capacitor filters, as opposed to digital filters, are analog sampled data systems. The signal remains in the analog domain, as the charge on a capacitor. Whether using an analog or digital sampled data system, the effects of sampling the signal must be considered.

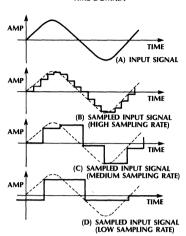

Figure 1 shows a time domain input and output signal of an analog sampled data system. In the ideal case, the sampled data system, samples the input signal instantaneously, or with an impulse function. The amplitude of each sample is equal to the instantaneous amplitude of the input signal. The output is a series of narrow pulses, each separated by time T, the sampling period.

#### 2.1 Aperture

Since an impulse function in the time domain corresponds to a flat spectrum in the frequency domain, the input spectrum is exactly reproduced in the frequency domain, however, in reality the sampling signal is periodic and has a finite pulse width. When convoluting a finite pulse width with an input spectrum  $F(i\omega)$  with unity amplitude, the result is found to be:

Figure 1: Signal Processing Systems

(1)

#### Figure 2: Analysis of a Sampled Signal

From this equation, the gain is a continuous function of frequency defined by  $(\tau/T)$  (sin  $(\omega\tau/2)/(\omega\tau/2)$ ) where  $\tau$  is the sample pulse width in seconds, T is the sample period in seconds, and  $\omega$  the frequency in radians per second.

The time and frequency domain plots for the finite pulse width sampled signal are shown in figure 2. Figure 2 is a plot of the previous equations where the frequency spectrum is formed around multiples of the sampling frequency. As long as the adjacent spectra do not overlay (aliasing distortion), the continuous signal can be reconstructed from the discrete samples.

To evaluate the amplitude distortion caused by having a finite pulse width, one can simply solve equation 1. Since the ML2111 has a zero-order hold  $\tau/T$  is unity. Assuming a 7.5 MHz sampling frequency and a bandwidth of 150 KHz, the amplitude distortion or attenuation is 5.7 × 10<sup>-3</sup> dB.

The equation shows that when the sampling frequency is 40-50 times greater than the bandwidth, the aperture effects are negligible.

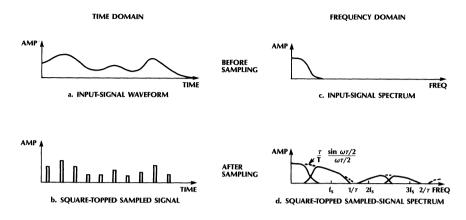

#### 2.2 Aliasing

Another potential source for distortion in a sampled data system is aliasing. Aliasing distortion occurs when the input frequency to a sampled data system contains frequency components above one half the sampling frequency. These higher frequency components beat with the sampling frequency and are reflected back into the baseband causing aliasing distortion.

The additional spectral components caused by sampling the input signal are the sum and differences of the input frequencies with multiples of the sampling frequency. For example, assume the input to a sampled data system is a sine wave with a frequency of 100 KHz ( $f_1$ ) sampled at 250 KHz ( $f_2$ ), as shown in figure 3a. The first few spectral components will be at: ( $f_i = 100$  KHz; original signal,  $f_s - f_i = 150$  KHz,  $f_s + f_i = 350$  KHz,  $2f_s - f_i = 400$  KHz,  $2f_s + f_i = 600$  KHz, . . .) Now assume  $f_i$  has a second harmonic, which would be at 200 KHz, the spectral components are shown in figure 3b. If our bandwidth of interest were from DC to  $f_s/2$ , then the  $f_s - 2f_i$ component interferes with the original signal. If we were to reconstruct the original signal by lowpass filtering it, we could not separate the aliased component,  $f_s - 2f_i = 50$ KHz, from the original signal.

If our bandwidth of interest is a bandpass, the aliased component may not interfere. For example, if the ML2111 were to be used as a four pole bandpass filter with a center frequency at 100 KHz and a Q = 10 as shown in figure 3c, then the aliasing components in the above example would be filtered out as shown in figure 3d. But if the ML2111 were to be used as a low pass filter, then the f<sub>s</sub> – 2f<sub>1</sub> aliased component would not be filtered out by the ML2111, and an anti-aliasing filter would be needed.

If the input signal is not band-limited, and the aliasing components fall within the bandwidth of interest, then a lowpass filter or anti-aliasing filter must be placed in front of the ML2111. This filter must be a continuous filter rather than a sampled data filter, however, the complexity of this filter is typically much less than the ML2111 filters, and its frequency response is less critical allowing for relaxed component tolerances.

Since no frequency component can be totally eliminated, one must determine the acceptable amplitude of the aliasing components that will *not* impact the Signal to Noise ratio of the system.

The higher the ratio of sampling frequency to input bandwidth, the lower the requirements on the antialiasing filter. Figure 4 shows the effects of sampling rate

rate on the separation of sampled signal spectra. Note the amount of overlap increases as the sampling frequency is decreased for a fixed input signal bandwidth. In general, the higher the sampling frequency, the less aliasing distortion. Since the ML2111's sampling frequency is typically either 50 or 100 times greater than the input bandwidth, the aliasing distortion may be negligible.

#### 2.3 Signal to Noise Ratio and Aliasing Distortion

To determine whether aliasing distortion could be a problem, one must first determine the Signal to Noise Ratio of the overall system. Aliasing distortion less than the signal to noise ratio is of no concern.

The data sheet specifies noise based on Q and bandwidth. From these specs one can deduce the S/N ratio of one bi-quad in the ML2111. Using a simplified example, a bandpass filter with a Q = 10 and a system clock to center frequency ratio of 50:1 has noise that is 262  $\mu$ Vrms over a 750 KHz bandwidth; taken from the specs in the data sheet. To determine the maximum input signal amplitude, one must consider the slew rate spec. The typical value is 2 V/ $\mu$ sec, however a comfortable safety margin is 1.495 V/ $\mu$ sec for the commercial temperature range and 1.256 V/ $\mu$ sec for the military temperature range. The slew rate =  $2\pi fA$ , where f is the maximum input frequency, and A is the peak amplitude in volts. Therefore A = 1.495E6/( $2^*\pi^*100E3$ ) = 2.3 Volts; and the S/N = 78 dB.

Based on a 100 KHz bandpass filter with a Q = 10.  $f_{CLK}$ :  $f_0 = 50:1$ , and a signal to noise ratio of 78 dB, what sort of anti-aliasing filter would be sufficient? One must first look at the spectrum of the input signal, particularly in the 4.895 MHz to 4.905 MHz frequency range since this is the range that will be reflected back into the bandwidth of interest, 95 KHz to 105 KHz. If the frequency components in the 4.895 MHz to 4.905 MHz are below 78 dB, they will have a minimum impact on the signal to noise ratio. Let's assume that these frequency components are down only 20 dB. Then the anti-aliasing filter will have to attenuate the frequencies in the 4.895 MHz to 4.095 MHz range by 78 - 20 = 58 dB, and pass the frequencies in the 95 KHz to 105 KHz frequency range with no attenuation. A simple two pole Butterworth filter with a cutoff frequency of 170 KHz will be sufficient, however there will be an attenuation of about 0.5 dB at 100 KHz due to this filter.

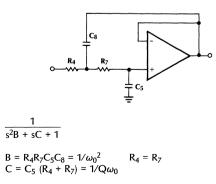

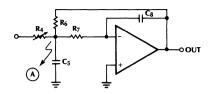

Figure 5a shows a Sallen-Key active filter capable of implementing two poles, and figure 5b shows a Rauch filter also implementing two poles. These two active filters are good examples to use for anti-aliasing and reconstruction filters. Using the Rauch filter for the above example,  $C_5 = 400$  pF,  $C_8 = 90$  pF, and  $R = R_4 = R_6 = R_7 = 5$  K $\Omega$ . Fortunately the cutoff frequency for the antialiasing and reconstruction filters are not critical since capacitors can vary 5% and resistors can vary 1%. Taking into account component tolerance for our example, the cutoff frequency can vary worst case from 152 KHz up to 178 KHz.

The important aspects to note are that one must first determine the signal to noise ratio in the bandwidth of interest. Based on this bandwidth, are there any frequencies that will be reflected back into the bandwidth of interest, and if so how much will they need to be attenuated? Remember that frequency components reflected back outside of the bandwidth of interest, will be filtered by the ML2111. Since the ratio of the sampling frequency to the center frequency is large on the ML2111, most designs will not need an anti-aliasing filter, and if they do, a simple two pole butterworth should suffice.

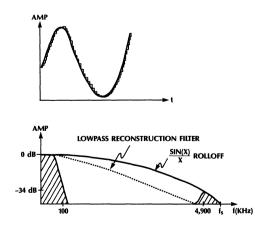

#### 2.4 Signal Reconstruction

The output signal of a switched capacitor filter contains higher frequency components since it is a sampled signal. Many systems can accommodate these higher frequency components; however, if they interfere with the system's performance, then a signal reconstruction filter can be employed.

A time domain and frequency domain plot of the output from the ML2111 is given in figure 6. The output signal changes amplitude every clock period. These sharp transitions elicit high frequency components in the output signal. Once again, the fact that the ratio of the sampling frequency to the input bandwidth is high, reduces these distortion effects. As a result of the sin (x)/x envelope, the higher frequency components are attenuated. For example, assuming the input bandwidth is 100 KHz and Figure 4: Effects of Sampling Rate on Aliasing Noise

TIME DOMAIN

AMP AMP AMP ALIASING NOISE ALIASING NOISE ALIASING NOISE ALIASING FREQ

FREQUENCY DOMAIN

the sampling rate is 5 MHz, the frequencies around 4.9 MHz are down 34 dB, and they degrade towards zero as the frequency reaches 5 MHz. A single pole reconstruction filter with a cutoff frequency at 200 KHz would add an additional attenuation of 27 dB at 4.9 MHz but would attenuate the output by 1 dB at 100 KHz. A two pole Butterworth as in figure 5a or 5b would yield 58 dB of attenuation at 4.9 MHz and only 0.5 dB at 100 KHz.

#### 3.0 Layout Considerations

The layout of any board with analog and digital circuitry combined mandates careful consideration. The most important steps in designing a low noise system are:

- 1. All power source leads should have a bypass capacitor to ground on each printed circuit board (PCB). At least one electrolytic bypass capacitor (50  $\mu$ F or more) per board is recommended at the point where all power traces from the ML2111 join prior to interfacing with the edge connector pins assigned to the power leads.

- 2. Layout the traces such that analog signal and capacitor leads are far from the digital clock.

- 3. Both grounds and power supply leads must have low resistance and inductance. This should be accomplished by using a ground plane where ever possible. Either multiple or extra large plated through holes should be used when passing the ground connections through the PCB.

- 4. Use a separate trace for clock ground, and connect it to the edge connector board ground.

- 5. Use ground plane on both sides of PC board.

- 6. All power pins on ICs should have 0.1  $\mu$ F and a 0.01  $\mu$ F capacitors in parallel tied to ground, and as close to the power pins as possible.

- 7. Stray capacitance, lead lengths, and traces, on pin 4 and 17, the negative input of the op amp, should be kept to a minimum, particularly for high frequency filters which are more sensitive.

#### Figure 5a. Sallen-Key Filter

Figure 5b. Rauch Filter

DC Gain:  $\frac{R_6}{R_4}$  = H(0) [Minimize Parasitic C at Node (A)]

Transfer function:  $\frac{H(0) (1/B)}{s^2 + s(C/B) + 1/B} = \frac{H(0) \omega_0^2}{s^2 + s(\omega_0/Q) + \omega_0^2}$

B =

$$R_6 R_7 C_8 C_5$$

C =  $\frac{R_6 R_7 C_8 + C_8 (R_6 + R_7) R_4}{R_4}$

Choose Butterworth response for example:

$$\begin{split} \omega_0 &= 2\pi [170 \text{ KHz}] \approx 1.06 \times 10^6 \text{ rad/s} \\ Q &= .707 \\ \text{say } R_4 &= R_7 = R_6 = R \implies 1/\omega_0^2 = R^2 C_8 C_5 \\ C &= R C_8 + C_8 (R_6 + R_7) = R C_8 + 2 C_8 R = 3 R C_8 \\ &= > \frac{C}{B} = \frac{3R C_8}{R^2 C_8 C_5} = \frac{3}{R C_5} = \frac{\omega_0}{Q} \\ &= > \begin{cases} C_5 &= \frac{3Q}{R\omega_0} & \text{say } R = 5 \text{ K}\Omega \\ C_8 &= \frac{1}{\omega_0^2 R^2 C_5} \end{cases} \end{split}$$

Figure 6: Signal Reconstruction

#### 3.1 Clocks and Output Loading

It is important to properly terminate the clock input to prevent overshoot. Each pin has protection diodes for Electro-Static Discharge (ESD), and any overshoot of more than 0.3 to 0.5 volts will be injected directly into the ML2111's ground and/or supplies. Matching the characteristic impedance of the line will prevent any ringing thus reduce clock noise.

When operating with high clock frequencies, the output of the op amp and integrators should be properly loaded. Ideally these outputs—LP, BP, and N—like to drive a total of 2 to 3 mA of peak current each. Assuming the output voltage swing is  $\pm 2$  volts, the sum of R<sub>5</sub> and R<sub>6</sub>, in mode 1c for example, should be 2 V/2 mA or about 1,000 ohms; assuming no other resistors are connected. Sometimes this is difficult to do if the ratios and loading cannot simultaneously be achieved. In this case an additional loading resistor placed as close as possible to the output pin will serve the purpose of properly loading the outputs.

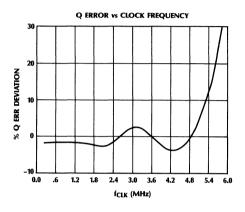

#### 4.0 Sweeping Filters

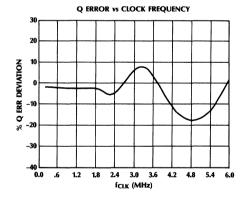

One particularly nice feature of sampled data filters is the fact that the center frequency of a filter is directly related to the clock frequency. For a lowpass filter, increasing the clock frequency increases the cutoff frequency. Even though the center frequency increases proportionally with the clock, Q stays constant. Therefore in a bandpass filter, increasing the clock frequency increases the center frequency as well as the bandwidth. Table 2 in the data sheet illustrates this relationship. (Note that there is some Q deviation as the system clock goes beyond a certain value. Refer to figure 2E in the data sheet for a graph of this phenomenon)

A good rule of thumb for the maximum rate a filter can be swept is that the Sweep Rate should be less than the square of the bandwidth of the filter. This will reduce attenuation of the passband as a result of sweeping the filter. The theoretical derivation of this approximation is as follows.

Assume we have a bandpass filter with an in-band signal that starts at t = 0. The output of the filter will exponentially increase until it reaches the steady state gain of the passband. After 4 time constants ( $\tau$ ), the output sine wave will be at 98% of its final amplitude.

Sweeping a filter is analogous to keeping the filter constant and sweeping the input frequency. To prevent the filter from attenuating the sweeping input signal by more than 2% or 0.16 dB:

Sweep Rate

$$< BW/4\tau$$

(2)

but the time constant can be approximated by:

and,

$$\tau \simeq Q/2\pi f_0$$

(3)

Q = f<sub>0</sub>/BW or BW = f<sub>0</sub>/Q (4)

substituting  $\tau$  and BW into equation (2) results in:

Sweep Rate

$$< \pi BW^2/2$$

(5)

#### 5.0 High Frequency Operation

There are three basic modes for the ML2111 — mode 1, 2 and 3. Within each mode there are several variations as shown in the table below.

| Mode 1*             | High Frequency Mode                                                           |

|---------------------|-------------------------------------------------------------------------------|

| 1, 1a, 1d<br>1b, 1c | $f_0$ up to 150 KHz; Q up to about 20** $f_0$ up to 100 KHz; Q up to about 30 |

| Mode 2              | Flexible for Notches                                                          |

| 2, 2a, 2b           | f <sub>0</sub> up to 30 KHz; Q up to about 30                                 |

| Mode 3              | Most Flexible/Low Component Count                                             |

| 3, 3a               | f <sub>0</sub> up to 30 KHz; Q up to about 30                                 |

Q and f<sub>0</sub> have an inverse relationship. This table is only an approximation. Actual performance depends on board layout and stray capacitance.

\*\* 15% or less Q deviation. Higher Q's can be realized with greater deviation.

Mode 1 is the only mode which has the input amplifier outside the resonant loop. This is important because the input amplifier reduces the bandwidth potential of the filter. Only Mode 1 can achieve filters with resonant frequencies up to 150 KHz.

Inserting an ML2111 into an MF10, LMF100, or LTC1060 socket and increasing the clock frequency does not automatically increase the bandwidth potential up to 150 KHz. If these pin-compatible parts were designed using Mode 1, the bandwidth improvements would be realized; however if they were used in another mode, there would be limited bandwidth improvements.

Complex, high order filters usually have pole pairs with different center frequencies; Elliptical and Chebyshev filters are two examples. To realize two pole pairs in one ML2111 with different center frequencies, one must either use two different clocks, or use a mode which allows the center frequency to be modified by external resistors.

Using different clock frequencies to realize poles with different center frequencies is not recommended. Besides the additional expense of providing more than one clock, the two system clocks may beat with each other and possibly result in side tones that falls within the passband of the filter. Additionally if anti-aliasing is needed, separate anti-aliasing filters would be needed for each stage.

Looking at tables 1 and 2 in the ML2111 data sheet, one can see the modes that allow the center frequency to be modified by external resistors. These modes each have an additional coefficient multiplied by  $f_{CLK}/100(50)$ . From the block diagrams one can see that the modes which allow the center frequency to be modified, feedback the LP output using a resistor divider. The modes that restrict the ratio to 50 or 100 have a unity gain LP feedback.

If the coefficient multiplied by  $f_{CLK}/100(50)$  is greater than or equal to 1, as in Mode 1b, then the ratio of  $f_{CLK}$  to  $f_0$ can be less than 50 or 100. Whereas if this coefficient is less than or equal to 1, then the ratio of  $f_{CLK}$ :  $f_0$  can be greater than or equal to 50 or 100. Reducing the ratio of  $f_{CLK}$  to  $f_0$  to less than 40 to 50 is not recommended. As the ratio of the sampling frequency to the center frequency is reduced, the approximation of a sample data filter to a continuous filter is reduced. Aperture effects increase, aliasing effects may increase, harmonics in the output increase, and the warpage between the discrete and the continuous filter increase. 40 to 50:1 is the minimum recommended ratio of  $f_{CLK}$  to  $f_0$ .

Based on the above arguments one might conclude that 100:1 is better than 50:1. In general this is true for switched capacitor filters, but not for the ML2111. The specifications in the data sheet show that a 50:1 ratio provides a more accurate Q than a 100:1, and a 50:1 ratio allows higher frequency filters.

Mode 3 is the most flexible since the center frequency can be greater than or less than  $f_{CLK}/100(50)$  by selecting  $R_2$  and  $R_4$ . Its also the most efficient since it has the lowest component count. However mode 3 can only work up to 30 to 40 KHz or Qs up to the 10 to 30 range; higher  $f_0$  can be obtained with lower Qs. Sometimes a small capacitor ( $C_4$ ) across  $R_4$  can compensate the filter response and offer less Q deviation. The value should be selected by setting  $C_4$  equal to  $1/2\pi R_4 BW$  where BW is approximately equal to 2 to 4 MHz.

Another reason mode 3 can only be used at lower frequencies is that there is a true sample and hold at the positive input of the summer. This sample and hold adds a 7.2 degree delay at the center frequency when using a 50:1 ratio (360°/50). By using a higher ratio this delay is lowered. Since the ML2111 allows a higher system clock than other competing devices, this delay can usually be made smaller for similar center frequencies.

In conclusion, for high frequency filters use Mode 1. For complex filters with various center frequencies use Mode 1c. In most cases one should choose 50:1 over 100:1 ratio for more accurate Q's and center frequencies.

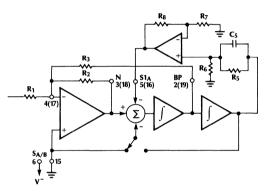

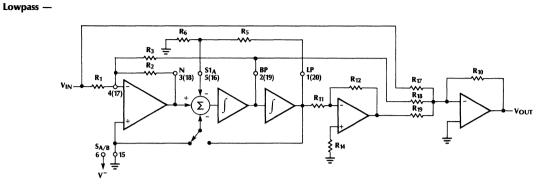

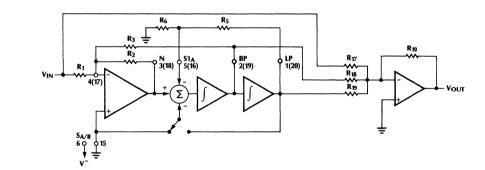

#### 5.1 A Flexible Building Block

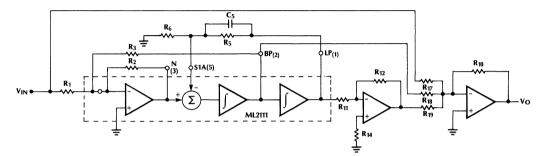

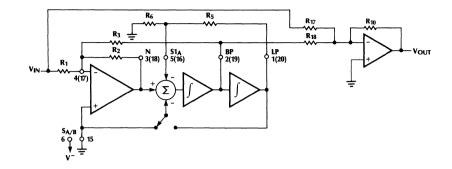

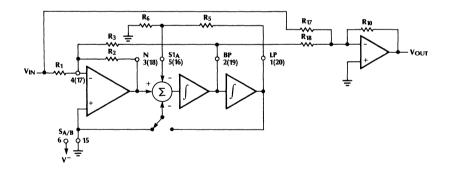

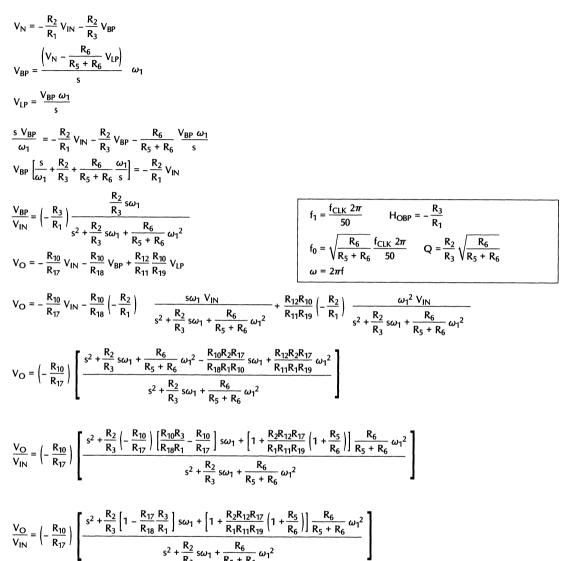

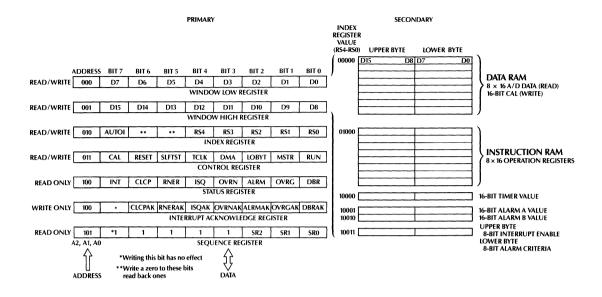

Figure 7 shows the block diagram of a second order section which includes both a complex pole pair and a complex zero pair. The poles are provided by the ML2111 and the zeros realized by one and sometimes two external op amps. This building block uses mode 1c which allows the poles to have a center frequency based on external resistors as well as the clock, plus it can be used in higher frequency filters since the op amp is outside of the resonant loop. The same feedforward circuit can be used on other modes as well, but for high

frequency filters, where each complex pole pair has a different center frequency, mode 1c is the best choice. As mentioned before, only when Butterworth filters are

desired, use mode 1 to achieve higher frequencies and a higher dynamic range. The transfer function for the flexible building block is given below.

$$\frac{V_{O}}{V_{IN}} = \left(-\frac{R_{10}}{R_{17}}\right) \left[\frac{s^{2} + \frac{R_{2}}{R_{3}}\left[1 - \frac{R_{17}}{R_{18}}\frac{R_{3}}{R_{1}}\right]s\omega_{1} + \left[1 + \frac{R_{2}R_{12}R_{17}}{R_{1}R_{19}}\left(1 + \frac{R_{5}}{R_{6}}\right)\right]\frac{R_{6}}{R_{5} + R_{6}}\omega_{1}^{2}}{s^{2} + \frac{R_{2}}{R_{3}}s\omega_{1} + \frac{R_{6}}{R_{5} + R_{6}}\omega_{1}^{2}}\right]$$

(6)

Figure 7: Flexible Building Block

At least one and sometimes two external op amps are required to realize the zeros. The first op amp serves as an inverter, while the second one sums the input signal with the lowpass and bandpass outputs. A fast op amp should usually be used with greater than 10 MHz bandwidth to minimize signal phase shifts. Depending on the application, sometimes a slower amplifier will suffice. In some cases no external op amp is necessary and the second op amp in the ML2111 if not being used will suffice. This was done in figure 34 in the data sheet.

With the Flexible Building Block a lowpass, highpass, notch, and allpass section can be realized by properly positioning the zero locations. Zero locations are chosen by selecting the appropriate resistors. The difference between the lowpass output provided by the ML2111 in mode 1c and the lowpass function realized by the flexible building block is that in mode 1c the response is monotonically decreasing, while the Flexible Building Block has a complex zero pair which inserts a ripple in the stop band and flattens out at high frequency.

Since the Flexible Building Block uses mode 1c, the pole equations remain the same whether there is feedforward or not. What changes is the zero location and the DC gain. The following equations are used to determine the pole locations and Q for the Flexible Building Block, which uses mode 1c.

$$f_0 = \frac{f_{CLK}}{100(50)} \sqrt{\frac{R_6}{R_5 + R_6}}$$

$$Q = \frac{R_3}{R_2} \sqrt{\frac{R_6}{R_5 + R_6}}$$

A handy set of equations to convert pole and zero locations given in rectangular coordinates to  $f_0$  and Q values is as follows:

Complex Pole =

$$\sigma$$

+ j $\omega$ ;

$f_0 = \sqrt{\frac{\sigma^2 + \omega^2}{2\pi}} \quad Q = \frac{1}{2}\sqrt{1 + (\omega/\sigma)^2}$

(7)

By cascading several of these building blocks, complex high frequency Elliptical filters can be realized.

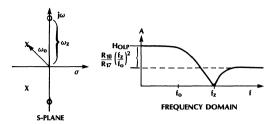

#### 5.2 Lowpass

For a lowpass design with a notch, the zeros should be placed on the j $\omega$  axis at frequencies greater than the poles' center frequency. In the numerator of the transfer function for equation 6, the coefficient for  $s\omega_1$  should be

set to zero; setting

$$\frac{R_3}{R_1} = \frac{R_{18}}{R_{17}}$$

.

Since  $\frac{R_6}{R_5 + R_6} \omega_1^2 = \omega_0^2$ , the coefficient

$(1 + \frac{R_2R_{12}R_{17}}{R_1R_{11}R_{19}}(1 + \frac{R_5}{R_6})$  determines the center frequency of the zero. In this form it is always greater than one, therefore the center frequency of the zero is always greater than the center frequency for the poles; hence a lowpass filter. The pole/zero location and the frequency response are shown below.

Equations for the lowpass configuration:

$$\frac{R_{17}}{R_{19}} = \frac{\left(\frac{12}{f_0}\right)^2 - 1}{\frac{R_2}{R_1}\left(1 + \frac{R_5}{R_6}\right)} \qquad f_Z = f_0 \sqrt{1 + \frac{R_2 R_{12} R_{17}}{R_1 R_{11} R_{19}}\left(1 + \frac{R_5}{R_6}\right)}$$

$$DC \text{ Gain} = H_{OLP} = \left(-\frac{R_{10}}{R_{17}}\right) \left(1 + \frac{R_2 R_{12} R_{17}}{R_1 R_{11} R_{19}}\left(1 + \frac{R_5}{R_6}\right)\right)$$

The ratio of the zero to the pole frequency determines the DC to high frequency attenuation.

When the zeros are at the same frequency as the poles the bi-quad becomes a notch, and there is no difference between the high frequency and low frequency gain. The larger the difference between the pole and zero frequencies, the greater the rejection. Figure 8 illustrates the relationship between pole/zero location and gain.

#### Figure 8: Varying fz and Keeping fo and Q Constant

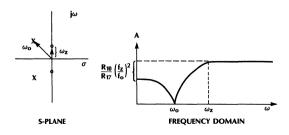

#### 5.3 Highpass

For a highpass filter the zeros must be less than the center frequency for the poles. The pole/zero plot and the frequency plot are shown below.

To place the zeros at a lower frequency than the poles the coefficient  $1 + \frac{R_2R_{12}R_{17}}{R_1R_{19}}\left(1 + \frac{R_5}{R_6}\right)$  must be less than one. This can be done by removing the inverter in figure 7, which makes the sign of  $R_{19}$  negative. To place the zeros on the j $\omega$  axis, once again  $\frac{R_3}{R_1} = \frac{R_{18}}{R_{17}}$ . Equations for the highpass configuration:

$$f_{Z} = f_{0} \sqrt{1 - \frac{R_{2}R_{12}R_{17}}{R_{1}R_{11}R_{19}} \left(1 + \frac{R_{5}}{R_{6}}\right)}$$

$$H_{OHP} = -\frac{R_{10}}{R_{17}}$$

#### 5.4 Notch

Even though mode 1c provides a notch output, the notch realized by the flexible building block achieves 0 dB of gain at DC and at high frequencies regardless of the Q value. The problem with the notch in mode 1c is that

$$H_{ON1} (f \rightarrow 0) = H_{ON2} (f \rightarrow f_{CLK}/2) = \frac{\sqrt{\frac{R_6}{R_5 + R_6}}}{Q}$$

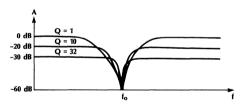

As Q increases  $H_{ON1,2}$  must decrease otherwise the bandpass output node, BP pin 2 or 19, will saturate. The restriction is that  $H_{OBP} = 1 = -R_3/R_1$ . Let's take a simple case when  $R_5 = 0$ , then  $H_{ON1} = H_{ON2} = 1/Q$ . The plot below shows the notch for different Q's in mode 1c.

#### Figure 9: Mode 1c Notch when $R_5 = 0$

To realize the notch using the Flexible Building Block the zeros must be placed on the j $\omega$  axis at the same resonant frequency as the poles. Therefore from equation 6,  $\frac{R_3}{R_1} = \frac{R_{18}}{R_{17}}$  and  $R_{19} \rightarrow \infty$ . Setting  $R_{19}$  equal to infinity means removing it from the circuit; which saves an op amp and a few resistors.  $H_{OBP}$  still must equal one, however the gain at DC and  $f_{CLK}/2$  is independent of Q;  $H_{ON1}$  (f  $\rightarrow$  0) =  $H_{ON2}$  (f  $\rightarrow f_{CLK}/2$ ) =  $-R_{10}/R_{17}$ . Tuning  $R_{18}$  adjusts the depth of the notch. See figure 34 in the data sheet for an example.

#### 5.5 Allpass Equalizer

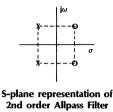

An allpass filter is used to linearize the filter's phase response. A linear phase response results in a constant group delay. An allpass filter keeps the gain constant and just shifts the phase. To keep the gain constant and only shift the phase, the poles and zeros must be equal but on opposite sides of the s-plane as shown below.

The Flexible Building Block can function as an allpass when  $R_{19} \rightarrow \infty$  and  $\frac{R_{17}R_3}{R_{18}R_1} = 2$ . The Transfer function for the allpass is:

$$\frac{V_{O}}{V_{IN}} = \left(-\frac{R_{10}}{R_{17}}\right) \frac{s^2 - \frac{R_2}{R_3}\omega_1 s + \frac{R_6}{R_5 + R_6}\omega_1^2}{s^2 + \frac{R_2}{R_3}\omega_1 s + \frac{R_6}{R_5 + R_6}\omega_1^2}$$

(8)

#### 5.6 Frequency Compensation

In some cases it is possible to improve the Q accuracy and minimize Q deviation by adding a capacitor (C5) in parallel with R<sub>5</sub> in figure 7. This capacitor serves as compensation for a pole at around 2.4 MHz in the output of LP. The zero location should be placed at around 2.4 MHz, where the internal pole is. Unfortunately C5 adds a pole as well as a zero to this branch. If this pole is too close to the zero, the benefit of C<sub>5</sub> is diminished. The zero location is:  $f_Z = 1/2\pi R_5 C_5$  and the pole location is:  $f_p$ =  $1/2\pi(R_5 \parallel R_6)C_5$ ,  $(R_5 \parallel R_6$  is the parallel equivalent resistance). The larger the ratio of the pole frequency to the zero frequency, the better this capacitor will serve.

The highest center frequency attained is when R5 equals zero. (Note: Practically speaking R5 should never be zero, to allow fine tuning of f<sub>0</sub>.) Unfortunately C<sub>5</sub> cannot properly compensate the 2.4 MHz internal pole with a negligible value for R5. To overcome this problem, compensation can be achieved at high frequencies using an op amp in the LP feedback branch as shown in figure 10.

The center frequency in mode 1c is calculated by the following equation:

$\frac{f_{CLK}}{f_0} = \frac{50}{\sqrt{k}}$  where k = Transfer function

With a passive feedback loop using  $R_5$  and  $R_6$ ,  $k = \frac{R_6}{R_5 + R_6}$ . However when using the op amp configuration as in figure 10, k =  $\left(\frac{R_6}{R_5 + R_6}\right)\left(1 + \frac{R_8}{R_7}\right)$ . When k = 1 the ratio is 50. Using active feedback in mode 1c has the unique advantage of allowing the ratio of clock to center frequency to be less than 50 by setting k greater than 1. It is not recommended to use ratios less than 40-50, however this feature does allow more freedom in tuning the center frequency of the pole above or below the ratio of 50. If the circuit uses a crystal for f<sub>CLK</sub>, and the pole needs to be tuned, R<sub>8</sub> could be a potentiometer to allow tuning of the pole. For this compensation to work  $\frac{R_8}{R}$  should be 4-9 to provide phase lead before phase lag.

#### Figure 10: Compensation Using Active Feedback for High **Frequency Poles**

$C_5$  = 33-66pF (Depends on board's parasitics)  $R_8 = 1800\Omega$ ;  $R_7 = 200$  $R_6 = 100\Omega$ ,  $R_5 = 900\Omega$

Using mode 1 instead of mode 1c as configured in figure 7, is a better solution for high frequency poles; however there are certain cases where mode 1 cannot be used. For example, if one of the two bi-guads in the ML2111 is already used in mode 1c, then the other one must also operate in mode 1c. It would be less expensive to add an op amp to the second bi-quad of an existing ML2111 than to add an additional ML2111 just to use one bi-quad operating in mode 1.

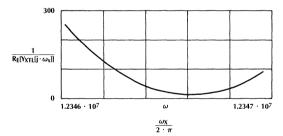

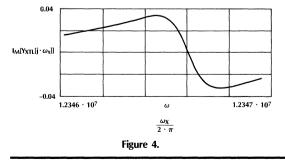

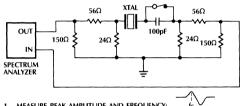

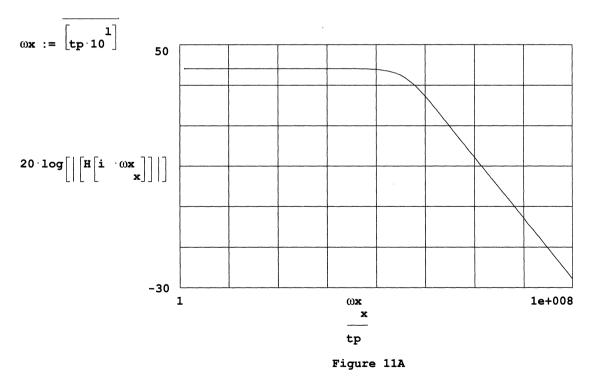

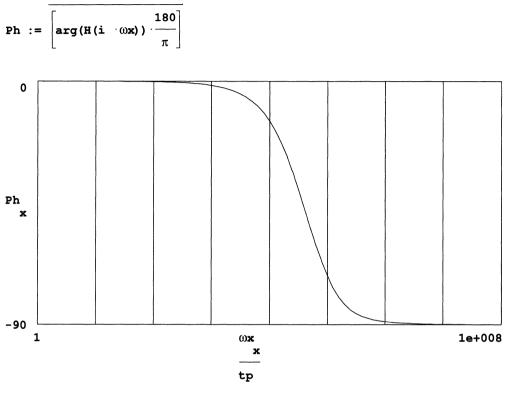

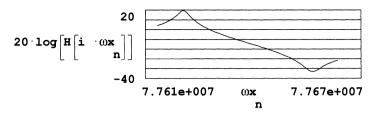

Figure 11a shows the Q accuracy vs. clock frequency in mode 1c using passive feedback for a Q approximately equal to 10. Q inaccuracy dramatically increases just beyond 100 KHz center frequency. Figure 11b shows Q accuracy vs. center frequency in mode 1c using active feedback with a DC transfer function of 1. The op amp used for this measurement was an AD5539, where

$\frac{R_8}{R_7} = \frac{R_5}{R_6} = 9$ . This op amp is a good choice because it has

a wide bandwidth, 220 MHz, and is low cost. The figure shows that Q deviation does not dramatically increase until well beyond 120 KHz; therefore for higher frequency operation and high Q, the use of mode 1c with active feedback is recommended.

#### Figure 11a: Mode 1c with Passive Feedback

$$\frac{R_3}{R_2}$$

= 10; R<sub>5</sub> = 0; R<sub>1</sub> = R<sub>3</sub> = 20K

Figure 11b: Mode 1c with Active Feedback

$$C_5 = 33pF; \frac{R_3}{R_2} = 10; R_5 = 0; R_1 = R_3 = 20K$$

#### 6.0 Design Methodology for Complex Filters

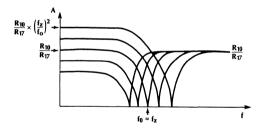

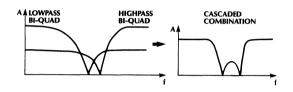

The previous section described how to use the Flexible Building Block to implement lowpass, highpass, notch, and allpass second order sections. Higher order filters are achieved by cascading these second order sections. For example an Elliptical notch is accomplished by cascading lowpass and highpass sections as shown in figure 12.

An Elliptical bandpass is also a combination of highpass and lowpass sections, except for a bandpass filter the cutoff frequency for the highpass bi-quads are lower than the cutoff frequency for the lowpass.

#### Figure 12: Fourth Order Elliptic Notch

Once the pole and zero location have been determined for the filter desired, the next step is to choose the proper mode of operation and translate the center frequency and Q values for each pole and zero into resistor values. If the pole and zero locations are given in real and imaginary values, they can be converted to  $f_0$ and Q by using equation 7.

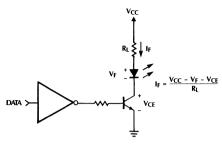

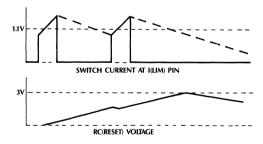

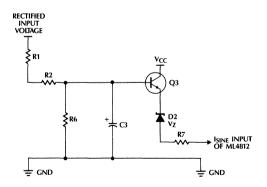

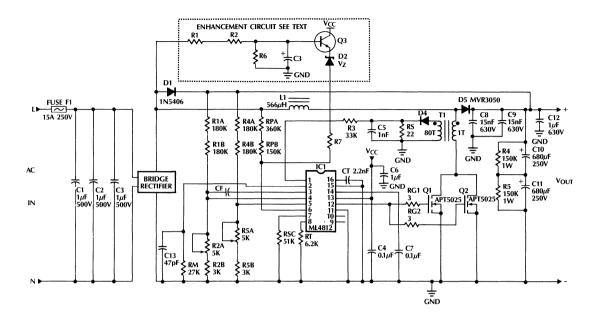

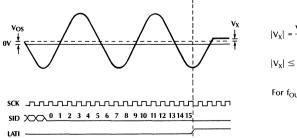

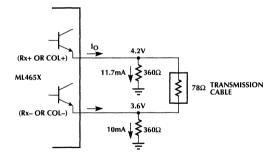

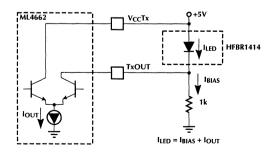

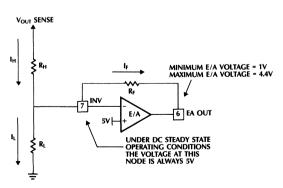

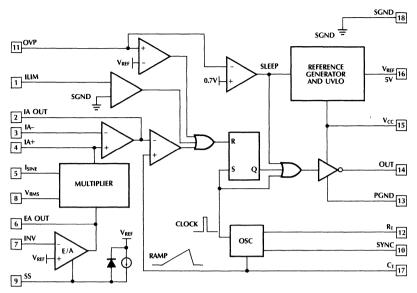

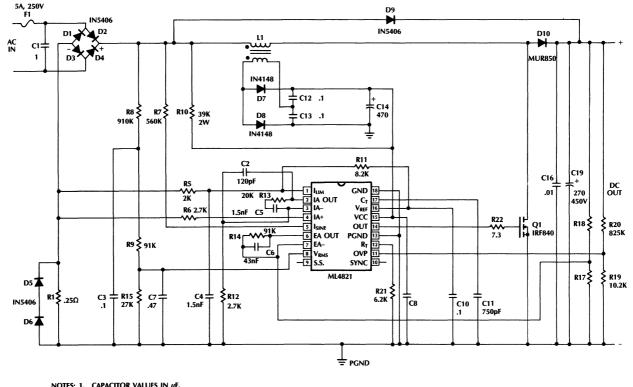

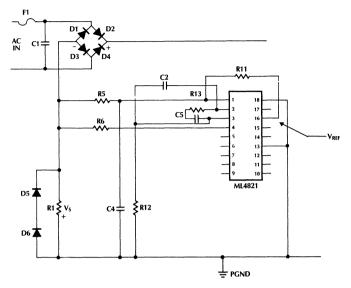

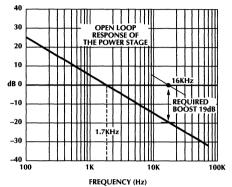

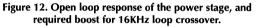

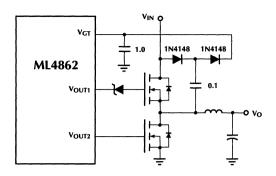

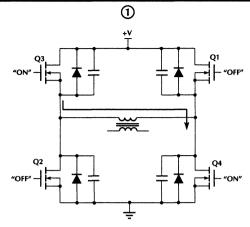

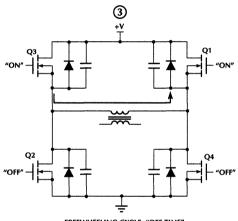

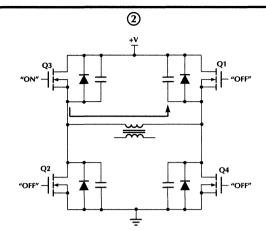

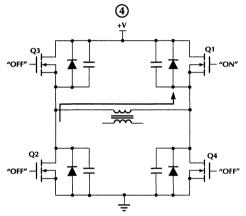

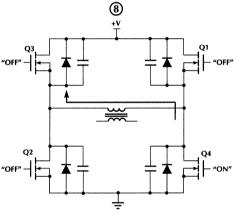

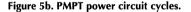

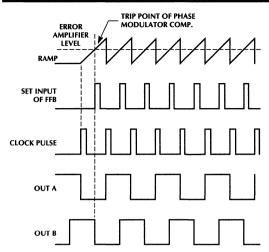

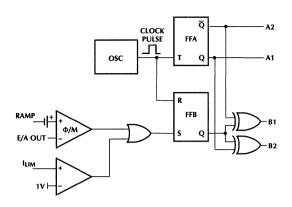

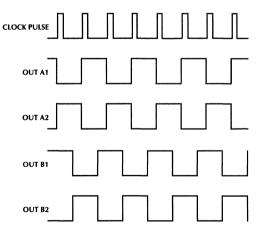

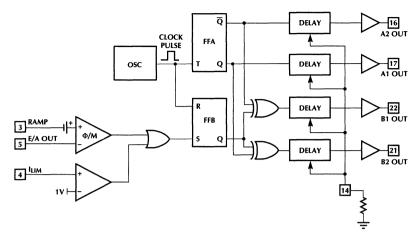

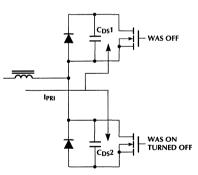

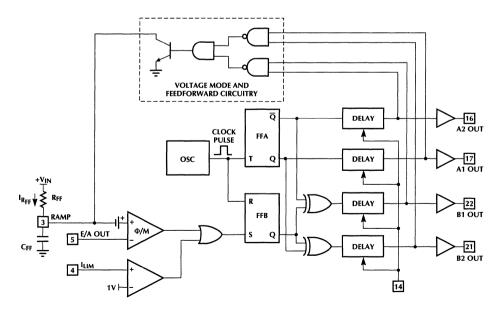

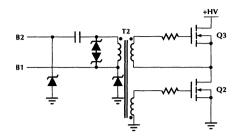

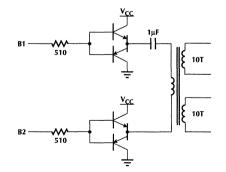

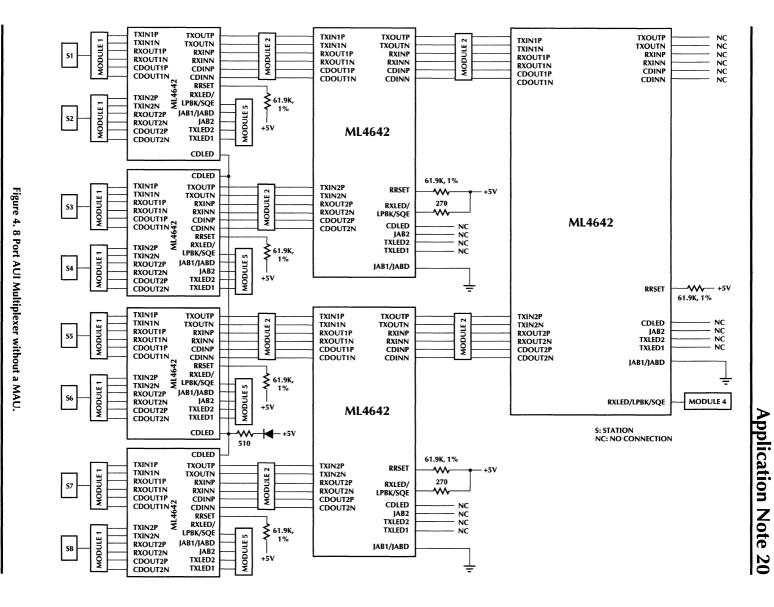

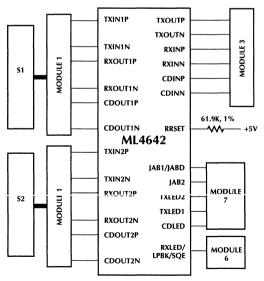

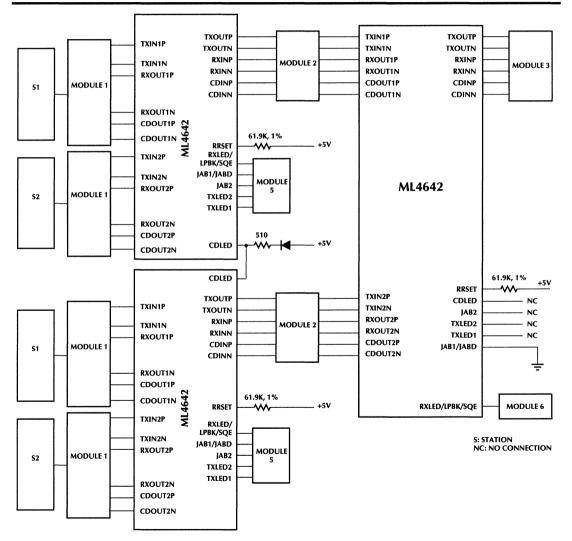

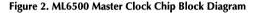

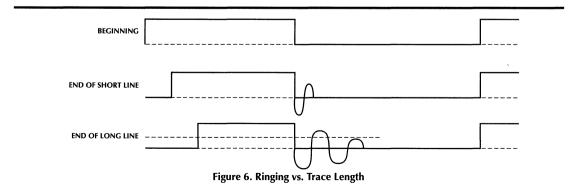

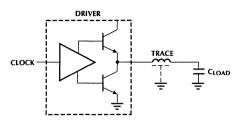

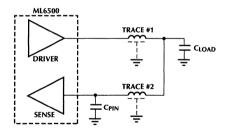

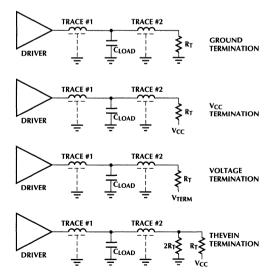

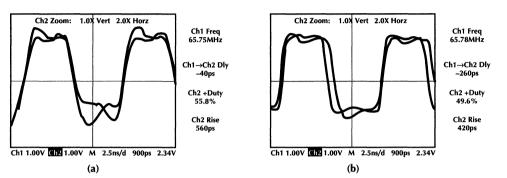

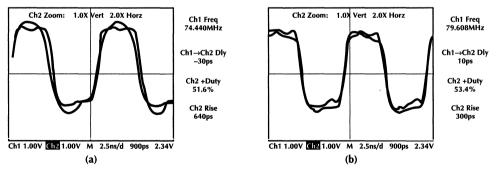

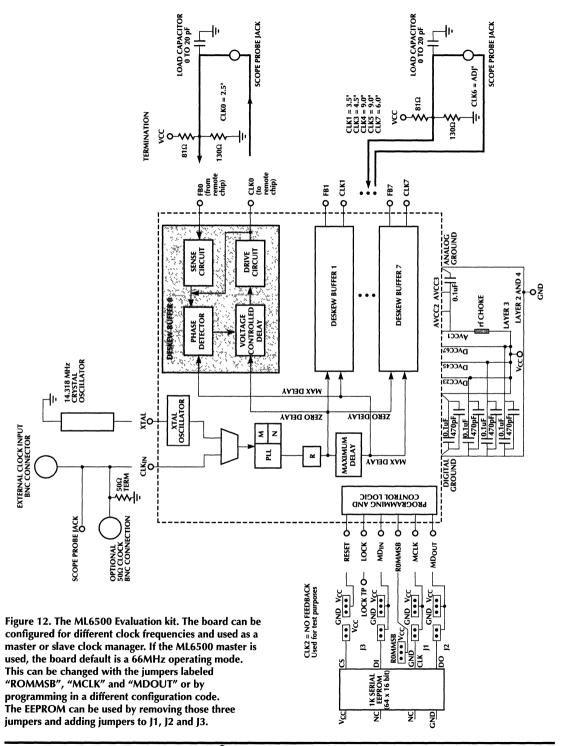

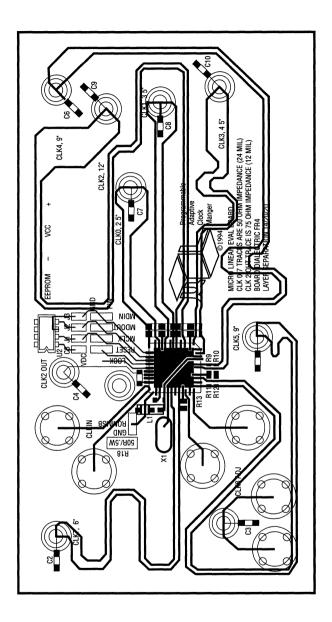

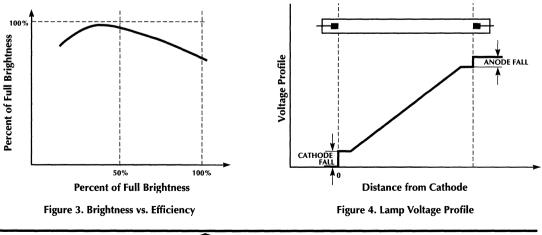

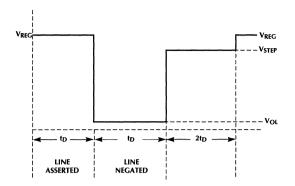

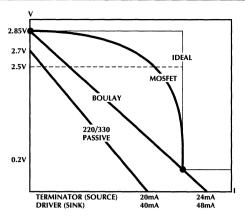

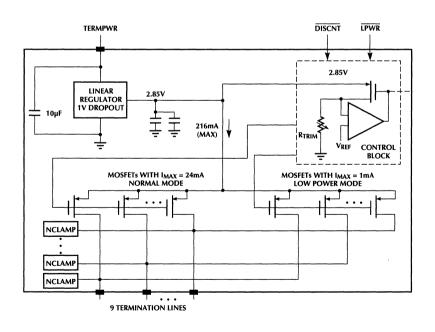

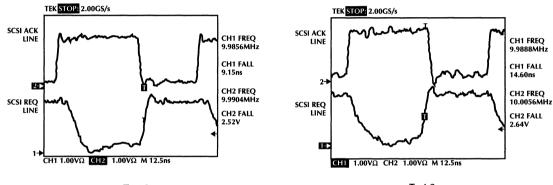

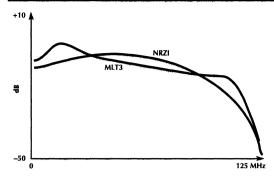

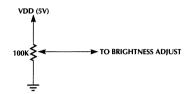

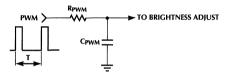

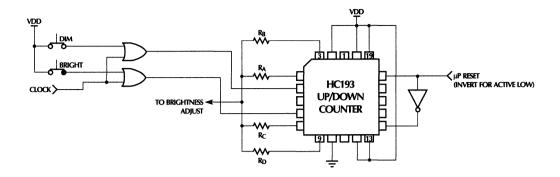

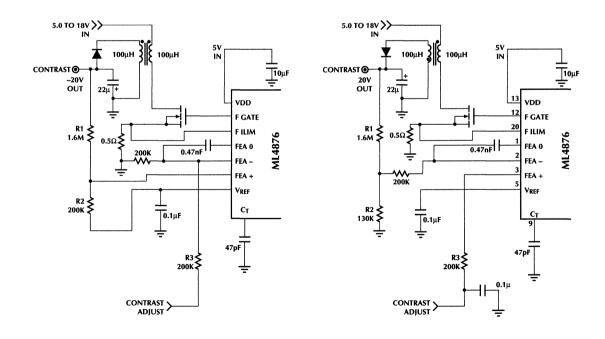

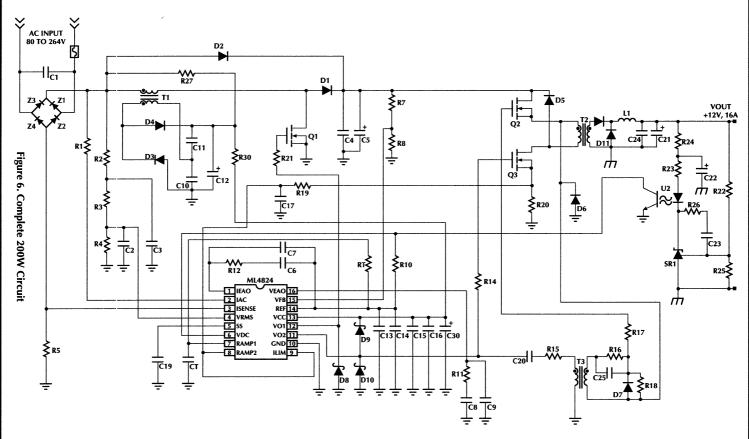

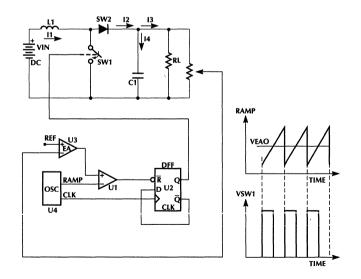

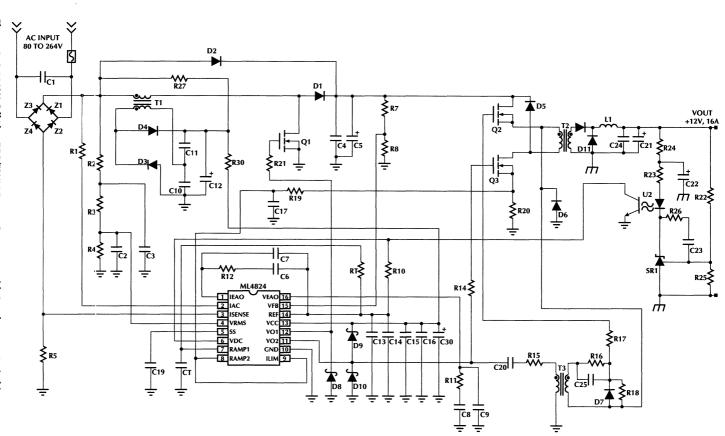

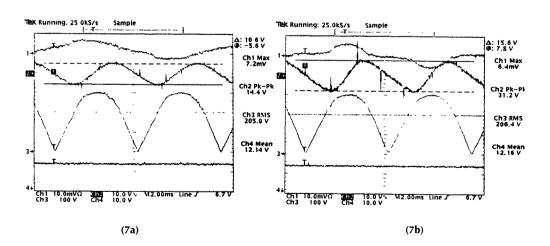

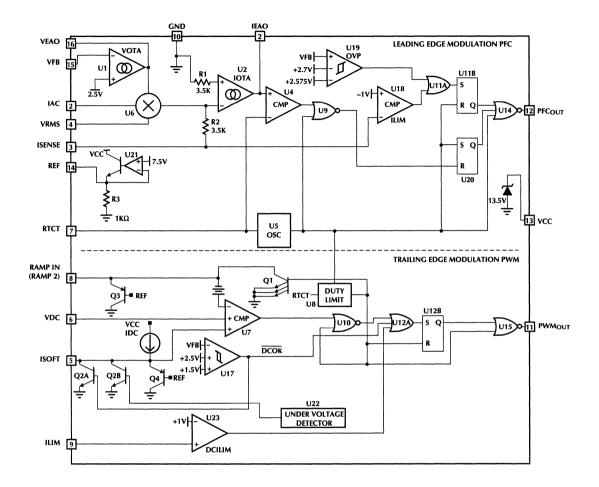

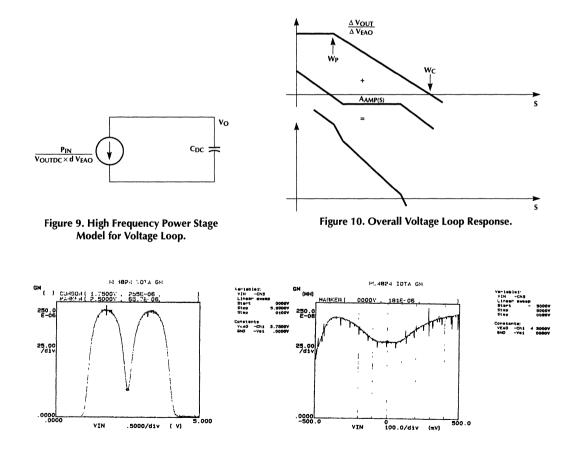

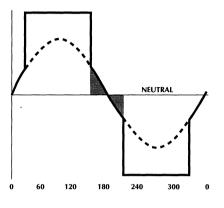

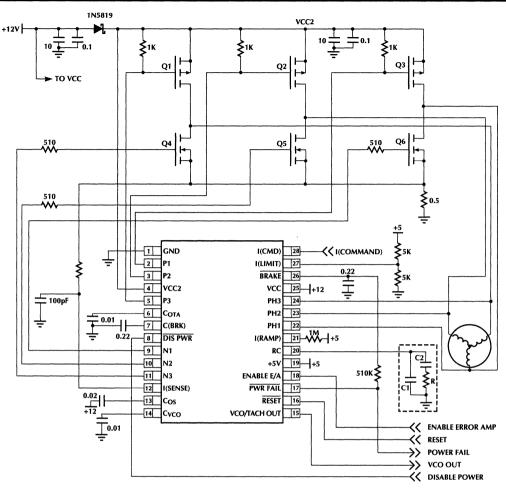

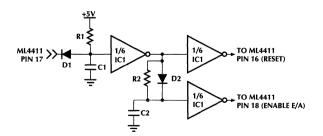

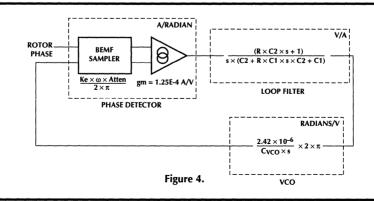

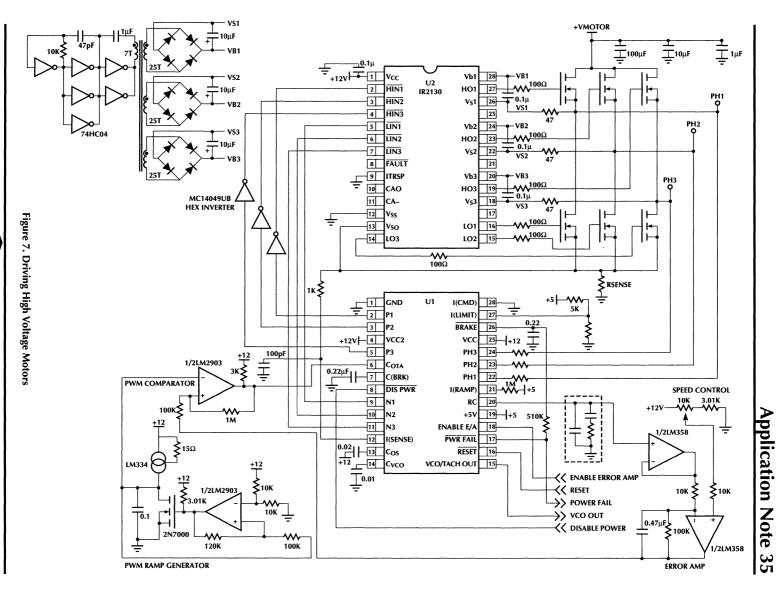

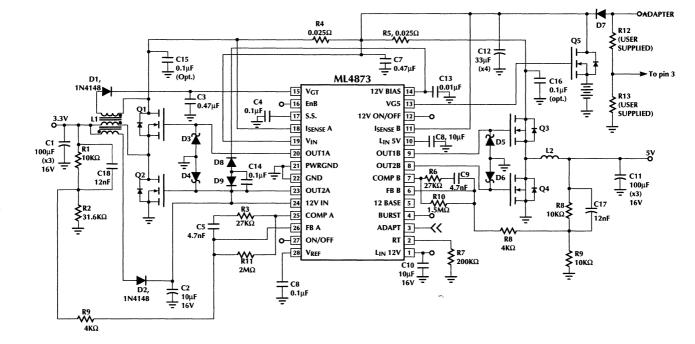

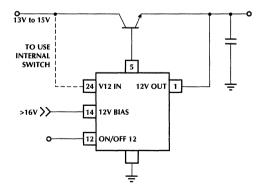

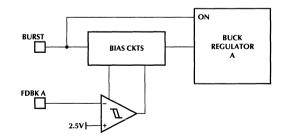

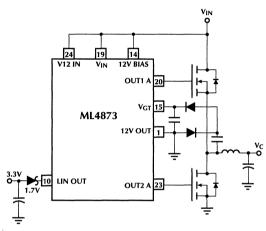

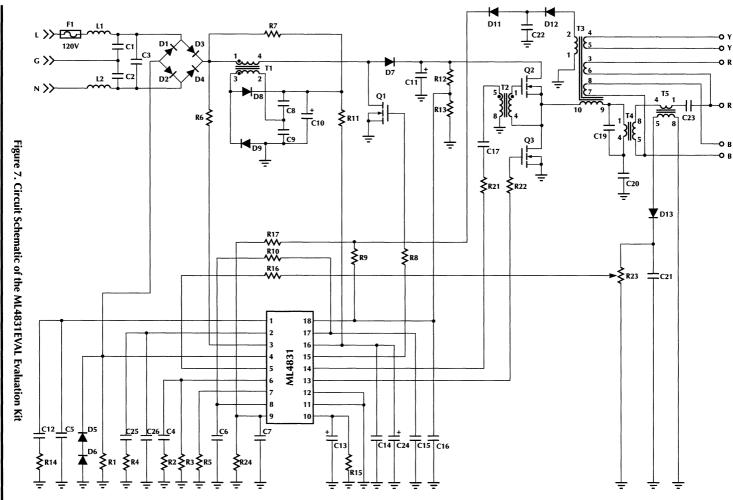

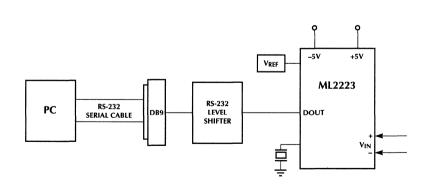

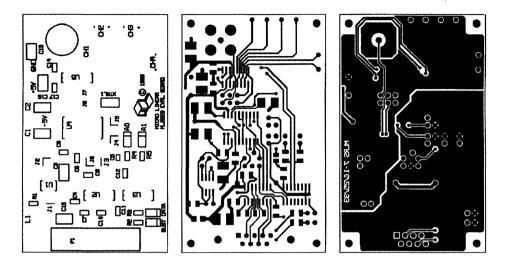

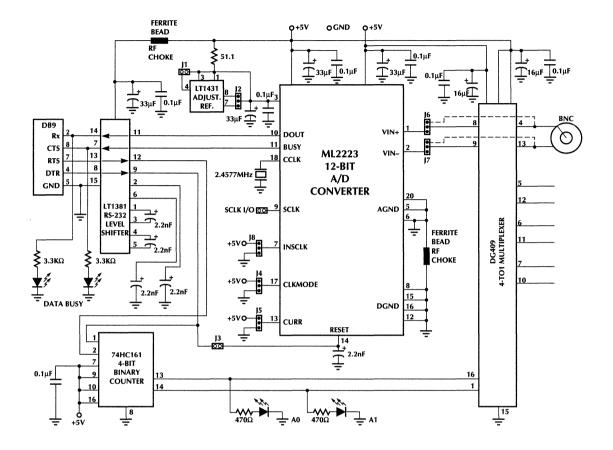

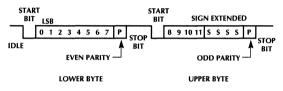

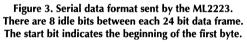

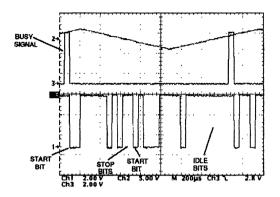

For center frequencies between 0 and 20 KHz, either mode 3 or mode 1c can be used. Sometimes mode 3 or mode 3a will result in a lower component count. However mode 3 should be used with caution since high Qs and high parasitic capacitance on pin 4 and 17 can lead to oscillations. This can usually be compensated by using a capacitor across R4, which provides some phase lead, and low value resistors such as 1-2 Kohms.