# 82077SL CHMOS SINGLE-CHIP FLOPPY DISK CONTROLLER

- Completely Compatible with Industry Standard 82077AA

- Single-Chip Laptop Desktop Floppy Disk Controller Solution

- 100% PC AT\* Compatible

- 100% PS/2\* Compatible

- 100% PS/2 Model 30 Compatible

- Fully Compatible with Intel's 386SL Microprocessor SuperSet

- Integrated Drive and Data Bus Buffers

- **Power Management Features**

- Application Software Transparency

- Programmable Powerdown Command

- Auto Powerdown and Wakeup Modes

- Two External Power Management Pins

- Typical Power Consumption in Power Down: Less than 95 μA

- Integrated Analog Data Separator

- 250 Kbits/sec

- 300 Kbits/sec

- 500 Kbits/sec

- 1 Mbits/sec

- Programmable Crystal Oscillator for On or Off

- Perpendicular Recording Support

- 12 mA Host Interface Drivers, 40 mA Disk Drivers

- Four Fully Decoded Drive Select and Motor Signals

- Programmable Write Precompensation Delays

- Addresses 256 Tracks Directly, Supports Unlimited Tracks

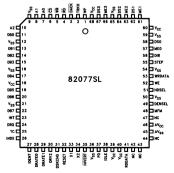

290410-1

- 16 Byte FIFO

- 68-Pin PLCC

# **■** High Speed Processor Interface

The 82077SL, a 24 MHz crystal, a resistor package, and a device chip select implements a complete laptop solution. All programmable options default to 82077AA compatible values. The dual PLL data separator has better performance than most board level/discrete PLL implementations. The FIFO allows better system performance in multi-master systems (e.g., Microchannel, EISA).

The 82077SL is a superset of 82077AA. The 82077SL incorporates power management features while maintaining complete compatibility with the 82077AA/8272A floppy disk controllers. It contains programmable power management features while integrating all of the logic required for floppy disk control. The power management features are transparent to any application software. There are two versions of 82077SL floppy disk controllers, the 82077SL and 82077SL-5. The only difference between the two products is that the 82077SL supports 1 Mbps data rate for the higher 4 MB density floppy disk drives and 82077SL-5 supports 500/300/250 Kbps data rate for high and low density floppy disk drives.

The 82077SL is fabricated with Intel's advanced CHMOS III technology and is available in a 68-lead PLCC (plastic) package.

Figure 1. 82077SL Pinout

\*PS/2 and PC AT are trademarks of IBM.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied. Information contained herein supersedes previously published specifications on these devices from Intel. May 1991

Order Number: 290410-001

# 82077SL CHMOS Single-Chip Floppy Disk Controller

| CONTENTS                                           | PAGE | CONTENTS                                      | PAGE                |

|----------------------------------------------------|------|-----------------------------------------------|---------------------|

| 1.0 INTRODUCTION                                   | 7    | 3.0 DRIVE INTERFACE                           | 15                  |

| 1.1 Perpendicular Recording Mode .                 | 8    | 3.1 Cable Interface                           | 15                  |

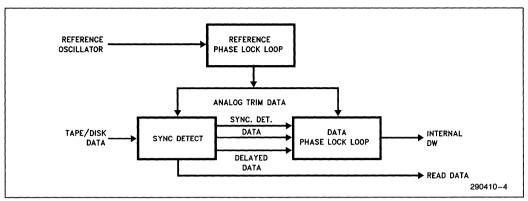

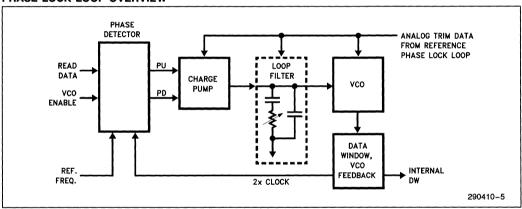

| 1.2 Power Management Scheme                        | 8    | 3.2 Data Separator                            | 15                  |

| 2.0 MICROPROCESSOR INTERFACE                       | 8    | 3.2.1 Jitter Tolerance .                      | 16                  |

| 2.1 Status, Data, and Control                      |      | 3.2.2 Locktime (t <sub>LOCK</sub> )           |                     |

| Registers                                          | 8    | 3.2.3 Capture Range                           |                     |

| 2.1.1a Status Register A<br>(SRA, PS/2 Mode)       | 8    | 3.3 Write Precompensation                     |                     |

| 2.1.1b Status Register A<br>(SRA, Model 30 Mode)   |      | 4.0 POWER MANAGEMENT FEATURES                 | 18                  |

| 2.1.2a Status Register B                           |      | 4.1 Oscillator Power Mana                     | gement 18           |

| (SRB, PS/2 Mode)                                   | 9    | 4.2 Part Power Manageme                       | ent18               |

| 2.1.2b Status Register B                           |      | 4.2.1 Powerdown Mode                          | s18                 |

| (SRB, Model 30 Mode)                               | 10   | 4.2.1a Direct Powerdow                        | vn18                |

| 2.1.3 Digital Output Register (DOR)                | 10   | 4.2.1b Auto Powerdowr                         | 18 18               |

| 2.1.4 Datarate Select Register                     | 10   | 4.2.2 Wake Up Modes                           | 19                  |

| (DSR)                                              | 11   | 4.2.2a Wake Up from D<br>Powerdown            |                     |

| 2.1.5 Main Status Register (MSR)                   |      | 4.2.2b Wake Up from A Powerdown               | uto<br>19           |

| 2.1.6 FIFO (Data)                                  | 12   | 4.3 Register Behavior                         |                     |

| 2.1.7a Digital Input Register (DIR, PC-AT Mode)    | 12   | 4.4 Pin Behavior                              |                     |

| 2.1.7b Digital Input Register                      |      | 4.4.1 System Interface                        | Pins 20             |

| (DIR, PS/2 Mode)                                   | 13   | 4.4.2 FDD Interface Pin                       | s20                 |

| 2.1.7c Digital Input Register (DIR, Model 30 Mode) | 14   | 5.0 CONTROLLER PHASES                         | 21                  |

| 2.1.8a Configuration Control                       |      | 5.1 Command Phases                            |                     |

| Register (ČCR, PC AT and PS/: Modes)               |      | 5.2 Execution Phases                          | 21                  |

| 2.1.8b Configuration Control                       | 14   | 5.2.1 Non-DMA Mode, from the FIFO to the      | Transfers<br>Host21 |

| Register (ČCR, Model 30 Mode)                      |      | 5.2.2 Non-DMA Mode, from the Host to the      | Transfers<br>FIFO21 |

| 2.2 RESET                                          |      | 5.2.3 DMA Mode, Trans<br>the FIFO to the Host | sfers from          |

| Reset                                              |      | 5.2.4 DMA Mode, Trans<br>the Host to the FIFO | sfers from          |

| ("Software" Reset)                                 |      | 5.2.5 Data Transfer Ter                       |                     |

| 2.3 DMA Transfers                                  | 15   | 5.3 Result Phase                              | 22                  |

|                                                    |      |                                               |                     |

| <b>CONTENTS</b> PA                  | GE   | CONTENTS                                           | PAGE  |

|-------------------------------------|------|----------------------------------------------------|-------|

| 6.0 COMMAND SET/DESCRIPTIONS        | 22   | 8.3 Compatibility with the FIFO                    | 42    |

| 6.1 Data Transfer Commands          |      | 8.4 Drive Polling                                  | 43    |

| 6.1.1 Read Data                     |      | 9.0 PROGRAMMING GUIDELINES                         | 43    |

| 6.1.2 Read Deleted Data             |      | 9.1 Command and Result Phase                       |       |

| 6.1.3 Read Track                    |      | Handshaking                                        | 43    |

| 6.1.4 Write Data                    |      | 9.2 Initialization                                 | 44    |

| 6.1.5 Write Deleted Data            |      | 9.3 Recalibrates and Seeks                         | 45    |

| 6.1.6 Verify                        |      | 9.4 Read/Write Data Operations                     | 45    |

| 6.1.7 Format Track                  |      | 9.5 Formatting                                     | 47    |

| 6.2 Control Commands                |      | 9.6 Verifies                                       |       |

| 6.2.1 Read ID                       | . 34 | 9.7 Powerdown State and Recove                     | ry 48 |

| 6.2.2 Recalibrate                   | . 34 | 9.7.1 Oscillator Power                             | 40    |

| 6.2.3 Seek                          | . 34 | Management                                         |       |

| 6.2.4 Sense Interrupt Status        | . 34 | 9.7.2 Part Power Management 9.7.2a Powerdown Modes |       |

| 6.2.5 Sense Drive Status            | . 35 | 9.7.2b Wake Up Modes                               |       |

| 6.2.6 Specify                       | . 35 | 9.7.2b wake op Modes                               | 49    |

| 6.2.7 Configure                     | . 35 | 10.0 DESIGN APPLICATIONS                           |       |

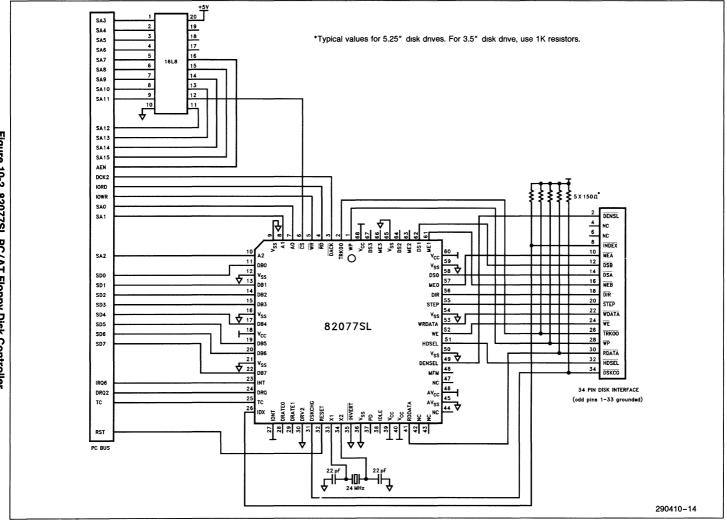

| 6.2.8 Version                       | . 36 | 10.1 PC/AT Floppy Disk Controlle                   | r 49  |

| 6.2.9 Relative Seek                 | . 36 | 10.1.1 PC/AT Floppy Disk Controller Architecture   | 40    |

| 6.2.10 Dumpreg                      | . 36 | 10.1.2 82077SL PC/AT Solutio                       |       |

| 6.2.11 Perpendicular Mode           |      | 10.1.2 820773L FC/AT 301010                        |       |

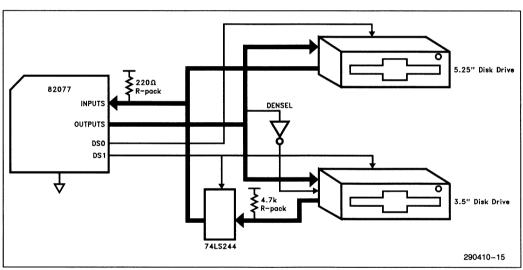

| Command                             |      | 10.2.1 3.5" Drives under the A                     |       |

| 6.2.12 Powerdown Mode Command       | 38   | Mode                                               |       |

| 6.3 Command Set Enhancements        |      | 10.2.2 3.5" Drives under the PS                    | 5/2   |

| 6.3.1 Perpendicular Mode            |      | Mode                                               |       |

| 6.3.2 Lock                          |      | 10.2.3 Combining 5.25" and 3.5                     |       |

|                                     |      |                                                    |       |

| 6.3.3 Enhanced Dumpreg Command      | . 39 | 11.0 DC SPECIFICATIONS                             |       |

| 7.0 STATUS REGISTER ENCODING        | 40   | 11.1 Absolute Maximum Ratings .                    |       |

| 7.1 Status Register 0               |      | 11.2 DC Characteristics                            |       |

| 7.2 Status Register 1               |      | 11.3 Oscillator                                    | 56    |

| 7.3 Status Register 2               |      | 12.0 AC SPECIFICATIONS                             | 57    |

| 7.4 Status Register 3               |      | 13.0 DATA SEPARATOR                                |       |

| •                                   |      | CHARACTERISTICS FOR FLOPP                          | Υ     |

| 8.0 COMPATIBILITY                   |      | DISK MODE                                          | 63    |

| 8.1 Register Set Compatibility      |      | 14.0 82077SL 68-LEAD PLCC                          |       |

| 8.2 PS/2 vs. AT vs. Mode 30 Mode    |      | PACKAGE THERMAL                                    | 2.4   |

| 8.2.1 PS/2 Mode<br>8.2.2 PC/AT Mode |      | CHARACTERISTICS                                    | 64    |

|                                     |      |                                                    |       |

| 8.2.3 Mode 30 Mode                  | 42   |                                                    |       |

**Table 1. 82077SL Pin Description**

| Symbol                                               | Pin#                                         | 1/0 |           | Description                                                                                                                                                                                                                        |               |             |                                                                                     |                  |   |

|------------------------------------------------------|----------------------------------------------|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|-------------------------------------------------------------------------------------|------------------|---|

| HOST IN                                              | TERFA                                        | CE  |           | ***************************************                                                                                                                                                                                            |               |             |                                                                                     |                  |   |

| RESET                                                | 32                                           | I   |           | RESET: A high level places the 82077SL in a known idle state. All registers are cleared except those set by the Specify command.                                                                                                   |               |             |                                                                                     |                  |   |

| <u>cs</u>                                            | 6                                            | ı   | СНІ       | CHIP SELECT: Decodes base address range and qualifies RD and WR inputs.                                                                                                                                                            |               |             |                                                                                     |                  |   |

| A0                                                   | 7                                            | ı   | ADI       | ADDRESS: Selects one of the host interface registers:                                                                                                                                                                              |               |             |                                                                                     |                  |   |

| A1<br>A2                                             | 8<br>10                                      |     | <b>A2</b> | A2 A1 A0 Access Type Register                                                                                                                                                                                                      |               |             |                                                                                     |                  |   |

|                                                      |                                              |     | 0         | 0                                                                                                                                                                                                                                  | 0             | R           | Status Register A                                                                   | SRA              |   |

| -                                                    |                                              |     | 0         | 0                                                                                                                                                                                                                                  | 1             | R           | Status Register B                                                                   | SRB              |   |

|                                                      |                                              |     | 0         | 1                                                                                                                                                                                                                                  | 0             | R/W         | Digital Output Register                                                             | DOR              |   |

|                                                      |                                              |     | 0         | 1                                                                                                                                                                                                                                  | 1             |             | Reserved                                                                            |                  |   |

|                                                      |                                              |     | 1         | 0                                                                                                                                                                                                                                  | 0             | R           | Main Status Register                                                                | MSR              |   |

|                                                      |                                              |     | 1         | 0                                                                                                                                                                                                                                  | 0             | w           | Data Rate Select Register                                                           | DSR              |   |

|                                                      |                                              |     | 1         | 0                                                                                                                                                                                                                                  | 1             | R/W         | Data (First In First Out)                                                           | FIFO             |   |

|                                                      |                                              |     | 1         | 1                                                                                                                                                                                                                                  | 0             |             | Reserved                                                                            |                  |   |

|                                                      |                                              |     | 1         | 1                                                                                                                                                                                                                                  | 1             | R           | Digital Input Register                                                              | DIR              |   |

|                                                      |                                              |     | 1         | 1                                                                                                                                                                                                                                  | 1             | w           | Configuration Control Register                                                      | CCR              | - |

| DB0<br>DB1<br>DB2<br>DB3<br>DB4<br>DB5<br>DB6<br>DB7 | 11<br>13<br>14<br>15<br>17<br>19<br>20<br>22 | 1/0 | DAI       | ABU                                                                                                                                                                                                                                | <b>JS:</b> Da | ata dus Wit | h 12 mA drive                                                                       |                  |   |

| RD                                                   | 4                                            | ı   | RE/       | ND: C                                                                                                                                                                                                                              | ontrol        | signal      |                                                                                     |                  |   |

| WR                                                   | 5                                            | ı   | WR        | ITE: (                                                                                                                                                                                                                             | Contro        | ol signal   |                                                                                     | - <del>1 1</del> |   |

| DRQ                                                  | 24                                           | 0   | but       | goes                                                                                                                                                                                                                               |               | h impedan   | sts service from a DMA controller.<br>ice in AT and Model 30 modes wh               |                  |   |

| DACK                                                 | 3                                            | ı   | cycl      | es. N                                                                                                                                                                                                                              | ormal         |             | Control input that qualifies the RE<br>ow, but is disabled in AT and Mode<br>e DOR. |                  |   |

| TC                                                   | 25                                           | ı   | disk      | TERMINAL COUNT: Control line from a DMA controller that terminates the current disk transfer. TC is accepted only while DACK is active. This input is active high in the AT, and Model 30 modes and active low in the PS/2TM mode. |               |             |                                                                                     |                  |   |

| INT                                                  | 23                                           | 0   | Nor       | INTERRUPT: Signals a data transfer in non-DMA mode and when status is valid. Normally active high, but goes to high impedance in AT, and Model 30 modes when the appropriate bit is set in the DOR.                                |               |             |                                                                                     |                  |   |

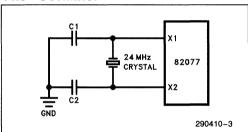

| X1<br>X2                                             | 33<br>34                                     |     | crys      |                                                                                                                                                                                                                                    | 1 may         |             | on for a 24 MHz fundamental mod<br>with a MOS level clock and X2 w                  |                  |   |

Table 1. 82077SL Pin Description (Continued)

| Symbol                   | Pin#                 | 1/0     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|--------------------------|----------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| HOST INTE                | RFACE                | (Conti  | nued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| IDENT                    | 27                   | 1       | IDENTITY: Upon Hardware RESET, this input (along with MFM pin) selects between the three interface modes. After RESET, this input selects the type of drive being accessed and alters the level on DENSEL. The MFM pin is also sampled at Hardware RESET, and then becomes an output again. Internal pullups on MFM permit a no connect.                                                                                                                                                                                    |  |  |  |  |  |

|                          |                      |         | IDENT MFM INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|                          |                      |         | 1 1 or NC AT Mode<br>1 0 ILLEGAL<br>0 1 or NC PS/2 Mode<br>0 0 Model 30 Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|                          |                      |         | AT MODE: Major options are: enables DMA Gate logic, TC is active high, Status Registers A & B not available.  PS/2 MODE: Major options are: No DMA Gate logic, TC is active low, Status Registers A & B are available.                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|                          |                      |         | Registers A & B are available.  MODEL 30 MODE: Major options are: enable DMA Gate logic, TC is active nigh, Status Registers A & B available.  After Hardware reset this pin determines the polarity of the DENSEL pin. IDENT at a logic level of "1", DENSEL will be active high for high (500 Kbps/1 Mbps) data rates (typically used for 5.25" drives). IDENT at a logic level of "0", DENSEL will be active low for high data rates (typically used for 3.5" drives). This assumes the INVERT pin to be tied to ground. |  |  |  |  |  |

| DISK CON                 | TROL (A              | II outp | uts have 40 mA drive capability)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| INVERT                   | 35                   | l       | INVERT: Strapping option. Determines the polartity of all signals in this section. Should be strapped to ground when using the internal buffers and these signals become active LOW. When strapped to VCC, these signals become active high and external inverting drivers and receivers are required.                                                                                                                                                                                                                      |  |  |  |  |  |

| ME0<br>ME1<br>ME2<br>ME3 | 57<br>61<br>63<br>66 | 0       | <b>ME0-3:</b> Decoded Motor enables for drives 0-3. The motor enable pins are directly controlled via the Digital Output Register.                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| DS0<br>DS1<br>DS2<br>DS3 | 58<br>62<br>64<br>67 | 0       | <b>DRIVE SELECT 0-3:</b> Decoded drive selects for drives 0-3. These outputs are decoded from the select bits in the Digital Output Register and gated by ME0-3.                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| HDSEL                    | 51                   | 0       | <b>HEAD SELECT:</b> Selects which side of a disk is to be used. An active level selects side 1.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| STEP                     | 55                   | 0       | STEP: Supplies step pulses to the drive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| DIR                      | 56                   | 0       | <b>DIRECTION:</b> Controls the direction the head moves when a step signal is present. The head moves toward the center if active.                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

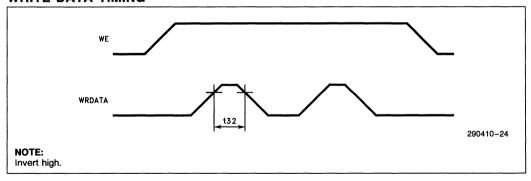

| WRDATA                   | 53                   | 0       | <b>WRITE DATA:</b> FM or MFM serial data to the drive. Precompensation value is selectable through software.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| WE                       | 52                   | 0       | WRITE ENABLE: Drive control signal that enables the head to write onto the disk.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| DENSEL                   | 49                   | 0       | <b>DENSITY SELECT:</b> Indicates whether a low (250/300 Kbps) or high (500 Kbps/1 Mbps) data rate has been selected.                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| DSKCHG                   | 31                   | ı       | DISK CHANGE: This input is reflected in the Digital Input Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

Table 1. 82077SL Pin Description (Continued)

| Symbol           | Pin#                                              | 1/0    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------|---------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DISK CON         | ITROL (                                           | All ou | tputs have 40 mA drive capability) (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DRV2             | 30                                                | ı      | <b>DRIVE2:</b> This indicates whether a second drive is installed and is reflected in Status Register A.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TRK0             | 2                                                 | 1      | TRACK0: Control line that indicates that the head is on track 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| WP               | 1                                                 | ı      | WRITE PROTECT: Indicates whether the disk drive is write protected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| INDX             | 26                                                | 1      | INDEX: Indicates the beginning of the track.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PLL SECT         | ION                                               |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RDDATA           | 41                                                | 1      | <b>READ DATA:</b> Serial data from the disk. INVERT also affects the polarity of this signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MFM              | 48                                                | 1/0    | MFM: At Hardware RESET, aids in configuring the 82077SL. Internal pull-up allows a no connect if a "1" is required. After reset this pin becomes an output and indicates the current data encoding/decoding mode (Note: If the pin is held at logic level "0" during hardware RESET it must be pulled to "1" after reset to enable the output. The pin can be released on the falling edge of hardware RESET to enable the output). MFM is active high (MFM). MFM may be left tied low after hardware reset, in this case the MFM function will be disabled. |

| DRATE0<br>DRATE1 | 28<br>29                                          | 0      | <b>DATARATEO-1:</b> Reflects the contents of bits 0,1 of the Data Rate Register. (Drive capability of +6.0 mA @ 0.4V and -4.0 mA @ 2.4V)                                                                                                                                                                                                                                                                                                                                                                                                                     |

| IDLE             | 38                                                | 0      | IDLE: This pin indicates that the part is in the IDLE state and can be powered down. IDLE state is defined as MSR = 80H, INT = 0, and the head being "unloaded" (as defined in Section 6.2.6). Whenever the part is in this state, IDLE pin is active high. If the part is powered down by the Auto Mode, IDLE pin is set high and if the part is powered down by setting the DSR POWERDOWN bit, IDLE pin is set low.                                                                                                                                        |

| PD               | 37                                                | 0      | POWERDOWN: This pin is active high whenever the part is in powerdown state, either via DSR POWERDOWN bit or via the Auto Mode. This pin can be used to disable external oscillator's output.                                                                                                                                                                                                                                                                                                                                                                 |

| MISCELL          | ANEOU                                             | S      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VCC              | 18<br>39<br>40<br>60<br>68                        |        | Voltage: +5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| GND              | 9<br>12<br>16<br>21<br>36<br>50<br>54<br>59<br>65 |        | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| AVCC             | 46                                                |        | Analog Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AVSS             | 45                                                |        | Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| NC               | 42<br>43<br>44<br>47                              |        | No Connection: These pins MUST be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

### 1.0 INTRODUCTION

The 82077SL is a single-chip floppy disk controller for portable PC designs, PC-ATTM, MicrochannelTM and EISA systems. The 82077SL includes all the power management features necessary to implement a powerful laptop and notebook solution. The 82077SL is fully compatible with the 82077AA. The pin out remains the same with the exception of two new powerdown status pins, PD and IDLE. These pins will replace the LOFIL and HIFIL pins on the 82077AA that are used to connect an external capacitor.

The 82077SL, a 24 MHz crystal, a resistor package and a chip select implement a complete design. The power management features of the 82077SL are designed to be transparent to all application software. The 82077SL will seem awake to the software even

when it is in powerdown mode. All drive control signals are fully decoded and have 40 mA drive buffers with selectable polarity. Signals returned from the drive are sent through on-chip input buffers with hysteresis for noise immunity. The integrated analog data separator needs no external compensation of components, yet allows for wide motor variation with exceptionally low soft error rates. The microprocessor interface has 12 mA drive buffers on the data bus plus 100% hardware register compatibility for PC-ATTM and MicrochannelTM systems. The 16-byte FIFO with programmable thresholds is extremely useful in multi-master systems (MicrochannelTM, EISA) or systems with large bus latency.

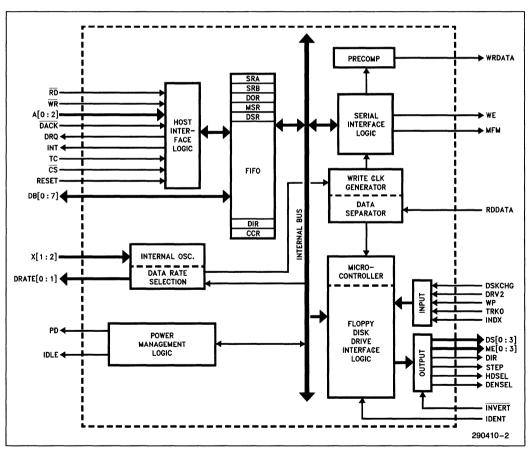

Upon hardware reset, (Pin 32) the 82077SL defaults to 8272A functionality. Figure 1-1 is a block diagram of the 82077SL.

Figure 1-1, 82077SL Block Diagram

# 1.1 Perpendicular Recording Mode

An added capability of the 82077SL is the ability to interface directly to perpendicular recording floppy drives. Perpendicular recording differs from the traditional longitudinal method by orienting the magnetic bits vertically. This scheme packs in more data bits for the same area.

The 82077SL with perpendicular recording drives can read standard 3.5" floppies as well as read and write perpendicular media. Some manufacturers offer drives that can read and write standard and perpendicular media in a perpendicular media drive.

A single command puts the 82077SL into perpendicular mode. All other commands operate as they normally do. The perpendicular mode requires the 1 Mbps data rate of the 82077SL. At this data rate, the FIFO eases the host interface bottleneck due to the speed of data transfer to or from the disk.

# 1.2 Power Management Scheme

While maintaining compatibility with 82077AA, the 82077SL contains a powerful set of features for conserving power. This enables the 82077SL to play an important role in the power sensitive environment of portable personal computers. These features are transparent to any application software.

The 82077SL supports two powerdown modes—direct powerdown and automatic powerdown. Direct powerdown refers to direct action by the software to powerdown without dependence on external factors. Automatic powerdown results from 82077SL's monitoring of the current conditions according to a previously programmed mode. The 82077SL contains a new powerdown command that via programming can be used to invoke auto powerdown. 82077SL is powered down whenever a set of conditions are satisfied. Any hardware reset disables the automatic powerdown command. Software resets have no effect on the POWERDOWN command parameters.

The 82077SL also supports powerdown of its internal crystal oscillator independent of the powerdown modes described above. By setting bit 5 in DSR register, the internal oscillator is turned off. This bit has sole control of the oscillator powerdown. This allows the internal oscillator to be turned off when an external oscillator is used.

## 2.0 MICROPROCESSOR INTERFACE

The interface consists of the standard asynchronous signals; RD, WR, CS, A0-A2, INT, DMA control and

a data bus. The address lines select between configuration registers, the FIFO and control/status registers. This interface can be switched between PC AT, Model 30, or PS/2TM normal modes. The PS/2TM register sets are a superset of the registers found in a PC-AT.

# 2.1 Status, Data and Control Registers

As shown below, the base address range is supplied via the  $\overline{\text{CS}}$  pin. For PC-ATTM or PS/2TM designs, the primary and secondary address ranges are 3F0 Hex to 37F Hex and 370 Hex to 377 Hex respectively.

| A2 | <b>A</b> 1 | A0 | Access<br>Type | Register                       |      |

|----|------------|----|----------------|--------------------------------|------|

| 0  | 0          | 0  | R              | Status Register A              | SRA  |

| 0  | 0          | 1  | R              | Status Register B              | SRB  |

| 0  | 1          | 0  | R/W            | Digital Output Register        | DOR  |

| 0  | 1          | 1  |                | Reserved                       |      |

| 1  | 0          | 0  | R              | Main Status Register           | MSR  |

| 1  | 0          | 0  | · W            | Data Rate Select Register      | DSR  |

| 1  | 0          | 1  | R/W            | Data (First In First Out)      | FIFO |

| 1  | 1          | 0  |                | Reserved                       |      |

| 1  | 1          | 1  | R              | Digital Input Register         | DIR  |

| 1  | 1          | 1  | w              | Configuration Control Register | CCR  |

In the following sections, the various registers are shown in their powerdown state. The "UC" notation stands for a value that is returned without change from the active mode. The notation " \* " means that the value is reflecting the actual status of the 82077SL, but the value is determinable in the powerdown state. "N/A" reflects the values of the pins indicated. "X" indicates that the value is undefined.

# 2.1.1a STATUS REGISTER A (SRA, PS/2 MODE)

This register is read-only and monitors the state of the interrupt pin and several disk interface pins. This register is part of the register set, and is not accessible in PC-AT mode.

This register can be accessed during powerdown state without waking up the 82077SL from its powerdown state.

| Bits            | 7              | 6°   | 5    | 4°   | 3     | <b>2</b> ° | 1°C | 0   |

|-----------------|----------------|------|------|------|-------|------------|-----|-----|

| Function        | INT<br>PENDING | DRV2 | STEP | TRKO | HDSEL | ĪNDX       | WP  | DIR |

| H/W Reset State | 0              | N/A  | 0    | N/A  | 0     | N/A        | N/A | 0   |

| Auto PD State   | 0*             | UC   | 0*   | 1    | 0*    | 1          | 1   | 0*  |

The INT PENDING bit is used by software to monitor the state of the 82077SL INTERRUPT pin. The bits marked with a "°" reflect the state of drive signals on the cable and are independent of the state of the INVERT pin.

The INT PENDING bit is low by definition for 82077SL to be in powerdown. The bits reflecting the floppy disk drive input pins (TRK0, INDEX and WP) are forced to an inactive state. The floppy disk drive outputs (HDSEL, STEP, and DIR) also go to their inactive, default state.

As a read-only register, there is no default value associated with a reset other than some drive bits will change with a reset. The INT PENDING, STEP, HDSEL, and DIR bits will be low after reset.

## 2.1.1b STATUS REGISTER A (SRA, MODEL 30 MODE)

| Bits            | 7              | 6   | 5           | 4    | 3     | 2    | 1   | 0   |

|-----------------|----------------|-----|-------------|------|-------|------|-----|-----|

| Function        | INT<br>PENDING | DRQ | STEP<br>F/F | TRK0 | HDSEL | INDX | WP  | DIR |

| H/W Reset State | 0              | 0   | 0           | N/A  | 1     | N/A  | N/A | 1   |

| Auto PD State   | 0*             | 0*  | 0           | 0    | 1*    | 0    | 0   | 1*  |

This register has the following changes in PS/2 Model 30 Mode. Disk interface pins (Bits 0, 1, 2, 3, & 4) are inverted from PS/2 Mode. The DRQ bit monitors the status of the DMA Request pin. The STEP bit is latched with the Step output going active and is cleared with a read to the DIR register, Hardware or Software RESET.

The DRQ bit is low by definition for 82077SL to be in powerdown. The bits reflecting the floppy disk drive input pins (TRK0, INDEX and WP) are forced to reflect an inactive state. The floppy disk drive outputs (HDSEL, STEP, and DIR) also go to their inactive, default state.

## 2.1.2a STATUS REGISTER B (SRB, PS/2 MODE)

This register is read-only and monitors the state of several disk interface pins. This register is part of the PS/2 register set, and is not accessible in PC-AT mode.

| Bits            | 7 | 6 | 5              | 4                | 3*               | 2  | 1          | 0          |

|-----------------|---|---|----------------|------------------|------------------|----|------------|------------|

| Function        | 1 | 1 | DRIVE<br>SEL 0 | WRDATA<br>TOGGLE | RDDATA<br>TOGGLE | WE | MOT<br>EN1 | MOT<br>EN0 |

| H/W Reset State | 1 | 1 | 0              | 0                | 0                | 0  | 0          | 0          |

| Auto PD State   | 1 | 1 | UC             | 0                | 0                | 0* | 0          | 0          |

As the only drive input, RDDATA TOGGLE's activity is independent of the INVERT pin level and reflects the level as seen on the cable.

The two TOGGLE bits do not read back the state of their respective pins directly. Instead, the pins drive a Flip/Flop which produces a wider and more reliably read pulse. Bits 6 and 7 are undefined and always return a 1.

After any reset, the activity on the TOGGLE pins are cleared. Drive select and Motor bits cleared by the RESET pin and not software resets.

| Bits            | 7    | 6   | 5   | 4             | 3             | 2         | 1   | 0   |

|-----------------|------|-----|-----|---------------|---------------|-----------|-----|-----|

| Function        | DRV2 | DS1 | DS0 | WRDATA<br>F/F | RDDATA<br>F/F | WE<br>F/F | DS3 | DS2 |

| H/W Reset State | N/A  | 1   | 1   | 0             | 0             | 0         | 1   | 1   |

| Auto PD State   | UC   | UC  | UC  | 0             | 0             | 0         | UC  | UC  |

# 2.1.2b STATUS REGISTER B (SRB, MODEL 30 MODE)

This register has the following changes in Model 30 Mode. Bits 0, 1, 5, and 6 return the decoded value of the Drive Select bits in the DOR register. Bits 2, 3, and 4 are set by their respective active going edges and are cleared by reading the DIR register. The WRDATA bit is triggered by raw WRDATA signals and is not gated by WE. Bits 2, 3, and 4 are cleared to a low level by either Hardware or Software RESET.

## 2.1.3 DIGITAL OUTPUT REGISTER (DOR)

The Digital Output Register contains the drive select and motor enable bits, a reset bit and a DMA GATE bit.

| Bits            | 7          | 6          | 5          | 4          | 3           | 2     | 1             | 0             |

|-----------------|------------|------------|------------|------------|-------------|-------|---------------|---------------|

| Function        | MOT<br>EN3 | MOT<br>EN2 | MOT<br>EN1 | MOT<br>EN0 | DMA<br>GATE | RESET | DRIVE<br>SEL1 | DRIVE<br>SEL2 |

| H/W Reset State | 0          | 0          | 0          | 0          | 0           | 0     | 0             | 0             |

| Auto PD State   | 0*         | 0*         | 0*         | 0*         | UC          | 1*    | UC            | UC            |

The MOT ENx bits directly control their respective motor enable pins (ME0-3). A one means the pin is active, the INVERT pin determines the active level. The DRIVE SELx bits are decoded to provide four drive select lines and only one may be active at a time. A one is active and the INVERT pin determines the level on the cable. Standard programming practice is to set both MOT ENx and DRIVE SELx bits at the same time.

Table 2-1 lists a set of DOR values to activate the drive select and motor enable for each drive.

| Table 2-1. Drive Activation values |           |  |  |  |  |  |

|------------------------------------|-----------|--|--|--|--|--|

| Drive                              | DOR Value |  |  |  |  |  |

| 0                                  | 1CH       |  |  |  |  |  |

| 1 1                                | 2DH       |  |  |  |  |  |

| 2                                  | 4EH       |  |  |  |  |  |

| 3                                  | 8FH       |  |  |  |  |  |

**Table 2-1. Drive Activation Values**

The DMAGATE bit is enabled only in PC-AT and Model 30 Modes. If DMAGATE is set low, the INT and DRQ outputs are tristated and the DACK and TC inputs are disabled. DMAGATE set high will enable INT, DRQ, TC, and DACK to the system. In PS/2 Mode DMAGATE has no effect upon INT, DRQ, TC or DACK pins and they are always active.

The DOR reset bit and the Motor Enable bits have to be inactive when the 82077SL is in powerdown. The DMAGATE and DRIVE SEL bits are unchanged. During powerdown, writing to the DOR does not awaken the 82077SL with the exception of activating any of the motor enable bits. Setting the motor enable bits active (high) will wake up the part.

This RESET bit clears the basic core of the 82077SL and the FIFO circuits when the LOCK bit is set to "0" (see Section 5.3.2 for LOCK bit definition). Once set, it remains set until the user clears this bit. This bit is set by a chip reset and the 82077SL is held in a reset state until the user clears this bit. The RESET bit has no effect upon this register.

|                 |              | •             | •     |               |               |               |               |               |

|-----------------|--------------|---------------|-------|---------------|---------------|---------------|---------------|---------------|

| Bits            | 7            | 6             | 5     | 4             | 3             | 2             | 1             | 0             |

| Function        | S/W<br>RESET | POWER<br>DOWN | PDOSC | PRE-<br>COMP2 | PRE-<br>COMP1 | PRE-<br>COMP0 | DRATE<br>SEL1 | DRATE<br>SEL0 |

| H/W Reset State | 0            | 0             | 0     | 0             | 0             | 0             | 1             | 0             |

| Auto PD State   | 0            | 0             | UC    | UC            | UC            | UC            | UC            | UC            |

### 2.1.4 DATARATE SELECT REGISTER (DSR)

This register ensures backward compatibility with the 82072 floppy controller and is write-only. Changing the data rate changes the timings of the drive control signals. To ensure that drive timings are not violated when changing data rates, choose a drive timing such that the fastest data rate will not violate the timing.

This register is identical to the one used in 82077AA with the exception of bit 5. This bit in the 82077SL denoted by PDOSC is used to implement crystal oscillator power management. The internal oscillator in the 82077SL can be programmed to be either powered on or off via the PDOSC bit. This capability is independent of the chip's powerdown state. In other words, auto powerdown mode and powerdown via activating POWERDOWN bit has no effect over the power state of the oscillator.

In the default state the PDOSC bit is low and the oscillator is powered up. When this bit is programmed to a one, the oscillator is shut off. Hardware reset clears this bit to a zero. Neither of the software resets (via DOR or DSR) have any effect on this bit. When an external oscillator is used, this bit can be set to reduce power consumption. When an internal oscillator is used, this bit can be set to turn off the oscillator to conserve power. However. PDOSC must go high only when the part is in the powerdown state, otherwise the part will not function correctly and must be hardware reset once the oscillator has turned back on and stabilized. Setting the PDOSC bit has no effect on the clock input to the 82077SL (the X1 pin). The clock input is separately disabled when the part is powered down.

S/W RESET behaves the same as DOR RESET except that this reset is self clearing.

POWERDOWN bit implements direct powerdown. Setting this bit high will put the 82077SL into the powerdown state regardless of the state of the part. The part is internally reset and then put into powerdown. No status is saved and any operation in progress is aborted. Unlike the 82077AA this mode of powerdown does not turn off the internal oscillator. Any hardware or software reset will exit the 82077SL from this powerdown state.

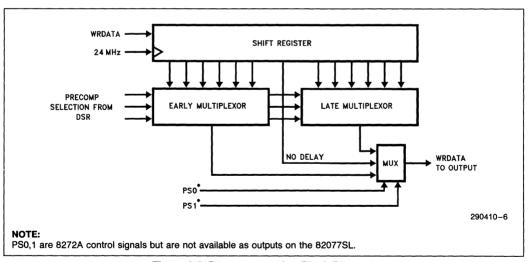

PRECOMP 0-2 adjusts the WRDATA output to the disk to compensate for magnetic media phenomena known as bit shifting. The data patterns that are sus-

ceptible to bit shifting are well understood and the 82077SL compensates the data pattern as it is written to the disk. The amount of precompensation is dependent upon the drive and media but in most cases the default value is acceptable.

The 82077SL starts precompensating the data pattern starting on Track 0. The CONFIGURE command can change the track that precompensating starts on. Table 2-2 lists the precompensation values that can be selected and Table 2-3 lists the default precompensation values. The default value is selected if the three bits are zeros.

DRATE 0-1 select one of the four data rates as listed in Table 2-4. The default value is 250 Kbps upon a chip ("Hardware") reset. Other ("Software") Resets do not affect the DRATE or PRECOMP bits.

**Table 2-2. Precompensation Delays**

| PRECOMP<br>432 | Precompensation Delay |

|----------------|-----------------------|

| 111            | 0.00 ns—DISABLED      |

| 001            | 41.67 ns              |

| 010            | 83.34 ns              |

| 011            | 125.00 ns             |

| 100            | 166.67 ns             |

| 101            | 208.33 ns             |

| 110            | 250.00 ns             |

| 000            | DEFAULT               |

**Table 2-3. Default Precompensation Delays**

| Data Rate | Precompensation Delays |

|-----------|------------------------|

| 1 Mbps    | 41.67 ns               |

| 500 Kbps  | 125 ns                 |

| 300 Kbps  | 125 ns                 |

| 250 Kbps  | 125 ns                 |

**Table 2-4. Data Rates**

| DRAT | ESEL | DATA RATE |          |  |  |

|------|------|-----------|----------|--|--|

| 1    | 0    | MFM       | FM       |  |  |

| 1    | 1    | 1 Mbps    | Illegal  |  |  |

| 0    | 0    | 500 Kbps  | 250 Kbps |  |  |

| 0    | 1    | 300 Kbps  | 150 Kbps |  |  |

| 1    | 0    | 250 Kbps  | 125 Kbps |  |  |

| 2.1.3 MAIN O'ATOO NEGIOTEN (MON) |     |     |            |            |              |              |              |              |  |  |

|----------------------------------|-----|-----|------------|------------|--------------|--------------|--------------|--------------|--|--|

| Bits                             | 7   | 6   | 5          | 4          | 3*           | 2            | 1            | 0            |  |  |

| Function                         | RQM | DIO | NON<br>DMA | CMD<br>BSY | DRV3<br>BUSY | DRV2<br>BUSY | DRV1<br>BUSY | DRV0<br>BUSY |  |  |

| H/W Reset State                  | 0   | Х   | Х          | Х          | Х            | Х            | Х            | Х            |  |  |

| Auto PD State                    | 1   | 0   | 0          | 0          | 0            | 0            | 0            | 0            |  |  |

#### 2.1.5 MAIN STATUS REGISTER (MSR)

The Main Status Register is a read-only register and is used for controlling command input and result output for all commands.

RQM—Indicates that the host can transfer data if set to a 1. No access is permitted if set to a 0.

DIO—Indicates the direction of a data transfer once RQM is set. A 1 indicates a read and a 0 indicates a write is required.

NON-DMA—This mode is selected in the SPECIFY command and will be set to a 1 during the execution phase of a command. This is for polled data transfers and helps differentiate between the data transfer phase and the reading of result bytes.

COMMAND BUSY—This bit is set to a one when a command is in progress. This bit will go active after the command byte has been accepted and goes inactive at the end of the results phase. If there is no result phase (SEEK, RECALIBRATE commands), this bit is returned to a 0 after the last command byte.

DRV x BUSY—These bits are set to ones when a drive is in the seek portion of a command, including seeks, and recalibrates.

#### 2.1.6 FIFO (DATA)

All command parameter information and disk data transfers go through the FIFO. The FIFO is 16 bytes in size and has programmable threshold values. Data transfers are governed by the RQM and DIO bits in the Main Status Register.

The FIFO defaults to an 8272A compatible mode after a "Hardware" reset (Reset via pin 32). "Software" Resets (Reset via DOR or DSR register) can also place the 82077SL into 8272A compatible mode if the LOCK bit is set to "0" (See section 5.3.2 for the definition of the LOCK bit). This maintains PC-AT hardware compatibility. The default values can be changed through the CONFIGURE command (enable full FIFO operation with threshold

control). The advantage of the FIFO is that it allows the system a larger DMA latency without causing a disk error. Table 2.5 gives several examples of the delays with a FIFO. The data is based upon the following formula:

Threshold#

$$\times \left| \frac{1}{\text{DATA RATE}} \times 8 \right| - 1.5 \,\mu\text{s} = \text{DELAY}$$

Table 2-5. FIFO Service Delay

| FIFO Threshold<br>Examples | Maximum Delay to Servicing at 1 Mbps Data Rate |  |  |  |  |  |  |

|----------------------------|------------------------------------------------|--|--|--|--|--|--|

| 1 byte                     | $1 \times 8$ μs $- 1.5$ μs $= 6.5$ μs          |  |  |  |  |  |  |

| 2 bytes                    | $2 \times 8 \mu s - 1.5 \mu s = 14.5 \mu s$    |  |  |  |  |  |  |

| 8 bytes                    | $8 \times 8 \mu s - 1.5 \mu s = 62.5 \mu s$    |  |  |  |  |  |  |

| 15 bytes                   | $15 \times 8 \mu s - 1.5 \mu s = 118.5 \mu s$  |  |  |  |  |  |  |

| FIFO Threshold<br>Examples | Maximum Delay to Servicing<br>at 500 Kbps Data Rate |

|----------------------------|-----------------------------------------------------|

| 1 byte                     | $1 \times 16 \mu s - 1.5 \mu s = 14.5 \mu s$        |

| 2 bytes                    | $2 \times 16$ μs $-1.5$ μs $=30.5$ μs               |

| 8 bytes                    | $8 \times 16 \mu s - 1.5 \mu s = 126.5 \mu s$       |

| 15 bytes                   | $15 \times 16 \mu s - 1.5 \mu s = 238.5 \mu s$      |

At the start of a command, the FIFO action is always disabled and command parameters must be sent based upon the RQM and DIO bit settings. As the 82077SL enters the command execution phase, it clears the FIFO of any data to ensure that invalid data is not transferred.

An overrun or underrun will terminate the current command and the transfer of data. Disk writes will complete the current sector by generating a 00 pattern and valid CRC.

# 2.1.7a DIGITAL INPUT REGISTER (DIR, PC-AT MODE)

This register is read only in all modes. In PC-AT mode only bit 7 is driven, all other bits remain tristated.

| Bits            | 7   | 6 | 5 | 4 | 3* | 2 | 1 | 0 |

|-----------------|-----|---|---|---|----|---|---|---|

| Function        | DSK | _ | _ | _ | _  | _ | _ |   |

| H/W Reset State | N/A |   | _ | _ | _  | _ | _ | _ |

| Auto PD State   | 0   |   | _ |   |    |   |   | _ |

DSKCHG monitors the pin of the same name and reflects the opposite value seen on the disk cable, regardless of the value of INVERT. The DSKCHG bit

is forced inactive along with all the inputs from the floppy disk drive. All the other bits remain tristated.

# 2.1.7b DIGITAL INPUT REGISTER (DIR, PS/2 MODE)

| Bits            | 7          | 6 | 5 | 4 | 3 | 2             | 1             | 0            |

|-----------------|------------|---|---|---|---|---------------|---------------|--------------|

| Function        | DSK<br>CHG | 1 | 1 | 1 | 1 | DRATE<br>SEL1 | DRATE<br>SEL0 | HIGH<br>DENS |

| H/W Reset State | N/A        | 1 | 1 | 1 | 1 | 1             | 0             | 1            |

| Auto PD State   | 0          | 1 | 1 | 1 | 1 | UC            | UC            | UC           |

The following is changed in PS/2 Mode: Bits 6, 5, 4, and 3 return a value of "1", and the DRATE SEL1-0 return the value of the current data rate selected (see Table 2-4 for values).

HIGH DENS is low whenever the 500 Kbps or 1 Mbps data rates are selected. This bit is independent of the effects of the IDENT and INVERT pins.

The DSKCHG bit is forced inactive along with all the inputs from the floppy disk drive. All the other bits (as applicable) remain unchanged.

Table 2-6 shows the state of the DENSEL pin when INVERT is low.

This pin is set high after a pin RESET and is unaffected by DOR and DSR resets.

Table 2-6. DENSEL Encoding

| Data Rate | IDENT* | DENSEL |  |  |  |  |  |  |

|-----------|--------|--------|--|--|--|--|--|--|

| 1 Mbps    | 0      | 0      |  |  |  |  |  |  |

|           | 1      | 1      |  |  |  |  |  |  |

| 500 Kbps  | 0      | 0      |  |  |  |  |  |  |

|           | 1      | 1      |  |  |  |  |  |  |

| 300 Kbps  | 0      | 1      |  |  |  |  |  |  |

|           | 1      | 0      |  |  |  |  |  |  |

| 250 Kbps  | 0      | 1      |  |  |  |  |  |  |

|           | 1      | 0      |  |  |  |  |  |  |

<sup>\*</sup>After ("Hardware") Chip Reset

| 2.1.7c | DIGITAL | INPUT | REGISTER | (DIR, | MODEL | 30 MODE) |

|--------|---------|-------|----------|-------|-------|----------|

|--------|---------|-------|----------|-------|-------|----------|

| Bits            | 7          | 6 | 5 | 4 | 3           | 2      | 1             | 0             |

|-----------------|------------|---|---|---|-------------|--------|---------------|---------------|

| Function        | DSK<br>CHG | 0 | 0 | 0 | DMA<br>GATE | NOPREC | DRATE<br>SEL1 | DRATE<br>SEL0 |

| H/W Reset State | N/A        | 0 | 0 | 0 | 0           | 0      | 1             | 0             |

| Auto PD State   | 1          | 0 | 0 | 0 | UC          | UC     | UC            | UC            |

The following is changed in Model 30 Mode: Bits 6, 5, and 4 return a value of "0", and Bit 7 (DSKCHG) is inverted in Model 30 Mode.

The DSKCHG bit is forced inactive along with all the inputs from the floppy disk drive. All the other bits (as applicable) remain unchanged.

Bit 3 reflects the value of DMAGATE bit set in the DOR register.

Bit 2 reflects the value of NOPREC bit set in the CCR register.

## 2.1.8a CONFIGURATION CONTROL REGISTER (CCR, PC AT and PS/2 MODES)

This register sets the datarate and is write only. In the PC-AT it is named the DSR.

| Bits            | 7 | 6 | 5 | 4 | 3 | 2 | 1             | 0             |

|-----------------|---|---|---|---|---|---|---------------|---------------|

| Function        | _ |   |   |   |   |   | DRATE<br>SEL1 | DRATE<br>SEL0 |

| H/W Reset State | _ | _ | _ | _ |   | _ | 1             | 0             |

| Auto PD State   | _ |   |   | _ |   | _ | UC            | UC            |

Refer to the table in the Data Rate Select Register for values. Unused bits should be set to 0.

## 2.1.8b CONFIGURATION CONTROL REGISTER (CCR, MODEL 30 MODE)

| Bits            | 7 | 6 | 5 | 4 | 3 | 2      | 1             | 0             |

|-----------------|---|---|---|---|---|--------|---------------|---------------|

| Function        | _ |   |   |   | _ | NOPREC | DRATE<br>SEL1 | DRATE<br>SEL0 |

| H/W Reset State |   |   | _ | _ | _ | 0      | 1             | 0             |

| Auto PD State   |   |   |   | _ |   | UC     | UC            | UC            |

NOPREC has no function, and is reset to "0" with a Hardware RESET only.

#### 2.2 RESET

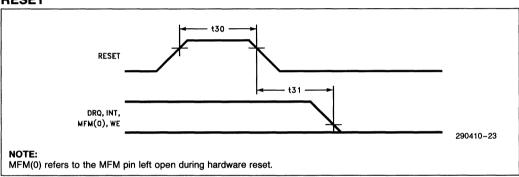

There are three sources of reset on the 82077SL; the RESET pin, a reset generated via a bit in the DOR and a reset generated via a bit in the DSR. All resets take the 82077SL out of the power down state.

On entering the reset state, all operations are terminated and the 82077SL enters an idle state. Activating reset while a disk write activity is in progress will corrupt the data and CRC.

On exiting the reset state, various internal registers are cleared, and the 82077SL waits for a new command. Drive polling will start unless disabled by a new CONFIGURE command.

## 2.2.1 RESET PIN ("HARDWARE") RESET

The RESET pin is a global reset and clears all registers except those programmed by the SPECIFY command. The DOR Reset bit is enabled and must be cleared by the host to exit the reset state.

# 2.2.2 DOR RESET vs DSR RESET ("SOFTWARE" RESET)

These two resets are functionally the same. The DSR Reset is included to maintain 82072 compatibility. Both will reset the 8272 core which affects drive status information. The FIFO circuits will also be reset if the LOCK bit is a "0" (See Section 5.3.2 for the definition of the LOCK bit). The DSR Reset clears itself automatically while the DOR Reset requires the host to manually clear it. DOR Reset has precedence over the DSR Reset. The DOR Reset is set automatically upon a pin RESET. The user must manually clear this reset bit in the DOR to exit the reset state.

The t30a specification in the A.C. Specifications gives the minimum amount of time that the DOR reset must be held active. This amount of time that the DOR reset must be held active is dependent upon the data rate. 82077SL requires that the DOR reset bit must be held active for at least 0.5  $\mu s$  at 250 Kbps. This is less than a typical ISA I/O cycle time.

## 2.3 DMA Transfers

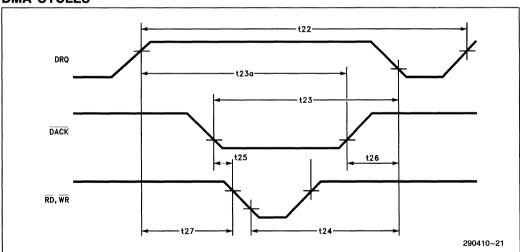

DMA transfers are enabled with the SPECIFY command and are initiated by the 82077SL by activating the DRQ pin during a data transfer command. The FIFO is enabled directly by asserting DACK and addresses need not be valid.

### 3.0 DRIVE INTERFACE

The 82077SL has integrated all of the logic needed to interface to a floppy disk which use floppy interface. All drive outputs have 40 mA drive capability and all inputs use a receive buffer with hysteresis. The internal analog data separator requires no external components, yet allows for an extremely wide capture range with high levels of read-data jitter, and ISV. The designer needs only to run the 82077SL disk drive signals to the disk or tape drive connector.

## 3.1 Cable Interface

The INVERT pin selects between using the internal buffers on the 82077SL or user supplied inverting

buffers. INVERT pulled to V<sub>CC</sub> disables the internal buffers; pulled to ground will enable them. There is no need to use external buffers with the 82077SL in typical PC applications.

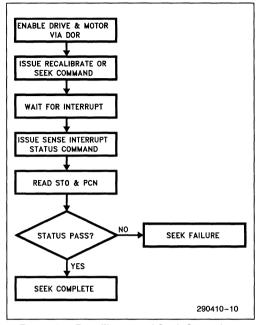

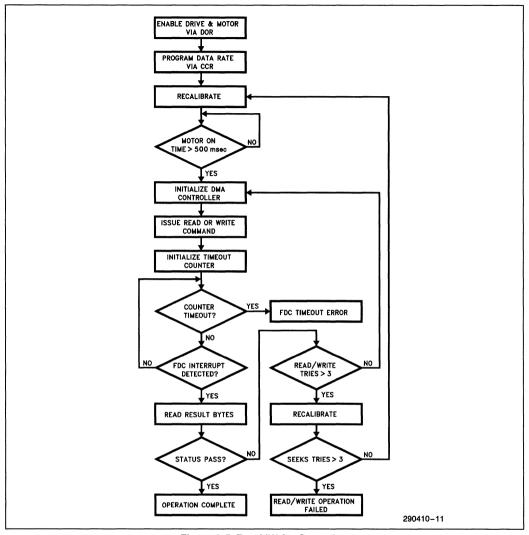

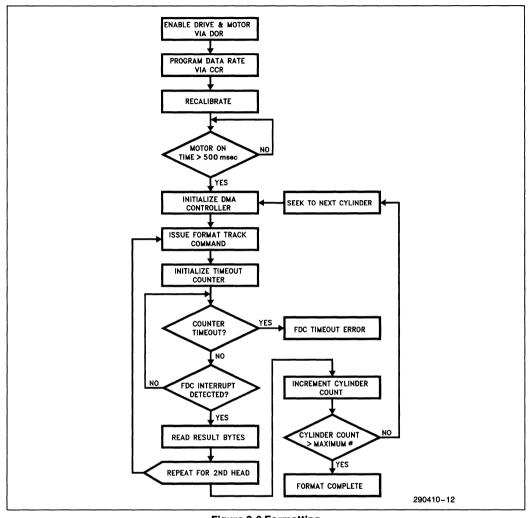

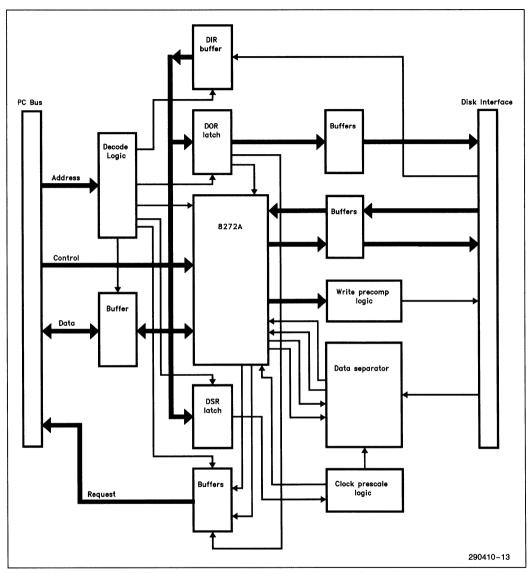

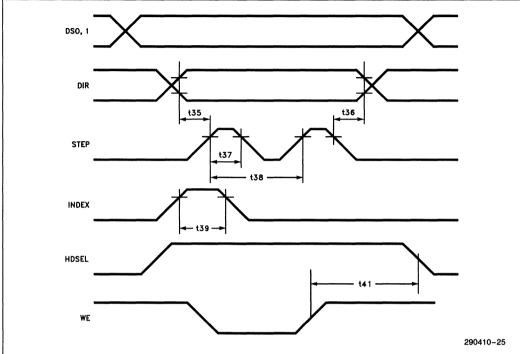

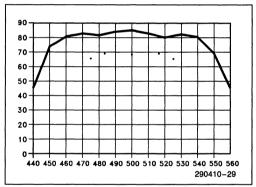

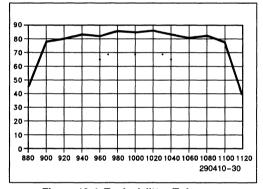

The polarity of the DENSEL pin is controlled through the IDENT pin, after hardware reset. For 5.25" drives a high on DENSEL tells the drive that either the 500 Kbps or 1 Mbps data rate is selected. For some 3.5" drives the polarity of DENSEL changes to a low for high data rates. See **Table 2-6 DENSEL Encoding** for IDENT pin settings.