**Microcomputer Programmable Logic Handbook**

1989

# Microcomputer Programmable Logic Handbook

# intel

## LITERATURE

To order Intel Literature or obtain literature pricing information in the U.S. and Canada call or write Intel Literature Sales. In Europe and other international locations, please contact your local sales office or distributor.

INTEL LITERATURE SALES P.O. BOX 58130 SANTA CLARA, CA 95052-8130 In the U.S. and Canada call toll free (800) 548-4725

## **CURRENT HANDBOOKS**

Product line handbooks contain data sheets, application notes, article reprints and other design information.

| TITLE                                                                                       | LITERATURE<br>ORDER NUMBER |

|---------------------------------------------------------------------------------------------|----------------------------|

| COMPLETE SET OF HANDBOOKS<br>(Available in U.S. and Canada only)                            | 231003                     |

| AUTOMOTIVE PRODUCTS HANDBOOK<br>(Not included in handbook set)                              | 231792                     |

| COMPONENTS QUALITY/RELIABILITY HANDBOOK                                                     | 210997                     |

| EMBEDDED CONTROL APPLICATIONS HANDBOOK                                                      | 270648                     |

| 8-BIT EMBEDDED CONTROLLER HANDBOOK                                                          | 270645                     |

| 16-BIT EMBEDDED CONTROLLER HANDBOOK                                                         | 270646                     |

| 32-BIT EMBEDDED CONTROLLER HANDBOOK                                                         | 270647                     |

| MEMORY COMPONENTS HANDBOOK                                                                  | 210830                     |

| MICROCOMMUNICATIONS HANDBOOK                                                                | 231658                     |

| MICROCOMPUTER PROGRAMMABLE LOGIC HANDBOOK                                                   | 296083                     |

| MICROPROCESSOR AND PERIPHERAL HANDBOOK<br>(2 volume set)                                    | 230843                     |

| MILITARY PRODUCTS HANDBOOK<br>(2 volume set. Not included in handbook set)                  | 210461                     |

| OEM BOARDS AND SYSTEMS HANDBOOK                                                             | 280407                     |

| PRODUCT GUIDE<br>(Overview of Intel's complete product lines)                               | 210846                     |

| SYSTEMS QUALITY/RELIABILITY HANDBOOK                                                        | 231762                     |

| INTEL PACKAGING OUTLINES AND DIMENSIONS<br>(Packaging types, number of leads, etc.)         | 231369                     |

| LITERATURE PRICE LIST (U.S. and Canada)<br>(Comprehensive list of current Intel Literature) | 210620                     |

| INTERNATIONAL LITERATURE GUIDE                                                              | E00029                     |

CG/LIT/100188

About Our Cover:

From robotics to lap-top computers, Intel's Erasable Programmable Logic Devices (EPLDs) are the most advanced in the microcomputer industry. How you personally choose to implement their power is only limited by your imagination.

# U.S. and CANADA LITERATURE ORDER FORM

| NAME:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                               |                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------|

| COMPANY:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                               |                                  |

| ADDRESS:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                               |                                  |

| CITY:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | STATE:                                                                                        | ZIP:                             |

| COUNTRY:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                               |                                  |

| PHONE NO.: ()                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ×                                                                                             |                                  |

| ORDER NO.         1           Image: Image |                                                                                               | QTY. PRICE TOTAL                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                               | X=                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                               | ×=                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                               | ×=                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                               | X=                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                               | Subtotal                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                               | Must Add Your<br>.ocal Sales Tax |

| Postage: add 10% of subtotal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                               | > Postage                        |

| Pay by check, money order, or include comp<br>accept VISA, MasterCard or American Expres<br>for delivery.<br>VISA 	MasterCard 	American Express                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ss. Make payment to Intel Liter                                                               | ature Sales. Allow 2-4 weeks     |

| Account No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                               |                                  |

| Signature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                               |                                  |

| Mail To: Intel Literature Sales<br>P.O. Box 58130<br>Santa Clara, CA 95052-8130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | International Customers of<br>should use the International or<br>Sales Office or Distributor. |                                  |

| For phone orders in the U.S. and Cana<br>Call Toll Free: (800) 548-4725                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ada                                                                                           |                                  |

Prices good until 12/31/89. Source HB

## INTERNATIONAL LITERATURE ORDER FORM

| NAME:        |                                       |                 |       |

|--------------|---------------------------------------|-----------------|-------|

| COMPANY:     |                                       |                 |       |

| ADDRESS:     |                                       |                 |       |

| CITY:        |                                       | _ STATE: ZIP:   |       |

| COUNTRY:     |                                       |                 |       |

| PHONE NO.: ( | )                                     |                 |       |

| ORDER NO.    | TITLE                                 | QTY. PRICE      | TOTAL |

|              |                                       | X=_             |       |

|              |                                       | X=_             |       |

|              | · · · · · · · · · · · · · · · · · · · | X=_             |       |

|              | ·                                     |                 |       |

|              |                                       | X=_             |       |

|              |                                       | X=_             |       |

|              |                                       |                 | ,     |

|              |                                       | X=              |       |

|              |                                       |                 |       |

|              |                                       | X=_             |       |

|              | ,                                     |                 |       |

|              |                                       | Must Add Your   |       |

|              |                                       | Local Sales Tax |       |

|              |                                       | Total           |       |

#### PAYMENT

Cheques should be made payable to your local Intel Sales Office (see inside back cover.)

Other forms of payment may be available in your country. Please contact the Literature Coordinator at your local Intel Sales Office for details.

The completed form should be marked to the attention of the LITERATURE COORDINATOR and returned to your local Intel Sales Office.

Intel the Microcomputer Company:

When Intel invented the microprocessor in 1971, it created the era of microcomputers. Whether used as microcontrollers in automobiles or microwave ovens, or as personal computers or supercomputers, Intel's microcomputers have always offered leading-edge technology. In the second half of the 1980s, Intel architectures have held at least a 75% market share of microprocessors at 16 bits and above. Intel continues to strive for the highest standards in memory, microcomputer components, modules, and systems to give its customers the best possible competitive advantages.

# PROGRAMMABLE LOGIC HANDBOOK

1989

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products:

Above, BITBUS, COMMputer, CREDIT, Data - Pipeline, ETOX, FASTPATH, Genius, i, î, ICE, iCEL, iCS, iDBP, iDIS, I<sup>2</sup>ICE, iLBX, i<sub>m</sub>, iMDDX, iMMX, Inboard, Insite, Intel, int<sub>e</sub>l, Intel376, Intel386, Intel486, int<sub>e</sub>IBOS, Intel Certified, Intelevision, int<sub>e</sub>ligent Identifier, int<sub>e</sub>ligent Programming, Intellec, Intellink, iOSP, iPDS, iPSC, iRMK, iRMX, iSBC, iSBX, iSDM, iSXM, KEPROM, Library Manager, MAPNET, MCS, Megachassis, MICROMAINFRAME, MULTIBUS, MULTICHANNEL, MULTIMODULE, ONCE, OpenNET, OTP, PC BUBBLE, Plug-A-Bubble, PROMPT, Promware, QUEST, QueX, Quick-Erase, Quick-Pulse Programming, Ripplemode, RMX/80, RUPI, Seamless, SLD, SugarCube, UPI, and VLSiCEL, and the combination of ICE, iCS, iRMX, iSBC, iSBX, iSXM, MCS, or UPI and a numerical suffix, 4-SITE, 376, 386, 486.

MDS is an ordering code only and is not used as a product name or trademark. MDS<sup>®</sup> is a registered trademark of Mohawk Data Sciences Corporation.

\*MULTIBUS is a patented Intel bus.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 58130 Santa Clara, CA 95052-8130

# **CUSTOMER SUPPORT**

#### **EPLD HOTLINE**

The Intel EPLD Technical Hotline is manned by applications personnel from 8:00 a.m. to 5:00 p.m. (PST) every business day. The number (U.S. and Canada) is 1-800-323-EPLD (1-800-323-3753).

#### **BBS**

Intel has a Bulletin Board System for registered iPLS II customers to electronically transfer information. A registered user with a modem can log onto the system. The current number is (916) 985-2308. If your communication software supports file transfers, you can receive utilities, software updates, and the latest information on EPLDs via the Bulletin Board.

#### **CUSTOMER SUPPORT**

Customer Support is Intel's complete support service that provides Intel customers with hardware support, software support, customer training, and consulting services. For more information contact your local sales offices.

After a customer purchases any system hardware or software product, service and support become major factors in determining whether that product will continue to meet a customer's expectations. Such support requires an international support organization and a breadth of programs to meet a variety of customer needs. As you might expect, Intel's customer support is quite extensive. It includes factory repair services and worldwide field service offices providing hardware repair services, software support services, customer training classes, and consulting services.

#### HARDWARE SUPPORT SERVICES

Intel is committed to providing an international service support package through a wide variety of service offerings available from Intel Hardware Support.

#### SOFTWARE SUPPORT SERVICES

Intel's software support consists of two levels of contracts. Standard support includes TIPS (Technical Information Phone Service), updates and subscription service (product-specific troubleshooting guides and COMMENTS Magazine). Basic support includes updates and the subscription service. Contracts are sold in environments which represent product groupings (i.e., iRMX<sup>®</sup> environment).

#### CONSULTING SERVICES

Intel provides field systems engineering services for any phase of your development or support effort. You can use our systems engineers in a variety of ways ranging from assistance in using a new product, developing an application, personalizing training, and customizing or tailoring an Intel product to providing technical and management consulting. Systems Engineers are well versed in technical areas such as microcommunications, real-time applications, embedded microcontrollers, and network services. You know your application needs; we know our products. Working together we can help you get a successful product to market in the least possible time.

#### **CUSTOMER TRAINING**

Intel offers a wide range of instructional programs covering various aspects of system design and implementation. In just three to ten days a limited number of individuals learn more in a single workshop than in weeks of self-study. For optimum convenience, workshops are scheduled regularly at Training Centers worldwide or we can take our workshops to you for on-site instruction. Covering a wide variety of topics, Intel's major course categories include: architecture and assembly language, programming and operating systems, BITBUS<sup>™</sup> and LAN applications.

## **Table of Contents**

| Alphanumeric Index                                                     | ix    |

|------------------------------------------------------------------------|-------|

| CHAPTER 1                                                              |       |

| Overview                                                               |       |

|                                                                        | 1-1   |

|                                                                        | 1-1   |

| CHAPTER 2                                                              |       |

| EPLDs—Erasable Programmable Logic Devices                              |       |

| DATA SHEETS                                                            |       |

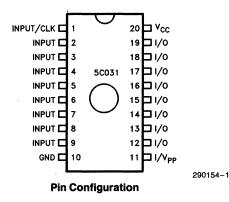

| 5C031, 300-Gate CHMOS H-Series Erasable Programmable Logic Device      |       |

| (H-EPLD)                                                               | 2-1   |

| 5C032, 300-Gate CHMOS H-Series Erasable Programmable Logic Device      |       |

| (H-EPLD)                                                               | 2-13  |

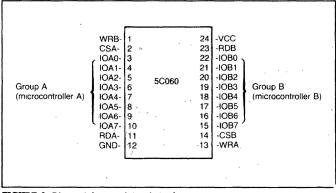

| 5C060, 600-Gate CHMOS H-Series Erasable Programmable Logic Device      |       |

| (H-EPLD)                                                               | 2-26  |

| 5C090, 900-Gate CHMOS H-Series Erasable Programmable Logic Device      | o 40  |

| (H-EPLD)                                                               | 2-42  |

| 5C121, 1200-Gate CHMOS H-Series Erasable Programmable Logic Device     | 2-59  |

| 5C180, 1800-Gate CHMOS Erasable Programmable Logic Device              | 2-74  |

| APPLICATION BRIEFS<br>AB-8 Implementing Cascaded Logic in the 5C121    | 0 100 |

| AB-9 5C121 As a Three and One-Half Digit Display Driver                | 2-100 |

| AB-9 SC121 As a Three and One-Han Digit Display Driver                 | 2-116 |

| AB-11 16-Bit Binary Counter Implementation Using the 5C060 EPLD        | 2-128 |

| AB-12 Designing a Mailbox Memory for Two 5C031s                        | 2-120 |

| AB-16 Atypical Latch/Register Construction in EPLDs                    | 2-152 |

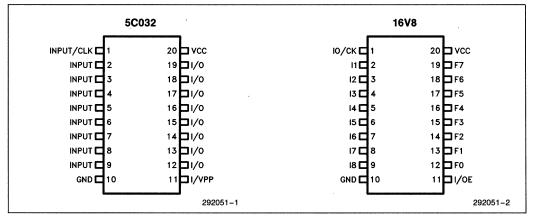

| AB-22 5C032-25 vs. 16V8-25: A Device Comparison                        |       |

| APPLICATION NOTES                                                      | 2 100 |

| AP-271 Applying the 5C121 Architecture                                 | 2-165 |

| AP-272 The 5C060 Unification of a CHMOS System                         |       |

| AP-276 Implementing a CMOS Bus Arbiter/Controller in the 5C060 EPLD    | 2-188 |

| AP-307 EPLDs, PLAS, and TTL—Comparing the "Hidden Costs" in Production | 2-198 |

| AP-321 Fitting the 5C180                                               | 2-220 |

| ENGINEERING REPORTS                                                    |       |

| ER-22 5C180 vs. EP1800: A Comparison of Device Specifications          | 2-233 |

| TECHNICAL PAPERS                                                       |       |

| Techniques for Modular EPLD Designs                                    | 2-241 |

| ARTICLE REPRINTS                                                       |       |

| AR-450 Crosspoint Switch: A PLD Approach                               | 2-251 |

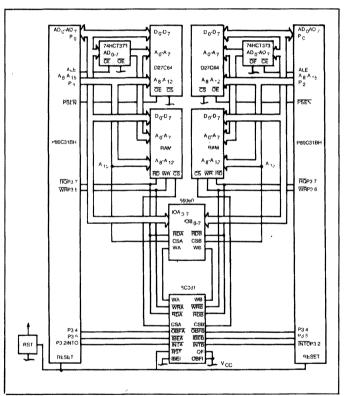

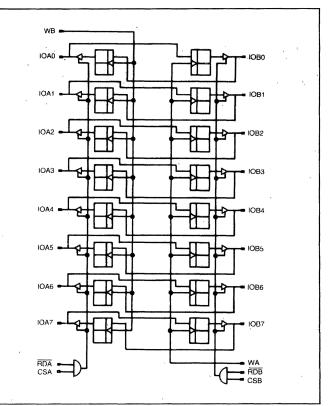

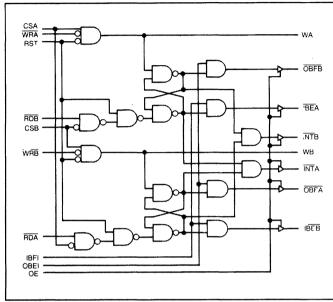

| AR-451 A Programmable Logic Mailbox for 80C31 Microcontrollers         | 2-255 |

| AR-454 Regain Lost I/O Ports with Erasable PLDs                        | 2-258 |

| CHAPTER 3                                                              |       |

| Advanced Architecture EPLDs                                            |       |

| DATA SHEETS                                                            |       |

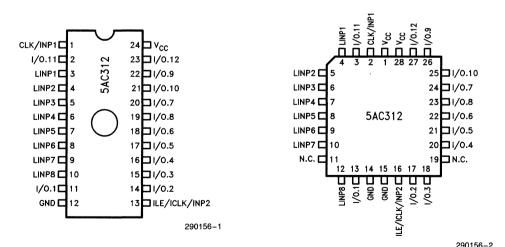

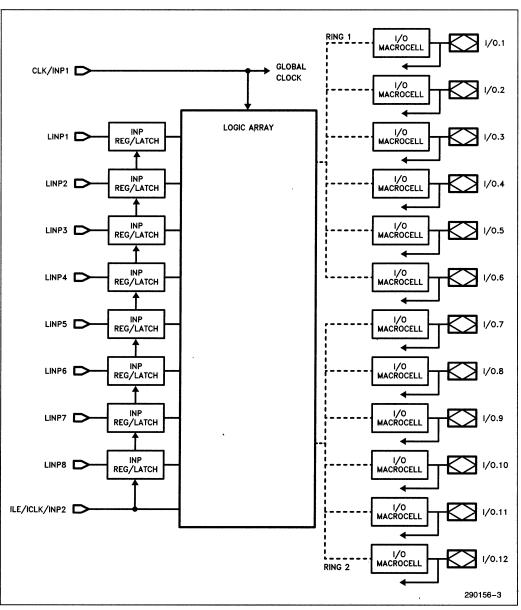

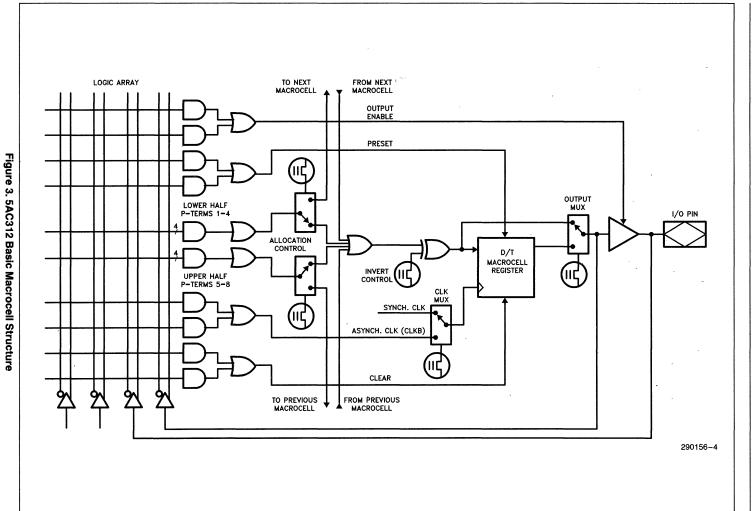

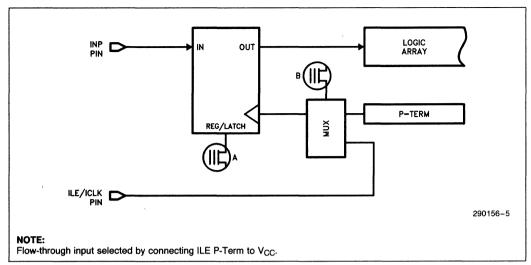

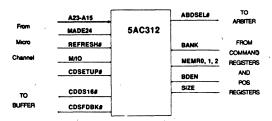

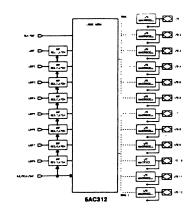

| 5AC312, 1-Micron CHMOS Erasable Programmable Logic Device              | 3-1   |

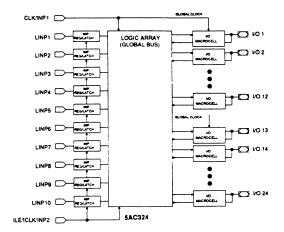

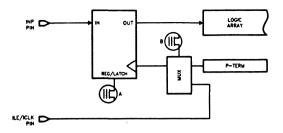

| 5AC324, 1-Micron CHMOS EPLD                                            | 3-19  |

| 85C508, Fast 1-Micron CHMOS EPLD                                       | 3-38  |

| 5CBIC, Programmable BUS Interface Controller                           | 3-45  |

| APPLICATION NOTES                                                      |       |

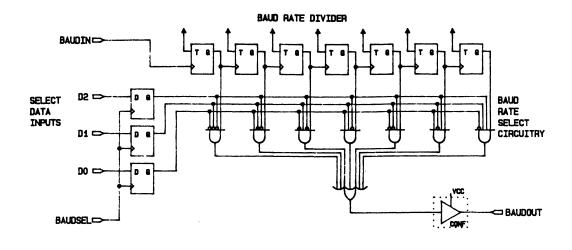

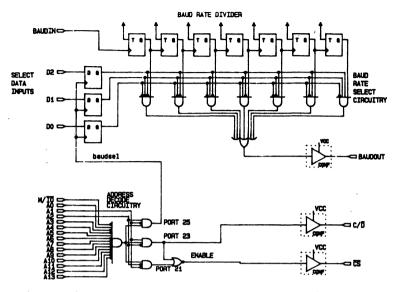

| AP-317 Implementing a PS/2 POS Using the 5AC312 EPLD                   | 3-62  |

| AP-319 Designing with the 5AC312/5AC324 EPLDs                          | 3-74  |

| TECHNICAL PAPERS                                                       |       |

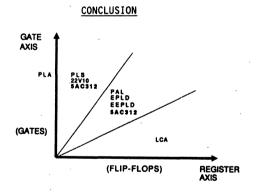

| Programmable and/Allocatable Based EPLD Addresses the Needs of Complex |       |

| Combinational and Sequential Designs.                                  | 3-83  |

| Advanced Architecture PLDs Solve Common State Machine Problems         | 3-91  |

,

## Table of Contents (Continued)

## **CHAPTER 4**

# Development Support Tools

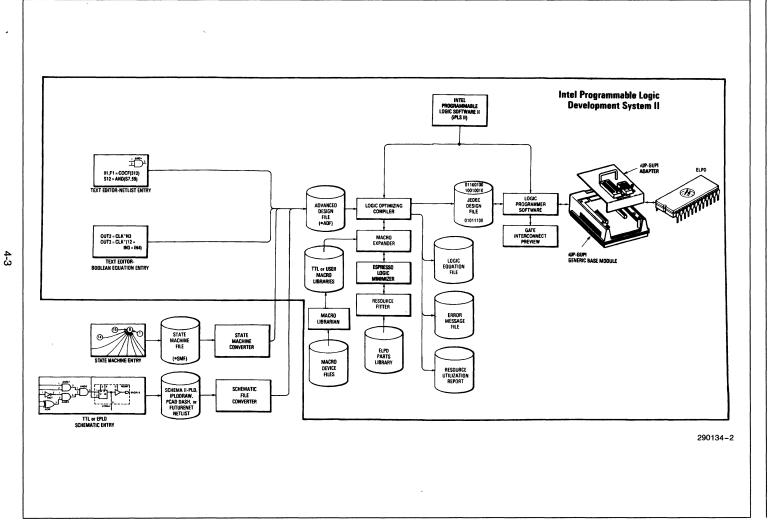

| iPLDS II, The Intel Programmable Logic Development System Version II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-1  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| iUP-PC, Intel Universal Programmer for the Personal Computer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-11 |

| iUP-200A/iUP-201A Universal PROM Programmers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-18 |

| PRODUCT BRIEFS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

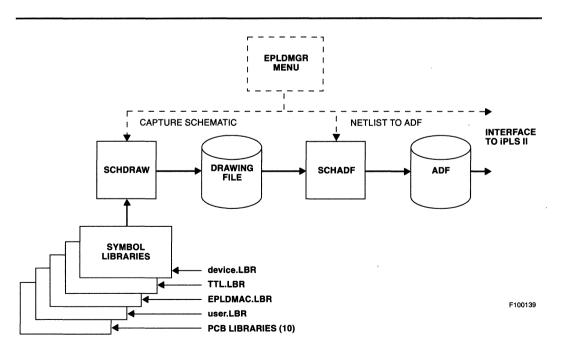

| SCHEMA II-PLD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-25 |

| iPLSII Macro Librarian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-26 |

| PLDUTIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-27 |

| UTILITIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

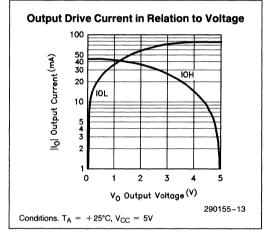

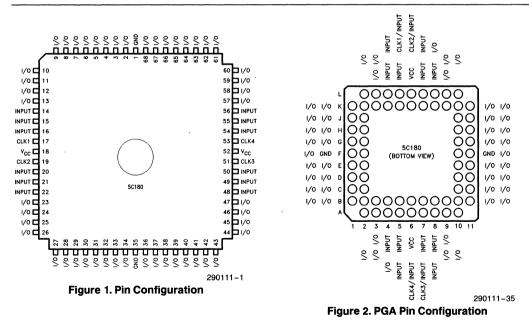

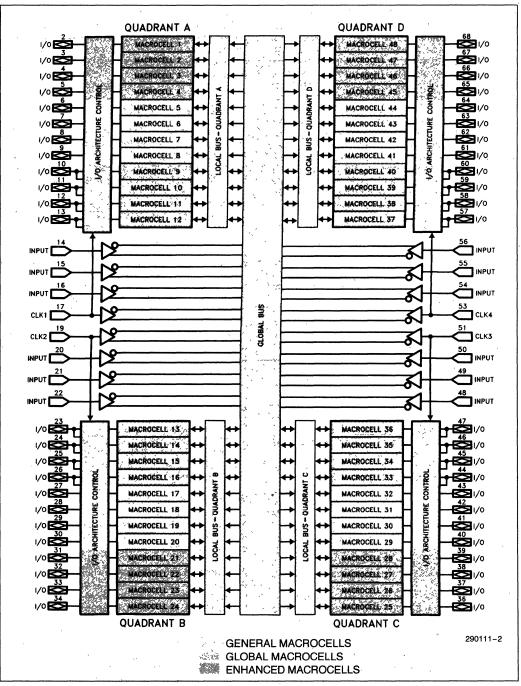

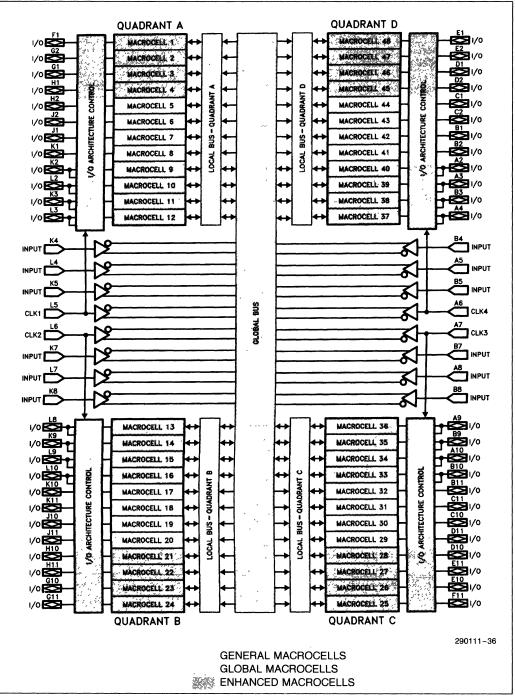

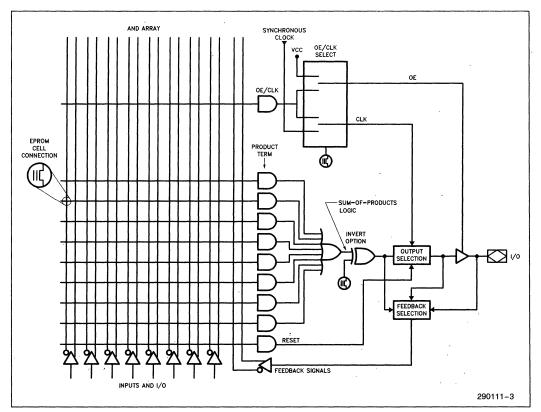

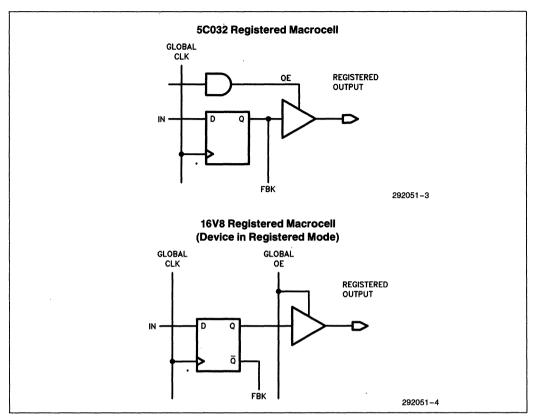

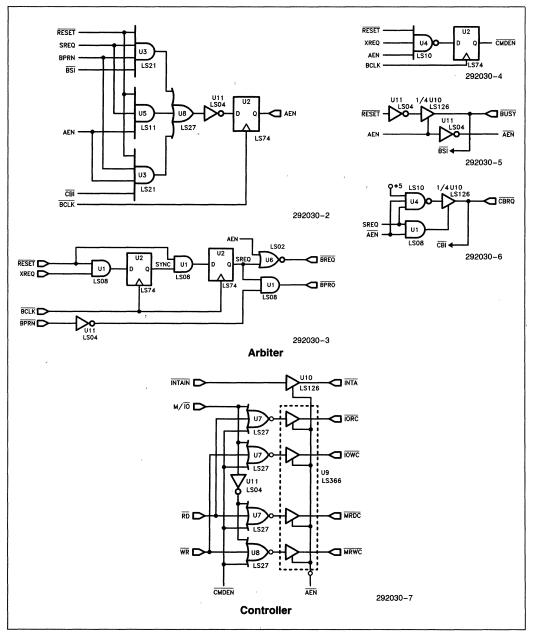

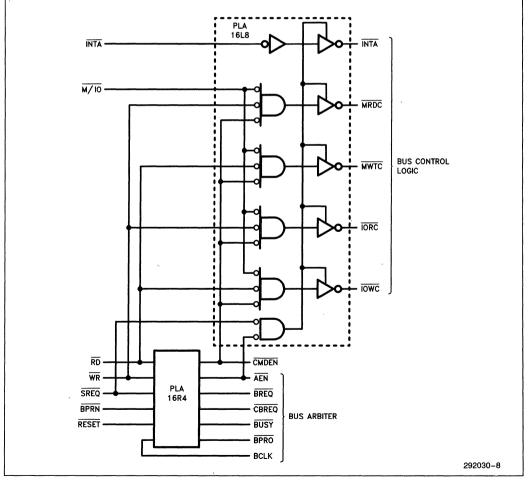

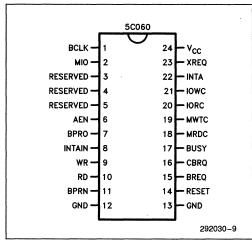

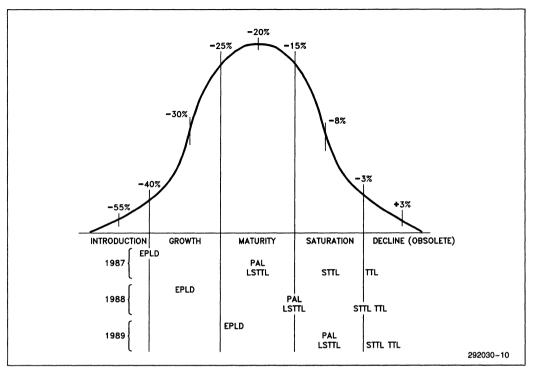

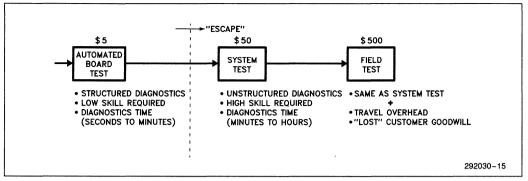

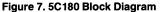

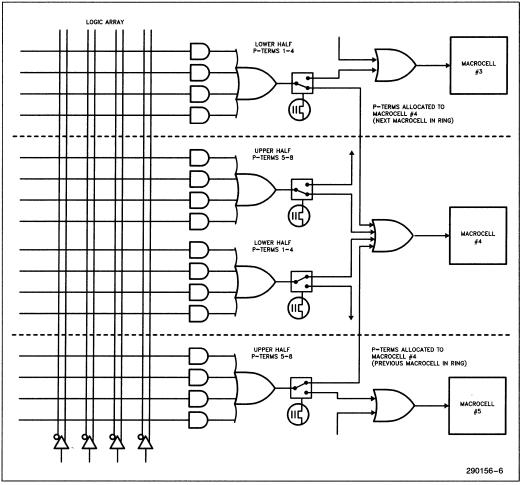

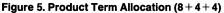

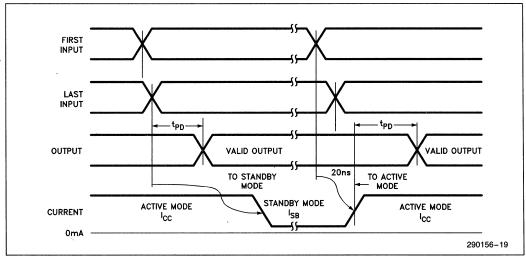

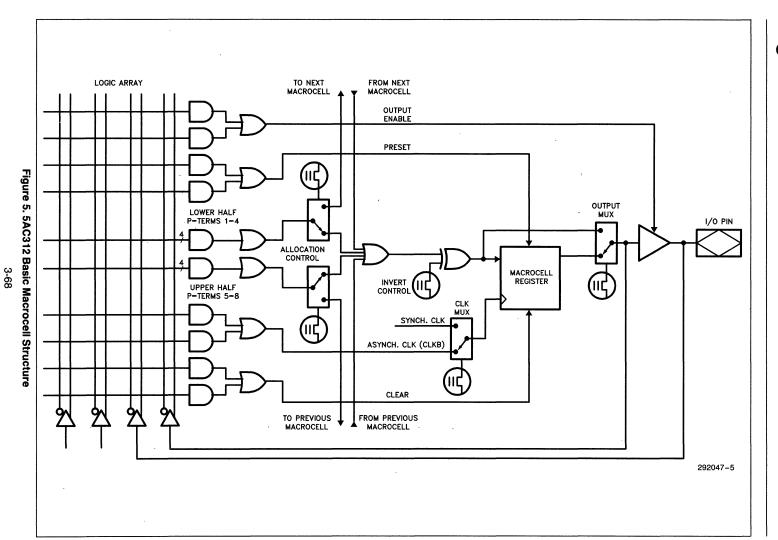

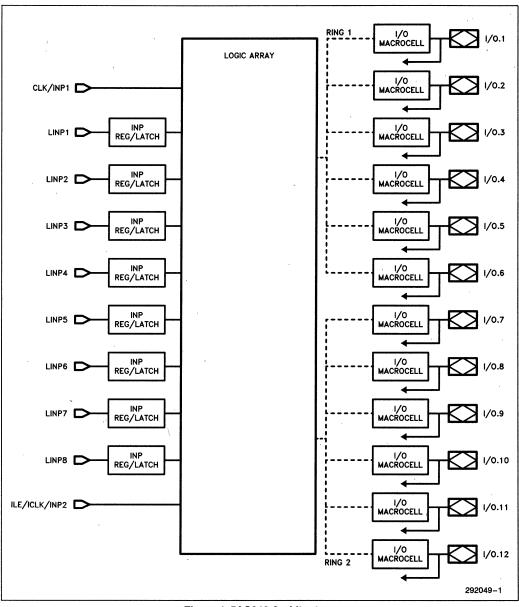

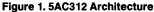

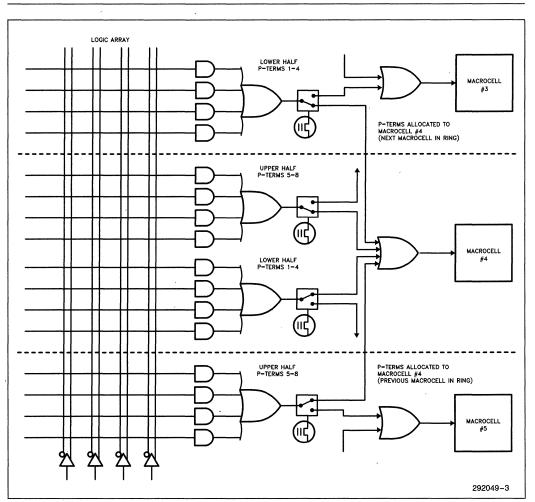

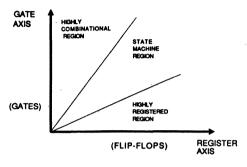

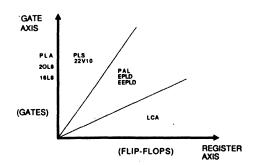

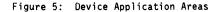

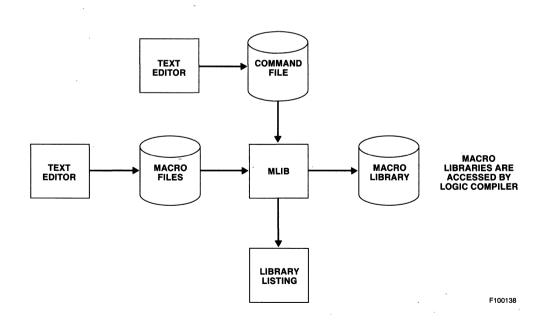

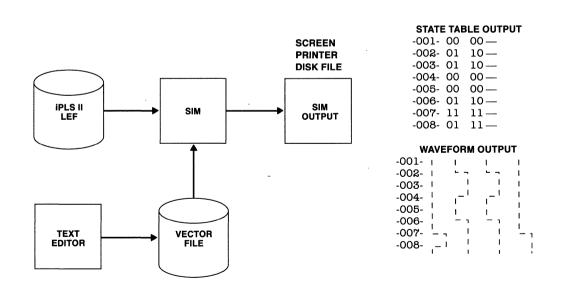

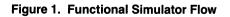

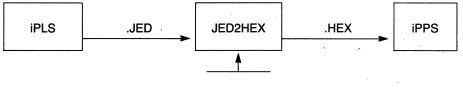

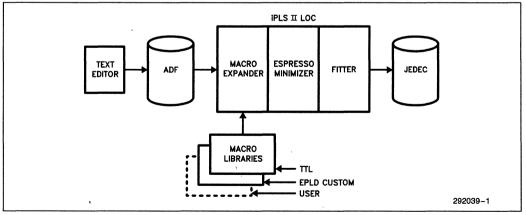

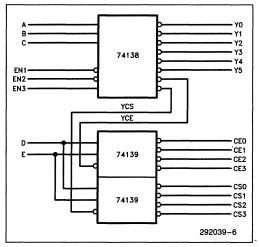

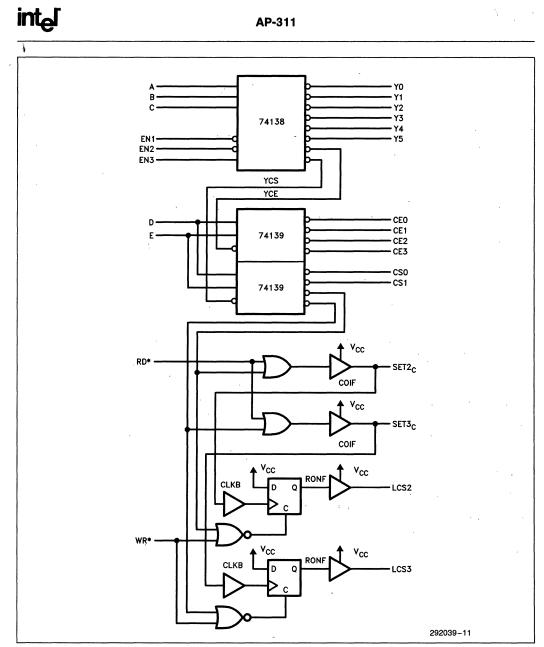

| PAL2ADF Utility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-29 |