# Embedded Controller Handbook

Volume II 16-Bit

# LITERATURE

To order Intel literature write or call:

Intel Literature Sales P.O. Box 58130 Santa Clara, CA 95052-8130 Toll Free Number: (800) 548-4725\*

Use the order blank on the facing page or call our **Toll Free** Number listed above to order literature. Remember to add your local sales tax and a 10% postage charge for U.S. and Canada customers, 20% for customers outside the U.S. Prices are subject to change.

#### 1988 HANDBOOKS

Product line handbooks contain data sheets, application notes, article reprints and other design information.

| NAME                                                                           | ORDER NUMBER | **PRICE IN<br>U.S. DOLLARS |

|--------------------------------------------------------------------------------|--------------|----------------------------|

| COMPLETE SET OF 8 HANDBOOKS<br>Save \$50.00 off the retail price of \$175.00   | 231003       | \$125.00                   |

| AUTOMOTIVE HANDBOOK (Not included in handbook Set)                             | 231792       | \$20.00                    |

| COMPONENTS QUALITY/RELIABILITY HANDBOOK (Available in July)                    | 210997       | \$20.00                    |

| EMBEDDED CONTROLLER HANDBOOK (2 Volume Set)                                    | 210918       | \$23.00                    |

| MEMORY COMPONENTS HANDBOOK                                                     | 210830       | \$18.00                    |

| MICROCOMMUNICATIONS HANDBOOK                                                   | 231658       | \$22.00                    |

| MICROPROCESSOR AND PERIPHERAL HANDBOOK (2 Volume Set)                          | 230843       | \$25.00                    |

| MILITARY HANDBOOK (Not included in handbook Set)                               | 210461       | \$18.00                    |

| OEM BOARDS AND SYSTEMS HANDBOOK                                                | 280407       | \$18.00                    |

| PROGRAMMABLE LOGIC HANDBOOK                                                    | 296083       | \$18.00                    |

| SYSTEMS QUALITY/RELIABILITY HANDBOOK                                           | 231762       | \$20.00                    |

| PRODUCT GUIDE Overview of Intel's complete product lines                       | 210846       | N/C                        |

| DEVELOPMENT TOOLS CATALOG                                                      | 280199       | N/C                        |

| INTEL PACKAGING OUTLINES AND DIMENSIONS Packaging types, number of leads, etc. | 231369       | N/C                        |

| LITERATURE PRICE LIST List of Intel Literature                                 | 210620       | N/C                        |

<sup>\*</sup>Good in the U.S. and Canada

About Our Cover:

A piano keyboard is deceptively simple. Essentially an array of on-off switches, with the application of human intelligence it can produce an infinite variety of sound. Embedded controllers provide the "hidden intelligence" found in thousands of products we use everyday.

<sup>\*\*</sup>These prices are for the U.S. and Canada only. In Europe and other international locations, please contact your local Intel Sales Office or Distributor for literature prices.

# Get Intel's Latest Technical Literature, Automatically!

### **Exclusive, Intel Literature Update Service**

Take advantage of Intel's year-long, low cost Literature Update Service and you will receive your first package of information followed by automatic quarterly updates on all the latest product and service news from Intel.

### Choose one or all five product categories update

Each product category update listed below covers in depth, all the latest Handbooks, Data Sheets, Application Notes, Reliability Reports, Errata Reports, Article Reprints, Promotional Offers, Brochures, Benchmark Reports, Technical Papers and much more...

#### 1. Microprocessors

Product line handbooks on Microprocessors, Embedded Controllers and Component Quality/Reliability, *Plus*, the Product Guide, Literature Guide, Packaging Information and 3 quarterly updates. \$70.00 Order Number: **555110**

#### 2. Peripherals

Product line handbooks on Peripherals, Microcommunications, Embedded Controllers, and Component Quality/Reliability, *Plus*, the Product Guide, Literature Guide, Packaging Information and 3 quarterly updates. \$50.00 Order Number: **555111**

#### 3. Memories =

Product line handbooks on Memory Components, Programmable Logic and Components Quality/Reliability, *Plus*, the Product Guide, Literature Guide, Packaging Information and 3 quarterly updates. \$50.00 Order Number: **555112**

#### 4. OEM Boards and Systems

Product line handbooks on OEM Boards & Systems, Systems Quality/Reliability, *Plus*, the Product Guide, Literature Guide, Packaging Information and 3 quarterly updates. \$50.00 Order Number: **555113**

#### 5. Software

Product line handbooks on Systems Quality/Reliability, Development Tools Catalog, Plus, the Product Guide, Literature Guide, Packaging Information and 3 quarterly updates. \$35.00 Order Number: **555114**

To subscribe, rush the Literature Order Form in this handbook, or call today, toll free (800) 548-4725.\*

Subscribe by March 31, 1988 and receive a valuable free gift.

The charge for this service covers our printing, postage and handling cost only.

Please note: Product manuals are not included in this offer.

Customers outside the U.S. and Canada should order directly from the U.S.

Offer expires 12/31/88.

\*Good in the U.S. and Canada.

# LITERATURE SALES ORDER FORM

| DDRESS:                                      | <u> </u>                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                          |

|----------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| TY:                                          | <del></del>                                | STA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TE: ZIP:                                                                                                 |

| OUNTRY:                                      |                                            | · .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | · · · · · · · · · · · · · · · · · · ·                                                                    |

| HONE NO.: (                                  | )                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                          |

| ORDER NO.                                    |                                            | TITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | QTY. PRICE TOTAL                                                                                         |

|                                              | ] ·                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ×=                                                                                                       |

|                                              | ]                                          | * *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ×=                                                                                                       |

|                                              | ]                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                          |

|                                              | 1                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ×=                                                                                                       |

|                                              | ] <del></del>                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ×=                                                                                                       |

| <del></del>                                  | ]                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | =                                                                                                        |

| <u>                                     </u> | ]                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ×=                                                                                                       |

|                                              | ]                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ×=                                                                                                       |

|                                              |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ×=                                                                                                       |

|                                              |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ×=                                                                                                       |

|                                              | ]                                          | State of the state |                                                                                                          |

| · · · · · · · · · · · · · · · · · · ·        |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Subtotal                                                                                                 |

| e e e e e e e e e e e e e e e e e e e        | a was in the                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Must Add Your                                                                                            |

|                                              |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Local Sales Tax                                                                                          |

| Must add appropria<br>10% U.S. and Can       | te postage to subtotal ada, 20% all other) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                          |

|                                              |                                            | e e e e e e e e e e e e e e e e e e e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Total                                                                                                    |

| Intel Literature Sa<br>Visa                  | ales Allow 2-4 weeks                       | for delivery.<br>press Expiration Date                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | r, or company purchase order paya                                                                        |

| gnature:                                     |                                            | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                          |

| lail To: Intel Lite<br>P.O. Box<br>Santa Cl  |                                            | should contact thei                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | tomers outside the U.S. and Cana<br>ir local Intel Sales Office or Distribu<br>of most Intel literature. |

European Literature Order Form in back of book.

Call Toll Free: (800) 548-4725 for phone orders

95052-8130

Intel the Microcomputer Company:

When Intel invented the microprocessor in 1971, it created the era of microcomputers. Whether used as microcontrollers in automobiles or microwave ovens, or as personal computers or supercomputers, Intel's microcomputers have always offered leading-edge technology. In the second half of the 1980s, Intel architectures have held at least a 75% market share of microprocessors at 16 bits and above. Intel continues to strive for the highest standards in memory, microcomputer components, modules, and systems to give its customers the best possible competitive advantages.

# EMBEDDED CONTROLLER HANDBOOK

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products:

Above, BITBUS, COMMputer, CREDIT, Data Pipeline, FASTPATH, GENIUS, i, î, ICE, iCEL, iCS, iDBP, iDIS, I²ICE, iLBX, i<sub>m</sub>, iMDDX, iMMX, Inboard, Insite, Intel, int<sub>e</sub>l, int<sub>e</sub>lBOS, Intel Certified, Intelevision, int<sub>e</sub>ligent Identifier, int<sub>e</sub>ligent Programming, Intellec, Intellink, iOSP, iPDS, iPSC, iRMK, iRMX, iSBC, iSBX, iSDM, iSXM, KEPROM, Library Manager, MAP-NET, MCS, Megachassis, MICROMAINFRAME, MULTIBUS, MULTICHANNEL, MULTIMODULE, MultiSERVER, ONCE, OPENNET, OTP, PC-BUBBLE, Plug-A-Bubble, PROMPT, Promware, QUEST, QueX, Quick-Pulse Programming, Ripplemode, RMX/80, RUPI, Seamless, SLD, SugarCube, SupportNET, UPI, and VLSiCEL, and the combination of ICE, iCS, iRMX, iSBC, iSBX, iSXM, MCS, or UPI and a numerical suffix, 4-SITE.

MDS is an ordering code only and is not used as a product name or trademark. MDS® is a registered trademark of Mohawk Data Sciences Corporation.

\*MULTIBUS is a patented Intel bus.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Distribution Mail Stop SC6-59 3065 Bowers Avenue Santa Clara, CA 95051

# **Table of Contents**

|     | Alphanumeric Index                                                           | viii           |

|-----|------------------------------------------------------------------------------|----------------|

| 8-1 | BIT PRODUCTS                                                                 |                |

|     | MCS®-48 FAMILY                                                               |                |

|     | Chapter 1                                                                    |                |

|     | MCS®-48 Single Component System                                              | 1-1            |

| ,   | Ohanday O                                                                    | ,              |

|     | MCS®-48 Expanded System                                                      | 2-1            |

|     | Chapter 3                                                                    | 2-1            |

|     | MCS®-48 Instruction Set                                                      | 3-1            |

|     |                                                                              | 3-1            |

| '   | Chapter 4 DATA SHEETS                                                        |                |

|     | 8243 MCS®-48 Input/Output Expander                                           | 4-1            |

|     | P8748H/P8749H/8048AH/8035AHL/8049AH/8039AHL/8050AH/8040AHL                   | 4-1            |

|     | HMOS Single-Component 8-Bit Production Microcontroller                       | 4-8            |

|     | D8748H/8749H HMOS-E Single-Component 8-Bit Microcomputer                     | 4-21           |

|     | MCS®-48 Express                                                              | 4-33           |

|     | MCS®-48 INDEX                                                                | 4-36           |

|     | MCS®-51 FAMILY                                                               |                |

|     | Chapter 5                                                                    |                |

|     | MCS®-51 Architectural Overview                                               | 5-1            |

|     |                                                                              | J-1            |

| ,   | Chapter 6 Hardware Description of the 8051, 8052 and 80C51                   | 6-1            |

|     |                                                                              | 0-1            |

| ,   | Chapter 7                                                                    | 4              |

|     | Hardware Description of the 83C51FA (83C252)                                 | 7-1            |

| (   | Chapter 8                                                                    |                |

|     | Hardware Description of the 83C152                                           | 8-1            |

| (   | Chapter 9                                                                    |                |

|     | MCS®-51 Programmer's Guide and Instruction Set                               | 9-1            |

| (   | Chapter 10                                                                   |                |

|     | DATA SHEETS                                                                  |                |

|     | 8031/8051/8031AH/8051AH/8032AH/8052AH/8751H/8751H-8 8-Bit HMOS               |                |

|     | and HMOS EPROM Microcontrollers                                              |                |

|     | 8051AHP 8-Bit Control-Oriented Microcontroller with Protected ROM            | 10-15          |

|     | 8031AH/8051AH/8032AH/8052AH/8751H/8751H-8 Express                            | 10-25          |

|     | 8751BH 8-Bit HMOS EPROM Microcontroller                                      | 10-27          |

|     | 8032BH/8052BH 8-Bit HMOS Microcontrollers                                    | 10-38<br>10-46 |

|     | 8752BH 8-Bit HMOS EPROM Microcontroller                                      | 10-46          |

|     | 80C31BH/80C51BH Express                                                      | 10-57          |

|     | 87C51 8-Bit CHMOS EPROM Microcontroller                                      | 10-69          |

|     | 87C51 Express                                                                | 10-71          |

|     | 87C51FA (87C252) CHMOS Single-Chip 8-Bit Microcontroller                     | 10-87          |

|     | 83C152A/80C152A Universal Communications Controller                          |                |

|     | 80C152JA/83C152JA/80C152JB Universal Communications Controller               |                |

|     | 27C64/87C64 64K (8K x 8) CHMOS Production and UV Erasable PROMs              |                |

|     | 87C257 256K (32K x 8) CHMOS UV Erasable PROM                                 |                |

|     | UPITM-452 CHMOS Programmable I/O Processor                                   | 10-157         |

|     | APPLICATION NOTES                                                            |                |

|     | AP-70 Using the Intel MCS®-51 Boolean Processing Capabilities                | 10-211         |

|     | AP-125 Designing Microcontroller Systems for Electrically Noisy Environments | 10-256         |

|     | AP-155 Oscillators for Microcontrollers                                      | 10-278         |

# Table of Contents (Continued)

| AP-252 Designing with the 80C51BH                                                           | 10-310<br>10-334 |

|---------------------------------------------------------------------------------------------|------------------|

| ARTICLE REPRINTS AR-409 Increased Functions in Chip Result in Lighter, Less Costly Portable |                  |

| Computer                                                                                    | 10-354           |

| AR-517 Using the 8051 Microcontroller with Resonant Transducers DEVELOPMENT SUPPORT TOOLS   | 10-359           |

| 8051 Software Packages                                                                      | 10-364           |

| iDCX 51 Distributed Control Executive                                                       |                  |

| ICETM 5100/252 In-Circuit Emulator for the MCS®-51 Family                                   |                  |

| 80C152 INDEX                                                                                |                  |

| THE RUPITM FAMILY                                                                           | 10 002           |

| Chapter 11                                                                                  |                  |

| The RUPITM-44 Family                                                                        | 11-1             |

| Chapter 12                                                                                  |                  |

| 8044 Architecture                                                                           | 12-1             |

| Chapter 13                                                                                  |                  |

| 8044 Serial Interface                                                                       | 13-1             |

| Chapter 14                                                                                  |                  |

| 8044 Application Examples                                                                   | 14-1             |

| Chapter 15 DATA SHEET                                                                       |                  |

| 8044AH/8344AH/8744H High Performance 8-Bit Microcontroller with On-Chip                     |                  |

| Serial Communication Controller                                                             | 15-1             |

| APPLICATION NOTE                                                                            |                  |

| AP-283 Flexibility in Frame Size with the 8044                                              | 15-27            |

| ARTICLE REPRINT                                                                             |                  |

| AR-307 Microcontroller with Integrated High Performance Communications Interface            | 15-57            |

| DEVELOPMENT SUPPORT TOOLS                                                                   | 10-07            |

| ICETM5100/044 In-Circuit Emulator for the RUPITM-44 Family                                  | 15-66            |

| MCS®-80/85 FAMILY                                                                           |                  |

| Chapter 16                                                                                  |                  |

| DATA SHEETS                                                                                 |                  |

| 8080A/8080A-1/8080A-2 8-Bit N-Channel Microprocessor                                        | 16-1<br>16-11    |

| 8155H/8156H/8155H-2/8156H-2 2048-Bit Static HMOS RAM with I/O Ports and                     | 10-11            |

| Timer                                                                                       | 16-31            |

| 8185/8185-2 1024 x 8-Bit Static RAM for MCS®-85                                             | 16-45            |

| 8224 Clock Generator and Driver for 8080A CPU                                               | 16-50            |

| 8228 System Controller and Bus Driver for 8080A CPU                                         | 16-55            |

| 8755A 16,384-Bit EPROM with I/O                                                             | 16-59            |

| 16-BIT PRODUCTS                                                                             |                  |

| MCS®-96 FAMILY                                                                              |                  |

| Chapter 17                                                                                  | 474              |

| MCS®-96 Architectural Overview                                                              | 17-1             |

| Chapter 18 MCS®-96 Instruction Set                                                          | 18-1             |

| Chapter 19                                                                                  | 10-1             |

| MCS®-96 Hardware Design Information                                                         | 19-1             |

|                                                                                             |                  |

# **Table of Contents (Continued)**

| Chapter 20                                                                     |         |

|--------------------------------------------------------------------------------|---------|

| 80C196KA Architectural Overview                                                | 20-1    |

| Chapter 21                                                                     |         |

| DATA SHEETS                                                                    |         |

| 809XBH/839XBH/879XBH with 8 or 16-Bit External Bus                             | 21-1    |

| 809XBH-10 Advanced 16-Bit Microcontroller with 8 or 16-Bit External Bus        | 21-44   |

| 809X-90, 839X-90                                                               |         |

| 809XBH/839XBH/879XBH Express                                                   |         |

| 809X-90, 839X-90 Express                                                       |         |

| 80C196KA 16-Bit High Performance CHMOS Microcontroller                         | 21-92   |

| APPLICATION NOTES                                                              |         |

| AP-248 Using the 8096                                                          | 21-119  |

| AP-275 An FFT Algorithm for MCS®-96 Products Including Supporting Routines     | 21 110  |

| and Examples                                                                   | 21-222  |

| DEVELOPMENT SUPPORT TOOLS                                                      | Z 1-222 |

| MCS®-96 Software Development Packages                                          | 21-207  |

| iDCX 96 Distributed Control Executive                                          |         |

| iSBE-96 Development Kit Single Board Emulator and Assembler for MCS®-96        | 21-307  |

| VLSiCE-96 In-Circuit Emulator for the 8X9X Family of Microcontrollers          | 21-313  |

| ICETM-196PC Real-Time Transparent 80C196 In-Circuit Emulator                   | 21-323  |

| MCS®-96 INDEX                                                                  |         |

| 80C196 INDEX                                                                   |         |

|                                                                                | 21-341  |

| 80186 FAMILY                                                                   |         |

| Chapter 22                                                                     |         |

| DATA SHEETS                                                                    |         |

| 80186 High Integration 16-Bit Microprocessor                                   |         |

| 80C186 High Integration 16-Bit Microprocessor                                  |         |

| 80188 High Integration 16-Bit Microprocessor                                   |         |

| 80C188 High Integration 16-Bit Microprocessor                                  |         |

| 82188 Integrated Bus Controller for 8086, 8088, 80186, 80188 Processors        | 22-225  |

| APPLICATION NOTES                                                              |         |

| AP-186 Introduction to the 80186 Microprocessor                                | 22-241  |

| AP-258 High Speed Numerics with the 80186, 80188 and 8087                      | 22-316  |

| AP-286 80186/188 Interface to Intel Microcontrollers                           | 22-332  |

| DEVELOPMENT SUPPORT TOOLS                                                      |         |

| 8086/80186 Software Packages                                                   |         |

| VAX/VMS Resident 8086/8088/80186 Software Development Packages                 | 22-383  |

| 8087 Support Library                                                           |         |

| 80287 Support Library                                                          |         |

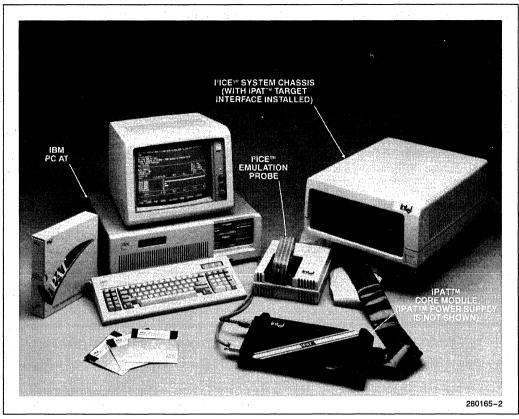

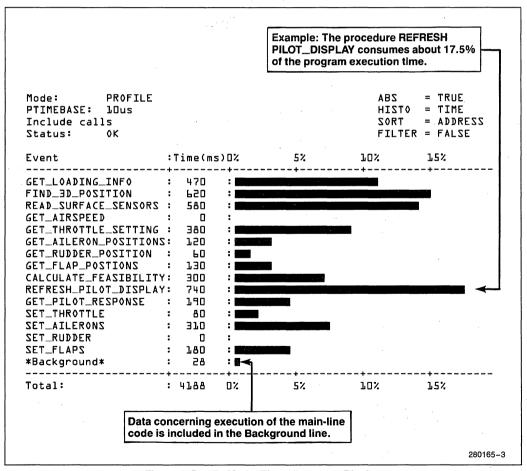

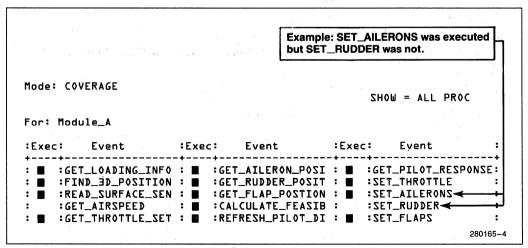

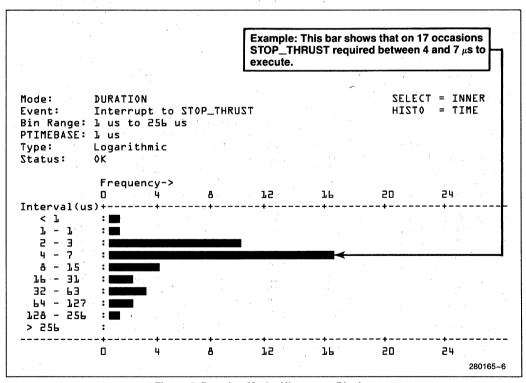

| iPAT Performance Analysis Tool                                                 | 22-399  |

| I <sup>2</sup> ICE™ Integrated Instrumentation and In-Circuit Emulation System | 22-412  |

| ICE™-186 In-Circuit Emulator                                                   | 22-424  |

|                                                                                |         |

# Alphanumeric Index

| 27C64/87C64 64K (8K x 8) CHMOS Production and UV Erasable PROMs                                             |        |

|-------------------------------------------------------------------------------------------------------------|--------|

| 80C152JA/83C152JA/80C152JB Universal Communications Controller                                              | 10-117 |

| 80C186 High Integration 16-Bit Microprocessor                                                               | 22-53  |

| B0C188 High Integration 16-Bit Microprocessor                                                               | 22-165 |

| 80C196KA Architectural Overview                                                                             | 20-1   |

| 80C196KA 16-Bit High Performance CHMOS Microcontroller                                                      | 21-92  |

| 80C31BH/80C51BH Express                                                                                     | 10-69  |

| 80C31BH/80C51BH 8-Bit CHMOS Microcontrollers                                                                | 10-57  |

| 80186 High Integration 16-Bit Microprocessor                                                                |        |

| 80188 High Integration 16-Bit Microprocessor                                                                |        |

| 80287 Support Library                                                                                       | 22-395 |