# Microsystem Components Handbook

Peripherals Volume II

# **LITERATURE**

To order Intel Literature write or call:

Intel Literature Sales P.O. Box 58130 Santa Clara, CA 95052-8130 Intel Literature Sales: (800) 548-4725 Other Inquiries: (800) 538-1876

Use the order blank on the facing page or call our Toll Free Number listed above to order literature. Remember to add your local sales tax and a 10% handling charge for U.S. customers, 20% for Canadian customers.

#### 1986 HANDBOOKS

Product Line handbooks contain data sheets, application notes, article reprints and other design information.

| NAME                                                                                       | ORDER NUMBER | *PRICE IN<br>U.S. DOLLARS |

|--------------------------------------------------------------------------------------------|--------------|---------------------------|

| COMPLETE SET OF 9 HANDBOOKS Get a 30% discount off the retail price of \$171.00            | 231003       | \$120.00                  |

| MEMORY COMPONENTS HANDBOOK                                                                 | 210830       | \$18.00                   |

| MICROCOMMUNICATIONS HANDBOOK                                                               | 231658       | \$18.00                   |

| MICROCONTROLLER HANDBOOK                                                                   | 210918       | \$18.00                   |

| MICROSYSTEM COMPONENTS HANDBOOK<br>Microprocessor and peripherals (2 Volume Set)           | 230843       | \$25.00                   |

| DEVELOPMENT SYSTEMS HANDBOOK                                                               | 210940       | \$18.00                   |

| OEM SYSTEMS HANDBOOK                                                                       | 210941       | \$18.00                   |

| SOFTWARE HANDBOOK                                                                          | 230786       | \$18.00                   |

| MILITARY HANDBOOK                                                                          | 210461       | \$18.00                   |

| QUALITY/RELIABILITY HANDBOOK                                                               | 210997       | \$20.00                   |

| PRODUCT GUIDE Overview of Intel's complete product lines                                   | 210846       | No charge                 |

| LITERATURE GUIDE Listing of Intel Literature                                               | 210620       | No charge                 |

| INTEL PACKAGING SPECIFICATIONS Listing of Packaging types, number of leads, and dimensions | 231369       | No charge                 |

<sup>\*</sup>These prices are for the U. S. and Canada only. In Europe and other international locations, please contact your local Intel Sales Office or Distributor for literature prices.

# U.S. LITERATURE ORDER FORM

| NAME:                                                               |                                                                                                             |                       |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------|

| COMPANY:                                                            |                                                                                                             |                       |

| ADDRESS:                                                            |                                                                                                             |                       |

| CITY:                                                               | STATE:                                                                                                      | ZIP:                  |

| COUNTRY:                                                            |                                                                                                             |                       |

| PHONE NO.: ()                                                       |                                                                                                             |                       |

| ORDER NO.                                                           | TITLE QTY                                                                                                   | PRICE TOTAL           |

|                                                                     |                                                                                                             | × =                   |

|                                                                     |                                                                                                             |                       |

|                                                                     |                                                                                                             | × =                   |

|                                                                     |                                                                                                             | . × =                 |

| -                                                                   |                                                                                                             | × =                   |

|                                                                     |                                                                                                             | ×=                    |

|                                                                     |                                                                                                             | × =                   |

|                                                                     |                                                                                                             | × =                   |

|                                                                     |                                                                                                             | ubtotal               |

| Add appropriate postage and handling to subtotal                    |                                                                                                             |                       |

| 10% U.S.                                                            |                                                                                                             | es Tax                |

| 20% Canada                                                          | Postage & Har                                                                                               | ndling                |

| Allow 2-4 weeks for delivery                                        |                                                                                                             | Total                 |

|                                                                     | eck or Money Order, payable to Intel Boo                                                                    | oks. Purchase Orders  |

| have a \$50.00 minimum<br>□ Visa □ MasterCard Expi                  | ration Date                                                                                                 |                       |

| Account No.                                                         |                                                                                                             |                       |

| Signature:                                                          |                                                                                                             |                       |

|                                                                     |                                                                                                             | 0                     |

| Mail To: Intel Literature Sales<br>PO. Box 58130<br>Santa Clara, CA | s Customers outside the U.S. and<br>tact the local Intel Sales Office<br>in the back of most Intel literatu | or Distributor listed |

Call Toll Free: (800) 548-4725 for phone orders

Prices good until 12/31/86.

95052-8130

Source HB

**Mail To:** Intel Literature Sales P.O. Box 58130

Santa Clara, CA 95052-8130

# MICROSYSTEM COMPONENTS HANDBOOK

1986

About Our Cover:

The design on our front cover is an abstract portrayal of the unlimited interface linking options available with Intel microsystem components. Intel microprocessors and associated peripherals are the building blocks which provide total systems development solutions. Intel's superior technology, reliability and support provides easier solutions to specific development problems. Thereby, cutting "time-to-market" and creating a greater market share.

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products:

Above, BITBUS, COMMputer, CREDIT, Data Pipeline, GENIUS, i,  $\frac{1}{1}$ , ICE, iCEL, iCS, iDBP, iDIS, I²ICE, iLBX, i $_{\rm m}$ , iMDDX,, iMMX, Insite, Intel, intel, intelBOS, Intelevision, intelligent Identifier, intelligent Programming, Intellec, Intellink, iOSP, iPDS, iPSC, iRMX, iSBC, iSBX, iSDM, iSXM, KEPROM, Library Manager, MCS, Megachassis, MICROMAINFRAME, MULTIBUS, MULTICHANNEL, MULTIMODULE, ONCE, OpenNET, Plug-A-Bubble, PROMPT, Promware, QUEST, QueX, Ripplemode, RMX/80, RUPI, Seamless, SLD, UPI, and VLSiCEL, and the combination of ICE, iCS, iRMX, iSBC, iSBX, MCS, or UPI and a numerical suffix.

MDS is an ordering code only and is not used as a product name or trademark. MDS® is a registered trademark of Mohawk Data Sciences Corporation.

\*MULTIBUS is a patented Intel bus.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Distribution Mail Stop SC6-59 3065 Bowers Avenue Santa Clara, CA 95051

# **Table of Contents**

| NUMERIC INDEX                                                                                                                    | Vİ           |

|----------------------------------------------------------------------------------------------------------------------------------|--------------|

| CHAPTER 1                                                                                                                        |              |

| OVERVIEW                                                                                                                         |              |

| Introduction                                                                                                                     | 1-1          |

| CHAPTER 2                                                                                                                        |              |

| 8080, 8085 MICROPROCESSORS                                                                                                       |              |

| DATA SHEETS                                                                                                                      |              |

| 8080A/8080A-1/8080A-2 8-Bit N-Channel Microprocessor                                                                             | 2-1          |

| 8085AH/8085AH-2/8085AH-1 8-Bit HMOS Microprocessor                                                                               | 2-10         |

| 8155H/8156H/8155H-2/8156H-2 2048-Bit Static HMOS RAM with I/O Ports and Timer<br>8185/8185-2 1024 x 8-Bit Static RAM for MCS®-85 |              |

| 8224 Clock Generator and Driver for 8080A CPU                                                                                    |              |

| 8228/8238 System Controller and Bus Driver for 8080A CPU                                                                         |              |

| 8237A/8237A-4/8237A-5 High Performance Programmable DMA Controller                                                               | 2-52         |

| 82C37A-5 CHMOS High Performance Programmable DMA Controller                                                                      |              |

| 8257/8257-5 Programmable DMA Controller                                                                                          |              |

| 8259A/8259A-2/8259A-8 Programmable Interrupt Controller                                                                          |              |

| 8755A/8755A-2 16, 384-Bit EPROM with I/O                                                                                         |              |

| APPLICATION NOTES                                                                                                                |              |

| AP-59 Using the 8259A Programmable Interrupt Controller                                                                          | 2-144        |

| CHAPTER 3                                                                                                                        |              |

| 8086, 8088, 80186, 80188 MICROPROCESSCORS                                                                                        |              |

| DATA SHEETS                                                                                                                      |              |

| 8086 16-Bit HMOS Microprocessor                                                                                                  |              |

| 80C86/80C86-2 16-Bit CHMOS Microprocessor                                                                                        |              |

| 80186 High Integration 16-Bit Microprocessor iAPX 88/10 8-Bit HMOS Microprocessor                                                |              |

| 80C88/80C88-2 8-Bit CHMOS Microprocessor                                                                                         |              |

| 80188 High Integration 8-Bit Microprocessor                                                                                      | 3-162        |

| 8087/8087-2/8087-1 Numeric Data Coprocessor                                                                                      | 3-218        |

| 8282/8283 Octal Latch                                                                                                            |              |

| 8284A/8284A-1 Clock Generator and Driver for iAPX 86, 88 Processors                                                              |              |

| 8286/8287 Octal Bus Transceiver                                                                                                  |              |

| 8288 Bus Controller for iAPX 86, 88 Processors                                                                                   |              |

| 82C88 CHMOS Bus Controller for 80C86, 80C88 Processors                                                                           | 3-275        |

| 82188 Integrated Bus Controller for iAPX 86, 88, 186, 188 Processors                                                             |              |

| 8289/8289-1 Bus Arbiter                                                                                                          | 3-299        |

| AP-67 8086 System Design                                                                                                         | 3-310        |

| AP-113 Getting Started with the Numeric Data Processor                                                                           |              |

| AP-186 Introduction to the 80186                                                                                                 | 3-435        |

| CHAPTER 4                                                                                                                        |              |

| 80286 MICROPROCESSORS                                                                                                            |              |

| DATA SHEETS                                                                                                                      |              |

| iAPX 286/10 High Performance Microprocessor                                                                                      |              |

| with Memory Management and Protection                                                                                            | 4-1          |

| 80287 80-Bit HMOS Numeric Processor Extension                                                                                    | 4-56<br>4-82 |

| 82258 Advanced Direct Memory Access Coprocessor                                                                                  |              |

| 82288 Bus Controller for iAPX 286 Processors                                                                                     |              |

| 82289 Bus Arbiter for iAPX 286 Processor Family                                                                                  |              |

| CHARTER 5                                                                                                                        |              |

| CHAPTER 5 80386 MICROPROCESSORS                                                                                                  |              |

| DATA SHEETS                                                                                                                      |              |

| 80386 High Performance Microprocessor with Integrated Memory Management                                                          | 5-1          |

| 82384 Clock Generator and Reset Interface for 80386 Processors                                                                   | 5-2          |

# -VOLUME 2-

| HAPTER 6                                                                              |         |

|---------------------------------------------------------------------------------------|---------|

| MEMORY CONTROLLERS                                                                    |         |

| DATA SHEETS                                                                           |         |

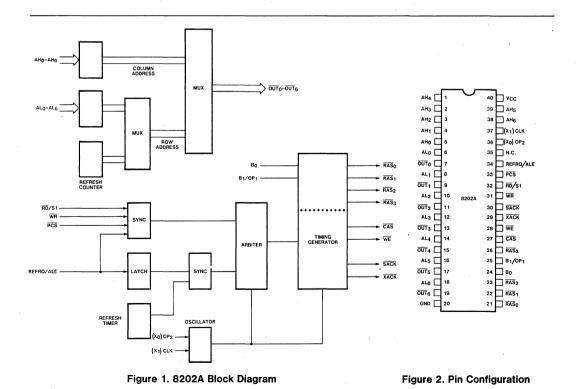

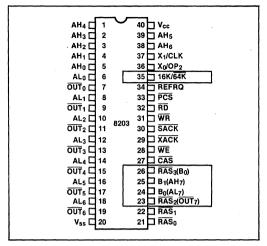

| 8202A Dynamic RAM Controller                                                          | . 6-    |

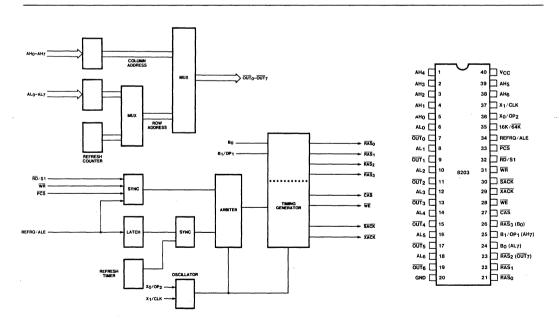

| 8203 64K Dynamic RAM Controller                                                       |         |

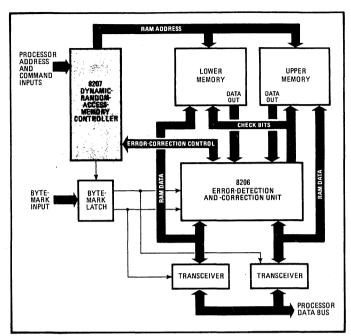

| 8206/8206-2 Error Detection and Correction Unit                                       | . 6-30  |

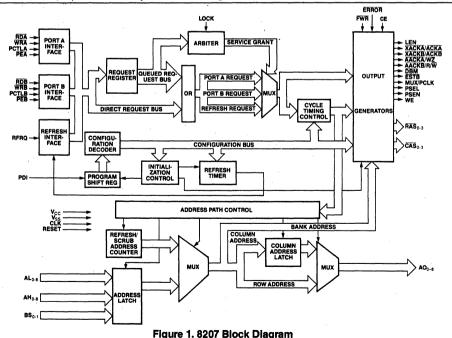

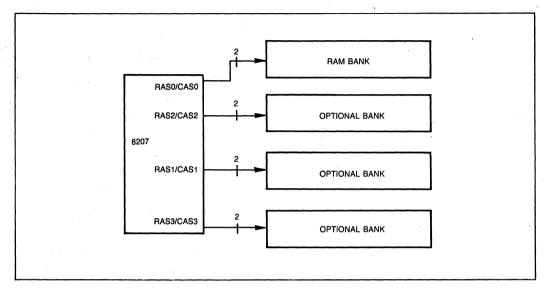

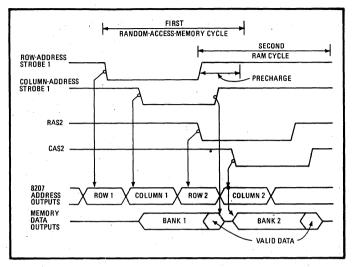

| 8207 Dual-Port Dynamic RAM Controller                                                 | . 6-52  |

| 8208 Dynamic RAM Controller                                                           |         |

| 82C08 CHMOS Dynamic RAM Controller                                                    |         |

| LISERS MANUAL                                                                         |         |

| Introduction                                                                          | . 6-15  |

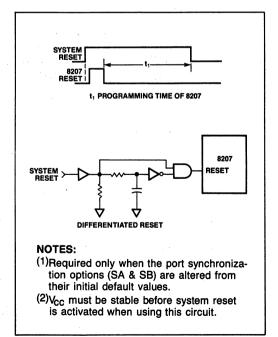

| Programming the 8207                                                                  | . 6-15  |

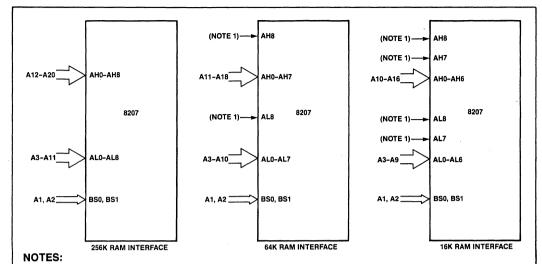

| RAM Interface                                                                         | 6 15    |

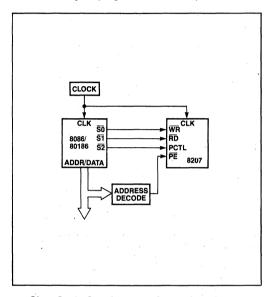

| Microprocessor Interfaces                                                             |         |

|                                                                                       |         |

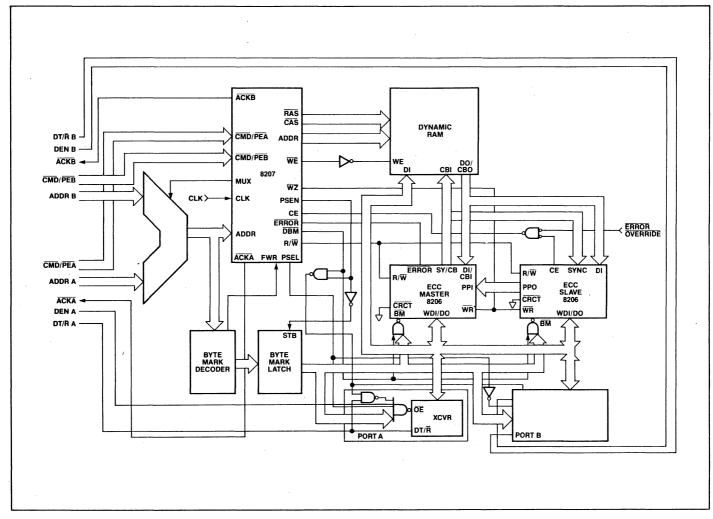

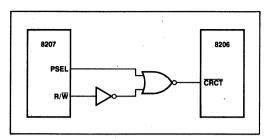

| 8207 with ECC (8206)                                                                  |         |

| Appendix                                                                              | 6-17    |

| APPLICATION NOTES AP-97A Interfacing Dynamic RAM to iAPX 86/88 Using the 8202A & 8203 |         |

|                                                                                       |         |

| AP-141 8203/8206/2164A Memory Design                                                  |         |

| AP-167 Interfacing the 8207 Dynamic RAM Controller to the iAPX 186                    |         |

| AP-168 Interfacing the 8207 Advanced Dynamic RAM Controller to the iAPX 286           | . 6-228 |

| ARTICLE REPRINTS                                                                      |         |

| AR-364 FAE News 1/84 "8208 with 186"                                                  | . 6-235 |

| AR-231 Dynamic RAM Controller Orchestrates Memory Systems                             | . 6-246 |

| SUPPORT PERIPHERALS                                                                   |         |

| DATA SHEETS                                                                           |         |

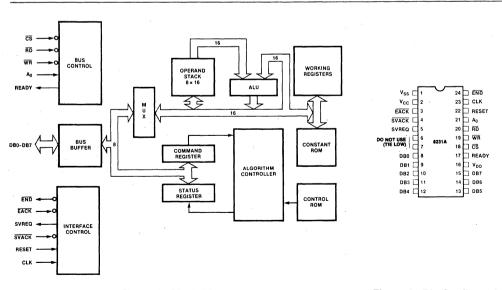

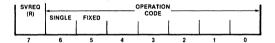

| 8231A Arithmetic Processing Unit                                                      | . 6-253 |

| 8253/8253-5 Programmable Interval Timer                                               | . 6-263 |

| 8254 Programmable Interval Timer                                                      | 6-274   |

| 82C54 CHMOS Programmable Interval Timer                                               | 6-290   |

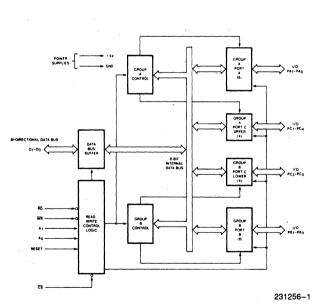

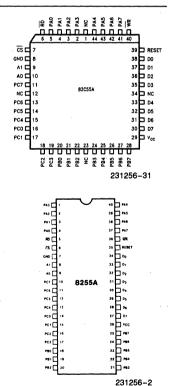

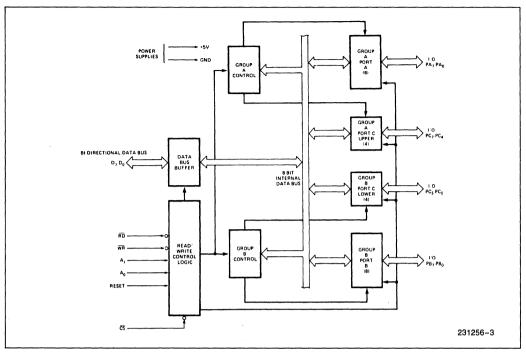

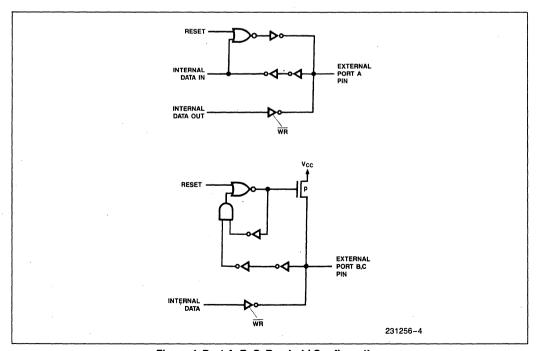

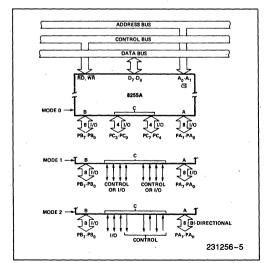

| 8255A/8255A-5 Programmable Peripheral Interface                                       | 6-307   |

| 82C55A CHMOS Programmable Peripheral Interface                                        | 6-328   |

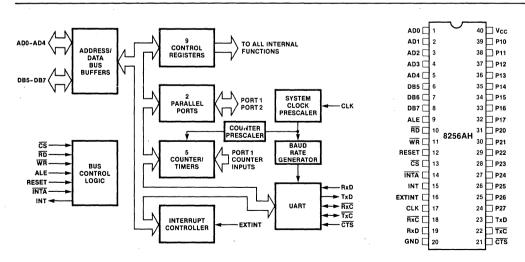

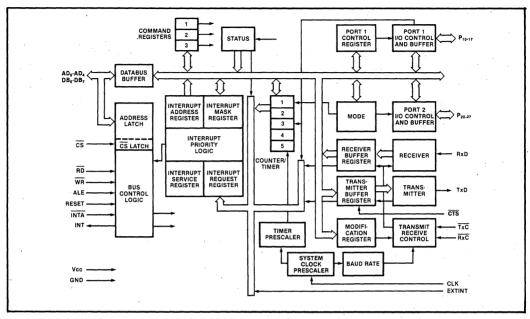

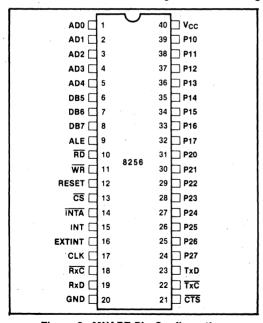

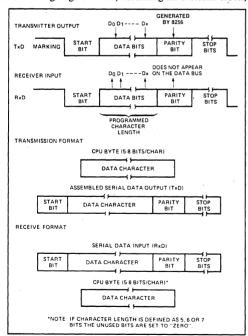

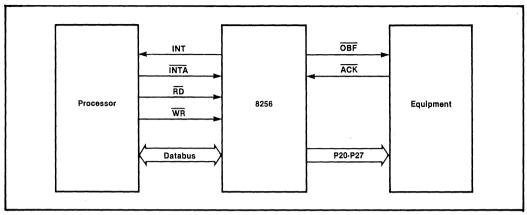

| 8256AH Multifunction Microprocessor Support Controller                                |         |

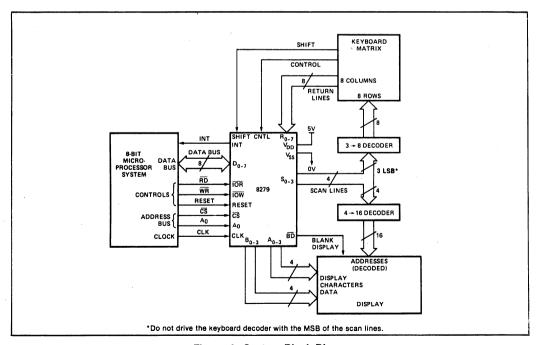

| 8279/8279-5 Programmable Keyboard/Display Interface                                   |         |

| APPLICATION NOTES                                                                     | . 0-31- |

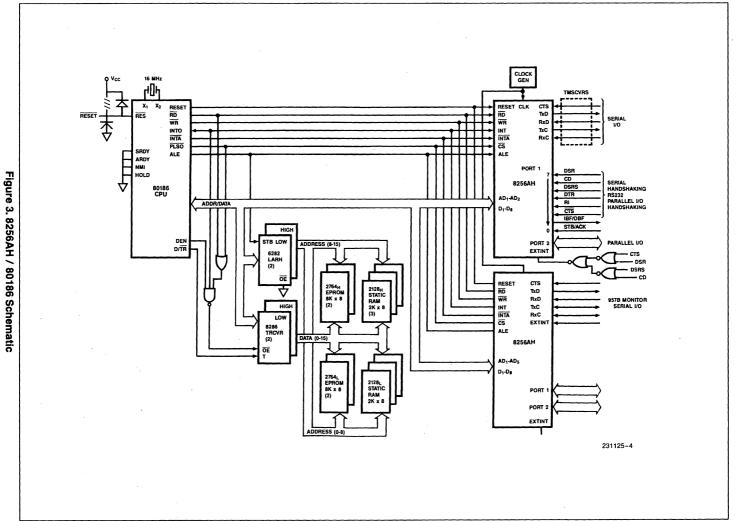

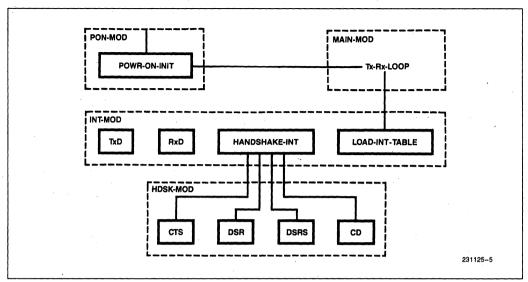

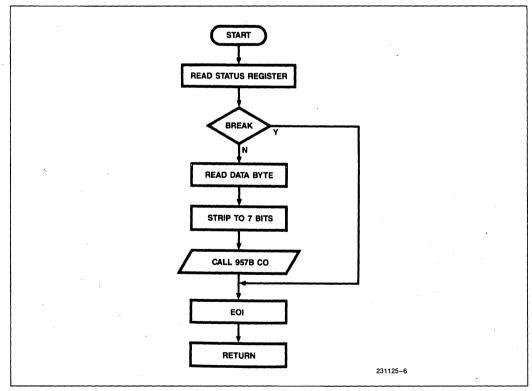

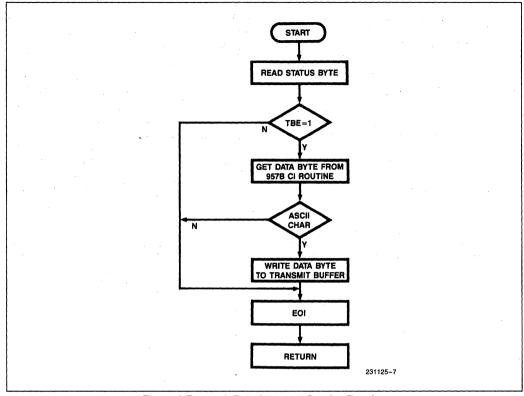

| AP-153 Designing with the 8256                                                        | 6 200   |

| AP-183 8256AH Application Note                                                        | 6-46    |

| FLOPPY DISK CONTROLLERS                                                               | 0-40    |

|                                                                                       |         |

| DATA SHEETS                                                                           | 0.47    |

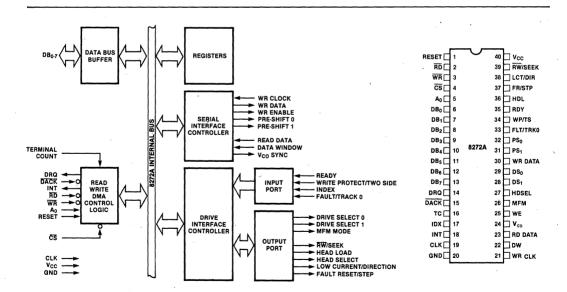

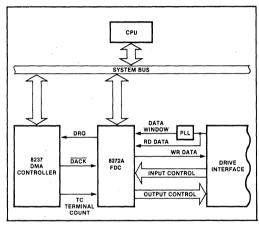

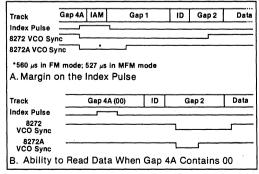

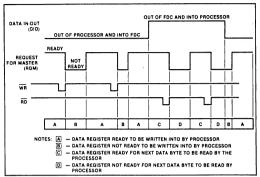

| 8272A Single/Double Density Floppy Disk Controller                                    | . 6-4/8 |

| APPLICATION NOTES                                                                     |         |

| AP-116 An Intelligent Data Base System Using the 8272                                 |         |

| AP-121 Software Design and Implementation of Floppy Disk Systems                      | . 6-538 |

| HARD DISK CONTROLLERS                                                                 |         |

| DATA SHEETS                                                                           |         |

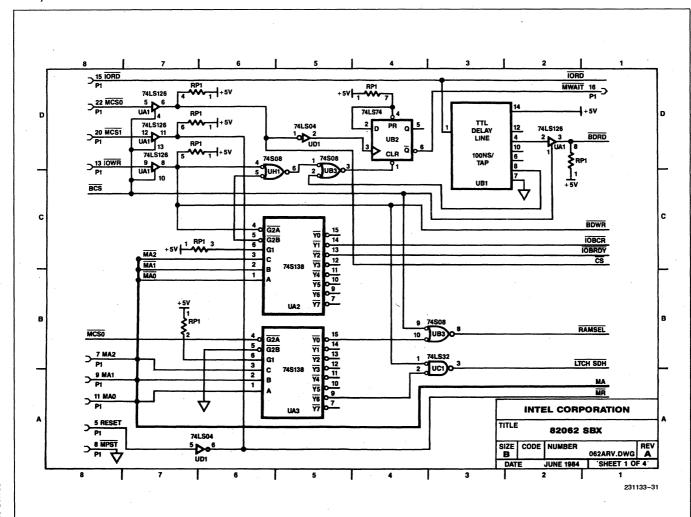

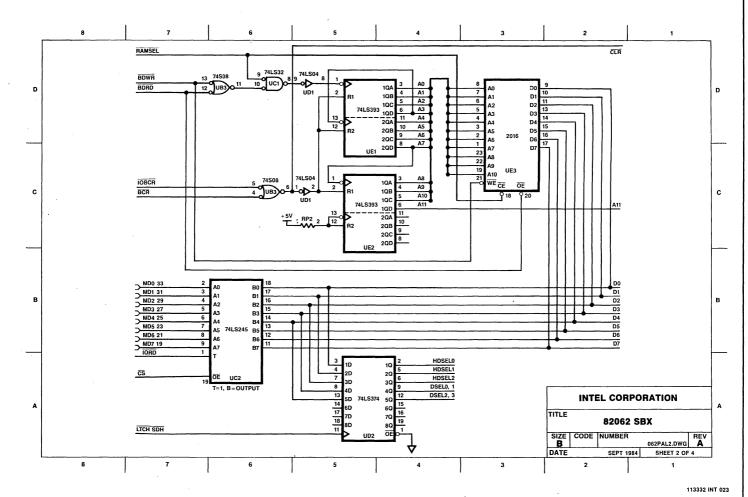

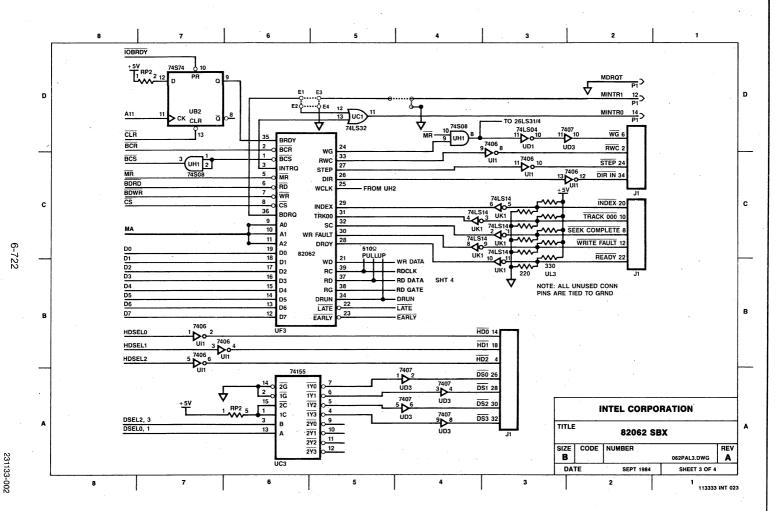

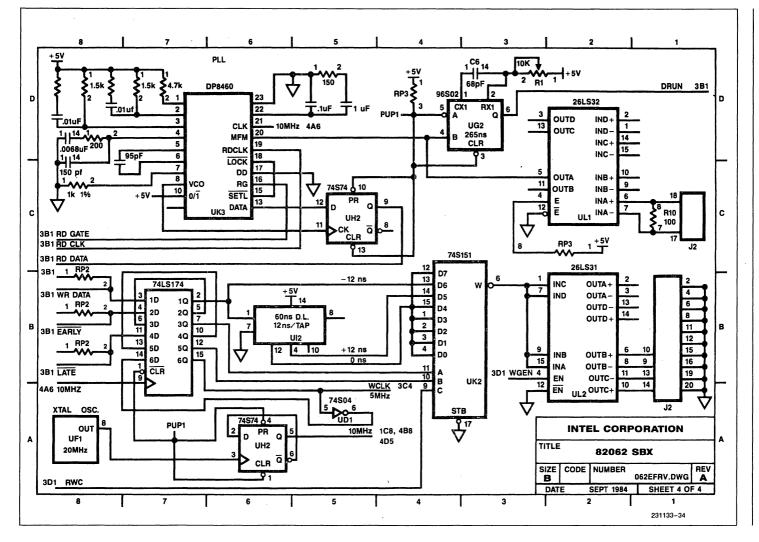

| 82062 Winchester Disk Controller                                                      | . 6-608 |

| 82064 Winchester Disk Controller with On-Chip Error Detection and Correction          | . 6-63  |

| APPLICATION NOTES                                                                     |         |

| AP-182 Multimode Winchester Controller Using the 82062                                | . 6-667 |

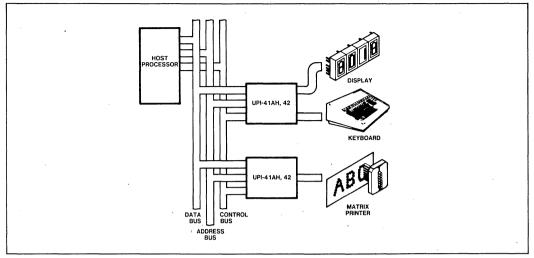

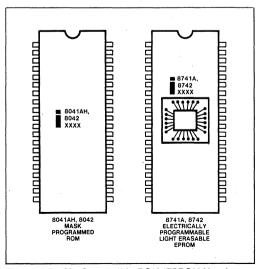

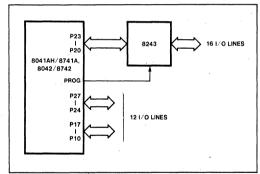

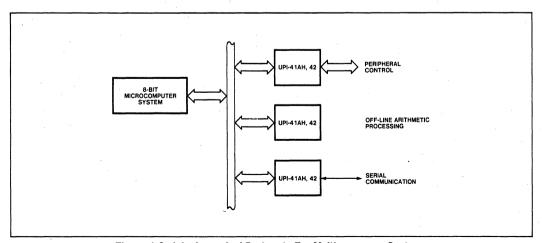

| UNIVERSAL PERIPHERAL INTERFACE SLAVE MICROCONTROLLERS                                 |         |

| DATA SHEETS                                                                           |         |

| UPI-452 Slave Microcontroller (8051)                                                  | . 6-729 |

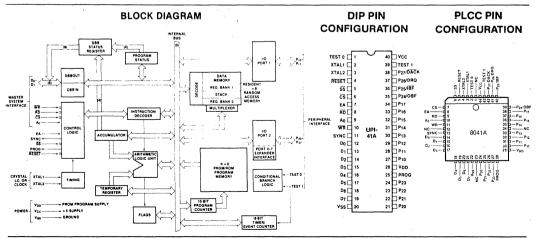

| UPI-41 8-Bit Slave Microcontroller                                                    | . 6-768 |

| UPI-42 8-Bit Slave Microcontroller                                                    |         |

| 8243 MCS-48 Input/Output Expander                                                     |         |

| UPI-41/42 USERS MANUAL                                                             |  |

|------------------------------------------------------------------------------------|--|

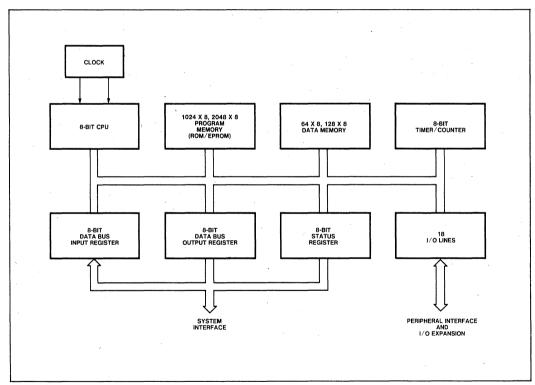

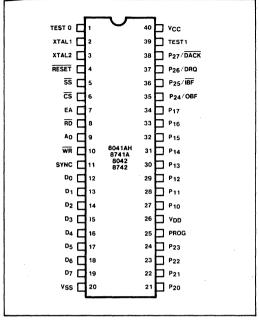

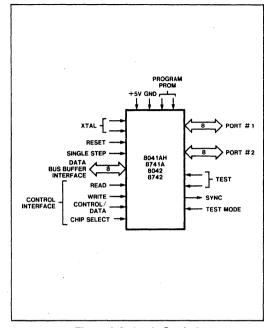

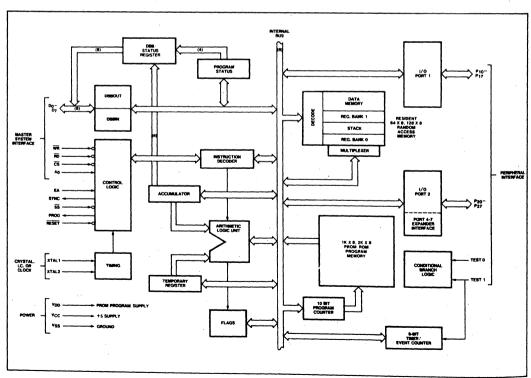

| Introduction 6-805                                                                 |  |

| Functional Description                                                             |  |

| Instruction Set                                                                    |  |

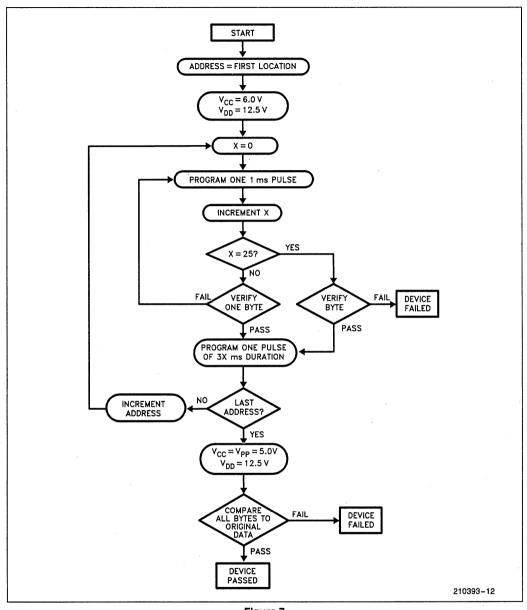

| Single-Step, Programming, and Power-Down Modes6-854                                |  |

| System Operation                                                                   |  |

| Applications                                                                       |  |

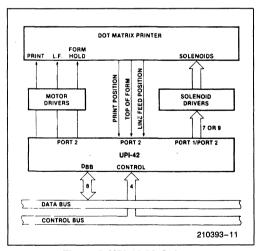

| AP-161 or 61 Complex Peripheral Control with the UPI-42                            |  |

| AP-90 An 8741A/8041A Digital Cassette Controller                                   |  |

| APPLICATION NOTES                                                                  |  |

| Applications Using the 8042 UPI™ Microcontroller                                   |  |

| SYSTEM SUPPORT                                                                     |  |

| ICE-42 8042 In-Circuit Emulator                                                    |  |

| MCS-48 Diskette-Based Software Support Package                                     |  |

| iUP-200/iUP-201 Universal PROM Programmers6-1017                                   |  |

|                                                                                    |  |

| CHAPTER 7                                                                          |  |

| ALPHANUMERIC TERMINAL CONTROLLERS                                                  |  |

| DATA SHEETS                                                                        |  |

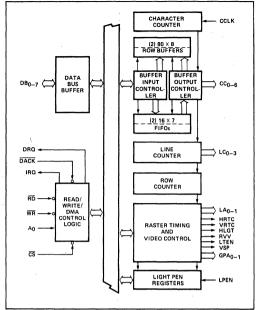

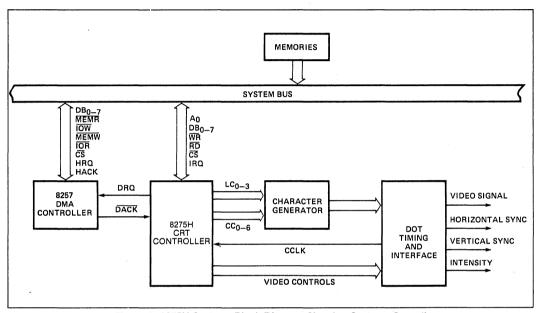

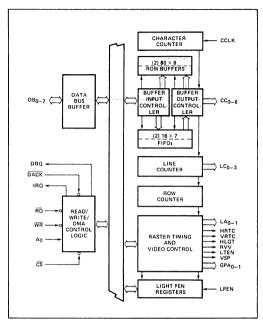

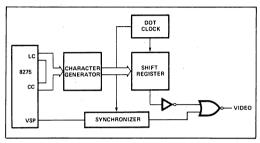

| 8275H Programmable CRT Controller                                                  |  |

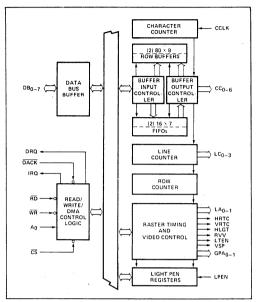

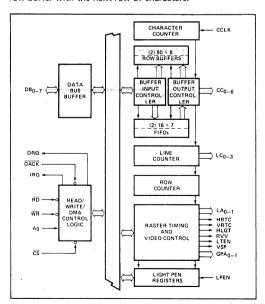

| 8276H Small System CRT Controller                                                  |  |

| APPLICATION NOTES                                                                  |  |

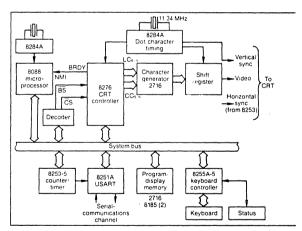

| AP-62 A Low Cost CRT Terminal Using the 8275                                       |  |

| ARTICLE REPRINTS                                                                   |  |

| AR-178 A Low Cost CRT Terminal Does More with Less                                 |  |

| DATA SHEETS                                                                        |  |

| 82720 Graphics Display Controller                                                  |  |

| ARTICLE REPRINTS                                                                   |  |

| AR-255 Dedicated VLSI Chip Lightens Graphic Display Design Load                    |  |

| AR-298 Graphics Chip Makes Low Cost High Resolution, Color Displays Possible 7-136 |  |

| TEXT PROCESSING PRODUCTS                                                           |  |

| DATA SHEETS                                                                        |  |

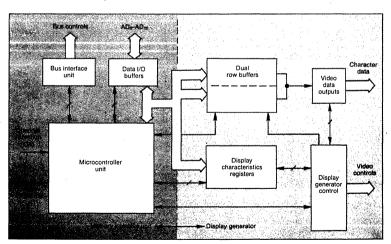

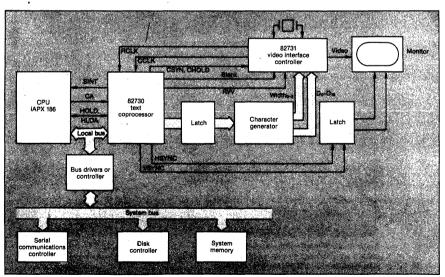

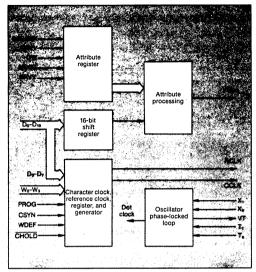

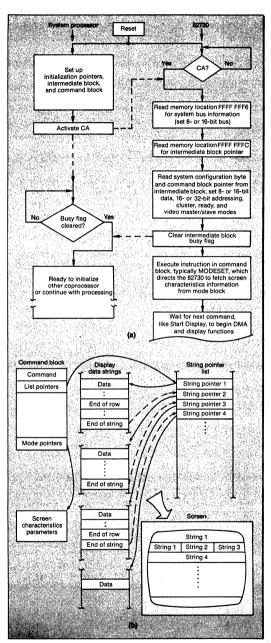

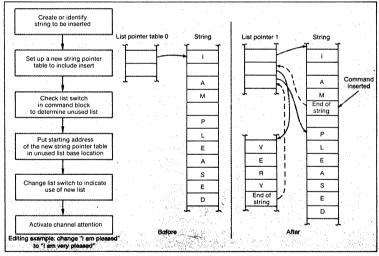

| 82730 Text Coprocessor 7-143                                                       |  |

| ARCHITECTURAL OVERVIEW                                                             |  |

| The 82786 CHMOS Graphics Coprocessor 7-187                                         |  |

| ARTICLE REPRINTS                                                                   |  |

| AR-305 Text Coprocessor Brings Quality to CRT Displays                             |  |

| AR-297 VLSI Coprocessor Delivers High Quality Displays                             |  |

| AR-296 Mighty Chips                                                                |  |

|                                                                                    |  |

| CHAPTER 8                                                                          |  |

| ERASABLE/PROGRAMMABLE LOGIC DEVICES                                                |  |

| DATA SHEETS                                                                        |  |

| 5C121 1200 Gate CHMOS H-Series Eraseable/Programmable Logic Device 8-1             |  |

| 5C060 600 Gate CHMOS H-Series Erasable/Programmable Logic Device                   |  |

|                                                                                    |  |

# Numeric Index

| 5C121 1200 Gate CHMOS H-Series Eraseable/Programmable Logic Device                      | . 8-1 |

|-----------------------------------------------------------------------------------------|-------|

| 5C060 600 Gate CHMOS H-Series Eraseable/Programmable Logic Device8                      |       |

| 80186 (iAPX 186) High Integration 16-Bit Microprocessor                                 | 435   |

| 80188 (iAPX 188) High Integration 8-Bit Microprocessor 3-                               | -162  |

| 80286 (iAPX 286/10) High Performance Microprocessor with Memory Management              |       |

| and Protection 4-1, 6-228, 6-                                                           |       |

| 80287 80-Bit HMOS Numeric Processor Extension4                                          | 1-56  |

| 80386 High Performance Microprocessor with Integrated Memory Management                 | . 5-1 |

| 8041A/8641A/8741A Universal Peripheral Interface                                        |       |

| 8041A/8641A/8741A Universal Peripheral Interface 8-Bit Slave Micro Controller           | .994  |

| 8042/8742 Universal Peripheral Interface                                                |       |

| 8-Bit Slave Micro Controller                                                            | 006   |

| 80452/83452/87452 Universal Peripheral Interface 8-Bit Slave Micro Controller 6-729, 6- | -805  |

| 8080A/8080A-1/8080A-2, 8-Bit N-Channel Microprocessor                                   | . 2-1 |

| 8085AH/8085AH-2/8085AH-1 8-Bit HMOS Microprocessors                                     | 2-10  |

| 8086 (iAPX 86/10) 16-Bit HMOS Microprocessor                                            | 181   |

| 80C86/80C86-2 16-Bit Microprocessor                                                     | 3-25  |

| 8087/8087-2/8087-1 Numeric Data Coprocessor                                             | 373   |

| 8088 (iAPX 88/10) 8-Bit HMOS Microprocessor                                             |       |

| 80C88/80C88-2 8-Bit CHMOS Microprocessor                                                | 133   |

| 8155H/8156H/8155H-2/8156H-2 2048-Bit Static HMOS RAM with I/O Ports and Timer2          |       |

| 8185/8185-2 1024 x 8-Bit Static RAM for MCS®-852                                        | 2-38  |

| 8202A Dynamic RAM Controller                                                            | ·181  |

| 8203 64K Dynamic RAM Controller                                                         | 217   |

| 8205 High Speed 1 out of 8 Binary Decoder                                               |       |

| 8206 Error Detection and Correction Unit                                                | 247   |

| 82062 Winchester Disk Controller                                                        |       |

| 82064 Winchester Disk Controller with On-Chip Error Detection and Correction 6-         |       |

| 8207 Dual-Port Dynamic RAM Controller 6-52, 6-150, 6-223, 6-228, 6-                     | 247   |

| 8208 Dynamic RAM Controller 6-98, 6-                                                    |       |

| 82C08 Dynamic RAM Controller 6-                                                         |       |

| 82188 Integrated Bus Controller for iAPX 86, 88, 186, 188 Processors 3-                 |       |

| 8224 Clock Generator And Driver for 8080A CPU2                                          |       |

| 82258 Advanced Direct Memory Access Coprocessor4                                        |       |

| 8228/8238 System Controller and Bus Driver for 8080A CPU                                |       |

| 82284 Clock Generator and Ready Interface for iAPX 286 Processors 4-                    | 139   |

| 82288 Bus Controller for iAPX 286 Processors 4-                                         | 148   |

| 82289 Bus Arbiter for iAPX 286 Processor Family4-                                       |       |

| 8231A Arithmetic Processing Unit 6-                                                     | 253   |

| 8237A/8237A-4/8237A-5 High Performance Programmable DMA Controller2                     |       |

| 82C37A-5 CHMOS High Performance Programmable DMA Controller2                            |       |

| 82384 Clock Generator And Reset Interface for 80386 Processors                          |       |

| 8243 MCS-48 Input/Output Expander 6-799, 6-                                             | -805  |

|                                                                                         |       |

| 6255/6255-5 Frogrammable interval rimer                             |          | • • • • • • | 0-203  |

|---------------------------------------------------------------------|----------|-------------|--------|

| 8254 Programmable Interval Timer                                    |          |             | 6-274  |

| 82C54 CHMOS Programmable Interval Timer                             |          |             | 6-290  |

| 8255A/8255A-5 Programmable Peripheral Interface                     |          |             | 6-307  |

| 82C55A CHMOS Programmable Peripheral Interface                      |          |             | 6-328  |

| 8256AH Multifunction Microprocessor Support Controller              | 6-357,   | 6-386,      | 6-461  |

| 8257/8257-5 Programmable DMA Controller                             |          |             | .2-78  |

| 8259A/8259A-2/8259A-8 Programmable Interrupt Controller             |          | . 2-95,     | 2-144  |

| 82C59A-2 CHMOS Programmable Interrupt Controller                    |          |             | 2-113  |

| 8272A Single/Double Density Floppy Disk Controller                  | . 6-478, | 6-497,      | 6-538  |

| 82720 Graphics Display Controller                                   | 7-205,   | 7-213,      | 7-216  |

| 82730 Text Coprocessor 7-136, 7-143, 7-205, 7-213, 7-216            |          |             |        |

| 8275H Programmable CRT Controller                                   |          |             |        |

| 8276H Small System CRT Controller                                   |          | 7-25        | , 7-84 |

| 82786                                                               |          |             | 7-187  |

| 8279/8279-5 Programmable Keyboard/Display Interface                 |          |             | 6-374  |

| 8282/8283 Octal Latch                                               |          |             | 3-241  |

| 8284A/8284A-1 Clock Generator and Driver for iAPX 86, 88 Processors |          |             | 3-246  |

| 82C84A/82C84A-5 CHMOS Clock Generator And Driver                    |          |             |        |

| For 80C86, 80C88 Processors                                         |          |             | 3-254  |

| 8286/8287 Octal Bus Transceiver 3-263                               |          |             |        |

| 8288 Bus Controller for iAPX 86, 88 Processors                      |          |             | 3-268  |

| 82C88 CHMOS Bus Controller for 80C86, 80C88 Processors              |          |             | 3-275  |

| 8289/8989-1 Bus Arbiter                                             |          |             | 3-299  |

| 8755A/8755A-2 16.384-Bit EPROM with I/O                             |          |             | 2-133  |

# **CUSTOMER SUPPORT**

#### **CUSTOMER SUPPORT**

Customer Support is Intel's complete support service that provides Intel customers with Customer Training, Software Support and Hardware Support.

After a customer purchases any system hardware or software product, service and support become major factors in determining whether that product will continue to meet a customer's expectations. Such support requires an international support organization and a breadth of programs to meet a variety of customer needs. Intel's extensive customer support includes factory repair services as well as worldwide field service offices providing hardware repair services, software support services and customer training classes.

#### HARDWARE SUPPORT

Hardware Support Services provides maintenance on Intel supported products at board and system level. Both field and factory services are offered. Services include several types of field maintenance agreements, installation and warranty services, hourly contracted services (factory return for repair) and specially negotiated support agreements for system integrators and large volume end-users having unique service requirements. For more information contact your local Intel Sales Office.

#### SOFTWARE SUPPORT

Software Support Service provides maintenance on software packages via software support contracts which include subscription services, information phone support, and updates. Consulting services can be arranged for on-site assistance at the customer's location for both short-term and long-term needs. For complex products such as NDS II or 12ICE, orientation/installation packages are available through membership in Insite User's Library, where customer-submitted programs are catalogued and made available for a minimum fee to members. For more information contact your local Intel Sales Office.

#### **CUSTOMER TRAINING**

Customer Training provides workshops at customer sites (by agreement) and on a regularly scheduled basis at Intel's facilities. Intel offers a breadth of workshops on microprocessors, operating systems and programming languages, etc. For more information on these classes contact the Training Center nearest you.

#### TRAINING CENTER LOCATIONS

To obtain a complete catalog of our workshops, call the nearest Training Center in your area.

| Boston             | (617) 692-1000    | London              | (0793) 696-000  |

|--------------------|-------------------|---------------------|-----------------|

| Chicago            | (312) 310-5700    | Munich              | (089) 5389-1    |

| San Francisco      | (415) 940-7800    | Paris               | (01) 687-22-21  |

| Washington, D.C.   | (301) 474-2878    | Stockholm           | (468) 734-01-00 |

| Israel             | (972) 349-491-099 | Milan               | 39-2-82-44-071  |

| Tokyo              | 03-437-6611       | Benelux (Rotterdam) | (10) 21-23-77   |

| Osaka (Call Tokyo) | 03-437-6611       | Copenhagen          | (1) 198-033     |

| Toronto, Canada    | (416) 675-2105    | Hong Kong           | 5-215311-7      |

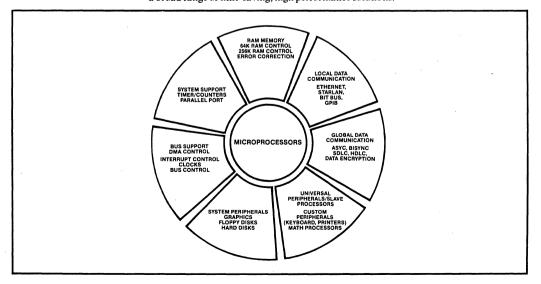

#### INTRODUCTION

Intel microprocessors and peripherals provide a complete solution in increasingly complex application environments. Quite often, a single peripheral device will replace anywhere from 20 to 100 TTL devices (and the associated design time that goes with them).

Built-in functions and standard Intel microprocessor/ peripheral interface deliver very real *time* and *performance* advantages to the designer of microprocessorbased systems.

#### REDUCED TIME TO MARKET

When you can purchase an off-the-shelf solution that replaces a number of discrete devices, you're also replacing all the design, testing, and debug *time* that goes with them.

#### **INCREASED RELIABILITY**

At Intel, the rate of failure for devices is carefully tracked. Highest reliability is a tangible goal that translates to higher reliability for your product, reduced downtime, and reduced repair costs. And as more and more functions are intergrated on a single VLSI device, the resulting system requires less power, produces less heat, and requires fewer mechanical connections—again resulting in greater system reliability.

#### **LOWER PRODUCTION COST**

By minimizing design time, increasing reliability, and

replacing numerous parts, microprocessor and peripheral solutions can contribute dramatically to lower product costs.

#### HIGHER SYSTEM PERFORMANCE

Intel microprocessors and peripherals provide the highest system performance for the demands of today's (and tomorrow's) microprocessor-based applications. For example, the 80386 32 bit offers the highest performance for multitasking, multiuser systems. Intel's peripheral products have been designed with the future in mind. They support all of Intel's 8, 16 and 32 bit processors.

#### **HOW TO USE THE GUIDE**

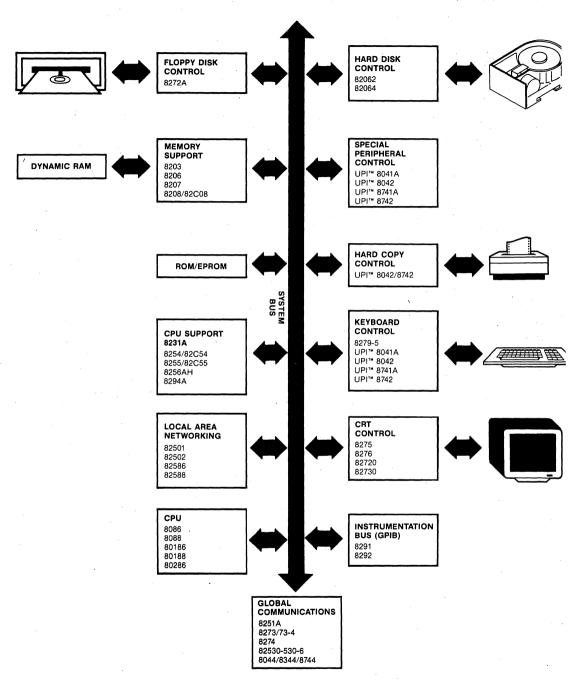

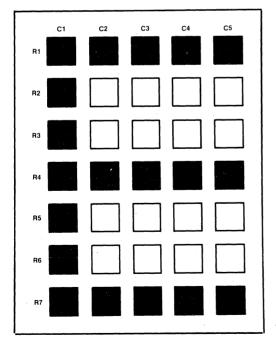

The following application guide illustrates the range of microprocessors and peripherals that can be used for the applictions in the vertical column of the left. The peripherals are grouped by the I/O function they control. CRT datacommunication, universal (user programmable), mass storage dynamic RAM controllers, and CPU/bus support.

An "X" in a horizontal application row indicates a potential peripheral or CPU, depending upon the features desired. For example, a conversational terminal could use either of the three display controllers, depending upon features like the number of characters per row or font capability. A "Y" indicates a likely candidate, for example, the 8272A Floppy Disk Controller in a small business computer.

The Intel microprocessor and peripherals family provides a broad range of time-saving, high performance solutions.

# intel's Microsystem Components Kit Solution

Get Your Kit Together!

# **APPLICATION CHART**

#### POTENTIAL APPLICATION X-TYPICAL APPLICATION Y

|                             | MIC                   | ROP             | ROC          | ESS           | ORS             | DI               | SPL               | AY                    |                | DAT           | A CC          | ММ           | UNI                     | CATI            | *                 | 6          | UPI            | DI              | sĸ             | DRA                                   | M C           | ONT   | ROL        |           | SUP      | POR                                     | RT |

|-----------------------------|-----------------------|-----------------|--------------|---------------|-----------------|------------------|-------------------|-----------------------|----------------|---------------|---------------|--------------|-------------------------|-----------------|-------------------|------------|----------------|-----------------|----------------|---------------------------------------|---------------|-------|------------|-----------|----------|-----------------------------------------|----|

| APPLICATION                 | 8088                  | 9808            | 80188        | 80186         | 80286           | 8275/76          | 82720             | 82730/731*            | 8251A          | 8273*         | 8274          | 8291A/92/94* | 82530                   | 82588*          | 82586/501/502     | 8044/8744* | 8042/8742      | 8272A           | 82062/064      | 8203*                                 | 8206          | 8207* | 8208*/C08* | 8254/C54  | 8255/C55 | 8256AH                                  |    |

| PERIPHERALS                 |                       |                 |              |               |                 |                  |                   |                       |                |               |               |              |                         |                 |                   |            |                |                 |                |                                       |               |       |            |           |          |                                         |    |

| Printers                    | X                     |                 | X            | Υ             |                 |                  | X                 | X.                    | X              |               |               | Х            | v Lamas and             | ne nazivo tiko  |                   | X          | X              |                 |                |                                       |               |       |            | Х         | X        | X                                       | L  |

| Plotters                    | X                     | Х               | X            | Υ             | V 4111          | l                |                   |                       | X              | l             |               | X            |                         |                 |                   | X          | X              |                 |                |                                       | l             |       |            |           | X        |                                         | 1. |

| Keyboards                   |                       |                 | X            | Υ             | dum sin         |                  | 2000              |                       | X              |               |               | Von erne     |                         |                 |                   | X          | X              |                 |                |                                       | attendance of |       | L          | .c. homes | X        | - 1                                     |    |

| MAŚS STORAGE                |                       |                 |              |               |                 |                  |                   |                       |                |               |               |              |                         |                 |                   |            |                |                 |                |                                       |               |       |            |           |          |                                         |    |

| Hard Disk                   | X                     | X               | Y            | Y             | VES:            |                  |                   |                       |                |               |               |              | a. Valida               |                 |                   |            |                | 3               | X              |                                       |               |       |            |           | Х        |                                         | L  |

| Mini Winchester             | X                     | l               | Y            | Υ             |                 |                  |                   | L                     | l              |               | l             |              |                         |                 |                   |            |                |                 | Υ.             | <u> </u>                              |               |       | I          | 1         |          | l                                       | 1  |

| Tape                        |                       |                 | X            | Y             |                 | 33.7             |                   |                       |                |               |               | 4            | 34.3                    |                 |                   | Х          | Х              |                 |                |                                       |               |       |            |           | Х        |                                         |    |

| Cassette                    | A000,                 | oi              | ÎΫ́          | Υ             |                 | AMX Jun          | o w w on me a     |                       | 20.00          |               | 4.5 - NONEMAN |              | O THE REAL PROPERTY.    | Inflored Screen |                   |            | Х              |                 | 3.4.7 (4.4     | 2 'ArAille                            |               | 1     |            |           | X        | AND | 1  |

| Floppy/Mini                 |                       | Calabian.       | Y            | Υ             | 73.5            | Z."              |                   |                       | ever et ver    |               |               |              |                         | 4.4             | 7                 |            | 1              | Υ               |                | * mar                                 | 70.00         |       | ~          |           |          |                                         | ľ  |

| COMMUNICATIONS              |                       |                 |              |               | MANAGES -       | 69.000           | N. OLJOMAN        | t its/countries       | nie rektieri   | 200,000       | w. w. der i r |              | · war and the state of  | 16164           |                   |            | v - / - v m    | i. n. r Mistory | enterna Voca   | thew von                              |               | 1 /2  |            |           |          | Aredonali/A                             | 1  |

| PBX                         | 33.33                 |                 | X            | Х             | Υ               |                  | 466               | 3,713                 | 1000           | X             | X             |              | X                       | y 10 g-111.     |                   | X          |                | 7.7             |                | Х                                     | Х             | X     | X          | X         | X        | X                                       | 1  |

| LANS                        | X                     | X               | Υ            | Υ             |                 | 1                |                   | 1000                  | ,              |               | X<br>X        |              | X                       | Х               | Y                 | Х          |                |                 |                |                                       |               |       |            | Х         |          | 1                                       | 1  |

| Modems                      | 3733                  |                 | 1357         |               |                 | - A3             | G. 25.            |                       | X              | 478           | X             |              | Х                       |                 | 7.53              | X          | Х              |                 |                | spend, to                             | 7.3.7         | . wy  | / V' Y === | 1 200     |          | 70                                      |    |

| Bisync                      | Section of the second | 111,111,242,244 | Foto mind to | m Water I i A | C. C. Washin X. | Consider verben. | la /www.indlane.i | Karani ada ani karani | X              | e as jemini i | X             | i di makani  |                         | Х               |                   | - Canno    |                | 411,00000       |                |                                       | trovatare un  |       | to Vary A  | X         |          | t-e-minatura                            | Ī  |

| SDLC/HDLC                   |                       |                 | STATE        | THE STATE     | 1837            | \$2.50°          |                   | 75                    |                | X             | x.            | 70 Y Y       | X                       | - : //          | 1 x 2 x 1         | Х          |                | 57.5            |                |                                       |               |       |            | Î         |          |                                         | 1  |

| Serial Backplane            | 2000                  | adiiijiesiin    | THE YELDES   | (4102226)     | · Makking       | ealit, 324 3     | enagligh like e   | gal ii wakii ii       | o Tarinada a r | X             | X             | downasia-r   | X                       |                 | х                 | x          | 2.22           | an harried      |                | · · · · · · · · · · · · · · · · · · · | Wanton Co.    | *     |            | ~ / :     |          | 1, 4,                                   | 1  |

| Central Office              | 35.63                 | X               | S 1979       | X             | Y               | 87.773           | 1850              | STATE                 | 753            | x             | Î             | 77.33        | X<br>X<br>X             |                 | - ( )             | x          | - E            |                 | 2000           | st                                    | X             | X     | X          | X         |          | Х                                       | 1- |

| Network Control             | azina                 | Y               | alaist.      | X             | Y               |                  | - Markey his      | Si Sanz               | لللفضنا        | Zahak.        | x             | 1) 0 1, y'am | x                       | Х               | Х                 | x          | to in the case | m' wasi, ,      |                | Louis adam                            | 1             |       | -257       | X         |          |                                         | 1  |

| OFFICE/BUS                  | <b>T</b>              | THE             | D-SE         | 288           |                 | 37.51            | <b>FF</b> 6       | F.S (2) A             | 1482           | TES.          | 1             | 2.77         | 278                     | WITH IT         |                   | 200        | 57,111         | *****           | 7.32           | 250                                   |               |       |            | 100       |          |                                         | ŀ  |

| Copier/FAX                  | X                     | 25752           | X            | Υ             |                 | Liller C         |                   | San charles           | inime-bilan    | or Millerdon  | ·             | Х            | المستثلاث               | الونيعاسات      | X                 | X          | X              | بمسم باب        | المذكر أستدريا | Litan, ye aire.                       | I.44          | 1     |            |           |          | X                                       | ľ  |

| Wordprocessor               | â                     | Х               | x.           | χ̈́           | Y               | Essi             | Х                 | Y                     | X              | 1000 A        | Hazs          | 200          | SOW                     | MARIE .         | .√}::             | Î x        | ·              | Y               |                | X                                     | X             | X     | X          | Y         | Υ        | Ŷ                                       | 1  |

| wordprocessor<br>Typewriter | res/Acti              |                 | X            |               |                 | ak irai          | Salah             |                       |                | Lingsto       |               | أشفشلها      | الشتملك                 |                 | 2000              | X          | х              | : <b></b>       | www.vii.india. | ĽΔ.                                   | 1             | 1 ^-  | - A.       |           | Ý        | -43×                                    | 1  |

|                             | 17757                 | v               | 1.           |               | 2.55            | geran            | Х                 | Υ                     | 1450           |               | X             | 015(16)      | Χ                       | Χ               | х                 | 100        | · ^ -          | 11,772          | 1777           |                                       | x             | 1     | 1 1 700    |           | ļ. '     |                                         | 1  |

| Electronic Mail             | المكاشا               | X               | X            | X<br>X<br>X   | х               | المارية المارية  | <del></del>       |                       | X              | والمستقدم     |               | L.C. Marin   | -Oknaii                 | 1. Disk.        | 6 3 <b>/A</b> _0. | X          | · marin        | بالعظب          |                |                                       |               |       | s alas m   | Υ         | X        | X                                       | t  |

| Transaction System          | ×                     | X               | â            | Q-            | <b>, ^</b> s    | х                | X                 | Х                     | Î.             | 75 SY         | 1,545         | 1513/15/     |                         | many v 1:1m     |                   | x          | х              |                 |                | 1170                                  | 1             |       | Х          | Y         | ^        | î                                       | 1  |

| Data Entry<br>COMPUTERS     | 10.00                 |                 | 1.25 L       | -A.           |                 | ·                | · ^               | <u>^</u>              | A.             | - frain       |               | ļ            |                         |                 | l                 | · ^        | -A.            | المشاد          |                |                                       | ļ             | 1     | -^-        | I         |          | · ^ -                                   | 1  |

| SM Bus Computer             | 57-5                  | Х               | Υ            | V             | · .             | 1 V              | V                 | V                     | v              | iner.         | v             |              | Χ                       | Ÿ               | v                 | v          | V              | Y               | v              | v                                     | l v           | ¥     | Y          | V         | V        | X                                       | 1  |

| PC                          | 1.                    | 1-0-            |              | X<br>X        | X               | X                | Y                 | Ϋ́Υ                   | X              | Sicale        | X             | Х            | X                       | X               | X                 | X          | X              | Y               | Y              | X                                     | X             | X     | X          | Y         | Y        | x                                       | 1  |

| Portable PC                 | Y                     | Х               | 27.5         | â             | <b>∤</b> ^ः     | _^               | 327               |                       | î              | 1.75          | .             | ^-           | ^·                      |                 | -^-               | 1.0        | Ç              | Ÿ               | '-             | Ŷ                                     | 1.^           | 1.0   | - ÷        | V         | Y        | Q.                                      | 1  |

|                             | X                     | Х               | Υ            | X             | X               | Con Land         | х                 | ماشتأدب               | X              |               | harran.       | - aliin w    | A STATE OF THE STATE OF | and a n         | ani ne s          | come.      | X              | Y               |                | X                                     |               | X     | X          | Y         | Y        | X                                       | -  |

| Home Computer               | ^                     | ^               | 1            | ^             | ^               | ł                | ^                 |                       | ^              | l             |               |              |                         |                 |                   |            | ^              | 1               |                | ^                                     |               | ^     | ^          | '         | '        | ^                                       | 1  |

| APPLICATION    Record   Record | <b>(</b>        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Conversational Graphics CRT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |

| Editing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |

| Editing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (               |

| Videotex                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |

| Videotex                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |

| Printing, Laser, Impact                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | X               |

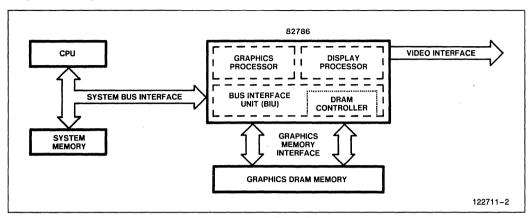

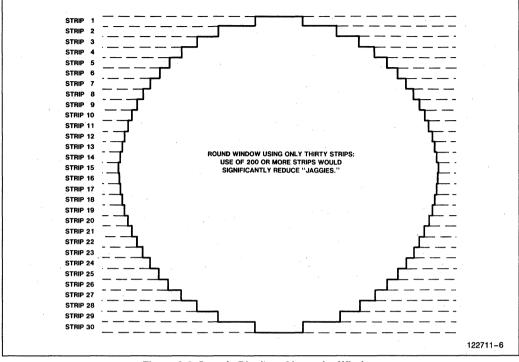

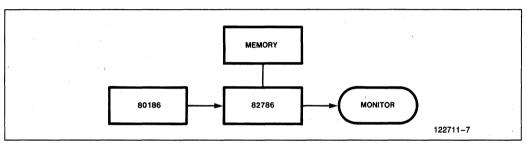

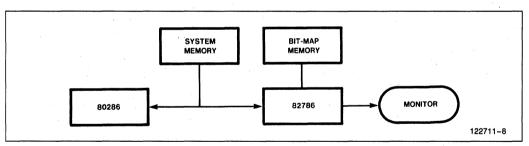

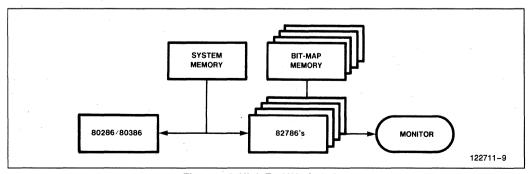

| Portable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | x               |