# Development Systems Handbook

intel

h

Order Number: 210940-003

## LITERATURE

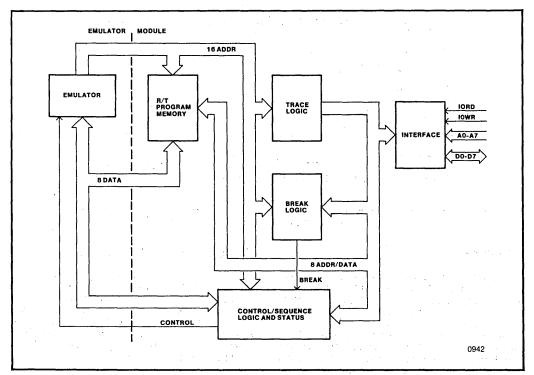

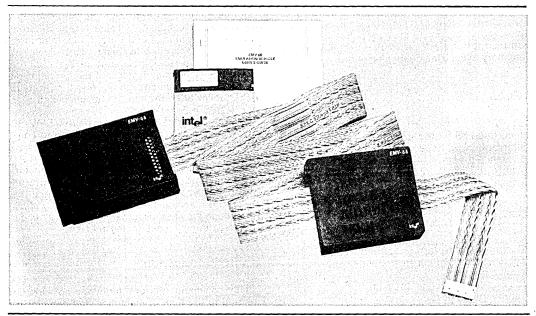

In addition to the product line handbooks listed below, the INTEL PRODUCT GUIDE (no charge, Order No. 210846-003) provides an overview of Intel's complete product lines and customer services.

Consult the INTEL LITERATURE GUIDE (Order No. 210620) for a listing of Intel literature. TO ORDER literature in the U.S., write or call the INTEL LITERATURE DEPARTMENT, 3065 Bowers Avenue, Santa Clara, CA 95051, (800) 538-1876, or (800) 672-1833 (California only). TO ORDER literature from international locations, contact the nearest Intel sales office or distributor (see listings in the back of most any Intel literature).

Use the order blank on the facing page or call our TOLL FREE number listed above to order literature. Remember to add your local sales tax.

#### **1985 HANDBOOKS**

Product line handbooks contain data sheets, application notes, article reprints and other design information.

|                                                                                                                                                       | <sup>*</sup> U.S. PRICE |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| QUALITY/RELIABILITY HANDBOOK (Order No. 210997-001)<br>Contains technical details of both quality and reliability programs and principles.            | \$15.00                 |

| CHMOS HANDBOOK (Order No. 290005-001)<br>Contains data sheets only on all microprocessor, peripheral, microcontroller and<br>memory CHMOS components. | \$12.00                 |

| MEMORY COMPONENTS HANDBOOK (Order No. 210830-004)                                                                                                     | \$18.00                 |

| TELECOMMUNICATION PRODUCTS HANDBOOK (Order No. 230730-003)                                                                                            | \$12.00                 |

| MICROCONTROLLER HANDBOOK (Order No. 210918-003)                                                                                                       | \$18.00                 |

| MICROSYSTEM COMPONENTS HANDBOOK (Order No. 230843-002)<br>Microprocessors and peripherals—2 Volume Set                                                | \$25.00                 |

| DEVELOPMENT SYSTEMS HANDBOOK (Order No. 210940-003)                                                                                                   | \$15.00                 |

| OEM SYSTEMS HANDBOOK (Order No. 210941-003)                                                                                                           | \$18.00                 |

| SOFTWARE HANDBOOK (Order No. 230786-002)                                                                                                              | \$12.00                 |

| MILITARY HANDBOOK (Order No. 210461-003)<br>Not available until June.                                                                                 | \$15.00                 |

| <b>COMPLETE SET OF HANDBOOKS (Order No. 231003-002)</b><br>Get a 25% discount off the retail price of \$160.                                          | \$120.00                |

| NAME:                                            |                                         | TITLE:                        |

|--------------------------------------------------|-----------------------------------------|-------------------------------|

| COMPANY:                                         |                                         |                               |

| ADDRESS:                                         |                                         |                               |

| CITY:                                            | STATE:                                  | ZIP:                          |

| COUNTRY:                                         |                                         |                               |

| PHONE NO.: ()                                    |                                         |                               |

| ORDER NO.                                        | TITLE                                   | QTY. PRICE TOTAL              |

|                                                  |                                         | × =                           |

|                                                  |                                         | × =                           |

|                                                  |                                         | × =                           |

|                                                  |                                         | × =                           |

|                                                  |                                         |                               |

|                                                  | - · · · · · · · · · · · · · · · · · · · | × =                           |

|                                                  | · .                                     | Subtotal                      |

| POSTAGE AND HANDLING:<br>Add appropriate postage | Your Loca                               | I Sales Tax                   |

| and handling to subtotal<br>10% U.S.             |                                         |                               |

| 20% Canada –                                     |                                         |                               |

| Allow 4-6 weeks for delivery                     |                                         | Total                         |

| Pay by Visa, MasterCard, Check or                | Money Order, payable to Intel           | Literature. Purchase Orde     |

| have a \$50.00 minimum.                          |                                         |                               |

|                                                  |                                         |                               |

| MasterCard                                       |                                         | Date                          |

| Signature:                                       |                                         | ·                             |

| Mail To: Intel Literature Distributio            | n Customers outside the                 | U.S. and Canada should c      |

| Mail Stop SC6-714<br>3065 Bowers Avenue          |                                         | s Office or Distributor liste |

| Santa Clara, CA 95051.                           | the back of this book.                  |                               |

Cut Along Dotted Line

이 나는 사람이 것 옷에 가져져졌다. 것 같아.

#### Mail To: Intel Literature Distribution Mail Stop SC6-714 3065 Bowers Avenue Santa Clara, CA 95051.

1.1

177

A Charles and A to get

1994 - 1995 - 1995 - 1995 - 1995 - 1995 - 1995 - 1995 - 1995 - 1995 - 1995 - 1995 - 1995 - 1995 - 1995 - 1995 -

ĪN

## DEVELOPMENT SYSTEMS HANDBOOK

## **JANUARY 1985**

About Our Cover:

The design on our front cover is an abstract portrayal of the systems creation or connection point. From this central sunburst of technology, peripheral design applications and Ethernet networking cables combine in an orchestrated manner symbolically indicating a development process that is in tune with the technological explosion. The design engineer can count on Intel's complete set of integrated tools for every facet of systems development.

1

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products:

BITBUS, COMMputer, CREDIT, Data Pipeline, GENIUS, i, <sup>1</sup>, ICE, iCS, iDBP, iDIS, I<sup>2</sup>ICE, iLBX, i<sub>m</sub>, iMDDX, iMMX, Insite, Intel, int<sub>e</sub>l, int<sub>e</sub>lBOS, Intelevision, int<sub>e</sub>ligent Identifier, int<sub>e</sub>ligent Programming, Intellec, Intellink, iOSP, IPDS, iRMX, iSBC, ISBX, ISDM, ISXM, KEPROM, Library Manager, MCS, Megachassis, MICROMAINFRAME, MULTIBUS, MULTICHANNEL, MULTIMODULE, OpeNET, Plug-A-Bubble, PROMPT, Promware, QUEST, QueX, Ripplemode, RMX/80, RUPI, Seamless, SLD, SYSTEM 2000, and UPI, and the combination of ICE, ICS, IRMX, ISBC, ISBX, MCS, or UPI and a numerical suffix.

MDS is an ordering code only and is not used as a product name or trademark. MDS \* is a registered trademark of Mohawk Data Sciences Corporation.

\* MULTIBUS is a patented Intel bus.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Department 3065 Bowers Avenue Santa Clara, CA 95051

©INTEL CORPORATION 1984

## **Table of Contents**

| ALPHANUMERIC INDEXvi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CHAPTER 1<br>Microcomputer Development Systems<br>Data Sheets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| iMDX 430/431/440/441 Intellec® Series IV Microcomputer Development System       1-1         iPDS™ Personal Development System       1-6         iPDS™-130 Optional Flexible External Disk Drive       1-17         iPDS™-Proto Kit       1-21         iMDX 557 iAPX Resident Processor Card Package       1-23         iMDX 511 Enhanced Human Interface       1-26         Model iMDX 750 Intellec® Series II/III/IV Winchester Subsystem       1-28         Application Note       1-21         AP-156 Designing Modules for iPDS™ and iUP Systems       1-31 |

| CHAPTER 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

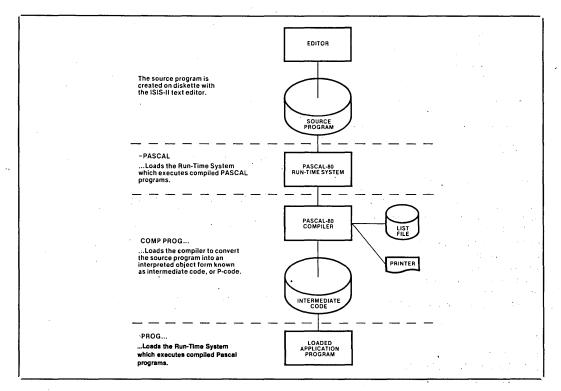

| Network Development Systems         Data Sheets         Network Development System II (NDS-II)         iMDX-580/581 ISIS Cluster Board Packages         Asynchronous Communication Link         Mainframe Link for Distributed Development                                                                                                                                                                                                                                                                                                                      |

| iNA 955 iRMX <sup>™</sup> NDS-II Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CHAPTER 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Microcomputer Software Development Tools<br>Data Sheets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Program Management Tools       .3-1         PSCOPE High-Level Program Debugger       .3-4         iRMX™ PSCOPE 86 High-Level Program Debugger       .3-9         NDS-II Electronic Mail       .3-20         8086 Software Toolbox       .3-22         AEDIT Text Editor       .3-24         ISIS-II Software Toolbox       .3-26         Insite       .3-28                                                                                                                                                                                                     |

| AP-162 PMT Tutorial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Article Reprints         AR-225 Debugging Catches up with High-Level Programming         AR-319 Software Development         AR-352 Integrated Environment Speeds System Development                                                                                                                                                                                                                                                                                                                                                                            |

| CHAPTER 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Microcomputer Development Languages<br>Data Sheets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

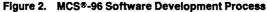

| iAPX 286 Software Development Packages                      | 4-1  |

|-------------------------------------------------------------|------|

| Pascal 286 Software Package                                 | 4-6  |

| PL/M 286 Software Package                                   | 4-9  |

| iAPX 86, 88 Software Development Packages for Series II/PDS | 4-13 |

| 86/88/186/188 Software Packages                             | 4-23 |

|                                                             |      |

## **Table of Contents**

|   | Fortran 80 8080/8085 ANS Fortran 77                                 |

|---|---------------------------------------------------------------------|

|   | Pascal 80 S/W Package                                               |

|   | PL/M 80 High Level Programming Language4-48                         |

|   |                                                                     |

|   | 8087 Software Support Package4-51                                   |

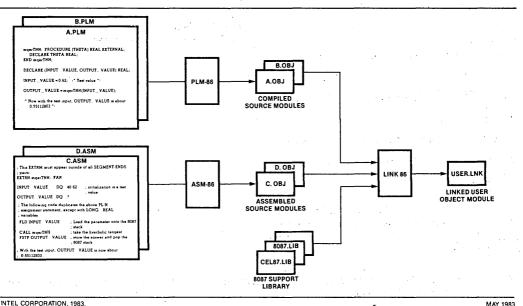

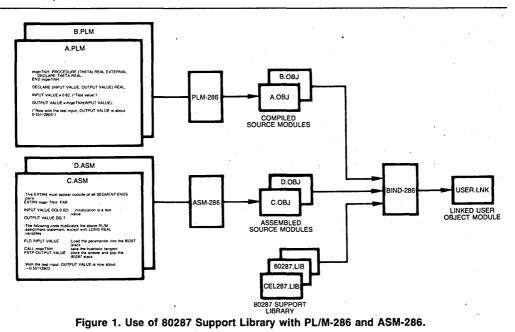

|   | 8087 Support Library                                                |

|   | 80287 Support Library                                               |

|   | 8089 IOP Software Support Package4-61                               |

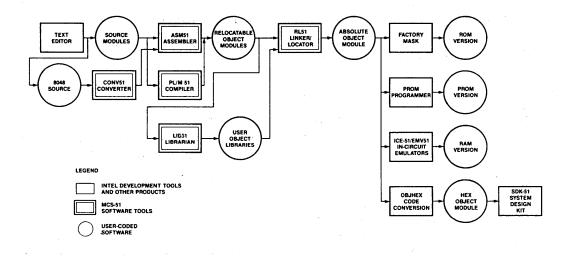

|   | 8051 Software Packages4-64                                          |

|   | MCS®-48 Diskette-Based Software Support Package4-73                 |

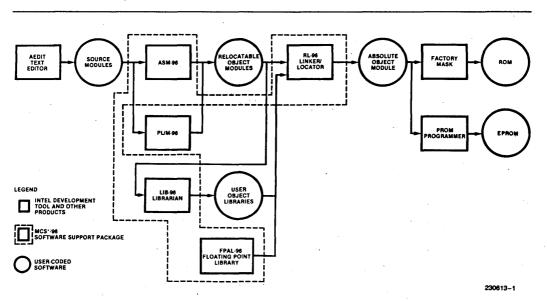

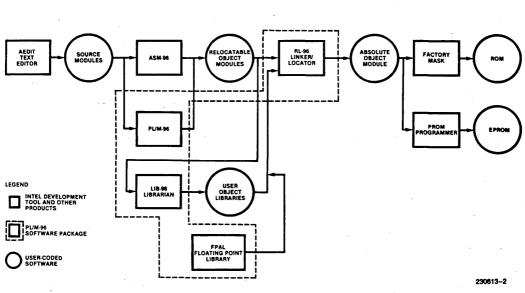

|   | MCS®-96 Software Development Packages4-75                           |

|   | VAX*/VMS* Resident iAPX-86/88/186 Software Development Packages4-83 |

|   | VAX*/VMS* Resident Software Development Packages for iAPX 286 4-90  |

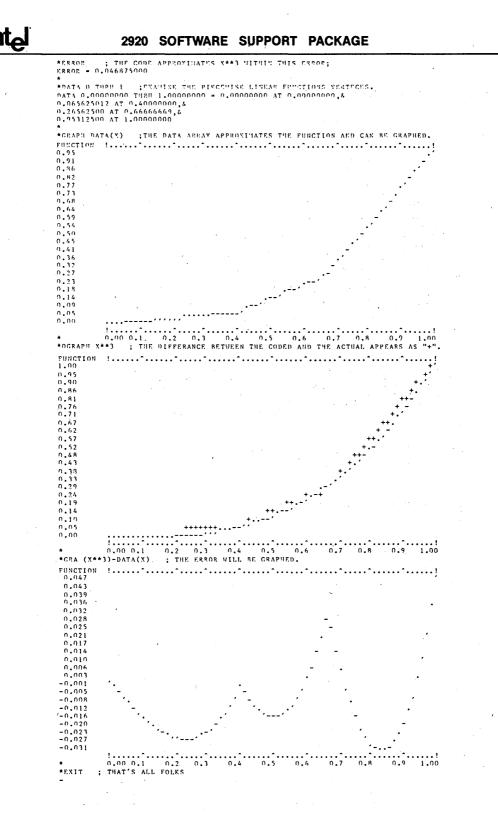

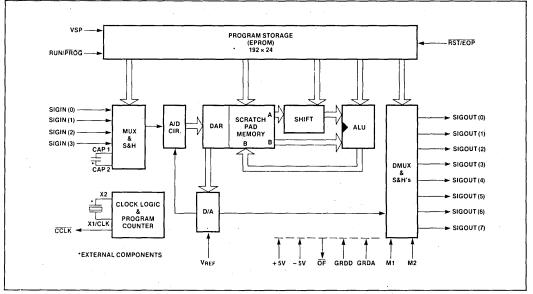

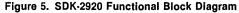

|   | 2920 Software Support Package                                       |

| A | rticle Reprints                                                     |

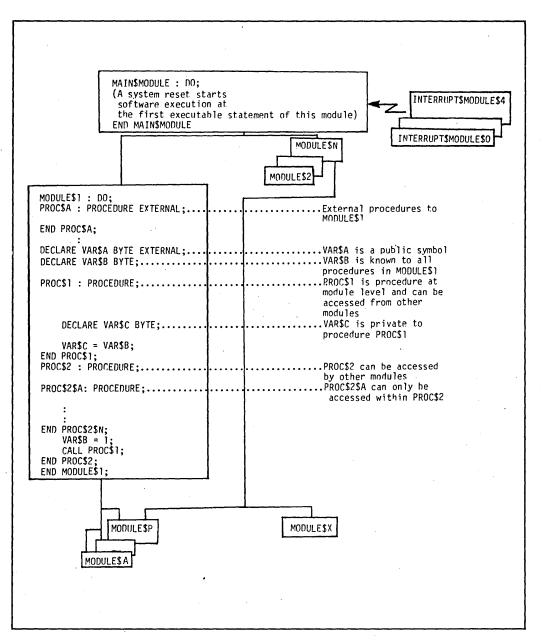

|   | AR-59 Modular Programming in PL/M4-107                              |

|   | AR-136 PL/M-86 Combines Hardware Access with High-Level             |

|   | Language Features                                                   |

|   | AR-200 Compiler Optimization Techniques                             |

|   | AR-239 PL/M-51: A High-Level Language for the                       |

|   | 8051 Microcontroller Family                                         |

|   | 0001 MI0100011101101 Chilling                                       |

#### **CHAPTER 5**

#### In-Circuit Emulators

#### **Data Sheets**

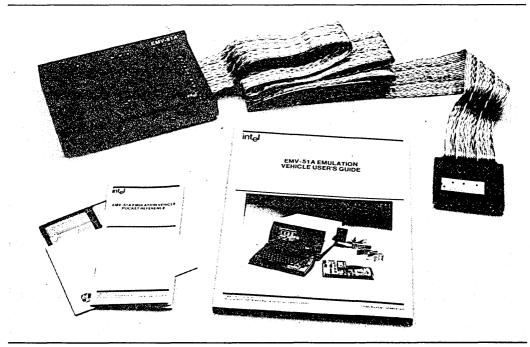

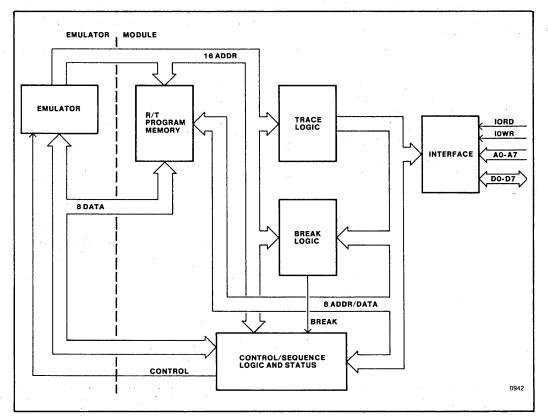

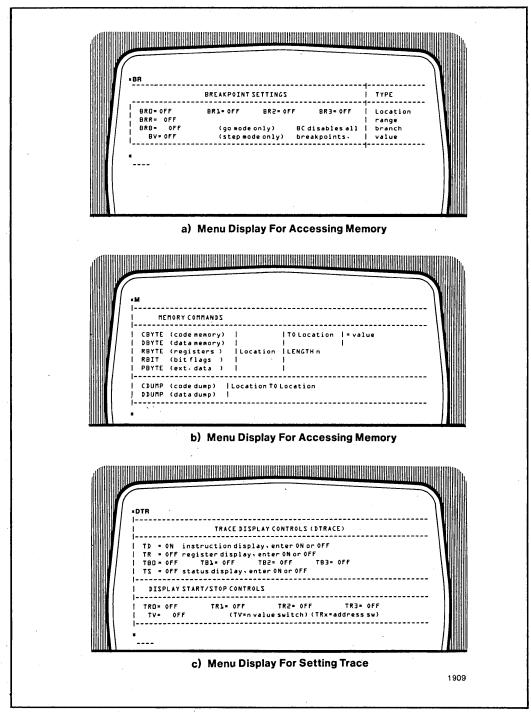

| EMV-51A 8051A Emulation Vehicle5-1                                                         |

|--------------------------------------------------------------------------------------------|

| EMV-44 Con 8044 Emulation Vehicle Conversion Package5-9                                    |

| EMV-88 iAPX 8088 Emulation Vehicle5-17                                                     |

| iSBE-96 Single Board Emulator5-28                                                          |

| I <sup>2</sup> ICE <sup>™</sup> Integrated Instrumentation and In-Circuit Emulation System |

| iLTA Logic Timing Analyzer                                                                 |

| ICE <sup>™</sup> -42 8042 In-Circuit Emulator                                              |

| ICE <sup>™</sup> -44 Module 8044 In-Circuit Emulator5-66                                   |

| ICE <sup>™</sup> -49A MCS <sup>®</sup> -48 In-Circuit Emulator                             |

| ICE <sup>™</sup> -51 8051 In-Circuit Emulator                                              |

| ICE-85B <sup>™</sup> MCS-85 In-Circuit Emulator with Multi-ICE <sup>™</sup>                |

| ICE <sup>™</sup> -86A iAPX 86 In Circuit Emulator                                          |

| ICE <sup>™</sup> -88A iAPX 88 In-Circuit Emulator5-103                                     |

#### **CHAPTER 6**

#### PROM Programming Data Sheets

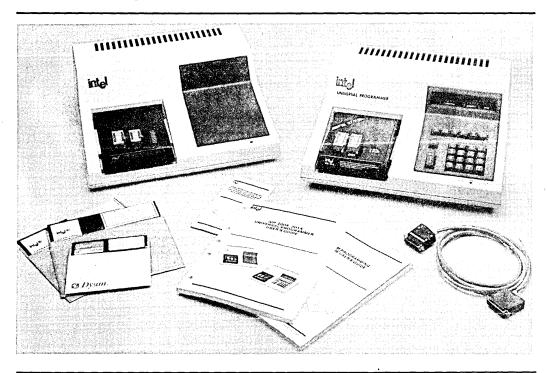

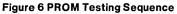

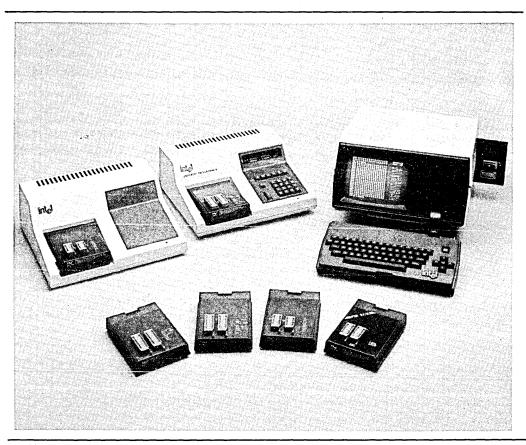

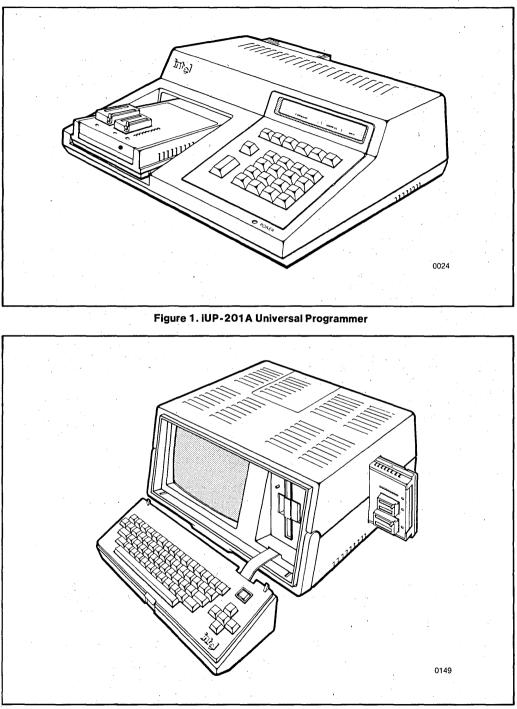

| iUP-200A/iUP-201A Universal PROM Programmers                                               |             |                   | 6-1  |

|--------------------------------------------------------------------------------------------|-------------|-------------------|------|

| PROM Programming Personality Modules                                                       |             |                   | 6-12 |

| Application Note                                                                           |             |                   |      |

| AP-179 PROM Programming with the Intel Personal<br>Development System (iPDS <sup>™</sup> ) | •••••       | • • • • • • • • • | 6-22 |

| CHAPTER 7                                                                                  |             |                   |      |

| System Design Kits                                                                         | · · · · · · | 1 A. A.           |      |

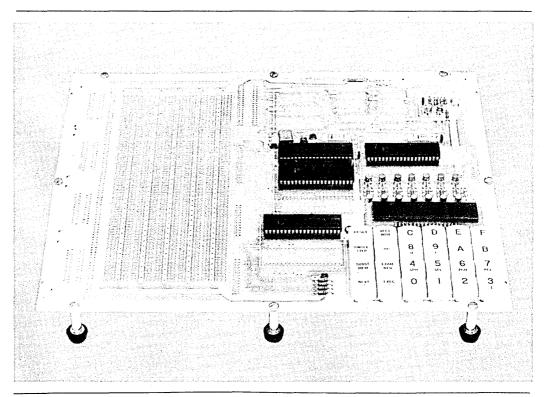

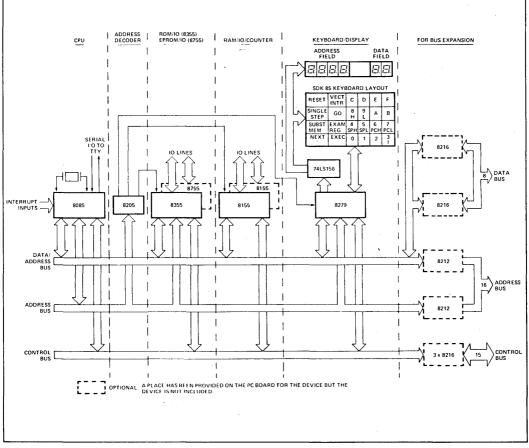

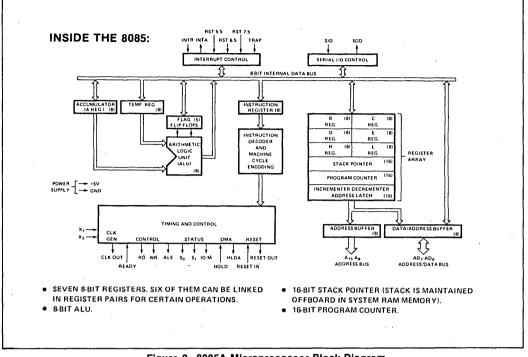

| SDK-85 MCS-85 <sup>™</sup> System Design Kit                                               |             |                   | 7-1  |

| SDK-85 MCS-85 <sup>1</sup> <sup>M</sup> System Design Kit                  | /-1    |

|----------------------------------------------------------------------------|--------|

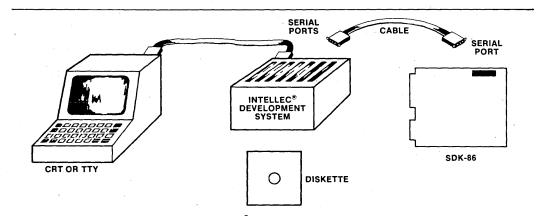

| SDK-86 MCS-86 <sup>TM</sup> System Design Kit                              | 7-7    |

| SDK-C86 MCS-86 <sup>™</sup> System Design Kit Software and Cable Interface | .7-13  |

| SDK-51 MCS <sup>®</sup> -51 System Design Kit                              | . 7-15 |

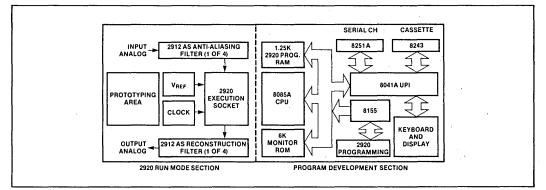

| SDK-2920 2920 System Design Kit                                            | . 7-20 |

## **Table of Contents**

#### **CHAPTER 8 Third Party Software**

| ata Sheets                                             |                                                                                                                                                                                                                                            |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Microsoft* Inc., BASIC-80 Interpreter Software Package | .8-1                                                                                                                                                                                                                                       |

| Microsoft* Inc., BASIC-80 Compiler Software Package    | . 8-4                                                                                                                                                                                                                                      |

| Digital Research Inc., CP/M* 2.2 Operating System      | .8-6                                                                                                                                                                                                                                       |

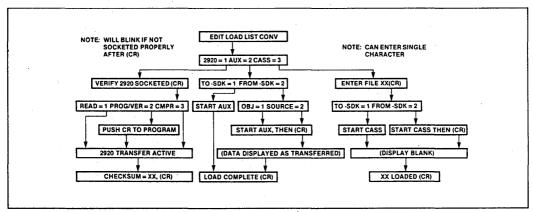

| Wordstar* Word Processing Software                     | .8-9                                                                                                                                                                                                                                       |

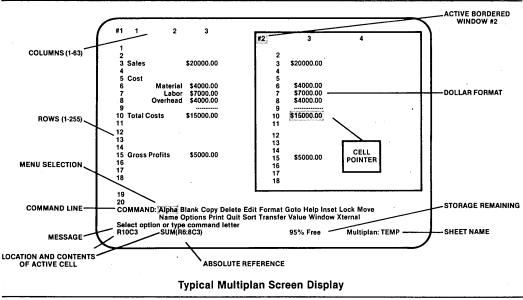

| Microsoft* Multiplan* Spreadsheet                      |                                                                                                                                                                                                                                            |

|                                                        | ata Sheets         Microsoft* Inc., BASIC-80 Interpreter Software Package         Microsoft* Inc., BASIC-80 Compiler Software Package         Digital Research Inc., CP/M* 2.2 Operating System         Wordstar* Word Processing Software |

۷

\*Please note: VAX and VMS are trademarks of Digital Equipment Corporation Microsoft and Multiplan are trademarks of Microsoft Corporation CP/M is a trademark of Digital Research Corporation Wordstar is a trademark of Micropro International

|                                                 | •      |

|-------------------------------------------------|--------|

| 2920 Software                                   |        |

| 464 464 464 464 464 464 464 464 464 464         |        |

| 8086 Software Toolbox                           |        |

| 86/88/186/188 Software                          |        |

| 8087 Software Support Library                   |        |

| 8087 Support Library                            |        |

| 8089 IOP Software                               |        |

| 80287 Support Library                           |        |

| AEDIT Text Editor                               | 1      |

| Asynchronous Communications Link                | 3      |

| BASIC-80 Compiler                               |        |

| BASIC-80 Interpreter                            |        |

| CP/M 2.2 Operating System                       |        |

| EMV-44                                          |        |

| EMV-51A                                         |        |

| EMV-88                                          | 1      |

| FORTRAN 80                                      |        |

| FORTRAN 86/88                                   |        |

| iAPX 86, 88 Software for Series II/PDS          |        |

| iAPX 286 Software                               | 1      |

| iC-86 C Compiler                                |        |

| I <sup>2</sup> ICE                              | 5      |

| ICE <sup>TM</sup> -42                           |        |

| ICETM-44                                        | 3      |

| ICETM-49A                                       | 4      |

| ICETM-51                                        | )      |

| ICETM-85B                                       | 3      |

| ICETM-86A                                       | 5      |

| ICETM-88A                                       |        |

| ILTA                                            |        |

| iMDX 430/431/440/441                            |        |

| IMDX 511                                        |        |

| IMDX 557                                        |        |

| IMDX 580/581                                    |        |

| IMDX 750                                        |        |

| INA 955                                         |        |

| Insite 3-26                                     |        |

| IPDS™ 1-6                                       |        |

| iPDS <sup>TM</sup> ·Proto                       |        |

| iPDS™-130                                       |        |

| IRMX™ PSCOPE 86                                 |        |

| iSBE                                            |        |

| ISIS-II Software Toolbox                        |        |

| iUP-200A/iUP-201A                               |        |

| Mainframe Link                                  |        |

| MCS <sup>®</sup> • 48 Diskette • Based Software | a.     |

| MCS <sup>®</sup> ·96 Software                   | 5      |

| Multiplan Spreadsheet                           | ĥ      |

| NDS-II 2-                                       |        |

| NDS-II Electronic Mail                          |        |

| Pascal 80                                       | 3      |

| Pascal 86/88                                    |        |

| Pascal 286                                      | 6      |

| PL/M-80                                         | R<br>R |

| PL/M 86/88/186/188                              | 1      |

| PL/M 286                                        | ۱<br>۵ |

| PL/M 200                                        |        |

| Program management roots                        |        |

| PROM                                            |        |

|                                                 | *      |

•

| DK-2920                                    | , |

|--------------------------------------------|---|

| DK-51                                      | j |

| DK-85                                      |   |

| DK-86                                      |   |

| DK-C86                                     |   |

| AX*/VMX* Resident iAPX 86/88/186 Software  | j |

| AX*/VMX* Resident Software for iAPX 286490 | ) |

| /ordstar                                   |   |

\*Please note:

VAX and VMS are trademarks of Digital Equipment Corporation Microsoft and Multiplan are trademarks of Microsoft Corporation CP/M is a trademark of Digital Research Corporation Wordstar is a trademark of Micropro International

, , -· · ·

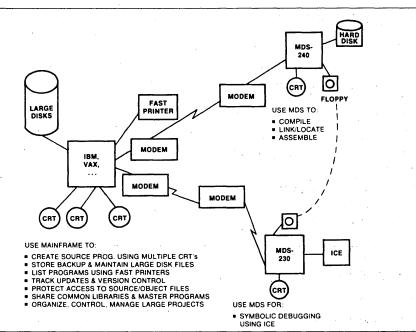

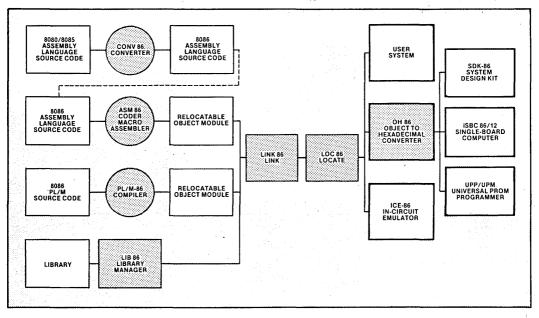

#### INTEL'S DEVELOPMENT ENVIRONMENT — THE COMPLETE SOLUTION

The emergence of high performance, low cost microprocessors has revolutionized the computer industry in the past decade. Many of today's advanced "chips" literally contain the computing power of mainframe computers that were commonly used just ten short years ago. The availability of these advanced processors has spawned many new products and vastly improved existing ones.

The rapid advances in microprocessor technology have also revolutionized the microprocessor system design process. The days of a single engineer developing all software and hardware for a given system are over. Most projects today consist of many engineers working in a team. And most projects are software intensive: a ratio of five to ten software engineers for every hardware designer is common.

Developing software intensive systems with large teams typically creates headaches for team members and project leaders alike. Large team development necessitates numerous team meetings, large numbers of software modules containing many interfaces, significant amounts of formal system documentation, and a long and tedious debug process. In addition, team members must share all types of project information: source code, object code, test suite results, etc. Project leaders in this environment must continually strive to meet project deadlines and contain costs. Intel offers a complete line of microcomputer development tools that help developers maintain tight project deadlines and minimize costs. For example, Intel's advanced software development tools and programming languages can boost an individual programmer's productivity and also simplify team management. Our powerful In Circuit Emulators (ICEs<sup>TM</sup>) minimize the risks associated with integrating system software with target hardware and thus ensure your projects are not delayed during this critical development phase. And Intel's state-of-the-art dedicated workstations, such as the Series IV Microcomputer Development System, are ideal development hosts for providing these remarkable tools at your fingertips. Moreover, as your team grows you can link team members together in a powerful network with NDS-II—the Network Development System. Because of our special knowledge of the processors we design, you can be assured that our tools are the most powerful available for the task at hand.

#### Software Tools Boost Programmer Productivity

Intel offers a wide range of software development tools that boost programmer productivity and minimize the costly administrative overhead that typically accompanies large software development projects.

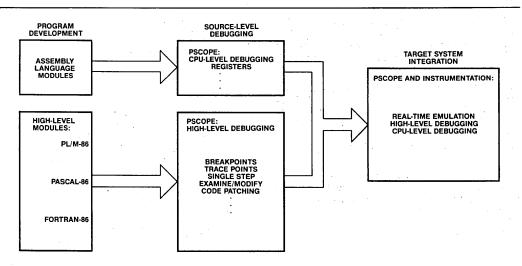

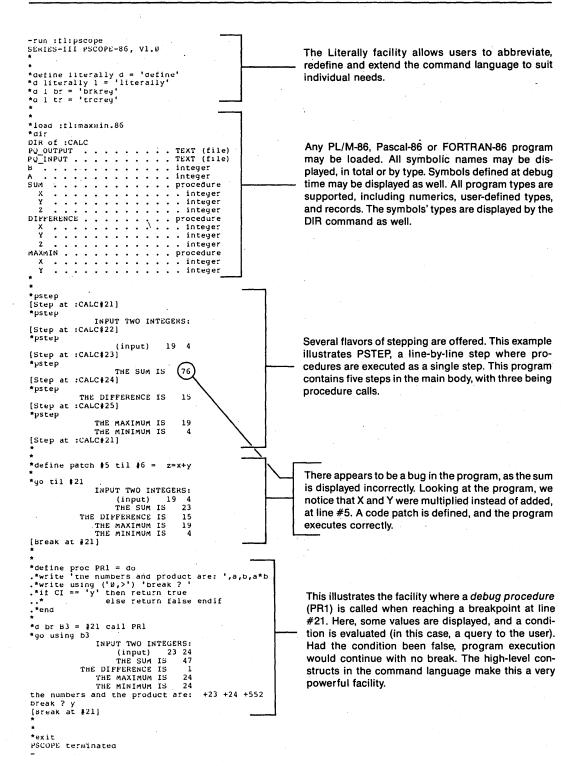

• PSCOPE Simplifies and Speeds Program Debugging

PSCOPE is a source-level symbolic debugger that allows the high-level language program-

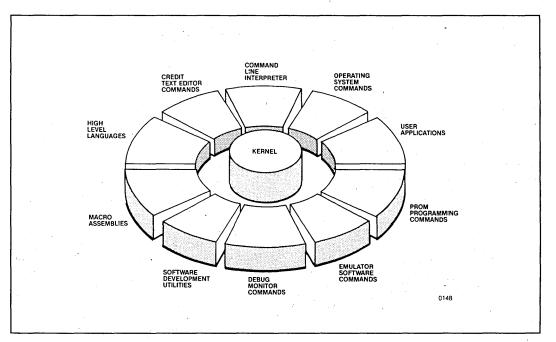

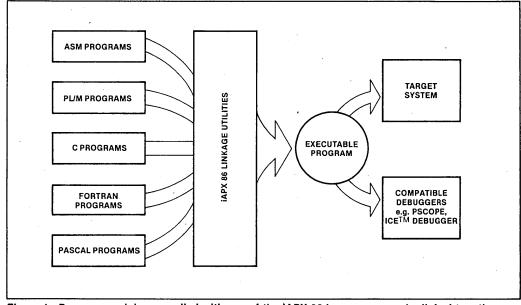

This chart illustrates the broad range of tools that simplify the development of products using Intel microprocessors and microcontrollers.

| Tools Available                                                                        | 8-Bit<br>μ Controller | 8051 | 8085 | 8096 | 8088 | 8086 | 80188 | 80186 | 80286 |

|----------------------------------------------------------------------------------------|-----------------------|------|------|------|------|------|-------|-------|-------|

| LANGUAGES<br>• Pascal<br>• FORTRAN<br>• PL/M<br>• C<br>• MACRO ASSEMBLERS              |                       | _    |      | -    |      |      |       |       |       |

| TOOLS<br>• PSCOPE<br>• SVCS; MAKE                                                      |                       |      | _    |      | _    | _    |       | _     | _     |

| INSTRUMENTATION<br>• IN-CIRCUIT EMULATORS<br>• I <sup>2</sup> ICE <sup>TM</sup> SYSTEM |                       | -    | . —  |      |      |      |       |       |       |

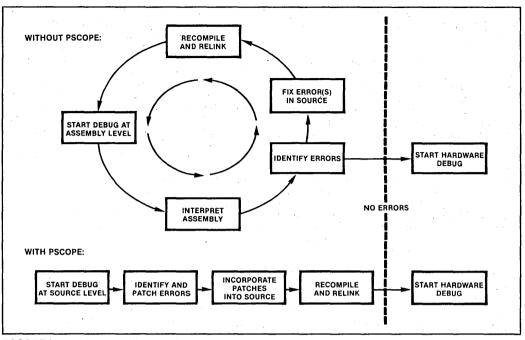

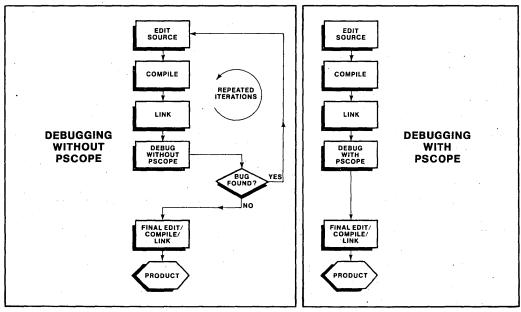

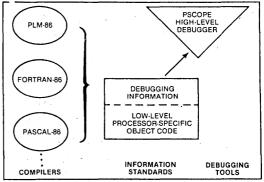

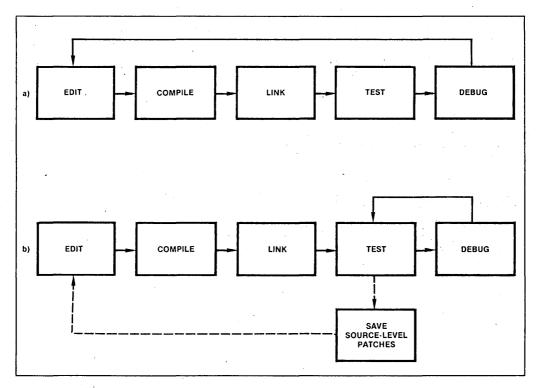

PSCOPE is an advanced, high-level language debugger that cuts many time consuming steps out of the software debugging process. PSCOPE enables users to correct software errors with "patches," eliminating many unnecessary edits, compiles and links.

mer to completely debug his code at the same level at which it was written. Breakpointing, tracing, and patching are all done in a faster and less error-prone manner than through obsolete machine-level debuggers. Since software testing and maintenance consume a greater portion of development life-cycle time and cost, PSCOPE debugging can significantly improve programming efficiency.

Program Management Tools Save Development and Administration Time

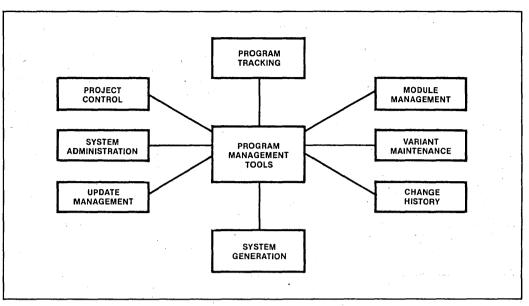

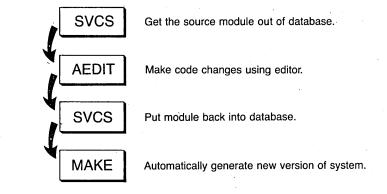

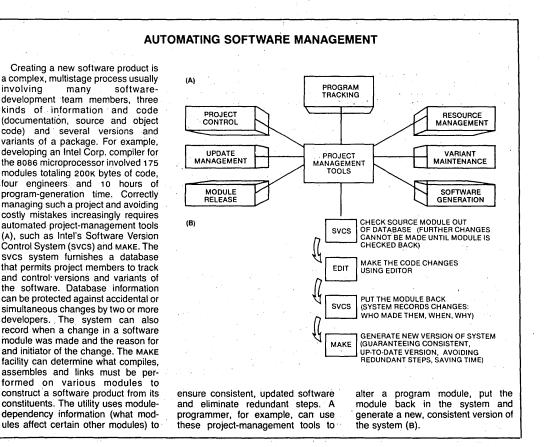

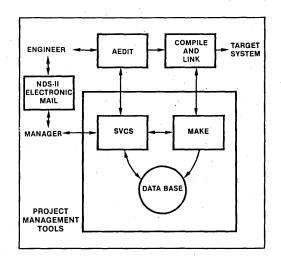

Intel Program Management Tools (PMTs) tighten your control over program changes, documentation, software maintenance, system generation, and program libraries reducing your administrative workload and time. Intel PMTs currently consist of two powerful utilities: the Software Version Control System (SVCS) and MAKE.

SVCS is a system database manager that simplifies software development and maintenance. You never have to waste time trying to manually keep track of software changes. SVCS tracks each change (including who made the change, what changed, when, and why) so that you can always be sure you are working with the current version of a given module. SVCS enforces individual discipline to enhance team cooperation and project control.

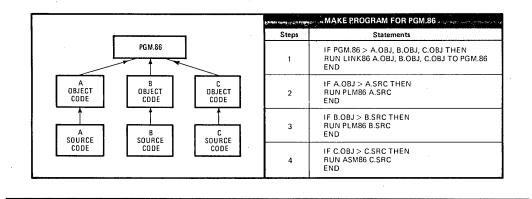

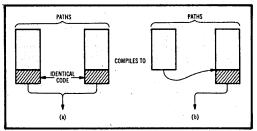

MAKE is an automatic system generation tool that can save hours and days of software generation time. It automatically finds the most recent modules, recompiles only the ones that need it, and generates a new system. All you do is create a specification of your system. MAKE does the rest.

MAKE works with SVCS to maintain the most current version of software—including up-to-the-minute source code changes from project software engineers. So you never waste time recompiling outdated modules or generating entire systems from outdated modules.

Together, Intel PMTs dramatically boost productivity by eliminating redundant steps. They save weeks—sometimes months—of software development time for any given project.

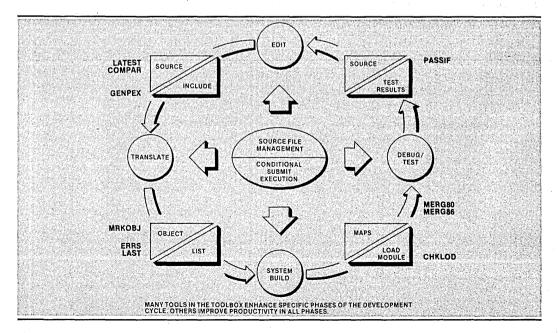

• Software Toolboxes Provide Programmers With an Arsenal of Productivity Aids

Intel's software toolboxes are collections of utilities that perform a variety of productivity-

Program Management Tools enable you to manage and easily integrate the efforts of many development team members.

oriented functions. The ISIS-II Software Toolbox offers conditional submit file control tools, source management tools, and other tools that operate at the ISIS-II command level. The 8086 Software Toolbox is a collection of 16-bit software tools that are valuable for text formatting and preparation, software testing and performance analysis, 286/287 software development, and a multitude of other applications:

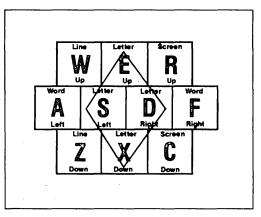

AEDIT Enables Programmers to Easily Enter Source Code and Text Files

Intel also offers AEDIT, an advanced editor that significantly improves programmer productivity. AEDIT was designed with the programmer in mind, and offers full screen editing, the ability to edit two files at once, features for manipulating large blocks of text, and a powerful macro command facility.

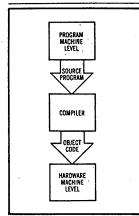

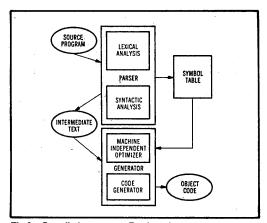

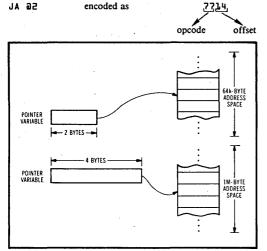

#### High-Level Languages Improve Software Quality and Programming Efficiency

High-level languages make programming easier. And Intel's efficient high-level language compilers do not sacrifice code quality for ease of use. Moreover, different languages can be used for the various modules which make up a software system. This allows programmers to choose the optimal language for each given module, and then link the modules together into high quality software systems. Intel provides complete high-level language support for all 8-bit and 16-bit Intel microprocessors. All Intel languages produce linkable and locatable object codes. In addition, Intel compilers pass information to debuggers to optimize the debug cycle. Standard languages supported include PL/M, Pascal, Fortran, Basic and C.

#### In-Circuit Emulators Simplify System Integration

Intel's In Circuit Emulators (ICEs<sup>TM</sup>) accelerate system integration to the fastest possible speed. By emulating the prototype to check out the hardware design, each processor specific ICE reduces system integration and hardware debug times to a minimum.

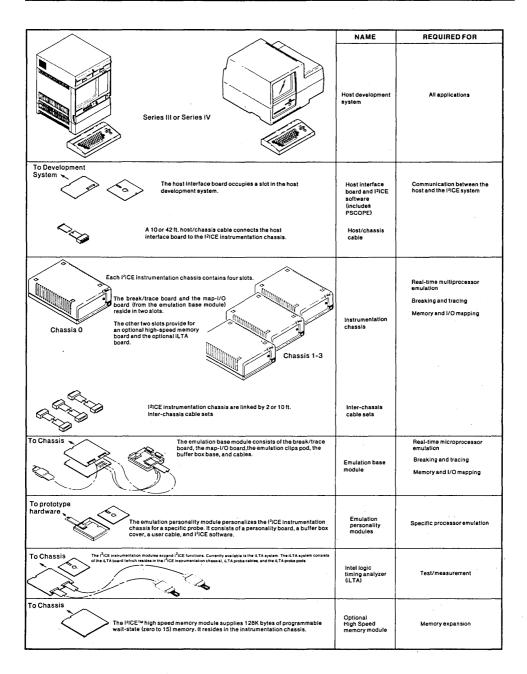

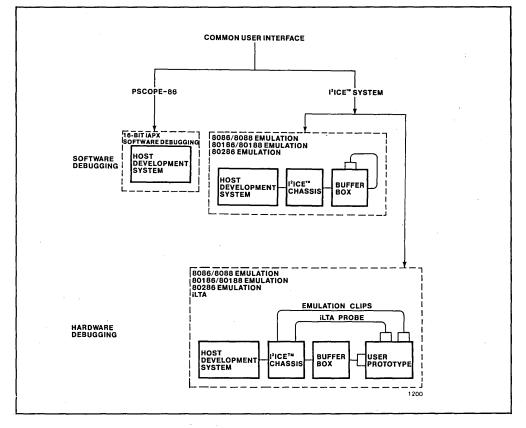

The premier ICE for all iAPX microprocessors is the  $I^2ICE^{TM}$  (Integrated Instrumentation and In-Circuit Emulation) Emulation System.

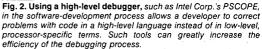

The  $I^2ICE$  system is a revolutionary tool which integrates in-circuit emulation, high-level software debugging and optional logic timing analysis into one system. With the  $I^2ICE$  system you shorten debugging time and obtain easier to understand debug data while reducing risks and product development time.

The  $I^2ICE$  system gives you full speed, real-time support for all Intel iAPX microprocessors. It also offers an arsenal of break and trace points so that your design team can set up complex, multi-nested test conditions.

The I<sup>2</sup>ICE system provides a single human interface across the spectrum of debugging and system integration tasks. This eliminates the slow-down problems inherent in multiple interfaces. And there is never the need to leave the high level language environment because the I<sup>2</sup>ICE system incorporates PSCOPE to ease the transition from software debug to hardware debug and hardware/software integration.

#### Powerful Workstations Put Development Tools Within Your Reach

Intel workstations, such as the Series IV, are your gateway to the Intel development methodology. Their computing power puts Intel development tools literally at your fingertips. Intel offers a variety of hosts, such as those mentioned below, that can match the size, budget, and complexity of your development projects. • Series IV Microcomputer Development System Provides Sophisticated Capabilities Not Found on Other Development Systems

Intel's Series IV is a 16-bit workstation offering many advanced features. Like foreground/background processing that allows you to do two things at once—dramatically increasing your productivity. A hierarchical file system that enables your file structure to be set up according to project requirements. And a friendly human interface speeds learning, eliminates the need to plow through manuals, and significantly improves ease of use.

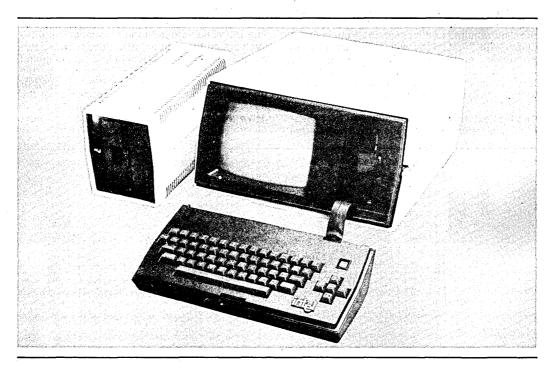

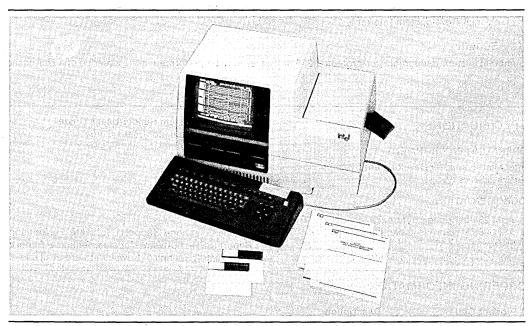

Personal Development System Enables Low-Cost Product Development and Support

The Personal Development System (iPDS<sup>TM</sup>) is a portable, low-cost system that provides total development support for smaller 8-bit

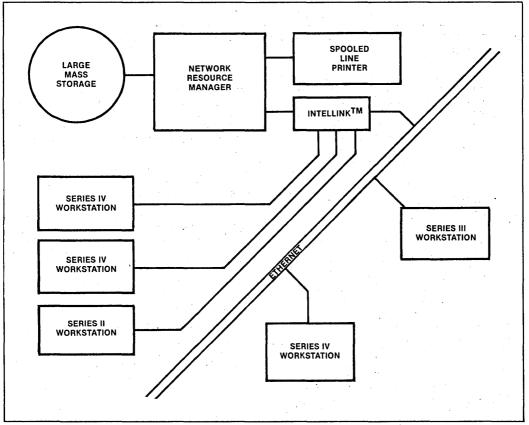

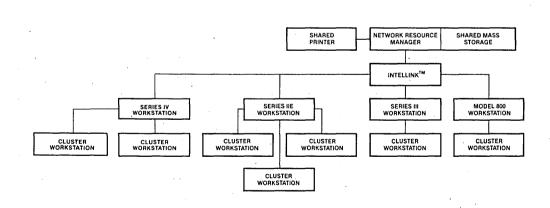

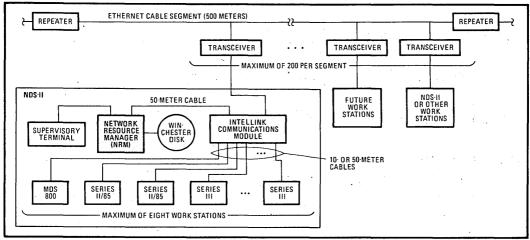

The NDS-II Network Development System is a comprehensive Local Area Network that increases the productivity of engineers as well as equipment. Team members can easily share information and common hardware such as line printers and mass storage.

applications. It also supports the CP/M operating system, so it can double as a personal computer for your engineers.

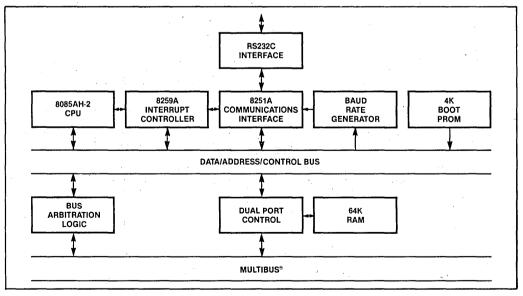

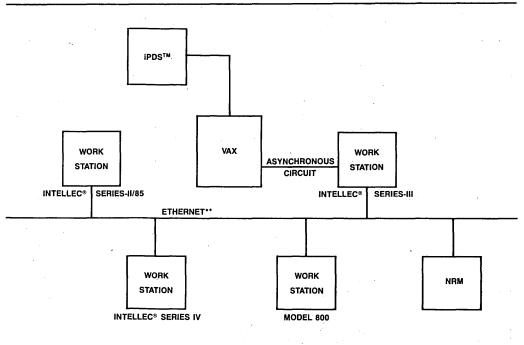

#### Networking Links Project Engineers Into A Powerful Team

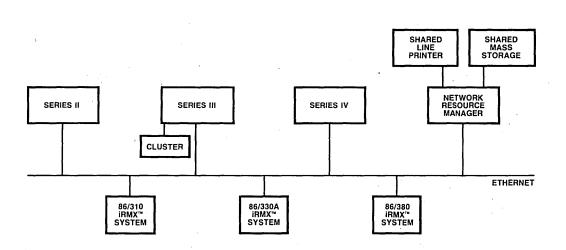

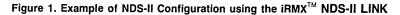

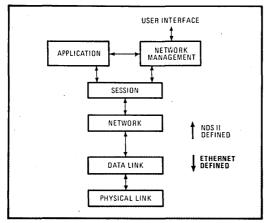

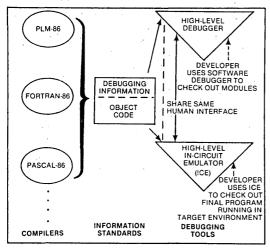

Intel's Networked Development System—NDS-II—is an Ethernet-based local area network that ties together Intel's development systems. It can increase the productivity of engineers as well as equipment.

For example, an engineer can use the Distributed Job Control service to send time-consuming tasks such as compiling to the NDS-II Network Resource Manager (NRM) for reassignment to a workstation that is not presently in use. The engineer can move on to other work at his/her terminal while the NRM completes the previous job.

NDS-II helps you get the most use out of your development dollars. Team members can share common hardware such as line printers and mass storage devices. In addition, NDS-II's modular approach provides a structure for orderly growth. A consistent upgrade path protects your investment in Intel development products.

#### Intel Offers Complete Development Support

Intel's support for your development project goes beyond the superior hardware and software tools described in this handbook—we deliver complete development solutions.

#### TRAINING

Intel offers training courses throughout the year at Intel Training Centers around the world. Courses can be tailored for either technical or management personnel.

#### **FIELD SUPPORT**

A worldwide network of Intel Field Service and Field Applications Engineers is available to assist you.

#### FIELD UPDATES

Intel customers are kept up-to-date on development system changes and enhancements to software via regular update mailings. "Hot-line" telephone support is also available.

#### DOCUMENTATION

Comprehensive product documentation is available including manuals, application notes and detailed data sheets. (A complete literature guide is available upon request.)

#### **USER'S PROGRAM LIBRARY**

Through INSITE (Intel's Software Index and Technology Exchange), Intel makes available a broad collection of programs that may substantially cut development time for you.

Intel offers complete advanced microsystem solutions. Solutions in hardware, Solutions in software, Solutions in customer support, Solutions that work together for you.

#### Find Out More

Contact the Intel sales or distributor office nearest you (see the back of this handbook) for more information today. a a substantia da angle a substantia a substantia. Angle a substantia da a Angle a substantia da a

and Robert All and All a All and A All and All and

(1) A second se second seco

(Automotic states and states of the second states of the second states are second states and states are second stat second states are s Sec. 1.

and a start of the second start and the second start of the secon

an an an Araba an Araba an Araba. An Araba an Araba an Araba an Araba an Araba Araba an Araba an Araba an Araba.

an server as g

and the second second

ни 1919 — Паралия — Парания Валики, 1913 1919 — Паралия — Парания Парания — Парани

## Microcomputer Development Systems

# intel

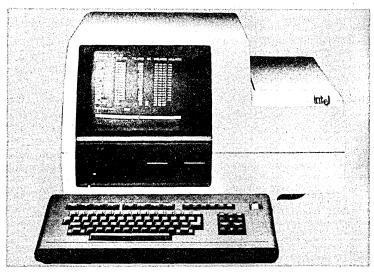

### IMDX 430/431/440/441 INTELLEC® SERIES IV MICROCOMPUTER DEVELOPMENT SYSTEM

- Complete Microcomputer Development System for the iAPX 86/87/88/186/188/286, the MCS<sup>®</sup> -80/85 and the MCS<sup>®</sup> -48/51/96 family microprocessors

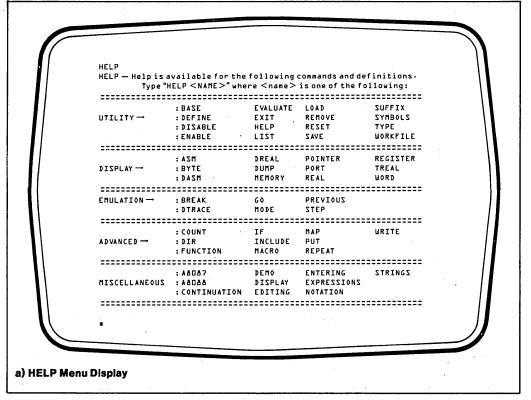

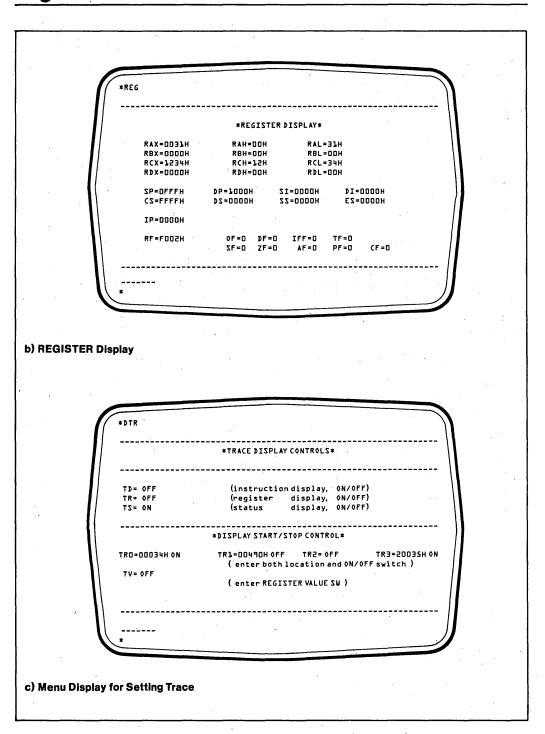

- Advanced, friendly human interface with menu-driven function keys, HELP, and syntax builder/checker capabilities for increased user productivity

- Foreground/Background multiprocessing for simultaneous execution of two jobs by a single user; increasing system throughput

- Multi-user capability for simultaneous operation by two users, significantly reducing system cost per user

- Hierarchical file system provides file sharing and protection for large software projects

- Software compatible with both Series IIE and Series IIIE development systems

- Supports PL/M, Pascal, C, and FORTRAN, and Basic high-level languages as well as assemblers

- Provides Program Management Tools (PMTs), advanced AEDIT text editor and supports powerful PSCOPE symbolic, source level debugger

- Can be fully integrated into the NDS-II Network Development System

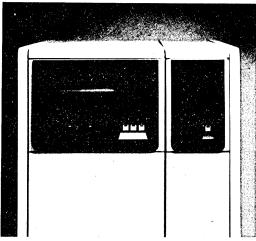

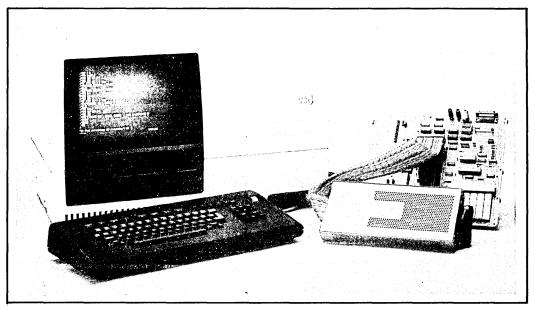

The Intellec® Series IV is a new generation development system specifically designed for supporting the iAPX family of advanced microprocessors. It also supports the MCS-80/85 and the MCS-48/51 families.

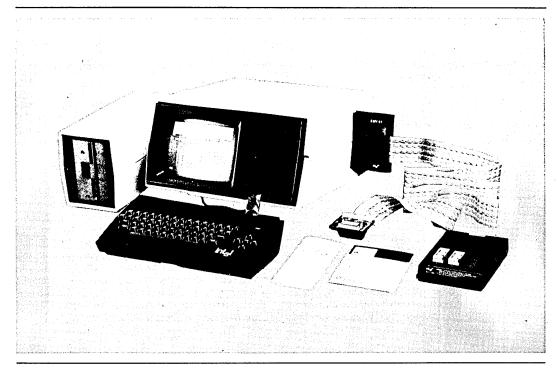

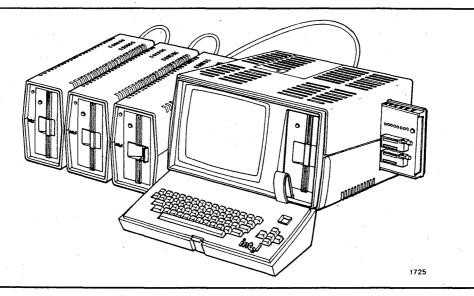

Figure 1. Intellec® Series IV Microcomputer Development System

Intel Corporation Assumes No Responsibility for the Use of Any Circuitry Other Than Circuitry Embodied in an Intel Product. No Other Circuit Patent Licenses are Implied. Information Contained Herein Supercedes Previously Published Specifications of These Devices from Intel.

©INTEL CORPORATION, 1983

MAY 1984 ORDER NUMBER: 230625-003

Series IV provides a state-of-the-art, easy-to-use, high performance host environment for running a wide variety of hardware and software development tools. A unique combination of tools provides an integrated microcomputer system design that results in highly improved designer productivity and considerable shortening of time to market. The length of the compile-link-load-debug-edit cycle is minimized by the friendly human interface, powerful and easy-to-use editors, a wide selection of language translators, source level debuggers, program management tools. The advanced operating system features a hierarchical file system, foreground/ background multitasking, and multi-user capability. Furthermore, the Series IV can serve as a powerful workstation on the NDS-II distributed processing network for high performance multi-user software development. The networking architecture supports a distributed co-operative processing environment. Tasks like compilations can be executed in the background mode or exported to an idle workstation while the user is in the middle of an interactive edit session. The key benefit of this approach is a much higher system throughput and programmer productivity than, for instance, a system designed for rawperformance and fast compilations only.

The Series IV is offered in four different versions, providing a range of storage and performance options so that the user may select the configuration to suit his/her stand-alone or networking development station needs. The four versions are not only compatible with one another, but are also software compatible with the current generation enhanced Series IIE/IIIE systems. Existing ISIS-compatible software can run directly on the Series IV under the ISIS operation system. Finally, the NDS-II network provides an ideal means for the various hosts, e.g., Series II/III/IV to work with each other, protecting the user's past, and present, and future investment.

#### **FUNCTIONAL DESCRIPTION**

#### Systems Components

The Intellec Series IV model 430/431 Microcomputer Development System is an easy-to-use highperformance system in one package. It includes a CPU board for each of the iAPX 88 and MCS® 85 processors and 640K bytes of system RAM. The system has eight function keys included in its detachable standard ASCII keyboard that also has cursor controls and uppercase/lowercase capability. These function keys are menu driven and, with the use of the syntax builder/checker, greatly reduce user keystrokes. Peripheral configurations include: Model iMDX 430WD, 440WD—two floppy disks, one 35MB Winchester; and Model iMDX 431, 441—one floppy disk, one 10MB Winchester.

The 5.25" drives, a green phosphor screen, and a detachable keyboard are all integrated into the system. The main chassis has ten MULTIBUS® slots (three 12" X 12", seven 6%" X 12") power supplies, fans and cables.

#### **Operating System Environments/Features**

The Series IV provides both an 8086/8088-based development environment and an 8080/8085 based development environment. The host execution mode is the 8086/8088, which runs under the iNDX operating system. To execute an 8080/8085 program, the ISIS-IV utility is invoked; entering the 8085 execution mode. All ISIS-compatible 8-bit software can thus be run directly on the Series IV, through a user interface that is compatible with ISIS-based development systems such as the Series II and the Series III.

#### **HIERARCHICAL FILE SYSTEM**

The iNDX operating system employs a hierarchical file system, providing file sharing and protection features. The hierarchical structure allows logical grouping of data. The structure resembles an inverted tree. The root of the system is called the logical system root. The system root logically "connects" the volumes within the file system. Each volume corresponds to a physical mass storage device. Volumes are further divided into files. Files can be either directory files or data files. Directory files contain references to further directory or data files. Data files contain only data.

It is not necessary to know the physical location of files to address them. Each file can be addressed by a path name, which is a character string recognized by the operating system.

The iNDX file system provides file protection features in the form of access rights. The owners of a file may set their access rights to their own files and separately set the WORLD's access rights (everyone else) to their files. File may thus be shared and also protected from accidental or deliberate addressing or destruction. Foreground/background processing capability allows the simultaneous execution of two jobs, resulting in improved system throughput. While a program is executing in the background, another program could be run in the foreground. For example, an interactive editor could be executing in the foreground while a compilation is taking place in the background.

A toggle key on the Series IV keyboard can be used to instantaneously move from one region to the other, allowing interactive operations in both foreground and background regions. For example, while a software debug session is taking place in the foreground, listing files can be displayed from the background.

#### **MULTI-USER CAPABILITY**

A low cost terminal can be attached to serial port 1. This terminal operates as an independent system, accessing one region, while the console and keyboard access the other region. In this mode two users will be able to perform software development tasks simultaneously at a significantly reduced cost per user.

#### The Human Interface

The Series IV is one of the easiest systems to learn and to use, as its human interface is designed to be friendly to both novice and expert users.

It offers eight softkeys that cut the number of keystrokes required to perform a function. On-line HELP provides instantaneous access to command definition, the menu-driven screen interface allows the user to see where he/she is at and to select the next operation. In conjunction with the soft function keys, it allows single key command invocation. The syntax builder and checker completes commands and insures proper command syntax before execution. Features such as type-ahead, auto-repeat keys, and quick view file facility are some of the many other human interface factors that improve programmer productivity.

#### The AEDIT Text Editor

The AEDIT text editor is one of the most powerful and easy-to-use editors available. It runs under the iNDX operating system and offers features such as:

Display and scroll text on the screen

- Move to any character position in the text file or to any point on the screen instantly

- Correct typing mistakes as you type

- Rewrite text by typing new characters over old ones

- Make insertions and deletions easily at any point in a file

- Find any string of characters and substitute another string, querying the operator if desired

- Move or copy sections of text within a file or to/from another file

- Create macros to execute several commands at once, thereby simplifying repetitive editing tasks

- Edit two files simultaneously

- Indent text and delimit long lines automatically

- View lines over 80 characters long

#### Languages and Utilities

The Series IV supports popular high-level languages such as PL/M, Pascal, FORTRAN, and C, as well as powerful "high-level" macro assemblers such as ASM86. In addition, iRMX<sup>™</sup> utilities such as ICU-86, PATCH utility, Files Utility, Crash analyzer and SDM 86 System Debug Monitor are supported by the Series IV.

The high-level language compilers produce code for the target processors. They also contain runtime floating-point arithmetic support for the 8087 Numeric Data Processor.

## PSCOPE, the High-Level Language Debugger

The Series IV supports the PSCOPE debugger, an interactive, symbolic debugger for FORTRAN, Pascal, and PL/M programs. Operations are performed on source statements, procedure entry points, labels, and variables, as opposed to machine instructions memory addresses. PSCOPE improves productivity in the debug phase of development and produces more reliable software. It allows the user to perform extensive tests and consistency checks on the programs, and it automates much of the testing.

#### **In-Circuit Emulators**

The Series IV supports a host of ICE modules including the powerful I<sup>2</sup>ICE<sup>™</sup> for iAPX family-

based development. These tools allow the debugging of microcomputer system hardware and software concurrently, saving considerable development cost and time.

#### **Network Capability**

The Series IV may be used as a high-performance workstation for use on the NDS-II Network Development System. It has complete access to all the network resources and facilities on the NDS-II. A stand-alone Series IV can be upgraded to an NDS-II workstation with the addition of an Ethernet\* Communication Board Set. The background partition of the Series IV may be made available as a network resource.

When configured as an NDS-II workstation, the Series IV can also serve as a host for up to four iMDX-580 ISIS cluster boards, providing a cost effective means for supporting incremental 8-bit software workstations on the network.

#### System Configurations

Series IV Systems are available in 110v, 60Hz; 220v and 100v, 50Hz models.

#### STAND-ALONE

#### IMDX 430WD Kit

A two floppy stand-alone system including detachable keyboard and integral green CRT that comes complete with a 30MB Winchester in a separate chassis. The CPU's are the 8088 and the 8085A-2.

#### **IMDX 431**

Stand-alone Intellec Development system with detachable keyboard and integral green CRT. Included in the main chassis is one 5.25" floppy and one 5.25" 10MB Winchester drive.

#### **IMDX 440WD Kit**

The same configuration as the iMDX 430WD, this model has an additional higher performance 8086 CPU.

#### IMDX 441 Kit

The same configuration as the iMDX 431, this model has an additional higher performance 8086 CPU.

#### NETWORK

#### iMDX 430WS Kit

A two floppy workstation that includes Ethernet NDS-II boards for network operation.

\*Ethernet is a trademark of Xerox Corp.

#### IMDX 440WS Kit

The same configuration as the iMDX 430WS, this system includes a high-performance option for resident 8086 execution and faster performance.

#### **IMDX 430 TO 440 UPGRADE**

#### **IMDX 434**

High-performance add-on option. Converts a model iMDX 430 or iMDX 431 to a model iMDX 440 or iMDX 441.

#### **NETWORK UPGRADE**

#### **IMDX 456**

Communication board set converts any Series IV stand-alone system to an NDS II workstation.

#### SECOND-USER TERMINALS

The following terminals have been tested and found to be interface-compatible with the Series IV CPIO board and can be used as second-user terminals.

LEAR SEIGLER, Model ADM 3A TELEVIDEO, Model 910+

The following terminals have been successfully tested for interface-compatibility, however they do not meet Intel environmental specifications: adverse electrostatic conditions may produce unpredictable screen output, requiring terminal or system reset.

Televideo, Model 925, 950 Adds Viewpoint 3A+ Qume 102 Hazeltine 1510

#### PHYSICAL CHARACTERISTICS

| Chassis |                  | Keyboard        |

|---------|------------------|-----------------|

| Width   | 26.5" (67.3 cm)  | 20.0" (50.8 cm) |

| Height  | 16.5" (41.9 cm)  | 3.0" (7.6 cm)   |

| Depth   | 18.5" (47.0 cm)  | 8.0" (20.3 cm)  |

| Weight  | 52 lb. (23.4 kg) | 7 lb. (3.1 kg)  |

#### ELECTRICAL CHARACTERISTICS

#### **DC Power Supplies**

| Volts Supplied | Amps Supplied |

|----------------|---------------|

| +5.1 ± 1%      | 45.0          |

| +12 ± 5%       | 3.0           |

| $-12 \pm 5\%$  | 2.0           |

| $-10 \pm 5\%$  | 0.5           |

| +12 ± 5%       | 5.0           |

#### **AC Requirements**

110v, 60Hz 220v, 50Hz

#### **Environmental Characteristics**

Operating Temperature — 10°C to 35°C (50°F to 95°F) Humidity — 10% — 95% (non-condensing)

#### Equipment Supplied

Series IV System

Series II/III to Series IV link software diskettes and cable

Series IV Software

- iNDX OS

- ISIS IV OS

- AEDIT

- Macroassemblers and utilities

- ICE™ software

- Prom Programmer Software

- Debug 88

- Program Management Tools (MAKE, SVCS)

- Diagnostics

#### Documentation Supplied

- Intellec Series IV Microcomputer Development System Overview, Order Number 121752

- Intellec Series IV Microcomputer Development System Installation and Checkout Manual, Order Number 121757

- Intellec Series IV Operating and Programming Guide, Order Number 121753

- Intellec Series IV Pocket Reference, Order Number 121760

- Intellec Series IVC ISIS-IV User's Guide, Order Number 121880

- Intellec Series IV ISIS-IV Pocket Reference, Order Number 121890

- AEDIT Text Editor User's Guide, Order Number 121756

- AEDIT Text Editor Pocket Reference, Order Number 121767

- DEBUG-88 User's Guide, Order Number 121758

- *iAPX 88 Book*, Order Number 210200

- iAPX 86, 88 User's Manual, Order Number 210201

- *iAPX 86, 88 Family Utilities User's Guide,* Order Number 121616

- MCS-80/85 Family User's Manual, Order Number 121506

- MCS-80/85 Utilities User's Guide for 8080/8085-Based Development Systems, Order Number 121617

- 8080/8085 Floating-Point Arithmetic Library User's Manual, Order Number 9800452

- An Introduction to ASM86, Order Number 121689

- ASM86 Macro Assembler Operating Instructions for 8086-Based Systems, Order Number 121628

- ASM86 Language Reference Manual, Order Number 121703

- ASM86 Macro Assembler Pocket Reference, Order Number 121674

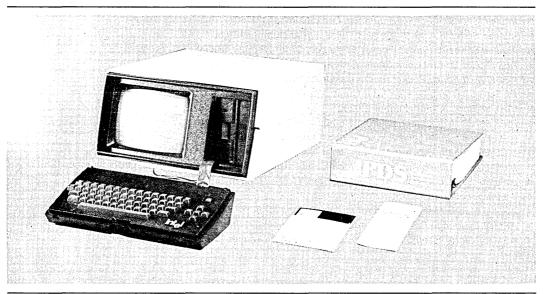

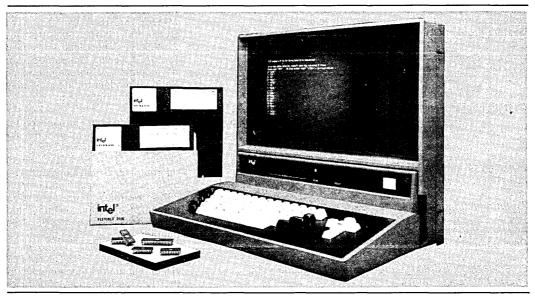

## iPDS<sup>™</sup> PERSONAL DEVELOPMENT SYSTEM

- Completely integrated computer system packaged in a compact rugged enclosure for portability

- Comprehensive design tool for 8 bit Intel microprocessors

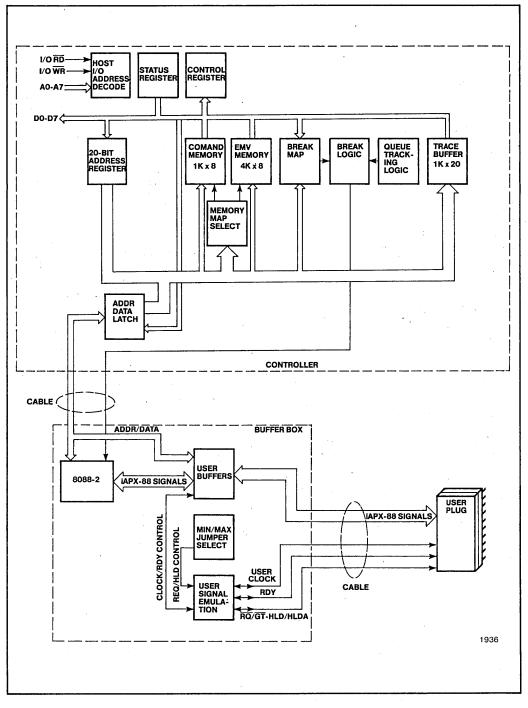

- Microprocessor Emulator (EMV) functions

- Dual processing capability

- Expandable using standard Multimodule™ cards

- Desk top computer for CP/M\* based applications

- 640 K byte Integral flexible disk drive; expandable to 1.28 million bytes

- Powerful ISIS-PDS disk operating system with relocating macro-assembler, and CRT-based editor

- Optional high level languages Fortran 80,PL/M 80, PL/M 88/86 and Basic

- Software compatible with previous Intellec systems

- PROM programming functions

- Bubble Memory option.

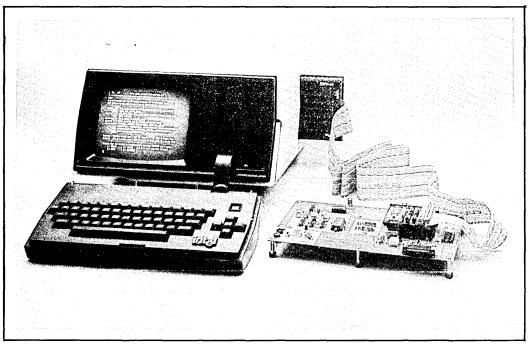

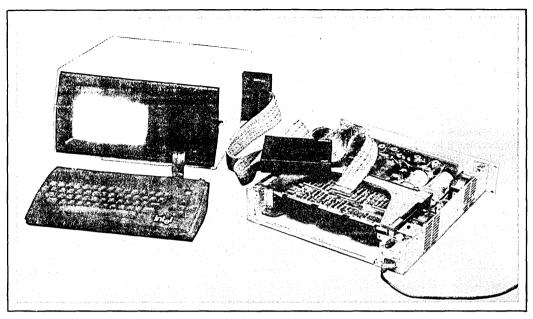

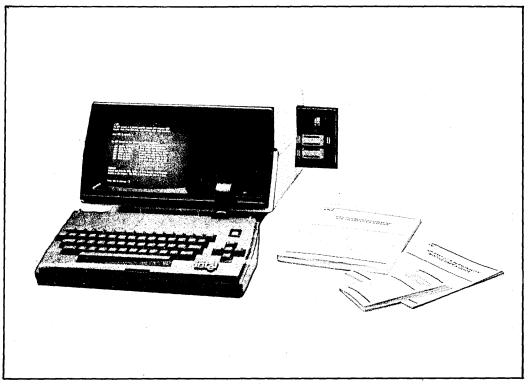

The iPDS Development System is a completely integrated computer system supporting the development of products incorporating Intel 8 bit microprocessors or microcontrollers. Used with its optional emulation vehicles (EMVs) and iUP PROM Programming Personality Modules, the iPDS system provides comprehensive support for integrated hardware and software development, product testing during manufacture, and customer support after the product is in the field. The unit is designed with portability in mind permitting the iPDS Development System to be conveniently transported around the laboratory and into the field. Extensive software is available thereby simplifying and speeding up product development. The software is designed to make the iPDS system easy to use for the novice as well as satisfying the needs of the experienced user. Used with the optional CP/M operating system, the iPDS system becomes a desk top computer that can execute CP/M compatible application programs.

The following are trademarks of Intel Corporation and its alfiliates and may be used only to identify Intel products: BXP, CREDIT, i, ICE, ICS, <sup>I</sup>m, Insite, Intel, INTEL, Intelevision, Intelie, iPDS, ISBC, ISBX, Library Manager, MCS, MAIN MULTIMODULE, Megachassis, Microamp, MULTIBUS, Plug-A-Bubble, PROMPT, Promware, RMX, UPI, µ Scope, System 2000, Micromainframe, and the combination of MCS, ICE, ISBC, IS

#### FUNCTIONAL DESCRIPTION

#### **Hardware Components**

The iPDS case comprises two high impact, shock resistant, poly-carbonate plastic enclosures, that when fitted together, provide a compact and fully enclosed unit. The main enclosure houses a CRT, flexible disk drive, power supply, and base processor printed board assembly. The second enclosure houses the keyboard. On the right side of the unit a spring loaded door allows insertion of an emulator module or an iUP PROM programming module. On the top, a hinged panel covers the storage space for cables and plug-in modules. The carrying handle is attached to the front of the main enclosure and folds away when the system is in use. In the closed position, the iPDS system is 8.15" high, 16" wide, 20" long, and conveniently fits under an airline seat. The basic unit weighs 27 pounds.

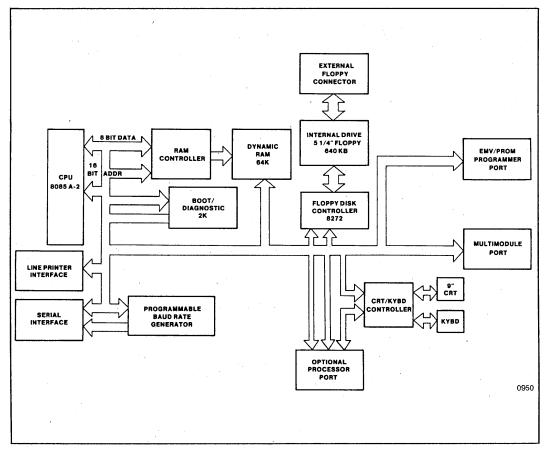

#### BASE PROCESSOR PRINTED BOARD ASSEMBLY-BPB

The Base Processor Board (BPB) contains the powerful 8085A microprocessor, 64K bytes of RAM, CRT/keyboard controller, floppy disk controller, serial I/O port, and parallel I/O port. There are interfaces for connection to the Optional Processor Board, Multimodule Adaptor Board, and the EMV/PROM Programming Adaptor Board.

#### INTEGRAL CRT

The CRT is a 9 inch green phosphor (P42) unit that displays 24 lines of 80 characters/line with a nominal 15.6 KHz vertical sweep rate. The CRT controller, based on an Intel 8085 and 8275 Programmable Controller Chip is located on the BPB. A single cable containing the signals, power, and ground connect it to the CRT. The contrast adjustment is accessible at the rear of the unit. A pull out bail allows the CRT to be placed in a comfortable operating position of 24 degrees to the horizontal. The standard ASCII set of 94 printable characters is displayable, including upper and lower case alpha characters, and the digits 0 through 9. Another 31 characters for character graphics are defined. If the Optional Processor Board is installed, the second processor shares the CRT with the base processor. The bottom part of the screen is assigned to the processor communicating with the keyboard. The top part of the screen displayed in reverse video is assigned to the other processor. The number of lines appearing on the screen for each processor can be completely controlled by the user via special function keys.

#### **KEYBOARD**

The keyboard is housed in a separate enclosure and a flat shielded cable connects it directly to the keyboard controller on the BPB. This 5" cable provides the flexibility to place the keyboard in a comfortable operating position relative to the main enclosure. A total of 61 keys include a typewriter keyset, cursor control keys, and function keys. Auto repeat is available for all keys and is implemented by the keyboard controller. If the Optional Processor Board is installed, it shares the keyboard with the base processor. Initially, the keyboard is assigned to the base processor. It can be assigned to the optional processor by pressing the special function key, FUNC-HOME. Subsequent use of the FUNC-HOME key alternates the keyboard assignment between the two processors.

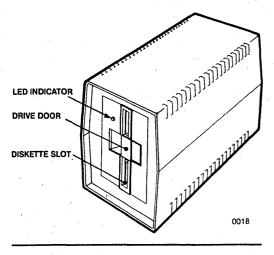

#### INTEGRAL FLOPPY DISK DRIVE

The integral floppy disk drive is a 5 1/4", doublesided, 96 tracks-per-inch drive. Diskettes are written double-sided, double density and provide 640 K bytes of formatted storage in the built-in drive. The floppy disk controller located on the BPB is based on the INTEL 8272 floppy disk controller chip, and can control one additional drive. The ISIS-PDS operating system supports the disk drives. If the Optional Processor Board is installed, the integral disk drive is shared by the two processors or it can be exclusively assigned to one of the processors. When shared, only one processor can access a drive at a time. However, the disk drive sharing is transparent to the user since the ISIS-PDS operating system controls the accessing of the drive and automatically resolves file contention.

#### INPUT/OUTPUT

The iPDS Development System contains two I/O channels located at the rear of the base enclosure and wired to the I/O ports on the Base Processor Board. The serial channel is an EIA RS-232-C interface for asynchronous and synchronous data transfer and is based on the Intel 8251 USART and 8253 timer. The interface can be software configured using the SERIAL command. Full duplex asynchronous operation from 110 to 19.2K baud is selectable.

The parallel I/O interface is an 8 bit parallel I/O port supporting a Centronics type printer. The

interface is implemented with an Intel 8255 Programmable Parallel Interface chip. A maximum transfer rate of 600 cps is supported.

#### **Software Components**

#### **ISIS-PDS OPERATING SYSTEM**

The ISIS-PDS operating system included with the basic iPDS system is designed with a major emphasis on ease of use and simplification of microcomputer development. It is based on the proven ISIS II operating system available on all intellec Microcomputer Development Systems.

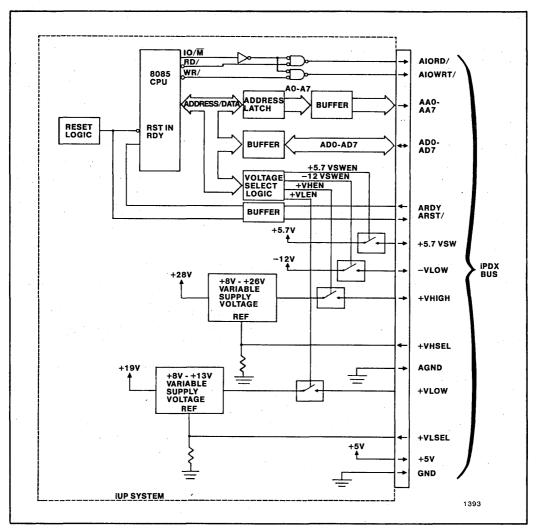

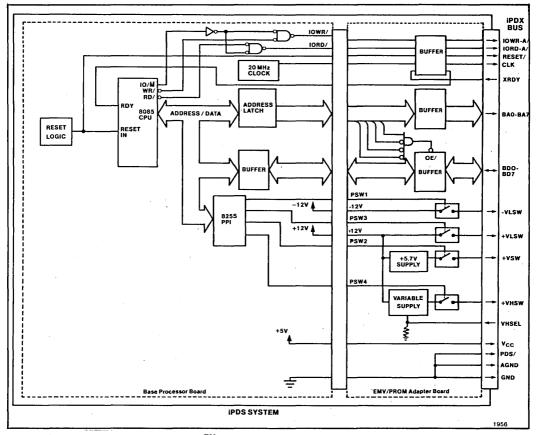

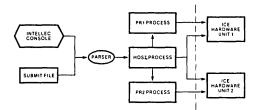

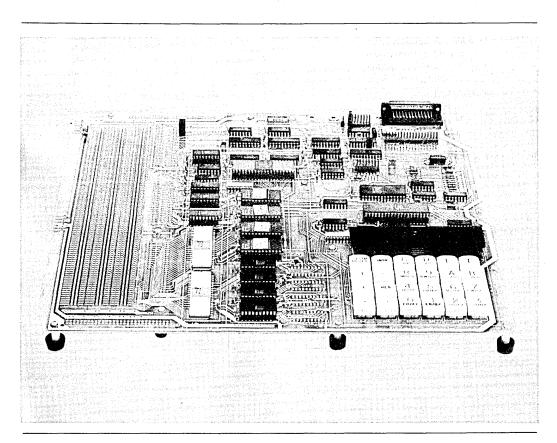

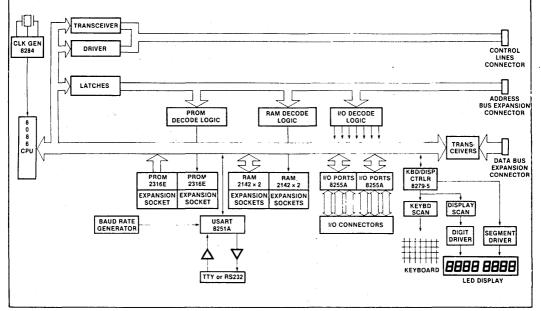

#### Figure 1. iPDS™ Block Diagram

ISIS-PDS has a comprehensive set of commands to control system operation. These commands can be divided into five functional groups.

- System Management Commands

- Device Management Commands

- File Management Commands

- Program Development Commands

- Program Execution Commands

SYSTEM MANAGEMENT COMMANDS HELP displays help information for operating system commands. ? displays the version number of the current Command Line Interpreter. FUNC-R software resets the processor to which the keyboard is currently assigned. FUNC-S switches the CRT display speed between a slow and fast speed. FUNC-T switches the keyboard between typewriter mode and locked upper case mode. FUNC-HOME switches the current foreground and background processors. FUNC-1 increases the display for the foreground processor by one line and decreases the background processor display by one line. FUNC-1 decreases the display for the foreground processor by one line and increases the background processor display by one line. **DEVICE MANAGEMENT COMMANDS** IDISK initially prepares disks and bubble memory for use with the operating system. ASSIGN displays or assigns the mapping of physical to logical devices. re-assigns the system output to the CRT display screen. FUNC <n> changes the system input from the keyboard to the file named JOB < n > .CSD where < n > is a one-digit number from 0 to 9. changes the system input from the keyboard to a file or device which is specified by the user. SERIAL initializes the serial I/O port. ATTACH assigns a row of multimodules to a processor. DETACH releases a row of multimodules from a processor. FILE MANAGEMENT COMMANDS DIR displays a list of the files stored on a disk or on bubble memory. ATTRIB displays and modifies the attributes of a file. COPY transfers files and appends files.

Table 1 summarizes these commands. The HELP commands are especially useful, providing the user with on-line assistance, eliminating frequent referencing of the manual.

| DELETE                | removes files from the disk.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RENAME                | changes the filename and/or extension of a file.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Ċ                     | displays the contents of a file on the screen.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PRC                   | OGRAM DEVELOPMENT COMMANDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| LIB                   | allows the user to manage a library of MCS-80/85 program modules.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| LINK                  | combines a number of object modules into a single<br>object module in an output file.                                                                                                                                                                                                                                                                                                                                                                                                                |

| LOCATE                | converts relocatable object programs into absolute<br>object programs by supplying memory addresses<br>throughout the program.                                                                                                                                                                                                                                                                                                                                                                       |

| HEXOBJ                | converts a program from hexadecimal file format to<br>absolute object format.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OBJHEX                | converts a program from absolute object format to<br>hexadecimal file format.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DEBUG                 | provides a minimum set of 8080/8085 debugging commands.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PRC                   | OGRAM EXECUTION COMMANDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <filename></filename> | loads and executes the object program named <filename>.</filename>                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SUBMIT                | reads an input SUBMIT file, creates a command file<br>containing ISIS commands, and executes<br>commands in sequence from the file created.                                                                                                                                                                                                                                                                                                                                                          |

| •                     | is a fast form of the SUBMIT command. One<br>command line is read from the SUBMIT file,<br>transformed into an ISIS command in memory, and<br>executed. No intermediate file is created.                                                                                                                                                                                                                                                                                                             |

| /                     | reads ISIS commands from a disk job file and<br>executes them in sequence. The / command is also<br>considered a device management command.                                                                                                                                                                                                                                                                                                                                                          |

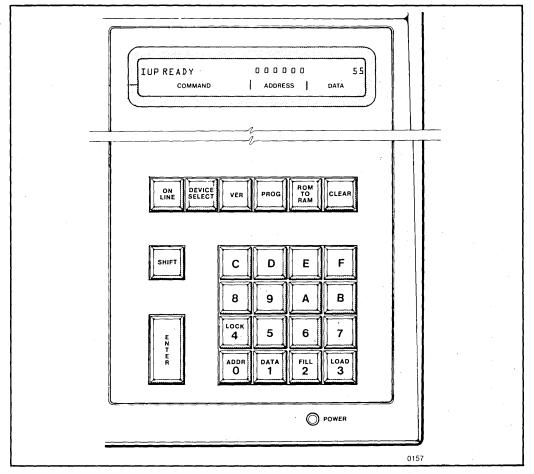

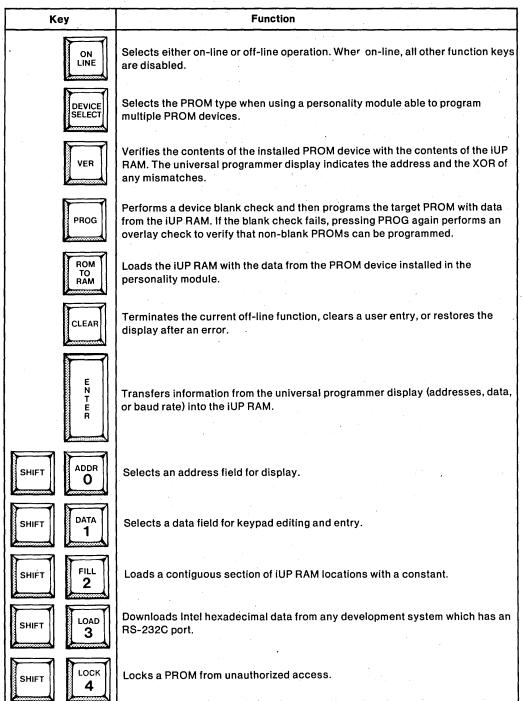

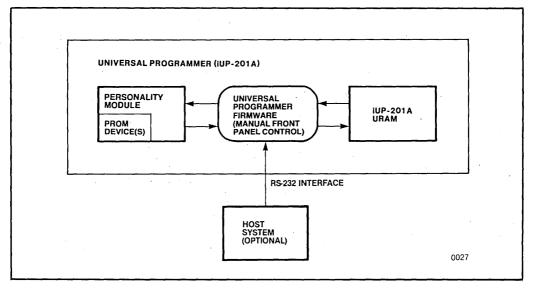

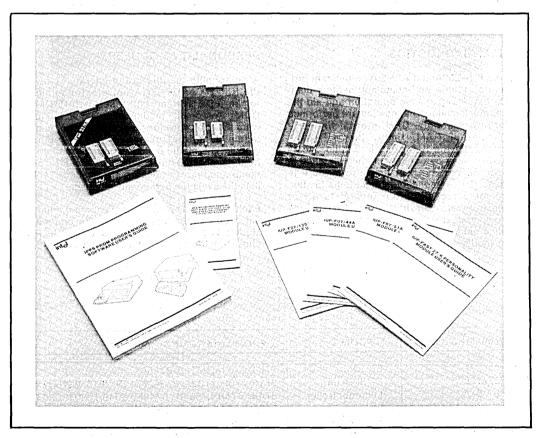

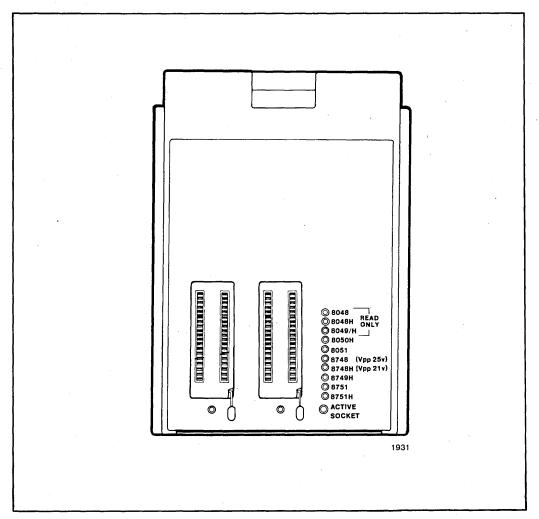

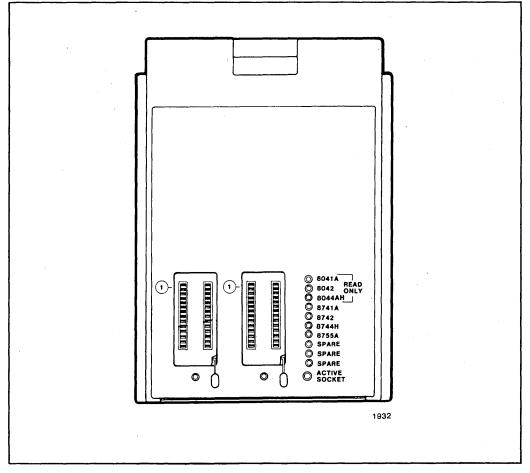

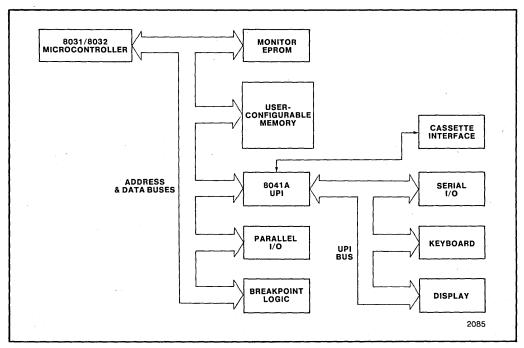

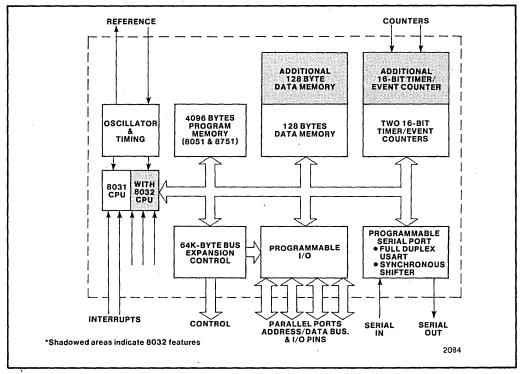

| JOB                   | stores a sequence of frequently used ISIS<br>commands in a job file as they are entered from the<br>keyboard without executing them until the sequence<br>is completely entered. Two job files, ABOOT.CSD<br>and BBOOT.CSD, deserve special mention. If either<br>of these files is present (ABOOT.CSD for Processor<br>A and BBOOT.CSD for Processor B) when the<br>system is initialized, commands are automatically<br>executed from the file. This feature can be used to<br>configure a system. |