intel

# Software Handbook

Order Number: 230786-001

intel

## SOFTWARE HANDBOOK

1984

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9(a) (9). Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and may only be used to identify Intel products:

BITBUS, COMMputer, CREDIT, Data Pipeline, GENIUS, i, î, ICE, iCS, iDBP, iDIS, I<sup>2</sup>ICE, iLBX, i<sub>m</sub>, iMMX, Insite, Intel, int<sub>e</sub>I, int<sub>e</sub>IBOS, Intelevision, int<sub>e</sub>ligent Identifier, int<sub>e</sub>ligent Programming, Intellec, Intellink, iOSP, iPDS, iSBC, iSBX, iSDM, iSXM, Library Manager, MCS, Megachassis, MICRO-MAINFRAME, MULTIBUS, MULTICHANNEL, MULTIMODULE, Plug-A-Bubble, PROMPT, Promware, QUEST, QUEX, Ripplemode, RMX/80, RUPI, Seamless, SOLO, SYSTEM 2000, and UPI, and the combination of ICE, iCS, iRMX, iSBC, MCS, or UPI and a numerical suffix.

The following are trademarks of the companies indicated and may only be used to identify products of the owners.

CP/M is a trademark of Digital Research, Inc.

DEC, DEC-10, DEC-20, PDP-11, DECnet, DECwriter, RSTS, and VAX are trademarks of Digital Equipment Corporation.

MDS is an ordering code only and is not used as a product name or trademark.

MDS® is a registered trademark of Mohawk Data Sciences Corporation.

Microsoft is a trademark of Microsoft, Inc.

© Intel Corporation, 1983

## Table of Contents

| CHAPTER 1<br>OVERVIEW<br>Introduction                                                        | 1-1                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER 2                                                                                    |                                                                                                                                                                            |

| OPERATING SYSTEMS                                                                            |                                                                                                                                                                            |

| Introduction                                                                                 | 2-1                                                                                                                                                                        |

| 8080/8085 Microprocessor Family                                                              |                                                                                                                                                                            |

| DATA SHEET                                                                                   |                                                                                                                                                                            |

| Digital Research Inc. CP/M 2.2 Operating System                                              | 2-2                                                                                                                                                                        |

| 8086/8088 Microprocessor Family                                                              |                                                                                                                                                                            |

| DATA SHEETS                                                                                  |                                                                                                                                                                            |

| iRMX 86 Operating System                                                                     | 2-5                                                                                                                                                                        |

| iRMX 88 Real-Time Multitasking Executive                                                     | 2-25                                                                                                                                                                       |

| Preconfigured iRMX 86 Operating System                                                       | 2-31                                                                                                                                                                       |

| iOSP 86 iAPX 86/30 and iAPX 88/30 Support PackageiMMX 800 MULTIBUS Message Exchange Software | 2-37<br>2-41                                                                                                                                                               |

| FACT SHEET                                                                                   | 2-41                                                                                                                                                                       |

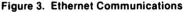

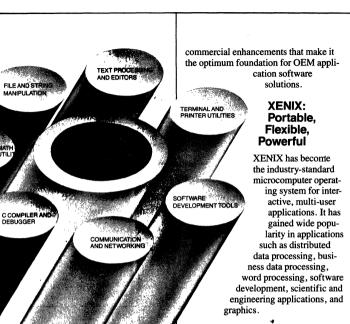

| XENIX 286 Operating Systems                                                                  | 2-45                                                                                                                                                                       |

| APPLICATION NOTE                                                                             | 2-40                                                                                                                                                                       |

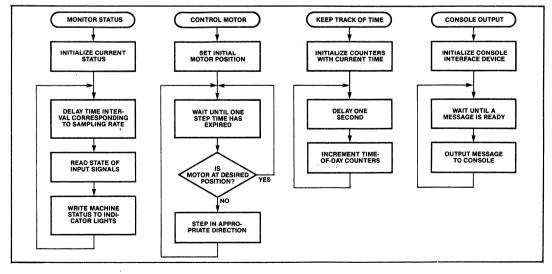

| AP-130 Using Operating Systems Processor's to Simplify Microcomputer Designs                 | 2-51                                                                                                                                                                       |

| ARTICLE REPRINTS                                                                             | 2-01                                                                                                                                                                       |

| AR-236 Let Operating Systems Aid in Component Designs                                        | 2-102                                                                                                                                                                      |

| AR-286 Software That Resides in Silicon                                                      |                                                                                                                                                                            |

| AR-287 Putting Real-Time Operating Systems to Work                                           |                                                                                                                                                                            |

| AR-288 Intel's Matchmaking Strategy: Marry iRMX Operating                                    |                                                                                                                                                                            |

| System with Hardware                                                                         | 2-128                                                                                                                                                                      |

| AR-289 iRMX 86 Has Functionality, Configurability                                            |                                                                                                                                                                            |

| CHAPTER 3                                                                                    |                                                                                                                                                                            |

|                                                                                              |                                                                                                                                                                            |

|                                                                                              |                                                                                                                                                                            |

| TRANSLATORS AND UTILITIES FOR PROGRAM DEVELOPMENT                                            | 0.1                                                                                                                                                                        |

| Introduction                                                                                 | 3-1                                                                                                                                                                        |

| Introduction                                                                                 | 3-1                                                                                                                                                                        |

| Introduction                                                                                 |                                                                                                                                                                            |

| Introduction                                                                                 | 3-3                                                                                                                                                                        |

| Introduction                                                                                 | 3-3<br>3-6                                                                                                                                                                 |

| Introduction                                                                                 | 3-3<br>3-6<br>3-10                                                                                                                                                         |

| Introduction                                                                                 | 3-3<br>3-6<br>3-10<br>3-12                                                                                                                                                 |

| Introduction                                                                                 | 3-3<br>3-6<br>3-10<br>3-12<br>3-15                                                                                                                                         |

| Introduction                                                                                 | 3-3<br>3-6<br>3-10<br>3-12                                                                                                                                                 |

| Introduction                                                                                 | 3-3<br>3-6<br>3-10<br>3-12<br>3-15                                                                                                                                         |

| Introduction                                                                                 | 3-3<br>3-6<br>3-10<br>3-12<br>3-15                                                                                                                                         |

| Introduction                                                                                 | 3-3<br>3-6<br>3-10<br>3-12<br>3-15<br>3-18                                                                                                                                 |

| Introduction                                                                                 | 3-3<br>3-6<br>3-10<br>3-12<br>3-15<br>3-18<br>3-28<br>3-32                                                                                                                 |

| Introduction                                                                                 | 3-3<br>3-6<br>3-10<br>3-12<br>3-15<br>3-18<br>3-28<br>3-32<br>3-35<br>3-39                                                                                                 |

| Introduction                                                                                 | 3-3<br>3-6<br>3-10<br>3-12<br>3-15<br>3-18<br>3-28<br>3-32<br>3-35<br>3-39<br>3-43                                                                                         |

| Introduction                                                                                 | 3-3<br>3-6<br>3-10<br>3-12<br>3-15<br>3-18<br>3-28<br>3-32<br>3-35<br>3-39<br>3-43<br>3-46                                                                                 |

| Introduction                                                                                 | 3-3<br>3-6<br>3-10<br>3-12<br>3-15<br>3-18<br>3-28<br>3-32<br>3-35<br>3-39<br>3-43<br>3-46<br>3-50                                                                         |

| Introduction                                                                                 | 3-3<br>3-6<br>3-10<br>3-12<br>3-15<br>3-18<br>3-28<br>3-32<br>3-35<br>3-39<br>3-43<br>3-46<br>3-50<br>3-53                                                                 |

| Introduction                                                                                 | 3-3<br>3-6<br>3-10<br>3-12<br>3-15<br>3-18<br>3-28<br>3-32<br>3-35<br>3-39<br>3-43<br>3-46<br>3-50<br>3-53<br>3-58                                                         |

| Introduction                                                                                 | 3-3<br>3-6<br>3-10<br>3-12<br>3-15<br>3-18<br>3-28<br>3-32<br>3-35<br>3-39<br>3-43<br>3-43<br>3-46<br>3-50<br>3-53<br>3-58<br>3-58<br>3-60                                 |

| Introduction                                                                                 | 3-3<br>3-6<br>3-10<br>3-12<br>3-15<br>3-18<br>3-28<br>3-32<br>3-35<br>3-39<br>3-43<br>3-46<br>3-50<br>3-53<br>3-58<br>3-58<br>3-60<br>3-64                                 |

| Introduction                                                                                 | 3-3<br>3-6<br>3-10<br>3-12<br>3-15<br>3-18<br>3-28<br>3-28<br>3-23<br>3-35<br>3-39<br>3-43<br>3-46<br>3-50<br>3-53<br>3-53<br>3-53<br>3-58<br>3-60<br>3-64<br>3-71         |

| Introduction                                                                                 | 3-3<br>3-6<br>3-10<br>3-12<br>3-15<br>3-18<br>3-28<br>3-32<br>3-35<br>3-39<br>3-43<br>3-46<br>3-50<br>3-53<br>3-58<br>3-58<br>3-60<br>3-64                                 |

| Introduction                                                                                 | 3-3<br>3-6<br>3-10<br>3-12<br>3-15<br>3-18<br>3-28<br>3-32<br>3-35<br>3-39<br>3-43<br>3-46<br>3-50<br>3-53<br>3-58<br>3-58<br>3-60<br>3-64<br>3-71<br>3-76                 |

| Introduction                                                                                 | 3-3<br>3-6<br>3-10<br>3-12<br>3-15<br>3-18<br>3-28<br>3-32<br>3-35<br>3-39<br>3-43<br>3-46<br>3-50<br>3-53<br>3-58<br>3-60<br>3-53<br>3-58<br>3-60<br>3-51<br>3-76<br>3-79 |

| Introduction                                                                                 | 3-3<br>3-6<br>3-10<br>3-12<br>3-15<br>3-18<br>3-28<br>3-32<br>3-35<br>3-39<br>3-43<br>3-46<br>3-50<br>3-53<br>3-58<br>3-58<br>3-60<br>3-64<br>3-71<br>3-76                 |

9

4

intel®

, P

.

| Single Chip Microcontroller Software DATA SHEETS                                   |             |

|------------------------------------------------------------------------------------|-------------|

| 2920 Software Support Package                                                      | 3-94        |

| MCS-48 Diskette-Based Software Support Package                                     |             |

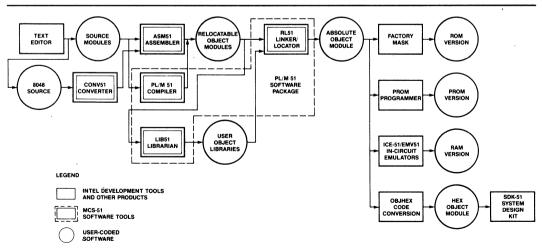

| PL/M 51 Software                                                                   | 3-110       |

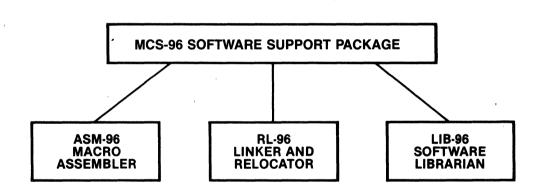

| MCS-96 Software Support Package                                                    | 3-114       |

| CHAPTER 4                                                                          |             |

| PRODUCTIVITY TOOLS AND COMMUNICATION SOFTWARE                                      | 4-1         |

| Program Development and Management Tools<br>DATA SHEETS                            | 4-1         |

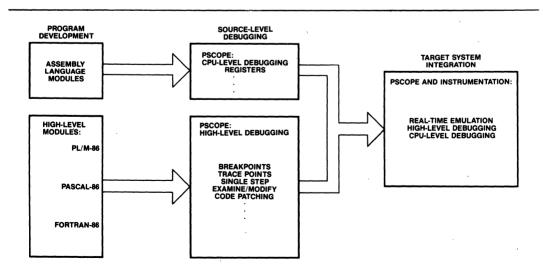

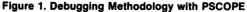

| PSCOPE High-Level Program Debugger                                                 | 4-2         |

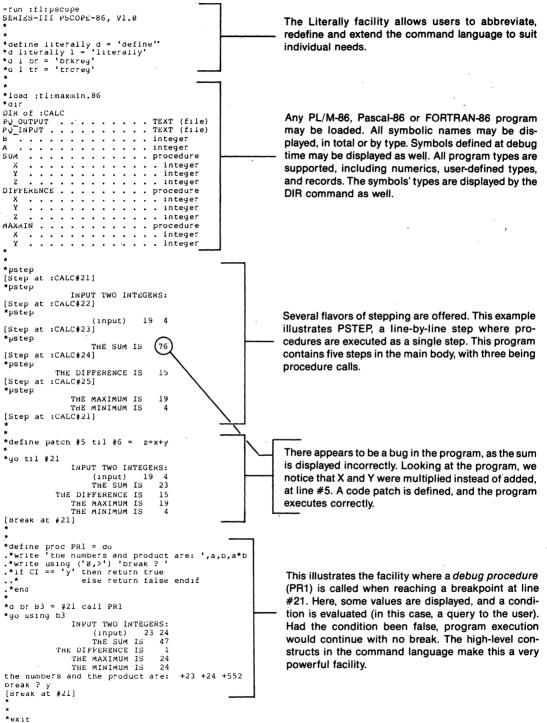

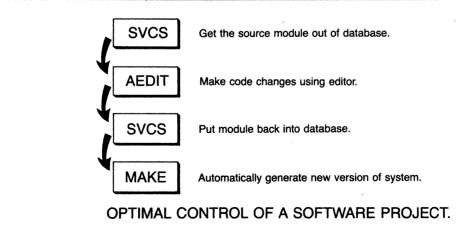

| Program Management Tools ISIS-II Software Toolbox                                  | 4-7<br>4-10 |

| 8086 Software Toolbox                                                              |             |

| AEDIT Text Editor                                                                  | 4-14        |

| CREDIT CRT-Based Text Editor                                                       | 4-16        |

| DATA SHEETS                                                                        |             |

| Mainframe Link for Distributed Development                                         |             |

| Intel Asynchronous Communications Link                                             |             |

| iNA 960 Network Software NDS-II Electronic Mail                                    |             |

|                                                                                    |             |

| CHAPTER 5<br>SYSTEM AND APPLICATIONS SOFTWARE                                      |             |

| FACT SHEETS                                                                        |             |

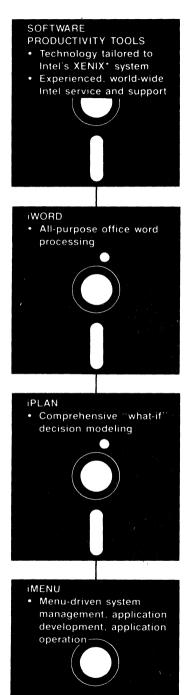

| XENIX Productivity Software Tools                                                  | 5-1         |

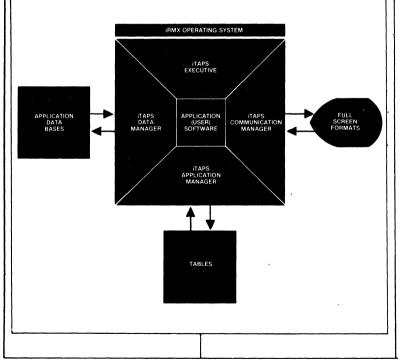

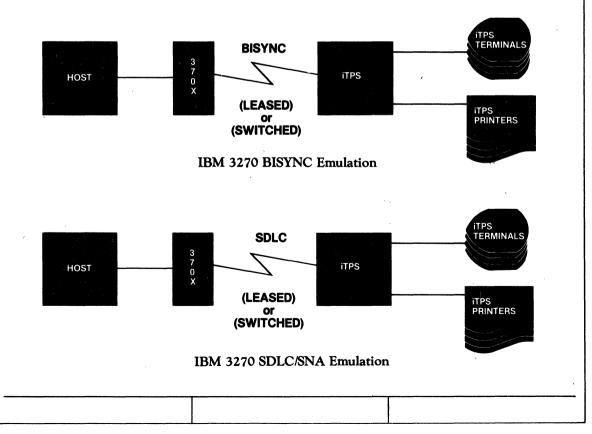

| iTPS Transaction Processing Systems Terminal Application Processing System (iTAPS) | 5-9         |

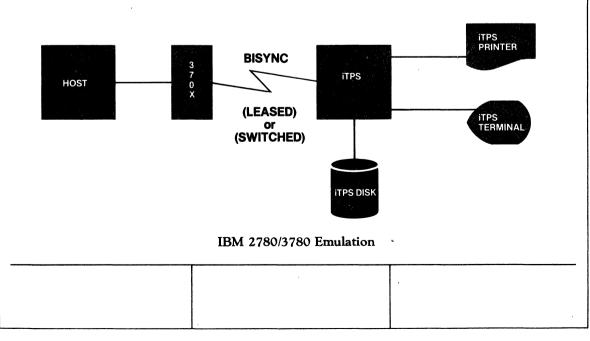

| iTPS Transaction Processing Systems Communications                                 | 5-12        |

| System 2000 Database Management System Sperry (Univac) 1100 Series                 | 5-16        |

| CHAPTER 6                                                                          |             |

| COMPONENT SOFTWARE                                                                 |             |

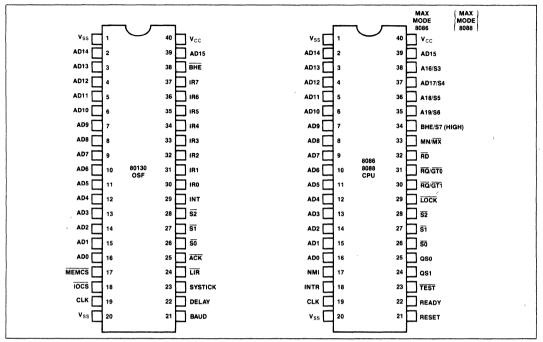

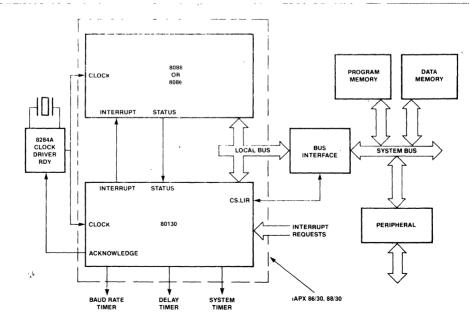

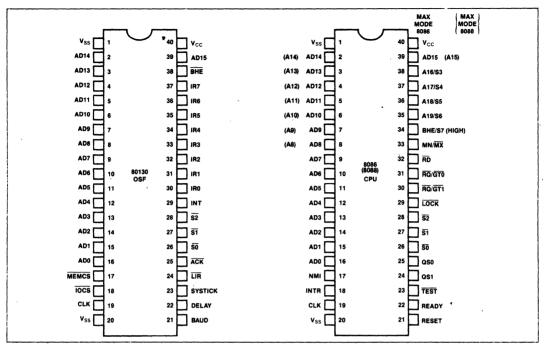

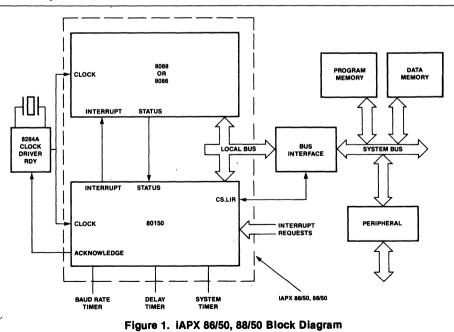

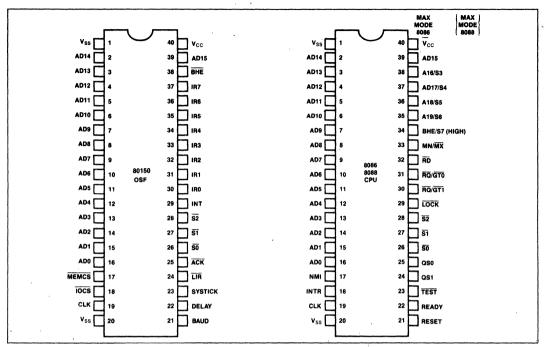

| DATA SHEETS<br>80130/80130-2 iAPX 86/30, 88/30, 186/30, 188/30 iRMX 86             |             |

| Operating System Processors                                                        | 6-1         |

| 80150/80150-2 iAPX 86/50, iAPX 88/50, 186/50, 188/50 CP/M 86                       | •           |

| Operating System Processors                                                        | 6-23        |

| CHAPTER 7                                                                          |             |

| USER LIBRARY                                                                       |             |

| Introduction                                                                       | 7-1         |

| User Library Insite User's Program Library                                         | 7-2         |

| Insite Submittal Requirements                                                      | 7-3         |

| Insite Index of Program                                                            | 7-5         |

|                                                                                    |             |

| Software Standards                                                                 | A-1         |

| APPENDIX B                                                                         |             |

| Software Support                                                                   | B-1         |

σ

## Software Handbook Overview

1

### SOFTWARE HANDBOOK OVERVIEW

Welcome to the Intel Software Handbook. This handbook is a complete guide to the software products and services offered by Intel.

Intel's software products follow the open systems strategy that allows Intel products to be purchased at the customers' desired level of integration. Hence these products are available for component, board, or systems applications. This open systems philosophy is backed by software standards that insure that the software can operate at numerous levels of integration. These software standards are described in the appendix.

Software for Intel's products is available both from Intel and from Independent Software Vendors (ISVs). For a complete listing of software available from ISVs, see the Intel Yellow Pages which is published annually by Intel. This handbook describes software products that are available through Intel, consisting of Intel-developed and ISV-developed products. Products that are offered by Intel have all been evaluated and tested to meet Intel's quality standard. They are backed by an extensive support organization described in the appendix.

· · ·

· · · · ·

. . . .

.

## **Operating Systems**

2

### **OPERATING SYSTEMS**

#### INTRODUCTION

The ability to convert advanced microprocessor technology into solutions for modern day problems begins with effective and efficient designs for new hardware products and architecture. However, a most critical element in the success of any microcomputer solution is the availability of a high quality, reliable operating system. Without this software counterpart, the technological advances cannot be fully implemented, nor their benefits fully realized.

The classic role of the microcomputer operating system can be outlined by viewing its major functions and purposes. The functions of the microcomputer operating system are threefold: 1) to manage system resources and the allocation of these resources to users; 2) to provide automatic functions such as initialization and start-up procedures; and 3) to provide an efficient, straightforward and consistent method for user programs to interface with the hardware subsystems, including a simple and friendly human interface. Typically, the operating systems have one of two main purposes. First, they can be used to develop a new software system that runs on another machine. These systems are usually large and fairly sophisticated. ISIS and \*XENIX are examples of such developmental operating systems. The second purpose for microcomputer operating systems is directed toward the execution of software programs for targeted application. The largest number of operating systems are of this type, including the RMX systems. The most critical requirement is for these application.

This rather neat and simple categorization of microcomputer operating systems, which has been useful in the past, is quickly becoming blurred. The rapid developments in microcomputer technology have increased the power and decreased the cost of microcomputers, allowing them to become applicable to the solution of a broader variety and more sophisticated set of problems. Microcomputer systems must increasingly provide such capabilities as multiprogramming, multitasking, multiprocessing, networking, as well as scheduling and priority determination. As systems become more complex, they must still remain responsive to real-time applications. Operating systems must be able to capitalize on the trends toward placing more and more software into silicon. This trend is blurring the distinction between the hardware and software subsystems. Microcomputer systems are also evolving to encompass both the developmental and target application purposes into one system.

These dramatic changes in technology place additional demands on operating systems. We see operating systems undergoing changes to consider the need for: 1) modularity and ease of configurability; 2) evolutionary, not revolutionary, path of growth; and 3) standardization in languages, networks and the operating system itself. The first need is required to allow the system to be a powerful development tool yet configurable to more specialized applications. The last two items are needed to provide protection of a firm's software investment, including the option to move toward silicon software.

The operating systems and executives in this section are state-of-the-art microcomputer systems that have taken to task the challenges posed by advancing microprocessor technology. These operating systems offer the widest range of solutions with the highest quality and most future-oriented software available today. Consequently, our customers can select the appropriately optimized option to achieve their price/performance goals and give them time-to-market advantage over their competitors.

\*XENIX is a trademark of Microsoft Corp.

## DIGITAL RESEARCH INC. CP/M\* 2.2 OPERATING SYSTEM

- High-performance, single-console operating system

- Simple, reliable file system matched to microcomputer resources

- Table-driven architecture allows field reconfiguration to match a wide variety of disk capacities and needs

- Extensive documentation covers all facts of CP/M applications

- More than 1,000 commercially available compatible software products

- General-purpose subroutines and table-driven data-access algorithms provide a truly universal data management system

- Upward compatibility from all previous versions

CP/M 2.2 is a monitor control program for microcomputer system and application uses on Intel 8080/8085-based microcomputer (see the *CP/M-86* \* *Operating System* data sheet for information on CP/M for Intel 8086/8088-based systems). CP/M provides a general environment for program execution, construction, storage, and editing, along with the program assembly and check-out facilities.

The CP/M monitor provides rapid access to programs through a comprehensive file management package. The file subsystem supports a named file structure, allowing dynamic allocation of file space as well as sequential and random file access. Using this system, a large number of distinct programs can be stored in both sourceand machine-executable form.

CP/M also supports a powerful context editor, Intel-compatible assembler, and debugger subsystems. Nearly all personal software programs can be bought configured to run under CP/M, several of which are available from Intel.

#### FEATURES

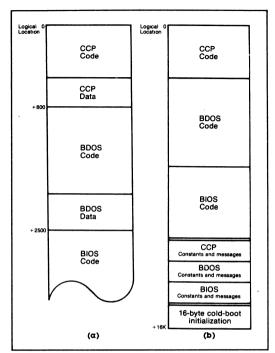

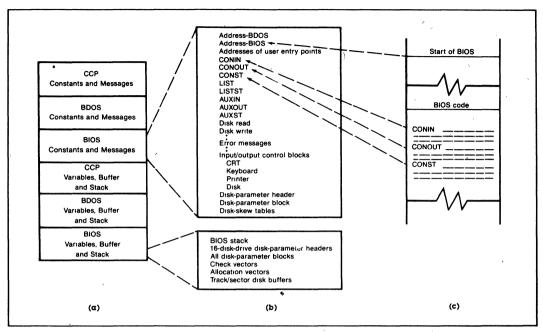

CP/M is logically divided into four distinct modules:

#### **BIOS—Basic I/O System**

- Provides primitive operations for access to disk drives and interface to standard peripherals (teletype, CRT, paper tape reader/punch, bubble memory, and user-defined peripherals)

- Allows user modification for tailoring to a particular hardware environment

#### **BDOS—Basic Disk Operating System**

- -Provides disk management for one to sixteen disk drives containing independent file directories

- Implements disk allocation strategies for fully dynamic file construction and minimization of head movement across the disk

- -Uses less than 4K of memory allowing plenty of memory space for applications programs

- -Uses less than 4K of memory

- -Makes programs transportable from system to system

- -Entry points include the following primitive operations which can be programmatically accessed:

- SEARCHLook for a particular disk file by<br/>nameOPENOpen a file for further operationsCLOSEClose a file after processingRENAMEChange the name of a particular file

- READ Read a record from a particular file

- WRITE Write a record to a particular file

- SELECT Select a particular disk drive for further operations

#### **CCP—Console Command Processor**

- -Provides primary user interface by reading and interpreting commands entered through the console

- -Loads and transfers control to transient programs, such as assemblers, editors, and debuggers

- ---Processes built-in standard commands including:

- ERA Erase specified files

- DIR List file names in the directory

- REN Rename the specified file

- SAVE Save memory contents in a file

- TYPE Display the contents of a file on the console

#### **TPA**—Transient Program Area

- -Holds programs which are loaded from the disk under command of the CCP

- Programs created under CP/M can be checked out by loading and executing these programs in the TPA

- -User programs, loaded into the TPA, may use the CCP area for the program's data area

- -Transient commands are specified in the same manner as built-in commands

- -Additional commands can be easily defined by the user

- -Defined transient commands include:

- PIP Peripheral Interchange Program —implements the basic media transfer operations necessary to load, print, punch, copy, and combine disk files; PIP also performs various reformatting and concatenation functions. Formatting options include parity-bit removal, case conversion, Intel hex file validation, subfile extraction, tab expansion, line number generation, and pagination

- ED Text Editor—allows creation and modification of ASCII files using extensive context editing commands: string substitution, string search, insert, delete and block move; ED allows text to be located by context, line number, or relative position with a macro command for making extensive text changes with a single command line

- ASM Fast 8080 Assembler—uses standard Intel mnemonics and pseudo operations with free-format input, and conditional assembly features

- DDT Dynamic Debugging Tool—contains an integral assembler/disassembler module that lets the user patch and display memory in either assembler mnemonic or hexadecimal form and trace program execution with full register and status display; instructions can be executed between breakpoints in real-time, or run fully monitored, one instruction at a time

- SUBMIT Allows a group of CP/M commands to be batched together and submitted to the operating system by a single command

- STAT Lists the number of bytes of storage remaining on the currently logged disks, provides statistical information about particular files, and displays or alters device assignments

- LOAD Converts Intel hex format to absolute binary, ready for direct load and execution in the CP/M environment

- SYSGEN Creates new CP/M system disks for back-up purposes

- MOVCPM Provides regeneration of CP/M systems for various memory configurations and works in conjunction with SYSGEN to provide additional copies of CP/M

#### BENEFITS

- —Easy implementation on any computer configuration which uses an Intel 8080/8085 Central Processing Unit (see the CP/M-86 data sheet for CP/M applications on the iAPX86 CPU)

- —iPDS version supports bubble memory option as an additional diskette drive. Also allows diskette duplication with a single drive

- -Extensive selection of CP/M-compatible programs allows production and support of a comprehensive software package at low cost

- -Field programmability for special-purpose operating system requirements

- ---Provides field specification of one to sixteen logical drives, each containing up to eight megabytes

- Files may contain up to 65,536 records of 128 bytes each but may not exceed the size of any single disk

- Each disk is designed for 64 distinct files—more directory entries may be allocated if necessary

#### SPECIFICATIONS

#### **Hardware Required**

- -Model 800 with 720 kit

- ---DS 235 kit or MDS 225 with 720 kit (integral drive supported except as system boot device)

Optional:

- RAM up to 64K

- -Additional floppy disk drives

- -Single density via 201 controller

- -Bubble memory and optional Shugart 460 5<sup>1</sup>/<sub>4</sub>" disk drive for iPDS

#### **Documentation Package**

#### Title

CP/M 2.2 documentation consisting of 7 manuals: An Introduction to CP/M Features and Facilities CP/M 2.2 User's Guide CP/M Assembler (ASM) User's Guide CP/M Dynamic Debugging Tool (DDT) User's Guide ED: A Context Editor for the CP/M Disk System User's Manual CP/M 2 Interface Guide

- Individual users are physically separated by user numbers, with facilities for file copy operations from one user area to another

- Relative-record random-access functions provide direct access to any of the 65,536 records of an eight-megabyte file

#### **Shipping Media**

(Specify by Alpha Character when ordering.)

- A-single density (IBM 3740/1 compatible)

- B-double density

- F-double-sided, double density 51/4" floppy (iPDS format)

#### Order Code P

#### **Product Description**

See Price List CP/M (Control Program for Microcomputers) is a disk-based operating system for the Intel 8080/8085-based systems. CP/M provides a general environment for program development, test, execution and storage. CP/M storage is available via a comprehensive, named-file structure supporting both sequential and random access. CP/M support tools include a Text Editor, a debugger, and an 8080/8085 assembler.

#### SUPPORT:

Intel offers several levels of support for this product, depending on the system configuration in which it is used. Please consult the price list for a detailed description of the support options available.

An Intel Software License required.

\*CP/M is a registered trademark of Digital Research, Inc.

<sup>\*</sup>CP/M-86, MP/M, CP/NET and MP/NET are trademarks of Digital Research, Inc.

# intel

## iRMX<sup>™</sup> 86 OPERATING SYSTEM

- Real-time processor management for time-critical iAPX 86 and iAPX 88 applications

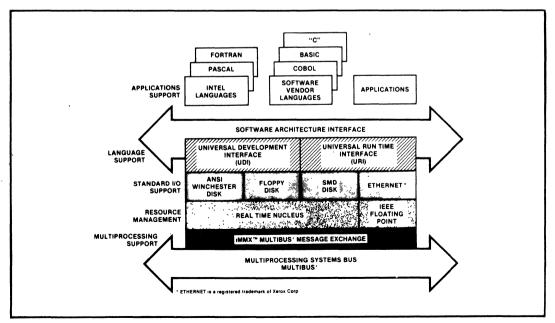

- On-target system development with Universal Development Interface (UDI)

- Configurable system size and function for diverse application requirements

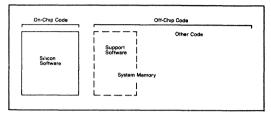

- All iRMX<sup>™</sup> 86 code can be (P)ROM'ed to support totally solid state designs

- Compatible operating system services for iAPX 86/30 and 88/30 Operating System Processors (iOSP<sup>™</sup> 86)

- Multi-terminal support with multi-user human interface

- Broad range of device drivers included for industry standard MULTIBUS<sup>®</sup> peripheral controllers

- Expandable to multi-processor systems with iMMX<sup>™</sup> 800 Message Exchange Software

- Extendable to iAPX 286 systems with iRMX<sup>™</sup> 286R option

- Powerful utilities for interactive configuration and real-time debugging

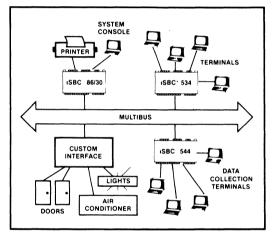

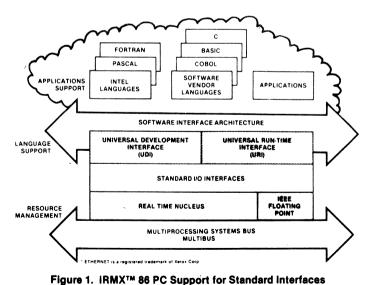

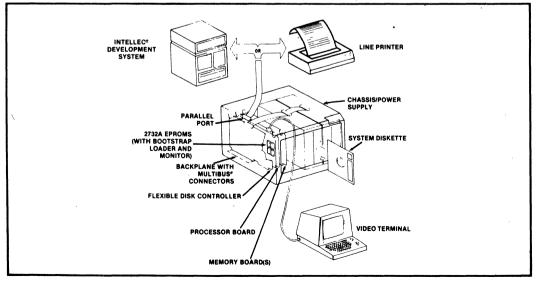

The iRMX<sup>™</sup> 86 Operating System is an easy-to-use, real-time, multi-tasking and multi-programmming software system designed to manage and extend the resources of iSBC<sup>®</sup> 86 and iSBC 88 Single Board Computers, as well as other iAPX 86- and iAPX 88-based microcomputers. iRMX 86 functions are available in silicon with the iAPX 86/30 and 88/30 Operating System Processors, in a user configurable software package, and fully integrated into the SYSTEM 86/300 Family of Microcomputer Systems. The Operating System provides a number of standard interfaces that allow iRMX 86 applications to take advantage of industry standard device controllers, hardware components, and a multitude of software packages developed by Independent Software Vendors (ISVs). Many high-performance features extend the utility of iRMX 86 Systems into applications such as data collection, transaction processing, and process control where immediate access to advances in VLSI technology is paramount. These systems may deliver real-time performance and explicit control over resources; yet also support applications with multiple users needing to simultaneously access terminals. The configurable layers of the System provide services ranging from interrupt management and standard device drivers for many sophisticated controllers, to data-file maintenance commands provided by a comprehensive multi-user human interface. By providing access to the standard Universal Development Interface (UDI) for each user terminal, Original Equipment Manufacturers (OEMs) can pass program development and target application capabilities to their users.

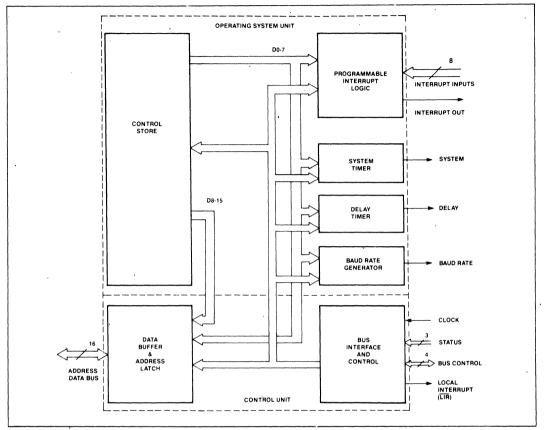

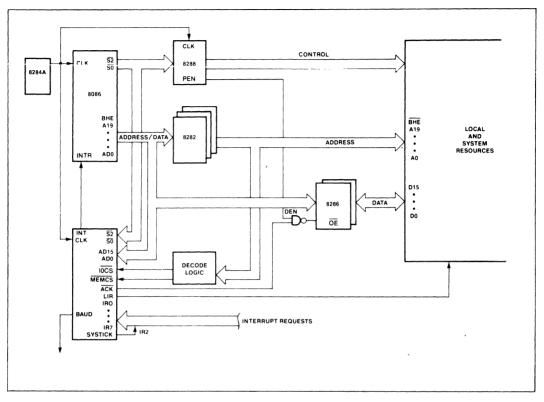

#### iRMX™ 86 VLSI Operating System

The following are trademarks of Intel Corporation and may be used only to describe Intel products Intel, ICE, IMMX, IOSP, IRMX, ISBC, ISBX, ISXM, MULTIBUS, MULTICHANNEL and MULTIMODULE Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied

3

The iRMX 86 Operating System is a complete set of system software modules that provide the resource management functions needed by computer systems. These management functions allow Original Equipment Manufacturers (OEMs) to best use resources available in microcomputer systems while getting their products to market quickly, saving time and money. Engineers are relieved of writing complex system software and can concentrate instead on their application software.

This data sheet describes the major features of the iRMX 86 Operating System. The benefits provided to engineers who write application software and to users who want to take advantage of improving microcomputer price and performance are explained. The first section outlines the system resource management functions of the Operating System and describes several system calls. The second section gives a detailed overview of iRMX 86 features aimed at serving both the iRMX 86 system designer and programmer, as well as the end users of the product into which the Operating System is incorporated.

#### FUNCTIONAL DESCRIPTION

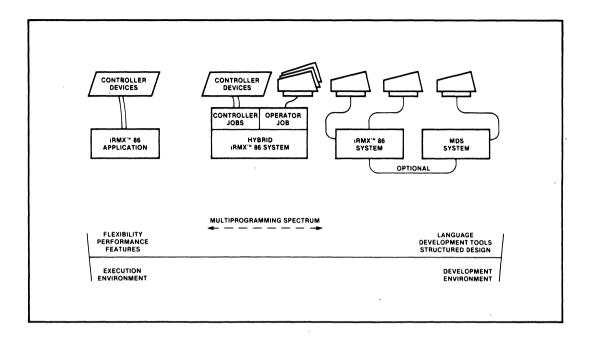

To take best advantage of iAPX 86 and 88 microprocessors in applications where the computer is required to perform many functions simultaneously, the iRMX 86 Operating System provides a multiprogramming environment in which many independent, multi-tasking application programs may run. The flexibility of independent environments allows application programmers to separately manage each application's resources during both the development and test phases.

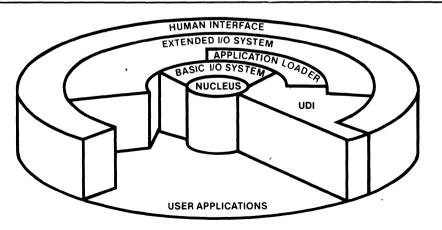

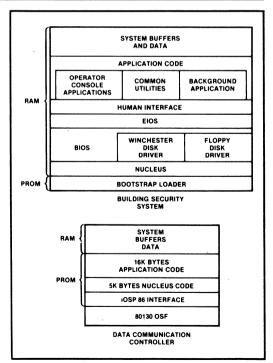

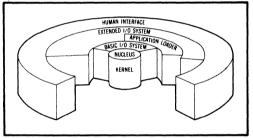

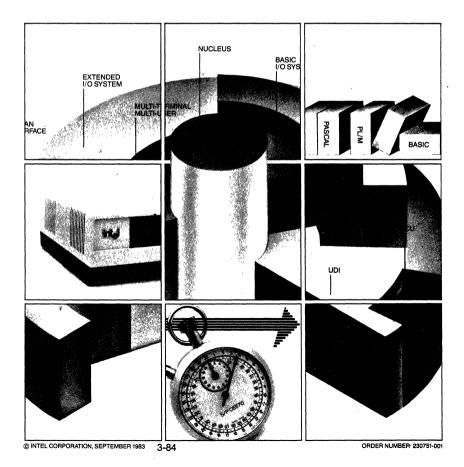

The resource management functions of the iRMX 86 System are supported by a number of configurable software layers. While many of the functions supplied by the innermost layer, the Nucleus, are required by all systems, all other functions are optional. The I/O systems, for example, need not be included in systems having no secondary storage requirement. Each layer provides functions that encourage application programmers to use modular design techniques which aid in quick development of easily maintainable programs.

The components of the iRMX 86 Operating System provide both implicit and explicit management of system resources. These resources include processor scheduling, up to one megabyte of system memory, up to 57 independent interrupt sources, all input and output devices, as well as directory and data files contained on mass storage devices and accessed by a number of independent users. Management of each of these system resources and how the resources can be shared between multiple processors and users is discussed in the following sections.

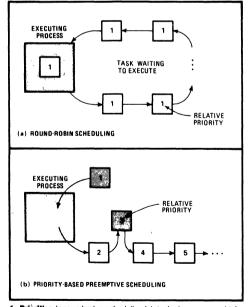

#### **Process Management**

To implement multi-tasking application systems, programmers require a method of managing the different processes of their application, and for allowing the processes to communicate with each other. The Nucleus layer of the iRMX 86 System provides a number of facilities to efficiently manage these processes, and to effectively communicate between them. These facilities are provided by system calls that manipulate data structures called tasks, jobs, semaphores, regions, and mailboxes. The iRMX 86 System refers to these structures as "objects".

Ł

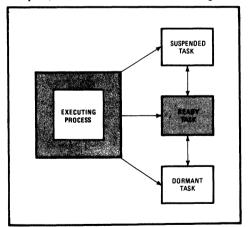

**Tasks** are the basic element of all applications built on the iRMX 86 Operating System. Each task is an entity capable of executing CPU instructions and issuing system calls in order to perform a function. Tasks are characterized by their register values (including those of an optional 8087 Numeric Processor Extension), a priority between 0 and 255, and the resources associated with them.

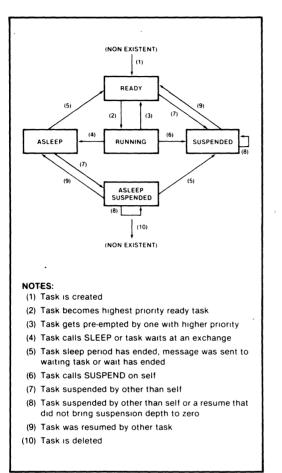

Each iRMX 86 task in the system is scheduled for operation by the iRMX 86 nucleus. Figure 1 shows the five states in which each task may be placed, and some examples of how a task may move from one state to another. The iRMX 86 nucleus ensures that each task is placed in the correct state, defined by the events in its external environment and by the task issuing system calls. Each task has a priority to indicate its relative importance and need to respond to its environment. The nucleus guarantees that the highest priority ready-to-run task is the task that runs.

Jobs are used to define the operating environment of a group of tasks. Jobs effectively limit the scope of an application by collecting all of its tasks and other objects into one group. Because the environment for execution of an application is defined by an iRMX 86 job, separate applications can be efficiently developed by separate development teams.

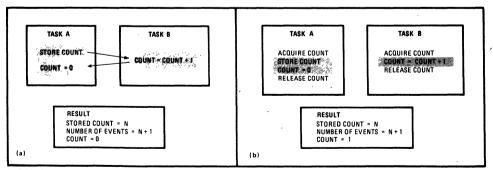

The iRMX 86 Operating System provides two primary techniques for real-time event synchronization in multitask applications: regions and semaphores.

**Regions** are used to restrict access to critical sections of code and data. Once the iRMX 86 Operating System gives a task access to resources guarded by a region, no other tasks may make use of the resources, and the task is given protection against deletion and suspension. Regions are typically used to protect data structures from being simultaneously updated by multiple tasks.

Semaphores are used to provide mutual exclusion between tasks. They contain abstract "units" that are sent between the tasks, and can be used to implement the cooperative sharing of resources.

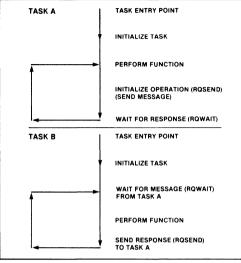

Figure 1. Task State Diagram

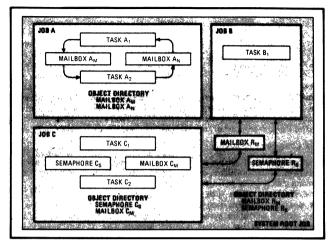

Multi-tasking applications must communicate information and share system resources among cooperating tasks. The iRMX 86 Operating System assigns a unique 16-bit number, called a token, to each object created in the System. Any task in possession of this token is able to access the object. The iRMX 86 Nucleus allows tasks to gain access to objects, and hence system resources, at run-time with two additional mechanisms: mailboxes and object directories.

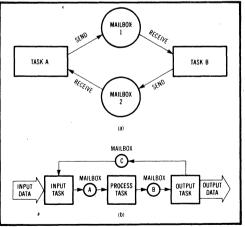

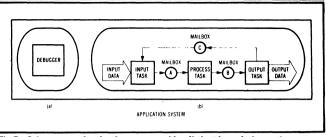

**Mailboxes** are used by tasks wishing to share objects with other tasks. A task may share an object by sending the object's token via a mailbox. The receiving task can check to see if a token is there, or can wait at the mailbox until a token is present.

**Object Directories** are also used to make an object available to other tasks. An object is made public by cataloging its token and name in a directory. In this manner, any task can gain access to the object by knowing its name, and job environment that contains the directory.

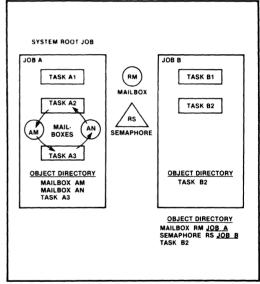

Three example jobs are shown in Figure 2 to demonstrate how two tasks can share an object that was not known to the programmers at the time the tasks were developed. Both Job 'A' and Job 'B' exist within the environment of the 'Root Job' that forms the foundation of all iRMX 86 systems. Each job possesses a directory in which tasks may catalog the name of an object. Semaphore 'RS', for example, is accessable by all tasks in the system, because its name is cataloged in the directory of the Root Job. Mailbox 'AN' can be used to transfer objects between Tasks 'A2' and 'A3' because its token is accessable in the object directory for Job 'A'

Table 1 lists the major functions of the iRMX 86 Nucleus that manage system processes.

Figure 2. Object Directories

#### Memory Management

Each job in an iRMX 86 System defines the amount of the one megabyte of addressable memory to be used by its tasks. The iRMX 86 Operating System manages system memory and allows jobs to share this critical resource by providing another object type: segments.

Segments are contiguous pieces of memory, between 16 Bytes and 64K Bytes in length, that exist within the environment of the job in which they were created. Segments form the fundamental piece of system memory used for task stacks, data storage, system buffers, loading programs from secondary storage, passing information between tasks, etc.

| System Call           | Function Performed                                                                                                                                                                                                |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RQ\$CREATE\$JOB       | Creates an environment for a number of tasks and other objects, as well as creating an initial task and its stack.                                                                                                |

| RQ\$DELETE\$JOB       | Deletes a job and all the objects currently defined within its bounds. All memory used<br>is returned to the job from which the deleted job was created.                                                          |

| RQ\$OFFSPRING         | Provides a list of all the current jobs created by the specified job.                                                                                                                                             |

| RQ\$CATALOG\$OBJECT   | Enters a name and token for an object into the object directory of a job.                                                                                                                                         |

| RQ\$UNCATALOG\$OBJECT | Removes an object's token and its name from a job's object directory.                                                                                                                                             |

| RQ\$LOOKUP\$OBJECT    | Returns a token for the object with the specified name found in the object directory of the specified job.                                                                                                        |

| RQ\$GET\$TYPE         | Returns a code for the type of object referred to by the specified token.                                                                                                                                         |

| RQ\$CREATE\$MAILBOX   | Creates a mailbox with queues for waiting tasks and objects with FIFO or PRIORITY discipline.                                                                                                                     |

| RQ\$DELETE\$MAILBOX   | Deletes a mailbox.                                                                                                                                                                                                |

| RQ\$SEND\$MESSAGE     | Sends an object to a specified mailbox. If a task is waiting, the object is passed to the<br>appropriate task according to the queuing discipline. If no task is waiting, the object is<br>queued at the mailbox. |

| RQ\$RECEIVE\$MESSAGE  | Attempts to receive an object token from a specified mailbox. The calling task may<br>choose to wait for a specified number of system time units if no token is available.                                        |

| RQ\$DISABLE\$DELETION | Prevents the deletion of a specified object by increasing its disable count by one.                                                                                                                               |

| RQ\$ENABLE\$DELETION  | Reduces the disable count of an object by one, and if zero, enables deletion of that<br>object.                                                                                                                   |

| RQ\$FORCE\$DELETE     | Forces the deletion of a specified object if the disable count is either 0 or 1.                                                                                                                                  |

| RQ\$CREATE\$TASK      | Creates a task with the specified priority and stack area.                                                                                                                                                        |

| RQ\$DELETE\$TASK      | Deletes a task from the system, and removes it from any queues in which it may be waiting.                                                                                                                        |

| RQ\$SUSPEND\$TASK     | Suspends the operation of a task. If the task is already suspended, its suspension<br>depth is increased by one.                                                                                                  |

| RQ\$RESUME\$TASK      | Resumes a task. If the task had been suspended multiple times, the suspension depth<br>is reduced by one, and it remains suspended.                                                                               |

| RQ\$SLEEP             | Causes a task to enter the ASLEEP state for a specified number of system time units.                                                                                                                              |

| RQ\$GET\$TASK\$TOKENS | Gets the token for the calling task or associated objects within its environment.                                                                                                                                 |

| RQ\$SET\$PRIORITY     | Dynamically alters the priority of the specified task.                                                                                                                                                            |

| RQ\$GET\$PRIORITY     | Obtains the current priority of a specified task.                                                                                                                                                                 |

| RQ\$CREATE\$REGION    | Creates a region, with an associated queue of FIFO or PRIORITY ordering discipline.                                                                                                                               |

| RQ\$DELETE\$REGION    | Deletes the specified region if it is not currently in use.                                                                                                                                                       |

| RQ\$ACCEPT\$CONTROL   | Gains control of a region only if the region is immediately available.                                                                                                                                            |

| RQ\$RECEIVE\$CONTROL  | Gains control of a region. The calling task may specify the number of system time units it wishes to wait if the region is not immediately available.                                                             |

| RQ\$SEND\$CONTROL     | Relinquishes control of a region.                                                                                                                                                                                 |

| RQ\$CREATE\$SEMAPHORE | Creates a semaphore.                                                                                                                                                                                              |

| RQ\$DELETE\$SEMAPHORE | Deletes a semaphore.                                                                                                                                                                                              |

| RQ\$SEND\$UNITS       | Increases a semaphore counter by the specified number of units.                                                                                                                                                   |

| RQ\$RECEIVE\$UNITS    | Attempts to gain a specified number of units from a semaphore. If the units are not immediately available, the calling task may choose to wait.                                                                   |

| Table 1  | Process | Management | System | Calls |

|----------|---------|------------|--------|-------|

| Table I. | F100633 | manayement | System | Calla |

The example in Figure 2 also demonstrates when information is shared between Tasks 'A2' and 'A3'; 'A2' only needs to create a segment, put the information in the memory allocated, and send it via the Mailbox 'AM' using the RQ\$SEND\$MESSAGE system call (see Table 1).Task 'A3' would get the message by using the RQ\$ RECEIVE\$MESSAGE system call. The Figure also shows how the receiving task could signal the sending task by sending an acknowledgement via the second Mailbox 'AN'.

Each job is created with both maximum and minimum limits set for its memory pool. Memory required by all objects and resources created in the job is taken from this pool. If more memory is required, a job may be allowed to borrow memory from the pool of its containing job (the job from which it was created). In this manner, initial jobs may efficienty allocate memory to jobs they subsequently create, without exactly knowing their requirements.

The iRMX 86 Operating System supplies other memory managment functions to search specific address ranges for available memory. The System performs this search at system initialization, and can be configured to ignore non-existent memory and addresses reserved for I/O devices and other application requirements.

Table 2 lists the major system calls used to manage the system memory.

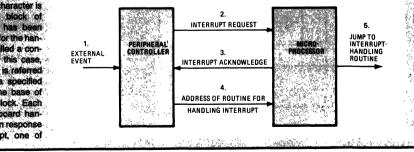

#### Interrupt Management

Real-time systems, by their nature, must respond to asynchronous and unpredictable events quickly. The iRMX 86 Operating System uses interrupts and the eventdriven nucleus described earlier to give real-time response to events. Use of a pre-emptive scheduling technique ensures that the servicing high priority events always take precedence over other system activities.

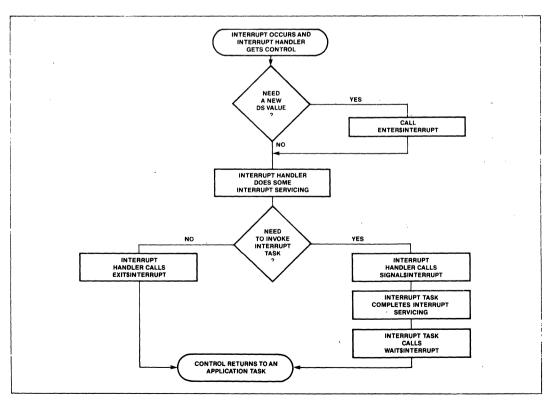

The iRMX 86 Operating System gives applications the flexibility to optimize either interrupt response time or interrupt response capability by providing two tiers of Interrupt Management. These two distinct tiers are managed by Interrupt Handlers and Interrupt Tasks.

Interrupt Handlers are the first tier of interrupt service. For small, simple functions, interrupt handlers are often the most efficient means of responding to an event. They provide faster response than interrupt tasks, but must be kept simple since interrupts (except the iAPX 86 and 88 non-maskable interrupt) are masked during their execution. When extended interrupt service is required, interrupt handlers "signal" a waiting interrupt task that, in turn, performs more complicated functions.

Interrupt Tasks are distinct tasks whose priority is associated with a hardware interrupt level. They are permitted

to make any iRMX 86 system call. While an interrupt task is servicing an interrupt, interrupts of lower priority are not allowed to pre-empt the system.

Table 3 shows the iRMX 86 System Calls provided to manage interrupts.

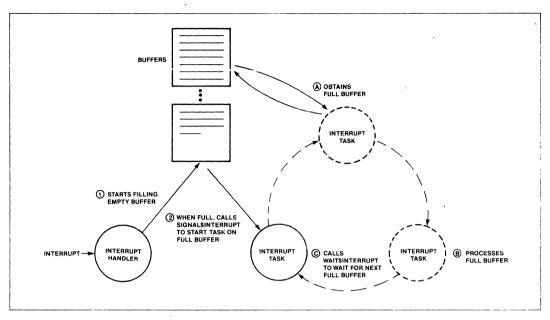

#### INTERRUPT MANAGEMENT EXAMPLE

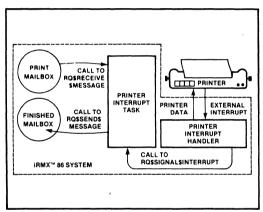

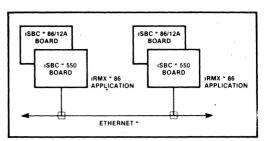

Figure 3 illustrates how the iRMX 86 Interrupt System may be used to output strings of characters to a printer. In the example, a mailbox named 'PRINT' is used by all tasks in the system to queue messages to be printed. Application tasks put the characters in segments that are transmitted to the printer interrupt service task via the PRINT Mailbox. Once printing is complete, the same interrupt task passes the messages on to another application via the FINISHED Mailbox so that an operator message can be displayed.

Figure 3. Interrupt Management Example

#### BASIC I/O SYSTEM

The Basic I/O System (BIOS) provides the direct access to I/O devices needed by real-time applications. The BIOS allows I/O functions to overlap other system functions. In this manner, application tasks make asynchronous calls to the iRMX 86 BIOS, and proceed to perform other activities. When the I/O request must be completed before an application can continue, the task waits at a mailbox for the result of the operation.

Some system calls provided by the BIOS are listed in Table 4.

The Basic I/O System communicates with peripheral devices through device drivers. These device drivers provide the System with four basic functions needed to control and communicate with devices: Initialize I/O, Finish I/O, Queue I/O, and Cancel I/O. Using the device driver interface, users of non-standard devices may write custom drivers compatible with the I/O System.

| System Call               | Function Performed                                                                                                                      |  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| RQ\$CREATE\$SEGMENT       | Dynamically allocates a memory segment of the specified size.                                                                           |  |

| RQ\$DELETE\$SEGMENT       | Deletes the specified segment by deallocating the memory.                                                                               |  |

| RQ\$GET\$POOL\$ATTRIBUTES | Returns attributes such as the minimum and maximum, as well as current size of the memory in the environment of the calling task's job. |  |

| RQ\$GET\$SIZE             | Returns the size (in bytes) of a segment.                                                                                               |  |

| RQ\$SET\$POOL\$MIN        | Dynamically changes the minimum memory requirements of the job environment<br>containing the calling task.                              |  |

#### Table 2. Memory Management System Calls

#### Table 3. Interrupt Management System Calls

.

| System Call           | Function Performed                                                                                                                                     |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RQ\$SET\$INTERRUPT    | Assigns an interrupt handler and, if desired, an interrupt task to the specified interrupt level. Usually the calling task becomes the interrupt task. |  |

| RQ\$RESET\$INTERRUPT  | Disables an interrupt level, and cancels the assignment of the interrupt handler for that level. If an interrupt task was assigned, it is deleted.     |  |

| RQ\$GET\$LEVEL        | Returns the number of the highest priority interrupt level currently being processed.                                                                  |  |

| RQ\$SIGNAL\$INTERRUPT | Used by an interrupt handler to signal the associated interrupt task that an interrupt has occurred.                                                   |  |

| RQ\$WAIT\$INTERRUPT   | Used by an interrupt task to SLEEP until the associated interrupt handler signals the<br>occurrence of an interrupt.                                   |  |

| RQ\$EXIT\$INTERRUPT   | Used by an interrupt handler to relinquish control of the System.                                                                                      |  |

| RQ\$ENABLE            | Enables the hardware to accept interrupts from a specified level.                                                                                      |  |

| RQ\$DISABLE           | Disables the hardware from accepting interrupts at or below a specified level.                                                                         |  |

#### Table 4. Key BIOS I/O Management System Calls

| System Call               | Function Performed                                                                                                      |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------|--|

| RQ\$A\$ATTACH\$FILE       | Creates a Connection to an existing file.                                                                               |  |

| RQ\$A\$CHANGE\$ACCESS     | Changes the types of accesses permitted to the specified user(s) for a specific file.                                   |  |

| RQ\$A\$CLOSE              | Closes the Connection to the specified file so that it may be used again, or so that the type of access may be changed. |  |

| RQ\$A\$CREATE\$DIRECTORY  | Creates a Named File used to store the names and locations of other Named Files.                                        |  |

| RQ\$A\$CREATE\$FILE       | Creates a data file with the specified access rights.                                                                   |  |

| RQ\$A\$DELETE\$CONNECTION | Deletes the Connection to the specified file.                                                                           |  |

| RQ\$A\$GET\$FILE\$STATUS  | Returns the current status of a specified file.                                                                         |  |

| RQ\$A\$OPEN               | Opens a file for either read, write, or update access.                                                                  |  |

| RQ\$A\$READ               | Reads a number of bytes from the current position in a specified file.                                                  |  |

| RQ\$A\$SEEK               | Moves the current data pointer of a Named or Physical file.                                                             |  |

| RQ\$A\$WRITE              | Writes a number of bytes at the current position in a file.                                                             |  |

| RQ\$WAIT\$IO              | Synchronizes a task with the I/O System by causing it to wait for I/O operation results.                                |  |

na b

,

The iRMX 86 Operating System includes a number of device drivers to allow applications to use standard USART serial communication devices, multiple CRTs and keyboards, bubble memories, diskettes, disks, a Centronics-type parallel printer, and many of Intel's iSBC and iSBX™ device controllers (see Table 9). If an application requires use of a non-standard device, users need only write a device driver to be included with the BIOS, and access it as if it were part of the standard system. For most random-access devices, this job is further simplified by using standard routines provided with the System. Use of this technique ensures that applications can remain device independent.

#### **MULTI-TERMINAL SUPPORT**

The iRMX 86 Terminal Support provides line editing and terminal control capabilities. The Terminal Support communicates with devices through simple drivers that do only character I/O functions. Dynamic terminal reconfiguration is provided so that attributes such as terminal type and line speed may be changed without modifying the application or the Operating System. Dynamic configuration may be typed in, generated programmatically or stored in a file and copied to a terminal I/O connection.

The iRMX 86 Terminal Support provides automatic translation of control characters to specific control sequences for each terminal. This translation enables applications using standard control characters to function with nonstandard terminals. The translation requirements for each terminal can be stored in terminal description files and copied to a connection, as described above.

#### **DISK I/O PERFORMANCE**

Table 5 shows iRMX 86 performance obtained using the iSBC 215 Winchester Disk and iSBX 218 Diskette Controllers under the specified conditions.

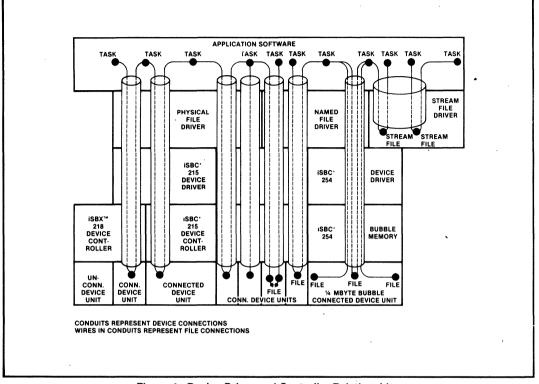

Each device driver can be used to interface to a number of separate and, in some cases, different devices (See Figure 4). The iSBC 215 Device Driver, supplied with the system, is capable of supporting the iSBC 215 Winchester Disk Controller, the iSBC 220 SMD Disk Controller, and the iSBX 218 Flexible Disk Controller (when mounted on an iSBC 215 board). Each device controller may, in turn, control a number of separate device units. In addition, each driver may control a number of like device controllers. This capability allows the use of large storage systems with a minimum of I/O system code to write or maintain.

#### **EXTENDED I/O SYSTEM**

The iRMX 86 Extended I/O System (EIOS) adds a number of I/O management capabilities to simplify access to

files. Whereas the BIOS provides users with the basic system calls needed for direct management of I/O resources, many users prefer to have the system perform all the buffering and synchronization of I/O requests automatically. The EIOS allows users to access I/O devices without having to write procedures for buffering data, or to specify particular devices with constant device names.

By performing device buffering automatically, the iRMX 86 EIOS optimizes accesses to disks and other devices. Often, when an application task asks the System to READ a portion of a file, the System is able to respond immediately with the data it has read in advance of the request. Similarly, the EIOS will not delay a task for writing data to a device unless it is specifically told to, or if its output buffers are filled.

Logical file and device names are provided by the EIOS to give applications complete file and device independence. Applications may send data to the 'line printer' (:LP:) without needing to know which specific device will be used as the printer. This logical name may, in fact, not be a printer at all, but it could be a disk file that is later scheduled for printing.

The EIOS uses the functions provided by the BIOS to synchronize individual I/O requests with results returned by device drivers. Most EIOS system calls are similar to the BIOS calls, except that they appear to suspend the operation of the calling task until the I/O requests are completed.

| Function                                    | Average<br>Character Throughput<br>Bytes per Second* |                    |

|---------------------------------------------|------------------------------------------------------|--------------------|

|                                             | Winchester Disk                                      | Diskette           |

| Single File Read                            | 42,000                                               | 15,800             |

| Two File Read<br>(Same Device)              | 36,800                                               | <sup>`</sup> 5,700 |

| Single File Write                           | 23,800                                               | 5,400              |

| Two File Write<br>(Different Devices)       | 36,200                                               | 6,900              |

| Read/Write Two Files<br>(Different Devices) | 38,900                                               | 6,000              |

<sup>&</sup>lt;sup>™</sup> These measurements were made in the following environment: Entire IRMX<sup>™M</sup> 86 operating system and application code and data located in on-board RAM of a 8-MHz ISBC® 86/30 Single Board Computer. Named files, each with a file size of 128 KBytes, were used with a device and volume granularity of 1 KBytes and six 1 KByte buffers. The disk interleave factor was 2. The ISBC 215 Winchester Controller was attached to two 20-Mbyte drives, and supported the ISBX<sup>™</sup> 218 Diskette Controller that, in turn, was attached to two double density 8'' diskette drives. This performance is, to a large part, restricted by the mechanical speed of the devices.

Figure 4. Device Driver and Controller Relationships

#### **File Management**

The iRMX 86 Operating System provides three distinct types of files to ensure efficient management of both program and data files: Named Files, Physical Files, and Stream Files. Each file type provides access to I/O devices through the standard device drivers mentioned earlier. The same device driver is used to access physical and named files for a given device.

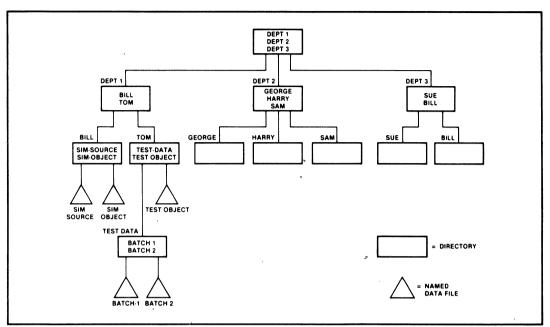

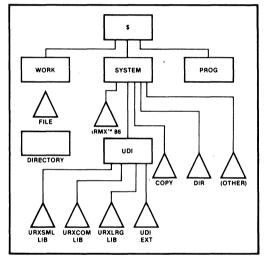

#### NAMED FILES

Named files allow users to access information on secondary storage by referring to a file with its ASCII name. The names of files stored on a device are stored in special files called directories. As directories are themselves named files, the iRMX 86 File System allows directories to contain the names of other directories. Figure 5 illustrates the resulting hierarchical file structure. This structure is useful for isolating file names to particular user applications, and for tailoring system data to the requirements of users and applications sharing storage devices. Using different branches on the directory tree, different users do not have to coordinate in naming their files to ensure unique names. Whenever a request is made involving a file name, the System will search the appropriate directory in order to find the necessary information about the file's size, access rights, and specific location on the storage device.

The iRMX 86 BIOS uses an efficient format for writing the directory and data information into secondary storage. This standard iRMX 86 format is fully compatible with the ISO Media standard, and other Intel systems such as the iRMX 88 Operating System. This structure enables the system to directly access any byte in a file, often without having to do additional I/O to access space allocation information. The maximum size of an individual file is  $2^{32}$  (4.3 billion) bytes.

#### EASE OF ACCESS

The hierarchical file structure is provided to isolate and organize collections of named files. To give operators fast and simple access to any level within the file tree, an ATTACHFILE command is provided. This command allows operators to give a logical name to a point in the tree so that a long sequence of characters need not be typed each time a file is referred to.

Figure 5. Hierarchical Named File Structure

#### **ACCESS PROTECTION**

Access to each Named File is protected by the rights assigned to each user by the owner of the file. Rights to read, append, update, and delete may be selectively granted to other users of the system. In general, users of Named Files are classified into one of three categories: User, Group, and World. Users and Groups are used when different programmers and programs need to share information stored in a file. The World classification is used when rights are to be granted to all who can use the system.

#### **PHYSICAL FILES**

Physical Files allow more direct device access than Named Files. Each Physical File occupies an entire device, treated as a single stream of individually accessable bytes. No access control is provided for Physical Files as they are typically used for such applications as driving a printing device, translating from one device format to another, driving a paper tape device, and controlling analog mechanisms.

#### STREAM FILES

Stream Files provide applications with a method of using iRMX 86 file management methods for data that does not need to go into secondary storage. Stream Files act as direct channels, through system memory, from one task to another. These channels are very useful to pro-

grams, for example, wishing to preserve file and device independence allowing data sent to a printer one time, to a disk file another time, and to another program on a different occasion.

#### **BOOTSTRAP AND APPLICATION LOADERS**

Two utilities are supplied with the System to load programs and data into system memory from secondary storage devices:

The **iRMX 86 Bootstrap Loader** can be configured to a size of less than 600 bytes of P(ROM), and is typically used to load the initial system from the system disk into memory, and begin its execution.

The **Application Loader** is typically used by application programs already running in the system to load additional programs and data from any secondary storage device. The Human Interface layer, for example, uses the Application Loader to load the non-resident Human Interface Commands. The Application Loader is capable of loading both relocatable and absolute code, as well as program overlays.

#### **Human Interface**

The flexibility of the interface between computer controlled machines and their users often determines the usability and ultimate success of the machines. Table 12 lists iRMX 86 Human Interface functions giving users and applications simple access to the file and system management capabilities described earlier. The process, interrupt, and memory managment functions described earlier, are performed automatically for Human Interface users.

#### **MULTI-USER ACCESS**

Using the multi-terminal support provided by the BIOS, the iRMX 86 Human Interface can support several simultaneous users. The real-time nature of the system is maintained by providing a priority for each user, and using the event-driven iRMX 86 Nucleus to schedule tasks. High-performance interrupt response is guaranteed even while users interact with various application packages. For example, multi-terminal support allows one person to be using the iRMX 86 Editor, while another compiles a FORTRAN 86 or PASCAL 86 program, while several others load and access applications.

Each terminal attached to the iRMX 86 multi-user Human Interface is automatically associated with a user, a memory pool, and an initial program to run when the terminal is connected. This association is made using a file that may be changed at any time. Changes are effective the next time the system is initialized.

The initial program specified for each terminal can be a special application program, a custom Human Interface, or the standard iRMX 86 Command Line Interpreter (CLI). For example, you may choose to use the Microsoft Basic Interpreter as this initial program. After system start-up, each terminal user would be able to run the interpreter without asking for it to be loaded. From the BASIC interpreter an operator, for example, could run a data collection program, written in BASIC, that communicates with several laboratory instruments, and prints charts and reports based on certain test results. When finished entering, changing, or running a BASIC program, the terminal would remain in BASIC for the next user.

Specifying an application program as a terminal's initial program makes the interface between operators and the computer system much simpler. Each operator need only be aware of the function of a particular application; not needing to interact with any unfamiliar functions also available on his application system.

Specifying the standard iRMX 86 Human Interface CLI as the initial program enables users of the terminals to access all iRMX 86 functions. This CLI makes it easy to manage iRMX 86 files, load and execute Intel-supplied and custom programs, and submit command files for later execution.

| Table 5. IRMX '* Heal-Time Performance   |                          |  |

|------------------------------------------|--------------------------|--|

| Real-Time<br>Function                    | Execution<br>Time (msec) |  |

| SUSPEND TASK                             | 0.45                     |  |

| INTERRUPT LATENCY<br>(to Handler)        | 0.20<br>(Max)            |  |

| INTERRUPT LATENCY<br>(to Handler)        | 0.03<br>(Typical)        |  |

| CONTEXT SWITCH CAUSED<br>BY INTERRUPT    | 0.68<br>(Max)            |  |

| SEND MESSAGE<br>(no context switch)      | 0.30                     |  |

| SEND MESSAGE<br>(with context switch)    | 0.57                     |  |

| SEND CONTROL<br>(no context switch)      | 0.19                     |  |

| SEND CONTROL<br>(with context switching) | 0.50                     |  |

| RECEIVE CONTROL<br>(no waiting)          | 0.25                     |  |

Context switch time is the time between executing in the context of a task, and the first instruction to execute in the context of another task.

These times were measured using an 8 MHz iSBC<sup>±</sup> 86/30 Single Board Computer with the standard configuration supported by the Preconfigured System, and all program and data stored in on-board dynamic RAM.

Figure 6. Typical iRMX<sup>™</sup> 86 Configurations

#### **FEATURE OVERVIEW**

The iRMX 86 Operating System is well suited to serve the demanding needs of real-time applications executing on complex microprocessor systems. The iRMX 86 System also provides many tools and features needed by real-time system developers and programmers. The following sections describe features useful in both the development and execution environments. The description of each feature outlines the advantages given to hardware and software engineers concerned with overall system cost, expandability with custom and industry standard options, and long-term maintenance of iRMX 86-based systems. The development environment features also describe the ease with which the iRMX 86 Operating System can be incorporated into overall system designs.

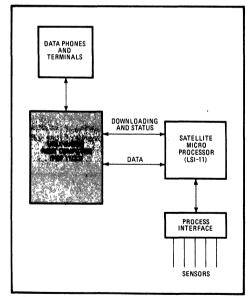

#### **Execution Environment Features**