## Memory Components Handbook

## LITERATURE

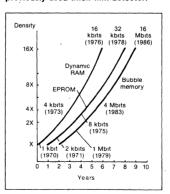

1983 will be a year of transition for Intel's catalog program. In order to better serve you, our customers, we are reorganizing many of our catalogs to more completely reflect product groups.

In addition to the new product line handbooks listed below, an INTEL PRODUCT GUIDE (Order No. 210846) will be available free of charge in March. This GUIDE will contain a listing of Intel's complete product line along with information on quality/reliability, packaging and ordering, customer training classes and product services.

Consult the Intel Literature Guide (no charge, Order No. 210620) for a complete listing of Intel literature. Literature is presently available in other forms for those handbooks that will not be published until later in the year. Write or call the Intel Literature Department, 3065 Bowers Avenue, Santa Clara, CA 95051, (800) 538-1876, or (800) 672-1833 (California only).

#### HANDBOOKS

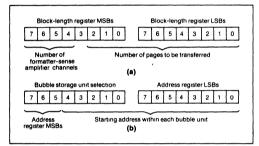

#### Memory Components Handbook (Order No. 210830)

Contains all application notes, article reprints, data sheets and other design information on RAMs, DRAMs, EPROMs, E<sup>2</sup>PROMs, Bubble Memories.

#### Microcontroller Handbook (Available in May)

Contains all application notes, article reprints, data sheets, and other user information on the MCS-48, MCS-51 (8-bit) and the new MCS-96 (16-bit) product families.

#### Military Handbook (Order No. 210461)

Contains complete data sheets on all military products.

#### Microprocessor and Peripherals Handbook (Order No. 210844)

Contains data sheets on all microprocessors and peripherals. (Individual User Manuals are also available on the 8085, 8086, 8088, 186, 286, etc.)

#### **Development Systems Handbook (Available in April)**

Contains data sheets on development systems and supporting software.

#### **OEM Systems Handbook (Available in May)**

Contains all application notes, article reprints and data sheets for OEM boards and systems.

#### Software Handbook (Available in May)

Contains software product overview as well as data sheets for all Intel software.

#### Quality/Reliability Standards Handbook (Available in April)

# intel

### MEMORY COMPONENT HANDBOOK

1983

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products:

BXP, CREDIT, i, ICE, I<sup>2</sup>ICE, ICS, iDBP, iDIS, iLBX, i<sub>m</sub>, iMMX, Insite, INTEL, int<sub>e</sub>I, Intelevision, Intellec, int<sub>e</sub>ligent Identifier<sup>™</sup>, int<sub>e</sub>IBOS, int<sub>e</sub>Iigent Programming<sup>™</sup>, Intellink, iOSP, iPDS, iRMS, iSBC, iSBX, iSDM, iSXM, Library Manager, MCS, Megachassis, Micromainframe, MULTIBUS, Multichannel<sup>™</sup> Plug-A-Bubble, MULTIMODULE, PROMPT, Ripplemode, RMX/80, RUPI, System 2000, and UPI, and the combination of ICE, iCS, iRMX, iSBC, MCS, or UPI and a numerical suffix.

MDS is an ordering code only and is not used as a product name or trademark. MDS<sup>®</sup> is a registered trademark of Mohawk Data Sciences Corporation.

\* MULTIBUS is a patented Intel bus.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Department 3065 Bowers Avenue Santa Clara, CA 95051

### **Table of Contents**

| Alphanumeric Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | v                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Memory Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-1                                                                                                      |

| CHAPTER 2 Intel Memory Technologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-1                                                                                                      |

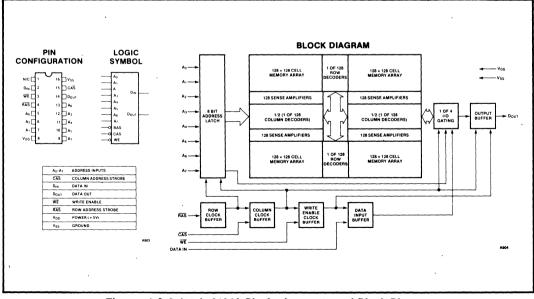

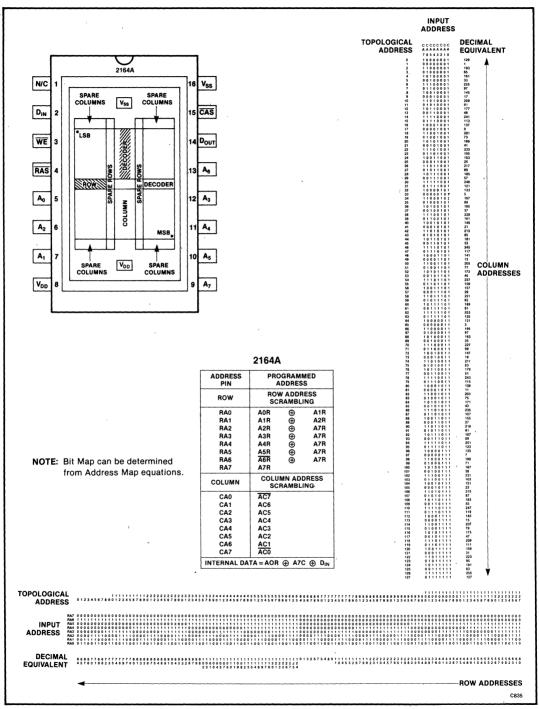

| CHAPTER 3<br>RAMs (Random Access Memories)<br>APPLICATION NOTES<br>AP-74 High Speed Memory System Design Using 2147H<br>AP-131 Intel 2164A 64K Dynamic RAM Device Description<br>AP-132 Designing Memory Systems with the 8K × 8 iRAM (2186/87)<br>AP-133 Designing Memory Systems for Microprocessors Using the Intel 2164A<br>and 2119 Dynamic RAM                                                                                                                                                                                                                                                                             | 3-22<br>3-40                                                                                             |

| and 2118 Dynamic RAMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-110<br>3-146<br>3-151<br>3-164                                                                         |

| AR-189 Keep Memory Design Simple Yet Cull Single-Bit Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-217                                                                                                    |

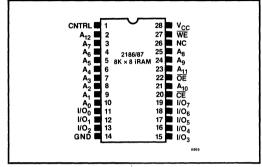

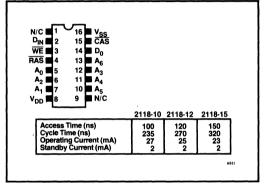

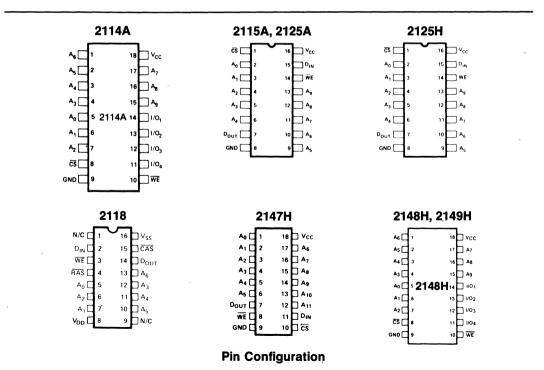

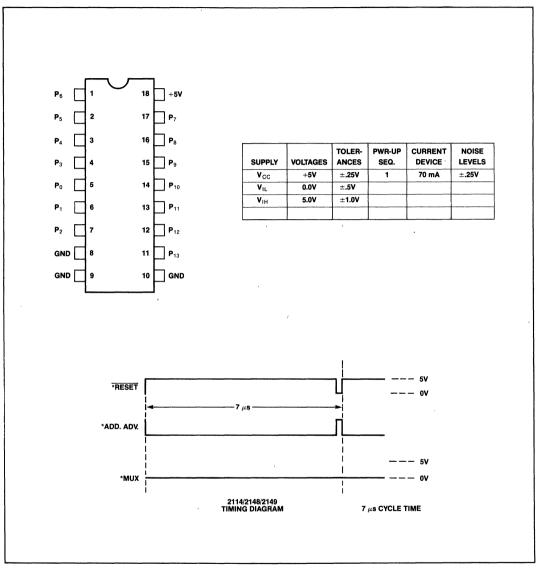

| 2114A, 1024 × 4-Bit Static RAM<br>2115A/2125A Family, High Speed 1K × 1-Bit Static RAM<br>2115H/2125H Family, High Speed 1K × 1-Bit Static RAM<br>2118 Family 16,384 × 1-Bit Dynamic RAM<br>2141, 4096 × 1-Bit Static RAM<br>2147H High Speed 4096 × 1-Bit Static RAM<br>2148H, 1024 × 4-Bit Static RAM<br>2148H, 1024 × 4-Bit Static RAM<br>2149H, 1024 × 4-Bit Static RAM<br>2164A Family 65,536 × 1-Bit Dynamic RAM<br>2186, 8192 × 8-Bit Integrated RAM<br>8203 64K Dynamic RAM Controller<br>8206 Error Detection and Correction Unit<br>8207 Advanced Dynamic RAM Controller<br>RAM Family Express Data Sheet<br>CHAPTER 4 | 3-228<br>3-233<br>3-238<br>3-249<br>3-255<br>3-259<br>3-263<br>3-267<br>3-281<br>3-288<br>3-303<br>3-322 |

| EPROMs (Erasable Programmable Read Only Memories)<br>APPLICATION NOTES<br>AP-151 The Int <sub>e</sub> ligent Programming <sup>™</sup> Algorithm Fast Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                          |

| for Intel EPROMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-1                                                                                                      |

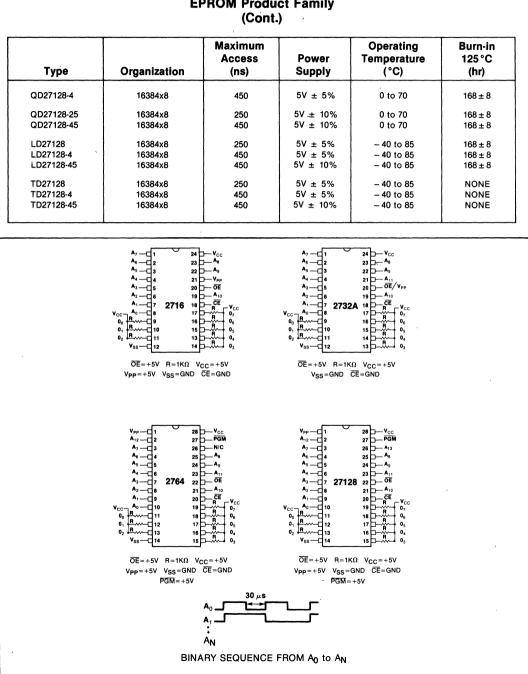

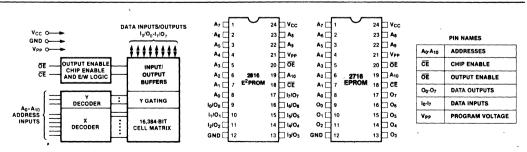

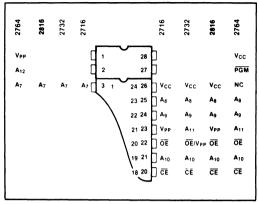

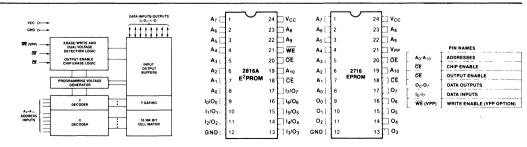

| 2716, 16K (2K x 8) UV Erasable PROM<br>2732A, 32K (4K x 8) UV Erasable PROM<br>2764, 64K (8K x 8) UV Erasable PROM<br>27128, 128K (16K x 8) UV Erasable PROM<br>27256, 256K (32K x 8) UV Erasable PROM<br>Express Data Sheet.                                                                                                                                                                                                                                                                                                                                                                                                    | 4-12<br>4-19<br>4-29<br>4-39                                                                             |

#### **CHAPTER 5**

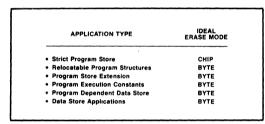

| E <sup>2</sup> PROMs (Electrically Erasable Programmable Read Only Memories)                 |       |

|----------------------------------------------------------------------------------------------|-------|

| 1982-1983 Designer's Guide to E <sup>2</sup> PROM Products                                   | 5-1   |

| APPLICATION NOTES                                                                            |       |

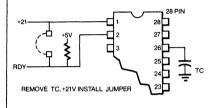

| AP-100 Reliability Aspects of a Floating Gate E <sup>2</sup> PROM                            |       |

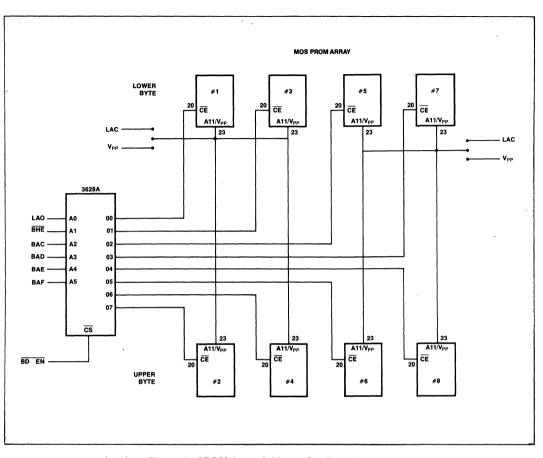

| AP-136 A MULTIBUS <sup>®</sup> -Compatible 2816 E <sup>2</sup> PROM Memory Board Description |       |

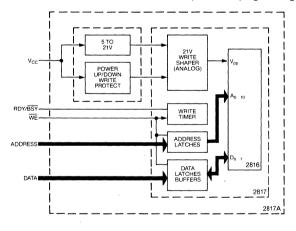

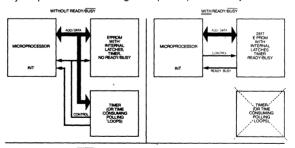

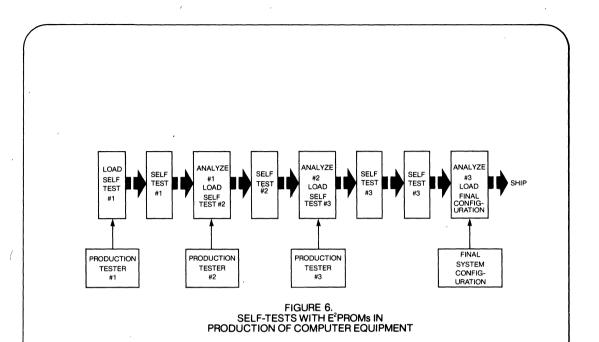

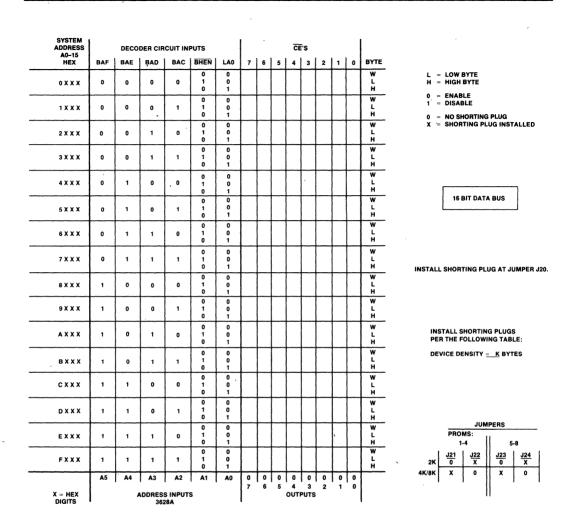

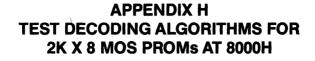

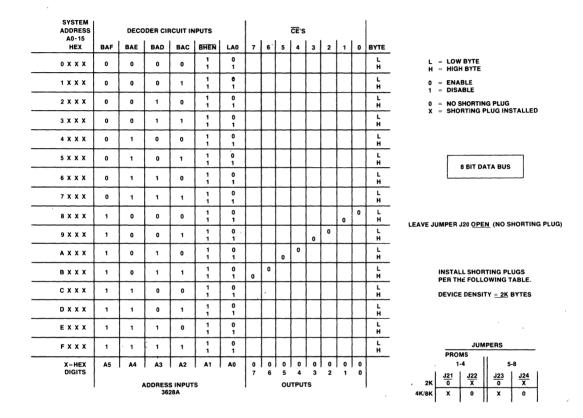

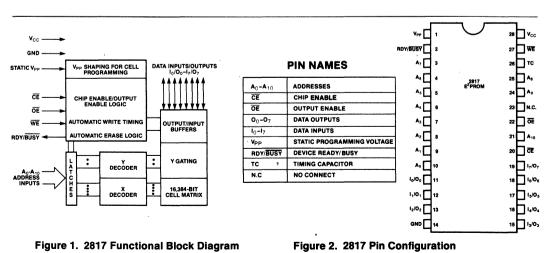

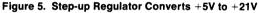

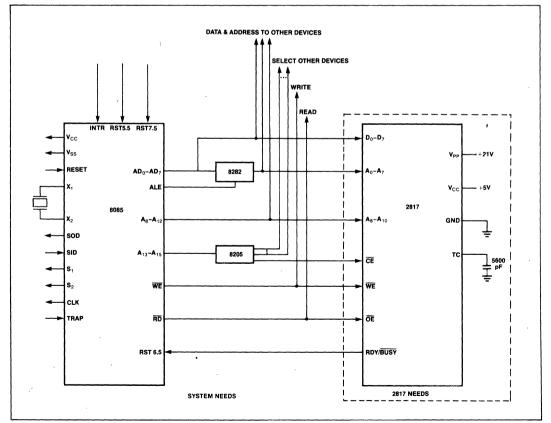

| AP-148 2817 Using the 2817 Intelligent E <sup>2</sup> PROM                                   | 5-67  |

| ARTICLE REPRINTS                                                                             |       |

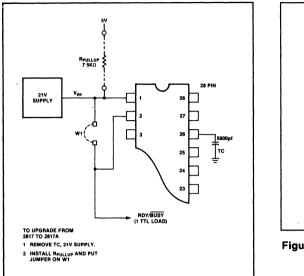

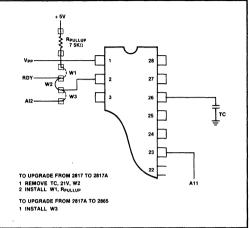

| AR-119 16-K EE-PROM Relies On Tunneling For Byte-Erasable Program Storage                    |       |

| AR-174 Hardware a Software Download Techniques with 2816                                     |       |

| AR-230 ROMs That Erase One Byte at a Time                                                    | 5-85  |

| DATA SHEETS                                                                                  |       |

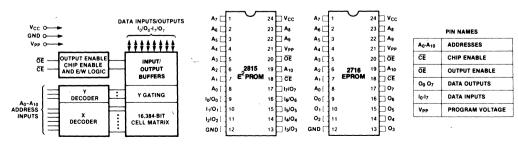

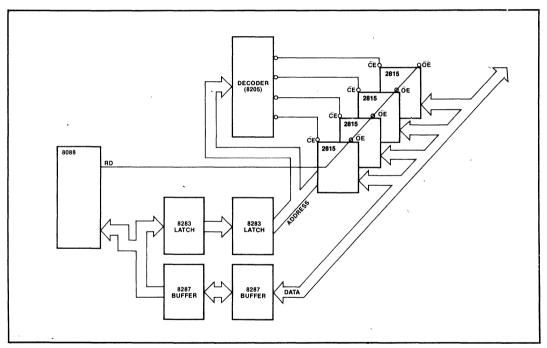

| 2815, 16K (2K x 8) Electrically Erasable PROM                                                | 5-90  |

| 2816, 16K (2K x 8) Electrically Erasable PROM                                                | 5-103 |

| 2816A, 16K (2K x 8) Electrically Erasable PROM                                               |       |

| 2817, 16K (2K x 8) Electrically Erasable PROM                                                | 5-128 |

| CHAPTER 6                                                                                    |       |

| Bubble Memory                                                                                |       |

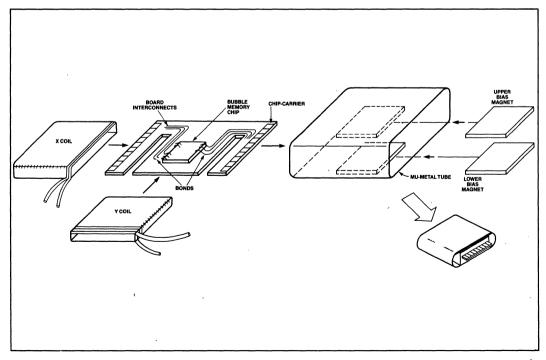

| Magnetic Bubble Primer                                                                       | 6-1   |

| APPLICATION NOTES                                                                            | 01    |

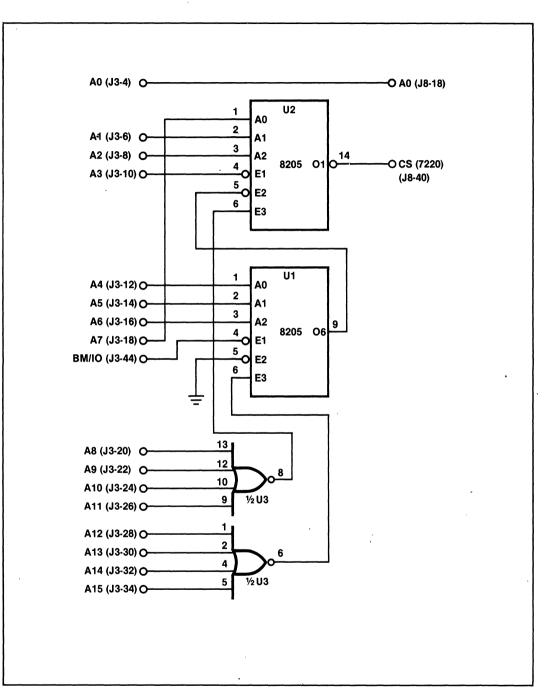

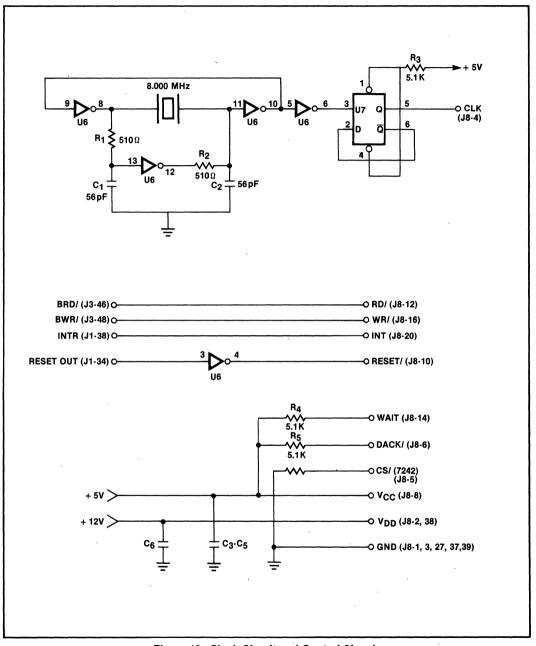

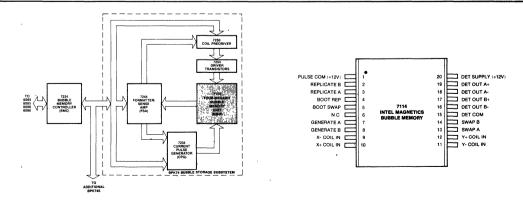

| AP-119 Microprocessor Interface for the BPK 72                                               | 6-15  |

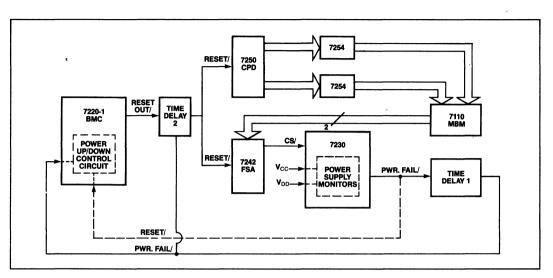

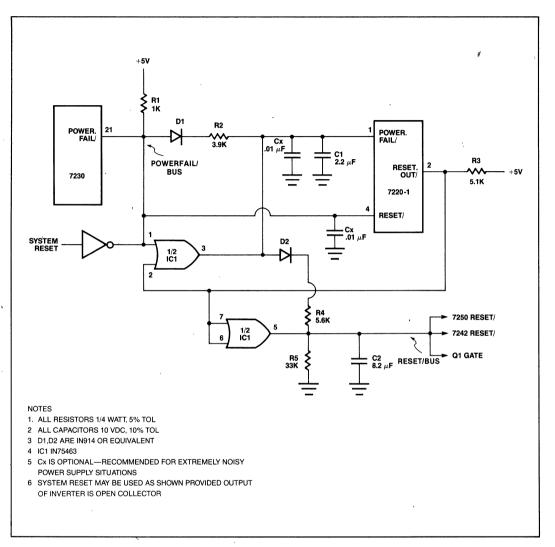

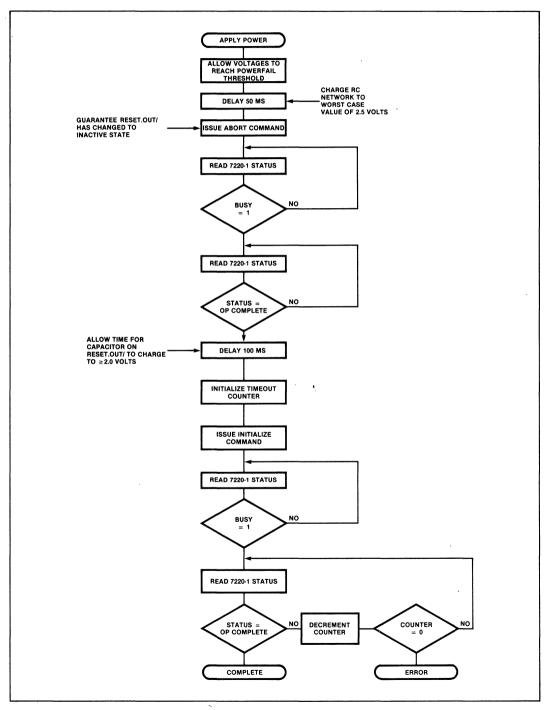

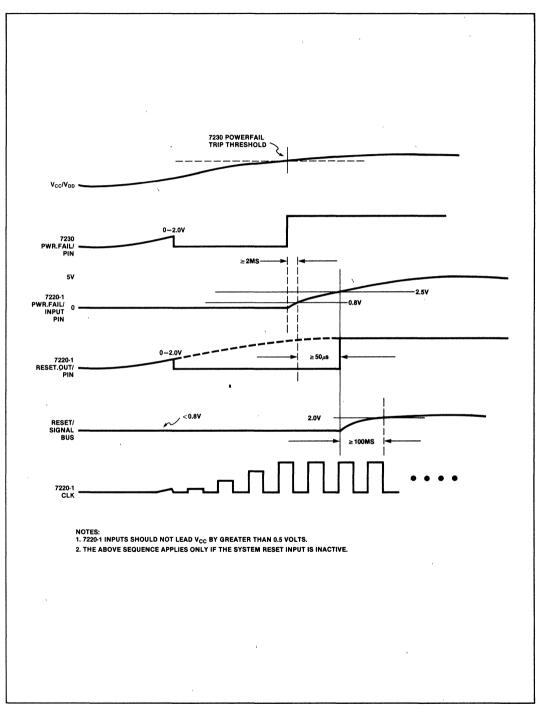

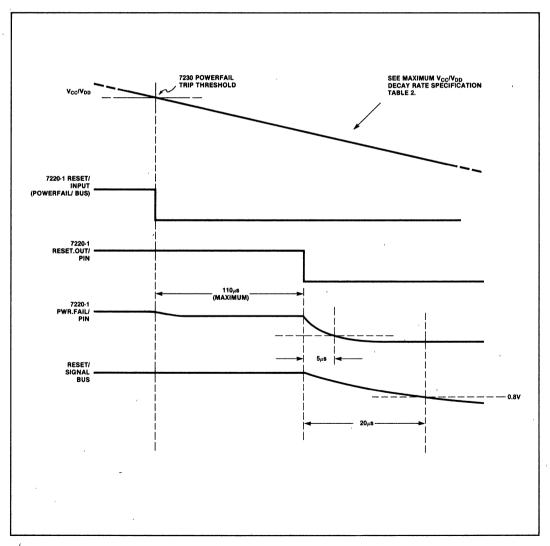

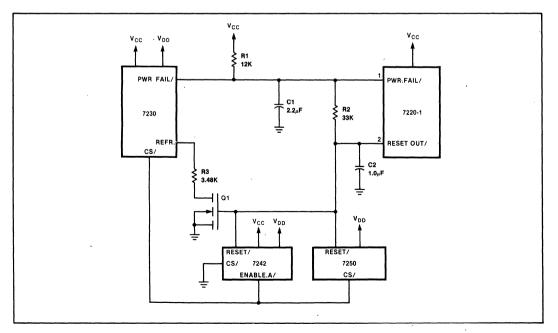

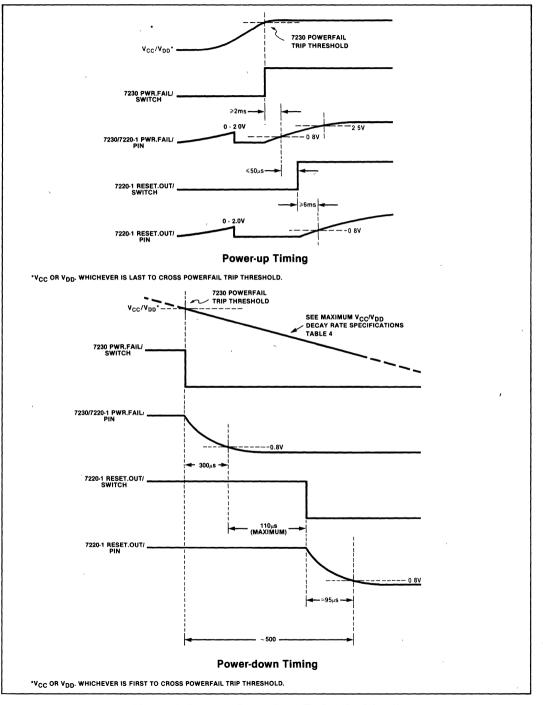

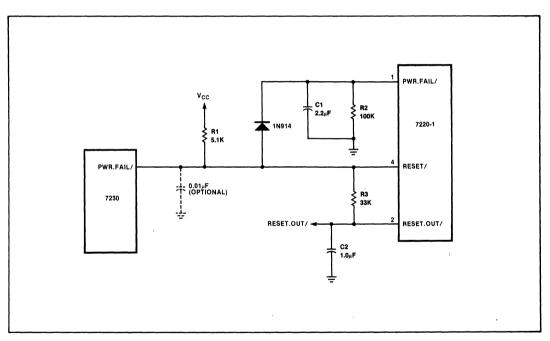

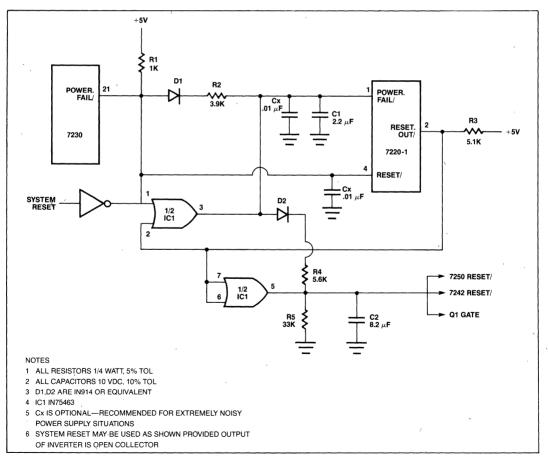

| AP-127 Powerfail Considerations for Magnetic Bubble Memories                                 |       |

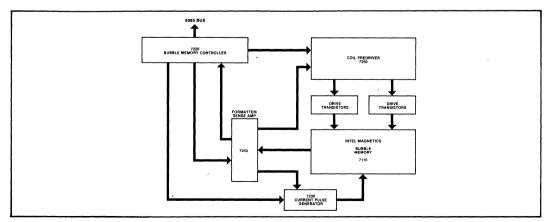

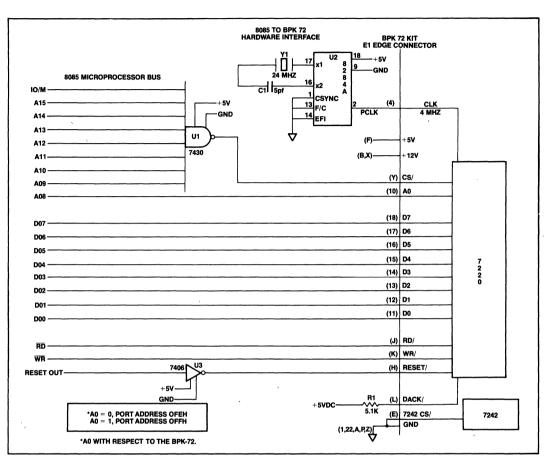

| AP-150 8085 to BPK 72 Interface                                                              |       |

| ARTICLE REPRINTS                                                                             | 0.00  |

| AR-243 Thin-film Detectors X-ray Lithography Deliver 4-Mbit Bubble Chip                      | 6-158 |

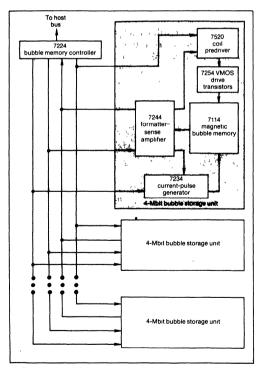

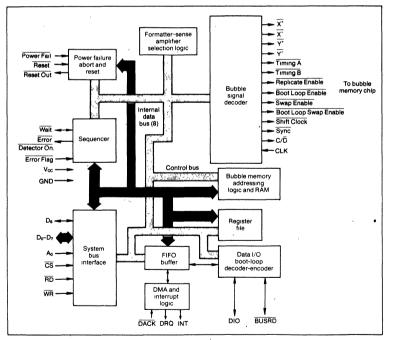

| AR-250 Bubble Chip Packs 4 Mbits Into 1-Mbit Space                                           |       |

| DATA SHEETS                                                                                  |       |

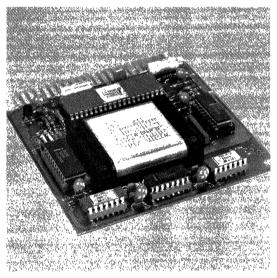

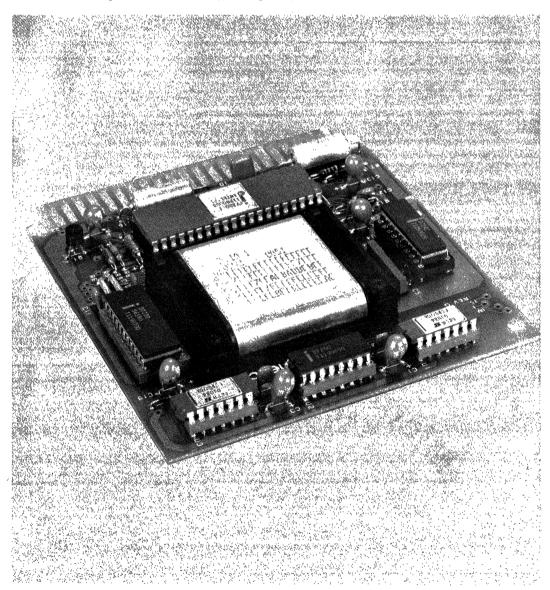

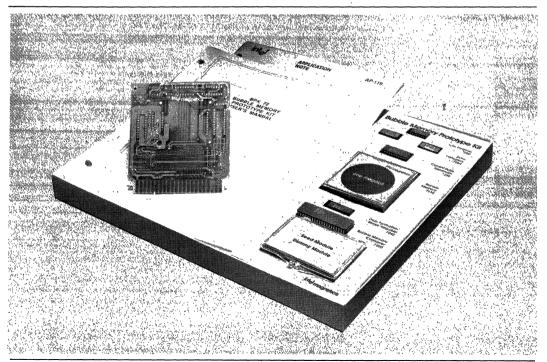

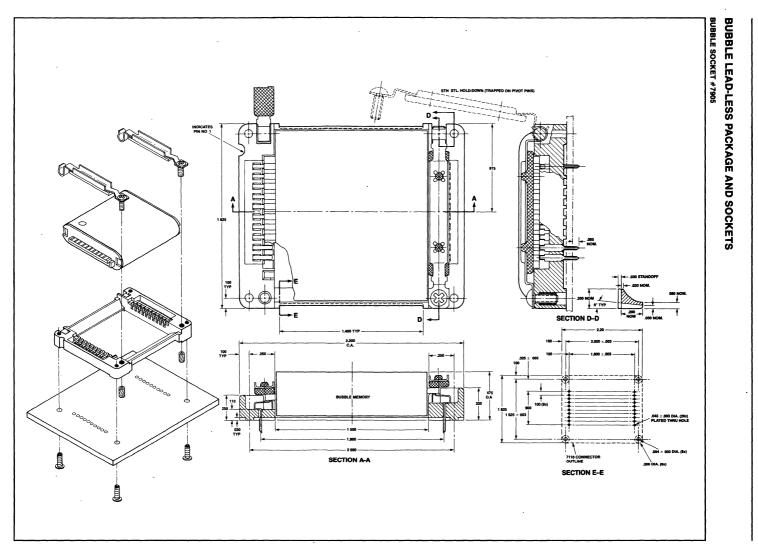

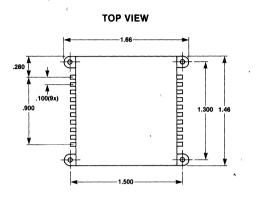

| BPK 72 Bubble Storage Prototype Kit                                                          | 6-169 |

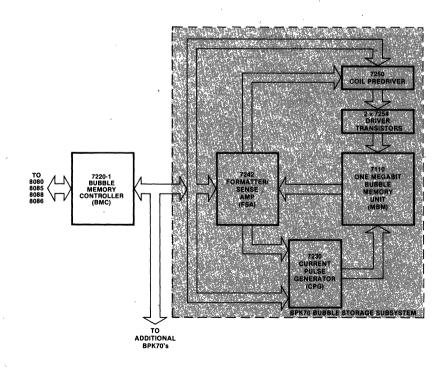

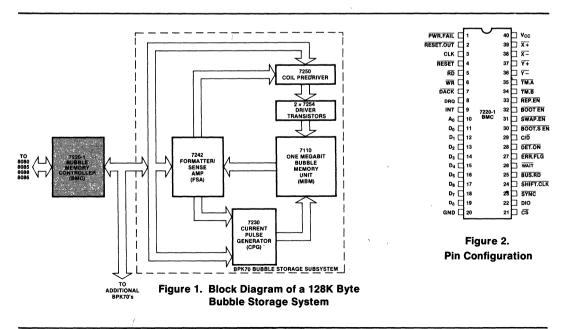

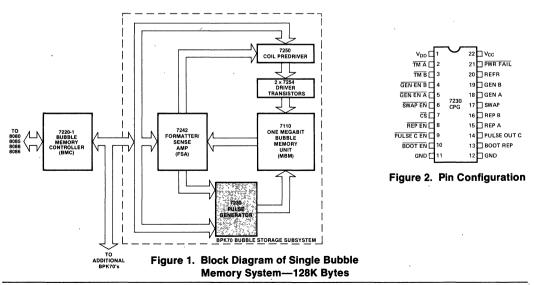

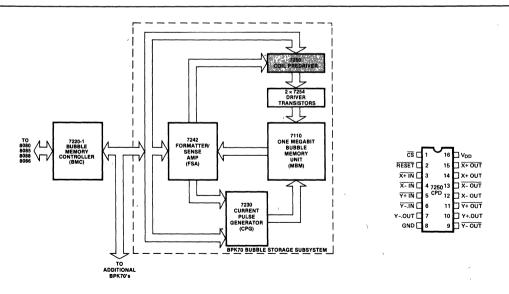

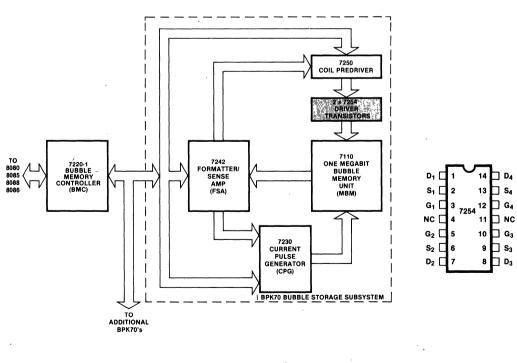

| BPK 70 1 Megabit Bubble Storage Subsystem                                                    |       |

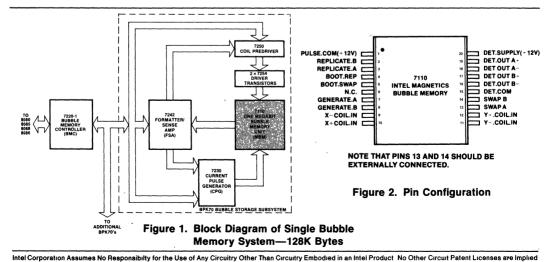

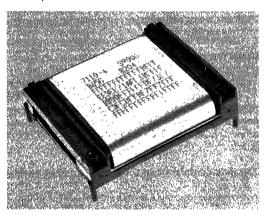

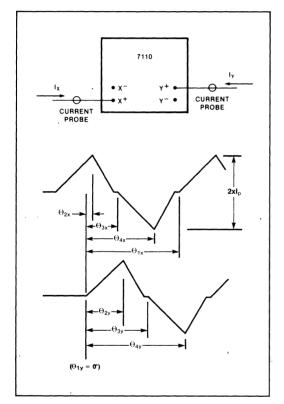

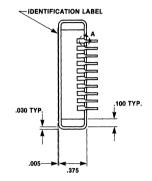

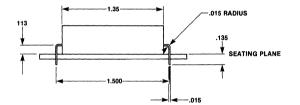

| 7110, 1 Megabit Bubble Memory Family                                                         |       |

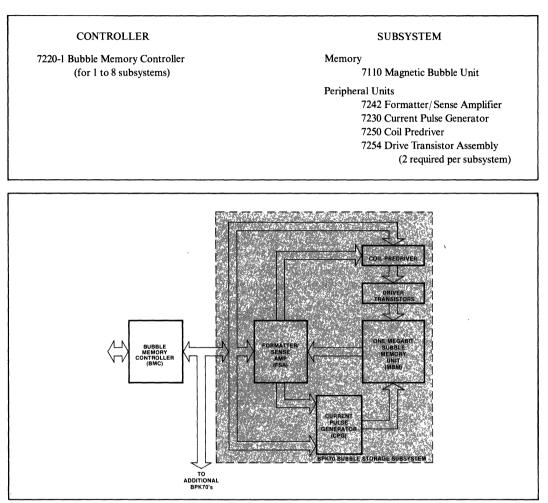

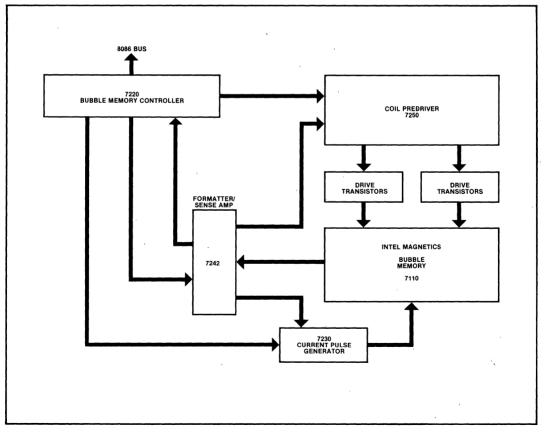

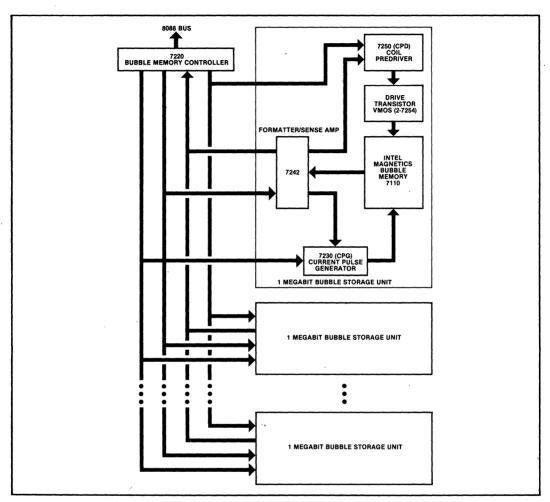

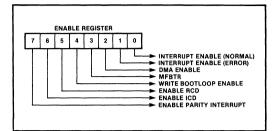

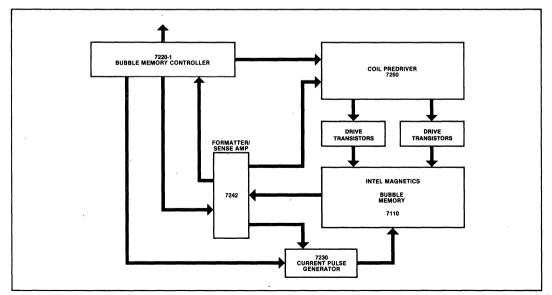

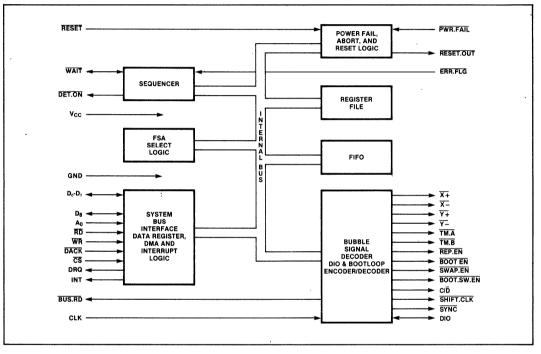

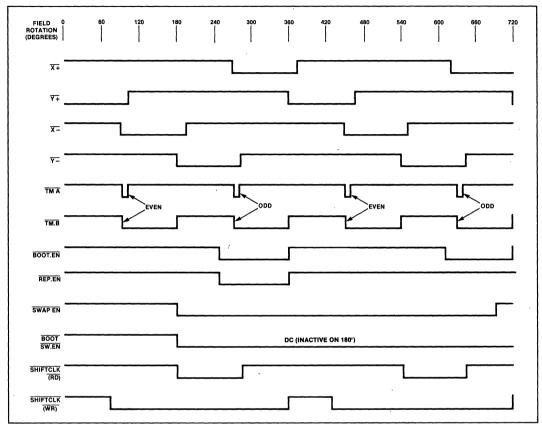

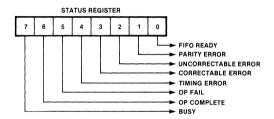

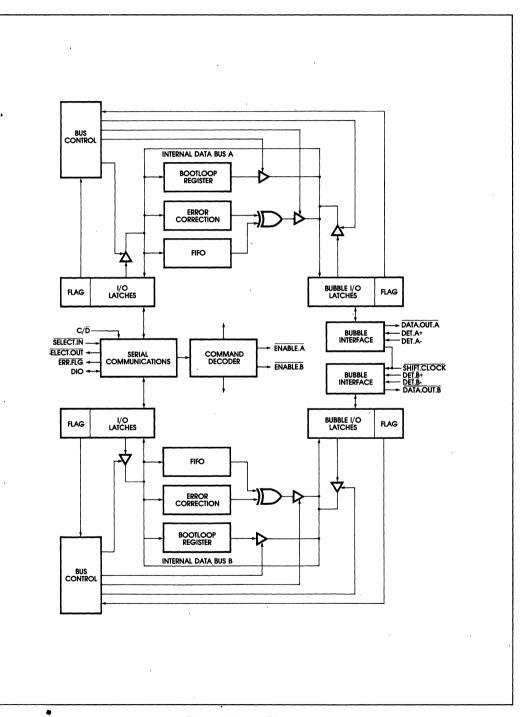

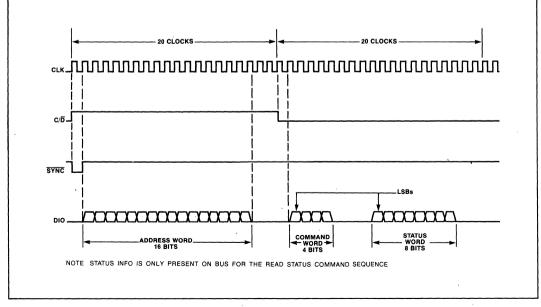

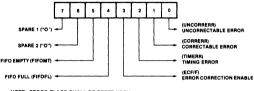

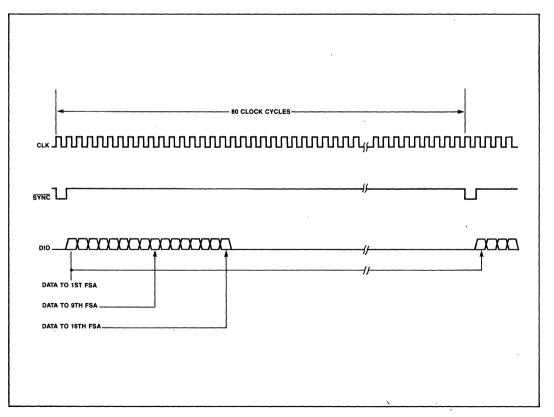

| 7220-1, Bubble Memory Controller                                                             | 6-184 |

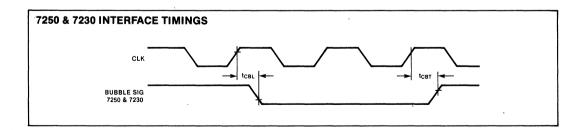

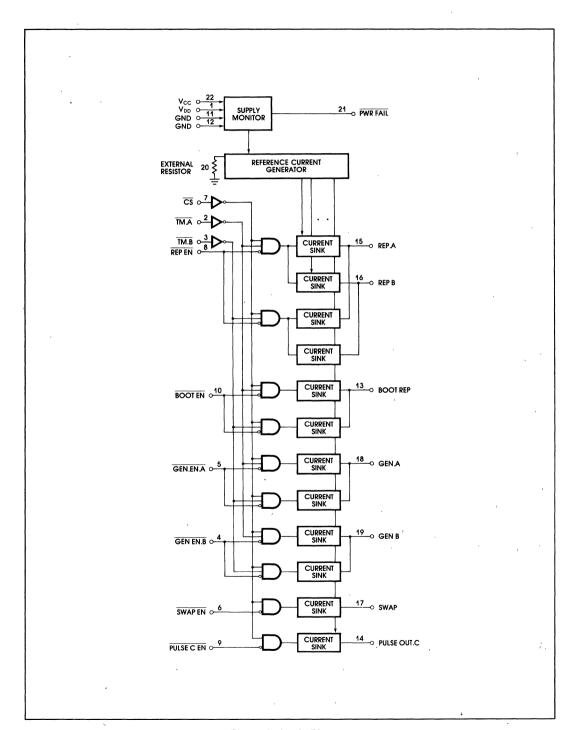

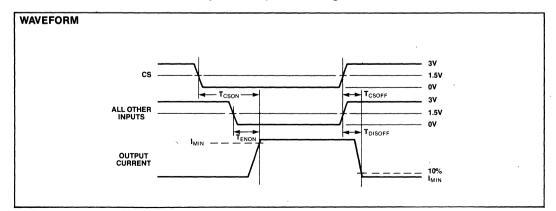

| 7230, Current Pulse Generator for Bubble Memories                                            | 6-199 |

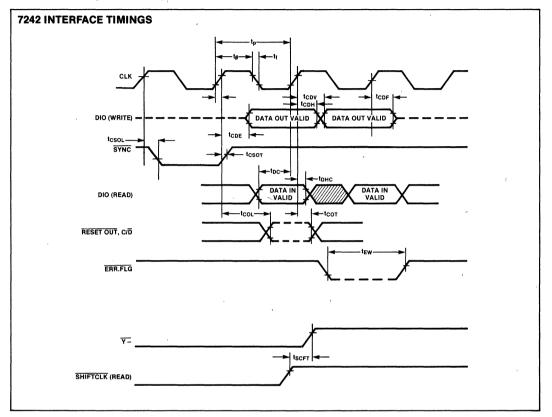

| 7242, Dual Formatter/Sense Amplifier for Bubble Memories                                     | 6-204 |

| 7250, Coil Pre-Driver for Bubble Memories                                                    |       |

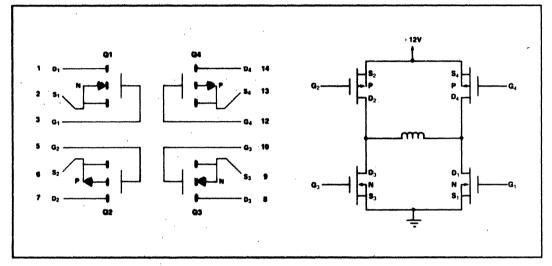

| 7254, Quad VMOS Drive Transistors for Bubble Memories                                        | 6-220 |

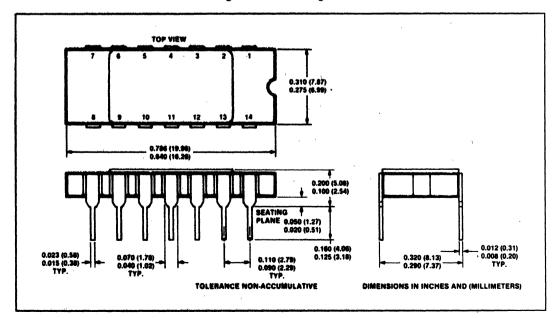

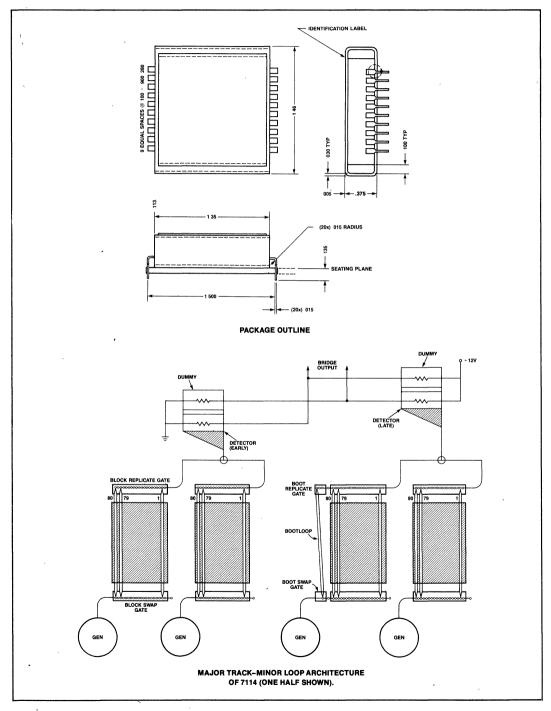

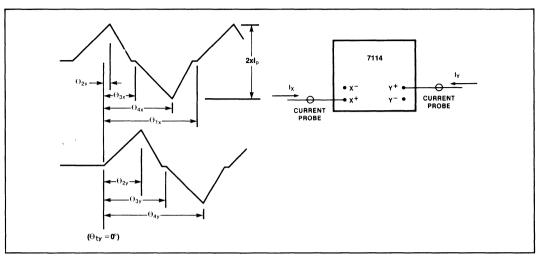

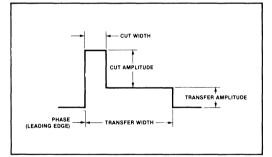

| 7114, 4-Megabit Bubble Memory                                                                | 6-223 |

| CHAPTER 7                                                                                    |       |

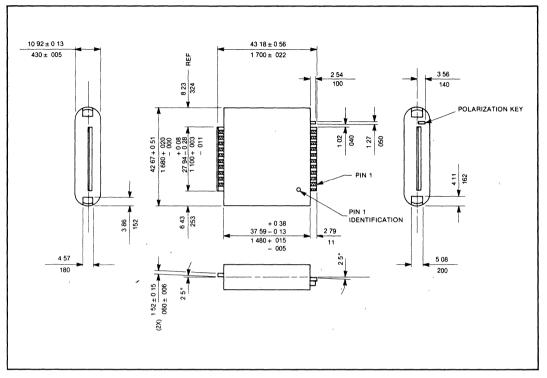

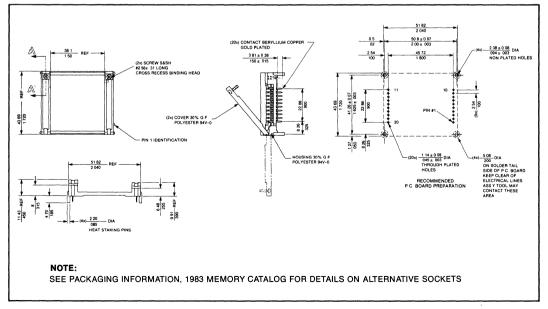

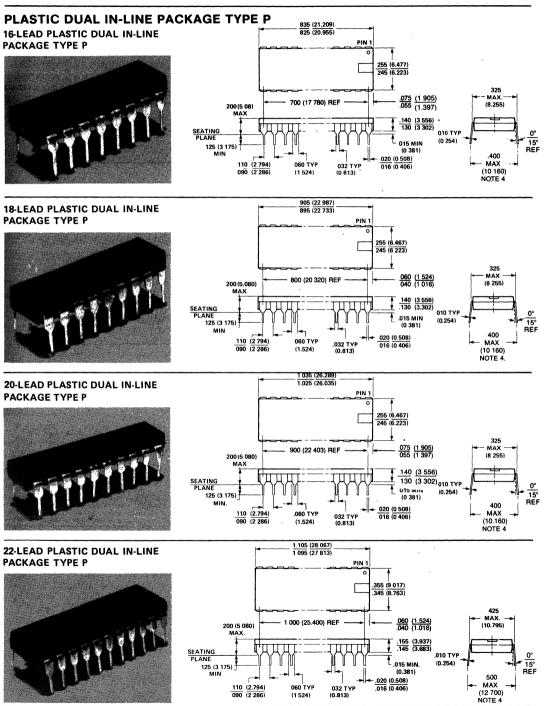

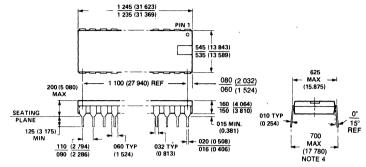

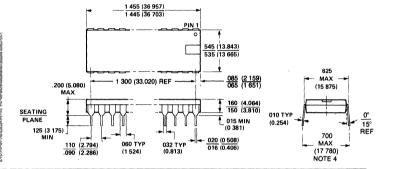

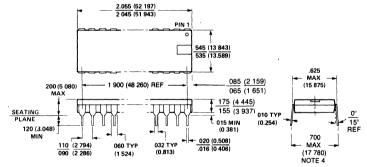

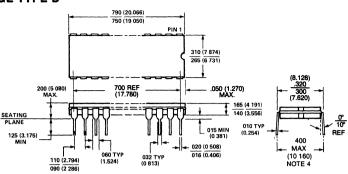

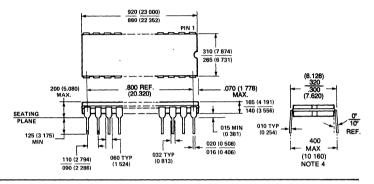

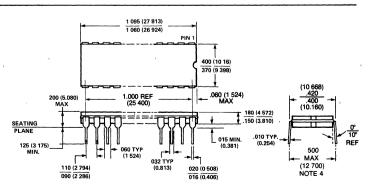

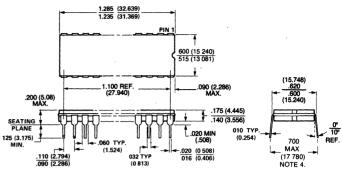

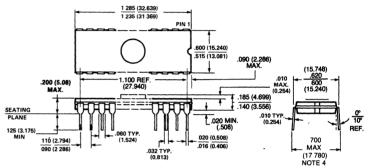

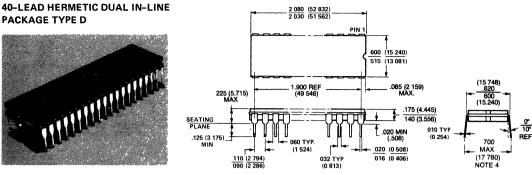

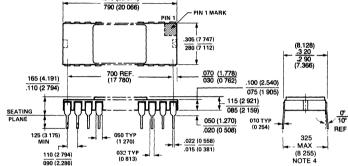

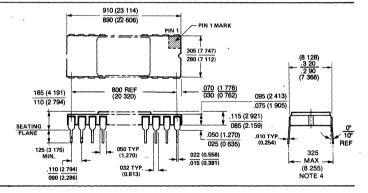

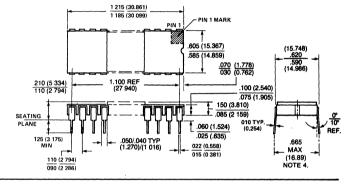

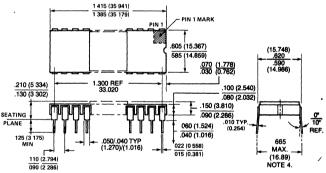

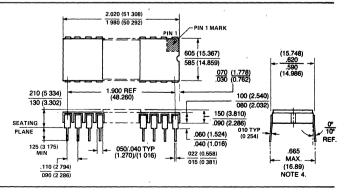

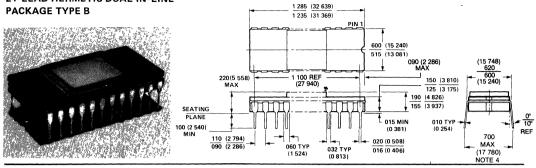

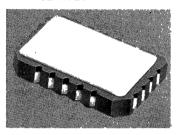

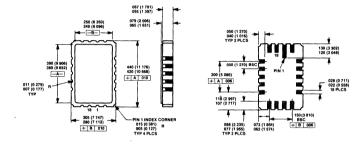

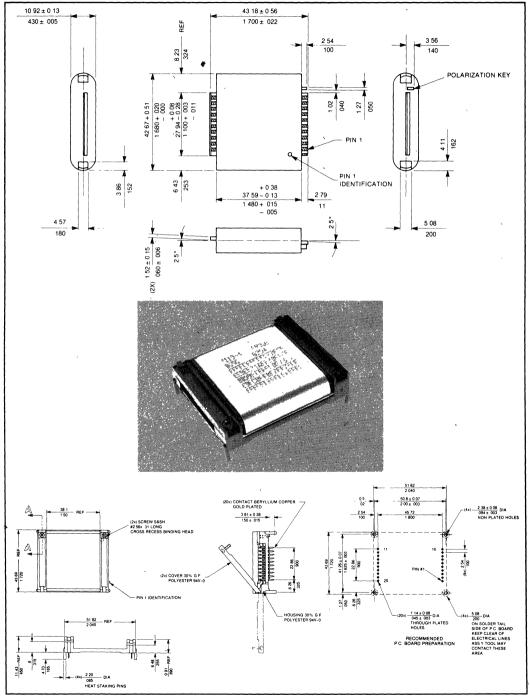

| ackaging Information | 7- |

|----------------------|----|

|----------------------|----|

### Alphanumeric Index

| 2114, 1024 x 4-Bit Static RAM                              | 4 |

|------------------------------------------------------------|---|

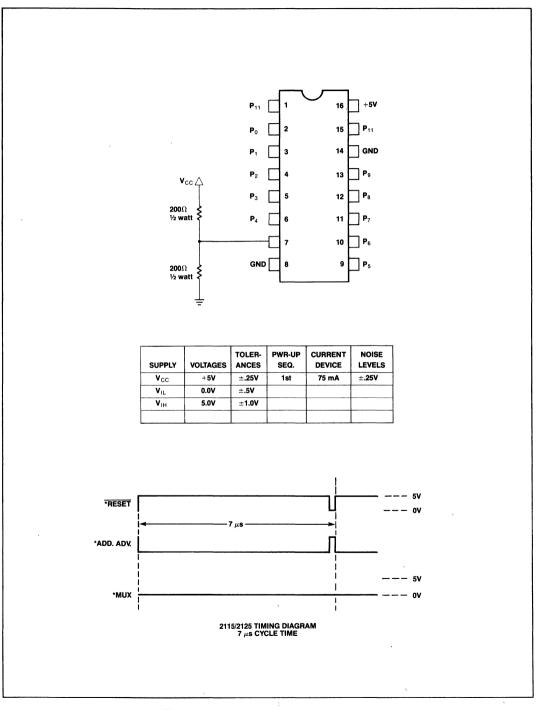

| 2115A/2125A Family, High Speed 1K x 1-Bit Static RAM       | 8 |

| 2115H/2125H Family, High Speed 1K x 1-Bit Static RAM       | 3 |

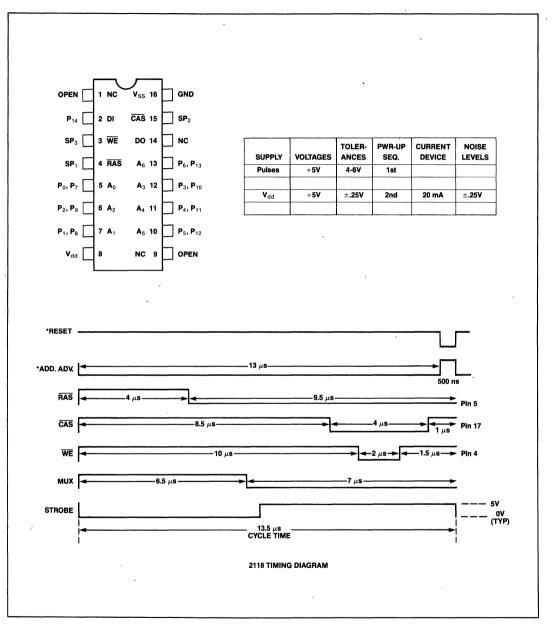

| 2118 Family 16,384 x 1-Bit Dynamic Ram                     |   |

| 2141, 4096 x 1-Bit Static RAM                              |   |

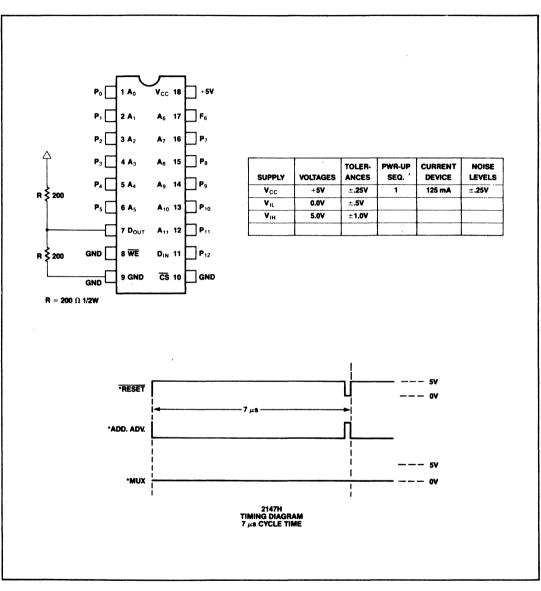

| 2147H High Speed 4096 x 1-Bit Static RAM                   | 5 |

| 2148H High Speed 1024 x 4-Bit Static RAM                   |   |

| 2149H High Speed 1024 x 4-Bit Static RAM                   | 3 |

| 2164A 65,536 x 1-Bit Dynamic RAM                           |   |

| 2186, 8192 x 8-Bit Integrated RAM                          |   |

| 27128, 128K (16K x 8) UV Erasable PROM                     |   |

| 2716, 16K (2K x 8) UV Erasable PROM                        | 5 |

| 27256, 256K (32K x 8) UV Erasable PROM                     |   |

| 2732A, 32K (4K x 8) UV Erasable PROM                       |   |

| 2764, 64K (8K x 8) UV Erasable PROM                        | 9 |

| 2815, 16K (2K x 8) Electrically Erasable PROM              | 0 |

| 2816, 16K (2K x 8) Electrically Erasable PROM              | 3 |

| 2816A, 16K (2K x 8) Electrically Erasable PROM 5-116       | 6 |

| 2817, 16K (4K x 8) Electrically Erasable PROM5-67,5-128    |   |

| 7110, 1 Megabit Bubble Memory Family6-176                  |   |

| 7114, 4-Megabit Bubble Memory                              | 3 |

| 7220-1, Bubble Memory Controller                           |   |

| 7230, Current Pulse Generator for Bubble Memories6-199     |   |

| 7242, Dual Formatter/Sense Amplifier for Bubble Memories   |   |

| 7250, Coil Pre-driver for Bubble Memories                  |   |

| 7254, Quad VMOS Drive Transistors for Bubble Memories6-220 |   |

| 8085 Microprocessor                                        |   |

| 8202A Dynamic RAM Controller                               |   |

| 8203 64K Dynamic RAM Controller                            |   |

| 8206 Error Detection and Correction Unit                   |   |

| 8207 Advanced Dynamic RAM Controller                       |   |

| BPK 70, 1 Megabit Bubble Storage Subsystem                 |   |

| BPK 72, Bubble Storage Prototype Kit6-15, 6-16             |   |

| iAPX-86 16-Bit HMOS Microprocessor                         |   |

| iAPX-88 8-Bit HMOS Microprocessor                          | υ |

۷

### PREFACE

This handbook has been prepared to provide a comprehensive grouping of technical literature covering Intel's memory products, with special emphasis on microprocessor applications. In addition, a brief summary of current memory technologies and basic segmentation of product lines is provided.

# Memory Overview

### CHAPTER I: MEMORY OVERVIEW

Joe Altnether

#### MEMORY BACKGROUND AND DEVELOPMENT

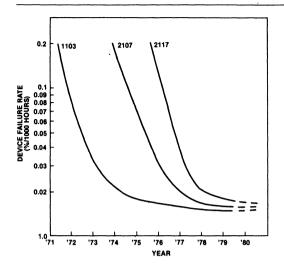

Only ten years ago MOS LSI memories were little more than laboratory curiosities. Any engineer brave enough to design with semiconductor memories had a simple choice of which memory type to use. The 2102 Static RAM for ease of use or the 1103 Dynamic RAM for low power were the only two devices available. Since then, the memory market has come a long way, the types of memory devices have proliferated, and more than 3,000 different memory devices are now available. Consequently, the designer has a lot to choose from but the choice is more difficult, and therefore, effective memory selection is based on matching memory characteristics to the application.

Memory devices can be divided into two main categories: volatile and non-volatile. Volatile memories retain their data only as long as power is applied. In a great many applications this limitation presents no problem. The generic term random access memory (RAM) has come to be almost synonymous with a volatile memory in which there is a constant rewriting of stored data.

In other situations, however, it is imperative that a nonvolatile device be used because it retains its data whether or not power is applied. An example of this requirement would be retaining data during a power failure. (Tape and disk storage are also non-volatile memories but are not included within the scope of this book which confines itself to solid-state technologies in an IC form factor.)

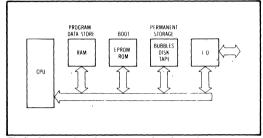

Thus, when considering memory devices, it's helpful to see how the memory in computer systems is segmented by applications and then look at the state-of-the-art in these cases.

#### **Read/Write Memory**

First examine read/write memory (RAM), which permits the access of stored memory (reading) and the ability to alter the stored data (writing).

Before the advent of solid-state read/write memory, active data (data being processed) was stored and retrieved from non-volatile core memory (a magneticstorage technology). Solid-state RAMs solved the size and power consumption problems associated with core, but added the element of volatility. Because RAMs lose their memory when you turn off their power, you must leave systems on all the time, add battery backup or store important data on a non-volatile medium before the power goes down.

Despite their volatility, RAMs have become very popular, and an industry was born that primarily fed computer systems' insatiable appetites for higher bit capacities and faster access speeds.

#### **RAM Types**

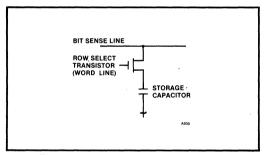

Two basic RAM types have evolved since 1970. Dynamic RAMs are noted for high capacity, moderate speeds and low power consumption. Their memory cells are basically charge-storage capacitors with driver transistors. The presence or absence of charge in a capacitor is interpreted by the RAM's sense line as a logical 1 or 0. Because of the charge's natural tendency to distribute itself into a lower energy-state configuration, however, dynamic RAMs require periodic charge refreshing to maintain data storage.

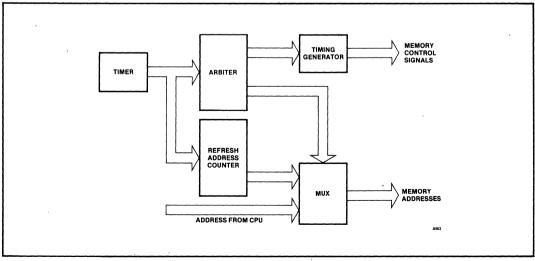

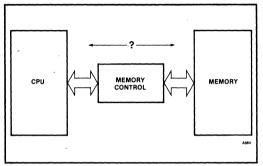

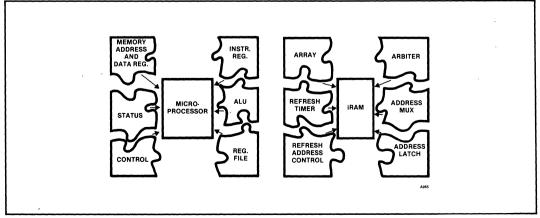

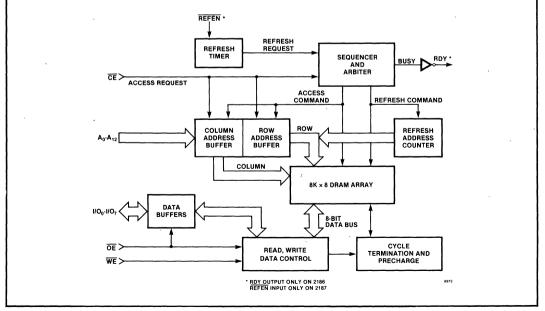

Traditionally, this requirement has meant that system designers had to implement added circuitry to handle dynamic RAM subsystem refresh. And at certain times, refresh procedures made the RAM unavailable for writing or reading; the memory's control circuitry had to arbitrate access. However, there are now two available alternatives that largely offset this disadvantage. For relatively small memories in microprocessor environments, the integrated RAM or iRAM provides all of the complex refresh circuitry on chip, thus, greatly simplifying the system design. For larger storage requirements, LSI dynamic memory controllers reduce the refresh requirement to a minimal design by offering a monolithic controller solution.

Where users are less concerned with space and cost than with speed and reduced complexity, the second RAM type — static RAMs — generally prove best. Unlike their dynamic counterparts, static RAMs store ones and zeros using traditional flip-flop logic-gate configurations. They are faster and require no refresh. A user simply addresses the static RAM, and after a very brief delay, obtains the bit stored in that location. Static devices are also simpler to design with than dynamic RAMs, but the static cell's complexity puts these nonvolatile chips far behind dynamics in bit capacity per square mil of silicon.

#### The iRAM

There is a way, however, to gain the static RAM's design-in simplicity but with the dynamic RAM's higher

capacity and other advantages. An integrated RAM or iRAM integrates a dynamic RAM and its control and refresh circuitry on one substrate, creating a chip that has dynamic RAM density characteristics, but looks like a static RAM to users. You simply address it and collect your data without worrying about refresh and arbitration.

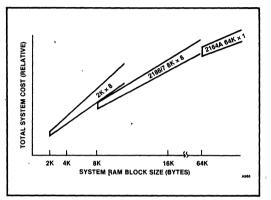

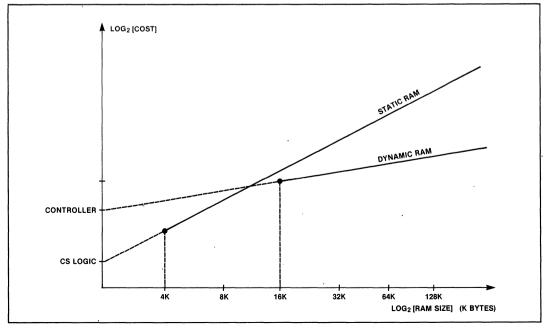

Before iRAM's introduction, users who built memory blocks smaller than 8K bytes typically used static RAMs because the device's higher price was offset by the support-circuit simplicity. On the other hand, users building blocks larger than 64K bytes usually opted for dynamic RAMs because density and power considerations began to take precedence over circuit complexity issues.

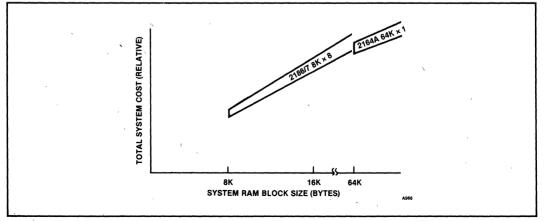

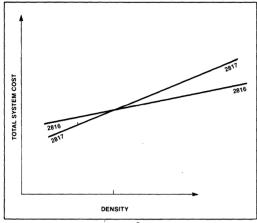

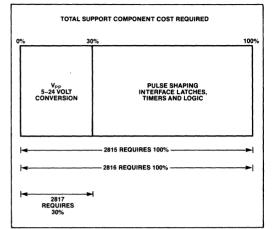

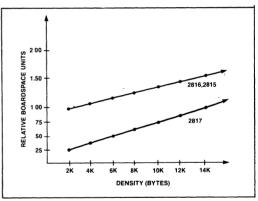

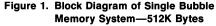

For the application area between these two limits, decisions had to depend on less straightforward tradeoffs. But iRAMs could meet this middle area's needs (See Figure 1).

#### **Read-Only Memory**

Another memory class, read-only memory (ROM), is similar to RAM in that a computer addresses it and then retrieves data stored at that address. However, ROM includes no mechanism for altering the data stored at that address — hence, the term read only.

ROM is basically used for storing information that isn't subject to change — at least not frequently. Unlike RAM, when system power goes down, ROM retains its contents.

ROM devices became very popular with the advent of microprocessors. Most early microprocessor applications were dedicated systems; the system's program was fixed and stored in ROM. Manipulated data could vary and was therefore stored in RAM. This application split caused ROM to be commonly called program storage, and RAM, data storage. The first ROMs contained cell arrays in which the sequence of ones and zeros was established by a metalization interconnect mask step during fabrication. Thus, users had to supply a ROM vendor with an interconnect program so the vendor could complete the mask and build the ROMs. Set-up charges were quite high — in fact, even prohibitive unless users planned for large volumes of the same ROM.

To offset this high set-up charge, manufacturers developed a user-programmable ROM (or PROM). The first such devices used fusible links that could be melted or "burned" with a special programmer system.

Once burned, a PROM was just like a ROM. If the burn program was faulty, the chip had to be discarded. But, PROMs furnished a more cost-effective way to develop program memory or firmware for low-volume purposes than did ROMs.

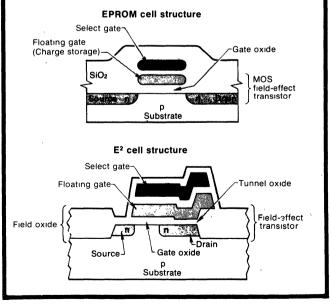

As one alternative to fusable-link programming, Intel pioneered an erasable MOS-technology PROM (termed an EPROM) that used charge-storage programming. It came in a standard ceramic DIP package but had a window that permitted die exposure to light. When the chip was exposed to ultraviolet light, high energy photons could collide with the EPROM's electrons and scatter them at random, thus erasing the memory.

The EPROM was obviously not intended for use in read/write applications, but it proved very useful in research and development for prototypes, where the need to alter the program several times is quite common. Indeed, the EPROM market consisted almost exclusively of development labs. As the fabrication process became mature, however, and volumes increased, EPROM's lower prices made them attractive even for medium-volume production-system applications.

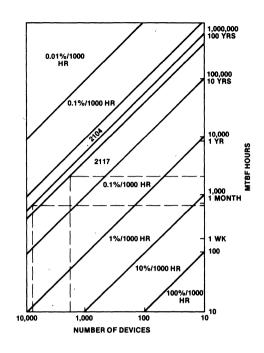

Figure 1. System Cost Graph

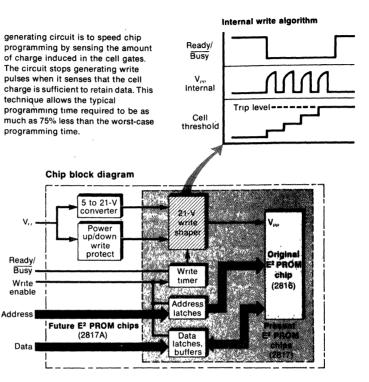

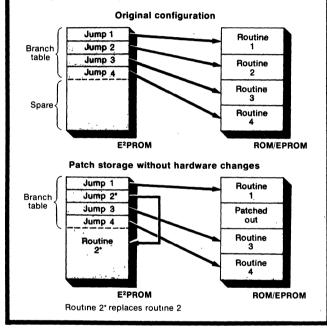

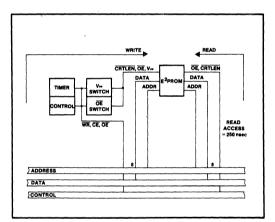

Another ROM technology advance occurred in 1980 with the introduction of Intel's 2816 - a 16K ROM that's user programmable and electrically erasable. Thus, instead of removing it from its host system and placing it under ultraviolet light to erase its program, the 2816 can be reprogrammed in its socket. Moreover, single bits or entire bytes can be erased in one operation instead of erasing the entire chip.

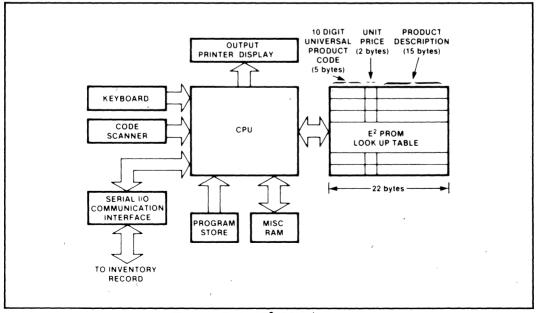

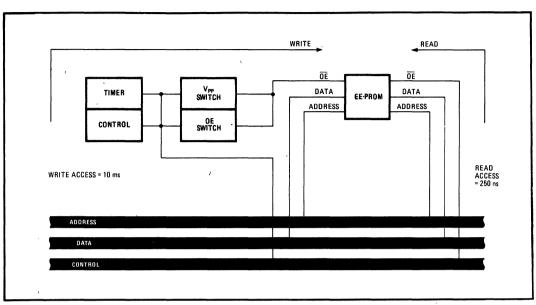

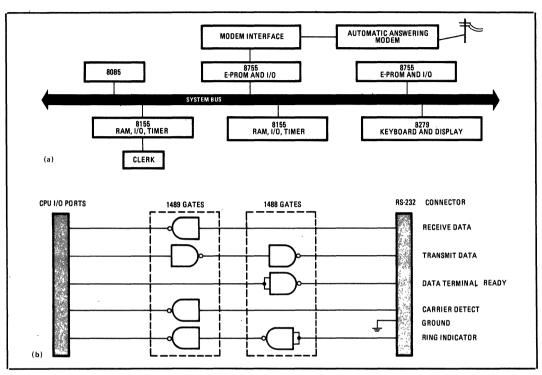

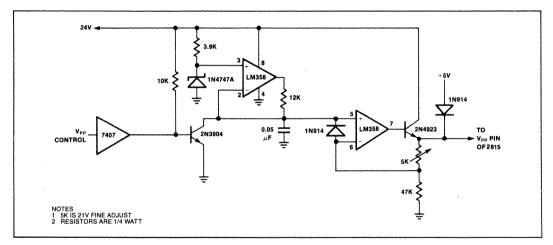

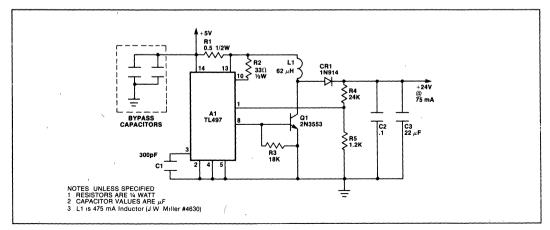

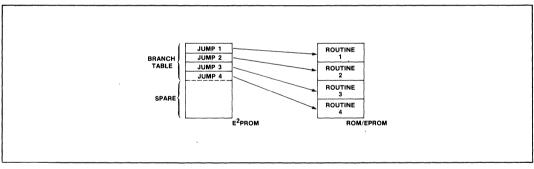

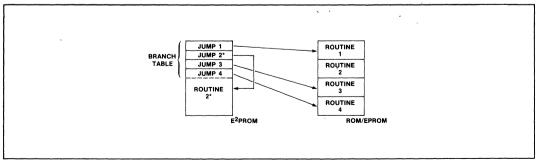

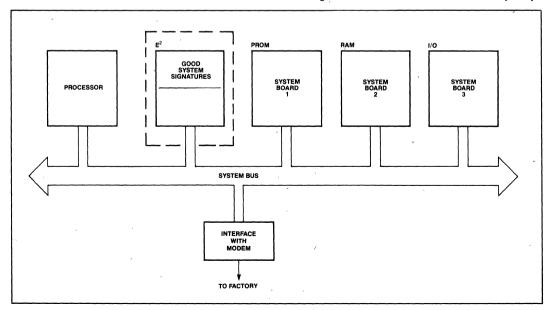

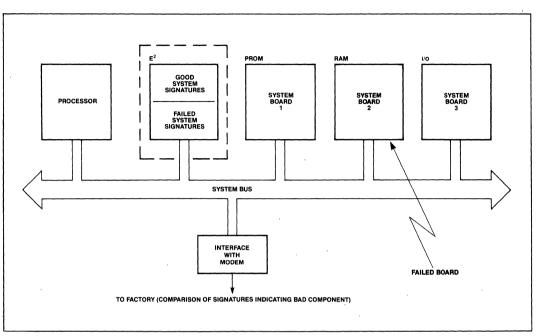

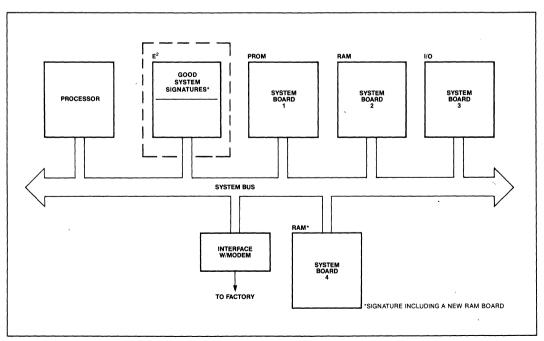

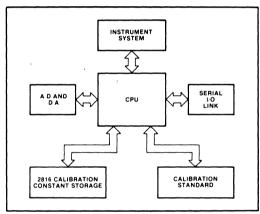

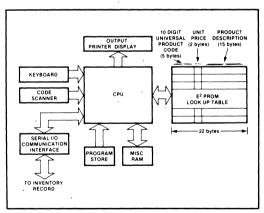

Such  $E^2$ PROMs (for electrically erasable programmable ROM) are opening up new applications. In pointof-sale terminals, for example, each terminal connects to a central computer but each can also handle moderate amounts of local processing. An  $E^2$ PROM can store discount information to be automatically figured in during a sales transaction. Should the discount change, the central computer can update each terminal via telephone lines by reprogramming that portion of the  $E^2$ PROM (Figure 2).

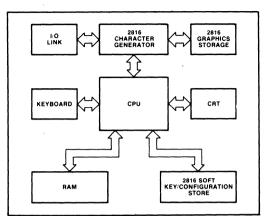

In digital instrumentation, an instrument could become self-calibrating using an E<sup>2</sup>PROM. Should the instrument's calibration drift outside specification limits, the system could employ a built-in diagnostic to reprogram a parametric setting in an E<sup>2</sup>PROM and bring the calibration back within limits.

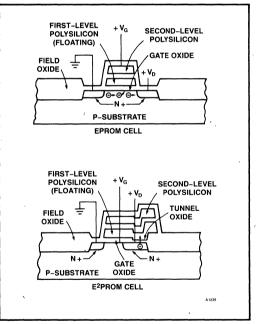

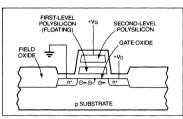

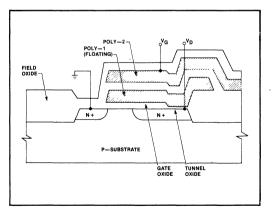

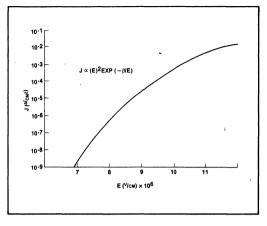

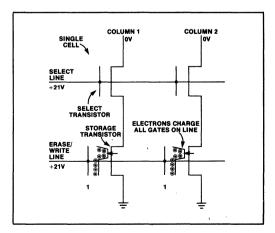

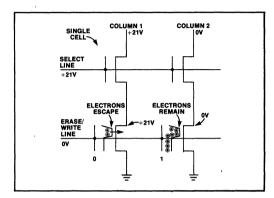

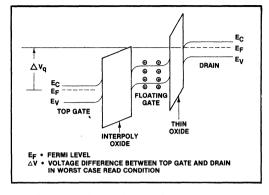

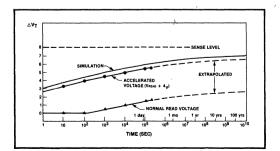

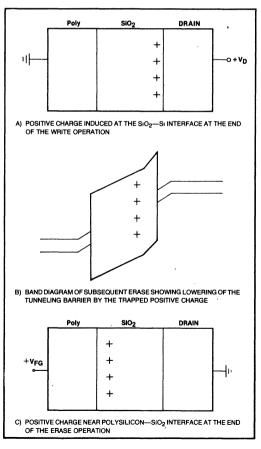

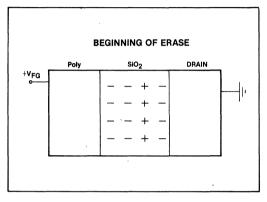

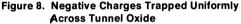

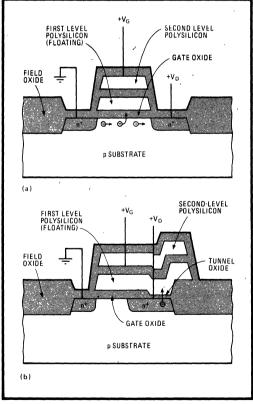

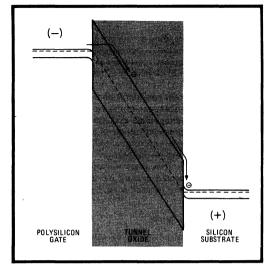

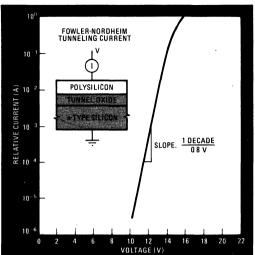

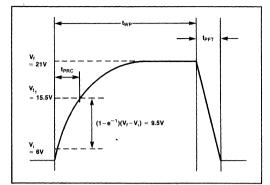

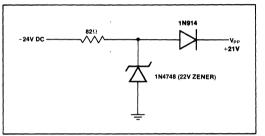

E<sup>2</sup>PROMs contain floating-gate tunnel-oxide (Flotox) cell structure. Based on electron tunneling through a thin (less than 200 Angstroms) layer of silicon dioxide, these cells permit writing and erasing with 21 Volt pulses.

During a read operation, the chips use conventional +5 Volt power.

#### **Bubble Memory**

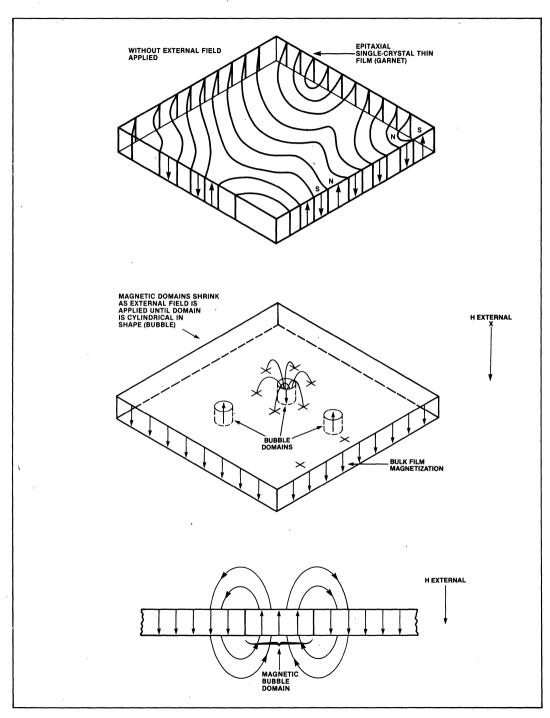

A very different device type, bubble memory was once considered the technology that would obsolete RAM components. This view failed to consider the inherent features and benefits of each technology. There is no question that RAMs have staked out a read/write applications area that is vast. Nevertheless, their volatility presents severe problems in more than a few applications. Remote systems, for example, might be unable to accept a memory that is subject to being wiped out should a power failure occur.

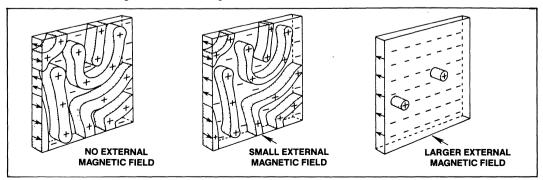

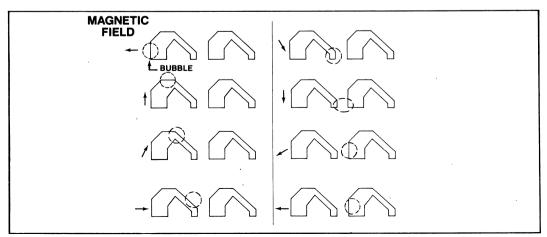

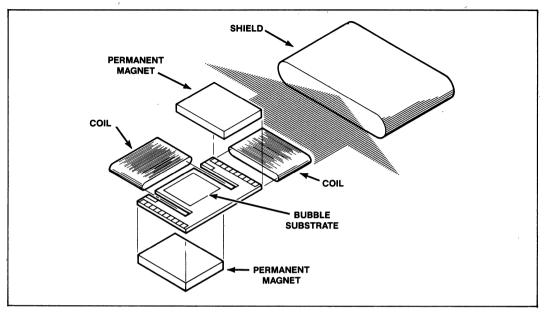

Bubble memories use a magnetic storage technique, roughly similar to the core memory concept but on a much smaller size and power-consumption scale. They are non-volatile and physically rugged. Thus, their first clear applications target has been in severe-environment and remote system sites. Portable terminals represent another applications area in which bubbles provide unique benefits.

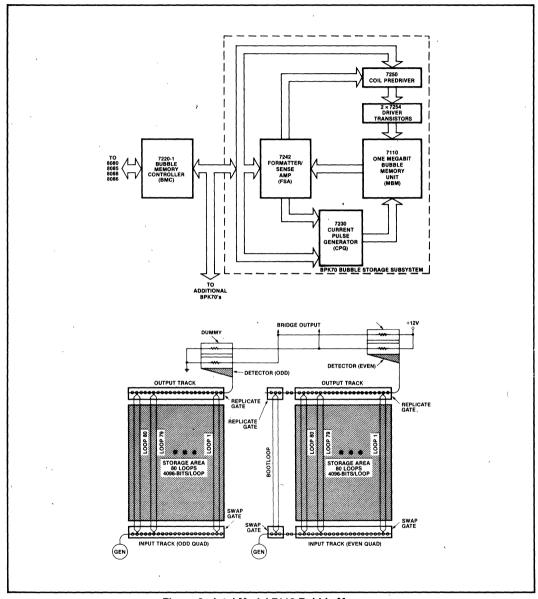

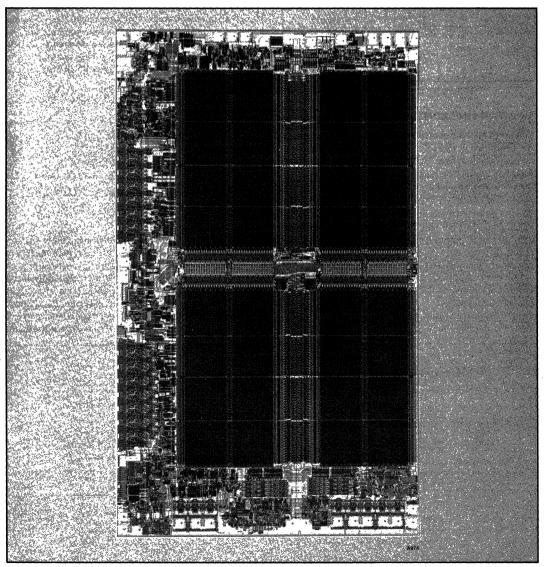

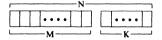

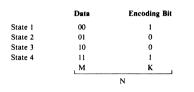

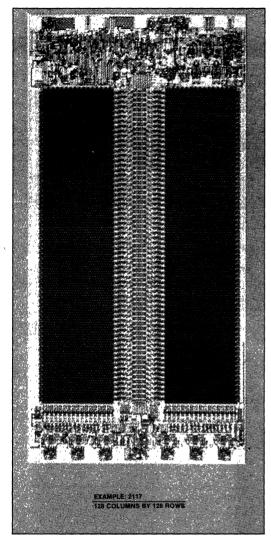

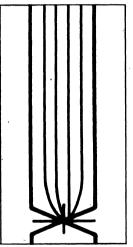

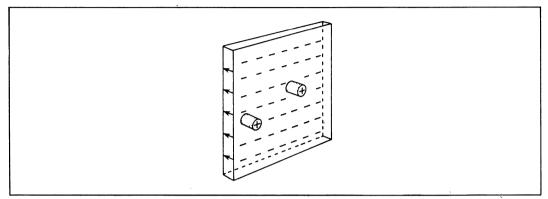

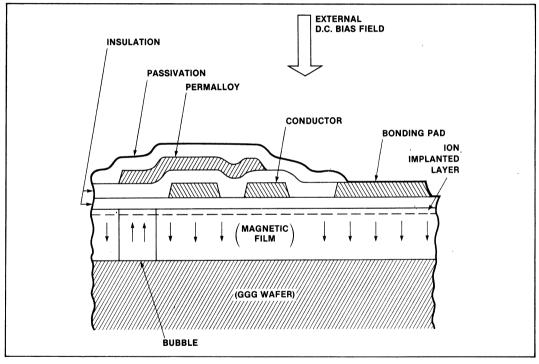

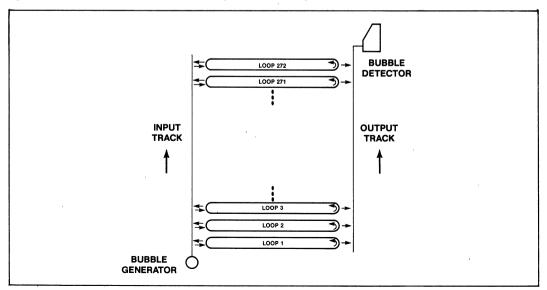

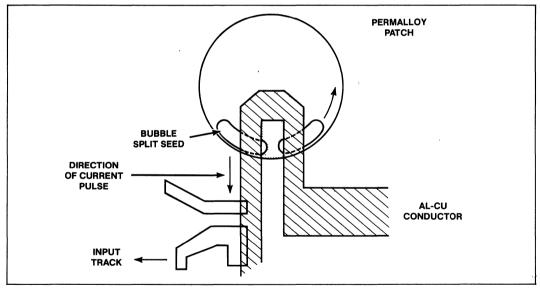

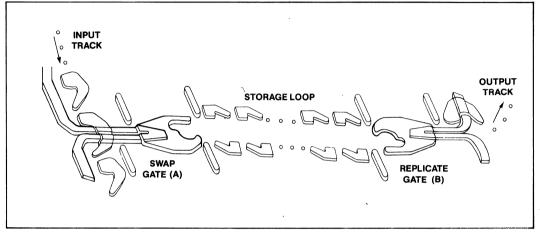

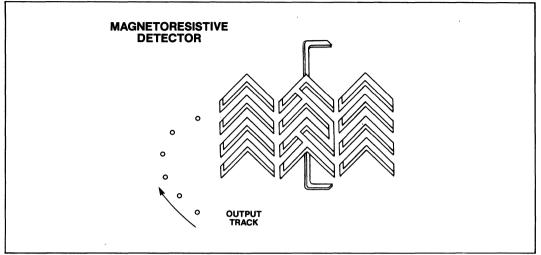

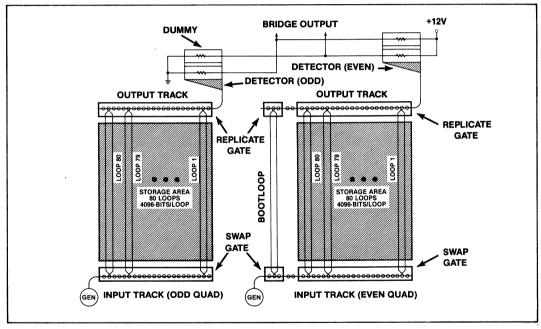

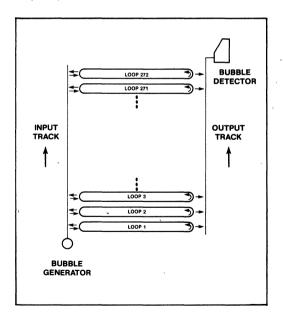

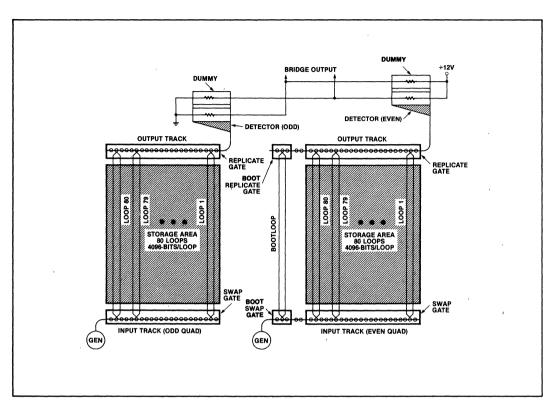

Considering bubble products, Intel's latest design provides 1,048,576 bits of data storage via a defect-tolerant technique that makes use of 1,310,720 total bits (Figure 3). Internally, the product consists of 256 storage loops of 4,086 bits each. Coupled with available control devices, this single chip can implement a 128K byte memory subsystem.

Figure 2. Typical E<sup>2</sup>PROM Application

MEMORY OVERVIEW

int

Figure 3. Intel Model 7110 Bubble Memory

#### SEGMENTATION OF MEMORY DEVICES

Besides the particular characteristics of each device that has been discussed, there are a number of other factors to consider when choosing a memory product, such as cost, power consumption, performance, memory architecture and organization, and size of the memory. Each of these factors plays a important role in the final selection process.

#### Performance

Generally, the term performance relates to how fast the device can operate in a given system environment. This

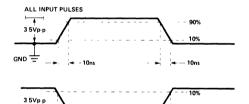

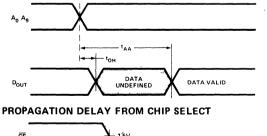

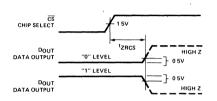

parameter is usually rated in terms of the access time. Fast SRAMs can provide access times as fast 20 ns, while the fastest DRAM cannot go much beyond the 100 ns mark. A bipolar PROM has an access time of 35 ns. RAM and PROM access is usually controlled by a signal most often referred to as Chip Select ( $\overline{CS}$ ).  $\overline{CS}$  often appears in device specifications. In discussing access times, it is important to remember that in SRAMs and PROMs, the access time equals the cycle time of the system whereas in DRAMs, the access time is always less than the cycle time.

#### Cost

There are many ramifications to consider when evaluating cost. Cost can be spread over factors such as design-in time, cost per device, cost per bit, size of memory, power consumption, etc.

Cost of design time is directly proportional to design complexity. For example, SRAMs generally require less design-in time than DRAMs because there is no refresh circuitry to consider. Conversely, the DRAM provides the lowest cost per bit because of its higher packing density.

#### **Memory Size**

Memory size is generally specified in the number of bytes (a byte is a group of eight bits). The memory size of a system is usually segmented depending upon the general equipment category. Computer mainframes and most of today's minicomputers use blocks of RAM substantially beyond 64K bytes — usually in the hundreds of thousands of bytes. For this size of memory, the DRAM has a significantly lower cost per bit. The additional costs of providing the refresh and timing circuitry are spread over many bits.

The microprocessor user generally requires memory sizes ranging from 2K bytes up to 64K bytes. In memories of this size, the universal site concept allows maximum flexibility in memory design.

#### **Power Consumption**

Power consumption is important because the total power required for a system directly affects overall cost. Higher power consumption requires bigger power supplies, more cooling, and reduced device density per board — all affecting cost and reliability. All things considered, the usual goal is to minimize power. Many memories now provide automatic power-down. With today's emphasis on saving energy and reducing cost, the memories that provide these features will gain an increasingly larger share of the market.

In some applications, extremely low power consumption is required, such as battery operation. For these appli-

cations, the use of devices made by the CMOS technology have a distinct advantage over the NMOS products. CMOS devices offer power savings of several magnitudes over NMOS. Non-volatile devices such as  $E^2PROMs$  are usually independent of power problems in these applications.

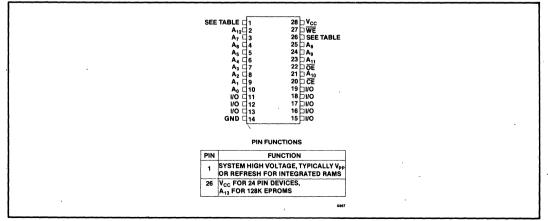

Power consumption also depends upon the organization of the device in the system. Organization usually refers to the width of the memory word. At the time of their inception, memory devices were organized as nK x 1 bits. Today, they are available in various configurations such as 4K×1, 16K×1, 64K×1, 1K×4, 2K×8, etc. As the device width increases, fewer devices are required to configure a given memory word --- although the total number of bits remains constant. The wider organization can provide significant savings in power consumption, because a fewer number of devices are required to be powered up for access to a given memory word. In addition, the board layout design is simpler due to fewer traces and better layout advantages. The wider width is of particular advantage in microprocessors and bit-slice processors because most microprocessors are organized in 8-bit or 16-bit architectures. A memory chip configured in the nK×8 organization can confer a definite advantage --- especially in universal site applications. All non-volatile memories other than bubble memories are organized nK×8 for this very reason.

#### **Types of Memories**

The first step to narrowing down your choice is to determine the type of memory you are designing — data store or program store. After this has been done, the next step is to prioritize the following factors:

Performance Power Consumption Density Cost

#### **Global Memory**

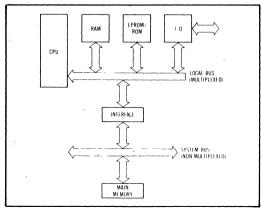

Generally, a global memory is greater than 64K bytes and serves as a main memory for a microprocessor system. Here, the use of dynamic RAMs for read/write memory is dictated to provide the highest density and lowest cost per bit. The cost of providing refresh circuitry for the dynamic RAMs is spread over a large number of memory bits, thus minimizing the cost impact. Bubbles would also be an excellent choice for global memory where high performance is not required. In addition, bubbles offer low cost per bit and non-volatility.

#### Local Memory

Local memories are usually less than 64K bytes and reside in the proximity of the processor itself — usually on the same PC board. Two types of memories are

often used in local memory applications: RAMs and E<sup>2</sup>PROMs/EPROMs. These devices all offer universal site compatibility and density upgrade.

#### Synchronous and Asynchronous Memories

Historically, there have been several definitions of convenience when describing synchronous and asynchronous memory devices. The question of which definition is the more appropriate boils down to a philosophical decision, and depends on whether the definition is narrowed to component operating parameters or expanded to system operating parameters.

One popular and accepted definition defines the two types of memories by relying on the most apparent difference. The synchronous memory possesses an internal address register which latches the current device address, but the asynchronous device lacks this capability. The logic of this definition is easy to follow: Register transfer or sequential logic is considered synchronous because it is clocked by a common periodic signal the system clock. Memories with internal address registers are also internally sequential logic arrays clocked by a signal, common throughout the memory system, and are, therefore, synchronous.

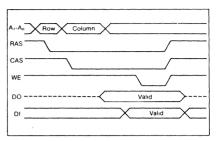

By the foregoing definition, asynchronous memories would require the device address be held valid on the bus throughout the memory cycle. Static RAMs fall into this category. In contrast, synchronous memories require the address to be valid only for a very short period of time just before, during, and just after the arrival of the address register clock. DRAMs and clocked static RAMs fall into this category.

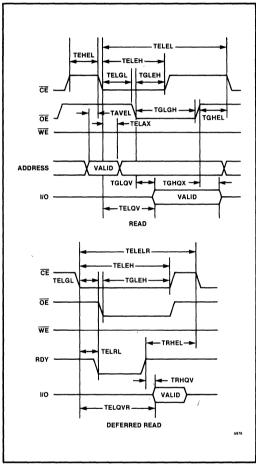

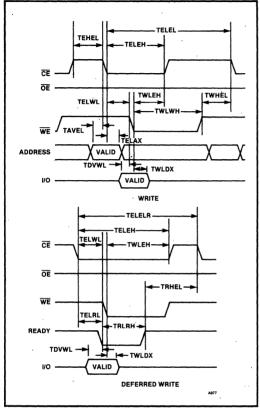

With the introduction of the 2186 and 2187 iRAMs, the preceding definition no longer fits, because both de-

vices have on chip address latches. Yet with respect to the system, one device operates synchronously and the other asynchronously.

Therefore, in considering memory devices or systems that operate within a specified cycle time, Intel defines a synchronous memory as one that responds in a predictable and sequential fashion, always providing data within the same time frame from the clock input. This allows a system designer to take advantage of the predictable access time and maximize his system performance by reducing or eliminating WAIT states.

Intel defines an asynchronous memory as one that (within the framework of the memory cycle specifications) does not output data in a predictable and repeatable time frame with respect to system timing. This is generally true of DRAM systems, where a refresh cycle, which occurs randomly skewed to the balance of the system timing, may be in progress at the time of a memory cycle request by the CPU. In this case, provision must be made to re-synchronize the system to the memory — usually with a READY signal. The 2186 iRAMs fit into this category, while the 2187 iRAMs are considered synchronous devices.

These definitions are somewhat broader in scope than those chosen in the past; however, as systems become implemented in silicon, a more global definition is required to encompass those former systems that are now silicon devices.

#### SUMMARY

Table 1 provides a summary of the various memory devices that have been discussed.

| Operating<br>From      | Read Sp<br>Fast                                                                                                                           | eed<br>Slow     | Write S<br>Fast | Speed<br>Slow       | Down<br>Load                 | Si:<br>Small     | ze<br>Large      | Removable<br>(Archive) | System<br>Level       |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|---------------------|------------------------------|------------------|------------------|------------------------|-----------------------|

| Mass                   |                                                                                                                                           | Bubbles<br>Disk |                 | Bubbles<br>Disk     | N/A                          |                  | Bubbles<br>Disk  | Bubbles<br>Disk        | Add on RAM<br>Bubbles |

| Boot                   | EPROM                                                                                                                                     |                 | N/A ·           | N/A                 | N/A                          | All <sup>2</sup> |                  |                        | N/A                   |

| Monitor                | EPROM                                                                                                                                     |                 | N/A             | · N/A               | N/A                          | Ali              |                  |                        | N/A                   |

| Buffer                 | Bytewide                                                                                                                                  | Bubbles         | Bytewide        | Bubbles             | N/A                          | All              | Bubbles<br>X1    |                        | Add in RAM<br>Bubbles |

| Diagnostics            | E <sup>2</sup> /EPROM/<br>RAM                                                                                                             |                 | Bytewide        | E <sup>2</sup> PROM | <sup>1</sup> Disk<br>Bubbles | All              | All <sup>3</sup> | Bubbles<br>Disk        | N/A                   |

| Operating<br>System    |                                                                                                                                           |                 | N/A             | N/A                 | <sup>1</sup> Disk<br>Bubbles | Ali              | X1               | Bubbles<br>Disk        | Add in/<br>Add on RAM |

| APP/PGM/<br>Data Store | E <sup>2</sup> /EPROM/<br>RAM                                                                                                             |                 | Bytewide<br>X 1 | E <sup>2</sup> PROM | <sup>1</sup> Disk<br>Bubbles | All              | X1               | Bubbles<br>Disk        | Add in/<br>Add on RAM |

|                        | <sup>1</sup> Down Loaded From Add on/Add in Bubbles<br><sup>2</sup> E <sup>2</sup> /EPROM Bytewides<br><sup>3</sup> X 1 Dram Bubbles Disk |                 |                 |                     |                              |                  |                  |                        |                       |

**Table 1. Segmentation of Memory Devices**

## Memory Technologies

· · · · · ·

### **CHAPTER 2: INTEL MEMORY TECHNOLOGIES**

Larry Brigham, Jr.

Most of this handbook is devoted to techniques and information to help you design and implement semiconductor memory in your application or system. In this section, however, the memory chip itself will be examined and the processing technology required to turn a bare slice of silicon into high performance memory devices is described. The discussion has been limited to the basics of MOS (Metal Oxide Semiconductor) technologies as they are responsible for the overwhelming majority of memory devices manufactured at Intel.

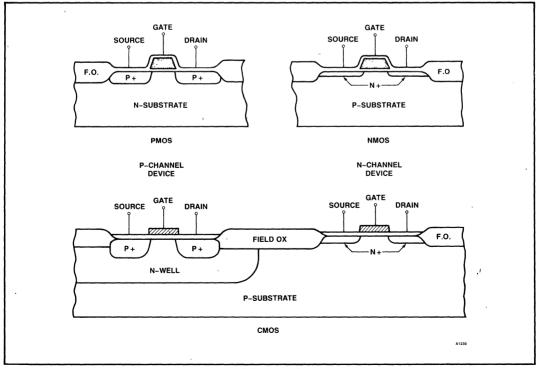

There are three major MOS technology families — PMOS, NMOS, and CMOS (Figure 1). They refer to the channel type of the MOS transistors made with the technology. PMOS technologies implement p-channel transistors by diffusing p-type dopants (usually Boron) into an n-type silicon substrate to form the source and drain. P-channel is so named because the channel is comprised of positively charged carriers. NMOS technologies are similar, but use n-type dopants (normally phosphorus or arsenic) to make n-channel transistors in p-type silicon substrates. N-channel is so named because the channel is comprised of negatively charged carriers. CMOS or Complementary MOS technologies combine both p-channel and n-channel devices on the same silicon. Either p- or n-type silicon substrates can be used, however, deep areas of the opposite doping type (called wells) must be defined to allow fabrication of the complementary transistor type.

Most of the early semiconductor memory devices, like Intel's pioneering 1103 dynamic RAM and 1702 EPROM were made with PMOS technologies. As higher speeds and greater densities were needed, most new devices were implemented with NMOS. This was due to the inherently higher speed of n-channel charge carriers (electrons) in silicon along with improved process margins. The majority of MOS memory devices in pro-

Figure 1. MOS Process Cross-sections

duction today are fabricated with NMOS technologies. CMOS technology has begun to see widespread commercial use in memory devices. It allows for very low power devices and these have been used for battery operated or battery back-up applications. Historically, CMOS has been slower than any NMOS device. Recently, however, CMOS technology has been improved to produce higher speed devices. Up to now, the extra cost processing required to make both transistor types has kept CMOS memories limited to those areas where the technology's special characteristics would justify the extra cost. In the future, the learning curve for high performance CMOS costs will make a larger and larger number of memory devices practical in CMOS.

In the following section, the basic fabrication sequence for an HMOS circuit will be described. HMOS is a high performance n-channel MOS process developed by Intel for 5 Volt single supply circuits. HMOS, along with its evolutionary counterparts HMOS II and HMOS III, CHMOS and CHMOS II (and their variants), comprise the process family responsible for most of the memory components produced by Intel today.

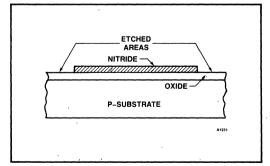

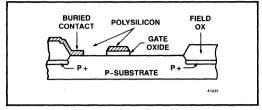

The MOS IC fabrication process begins with a slice (or wafer) of single crystal silicon. Typically, it's 100 or 125 millimeter in diameter, about a half millimeter thick, and uniformly doped p-type. The wafer is then oxidized in a furnace at around 1000°C to grow a thin layer of silicon dioxide (SiO<sub>2</sub>) on the surface. Silicon nitride is then deposited on the oxidized wafer in a gas phase chemical reactor. The wafer is now ready to receive the first pattern of what is to become a many layered complex circuit. The pattern is etched into the silicon nitride using a process known as photolithography, which will be described in a later section. This first pattern (Figure 2) defines the boundaries of the active regions of the IC, where transistors, capacitors, diffused resistors, and first level interconnects will be made.

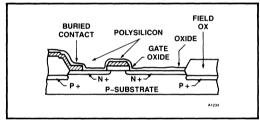

Figure 2. First Mask

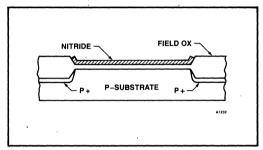

The patterned and etched wafer is then implanted with additional boron atoms accelerated at high energy. The boron will only reach the silicon substrate where the nitride and oxide was etched away, providing areas doped strongly p-type that will electrically separate active areas. After implanting, the wafers are oxidized again and this time a thick oxide is grown. The oxide only grows in the etched areas due to silicon nitride's properties as an oxidation barrier. When the oxide is grown, some of the silicon substrate is consumed and this gives a physical as well as electrical isolation for adjacent devices as can be seen in Figure 3.

Figure 3. Post Field Oxidation

Having fulfilled its purpose, the remaining silicon nitride layer is removed. A light oxide etch follows taking with it the underlying first oxide but leaving the thick (field) oxide.

Now that the areas for active transistors have been defined and isolated, the transistor types needed can be determined. The wafer is again patterned and then if special characteristics (such as depletion mode operation) are required, it is implanted with dopant atoms. The energy and dose at which the dopant atoms are implanted determines much of the transistor's characteristics. The type of the dopant provides for depletion mode (n-type) or enhancement mode (p-type) operation.

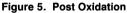

The transistor types defined, the gate oxide of the active transistors are grown in a high temperature furnace. Special care must be taken to prevent contamination or inclusion of defects in the oxide and to ensure uniform consistent thickness. This is important to provide precise, reliable device characteristics. The gate oxide layer is then masked and holes are etched to provide for direct gate to diffusion ("buried") contacts where needed.

The wafers are now deposited with a layer of gate material. This is typically poly crystaline silicon ("poly") which is deposited in a gas phase chemical reactor similar to that used for silicon nitride. The poly is then doped (usually with phosphorus) to bring the sheet resistance down to 10-20 ohms/square. This layer is also used for circuit interconnects and if a lower resistance is required, a refractory metal/polysilicon composite or refractory metal silicide can be used instead. The gate layer is then patterned to define the actual transistor gates and interconnect paths (Figure 4).

Figure 4. Post Gate Mask

The wafer is next diffused with n-type dopant (typically arsenic or phosphorus) to form the source and drain junctions. The transistor gate material acts as a barrier to the dopant providing an undiffused channel self-aligned to the two junctions. The wafer is then oxidized to seal the junctions from contamination with a layer of SiO<sub>2</sub> (Figure 5).

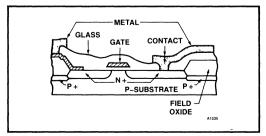

A thick layer glass is then deposited over the wafer to provide for insulation and sufficiently low capacitance between the underlying layers and the metal interconnect signals. (The lower the capacitance, the higher the inherent speed of the device.) The glass layer is then patterned with contact holes and placed in a high temperature furnace. This furnace step smooths the glass surface and rounds the contact edges to provide uniform metal coverage. Metal (usually aluminum or aluminum/silicon) is then deposited on the wafer and the interconnect patterns and external bonding pads are defined and etched (Figure 6). The wafers then receive a low temperature (approximately 500°C) alloy that insures good ohmic contact between the Al and diffusion or poly.

Figure 6. Completed Circuit (without passivation)

At this point the circuit is fully operational, however, the top metal layer is very soft and easily damaged by handling. The device is also susceptible to contamination or attack from moisture. To prevent this the wafers are sealed with a passivation layer of silicon nitride or a silicon and phosphorus oxide composite. Patterning is done for the last time opening up windows only over the bond pads where external connections will be made.

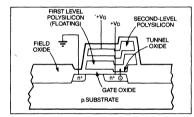

This completes basic fabrication sequence for a single poly layer process. Double poly processes such as those used for high density Dynamic RAMs, EPROMs, and E<sup>2</sup>PROMs follow the same general process flow with the addition of gate, poly deposition, doping, and interlayer dielectric process modules required for the additional poly layer (Figure 7). These steps are performed right after the active areas have been defined (Figure 3) providing the capacitor or floating gate storage nodes on those devices.

Figure 7. Double Poly Structure

After fabrication is complete, the wafers are sent for testing. Each circuit is tested individually under conditions designed to determine which circuits will operate properly both at low temperature and at conditions found in actual operation. Circuits that fail these tests are inked to distinguish them from good circuits. From here the wafers are sent for assembly where they are sawed into individual circuits with a paper-thin diamond blade. The inked circuits are then separated out and the good circuits are sent on for packaging. Packages fall into two categories — hermetic and nonhermetic. Hermetic packages are Cerdip, where two ceramic halves are sealed with a glass fritt, or ceramic with soldered metal lids. An example of hermetic package assembly is shown in Table 1. Non-hermetic packages are molded plastics.

The ceramic package has two parts, the base, which has the leads and die (or circuit) cavity, and the metal lid. The base is placed on a heater block and a metal alloy preform is inserted. The die is placed on top of the preform which bonds it to the package. Once attached, wires are bonded to the circuit and then connected to the leads. Finally the package is placed in a dry inert atmosphere and the lid is soldered on.

The cerdip package consists of a base, lead frame, and lid. The base is placed on a heater block and the lead

frame placed on top. This sets the lead frame in glass attached to the base. The die is then attached and bonded to the leads. Finally the lid is placed on the package and it is inserted in a seal furnace where the glass on the two halves melt together making a hermetic package.

In a plastic package, the key component is the lead frame. The die is attached to a pad on the lead frame and bonded out to the leads with gold wires. The frame then goes to an injection molding machine and the package is formed around the lead frame. After mold the excess plastic is removed and the leads trimmed.

After assembly, the individual circuits are retested at an elevated operating temperature to assure critical operating parameters and separated according to speed and power consumption into individual specification groups.

| Flow     | Process/Materials                      | Typical Item                                                                               | Frequency                                | Criteria                             |

|----------|----------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------|

| Ŷ        | Wafer                                  |                                                                                            |                                          | ·                                    |

| \$       | Die saw, wafer break                   |                                                                                            |                                          |                                      |

| ¢        | Die wash and plate                     |                                                                                            | e.                                       |                                      |

|          | Die visual inspection                  | Passivation, metal                                                                         | 100% of die                              |                                      |

|          | QA gate                                |                                                                                            | Every lot                                | 0/76, LTPD = 5%                      |

| ¢        | Die attach<br>(Process monitor)        | Wet out                                                                                    | $4 \times /operator/shift$               | 0/11 LTPD = 20%                      |

| <b> </b> | Post die attach visual                 |                                                                                            | 100% of devices                          |                                      |

| ¢        | Wire bond<br>(Process monitor)         | Orientation, lead dressing, etc.                                                           | 4 × /operator/<br>machine/shift          |                                      |

| 4        | Post bond inspection                   |                                                                                            | 100% devices                             |                                      |

|          | QA gate                                | All previous items                                                                         | every lot                                | 1/129, LTPD = 3%                     |

|          | Seal and Mark<br>(Process monitor)     | Cap align, glass<br>integrity, moisture                                                    | 4 × /furnace/shift                       | 0/ <u>1</u> 5, LTPD = 15%            |

| <b></b>  | Temp cycle                             |                                                                                            | 10 × to mil std.<br>883 cond. C          | 1/11, LTPD = 20%                     |

|          | Hermeticity check<br>(Process monitor) | F/G leak                                                                                   | 100% devices                             |                                      |

| ¢        | Lead Trim<br>(Process monitor)         | Burrs, etc. (visual)<br>Fine leak                                                          | 4 × /station/shift<br>2 × /station/shift | 0/15, LTPD = 15%<br>1/129, LTPD = 3% |

| †        | External visual                        | Solder voids, cap alignment, etc.                                                          | 100% devices                             |                                      |

| 1.       | QA gate                                | All previous items                                                                         | All lots                                 | 1/129, LTPD = 3%                     |

|          | Class test<br>(Process monitor)        | Run standards<br>(good and reject)<br>Calibrate every<br>system using<br>"autover" program | Every 48 hrs.                            |                                      |

| 2.       | Mark and Pack                          | ;                                                                                          |                                          |                                      |

| 20       | Final QA                               | (See attached)                                                                             | •                                        |                                      |

#### Table 1. 2164A Hermetic Package Assembly

1. Units for assembly reliability monitor. 2. Units for product reliability monitor.

The finished circuits are marked and then readied for shipment.

The basic process flow described above may make VLSI device fabrication sound straightforward, however, there are actually hundreds of individual operations that must be performed correctly to complete a working circuit. It usually takes well over two months to complete all these operations and the many tests and measurements involved throughout the manufacturing process. Many of these details are responsible for ensuring the performance, quality, and reliability you expect from Intel products. The following sections will discuss the technology underlying each of the major process elements mentioned in the basic process flow.

#### PHOTOLITHOGRAPHY

The photo or masking technology is the most important part of the manufacturing flow if for no other reason than the number of times it is applied to each wafer. The manufacturing process gets more complex in order to make smaller and higher performance circuits. As this happens the number of masking steps increases, the features get smaller, and the tolerance required becomes tighter. This is largely because the minimum size of individual pattern elements determine the size of the whole circuit, effecting its cost and limiting its potential complexity. Early MOS IC's used minimum geometries (lines or spaces) of 8-10 microns (1 micron=10<sup>-6</sup> meter  $\approx$  1/25,000 inch). The n-channel processes of the mid 1970's brought this down to approximately 5 microns, and today minimum geometries are less than 2 microns in production. This dramatic reduction in feature size was achieved using the newer high resolution photo resists and optimizing their processing to match improved optical printing systems.

A second major factor in determining the size of the circuit is the registration or overlay error. This is how accurately one pattern can be aligned to a previous one. Design rules require that space be left in all directions according to the overlay error so that unrelated patterns do not overlap or interfere with one another. As the error space increases the circuit size increases dramatically. Only a few years ago standard alignment tolerances were  $\geq \pm 2$  microns; now advanced Intel processes have reduced this dramatically due mostly to the use of advanced projection and step and repeat exposure equipment.

The wafer that is ready for patterning must go through many individual steps before that pattern is complete. First the wafer is baked to remove moisture from its surface and is then treated with chemicals that ensure good resist adhesion. The thick photoresist liquid is then applied and the wafer is spun flat to give a uniform coating, critical for high resolution. The wafer is baked at a low temperature to solidify the resist into gel. It is then exposed with a machine that aligns a mask with the new pattern on it to a previously defined layer. The photoresist will replicate this pattern on the wafer.

Negative working resists are polymerized by the light and the unexposed resist can be rinsed off with solvents. Positive working resists use photosensitive polymerization inhibitors that allow a chemically reactive developer to remove the exposed areas. The positive resists require much tighter control of exposure and development but yield higher resolution patterns than negative resistance systems.

The wafer is now ready to have its pattern etched. The etch procedure is specialized for each layer to be etched. Wet chemical etchants such as hydrofluoric acid for silicon oxide or phosphoric acid for aluminum are often used for this. The need for smaller features and tighter control of etched dimensions is increasing the use of plasma etching in fabrication. Here a reactor is run with a partial vacuum into which etchant gases are introduced and an electrical field is applied. This yields a reactive plasma which etches the required layer.

The wafer is now ready for the next process step. Its single journey through the masking process required the careful engineering of mechanics, optics, organic chemistry, inorganic chemistry, plasma chemistry, physics, and electronics.

#### DIFFUSION

The picture of clean room garbed operators tending furnace tubes glowing cherry red is the one most often associated with IC fabrication. These furnace operations are referred to collectively as diffusion because they employ the principle of solid state diffusion of matter to accomplish their results. In MOS processing, there are three main types of diffusion operations: predeps, drives, and oxidations.

Predeposition, or "predep," is an operation where a dopant is introduced into the furnace from a solid, liquid, or gaseous source and at the furnace temperature (usually 900-1200°C) a saturated solution is formed at the silicon surface. The temperature of the furnace, the dopant atom, and rate of introduction are all engineered to give a specific dose of the dopant on the wafer. Once this is completed the wafer is given a drive cycle where the dopant left at the surface by the predep is driven into the wafer by high temperatures. These are generally at different temperatures than the predeps and are designed to give the required junction depth and concentration profile.

Oxidation, the third category, is used at many steps of the process as was shown in the process flow. The temperature and oxidizing ambient can range from 800 to 1200°C and from pure oxygen to mixtures of oxygen and other gases to steam depending on the type of oxide required. Gate oxides require high dielectric breakdown strength for thin layers (between .01 and .1 micron) and very tight control over thickness (typically  $\pm$  .005 micron or less than  $\pm$  1/5,000,000 inch), while isolation oxides need to be quite thick and because of this their dielectric breakdown strength per unit thickness is much less important.

The properties of the diffused junctions and oxides are key to the performance and reliability of the finished device so the diffusion operations must be extremely well controlled for accuracy, consistency and purity.

#### ION IMPLANT

Intel's high performance products require such high accuracy and repeatability of dopant control that even the high degree of control provided by diffusion operations is inadequate. However, this limitation has been overcome by replacing critical predeps with ion implantation. In ion implantation, ionized dopant atoms are accelerated by an electric field and implanted directly into the wafer. The acceleration potential determines the depth to which the dopant is implanted.

The charged ions can be counted electrically during implantation giving very tight control over dose. The ion implanters used to perform this are a combination of high vacuum system, ion source, mass spectrometer, linear accelerator, ultra high resolution current integrator, and ion beam scanner. You can see that this important technique requires a host of sophisticated technologies to support it.

#### THIN FILMS

Thin film depositions make up most of the features on the completed circuit. They include the silicon nitride for defining isolation, polysilicon for the gate and interconnections, the glass for interlayer dielectric, metal for interconnection and external connections, and passivation layers. Thin film depositions are done by two main methods: physical deposition and chemical vapor deposition. Physical deposition is most common for depositing metal. Physical depositions are performed in a vacuum and are accomplished by vaporizing the metal with a high energy electron beam and redepositing it on the wafer or by sputtering it from a target to the wafer under an electric field.

Chemical vapor deposition can be done at atmospheric pressure or under a moderate vacuum. This type of deposition is performed when chemical gases react at the wafer surface and deposit a solid film of the reaction product. These reactors, unlike their general industrial counterparts, must be controlled on a microscale to provide exact chemical and physical properties for thin films such as silicon dioxide, silicon nitride, and polysilicon.

The fabrication of modern memory devices is a long, complex process where each step must be monitored, measured and verified. Developing a totally new manufacturing process for each new product or even product line takes a long time and involves significant risk. Because of this, Intel has developed process families, such as HMOS, on which a wide variety of devices can be made. These families are scalable so that circuits need not be totally redesigned to meet your needs for higher performance.<sup>1</sup> They are evolutionary (HMOS I, HMOS II, HMOS III, CHMOS) so that development time of new processes and products can be reduced without compromising Intel's commitment to consistency, quality, and reliability.

The manufacture of today's MOS memory devices requires a tremendous variety of technologies and manufacturing techniques, many more than could be mentioned here. Each requires a team of experts to design, optimize, control and maintain it. All these people and thousands of others involved in engineering, design, testing and production stand behind Intel's products.

Because of these extensive requirements, most manufacturers have not been able to realize their needs for custom circuits on high performance, high reliability processes. To address this Intel's expertise in this area is now available to industry through the silicon foundry. Intel supplies design rules and support to design and debug circuits. This includes access to Intel's n-well CHMOS technology. Users of the foundry can now benefit from advanced technology without developing processes and IC manufacturing capability themselves.

<sup>&</sup>lt;sup>1</sup> R. Pashley, K. Kokkonen, E. Boleky, R. Jecmen, S. Liu, and W. Owen, "H-MOS Scales Traditional Devices to Higher Performance Level," *Electronics*, August 18, 1977.

## Random Access Memories

•

## APPLICATION NOTE

**AP-74**

#### INTRODUCTION

The Intel® 2147H is a 4096-word by 1-bit Random Access Memory, fabricated using Intel's reliable HMOS II technology. HMOS II, the second generation HMOS, is Intel's high performance nchannel silicon gate technology, making simple, high speed memory systems a reality. The purpose of this application note is to describe the 2147H operation and discuss design criteria for high speed memory systems.

#### TECHNOLOGY

When Intel introduced the HMOS 2147, MOS static RAM performance took a quantum leap by combining scaling, internal substrate bias generation, and automatic powerdown. As a result, the 2147 has an access time of 55ns, density of 4096 bits, and power consumption of .99W active and .165W standby.

The high performance of the 2147 is further enhanced by the 2147H using HMOS II, a scaled HMOS process increasing the speed at the same power level which involves more than scaling dimensions.

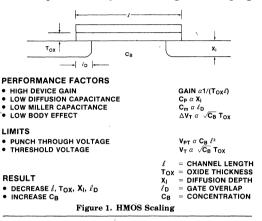

Figure 1 shows the cross section of an HMOS device and lists the parameters of scaling, one of which is high device gain. The slew rate of an amplifier or device is proportional to the gain. Because faster switching speeds occur with high gain, the gain is maximized for high speed. Device gain is inversely proportional to the oxide thickness  $(T_{OX})$  and device length (l), consequently, scaling these dimensions increases the gain.

Another factor which influences performance is unwanted capacitance which appears in two forms - - diffusion and Miller. Diffusion capacitance is directly proportional to the diffusion depth (X<sub>i</sub>) into the silicon, thus X<sub>i</sub> must be reduced. Miller capacitance, the same phenomenon that occurs in the macro world of discrete devices, is proportional to the overlap length of the gate and the source  $(\mathcal{L}_{D})$ . Capacitance on the input shunts the high frequency portion of the input signal so that the device can only respond to low frequencies. Secondly, capacitance from the drain to the gate forms a feedback path creating an integrator or low pass filter which degrades the high frequency performance. This effect is minimized by reducing  $l_{\rm D}$ .

One of the limits on scaling is punch through voltage, which occurs when the field strength is too high, causing current to flow when the device is "turned off". Punch through voltage is a function of channel length  $(\not L)$  and doping concentration (C<sub>B</sub>), thus channel shortening can be compensated by increasing the doping

concentration. This has the additional advantage of balancing the threshold voltage which was decreased by scaling the oxide thickness for gain.

#### Comparison

Comparing scaling theory to HMOS II scaling in Table I, note that HMOS II agrees with scaling theory except for the supply voltage. It is left constant at +5V to maintain TTL compatibility. Had the voltage been scaled, the power would have been reduced by  $1/K^3$  rather than 1/K, but the device would not have been TTL compatible.

#### Table I. Scaling

|                      | Theory           | HMOS II |

|----------------------|------------------|---------|

| Dimensions           | 1/K              | 1/K     |

| Substrate Doping     | к                | к       |

| Voltage              | 1/K              | 1       |

| Device Current       | 1/K              | 1       |

| Capacitance A/T      | 1/K              | 1/K     |

| Time Delay VC/I      | 1/K              | 1/K     |

| Power Dissipation VI | 1/K <sup>2</sup> | 1       |

| Power Delay Product  | 1/K <sup>3</sup> | 1/K     |

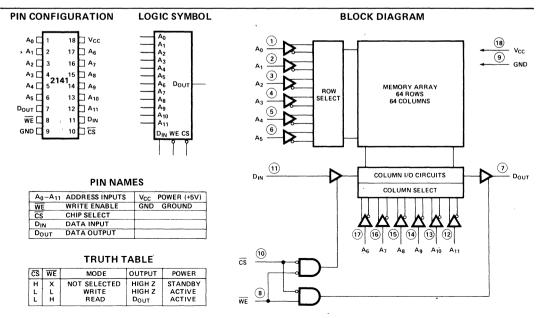

#### THE DEVICE

The 2147H is TTL compatible, operates from a single +5 volt supply, and is easy to use.

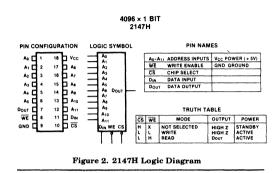

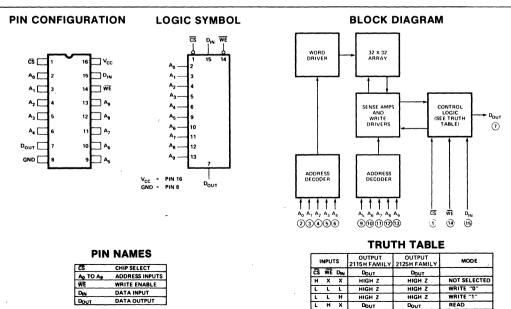

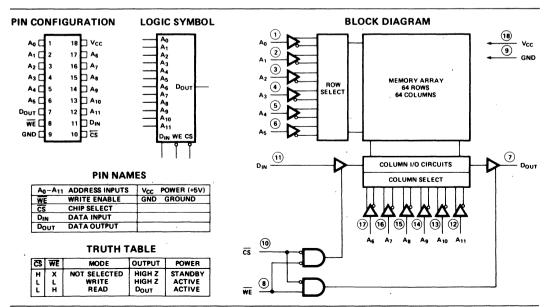

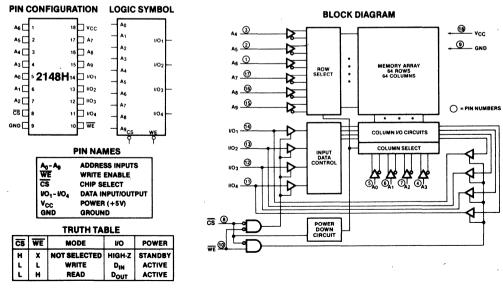

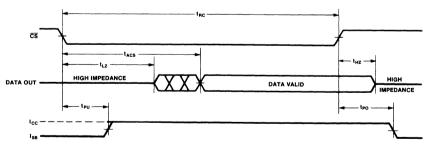

Figure 2 shows the pin configuration and the logic symbol. The 2147H is compatible with the 2147 allowing easy system upgrade. Contained in an industry standard 18-pin dual in-line package the 2147H is organized as 4096 words of 1 bit. To access each of these words, twelve address lines are required. In addition, there are two control signals:  $\overline{CS}$ , which activates the RAM; and  $\overline{WE}$ ,

AP-74

which controls the write function. Separate data input and output are available. Logical operation of the 2147H is shown in the truth table. The output is in the high impedance or three-state mode unless the RAM is being read. Power consumption switches from standby to active under control of  $\overline{\text{CS}}$ .

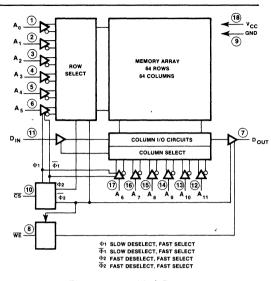

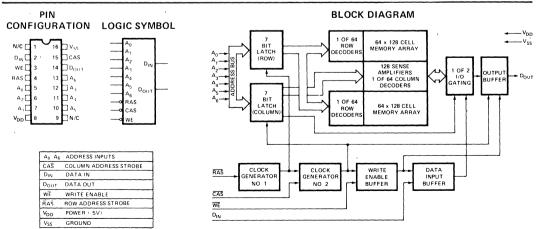

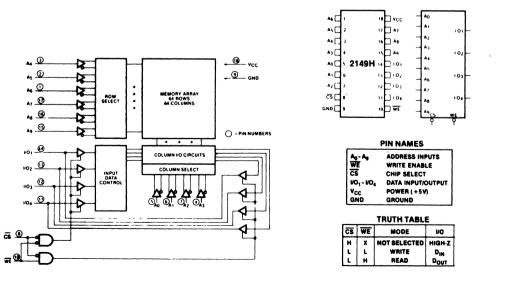

Internal structure of the 2147H is shown in the block diagram of Figure 3. The major portions of the device are: addresses, control ( $\overline{CS}$  and  $\overline{WE}$ ), the memory array and a substrate bias generator, which is not shown.

The memory is organized into a two-dimensional array of 64 rows and 64 columns of memory cells. The lower-order six addresses decode one of 64 to select the row while the upper-order six addresses decode to select one column. The intersection of the selected row and the selected column locate the desired memory cell. Additional logic in the column selection circuit controls the flow of data to the array and as stated in the truth table,  $\overline{\rm WE}$  controls the output buffer.

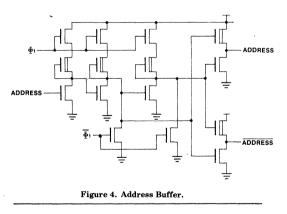

As shown in Figure 4, the first three stages of the address buffer are designed with an additional transistor. In each stage, the lowest transistors are the active devices, the middle transistors are load devices, while the upper transistors, controlled by  $\Phi_1$ , are the key to low standby power. Forming an AND function with the active devices, the upper transistors are turned off when the 2147H is not active, minimizing power consumption. Without them, at least one stage of these cascaded amplifiers would always be consuming power.

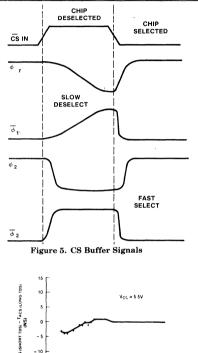

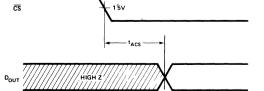

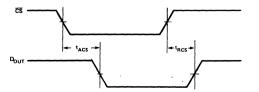

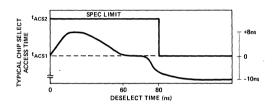

The signal  $\Phi_1$ , and its inverse  $\overline{\Phi}_1$ , are generated from CS. They are part of an innovative design not found in the earlier 2147. Their function is to minimize the effects at short deselect times on the Chip Select access time,  $t_{ACS}$ .

Figure 3. 2147H Block Diagram

For both the 2147 and the 2147H, access is delayed until the address buffers are activated by chip selection. In the standard 2147, priming during deselection compensates for this delay by speeding up the access elsewhere in the circuitry. For short deselect times, however, full compensation does not occur because priming is incomplete. The result is a pushout in tACS for short deselect times.

3-3

In the 2147H, the address buffers are controlled by  $\Phi_1$ , which is shaped as shown in Figure 5.  $\Phi_1$  activates rapidly for fast select time. However,  $\Phi_1$ deactivates slowly, keeping the address buffers active during short deselect times to speed access. As shown in Figure 6, this design innovation keeps t<sub>ACS</sub> pushout to less than 1 ns.

20 30 TDS (NS

Figure 6. CS Access Vs. Deselect Time

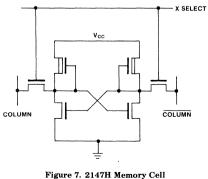

Figure 7 shows the standard six-transistor cell. Configured as a bi-stable flip-flop, the memory cell uses two transistors for loads and two for active devices so that the data is stored twice as true and compliment. The two remaining transistors enable data onto the internal I/O bus. Unlike the periphery, the cell is not powered down during deselect time to sustain data indefinitely.

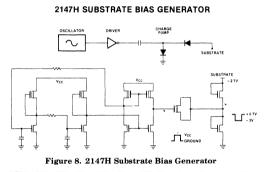

The 2147H has an internal bias generator. Bias voltage allows the use of high resistivity substrate by adjusting the threshold voltages. In addition, it reduces the effect of bulk silicon capacitance. As a result, performance is enhanced. Bias voltage is generated by capacitively coupling the output of a ring oscillator to a charge pump connected to the substrate. Internally generated bias permits the 2147H to operate from a single +5 volt supply, maintaining TTL compatibility.

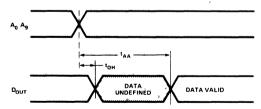

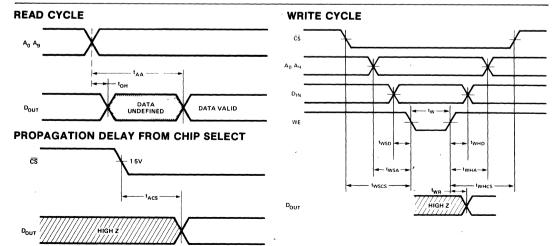

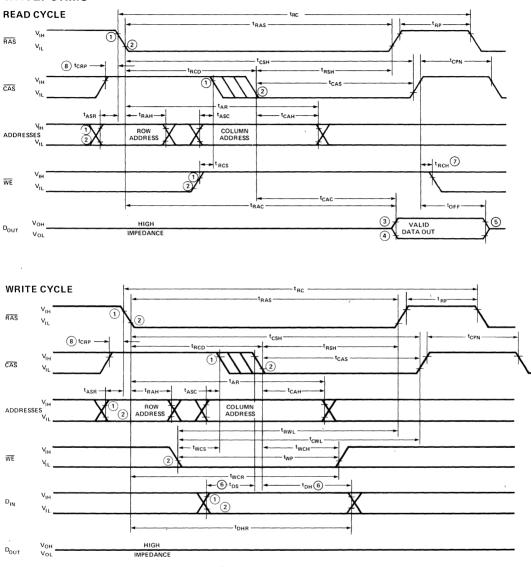

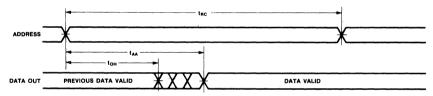

#### DEVICE OPERATION READ MODE

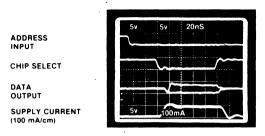

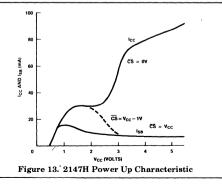

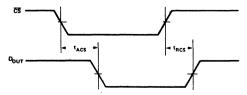

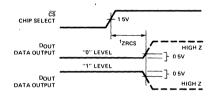

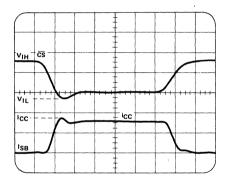

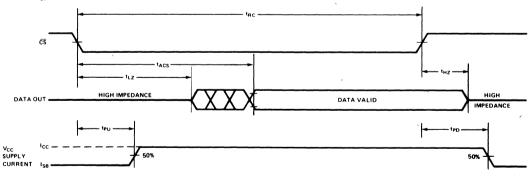

With power applied and  $\overline{CS}$  at greater than 2V, the 2147H is in the standby mode, drawing less than 30mA. Activating  $\overline{CS}$  begins access of the cell as defined by the state of the addresses. Data is transferred from the cell to the output buffer. Because the cell is static, the read operation is nondestructive. Device access and current are shown in Figure 9. Maximum access relative to the leading edge of  $\overline{CS}$  is 35 ns for a 2147H-1. Without clocks, data is valid as long as address and control are maintained.

#### WRITE MODE

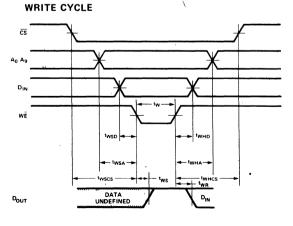

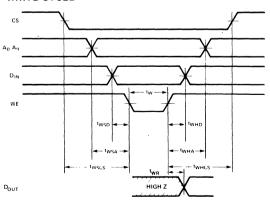

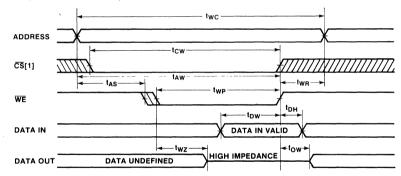

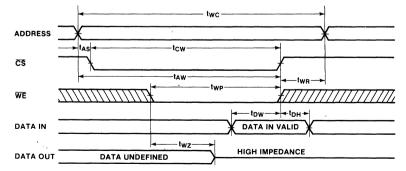

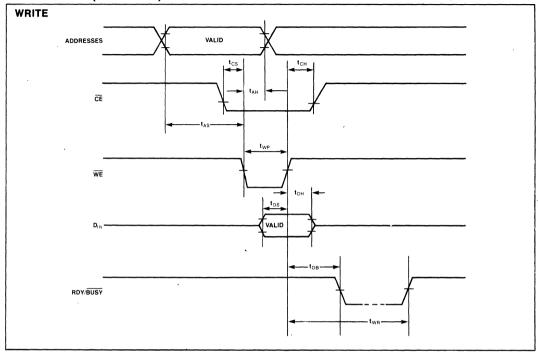

Data is modified when the write enable  $\overline{WE}$  is activated during a cycle. At this time, data present at the input is duplicated in the cell specified by the address. Data is latched into the cell on the trailing edge of WE, requiring that setup and hold times relative to this edge be maintained.

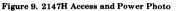

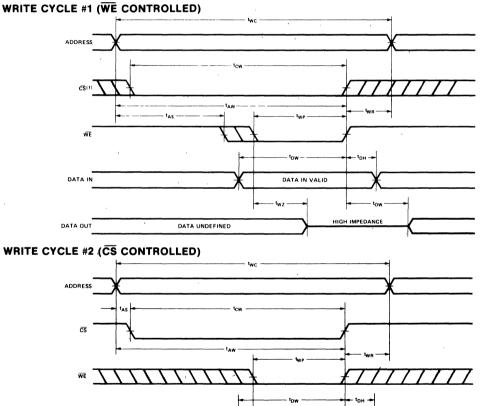

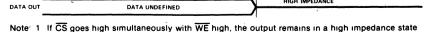

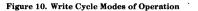

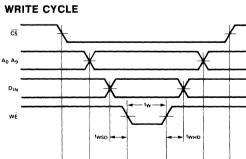

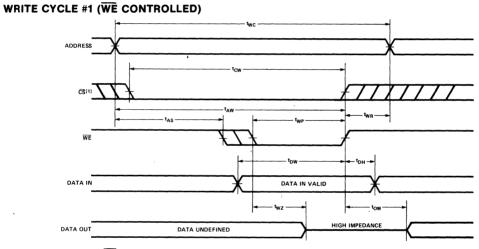

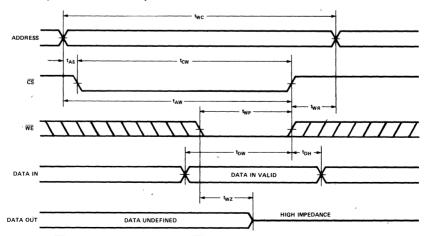

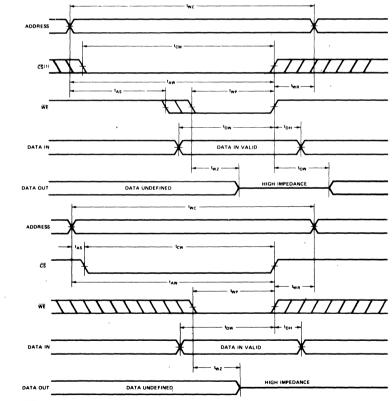

Two modes of operation are allowed in a write cycle, as shown in Figure 10. In the first mode, the write cycle is controlled by  $\overline{WE}$ , while in the other cycle, the cycle is controlled by  $\overline{CS}$ . In a  $\overline{WE}$  controlled cycle,  $\overline{CS}$  is held active while addresses change and the  $\overline{WE}$  signal is pulsed to establish memory cycles. In the  $\overline{CS}$  controlled cycle,  $\overline{WE}$  is maintained active while addresses again thange and  $\overline{CS}$  changes state to define cycle length. This flexible operation eases the use and makes the 2147H applicable to a wide variety of system designs.

#### WAVEFORMS

DATA IN

DATA IN VALID

HIGH IMPEDANCE

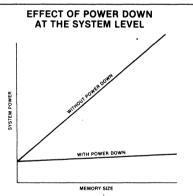

Power consumed by a memory system is the product of the number of devices, the voltage applied, and the average current:

#### Equation 1

$$P = NVI_{AVE}$$

where:

P = Power

N = Number of devices

V = Voltage applied

IAVE = Average current/device

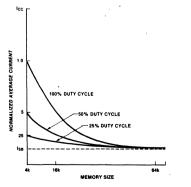

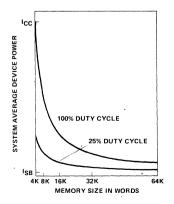

Without power down, the average current is approximately the operating current. System power increases linearily with the number of devices. With power down, power consumption increases in proportion to the standby current with increasing number of memory devices. Curves in Figure 11 illustrate the difference which results from the majority of devices being in standby with a very small portion of the devices

active or being accessed. For a system with power down, the average current of a device in the system is the sum of total active current and the total standby current divided by the number of devices in the system. For an X1 memory such as the 2147H, the number of active devices in most systems will be equal to the number of bits/word, m. Therefore, the number of devices in standby is the difference between N and M. IAVE is expressed mathematically:

#### **Equation 2**

where:

N m = Number of active devices IACT = Active current ISB = Standby current

IAVE= mIACT + (N-m) ISB

The graph of Figure 12 shows the relation between average device current and memory size for automatic power down. For large memories the average device current approaches the standby current. Total system power usage, P, is calculated by substituting Equation 2 into Equation 1.

$$P = V[mI_{ACT} + (N-m) I_{SB}]$$

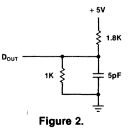

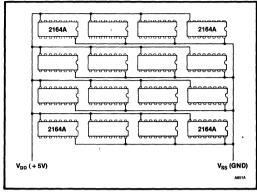

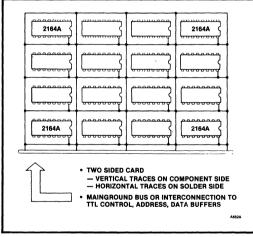

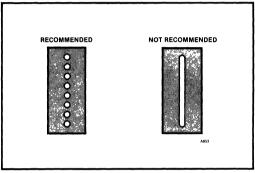

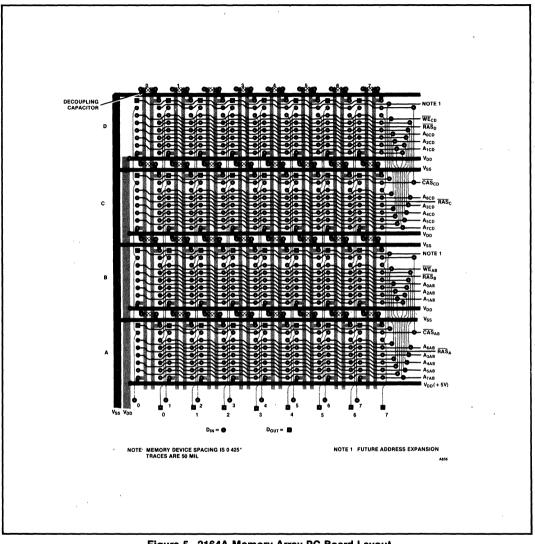

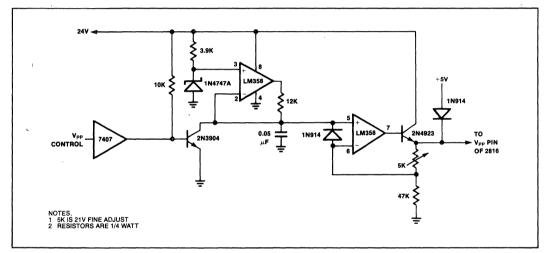

Comparison of power consumption of a system with and without power down illustrates the power savings. Assume a 64K by 18-bit memory constructed with 4KX1 devices. Active current of one device is 180mA and standby current is 30mA. Duty cycle is assumed to be 100% and voltage is 5 volts. The number of devices in the system is: