# inte

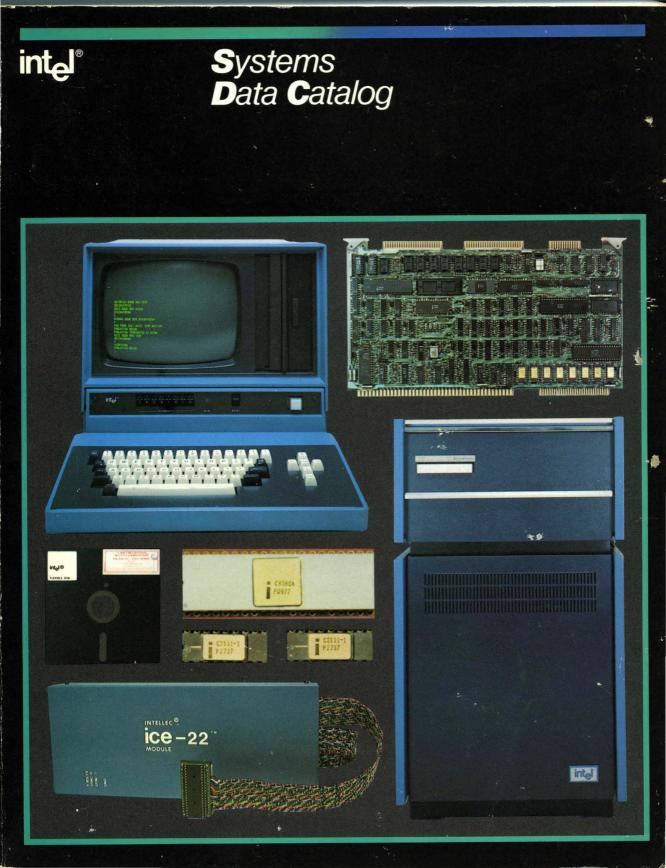

# SYSTEMS DATA CATALOG

**JANUARY 1981**

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9 (a) (9). Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and may only be used to identify Intel products:

| BXP            | Intelevision    | MULTIBUS*   |

|----------------|-----------------|-------------|

| CREDIT         | Intellec        | MULTIMODULE |

| i              | iSBC            | PROMPT      |

| ICE            | iSBX            | Promware    |

| ICS            | Library Manager | RMX         |

| i <sub>m</sub> | MCS             | UPI         |

| Insite         | Megachassis     | μScope      |

| Intel          | Micromap        |             |

and the combinations of ICE, iCS, iSBC, MCS or RMX and a numerical suffix.

MDS is an ordering code only and is not used as a product name or trademark. MDS<sup>®</sup> is a registered trademark of Mohawk Data Sciences Corporation.

\*MULTIBUS is a patented Intel bus.

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

## Quality Assurance Flow Chart CHAPTER 1

ļ

| Single Board Computers                                                                                           |      |

|------------------------------------------------------------------------------------------------------------------|------|

| iSBC 80/04 Single Board Computer                                                                                 | 1-1  |

| iSBC 80/05 or (pSBC 80/05*) Single Board Computer                                                                | 1-7  |

| iSBC 80/10B or (pSBC 80/10B*) Single Board Computer                                                              | 1-12 |

| iSBC 80/20-4 or (pSBC 80/20-4*) Single Board Computer                                                            | 1-19 |

| iSBC 80/24 or (pSBC 80/24*) Single Board Computer                                                                | 1-26 |

| iSBC 80/30 or (pSBC 80/30*) Single Board Computer                                                                | 1-35 |

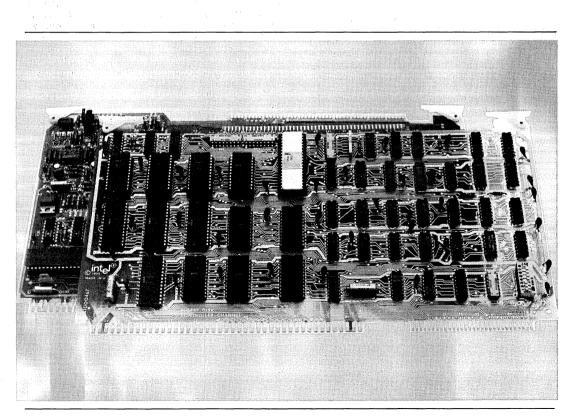

| iSBC 86/12A or (pSBC 86/12A*) Single Board Computer                                                              | 1-43 |

| iSBC 88/40 Measurement and Control Computer                                                                      | 1-51 |

| iSBC 310 High Speed Mathematics Unit                                                                             | 1-59 |

|                                                                                                                  |      |

| CHAPTER 2                                                                                                        |      |

| iSBX™ MULTIMODULE™ Boards                                                                                        |      |

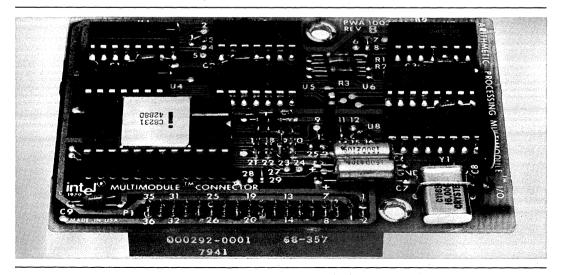

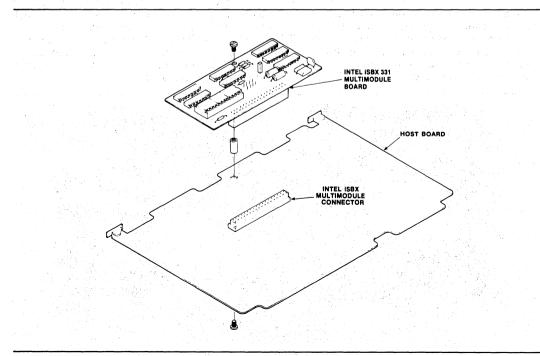

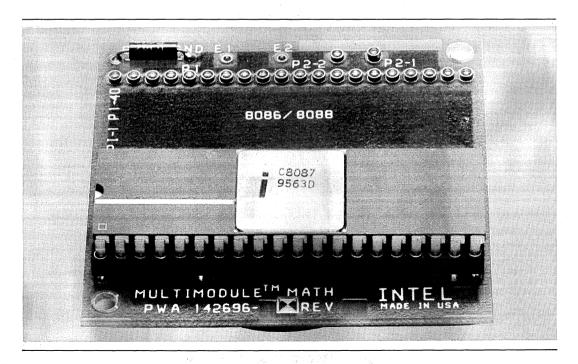

| iSBX 331 Fixed Floating Point Math MULTIMODULE Board                                                             | 2-1  |

| iSBX 332 Floating Point Math MULTIMODULE Board                                                                   | 2-7  |

| iSBX 350 Parallel I/O MULTIMODULE Board                                                                          | 2-12 |

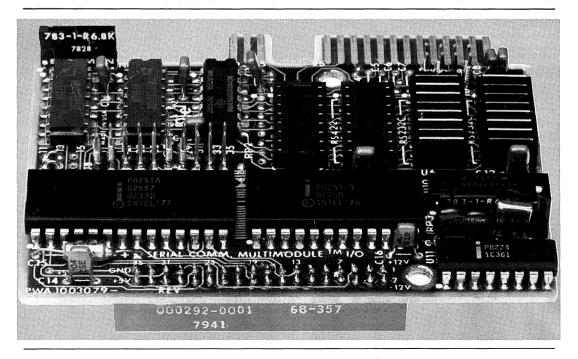

| iSBX 351 Serial I/O MULTIMODULE Board                                                                            | 2-16 |

|                                                                                                                  | 2-10 |

| CHAPTER 3                                                                                                        |      |

|                                                                                                                  |      |

| iCS™ Industrial Control Series                                                                                   | 0.4  |

| iCS 80 Industrial Chassis                                                                                        | 3-1  |

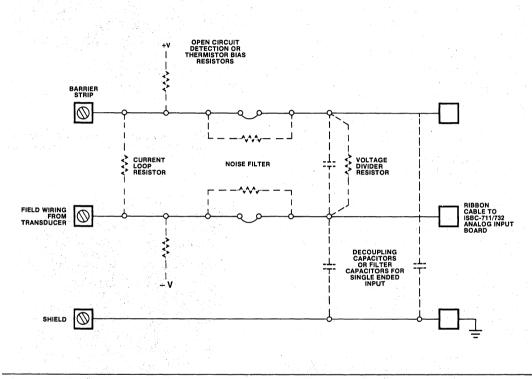

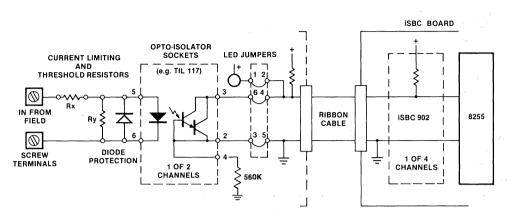

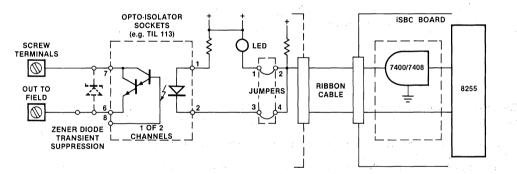

| iCS 910/920/930 Signal Conditioning/Termination Panels                                                           | 3-6  |

| iSBC 941 Industrial Digital Processor                                                                            | 3-14 |

| was a second a second |      |

| CHAPTER 4                                                                                                        |      |

| Run-Times Systems Software                                                                                       |      |

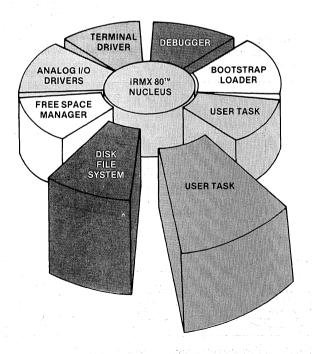

| iRMX /80 Real-Time Multi-Tasking Executive                                                                       | 4-1  |

| iSBC 801 FORTRAN Run-Time Package                                                                                | 4-6  |

| iSBC 802 BASIC-80 Configurable RMX/80 Disk-Based Interpreter                                                     | 4-9  |

| iRMX 86 Operating System                                                                                         | 4-13 |

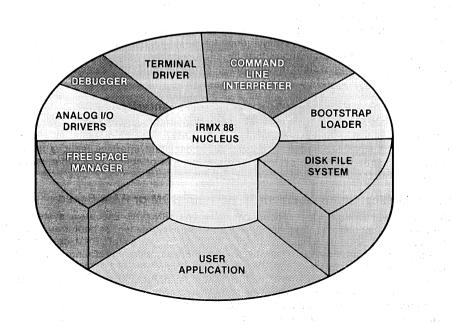

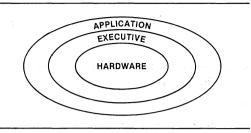

| iRMX 88 Real-Time Multi-Tasking Executive                                                                        | 4-25 |

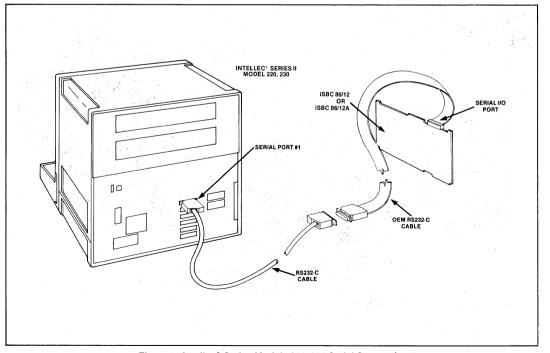

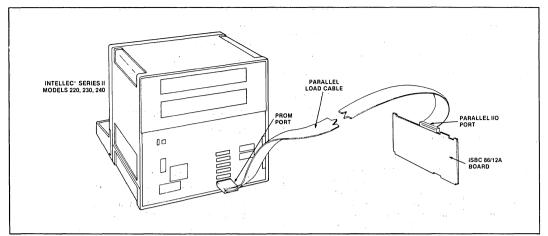

| iSBC 957A Intellec-iSBC 86/12A Interface and Execution Package                                                   | 4-31 |

|                                                                                                                  |      |

| CHAPTER 5                                                                                                        |      |

| Peripheral Controllers                                                                                           |      |

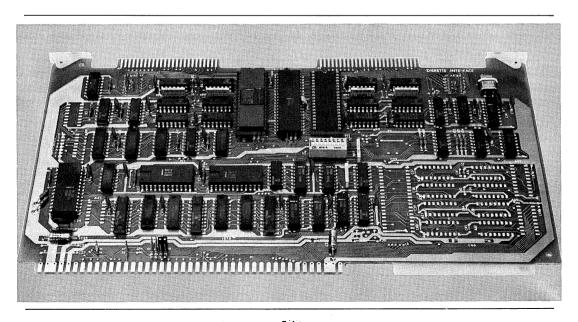

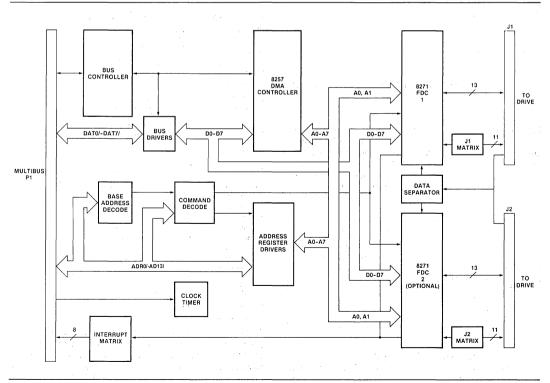

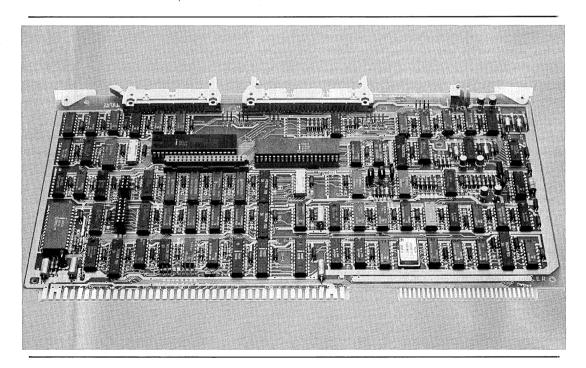

| iSBC 202 Double Density Diskette Controller                                                                      | 5-1  |

| iSBC 204 Single Density Flexible Diskette Controller                                                             | 5-4  |

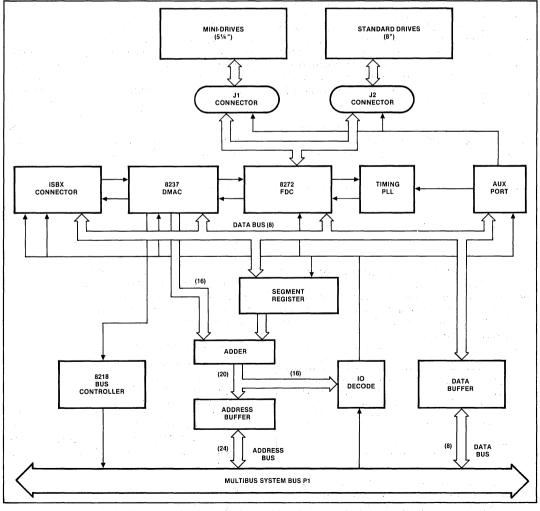

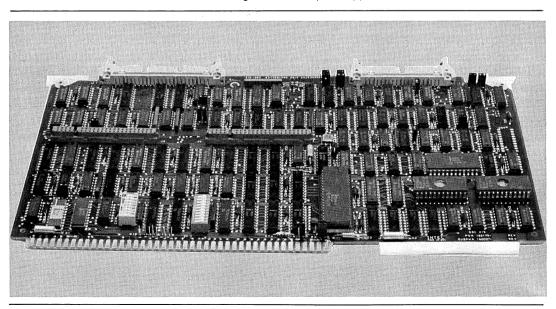

| iSBC 208 Flexible Disk Controller                                                                                | 5-8  |

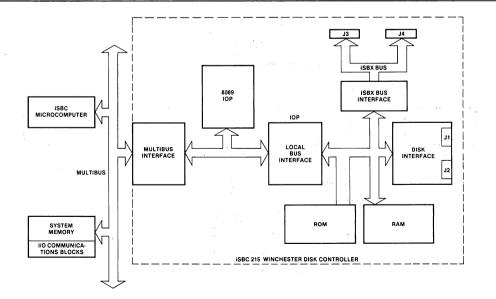

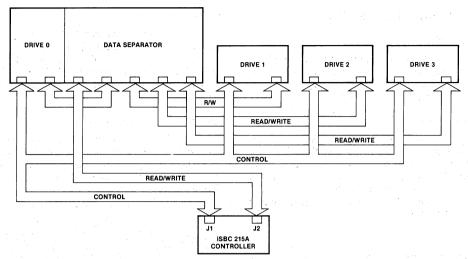

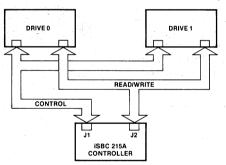

| iSBC 215A/iSBC 215B Winchester Disk Controller                                                                   | 5-12 |

| iSBC 218 Flexible Disk Controller                                                                                | 5-12 |

|                                                                                                                  | 5-21 |

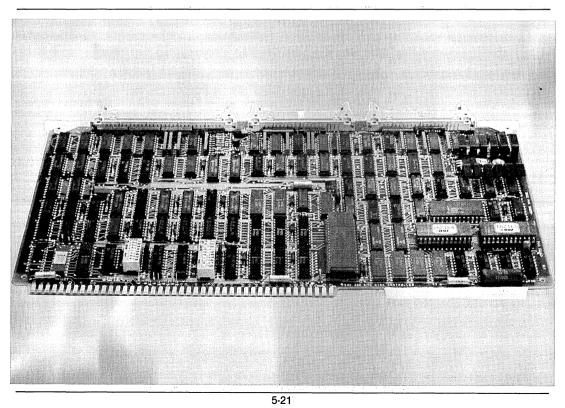

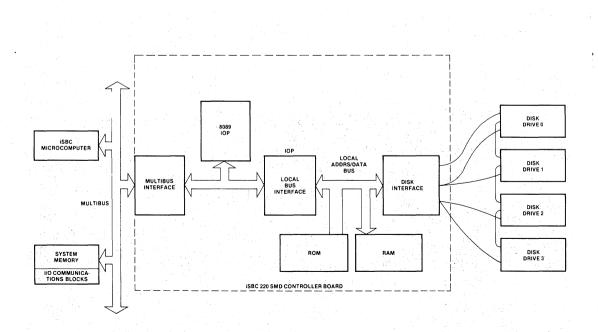

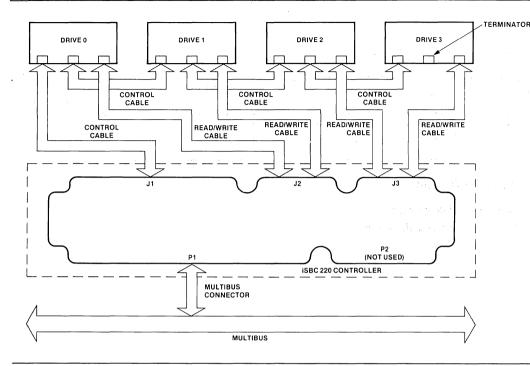

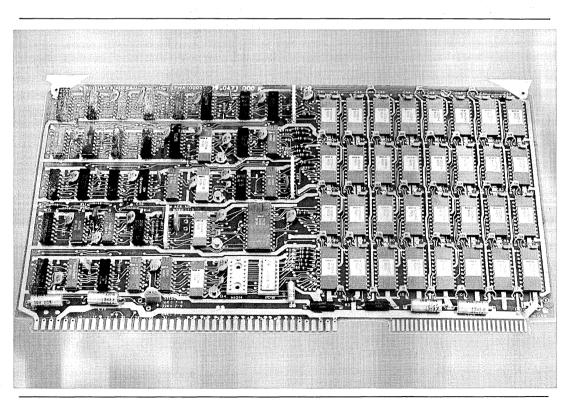

| iSBC 220 SMD Disk Controller                                                                                     | 5-21 |

|                                                                                                                  |      |

| CHAPTER 6                                                                                                        |      |

| Memory Expansion Boards                                                                                          |      |

| iSBC 016 16K-Byte RAM Memory Board                                                                               | 6-1  |

| iSBC 032/048/064 RAM Memory Boards                                                                               |      |

| iSBC 090 Memory System                                                                                           | 6-5  |

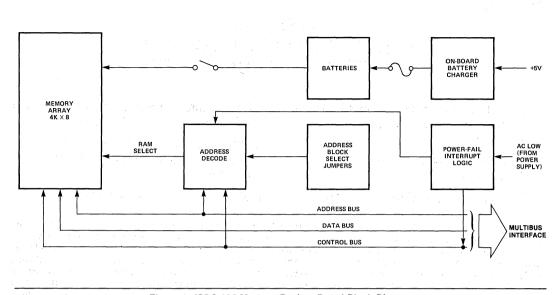

| iSBC 094 4K-Byte CMOS RAM Memory Battery Backup Board                                                            | 6-9  |

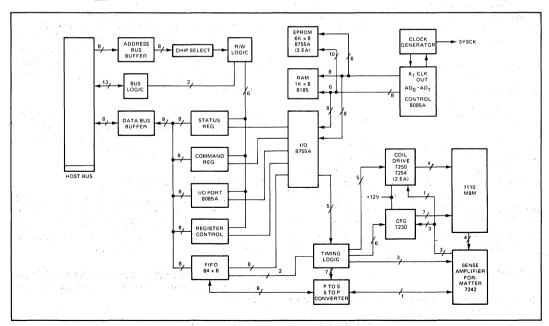

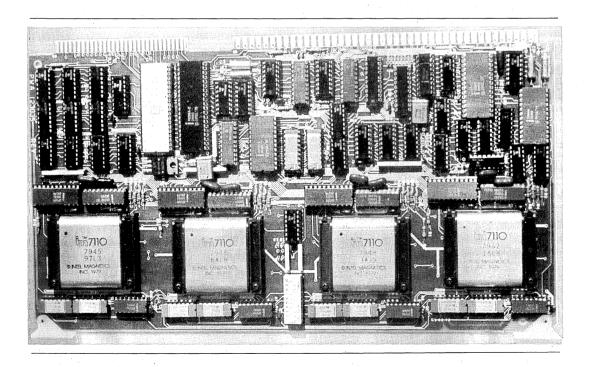

| iSBC 250 1 Megabit Bubble Memory Board                                                                           | 6-12 |

| iSBC 254 Bubble Memory Board                                                                                     | 6-15 |

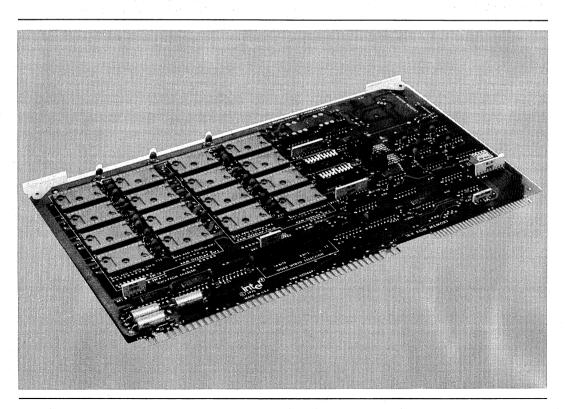

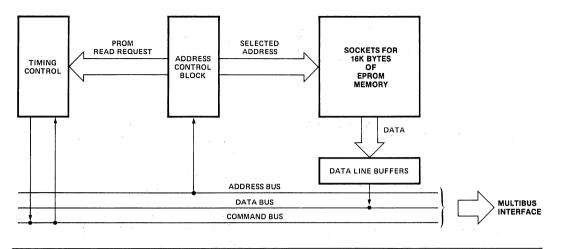

| iSBC 416 16K EPROM Expansion Board                                                                               | 6-16 |

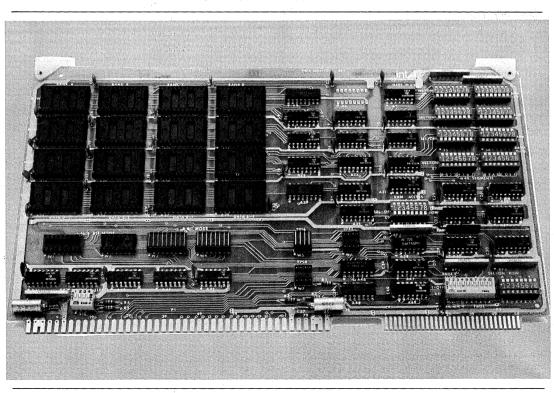

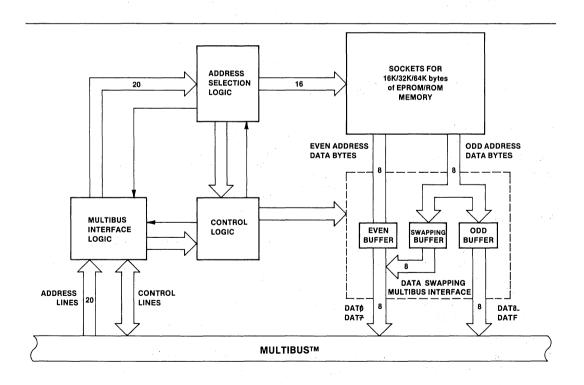

| iSBC 464 or (pSBC 464*) 64K-Byte EPROM Expansion Board                                                           | 6-18 |

| iSBC 108A/116A Combination Memory and I/O Expansion Boards                                                       | 6-21 |

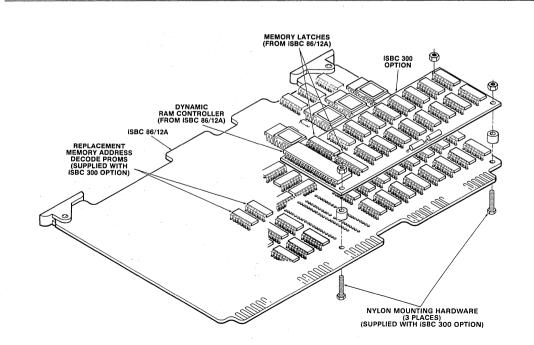

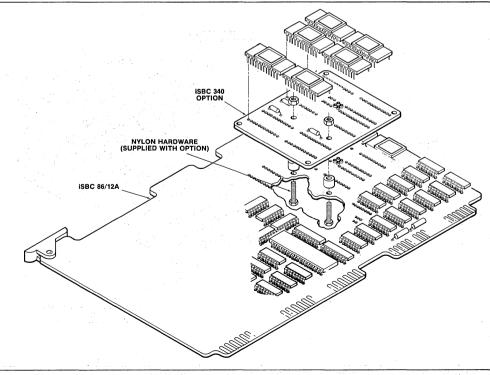

| iSBC 300 or (pSBC 300*) 32K-Byte RAM Expansion Module iSBC 340 or (pSBC 340*)                                    |      |

| 16K-Byte EPROM Expanison Module                                                                                  | 6-29 |

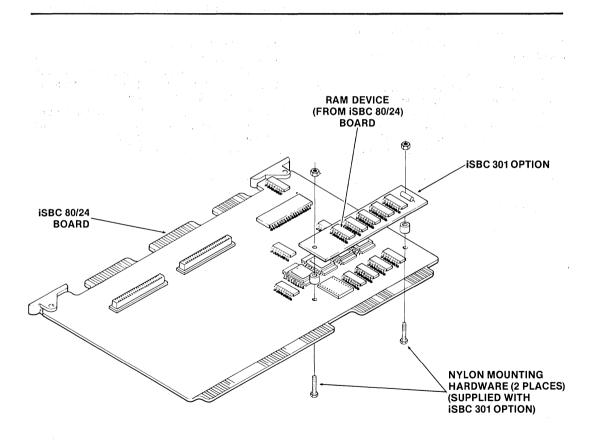

| iSBC 301 4K-Byte RAM MULTIMODULE Board                                                                           | 6-30 |

|                                                                                                                  |      |

| CHAPTER 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

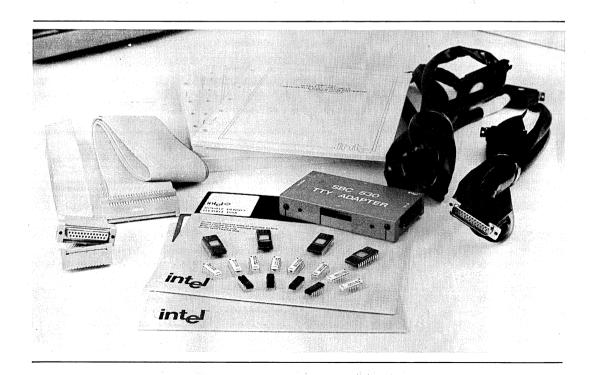

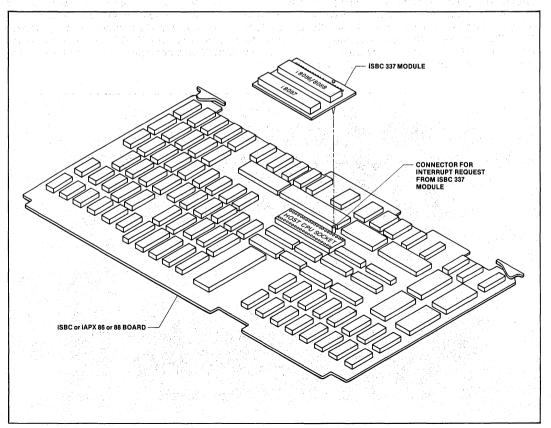

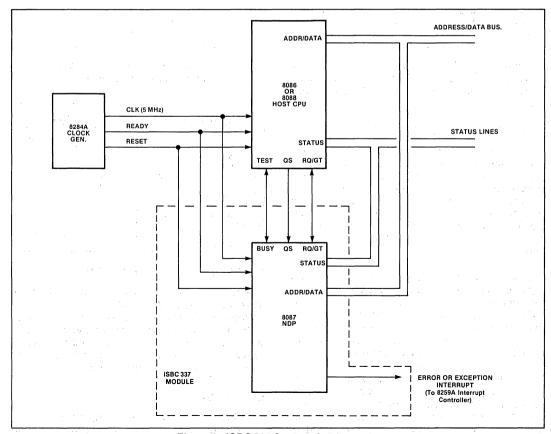

| Digital I/O Expansion and Signal Conditioning Boards<br>iSBC 337 MULTIMODULE Numeric Data Processor<br>iSBC 501 Direct Memory Access Controller.<br>iSBC 508 I/O Expansion Board<br>iSBC 517 Combination I/O Expansion Board<br>iSBC 519 or (pSBC 519*) Programmable I/O Expansion Board<br>iSBC 530 Teletypewriter Adapter.<br>iSBC 556 Optically Isolated I/O Board<br>iSBC 569 Intelligent Digital Controller                                                              | 7-9<br>7-13<br>7-15<br>7-19<br>7-23<br>7-25 |

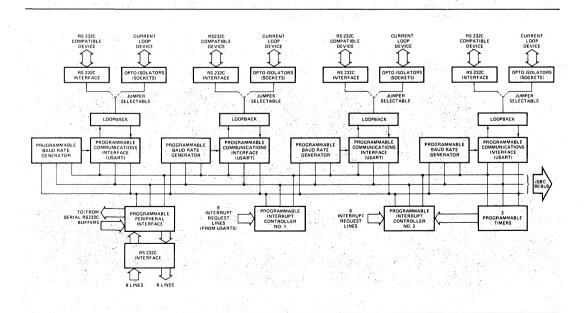

| CHAPTER 8<br>Communication Controllers<br>iSBC 534 or (pSBC 534*) Four Channel Communications Expansion Board<br>iSBC 544 Intelligent Communications Controller                                                                                                                                                                                                                                                                                                               | 8-1<br>8-5                                  |

| CHAPTER 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1997 (N. 19                                 |

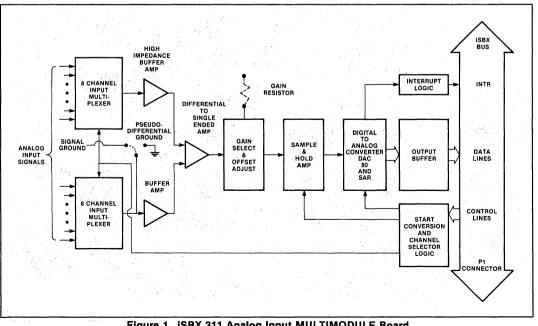

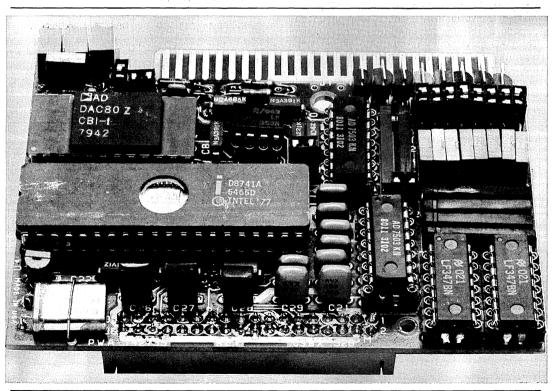

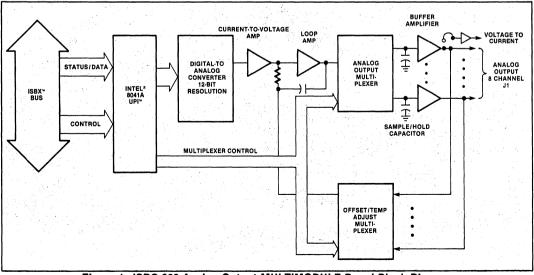

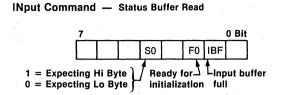

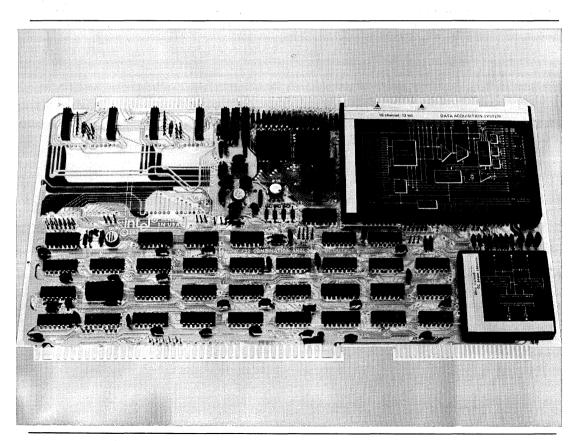

| Analog I/O Expansion & Signal Conditioning Boards         iSBX 311 Analog Input MULTIMODULE Board         iSBX 328 Analog Output MULTIMODULE Expansion Board         iSBX 711 Analog Input Board         iSBX 724 Analog Output Board         iSBX 732 Analog Combination I/O Board                                                                                                                                                                                           | 9-5<br>9-9<br>9-13                          |

| CHAPTER 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                             |

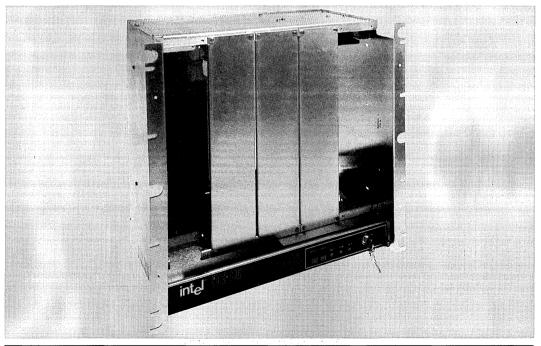

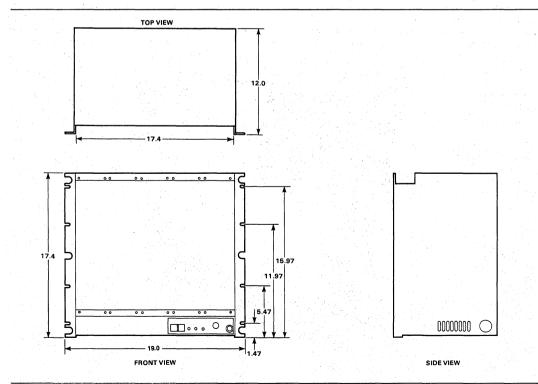

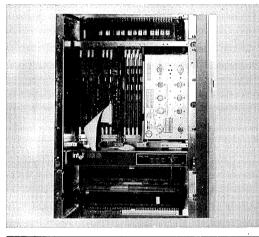

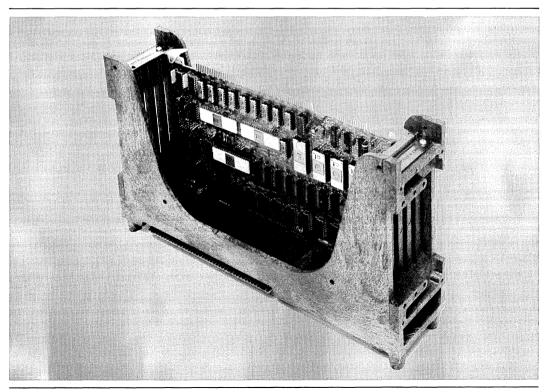

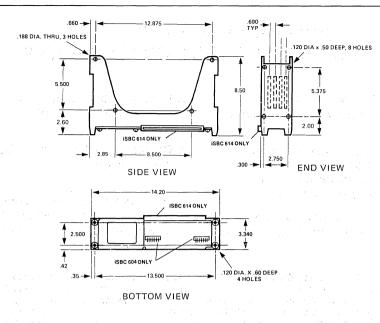

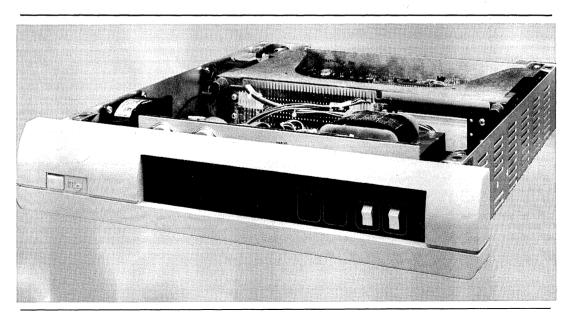

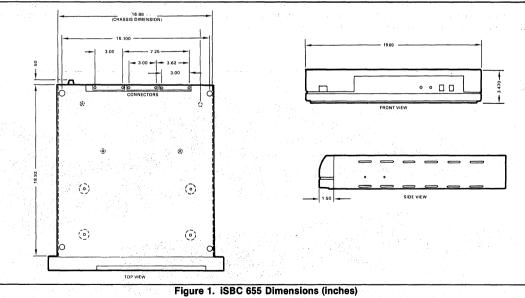

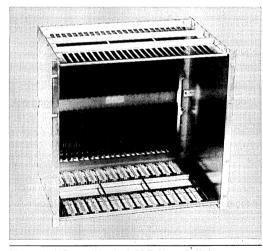

| System Packaging & Power Supplies<br>ISBC 604/614 or (pSBC 604/614*) Modular Cardcage/Backplane<br>ISBC 655 System Chassis<br>ISBC 660 System Chassis<br>ISBC 635 Power Supply<br>ISBC 640 Power Supply                                                                                                                                                                                                                                                                       | 10-5<br>10-8                                |

| CHAPTER 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                             |

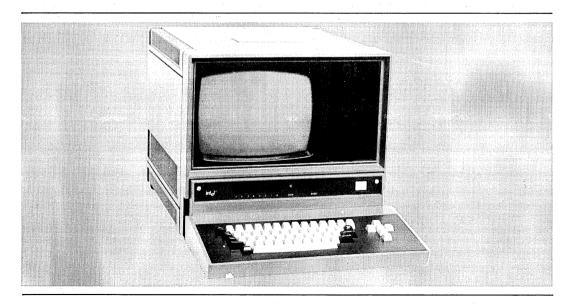

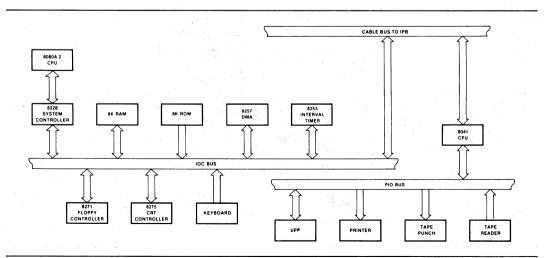

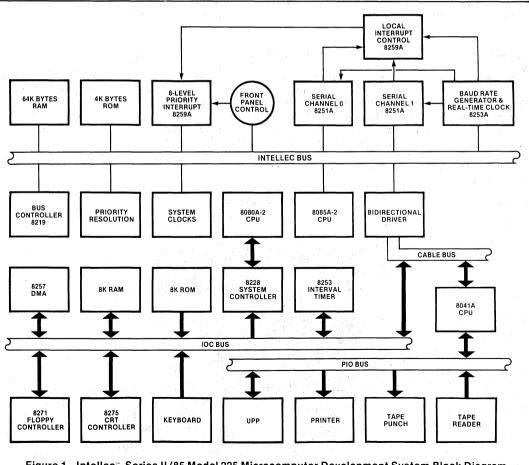

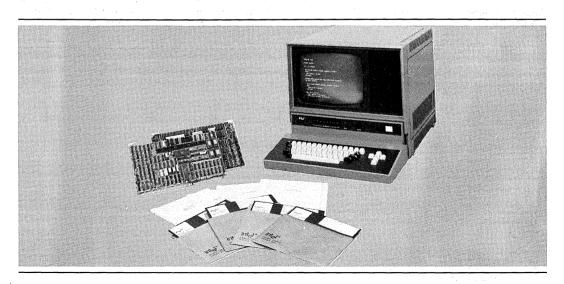

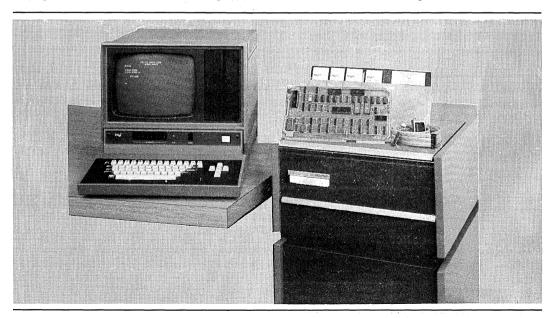

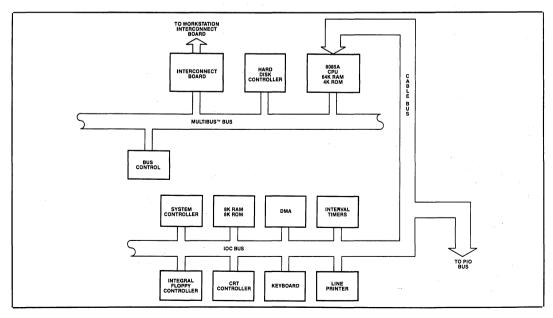

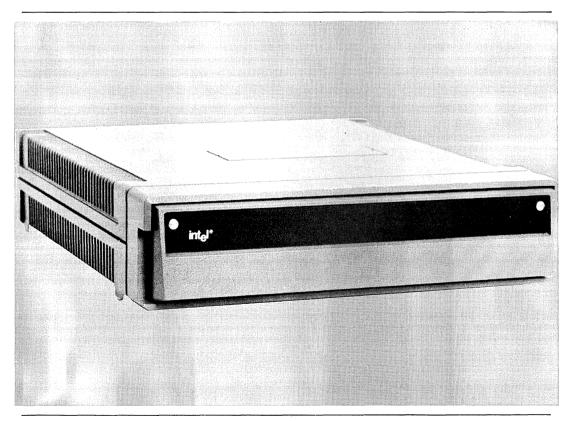

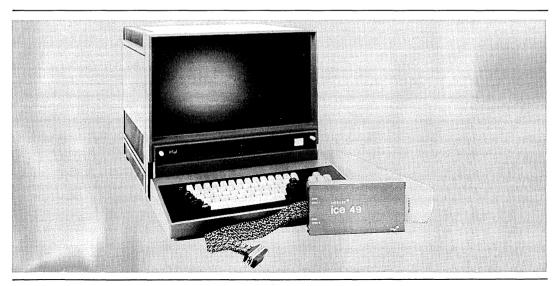

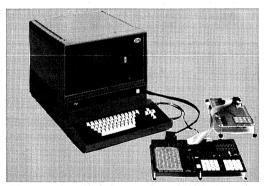

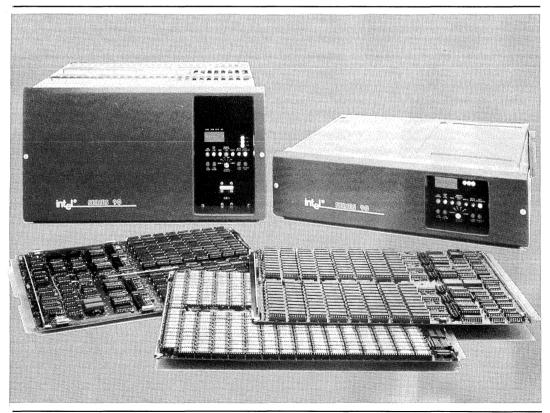

| Microcomputer Development Systems         Introduction - New Dimensions in Development Solutions         Model 120 Intellec Series II Microcomputer Development System         Model 225 Intellec Series II/85 Microcomputer Development System         Model 286 Intellec Series III Microcomputer Development System         Model 286 Intellec Series III Microcomputer Development System         Model 280 Network Manager Intellec Network Development System-1 (NDS-1) | 11-3<br>11-7<br>11-12                       |

| CHAPTER 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                             |

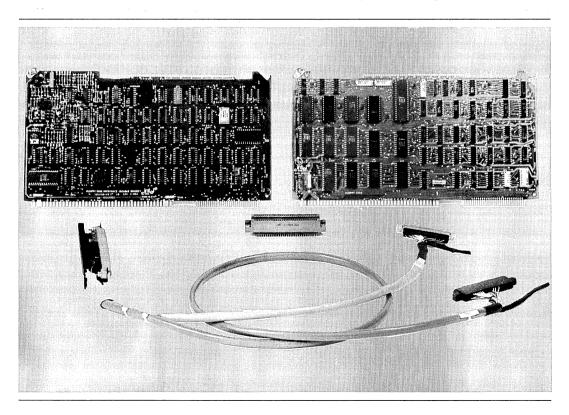

| Microcomputer Development Systems Options<br>Expansion Chassis Intellec Series II Microcomputer Development System<br>Model 503 Double Density Upgrade Kit for Intellec Microcomputer Development System<br>Model 505 Intergrated Processor Card<br>Model 556 iAPX 86 Resident Processor Board Package<br>Model 590 Network Manager Upgrade Package Intellec Network Development System-1                                                                                     | 12-5<br>12-8                                |

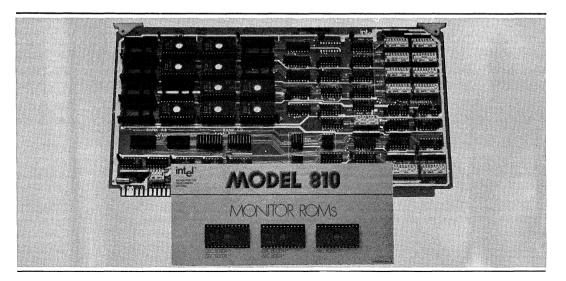

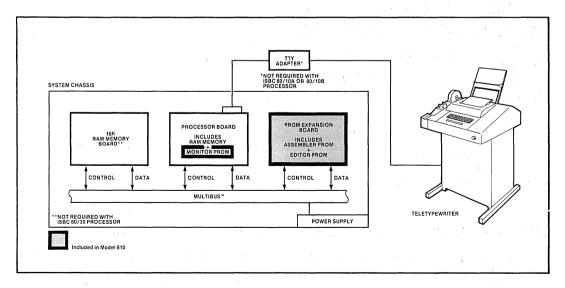

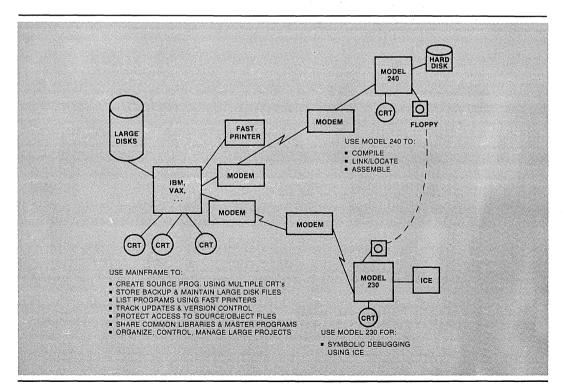

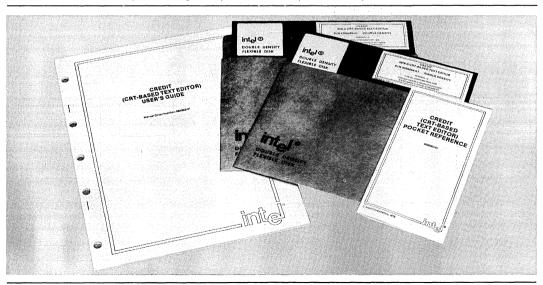

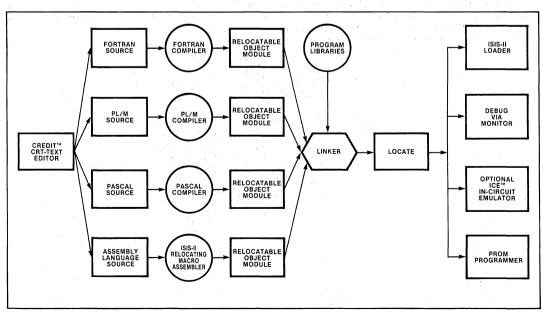

| (NDS-1)<br>Model 810 Software Development Module<br>Mainframe Link for Distributed Development<br>Credit CRT-Based Text Editor Microcomputer Development Systems                                                                                                                                                                                                                                                                                                              | 12-11<br>12-14<br>12-18<br>12-21            |

| CHAPTER 13<br>Flexible and Hard Disk Systems<br>Intellec Single/Double Density Flexible Disk System                                                                                                                                                                                                                                                                                                                                                                           |                                             |

| CHAPTER 14<br>MCS 80/85™ Development Systems and Options                                                                                                                                                                                                                                                                                                                                                                                                                      |                                             |

| FORTRAN 80 8080/8085 ANS FORTRAN 77 Intellec Resident Compiler | 14-1 |

|----------------------------------------------------------------|------|

| Basic-80 Extended ANS 1978 Basic Intellec Resident Interpreter | 14-5 |

|                                                                |      |

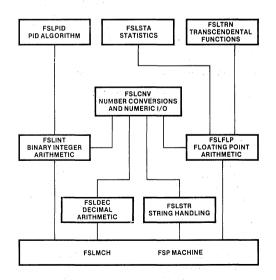

| 8080/8085 Fundamental Support Package (FSP)                 | 14-8          |

|-------------------------------------------------------------|---------------|

|                                                             | 14-12         |

|                                                             | 14-16         |

|                                                             | 14-19         |

|                                                             | 14-24         |

|                                                             | 14-26         |

|                                                             | 14-28         |

|                                                             | 14-34         |

| OUADTED 15                                                  |               |

| CHAPTER 15                                                  |               |

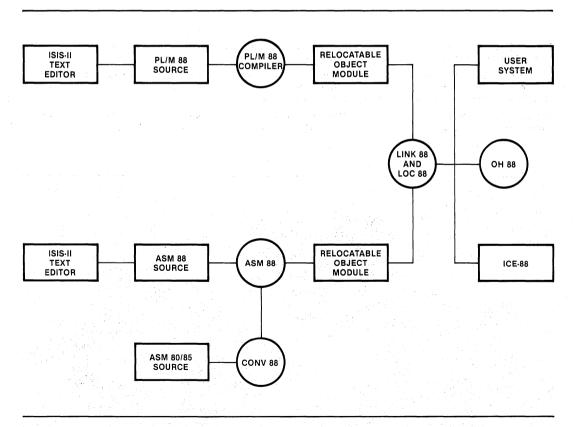

| iAPX 86/88 Support Options                                  | 45.4          |

| Series II 8086/8088 Software Development Packages           | 15-1<br>15-11 |

| PL/M 86/88 Software Package                                 | 15-11         |

| PASCAL 86/88 Software Package                               | 15-10         |

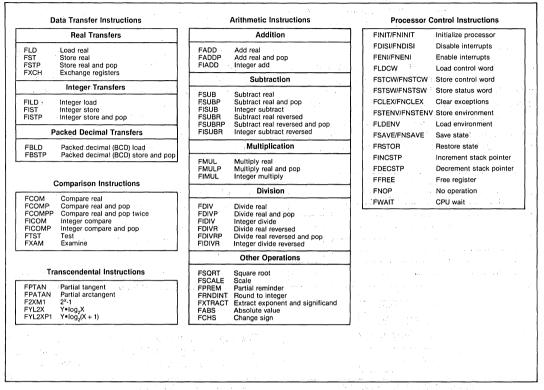

| 8087 Software Support Package                               | 15-19         |

|                                                             | 15-22         |

|                                                             | 15-25         |

|                                                             | 15-30         |

|                                                             | 15-36         |

|                                                             | 10-00         |

| CHAPTER 16                                                  |               |

| Prototype Microcomputer Kits                                |               |

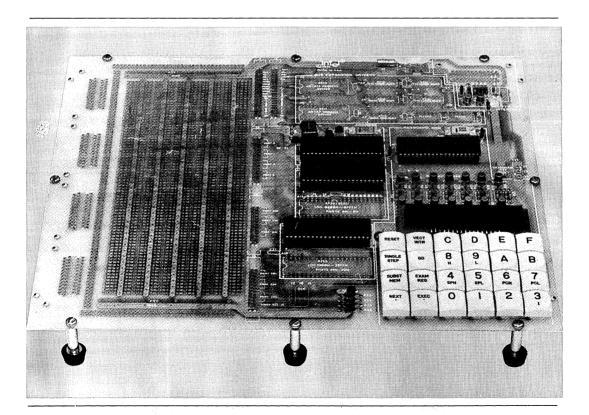

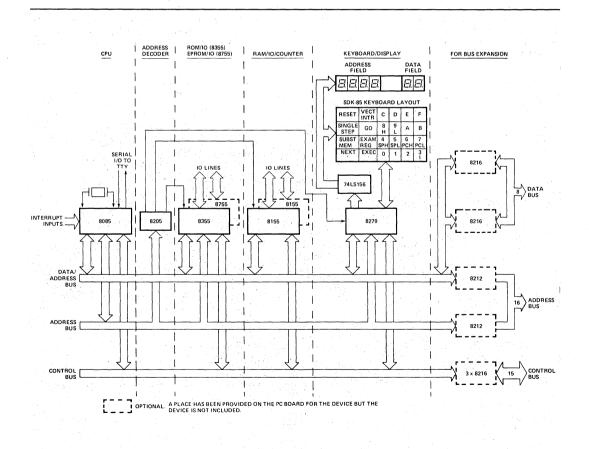

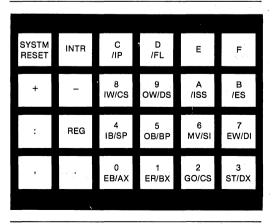

| SDK-85, MCS-85 System Design Kit                            | 16-1          |

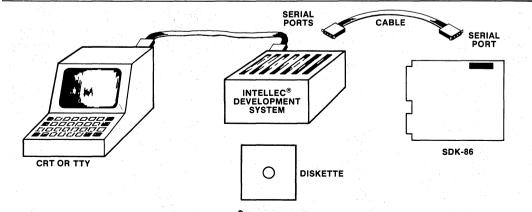

| SDK-86, MCS-86 System Design Kit                            | 16-7          |

| SDK-C86, MCS-86 System Design Kit                           |               |

| Software and Cable Interface to Intellec Development System | 16-13         |

| CHAPTER 17                                                  |               |

| MCS-48™ Development Systems                                 |               |

| MCS-48 Diskette-Based Software Support Package              | 17-1          |

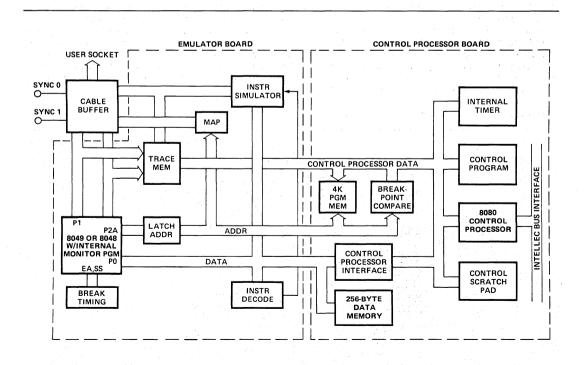

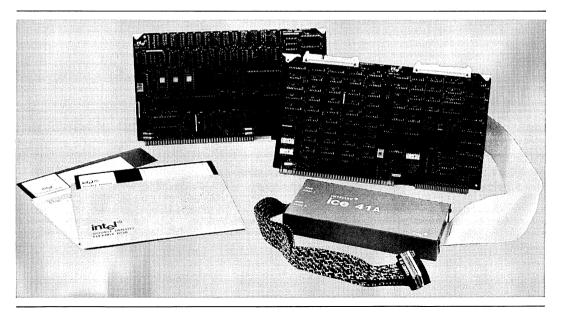

| ICE-49, MCS-48 In-Circuit Emulator                          | 17-3          |

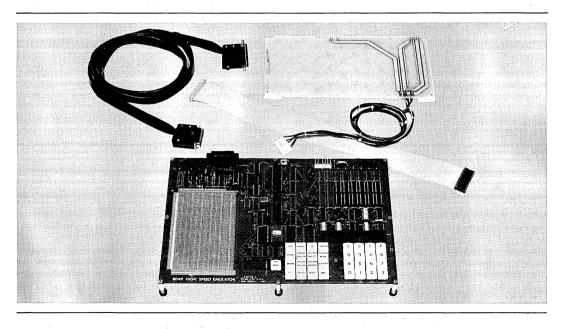

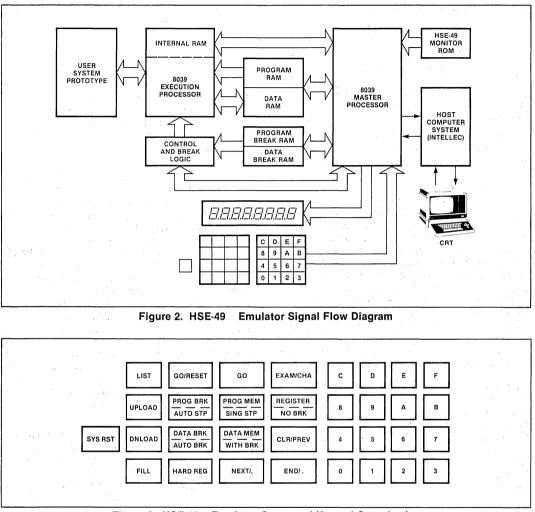

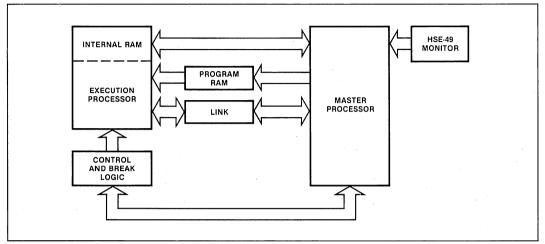

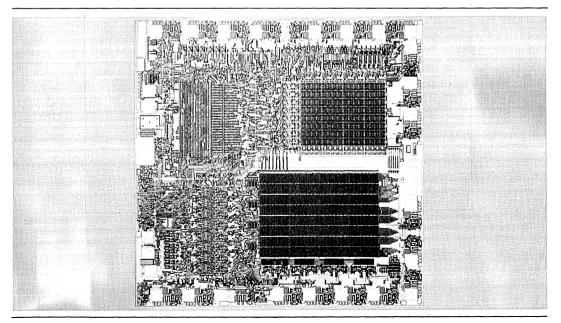

| HSE-49 High Speed Emulator                                  | 17-7          |

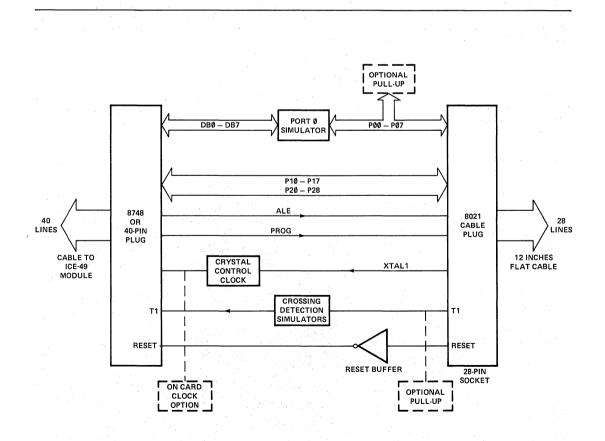

| EM1 8021 Emulation Board                                    | 17-13         |

|                                                             | 17-16         |

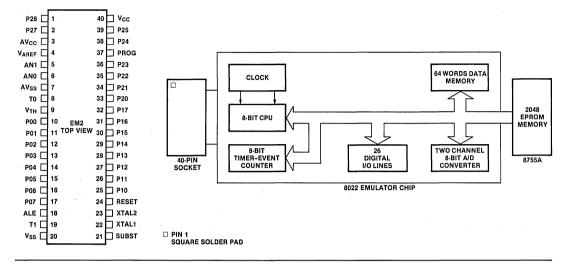

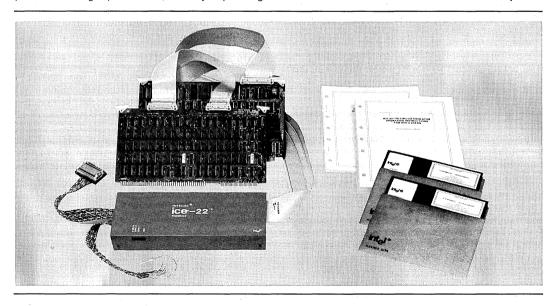

| ICE-22, 8022 In-Circuit Emulator                            | 17-19         |

| CHAPTER 18                                                  |               |

| MCS-51 <sup>TM</sup> Development Systems                    |               |

| 8051 Software Development Package                           | 18-1          |

| CHAPTER 19                                                  |               |

| UPI-41A™ Development Systems                                |               |

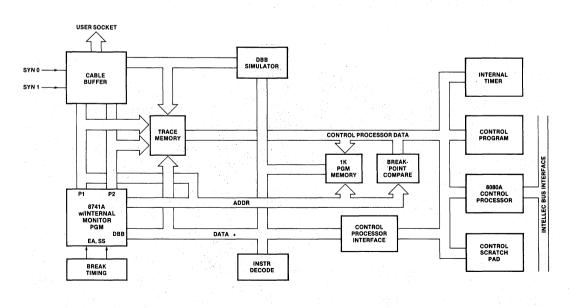

| ICE-41A, UPI-41A In-Circuit Emulator                        | 19-1          |

|                                                             | 13-1          |

| CHAPTER 20                                                  |               |

| 2920 Signal Processor Development Systems                   |               |

| 2920 Software Support Package                               | 20-1          |

| CHAPTER 21                                                  |               |

| Memory Systems                                              |               |

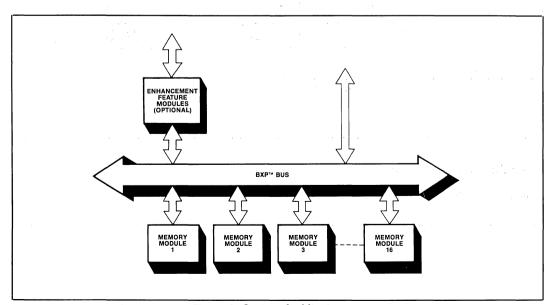

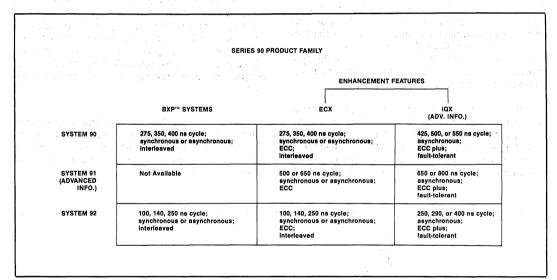

| Introduction                                                | 21-1          |

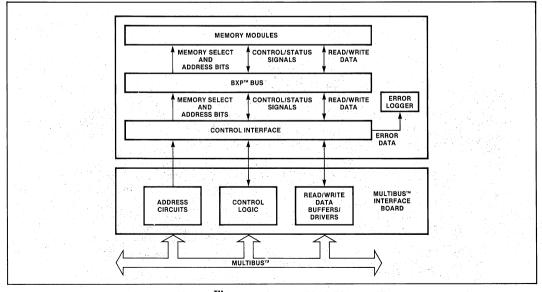

| Series 90 General Purpose Memory System                     | 21-2          |

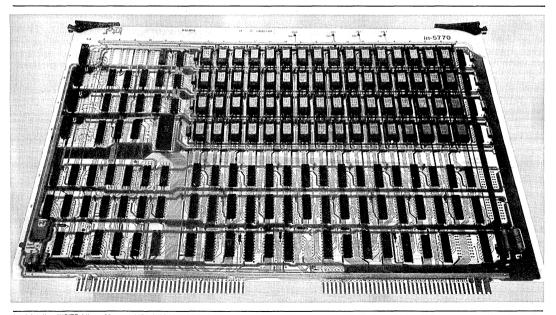

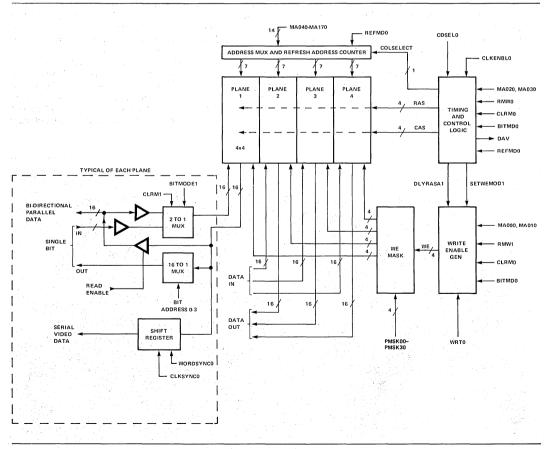

| in-5770 Video Refresh Memory System                         | 21-5          |

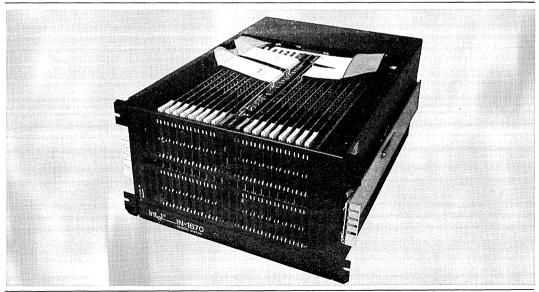

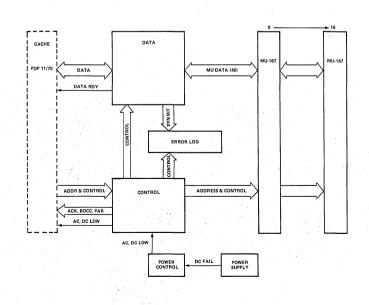

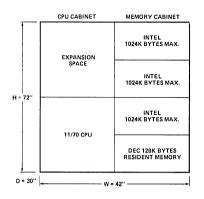

| in-1670, PDP*-11/70 Add-On Memory System                    | 21-11         |

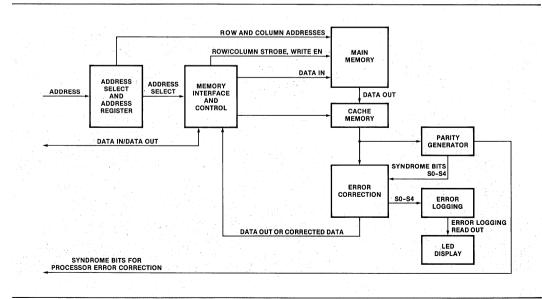

| in-5150 Eclipse Add-In Memory                               | 21-15         |

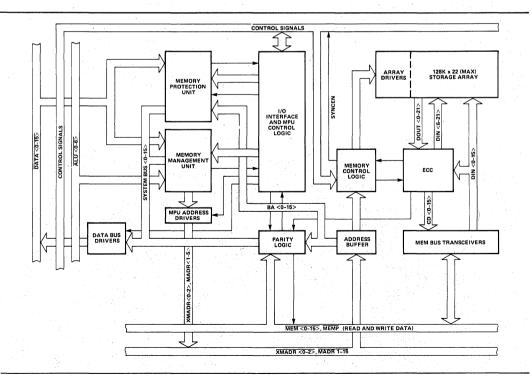

| in-5160 Nova 3 Add-In Memory                                | 21-19         |

| MU-5780 VAX-11/780 Add-In Memory Card                       | 21-24         |

| CHAPTER 22                                                  |               |

| Insite™ User's Program Library                              | 22-1          |

|                                                             | '             |

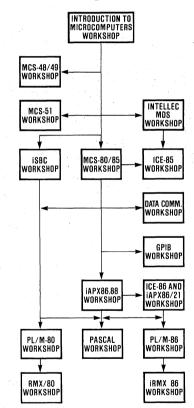

| CHAPTER 23 Intel Microcomputer Workshops                    | 00 4          |

| · _ 프로그램 · · · · · · · · · · · · · · · ·                    | 23-1          |

| CHAPTER 24                                                  |               |

| Product Service                                             | 24-1          |

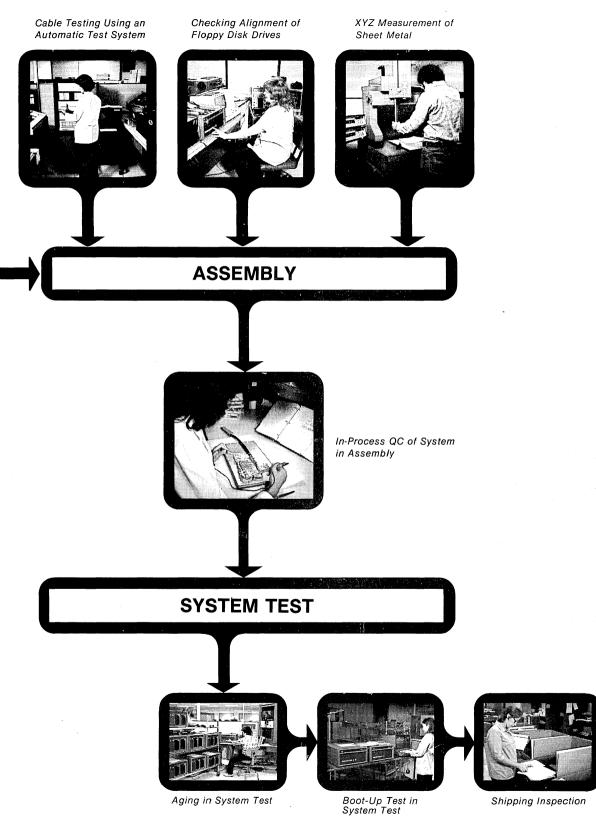

# QUALITY ASSURANCE

## A typical product flow

Gold Thickness Measurement on Raw Boards

Kit Audit

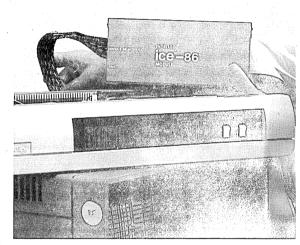

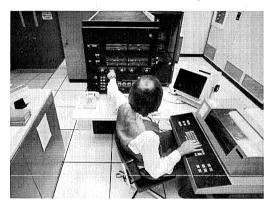

Automatic Test Systems Utilized in Board Testing

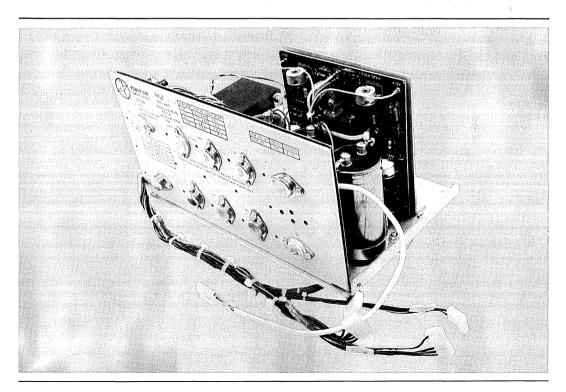

Single Board Computer Test Fixture

Visual Inspection of Printed Wire Assemblies

Ovens Utilized for Board Pre-Bake

# Single Board Computers

int

## iSBC 80/04 SINGLE BOARD COMPUTER

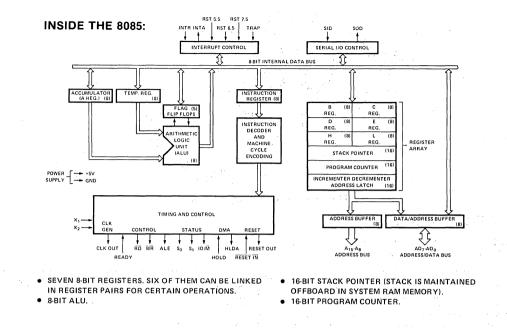

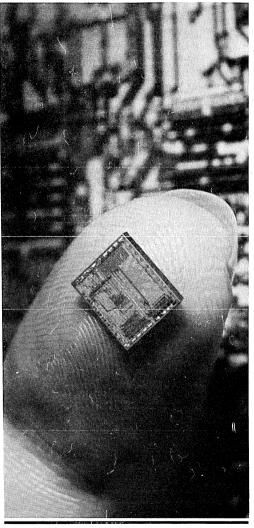

- 8085A CPU used as central processor

- 256 bytes of static read/write memory

- Sockets for 4K bytes of erasable reprogrammable read only memory

- 22 programmable parallel I/O lines with sockets for interchangeable line drivers and terminators

- Optimized for stand-alone applications with provisions for on-board + 5V regulator, heat sink, and mounting holes for attachment to user's equipment

- Programmable 14-bit binary timer

- TTL serial I/O interface with hole patterns for RS232C line drivers and receivers

- Four-level vectored interrupt

- Upward compatibility with iSBC 80/05

- Single + 5V power supply

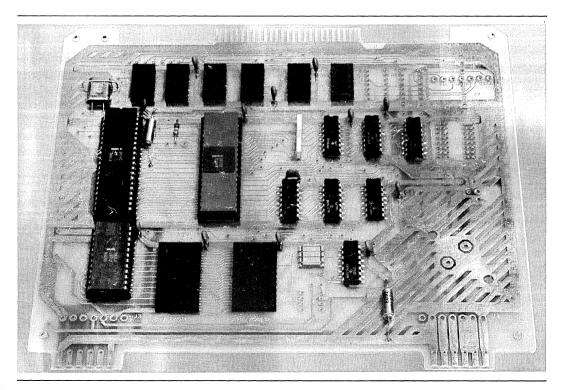

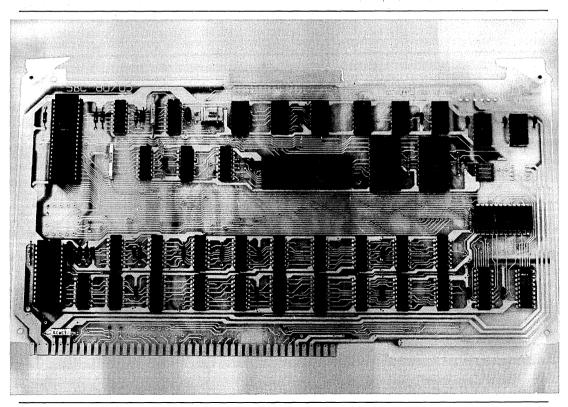

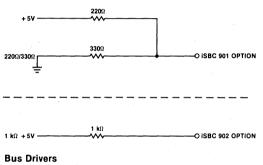

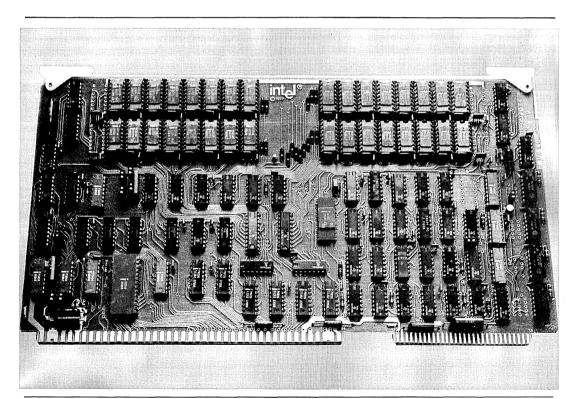

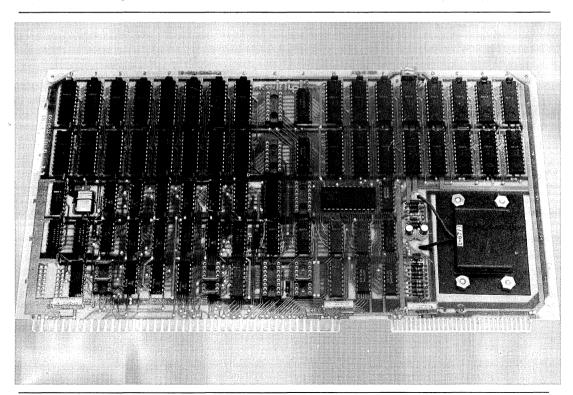

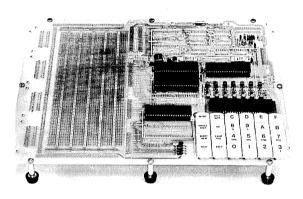

The iSBC 80/04 Single Board Computer is a member of Intel's complete line of OEM computer systems which take full advantage of Intel's LSI technology to provide economical, self-contained computer-based solutions for OEM applications. The iSBC 80/04 is a complete computer system on a single 6.75 × 7.85-inch printed circuit card. The CPU, system clock, read/write memory, nonvolatile read only memory, I/O ports and drivers, serial interface, priority interrupt logic, and programmable timer all reside on the board.

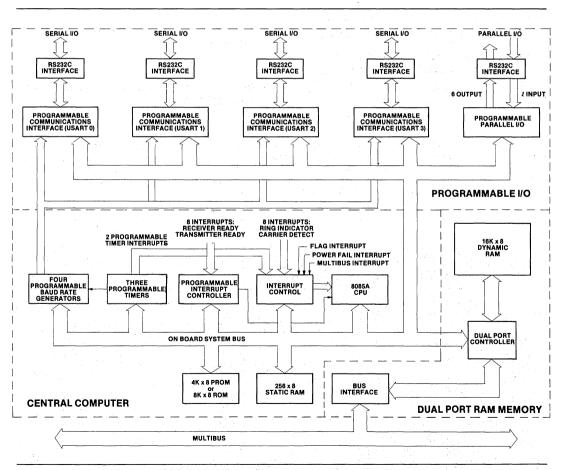

## FUNCTIONAL DESCRIPTION

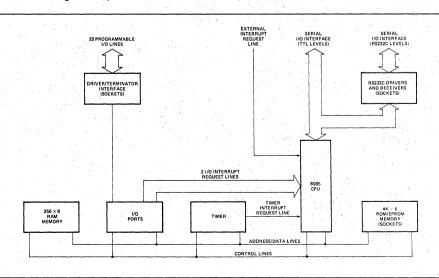

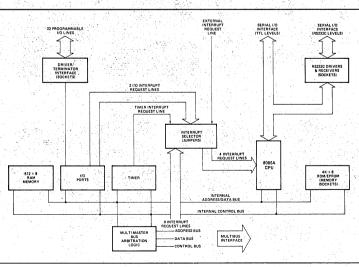

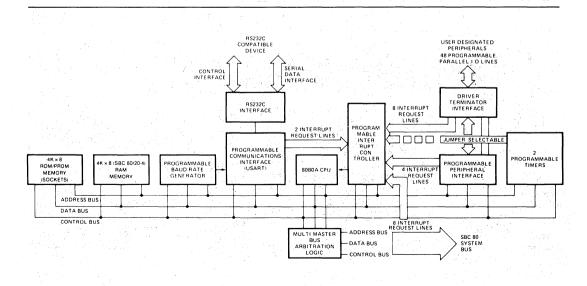

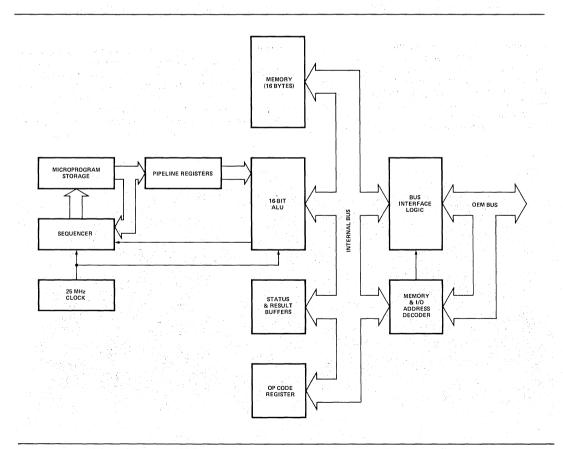

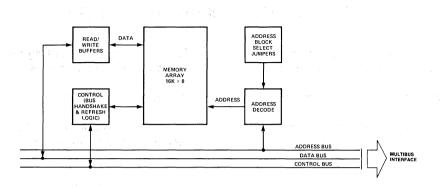

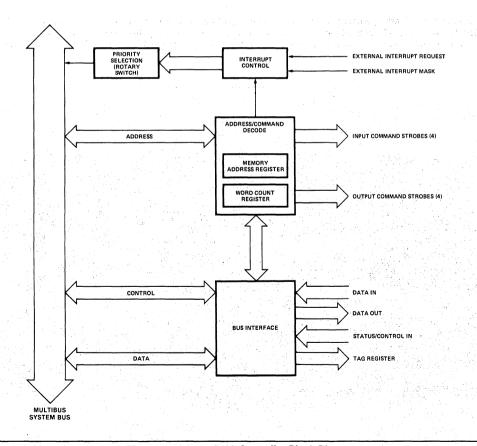

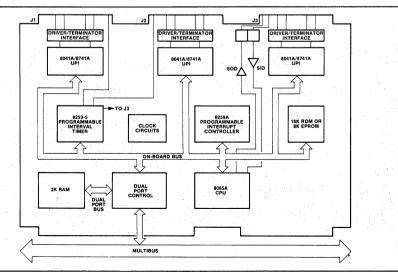

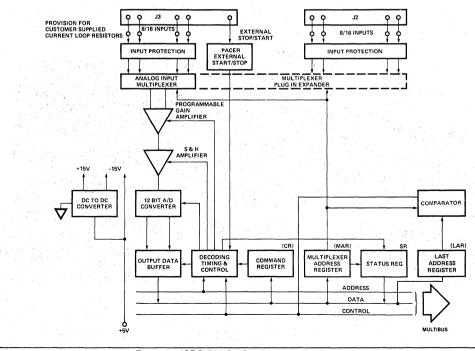

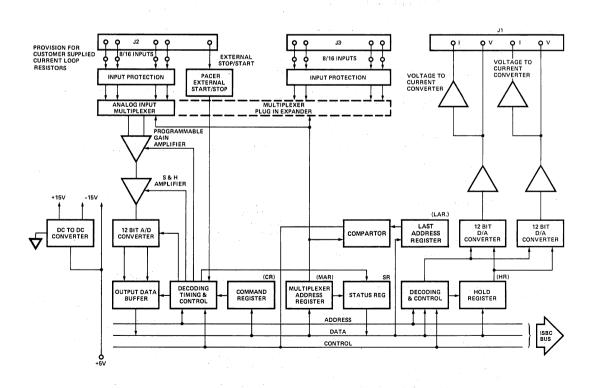

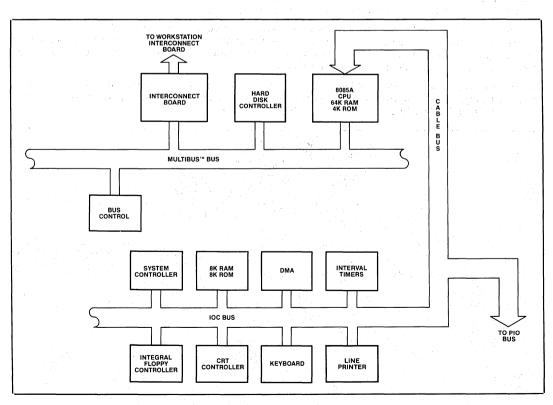

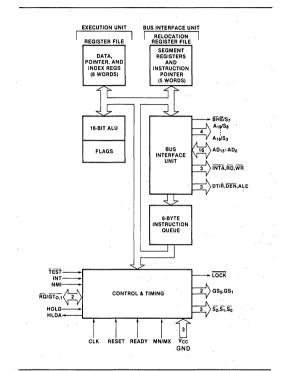

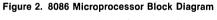

Intel's powerful 8-bit n-channel 8085A CPU, fabricated on a single LSI chip, is the central processor for the iSBC 80/04. The 8085A CPU is directly software compatible with the popular intel 8080A CPU. The 8085A contains six 8-bit general purpose registers and an accumulator. The six general purpose registers may be addressed individually or in pairs, providing both single and double precision operators. Minimum on-board instruction execution time is 2.03 microseconds. A block diagram of iSBC 80/04 functional components is shown in Figure 1.

## **Memory Addressing**

The 8085A CPU has a 16-bit program counter which allows addressing of up to 65,536 bytes of memory. An external stack, located within any portion of iSBC 80/04 read/write memory, may be used as a last-in/first-out storage area for the contents of the program counter, flags, accumulator, and all of the six general purpose registers. A 16-bit stack pointer controls the addressing of this external stack. This stack provides subroutine nesting bounded only by memory size.

#### **Memory Capacity**

The iSBC 80/04 contains 256 bytes of read/write memory using the Intel 8155 RAM/IO/Timer. Two sockets for up to 4K bytes of nonvolatile read only memory are provided on the board. Read only memory may be added in 2K-byte increments using Intel 2716 erasable and electrically reprogrammable ROMs (EPROMs) or Intel 2316E masked ROMs. Optionally, if only 2K bytes are required, read only memory may be added in 1K-byte increments using Intel 2708 EPROMs or Intel 2608 masked ROMs.

## Parallel I/O Interface

The iSBC 80/04 contains 22 programmable parallel I/O lines implemented using the I/O ports of the Intel 8155

RAM/IO/Timer. The system software is used to configure the I/O lines in any combination of unidirectional input or output ports as indicated in Table 1. The I/O interface may, therefore, be customized to meet specific peripheral requirements. In order to take full advantage of the large number of possible I/O configurations, sockets are provided for interchangeable I/O line drivers and terminators. Hence, the flexibility of the I/O interface is further enhanced by the capability of selecting the appropriate combination of optional line drivers and terminators to provide the required sink current, polarity, and drive/termination characteristics for each application. The 22 programmable I/O lines and signal ground lines are brought out to a 50-pin edge connector that mates with flat, woven, or round cable.

#### Stand-Alone Applications

The iSBC 80/04 is designed to be a cost-effective solution for applications requiring a self-contained computer on a single board without the need for external memory or I/O options. In order to help minimize power supply cost in small systems, the iSBC 80/04 includes provision for an on-board + 5V regulator allowing unregulated voltage to be connected directly on the board. Regulated DC voltages are applied to the board through two 12-pin edge connectors which mate with flat, woven, or round cables. The iSBC 80/04 also includes pins that will accept MOLEX-type connectors for connection of regulated DC voltages. Mounting holes are provided in the corners of the iSBC 80/04 board which permit direct attachment to the user's equipment, thereby eliminating the need for cardcage and backplane.

## Compatibility with iSBC 80/05

The iSBC 80/04 is fully upward compatible with the iSBC 80/05 Single Board Computer. Pin assignments for parallel I/O, serial I/O, and regulated DC voltages are

Figure 1. ISBC Block Diagram Showing Functional Components

|       |           | Mode of Operation<br>Unidirectional |         |                      |        |    |

|-------|-----------|-------------------------------------|---------|----------------------|--------|----|

| Port  | Lines     | Inj                                 | Input   |                      | Output |    |

| (qty) | Unlatched | Latched &<br>Strobed                | Latched | Latched &<br>Strobed | ' .    |    |

| 1     | 8         | х                                   | X       | X                    | Х      |    |

| 2     | 8         | X                                   | X       | X                    | X      |    |

| 3     | 3         | X                                   |         | Х                    |        | X1 |

| 4     | 3         | Х                                   |         | Х                    |        | χ2 |

#### Table 1. Input/Output Port Modes of Operation

#### Notes

1. Port 3 must be used as a control port when port 1 is used as a latched and strobed input or a latched and strobed output port.

2. Port 4 must be used as a control port when port 2 is used as a latched and strobed input or a latched and strobed output port.

indentical to those of the iSBC 80/05. Additionally, software developed for the iSBC 80/04 will execute directly in the iSBC 80/05. In addition to the iSBC 80/04 features, the iSBC 80/05 contains a total of 512 bytes of read/write memory, allows for expansion of memory and I/O capacity, and provides full MULTIBUS arbitration control for multimaster applications.

## **Programmable Timer**

The iSBC 80/04 provides a fully programmable binary 14-bit interval timer utilizing the Intel 8155 RAM/IO/Timer. The systems designer simply configures the time via software to meet system requirements. Whenever a given timer delay is needed, software commands to the programmable timer select the desired functions. Four functions are available as shown in Table 2. The contents of the timer counter may be read at any time during system operation.

| Function                      | Operation                                                                                                                                                                                                      |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Programmable<br>pulse         | Timer out goes low during the sec-<br>ond half of count. Therefore, the<br>count loaded in the count length<br>register should be twice the pulse<br>width desired.                                            |

| Square wave<br>rate generator | Timer out remains high until one-<br>half the count has been completed,<br>and goes low for the other half of the<br>count. The count length is auto-<br>matically reloaded when terminal<br>count is reached. |

| Rate generator                | Divide by N counter. A repetitive<br>timer out low pulse is generated and<br>new timeout initiated every time ter-<br>minal count is reached.                                                                  |

| Programmable<br>strobe        | A single low pulse is generated upon<br>reaching terminal count. This func-<br>tion is extremely useful for genera-<br>tion of real-time clocks.                                                               |

## Serial I/O Interface

The iSBC 80/04 prvides serial I/O capability through the serial input data (SID) and serial output data (SOD) functions of the Intel 8085A CPU. These functions are controlled exclusively by software through execution of the 8085A RIM and SIM instructions. The baud rate for the serial I/O interface is determined by the system time available for execution of serial I/O support software. Hence, the maximum baud rate supported by the iSBC 80/04 is solely dependent on the overall system real-time software requirements. Serial I/O signals are TTL compatible, and hole patterns are provided on the board for optional installation of RS232C line drivers and receivers.

## Interrupt Capability

The iSBC 80/04 takes advantage of the powerful interrupt processing capability of the 8085A CPU. Interrupt requests are routed to four interrupt inputs of the 8085A CPU (i.e., TRAP, RST 7.5, RST 6.5, and RST 5.5 in order of priority, TRAP highest), and each input generates a unique memory address (i.e., TRAP:  $26_{16}$ , RST 7.5:  $3C_{16}$ , RST 6.5:  $34_{16}$ , RST 5.5:  $2C_{16}$ ). A single 8085A jump instruction at each of these addresses then provides linkage to locate each interrupt service routine independently anywhere in memory. All interrupt inputs with the exception of one (TRAP) may be masked via software. The trap interrupt should be used for conditions such as power-down sequences which require attention by the 8085A CPU.

Interrupt Generation — The iSBC 80/04 accepts interrupts from four sources. An interrupt is automatically generated by the programmable interval timer/event counter upon completion of the selected function. Two interrupts are automatically generated by the I/O ports section of the 8155 when ports 1 or 2 of the 8155 are programmed to operate in the "latched and strobed" mode (see Table 1). The fourth interrupt source is available to the user and should be used to inform the 8085A CPU of catastrophic errors such as power failure. This userdefined source is connected to the trap input of the 8085A CPU.

## Systems Development Capability

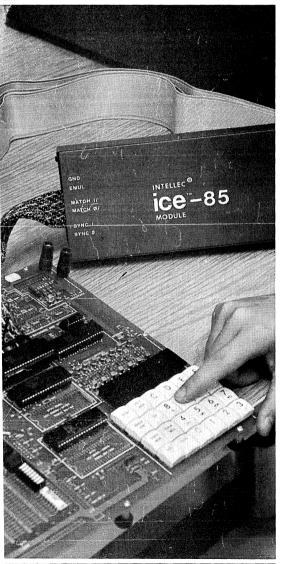

The development cycle of the iSBC 80/04-based products may be significantly reduced using an Intellec microcomputer development system. The resident macroassembler, text editor, and system monitor greatly simplify the design, development, and debug of iSBC 80/04 system software. An optional diskette operating system provides a relocating macroassembler, a relocating loader and linkage editor, and a library manager. A unique in-circuit emulator (ICE-85) option provides the capability of developing and debugging software directly on the iSBC 80/04.

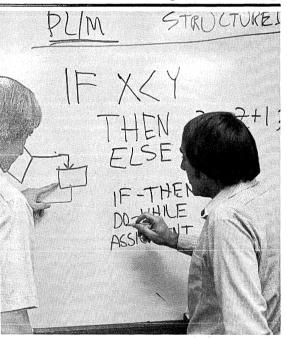

## Programming Capability

PL/M-80 — Intel's high level programming language, PL/M, is also available as a resident Intellec microcomputer development system option. PL/M provides the capability to program in a natural, algorithmic language and eliminates the need to manage register usage or allocate memory. PL/M programs can be written in a much shorter time than assembly language programs for a given application.

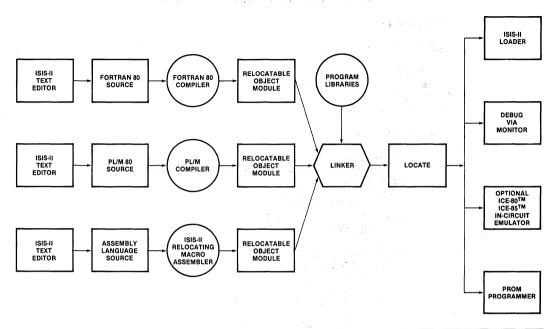

FORTRAN-80 — For applications requiring computational and formatted I/O capabilities, the high level FORTRAN-80 programming language is also available as a resident option of the Intellec system. The FOR-TRAN compiler produces relocatable object code that may be easily linked with PL/M or assembly language program modules. This gives the user a wide flexibility in developing software.

## SPECIFICATIONS

#### Word Size

Instruction — 8, 16, or 24 bits Data — 8 bits

#### Cycle Time

Basic Instruction Cycle — 2.03  $\mu s,~\pm 0.1\%$

#### Note

Basic instruction cycle is defined as the fastest instruction (i.e., four clock cycles).

#### Memory Addressing

ROM/EPROM - 0-0FFFH

RAM — 3F00<sub>H</sub>

## Memory Capacity

ROM/EPROM — 4K bytes (sockets only) RAM — 256 bytes

#### I/O Addressing

On-Board Programming I/O - see Table 1

| Port<br>Control | 8155<br>Port 1 | 8155<br>Port 2 | 8155<br>3&4 |    |    | 8155 Timer<br>High-Order<br>Byte |

|-----------------|----------------|----------------|-------------|----|----|----------------------------------|

| Address         | 00             | 01             | 02          | 03 | 04 | 05                               |

## I/O Capacity

Parallel — 22 programmable lines (see Table 1)

#### **Serial Communications Characteristics**

SID and SOD functions of the 8085 CPU are used for serial I/O. Controlled by software through RIM and SIM instructions of the 8085A CPU. Baud rate determined by system time available for serial I/O handling. On-board timer may be used to greatly ease serial I/O timing requirements.

#### Interrupts

Four-level interrupt routed to 8085 CPU interrupt inputs. Each interrupt automatically vectors the processor to a unique memory location.

| Condition    | Interrupt<br>Input                    | Memory<br>Address | Priority  | Туре          |

|--------------|---------------------------------------|-------------------|-----------|---------------|

| User-defined | TRAP                                  | 2416              | Highest   | Non-maskable  |

| Timer        | RST 7.5                               | 3C16              |           | Maskable      |

| I/O Port 2   | RST 6.5                               | 3416              | l° ∳ -    | Maskable      |

| I/O Port 1   | RST 5.5                               | 2C16              | Lowest    | Maskable      |

| the second   | · · · · · · · · · · · · · · · · · · · | 1. Star           | 1.1.1.1.1 | a a prosi sub |

#### Timer

Input Frequency Reference — 122.88 kHz  $\pm$  0.1% (8.14  $\mu s$  period nominal)

Output Frequencies/Timing Intervals

| Function                                                                                                         | Timer/Counter |           |  |

|------------------------------------------------------------------------------------------------------------------|---------------|-----------|--|

| and the second | Min           | Max       |  |

| Programmable pulse                                                                                               | 8.14 µs       | 66.67 ms  |  |

| Square wave rate generator                                                                                       | 7.50 Hz       | 61.44 kHz |  |

| Rate generator                                                                                                   | 7.50 Hz       | 61.44 kHz |  |

| Programmable strobe                                                                                              | 8.14 μs       | 133.33 ms |  |

#### Interfaces

#### Parallel I/O - All signals TTL compatible

Interrupt Request — All TTL compatible (active-low) Serial I/O — TTL; hole patterns available for user installation of RS232C line drivers and receivers

## System Clock (8085 CPU)

1.966 MHz ± 0.1%

## Connectors

| Inte         | ərfacə                   | Pins<br>(no.)          | Center<br>(in.) | Mating Connectors <sup>1</sup>                                 |

|--------------|--------------------------|------------------------|-----------------|----------------------------------------------------------------|

|              | + 5V, + 12V,             | 7                      | 0.156           | Molex 09-66-1071<br>Connector<br>Molex 09-50-7071<br>Connector |

|              | – 5V <sup>2</sup>        | single-<br>sided       |                 | AMP 87194-6<br>Connector<br>AMP 3-87025-4<br>Connector         |

| Voltages     | + 5V, - 12V <sup>3</sup> | 7<br>single-           | 0.156           | Molex 09-66-1071<br>Connector<br>Molex 09-50-7071<br>Connector |

| Voltages   + | + 50, - 120              | sided                  | 0.150           | AMP 87194-6<br>Connector<br>AMP 3-87025-4<br>Connector         |

|              | Unregulated              | 2                      |                 | Molex 09-66-1021<br>Connector<br>Molex 09-50-7021<br>Connector |

|              | + 5V                     | single-<br>sided       | 0.156           | AMP 89194-1<br>Connector<br>AMP 2-87025-5<br>Connector         |

| Para         | illei I/O                | 50<br>double-<br>sided | 0.1             | 3M 3415-000<br>(flat cable)                                    |

|              |                          | 7                      |                 | Molex 09-66-1071<br>Connector<br>Molex 09-50-7071<br>Connector |

| Ser          | ial I/O                  | single-<br>ended       | 0.156           | AMP 87194-6<br>Connector<br>AMP 3-87025-4<br>Connector         |

an e chatta

#### Notes

1. Connectors and pins from a given vendor may only be used with connectors and pins from the same vendor.

2. A single 86-contact edge-on connector may be used to connect the two groups of regulated voltages (i.e., +5V, +12V, -5V, and +5V, -12V).

3. Required only when RS232C line drivers and receivers are used.

## Line Drivers and Terminators

**I/O Drivers** — The following line drivers are all compatible with the I/O driver sockets on the iSBC 80/04:

| Driver | Characteristic | c Sink Current (mA) |  |

|--------|----------------|---------------------|--|

| 7438   | I,OC           | 48                  |  |

| 7437   | 1              | 48                  |  |

| 7432   | NI             | 16                  |  |

| 7426   | I,OC           | 16                  |  |

| 7409   | NI,OC          | 16                  |  |

| 7408   | NI             | 16                  |  |

| 7403   | I,OC           | 16                  |  |

| 7400   | 1              | 16                  |  |

Note

I = inverting; NI = non-inverting; OC = open collector.

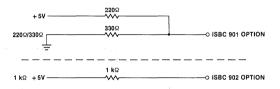

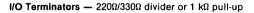

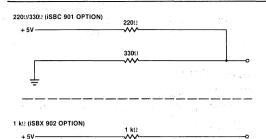

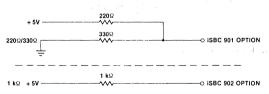

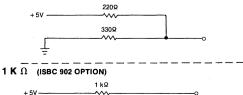

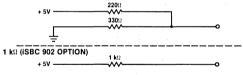

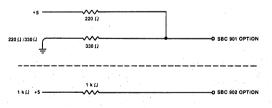

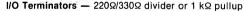

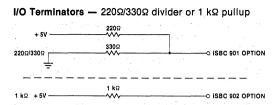

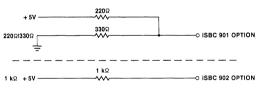

**I/O Terminators** — Intel provides  $220\Omega/330\Omega$  divider and 1 k $\Omega$  pull-up resistive terminator packs for termination of I/O lines programmed as inputs. These options are as follows:

## **RS232C Drivers and Receivers**

The following RS232C drivers and receivers are compatible with the RS232C socket on the iSBC 80/04: RS232C Driver — National DS1488 or TI SN75188 RS232C Receiver — National DS1490 or TI SN75189

#### Sockets

Sockets may be installed in the hole patterns provided for the RS232C drivers and receivers. The following sockets are compatible with the iSBC 80/04: TI C93-14-02 and SCANBE US-2-14-160-N-B.

## **Compatible Voltage Regulator**

National LM 323 — 3A, 5V Positive Regulator Fairchild μA7805 KM — 1A, 5V Positive Regulator

#### Compatible Heat Sink

IERC — LA Series or AAVID Engineering, Inc. — Series 5051

#### Physical Characteristics

Width — 7.85 in. (19.94 cm) Height — 6.75 in. (17.15 cm) Depth — 0.50 in. (1.27 cm) Weight — 6.0 oz (169.9 gm)

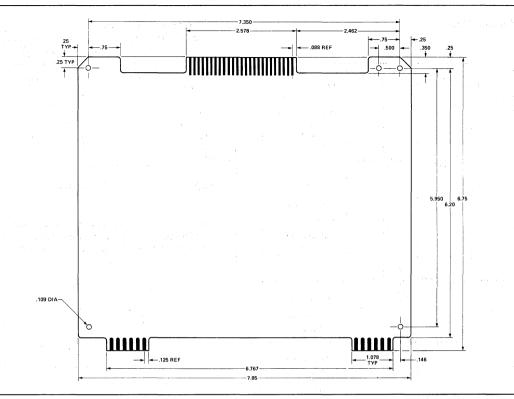

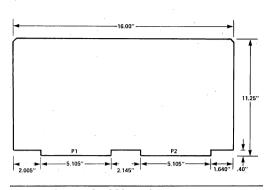

Figure 2. iSBC 80/04 Dimensions

## Electrical Characteristics DC Power Requirements

| Voltage<br>(±5%)     | Without<br>PROM <sup>1</sup><br>(max) | With 2716<br>EPROM <sup>2</sup><br>(max) | With 2708<br>EPROM <sup>3</sup><br>(max) |

|----------------------|---------------------------------------|------------------------------------------|------------------------------------------|

| $V_{CC} = +5V$       | I <sub>CC</sub> = 600 mA              | 1.45A                                    | 1.25A                                    |

| $V_{DD} = + 12V^{4}$ | $I_{DD} = 0$                          | 7 mA <sup>5</sup>                        | 137 mA                                   |

| $V_{BB} = -5V^{4}$   | $I_{BB} = 0$                          | 0                                        | 90 mA                                    |

| $V_{AA} = -12V^{5}$  | I <sub>AA</sub> = 0                   | 23 mA <sup>5</sup>                       | 23 mA <sup>5</sup>                       |

#### Notes

1. Does not include power required for optional EPROM/ROM, I/O drivers, and I/O terminators.

2. With two Intel 2716 EPROMs and  $220\Omega/330\Omega$  terminators installed for 22 input ports; all terminator inputs low.

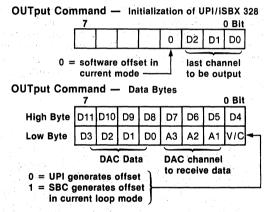

3. With two Intel 2708 EPROMs and  $220\Omega/330\Omega$  terminators installed for 22 input ports; all terminator inputs low.

4. Required for 2708 EPROMs.

5. Required only when RS232C capability required.

## Environmental Characteristics

Operating Temperature - 0°C to + 55°C

## **Reference Manual**

9800482-02 - iSBC 80/04 Hardware Reference Manual (NOT SUPPLIED)

Reference manuals are shipped with each product only if designated SUPPLIED (see above). Manuals may be ordered from any Intel sales representative, distributor office or from Intel Literature Department, 3065 Bowers Avenue, Santa Clara, California 95051.

## **ORDERING INFORMATION**

Part Number SBC 80/04 **Description** Single Board Computer

# iSBC 80/05 or (pSBC 80/05\*) SINGLE BOARD COMPUTER

8085A CPU used as central processor

int

- 512 bytes of static read/write memory

- Sockets for 4K bytes of erasable reprogrammable or masked read only memory

- 22 programmable parallel I/O lines with sockets for interchangeable line drivers and terminators

- Full MULTIBUS control logic allowing up to 16 masters to share system bus

- Programmable 14-bit binary timer

- TTL serial I/O interface with sockets for RS232C line drivers and receivers

- Four-level vectored interrupt

- Fully compatible with optional iSBC expansion boards and peripherals

- Single + 5V power supply

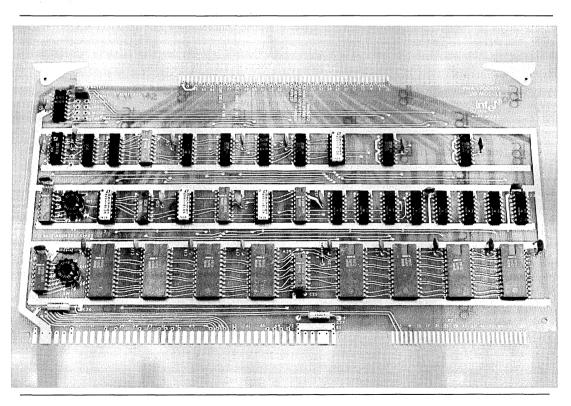

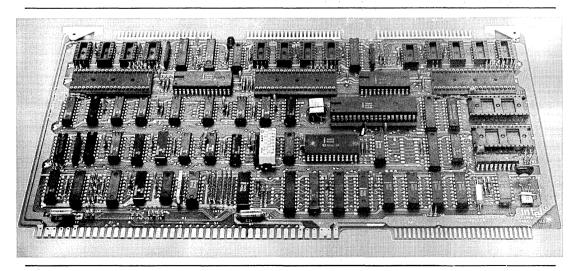

The iSBC 80/05 Single Board Computer is a member of Intel's complete line of OEM computer systems which take full advantage of Intel's LSI technology to provide economical, self-contained computer-based solutions for OEM applications. The iSBC 80/05 is a complete computer system on a single 6.75 x 12.00-inch printed circuit card. The CPU, system clock, read/write memory, nonvolatile read only memory, I/O ports and drivers, serial interface, priority interrupt logic, programmable timer, MULTIBUS control logic, and bus expansion buffers all reside on the board.

\*Same product, manufactured by Intel Puerto Rico, Inc.

## FUNCTIONAL DESCRIPTION

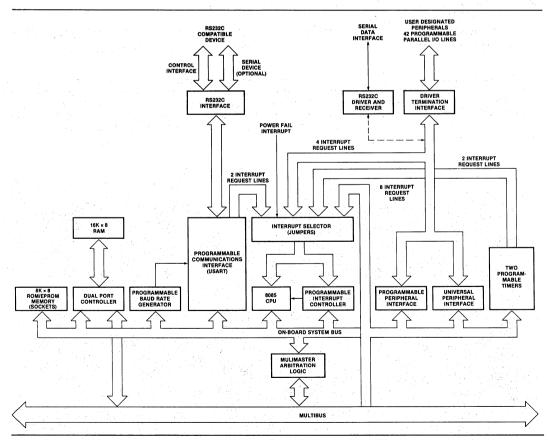

Intel's powerful 8-bit n-channel 8085 CPU, fabricated on a single LSI chip, is the central processor for the iSBC 80/05. The 8085A CPU is directly software compatible with the popular Intel 8080A CPU. The 8085A contains six. 8-bit general purpose registers and an accumulator. The six general purpose registers may be addressed individually or in pairs, providing both single and double precision operators. Minimum on-board instruction execution time is 2.03 microseconds. A block diagram of iSBC 80/05 functional components is shown in Figure 1.

## **Memory Addressing**

The 8085A CPU has a 16-bit program counter which allows direct addressing of up to 65,536 bytes of memory. An external stack, located within any portion of read/write memory, may be used as a last-in/first-out storage area for the contents of the program counter, flags, accumulator, and all of the six general purpose registers. A 16-bit stack pointer controls the addressing of this external stack. This stack provides subroutine nesting bounded only by memory size.

#### **Memory Capacity**

The iSBC 80/05 contains 512 bytes of read/write memory using Intel's low power static RAMs. Two sockets for up to 4K bytes of nonvolatile read only memory are provided on the board. Read only memory may be added in 2K-byte increments using Intel 2716 erasable and electrically reprogrammable ROMs (EPROMs) or Intel 2316E masked ROMs. Optionally, if only 2K bytes are required, read only memory may be added in 1K-byte increments using Intel 2708 EPROMs or Intel 2608 masked ROMs.

## Parallel I/O Interface

The iSBC 80/05 contains 22 programmable parallel I/O lines implemented using the I/O ports of the Intel 8155 RAM/IO/Timer. The system software is used to configure the I/O lines in any combination of unidirectional input or output ports as indicated in Table 1. The I/O interface may, therefore, be customized to meet specific peripheral requirements. In order to take full advantage of the large number of possible I/O configurations, sockets are provided for interchangeable I/O line drivers and terminators. Hence the flexibility of the I/O interface is further enhanced by the capability of selecting the appropriate combination of optional line drivers and terminators to provide the required sink current, polarity, and drive/termination characteristics for each application. The 22 programmable I/O lines and signal ground lines are brought out to a 40-pin edge connector that mates with flat, woven, or round cable.

## **Multimaster Capability**

The iSBC 8085A is a full computer on a single board with resources capable of supporting a great variety of OEM system requirements. For those applications requiring additional processing capacity and the benefits of multiprocessing (i.e., several CPUs and/or controllers logically share systems tasks with communication over the system bus), the iSBC 80/05 provides full MULTIBUS arbitration control logic. This control logic allows up to three bus masters (i.e., any combination of iSBC 80/05, ISBC 80/20-4, DMA controller, diskette controller, etc.) to share the system bus in serial (daisy-chain) priority fashion, and up to 16 masters may share the MULTIBUS with the addition of an external priority network. The MULTIBUS arbitration logic operates synchronously with a MULTIBUS clock (provided by the iSBC 80/05 or optionally connected directly to the MULTIBUS clock) while data is transferred via a handshake between the master and slave modules. This allows different speed controllers to share resources on the same bus, and for transfers via the bus to proceed asynchronously. Thus, transfer speed is dependent on transmitting and receiving devices only. This design prevents slow master modules from being handicapped in their attempts to

Figure 1. iSBC 80/05 Block Diagram Showing Functional Components

|      |       | Mode of Operation<br>Unidirectional |                      |         |                      |         |

|------|-------|-------------------------------------|----------------------|---------|----------------------|---------|

| Port | Lines |                                     |                      | Input   |                      | Control |

|      | (qty) | Unlatched                           | Latched &<br>Strobed | Latched | Latched &<br>Strobed | •       |

| 1    | 8     | Х                                   | Х                    | Х       | Х                    |         |

| 2    | 8     | X                                   | Х                    | Х       | X                    |         |

| 3    | 3     | X                                   |                      | х       |                      | X1      |

| 4    | 3     | Х                                   |                      | Х       |                      | X2      |

#### Table 1. Input/Output Modes of Operation

#### Notes

1. Port 3 must be used as a control port when port 1 is used as a latched and strobed input or a latched and strobed output port.

2. Port 4 must be used as a control port when port 2 is used as a latched and strobed input or a latched and strobed output port.

gain control of the bus, but does not restrict the speed at which faster modules can transfer data via the same bus. The most obvious applications for the master-slave capabilities of the bus are multiprocessor configurations, high speed direct-memory-access (DMA) operations and high speed peripheral control, but are by no means limited to these three.

## **Programmable Timer**

The iSBC 80/05 provides a fully programmable binary 14-bit interval timer utilizing the Intel 8155 RAM/IO/ Timer. The system designer simply configures the timer via software to meet system requirements. Whenever a given time delay is needed, software commands to the programmable timer select the desired function. Four functions are available as shown in Table 2. The contents of the timer counter may be read at any time during system operation.

#### Serial I/O Interface

The iSBC 80/05 provides serial I/O capability through the serial input data (SID) and serial output data (SOD) functions of the Intel 8085A CPU. These functions are controlled exculsively by software through execution of the 8085A RIM and SIM instructions. The baud rate for the serial I/O interface is determined by the system time available for execution of serial I/O support software. Hence, the maximum baud rate supported by the iSBC 80/05 is solely dependent on the overall system realtime software requirements. Serial I/O signals are TTL compatible and sockets are provided on the board for optional connection of RS232C line drivers and receivers.

## Interrupt Capability

The iSBC 80/05 takes advantage of the powerful interrupt processing capability of the 8085A CPU. Interrupt requests are routed to the four interrupt inputs of the 8085A CPU (i.e., TRAP, RST 7.5, RST 6.5, and RST 5.5 in order of priority, TRAP highest), and each input generates a unique memory address (i.e., TRAP: 24<sub>16</sub>, RST 7.5: 3C<sub>16</sub>, RST 6.5: 34<sub>16</sub>, RST 5.5: 2C<sub>16</sub>). A single 8085A jump

| Table 2. | Programmable | Timer | Functions |

|----------|--------------|-------|-----------|

|----------|--------------|-------|-----------|

| Function                      | Operation                                                                                                                                                                                                        |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Programmable<br>pulse         | Timer out goes low during the<br>second half of count. Therefore, the<br>count loaded in the count length<br>register should be twice the pulse<br>width desired.                                                |

| Square wave<br>rate generator | Timer out will remain high until one-<br>half the count has been completed,<br>and go low for the other half of the<br>count. The count length is auto-<br>matically reloaded when terminal<br>count is reached. |

| Rate generator                | Divide by N counter. A repetitive<br>timer out low pulse is generated and<br>new timeout initiated every time ter-<br>minal count is reached.                                                                    |

| Programmable<br>strobe        | A single low pulse is generated upon<br>reaching terminal count. This func-<br>tion is extremely useful for genera-<br>tion of real-time clocks.                                                                 |

instruction at each of these addresses then provides linkage to locate each interrupt service routine independently anywhere in memory. All interrupt inputs with the exception of one (TRAP) may be masked via software. The trap interrupt should be used for conditions such as power-down sequences which require immediate attention by the 8085A CPU.

## **Expansion Capabilities**

Memory and I/O capacity may be expanded and additional functions added using Intel MULTIBUS compatible expansion boards. High speed integer and floatingpoint arithmetic capabilities may be added by using the ISBC 310 High Speed Mathematics Unit. Memory may be expanded to 65,536 bytes by adding user specified combinations of RAM boards, EPROM boards, or combinations boards. Input/output capacity may be increased by adding digital I/O and analog I/O expansion boards. Mass storage capability may be achieved by adding single or double density diskette controllers as subsystems. Modular expandable backplanes and cardcages are avialable to support multiboard systems.

## Systems Development Capability

The development cycle of iSBC 80/05-based products may be significantly reduced using an Intellec microcomputer development system. The resident macroassembler, text editor, and system monitor greatly simplify the design, development, and debug of iSBC 80/05 system software. An optional diskette operating system provides a relocating macroassembler, a relocating loader and linkage editior, and a library manager. A unique in-circuit emulator (ICE-85) option provides the capability of developing and debugging software directly on the iSBC 80/05.

#### **Programming Capability**

**PL/M-80** — Intel's high level programming language, PL/M, is also available as a resident Intellec microcomputer development system option. PL/M provides the capability to program in a natural, algorithmic language and eliminates the need to manage register usage or allocate memory. PL/M programs can be written in a much shorter time than assembly language programs for a given application.

## SPECIFICATIONS

#### Word Size

Instruction — 8, 16, or 24 bits Data — 8 bits

## Cycle Time

**Basic Instruction Cycle** — 2.03  $\mu$ s, ± 0.1%

Basic instruction cycle is defined as the fastest instruction (i.e., four clock cycles).

#### Memory Addressing

ROM/EPROM — 0-0FFF<sub>H</sub> RAM — 3E00<sub>H</sub>

## Memory Capacity

**On-Board ROM/EPROM** — 4K bytes (with Intel 2716) or 2K bytes (with Intel 2708)

On-Board RAM - 512 bytes

**Off-Board Expansion** — Up to 65,536 bytes in user specified combination of RAM, ROM, and PROM

## I/O Addressing

On-Board Programmable I/O - see Table 1

| Port<br>Control | 8155<br>Port 1 | 8155<br>Port 2 | 8155<br>Ports<br>3 & 4 | 8155<br>Port | 8155 Timer<br>Low-Order<br>Byte |    |

|-----------------|----------------|----------------|------------------------|--------------|---------------------------------|----|

| Address         | 00             | 01             | 02                     | 03           | 04                              | 05 |

#### I/O Capacity

Parallel - 22 programmable lines (see Table 1)

## Note

The iSBC 80/05 may be expanded to 1102 programmable input/output lines by using optional iSBC 80  $\ensuremath{\text{I/O}}$  boards.

## **Serial Communications Characteristics**

SID and SOD functions of the 8085A CPU are used for serial I/O. They are controlled by software through RIM

and SIM instructions of the 8085A CPU. Baud rate is determined by system time available for serial I/O handling. On-board timer may be used to greatly ease serial I/O timing requirements.

#### Interrupts

Four-level interrupt routed to 8085A CPU interrupt inputs. Each interrupt automatically vectors the processor to a unique memory location.

| Interrupt<br>Input | Memory<br>Address | Priority      | Туре         |

|--------------------|-------------------|---------------|--------------|

| TRAP               | 2416              | Highest       | Non-maskable |

| RST 7.5            | 3C16              |               | Maskable     |

| RST 6.5            | 3416              | :.:: <b>∀</b> | Maskable     |

| RST 5.5            | 2C16              | Lowest        | Maskable     |

#### Timer

Input Frequency Reference — 122.88 kHz  $\pm$  0.1% (8.14  $\mu$ s period nominal)

#### **Output Frequencies/Timing Intervals**

| Function                   | Timer/Counter |           |

|----------------------------|---------------|-----------|

|                            | Min           | Max       |

| Programmable pulse         | 8.14 µs       | 66.67 ms  |

| Square wave rate generator | 7.50 Hz       | 61.44 kHz |

| Rate generator             | 7.50 Hz       | 61.44 kHz |

| Programmable strobe        | 8.14 μs       | 133.33 ms |

#### Interfaces

Bus — All signals TTL compatible

Parallel I/O - All signals TTL compatible

Interrupt Request — All TTL compatible (active-low) Serial I/O — TTL; sockets available for RS232C line drivers and receivers

#### System Clock (8085A CPU)

1.966 MHz ± 0.1%

| Interface               | Lines<br>(qty)  | Centers<br>(in.) | Mating Connector                                               |

|-------------------------|-----------------|------------------|----------------------------------------------------------------|

| Bus                     | 86 double-sided | 0.156            | Viking 2KH43/9AMK12                                            |

| Parallel I/O            | 50 double-sided | 0.100            | 3M 3415-000                                                    |

| Serial I/O <sup>1</sup> | 1               | 0.156            | Molex 09-66-1071<br>Connector<br>Molex 09-50-7071<br>Connector |

| Senar I/O               | 7 single-sided  |                  | AMP 87194-6<br>Connector<br>AMP 3-87025-4<br>Connector         |

#### Note

1. Connectors and pins from one vendor may only be used with connectors and pins from the same vendor.

## Line Drivers and Terminators

**I/O Drivers** — The following line drivers are all compatible with the I/O driver sockets on the iSBC 80/05:

| Driver | Driver Characteristic Sink Cu            |    |

|--------|------------------------------------------|----|

| 7438   | I,OC                                     | 48 |

| 7437   | ,                                        | 48 |

| 7432   | NI N | 16 |

| 7426   | I,OC                                     | 16 |

| 7409   | NI,OC                                    | 16 |

| 7408   | NI                                       | 16 |

| 7403   | I,OC                                     | 16 |

| 7400   | 1 · · · ·                                | 16 |

#### Note

I = inverting; NI = non-inverting; OC = open collector.

**I/O Terminators** — Intel provides  $220\Omega/330\Omega$  divider and 1 k $\Omega$  pull-up resistive terminator packs for termination of I/O lines programmed as inputs. These options are as follows:

#### **Bus Drivers**

| Driver   | Characteristic | Sink Current (mA) |

|----------|----------------|-------------------|

| Data     | Tri-state      | 50                |

| Address  | Tri-state      | 50                |

| Commands | Tri-stc*e      | 32                |

#### **RS232C Drivers and Receivers**

The following RS232C drivers and receivers are compatible with the RS232C socket on the iSBC 80/05: RS232C Driver — National DS1488 or TI SN75188 RS232C Receiver — National DS1490 or TI SN75189

## **Physical Characteristics**

Width — 12.00 in. (30.49 cm) Height — 6.75 in. (17.15 cm) Depth — 0.50 in. (1.27 cm) Weight — 12.0 oz (339.8 gm)

## **Electrical Characteristics**

## **DC Power Requirements**

| Voltage<br>(±5%)     | Without<br>PROM <sup>1</sup><br>(max) | With 2716<br>EPROM <sup>2</sup><br>(max) | With 8708<br>EPROM <sup>3</sup><br>(max) |

|----------------------|---------------------------------------|------------------------------------------|------------------------------------------|

| $V_{CC} = +5V$       | I <sub>CC</sub> = 1.80 mA             | 2.65A                                    | 2.45A                                    |

| $V_{DD} = + 12V^{4}$ | $I_{DD} = 0$                          | 7 mA <sup>5</sup>                        | 137 mA                                   |

| $V_{BB} = -5V^4$     | I <sub>BB</sub> = 0                   | 0                                        | 90 mA                                    |

| $V_{AA} = -12V^{5}$  | $I_{AA} = 0$                          | 23 mA <sup>5</sup>                       | 23 mA <sup>5</sup>                       |

Notes

1. Does not include power required for optional EPROM/ROM, I/O drivers, and I/O terminators.

2. With two Intel 2716 EPROMs and 220Ω/330Ω terminators installed for 22 input ports; all terminator inputs low.

3. With two Intel 2708 EPROMs and  $220\Omega/330\Omega$  terminators installed for 22 input ports; all terminator inputs low.

4. Required for 2708 EPROMs.

5. Required only when RS232C capability required.

## **Environmental Characteristics**

Operating Temperature - 0°C to + 55°C.

#### **Reference Manual**

9800483D — iSBC 80/05 Hardware Reference Manual (NOT SUPPLIED)

Reference manuals are shipped with each product only if designated SUPPLIED (see above). Manuals may be ordered from any Intel sales representative, distributor office or from Intel Literature Department, 3065 Bowers Avenue, Santa Clara, California 95051.

## **ORDERING INFORMATION**

| Part Number | Descriptio   |

|-------------|--------------|

| SBC 80/05   | Single Board |

scription le Board Computer

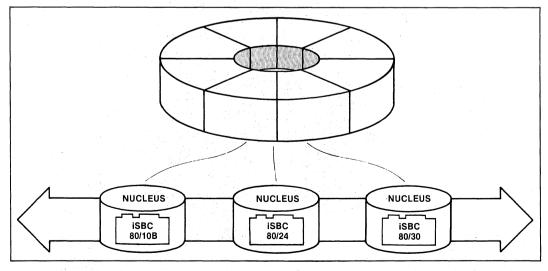

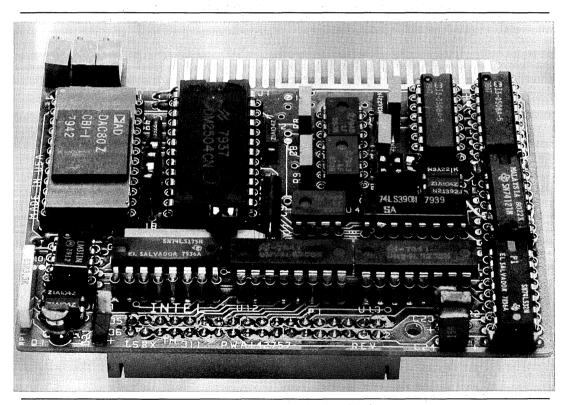

# iSBC 80/10B or (pSBC 80/10B\*) SINGLE BOARD COMPUTER

- Upward compatible with iSBC 80/10A Single Board Computer

- 8080A CPU used as central processing unit

- One iSBX bus socket for iSBX MULTIMODULE board expansion

- 1K byte of read/write memory with sockets for expansion up to 4K bytes

- Sockets for up to 16K bytes of read only memory

- 48 programmable parallel I/O lines with sockets for interchangeable line drivers and terminators

- Programmable synchronous/asynchronous communications interface with selectable RS232C or teletypewriter compatibility

- Single level interrupt with 11 interrupt sources

- Auxiliary power bus and power-fail interrupt control logic for RAM battery backup

- 1.04-millisecond interval timer

- Limited master MULTIBUS interface

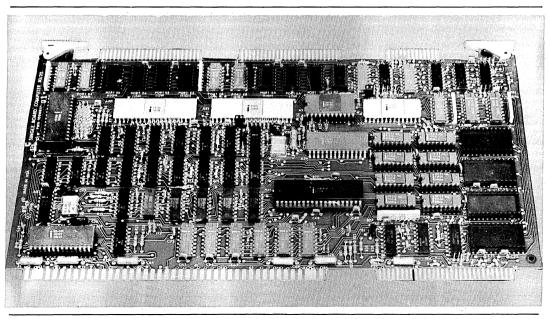

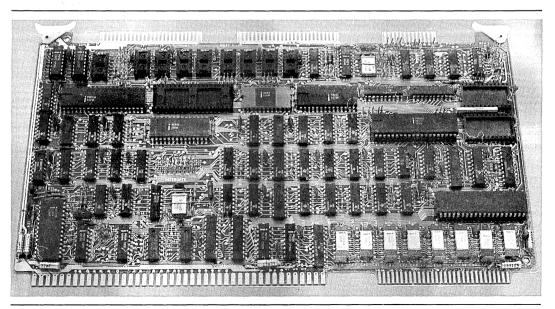

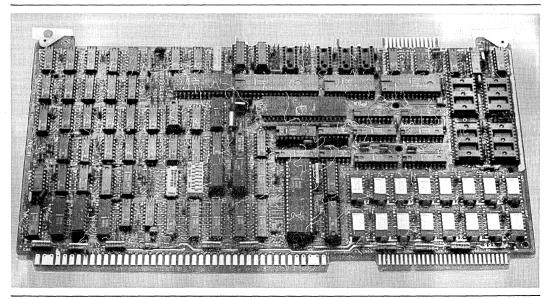

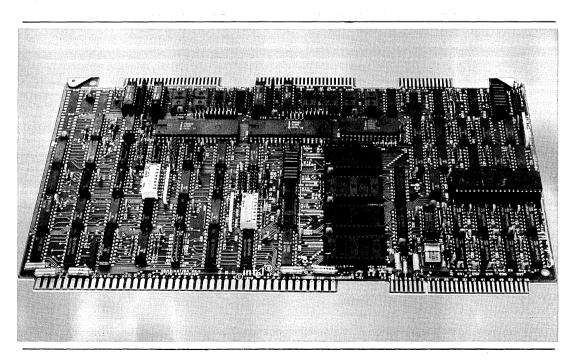

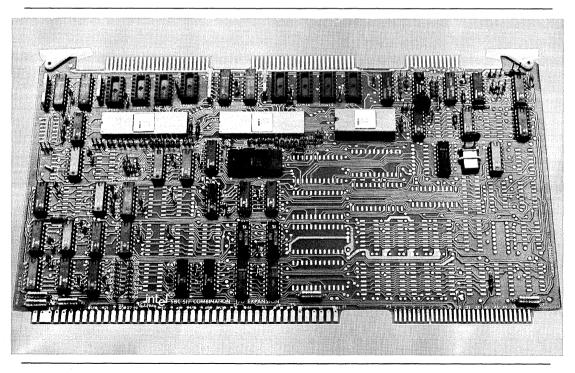

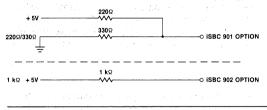

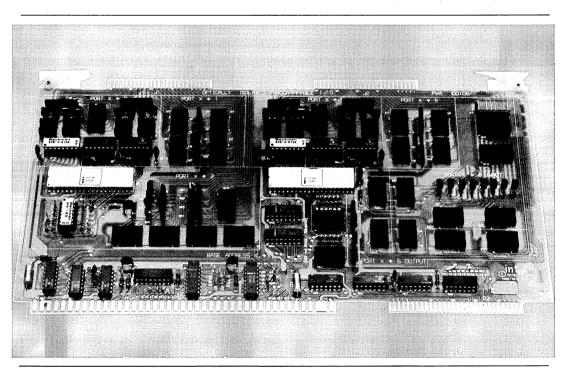

The Intel® iSBC 80/10B board is a member of Intel's complete line of OEM microcomputer systems which take full advantage of Intel's LSI technology to provide economical, self-contained computer-based solutions for OEM applications. The iSBC 80/10B board is a complete computer system on a single 6.75 x 12.00-inch printed circuit card. The CPU, system clock, iSBX bus interface, read/write memory, read only memory sockets, I/O ports and drivers, serial communications interface, bus control logic, and drivers all reside on the board.

\*Same product, manufactured by Intel Puerto Rico, Inc.

## FUNCTIONAL DESCRIPTION

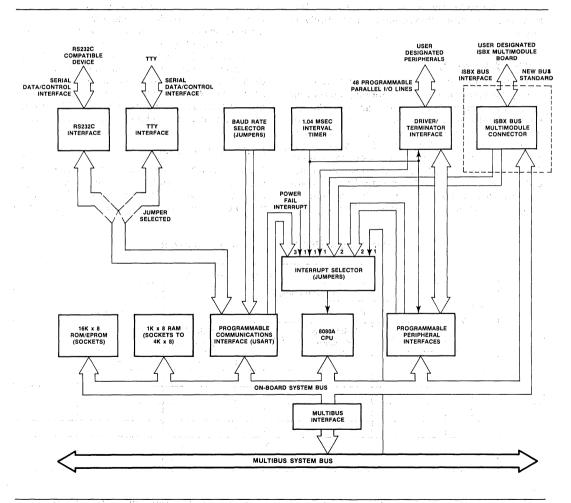

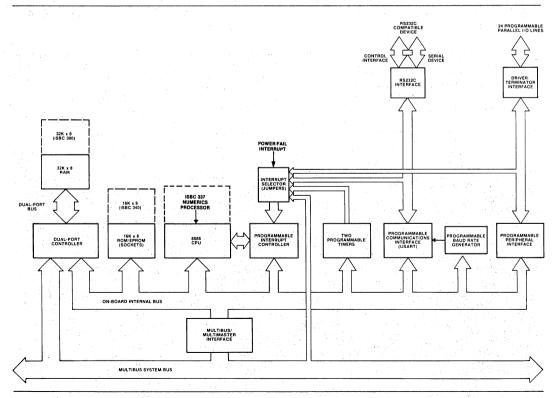

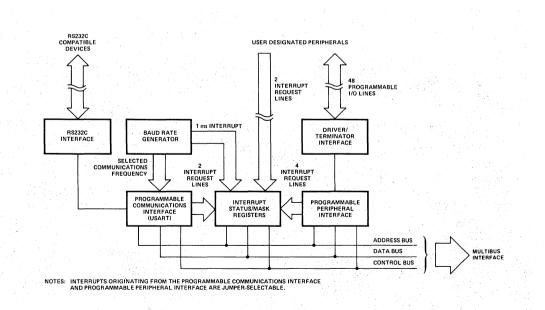

Intel's powerful 8-bit n-channel MOS 8080A CPU, fabricated on a single LSI chip, is the central processor for the iSBC 80/10B board. The 8080A contains six 8-bit general purpose registers and an accumulator. The six general purpose registers may be addressed individually or in pairs, providing both single and double precision operators. A block diagram of iSBC 80/10B board functional components is shown in Figure 1.

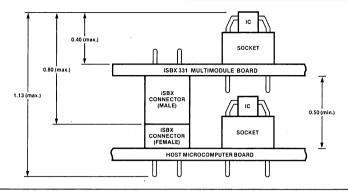

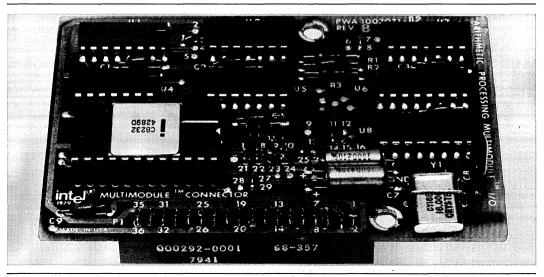

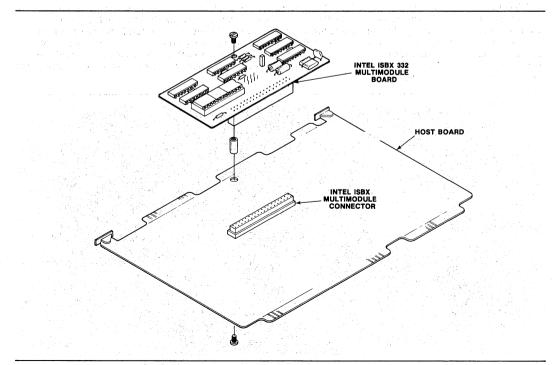

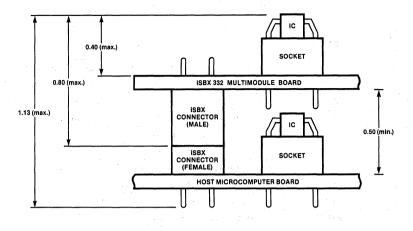

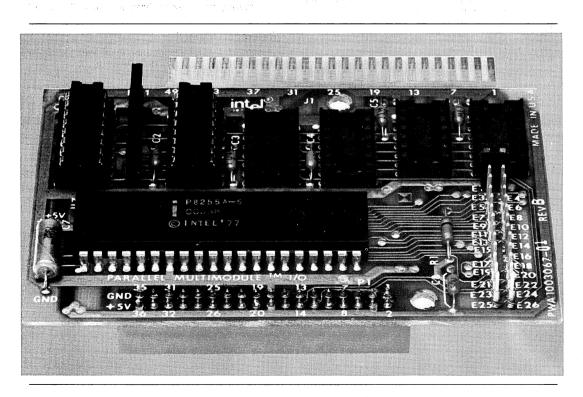

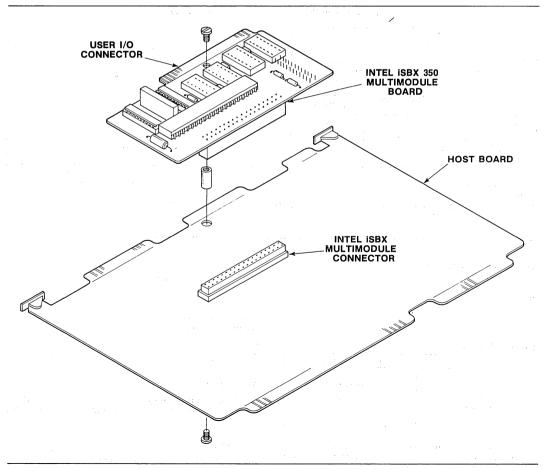

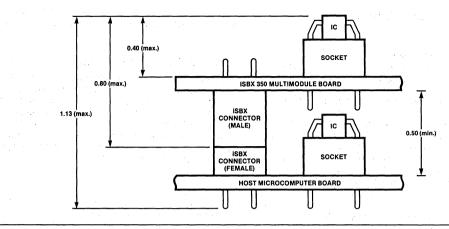

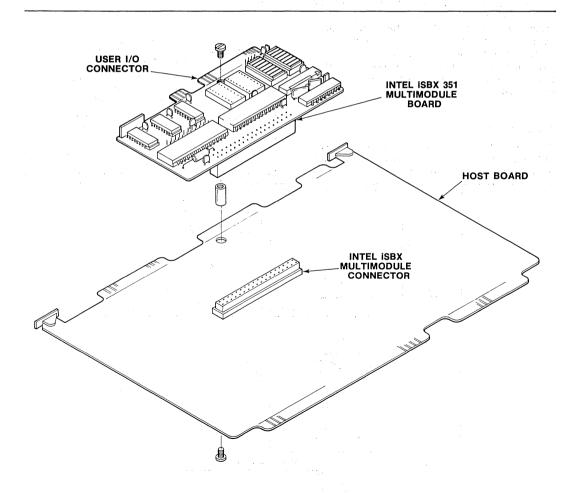

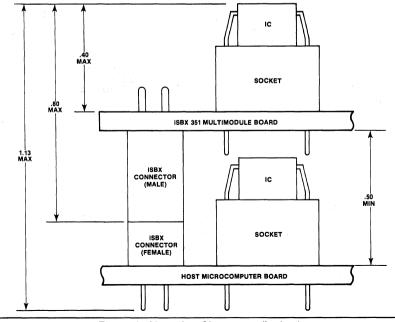

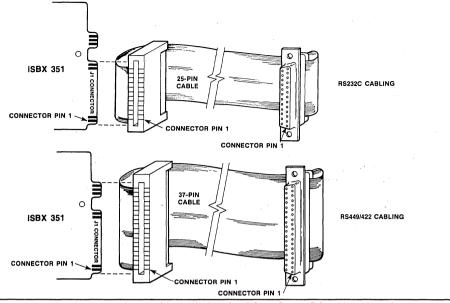

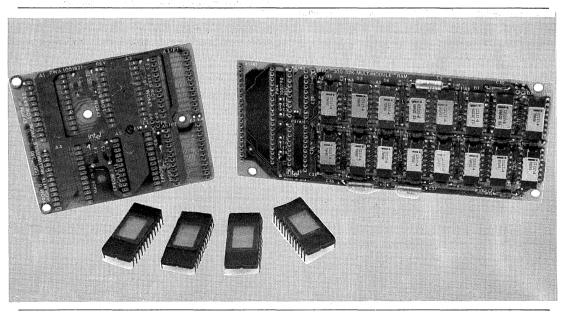

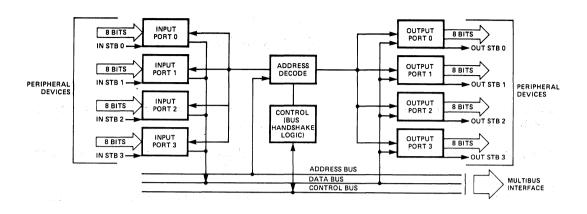

# iSBX Bus MULTIMODULE Board Expansion

The new iSBX bus interface brings an entirely new dimension to system design offering incremental

on-board expansion with small iSBX boards. One iSBX bus connector interface is provided to accomplish plug-in expansion with any iSBX MULTIMODULE board. iSBX boards are available to provide expansion equivalent to the I/O available on the iSBC 80/10B board or the user may configure entirely new functionality such as math directly onboard. The iSBX 350 programmable I/O MULTI-MODULE board provides 24 I/O lines using an 8255A programmable peripheral interface. Therefore, the iSBX 350 module together with the iSBC 80/10B board may offer 72 lines of programmable I/O. Alternately, a serial port may be added using the iSBX 351 serial I/O multimodule board or math may be configured on-board with the iSBX 332 floating point math MULTIMODULE board.

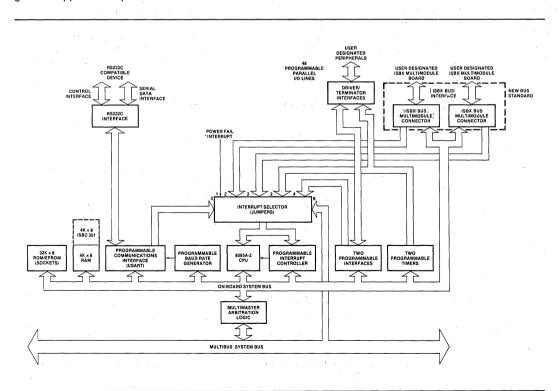

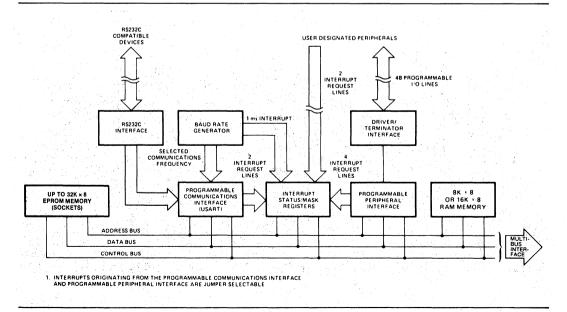

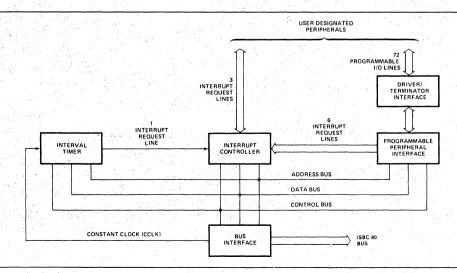

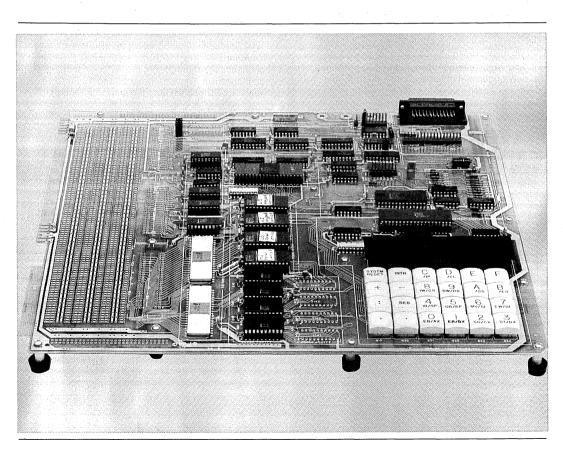

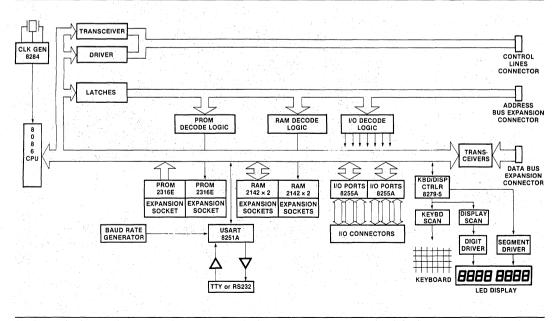

Figure 1. iSBC 80/10B Single Board Computer Block Diagram

The iSBX board is a logical extension of the onboard programmable I/O and is accessed by the iSBC 80/10B single board computer as common I/O port locations. The iSBX board is coupled directly to the 8080A CPU and therefore becomes an integral element of the iSBC 80/10B single board computer providing optimum performance.

## **Memory Addressing**

The 8080A has a 16-bit program counter which allows direct addressing of up to 64K bytes of memory. An external stack, located within any portion of read/write memory, may be used as a last-in/first-out storage area for the contents of the program counter, flags, accumulator, and all of the six general purpose registers. A 16-bit stack pointer controls the addressing of this external stack. This stack provides subroutine nesting bounded only by memory size.

## **Memory Capacity**

The iSBC 80/10B board contains 1K bytes of read/write static memory. In addition, sockets for up to 4K bytes of RAM memory are provided on board. Read/write memory may be added in 1K byte increments using two 1Kx4 Intel 2114A-5 static RAMs. All on-board RAM read and write operations are performed at maximum processor speed. Sockets for up to 16K bytes of nonvolatile read-only-memory may be added in 1K byte increments up to 4K bytes (using Intel 2708, 2758, or 2608); in

2K byte increments up to 8K bytes (using Intel 2716 or 2316A); or in 4K byte increments up to 16K bytes (using Intel 2732). All on-board ROM or EPROM read operations are performed at maximum processor speed.

## Parallel I/O Interface

The iSBC 80/10B board contains 48 programmable parallel I/O lines implemented using two Intel 8255A programmable peripheral interfaces. The system software is used to configure the I/O lines in any combination of unidirectional input/output. and bidirectional ports indicated in Table 1. Therefore, the I/O interface may be customized to meet specific peripheral requirements. In order to take full advantage of the large number of possible I/O configurations, sockets are provided for interchangeable I/O line drivers and terminators. Hence, the flexibility of the I/O interface is further enhanced by the capability of selecting the appropriate combination of optional line drivers and terminators to provide the required sink current, polarity, and drive/termination characteristics for each application. The 48 programmable I/O lines and signal ground lines are brought out to two 50-pin edge connectors that mate with flat cable or round cable.

## Serial I/O Interface

A programmable communications interface using the Intel® 8251A Universal Synchronous/Asynchronous Receiver/Transmitter (USART) is contained on the board. A jumper selectable baud rate

|      |                |       | an a | Mode of              | Operation |                      |         |  |

|------|----------------|-------|------------------------------------------|----------------------|-----------|----------------------|---------|--|

|      |                |       | Unidirec                                 |                      |           |                      |         |  |

| Port | Lines<br>(qty) | In    | put                                      | Output               |           | Bidirectional        | Control |  |

|      |                | (4.37 | Unlatched                                | Latched &<br>Strobed | Latched   | Latched &<br>Strobed |         |  |

| 1    | 8              | X     | X                                        | X                    | X         | X                    |         |  |

| 2    | 8              | X     | X                                        | X                    | X         | -                    |         |  |

| 3    | 8              | ×     |                                          | X                    |           |                      | X1      |  |

| 4    | .8             | X     |                                          | X                    |           |                      |         |  |

| 5    | 8              | x     | and an an an                             | X                    |           |                      |         |  |

| 6    | 4              | x     |                                          | X                    |           |                      |         |  |

|      | 4              | X     |                                          | X                    |           |                      |         |  |

#### Table 1. Input/Output Port Modes of Operation

#### Notes

Port 3 must be used as a control port when either port 1 or port 2 are used as a latched and strobed input or a latched and strobed output port or port 1 is used as a bidirectional port.

0

generator provides the USART with all common communications frequencies. The USART can be programmed by the system software to select the desired synchronous or asynchronous serial data transmission technique (including IBM Bi-Sync). The mode of operation (i.e., synchronous or asynchronous), data format, control character format and parity are all under program control. The 8251A provides full duplex, double-buffered transmit and receive capability. Parity, overrun, and framing error detection are all incorporated in the USART. The inclusion of jumper selectable TTY or RS232C compatible interfaces on the board, in conjunction with the USART, provides a direct interface to teletypes, CRTs, RS232C compatible cassettes, and asynchronous and synchronous modems. The RS232C or TTY command lines, serial data lines, and signal ground lines are brought out to a 26-pin edge connector that mates with RS232C compatible flat or round cable.

## Interrupt Capability

Interrupt requests may originate from 11 sources. Two jumper selectable interrupt requests can be automatically generated by the programmable peripheral interface when a byte of information is ready to be transferred to the CPU (i.e., input buffer is full) or a byte of information has been transferred to a peripheral device (i.e., output buffer is empty). Three jumper selectable interrupt requests can be automatically generated by the USART when a character is ready to be transferred to the CPU (i.e., receive channel buffer is full), a character is ready to be transmitted (i.e., the USART is ready to accept a character from the CPU), or when the transmitter is empty (i.e., the USART has no character to transmit). These five interrupt request lines are all maskable under program control. Two interrupt request lines may be interfaced directly to user designated peripheral devices; one via the MULTI-BUS system bus and the other via the I/O edge connector. One jumper selectable interrupt request may be interfaced to the power-fail interrupt control logic. One jumper selectable interrupt request may originated from the interval timer. Two general purpose interrupt requests are jumper selectable from the iSBX interface. These two signals permit a user installed MULTIMODULE board to interrupt the 8080A CPU. The eleven interrupt request lines share a single CPU interrupt level. When an interrupt request is recognized, a restart instruction (RESTART 7) is generated. The processor responds by suspending program execution and executing a user defined interrupt service routine originating at location 3816.

## **Power-Fail Control**

A power-fail interrupt may be detected through the AC-low signal generated by the power supply. This signal may be configured to interrupt the 8080A CPU to initiate an orderly power down instruction sequence.

## **Interval Timer**

A 1.04 millisecond timer is available for interval interrupts or as a clock output to the parallel I/O connector. The timer output is jumper selectable to the programmable parallel interface, the parallel I/O connector (J1), or directly to the 8080A CPU.

## MULTIBUS System Expansion Capabilities

Memory and I/O capacity may be expanded and additional functions added using Intel MULTIBUS™ system compatible expansion boards. Memory may be expanded to 65,536 bytes by adding user specified combinations of RAM boards, EPROM boards, or combination boards. Input/output capacity may be increased by adding digital I/O and analog I/O expansion boards. In addition, the iSBC 80/10B board performs as a limited bus master in that it must occupy the lowest priority when used with other MULTIBUS masters. The bus master may take control of the MULTIBUS system bus by halting the iSBC 80/10B board program execution. Mass storage capability may be achieved by adding single density diskette, double density diskette, or hard disk controllers. Modular expandable backplanes and cardcages are available to support multiboard systems.

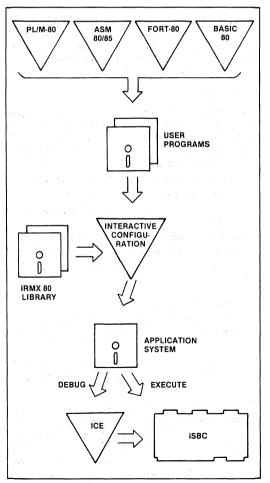

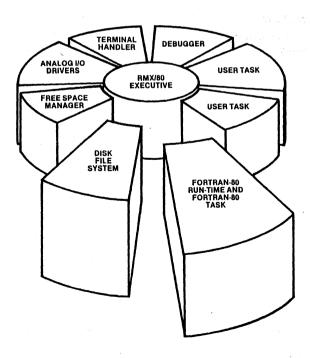

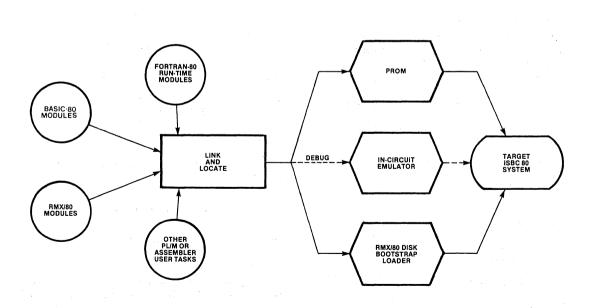

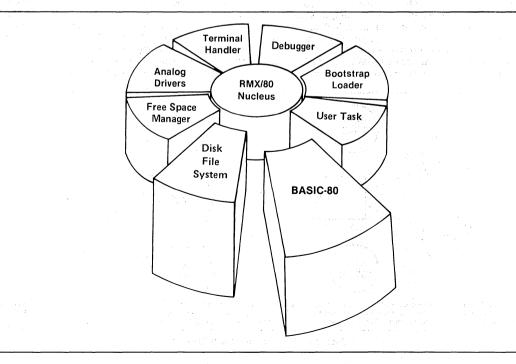

## **Real-Time Software**

The RMX/80 executive, which contains all major real-time facilities including priority-based system resource allocation, intertask communication and control, interrupt driven control for standard I/O devices, and interrupt handling, occupies 2K bytes of memory which can be stored on-board in EPROM. Optional linkable and relocatable modules for console control (CRT or TTY), disk file system, and analog subsystems are provided with the RMX/80 package. User configurability is aided on the Intellec microcomputer development system by the Interactive Configuration Utility program provided with the RMX/80 package.

## System Development Capability

The development cycle of iSBC 80/10B-based products may be significantly reduced using Intel's system development tools available today. The

Intellec Series II family of compatible microcomputer development systems provides a range of capability from a low cost disk-based edit debug workstation to a high performance, fully compatible hard-disk-based software development system. Also, a unique in-circuit emulator (ICE-80) option provides the capability of developing and debugging software directly on the iSBC 80/10B board.

## Programming Capability

**PL/M-80** — Intel's high level programming language, PL/M, is also available as a resident Intellec microcomputer development system option. PL/M provides the capability to program in a natural, algorithmic language and eliminates the need to manage register usage or allocate memory. PL/M programs can be written in a much shorter time than assembly language programs for a given application.

FORTRAN-80 — For applications requiring computational and formatted I/O capabilities, the ANSI 77 standard high level FORTRAN-80 programming language is available as a resident option of the Intellec system. The FORTRAN compiler produces

## **SPECIFICATIONS**

| Page 1. pl - Miles et | 공연 이 지수는 것이 같아. | 이번 모양을 관심하는      |            |

|-----------------------|-----------------|------------------|------------|

| Word Size             |                 | ં તેલું હતું છે. | કુ સમય છે. |

| Instruction - 8,      | 16, or 24 bits  |                  |            |

| Data - 8 bits         |                 | stra galata      | en bes     |

#### Cycle Time

**Basic Instruction Cycle** — 1.95  $\mu$ sec Note Basic instruction cycle is defined as the fastest instruction (i.e.,

four clock cycles) serves a magnitude to the destruction (i.e.,

# Memory Addressing

0-0FFF using 2708, 2758 0-1FFF using 2716, 2316E 0-3FFF using 2732

#### On-Board RAM

- 3C00-3FFF with no RAM expansion

- 3000-3FFF with 2114A-5 expansion

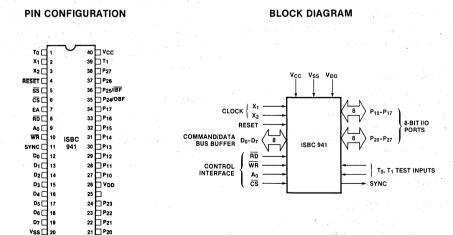

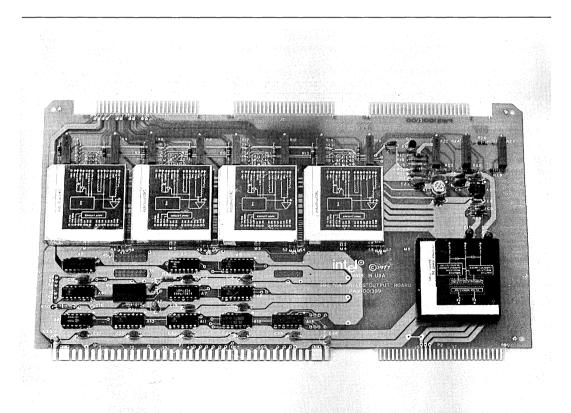

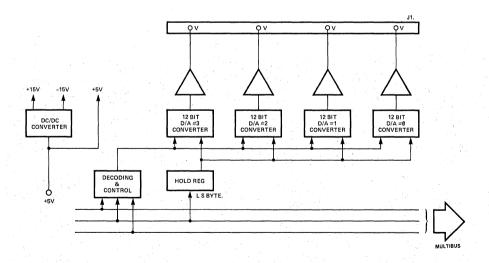

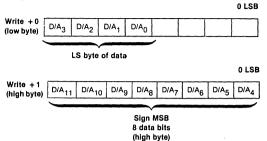

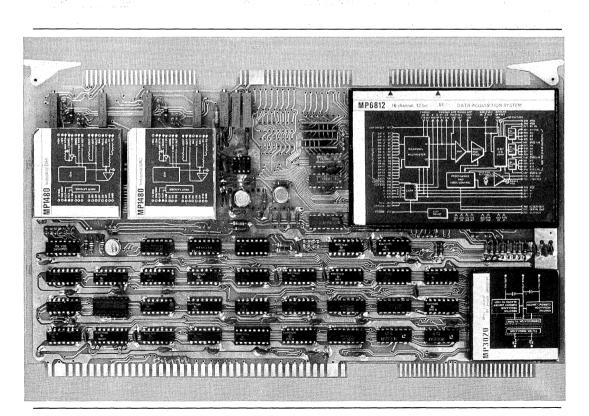

- Note