# PRELIMINARY MCS<sup>™</sup> 40 MICROCOMPUTER SET ADVANCE SPECIFICATIONS

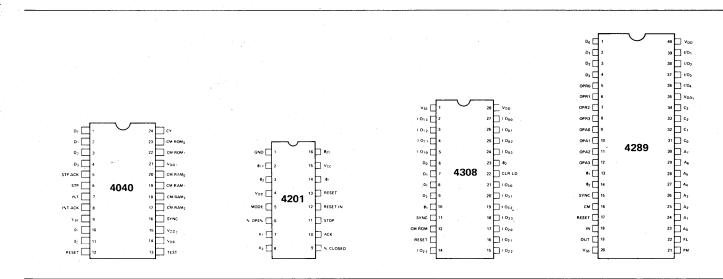

Intel will soon introduce four new integrated circuits to further enhance the low-cost advantages of using the MCS-40 Microcomputer Set and allow its use in applications not before possible. These devices are both functionally and electrically compatible with current MCS-4 devices. The accompanying pages present a functional description of these new devices. Electrical specifications will be published as soon as the devices are fully characterized.

# 4040 – Central Processor Unit

- Functionally and electrically identical to Interrupt capability 4004 CPU Single step operation 14 new instuctions (60 total) including 8K byte memory addressing capability Logical Operations and Read Program 24 index registers Memory Subroutine nesting to 7 levels 4201 – Clock Generator Crystal controlled oscillator Generates power on reset for MCS-4 **Directly drives MCS-4 set** Provides single step circuit for 4040 4308 – Mask Programmable ROM 1K x 8 program storage Equivalent of (4) 4001 ROM's Four independent 4-bit I/O ports 4289 — Standard Memory Interface

- Single package equivalent of 4008/4009

- Allows use of 2 µsec memories with MCS-4

- Direct interface to all standard memories: TTL, NMOS, PMOS, CMOS

THE MCS-4 USER'S MANUAL SHOULD BE REFERENCED FOR A MORE BASIC UNDERSTANDING OF THE SYSTEM.

#### 4040 CENTRAL PROCESSOR UNIT

#### 1. Introduction

The 4040 is a single chip 4-bit parallel MOS central processor. It is intended as an enhanced version of the 4004 and as such retains all of the functional capability of that device. It does, however, provide several significant improvements in hardware and software. These are listed briefly here and will be described in detail in the body of this preliminary specification.

#### 1.1 Extended Instruction Set

The 4040 software contains all of the 4004 instruction set and includes an additional 14 instructions, providing:

. HALT

- . Logical operations between accumulator and a designated index register.

- . INTERRUPT DISABLE, ENABLE FUNCTIONS

- . ROM BANK switching

- . Index register bank switching

This instruction set is described in detail in Section 4.

#### 1.2 Hardware Interrupt Logic

The 4040 contains the necessary hardware to accept and process single level interrupts. To facilitate this, the address stack has been increased from 4 x 12 bits to 8 x 12 bits, allowing up to seven levels of subroutine nesting. In addition, the index register array has been increased

from sixteen 4-bit registers to twenty-four 4-bit registers. The interrupt logic is explained in detail in Section 3.2.

#### 1.3. Hardware STOP Logic

The 4040 is provided with a STOP control which allows the user to halt the processor at any instruction cycle. This feature allows the implementation of a 'single step' operation for program debugging (see Section 3.1 and Appendix II for detailed descriptions).

#### 1.4 Expanded ROM Capacity

The 4040 can directly address up to 8K x 8 words of ROM with no external logic required.

#### 1.5 More Flexible Interface and System Configurations

The 4040 is provided with separate power supply pins for the timing circuitry and for the output buffers. These features allow a low-power standby mode by shutting off the main power supply and operating only the timing. Since the output buffers have a separate supply they can be directly interfaced to other circuit types such as N-channel MOS or CMOS. For single-supply systems all three power supply pins can be tied together.

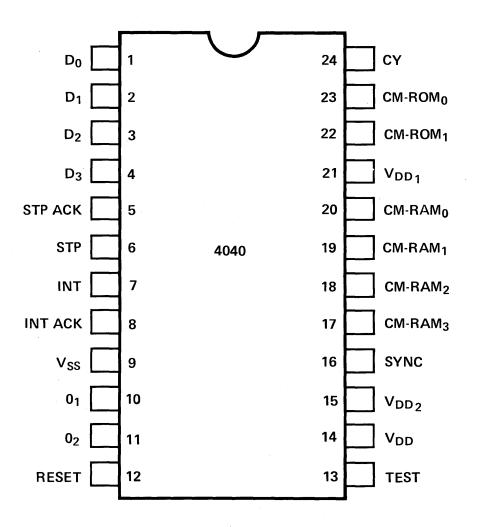

#### 2. General Description of Hardware

The 4040 is packaged in a 24 pin ceramic DIP. The pin configuration is shown in the following figure. A brief functional description of each pin is given in Section 2.1.

4040 PIN CONFIGURATION 2.1 Pin Description

| Pin # | Designation | Description of Function |

|-------|-------------|-------------------------|

|       |             |                         |

- 1 4  $D_0 D_3$  Bidirectional data bus. All address and data communication between the processor and the RAM and ROM chips is handled by way of these 4 lines.

- 5 STPA STOP ACKNOWLEDGE ouput. This signal acknowledges receipt that the machine has stopped. Output is "open drain" requiring pull-down resistor to V<sub>DD</sub>.

- 6 STP STOP input signal. A logic "1" level at this input causes the processor to enter the STOP mode.

7 INT INTERRUPT input signal. A logic "1" level at this input causes the processor to enter the INTERRUPT mode.

8 INTA INTERRUPT ACKNOWLEDGE output. This signal acknowledges receipt of an INTERRUPT command and prevents additional INTERRUPTs from entering the processor. INTERRUPT ACKNOWLEDGE remains active until cleared by the execution of the new BRANCH BACK and SRC (BBS) instruction. The output is "open drain", requiring a pull-down resistor to V<sub>DD</sub>.

| <u>Pin #</u> | Designation                     | Description of Function                     |

|--------------|---------------------------------|---------------------------------------------|

| 9            | v <sub>ss</sub>                 | Circuit GND potential - most positive       |

|              |                                 | supply voltage.                             |

| 10,11        | ø <sub>1</sub> , ø <sub>2</sub> | Non-overlapping clock signals which de-     |

|              |                                 | termine processor timing.                   |

| 12           | RESET                           | RESET input. A "1" level applied to this    |

|              |                                 | pinclears all flag and status flip-flops    |

|              |                                 | and forces the program counter to 0. To     |

|              |                                 | completely clear all of the address and     |

|              |                                 | index registers, RESET must be applied for  |

|              |                                 | 96 clock cycles (12 machine cycles).        |

| 13           | TEST                            | TEST input. The logical state of this       |

|              |                                 | input can be examined with the JCN instruc- |

|              |                                 | tion.                                       |

| 14           | v <sub>DD</sub>                 | Main supply voltage to the processor.       |

|              |                                 | Value must be $V_{SS}$ -15.0V $\pm$ 5%.     |

| 15           | V <sub>DD2</sub>                | Supply voltage for output buffers. May      |

|              |                                 | be varied depending on interface condi-     |

|              |                                 | tions.                                      |

| 16           | SYNC                            | SYNC output. Synchronization signal gener-  |

|              |                                 | ated by the processor and sent to ROM and   |

|              |                                 | RAM chips. Indicates beginning of instruc-  |

|              |                                 | tion cycle.                                 |

|              |                                 |                                             |

Pin # Designation Description of Function

17 - 20 CM-RAM CM-RAM CM-RAM Outputs. These outputs act as bank select signals for the 4002 RAM chips in the system.

21  $V_{DD1}$  Supply voltage for timing circuit. Value must be  $V_{SS}$  -15.0V ± 5%. Allows low power standby operation.

22,23 CM-ROM - CM-ROM outputs. These outputs act as bank select signals for the ROM chips in the system.

24 CY CARRY output buffer. The state of the CY flip-flop is presented at this output and is updated at  $X_1$ . The output is "open drain" requiring a pull-down resistor to  $V_{DD}$ .

#### 2.2 Basic Circuit Timing

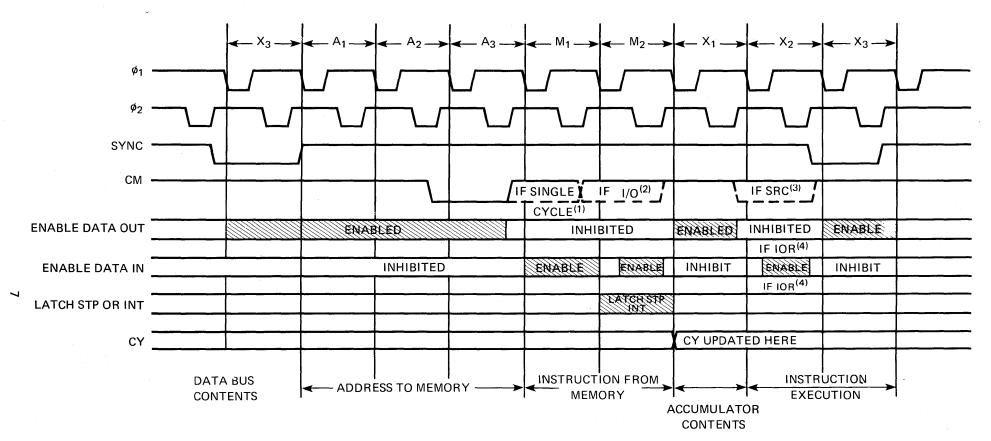

The basic system timing for the 4040 is identical to that used for the 4004, as shown in the following figure. Two non-overlapping clock signals,  $\emptyset_1$  and  $\emptyset_2$ , are used to define the basic timing. The start of an instruction cycle is indicated by the SYNC signal, which is generated by the processor and sent to the various ROM and RAM or peripheral chips in the system. An instruction cycle consists of the following operations:

- 1. The 12-bit content of the program counter is sent out to the ROM chips in three 4-bit groups during  $A_1$ ,  $A_2$ ,  $A_3$ .

- 2. The 8-bit instruction or data from the addressed ROM loca-

#### 4040 TIMING

#### NOTES:

- CM-ROM, RAM SIGNALS WILL BE PRESENT AT M<sub>1</sub> FOR ANY SINGLE CYCLE INSTRUCTION OR FOR THE FIRST CYCLE OF A DOUBLE CYCLE INSTRUCTION.

- 2. CM-ROM, RAM SIGNALS WILL BE PRESENT AT  $M_2$  FOR ANY OF THE SIXTEEN I/O GROUP INSTRUCTIONS.

- **3.** CM-ROM, RAM SIGNALS WILL BE PRESENT AT X<sub>2</sub> DURING EXECUTION OF AN SRC INSTRUCTION.

- IOR MEANS ONE OF THE I/O READ INSTRUCTIONS: SBM, ROM, RDR, ADM, RDØ, RD1, RD2, RD3.

tion is received by the processor at  $M_1$  and  $M_2$  at which time the instruction is decoded.

3. Instruction execution occurs during X<sub>1</sub>, X<sub>2</sub>, and X<sub>3</sub>. Data or address information may be sent to output ports or RAM chips; data may be received from input ports or RAM chips; or data may be operated on within the processor.

The data bus contents at the various times of the instruction cycle are defined just as for the 4004 with the exception of the data at  $X_1$ . The 4040 outputs the contents of the accumulator at  $X_1$  for program debugging purposes, whereas the 4004 simply copies the data which it received at  $M_2$ . The data bus contents at  $X_2$  and  $X_3$  depend on the instruction being executed; a listing for each individual instruction is contained in Appendix III.

An additional change to the basic timing occurs with the generation of the CM-ROM, CM-RAM signals at  $M_1$ . This will occur for all single cycle instructions and for the first cycle of all double cycle instructions. This feature allows external logic to distinguish between instruction information and address or data at  $M_1$  and  $M_2$  time.

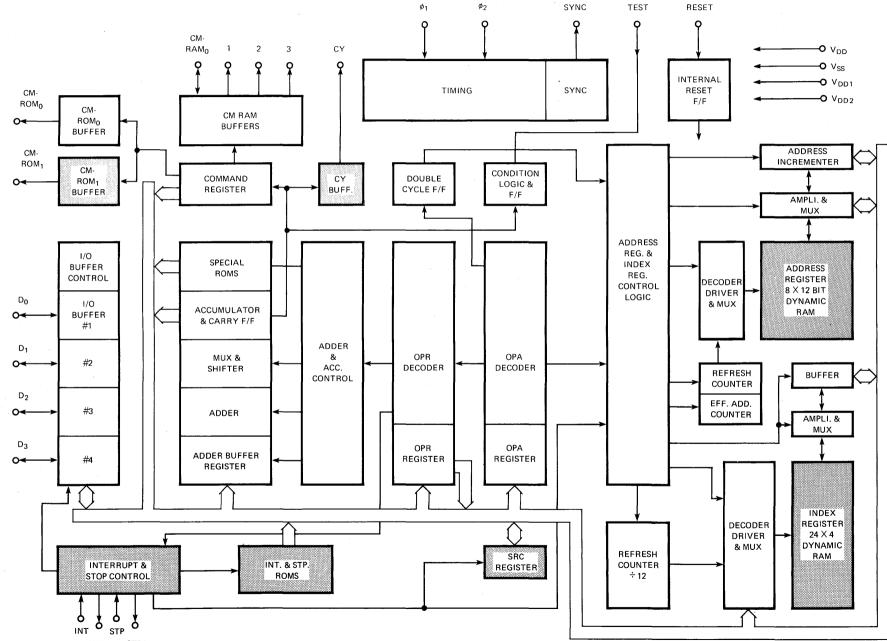

# 2.3 Basic Description of Major Circuit Blocks

The following figure is a block diagram of the 4040 indicating the major circuit blocks and their interconnections. The following major functional blocks are contained in the 4040:

1. Address register stack and address incrementer.

- 2. Index register array.

- 3. 4-bit adder/accumulator.

4040 BLOCK DIAGRAM

INTA STPA

4040

- 4. Instruction register/decoder and control logic.

- 5. Hardware interrupt and stop control.

- Peripheral circuits for controlling timing and external communication.

A brief functional description of each of these major elements is given below.

2.3.1 Address Register and Address Incrementer

The address register is a dynamic RAM array of 8 x 12 bits operating as a push-down stack. One level of the stack is used to store the effective address, leaving seven levels available for subroutine calls and interrupt processing. The stack address is provided by the effective address counter to the decoder.

The contents of the selected address register are stored in the address buffer and multiplexed to the internal bus during  $A_1$ ,  $A_2$ , and  $A_3$  in 4-bit slices. The contents of the address buffer are incremented by a 4-bit carrylook-ahead circuit following the outputting of each 4bit slice. The incremented value is transferred back to the address buffer and written back into the selected address register.

Since the array is dynamic, provision is made for refreshing the stored data. A 3-bit refresh counter is multiplexed to the stack decoder for this purpose.

# 2.3.2 Index Register Array

The index register is a dynamic RAM array of  $12 \times 8$  bits organized as three banks of  $4 \times 8$  bits. Two of

the banks have identical address locations and so must be individually selected with the SIBØ, 1 instructions. The third bank is always available for use. Section 3.2.1.1 describes the index register array organization in detail.

Two modes of operation are possible for the index register array. In one mode the array provides 24 directly addressable 4-bit storage locations for intermediate computation or control purposes. In the second mode the array provides 12 pairs of register locations for addressing RAM and ROM or for storing data fetched from ROM.

Index register addressing is provided by the internal bus for normal read/write operations and by a refresh counter for refresh operation. The addresses are multiplexed to the array decoder.

The content of the selected register is stored in a temporary register and multiplexed to the internal bus. During write operations the internal bus contents are transferred to the temporary register and then to the selected index register.

#### 2.3.3 SRC Register

The SRC register is an 8-bit dynamic latch which stores the contents of the designated index register pair during the execution of the SRC instruction. This 8-bit value is sent to the ROM and RAM chips as an address 4040

for a succeeding I/O instruction (see detailed description in Sec. 4.) The SRC register is used to hold this value in the case that an interrupt should occur, thus allowing the value to be restored when a return from interrupt is made. The SRC register is not loadable during an interrupt routine.

#### 2.3.4 4-Bit Adder/Accumulator

The 4-bit adder is of the ripple-through carry type. One term of the addition comes from the "Adder Buffer" register which communicates with the internal bus on one side and can transfer to the adder data or data. The other term of the addition comes from the accumulator and carry flip-flop. Both data and data can be transferred. The output of the adder is transferred to the accumulator and carry FF. The accumulator is provided with a shifter to implement shift right and shift left instructions. The accumulator communicates also with the command register, with special ROMs, with the condition logic, and with the internal bus. The command register holds a 3-bit code used for CM-RAM line switching. The special ROMs perform a code conversion for DAA (decimal adjust accumulator) and KBP (process keyboard) instructions. The special ROMs communicate with the internal bus. The condition logic senses ADD = 0 and ACC = 0 conditions, the state of the carry FF, and the state of an external signal (TEST) to implement JCN (jump on condition) and ISZ (increment index register skip if zero) instructions.

#### 2.3.5 Instruction Register/Decoder and Control Logic

The instruction register is loaded with the content of the internal bus at  $M_1$  and  $M_2$  through a multiplexer and holds the instruction fetched from ROM. The instructions are decoded in the instruction decoder and appropriately gated with timing signals to provide the control signals for the various functional blocks. A single cycle FF is reset from one of 5 double-length instructions. Double-length instructions are instructions that need two system cycles (16 clock cycles) for their execution. A condition FF controls JCN and ISZ instruction and is set by the condition logic.

#### 2.3.6 INTERRUPT and STOP Control Logic

The 4040 is provided with hardware INTERRUPT and STOP controls which override the normal processor operation. The INTERRUPT logic detects and acknowledges the presence of an INTERRUPT signal and forces the processor to execute a JMS instruction to location 003. Section 3.2 discusses in detail the timing and operation of the INTERRUPT control as well as the additional 4040 features which enhance its use. Examples of INTERRUPT processing routines are given in Appendix 1B.

The STOP control logic behaves in a similar manner by detecting and acknowledging the presence of a STOP signal. The processor is forced to execute a NOP instruction and will remain in the STOP condition 4040

until the STOP signal is removed. Section 3.1 presents a detailed description of the STOP/HALT operating mode.

# 2.3.7 Peripheral Circuits

This includes:

- a. The data bus input-output buffers communicating between data pads and internal bus.

- b. Timing and SYNC generator.

- c. 2 CM-ROM and 4 CM-RAM output buffers.

- d. POWER-ON-CLEAR flip-flop.

During RESET, all RAMs and static FF's are cleared, and the data bus is set to "0". After RESET, program control will start from "0" and  $CM-ROM_{g}$ ,  $CM-RAM_{g}$  will be selected. In addition, the INTERRUPT logic will be disabled and INDEX register bank g will be selected.

#### 3. 4040 New Operating Features

The following features will be described in detail:

- . STOP/HALT mode logic

- . INTERRUPT mode logic

- . Extended ROM addressing capability

#### 3.1 STOP/HALT Mode Operation

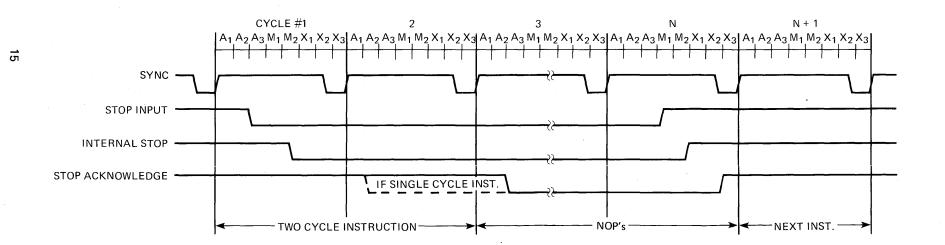

The normal processor cycle of the 4040 may be "stopped" at any point in an instruction sequence by one of two methods. A logic "1" level may be applied to the STOP input pin, in which case the processor will complete the current instruction and then enter the STOP mode. The timing for this operation is shown in the following figure and the sequence of events is outlined below:

**STOP TIMING**

- a. During instruction cycle #1 the state of the STOP pin is gated into the internal STOP latch at M<sub>2</sub>.

- b. At  $A_1$  of the next single cycle instruction the STOP flipflop will be set. In the example shown, the processor was executing a double cycle instruction when the STOP signal was first applied. It was allowed to complete the full instruction, hence the STOP flip-flop was not set until  $A_1$  of instruction cycle #3. The buffered output of the STOP flip-flop is used as a STOP ACKNOWLEDGE signal.

- c. During instruction cycle #3 and all succeeding instruction cycles, the content of the program counter is sent out at  $A_1$ ,  $A_2$ , and  $A_3$ . The program counter is not allowed to increment, however, effectively "stopping" the processor at a give location. In addition the data bus input buffers are prevented from receiving information at  $M_1$  and  $M_2$  times and a NOP instruction is forced on the internal data bus.

- d. The processor remains in this NOP loop until the external STOP signal is returned to a logic "0" level during instruction cycle N. The new information is gated into the STOP latch at  $M_2$ , allowing the STOP flip-flop to reset at  $X_3$  of the instruction cycle N. Normal processor operation resumes at instruction cycle N + 1.

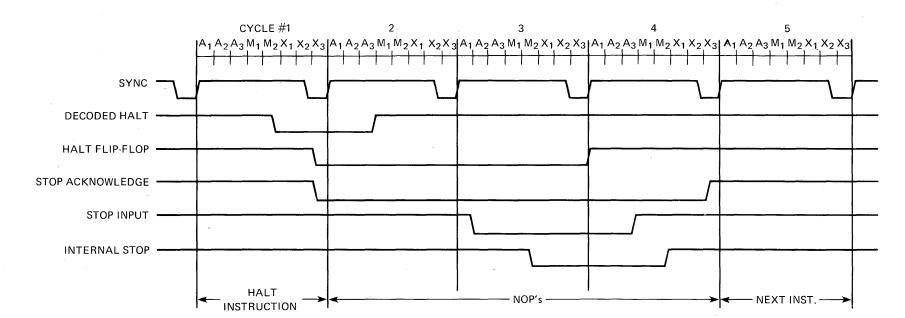

#### 3.1.1 HALT Mode

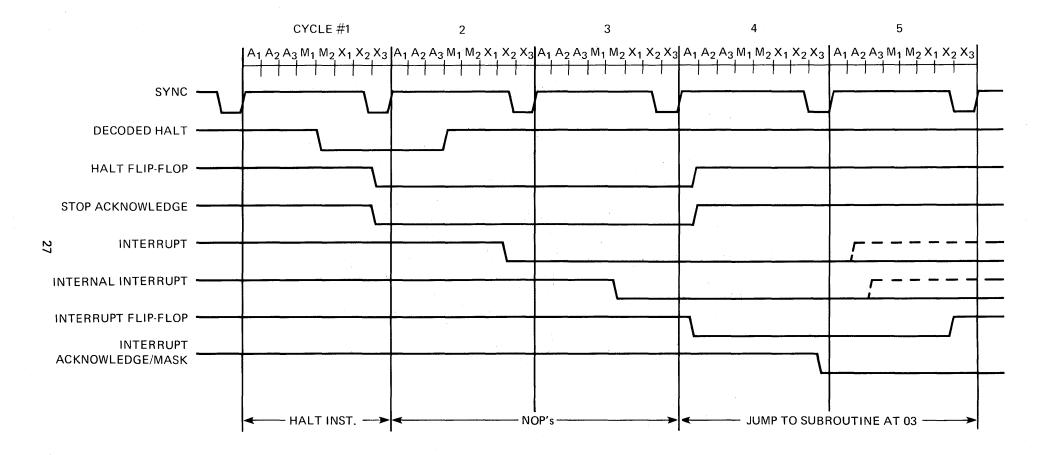

Entry to the STOP mode may also be gained through the use of the HALT (HLT) instruction as shown in the following figure. In this case the processor executes

the HLT instruction and causes the HALT and STOP flip-flops to be set at X<sub>3</sub> of instruction cycle #1. The processor is forced to execute NOP's at instruction cycle #2 and all successive cycle times until removed from the HALT mode.

Exit from the HALT mode can be gained in two ways, one of which is also shown in the following figure. At instruction cycle #N, a logic "1" level is applied to the STOP input and is in turn latched by the STOP latch at  $M_2$ . A logic "1" in the STOP latch causes the HALT flipflop to be reset at  $A_1$  of cycle #n + 1. The processor is now in the normal STOP mode and can be released as described in (d) above.

The second means of exiting from the HALT condition is by way of the INTERRUPT input and will be described in Section 3.2.

#### 3.1.2 DATA BUS Contents

The data bus contents during STOP/HALT mode are shown. For program debugging purposes the following information is available:

A<sub>1</sub>, A<sub>2</sub>, A<sub>3</sub> 12-bit address from internal program counter.

M<sub>1</sub>, M<sub>2</sub> 8-bit instruction from addressed ROM location. Internally the processor executes NOP.

X<sub>1</sub> 4-bit contents of ACCUMULATOR. X<sub>2</sub>, X<sub>3</sub> 8-bit contents of internal SRC register

17

# HALT TIMING (EXIT USING STOP INPUT)

which stores the value of the last SRC address. CM-ROM and CM-RAM signals are not present at  $X_2$  in this case. (See Section 3.2 for complete description of operation of SRC register.)

4040

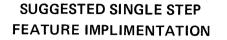

# 3.1.3 Single Step Operation

The STOP control provides a convenient means of program debugging by allowing a "single step" operation. Appendix II describes the necessary hardware and timing.

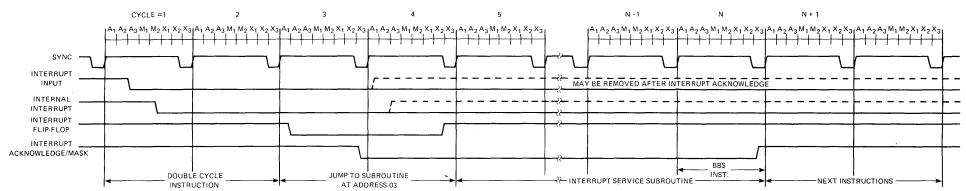

#### 3.2 INTERRUPT Mode

The 4040 is provided with an asynchronous INTERRUPT input and an INTERRUPT ACKNOWLEDGE output. The following figure presents the basic timing for the INTERRUPT mode. The sequence of events is as follows:

- a. During instruction cycle #1 an INTERRUPT occurs and is gated into the INTERRUPT LATCH during M2.

- b. At A<sub>1</sub> of the next single cycle instruction the INTERRUPT flip-flop is set. As in the case of the STOP example, if the processor is executing a double cycle instruction it is allowed to complete it.

- c. During instruction cycle #3 the program counter is prevented from incrementing and the data input buffers are inhibited at  $M_1$  and  $M_2$ . A JUMP TO SUBROUTINE (JMS) instruction is forced on the internal data bus. The subroutine address is forced to be page 0, location 3. At  $X_3$  the INTERRUPT ACKNOWLEDGE flip-flop is set and its

# INTERRUPT TIMING

INTERNOFT

buffered output is available on the INTERRUPT ACKNOWLEDGE pin. The instruction at location 0, 3 begins the interrupt processing routine.

4040

d. The INTERRUPT ACKNOWLEDGE flip-flop remains set until the interrupt has been processed and the new BRANCH BACK & SRC (BBS) instruction has been executed (instruction cycle #N). No new INTERRUPT can be entered while INTERRUPT ACKNOWLEDGE is active. Note that the INTERRUPT signal may be removed after INTERRUPT ACKNOWLEDGE occurs.

#### 3.2.1 Saving and Restoring Processor Status

To have an effective interrupt handling capability the processor must be capable of saving current program and status register values and restoring same when the interrupt processing is complete. In the 4040 the following values must be saved:

a. Content of ACCUMULATOR and CARRY flip-flop.

- b. Content of COMMAND REGISTER.

- c. Content of as many INDEX REGISTERS as required.

- d. The value of the last SRC address sent out prior to interrupt.

e. Content of the PROGRAM COUNTER.

f. The current ROM bank  $(CM-ROM_0 + CM-ROM_1)$ .

To facilitate the items listed, a number of new hardware features have been included in the 4040 and are described in the following paragraphs.

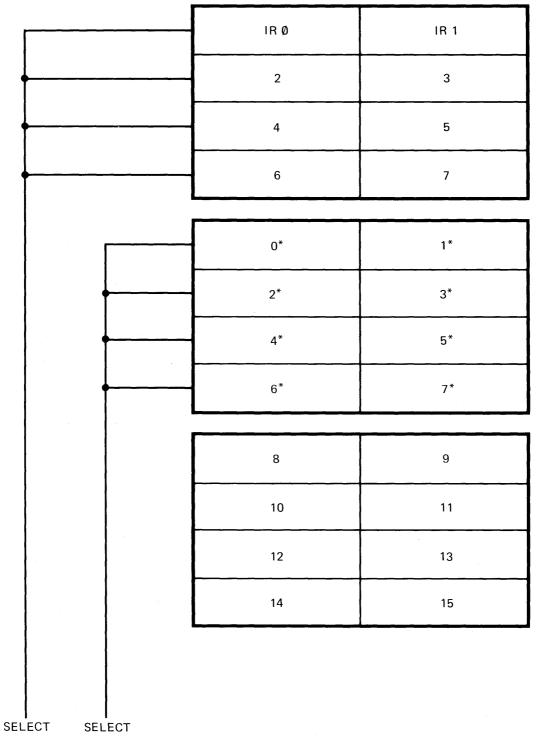

# 3.2.1.1 Expanded Index Register Array

Saving status values requires having temporary storage locations available in the index

register array. For this reason the 4040 is provided with 8 additional index registers (4 register pairs) providing a total of 24 4-bit registers (12 8-bit register pairs). The array is organized into three 8 register banks. Bank  $\emptyset$  and Bank 1 are individually selectable by using the SELECT INDEX BANK (SB $\emptyset$ , SB1) instructions. The upper bank, that one containing registers 8 - 15, is always available for storage. Appendix I.b provides examples of interrupt routines and demonstrates the use of the index register banks as well as all other features listed here.

Note that both Bank Ø and Bank 1 contain the same individual address locations. This feature allows those instructions which reference specific register locations to be executed from either index register bank. Thus the JUMP INDIRECT (JIN) instruction and the logical instructions OR4, OR5, AN6, AN7 reference two different sets of registers, e.g. a JIN instruction can reference register pair #0 in Bank Ø or in Bank 1.

The BANK SELECT flip-flop is automatically saved and restored during interrupts. Thus a user may wish to operate

# INDEX REGISTER ORGANIZATION

BANK Ø BANK 1 in Bank Ø until interrupted then switch to Bank 1. When the BBS instruction is executed to return from interrupt, previous Bank will automatically be selected for the next instruction.

After application of a RESET signal, Bank  $\emptyset$  will be selected.

# 3.2.1.2 SRC Register

When the 4040 executes an SRC instruction, the 4-bit values sent out at X<sub>2</sub> and X<sub>3</sub> are stored internally in the 8-bit SRC register. The SRC register is locked out during the interrupt routine by the INTERRUPT ACKNOWLEDGE flip-flop. Thus, any SRC instruction executed during an interrupt routine will not affect the value in the SRC register. The last instruction in the interrupt routine must be a BRANCH BACK and SRC (BBS), another new instruction which restores the program counter (see below) and sends out the contents of the SRC register at  $X_2$  and  $X_3$ , and generates the appropriate CM-ROM and CM-RAM at X2. This restores the ROM and RAM select logic to their preinterrupt conditions.

# 3.2.1.3 Extended Address Register Stack

The address stack of the 4040 is an 8 x 12 bit array (compared to 4 x 12 bits in the 4004). One level of the stack is required for the

program counter; hence seven levels of subroutines may be nested using the 4040.

When an interrupt occurs the program counter is not incremented, but is stored down one level in the stack by the execution of the forced JMS instruction. This value is restored by the execution of the BBS instruction at the end of the interrupt routine.

# 3.2.1.4 General Information Applying to Interrupt

- The 4040 is capable of servicing one interrupt at a time. The INTERRUPT ACKNOWLEDGE signal is used internally to prevent a second interrupt from being entered until the first is completely serviced.

- Two instructions, INTERRUPT ENABLE (EIN) and INTERRUPT DISABLE (DIN) are provided for protecting sequences of instructions from being interrupted. These are described in detail in Section 4.

- The RESET signal serves to disable interrupt. If the processor is started from a RESET condition an EIN instruction must be performed before an interrupt will be recognized.

- If an INTERRUPT and STOP signal occur such that they are both latched at M<sub>2</sub> of the same instruction cycle, the STOP logic will have

4040

priority, and must be cleared before the interrupt can be recognized.

As mentioned in Section 3.1.2 the INTERRUPT control may be used to exit from a HALT condition. The timing for this is shown, The processor enters the HALT mode at instruction cycle #1 and remains in that mode until the INTERRUPT signal is recognized at instruction cycle #4. When the INTERRUPT flip-flop is set, it causes the HALT flip-flop to be reset. The processor is then in the INTERRUPT In this way a processor could be used mode. in a completely asynchronous control application in which the INTERRUPT signal would begin the processing routine. When the routine was complete the processor would execute the HLT instruction and wait for a new INTERRUPT.

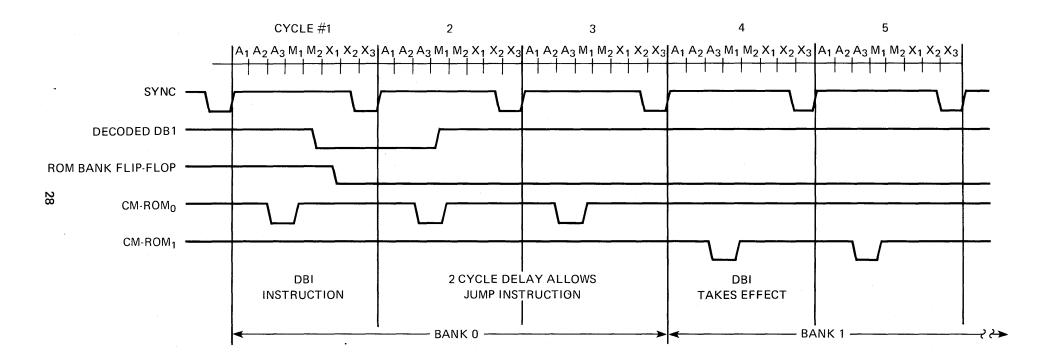

#### 3.3 Extended ROM Addressing Capability

The 4040 is equipped with two CM-ROM output buffers, each of which can be used to select a bank of sixteen 256 x 8 ROMs. A total of 8K x 8-bit words can be directly addressed. Bank switching is accomplished through the use of two new instructions, DESIGNATE BANK  $\emptyset$  (DB $\emptyset$ ) and DESIGNATE BANK 1 (DB1). Both of these instructions take effect on the third cycle following their execution. Appendix I.a provides example

# HALT TIMING (EXIT USING INTERRUPT)

#### **ROM BANK SWITCHING**

uses of the DBØ, 1 instructions.

Since the INTERRUPT control logic will force a JMS to page  $\emptyset$ , location 3, the first few instructions of the interrupt routine will have to be duplicated in both ROM banks (see Appendix I.b).

The fact that the bank switching operation requires three instruction cycles to be completed means that an INTERRUPT cannot occur during those three cycles. For this reason the INTERRUPT logic is internally disabled during the execution of DBØ or DB1.

4. Definition of Instruction Set

The 4040 is functionally compatible with the 4004 and therefore recognizes all 46 instructions valid for the 4004. In addition, the 4040 recognizes 14 new instructions giving a total of 60 instructions in the set. The instruction format is, of course, identical to that used in the 4004.

Four groups of instructions can be defined as follows:

- Machine Instructions This group of 16 instructions are designated by an OPR code of 0000 - 1101. Within this group is contained a second group which is designated supplemental group.

- Supplemental Group This group of 14 instructions is designated by an OPR code of 0000 and an OPA code of 0001 - 1110.

These are the new instructions which have been added to the 4040.

- c. I/O Group Designated by an OPR code of 1110, this group of 16 instructions is used for transferring data between the processor and the RAM chips or I/O circuits.

d. Accumulator Group - This group of 14 instructions is designated by an OPR code of 1111 and operates only on the accumulator/carry flip-flop, the special ROMs and the command register.

The 4004 instruction set is well documented elsewhere (see MCS-4 Users' Manual) and therefore will not be described here. The new supplemental group will be described in detail below:

| 4.1 | New | Instructions | for | 4040 | - | Detailed | Description |

|-----|-----|--------------|-----|------|---|----------|-------------|

|-----|-----|--------------|-----|------|---|----------|-------------|

| MNEMONIC | OPR  | OPA  | DESCRIPTION                        |

|----------|------|------|------------------------------------|

| HLT      | 0000 | 0001 | The processor sets the HALT and    |

|          |      |      | STOP flip-flops. Program counter   |

|          |      |      | incrementer and data input buffers |

|          |      |      | are inhibited. The processor ex-   |

|          |      |      | ecutes NOP continuously; continua- |

|          |      |      | tion can occur by means of STOP or |

|          |      |      | INTERRUPT control.                 |

BBS 0000 0010 This instruction is a combination of BRANCH BACK and SRC. The effective address counter is decremented and program control is returned to the location saved by the forced JMS which occurred during the interrupt routine. In addition, the content of the SRC register is sent out at  $X_2$  and  $X_3$  of the instruction cycle, thus restoring

| MNEMONIC | OPR  | OPA  | DESCRIPTION                                                                                                                                                                                                                                     |

|----------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |      |      | the I/O port or RAM location address.                                                                                                                                                                                                           |

| LCR      | 0000 | 0011 | The 4-bit contents of the COMMAND<br>REGISTER are transferred to the<br>ACCUMULATOR. This allows saving<br>the command register values before<br>processing the interrupt.                                                                      |

| OR4      | 0000 | 0100 | The 4-bit contents of index register<br>#4 are logically "OR-ed" with the<br>ACCUMULATOR. The result is placed<br>in the ACCUMULATOR and the CARRY<br>flip-flop is unaffected. Logically<br>the result is :<br>$ACC_n \leftarrow ACC_n + IR4_n$ |

| OR5      | 0000 | 0101 | The 4-bit contents of index register<br>#5 are logically "OR-ed" with the<br>ACCUMULATOR.                                                                                                                                                       |

| AN6      | 0000 | 0110 | The 4-bit contents of index register<br>#6 are logically "AND-ed" with the<br>ACCUMULATOR. The result is placed<br>in the ACCUMULATOR and the CARRY<br>IS unaffected. Logically the result<br>is:                                               |

$A_{CCn} \leftarrow ACC_n \cdot IR6_n$

| MNEMONIC | OPR  | OPA  | DESCRIPTION                                  |

|----------|------|------|----------------------------------------------|

| AN7      | 0000 | 0111 | The 4-bit contents of index regis-           |

|          |      |      | ter #7 are logically "AND-ed" with           |

|          |      |      | the ACCUMULATOR.                             |

| dbø      | 0000 | 1000 | DESIGNATE ROM BANK $\emptyset$ . The most    |

|          |      |      | significant bit of the COMMAND REGIS-        |

|          |      |      | TER, $CR_3$ , is reset. On the third         |

|          |      |      | instruction cycle following its              |

|          |      |      | execution, it causes CM-ROMØ to be           |

|          |      |      | activated.                                   |

| DB1      | 0000 | 1001 | DESIGNATE ROM BANK 1. The most               |

|          |      |      | significant bit of the COMMAND REGIS-        |

|          |      |      | TER, CR <sub>3</sub> , is set. On the third  |

|          |      |      | instruction cycle following its              |

|          |      |      | execution, it causes CM-ROM1 to              |

|          |      |      | be activated.                                |

| SBØ      | 0000 | 1010 | SELECT INDEX REGISTER BANK $\emptyset$ . The |

|          |      |      | index register bank select flip-flop         |

|          |      |      | is reset. Index registers 0 - 7,             |

|          |      |      | 8 - 15 will be available for program         |

|          |      |      | use.                                         |

| SB1      | 0000 | 1011 | SELECT INDEX REGISTER BANK 1. The            |

|          |      |      | index register bank select flip-flop         |

|          |      |      | is set. Index registers 0* - 7*,             |

|          |      | •    | 8 – 15 will be available for program         |

|          |      |      | use.                                         |

| MNEMONIC | OPR  | OPA  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                    |

|----------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EIN      | 0000 | 1100 | ENABLE INTERRUPT. Internal interrupt detection logic is enabled.                                                                                                                                                                                                                                                                                                               |

| DIN      | 0000 | 1101 | DISABLE INTERRUPT. Internal interrupt detection logic is disabled.                                                                                                                                                                                                                                                                                                             |

| RPM      | 0000 | 1110 | READ PROGRAM MEMORY. This instruc-<br>tion can be used only with the 4289<br>Standard Memory and I/O Interface<br>Chip. The contents of the previously<br>selected half-byte of program memory<br>are transferred to the 4040 and<br>loaded to the ACCUMULATOR. A First/<br>Last sequence flip-flop regulates<br>the transfer. Two RPMs are required<br>for instruction fetch. |

#### APPENDIX I

#### PROGRAMMING EXAMPLES

# I. USE OF DBØ AND DB1

The DB instructions present a convenient method of switching from one ROM bank to another. As shown in the following examples the bank switch is delayed until the 3rd instruction cycle after the DB is executed.

#### EXAMPLE A

|                  | Locatic<br>Page / |                          | Instruction                 | Comment                                                                                                     |

|------------------|-------------------|--------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------|

| 0<br>0<br>0<br>0 | 2<br>2<br>2<br>2  | 107<br>108<br>109<br>110 | X X X<br>DB1<br>JUN 1<br>27 | Designate Bank 1.<br>During this instruction cycle<br>a "1" is loaded in bit #3 of<br>the command register. |

| 1                | 1                 | 27                       | x x x                       | JUN occurred to Bank l because<br>CM-ROM <sub>l</sub> has been activated.                                   |

| 1<br>1<br>1      | 1<br>1<br>1       | 63<br>64<br>65           | DBØ<br>ISZ 3<br>151         | Designate Bank Ø.                                                                                           |

| 0                | 1                 | 66                       | x x x                       | Program jumps here if $(IR_3) = 0$ .                                                                        |

| 0                | 1                 | 151                      | ххх                         | Program jumps here if (IR <sub>3</sub> ) $\neq$ 0.                                                          |

\* Bank # 0, 1

Page # 0 - 15

Word # 0 - 255

#### EXAMPLE B

|        | Locatic<br>Page / |            | Instruction  | Comment                                                                                          |

|--------|-------------------|------------|--------------|--------------------------------------------------------------------------------------------------|

| 0<br>0 | 7<br>7            | 131<br>132 | X X X<br>DBl | Designate Bank 1.                                                                                |

| 0<br>0 | 7<br>7            | 133<br>134 | JMS 2<br>96  | Address 7, 135 saved in stack.                                                                   |

| 1<br>• | 2                 | 96<br>•    | x x x<br>•   | JMS occurs to 1, 2, 96 since<br>CM-ROM, is activated at this<br>instruction cycle.               |

| 1<br>1 | 2<br>2            | 170<br>171 | DBØ<br>XCH 7 | Designate Bank Ø.                                                                                |

| 1      | 2                 | 172        | BBL          | Address 7, 135 pulled from stack and placed in PC; branch back                                   |

| 0      | 7                 | 135        | ххх          | occurs to 7, 135 in Bank $\emptyset$ because CM-ROM, is activated during this instruction cycle. |

### II. INTERRUPT PROCESSING

An interrupt processing routine is, in general, composed of three parts:

- a) The instructions required to save the current processor status.

- b) A portion which determines and services the interrupting device.

- c) The instructions required to restore program control to the pre-interrupt conditions.

In the first example, the processor is used with a single ROM bank, and index register Bank 1 is used to save status (accumulator/carry, command register). The six remaining registers in IR Bank 1 are available for interrupt servicing. In addition to being relatively simple, this scheme has the advantage of saving processor status with the fewest number of instructions. Note that since only one ROM bank is available, it is only necessary to save the lower three bits of CR. This allows saving the CR and CY in the same register location.

In Example B, both ROM banks are used and all eight registers of IR Bank 1 are required to service the interrupt. Since the forced JMS instruction can occur in either ROM bank, the instructions

required to save ACC and CR must be located in each bank. If more than eight register locations are required for interrupt servicing, additional instructions will be required to save the values of the upper eight IR.

EXAMPLE A

|                            | Locatio<br>Page /               |                                      | Instruction                         | Comment                                                                                                                                                                                                                                                                                                                |

|----------------------------|---------------------------------|--------------------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                          | 6                               | 82                                   | SRC 4                               | (IR 8,9) sent to ROM & RAM,<br>Load SRC Reg.                                                                                                                                                                                                                                                                           |

| 0<br>0<br>0                | 6<br>6<br>6                     | 83<br>84<br>84                       | INC 9<br>(JMS Ø)<br>(3)             | Interrupt occurs here.<br>Interrupt acknowledged, 6,84<br>saved in stack; instruction at<br>6,84 ignored.                                                                                                                                                                                                              |

| 0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0 | 3<br>4<br>5<br>6<br>7<br>8<br>9      | SB1<br>XCH 7<br>LCR<br>RAL<br>XCH 6 | <pre>Select IR Bank 1.<br/>(ACC)→IR7* - ACC saved.<br/>(CR)→ACC<br/>(CY)→ACC<sub>0</sub>, Acc<sub>0</sub>→Acc<sub>1</sub>Acc<sub>3</sub>→CY<br/>(ACC)→IR6* CY, CR saved.<br/>Routine for determing and<br/>servicing interrupt is executed<br/>here.</pre>                                                             |

| 0                          | P                               | n<br>n+1<br>n+2<br>n+3<br>n+4<br>n+5 | SBØ<br>BBS                          | <pre>(IR6*)→ACC<br/>ACC<sub>0</sub>→CY - CY restored<br/>ACC<sub>0</sub>→CR<sub>0</sub>, ACC<sub>1</sub>→CR<sub>1</sub>, ACC<sub>2</sub>→CR<sub>2</sub>,<br/>CR restored.<br/>(IR7*)→ACC<br/>Select IR Bank Ø.<br/>Address 6,84 loaded into PC;<br/>contents of SRC register sent<br/>out;<br/>program restored.</pre> |

| 0                          | 6                               | 84                                   | WRM                                 | program restored.                                                                                                                                                                                                                                                                                                      |

#### APPENDIX II

### SINGLE STEP MODE

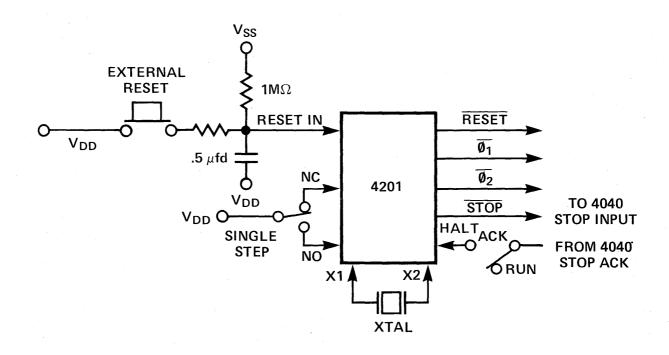

Fig. Cl shows a possible circuit configuration for operating in single step mode. The circuit uses the positive going (turn-off) edge of STOP ACKNOWLEDGE to generate a new STP signal. Operation is as follows:

- (a) With the toggle switch in the SINGLE-STEP position, the line STP is at a logic "l" level and the processor is in the STOP mode.

- (b) Depressing the single-step push button causes a negative going pulse to be generated at point (A), in turn causing STP to return to a positive level. The duration of this pulse is determined by the R/C combination and must be greater than one instruction cycle.

- (c) The processor will cause STPA to return to a logic "0" level indicating that it is no longer in STOP mode. This signal is inverted and then used to reset the O/S causing STP to return to logic "1".

- (d) The "new" STP signal will be latched up and acknowledged after one instruction has been executed.

## APPENDIX III

÷ .

|             | DATA @ X <sub>2</sub>                           | DATA @ X <sub>3</sub>       |                                                                                 |

|-------------|-------------------------------------------------|-----------------------------|---------------------------------------------------------------------------------|

| INSTRUCTION | D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> Dø | $D_3 D_2 D_1 D_{\emptyset}$ | COMMENTS                                                                        |

|             |                                                 |                             |                                                                                 |

| NOP         | 1 1 1 1                                         | 1 1 1 1                     |                                                                                 |

| HLT         | 1 1 1 1                                         | 1 1 1 1                     | After execution of<br>HLT, processor enters                                     |

| BBS         | (SRCH)                                          | (SRCL)                      | STOP mode.<br>(SRCH) means contents<br>of 4 high order bits<br>of SRC register. |

| LCR         | (COM. REG)                                      | 1 1 1 1                     |                                                                                 |

| OR4         | (0100)                                          | 1 1 1 1                     |                                                                                 |

| OR5         | (0101)                                          | 1 1 1 1                     |                                                                                 |

| AN6         | (0110)                                          | 1 1 1 1                     |                                                                                 |

| AN7         | (0111)                                          | 1 1 1 1                     |                                                                                 |

| DBØ         | 1 1 1 1                                         | 1 1 1 1                     |                                                                                 |

| DB1         | 1 1 1 1                                         | 1 1 1 1                     |                                                                                 |

| SBØ         | 1 1 1 1                                         | 1 1 1 1                     |                                                                                 |

| SB1         | 1 1 1 1                                         | 1 1 1 1                     |                                                                                 |

| ElN         | 1 1 1 1                                         | 1 1 1 1                     |                                                                                 |

| DIN         | 1 1 1 1                                         | 1 1 1 1                     |                                                                                 |

| RPM         | (P.M.)                                          | (P.M.)                      | Program memory content                                                          |

|             |                                                 |                             |                                                                                 |

## 4201 CLOCK GENERATOR

#### 1.0 Introduction

The 4201 is a CMOS MSI integrated circuit designed to fill the clock requirements of the MCS-4 microcomputer set. The 4201 contains a crystal controlled oscillator (XTAL external), clock generation circuitry, and both MOS and TTL level clock driver circuits.

The 4201 also performs the power on reset function required by MCS-4 components and provides the logic necessary to implement the single-step function of the 4040 central processor unit.

## 2.0 Hardware Description

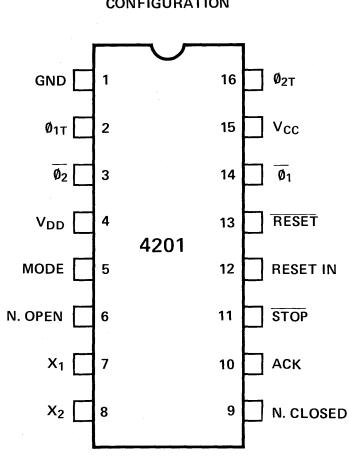

The 4201 is packaged in a 16-pin plastic DIP. The pin configuration is shown in the following figure, and a functional description of each pin is given below:

| <u>Pin #</u> | Designation     | Description                                                      |

|--------------|-----------------|------------------------------------------------------------------|

| 1            | GND             | Circuit ground potential                                         |

| 2            | ØlT             | Phase 1 TTL level clock output (2ma-sink).                       |

| 3            | ø2              | Phase 2 MOS level clock output. Directly                         |

|              |                 | drives all MCS-4 components (up to 250pf).                       |

| 4            | V <sub>DD</sub> | Main Power Supply Pin. V <sub>DD</sub> = V <sub>SS</sub> -15V+5% |

| 5            | MODE            | Counter mode control pin. Determines whether                     |

|              |                 | counter divides basic frequency by 4 or 7.                       |

|              | · .             | Model 1 = V <sub>SS</sub>                                        |

|              |                 | Model 2 = $V_{DD}$                                               |

|              |                 | 40                                                               |

4201 PIN CONFIGURATION 6 N. OPEN Input of single step circuitry to which normally open contact of SPDT switch is connected.

7 X1 External Crystal Connection

8 X2 External Crystal Connection

9 N. CLOSED Input of single step circuitry to which normally closed contact of SPDT switch is connected.

10 ACK Acknowledge input to single step circuitry normally connected to stop acknowledge output of 4040.

11 STOP Stop output of single step circuitry normally connected to stop input of 4040.

12 RESET IN Input to which RC network is connected to provide power-on reset timing.

13 RESET Reset signal output which directly connects to all MCS-4 reset inputs.

14  $\overline{\emptyset 1}$  Phase 1 MOS level clock output. Directly drives all MCS-4 clock inputs (up to 250pf).

15 V<sub>CC</sub> Circuit reference potential--most positive supply voltage.

Ø2T Phase 1 TTL level clock output (2ma-sink).

42

## **4201 IMPLEMENTATION**

## 3.0 Functional Description

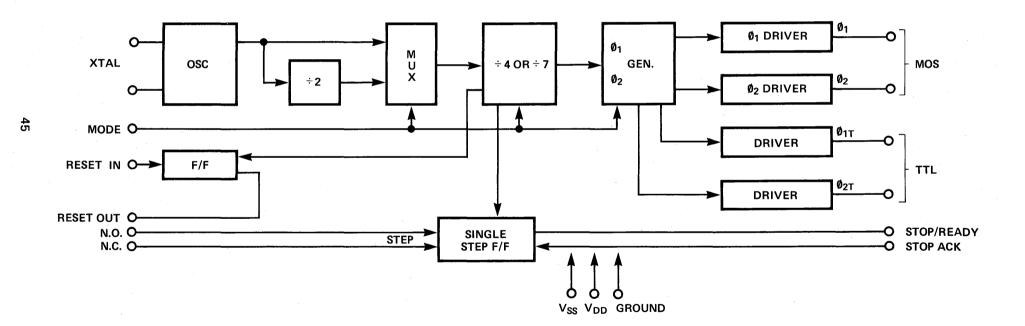

The 4201 consists of the following functional blocks:

#### 3.1 Crystal Oscillator

The oscillator is a simple series mode crystal-type circuit consisting of two inverters biased in the active region, and a series crystal element.

#### 3.2 Programmable Shift Register

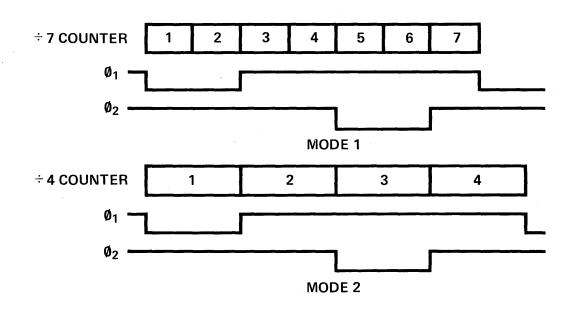

The shift register in the 4201 divides the master clock and generates the proper states for generating the desired twophase clock. The circuit is a seven-bit dynamic device which circulates a logical "1" through a field of zeroes. The output of the various stages are then combined to provide the proper clock waveforms.

In order to maintain the proper clock timing over the full operating frequency range of the MCS-4, the shift register is programmable (using mode pin) as either a 7-bit or 4-bit device. When in the 4-bit mode the clock is divided by 2 and the relationship between the phases is equal; that is,  $\emptyset_1$  pulse width,  $\emptyset_2$  pulse width,  $\emptyset_1$  to  $\emptyset_2$  and  $\emptyset_2$  to  $\emptyset_1$  times are all equal.

#### 3.3 Phase Decoder

A simple gate complex is used to decode the shift register outputs to provide phase 1 and phase 2 clock waveforms. This circuitry is controlled by the mode input to achieve the two sets of timing discussed in the previous section.

4201 BLOCK DIAGRAM

## 3.4 Output Buffers

There are two sets of output buffers for the 2 phase clock. One set is the MOS level drivers designed to directly drive a full complement of MCS-4 components. These outputs can drive approximately 250pf loads with transition times of less than 50ns. The second set provides TTL compatible outputs which can drive one standard TTL load.

### 3.5 Reset Circuit

The reset circuit is simply a level detector and driver stage. An external RC netword connected between  $V_{DD}$  and  $V_{SS}$  at the reset input pin of the 4201 provides the required power-on delay. A  $1M\Omega/.5\mu$ fd combination will insure a 300ms reset pulse.

A reset pulse can be generated externally by discharging the external capacitor.

In addition to driving members of the MCS-4 externally, the reset pulse is used internally for initializing the single step circuitry.

### 3.6 Single Step Control

The 4201 contains the necessary circuitry for allowing the 4040 CPU to execute instructions one at a time. Using the stop input and stop acknowledge output of the 4040, the 4201 generates a pulse that allows the 4040 to perform only one instruction. The stop command can be provided by a SPDT pushbutton directly since bebouncing is provided by the 4201. A SPST toggle switch, in series with the ACK line, provides th the Run/Halt feature.

## 4201 SHIFT REGISTER MODES

#### 4308 READ ONLY MEMORY

### 1.0 Introduction

The 4308 is a 1024 x 8-bit word ROM memory with four I/O ports. It is designed for the MCS-4 system, and is operationally compatible with all existing MCS-4 elements. The 4308 is functionally identical to four 4001 chips. It has 16 I/O lines arranged in four groups of four lines. Port selection and accessibility is accomplished as previously, with the 4001. In addition, 4308 has input I/O buffer storage, and is packaged in a 28-pin DIP. A substitution of four 4001 programs can be incorporated in one 4308, including I/O, with no other consideration.

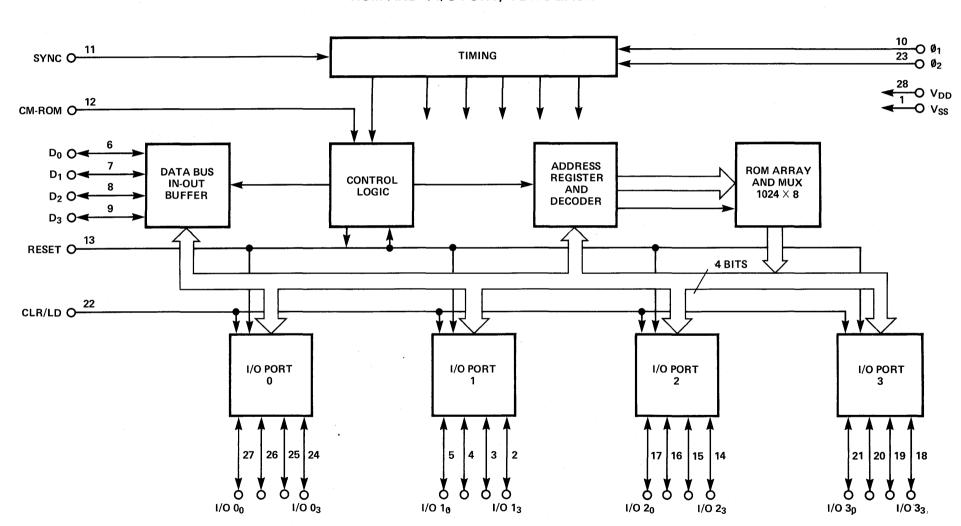

#### 2.0 General Description

The 4308 ROM memory is arrayed 1024 x 8-bit words. As in the 4001, the Al - A3 time periods are used to address the ROM contents. The 4308 decodes the first ten bits of the address to select 1 out of 1024 words, 8-bits wide. The remaining two bit selects a package number, one of four combinations are possible per ROM bank. The package (chip select) number is selected by a metal mask option. As with the 4001, instruction information is available in two 4-bit segments during  $M_1$  and  $M_2$  time periods. A 4004 system can accommodate up to four 4308's while a 4040 system can utilize up to eight devices. Since the 4308 is compatible with all components of the MCS-4 system, 4308 and 4001 can be mixed on one memory bank as long as the chip select addresses are mutually exclusive.

4308 PIN CONFIGURATION

4308 1024  $\times$  8 BIT MASK PROGRAMMABLE ROM AND 4 I/O PORT, 4 BITS EACH

As an I/O device, the 4308 ROM recognizes the same class of I/O instructions (SRC, WRR, and RDR) as that of the 4001 ROM. Each of the four I/O ports are program selectable. Each of the four lines can be specified as either inputs or outputs. This is done via the metal mask option. A complete description of the I/O option capabilities are given in Section 3.0. The 4308 has an input storage buffer for utilization with those I/O pins designated as inputs. A common strobe line allows the asynchronous loading of data from the I/O lines. This same strobe line can also serve as a clear to the I/O output port buffers when desig-This line is common to all ports on a 4308 and when nated. toggled, will effect those I/O lines connected by the metal mask option. For an input line, if the strobe line is left unconnected, or if it is pulled up  $(V_{SS})$ , then the output of the buffer will follow the input.

4308

#### 2.1 Pin Description

| <u>Pin #</u> | Designators                           | Description of Function            |

|--------------|---------------------------------------|------------------------------------|

| 1            | VSS                                   | Circuit GND potentialmost positive |

| ·            |                                       | supply voltage.                    |

| 2 - 5        | 1/01 <sub>3</sub> - 1/01 <sub>ø</sub> | Four I/O ports consisting of 4 bi- |

| 14 - 17      | $1/02_{3} - 1/02_{g}$                 | directional and selectable lines   |

| 18 - 21      | 1/03 <sub>3</sub> - 1/03 <sub>Ø</sub> | which are selectively compatible   |

| 24 - 27      | 1/0ø <sub>3</sub> - 1/0ø <sub>ø</sub> | to a host of logic families.       |

| 10, 23       | Ø1, Ø2                                | Non-overlapped clock signals which |

|              |                                       | determine device timing.           |

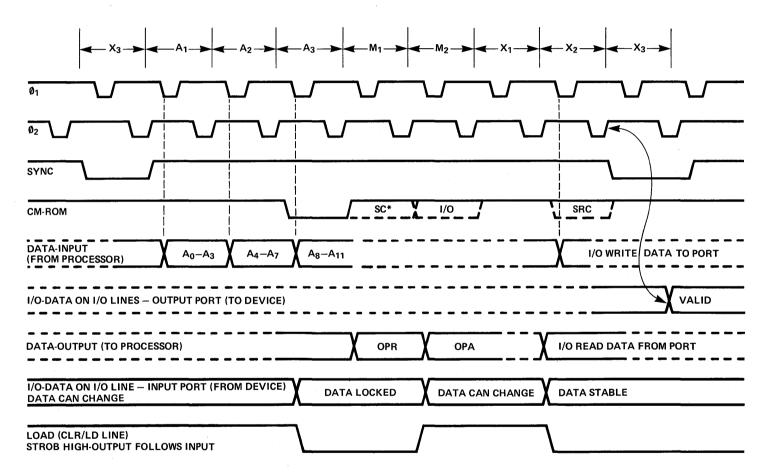

## **4308 EXTERNAL TIMING**

**\*REFER TO MCS 4040 SPECIFICATION**

| <u>Pin#</u> | Designators | Description of Function                 |

|-------------|-------------|-----------------------------------------|

| 11          | SYNC        | System synchronization signal gener-    |

|             |             | ated by processor.                      |

| 12          | CM-ROM      | Chip enable generated by the processor. |

| 13          | RESET       | Reset input. A "l" level on this        |

|             |             | pin will clear internal flip-flops      |

|             |             | and buffers. The input buffers are not  |

|             |             | cleared by this signal.                 |

| 22          |             | Class/I and input When this option      |

| 22          | CLR/LD      | Clear/Load input. When this option      |

is selected, a "1" to "0" state change will cause the output buffer to clear or the input buffer to load the contents of I/O bus. This bus is common to all I/O ports and is TTL compatible.

28

Main supply voltage value must be  $V_{SS} - 15.0V \pm 5$ %.

## 2.2 Basic Timing

v<sub>dd</sub>

Referring to the timing diagrams, at the beginning of each instruction sequence, a SYNC pulse is generated externally to synchronize the processor with the various components of the system. This pulse, along with the clock inputs  $\emptyset_1$  and  $\emptyset_2$ , is used in the 4308 as an input to a timing register. During time Al, A2, and A3 the address is sequentially

53

accepted from the data bus and decoded. During time A3, the CM-ROM line will be active, and if the 2-bit (highest order) chip select matches the metal pre-programmed chip select option, the ROM will respond to the current address.

At time M1, M2, the instruction OPR, OPA will be placed on the data bus for the processor. The 4308 responds to 3 I/O instructions in the 4004/4040 instruction set - SRC, RDR, and WRR.

The SRC or Send Register Control instruction is used to designate a set of 4 I/O lines (1 port) on a particular ROM which are to be used for subsequent ROM I/O operations. When this instruction is executed by the processor, the processor sends a 4-bit code to the ROM during  $X_2$ , and CM-ROM goes to a "1". The first two bits ( $D_3$ ,  $D_4$ ) of this code select a group of 1 out of 4 possible 4308, and the last two bits select a particular port (1 of 4 ports). This port remains selected until the next SRC instruction is executed.

As in the 4001, the WRR (write to ROM port) instruction will cause the contents of the accumulator to be transferred to a previously selected ROM port. As in both the RDR and WRR operations, the CM-ROM line will become active during time M2, and if the ROM has a previously selected I/O port it will respond to the I/O in two ways. For a WRR accumulator, data will be transferred to an internal ROM selected output port flip-flops during X2. Data will be available

4308 I/O PIN OPTIONS

on the I/O line from time X3  $\cdot \overline{\beta}_2$ . The data will remain on the bus until a new WRR occurs, a reset occurs, or a clear (CLR/LD line) is generated. The RDR instruction will transfer information from the input port flip-flops of a previously selected port. Prior to RDR instruction the user should insure that the input flip-flops have been loaded via the CLR/LD strobe if the load strobe is specified. If the load strobe is not specified, information on the input lines will be loaded into the accumulator at the time of the RDR. Input ports or lines are TTL compatible as well as the CLR/LD line. Outputs require external pull-up and +5V, -10V supply.

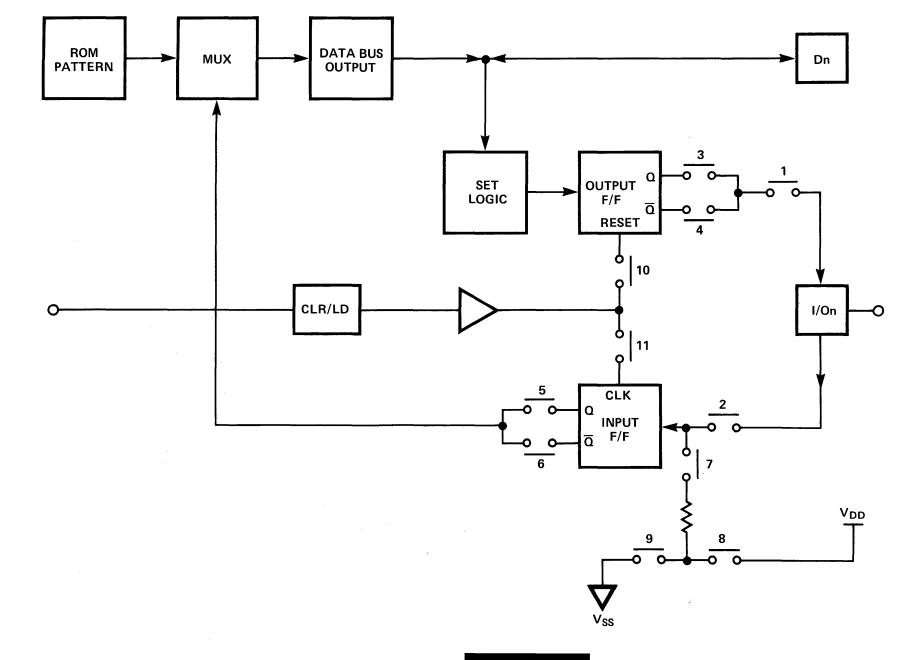

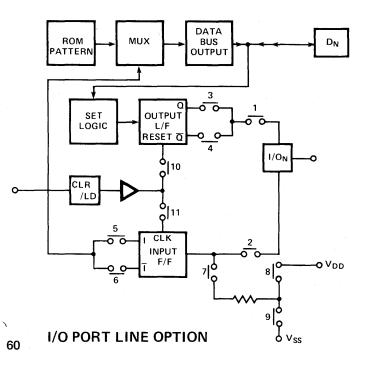

#### 3.0 I/O Options

The 4308 offers all of the feasibilities found in the 4001. In addition, there are enhancements over the 4001:

- 1. The user can programmably clear any or all output ports with the CL/LD signal.

- 2. When operated as an input port, both the inverting and noninverting inputs paths are TTL compatible.

- By selecting the LD option, the input buffer becomes an input flip-flop and the CL/LD signal becomes an asynchronous clock for loading data.

Referring to the block diagram of the single I/O pin illustrating the various options, it should be noted that the option numbering differs from that of 4001. Certain pin combination are mutually exclusive and should not be specified together. There are also certain invalid combinations. The following combinations should

be avoided:

```

8, 9

5, 6

3, 4

10, 11

```

Examples of some common desired option/connections are:

(a) I/O pin inputs\*

non-inverting 11, 2, 5, 7, 9 (TTL) - 2, 5, 7, 8 inverting 11, 2, 6, 7, 9 (TTL) - 2, 6, 7, 8

(b) I/O pin outputs

non-inverting 3, 1 (10 optional)

inverting 4, 1 (10 optional)

Other combinations exist and should be used with caution.

For TTL compatibility on the I/O lines, the supply voltage should be  $V_{DD} = -10V \pm 5\%$ ,  $V_{SS} = +5V \pm 5\%$ ,  $V_{DD1} = GND$ . External pullup is required for outputs.

All 4308 metal masked ROM orders must be submitted on forms provided by Intel. Programming information should be provided in the form of computer punched cards or punched tape. In either case, a print-out of the truth table must accompany the order. Refer to the Appendix for complete pattern specification and a sample 4308 ROM form.

\*NOTE: Option 11 need not be specified if an unbuffered input is desired. This is equivalent to a 4001 input.

#### 4308 INPUT FORMAT

The 4308 programming information should be provided in the form of computer punched cards or punched paper tape. The input format is found in the <u>Intel General Component Catalog</u>, and reproduced here for your convenience. The following enhancement has been added to assist in the preparation of programs. These features are optional:

A. The character "X" to be included with "P" and "N" in data word, where "X" indicates "don't care". The bit will be assigned a value which will have the least impact on the dynamic operation of the ROM. A fully assigned listing will be returned to the customer for approval.

B. The use of a format; B\*nnnnF to indicate that the preceding word should be repeated nnnnn times, (where "nnn" is a decimal number). It should be noted that "nnnnn" can be no greater than 1023 for

the 4308.

The above two options permits the user to default the last "nnn" ROM words to a "don't care" value.

Due to the I/O customizing option of the 4308, the following header information should be appended to the usual programming input. This information provided on a header is optional. The 4308 custom ROM order form should accompany the program whether the header is used or not.

Each tape should start with a device identifier

#### "14308-"

where the "I" and the "-" serve as delimiters, just as "B" and "F" do for data words. This could be preceded by any data not containing

an "I".

This should be followed by the chip select information encoded as a decimal number and enclosed by "C" and "S", as in:

"CdS" =  $\emptyset - 3$

Finally, the I/O options would be specified on a port-by-port basis (refer to ROM form) with the connections to be made separated by commas, and enclosed in parenthesis:

"(nl, n2, n3...nll)".

Example:

| "()"           | indicates no connection              |

|----------------|--------------------------------------|

| "(1)"          | indicates only #1                    |

| "(2, 5, 7, 9)" | indicates connections 2, 5, 7, and 9 |

So, a 4308 tape might be:

.

I4308-CØ3S (1,3) (2,7,5,9)...(1,4) B . . F . .

#### 4308 Metal Masked ROM

All custom ROM orders must be submitted on forms provided by Intel. Programming information should be sent in the form of computer punched cards or punched paper tape. In either case, a print-out of the truth table must accompany the order. Refer to the 4308 Data Catalog for complete pattern specifications. Additional forms are available from Intel.

|             | Intel use |      |

|-------------|-----------|------|

| CUSTOMER    | S#        | PPPP |

| ADDRESS     | STD       | ZZ   |

| P.O. NUMBER | APP       | DD   |

| DATE        | DATE      | I/O  |

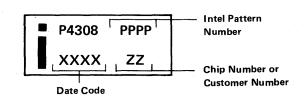

#### INTEL STANDARD MARKING

The marking as shown at right must contain the Intel logo, the product type (P4308), the four digit Intel pattern number (PPPP), a date code (XXXX), and the two digit chip number (DD). An optional customer identification number may be substituted for the chip number (ZZ).

Optional Customer Number (Maximum 6 characters or spaces)

#### **ROM DESCRIPTION**

| Chip Se | lect | Valı | ue (0- | -3) | • | (1 | Vlust | be | spec | cified. | .) |

|---------|------|------|--------|-----|---|----|-------|----|------|---------|----|

|         |      |      |        |     |   |    |       |    |      |         |    |

In the table below, select the connections which should be

made for each of the 16 I/O port input lines. Avoid the use of illegal options-refer to the 4308 Data Catalog.

Mark the appropriate box for an option connection. Leave blank for a no connection.

| ( PIN              | ( PIN |   |   | OPTION |   |   |   |   |   |   |    |    |

|--------------------|-------|---|---|--------|---|---|---|---|---|---|----|----|

| I/O 0 <sub>0</sub> | 27    | 1 | 2 | 3      | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| I/O 0 <sub>1</sub> | 26    | 1 | 2 | 3      | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 1/O 02             | 25    | 1 | 2 | 3      | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| I/O 0 <sub>3</sub> | 24    | 1 | 2 | 3      | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| I/O 1 <sub>0</sub> | 5     | 1 | 2 | 3      | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| I/O 1 <sub>1</sub> | 4     | 1 | 2 | 3      | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| I/O 1 <sub>2</sub> | 3     | 1 | 2 | 3      | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| I/O 1 <sub>3</sub> | 2     | 1 | 2 | 3      | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| I/O 20             | 17    | 1 | 2 | 3      | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| I/O 21             | 16    | 1 | 2 | 3      | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| I/O 22             | 15    | 1 | 2 | 3      | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 1/O 23             | 14    | 1 | 2 | 3      | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 1/O 3 <sub>0</sub> | 21    | 1 | 2 | 3      | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 1/0 3 <sub>1</sub> | 20    | 1 | 2 | 3      | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| I/O 3 <sub>2</sub> | 19    | 1 | 2 | 3      | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 1/O 3 <sub>3</sub> | 18    | 1 | 2 | 3      | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

## Input Format

#### I. ROM and PROM Truth Table Format

Programming information should be sent in the form of computer punched cards or punched paper tape. When using the 7600C or MCS programmers (see Section II), punched paper tape should be used. In all cases, a printout of the truth table should be accompanied with the order.

- The following general format is applicable to the programming information sent to Intel:

- 1. A data field should start with the most significant bit and end with the least significant bit.

- 2. The data field should consist of P's and N's. A P is to indicate a high level output (most positive) and an N a low level output (most negative). If the programming information is sent on a punched paper tape, then a start character, B, and an end character, F, must be used in the data field.

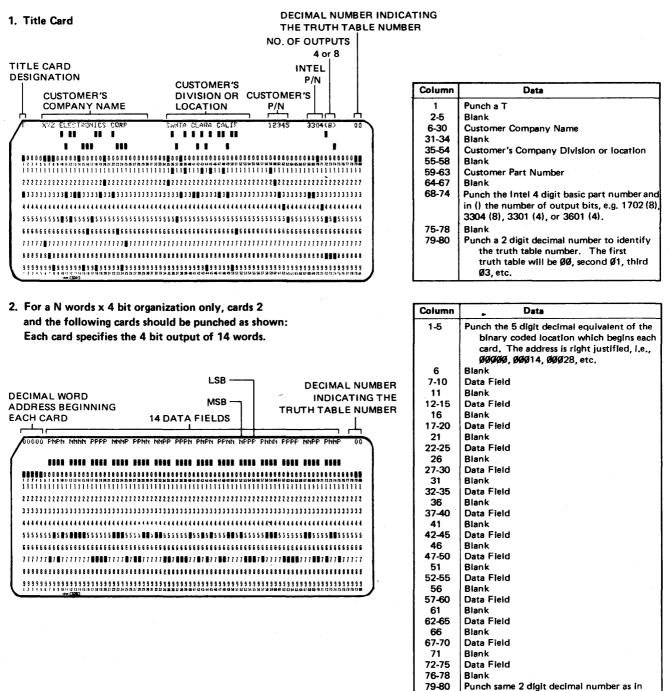

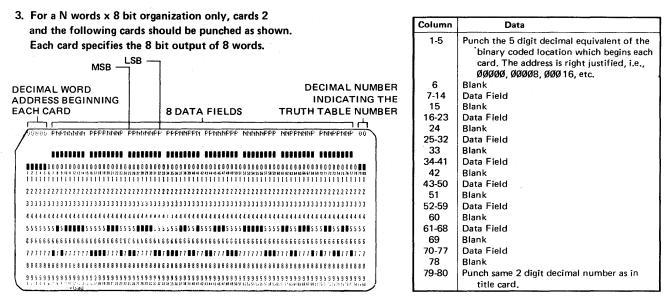

#### A. Punched Card Format

An 80 column Hollerith card (preferably interpreted) punched by an IBM 026 or 029 keypunch should be submitted. The first card will be a title card. The format is as follows:

title card.

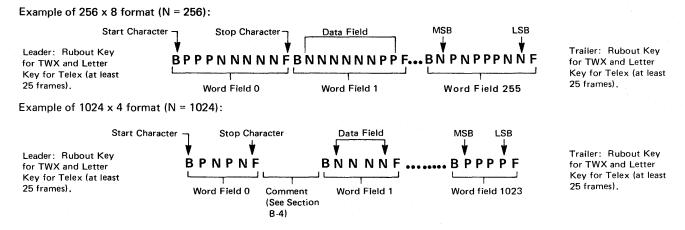

#### B. Paper Tape Format

The paper tapes which should be used are the:

- 1. 1" wide paper tape using 7 or 8 bit ASCII code, such as a model 33 ASR teletype produces, or the

- 2. 11/16" wide paper tape using 5 bit Baudot code, such as a Telex produces.

The format requirements are as follows:

- 1. All word fields are to be punched in consecutive order, starting with word field Ø (all addresses low). There must be exactly N word fields for the N x 8 or N x 4 ROM organization.

- 2. Each word field must begin with the start character B and end with the stop character F. There must be exactly 8 or 4 data characters between the B and F for the N x 8 or N x 4 organization respectively.

NO OTHER CHARACTERS, SUCH AS RUBOUTS, ARE ALLOWED ANYWHERE IN A WORD FIELD. If in preparing a tape, an error is made, the entire word field, including the B and F must be rubbed out. Within the word field, a P results in a high level output, and an N results in a low level output.

- 3. Preceding the first word field and following the last word field, there must be a leader/trailer length of at least 25 characters. This should consist of rubout punches (letter key for Telex tapes)

- 4. Between word fields, comments not containing B's or F's may be inserted. Carriage return and line feed characters should be inserted (as a "comment") just before each word field (or at least between every four word fields). When these carriage returns, etc. are inserted, the tape may be easily listed on the teletype for purposes of error checking. The customer may also find it helpful to insert the word number (as a comment) at least every four word fields.

- 5. Included in the tape before the leader should be the customer's complete Telex or TWX number and if more than one pattern is being transmitted, the ROM pattern number.

- 6. MSB and LSB are the most and least significant bit of the device outputs. Refer to the data sheet for the pin numbers.

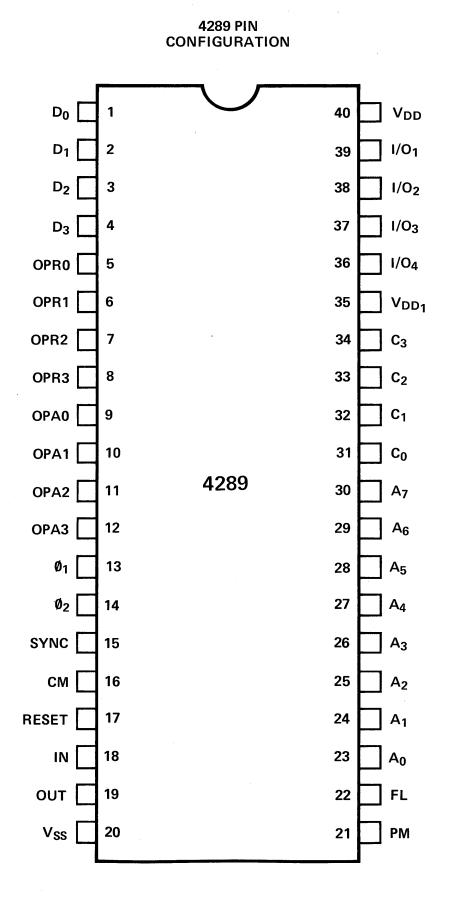

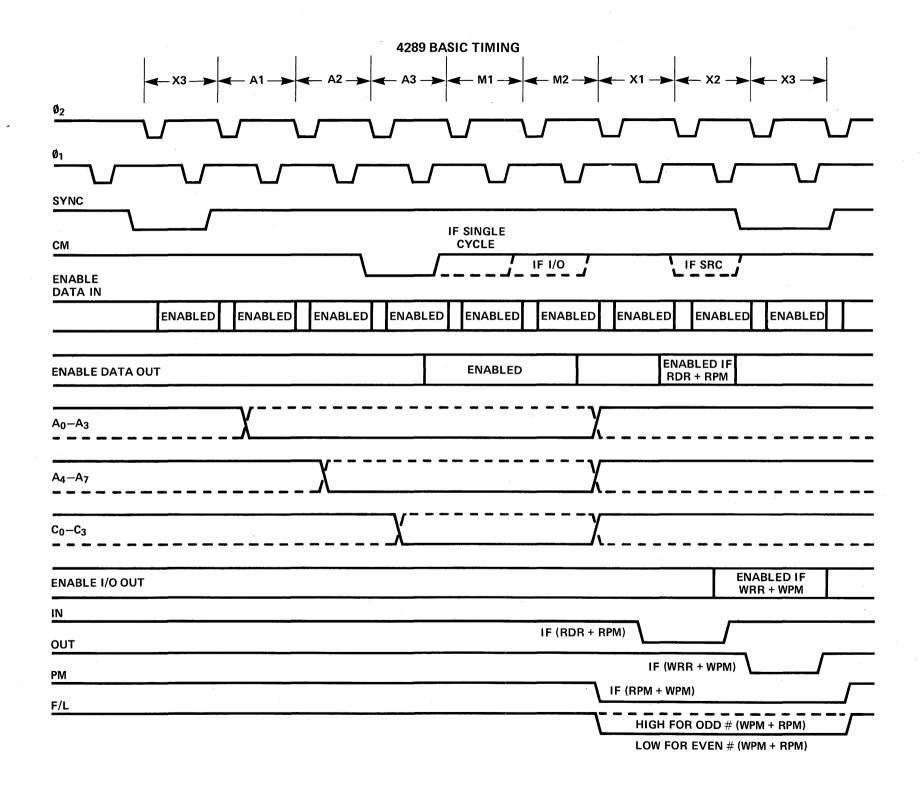

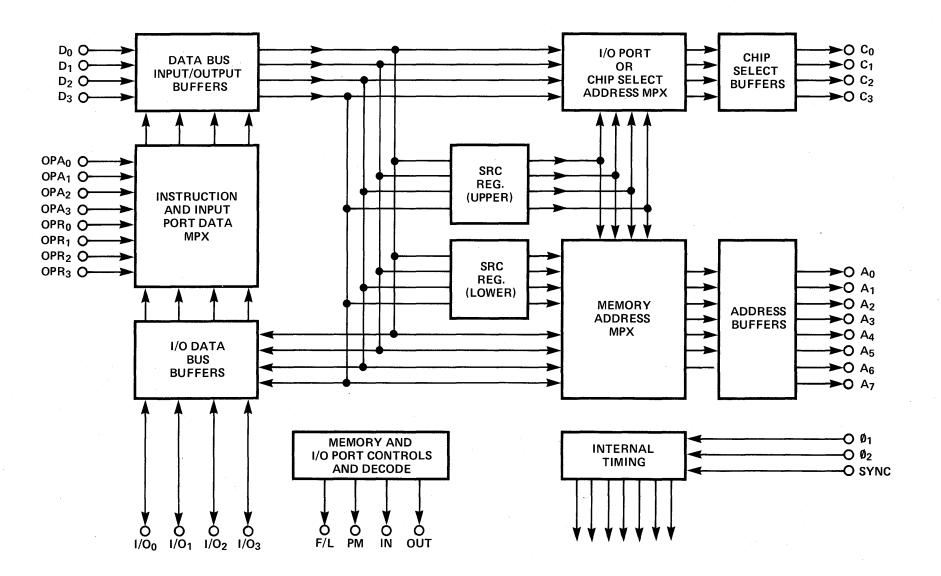

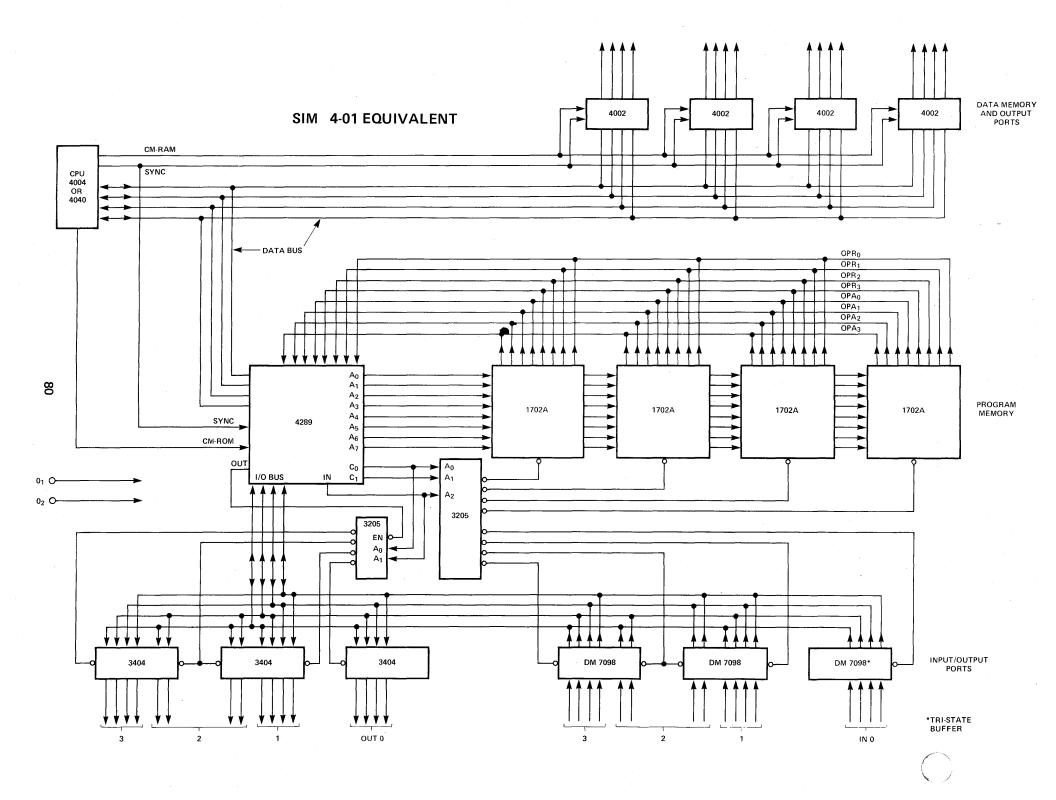

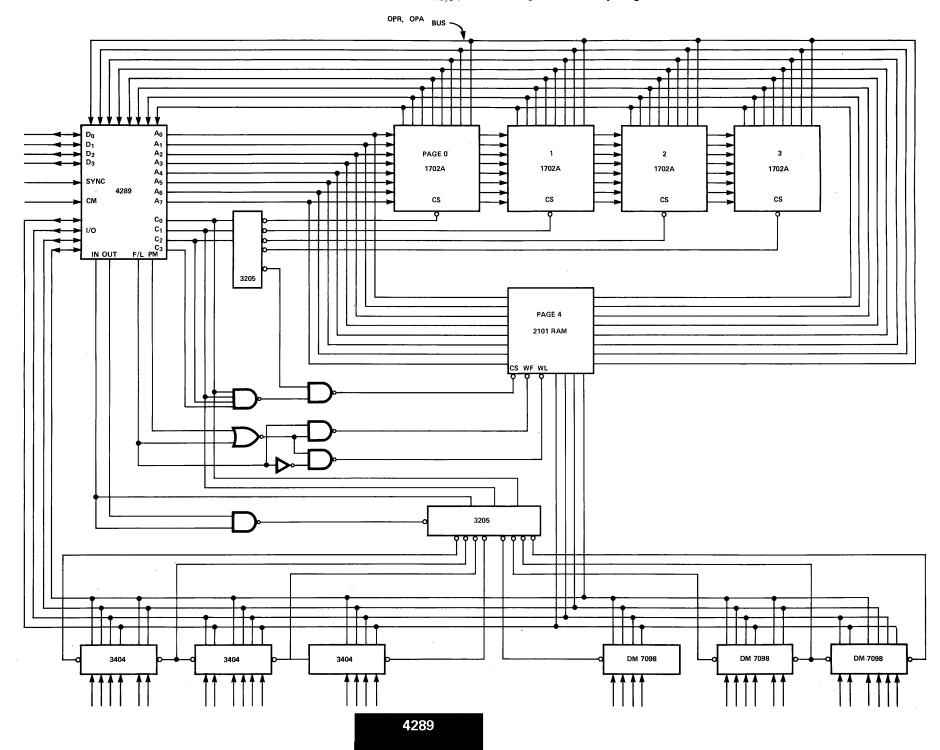

#### 4289 STANDARD MEMORY INTERFACE

#### 1.0 Introduction

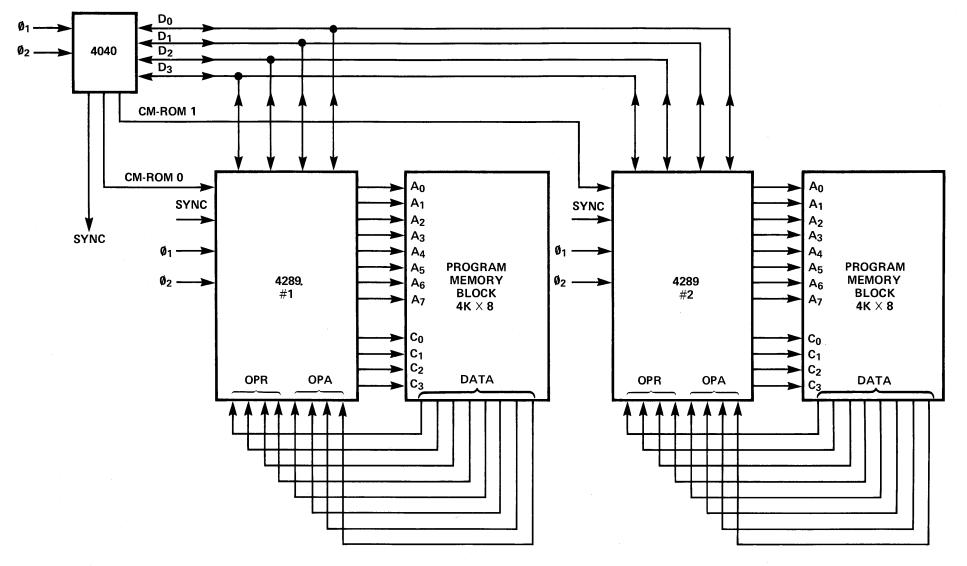

The 4289 is a single chip replacement for the 4008/4009 STANDARD MEMORY and I/O INTERFACE set. Like that set, it enables the 4-bit microprocessor chip (4004 or 4040) to be used with "standard" memory components such as 1702 PROM's or 2102 RAM's and general purpose input/output devices.

A number of improvements as well as additions have been incorporated into the 4289 aside from the single chip package. These are listed here and described in detail in Sections 2 and 3.

1.1 A change in internal timing has been made which will allow using PROGRAM MEMORY components with access times as great as 2.1µseconds (address to output).

4289

- 1.2 A new instruction, READ PROGRAM MEMORY (RPM) which is included in the 4040 instruction set, is recognized by the 4289. Section 3.3 provides a detailed description of RPM.

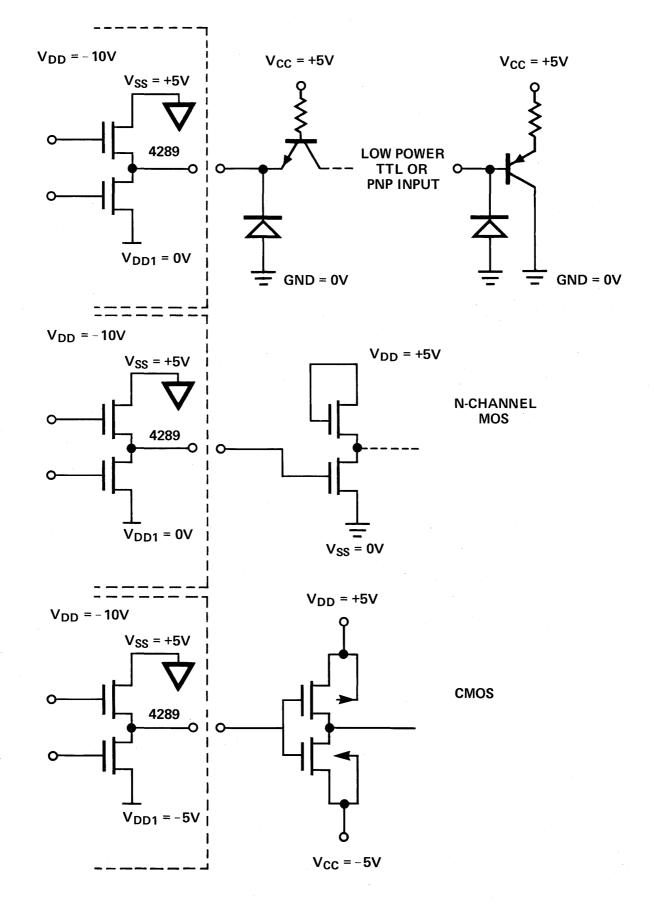

- 1.3 A separate supply voltage, V<sub>DD1</sub>, has been provided for the ADDRESS and CHIP SELECT buffers. This simplifies the problem of interfacing to n-channel/TTL-compatible memories. See Appendix for examples.

1.4 A RESET pin has been added which simplifies control over the FIRST/LAST flip-flop (see Section 3.3). It is not necessary to power down the chip to perform the reset function.

## 2.0 Description of Basic Hardware

The 4289 is packaged in a 40-pin plastic DIP. The pin configuration and a brief functional description of each pin is given in Section 2.1.

## 2.1 Pin Function Description

| <u>Pin #</u> | Designation                    | Description                                                                                                                                    |

|--------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 - 4        | <sup>D</sup> ø <sup>−D</sup> 3 | Bidirectional data bus. All address,                                                                                                           |

|              |                                | instruction and data communication be-                                                                                                         |

|              |                                | tween processor and the PROGRAM MEMORY                                                                                                         |

|              |                                | or I/O ports is transmitted on these                                                                                                           |

|              |                                | 4 pins.                                                                                                                                        |

| 5 - 8        | oprø-opr3                      | The high order 4 bits (OPR) of the instruction from the PROGRAM MEMORY are transferred to the 4289 on these pins. Same as $D_5'-D_8'$ on 4009. |

| 9 - 12       | OPAø-OPA3                      | The low order 4 bits (OPA) of the in-                                                                                                          |

struction are transferred to the 4289. Same as  $D_1'-D_4'$  on 4009.

$13 - 14 \ \emptyset_1 - \emptyset_2$

Non-overlapping clock signals which are used to generate the basic chip timing.

| <u>Pin #</u> | Designation     | Description                            |

|--------------|-----------------|----------------------------------------|

| 15           | SYNC            | Synchronization input signal driven    |

|              |                 | by SYNC output of processor.           |

| 16           | СМ              | Command input driven by CM-ROM output  |

|              |                 | of processor. Used for decoding SRC    |

|              |                 | and I/O instructions.                  |

| 17           | RESET           | RESET input. A logic "l" level applied |

|              |                 | to this input resets the CM flip-flop  |

|              |                 | and FIRST/LAST flip-flop.              |

| 18           | IN              | Output signal generated by 4289 when   |

|              |                 | the processor executes an RDR or RPM   |

|              |                 | instruction.                           |

| 19           | OUT             | Output signal generated by the 4289    |

|              |                 | when the processor executes a WRR or   |

|              |                 | WPM instruction.                       |

| 20           | V <sub>SS</sub> | Circuit GND potential; most positive   |

|              |                 | supply voltage.                        |

| 21           | РМ              | Output signal generated by the 4289    |

|              |                 | when the processor executes an RPM or  |

|              |                 | WPM instruction.                       |

| 22           | F/L             | Output signal generated by the 4289 to |

|              |                 | indicate which half-byte of PROGRAM    |

|              |                 | MEMORY is to be operated on.           |

|              |                                    | 3                                                   |

|--------------|------------------------------------|-----------------------------------------------------|

| <u>Pin #</u> | Designation                        | Description                                         |

| 23 - 30      | Aø <sup>-A</sup> 7                 | Address output buffers. The demulti-                |

|              |                                    | plexed address values generated by the              |

|              |                                    | 4289 from the address data supplied                 |

|              |                                    | by the processor at $A_1$ and $A_2$ .               |