intal

## INTRODUCTION TO THE INTEL386<sup>™</sup> SL MICROPROCESSOR SUPERSET TECHNICAL OVERVIEW

## LITERATURE

To order Intel Literature or obtain literature pricing information in the U.S. and Canada call or write Intel Literature Sales. In Europe and other international locations, please contact your *local* sales office or distributor.

INTEL LITERATURE SALES P.O. BOX 7641 Mt. Prospect, IL 60056-7641

Intal®

In the U.S. and Canada call toll free (800) 548-4725 This 800 number is for external customers only.

### **CURRENT HANDBOOKS**

Product line handbooks contain data sheets, application notes, article reprints and other design information. All handbooks can be ordered individually, and most are available in a pre-packaged set in the U.S. and Canada.

| TITLE                                                         | INTEL<br>ORDER NUMBER | ISBN          |

|---------------------------------------------------------------|-----------------------|---------------|

| SET OF THIRTEEN HANDBOOKS<br>(Available in U.S. and Canada)   | 231003                | N/A           |

| CONTENTS LISTED BELOW FOR INDIVIDUAL                          | ORDERING:             |               |

| COMPONENTS QUALITY/RELIABILITY                                | 210997                | 1-55512-132-2 |

| EMBEDDED APPLICATIONS                                         | 270648                | 1-55512-123-3 |

| 8-BIT EMBEDDED CONTROLLERS                                    | 270645                | 1-55512-121-7 |

| 16-BIT EMBEDDED CONTROLLERS                                   | 270646                | 1-55512-120-9 |

| 16/32-BIT EMBEDDED PROCESSORS                                 | 270647                | 1-55512-122-5 |

| MEMORY PRODUCTS                                               | 210830                | 1-55512-117-9 |

| MICROCOMMUNICATIONS                                           | 231658                | 1-55512-119-5 |

| MICROCOMPUTER PRODUCTS                                        | 280407                | 1-55512-118-7 |

| MICROPROCESSORS                                               | 230843                | 1-55512-115-2 |

| PACKAGING                                                     | 240800                | 1-55512-128-4 |

| PERIPHERAL COMPONENTS                                         | 296467                | 1-55512-127-6 |

| PRODUCT GUIDE<br>(Overview of Intel's complete product lines) | 210846                | 1-55512-116-0 |

| PROGRAMMABLE LOGIC                                            | 296083                | 1-55512-124-1 |

| ADDITIONAL LITERATURE:<br>(Not included in handbook set)      |                       |               |

| AUTOMOTIVE HANDBOOK                                           | 231792                | 1-55512-125-x |

| INTERNATIONAL LITERATURE GUIDE<br>(Available in Europe only)  | E00029                | <b>N/A</b>    |

| CUSTOMER LITERATURE GUIDE                                     | 210620                | N/A           |

| MILITARY HANDBOOK<br>(2 volume set)                           | 210461                | 1-55512-126-8 |

| SYSTEMS QUALITY/RELIABILITY                                   | 231762                | 1-55512-046-6 |

|                                                               |                       |               |

## U.S. and CANADA LITERATURE ORDER FORM

| NAME:                                                             |                                           |                                    |                                                                     |                               |       |

|-------------------------------------------------------------------|-------------------------------------------|------------------------------------|---------------------------------------------------------------------|-------------------------------|-------|

| COMPANY:                                                          |                                           |                                    |                                                                     |                               |       |

| ADDRESS:                                                          |                                           |                                    |                                                                     |                               |       |

| CITY:                                                             |                                           |                                    | STATE:                                                              | ZIP:                          |       |

| COUNTRY:                                                          |                                           |                                    |                                                                     |                               |       |

| PHONE NO.: _(                                                     | )                                         |                                    |                                                                     |                               |       |

| ORDER NO.                                                         | т                                         | ITLE                               | QTY.                                                                | PRICE                         | TOTAL |

|                                                                   |                                           |                                    |                                                                     | ×                             | =     |

|                                                                   |                                           |                                    |                                                                     | ×                             | =     |

|                                                                   |                                           |                                    |                                                                     | ×                             | =     |

|                                                                   |                                           |                                    |                                                                     | ×                             | =     |

|                                                                   |                                           |                                    |                                                                     | ×                             | =     |

|                                                                   |                                           |                                    |                                                                     | ×                             | =     |

|                                                                   |                                           |                                    |                                                                     | ×                             | =     |

|                                                                   |                                           |                                    |                                                                     | ×                             | =     |

|                                                                   |                                           |                                    |                                                                     | ×                             | =     |

|                                                                   |                                           |                                    |                                                                     | ×                             | =     |

|                                                                   |                                           |                                    |                                                                     | Subtotal                      |       |

| <b></b>                                                           |                                           |                                    |                                                                     | ust Add Your<br>cal Sales Tax |       |

| Include postage:<br>Must add 15% of Subtotal to                   | o cover U.S.                              |                                    |                                                                     | → Postage                     |       |

| and Canada postage. (20%                                          | all other.)                               |                                    |                                                                     |                               |       |

| Pay by check, money orde accept VISA, MasterCard o delivery.      | er, or include comp<br>or American Expres | any purchase or<br>s. Make payment | der with this form<br>to Intel Literature                           |                               |       |

| UISA 🗌 MasterCard                                                 | American Expre                            | ss Expiration Da                   | ate                                                                 |                               |       |

| Account No                                                        |                                           |                                    |                                                                     |                               |       |

| Signature                                                         |                                           |                                    |                                                                     |                               |       |

| Mail To: Intel Literature Sa<br>P.O. Box 7641<br>Mt. Prospect, IL |                                           | should use the                     | <b>customers</b> outsid<br>International orde<br>al Sales Office or | er form on the                |       |

# For phone orders in the U.S. and Canada Call Toll Free: (800) 548-4725

### INTERNATIONAL LITERATURE ORDER FORM

| NAME:         |       |        |                       |

|---------------|-------|--------|-----------------------|

| COMPANY:      |       |        |                       |

| ADDRESS:      |       |        |                       |

| CITY:         |       | STATE: | ZIP:                  |

|               |       |        |                       |

| PHONE NO.: _( | )     |        |                       |

| ORDER NO.     | TITLE | QTY.   | PRICE TOTAL           |

|               |       | ×      | =                     |

|               |       | ×      | =                     |

|               |       | ×      | =                     |

|               |       | ×      | =                     |

|               |       | ×      | =                     |

|               |       | ×      | =                     |

|               |       | ×      | =                     |

|               |       | ×      | =                     |

|               |       | ×      | =                     |

|               |       |        | =                     |

|               |       |        | Subtotal              |

|               |       | Must   | Add Your<br>Sales Tax |

|               |       | 2004.  | Total                 |

#### PAYMENT

Cheques should be made payable to your *local* Intel Sales Office (see inside back cover).

Other forms of payment may be available in your country. Please contact the Literature Coordinator at your *local* Intel Sales Office for details.

The completed form should be marked to the attention of the LITERATURE COORDINATOR and returned to your *local* Intel Sales Office.

int<sub>e</sub>l®

# Intel 386<sup>™</sup>SL MICROPROCESSOR SUPERSET

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel products:

376, Above, ActionMedia, BITBUS, Code Builder, DeskWare, Digital Studio, DVI, EtherExpress, ETOX, FaxBACK, Grand Challenge, i, i287, i386, i387, i486, i487, i750, i860, i960, ICE, iLBX, inboard, Intel, Intel287, Intel386, Intel387, Intel486, Intel487, Intel inside., Intellec, IPSC, IRMX, ISBC, ISBX, IWARP, LANPrint, LANSelect, LANShell, LANSight, LANSpace, LANSpool, MAPNET, Matched, MCS, Media Mail, NetPort, NetSentry, OpenNet, PRO750, ProSolver, READY-LAN, Reference Point, RMX/80, SatisFAXtion, Snapin 386, Storage Broker, SugarCube, The Computer Inside., TokenExpress, Visual Edge, and WYPIWYF

MDS is an ordering code only and is not used as a product name or trademark, MDS is a registered trademark of Mohawk Data Sciences Corporation.

CHMOS and HMOS are patented processes of Intel Corp.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

Additional copies of this manual or other Intel literature may be obtained from.

Intel Corporation Literature Sales P.O. Box 7641 Mt. Prospect, IL 60056-7641

©INTEL CORPORATION 1991

## INTEL SERVICE

### INTEL'S COMPLETE SUPPORT SOLUTION WORLDWIDE

Intel Service is a complete support program that provides Intel customers with hardware support, software support, customer training, and consulting services. For detailed information contact your local sales offices.

Service and support are major factors in determining the success of a product or program. For Intel this support includes an international service organization and a breadth of service programs to meet a variety of customer needs. As you might expect, Intel service is extensive. It can start with On-Site Installation and Maintenance for Intel and non-Intel systems and peripherals, Repair Services for Intel OEM Modules and Platforms, Network Operating System support for Novell NetWare and Banyan VINES software, Custom Integration Services for Intel Platforms, Customer Training, and System Engineering Consulting Services. Intel maintains service locations worldwide. So wherever you're using Intel technology, our professional staff is within close reach.

### **ON-SITE INSTALLATION AND MAINTENANCE**

Intel's installation and maintenance services are designed to get Intel and Intel-based systems and the networks they use up and running-fast. Intel's service centers are staffed by trained and certified Customer Engineers throughout the world. Once installed, Intel is dedicated to keeping them running at maximum efficiency, while controlling costs.

### **REPAIR SERVICES FOR INTEL OEM MODULES AND PLATFORMS**

Intel offers customers of its OEM Modules and Platforms a comprehensive set of repair services that reduce the costs of system warranty, maintenance, and ownership. Repair services include module or system testing and repair, module exchange, and spare part sales.

### NETWORK OPERATING SYSTEM SUPPORT

An Intel software support contract for Novell NetWare or Banyan VINES software means unlimited access to troubleshooting expertise any time during contract hours—up to seven days per week, twenty-four hours per day. To keep networks current and compatible with the latest software versions, support services include access to minor releases and "patches" as made available by Novell and Banyan.

### **CUSTOM SYSTEM INTEGRATION SERVICES**

Intel Custom System Integration Services enable resellers to order completely integrated systems assembled from a list of Intel386<sup>™</sup> and Intel486<sup>™</sup> microcomputers and validated hardware and software options. These services are designed to complement the reseller's own integration capabilities. Resellers can increase business opportunities, while controlling overhead and support costs.

### **CUSTOMER TRAINING**

Intel offers a wide range of instructional programs covering various aspects of system design and implementation. In just three to five days a limited number of individuals learn more in a single workshop than in weeks of self-study. Covering a wide variety of topics, Intel's major course categories include: architecture and assembly language, programming and operating systems, BITBUS<sup>™</sup>, and LAN applications.

### SYSTEM ENGINEERING CONSULTING

Intel provides field system engineering consulting services for any phase of your development or application effort. You can use our system engineers in a variety of ways ranging from assistance in using a new product, developing an application, personalizing training and customizing an Intel product to providing technical and management consulting. Working together, we can help you get a successful product to market in the least possible time.

### TABLE OF CONTENTS

| PREFACE                                                  | v   |

|----------------------------------------------------------|-----|

| Manual Objectives and Organization                       | vi  |

| Related Publications                                     | vii |

| CHAPTER 1: PRODUCT HIGHLIGHTS                            | 1   |

| Technological Challenges of Modern PCs                   |     |

| The Intel386 <sup>™</sup> SL Microprocessor SuperSet     |     |

| System Design Options                                    |     |

| Clock Frequency Options                                  |     |

| Performance Factors                                      |     |

| Guaranteed Compatibility                                 |     |

| The Expanding Horizons of PC Design                      |     |

| Intermediate Design Options                              |     |

| A New Class of "Hybrid" PCs                              |     |

| Product Highlights Summary                               |     |

|                                                          |     |

| CHAPTER 2: HARDWARE SYSTEM ARCHITECTURE                  |     |

| Functional Partitioning                                  |     |

| Intel386 SL Microprocessor Functions                     |     |

| 82360SL Peripheral I/O Subsystem Functions               |     |

| 82760SL VGA Graphics Control Subsystem Functions         |     |

| External Memory Arrays                                   |     |

| System Interconnect Buses                                |     |

| Main Memory Options                                      |     |

| SRAM Main Memory                                         |     |

| DRAM Main Memory                                         |     |

| Memory System Sizing and Control Mechanisms              |     |

| Cache Memory System                                      |     |

| Configuration Options                                    |     |

| Cache Performance Factors                                |     |

| Cache Power-Consumption Factors                          |     |

| BIOS Memory Array                                        |     |

| Flash Memory Support                                     |     |

| Graphics Display Subsystem                               |     |

| CRT Display Modes                                        |     |

| LCD Display Modes                                        |     |

| Display Buffer Memory                                    |     |

| Display Control Mechanisms<br>System Timing Requirements |     |

| Hardware Architecture Summary                            |     |

| Hardware Architecture Summary                            |     |

| CHAPTER 3: SOFTWARE SYSTEM ARCHITECTURE                       | 33 |

|---------------------------------------------------------------|----|

| Intel386 Microprocessor Family Architecture Overview          | 33 |

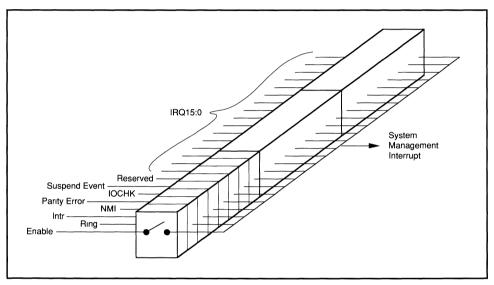

| Architectural Extensions for System Management                | 34 |

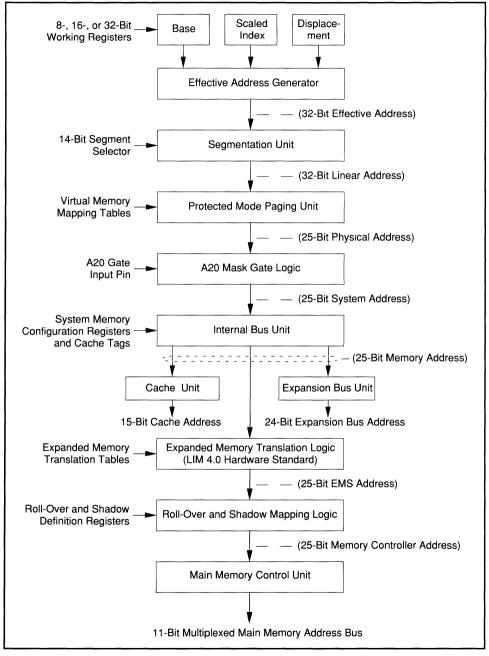

| Memory System Management                                      | 35 |

| Virtual Memory Paging                                         |    |

| LIM 4.0 Memory Expansion                                      | 35 |

| ROM Shadowing                                                 |    |

| Memory Backfilling and Roll-Over                              | 36 |

| Memory Region Retargeting Logic                               |    |

| CPU and Memory Configuration and Control Registers            |    |

| Standard Peripheral Interface Registers                       | 38 |

| VGA Graphics System Registers                                 |    |

| New Peripheral I/O Facilities                                 |    |

| Peripheral Control Register "Shadow" Latches                  |    |

| Compatibility Safeguards                                      |    |

| A20 Pin Mask                                                  |    |

| Non-Cachability of Memory-Mapped I/O                          |    |

| Cache Invalidation on LIM Page Changes                        |    |

| Concealing Peripherals From Applications Programs             |    |

| Software Architecture Summary                                 | 47 |

| CHAPTER 4: POWER-MANAGEMENT STRATEGY                          | 49 |

| Power Management Overview                                     |    |

| Basic Power Reduction Techniques                              |    |

| Power Management Hardware Requirements                        | 51 |

| Power Management Hazards to Software Compatibility            | 51 |

| Hardware Support for Power Management                         | 52 |

| Intel386 SL Microprocessor SuperSet Power Management Strategy |    |

| Central Processor Power Reductions                            | 53 |

| Math Coprocessor Power Reductions                             |    |

| Peripheral Power Reductions                                   |    |

| Memory System Power Reductions                                |    |

| Graphics Display System Power Reductions                      |    |

| Software Support for Power Management                         |    |

| System Management Interrupt                                   |    |

| Private System Management Memory                              |    |

| SMI Mode Independence                                         |    |

| Power Management Software Design                              |    |

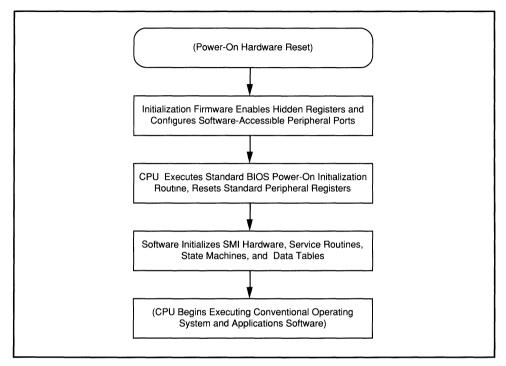

| System Management Mode Initialization                         |    |

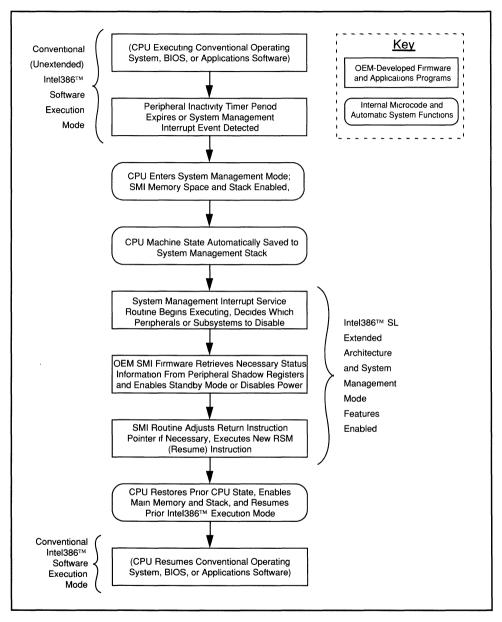

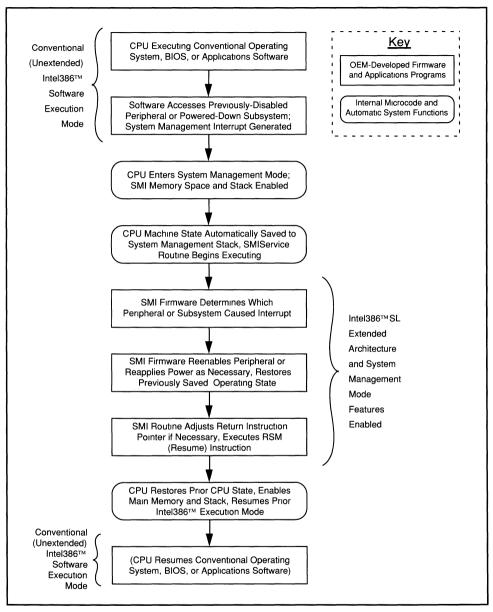

| Entry and Exit to SMI Service Routines                        |    |

| Power Management Hardware Design Issues                       |    |

| Power Management Summary                                      | 63 |

| CHAPTER 5: SYSTEM DESIGN EXAMPLES |    |

|-----------------------------------|----|

| Ultra-Compact "Palm-Top" PC       | 65 |

| Note-Pad PC                       |    |

| Notebook PC                       |    |

| Lap-Top PC                        | 69 |

Intel386<sup>™</sup> SL Microprocessor SuperSet Delivers Full ISA Compatibility in the Smallest Possible Footprint

## PREFACE

The Intel386<sup>™</sup> SL Microprocessor SuperSet is the newest addition to the Intel386 32-bit microprocessor product line. Contained within just two VLSI components are virtually all of the critical elements needed for a range of microcomputer-based products, from checkbook-sized "palm-top" personal computers and notebook computers to full-featured, fully-expandable lap-top portables.

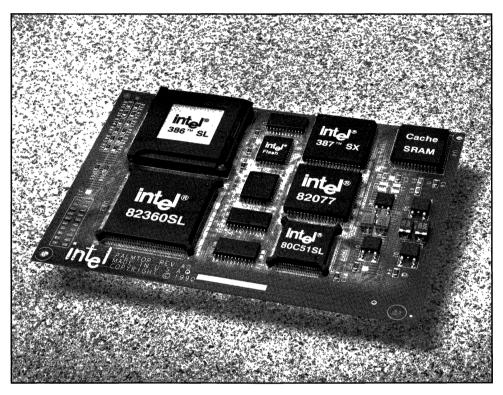

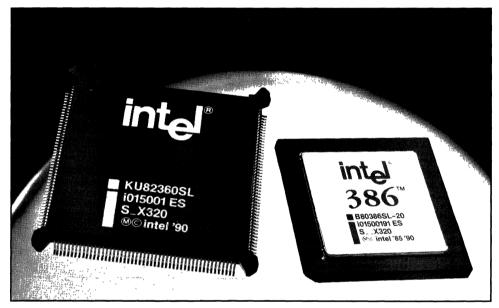

The Intel386 SL Microprocessor SuperSet includes two components which provide: the Intel386 SL central processing unit that is fully compatible with the Intel386 microprocessor architecture, main memory and bus interface control system; and the 82360SL peripheral I/O subsystem.

The components bring a number of new design techniques to the personal computer world for the first time. For instance:

- Extensions to the processor architecture support a new system-management mode with which OEM firmware can monitor and control hardware operation and conserve battery power without sacrificing Intel386 software compatibility

- Processor and peripheral clock frequencies can be adjusted dynamically to conserve power without sacrificing overall system performance

- Each component's internal design is fully static so the clock can be stopped without losing critical data

- SmartHit cache control logic boosts performance and saves power by eliminating unneeded memory transfers

- FlexLogic circuitry lets software control all operating characteristics and decouple system behavior from hardware design

- An uncommitted ideaPort interface lets original equipment manufacturers develop unique new value-added functions transparent to existing software

The components contain more than 1.5 million transistors in all and are fabricated from Intel's one-micron CHMOS-IV technology. While SL SuperSet-based systems benefit from the highest possible integration level, they also deliver significantly better performance than is possible with conventional technology.

The Intel386 SL SuperSet components comply with all Industry Standard Architecture (ISA) design conventions and are thus fully compatible with the IBM PC/AT personal computer and its derivatives. Systems built with the Intel SL SuperSet can therefore run all existing business and scientific applications developed for the 8086, 80286, 80386, and 80486 microprocessors. The SL SuperSet likewise supports all popular microprocessor operating systems developed for the original 8086 and Intel386 Family architecture, including MS-DOS<sup>+</sup>, OS/2\*\*, Windows\*\*, Windows-386\*\*, and UNIX<sup>++</sup> System V.

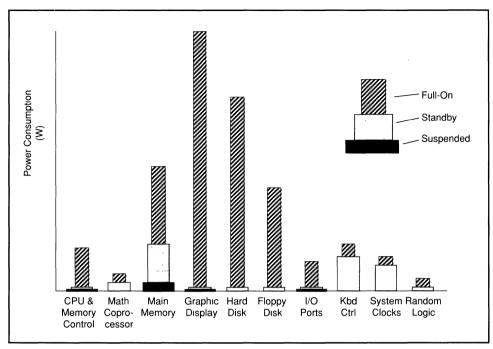

Moreover, each component reduces power requirements to an absolute minimum, not just for the chips themselves but for the main memory, display interface, and other system components. Reductions in run-time power in turn extend the useful operating life of battery-operated portable computers, and automatic built-in stand-by modes stretch the battery life of idle systems still further.

### Manual Objectives and Organization

This manual serves as a basic introduction and overview for the full Intel386 SL Microprocessor SuperSet family, and is intended to help hardware and software engineers and managers evaluate the suitability of the products for personal computers and other application areas.

Since the Intel386 SL SuperSet combines the functions of an entire computer system into just a few components, different readers will view the Intel SuperSet from different perspectives. Hardware engineers will want to understand how the products connect to other system components. Programmers developing basic I/O system (BIOS) software must understand the capabilities of the on-chip peripheral registers in order to initialize the PC with the desired characteristics.

Marketing managers may wish to understand how price reductions allowed by slower memories and support components affect overall system performance, and how Intel SL SuperSet hardware lets them augment built-in functions with external circuitry for greater flexibility and product differentiation. Those concerned with the problems of allocating a limited battery-power budget among system resources and peripherals must understand the power-management options and capabilities supported by each chip.

In order to address different reader perspectives, this manual is divided into five chapters. **Chapter 1** is an overview of product-line highlights and surveys a range of personal computer configurations that will benefit from various SL SuperSet features. **Chapter 2** discusses system hardware design, including the functions performed by each SL SuperSet component and how the components interact with other system elements.

Intel386<sup>TM</sup> SL, Intel386<sup>TM</sup>, and Intel486<sup>TM</sup> are trademarks of Intel Corporation CHMOS-IV is a patented process technology of Intel Corporation

<sup>†</sup> MS-DOS® is a registered trademark of Microsoft Corporation.

<sup>\*\*</sup> OS/2<sup>™</sup>, Windows, and Windows-386 are trademarks of Microsoft Corporation.

<sup>††</sup> UNIX® is a registered trademark of AT&T.

**Chapter 3** covers the processor architecture and memory-address mapping facilities, and explores software design issues related to the on-chip peripheral facilities and configuration options.

**Chapter 4** goes into greater depth explaining the new system management mode, especially as it relates to power management, and discusses its special software requirements. The block diagrams in **Chapter 5** show example system configurations supported by the Intel SL SuperSet, and shows how individual OEMs can add unique functions to the Intel SL SuperSet to expand its end-user capabilities.

### **Related Publications**

This manual gives only a glimpse of the architecture and peripheral capabilities of the Intel386 SL Microprocessor SuperSet, and makes no attempt to describe its underlying instruction set, electrical specifications, or timing parameters. For design information of this type consult the following related publications:

- Intel386<sup>™</sup> SL Microprocessor SuperSet System Design Guide, Intel Order No. 240816

- Intel386<sup>™</sup> SL Microprocessor SuperSet Programmer's Reference Manual, Intel Order No. 240815

- Intel386<sup>™</sup> SL Microprocessor SuperSet Data Sheet, Intel Order No. 240814

- Intel386<sup>™</sup> Microprocessor Software Writer's Guide, Intel Order No. 231499

# Chapter 1 Product Highlights

## CHAPTER 1 PRODUCT HIGHLIGHTS

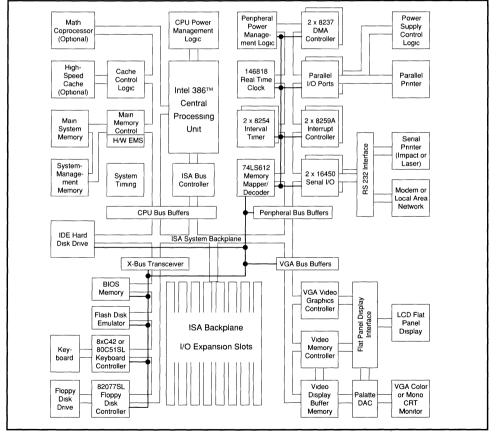

The personal computer industry has expanded in ways its creators never expected. On the one hand, designers have converged on a well-defined set of processor, memory, peripheral, and system backplane functions that are now part of all industry-standard personal computers (see Figure 1-1). On the other hand, the simple, conventional desktop computer systems of the mid '80s have evolved into a bewildering array of physical configurations. New peripheral devices and new system capabilities continue to augment the basic functions of early PCs.

Figure 1-1. Industry-Standard PCs Contain a Common Set of System Functions and Peripherals

While the performance delivered by high-end PCs continues to soar, the market now demands a range of alternative designs, at different price points, in different form-factors. Satisfying this demand poses a whole new set of challenges to today's microcomputer hardware and software engineers.

### **Technological Challenges of Modern PCs**

Standard microcomputers no longer seem as "micro" as they once did. When PCs must compete for desk space with telephones, modems, facsimile machines, and other desk-top clutter, it's important to keep the PC footprint small.

This is especially true for portable PCs. If it's bigger than a bread box it's no longer in vogue: today's users prefer systems that fit a briefcase or coat pocket. Shrinking enclosures demand ever-smaller circuit boards, so the components used must be the most highly integrated devices achievable within a given state of the art.

The challenge posed by battery-powered portable systems is doubly severe. Not only are size constraints tight, but power conservation is critical. Battery size and capacity are limited, so the less power the PC consumes, the longer it can go between charges. Unfortunately, past efforts to include power-management capabilities have had mixed success: ports, programs, and new resources needed for power-management functions unavoidably introduced a hazard that existing software might malfunction on the revised hardware.

Efforts to reconcile the competing factors of performance, size, power consumption, and software compatibility have created new opportunities and market niches for a remarkable variety of PC configurations. In order to differentiate their products from the competition, PC designers seek to provide unique features such as innovative hardware design, effective packaging technology, fast and convenient mass storage, or more natural user interfaces (NUIs).

A mouse, track-ball, or note-pad stylus for handwritten data, or other novel input devices often augment the standard keyboard, while circuitry for speech recognition and gesture detection may allow more intuitive control paradigms. Thus the components from which modern PCs are built must leave the hardware designer complete flexibility in adapting and extending his product with unique functionality.

At the same time, however, modern PCs must guarantee their users absolute compatibility with the wealth of applications software developed since the PC business began. This compatibility must be assured at all levels of hardware and software: within the processor itself, its memory control systems, the peripherals it supports, and the bus interface through which third-party add-in boards expand system functions.

### The Intel386 SL Microprocessor SuperSet

The Intel386 SL Microprocessor SuperSet (Figure 1-2) addresses each of the above concerns. At its heart is a full-featured 32-bit central processor unit that is fully compatible with the industry-standard Intel386 microprocessor architecture. Built into the CPU are a main-memory subsystem controller with a large address space and extensive address translation and remapping logic, tag registers and control logic needed for a cache memory system, and support for an optional Intel387<sup>™</sup> SX Math CoProcessor.

Figure 1-2. The Intel386<sup>™</sup> SL Microprocessor SuperSet Includes Two Highly-Integrated Components

Supporting the processor are a host of general-purpose peripheral interface devices, including serial ports, parallel ports, timers, interrupt controllers, keyboard and disk interfaces. Special power-management circuitry within each chip makes the most efficient use possible of limited power supplies.

### **System Design Options**

The Intel386 SL Microprocessor SuperSet gives hardware designers a tremendous degree of flexibility, as shown in Table 1-1. The main system memory and display buffers can be built with static (SRAM) or dynamic (DRAM) memory devices of various sizes and speeds, with optional cache subsystems and non-volatile Flash EPROM arrays. End users can add memory in various combinations and configurations, typically by inserting single in-line memory modules (SIMMs) or credit-card-style expansion modules. The SL SuperSet can detect the size and configuration of installed memory during system initialization, and software can then adjust address multiplexing, control, and interleave schemes accordingly.

| Feature                          | Design Options                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Central Processing Unit          | Real Mode, 286 Protected Mode, 32-Bit Intel386 Protected Mode,<br>Operating Modes                                                                                                                                                                                                                                                                                                                                                             |

| Virtual 8086 Mode                |                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CPU Frequency Control            | 25 MHz (Maximum); Reduced Frequency (Maximum +2, +4, or +8);<br>or Fully-Static (Stopped Clock)                                                                                                                                                                                                                                                                                                                                               |

| Math Coprocessor Support         | Interface for Optional Intel387 SX Math CoProcessor                                                                                                                                                                                                                                                                                                                                                                                           |

| Coprocessor Frequency<br>Control | 25 MHz Maximum Frequency ÷1, ÷2, ÷4, ÷8, or ÷16                                                                                                                                                                                                                                                                                                                                                                                               |

| Main Memory Type                 | Static (SRAM) or Dynamic (DRAM)                                                                                                                                                                                                                                                                                                                                                                                                               |

| Main Memory Capacity             | 512 Kilobytes to 20 Megabytes                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Cache Memory Support             | None, 16K, 32K, or 64K bytes; Direct Mapped, Two-Way, or Four-<br>Way Set Associative                                                                                                                                                                                                                                                                                                                                                         |

| Memory Expansion                 | Standard 386 CPU Paged Memory Management, plus Hardware<br>Support for LIM 4.0 Memory Expansion Standard                                                                                                                                                                                                                                                                                                                                      |

| Main Memory Parity Support       | Optional Parity Generation and Verification Logic On-Chip                                                                                                                                                                                                                                                                                                                                                                                     |

| Main Memory Enhancements         | Optional Automatic EPROM Shadowing, Backfill, and Roll-Over                                                                                                                                                                                                                                                                                                                                                                                   |

| BIOS Memory Support              | ROMs, Conventional EPROMs, or Flash EPROMs; 64K–128K bytes; 8- or 16-bit Bus Width; 0–15 wait states;                                                                                                                                                                                                                                                                                                                                         |

| Mass Storage Support             | Floppy Disk Controller Interface; IDE Hard Disk Interface; and<br>Flash EPROM Disk Emulation                                                                                                                                                                                                                                                                                                                                                  |

| Video Graphics Device Types      | Monochrome STN LCD panels, TFT LCD Displays                                                                                                                                                                                                                                                                                                                                                                                                   |

| Video Graphics Standards         | IBM VGA Standard                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DMA Controller Frequency         | Bus Clock Frequency ÷1, ÷2, or Stopped Clock                                                                                                                                                                                                                                                                                                                                                                                                  |

| Keyboard Controller Frequency    | System Clock Frequency +2, +4, or Stopped Clock                                                                                                                                                                                                                                                                                                                                                                                               |

| Power Conservation Modes         | Fully-Programmable: Processors and peripherals can be individu-<br>ally configured for an arbitrary range of power-conservation modes,<br>from Full-speed/Full-power execution to Low-frequency or<br>Stopped-clock/Ultra-low-power mode. OEM-developed firmware<br>can institute individual CPU, memory, and peripheral power-<br>management policies based on system-wide power-usage<br>patterns, computational load, and user preferences |

### Table 1-1. The Intel386<sup>™</sup> SL Microprocessor SuperSet Leaves OEMs a Choice of System Design Options

The SL SuperSet includes all of the peripheral devices now standard in ISA PCs, including serial and parallel ports, interrupt and DMA controllers, timers, and so forth. And, the forthcoming display subsystem is compatible with the IBM VGA standard using standard monochrome STN LCD panels and color TFT LCD displays. The SL SuperSet supports solid-state Flash EPROM disk emulators in addition to rotating media for conventional diskettes and hard drives. Using Intel's FlexLogic configuration scheme, each such peripheral can be enabled, disabled, or reconfigured in various operating modes as needed, all under software control.

### **Clock Frequency Options**

The Intel386 SL Microprocessor SuperSet components allow clock frequencies up to 25 MHz. When battery life is more critical than performance, the clock can be divided by a software-selectable factor to produce a slower, more power-efficient effective CPU frequency. Memory, I/O system, and coprocessor clock frequencies are all likewise software controlled, independent of each other and of the main CPU.

Portable systems can therefore conserve power by running at slower speeds during long periods of text entry, database downloading, or activities that take little computational power. During periods of intense computation, such as searching, sorting, or cataloguing a database, or recomputing a large spreadsheet, the system can switch back to its fastest CPU frequency, for what is sometimes called "turbo" operation.

The number of CPU cycles taken for each memory or expansion-bus access is software adjustable to compensate for different CPU operating frequencies. An SRAM that needs several wait states at the highest CPU frequency, for example, may run without wait states when the clock divides by four. Thus the CPU clock can be slowed without degrading system performance proportionately.

### **Performance Factors**

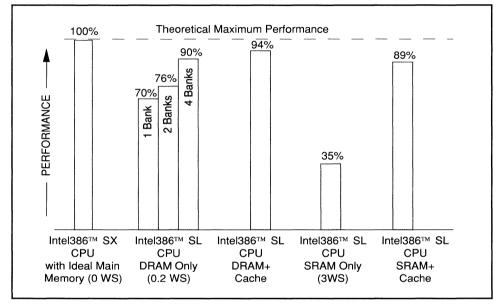

While hardware designers worry about physical system size, complexity, and power consumption, end users are more concerned with system throughput. The SL SuperSet's central processor and all of its supporting circuitry provide designers with the benefits of high integration and low power consumption without sacrificing the end-user performance expected of 386 microprocessor-based PCs.

Specially-tuned control logic and the cache memory subsystem let the SL SuperSet use relatively slow, low-cost memory components without sacrificing performance. Systems that manipulate extensive scientific or engineering data can add an optional floating-point math coprocessor. The coprocessor operating frequency can be adjusted under software control according to its computational load. To save further power, the coprocessor can be configured separately from the main CPU, or disabled entirely when not in use.

### **Guaranteed Compatibility**

Each Intel386 SL Microprocessor SuperSet component complies with all industrystandard PC design conventions. Extensions to the basic CPU architecture provide facilities for configuring system hardware, switching modes, and managing system power consumption, totally transparent to existing software. The new System Management Mode provides a new, dedicated interrupt vector and a new control instruction for supervisory control and power management functions. Software and data structures needed to support these functions all reside in a memory partition that is inaccessible to conventional software. Unlike conventional design approaches, SL SuperSet-based systems do not depend on "terminate and stay resident" (TSR) routines that can interfere with existing application programs.

While the SL SuperSet includes a number of new capabilities for power-reduction, each circumvents the hazards found in conventional design techniques. Each new capability is supported by an extension to the basic Intel386 architecture, rather than by appropriating some aspect of the original architecture that may or may not be needed for a particular piece of software. All of the resources of the original 8086, 80286, and Intel386 Family processors are thus preserved intact, ensuring full compatibility with all existing application programs and operating systems.

Systems built with these products can therefore be made fully compatible at both the hardware and software levels with all existing business and scientific applications programs developed for the 8086, 80286, and Intel386 Family microprocessors and all of the 8086 and Intel386 microprocessor operating systems now in use, including MS-DOS, OS/2, Windows 3.0, Windows-386, and UNIX System V.

### The Expanding Horizons of PC Design

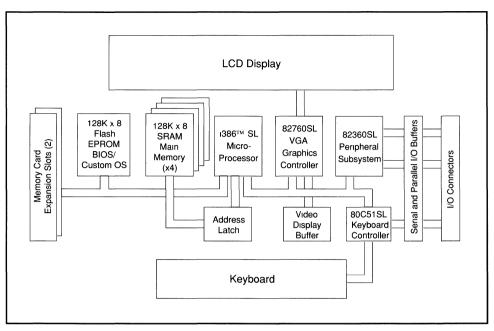

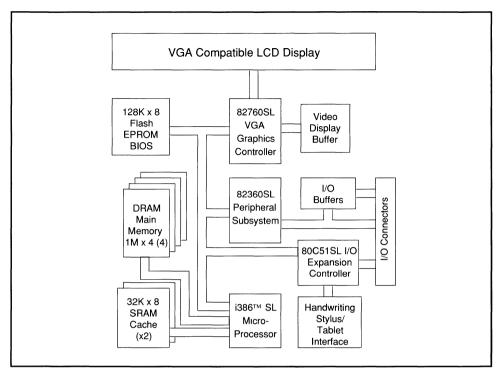

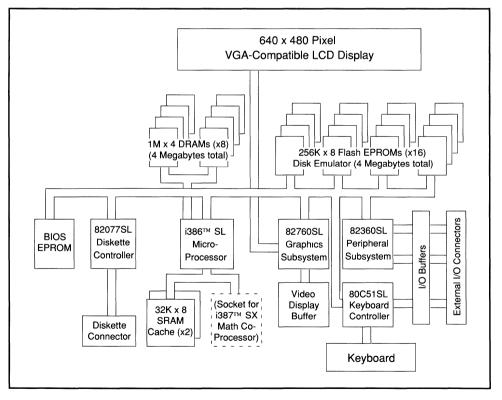

The SL SuperSet is versatile enough to be used in personal computers spanning a spectrum of hardware configurations. At one extreme might be the tiny, palm-top PC shown in Figure 1-3. Computers with this form-factor have compact keyboards, small LCD matrix displays, ROM or Flash EPROM-based operating-system and applications software, and a moderate amount of data memory, typically implemented using low-power static (SRAM) devices. Operating power is supplied by replaceable penlight cells or a small rechargeable battery.

Such a product may connect to larger host computers through a serial cable or modem for transferring program and data files, and may augment its memory capacity via credit-card-sized expansion boards. A step above palm-top PCs are small note-pad-sized computers with larger displays and easier-to-use keyboards. In both markets, however, physical size, weight, cost, and power preservation factors outweigh raw performance and expandability concerns.

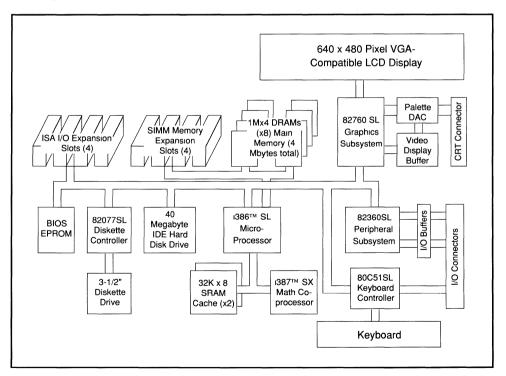

At the other end of the spectrum are conventional desk-top computers with high-resolution color CRT displays, full-function keyboards, and mouse input devices (see Figure 1-4). With circuit-board area and power consumption at less of a premium, such systems may include internal high-capacity hard disks, built-in modems, a local-area network interface, and expansion connectors for a range of serial and parallel printers, optical scanners, and external CD-ROM disk drives.

Figure 1-4. Typical Desk-Top PC Configuration

While desktop configurations also benefit from a small design footprint and low entrylevel system cost, it's critical that their design not be limited with respect to performance, upgradeable memory capacity, and compatibility with off-the-shelf applications software and standard I/O expansion boards. The main memory in such configurations is typically DRAM based, with from 1 to 32 megabytes. High-speed SRAM caches may also be included to improve the performance of DRAM main memory.

### **Intermediate Design Options**

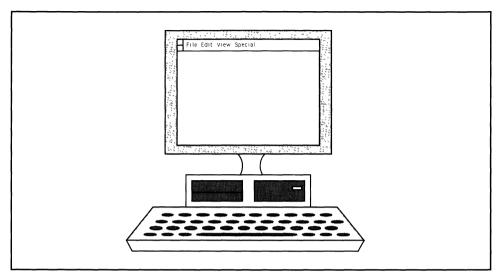

Between these extremes one can envision a tremendous variety of design options (see Figure 1-5). Today's portable computers range in size from "lap-top" to "luggable". Power supplies support both plug-in and battery-powered operating modes. Display technologies range from simple LCD displays to large monochrome and color CRTs. Mass storage options include some combination of internal floppy-disk drives, hard disks, or solid-state disk emulators.

# Figure 1-5. The Intel386<sup>™</sup> SL Microprocessor SuperSet is Designed for Applications from Battery-Powered Palm-Top PCs to Fully-Expandable Desk-Top Systems

All PCs, however, share the a need for speed and software flexibility. Today's graphical user interfaces (GUIs) and newly-emerging "natural user interfaces" (NUIs) demand the 32-bit precision, higher performance, expanded address range, and software protection mechanisms provided by the Intel386 architecture.

Other features of the SL SuperSet benefit PC configurations throughout the size, price, and complexity continuum. High integration is vital to palm-top designs, but can also shrink desk-top systems. Reduced power demands extend battery life, but can also reduce the size and cost of A.C. power supplies and eliminate cooling fans. Extensions to the CPU architecture can provide increased data security and improve system integrity. Systems of all sizes built with the SL SuperSet can deliver significantly better performance than those that use less sophisticated technology.

### A New Class of "Hybrid" PCs

Each system shown in Figure 1-5 can be built with conventional technology, of course, if one is willing to make compromises in price, performance, and power consumption. Designers can optimize whichever factors they choose for a particular configuration at the hardware level by making corresponding trade-offs in control logic and component selection.

The Intel386 SL Microprocessor SuperSet family, however, uses the same components for all PC form factors and levels of complexity, with power and performance trade-offs accomplished by software. FlexLogic control circuitry enables functions appropriate to each configuration. CPU operating frequencies can be selected, memory control algorithms can be refined, and peripheral modes can be enabled dynamically, according to computational load, in order to optimize both performance and battery life.

The ability to adjust the behavior of fixed hardware through software makes it possible to build a new class of "hybrid" PCs (see Figure 1-6) that function in multiple modes. For home or office use such a system would behave like a conventional office PC; i.e., it would have a full-size color CRT, keyboard, and mouse, include diskette and high-capacity hard-disk drives, attach to a telephone jack or local-area network, have slots for standard I/O expansion boards, and draw A.C. power from the wall. In desk-top mode this system would continuously deliver the uncompromised performance levels users expect from 386-microprocessor-class PCs.

If the computer was needed elsewhere, however, a small "compute engine" module consisting of the central processor and main memory and a solid-state disk emulator could detach from its desk-top docking module and become a fully-functional standalone unit, with its own integrated keyboard, flat-panel LCD display, and internal battery power. Space and power considerations might change somewhat the way the portable configuration operates—its system clock rate, memory size, or mass storage capacity may be reduced, or it may run a special ROM-based version of the host operating system—but each configuration would use the same processor and basic system memory, run the same utilities and applications programs, and retrieve and update the same text and data files.

Figure 1-6. Stand-Alone Portable Module Acts as the Compute Engine of a Hybrid PC Design

### **Product Highlights Summary**

As portable, battery-powered personal computers come into widespread use, microprocessors must provide new features and facilities tailored to such systems. Such systems require the highest level of system integration and the minimum possible power consumption, while sustaining the performance and flexibility users have come to expect from the Intel386 microprocessor family. The Intel386 SL Microprocessor SuperSet is the first pair of fully-integrated 32-bit personal computer chips designed expressly for portable computers, and provides system hardware and software designers with a wide range of options with which they can develop PC products that would be difficult or impossible to build with conventional technology.

# Chapter 2 Hardware System Architecture

## CHAPTER 2 HARDWARE SYSTEM ARCHITECTURE

The Intel386 SL Microprocessor SuperSet lets personal computers take advantage of the highest possible level of system integration, while at the same time preserving complete freedom in selecting a combination of system features, power/performance trade-offs, and value-added enhancements.

The SL SuperSet combines essentially all of the components needed to build an industrystandard personal computer within just two components: the Intel386 SL central processor, main memory, and bus interface control system; and the 82360SL peripheral component subsystem. The only other components needed for a complete, working PC are various memory arrays, a keyboard interface, graphics controller, and electrical buffers for certain optional peripherals.

This chapter first reviews the general functions performed by each of the SL SuperSet components, and then discusses some of the options and degrees of flexibility allowed in the design of the various memory arrays and display subsystem.

### **Functional Partitioning**

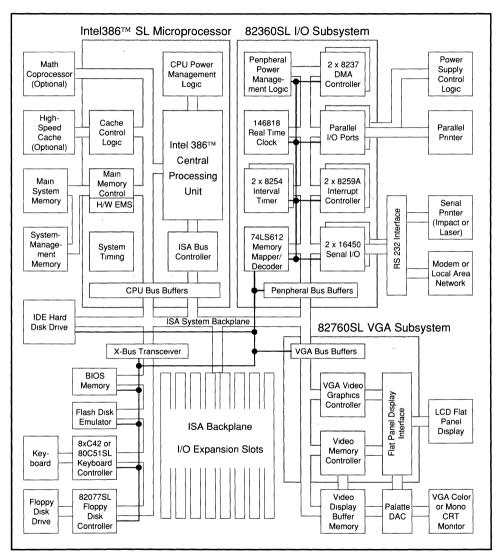

Intel SL SuperSet-based products will generally contain each of the functional blocks shown in Figure 2-1. The functions performed by each block are described briefly below.

Figure 2-1. Intel 386<sup>™</sup> SL Microprocessor SuperSet Family Components Bring Together All Critical PC Functions

# Intel386 SL Microprocessor Functions

The Intel386 SL Microprocessor is highly integrated, both in its transistor count and the functions it performs. At the heart of the device is a central processing unit (CPU) compatible with the Intel386microprocessor. The CPU has been fully re-engineered for low-power static (stopped-clock) operation, and its architecture has been augmented with extensions needed for general-purpose system-management functions, as described in **Chapter 4**.

The CPU contains the same paged-memory-management system that is standard on all Intel386microprocessors. In addition, on-chip hardware implements an expanded memory system (EMS) compatible with the Lotus/Intel/Microsoft (LIM 4.0) standard. Address-mapping and control logic within the Intel386 SL processor can "shadow" BIOS ROMs with faster memory devices, and supports all common memory roll-over and back-filling schemes. The Intel386 SL processor contains all the control and interface logic needed to drive directly a 20-megabyte main memory system and a smaller, faster, optional cache.

The Intel386 SL processor also contains bus drivers and control circuitry for two expansion interfaces. A high-performance peripheral-interface bus communicates with devices on the same circuit board as the SL SuperSet, while an ISA-compatible "system backplane" bus communicates with industry-standard peripheral add-in boards. On-chip control logic automatically routes each memory or I/O operation to the appropriate memory array, cache, peripheral bus, or backplane, without involving the operating system or applications software in any way.

All system configuration logic in the Intel386 SL processor is initialized under software control. This FlexLogic control system may be reconfigured at run-time to match the system hardware design, the size and type of main memory and peripherals currently installed, and the end-user's power consumption and performance goals.

# 82360SL Peripheral I/O Subsystem Functions

The 82360SL Peripheral I/O Subsystem contains dedicated logic to perform a number of CPU and memory support functions, a complete set of input/output (I/O) peripherals including serial ports, parallel ports, timers, and interrupt and DMA controllers, and interfaces for separate keyboard, diskette, and IDE hard-disk-drive controllers. The peripheral registers can be configured under software control to operate exactly like the discrete components commonly found in industry-standard PCs. See **Chapter 3** for information on the standard peripherals and their configuration options.

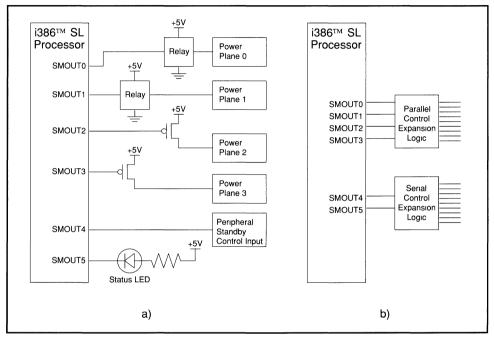

Processor and memory support functions contained in the 82360SL eliminate most of the external random-logic "glue" that might otherwise be required. The 82360SL provides internal variable-frequency clock generators for the CPU, backplane, video subsystem, and external math coprocessor. These features are discussed in **Chapter 4**.

Finally, the 82360SL contains an extensive set of power-management control facilities which further reduce energy requirements of battery-powered portable computers. A special low-power DRAM refresh timer keeps the main system memory alive and refreshed when the CPU is otherwise inactive. These, too, are discussed in **Chapter 4**. All of the standard peripheral registers, clock-generation logic, and power-management facilities have been designed to ensure compatibility with all existing operating systems and applications software.

# 82760SL VGA Graphics Control Subsystem Functions

The 82760SL VGA Graphics Control Subsystem will implement all of the control logic needed for a complete display subsystem fully compatible at the register level with the IBM VGA standard. It will be configured to connect to either monochrome or full-color CRTs or flat-panel liquid-crystal display (LCD) technologies with resolution up to 640 x 480 pixels, or 800 x 600 pixels, and will automatically translate each of 256 colors into up to 64 gray levels for monochrome displays.

The 82760SL will include power-management circuitry that keeps track of display system usage and determines when it's safe to power-down flat-panel backlights or the display interface circuitry. These features are also discussed in **Chapter 4**.

# **External Memory Arrays**

The block labeled "Main System Memory" in Figure 2-1 generally holds the computer's operating system software, application programs loaded from disk, and temporary data or files. The Intel386 SL processor hooks directly to either SRAM or DRAM memory devices with total capacity from 512 Kilobytes to 20 megabytes, with optional parity. Depending on the type and size of the memory devices involved, control logic generates the appropriate chip-select, bank-select, byte-enable, and read and write control signals.

The Intel386 SL processor also contains control logic for a smaller, optional memory array labeled "High-Speed Cache" in Figure 2-1. The internal control unit includes the tag bits and comparators needed for a variety of cache sizes and configurations. The cache interface requires no "glue": separate, dedicated pins drive all cache address and data buses and generate all chip-select and byte-enable control signals, so external cache systems consist of just one, two, or four memory components.

The block labeled "BIOS Memory" indicates ROM, EPROM, or Flash EPROM memory devices that hold the basic I/O system software for ISA computers. The same array may also contain system-specific initialization and configuration software, and may contain interrupt and trap-handler routines used for power-management software.

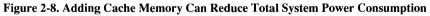

The SL SuperSet supports two additional optional memory arrays for special system functions. The "Flash Disk Emulator" block contains non-volatile memory devices used to replace or augment conventional disks and diskette drives with a solid-state file-storage system. This memory can be arbitrarily large, and can hold OS code, application programs, and important data files indefinitely, even with all power removed from the system.

The optional memory block labeled "System Management Memory" in Figure 2-1 holds code and data needed by supervisory system functions, information that would normally be concealed from OS and application programs. Portions of this memory may be implemented with Flash EPROMs or micro-power static RAMs, in which case critical system status information can be retained when power to the rest of the computer is disabled. With the proper software, this facility lets the computer power itself down when idle, and later resume program execution automatically at the exact point it ceased. System management functions are explained in **Chapter 4**.

Finally, a separate, dedicated DRAM memory array labeled "Video Memory" holds the display buffer used by the video graphics subsystem. The 82760SL directly supplies all address signals, data buses, and control strobes used by the display buffer, providing a truly "glue-less" memory interface

# System Interconnect Buses

The various pins on the SL SuperSet components generally connect to corresponding pins on other components, external memory arrays, peripherals, or the expansion bus. Certain pins supply the clock signal inputs to each device and support the various power management functions. Others pass control and status information between chips and supply pre-decoded chip-select signals, eliminating external random-logic "glue".

All signal pins that connect to the bus labeled "ISA System Backplane" in Figure 2-1 can drive directly up to eight standard expansion slots. These include 24-bit system and local address (SA and LA) buses and a 16-bit system data (SD) bus. A control bus supervises memory and I/O read and write operations and services requests for interrupts and direct-memory-access (DMA) transfers. Table 2-1 summarizes the SL SuperSet pins that attach directly to the ISA backplane connectors.

| i386™ SL | 82360SL | Signal Mnemonic  | Signal Function                      |

|----------|---------|------------------|--------------------------------------|

| Х        | Х       | SD15:0           | System Data Bus                      |

| Х        |         | SA19:17          | System Address Bus                   |

| Х        | Х       | SA16:0           | System Address Bus                   |

| Х        | Х       | LA23:17          | Local Address Bus                    |

|          | Х       | SMEMW#           | System Memory Write                  |

|          | Х       | SMEMR#           | System Memory Read                   |

| Х        | Х       | MEMW#            | Memory Write                         |

| Х        | Х       | MEMR#            | Memory Read                          |

| Х        | Х       | IOW#             | I/O Port Write                       |

| Х        | Х       | IOR#             | I/O Port Read                        |

|          | Х       | AEN              | System Address Enable                |

|          | Х       | IRQ15:10, 8:3, 1 | System Backplane Interrupt Requests  |

| Х        | Х       | IRQ9             | VGA Interrupt Request                |

|          | Х       | DRQ7:5,3:0       | Direct Memory Access Requests        |

|          | Х       | DACK7:5,3:0      | Direct Memory Access Acknowledge     |

| Х        | Х       | SBHE#            | System Bus High Enable               |

|          | Х       | тс               | Terminal DMA Transfer Cycle Count    |

| Х        | Х       | IOCHRDY          | I/O Channel Ready                    |

| Х        | Х       | 0WS#             | Zero Wait-State Transfer             |

|          | Х       | REFRESH#         | System Memory Refresh Cycle          |

| Х        | Х       | MASTER#          | AT Bus Master                        |

| Х        | Х       | BALE             | Buffered Address Latch Enable        |

|          | Х       | RESETDRV         | Cold System Reset                    |

|          | Х       | OSC              | System Bus Oscillator                |

| Х        |         | MEMCS16#         | 16-Bit Mem Transfer Mode Chip Select |

| х        | Х       | IOCS16#          | 16-Bit I/O Transfer Mode Chip Select |

|          | Х       | IOCHCHK#         | I/O Channel Check                    |

| Х        | X       | SYSCLK           | System Clock                         |

| Table 2-1, SI  | SuperSet Expans    | tion Bus Pins | Directly Drive  | the ISA Backplane |

|----------------|--------------------|---------------|-----------------|-------------------|

| 1 abic 2-1. SI | 2 Super Set Expans | non bus i ms  | Differing Drive | the ISA Dataplane |

### **Main Memory Options**

The Intel386 SL processor contains control and interface logic for main memory arrays built with either static (SRAM) or dynamic (DRAM) memory devices, with or without parity. The address and control functions performed by Intel386 SL processor pins vary, depending on the memory type selected. Address signals can be either latched or multiplexed, and control outputs can provide bank-select, chip-select, and byte-enable signals as appropriate for the sizes of memory components currently installed. DRAM refresh sequencing and parity generation and verification (if enabled) are automatic.

# SRAM Main Memory

Power consumption is critical in palm-top and note-pad sized computers. For maximum battery life, such systems generally use low-power SRAMs for their main memory systems. An SRAM device draws essentially no power except when it is accessed. Since only one location can be addressed at a time, the total power consumption of an SRAM-based main memory system is slight, no matter what its size.

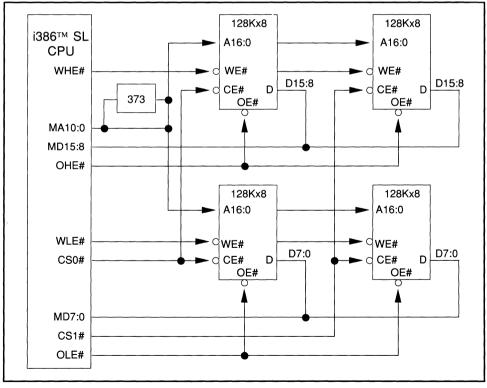

Figure 2-2 shows a simple 128K-byte main-memory system built with four SRAM chips, each driven directly by Intel386 SL CPU output pins. The Intel386 SL CPU can supply an arbitrary 22-bit address value in two stages, high-order half first, through pins MA10:0. To save time, ensuing accesses within the same 2K-byte page update only the low-order address bits.

The top address bits are also decoded internally to produce chip-select outputs (CS3:0#) for up to four SRAM memory banks. System configuration software determines the size of each bank. By decoding different sets of high-order address bits, the bank-select outputs can support memory systems with programmable bank size.

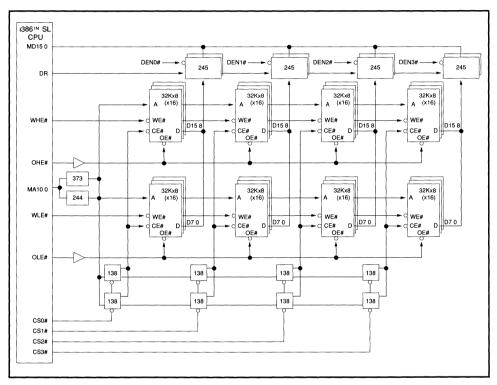

Data bus MD15:0 transfers one or two bytes of data at a time. Transfer-type information is internally combined with memory address bit 0 to produce individual output-enable and write-enable signals for the high- and low-order bytes of the array (OHE#, OLE#, WHE#, and WLE#). SRAM configurations are expandable up to 20 megabytes with external buffers and decoders. Figure 2-3 shows a 4 megabyte SRAM main-memory configuration.

Figure 2-3. Typical Four-Bank, 4-Megabyte Buffered SRAM Memory Configuration

# **DRAM Main Memory**

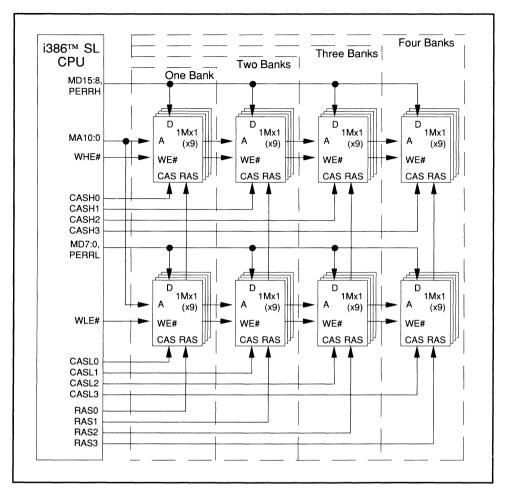

High-capacity main-memory arrays generally require fewer chips when built using DRAM devices. The DRAM control logic built into the Intel386 SL processor is extremely flexible. DRAM arrays can be 16 or 18 bits wide depending on whether automatic parity verification is enabled. Dedicated RAS#, CAS#, and WE# strobes are provided separately for the high- and low-order bytes of each DRAM bank. Figure 2-4 shows a four-bank, 20-megabyte DRAM memory array.

Figure 2-4. Four-Bank, 32-Megabyte Dynamic RAM Memory Configuration

The DRAM controller supports three different memory speeds. The number of CPU cycles allotted to each transfer varies to compensate for different CPU frequencies and memory speeds. One, two, three or four banks may be installed at a time. With two or four banks installed, accesses are interleaved between banks one and two, three and four for higher transfer rates.

With four banks installed, each pair may be a different size, allowing a range of memory configurations with total capacity from 512K to 20M bytes (see Table 2-2 for all possible DRAM configurations). Pins MA10:0 multiplex different sets of address bits according to the number of DRAM banks installed and the size and interleave mode of the components in each bank.

|        | Individual Bank | Size (x 16 bits) |        | Total System     |

|--------|-----------------|------------------|--------|------------------|

| Bank 0 | Bank 1          | Bank 2           | Bank 3 | Capacity (Bytes) |

| 512K   | 512K            | _                |        | 2 Meg            |

| 512K   | 512K            | 1 Meg            | —      | 4 Meg            |

| 512K   | 512K            | _                | 1 Meg  | 4 Meg            |

| 512K   | 512K            | 1 Meg            | 1 Meg  | 6 Meg            |

| 512K   | 512K            | 4 Meg            |        | 10 Meg           |

| 512K   | 512K            |                  | 4 Meg  | 10 Meg           |

| 512K   | 512K            | 4 Meg            | 1 Meg  | 12 Meg           |

| 512K   | 512K            | 1 Meg            | 4 Meg  | 12 Meg           |

| 512K   | 512K            | 4 Meg            | 4 Meg  | 18 Meg           |

| 1 Meg  |                 |                  |        | 2 Meg            |

| 1 Meg  |                 | 1 Meg            |        | 4 Meg            |

| 1 Meg  |                 |                  | 1 Meg  | 4 Meg            |

| 1 Meg  |                 | 1 Meg            | 1 Meg  | 6 Meg            |

| 1 Meg  |                 | 4 Meg            |        | 10 Meg           |

| 1 Meg  |                 |                  | 4 Meg  | 10 Meg           |

| 1 Meg  |                 | 4 Meg            | 1 Meg  | 12 Meg           |

| 1 Meg  |                 | 1 Meg            | 4 Meg  | 12 Meg           |

| 1 Meg  |                 | 4 Meg            | 4 Meg  | 18 Meg           |

| 1 Meg  | 1 Meg           |                  |        | 4 Meg            |

| 1 Meg  | 1 Meg           | 1 Meg            |        | 6 Meg            |

| 1 Meg  | 1 Meg           |                  | 1 Meg  | 6 Meg            |

| 1 Meg  | 1 Meg           | 1 Meg            | 1 Meg  | 8 Meg            |

| 1 Meg  | 1 Meg           | 4 Meg            |        | 12 Meg           |

| 1 Meg  | 1 Meg           |                  | 4 Meg  | 12 Meg           |

| 1 Meg  | 1 Meg           | 4 Meg            | 1 Meg  | 14 Meg           |

| 1 Meg  | 1 Meg           | 1 Meg            | 4 Meg  | 14 Meg           |

| 1 Meg  | 1 Meg           | 4 Meg            | 4 Meg  | 20 Meg           |

| 1 Meg  | 4 Meg           |                  |        | 10 Meg           |

| 1 Meg  | 4 Meg           | 1 Meg            |        | 12 Meg           |

| 1 Meg  | 4 Meg           |                  | 1 Meg  | 12 Meg           |

| 256K   | 256K            |                  |        | 1 Meg            |

| 256K   | 256K            | 1 Meg            |        | 3 Meg            |

| 256K   | 256K            |                  | 1 Meg  | 3 Meg            |

| 256K   | 256K            | 1 Meg            | 1 Meg  | 5 Meg            |

| 256K   | 256K            | 4 Meg            |        | 9 Meg            |

| 256K   | 256K            |                  | 4 Meg  | 9 Meg            |

#### Table 2-2. Intel 386<sup>™</sup>SL Processor Control Logic Supports DRAM Configurations Up to 20 Mbytes

A number of special Intel386 SL processor facilities reduce DRAM power consumption. Only the memory devices involved in each transfer are enabled. With page-mode DRAMs, successive transfers within the same page produce CAS#-only transfer cycles for greater speed and reduced lower power. The refresh rate is programmable, and the controller can perform CAS# before RAS# refresh sequencing to reduce power-supply transients ("spiking"), improve performance, and increase power efficiency.

### **Memory System Sizing and Control Mechanisms**

The characteristics of the main memory controller, including the type and operating mode of the devices used, the number of the installed banks, and the size of each bank are configured through software at initialization time. System initialization software can test the size and characteristics of memory components currently installed and dynamically adjust memory-control algorithms according to the results of those tests. A number of control pins alter their function depending on the basic memory technology selected; the alternate functions performed by each of these pins is shown in Table 2-3. For further details, consult the **Intel 386**<sup>TM</sup> SL Microprocessor SuperSet Programmer's Reference Manual.

| Signal Mnemonic | DRAM-Mode Pin Function       | SRAM-Mode Pin Function     |

|-----------------|------------------------------|----------------------------|

| CMUX0           | CAS, Low Byte, Bank 3        | Transceiver Direction      |

| CMUX1           | CAS, High Byte, Bank 3       | Address Latch Enable       |

| CMUX2           | CAS, Low Byte, Bank 2        | Transceiver Enable, Bank 3 |

| CMUX3           | CAS, High Byte, Bank 2       | Transceiver Enable, Bank 2 |

| CMUX4           | CAS, Low Byte, Bank 1        | Transceiver Enable, Bank 1 |

| CMUX5           | CAS, High Byte, Bank 1       | Transceiver Enable, Bank 1 |

| CMUX6           | CAS, Low Byte, Bank 0        | Transceiver Enable, Bank 0 |

| CMUX7           | CAS, High Byte, Bank 0       | Transceiver Enable, Bank 0 |

| CMUX8           | RAS, Bank 3                  | Chip Enable, Bank 3        |

| CMUX9           | RAS, Bank2                   | Chip Enable, Bank 2        |

| CMUX10          | RAS, Bank1                   | Chip Enable, Bank 1        |

| CMUX11          | RAS, Bank0                   | Chip Enable, Bank 0        |

| CMUX12          | Low-Order Byte Parity Error  | Low-Byte Output Enable     |

| CMUX13          | High-Order Byte Parity Error | High-Byte Output Enable    |

|                 |                              |                            |

#### Table 2-3. Intel SL SuperSet Multifunction Main Memory Control Signals

### **Cache Memory System**

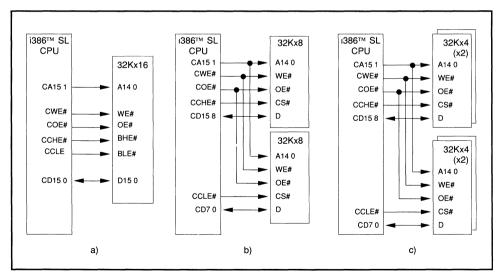

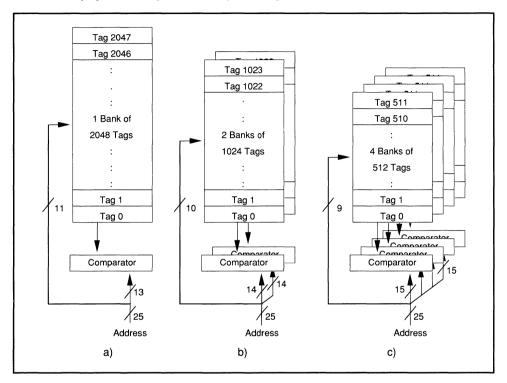

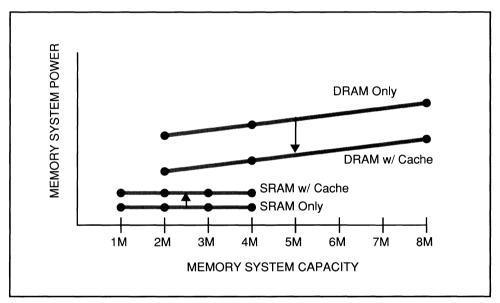

High-performance computers traditionally include cache memory to reduce main memory latency and boost system throughput, albeit at the expense of increased system complexity and power requirements. The optional high-speed cache system supported by the SL SuperSet allows the simplest possible implementation, and can both improve CPU performance and reduce system power consumption.