THE

TRANSPUTER

DATABOOK

INMOS Limited 1000 Aztec West Almondsbury Bristol BS12 4SQ UK Telephone (0454) 616616 Telex 444723

INMOS Japan K.K.

4th Floor No 1 Kowa Bldg

11-41 Akasaka 1-chome

Minato-ku

Tokyo 107

Japan

Telephone 03-505 2840

Telex J29507 TEI JPN

Fax 03-505 2844

INMOS Corporation PO Box 16000 Colorado Springs CO 80935 USA Telephone (719) 630 4000 Telex (Easy Link) 629 44 936

INMOS SARL Immeuble Monaco 7 rue Le Corbusier SILIC 219 94518 Rungis Cedex France Telephone (1) 46.87.22.01 Telex 201222 INMOS GmbH Danziger Strasse 2 8057 Eching Munich West Germany Telephone (089) 319 10 28 Telex 522645

### LOCAL U.S. SALES OFFICES

INMOS Corporation 200 E Sandpointe Suite 650 Santa Ana CA 92707 Telephone(714) 957 6018

INMOS Corpoation 2620 Augustine Drive Suite 100 Santa Clara CA 95054 Telephone (408) 727 7771

INMOS Corporation 12400 Whitewater Drive Suite 120 Minnetonka MN 55343 Telephone (612) 932 7121 INMOS Corporation 6025-G Atlantic Blvd Norcross GA 30071 Telephone (404) 242 7444

INMOS Corporation 5 Burlington Woods Drive Suite 201 Burlington MA 01803 Telephone (617) 229 2550

INMOS Corporation 10200 E Girard Avenue Suite B239 Denver CO 80231 Telephone (303) 368 0561 INMOS Corporation 14643 Dallas Parkway Suite 730 Dallas TX 75240 Telephone (214) 490 9522

INMOS Corporation 9861 Broken Land Parkway Suite 320 Columbia MD 21046 Telephone (301) 995 6952

INMOS Corporation PO Box 272 Fishkill NY 12524 Telephone (914) 897 2422

### **INMOS Databook Series**

Transputer Databook Military Micro-products Databook

Transputer Support Databook: Development and Sub-systems

Memory Databook Graphics Databook Digital Signal Processing Databook

Transputer Applications Notebook: Architecture and Software Transputer Applications Notebook: Systems and Performance

Copyright ©INMOS Limited 1989

INMOS reserves the right to make changes in specifications at any time and without notice. The information furnished by INMOS in this publication is believed to be accurate; however, no responsibility is assumed for its use, nor for any infringement of patents or other rights of third parties resulting from its use. No licence is granted under any patents, trademarks or other rights of INMOS.

, Inmos, IMS and occam are trademarks of the INMOS Group of Companies.

INMOS is a member of the SGS-THOMSON Microelectronics Group.

INMOS document number: 72 TRN 203 01

## TRANSPUTER DATABOOK

### **Contents overview**

| 1  | INMOS                     | 1   |

|----|---------------------------|-----|

| 2  | Transputer architecture   | 5   |

| 3  | Transputer overview       | 27  |

| 4  | IMS T805 engineering data | 47  |

| 5  | IMS T801 engineering data | 127 |

| 6  | IMS T800 engineering data | 189 |

| 7  | IMS T425 engineering data | 261 |

| 8  | IMS T414 engineering data | 333 |

| 9  | IMS T222 engineering data | 399 |

| 10 | IMS T225 preview          | 453 |

| 11 | IMS M212 preview          | 463 |

| 12 | IMS C004 engineering data | 479 |

| 13 | IMS C011 engineering data | 503 |

| 14 | IMS C012 engineering data | 529 |

| A  | Quality and Reliability   | 551 |

| В  | Index                     | 557 |

### Contents

|   | Preface      |                  |                                     | xix      |

|---|--------------|------------------|-------------------------------------|----------|

|   | Notation and | nomencla         | ature                               | xx       |

|   |              |                  |                                     |          |

| 1 | INMOS        |                  |                                     | 1        |

|   | 1 Introd     | duction          |                                     | 2        |

|   | 1.1          | Manuf            | acturing                            | 2        |

|   | 1.2          | Assen            | nbly                                | 2        |

|   | 1.3          | Test             |                                     | 2        |

|   | 1.4          |                  | y and Reliability                   | 2        |

|   | 1.5          | Militar          |                                     | 2        |

|   | 1.6          |                  | Developments                        | 3        |

|   |              | 1.6.1            | Research and Development            | 3        |

|   |              | 1.6.2            | Process Developments                | 3        |

|   | <b>T</b>     |                  |                                     |          |

| 2 | Transputer   | archited         | cture                               | 5        |

|   | 1            |                  |                                     |          |

|   | 1 Introd     | duction<br>Overv | low                                 | 6        |

|   | 1.1          | Overv            | Transputers and occam               | 7        |

|   | 1.2          | Systol           | m design rationale                  |          |

|   | 1.2          | 1.2.1            | Programming                         | 8        |

|   |              | 1.2.2            | Hardware                            | 9        |

|   |              | 1.2.3            |                                     | 9        |

|   | 1.3          |                  | ms architecture rationale           | 9        |

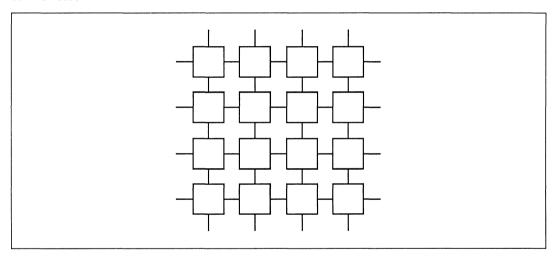

|   |              | 1.3.1            | Point to point communication links  | 9        |

|   |              | 1.3.2            | Local memory                        | 10       |

|   | 1.4          |                  | nunication                          | 10       |

|   |              |                  |                                     |          |

|   |              | .m model         |                                     | 12       |

|   | 2.1          | Overv            |                                     | 12       |

|   | 2.2          |                  | n overview                          | 13       |

|   |              | 2.2.1            | Processes                           | 13       |

|   |              |                  | Assignment                          | 13       |

|   |              |                  | Input                               | 13       |

|   |              |                  | Output                              | 13       |

|   |              | 2.2.2            | Constructions                       | 14       |

|   |              |                  | Sequence<br>Parallel                | 14<br>14 |

|   |              |                  | Communication                       | 15       |

|   |              |                  | Conditional                         | 15       |

|   |              |                  | Alternation                         | 15       |

|   |              |                  | Loop                                | 16       |

|   |              |                  | Selection                           | 16       |

|   |              |                  | Replication                         | 16       |

|   |              | 2.2.3            | Types                               | 17       |

|   |              | 2.2.4            | Declarations, arrays and subscripts | 17       |

|   |              | 2.2.5            | Procedures                          | 18       |

|   |              | 2.2.6            | Functions                           | 18       |

|   |              | 2.2.7            | Expressions                         | 18       |

|   |              |                  |                                     |          |

|                                         |      |             | 2.2.8 Timer                                       | 19 |

|-----------------------------------------|------|-------------|---------------------------------------------------|----|

|                                         |      |             | 2.2.9 Peripheral access                           | 19 |

|                                         |      | 2.3         | Configuration                                     | 20 |

|                                         |      |             | PLACED PAR                                        | 20 |

|                                         |      |             | PRI PAR                                           | 20 |

|                                         |      |             | 2.3.1 INMOS standard links                        | 20 |

|                                         | 3    | Error       | handling                                          | 21 |

|                                         |      |             |                                                   |    |

|                                         | 4    |             | ram development                                   | 22 |

|                                         |      | 4.1         | Logical behaviour                                 | 22 |

|                                         |      | 4.2         | Performance measurement                           | 22 |

|                                         |      | 4.3         | Separate compilation of OCCAM and other languages | 22 |

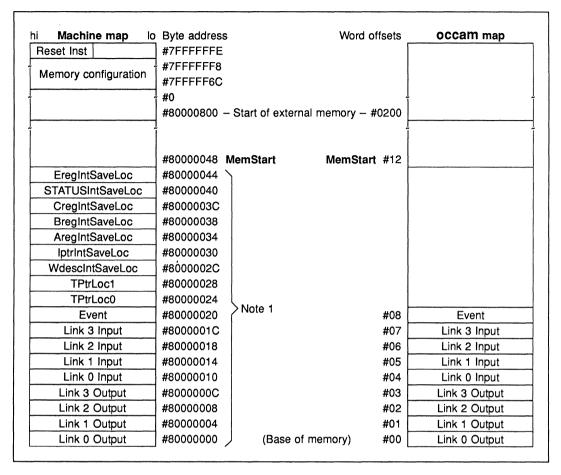

|                                         |      | 4.4         | Memory map and placement                          | 23 |

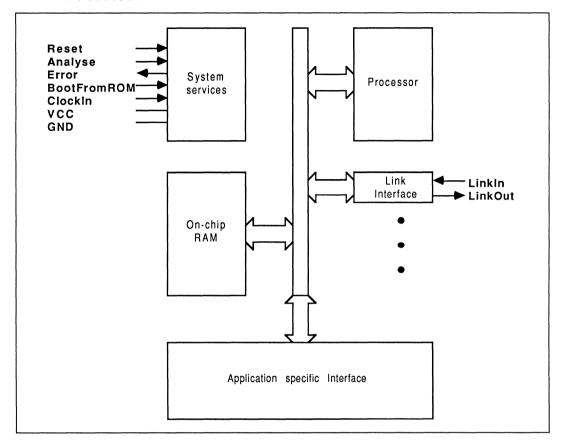

|                                         | 5    | Physi       | ical architecture                                 | 24 |

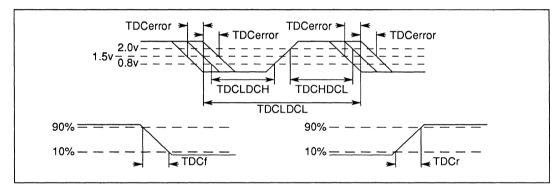

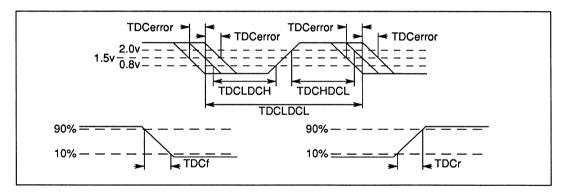

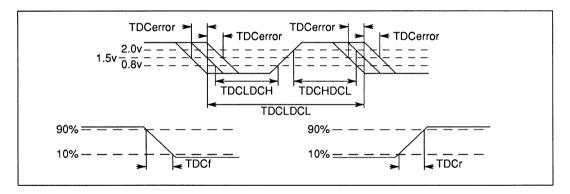

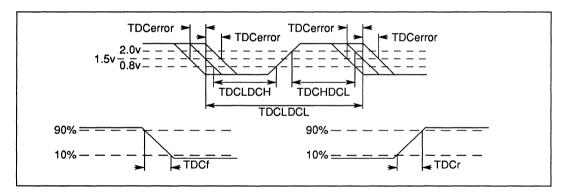

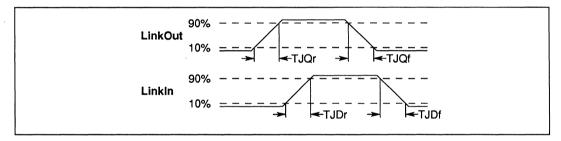

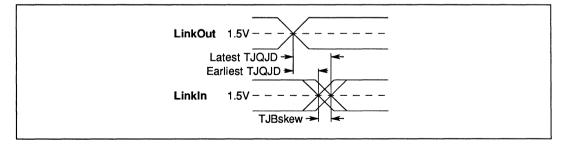

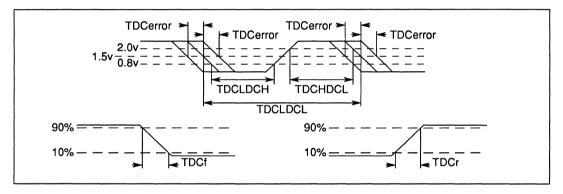

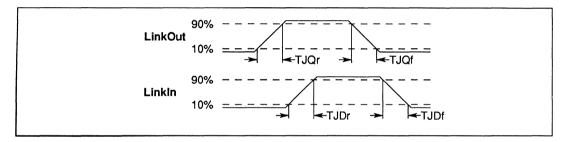

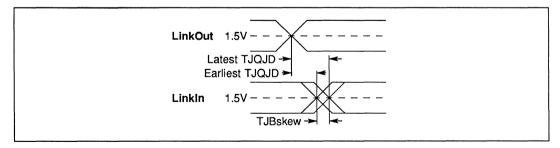

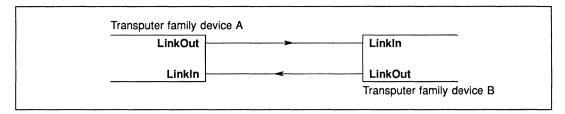

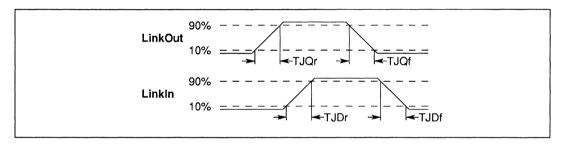

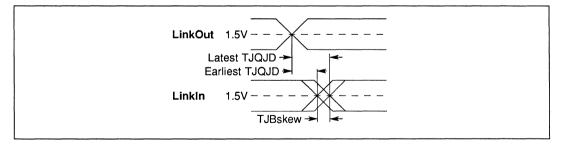

|                                         |      | 5.1         | INMOS serial links                                | 24 |

|                                         |      |             | 5.1.1 Overview                                    | 24 |

|                                         |      |             | 5.1.2 Link electrical specification               | 24 |

|                                         |      | 5.2         | System services                                   | 24 |

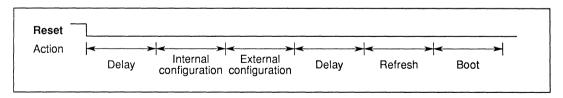

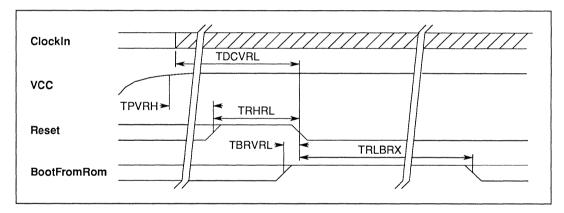

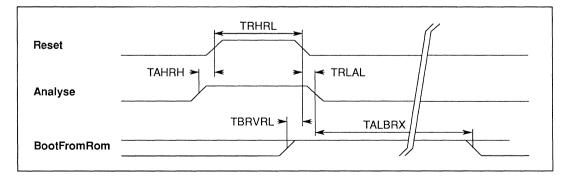

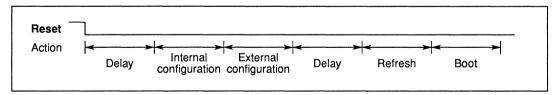

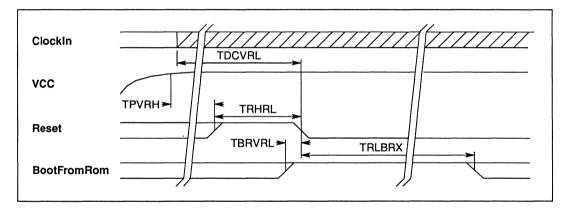

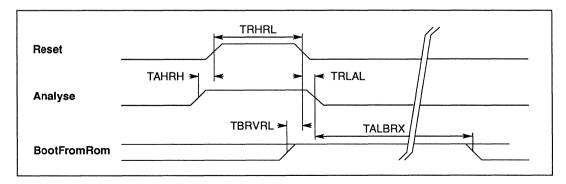

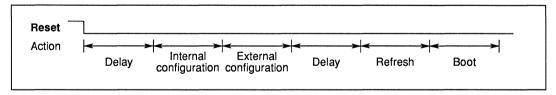

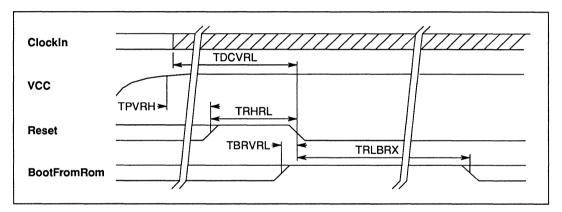

|                                         |      |             | 5.2.1 Powering up and down, running and stopping  | 24 |

|                                         |      |             | 5.2.2 Clock distribution                          | 25 |

|                                         |      | 5.3         | Bootstrapping from ROM or from a link             | 25 |

| *************************************** |      | 5.4         | Peripheral interfacing                            | 25 |

|                                         |      |             |                                                   |    |

| 3                                       | Trar | sputer      | overview                                          | 27 |

|                                         | 1    | Introd      | duction                                           | 28 |

|                                         |      |             |                                                   |    |

|                                         | 2    | The t       | ransputer: basic architecture and concepts        | 29 |

|                                         |      | 2.1         | A programmable device                             | 29 |

|                                         |      | 2.2         | occam                                             | 29 |

|                                         |      | 2.3         | VLSI technology                                   | 29 |

|                                         |      | 2.4         | Simplified processor with micro-coded scheduler   | 30 |

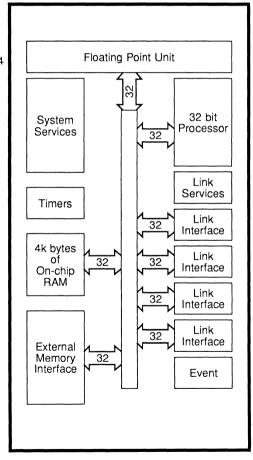

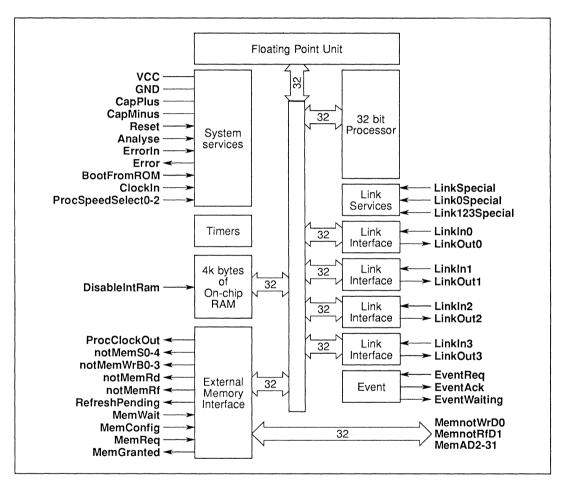

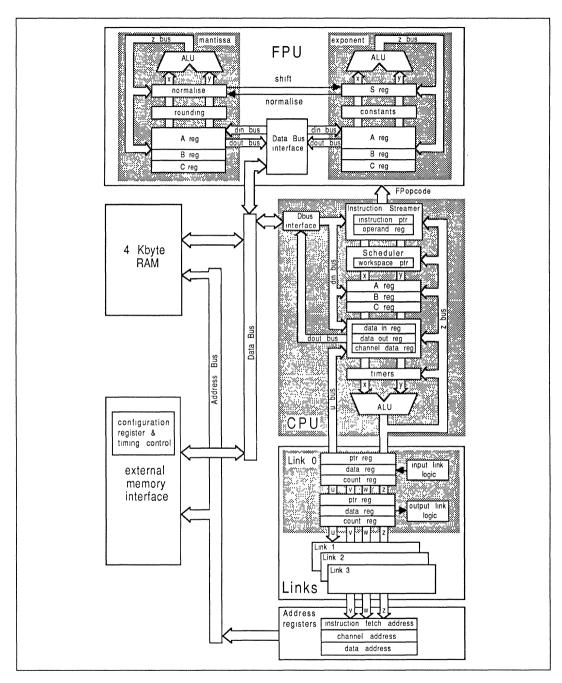

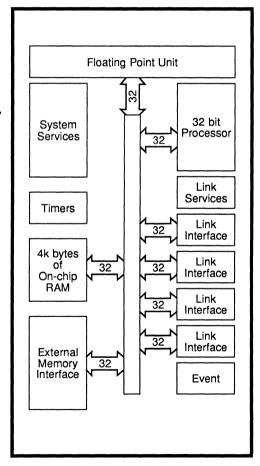

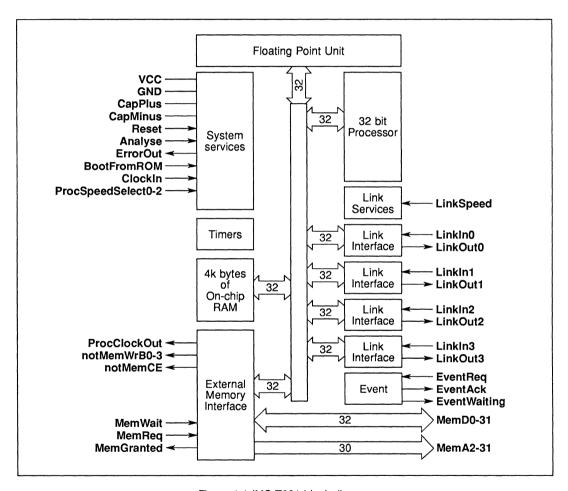

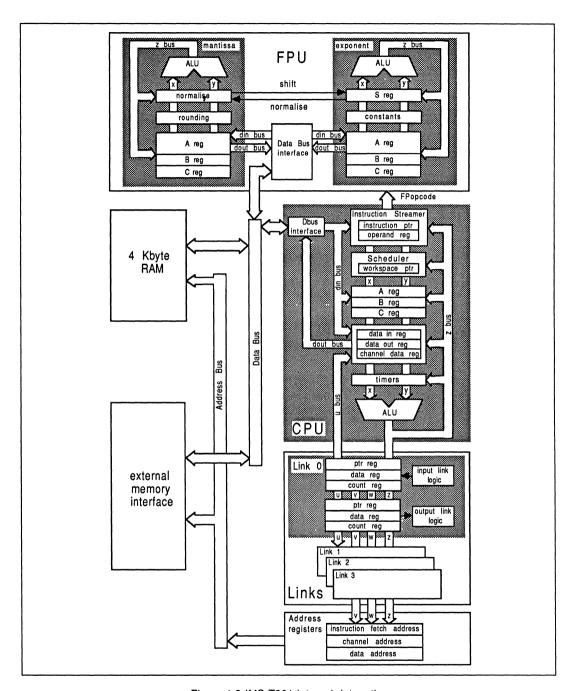

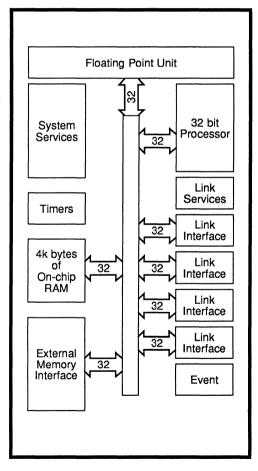

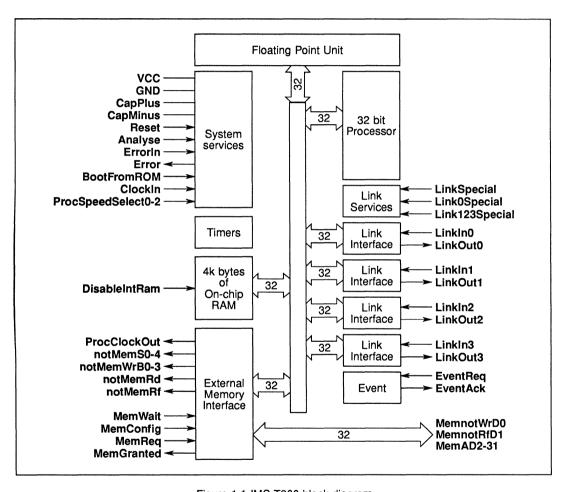

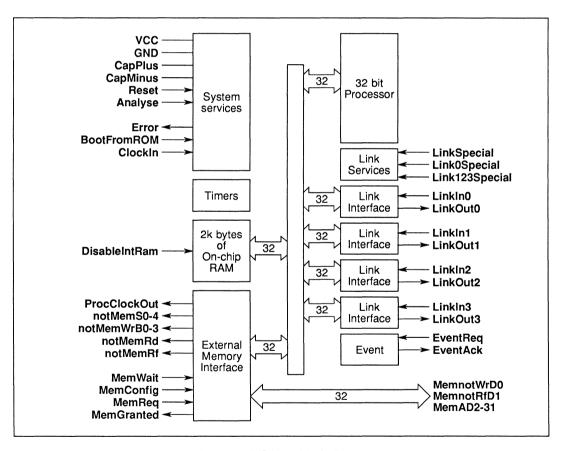

|                                         | 3    | Trans       | sputer internal architecture                      | 31 |

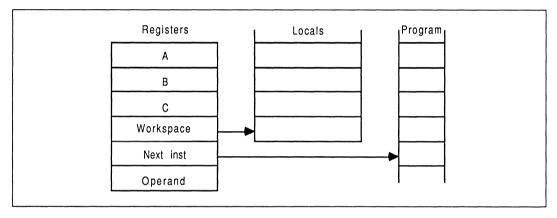

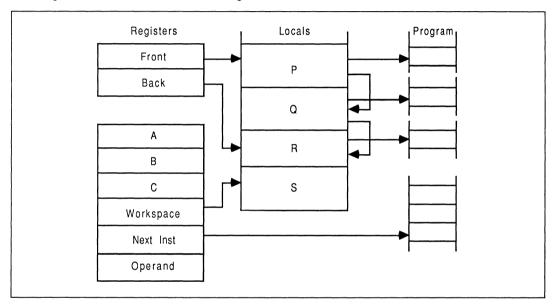

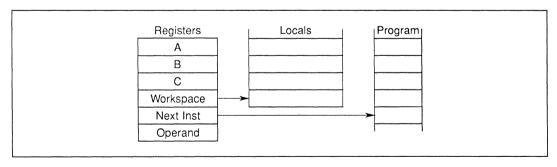

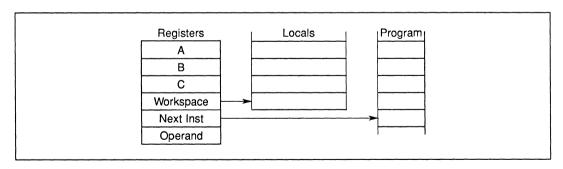

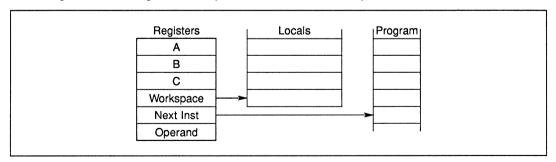

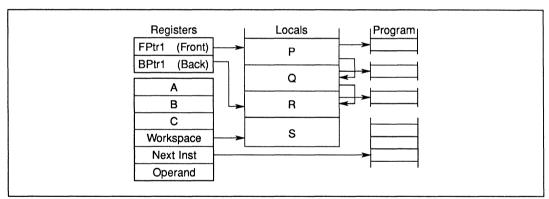

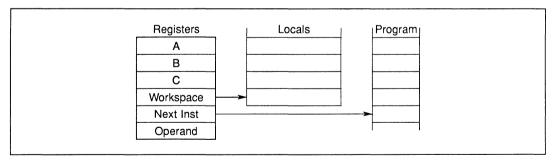

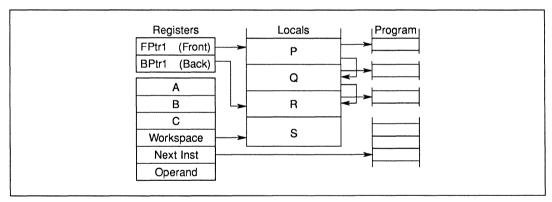

|                                         |      | 3.1         | Sequential processing                             | 32 |

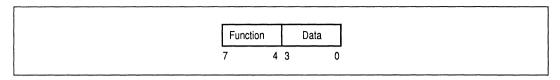

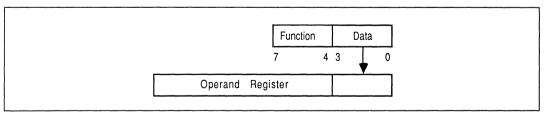

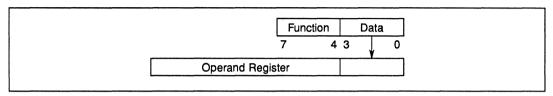

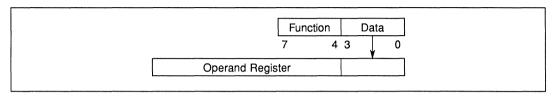

|                                         |      | 3.2         | Instructions                                      | 32 |

|                                         |      | <del></del> | 3.2.1 Direct functions                            | 33 |

|                                         |      |             | 3.2.2 Prefix functions                            | 33 |

|                                         |      |             | 3.2.3 Indirect functions                          | 34 |

|                                         |      |             | 3.2.4 Efficiency of encoding                      | 34 |

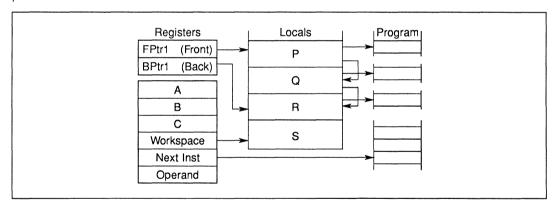

|                                         |      | 3.3         | Support for concurrency                           | 34 |

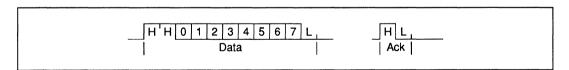

|                                         |      | 3.4         | Communications                                    | 36 |

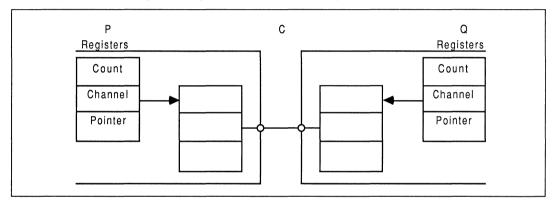

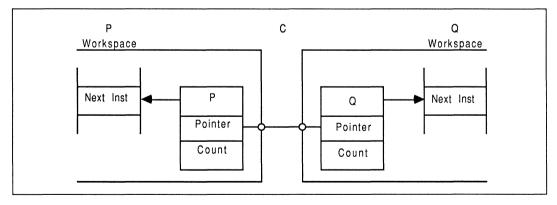

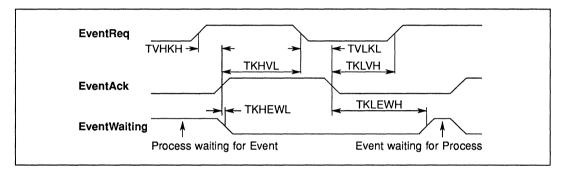

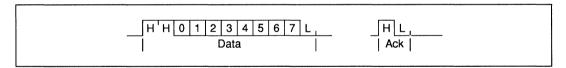

|                                         |      |             | 3.4.1 Internal channel communication              | 36 |

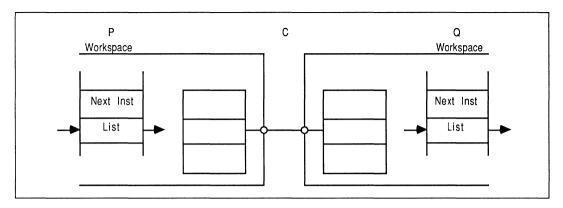

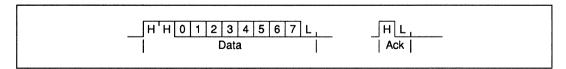

|                                         |      |             | 3.4.2 External channel communication              | 38 |

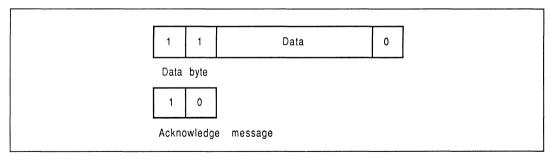

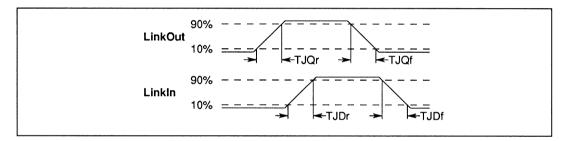

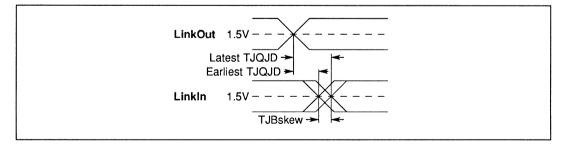

|                                         |      |             | 3.4.3 Communication links                         | 39 |

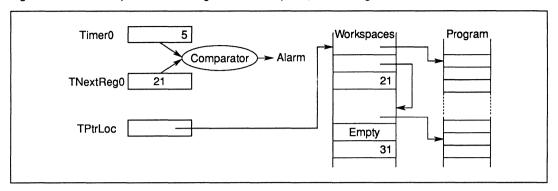

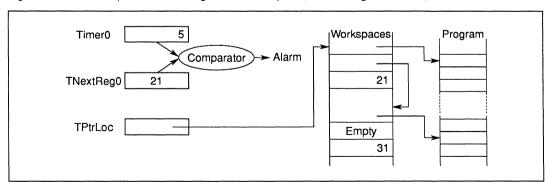

|                                         |      | 3.5         | Timer                                             | 40 |

|                                         |      | 3.6         | Alternative                                       | 40 |

|                                         |      | 3.7         | Floating point instructions                       | 40 |

|                                         |      |             | 3.7.1 Optimising use of the stack                 | 41 |

|                                         |      |             | 3.7.2 Concurrent operation of FPU and CPU         | 41 |

|                                         |      | 3.8         | Floating point unit design                        | 42 |

|   |       | 3.9        | Graphic           | s capability                                | 43       |

|---|-------|------------|-------------------|---------------------------------------------|----------|

|   |       |            | 3.9.1             | Example - drawing coloured text             | 43       |

|   |       |            |                   |                                             |          |

|   | 4     | Conc       | lusion            |                                             | 45       |

|   | 1840  | TOOL -     |                   |                                             |          |

| 4 | IIVIS | 1805 e     | ngineerin         | g data                                      | 47       |

|   | 1     | Introd     | duction           |                                             | 48       |

|   |       |            |                   |                                             |          |

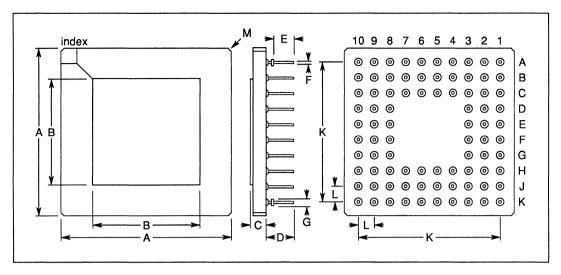

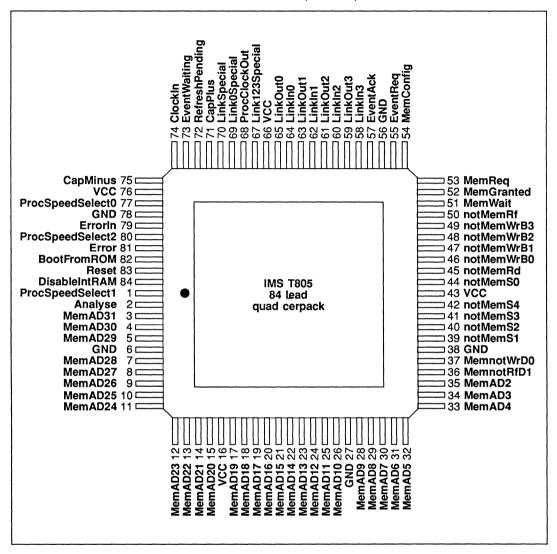

|   | 2     | Pin d      | esignations       | 3                                           | 51       |

|   |       |            |                   |                                             |          |

|   | 3     | Proce      |                   |                                             | 52       |

|   |       | 3.1        | Register          |                                             | 52       |

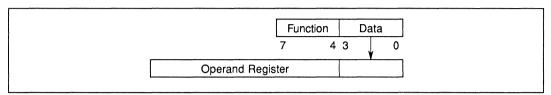

|   |       | 3.2        | Instructi         |                                             | 53       |

|   |       |            |                   | Direct functions                            | 53       |

|   |       |            |                   | Prefix functions                            | 53       |

|   |       |            |                   | Indirect functions                          | 54       |

|   |       |            |                   | Expression evaluation                       | 54<br>54 |

|   |       | 3.3        |                   | Efficiency of encoding less and concurrency | 55       |

|   |       | 3.4        | Priority          | es and concurrency                          | 56       |

|   |       | 3.5        |                   | nications                                   | 56       |

|   |       | 3.6        | Block m           |                                             | 57       |

|   |       | 3.7        | Timers            |                                             | 57       |

|   |       |            | 11111010          |                                             |          |

|   | 4     | Instru     | ction set s       | summary                                     | 59       |

|   |       | 4.1        |                   | duling points                               | 60       |

|   |       | 4.2        |                   | structions                                  | 61       |

|   |       | 4.3        | Debugg            | ing support                                 | 61       |

|   |       | 4.4        | Floating          | point errors                                | 61       |

|   |       |            |                   |                                             |          |

|   | 5     | Float      | ing point u       | nit                                         | 69       |

|   |       |            |                   |                                             |          |

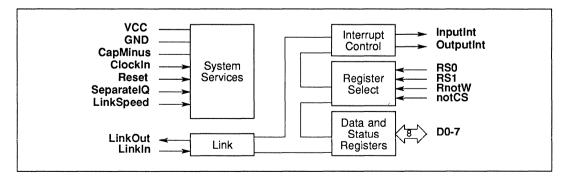

|   | 6     |            | m services        |                                             | 71       |

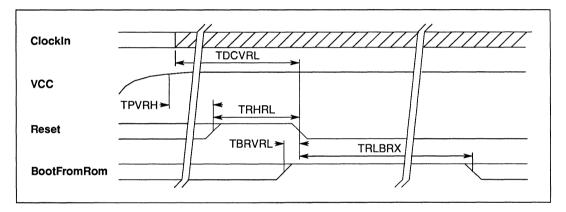

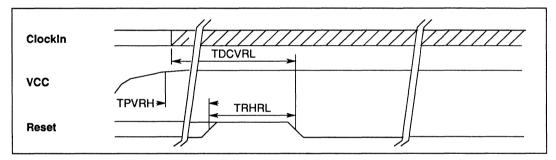

|   |       | 6.1        | Power             |                                             | 71       |

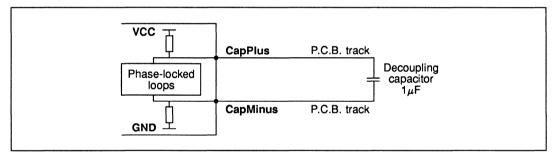

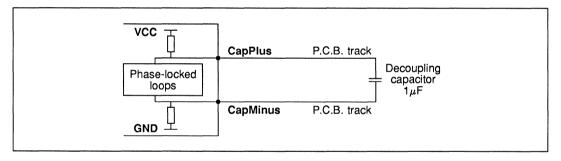

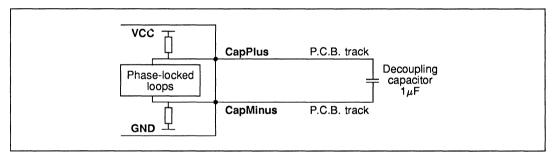

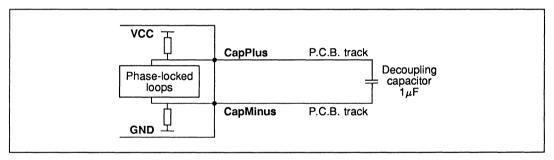

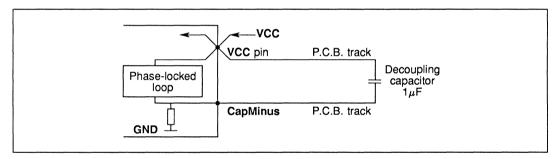

|   |       | 6.2        |                   | s, CapMinus                                 | 71       |

|   |       | 6.3        | Clockin           | and Calando O                               | 71       |

|   |       | 6.4        |                   | eedSelect0-2                                | 72       |

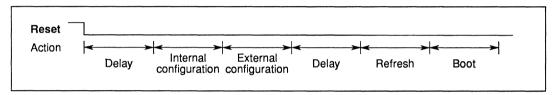

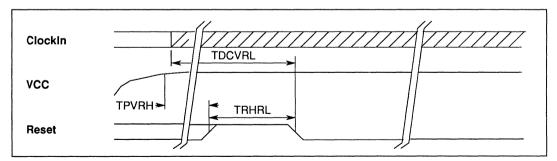

|   |       | 6.5<br>6.6 | Reset<br>Bootstra | 2N                                          | 73<br>73 |

|   | ·     | 6.7        | Peek an           |                                             | 75       |

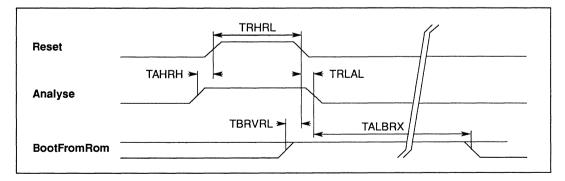

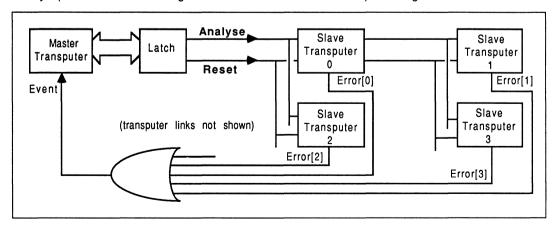

|   |       | 6.8        | Analyse           |                                             | 75       |

|   |       | 6.9        | Error, E          |                                             | 76       |

|   |       |            |                   |                                             |          |

|   | 7     | Memo       | orv               |                                             | 77       |

|   | ····  |            |                   |                                             |          |

|   | 8     | Exter      | nal memor         | y interface                                 | 79       |

|   |       | 8.1        | Pin fund          |                                             | 80       |

|   |       |            | 8.1.1             | MemAD2-31                                   | 80       |

|   |       |            | 8.1.2             | notMemRd                                    | 80       |

|   |       |            | 8.1.3             | MemnotWrD0                                  |          |

|   |       |            | 8.1.4             | notMemWrB0-3                                | 80       |

|   |       |            | 8.1.5             | notMemS0-4                                  | 80       |

|   |                                        |         | 8.1.6 MemWait                                   | 80  |

|---|----------------------------------------|---------|-------------------------------------------------|-----|

|   |                                        |         | 8.1.7 MemnotRfD1                                | 80  |

|   | ************************************** |         | 8.1.8 notMemRf                                  | 80  |

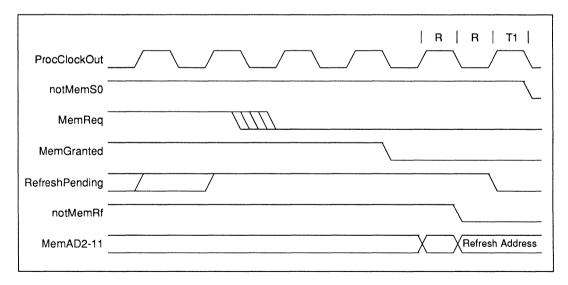

|   |                                        |         | 8.1.9 RefreshPending                            | 80  |

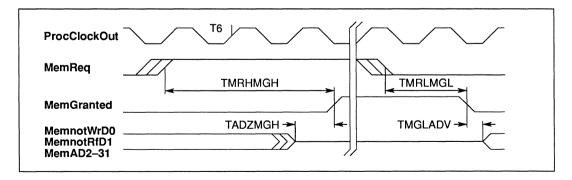

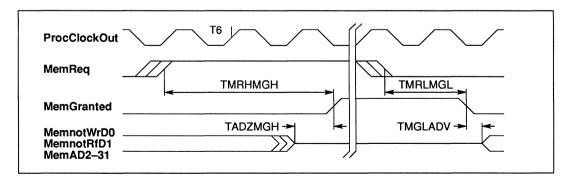

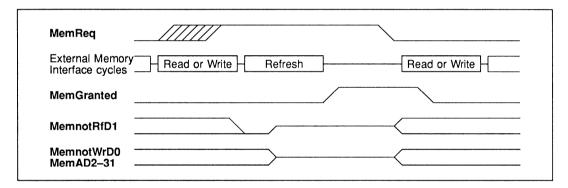

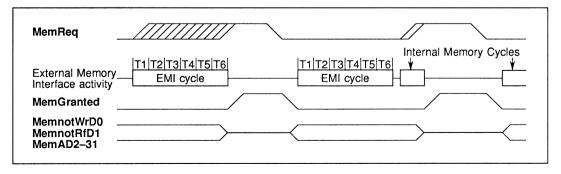

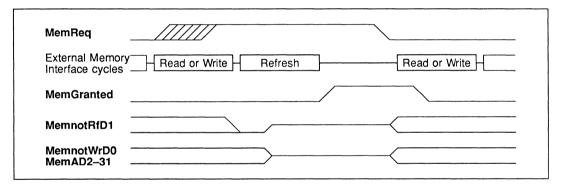

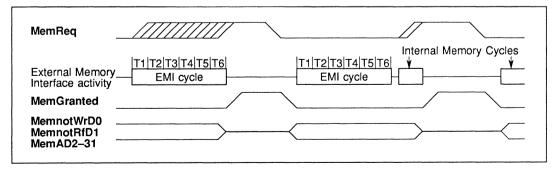

|   |                                        |         | 8.1.10 MemReq, MemGranted                       | 81  |

|   |                                        |         | 8.1.11 MemConfig                                | 81  |

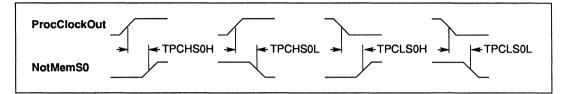

|   |                                        |         | 8.1.12 ProcClockOut                             | 82  |

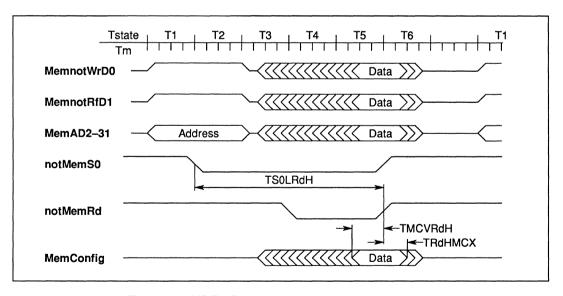

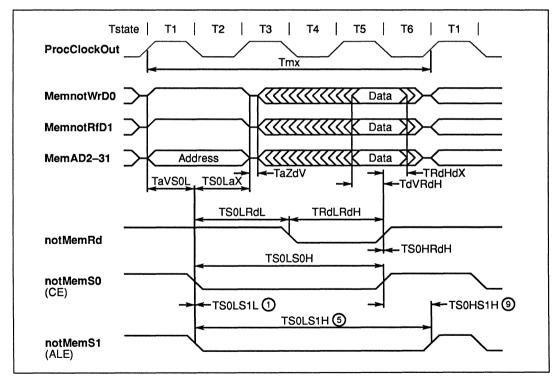

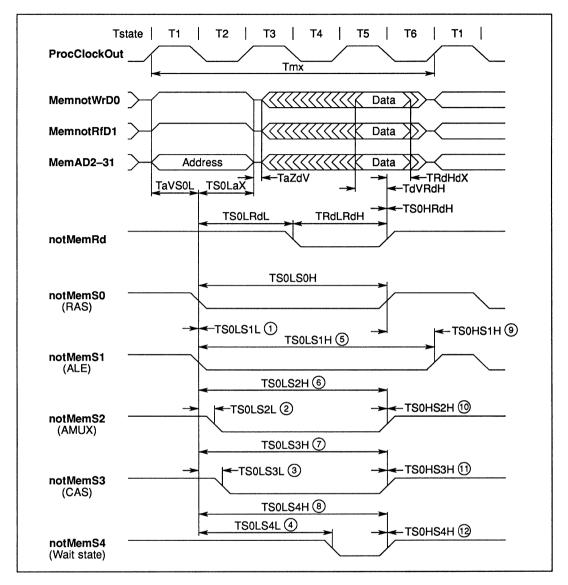

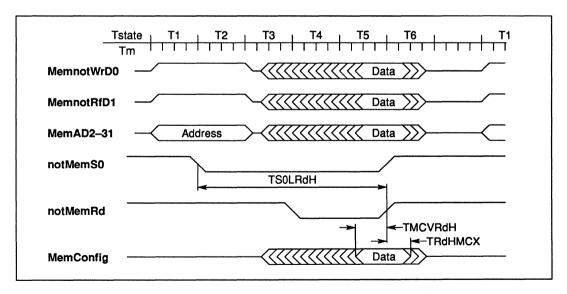

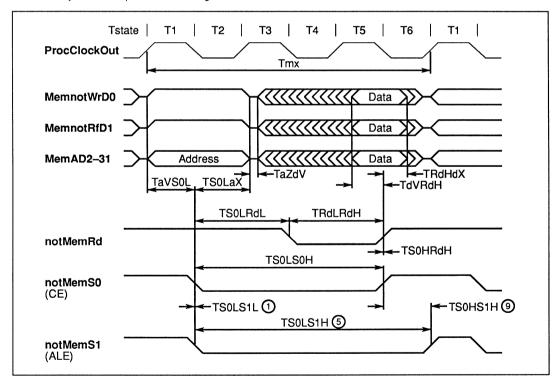

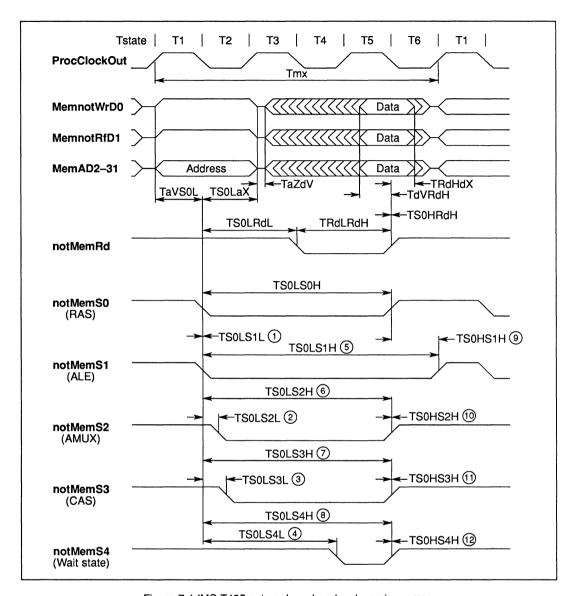

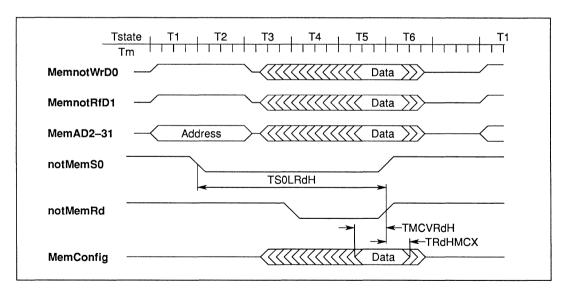

|   |                                        | 8.2     | Read cycle                                      | 83  |

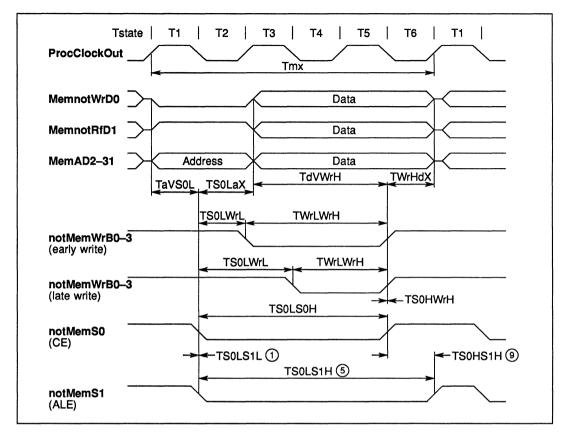

|   |                                        | 8.3     | Write cycle                                     | 88  |

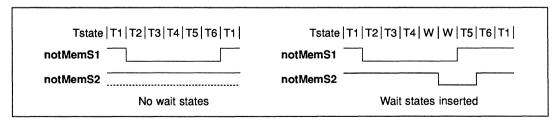

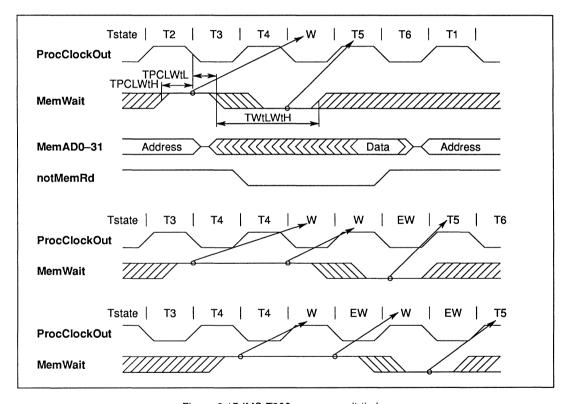

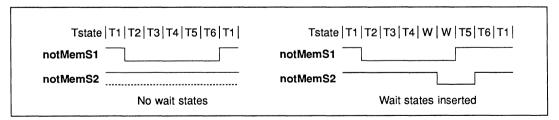

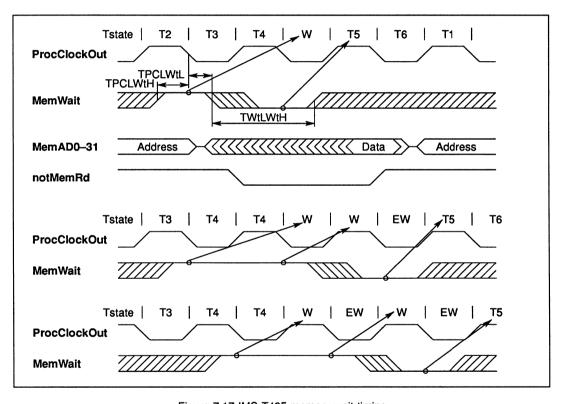

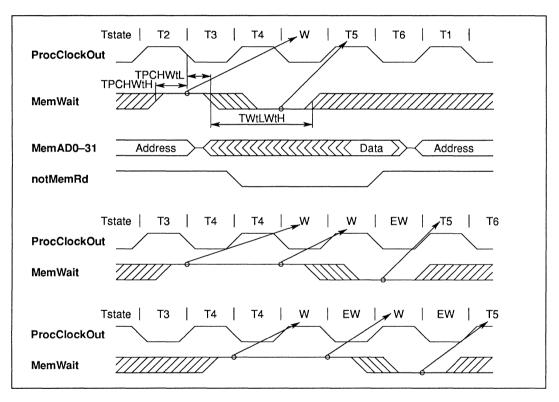

|   |                                        | 8.4     | Wait                                            | 89  |

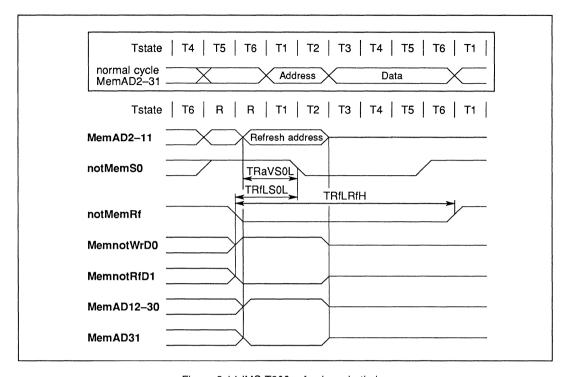

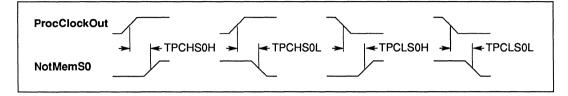

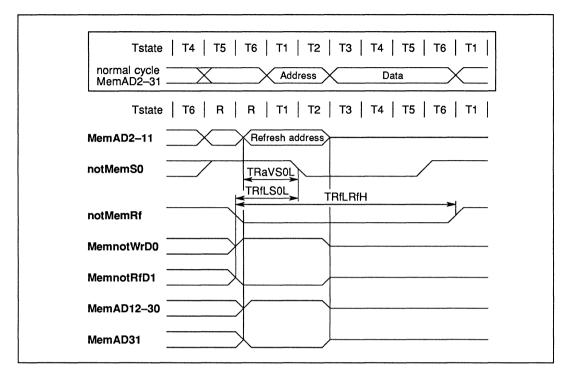

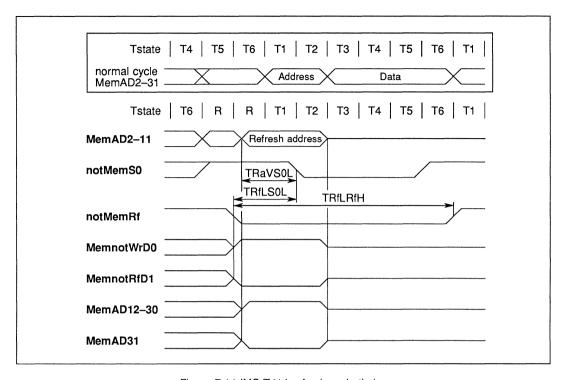

|   |                                        | 8.5     | Memory refresh                                  | 91  |

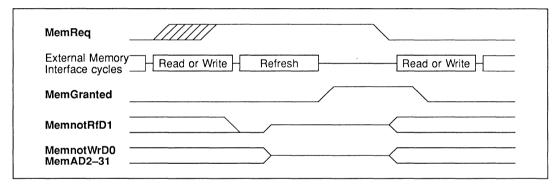

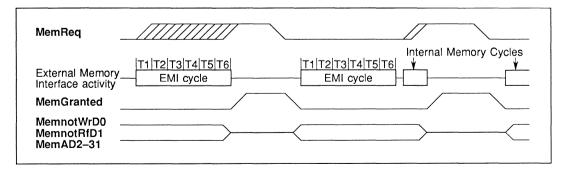

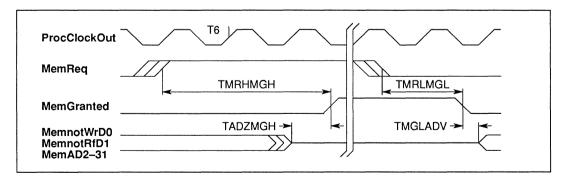

|   |                                        | 8.6     | Direct memory access                            | 94  |

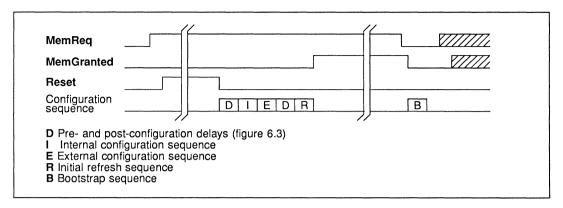

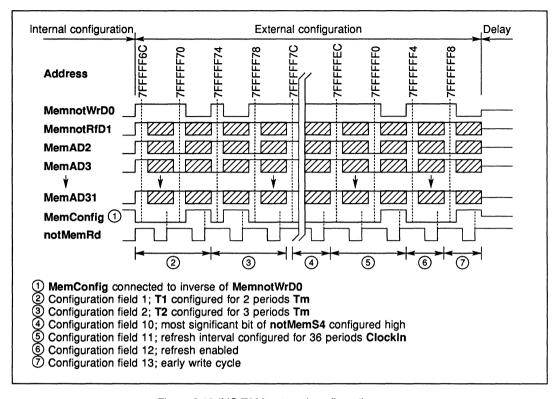

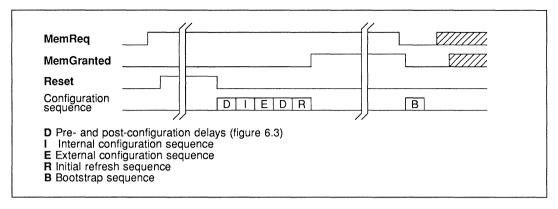

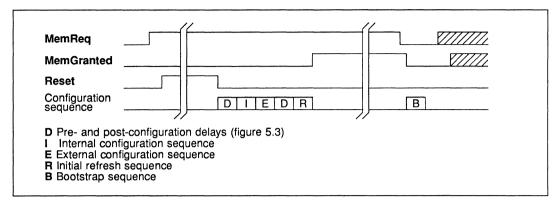

|   |                                        | 8.7     | Memory configuration                            | 96  |

|   |                                        |         | 8.7.1 Internal configuration                    | 96  |

|   |                                        |         | 8.7.2 External configuration                    | 98  |

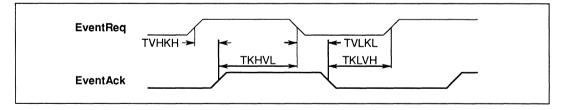

|   | 9                                      | Events  | 3                                               | 103 |

|   | 10                                     | Links   |                                                 | 105 |

|   |                                        | Liiks   |                                                 | 100 |

|   | 11                                     | Electri | ical specifications                             | 108 |

|   |                                        | 11.1    | DC electrical characteristics                   | 108 |

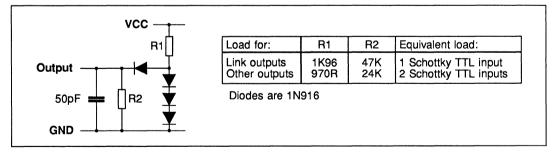

|   |                                        | 11.2    | Equivalent circuits                             | 109 |

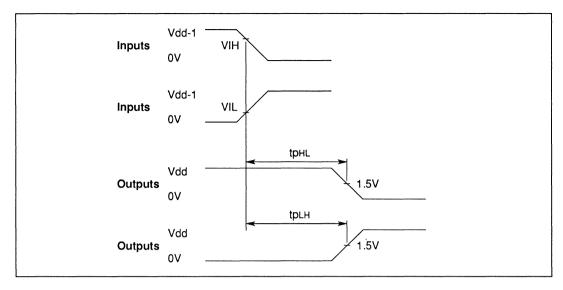

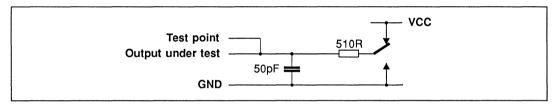

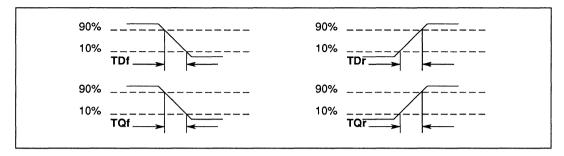

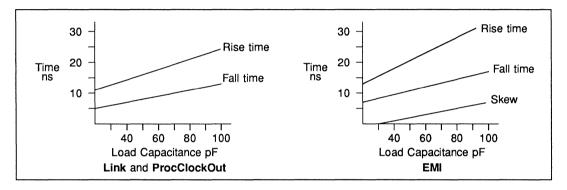

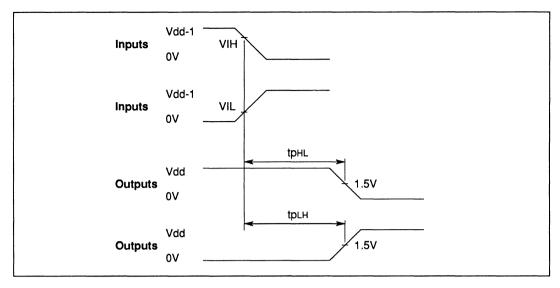

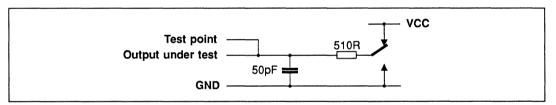

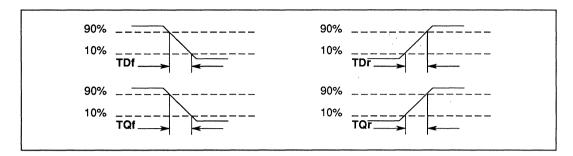

|   |                                        | 11.3    | AC timing characteristics                       | 110 |

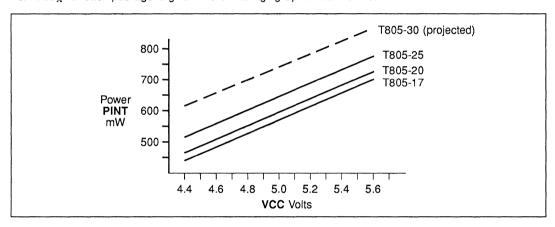

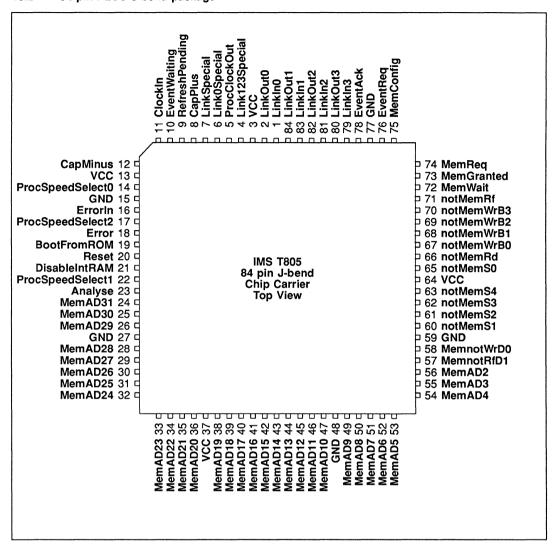

|   |                                        | 11.4    | Power rating                                    | 112 |

|   | 12                                     | Perfor  | mance                                           | 113 |

|   |                                        | 12.1    | Performance overview                            | 113 |

|   |                                        | 12.2    | Fast multiply, TIMES                            | 115 |

|   |                                        | 12.3    | Arithmetic                                      | 116 |

|   |                                        | 12.4    | Floating point operations                       | 117 |

|   |                                        |         | 12.4.1 Floating point functions                 | 117 |

|   |                                        |         | 12.4.2 Special purpose functions and procedures | 118 |

|   |                                        | 12.5    | Effect of external memory                       | 118 |

|   |                                        | 12.6    | Interrupt latency                               | 119 |

|   | 13                                     | Packa   | ge specifications                               | 120 |

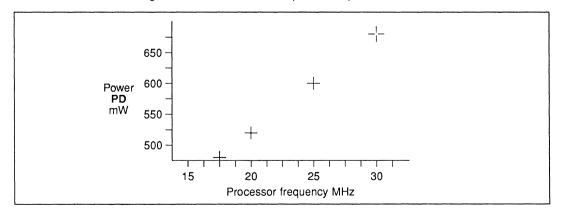

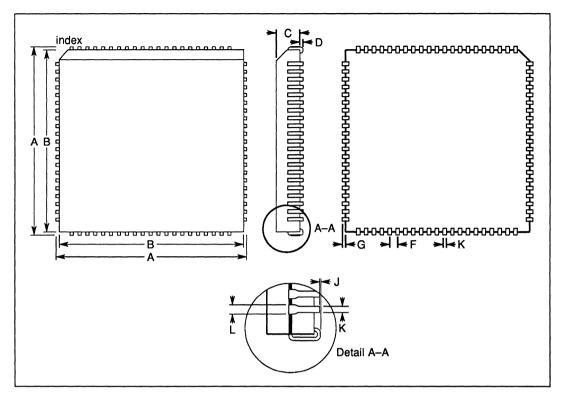

|   |                                        | 13.1    | 84 pin grid array package                       | 120 |

|   |                                        | 13.2    | 84 pin PLCC J-bend package                      | 122 |

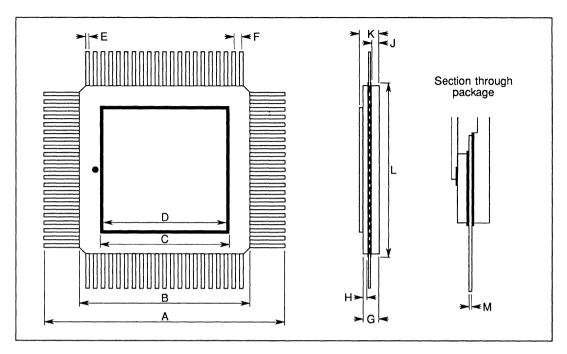

|   |                                        | 13.3    | 84 lead quad cerpack package                    | 124 |

|   | 14                                     | Orderi  | ng                                              | 126 |

| 5 | IMS                                    | T801 en | ngineering data                                 | 127 |

|   | 1                                      | Introdi |                                                 | 128 |

|   |                                        | mirodi  | uction                                          | ·   |

|   | 2                                      | Pin de  | esignations                                     | 131 |

| 3       | Proce    |                              | 132                                                                                                              |

|---------|----------|------------------------------|------------------------------------------------------------------------------------------------------------------|

|         | 3.1      | Registers                    | 132                                                                                                              |

|         | 3.2      | Instructions                 | 133                                                                                                              |

|         |          | 3.2.1 Direct functions       | 133                                                                                                              |

|         |          | 3.2.2 Prefix functions       | 133                                                                                                              |

|         |          | 3.2.3 Indirect functions     | 134                                                                                                              |

|         |          | 3.2.4 Expression evaluation  | 134                                                                                                              |

|         |          | 3.2.5 Efficiency of encoding | 134                                                                                                              |

|         | 3.3      | Processes and concurrency    | 135                                                                                                              |

|         | 3.4      | Priority                     | 136                                                                                                              |

|         | 3.5      | Communications               | 136                                                                                                              |

|         | 3.6      | Block move                   | 137                                                                                                              |

|         | 3.7      | Timers                       | 137                                                                                                              |

| 4       | Inetru   | ction set summary            | 139                                                                                                              |

| <b></b> | 4.1      | Descheduling points          | 140                                                                                                              |

|         | 4.2      | Error instructions           | 141                                                                                                              |

|         | 4.3      | Debugging support            | 141                                                                                                              |

|         | 4.4      | Floating point errors        | 141                                                                                                              |

|         | 7.7      | Troating point errors        | 141                                                                                                              |

| 5       | Floatir  | ng point unit                | 149                                                                                                              |

|         | 1 104111 | ng point aint                | 170                                                                                                              |

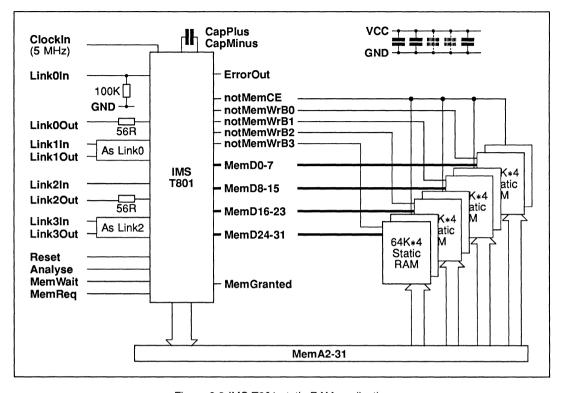

| 6       | System   | m services                   | 151                                                                                                              |

|         | 6.1      | Power                        | 151                                                                                                              |

|         | 6.2      | CapPlus, CapMinus            | 151                                                                                                              |

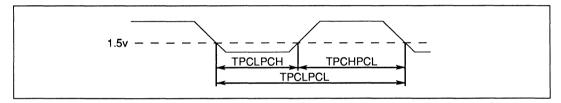

|         | 6.3      | Clockin                      | 151                                                                                                              |

|         | 6.4      | ProcSpeedSelect0-2           | 152                                                                                                              |

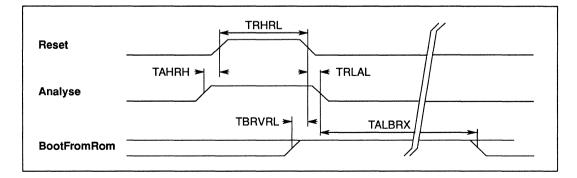

|         | 6.5      | Reset                        | 153                                                                                                              |

|         | 6.6      | Bootstrap                    | 153                                                                                                              |

|         | 6.7      | Peek and poke                | 155                                                                                                              |

|         | 6.8      | Analyse                      | 155                                                                                                              |

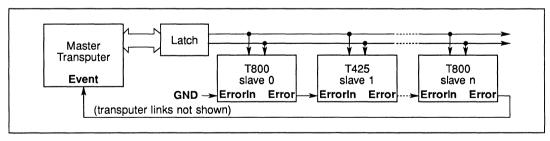

|         | 6.9      | ErrorOut                     | 156                                                                                                              |

|         |          |                              | and the second |

| 7       | Memo     | ory                          | 157                                                                                                              |

|         |          |                              |                                                                                                                  |

| 8       | Extern   | nal memory interface         | 159                                                                                                              |

|         | 8.1      | Pin functions                | 160                                                                                                              |

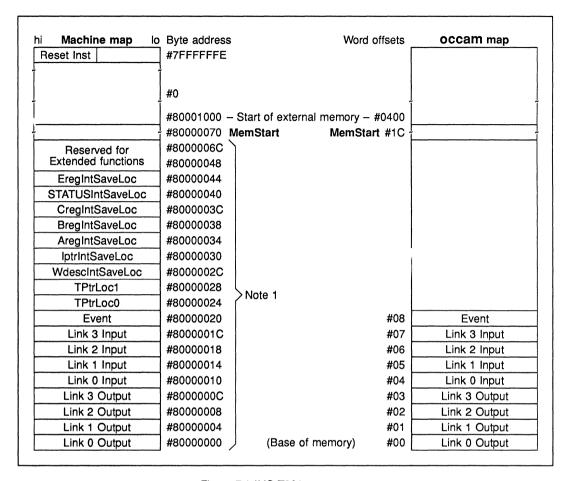

|         |          | 8.1.1 MemA2-31               | 160                                                                                                              |

|         |          | 8.1.2 MemD0-31               | 160                                                                                                              |

|         |          | 8.1.3 notMemCE               | 160                                                                                                              |

|         |          | 8.1.4 notMemWrB0-3           | 161                                                                                                              |

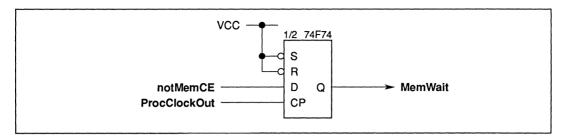

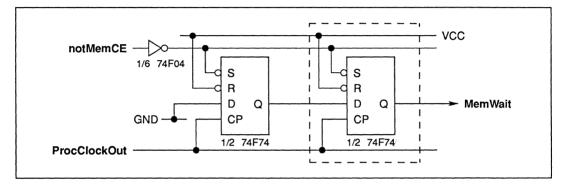

|         |          | 8.1.5 MemWait                | 161                                                                                                              |

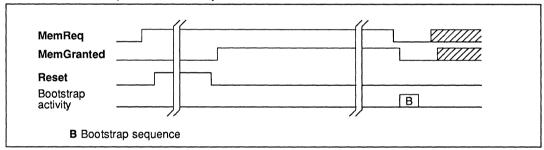

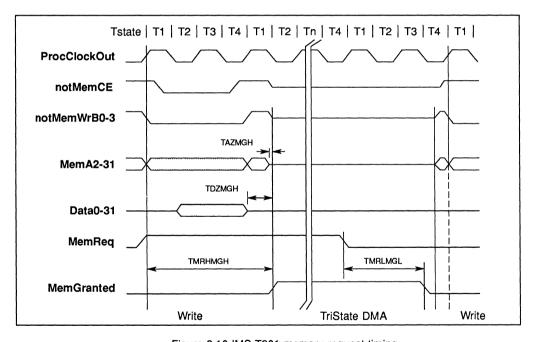

|         |          | 8.1.6 MemReq, MemGranted     | 161                                                                                                              |

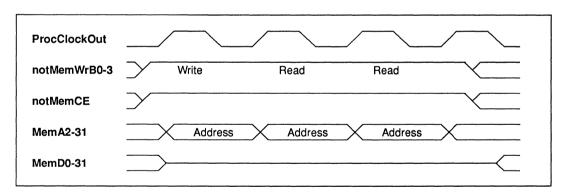

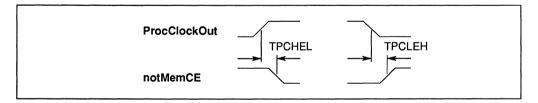

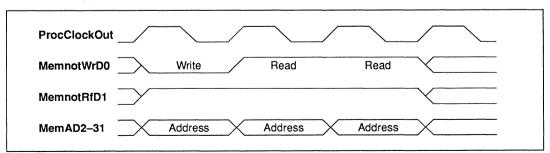

|         |          | 8.1.7 ProcClockOut           | 162                                                                                                              |

|         | 8.2      | Read cycle                   | 163                                                                                                              |

|         | 8.3      | Write cycle                  | 164                                                                                                              |

|         | 8.4      | Wait                         | 165                                                                                                              |

|         | 8.5      | Direct memory access         | 167                                                                                                              |

|         | F        |                              | 400                                                                                                              |

| 9       | Event    | 3                            | 169                                                                                                              |

| 10      | Links    |                              | 171                                                                                                              |

| 10      | LIIIKS   |                              | 171                                                                                                              |

|   | 11   | Electrical specifications |                                                                                                                                                                                                                                                                                                                                                                          |     |  |  |

|---|------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

|   |      | 11.1                      | DC electrical characteristics                                                                                                                                                                                                                                                                                                                                            | 174 |  |  |

|   |      | 11.2                      | Equivalent circuits                                                                                                                                                                                                                                                                                                                                                      | 175 |  |  |

|   |      | 11.3                      | AC timing characteristics                                                                                                                                                                                                                                                                                                                                                | 176 |  |  |

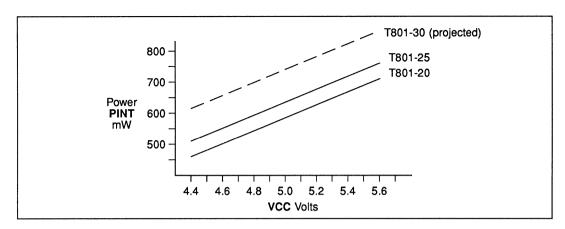

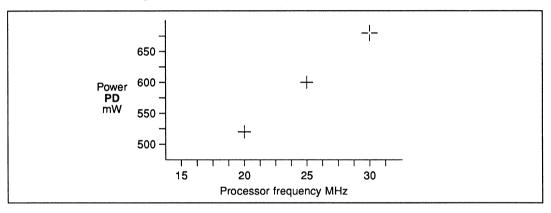

|   |      | 11.4                      | Power rating                                                                                                                                                                                                                                                                                                                                                             | 177 |  |  |

|   | 12   | Perfo                     | rmance                                                                                                                                                                                                                                                                                                                                                                   | 179 |  |  |

|   |      | 12.1                      | Performance overview                                                                                                                                                                                                                                                                                                                                                     | 179 |  |  |

|   |      | 12.2                      | Fast multiply, TIMES                                                                                                                                                                                                                                                                                                                                                     | 181 |  |  |

|   |      | 12.3                      | Arithmetic                                                                                                                                                                                                                                                                                                                                                               | 182 |  |  |

|   |      | 12.4                      | Floating point operations                                                                                                                                                                                                                                                                                                                                                | 183 |  |  |

|   |      |                           | 12.4.1 Floating point functions                                                                                                                                                                                                                                                                                                                                          | 183 |  |  |

|   |      |                           |                                                                                                                                                                                                                                                                                                                                                                          | 184 |  |  |

|   |      | 12.5                      |                                                                                                                                                                                                                                                                                                                                                                          | 184 |  |  |

|   |      | 12.6                      | Interrupt latency                                                                                                                                                                                                                                                                                                                                                        | 185 |  |  |

|   | 13   | Packa                     | age specifications                                                                                                                                                                                                                                                                                                                                                       | 186 |  |  |

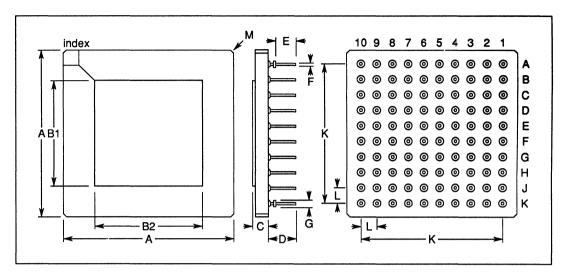

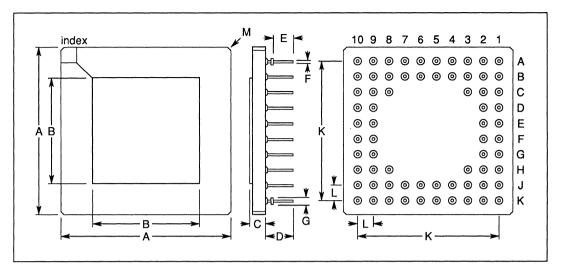

|   |      | 13.1                      | 100 pin grid array package                                                                                                                                                                                                                                                                                                                                               | 186 |  |  |

|   | 14   | Order                     | ring                                                                                                                                                                                                                                                                                                                                                                     | 188 |  |  |

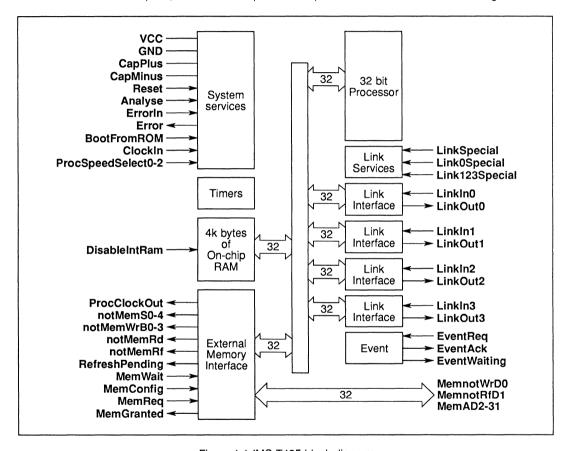

| 6 | IMS  | T800 ei                   | ngineering data                                                                                                                                                                                                                                                                                                                                                          | 189 |  |  |

|   |      |                           |                                                                                                                                                                                                                                                                                                                                                                          |     |  |  |

|   | 1    | Introd                    | duction                                                                                                                                                                                                                                                                                                                                                                  | 190 |  |  |

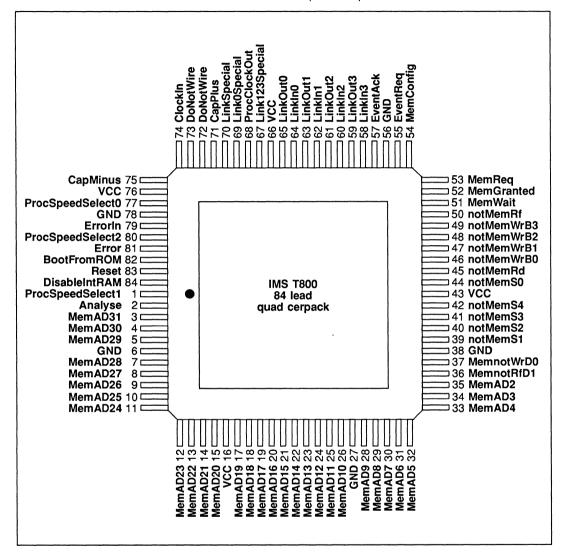

|   | 2    | Pin d                     | esignations                                                                                                                                                                                                                                                                                                                                                              | 192 |  |  |

|   | 3    | Proce                     | DC electrical characteristics  Equivalent circuits  AC timing characteristics  Power rating  ormance  Performance overview  Fast multiply, TIMES  Arithmetic  Floating point operations  12.4.1 Floating point functions  12.4.2 Special purpose functions and procedures  Effect of external memory  Interrupt latency  kage specifications  100 pin grid array package |     |  |  |

|   |      | 3.1                       | Registers                                                                                                                                                                                                                                                                                                                                                                | 193 |  |  |

|   |      | 3.2                       | Instructions                                                                                                                                                                                                                                                                                                                                                             | 194 |  |  |

|   |      |                           |                                                                                                                                                                                                                                                                                                                                                                          | 194 |  |  |

|   |      |                           |                                                                                                                                                                                                                                                                                                                                                                          | 194 |  |  |

|   |      |                           |                                                                                                                                                                                                                                                                                                                                                                          | 195 |  |  |

|   | ·    |                           |                                                                                                                                                                                                                                                                                                                                                                          | 195 |  |  |

|   | ···· |                           |                                                                                                                                                                                                                                                                                                                                                                          | 195 |  |  |

|   |      | 3.3                       |                                                                                                                                                                                                                                                                                                                                                                          | 196 |  |  |

|   |      | 3.4                       |                                                                                                                                                                                                                                                                                                                                                                          | 197 |  |  |

|   |      | 3.5                       |                                                                                                                                                                                                                                                                                                                                                                          | 197 |  |  |

|   |      | 3.6                       |                                                                                                                                                                                                                                                                                                                                                                          | 198 |  |  |

|   |      | 3.7                       | Timers                                                                                                                                                                                                                                                                                                                                                                   | 198 |  |  |

|   | 4    |                           |                                                                                                                                                                                                                                                                                                                                                                          | 200 |  |  |

|   |      | 4.1                       |                                                                                                                                                                                                                                                                                                                                                                          | 201 |  |  |

|   |      | 4.2                       |                                                                                                                                                                                                                                                                                                                                                                          | 202 |  |  |

|   |      | 4.3                       | Floating point errors                                                                                                                                                                                                                                                                                                                                                    | 202 |  |  |

|   | 5    | Floati                    | ing point unit                                                                                                                                                                                                                                                                                                                                                           | 209 |  |  |

| 6  | Systen       | n services                                      | 211        |

|----|--------------|-------------------------------------------------|------------|

|    | 6.1          | Power                                           | 211        |

|    | 6.2          | CapPlus, CapMinus                               | 211        |

|    | 6.3          | Clockin                                         | 211        |

|    | 6.4          | ProcSpeedSelect0-2                              | 212        |

|    | 6.5          | Reset                                           | 213        |

|    | 6.6          | Bootstrap                                       | 213        |

|    | 6.7          | Peek and poke                                   | 215        |

|    | 6.8          | Analyse                                         | 215        |

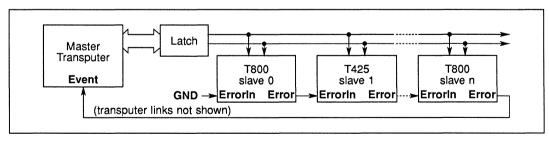

|    | 6.9          | Error, Errorin                                  | 216        |

|    |              |                                                 |            |

| 7  | Memo         | ry                                              | 217        |

|    |              |                                                 |            |

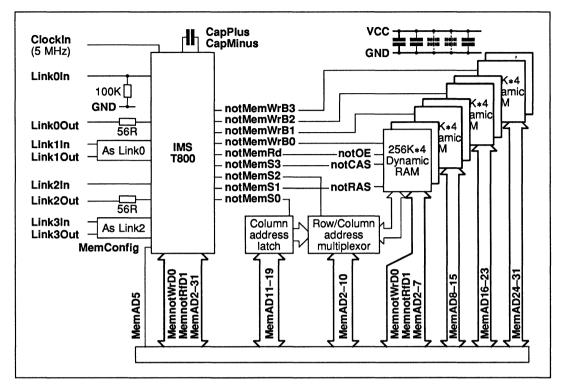

| 8  |              | al memory interface                             | 219        |

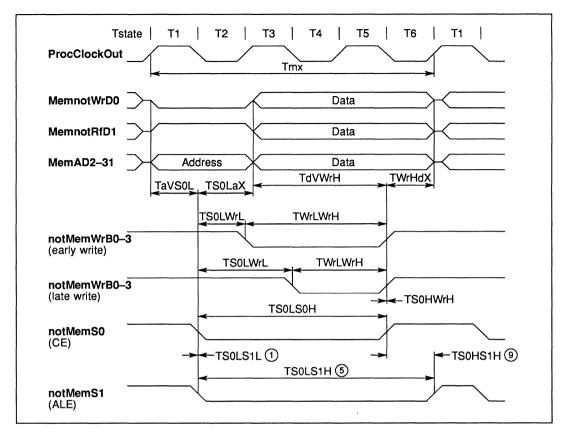

|    | 8.1          | ProcClockOut                                    | 219        |

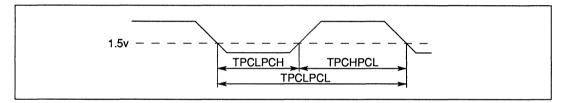

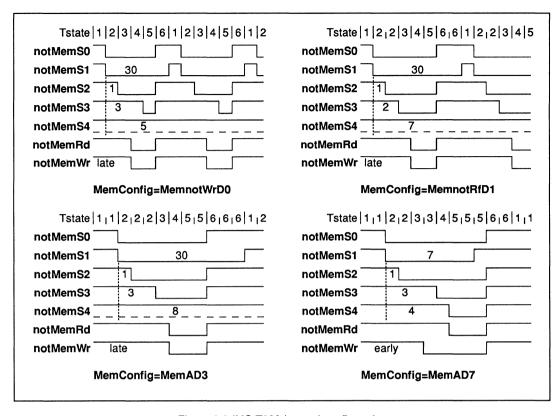

|    | 8.2          | Tstates                                         | 219        |

|    | 8.3          | Internal access                                 | 220        |

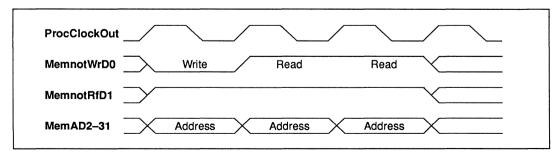

|    | 8.4          | MemAD2-31                                       | 221        |

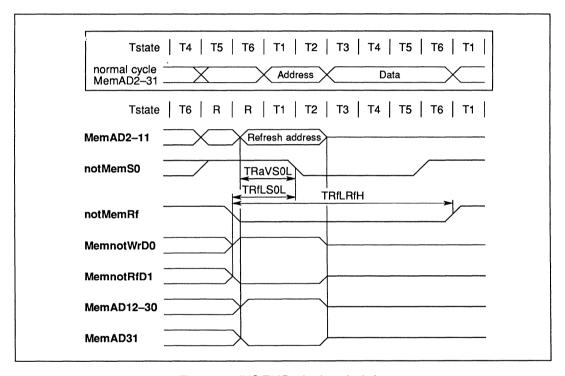

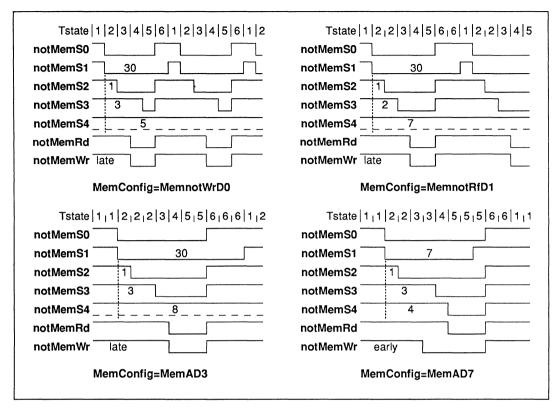

|    | 8.5          | MemnotWrD0                                      | 221        |

|    | 8.6          | MemnotRfD1                                      | 221        |

|    | 8.7          | notMemRd                                        | 221        |

|    | 8.8          | notMemS0-4                                      | 221        |

|    | 8.9          | notMemWrB0-3                                    | 225        |

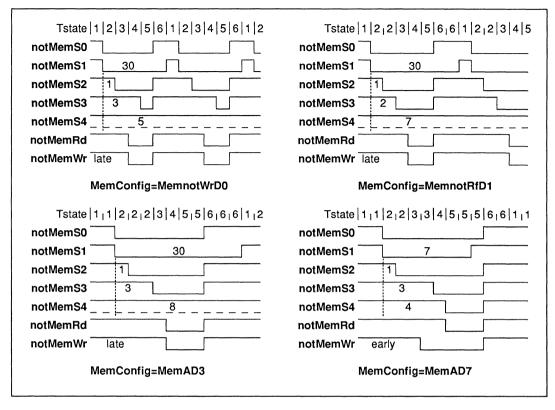

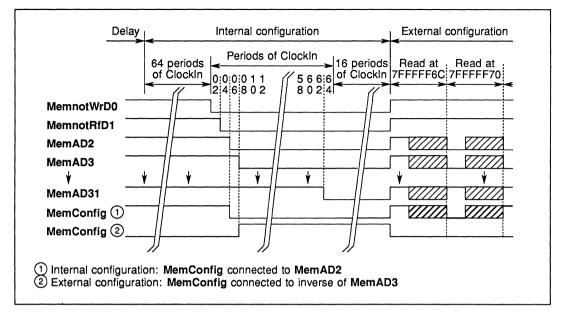

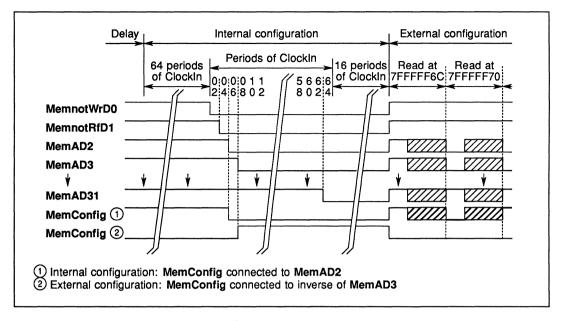

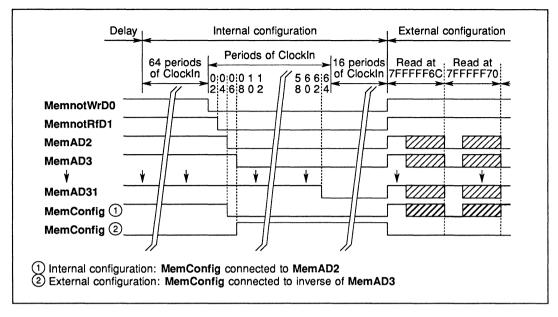

|    | 8.10         | MemConfig                                       | 228        |

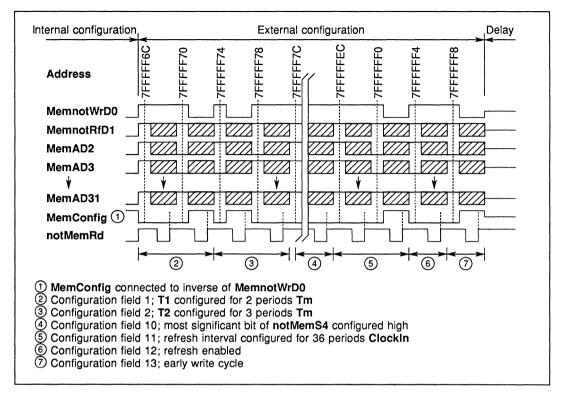

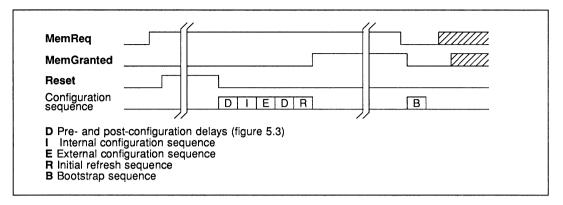

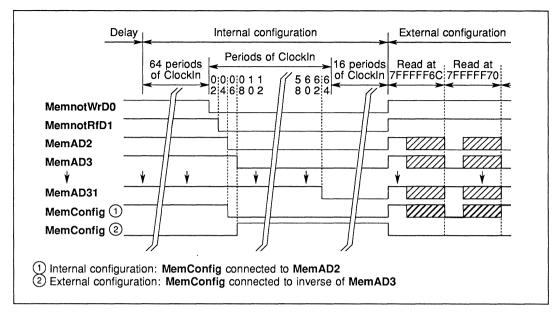

|    |              | 8.10.1 Internal configuration                   | 228        |

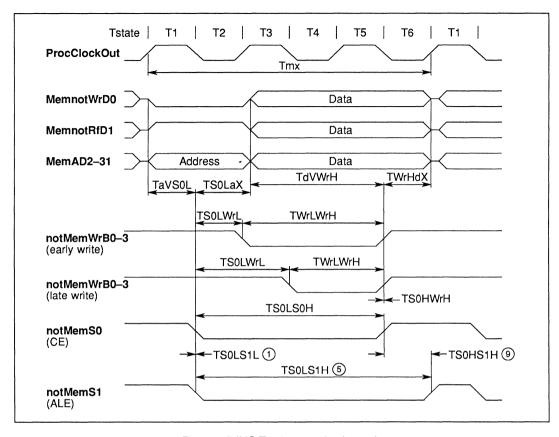

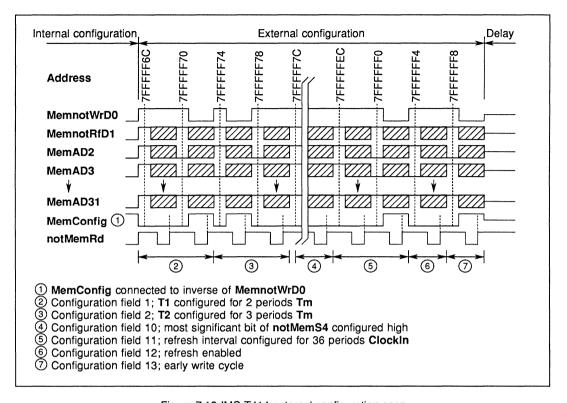

|    |              | 8.10.2 External configuration                   | 230        |

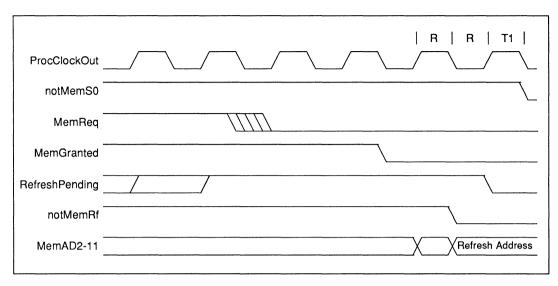

|    | 8.11         | notMemRf                                        | 235        |

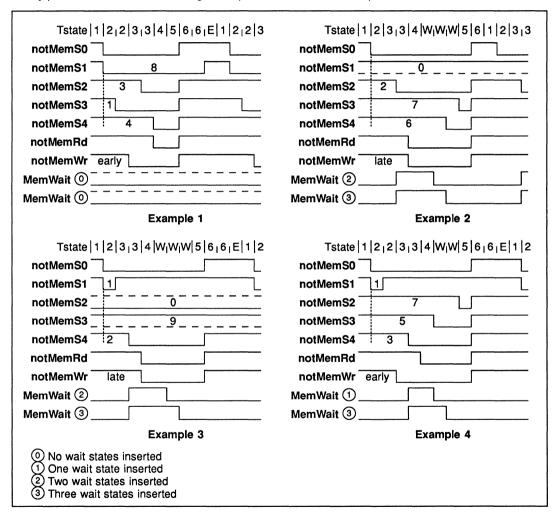

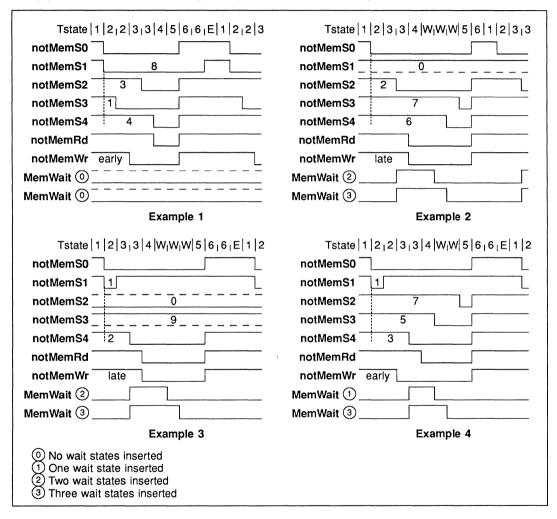

|    | 8.12         | MemWait                                         | 236        |

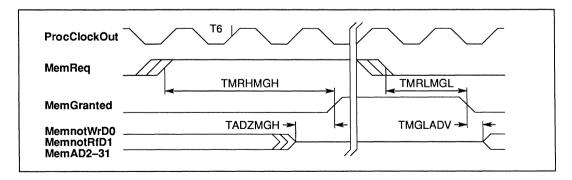

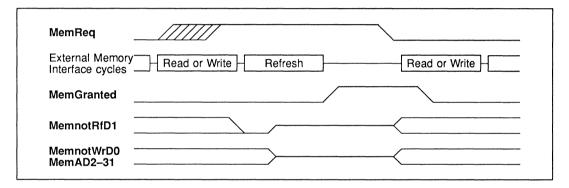

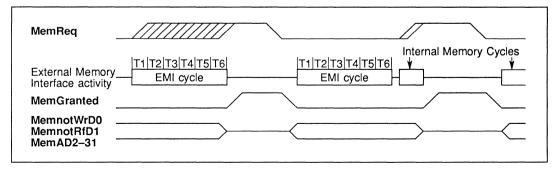

|    | 8.13         | MemReq, MemGranted                              | 238        |

|    |              |                                                 |            |

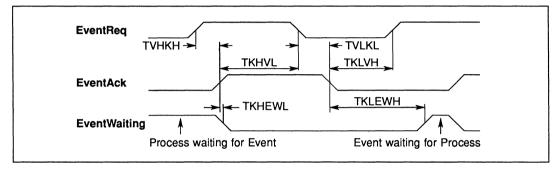

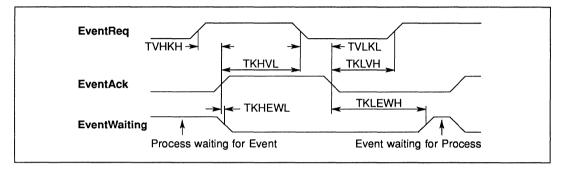

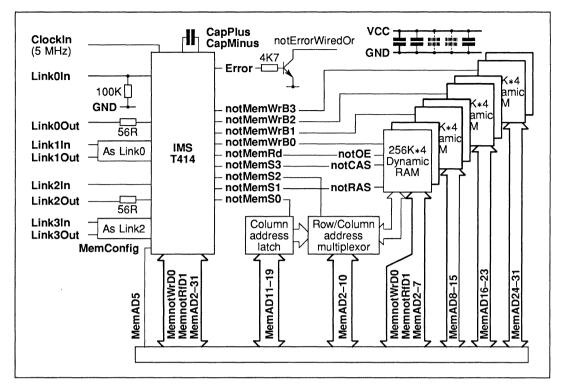

| 9  | Events       |                                                 | 240        |

|    | WHAT CO      |                                                 |            |

| 10 | Links        |                                                 | 241        |

|    |              |                                                 |            |

| 11 |              | cal specifications                              | 244        |

|    | 11.1         | DC electrical characteristics                   | 244        |

|    | 11.2         | Equivalent circuits                             | 245        |

|    | 11.3         | AC timing characteristics                       | 246        |

|    | 11.4         | Power rating                                    | 248        |

|    |              |                                                 |            |

| 12 |              | mance                                           | 249        |

|    | 12.1         | Performance overview                            | 249        |

|    | 12.2         | Fast multiply, TIMES                            | 251        |

|    | 12.3         | Arithmetic                                      | 252        |

|    | 12.4         | Floating point operations                       | 253        |

|    |              | 12.4.1 Floating point functions                 | 253        |

|    | 10.5         | 12.4.2 Special purpose functions and procedures | 254        |

|    | 12.5<br>12.6 | Effect of external memory                       | 254<br>255 |

|    | 1∠.0         | Interrupt latency                               | 255        |

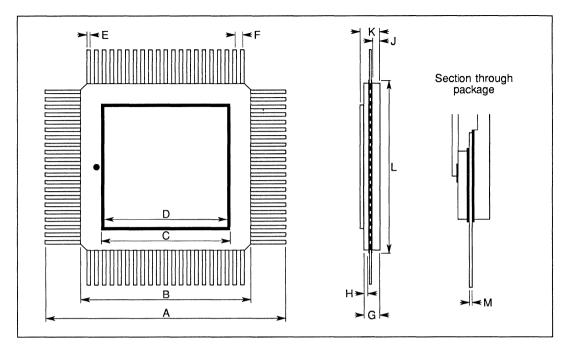

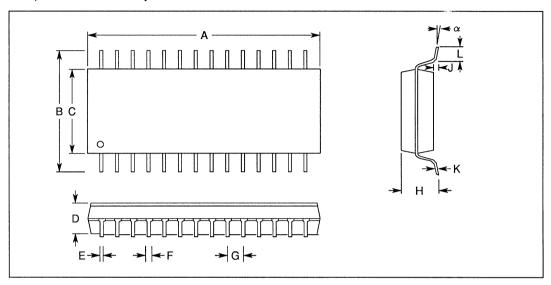

|    | 13      | Packa  | ige specifi        |                        | 256        |

|----|---------|--------|--------------------|------------------------|------------|

|    |         | 13.1   |                    | grid array package     | 256        |

|    |         | 13.2   | 84 lead            | quad cerpack package   | 258        |

|    |         |        |                    |                        |            |

|    | 14      | Order  | ring               |                        | 260        |

|    |         |        |                    |                        |            |

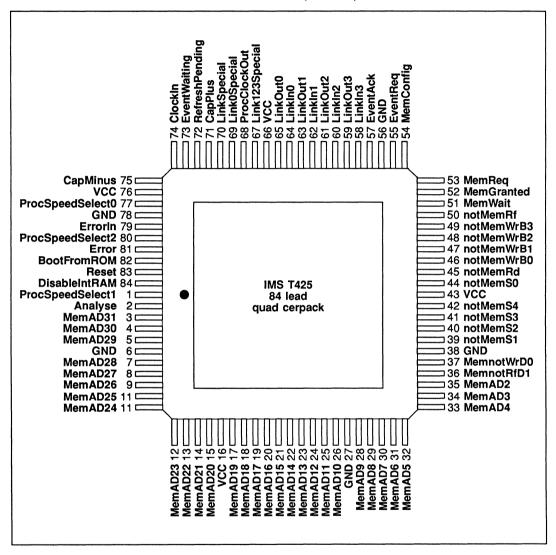

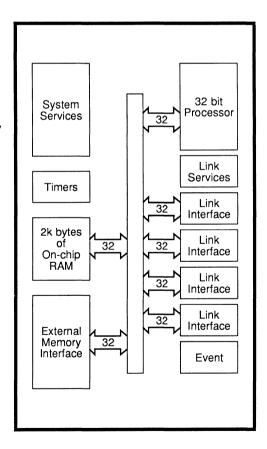

| 7  | IMS     | T425 e | ngineerii          | ng data                | 261        |

|    |         |        |                    |                        |            |

|    | 1       | Introd | duction            |                        | 262        |

|    |         |        |                    |                        |            |

|    | 2       | Pin d  | esignation         | IS                     | 264        |

|    |         |        |                    |                        | 005        |

|    | 3       | Proce  |                    |                        | 265        |

|    |         | 3.1    | Registe<br>Instruc |                        | 265        |

|    |         | 3.2    | 3.2.1              | Direct functions       | 266<br>266 |

|    |         |        | 3.2.1              | Prefix functions       | 266        |

|    |         |        | 3.2.3              | Indirect functions     | 267        |

|    |         |        | 3.2.3              | Expression evaluation  | 267        |

|    |         |        | 3.2.5              | Efficiency of encoding | 267        |

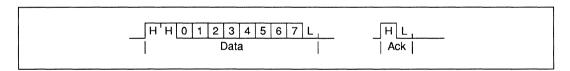

|    |         | 3.3    |                    | ses and concurrency    | 268        |

|    |         | 3.4    | Priority           |                        | 269        |

|    |         | 3.5    |                    | unications             | 269        |

| un |         | 3.6    | Block              |                        | 270        |

|    |         | 3.7    | Timers             |                        | 270        |

|    |         | 3.7    | 11111013           |                        | 210        |

|    | 4       | Instru | uction set         | summary                | 272        |

|    | •       | 4.1    |                    | eduling points         | 273        |

|    |         | 4.2    |                    | nstructions            | 274        |

|    |         | 4.3    | Debug              | ging support           | 274        |

|    |         |        |                    | 3 - 11                 |            |

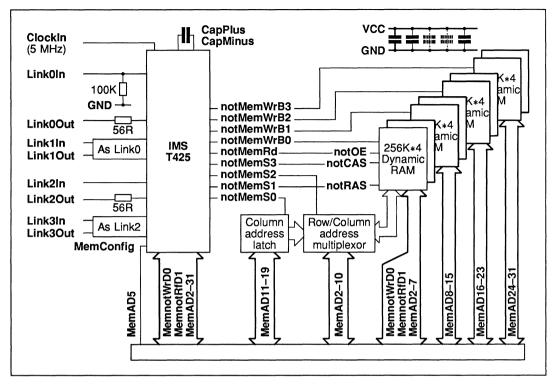

|    | 5       | Syste  | m service          | S                      | 280        |

|    |         | 5.1    | Power              |                        | 280        |

|    |         | 5.2    | CapPlu             | s, CapMinus            | 280        |

|    |         | 5.3    | Clockir            |                        | 280        |

|    | <u></u> | 5.4    | ProcSp             | eedSelect0-2           | 281        |

|    |         | 5.5    | Reset              |                        | 282        |

|    |         | 5.6    | Bootsti            | rap                    | 282        |

|    |         | 5.7    | Peek a             | nd poke                | 284        |

|    |         | 5.8    | Analys             | e                      | 284        |

|    |         | 5.9    | Error, E           | Errorin                | 285        |

|    |         |        |                    |                        |            |

|    | 6       | Memo   | ory                |                        | 286        |

|    |         |        |                    |                        |            |

|    | 7       |        |                    | ry interface           | 288        |

|    |         | 7.1    | ProcCl             |                        | 288        |

|    |         | 7.2    | Tstates            |                        | 288        |

|    |         | 7.3    |                    | Laccess                | 289        |

|    |         | 7.4    | MemA               |                        | 290        |

|    |         | 7.5    | Memno              |                        | 290        |

|    |         | 7.6    | Memno              |                        | 290        |

|    |         | 7.7    | notMen             | nRd                    | 290        |

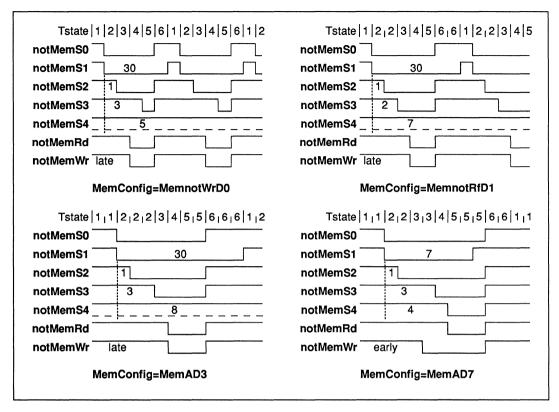

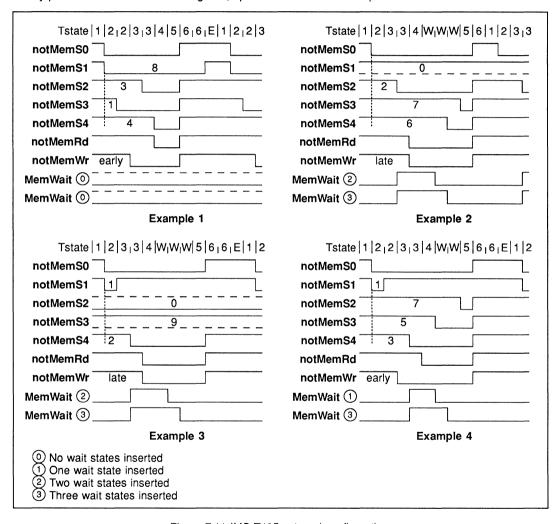

|   |          | 7.8                                    | notMemS0-4                                      | 290 |

|---|----------|----------------------------------------|-------------------------------------------------|-----|

|   |          | 7.9                                    | notMemWrB0-3                                    | 294 |

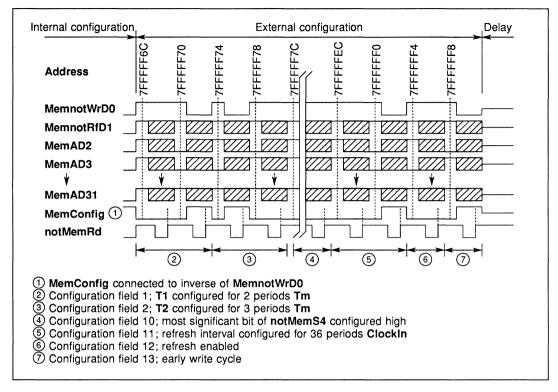

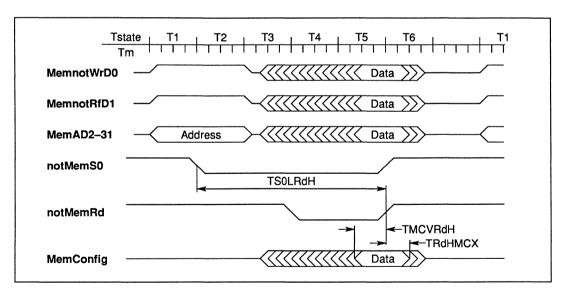

|   |          | 7.10                                   | MemConfig                                       | 297 |

|   |          |                                        | 7.10.1 Internal configuration                   | 297 |

|   |          |                                        | 7.10.2 External configuration                   | 299 |

|   |          | 7.11                                   | RefreshPending                                  | 304 |

|   |          | 7.12                                   | notMemRf                                        | 305 |

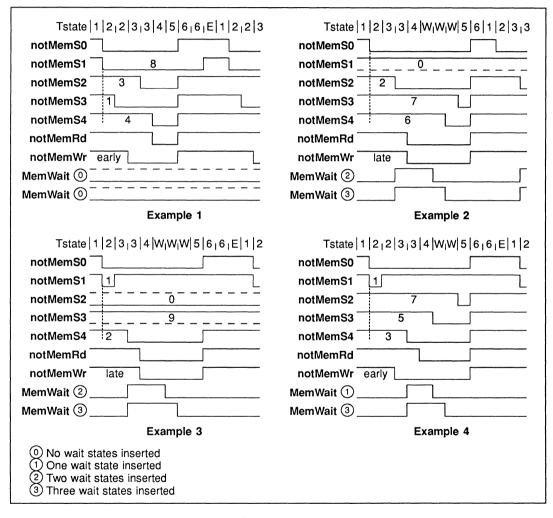

|   |          | 7.13                                   | MemWait                                         | 306 |

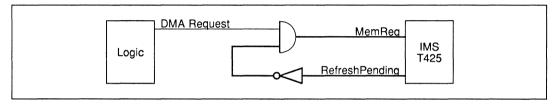

|   |          | 7.14                                   | MemReq, MemGranted                              | 308 |

|   | 8        | Events                                 | S                                               | 310 |

|   | 9        | Links                                  |                                                 | 312 |

|   | 10       | Flectr                                 | ical specifications                             | 315 |

|   |          | 10.1                                   | DC electrical characteristics                   | 315 |

|   |          | 10.2                                   | Equivalent circuits                             | 316 |

|   |          | 10.3                                   | AC timing characteristics                       | 317 |

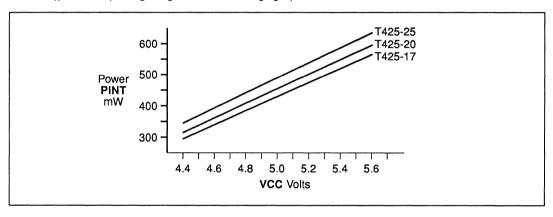

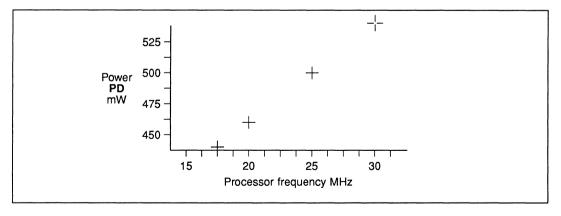

|   |          | 10.4                                   | Power rating                                    | 319 |

|   | 11       | Porfor                                 | mance                                           | 320 |

|   |          | 11.1                                   | Performance overview                            | 320 |

|   |          | 11.2                                   | Fast multiply, TIMES                            | 322 |

|   |          | 11.3                                   | Arithmetic                                      | 322 |

|   |          | 11.4                                   | Floating point operations                       | 323 |

|   |          | 11.7                                   | 11.4.1 Special purpose functions and procedures | 324 |

|   |          | 11.5                                   | Effect of external memory                       | 324 |

|   |          | 11.6                                   | Interrupt latency                               | 325 |

|   |          | 11.0                                   | menapt laterioy                                 |     |

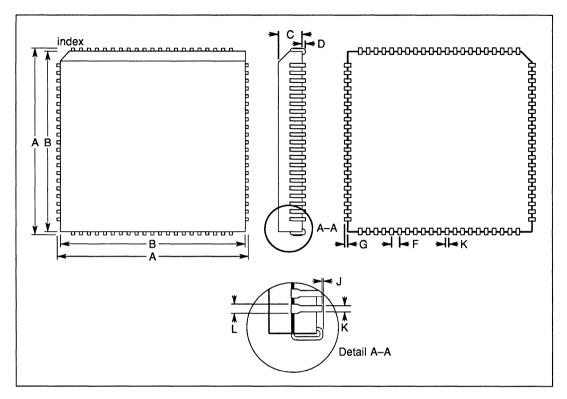

|   | 12       | Packa                                  | ge specifications                               | 326 |

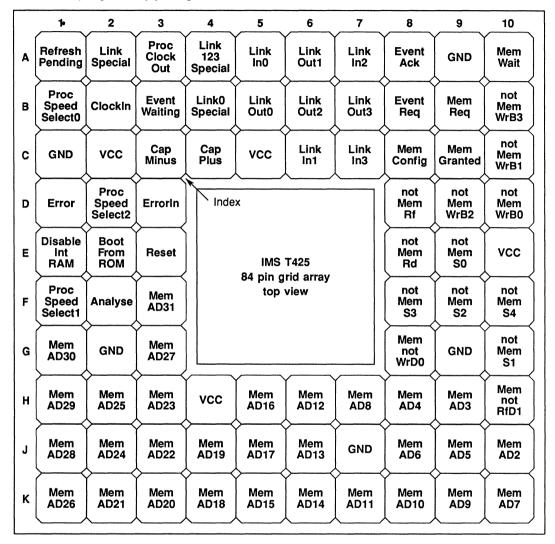

|   |          | 12.1                                   | 84 pin grid array package                       | 326 |

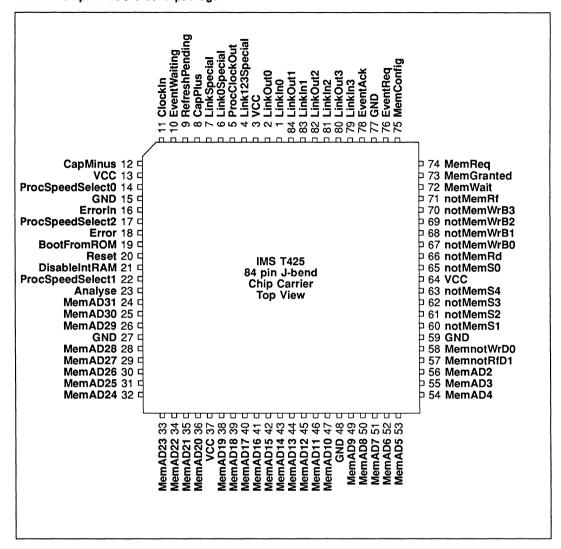

|   |          | 12.2                                   | 84 pin PLCC J-bend package                      | 328 |

|   |          | 12.3                                   | 84 lead quad cerpack package                    | 330 |

|   | 13       | Orderi                                 | ing                                             | 332 |

|   |          |                                        |                                                 |     |

| 8 | IMS      | T414 er                                | ngineering data                                 | 333 |

|   | 1        | Introd                                 | uction                                          | 334 |

|   | 2        | Pin de                                 | esignations                                     | 336 |

|   | 3        | Proces                                 | CCOL                                            | 337 |

|   | <u> </u> | 3.1                                    | Registers                                       | 337 |

|   |          | 3.2                                    | Instructions                                    | 338 |

|   |          | U.L                                    | 3.2.1 Direct functions                          | 338 |

|   |          |                                        | 3.2.2 Prefix functions                          | 338 |

|   |          |                                        | 3.2.3 Indirect functions                        | 339 |

|   |          | ······································ | 3.2.4 Expression evaluation                     | 339 |

|   |          |                                        | 3.2.5 Efficiency of encoding                    | 339 |

|   |          | 3.3                                    | Processes and concurrency                       | 340 |

|   |          | 3.4                                    | Priority                                        | 341 |

|   |          | 2.5                                    | Communications                                  | 2/1 |

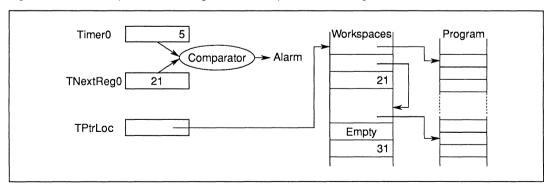

| <br>                                        | 3.6     | Timers                        | 342 |

|---------------------------------------------|---------|-------------------------------|-----|

| <br>4                                       | Instru  | ction set summary             | 343 |

|                                             | 4.1     | Descheduling points           | 344 |

| <br>                                        | 4.2     | Error instructions            | 344 |

| <br>                                        | 7.4     | Error mattactions             |     |

| <br>5                                       | Systen  | m services                    | 349 |

|                                             | 5.1     | Power                         | 349 |

| <br>                                        | 5.2     | CapPlus, CapMinus             | 349 |

|                                             | 5.3     | Clockin                       | 349 |

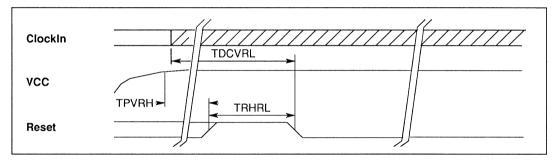

|                                             | 5.4     | Reset                         | 351 |

| ***************************************     | 5.5     | Bootstrap                     | 351 |

|                                             | 5.6     | Peek and poke                 | 353 |

|                                             | 5.7     | Analyse                       | 353 |

| <br>                                        | 5.8     | Error                         | 354 |

| <br>6                                       | Memo    | M.                            | 355 |

| <br>                                        | Wento   | ıy                            | 333 |

| <br>7                                       | Extern  | nal memory interface          | 357 |

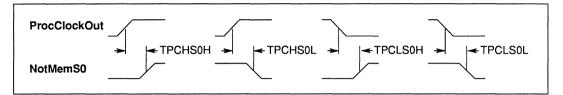

|                                             | 7.1     | ProcClockOut                  | 357 |

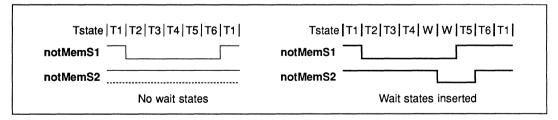

| <br>                                        | 7.2     | Tstates                       | 357 |

| <br>                                        | 7.3     | Internal access               | 358 |

| <br>                                        | 7.4     | MemAD2-31                     | 359 |

| <br>                                        | 7.5     | MemnotWrD0                    | 359 |

| <br>·                                       | 7.6     | MemnotRfD1                    | 359 |

|                                             | 7.7     | notMemRd                      | 359 |

| <br>······································  | 7.8     | notMemS0-4                    | 359 |

|                                             | 7.9     | notMemWrB0-3                  | 363 |

|                                             | 7.10    | MemConfig                     | 366 |

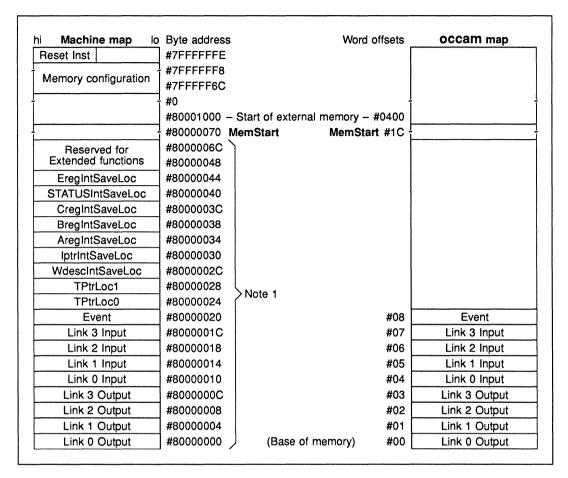

|                                             |         | 7.10.1 Internal configuration | 366 |

|                                             |         | 7.10.2 External configuration | 368 |

|                                             | 7.11    | notMemRf                      | 373 |

|                                             | 7.12    | MemWait                       | 374 |

|                                             | 7.13    | MemReq, MemGranted            | 376 |

| <br>8                                       | Events  |                               | 378 |

| <br>                                        | Lvents  |                               | 370 |

| 9                                           | Links   |                               | 379 |

|                                             |         |                               |     |

| <br>10                                      |         | ical specifications           | 382 |

| <br>                                        | 10.1    | DC electrical characteristics | 382 |

| <br>                                        | 10.2    | Equivalent circuits           | 383 |

| <br>                                        | 10.3    | AC timing characteristics     | 384 |

| <br>*************************************** | 10.4    | Power rating                  | 386 |

| <br>11                                      | Perfori | mance                         | 387 |

| <br>                                        | 11.1    | Performance overview          | 387 |

| <br>                                        | 11.2    | Fast multiply, TIMES          | 389 |

| <br><del></del>                             | 11.3    | Arithmetic                    | 389 |

| <br>                                        | 11.4    | Floating point operations     | 390 |

| <br>                                        | 11.5    | Effect of external memory     | 391 |

| <br>                                        | 11.6    | Interrupt latency             | 392 |

|                                             |         |                               |     |

|   | 12                                      | Packa   | ge specifications            | 393 |

|---|-----------------------------------------|---------|------------------------------|-----|

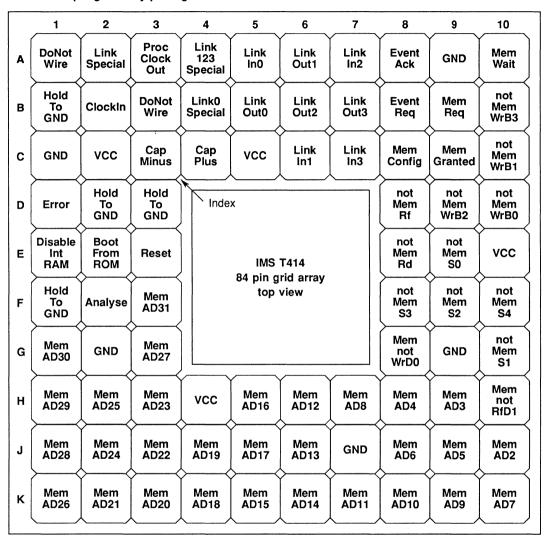

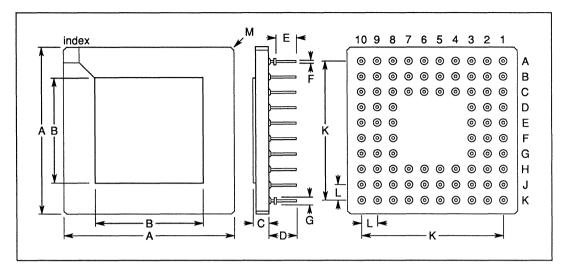

|   |                                         | 12.1    | 84 pin grid array package    | 393 |

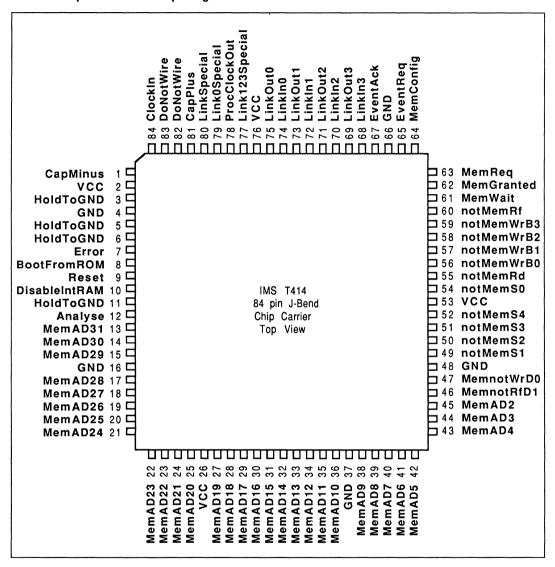

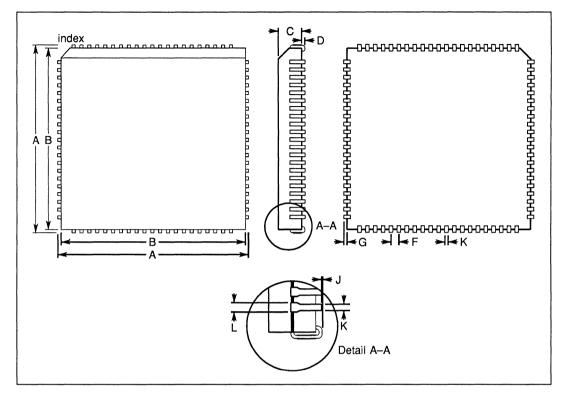

|   |                                         | 12.2    | 84 pin PLCC J-bend package   | 395 |

|   | 13                                      | Orderi  | ing                          | 397 |

|   | 13                                      | Orden   | ing                          |     |

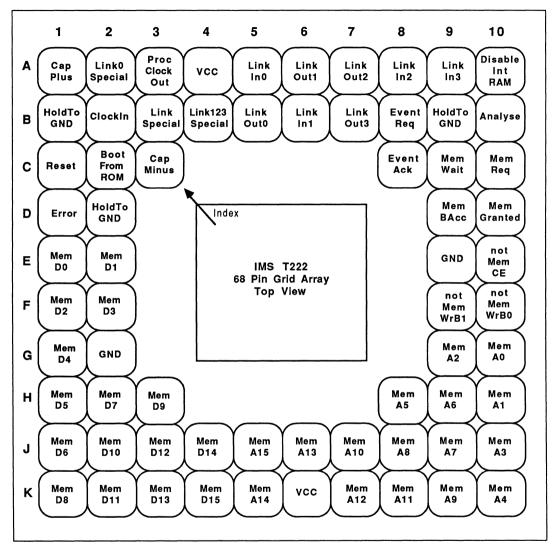

| 9 | IMS                                     | T222 en | ngineering data              | 399 |

|   |                                         |         |                              | 400 |

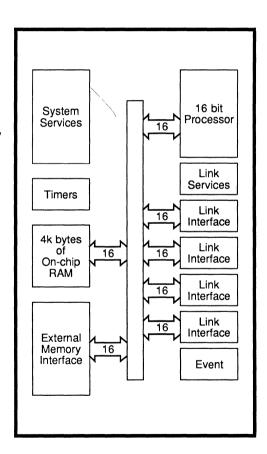

|   | 1                                       | Introd  | uction                       | 400 |

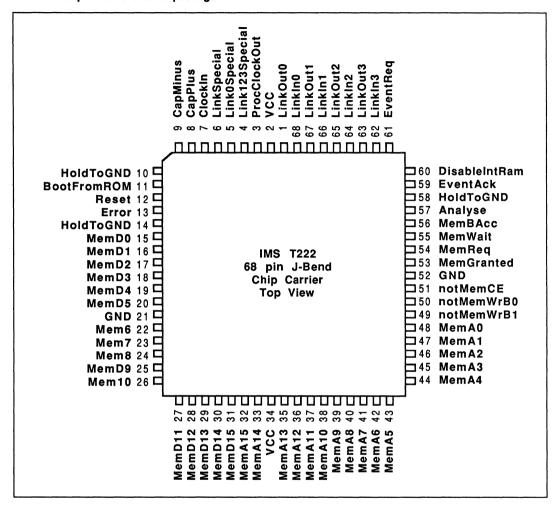

|   | 2                                       | Pin de  | esignations                  | 402 |

|   |                                         |         |                              |     |

|   | 3                                       | Proces  |                              | 403 |

|   |                                         | 3.1     | Registers                    | 403 |

|   |                                         | 3.2     | Instructions                 | 404 |

|   |                                         |         | 3.2.1 Direct functions       | 404 |

|   |                                         |         | 3.2.2 Prefix functions       | 404 |

|   | *************************************** |         | 3.2.3 Indirect functions     | 405 |

|   |                                         |         | 3.2.4 Expression evaluation  | 405 |

|   |                                         |         | 3.2.5 Efficiency of encoding | 405 |

|   |                                         | 3.3     | Processes and concurrency    | 406 |

|   |                                         | 3.4     | Priority                     | 407 |

|   |                                         | 3.5     | Communications               | 407 |

|   |                                         | 3.6     | Timers                       | 408 |

|   | 4                                       | Instru  | ction set summary            | 409 |

|   |                                         | 4.1     | Descheduling points          | 410 |

|   |                                         | 4.2     | Error instructions           | 410 |

|   | 5                                       | System  | m services                   | 415 |

|   |                                         | 5.1     | Power                        | 415 |

|   |                                         | 5.2     | CapPlus, CapMinus            | 415 |

|   |                                         | 5.3     | Clockin                      | 415 |

|   |                                         | 5.4     | Reset                        | 416 |

|   |                                         | 5.5     | Bootstrap                    | 416 |

|   |                                         | 5.6     | Peek and poke                | 418 |

|   |                                         | 5.7     | Analyse                      | 418 |

|   |                                         | 5.8     | Error                        | 419 |

|   |                                         |         |                              | 100 |

|   | 6                                       | Memo    | ory                          | 420 |

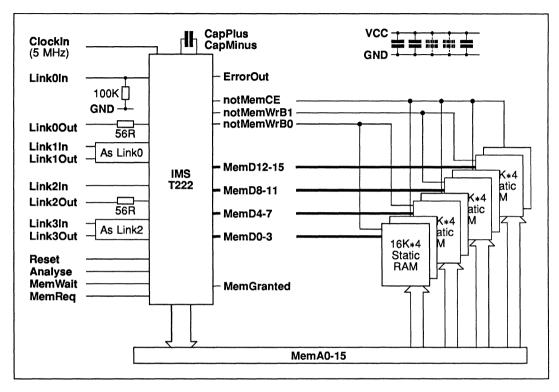

|   | 7                                       | Extern  | nal memory interface         | 422 |

|   |                                         | 7.1     | ProcClockOut                 | 422 |

|   |                                         | 7.2     | Tstates                      | 423 |

|   |                                         | 7.3     | Internal access              | 423 |

|   |                                         | 7.4     | Mem A0-15                    | 423 |

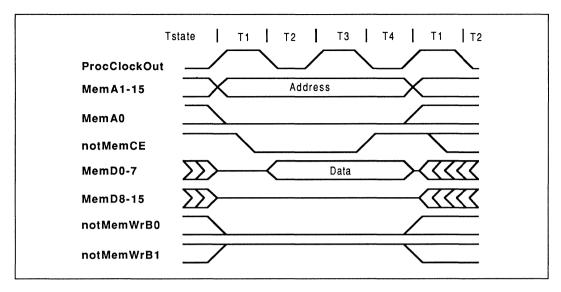

|   |                                         | 7.5     | MemD0-15                     | 423 |

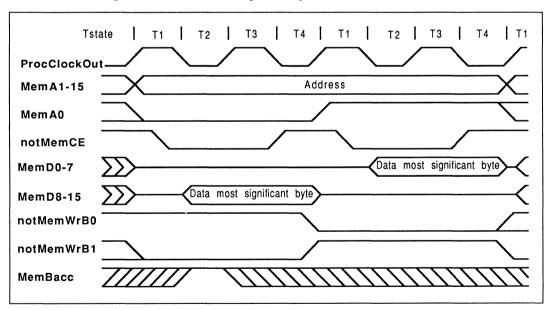

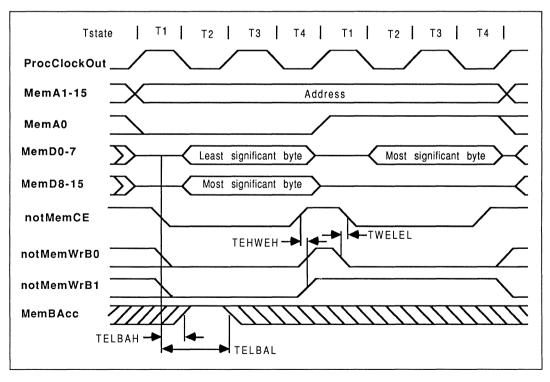

|   |                                         | 7.6     | notMemWrB0-1                 | 424 |

|   |                                         | 7.7     | notMemCE                     | 426 |

|   |                                         | 7.8     | MemBAcc                      | 428 |

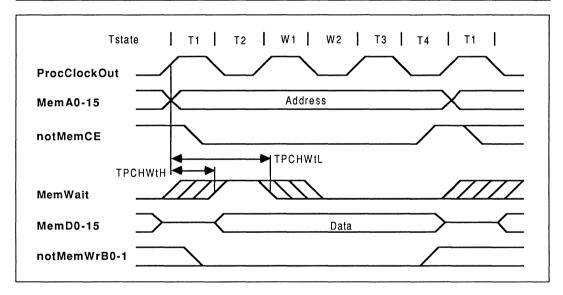

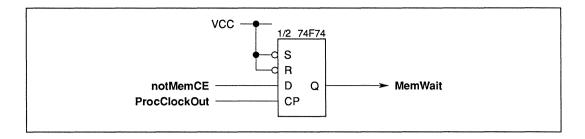

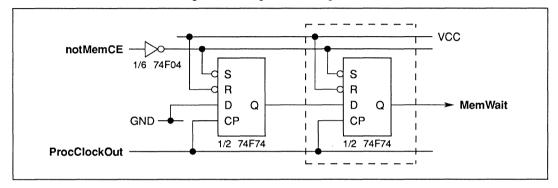

|   |                                         | 7.9     | MemWait                      | 429 |

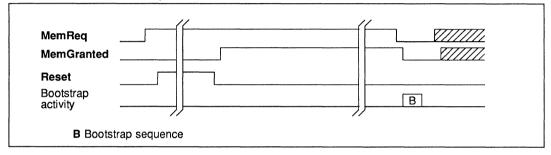

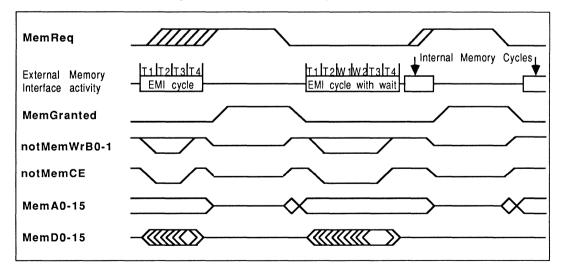

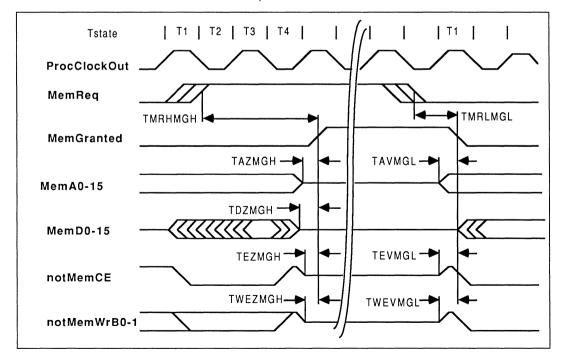

|   |                                         | 7.10    | MemReq, MemGranted           | 431 |

|   |                                         |         |                              |     |

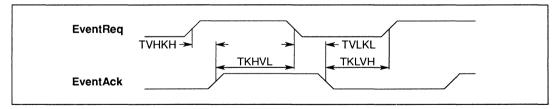

|             | 8                  | Events           | 3         |                          | 433 |

|-------------|--------------------|------------------|-----------|--------------------------|-----|

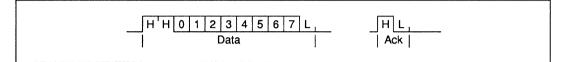

|             | 9                  | Links            |           |                          | 434 |

|             |                    |                  |           |                          |     |

|             | 10                 |                  |           | ifications               | 437 |

|             |                    | 10.1             |           | ctrical characteristics  | 437 |

|             |                    | 10.2             |           | lent circuits            | 438 |

|             |                    | 10.3             |           | ing characteristics      | 439 |

|             |                    | 10.4             | Power     | rating                   | 441 |

|             | 11                 | Perfor           | mance     |                          | 442 |

|             |                    | 11.1             |           | mance overview           | 442 |

|             |                    | 11.2             |           | ultiply, TIMES           | 444 |

|             |                    | 11.3             | Arithm    |                          | 444 |

|             |                    | 11.4             |           | g point operations       | 445 |

|             |                    | 11.5             |           | of external memory       | 446 |

|             |                    | 11.6             |           | pt latency               | 447 |

|             |                    |                  |           |                          |     |

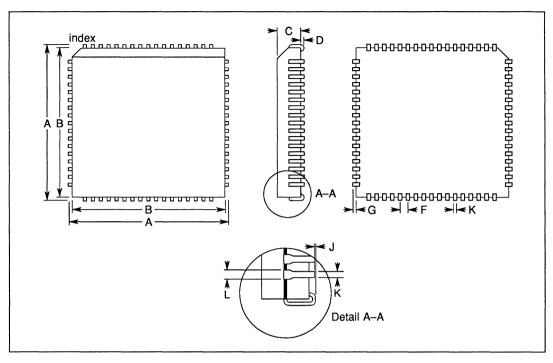

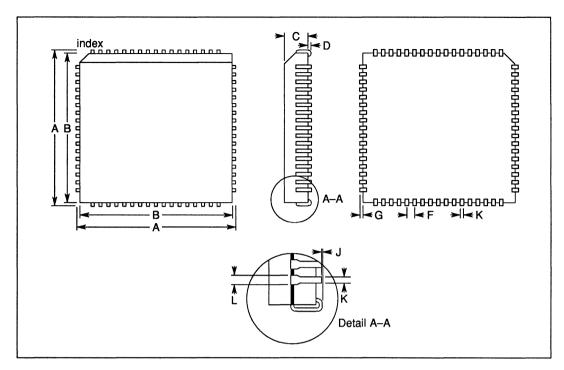

|             | 12                 |                  | ge specif | fications                | 448 |

|             |                    | 12.1             | 68 pin    | grid array package       | 448 |

|             |                    | 12.2             | ьв ріп    | PLCC J-bend package      | 450 |

|             | 13                 | Orderi           | ng        |                          | 452 |

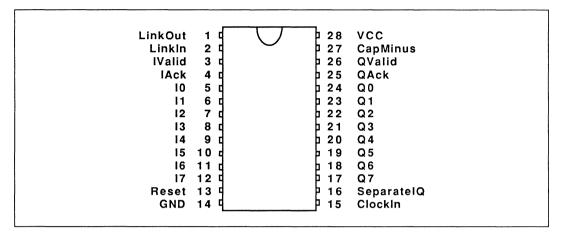

| 10          | IMS                | IMS T225 preview |           |                          |     |

| <del></del> |                    |                  |           |                          | 453 |

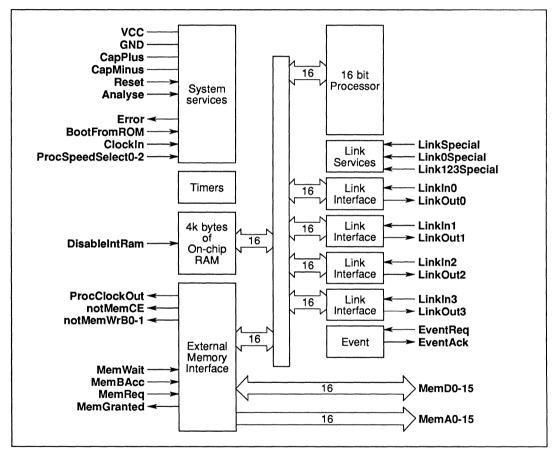

|             | 1                  | Introd           | uction    |                          | 454 |

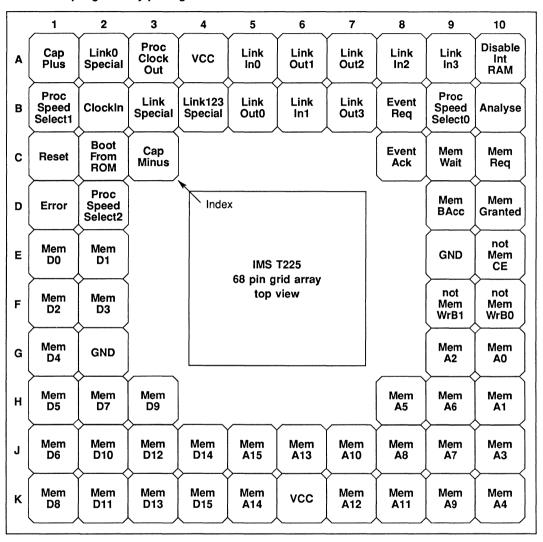

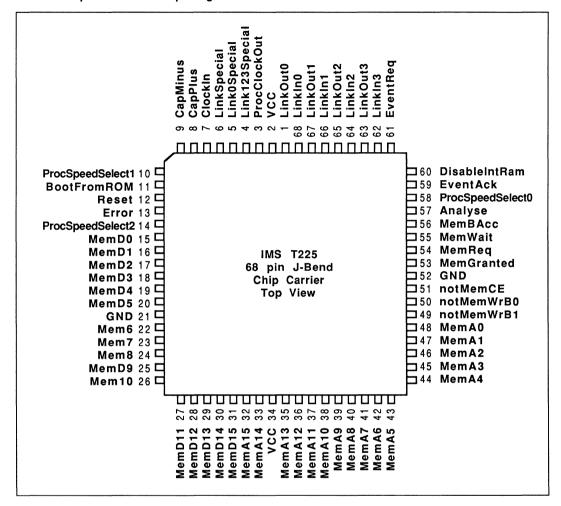

|             | 2                  | Pin de           | signatio  | ns                       | 456 |

|             |                    |                  |           |                          |     |

|             | 3                  | Instru           | ction set | summary                  | 457 |

|             | 4                  | Packa            | ge speci  | fications                | 459 |

|             |                    | 4.1              |           | grid array package       | 459 |

|             |                    | 4.2              | 68 pin    | PLCC J-bend package      | 460 |

|             |                    |                  |           |                          |     |

|             | 5                  | Orderi           | ng        |                          | 461 |

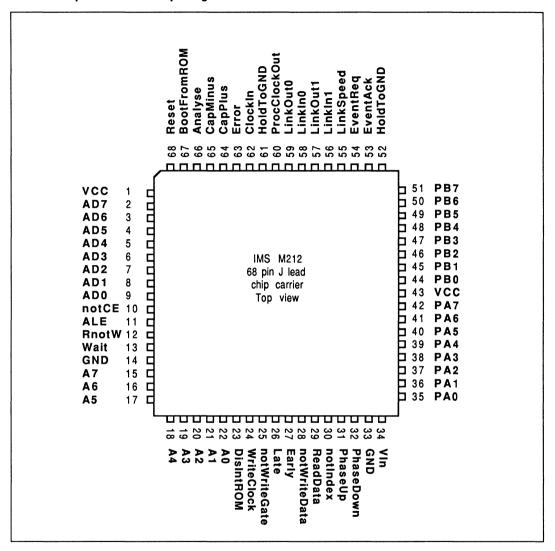

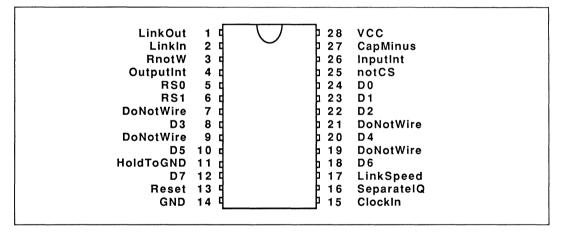

| 11          | IMS M212 preview 4 |                  |           |                          |     |

|             | 1                  | Introd           | uction    |                          | 464 |

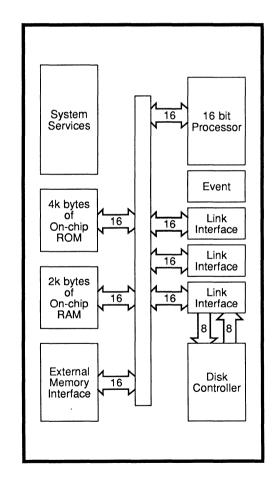

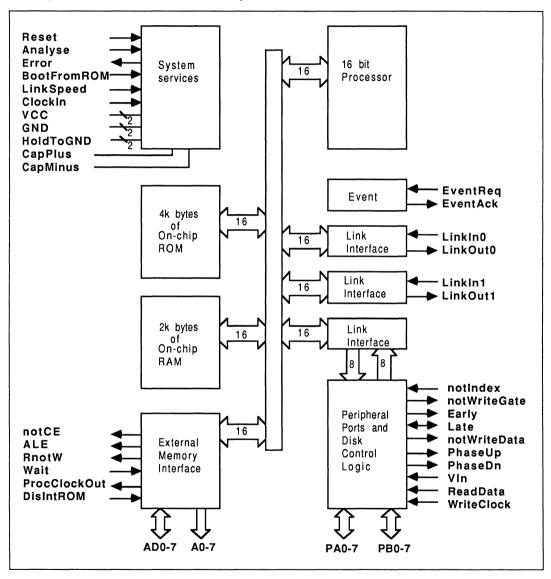

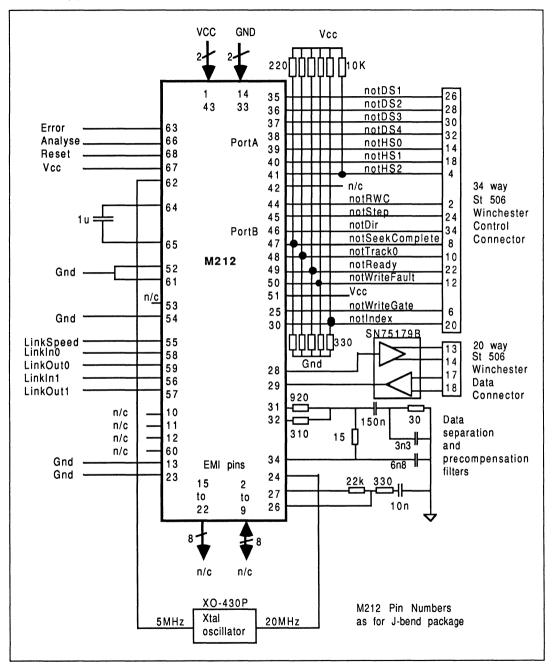

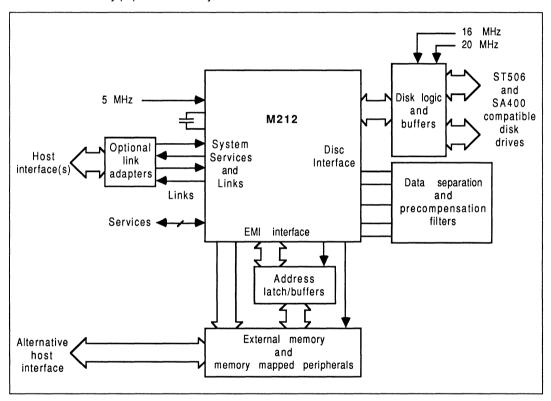

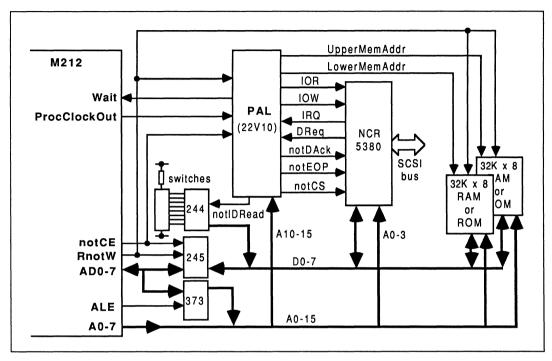

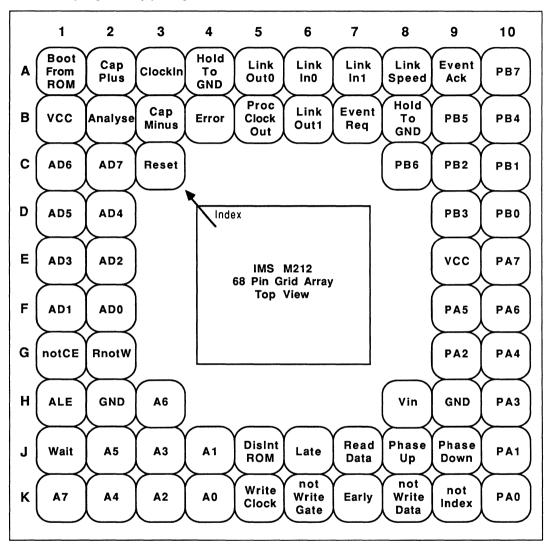

|             |                    | 1.1              |           | 212 peripheral processor | 465 |

|             |                    | 1.1              | 1.1.1     | Central processor        | 465 |

|             |                    |                  | 1.1.2     | Peripheral interface     | 465 |

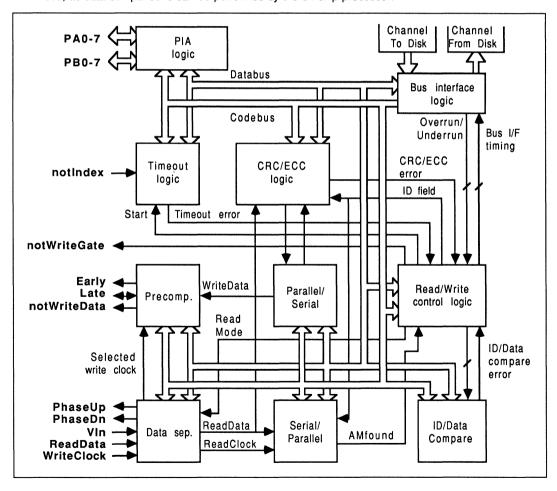

|             |                    |                  | 1.1.3     | Disk controller          | 465 |

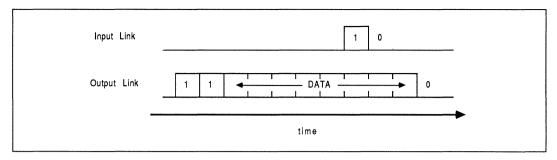

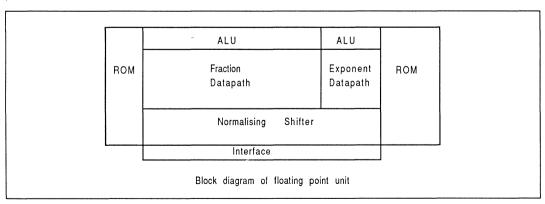

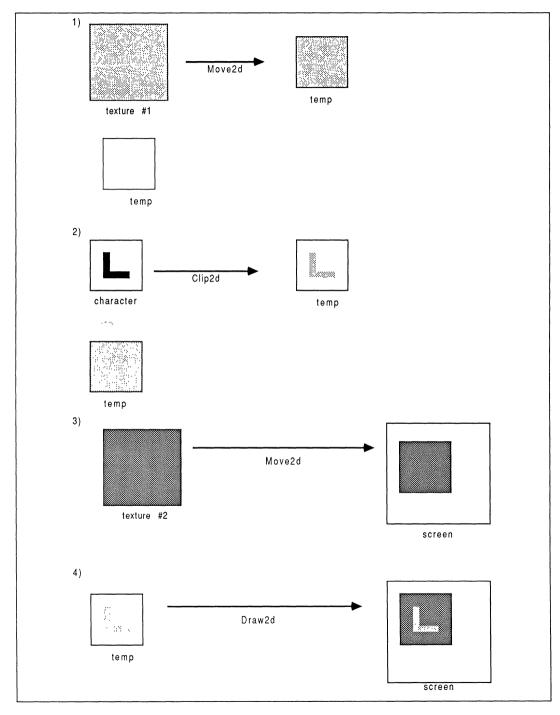

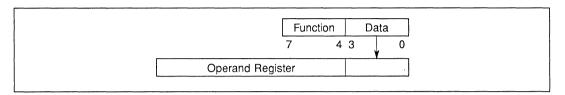

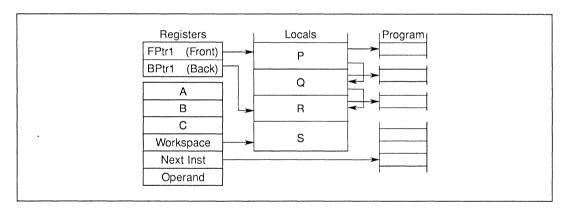

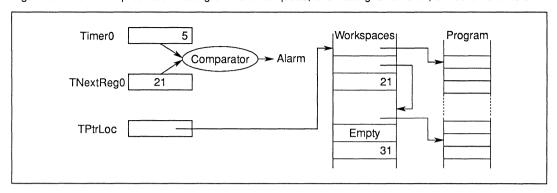

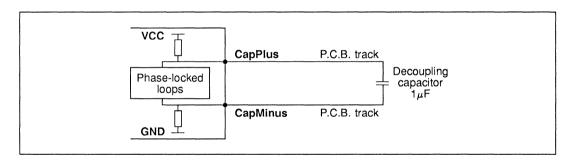

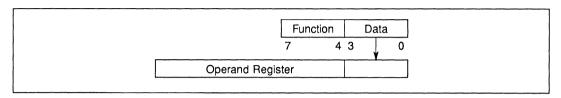

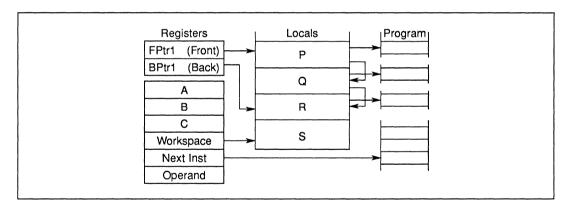

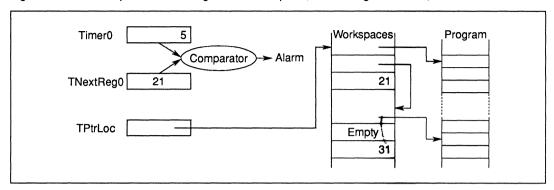

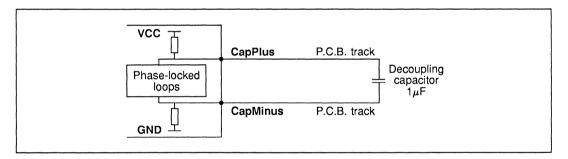

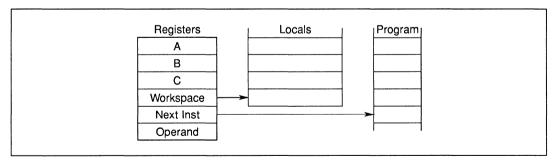

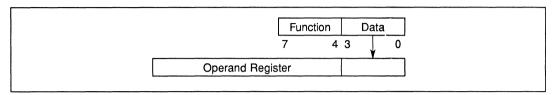

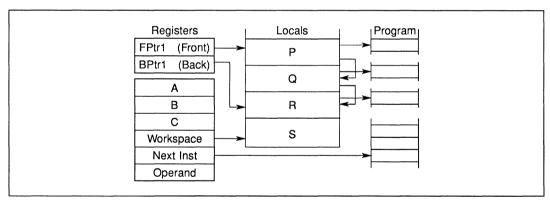

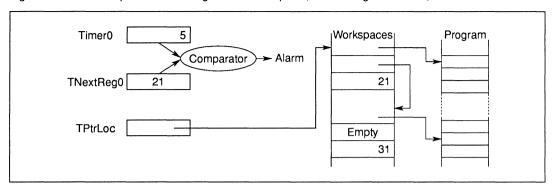

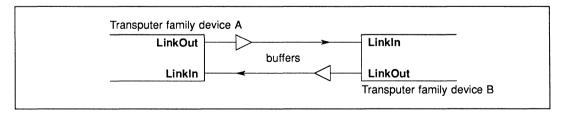

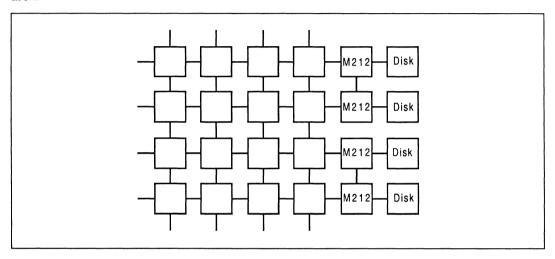

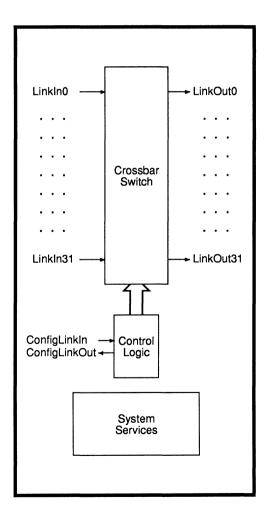

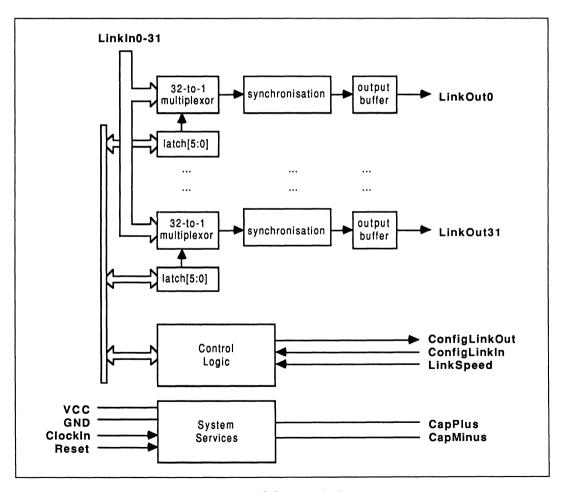

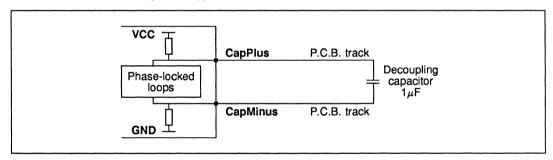

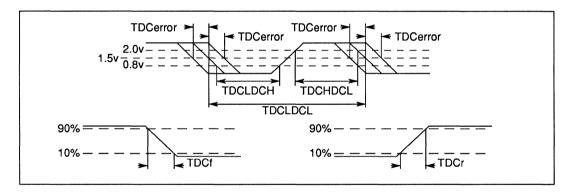

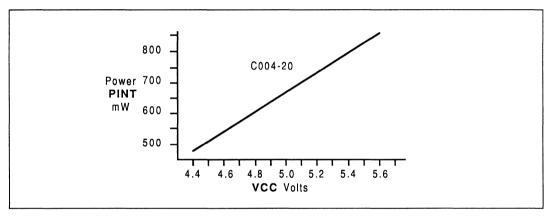

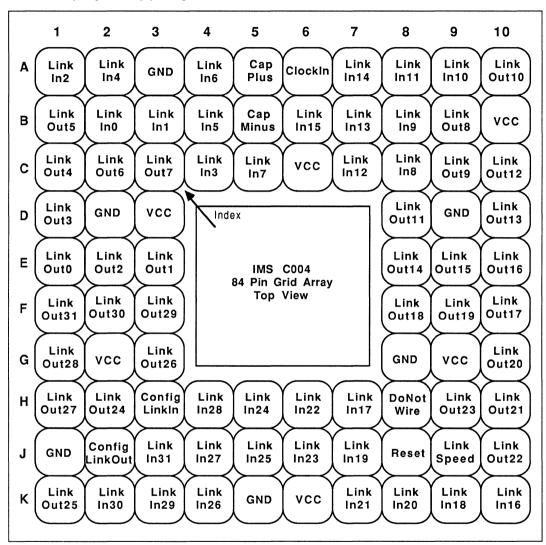

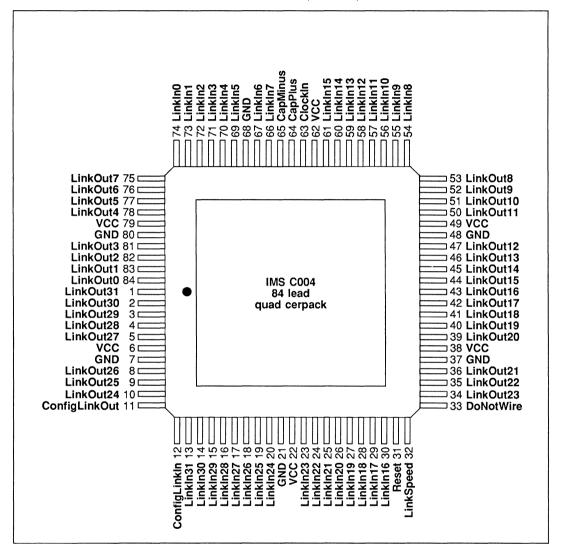

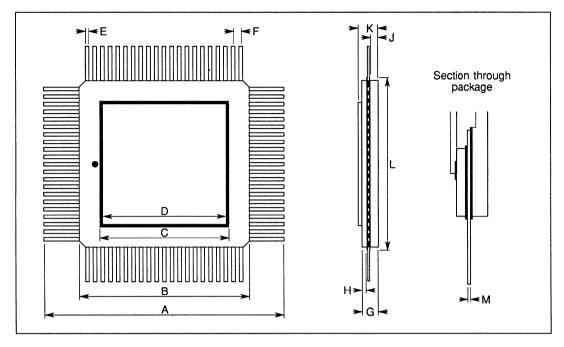

|             |                    |                  | 1.1.4     | Links                    | 466 |