1995 RISC MICROPROCESSOR PROCESSORS, SUPPORT COMPONENTS, SOFTWARE, & BOARD-LEVEL PRODUCTS DATA BOOK

Integrated Device Technology, Inc.

11

ORTON

11

Integrated Device Technology, Inc.

# 1995 RISC MICROPROCESSORS DATA BOOK

2975 Stender Way, Santa Clara, California 95054 Telephone: (800) 345-7015 • TWX: 910-338-2070 • FAX: (408) 492-8674 Printed in U.S.A. ©1995 Integrated Device Technology, Inc.

.

•

# **CONTENTS OVERVIEW**

For ease of use for our customers, Integrated Device Technology provides four separate data books - Logic, Specialized Memories and Modules, RISC and RISC SubSystems, and Static RAM.

IDT's 1995 RISC Data Book is comprised of new and revised data sheets for the RISC and RISC Subsystems product groups. Also included is a current packaging section for the products included in this book. This section will be updated in each subsequent data book to reflect packages offered for products included in that book.

The 1995 RISC Data Book's Table of Contents contains a listing of the products contained in that data book only. In the past we have included products that appeared in other IDT data books. The numbering scheme for the book is as follows: the number in the bottom center of the page denotes the section number and the sequence of the data sheet within that section, (i.e. 5.5 would be the fifth data sheet in the fifth section). The number in the lower right hand corner is the page number of that particular data sheet.

Integrated Device Technology, a recognized leader in high-speed CMOS technology, produces a broad line of products. This enables us to provide a complete CMOS solution to designers of high-performance digital systems. Not only do our product lines include industry standard devices, they also feature products with faster speed, lower power, and package and/or architectural benefits that allow the designer to achieve significantly improved system performance.

To find ordering information: Ordering Information for all products in this book appears in Section 1, along with the Package Outline Index, Product Selector Guides, and Cross Reference Guides. Reference data on our Technology Capabilities and Quality Commitments is included in separate sections (2 and 3, respectively).

To find product data: Start with the Table of Contents, organized by product line (page 1.2), or with the Numeric Table of Contents (page 1.4). These indexes will direct you to the page on which the complete technical data sheet can be found. Data sheets may be of the following type:

**PRODUCT BRIEF** — contains initial descriptions, subject to change, for products that are in development, also includes a features listing.

ADVANCE INFORMATION — contain initial descriptions, subject to change, for products that are in development.

**PRELIMINARY** — contain descriptions for products soon to be, or recently, released to production, including features, pinouts and block diagrams. Timing data are based on simulation or initial characterization and are subject to change upon full characterization.

**FINAL** — contain minimum and maximum limits specified over the complete supply and temperature range for full production devices.

New products, product performance enhancements, additional package types and new product families are being introduced frequently. Please contact your local IDT sales representative to determine the latest device specifications, package types and product availability.

# LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of IDT.

- Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support

or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the

labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Note: Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.

The IDT logo is a registered trademark, and BUSMUX, Flexi-pak, BiCEMOS, CacheRAM, CEMOS, FASTX, Flow-thruEDC, IDT/c, IDT/envY, IDT/kit, IDT/sae, IDT/sim, IDT/ux, MacStation, REALB, RISC SubSystem, RISController, RISCore, RISCompiler, RISC Windows, RISChipset, SmartLogic, SyncFIFO, TargetSystem, Orion, R36100, R3041, R3051, R3052, R3071, R3081, R3710, R3715, R3720, R3721, R3740, R4400, R4600, R4650 and R4700 are trademarks of Integrated Device Technology, Inc.

MIPS and RISCross are registered trademarks of MIPS Computer Systems; Windows is a registered trademark of MicroSoft Corporation; UNIX is a registered trademark of AT & T; Appletalk is a registered trademark of Apple Computer, Inc.; PostScript is a registered trademark of Adobe Systems; Sun-4, Sparc, and SunOS are registered trademarks of SUN Microsystems, Inc.; IRIX 5.2 is a registered trademark of SUN Microsystems, Inc.; PostScript is a registered trademark of Adobe Systems; Sun-4, Sparc, and SunOS are registered trademarks of SUN Microsystems, Inc.; IRIX 5.2 is a registered trademark of Silicon Graphics, Inc.

# 1995 RISC DATA BOOK TABLE OF CONTENTS

PAGE

# **GENERAL INFORMATION**

| Contents Overview               | 1.1 |

|---------------------------------|-----|

| Table of Contents               | 1.2 |

| Numeric Table of Contents       | 1.3 |

| Ordering Information            | 1.4 |

| IDT Package Marking Description | 1.5 |

| RISC Product Selector Guide     |     |

# **TECHNOLOGY AND CAPABILITIES**

| IDTLeading the CMOS Future        | 2.1 |

|-----------------------------------|-----|

| IDT Military and DESC-SMD Program |     |

| Radiation Hardened Technology     |     |

| IDT Leading Edge CMOS Technology  | 24  |

| Superior Quality and Reliability  |     |

| Superior duality and residently   | 2.0 |

# QUALITY AND RELIABILITY

| Quality, Service and Performance                                         | 3.1 |

|--------------------------------------------------------------------------|-----|

| IDT Quality Conformance Program                                          | 3.2 |

| Radiation Tolerant/Enhanced/Hardened Products for Radiation Environments |     |

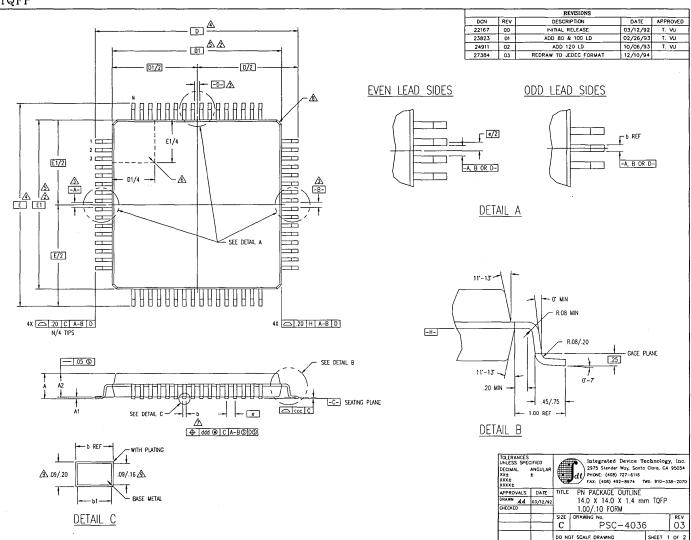

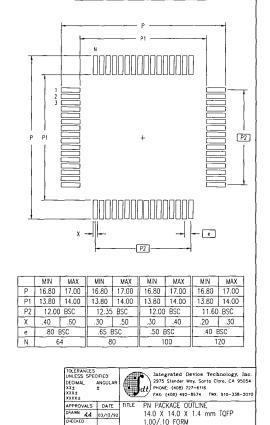

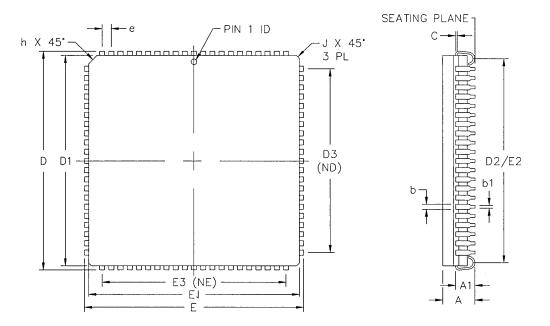

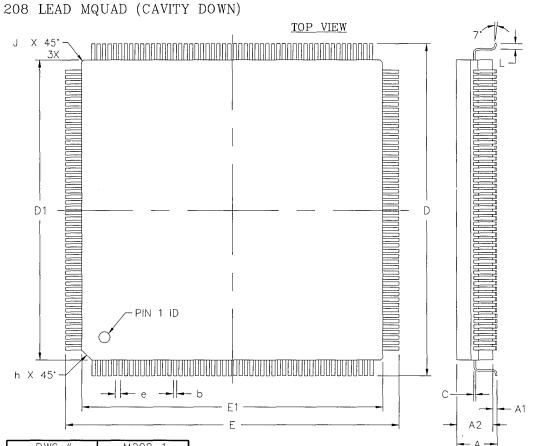

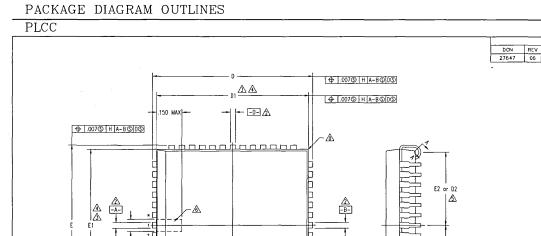

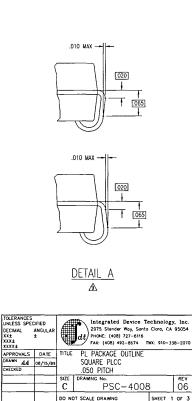

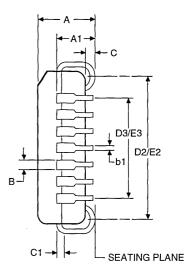

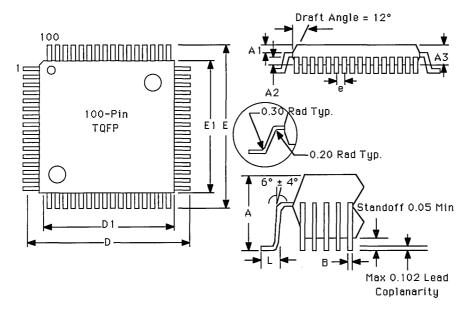

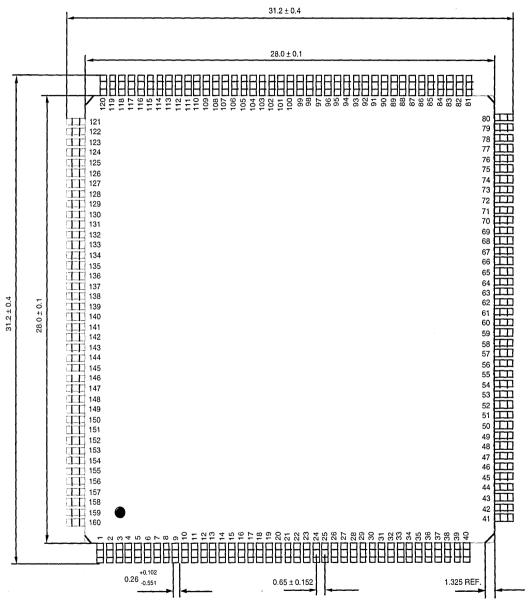

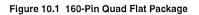

# PACKAGE DIAGRAM OUTLINES

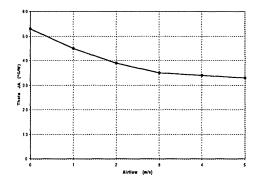

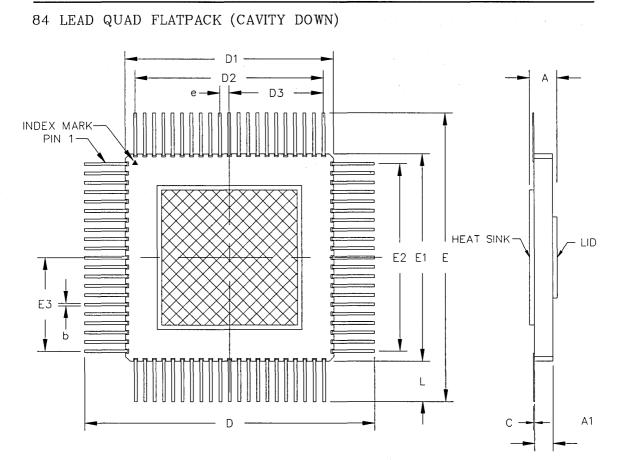

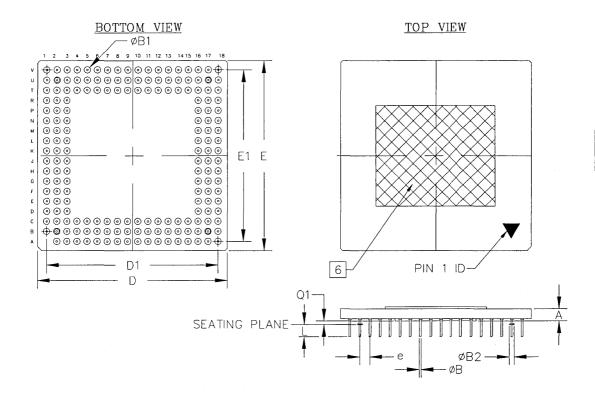

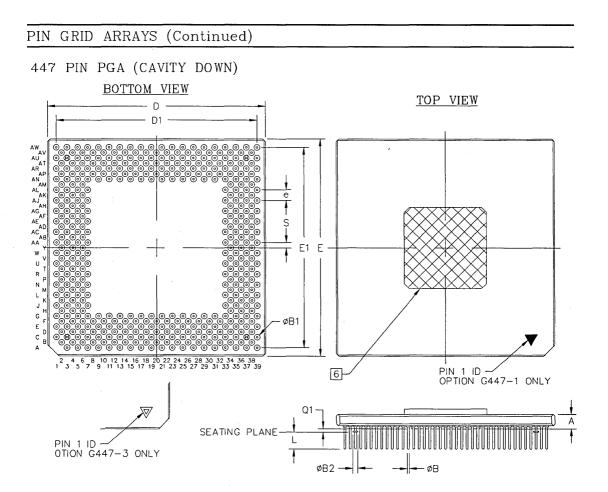

| Thermal Performance Calculations for IDT's Packages | 4.1 |

|-----------------------------------------------------|-----|

| Package Diagram Outline Index                       | 4.2 |

| Monolithic Package Diagram Outlines                 | 4.3 |

# **RISC PROCESSING COMPONENTS**

| IDT79R3000A        | RISC CPU Core Processor                                     | 5.1  |

|--------------------|-------------------------------------------------------------|------|

| IDT79R3041         | Integrated RISController <sup>™</sup> for Low-Cost Systems  | 5.2  |

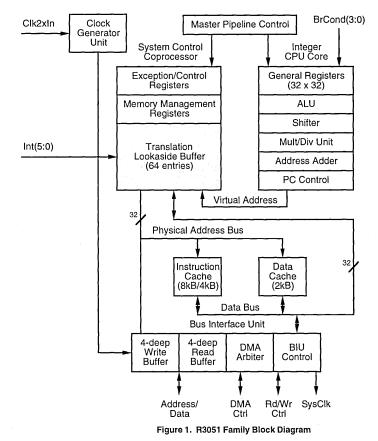

| IDT79R3051/79R3052 | IDT79R3051/79R3052 RISControllers™                          | 5.3  |

| IDT79R3071         | IDT79R3071 RISController <sup>™</sup>                       | 5.4  |

| IDT79R3081         | IDT79R3081 RISController <sup>™</sup> with FPA              | 5.5  |

| IDT79R36100        | IDT79R361 Highly Integrated RISController <sup>™</sup>      | 5.6  |

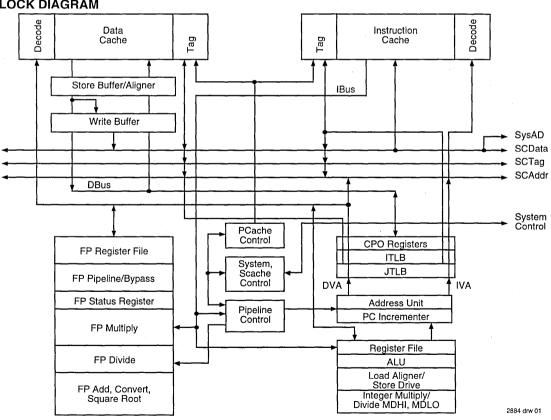

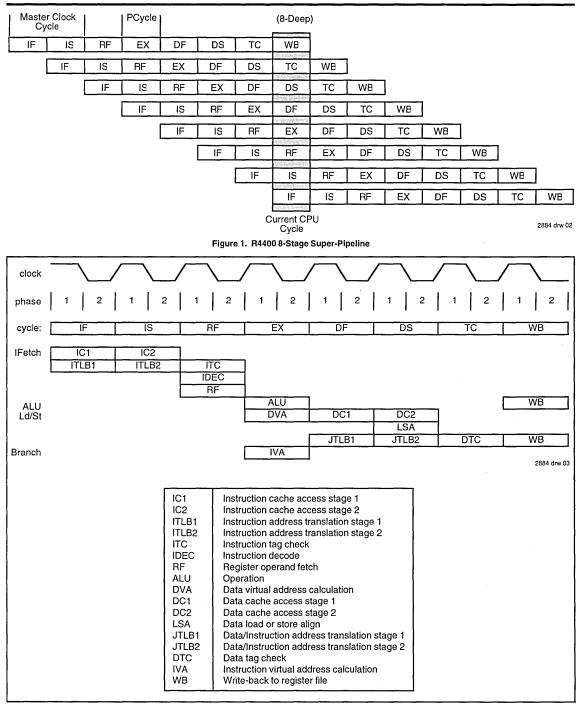

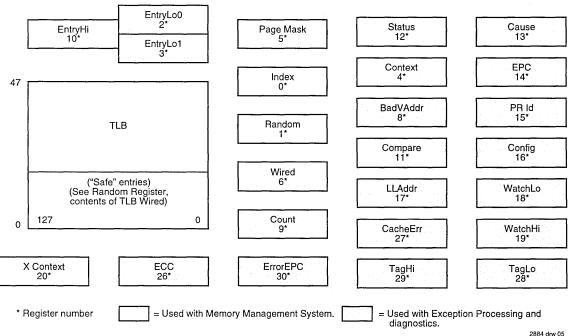

| IDT79R4400         | Third-Generation 64-Bit Super-Pipelined RISC Microprocessor | 5.7  |

| IDT79R4600         | Fourth-Generation 64-Bit RISC Microprocessor                | 5.8  |

| IDT79R4650         | Embedded 64-Bit RISC Orion <sup>™</sup> Microprocessor      | 5.9  |

| IDT79R4700         | Enhanced Orion <sup>™</sup> 64-Bit RISC Microprocessor      | 5.10 |

# **RISC SUPPORT COMPONENTS**

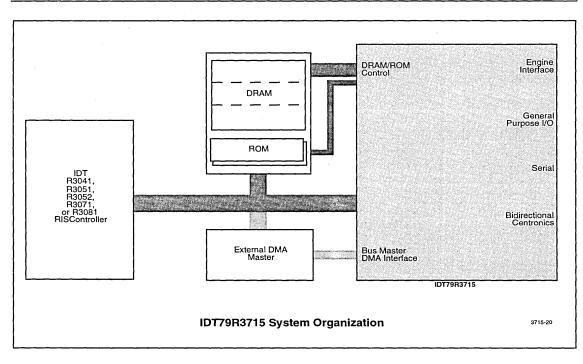

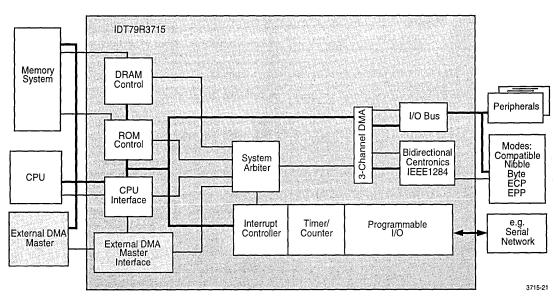

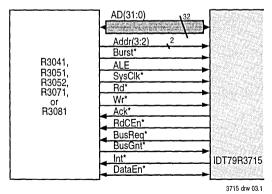

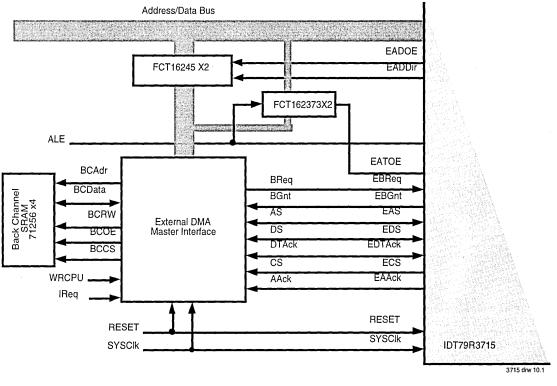

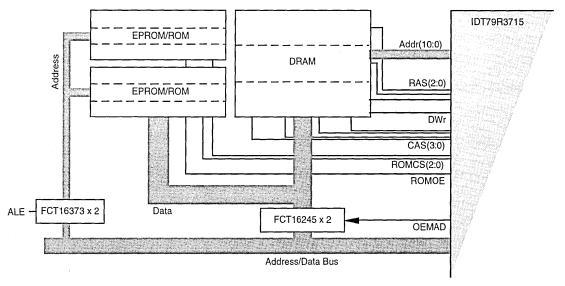

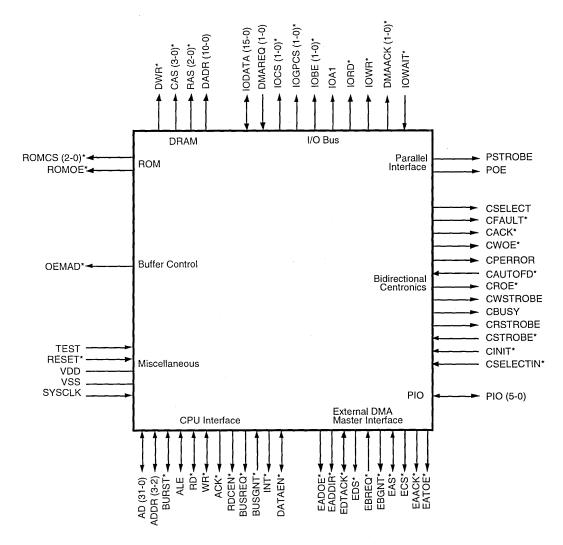

| IDT79R3715    | Single-Chip System Controller                                                              | 6.1 |

|---------------|--------------------------------------------------------------------------------------------|-----|

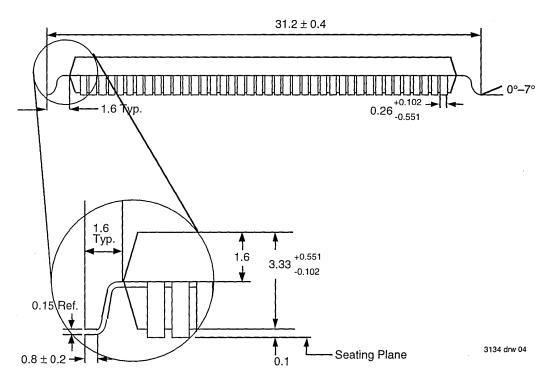

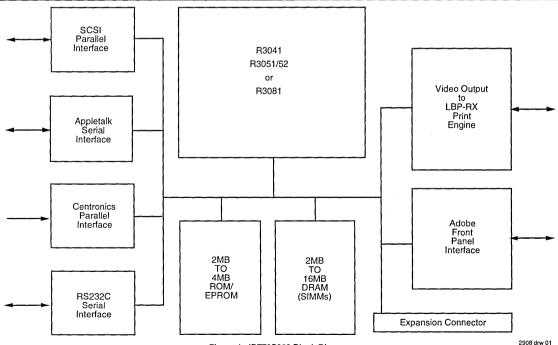

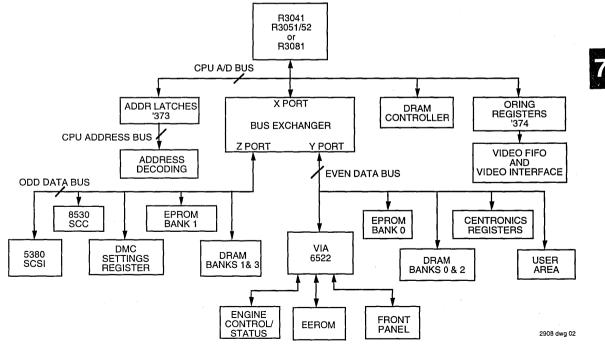

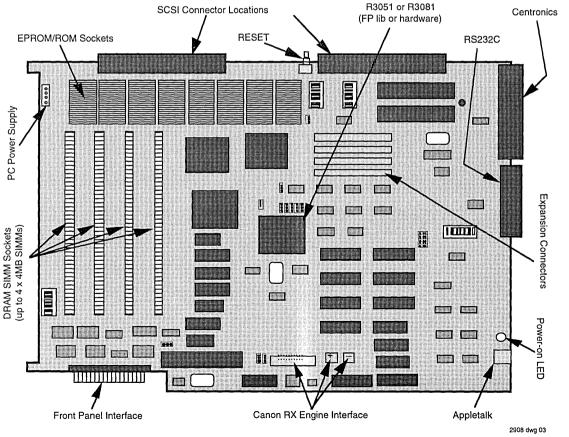

| IDT79R3710/40 | Laser Printer Integrated System Controller for IDT R30xx RISController <sup>™</sup> Family |     |

|               | w/Adobe <sup>™</sup> Frame Buffer Compression                                              | 6.2 |

| IDT79R4761    | Orion <sup>™</sup> Family Memory and I/O Controller                                        | 6.3 |

| IDT79R4762    | Orion <sup>™</sup> Family PCI to Orion <sup>™</sup> Bridge                                 | 6.4 |

|               |                                                                                            |     |

# 1995 RISC DATA BOOK (Continued)

# **RISC DEVELOPMENT SUPPORT PRODUCTS**

| Third Party Development | Tools and Applications Software for IDT RISC Processors                                              | 7.1  |

|-------------------------|------------------------------------------------------------------------------------------------------|------|

| Training Class          | Applications Development with IDT RISControllers <sup>™</sup> and Orion <sup>™</sup> Microprocessors | 7.2  |

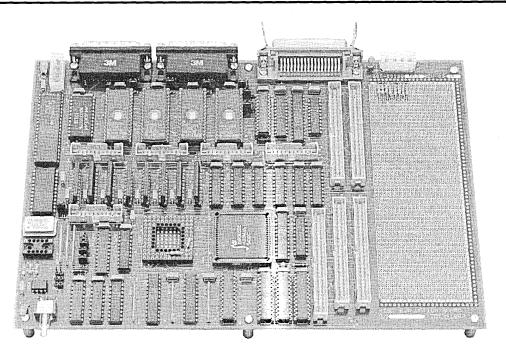

| IDT79S389               | Laser Printer Controller—3051 Family Reference Platform for Postscript <sup>™</sup> Level 2          |      |

|                         | Software from Adobe <sup>™</sup>                                                                     | 7.3  |

| IDT79S385A              | R3051 <sup>™</sup> Family Evaluation Kit                                                             | 7.4  |

| IDT 79S341              | R3041 <sup>™</sup> Evaluation Kit                                                                    | 7.5  |

| IDT79S381               | R3081 <sup>™</sup> Evaluation Kit                                                                    | 7.6  |

| IDT79S460               | R4600 <sup>™</sup> Evaluation and Development Platform                                               | 7.7  |

| IDT79S464               | Orion <sup>™</sup> 79R464 Evaluation Kit                                                             | 7.8  |

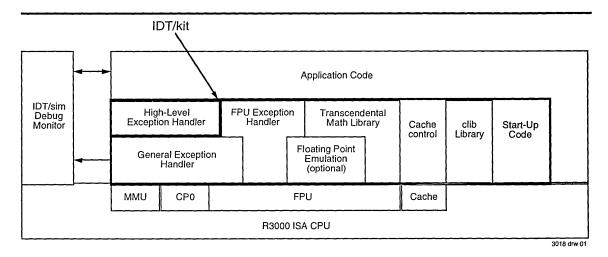

| IDT7RS901               | IDT/sim <sup>™</sup> System Integration Manager ROMable Debugging Kernel                             | 7.9  |

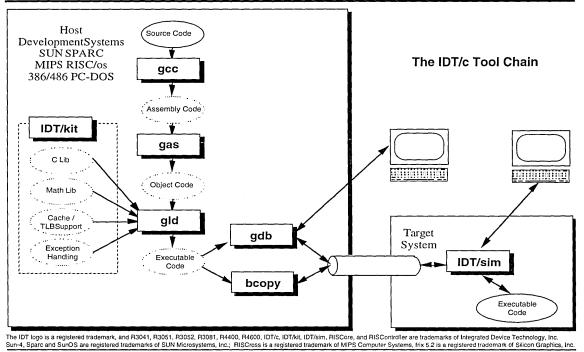

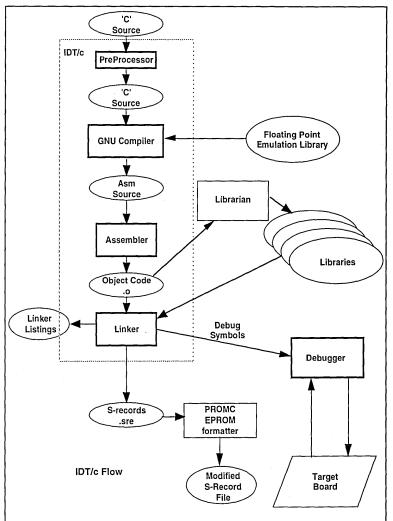

| IDT7RS930               | IDT/c <sup>™</sup> Multihost GNU C-Compiler System                                                   | 7.10 |

| IDT7RS909               | IDT/kit <sup>™</sup> Kernel Integration Toolkit                                                      | 7.11 |

# IDT SALES OFFICE, REPRESENTATIVE AND DISTRIBUTOR LOCATIONS

# NUMERICAL TABLE OF CONTENTS

## PART NO.

| IDT79R3000A             | RISC CPU Core Processor                                                                              | 5.1  |

|-------------------------|------------------------------------------------------------------------------------------------------|------|

| IDT79R3041              | Integrated RISController <sup>™</sup> for Low-Cost Systems                                           | 5.2  |

| IDT79R3051/79R3052      | IDT79R3051/79R3052 RISControllers <sup>™</sup>                                                       | 5.3  |

| IDT79R3071              | IDT79R3071 RISController <sup>™</sup>                                                                | 5.4  |

| IDT79R3081              | IDT79R3081 RISController <sup>™</sup> with FPA                                                       | 5.5  |

| IDT79R36100             | IDT79R361 Highly Integrated RISController <sup>™</sup>                                               | 5.6  |

| IDT79R3710/40           | Laser Printer Integrated System Controller for IDT R30xx RISController <sup>™</sup> Family           |      |

|                         | w/Adobe™ Frame Buffer Compression                                                                    | 6.2  |

| IDT79R3715              | Single-Chip System Controller                                                                        | 6.1  |

| IDT79R4400              | Third-Generation 64-Bit Super-Pipelined RISC Microprocessor                                          | 5.7  |

| IDT79R4600              | Fourth-Generation 64-Bit RISC Microprocessor                                                         | 5.8  |

| IDT79R4650              | Embedded 64-Bit RISC Orion <sup>™</sup> Microprocessor                                               | 5.9  |

| IDT79R4700              | Enhanced Orion <sup>™</sup> 64-Bit RISC Microprocessor                                               | 5.10 |

| IDT79R4761              | Orion <sup>™</sup> Family Memory and I/O Controller                                                  | 6.3  |

| IDT79R4762              | Orion <sup>™</sup> Family PCI to Orion <sup>™</sup> Bridge                                           | 6.4  |

| IDT79S341               | R3041 <sup>™</sup> Evaluation Kit                                                                    | 7.5  |

| IDT79S381               | R3081 <sup>™</sup> Evaluation Kit                                                                    | 7.6  |

| IDT79S389               | Laser Printer Controller—3051 Family Reference Platform for Postscript <sup>™</sup> Level 2          |      |

|                         | Software from Adobe <sup>™</sup>                                                                     | 7.3  |

| IDT79S385A              | R3051 <sup>™</sup> Family Evaluation Kit                                                             | 7.4  |

| IDT79S460               | R4600 <sup>™</sup> Evaluation and Development Platform                                               | 7.7  |

| IDT79S464               | Orion <sup>™</sup> 79R464 Evaluation Kit                                                             | 7.8  |

| IDT7RS901               | IDT/sim <sup>™</sup> System Integration Manager ROMable Debugging Kernel                             | 7.9  |

| IDT7RS909               | IDT/kit <sup>™</sup> Kernel Integration Toolkit                                                      | 7.11 |

| IDT7RS930               | IDT/c <sup>™</sup> Multihost GNU C-Compiler System                                                   | 7.10 |

| Third Party Development | Fools and Applications Software for IDT RISC Processors                                              | 7.1  |

| Training Class          | Applications Development with IDT RISControllers <sup>™</sup> and Orion <sup>™</sup> Microprocessors | 7.2  |

PAGE

1

# **ORDERING INFORMATION**

When ordering by TWX or Telex, the following format must be used:

- A. Complete Bill To.

- B. Complete Ship To.

- C. Purchase Order Number.

- D. Certificate of Conformance. Y or N.

- E. Customer Source Inspection. Y or N.

- F. Government Source Inspection. Y or N

- G. Government Contract Number and Rating.

- H. Requested Routing.

- I. IDT Part Number -

- Each item ordered must use the complete part number exactly as listed in the price book.

- J. SCD Number Specification Control Document (Internal Traveller).

- K. Customer Part Number/Drawing Number/Revision Level -

- Specify whether part number is for reference only, mark only, or if extended processing to customer specification is required.

- L. Customer General Specification Numbers/Other Referenced Drawing Numbers/Revision Levels.

- M. Request Date With Exact Quantity.

- N. Unit Price.

- O. Special Instructions, Including Q.A. Clauses, Special Processing.

Federal Supply Code Number/Cage Number — 61772 Dun & Bradstreet Number — 03-814-2600 Federal Tax I.D. — 94-2669985

Federal Tax I.D. - 94-26

TLX# — 887766

FAX# --- 408-727-3468

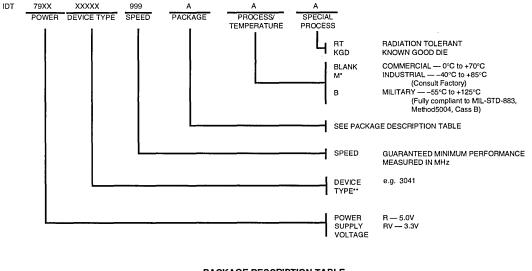

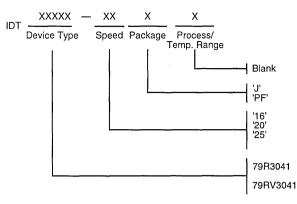

## PART NUMBER DESCRIPTION

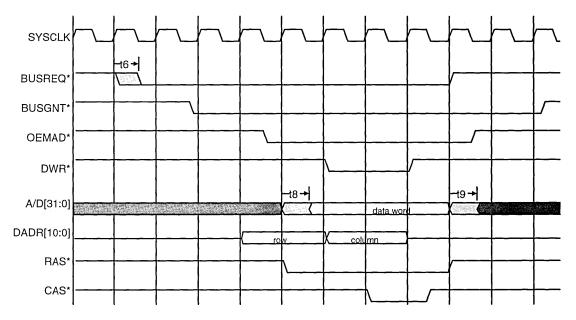

#### PACKAGE DESCRIPTION TABLE

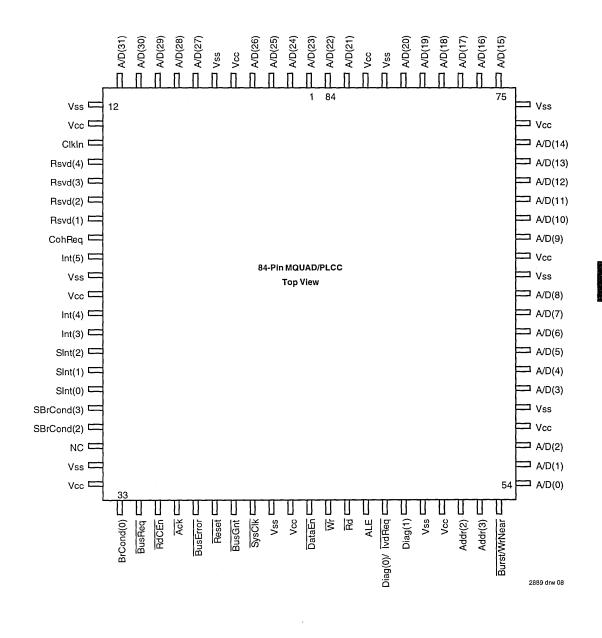

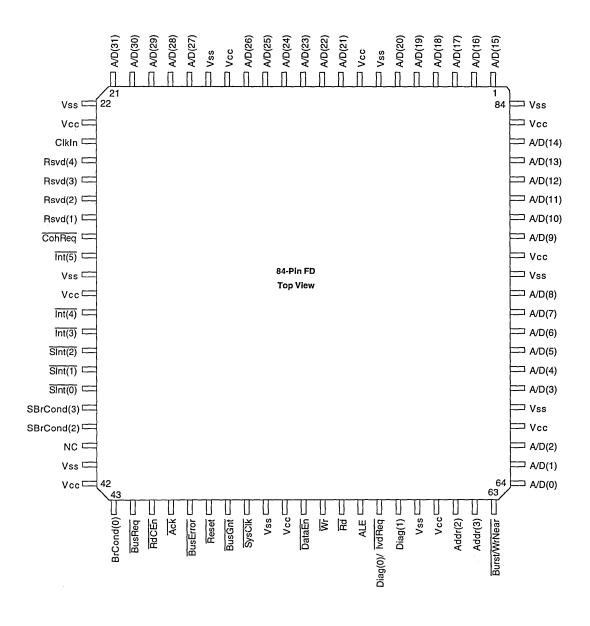

|   | J  | 84-lead PLCC                |

|---|----|-----------------------------|

|   | PF | 100-lead TQFP               |

|   |    | 160-Lead PQFP               |

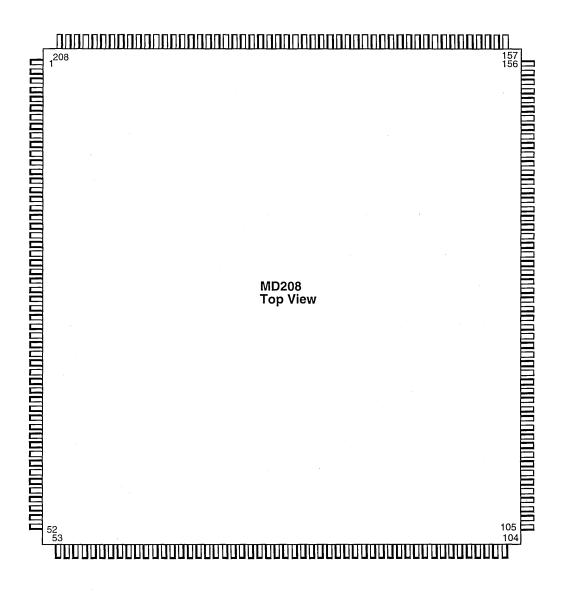

|   |    | 208-Lead PQFP               |

|   | MJ | 84-lead MQUAD               |

|   | FD | 84-lead Cavity-down Flatpak |

|   | G  | 179-pin PGA                 |

|   |    | 447-pin PGA                 |

|   | GL | Extended lead 447-pin PGA   |

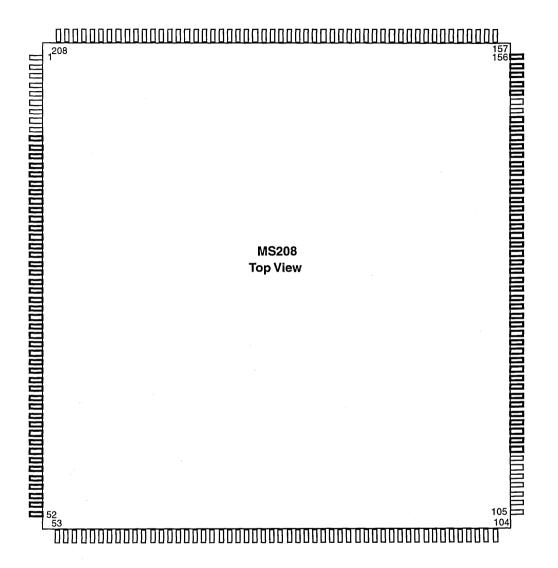

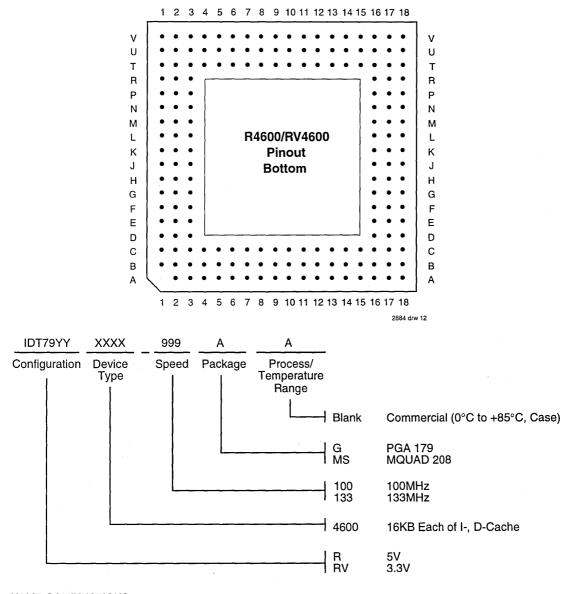

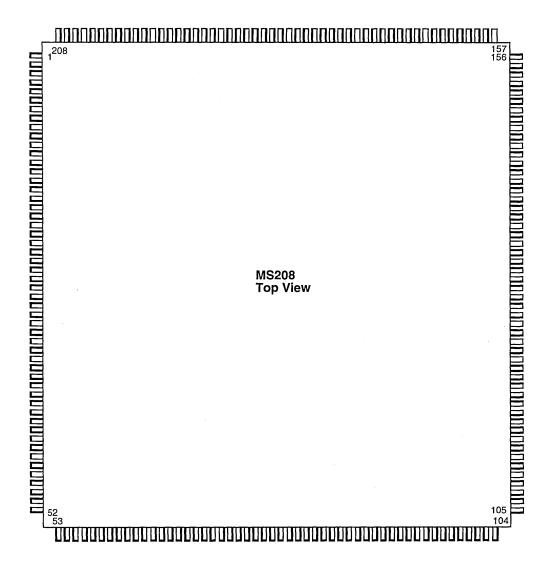

| i | MS | 208-lead MQUAD              |

|   |    |                             |

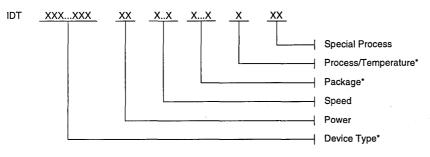

# IDT PACKAGE MARKING DESCRIPTION

## PART NUMBER DESCRIPTION

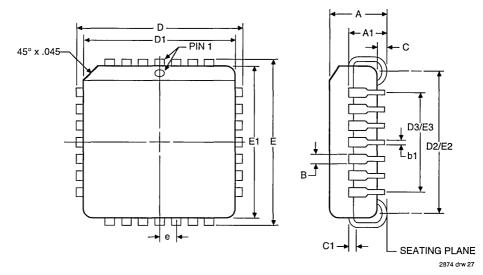

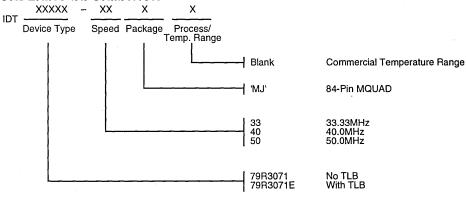

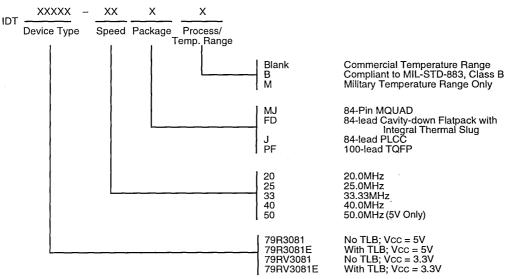

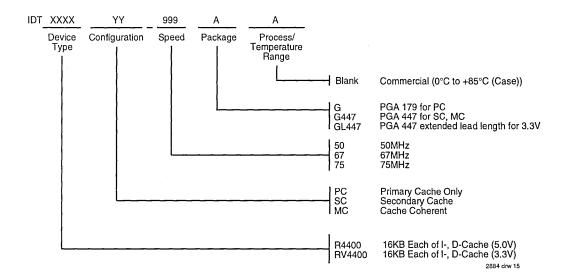

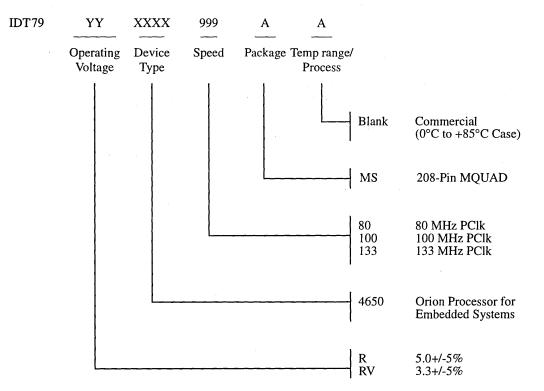

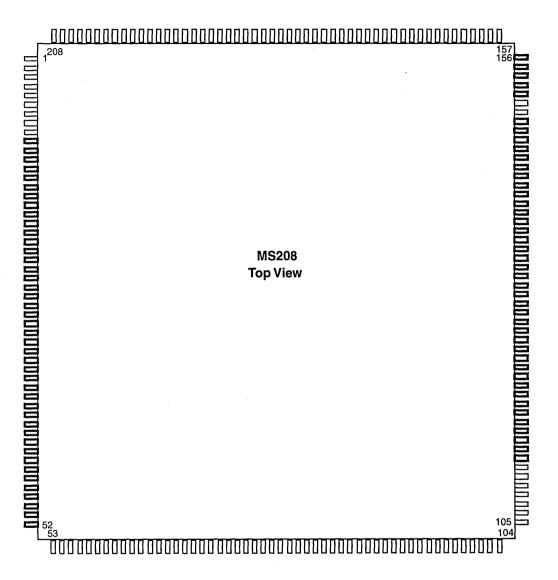

IDT's part number identifies the basic product, speed, power, package(s) available, operating temperature and processing grade. Each data sheet has a detailed description, using the part number, for ordering the proper product for the user's application. The part number is comprised of a series of alpha-numeric characters:

- 1. An "IDT" corporate identifier for Integrated Device Technology, Inc.

- 2. A basic device part number composed of alpha-numeric characters.

- A device power identifier, composed of one or two alpha characters, is used to identify the power options. In most cases, the following alpha characters are used: "R" is used for 5.0V compliant products.

"RV" is used for 3.3V compliant products.

- A device speed identifier, when applicable, is either alpha characters, such as "A" or "B", or numbers, such as 20 or 45. The speed units, depending on the product, are in nanoseconds or megahertz.

- A package identifier, composed of one or two characters. The data sheet should be consulted to determine the packages available and the package identifiers for that particular product.

- 6. A temperature/process identifier. The product is available in either the commercial or military temperature range, processed to a commercial specification, or the product is available in the military temperature range with full compliance to MIL-STD-883. Many of IDT's products have burn-in included as part of the standard commercial process flow.

- A special process identifier, composed of alpha characters, is used for products which require radiation enhancement (RE) or radiation tolerance (RT).

Example for Monolithic Devices:

\* Field Identifier Applicable To All Products

2507 drw 01

#### ASSEMBLY LOCATION DESIGNATOR

IDT uses various locations for assembly. These are identified by an alpha character in the last letter of the date code marked on the package. Presently, the assembly location alpha character is as follows:

- V = Penang, hermetic

- I = Anam, Korea

- T = Hong Kong

- A = USA

- G = USA, hermetic

- M = USA, plastic

- P = Api, Phillipines

- H = Penang, plastic

## MIL-STD-883C COMPLIANT DESIGNATOR

IDT ships certain military products which are compliant to the latest revision of MIL-STD-883C. Such products are identified by a "C" designation on the package. The location of this designator is specified by internal documentation at IDT.

# HIGH-SPEED CMOS MICROPROCESSOR FAMILY PRODUCT SELECTOR GUIDE

# High-Speed CMOS Microprocessor Family

- Broadest range of high-performance to low-cost, code-compatible RISC processors: R3000A, R4000 CPUs, R3041/51/52/81 RISControllers, R4600, R4650, and R4700

- R4400—third-generation high-performance 64-bit CPU and FPA with on-chip cache

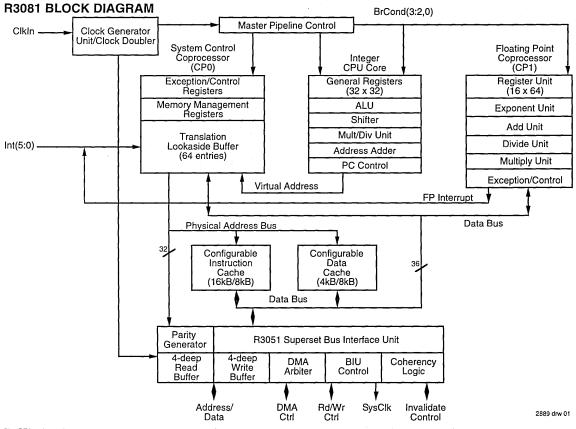

- R3051/52/81/41 RISController Family—designed for lowercost embedded systems, all code-compatible with original R3000

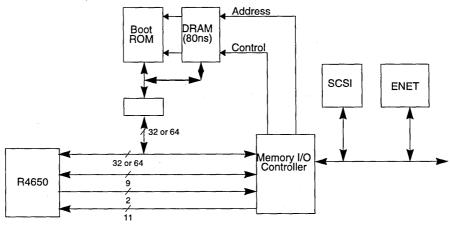

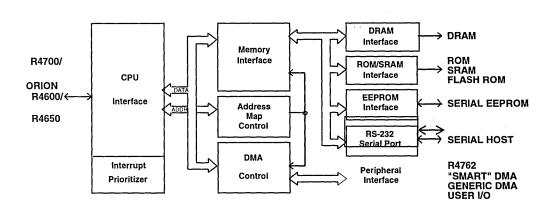

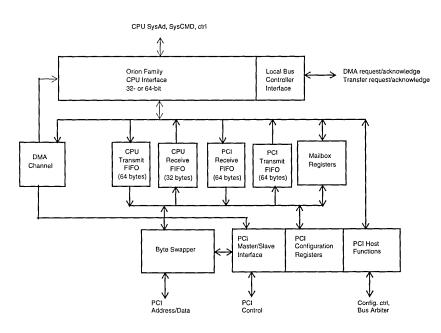

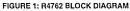

- Support chips designed for RISC systems: R3715 System Controller, R3740 Laser Printer Controller, R4761 Orion Family System Controller, and R4762 Orion Family PCI Bridge Chip

- Applications range from real-time control to multiprocessing systems

- Optimizing compilers

|                |                                                                                                                                                                                                             |                         |        | Data<br>Book |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------|--------------|

| Number         | Description                                                                                                                                                                                                 | Pkgs.                   | Avail. | Page         |

| RISC CMOS MICH | ROPROCESSORS                                                                                                                                                                                                |                         |        |              |

| IDT79R4400     | Very high-performance, highly integrated 64-bit CPU,<br>fully binary compatible with the R3000A. Combines<br>CPU, floating-point and 16/32KB of cache, capable of over<br>50 VAX mips sustained performance | 447PGA<br>179PGA        | NOW    | 5.6          |

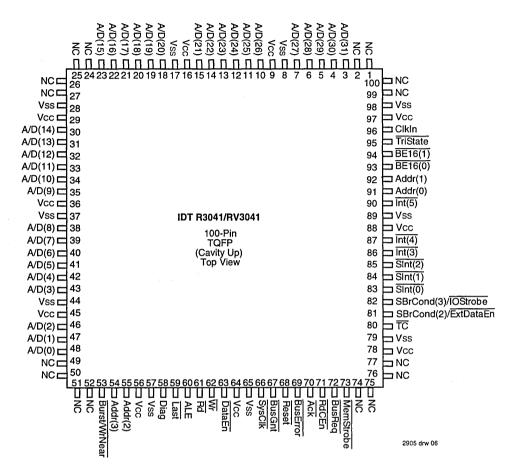

| IDT79R3041     | RISController, 2.5KB cache, R3000A core, 4-deep read/<br>write buffers, low-cost packaging, pin-compatible with R3051/52/81                                                                                 | 84PLCC<br>100PF         | NOW    | 5.2          |

| IDT79R3051/52  | RISControllers, 6KB or 10KB on-chip cache, R3000A<br>CPU core, and 4-deep read/write buffers, low-cost<br>84-pin packaging                                                                                  | 84PLCC<br>84MJ          | NOW    | 5.2          |

| IDT79R3081     | RISController, 20KB on-chip, R300 CPU core,<br>R3010A Floating Point Accelerator, 4-deep read/write<br>buffers, pin-compatible with R3041/51/52                                                             | 84MJ<br>84FD<br>100PQFP | NOW    | 5.3          |

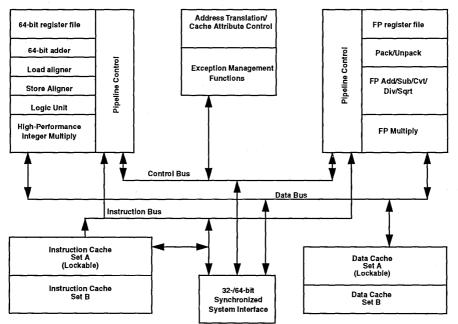

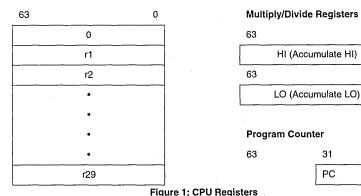

| IDT79R4600     | Very high-performance, highly integrated 64-bit CPU,<br>fully binary compatible with the R3000A. Combines CPU,<br>floating-point and 32KB of cache, capable of over 175 mips<br>sustained performance       | 179PGA<br>208 MQUAD     | NOW    | 5.4          |

| IDT79R4650     | R4600 derivative capable of 66.7 Million Integer Multiply-<br>Accumulate Operations/sec @ 133MHz and 175 mips sustained<br>performance. Combines CPU, floating-point and 16KB of cache.                     | 208MQUAD                | NOW    | 5.5          |

| IDT79R4700     | Pin-compatible with the R4600, the R4700 is an enhanced version of the R4600. Combines CPU, floating-point and 32KB of cache, capable of over 225 mips sustained performance                                | 179PGA<br>208MQUAD      | NOW    | 5.6          |

· Low-cost Evaluation Boards available

#### High-Speed CMOS RISC Microprocessor Family (Cont'd)

| Dent Mussiker  | Providenter de la companya de | an sharan<br>An sharan                   | A      | Data<br>Book |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------|--------------|--|

| Part Number    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | · · · · ·                                | Avail. | Page         |  |

| R3000 FAMILY E | VALUATION_KITS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                          |        |              |  |

| IDT79S341      | R3041 Family Evaluation Board. Complete, self-contained syste<br>only a power supply and simple terminal to be operational. Kit co<br>R3041 CPU, 1MB of DRAM, IDT/sim monitor in EPROM, serial I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ontains                                  | NOW    | 7.5          |  |

| IDT79S385A     | R305X Family Evaluation Board. Complete, self-contained syste<br>only a power supply and simple terminal to be operational. Kit cc<br>R3052E CPU, 1MB of DRAM, IDT/sim monitor in EPROM, seria<br>Supplied with all schematics, PAL equations and user's manual.<br>DOS version of the IDT/c compiler (see 7RS903) and a sample                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ontains<br>I I/O ports.<br>Also includes | NOW    | 7.4          |  |

| IDT79S381      | R3081 Family Evaluation Board. Complete, self-contained syste<br>only a power supply and simple terminal to be operational. Kit co<br>R3081 CPU, 2MB of DRAM, IDT/sim monitor in EPROM, serial I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ontains                                  | NOW    | 7.6          |  |

| IDT79S460      | R4600 Family Evaluation Board. Complete, self-contained syste<br>only a power supply and simple terminal to be operational. Kit co<br>R4600 CPU, 1MB of DRAM, IDT/sim monitor in EPROM, serial I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ontains                                  | NOW    | 7.7          |  |

#### **R3000 FAMILY SOFTWARE DEVELOPMENT TOOLS**

| IDT79S901 | IDT/sim System Integration Manager (see RISC SubSystems for description) | NOW | 7.8  |

|-----------|--------------------------------------------------------------------------|-----|------|

| IDT79S903 | IDT/c C-Compiler (see RISC SubSystems for description)                   | NOW | 7.9  |

| IDT79S909 | IDT/kit Kernel Integration Toolkit (see RISC SubSystems for description) | NOW | 7.10 |

|           |                                                                          |     |      |

#### Integrated RISC Design Solutions

IDT is committed to providing complete integrated RISC solutions by combining expertise in silicon process technology with leadership products in development systems and software. Long an industry leader in producing the fastest static RAMs for cache memory and high-speed logic for memory interface, IDT offers:

- Dedicated RISC support chips

- · Development tools such as multi-hosted Cross Compilers

- · CPU and cache modules

- RISC evaluation and prototyping vehicles

- Monitors and debuggers

2

# RISC SubSystems—RISC Without Risk ..... IDT Provides Total RISC System Solutions!

#### FASTER SYSTEMS: FASTER DESIGN CYCLES

Using RISC technology, you can build systems that will run rings around an old x86 or 680x0 design. IDT's RISC SubSystems Division can help you get your design completed in record time. IDT has proven RISC design and manufacturing experience that you can rely on. Exploit our expertise by having IDT design *AND* manufacture your board. Or integrate one of our pre-built, fullytested modules into your design.

#### Architectural Expertise

IDT brings together a unique combination of component knowledge, software skills, and board design experience as the foundation for developing a board-level product that meets your needs. As experienced system architects, we understand that component knowledge alone is not enough—that the interface between hardware and software is critical to a successful design. We have spent years honing our architectural expertise to include an in-depth understanding of both the hardware and software issues so our designs produce the performance you expect.

#### Fast Development Cycle

IDT uses the most advanced engineering tools in our hardware development lab. We have qualified quick-turn PCB fab houses and our own fully-equipped advanced manufacturing area, so new fabs can be assembled and sent into debug in a matter of days. In addition, IDT has developed the best software diagnostic tools available for MIPS RISC debug. Spotting behavioral patterns in malfunctioning systems and quickly identifying and fixing the hardware or software problem is key to maintaining a time-critical development cycle—and we want you to be first to market!

#### **Optimized Designs**

IDT is a premier supplier of RISC assemblies. Our expertise in handling layout, termination, and component selection issues is unmatched, and we use the latest tools for PCB layout, routing and design simulation. Our design team is fast and experienced, coordinating component selection with availability of the latest technology, and using ASICs where appropriate to improve performance and reduce space and cost. To date, we have designed and produced more different MIPS RISC assemblies than anyone else, optimizing every design for the highest possible performance per dollar.

#### **Total Support**

On-going support means on-time deliveries. IDT has on-going vendor TQM programs with suppliers of critical components to ensure on-time delivery of in-spec material. Our manufacturing organization is experienced in building very high-speed boards with tight tolerances and high-pin-count surface-mount components. And our design team is on-call to solve problems quickly if difficulties arise during production. We provide total support—from board design and software porting through production and test—because our success depends on your success!

#### Modules

Our modules contain the RISC CPU, Floating Point Accelerator, and all the cache memory. Most include clock control, interrupt and initialization logic, and read and write buffers, as well. All the components are surface-mounted on small, plug-in PC boards, burned-in and tested at the rated speed. All the tricky timing, and high-speed design is done and tested for you. The modules can be plugged into motherboards containing main memory, I/O, and the rest of the system, all of which is relatively low-speed and is easy to lay out using conventional design techniques.

#### **Custom Subsystems**

For custom boards that meet your unique requirements, we can develop a complete product specification, design the boards, deliver prototypes, and provide production units in any quantities. Many customers have found this to be a cost-effective way to augment their own engineering resources, and to procure material that exactly meets their needs without all the headaches of purchasing, material control, and on-going product and manufacturing engineering.

#### **Printer Controllers**

IDT has designed and produced a number of printer controllers, using both custom and standard hardware solutions. IDT's boardlevel products have been used to run Adobe PostScript\*\*, PCL5 emulation, and Pipeline Associates' color PostScript emulation. IDT is a licensee for Adobe's CPSI interpreter, and can develop a flexible true Adobe solution in a variety of hardware and software environments.

| Model       | Description                                                                           |

|-------------|---------------------------------------------------------------------------------------|

| Custom Desi | gns                                                                                   |

|             | Plotter Controllers                                                                   |

|             | Add-In Cards to EISA/ISA Bus                                                          |

|             | Add-in Cards for Macintosh                                                            |

|             | Laser Printer Controllers                                                             |

| Software    |                                                                                       |

|             | Adobe CPSI PostScript Application Development                                         |

|             | <ul> <li>UNIX<sup>™</sup> Porting, and Driver Development</li> </ul>                  |

|             | <ul> <li>C-EXECUTIVE<sup>™</sup> Real Time OS</li> </ul>                              |

|             | <ul> <li>Interprocessor Communication between RISC Subsystem and Mac or PC</li> </ul> |

GENERAL INFORMATION

# **TECHNOLOGY AND CAPABILITIES**

QUALITY AND RELIABILITY

PACKAGE DIAGRAM OUTLINES

**RISC PROCESSING COMPONENTS**

**RISC SUPPORT COMPONENTS**

RISC DEVELOPMENT SUPPORT PRODUCTS

# **IDT...LEADING THE CMOS FUTURE**

A major revolution is taking place in the semiconductor industry today. A new technology is rapidly displacing older NMOS and bipolar technologies as the workhorse of the '80s and beyond. That technology is high-speed CMOS. Integrated Device Technology, a company totally predicated on and dedicated to implementing high-performance CMOS products, is on the leading edge of this dramatic change.

Beginning with the introduction of the industry's fastest CMOS 2K x 8 Static RAM, IDT has grown into a company with multiple divisions producing a wide range of high-speed CMOS circuits that are, in almost every case, the fastest available. These advanced products are produced with IDT's proprietary CMOS technology, a twin-well, dry-etched, stepperaligned process utilizing progressively smaller dimensions.

From inception, IDT's product strategy has been to apply the advantages of its extremely fast CMOS technology to produce the integrated circuit elements required to implement high-performance digital systems. IDT's goal is to provide the circuits necessary to create systems which are far superior to previous generations in performance, reliability, cost, weight, and size. Many of the company's innovative product designs offer higher levels of integration, advanced architectures, higher density packaging and system enhancement features that are establishing tomorrow's industry standards. The company is committed to providing its customers with an everexpanding series of these high-speed, lower-power IC solutions to system design needs.

IDT's commitment, however, extends beyond state-of-theart technology and advanced products to providing the highest level of customer service and satisfaction in the industry. Manufacturing products to exacting quality standards that provide excellent, long-term reliability is given the same level of importance and priority as device performance. IDT is also dedicated to delivering these high-quality advanced products on time. The company would like to be known not only for its technological capabilities, but also for providing its customers with quick, responsive, and courteous service.

IDT's product families are available in both commercial and military grades. As a bonus, commercial customers obtain the benefits of military processing disciplines, established to meet or exceed the stringent criteria of the applicable military specifications.

IDT is the leading U.S. supplier of high-speed CMOS circuits. The company's high-performance fast SRAM, FCT logic, high-density modules, FIFOs, multi-port memories, BiCMOS ECL I/O memories, RISC SubSystems, and the 32-and 64-bit RISC microprocessor families complement each other to provide high-speed CMOS solutions for a wide range of applications and systems.

Dedicated to maintaining its leadership position as a stateof-the-art IC manufacturer, IDT will continue to focus on maintaining its technology edge as well as developing a broader range of innovative products. New products and speed enhancements are continuously being added to each of the existing product families, and additional product families are being introduced. Contact your IDT field representative or factory marketing engineer for information on the most current product offerings. If you're building state-of-the-art equipment, IDT wants to help you solve your design problems.

# IDT MILITARY AND DESC-SMD PROGRAM

IDT is a leading supplier of military, high-speed CMOS circuits. The company's high-performance Static RAMs, FCT Logic Family, Complex Logic (CLP), FIFOs, Specialty Memories (SMP), ECL I/O BiCMOS Memories, 32-bit RISC Microprocessor, RISC Subsystems and high-density Subsystems Modules product lines complement each other to provide high-speed CMOS solutions to a wide range of military applications and systems. Most of these product lines offer Class B products which are fully compliant to the latest revision of MIL-STD-883, Paragraph 1.2.1. In addition, IDT offers Radiation Tolerant (RT), as well as Radiation Enhanced (RE), products.

IDT has an active program with the Defense Electronic Supply Center (DESC) to list all of IDT's military compliant devices on Standard Military Drawings (SMD). The SMD program allows standardization of militarized products and reduction of the proliferation of non-standard source control drawings. This program will go far toward reducing the need for each defense contractor to make separate specification control drawings for purchased parts. IDT plans to have SMDs for many of its product offerings. Presently, IDT has 88 devices which are listed or pending listing. The devices are from IDT's SRAM, FCT Logic family, Complex Logic (CLP), FIFOs and Specialty Memories (SMP) product families. IDT expects to add another 20 devices to the SMD program in the near future. Users should contact either IDT or DESC for current status of products in the SMD program.

| SMD        |                |            | SMD         |            | SMD                |

|------------|----------------|------------|-------------|------------|--------------------|

| SRAM IDT   |                | 5962-93177 | 7206L       | 5962-88654 | 54FCT640/A         |

|            |                | 5962-92069 | 72141L      | 5962-88655 | 54FCT534/A         |

| 84036      | 6116           | 5962-92101 | 72215LB     | 5962-89767 | 54FCT540/A         |

| 5962-88740 | 6116LA         | 5962-93138 | 72220L      | 5962-89766 | 54FCT541/A         |

| 84132      | 6167           | 5962-92057 | 72225LB     | 5962-89733 | 54FCT191/A         |

| 5962-86015 | 7187           | 5962-93189 | 72245LB     | 5962-89732 | 54FCT241/A         |

| 5962-86859 | 6198/7198/7188 | 5962-91757 | 72200L      | 5962-89652 | 54FCT399/A         |

| 5962-86705 | 6168           |            |             | 5962-89513 | 54FCT574/A         |

| 5962-85525 | 7164           |            |             | 5962-89731 | 54FCT833A/B        |

| 5962-88552 | 71256L         | CLP        |             | 5962-89730 | 54FCT543/A         |

| 5962-88662 | 71256S         | 5962-87708 | 39C10B & C  | 5962-90901 | 29FCT52A/B/C       |

| 5962-88611 | 71682L         | 5962-88533 | 49C460A/B/C | 5962-92205 | 29FCT520AT/BT/CT   |

| 5962-89891 | 7198           | 5962-88613 | 39C60/A     | 5962-92157 | 49FCT805/A/806/A   |

| 5962-89892 | 6198           | 5962-88643 | 49C410      | 5962-92233 | 54FCT138T/AT/CT    |

| 5962-89690 | 6116           | 5962-86873 | 7216L       | 5962-92208 | 54FCT157T/AT/CT    |

| 5962-38294 | 7164           | 5962-87686 | 7217L       | 5962-92208 | 54FCT161T/AT/CT    |

| 5962-89692 | 7188           | 5962-88733 | 7210        |            |                    |

| 5962-89712 | 71982          | 5962-92122 | 49C465/A    | 5962-92210 | 54FCT163T/AT/CT    |

| 5962-89790 | 71682          | 0002 02122 | 400400//    | 5962-90669 | 54FCT193/A         |

|            |                | LOGIC      | IDT         | 5962-92213 | 54FCT240T/AT/CT    |

| SMP        |                |            |             | 5962-92232 | 54FCT241T/AT/CT    |

|            |                | 5962-87630 | 54FCT244/A  | 5962-92203 | 54FCT244T/AT/CT    |

| 5962-86875 | 7130/7140      | 5962-87629 | 54FCT245/A  | 5962-92214 | 54FCT245T/AT/CT    |

| 5962-87002 | 7132/7142      | 5962-86862 | 54FCT299/A  | 5962-92211 | 54FCT257T/AT/CT    |

| 5962-88610 | 7133SA/7143SA  | 5962-87644 | 54FCT373/A  | 5962-92215 | 54FCT273T/AT/CT    |

| 5962-88665 | 7133LA/7143LA  | 5962-87628 | 54FCT374/A  | 5962-92216 | 54FCT299T/AT/CT    |

| 5962-89764 | 7134           | 5962-87627 | 54FCT377/A  | 5962-92217 | 54FCT373T/AT/CT    |

| 5962-91508 | 7006           | 5962-87654 | 54FCT138/A  | 5962-92218 | 54FCT374T/AT/CT    |

| 5962-91617 | 7025           | 5962-87655 | 54FCT240/A  | 5962-92219 | 54FCT377T/AT/CT    |

| 5962-91662 | 7024           | 5962-87656 | 54FCT273/A  | 5962-92212 | 54FCT399T/AT/CT    |

| 5962-93153 | 7014S          | 5962-89533 | 54FCT861A/B | 5962-92234 | 54FCT521T/AT/BT/CT |

|            |                | 5962-89506 | 54FCT827A/B | 5962-92236 | 54FCT534T/AT/CT    |

| FIFO       | IDT            | 5962-88575 | 54FCT841A/B | 5962-92220 | 54FCT540T/AT/CT    |

| 5962-87531 | 7201LA         | 5962-88608 | 54FCT821A/B | 5962-92237 | 54FCT541T/AT/CT    |

| 5962-86846 | 72404L         | 5962-88543 | 54FCT521/A  | 5962-92221 | 54FCT543T/AT/CT    |

| 5962-88669 | 7203S          | 5962-88640 | 54FCT161/A  | 5962-92238 | 54FCT573T/AT/CT    |

| 5962-89568 | 72035<br>7204L | 5962-88639 | 54FCT573/A  | 5962-92222 | 54FCT574T/AT/CT    |

|            |                | 5962-88656 | 54FCT823A/B | 5962-92244 | 54FCT645T/AT/CT    |

| 5962-89536 | 7202LA         | 5962-88657 | 54FCT163/A  | 5962-92223 | 54FCT646T/AT/CT    |

| 5962-89863 | 7201SA         | 5962-88674 | 54FCT825A/B | 5962-92246 | 54FCT652T/AT/CT    |

| 5962-89523 | 72403L         | 5962-88661 | 54FCT863A/B | 5962-92225 | 54FCT821AT/BT/CT   |

| 5962-89666 | 7200L          | 5962-88736 | 29FCT520A/B | 5962-92229 | 54FCT823AT/BT/CT   |

| 5962-89942 | 72103L         | 5962-88775 | 54FCT646/A  | 5962-92230 | 54FCT825AT/BT/CT   |

| 5962-89943 | 72104L         | 5962-89508 | 54FCT139/A  | 5962-92247 | 54FCT827AT/BT/CT   |

| 5962-89567 | 7203L          | 5962-89665 | 54FCT824A/B |            |                    |

| 5962-90715 | 7204S          | 5962-88651 | 54FCT533/A  | RISC       |                    |

| 5962-91677 | 7205L          | 5962-88653 | 54FCT645/A  | 5962-94550 | 79R3081E           |

|            |                |            |             |            |                    |

|            | SMD                | LOGIC                    | IDT                                | 5962-92244 | 54FCT645T/AT/CT  |

|------------|--------------------|--------------------------|------------------------------------|------------|------------------|

| SRAM       | IDT                | 5962-87630               | 54FCT244/A                         | 5962-92223 | 54FCT646T/AT/CT  |

| 84036      | 6116               | 5962-87629               | 54FCT245/A                         | 5962-92246 | 54FCT652T/AT/CT  |

| 5962-88740 | 6116LA             | 5962-86862               | 54FCT299/A                         | 5962-92225 | 54FCT821AT/BT/CT |

| 84132      | 6167               | 5962-87644               | 54FCT373/A                         | 5962-92229 | 54FCT823AT/BT/CT |

| 5962-86015 | 7187               | 5962-87628               | 54FCT374/A                         | 5962-92230 | 54FCT825AT/BT/CT |

| 5962-86859 | 6198/7198/7188     | 5962-87627               | 54FCT377/A                         | 5962-92247 | 54FCT827AT/BT/CT |

| 5962-86705 | 6168               | 5962-87654               | 54FCT138/A                         |            |                  |

| 5962-85525 | 7164               | 5962-87655               | 54FCT240/A                         | RISC       | IDT              |

| 5962-88552 | 71256L             | 5962-87656               | 54FCT273/A                         | 5962-94550 | 79R3081E         |

| 5962-88662 | 71256S             | 5962-89533               | 54FCT861A/B                        | 0002 04000 |                  |

| 5962-88611 | 712503<br>71682L   | 5962-89506               | 54FCT827A/B                        |            |                  |

| 5962-89891 | 7198               | 5962-88575               | 54FCT841A/B                        |            |                  |

|            |                    | 5962-88608               | 54FCT821A/B                        |            |                  |

| 5962-89892 | 6198               | 5962-88543               | 54FCT521/A                         |            |                  |

| 5962-89690 | 6116               |                          | 54FCT161/A                         |            |                  |

| 5962-38294 | 7164               | 5962-88640               |                                    |            |                  |

| 5962-89692 | 7188               | 5962-88639               | 54FCT573/A                         |            |                  |

| 5962-89712 | 71982              | 5962-88656               | 54FCT823A/B                        |            |                  |

| 5962-89790 | 71682              | 5962-88657               | 54FCT163/A                         |            |                  |

|            |                    | 5962-88674               | 54FCT825A/B                        |            |                  |

| SMP        |                    | 5962-88661               | 54FCT863A/B                        |            |                  |

| 5962-86875 | 7130/7140          | 5962-88736               | 29FCT520A/B                        |            |                  |

| 5962-87002 | 7132/7142          | 5962-88775               | 54FCT646/A                         |            |                  |

| 5962-88610 | 7133SA/7143SA      | 5962-89508               | 54FCT139/A                         |            |                  |

| 5962-88665 | 7133LA/7143LA      | 5962-89665               | 54FCT824A/B                        |            |                  |

| 5962-89764 | 7134               | 5962-88651               | 54FCT533/A                         |            |                  |

| 5962-91508 | 7006               | 5962-88653               | 54FCT645/A                         |            |                  |

| 5962-91617 | 7025               | 5962-88654               | 54FCT640/A                         |            |                  |

| 5962-91662 | 7024               | 5962-88655               | 54FCT534/A                         |            |                  |

| 5962-93153 | 7014S              | 5962-89767               | 54FCT540/A                         |            |                  |

|            |                    | 5962-89766               | 54FCT541/A                         |            |                  |

| FIFO       | IDT                | 5962-89733               | 54FCT191/A                         |            |                  |

| 5962-87531 | 7201LA             | 5962-89732               | 54FCT241/A                         |            |                  |

| 5962-86846 | 72404L             | 5962-89652               | 54FCT399/A                         |            |                  |

| 5962-88669 | 7203S              | 5962-89513               | 54FCT574/A                         |            |                  |

| 5962-89568 | 7204L              | 5962-89731               | 54FCT833A/B                        |            |                  |

| 5962-89536 | 7202LA             | 5962-89730               | 54FCT543/A                         |            |                  |

| 5962-89863 | 7201SA             | 5962-90901               | 29FCT52A/B/C                       |            |                  |

| 5962-89523 | 72403L             | 5962-92205               | 29FCT520AT/BT/CT                   |            |                  |

| 5962-89666 | 7200L              | 5962-92157               | 49FCT805/A/806/A                   |            |                  |

| 5962-89942 | 72103L             | 5962-92233               | 54FCT138T/AT/CT                    |            |                  |

| 5962-89943 | 72104L             | 5962-92208               | 54FCT157T/AT/CT                    |            |                  |

| 5962-89567 | 7203L              | 5962-92209               | 54FCT161T/AT/CT                    |            |                  |

| 5962-90715 | 7204S              | 5962-92210               | 54FCT163T/AT/CT                    |            |                  |

| 5962-91677 | 7205L              | 5962-90669               | 54FCT193/A                         |            |                  |

| 5962-93177 | 7206L              | 5962-92213               | 54FCT240T/AT/CT                    |            |                  |

| 5962-92069 | 7200L<br>72141L    | 5962-92232               | 54FCT241T/AT/CT                    |            |                  |

| 5962-92101 | 72141L<br>72215LB  | 5962-92203               | 54FCT244T/AT/CT                    |            |                  |

| 5962-93138 | 72220L             | 5962-92214               | 54FCT245T/AT/CT                    |            |                  |

|            | 72220L<br>72225LB  | 5962-92211               | 54FCT257T/AT/CT                    |            |                  |

| 5962-92057 | 72225LB<br>72245LB | 5962-92215               | 54FCT273T/AT/CT                    |            |                  |

| 5962-93189 |                    | 5962-92216               | 54FCT299T/AT/CT                    |            |                  |

| 5962-91757 | 72200L             | 5962-92217               | 54FCT373T/AT/CT                    |            |                  |

|            | IDT                | 5962-92218               | 54FCT374T/AT/CT                    |            |                  |

| CLP        |                    | 5962-92218               | 54FCT377T/AT/CT                    |            |                  |

| 5962-87708 | 39C10B & C         | 5962-92219               | 54FCT399T/AT/CT                    |            |                  |

| 5962-88533 | 49C460A/B/C        |                          | 54FCT521T/AT/BT/CT                 |            |                  |

| 5962-88613 | 39C60/A            | 5962-92234               |                                    |            |                  |

| 5962-88643 | 49C410             | 5962-92236               | 54FCT534T/AT/CT                    |            |                  |

| 5962-86873 | 7216L              | 5962-92220               | 54FCT540T/AT/CT                    |            |                  |

| 5962-87686 | 7217L              | 5962-92237               | 54FCT541T/AT/CT                    |            |                  |

| 5962-88733 | 7210               | 5962-92221               | 54FCT543T/AT/CT                    |            |                  |

|            |                    |                          |                                    |            |                  |

| 5962-92122 | 49C465/A           | 5962-92238<br>5962-92222 | 54FCT573T/AT/CT<br>54FCT574T/AT/CT |            |                  |

# **RADIATION HARDENED TECHNOLOGY**

On an order by order basis IDT can manufacture and supply radiation hardened products for military/aerospace applications. Utilizing special processing and starting materials, IDT's radiation hardened devices survive in hostile radiation environments. In Total Dose, Dose Rate, and environments where single event upset is of concern, IDT products are designed to continue functioning without loss of performance. IDT can supply most of its products on these processes. Total Dose radiation testing is performed in-house on an ARACOR X-Ray system. External facilities are utilized for device research on gamma cell, LINAC and other radiation equipment. IDT has an on-going research and development program for improving radiation handling capabilities (See "IDT Radiation Tolerant/Enhanced Products for Radiation Environments" in Section 3) of IDT products/processes.

# **KNOWN GOOD DIE**

Emerging high performance electronic systems require smaller and smaller form-factors. IDT is meeting these design challenges by offering Known Good Die (KGD) in addition to its broad array of small form-factor packages. The IDT KGD manufacturing process enables IDT to offer die that have received the same electrical tests, burn-in, and speed sorting at elevated temperatures as shipped packaged products. Via IDT KGD, users are able to manufacture cost-efficient and reliable multi-chip modules (MCMs), hybrids, and other highdensity interconnect products. All IDT KGD, at the completion of their test flow, receive 100% die visual inspection and are packed within Gel-Pak<sup>™</sup> containers. The Gel-Pak<sup>™</sup> containers are then placed in vacuum sealed ESD wrappers prior to shipping. Delivered KGD products have superior yield, quality, and reliability over standard raw die offerings. Most IDT products can be offered as "KGD", and commercial, industrial or military temperatures can be considered.

1

# IDT LEADING EDGE CEMOS TECHNOLOGY

## THE PRODUCTIVITY REVOLUTION

New microprocessor-based systems enhance productivity by improving the accessibility and usability of information. By connecting systems through a network, data can be transmitted instantly, anywhere in the world. Using affordable computing systems, information can be located, retrieved, analyzed, and displayed as needed.

The systems that provide these capabilities are built around the microprocessor, and IDT's products maximize the potential of these microprocessor-based systems. As sales of these productivity-enhancing systems grow, so do the markets for IDT products.

# INNOVATIVE PRODUCTS FOR MORE PRO-DUCTIVE SYSTEMS

IDT markets products from four product groups: SRAMs, Specialty Memory Products, Logic products, and RISC Microprocessors.

Our strategy is to define, develop, and manufacture products that help our customers deliver greater value to their customers. We develop products in partnership with customers who are leaders in markets that fuel the productivity revolution, such as high-performance desktop and server computing, data communications and networking, and office automation. These customers use our products to build systems that are faster, less costly, and more productive.

Our customers are also building systems that are energyefficient. Designers are developing 3.3V systems to comply with the governmental Energy Star requirements. We have a competitive advantage because our CMOS VII technology was specifically designed to maintain higher speeds at this lower voltage.

Customers using high-performance microprocessors to build desktop computers and file servers can improve the performance of their products by incorporating cache memory systems. Cache memory systems are constructed with highspeed SRAMs, cache tag memories, and control logic. We are a recognized technology leader in SRAMs and the world's leading supplier of cache tag memories. Today, we supply these products both as discrete components and in the form of complete high-density cache memory modules used with PowerPC<sup>™</sup>, Intel 486<sup>™</sup>, Pentium<sup>™</sup> processor, and our own RISC microprocessors. We are working with manufacturers of both the microprocessors and their associated chipsets to develop new cache memory products that will maximize the performance of future microprocessor-based systems.

Customers building digital data communications and networking equipment use FIFO and dual-port memory products that are designed for these applications. FIFOs and dual-ports are uniquely suited to exchanging data between systems that operate at different speeds or use different protocols, a

R4600 and Orion are trademarks of Integrated Device Technology, Inc PowerPC is a trademark of Motorola Penitum processor and 1466 are trademarks of Intel Corporation Windows NT is a trademark of Microsoft Corporation UNIX is a registered trademark of AT&T common requirement in communications systems. We are the market leader in these SMP product areas, and we have introduced the industry's largest number of product and technology innovations over the years. Development work is now under way to design a family of products for the emerging ATM (Asynchronous Transfer Mode) market, which is expected to grow dramatically over the next several years.

Every high-performance system needs high-speed logic parts to connect memories, microprocessors, communications circuits, and other system components. We have been the performance leader in high-speed FCT logic devices since we pioneered these products in 1985, and we currently offer more than 150 different logic products. We have also introduced two new ultra-small packaging choices for our logic products, ideal for use in compact desktop and portable systems, as well as in PCMCIA cards, which are credit-card sized modules that add functionality to personal computers.

Customers who build high-performance office automation and communications systems are taking advantage of our family of 32-bit and 64-bit software-compatible RISC microprocessors, based on the extendable architecture developed by MIPS Technologies. The 20+ different microprocessors in our RISC family offer customers a wider range of price/ performance choices than competing microprocessor families. Software compatibility allows designers to choose one microprocessor for a particular product and then easily upgrade to a higher-performing version, in many cases simply by removing one device and plugging in another. Our 32-bit RISC microprocessor products are winning acceptance in a variety of embedded applications, including laser printers, network routers, and graphics display terminals.

In fiscal 1994, we introduced our 64-bit R4600<sup>™</sup> Orion<sup>™</sup> processor. This microprocessor provides leading-edge performance for embedded applications, such as laser printers and networking systems, and is also used in file servers and workstations that run UNIX® and Microsoft's new Windows NT<sup>™</sup> operating systems.

## ADVANCING OUR OWN PRODUCTIVITY

We participate in the productivity revolution both as a technology enabler and as a beneficiary. While our products enhance the productivity of our customers' microprocessorbased systems, we improve our own internal productivity by developing new manufacturing technologies, re-engineering workflows, and by adopting new electronic systems.

One of the primary ways we increase internal productivity is by developing and implementing advanced technologies. New process technologies result in smaller die, and new production equipment allows the use of larger wafers. The combination of smaller die and larger wafers allows us to generate significantly more devices per wafer. Migrating to an advanced 0.6-micron CMOS fabrication process in fiscal 1994 not only resulted in smaller die, it also improved product performance, increased yields, and lowered unit costs. Our new CMOS VIII 0.5-micron process is expected to extend our process technology momentum.

Because we have our own fabrication facilities, we control critical manufacturing operations, giving us a competitive advantage as we continue to improve our productivity. IDT has two sub-micron 6" wafer fabrication facilities, located in San José and Salinas, California, and a high-volume assembly and test facility in Penang, Malaysia. To support future growth, we have built a new sub-micron 8" wafer fabrication facility in Hillsboro, Oregon that will be fully operational in fiscal 1997, and an additional 40,000-square-foot building for test and assembly in Penang.

Manufacturing productivity is also improved by adjusting work schedules to increase the output from equipment already in place and improving product development cycles. Updated computer-aided design tools shorten product design times and improve the functionality of new product prototypes. For example, the R4600 Orion processor was designed by Quantum Effect Design, Inc., an IDT affiliate operating on-site, in just 21 months, which is a remarkably short development cycle for such a complex product.

Improvements in quality are the direct result of improvements in productivity. Our manufacturing quality levels have been improving for several years. In fiscal 1993, IDT was one of the first semiconductor companies to achieve ISO 9000 registration for wafer fabrication activities. ISO 9000 is a worldwide quality systems standard, and certification provides an important competitive advantage in both domestic and international markets. All of our manufacturing facilities are now ISO 9000 certified.

Customer service and support have been directly enhanced by many of our productivity improvements. New planning and scheduling systems allow us to improve our efficiency and predictability for meeting delivery commitments to customers. Expanded computer systems allow the migration of order services to field sales offices, bringing support closer to the customer. Increased use of EDI (Electronic Data Interchange) allows customers to directly enter orders and check order status, resulting in more timely information with less paperwork.

Improving productivity continues to be a key issue for technology companies. By continuing to improve internal productivity and manufacture quality products that support the productivity revolution, we expect to enhance the value of our company to our shareholders, our employees, and our customers.

# SUPERIOR QUALITY AND RELIABILITY

Maintaining the highest standards of quality in the industry on all products is the basis of Integrated Device Technology's manufacturing systems and procedures. From inception, quality and reliability are built into all of IDT's products. Quality is "designed in" at every stage of manufacturing – as opposed to being "tested-in" later – in order to ensure impeccable performance.

Dedicated commitment to fine workmanship, along with development of rigid controls throughout wafer fab, device assembly and electrical test, create inherently reliable products. Incoming materials are subjected to careful inspections. Quality monitors, or inspections, are performed throughout the manufacturing flow.

IDT military grade monolithic hermetic products are designed to meet or exceed the demanding Class B reliability levels of MIL-STD-883 and MIL-I-38535, as defined by Paragraph 1.2.1 of MIL-STD-883.

Product flow and test procedures for all monolithic hermetic military grade products are in accordance with the latest revision and notice of MIL-STD-883. State-of-the-art production techniques and computer-based test procedures are coupled with tight controls and inspections to ensure that products meet the requirements for 100% screening. Routine quality conformance lot testing is performed as defined in MIL-STD-883, Methods 5004 and 5005.

For IDT module products, screening of the fully assembled substrates is performed, in addition to the monolithic level screening, to assure package integrity and mechanical reliability. All modules receive 100% electrical tests (DC, functional and dynamic switching) to ensure compliance with the "subsystem" specifications.

By maintaining these high standards and rigid controls throughout every step of the manufacturing process, IDT ensures that commercial, industrial and military grade products consistently meet customer requirements for quality, reliability and performance.

### SPECIAL PROGRAMS

**Class S.** IDT also has manufacturing, screening and test capabilities in-house (except X-ray and some Group D tests) to perform Class S processing per MIL-STD-883 and has supplied Class S products on several programs.

Radiation Hardened. IDT has developed and supplied several levels of radiation hardened products for military/ aerospace applications to perform at various levels of dose rate, total dose, single event upset (SEU), upset and latchup. IDT products maintain nearly their same high-performance levels built to these special process requirements. The company has in-house radiation testing capability used both in process development and testing of deliverable product. IDT also has a separate group within the company dedicated to supplying products for radiation hardened applications and to continue research and development of process and products to further improve radiation hardening capabilities.

. . .

TECHNOLOGY AND CAPABILITIES

**GENERAL INFORMATION**

# QUALITY AND RELIABILITY

PACKAGE DIAGRAM OUTLINES

**RISC PROCESSING COMPONENTS**

**RISC SUPPORT COMPONENTS**

RISC DEVELOPMENT SUPPORT PRODUCTS

3

6

# **QSP-QUALITY, SERVICE AND PERFORMANCE**

Quality from the beginning, is the foundation for IDT's commitment to supply consistently high-quality products to our customers. IDT's quality commitment is embodied in its all pervasive Total Quality Commitment (TQC) process. Everyone who influences the quality of the product–from the designer to the shipping clerk–is committed to constantly improving the quality of their actions.

## **IDT QUALITY PHILOSOPHY**

"To make quantitative constant improvement in the quality of our actions that result in the supply of leadership products in conformance to the requirements of our customers."

## **IDT's ASSURANCE STRATEGY FOR TQC**

Measurable standards are essential to the success of TQC. All the processes contributing to the final quality of the product need to be monitored, measured and improved upon through the use of statistical tools.

|              | DEVELOPMENT |

|--------------|-------------|

|              | I           |

|              | FAB         |

|              | I           |

| PRODUCT FLOW | ASSEMBLY    |

|              | 1           |

|              | TEST        |

|              | I           |

|              | SHIP        |

Our customers receive the benefit of our optimized systems. Installed to enhance quality and reliability, these systems provide accurate and timely reporting on the effectiveness of manufacturing controls and the reliability and quality performance of IDT products and services.

> ORDER ENTRY I PRODUCTION CONTROL I SHIPPING I CUSTOMER SUPPORT

These systems and controls concentrate on TQC by focusing on the following key elements:

#### **Statistical Techniques**

SERVICE FLOW

Using statistical techniques, including Statistical Process Control (SPC) to determine whether the product/ processes are under control.

#### Standardization

Implementing policies, procedures and measurement techniques that are common across different operational areas.

#### Documentation

Documenting and training in policies, procedures, measurement techniques and updating through characterization/ capability studies.

#### **Productivity Improvement**

Using constant improvement teams made up from employees at all levels of the organization.

#### Leadership

Focusing on quality as a key business parameter and strategic strength.

#### **Total Employee Participation**

Incorporating the TQC process into the IDT Corporate Culture.

#### **Customer Service**

Supporting the customer, as a partner, through performance review and pro-active problem solving.

#### **People Excellence**

Committing to growing, motivating and retaining people through training, goal setting, performance measurement and review.

#### PRODUCT FLOW

Product quality starts here. IDT has mechanisms and procedures in place that monitor and control the quality of our development activities. From the calibration of design capture libraries through process technology and product characterization that establish whether the performance, ratings and reliability criteria have been met. This includes failure analysis of parts that will improve the prototype product.

At the pre-production stage once again in-house qualification tests assure the quality and reliability of the product. All specifications and manufacturing flows are established and personnel trained before the product is placed into production.

#### Manufacturing

To accomplish continuous improvement during the manufacturing stage, control items are determined for major manufacturing conditions. Data is gathered and statistical techniques are used to control specific manufacturing processes that affect the quality of the product. In-process and final inspections are fed back to earlier processes to improve product quality. All product is burnedin (where applicable) before 100% inspection of electrical characteristics takes place.

Products which pass final inspection are then subject to Quality Assurance and Reliability Tests. This data is used to improve manufacturing processes and provide reliability predictions of field applications.

#### Inventory and Shipping

Controls in shipping focus on ensuring parts are identified and packaged correctly. Care is also taken to see that the correct paperwork is present and the product being shipped was processed correctly.

#### SERVICE FLOW

Quality not only applies to the product but to the quality of -service we give our customers. Services is also constantly monitored for improvement.

#### **Order Procedures**

Checks are made at the order entry stage to ensure the correct processing of the Customer's product. After verification and data entry the Acknowledgements (sent to Customers) are again checked to ensure details are correct. As part of the TQC process, the results of these verifications are analyzed using statistical techniques and corrective actions are taken.

#### **Production Control**

Production Control (P.C.) is responsible for the flow and logistics of material as it moves through the manufacturing processes. The quality of the actions taken by P.C. greatly impinges on the quality of service the customer receives. Because many of our customers have implemented Just-in-Time (JIT) manufacturing practices, IDT as a supplier also has to adopt these same disciplines. As a result, employees receive extensive training and the performance level of key actions are kept under constant review. These key actions include:

Quotation response and accuracy. Scheduling response and accuracy. Response and accuracy of Expedites. Inventory, management, and effectiveness. On time delivery.

#### **Customer Support**

IDT has a worldwide network of sales offices and Technical Development Centers. These provide local customer support on business transactions, and in addition, support customers on applications information, technical services, benchmarking of hardware solutions, and demonstration of various Development Workstations.

The key to continuous improvement is the timely resolution of defects and implementation of the corrective actions. This is no more important than when product failures are found by a customer. When failures are found at the customer's incoming inspection, in the production line, or the field application, the Division Quality Assurance group is the focal point for the investigation of the cause of failure and implementation of the corrective action. IDT constantly improves the level of support we give our customers by monitoring the response time to customers that have detected a product failure. Providing the ecustomer with an analysis of the failure, including corrective actions and the statistical analysis of defects, brings CQI full circle–full support of our customers and their designs with high-quality products.

#### SUMMARY

In 1990, IDT made the commitment to "Leadership through Quality, Service, and Performance Products".

We believe by following that credo IDT and our cusotmers will be successful in the coming decade.With the implementation of the TQC strategy within the company, we will satisfy our goal...

"Leadership through Quality, Service and Performance Products".

# IDT QUALITY CONFORMANCE PROGRAM

# A COMMITMENT TO QUALITY

Integrated Device Technology's monolithic assembly products are designed, manufactured and tested in accordance with the strict controls and procedures required by Military Standards. The documentation, design and manufacturing criteria of the Quality and Reliability Assurance Program were developed and are being maintained to the most current revisions of MIL-38510 as defined by paragraph 1.2.1 of MIL-STD-883 and MIL-STD-883 requirements.