# Integrated Device Technology, Inc.

# 1991 RISC DATA BOOK

# **GENERAL INFORMATION**

TECHNOLOGY AND CAPABILITIES

QUALITY AND RELIABILITY

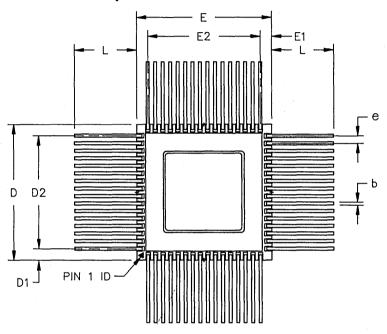

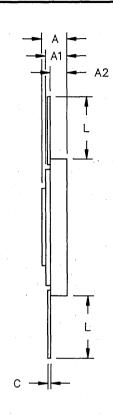

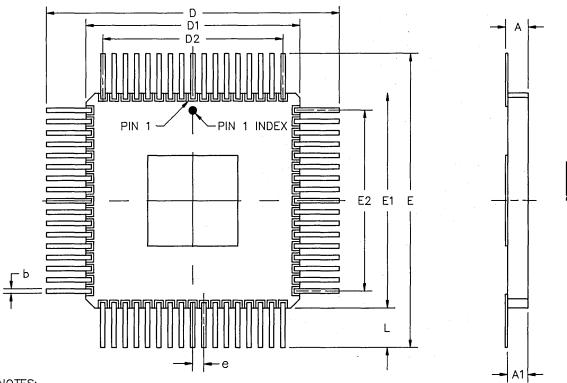

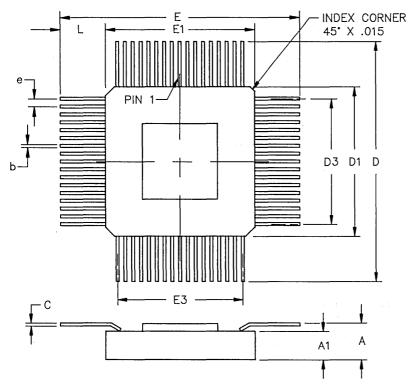

PACKAGE DIAGRAM OUTLINES

RISC PROCESSING COMPONENTS

3)

RISC SUPPORT COMPONENTS

6

RISC MODULE PRODUCTS

7

RISC DEVELOPMENT SUPPORT

3)

APPLICATION NOTES

#### **CONTENTS OVERVIEW**

Historically, Integrated Device Technology has presented our product offerings entirely under one cover. For ease of use for our customers, we have divided the products into four separate data books — Logic, Specialized Memory, RISC and Static RAM.

IDT's 1991 RISC Data Book is comprised of new and revised data sheets and application notes for the RISC and RISC Subsystem product lines. Also included is a current, complete packaging section for all IDT product groups. This section will be updated in each subsequent data book with the latest available packages.

The RISC Data Book's Table of Contents contains a listing of the products contained in the 1991 RISC Data Book, as well as those products which are contained in the other three data books. The numbering scheme is slightly different from the past. The number in the bottom center of the page denotes the section number and the sequence of the data sheet within that section, (i.e. 5.5 would be the fifth data sheet in the fifth section). The number in the lower right hand corner is the page number of that particular data sheet.

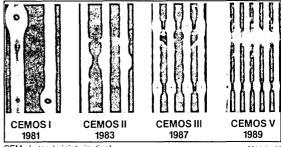

Integrated Device Technology, a recognized leader in high-speed CMOS technology, produces a broad line of products, enabling us to provide a complete CMOS solution to designers of high-performance digital systems. Our products include industry standard devices, as well as products with speed, lower power, package and/or architectural benefits that allow the designer to achieve significantly improved system performance.

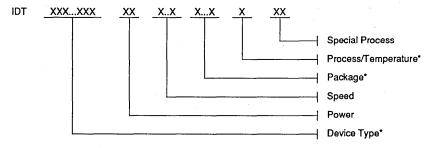

Use this book to find ordering information: Start with the Ordering Information chart at the back of each data sheet or the Cross Reference Guides (in Section 1), along with the Package Outline Index (page 4.2), to compose the complete IDT part number. Reference data on our Technology Capabilities and Quality Commitments are included in separate sections (2 and 3, respectively).

Use this book to find product data: Start with the Table of Contents, organized by product line (page 1.3), or with the Numeric Table of Contents across all product lines (page 1.4). These indexes will direct you to the page on which the complete technical data sheet can be found. Data sheets may be of the following type:

**ADVANCE INFORMATION** — contain initial descriptions, subject to change, for products that are in development, including features and block diagrams.

**PRELIMINARY** — contain descriptions for products soon to be, or recently, released to production, including features, pinouts and block diagrams. Timing data are based on simulation or initial characterization and are subject to change upon full characterization.

**FINAL** — contain minimum and maximum limits specified over the complete supply and temperature range for full production devices.

New products, product performance enhancements, additional package types and new product families are being introduced frequently. Please contact your local IDT sales representative to determine the latest device specifications, package types and product availability.

#### LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of IDT.

- 1. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose fallure to perform can be reasonably expected to cause the fallure of the life support device or system, or to affect its safety or effectiveness.

Note: Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.

# 1991 RISC DATA BOOK SUMMARY TABLE OF CONTENTS

|                                                                                                                                                                                                                                                                         | PAGE                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| GENERAL INFORMATION Contents Overview                                                                                                                                                                                                                                   | 1.2<br>1.3<br>1.4               |

| TECHNOLOGY AND CAPABILITIES  IDTLeading the CMOS Future  IDT Military and DESC-SMD Program.  Radiation Hardened Technology  IDT Leading Edge CEMOS Technology  Surface Mount Technology  State-of-the-Art Facilities and Capabilities  Superior Quality and Reliability | 2.2<br>2.3<br>2.4<br>2.5<br>2.6 |

| QUALITY AND RELIABILITY  Quality, Service and Performance  IDT Quality Conformance Program  Radiation Tolerant/Enhanced/Hardened Products for Radiation Environments                                                                                                    | 3.2                             |

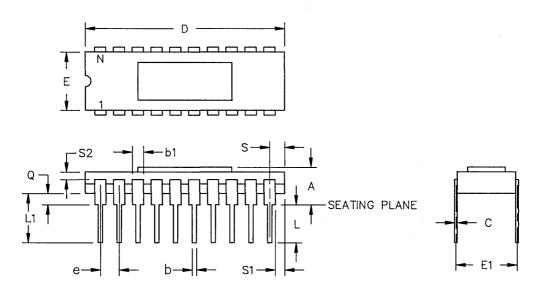

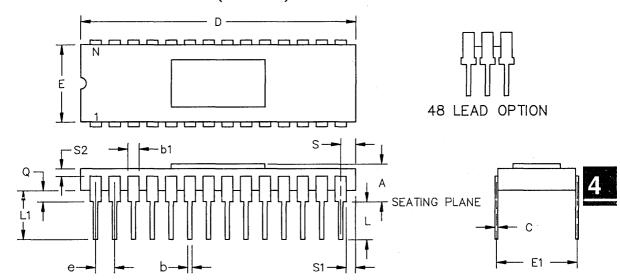

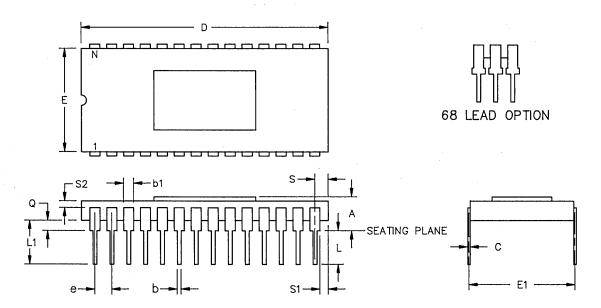

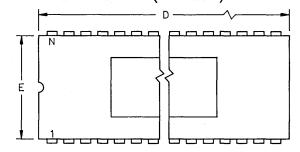

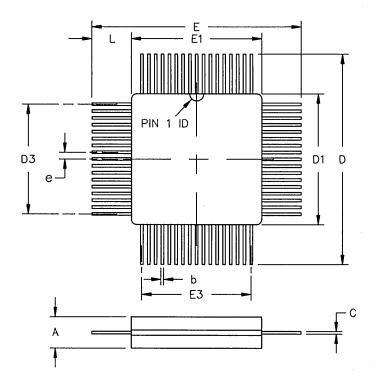

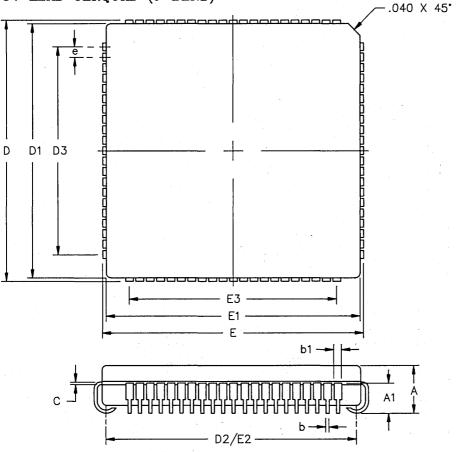

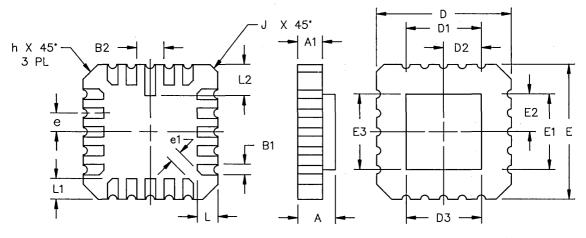

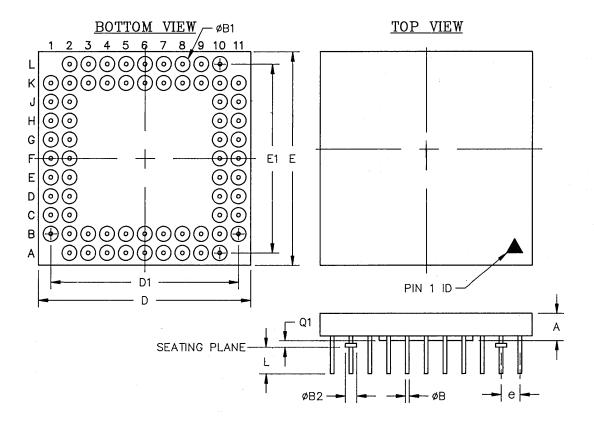

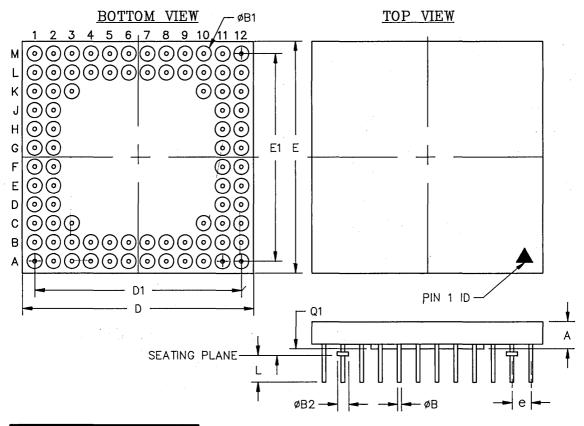

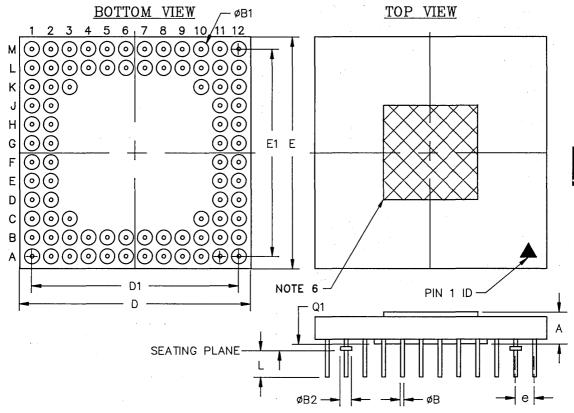

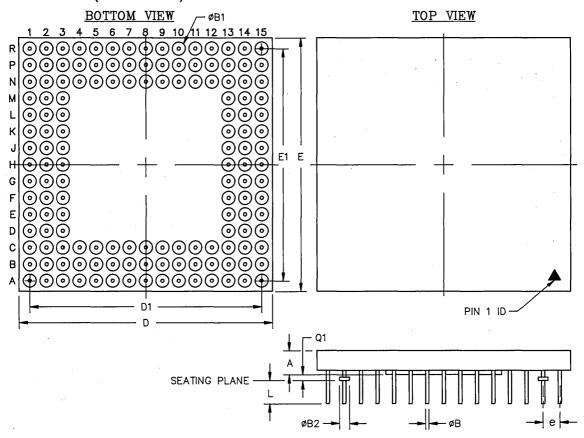

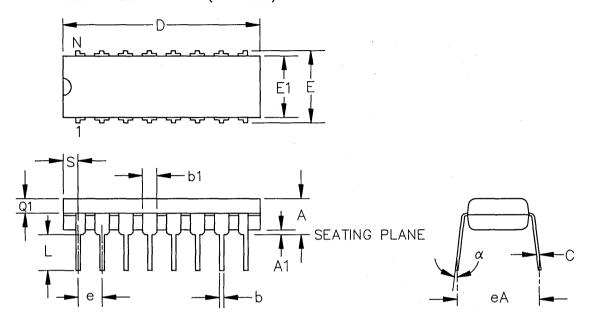

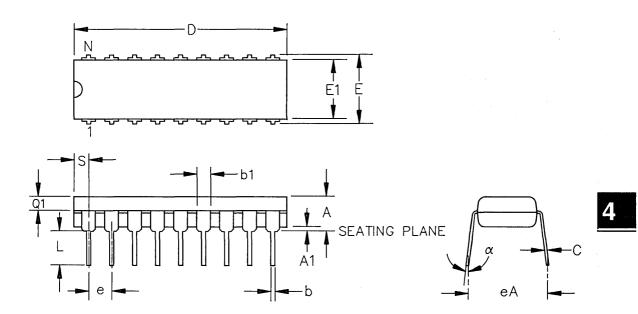

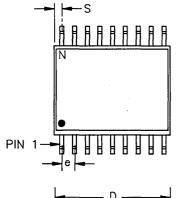

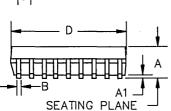

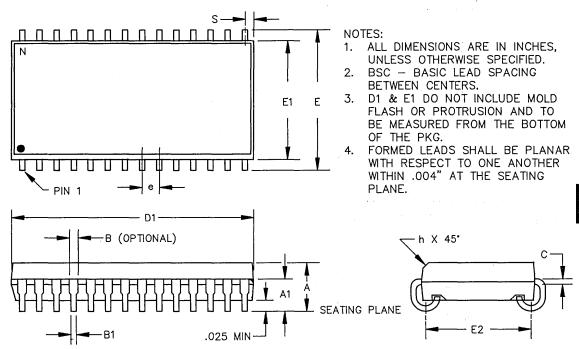

| PACKAGE DIAGRAM OUTLINES Thermal Performance Calculations for IDT's Packages Package Diagram Outline Index Monolithic Package Diagram Outlines                                                                                                                          | 4.2                             |

| RISC PROCESSING COMPONENTS RISC Processing Components Products                                                                                                                                                                                                          | 5.1                             |

| RISC SUPPORT COMPONENTS RISC Support Components Products                                                                                                                                                                                                                | 6.1                             |

| RISC MODULE PRODUCTS RISC Module Products                                                                                                                                                                                                                               | 7.1                             |

| RISC DEVELOPMENT SUPPORT RISC Development Support Products                                                                                                                                                                                                              | 8.1                             |

| APPLICATION NOTES  RISC Microprocessor Products Application Notes                                                                                                                                                                                                       | 9.1<br>9.16                     |

| IDT SALES OFFICE, REPRESENTATIVE AND DISTRIBUTOR LOCATIONS                                                                                                                                                                                                              |                                 |

| SUMMARY TABLE OF CONTENTS (CONTINUED)         | воок  |

|-----------------------------------------------|-------|

| LOGIC DATA BOOK                               |       |

| Complex Logic Products                        | LOGIC |

| Standard Logic Products                       | LOGIC |

| SPECIALIZED MEMORIES DATA BOOK                |       |

| ECL Products                                  | SMP   |

| FIFO Products                                 | SMP   |

| Specialty Memory Products                     | SMP   |

| Specialty Memory Products Subsystems Products | SMP   |

| SRAM DATA BOOK                                |       |

| CEMOS Static RAMs with Power Down Products    | SRAM  |

| High-Speed BICEMOS Static BAM Products        | •     |

# 1991 RISC DATA BOOK TABLE OF CONTENTS

|                      |                                                      | PAGE |

|----------------------|------------------------------------------------------|------|

| GENERAL INFO         | RMATION                                              |      |

|                      | THEATON                                              | 1.1  |

|                      | ontents                                              |      |

| •                    | VIIIIII                                              |      |

|                      | ntents                                               |      |

|                      | g Description                                        |      |

| TECHNOLOGY           | AND CAPABILITIES                                     |      |

|                      | MOS Future                                           | 2.1  |

|                      | SC-SMD Program                                       |      |

| . •                  | Technology                                           |      |

|                      | EMOS Technology                                      |      |

| Surface Mount Tech   | nology                                               | 2.5  |

|                      | lities and Capabilities                              |      |

| Superior Quality and | Reliability                                          | 2.7  |

| QUALITY AND F        |                                                      |      |

| Quality, Service and | Performance                                          | 3.1  |

|                      | ance Program                                         |      |

| Radiation Tolerant/E | nhanced/Hardened Products for Radiation Environments | 3.3  |

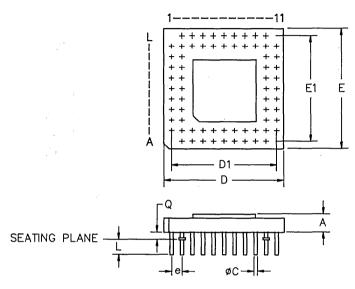

| PACKAGE DIAG         | RAM OUTLINES                                         | •    |

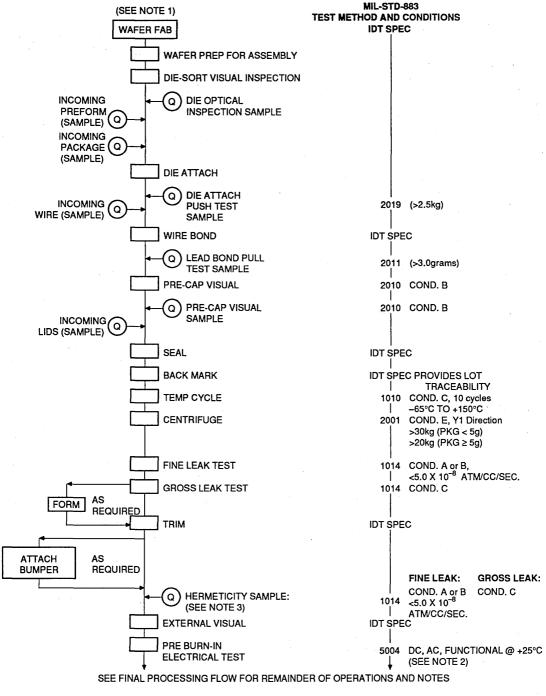

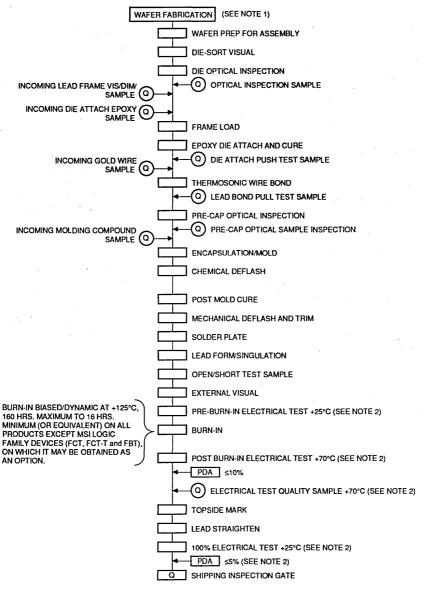

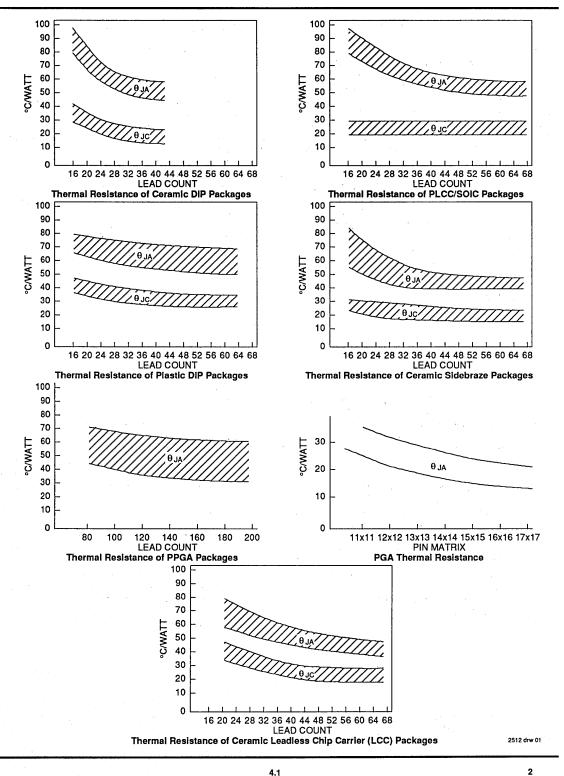

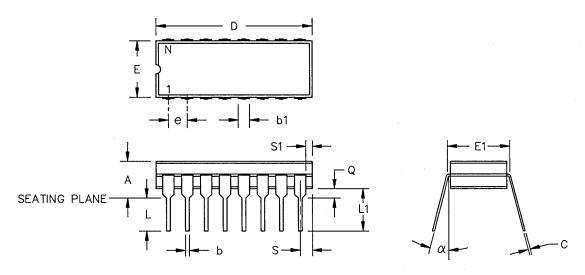

| Thermal Performanc   | e Calculations for IDT's Packages                    | 4.1  |

|                      | utline Index                                         |      |

|                      | Diagram Outlines                                     |      |

| RISC PROCESS         | ING COMPONENTS                                       | *    |

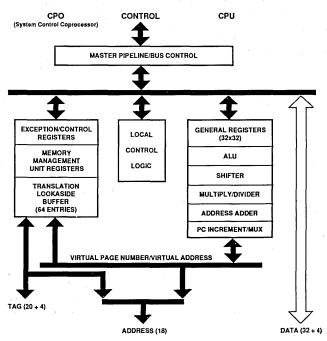

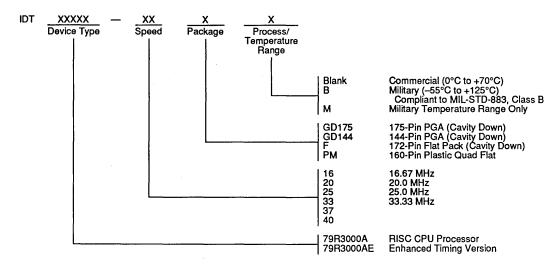

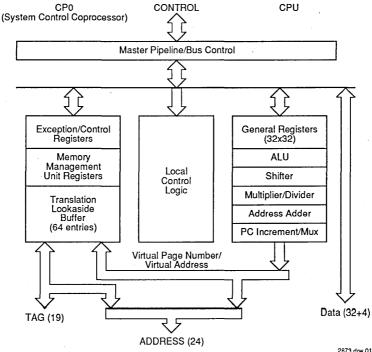

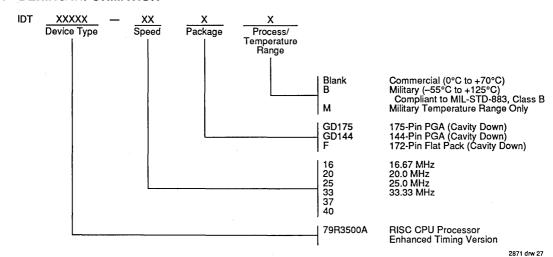

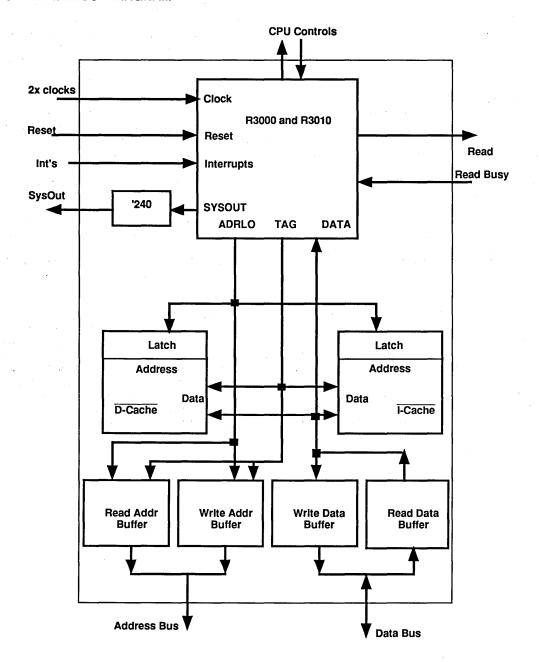

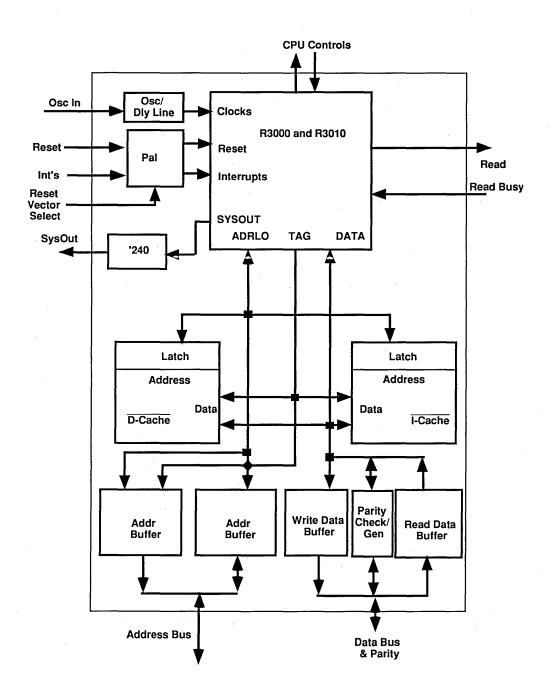

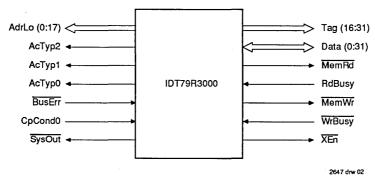

| IDT79R3000A          | RISC CPU Processor                                   | 5.1  |

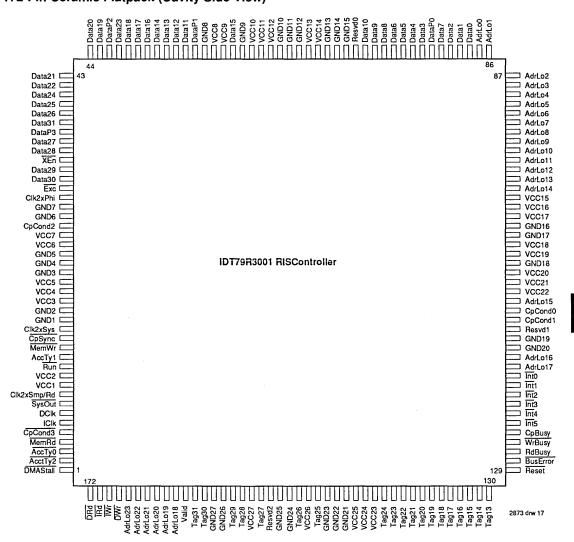

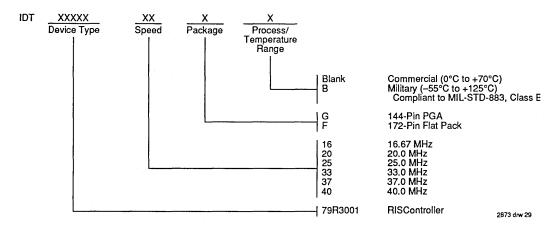

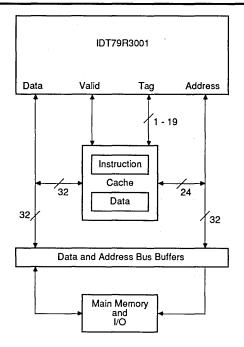

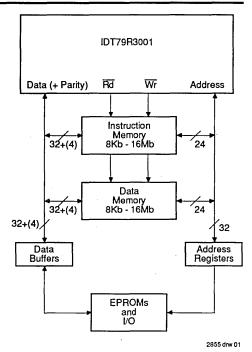

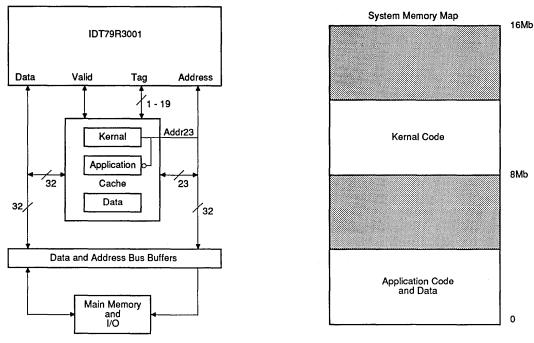

| IDT79R3001           | RISController™                                       | 5.2  |

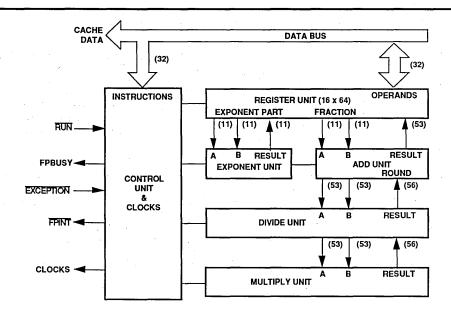

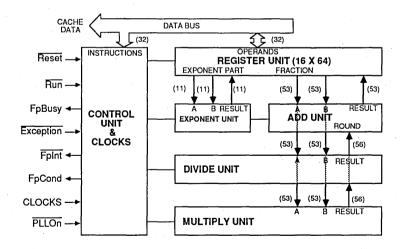

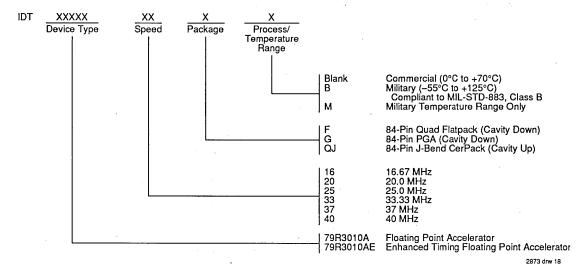

| IDT79R3010A          | RISC Floating Point Accelerator (FPA)                |      |

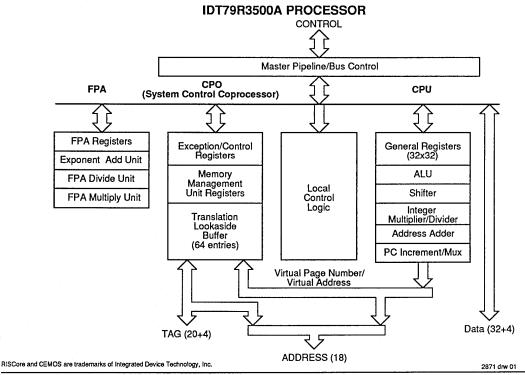

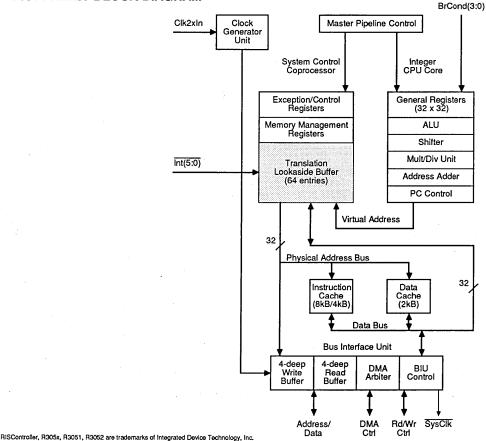

| IDT79R3500           | RISC CPU Processor RISCore™                          |      |

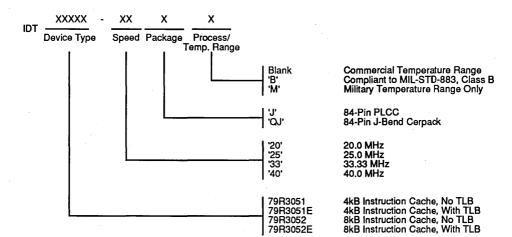

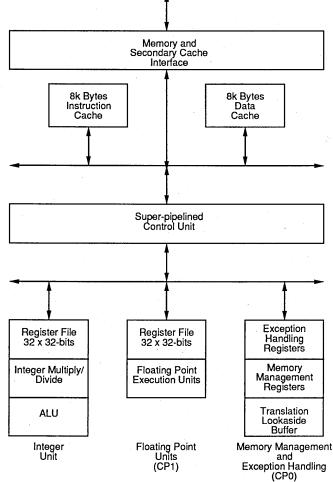

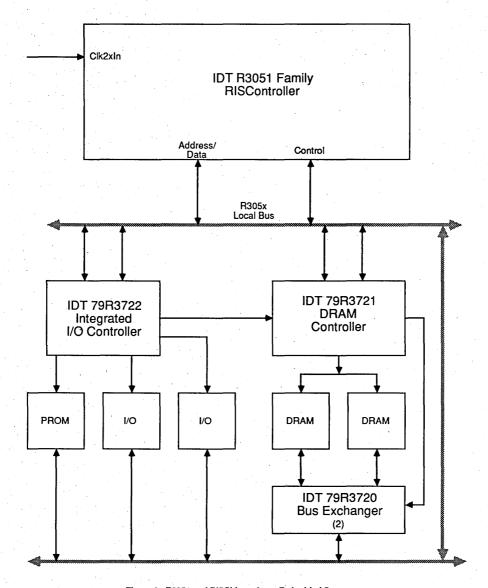

| IDT79R3051           | IDT79R3051 Family of Integrated RISControllers™      |      |

| IDT79R4000           | Third Generation RISC Microprocessor                 | 5.6  |

| RISC SUPPORT         |                                                      |      |

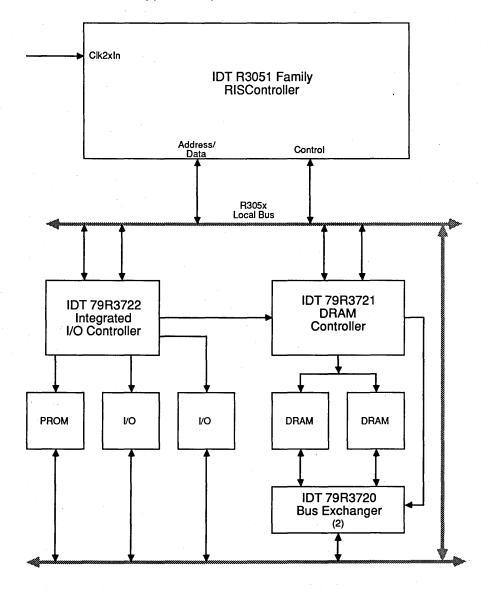

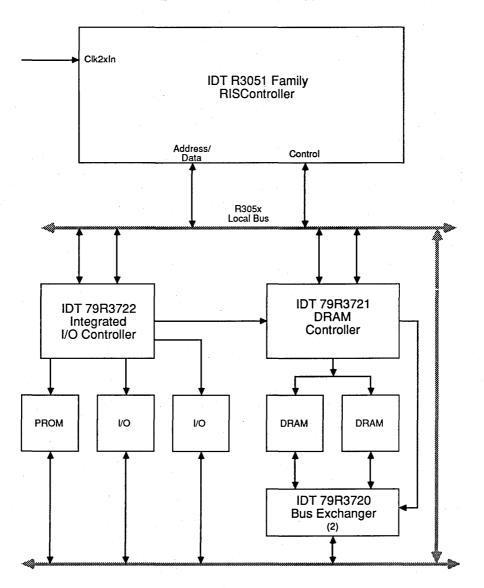

| IDT79R3720           | Bus Exchanger for R3051 Family                       | 6.1  |

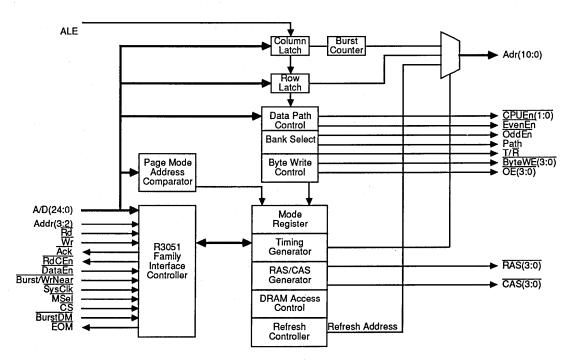

| IDT79R3721           | DRAM Controller for R3051 Family                     |      |

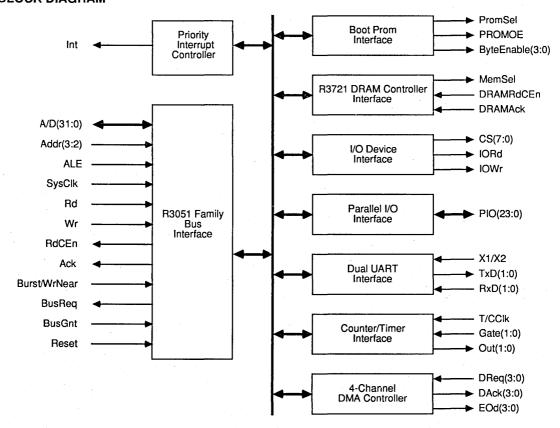

| IDT79R3722           | I/O Interface Controller for R3051 Family            |      |

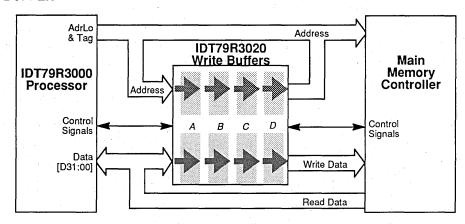

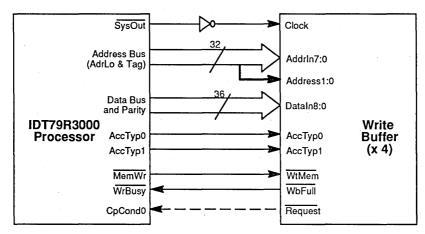

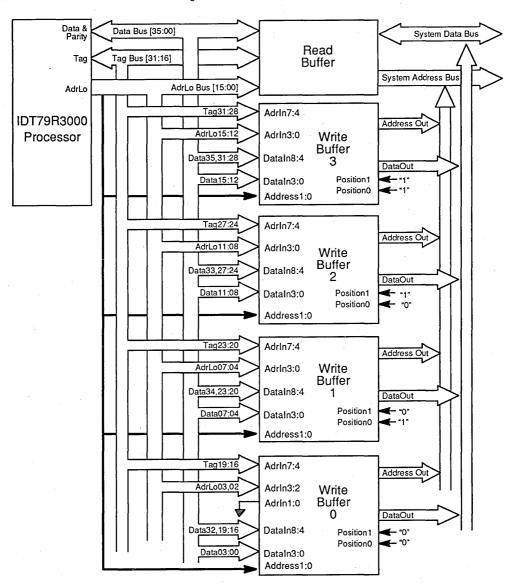

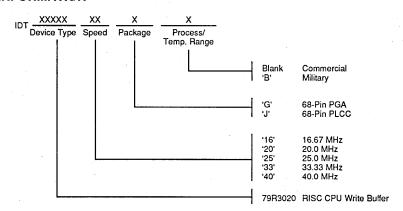

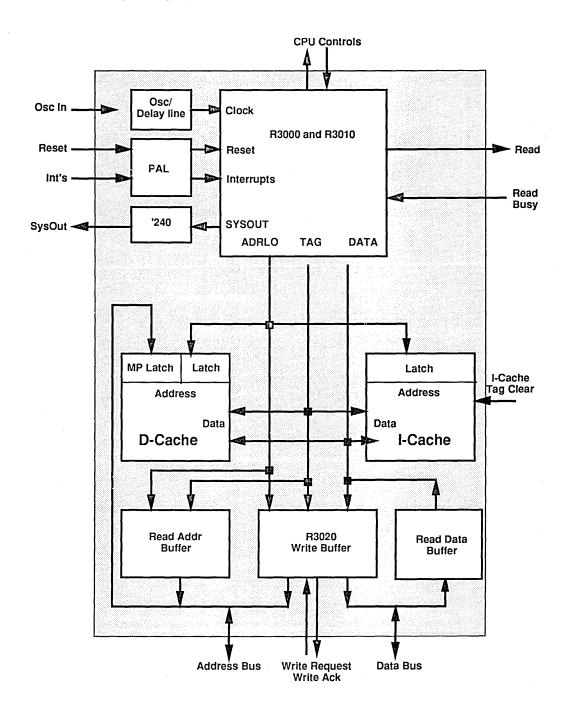

| IDT79R3020           | RISC CPU Write Buffer                                |      |

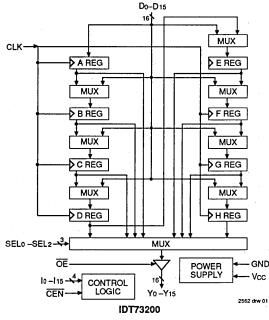

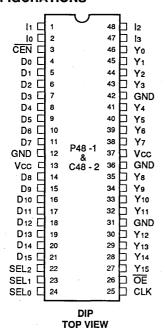

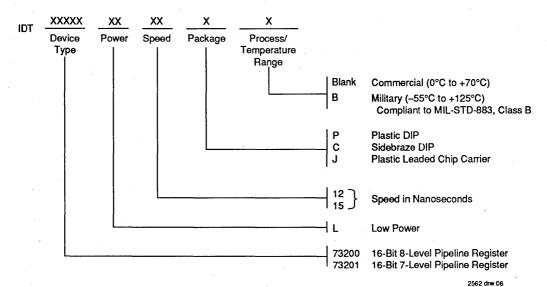

| IDT73200L            | 16-Bit CMOS Multilevel Pipeline Registers            |      |

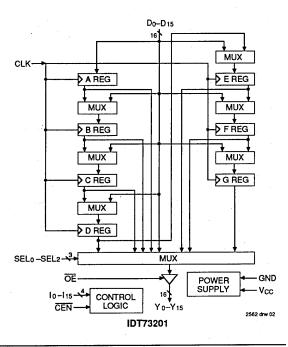

| IDT73201L            | 16-Bit CMOS Multilevel Pipeline Registers            |      |

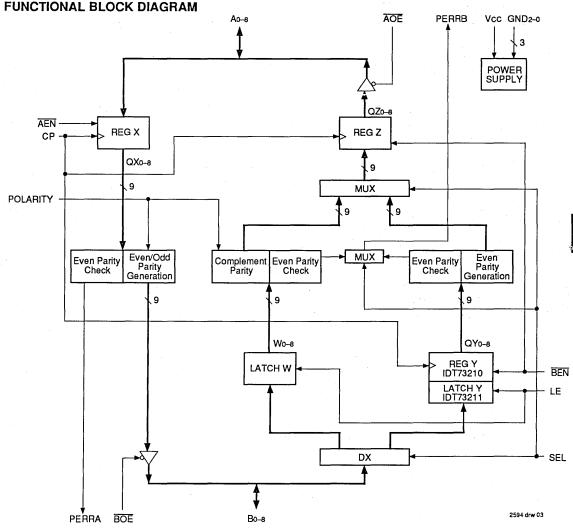

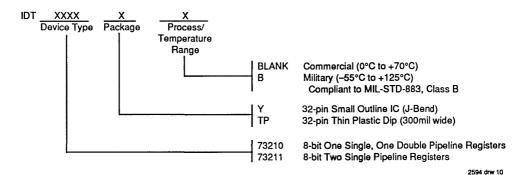

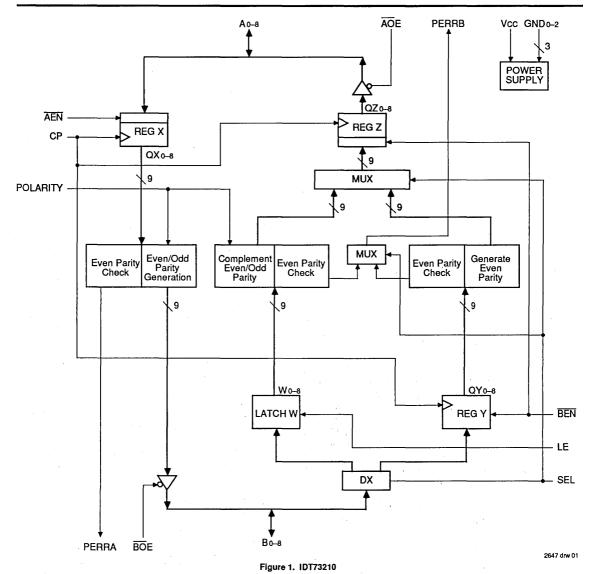

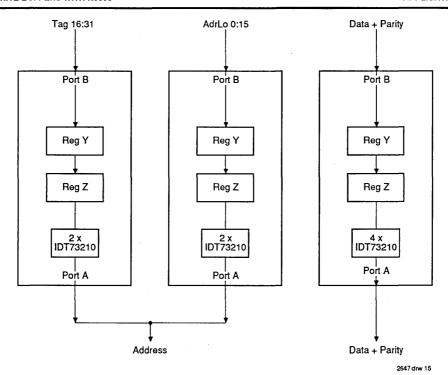

| IDT73210             | Fast CMOS Octal Register Transceiver with Parity     |      |

| IDT73211             | Fast CMOS Octal Register Transceiver with Parity     | 6.6  |

| RISC MODULE F        |                                                      |      |

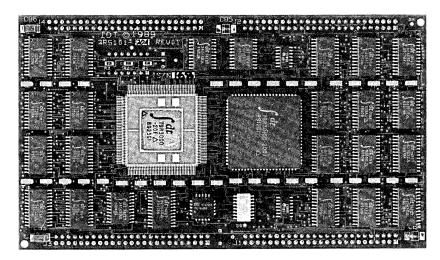

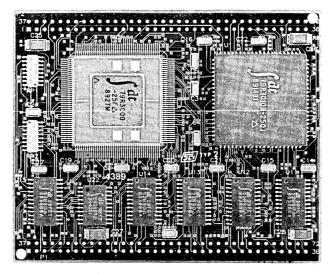

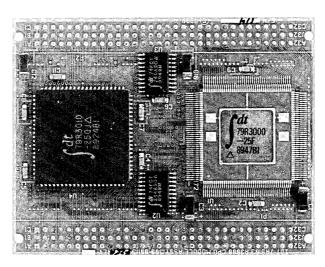

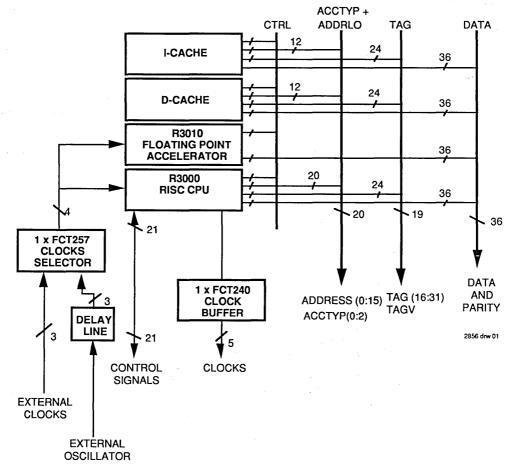

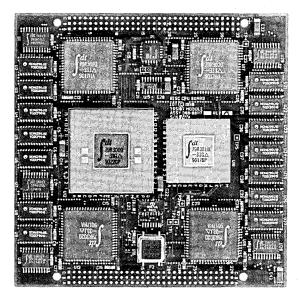

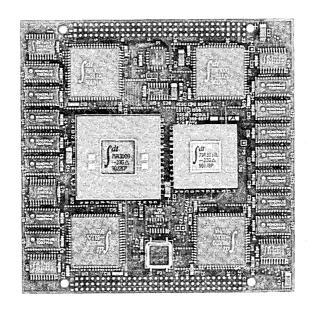

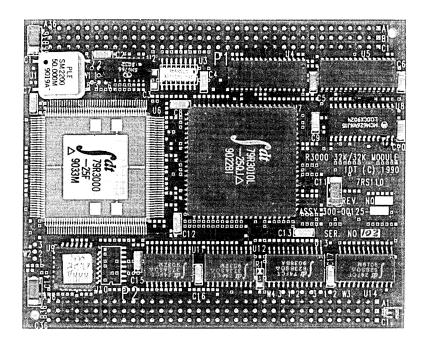

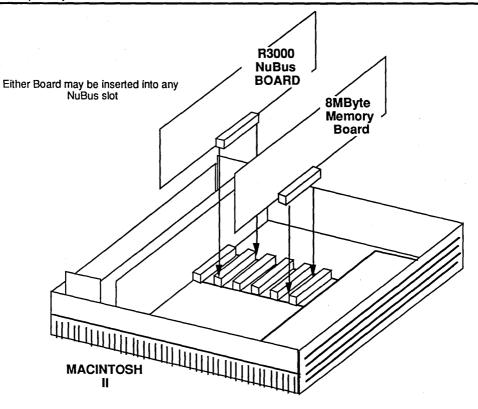

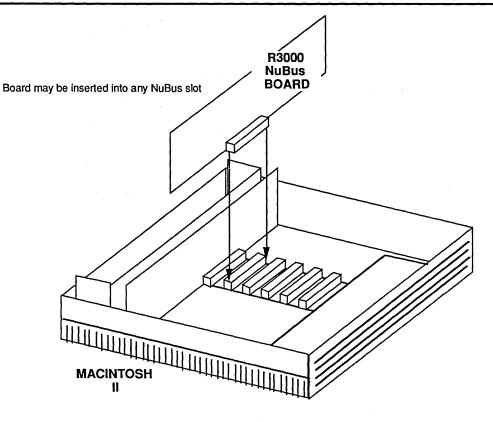

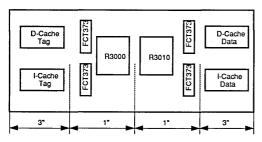

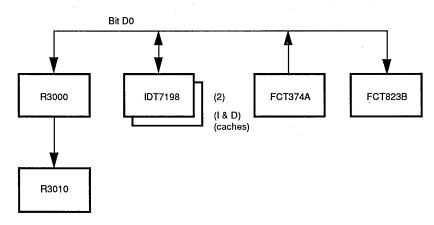

| IDT7RS101            | R3000 CPU Modules for General Applications           |      |

| IDT7RS102            | R3000 CPU Modules for Compact Systems                |      |

| IDT7RS103            | R3000 CPU Modules for Compact Systems                |      |

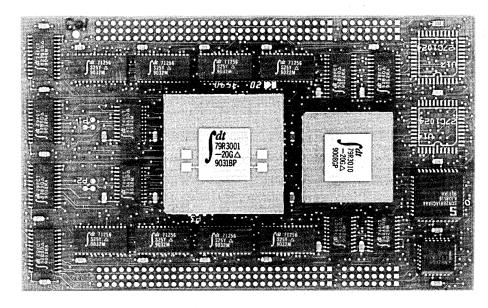

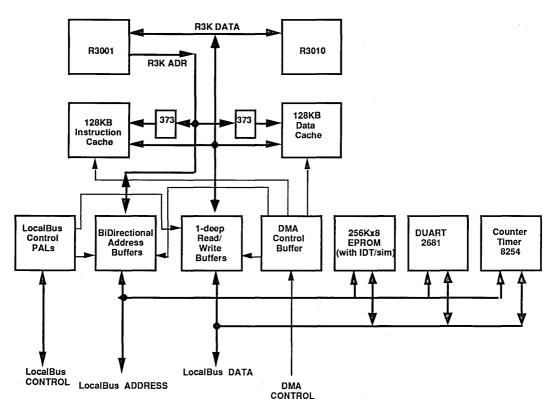

| IDT7RS104            | R3001 RISC Engine for Embedded Controllers           | 7.4  |

| 1991 RISC DATA BO      | OK (CONTINUED)                                                                             | PAGE |

|------------------------|--------------------------------------------------------------------------------------------|------|

| RISC MODULE PRODUC     | TS (CONTINUED)                                                                             |      |

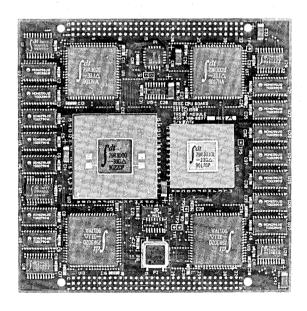

| IDT7RS107              | R3000 CPU Modules for High Performance and MultiProcessor Systems                          | 7.5  |

| IDT7RS108              | R3000 CPU Modules with 256K Caches                                                         | 7.6  |

| IDT7RS109              | R3000 CPU Modules with 256K Caches                                                         | 7.7  |

| IDT7RS110              | Plug Compatible Family of R3000 CPU Modules                                                | 7.8  |

| DIOC DEVEL OBMEN       | TOURRORT                                                                                   |      |

| RISC DEVELOPMEN        |                                                                                            |      |

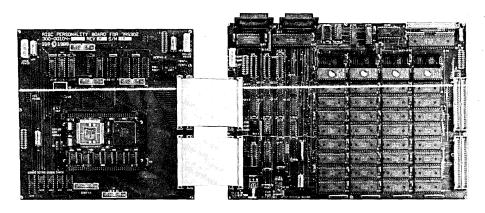

| RC32xx                 | IDT RISC Development Host Systems                                                          | 8.1  |

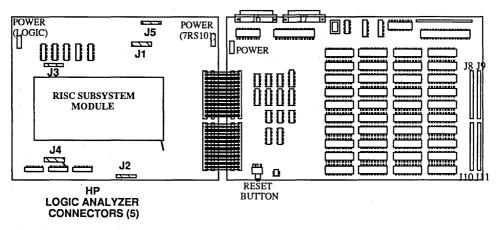

| IDT7RS300 Series       | Prototyping Platform for Any IDT CPU Module                                                | 8.2  |

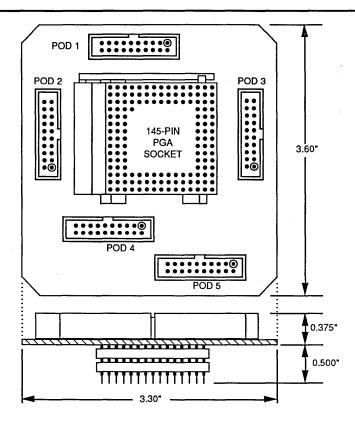

| IDT7RS363              | R3000 PGA Adaptor                                                                          |      |

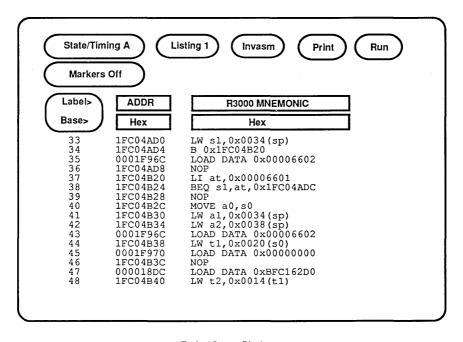

| IDT7RS364              | R3000 Disassembler for Use with the HP 16500 Logic Analyzer                                | 8.4  |

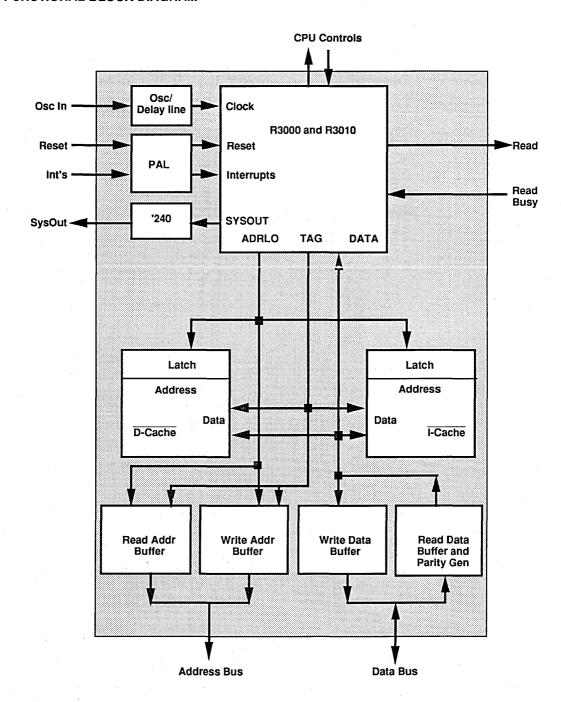

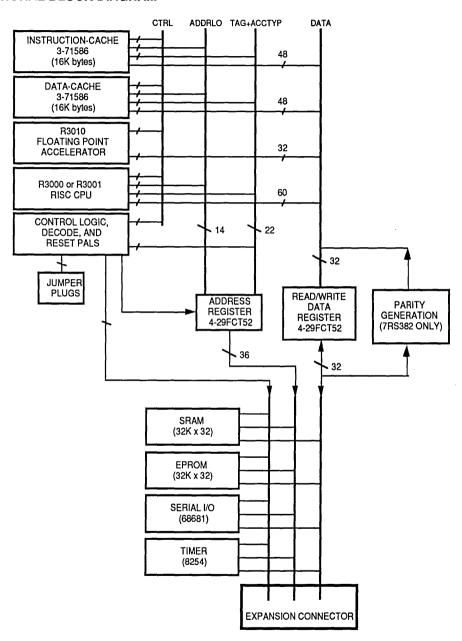

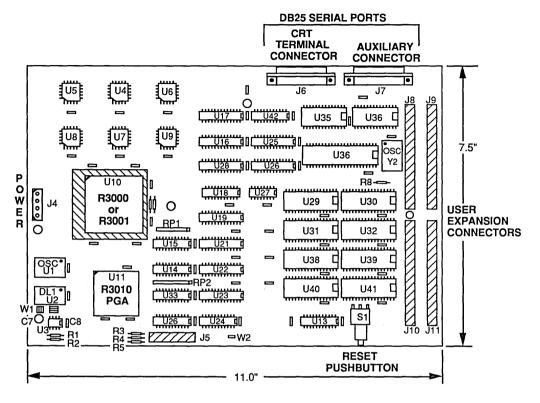

| IDT7RS382              | R3000 and R3001 Evaluation Boards                                                          | 8.5  |

| IDT7RS383              | R3000 and R3001 Evaluation Boards                                                          | 8.5  |

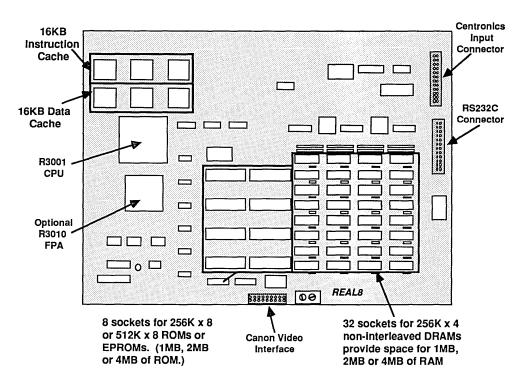

| IDT7RS388              | REAL8™ R3000 Laser Printer Controller Evaluation System                                    | 8.6  |

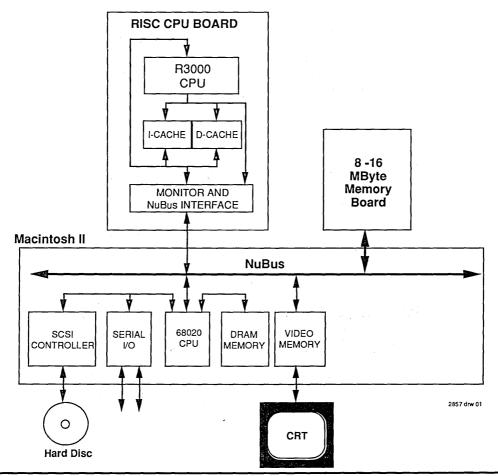

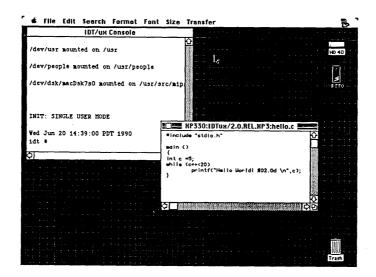

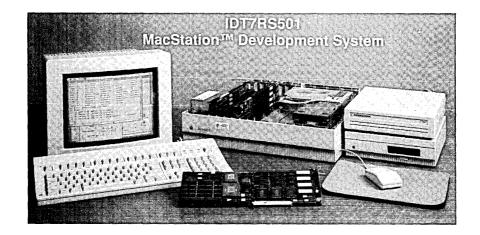

| IDT7RS502              | MacStation 2 R3000 Development System                                                      | 8.7  |

| IDT7RS503              | MacStation 3 R3000 Development System                                                      | 8.8  |

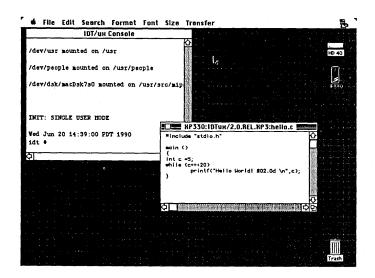

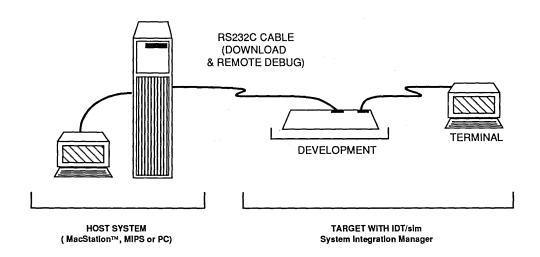

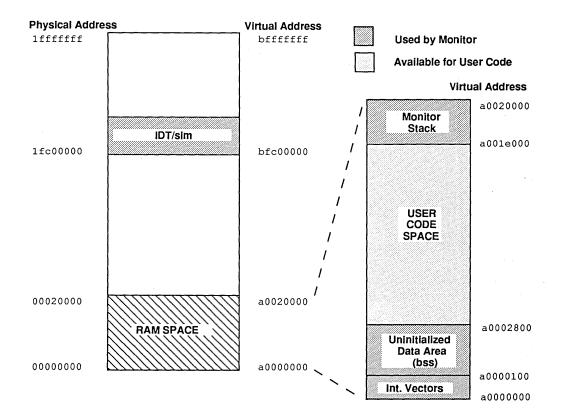

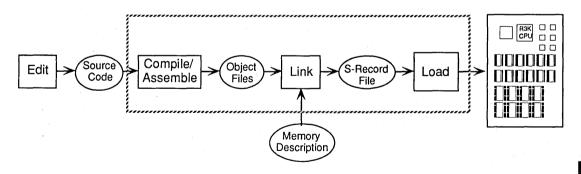

| IDT7RS901              | IDT/sim System Integration Manager ROMable Debugging Kernal                                | 8.9  |

| IDT7RS903              | IDT/c Multi-Host C-Compiler System                                                         |      |

| IDT7RS904              | Cross Assembler for IBM PCs and Clones                                                     |      |

| IDT7RS905              | IDT/fp Floating Point Library for Use with R3000 Compilers                                 |      |

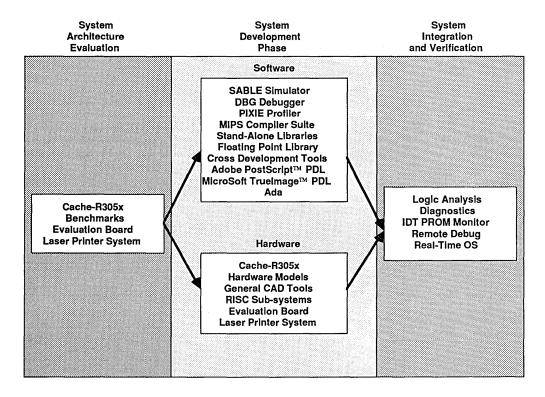

|                        | Third Party Development Support                                                            |      |

| APPLICATION NOTE       |                                                                                            |      |

|                        | oducts Application Notes                                                                   |      |

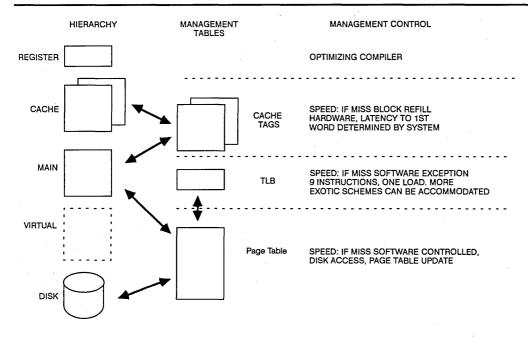

| AN-19                  | RISC and the Memory Hierarchy                                                              |      |

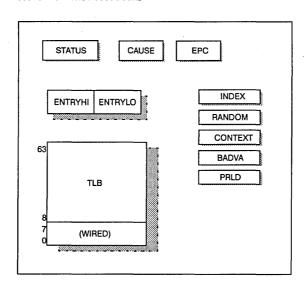

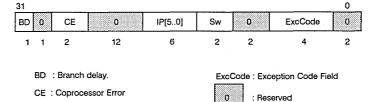

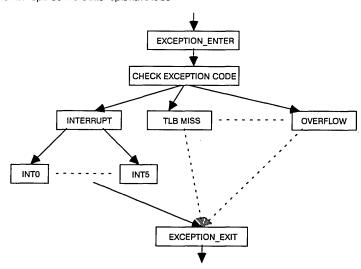

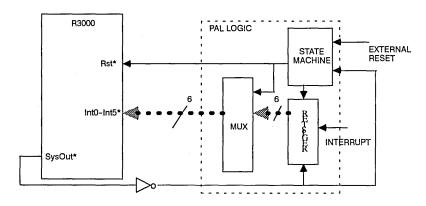

| AN-26                  | Interrupt Latency and Handling in the IDT79R3000                                           |      |

| AN-27                  | Cache Design Considerations Using the IDT79R3000                                           |      |

| AN-28                  | Using the IDT79R3000 in a Multiprocessor Organization                                      | 9.4  |

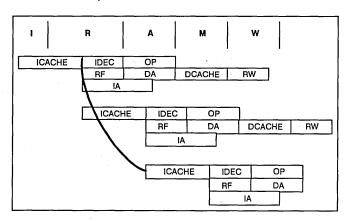

| AN-33                  | The Effect of Branch, Load and Store Latencies on RISC Processor  Performance              | 9.5  |

| AN-55                  | Design Techniques for Lowering Power Consumption in RISC Designs                           |      |

| AN-58                  |                                                                                            |      |

| AN-61                  | Parity in the IDT RISC Family                                                              |      |

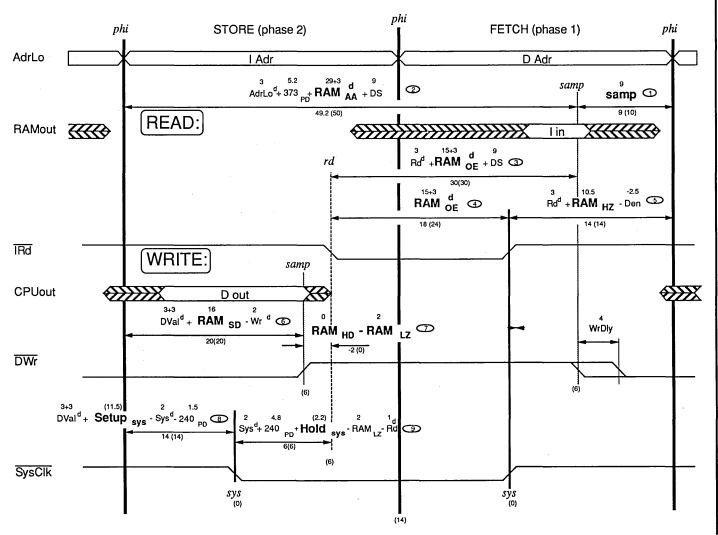

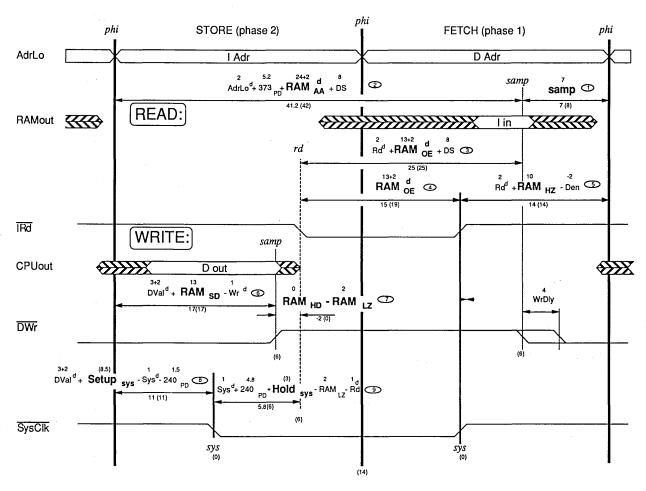

| · · · · · = ·          | R3000 33MHz Specification and Cache Timing                                                 |      |

| AN-62                  | R3000 Family Software Tools for Performance Analysis                                       | 9.9  |

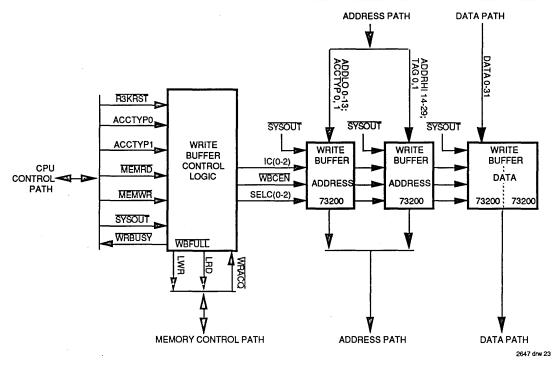

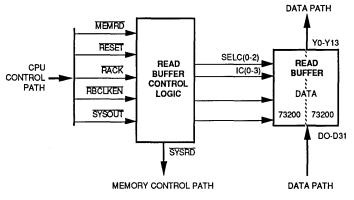

| AN-65                  | Using the IDT73210 as a One-Deep Read and Write Buffer with the IDT79R3000/3001            | 9.10 |

| AN-66                  | Designing Embedded Control Applications with the R3001 RISController                       |      |

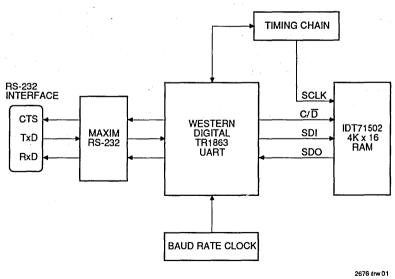

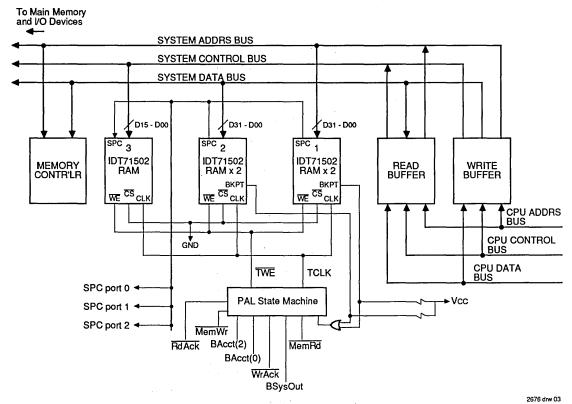

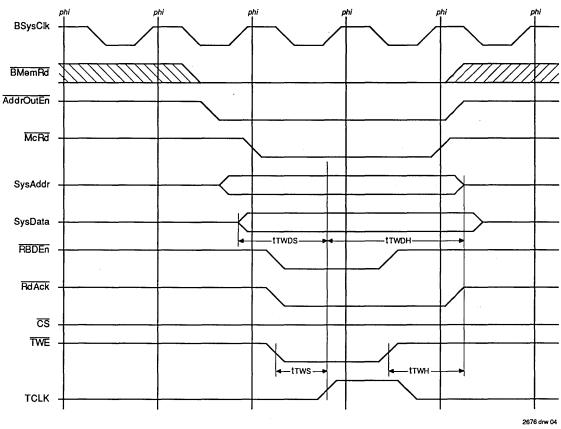

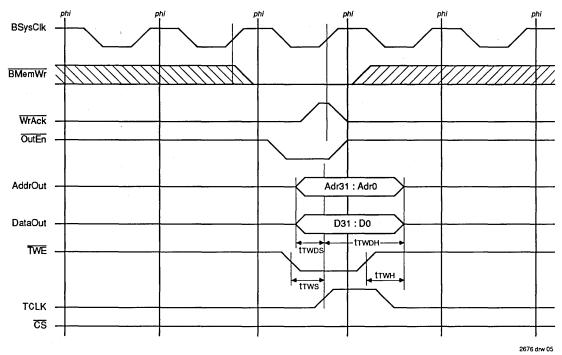

| AN-67                  | Using IDT71502 RAMs in a Real-Time Debugging Tool for an R3000 Microprocessor-Based System | 9.12 |

| AN-76                  |                                                                                            | -    |

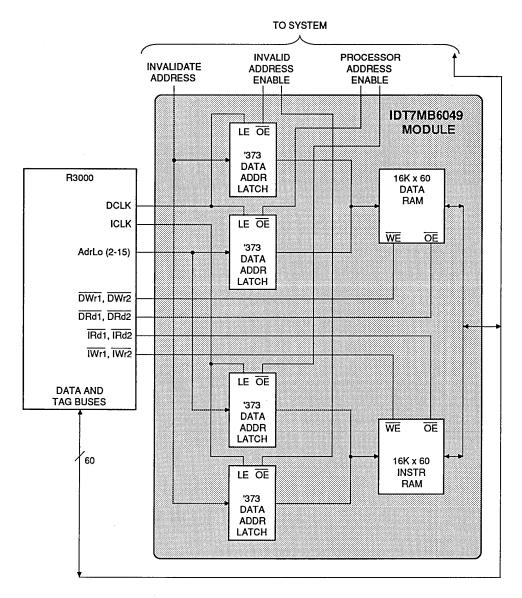

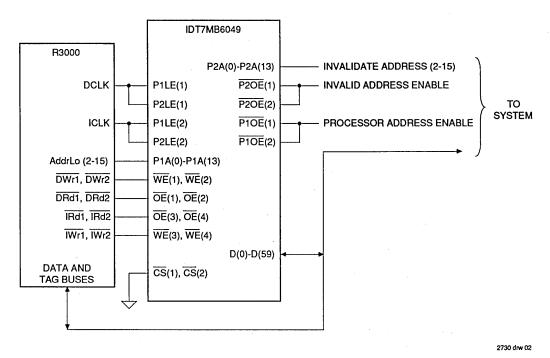

| · · · · · ·            | Using the IDT7MB6049 Cache Module for Single and Multiprocessor Systems                    | 9.13 |

| AN-77                  | R3001 Specification and Cache Timing                                                       | 9.14 |

| RISC Microprocessor Co | onference Papers                                                                           |      |

| CP-01                  | A Powerful Development Tool for the IDT79R3000 RISC Family                                 | 9.15 |

| CP-02                  | Developing Applications for the IDT79R3000 RISC Microprocessor                             | 9.16 |

| CP-03                  | IDT's R3001 Simplifies Design of High-Performance Control Systems                          | 9.17 |

| IDT SALES OFFICE,      | REPRESENTATIVE AND DISTRIBUTOR LOCATIONS                                                   |      |

## 1990-91 LOGIC DATA BOOK

The following is a listing of the data sheets located in the 1990-91 Logic Data Book available under separate cover:

| COMPLEX LOGIC PRODUCTS |                                                           | PAGI |

|------------------------|-----------------------------------------------------------|------|

| DSP AND MICROSLICET    | PRODUCTS                                                  |      |

| IDT39C01               | 4-Bit Microprocessor Slice                                | 5.1  |

| IDT39C10               | 12-Bit Sequencer                                          | 5.2  |

| IDT49C402              | 16-Bit Microprocessor Slice                               | 5.3  |

| IDT49C410              | 16-Bit Sequencer                                          | 5.4  |

| IDT7210L               | 16 x 16 Parallel Multiplier-Accumulator                   | 5.5  |

| IDT7216L               | 16 x 16 Parallel Multiplier                               | 5.6  |

| IDT7217L               | 16 x 16 Parallel Multiplier (32 Bit Output)               | 5.6  |

| IDT7381L               | 16-Bit CMOS Cascadable ALU                                | 5.7  |

| IDT7383L               | 16-Bit CMOS Cascadable ALU                                | 5.7  |

| READ/WRITE BUFFER P    | RODUCTS                                                   |      |

| IDT73200L              | 16-Bit CMOS Multilevel Pipeline Register                  | 5.8  |

| IDT73201L              | 16-Bit CMOS Multilevel Pipeline Register                  | 5.8  |

| IDT73210               | Fast Octal Register Transceiver w/Parity                  | 5.9  |

| IDT73211               | Fast Octal Register Transceiver w/Parity                  | 5.9  |

| FRROR DETECTION ANI    | D CORRECTION PRODUCTS                                     |      |

| IDT39C60               | 16-Bit Cascadable EDC                                     | 5.10 |

| IDT49C460              | 32-Bit Cascadable EDC.                                    | 5.11 |

| IDT49C465              | 32-Bit CMOS Flow-ThruEDC Unit                             | 5.12 |

| IDT49C466              | 64-BIT CMOS Flow-ThruEDC Unit                             | 5.13 |

| GRAPHICS PRODUCTS      |                                                           |      |

| IDT75C457              | CMOS Single 8-Bit PaletteDAC™ for True Color Applications | 5.14 |

| IDT75C458              | Triple 8-Bit PaletteDAC™                                  | 5.15 |

| IDT75C48               | 8-Bit Flash ADC                                           | 5.16 |

| IDT75C58               | 8-Bit Flash ADC with Overflow Output                      | 5.17 |

| 074404004004           |                                                           |      |

| STANDARD LOGIC F       |                                                           |      |

| IDT29FCT52T            | Non-inverting Octal Registered Transceiver                | 6.1  |

| IDT29FCT53T            | Inverting Octal Registered Transceiver                    | 6.1  |

| IDT29FCT520T           | Multi-level Pipeline Register                             | 6.2  |

| IDT29FCT521T           | Multi-level Pipeline Register                             | 6.2  |

| IDT54/74FCT138T        | 1-of-8 Decoder                                            | 6.3  |

| IDT54/74FCT139T        | Dual 1-of-4 Decoder                                       | 6.4  |

| IDT54/74FCT151T        | 8-Input Multiplexer                                       | 6.5  |

| IDT54/74FCT251T        | 8-Input Multiplexer w/3-State                             | 6.5  |

| IDT54/74FCT157T        | Quad 2-Input Multiplexer                                  | 6.6  |

| IDT54/74FCT257T        | FQuad 2-Input Multiplexer w/3-State                       | 6.6  |

| IDT54/74FCT161T        | Synchronous Binary Counter w/Asynchronous Master Reset    | 6.7  |

| IDT54/74FCT163T        | Synchronous Binary Counter w/Synchronous Reset            | 6.7  |

| IDT54/74FCT191T        | Up/Down Binary Counter w/Preset and Ripple Clock          | 6.8  |

| IDT54/74FCT193T        | Up/Down Binary Counter w/Separate Up/Down Clocks          | 6.9  |

| IDT54/74FCT240T        | Inverting Octal Buffer/Line Driver                        | 6.10 |

| IDT54/74FCT241T        | Non-inverting Octal Buffer/Line Driver                    | 6.10 |

| IDT54/74FCT244T        | Non-inverting Octal Buffer/Line Driver                    | 6.10 |

| IDT54/74FCT540T        | Inverting Octal Buffer/Line Driver                        | 6.10 |

| IDT54/74FCT541T        | Non-inverting Octal Buffer/Line Driver                    | 6.10 |

| IDT54/74FCT245T        | Non-inverting Octal Transceiver                           | 6.11 |

| 1990-91 LOGIC DATA | A BOOK (CONTINUED)                                          | PAGE |

|--------------------|-------------------------------------------------------------|------|

| STANDARD LOGIC PRO | DUCTS (CONTINUED)                                           |      |

| IDT54/74FCT640T    | Inverting Octal Transceiver                                 | 6.11 |

| IDT54/74FCT645T    | Non-inverting Octal Transceiver                             | 6.11 |

| IDT54/74FCT273T    | Octal D Flip-Flop w/Common Master Reset                     | 6.12 |

| IDT54/74FCT299T    | 8 Input Universal Shift Register w/Common Parallel I/O Pins | 6.13 |

| IDT54/74FCT373T    | Non-inverting Octal Transparent Latch w/3-State             | 6.14 |

| IDT54/74FCT533T    | Inverting Octal Transparent Latch w/3-State                 | 6.14 |

| IDT54/74FCT573T    | Non-inverting Octal Transparent Latch w/3-State             | 6.14 |

| IDT54/74FCT374T    | Non-inverting Octal D Register                              | 6.15 |

| IDT54/74FCT534T    | Inverting Octal D Register                                  | 6.15 |

| IDT54/74FCT574T    | Non-inverting Octal D Register                              | 6.15 |

| IDT54/74FCT377T    | Octal D Flip-Flop w/Clock Enable                            | 6.16 |

| IDT54/74FCT399T    | Quad Dual-Port Register                                     | 6.17 |

| IDT54/74FCT521T    | 8-Bit Identity Comparator                                   | 6.18 |

| IDT54/74FCT543T    | Non-inverting Octal Latched Transceiver                     | 6.19 |

| IDT54/74FCT646T    | Non-inverting Octal Registered Transceiver                  | 6.20 |

| IDT54/74FCT648T    | Inverting Octal Registered Transceiver                      | 6.20 |

| IDT54/74FCT651T    | Inverting Octal Registered Transceiver                      | 6.20 |

| IDT54/74FCT652T    | Non-inverting Octal Registered Transceiver                  | 6.20 |

| IDT54/74FCT620T    | Inverting Octal Bus Transceiver w/3-State                   | 6.21 |

| IDT54/74FCT623T    | Non-inverting Octal Bus Transceiver w/3-State               | 6.21 |

| IDT54/74FCT621T    | Non-inverting Octal Bus Transceiver (Open Drain)            | 6.22 |

| IDT54/74FCT622T    | Inverting Octal Bus Transceiver (Open Drain)                | 6.22 |

| IDT54/74FCT821T    | 10-Bit Non-inverting Register w/3-State                     | 6.23 |

| IDT54/74FCT823T    | 9-Bit Non-inverting Register w/Clear & 3-State              | 6.23 |

| IDT54/74FCT825T    | 8-Bit Non-inverting Register w/Clear & 3-State              | 6.23 |

| IDT54/74FCT827T    | 10-Bit Non-inverting Buffer                                 | 6.24 |

| IDT54/74FCT828T    | 10-Bit Inverting Buffer                                     | 6.24 |

| IDT54/74FCT841T    | 10-Bit Non-inverting Latch                                  | 6.25 |

| IDT54/74FCT843T    | 9-Bit Non-inverting Latch                                   | 6.25 |

| IDT54/74FCT845T    | 8-Bit Non-inverting Latch                                   | 6.25 |

| IDT29FCT52         | Non-inverting Octal Registered Transceiver                  | 6.26 |

| IDT29FCT53         | Inverting Octal Registered Transceiver                      | 6.26 |

| IDT29FCT520        | Multi-level Pipeline Register                               | 6.27 |

| IDT49FCT661        | 16-Bit Synchronous Binary Counter                           | 6.28 |

| IDT49FCT804        | High-Speed Tri-Port Bus Multiplexer                         | 6.29 |

| IDT49FCT805        | Buffer/Clock Driver w/Guaranteed Skew                       |      |

| IDT49FCT806        | Buffer/Clock Driver w/Guaranteed Skew                       | 6.30 |

| IDT49FCT818        | Octal Register with SPC™                                    | 6.31 |

| IDT49C25           | Microcycle Length Controller                                | 6.32 |

| IDT39C8XX          | IDT39C8XXX Family                                           | 6.33 |

| IDT54/74FCT138     | 1-of-8 Decoder                                              | 6.34 |

| IDT54/74FCT139     | Dual 1-of-4 Decoder                                         | 6.35 |

| IDT54/74FCT161     | Synchronous Binary Counter w/Asynchronous Master Reset      | 6.36 |

| IDT54/74FCT163     | Synchronous Binary Counter w/Synchronous Reset              | 6.36 |

| IDT54/74FCT182     | Carry Lookahead Generator                                   | 6.37 |

| IDT54/74FCT191     | Up/Down Binary Counter w/Preset and Ripple Clocks           | 6.38 |

| IDT54/74FCT193     | Up/Down Binary Counter w/Separate Up/Down Clocks            | 6.39 |

| IDT54/74FCT240     | Inverting Octal Buffer/Line Driver                          | 6.40 |

| IDT54/74FCT241     | Non-inverting Octal Buffer/Line Driver                      | 6.40 |

| IDT54/74FCT244     | Non-inverting Octal Buffer/Line Driver                      | 6.40 |

| IDT54/74FCT540     | Inverting Octal Buffer/Line Driver                          | 6.40 |

| IDT54/74FCT541     | Non-inverting Octal Buffer/Line Driver                      | 6.40 |

| IDT54/74FCT245     | Non-inverting Octal Transceiver                             | 6.41 |

| IDT54/74FCT640     | Inverting Octal Transceiver                                 | 6.41 |

1.3

| 1990-91 LOGIC DATA              | A BOOK (CONTINUED)                                                | PAGE |

|---------------------------------|-------------------------------------------------------------------|------|

| STANDARD LOGIC PRO              | DUCTS (CONTINUED)                                                 |      |

| IDT54/74FCT645                  | Non-inverting Octal Transceiver                                   | 6.41 |

| IDT54/74FCT273                  | Octal D Flip-Flop w/Common Master Reset                           | 6.42 |

| IDT54/74FCT299                  | 8-Input Universal Shift Register w/Common Parallel I/O Pins       | 6.43 |

| IDT54/74FCT373                  | Non-inverting Octal Transparent Latch                             | 6.44 |

| IDT54/74FCT533                  | Inverting Octal Transparent Latch                                 | 6.44 |

| IDT54/74FCT573                  | Non-inverting Octal Transparent Latch                             | 6.44 |

| IDT54/74FCT374                  | Non-inverting Octal D Flip-Flop                                   | 6.45 |

| IDT54/74FCT534                  | Inverting Octal D Flip-Flop w/3-State                             | 6.45 |

| IDT54/74FCT574                  | Non-inverting Octal D Register w/3-State                          | 6.45 |

| IDT54/74FCT377                  | Octal D Flip-Flop w/Clock Enable                                  | 6.46 |

| IDT54/74FCT399                  | Quad Dual-Port Register                                           | 6.47 |

| IDT54/74FCT521                  | 8-Bit Identity Comparator                                         | 6.48 |

| IDT54/74FCT543                  | Non-inverting Octal Latched Transceiver                           | 6.49 |

| IDT54/74FCT646                  | Non-inverting Octal Registered Transceiver                        | 6.50 |

| IDT54/74FCT821                  | 10-Bit Non-inverting Register w/3-State                           | 6.51 |

| IDT54/74FCT823                  | 9-Bit Non-inverting Register w/Clear & 3-State                    | 6.51 |

| IDT54/74FCT824                  | 9-Bit Inverting Register w/Clear & 3-State                        | 6.51 |

| IDT54/74FCT825                  | 8-Bit Non-inverting Register                                      | 6.51 |

| IDT54/74FCT827                  | 10-Bit Non-inverting Buffer                                       | 6.52 |

| IDT54/74FCT833                  | 8-Bit Transceiver w/Parity                                        | 6.53 |

| IDT54/74FCT841                  | 10-Bit Non-inverting Latch                                        | 6.54 |

| IDT54/74FCT843                  | 9-Bit Non-inverting Latch                                         | 6.54 |

| IDT54/74FCT844                  | 9-Bit Inverting Latch                                             | 6.54 |

| IDT54/74FCT845                  | 8-Bit Non-inverting Latch                                         | 6.54 |

| IDT54/74FCT861                  | 10-Bit Non-inverting Transceiver                                  | 6.55 |

| IDT54/74FCT863                  | 9-Bit Non-inverting Transceiver                                   | 6.55 |

| IDT54/74FCT864                  | 9-Bit Inverting Transceiver                                       | 6.55 |

| IDT54/74FBT240                  | Inverting Octal Buffer/Line Driver                                | 6.56 |

| IDT54/74FBT241                  | Non-inverting Octal Buffer/Line Driver                            | 6.57 |

| IDT54/74FBT244                  | Non-inverting Octal Buffer/Line Driver                            | 6.58 |

| IDT54/74FBT245                  | Non-inverting Octal Transceiver                                   | 6.59 |

| IDT54/74FBT373                  | Octal Transparent Latch w/3-State                                 | 6.60 |

| IDT54/74FBT374                  | Non-inverting Octal D Register                                    | 6.61 |

| IDT54/74FBT540                  | Inverting Octal Buffer                                            | 6.62 |

| IDT54/74FBT541                  | Non-inverting Octal Buffer                                        | 6.62 |

| IDT54/74FBT821                  | 10-Bit Non-inverting Register                                     | 6.63 |

| IDT54/74FBT823                  | 9-Bit Inverting Register                                          | 6.64 |

| IDT54/74FBT827                  | Non-inverting 10-Bit Buffers/Driver                               | 6.65 |

| IDT54/74FBT828                  | Inverting10-Bit Buffers/Driver                                    | 6.65 |

| IDT54/74FBT841                  | 10-Bit Non-inverting Latch                                        | 6.66 |

| IDT54/74FBT2240                 | Inverting Octal Buffer/Line Driver w/25Ω Series Resistor          | 6.67 |

| IDT54/74FBT2244                 | Inverting Octal Buffer/Line Driver w/25Ω Series Resistor          | 6.68 |

| IDT54/74FBT2373                 | Octal Transparent Latch w/3-State & 25Ω Series Resistor           | 6.69 |

| IDT54/74FBT2827                 | Non-inverting 10-Bit Buffers/Driver w/25 $\Omega$ Series Resistor | 6.70 |

| IDT54/74FBT2828                 | Inverting 10-Bit Buffers/Driver w/25Ω Series Resistor             | 6.70 |

| IDT54/74FBT2841                 | 10-Bit Memory Latch w/25Ω Series Resistor                         | 6.71 |

| APPLICATION AND TECHNICAL NOTES |                                                                   |      |

| <b>Complex Logic Products</b>   | Technical Notes                                                   |      |

| TN-02                           | Build a 20MIP Data Processing Unit                                | 7.1  |

| TN-03                           | Using the IDT49C402A ALLI                                         | 7.2  |

1.3 5

| 1990-91 LOG    | IC DATA BOOK (CONTINUED)                                          | PAGE |

|----------------|-------------------------------------------------------------------|------|

| Complex Logic  | Products Application Notes                                        |      |

| AN-03          | Trust Your Data with A High-Speed CMOS 6-, 32- or 64-Bit EDC      | 7.3  |

| AN-06          | 16-Bit CMOS Slices — New Building Blocks Maintain Microcode       |      |

|                | Compatibility Yet Increase Performance                            | 7.4  |

| AN-17          | FIR Filter Implementation Using FIFOs and MACs                    | 7.5  |

| AN-24          | Designing with the IDT49C460 and IDT39C60 Error Detection and     |      |

|                | Correction Units                                                  | 7.6  |

| AN-32          | Implementation of Digital Filters Using IDT7320, IDT7210, IDT7216 | 7.7  |

| AN-35          | Address Generator in Matrix Unit Operation Engine                 | 7.8  |

| AN-37          | Designing High-Performance Systems Using the IDT PaletteDAC™      |      |

| AN-63          | Using the IDT75C457's PaletteDAC™ in True Color and Monochrome    |      |

|                | Graphics Applications                                             | 7.10 |

| AN-64          | Protecting Your Data with IDT's 49C465 32-Bit Flow-thruEDC™ Unit  |      |

| AN-65          | Using IDT73200 or IDT73210 as Read and Write Buffers with R3000   |      |

| Standard Logic | Application Notes                                                 | 7.13 |

| AN-47          | Simultaneous Switching Noise                                      | 7.14 |

| AN-48          | Using High-Speed Logic                                            | 7.15 |

| AN-49          | Characteristics of PCB Traces                                     | 7.16 |

| AN-50          | Series Termination                                                |      |

| AN-51          | Power Dissipation in Clock Drivers                                | 7.18 |

| AN-52          | FCT Output Structures and Characteristics                         | 7.19 |

| AN-53          | Power-Down Operation                                              |      |

| AN-54          | FCT-T Logic Family                                                |      |

| Standard Logic | Technical Bulletins                                               |      |

### SPECIALIZED MEMORIES DATA BOOK

The following is a listing of the data sheets located in the 1990-91 Specialized Memories Data Book available under separate cover:

| IDT10484                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ECL PRODUCTS  |                                              | PAGE |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------------------------------|------|

| IDT100484                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IDT10484      | 4K x 4 ECL 10K SRAM (Corner Power)           | 5.1  |

| IDT10A484                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IDT100484     |                                              |      |

| IDT100A484                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | IDT101484     | 4K x 4 ECL 101K SRAM (Corner Power)          | 5.1  |

| IDT1014AB4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | IDT10A484     | 4K x 4 ECL 10K SRAM (Center Power)           | 5.2  |

| IDT10490                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IDT100A484    | 4K x 4 ECL 100K SRAM (Center Power)          | 5.2  |

| IDT100490                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IDT101A484    | 4K x 4 ECL 101K SRAM (Center Power)          | 5.2  |

| IDT101490                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IDT10490      | 64K x 1 ECL 10K SRAM                         | 5.3  |

| IDT10494                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IDT100490     | 64K x 1 ECL 100K SRAM                        | 5.3  |

| IDT10494                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IDT101490     | 64K x 1 ECL 101K SRAM                        | 5.3  |

| IDT101494                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IDT10494      |                                              | 5.4  |

| IDT10496LL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | IDT100494     | 16K x 4 ECL 100K SRAM                        | 5.4  |

| IDT100496LL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | IDT101494     | 16K x 4 ECL 101K SRAM                        | 5.4  |

| IDT100496LL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | IDT10496LL    |                                              | 5.5  |

| IDT10496RL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | IDT100496LL   |                                              | 5.5  |

| IDT100496RL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | IDT101496LL   | · · · · · · · · · · · · · · · · · · ·        | 5.5  |

| IDT101496RL   16K x 4 Self-Timed Reg Input, Latch Output   5.6   IDT10497   16K x 4 Synchronous Write, Latch Output   5.7   IDT100497   16K x 4 Synchronous Write, Latch Output   5.7   IDT10497   16K x 4 Synchronous Write, Latch Output   5.7   IDT10498   16K x 4 Conditional Write, Latch Output   5.8   IDT100498   16K x 4 Conditional Write, Latch Output   5.8   IDT100498   16K x 4 Conditional Write, Latch Output   5.8   IDT10504   64K x 4 ECL 10K SRAM   5.9   IDT10504   64K x 4 ECL 10K SRAM   5.9   IDT10504   64K x 4 ECL 10K SRAM   5.9   IDT1050504   64K x 4 ECL 10K SRAM   5.9   IDT10506LL   64K x 4 Self-Timed Latch Input, Latch Output   5.10   IDT10506LL   64K x 4 Self-Timed Latch Input, Latch Output   5.10   IDT10506LL   64K x 4 Self-Timed Latch Input, Latch Output   5.10   IDT10506LL   64K x 4 Self-Timed Reg Input, Latch Output   5.11   IDT10506RL   64K x 4 Self-Timed Reg Input, Latch Output   5.11   IDT10506RL   64K x 4 Self-Timed Reg Input, Latch Output   5.11   IDT10506RL   64K x 4 Self-Timed Reg Input, Latch Output   5.11   IDT10506RL   64K x 4 Self-Timed Reg Input, Latch Output   5.11   IDT10507   64K x 4 Synchronous Write, Latch Output   5.12   IDT10507   16K x 4 Synchronous Write, Latch Output   5.12   IDT10507   16K x 4 Synchronous Write, Latch Output   5.12   IDT10508   64K x 4 Conditional Write, Latch Output   5.13   IDT10509   32K x 9 ECL 10K SRAM   5.14   IDT10509   32K x 9 ECL 10K SRAM   5.14 | IDT10496RL    | 16K x 4 Self-Timed Reg Input, Latch Output   | 5.6  |

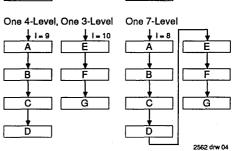

| IDT10497                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IDT100496RL   | 16K x 4 Self-Timed Reg Input, Latch Output   | 5.6  |