INTERNATIONAL CMOS TECHNOLOGY, INC.

# CMOS Programmable Products

**General Information**

**CMOS Serial EEPROMs**

**CMOS High Speed PROMs**

**CMOS High Speed EPROMs**

**CMOS PEEL Devices**

**CMOS PEEL Arrays**

**Development Tools**

**Article Reprints**

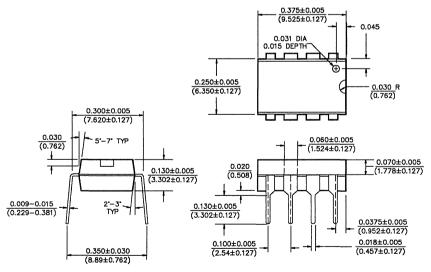

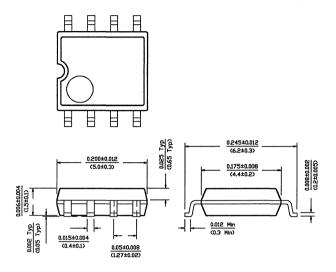

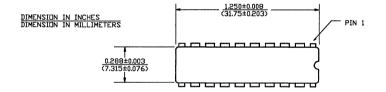

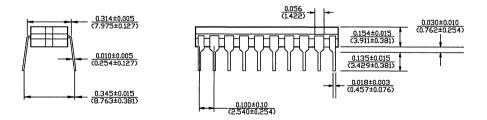

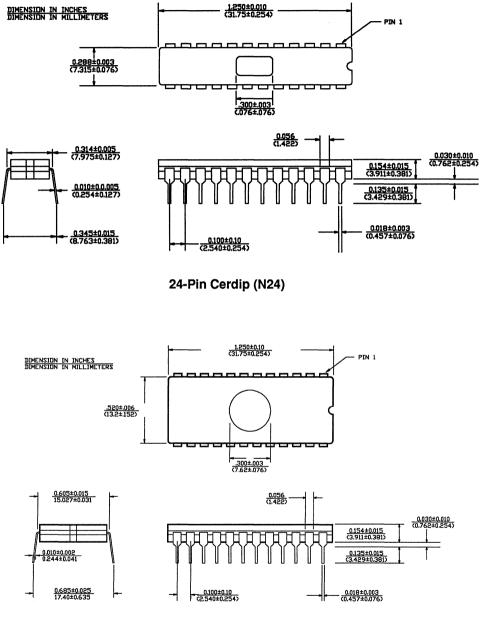

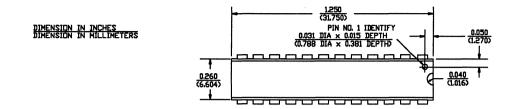

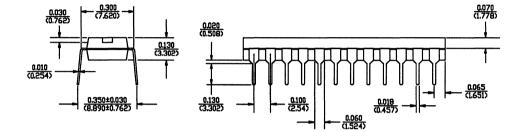

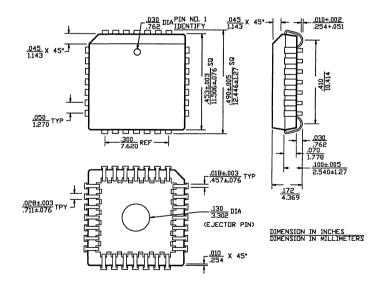

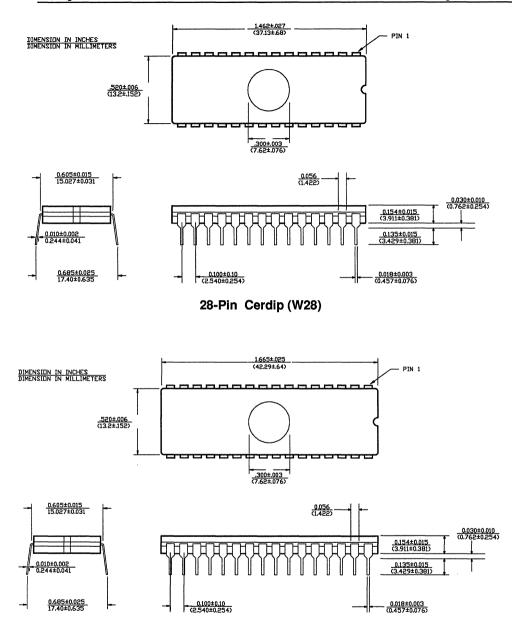

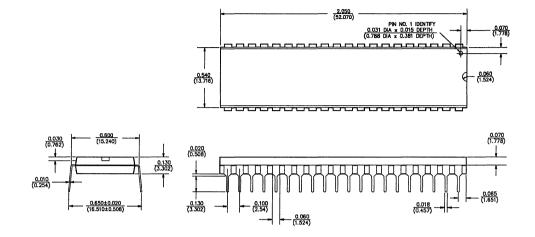

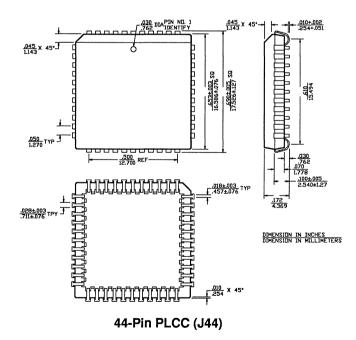

Package Information

Sales Representatives and Distributors

#### **Preliminary Designation**

The "Preliminary" designation on an ICT data sheet indicates that the product is not fully characterized. The specifications are subject to change, are based on design goals or preliminary part evaluation, and are not guaranteed. ICT or an authorized sales representative should be consulted for current information before using this product

#### Specifications, Patents, Life Support Policy, Trademarks

ICT reserves the right to make changes in specifications at any time and without notice. The information furnished by ICT in this publication is believed to be accurate and reliable. However, no responsibility is assumed by ICT for its use, nor for any infringements of patents of other rights of third parties resulting from its use. No license is granted under any patents or patent rights of ICT. ICT's products are not authorized for use as critical components in life support devices or systems without the written approval of the president of International CMOS Technology, Inc. Life support devices, or systems, are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### Trademarks

PEEL<sup>™</sup>, APEEL<sup>™</sup> and PACE<sup>™</sup> are trademarks of International CMOS Technology Inc. PAL® and PALASM® are registered trademarks of Monolithic Memories Inc GAL® is a registered trademark of Lattice Semiconductor Corp. ABEL<sup>™</sup> is a trademark of Data I/O Corporation CUPL<sup>™</sup> is a trademark of Assisted Technology Wordstar® is a registered trademark of MicroPro International Corporation

### ICT 1990 Data Book Copyright

This document is copyrighted. All rights are reserved. This document may not, in whole or in part, be copied, photocopied, reproduced, translated or reduced to any electronic medium or machine readable form without prior written consent from International CMOS Technology Inc.

©1989 International CMOS Technology Inc. 2125 Lundy Avenue San Jose, CA 95131

# **Table of Contents**

## **1.0 General Information**

| ICT Product Overview        | 1-1  |

|-----------------------------|------|

| ICT Quality and Reliability | 1-5  |

| Product Selection Guides    |      |

| Ordering Information        | 1-13 |

| Cross Reference Guides      |      |

## 2.0 CMOS Serial EEPROMs

| CMOS Serial EEPROM Features        | 2-1  |

|------------------------------------|------|

| 93C46 (1K-bit)                     |      |

| 93C46A (1K-bit)                    | 2-8  |

| 93C56A (2K-bit)                    |      |

| 93C66A (4K-bit)                    | 2-13 |

| 93CX46 (1K-bit, Extended Voltgage) |      |

| 93CX56 (2K-bit, Extended Voltgage) | 2-23 |

| 93CX66 (4K-bit, Extended Voltgage) |      |

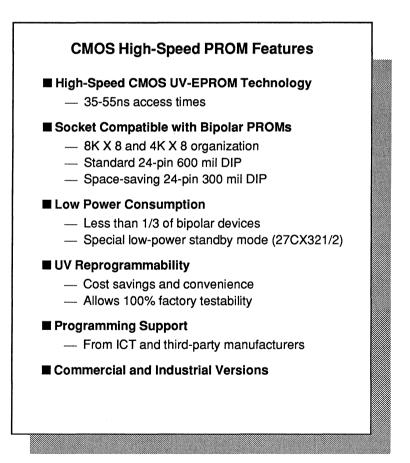

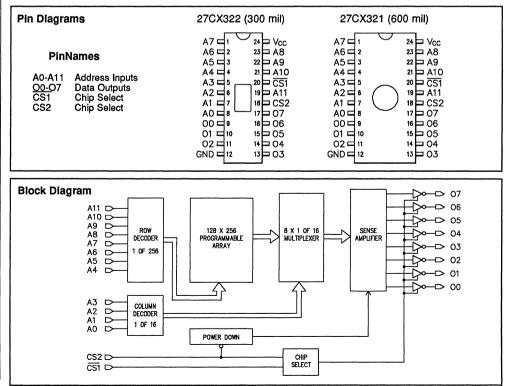

## 3.0 CMOS High-Speed PROMs

| CMOS High Speed PROM Features | 3-1 |

|-------------------------------|-----|

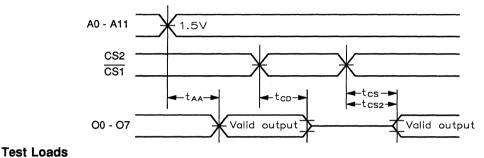

| 27CX321/322 (4K x 8)          | 3-2 |

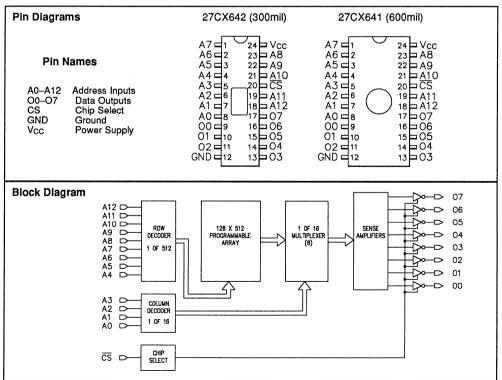

| 27CX641/642 (8K x 8)          |     |

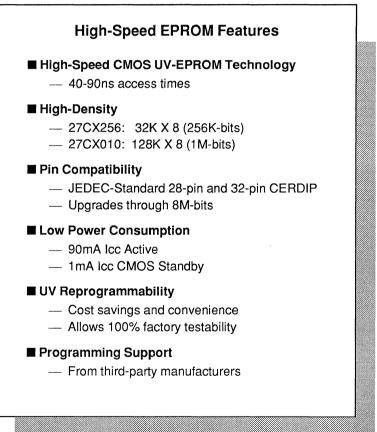

# 4.0 CMOS High-Speed EPROMs

| CMOS High Speed EPROM Features | 4-1 |

|--------------------------------|-----|

| 27CX010 (128K x 8)             |     |

| 27CX256 (32K x 8)              |     |

## 5.0 CMOS PEEL Devices

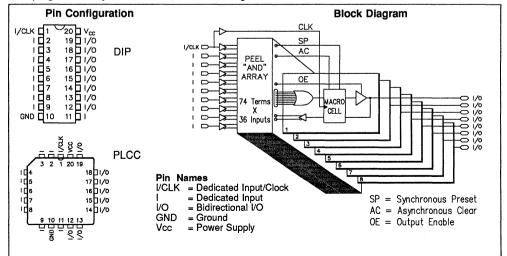

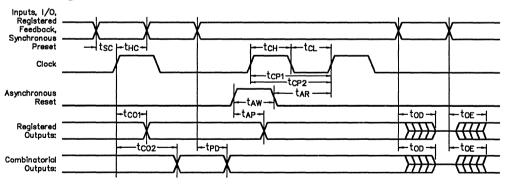

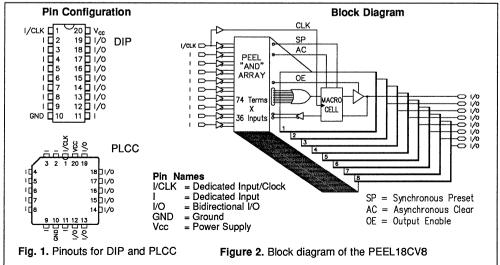

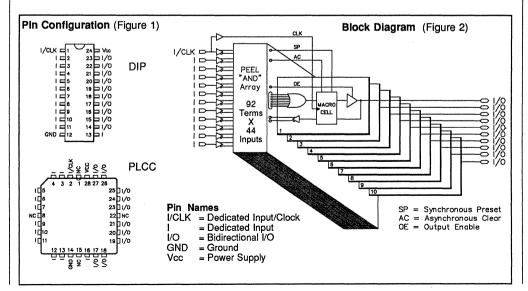

| PEEL18CV8       5-2         PEEL18CV8-15       5-10         PEEL18CV8-10       5-13         PEEL20CG10       5-14         PEEL20CG10-12       5-21         PEEL22CV10       5-22         PEEL22CV10-12       5-29         PEEL173       5-30         PEEL173       5-45         PEEL253       5-41         PEEL273       5-50         PEEL273       5-54         PEEL273-15       5-54         PEEL273-15       5-54 | PEEL Device Features   | 5-1  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|

| PEEL18CV8-15       5-10         PEEL18CV8-10       5-13         PEEL20CG10       5-14         PEEL20CG10-12       5-21         PEEL22CV10       5-22         PEEL22CV10-12       5-29         PEEL22CV10Z       5-30         PEEL153       5-37         PEEL173       5-45         PEEL253       5-41         PEEL273       5-50         PEEL273-15       5-54                                                       | PEEL18CV8              | 5-2  |

| PEEL18CV8-10       5-13         PEEL20CG10       5-14         PEEL20CG10-12       5-21         PEEL22CV10       5-22         PEEL22CV10-12       5-29         PEEL22CV10Z       5-30         PEEL153       5-37         PEEL173       5-45         PEEL253       5-41         PEEL273       5-50         PEEL273-15       5-54                                                                                       |                        | 5-10 |

| PEEL20CG10-12       .5-21         PEEL22CV10       .5-22         PEEL22CV10-12       .5-29         PEEL22CV10Z       .5-30         PEEL153       .5-37         PEEL173       .5-45         PEEL173-15       .5-41         PEEL273       .5-50         PEEL273-15       .5-54                                                                                                                                         |                        | 5-13 |

| PEEL22CV10                                                                                                                                                                                                                                                                                                                                                                                                           | PEEL20CG10             | 5-14 |

| PEEL22CV10                                                                                                                                                                                                                                                                                                                                                                                                           | PEEL20CG10-12          | 5-21 |

| PEEL22CV10Z 5-30<br>PEEL153 5-37<br>PEEL173 5-45<br>PEEL173-15 5-49<br>PEEL253 5-41<br>PEEL273 5-50<br>PEEL273-15 5-54                                                                                                                                                                                                                                                                                               |                        | 5-22 |

| PEEL153                                                                                                                                                                                                                                                                                                                                                                                                              | PEEL22CV10-12          | 5-29 |

| PEEL153                                                                                                                                                                                                                                                                                                                                                                                                              | PEEL22CV10Z            | 5-30 |

| PEEL173-15                                                                                                                                                                                                                                                                                                                                                                                                           |                        | 5-37 |

| PEEL253                                                                                                                                                                                                                                                                                                                                                                                                              | PEEL173                | 5-45 |

| PEEL273                                                                                                                                                                                                                                                                                                                                                                                                              | PEEL173-15             | 5-49 |

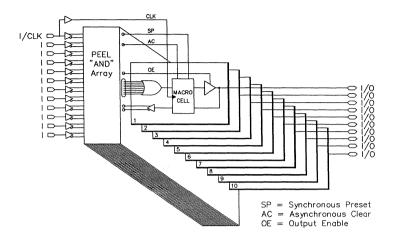

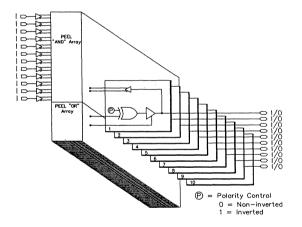

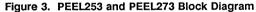

| PEEL273-15                                                                                                                                                                                                                                                                                                                                                                                                           | PEEL253                | 5-41 |

|                                                                                                                                                                                                                                                                                                                                                                                                                      | PEEL273                | 5-50 |

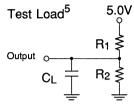

| PEEL Device Test Loads5-55                                                                                                                                                                                                                                                                                                                                                                                           | PEEL273-15             | 5-54 |

|                                                                                                                                                                                                                                                                                                                                                                                                                      | PEEL Device Test Loads | 5-55 |

## 6.0 CMOS PEEL Arrays

| PEEL Array Features | 6-1 |

|---------------------|-----|

| PA7024              |     |

| PA7040              |     |

# 7.0 Development Tools

| PDS-1 PEEL Development System      | 7-1 |

|------------------------------------|-----|

| PEEL Device Development Software   |     |

| PACE Advanced Development Software | 7-3 |

| Programming Support                |     |

# 8.0 Article Reprints

| Logical Design Techniques for Architecturally Enhanced EEPLDs | . 8-1  |

|---------------------------------------------------------------|--------|

| Electrically Erasable CMOS PLDs Conquer Tradeoff Dilemmas     | . 8-11 |

| PLD Synchronizes Asynchronous Inputs                          | .8-19  |

| Benefits from EEPLDs are Company-Wide                         | .8-21  |

| Logic Array Family Blends PGA and PLD Attributes              | .8-25  |

| ICT Architecture Boosts PGA Speeds and Densities              | .8-29  |

| ICT Unveils High Density Programmable Logic Architecture      | . 8-31 |

| The PLD/FPGA Trade-Off                                        | .8-33  |

| PEEL Arrays-Bridging the Gap Between PLDs and FPGAs           | . 8-37 |

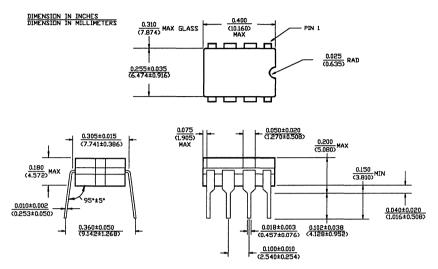

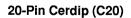

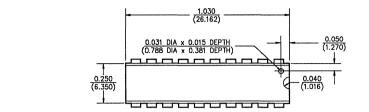

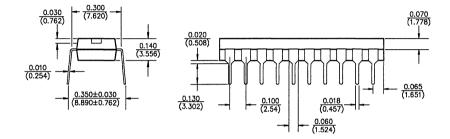

# 9.0 Package Information

| ckage Diagrams9-1 |

|-------------------|

|-------------------|

# **10.0** Sales Representatives and Distributors

| Headquarters and Regional Offices                    | 10-1 |

|------------------------------------------------------|------|

| North America Sales Representatives                  | 10-1 |

| North America Distributors                           | 10-2 |

| International Sales Representatives and Distributors | 10-3 |

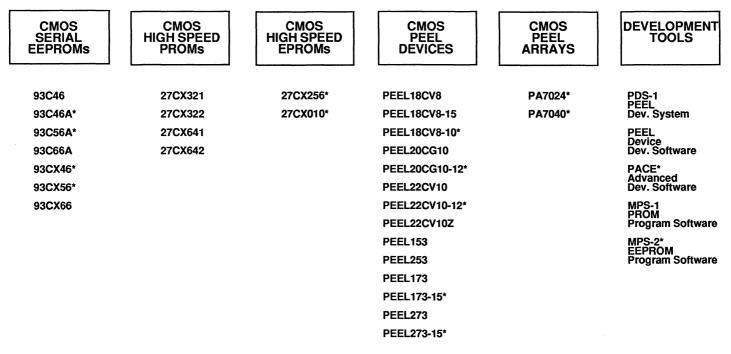

International CMOS Technology, Inc. (ICT) is pleased to bring to you our 1990 CMOS Programmable Products Data Book. ICT's technical expertise in non-volatile memory technologies has allowed us to produce a broad spectrum of leading-edge user-programmable integrated circuits. Our 1990 product line, which has doubled from last year, offers over thirty products with the features, performance and development support needed by designers today.

This year's offering includes several product innovations: including: the 93CX46/56/66 series of extended voltage EEPROMs, the worlds fastest 1-Meg EPROM the 27CX010, the high density PA7024/40 logic arrays, and the unique PACE Advanced Development Software.

In addition to our product line expansion, we have enhanced our existing strategic alliances and created new alliances with several major semiconductor manufacturers, thus assuring high-volume manufacturing capability to support our accelerated growth. ICT has also continued its serious commitment to quality and reliability. This commitment starts with the inherent reliability and testability of ICT's CMOS EPROM and EEPROM technologies and is enhanced through our advanced design, manufacturing and testing techniques. Service and customer satisfaction are the primary goals of ICT's quality team.

We at ICT thank you for your interest in ICT products and know you will find our 1990 data book useful in your future programmable IC design efforts.

Drew Allen Osterman President and CEO

**General Information**

# **ICT Product Line**

\* New Products

۱.

# **ICT Product Overview**

International CMOS Technology, Inc. (ICT) designs, manufactures, and markets user-programmable integrated circuits. With expertise in technology and circuit design, the company has combined complimentary-metal-oxide-semiconductor (CMOS) with electricallyerasable (EE) or ultra-violet-erasable (UV) memory technologies to create non-volatile programmable memories and logic devices.

Founded in 1983 in the heart of California's Silicon Valley, ICT initially entered the mainstream semiconductor industry by successfully producing the world's first 5V-only CMOS EEPROM (the 93C46). Since then, ICT has continued to introduce state-of-the-art CMOS ICs. The current product line families are listed below:

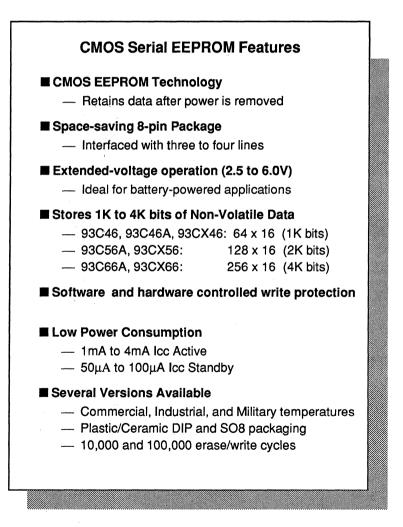

## **CMOS Serial EEPROMs**

ICT's CMOS Serial EEPROMs provide in-system-programmable nonvolatile data storage (that is, the data programmed, remains even after power is removed). Unlike parallel EEPROMs, ICT's serial EEPROMs offers low power consumption, low cost, space efficiency, and a 3 or 4 line interface that is easy to use with popular microcomputers. ICT's 1,024-bit 93C46 has become an industry standard with features that are ideal for high-volume, low density, data storage applications such as meters, alarms, locks, ID tags, appliances, telephones and VCRs.

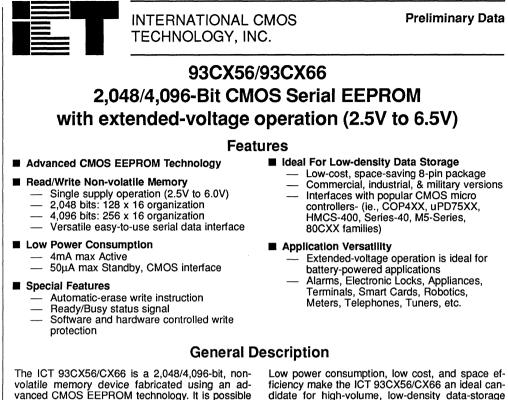

ICT's second generation family of CMOS Serial EEPROMs include 1K-bit, 2K-bit, and 4K-bit devices in both 5V-only and extended-voltage (2.5V-6.0V) versions. Besides higher densities, the new EEPROMs offer new features such as an autoerase write instruction and both hardware and software write protection. The extended voltage version EEPROMs, the 93CX46, 93CX56, and 93CX66, are ideal for battery-powered applications which must operate from high to low voltages and consume as little power as possible.

## CMOS High-Speed PROMs and EPROMs

ICT offers two related product families that are both based on highspeed CMOS EPROM technology. The CMOS PROMs are available in 24-pin DIP packages that are compatible with bipolar PROM pinouts. The CMOS EPROMs come in 28-pin and 32-pin packages with JEDEC standard EPROM pin-outs. Both families offer the high speed operation.

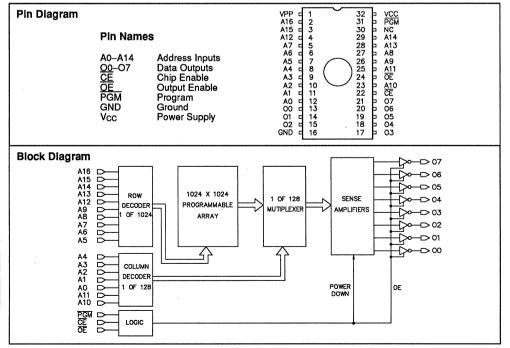

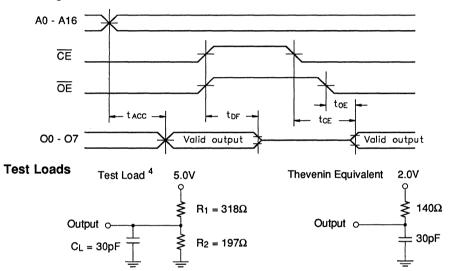

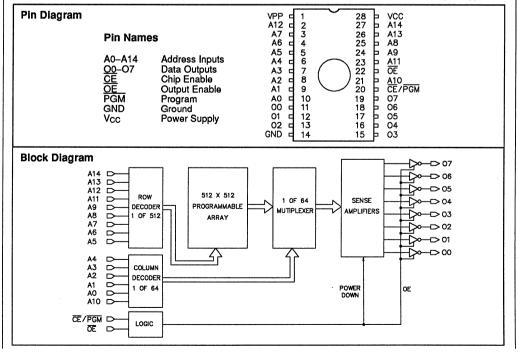

ICT's High-Speed PROM family, with access times as fast as 35ns and densities of 32K (4Kx8) and 64K (8Kx8), are frequently used in computation-intensive applications, such as digital signal processing (DSP), high speed modems, and video graphics controllers. Unlike common Bipolar PROMs, ICT's CMOS PROMs offer low-power consumption and reprogrammability which reduces system development and field-retrofit costs permitting the devices to accommodate code changes. Reprogrammability also enhances testability, allowing 100% factory testing for program and function. ICT's High-Speed CMOS EPROMs give systems design engineers the speed and density required for "no wait-state" operation with today's 16-bit and 32-bit microprocessors. The family of JEDECstandard 32-pin and 28-pin EPROMs, initially offer densities of 1M (128Kx8) and 256K (32Kx8), at speeds as fast as 55ns and 40ns respectively. Pin-out compatibility allows for easy upgrades through 8 Megabits. Processed in an advanced 1.0 micron CMOS technology, these devices offer the fastest access times per density available along with low power consumption and UV-reprogrammability.

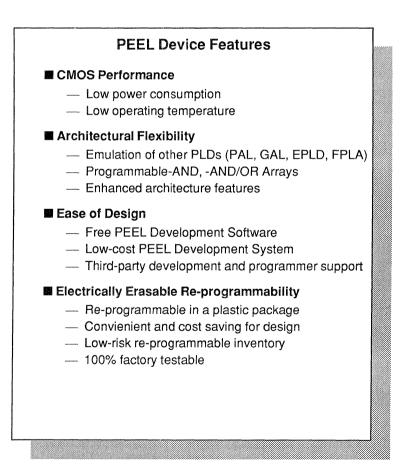

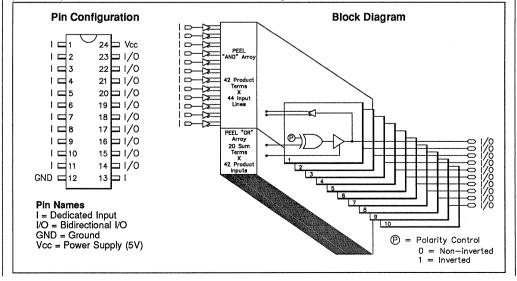

### **CMOS PEEL Devices**

Programmable logic devices (PLDs) in effect allow system designers to "write on silicon" and create custom logic functions in user-programmable off-the-shelf parts. The main benefits of PLD technology are the reduction of system parts count and quicker design turn-around. In a typical design, a single PLD can replace four or more standard logic packages. The design approach used with PLDs also reduces the time required to turn a design concept into a working circuit.

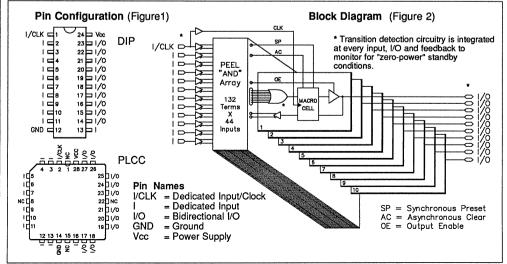

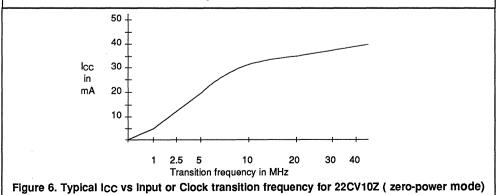

ICT's CMOS Programmable Electrically-Erasable Logic (PEEL) Devices offer several advantages over early-generation PLDs most of which are fabricated in bipolar technology. Unlike bipolar and other one-time-programmable PLDs, PEEL devices, give the designer a reprogrammable and completely tested alternative in a plastic package. Each PEEL device is programmed and tested during manufacturing to ensure 100% programming and function yield. PEEL devices also offer low-power consumption ranging from 1/2 to 1/8 that of standard PLDs. Ultra-low power consumption can be achieved using the "Zero-Power" PEEL22CV10Z.

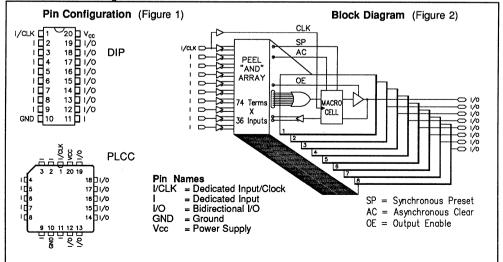

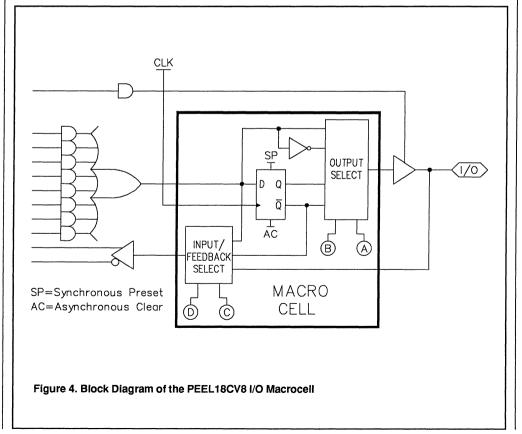

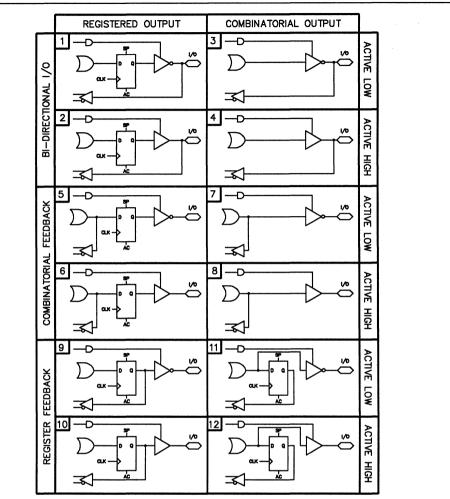

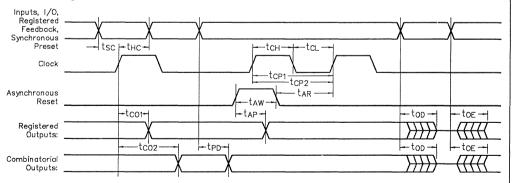

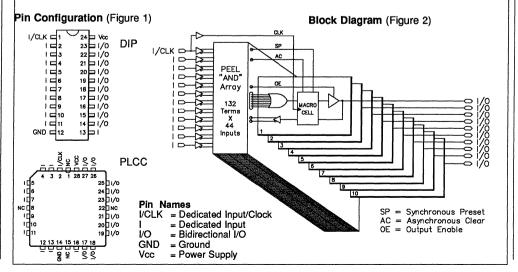

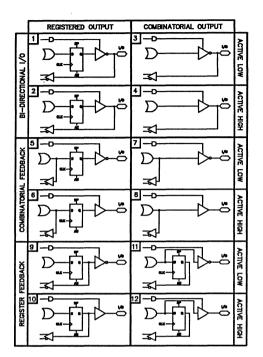

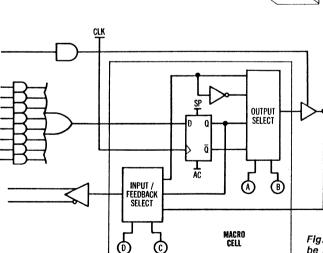

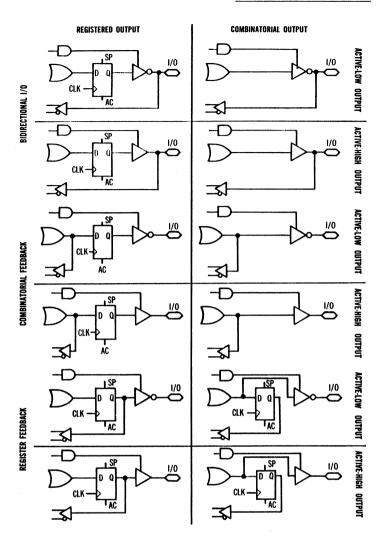

A key feature of PEEL devices are their enhanced architectures enabling them to take on the identity of a variety of popular 20 and 24-pin PLDs (PAL, GAL, EPLD, FPLA). For example, the PEEL18CV8 can emulate over 25 different PLDs with automatic translation via the PEEL Device Development Software. Thus, users can simplify inventories to a few PEEL devices and take advantage of PEEL low power consumption and EE-reprogrammability. The PEEL enhanced architectures also offer additional features such as a twelve configuration macro-cell, more product terms, and independent output enables, all of which allow designers to get more logic in each device.

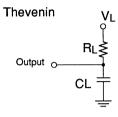

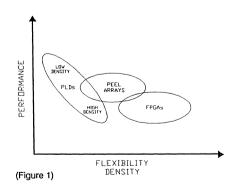

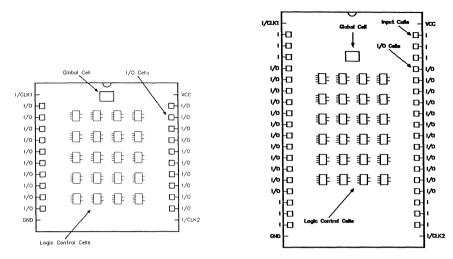

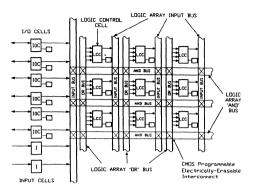

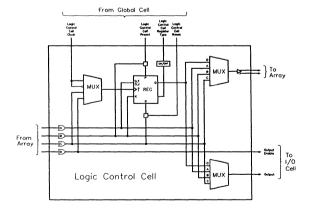

### **PEEL Arrays**

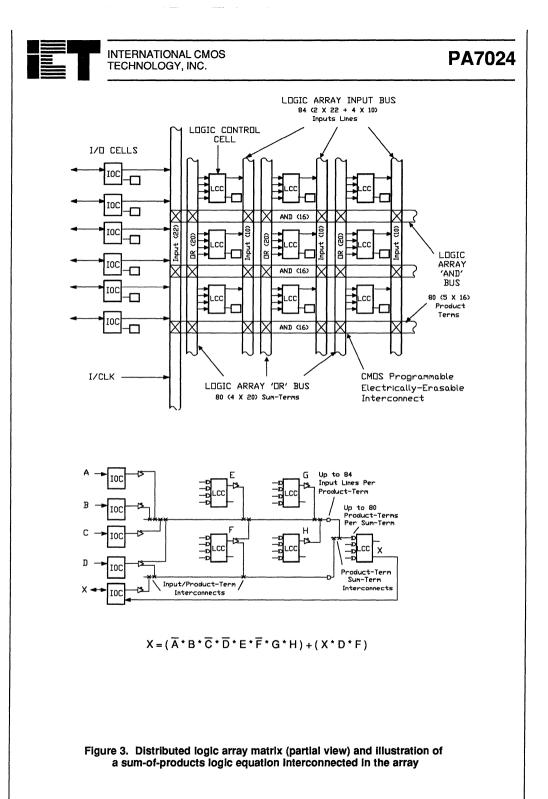

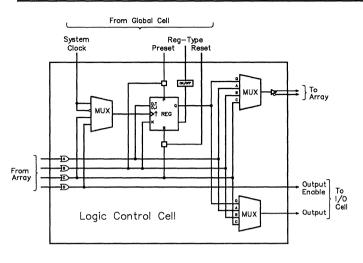

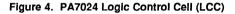

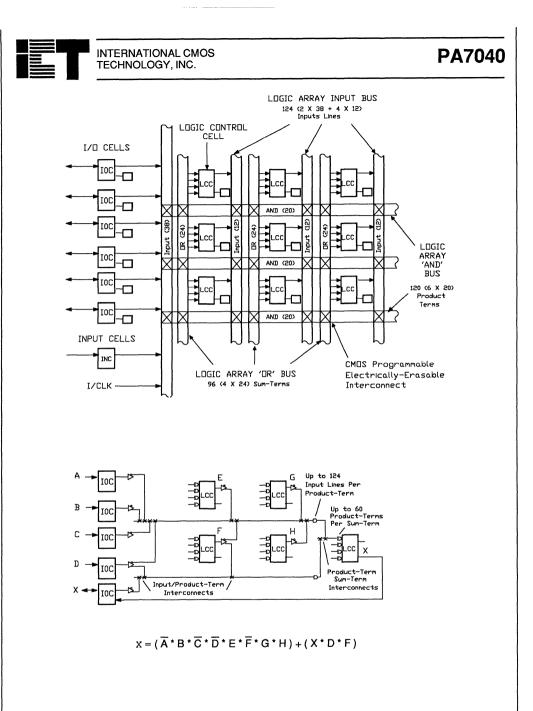

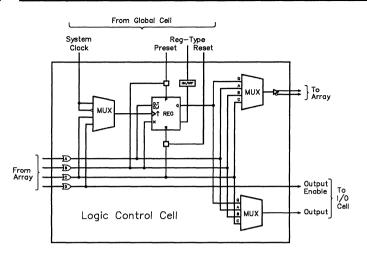

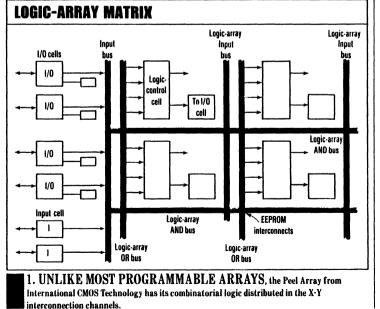

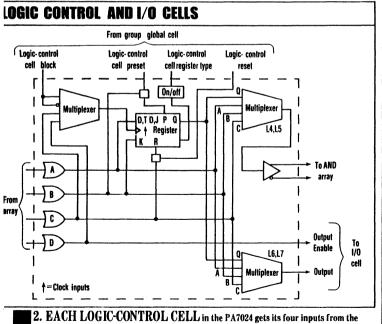

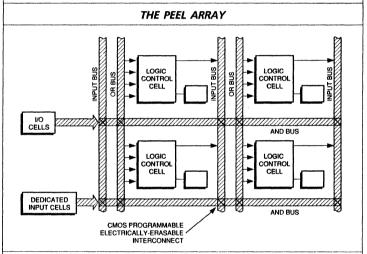

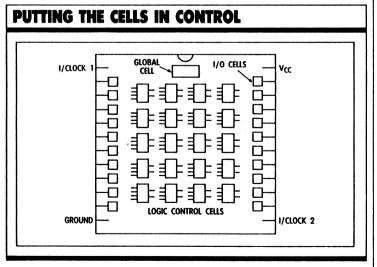

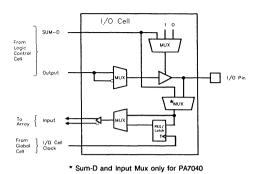

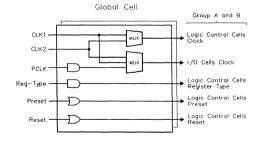

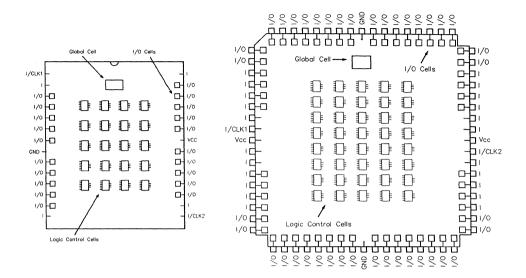

One of ICT's newest product families, PEEL Arrays are user-configurable high density ICs for creating multi-level, I/O buried, logic circuits. Designed in ICT's advanced 1-micron CMOS EE-technology, PEEL Arrays combine: the "wide-gate" speed performance of conventional PLDs, the architectural flexibility associated with Field Programmable Gate Arrays and a "best of both worlds" design methodology. PEEL Arrays offer all the same technology benefits of PEEL devices but at much higher levels of density and flexibility. The initial members of this family include the PA7024 and PA7040.

### **Development Tools**

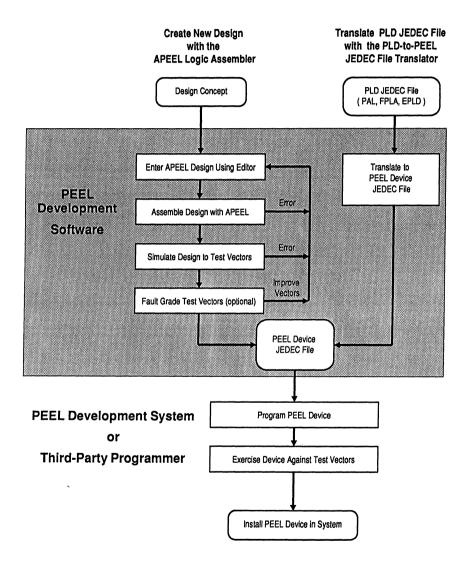

To support ICT's complete line of user-programmable products ICT offers software and programmer development tools for its PEEL Devices, PEEL Arrays and memory products. For PEEL Devices, ICT provides free PEEL Device development software as well as a low cost, easy-to-use, PC-based development system (PDS-1) which consists of design software, programmer and tester. For PEEL Arrays and PEEL Devices, the PACE Advanced Development Software offers an innovative and efficient method of design. Additionally, ICT's PROM and EEPROM memory products can be programmed using the PDS-1 system in conjunction with the MPS programming software.

# ICT Quality and Reliability

International CMOS Technology (ICT) is dedicated to providing its customers with integrated circuits that are designed, manufactured, tested, and serviced to the highest level of Quality and Reliability. From product definition through full production, ICT has developed and implemented a system designed to continually produce leading-edge CMOS products that meet, and usually exceed all customer requirements. At ICT, we recognize that product excellence is only obtained by a continuous commitment to be the leader in quality and reliability. ICT's quality and reliability programs are separated into the following categories:

## **Quality and Reliability by Design**

ICT's design philosophy emphasizes quality and reliability during every part of the design cycle. Conservative design rules and extensive logic and circuit simulation are performed over extreme operating conditions. During circuit and process design, special attention is paid to problems such as CMOS latch-up and electrostatic discharge (ESD). For example, ICT's I/O pins are prevented from CMOS latchup by a double guard-ring designed into all products. Also ICT designers have developed and implemented techniques to protect all products from electrostatic discharge (ESD) up to 2000V on all I/O pins. Special features are also designed into ICT products to improve the reliability of the device. As an example, all of ICT's second generation EEPROMs have a Program Enable (PE) hardware write protection designed to prevent against inadvertent writes during system power-up and power-down. These type of design considerations enhance the product's reliability in actual system applications.

### **Initial Device Qualification**

Tests have been developed to observe the life expectancy of each new product. In order to qualify a new product, packaged parts from a minimum of three different lots must be scrutinized for electrical functionality and reliability over extreme temperature and voltage conditions. Tests include operating life, data retention, endurance, temperature cycling, temperature/humidity bias, ESD, and latch-up. Pre-determined reliability goals must be met in order for a product to pass qualification. All procedures and results are carefully documented for future reference. This qualification validates the device, package, and supplier. Therefore, whenever design rules are adjusted, a new foundry or assembly facility is used, or a new package type is introduced, a re-qualification of the product must be completed.

A Dynamic High-Temperature Operating Life (DHTOL) test is a standard approach used to evaluate the reliability of a product under accelerated conditions. Data is gathered at the rated ambient temperature and the devices are biased as they would be in actual operation. The devices are exercised by constantly switching the inputs. This DHTOL test is set for a continuous operation typically at an ambient temperature of 125°C and a duration of test equal to 1,000 hours. The results of the DHTOL test are recorded in a datalog and made available for future reference.

At the cell level, data retention is a function of the floating gate's ability to retain charge. Data retention failures in a floating gate structure are commonly caused by dielectric defects and can be accelerated by high temperature bake stress. ICT's products are designed to provide data retention for at least ten years at the maximum rated temperature which is equivalent to over forty years of data retention at 55°c. ICT uses an industry standard endurance specification that for any lot of devices shipped, fewer than 5% of the units will cease to cycle properly before the specified limit when cycled at room temperature. ICT continually samples production lots of products by bulk programming and erasing the units for the specified cycles to assure the product meets ICT's endurance criteria.

## **Ongoing Monitor Qualification**

Although initial device qualification is an essential step to a product release, all products must be constantly monitored to ensure the reliability of the device. Production lots are sampled every quarter, and are subject to the same initial qualification tests, such as the DHTOL test and endurance test. All results are again documented, and failures are carefully analyzed in order to find long term improvements to the product. An example of the ongoing monitor program includes: Operating Life Test, Data Retention Bake and Cycling Endurance.

## **Quality and Reliability by Test**

ICT has developed a test flow to ensure that all products shipped to customers are of the highest quality and reliability. Each device is erased, programmed, and read at Wafer Sort, Package Test, Post-Bake Final Test, and QA Test to guarantee electrical characteristics over the entire operating temperature range and functionality of the part. Test programs are developed to screen out those devices which fail to meet data sheet specifications. Additionally since all ICT's products are programmable, every unit shipped is subjected to a data retention bake which verifies the ability to retain data for at least ten years over the entire temperature range. This is the equivalent of over forty years of data retention at  $55^{\circ}c$ .

## **Customer Service**

Customer service plays an important role in quality assurance. Customer product concerns are serviced and documented with failure analysis reports that states the problem and suggests a corrective solution. All ICT employees are a part of the customer service team, whose goal is to provide customer satisfaction.

## **CMOS Serial EEPROM Selection Guide**

| PART#    | DESCRIPTION                               | PINS | SPEED | Icc/Isb    | TEMP <sup>(1)</sup> | PACKAGE <sup>(2)</sup> |

|----------|-------------------------------------------|------|-------|------------|---------------------|------------------------|

| 93C46C   | 64 x 16 bit Serial EEPROM                 | 8    | n/a   | 3mA/0.1mA  | с                   | C8                     |

| 93C46CI  | 64 x 16 bit Serial EEPROM                 | 8    | n/a   | 6mA/0.1mA  | I                   | C8                     |

| 93C46CM  | 64 x 16 bit Serial EEPROM                 | 8    | n/a   | 7mA/0.1mA  | м                   | C8                     |

| 93C46P   | 64 x 16 bit Serial EEPROM                 | 8    | n/a   | 3mA/0.1mA  | С                   | P8                     |

| 93C46PE  | 93C46 with 100k cycle endurance           | 8    | n/a   | 3mA/0.1mA  | С                   | P8                     |

| 93C46PIE | 93C46I with 100k cycle endurance          | 8    | n/a   | 6mA/0.1mA  | I                   | P8                     |

| 93C46PI  | 64 x 16 bit Serial EEPROM                 | 8    | n/a   | 6mA/0.1mA  | I                   | P8                     |

| 93C46PM  | 64 x 16 bit Serial EEPROM                 | 8    | n/a   | 7mA/0.1mA  | м                   | P8                     |

| 93C46S   | 64 x 16 bit Serial EEPROM                 | 8    | n/a   | 3mA/0.1mA  | С                   | S8                     |

| 93C46SI  | 64 x 16 bit Serial EEPROM                 | 8    | n/a   | 6mA/0.1mA  | I                   | S8                     |

| 93C46AP  | 64 x 16 bit Serial EEPROM                 | 8    | n/a   | 3mA/0.1mA  | с                   | P8                     |

| 93C46API | 64 x 16 bit Serial EEPROM                 | 8    | n/a   | 6mA/0.1mA  | I                   | P8                     |

| 93C46APM | 64 x 16 bit Serial EEPROM                 | 8    | n/a   | 7mA/0.1mA  | м                   | P8                     |

| 93C46AK  | 64 x 16 bit Serial EEPROM                 | 8    | n/a   | 3mA/0.1mA  | с                   | K8                     |

| 93C46AS  | 64 x 16 bit Serial EEPROM                 | 8    | n/a   | 3mA/0.1mA  | С                   | S8                     |

| 93C46AKI | 64 x 16 bit Serial EEPROM                 | 8    | n/a   | 6mA/0.1mA  | I.                  | K8                     |

| 93C46ASI | 64 x 16 bit Serial EEPROM                 | 8    | n/a   | 6mA/0.1mA  | I                   | S8                     |

| 93C56AP  | 128 x 16 bit Serial EEPROM                | 8    | n/a   | 3mA/0.05mA | С                   | P8                     |

| 93C56API | 128 x 16 bit Serial EEPROM                | 8    | n/a   | 6mA/0.1mA  | I                   | P8                     |

| 93C56APM | 128 x 16 bit Serial EEPROM                | 8    | n/a   | 7mA/0.2mA  | м                   | P8                     |

| 93C56AK  | 128 x 16 bit Serial EEPROM                | 8    | n/a   | 3mA/0.05mA | С                   | K8                     |

| 93C56AKI | 128 x 16 bit Serial EEPROM                | 8    | n/a   | 6mA/0.1mA  | I                   | K8                     |

| 93C66AP  | 256 x 16 bit Serial EEPROM                | 8    | n/a   | 3mA/0.05mA | С                   | P8                     |

| 93C66API | 256 x 16 bit Serial EEPROM                | 8    | n/a   | 6mA/0.1mA  | I                   | P8                     |

| 93C66APM | 256 x 16 bit Serial EEPROM                | 8    | n/a   | 7mA/0.2mA  | М                   | P8                     |

| 93C66AK  | 256 x 16 bit Serial EEPROM                | 8    | n/a   | 3mA/0.05mA | С                   | K8                     |

| 93C66AKI | 256 x 16 bit Serial EEPROM                | 8    | n/a   | 6mA/0.1mA  | 1                   | K8                     |

| 93CX46P  | 64 x 16 bit Serial EEPROM (2.5V to 6.0V)  | 8    | n/a   | 3mA/0.05mA | с                   | P8                     |

| 93CX46PI | 64 x 16 bit Serial EEPROM (2.5V to 6.0V)  | 8    | n/a   | 6mA/0.1mA  | 1                   | P8                     |

| 93CX46PM | 64 x 16 bit Serial EEPROM (2.5V to 6.0V)  | 8    | n/a   | 7mA/0.2mA  | М                   | P8                     |

| 93CX46K  | 64 x 16 bit Serial EEPROM (2.5V to 6.0V)  | 8    | n/a   | 3mA/0.05mA | с                   | K8                     |

| 93CX46KI | 64 x 16 bit Serial EEPROM (2.5V to 6.0V)  | 8    | n/a   | 6mA/0.1mA  | T                   | K8                     |

| 93CX56P  | 128 x 16 bit Serial EEPROM (2.5V to 6.0V) | 8    | n/a   | 4mA/0.05mA | С                   | P8                     |

### CMOS Serial EEPROM Selection Guide (cont.)

| PART#    | DESCRIPTION                               |   | SPEED | ICC/ISB    | TEMP <sup>(1)</sup> PACKAGE <sup>(2)</sup> |    |

|----------|-------------------------------------------|---|-------|------------|--------------------------------------------|----|

| 93CX56PI | 128 x 16 bit Serial EEPROM (2.5V to 6.0V) | 8 | n/a   | 6mA/0.1mA  | I.                                         | P8 |

| 93CX56PM | 128 x 16 bit Serial EEPROM (2.5V to 6.0V) | 8 | n/a   | 8mA/0.2mA  | м                                          | P8 |

| 93CX56K  | 128 x 16 bit Serial EEPROM (2.5V to 6.0V) | 8 | n/a   | 4mA/0.05mA | с                                          | K8 |

| 93CX56KI | 128 x 16 bit Serial EEPROM (2.5V to 6.0V) | 8 | n/a   | 6mA/0.1mA  | 1                                          | K8 |

| 93CX66P  | 256 x 16 bit Serial EEPROM (2.5V to 6.0V) | 8 | n/a   | 4mA/0.05mA | С                                          | P8 |

| 93CX66P1 | 256 x 16 bit Serial EEPROM (2.5V to 6.0V) | 8 | n/a   | 6mA/0.1mA  | ł                                          | P8 |

| 93CX66PM | 256 x 16 bit Serial EEPROM (2.5V to 6.0V) | 8 | n/a   | 8mA/0.2mA  | м                                          | P8 |

| 93CX66K  | 256 x 16 bit Serial EEPROM (2.5V to 6.0V) | 8 | n/a   | 4mA/0.5mA  | С                                          | K8 |

| 93CX66KI | 256 x 16 bit Serial EEPROM (2.5V to 6.0V) | 8 | n/a   | 6mA/0.1mA  | I                                          | K8 |

<sup>(2)</sup>Package Codes: See section 9.0 for package drawings C = Ceramic DIP

K = 8 Pin SOIC (standard pin-out)

N = Windowed Ceramic DIP (300 mil)

P = Plastic DIP

S = 8 Pin SOIC (rotated pin-out) W = Windowed Ceramic DIP (600 mil)

<sup>(1)</sup>Temperature range codes: C = Commercial 0°C to +70°C I = Industrial -40°C to +85°C

M = Military -55°C to +125°C

<sup>(1)</sup>Temperature range codes: C = Commercial 0°C to +70°C

I = Industrial -40°C to +85°C

### **CMOS High Speed PROM and EPROM Selection Guide**

| PART#        | DESCRIPTION                 | PINS | SPEED | Icc/IsB     | TEMP <sup>(1</sup> | PACKAGE <sup>(2)</sup> |

|--------------|-----------------------------|------|-------|-------------|--------------------|------------------------|

| 27CX321C-35  | 4k x 8 bit High Speed PROM  | 24   | 35ns  | 40mA/0.5mA* | с                  | W24                    |

| 27CX321C-40  | 4k x 8 bit High Speed PROM  | 24   | 40ns  | 40mA/0.5mA* | с                  | W24                    |

| 27CX321C-45  | 4k x 8 bit High Speed PROM  | 24   | 45ns  | 40mA/0.5mA* | с                  | W24                    |

| 27CX321CI-45 | 4k x 8 bit High Speed PROM  | 24   | 45ns  | 60mA/0.5mA* | I                  | W24                    |

| 27CX321CI-55 | 4k x 8 bit High Speed PROM  | 24   | 55ns  | 60mA/0.5mA* | I                  | W24                    |

| 27CX322C-35  | 4k x 8 bit High Speed PROM  | 24   | 35ns  | 40mA/0.5mA* | С                  | N24                    |

| 27CX322C-40  | 4k x 8 bit High Speed PROM  | 24   | 40ns  | 40mA/0.5mA* | С                  | N24                    |

| 27CX322C-45  | 4k x 8 bit High Speed PROM  | 24   | 45ns  | 40mA/0.5mA* | С                  | N24                    |

| 27CX322CI-45 | 4k x 8 bit High Speed PROM  | 24   | 45ns  | 60mA/0.5mA* | I                  | N24                    |

| 27CX322CI-55 | 4k x 8 bit High Speed PROM  | 24   | 55ns  | 60mA/0.5mA* | I                  | N24                    |

| 27CX641C-35  | 8k x 8 bit High Speed PROM  | 24   | 35ns  | 90mA        | с                  | W24                    |

| 27CX641C-40  | 8k x 8 bit High Speed PROM  | 24   | 40ns  | 80mA        | с                  | W24                    |

| 27CX641C-45  | 8k x 8 bit High Speed PROM  | 24   | 45ns  | 80mA        | с                  | W24                    |

| 27CX641C-55  | 8k x 8 bit High Speed PROM  | 24   | 55ns  | 80mA        | С                  | W24                    |

| 27CX641CI-45 | 8k x 8 bit High Speed PROM  | 24   | 45ns  | 120mA       | I                  | W24                    |

| 27CX641CI-55 | 8k x 8 bit High Speed PROM  | 24   | 55ns  | 120mA       | 1                  | W24                    |

| 27CX642C-35  | 8k x 8 bit High Speed PROM  | 24   | 35ns  | 90mA        | с                  | N24                    |

| 27CX642C-40  | 8k x 8 bit High Speed PROM  | 24   | 40ns  | 80mA        | с                  | N24                    |

| 27CX642C-45  | 8k x 8 bit High Speed PROM  | 24   | 45ns  | 80mA        | с                  | N24                    |

| 27CX642C-55  | 8k x 8 bit High Speed PROM  | 24   | 55ns  | 80mA        | С                  | N24                    |

| 27CX642CI-45 | 8k x 8 bit High Speed PROM  | 24   | 45ns  | 120mA       | I                  | N24                    |

| 27CX642CI-55 | 8k x 8 bit High Speed PROM  | 24   | 55ns  | 120mA       | I                  | N24                    |

| 27CX256C-40  | 32k x 8 bit Hgh Speed EPROM | 28   | 40ns  | 90mA        | с                  | N28                    |

| 27CX256C-45  | 32k x 8 bit Hgh Speed EPROM | 28   | 45ns  | 90mA        | с                  | N28                    |

| 27CX256C-70  | 32k x 8 bit Hgh Speed EPROM | 28   | 70ns  | 90mA        | с                  | N28                    |

| 27CX010C-55  | 128k x 8 High Speed EPROM   | 32   | 55ns  | 90mA/1mA    | с                  | W2                     |

| 27CX010C-70  | 128k x 8 High Speed EPROM   | 32   | 70ns  | 90mA/1mA    | с                  | W2                     |

| 27CX010C-90  | 128k x 8 High Speed EPROM   | 32   | 90ns  | 90mA/1mA    | с                  | W2                     |

<sup>(2)</sup>Package Codes: See section 9.0 for package drawings

C = Ceramic DIP

N = Windowed Ceramic DIP (300 mil)

P = Plastic DIP

W = Windowed Ceramic DIP (600 mil)

\*typical standby current

## **CMOS PEEL Device Selection Guide**

| PART #         | DESCRIPTION                                   | PINS | SPEED | lcc mA      | TEMP <sup>(1</sup> | PACKAGE <sup>(2)</sup> |

|----------------|-----------------------------------------------|------|-------|-------------|--------------------|------------------------|

| PEEL18CV8P-10  | PLD superset 12 config, I/O macrocells (8)    | 20   | 10ns  | 80+0.5/MHz  | с                  | P20                    |

| PEEL18CV8P-12  | PLD superset 12 config, I/O macrocells (8)    | 20   | 12ns  | 80+0.5/MHz  | с                  | P20                    |

| PEEL18CV8P-15  | PLD superset 12 config, I/O macrocells (8)    | 20   | 15ns  | 80+0.5/MHz  | с                  | P20                    |

| PEEL18CV8P-20  | PLD superset 12 config, I/O macrocells (8)    | 20   | 20ns  | 80+0.5/MHz  | С                  | P20                    |

| PEEL18CV8P-25  | PLD superset 12 config, I/O macrocells (8)    | 20   | 25ns  | 20+0.7/MHz  | С                  | P20                    |

| PEEL18CV8P-35  | PLD superset 12 config, I/O macrocells (8)    | 20   | 35ns  | 20+0.7/MHz  | С                  | P20                    |

| PEEL18CV8PI-25 | Industrial Temperature Range PEEL18CV8        | 20   | 25ns  | 30+0.7/MHz  | I                  | P20                    |

| PEEL18CV8PI-35 | Industrial Temperature Range PEEL18CV8        | 20   | 35ns  | 30+0.7/MHz  | T                  | P20                    |

| PEEL18CV8J-10  | Surface mount PLCC PEEL18CV8                  | 20   | 10ns  | 80+0.5/MHz  | С                  | J20                    |

| PEEL18CV8J-12  | Surface mount PLCC PEEL18CV8                  | 20   | 12ns  | 80+0.5/MHz  | с                  | J20                    |

| PEEL18CV8J-15  | Surface mount PLCC PEEL18CV8                  | 20   | 15ns  | 80+0.5/MHz  | С                  | J20                    |

| PEEL18CV8J-20  | Surface mount PLCC PEEL18CV8                  | 20   | 20ns  | 80+0.5/MHz  | С                  | J20                    |

| PEEL18CV8J-25  | Surface mount PLCC PEEL18CV8                  | 20   | 25ns  | 20+0.7/MHz  | С                  | J20                    |

| PEEL18CV8J-35  | Surface mount PLCC PEEL18CV8                  | 20   | 35ns  | 20+0.7/MHz  | С                  | J20                    |

| PEEL20CG10P-12 | PLD superset 12 config, I/O macrocells (10)   | 24   | 12ns  | 105+0.5/MHz | с                  | P24                    |

| PEEL20CG10P-15 | PLD superset 12 config, I/O macrocells (10)   | 24   | 15ns  | 105+0.5/MHz | с                  | P24                    |

| PEEL20CG10P-20 | PLD superset 12 config, I/O macrocells (10)   | 24   | 20ns  | 65+0.5/MHz  | С                  | P24                    |

| PEEL20CG10P-25 | PLD superset 12 config, I/O macrocells (10)   | 24   | 25ns  | 55+0.5/MHz  | с                  | P24                    |

| PEEL20CG10P-35 | PLD superset 12 config, I/O macrocells (10)   | 24   | 35ns  | 55+0.5/MHz  | С                  | P24                    |

| PEEL20CG10J-12 | Surface mount PLCC PEEL20CG10                 | 24   | 12ns  | 105+0.5/MHz | с                  | P24                    |

| PEEL20CG10J-15 | Surface mount PLCC PEEL20CG10                 | 24   | 15ns  | 105+0.5/MHz | С                  | P24                    |

| PEEL20CG10J-20 | Surface mount PLCC PEEL20CG10                 | 24   | 20ns  | 65+0.5/MHz  | С                  | P24                    |

| PEEL20CG10J-25 | Surface mount PLCC PEEL20CG10                 | 24   | 25ns  | 55+0.5/MHz  | с                  | P24                    |

| PEEL20CG10J-35 | Surface mount PLCC PEEL20CG10                 | 24   | 35ns  | 55+0.5/MHz  | С                  | P24                    |

| PEEL22CV10P-12 | PLD superset 4/12 config, I/O macrocells (10) | 24   | 12ns  | 105+0.5/MHz | с                  | P24                    |

| PEEL22CV10P-15 | PLD superset 4/12 config, I/O macrocells (10) | 24   | 15ns  | 105+0.5/MHz | С                  | P24                    |

| PEEL22CV10P-20 | PLD superset 4/12 config, I/O macrocells (10) | 24   | 20ns  | 65+0.5/MHz  | С                  | P24                    |

| PEEL22CV10P-25 | PLD superset 4/12 config, I/O macrocells (10) | 24   | 25ns  | 55+0.5/MHz  | С                  | P24                    |

| PEEL22CV10P-35 | PLD superset 4/12 config, I/O macrocells (10) | 24   | 35ns  | 55+0.5/MHz  | с                  | P24                    |

| PEEL22CV10J-12 | Surface mount PLCC PEEL22CV10                 | 24   | 12ns  | 105+0.5/MHz | С                  | P24                    |

| PEEL22CV10J-15 | Surface mount PLCC PEEL22CV10                 | 24   | 15ns  | 105+0.5/MHz | с                  | P24                    |

| PEEL22CV10J-20 | Surface mount PLCC PEEL22CV10                 | 24   | 20ns  | 65+0.5/MHz  | с                  | P24                    |

| PEEL22CV10J-25 | Surface mount PLCC PEEL22CV10                 | 24   | 25ns  | 55+0.5/MHz  | с                  | P24                    |

## CMOS PEEL Device Selection Guide (cont.)

| PART #          | DESCRIPTION                               | PINS | SPEED | lcc mA      | TEMP <sup>(1</sup> | PACKAGE <sup>(2)</sup> |

|-----------------|-------------------------------------------|------|-------|-------------|--------------------|------------------------|

| PEEL22CV10J-35  | Surface mount PLCC PEEL22CV10             | 24   | 35ns  | 55+0.5/MHz  | с                  | P24                    |

| PEEL22CV10ZP-20 | Zero Power 12 config, I/O macrocells (10) | 24   | 20ns  | 65+0.5/MHz* | с                  | P24                    |

| PEEL22CV10ZP-25 | Zero Power 12 config, I/O macrocells (10) | 24   | 25ns  | 55+0.5/MHz* | С                  | P24                    |

| PEEL22CV10ZP-35 | Zero power 12 config, I/O macrocells (10) | 24   | 35ns  | 55+0.5/MHz* | с                  | P24                    |

| PEEL22CV10ZJ-25 | Surface mount PLCC PEEL22CV10Z            | 24   | 25ns  | 55+0.5/MHz* | с                  | P24                    |

| PEEL22CV10ZJ-35 | Surface mount PLCC PEEL22CV10Z            | 24   | 35ns  | 55+0.5/MHz* | с                  | P24                    |

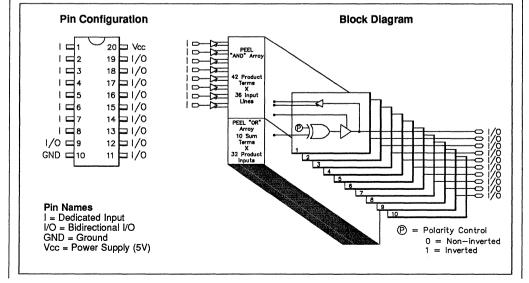

| PEEL153P-30     | FPLA prog AND/OR/polarity                 | 20   | 30ns  | 35+1.0/MHz  | с                  | P20                    |

| PEEL153P-35     | FPLA prog AND/OR/polarity                 | 20   | 35ns  | 35+1.0/MHz  | с                  | P20                    |

| PEEL173P-15     | FPLA prog AND/OR/polarity                 | 24   | 15ns  | 60+0.5/MHz  | с                  | P24                    |

| PEEL173P-30     | FPLA prog AND/OR/polarity                 | 24   | 30ns  | 35+1.0/MHz  | с                  | P24                    |

| PEEL173P-35     | FPLA prog AND/OR/polarity                 | 24   | 35ns  | 35+1.0/MHz  | с                  | P24                    |

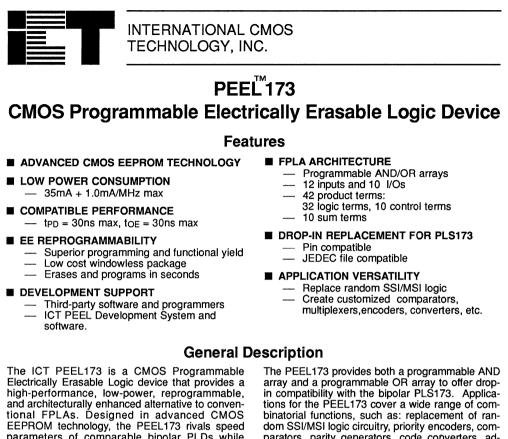

| PEEL253P-30     | Enhanced FPLA prog AND/OR/polarity        | 20   | 30ns  | 35+1.0/MHz  | с                  | P20                    |

| PEEL253P-35     | Enhanced FPLA prog AND/OR/polarity        | 20   | 35ns  | 35+1.0/MHz  | с                  | P20                    |

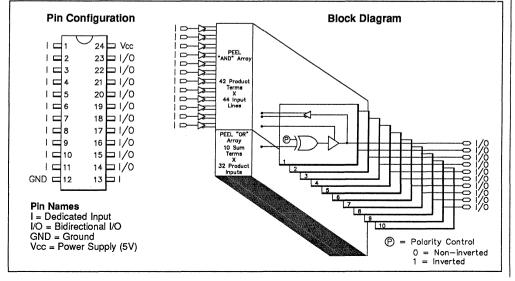

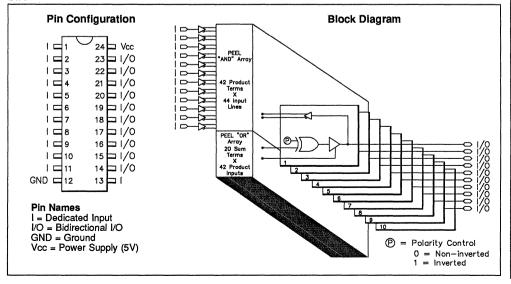

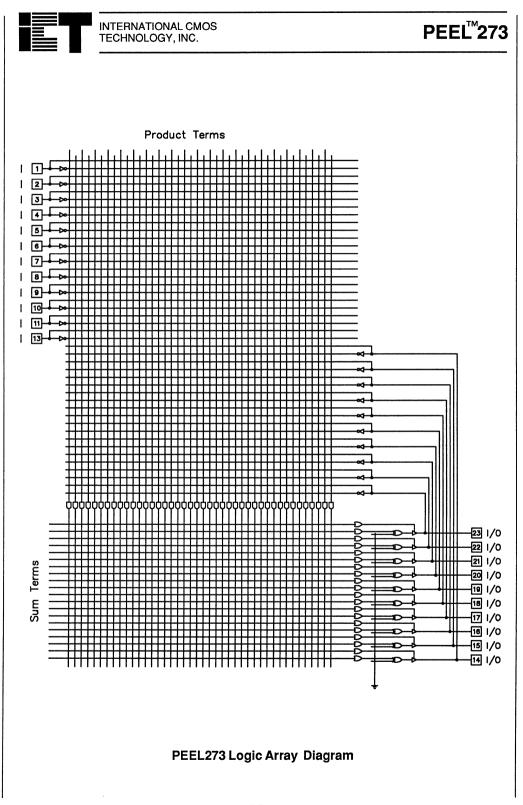

| PEEL273P-15     | FPLA prog AND/OR/polarity                 | 24   | 15ns  | 60+0.5/MHz  | с                  | P24                    |

| PEEL273P-30     | Enhanced FPLA prog AND/OR/polarity        | 24   | 30ns  | 35+1.0/MHz  | с                  | P24                    |

| PEEL273P-35     | Enhanced FPLA prog AND/OR/polarity        | 24   | 35ns  | 35+1.0/MHz  | С                  | P24                    |

\*Icc standby for zero-power mode is 200 $\mu A$

| <sup>(2)</sup> Package Codes: See section 9.0 for package drawing | js |

|-------------------------------------------------------------------|----|

| C = Ceramic PIP                                                   |    |

| B Blactic DIB                                                     |    |

P = Plastic DIF J = PLCC

N = Windowed Ceramic DIP (300 mil)

<sup>(1)</sup>Temperature range codes: C = Commercial  $0^{\circ}$ C to +70°C I = Industrial -40°C to +85°C

- - -

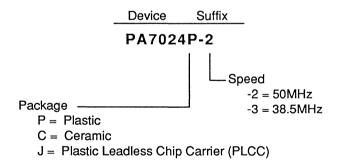

### **CMOS PEEL Array Selection Guide**

| PART #    | DESCRIPTION              | PINS | SPEED   | ícc mA      | TEMP <sup>(</sup> | <sup>1)</sup> PACKAGE <sup>(2)</sup> |

|-----------|--------------------------|------|---------|-------------|-------------------|--------------------------------------|

| PA7024P-2 | High density logic array | 24   | 50MHz   | 100+0.5/MHz | с                 | P24                                  |

| PA7024P-3 | High density logic array | 24   | 38.5MHz | 100+0.5/MHz | с                 | P24                                  |

| PA7024J-2 | High density logic array | 24   | 50MHz   | 100+0.5/MHz | С                 | J24                                  |

| PA7024J-3 | High density logic array | 24   | 38.5MHz | 100+0.5/MHz | с                 | J24                                  |

| PA7040P-2 | High density logic array | 40   | 50MHz   | 120+0.5/MHz | с                 | P40                                  |

| PA7040P-3 | High density logic array | 40   | 38.5MHz | 120+0.5/MHz | С                 | P40                                  |

| PA7040J-2 | High density logic array | 40   | 50MHz   | 120+0.5/MHz | с                 | J40                                  |

| PA7040J-3 | High density logic array | 40   | 38.5MHz | 120+0.5/MHz | С                 | J40                                  |

$^{(2)} \textbf{Package Codes:}$  See section 9.0 for package drawings C = Ceramic DIP

<sup>(1)</sup>Temperature range codes: C = Commercial 0°C to +70°C

J = PLCC

N = Windowed Ceramic DIP (300 mil) P = Plastic DIP S = 8 Pin SOIC

W = Windowed Ceramic DIP (600 mil)

# **Ordering Information**

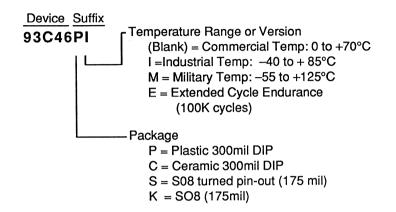

## **CMOS Serial EEPROMs**

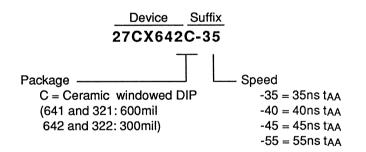

## **CMOS High-Speed Erasable PROMs**

\_ \_

# **Ordering Information**

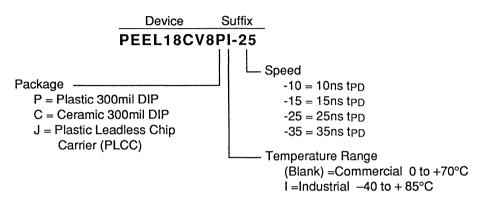

## **CMOS PEEL Devices**

## **CMOS PEEL Arrays**

# Serial EEPROM Cross Reference

| Asahi 🖙 ICT                                                                                                                                  | NCR IS ICT                                                                                                                                                                                                                                                                         | Rohm 🖙 ICT                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| 93CX4693CX46<br>93CX5693CX56<br>93CX6693CX66                                                                                                 | NCR5930893C46P                                                                                                                                                                                                                                                                     | BR93C46P 93C46P                                           |

| Catalyst 🖙 ICT                                                                                                                               | National 🖙 ICT                                                                                                                                                                                                                                                                     | Samsung 🖙 ICT                                             |

| CAT93C46P93C46P<br>CAT93C46PI93C46PI<br>CAT93C46K93C46AK<br>CAT35C102P93C56AP<br>CAT33C102P93CX56P<br>CAT35C104P93CK56P<br>CAT33C104P93CK56P | NMC9346N         93C46P           NMC9346EN         93C46PI           NMC9346MN         93C46PM           NMC9346M         93C46AK           NMC93246N         93C46AF           NMC93C46N         93C46AP           NMC93C56N         93C66AP           NMC93C66N         93C66AP | KM93C46                                                   |

| XLS93C46P93C46P<br>XLI93C46P93C46PI                                                                                                          | Oki nege ICT                                                                                                                                                                                                                                                                       |                                                           |

| Hyundai 📾 ICT                                                                                                                                | MSM1681193C46P<br>MSM16811GS93C46S                                                                                                                                                                                                                                                 | Thompson ឆេះ         ICT           TS93C46         93C46P |

| HY93C46S93C46P<br>HY93C46ES93C46PI<br>HY93C46J93C46S                                                                                         |                                                                                                                                                                                                                                                                                    |                                                           |

# **PROM and EPROM Cross Reference**

| AMD/MMI ESP ICT                                              | Fairchild 🖙 ICT                                   | Raytheon 🖙 ICT           |

|--------------------------------------------------------------|---------------------------------------------------|--------------------------|

| Am 27S43A 27CX321C-40                                        | 93Z565AC 27CX641C-45                              | R2971S 27CX322C-45       |

| Am27S43 27CX321C-45                                          | 93Z565C 27CX641C-55                               | 39VP864D 27CX641C-55     |

| Am27S49AC 27CX641C-45                                        | 93Z667C-40 27CX642C-40                            | 39VP865S 27CX642C-55     |

| Am27S49C 27CX641C-55                                         | 93Z667C-45 27CX642C-45                            |                          |

| 63S381A 27CX321C-35                                          | 93Z667C-55 27CX642C-55                            |                          |

| 63S3281 27CX321C-45                                          |                                                   | Signetics 🖙 ICT          |

| 27H010C-55 27CX010C-55                                       | Fujitsu 🖙 ICT                                     | N82HS321A 27CX321C-35    |

| 27H010C-70 27CX010C-70                                       | MB7142H 27CX321C-45                               | N82HS321 27CX321C-45     |

| 27H010C-90 27CX010C-90                                       | MB7144Y 27CX641C-45                               | N82HS641AN 27CX641C-45   |

|                                                              | MB7144H 27CX641C-40                               | N82HS641AF 27CX641C-45   |

| Atmel 🖙 ICT                                                  |                                                   | N82HS641N 27CX641C-55    |

| AT27HC641-40DC . 27CX641C-40                                 | Goldstar 🖙 ICT                                    | N82HS641FN 27CX641C-55   |

| AT27HC641-45DC . 27CX641C-45                                 | GM57HC64-45 27CX641C-45                           | 27HC641-55 27CX641C-55   |

| AT27HC641-55DC . 27CX641C-55<br>AT27HC642-40DC . 27CX642C-40 | GM57HC64-55 27CX641C-55                           |                          |

| AT27HC642-45DC . 27CX642C-45                                 |                                                   | Wafer Scale 🖙 ICT        |

| AT27HC642-55DC . 27CX642C-55                                 | Harris IS ICT                                     | WS57C43B-35 27CX321C-35  |

| Cypress IS ICT                                               |                                                   | WS57C43B-45D 27CX321C-45 |

|                                                              | HM-76321A-5 27CX321C-45                           | WS57C43B-35T 27CX321C-35 |

| CY7C264-40WC 27CX641C-40                                     | HM-76321-5 27CX321C-55<br>HM-76641A-5 27CX641C-45 | WS57C43B-45T 27CX321C-45 |

| CY7C264-45WC 27CX641C-45<br>CY7C264-55WC 27CX641C-55         | HM-76641-5 27CX641C-55                            | WS57C49B-40D 27CX641C-40 |

| 0170204-0300027070410-03                                     |                                                   | WS57C49B-45D 27CX641C-45 |

| CY7C261-40WC 27CX642C-40                                     |                                                   | WS57C49B-55D 27CX641C-55 |

| CY7C263-40WC 27CX642C-40<br>CY7C261-45WC 27CX642C-45         | National III ICT                                  | WS57C49B-40T 27CX641C-40 |

| CY7C263-45WC 27CX642C-45                                     | DM87S321 27CX321C-45                              | WS57C49B-45T 27CX641C-45 |

| CY7C261-55WC 27CX642C-55                                     | DM87S421 27CX322C-45                              | WS57C49B-55T 27CX641C-55 |

| CY7C263-55WC 27CX642C-55                                     |                                                   |                          |

|                                                              |                                                   |                          |

# PEEL Device Cross Reference \*

|                                                         | AMD/MMI, 🖙 ICT<br>National | AMD/MMI, CSF ICT<br>National, T.I. |

|---------------------------------------------------------|----------------------------|------------------------------------|

| PEEL18CV8P-35 PEEL18CV8-35<br>PEEL18CV8-25 PEEL18CV8-25 | PAL20L10PEEL173-35         | PAL18P8A PEEL18CV8-25              |

| FEEL100 V0-25 FEEL100 V0-25                             | or PEEL273-35              | PAL16RP4A PEEL18CV8-25             |

| PEEL20CG10-25 PEEL20CG10-25                             | orPEEL20CG10-35            | PAL16RP6A PEEL18CV8-25             |

| PEEL20CG10-35 PEEL20CG10-35                             | PAL20L10A PEEL173-30       | PALIGRP8A PEEL18CV8-25             |

| PEEL22CV10-35 PEEL22CV10-35                             | orPEEL273-30               | PAL16L8 PEEL18CV8-25               |

| PEEL22CV10-25 PEEL22CV10-25                             | orPEEL20CG10-25            | PAL16L8A PEEL18CV8-35              |

| PEEL22CV10Z-35 . PEEL22CV10Z-35                         | PAL16C1PEEL153-35          | PAL16L8A2 PEEL18CV8-35             |

| PEEL22CV10Z-25 . PEEL22CV10Z-25                         | PAL16C1A2 PEEL153-35       | PAL16L8A4 PEEL18CV8-35             |

|                                                         | PAL10H8PEEL18CV8-35        | PAL16L8B PEEL18CV8-15              |

| PEEL153-35 PEEL153-35<br>PEEL153-30 PEEL153-30          | PAL10H8A PEEL18CV8-25      | PAL16L8B2 PEEL18CV8-25             |

| PEEL153-30 PEEL153-30                                   | PAL10H8A2 PEEL18CV8-35     | PAL16L8B4 PEEL18CV8-35             |

| PEEL173-35 PEEL173-35                                   | PAL10L8                    | TALIOLOD4 TELEIOOV0-00             |

| PEEL173-30 PEEL173-30<br>PEEL253-35 PEEL253-35          | PAL10L8A PEEL18CV8-25      | PAL16R4 PEEL18CV8-35               |

| PEEL253-35 PEEL253-35<br>PEEL253-30 PEEL253-30          | PAL10L8A2 PEEL18CV8-35     | PAL16R4A PEEL18CV8-25*             |

| PEEL253-30 PEEL253-30<br>PEEL273-35 PEEL273-35          |                            | PAL16R4A2 PEEL18CV8-35             |

| PEEL273-35 PEEL273-35<br>PEEL273-30 PEEL273-30          | PAL12H6 PEEL18CV8-35       | PAL16R4A4 PEEL18CV8-35             |

| PEEL273-30 PEEL273-30                                   | PAL12H6A PEEL18CV8-25      | PAL16R4B PEEL18CV8-15              |

|                                                         | PAL12H6A2 PEEL18CV8-35     | PAL16R4B2 PEEL18CV8-25             |

|                                                         | PAL12L6PEEL18CV8-35        | PAL16R4B4 PEEL18CV8-35             |

|                                                         | PAL12L6A PEEL18CV8-25      | PAL16R6 PEEL18CV8-35               |

| AMD/MMI, DE ICT                                         | PAL12L6A2 PEEL18CV8-35     | PAL16R6A PEEL18CV8-25*             |

| National                                                | PAL14H4 PEEL18CV8-35       | PAL16R6A2 PEEL18CV8-35             |

|                                                         | PAL14H4A PEEL18CV8-25      | PAL16R6A4 PEEL18CV8-35             |

| PAL16HD8 PEEL18CV8-35                                   | PAL14H4A2 PEEL18CV8-35     | PAL16R6B PEEL18CV8-15              |

| PAL16HD8L PEEL18CV8-35                                  | PAL14L4 PEEL18CV8-35       | PAL16R6B2 PEEL18CV8-25             |

| PAL16HD8A PEEL18CV8-25                                  | PAL14L4A PEEL18CV8-25      | PAL16R6B4 PEEL18CV8-35             |

| PAL16LD8 PEEL18CV8-35                                   | PAL14L4A2 PEEL18CV8-35     |                                    |

| PAL16LD8L PEEL18CV8-35                                  |                            | PAL16R8 PEEL18CV8-35               |

| PAL16LD8A PEEL18CV8-25                                  | PAL16H2 PEEL18CV8-35       | PAL16R8A PEEL18CV8-25*             |

|                                                         | PAL16H2A PEEL18CV8-25      | PAL16R8A2 PEEL18CV8-35             |

|                                                         | PAL16H2A2 PEEL18CV8-35     | PAL16R8A4 PEEL18CV8-35             |

|                                                         | PAL16L2PEEL18CV8-35        | PAL16R8B PEEL18CV8-15              |

|                                                         | PAL16L2A PEEL18CV8-25      | PAL16R8B2 PEEL18CV8-25             |

|                                                         | PAL16L2A2 PEEL18CV8-35     | PAL16R8B4 PEEL18CV8-35             |

|                                                         |                            |                                    |

PEEL devices may be used as direct replacements for the PLDs indicated without modifying the original design. The original design is translated to an equivalent PEEL design by using ICT's JEDEC file translator (provided in the free PEEL Development software).

| AMD/MMI II ICT         | Altera 🖙 ICT                            | Intel EST ICT                   |

|------------------------|-----------------------------------------|---------------------------------|

| National, T.I.         | EP310PEEL18CV8-35                       | 5C031PEEL18CV8-35               |

| PAL20L8APEEL20CG10-25  | EP310-2PEEL18CV8-35                     | 5C032PEEL18CV8-35               |

| PAL20L8A2PEEL20CG10-35 | EP310IPEEL18CV8I-45                     |                                 |

| orPEEL173-35           | EP320PEEL18CV8-35                       |                                 |

| or PEEL273-35          | EP320-2PEEL18CV8-35                     | Signetics Kar ICT               |

| PAL20R4APEEL20CG10-25  | EP320-1PEEL18CV8-25                     | -                               |

| PAL20R4A2PEEL20CG10-35 | EP320IPEEL18CV8I-35                     | PLHS18P8APEEL18CV8-25           |

| PAL20R6APEEL20CG10-25  |                                         | PLS153 <sup>†</sup> PEEL153-35  |

| PAL20R6A2PEEL20CG10-35 |                                         | orPEEL253-35                    |

|                        |                                         | PLS153A <sup>†</sup> PEEL153-30 |

| PAL20R8APEEL20CG10-25  | Cypress 🖙 ICT                           | orPEEL253-30                    |

| PAL20R8A2PEEL20CG10-35 | PALC16L8-25PEEL18CV8-25                 | +                               |

| PAL12L10PEEL173-35     | PALC16L8-35PEEL18CV8-35                 | PLS173 <sup>†</sup> PEEL173-30  |

| orPEEL273-35           |                                         | orPEEL273-30                    |

| or PEEL20CG10-35       | PALC16R4-25PEEL18CV8-25                 |                                 |

| PAL14L4PEEL173-35      | PALC16R4-35PEEL18CV8-35                 |                                 |

| or PEEL273-35          | PALC16R6-25PEEL18CV8-25                 | Lattice FS ICT                  |

| orPEEL20CG10-35        | PALC16R6-35PEEL18CV8-35                 | National                        |

| PAL16L6PEEL173-35      | PALC16R8-25PEEL18CV8-25                 | GAL16V8-15LPEEL18CV8-15         |

| or PEEL273-35          | PALC16R8-35PEEL18CV8-35                 | GAL16V8-25LPEEL18CV8-25         |

| or PEEL20CG10-35       | PALC20G10-25PEEL20CG10-25               | GAL16V8-25QPEEL18CV8-25         |

| PAL18L4PEEL173-35      | PALC20G10-35PEEL20CG10-35               | GAL16V8-35LPEEL18CV8-35         |

| orPEEL273-35           |                                         | GAL16V8-35QPEEL18CV8-35         |

| orPEEL20CG10-35        | PALC22V10-25 <sup>†</sup> PEEL22CV10-25 | GAL20V8-25PEEL20CG10-25         |

|                        | PALC22V10-35 <sup>†</sup> PEEL22CV10-35 | GAL20V8-35PEEL20CG10-35         |

| PAL20L2PEEL173-35      |                                         |                                 |

| orPEEL273-35           |                                         |                                 |

| orPEEL20CG10-35        | L                                       |                                 |

† Devices marked with this symbol are JEDEC-file compatible with the PEEL device referenced. No translation is required to use a PEEL device as a direct replacement.

\* Consult factory for other speed options.

1-19

-

**CMOS Serial EEPROMs**

-

# **CMOS Serial EEPROMs**

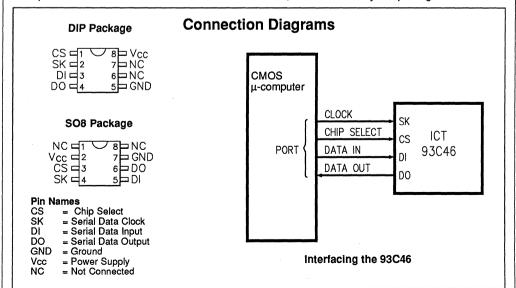

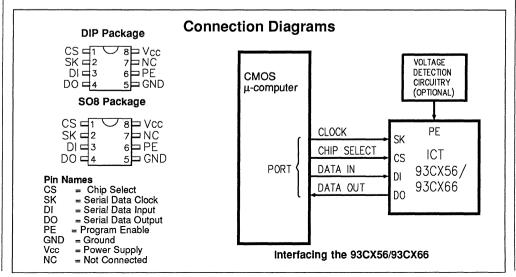

The ICT CMOS Serial EEPROMs provide a practical solution for today's CMOS systems requiring non-volatile data storage. All ICT serial EEPROMs can easily be interfaced with the popular micro-controllers and processors.

INTERN TECHN

### INTERNATIONAL CMOS TECHNOLOGY, INC.

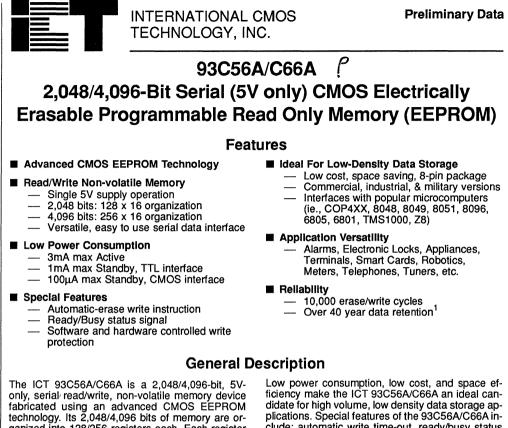

## 93C46 1,024-Bit Serial (5V only) CMOS Electrically Erasable Programmable Read Only Memory (EEPROM)

### Features

#### Advanced CMOS EEPROM Technology

#### Read/Write Non-volatile Memory

- --- Single 5V supply operation

- 1,024 bits, 64 x 16 organization

- Versatile, easy to use serial data interface

- Low Power Consumption

- 3mA max Active

- 1mA max Standby, TTL interface

- 100µA max Standby, CMOS interface

#### Special Features

- Automatic write cycle time-out

- Ready/Busy status signal

- Software controlled write protection

#### ■ Ideal For Low-Density Data Storage

- Low cost, space saving, 8-pin package

- Commercial, industrial, & military versions

- Interfaces with popular microcomputers (ie., COP4XX, 8048, 8049, 8051, 8096, 6805, 6801, TMS1000, Z8)

- Application Versatility

- Alarms, Electronic Locks, Appliances, Terminals, Smart Cards, Robotics, Meters, Telephones, Tuners, etc.

- Reliability

- 10,000 or 100,000 erase/write cycles

- Over 40 year data retention

### **General Description**

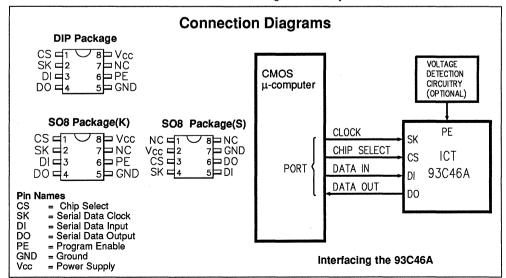

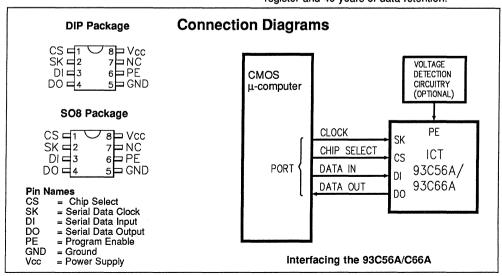

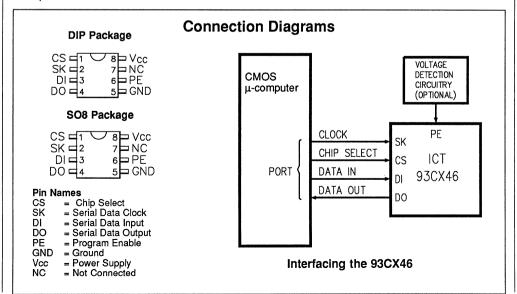

The ICT 93C46 is a 1,024-bit, 5V-only, serial read/write, non-volatile memory device fabricated using an advanced CMOS EEPROM technology. Its 1,024 bits of memory are organized into 64 registers each. Each register is individually addressable for serial read or write operations. A versatile serial interface consisting of chip select, clock, datain and data-out, can easily be controlled by popular microcomputers (ie., COP4XX, 8048, 8049, 8051, 6805, 6801, TMS1000,Z8) or standard microprocessors. Low power consumption, low cost, and space efficiency make the ICT 93C46 an ideal candidate for high volume, low density data storage applications. Special features of the 93C46 include: automatic write time-out, ready/busy status signal, software controlled write protection, and ultra-low standby power mode when deselected (CS low). Additionally, the 93C46 offers functional compatibility with existing NMOS serial EEPROMs. The 93C46 is designed for applications requiring 10,000 or 100,000 erase/write cycles per register.

INTERNATIONAL CMOS TECHNOLOGY, INC.

### **Function Description**

### **Device Operation**

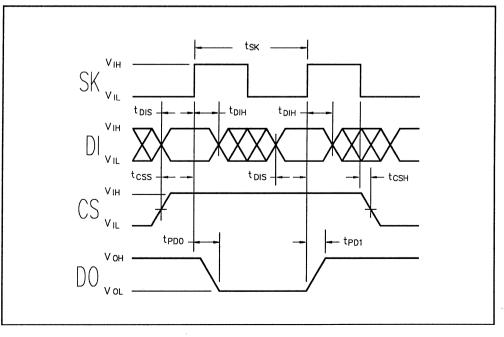

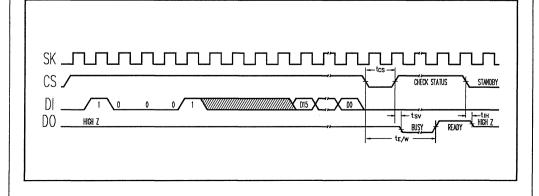

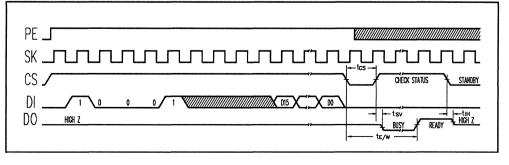

The ICT 93C46 is a serial 1,024-bit non-volatile memory device organized as 64 registers by 16 bits. Each register is independently addressable for read, write, or erase operations. Seven, 9-bit instructions control the operation of the device. These instructions are clocked into the data input (DI) pin in a serial fashion as controlled by the chip select (CS) and serial data clock (SK) inputs. The instructions include: read; write; erase; erase/write enable; erase/write disable; write all; and erase all registers.

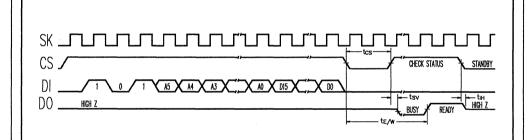

The format of each 9-bit instruction-starting with the most significant bit-is as follows: start bit (logical "1"); a two-bit op code; and an eight-bit address. The DO pin is normally in a high-impedance state, except when reading data from the device, or when checking the BUSY/READY status after a programming operation. The BUSY/READY status can be determined after a programming operation by selecting the device (CS high) and polling the DO pin. DO low indicates that the programming operation is not completed, while DO high indicates that the device is ready for the next operation. DO will return to the high-impedance state when the next instruction is initiated.

The 93C46 operates on a single supply voltage, which may range from 4.5 Volts to 5.5 Volts, and will generate, on chip, the high voltage required for any programming operation.

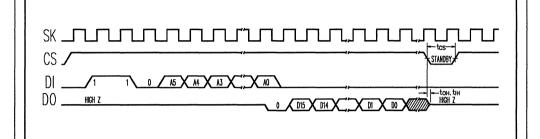

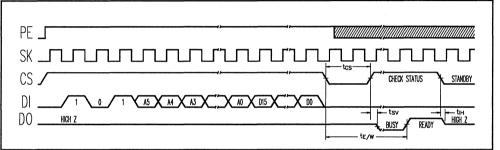

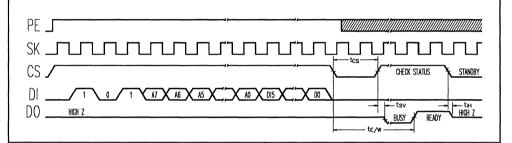

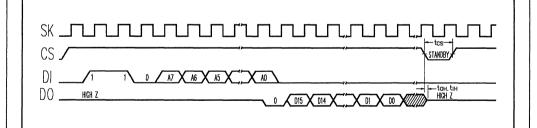

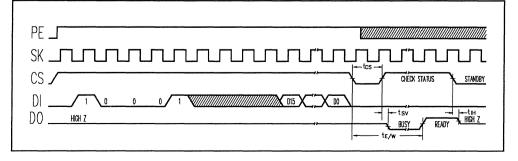

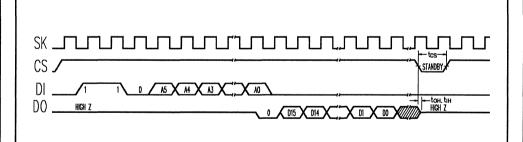

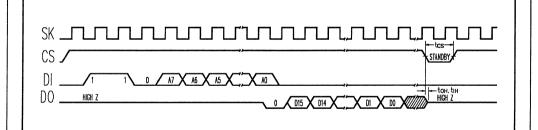

### Read (READ)

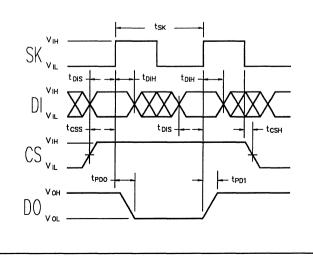

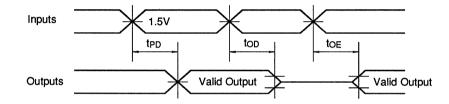

The read (READ) instruction outputs serial data on the DO pin. After a read instruction is received, the instruction and the address are decoded. Then data is transferred from the selected memory register to a 16-bit shift register and DO comes out of the highimpedance state. After sending a dummy bit (logical "0"), the 16-bit data string is shifted out of the device. The DO transitions occur on the rising edge of the clock and the data is stable after the specified delay tpo or tpp1.

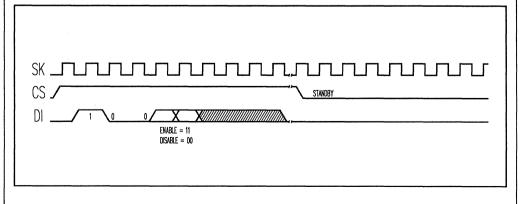

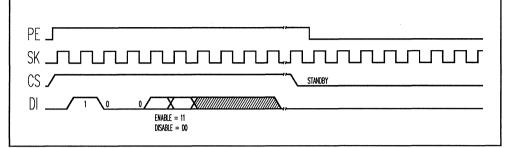

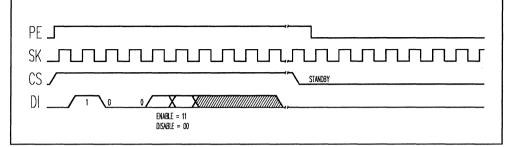

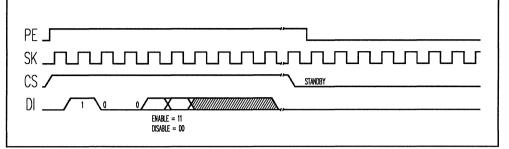

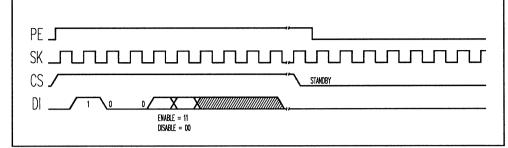

# Erase/Write Enable and Disable (EWEN and EWDS)

The 93C46 powers up in the programming-disable state. Any programming after power-up, or following a write disable (WDS) instruction, must first be preceded by a write enable (WEN) instruction. Once enabled, programming remains enabled until a write disable (WDS) instruction is executed or power is removed from the device. The write disable instruction disables all programming functions of the 93C46 and can be used to prevent accidentally disturbing data in the device. Data can be read from the 93C46 regardless of the programming enable/disable status.

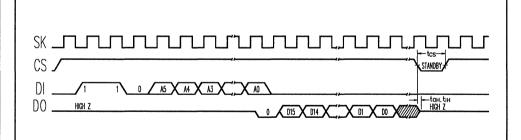

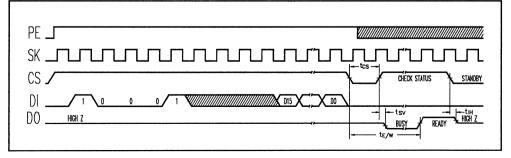

### Erase (ERASE)

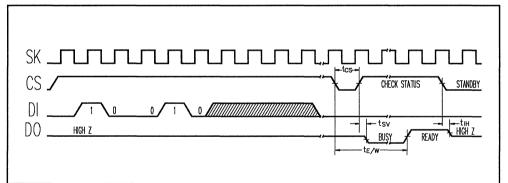

It is necessary to erase each register (all bits set to logical "1") before writing to it (certain bits set to logical "0"). After receiving the erase instruction, CS (chip select) must be held low for a minimum period specified by tcs. After inputting an erase instruction, the falling edge of CS initiates the self-timed write cycle. After observing tcs, the READY/BUSY status of the device can be determined by selecting the device and polling the DO pin.

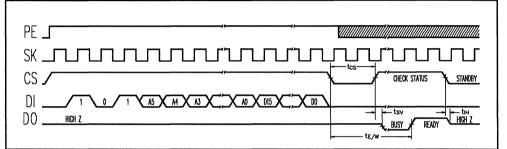

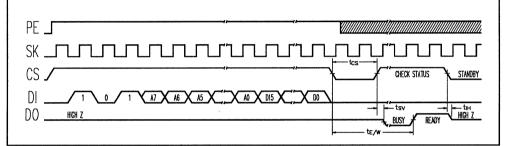

### Write (WRITE)

The write instruction (opcode plus address to be written to) is followed by 16 bits of data to be written into the specified address. After the last bit of data (Do) has been clocked into the DI pin, the CS (chip select) must be brought low before the next rising edge of the SK clock and held low for the minimum period specified by tcs. The falling edge of CS initiates the self-timed programming cycle. It is not necessary to clock the SK pin after initiating the self-timed write mode. The READY/BUSY status of the device can be determined by selecting the device and polling the DO pin.

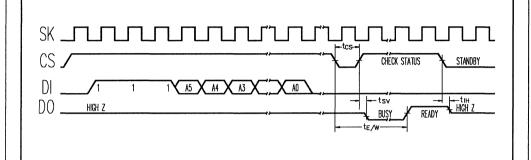

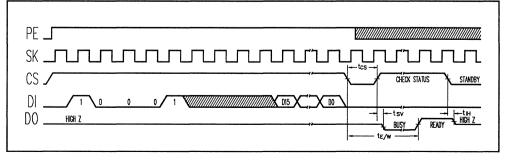

### Write All (WRAL)

The write-all (WRAL) instruction simultaneously programs all registers with the data pattern specified in the instruction. After receiving the write-all instruction and 16 bits of data, CS (chip select) must be held low for a minimum period specified by tcs. The falling edge of CS initiates the self-timed write cycle. It is not necessary to clock the SK pin after initiating the self-timed write-all mode. The BUSY/READY status of the device can be determined by selecting the device and polling the DO pin.

#### Erase All (ERAL)

Entire chip erasing is provided for ease of programming. The erase-all (ERAL) instruction simultaneously programs every bit on the chip to a logical "1". After receiving the erase-all instruction, CS (chip select) must be held low for a minimum period specified by tcs. The falling edge of CS initiates the self-timed write cycle. It is not necessary to clock the SK pin after initiating the self-timed erase-all mode. The BUSY/READY status of the device can be determined by selecting the device and polling the DO pin.

### Absolute Maximum Ratings

Exposure to absolute maximum ratings over extended periods of time may affect device reliability. Exceeding absolute maximum ratings may cause permanent damage

| Symbol | Parameter                  | Conditions           | Rating             | Unit |

|--------|----------------------------|----------------------|--------------------|------|

| Vcc    | Supply Voltage             | Relative to GND      | - 0.6 to +7.0      | v    |

| Vio    | Voltage Applied to Any Pin | Relative to GND      | - 0.6 to Vcc + 0.6 | V    |

| Tst    | Storage Temperature        |                      | - 65 to + 150      | °C   |

| TLT    | Lead Temperature           | Soldering 10 seconds | + 300              | °C   |

| Operat           | ing Ranges                       | Comr    | nercial | Indu | strial  | Mili | tary    |    |

|------------------|----------------------------------|---------|---------|------|---------|------|---------|----|

| Symbol Parameter |                                  | 93C46 9 |         | 93C  | 93C46 I |      | 93C46 M |    |

| -,               |                                  | Min     | Max     | Min  | Max     | Min  | Max     |    |

| Vcc              | Supply Voltage                   | 4.5     | 5.5     | 4.5  | 5.5     | 4.5  | 5.5     | V  |

| TA               | Ambient Temperature <sup>1</sup> | 0       | + 70    | - 40 | + 85    | - 55 | + 125   | °C |

DC and AC Electrical Characteristics

Over the operating range

| Symbol      | Parameter                                           | Conditions                                                              | 93C46 93C46 I 93C46 |       | 16 M  | Unit  |       |       |    |

|-------------|-----------------------------------------------------|-------------------------------------------------------------------------|---------------------|-------|-------|-------|-------|-------|----|

|             |                                                     |                                                                         | Min                 | Max   | Min   | Max   | Min   | Max   |    |

| Icc         | Power Supply Current,<br>Active, TTL/CMOS Interface | V <sub>CC</sub> = 5.5V, CS=SK=V <sub>IH</sub><br>DO = Open, f = 250 KHz |                     | 3     |       | 6     |       | 7     | mA |

| ICCSB1      | Supply Current, Standby,<br>TTL/CMOS Interface      | Vcc = 5.5V, CS = VIL<br>DO = Open                                       |                     | 1     |       | 3     |       | 3     | mA |

| ICCSB2      | Supply Current, Standby,<br>CMOS Interface          |                                                                         |                     | 100   |       | 100   |       | 100   | μA |

| ViH         | Input HIGH Level                                    |                                                                         | 2.0                 | Vcc+1 | 2.0   | Vcc+1 | 2.0   | Vcc+1 | V  |

| VIL         | Input LOW Level                                     |                                                                         | - 0.1               | 0.8   | - 0.1 | 0.8   | - 0.1 | 0.8   | V  |

| Vон         | Output HIGH Voltage                                 | lон = - 0.4mA                                                           | 2.2                 |       | 2.2   |       | 2.2   |       | V  |

| Vol         | Output LOW Voltage                                  | $I_{OL} = 2.1 \text{mA}$                                                |                     | 0.4   |       | 0.4   |       | 0.4   | V  |

| lu          | Input Leakage Current                               | V <sub>IN</sub> = 5.5V                                                  |                     | 10    |       | 10    |       | 10    | μΑ |

| llo         | Output Leakage Current                              | Vo=5.5V, CS=0, Vcc $\leq$ 5.5V                                          |                     | 10    |       | 10    |       | 10    | μΑ |

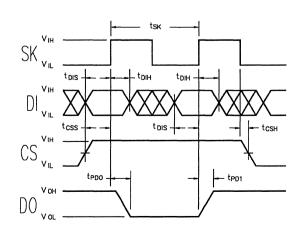

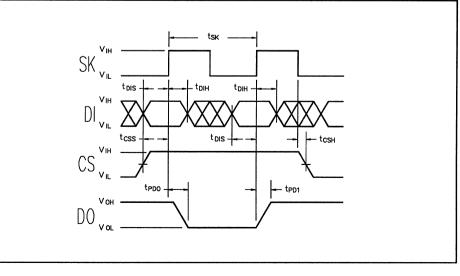

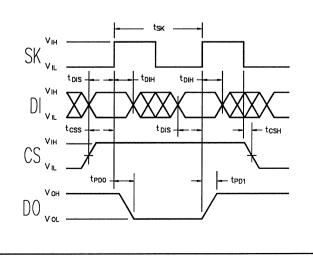

| tskp        | SK Period                                           |                                                                         | 4                   | 0     | 4     | 0     | 4     | 0     | μs |

| tskw        | SK Pulse Width                                      | High or Low                                                             | 1                   |       | 1     |       | 1     |       | μs |

| tcss        | CS High to SK High Delay                            |                                                                         | 200                 |       | 200   |       | 200   |       | ns |

| tcsH        | SK Low to CS Low Delay                              |                                                                         | 0                   |       | 0     |       | 0     |       | ns |

| tDIS        | Data Setup Time (Write)                             |                                                                         | 400                 |       | 400   |       | 400   |       | ns |

| tDIH        | Data Hold Time (Write)                              |                                                                         | 400                 |       | 400   |       | 400   |       | ns |

| tPD1        | Serial Clock to Output                              | $C_L \approx 100 \text{pF}, V_{OL} = 0.8 \text{V},$                     |                     | 2     |       | 2     |       | 2     | μs |

| tpD0        | Delay                                               | V <sub>OH</sub> = 2.0V, V <sub>IL</sub> = 0.45V,<br>VIH = 2.4V          |                     |       |       |       |       |       |    |

| t∈/w        | Self-timed Program Cycle <sup>2</sup>               |                                                                         |                     | 10    |       | 10    |       | 10    | ms |

| tcs         | Min CS Low Time                                     |                                                                         | 1                   |       | 1     |       | 1     |       | μs |

| tsv         | CS to Status Valid                                  | CL = 100pF                                                              |                     | 1     |       | 1     |       | 1     | μs |

| tон,<br>tiн | Falling Edge of CS to DO High Impedence             |                                                                         |                     | 400   |       | 400   |       | 400   | ns |

INTERNATIONAL CMOS TECHNOLOGY, INC.