#### PRELIMINARY, MARCH 1995

### **FEATURES**

- Hardware 2-D Video Zoom

- Resolutions up to 1280 x 1024

- Non-Integer Ratios

- From 1:1 to 32:1

- Independent X and Y

- 8, 15, 16 or 24 bit modes

- Hardware Video Filter

- Resolutions up to 1280 x 1024

- Zoom-tracking 2-D Digital Filter

- Filters Non-Integer Zooms

- 8, 15, 16 or 24 bit modes

- For Software or Hardware Zoom

- 170, 135 and 110 MHz Versions

- Zoom/Filter up to 135 MHz

- 24-bit Pixel Port

- 8, 15, 16 or 24 bit-per-pixel modes

XGA<sup>TM</sup>, HICOLOR<sup>TM</sup>, TARGA<sup>TM</sup>

- Pixel-by-Pixel mode switching

- On-Chip clock doubler

- Dual programmable PLL clock synthesizers

DSP-based ZOOMDACTM

with Dual Clock Synthesizers

- On-Chip Voltage Reference

- Software-readable output sense

- Device and manufacturer ID

- Delay Compensated Horiz. Sync

- Anti-Sparkle circuitry

- Low power 5 volt CMOS

- Power-Down for Battery and Green PCs

- 68-pin PLCC

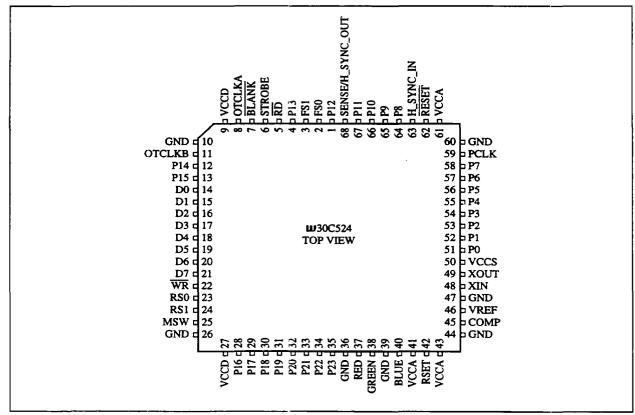

# FIGURE1: PIN DIAGRAM: w30C524

N

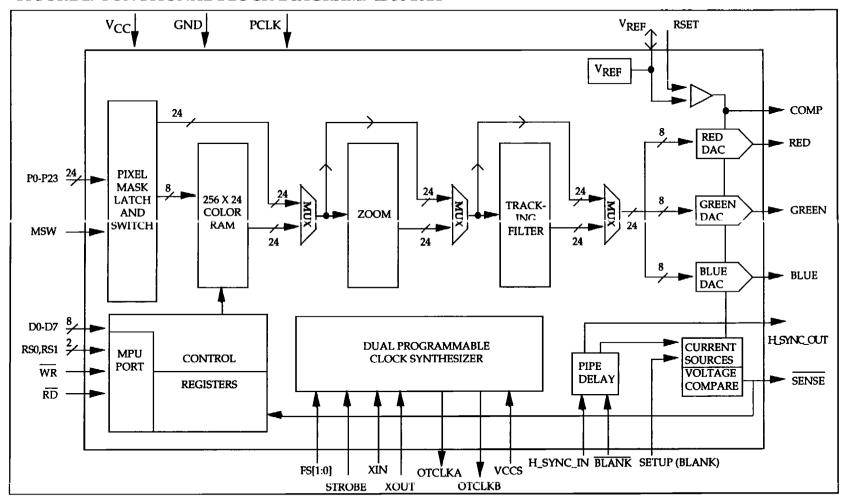

FIGURE 2: FUNCTIONAL BLOCK DIAGRAM: W30C524

#### **APPLICATIONS**

- True-Color Super-VGA

- Add-in card or motherboard

- Desktop, Notebook and Green PC's

- Screen resolution up to:

- 1600 x 1200, 8-bit per pixel, 60Hz

- 1280 x 1024, 24-bit per pixel, 76Hz

- 1024 x 768, 24-bit pixel, 127Hz

- 800 x 600, 24-bit per pixel, 200Hz

Software readable unique manufacturer and IC IDs allow for intelligent BIOS and plug-and-play board implementations.

Software controlled power-down modes are included for battery or green-PC applications.

# DESCRIPTION

The **W**30C524 is an advanced, high-performance super VGA RAM/DAC with dual programmable clock synthesizer specially enabled for Video for Windows, MPEG, and other video playback applications.

Built-in video zoom circuitry allows playback of larger video windows without sacrificing speed. An advanced 2-D tracking filter further enhances the video by removing the jagged zoom artifacts. The resulting video is enlarged and smooth without sacrificing frame rate.

A 24-bit pixel interface allows higher data throughput for more colors at higher screen resolutions. In 8-bit pixel modes, an on-chip 2-1 data multiplexer and on-chip clock doubler reduces external clock frequencies for easier FCC certification.

With 8,15,16 and 24 bit-per-pixel modes, the **W**30C524 supports all the major image formats, including XGA™, HICOLOR™ and TARGA™ formats. In addition to VGA compatible 18-bit modes to select 256 color look-up-table allows 8-bit modes to select 256 colors from the expanded 16 million color palette. Pixel-by-pixel mode switching allows mixing different image pixel formats on a single screen.

The device contains two programmable PLL clock synthesizers. Upon hardware reset, the clock synthesizers boot up to standard VGA and SVGA clock frequencies.

**Table 1: Pin description**

| Pin Name            | ī/O | Pin #                                | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------|-----|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCCD                | -   | 9, 27                                | Power, Digital. Connect these pins to +5 volts. These pins can be connected to the filtered supply plane or connected to the digital supply plane of the RAMDAC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| GND                 |     | 10, 26, 36,<br>39, 44, 47, 60        | Ground. Connect these pins to circuit ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VCCS                | -   | 50                                   | Power, Clock Synthesizer. Connect this pin to +5 volts. This can be a separate supply from the RAMDAC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VCCA                |     | 41, 43, 61                           | Power, Analog. Connect this pin to +5 volts. These pins supply the power for the analog DACs and PLL portion of the clock synthesizers. This pin should be connected to a filtered supply plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| P0-P23              | I   | 51-58, 64-67,<br>1, 4, 12, 13, 28-35 | Pixel Inputs: TTL compatible. These pins are latched on the rising edge of PCLK. Unused inputs should be connected to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RSET                | I   | 42                                   | Reference: An external resistor (RSET) is connected between the RSET pin and GND to control the magnitude of the full-scale current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| СОМР                | I   | 45                                   | Compensation Pin: Bypass this pin with an external 0.1µf capacitor to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $V_{ref}$           |     | 46                                   | Voltage Reference: Bypass this pin with an external 0.1µf capacitor to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SENSE<br>H_SYNC_OUT | 0   | 68                                   | SENSE or H_SYNC_OUT (Both Active-Low): TTL compatible. If Control Register [7] is "0" (powerup default), this pin functions as the monitor detect signal SENSE is a logic 0 if one or more of the red, green, or blue outputs has exceeded the internal voltage reference level of 340mV. If Control Register [7] is "1", this output pin changes function to become a delayed version of the H_SYNC_IN input signal. The delay is matched to the internal delays of the signal. The delay is matched to the internal delays of the w 30C524 logic in all modes and this output is the preferred source with which to drive the CRT Horizontal Sync input. |

IC WORKS W30C524

Table 1: Pin description (cont)

| Pin Name  | I/O | Pin#   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCLK      | I   | 59     | Pixel Clock: TTL compatible. The rising edge of the pixel clock latches the pixels, H_SYNC_IN and BLANK inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| BLANK     | I   | 7      | Blank (Active-Low): TTL compatible BLANK is latched on the rising edge of PCLK. When BLANK is low, the 1.44mA current source on the analog outputs will be turned off and the DACs ignore digital input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RESET     | I   | 62     | TTL compatible. Resets internal registers to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| H_SYNC_IN | I   | 63     | H_SYNC_IN is active low. In addition to providing synchronization for the internal zoom and filter logic, this input is delayed to latch the internal delays of the \$\textbf{W}\sigma 30C524\$ and output as H_SYNC_IN to drive the monitor. H_SYNC_IN does not affect the video DAC levels.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| D0-D7     | I/O | 14-21  | Data Bus: TTL compatible. Data is transferred between the data bus and the internal registers under control of the $\overline{RD}$ and $\overline{WR}$ signals. In an MPU wire operation, D0-D7 is latched on the rising edge of $\overline{WR}$ . To read data D0-D7 for the device $\overline{RD}$ must be in an active low state. The rising edge of the $\overline{RD}$ signal indicates the end of a read cycle. Following the read cycle, the data bus will to go a high impedance state. Note: for 6-bit operation, color data is contained in the lower six bits of the data bus. D0 is the LSV and D5 is the MSB. When the MPU writes color data, D6 and D7 are ignored. During MPU read cycles, D6 and D7 are a logic 0. |

| WR        | I   | 22     | Write (Active-Low): TTL compatible. $\overline{WR}$ controls the data transfer from the data bus to the selected internal register. D0-D7 data is latched at the rising edge of $\overline{WR}$ , and RS0-RS1 data is latched at the falling edge of $\overline{WR}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RD        | I   | 5      | Read (Active-Low): TTL Compatible. When $\overline{RD}$ is low, data transfers from the selected internal register to the data bus. RS0-RS1 is latched on the falling edge of $\overline{RD}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RS0-RS1   | I   | 23, 24 | Register Select: TTL compatible. These inputs are sampled on the falling edge of the $\overline{RD}$ or $\overline{WR}$ to determine which one of the internal registers is to be accessed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Table 1: Pin description (cont)

| Pin Name            | I/O | Pin#       | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RED, GREEN,<br>BLUE | I   | 37, 38, 40 | Color Signals: These pins are analog outputs. High-<br>impendance current sources are capable of driving a<br>double-terminated 75 coaxial cable                                                                                                                                                                                                                                                                                                                  |

| MSW                 | I   | 25         | Mode Switch: Input to change the RAMDAC mode. The RAMDAC interprets the incoming data on a pixel by pixel basis based on the mode. Ground if not used.                                                                                                                                                                                                                                                                                                            |

| XIN                 | I   | 48         | Crystal Input. Connect external crystal or stable frequency source to interrial crystal oscillator. The recommended frequency is 14.318 MHz system clock. When using a crystal, connect across XIN and XOUT.                                                                                                                                                                                                                                                      |

| XOUT                | I   | 49         | Crystal Ouput. Connect external crystal to internal crystal oscillator. All passive components are integrated on-chip to implement a tuned resonant circuit. Leave this pin floating when using a stable external frequency source connected to XIN.                                                                                                                                                                                                              |

| OTCLKA              | 0   | 8          | Ouput Clock A. TTL compatible. Output clock from analog PLL synthesizer A.                                                                                                                                                                                                                                                                                                                                                                                        |

| OTCLKB              | 0   | 11         | Output Clock B. TTL compatible. Output clock from analog PLL synthesizer B.                                                                                                                                                                                                                                                                                                                                                                                       |

| FS[1:0]             | I   | 3, 2       | Frequency Select Lines. TTL compatible. Clock frequency select lines. These lines select the register set that determines the frequency of the clock synthesizers. The FS[1:0] pins select the register sets when CC[7] and CC[3] = 0. When CC[7] and CC[3] = 1, bits in the CC register select the register sets.                                                                                                                                                |

| STROBE              | I   | 6          | STROBE. TTL compatible. Input for strobing the reference frequency select lines. FS[1:0] lines are connected to an internal transparent latch. When STROBE is high, data cannot be written to FS[1:0]. When STROBE is low, the latch is closed and data cannot be written to FS[1:0]. The falling edge of STROBE latches the FS[1:0] lines. If STROBE is tied permanently high, care must be taken to insure there is no noise or glitches on the FS[1:0] inputs. |

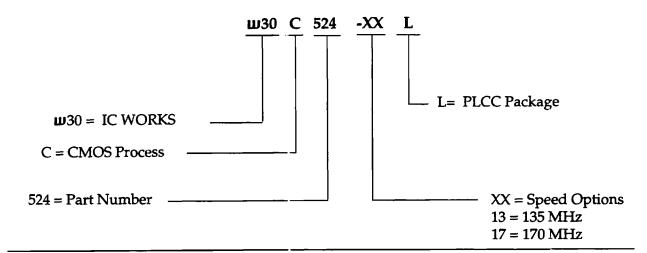

## ORDERING INFORMATION

### **VALID PART NUMBER**

ш30С524 - 13L, ш30С524 - 17L

IC WORKS, Inc. 3725 North First Street San Jose, CA 95134-1700 Tel: (408) 922-0202

Fax: (408) 922-0833

IC WORKS, Inc. reserves the right to amend or discontinue product development without notice. Circuit and timing diagrams used to describe IC WORKS products operation and applications are included as a means of illustrating a typical product application. Complete information for design purposes is not necessarily given. This information has been carefully checked and is believed to be entirely reliable. IC WORKS, however, will not assume any responsibility for inaccuracies.

### LIFE SUPPORT APPLICATIONS:

IC WORKS products are not designed for use in life support applications, devices, or systems where malfunctions of the IC WORKS product can reasonably be expected to result in personal injury. IC WORKS customers using or selling IC WORKS products for use in such applications do so at their own risk and agree to fully indemnify IC WORKS for any damages resulting in such improper use or sale.

Document No. 30C524/00/0395