# CDP6805 CMOS MICROCONTROLLERS & PERIPHERALS 1995

#### HARRIS SEMICONDUCTOR

In December 1988, Harris Semiconductor acquired the General Electric Solid State division, thereby adding former GE, RCA, and Intersil devices to the Harris Semiconductor line.

This CDP6805 CMOS Microcontrollers & Peripherals data book represents the full line of Harris Semiconductor CDP6805 products for commercial applications and supersedes previously published CDP6805 data books under the Harris, GE, RCA or Intersil names. For a complete listing of all Harris Semiconductor products, please refer to the Product Selection Guide (PSG201.21).

For complete details order the data sheet by using Harris AnswerFAX (see Section 9) or through Sector Applications (page iv). When using Harris AnswerFAX, the file number is used as the AnswerFAX document number.

Literature requests can be directed to:

#### Harris Semiconductor Data Services P.O. Box 883, MS 53-204 Melbourne, FL 32902 Phone: 1-800-442-7747 Fax: 407-724-7240

See Section 9 for Information Available on AnswerFAX Phone: (407) 724-7800

#### U.S. HEADQUARTERS

Harris Semiconductor 2401 Palm Bay Road N. E. Palm Bay, Florida 32905 TEL: (407) 724-7000

#### SOUTH ASIA

Harris Semiconductor H.K. Ltd 13/F Fourseas Building 208-212 Nathan Road Tsimshatsui, Kowloon Hong Kong TEL: (852) 723-6339

#### **EUROPEAN HEADQUARTERS**

Harris Semiconductor Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: 32 2 724 21 11

#### NORTH ASIA

Harris K.K. Kojimachi-Nakata Bldg. 4F 5-3-5 Kojimachi Chiyoda-ku, Tokyo 102 Japan TEL: (81) 3-3265-7571 TEL: (81) 3-3265-7572 (Sales)

Copyright © Harris Corporation 1995 (All Rights Reserved) Printed in USA, 1/1995

i

Harris Semiconductor products are sold by description only. All specifications in this product guide are applicable only to packaged products; specifications for die are available upon request. Harris reserves the right to make changes in circuit design, specifications and other information at any time without prior notice. Accordingly, the reader is cautioned to verify that information in this publication is current before placing orders. Reference to products of other manufacturers are solely for convenience of comparison and do not imply total equivalency of design, performance, or otherwise.

### **TECHNICAL ASSISTANCE**

For technical assistance on Harris products listed in this product selection guide, please contact the Field Applications Engineering staff available at one of the following Harris Sales Offices:

| UNITED STATES  |                          |  |  |  |  |

|----------------|--------------------------|--|--|--|--|

| CALIFORNIA     | Costa Mesa               |  |  |  |  |

|                | San Jose                 |  |  |  |  |

| FLORIDA        | Palm Bay                 |  |  |  |  |

| GEORGIA        | Duluth                   |  |  |  |  |

| ILLINOIS       | Schaumburg               |  |  |  |  |

| INDIANA        | Carmel                   |  |  |  |  |

| MASSACHUSETTS  | Burlington               |  |  |  |  |

| NEW JERSEY     | Voorhees                 |  |  |  |  |

| NEW YORK       | Hauppauge516-342-0291    |  |  |  |  |

|                | Wappingers Falls         |  |  |  |  |

| TEXAS          | Dallas                   |  |  |  |  |

| INTERNATIONAL  |                          |  |  |  |  |

| FRANCE         | Paris                    |  |  |  |  |

| GERMANY        | Munich                   |  |  |  |  |

| HONG KONG      | Kowloon                  |  |  |  |  |

| ITALY          | Milano 39-2-262-0761     |  |  |  |  |

| JAPAN          | Tokyo 81-3-3265-7571     |  |  |  |  |

| KOREA          | Seoul 82-2-551-0931      |  |  |  |  |

| SINGAPORE      | Singapore65-291-0203     |  |  |  |  |

| TAIWAN         | Taipei                   |  |  |  |  |

| UNITED KINGDOM | Camberley 44-2-766-86886 |  |  |  |  |

\_

For literature requests, please contact Harris at 1-800-442-7747 (1-800-4HARRIS) or call Harris AnswerFAX for immediate fax service at 407-724-7800.

# **CDP6805**

# **GENERAL INFORMATION**

#### **ALPHA NUMERIC PRODUCT INDEX**

| CDP6402     | CMOS Universal Asynchronous Receiver/Transmitter (UART)                  | 5-3   |

|-------------|--------------------------------------------------------------------------|-------|

| CDP6402C    | CMOS Universal Asynchronous Receiver/Transmitter (UART)                  | 5-3   |

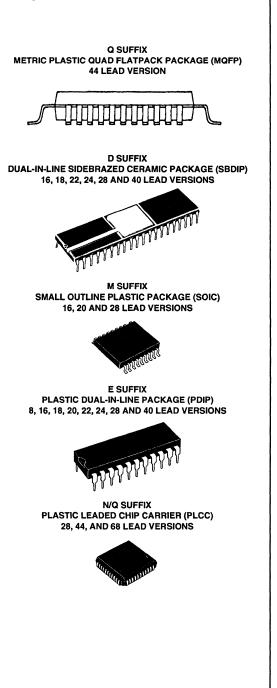

| CDP65C51    | CMOS Asynchronous Communications Interface Adapter (ACIA)                | 5-12  |

| CDP65C51A   | CMOS Asynchronous Communications Interface Adapter (ACIA)                | 5-12  |

| CDP6805E2   | CMOS 8-Bit Microprocessor                                                | 3-16  |

| CDP6805E2C  | CMOS 8-Bit Microprocessor                                                | 3-16  |

| CDP6805E3   | CMOS 8-Bit Microprocessor                                                | 3-16  |

| CDP6805E3C  | CMOS 8-Bit Microprocessor                                                | 3-16  |

| CDP6805F2   | CMOS High Performance Silicon Gate 8-Bit Microcontroller                 | 2-117 |

| CDP6805F2C  | CMOS High Performance Silicon Gate 8-Bit Microcontroller                 | 2-117 |

| CDP6805G2   | CMOS High Performance Silicon Gate 8-Bit Microcontroller                 | 2-133 |

| CDP6805G2C  | CMOS High Performance Silicon Gate 8-Bit Microcontroller                 | 2-133 |

| CDP6818     | CMOS Real-Time Clock With RAM.                                           | 5-30  |

| CDP6818A    | CMOS Real-Time Clock With RAM                                            | 5-49  |

| CDP6823     | CMOS Parallel Interface                                                  | 5-68  |

| CDP6853     | CMOS Asynchronous Communications Interface Adapter (ACIA) with MOTEL Bus | 5-82  |

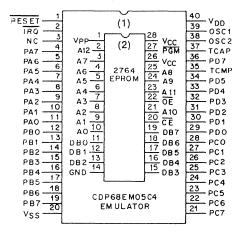

| CDP68EM05C4 | CMOS High Performance Silicon Gate 8-Bit Microcontroller Emulator.       | 3-3   |

NOTE: Compatible Products listed are not located within this data book, but may be acquired through the Harris AnswerFAX system. Please refer to Section 9 for further information.

# GENERAL INFORMATION

PAGE

1

#### ALPHA NUMERIC PRODUCT INDEX (Continued)

PAGE

| CDP68EM05C4N | CMOS High Performance Silicon Gate 8-Bit Microcontroller Emulator.                                | 3-3  |

|--------------|---------------------------------------------------------------------------------------------------|------|

| CDP68EM05D2  | CMOS High Performance Silicon Gate 8-Bit Microcontroller Emulator                                 | 3-9  |

| CDP68EM05D2N | CMOS High Performance Silicon Gate 8-Bit Microcontroller Emulator.                                | 3-9  |

| CDP68HC05C4  | 8-Bit Microcontroller Series                                                                      | 2-3  |

| CDP68HC05C8  | 8-Bit Microcontroller Series                                                                      | 2-3  |

| CDP68HC05D2  | 8-Bit Microcontroller                                                                             | 2-54 |

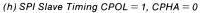

| CDP68HC05J3  | 8-Bit Microcontroller Series                                                                      | 2-94 |

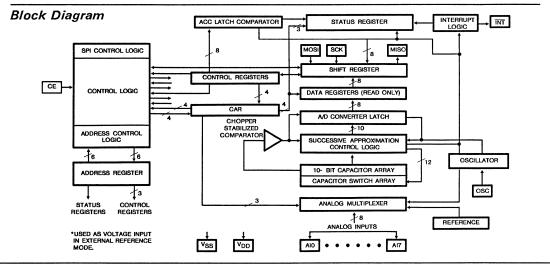

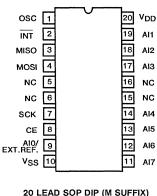

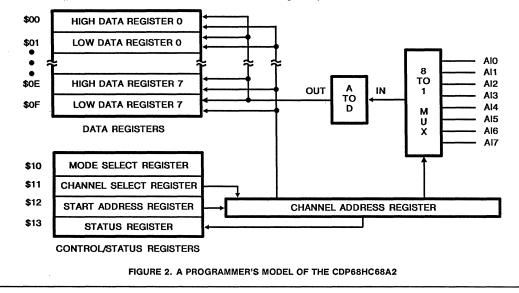

| CDP68HC68A2  | CMOS Serial 10-Bit A/D Converter                                                                  | 6-3  |

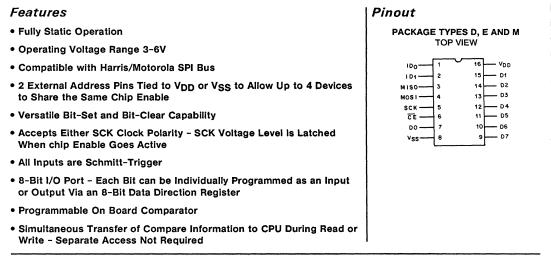

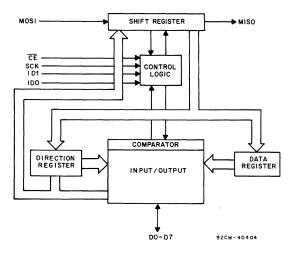

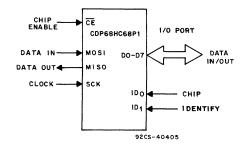

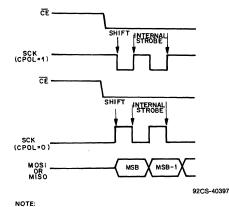

| CDP68HC68P1  | CMOS Serial 8-Bit Input/Output Port                                                               | 6-20 |

| CDP68HC68R1  | CMOS 128 Word by 8-Bit Static RAM                                                                 | 6-28 |

| CDP68HC68R2  | CMOS 256 Word by 8-Bit Static RAM.                                                                | 6-28 |

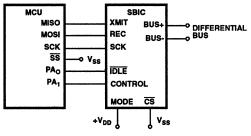

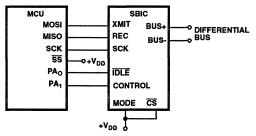

| CDP68HC68S1  | Serial Multiplexed Bus Interface                                                                  | 6-34 |

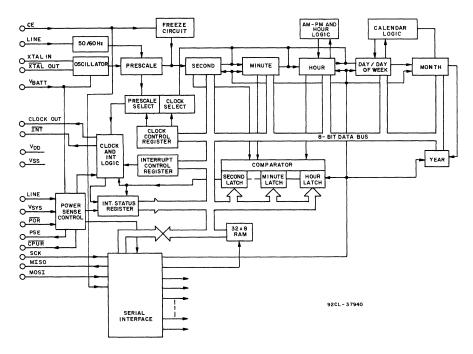

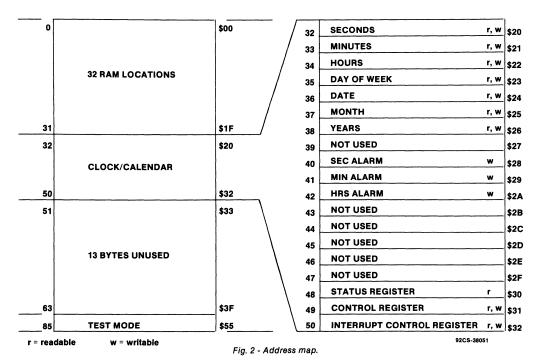

| CDP68HC68T1  | CMOS Serial Real-Time Clock With RAM and Power Sense/Control.                                     | 6-48 |

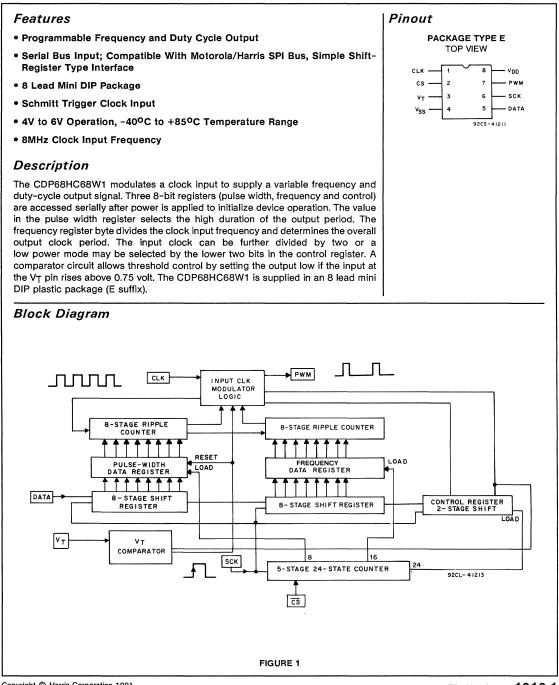

| CDP68HC68W1  | CMOS Serial Digital Pulse Width Modulator                                                         | 6-66 |

| CDP68HCL05C4 | 8-Bit Microcontroller Series.                                                                     | 2-3  |

| CDP68HCL05C8 | 8-Bit Microcontroller Series                                                                      | 2-3  |

| CDP68HSC05C4 | 8-Bit Microcontroller Series                                                                      | 2-3  |

| CDP68HSC05C8 | 8-Bit Microcontroller Series.                                                                     | 2-3  |

| HIP7030A0    | J1850 8-Bit 68HC05 Microcontroller Emulator Version (See Note) AnswerFAX Document Number 3645     | 3-1  |

| HIP7030A2    | J1850 8-Bit 68HC05 Microcontroller (See Note)<br>AnswerFAX Document Number 3646                   | 2-1  |

| HIP7038A8    | J1850 8-Bit 68HC05 Microcontroller 8K EEPROM Version (See Note)<br>AnswerFAX Document Number 3647 | 2-1  |

NOTE: Compatible Products listed are not located within this data book, but may be acquired through the Harris AnswerFAX system. Please refer to Section 9 for further information.

.

### **PRODUCT INDEX BY FAMILY**

| N | MICROCONTROLLERS P                                      |                                                                                                |       |  |  |

|---|---------------------------------------------------------|------------------------------------------------------------------------------------------------|-------|--|--|

|   | CDP68HC05C4, C8<br>CDP68HCL05C4, C8<br>CDP68HSC05C4, C8 | 8-Bit Microcontroller Series                                                                   | 2-3   |  |  |

|   | CDP68HC05D2                                             | 8-Bit Microcontroller                                                                          | 2-54  |  |  |

|   | CDP68HC05J3                                             | 8-Bit Microcontroller Series                                                                   | 2-94  |  |  |

|   | CDP6805F2,<br>CDP6805F2C                                | CMOS High Performance Silicon Gate 8-Bit Microcontroller                                       | 2-117 |  |  |

|   | CDP6805G2,<br>CDP6805G2C                                | CMOS High Performance Silicon Gate 8-Bit Microcontroller                                       | 2-133 |  |  |

|   | HIP7030A2                                               | J1850 8-Bit 68HC05 Microcontroller (See Note) AnswerFAX Document Number 3646                   | 2-1   |  |  |

|   | HIP7038A8                                               | J1850 8-Bit 68HC05 Microcontroller 8K EEPROM Version (See Note) AnswerFAX Document Number 3647 | 2-1   |  |  |

#### MICROPROCESSORS

| CDP68EM05C4,<br>CDP68EM05C4N     | CMOS High Performance Silicon Gate 8-Bit Microcontroller Emulators                            | 3-3  |

|----------------------------------|-----------------------------------------------------------------------------------------------|------|

| CDP68EM05D2,<br>CDP68EM05D2N     | CMOS High Performance Silicon Gate 8-Bit Microcontroller Emulators                            | 3-9  |

| CDP6805E2, E2C<br>CDP6805E3, E3C | CMOS 8-Bit Microprocessors.                                                                   | 3-16 |

| HIP7030A0                        | J1850 8-Bit 68HC05 Microcontroller Emulator Version (See Note) AnswerFAX Document Number 3645 | 3-1  |

#### SPI SERIAL BUS PERIPHERALS

| Octal Low Side Power Driver with Serial Bus Control (See Note) AnswerFAX Document Number 2767 | 6-1                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMOS Serial 10-Bit A/D Converter                                                              | 6-3                                                                                                                                                                                                                                                                                             |

| CMOS Serial 8-Bit Input/Output Port                                                           | 6-20                                                                                                                                                                                                                                                                                            |

| CMOS 128 Word (CDP68HC68R1) and 256 Word (CDP68HC68R2) by 8-Bit Static RAMs                   | 6-28                                                                                                                                                                                                                                                                                            |

| Serial Multiplexed Bus Interface                                                              | 6-34                                                                                                                                                                                                                                                                                            |

| CMOS Serial Real-Time Clock With RAM and Power Sense/Control                                  | 6-48                                                                                                                                                                                                                                                                                            |

| CMOS Serial Digital Pulse Width Modulator                                                     | 6-66                                                                                                                                                                                                                                                                                            |

|                                                                                               | AnswerFAX Document Number 2767<br>CMOS Serial 10-Bit A/D Converter<br>CMOS Serial 8-Bit Input/Output Port<br>CMOS 128 Word (CDP68HC68R1) and 256 Word (CDP68HC68R2)<br>by 8-Bit Static RAMs<br>Serial Multiplexed Bus Interface<br>CMOS Serial Real-Time Clock With RAM and Power Sense/Control |

NOTE: Compatible Products listed are not located within this data book, but may be acquired through the Harris AnswerFAX system. Please refer to Section 9 for further information. 1

### PRODUCT INDEX BY FAMILY (Continued)

| 8 | 8-BIT BUS PERIPHERALS  |                                                                          |      |  |  |

|---|------------------------|--------------------------------------------------------------------------|------|--|--|

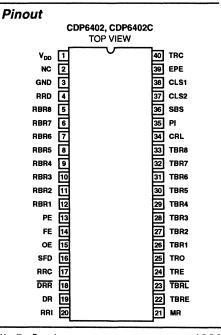

|   | CDP6402,<br>CDP6402C   | CMOS Universal Asynchronous Receivers/Transmitters (UART)                | 5-3  |  |  |

|   | CDP65C51,<br>CDP65C51A | CMOS Asynchronous Communications Interface Adapters (ACIA)               | 5-12 |  |  |

|   | CDP6818                | CMOS Real-Time Clock With RAM                                            | 5-30 |  |  |

|   | CDP6818A               | CMOS Real-Time Clock With RAM                                            | 5-49 |  |  |

|   | CDP6823                | CMOS Parallel Interface                                                  | 5-68 |  |  |

|   | CDP6853                | CMOS Asynchronous Communications Interface Adapter (ACIA) with MOTEL Bus | 5-82 |  |  |

NOTE: Compatible Products listed are not located within this data book, but may be acquired through the Harris AnswerFAX system. Please refer to Section 9 for further information.

## **Product Overview**

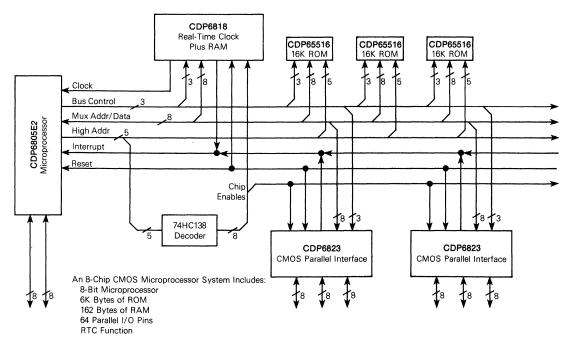

The Harris CDP6805/68HC05 family of high speed CMOS microcontrollers, microprocessors, and peripherals provides a cost efficient solution for diverse automotive, consumer, industrial, telecom, and military applications. The family is based on the established 6805 8-bit architecture. The entire family is built using CMOS technology and offers:

- Low Power Drain with μA dissipations and operation down to 2 volts, the Harris CDP68HC05 family is a natural choice for battery operated systems, battery backed-up systems, and systems in which heat generation is a primary concern.

- High Noise Immunity and Wide Operating Temperature Range (up to -55°C to +125°C) - allows these CMOS devices to be used in the most demanding automotive and industrial applications.

- Wide Operating Voltage Range reduces the need for expensive regulated power supplies and allows the design engineer to concentrate on other aspects of the system.

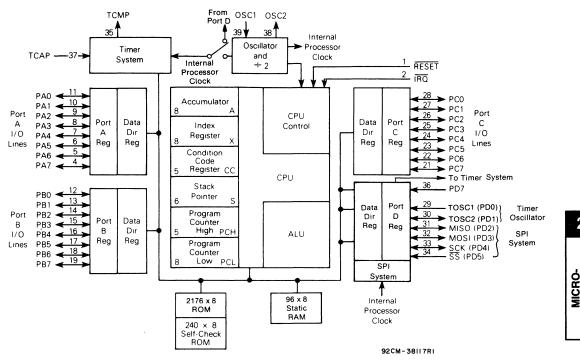

#### CDP6805/CDP68HC05 Microcontrollers and Microprocessors

The CDP6805 ('05) and CDP68HC05 ('HC05) families provide a selection of 8-bit microcontrollers and microprocessors. The 'HC05 family is built using a 1.5 micron, CMOS technology which features CPU cycle times down to 200ns. The '05 family is built using a 3 micron, CMOS technology which provides CPU cycle times down to 480ns.

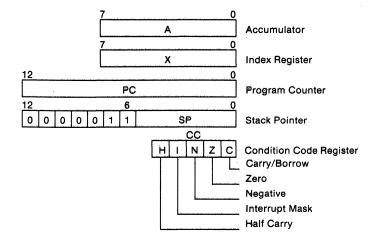

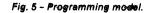

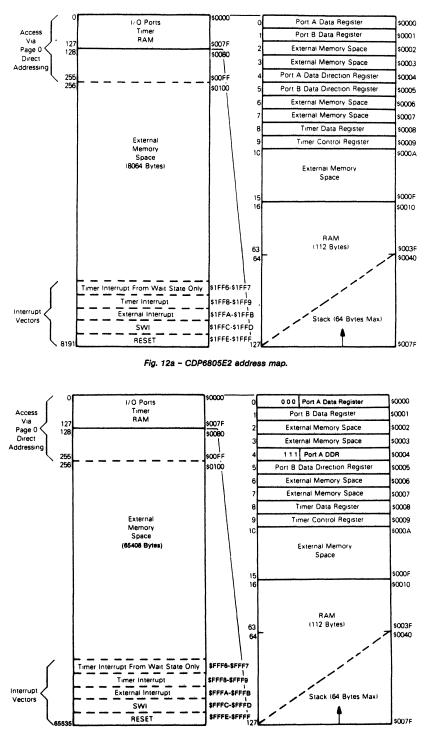

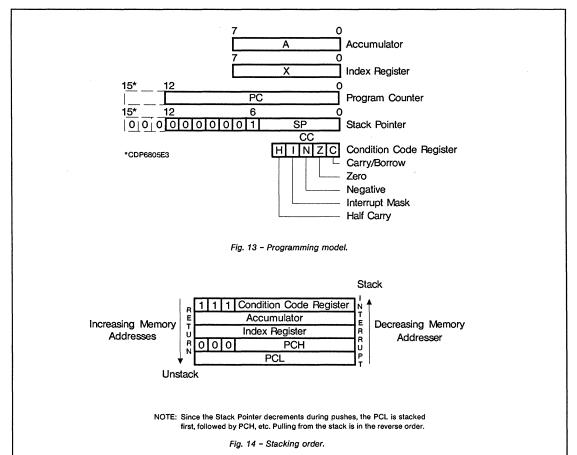

A common base instruction set and CPU register architecture, is shared by all members of the '05 and 'HC05 families. The 'HC05 instruction set has been extended with the addition of an 8 x 8 unsigned multiply opcode (MUL). The complete set of instructions is detailed in Section 4 of this book.

The CDP68HC05C4, CDP68HC05C8, CDP68HC05D2, CDP68HC05J3, and HIP7030A2 are microcontroller members of the 1.5 micron, 'HC05 family. Each is a self contained MCU with varying implementations of on-chip ROM, RAM, timer, port, and I/O functions. The CDP68EM05C4, CDP68EM05D2, and HIP7030A0 are microprocessor members of the 'HC05 family. Each shares the same RAM and I/O features as the equivalent MCU type, and provides address and data interface lines for connection to up to 8K of external ROM.

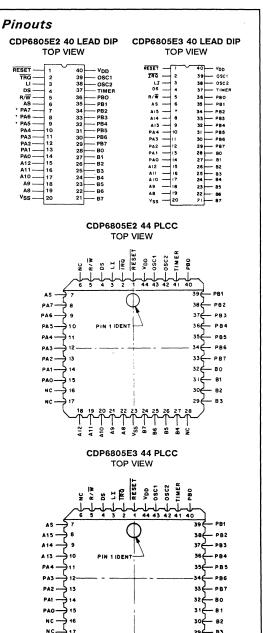

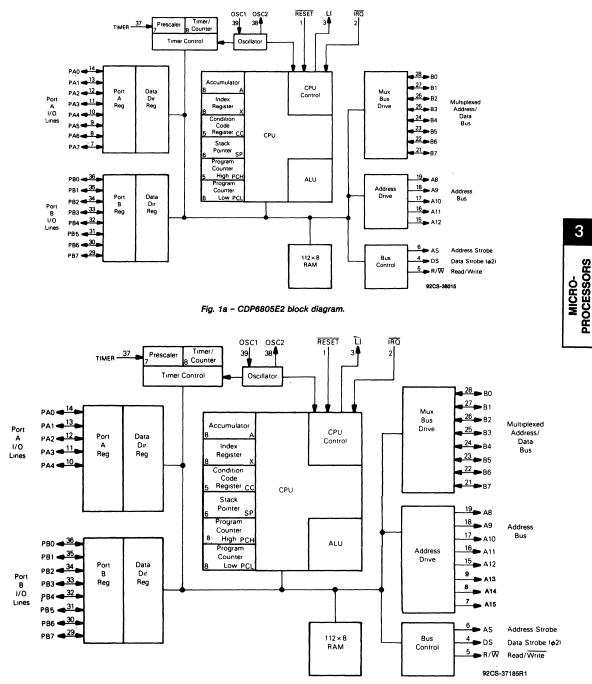

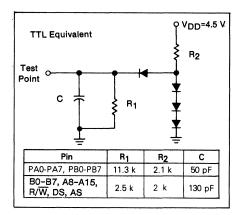

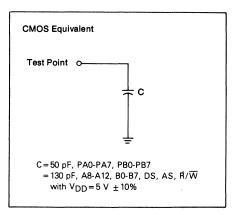

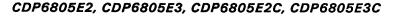

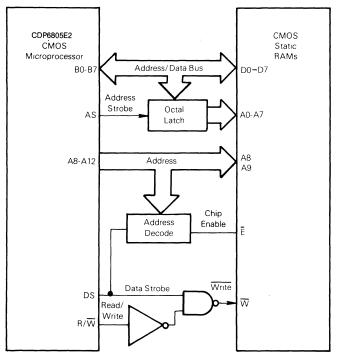

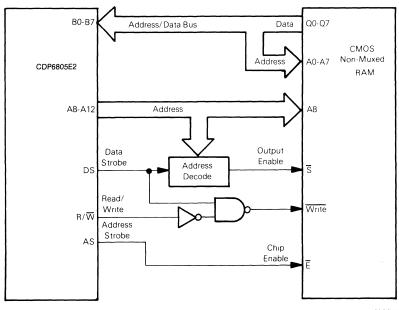

The CDP6805F2 and CDP6805G2 are microcontroller members of the 3 micron, '05 family. Each is a self contained MCU with on-chip ROM, RAM, timer, and I/O functions. The CDP6805E2 and CDP6805E3 are microprocessor members of the '05 family. They contain internal RAM, timer, and port logic, and feature address and data interface lines for connection to external memory. The CDP6805E2 can access up to 8K of memory, while the CDP6805E3 can access up to 64K of memory. All of the microcontrollers specified in this data book are masked ROM devices. The ROM code is inserted via photomasking techniques during the manufacture of the microcontrollers. This method of implementing code results in the lowest possible cost per device. Semiconductor manufacturing is based on *batch* processing. A single batch of 68HC05 microcontrollers typically produces 10,000 devices. Any device which Harris does not sell to the owner of the ROM code has no value. As a result *minimum order quantities* (MOQs) are established for all masked ROM devices. The low piece price generally makes masked ROM devices suitable for production runs of 5,000+ pieces (i.e. - 5 x MOQ). For lower volume designs, microprocessor equivalents should be considered. Contact your Harris sales representative for details on specific microcontrollers.

Section 2 provides complete technical data on the '05 and 'HC05 microcontrollers. Technical data on the microprocessor products is presented in Section 3. Note that the HIP7030A0 and HIP7030A2 are featured in the Harris Intelligent Power ICs data book.

#### CDP6805/CDP68HC05 Peripheral Devices

Section 5 and Section 6 contain detailed information on the extensive selection of peripherals designed specifically for use with the '05 and 'HC05 families of processors.

The 8-bit bus peripherals, contained in Section 5, are intended for use with microprocessors which have external address and data bus signals. These devices are also useful with many non-6805 processors.

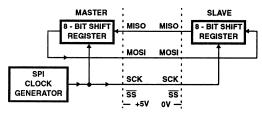

The serial peripheral interface (SPI) devices, detailed in Section 6, are designed to work on the SPI bus of the 'HC05 family of controllers (see Section 2 for information on the SPI bus). In addition to the peripherals contained in this data book, other SPI compatible devices are offered by Harris. In particular, the Intelligent Power ICs data book contains specfications of the CA3282 octal solenoid driver, the HIP008/81 quad power drivers, the HIP7010 J1850 multiplex wiring interface, and the HIP9020 engine knock sensor.

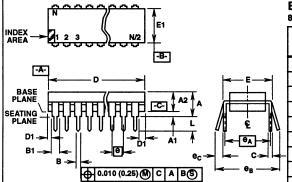

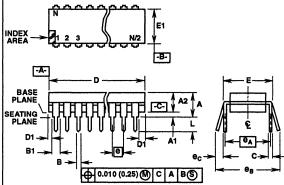

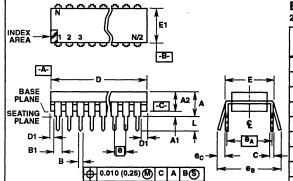

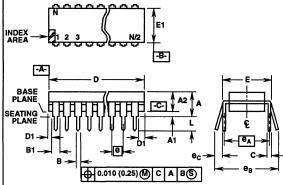

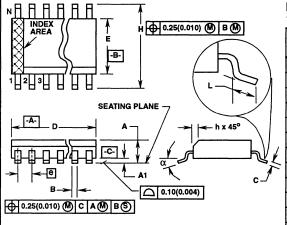

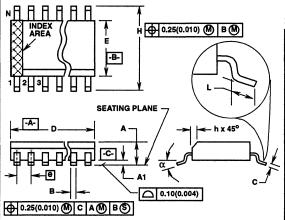

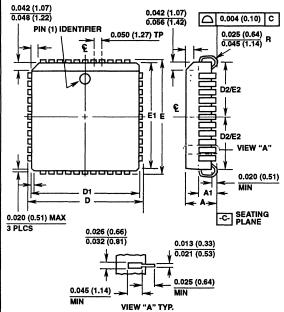

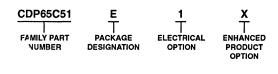

#### **Packaging Options**

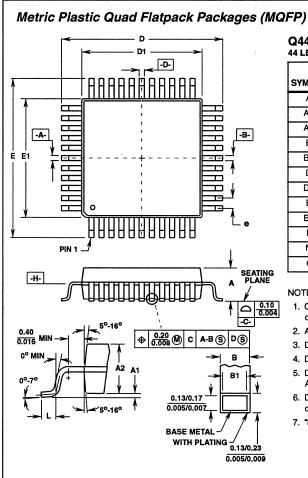

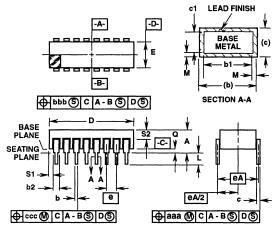

All of the devices featured in this data book are offered in PDIP (dual-in-line plastic) packages for through-hole assemblies. The majority of devices is also offered in surface mount (SMD) versions. Three types of packages are used to satisfy customers' SMD needs: PLCC (plastic leaded chip carrier); SOIC (small outline integrated circuit package); and MPQFP (metric plastic quad flatpack). Many of the 3 micron devices are also available in ceramic, dual-in-line, metal seal, packages for applications which require ceramic through-hole assembly.

Section 7 provides detailed information on all of the packaging options.

#### **Ordering Masked ROM Devices**

Manufacturing a masked ROM microcontroller requires that the customer's code be translated to a topological representation on a photomask. Section 8 covers the means by which a customer can provide ROM mask information to Harris. Ordering of masked ROM microcontrollers must be coordinated through a Harris sales representative. The information specified in Section 8 must be provided to allow proper generation of the photomask.

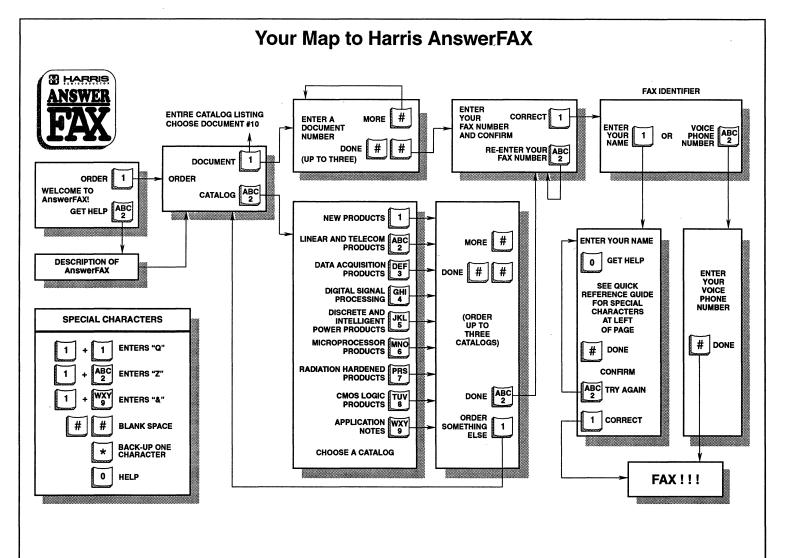

#### Harris AnswerFAX - Automated FAX Response System

The current version of data sheets for Harris products can be obtained via the Harris AnswerFAX system. Section 9 provides information on accessing the AnswerFAX system.

#### **Application Notes**

Application Notes covering the '05 and 'HC05 family of MCUs, CPUs, and peripherals can be obtained via the Harris AnswerFAX system. Section 9 provides a listing of the currently available documents.

# **CDP6805**

HIP7038A8

# 2

# MICROCONTROLLERS

|                                                         |                                                          | PAGE     |

|---------------------------------------------------------|----------------------------------------------------------|----------|

| MICROCONTROLLER D                                       | ATA SHEETS                                               |          |

| CDP68HC05C4, C8<br>CDP68HCL05C4, C8<br>CDP68HSC05C4, C8 | 8-Bit Microcontroller Series                             | 2-3      |

| CDP68HC05D2                                             | 8-Bit Microcontroller                                    | 2-54     |

| CDP68HC05J3                                             | 8-Bit Microcontroller Series                             | 2-94     |

| CDP6805F2,<br>CDP6805F2C                                | CMOS High Performance Silicon Gate 8-Bit Microcontroller | 2-117    |

| CDP6805G2,<br>CDP6805G2C                                | CMOS High Performance Silicon Gate 8-Bit Microcontroller | 2-133    |

| COMPATIBLE PRODUCT                                      | rs (See Note)                                            |          |

| HIP7030A2                                               | J1850 8-Bit 68HC05 MicrocontrollerAnswerFAX Document Num | ber 3646 |

J1850 8-Bit 68HC05 Microcontroller 8K EEPROM Version . . . AnswerFAX Document Number 3647

NOTE: Compatible Products listed are not located within this data book, but may be acquired through the Harris AnswerFAX system. Please refer to Section 9 for further information. 2

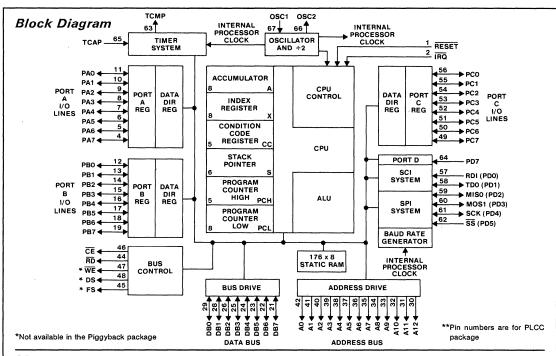

# CDP68HC05C4, C8 CDP68HCL05C4. C8 CDP68HSC05C4, C8

### 8-Bit Microcontroller Series

#### January 1995

#### Features

The following are some of the hardware and software highlights of the CDP68HC05C4 family of HCMOS Microcomputers.

#### HARDWARE FEATURES (All Types)

- HCMOS Technology

- 8-Bit Architecture

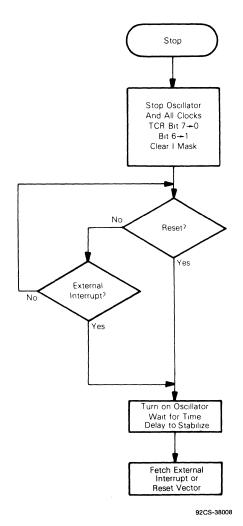

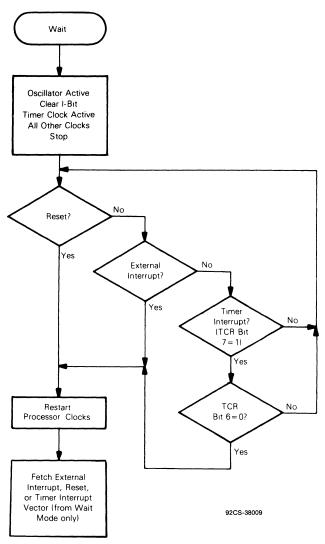

- Power-Saving STOP, WAIT and Data Retention Modes

- Fully Static Operation

- On-Chip Memory

- CDP68HC05C4, CDP68HCL05C4, CDP68HSC05C4

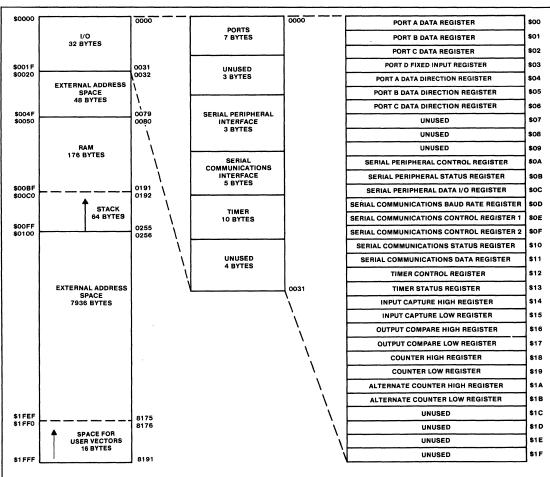

- 176 Bytes of RAM

- 4160 Bytes of User ROM

- CDP68HC05C8, CDP68HCL05C8, CDP68HSC05C8

- 176 Bytes of RAM

- 7744 Bytes of User ROM

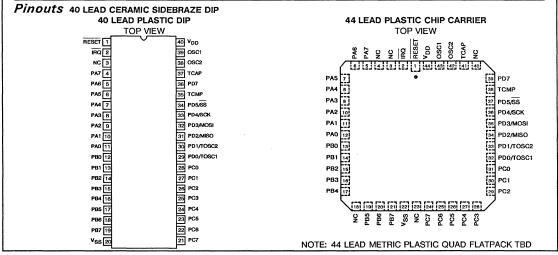

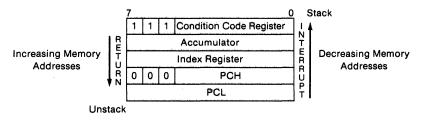

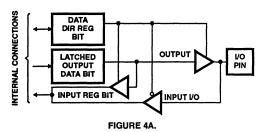

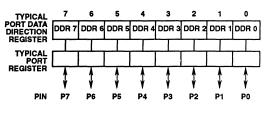

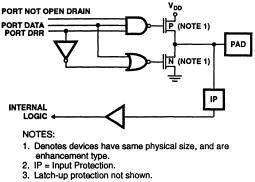

- 24 Bidirectional I/O Lines and 7 Input-Only Lines

- Internal 16-Bit Timer

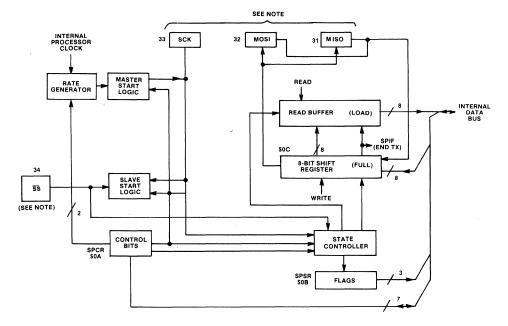

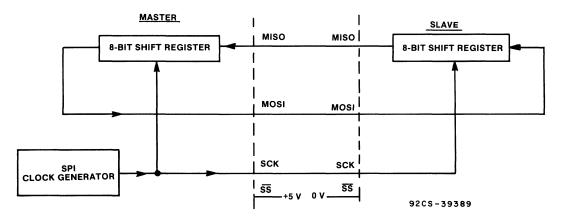

- Serial Communications Interface (SCI) System

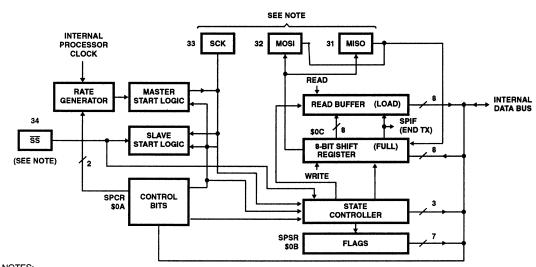

- Serial Peripheral Interface (SPI) System

- Self-Check Mode

- External, Timer, SCI, and SPI Interrupts

- Master Reset and Power-On Reset

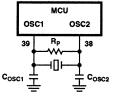

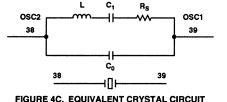

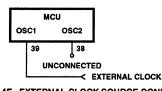

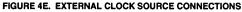

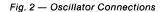

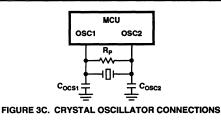

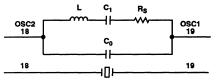

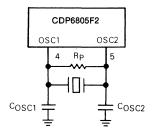

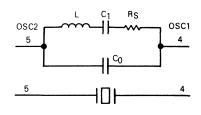

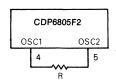

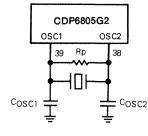

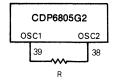

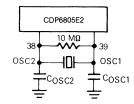

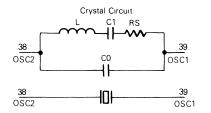

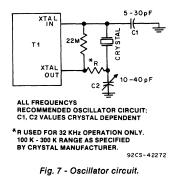

- On-Chip Oscillator with RC or Crystal Mask Options

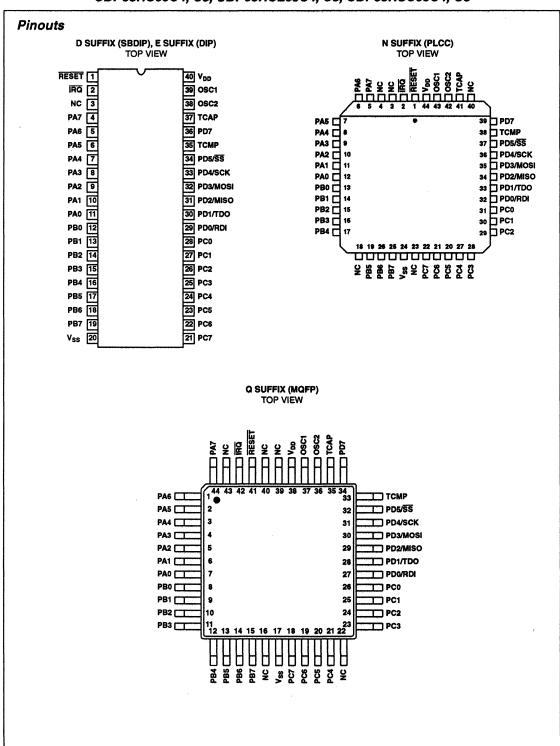

- 40 Lead Dual-In-Line, 44 Lead+ Plastic Chip Carrier, and 44 Lead Metric Plastic Quad Flatpack Packages

- CDP68HC05C4, CDP68HC05C8

- 4.2MHz Operating Frequency (2.1MHz Internal Bus Frequency) at 5V; 2.0MHz (1.0MHz Internal Bus) at 3.0V

- Single 3.0V to 6.0V Supply (2.0V Data Retention Mode)

- CDP68HCL05C4, CDP68HCL05C8

- Lower Supply Current, IDD in RUN, WAIT and STOP Modes at 5.5V, 3.6V and 2.4V

- Single 2.4V to 6.0V Supply (2V Data Retention Mode)

- CDP68HSC05C4, CDP68HSC05C8

- 8.0MHz Operating Frequency (4.0MHz Internal Bus Frequency)

- Single 3.0V to 6.0V Supply (2.0V Data Retention Mode)

#### SOFTWARE FEATURES

- Similar to MC6800

- 8 x 8 Unsigned Multiply Instruction

- · Efficient Use of Program Space

- Versatile Interrupt Handling

- True Bit Manipulation

- Addressing Modes with Indexed Addressing for Table

- Efficient Instruction Set

- Memory Mapped I/O

- Two Power-Saving Standby Modes

- Upward Software Compatible with the CDP6805 **CMOS Family**

#### Description

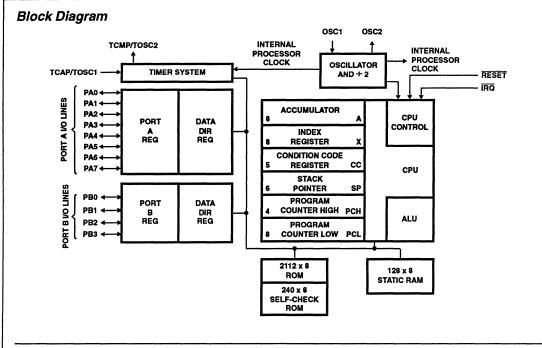

The CDP68HC05C4 HCMOS Microcomputer is a member of the CDP68HC05 family of low-cost single chip microcomputers. This 8-bit microcomputer unit (MCU) contains an onchip oscillator, CPU, 176 bytes of RAM, 4160 bytes of user ROM, I/O, two serial interface systems, and timer. The fully static design allows operation at frequencies down to DC, further reducing its already low-power consumption.

The CDP68HC05C8 is similar to the CDP68HC05C4 except for the size of on-chip ROM. The CDP68HC05C8 has 7744 bytes of on-chip user ROM. All information pertaining to the CDP68HC05C4 MCU applies to the CDP68HC05C8 with the exception of the memory description.

The CDP68HCL05C4 and CDP68HCL05C8 MCU devices are low-power versions of the CDP68HC05C4 and CDP68HC05C8, respectively. They contain all the features of the CDP68HC05C4 and CDP68HC05C8 with additional features of lower power consumption in the RUN, WAIT and STOP modes; and low voltage operation down to 2.4V.

The CDP68HSC05C4 and CDP68HSC05C8 MCU devices are high-speed versions of the CDP68HC05C4 and CDP68HC05C8, respectively. They also contain all the features of the CDP68HC05C4 and CDP68HC05C8 with the additional capability of higher frequency operation at 8.0MHz.

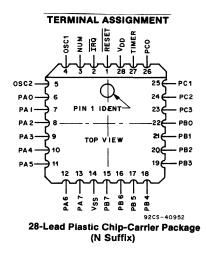

† Pin number references throughout this specification refer to the 40 lead DIP. See pinouts for cross reference.

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper I.C. Handling Procedures. Copyright C Harris Corporation 1994 2-3

#### CDP68HC05C4, C8, CDP68HCL05C4, C8, CDP68HSC05C4, C8

† 7744 bytes of ROM for: CDP68HC05C8, CDP68HCL05C8, CDP68HSC05C8.

#### **Power Considerations**

The average chip-junction temperature,  $\mathsf{T}_{\mathsf{J}},$  in  ${}^{o}\!\mathsf{C}$  can be obtained from:

$T_{J} = T_{A} + (P_{D} \bullet \theta_{JA})$

Where:  $T_A = Ambient Temperature, ^{O}C$  $\theta_{JA} = Package Thermal Resistance,$  $Junction-to-Ambient, ^{O}C/W$

$$P_D = P_{INT} + P_{I/O}$$

$\begin{array}{l} \mathsf{P}_{\mathsf{INT}} = \mathsf{I}_{\mathsf{CC}} \times \mathsf{V}_{\mathsf{CC}}, \text{ Watts - Chip Internal Power} \\ \mathsf{P}_{\mathsf{I/O}} = \mathsf{Power Dissipation on Input and Output} \\ \mathsf{Pins - User Determined} \end{array}$

For most applications  $P_{I/O} < P_{INT}$  and can be neglected.

An approximate relationship between  $\mathsf{P}_D$  and  $\mathsf{T}_J$  (if  $\mathsf{P}_{I\!/\!O}$  is neglected) is:

$$P_D = K + (T_J + 273^{\circ}C)$$

(EQ. 2)

Solving Equation 1 and Equation 2 for K gives:

$$K = P_D \bullet (T_A + 273^{\circ}C) + \theta_{JA} \bullet P_D 2$$

(EQ. 3)

Where K is a constant pertaining to the particular part. K can be determined from Equation 3 by measuring P<sub>D</sub> (at equilibrium) for a known T<sub>A</sub>. Using this value of K the values of P<sub>D</sub> and T<sub>J</sub> can be obtained by solving Equation 1 and Equation 2 iteratively for any value of T<sub>A</sub>.

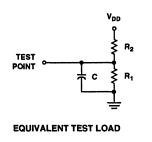

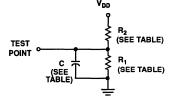

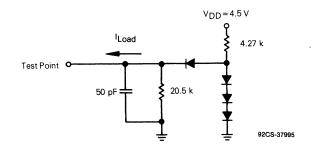

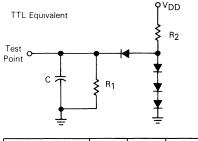

| PINS                     | R1      | R2     | С     |

|--------------------------|---------|--------|-------|

| V <sub>DD</sub> = 4.5V   |         |        |       |

| PA0-7, PB0-7, PC0-7, PD6 | 3.26kΩ  | 2.38kΩ | 50pF  |

| PD1-4                    | 1.9kΩ   | 2.26kΩ | 200pF |

| V <sub>DD</sub> = 3.0V   |         |        |       |

| PA0-7, PB0-7, PC0-7, PD6 | 10.19kΩ | 6.32kΩ | 50pF  |

| PD1-4                    | 6kΩ     | 6kΩ    | 200pF |

#### Absolute Maximum Ratings Voltages Referenced to V<sub>SS</sub>

Storage Temperature Range, T<sub>STG</sub> .....-65°C to +150°C

#### **Thermal Information**

| Thermal Resistance            | θ <sub>JA</sub> |

|-------------------------------|-----------------|

| Ceramic Dual-In-Line          | . 50°C/W        |

| Plastic Dual-In-Line          |                 |

| Plastic Chip Carrier          | .70°C/W         |

| Metric Plastic Quad Flat Pack | 120°C/W         |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### **DC Electrical Specifications** $V_{DD} = 5V \pm 10\%$ , $V_{SS} = 0V$ , $T_A = -40^{\circ}C$ to $+125^{\circ}C$ , Unless Otherwise Specified.

| PARAMETER                                                                      | SYMBOL          | CONDITIONS                                       | MIN                  | ТҮР | MAX                 | UNITS        |

|--------------------------------------------------------------------------------|-----------------|--------------------------------------------------|----------------------|-----|---------------------|--------------|

| Output Voltage                                                                 | V <sub>OL</sub> | Ι <sub>LOAD</sub> < 10μΑ                         | - 1                  | -   | 0.1                 | V            |

|                                                                                | V <sub>OH</sub> | 1                                                | V <sub>DD</sub> -0.1 | •   | -                   | v            |

| Output High Voltage                                                            |                 |                                                  |                      |     | 1                   |              |

| PA0-7, PB0-7, PC0-7, TCMP                                                      | V <sub>OH</sub> | I <sub>LOAD</sub> = -0.8mA                       | V <sub>DD</sub> -0.8 | -   | <u> </u>            | v            |

| PD1-4                                                                          | V <sub>OH</sub> | I <sub>LOAD</sub> = -1.6mA                       | V <sub>DD</sub> -0.8 | -   | -                   | v            |

| Output Low Voltage<br>PA0-7, PB0-7, PC0-7, PD1-4, TCMP                         | V <sub>OL</sub> | I <sub>LOAD</sub> = 1.6mA                        | -                    | -   | 0.4                 | v            |

| Input High Voltage, PA0-7, PB0-7, PC0-7, PD0-5,<br>PD7, TCAP, IRQ, RESET, OSC1 | V <sub>IH</sub> |                                                  | 0.7•V <sub>DD</sub>  | -   | V <sub>DD</sub>     | v            |

| Input Low Voltage, PA0-7, PB0-7, PC0-7, PD0-5,<br>PD7, TCAP, IRQ, RESET, OSC1  | V <sub>IL</sub> |                                                  | V <sub>SS</sub>      | -   | 0.2•V <sub>DD</sub> | v            |

| Data Retention Mode                                                            | V <sub>RM</sub> | $T_A = 0^{\circ}C$ to $+70^{\circ}C$             | 2                    | -   | •                   | v            |

| Supply Current (See Notes)                                                     |                 |                                                  |                      |     | 1                   |              |

| Run                                                                            | I <sub>DD</sub> |                                                  | -                    | 3.5 | 7                   | mA           |

| WAIT                                                                           | IDD             |                                                  | - 1                  | 1.6 | 4                   | mA           |

| STOP                                                                           | I <sub>DD</sub> | T <sub>A</sub> = 25°C                            | - 1                  | 2   | 50                  | μΑ           |

|                                                                                |                 | $T_A = 0^{\circ}C$ to $+70^{\circ}C$             |                      | •   | 140                 | μA           |

|                                                                                |                 | $T_A = -40^{\circ}C$ to $+85^{\circ}C$           | -                    | -   | 180                 | μΑ           |

|                                                                                | 1. A            | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$ |                      | •   | 250                 | μA           |

| I/O Ports Hi-Z Leakage Current<br>PA0-7, PB0-7, PC0-7, PD1-4                   | l <sub>IL</sub> |                                                  | -                    | -   | ±10                 | μΑ           |

| Input Current<br>RESET, IRQ, TCAP, OSC1, PD0, PD5, PD7                         | l <sub>in</sub> |                                                  | -                    | -   | ±1                  | _ μ <b>Α</b> |

| Capacitance Ports (As Input or Output)                                         | Солт            |                                                  | -                    | -   | 12                  | pF           |

| RESET, IRQ, TCAP, OSC1, PD0-5, PD7                                             | C <sub>IN</sub> |                                                  | -                    | •   | 8                   | pF           |

NOTES:

This device contains circuitry to protect the inputs against damage due to high static voltages of electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit. For proper operation it is recommended that V<sub>IN</sub> and V<sub>OUT</sub> be constrained to the range V<sub>SS</sub><(V<sub>IN</sub> or V<sub>OUT</sub>)<V<sub>DD</sub>. Reliability of operation is enhanced if unused inputs except OSC2 are connected to an appropriate logic voltage level (e.g., either V<sub>SS</sub> or V<sub>DD</sub>).

2. All values shown reflect average measurement.

3. Typical values at midpoint of voltage range, 25°C only.

- 4. WAIT I<sub>DD</sub>: Only timer system active (SPE = TE = RE = 0). If SPI, SCI active (SPE = TE = RE = 1) add 10% current draw.

- Run (Operating) I<sub>DD</sub>, WAIT I<sub>DD</sub>: Measured using external square-wave clock source (f<sub>OSC</sub> = 4.2MHz), all inputs 0.2V from rail, no DC loads, less than 50pF on all outputs, C<sub>L</sub> = 20pF on OSC2.

6. WAIT, STOP I<sub>DD</sub>: All ports configured as inputs,  $V_{IL} = 0.2V$ ,  $V_{IH} = V_{DD} - 0.2V$ .

7. STOP  $I_{DD}$  measured with OSC1 =  $V_{SS}$ .

8. WAIT I<sub>DD</sub> is affected linearly by the OSC2 capacitance.

| Specifications CDP68HC05C4, CD |  |  |  |  | CDP6 | BHC | 05 <b>C</b> 8 |  |  |

|--------------------------------|--|--|--|--|------|-----|---------------|--|--|

|                                |  |  |  |  |      | _   |               |  |  |

| PARAMETER                                                                      | SYMBOL           | CONDITIONS                                       | MIN                  | ТҮР | MAX                 | UNITS |

|--------------------------------------------------------------------------------|------------------|--------------------------------------------------|----------------------|-----|---------------------|-------|

| Output Voltage                                                                 | V <sub>OL</sub>  | I <sub>LOAD</sub> ≤ 10µА                         | -                    | -   | 0.1                 | v     |

|                                                                                | V <sub>он</sub>  |                                                  | V <sub>DD</sub> -0.1 | -   | •                   | v     |

| Output High Voltage                                                            |                  |                                                  |                      |     |                     |       |

| PA0-7, PB0-7, PC0-7, TCMP                                                      | V <sub>он</sub>  | I <sub>LOAD</sub> = -0.2mA                       | V <sub>DD</sub> -0.3 | -   | -                   | v     |

| PD1-4                                                                          | V <sub>OH</sub>  | I <sub>LOAD</sub> = -0.4mA                       | V <sub>DD</sub> -0.3 | -   | -                   | v     |

| Output Low Voltage<br>PA0-7, PB0-7, PC0-7, PD1-4, TCMP                         | V <sub>OL</sub>  | I <sub>LOAD</sub> = 0.4mA                        | -                    | -   | 0.3                 | v     |

| Input High Voltage, PA0-7, PB0-7, PC0-7, PD0-5,<br>PD7, TCAP, IRQ, RESET, OSC1 | VIH              |                                                  | 0.7•V <sub>DD</sub>  | -   | V <sub>DD</sub>     | v     |

| Input Low Voltage, PA0-7, PB0-7, PC0-7, PD0-5,<br>PD7, TCAP, IRQ, RESET, OSC1  | VIL              |                                                  | V <sub>SS</sub>      | -   | 0.2•V <sub>DD</sub> | v     |

| Data Retention Mode                                                            | V <sub>RM</sub>  | $T_{A} = 0^{\circ}C \text{ to } +70^{\circ}C$    | 2                    | -   | -                   | v     |

| Supply Current (See Notes)                                                     |                  |                                                  |                      |     |                     |       |

| Run                                                                            | I <sub>DD</sub>  |                                                  | -                    | 1   | 2.5                 | mA    |

| WAIT                                                                           | I <sub>DD</sub>  |                                                  | •                    | 0.5 | 1.4                 | mA    |

| STOP                                                                           | I <sub>DD</sub>  | T <sub>A</sub> = 25°C                            | -                    | 1   | 30                  | μA    |

|                                                                                |                  | $T_A = 0^{\circ}C$ to +70°C                      | -                    | -   | 80                  | μΑ    |

|                                                                                |                  | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$    | -                    | -   | 120                 | μΑ    |

|                                                                                |                  | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$ | -                    | -   | 175                 | μΑ    |

| I/O Ports Hi-Z Leakage Current<br>PA0-7, PB0-7, PC0-7, PD1-4                   | հլ               |                                                  | -                    | -   | ±10                 | μА    |

| Input Current<br>RESET, IRQ, TCAP, OSC1, PD0, PD5, PD7                         | I <sub>IN</sub>  |                                                  |                      | -   | ±1                  | μA    |

| Capacitance Ports (As Input or Output)                                         | С <sub>олт</sub> |                                                  | -                    | -   | 12                  | pF    |

| RESET, IRQ, TCAP, OSC1, PD0-5, PD7                                             | CIN              |                                                  | -                    | -   | 8                   | pF    |

NOTES:

1. All values shown reflect average measurement.

. .. ...

2. Typical values at midpoint of voltage range, 25°C only.

3. WAIT IDD: Only timer system active (SPE = TE = RE = 0). If SPI, SCI active (SPE = TE = RE = 1) add 10% current draw.

Run (Operating) I<sub>DD</sub>, WAIT I<sub>DD</sub>: Measured using external square-wave clock source (f<sub>OSC</sub> = 4.2MHz), all inputs 0.2V from rail, no DC loads, less than 50pF on all outputs, C<sub>L</sub> = 20pF on OSC2.

5. WAIT, STOP I<sub>DD</sub>: All ports configured as inputs,  $V_{IL} = 0.2V$ ,  $V_{IH} = V_{DD} - 0.2V$ .

6. STOP I<sub>DD</sub> measured with OSC1 = V<sub>SS</sub>.

7. WAIT I<sub>DD</sub> is affected linearly by the OSC2 capacitance.

| PARAMETER                                                              | SYMBOL                            | MIN      | MAX | UNITS |

|------------------------------------------------------------------------|-----------------------------------|----------|-----|-------|

| Frequency Of Operation                                                 |                                   |          |     |       |

| Crystal Option                                                         | fosc                              | -        | 4.2 | MHz   |

| External Clock Option                                                  | fosc                              | DC       | 4.2 | MHz   |

| Internal Operating Frequency                                           |                                   |          |     |       |

| Crystal (f <sub>OSC</sub> + 2)                                         | f <sub>OP</sub>                   | -        | 2.1 | MHz   |

| External Clock (f <sub>OSC</sub> + 2)                                  | f <sub>OP</sub>                   | DC       | 2.1 | MHz   |

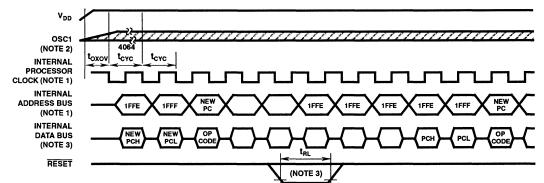

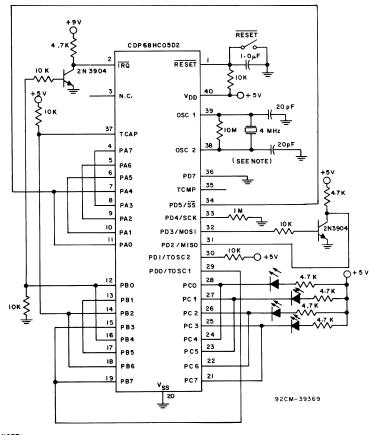

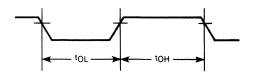

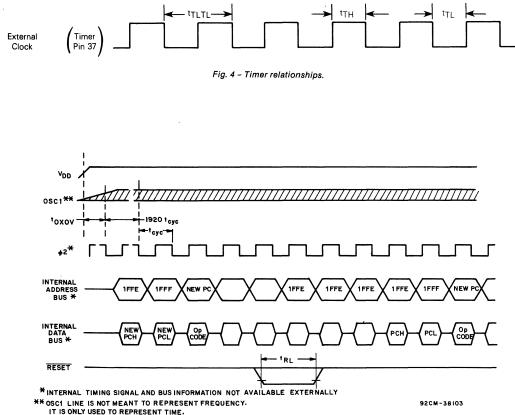

| Cycle Time (See Figure 11)                                             | tсус                              | 480      | -   | ns    |

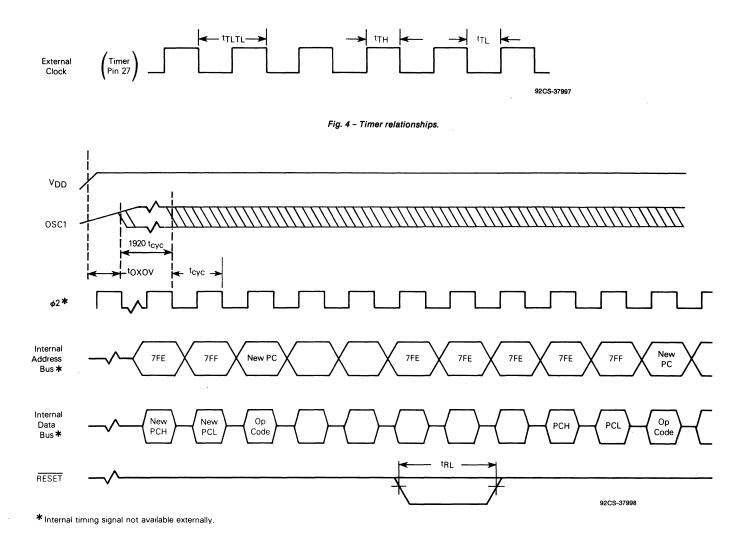

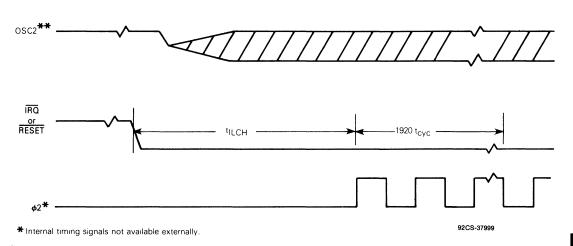

| Crystal Oscillator Start-up Time for AT-cut Crystal (See Figure 11)    | toxov                             | -        | 100 | ms    |

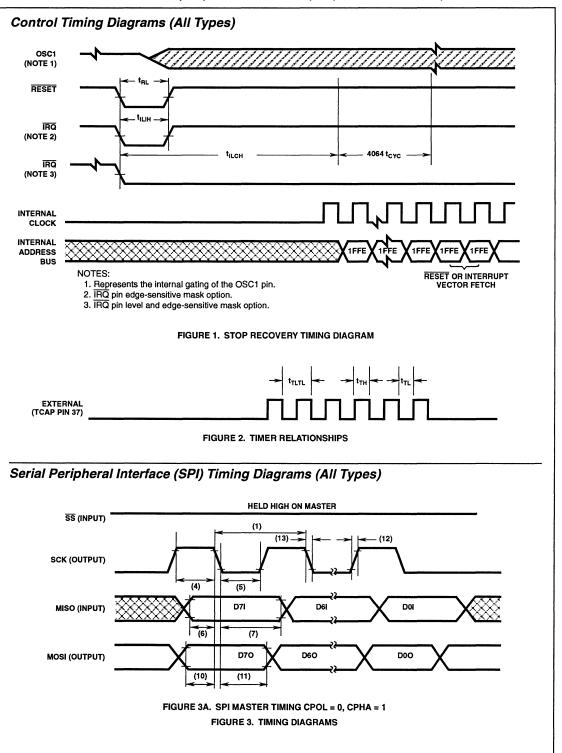

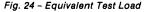

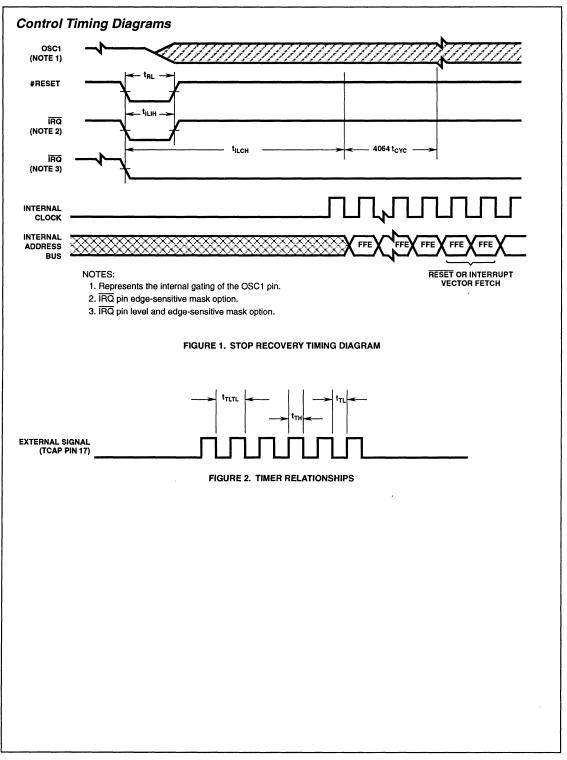

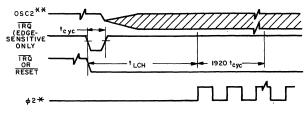

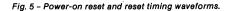

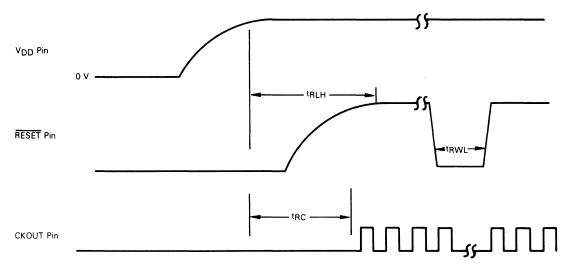

| Stop Recovery Start-up Time (AT-cut Crystal Oscillator) (See Figure 1) | tilch                             | -        | 100 | ms    |

| RESET Pulse Width (See Figure 11)                                      | t <sub>RL</sub>                   | 1.5      | •   | tcyc  |

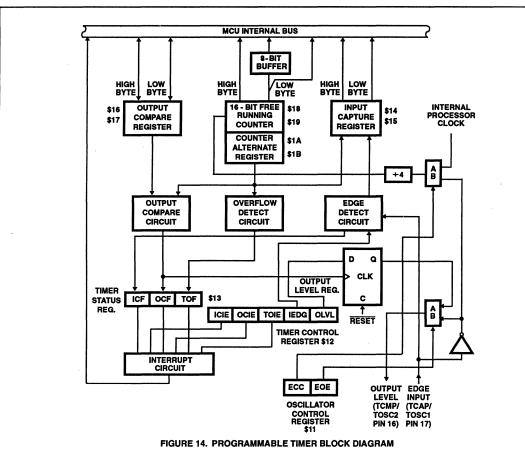

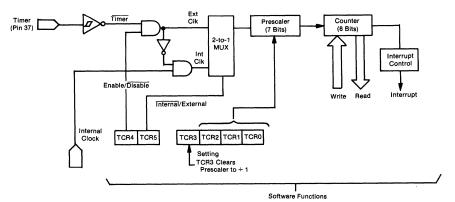

| Timer                                                                  |                                   |          |     |       |

| Resolution (Note 2)                                                    | t <sub>RES</sub>                  | 4        | -   | tcyc  |

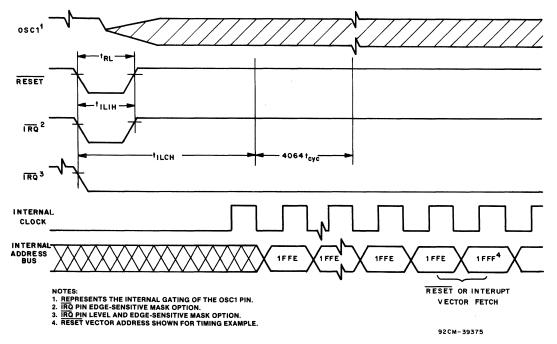

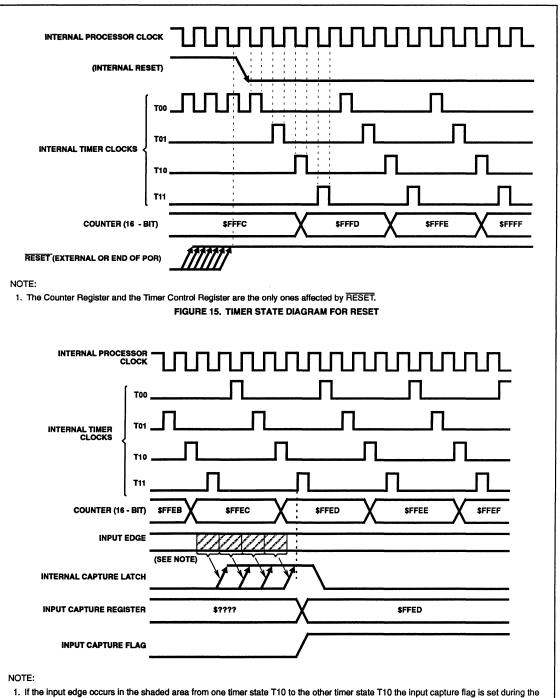

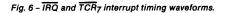

| Input Capture Pulse Width (See Figure 2)                               | t <sub>TH</sub> , t <sub>TL</sub> | 125      | -   | ns    |

| Input Capture Pulse Period (See Figure 2)                              | t <sub>TLTL</sub>                 | (Note 3) | -   | tcyc  |

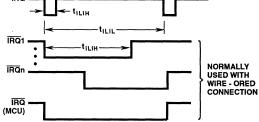

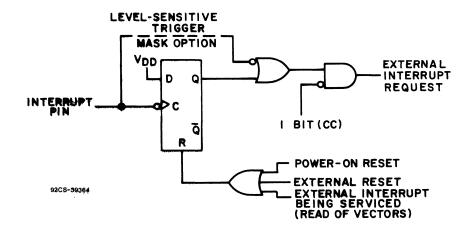

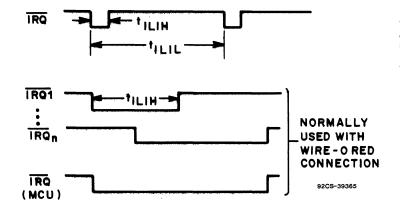

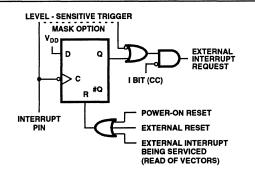

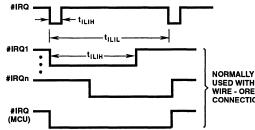

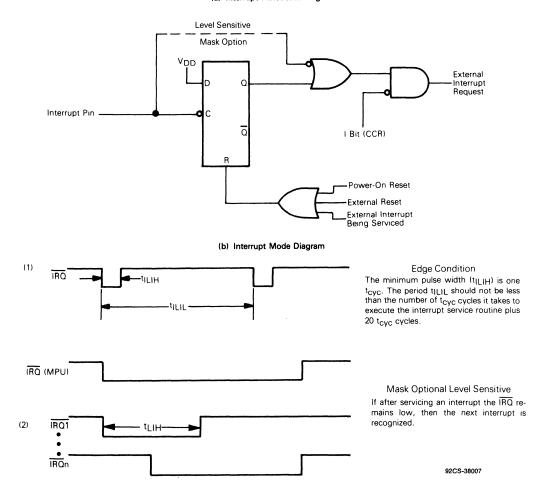

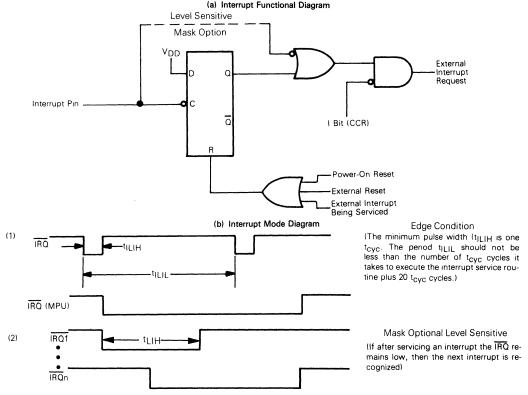

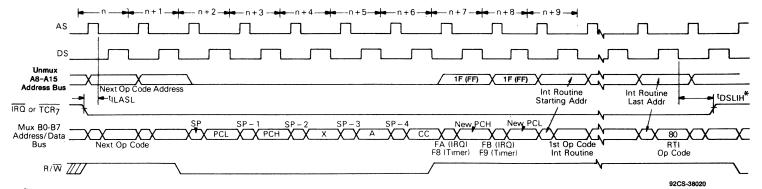

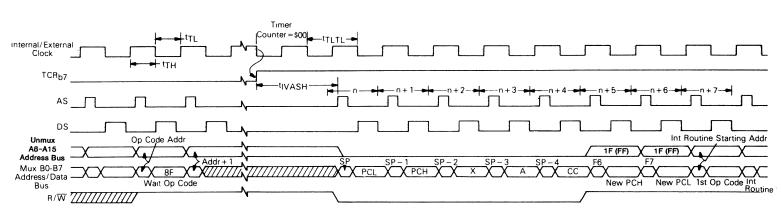

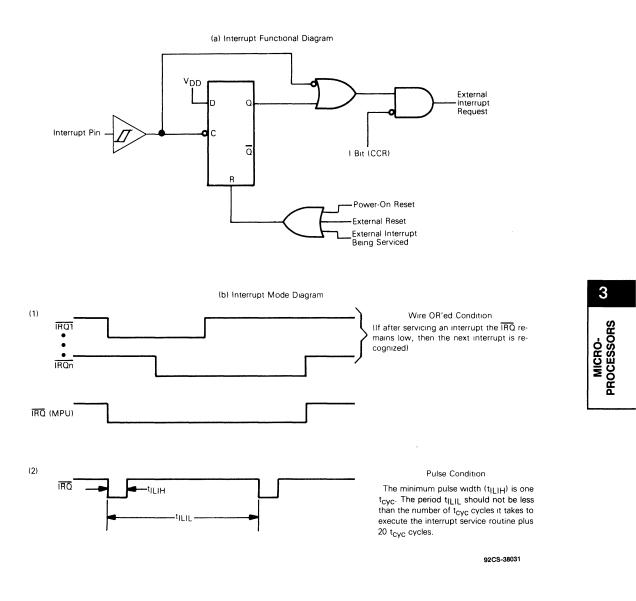

| Interrupt Pulse Width Low (Edge-Triggered) (See Figure 14)             | tılıн                             | 125      | -   | ns    |

| Interrupt Pulse Period (See Figure 14)                                 | t <sub>ын</sub>                   | (Note 1) | -   | tcyc  |

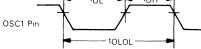

| OSC1 Pulse Width                                                       | toH, toL                          | 90       | -   | ns    |

NOTES:

1. The minimum period t<sub>ILIL</sub> should not be less than the number of cycle times it takes to execute the interrupt service routine plus 21 t<sub>CYC</sub>.

2. Since a 2-bit prescaler in the timer must count four internal cycles (t<sub>CYC</sub>), this is the limiting minimum factor in determining the timer resolution.

3. The minimum period t<sub>TLTL</sub> should not be less than the number of cycle times it takes to execute the capture interrupt service routine plus 24 t<sub>CYC</sub>.

| PARAMETER                                                              | SYMBOL                            | MIN      | МАХ | UNITS |

|------------------------------------------------------------------------|-----------------------------------|----------|-----|-------|

| Frequency Of Operation                                                 |                                   |          |     |       |

| Crystal Option                                                         | fosc                              | -        | 2.0 | MHz   |

| External Clock Option                                                  | fosc                              | DC       | 2.0 | MHz   |

| Internal Operating Frequency                                           |                                   |          |     |       |

| Crystal (f <sub>OSC</sub> + 2)                                         | f <sub>OP</sub>                   | -        | 1.0 | MHz   |

| External Clock (f <sub>OSC</sub> + 2)                                  | f <sub>OP</sub>                   | DC       | 1.0 | MHz   |

| Cycle Time (See Figure 11)                                             | tcyc                              | 1000     | -   | ns    |

| Crystal Oscillator Start-up Time for AT-cut Crystal (See Figure 11)    | toxov                             | -        | 100 | ms    |

| Stop Recovery Start-up Time (AT-cut Crystal Oscillator) (See Figure 1) | t <sub>ILCH</sub>                 | -        | 100 | ms    |

| RESET Pulse Width (See Figure 11)                                      | t <sub>RL</sub>                   | 1.5      | -   | tcyc  |

| Timer                                                                  |                                   |          |     |       |

| Resolution (Note 2)                                                    | t <sub>RES</sub>                  | 4        | -   | tcyc  |

| Input Capture Pulse Width (See Figure 2)                               | t <sub>TH</sub> , t <sub>TL</sub> | 250      | -   | ns    |

| Input Capture Pulse Period (See Figure 2)                              | t <sub>TLTL</sub>                 | (Note 3) | •   | tcyc  |

| Interrupt Pulse Width Low (Edge-Triggered) (See Figure 14)             | ţгін                              | 250      |     | ns    |

| Interrupt Pulse Period (See Figure 14)                                 | ţгін                              | (Note 1) | -   | tcyc  |

| OSC1 Pulse Width                                                       | t <sub>OH</sub> , t <sub>OL</sub> | 200      | -   | ns    |

NOTES:

1. The minimum period t<sub>ILIL</sub> should not be less than the number of cycle times it takes to execute the interrupt service routine plus 21 t<sub>CYC</sub>.

2. Since a 2-bit prescaler in the timer must count four internal cycles ( $t_{CYC}$ ), this is the limiting minimum factor in determining the timer resolution. 3. The minimum period  $t_{TLTL}$  should not be less than the number of cycle times it takes to execute the capture interrupt service routine plus 24  $t_{CYC}$ .

#### Specifications CDP68HC05C4, CDP68HC05C8

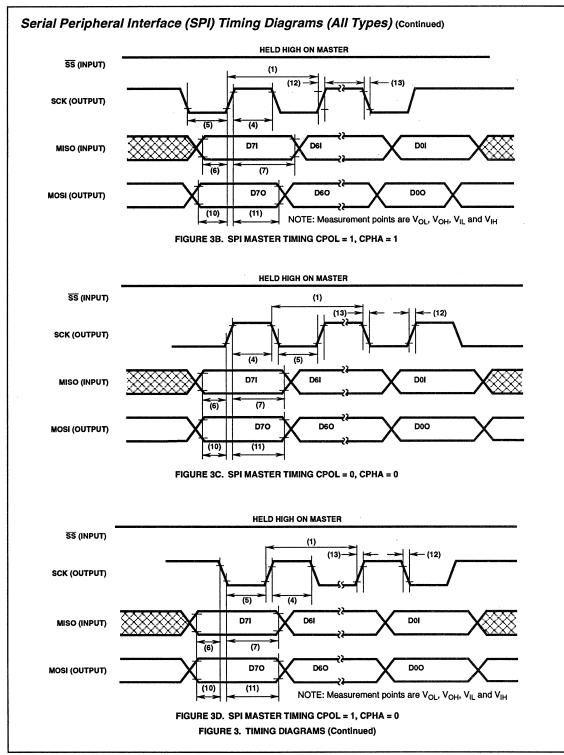

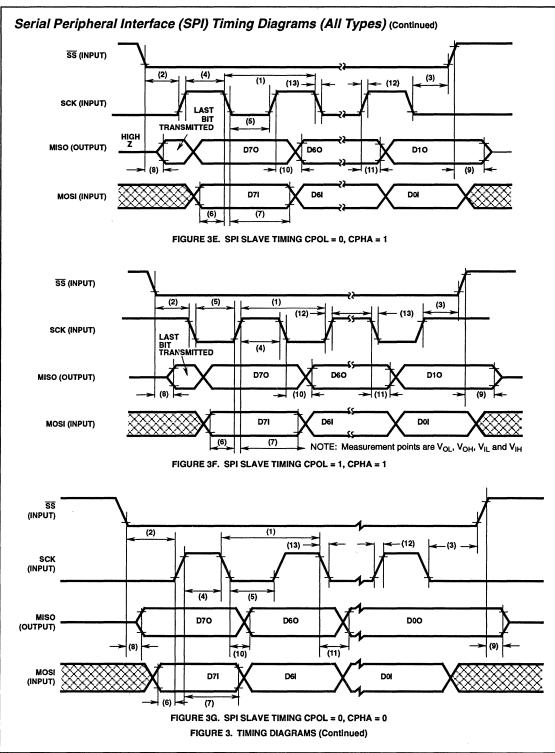

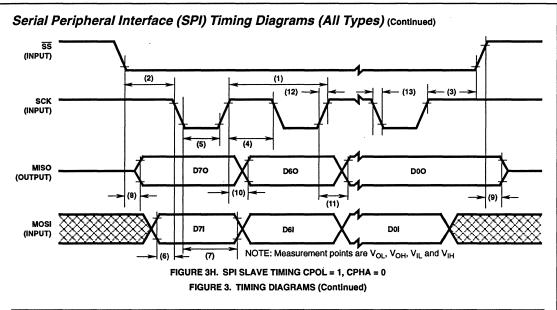

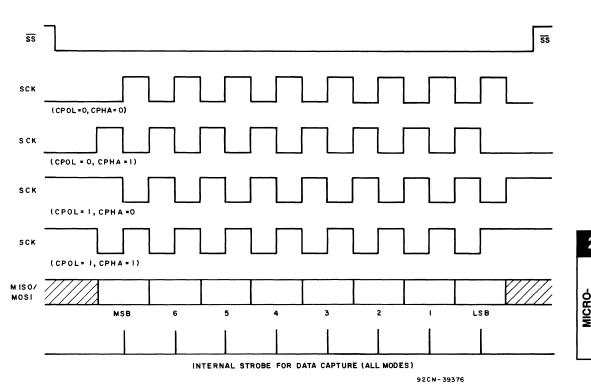

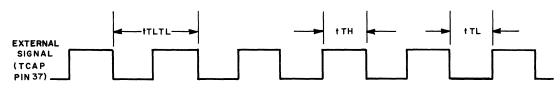

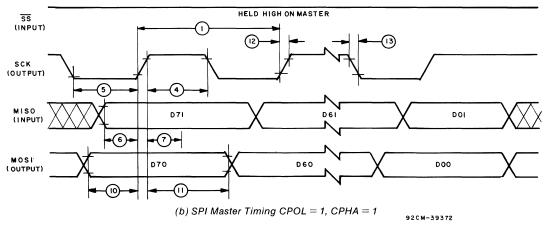

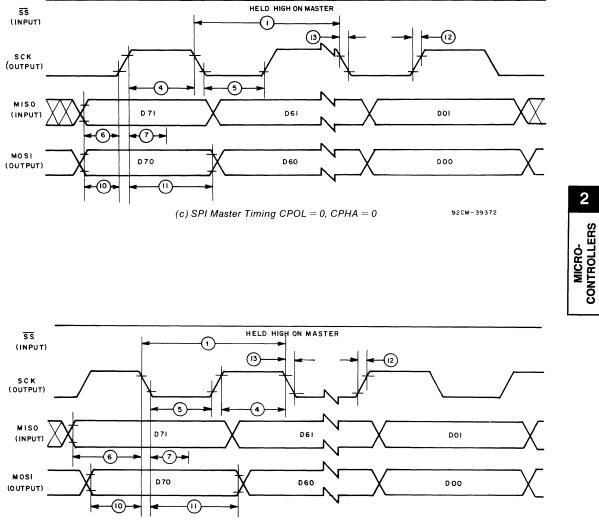

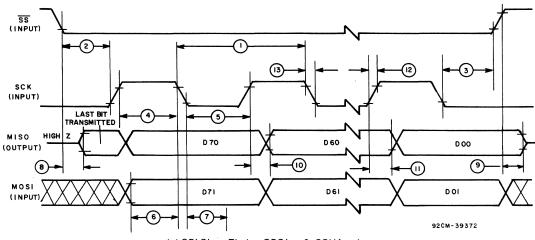

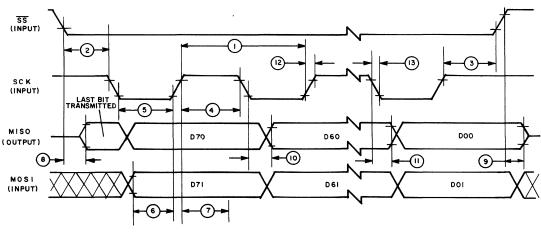

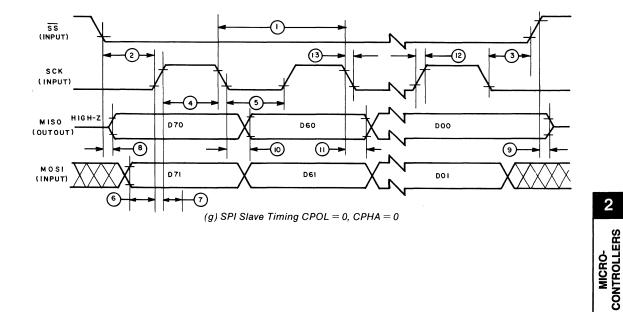

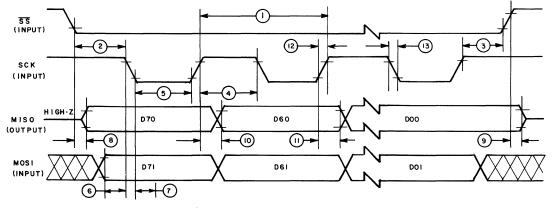

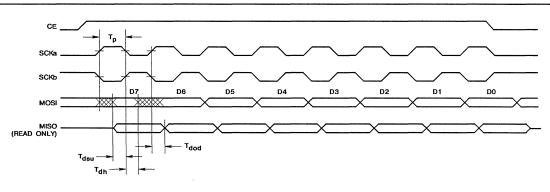

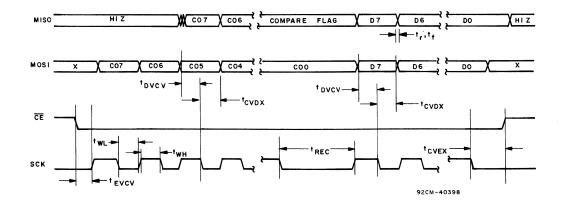

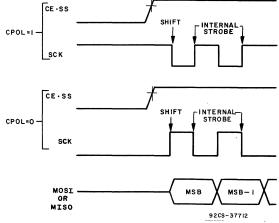

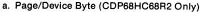

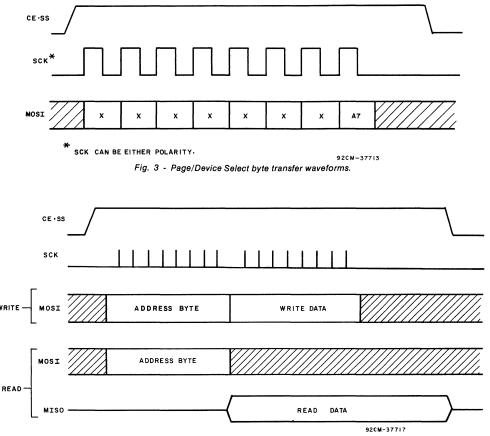

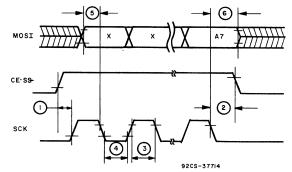

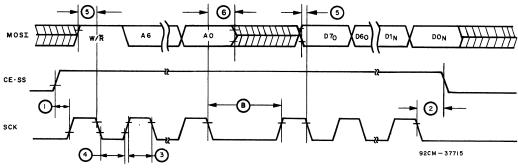

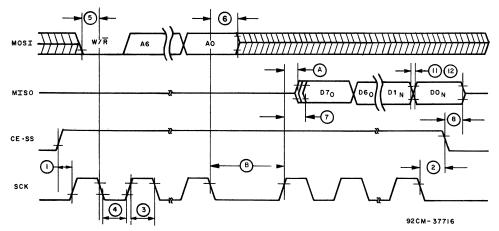

# Serial Peripheral Interface (SPI) Timing (See Figure 3) $V_{DD} = 5V \pm 10\%$ , $V_{SS} = 0V$ , $T_A = -40^{\circ}$ C to +125°C Unless Otherwise Specified.

| UMBER | PARAMETER                                                   | SYMBOL                | MIN      | MAX | UNITS                   |

|-------|-------------------------------------------------------------|-----------------------|----------|-----|-------------------------|

|       |                                                             |                       |          |     |                         |

|       | Operating Frequency<br>Master                               | form                  | DC       | 0.5 | f <sub>OP</sub> (Note 3 |

|       | Slave                                                       | fop(M)                | DC       | 2.1 | MHz                     |

|       |                                                             | f <sub>OP(S)</sub>    |          | 2.1 |                         |

| 1     | Cycle Time<br>Master                                        |                       | 2.0      | _   | 1                       |

|       | Slave                                                       | <sup>1</sup> CYC(M)   | 480      | •   | toyo                    |

|       |                                                             | <sup>t</sup> CYC(S)   | 400      | -   | ns                      |

| 2     | Enable Lead Time<br>Master                                  |                       | (Note 1) | _   |                         |

|       | Slave                                                       | LEAD(M)               | 240      |     |                         |

|       |                                                             | t <sub>LEAD(S)</sub>  | 240      | -   | ns                      |

| 3     | Enable Lag Time<br>Master                                   |                       | (Note 1) | _   |                         |

|       |                                                             | tLAG(M)               | 240      |     | +                       |

|       | Slave                                                       | t <sub>LAG(S)</sub>   | 240      | -   | ns                      |

| 4     | Clock (SCK) High Time<br>Master                             |                       | 340      |     |                         |

|       | ,                                                           | tw(sckh)M             |          | -   | ns                      |

|       | Slave                                                       | tw(sckh)s             | 190      | -   | ns                      |

| 5     | Clock (SCK) Low Time                                        |                       | 240      | -   |                         |

|       | Master                                                      | <sup>t</sup> w(sckl)M | 340      |     | ns                      |

|       | Slave                                                       | tw(SCKL)S             | 190      | -   | ns                      |

| 6     | Data Setup Time (Inputs)                                    |                       | 100      |     |                         |

|       | Master                                                      | t <sub>SU(M)</sub>    | 100      | -   | ns                      |

|       | Slave                                                       | tsu(s)                | 100      | -   | ns                      |

| 7     | Data Hold Time (Inputs)                                     |                       | 100      |     |                         |

|       | Master                                                      | t <sub>H(M)</sub>     | 100      | -   | ns                      |

|       | Slave                                                       | t <sub>H(S)</sub>     | 100      | -   | ns                      |

| 8     | Access Time (Time to Data Active from High Impedance State) |                       |          | 400 |                         |

|       | Slave                                                       | t <sub>A</sub>        | 0        | 120 | ns                      |

| 9     | Disable Time (Hold Time to High Impedance State)            |                       |          | 040 |                         |

|       | Slave                                                       | t <sub>DIS</sub>      | •        | 240 | ns                      |

| 10    | Data Valid Time                                             |                       | 0.05     |     |                         |

|       | Master (Before Capture Edge)                                | t <sub>V(M)</sub>     | 0.25     | -   | tcyc(M)                 |

|       | Slave (After Enable Edge) (Note 2)                          | t <sub>V(S)</sub>     | -        | 240 | ns                      |

| 11    | Data Hold Time (Outputs)                                    |                       | 0.05     |     |                         |

|       | Master (After Capture Edge)                                 | t <sub>HO(M)</sub>    | 0.25     | -   | <sup>t</sup> CYC(M)     |

|       | Slave (After Enable Edge)                                   | t <sub>HO(S)</sub>    | 0        | -   | ns                      |

| 12    | Rise Time ( $V_{DD} = 20\%$ to 70%, $C_L = 200pF$ )         |                       |          |     |                         |

|       | SPI Outputs (SCK, MOSI, MISO)                               | t <sub>R(M)</sub>     | -        | 100 | ns                      |

|       | SPI Inputs (SCK, MOSI, MISO, SS)                            | t <sub>R(S)</sub>     | -        | 2.0 | μs                      |

| 13    | Fall Time ( $V_{DD}$ = 20% to 70%, $C_{L}$ = 200pF)         |                       |          |     |                         |

|       | SPI Outputs (SCK, MOSI, MISO)                               | t <sub>F(M)</sub>     | -        | 100 | ns                      |

|       | SPI Inputs (SCK, MOSI, MISO, SS)                            | t <sub>F(S)</sub>     | -        | 2.0 | μs                      |

NOTES:

1. Signal Production depends on software.

2. Assumes 200pF load on all SPI pins.

Note that the units this specification uses is f<sub>OP</sub> (internal operating frequency), not MHz! In the master mode the SPI bus is capable of running at one-half of the devices's internal operating frequency, therefore 1.05MHz maximum. MICRO-CONTROLLERS

2-9

| NUMBER | PARAMETER                                                        | SYMBOL                | MIN      | MAX | UNITS                   |

|--------|------------------------------------------------------------------|-----------------------|----------|-----|-------------------------|

|        | Operating Frequency                                              |                       |          |     |                         |

|        | Master                                                           | fop(M)                | DC       | 0.5 | f <sub>OP</sub> (Note 3 |

|        | Slave                                                            | f <sub>OP(S)</sub>    | DC       | 1.0 | MHz                     |

| 1      | Cycle Time                                                       |                       |          |     |                         |

|        | Master                                                           | t <sub>CYC(M)</sub>   | 2.0      | -   | tcyc                    |

|        | Slave                                                            | t <sub>CYC(S)</sub>   | 1.0      | -   | μs                      |

| 2      | Enable Lead Time                                                 |                       |          |     |                         |

|        | Master                                                           | t <sub>LEAD(M)</sub>  | (Note 1) | -   | -                       |

|        | Slave                                                            | t <sub>LEAD(S)</sub>  | 500      | -   | ns                      |

| 3      | Enable Lag Time                                                  |                       |          |     |                         |

|        | Master                                                           | tLAG(M)               | (Note 1) | -   | -                       |

|        | Slave                                                            | t <sub>LAG(S)</sub>   | 500      | -   | ns                      |

| 4      | Clock (SCK) High Time                                            |                       |          |     |                         |

|        | Master                                                           | tw(sckh)M             | 720      | -   | ns                      |

|        | Slave                                                            | tw(sckh)s             | 400      | •   | ns                      |

| 5      | Clock (SCK) Low Time                                             |                       |          |     |                         |

|        | Master                                                           | <sup>t</sup> w(sckl)M | 720      | -   | ns                      |

|        | Slave                                                            | tw(sckl)s             | 400      | •   | ns                      |

| 6      | Data Setup Time (Inputs)                                         |                       |          |     |                         |

|        | Master                                                           | t <sub>SU(M)</sub>    | 200      | -   | ns                      |

|        | Slave                                                            | t <sub>SU(S)</sub>    | 200      | •   | ns                      |

| 7      | Data Hold Time (Inputs)                                          |                       |          |     |                         |

|        | Master                                                           | t <sub>H(M)</sub>     | 200      | -   | ns                      |

|        | Slave                                                            | t <sub>H(S)</sub>     | 200      | •   | ns                      |

| 8      | Access Time (Time to Data Active from High Impedance State)      |                       |          |     |                         |

|        | Slave                                                            | t <sub>A</sub>        | 0        | 250 | ns                      |

| 9      | Disable Time (Hold Time to High Impedance State)                 |                       |          |     |                         |

|        | Slave                                                            | t <sub>DIS</sub>      | -        | 500 | ns                      |

| 10     | Data Valid Time                                                  |                       |          |     |                         |

|        | Master (Before Capture Edge)                                     | tv(M)                 | 0.25     | -   | <sup>t</sup> CYC(M)     |

|        | Slave (After Enable Edge) (Note 2)                               | t <sub>V(S)</sub>     | •        | 500 | ns                      |

| 11     | Data Hold Time (Outputs)                                         |                       |          |     |                         |

|        | Master (After Capture Edge)                                      | t <sub>HO(M)</sub>    | 0.25     | -   | <sup>t</sup> CYC(M)     |

|        | Slave (After Enable Edge)                                        | t <sub>HO(S)</sub>    | 0        | -   | ns                      |

| 12     | Rise Time (V <sub>DD</sub> = 20% to 70%, C <sub>L</sub> = 200pF) |                       |          |     |                         |

|        | SPI Outputs (SCK, MOSI, MISO)                                    | <sup>t</sup> R(M)     | •        | 200 | ns                      |

|        | SPI Inputs (SCK, MOSI, MISO, SS)                                 | t <sub>R(S)</sub>     | -        | 2.0 | μs                      |

| 13     | Fall Time (V <sub>DD</sub> = 20% to 70%, C <sub>L</sub> = 200pF) |                       |          |     |                         |

|        | SPI Outputs (SCK, MOSI, MISO)                                    | t <sub>F(M)</sub>     | •        | 200 | ns                      |

|        | SPI Inputs (SCK, MOSI, MISO, SS)                                 | t <sub>F(S)</sub>     | -        | 2.0 | μs                      |

NOTES:

1. Signal Production depends on software.

2. Assumes 200pF load on all SPI pins.

3. Note that the units this specification uses is f<sub>OP</sub> (internal operating frequency), not MHz! In the master mode the SPI bus is capable of running at one-half of the devices's internal operating frequency, therefore 0.05MHz maximum.

#### Specifications CDP68HCL05C4, CDP68HCL05C8

| PARAMETER                                                                      | SYMBOL          | CONDITIONS                                    | MIN                  | ТҮР       | MAX                 | UNITS |

|--------------------------------------------------------------------------------|-----------------|-----------------------------------------------|----------------------|-----------|---------------------|-------|

| Output Voltage                                                                 | V <sub>OL</sub> | I <sub>LOAD</sub> ≤10μA                       | -                    | •         | 0.1                 | v     |

|                                                                                | V <sub>OH</sub> | 1                                             | V <sub>DD</sub> -0.1 | •         | -                   | v     |

| Output High Voltage                                                            |                 |                                               |                      |           |                     |       |

| PA0-7, PB0-7, PC0-7, TCMP                                                      | V <sub>он</sub> | l <sub>LOAD</sub> = -0.8mA                    | V <sub>DD</sub> -0.8 | -         | -                   | v     |

| PD1-4                                                                          | V <sub>OH</sub> | I <sub>LOAD</sub> = -1.6mA                    | V <sub>DD</sub> -0.8 | -         | -                   | v     |

| Output Low Voltage<br>PA0-7, PB0-7, PC0-7, PD1-4, TCMP                         | V <sub>OL</sub> | I <sub>LOAD</sub> = 1.6mA                     | -                    | -         | 0.4                 | v     |

| Input High Voltage, PA0-7, PB0-7, PC0-7, PD0-5,<br>PD7, TCAP, IRQ, RESET, OSC1 | ViH             |                                               | 0.7•V <sub>DD</sub>  | •         | V <sub>DD</sub>     | v     |

| Input Low Voltage, PA0-7, PB0-7, PC0-7, PD0-5,<br>PD7, TCAP, IRQ, RESET, OSC1  | V <sub>IL</sub> |                                               | V <sub>SS</sub>      | -         | 0.2•V <sub>DD</sub> | v     |

| Data Retention Mode                                                            | V <sub>RM</sub> | $T_A = 0^{\circ}C$ to $+70^{\circ}C$          | 2                    | -         | -                   | v     |

| Supply Current (See Notes)                                                     |                 |                                               |                      | (kengton) | 1                   |       |

| Run                                                                            | I <sub>DD</sub> |                                               |                      | -         | 5                   | mA    |

| WAIT                                                                           | I <sub>DD</sub> |                                               | -                    | -         | 2.75                | mA    |

| STOP                                                                           | I <sub>DD</sub> | T <sub>A</sub> = 25°C                         | · ·                  | -         | 15                  | μΑ    |

|                                                                                |                 | $T_{A} = 0^{\circ}C \text{ to } +70^{\circ}C$ |                      | -         | 25                  | μA    |

| VO Ports Hi-Z Leakage Current<br>PA0-7, PB0-7, PC0-7, PD1-4                    | Ι <sub>ΙL</sub> |                                               | -                    | -         | ±1                  | μΑ    |

| Input Current<br>RESET, IRQ, TCAP, OSC1, PD0, PD5, PD7                         | l <sub>in</sub> |                                               | -                    | -         | ±1                  | μA    |

| Capacitance Ports (As Input or Output)                                         | Солт            |                                               | -                    | -         | 12                  | pF    |

| RESET, IRQ, TCAP, OSC1, PD0-5, PD7                                             | CIN             |                                               | -                    | -         | 8                   | pF    |

NOTES:

1. All values shown reflect average measurement.

2. Typical values at midpoint of voltage range, 25°C only.

3. WAIT I<sub>DD</sub>: Only timer system active (SPE = TE = RE = 0). If SPI, SCI active (SPE = TE = RE = 1) add 10% current draw.

Run (Operating) I<sub>DD</sub>, WAIT I<sub>DD</sub>: Measured using external square-wave clock source (f<sub>OSC</sub> = 4.2MHz), all inputs 0.2V from rail, no DC loads, less than 50pF on all outputs, C<sub>L</sub> = 20pF on OSC2.

5. WAIT, STOP I\_DD: All ports configured as inputs, V\_IL = 0.2V, V\_IH = V\_DD - 0.2V.

6. STOP I<sub>DD</sub> measured with OSC1 =  $V_{SS}$ .

7. WAIT  $\ensuremath{\mathsf{I}_{\text{DD}}}$  is affected linearly by the OSC2 capacitance.

#### Specifications CDP68HCL05C4, CDP68HCL05C8

| PARAMETER                                                                      | SYMBOL           | CONDITIONS                                  | MIN                  | ТҮР | MAX                 | UNITS |

|--------------------------------------------------------------------------------|------------------|---------------------------------------------|----------------------|-----|---------------------|-------|

| Output Voltage                                                                 | V <sub>OL</sub>  | I <sub>LOAD</sub> ≤ 10μA                    | -                    | •   | 0.1                 | v     |

|                                                                                | V <sub>OH</sub>  |                                             | V <sub>DD</sub> -0.1 | -   | -                   | v     |

| Output High Voltage                                                            |                  |                                             |                      |     |                     |       |

| PA0-7, PB0-7, PC0-7, TCMP                                                      | V <sub>OH</sub>  | I <sub>LOAD</sub> = -0.2mA                  | V <sub>DD</sub> -0.3 | -   | -                   | v     |

| PD1-4                                                                          | V <sub>OH</sub>  | I <sub>LOAD</sub> = -0.4mA                  | V <sub>DD</sub> -0.3 | •   | -                   | v     |

| Output Low Voltage<br>PA0-7, PB0-7, PC0-7, PD1-4, TCMP                         | V <sub>OL</sub>  | I <sub>LOAD</sub> = 0.4mA                   | -                    | •   | 0.3                 | v     |

| Input High Voltage, PA0-7, PB0-7, PC0-7, PD0-5,<br>PD7, TCAP, IRQ, RESET, OSC1 | VIH              |                                             | 0.7•V <sub>DD</sub>  | -   | V <sub>DD</sub>     | v     |

| Input Low Voltage, PA0-7, PB0-7, PC0-7, PD0-5,<br>PD7, TCAP, IRQ, RESET, OSC1  | V <sub>IL</sub>  |                                             | V <sub>SS</sub>      | Ŧ   | 0.2•V <sub>DD</sub> | v     |

| Data Retention Mode                                                            | V <sub>RM</sub>  | $T_A = 0^{\circ}C$ to $+70^{\circ}C$        | 2                    | -   | -                   | v     |

| Supply Current (3.6V <sub>DC</sub> at f <sub>OSC</sub> = 2MHz)                 |                  |                                             |                      |     |                     |       |

| Run                                                                            | IDD              |                                             |                      | •   | 1.75                | mA    |

| WAIT                                                                           | I <sub>DD</sub>  |                                             | -                    | •   | 900                 | μA    |

| STOP                                                                           | I <sub>DD</sub>  | T <sub>A</sub> = 25°C                       | - 1                  | -   | 5                   | μA    |

|                                                                                |                  | $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$ | •                    | •   | 10                  | μA    |

| Supply Current (2.4V <sub>DC</sub> at f <sub>OSC</sub> = 1MHz)                 |                  |                                             |                      | *** |                     |       |

| Run                                                                            | I <sub>DD</sub>  |                                             |                      | -   | 750                 | μA    |

| WAIT                                                                           | I <sub>DD</sub>  |                                             | -                    |     | 400                 | μΑ    |

| STOP                                                                           | IDD              | T <sub>A</sub> = 25°C                       | -                    | -   | 2.0                 | μA    |

|                                                                                |                  | $T_A = 0^{\circ}C$ to $+70^{\circ}C$        | -                    | -   | 5.0                 | μΑ    |

| I/O Ports Hi-Z Leakage Current<br>PA0-7, PB0-7, PC0-7, PD1-4                   | կլ               |                                             | -                    | -   | ±1                  | μА    |

| Input Current<br>RESET, IRQ, TCAP, OSC1, PD0, PD5, PD7                         | I <sub>IN</sub>  |                                             | -                    | -   | ±1                  | μА    |

| Capacitance Ports (As Input or Output)                                         | С <sub>олт</sub> |                                             | -                    | -   | 12                  | pF    |

| RESET, IRQ, TCAP, OSC1, PD0-5, PD7                                             | CIN              |                                             |                      | +   | 8                   | pF    |

NOTES:

1. All values shown reflect average measurement.

2. Typical values at midpoint of voltage range, 25°C only.

3. WAIT IDD: Only timer system active (SPE = TE = RE = 0). If SPI, SCI active (SPE = TE = RE = 1) add 10% current draw.

Run (Operating) I<sub>DD</sub>, WAIT I<sub>DD</sub>: Measured using external square-wave clock source, all inputs 0.2V from rail, no DC loads, less than 50pF on all outputs, C<sub>L</sub> = 20pF on OSC2.

5. WAIT, STOP I<sub>DD</sub>: All ports configured as inputs, V<sub>IL</sub> = 0.2V, V<sub>IH</sub> = V<sub>DD</sub> -0.2V.

6. STOP I<sub>DD</sub> measured with OSC1 = V<sub>SS</sub>.

7. WAIT  $I_{\mbox{\scriptsize DD}}$  is affected linearly by the OSC2 capacitance.

| PARAMETER                                                              | SYMBOL                            | MIN      | MAX | UNITS |

|------------------------------------------------------------------------|-----------------------------------|----------|-----|-------|

| Frequency Of Operation                                                 |                                   |          |     |       |

| Crystal Option                                                         | fosc                              | -        | 4.2 | MHz   |

| External Clock Option                                                  | fosc                              | DC       | 4.2 | MHz   |

| Internal Operating Frequency                                           |                                   |          |     |       |

| Crystal (f <sub>OSC</sub> + 2)                                         | f <sub>OP</sub>                   | •        | 2.1 | MHz   |

| External Clock(f <sub>OSC</sub> + 2)                                   | fop                               | DC       | 2.1 | MHz   |

| Cycle Time (See Figure 11)                                             | tсус                              | 480      | •   | ns    |

| Crystal Oscillator Start-up Time for AT-cut Crystal (See Figure 11)    | toxov                             | •        | 100 | ms    |

| Stop Recovery Start-up Time (AT-cut Crystal Oscillator) (See Figure 1) | t <sub>ILCH</sub>                 | -        | 100 | ms    |

| RESET Pulse Width (See Figure 11)                                      | t <sub>RL</sub>                   | 1.5      | -   | tcyc  |

| Timer                                                                  |                                   |          |     |       |

| Resolution (Note 2)                                                    | t <sub>RES</sub>                  | 4        | -   | tcyc  |

| Input Capture Pulse Width (See Figure 2)                               | t <sub>TH</sub> , t <sub>TL</sub> | 125      | -   | ns    |

| Input Capture Pulse Period (See Figure 2)                              | t <sub>TLTL</sub>                 | (Note 3) | •   | tcyc  |

| Interrupt Pulse Width Low (Edge-Triggered) (See Figure 14)             | t <sub>iLIH</sub>                 | 125      | -   | ns    |

| Interrupt Pulse Period (See Figure 14)                                 | ţ                                 | (Note 1) | -   | tcyc  |

| OSC1 Pulse Width                                                       | toH, toL                          | 90       | •   | ns    |

#### Specifications CDP68HCL05C4, CDP68HCL05C8

NOTES:

1. The minimum period t<sub>ILIL</sub> should not be less than the number of cycle times it takes to execute the interrupt service routine plus 21 t<sub>CYC</sub>.

2. Since a 2-bit prescaler in the timer must count four internal cycles (t<sub>CYC</sub>), this is the limiting minimum factor in determining the timer resolution.

3. The minimum period t<sub>TLTL</sub> should not be less than the number of cycle times it takes to execute the capture interrupt service routine plus 24 t<sub>CYC</sub>.

Control Timing V<sub>DD</sub> = 2.4V - 3.6V, V<sub>SS</sub> = 0V, T<sub>A</sub> = 0°C to +70°C, Unless Otherwise Specified.

| PARAMETER                                                              | SYMBOL                            | 3.6\     | / <sub>DC</sub> | 2.4      | VDC |                  |

|------------------------------------------------------------------------|-----------------------------------|----------|-----------------|----------|-----|------------------|

| PARAMETER                                                              | STMBUL                            | MIN      | MAX             | MIN      | MAX |                  |

| Frequency Of Operation                                                 |                                   |          |                 |          |     | 1                |

| Crystal Option                                                         | fosc                              | -        | 2.0             | -        | 1.0 | MHz              |

| External Clock Option                                                  | fosc                              | DC       | 2.0             | DC       | 1.0 | MHz              |

| Internal Operating Frequency                                           |                                   |          |                 |          |     |                  |

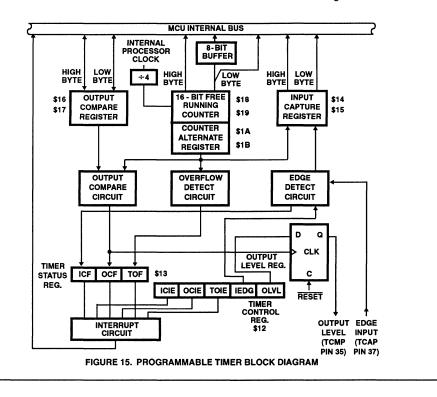

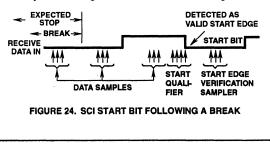

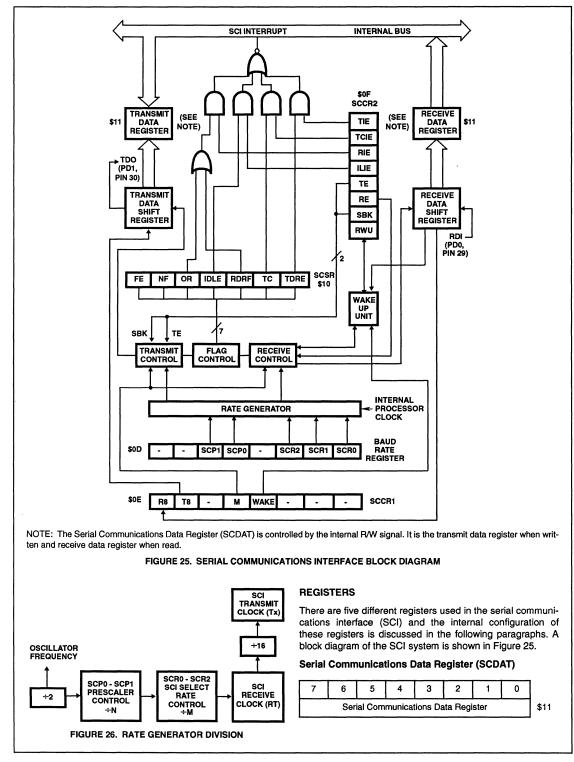

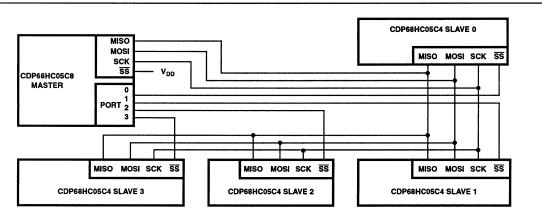

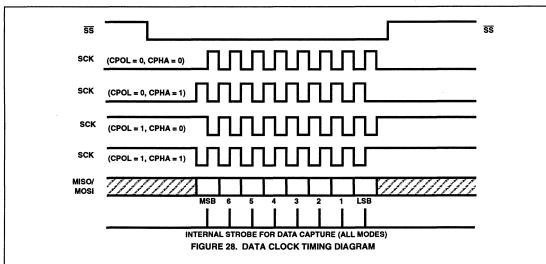

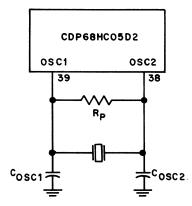

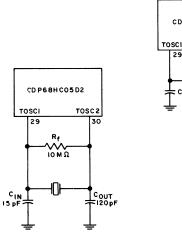

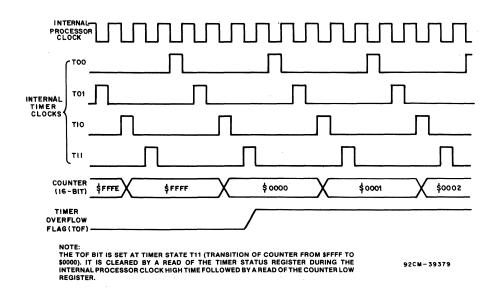

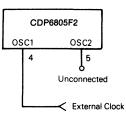

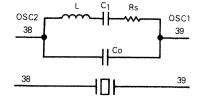

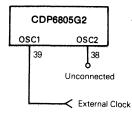

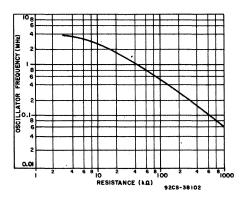

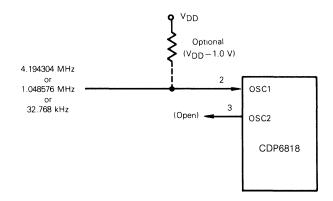

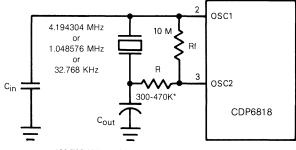

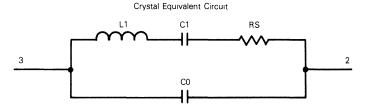

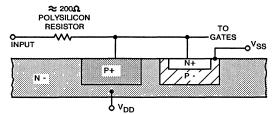

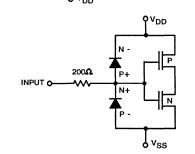

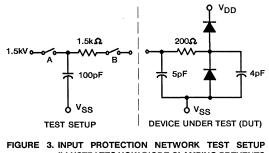

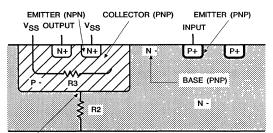

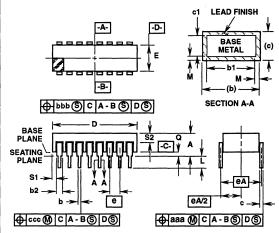

| Crystal (f <sub>OSC</sub> + 2)                                         | f <sub>OP</sub>                   | -        | 1.0             | -        | 0.5 | MHz              |