# 1976

SENERAL INSTRUMENT CORPORATION

# **MOS DATA 1976** • SECTIONS

5

10

| GENERA | ΔIII | VIEUBIN | MOITA | /INDEX |

|--------|------|---------|-------|--------|

**CALCULATORS**

**CLOCKS/CLOCK RADIOS**

RADIO/TELEVISION/TV GAMES

**ELECTRONIC ORGANS/FREQUENCY DIVIDERS**

**APPLIANCE TIMERS**

**TELECOMMUNICATIONS**

DATA COMMUNICATIONS

**COUNTERS/DIGITAL METERS**

**MICROPROCESSORS**

RANDOM ACCESS MEMORIES

**ELECTRICALLY ALTERABLE READ ONLY MEMORIES**

**READ ONLY MEMORIES**

KEYBOARD ENCODERS/CHARACTER GENERATORS

PACKAGE OUTLINES/SALES OFFICES

# GENERAL INSTRUMENT MICROELECTRONICS

# A TOTAL TECHNOLOGICAL SERVICE

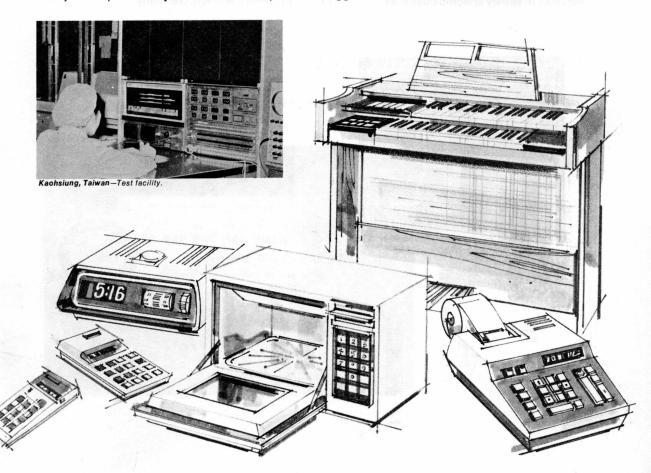

Hicksville, New York—Test area.

Hicksville, New York-Microelectronics World Headquarters.

General Instrument Microelectronics is one of the world's leading manufacturers of MOS (metal oxide semiconductor) LSI (large scale integration) products. A pioneer in MOS/LSI in 1966, General Instrument is now a worldwide supplier of volume microelectronic products.

GI has facilities in every major market, providing customers with the full spectrum of services: new product development... applications engineering support...circuit manufacturing.

# Strategically Located Plants

General Instrument operates four production facilities in the United States, Europe and the Far East. The plants at Glenrothes, Scotland; Chandler, Arizona and

Hicksville, New York have full capability for design, mask making, diffusion, assembly, test and quality assurance. The factory in Kaohsiung, Taiwan is specifically set up for high volume assembly, test, quality assurance and Far East applications assistance.

In addition to providing nearby sources of supply on three continents, each plant has a backup facility designated as an in-house second source to insure uninterrupted delivery. Common processes and equipment are employed and major product styles are always produced in at least two separate locations. To maintain uniform standards from plant to plant, the quality assurance group at each facility reports to a worldwide quality assurance director.

Because General Instrument has a comprehensive exposure to the world MOS market, it has been able to structure its facilities to conform to evolving customer needs. Production capabilities are concentrated in product areas of greatest volume. Furthermore, cost effectiveness is enhanced because import duties are saved on locally manufactured products.

# **Broad Product Lines**

General Instrument Microelectronics offers the widest range of standard LSI circuits in the industry. The company's off-the-shelf microcircuit portfolio consists of over 200 different MOS/LSI devices for a diversity of markets: consumer, calculator, tele – communications, and data management.

Chandler, Arizona-Electron Beam Evaporation.

As a leading supplier of consumer microelectronics, General Instrument manufactures MOS/LSI circuits for clocks, clock radios, TV tuners, remote control, appliance timers, radio and high fidelity systems. GI is a leading supplier of LSI for video games; the AY-3-8500 was the first single chip LSI product to provide six different games with on-screen scoring and realistic sound.

General Instrument is the largest independent manufacturer of microcircuits for hand held and printing calculators. The product selection ranges from the basic functions to advanced scientific and printing calculator LSI.

Glenrothes, Scotland-Assembly operation.

As an outgrowth of General Instrument Corporation's long experience in telecommunications, GI Microelectronics has introduced a series of standard telephone circuits for use in the conversion of telephone apparatus from electromechanical to all-electronic operation. These circuits are being sold to the independent producers of telephone equipment around the world.

This catalog not only contains an extensive range of products but offers the widest choice of circuits within each specific family. Note, for example, the microprocessor and memory product line. In addition to supplying ROMs and RAMs, General Instrument Microelectronics has introduced a major new product style. It's the EAROM,

or electrically alterable ROM, which combines the reprogrammability of the RAM with the non-volatility of the ROM. Further, GI's 4K Static RAM is particularly suited for use with microprocessors for data terminals and telecommunications.

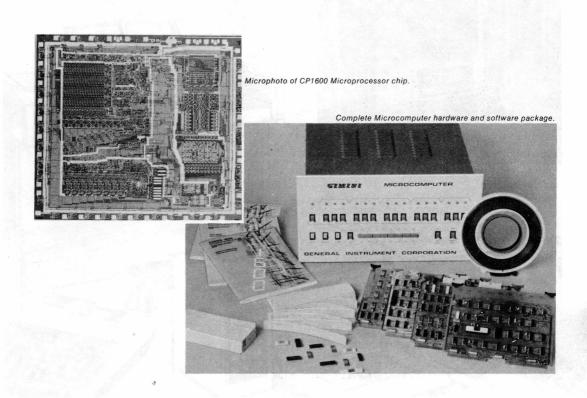

The CP1600 Microprocessor, which General Instrument developed jointly with Honeywell, is the world's most powerful 16 bit microprocessor. For the first time, the logic byte size, or computing power, of mini-computer hardware is made available in a single chip of silicon.

# **Continuing Cost Effectiveness**

General Instrument helps you to compete. Our high volume orientation, coupled with aggressive cost reduction, has made

possible products previously beyond the reach of the everyday consumer. The GI Mini-Pak, introduced for calculator and consumer products, provides a further saving in labor and material for the GI Microelectronics customer.

# **Advanced Design Centers**

MOS design and development centers are maintained at Glenrothes, Scotland; Hicksville, New York and Chandler, Arizona. Research and development for new processes and products are conducted at each of these locations.

# **Custom Design Services**

In addition to its extensive catalog of standard products, General Instrument Microelectronics provides custom design services to satisfy specific customer requirements. In some cases, the custom application is best served by software or firmware programming of a standard microprocessor. In other cases, a custom chip layout is more cost effective.

These services may be arranged through any of the Microelectronics sales offices.

# **Applications Assistance Around the Globe**

To provide the special applications assistance that customers may require, General Instrument Microelectronics maintains fully staffed Applications Centers at strategic locations around the world...

U.S.A.—Hicksville, New York / Chandler, Arizona

EUROPE—Glenrothes, Scotland / London, England / Munich, Germany

ASIA—Kaohsiung, Taiwan / Tokyo, Japan / Hong Kong

SOUTH AMERICA-Sao Paulo, Brazil

Arrangements can be made for immediate assistance from these centers by contacting any of the sales offices listed in this catalog.

# **Corporate Support**

General Instrument Microelectronics is backed by the full resources of the General Instrument Corporation, which has for over 50 years been among the leaders in the application of modern electronics to entertainment, industrial, military, data and communications systems. The skills,

production techniques and technological know-how of the entire General Instrument organization are utilized by GI Microelectronics to further improve its products and customer services.

Among the other electronic components manufactured by General Instrument are discrete semiconductors, relays, display devices and TV components. GI also produces CATV equipment, off-track and on-track wagering systems and equipment for defense applications.

Hicksville, New York-Pattern generator.

Hicksville, New York— Computer-aided design system.

# PART NUMBER INDEX

| NUMBER SE               |          | PAGE | NUMBER           | SECTION | PAGE | PART<br>NUMBER      | SECTION       | PAGE     |

|-------------------------|----------|------|------------------|---------|------|---------------------|---------------|----------|

| Α,                      | ECTION I | AGE  |                  | SECTION | FAGE | HOMBEN              |               |          |

| AY-1-0212               | 5        | 91   | AY-6-1013        | 8       | 145  | 1/01600 .           | 10            | 202      |

| AY-1-0212A              |          |      | AY-6-4016        | 8       | 154  | LP1000              | 10            | 216      |

| AY-1-1006               |          |      | C-583            | 2       | 21   |                     | 10            |          |

|                         | 5        |      |                  | 2       |      |                     | 10            |          |

| AY-1-1313               | 5        | 100  | C-589            | 2       | 23   | LP6000              |               |          |

| AY-1-2006               |          |      | C-593            | 2       | 24   | LP8000              | 10            | 216      |

| AY-1-5050               |          |      | C-594            | 2       | 25   | MC1600              | 10            | 203      |

| AY-1-5051               |          |      |                  | 2       |      | l.                  |               |          |

| AY-1-6721/5 AY-1-6721/6 | 5        | 100  |                  | 2       |      | MEM1056<br>MEM1056B | 9             |          |

|                         |          |      |                  | 2       |      |                     |               |          |

| AY-3-0214               |          |      |                  | 2       |      |                     | 10            |          |

| AY-3-0215               |          |      |                  | 2       |      | PIC1650 .           | 10            | 213      |

| AY-3-0216               |          |      | C-683D           |         |      | PM1600              | 10            | 204      |

| AY-3-1014A              |          |      | C-685<br>C-685D  | 2       |      | RA-3-4200           | 11            | 228      |

| AY-3-1015<br>AY-3-8500  |          |      | C-685D           |         |      | RA-3-4256           |               |          |

| AY-3-8500 AY-3-8500-1   |          |      | C-009D           |         |      | RA-3-4256A          |               |          |

| AY-3-9400               |          |      | C-717            |         |      | RA-3-4256E          | 3 11          | 224      |

| AY-3-9410               |          |      |                  | 2       |      | RA-3-4402           | 11            | 232      |

| AY-5-1013               |          |      |                  | 2       |      | RO-3-2513           | 14            | 299      |

| AY-5-1013<br>AY-5-1013A | 8        | 145  |                  |         |      |                     | 13            |          |

| AY-5-1016               | Ω        | 154  | CC1600           |         |      |                     | 13            |          |

| AY-5-1010 AY-5-1200A    | 3        | 36   | CF-583           |         |      | RO-3-5120           | 13            | 268      |

|                         | 3        |      | CF-585           |         |      | RO-3-8316A          | A 13          | 273      |

| AY-5-1203A              |          |      | CF-589           |         |      | RO-3-8316E          |               |          |

| AY-5-1204A              |          |      |                  | 2       |      | RO-3-9316/          |               |          |

| AY-5-1224A              |          |      | CF-594<br>CF-595 | 2<br>2  |      | RO-3-9316           |               |          |

| AY-5-1230               |          |      |                  | 2<br>2  |      | RO-3-16384          |               |          |

| AY-5-1315               | 5        | 102  |                  | 2       |      | RO-3-20480          |               |          |

| AY-5-1317A              | 5        | 104  | CF-599           | 2       | 29   | RO-5-1302           |               |          |

| AY-5-2376               |          |      |                  |         |      |                     | 3 14          |          |

| AY-5-3500               |          |      |                  | 2       |      | RO-5-5184           |               |          |

| AY-5-3507<br>AY-5-3510  |          |      | CK3000           | 3       | 41   | RO-5-8192           |               |          |

| AY-5-3600               |          |      | CK3100           |         |      | RO-6-1024           |               |          |

| AY-5-4007               | 9        | 172  | CK3200           |         |      | RO-6-1024           |               |          |

| AY-5-4007A              | 9        | 172  | CK3300           |         |      | RO-6-2048           |               |          |

| AY-5-4007D              | 9        | 172  | CK3400           | 3       | 46   | RO-6-2048           |               |          |

| AY-5-4057               | 9        | 178  | CP1600           | 10      | 192  | RO-7-1024           |               |          |

| AY-5-5053               |          |      | CP1600A .        |         |      | RO-7-1024           |               |          |

| AY-5-5054               | 9        | 186  | CT7000           |         |      | RO-7-2048/          |               |          |

| AY-5-8100               |          |      |                  |         |      | RO-7-2048           |               |          |

| AY-5-8101               |          |      | ER1105           | 12      | 238  | RM1600              | 10            | 205      |

| AY-5-8300               |          |      | ER1400           |         |      | RM1601              | 10            | 206      |

| AY-5-8302<br>AY-5-8310  |          | 1    | ER2050<br>ER2401 |         |      | S1600               | 10            | 207      |

| AY-5-8410               |          |      | ER2800           |         |      | SAA1024 .           | 4             | 66       |

| AY-5-8411               |          |      | ER3400           |         |      | SAA1025 .           |               |          |

| AY-5-8420               |          |      | GIMINI           |         |      | SAL1600 .           |               |          |

| AY-5-9100               |          |      |                  |         |      | 1                   |               |          |

| AY-5-9200               |          |      | GP1600           | 10      | 201  | SL Series           | Contact any   | GI Sales |

| AY-5-9300               | 7        | 130  |                  |         |      | SS Series           | Office for de | tails.   |

| AY-5-9500               | 7        | 134  |                  |         |      |                     |               |          |

| AY-5-9800               |          |      |                  |         |      |                     |               |          |

# **III** FUNCTIONAL INDEX

| CALCUL                | ATORS                                                                                                                                              |                   |              |                    |                 | Secti   | on 2        |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------|--------------------|-----------------|---------|-------------|

| Description           | Function                                                                                                                                           | 9V<br>Fluorescent | 9V LED       | 9V LED<br>(Direct) | 15V Fluorescent | 15V LED | PAGE<br>NO. |

|                       | 4 functions and percent key.                                                                                                                       | CF-683            | C-683        | C-683D             | CF-583          | C-583   | 21          |

| 8 DIGIT<br>BASIC      | 4 functions, percent key, one-key or multi-key memory.                                                                                             | CF-685            | C-685        | C-685D             | CF-585          | C-585   | 22          |

| 8 DIGIT<br>ALGEBRA    | 4 functions, percent key, x <sup>2</sup> , Jx, 1/x, +/-, one-ke choice of 20 to 29 keys.                                                           | y or multi-key m  | emory,       | C-689D             | CF-589          | C-589   | 23          |

|                       | 4 functions and percent key.                                                                                                                       |                   |              |                    | CF-593          | C-593   | 24          |

| 9 DIGIT<br>BASIC      | 4 functions, percent key, one-key memory.                                                                                                          | ,                 |              |                    | CF-594          | C-594   | 25          |

|                       | 4 functions, percent key, multi-key memory.                                                                                                        |                   |              |                    | CF-595          | C-595   | 26          |

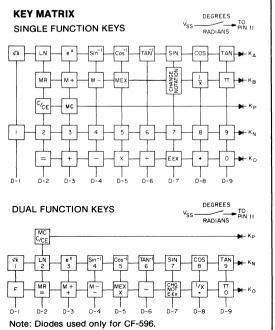

|                       | Basic 4 functions, scientific notation, 'sin, cos, to square root, pi, natural logs, 1/x, e³, memory exponent* range ±99, choice of 19 to 35 keys. |                   |              |                    | CF-596          | C-596   | 27          |

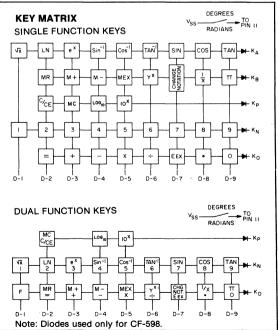

| 9 DIGIT<br>SCIENTIFIC | All the above plus: 0 to 10 <sup>®</sup> degree trig rang accuracy of transcendentals, choice of 21 to 3                                           |                   | , extended   | digit              | CF-598          | C-598   | 28          |

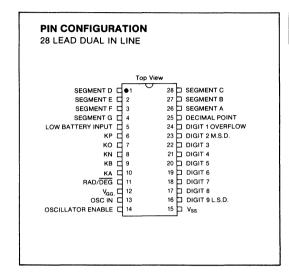

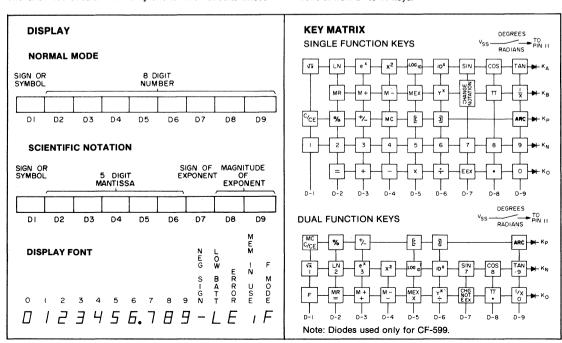

|                       | All the above plus: two levels of parenthesis,                                                                                                     | (², %, +/-, choic | e of 24 to 4 | 1 keys.            | CF-599          | C-599   | 29          |

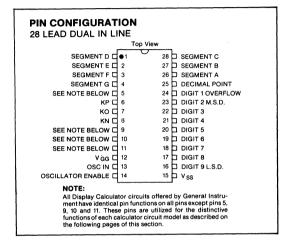

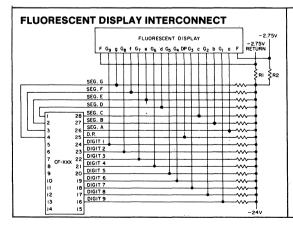

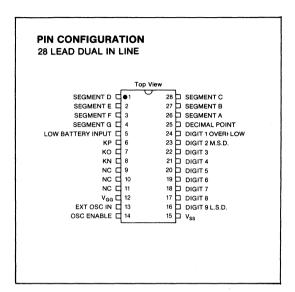

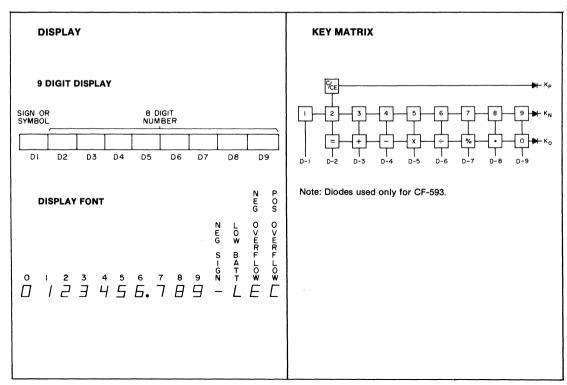

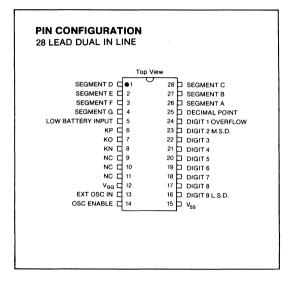

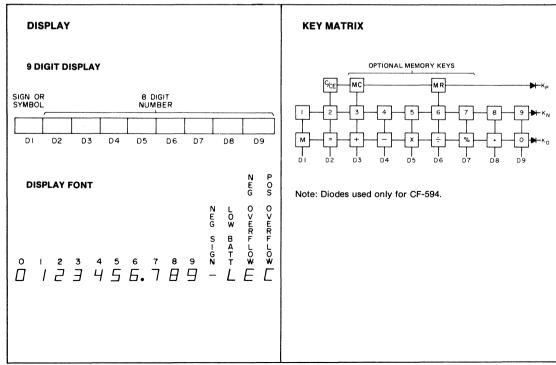

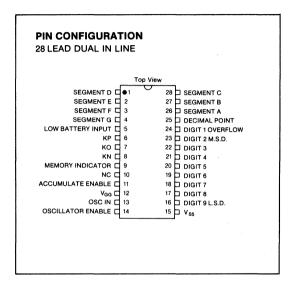

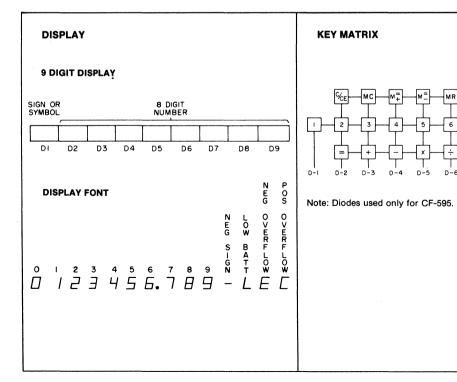

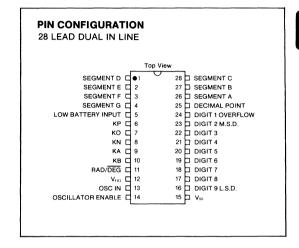

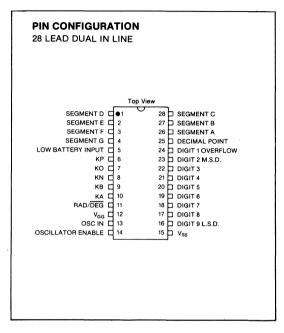

The C-500/C-600 series are pin-for-pin compatible chips designed to fit in the same basic PC board. All have automatic constant in 4 functions, floating decimal, on-board oscillator, single power supply, and drive LED segments or fluorescent displays directly. All are in a 28 lead DIP.

| DESCRIPTION                      | FUNCTION                                                                                                           | MEMORY<br>FUNCTION                                          | PART<br>NUMBER  | PACKAGE | FEATURES                               | PAGE<br>NO. |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------|---------|----------------------------------------|-------------|

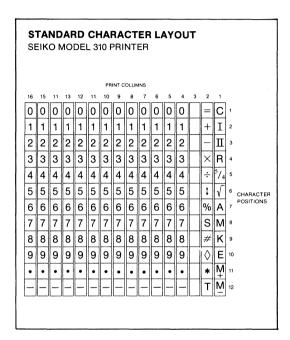

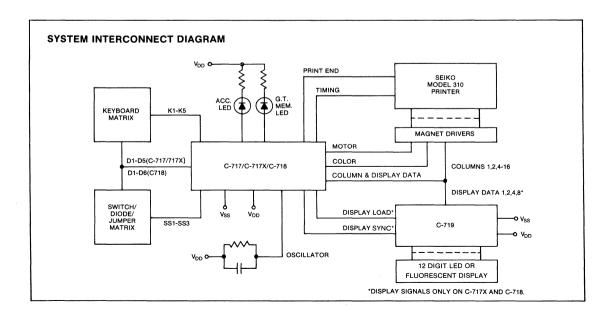

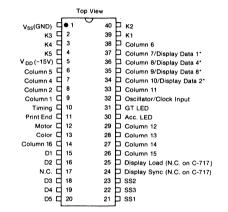

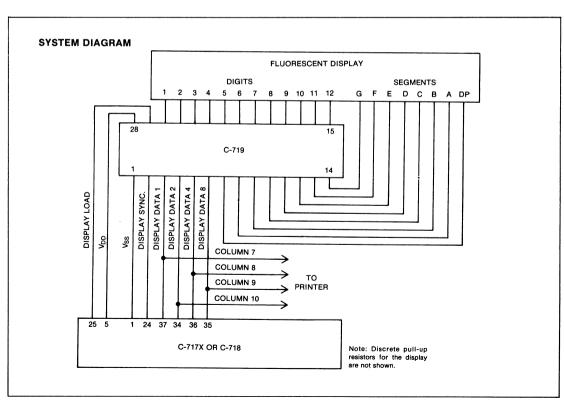

|                                  | Basic 4 functions and percent,<br>automatic constant in multiply<br>and divide, repeat add/subtract,               | Accumulator and<br>Grand Total<br>Memories                  | C-717<br>C-717X |         | Interfaces with the Shinshu            | 31          |

| 12 DIGIT<br>PRINTING             | decimal select mode, memory-in-<br>use indicator, rounding options,<br>non-add(#)/date key, and other<br>features. | Accumulator, item counter, and four-key independent memory. | *C-718          | 40 DIP  | Seiki Model 310 impact printer.        | 32          |

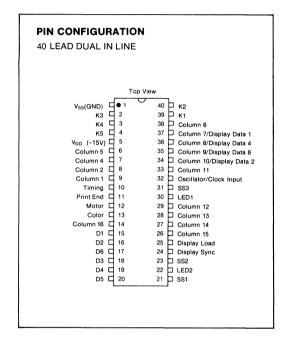

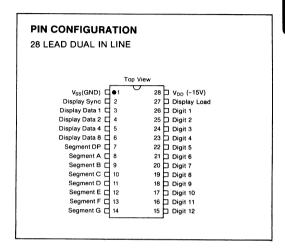

| PRINTER-<br>DISPLAY<br>INTERFACE | Adds display capability to the C-717X and C-718 printing calculator circuits.                                      | _                                                           | *C-719          | 28 DIP  | For both LED and fluorescent displays. | 33          |

\*For future release.

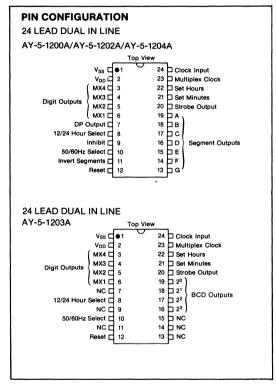

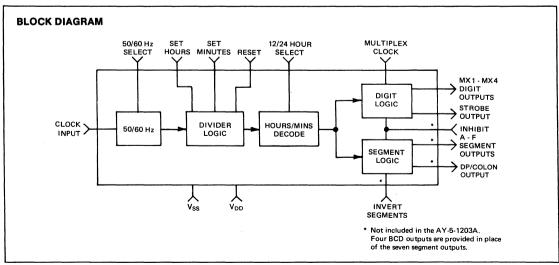

| DESCRIPTION                         | FUNCTION                     | PART<br>NUMBER          | DISPLAY TYPE             | FLASHING<br>SECONDS | ZERO<br>BLANKING | 50/60 Hz<br>OPERATION | PACKAGE                                | FEATURES                                                                                            | PAGE<br>NO. |

|-------------------------------------|------------------------------|-------------------------|--------------------------|---------------------|------------------|-----------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------|-------------|

|                                     |                              | AY-5-1200A              | 7-SEGMENT<br>FLUORESCENT |                     | 1                | -                     | 24 DIP                                 | Direct fluorescent display drive.                                                                   | 36          |

|                                     |                              | AY-5-1202A              | 7-SEGMENT<br>FLUORESCENT | 1                   | 1                | -                     | 24 DIP                                 | Direct fluorescent display drive.                                                                   | 36          |

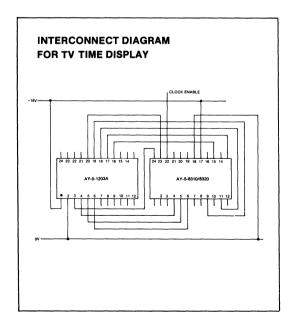

| 4 DIGIT                             | 12/24 hour<br>clock          | AY-5-1203A              | BCD OUTPUTS              | 1                   |                  | 1                     | 24 DIP                                 | See AY-5-8320<br>TV circuit.                                                                        | 36          |

|                                     |                              | AY-5-1204A              | 7-SEGMENT<br>FLUORESCENT | 1                   |                  | 1                     | 24 DIP                                 | Direct fluorescent display drive.                                                                   | 36          |

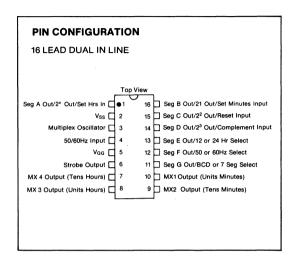

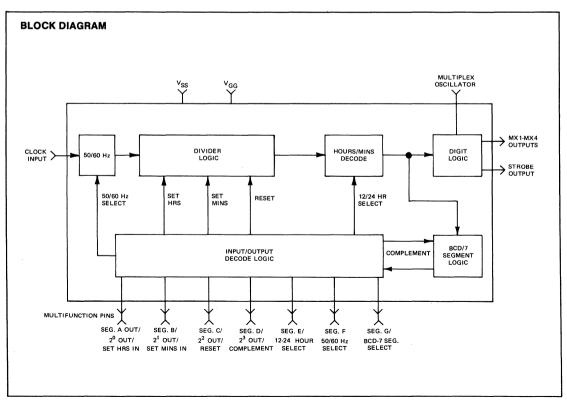

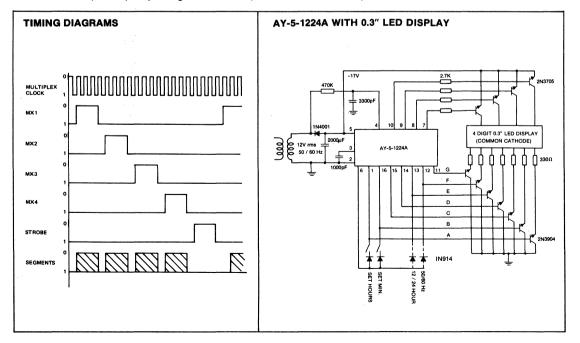

| A                                   | AY-5-1224A                   | BCD OR<br>7-SEGMENT LED |                          | 1                   | 1                | 16 DIP                | Zero blanking in<br>12 hour mode only. | 38                                                                                                  |             |

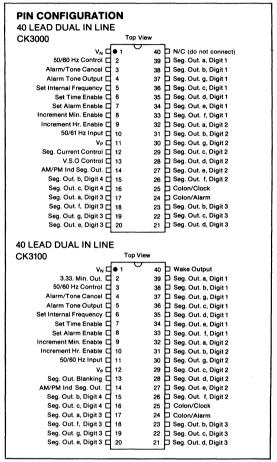

|                                     | 12 hour clock,               | CK3000                  | 7-SEGMENT PLASMA         | _                   | -                | -                     | 40 DIP                                 | Snooze alarm,<br>individual digit<br>drive.                                                         | 41          |

|                                     | 24 hour alarm                | CK3100                  | 7-SEGMENT LED            | 1                   | 1                | -                     | 40 DIP                                 | Snooze alarm;<br>individual digit<br>drive.                                                         | 41          |

| 4 DIGIT<br>WITH ALARM<br>AND DIRECT | 12/24 hour<br>clock, 24 hour | CK3200                  | 7-SEGMENT PLASMA         | -                   | -                |                       | 28 DIP                                 | Snooze alarm,<br>duplexed digits.                                                                   | 46          |

| DISPLAY DRIVE                       | alarm                        | CK3400                  | 7-SEGMENT LED            | <b>"</b>            | <b>1</b>         | 1                     | 28 DIP                                 | Snooze alarm,<br>duplexed digits.                                                                   | 46          |

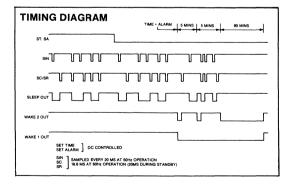

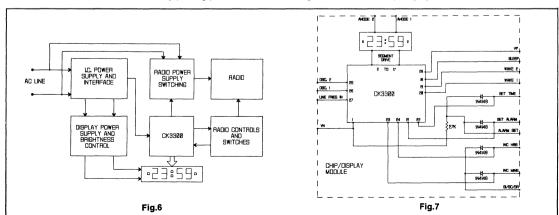

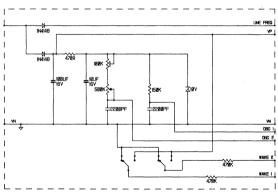

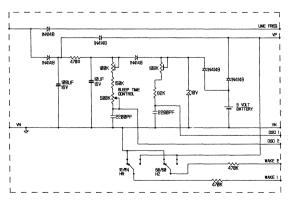

|                                     | 12/24 hour<br>clock radio    | CK3300                  | 7-SEGMENT LED            | 1                   | v                | ,                     | 28 DIP                                 | Snooze alarm,<br>duplexed digits,<br>sleeptimer, time-<br>switch, battery<br>standby<br>capability. | 52          |

# FUNCTIONAL INDEX

| RADIO / TEI                  | LEVISION / TV GA                                                                           | MES                      |                   |         | Section                                                                                                                                                                       | on 4        |

|------------------------------|--------------------------------------------------------------------------------------------|--------------------------|-------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION                  | FUNCTION                                                                                   | PART<br>NUMBER           | POWER<br>SUPPLIES | PACKAGE | FEATURES                                                                                                                                                                      | PAGE<br>NO. |

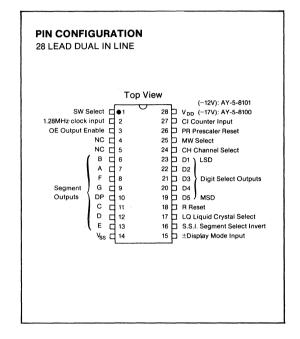

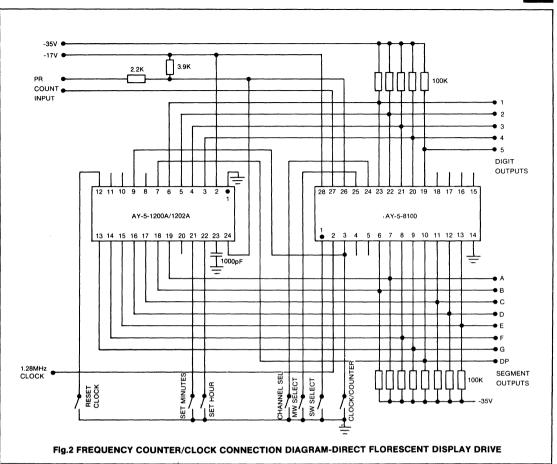

| RADIO RECEIVER               | Counts & displays MW, SW,                                                                  | AY-5-8100                | GND, -17          |         | 41/2 digit display; MW 2999 kHz, SW 29.995<br>MHz, VHF 299.95 MHz; 0 to 99 FM channel                                                                                         | -           |

| FREQUENCY<br>COUNTER/DISPLAY | and VHF frequencies                                                                        | AY-5-8101                | GND, -12          | 28 DIP  | indication (European standard), 7-segment outputs.                                                                                                                            | 72          |

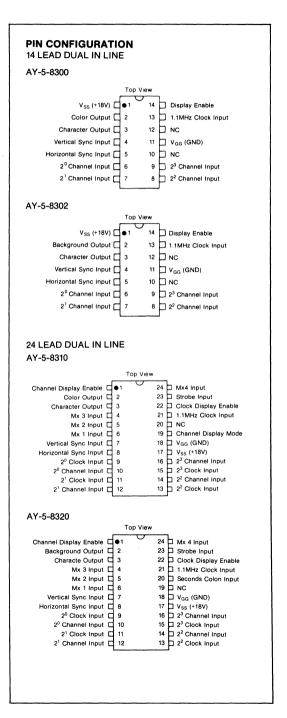

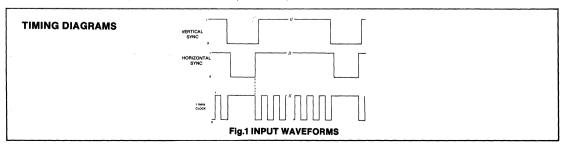

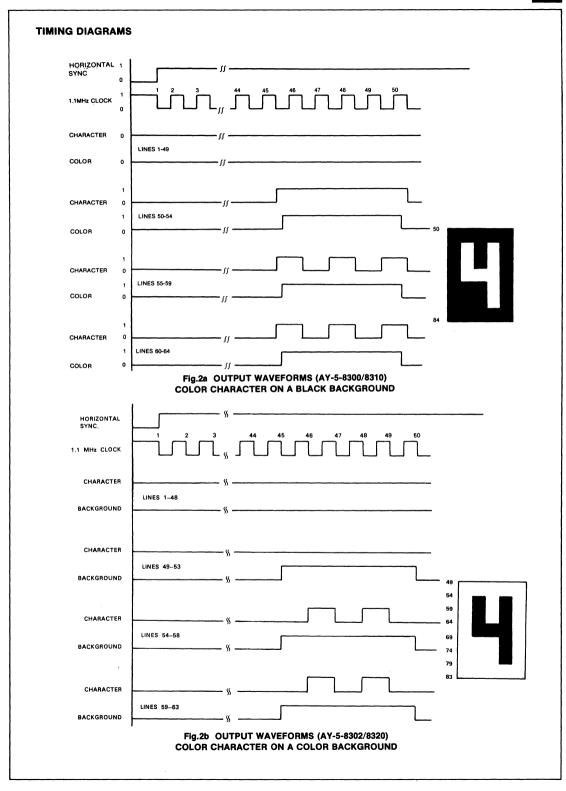

| TV CHANNEL                   | Displays channels 0—15 on TV screen.                                                       | AY-5-8300                | + 18. GND         | 14 DIP  | Display is positioned at top-right corner.<br>Capable of color numerals/black                                                                                                 | 76          |

| DISPLAY                      | Displays channels 1-16 on<br>TV screen                                                     | AY-5-8302                | 1 10, GND         | 14 017  | background. Automatic display recall.                                                                                                                                         | 70          |

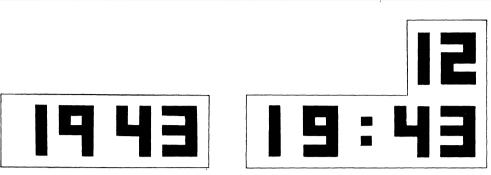

| TV CHANNEL/TIME              | Displays channels 0—15 or 00—99 or time on TV screen.                                      | AY-5-8310                | + 18. GND         | 24 DIP  | Display is positioned at top-right corner.<br>Capable of color numerats/black back-<br>ground and either separate (AY-5-8310) or<br>simultaneous (AY-5-8320) time and channel | 76          |

| DISPLAY                      |                                                                                            | AY-5-8320                | + 10, GIND        | 24 DIF  | display (see AY-5-1203A clock circuit), with flashing seconds and colon. Automatic display recall.                                                                            | /6          |

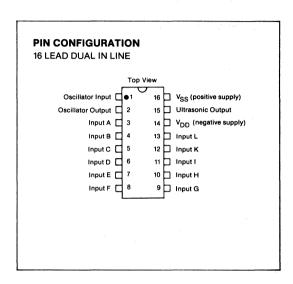

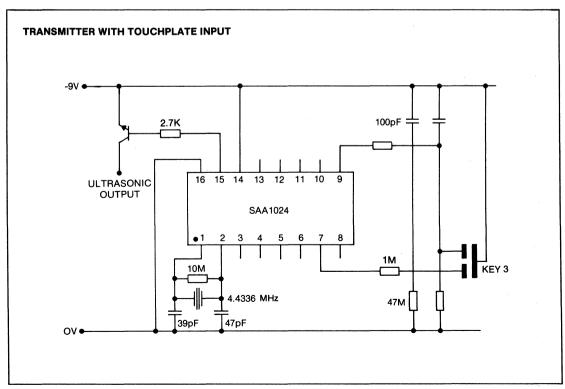

|                              | Transmitter                                                                                | SAA 1024                 | 9V<br>BATTERY     | 16 DIP  | 30 ultrasonic control channels, 34-44 kHz.<br>Utilizes a 4.4 MHz TV crystal for accuracy.                                                                                     | 66          |

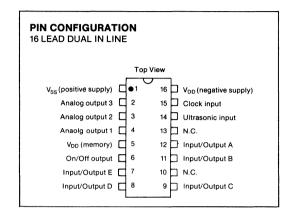

| TV REMOTE                    | Receiver                                                                                   | SAA 1025                 | SEE DATA<br>SHEET | 16 DIP  | Power on/off output, 16 TV channel selection (& 5 spares), brightness, saturation and volume analog outputs.                                                                  | 68          |

| CONTROL                      | Transmitter                                                                                | *AY-5-8410               | GND, -15          | -       | 23 channels, either local control                                                                                                                                             | 82          |

|                              | Transmitter                                                                                | *AY-5-8411               | 9V BATTERY        | -       | at receiver or remote control.                                                                                                                                                | 02          |

|                              | Receiver                                                                                   | *AY-5-8420               | GND, -15          | -       | 63 channels with error-detection.                                                                                                                                             | 83          |

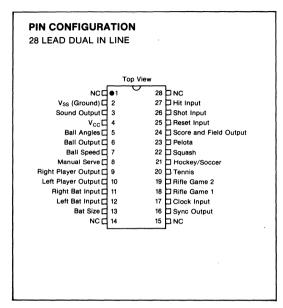

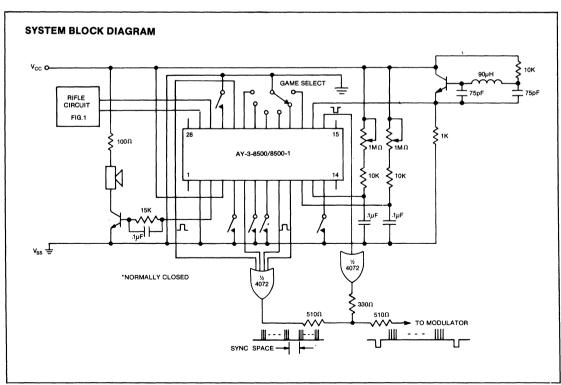

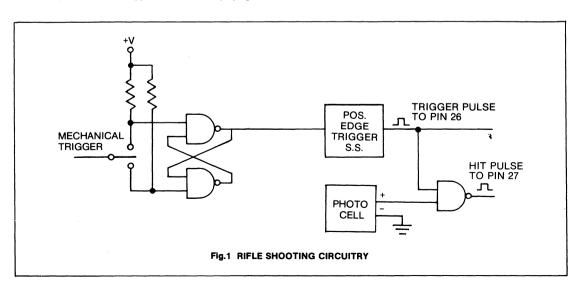

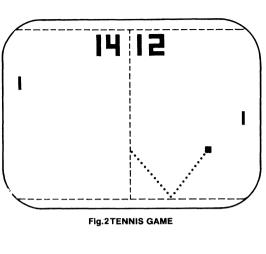

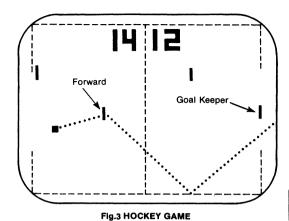

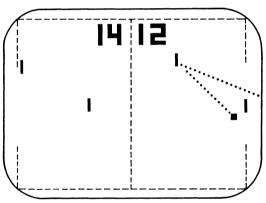

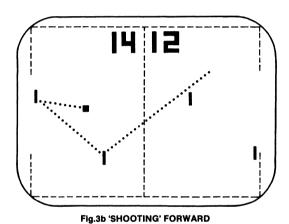

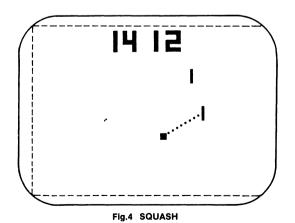

| TV GAMES                     | Add-on for TV sets. 6 games: tennis, squash, hockey (soccer), pelota, rifle shooting 1 & 2 | AY-3-8500<br>AY-3-8500-1 | 9V<br>BATTERY     | 24 DIP  | 3 two-person and 3 one-person games.<br>Automatic scoring (displayed on TV screen),<br>realistic sounds, visually defined playing<br>area, 525 and 625 line standards.        | 84          |

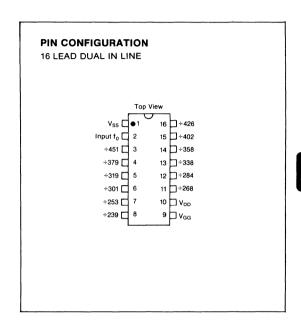

| ELECTRO                         | NIC ORGANS / FF                                       | REQUEN         | CY DIVID             | ERS               |         | Section                                                                   | on 5        |

|---------------------------------|-------------------------------------------------------|----------------|----------------------|-------------------|---------|---------------------------------------------------------------------------|-------------|

| DESCRIPTION                     | FUNCTION                                              | PART<br>NUMBER | MAXIMUM<br>FREQUENCY | POWER<br>SUPPLIES | PACKAGE | FEATURES                                                                  | PAGE<br>NO. |

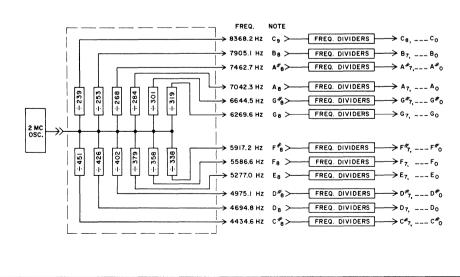

| MASTER<br>FREQUENCY             | Generates a complete octave                           | AY-1-0212      | 1.5 MHz              | +12. GND          | 16 DIP  | 250 kHz minimum                                                           | 91          |

| GENERATOR                       | of musical frequencies                                | AY-1-0212A     | 2.5 MHz              | + 12, GND         | 16 DIP  | frequency                                                                 | 91          |

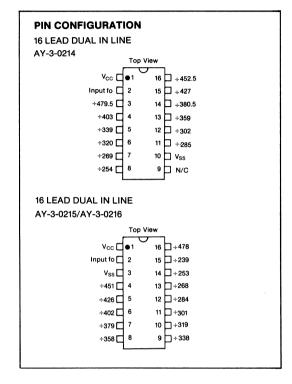

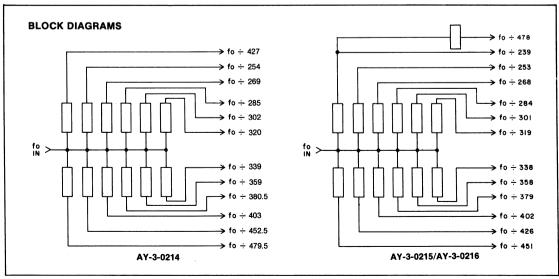

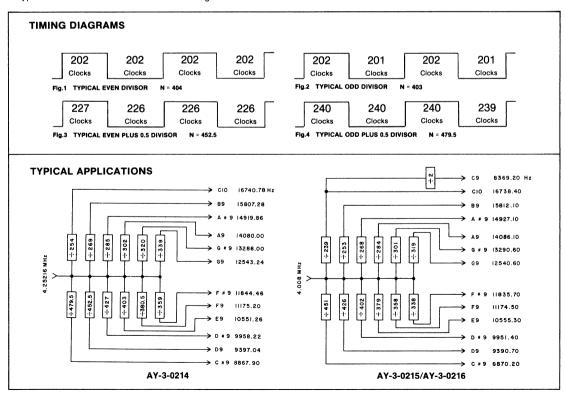

|                                 |                                                       | AY-3-0214      |                      |                   |         | 12 outputs, 50% duty cycle                                                |             |

| TOP OCTAVE<br>GENERATOR         | Generates top octave scale                            | AY-3-0215      | 4.5 MHz              | + 10 to + 16, GND | 16 DIP  | 13 outputs, 50% duty cycle                                                | 94          |

|                                 |                                                       | AY-3-0216      |                      |                   |         | 13 outputs, 30% duty cycle                                                |             |

| PRIORITY<br>LATCHING<br>NETWORK | Establishes priority level of 13 latch inputs/outputs | AY-1-1313      | 20 kHz               | GND, -12, -27     | 40 DIP  | Stackable for expanded latching/priority function.                        | 100         |

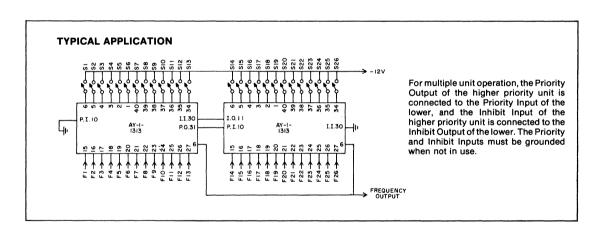

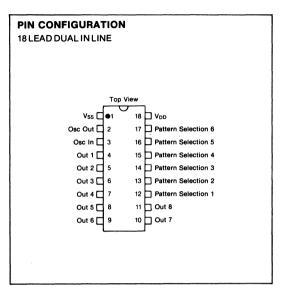

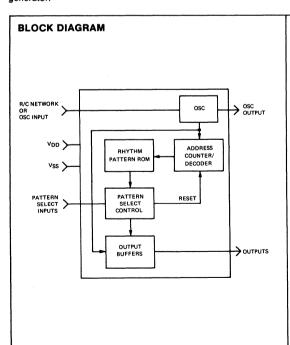

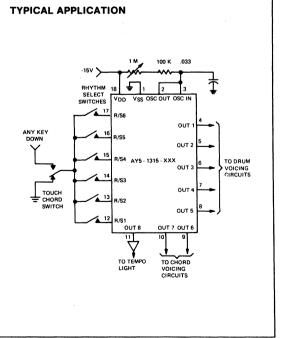

| RHYTHM<br>GENERATOR             | Generates 6 rhythms. drives<br>8 instruments          | AY-5-1315      | 10 kHz               | GND, -15          | 18 DIP  | Resets for coupling chords to rhythm. 32 beat pattern. Mask programmable. | 102         |

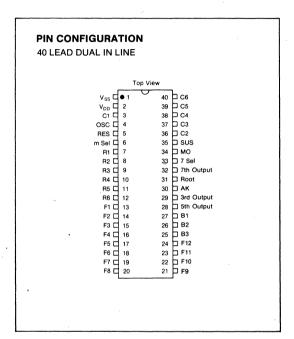

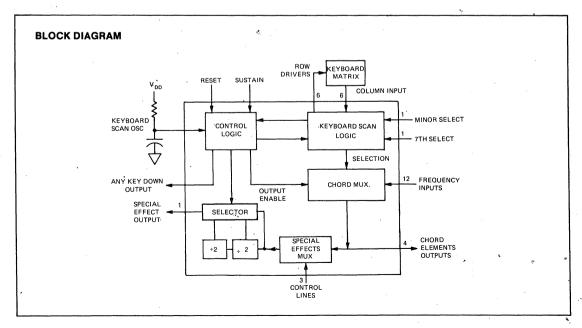

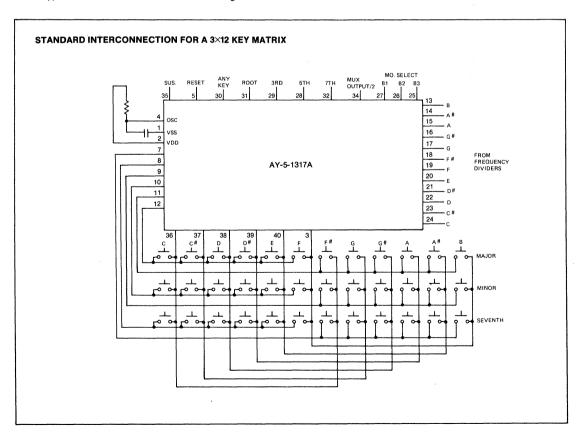

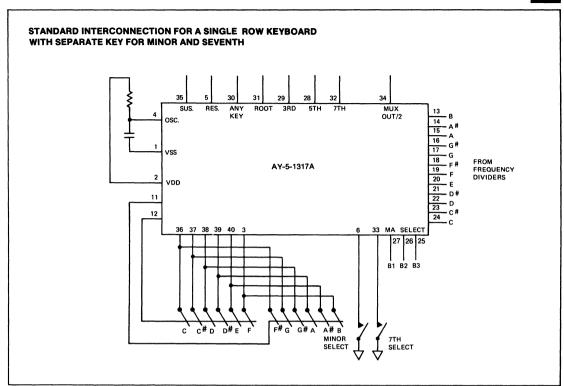

| CHORD<br>GENERATOR              | Produces major, minor, 7th chords, walking bass       | AY-5-1317A     | 50 kHz               | GND, -15          | 40 DIP  | Mixed outputs, sustain, top<br>key priority                               | 104         |

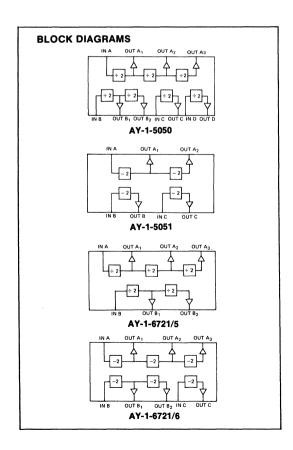

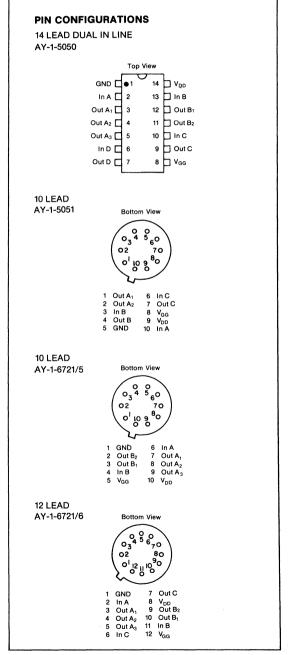

|                                 | 4 stage                                               | AY-1-5051      | 1 MHz                | GND, -13, -27     | 10 TO   | Arranged 2+1+1                                                            | 108         |

|                                 | 5 stage                                               | AY-1-6721/5    | 1 MHz                | GND, -13, -27     | 10 TO   | Arranged 3+2                                                              | 108         |

|                                 |                                                       | AY-1-6721/6    | 1 MHz                | GND, -13, -27     | 12 TO   | Arranged 3+2+1                                                            | 108         |

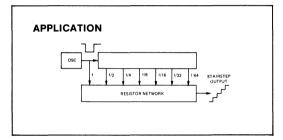

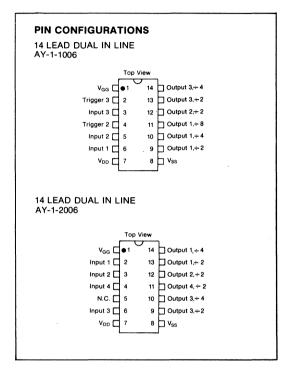

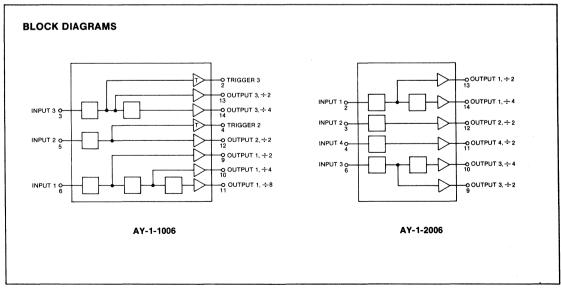

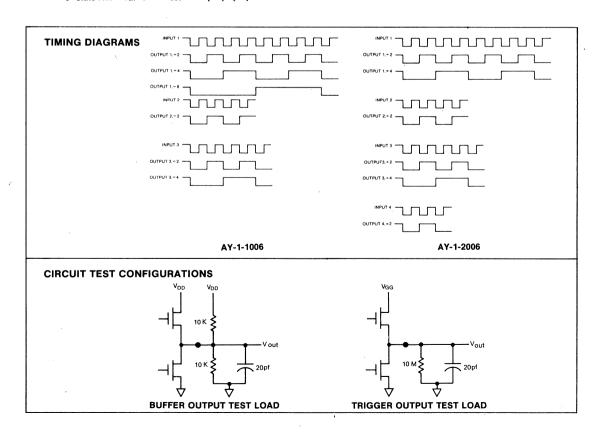

| FREQUENCY<br>DIVIDERS           | 6 stage                                               | AY-1-1006      | 50 kHz               | GND, -12, -27     | 14 DIP  | Arranged 3+2+1                                                            | 96          |

| DIVIDENS                        |                                                       | AY-1-2006      | 50 kHz               | GND, -12, -27     | 14 DIP  | Arranged 2+2+1+1                                                          | 96          |

|                                 |                                                       | AY-1-5050      | 1 MHz                | GND, -13, -27     | 14 DIP  | Arranged 3+2+1+1                                                          | 108         |

|                                 | 7 stage                                               | AY-1-1007B     | 50kHz                | GND, -12, -27     | 14 DIP  | Arranged 3+2+1+1,<br>power-on reset                                       | 98          |

| APPLIANC            | E TIMERS                                                                      |                |                   |         | Sect                                                                                                                                                          | on 6        |

|---------------------|-------------------------------------------------------------------------------|----------------|-------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION         | FUNCTION                                                                      | PART<br>NUMBER | POWER<br>SUPPLIES | PACKAGE | FEATURES                                                                                                                                                      | PAGE<br>NO. |

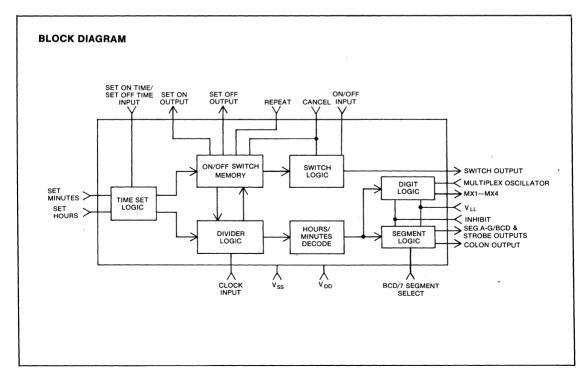

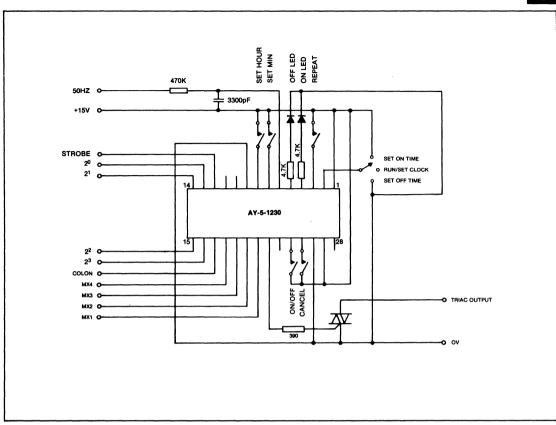

| CLOCK TIMER         | 24 hour programmable,<br>repeatable on/off time switch<br>with 24 hour clock. | AY-5-1230      | GND, -17          | 28 DIP  | 50 Hz input (60 Hz option on request), BCD or 7-segment direct fluorescent display drive outputs, zero blanking, 24 hour display (12 hour option on request). | 112         |

| COUNT-DOWN<br>TIMER | Keyboard programmable count-down timer with 99 min/99 sec capability.         | *CT 7000       | GND, -15          | 40 DIP  | 60 Hz input, drives 4 digit display, end-of-<br>count audio output.                                                                                           | 116         |

# **■ FUNCTIONAL INDEX**

| TELECO                                         | MMUNICATIO                                                | NS             |                   |                     | Secti                                                                                       | on 7        |

|------------------------------------------------|-----------------------------------------------------------|----------------|-------------------|---------------------|---------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION                                    | FUNCTION                                                  | PART<br>NUMBER | POWER<br>SUPPLIES | PACKAGE             | FEATURES                                                                                    | PAGE<br>NO. |

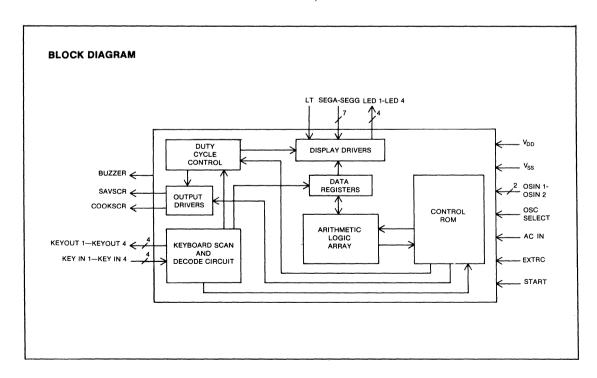

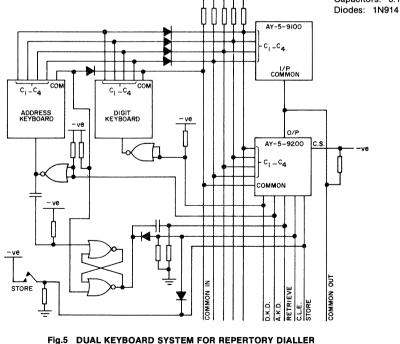

| PUSH BUTTON<br>TELEPHONE<br>DIALLER<br>CIRCUIT | Converts push button input to rotary dial pulses          | AY-5-9100      | SEE DATA SHEET    | 18 DIP              | Programmable timing, one-call memory, optional re-<br>dial and access pause capability.     | 120         |

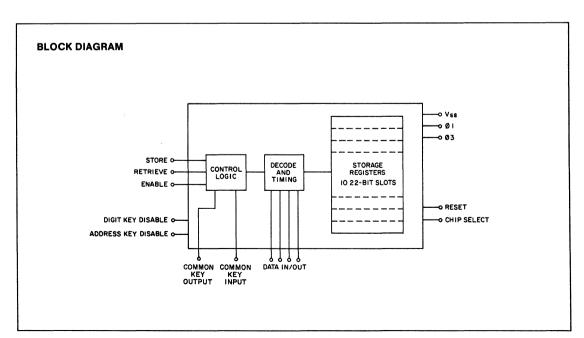

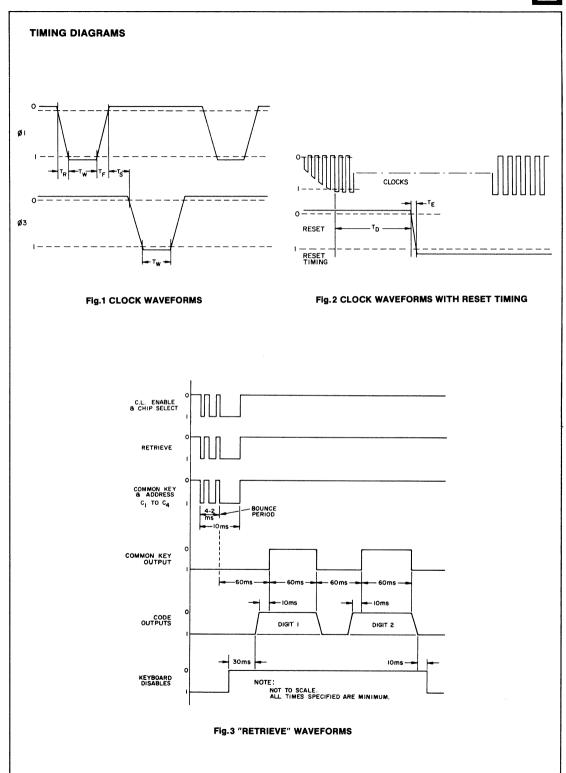

| REPERTORY<br>DIALLER                           | Stores ten telephone numbers                              | AY-5-9200      | SEE DATA SHEET    | 16 DIP              | Complements AY-5-9100 to enable storage of up to ten 22-digit telephone numbers. Stackable. | 124         |

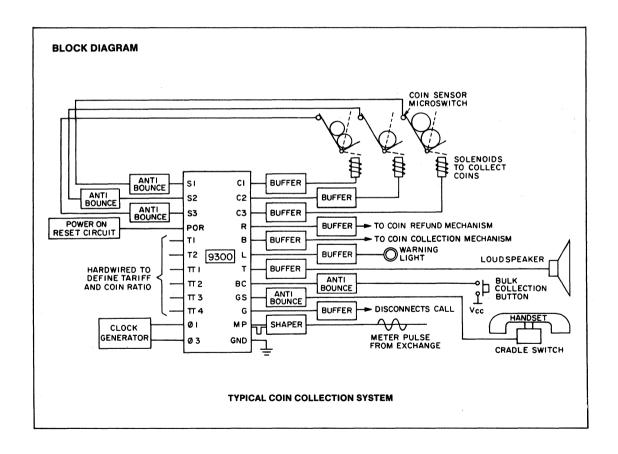

| COINBOX<br>CIRCUIT                             | Controls the operation of a standard pay telephone        | AY-5-9300      | SEE DATA SHEET    | 24 DIP              | Up to 3 coin denominations recognized. 16 selectable coin value ratios.                     | 130         |

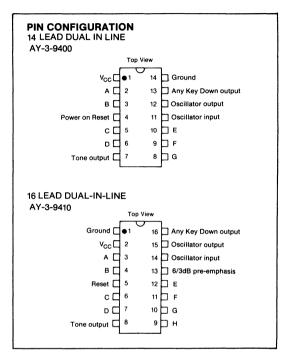

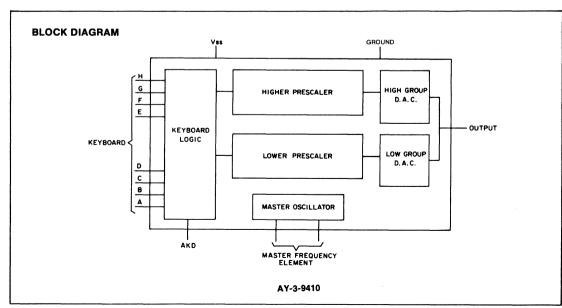

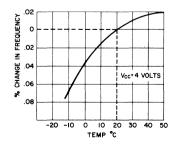

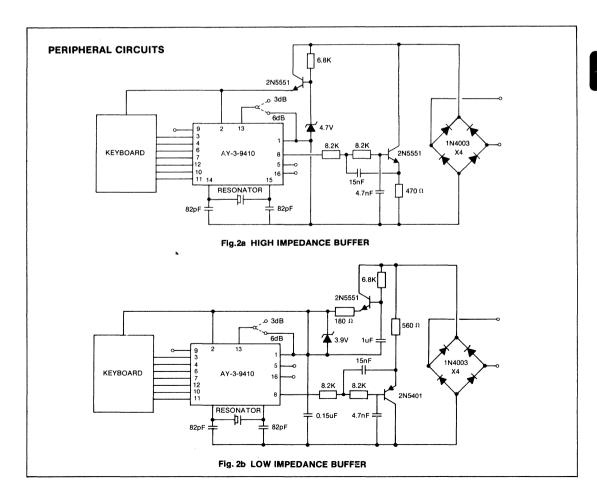

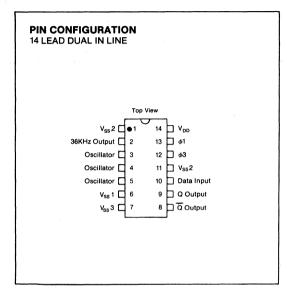

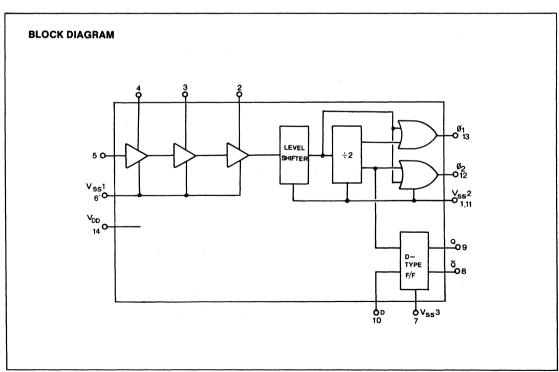

| DUAL TONE<br>MULTI-                            | Generates MF/tone                                         | AY-3-9400      | +5, GND           | 14 DIP              | With a low cost ceramic resonator, generates 12 tone pairs.                                 | 131         |

| FREQUENCY<br>GENERATOR                         | telephone frequencies                                     | AY-3-9410      | +5, GND           | 16 DIP              | Same as AY-3-9400 but generates 16 tone pairs for data transmission.                        | 131         |

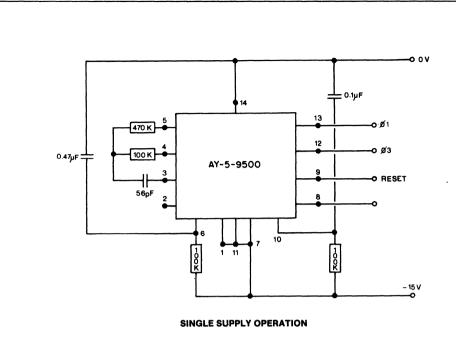

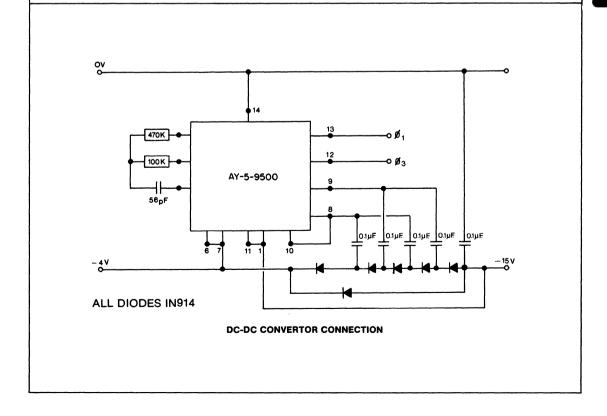

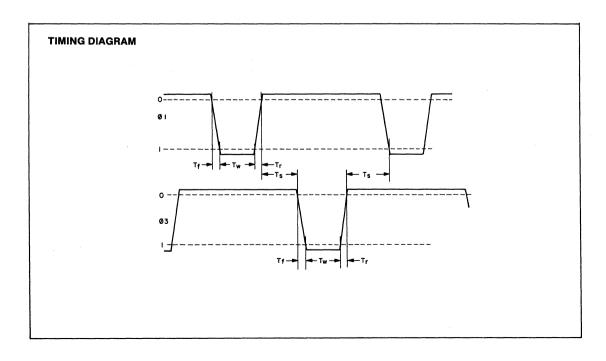

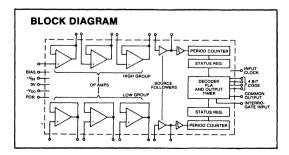

| C-MOS CLOCK<br>GENERATOR                       | Generates 2-phase clocks from a single power supply       | AY-5-9500      | SEE DATA SHEET    | 14 DIP              | Generates 2-phase clocks for AY-5-9100 & AY-5-9200.                                         | 134         |

| MULTI-<br>FREQUENCY<br>RECEIVER                | Detects and converts<br>MF/Tone telephone<br>frequencies. | *AY-5-9800     | SEE DATA SHEET    | 28 DIP or<br>40 DIP | Many programmable features provide wide applications.                                       | 137         |

| DATA CO               | MMUNIC                                           | ATIONS                 |                           |               |               |                |                   |         | Sectio                    | n 8         |

|-----------------------|--------------------------------------------------|------------------------|---------------------------|---------------|---------------|----------------|-------------------|---------|---------------------------|-------------|

| DESCRIPTION           | FUNCTION                                         | PART<br>NUMBER         | REPLACES<br>(PIN-FOR-PIN) | BAUD<br>RANGE | MAX.<br>FREQ. | TEMP.<br>RANGE | POWER<br>SUPPLIES | PACKAGE | FEATURES                  | PAGE<br>NO. |

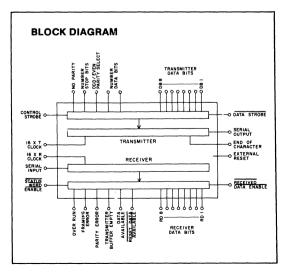

|                       |                                                  | *AY-3-1015             |                           | 0 to 30 kb    | 480 kHz       | 0 to 70        | +5, GND           | 40 DIP  | 1, 1.5, or 2<br>stop bits | 149         |

|                       | Complete 5-8                                     | †AY-6-1013             | AMI S1757<br>SIG 2536     | 0 to 20 kb    | 320 kHz       | -55 to +125    |                   |         | ·                         |             |

| UAR/T®                | bit serial/<br>parallel,                         | AY-5-1013              | SMC COM2505<br>TITMS6011  | 0 to 30 kb    | 480 kHz       | 0 to 70        | +5, GND,<br>-12   | 40 DIP  | 1 or 2 stop bits          | 145         |

|                       | parallel/serial<br>interface                     | AY-5-1013A             | WD TR1402A<br>WD TR1602A  | 0 to 40 kb    | 640 kHz       | 0 to 70        |                   |         |                           |             |

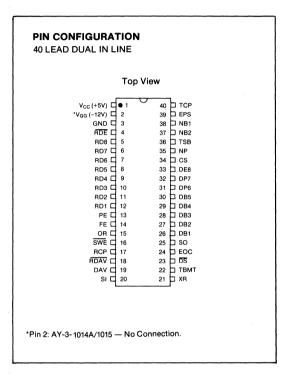

|                       |                                                  | *AY-3-1014A            |                           | 0 to 30 kb    | 480 kHz       | 0 to 70        | +5, GND           | 40 DIP  | 1, 1.5, or 2<br>stop bits | 149         |

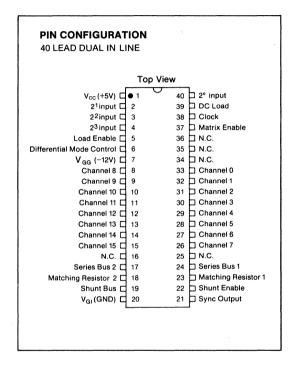

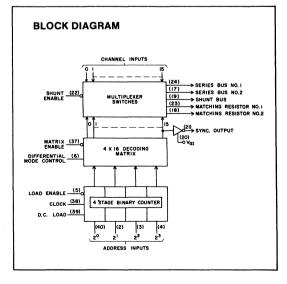

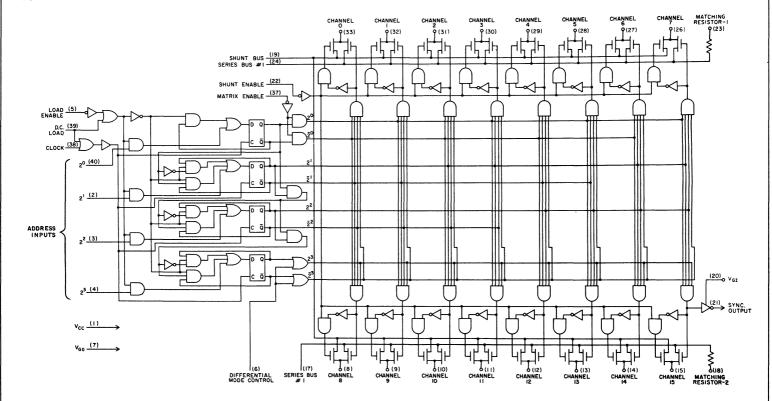

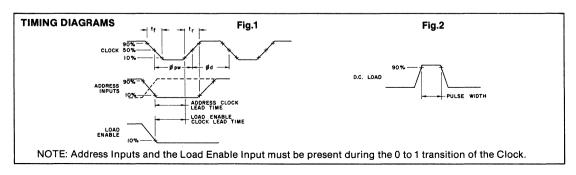

| RANDOM/<br>SEQUENTIAL | Multiplexes 16<br>analog chan-<br>nels, current, | AY-5-1016              |                           |               | 0.444         | 0 to 70        | +5, GND,          | 40.010  |                           | 154         |

| ACCESS<br>MULTIPLEXER | voltage, or<br>differential<br>mode              | <sup>†</sup> AY-6-4016 | _                         | _             | 2 MHz         | -55 to +125    | -12               | 40 DIP  |                           | 154         |

†Also available with MIL STD 883 screening (add suffix TX to part number). \*UAR/T is a registered trademark of General Instrument Corporation.

| COUNTER                               | RS / DIGITAL N                                                                    | METERS         |                         |                    |                   |         | Section                                                              | on 9        |

|---------------------------------------|-----------------------------------------------------------------------------------|----------------|-------------------------|--------------------|-------------------|---------|----------------------------------------------------------------------|-------------|

| DESCRIPTION                           | FUNCTION                                                                          | PART<br>NUMBER | MAX. COUNT<br>FREQUENCY | DISPLAY<br>CURRENT | POWER<br>SUPPLIES | PACKAGE | FEATURES                                                             | PAGE<br>NO. |

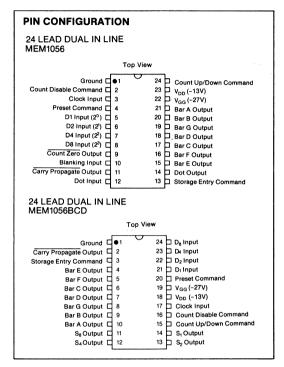

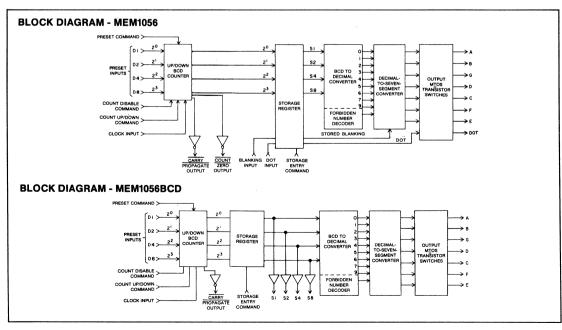

| 1 DIGIT<br>COUNTER                    | Counts & decodes one decade to BCD outputs.                                       | MEM 1056BCD    | 1.0 MHz                 | _                  | GND, -13, -27     | 24 DIP  | BCD outputs.                                                         | 162         |

| 1 DIGIT<br>COUNTER/<br>DISPLAY DRIVER | Counts & decodes one decade to 7-segment outputs.                                 | MEM 1056       | 1.0 MHz                 | 1.0 mA             | GND, -13, -27     | 24 DIP  | 7-segment outputs                                                    | 162         |

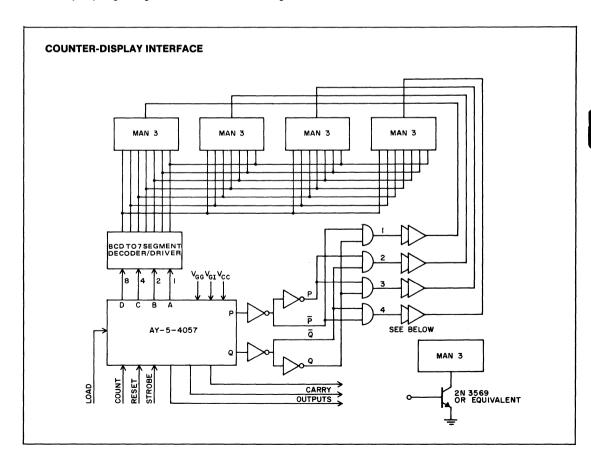

| 4 DIGIT<br>COUNTER                    | Counts, stores & decodes four decades to BCD outputs.                             | AY-5-4057      | 500 kHz                 | _                  | +5, GND, -12      | 16 DIP  | BCD outputs                                                          | 178         |

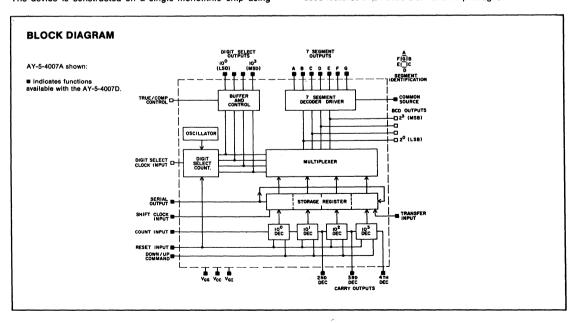

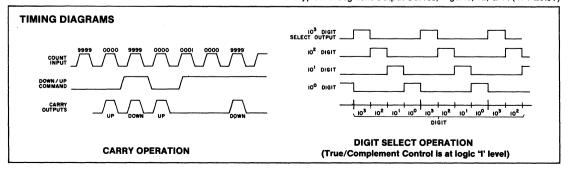

|                                       | Counts (us on down)                                                               | AY-5-4007      |                         |                    |                   | 24 DIP  | BCD outputs, true/<br>complement control                             | 172         |

| 4 DIGIT<br>COUNTER/<br>DISPLAY DRIVER | Counts (up or down),<br>stores & decodes four<br>decades to 7-segment<br>outputs. | AY-5-4007A     | 600 kHz                 | 25 mA/V            | +5, GND, -12      | 40 DIP  | Includes features of<br>AY-5-4007 & 4007D.                           | 172         |

|                                       | outputs.                                                                          | AY-5-4007D     |                         |                    |                   | 24 DIP  | Serial count output, three carry outputs                             | 172         |

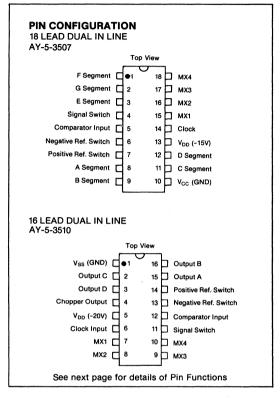

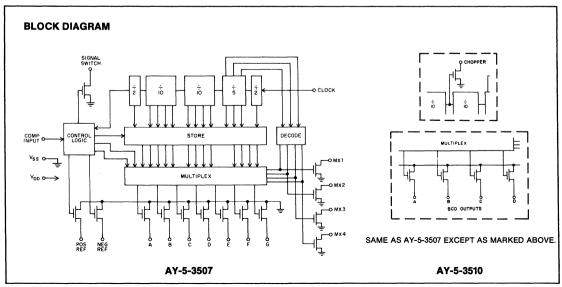

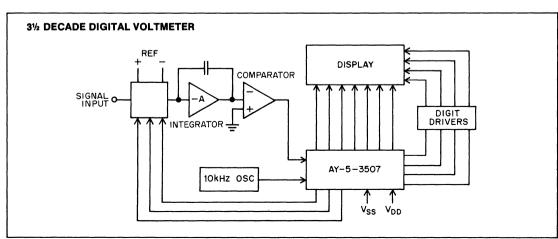

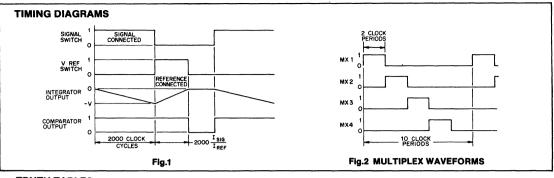

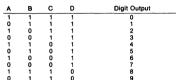

| 3½ DIGIT DVM                          | DVM logic incorporating                                                           | AY-5-3507      | 40 kHz                  | 6 mA               | GND,15            | 18 DIP  | Range to 1999, 7-<br>segment outputs                                 | 168         |

| CIRCUIT                               | dual ramp integration                                                             | AY-5-3510      | 40 KHZ                  | -                  | GND, -15          | 16 DIP  | Range to 1999, BCD outputs                                           | 168         |

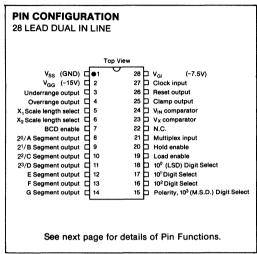

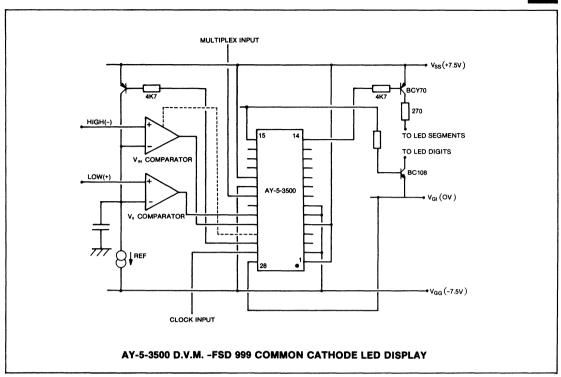

| 3% DIGIT DVM<br>CIRCUIT               | DVM logic incorporating single ramp integration                                   | AY-5-3500      | 200 kHz                 | 6 mA               | GND, -7.5, -15    | 28 DIP  | 3 ranges: 999, 1999,<br>2999. Dual polarity,<br>BCD & 7-seg. outputs | 163         |

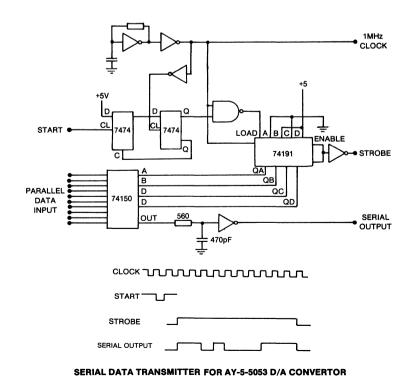

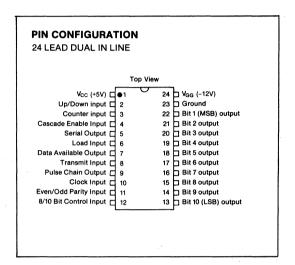

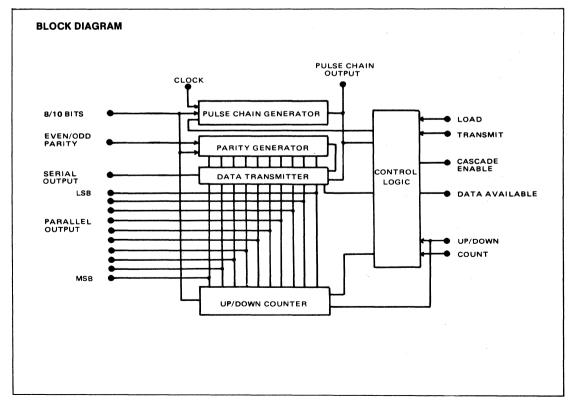

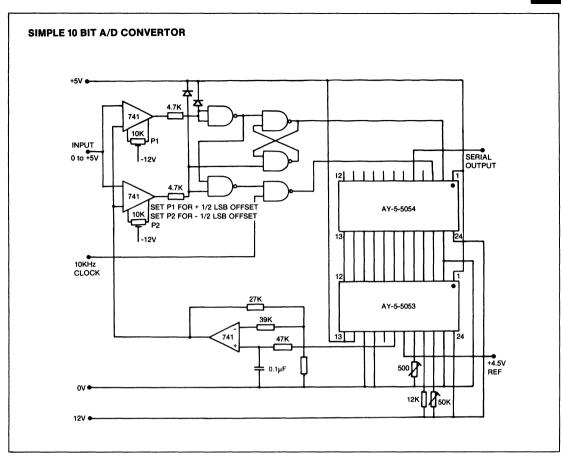

| 10 BIT D/A<br>CONVERTOR               | Ladderless D/A converter                                                          | AY-5-5053      | SEE DATA SHEET          | _                  | +5, GND, -12      | 24 DIP  | Employs stochastic techniques.                                       | 181         |

| A/DCONVERTOR<br>CONTROL               | With AY-5-5053,<br>performs A/D with<br>transmitter facility.                     | AY-5-5054      | SEE DATA SHEET          | _                  | +5, GND, -12      | 24 DIP  | For use in remote sensing applications.                              | 186         |

# FUNCTIONAL INDEX

| MICROPROCESSORS                                                                                                                                                                                                                                                |                |                             |                                     |                 |                   | Section          | 10          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------|-------------------------------------|-----------------|-------------------|------------------|-------------|

| DESCRIPTION                                                                                                                                                                                                                                                    | PART<br>NUMBER | INTERNAL<br>REGISTER<br>ADD | CLOCKS/<br>FREQUENCY/<br>MICROCYCLE | INTER-<br>FACE  | POWER<br>SUPPLIES | PACKAGE          | PAGE<br>NO. |

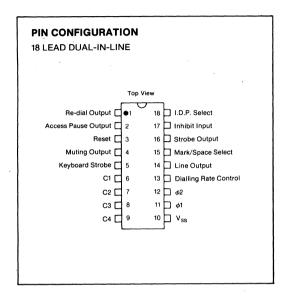

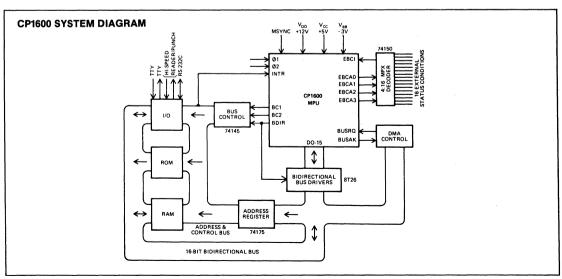

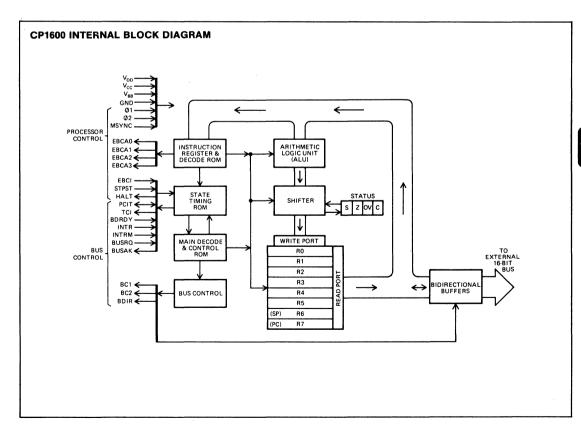

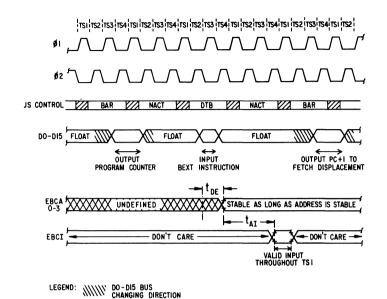

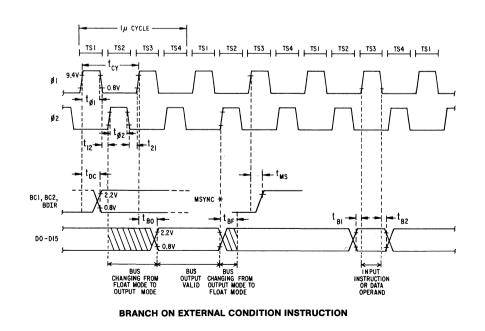

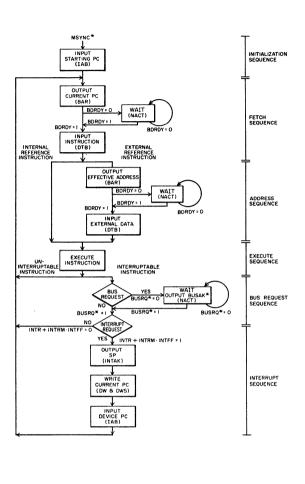

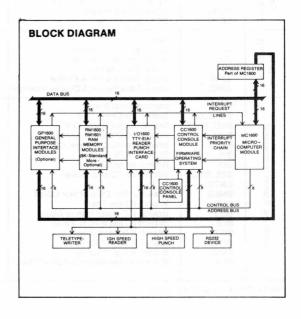

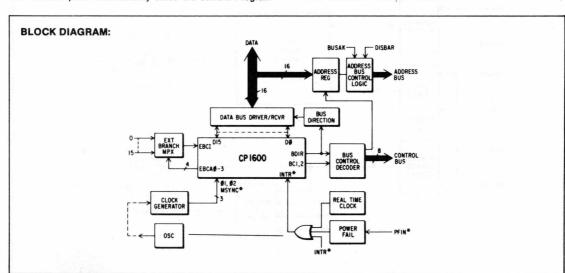

| 16 BIT—High performance, N-Channel, single-chip with 3rd generation minicomputer architecture, 87 basic instructions, 8 general purpose 16 bit registers, last-in/first-out stack of unlimited                                                                 | CP1600         | 3.6 μs                      | 2/3.3 MHz/ 600 ns.                  | TTL             | +12, +5,          | 40.010           | 192         |

| depth, 65K memory address capability, dual level priority interrupt system, and Direct Memory Access capability.                                                                                                                                               | *CP1600A       | 2.4 μs                      | 2/5 MHz/ 400 ns.                    | 111             | GND, -3           | 40 DIP           | 192         |

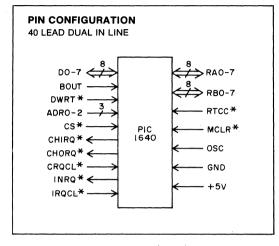

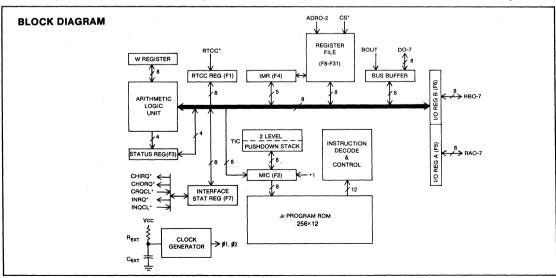

| 8 BIT—PIC: A single-chip byte oriented micro-programmable interface controller for low cost microprocessor/peripheral device interfacing. An internal ROM microprogram defines the overall functional characteristics and operational waveforms on each of the | *PIC 1640      |                             | 4/4/41-/4                           |                 | LE CND            | 40 DIP           | 210         |

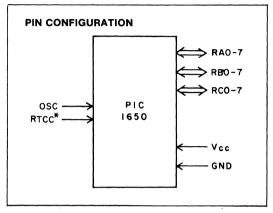

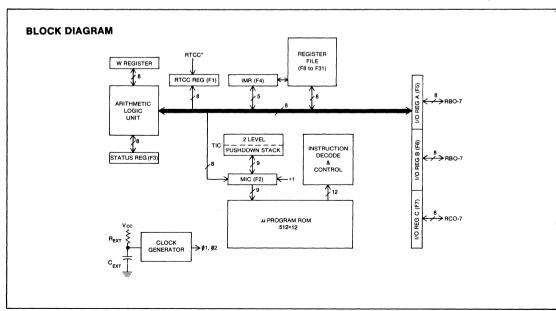

| general purpose I/O lines. Both products emphasize control and interface functions. PIC 1650 design/instruction set also supports computing functions. Full software support and a Hardware Emulator are available.                                            | *PIC 1650      | 1μs                         | 1/4 MHz/1μs                         | TTL             | +5, GND           | 40 DIP<br>28 DIP | 213         |

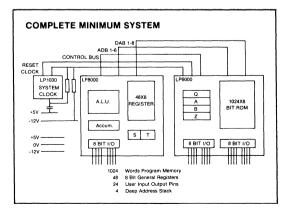

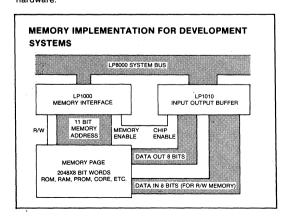

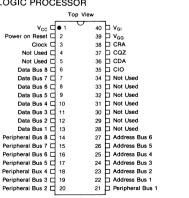

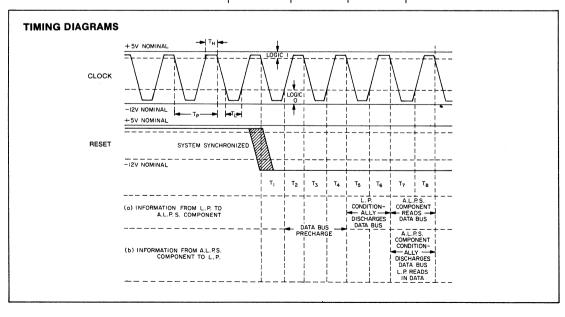

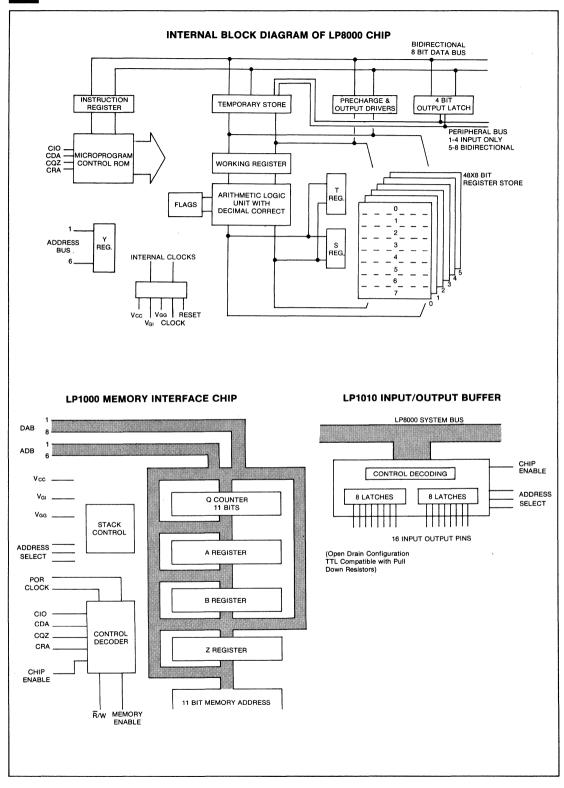

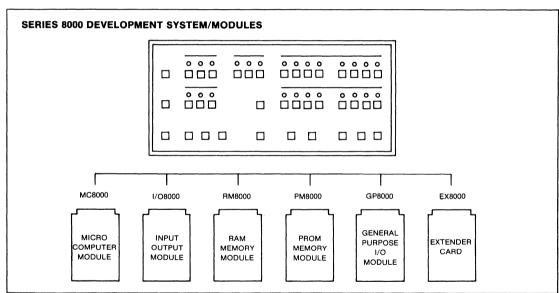

| ORIT ALDS: Advanced Losis Drangeling System A bit of 5 D                                                                                                                                                                                                       | LP 8000        |                             |                                     |                 |                   | 40 DIP           | 216         |

| BBIT — ALPS: Advanced Logic Processing System. A kit of 5 P-<br>Channel arrays consisting of microprocessor, ROM, I/O, memory<br>interface (to standard, RAM, ROM, PROM), and a clock/reset                                                                    | LP 6000        | ]                           |                                     | TTLor           |                   | 40 DIP           | 216         |

| generator circuit. The microprocessor contains an 8 bit accumulator,                                                                                                                                                                                           | LP 1010        | 5.5μs                       | 1/720 kHz/694 ns.                   | high<br>level   | +5, GND,<br>-12   | 40 DIP           | 216         |

| 48 internal registers, binary and decimal capability, and an input/<br>output port allowing simple systems to be configured with as few as                                                                                                                     | LP 1000        |                             |                                     | (open<br>drain) |                   | 40 DIP           | 216         |

| two chips.                                                                                                                                                                                                                                                     | LP 1030        | ]                           | 1                                   |                 |                   | 8 DIP            | 216         |

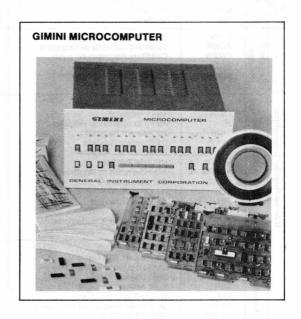

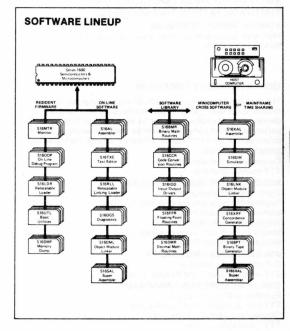

General Instrument offers a "total product family" approach to microprocessor circuits including the circuits described here plus a full complement of semiconductor circuits, PC card modules, prototype development hardware, extensive software support and comprehensive documentation. For further information call the sales office nearest you.

\*For future release

| RAND             | OM ACCES               | S MEMO         | RIES                      |                            | 0                 | Section 11 |                      |             |  |  |

|------------------|------------------------|----------------|---------------------------|----------------------------|-------------------|------------|----------------------|-------------|--|--|

| BITS/<br>MODE    | MEMORY<br>ORGANIZATION | PART<br>NUMBER | REPLACES<br>(PIN-FOR-PIN) | ACCESS TIME/<br>CYCLE TIME | POWER<br>SUPPLIES | PACKAGE    | FEATURES             | PAGE<br>NO. |  |  |

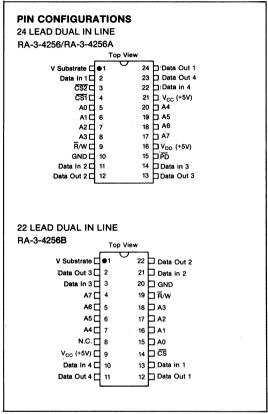

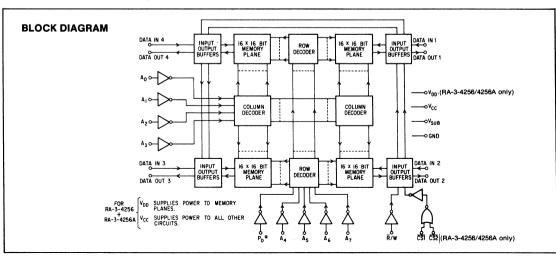

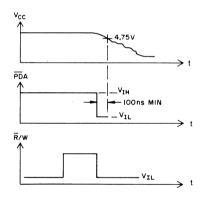

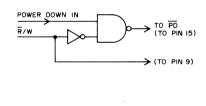

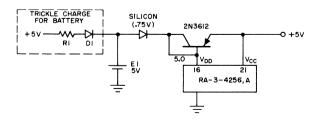

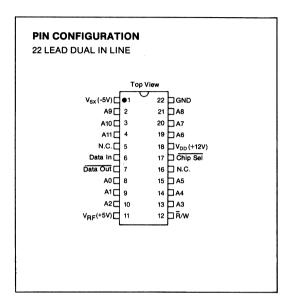

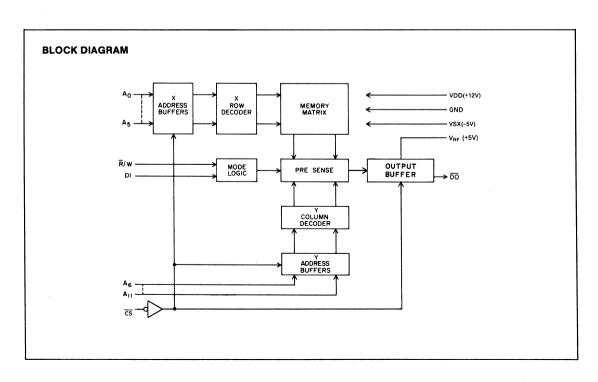

|                  |                        | RA-3-4256      | _                         | 500ns/500 ns               | +5, GND           | 24 DIP     | Power down mode      | 224         |  |  |

| 1024 /<br>STATIC | 256 x 4                | RA-3-4256A     | _                         | 650ns/650ns                | +5, GND           | 24 DIP     | Power down mode      | 224         |  |  |

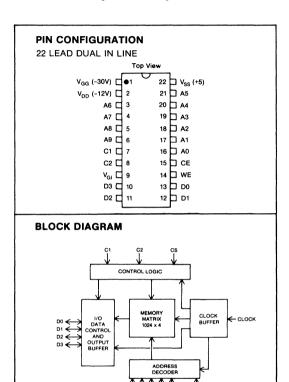

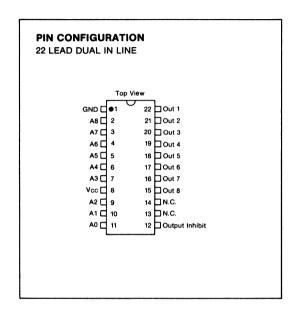

| STATIO           |                        | RA-3-4256B     | _                         | 650ns/650ns                | +5, GND           | 22 DIP     |                      | 224         |  |  |

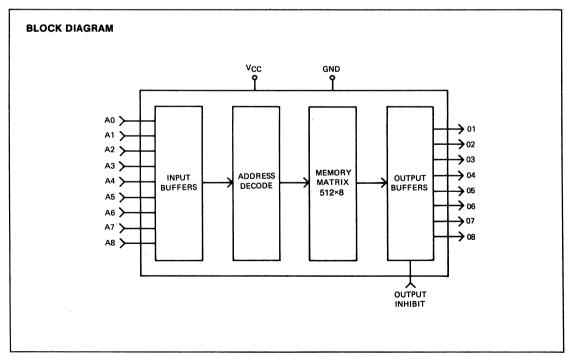

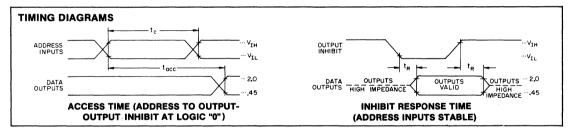

| 4096 /           |                        | RA-3-4200      | SEMI 4200                 | 215ns/400ns                | +12, +5, GND, -5  | 22 DIP     | TTL output           | 228         |  |  |

| STATIC           | 4096 x 1               | RA-3-4402      | SEMI 4402                 | 200ns/350ns                | +12, GND, -5      | 22 DIP     | Differential outputs | 232         |  |  |

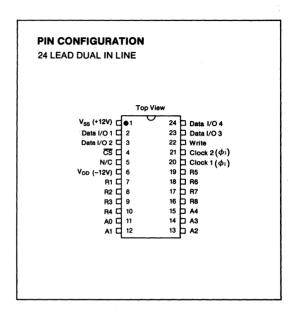

| ELEC | TRICALLY A             | LTERAB         | LE READ             | ONLY          | MEMO                | PRIES                 |                    |         | Section 12              |             |

|------|------------------------|----------------|---------------------|---------------|---------------------|-----------------------|--------------------|---------|-------------------------|-------------|

| BITS | MEMORY<br>ORGANIZATION | PART<br>NUMBER | READ<br>ACCESS TIME | ERASE<br>TIME | ERASE<br>MODE       | WRITE<br>TIME         | POWER<br>SUPPLIES  | PACKAGE | FEATURES                | PAGE<br>NO. |

| 512  | 32 x 16                | ER 2050        | <b>4</b> μs         | 100 ms        | WORD<br>(16 BIT)    | 100ms/<br>16 BIT WORD | +5, -29            | 28 DIP  |                         | 246         |

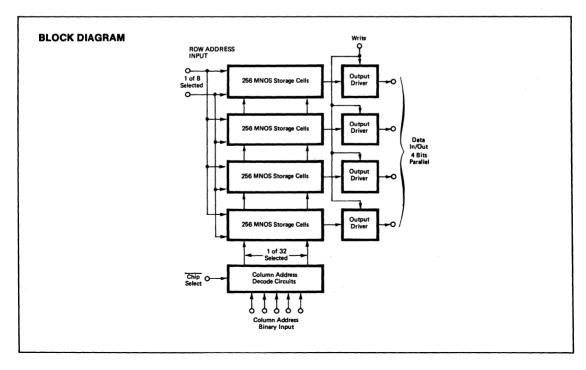

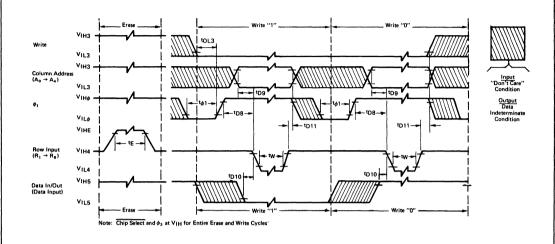

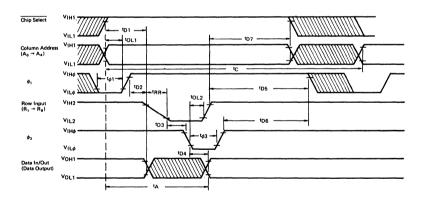

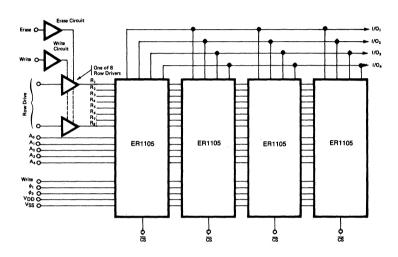

| 1024 | 256 x 4                | ER 1105        | 2μs                 | 100 ms        | BLOCK<br>(32 x 1)   | 10 ms/<br>4 BIT WORD  | +12, -12           | 24 DIP  |                         | 238         |

| 1400 | 100 x 14               | ER1400         | 3.4 ms              | 100 ms        | WORD<br>(14 BIT)    | 100ms/<br>14 BIT WORD | -35                | 8 TO    | 10 year<br>data storage | 243         |

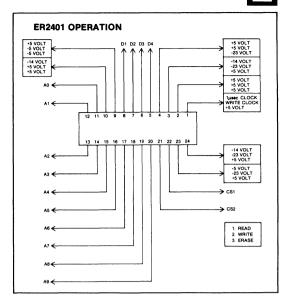

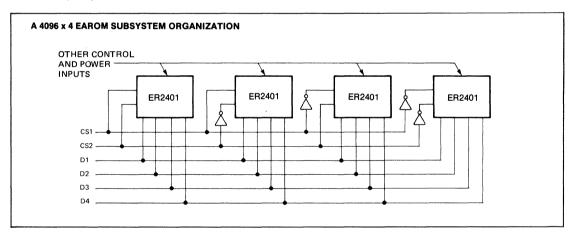

| 4096 | 10044                  | ER 2401        | 2μs                 | 100 ms.       | BLOCK<br>(1024 x 4) | 10 ms/<br>4 BIT WORD  | +5, -5<br>-14, -24 | 24 DIP  | @ 70°C                  | 248         |

| 4096 | 1024 x 4               | *ER3400        | 600ns               | 1ms           | WORD<br>(4 BIT)     | 100μs/<br>4 BIT WORD  | +5,-12,<br>-30     | 22 DIP  |                         | 255         |

| 8192 | 2048 x 4               | *ER2800        | 2μs                 | 100 ms        | BLOCK<br>(2048 x 4) | 20ms/<br>4 BIT WORD   | +5, -5<br>-14, -24 | 24 DIP  |                         | 254         |

\*For future release.

# FUNCTIONAL INDEX

| READ O             | NLY   | MEMORIE                | S                        |                              |                 |                    |                   |         | Section                                 | า 13        |

|--------------------|-------|------------------------|--------------------------|------------------------------|-----------------|--------------------|-------------------|---------|-----------------------------------------|-------------|

| DESCRIPTION        | BITS  | MEMORY<br>ORGANIZATION | PART<br>NUMBER           | REPLACES<br>(PIN-FOR-PIN)    | ACCESS<br>TIME  | CLOCKS/<br>VOLTAGE | POWER<br>SUPPLIES | PACKAGE | FEATURES                                | PAGE<br>NO. |

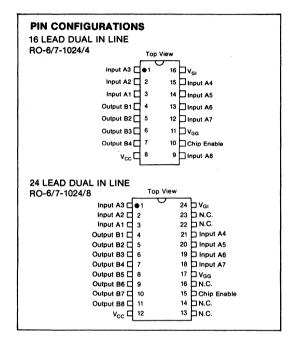

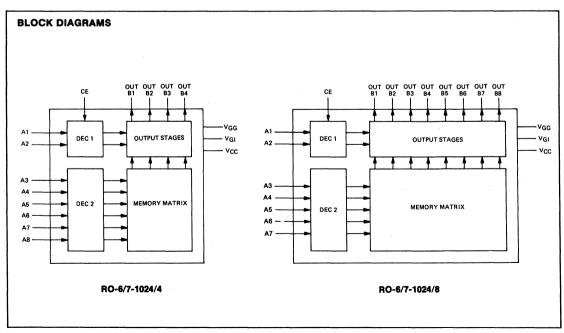

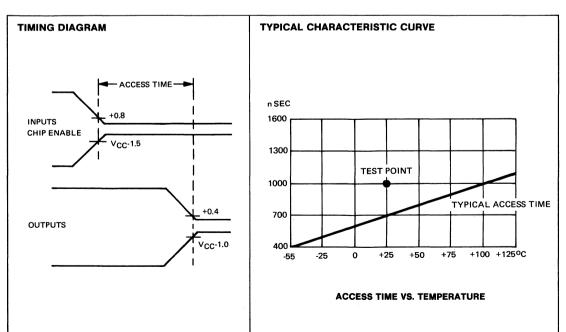

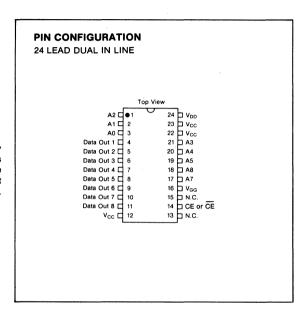

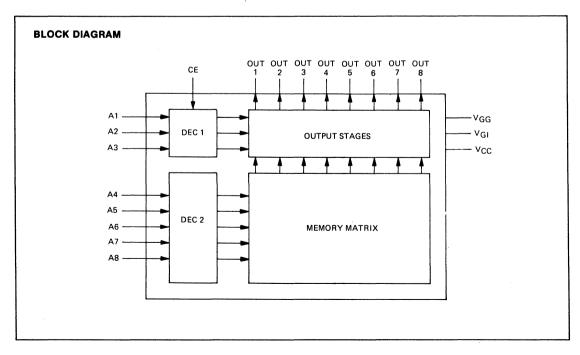

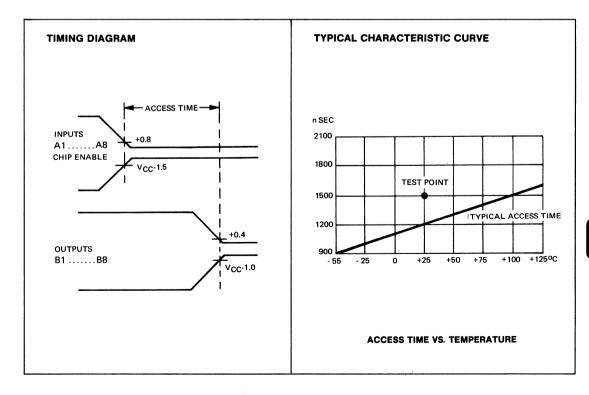

|                    | 1024  | 256 x 4                | RO-7-1024/4              | _                            | 1μs (typ.)      | STATIC             | +5, GND,<br>-12   | 16 DIP  | RO-6-1024/4 avail.<br>for -55° to +125° | 258         |

|                    | 1024  | 128 x 8                | RO-7-1024/8              | _                            | 1μs (typ.)      | STATIC             | +5, GND,<br>-12   | 24 DIP  | RO-6-1024/8 avail.<br>for -55° to +125° | 258         |

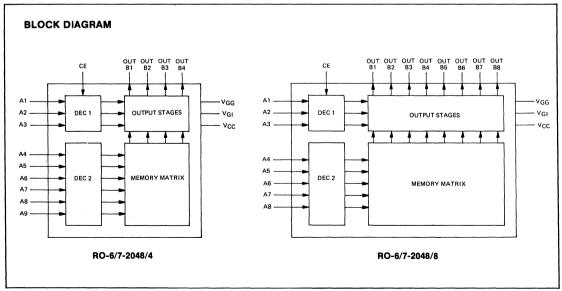

|                    |       | 512 x 4                | RO-7-2048/4              | _                            | 1.5μs<br>(typ.) | STATIC             | +5, GND,<br>-12   | 24 DIP  | RO-6-2048/4 avail.<br>for -55° to +125° | 262         |

|                    | 2048  | 256 x 8                | RO-7-2048/8              |                              | 1.5μs<br>(typ.) | STATIC             | +5, GND,<br>-12   | 24 DIP  | RO-6-2048/8 avail.<br>for -55° to +125° | 262         |

|                    |       | 250 X 6                | RO-5-1302                | INTEL 1302                   | 1.5μs<br>(typ.) | STATIC             | +5, GND,<br>-12   | 24 DIP  | Mask programmable<br>version of 1702    | 260         |

| GENERAL<br>PURPOSE | 2560  | 512 x 5                | RO-3-2560                | _                            | 450 ns.         | STATIC             | +5, GND           | 18 DIP  |                                         | 264         |

|                    | 4096  | 512 x 8                | RO-3-4096                | _                            | 500 ns.         | STATIC             | +5, GND           | 22 DIP  |                                         | 266         |

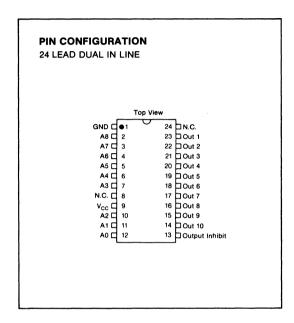

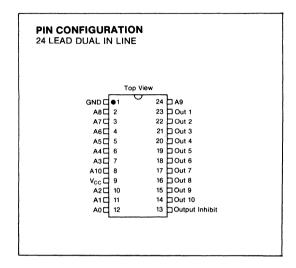

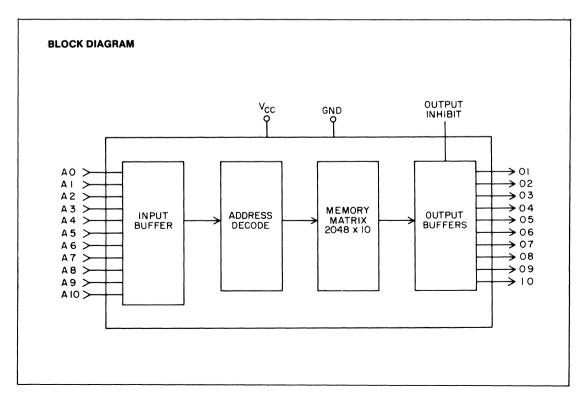

|                    | 5120  | 512 x 10               | RO-3-5120                | EA 4000                      | 500 ns.         | STATIC             | +5, GND           | 24 DIP  |                                         | 268         |

|                    | 8192  | 2048 x 4               | RO-5-8192                | AMI S8865<br>TI TMS4000      | 1.2μs<br>(typ.) | 2/TTL              | +5, -12           | 24 DIP  |                                         | 270         |

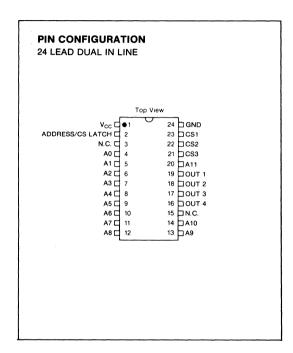

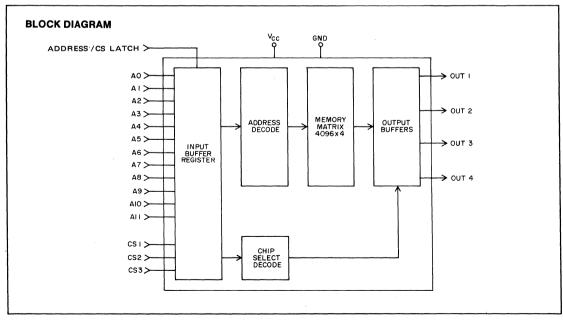

|                    |       | 4096 x 4               | RO-3-16384               | AMI S8996                    | 1μs             | STATIC             | +5, GND           | 24 DIP  | Address/CS latch                        | 278         |

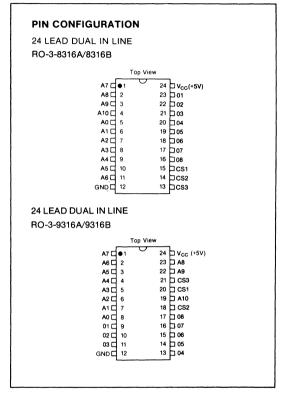

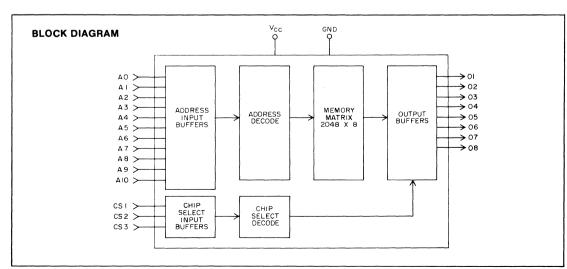

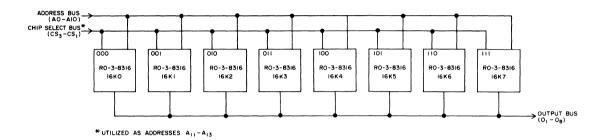

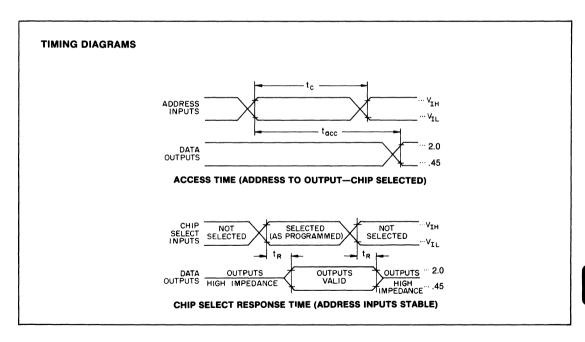

|                    | 16384 | 2048 x 8               | RO-3-8316A<br>RO-3-9316A | INTEL 2316,A<br>INTEL 4316.A | 850 ns.         | STATIC             | +5. GND           | 24 DIP  |                                         | 273         |

|                    |       | 2048 X 8               | RO-3-8316B<br>RO-3-9316B | INTEL 4316,A                 | 450 ns.         | STATIC             | TO, GND           | 24 DIP  |                                         | 2/3         |

|                    | 20480 | 2048 x 10              | *RO-3-20480              | _                            | 500 ns.         | STATIC             | +5, GND           | 24 DIP  |                                         | 281         |

Note: All Read Only Memories are mask-programmable.

\*For future release.

| KEYBOA                 | RD   | ENCODE                 | RS / CHA       | RACTER                    | GENER                      | RATOR                    | S               |         | Sectio                                                   | n 14        |

|------------------------|------|------------------------|----------------|---------------------------|----------------------------|--------------------------|-----------------|---------|----------------------------------------------------------|-------------|

| DESCRIPTION            | BITS | MEMORY<br>ORGANIZATION | PART<br>NUMBER | REPLACES<br>(PIN-FOR-PIN) | ACCESS<br>TIME             | CLOCKS/<br>VOLTAGE       | POWER SUPPLIES  | PACKAGE | FEATURES                                                 | PAGE<br>NO. |

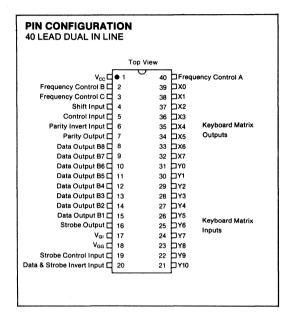

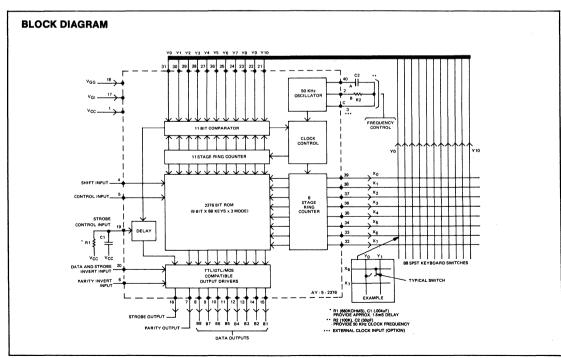

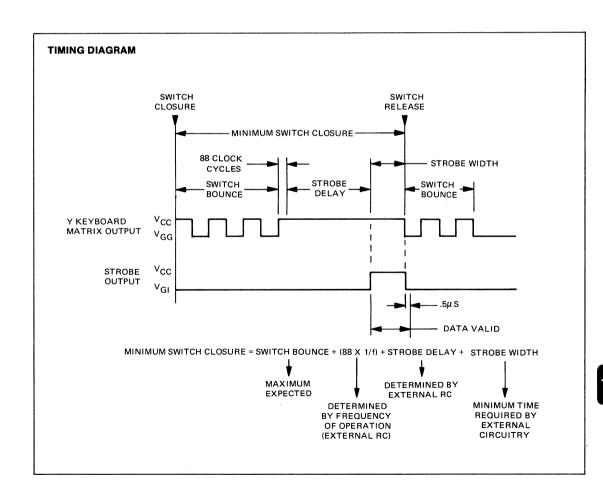

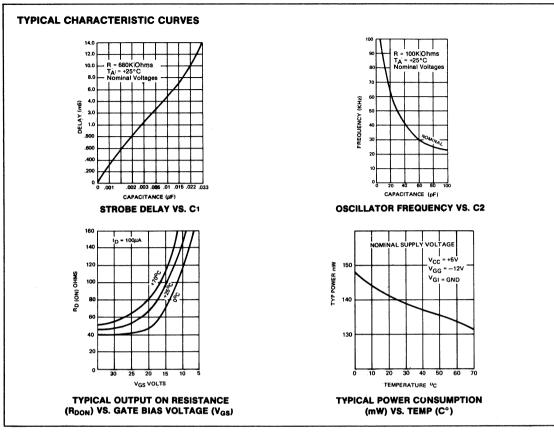

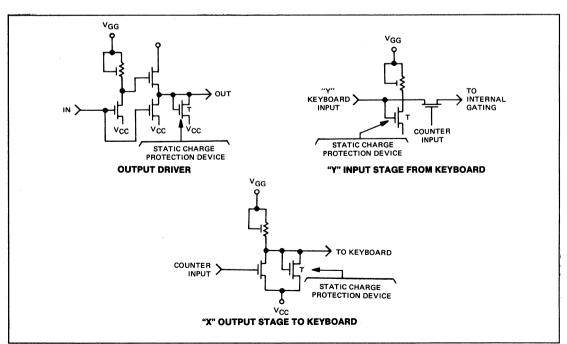

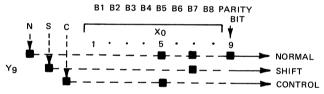

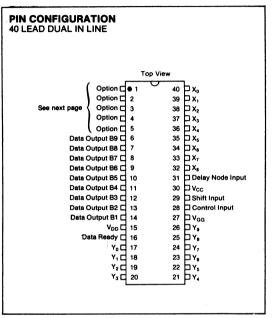

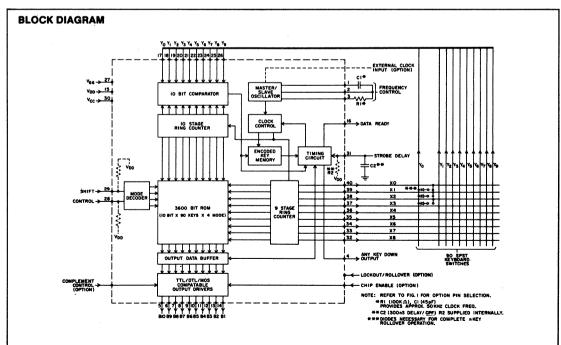

| KEYBOARD               | 2376 | 88 x 3 x 9             | AY-5-2376      | SMC KR2376                | 10-100<br>KHz SCAN<br>RATE | 1/TTL OR<br>INT. OSC.    | +5, GND,<br>-12 | 40 DIP  | 2 key rollover, 88<br>keys, 3 modes                      | 284         |

| ENCODER                | 3600 | 90 x 4 x 10            | AY-5-3600      | SMC KR3600                | 10-100<br>kHz SCAN<br>RATE | 1/TTL OR<br>INT. OSC.    | +5, GND,<br>-12 | 40 DIP  | 2/N key rollover, 90<br>keys, 4 modes                    | 289         |

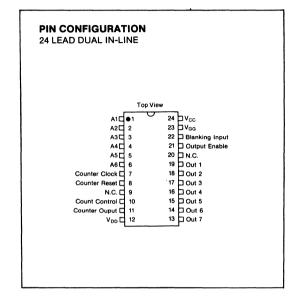

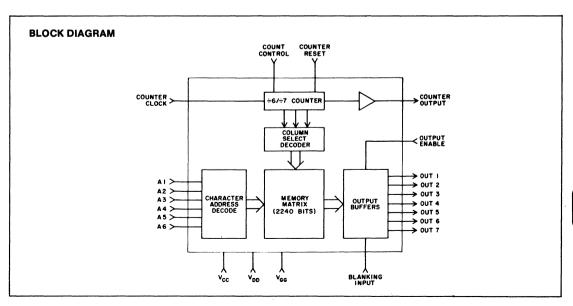

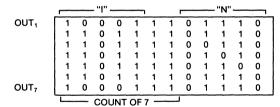

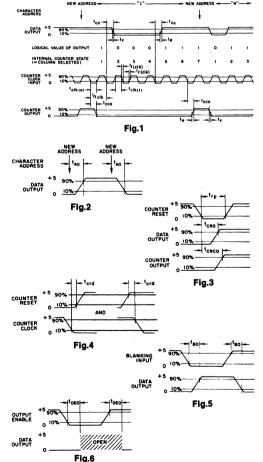

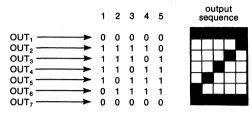

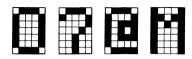

|                        | 2240 | 64 x 5 x 7             | RO-5-2240S     | MK 2302<br>FSC 3257       | 1μs (typ.)                 | 1/TTL<br>FOR<br>SCANNING | +5, GND,<br>-12 | 24 DIP  | 5 x 7 characters,<br>column output, on-<br>chip scanning | 295         |

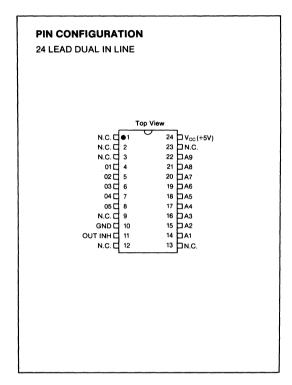

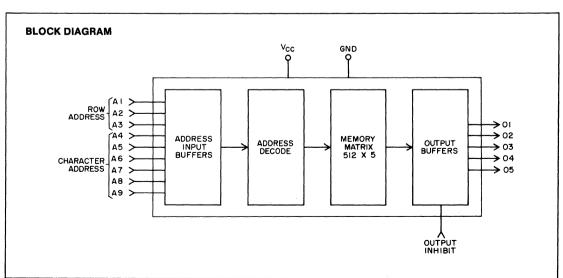

| CHARACTER<br>GENERATOR | 2560 | 64 x 8 x 5             | RO-3-2513      | SIG 2513                  | 450 ns.                    | STATIC                   | +5, GND         | 24 DIP  | 5 x 7 characters,<br>row output                          | 299         |

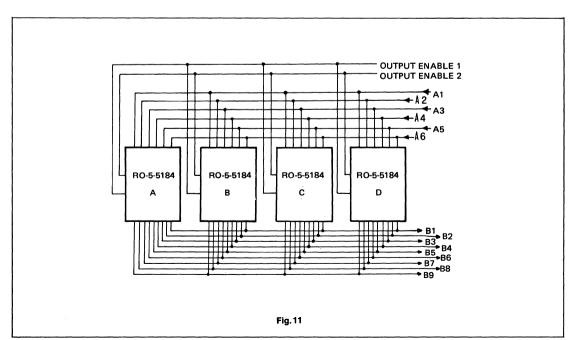

|                        | 5184 | 64×9×9                 | RO-5-5184      | -                         | 5μs (typ.)                 | 1/TTL<br>FOR<br>SCANNING | +5, GND,<br>-12 | 24 DIP  | 9 x 9 characters, on-<br>chip left/right<br>scanning     | 303         |

Note: All Keyboard Encoders and Character Generators are mask-programmable.

| STA  | TIC SHIFT    | REGISTER              | RS (Conta                 | ict any GI S             | ales Offi        | ce for de          | tails.)           |                |                                    |

|------|--------------|-----------------------|---------------------------|--------------------------|------------------|--------------------|-------------------|----------------|------------------------------------|

| BITS | ORGANIZATION | 0° to 70°<br>PART NO. | -55° to +125°<br>PART NO. | OPERATING<br>FREQ. RANGE | INPUT/<br>OUTPUT | CLOCKS/<br>VOLTAGE | POWER<br>SUPPLIES | PACKAGES       | FEATURES                           |

|      | VARIABLE     | SS-5-1032             | SS-6-1032                 | DC-1 MHz                 | TTL              | 1/TTL              | +5, GND,<br>-12   | 16 DIP         | 6 S/R's arranged<br>1-1-2-4-8-16   |

| 32   | DUAL 16      | ‡SS-5-8211            | SS-6-8211                 | DC-2 MHz                 | TTL              | 1/TTL              | +5, GND,          | 16 DIP         | Set control dual<br>input selector |

|      |              | †\$\$-5-8212          | SS-6-8212                 | DC-2 MHz                 |                  |                    | -12               | 8/14 DIP, 8 TO |                                    |

| 64   | QUAD 16      | †SL-5-4016            | _                         | DC-2 MHz                 | TTL              | 1/TTL              | +5, GND,<br>-12   | 14 DIP         |                                    |

| 100  | DUAL 50      | † SL-5-2050           | SL-6-2050                 | DC-1 MHz                 | TTL              | 1/TTL              | +5, GND.          | 8/14 DIP, 8 TO |                                    |

| 100  | QUAD 25      | †SL-5-4025            | SL-6-4025                 | DC-1 MHz                 | '''              | 1/116              | -12               | 14 DIP         |                                    |

| 128  | DUAL 64      | †SL-5-2064            | SL-6-2064                 | DC-1 MHz                 |                  | 4/771              | +5, GND,          | 8/14 DIP, 8 TO |                                    |

| 128  | QUAD 32      | †SL-5-4032            | SL-6-4032                 | DC-1 MHz                 | TTL              | 1/TTL              | -12               | 14 DIP         |                                    |

| 200  | DUAL 100     | †SL-5-C2100           | -                         | DC-2 MHz                 | TTL              | 1/TTL              | +5, GND,<br>-12   | 14 DIP, 8 TO   |                                    |

| 050  | DUAL 100     | †SL-5-2128            | _                         | DC-1 MHz                 | 771              | +'5 GNC            | +5, GND,          | 8/14 DIP. 8 TO |                                    |

| 230  | 256 DUAL 128 | SL-5-C2128            | I -                       | DC-2 MHz                 | TTL              | 1/TTL              | -12               | 6/14 DIP, 8 TO |                                    |

‡Available in Europe as part number SS-7-2016 (16 lead plastic DIP only)

†Available in Europe as part number SS-7/SL-7 (14 lead plastic DIP only).

# PIN-FOR-PIN REPLACEMENT INDEX

AMI GI

DEVICE NO. REPLACEMENT

S1757 ... AY-5-1013/1013A

S1757 ... AY-3-1014A/1015

S2470 ... AY-1-1006

S8865 ... RO-5-8192

S8996 ... RO-3-16384

ELECTRONIC

ARRAYS GI

REPLACEMENT

EA4000 . . . . . . . RO-3-5120

EMM/SEMI

GI

DEVICE NO.

REPLACEMENT

4200

RA-3-4200

4402

RA-3-4402

FAIRCHILD GI

DEVICE NO.

DEVICE NO. REPLACEMENT 3257 ...... RO-5-2240S

**INTEL** GI

2316A . . . . . . . . RO-3-8316A/8316B 8316A . . . . . . . . RO-3-8316A/8316B

MOSTEK GI

DEVICE NO. REPLACEMENT

MK2302 ... RO-5-2240S

MK50240 ... AY-3-0215

MK50241 ... AY-3-0216

MK50242 ... AY-3-0214

MK50242 ... AY-1-0212

**NATIONAL** GI

DEVICE NO. REPLACEMENT

MM5303 ... AY-5-1013/1013A

MM5303 ... AY-3-1014A/1015

MM5823 ... AY-1-2006

MM5824 ... AY-1-1006

**SIGNETICS** GI

SMC GI

DEVICE NO. REPLACEMENT

COM2505 .... AY-5-1013/1013A

COM2505 .... AY-3-1014A/1015

KR2376 .... AY-5-2376

KR3600 .... AY-5-3600

**WESTERN**

**DIGITAL** GI

DEVICE NO. REPLACEMENT TR1602 . . . . . . AY-5-1013/1013A TR1602 . . . . . . AY-3-1014A/1015

**TEXAS**

INSTRUMENTS GI

DEVICE NO. REPLACEMENT TMS0803 . . . . C-593 TMS0851 . . . . CF-593 TMS4000 . . . . RO-5-8192

TMS5001 .... AY-5-3600

TMS6011 ..... AY-5-1013/1013A TMS6011 ..... AY-3-1014A/1015

| , |  |  |  |

|---|--|--|--|

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

C/CF-583 C/CF-683 C-683D C/CF-589 C/CF-585 C/CF-685 C-685D C-689D C/CF-593 C/CF-594 C/CF-595 C/CF-596 C/CF-598 C/CF-599 C-717 C-717X C-718 C-719

C/CF-580 SERIES C/CF-590 SERIES C/CF-680 SERIES

# **GENERAL INFORMATION**

# **Display Calculator Circuits**

## **FEATURES**

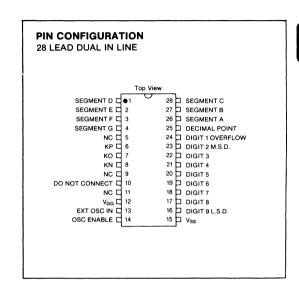

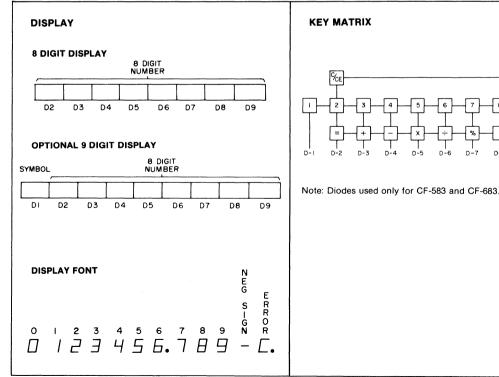

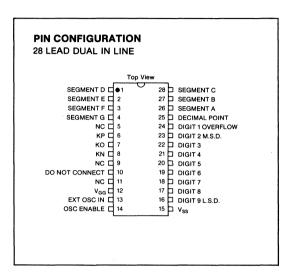

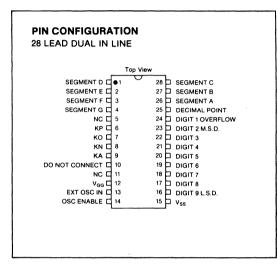

- Printed circuit board compatibility of circuits.

- Direct segment drive for LED displays (C-XXX)

- Direct segment and digit drive for LED displays (C-XXXD)

- Direct fluorescent display drive (CF-XXX)

- Algebraic operation

- Automatic constant

- Floating point operation

- Constant or chain operation (no switch required)

- Leading zero suppression

- Automatic power-on clear

- Internal clock (on-chip oscillator)

- Internal keyboard debounce logic

## DESCRIPTION

General Instrument's broad line of display calculator circuits, the C/CF-500 Series and the C/CF-600 Series, consists of pin-for-pin compatible circuits designed to fit in the same basic PC board. This provides a high degree of flexibility in calculator models manufactured while minimizing the tooling required.

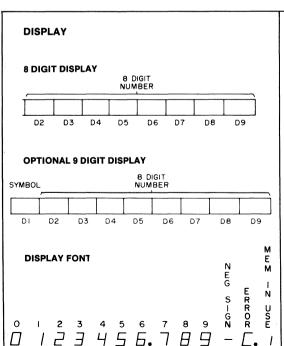

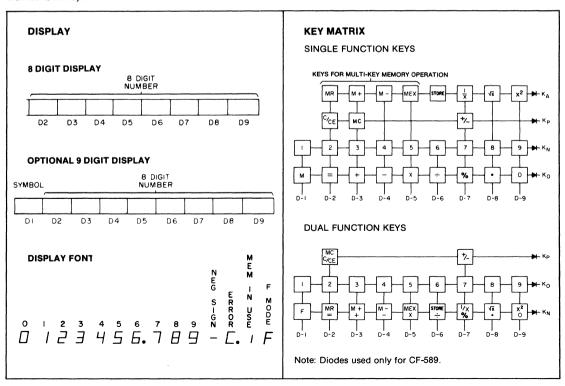

| Description        | Function                                                                                                     | 9V<br>Fluorescent                                                                                                                                                                                                                 | 9V LED | 9V LED<br>(Direct) | 15V Fluorescent | 15V LED |  |  |

|--------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------|-----------------|---------|--|--|

|                    | 4 functions and percent key.                                                                                 | CF-683                                                                                                                                                                                                                            | C-683  | C-683D             | CF-583          | C-583   |  |  |

| 8 DIGIT<br>BASIC   | 4 functions, percent key, one-key or multi-key memory.                                                       | L CF-685 L C-685 L C-685 D                                                                                                                                                                                                        |        |                    |                 |         |  |  |

| 8 DIGIT<br>ALGEBRA | 4 functions, percent key, $x^2, \sqrt{x}$ , $1/x$ , $+/-$ , one-key choice of 20 to 29 keys.                 | functions, percent key, $x^2, \sqrt{x}$ , $1/x$ , +/-, one-key or multi-key memory, choice of 20 to 29 keys.                                                                                                                      |        |                    |                 |         |  |  |

|                    | 4 functions and percent key.                                                                                 | 4 functions and percent key.                                                                                                                                                                                                      |        |                    |                 |         |  |  |

| 9 DIGIT<br>BASIC   | 4 functions, percent key, one-key memory.                                                                    |                                                                                                                                                                                                                                   |        |                    | CF-594          | C-594   |  |  |

|                    | 4 functions, percent key, multi-key memory.                                                                  |                                                                                                                                                                                                                                   |        |                    | CF-595          | C-595   |  |  |

| 9 DIGIT            |                                                                                                              | Basic 4 functions, scientific notation, sin, cos, tan, arc sin, arc cos, arc tan, memory, square root, pi, natural logs, 1/x, e <sup>x</sup> , memory exchange, degrees and radians, exponent range ±99, choice of 19 to 35 keys. |        |                    |                 |         |  |  |

| SCIENTIFIC         | All the above plus: 0 to 10 <sup>98</sup> degree trig range, accuracy of transcendentals, choice of 21 to 38 | digit                                                                                                                                                                                                                             | CF-598 | C-598              |                 |         |  |  |

|                    | All the above plus: two levels of parenthesis, x2                                                            | 1 keys.                                                                                                                                                                                                                           | CF-599 | C-599              |                 |         |  |  |

## I THE FOLLOWING APPLY AS NOTED:

#### A. AUTOMATIC CONSTANT (All circuits)

The answer from any operation is entered automatically as a Constant by the = key without a constant switch. The Constant may then be used with all five functions and the answer from any Constant calculation can be used for further calculations without re-entry. This provides an extremely powerful facility for solving many complex equations without the need for writing down or remembering intermediate results. It is particularly useful for raising to a power, compound interest calculations, nth roots, depreciation calculations, etc. In constant multiplication, the constant is the first entered number (constant multiplicand). In division, addition and subtraction, the constant is the second entered number. The completion of the first operation with the depression of the = key initiates the storage of the constant number. For subsequent operations it is only necessary to enter a number and depress the = key.

# B. DECIMAL ALIGNMENT (C/CF-593, C/CF-594, C/CF-595)

The results of addition or subtraction will remain aligned to the preceding number having the most decimal places. This feature allows computation in the dollar and cents mode without suppression of the zeros to the right of the decimal point. If a right shift is needed to keep the eight most significant digits, the least significant digits are lost. The results of multiplication and division will be completely right adjusted such that only the most significant digits are displayed except during overflow.

## C. CAPACITY (All except Scientific Circuits)

For the C/CF-580 Series and the C/CF-680 Series, in the case of overflow, the eight most significant digits are displayed (seven digits and minus sign for negative answers) all decimal points are lit and the keyboard is locked out. Only the operation of the clear key will allow continued operation. On depression of the clear key, the decimal point is shifted eight places to the left of its actual position.

For the C/CF-593, 594 and 595, in the case of overflow, the overflow symbol is displayed, and the decimal point shifted eight places to the left of its actual position. Under these conditions, the keyboard is locked out such that only the operation of the clear key will allow continued operation.

In all cases, for an attempted entry requiring more than eight display digits, the most significant digits are protected upon the attempted entry of another digit. The keyboard is not locked out and operations are still able to be performed.

When division by zero is attempted, an overflow condition results and a zero is displayed.

# D. PERCENT KEY (all except C/CF-596 and 598)

Multiplies the two preceding entries and divides by 100, and when followed by = gives add-on and discount: A+B% yields (AB/100); A+B%=yields A+(AB/100). A-B% yields (AB/100); A-B%=yields A-(AB/100).

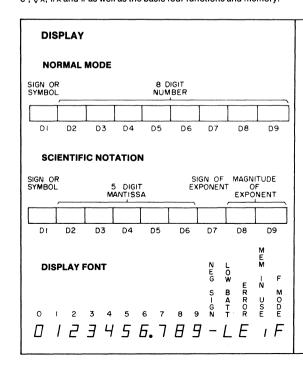

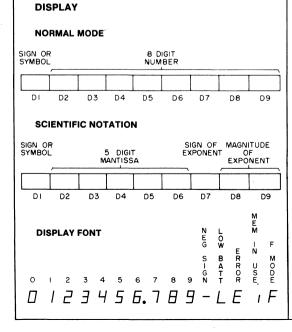

# E. CHANGE NOTATION KEY (Scientific Circuits)

Depression of the CHG NOT key will convert the displayed number to scientific notation, if it is in the "normal" mode, or it will display the 8 most significant digits of a scientific mantissa with the decimal point correctly located (even if it falls beyond the display area) and trailing zeroes shall be blanked. In addition, for numbers less than one, the digits are left shifted until all leading zeroes have been eliminated.

## F. EXPONENT KEY (Scientific Circuits)

**EEX:** This key operates as follows: The EEX key sets the two right most digits to zero, the third digit from the right is blanked and the calculator is conditioned to accept sign and numeral keys to define the exponent value of the number entry. If the mantissa had numbers in any of the last three digit positions, these are retained but not displayed.

# G. FUNCTION KEY OPERATIONS (Used only with dual-function keys)

Depression of the F key sets the calculator in the "Function" mode and the F indicator is lit. The dual function keys will then function as indicated by their upper case designation. Single function keys directly perform the indicated function.

Depression of the second key of the sequence resets the "Function" mode and the F indicator is turned off when the answer is displayed. The "Function" mode can also be reset by a second depression of the F key.

I THE FOLLOWING APPLY AS NOTED TO CIRCUITS WITH MEMORY:

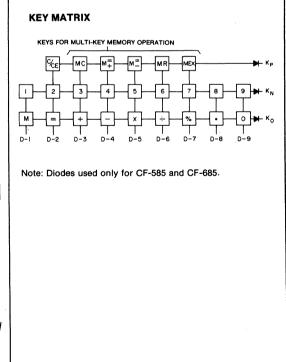

# A. MEMORY DESCRIPTION: One-Key memory as provided in C/CF-585, 589, 594, 685, C-685D & C-689D.

M: The Memory key is used in conjunction with other function keys to define a two key sequence which sets a mode of operation associated with the memory register and terminates any immediately preceding entry.

Operation of the M key followed by + adds the contents of the display register to the memory register without altering the contents of the display register.

Operation of the M key followed by – subtracts the contents of the display register without altering the contents of the display register.

Operation of the M key followed by = transfers the contents of the memory register into the display register without altering the contents of the memory register.

Operation of the M key followed by C/CE clears the contents of the memory register.

Operation of the M key followed by the X key performs a memorydisplay exchange function. The contents of the memory register are brought out to the display register and the contents of the display register are written into the memory register, replacing the previous contents of the memory register.

Operation of the M key followed by any key other than +, -, X, =, or C/CE shall reset the M condition and act upon the subsequent entry as if the M had not been entered.

In addition, two optional keys are provided with the C/CF-594 for operation as follows:

**MR, MEMORY READ:** Functions identically to the M = sequence above

MC, MEMORY CLEAR: Functions identically to the M C/CE sequence above.

# B. MEMORY DESCRIPTION: Multi-key memory as provided in all algebra and scientific circuits

MR, MEMORY READ: Functions identically to the M = sequence above.

MC, MEMORY CLEAR: Functions identically to the M C/E sequence above.

M+, MEMORY PLUS: Functions identically to the M+ sequence above

$\mathbf{M-},\mathbf{MEMORY\ MINUS:}$  Functions identically to the  $\mathbf{M-}$  sequence above.

**MEX, MEMORY EXCHANGE:** Functions identically to the MX sequence above.

In addition, the C/CF-589 and C-689D are provided with a STORE key which transfers the contents of the display to memory without changing the display.

# C. MEMORY DESCRIPTION: Multi-key memory as provided in C/CF-585, 595, 685 and C-685D.

MC, MEMORY CLEAR: clears the memory while leaving the display intact.

MR, MEMORY READ: transfers the data in memory to the display without changing the memory.

MŢ, MEMORY EQUALS/PLUS: completes the preceding operation, displays the result, and adds the result to the memory.

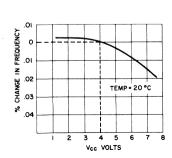

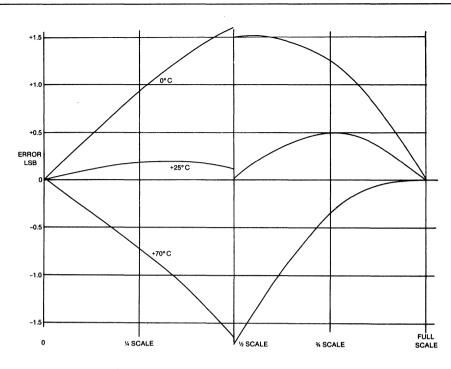

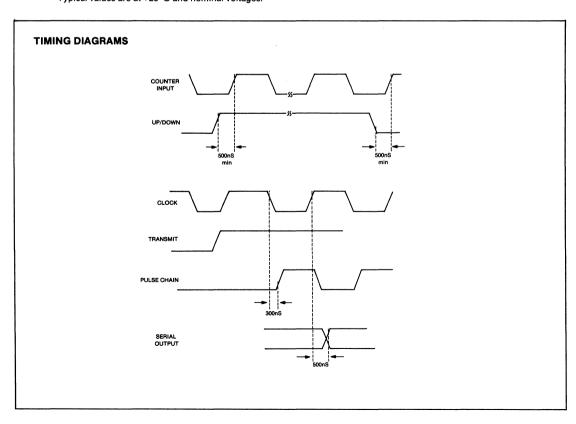

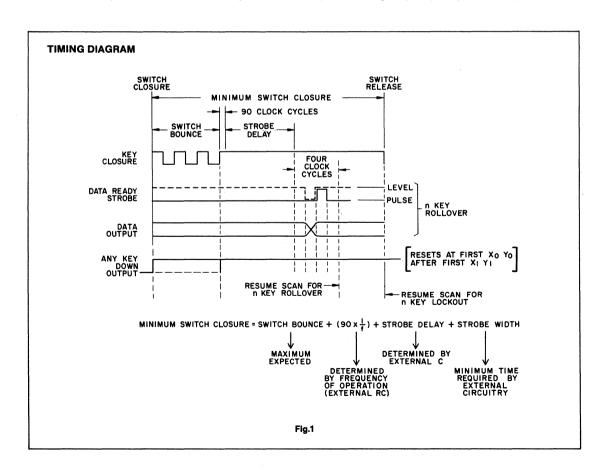

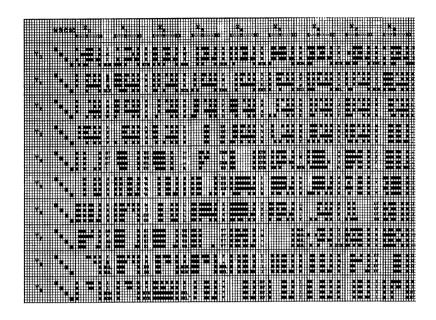

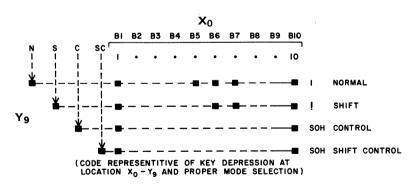

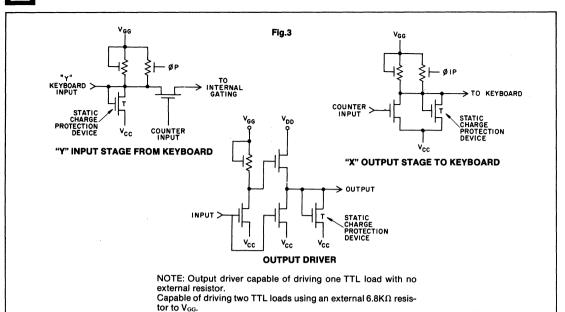

M≡,MEMORY EQUALS/MINUS: completes the preceding operation , displays the result and subtracts the result from the memory.