# FUĴITSU

# SPARClite

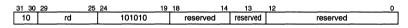

Embedded Processor User's Manual

SPARClite Embedded Processor User's Manual

1993

FUJITSU

## SPARClite User's Manual

Fujitsu Microelectronics, Inc.

Semiconductor Division

# Credits

Book design & illustration by Communication Graphics. This book, excluding the cover, was illustrated, and produced on Macintosh Computers using FrameMaker® workstation publishing software.

Cover design by Gregg Robles.

## TRADEMARKS

NICE is a trademark of Fujitsu Microelectronics, Inc.

SPARC is a registered trademark of SPARC International, Inc. based on technology developed by Sun Microsystems, Inc. SPARClite is a trademark of SPARC International exclusively licensed to Fujitsu Microelectronics, Inc. SPARCstation is a trademark of SPARC International, Inc. Products bearing the SPARC trademarks are based on an architecture develped by Sun Microsystems, Inc.

Macintosh is a registered trademark of Apple Computer, Inc. FrameMaker is a registered trademark of Frame Technology Corporation.

Copyright © 1993 Fujitsu Microelectronics, Inc., Semiconductor Division.

All rights reserved. This publication contains information considered proprietary by Fujitsu Limited and Fujitsu Microelectronics, Inc. No part of this document may be copied or reproduced in any form or by any means or transferred to any third party without the prior written consent of Fujitsu Microelectronics, Inc.

Circuit diagrams utilizing Fujitsu products are included as a means of illustrating typical semiconductor applications. Consequently, complete information sufficient for design purposes is not necessarily given.

Fujitsu limited and its subsidiaries reserve the right to change products or specifications without notice. Fujitsu advises its customers to obtain the latest version of device specifications to verify, before placing orders, that the information being relied upon by the customer is current.

The information contained in this document does not convey any license under copyrights, patent rights or trademarks claimed and owned by Fujitsu Limited or its subsidiaries. Fujitsu assumes no liability for Fujitsu applications assistance, customer's product design, or infringement of patents arising from use of semiconductor devices in such systems' designs. Nor does Fujitsu warrant or represent that any patent right, copyright, or other intellectual property right of Fujitsu covering or relating to any combination, machine, or process in which such semiconductor devices might be or are used.

Fujitsu Microelectronics, Inc.'s Semiconductor Division's products are not authorized for use in life support devices or systems. Life support devices or systems are device or systems which are:

#### 1. Intended for surgical implant into the human body.

2. Designed to support or sustain life; and when properly used according to label instructions, can reasonably be expected to cause significant injury to the user in the event of failure.

The information contained in this document has been carefully checked and is believed to be entirely accurate. However, Fujitsu Limited and Fujitsu Microelectronics, Inc. assume no responsibility for inaccuracies.

This document is published by the marketing department of Fujitsu Microelectronics, Inc., Semiconductor Division, 3545 North First Street, San Jose, California, U.S.A. 95134-1804.

| Preface            | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | •   | ••• | 1 |

|--------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|-----|---|

| Section 1: MB86930 | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | •   | 1-  | 1 |

| Section 2: MB86931 | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | . 4 | 1-  | 1 |

| Section 3: MB86932 | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | . E | 31- | 1 |

| Section 4: MB86933 | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | .0  | :1- | 1 |

Contents

#### Contents

# About This Manual

SPARClite<sup>™</sup> is a family of microprocessors which conform to Version 8 of the SPARC architecture and which have been optimized for use in embedded control. This manual is the definitive guide for understanding this family of embedded processors. It describes both the SPARClite architecture and the first four members of the family - the MB86930, MB86931, MB86932, and MB86933. The intended audience for this manual is both hardware systems designers and applications programmers.

#### Organization

This manual is divided into four sections, each with its own table of contents.

- Section 1 describes the SPARClite architecture and specifically, the MB86930 microprocessor (the first member of the SPARClite family). This section can be read by itself for an understanding of the SPARClite architecture or the MB86930 processor.

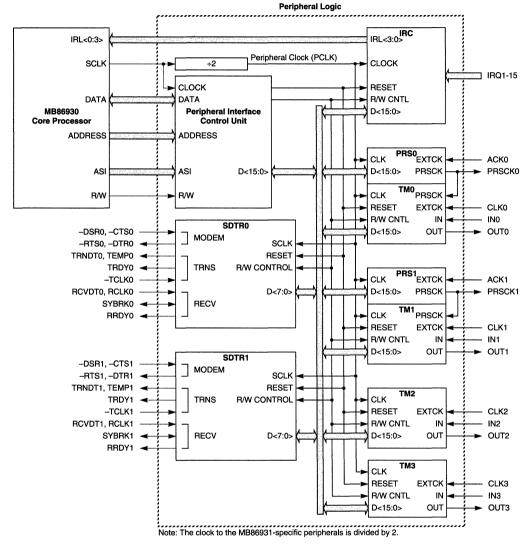

- Section 2 describes the MB86931 which is a superset of the MB86930. This section describes only the additional feature set of the MB86931 and therefore should be read after section 1.

- Section 3 describes the MB86932 which is a superset of the MB86930. This section describes only the additional feature set of the MB86932 and therefore should be read after section 1.

-I

• Section 4 describes the MB86933 which is a subset of the MB86930. Unlike sections 2 and 3, this section contains a complete description of the MB86933 and can be read independently of all other sections.

#### Notation

This manual uses the following notational conventions:

- Active-low signal names are preceded with a dash, as in –RESET.

- Numerals without any special prefix are in base 10. Hexadecimal numerals are preceded by 0x, and binary numerals are preceded by 0b. Thus, 28 = 0x1C = 0b11100.

#### **Related Literature**

Additional information can be found in the following documents:

- MB86930 SPARClite 32-Bit RISC Embedded Processor Data Sheet—Describes the MB86930 processor in detail, including complete physical, electrical, and timing characteristics. Available from Fujitsu Microelectronics' Semiconductor Division.

- MB86931 SPARClite 32-Bit RISC Embedded Processor Data Sheet—Describes the MB86931 processor in detail, including complete physical, electrical, and timing characteristics. Available from Fujitsu Microelectronics' Semiconductor Division.

- MB86932 SPARClite 32-Bit RISC Embedded Processor Data Sheet—Describes the MB86932 processor in detail, including complete physical, electrical, and timing characteristics. Available from Fujitsu Microelectronics' Semiconductor Division.

- MB86933 SPARClite 32-Bit RISC Embedded Processor Data Sheet—Describes the MB86933 processor in detail, including complete physical, electrical, and timing characteristics. Available from Fujitsu Microelectronics' Semiconductor Division.

- SPARClite Application Notes Discuss specific design issues in detail. Available from Fujitsu Microelectronics' Semiconductor Division.

- The SPARC Architecture Manual (version 8) This document is a more detailed description of the version 8 SPARC architecture on which the SPARClite family is based. Available from SPARC International, Menlo Park, California.

# MB86930

MB86930 - SPARClite User's Manual

####

### Chapter 1: Section 1: MB86930

### Chapter 1: Overview

| 1.1 General Description           |      |

|-----------------------------------|------|

| 1.2 Special Features              |      |

| 1.3 Programmer's Model            |      |

| 1.3.1 Program Modes               |      |

| 1.3.2 Memory Organization         |      |

| 1.3.3 Registers                   |      |

| 1.3.4 Data Types                  |      |

| 1.3.5 Instructions                |      |

| 1.3.6 Data and Instruction Caches |      |

| 1.3.7 Interrupts and Traps        |      |

| 1.4 Internal Architecture         |      |

| 1.4.1 Integer Unit                |      |

| 1.4.2 Data and Instruction Caches |      |

| 1.4.3 Bus Interface Unit          |      |

| 1.4.4 Debug Support Unit          |      |

| 1.5 External Interface            |      |

| 1.5.1 Signals                     |      |

| 1.5.2 Bus Operation               |      |

| 1.5.3 System Support Functions    |      |

| 1.6 Development-Support Tools     | 1.10 |

### Chapter 2: Programmer's Model

| 2.1 Program Modes                                                                                                                                                                                                                                                                                                        |              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 2.2 Memory Organization                                                                                                                                                                                                                                                                                                  | 2-2          |

| 2.3 Registers                                                                                                                                                                                                                                                                                                            |              |

| <ul> <li>2.3.1 Register Windows</li> <li>2.3.2 Special Uses of the r Registers</li></ul>                                                                                                                                                                                                                                 | 2-7<br>2-7   |

| 2.3.4 Memory-Mapped Control Registers                                                                                                                                                                                                                                                                                    |              |

| 2.5 Instructions                                                                                                                                                                                                                                                                                                         |              |

| <ul> <li>2.5.1 Instructions</li> <li>2.5.2 Logical Instructions</li> <li>2.5.3 Arithmetic and Shift Instructions</li> <li>2.5.4 Control Transfer Instructions</li> <li>2.5.5 Load and Store Instructions</li> <li>2.5.6 Read and Write Control Register Instructions</li> <li>2.6 Data and Instruction Caches</li> </ul> |              |

| 2.6.1 Structure<br>2.6.2 Operation                                                                                                                                                                                                                                                                                       |              |

| 2.7 Interrupts and Traps                                                                                                                                                                                                                                                                                                 |              |

| 2.7.1 Trap Types<br>2.7.2 Trap Behavior<br>2.7.3 Reset and Error Modes                                                                                                                                                                                                                                                   | 2-51<br>2-53 |

| 2.8 Debug Support Unit                                                                                                                                                                                                                                                                                                   |              |

| <ul><li>2.8.1 Monitor Mode</li><li>2.8.2 Breakpoint Registers</li><li>2.8.3 Breakpoint Traps</li></ul>                                                                                                                                                                                                                   | 2-57         |

| 2.9 SPARC Compliance                                                                                                                                                                                                                                                                                                     |              |

### Chapter 3: Internal Architecture

| 3.1 Integer Unit                                   |      |

|----------------------------------------------------|------|

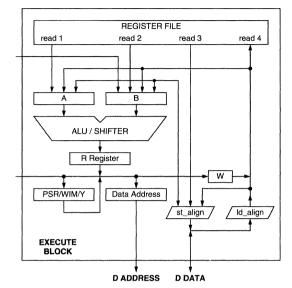

| 3.1.1   Block                                      |      |

| 3.1.2 A Block                                      |      |

| 3.1.3 E Block                                      |      |

| 3.1.4 Programmer-Visible State and Processor State |      |

| 3.1.5 IU Support for Debugging                     |      |

| 3.2 Data and Instruction Caches                    | 3-16 |

| 3.3 Bus Interface Unit                             | 3-17 |

| 3.3.1 Buffers                                      |      |

| 3.3.2 Exception Handling                           |      |

| 3.3.3 Effect on the Pipeline                       |      |

### Chapter 4: External Interface

| 4.1 Signals                          |     |

|--------------------------------------|-----|

| 4.1.1 Processor Control and Status   |     |

| 4.1.2 Memory Interface               |     |

| 4.1.3 Bus Arbitration                | 4-6 |

| 4.1.4 Peripheral Functions           |     |

| 4.1.5 Emulator Bus                   |     |

| 4.1.6 Test and Boundary-Scan         |     |

| 4.2 Bus Operation                    |     |

| 4.2.1 Exception Handling             |     |

| 4.2.2 Bus Cycles                     |     |

| 4.3 System Support Functions         |     |

| 4.3.1 System-Configuration Registers |     |

| 4.3.2 Same-Page Detection            |     |

| 4.3.3 Programmable Timer             |     |

#### **Chapter 5: Programming Considerations**

| 5.1 Initialization                                                                                                                                                                                                                                                                                                                                                                   |                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 5.1.1 Establishing the Processor State                                                                                                                                                                                                                                                                                                                                               | 5-2                                                              |

| 5.1.2 Configuring the System                                                                                                                                                                                                                                                                                                                                                         |                                                                  |

| 5.1.3 Initializing the On-Chip Cache                                                                                                                                                                                                                                                                                                                                                 | 5-4                                                              |

| 5.2 Trap Handling                                                                                                                                                                                                                                                                                                                                                                    |                                                                  |

| 5.3 Register and Stack Management                                                                                                                                                                                                                                                                                                                                                    |                                                                  |

| 5.3.1 Registers                                                                                                                                                                                                                                                                                                                                                                      |                                                                  |

| 5.3.2 Memory Stack                                                                                                                                                                                                                                                                                                                                                                   |                                                                  |

| 5.3.3 Functions Returning Aggregate Values                                                                                                                                                                                                                                                                                                                                           | 5-17                                                             |

| 5.3.4 Leaf Procedure Optimization                                                                                                                                                                                                                                                                                                                                                    |                                                                  |

| 5.3.5 Register Allocation Within a Window                                                                                                                                                                                                                                                                                                                                            |                                                                  |

| 5.3.6 Other Register and Window Usage Models                                                                                                                                                                                                                                                                                                                                         | 5-23                                                             |

| 5.4 Cache Management                                                                                                                                                                                                                                                                                                                                                                 | 5-24                                                             |

| 5.5 Division Routines Using the DIVScc Instruction                                                                                                                                                                                                                                                                                                                                   | 5-25                                                             |

| <b>J.J Division Rounnes Using the Division instruction</b>                                                                                                                                                                                                                                                                                                                           |                                                                  |

| -                                                                                                                                                                                                                                                                                                                                                                                    |                                                                  |

| 5.5.1 Simple Divide Step Examples                                                                                                                                                                                                                                                                                                                                                    | 5-25                                                             |

| -                                                                                                                                                                                                                                                                                                                                                                                    | 5-25<br>5-27                                                     |

| <ul> <li>5.5.1 Simple Divide Step Examples</li> <li>5.5.2 Signed Division with Doubleword Dividend (divs2)</li> <li>5.5.3 Signed Division with Word Dividend (divs1)</li> <li>5.5.4 Unsigned Division with Doubleword Dividend (divu2)</li> </ul>                                                                                                                                    |                                                                  |

| <ul> <li>5.5.1 Simple Divide Step Examples</li> <li>5.5.2 Signed Division with Doubleword Dividend (divs2)</li> <li>5.5.3 Signed Division with Word Dividend (divs1)</li> <li>5.5.4 Unsigned Division with Doubleword Dividend (divu2)</li> <li>5.5.5 Unsigned Division with Word Dividend (divu1)</li> </ul>                                                                        | 5-25<br>5-27<br>5-30<br>5-32<br>5-33                             |

| <ul> <li>5.5.1 Simple Divide Step Examples</li> <li>5.5.2 Signed Division with Doubleword Dividend (divs2)</li> <li>5.5.3 Signed Division with Word Dividend (divs1)</li> <li>5.5.4 Unsigned Division with Doubleword Dividend (divu2)</li> </ul>                                                                                                                                    | 5-25<br>5-27<br>5-30<br>5-32<br>5-33                             |

| <ul> <li>5.5.1 Simple Divide Step Examples</li> <li>5.5.2 Signed Division with Doubleword Dividend (divs2)</li> <li>5.5.3 Signed Division with Word Dividend (divs1)</li> <li>5.5.4 Unsigned Division with Doubleword Dividend (divu2)</li> <li>5.5.5 Unsigned Division with Word Dividend (divu1)</li> </ul>                                                                        |                                                                  |

| <ul> <li>5.5.1 Simple Divide Step Examples</li></ul>                                                                                                                                                                                                                                                                                                                                 | 5-25<br>.5-27<br>5-30<br>.5-32<br>5-33<br>.5-33<br>.5-34<br>5-37 |

| <ul> <li>5.5.1 Simple Divide Step Examples</li> <li>5.5.2 Signed Division with Doubleword Dividend (divs2)</li> <li>5.5.3 Signed Division with Word Dividend (divs1)</li> <li>5.5.4 Unsigned Division with Doubleword Dividend (divu2)</li> <li>5.5.5 Unsigned Division with Word Dividend (divu1)</li> <li>5.5.6 Divide Step In Support Of A To D Converter Compensation</li> </ul> |                                                                  |

| <ul> <li>5.5.1 Simple Divide Step Examples</li></ul>                                                                                                                                                                                                                                                                                                                                 |                                                                  |

| <ul> <li>5.5.1 Simple Divide Step Examples</li></ul>                                                                                                                                                                                                                                                                                                                                 |                                                                  |

| <ul> <li>5.5.1 Simple Divide Step Examples</li></ul>                                                                                                                                                                                                                                                                                                                                 |                                                                  |

| <ul> <li>5.5.1 Simple Divide Step Examples</li></ul>                                                                                                                                                                                                                                                                                                                                 |                                                                  |

### Chapter 6: System Design Considerations

| 6.1 Clocks                                                                                                                                                                                                                                               |      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 6.2 Memory and I/O Interfacing                                                                                                                                                                                                                           |      |

| <ul> <li>6.2.1 Interfacing SRAM</li> <li>6.2.2 Interfacing Page-Mode DRAM</li> <li>6.2.3 Interfacing EPROM and Other Devices with Slow Turn-off</li> <li>6.2.4 Illegal Memory Accesses</li> <li>6.2.5 I/O Interfacing Example: Ethernet Device</li></ul> |      |

| 6.3 DMA and Bus Arbitration                                                                                                                                                                                                                              |      |

| 6.4 MB86940 Peripheral Chip                                                                                                                                                                                                                              | 6-10 |

| 6.4.1 Interrupt Control<br>6.4.2 Counter/Timers<br>6.4.3 USARTs                                                                                                                                                                                          | 6-11 |

| 6.5 In-Circuit Emulation                                                                                                                                                                                                                                 | 6-11 |

| 6.6 Physical Design Issues                                                                                                                                                                                                                               | 6-12 |

#### **Chapter 7: Instruction Set**

| 7.1 Suggested Assembly Language Syntax |     |

|----------------------------------------|-----|

| 7.1.1 Register Names                   |     |

| 7.1.2 Special Symbol Names             | 7-2 |

| 7.1.3 Values                           |     |

| 7.1.4 Labels                           |     |

| 7.1.5 Comments                         |     |

| 7.2 Syntax Design                      |     |

| 7.3 Synthetic Instructions             |     |

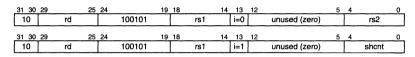

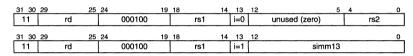

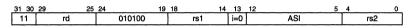

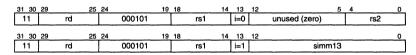

| 7.4 Binary Opcodes                     |     |

| 7.5 Instruction Set                    |     |

#### **Chapter 8: JTAG**

| 8.1 Introduction                   |      |

|------------------------------------|------|

| 8.2 Test Access Ports (TAP)        |      |

| 8.2.1 TCK                          | 8-2  |

| 8.2.2 TMS                          |      |

| 8.2.3 TDI                          | 8-3  |

| 8.2.4 TDO                          |      |

| 8.2.5 –TRST                        | 8-3  |

| 8.3 Test Instructions              |      |

| 8.3.1 BYPASS                       | 8-4  |

| 8.3.2 SAMPLE/PRELOAD               |      |

| 8.3.3 EXTEST                       | 8-5  |

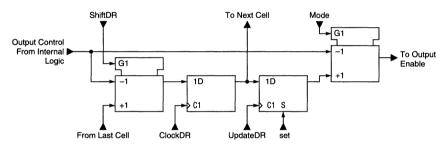

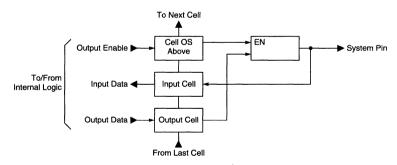

| 8.3.4 JTAG Cells                   |      |

| 8.3.5 Input Cell                   | 8-5  |

| 8.3.6 Output Cell                  | 8-6  |

| 8.3.7 I/O Cell                     | 8-6  |

| 8.3.8 Output Cell with Set         | 8-6  |

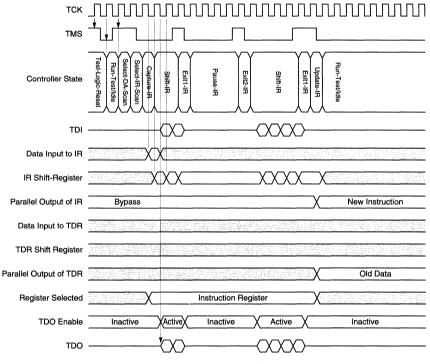

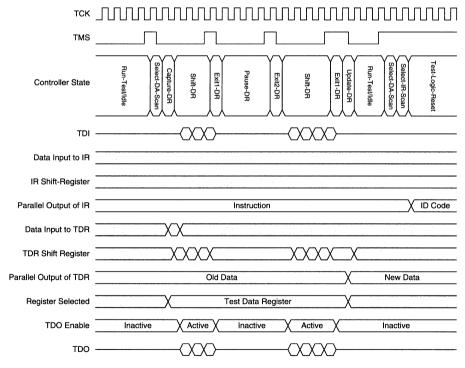

| 8.4 Operation                      |      |

| 8.5 The TAP Controller             |      |

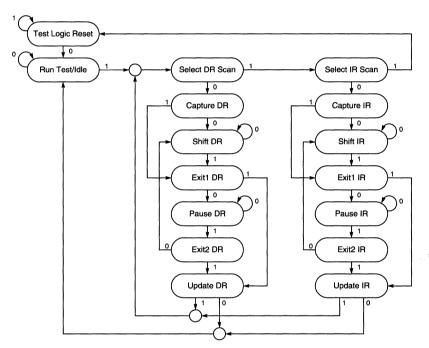

| 8.5.1 TAP Controller State Diagram | 8-10 |

| 8.6 MB86930 JTAG Pin List          |      |

# Overview

The SPARClite family is a collection of SPARC-based microprocessors optimized for use in embedded systems. Processors in the SPARClite family conform to the SPARC version 8 architecture definition; in particular, they are fully compatible with existing SPARC code and existing SPARC development environments. The MB86930 processor is the first member of the SPARClite family. This chapter provides a quick introduction to the processor architecture and the MB86930 in particular. Subsequent chapters will review this material in more detail.

#### **1.1 General Description**

The MB86930 is a high-performance processor suitable for use in embedded control applications such as printers, scanners, robotic machinery, telecom switches and monitors, and I/O subsystems. It operates at clock speeds up to 50 MHz, executing SPARC instructions at a maximum rate of 46 MIPs, and includes 2 Kbytes of instruction and 2 Kbytes of data cache on chip. It is available in a variety of packages, depending on clock-speed and power-dissipation requirements.

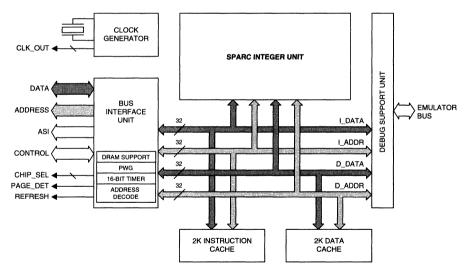

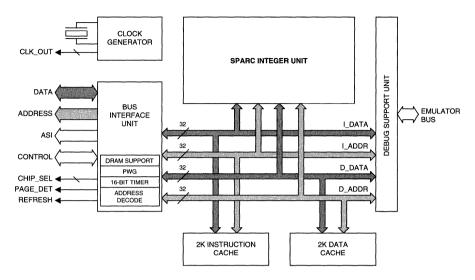

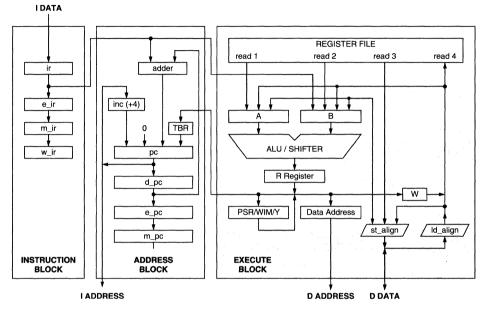

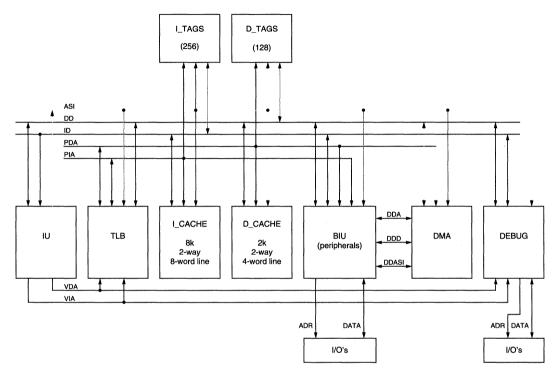

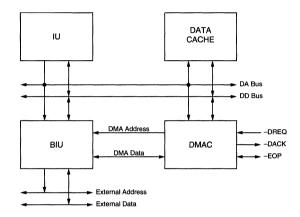

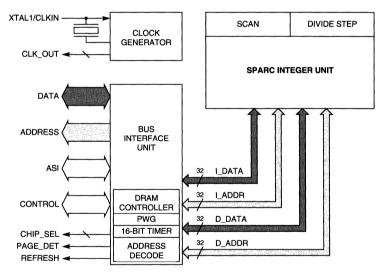

The processor consists of a Harvard (Aiken) architecture Integer Unit (IU) core, instruction and data caches, a Bus Interface Unit (BIU), and an In-Circuit Emulator Unit (EMU). These units are connected internally over separate instruction and data buses, and to external memory and I/O over a unified (instruction and data) bus which carries 32 bits of address and 32 bits of data.

The register file in the IU implements 8 register windows. An integer multiply unit (MU) within the IU speeds applications which require integer multiplication. The processor uses software to emulate floating-point instructions at rates up to 1 MFLOP.

The internal instruction and data caches make it possible to sustain a processing rate close to one cycle per instruction by providing the IU at 50 MHz with a maximum aggregate data throughput of 400 Mbytes/sec (two 32-bit words per cycle). The maximum external data throughput is 200 Mbytes/sec (1 word per cycle). In many applications, the internal caches make it possible to maintain high throughput even with slow external memory; SPARClite is therefore a cost-effective solution in embedded control applications that require high processing throughput but cannot tolerate the cost of large, high-speed memories.

The MB86930 is designed with Fujitsu's AS technology, a  $1\mu$  and 3-level metal process with minimum drawn transistor lengths of  $0.8\mu$ . The design of the data path and other arrayed blocks is fully custom to optimize die area and speed. Random control blocks are based on standard cells. All circuits are fully static.

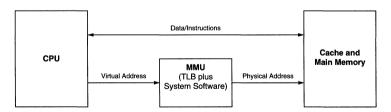

While it does provide a mechanism for code and data protection, the MB86930 is optimized for embedded applications which do not require virtual-to-physical address translation. Using an MB86930 processor in a virtual-memory system, while possible, would require an external Memory Management Unit for address translation.

#### **1.2 Special Features**

This section lists some of the features which give the MB86930 its superior speed, flexibility and efficiency and make it an ideal choice for a wide variety of low cost, high-performance embedded systems.

- Fast Instruction Execution: The instruction set is streamlined and hardwired for fast execution, with most instructions executing in a single cycle. At 50 (40,30,20) MHz, the MB86930 executes instructions at a peak rate of 50 (40,30,20) MIPs, and can sustain performance of 46 (37,28,18) MIPs. The Integer Unit (IU) features a 5-stage pipeline which has been designed to handle data interlocks, has an optimized branch handler for efficient control transfers, and a bus interface to handle single cycle bus accesses to on-chip cache.

- Large Register Set: An internal register file consisting of 136 registers organized into eight overlapping windows speeds interrupt response time and context switches. The register file minimizes accesses to memory during procedure linkages and facilitates passing of parameters and assignment of variables, reducing code in many programs. Reduced code, in turn, can fit more easily into the instruction cache.

**Overview - Special Features**

# FUĴÎTSU

- **On-Chip Caches:** On-chip data and instruction caches decouple the processor from external memory latency. The caches are organized as two-way set-associative for improved hit rates, as compared with direct-mapped caches.

- **Cache Locking:** Both data and instruction entries can be locked into their respective caches to ensure deterministic response and highest performance for critical or frequently recurring routines. Maximum flexibility has been designed into the cache to allow all or selected portions to be locked.

- Separate Instruction and Data Paths On-Chip: Separate 32-bit instruction and data buses provide a high-bandwidth interface between the IU and on-chip cache. These buses support single cycle instruction execution as well as single cycle data transfers with the cache. The on-chip bus design also supports future expansion of the MB86930.

- **System Support Functions:** The requirement for glue logic between the MB86930 and the system is minimized by providing programmable chip selects, programmable wait-state circuitry, and support for connection to fast page-mode DRAM. Multiple bus masters are supported through a simple handshake protocol.

- **Clock Generator:** To simplify clock design, a crystal can be connected directly to the on-chip oscillator, or an external clock source can be used. A phase-locked loop minimizes the skew between on- and off-chip clocks.

- Enhanced Instruction Set: The MB86930 incorporates a fast integer multiply instruction which executes in a fast 5, 3 or 2 cycles for 32-bit, 16-bit or 8-bit operands. An integer divide-step instruction cuts divide times by a factor of 5 to 10 over previous SPARC implementations. A scan instruction supports a single-cycle search for the most significant non-sign bit in a word.

- **Fully Static Circuit Design:** Its static design gives the MB86930 superior noise immunity. Future members of the SPARClite family will support a low-power mode, in which the processor clock can be slowed or stopped for arbitrary periods of time to reduce operating current with no loss of internal state.

- **Test and Debug Interface:** The MB86930 supports production test through industry standard JTAG boundary scan. Hardware emulation is supported with on-chip breakpoint and single step logic. A dedicated emulator bus provides a means to trace transactions between the integer unit and on-chip cache.

#### 1.3 Programmer's Model

This section briefly introduces those aspects of the SPARClite processor architecture which are visible to software: the user and supervisor modes of program execution; the organization of the address space; the processor's register set, supported data types, and instruction set; the on-chip caches; and interrupts and traps. Each of the topics discussed here is developed more fully in subsequent chapters.

#### 1.3.1 Program Modes

The SPARClite architecture supports protection in multitasking environments by providing two mutually exclusive modes of program execution, *user mode* and *supervisor mode*. Certain instructions are privileged, and can only be executed when the processor is in supervisor mode. Any attempt to execute a privileged instruction in user mode causes a trap.

Typically, application programs run in user mode, while operating systems run in supervisor mode. On reset, the processor is in supervisor mode. To enter user mode, software must clear a bit in the Processor State Register. The processor enters supervisor mode from user mode only when a hardware reset, an interrupt, or a trap occurs.

#### 1.3.2 Memory Organization

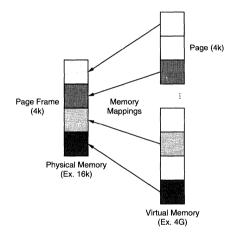

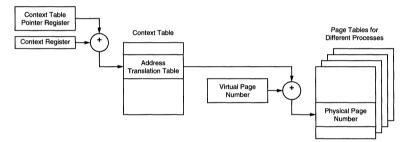

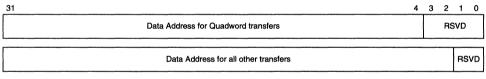

The processor can directly address up to 1 Terabyte of memory, organized into 256 address spaces of 4 GB each. Every external access involves an 8–bit Address Space Identifier (ASI), as well as a 32-bit address. The ASI selects one of the address spaces, and the 32-bit address selects a location within that space.

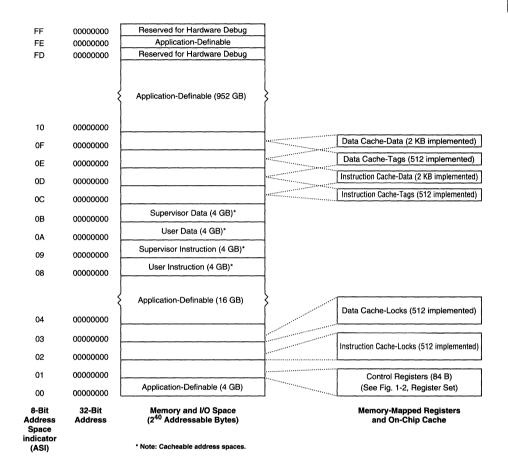

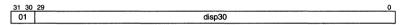

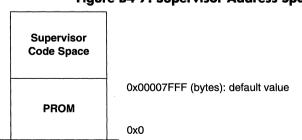

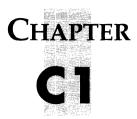

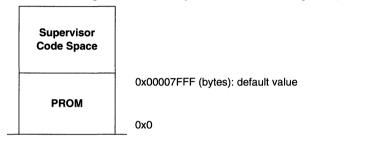

The use of four of the address spaces are defined in the SPARC architecture: the User Instruction, Supervisor Instruction, User Data, and Supervisor Data spaces. SPARClite defines additional address spaces, which are used for memory-mapped control registers and for the data and instruction caches; two further address spaces are reserved for hardware debug. The remaining spaces are application-definable; any of them can be used for either data memory or I/O. All I/O is memory-mapped. The organization of the entire addressable range is illustrated in Figure 1-1.

# FUĴÎTSU

Figure 1-1. Address-Space Organization

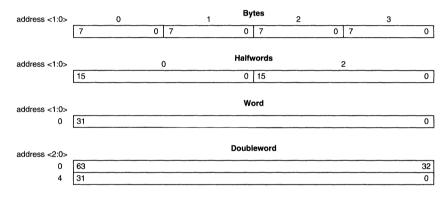

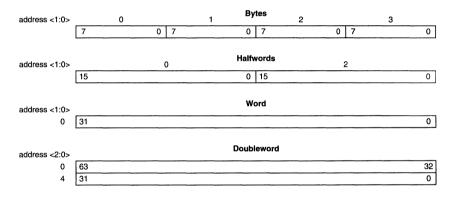

Loads and stores are the only instructions that cause external accesses. Versions of these instructions exist for transferring bytes, half-words, words and double words between external memory (or I/O) and processor registers. In user mode, only the user instruction and data spaces are accessible; accessing any of the remaining 254 address spaces requires the processor to be in supervisor mode.

The MB86930 processor does not contain memory-management hardware; virtual-address translation can be handled by software, or by an external memorymanagement unit with the on-chip caches disabled.

#### 1.3.3 Registers

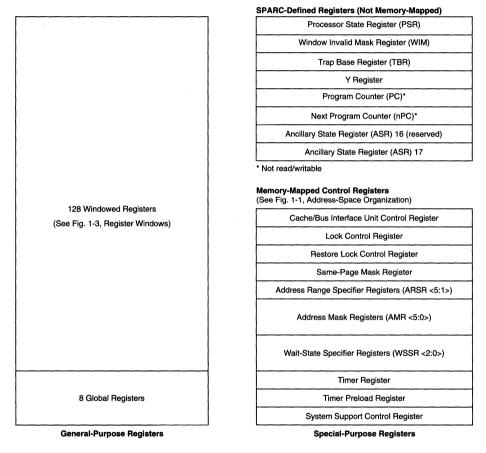

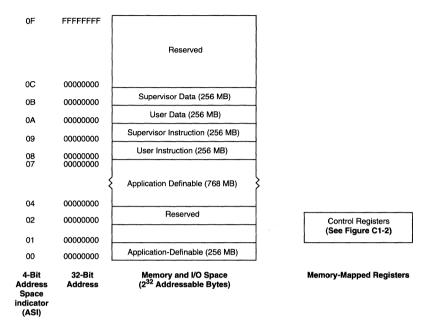

All registers are 32 bits wide. There are *general-purpose registers*, whose contents have no pre-assigned meaning, and *special-purpose registers*, which contain control and status information or special data values. Some of the special-purpose registers are defined in the SPARC architecture; the rest are SPARClite- or device-specific. The non-SPARC special-purpose registers are memory-mapped. The general-purpose registers, and the special-purpose Y Register, are the only ones which can be accessed in user mode. The register set is illustrated in Figure 1-2.

Figure 1-2. Register Set

#### **General-Purpose Registers**

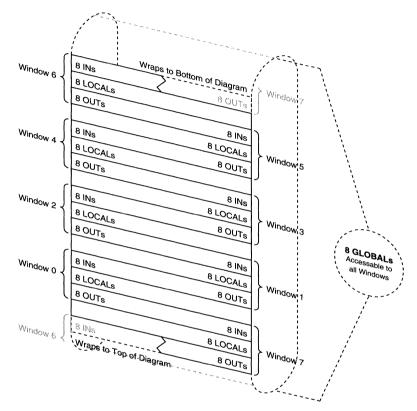

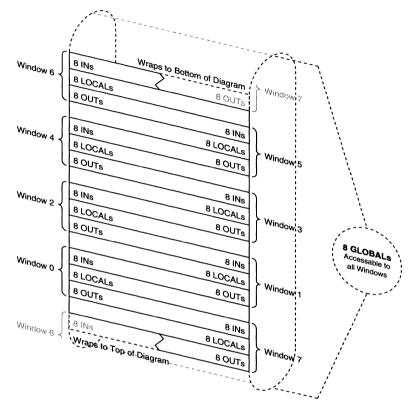

In the MB86930, there are 136 general-purpose registers; 8 of these are *global registers*; the other 128 are divided into 8 overlapping blocks, or *windows*. Each

Overview - Programmer's Model

# FUJITSU

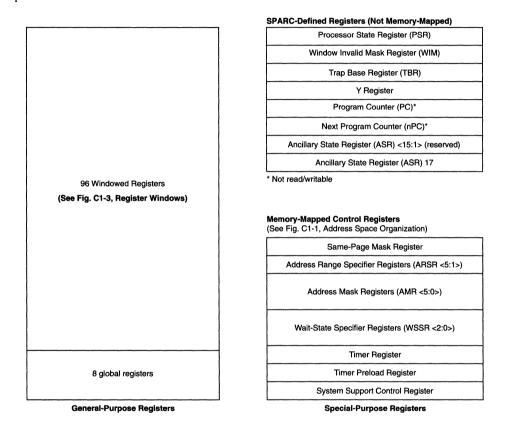

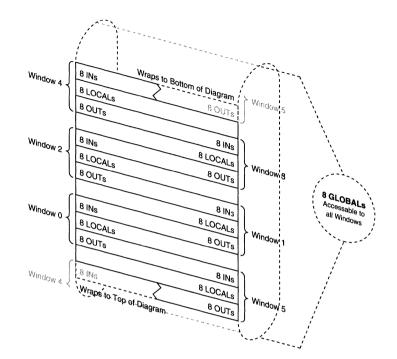

window contains 24 registers. Of these, 8 are *local* to the window, 8 are *"out"* registers shared with the adjacent window below, and 8 are *"in"* registers shared with the adjacent window above. This organization is illustrated in Figure 1-3.

Figure 1-3. Register Windows

At any given time, 32 general-purpose registers can be accessed directly: the 8 global registers, and the 24 registers of the currently active window. The value in the Current Window Pointer (CWP) field of the Processor State Register (PSR) determines which window is active.

The overlap between adjacent windows makes it easy to pass parameters to a subroutine. Values to be passed are written to the "out" registers of the current window, which are the same as the "in" registers of the adjacent window. A SAVE instruction can then be used to decrement the Current Window Pointer, making the parameter values available to the subroutine without moving any data. A RESTORE instruction can be used to increment the CWP upon return

from the subroutine. In effect, the general-purpose registers cache the top portion of the run-time stack.

The window overlap also speeds interrupt handling, as interrupts automatically decrement the CWP, giving the interrupt routing its own window. The SPARC architecture requires a free window to be available to handle these traps.

#### **Special-Purpose Registers**

The special-purpose registers include the control and status registers defined by the SPARC architecture, plus a collection of memory-mapped registers which control peripheral functions.

Special instructions exist for reading and writing each of the SPARC control and status registers, except for the Program Counter and the Next Program Counter. The Y Register can be read and written in user mode; the instructions that access the other SPARC-defined registers are privileged.

The memory-mapped registers can be read and written with the alternate-space load and alternate-space store instructions, which are also privileged.

The SPARC-defined registers, shown in Figure 1-2 above, are:

- Processor State Register (PSR)—The primary processor control and status register. It contains *mode* fields, which are set by the operating system to configure the processor, and *status* fields, which are set by the processor to indicate the effects of instruction execution.

- Window Invalid Mask Register (WIM)—Used by software to detect the occurrence of register file underflows and overflows. It contains one mask bit for each register window. If an operation which normally increments or decrements the Current Window Pointer would cause the CWP to point to a window whose corresponding WIM bit equals 1, a trap occurs.

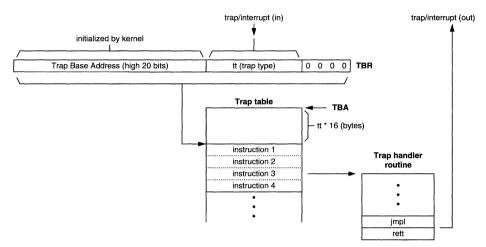

- Trap Base Register (TBR)—Contains three fields used by the processor to generate the address of the service routine when an interrupt or trap occurs.

- Y Register—Used in stepwise multiplication and division routines based on the MULScc and DIVScc instructions. Also used for integer multiply operations.

- Program Counter (PC)—Contains the word address of the instruction currently being executed by the Integer Unit. The PC cannot be directly read or written.

- Next Program Counter (nPC)—Contains the word address of the next instruction to be executed, assuming that no trap occurs. The nPC cannot be directly read or written.

- Ancillary State Registers (ASR[31:1])—The SPARC definition includes 31 Ancillary State Registers, 15 of which (ASR[15:1]) are reserved for future use.

The remaining ASR's can be defined and used in any way by SPARC implementations. SPARClite defines the following ASR:

ASR17— Used to enable and disable single-vector trapping. (When this feature is enabled, all traps vector to a single location.) Single vector trapping provides a small memory alternative to the standard 1K word trap table.

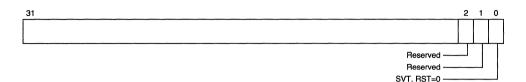

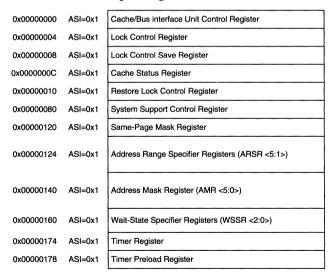

The memory-mapped SPARClite-specific registers, shown in Figure 1-2, are:

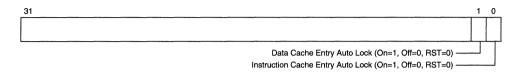

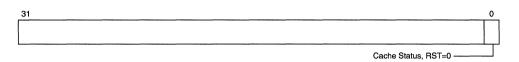

- Cache/Bus Interface Unit Control Register—Controls the operation of the data and instruction caches, and the write and prefetch buffers of the Bus Interface Unit.

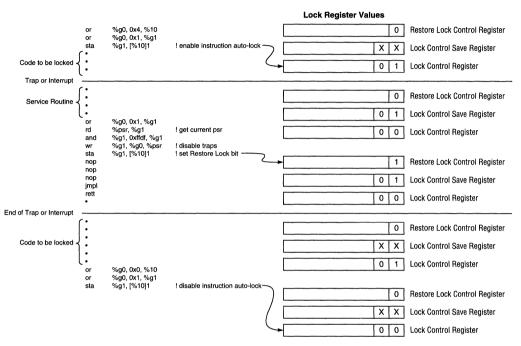

- Lock Control Register—Controls the locking of individual entries in the data and instruction caches.

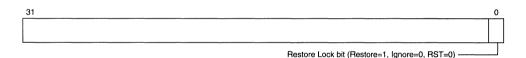

- Restore Lock Control Register—Enables or disables the restoration of the Lock Control Register upon return from an interrupt or a hardware trap.

- Same-Page Mask Register—Controls the operation of the same-page detection logic by specifying which bits of the current ASI and address are to be compared with those of the previous ASI and address.

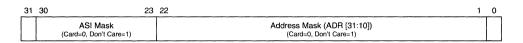

- Address Range Specifier Registers (ARSR[5:1])—Control the assertion of the Chip-Select outputs (–CS[5:1]). –CSn is asserted when the value on the address bus falls in the address range specified by ARSRn. –CS0 is asserted on accesses to the lowest address range in Supervisor Instruction Space.

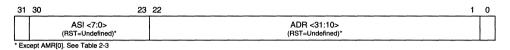

- Address Mask Registers (AMR[5:0])—AMRn controls the comparison of the current address with ARSRn by specifying which bits are to be compared and which are "don't cares."

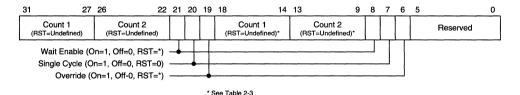

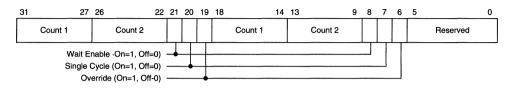

- Wait-State Specifier Registers (WSSR[2:0])—Determine, for each address range, the number of clock cycles between the time an address in that range appears on the address bus and the time the processor automatically generates the –READY signal. This makes it possible for memory and I/O devices with different access times to be connected to the processor without additional logic.

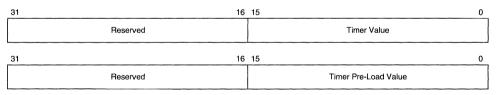

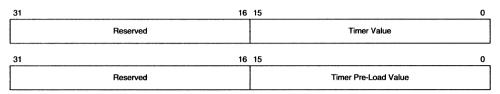

- Timer Register—Contains the current timer count.

- Timer Pre-Load Register—Contains the value which is loaded into the timer when the timer overflows.

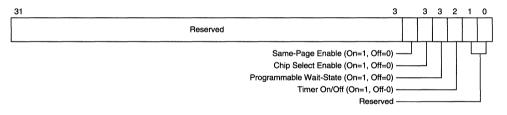

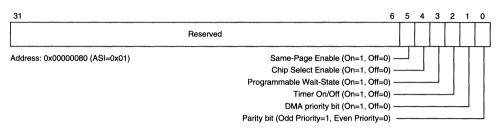

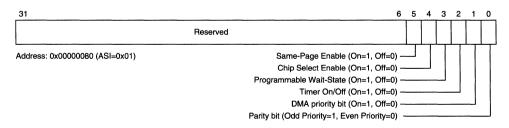

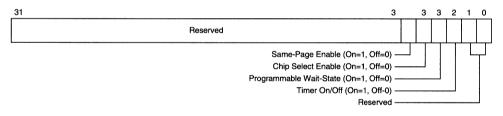

- System Support Control Register—Enables or disables same-page detection, chip-select, programmable wait-states, and the timer, independently of one another.

### 1.3.4 Data Types

SPARClite instructions support the Signed Integer, Unsigned Integer, and Tagged data formats of the SPARC definition. The Integer types are supported in byte (8-bit), half-word (16-bit), word (32-bit), and double-word (64-bit) widths. The

Tagged type is one word (32 bits) in width. Hardware support is not provided for the floating-point types; these can be handled in software.

#### 1.3.5 Instructions

SPARClite provides an upward-compatible superset of the SPARC (version 8) instruction set. The additional instructions—integer divide-step, and scan for first changed bit — are supported for the sake of higher performance in embedded applications. Table 1-1 lists the SPARClite instruction set. In the MB86930 processor, the floating-point and coprocessor instructions defined in the SPARC architecture are trapped for software emulation.

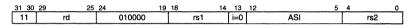

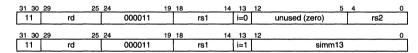

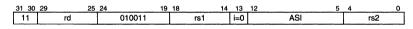

Each instruction is a single 32-bit word. The instruction set can be divided into five functional groups:

- 1. *Logical*—Bit-wise boolean operations. Each logical instruction comes in two versions: one leaves the integer condition codes in the Processor State Register unchanged; the other changes the condition codes as a side effect.

- 2. *Arithmetic and Shift*—Integer arithmetic, logical and arithmetic shifts. Besides the standard arithmetic operations, SPARC provides instructions to perform tagged arithmetic. In tagged arithmetic, the two least-significant bits of each operand are used to indicate the (user-defined) data type of the operand. The tagged arithmetic instructions set a condition code if the tag of an operand is not zero.

Besides the arithmetic instructions defined in the SPARC architecture, SPARClite provides:

- A *divide-step* instruction, which can be used to construct efficient iterative integer division algorithms.

- A *scan* instruction, which determines the first bit in a word which differs from the most-significant bit. The scan instruction can be used to simplify and accelerate many important operations, like normalizing numbers with redundant sign bits.

Most of the arithmetic instructions come in two versions: one of them leaves the integer condition codes unchanged, while the other changes the condition codes as a side effect of execution.

- 3. *Control Transfer*—Branches, calls, jumps, returns from trap, and conditional traps. The target address of the control transfer is computed either by adding a specified offset to the value in the Program Counter, or by adding two source operands. The transfer of control either occurs immediately after the control transfer instruction, or is delayed for one further instruction.

- 4. *Load and Store*—External accesses. Load and store are the only instructions that read and write to external devices (including memory). Bytes, half-words, words and double words can be transferred to and from processor registers.

Special instructions access alternate address spaces. Attempts at unaligned accesses are trapped, and must be carried out under software control.

5. *Read and Write Control Registers*—Access the Program State Register, Window-Invalid Mask Register, Trap-Base Register, Y Register, and Ancillary State Registers. There are also instructions for incrementing and decrementing the Current Window Pointer. With one exception, writes to the control registers are delayed for three instruction cycles. The three instructions following a write, therefore, should not attempt to use or modify the values written. A write to the Y Register, however, is not delayed: it is completed before the next instruction is executed.

| Group      | Opcode                                                                                   | Name                                                                                                                                                                                     |

|------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Logical    | AND (ANDcc)<br>ANDN (ANDNcc)<br>OR (ORcc)<br>ORN (ORNcc)<br>XOR (XORcc)<br>XNOR (XNORcc) | And (and modify cc)<br>And Not (and modify icc)<br>Inclusive-Or (and modify icc)<br>Inclusive-Or Not (and modify icc)<br>Exclusive-Or (and modify icc)<br>Exclusive-Nor (and modify icc) |

| Arithmetic | ADD (ADDcc)<br>ADDX (ADDXcc)                                                             | Add (and modify icc)<br>Add with Carry (and modify icc)                                                                                                                                  |

|            | TADDcc (TADDccTV)                                                                        | Tagged Add and modify icc (and Trap on overflow)                                                                                                                                         |

|            | SUB (SUBcc)<br>SUBX (SUBXcc)                                                             | Subtract (and modify icc)<br>Subtract with Carry (and modify icc)                                                                                                                        |

|            | TSUBcc (TSUBccTV)                                                                        | Tagged Subtract and modify icc (and Trap on overflow)                                                                                                                                    |

|            | MULScc                                                                                   | Multiply Step and modify icc                                                                                                                                                             |

|            | SMUL<br>UMUL<br>SMULcc<br>UMULcc<br>DIVScc<br>SCAN                                       | Signed Multiply<br>Unsigned Multiply<br>Signed Multiply (and modify icc)<br>Unsigned Multiply (and modify icc)<br>Divide-Step (and Modify icc)<br>Scan for bit different than MSB        |

| Shift      | SLL<br>SRL<br>SRA                                                                        | Shift Left Logical<br>Shift Right Logical<br>Shift Right Arithmetic                                                                                                                      |

| Control    | Bicc                                                                                     | Branch on integer condition codes                                                                                                                                                        |

| Transfer   | CALL<br>JMPL                                                                             | Call<br>Jump and Link                                                                                                                                                                    |

|            | RETT                                                                                     | Return from Trap                                                                                                                                                                         |

|            | Ticc                                                                                     | Trap on integer condition codes                                                                                                                                                          |

#### Table 1-1: Instruction Set

| Group                                     | Opcode                                                                    | Name                                                                                                                                                                                                                           |

|-------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Load<br>and Store                         | LDSB (LDSBA)<br>LDSH (LDSHA)<br>LDUB (LDUBA)<br>LDUH (LDUHA<br>LDD (LDDA) | Load Signed Byte (from Alternate space)<br>Load Signed Halfword (from Alternate space)<br>Load Unsigned Byte (from Alternate space)<br>Load Unsigned Halfword (from Alternate space)<br>Load Doubleword (From Alternate space) |

|                                           | STB (STBA)<br>STH (STHA)<br>ST (STA)<br>STD (STDA)                        | Store Byte (into Alternate Space)<br>Store Halfword (into Alternate space)<br>Store Word (into Alternate space)<br>Store Doubleword (into Alternate space)                                                                     |

|                                           | LDSTUB (LDSTUBA)<br>SWAP (SWAPA)                                          | Atomic Load-Store Unsigned Byte (in Alternate space)<br>Swap r Register with Memory (in Alternate space)                                                                                                                       |

|                                           | SAVE<br>RESTORE                                                           | Save caller's window<br>Restore caller's window                                                                                                                                                                                |

|                                           | SETHI                                                                     | Set High 22 bits of r register                                                                                                                                                                                                 |

| Read and<br>Write<br>Control<br>Registers | RDY<br>RDPSR<br>RDWIM<br>RDTBR<br>RDASR                                   | Read Y register<br>Read processor State Register<br>Read Window invalid Mask Register<br>Read Trap Base Register<br>Read Ancillary State Register                                                                              |

|                                           | WRY<br>WRPSR<br>WRWIM<br>WRTBR<br>WRASR                                   | Write Y register<br>Write processor State Register<br>Write Window invalid Mask Register<br>Write Trap Base Register<br>Write Ancillary State Register                                                                         |

|                                           | UNIMP                                                                     | Unimplemented instruction                                                                                                                                                                                                      |

Table 1-1: Instruction Set (Continued)

#### 1.3.6 Data and Instruction Caches

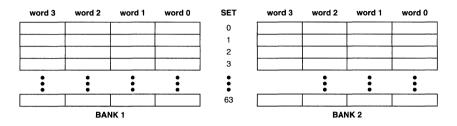

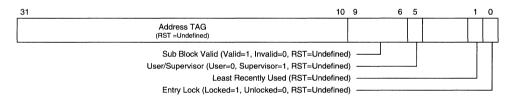

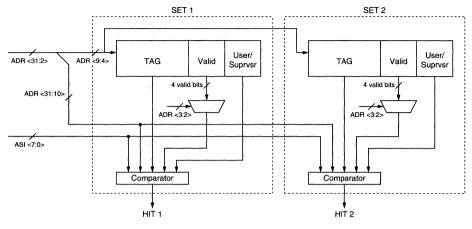

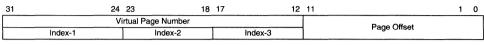

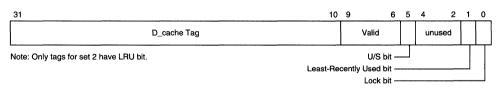

Each member of the SPARClite family contains separate data and instruction caches on-chip. In the MB86930 processor, each cache is 2 Kbytes in size, organized into two banks of sixty-four 4-word lines. Each cache line has a 22-bit *address tag*, which indicates the memory location to which the line is currently mapped. A cache line, together with its address tag and status bits, is often called a *cache entry*. The organization of each cache is *two-way set associative*; that is, each address in memory can be mapped to either of two locations in the cache.

There are three modes of cache operation: *normal, global locking,* and *local locking.* In normal mode, when the integer unit requests a read to a data or instruction address which is not found in the appropriate cache, the memory block containing the requested address is read into the cache, replacing one of the current cache entries. The locking modes prevent either an entire cache, or just selected entries, from being over written in this way. The locking modes thus allow time-critical routines to be locked into cache. Thanks to the set-associative organization, as much as one whole bank of a cache can be locked while the remaining bank continues to operate as a direct-mapped cache.

In normal mode, the data cache uses a write-through update policy, and allocates a cache entry only on a load. Writes to locked data entries, however, are not written through to main memory. In this way, a portion of the data cache can be used as fast on-chip RAM which is not mapped to external memory.

Cache tags and data are memory-mapped, and can be directly read and written using the alternate-space load and store instructions. These instructions are privileged.

Subsequent chapters discuss the cache in greater detail: *Programmer's Model* discusses cache locking; *Programming Considerations* contains hints for using the onchip cache to best advantage.

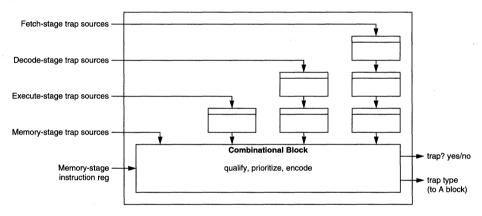

### 1.3.7 Interrupts and Traps

In this manual, we distinguish between *interrupts*—which are initiated by external interrupt signals, asynchronously with respect to processor operations, and *traps*—which are caused by instructions, and so are necessarily synchronous. During system operation, external interrupts are generally unavoidable; traps, however, can and should be kept to a minimum by careful software design and testing.

Interrupt response time is critical in many embedded applications. The total response time includes the time required for the processor to finish its current task after recognizing an interrupt, and the time required to switch contexts (if necessary) and begin executing the interrupt service routine. In the SPARClite family, non-interruptible multi-cycle events are minimized, (i.e., Cache refills which take multiple cycles to completely fill a cache line, are designed so they can be interrupt after every word load). This reduces both average and maximum interrupt latency. When an interrupt is detected, the processor switches to a new window. In this way, the current values in the general-purpose registers don't have to be saved before interrupt service begins. Furthermore, service routines can be locked into the cache, making them available for immediate access.

The MB86930 processor provides direct support for 15 distinct interrupt priority levels; each level can service multiple interrupt sources. Supervisor-mode software can mask up to 14 of these levels; the highest level is non-maskable (if ET=1).

An interrupt or trap (other than reset) causes control to be transferred to an address generated by the Trap Base Register. One field in the TBR contains the base address of the trap dispatch table. Normally, an 8-bit *trap type number* serves as an offset into this table. When *single-vector trapping* is enabled, however, control

passes to the base address of the trap table (with tt=0), regardless of the trap type. Reset always traps to address 0.

Up to 256 trap types can be distinguished on the basis of the 8-bit trap type number. Of these, half are reserved for hardware interrupts and traps; all but one of the others are programmer-initiated (see the discussion of the Ticc instruction in the *Programmer's Model* chapter). One trap type is defined in SPARClite to support in-circuit emulation. The various trap types are listed, in order of priority, in Table 1-2.

| Тгар                         | Priority | tt      |

|------------------------------|----------|---------|

| reset                        | 1        | _       |

| instruction_breakpoint       | 1.5      | 255     |

| data_breakpoint              | 1.5      | 255     |

| instruction_access_exception | 2        | 1       |

| privileged_instruction       | 3        | 3       |

| illegal_instruction          | 4.       | 2       |

| fp_disabled                  | 5        | 4       |

| cp_disabled                  | 5        | 36      |

| window_overflow              | 6        | 5       |

| window_underflow             | 7        | 6       |

| mem_address_not_aligned      | 8        | 7       |

| data_access_exception        | 10       | 9       |

| tag_overflow                 | 11       | 10      |

| trap_instruction (Ticc)      | 12       | 128 255 |

| interrupt_level_15           | 14       | 31      |

| interrupt_level_14           | 15       | 30      |

| interrupt_level_13           | 16       | 29      |

| interrupt_level_12           | 17       | 28      |

| interrupt_level_11           | 18       | 27      |

| interrupt_level_10           | 19       | 26      |

| interrupt_level_9            | 20       | 25      |

| interrupt_level_8            | 21       | 24      |

| interrupt_level_7            | 22       | 23      |

| interrupt_level_6            | 23       | 22      |

| interrupt_level_5            | 24       | 21      |

| interrupt_level_4            | 25       | 20      |

| interrupt_level_3            | 26       | 19      |

| interrupt_level_2            | 27       | 18      |

| interrupt_level_1            | 28       | 17      |

#### Table 1-2: Trap Types and Priorities

The expression *trapped instruction* refers, in the case of a synchronous trap, to the instruction which caused it. In the case of an interrupt, the trapped instruction is the one which was about to execute when the interrupt occurred.

The Integer Unit supports *precise traps*—when an interrupt or trap occurs, the saved state of the processor reflects the completion of all instructions prior to the trapped instruction, but no subsequent instructions (including the trapped

Overview - Programmer's Model

instruction). Hardware guarantees that upon return from the service routine, the Program Counter points to the trapped instruction or the following instruction if the trapped instruction was emulated.

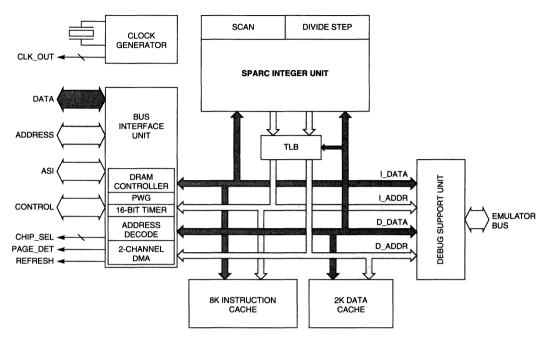

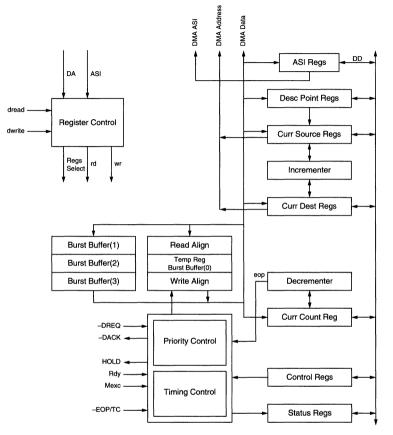

#### 1.4 Internal Architecture

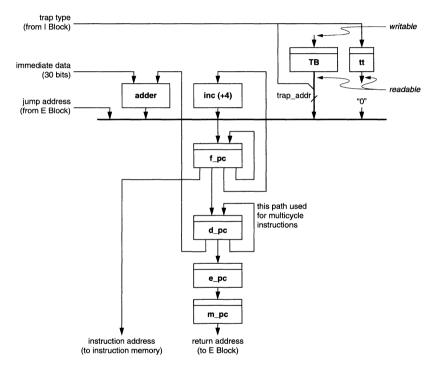

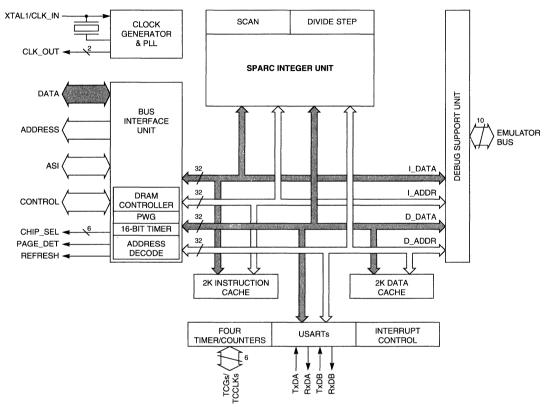

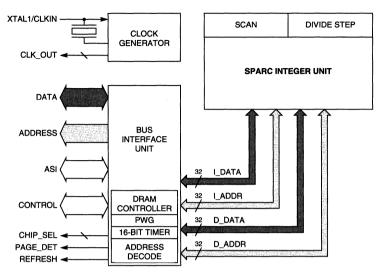

The internal architecture of SPARClite family processors is illustrated in Figure 1-4. The processor core consists of an Integer Unit which implements a superset of the SPARC integer instruction set. Separate on-chip caches are provided for data and instructions. The Bus Interface Unit handles the interface between the processor and the system. A Clock Generator with built-in phase-locked loop simplifies system clock design. Finally, the Debug Support Unit provides hardware support for in-circuit emulation. Internally, the various functional units are connected by separate instruction and data buses. For connection with external memory and I/O, a unified address bus and a unified data bus are extended off-chip. The main functional units are discussed briefly below, and more fully in the *Internal Architecture* chapter.

Figure 1-4. Internal Architecture (Block Diagram)

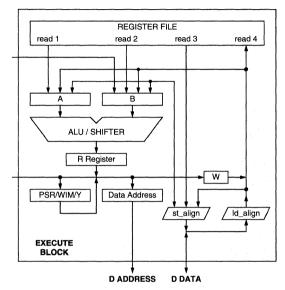

#### 1.4.1 Integer Unit

The Integer Unit (IU) is a compact, fully custom implementation of the SPARC architecture. The IU is hard-wired for high performance. Its internal functional units are designed around a modular architecture and can be customized to meet different application requirements. In the MB86930, for example, this flexibility

was used to provide direct hardware support for integer multiplication, and to extend the SPARC instruction set by supporting divide-step and scan instructions.

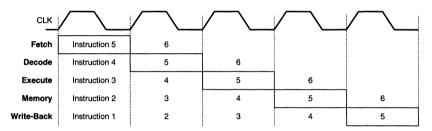

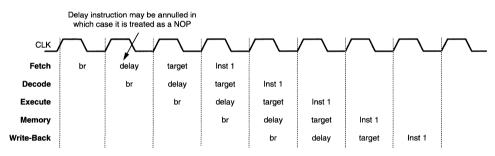

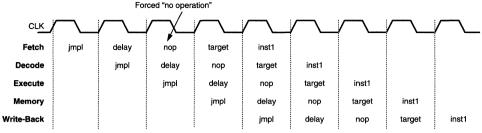

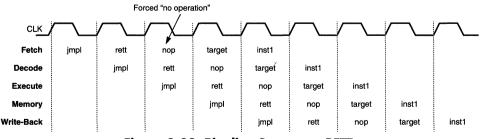

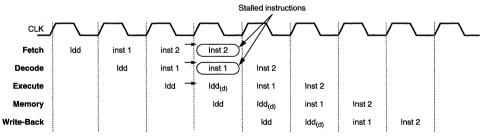

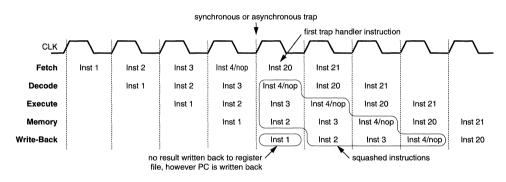

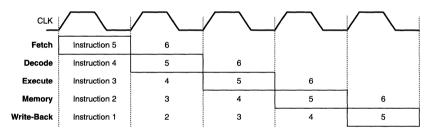

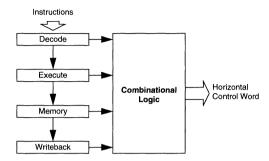

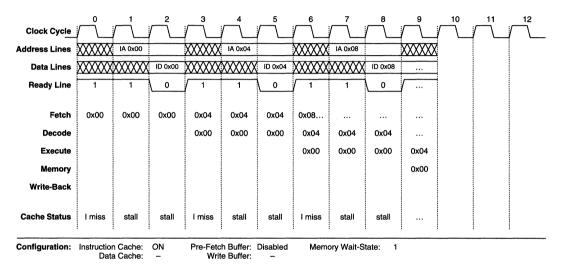

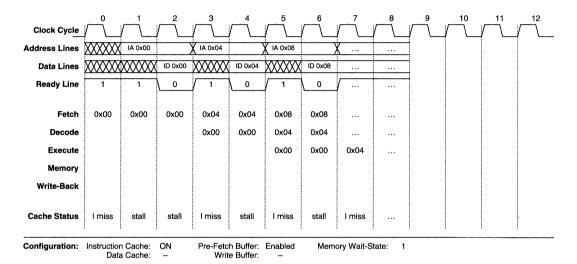

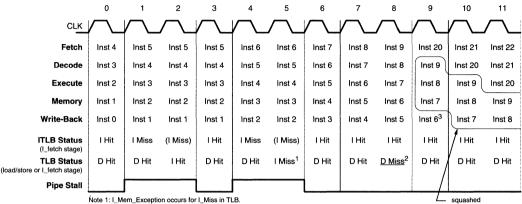

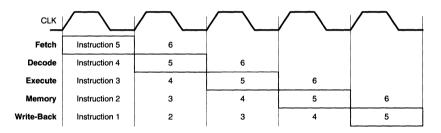

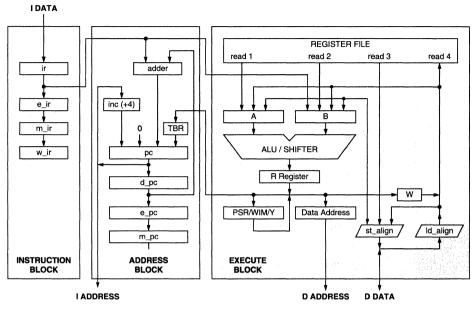

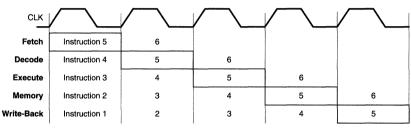

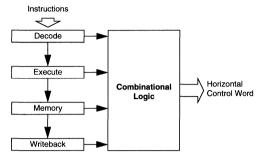

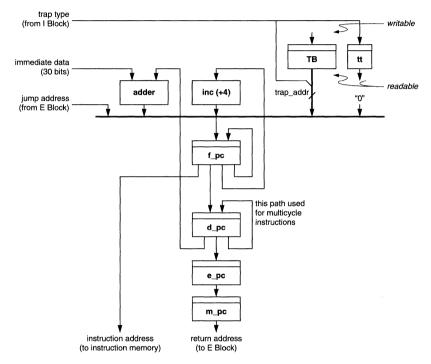

The IU implements a five-stage instruction pipeline to allow a sustained execution rate of nearly one instruction per cycle. The operation of the pipeline under ideal conditions is illustrated in Figure 1-5. The pipeline consists of the following stages:

- Fetch (F)—One of the instruction memory spaces is addressed and returns an instruction. (Figure 1-5 below assumes a hit in the instruction cache.)

- Decode (D)—The instruction is decoded; the register file is addressed and returns operands.

- Execute (E)—The ALU computes a result.

- Memory (M)—External memory is addressed (for load and store instructions only; this stage is idle for other instructions).

- Writeback (W)—The result (or loaded memory datum) is written into the register file.

Figure 1-5. Instruction Pipeline

No instructions execute out-of-order; that is, if instruction A enters the pipeline before instruction B, then instruction A necessarily reaches the writeback stage before instruction B does. Conditions which hold up the pipeline, and the effect of traps on pipeline operations, are discussed in the *Internal Architecture* chapter.

#### 1.4.2 Data and Instruction Caches

The on-chip data and instruction caches allow designers to build high-performance systems without incurring the cost of fast external memory and the associated control logic.

In the MB86930 processor, each cache is 2 Kbytes in size, organized into two banks of sixty-four 16-byte lines. Cache lines are refilled in 4-byte increments to avoid the interrupt latency incurred by long, uninterruptible cache line replacements.

```

Overview - Internal Architecture

```

The data and instruction caches are accessed independently over separate data and instruction buses, allowing data to be loaded from and stored to cache concurrently with instruction fetches.

### 1.4.3 Bus Interface Unit

The Bus Interface Unit (BIU) contains the logic which allows the processor to communicate with the system. The BIU receives requests for external memory and I/O accesses from the cache control logic. When the BIU performs a read, it returns the data to both the cache and the IU. Parallel paths make the data available to the IU in the same cycle that it is written to the cache.

The BIU has a one-word (32-bit) write buffer to hide external memory latency from the IU. The BIU also has a one-word prefetch buffer for instruction fetches. These buffers are enabled or disabled by bits in the Cache/Bus Interface Unit Control Register.

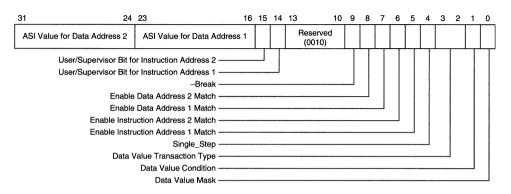

#### 1.4.4 Debug Support Unit

The Debug Support Unit supports hardware emulation with on-chip breakpoint and single-step logic. A dedicated emulator bus is extended off-chip from the debug unit; the emulator bus makes it possible to trace transactions between the Integer Unit and on-chip cache.

### 1.5 External Interface

The processor's external interface consists of signals, bus operations, and system support functions. This section gives an overview; details are discussed more fully in the *External Interface* chapter. The *System Design Considerations* chapter discusses issues that are likely to arise in the design of any SPARClite system.

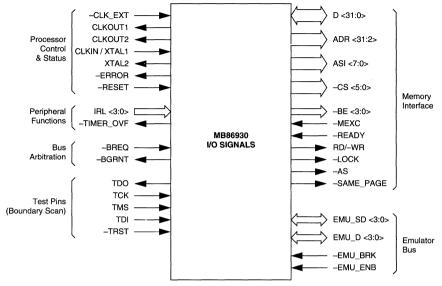

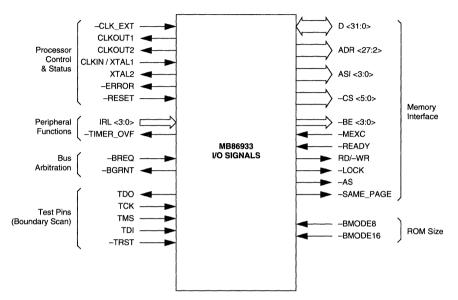

### 1.5.1 Signals

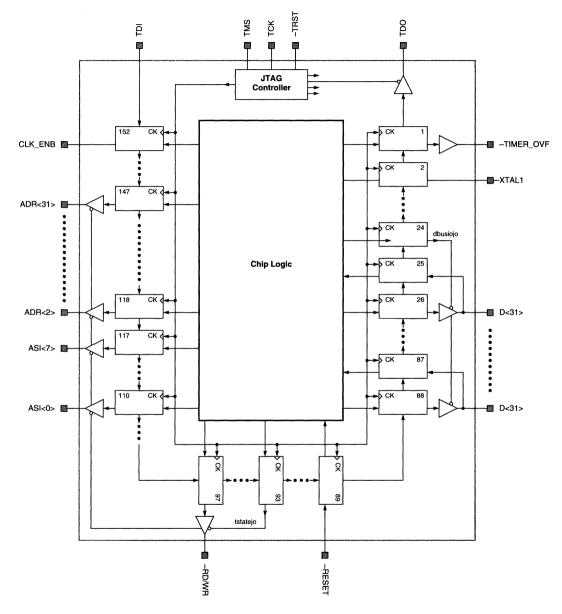

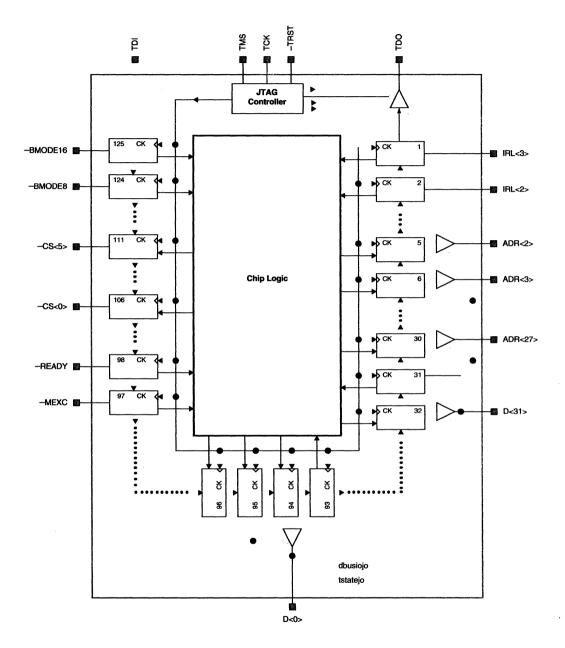

The processor's external signals, illustrated in Figure 1-6, can be grouped by function:

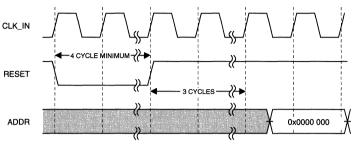

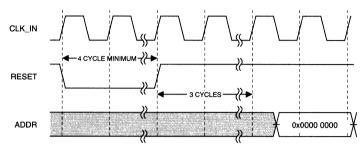

- Processor Control and Status—Reset, error, and clock signals.

- Memory Interface—Data and address buses, ASI and byte-enables, chipselects, and other control signals used to access external memory and memory-mapped devices.

- Bus Arbitration—Signals used by external devices in requesting, and by the processor in granting, control of the bus.

- Peripheral Functions—Interrupt-requests and timer overflow.

- Emulator Bus—Signals to support in-circuit emulation.

• Boundary-Scan—Test signals used for hardware verification.

Figure 1-6. Input and Output Signals

#### 1.5.2 Bus Operation

At any given time, the Bus Interface Unit is handling requests for external memory and I/O operations, arbitrating for bus access, or idle. From the point of view of the external system, bus transactions are handled in fairly standard ways:

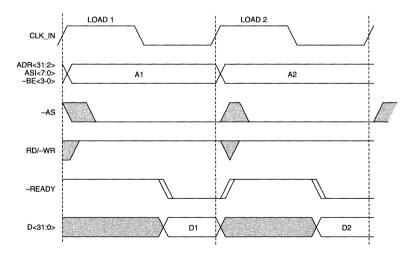

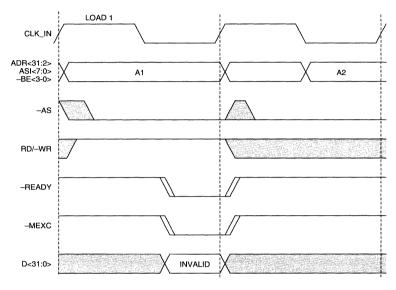

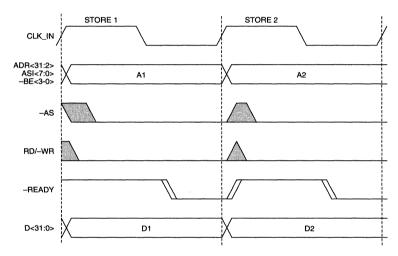

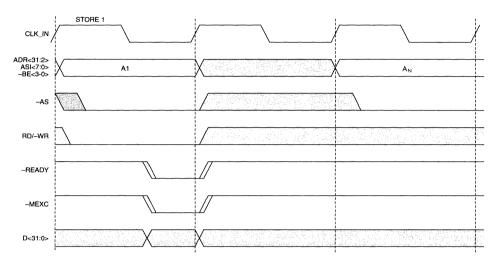

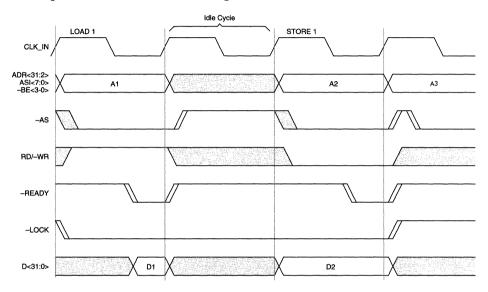

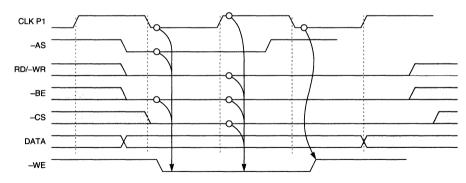

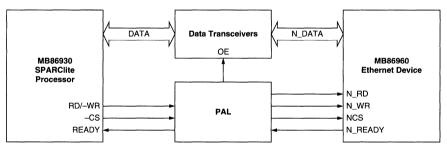

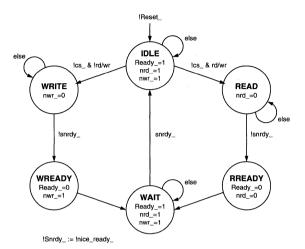

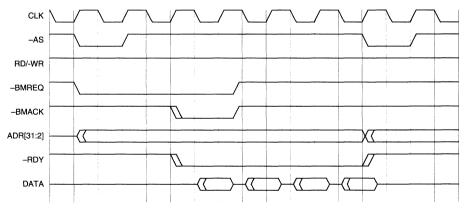

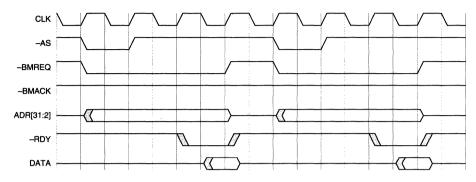

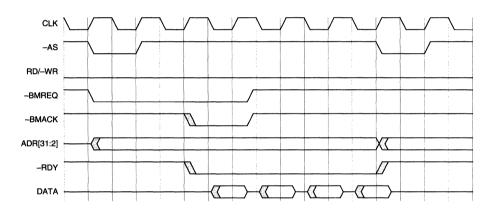

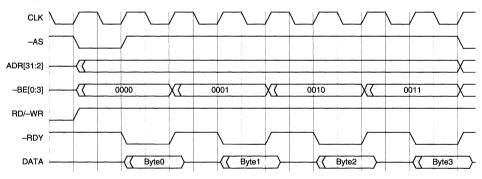

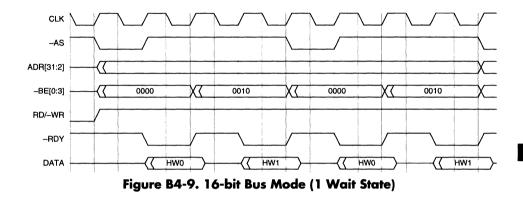

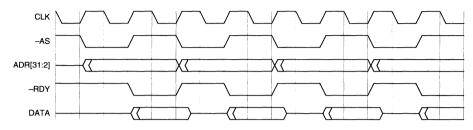

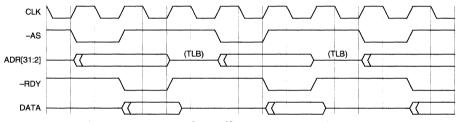

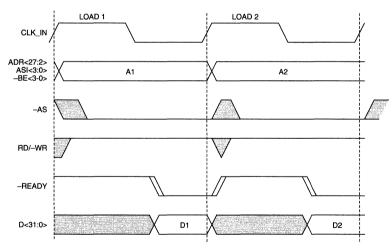

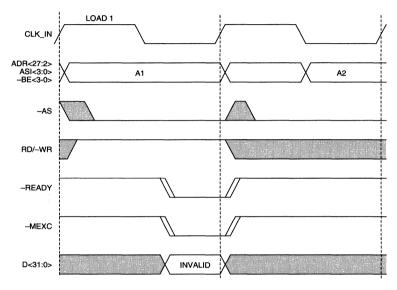

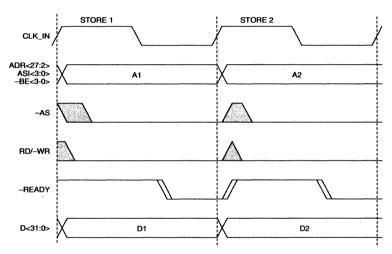

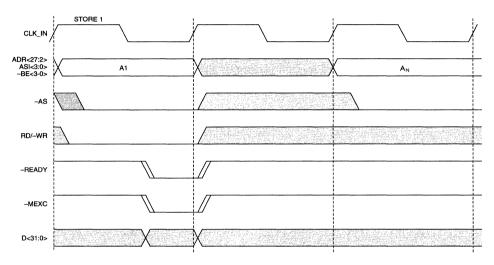

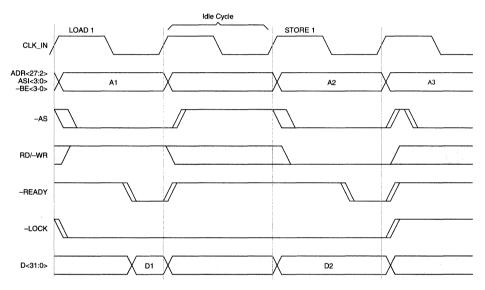

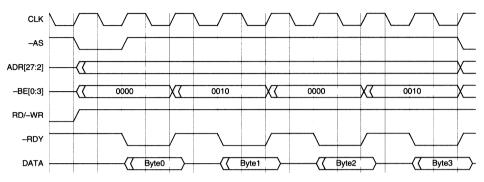

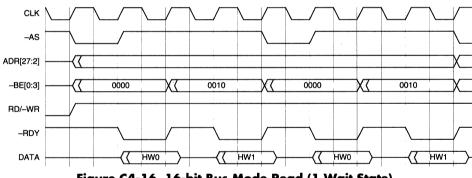

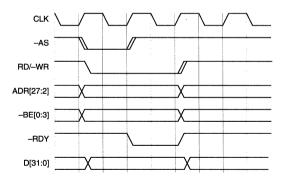

• Memory and I/O Operations—Read and write transactions are initiated with the BIU asserting the –AS signal. The RD/–WR output indicates the transaction type. The –BE[3:0] outputs indicate the transaction width. The BIU drives the address and ASI signals, and either drives (on stores) or reads (on loads) the signals on the data bus. The transaction ends when the external system or programmable wait-state generator asserts –READY.

An atomic load-store is executed as a load followed by a store, with no operation allowed in between. The –LOCK output is asserted to indicate that the bus is being used for more than one consecutive memory operation.

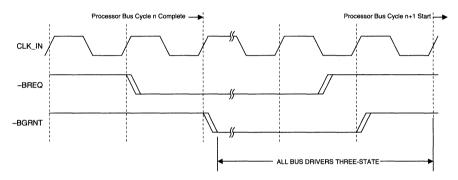

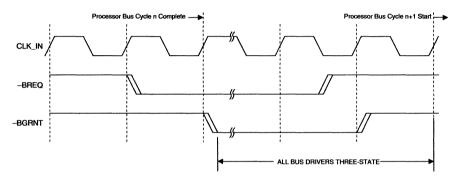

• Arbitration—Any external device can request ownership of the bus by asserting the –BREQ signal. The BIU three-states its bus drivers and asserts –BGRNT to indicate that it is relinquishing control of the bus. On completion of its transaction, the external device de-asserts –BREQ; the BIU responds by de-asserting –BGRNT in the following cycle.

The *External Interface* chapter gives further details concerning bus operations, with timing diagrams, a bus state diagram, and a discussion of transactions that are interrupted by exceptions.

#### 1.5.3 System Support Functions

Built-in system support functions help to minimize the amount of glue logic required in the external system. The support includes a set of system-configuration registers, a timer for generating refresh requests, and same-page detection logic.

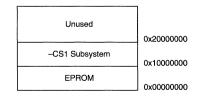

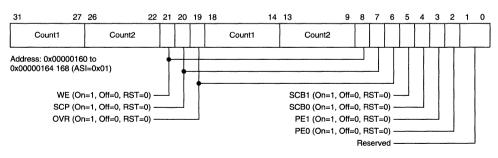

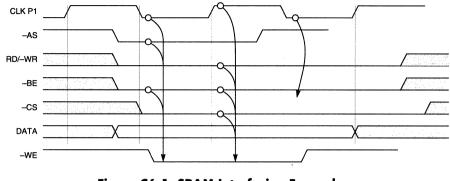

The system-configuration registers (Address Range Specifiers, Address Masks, and Programmable Wait-State Specifiers) allow software to define six different address ranges. When an address driven by the processor is in one of these ranges, the corresponding Chip-Select (–CS) pins are asserted. After a number of clock cycles determined by the corresponding Programmable Wait-State Specifier, the processor automatically generates the –READY signal. This makes it possible for memory and I/O devices with different access times to be connected to the processor without additional logic.

The programmable timer causes the –TIMER\_OVF output signal to be asserted at software-defined intervals. This signal can be used to initiate DRAM refresh cycles, or to control other periodic events in the external system.

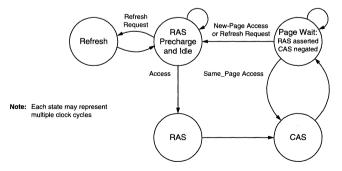

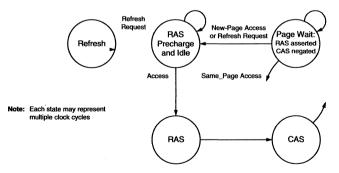

The same-page detection logic determines whether the address of the current memory transaction is on the same page as the previous transaction. If it is, the processor asserts the –SAME\_PAGE signal. The system can then take advantage of the fast consecutive accesses possible within the page boundaries of fast-page mode DRAM.

### 1.6 Development-Support Tools

A full range of development tools are available to support the development of your SPARClite application. The emergence of SPARC as the industry standard engineering workstation architecture provides a fully supported and cost effective source of native development environments. Furthermore, tools targeted at embedded systems development are available as well.

Solutions are available to meet your emulation, logic analysis, logic modeling, architectural simulation, real-time operating system, PC environment, benchmarking and prototyping requirements. Call the SPARClite customer hotline for a complete list of support solutions.

# Programmer's Model

This chapter presents the SPARClite processor architecture as a collection of resources available to software. It discusses the user and supervisor modes, the organization of the address space, the processor registers, the supported data types, the instruction set, the on-chip caches, interrupts and traps and debug support. A separate section describes the internal state of the processor after reset.

The *Programming Considerations* chapter contains information about how to use these processor resources to best advantage.

#### 2.1 Program Modes

The SPARC architecture provides two mutually exclusive modes of program execution, *user mode* and *supervisor mode*. The processor is in supervisor mode when the S bit of the Processor State Register (PSR) is 1, and in user mode when this bit is 0. Instructions which access either special-purpose registers or alternate memory spaces are privileged; the use of *privileged* instructions is restricted to supervisor mode.

The distinction between user and supervisor modes provides system protection in multitasking environments. System code runs in supervisor mode and has full access to processor resources, while application code runs in user mode and is kept from having unwanted side effects. Embedded systems connected to a network can use a protection scheme based on the distinction between user and supervisor modes. In such a scheme, network service routines intended to have system-wide effects run in supervisor mode. Routines intended to have only local effects, on the other hand, run in user mode.

In many embedded systems, however, this hierarchy is not required, and the processor can operate exclusively in supervisor mode. In this way, application code can directly manipulate the Current Window Pointer (in the PSR) and other processor control fields.

On reset, the processor is in supervisor mode. To enter user mode, software must clear the S bit in the PSR. The processor enters supervisor mode from user mode only when a hardware reset, an interrupt, or a trap occurs. A return from trap (RETT) instruction restores the value the S bit had before the trap was taken.

# 2.2 Memory Organization

The processor can directly address up to 1 Terabyte of memory, organized into 256 address spaces of 4 GB each. These address spaces may or may not overlap in physical memory, depending on the system design. Every external access involves an 8–bit Address Space Identifier (ASI) as well as a 32-bit address. The ASI selects one of the address spaces, and the address selects a word within that space (see Table 2-1). Only the user instruction and data spaces are available in user mode; accessing any of the other 254 address spaces requires the processor to be in supervisor mode.

| ASI <7:0>         | Address Space                |

|-------------------|------------------------------|

| 0x1               | Control Register             |

| 0x2               | Instruction Cache Lock       |

| 0x3               | Data Cache Lock              |

| 0x4 - 0x7         | Application Definable        |

| 0x8               | User Instruction Space       |

| 0x9               | Supervisor Instruction Space |

| 0xA               | User Data Space              |

| 0xB               | Supervisor Data Space        |

| 0xC               | Instruction Cache Tag RAM    |

| 0xD               | Instruction Cache Data RAM   |

| 0xE               | Data Cache Tag RAM           |

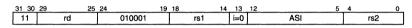

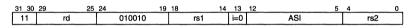

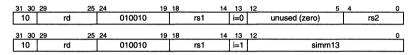

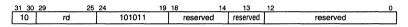

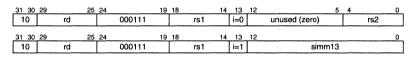

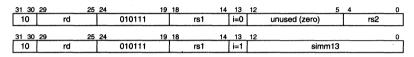

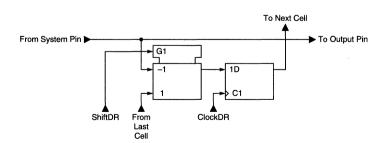

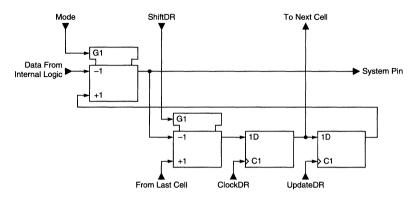

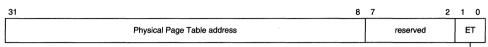

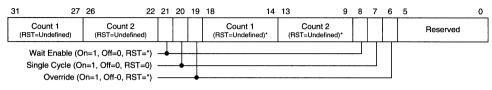

| 0xF               | Data Cache Data RAM          |