# FERRANTI

### Technical Handbook Standard ICs

Converter Voltage Reference Telecom Industrial

#### © FERRANTI plc 1984

The copyright in this work is vested in Ferranti plc and this document is issued for the purpose only for which it is supplied. No licence is implied for the use of any patented feature. It must not be reproduced in whole or in part, or used for tendering of manufacturing purposes except under an agreement or with the consent in writing of Ferranti plc and then only on the condition that this notice is included in any such reproduction. Information furnished is believed to be accurate but no liability in respect of any use of it is accepted by Ferranti plc.

Änderungen und Irrtümer sind vorbehalten.

Ausgabe 3 März 1985 Druck: Werbedruck Seibold

Widenmayerstraße 5 8000 München 22 Telefon (089) 236804-0

Telex 523980 Telefax (089) 299718

## FERRANTI

### Standard IC Datahandbook

| Content                       | Section |

|-------------------------------|---------|

| Product Selection Guide       | С       |

| Data Converter Digital Analog | 1       |

| Data Converter Analog Digital | 2       |

| Digitalvoltmeter              | 2       |

| Precision Voltage References  | 3       |

| Telecom Circuits              | 4       |

| Industrial                    | 5       |

| Package Details               | 6       |

| Application Notes             | 7       |

| Quality Assurance Program     | 8       |

| Semi-Custom-ICs               | 9       |

### **Product Selection Guide**

| Section | ٦                |                                                                                        | page  |

|---------|------------------|----------------------------------------------------------------------------------------|-------|

| Alpha   | numerical I      | ndex                                                                                   | C-5   |

| 1. Digi | ital to Anal     | ogue Converters                                                                        | 1-1   |

|         |                  | lection Guide                                                                          | 1-2   |

|         | Orientation      |                                                                                        | 1-3   |

|         | ZN425            | 8 Bit D/A-A/D-Converter with Refer. and Counter                                        | 1-11  |

|         | ZN426<br>ZN428   | 8 Bit D/A-Converter with Refer and Counter                                             | 1-19  |

|         | 211420           | 8 Bit $\mu$ P-compatible DAC with<br>Reference and Latched Inputs                      | 1-25  |

|         | ZN429            | 8 Bit Low Cost D/A-Converter                                                           | 1-35  |

|         | ZN423<br>ZN434   | 4 Bit Low Cost D/A-Converter                                                           | 1-35  |

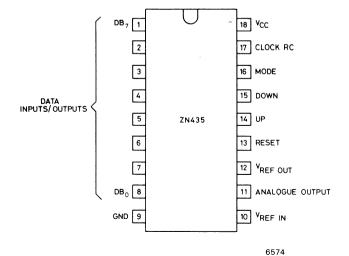

|         | ZN435            | 8 Bit D/A-A/D-Converter with Reference.                                                | 1-45  |

|         | 211100           | Clock-Generator and Up/Down Counter                                                    | 1 40  |

|         | ZN436            | 6 Bit Low Cost D/A-Converter                                                           | 1-57  |

|         | ZN558            | 8 Bit D/A-Converter with Latched Inputs                                                | 1-63  |

|         |                  |                                                                                        |       |

| 2. Ana  | logue to D       | igital Converters                                                                      | 2-1   |

|         | Product Se       | lection Guide                                                                          | 2-2   |

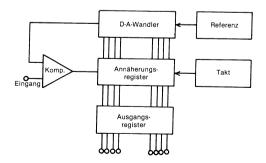

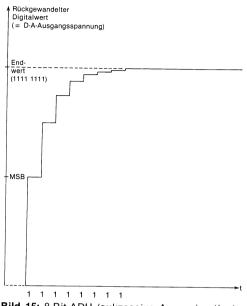

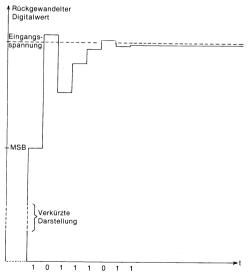

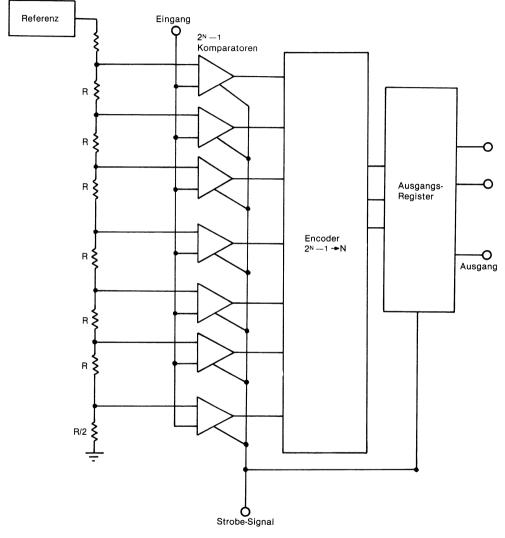

|         | Orientation      |                                                                                        | 2-3   |

|         | ZN425            | 8 Bit A/D-D/A-Converter, see D/A-Section                                               | 1-11  |

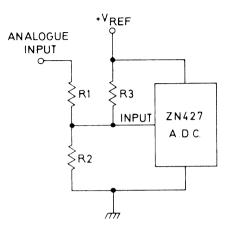

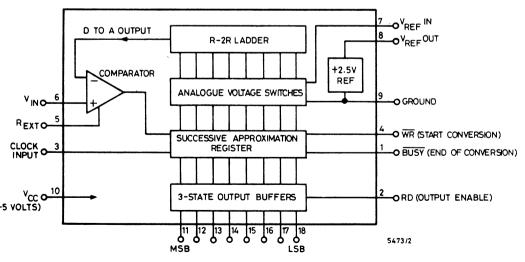

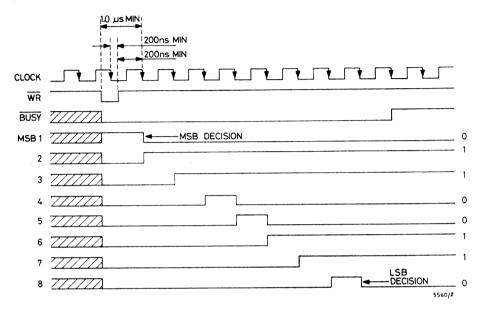

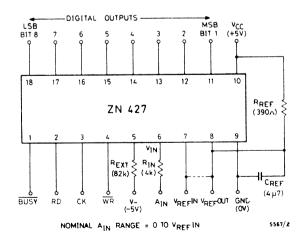

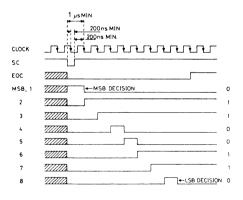

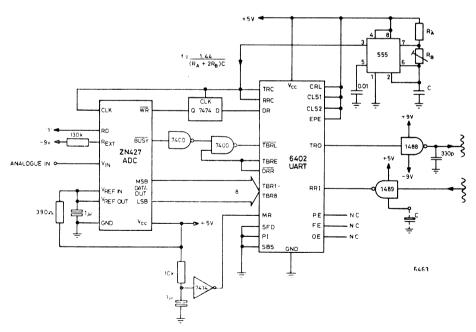

|         | ZN427            | 8 Bit $\mu$ P-compatible Converter with Reference,                                     | 2-15  |

|         |                  | Successive Approximation                                                               |       |

|         | ZN432            | 10 Bit Fast Converter with Reference                                                   | 2-33  |

|         |                  | Succ. Approx., serial and parallel Outputs                                             |       |

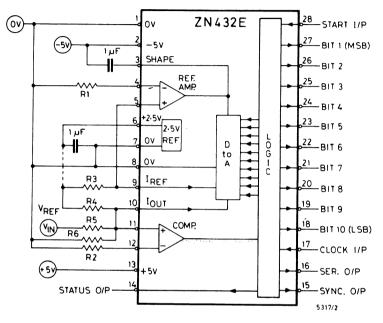

|         | ZN432E           | 10 Bit Fast ADC with Reference, Low Cost                                               | 2-43  |

|         |                  | Plastic Version                                                                        |       |

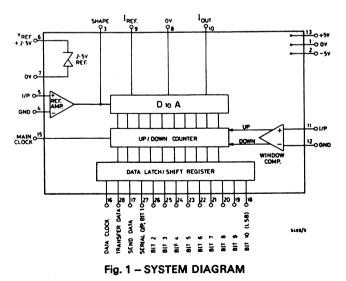

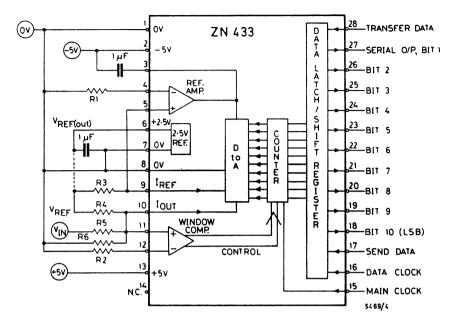

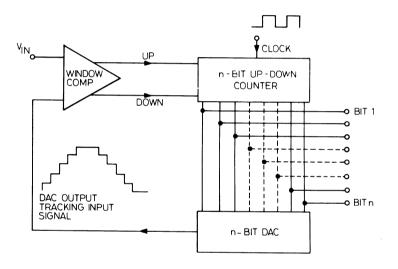

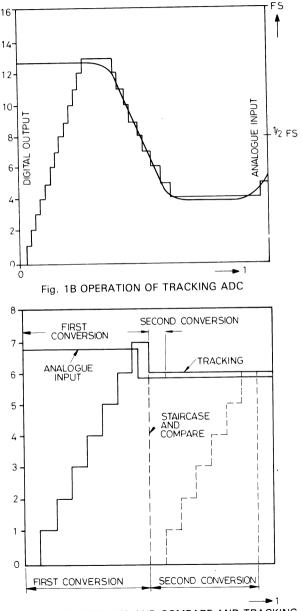

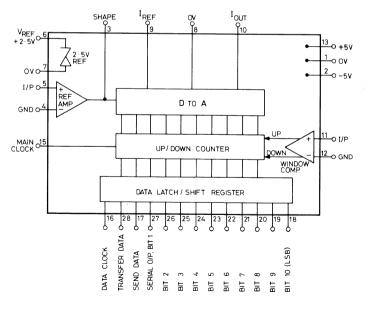

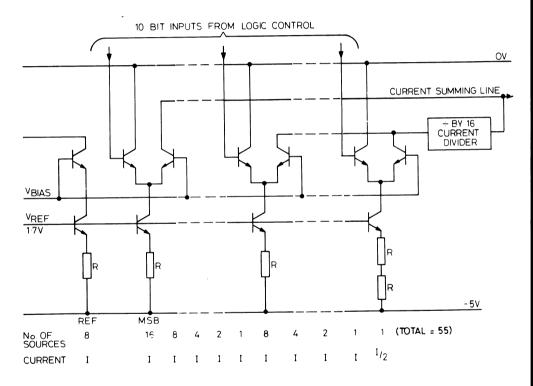

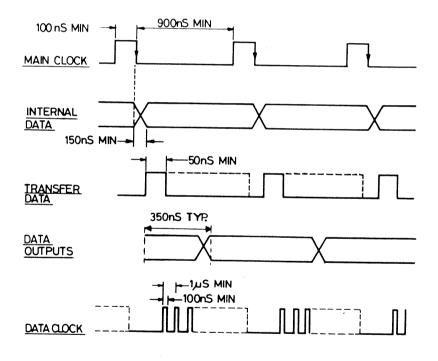

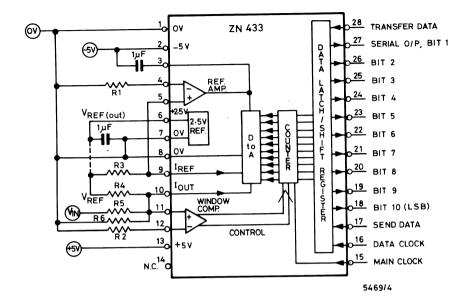

|         | ZN433            | 10 Bit Fast ADC with Reference, Tracking System                                        | 2-51  |

|         | ZN435            | 8 Bit A/D-D/A-Converter, see D/A-Section on chip                                       | 1-45  |

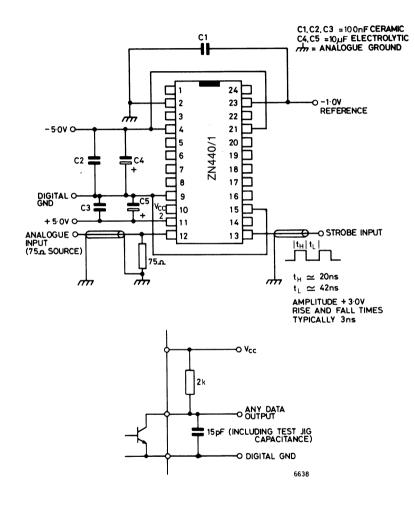

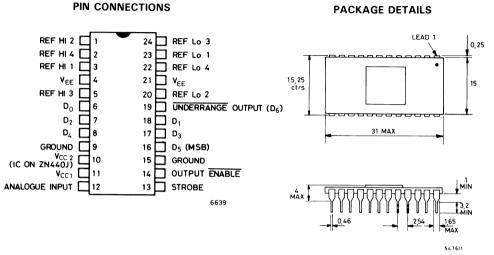

|         | ZN440/441        | 6 Bit Flash-Converter for Video Systems 16/10 MHz                                      | 2-61  |

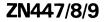

|         | ZN447            | 8 Bit $\mu$ P-compatible Converter with Reference and                                  | 2-77  |

|         | 711440           | Clock-Generator, Successive Approximation, 1/4LSB                                      |       |

|         | ZN448<br>ZN449   | 8 Bit ADC, 1/2LSB Version of ZN447                                                     | 2-77  |

|         | ZN449<br>ZN450   | 8 Bit ADC, 1 LSB Version of ZN447                                                      | 2-77  |

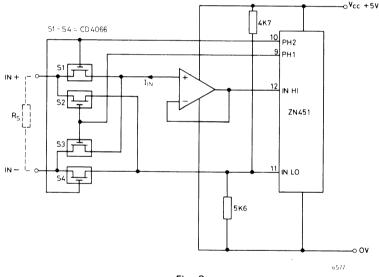

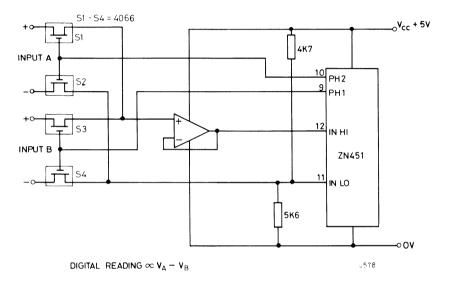

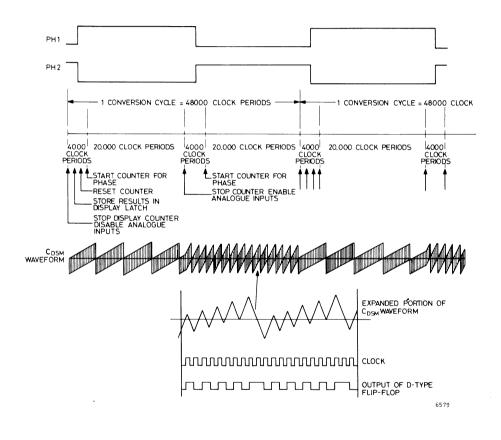

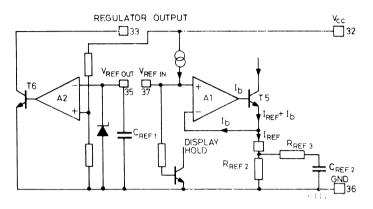

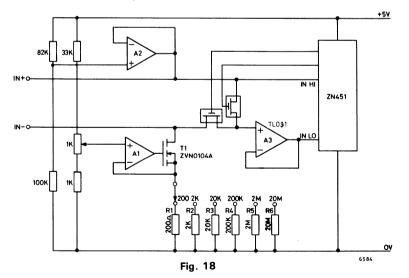

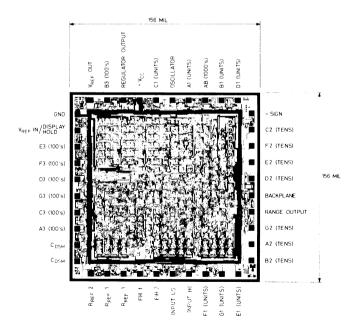

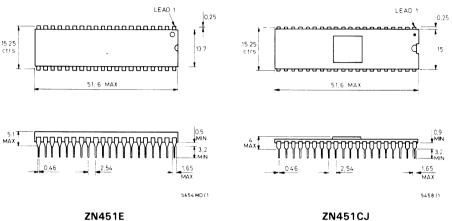

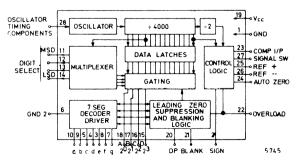

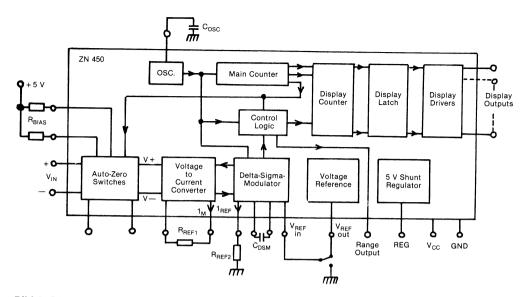

|         | ZN450<br>ZN451   | 3½Digit DVM Circuit for direct LC-Display Drive 200mV FS                               | 2-99  |

|         | ZN451<br>ZN501/2 | 3 <sup>1</sup> / <sub>2</sub> Digit DVM Circuit for direct LC-Display Drive 2mV FS     | 2-122 |

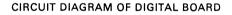

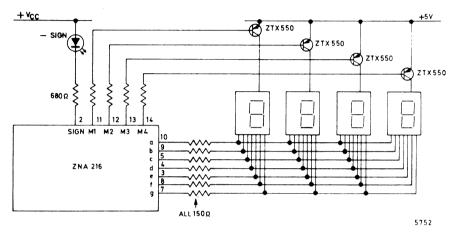

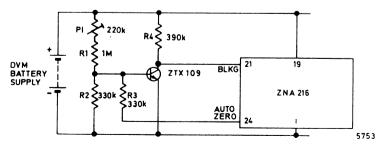

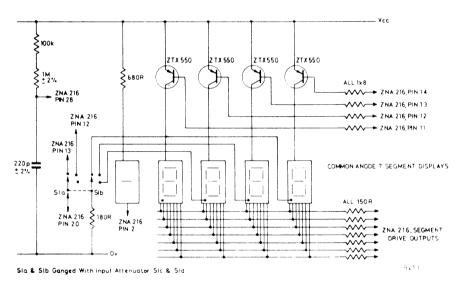

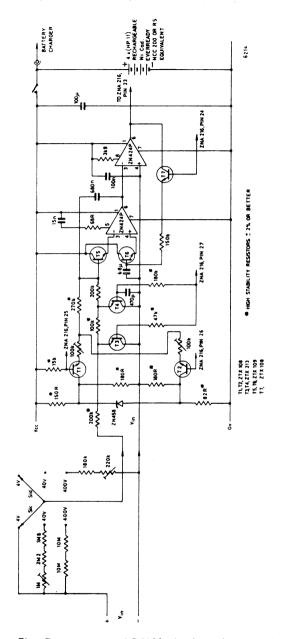

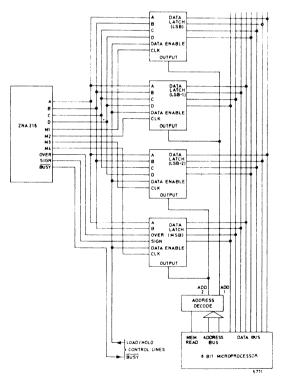

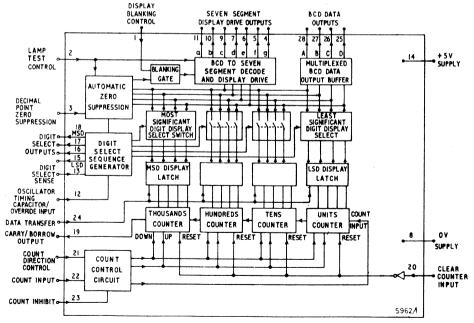

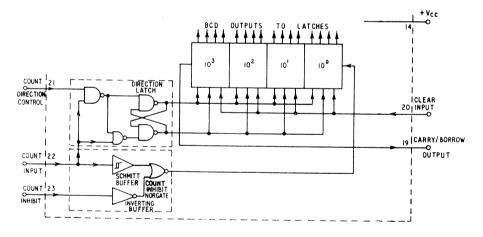

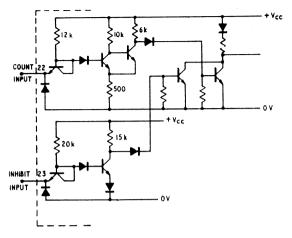

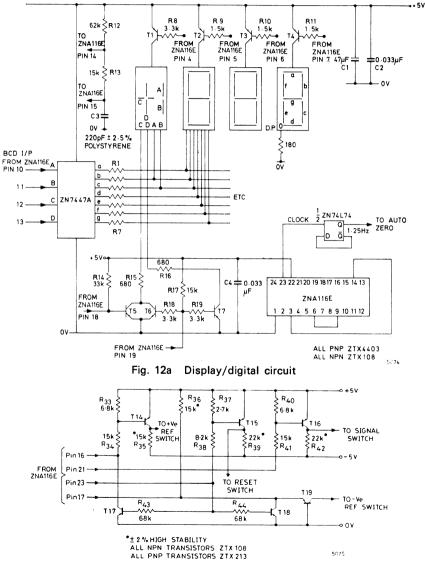

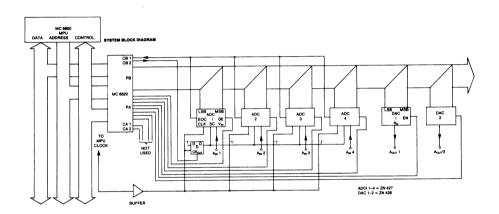

|         | ZNA116           | 10 Bit ADC μP-compatible, Tristate Outputs<br>3½Digit DVM Circuit for MPX-LED-Displays | 2-146 |

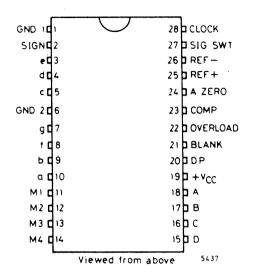

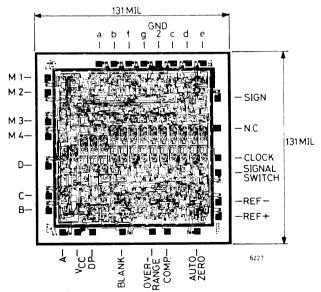

|         | ZNA110<br>ZNA216 | 334 Digit DVM Circuit for MPX LED Displays                                             | 2-162 |

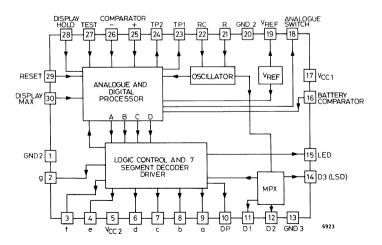

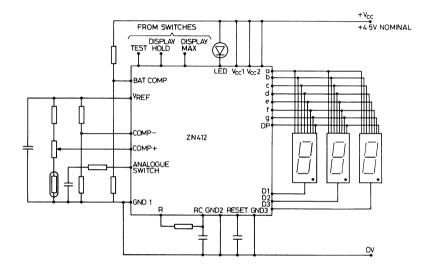

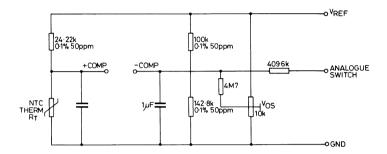

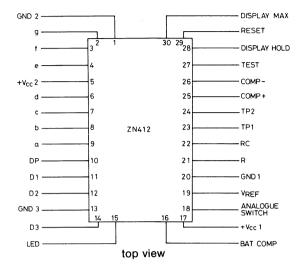

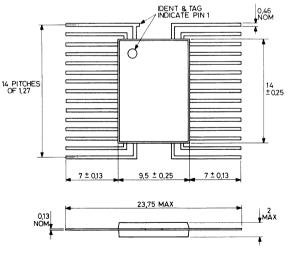

|         | ZN412            | 3¾Digit DVM Circuit for MPX-LED-Displays<br>Digital Clinical Thermometer               | 2-176 |

|         |                  |                                                                                        | 2-192 |

| 3. Precis | ion Voltage R                                                                                                                       | leferences                                                                                                                                                                                                                                                                                                                                                                                 | 3-1                                                                                 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

|           | Product Selec<br>ZN404<br>ZN423<br>ZN458,A,B<br>ZNREF Series<br>ZNREF 025<br>ZNREF 040<br>ZNREF 050<br>ZNREF 062<br>ZNREF 100       | 2,45 V Precision Voltage Reference<br>1,26 V Precision Voltage Reference<br>2,45 V Precision Voltage Reference                                                                                                                                                                                                                                                                             | 3-2<br>3-3<br>3-6<br>3-13<br>3-17<br>3-21<br>3-25<br>3-29<br>3-33<br>3-37           |

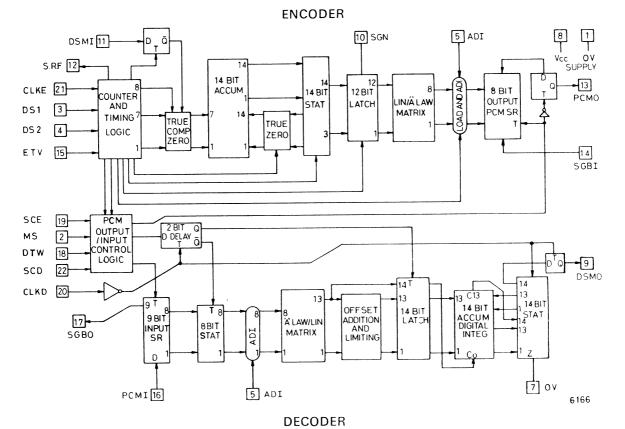

| 4. Teleco | omcircuits                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                            | 4-1                                                                                 |

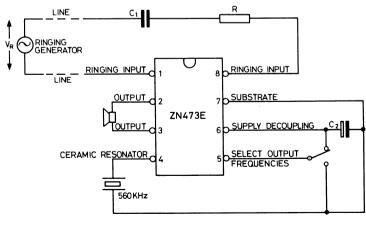

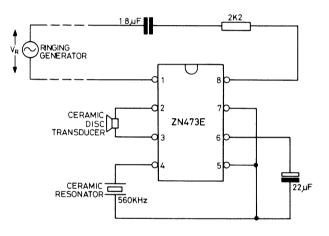

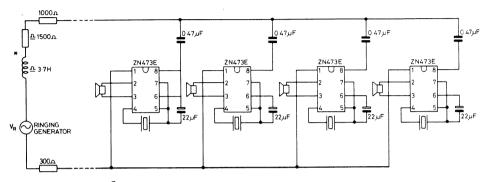

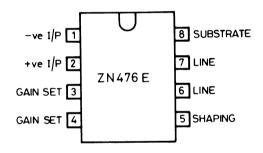

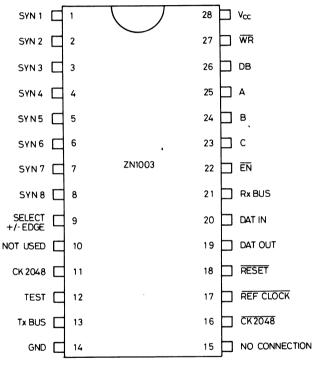

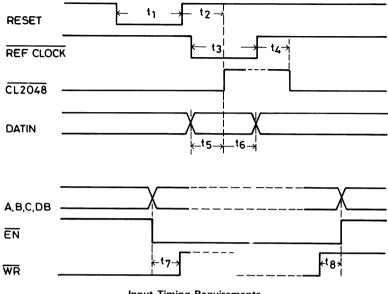

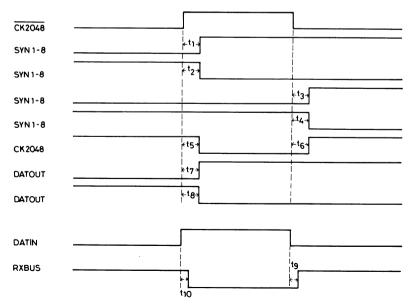

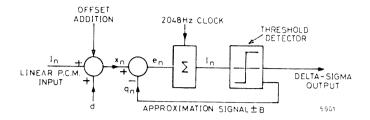

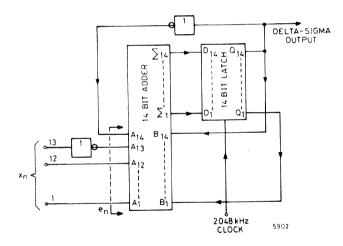

|           | Product Selec<br>ZN PCM 1<br>ZN PCM 2<br>ZN PCM 3<br>ZN470<br>ZN473<br>ZN475<br>ZN476<br>ZN476<br>ZN477<br>ZN478<br>ZN480<br>ZN1003 | ction<br>Single Channel Codec<br>Delta Sigma Modulator/Demodulator<br>Single Chip Synchronous Codec<br>Microphone Amplifier with Bridge<br>Tone Ringer with Dial Pulse Reject<br>Microphone Amp. with Half Bridge<br>Microphone Amp. with Bridge<br>Microphone Amp. with Bridge<br>Microphone Amp. Low Voltage<br>Ring detector with Dial Pulse Reject<br>Eight Channel Time Slot Assigner | 4-2<br>4-16<br>4-24<br>4-35<br>4-42<br>4-49<br>4-53<br>4-57<br>4-61<br>4-65<br>4-69 |

| 5. Indus  | trial                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                            | 5                                                                                   |

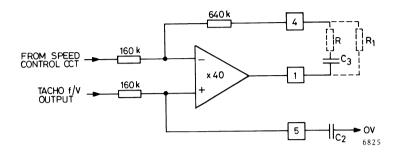

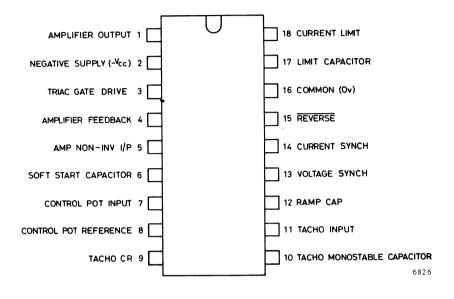

|           | ZN411<br>ZN414/5/6<br>ZN424<br>ZN459                                                                                                | ction<br>Precision Servo Circuit<br>Motor Speed Controller<br>AM-Radio Receiver<br>Gated Operational Ampl.<br>Ultra Low Noise Amplif.<br>Ultra Low Noise Preamplifier                                                                                                                                                                                                                      | 5-1<br>5-2<br>5-17<br>5-37<br>5-49<br>5-61<br>5-70                                  |

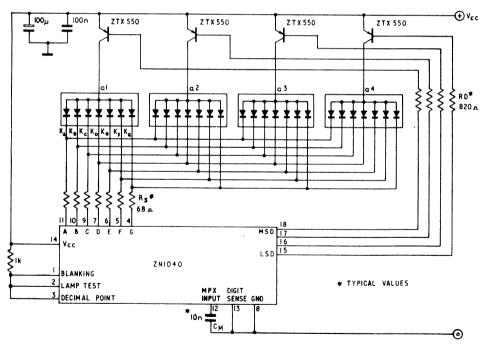

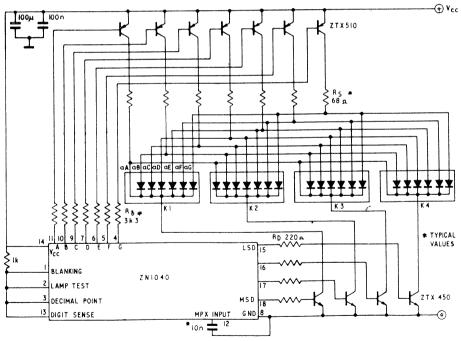

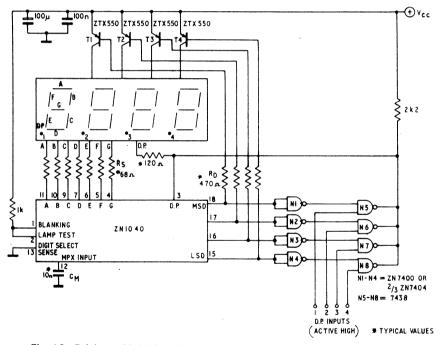

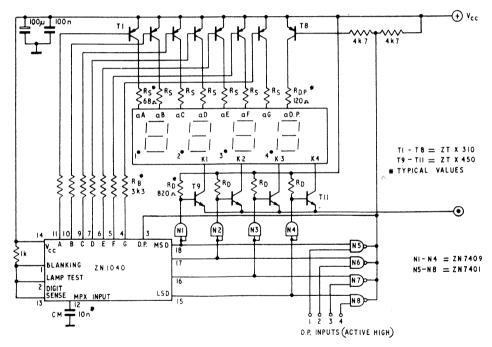

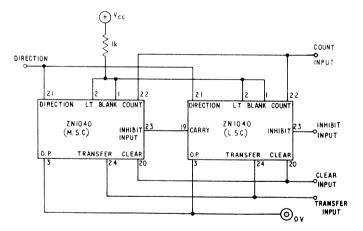

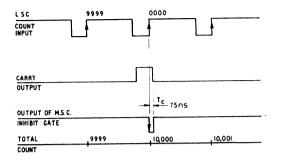

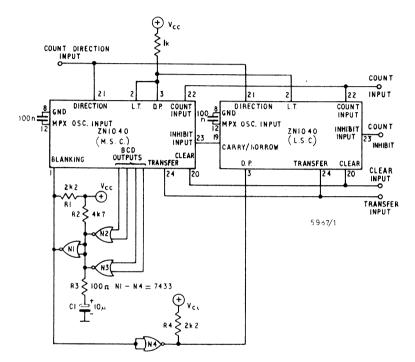

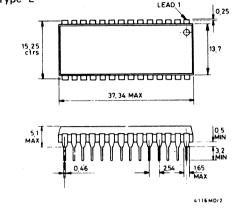

ZN1040ERD 4 Digit up/down Counter with LED Driver

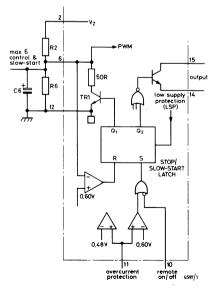

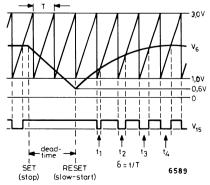

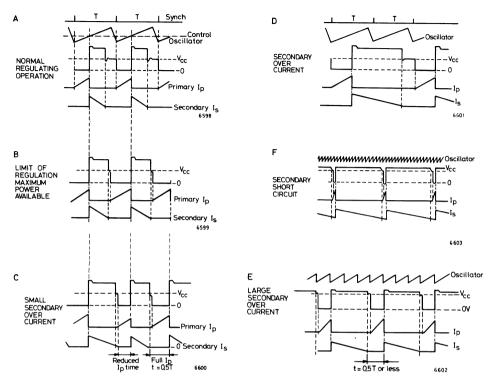

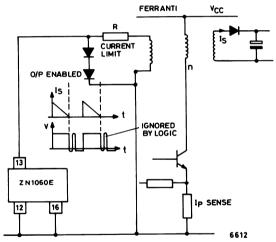

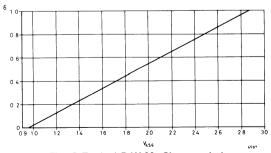

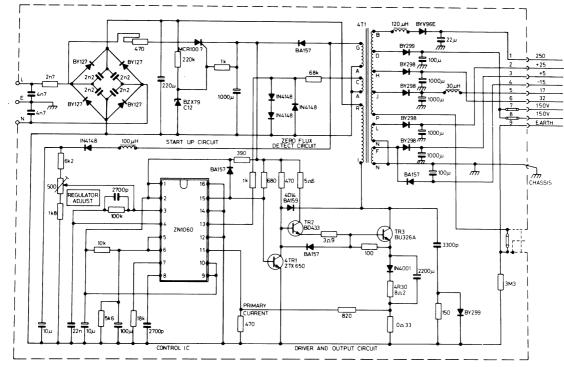

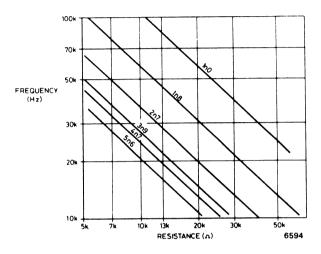

Switch Mode Controller-Driver

Switch Mode Controller Dual out

TV Synchronising Pulse Generator

**Dual Pico-Ampere Diode** Precision Counter Timer

TV Pattern Generator

ZN490

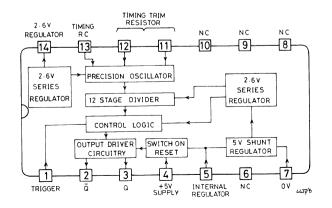

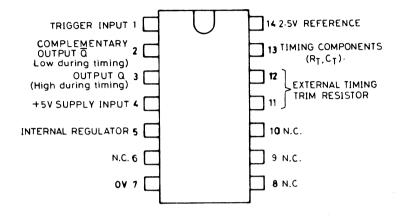

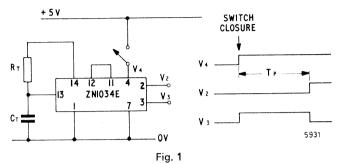

ZN1034

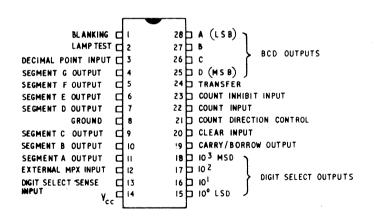

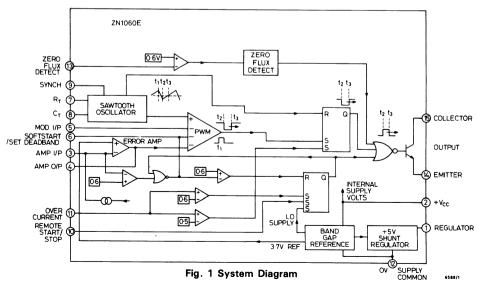

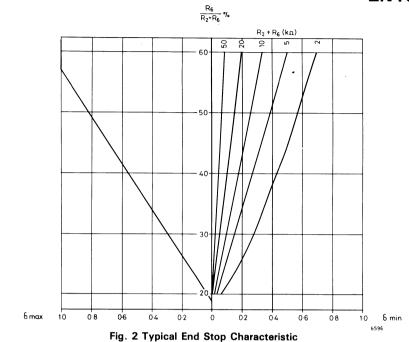

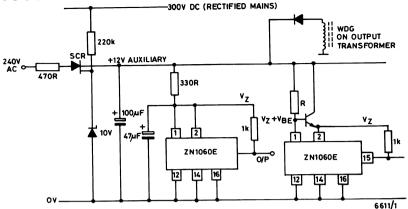

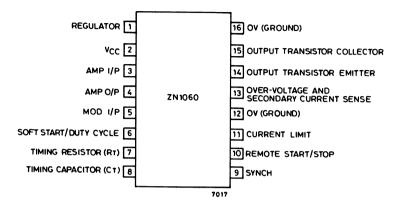

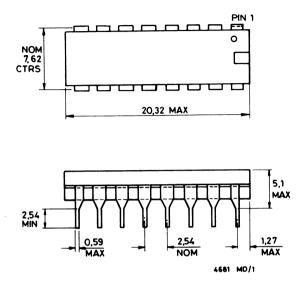

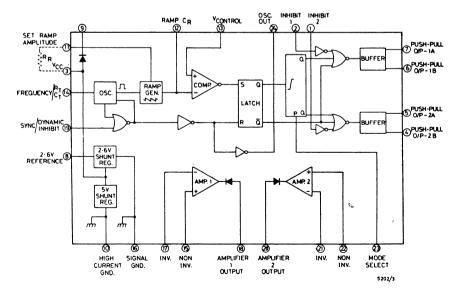

ZN1060

ZN1066 ZNA134

ZNA234

5-79

5-81

5-116

5-138

5-150

5-173

5-181

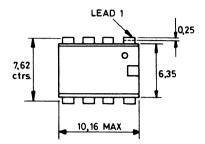

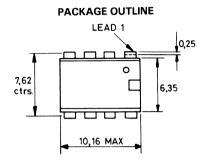

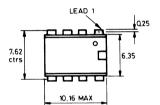

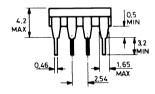

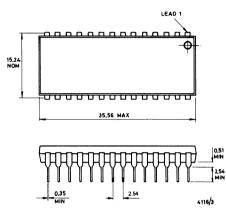

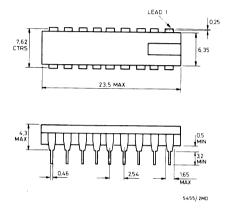

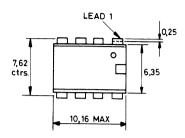

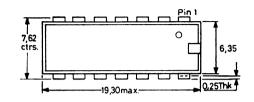

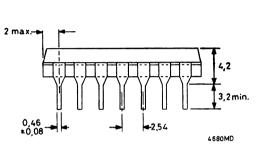

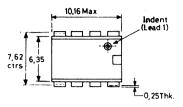

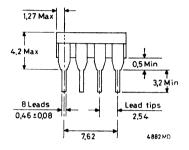

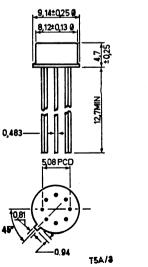

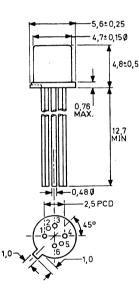

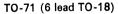

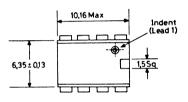

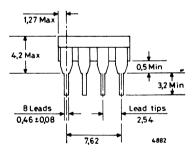

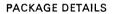

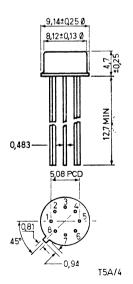

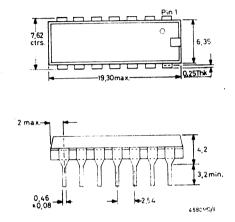

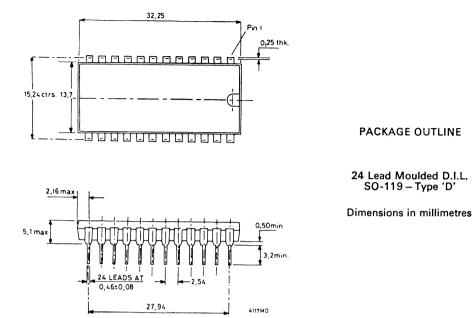

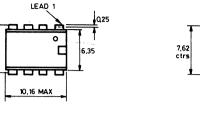

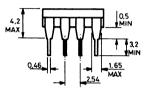

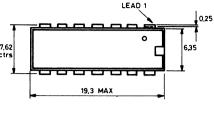

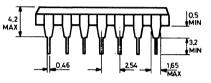

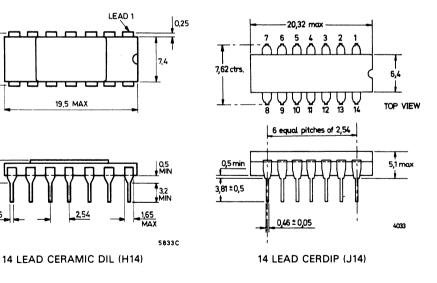

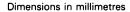

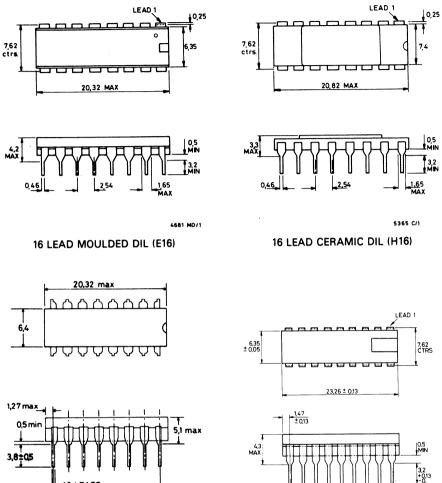

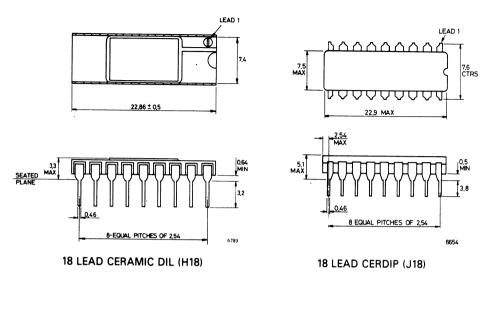

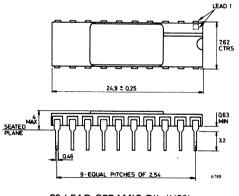

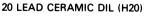

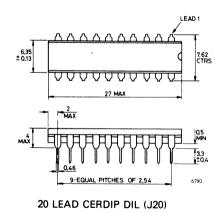

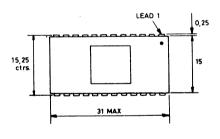

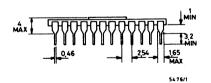

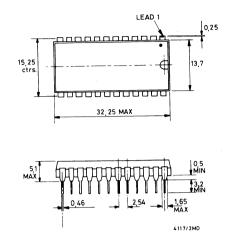

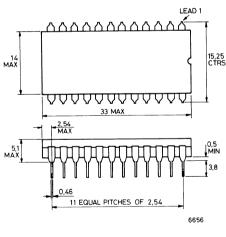

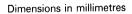

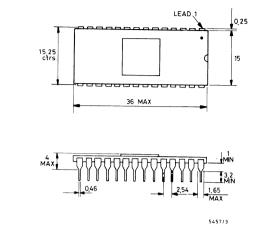

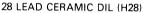

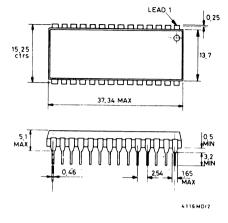

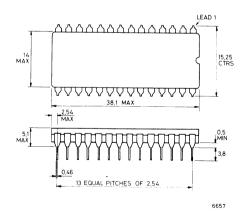

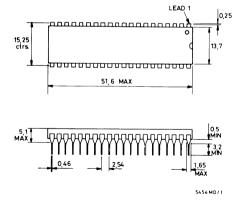

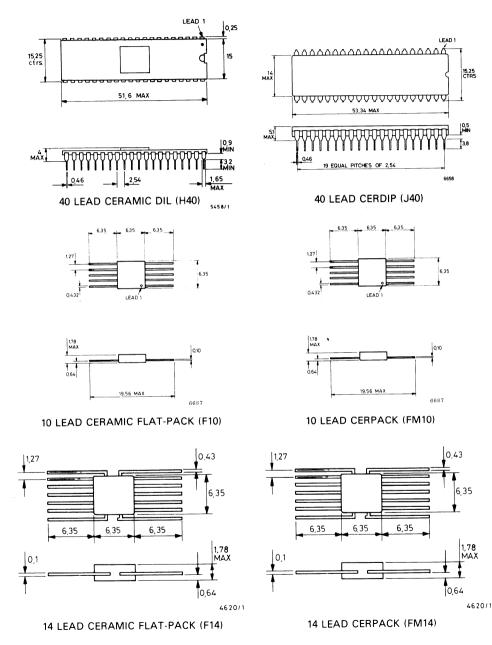

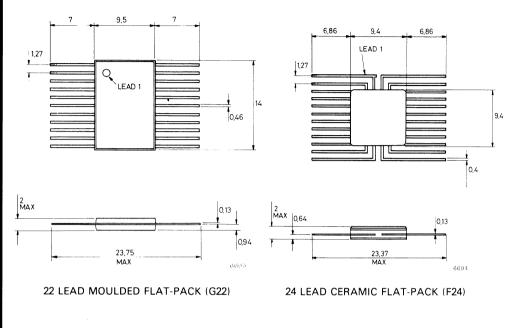

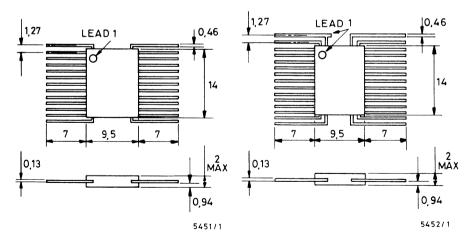

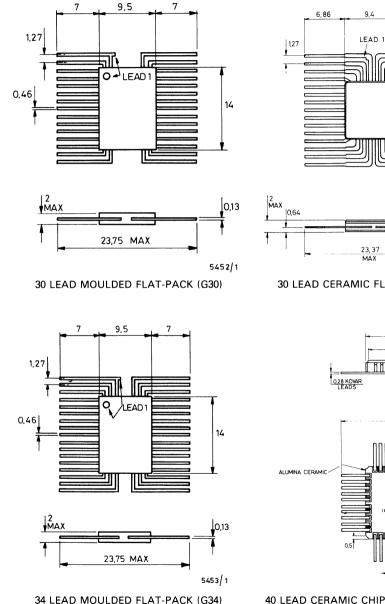

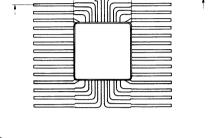

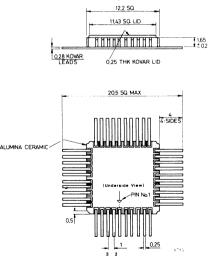

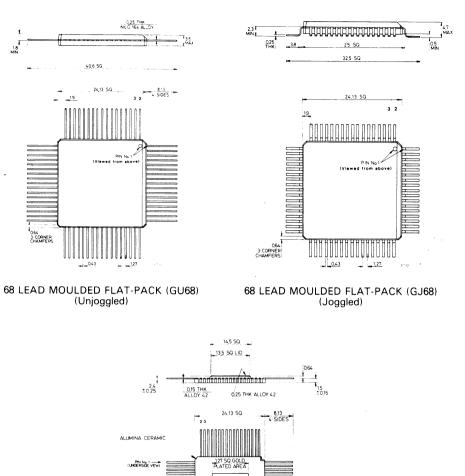

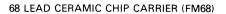

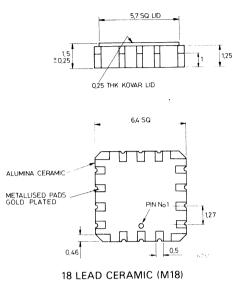

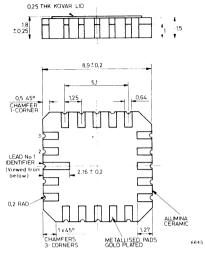

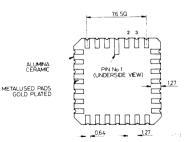

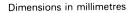

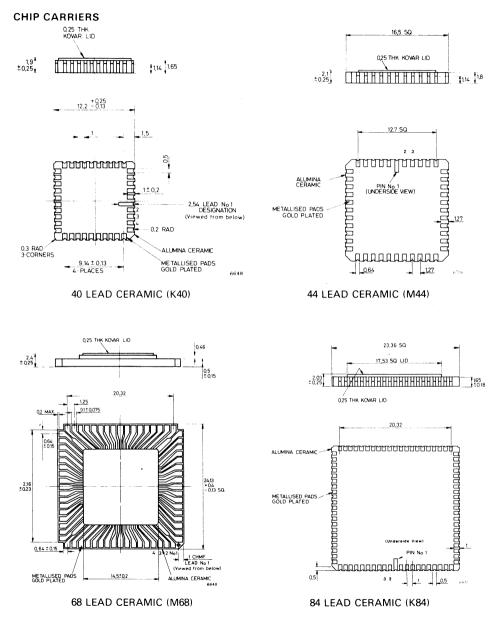

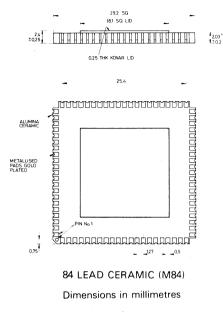

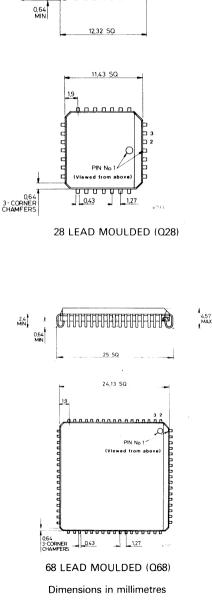

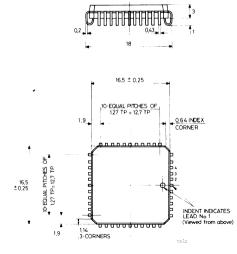

| 6. Package Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6-1                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 7. Application Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7-1                                                                                     |

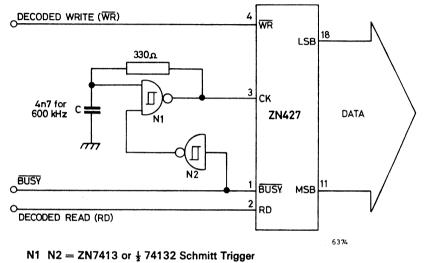

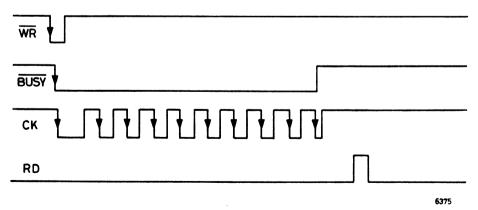

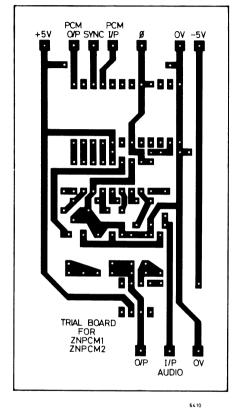

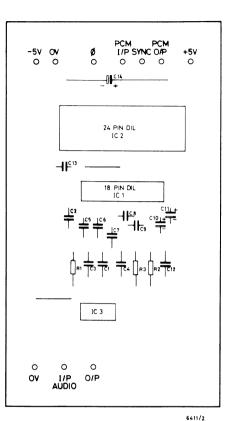

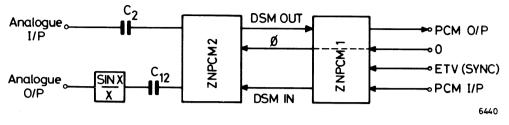

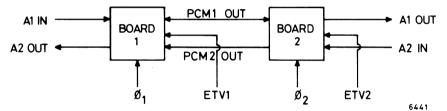

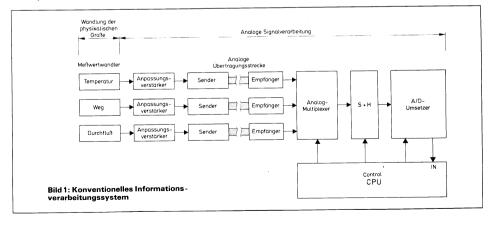

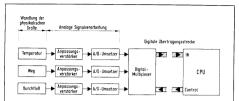

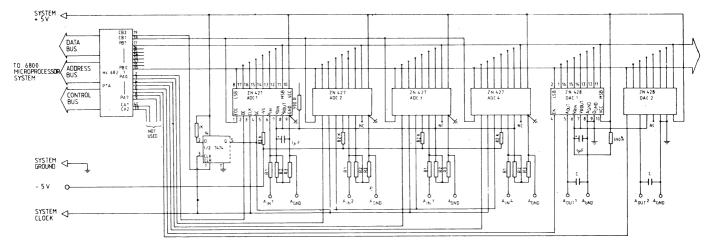

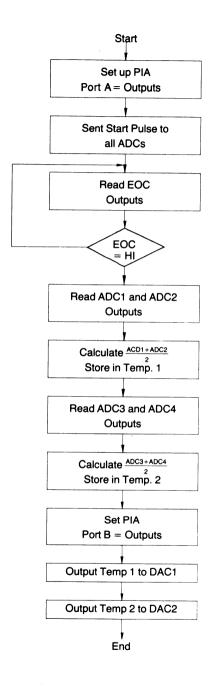

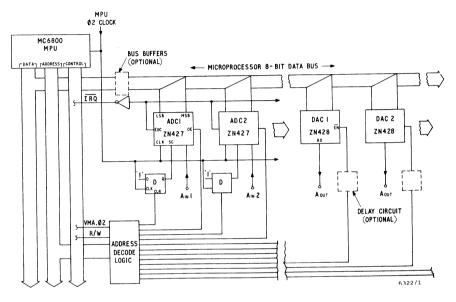

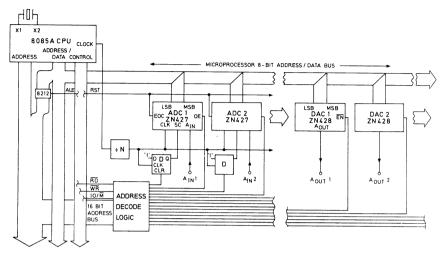

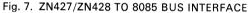

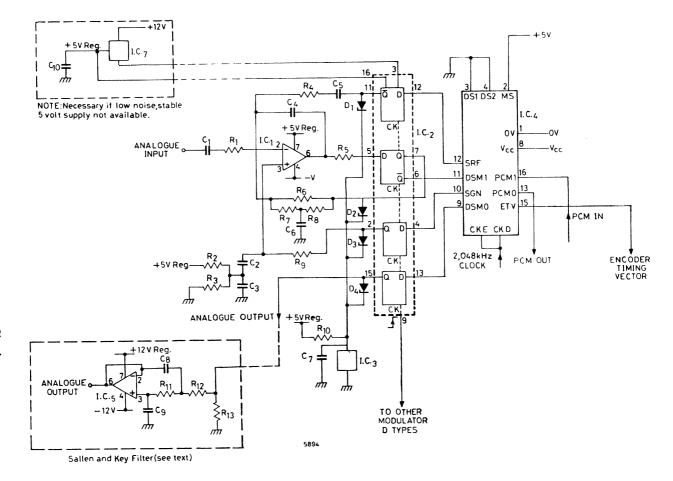

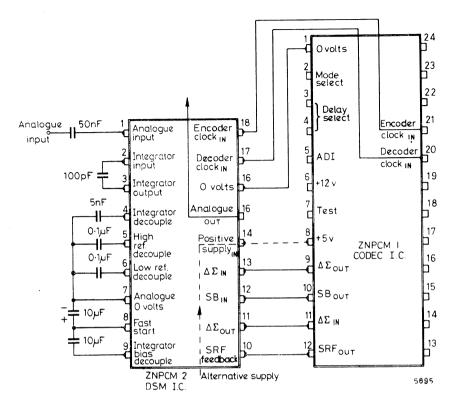

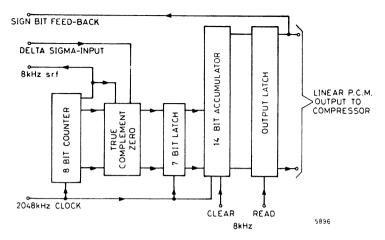

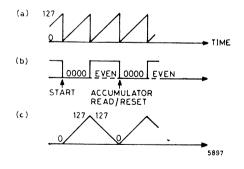

| A/D-Umsetzer - ihre Parameter, die Wandlungsver-<br>fahren und Anwendungsbeispiele<br>Prinzipien der Analog-Digital-Wandlung<br>Analoges Ein-/Ausgabesystem für den μP 6800<br>Applications of the ZN425 8 bit A/D-D/A-Converter<br>Microprocessor Interfacing using the ZN427/ZN428<br>Data Converters<br>Direct Bus Interfacing using the ZN427/ZN428<br>Data Converters<br>Microprocessor Interfacing using the ZN427<br>10 bit Data Converter<br>A Serial Interface for the ZN427 A/D Converter<br>A Single Channel Codec (ZN PCM 1/ZN PCM2)<br>ZN 433 Monolithic 10 Bit Tracking ADC | 7-3<br>7-13<br>7-25<br>7-31<br>7-61<br>7-87<br>7-97<br>7-107<br>7-107<br>7-115<br>7-131 |

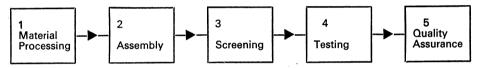

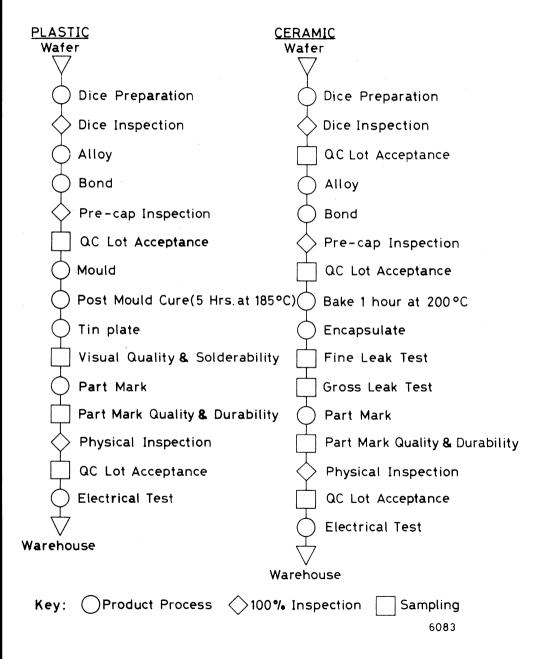

| 8. Qualitäty Assurance Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8-1                                                                                     |

| Ferranti Quality Assurance Program<br>Processing<br>Assembly<br>Screening<br>Testing<br>Quality Assurance<br>Acceptable Quality Levels                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8-2<br>8-2<br>8-5<br>8-5<br>8-5<br>8-5<br>8-6                                           |

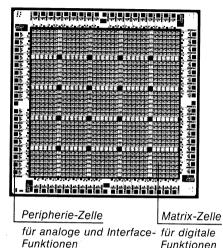

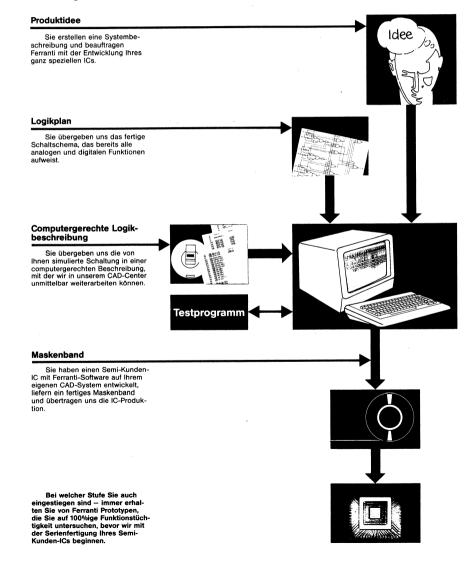

| 9. Semi-Custom-ICs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9-1                                                                                     |

### ALPHANUMERICAL INDEX

|           |                                                  | page           |

|-----------|--------------------------------------------------|----------------|

| ZN404     | 2,45 V Precision Voltage Reference               | 3-3            |

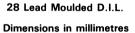

| ZN409     | Precision Servo Circuit                          | 5-2            |

| ZN411     | Motor Speed Controller                           | 5-17           |

| ZN412     | Digital Clinical Thermometer                     | 2-192          |

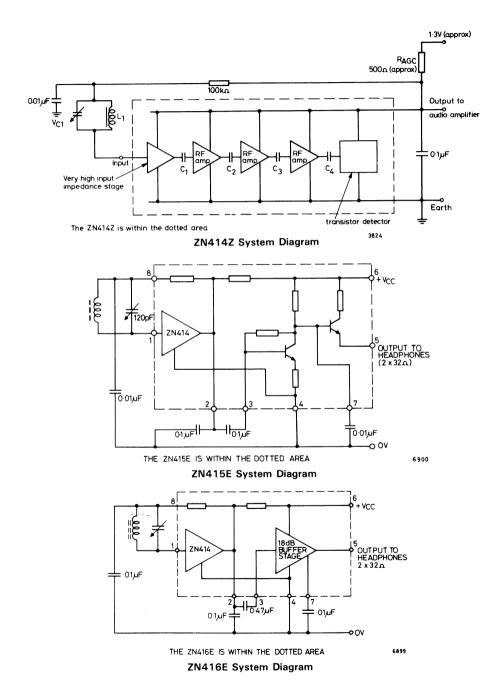

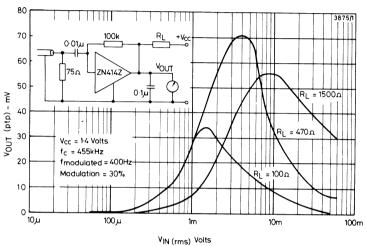

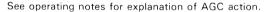

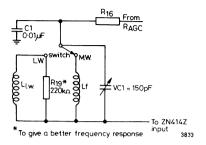

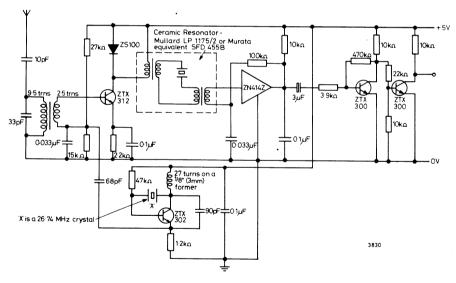

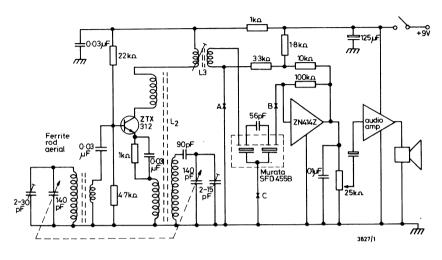

| ZN414/5/6 | AM-Radio Receivers                               | 5-37           |

| ZN423     | 1,26 V Precision Voltage Reference               | 3-6            |

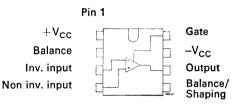

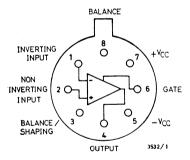

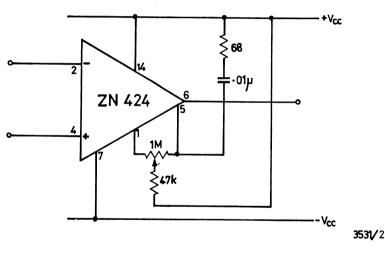

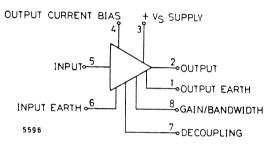

| ZN424     | Gated Operational Amplifier                      | 5-49           |

| ZN425     | 8 Bit D/A-A/D-Converter                          | 1-11           |

| ZN426     | 8 Bit D/A-Converter                              | 1-19           |

| ZN427     | 8 Bit A/D-Converter, $\mu$ P-compatible          | 2-15           |

| ZN428     | 8 Bit D/A-Converter, µP-compatible               | 1-25           |

| ZN429     | 8 Bit D/A-Converter, Low Cost                    | 1-35           |

| ZN432     | 10 Bit A/D-Converter, Succ. Approximation        | 2-33           |

| ZN432E    | 10 Bit A/D-Converter, Plastic, Low Cost          | 2-43           |

| ZN433     | 10 Bit A/D-Converter, Tracking                   | 2-51           |

| ZN434     | 4 Bit D/A-Converter, Low Cost                    | 1-41           |

| ZN435     | 8 Bit D/A-A/D-Converter                          | 1-45           |

| ZN436     | 6 Bit D/A-Converter, Low Cost                    | 1-57           |

| ZN440/1   | 6 Bit Flash Video-Converter, 16/10 MHz           | 2-61           |

| ZN447     | 8 Bit A/D-Converter, $\mu$ P-compatible, 1/4 LSB | 2-77           |

| ZN448     | 8 Bit A/D-Converter, $\mu$ P-compatible, 1/2 LSB | 2-77           |

| ZN449     | 8 Bit A/D-Converter, $\mu$ P-compatible, 1 LSB   | 2-77           |

| ZN450     | 3 1/2 Digit DVM-Circuit for LC-Displays          | 2-99           |

| ZN451     | 3 1/2 Digit DVM-Circuit for LC-Displays          | 2-122          |

| ZN458     | 2,45 V Precision Voltage Reference               | 3-13           |

| ZN459     | Ultra Low Noise Amplifier                        | 5-61           |

| ZN460     | Ultra Low Noise Preamplifier                     | 5-70           |

| ZN470/2   | Microphone Amplifier with Bridge                 | 4-35           |

| ZN473     | Tone Ringer with Dial Pulse Reject               | 4-42           |

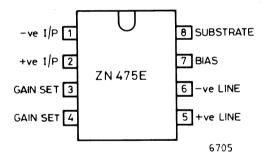

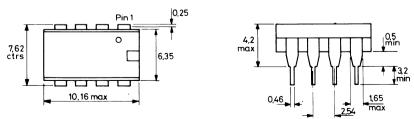

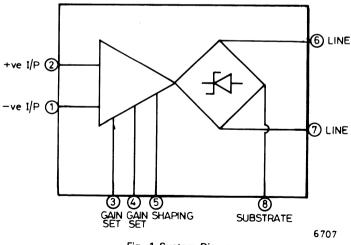

| ZN475     | Microphone Amplifier with Half Bridge            | 4-49           |

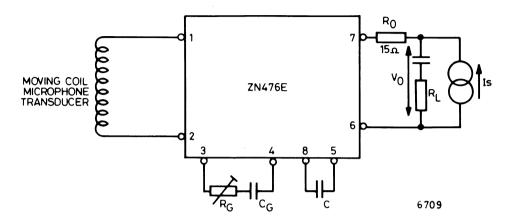

| ZN476     | Microphone Amplifier with Bridge                 | 4-53           |

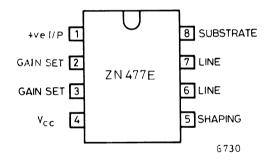

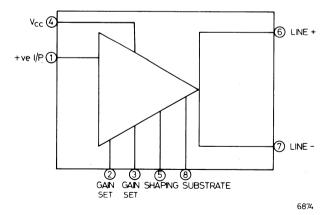

| ZN477     | Microphone Amplifier with Bridge                 | 4-57           |

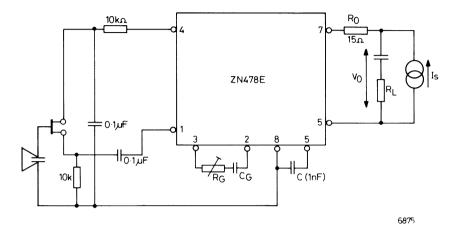

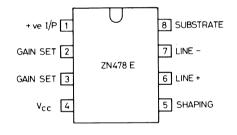

| ZN478     | Microphone Amplifier Low Voltage                 | 4-61           |

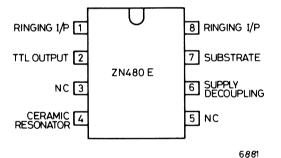

| ZN480     | Ring detector with dial pulse reject             | 4-65           |

| ZN490     | Dual Pico Ampere Diode                           | 5-79           |

| ZN501/2   | 10 Bit ADC $\mu$ P-compatible, Tristate          | 2-146          |

| ZN558     | 8 Bit DAC with latched Input                     | 1-63           |

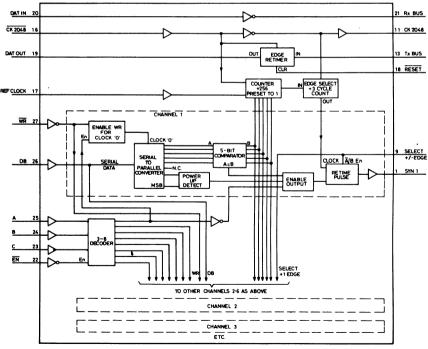

| ZN1003    | Time Slot Assigner                               | 4-69           |

| ZN1034    | Precision Counter Timer                          | 5-81           |

| ZN1040    | 4 digit up/down Counter with LED-Driver          | 5-116<br>5-138 |

| ZN1060    | Switch Mode Controller-Driver                    | 5-138          |

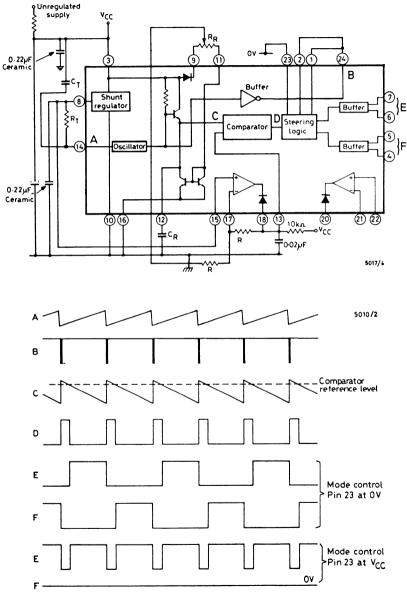

| ZN1066    | Switch Mode Controller, Dual Out                 | 5-150          |

ALPHANUMERICAL INDEX (cntd)

|           |                                               | page  |

|-----------|-----------------------------------------------|-------|

| ZNA116    | 3 1/2 Digit DVM-Circuit for MPX-LED-Displays  | 2-162 |

| ZNA134    | TV Synchronising Pulse Generator              | 5-173 |

| ZNA216    | 3 3/4 Digit DVM-Circuit for MPX-LED-Displays  | 2-176 |

| ZNA234    | TV Pattern Generator                          | 5-181 |

| ZNPCM1    | Single Channel Codec                          | 4-2   |

| ZNPCM2    | Delta Sigma Modulator/Demodulator             | 4-16  |

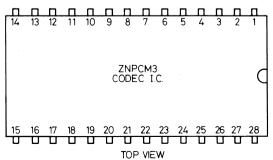

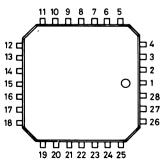

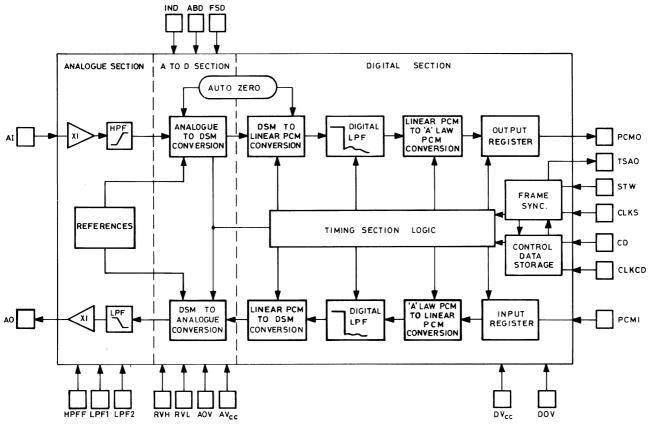

| ZNPCM3    | Single Chip Synchronous Codec                 | 4-24  |

| ZNREF 025 | 2,5 V Precision Voltage Reference (trimmable) | 3-21  |

| ZNREF 040 | 4,0 V Precision Voltage Reference (trimmable) | 3-25  |

| ZNREF 050 | 5,0 V Precision Voltage Reference (trimmable) | 3-29  |

| ZNREF 062 | 6,2 V Precision Voltage Reference (trimmable) | 3-33  |

| ZNREF 100 | 10 V Precision Voltage Reference (trimmable)  | 3-37  |

### 1. Digital-to-Analogue Converters

|                     |                                                                                | Contents |

|---------------------|--------------------------------------------------------------------------------|----------|

|                     |                                                                                | page     |

| 1. Digital to Analo | gue Converters                                                                 | 1-1      |

| Product Sel         | ection Guide                                                                   | 1-2      |

| Orientation         |                                                                                | 1-3      |

| ZN425               | 8 Bit D/A-A/D-Converter with Refer. and Counter                                | 1-11     |

| ZN426               | 8 Bit D/A-Converter with Refer and Counter                                     | 1-19     |

| ZN428               | 8 Bit $\mu$ P-compatible DAC with<br>Reference and Latched Inputs              | 1-25     |

| ZN429               | 8 Bit Low Cost D/A-Converter                                                   | 1-35     |

| ZN423<br>ZN434      | 4 Bit Low Cost D/A-Converter                                                   | 1-41     |

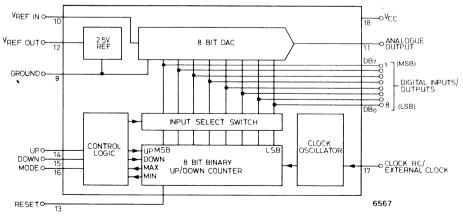

| ZN435               | 8 Bit D/A-A/D-Converter with Reference,<br>Clock-Generator and Up/Down Counter | 1-45     |

| ZN436               | 6 Bit Low Cost D/A-Converter                                                   | 1-57     |

| ZN558               | 8 Bit D/A-Converter with Latched Inputs                                        | 1-63     |

### **PRODUCT SELECTION GUIDE D TO A CONVERTERS**

| TYPE          | USEFUL     | SETTLING | ON-CHIP           | INPUT    | TEMPERATURE  | FEATURES                                 | PAGE |

|---------------|------------|----------|-------------------|----------|--------------|------------------------------------------|------|

|               | RESOLUTION | TIME     | REFERENCE         | LATCH    | RANGE        |                                          |      |

|               | (BITS)     | (µS)     |                   | <u> </u> | (°C)         |                                          |      |

| ZN425E SERIES | 8 to 6     | 1        | +                 |          | 0 to 70      | D to A with on-chip counter              | 1-11 |

| ZN425J-8      | 8          | 1        | +                 | -        | -55 to +125  | D to A with on-chip counter              | 1-11 |

| ZN426E SERIES | 8 to 6     | 1        | +                 | - '      | 0 to 70      | TTL and CMOS compatible                  | 1-19 |

| ZN426J-8      | 8          | 1        | +                 | _        | -55 to +125  | TTL and CMOS compatible                  | 1-19 |

| ZN428E-8      | 8          | 0,8      | +                 | +        | 0 to 70      | Microprocessor, TTL and CMOS compatible  | 1-25 |

| ZN428J-8      | 8          | 0,8      | +                 | +        | -55 to +125  | Microprocessor, TTL and CMOS compatible  | 1-25 |

| ZN429E-8      | 8          | 1        | _ /               | _ !      | 0 to 70      | Low cost, TTL and CMOS compatible        | 1-35 |

| ZN429J-8      | 8          | 1        | _ !               | ·        | -55 to +125  | Low cost, TTL and CMOS compatible        | 1-35 |

| ZN434E        | 4          | 0,3      | V <sub>cc/2</sub> | -        | 0 to 70      | Low cost, TTL and CMOS compatible        | 1-41 |

| ZN435E        | 8          | 0,8      | +                 | -        | 0 to 70      | D to A, up/down counter, clock-generator | 1-44 |

| ZN435J        | 8          | 0,8      | +                 | -        | -55 to +125  | D to A, up/down counter, clock-generator | 1-44 |

| ZN436E        | 6          | 1        | _                 | -        | 0 to 70      | Low cost, TTL and CMOS compatible        | 1-63 |

| ZN436J        | 6          | 1        | _                 |          | -55 to +125  | Low cost, TTL and CMOS compatible        | 1-63 |

| ZN558E        | 8          | 0,8      | +                 | +        | 0 to 70      | compatible to AD558 8 Bit Latched Input  | 1-63 |

| ZN558J        | 8          | 0,8      | +                 | +        | –55 to +125° | compatible to AD558 8 Bit Latched Input  | 1-63 |

|               |            |          |                   |          |              |                                          | 1 2  |

### 1. DIGITAL TO ANALOGUE CONVERTERS

A Digital to Analogue converter (DAC) is a device which converts a digital data input into a corresponding analogue output. This output usually takes the form of a voltage or current.

### 1.1 Ideal Output Characteristics

If a unipolar voltage output and normal binary input coding are assumed, then the ideal transfer function of a linear DAC may be written as:

$V_{out} = V_{FS} (B_{1}.2^{-1} + B_{2}.2^{-2} + B_{3}.2^{-3} + \dots + B_{n}.2^{-n})$

where  $B_1$  is the most significant bit input (MSB) and  $B_n$  is the least significant bit input (LSB). Bits 1 to n can each assume a value of '1' or '0'. The number of bit inputs a DAC possesses is known as the RESOLUTION of the converter.

The smallest increment of output voltage is that contributed by the LSB and is equal to  $V_{\text{FS}}.2^{\text{-n}}.$

The terms 'MSB', 'LSB' etc., are frequently used interchangeably to describe either the digital input or the corresponding analogue output.

The maximum output from a DAC is known as full-scale output (V<sub>FSO</sub>). It occurs when all inputs are '1' and is equal to  $V_{FS}\left(\frac{(2^n-1)}{2^n}\right)$ . For example the maximum output of a 3-bit DAC is  $\frac{7}{8}V_{FS}$ .

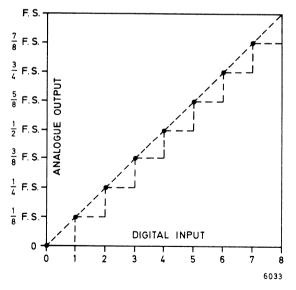

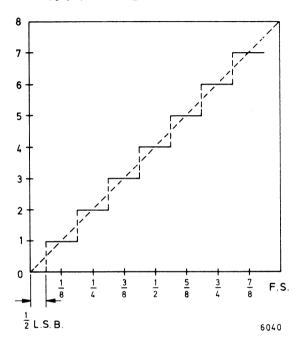

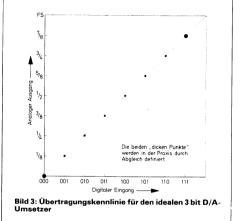

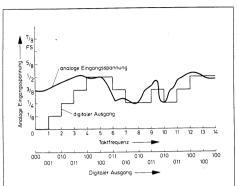

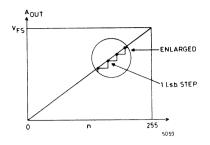

The transfer function graph of an ideal 3-bit DAC is shown in figure 1. For each of the 8 input codes there exists a discrete analogue output

Fig. 1. Transfer Characteristic of Ideal 3-bit DAC

level, represented by a point on the graph. It should be emphasised that the transfer characteristic is not a continuous function and it is, therefore, not strictly correct to join the points with a continuous line, since this would imply that non-integral input codes and corresponding levels existed. However, a straight line is often drawn between zero and full scale to represent the 'ideal' transfer function on which all the points should lie.

Similarly, if the input code of a DAC is incremented using, say, a binary counter and clock generator, then the analogue output will be a staircase waveform. DAC transfer functions are frequently drawn as a staircase, since this is a convenient way of illustrating various errors that may occur in a DAC. However, such a graph is, strictly speaking, a plot of analogue output v. time rather than output v. input code.

### **1.2 Practical DAC Circuits**

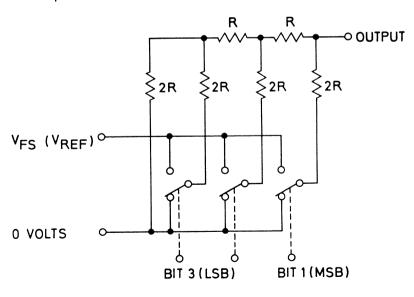

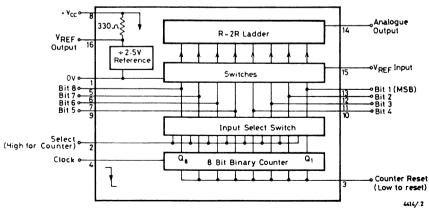

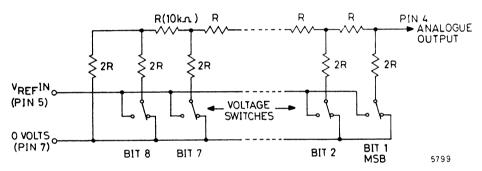

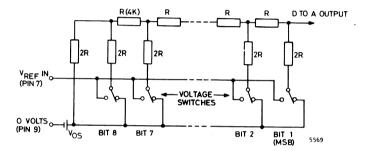

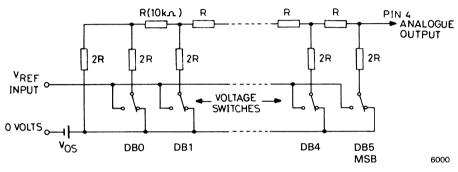

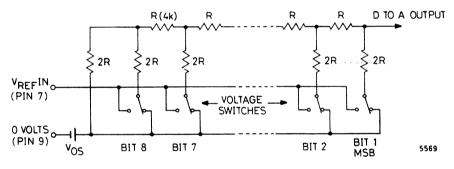

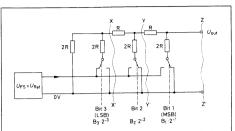

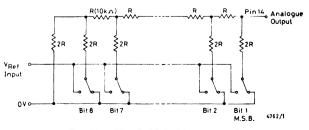

Figure 2 shows an example of a 3-bit DAC circuit based on a voltageswitching R-2R ladder network, a technique widely used in Ferranti converters.

Each 2R element is connected either to 0 volts or  $V_{FS}$  ( $V_{REF}$ ) by transistor switches. Binary weighted voltages are produced at the output of the R-2R ladder, the value being proportional to the digital input number.

Fig. 2. 3-bit Voltage Switching DAC

For example, it is fairly easy to see that if bit 1 is '1' and bits 2 and 3 are '0' then an output of  $V_{FS/2}$  is produced. This is because the resistance of the ladder looking from the output through the first R is 2R, which forms a 2:1 attenuator with the 2R in series with the MSB switch. Output voltages for other input codes can similarly be calculated, and it can be seen that the ladder may be extended to any number of bits.

The voltage switching ladder technique is used in the ZN426, ZN428 and ZN429 series of D to A converters and also in the ZN425 dualpurpose A to D/D to A converter.

### 1.3 D to A Parameters and Definitions

### 1.3.1 Converter Errors

The ideal DAC assumes that all the resistors are perfectly matched and that the switches have zero resistance. In a practical converter this will not be the case and various errors will occur in the output.

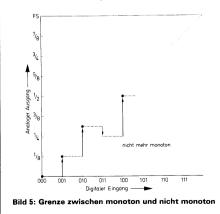

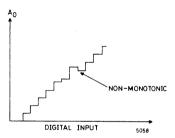

#### 1.3.2 Monotonicity

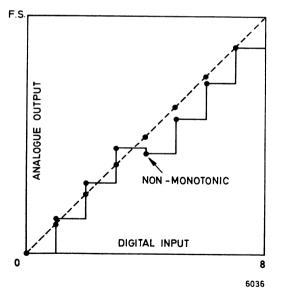

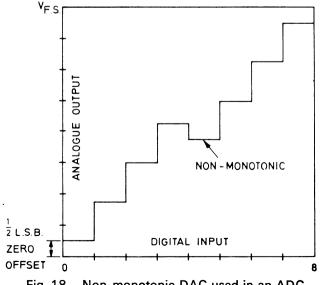

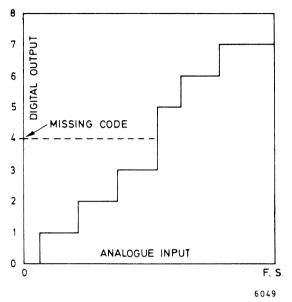

When the input code of a DAC is increased in 1 LSB steps the analogue output of the DAC should also increase, staircase fashion. If the output always increases in this manner then the DAC is said to be monotonic, i.e. the output is a single-valued function of the input. If, due to errors in the bit weighting, the output of the DAC decreases at any step, as shown in figure 3, then the DAC is said to be non-monotonic.

Fig. 3. Non-monotonic DAC

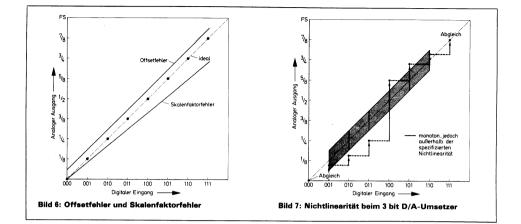

### 1.3.3 Offset (Zero Error)

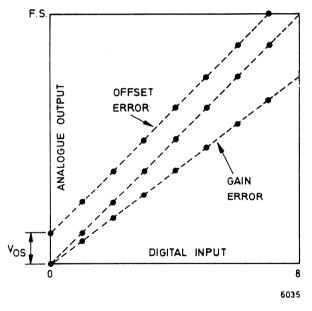

Assuming unipolar operation and normal binary coding, when the input code is zero then the DAC output should also be zero. However, due to package lead resistances and offset voltages in the switches this will not be the case, and a small output offset may exist. This has the effect of shifting the transfer function so that it no longer passes through zero, as shown in figure 4.

#### 1.3.4 Gain Error

If the reference voltage of a DAC is exactly the nominal value then the transfer characteristics of the converter should follow the ideal straight line. However, due to imperfections in the converter the transfer function may diverge from this line, as shown in figure 4. This error is known as gain error and is the difference between the slope of the actual transfer characteristic and the slope of the ideal transfer characteristic.

Fig. 4. Illustrating Offset and Gain Errors

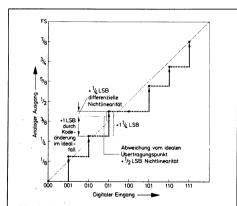

#### 1.3.5 Linearity Errors

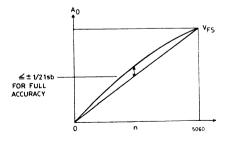

Offset and gain errors may be trimmed out so that the end points of the transfer characteristic lie at zero and  $V_{FSO}$ . However, even when this has been done, some or all of the intermediate points may not lie on the 'ideal' line. These errors, which cannot be trimmed out, are known as linearity errors.

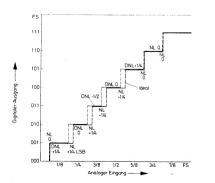

### 1.3.6 Non-Linearity (Linearity Error)

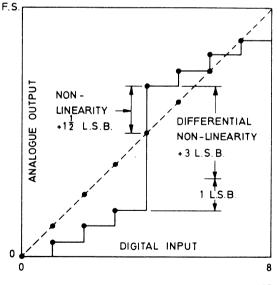

This is the maximum amount, given either as a percentage of full scale or a fraction of an LSB, by which any point on the transfer characteristic deviates from the ideal straight line passing through zero and V<sub>FSO</sub>. Non-linearity is illustrated in figure 5. A linearity error within the range  $\pm \frac{1}{2}$  LSB assures monotonic operation. Note however that the converse is not true and a DAC may still be monotonic with large linearity errors, which is also shown by figure 5.

### 1.3.7 Differential Non-linearity

This is the maximum difference, specified as a fraction of an LSB, between the actual and ideal size of any one LSB analogue increment. This can be seen as an error in the step height of a DAC staircase. A positive value of differential non-linearity means that the step height is larger than nominal, whilst a negative value means that it is smaller than nominal. If it is more negative than -1 LSB then the DAC is non-monotonic. However, positive differential non-linearity may assume any value and a DAC can still be monotonic, as shown in figure 5.

6037

Fig. 5. Illustrating Linearity Errors

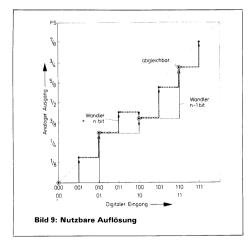

### 1.3.8 Resolution

As stated earlier, the resolution of a DAC is simply the number of bit inputs that a DAC possesses, which indicates the smallest analogue increment that the converter can produce as a fraction of  $V_{FS}$ , e.g. 8 bits = 1 part in 2<sup>8</sup> (256). Resolution implies nothing about the accuracy of a DAC, which is defined by linearity and other errors.

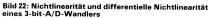

### 1.3.9 Useful Resolution

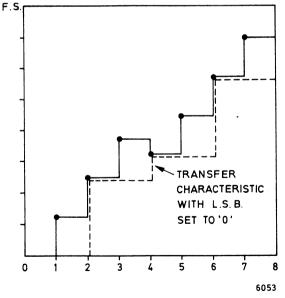

If an n bit DAC has a differential non-linearity of say -1.5 LSB then it is non-monotonic. However, if the LSB input is made permanently '0' then the DAC becomes an n-1 bit device with an LSB equal to twice the original LSB. The differential non-linearity error thus becomes -0.75 (new) LSB and the device is monotonic at a resolution of n-1 bits. This is illustrated in figure 6, which shows the transfer characteristic of a 3-bit DAC that has a useful resolution of 2 bits.

Due to manufacturing tolerances a proportion of n-bit converters will have only n-1 or n-2 bit useful resolution. In applications not requiring n -bit useful resolution these reduced resolution versions offer a significant price advantage. The useful resolution of Ferranti DACs is guaranteed over their full operating temperature range.

Fig. 6. Non-monotonic 3-bit DAC With a Useful Resolution of 2 bits

**1.3.10 Settling Time** is the time taken after a transition of the input code for the output of a DAC to settle to within  $\pm \frac{1}{2}$  LSB of its final value. This varies depending on which bits are being changed. It may be specified for a change of 1 LSB which generally gives the most optimistic (fastest) figure. More conservative figures are given by the most major transition (where the MSB changes in one direction and all other bits change in the opposite direction, e.g. 01111111 to 10000000 to 11111111) or vice versa.

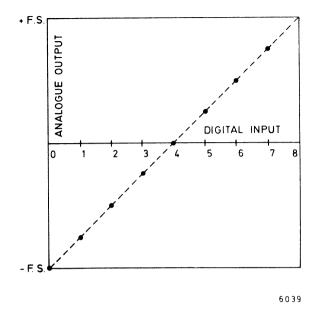

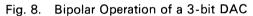

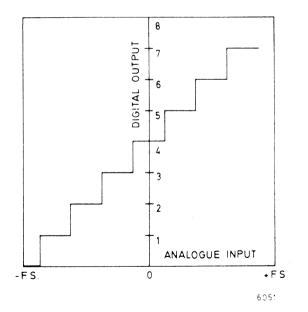

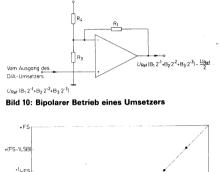

### 1.4 **Bipolar Operation**

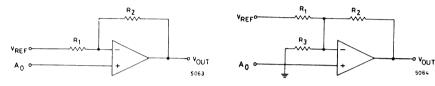

The discussion so far has been concerned only with DACs producing a single polarity (usually positive) output voltage. In some applications a bipolar (both positive and negative) output range may be required.

This can be achieved by adding a negative offset of  $\frac{V_{REF}}{2}$  to the

analogue output, as shown in figure 7. For all input codes where the MSB is '0' the output voltage is then negative, and for output codes where the MSB is '1' the output voltage is positive. Where the input coding is normally binary but the output voltage is offset by  $\frac{-V_{REF}}{2}$

then the input code is referred to as offset binary.

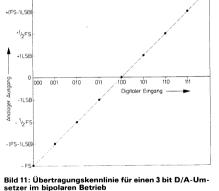

The transfer function of a 3-bit DAC with offset binary coding is shown in figure 8.

Fig. 7. Bipolar Operation of a DAC

### 8 Bit D/A-A/D-Converter

#### FEATURES

- 8, 7 and 6 bit Accuracy

- 0°C to +70°C (ZN425E Series)

- -55°C to +125°C (ZN425J-8)

- TTL and 5V CMOS Compatible

- Single +5V Supply

- Settling Time (D to A) 1 μsec Typical

- Conversion Time (A to D) 1 msec typical, using ramp and compare.

- Extra Components Required

- D-A : Reference capacitor (direct voltage output through 10 kΩ typ.)

- A-D : Comparator, gate, clock and reference capacitor

#### DESCRIPTION

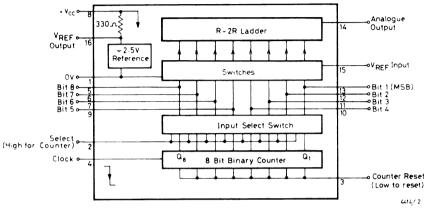

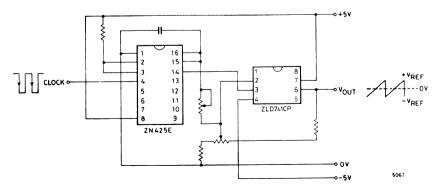

The ZN425 is a monolithic 8-bit digital to analogue converter containing an R-2R ladder network of diffused resistors with precision bipolar switches, and in addition a counter and a 2.5V precision voltage reference. The counter is a powerful addition which allows a precision staircase to be generated very simply merely by clocking the counter.

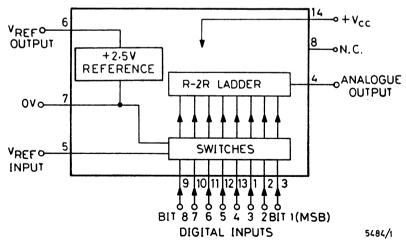

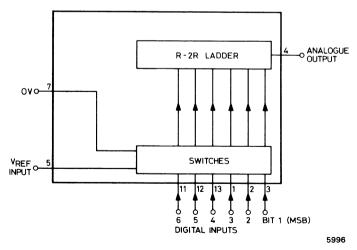

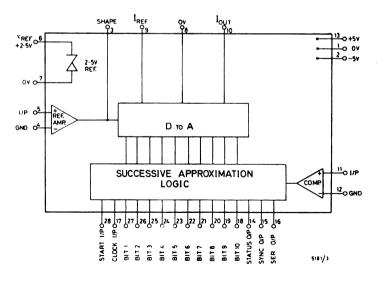

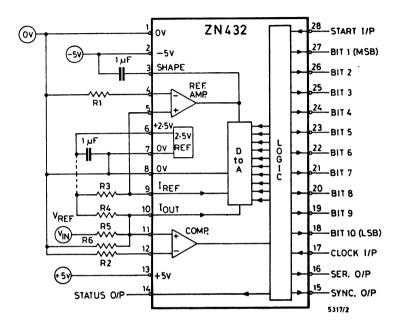

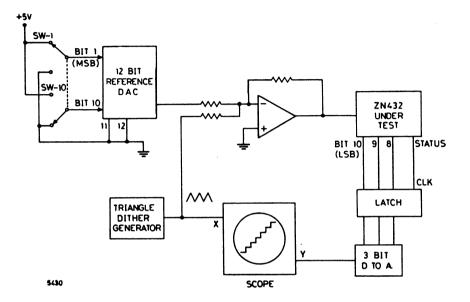

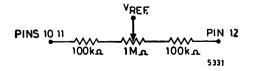

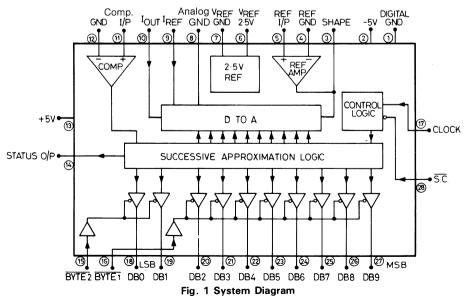

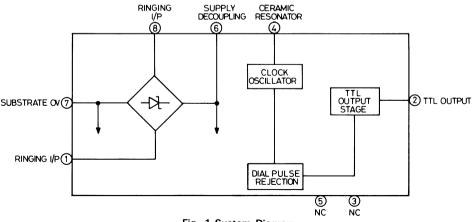

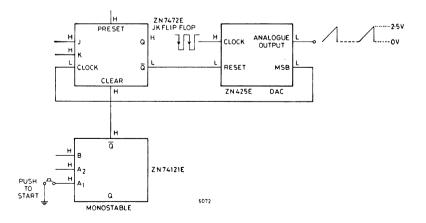

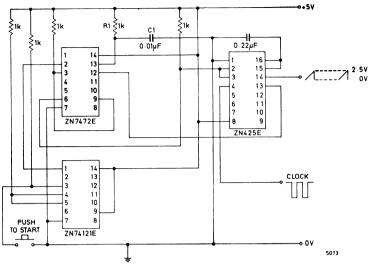

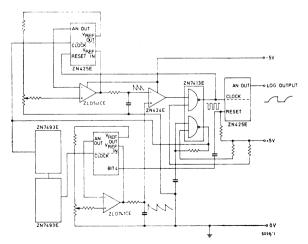

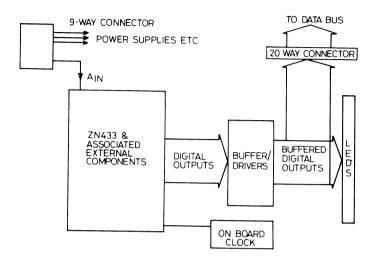

Fig. 1 - System Diagram

#### INTRODUCTION

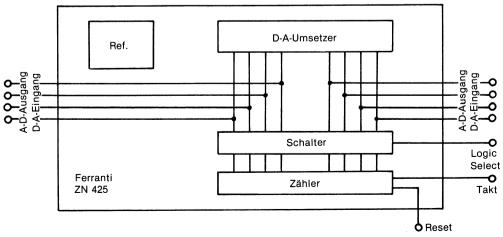

The ZN425 is an 8-bit dual mode digital to analogue/analogue to digital converter. It contains an 8-bit D to A converter using an advanced design of R-2R ladder network and an array of precision bipolar switches plus an 8-bit binary counter and a 2.5 volt precision voltage reference all on a single monolithic chip.

The special design of ladder network results in full 8-bit accuracy using normal diffused resistors.

The use of the on-chip reference voltage is pin optional to retain flexibility. An external fixed or varying reference may therefore be substituted.

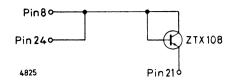

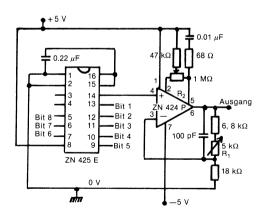

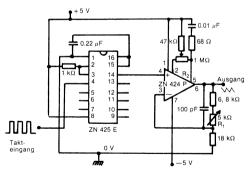

By including on the chip an 8-bit binary counter, analogue to digital conversion can be obtained simply by adding an external comparator (ZN424P) and clock inhibit gating (ZN7400E).

By simply clocking the counter the ZN425 can be used as a self-contained precision ramp generator.

A logic input select switch is incorporated which determines whether the precision switches accept the outputs from the binary counter or external digital inputs depending upon whether the control signal is respectively high or low.

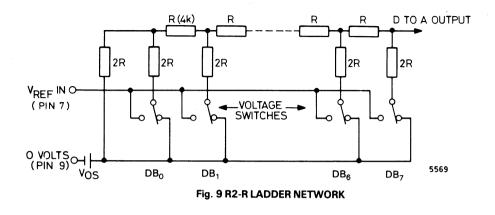

The converter is of the voltage switching type and uses an R-2R resistor ladder network as shown in Fig. 2.

Fig. 2 – The R-2R Ladder Network

Each 2R element is connected either to 0V or  $V_{REF}$  by transistor switches specially designed for low offset voltage (typically 1 millivolt).

Binary weighted voltages are produced at the output of the R-2R ladder, the value depending on the digital number applied to the bit inputs.

#### **ORDERING INFORMATION**

| Operating Temperature | 8-bit Accuracy | 7-bit Accuracy | 6-bit Accuracy | Package |

|-----------------------|----------------|----------------|----------------|---------|

| 0°C to +70°C          | ZN425E-8       | ZN425E-7       | ZN425E-6       | Plastic |

| –55°C to +125°C       | ZN425J-8       | -              |                | Ceramic |

#### ABSOLUTE MAXIMUM RATINGS

| Supply voltage V <sub>CC</sub>                  | +7·0 volts                   |

|-------------------------------------------------|------------------------------|

| Max. voltage, logic and V <sub>REF</sub> inputs | +5·5 volts See note 3        |

| Operating temperature range                     | 0°C to +70°C (ZN425E Series) |

|                                                 | –55°C to +125°C (ZN425J-8)   |

| Storage temperature range                       | –55°C to +125°C              |

### CHARACTERISTICS (at $T_{amb} = 25$ °C and $V_{CC} = +5$ volts unless otherwise specified).

#### Internal voltage reference

| Parameter                                | Symbol           | Min. | Тур. | Max. | Units  | Conditions              |

|------------------------------------------|------------------|------|------|------|--------|-------------------------|

| Output voltage                           | V <sub>REF</sub> | 2.4  | 2.55 | 2.7  | volts  | I = 7.5  mA  (internal) |

| Slope resistance                         | R <sub>s</sub>   |      | 2    | 4    | ohms   | I = 7.5  mA  (internal) |

| V <sub>REF</sub> Temperature coefficient |                  | -    | 40   | _    | ppm/*C | I = 7.5  mA  (internal) |

Note: The internal reference requires a  $0.22 \,\mu\text{F}$  stabilising capacitor between pins 1 and 16.

#### 8-Bit D to A Converter and Counter

| Parameter                                                                 | Symbol          | Min.             | Тур.      | Max.        | Units                                | Conditions                                               |

|---------------------------------------------------------------------------|-----------------|------------------|-----------|-------------|--------------------------------------|----------------------------------------------------------|

| Resolution                                                                |                 | 8                |           |             | bits                                 |                                                          |

| Accuracy ZN425J-8<br>(useful ZN425E-8<br>resolution) ZN425E-7<br>ZN425E-6 |                 | 8<br>8<br>7<br>6 |           |             | bits<br>bits<br>bits<br>bits<br>bits | V <sub>REF</sub> Input =<br>2 to 3V                      |

| Non-linearity                                                             |                 |                  |           | $\pm 0.5$   | L.S.B.                               | See Note 3                                               |

| Differential non-linearity                                                |                 |                  | $\pm 0.5$ |             | L.S.B.                               | See Note 6                                               |

| Settling time                                                             |                 | —                | 1.0       |             | μs                                   | 1 L.S.B. step                                            |

| Settling time to 0 · 5 L.S.B.                                             |                 | _                | 1 · 5     | 2.5         | μs                                   | All bits ON toOFF<br>or OFF to ON                        |

| Offset voltage ZN425J-8<br>ZN425E-8<br>ZN425E-6<br>ZN425E-7               | V <sub>os</sub> |                  | 8<br>3    | 12<br>8     | mV<br>mV                             | All bits OFF<br>See Note 3                               |

| Full scale output                                                         |                 | 2 · 545          | 2 · 550   | 2 · 555     | volts                                | All bits ON<br>Ext. V <sub>REF</sub> =2 <sup>.</sup> 56V |

| Full scale temperature coeff.                                             |                 |                  | 3         |             | ppm/°C                               | Ext. V <sub>REF</sub> =2 <sup>.</sup> 56V                |

| Non-linearity error temp. coeff.                                          |                 |                  | 7.5       | _           | ppm/°C                               | Relative to F.S.R.                                       |

| Analogue output resistance                                                | R <sub>o</sub>  |                  | 10        | -           | kΩ                                   |                                                          |

| External reference voltage                                                |                 | 0                | —         | 3.0         | volts                                |                                                          |

| Supply voltage                                                            | V <sub>cc</sub> | 4·5              | -         | <b>5</b> .5 | volts                                | See Note 3                                               |

| Supply current                                                            | ا.              | _                | 25        | 35          | mA                                   |                                                          |

| High level input voltage                                                  | VIH             | 2.0              | -         | —           | volts                                | See Notes 1 and 2                                        |

| Low level input voltage                                                   | V <sub>IL</sub> | _                | -         | 0.7         | volts                                |                                                          |

#### CHARACTERISTICS (continued).

| Parameter                                             | Symbol          | Min. | Тур. | Max.  | Units | Conditions                                         |

|-------------------------------------------------------|-----------------|------|------|-------|-------|----------------------------------------------------|

| High level input current                              | I <sub>IH</sub> | -    |      | 10    | μΑ    | $V_{CC} = max.$<br>$V_1 = 2 \cdot 4V$              |

|                                                       |                 |      |      | 100   | μA    | $V_{CC} = max.$<br>$V_1 = 5.5V$                    |

| Low level input current,<br>bit inputs                | I <sub>IL</sub> |      | _    | -0.68 | mA    | $V_{CC} = max.$<br>$V_1 = 0.3V$                    |

| Low level input current, clock reset and input select | I <sub>L</sub>  | _    |      | -0.18 | mA    |                                                    |

| High level output current                             | I <sub>он</sub> | _    | _    | -40   | μA    |                                                    |

| Low level output current                              | IOL             |      |      | 1.6   | mA    |                                                    |

| High level output voltage                             | V <sub>он</sub> | 2.4  | —    |       | volts | $V_{CC} = min.$<br>Q = 1<br>$I_{load} = -40 \mu A$ |

| Low level output voltage                              | V <sub>OL</sub> | -    |      | 0.4   | volts | $V_{CC} = min.$<br>Q = 0<br>$I_{load} = 1.6 mA$    |

| Maximum counter clock<br>frequency                    | f <sub>c</sub>  | 3    | 5    | -     | MHz   | See Note 5                                         |

| Reset pulse width                                     | t <sub>R</sub>  | 200  | -    | —     | ns    | See Note 4                                         |

#### Notes:

- 1. The Input Select pin (2) must be held low when the bit pins (5, 6, 7, 9, 10, 11, 12 and 13) are driven externally.

- 2. To obtain counter outputs on bit pins the Input Select pin (2) should be taken to  $+V_{CC}$  via a 1 k $\Omega$  resistor.

- 3. The ZN425J differs from the ZN425E in the following respects:

- (a) For the ZN425J, the maximum linearity error may increase to  $\pm 1$  LSB over the temperature ranges –55 °C to 0 °C and + 70 °C to +125 °C.

- (b) Maximum operating voltage. Between 70°C and 125°C the maximum supply voltage is reduced to 5.0V.

- (c) Offset voltage. The difference is due to package lead resistance. This offset will normally be removed by the setting up procedure, and because the offset temperature coefficient is low, the specified accuracy will be maintained.

- 4. The device may be reset by gating from its own counter.

- 5. F<sub>max</sub> in A/D mode is 300 kHz, see page 1-18

- 6. Monotonic over full operating temperature range at resolution appropriate to accuracy.

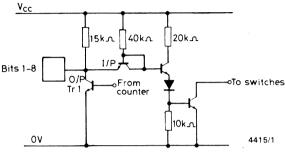

If Pin 2 is high then the output equals the Q output of the corresponding counter.

If Pin 2 is low then the output transistor, Tr1 is held off.

Fig. 3 - Bit Inputs/Outputs

#### APPLICATIONS

#### 1. 8-bit D to A Converter

The ZN425 gives an analogue voltage output directly from pin 14 therefore the usual current to voltage converting amplifier is not required. The output voltage drift, due to the temperature coefficient of the Analogue Output Resistance R<sub>o</sub>, will be less than 0.004% per °C (or 1 L.S.B./ 100°C) if R<sub>L</sub> is chosen to be  $\geq 650 \text{ k}\Omega$ .

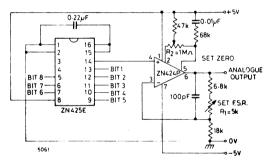

In order to remove the offset voltage and to calibrate the converter a buffer amplifier is necessary. Fig. 4 shows a typical scheme using the internal reference voltage. To minimise temperature drift in this and similar applications the source resistance to the inverting input of the operational amplifier should be approximately 6 k $\Omega$ . The calibration procedure is as follows:

- i. Set all bits to OFF (low) and adjust  $R_2$  until  $V_{out} = 0.000V$ .

- ii. Set all bits to ON (high) and adjust R1 until Vout = Nominal full scale reading 1 L.S.B.

- ili. Repeat i. and ii.

e.g. Set F.S.R. to

$$+3.840$$

volts  $-1$  L.S.B.

=  $3.825$  volts

(1 L.S.B. =  $\frac{3.84}{256}$  =  $15.0$  millivolts.)

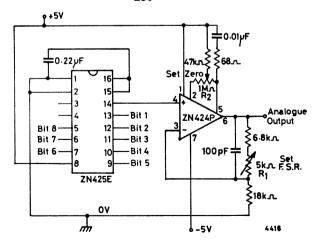

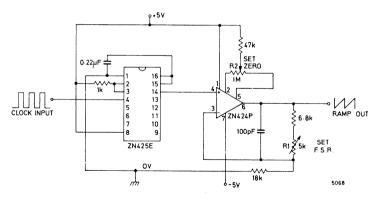

Fig. 4 - 8-bit Digital to Analogue Converter

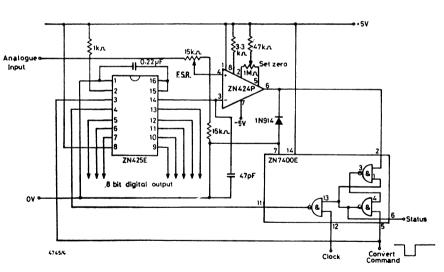

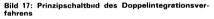

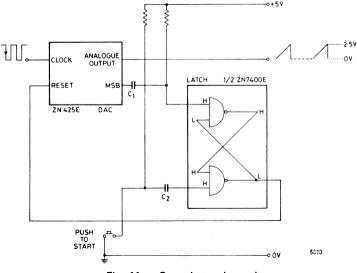

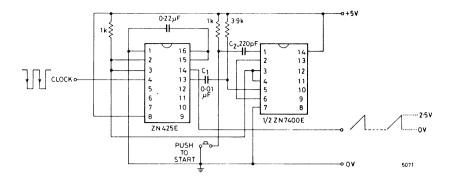

#### 2. 8-bit Analogue to Digital Converter

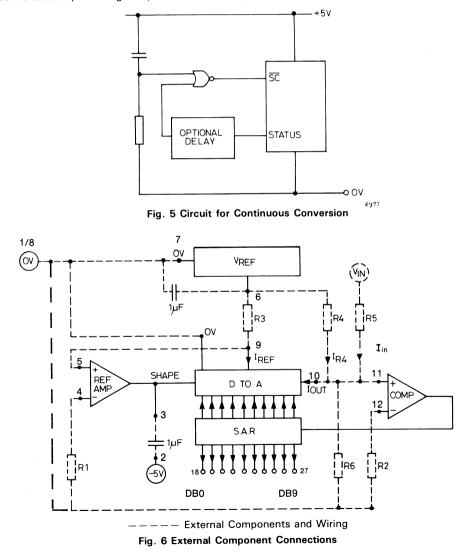

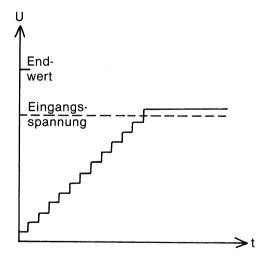

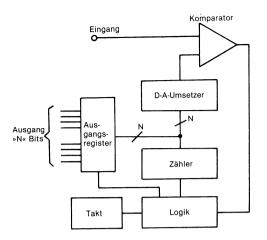

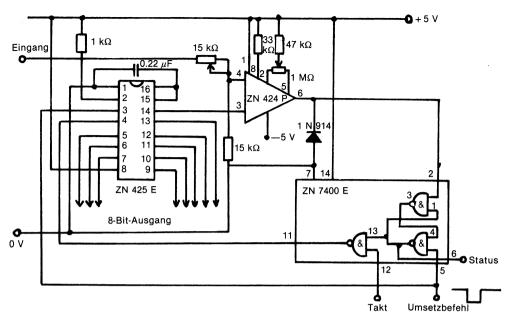

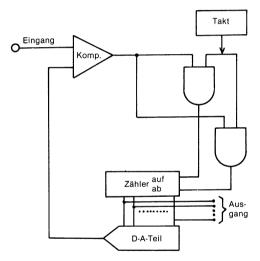

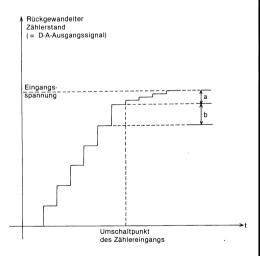

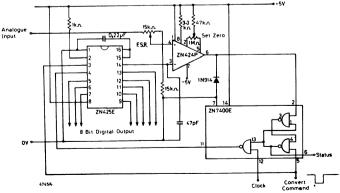

A counter type ADC can be constructed by adding a voltage comparator and a latch as in Fig. 5. On the negative edge of the CONVERT COMMAND pulse (15  $\mu$ s minimum) the counter is set to zero and the STATUS latch to logical 1. On the positive edge the gate is opened, enabling clock pulses to be fed to the counter input of the ZN425. The minimum negative clock pulse width to the ZN425 is 100 ns. The analogue output of the ZN425 ramps until it equals the voltage on the other input of the comparator. At this point the comparator output goes low and resets the STATUS latch to logical 0 from the status latch indicates that the 8 bit digital output is a valid representation of the analogue input voltage.

A small capacitor of 47 pF is added to the ZN425 output to stop any positive going glitches prematurely resetting the status latch. This capacitance is in parallel with the ZN425 output capacitance (20–30 pF) and they form a time constant with the ZN425 output resistance (10 k $\Omega$ ). This time constant is the main limit to the maximum clock frequency. With a fast comparator the clock frequency can be up to 300 kHz. Using the ZN424P as a comparator the clock frequency should be restricted to 100 kHz. The conversion time varies with the input, being a maximum for full scale input.

Maximum conversion time =

256 clock frequency in Hz seconds

Fig. 5 - 8-bit Analogue to Digital Converter

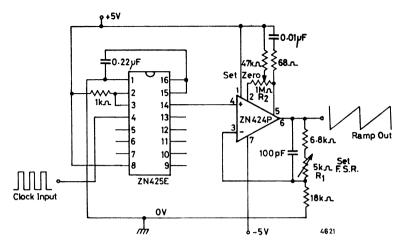

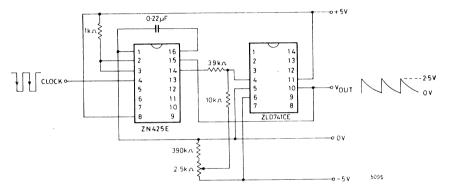

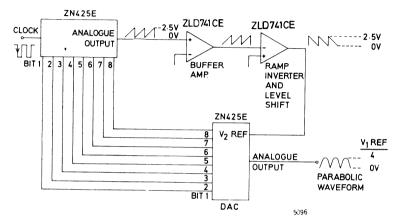

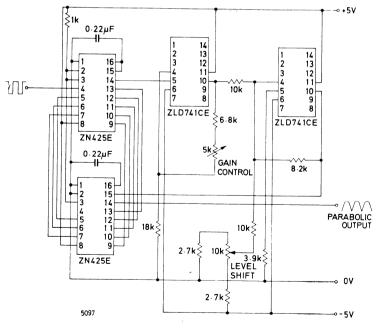

#### 3. Precision Ramp Generator

The inclusion of an 8-bit binary counter on the chip gives the ZN425 a useful ramp generator function. The circuit, Fig. 6 uses the same buffer stages as the D to A converter. The calibration procedure is also the same. Holding pin 2 low will set all bits to ON and if RESET is taken low with pin 2 high all the bits are turned OFF. If the end voltages of the ramp are not required to be set accurately then the buffer stage could be omitted and the voltage ramp will appear directly at pin 14.

Fig. 6 - Precision Ramp Generator

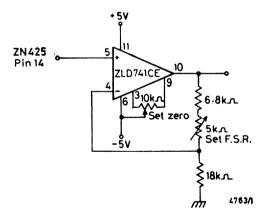

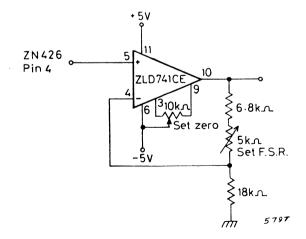

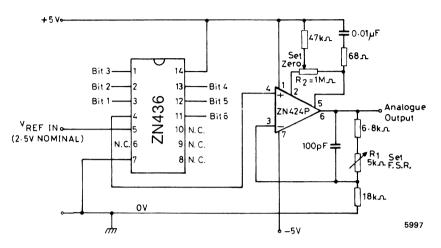

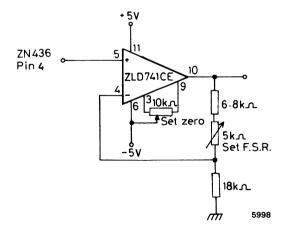

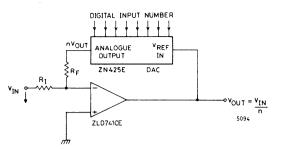

#### 4. Alternative Output Buffer using the ZLD741

The following circuit, employing the ZLD741 operational amplifier, may be used as the output buffer for both the 8-bit Digital to Analogue Converter (Fig. 4) and the Precision Ramp Generator (Fig. 6).

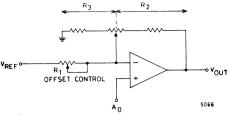

Fig. 7 - The ZLD741 as Output Buffer

#### 5. Further Applications

Details of a wide range of additional applications, described in the Ferranti publication 'Application Report-ZN425 8-bit A-D/D-A Converter', are also available.

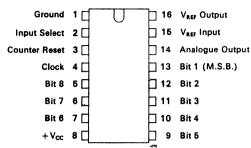

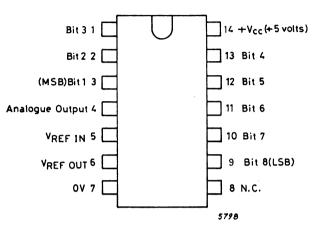

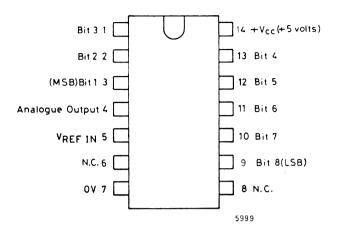

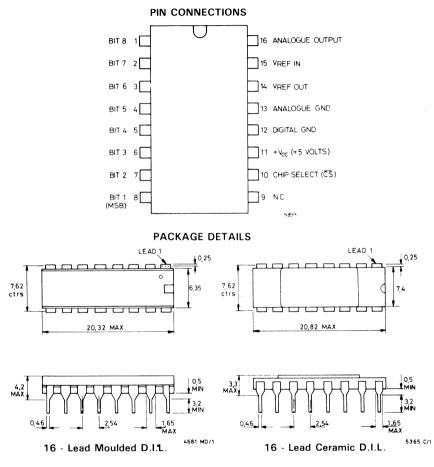

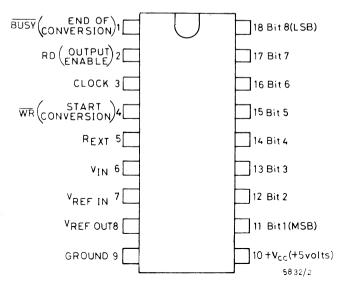

PIN CONNECTIONS

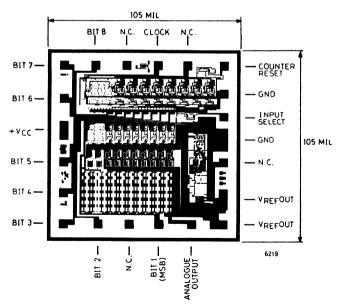

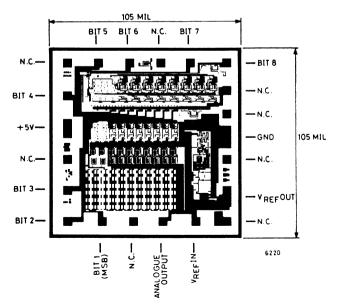

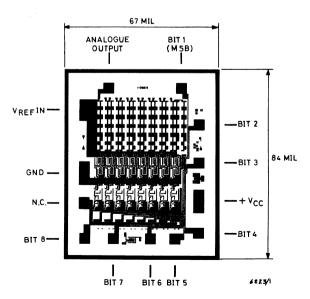

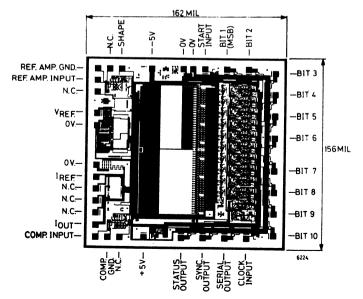

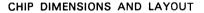

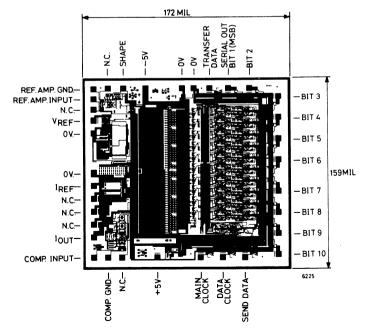

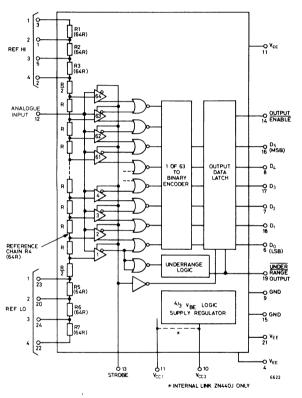

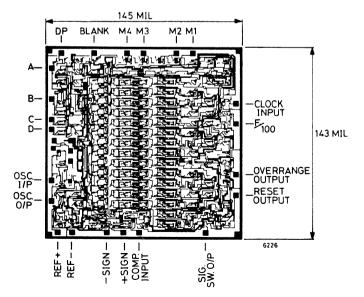

CHIP DIMENSIONS AND LAYOUT

### 8 Bit Monolithic D to A Converter

#### **FEATURES**

- 8, 7 and 6-bit Accuracy

- ZN426E Series Commercial Temp. Range 0°C to +70°C

- ZN426J-8 Military Temp. Range -55°C to +125°C

- TTL and 5V CMOS Compatible

- Single +5V Supply

- Settling Time 1 μsec. Typical

- Only Reference Capacitor and Resistor required

#### DESCRIPTION

The ZN426 is a monolithic 8-bit digital to analogue converter containing an R-2R ladder network of diffused resistors with precision bipolar switches and a 2.5V precision voltage reference.

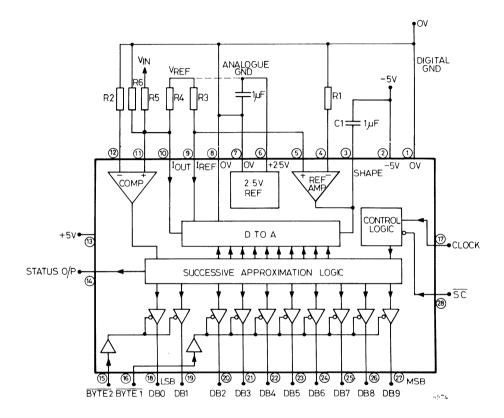

Fig. 1. System Diagram

#### INTRODUCTION

The ZN426 is an 8-bit digital to analogue converter. It contains an advanced design of R-2R ladder network and an array of precision bipolar switches plus a 2.5 volt precision voltage reference all on a single monolithic chip.

The special design of ladder network results in full 8-bit accuracy using normal diffused resistors.

The use of the on-chip reference voltage is pin optional to retain flexibility. An external fixed or varying reference may therefore be substituted. In this case there is no need to supply power to the internal reference so  $R_{BFF}$  and  $C_{BFF}$  can be omitted.

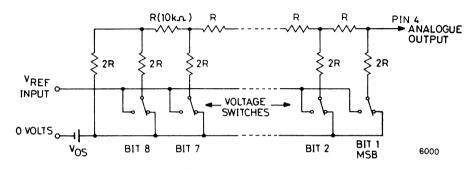

The converter is of the voltage switching type and uses an R-2R resistor ladder network as shown in Fig. 2.

Fig. 2. The R-2R Ladder Network

Each 2R element is connected either to 0V or V<sub>REF</sub> by transistor switches specially designed for low offset voltage (typically 1 millivolt).

**Binary weighted voltages are produced at the output of the R-2R ladder**. the value depending on the **digital number applied to the bit inputs**.

#### **ORDERING INFORMATION**

| Operating Temperature | 8-bit accuracy | 7-bit accuracy | 6-bit accuracy | Package |

|-----------------------|----------------|----------------|----------------|---------|

| 0 to +70°C            | ZN426E-8       | ZN426E-7       | ZN426E-6       | Plastic |

| –55 to +125°C         | ZN426J-8       | _              | _              | Ceramic |

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply voltage V <sub>CC</sub>                  | •• | +7.0 volts   |

|-------------------------------------------------|----|--------------|

| Max. voltage, logic and V <sub>REF</sub> inputs | •• | +5.5 volts   |

| Storage temperature range                       | •• | 55 to +125°C |

| Parameter                                            | Symbol | Min.   | Тур.  | Max.  | Units        | Conditions                                       |

|------------------------------------------------------|--------|--------|-------|-------|--------------|--------------------------------------------------|

| Converter<br>Resolution                              |        | 8      |       |       | bits         |                                                  |

| Accuracy (useful resolution)<br>ZN426J-8<br>ZN426E-8 |        | 8      | _     |       | bits         | V <sub>REF</sub> input<br>= 2.0 to 3.0 volts     |

| ZN426E-7<br>ZN426E-7<br>ZN426E-6                     |        | 7<br>6 |       | _     | bits<br>bits | = 2.0 to 3.0 volts                               |

| Non-linearity                                        |        |        |       | ±0.5  | L.S.B.       | Note 1                                           |

| Differential non-linearity                           |        | —      | ±0.5  |       | L.S.B.       | Note 2                                           |

| Settling time to 0.5 L.S.B.                          |        | _      | 1.0   |       | μs           | 1 L.S.B. step                                    |

| Settling time to 0.5 L.S.B.                          |        |        | 2.0   |       | μs           | All bits ON to OFF<br>or OFF to ON               |

| Offset voltage ZN426J-8<br>ZN426E-8                  | Vos    |        | 5.0   | 8.0   | mV           | All bits OFF                                     |

| ZN426E-7<br>ZN426E-7<br>ZN426E-6                     |        |        | 3.0   | 5.0   | mV           | Note 1                                           |

| V <sub>OS</sub> temperature coefficient              |        |        | 5     |       | μV/°C        |                                                  |

| Full scale output                                    |        | 2.545  | 2.550 | 2.555 | volts        | All bits ON<br>Ext. V <sub>REF</sub> =<br>2.560V |

| Full scale temp. coefficient                         |        |        | 3     |       | ppm/°C       | Ext. V <sub>REF</sub> =<br>2.560V                |

| Non-linearity temp. coeff.                           |        |        | 7.5   |       | ppm/°C       | Relative to F.S.R.                               |

### ELECTRICAL CHARACTERISTICS ( $V_{CC} = +5$ volts, $T_{amb} = 25$ °C unless otherwise specified).

#### Notes:

- 1. The ZN426J-8 differs from the ZN426E-8 in the following respects :

- (a) For the ZN426J-8, the maximum linearity error may increase to ±0.4% FSR i.e. ±1 LSB over the temperature ranges −55°C to 0°C and +70°C to +125°C.

- (b) Offset voltage. The difference is due to package lead resistance. This offset will normally be removed by the setting up procedure, and because the offset temperature coefficient is low, the specified accuracy will be maintained.

- 2. Monotonic over full temperature range at resolution appropriate to accuracy.

ELECTRICAL CHARACTERISTICS (continued)

| Parameter                                       | Symbol           | Min.  | Тур. | Max.  | Units  | Conditions                                       |

|-------------------------------------------------|------------------|-------|------|-------|--------|--------------------------------------------------|

| Analogue output resistance                      | R <sub>o</sub>   |       | 10   |       | kΩ     |                                                  |

| External reference voltage                      |                  | 0     |      | 3.0   | volts  |                                                  |

| Supply voltage                                  | V <sub>cc</sub>  | 4.5   |      | 5.5   | Volts  |                                                  |

| Supply current                                  | I <sub>s</sub>   | -     | 5    | 9     | mA     |                                                  |

| High level input voltage                        | VIH              | 2.0   |      |       | volts  |                                                  |

| Low level input voltage                         | VIL              |       | _    | 0.7   | volts  |                                                  |

| High level input current                        | I <sub>IH</sub>  | _     |      | 10    | μΑ     | $V_{CC} = max.,$<br>$V_1 = 2.4V$                 |

|                                                 |                  |       |      | 100   | μΑ     | V <sub>CC</sub> = max.,<br>V <sub>1</sub> = 5.5V |

| Low level input current                         | IIL              | —     | _    | -0.18 | mA     | $V_{CC} = max.,$<br>$V_{I} = 0.3V$               |

| Internal Voltage<br>Reference<br>Output voltage | V <sub>REF</sub> | 2.475 | 2.55 | 2.625 | volts  | <i>Note*</i><br>R <sub>REF</sub> = 390Ω          |

| Slope resistance                                | R <sub>s</sub>   | _     | 1    | 2     | ohms   | $R_{REF} = 390\Omega$                            |

| V <sub>REF</sub> temperature coefficient        |                  | —     | 40   | —     | ppm/°C | $R_{REF} = 390\Omega$                            |

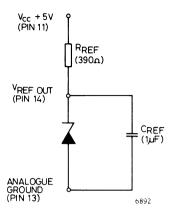

*Note*<sup>•</sup> The internal reference requires a 1  $\mu$ F stabilising capacitor between pins 7 and 6 (C<sub>REF</sub>) and a 390 $\Omega$  resistor between pins 14 and 6 (R<sub>REF</sub>).

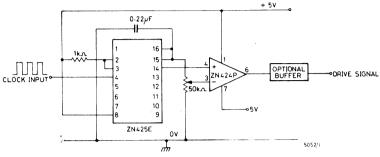

#### APPLICATIONS

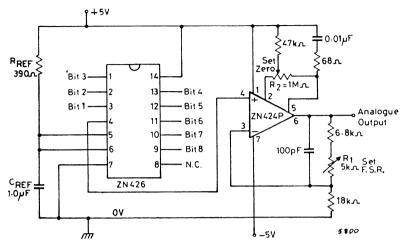

#### 1. 8-bit D to A Converter

The ZN426 gives an analogue voltage output directly from pin 4 therefore the usual current to voltage converting amplifier is not required. The output voltage drift, due to the temperature coefficient of the Analogue Output Resistance R<sub>o</sub>, will be less than 0.004% per °C (or 1 L.S.B./ 100°C) if R<sub>L</sub> is chosen to be  $\geq 650 \text{ k}\Omega$

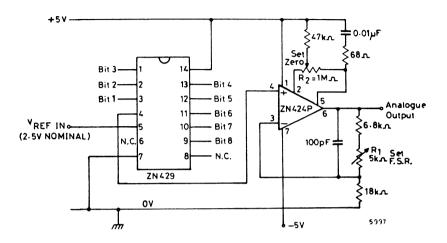

In order to remove the offset voltage and to calibrate the converter a buffer amplifier is necessary. Fig. 3 shows a typical scheme using the internal reference voltage. To minimise temperature drift in this and similar applications the source resistance to the inverting input of the operational amplifier should be approximately  $6 \ k\Omega$ . The calibration procedure is as follows:

i. Set all bits to OFF (low) and adjust  $R_2$  until  $V_{out} = 0.000V$ .

*ii.* Set all bits to ON (high) and adjust R<sub>1</sub> until V<sub>out</sub> = Nominal full scale reading -1 L.S.B.

iii. Repeat i. and ii.

e.g. Set F.S.R. to +3.840 volts -1 L.S.B. = 3.825 volts

$$(1 \text{ L.S.B.} = \frac{3 \cdot 84}{256} = 15.0 \text{ millivolts.})$$

Fig. 3. 8-bit Digital to Analogue Converter

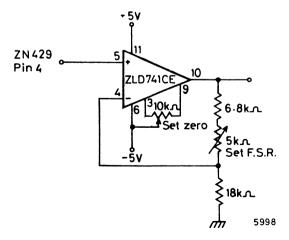

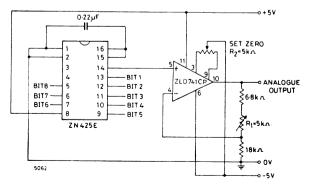

#### Alternative Output Buffer using the ZLD741

The following circuit, employing the ZLD741 operational amplifier, may be used as the output buffer (Fig. 3).

Fig. 4. The ZLD741 as Output Buffer

**PIN CONNECTIONS**

#### CHIP DIMENSIONS AND LAYOUT

### ZN428E-8 ZN428J-8

### 8 Bit Latched Input Monolithic D to A Converter

#### FEATURES

- Contains DAC with data latch and on-chip reference.

- Guaranteed monotonic over the full operating temperature range

- Single +5V supply Microprocessor compatible

- TTL and 5V CMOS compatible

- 800 ns settling time Complementary to ZN427 A to D Series

- ZN428E-8 Commercial temperature range 0°C to +70°C

- ZN428J-8 Military temperature range -55°C to +125°C

#### **GENERAL DESCRIPTION**

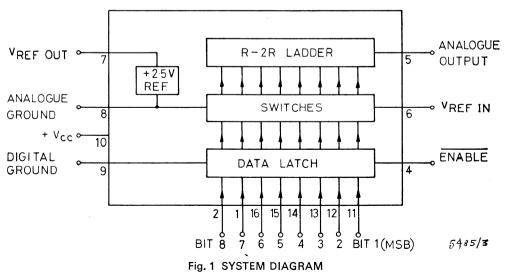

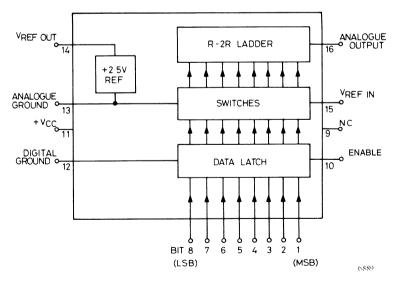

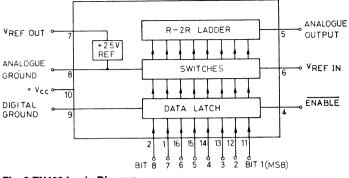

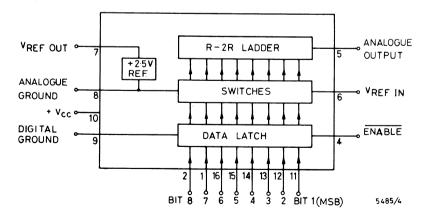

The ZN428 is a Monolithic 8 bit D to A converter with input latches to facilitate updating from a data bus. The latch is transparent when Enable is LOW and the data is held when Enable is taken HIGH. The ZN428 also contains a 2.5 volt reference the use of which is pin optional to retain flexibility. An external fixed or varying reference may therefore be substituted.

### ZN428E-8/J-8

#### ABSOLUTE MAXIMUM RATINGS

| Supply voltage V <sub>CC</sub>                 | •• | •• |    | • • | +7.0 volts                                            |

|------------------------------------------------|----|----|----|-----|-------------------------------------------------------|

| Max. voltage, logic and V <sub>REF</sub> input |    |    |    |     | +V <sub>cc</sub>                                      |

| Operating temperature range                    | •• | •• | •• | ••  | 0°C to +70°C (ZN428E-8)<br>-55°C to +125°C (ZN428J-8) |

| Storage temperature range                      |    | •• |    | ••  | –55°C to +125°C                                       |

| Analogue Ground to Digital Ground              | •• | •• | •• |     | $\ldots \pm 200 \text{ mV}$                           |

### ELECTRICAL CHARACTERISTICS (V\_{CC} = +5 volts, T\_{amb} = 25 \,^{\circ}\text{C} unless otherwise specified).

| Parameter                                             | Min.    | Тур.  | Max.      | Units  | Conditions                                                             |

|-------------------------------------------------------|---------|-------|-----------|--------|------------------------------------------------------------------------|

| Internal Voltage<br>Reference<br>Output voltage       | 2.475   | 2.550 | 2.625     | volts  | $R_{\text{REE}} = 390\Omega$                                           |

| Slope resistance                                      |         | 0.5   | 2         | Ω      | $\begin{cases} R_{REF} = 390\Omega \\ C_{REF} = 1 \ \mu F \end{cases}$ |

| V <sub>REFOUT</sub> T.C.                              |         | 50    |           | ppm/°C |                                                                        |

| Reference current                                     | 4       |       | 15        | mA     | Note 1                                                                 |

| D to A Converter<br>Linearity error                   |         |       | ±0.5      | LSB    | 2.0V ≼V <sub>REF IN</sub> ≼3.0V                                        |

| Differential non-linearity                            |         | ±0.5  |           | LŞB    |                                                                        |

| Linearity error T.C.                                  |         | ±3    |           | ppm/°C |                                                                        |

| Differential non-linearity T.C.                       |         | ±6    |           | ppm/°C |                                                                        |

| Offset voltage                                        |         | 2     | 5         | mV     | All bits OFF                                                           |

| Offset voltage T.C.                                   |         | ±6    |           | μV/°C  |                                                                        |

| Full scale output                                     | 2.545   | 2.550 | 2.555     |        | External reference                                                     |

| Full scale output T.C.                                |         | 2     |           | ppm/°C | $V_{\text{REF IN}} = 2.560 \text{ volts,}$<br>all bits ON              |

| Analogue output resistance                            |         | 4     |           | kΩ     |                                                                        |

| External reference voltage                            | 0       |       | 3.0       | volts  |                                                                        |

| Settling time to 0.5 LSB                              |         | 800   |           | ns     | 1 LSB Major Transition<br>(Note 2)                                     |

|                                                       |         | 1.25  |           | μs     | All bits ON to OFF or<br>OFF to ON (Note 2)                            |

| Operating temperature range :<br>ZN428E-8<br>ZN428J-8 | 0<br>55 |       | 70<br>125 | с<br>с |                                                                        |

| Supply voltage (V <sub>CC</sub> )                     | 4.5     | 5.0   | 5.5       | volts  |                                                                        |

Note 1 See REFERENCE Note 2  $R_L = 10 \text{ M}\Omega$ ,  $C_L = 10 \text{ pF}$ .

### ZN428E-8/J-8

#### **ELECTRICAL CHARACTERISTICS** (continued)

|                                                                                      | Min. | Тур. | Max. | Units | Conditions                                                               |

|--------------------------------------------------------------------------------------|------|------|------|-------|--------------------------------------------------------------------------|

| Supply current                                                                       |      | 20   | 30   | mA    | Note 3                                                                   |

| Power consumption                                                                    |      | 100  |      | mW    |                                                                          |

| Logic<br>(over specified operating<br>temperature range)<br>High level input voltage | 2.0  |      |      | v     |                                                                          |

| Low level input voltage                                                              |      |      | 0.8  | v     |                                                                          |

| High level input current                                                             |      |      | 60   | μΑ    | V <sub>IN</sub> = 5.5V                                                   |

|                                                                                      |      |      | 20   | μΑ    | $V_{1N} = 5.5V$<br>$V_{CC} = Max.$<br>$V_{1N} = 2.4V$<br>$V_{CC} = Max.$ |

| Low level input current                                                              |      |      | -5   | μA    | $V_{IN} = 0.4V$<br>$V_{CC} = Max.$                                       |

| Input Clamp Diode Voltage                                                            |      | -1.5 |      | v     | I <sub>IN</sub> = -8 mA                                                  |

| Enable pulse width                                                                   | 100  |      |      | ńs    |                                                                          |

| Data set-up time                                                                     | 150  |      |      | ns    | Note 4                                                                   |

| Data hold time                                                                       | 10   |      |      | ns    | Note 5                                                                   |

|                                                                                      |      |      |      |       |                                                                          |

Note 3 All inputs HIGH ( $V_{1H} = 3.5$  volts).

Note 4 Set up time before Enable goes high.

Note 5 Hold time after Enable goes high.

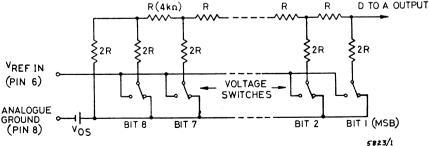

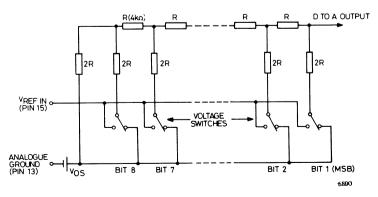

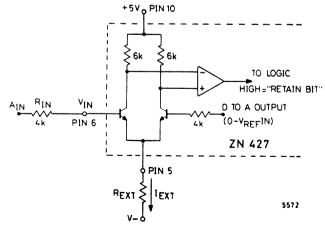

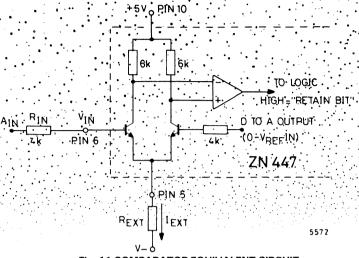

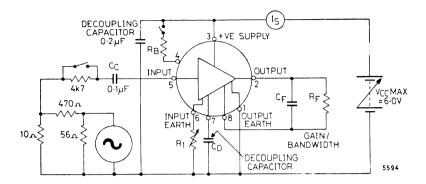

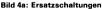

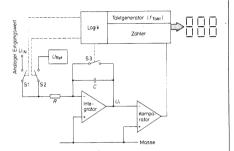

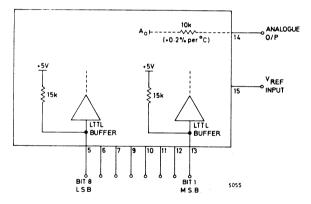

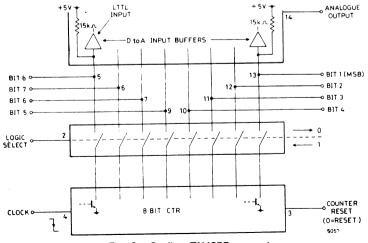

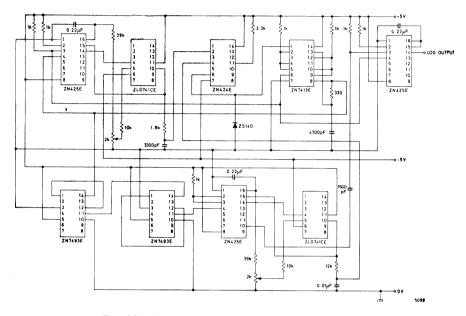

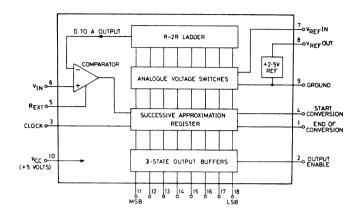

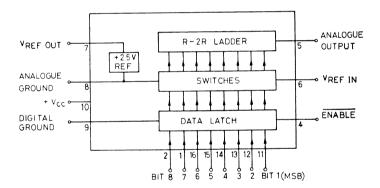

#### **D to A CONVERTER**

The converter is of the voltage switching type and uses an R-2R ladder network as shown in Fig. 2. Each 2R element is connected to 0V or  $V_{REF\,IN}$  by transistor voltage switches specially designed for low offset voltage (<1 millivolt). A binary weighted voltage is produced at the output of the R-2R ladder.

Fig. 2. The R-2R Ladder Network

### ZN428E-8/J-8

Analogue Output =

$$\frac{n}{256} (V_{REF IN} - V_{OS}) + V_{OS}$$

where n is the digital input to the D to A from the data latch.

$V_{OS}$  is a small offset voltage produced by the D to A switch currents flowing through the package lead resistance. The value of  $V_{OS}$  is tyically 1 mV. This offset will normally be removed by the setting up procedure (see APPLICATIONS section) and because the offset temperature coefficient is low ( $\pm 6 \mu V/$ °C) the effect on accuracy is negligible.

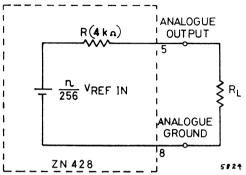

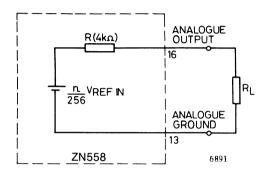

Fig. 3. Analogue Output Equivalent Circuit

Fig. 3 shows an equivalent circuit of the output (ignoring  $V_{OS}$ ). The output resistance R has a temperature coefficient of +0.2% per °C.

The gain drift due to this is  $\frac{0.2R}{R+R_L}$  % per °C

RL should be chosen to be as large as possible to make the gain drift small. As an example if  $R_L = 400 \text{ k}\Omega$  then the gain drift due to the T.C. of R for a 100°C change in ambient temperature will be less than 0.2%. Alternatively the ZN428 can be buffered by an amplifier (see APPLICATIONS section).

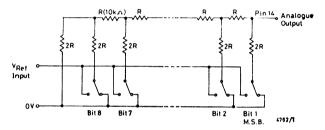

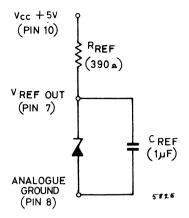

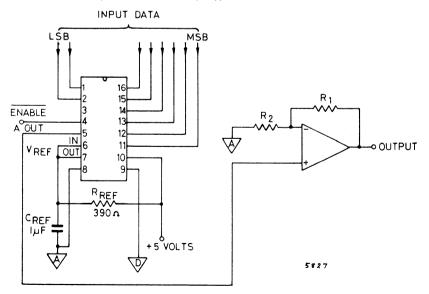

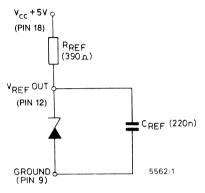

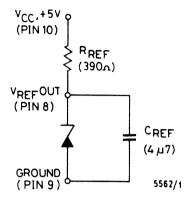

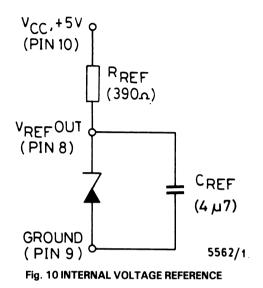

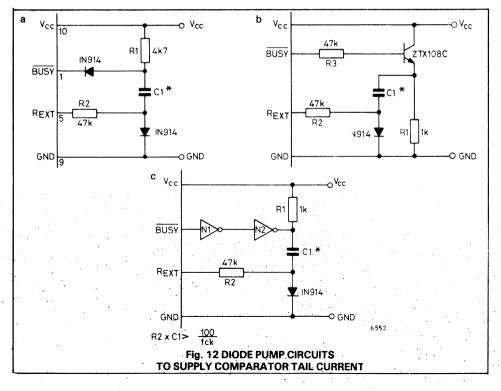

#### REFERENCE

#### (a) Internal Reference

The internal reference is an active band gap circuit which is equivalent to a 2.5 volt Zener diode with a very low slope impedance (Fig. 4). A resistor ( $R_{REF}$ ), should be connected between  $+V_{CC}$  (pin 10) and pin 7. The recommended value of  $390\Omega$  will supply a nominal reference current of (5.0-2.5)/0.39 = 6.4 mA. A stabilising/decoupling capacitor,  $C_{REF} = 1 \,\mu$ F is required between pins 7 and 8 for internal reference operation,  $V_{REFOUT}$  (pin 7) being connected to  $V_{REF IN}$  (pin 6).

Up to five ZN428s may be driven from one internal reference (there is no need to reduce R<sub>REF</sub>) This useful feature saves power and gives excellent gain tracking between the converters.

#### (b) External Reference

If required an external reference voltage may be connected to  $V_{REF IN}$ . The slope resistance of such a reference source should be less than  $\frac{2.5}{n} \Omega$ , where n is the number of converters supplied.  $V_{REF IN}$  can be varied from 0 to +3 volts for ratiometric operation. The ZN428 is guaranteed monotonic for  $V_{REF IN}$  above 2 volts.

Fig. 4. Internal Voltage Reference

#### LOGIC

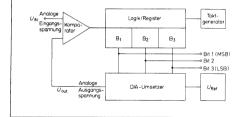

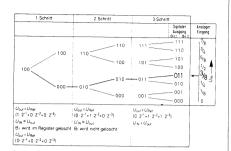

Input coding is binary for unipolar operation and offset binary for bipolar operation. When the Enable input is low the data inputs drive the D to A directly. When Enable goes high the input data word is held in the data latch.

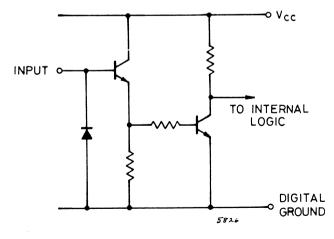

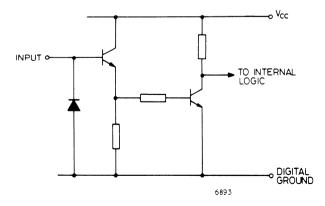

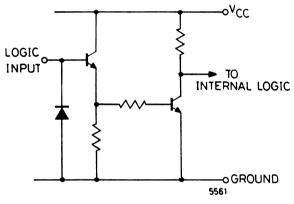

The equivalent circuit for the data and clock inputs is shown in Fig. 5.

The ZN428 is provided with separate analogue and digital ground connections. The circuit will operate correctly with as much as  $\pm 200$  mV between the two grounds.

Fig. 5. Equivalent Circuit of All Inputs

### APPLICATIONS

### (1) Unipolar D to A Converter

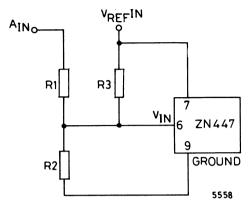

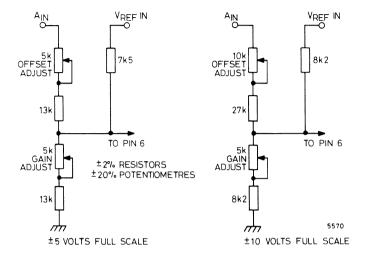

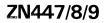

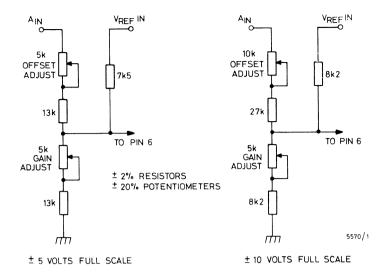

The nominal output range of the ZN428 is 0 to  $V_{REF\,IN}$  through a 4 k $\Omega$  resistance. Other output ranges can readily be obtained by using an external amplifier.

The general scheme (Fig. 6) is suitable for amplifiers with input bias currents less than 1.5 µA.

The resulting full scale range is given by

$$V_{OUT} FS = \left(1 + \frac{R1}{R2}\right) V_{REF IN} = G. V_{REF IN}$$

The impedance at the inverting input is R1//R2 and for low drift with temperature this parallel combination should be equal to the ladder resistance (4 k $\Omega$ ). The required nominal values of R1 and R2 are given by R1 = 4G k $\Omega$  and R<sub>2</sub> = 4G/(G-1) k $\Omega$ .

Using these relationships a table of nominal resistance values for  $\rm R_1$  and  $\rm R_2$  can be constructed for V\_{REF IN} = 2.5 volts.

| Output Range | G | R <sub>1</sub> | R <sub>2</sub> |

|--------------|---|----------------|----------------|

| +5V          | 2 | 8kΩ            | 8kΩ            |

| +10V         | 4 | 16kΩ           | 5.33kΩ         |

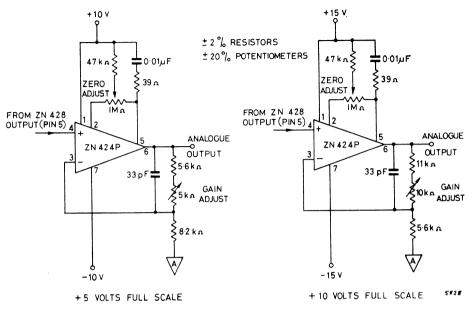

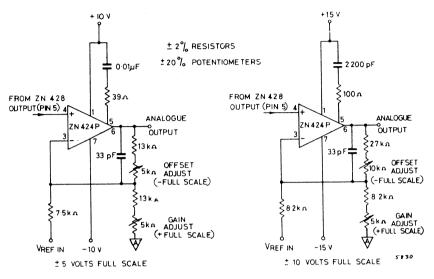

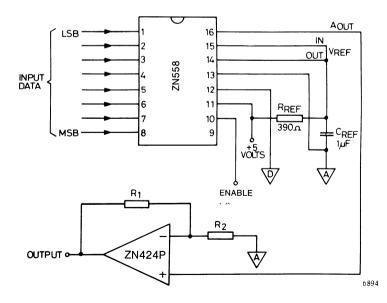

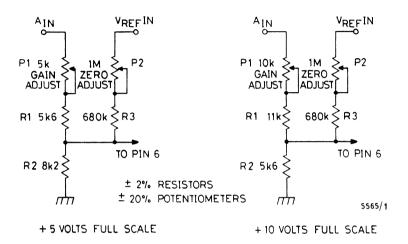

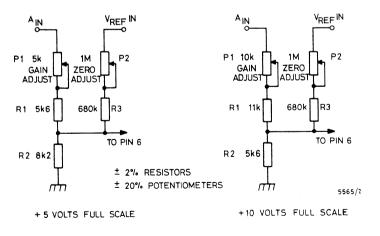

For gain setting  $R_1$  is adjusted about its nominal value. Practical circuit realisations (including amplifier stabilising components) for +5V and +10V output ranges are given in Fig. 7. Settling time for a major transition is 1.5  $\mu$ s typical.

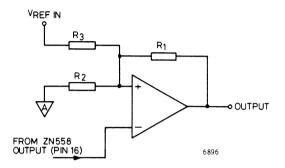

Fig. 6. Unipolar operation - Basic Circuit

### UNIPOLAR ADJUSTMENT PROCEDURE

- (i) Set all bits to OFF (low) with Enable low and adjust zero until  $V_{OUT} = 0.0000V$ .

- (ii) Set all bits ON (high) and adjust gain until  $V_{OUT} = FS 1 LSB$ .

|                   |         |           | ~                       |

|-------------------|---------|-----------|-------------------------|

| Output Range, +FS | LSB     | FS – 1LSB |                         |

| +5V               | 19.5 mV | 4.9805V   | $1LSB = \frac{FS}{256}$ |

| +10V              | 39.1 mV | 9.9609V   | 250                     |

|                   |         |           |                         |

### UNIPOLAR SETTING UP POINTS

### UNIPOLAR LOGIC CODING

| Input Code                                                     | Analogue Output                                                                           |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| (Binary)                                                       | (Nominal value)                                                                           |

| 1111111<br>1111110<br>1100000<br>1000001<br>1000000<br>0111111 | FS - 1LSB<br>FS - 2LSB<br># FS<br># FS + 1LSB<br># FS<br># FS - 1LSB<br># FS<br>1LSB<br>0 |

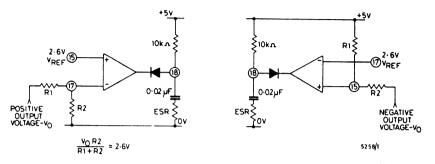

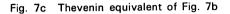

### (2) Bipolar D to A Converter

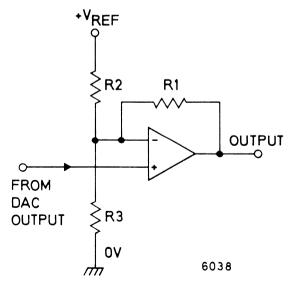

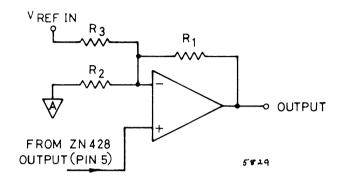

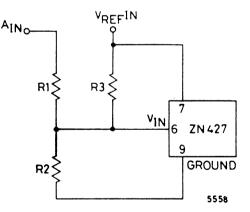

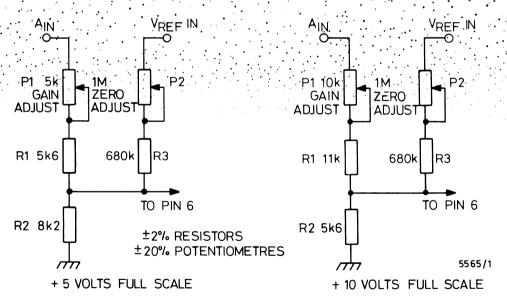

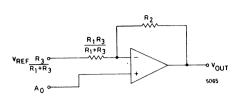

For bipolar operation the output from the ZN428 is offset by half full scale by connecting a resistor  $R_3$  between  $V_{REF IN}$  and the inverting input of the buffer amplifier (Fig. 8).

Fig. 8. Bipolar Operation - Basic Circuit

When the digital input to the ZN428 is zero the analogue output is zero and the amplifier output should be –Full scale. An input of all ones to the D to A will give a ZN428 output of  $V_{\text{REF IN}}$  and the amplifier output required is + Full scale. Also, to match the ladder resistance the parallel combination of  $R_1$ ,  $R_2$  and  $R_3$  should be 4 k $\Omega$ .

The nominal values of R<sub>1</sub>, R<sub>2</sub> and R<sub>3</sub> which meet these conditions are given by

$$R_1 = 8G k\Omega$$

,  $R_2 = 8G/(G-1) k\Omega$  and  $R_3 = 8 k\Omega$

where the resultant output range is  $\pm G V_{REF IN}$ .

A bipolar output range of  $\pm V_{\text{REF IN}}$  (which corresponds to the basic unipolar range 0 to  $V_{\text{REF IN}}$ ) is obtained if  $R_1 = R_3 = 8 \, k\Omega$  and  $R_2 = \infty$ .

Assuming that V\_{REF IN}=2.5 volts the nominal values of resistors for  $\pm 5V$  and  $\pm 10V$  output ranges are given in the following table :

| Output Range | G | R <sub>1</sub> | R <sub>2</sub> | R <sub>3</sub> |

|--------------|---|----------------|----------------|----------------|

| ±5V          | 2 | 16 kΩ          | 16 kΩ          | 8 kΩ           |

| ±10V         | 4 | 32 kΩ          | 10.66 kΩ       | 8 kΩ           |

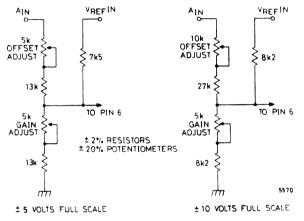

Minus full scale (offset) is set by adjusting  $R_1$  about its nominal value relative to  $R_3$ . Plus full scale (gain) is set by adjusting  $R_2$  relative to  $R_1$ .

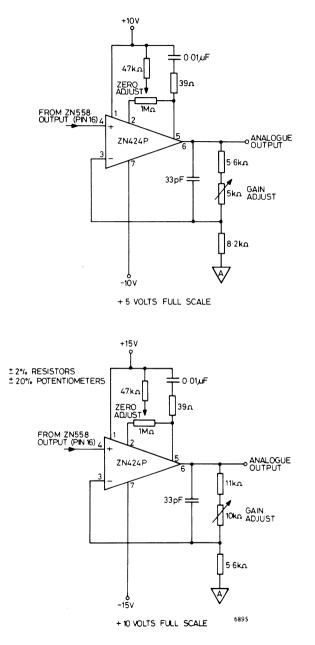

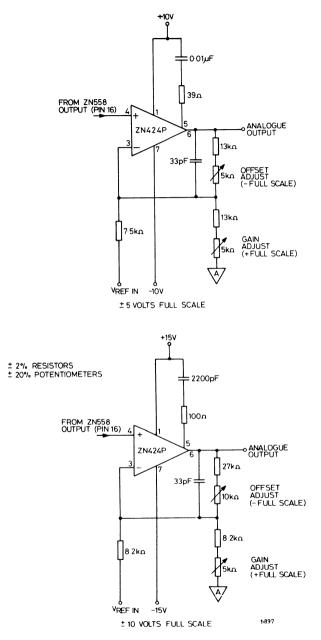

Practical circuit realisations are given in Fig. 9. Note that in the  $\pm$ 5V case R<sub>3</sub> has been chosen as 7.5 k $\Omega$  (instead of 8.2 k $\Omega$ ) to get a more symmetrical range of adjustment using standard potentiometers. Settling time for a major transition is 1.5  $\mu$ s typical.

Fig. 9. Bipolar Operation - Component Values

### **Bipolar Adjustment Procedure**

- (1) Set all bits to OFF (low) with Enable low and adjust offset until the amplifier output reads -Full Scale.

- (2) Set all bits ON (high) and adjust gain until the amplifier output reads + (Full Scale 1LSB).

| Input Range, $\pm$ FS | LSB     | -FS       | +(FS-1LSB) |                          |

|-----------------------|---------|-----------|------------|--------------------------|

| ±5V                   | 39.1 mV | -5.0000V  | +4.9609V   | $1LSB = \frac{2FS}{256}$ |

| ±10V                  | 78.1 mV | -10.0000V | +9.9219V   | 200                      |

### **BIPOLAR SETTING UP POINTS**

### BIPOLAR LOGIC CODING

| Input Code                                                      | Analogue Output                                                                                                              |

|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| (Offset Binary)                                                 | (Nominal Value)                                                                                                              |

| 1111111<br>1111110<br>1100000<br>1000000<br>0111111<br>01000000 | + (FS - 1LSB)<br>+ (FS - 2LSB)<br>+ $\frac{1}{2}$ FS<br>+ 1LSB<br>0<br>- 1LSB<br>- $\frac{1}{2}$ FS<br>- (FS - 1LSB)<br>- FS |

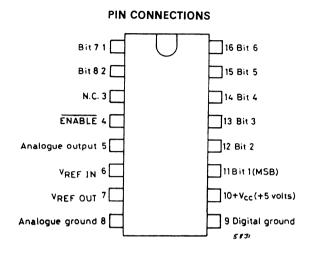

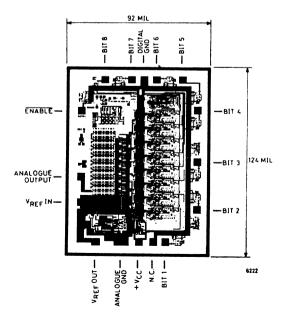

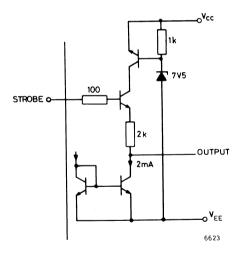

## CHIP DIMENSIONS AND LAYOUT

## 8 Bit D/A-Converter, Low Cost

### **FEATURES**

- 8, 7 and 6-bit Accuracy

- ZN429E Series Commercial Temp. Range 0\*C to +70\*C

- ZN429J-8 Military Temp. Range -55°C to +125°C

- TTL and 5V CMOS Compatible

- Single +5V Supply

- Settling Time 1 μsec. Typical

- Designed for low-cost applications

### DESCRIPTION

The ZN429 is a monolithic 8-bit digital to analogue converter containing an R-2R ladder network of diffused resistors with precision bipolar switches.

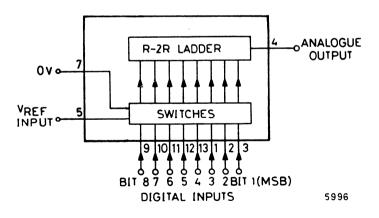

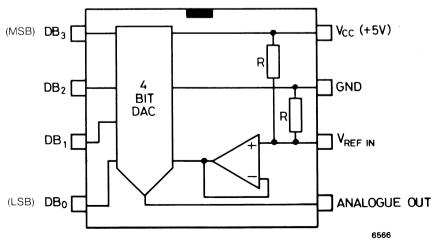

Fig. 1. System Diagram

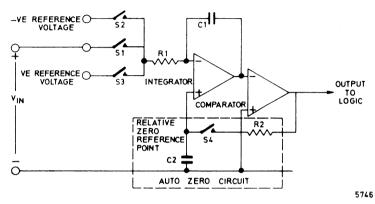

### INTRODUCTION