F8 USER'S GUIDE

# **F8 USER'S GUIDE**

# 67095665

Copyright © Fairchild Camera and Instrument Corporation 1976

``````

# F8 USER'S GUIDE

# 67095665

PAGE

| <u>R</u> | <u>s</u> | DATE    |

|----------|----------|---------|

| A        | 0        | 2/13/76 |

| B        | 0        | 5/1/76  |

# TABLE OF CONTENTS

#### SECTION

TITLE

| FAGE | PA | GE |

|------|----|----|

|------|----|----|

| 1.0<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6 | The F8 Microcomputer SystemFrom Logic Device to Microcomputer |

|-----------------------------------------------|---------------------------------------------------------------|

| 2.0                                           | The 3850 CPU                                                  |

| 2.1                                           | Device Organization.                                          |

| 2.1.1                                         | The Arithmetic and Logic Unit                                 |

| 2.1.2                                         | The Instruction Register   2-2                                |

| 2.1.2                                         | The Accumulator.                                              |

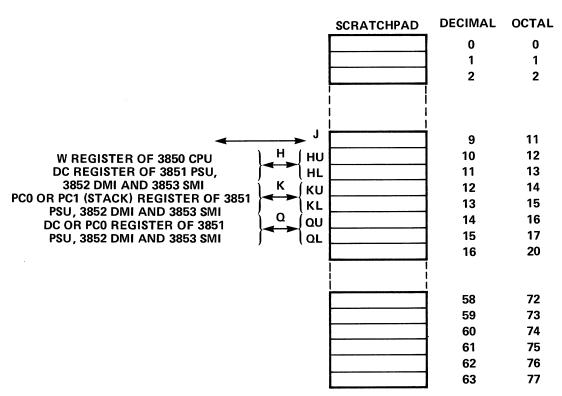

| 2.1.4                                         | The Scratchpad and ISAR                                       |

| 2.1.4                                         |                                                               |

|                                               | 0                                                             |

| 2.1.6                                         | The Control Unit         2-4                                  |

| 2.1.7                                         | Interrupt Logic                                               |

| 2.1.8                                         | Power On Detect                                               |

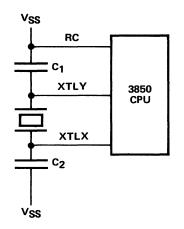

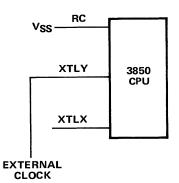

| 2.1.9                                         | Clock Circuits                                                |

| 2.1.10                                        | The Data Bus                                                  |

| 2.1.11                                        | I/O Ports                                                     |

| 2.2                                           | Signal Descriptions and Electrical Characteristics            |

| 2.2.1                                         | Signal Descriptions                                           |

| 2.2.2                                         | Electrical Specifications                                     |

| 2.3                                           | Clock Circuits                                                |

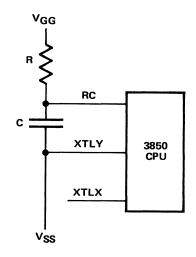

| 2.3.1                                         | Crystal Mode                                                  |

| 2.3.2                                         | External Mode                                                 |

| 2.3.3                                         | RC Mode (3850-1 Only)                                         |

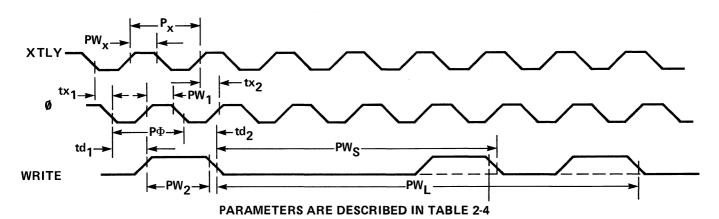

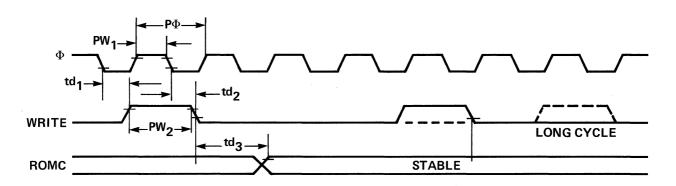

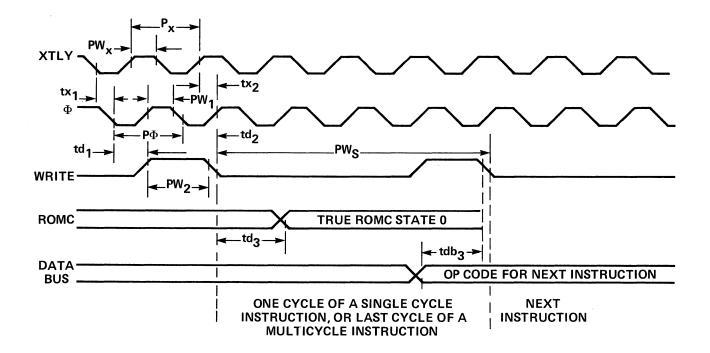

| 2.3.4                                         | Timing Signal Characteristics                                 |

| 2.4                                           | Instruction Execution                                         |

| 2.4.1                                         |                                                               |

| 2.4.1                                         |                                                               |

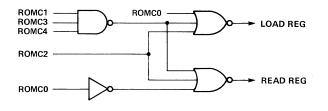

|                                               | The ROMC Signals    2-8                                       |

| 2.4.3                                         | Instruction Execution Sequence                                |

| 2.4.4                                         | Referencing Memory                                            |

| 2.4.5                                         | Memory-to-Memory Data Transfers                               |

| 2.4.6                                         | Input/Output Interfacing                                      |

| 2.4.7                                         | Interrupts                                                    |

| 2.5                                           | Instruction Set Summary                                       |

| 3.0                                           | The 3851 Program Storage Unit (PSU)                           |

| 3.1                                           | Device Organization.                                          |

| 3.1.1                                         | 5                                                             |

|                                               | ROM Storage                                                   |

| 3.1.2                                         | The Program Counter (PC0) and Data Counter (DC0)              |

| 3.1.3                                         | Page Select and Address Space    3-2                          |

| 3.1.4                                         | Addressing Consistency in Multiple Memory Devices             |

| 3.1.5                                         | The Stack Register PC1                                        |

| 3.1.6                                         | Incrementer Adder Logic                                       |

|                                               |                                                               |

### **TABLE OF CONTENTS (Continued)**

### TITLE

| 3.0    | The 3851 Program Storage Unit (PSU) (Continued)                        |              |

|--------|------------------------------------------------------------------------|--------------|

| 3.1.7  | Interrupt Logic                                                        | 3-4          |

| 3.1.8  |                                                                        | 3-4          |

| 3.1.9  | The Data Bus                                                           | 3-4          |

| 3.1.10 | I/O Ports                                                              | 3-4          |

| 3.2    | Signal Descriptions, Electrical Characteristics and Mask Options       | 3-5          |

| 3.2.1  | Signal Descriptions                                                    | 3-5          |

| 3.2.2  | Mask Options                                                           | 3-7          |

| 3.2.3  | Card Format Used to Define 3851 PSU Mask Options                       | 3-7          |

| 3.2.4  | Paper Tape and Cartridge Format Used to Define 3851 PSU Mask Options . | 3-8          |

| 3.2.5  | Electrical Specifications                                              | 3-8          |

| 3.3    | Clock Timing                                                           | 3-8          |

| 3.4    | Instruction Execution                                                  | 3-8          |

| 3.4.1  | Data Output by the PSU                                                 | 3-13         |

| 3.4.2  | Data Input to the PSU                                                  | 3-13         |

| 3.4.3  | Input/Output Interfacing                                               | 3-13         |

| 3.5    | The Programmable Timer                                                 | 3-15         |

| 3.6    | Interrupt Logic                                                        | 3-17         |

| 3.6.1  | Interrupt Logic Organization                                           | 3-17         |

| 3.6.2  | Interrupt Acknowledge Sequence                                         | 3-20         |

| 3.6.3  | Interrupt Address Vector                                               | 3-21         |

| 3.6.4  | Interrupt Signals Timing                                               | 3-21         |

|        |                                                                        |              |

| 4.0    | The 3852 Dynamic Memory Interface (DMI)                                |              |

| 4.1    | Device Organization                                                    | 4-1          |

| 4.1.1  | Dynamic Memory Interface                                               | 4-1          |

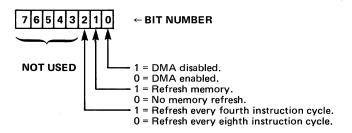

| 4.1.2  | DMA and Refresh Control                                                | 4-1          |

| 4.1.3  | I/O Ports                                                              | 4-2          |

| 4.2    | Signal Descriptions and Electrical Characteristics                     | 4-2          |

| 4.2.1  | Signal Descriptions                                                    | 4-2          |

| 4.2.2  | DC Electrical Specifications                                           | 4-3          |

| 4.3    | The 3852 DMI Address Space                                             | 4-3          |

| 4.3.1  | Dynamic RAM Address Space                                              | 4-4          |

| 4.3.2  | 3852 DMI Address Registers' Address Space                              | 4-5          |

| 4.3.3  | Address Contentions                                                    | 4-6          |

| 4.4    |                                                                        | 4-7          |

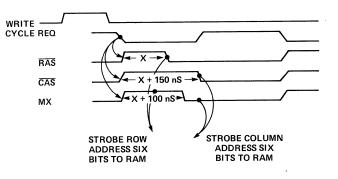

| 4.4.1  | Timing Signals Received by the 3852 DMI                                | 4-7          |

| 4.4.2  | Timing Signals Output by a 3852 DMI                                    | 4-7          |

| 4.5    | Instruction Execution                                                  | 4-11         |

| 4.5.1  | Data Output by RAM                                                     | 4-11         |

| 4.5.2  | Data Output by the 3852 DMI                                            | 4-12         |

| 4.5.3  | Data Input to RAM                                                      | 4-12         |

| 4.5.4  | Data Input to the 3852 DMI                                             | 4-12         |

| 4.5.5  |                                                                        |              |

|        | Input/Output                                                           | 4-12         |

| 4.5.6  | Input/Output                                                           | 4-12<br>4-13 |

|        |                                                                        |              |

| 4.5.6  | System Initialization                                                  | 4-13         |

SECTION

# **TABLE OF CONTENTS (Continued)**

| SECTION             | TITLE                                                           | PAGE |

|---------------------|-----------------------------------------------------------------|------|

| 5.0                 | The 3853 Static Memory Interface (SMI)                          |      |

| 5.1                 | Device Organization                                             | 5-2  |

| 5.1.1               | Memory Addressing Logic                                         | 5-2  |

| 5.1.2               | Timer and Interrupt Logic                                       | 5-2  |

| 5.1.3               | I/O Ports                                                       | 5-2  |

| 5.2                 | Signal Descriptions and Electrical Characteristics              | 5-3  |

| 5.2.1               | Signal Descriptions                                             | 5-3  |

| 5.2.2               |                                                                 | 5-4  |

| 5.3                 |                                                                 | 5-4  |

| 5.4                 | Instruction Execution                                           | 5-4  |

| 5.4                 |                                                                 | 5-4  |

| 6.0                 | The 3854 Direct Memory Access Controller (DMA)                  |      |

| 6.1                 | Device Organization                                             | 6-1  |

| 6.1.1               | I/O Ports                                                       | 6-1  |

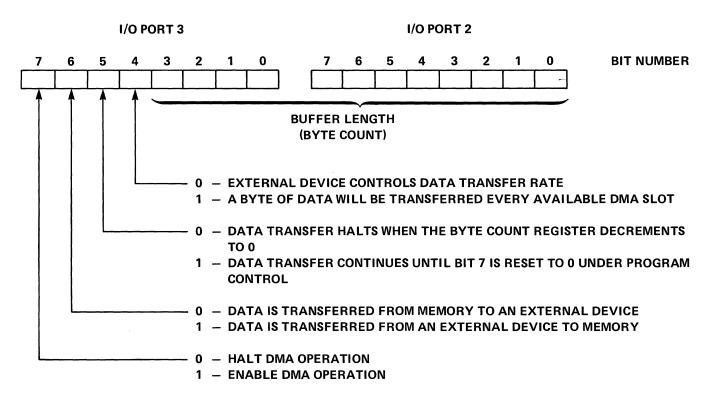

| 6.1.2               | DMA Options                                                     | 6-1  |

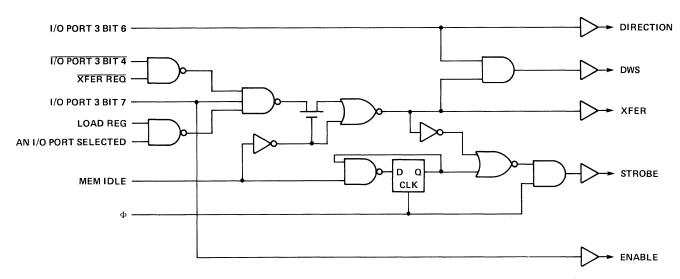

| 6.1.3               | DMA Control Logic                                               | 6-3  |

| 6.1.4               | Increment and Decrement Logic                                   | 6-4  |

| 6.1.5               | The Data and Address Busses                                     | 6-4  |

| 6.2                 | Signal Descriptions and Electrical Characteristics              | 6-4  |

| 6.2.1               | Signal Descriptions                                             | 6-4  |

| 6.3                 |                                                                 | 6-7  |

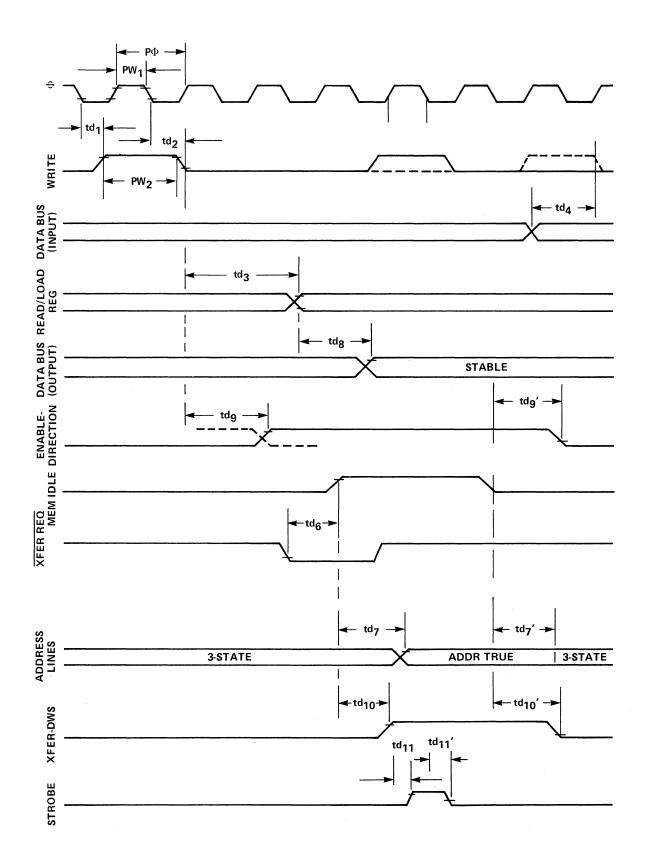

| 6-4                 | DMA I/O Operation                                               | 6-7  |

| 7.0                 | The 3861 Peripheral Input/Output (PIO)                          |      |

| 7.1                 |                                                                 | 71   |

|                     |                                                                 | 7-1  |

| 7.1.1               |                                                                 | 7-1  |

| 7.1.2               |                                                                 | 7-2  |

| 7.1.3               | The Data Bus                                                    | 7-2  |

| 7.1.4               | I/O Ports                                                       | 7-2  |

| 7.2                 | Signal Descriptions, Electrical Characteristics                 | 7-2  |

| 7.2.1               | Signal Descriptions                                             | 7-2  |

| 7.2.2               | Electrical Specifications                                       | 7-3  |

| 7.3                 | Clock Timing                                                    | 7-3  |

| 7.4                 | Instruction Execution                                           | 7-3  |

| 7.4.1               | Data Output by the PIO                                          | 7-3  |

| 7.4.2               | Data Input to the PIO                                           | 7-6  |

| 7.4.3               | Input/Output Instruction                                        | 7-6  |

| 7.5                 | Input/Output Interfacing.                                       | 7-7  |

| 7.6                 | Programmable Timer                                              | 7-8  |

| 7.7                 |                                                                 | 7-9  |

| 8.0                 | (Pending)                                                       |      |

| 9.0                 | (Pending)                                                       |      |

| 10.0                | (Pending)                                                       |      |

| <b>11.0</b><br>11.1 | <b>3850 CPU-3851 PSU Systems</b> Single 3851 PSU Configurations | 11-1 |

iii RBS0 5-1-76

# TABLE OF CONTENTS (Continued)

| SECTION    | TITLE                                                                                                                                                                         |      |  |  |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|--|

| 11.0       | 3850 CPU-3851 PSU Systems (Continued)                                                                                                                                         |      |  |  |  |  |

| 11.1.1     | I/O in Single 3851 PSU Configurations                                                                                                                                         | 11-1 |  |  |  |  |

| 11.1.2     | Connections to the Data Bus in Single 3851 PSU Configurations                                                                                                                 | 11-3 |  |  |  |  |

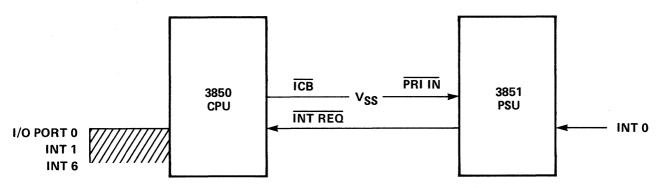

| 11.1.3     | Interrupt Processing in Single 3851 PSU Configurations                                                                                                                        | 11-3 |  |  |  |  |

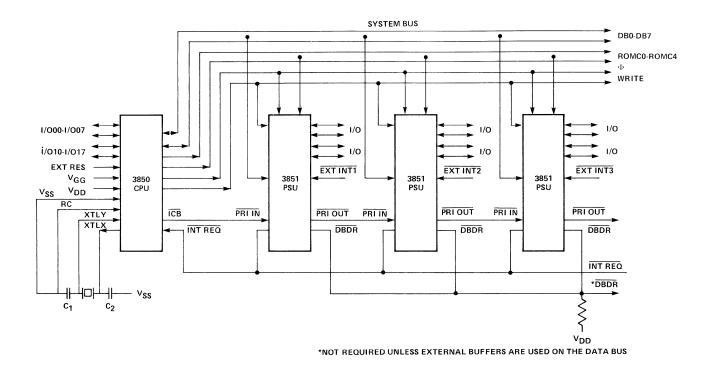

| 11.2       | Multiple PSU Configurations                                                                                                                                                   | 11-5 |  |  |  |  |

| 11.2.1     | I/O in Multiple 3851 PSU Configurations                                                                                                                                       | 11-5 |  |  |  |  |

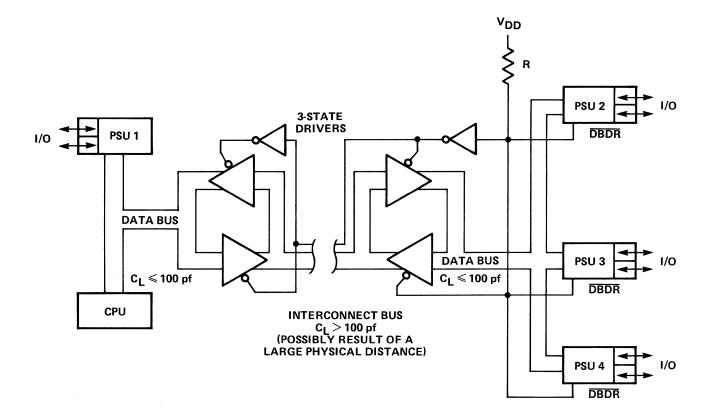

| 11.2.2     | Connections to the Data Bus in Multiple 3851 PSU Configurations.                                                                                                              | 11-7 |  |  |  |  |

| 11.2.3     | Interrupt Processing in Multiple 3851 PSU Configurations                                                                                                                      | 11-7 |  |  |  |  |

| 12.0       | F8 Configurations that Include 3852 DMI and 3853 SMI Devices                                                                                                                  |      |  |  |  |  |

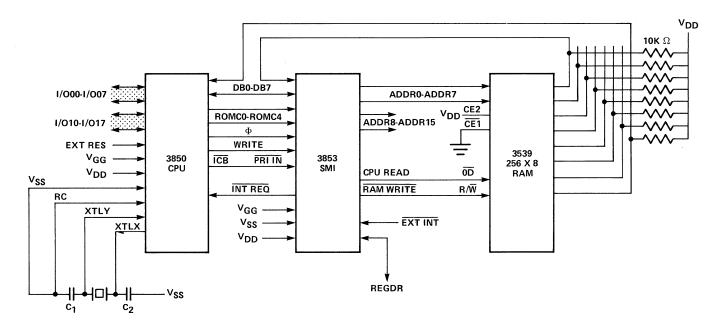

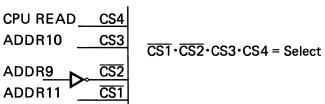

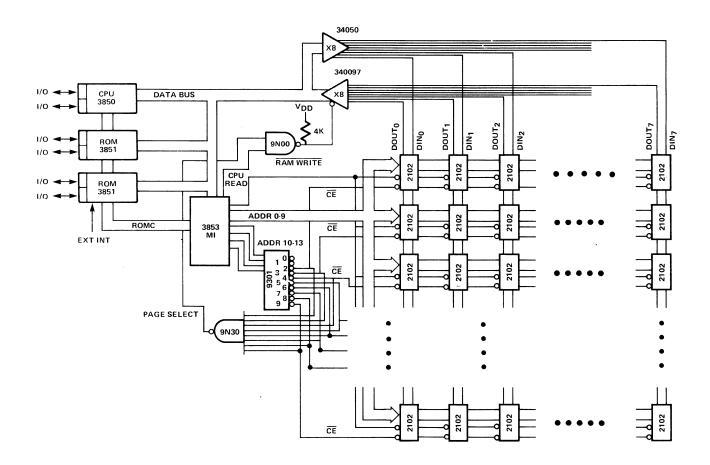

| 12.1       | Small CPU-RAM Configurations                                                                                                                                                  | 12-1 |  |  |  |  |

| 12.1.1     | Small CPU-RAM Configurations without a PSU                                                                                                                                    | 12-1 |  |  |  |  |

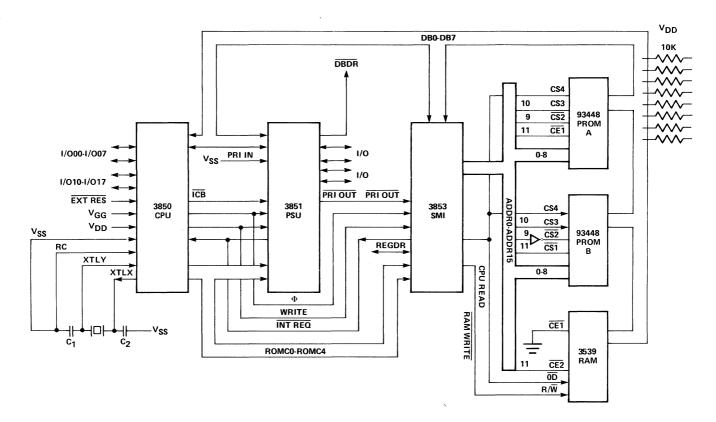

| 12.1.2     | Small CPU-RAM Configurations with a PSU                                                                                                                                       | 12-2 |  |  |  |  |

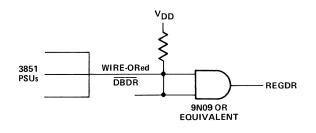

| 12.1.3     | Connecting the REGDR Input                                                                                                                                                    | 12-2 |  |  |  |  |

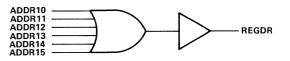

| 12.2       | Large F8 Configurations with Mixed Memory                                                                                                                                     | 12-4 |  |  |  |  |

| 12.3       | Interfacing Very Large Memories                                                                                                                                               | 12-6 |  |  |  |  |

| 12.4       | Interfacing to Slow Memories                                                                                                                                                  | 12-8 |  |  |  |  |

| 12.5       | Interrupt Processing in F8 Configurations that Include ROM and RAM                                                                                                            | 12-8 |  |  |  |  |

| 13.0       | Using Direct Memory Access                                                                                                                                                    |      |  |  |  |  |

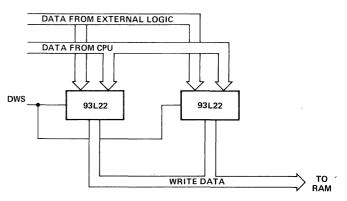

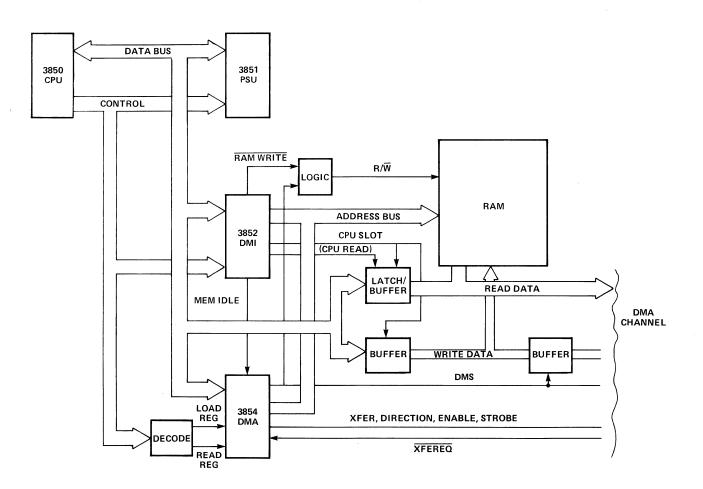

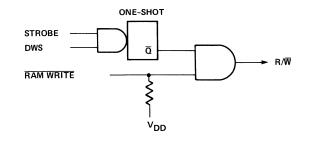

| 13.1       | A Simple DMA Configuration                                                                                                                                                    | 13-1 |  |  |  |  |

| 13.1.1     | RAM Array Interface                                                                                                                                                           | 13-1 |  |  |  |  |

| 13.1.2     | 3854 DMA Device Signals                                                                                                                                                       | 13-2 |  |  |  |  |

| 13.1.3     | DMA Timing during Transfer of One Byte                                                                                                                                        | 13-3 |  |  |  |  |

| 13.1.4     | DMA Timing during a Block Transfer                                                                                                                                            | 13-3 |  |  |  |  |

| 13.1.5     | DMA and Refresh Rates                                                                                                                                                         | 13-4 |  |  |  |  |

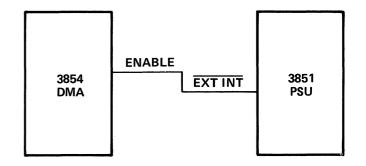

| 13.2       | Using an Interrupt to Identify the End of a DMA Transfer                                                                                                                      | 13-5 |  |  |  |  |

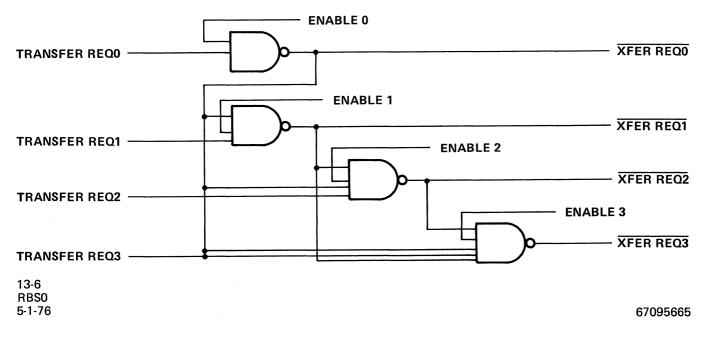

| 13.3       | Including more than One 3854 DMA Device in a Configuration                                                                                                                    | 13-6 |  |  |  |  |

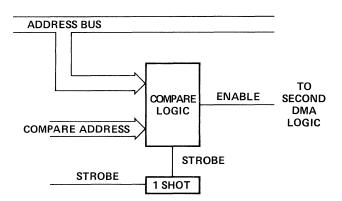

| 13.4       | Catching DMA on the Fly                                                                                                                                                       | 13-7 |  |  |  |  |

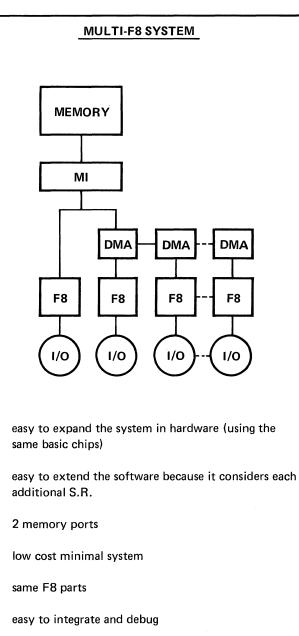

| 14.0       | Multiprocessor Configurations and Applications                                                                                                                                |      |  |  |  |  |

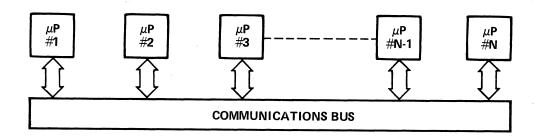

| 14.1       | Multiprocessor Configurations                                                                                                                                                 | 14-1 |  |  |  |  |

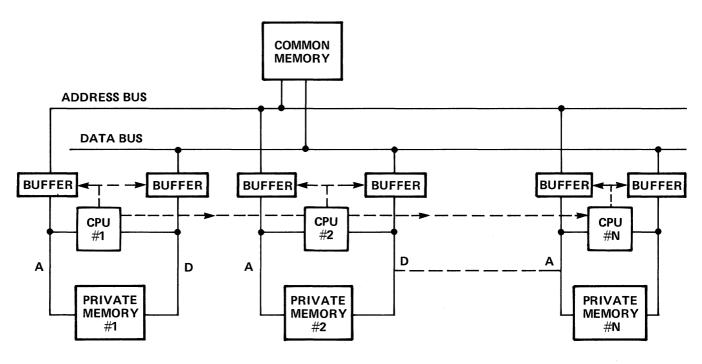

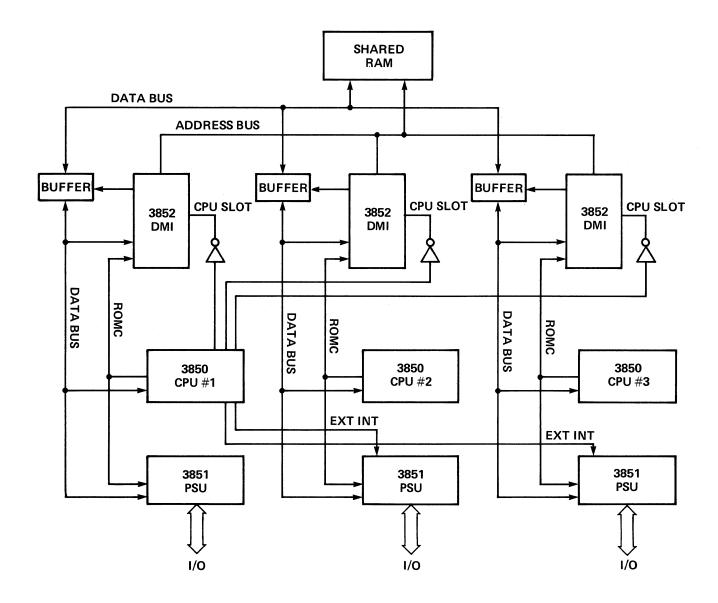

| 14.1.1     | Network with Communications Bus Link                                                                                                                                          | 14-1 |  |  |  |  |

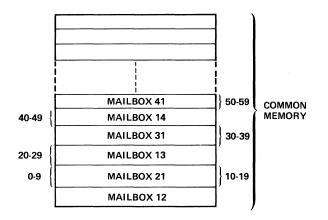

| 14.1.2     | Network with Shared Common Memory                                                                                                                                             | 14-3 |  |  |  |  |

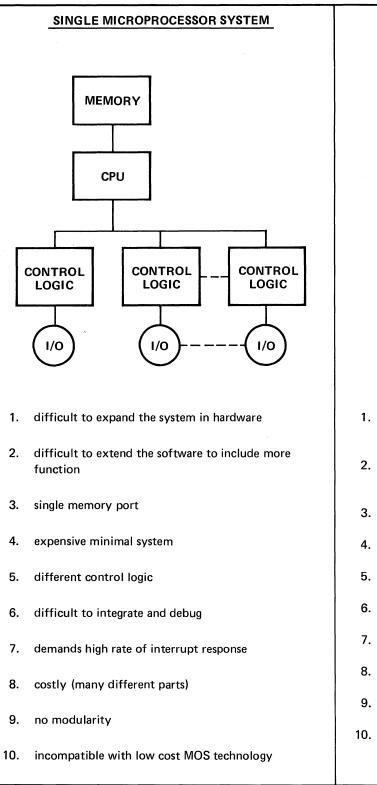

| 14.2       | A Comparison between the Single Microprocessor System and the                                                                                                                 |      |  |  |  |  |

|            | Multiprocessor Network                                                                                                                                                        | 14-9 |  |  |  |  |

| Appendix A | FAIR-BUG – 3851A PSU (SL 31162) Specifications<br>3508 Future Product Description. 8192-Bit Read-Only Memory<br>3516 Future Product Description. 16K-Bit MOS Read-Only Memory |      |  |  |  |  |

# LIST OF ILLUSTRATIONS

### FIGURE

### TITLE

#### PAGE

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>1-6<br>1-7<br>1-8<br>1-9<br>1-10<br>1-11<br>1-12<br>1-13<br>1-14<br>1-15<br>1-16<br>1-17<br>1-18 | A Logic Device Using Control Signals       1         A Universal Logic Device       1         An Elementary Central Processing Unit       1         A Simple CPU with Memory       1         The Concept of an Interrupt       1         Memory as a Buffer between External Logic and the CPU       1         Functional Logic of a Complete Microcomputer System       1         F8 Microcomputer Timing       1         A Two-Device Configuration Consisting of a 3850 CPU and a 3851 PSU       1         3852 Dynamic Memory Interface Device Logic       1         3861 Peripheral Input/Output Device Logic       1         3854 Direct Memory Access Device Logic       1         Discrete vs. Microprocessor Approach       1         Instructions Linking Program Counter       1         Instructions Linking Data Counter       1 | 1-1<br>1-2<br>1-2<br>1-3<br>1-3<br>1-4<br>1-5<br>1-5<br>1-5<br>1-5<br>1-5<br>1-8<br>1-9<br>1-9<br>1-12<br>1-14<br>1-15<br>1-16 |

|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

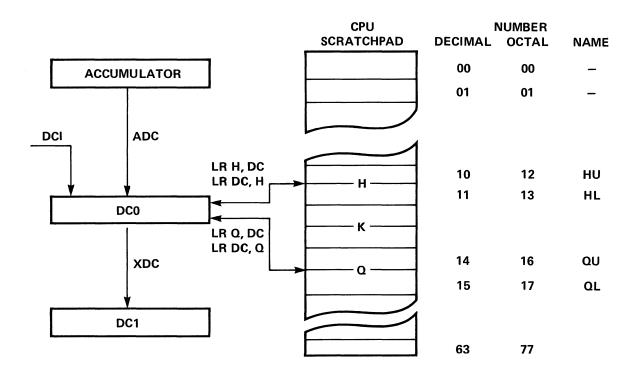

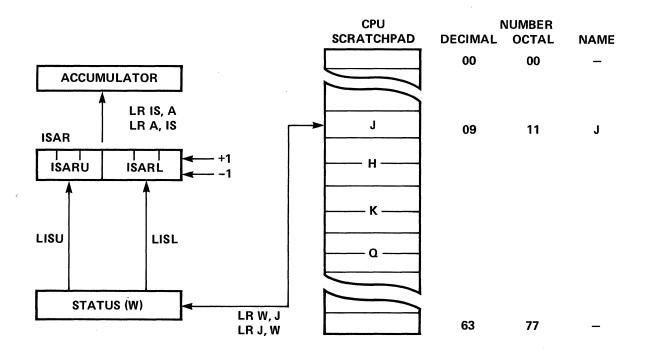

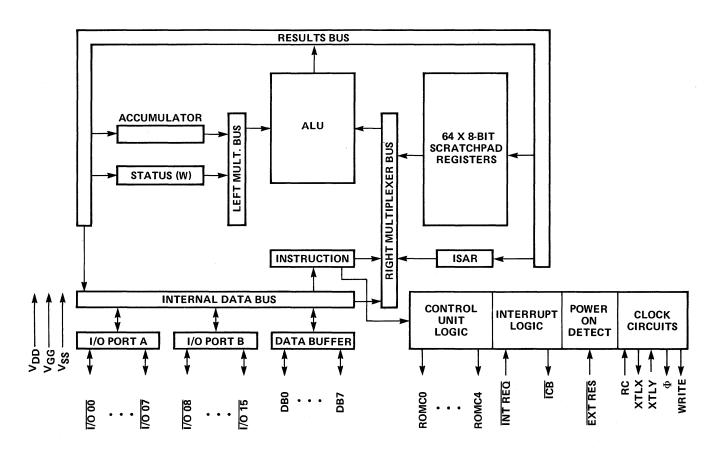

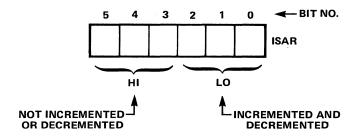

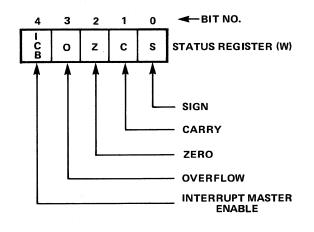

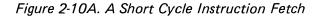

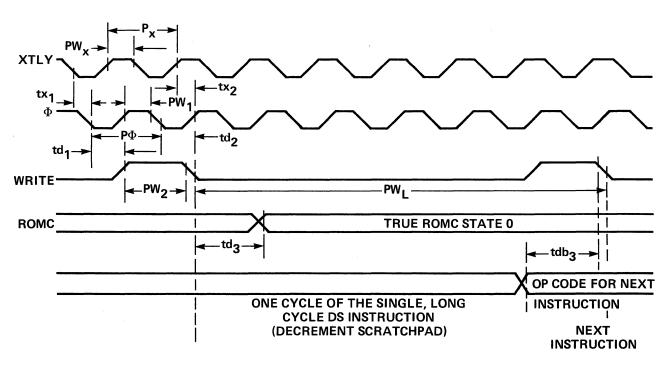

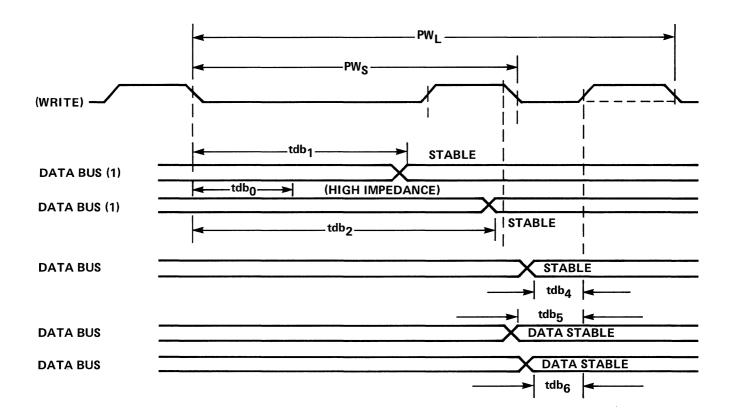

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9<br>2-10A<br>2-10B<br>2-11<br>2-12<br>2-13<br>2-14<br>2-15<br>3-1        | Logical Organization and Pins for the 3850 CPU .<br>The ISAR Register .<br>The 3850 CPU Scratchpad Registers .<br>3850 CPU Pin Assignments .<br>Crystal Mode Clock Generation .<br>External Mode Clock Generation .<br>RC Mode Clock Generation .<br>Timing Signal Specifications .<br>ROMC Signals Output by 3850 CPU .<br>A Short Cycle Instruction Fetch .<br>A Long Cycle Instruction Fetch (During DS Only) .<br>Memory Reference Timing .<br>An F8 I/O Port Bit .<br>Timing for Data Input or Output at I/O Port Pins .<br>Interrupt Signals Timing .<br>Instructions that Move Data between the Scratchpad and Registers .                                                                                                                                                                                                             | 2-1<br>2-2<br>2-3<br>2-5<br>2-7<br>2-7<br>2-7<br>2-7<br>2-7<br>2-7<br>2-7<br>2-7<br>2-7<br>2-7                                 |

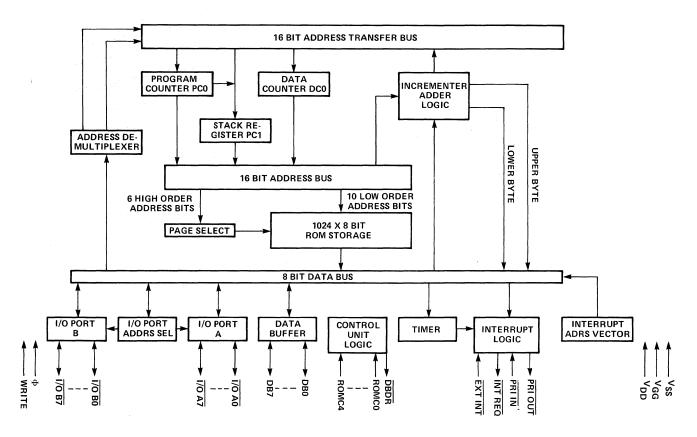

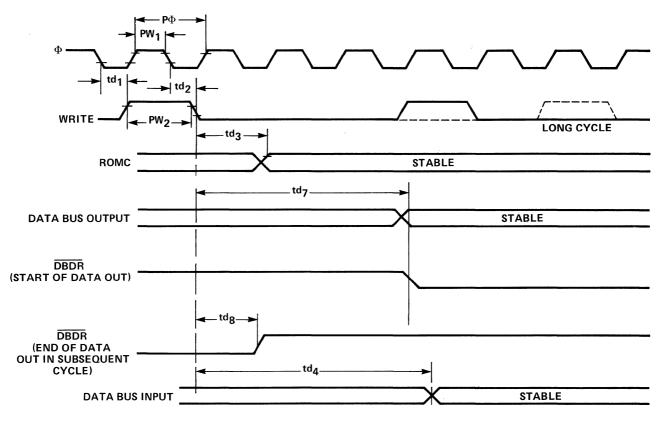

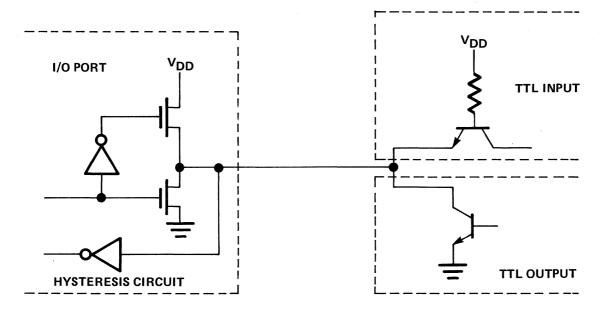

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10<br>3-11                                                         | 3851 PSU Pin Assignments       3851 PSU Data Bus Timing         3851 PSU Data Bus Timing       3851 PSU Data Bus Timing         Standard Pull-up Configuration       3851 PSU Data Bus Timing         Open Drain Configuration       3851 PSU Data Bus Timing         Driver Pull-up Configuration       3851 PSU Data Bus Timing         Timing at PSU I/O Ports       3851 PSU I/O Ports         Timer Block Diagram       3851 PSU Interrupt Logic         Conceptual Illustration of 3851 PSU Interrupt Logic       3851 PSU Interrupt Logic                                                                                                                                                                                                                                                                                              | 3-2<br>3-5<br>3-11<br>3-14<br>3-14<br>3-15<br>3-16<br>3-16<br>3-17<br>3-18<br>3-19                                             |

RBS0 5-1-76

v

# LIST OF ILLUSTRATIONS (Continued)

| FIGURE       | TITLE                                                                                               | PAGE                    |

|--------------|-----------------------------------------------------------------------------------------------------|-------------------------|

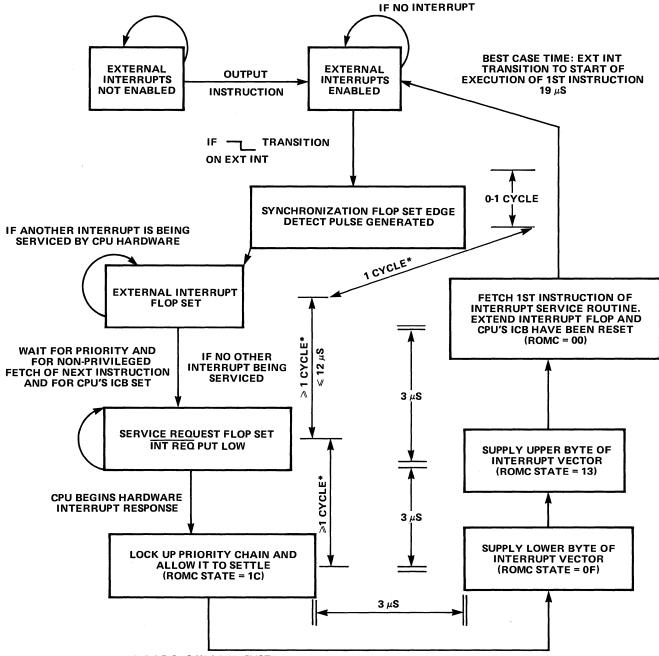

| 3-12<br>3-13 | External Interrupt Sequence                                                                         | 3-19<br>3-22            |

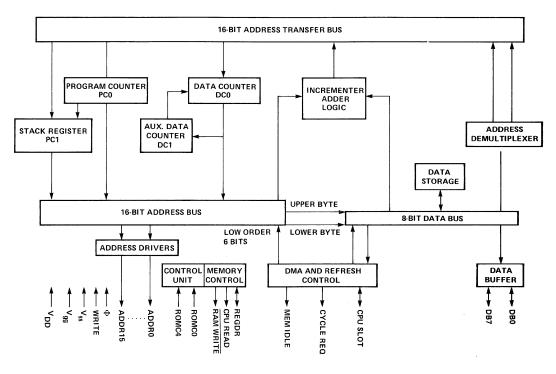

| 4-1          | Logic Organization and Pins for the 3852 DMI                                                        | 4-1                     |

| 4-2          | 3852 DMI Pin Assignments                                                                            | 4-2                     |

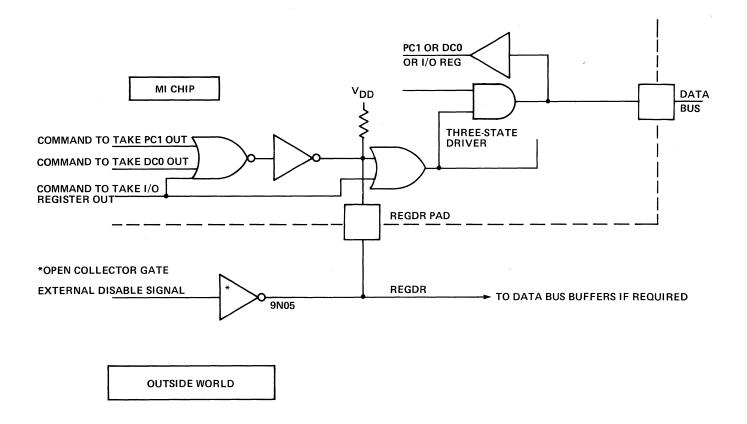

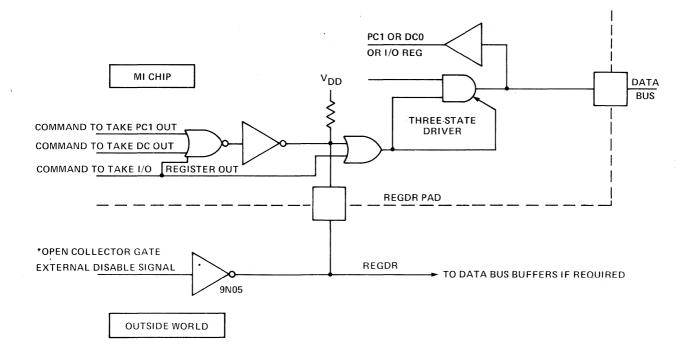

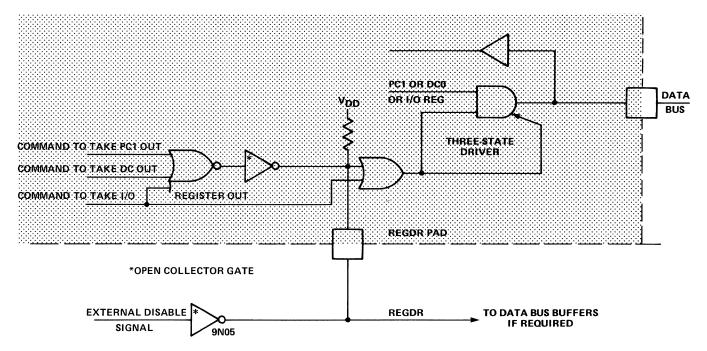

| 4-3          | REGDR Controls Data Bus Drivers                                                                     | 4-4                     |

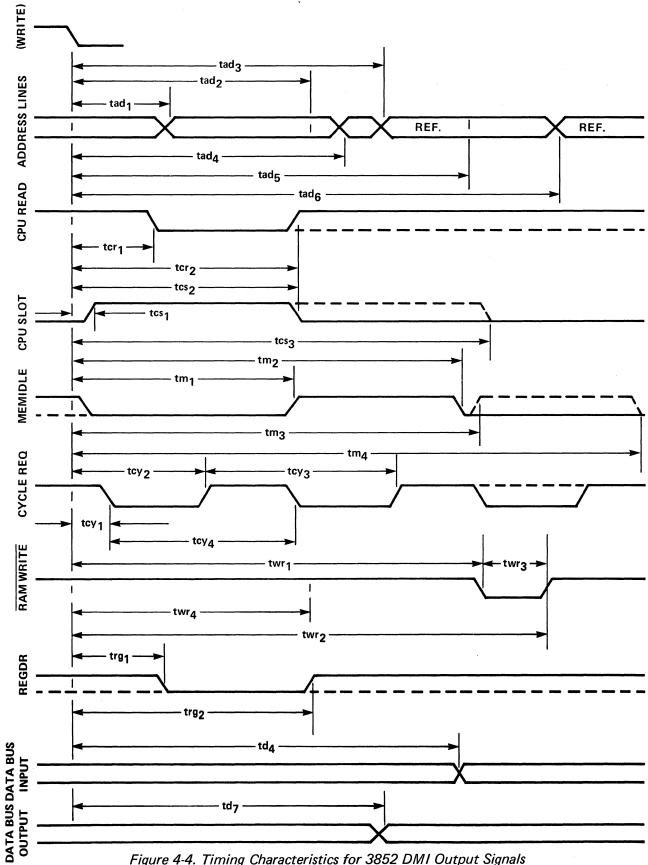

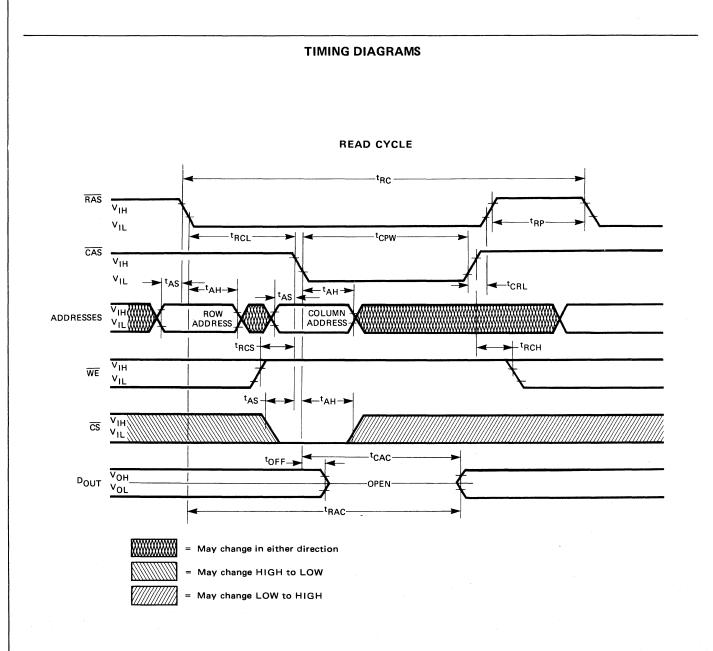

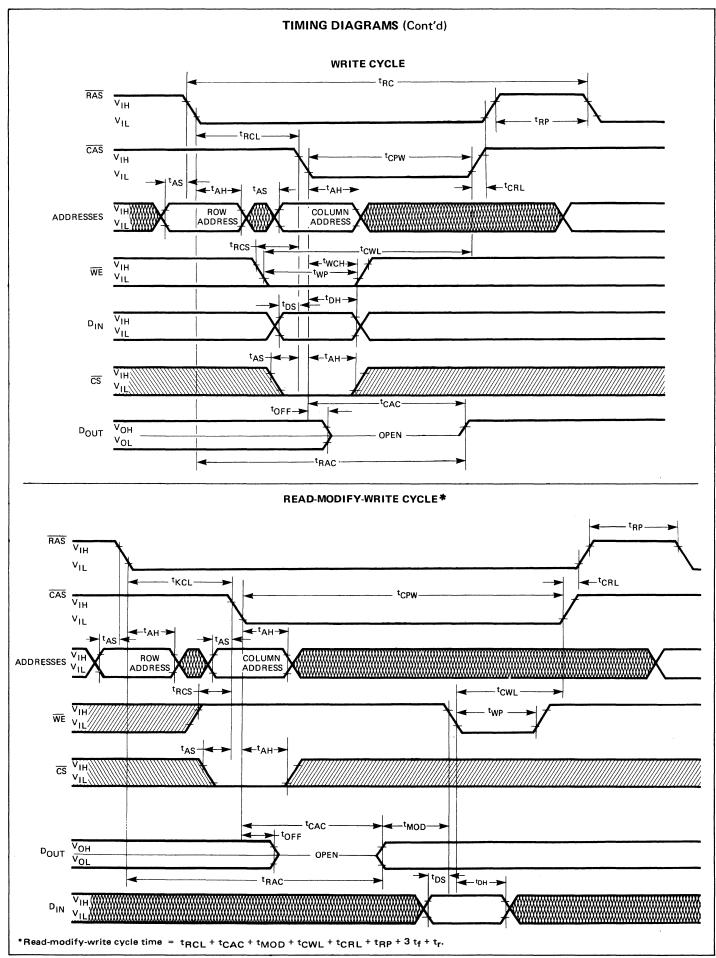

| 4-4          | Timing Characteristics for 3852 DMI Output Signals                                                  | 4-8                     |

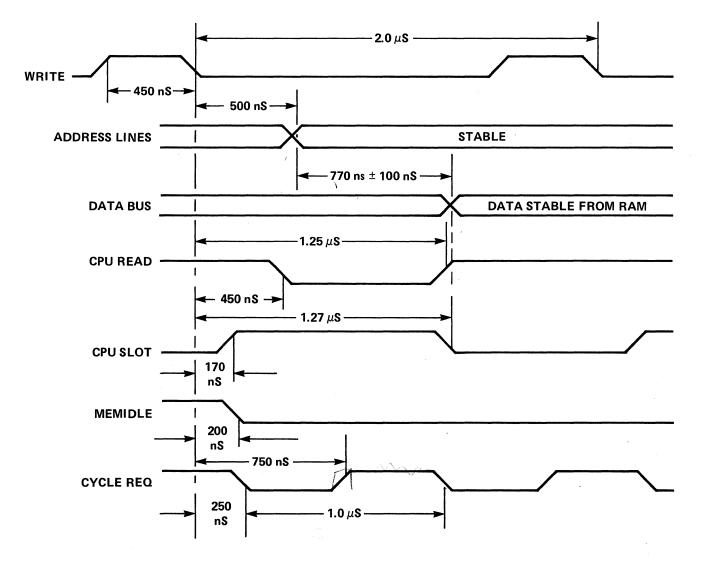

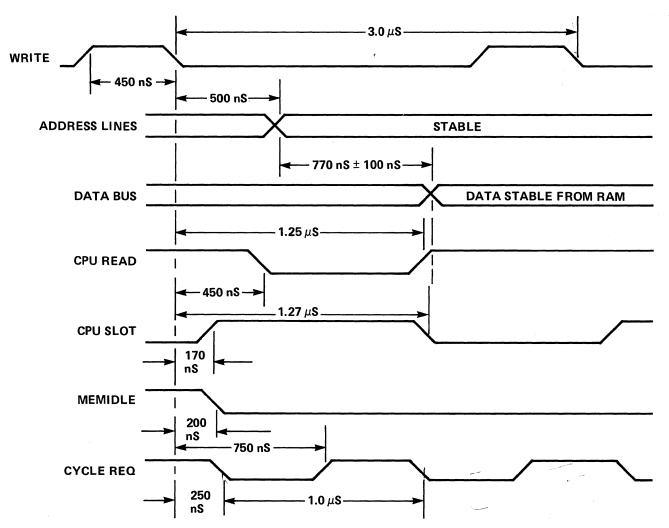

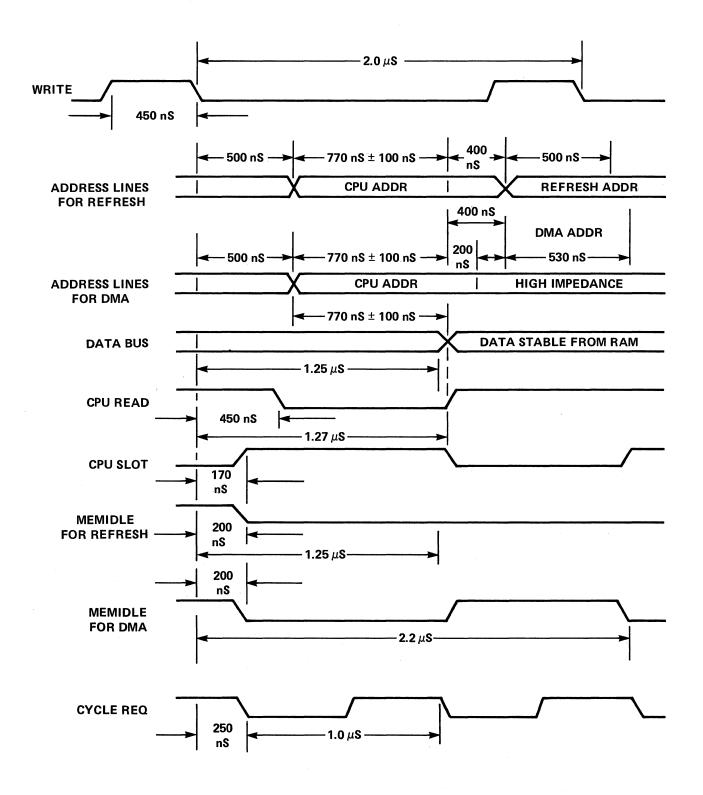

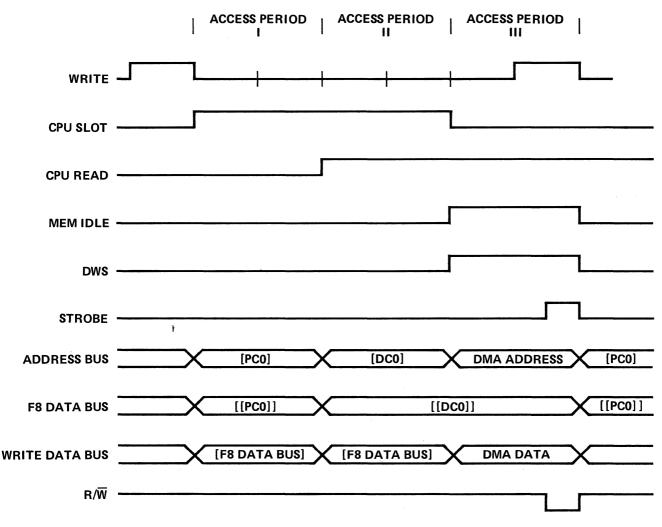

| 4-5          | 3852 DMI Timing Signals Output during a Short Cycle Memory Read, with Address from PCO              | 4-10                    |

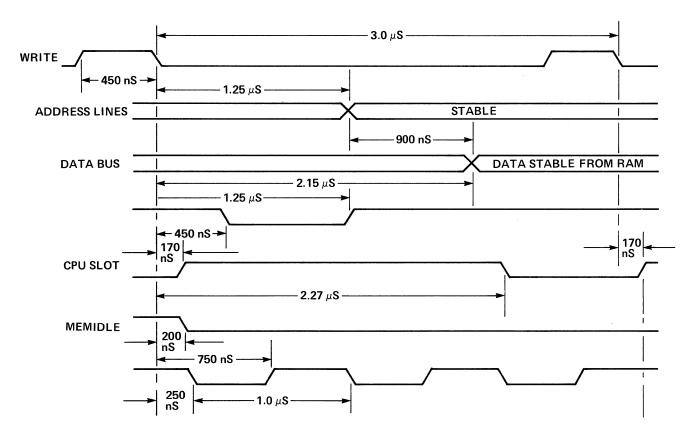

| 4-6          | 3852 DMI Timing Signals Output during a Long Cycle Memory Read, with Address Out of Program Counter | 4-11                    |

| 4-7          | 3852 DMI Timing Signals Output during a Long Cycle Memory Read, with Address Out of Data Counter    | 4-13                    |

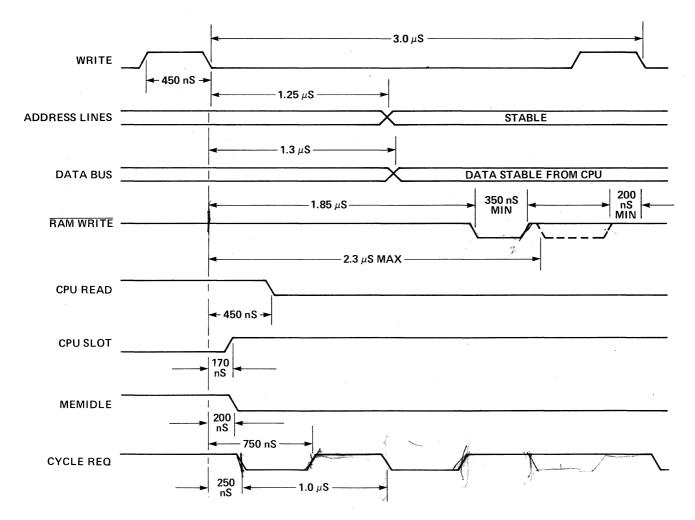

| 4-8          | 3852 DMI Timing Signals Output during a Write to Memory                                             | 4-14                    |

| 4-9          | Interpretation of Signals Output by the 3852 DMI                                                    | 4-14                    |

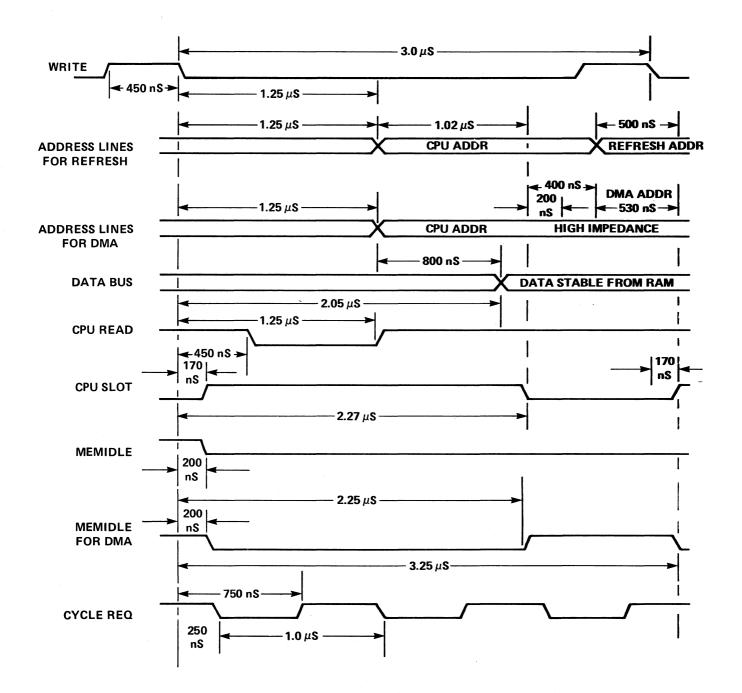

| 4-10         | Timing for Memory Refresh and DMA during a Short Cycle Memory Read,                                 |                         |

| +10          | with Address Out of Program Counter.                                                                | 4-20                    |

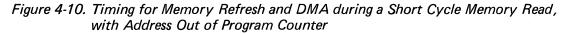

| 4-11         | Timing for Memory Refresh and DMA during a Long Cycle Memory Read,                                  | 120                     |

|              | with Address Out of Program Counter                                                                 | 4-21                    |

| 4-12         | Timing for Memory Refresh and DMA during a Long Cycle Memory Read,                                  |                         |

|              | with Address Out of Data Counter                                                                    | 4-22                    |

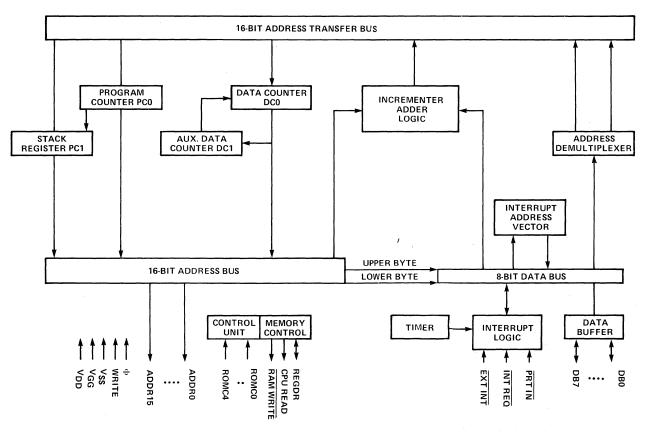

| 5-1          | Logic Organization and Pins for the 3853 SMI                                                        | 5-1                     |

| 5-2          | 3853 SMI Pin Assignments                                                                            | 5-3                     |

| 5-3          | REGDR Controls Data Bus Drivers                                                                     | 5-4                     |

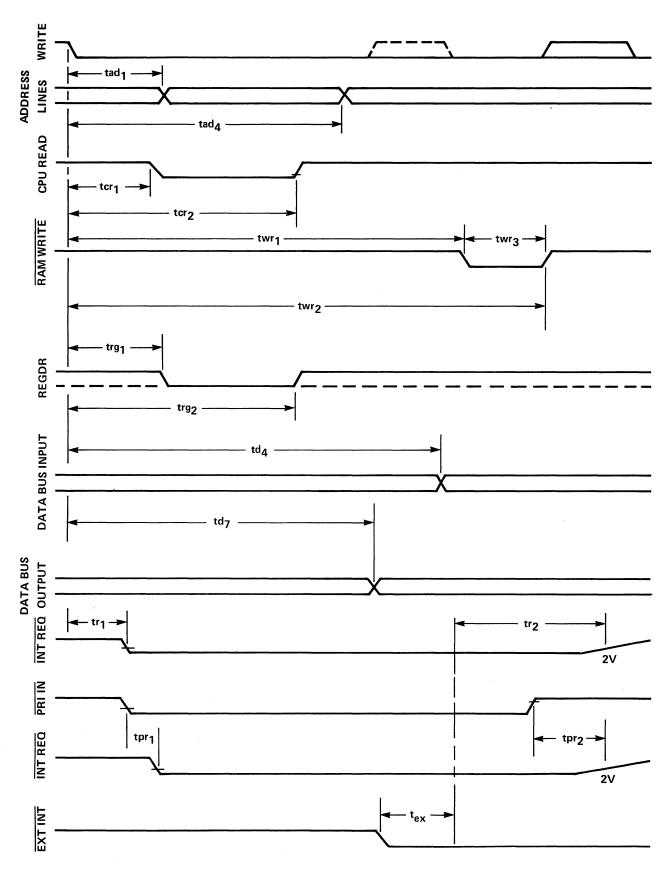

| 5-4          | 3853 Signal Timing                                                                                  | 5-5                     |

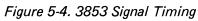

| 5-5          | 3853 SMI Timing Signals Output during a Short Cycle, Memory Read Using PCO                          | 5-6                     |

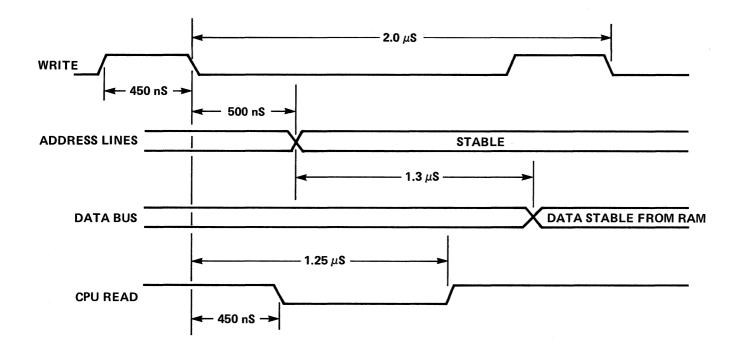

| 5-6          | 3853 SMI Timing Signals Output during a Long Cycle Memory Read,                                     |                         |

|              | with Address Out of Program Counter.                                                                | 5-6                     |

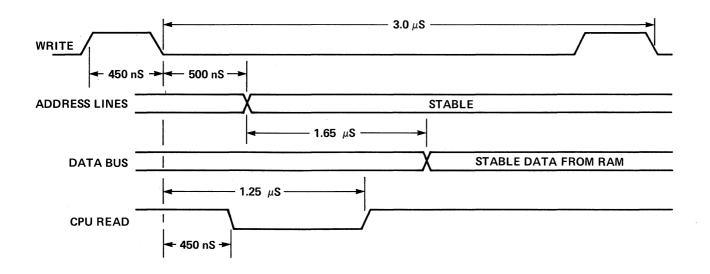

| 5-7          | 3853 SMI Timing Signals Output during a Long Cycle Memory Read,                                     |                         |

|              | with Address Out of Data Counter                                                                    | 5-7                     |

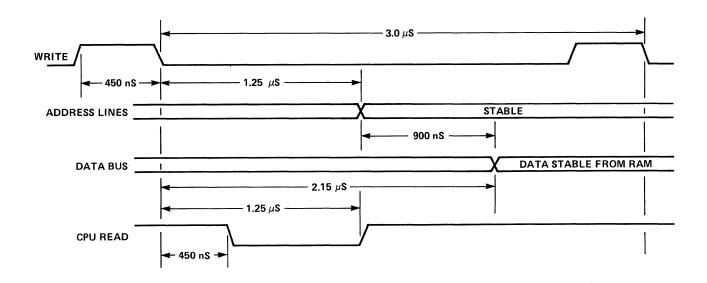

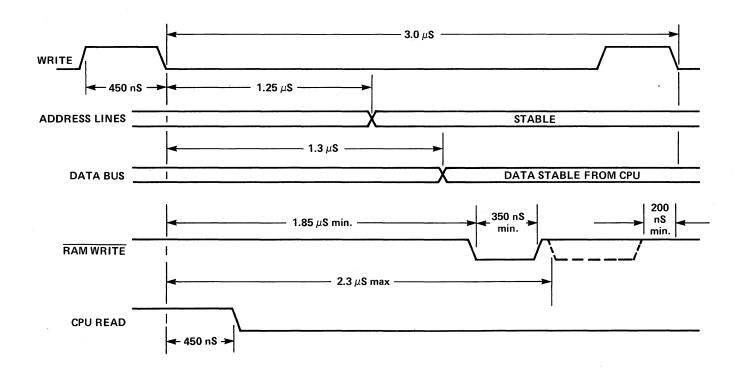

| 5-8          | 3853 SMI Timing Signals Output during a Write to Memory                                             | 5-7                     |

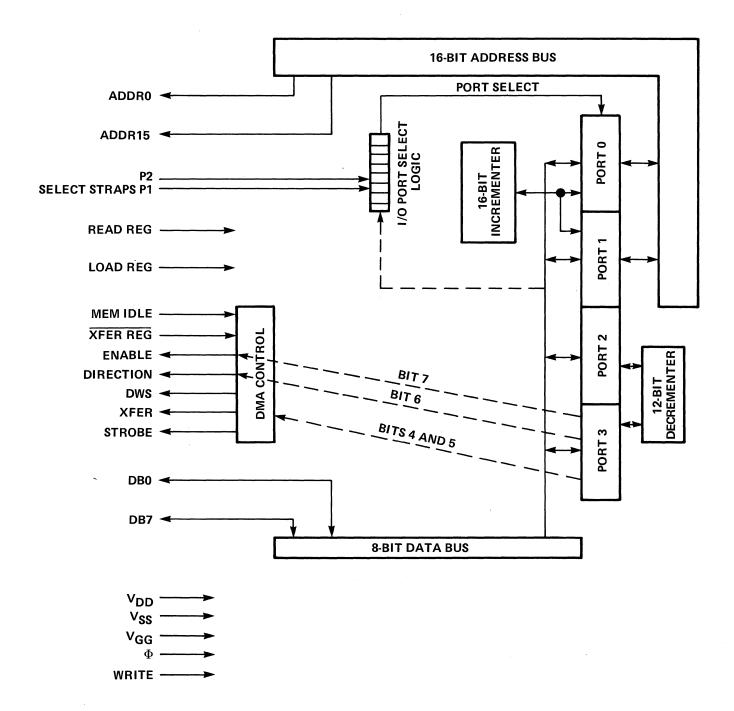

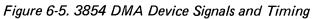

| 6-1          | Logical Organization and Pins for the 3854 DMA Device                                               | 6-2                     |

| 6-2          | How PORT2 and PORT3 are Used to Control DMA Operations                                              | 6-3                     |

| 6-3          | 3854 DMA Pin Assignments                                                                            | 6-4                     |

| 6-4          | DMA Control Signals Output by the 3854 DMA Device                                                   | 6-5                     |

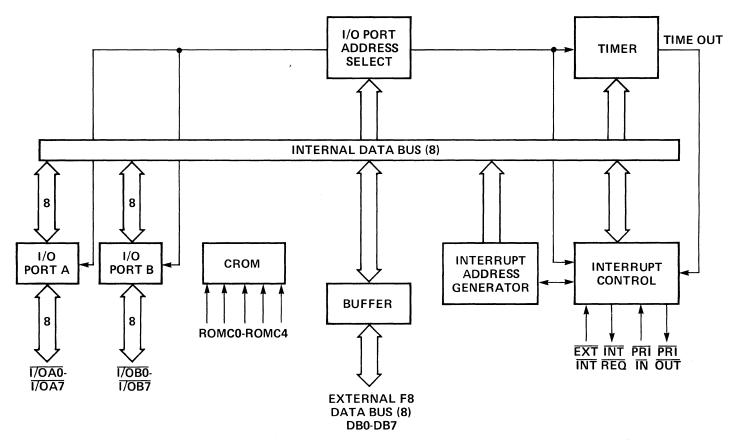

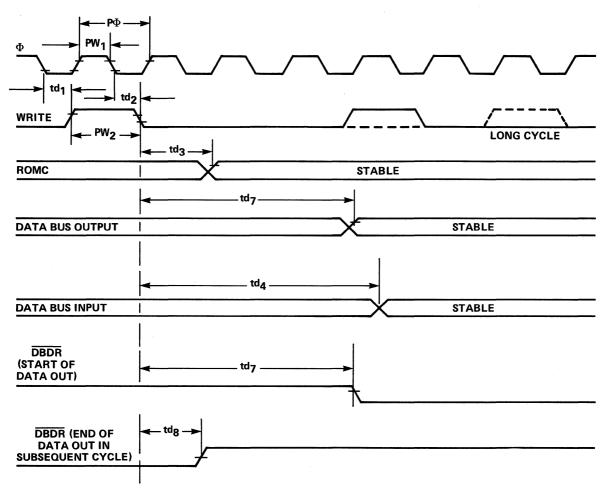

| 6-5          | 3854 DMA Device Signals and Timing                                                                  | 6-9                     |

| 00           |                                                                                                     | 00                      |

| 7-1          | Logical Organization and Pins for the 3861 PIO                                                      | 7-1                     |

| 7-2          | 3861 PIO Pin Assignments                                                                            | <i>.</i><br>7-2         |

| 7-3          | 3861 PIO Data Bus Timing                                                                            | 7-6                     |

| 7-4          | Timing at PIO I/O Ports                                                                             | 7-8                     |

| 7-5          | An F8 I/O Port Bit                                                                                  | 7-0<br>7-9              |

| 7-5<br>7-6   | Interrupt Logic Signals' Timing                                                                     | 7- <del>3</del><br>7-10 |

| <i>1</i> ⁼0  |                                                                                                     | 7-10                    |

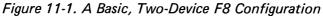

| 11-1         | A Basic, Two-Device F8 Configuration                                                                | 11-1                    |

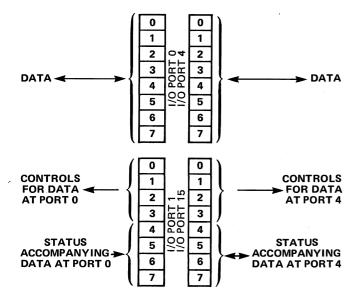

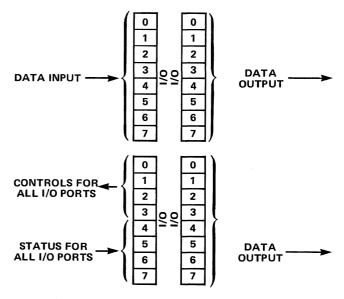

| 11-2         | I/O Ports Divided into Two Subsystems for a Two-Device F8 Configuration                             | 11-2                    |

| 11-3         | I/O Ports Divided into Three Unidirectional Data Ports and One Control/Status                       |                         |

| -            | Port for a Two-Device F8 Configuration                                                              | 11-2                    |

### LIST OF ILLUSTRATIONS (Continued)

| FIGURE                                                       | TITLE                                                                                                                                                                                                                                                                                                        | PAGE                                                         |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

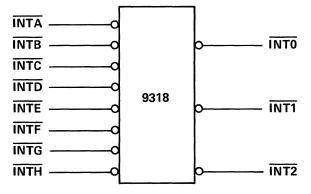

| 11-4<br>11-5<br>11-6<br>11-7                                 | Handling Multiple Interrupts in a Two-Device F8 Configuration                                                                                                                                                                                                                                                | 11-4<br>11-6<br>11-7<br>11-8                                 |

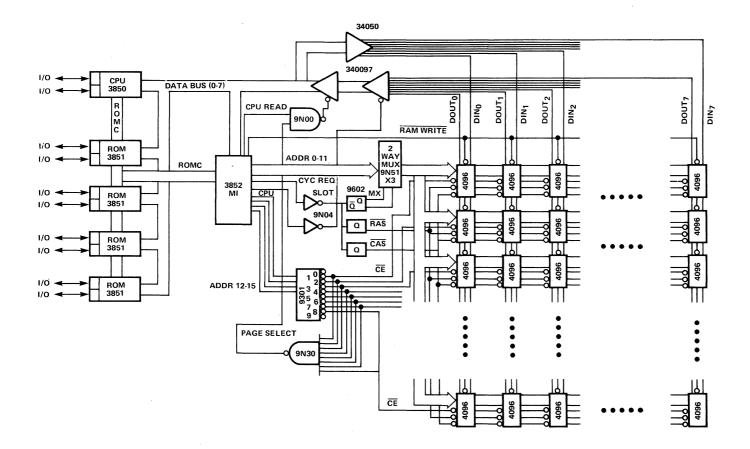

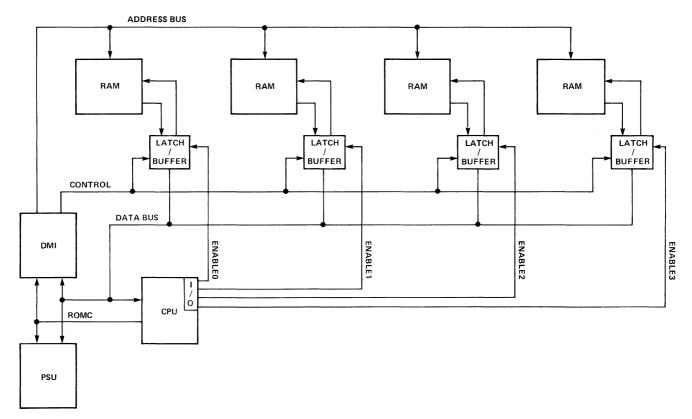

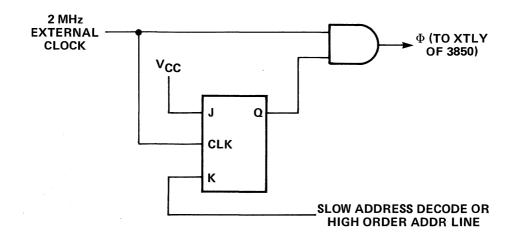

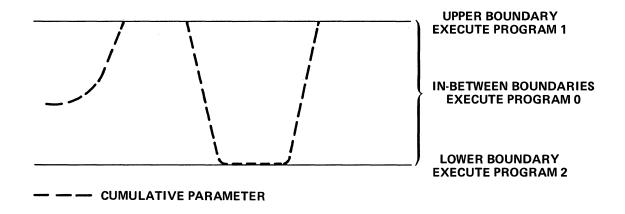

| 12-1<br>12-2<br>12-3<br>12-4<br>12-5<br>12-6<br>12-7<br>12-8 | Interfacing RAM using a 3853 SMIInterfacing ROM and RAM using a 3853 SMIREGDR Controls Data Bus Drivers2K ROM and 8K RAM Configuration using 2102 Memory Devices4K ROM and 32K RAM Configuration using 4096 DevicesMemory Bank SwitchingModifying Clock Period under Hardware ControlBang-Bang Control Logic | 12-2<br>12-3<br>12-4<br>12-5<br>12-6<br>12-7<br>12-7<br>12-9 |

| 13-1<br>13-2<br>13-3                                         | A Typical DMA Configuration                                                                                                                                                                                                                                                                                  | 13-2<br>13-4<br>13-5                                         |

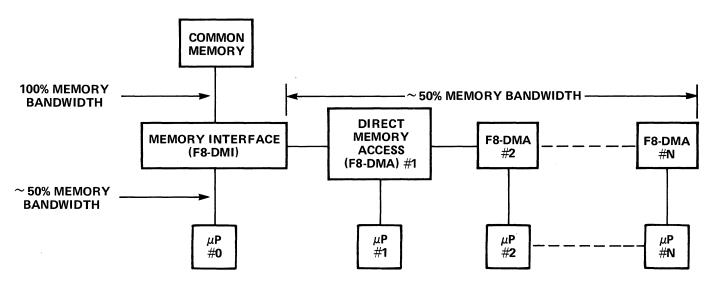

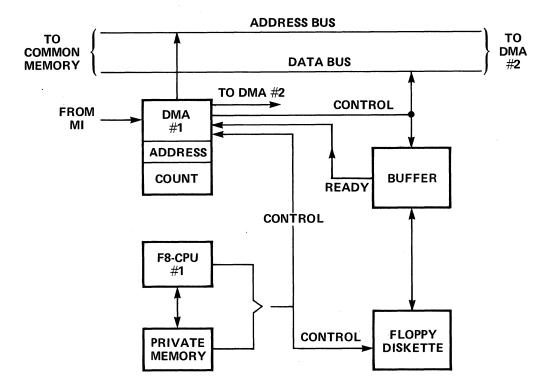

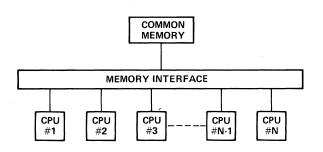

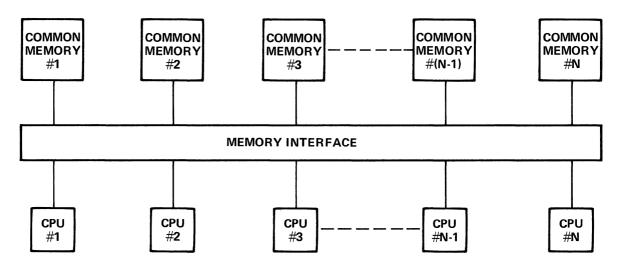

| 14-1<br>14-2<br>14-3<br>14-4<br>14-5<br>14-6<br>14-7         | Communication Oriented Microprocessor Network using a Common<br>Communications Bus                                                                                                                                                                                                                           | 14-2<br>14-2<br>14-2<br>14-3<br>14-4<br>14-5                 |

| 14-8<br>14-9<br>14-10<br>14-11<br>14-12                      | of Figure 14-6)                                                                                                                                                                                                                                                                                              | 14-6<br>14-6<br>14-7<br>14-7<br>14-8<br>14-9                 |

# LIST OF TABLES

| TABLE                                         | TITLE                                                                                                                                                                                                                                                                                 | PAGE                                              |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5               | Number of F8 Devices that can be in a Standard, One CPU F8 Configuration       .         Input/Output Instructions       .         Arithmetic/Logical Instructions       .         Address Register Control Instructions       .         ISAR and Status Control Instructions       . | 1-10<br>1-16<br>1-17<br>1-18<br>1-18              |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7 | A Summary of Status Bits                                                                                                                                                                                                                                                              | 2-4<br>2-5<br>2-9<br>2-10<br>2-12<br>2-16<br>2-17 |

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5               | 3851 PSU Signals                                                                                                                                                                                                                                                                      | 3-5<br>3-6<br>3-9<br>3-10<br>3-11                 |

| 4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6        | 3852 DMI Signal Summary                                                                                                                                                                                                                                                               | 4-3<br>4-5<br>4-9<br>4-12<br>4-15<br>4-16         |

| 5-1<br>5-2<br>5-3                             | 3853 SMI Signal Summary                                                                                                                                                                                                                                                               | 5-3<br>5-8<br>5-9                                 |

| 6-1<br>6-2<br>6-3<br>6-4                      | Address of I/O Ports Used by 3854 DMA Devices                                                                                                                                                                                                                                         | 6-1<br>6-4<br>6-5<br>6-8                          |

| 7-1<br>7-2<br>7-3<br>7-4<br>7-5<br>7-6        | 3861 Port and Address Assignments (HEX)                                                                                                                                                                                                                                               | 7-2<br>7-2<br>7-3<br>7-4<br>7-5<br>7-7            |

| 12-1<br>12-2                                  | Required 3853 SMI Memory Characteristics                                                                                                                                                                                                                                              | 12-8<br>12-8                                      |

# LIST OF TABLES (Continued)

| TABLE | TITLE                                                                             | PAGE  |

|-------|-----------------------------------------------------------------------------------|-------|

| 12-3  | Required 3852 DMI Memory Characteristics with DMA                                 | 12-8  |

| 13-1  | DMA and Refresh Rates                                                             | 13-6  |

| 14-1  | A Comparison between a Single Processor System and a Microprocessor Network $\ .$ | 14-10 |

1.0 The F8 Microcomputer System

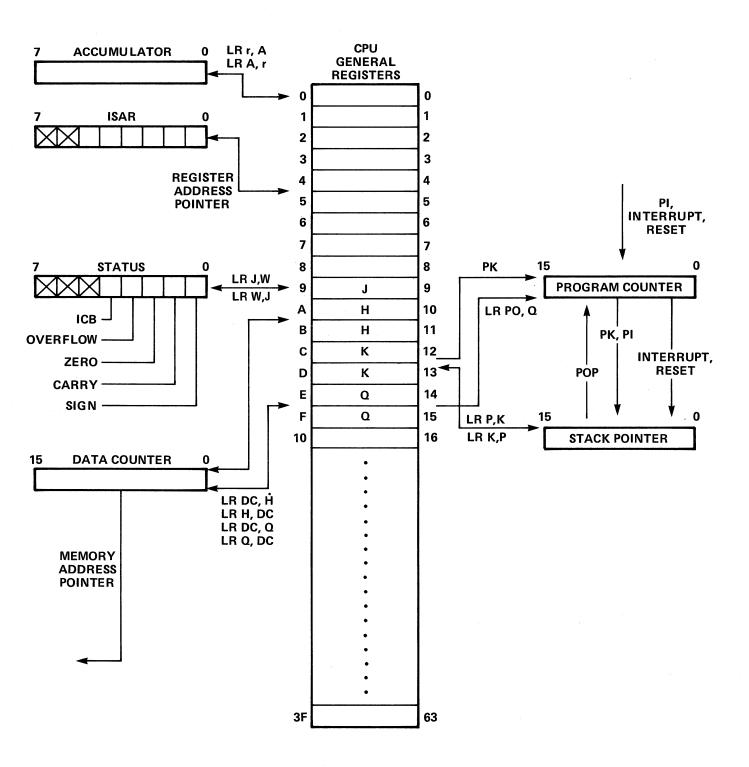

2.0 The 3850 CPU

3.0 The 3851 Program Storage Unit (PSU)

4.0 The 3852 Dynamic Memory Interface (DMI)

5.0 The 3853 Static Memory Interface (SMI)

6.0 The 3854 Direct Memory Access Controller (DMA)

7.0 The 3861 Peripheral Input/Output (PIO)

8.0 (Pending)

9.0 (Pending)

10.0 (Pending)

11.0 3850 CPU-3851 PSU Systems

12.0 F8 Configurations that Include 3852 DMI and 3853 SMI Devices

**13.0 Using Direct Memory Access**

14.0 Multiprocessor Configurations and Applications

Appendix A. FAIR-BUG – 3851A PSU (SL 31162) Specifications

3508 Future Product Description. 8192-Bit Read-Only Memory

3516 Future Product Description. 16K-Bit MOS Read-Only Memory

1.0 The F8 Microcomputer System

# THE F-8 MICROCOMPUTER SYSTEM

Microcomputers represent a new concept in logic design: A single logic device capable of performing any logic operation.

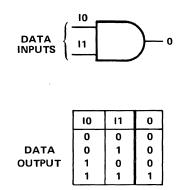

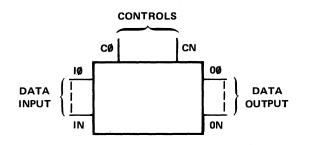

The most elementary logic device receives one or more input signals and immediately generates output signals that may be defined as a function of the input signal via an appropriate truth table. Consider a simple AND gate, as illustrated in Figure 1-1.

Figure 1-1. A Very Elementary Logic Device

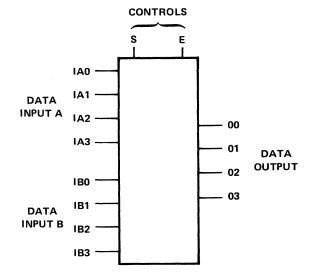

In Figure 1-1, both the input signals and the output signals may be described as data. A slightly more complex logic device will introduce signals which are not data, but rather provide control. Consider the latched dual input, four-bit multiplexer buffer illustrated in Figure 1-2.

The device illustrated in Figure 1-2 has taken two subtle steps toward becoming a microcomputer.

First, two control signals have been added.

Second, a four bit data unit has been defined.

Consider the two control signals; select (S) determines whether inputs A or inputs B will be outputs. Enable (E) determines when the selected input will be output. Until E goes true, the buffer disconnects itself from external logic by presenting a high impedance at its output pins.

Why is this logic device 4 bits wide? The answer, simply, is that the processing of parallel binary data

#### Figure 1-2. A Logic Device Using Control Signals

is a sufficiently common event for a 4-bit device to be justifiable in preference to four 1-bit devices; and a 4-bit device costs very little more than a 1-bit device, so using the 4-bit device will greatly reduce costs. This being the case, why not standardize on 8-bit devices? or 16-bit devices? The answer is that a logic designer must worry about the size of a DIP (Dual Inline Package). Economics dictate that any application must be implemented on as few PC cards as possible; therefore, using 40-pin DIPs, where a 20-pin DIP would do as well, wastes PC card space.

#### 1.1 FROM LOGIC DEVICE TO MICROCOMPUTER

A relatively small conceptual step is all that is needed to go from the latched, dual input, buffer illustrated in Figure 1-2, to a microcomputer. Assume that semiconductor state of the art has reached the point where logic to implement every single device in the Fairchild TTL Data Book can be provided on a single chip. This device would have the same three types of signals as the latched, dual input buffer; namely, data input, data output and control. This is illustrated in Figure 1-3.

67095665

1-1 RBS0 5-1-76

#### Figure 1-3. A Universal Logic Device

Resolving two aspects of the universal logic device illustrated in Figure 1-3 will provide the foundation for the design of any microcomputer. What will be the data width for the device and what will be the nature of the control signals?

Selecting a microcomputer's data width is about the same as selecting the data width for any parallel logic device. The selection is made by trading off the number of DIP pins available, against the way in which these pins can be used. This trade off has most frequently led to an 8-bit data width. In order to understand microcomputers in general, justifying this data width is not of any importance. It is sufficient to point out that while 4 bit and 16 bit microcomputers are available, 8 bit microcomputers are the most common.

There are, perhaps, ten thousand different logic devices listed in any complete catalog. Does this mean that fourteen control pins will be needed to provide sufficient selection options? Indeed, no. It would most certainly be impractical to faithfully reproduce ten thousand sets of logic on a single chip. A relatively small number of unique operations provides the basis for any logic device. By implementing this small number of unique operations on the single chip and by providing the means to correctly combine or sequence these elementary operations, a microcomputer can perform as though all ten thousand devices had been faithfully reproduced.

These are the basic functions out of which any logic device may be built:

- Binary addition and subtraction. Subtraction can be (and usually is), replaced by the complement function, since most microromputers use twos complement binary arithmetic.

- 2. Boolean logic operators, including AND, OR and Exclusive OR. The NOT function is taken care of by having a complement.

3. Real time control. This is a more comprehensive equivalent of the enable strobe.

Binary arithmetic and Boolean Logic are described in "A Guide to Programming the F8 Microcomputer." Items 1 and 2 above are combined into a piece of logic called the "Arithmetic and Logic Unit" (or ALU).

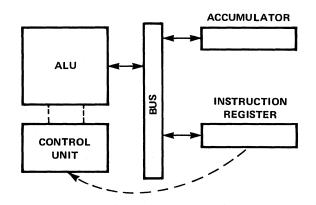

Because the actual manipulative logic of the microcomputer is implemented as a set of basic functions, rather than as a compendium of well known logic devices, the whole concept of logic design changes when using a microcomputer. To be specific, when using a microcomputer, logic is broken down into a serial stream of basic operations. This serial stream of basic operations is created by programming the microcomputer in real time. Three pieces of logic must be added to the ALU in order to make this possible:

- 1. There must be a register which holds the control input. The control input is referred to as an instruction, and the register which holds it is referred to as the "Instruction Register."

- 2. There must be logic capable of decoding the instruction register's contents. This logic must then enable appropriate logic within the ALU, so that the operations specified by the control input occur.

- 3. There must be an additional data register capable of buffering data input to and output by the ALU. This register is named the "Accumulator."

Combining these three requirements, Figure 1-4 illustrates a group of logic which is often referred to as a "Central Processing Unit" (or CPU). The sequence of instructions which, taken together, cause the CPU to respond as required by an application, is referred to as a "Program."

Figure 1-4. An Elementary Central Processing Unit

1-2 RBS0 5-1-76

67095665

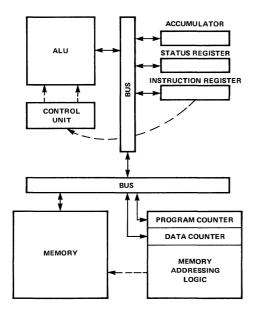

Since the Accumulator is a buffer for transient data, a status register will be added to the CPU. This register will record the condition of the most recent ALU operation. Conditions such as a zero or nonzero result, or a positive or negative result will be recorded.

Consider next, the source of the instruction code sequence and the source or destination of data. The instruction sequence, or program, is a definable and non-varying specification for any application; as such, it will usually become a Read Only Memory. This ROM is going to need an address register which, at any time, identifies the location from which the next instruction code will be fetched. This register is referred to as a Program Counter. Data, likewise, is going to need memory and an address register identifying the memory location which is the current data source or destination; however, data will require some Read/Write Memory, since some memory will have to serve as a data destination, as well as a data source. Adding program and data storage logic to a microcomputer system results in Figure 1-5.

Figure 1-5. A Simple CPU with Memory

A basic necessity of any microcomputer system is a conduit for transmitting data to or from external logic. I/O ports serve this purpose. An I/O port is a bi-directional, 8 bit buffer, communicating on one side with external logic and on the other side with the microcomputer system. The I/O port also provides the third basic functions required of a microcomputer: the equivalent of enable logic. In a microcomputer system, the enable signal becomes an instruction which causes data to be output to, or input from an I/O port.

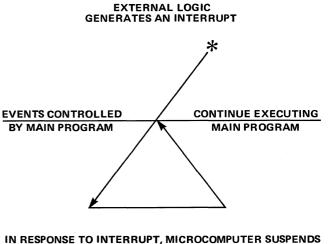

There is a further type of communication that occurs in microcomputer systems, but has no discrete logic parallel; it is the Interrupt. Observe that the microcomputer described thus far provides no means for external logic to initiate asynchronous communication. External logic is, in effect, at the mercy of the microcomputer. Unless the microcomputer program includes instructions to access an I/O port, external logic has no way of communicating with the microcomputer. This means that microcomputer program logic must be all encompassing enough to anticipate any external event which may occur. In many cases, such a program simply cannot exist. The interrupt is a signal which external logic transmits to the microcomputer in order to deflect the microcomputer program temporarily, to serve external logic's immediate needs. This concept is illustrated in Figure 1-6. "A Guide to Programming the Fairchild F8 Microcomputer" provides a thorough description of what interrupts are and how to use them.

IN RESPONSE TO INTERRUPT, MICROCOMPUTER SUSPENDS MAIN PROGRAM AND EXECUTES A SPECIAL INTERRUPT SERVICE ROUTINE

Figure 1-6. The Concept of an Interrupt

The F8 microcomputer makes additional use of interrupt logic to provide a real time capability via a programmable timer. The programmable timer is an 8 bit shift register which may be loaded with a value that specifies a fixed time period at the end of which an interrupt is generated. The programmable timer provides the microcomputer with the

> 1-3 RBS0 5-1-76

ability to synchronize events within the system to real time outside the system.

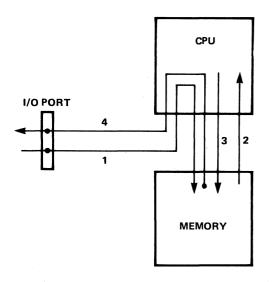

At this point, a microcomputer system may be visualized as consisting of data manipulation logic within the CPU, plus large data buffers provided by memory. I/O ports constitute relatively small conduits through which data passes to or from external logic. Since memory buffers within the microcomputer system may be quite large, there will be an additional step required by logic that uses a microcomputer, an additional step which would not exist were discrete logic being used: raw data will be loaded into or out of memory buffers before or after being processed. This is illustrated in Figure 1-7.

**1 DATA TO MEMORY**

2 DATA TRANSMITTED AS INPUT TO CPU

**3 DATA TO MEMORY AS OUTPUT FROM CPU**

4 DATA OUTPUT FROM MEMORY

Figure 1-7. Memory as a Buffer between External Logic and the CPU

Using input and output instructions, the normal sequence of events required to output data from the microcomputer to external logic, is to load the data from memory into the accumulator, then transmit data from the accumulator to an I/O port. To input data, the data is first loaded from an I/O port into the accumulator, then it is moved from the accumulator to memory. If a large block of data is to be moved between memory and an external device, then time will be wasted performing the data movement in two steps. In addition, the CPU

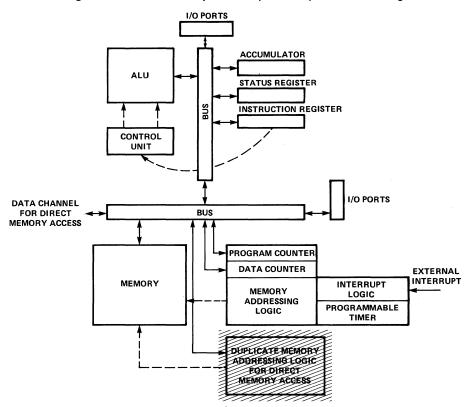

1-4 RBS0 5-1-76 will be tied up implementing what is nothing more than simple data movement. This being the case, a separate path is provided between memory and external devices and this path is referred to as Direct Memory Access. Figure 1-8 now illustrates the complete logic of a microcomputer system. A great deal more could be said about the logic illustrated in Figure 1-8, and it has been said in the "Guide to Programming the F8 Microcomputer." This book assumes the reader understands all the concepts summarized thus far; if this assumption is incorrect, return to the "Guide to Programming the F8 Microcomputer."

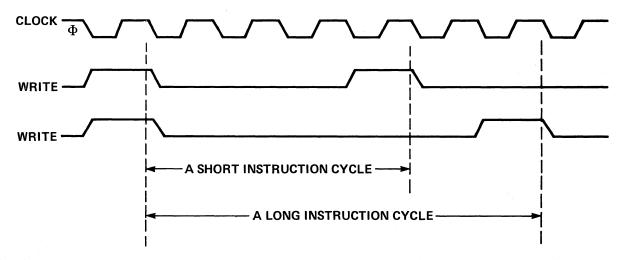

#### **1.2 TIMING IN MICROCOMPUTER SYSTEMS**

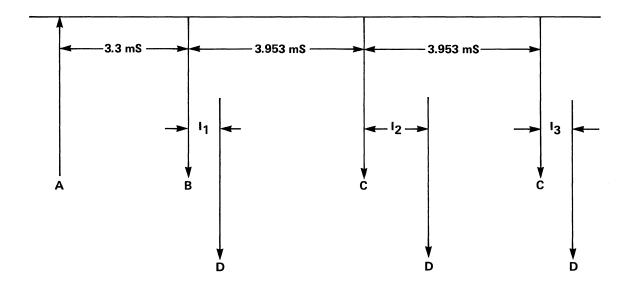

Microcomputers are inherently synchronous devices. This is a necessity, since the complications of sequencing logic in innumerable different ways would become too complex to handle if logic were asynchronous. The entire microcomputer system is therefore driven by a clock and operations within the system occur within well defined instruction cycles. A register manipulation, such as doing a binary add of memory to the Accumulator and placing the result back into the Accumulator, takes one complete instruction cycle. The F8 instruction cycle is illustrated in Figure 1-9. It is the period between two trailing edges of a WRITE clock. Most of the F8 instruction cycles are short cycles (4 $\Phi$ periods long), however long cycles ( $6\Phi$  periods long) are used when data transfers between two circuits require a longer time than is available in a short cycle.

#### 1.3 THE DEVICES OF THE F8 MICROCOMPUTER SYSTEM

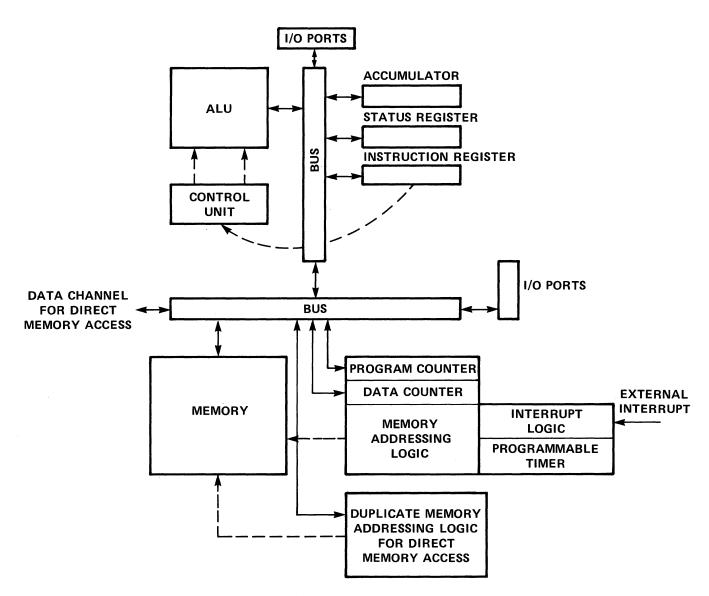

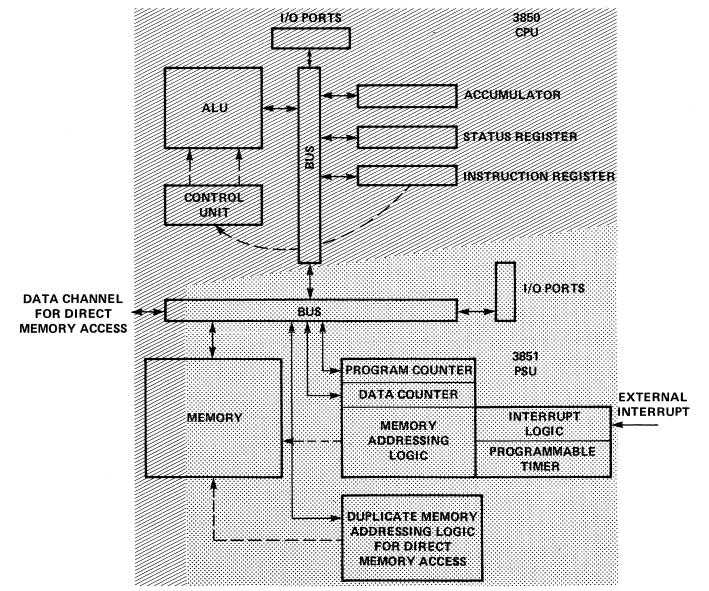

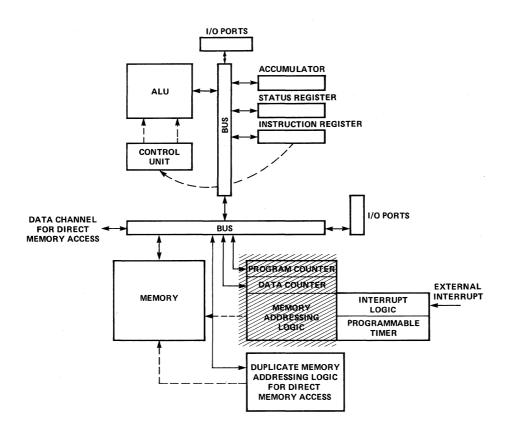

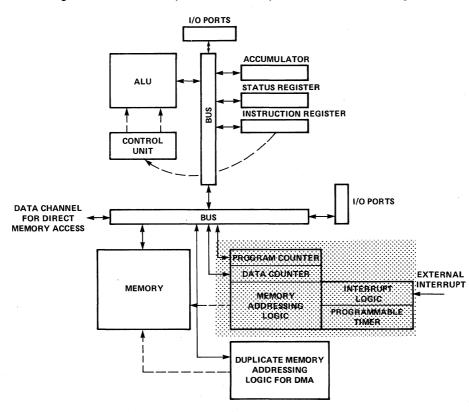

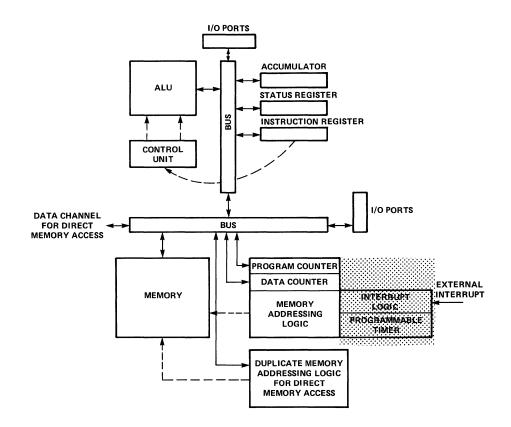

Consider now how the total logic of a microcomputer as illustrated in Figure 1-8, is implemented on various devices of the F8 microcomputer system.

The distribution of logic among various devices of a microcomputer system is one of the most variable features of microcomputers in general. This results from the fact that by sheer coincidence, the requirements for a logic replacement device is quite similar in architecture to the traditional computer. The first microcomputers were developed as very small computers for use in intelligent terminals. The F8, on the other hand, was designed after the microcomputer industry had started to take a recognizable form and intelligent decisions could be made regarding the most economical implemen-

67095665

Figure 1-8. Functional Logic of a Complete Microcomputer System

tation of logic for a logic replacement product. For this reason, logic distribution differs significantly when the F8 is compared with predecessor microcomputers.

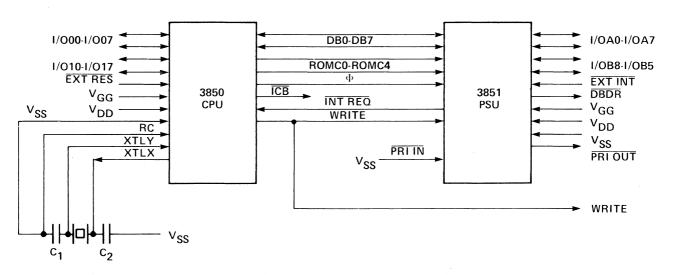

It would appear to be a truism that the most important features of any application is its complexity. Therefore it makes sense to implement logic on devices in terms of application complexity, rather than in terms of traditional computer function. The F8 microcomputer system is the only one that takes this approach. Refer to Figure 1-10. Two F8 devices, the 3850 CPU and the 3851 PSU, together implement all the basic necessities of a small microcomputer system. For the F8 to be implemented in this intelligent way, these three features of the F8 had to contradict old computer concepts:

- 1. A small amount of RAM is implemented within the CPU as a scratchpad memory.

- 2. Memory addressing logic is implemented in the memory devices and not in the CPU.

- I/O ports are implemented in the CPU and memory devices, rather than requiring separate I/O devices.

A logic designer is unlikely to see anything especially revolutionary about the logic distribution illustrated in Figure 1-10. Indeed, the only revolutionary thing about it is that it does not conform to traditional data processing computer concepts; but then,

Figure 1-10. A Two-Device Configuration Consisting of a 3850 CPU and a 3851 PSU

1-6 RBS0 5-1-76 traditional data processing computers were never built to replace discrete logic.

The 3850 CPU must be present in all F8 configurations, and as a minimum either a 3851 PSU or a memory interface device (3852 or 3853) with standard ROM/PROM. Any of the three memory oriented circuits may be used together or singly in the same system. In addition, when system needs dictate, multiple units of the same type may be used. For example, if 2K words of ROM, 64 bytes of RAM, and six I/O ports are required, one 3850 and two 3851s may comprise the system. If larger RAM or ROM is required the system may consist of one 3850, one 3853 and the appropriate amount of standard memory packages.

As soon as an application becomes complex enough to require large amounts of RAM, or when the custom marking process associated with the 3851 is too cumbersome, the 3852 Dynamic Memory Interface (DMI) or the 3853 Static Memory Interface (SMI) devices may be used to replace the 3851 PSU. Each of these devices interpret control signals output by the 3850 CPU in order to generate the standard address and control signals required by off-the-shelf dynamic and static memory devices. Figures 1-11 and 1-12 illustrate the logic which is provided by the 3852 DMI and 3853 SMI devices, respectively. A 4-chip system, which is the equivalent of the 2-chip system but which does not require the customized 3851 PSU, can be built of a 3850 CPU, 3853 SMI, 3861 PIO, and standard ROM/ PROM.

Applications that require additional I/O and interrupt ability but that do not need the program storage of the 3851 Program Storage Unit (PSU) can use the 3861 Peripheral Input/Output (PIO). This device interprets the control signals of the 3850 CPU to drive two I/O ports of 8 bits each. Interrupt logic and a programmable timer are also on the device. Figure 1-13 illustrates the logic provided by the 3861 PIO device.

The final device of the F8 microcomputer system is the 3854 Direct Memory Access (DMA) device. Figure 1-14 illustrates the logic implemented on this device. The 3854 DMA device, working in conjunction with the 3852 DMI device, generates the control and address signals needed to implement data transfer between memory and external logic. This data transfer occurs in parallel with normal events occurring within the F8 microcomputer system.

Table 1-1 illustrates how F8 devices provide capabilities needed by various applications. Note the strong correlation between number of devices and complexity of application.

#### 1.4 F8 BUS STRUCTURE

F8 system components are connected through an F8 system bus. This system bus is composed of the following elements:

- Data Bus (8 lines) DB0-DB7

- Control Lines (5 lines) ROMC0-ROMC4

- Clocks  $\Phi$ , WRITE (2 lines), and

- Interrupt lines PRI IN, PRI OUT, INT REQ (3 lines)

#### DATA BUS (DB0-DB7)

These eight (8) bi-directional lines are used to transfer data, addresses, and input/output signals between various devices, including memories, in an F8 system. Within a system only one device may be driving signals on the Data Bus at any given time.

#### CONTROL LINES (ROMCO-ROMC4)

These five (5) lines transmit thirty-two different commands from the F8 CPU to the rest of the devices in the system. At the beginning of each cycle, the CPU decodes the instruction and a command is presented on these lines to indicate the operation to be performed during the current cycle by the rest of the system.

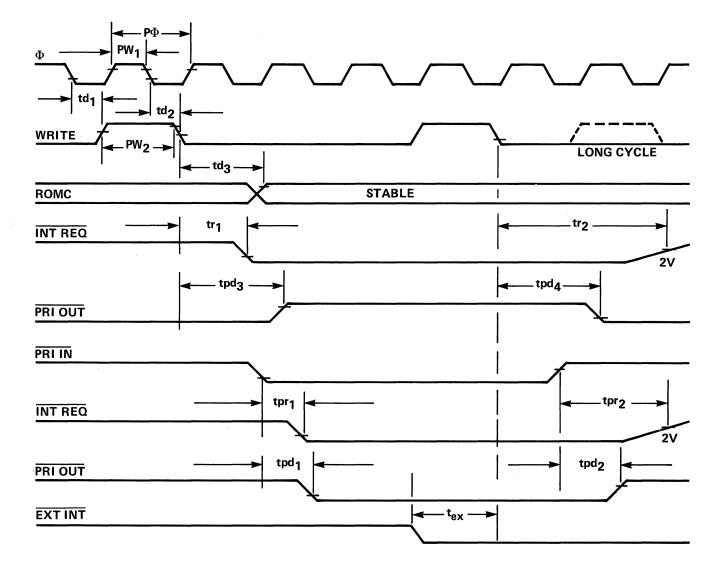

#### $\Phi$ , WRITE CLOCKS

These two (2) lines carry the necessary timing information required from the F8 CPU to the rest of the system. ' $\Phi$ ' is the basic clock—normally 2 MHz—generated by the F8 CPU timing circuits. 'WRITE' clock is a signal having a pulse-width of one ' $\Phi$ ' period, and having a period of either four ' $\Phi$ ' clock cycles or six ' $\Phi$ ' clock cycles. All the registers and flip-flops (except for the scratchpad, which is static) in the F8 devices are either updated or refreshed during the active state of the 'WRITE' clock.

#### **INTERRUPT LINES (3)**

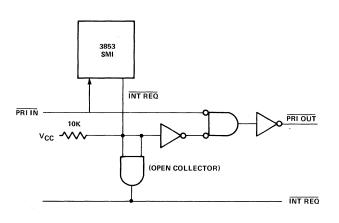

INT REQ is a signal from the other F8 devices to the CPU that indicates that an interrupt is requested. PRIORITY IN and PRIORITY OUT are signals used to connect various interrupt circuits into a priority daisy chain.

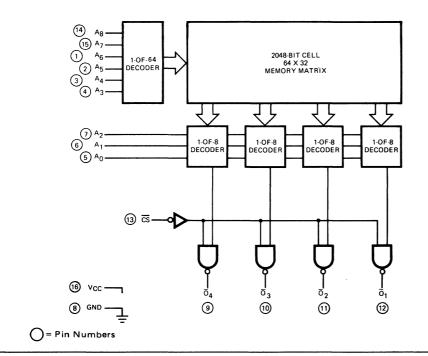

Figure 1-11. 3852 Dynamic Memory Interface Device Logic

Figure 1-12. 3853 Static Memory Interface Device Logic

Figure 1-13. 3861 Peripheral Input/Output Device Logic

Figure 1-14. 3854 Direct Memory Access Device Logic

|             | LOGIC I         | LOGIC PROVIDED |            |       | NUMBER         |                                                                                                                                                   |

|-------------|-----------------|----------------|------------|-------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| DEVICE      | BYTES OF MEMORY | I/O*<br>PORTS  | INTERRUPTS | TIMER | IN<br>SYSTEM** | COMMENTS                                                                                                                                          |

| 3850<br>CPU | 64 RAM          | 2              |            |       | 1              | RAM is independent of external memory                                                                                                             |

| 3851<br>PSU | 1024 ROM        | 2              | 1          | 1     | 0 to 64        | Maximum memory in<br>system equals 64 X 1024<br>bytes                                                                                             |

| 3852<br>DMI |                 |                |            |       | 0 ör 1         | 3852 DMI must be present<br>for 3854 DMA to be present.<br>Either 3852 DMI or 3853<br>SMI will be present in systems<br>with external ROM/RAM. Up |

| 3853<br>SMI |                 |                | 1          | 1     | 0 or 1         | to 64K bytes can be address-<br>ed. Maximum memory equal<br>65,536 minus PSU memory<br>RAM/ROM/PROM may be<br>intermixed.                         |

| 3861<br>PIO |                 | 2              | 1          | 1     | 0 to 64        | Ports, interrupt, and timer same as those of 3851 PSU                                                                                             |

| 3854<br>DMA |                 |                |            |       | 0 to 4         | Provides logic for a DMA<br>channel. If present, a 3852<br>DMI must also be present.                                                              |

Table 1-1. Number of F8 Devices that can be in a Standard, One CPU F8 Configuration

\*The number of I/O ports listed refers to the number of I/O ports available to external devices and excludes internal buffers addressed as I/O ports.

\*\*These numbers apply to single CPU configurations that use none of the special expansion techniques described in Section 7 through 10.

#### 1.5 F8 I/O AND INTERRUPT

I/O ports and the interrupt structure are distributed throughout the F8 system.

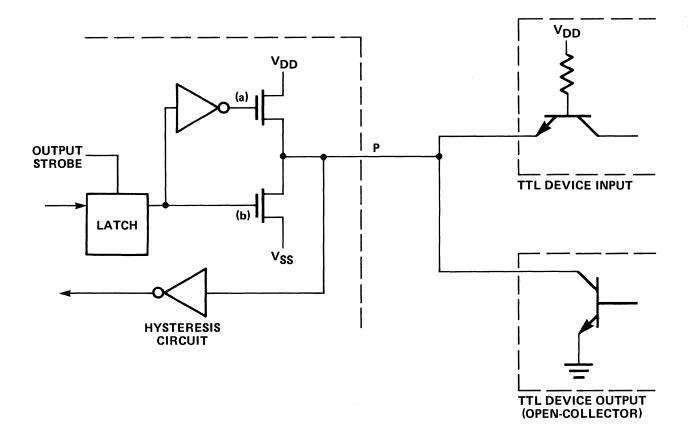

Characteristics common to all I/O ports in F8 devices can be summarized as follows:

- Each has a unique 8-bit I/O address

- Each can be used for output or input on a bit basis

- Latches in the port hold output data

- Output data is "wire-ORed" with input data (an internal pull-up is provided)

- Input and output are TTL compatible.

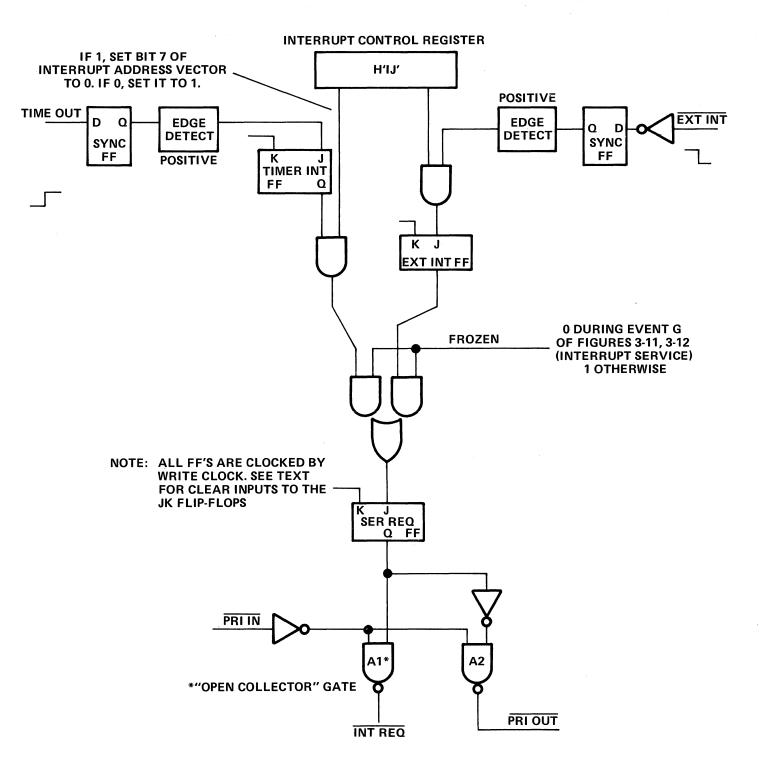

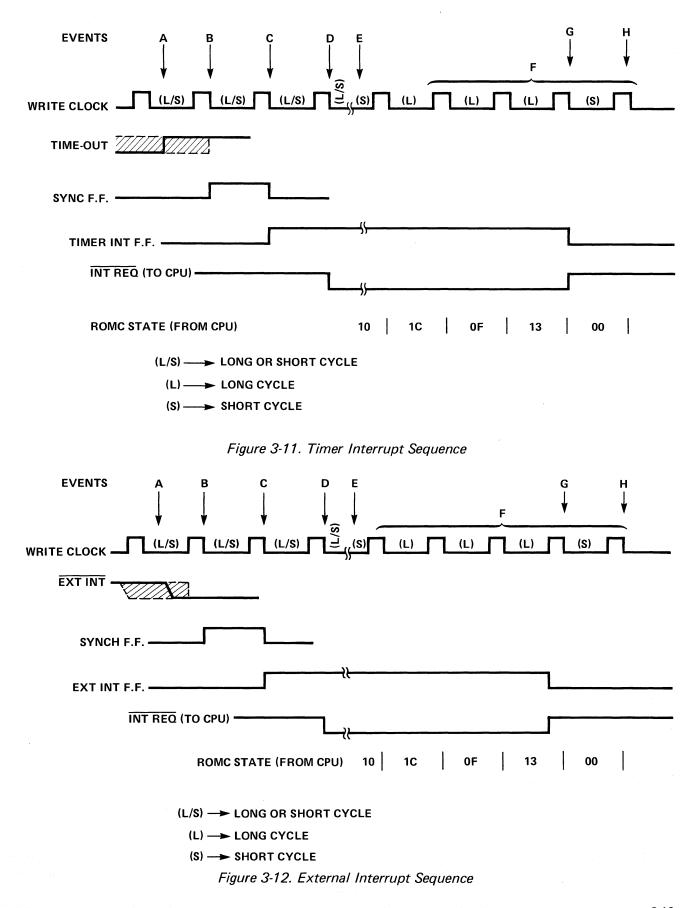

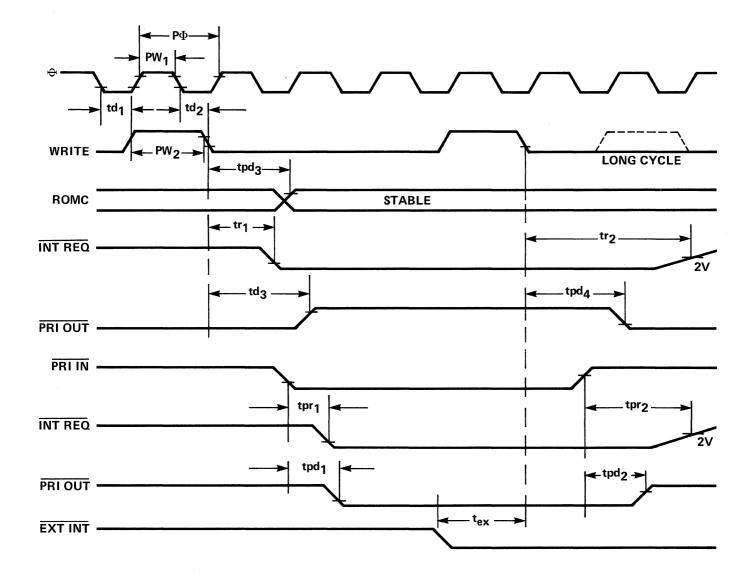

Interrupt capability allows external stimulus to stop normal processing and to force processing to an interrupt service routine. The interrupt structure is also distributed throughout the F8 system. The interrupt sequence begins with the transition of an input line (External Interrupt); the F8 system takes over from that point to assign priorities, to generate an interrupt vector address, and to direct program execution to that interrupt location. Each PSU, PIO, and SMI has its own independent interrupt structure; each has its own external interrupt input and interrupt vector. The CPU has the task of directing program execution to the vector address; the other F8 chips have the task of accepting the interrupt input and of generating the interrupt vector. Interrupts may also be generated by internal timers.

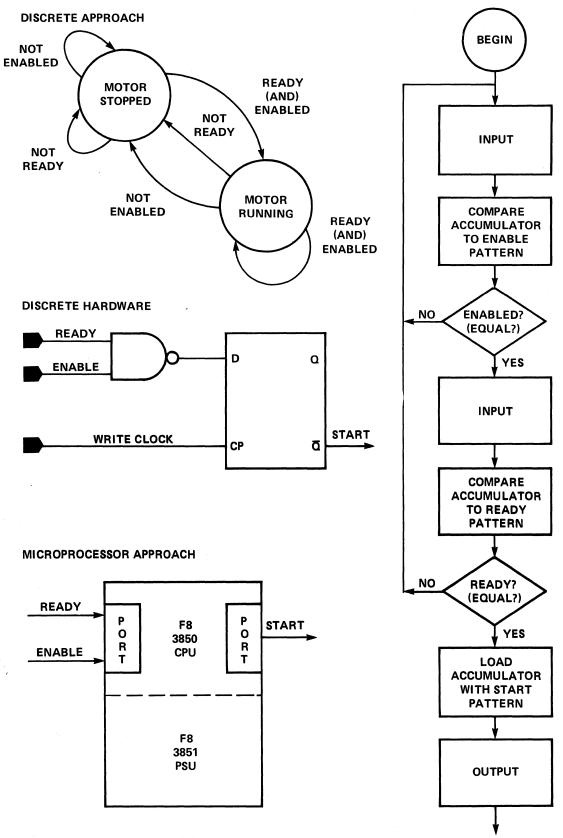

### 1.6 F8 INSTRUCTION SET

The instruction set of a microprocessor is the tool used to shape the microprocessor to fit a particular application, just as NAND gates and flip-flops were the tools used in discrete TTL logic design. The designer must make a transition as he picks up the tools of a microprocessor design. With TTL logic, the design concentrated on state diagrams and on the conditions that cause transition between states. In microprocessor design, the state diagram is transformed into a flow chart, an outline of the serial stream of operations. Each operation is implemented with a set of instructions. States become equivalent to the contents of the microprocessor registers. One of the most significant registers of the microprocessor is the Program Counter (PC0). This register keeps track of the address of the next instruction to be executed. The NAND gate, which simultaneously tested a number of conditions to determine a state transition, is replaced by a serial sequence of conditional branch instructions, each of which alter the Program Counter contents if the specified condition is matched.

Figure 1-15 illustrates a simple problem solved in two ways-by TTL design and by microprocessor design. Two conditions, READY and ENABLE, are necessary before a signal START can activate a motor. The TTL design combines the two conditions in a NAND gate and clocks the NAND gate output through a flip-flop. The microprocessor design uses a flow chart in place of the logic symbols. The two input conditions, READY and ENABLE, are assumed connected to two different I/O ports. Compare instructions set the zero status flag if the input instruction loaded the desired bits into the accumulator. Conditional branch instructions in turn test the status flag. Only if both input signals are "1" does the program get down to the step that uses the output instruction to set the signal START to "1". This simple problem exemplifies the effectiveness of the microprocessor approach to system design.

The F8 instruction set is categorized into four groups:

- Input/Output

- Arithmetic/Logical: Accumulator group

Immediate reference group Scratchpad reference group Memory reference group

Address Register Control: Program counter

group Conditional branch group Data counter group Q, K, H and J register group

ISAR and status control

The following paragraphs are an overview of the instruction set; a more complete discussion of programming is found in the book "A Guide to Programming the F8 Microcomputer."

Just as the two chip system shown in Section 1-3 emphasized I/O capability and compact systems, so too does the F8 instruction set emphasize I/O, bit manipulation, fast powerful scratchpad manipulation, and short one byte instructions. The F8 logic design complements the power of the instruction set; for instance, branch instructions save bytes and time by using relative addressing. Low address I/O ports can be accessed by one byte instructions. Twelve scratchpad registers are directly addressable.

**Input/Output Instructions** — Within the input/ output category are the instructions that bring data from the external world, via the I/O port, into the accumulator. Once into the accumulator, the arithmetic/logical instructions can begin manipulating and testing the data bits. The input/output instructions are given in Table 1-2. Input/output instructions use two modes of I/O port addressing:

Short Direct Addressing: One byte input/output instructions have the op code as the high order 4-bit and the I/O address as the low 4-bits. Ports 00 through 0F (HEX) may be addressed.

Long Direct Addressing: In these two byte instructions, the I/O port address is contained in the second byte of the instruction. Any port may be accessed.

Arithmetic/Logical Instructions — Within the arithmetic/logical category are the instructions that manipulate data bytes. Instructions within this category are given in Table 1-3. Functions available are:

$\begin{array}{r} \mathsf{ACC} \leftarrow \mathsf{ACC} \ + \ \mathsf{B} \ (\mathsf{Binary} \ \mathsf{Add}) \\ \mathsf{ACC} \leftarrow \mathsf{ACC} \ + \ \mathsf{B} \ (\mathsf{Decimal} \ \mathsf{Add}) \\ \mathsf{ACC} \leftarrow \mathsf{ACC} \ \Delta \ \mathsf{B} \ (\mathsf{Logical} \ \mathsf{AND}) \\ \mathsf{ACC} \leftarrow \mathsf{ACC} \ \heartsuit \ \mathsf{B} \ (\mathsf{Logical} \ \mathsf{OR}) \\ \mathsf{ACC} \leftarrow \mathsf{ACC} \ \heartsuit \ \mathsf{B} \ (\mathsf{Logical} \ \mathsf{OR}) \\ \mathsf{ACC} \leftarrow \mathsf{ACC} \ + \ \mathsf{B} \ (\mathsf{Exclusive} \ \mathsf{OR}) \\ \mathsf{Status} \ \mathsf{Flags} \leftarrow \ \mathsf{B} - \mathsf{ACC} \ (\mathsf{Two's} \ \mathsf{Complement} \\ \mathsf{Subtract}) \end{array}$

- ACC  $\leftarrow \overline{\text{ACC}}$  (One's Complement)

- ACC ← (Logical Shifts) ACC

#### MICROPROCESSOR HARDWARE

1-12 RBS0 5-1-76

67095665

The accumulator is involved in all of the above operations. Two variable operations, such as ADD, always use the accumulator as one of the operands. The result of the operation is always loaded back into the accumulator. The second operand for the arithmetic/logical functions can have three sources:

- Scratchpad memory within the 3850 CPU for the scratchpad reference group.

- Memory within a 3851 PSU, or standard RAM/ ROM for the memory reference group.

- Immediate values stored with the instruction as its second byte for the immediate reference group.

Addressing modes for the arithmetic/logical instructions are:

#### Scratchpad Register Group -

Direct Register Addressing – This mode of addressing may be used to directly reference some scratchpad registers. By including the register number in the one-byte instruction, the first 12 of the 64 scratchpad registers may be referenced directly. Indirect Register Addressing – All 64 scratchpad registers may be indirectly referenced, using the Indirect Scratchpad Address Register (ISAR) in the CPU. This 6-bit register acts as a pointer to the scratchpad memory. It is either incremented, decremented or left unchanged after accessing the scratchpad register.

#### Memory Reference Group -

Indirect Memory Addressing – A 16-bit indirect address register, the Data Counter, points to either data or constants in bulk memory. A group of onebyte instructions is provided to manipulate this area of memory. These instructions imply that the Data Counter is pointing to the desired memory byte. The Data Counter is self-incrementing, allowing for an entire data field to be scanned and manipulated without requiring special instructions to increment its content.

#### Immediate Reference Group --

Short Immediate Addressing – Instructions whose addressing mode is Short Immediate have the instruction op code as the first four bits and the operand as the last four bits. They are all one-byte instructions.

Long Immediate Addressing - In these two-byte instructions, the first instruction byte is the op code and the second byte is the 8-bit operand.

Address Register Control Instructions – The instructions of this category are given in Table 1-4.

These instructions manipulate the Program Counter (PC0), the stack register (PC1), the primary Data Counter (DC0), and the secondary Data Counter (DC1).

Normally the Program Counter increments after each instruction, addressing one instruction after another. Jumps and branches are used to alter this sequence; jumps load a 16-bit value into PCO while branches add or subtract an offset to PCO.

Subroutines make use of instructions that save and that reload the contents of the Program Counter. A subroutine is a segment of programming that performs a specific task which is needed at several different places in a program. Each time a subroutine call is made, the processor executes the instruction stream of the subroutine. When execution of the subroutine is complete, control returns to the instruction immediately following the subroutine call. Special instructions are used to call a subroutine—push instructions. A push is like a jump except that the next address after the push instruction is saved in the Stack Register (PC1).

The POP instruction reloads the Program Counter (PC0) from the Stack Register (PC1). Thus a return to the main program after execution of a subroutine is accomplished.

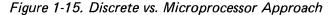

Subroutines may be nested, which means that a call to a second subroutine may occur during the execution of a first subroutine. Nested subroutines require that more than one value from the Program Counter be saved. The F8 microprocessor dedicates pairs of stratchpad registers in the 3850 CPU which are used to save and then to reload the Stack Register (PC1) as well as the Data Counter (DC0). The interrelationship of the scratchpad registers and the address registers is shown in Figure 1-16.

Other single byte instructions of the address register control category link the K and Q scratchpad registers to the accumulator so that they may be stored elsewhere. Thus, a stack may be created. The PK and LR PO, Q instructions can be used to push or jump addresses dynamically created during the program's execution.

Conditional branch instructions also modify the Program Counter. The branch instructions test selected status flags and will either modify the program counter if the test is satisfied or will otherwise continue to the next sequential instruction.

Figure 1-16. Instructions Linking Program Counter

Since branches are the decision making tools, they are frequently used. The F8 has a large number of branch instructions, providing ease of programming. A test can be made for either a single status flag being true or false or for a combination of flags, such as "branch if a result is positive OR produced a carry." The four status flags are overflow, zero, carry, and sign. Branch instructions can move the Program Counter forwards or backwards.

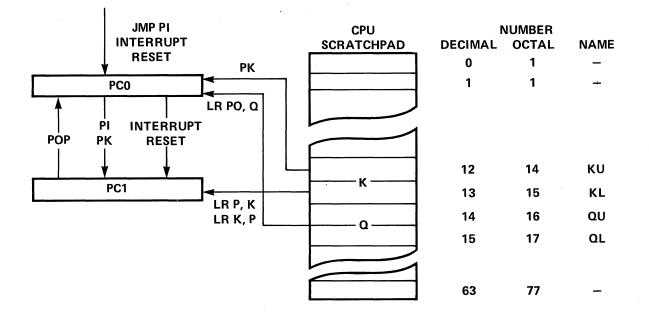

The primary Data Counter register (DC0) supplies the indirect address used by the memory referencing arithmetic/logical instructions. The Data Counter may be used to access data bytes or tables of data, such as a table of 256 entries that matches ASCII values to EBCDIC values. Sometimes the location of the data byte is fixed; in such a case the DCI instruction is used to load DC0 using the 2-byte immediate operand. At other times, such as table look-ups, the value loaded into DC0 is not fixed but rather is the result of a calculation made during program execution. In such an instance, the Data Counter may be loaded from the scratchpad registers. Table 1-4 gives the instructions that manipulate DC0. Some of these instructions link DC0 to dedicated pairs of scratchpad registers. The scratchpad registers and their linkage to DCO are given in Figure 1-17.

The linkages of DC0 to the scratchpad are used for calculating values to be loaded into DC0; they are also used for loading and storing DC0. Notice that the H register pair is within the direct addressing range of the arithmetic/logical scratchpad instructions. The registers of the Q pair are linked by one-byte byte load and store instructions to the accumulator.

The ADC instruction adds the accumulator to the contents of the Data Counter. The Q register pair is linked to both the Data Counter and the program counter; this path can be used to transfer a value from DC0 to PC0 after a jump value is calculated in DC0 using the ADC instruction.

The memory interface devices have two data counters, DC0 and DC1. The secondary data counter, DC1, is useful for programs working with two blocks of memory.The H and Q register pairs come into use if three blocks are being handled, such as when going "A (+) B (into) C."

The addressing modes used in the program control category are:

*Implied Addressing* – The data for these one-byte instructions are implied by the actual instruction.

Figure 1-17. Instructions Linking Data Counter

For example, the POP instruction automatically implies that the content of the Program Counter will be set to the value contained in the Stack Register.

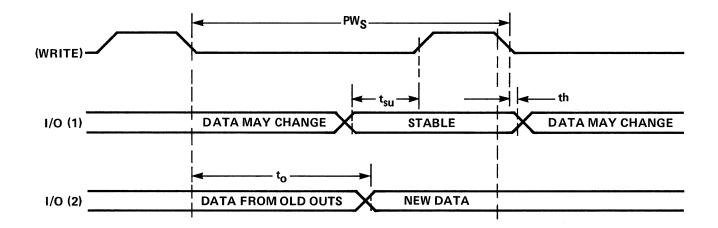

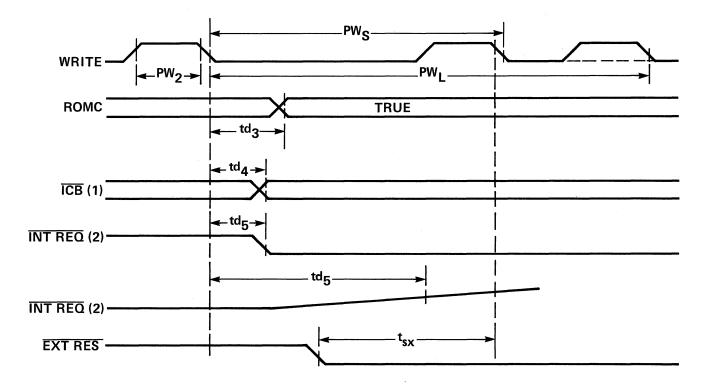

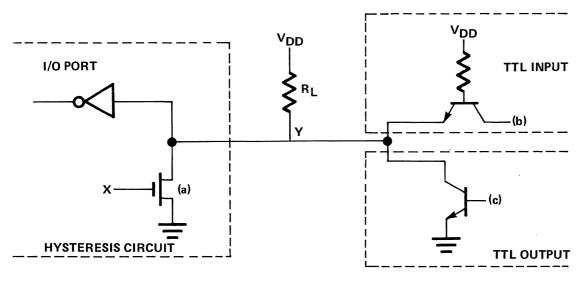

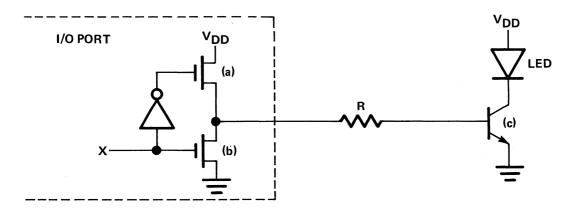

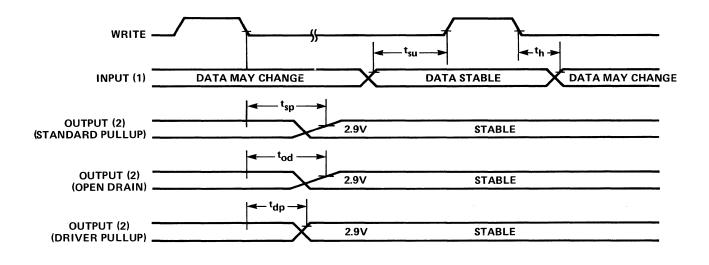

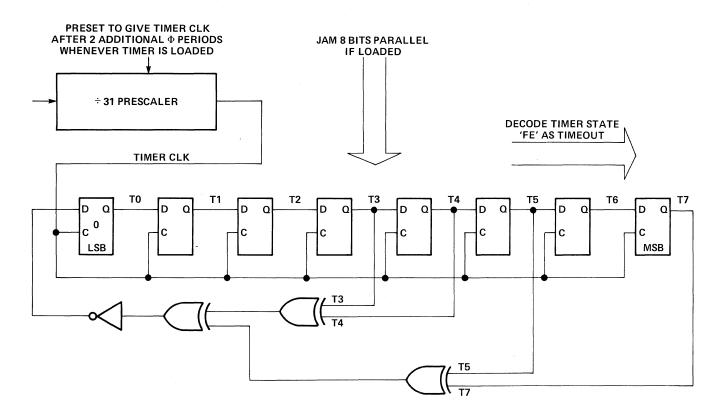

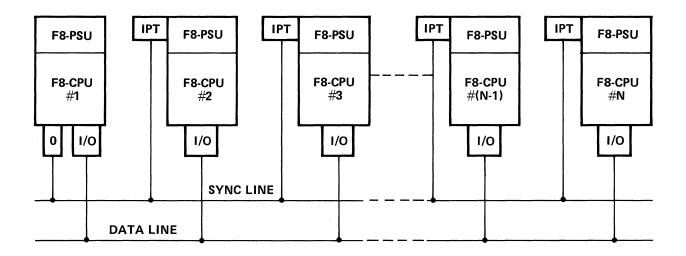

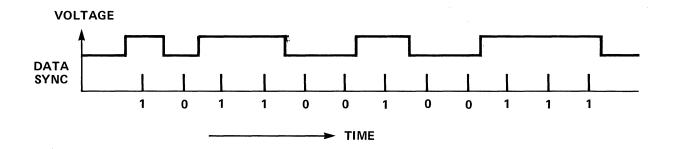

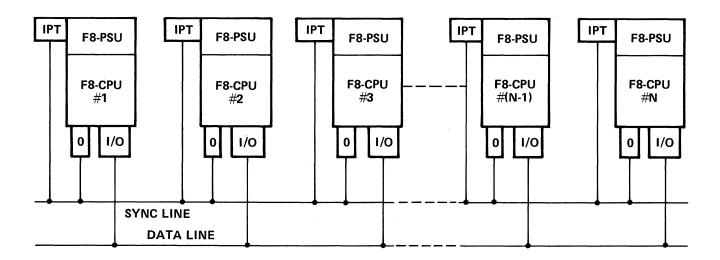

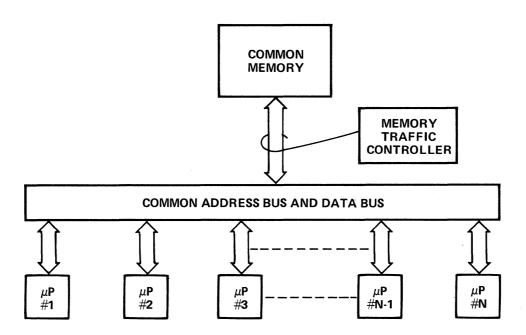

*Relative Addressing* — All F8 branch instructions use the relative addressing mode. Whenever a branch is taken, the Program Counter is updated by an 8-bit relative address contained in the second byte of instructions. A branch may extend 128 locations forward or 127 locations backward from the address of the branch instruction.