## FAIRCHILD SEMICONDUCTOR

# 9500 Series · High Speed Logic

MAY 1971

#### CONTENTS

| Fairchild 9500 Easy ECL Family                         |

|--------------------------------------------------------|

| Advantages of Temperature Compensated ECL              |

| Product Summary                                        |

| Data Sheets                                            |

| Design Information                                     |

| 9500 System Application and Wiring Rules               |

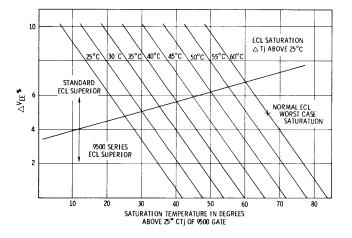

| Temperature Compensated ECL                            |

| Applications of the 9538 ECL/MSI High Speed Decoder 99 |

| •                                                      |

|                                                        |

|                                                        |

|                                                        |

### **ERRATA SHEET-9500 ECL BROCHURE**

|         | Page   | Product | Description                               |                                                                |                                                                                 |                                                                                                  |                                          |      |

|---------|--------|---------|-------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------|------|

|         | 6      | 95HO0   | M <sub>R</sub> is active HIGH             | , PE is activ                                                  | e LOW                                                                           |                                                                                                  |                                          |      |

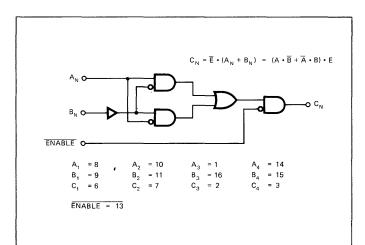

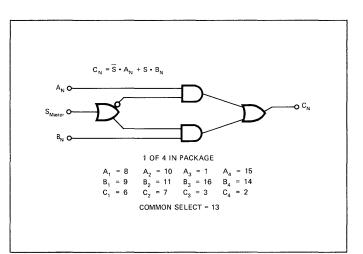

|         | 15     | 9578    | Pin Connections:<br>Active LOW ena        | C1 = 6                                                         | A <sub>2</sub> = 10<br>B <sub>2</sub> = 11<br>C <sub>2</sub> = 7                | $B_{3} = 16$                                                                                     | A4 = 15<br>B4 = 14<br>C4 = 2             |      |

|         | 15     | 9579    | Pin Connections:                          | B1 = 8<br>C1 = 7                                               | B <sub>2</sub> = 10<br>C <sub>2</sub> = 6                                       | B <sub>3</sub> = 1<br>C <sub>3</sub> = 2                                                         | A <sub>3</sub> = 13<br>B4 = 15<br>C4 = 3 |      |

|         |        |         | Select = 13 (A s                          | elect HIGH,                                                    | , B select LO                                                                   | W)                                                                                               |                                          |      |

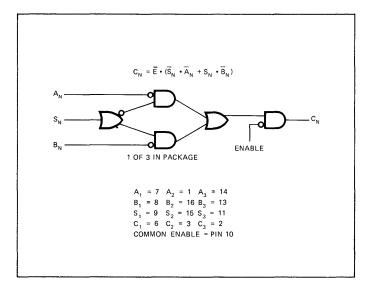

|         | 16     | 9580    | Pin Connections:<br>Active LOW ena        | B <sub>1</sub> = 7<br>C <sub>1</sub> = 9<br>S <sub>1</sub> = 6 | $A_2 = 16$<br>$B_2 = 1$<br>$C_2 = 15$<br>$S_2 = 3$<br>select HIGH               | B <sub>3</sub> = 14<br>C <sub>3</sub> = 11<br>S <sub>3</sub> = 2                                 | (/م <del>ا</del> د                       |      |

|         |        |         | $A_N$ and $B_N$ inp<br>gate is active LO  | outs are act                                                   |                                                                                 |                                                                                                  |                                          |      |

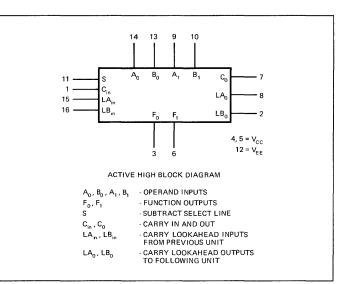

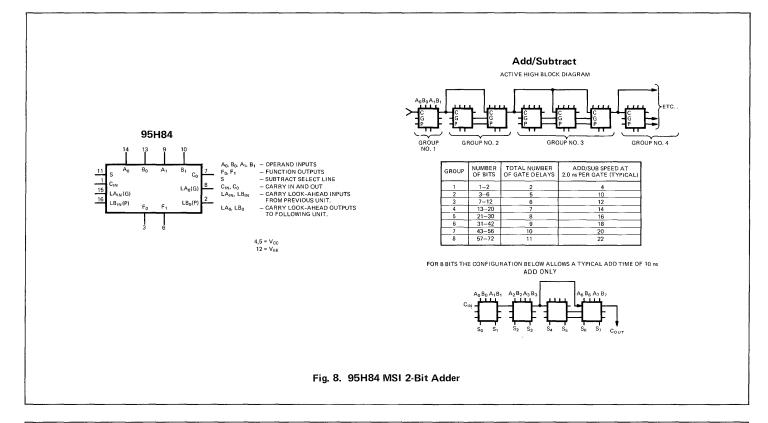

|         | 17, 83 | 95H84   | Pin Connections:                          | A <sub>1</sub> = 9<br>B <sub>0</sub> = 13                      | C <sub>IN</sub> = 1<br>LA <sub>IN</sub> = 16<br>LB <sub>IN</sub> = 15<br>S = 11 | F <sub>1</sub> = 6<br>LA <sub>OUT</sub> =                                                        | 2                                        |      |

|         |        |         | ADD/SU                                    | BTRACT (T                                                      | wo's Complem                                                                    | enț)                                                                                             |                                          |      |

| ADD SUB |        |         |                                           | 95H84 LAO<br>N LBO                                             |                                                                                 | С <sub>ІМ</sub> Со<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$<br>\$ |                                          | ETC. |

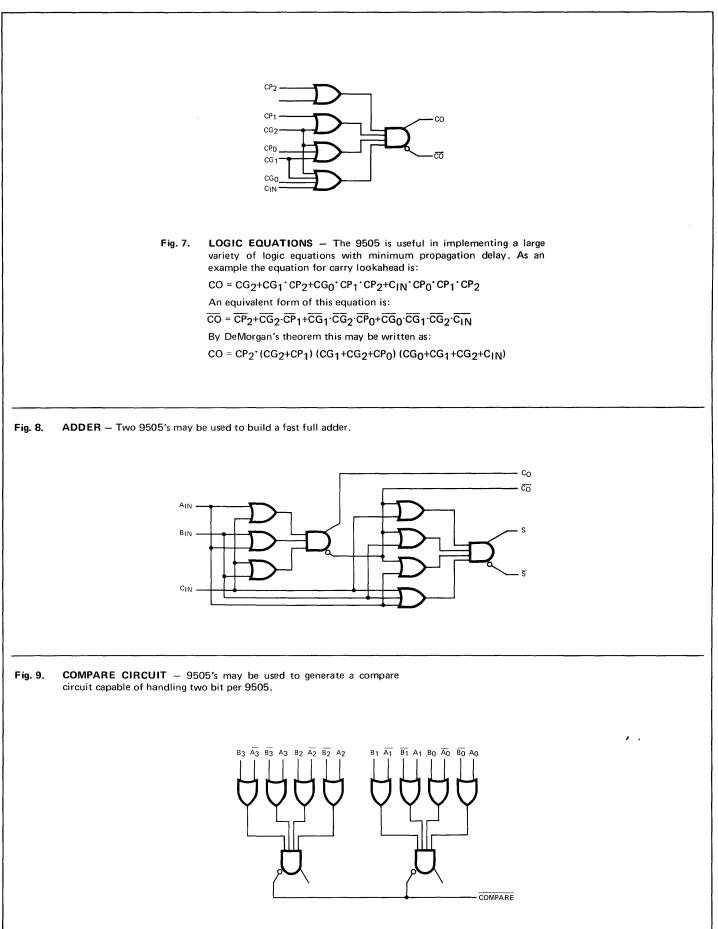

|         | 37     | 9505    | Fig. 8: One input c                       | of unused O                                                    | R gate must                                                                     | be HIGH.                                                                                         |                                          |      |

| ·       | 70     | 95H90   | A.C. Electrical Cha<br>and bottom of page |                                                                | : Note 1: Se                                                                    | e functional                                                                                     | description                              |      |

|         | 72     | 95H9O   | Fig. 8: (ECL to ⊺<br>be 220Ω.             | TTL) collect                                                   | tor load resi                                                                   | stor of 2N5                                                                                      | 771 should                               |      |

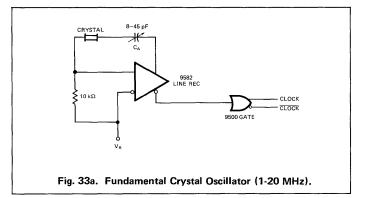

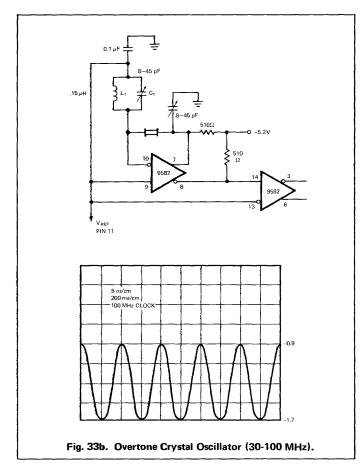

92 Sys. Appl. Fig. 33A Crystal Oscillator: Output driving crystal is active LOW, and Wiring output driving buffer gate is active HIGH. Rules

SEMICONDUCTOR

D.

FAIRCHIL

| S                                                                                  | SI                              |                |                                                     |                                           | MSI           |                                                                                                         | - THE REAL                                                |                                                  | Interface                                           |  |  |  |  |  |

|------------------------------------------------------------------------------------|---------------------------------|----------------|-----------------------------------------------------|-------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------|--|--|--|--|--|

| Gates<br>95L22<br>Dual                                                             | Flip Flops                      | Decoders       | Multiplexers                                        | Registers                                 | Latches       | Operators                                                                                               | Counters                                                  | Memory                                           |                                                     |  |  |  |  |  |

| 95L23<br>Triple<br>95L24<br>Quad                                                   |                                 |                |                                                     |                                           |               |                                                                                                         |                                                           |                                                  |                                                     |  |  |  |  |  |

| 9502<br>Dual<br>9503<br>Triple<br>9504<br>Quad<br>9505<br>DR/And<br>507<br>uad And | 9528<br>Dual D                  | 9538<br>1 of 8 | 9579<br>Quad 2<br>9580<br>Trip 2<br>9581<br>8 Input |                                           | 9534<br>4 Bit | 9578<br>Ex-Or/<br>Comp-<br>arator                                                                       |                                                           | 95410<br>256 Bit<br>Ram                          | 9582<br>Receiver/<br>Amplifier<br>9595<br>Converter |  |  |  |  |  |

| 95H02<br>Dual<br>95H03<br>Triple<br>95H04<br>Quad                                  | 95H28<br>Dual D<br>95H29<br>J-K |                |                                                     | 95H39<br>Multi-<br>port<br>95H00<br>4 Bit |               | 95H55<br>5-Bit<br>Comp-<br>arator<br>95H42<br>Carry<br>95H41<br>4 Bit<br>ALU<br>95H84<br>2 Bit<br>Adder | 95H10<br>Decimal<br>95H16<br>Binary<br>95H90<br>Prescaler | 95400<br>64 Bit<br>Ram<br>95401<br>16 Bit<br>Ram |                                                     |  |  |  |  |  |

### FAIRCHILD 9500 EASY ECL FAMILY

## FAIRCHILD 9500 EASY ECL

ECL offers both maximum speed performance and optimum logic flexibility in the design of high speed systems. Circuit features such as Wired-OR, complementary outputs and series gating permit the implementation of many digital functions with lower package count and therefore lower component cost, with similar system power dissipation, than with high speed TTL.

9500 ECL incorporates unique design features, including temperature compensation and on chip terminating resistors to eliminate many of the application problems (low noise margin and instability) associated with earlier forms of ECL. In addition the basic gate characteristics have been chosen to allow the use of more relaxed wiring rules and therefore lower cost interconnection methods than any logic family in the same speed range.

By taking advantage of Fairchild's experience in designing high speed custom circuits the 9500 user will have at his disposal one of the best planned circuit families available. The intermixing of high speed and very high speed ECL technologies, and basic gates with complex MSI functions in a single logic family allows a designer to optimise a system to his particular cost-performance goal.

The 9500 product range has been planned around the requirements of the three basic application areas for high speed circuits.

#### **ADVANTAGES**

- Transmission line compatible

- Can be fully terminated

- Minimum line reflections

- Low transient noise susceptibility

- High fan in/fan out possible across speed range

- No additional inversion delay

- Two logic decisions per gate delay

- Up to 30% lower system package count

- Low crosstalk

- Simpler wiring rules for same system speed

- Low internal noise generation

- Constant power dissipation across frequency range

- Circuitry oriented to design of very high speed, medium power MSI functions

| Computers | <ul> <li>Basic Gates in 2.5 ns and 1.5 ns ranges,</li> </ul> |

|-----------|--------------------------------------------------------------|

|           | complex gate functions, dual D flip-flops,                   |

|           | latches scratchpad memories, decoders,                       |

|           | registers, adders.                                           |

- Communications Prescalers, mixers, broad band amplifiers, oscillators, multiplexers, decoders.

- Instrumentation High speed flip-flops for 100 MHz and 250 MHz applications, multiplexers, demultiplexers, line receivers.

This dynamic logic family will continue to expand as technology and applications demand. All additions to the 9500 range will be compatible with the present devices, permitting upgrading of existing designs to take advantage of economic and performance improvements as they become available.

#### SYSTEMS ADVANTAGES OF ECL

In addition to the maximum possible operating speeds, ECL also offers many advantages over other logic forms for the design of digital systems.

#### FEATURE

HIGH INPUT/LOW OUTPUT IMPEDANCE

COMPLEMENTARY OUTPUTS/WIRE-OR CAPABILITY

HIGHER NOISE MARGIN RELATIVE TO LOGIC SWING. LOWER EDGE SPEED RELATIVE TO DELAY

CONSTANT SUPPLY CURRENT DRAIN

SERIES GATING, EMITTER AND COLLECTOR DOTTING, ETC.

#### 9500 TEMPERATURE COMPENSATED ECL -

Significant applications characteristics of 9500 are:

• Temperature Compensation

Logic levels remain constant across range  $0^{\circ}$ C to  $75^{\circ}$ C. Maintains maximum system noise immunity and eliminates saturation problems.

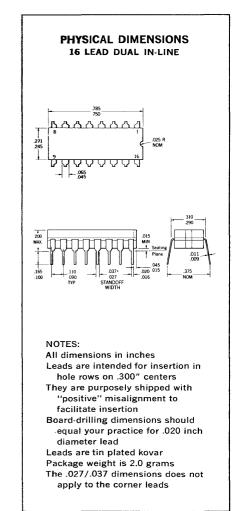

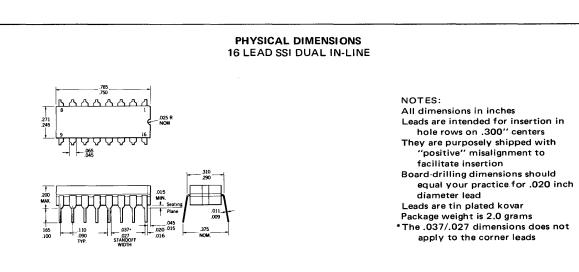

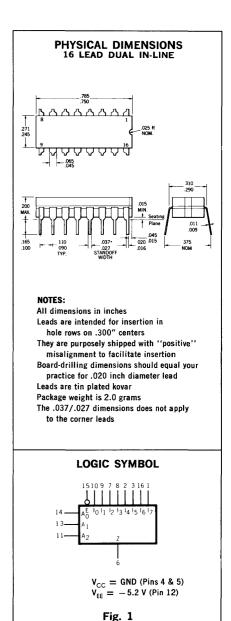

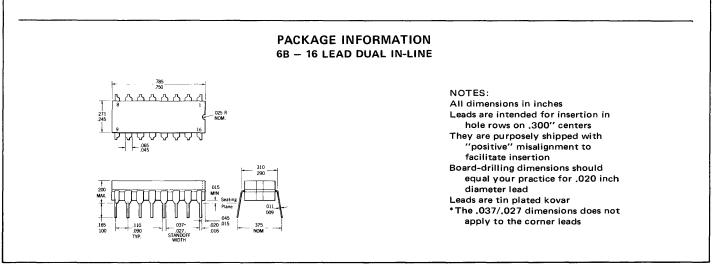

• Packaging

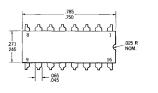

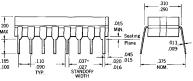

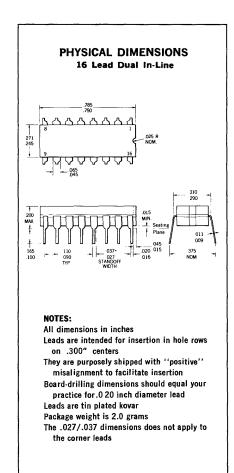

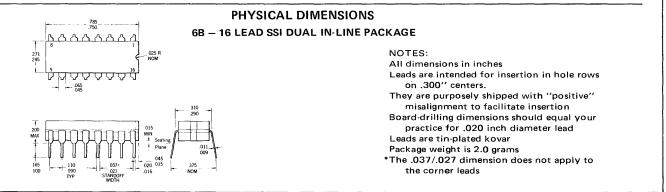

Hermetic 16 pin Dual In-Line Package

Internal Pull Down Resistors

Point to point wiring up to 8" on single sided boards permitted by internal 2 k ohm resistors and choice of edge rates. These resistors also eliminate oscillation problems and allow unused inputs to be left open.

• Low Crosstalk And Noise Generation

Insured by provision of split  $V_{CC}$  lines and location of supply pins.

• 50 Ohm Line Drive Capability

Output transistors designed to drive a 50 ohm terminated line and a fanout of 10 loads simultaneously.

• Single Power Supply

9500 elements are specified for use with a single power supply.

MSI Flexibility

The 9500 product range has been designed to take maximum advantage of MSI performance in logic flexibility, economy and speed-power optimisation. Basic building blocks are aimed at computing, communications and instrumentation applications.

• Cost Effectiveness

Low cost processing, together with above features insure simple applications rules and lowest cost hardware and components for high speed systems.

#### 9500 ECL FAMILY CHARACTERISTICS

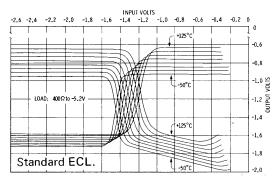

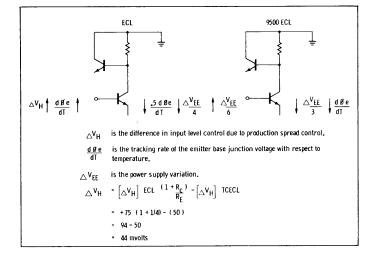

The 9500 circuit uses the same basic configuration as conventional ECL with the addition of temperature compensated internal reference and current source networks. These maintain the logic ZERO state insensitive to temperature variations. Logic ONE is clamped to ZERO by the collector cross-coupling diode network.

The temperature compensation networks require only minimal additional chip area for the gate functions. On MSI and complex gate elements the additional area is insignificant as compensation is only applied to the output nodes.

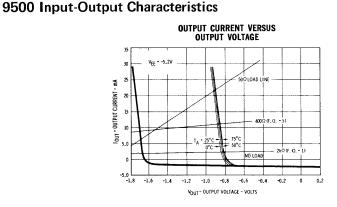

With -5.2 volt V<sub>EE</sub> logic ONE is typically V<sub>OH</sub> = -850 mV and logic ZERO V<sub>OL</sub> = -1700 mV. These levels will interface directly with other ECL families, and with DTL and TTL using simple discrete and monolithic interface circuits. 9500 elements can also be operated from a positive supply if desired. (See Fairchild Application Brief 157).

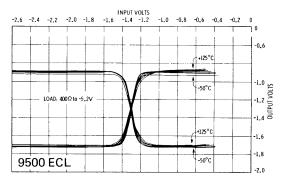

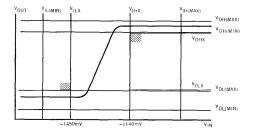

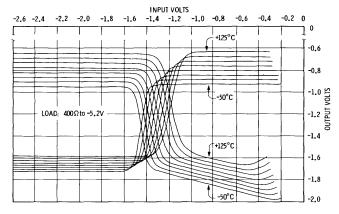

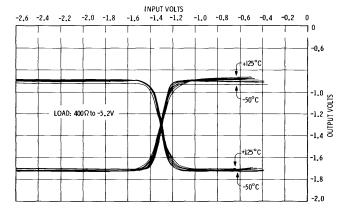

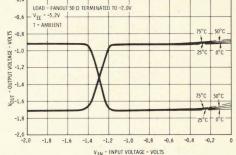

### Conventional ECL vs. 9500 Transfer Characteristics

## **PRODUCT ANNOUNCEMENT SCHEDULE**

#### AVAILABLE NOW IN QUANTITY

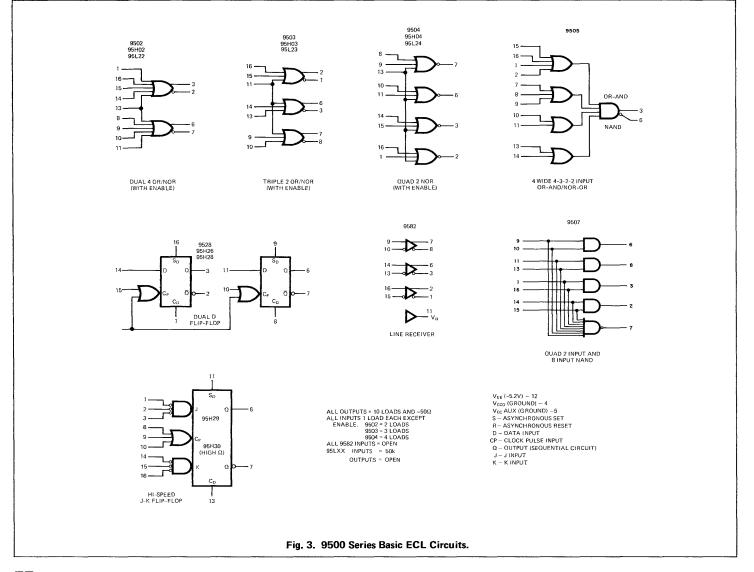

- 9502 Dual 4-Input OR/NOR Gate

- 9503 Triple 2-Input OR/NOR Gate

- 9504 Quad 2-Input NOR Gate

- 9505 Quad OR-AND Gate

- 9528 "Dual D" Flip Flop9538 3 Line/8 Line Decoder

- 9581 8-Input Multiplexer

- 9582 Multifunction Receiver/ Amplifier

- 95H90 High Speed VHF Prescaler

- 9595 Level Converter

### AVAILABLE 3RD QUARTER 1971

- 9507 Quad-AND-NAND Gate

- 95H02 High Speed 9502 (Dual 4-Input OR/NOR Gate)

- 95H03 High Speed 9503 (Triple 2-Input OR/NOR Gate)

- 95H04 High Speed 9504 (Quad 2-Input NOR Gate)

- \*95H22 High ohm option of the High Speed Dual 4-Input Gate

- 95L22 Low Power Dual Gate

- \*95H23 High ohm option of the High Speed Triple 2-Input Gate

- 95L23 Low Power Triple Gate

- \*95H24 High ohm option of the High Speed Quad 2-Input Gate 95L24 Low Power Quad Gate

- 95L24 Low Fower Quad Gate

- 95H29 High Speed J-K Flip Flop

- \*95H30 High ohm option of the High Speed J-K Flip Flop 9534 Quad Latch

- 95400 High Speed 64 Bit Scratch Pad

- 9578 Quad Exclusive-Or Gate/4–Bit Comparator

- 9579 Quad 2-Input Multiplexer

- 9580 Triple 2-Input Multiplexer

- 95H84 High Speed 2-Bit Adder/Subtractor

### AVAILABLE 4TH QUARTER 1971

- 95H00 High Speed 4-Bit Universal Register

- 95H10 High Speed Synchronous Decade Counter

- 95H16 High Speed Synchronous Binary Counter

- \*95H26 High ohm option of the High Speed Dual D Flip Flop

- 95H28 High Speed Dual D Flip Flop

- 95H39 High Speed Multiport Register

- 95H41 High Speed 4-Bit ALU

- 95H42 High Speed Carry Lookahead

- 95H55 High Speed 5-Bit Comparator

\*Special Order

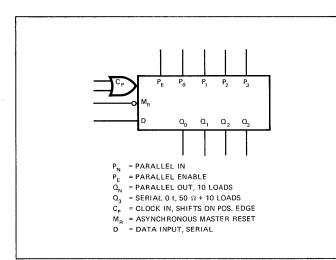

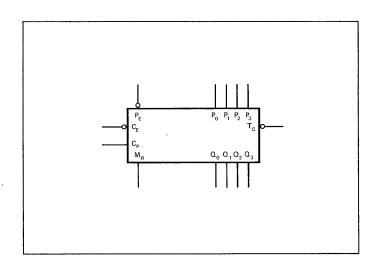

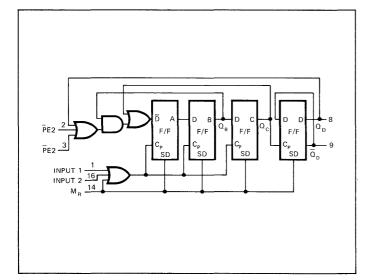

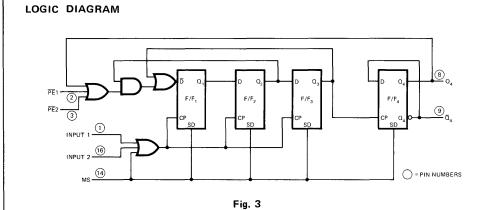

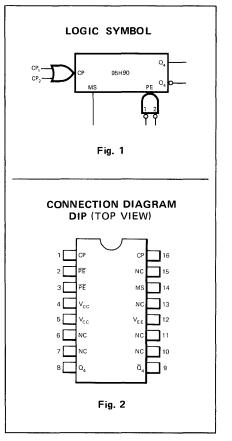

### 95H00 FOUR BIT UNIVERSAL SHIFT REGISTER

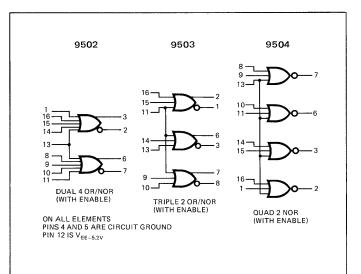

### 9502·9503·9504 BASIC GATES

**DESCRIPTION** The 95H00 is a four bit Parallel/Serial In, Parallel/ Serial Out Universal shift register. High speed ECL technology permits storage, shifting, counting and serial code conversion in excess of 150 MHz.

Features include assertion outputs on each state, overriding asynchronous master reset, serial and parallel D type inputs and a gated clock. Availability of all these features on one chip significantly improves the reliability, performance, and power consumption of high speed systems.

- HIGH SPEED . . . 150 MHz SHIFT FREQUENCY

- D TYPE INPUT IN SERIAL AND PARALLEL

- GATED CLOCK INPUT

- ASYNCHRONOUS MASTER RESET

- 50  $\Omega$  drive on Q3 output

- WIRED OR CAPABILITY

- SEPARATE CURRENT SWITCH EMITTER FOLLOWER  $V_{CC}$  PINS ELIMINATE NOISE COUPLING

- TEMPERATURE COMPENSATION

- INTERNAL PULL DOWN

- SINGLE -5.2 VOLT POWER SUPPLY

- HERMETIC CERAMIC 16 PIN DIP

- COMPLEX MULTI-GATE CHIP REDUCES PACKAGE COUNT & POWER

**DESCRIPTION** The 9502, 9503 and 9504 are temperature compensated OR/NOR Gates employing a nonsaturating current switch, emitter follower configuration to achieve high speed. The elements are intended for the design of high speed central processors, terminals, instrumentation and digital communications systems.

Input and output 2K  $\Omega$  pulldown resistors eliminate the necessity for external termination of lines up to 6-8 inches and unused logic inputs. Package pin locations are chosen to reduce internal noise generation and crosstalk.

- HIGH SPEED . . . 2.3 ns PER GATE

- SEPARATE V<sub>CC</sub> PINS ELIMINATE NOISE COUPLING

- TEMPERATURE COMPENSATION

- INTERNAL PULLDOWN RESISTORS

- COMMON ENABLE INPUTS

- LOW CROSSTALK AND NOISE GENERATION

- WIRE-OR CAPABILITY

- 50  $\Omega$  LINE DRIVING CAPABILITY

- COMPLEMENTARY OR/NOR OUTPUTS (9502, 9503)

- SINGLE -5.2V POWER SUPPLY

- HERMETIC CERAMIC 16 PIN DUAL IN-LINE PACKAGE

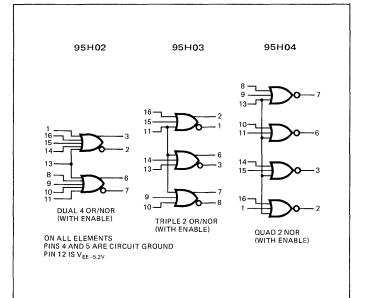

### 95H02·95H03·95H04 9505 4 WIDE **CLOCK DRIVER**/ HIGH SPEED GATES

# **OR-AND GATE**

DESCRIPTION The 95H02, H03 and H04 are temperature compensated OR/NOR Gates employing a nonsaturating current switch, emitter follower configuration to achieve a very high speed. The elements are intended for use where higher logic speeds and faster edges than standard 9500 gates are required, as in clock and flip-flop driving.

These gates will improve available speed performance of 9528 flip-flops and 9534 latches in counting and register application.

- HIGH SPEED . . . 1.6 ns PER GATE

- SEPARATE CURRENT SWITCH AND EMITTER FOLLOWER V<sub>CC</sub> PINS - ELIMINATES NOISE COUPLING

- **TEMPERATURE COMPENSATION**

- INTERNAL PULLDOWN RESISTORS •

- COMMON ENABLE INPUTS

- LOW CROSSTALK AND NOISE GENERATION

- WIRE-OR CAPABILITY

- 50  $\Omega$  LINE DRIVING CAPABILITY

- COMPLEMENTARY OR/NOR OUTPUTS (95H02, H03)

- SINGLE -5.2V POWER SUPPLY

- HERMETIC CERAMIC 16 PIN DUAL IN-LINE PACKAGE .

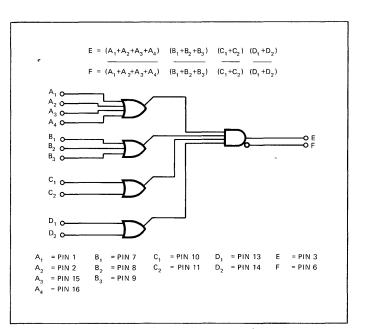

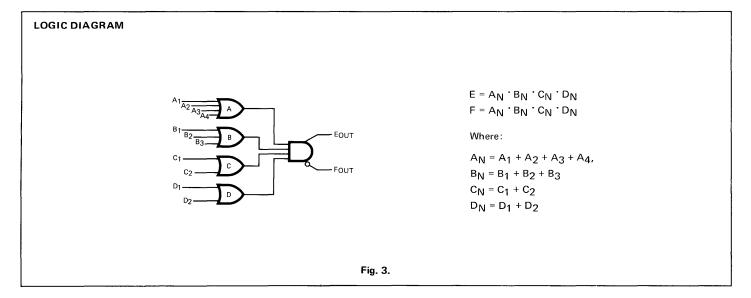

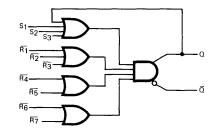

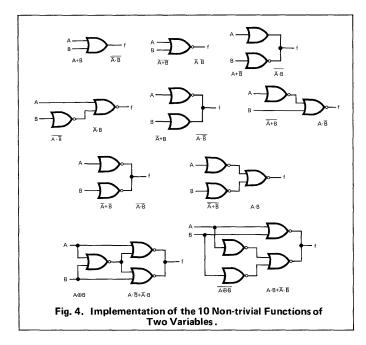

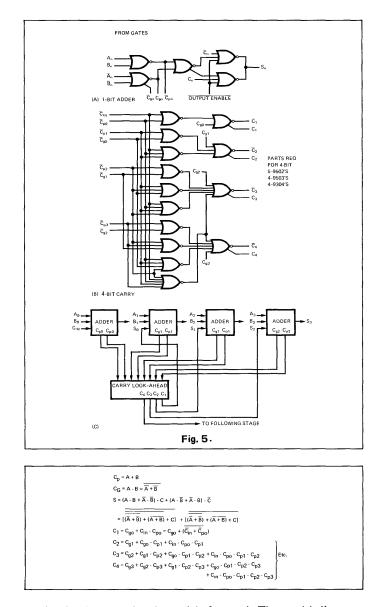

DESCRIPTION The 9505 is a temperature compensated OR-AND gate that achieves in slightly over one basic gate delay the AND of four different OR'ed functions.

The NOR outputs of the four OR gates are OR'ed to derive the OR-NOR function.

This element is useful in the design of Arithmetic Logic Units for construction of adders, subtracters, multipliers etc. Just two 9505's will implement a full carry adder function,

- HIGH SPEED . . . 2.7 ns OR-AND, 2.5 ns NOR-OR

- SEPARATE CURRENT SWITCH & EMITTER FOLLOWER  $\mathsf{V}_{\mathsf{CC}}$ . PINS - ELIMINATES NOISE COUPLING

- **TEMPERATURE COMPENSATED**

- INTERNAL 2K PULL DOWN RESISTORS

- COMPLEX LOGIC FUNCTION REDUCES PACKAGE COUNT

- WIRE OR CAPABILITY

- 50  $\Omega$  LINE DRIVING CAPABILITY

- SINGLE -5.2V POWER SUPPLY

- HERMETIC CERAMIC 16 PIN DUAL IN-LINE PACKAGE

## 9507 QUAD AND/NAND

### 95H10 MSI BCD DECADE COUNTER

**DESCRIPTION** The 9507 is a Temperature Compensated Quad EC $\mu$ L AND gate using series gating and collector and emitter dotting to achieve the logical functions within approximately one gate delay.

The uses are for any logical AND or 8 input NAND function with higher speed than similar logic implemented with standard gates. This element is designed to increase speed and reduce package count in high performance processors and controllers.

- HIGH SPEED . . . 2.6 ns PER GATE

- 8 INPUT LOGIC NAND IN ONE GATE DELAY

- SEPARATE NON-STANDARD ECL LOGIC FUNCTIONS --4 DUAL AND GATES

- HIGHER SYSTEM RELIABILITY AND LOWER COST BY ELIM-INATING COMPLEX WIRING OF OR/NOR GATES

- SEPARATE CURRENT SWITCH & EMITTER FOLLOWER  $\mathsf{V}_{\mathsf{CC}}$  PINS

- TEMPERATURE COMPENSATION

- INTERNAL PULLDOWN RESISTORS

- LOW CROSSTALK AND NOISE GENERATION

- WIRE OR CAPABILITY

- 50  $\Omega$  LINE DRIVING CAPABILITY

- SINGLE -5.2V POWER SUPPLY

- HERMETIC CERAMIC 16 PIN DIP

**DESCRIPTION** The 95H10 is a high speed synchronously presettable 8421 BCD decade counter. It is a synchronously presettable, multifunction MSI building block useful for a large number of counting, digital integration, and conversion applications. Up to 9 decades can be cascaded with no speed degradation using the standard 9500 gates. With 95H00 gates a multidecade synchronous load counter to over 150 MHz can be built. Typical counter frequency is over 180 MHz or easy frequency increase to over 250 MHz with the 95H29 JK Flip Flop.

Features include assertion inputs and outputs on each of the 4 master slave counting flip flop. Terminal count is generated internally in a manner that allows synchronous loading at nearly the speed of the basic counter. When the parallel load feature is not needed, the CE input may be used as a clock gate regardless of clock input level. Availability of all these features on one chip significantly improves the reliability, performance and power consumption of high speed systems.

- HIGH SPEED COUNT . . . 180 MHz TYPICAL COUNT FREQUENCY

- HIGH SPEED SYNCHRONOUSLY LOAD . . . OVER 150 MHz SYNCHRONOUS LOAD FREQUENCY

- INTERNAL COUNT ENABLE

- EXPANDABLE TO OVER 250 MHz WITH THE 95H29

- ASYNCHRONOUS MASTER RESET

- 50  $\Omega$  or fanout of 10 on each output

- WIRE OR CAPABILITY

- SEPARATE CURRENT SWITCH EMITTER FOLLOWER  $\mathsf{V}_{\mathsf{CC}}$  PINS ELIMINATE NOISE COUPLING

- **TEMPERATURE COMPENSATION**

- INTERNAL PULLDOWN FOR DIRECT LOW COST WIRING

- SINGLE -5.2 VOLT POWER SUPPLY

- HERMETIC CERAMIC 16 PIN DIP

- COMPLEX MULTI-GATE CHIP REDUCES PACKAGE COUNT AND POWER

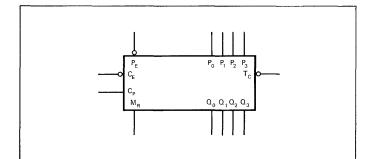

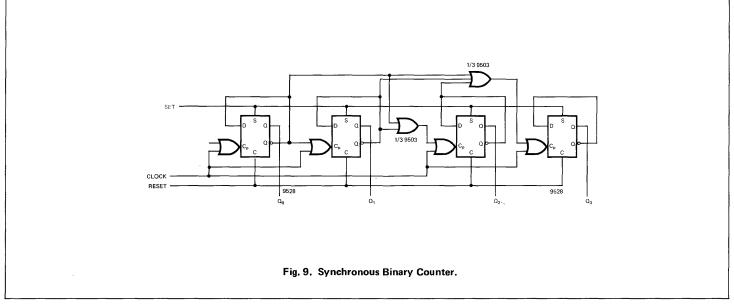

### 95H16 MSI 4-BIT **BINARY COUNTER**

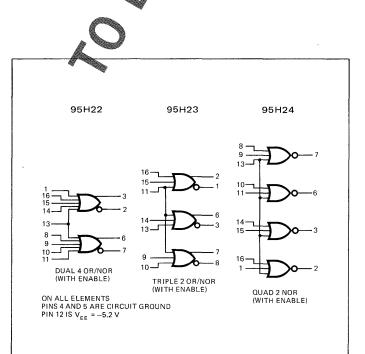

### 95H22·95H23·95H24 **CLOCK DRIVER**/ HIGH SPEED GATES

**DESCRIPTION** The 95H16 is a high speed synchronously presettable 4-Bit Binary counter. It is a synchronously presettable, multifunction MSI building block useful for a large number of counting, digital, integration, and conversion applications. Up to 9 devices can be cascaded with no speed degradation using the standard 9500 gates. With 95H00 gates a multidecade synchronous load counter to over 150 MHz can be built, Typical count frequency is over 180 MHz or easy frequency increase to over 250 MHz with the 95H29 JK Flip Flop.

Features include assertion inputs and outputs on each of the 4 master slave counting flip flop. Terminal count is generated internally in a manner that allows synchronous loading at nearly the speed of the basic counter. When the parallel load feature is not needed, the CE input may be used as a clock gate regardless of clock input level. Availability of all these features on one chip significantly improves the reliability, performance and power consumption of high speed systems.

- HIGH SPEED COUNT ... 180 MHz TYPICAL COUNT FREQUENCY

- HIGH SPEED SYNCHRONOUSLY LOAD . . . OVER 150 MHz SYNCHRONOUS LOAD FREQUENCY

- INTERNAL COUNT ENABLE

- EXPANDABLE TO OVER 250 MHz WITH THE 95H29

- ASYNCHRONOUS MASTER RESET

- 50  $\Omega$  or fanout of 10 on each output

- WIRE OR CAPABILITY

- SEPARATE CURRENT SWITCH EMITTER FOLLOWER VCC PINS - ELIMINATE NOISE COUPLING

- **TEMPERATURE COMPENSATION**

- INTERNAL PULLDOWN FOR DIRECT LOW COST WIRING

- SINGLE -5.2 VOLT POWER SUPPLY

- HERMETIC CERAMIC 16 PIN DIP

- COMPLEX MULTI-GATE CHIP REDUCES PACKAGE COUNT AND POWER

DESCRIPTION The 95H22, H23 and H24 are temper . comnensated OR/NOR Gates employing a nonsaturating current switch, emitter follower configuration to achieve a very high speed. The elements are intended for use where higher logic speeds and faster edges than standard 9500 gates are required, as in clock and flip-free driving.

These gates will improve available speed performance of 9528 flip-flops and 9534 latches in counting and register application.

- HIGH SPEED . . . 1.6 ns PER GA ٠

- SEPARATE CURRENT SWITCH AND EMITTER FOLLOWER V<sub>CC</sub> PINS - ELIMINATES NOISE COUPLING

- TEMPERATURE COMPENSATION

- INTERNAL 50 K  $\Omega \rm RESISTORS$  FOR GREATER FANOUT .

- COMMON ENABLE INPUTS LOW CROSSTALK AND NOTE GENERATION

- WIRE-OR CAPABILITY

- 50  $\Omega$  LINE DRIVING CAPABILITY COMPLEMENTARY OF NOR OUTPUTS (95H22, H23) SINGLE –5.2V POWER SUPPLY

- HERMETIC CERAMIC 16 PIN DUAL IN-LINE PACKAGE

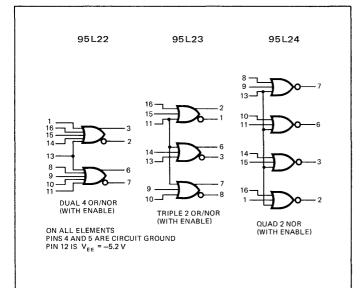

### 95L22.95L23.95L24 LOW POWER GATES

### 95H26 **VERY HIGH SPEED DUAL D FLIP-FLOP**

DESCRIPTION The 95L22, L23, and L24 are temperature compensated EC $\mu$ L OR/NOR Gates employing a non-saturating current switch, emitter follower configuration to achieve high speed. These elements are intended for use where power is to be minimized. External pulldown resistors are needed for all outputs. For longer lines series termination may be used to further reduce system power.

These gates will improve available power performance of ECL systems where speed degrading due to fanout and loading can be tolerated.

- LOW POWER . . . 20 MW PER GATE

- HIGH SPEED . . . 2.0 ns INTO 50 OHMS

- **TEMPERATURE COMPENSATION**

- . INTERNAL 50 K  $\Omega$  resistors on inputs

- COMMON ENABLE INPUTS

- 50  $\Omega$  LINE DRIVE CAPABILITY

- WIRE-OR CAPABILITY

- **PIN COMPATIBLE WITH OTHER 9500 GATES**

- SINGLE -5.2 VOLT POWER SUPPLY

- HERMETIC CERAMIC 16 PIN DUAL IN-LINE PACKAGE

DESCRIPTION The 95H26 is a high speed, temperature compensated ECµL dual D (data) flip-flop compatible with all other membra the 9500 series of EC $\mu$ L circuits. The device is versatile and pe implementation of high speed counters, registers, and control circuits.

FUNCTIONAL DESCRIPTION Each D Flip-Flop consists of both a master and a slave. While the clock is LOW the slave is eld steady, but the information on the D input is permitted to enter the master. The next clock transition from LOW to HIGH locks the master in its present state making it insensitive to the D input and connects he slave to the master causing the new information to be reflected on the outputs. Logic races are avoided by offsetting the mathematical and slave thresholds to avoid simultaneous switching when low speed enges are encountered in the system.

The internal clock is the OR of two clock muts, one common to both flip-flops. The ORed clock permits the one input as a clock pulse input and the other as an active low enable.

- 260 MHz OPERATION

- SEPARATE CURRENT SWITCH AND EMITTER FOLLOWER  $V_{\mbox{CC}}$  PINS – ELIMINATES NOISE COUPLING TEMPERATURE COMPENSATION

- INTERNAL 50 K  $\Omega$  resistors for greater fanout master-slave circuit

- SEPARATE DIRECT SET AND CLEAR INPUTS

- BOTH COMMON AND SEPARATE CLOCK INPUTS

- WIRED-OR CARABILITY ON OUTPUTS

- 50  $\Omega$  LINE DRIVING CAPABILITY

- SINGLE -52 COLT POWER SUPPLY

- HERMETIC CERAMIC 16 PIN DUAL IN-LINE PACKAGE

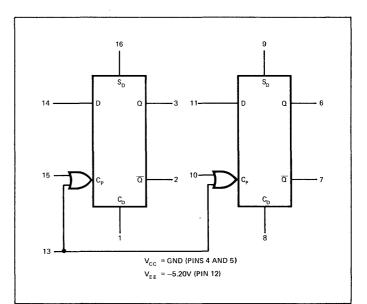

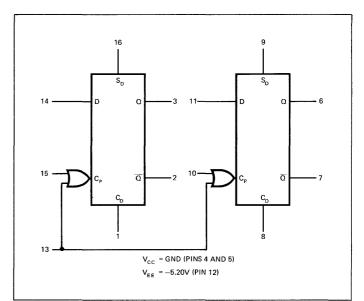

### 9528 HIGH SPEED DUAL D FLIP-FLOP

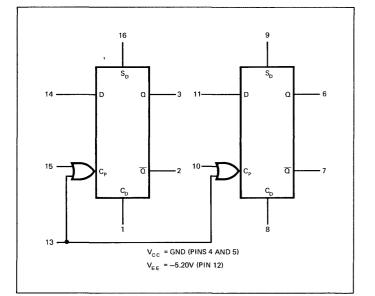

### 95H28 VERY HIGH SPEED DUAL D FLIP-FLOP

**DESCRIPTION** The 9528 is a high speed, temperature compensated EC $\mu$ L dual D (data) flip-flop compatible with all other members of the 9500 series of EC $\mu$ L circuits. The device is versatile and permits easy implementation of high speed counters, registers, and control circuits.

**FUNCTIONAL DESCRIPTION** Each D Flip-Flop consists of both a master and a slave. While the clock is LOW the slave is held steady, but the information on the D input is permitted to enter the master. The next clock transition from LOW to HIGH locks the master in its present state making it insensitive to the D input and connects the slave to the master causing the new information to be reflected on the outputs, Logic races are avoided by offsetting the master and slave thresholds to avoid simultaneous switching when low speed edges are encountered in the system.

The internal clock is the OR of two clock inputs, one common to both flip-flops. The ORed clock permits the use of one input as a clock pulse input and the other as an active low enable.

- 160 MHz OPERATION

- SEPARATE CURRENT SWITCH AND EMITTER FOLLOWER V<sub>CC</sub> PINS – ELIMINATES NOISE COUPLING

- TEMPERATURE COMPENSATION

- INTERNAL PULLDOWN RESISTORS

- MASTER-SLAVE CIRCUIT

- SEPARATE DIRECT SET AND CLEAR INPUTS

- BOTH COMMON AND SEPARATE CLOCK INPUTS

- WIRED-OR CAPABILITY ON OUTPUTS

- 50  $\Omega$  LINE DRIVING CAPABILITY

- SINGLE -5.2 VOLT POWER SUPPLY

- HERMETIC CERAMIC 16 PIN DUAL IN-LINE PACKAGE

**DESCRIPTION** The 95H28 is a high speed, temperature compensated EC $\mu$ L dual D (data) flip-flop compatible with all other members of the 9500 series of EC $\mu$ L circuits. The device is versatile and permits easy implementation of high speed counters, registers, and control circuits.

**FUNCTIONAL DESCRIPTION** Each D Flip-Flop consists of both a master and a slave. While the clock is LOW the slave is held steady, but the information on the D input is permitted to enter the master. The next clock transition from LOW to HIGH locks the master in its present state making it insensitive to the D input and connects the slave to the master causing the new information to be reflected on the outputs. Logic races are avoided by offsetting the master and slave thresholds to avoid simultaneous switching when low speed edges are encountered in the system.

The internal clock is the OR of two clock inputs, one common to both flip-flops. The ORed clock permits the use of one input as a clock pulse input and the other as an active low enable.

- 260 MHz OPERATION

- SEPARATE CURRENT SWITCH AND EMITTER FOLLOWER  $V_{CC}\ \text{PINS}\ -$  ELIMINATES NOISE COUPLING

- TEMPERATURE COMPENSATION

- INTERNAL PULLDOWN RESISTORS

- MASTER-SLAVE CIRCUIT

- SEPARATE DIRECT SET AND CLEAR INPUTS

- BOTH COMMON AND SEPARATE CLOCK INPUTS

- WIRED-OR CAPABILITY ON OUTPUTS

- 50  $\Omega$  LINE DRIVING CAPABILITY

- SINGLE -5.2 VOLT POWER SUPPLY

- HERMETIC CERAMIC 16 PIN DUAL IN-LINE PACKAGE

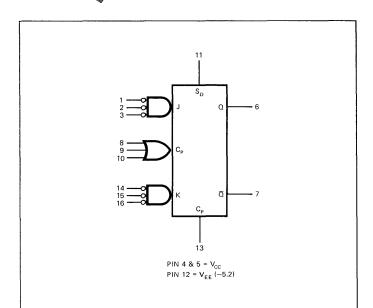

# 95H29 VERY HIGH 95H30 VERY HIGH SPEED J-K FLIP-FLOP SPEED J-K FLIP-FLOP

**DESCRIPTION** The 95H29 is a Hi-Speed edge-triggered  $\overline{J}$  K Master-Slave flip-flop with both direct set and clear inputs. The  $\overline{J}$ ,  $\overline{K}$  and Clock functions are the active low AND of three inputs. With these inputs this device may be used effectively in counters, registers and other applications where data must be stored or shifted at a high rate.

In addition the full frequency range may be used effectively as a prescaler and controlled divider for frequencies up to 250 MHz.

- 250 MHz OPERATION

- ASYNCHRONOUS DIRECT SET AND CLEAR

- MASTER-SLAVE CIRCUIT

- NON-ONES CATCHING .

- SEPARATE CURRENT SWITCH & EMITTER FOLLOWER • V<sub>CC</sub> PINS

- J AND K INPUTS

- INTERNAL PULLDOWN RESISTORS

- WIRED-OR CAPABILITY ON OUTPUTS •

- 50  $\Omega$  LINE DRIVING CAPABILITY .

- **TEMPERATURE COMPENSATION** ٠

- SINGLE -5.2 VOLT POWER SUPPLY •

- HERMETIC CERAMIC 16 PIN DIP

DESCRIPTION The 95H30 is a Hi-Speed edge-tragered K Master-Slave flip-flop with both direct set and clear inputs. The  $\overline{K}$  and Clock functions are the active low AND of three inputs. With these inputs this device may be used effectively in counters, registers and other applications where data must be stored or shifted at a high rate.

In addition the full frequency range m ed effectively as a prescaler and controlled divider for freque jes ᠾ to 250 MHz.

- **250 MHz OPERATION**

- ASYNCHRONOUS DIRECT ST D CLEAR

- MASTER-SLAVE CIRCUIT

- NON-ONES CATCHING

- SEPARATE CURRENT SWITCH & EMITTER FOLLOWER V<sub>CC</sub> PINS

- **J** AND **K** INPUTS

- INTERNAL 50K  $\Omega$  (NPUT RESISTORS FOR GREATER FANOUT

- WIRED-OR CAPABILITY ON OUTPUTS 50  $\Omega$  LINE DRIVING CAPABILITY

- TEMPERATURE COMPENSATION

- SINGLE 2 VOLT POWER SUPPLY

- SERAMIC 16 PIN DIP HERMETIC

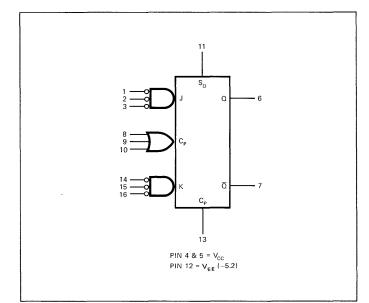

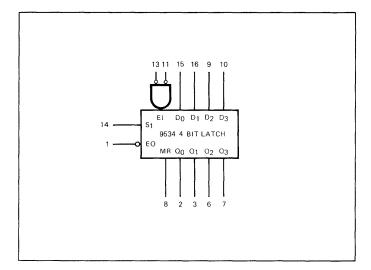

### 9534 QUAD LATCH WITH INPUT AND OUTPUT ENABLES

### 9538 OCTAL DECODE-3 LINE/8 LINE

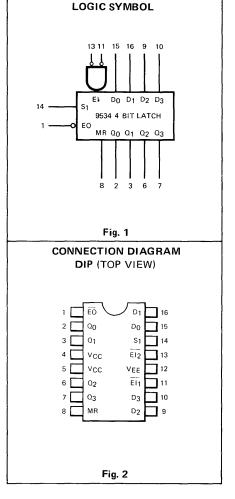

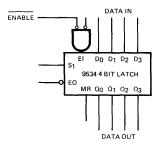

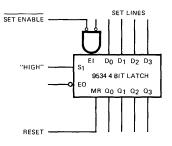

**DESCRIPTION** The 9534 quad D latch will store four bits of information simultaneously. Two Input enable inputs and a common output enable allow maximum logic flexibility. A common Select input selects 'D' type or 'Set' type of operation. A common reset clears the device so that the 1's catching feature may be used when desired.

This element is designed as a storage buffer for high speed registers in arithmetic logic units and parallel-serial conversion in communication systems.

- HIGH SPEED . . . 4.3 ns TYPICAL DATA DELAYS 'S

- COMMON LATCH ENABLE

- COMMON MASTER RESET

- COMMON SELECT FOR 'D' OR 'SET'

- COMPLEX MULTIGATE CHIP REDUCES PACKAGE COUNT

- EASILY EXPANDED TO LARGE HIGH SPEED MEMORY

- WIRED-OR CAPABILITY

- SEPARATE CURRENT SWITCH AND EMITTER FOLLOWER V<sub>CC</sub> PINS – ELIMINATES NOISE COUPLING

- TEMPERATURE COMPENSATION

- INTERNAL PULLDOWN

- 50  $\Omega$  LINE DRIVE CAPABILITY

- SINGLE -5.2 VOLT POWER SUPPLY

- HERMETIC CERAMIC 16 PIN DIP

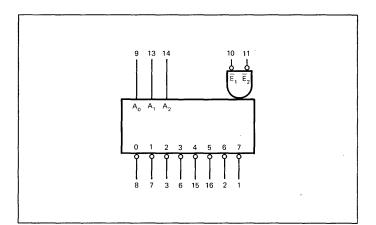

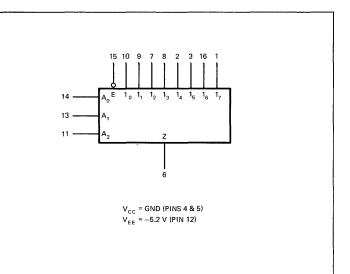

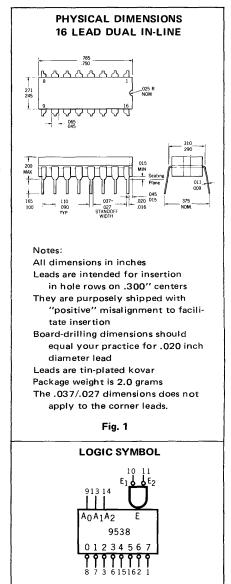

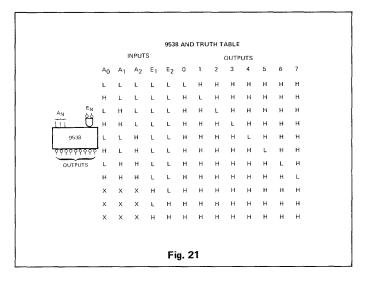

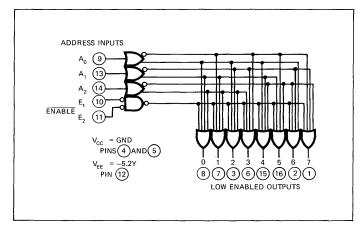

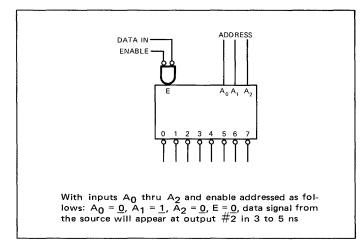

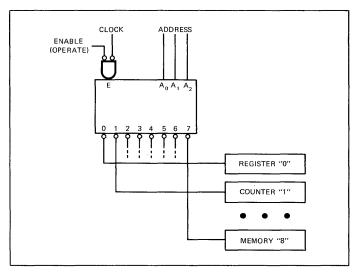

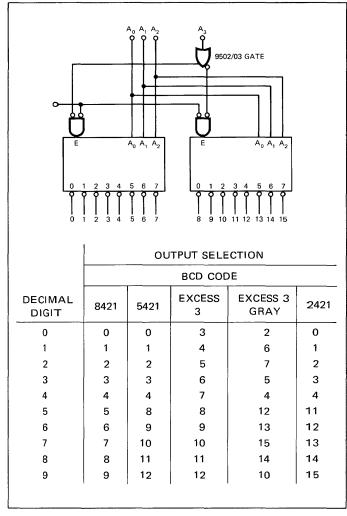

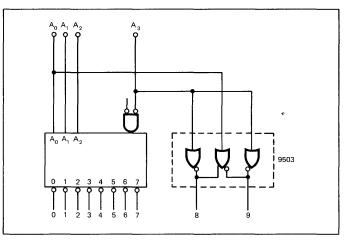

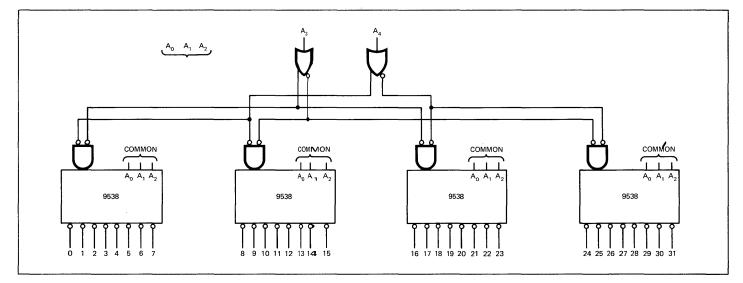

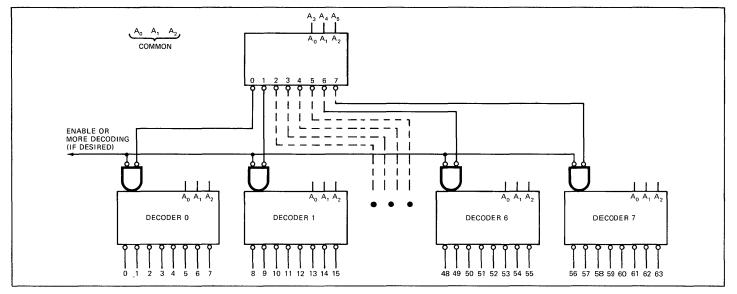

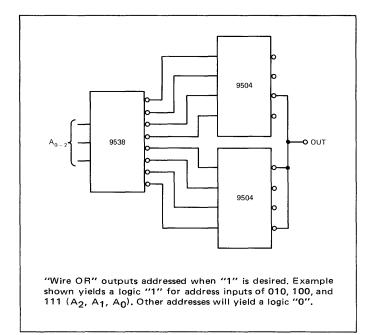

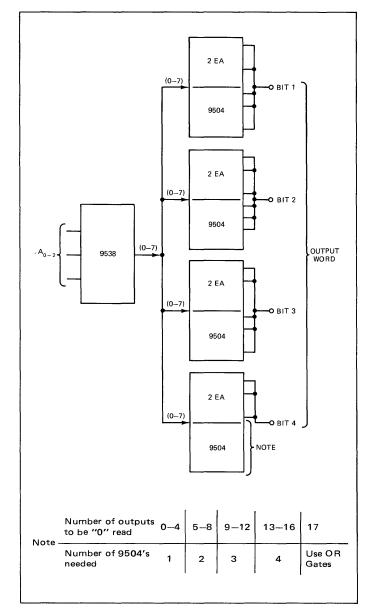

**DESCRIPTION** The 9538 decoder accepts three binary address inputs and under control of the enables activate one of the eight active low outputs. Both enables must be low for any output to go low.

The ECL 9538 may be used as a demultiplexer by connecting a data source to one of the enable inputs. The other enable input will function as a data enable line while inputs  $A_0$ ,  $A_1$ , and  $A_2$  select the desired data output line (0 through 7).

The 9538 is particularly useful in memory expansion and register or peripheral selection applications.

- HIGH SPEED . . . 4 ns FROM ADDRESS TO OUTPUT

- USEABLE FOR DEMULTIPLEXING 2 ENABLE INPUTS

- OUTPUTS ACTIVE LOW FOR ENABLING WITH OTHER MEMBERS OF THE 9500 FAMILY

- NO INVERSION FROM ENABLE TO SELECTED OUTPUT

- WIRED-OR CAPABILITY

- SEPARATE CURRENT SWITCH EMITTER FOLLOWER V<sub>CC</sub> PINS – ELIMINATE NOISE COUPLING

- TEMPERATURE COMPENSATION

- INTERNAL PULL DOWN

- 50  $\Omega$  LINE DRIVE CAPABILITY

- SINGLE -5.2 VOLT POWER SUPPLY

- HERMETIC CERAMIC 16 PIN DIP

- COMPLEX MULTI-GATE CHIP REDUCES PACKAGE COUNT & POWER

### 95H41 MSI 4 BIT ALU 95H55 MSI 5 BIT 95H42 MSI CARRY LOOKAHEAD UNIT

## COMPARATOR WITH **ENABLE**

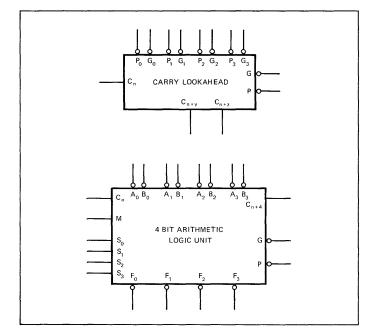

DESCRIPTION The 95H41 is a 4 Bit High Speed Arithmetic Logic Unit (ALU) which can perform all the possible 16 logic operations on two variables and a variety of arithmetic operations; the Add and Subtract modes being the most important. This ALU is ideally suited for mini-computers, data processors, peripheral systems, and instrument systems. The functions found in the successful TTL 9341/54181 have been used to define this ECL/MSI. Although not as fast as the 95H84 2 Bit Adder/Subtractor the multiple functions permit reduced package count for the multiple function applications.

Features include: All 16 operations of two variables - Exclusive OR, Comparator, AND, NAND, OR, NOR, plus ten other logic operations. The experience gained from use of the TTL equivalent can be directly applied to this high speed ECL MSI. The 95H42 is the Carry Lookahead Generator.

- . HIGH SPEED . . . TYPICAL 4 BIT ADD OF 5 ns

- COMPLEX MULTIFUNCTION CHIP REDUCES PACKAGE AND POWER REQUIREMENTS

- 50  $\Omega$  or fanout of 10 on each output

- WIRE-OR CAPABILITY

- SEPARATE CURRENT SWITCH, EMITTER FOLLOWER VCC PINS - ELIMINATE NOISE COUPLING

- **TEMPERATURE COMPENSATION**

- INTERNAL PULLDOWN FOR DIRECT LOW COST WIRING

- SINGLE -5.2 VOLT SUPPLY

- **HERMETIC CERAMIC 24 PIN DIP**

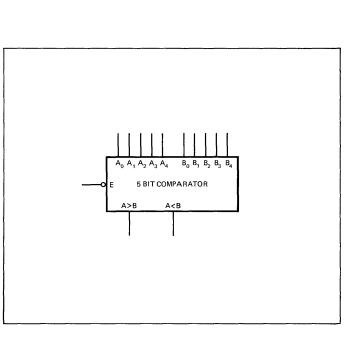

DESCRIPTION The 95H55 is a high speed expandable 5 Bit Comparator which provides comparisons between two 5 bit words and gives two outputs, "Less Than" and "Greater Than", "Equal To" can be obtained by ORing the "Less Than" and "Greater Than" outputs. A high level on the Enable function forces both outputs low.

Features include easy expansion to larger word comparisons and very high speed operation. Experience gained in use of the TTL 9324 can be directly applied to the 95H55.

- HIGH SPEED . . . 1.0 ns INTERNAL GATE DELAYS

- "GREATER THAN" AND "LESS THAN" IN ONE DEVICE

- OUTPUT ENABLE INPUT IS ACTIVE LOW FOR EASE OF USE WITH OTHER MEMBERS OF THE 9500 FAMILY

- WIRE-OR CAPABILITY

- 50  $\Omega$  or fanout of 10 on each output

- SEPARATE CURRENT SWITCH EMITTER FOLLOWER V<sub>CC</sub> PINS - ELIMINATE NOISE COUPLING

- **TEMPERATURE COMPENSATED**

- INTERNAL PULLDOWN RESISTORS FOR DIRECT LOW COST WIRING

- SINGLE -5.2 VOLT POWER SUPPLY

- **HERMETIC CERAMIC 16 PIN DIP**

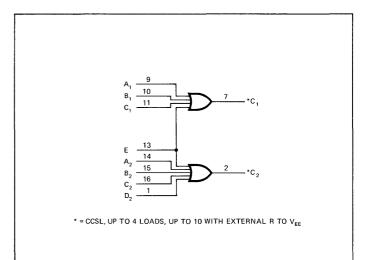

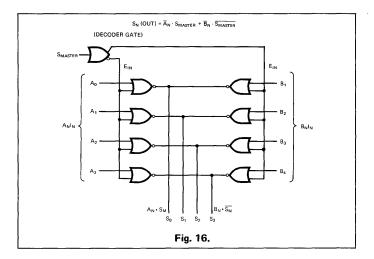

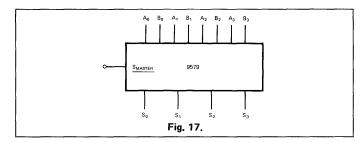

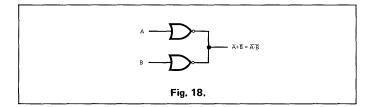

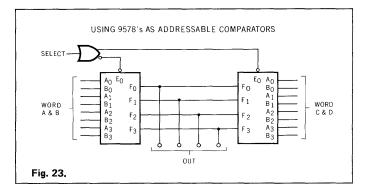

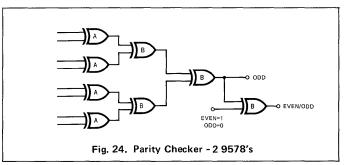

### 9578 QUAD EXCLUSIVE - OR WITH ENABLE, 4 BIT COMPARATOR

### 9579 QUAD 2 INPUT MULTIPLEXER WITH COMMON SELECT

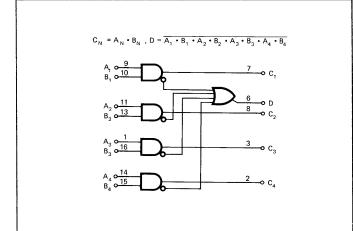

**DESCRIPTION** The 9578 provides four exclusive OR gates in one package using internal gating to achieve the logic function within approximately one gate delay. An additional enable gate is included so that all outputs may be held low if desired. With four of these devices a 16 bit compare function may be built with one gate delay. This element is useful in many applications such as data comparison, parity generation and checking, frequency mixing, decision and code conversion, etc.

- HIGH SPEED . . . 3.0 ns FOR EX-OR

- COMMON ENABLE

- WIRED OR CAPABILITY

- SEPARATE CURRENT SWITCH EMITTER FOLLOWER V<sub>CC</sub>PINS – ELIMINATE NOISE COUPLING

- TEMPERATURE COMPENSATION

- INTERNAL PULLDOWN

- 50  $\Omega$  LINE DRIVE CAPABILITY

- SINGLE -5.2 VOLT POWER SUPPLY

- HERMETIC CERAMIC 16 PIN DIP

- COMPLEX MULTI-GATE CHIP REDUCES PACKAGE COUNT & POWER

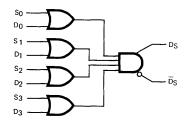

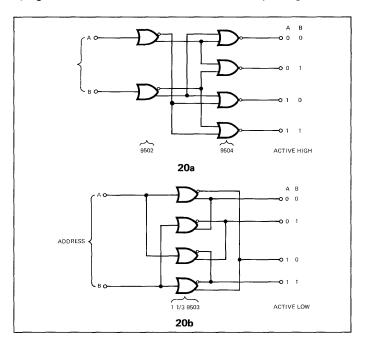

**DESCRIPTION** The 9579 is a Temperature Compensated logic equivalent of a 4 pole -2 position switch. It will select logically one of two groups of 4 data sources with a common select line. This high speed switch operates within about one 9500 gate delay and provides a significant increase in reliability and power savings by delivering this function in one 16 pin package.

- HI-SPEED . . . 3.0 ns FROM SELECT TO OUTPUT

- COMMON SELECT

- WIRED OR CAPABILITY

- SEPARATE CURRENTSWITCH EMITTER FOLLOWER V<sub>CC</sub>PINS – ELIMINATE NOISE COUPLING

- TEMPERATURE COMPENSATION

- INTERNAL PULL DOWN

- 50  $\Omega$  LINE DRIVE CAPABILITY

- SINGLE -5.2 VOLT POWER SUPPLY

- HERMETIC CERAMIC 16 PIN DIP

- COMPLEX MULTI-GATE CHIP REDUCES PACKAGE COUNT & POWER

### 9580 TRIPLE 2 INPUT 9581 MULTIPLEXER WITH 1 OF COMMON ENABLE

## 9581 1 OF 8 MULTIPLEXER

**DESCRIPTION** The 9580 multiplexer is the logic equivalent of 3 single pole, two position switches.

By the use of the separate select lines the 9580 may be interconnected as a 4 input multiplexer.

The output Enable function allows ease of expansion into more complex elements by use of the wired OR feature. For example with the additional use of a standard gate two 9580's will expand into a triple 4 input multiplexer, useful in register and peripheral applications.

- HIGH SPEED . . . 3.0 ns FROM SELECT TO OUTPUT

- SEPARATE SELECTS

- COMMON ENABLE

- INTERCONNECTS TO 4 INPUT MULTIPLEXER

- WIRED OR CAPABILITY

- SEPARATE CURRENT SWITCH EMITTER FOLLOWER V<sub>CC</sub> PINS - ELIMINATE NOISE COUPLING

- TEMPERATURE COMPENSATION

- INTERNAL PULL DOWN

- 50  $\Omega$  LINE DRIVER CAPABILITY

- SINGLE -5.2 VOLT POWER SUPPLY

- HERMETIC CERAMIC 16 PIN DIP

- COMPLEX MULTI-GATE CHIP REDUCES PACKAGE COUNT & POWER

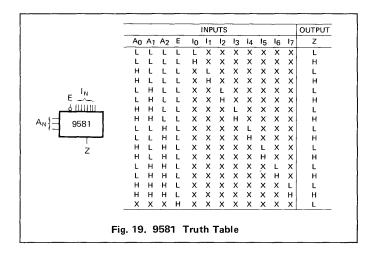

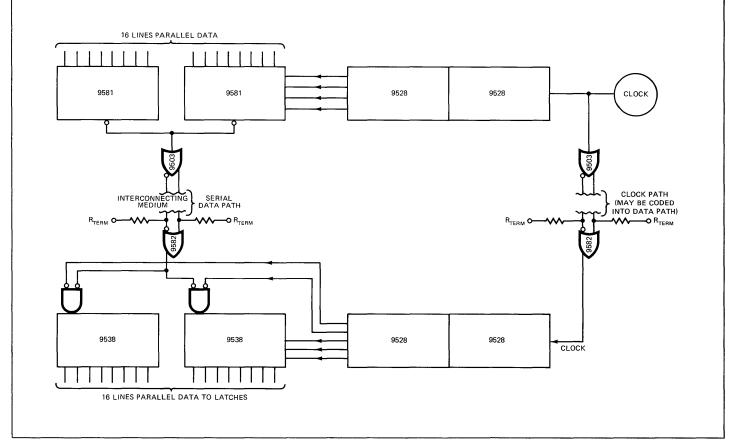

**DESCRIPTION** The 9581 eight input multiplexer is fundamentally a high speed semiconductor implementation of a single-pole eight-position switch. Three address lines select one out of the eight data inputs and feed this input to the output (Z). An active low enable forces the output LOW if held HIGH.

The 9581 provides the ability to select from or sequence eight data sources. It may therefore be used as a parallel to serial converter by sequentially advancing through the input address combinations.

The device may also be used as a universal logic element capable of generating any function of four variables by proper manipulation of the inputs. The wire-ORable outputs and the input enable permit easy expansion of several 9581's to form multiplexers with more than eight inputs.

- HIGH SPEED . . . 3.2 ns DATA

- ACTIVE LOW ENABLE INTERFACES WITH OTHER MEMBERS OF THE LINE

- PARALLEL TO SERIAL CONVERTER

- WIRED OR CAPABILITY

- SEPARATE CURRENT SWITCH EMITTER FOLLOWER V<sub>CC</sub> PINS — ELIMINATE NOISE COUPLING

- TEMPERATURE COMPENSATION

- INTERNAL PULL DOWN

- 50  $\Omega$  LINE DRIVE CAPABILITY

- SINGLE –5.2 VOLT POWER SUPPLY

- HERMETIC CERAMIC 16 PIN DIP

- COMPLEX MULTI-GATE CHIP REDUCES PACKAGE COUNT & POWER

### 9582 MULTI-FUNCTION 95H84 2 BIT LINE RECEIVER/ AMPLIFIER

# ADDER/SUBTRACTOR

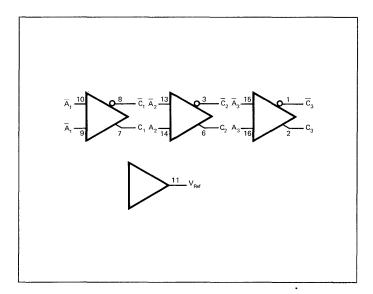

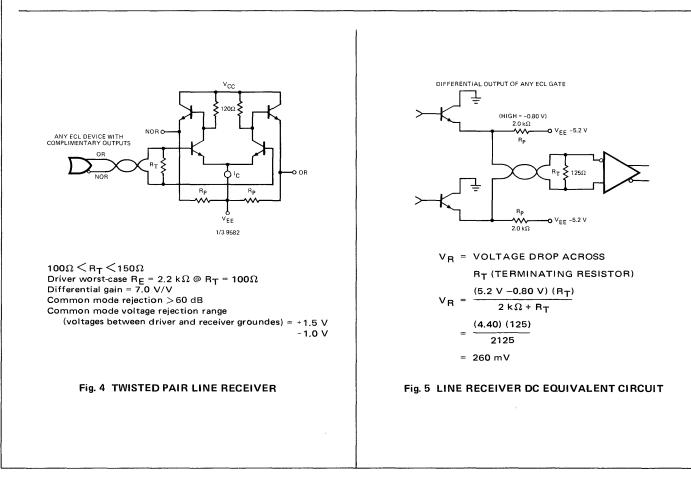

**DESCRIPTION** The 9582 is 3 differential input amplifiers. Both the true and complement outputs are temperature compensated to be compatible with other ECL 9500 products. With appropriate connection of the base pins the device will function as a differential line receiver; Schmitt trigger; high speed comparator; broad band video, IF. or R.F. amplifier; or oscillator,  $V_{\text{ref}}$  is made available to allow use of this device as a high input impedance buffer gate.

- DIFFERENTIAL INPUT .

- . TRUE AND COMPLEMENT OUTPUT

- HIGH INPUT IMPEDANCE .

- HIGH SPEED . . . 3.0 ns

- **OUTPUTS PRE-LOADED WITH 2K**

- . WIRED OR CAPABILITY

- SEPARATE CURRENT SWITCH EMITTER FOLLOWER V<sub>CC</sub> PINS • - ELIMINATE NOISE COUPLING

- **TEMPERATURE COMPENSATION**

- . 50  $\Omega$  LINE DRIVER CAPABILITY

- . SINGLE -- 5.2 VOLT POWER SUPPLY

- **HERMETIC CERAMIC 16 PIN DIP**

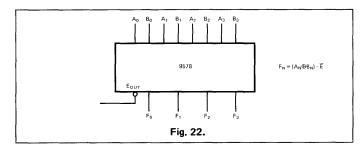

**DESCRIPTION** Performs addition and subtraction on two bits with full internal carry look ahead expandable between units. No additional carry look ahead unit is required. Can be implemented to add or subtract 2 64 bit words within 20 nsec at a power comparable to a TTL adder with carry look ahead units.

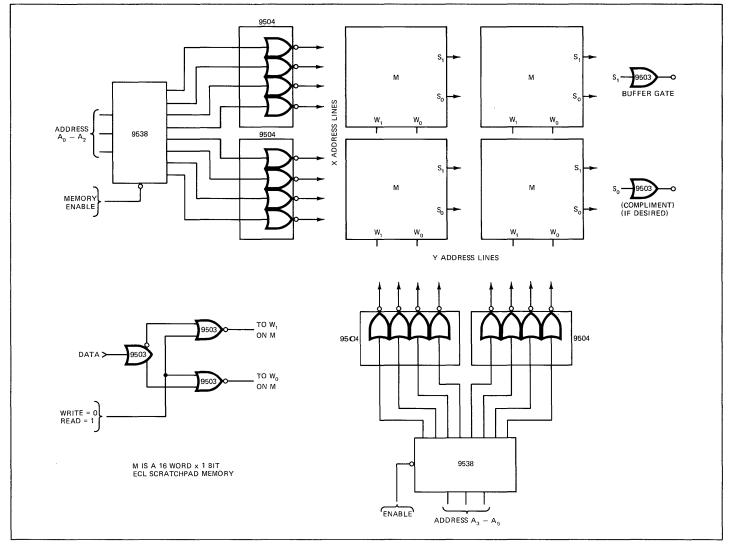

An arithmetic logic unit using 95H84 for adders, 9528 and 34 for registers and a scratchpad memory of 9538 and 95H40 could effectively process 32 bit words at a 40 MHz clock rate using a multiphase clocking scheme

- HIGH SPEED . . . 1.5 ns INTERNAL GATE DELAYS

- ADDS AND SUBTRACTS WITH ONE DEVICE

- INTERNAL CARRY LOOKAHEAD

- WIRED OR CAPABILITY

- SEPARATE CURRENT SWITCH EMITTER FOLLOWER V<sub>CC</sub> PINS - ELIMINATE NOISE COUPLING

- **TEMPERATURE COMPENSATION**

- INTERNAL PULL DOWN

- 50  $\Omega$  LINE DRIVE CAPABILITY

- SINGLE -5.2 VOLT POWER SUPPLY

- **HERMETIC CERAMIC 16 PIN DIP**

- COMPLEX MULTI-GATE CHIP REDUCES PACKAGE COUNT & POWER

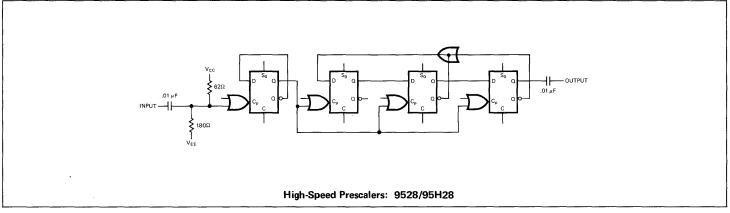

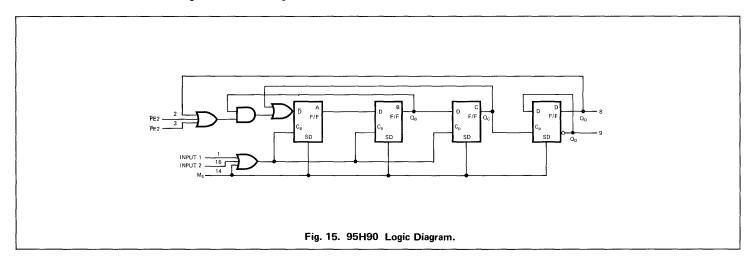

### 95H90 VHF PRESCALER ÷ 10/11

### 9595 DUAL ECL/TTL CONVERTER

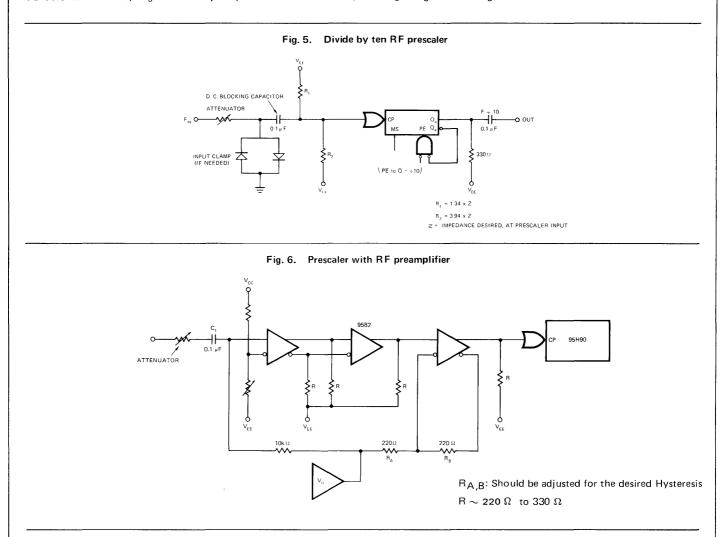

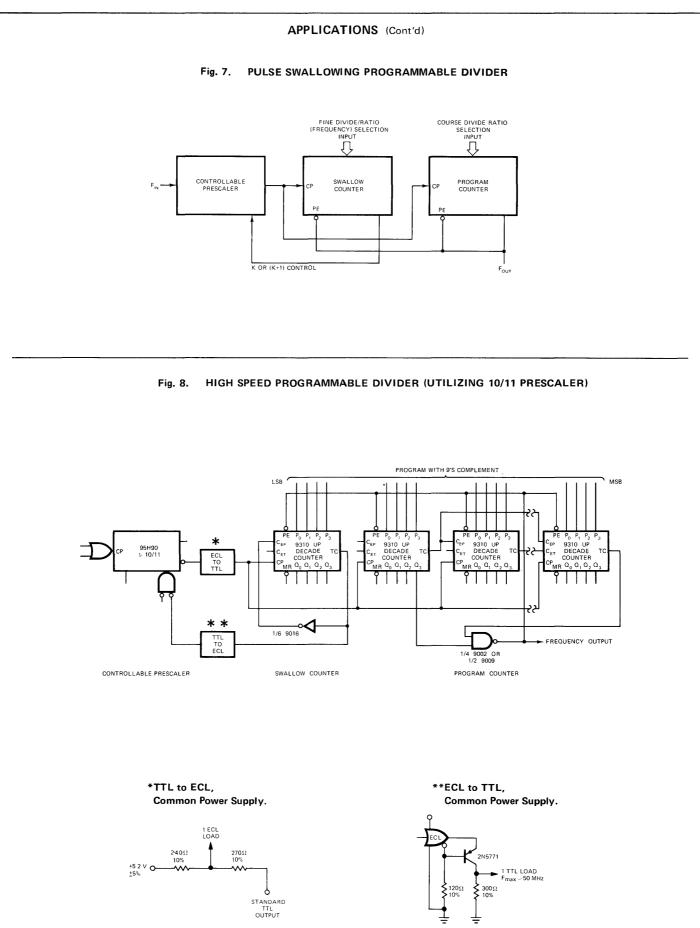

**DESCRIPTION** The 95H90 prescaler is a high speed ECL MSI designed specifically for the communication and instrumentation manufacturer. In its simplest use it will divide any clock frequency up to 250 MHz, by 10. By using the 9590 with other control logic a divide by 10/11 logic control element allows a divide by "N" counter to be constructed with a max frequency over 250 MHz.

By keeping all the high speed logic manipulation "on chip", a dramatic decrease in power and increase in reliability and wire-ability are made available at much lower cost than a comparable SSI function.

- HIGH SPEED . . . 300 MHz

- ÷10/11 ENABLE

- HIGH SPEED RESET

- WIRED OR CAPABILITY

- SEPARATE CURRENTSWITCH EMITTER FOLLOWER V<sub>CC</sub> PINS ELIMINATE NOISE COUPLING

- TEMPERATURE COMPENSATION

- INTERNAL PULL DOWN

- 50  $\Omega$  LINE DRIVE CAPABILITY

- SINGLE –5.2 VOLT POWER SUPPLY

- HERMETIC CERAMIC 16 PIN DIP

- COMPLEX MULTI-GATE CHIP REDUCES PACKAGE COUNT & POWER

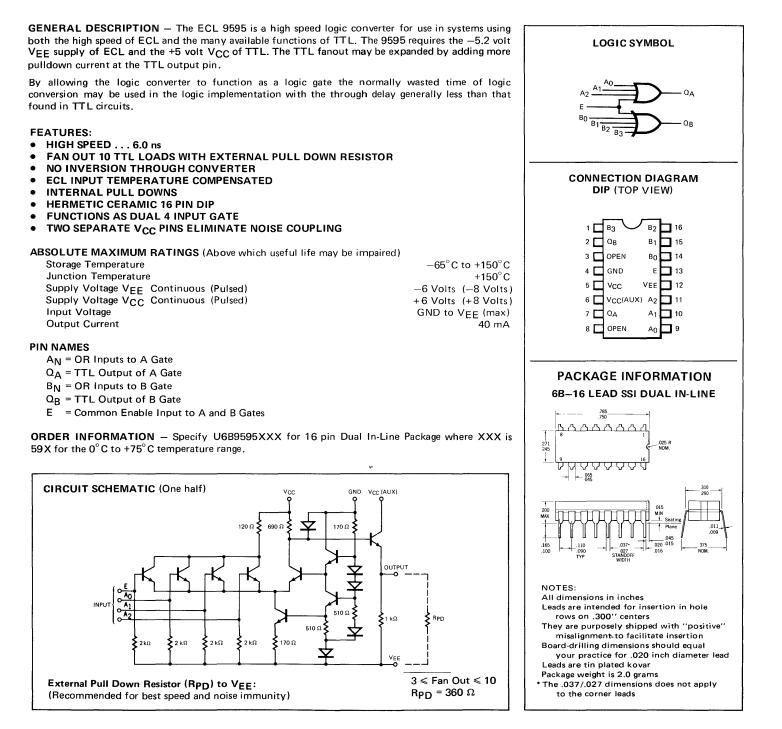

**DESCRIPTION** The 9595 is a high speed logic converter for use in systems using both the high speed of ECL and the many available functions of TTL. The 9595 requires the -5.2 volt V<sub>EE</sub> supply of ECµL and the +5 volt V<sub>CC</sub> of TTL. The TTL fanout of 4 may be expanded by adding more pulldown current at the TTL output pin.

By allowing the logic converter to function as a logic gate the normally wasted time of logic conversion may be used in the logic implementation with the through delay generally less than that found in TTL circuits.

- HIGH SPEED . . . 6 ns

- FAN OUT 10

- NO INVERSION THROUGH CONVERTER

- ECL INPUT TEMPERATURE COMPENSATED

- INTERNAL PULL DOWNS

- HERMETIC CERAMIC 16 PIN DIP

- FUNCTIONS AS DUAL 2 INPUT GATE

- MULTIPLE LOGIC GATE CAPABILITY

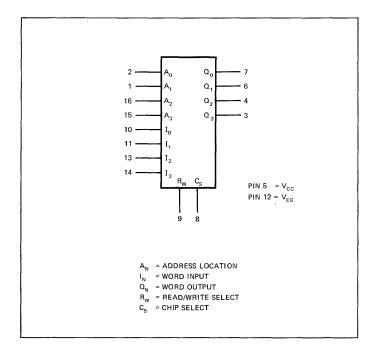

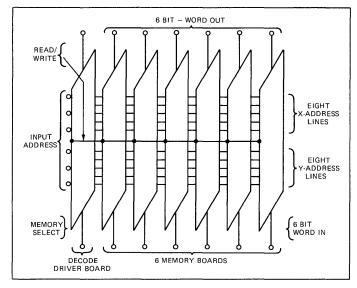

### 95400 64 BIT MEMORY

**DESCRIPTION** The 95400 is a very high speed 64 bit memory organized 16 words by 4 bits. Internal decoding is employed with the 16 words selected through four address lines. A chip select input, read/ write control line, and OR-tieable outputs are also provided.

The 16x4 organization was chosen as optimum for small high speed scratchpad applications. For word capacities in excess of 16, the 9538 decoder will permit expansion with very little decrease in overall speed.

- HIGH SPEED . . . 12 ns ACCESS TIME

- LARGE CAPACITY 64 BITS

- OPTIMIZED FOR SMALL WORDS 16 x 4

- HIGH SPEED CHIP ENABLE FOR EASE OF EXPANSION

- WIRED-OR CAPABILITY

- **TEMPERATURE COMPENSATION**

- ALL INPUTS AND OUTPUTS OPEN FOR EASE OF EXPANSION

- 50  $\Omega$  LINE DRIVE CAPABILITY

- SINGLE -5.2 VOLT POWER SUPPLY

- HERMETIC CERAMIC 16 PIN DIP

- COMPLEX MULTI-GATE CHIP REDUCES PACKAGE COUNT & POWER

### 95401 16 BIT SCRATCHPAD MEMORY

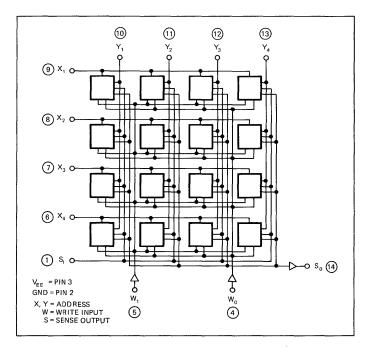

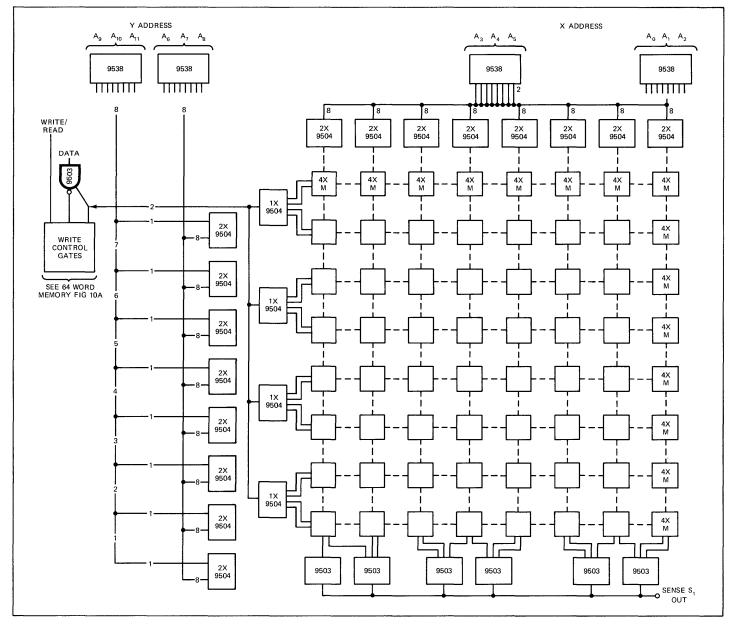

**DESCRIPTION** This element is a 16 bit monolithic integrated memory element designed for use in very high speed scratchpad memory applications. The element consists of 16 nonsaturating bistable storage cells arranged in an addressable four-by-four matrix.

The logic diagram below indicates the X and Y address lines, sense zero and sense one,  $S_0$ ,  $S_1$  and write zero and write one.  $W_0$ ,  $W_1$ , pin locations.

All outputs are normal logic "0" for ease of expansion to larger word sizes.

A desired bit location is selected by raising the coincident X-Y address lines to a logic "1" (typically -0.8 volts) and holding the nonselected address lines at logic "0" (typically -1.6 volts). The data, and its complement stored at the addressed location are read at the sense output terminals. If a "1" is stored, terminal S<sub>1</sub> will be at logical "1", if "0" is stored, terminal S<sub>0</sub> will be at "1".

Writing a logical "1" is accomplished by raising  $W_1$  to "1" and addressing the appropriate location, as for sensing. A logic "0" is stored by applying "1" to terminal  $W_0$ .

This element is available in the hermetically sealed, 14 lead ceramic Dual-In-line Package, suitable for operation over the temperature range  $0^{\circ}$ C to 75°C. This device is second sourced by RCA as the CD2155D.

- HIGH SPEED ACCESS TIME <6 ns, READ/WRITE CYCLE TIME <18 ns</li>

- OUTPUT WIRE OR FACILITY FOR WORD EXPANSION

- NON-DESTRUCTIVE READ-OUT

- TRUE AND COMPLEMENTARY OUTPUTS PROVIDED

- 50  $\Omega$  LINE DRIVE CAPABILITY

- ECL COMPATIBLE LOGIC "1" TYPICALLY -0.8V - LOGIC "0" TYPICALLY -1.6V

- SINGLE POWER SUPPLY (-5.0V/-5.2V)

- POWER DISSIPATION TYPICALLY 300 mW

### HIGH SPEED GATES FAIRCHILD TEMPERATURE COMPENSATED ECL

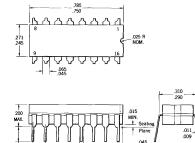

**GENERAL DESCRIPTION** — The 9502, 9503 and 9504 are temperature compensated  $EC_{\mu}L$  OR/NOR Gates employing a nonsaturating current switch, emitter follower configuration to achieve high speed. The elements are intended for the design of high speed central processors, terminals, instrumentation and digital communications systems.

All 9500 series elements incorporate a unique temperature compensation network. This insures that significant parameters such as logic levels, noise margin and speed remain relatively constant over a wide temperature range. Input and output 2 k $\Omega$  pulldown resistors eliminate the necessity for external termination of lines up to 6-8 inches and unused logic inputs. Package pin locations are chosen to reduce internal noise generation and crosstalk.

The devices are packaged in the hermetic CERAMIC, 16 pin Dual In-Line Package and specified for operation over the temperature range  $0^{\circ}$ C to 75°C.

• HIGH SPEED . . . 2.3 ns PER GATE

- + SEPARATE CURRENT SWITCH AND EMITTER FOLLOWER V $_{

m CC}$  PINS Eliminates noise coupling

- TEMPERATURE COMPENSATION

- INTERNAL PULLDOWN RESISTORS

- COMMON ENABLE INPUTS

- LOW CROSSTALK AND NOISE GENERATION

- WIRE-OR CAPABILITY

- 50  $\boldsymbol{\Omega}$  line driving capability

- COMPLEMENTARY OR/NOR OUTPUTS (9502, 9503)

- SINGLE —5.2 V POWER SUPPLY

- HERMETIC CERAMIC 16 PIN DUAL IN-LINE PACKAGE

ABSOLUTE MAXIMUM RATINGS (above which useful life may be impaired)

| Storage Temperature                         |  |

|---------------------------------------------|--|

| Junction Temperature                        |  |

| Supply Voltage V <sub>FF</sub> (Continuous) |  |

| Supply Voltage V <sub>FF</sub> (Pulsed)     |  |

| Input Voltage                               |  |

| Output Current                              |  |

#### **ORDER INFORMATION**

Specify U6B9502XXX for 16 pin Dual In-Line Package where XXX is 59X for the 0 °C to +75 °C temperature range for 9502 gate. Substitute 9503 or 9504 for other elements.

-65°C to +150°C

GND to  $V_{EE}$  (max)

+150°C

-6 Volts

-8 Volts

40 mA

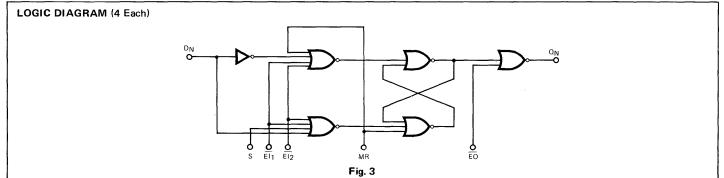

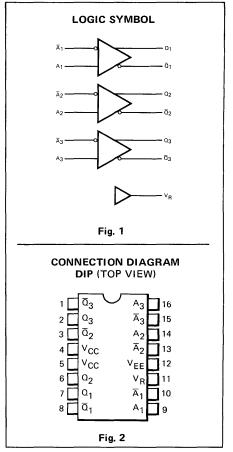

#### FUNCTIONAL DESCRIPTION

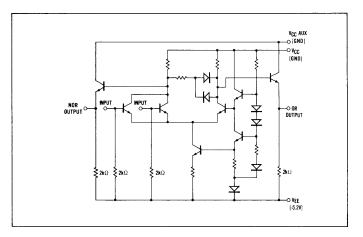

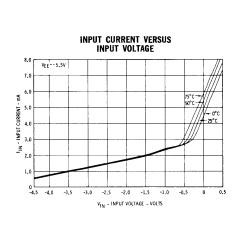

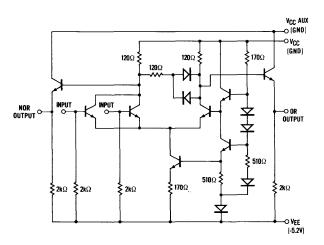

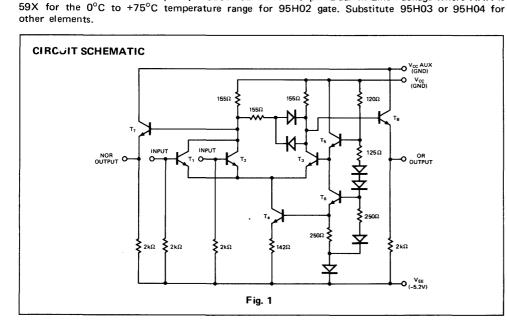

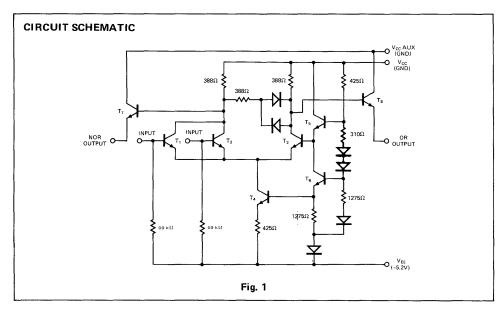

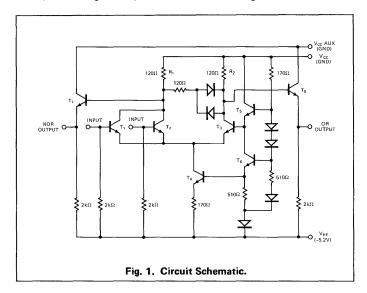

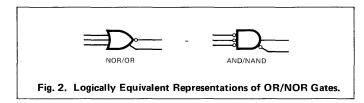

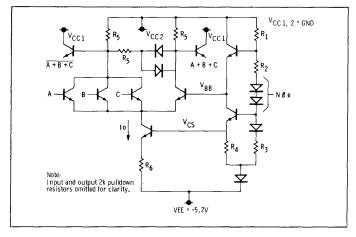

The 9500 Series Temperature Compensated  $EC_{\mu}L$  Gates are based on the current switch-emitter follower (CSEF), or emitter coupled ( $EC_{\mu}L$ ), configuration of Figure 1. Additional circuit complexity compared with conventional  $EC_{\mu}L$  is incorporated to improve system operating characteristics. This includes temperature compensation networks to insure that logic levels and thresholds, set by the on chip bias driver, are essentially independent of temperature. On chip output emitter follower and input pulldown 2 k ohm resistors reduce external components normally required for short line termination and unused logic inputs. A current source in the tail of the differential amplifier equalizes ONE and ZERO level noise margins by removing the NOR side saturation knee, and also improves saturation temperature dependency.

Defining logic "ONE" as  $V_{OH} = -895$  mV (typ) and logic "ZERO" as  $V_{OL} = -1710$  mV (typ), the elements perform the logical NOR and OR functions. The opposite definition specifies NAND/AND operation. All parameters specified in the characteristics are defined by the algebraic maximum and minimum limits.

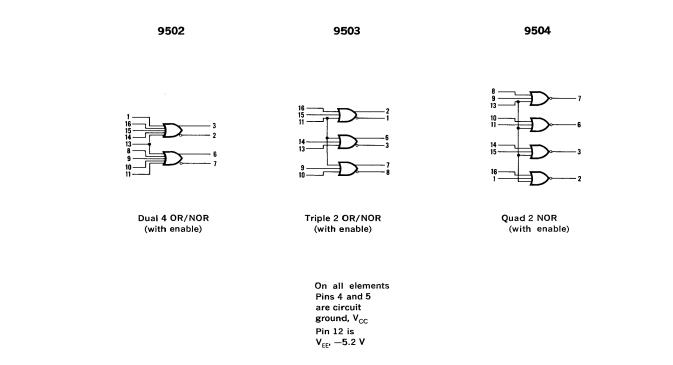

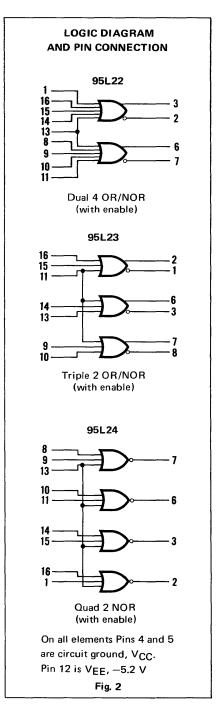

Gate pin configurations are indicated in Fig. 2. An input enable line common to all gates in each package is provided for additional logical flexibility.

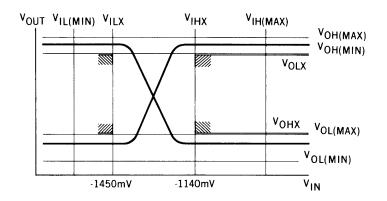

#### Fig. 1 - CIRCUIT SCHEMATIC

#### Fig. 2 - LOGIC DIAGRAM AND PIN CONNECTION

| SYMBOL              | CHARACTERISTIC                   | 0°C  |      |       | +25°C |      |       | +75°C |      |       | UNITS | CONDITIONS                                  |

|---------------------|----------------------------------|------|------|-------|-------|------|-------|-------|------|-------|-------|---------------------------------------------|

|                     |                                  | MIN. | TYP. | MAX.  | MIN.  | TYP. | MAX.  | MIN.  | TYP. | MAX.  |       |                                             |

| I <sub>IN</sub> (1) | Input Current at V <sub>IH</sub> |      |      |       |       |      |       |       |      |       |       |                                             |

|                     | Standard Gate                    |      | 2.30 | 3.15  |       | 2.25 | 3.10  |       | 2.15 | 3.00  | mA    | V _ 900 mV                                  |

|                     | Enable Lines                     |      |      |       |       |      |       |       |      |       |       | $V_{IH} = -900 \text{ mV}$ to each input    |

|                     | 9502                             |      | 4.60 | 6.30  |       | 4.50 | 6.20  |       | 4.30 | 6.00  | mA    | sequentially                                |

|                     | 9503                             |      | 6.90 | 9.45  |       | 6.75 | 9.30  |       | 6.45 | 9.00  | mA    | sequentially                                |

|                     | 9504                             |      | 9.20 | 12.60 |       | 9.00 | 12.40 |       | 8.60 | 12.00 | mA    |                                             |

| I <sub>IN</sub> (0) | Input Current at V <sub>IL</sub> |      |      |       |       |      |       |       |      |       |       |                                             |

|                     | Standard Gate                    |      | 1.80 | 2.40  |       | 1.75 | 2.35  |       | 1.65 | 2.25  | mA    | $V_{11} = -1700 \text{ mV}$                 |

|                     | Enable Lines                     |      |      |       |       |      |       |       |      |       |       | to each input<br>sequentially               |

|                     | 9502                             |      | 3.60 | 4.80  |       | 3.50 | 4.70  |       | 3.30 | 4.50  | mA    |                                             |

|                     | 9503                             |      | 5.40 | 7.20  |       | 5.25 | 7.05  |       | 4.95 | 6.75  | mA    |                                             |

|                     | 9504                             |      | 7.20 | 9.60  |       | 7.00 | 9.40  |       | 6.60 | 9.00  | mA    |                                             |

| I <sub>PD</sub>     | Power Supply Current             |      |      |       |       |      |       |       |      |       |       |                                             |

|                     | 9502                             | 25   | 33   | 43    | 29    | 35   | 44    | 30    | 37   | 48    | mA    | All inputs                                  |

|                     | 9503                             | 35   | 46   | 59    | 40    | 48   | 60    | 40    | 51   | 65    | mA    | open                                        |

|                     | 9504                             | 40   | 52   | 67    | 45    | 54   | 68    | 41    | 57   | 74    | mA    |                                             |

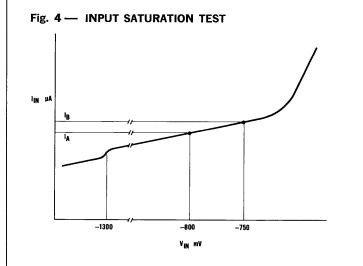

| $\Delta I_{IN}$     | Input                            |      |      |       |       |      |       |       |      |       |       | See Fig. 4                                  |

|                     | Saturation                       |      |      |       |       |      |       |       |      | 50    | μA    | $\Delta I_{\rm IN} = I_{\rm B} - I_{\rm A}$ |

|                     | Test                             |      |      |       |       |      |       |       |      |       |       | $I_A = I_{IN} @$                            |

|                     |                                  |      |      |       |       |      |       |       |      |       |       | $V_{IN} = 800 \text{ mV}$                   |

|                     | ]                                | ļ    |      |       |       |      |       | )     |      |       |       | $I_{B} = I_{IN} @$                          |

|                     |                                  |      |      |       |       |      |       |       |      |       |       | $V_{1N} = 750 \text{ mV}$                   |

#### A.C. ELECTRICAL CHARACTERISTICS (Industrial Temperature Range 0°C to +75°C)

| SYMBOL          | CHARACTERISTIC                           | 0°C  |      |      | 1    | +25°0      | ;          |      | +75°( | C    | UNITS | CONDITIONS                                                                              |

|-----------------|------------------------------------------|------|------|------|------|------------|------------|------|-------|------|-------|-----------------------------------------------------------------------------------------|

|                 |                                          | MIN. | TYP. | MAX. | MIN. | TYP.       | MAX.       | MIN. | TYP.  | MAX. |       |                                                                                         |

| t <sub>pd</sub> | Propagation Delay                        |      |      |      |      |            |            |      |       |      |       |                                                                                         |

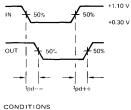

| P0              | t <sub>pd</sub>                          |      | 2.3  |      |      | 2.3        | 3.5        |      | 2.5   |      | ns    | See Fig. 5                                                                              |

|                 | t <sub>pd++</sub>                        |      | 2.2  |      |      | 2.2        | 3.5        |      | 2.4   |      | ns    | $R_{L} = 50 \Omega \text{ to } -2.0 \text{ V}$                                          |

|                 | t <sub>pd-+</sub>                        |      | 2.4  |      |      | 2.4        | 3.5        |      | 2.6   |      | ns    | С <sub>L</sub> <5.0 pF                                                                  |

|                 | t <sub>pd+-</sub>                        |      | 2.5  |      |      | 2.5        | 3.2        |      | 2.7   |      | ns    | $t_r = t_f = 2.5 \text{ ns}$                                                            |

| t <sub>r</sub>  | Rise Time                                | 1.5  |      | 4.5  | 1.5  | 3.0        | 4.5        | 1.5  |       | 4.5  | ns    | See Fig. 5<br>$R_L = 50 \Omega \text{ to} -2.0 \text{ V}$<br>$C_L < 5.0 \text{ pF}$     |

| t <sub>f</sub>  | Fall Time                                | 1.5  |      | 4.5  | 1.5  | 3.0        | 4.5        | 1.5  |       | 4.5  | ns    | See Fig. 5<br>$R_{L} = 50 \Omega \text{ to} -2.0 \text{ V}$<br>$C_{L} < 5.0 \text{ pF}$ |

| I <sub>T</sub>  | Transient Input Current<br>Standard Gate |      |      |      |      | 2.5        | 3.5        |      |       |      | mA    | See Fig. 6 on Page 5                                                                    |

|                 | Enable Lines<br>9502                     |      |      |      |      | 3.4        | 4.5        |      |       |      | mA    |                                                                                         |

|                 | 9502                                     |      |      |      |      | 3.4<br>4.7 | 4.5<br>5.7 |      |       |      | mA    |                                                                                         |

|                 | 9504                                     |      |      |      |      | 5.0        | 6.0        |      |       |      | mA    |                                                                                         |

| t <sub>pd</sub> | Propagation Delay                        |      |      |      |      |            |            |      |       |      |       |                                                                                         |

| P.0             | t <sub>pd</sub>                          |      | 2.6  |      |      | 2.6        | 3.5        |      | 2.8   | 1    | ns    | See Fig. 5                                                                              |

|                 | t <sub>pd++</sub>                        |      | 2.5  |      |      | 2.5        | 3.5        |      | 2.7   |      | ns    | $R_{L} = 50 \Omega \text{ to} - 2.0 \text{ V}$                                          |

|                 | t <sub>pd-+</sub>                        |      | 2.7  |      |      | 2.7        | 3.5        |      | 2.9   |      | ns    | $C_{L} = 15 \text{ pF} \pm 5\%$                                                         |

|                 | $t_{pd+-}$                               |      | 2.8  |      |      | 2.8        | 3.5        |      | 3.0   |      | ns    | $t_r = t_f = 2.5 \text{ ns}$                                                            |

|                  |                                                                                                            |                       |       |                         |                   | LIMITS |               |                      |       |                         |                |                                                                                                                                                                                                                                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------|-----------------------|-------|-------------------------|-------------------|--------|---------------|----------------------|-------|-------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYMBOL           | CHARACTERISTIC                                                                                             | 0°C<br>Min. Typ. Max. |       | +25°C<br>MIN. TYP. MAX. |                   | MIN.   | +75°C<br>TYP. | MAX.                 | UNITS | CONDITIONS              |                |                                                                                                                                                                                                                                                                                                                      |

| V <sub>он</sub>  | Output High Voltage<br>F.O. = 1 gate<br>F.O. = 5 gates<br>$50 \Omega \text{ to} -2.0 \text{ V}$            | 900<br>940<br>975     | -890  | 800<br>840<br>875       | -940              |        |               | -940                 |       |                         | mV<br>mV<br>mV | $\begin{array}{l} {\sf V}_{\rm IL}=-1700~{\rm mV}\\ {\rm for~NOR~gate}\\ {\sf V}_{\rm IH}=-900~{\rm mV}\\ {\rm for~OR~gate} \end{array}$                                                                                                                                                                             |

| V <sub>OL</sub>  | Output Low Voltage<br>F.O. = 1 gate<br>F.O. = 5 gates<br>$50 \Omega \text{ to } -2.0 \text{ V}$            | 1785                  | -1710 | —1595<br>—1635<br>—1625 | -1785             | -1710  | -1635         | -1785                | -1710 |                         | mV<br>mV<br>mV | $V_{\rm IL} = -1700 \text{ mV}$<br>for OR gate<br>$V_{\rm IH} = -900 \text{ mV}$<br>for NOR gate                                                                                                                                                                                                                     |

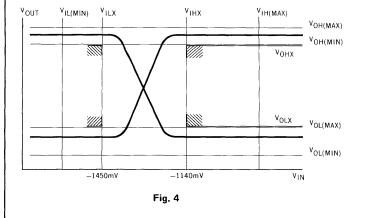

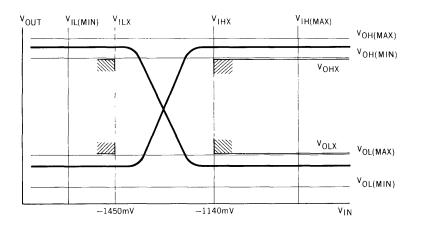

| V <sub>онх</sub> | Output High Voltage<br>at $V_{IN}$ (threshold)<br>F.0. = 1 gate<br>F.0. = 5 gates<br>50 $\Omega$ to -2.0 V | 910<br>950<br>985     |       |                         | 910<br>950<br>985 |        |               | —900<br>—950<br>—985 |       |                         | mV<br>mV<br>mV | $ \begin{array}{l} \text{See Fig. 3} \\ \text{V}_{\text{ILX}} = -1450 \text{ mV} \\ \text{for NOR gate} \\ \text{V}_{\text{IHX}} = -1140 \text{ mV} \\ \text{for OR gate} \end{array} \\ \begin{array}{l} \text{To each} \\ \text{input} \\ \text{sequentially} \\ (\text{other input} \\ \text{open}) \end{array} $ |

| V <sub>OLX</sub> | Output Low Voltage<br>at $V_{1N}$ (threshold)<br>F.O. = 1 gate<br>F.O. = 5 gates<br>50 $\Omega$ to -2.0 V  |                       |       |                         | -                 |        |               |                      |       | —1585<br>—1625<br>—1615 | mV             | See Fig. 3<br>$V_{ILX} = -1450 \text{ mV}$ To each<br>input<br>for OR gate<br>$V_{IHX} = -1140 \text{ mV}$ (other input<br>for NOR gate<br>open)                                                                                                                                                                     |

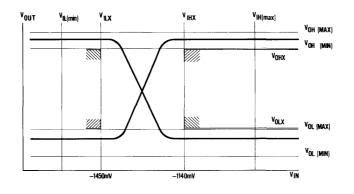

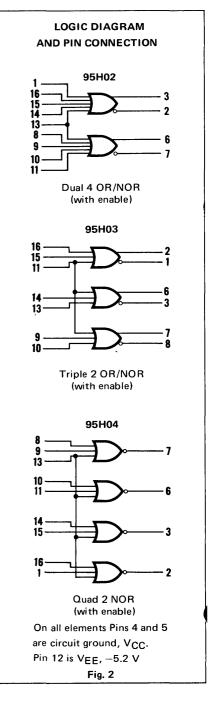

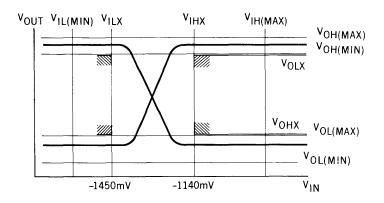

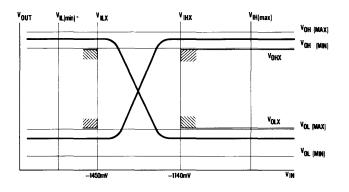

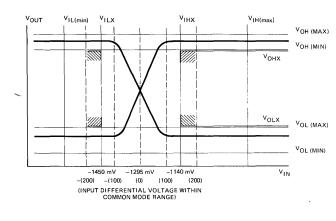

Fig. 3 --- NOISE MARGIN SPECIFICATION POINTS

Corner points indicated on the transfer characteristics represent the worst case points (thresholds) at which the device will start to switch. The values  $V_{\rm ILX}$  and  $V_{\rm IHX}$  define the maximum width of the transition region.

This test insures that the input transistor is not in saturation at  $V_{\rm IN} = 750$  mV. This represents a worst case condition with the driving gate at  $V_{\rm OH}$  (min) = 750 mV (ie. for  $T_{\rm A} = 75^{\circ}$ C this is equivalent to driving gate into F0 = 1 with its power supply at .--5%).

Saturation is defined as no increase in collector current for 20% increase in base drive current  $I_{\rm R}$ . The effect is to increase  $t_{\rm orb}$ .

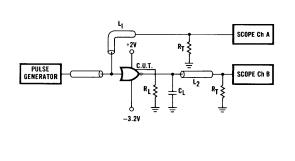

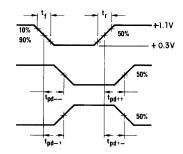

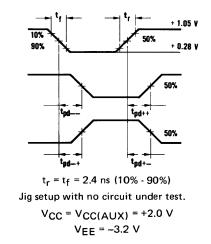

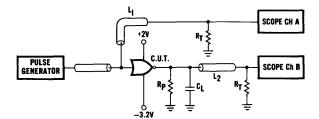

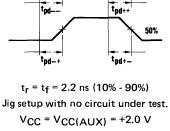

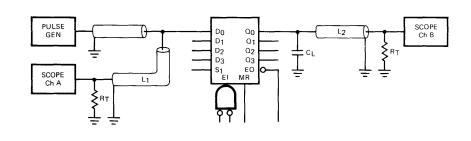

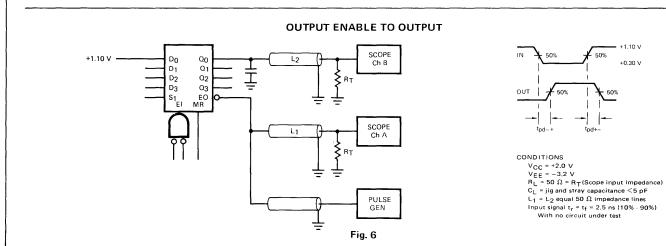

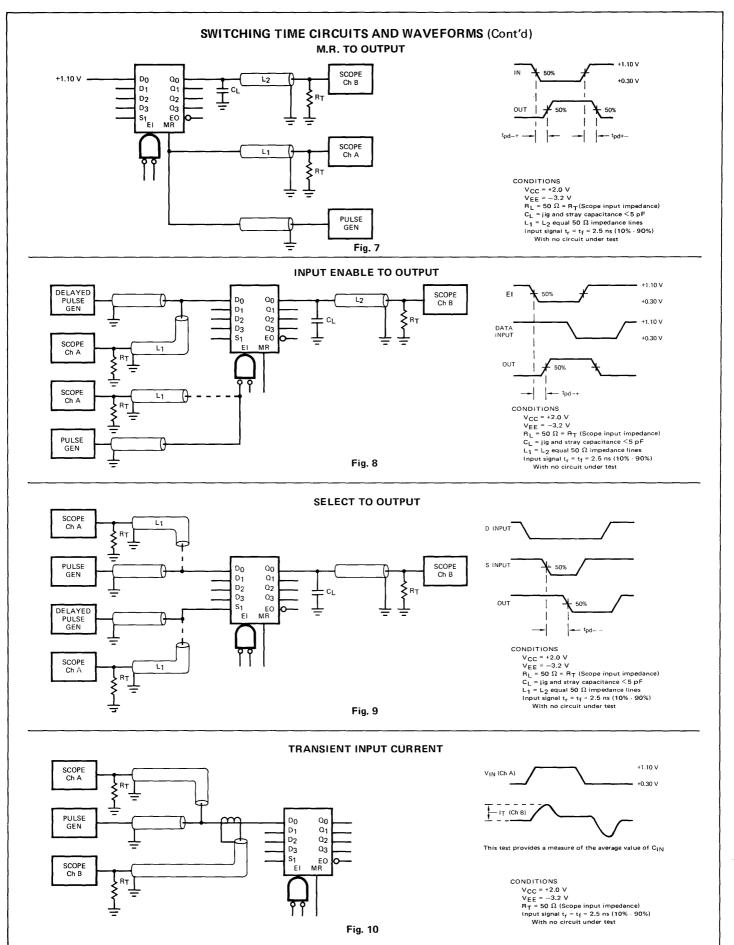

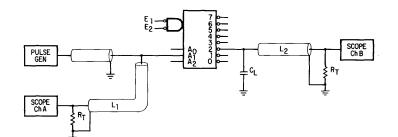

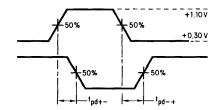

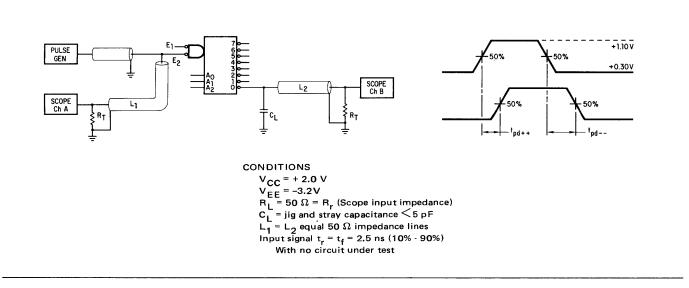

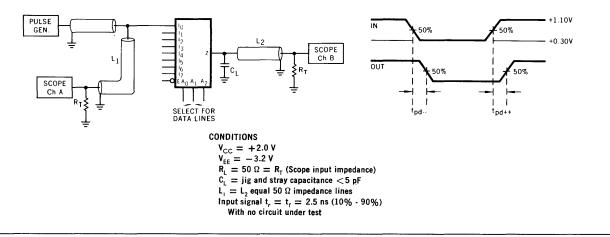

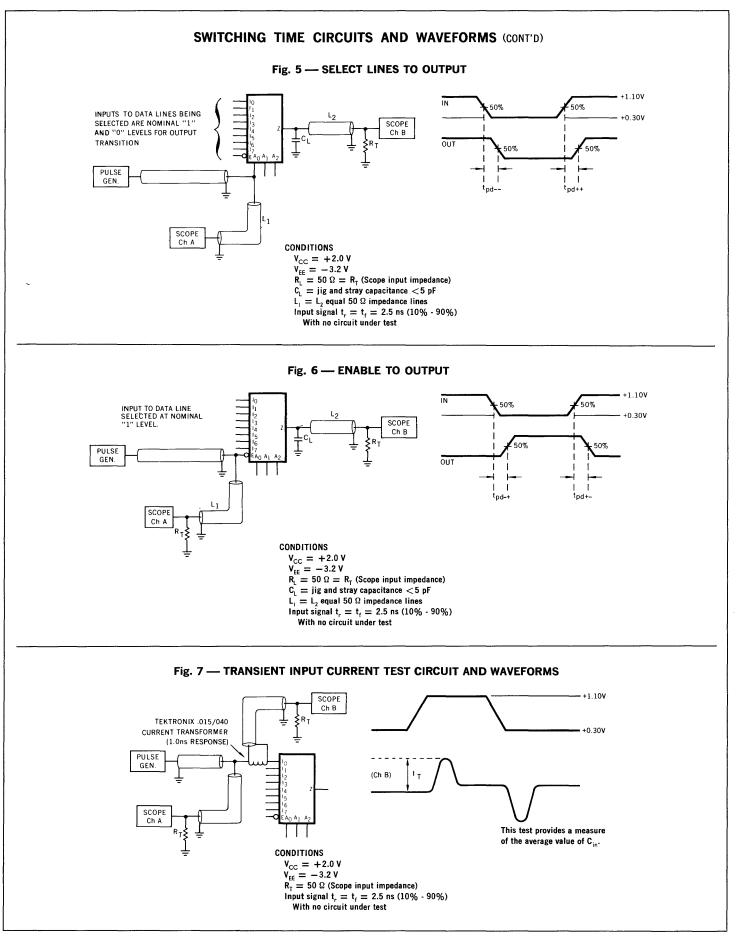

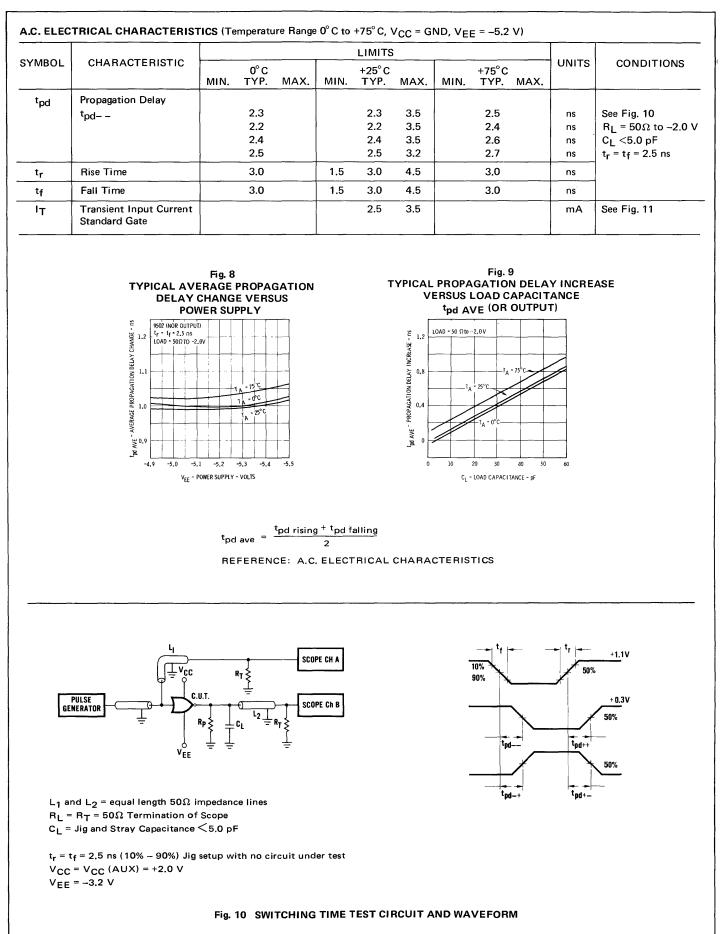

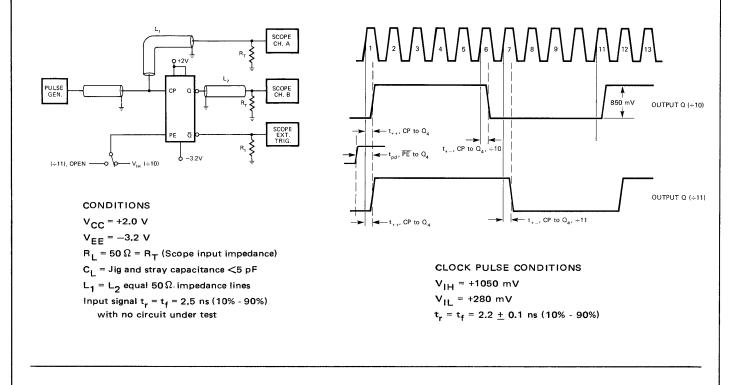

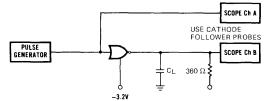

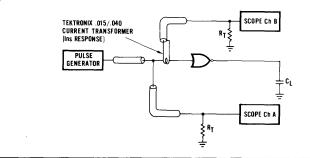

#### Fig. 5 — SWITCHING TIME TEST CIRCUIT AND WAVEFORM

$t_r = t_f = 2.5$  ns (10% - 90%) Jig setup with no circuit under test  $V_{_{\rm CC}} = V_{_{\rm CC}}$  (AUX) = +2.0 V  $V_{_{\rm EE}} = -3.2$  V

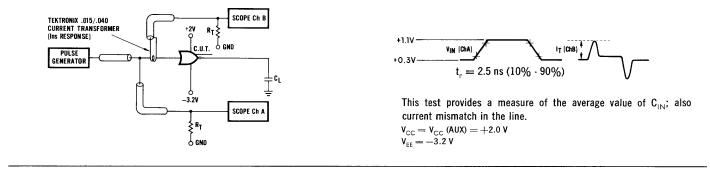

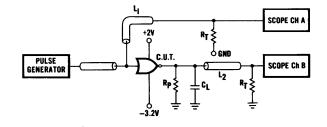

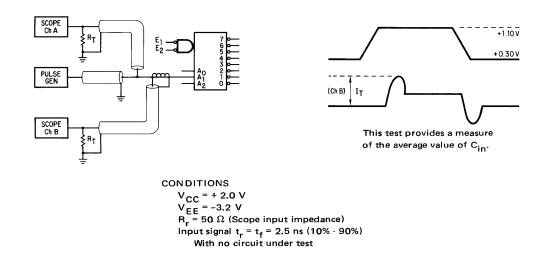

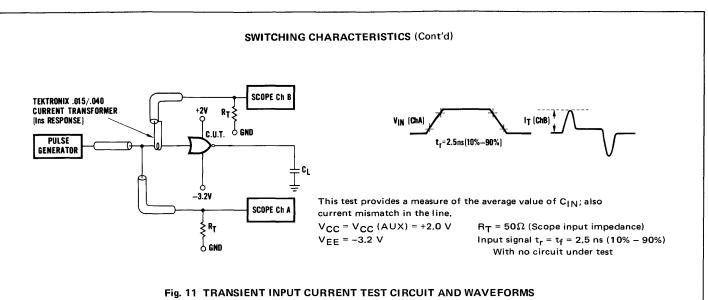

#### Fig. 6 --- TRANSIENT INPUT CURRENT TEST CIRCUIT AND WAVEFORMS

- $L_{_{\rm I}}$  and  $L_{_{\rm 2}}=$  equal length 50  $\Omega$  impedance lines

- $\mathrm{R_L}=\mathrm{R_T}=50~\Omega$  Termination of Scope

- $C_L = Jig$  and Stray Capacitance < 5.0 pF

Logic levels for Figs. 5 and 6 are nominal values at 50  $\Omega$  fanout determined by indicated power supplies. These values chosen to permit use of scope 50  $\Omega$  termination to ground. Decoupling 0.1  $\mu F$  from GND to  $V_{\rm FF}.$

### FAIRCHILD ECL • 9502 • 9503 • 9504

.

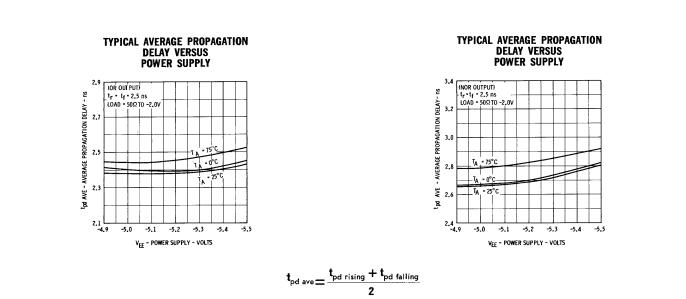

#### TYPICAL AVERAGE PROPAGATION DELAY VERSUS POWER SUPPLY

#### APPLICATIONS NOTES

#### INTERCONNECTION RECOMMENDATIONS

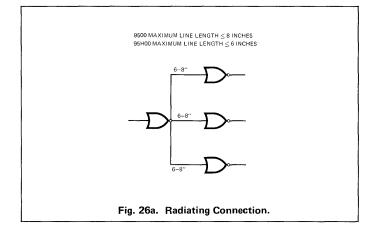

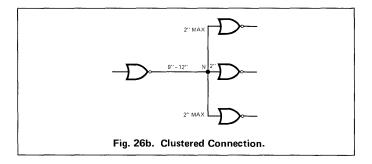

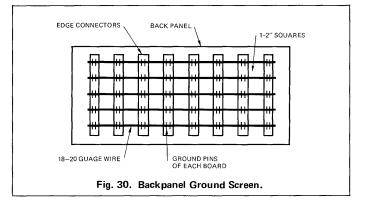

All high speed  $EC_{\mu L}$  circuits demand that special precautions be taken for optimum system performance. A ground plane must be provided for a good, low impedance, ground current return path and to transform interconnections into microstrip transmission lines. The voltage supply line should be well decoupled with small ceramic capacitors throughout each card between  $V_{EE}$  and the ground plane and by including at least one larger tantalum capacitor per card.

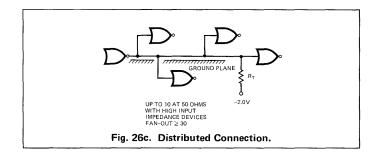

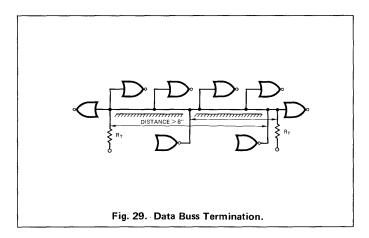

Typical microstrip lines have a characteristic impedance between 50 and 150 ohms with the lower being more desirable in  $EC_{\mu}L$  systems. For local interconnects the internal 2 k $\Omega$  resistors provide adequate termination but for optimum performance lines longer than 6 or 8 inches in length should be terminated in their characteristic impedance.

Lines up to 12 inches may be left unterminated if a degraded waveform can be tolerated with the resultant decrease in speed and increase in ringing.

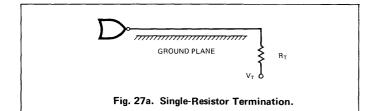

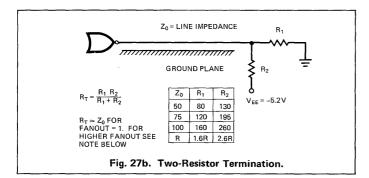

Microstrip interconnections may be terminated by a resistor to a -2 volt supply:  $R = \frac{Z_{\odot}}{1 - NZ_{\odot}/2000}$  where  $Z_{\odot}$  is the characteristic impedance

of the line and N is the number of loads. Alternately, a 2 resistor divider network may be used with  $R_1 = 1.6$  R connected to ground and  $R_2 = 2.6$  R connected to  $V_{EE}$ .

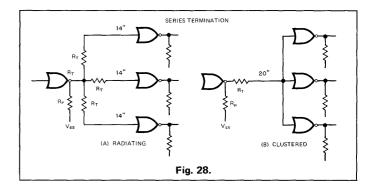

Series terminating resistors decrease noise immunity and slow rise and fall times, but can still be used if these effects are tolerable. In addition, care must be taken to avoid glitches in the threshold region of the waveform occurring at certain combinations of line length and series resistor value.

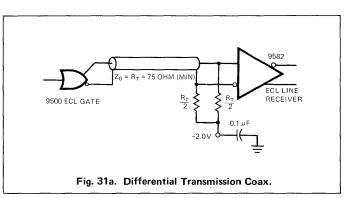

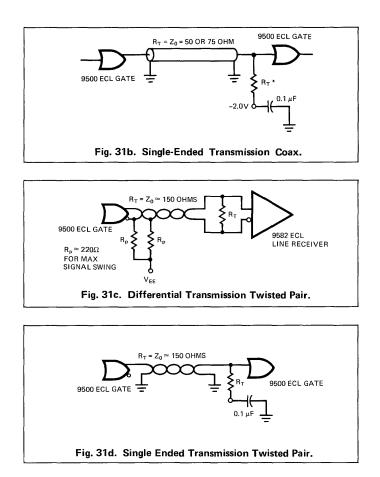

A single terminated wire running over a ground screen can be used for backpanel interconnections up to 4 or 5 inches in length, but terminated coaxial cables or terminated twisted pairs of wire are required for longer interconnections.

#### LINE DRIVING CAPABILITY

The 9500 series  $EC_{\mu}L$  circuits are capable of driving fairly long lines if the previous recommendations are followed. 50 ohm coaxial cables 10 feet in length or longer and properly terminated may be driven with almost no degradation in the waveform. The normal delay due to the finite speed of the signal traveling down the cable will be encountered in addition to a slight decrease in signal swing. This decrease caused by the attenuation of the cable (about 40 mV for 10 feet of 50 ohm coax) will lower the noise immunity of the receiving circuit by the same amount. Care must be exercised to ensure the ground potentials at the driving and receiving ends of a line are equal and no differential noise is present.

### VERY HIGH SPEED GATES FAIRCHILD TEMPERATURE COMPENSATED ECL

**GENERAL DESCRIPTION** – The 95H02, 95H03 and 95H04 are temperature compensated ECL OR/NOR Gates employing a nonsaturating current switch, emitter follower configuration to achieve high speed. The elements are intended for the design of high speed central processors, terminals, instrumentation and digital communications systems.

All 9500 series elements incorporate a unique temperature compensation network. This insures that significant parameters such as logic levels, noise margin and speed remain relatively constant over a wide temperature range. Input and output  $2 k\Omega$  pulldown resistors eliminate the necessity for external termination of lines up to 6-8 inches and unused logic inputs. Package pin locations are chosen to reduce internal noise generation and crosstalk.

The devices are packaged in the hermetic CERAMIC, 16 pin Dual In-Line Package and specified for operation over the temperature range  $0^{\circ}$  C to  $75^{\circ}$  C.

- PIN IDENTICAL TO LOWER SPEED GATES (9502 9503 9504)

- VERY HIGH SPEED . . . 1.7 ns PER GATE

- SEPARATE CURRENT SWITCH AND EMITTER FOLLOWER  $\mathsf{V}_{\mathsf{CC}}$  PINS ELIMINATES NOISE COUPLING

ORDER INFORMATION - Specify U6B95H02XX for 16 pin Dual In-Line Package where XXX is

- TEMPERATURE COMPENSATION

- INTERNAL PULLDOWN RESISTORS

- COMMON ENABLE INPUTS

- LOW CROSSTALK AND NOISE GENERATION

- WIRED-OR CAPABILITY

- 50 Ω LINE DRIVING CAPABILITY

- COMPLEMENTARY OR/NOR OUTPUTS (9502, 9503)

- SINGLE -5.2 V POWER SUPPLY

- HERMETIC CERAMIC 16 PIN DUAL IN-LINE PACKAGE

**FUNCTIONAL DESCRIPTION** – The 9500 Series Temperature Compensated ECL Gates are based on the current switch-emitter follower (CSEF), or emitter coupled (ECL), configuration of Figure 1. Additional circuit complexity compared with conventional ECL is incorporated to improve system operating characteristics. This includes temperature compensation networks to insure that logic levels and thresholds, set by the on chip bias driver, are essentially independent of temperature. On chip output emitter follower and input pulldown 2 k ohm resistors reduce external components normally required for short line termination and unused logic inputs. A current source in the tail of the differential amplifier equalizes ONE and ZERO level noise margins by removing the NOR side saturation knee, and also improves saturation temperature dependency.

Defining logic "ONE" as  $V_{OH} = -900 \text{ mV}$  (typ) and logic "ZERO" as  $V_{OL} = -1700 \text{ mV}$  (typ), the elements perform the logical NOR and OR functions. The opposite definition specifies NAND/AND operation. All parameters specified in the characteristics are defined by the algebraic maximum and minimum limits.

Gate pin configurations are indicated in Fig. 2. An input enable line common to all gates in each package is provided for additional logical flexibility.

#### ABSOLUTE MAXIMUM RATINGS (above which useful life may be impaired)

| Storage Temperature             | -65°C to +150°C  |

|---------------------------------|------------------|

| Junction Temperature            | +150°C           |

| Supply Voltage VEE (Continuous) | -6 Volts         |

| Supply Voltage VEE (Pulsed)     | –8 Volts         |

| Input Voltage                   | GND to VEE (max) |

| Output Current                  | 40 mA            |

#### D.C. ELECTRICAL CHARACTERISTICS (Operating Temperature Range: T<sub>A</sub> = 0°C to 75°C, V<sub>CC</sub> = GND, V<sub>EE</sub> = ~5.2 V)

| 0)/1100:        |                                                                         |                       | LIMITS               |                      |       |                                               |                                                                                                                      |

|-----------------|-------------------------------------------------------------------------|-----------------------|----------------------|----------------------|-------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| SYMBOL          | CHARACTERISTIC                                                          | MIN.                  | TYP.                 | MAX.                 | UNITS |                                               | CONDITIONS                                                                                                           |

| V <sub>OH</sub> | Output Voltage High                                                     |                       | 860<br>910<br>950    |                      | mV    | FO = 1 Gate<br>FO = 5 Gates<br>50 Ω to -2.0 V | V <sub>IN</sub> = V <sub>IL</sub> = -1700 mV for NOR Gate<br>V <sub>IN</sub> = V <sub>IH</sub> = -900 mV for OR Gate |

| VOL             | Output Voltage Low                                                      |                       | 1690<br>1740<br>1720 |                      | mV    | FO = 1 Gate<br>FO = 5 Gates<br>50 Ω to2.0 V   | $V_{IN} = V_{IH} = -900 \text{ mV}$ for NOR Gate<br>$V_{IN} = V_{IL} = -1700 \text{ mV}$ for OR Gate                 |

| Vонх            | Output Voltage High<br>at V <sub>IN</sub> = V <sub>IX</sub> (Threshold) | -930<br>-970<br>-1010 |                      |                      | mV    | FO = 1 Gate<br>FO = 5 Gates<br>50 Ω to -2.0 V | See Fig. 3<br>VIN = VILX =1450 mV for NOR Gat<br>VIN = VIHX =1140 mV for OR Gate                                     |

| VOLX            | Output Voltage Low<br>at V <sub>IN</sub> = V <sub>IX</sub> (Threshold)  |                       |                      | 1605<br>1655<br>1635 | mV    | FO = 1 Gate<br>FO = 5 Gates<br>50 Ω to -2.0 V | See Fig. 3<br>VIN = VILX = -1450 mV for OR Gate<br>VIN = VIHX = -1140 mV for NOR Gat                                 |

| VIHX            | Guaranteed Input High<br>Threshold Voltage                              | 1140                  |                      |                      | mV    |                                               | Guaranteed Input High<br>Threshold Voltage                                                                           |

| VILX            | Guaranteed Input Low<br>Threshold Voltage                               |                       |                      | -1450                | mV    |                                               | Guaranteed Input Low<br>Threshold Voltage                                                                            |

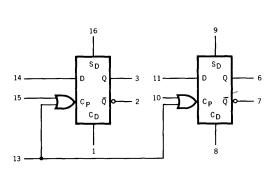

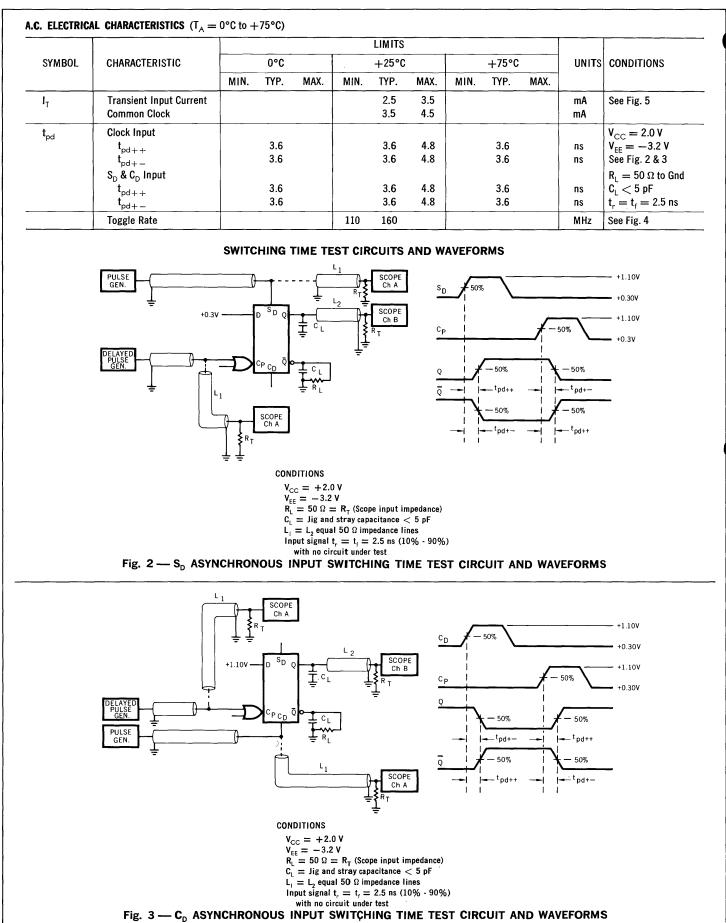

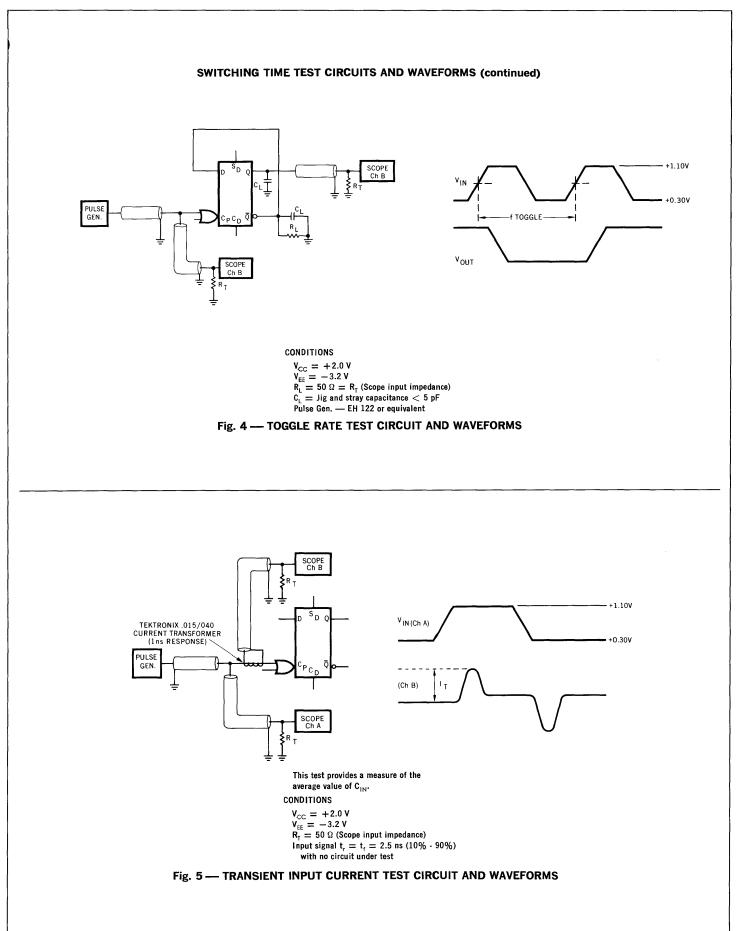

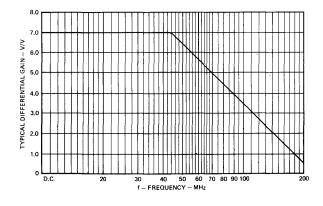

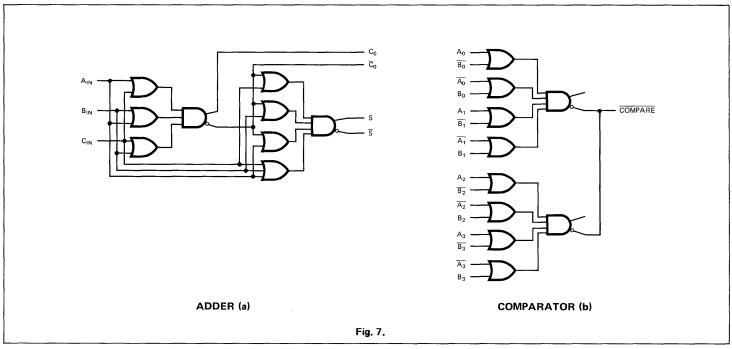

| VIN(H)          | Input Current High                                                      |                       | 2.40                 | 3.58                 | mA    |                                               | V <sub>IN</sub> = -900 mV to Common<br>Enable Input                                                                  |