# 82C614 DATA BOOK

September 1990 Revision 1.6

CHIPS AND TECHNOLOGIES, INC. 3050 ZANKER ROAD SAN JOSE, CA 95134 (408) 434-0600

A

E 2098116 0009500 389 E

### **COPYRIGHT NOTICE**

Copyright @ 1990, Chips and Technologies, Inc. ALL RIGHTS RESERVED.

This manual is copyrighted by Chips and Technologies, Inc. You may not reproduce, transmit, transcribe, store in a retrieval system, or translate into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, any part of this publication without the express written permission of Chips and Technologies.

### TRADEMARKS

CHIPS, MicroCHIP, CHIPS/250 and CHIPS/280 are trademarks of Chips and Technologies, Incorporated.

IBM, IBM PC, and IBM PC AT are registered trademarks of International Business Machines Corporation. MicroChannel is a trademark of International Business Machines Corporation.

MS-DOS is a registered trademark of Microsoft Corporation.

Intel, 386, 387, 386SX and 387SX are trademarks of Intel Corporation

### DISCLAIMER

Chips and Technologies, Inc. makes no representations or warranties regarding the contents of this manual. We reserve the right to revise the manual or make changes in the specifications of the product described within it at any time without notice and without obligation to notify any person of such revision or change.

The information contained in this manual is provided for general use by our customers. Our customers should be aware that the personal computer field is the subject of many patents. Our customers should ensure that they take appropriate action so that their use of our products does not infringe upon any patents. It is the policy of Chips and Technologies, Inc. to respect the valid patent rights of third parties and not to infringe upon or assist others to infringe upon such rights.

### **RESTRICTED RIGHTS LEGEND**

Use, duplication, or disclosure by the Government is subject to restrictions set forth in subparagraph  $(c)(1)(\ddot{u})$  of the Rights in Technical Data and Computer Software clause at 252.277-7013.

**Revision 1.6**

2098176 0009201 512 📰

Page 1

## **Table of Contents**

| 1.0 Ove | view                             | 4    |

|---------|----------------------------------|------|

| 1.      | MicroChannel Interface           |      |

| 1.      | Local Interface                  | 5    |

| 1.      | DMA Channels                     | ~ 6  |

| 1       | FIFO Buffers                     |      |

| £.      |                                  |      |

| 1.      | 5 Initialization ROM             | 6    |

| 2.0 Reg | sters                            |      |

| 2       |                                  |      |

| 2       | 2 POS Registers                  | Ξġ.  |

| 2       |                                  | 12   |

| 2       |                                  | - 14 |

| Z.      | 4 Multifunction Pin Registers    | . 20 |

| 2       | 5 Programmable Decoded Registers | . 21 |

| 2       | 6 Other Registers                | . 24 |

| 2       | 7 DMA Registers                  | . 25 |

| 2 A D-  |                                  | 20   |

|         | ic Operation                     |      |

| 3       |                                  | . 32 |

| 3       |                                  | . 43 |

| 3       |                                  | 47   |

| 3       | 4 Data Sizes                     | 49   |

| 3       | 5 CHCK Interrupt                 | . 54 |

| 3       |                                  | 55   |

| ž       |                                  |      |

| 3       |                                  | 57   |

|         |                                  |      |

| 3       | 9 Fixed Decodes                  | 61   |

| 3       | 10 Data Parity                   | 62   |

| 3       | 11 Streaming Data                |      |

|         | 12 Extended POS                  | 63   |

| -       |                                  |      |

| 3       | 13 Multifunction Pins            | 64   |

| 3       | 14 Multifunction Pin Programming | 69   |

| A A D:- | out Summary                      | 70   |

|         | 1 MicroChannel Pins              |      |

|         |                                  | /0   |

|         | 2 Adapter Side Pins              |      |

|         | 3 Pin List (by pin number)       |      |

| 4       | 4 Pin List (by pin name)         | 72   |

| 5.0 Pir | Descriptions                     | 73   |

| 6.0 0-  | erating Considerations           |      |

|         | 1 Absolute Maximum Ratings       |      |

|         | 2 Aparting Conditions            |      |

|         | 2 Operating Conditions           | 00   |

|         | 3 DC Characteristics             | 80   |

## Table of Contents (continued)

| 7.0 AC Ch  | aracteristics                                                                                                                     |     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|

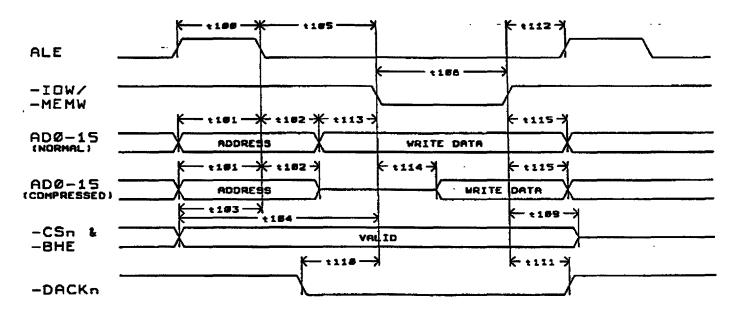

| 7.1        | Local Bus Cycles (normal)                                                                                                         |     |

| 7.2        | Local Bus Cycles (compressed)                                                                                                     |     |

| 73         | MicroChannel Bus Cycles (slave)                                                                                                   | 85  |

| 7.4        | Local Bus Cycles (normal)<br>Local Bus Cycles (compressed)<br>MicroChannel Bus Cycles (slave)<br>MicroChannel Bus Cycles (master) | 92  |

| 8.0 Timing | Diagrams                                                                                                                          |     |

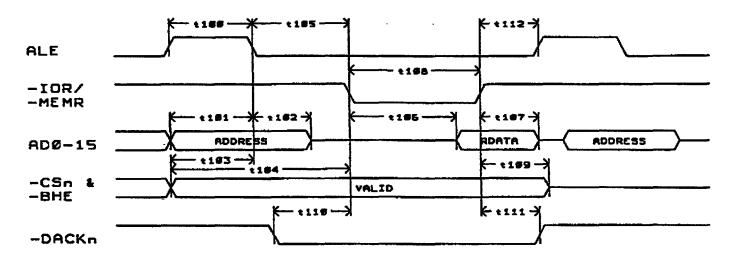

| 8.1 ~      | Local Bus Read Cycle                                                                                                              |     |

| 82         | Local Bus Write Cycle                                                                                                             | 102 |

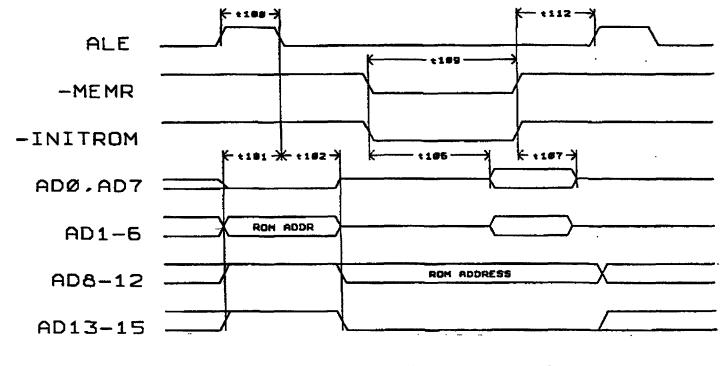

| 8.3        | Local Bus Init ROM Timing                                                                                                         |     |

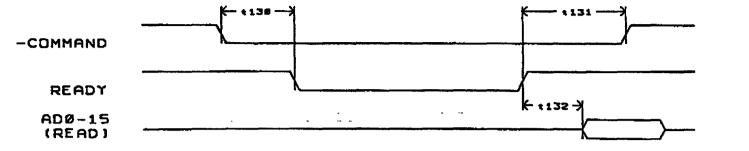

| 8.4        | Diagrams<br>Local Bus Read Cycle<br>Local Bus Write Cycle<br>Local Bus Init ROM Timing<br>Local Bus Ready Timing                  |     |

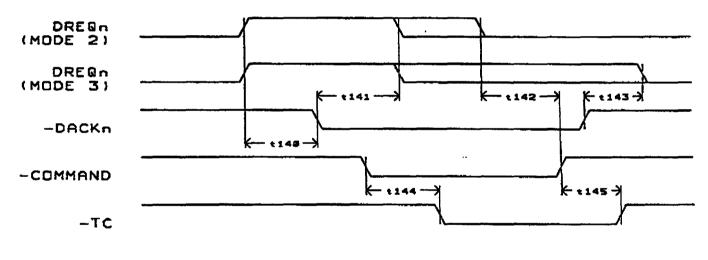

| 8.5        | Local Bus DREQ Timing                                                                                                             |     |

| Appendix   | A                                                                                                                                 |     |

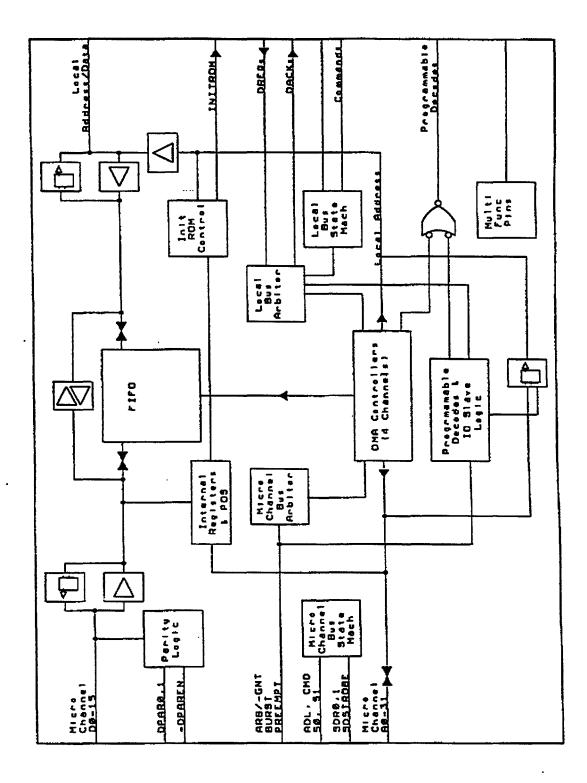

|            | 820614 Block Diagram                                                                                                              | 106 |

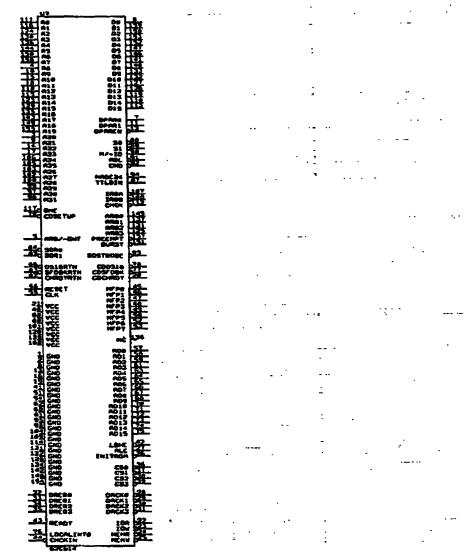

|            | 82C614 Bus Master/Suggested Logic Symbol                                                                                          | 107 |

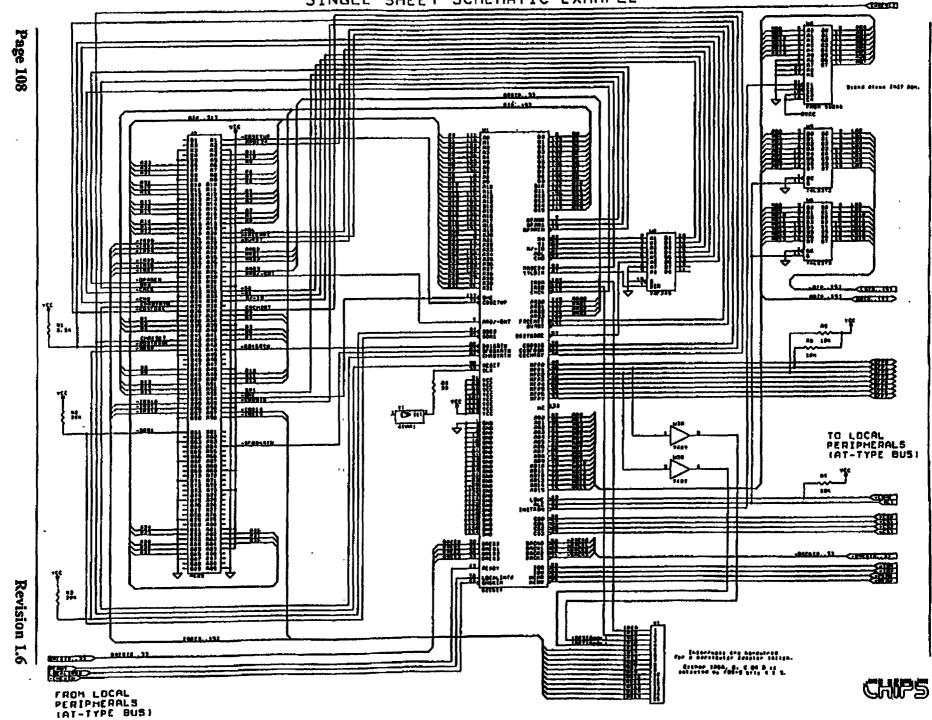

|            | 82(614 Application Example                                                                                                        | 102 |

|            | A                                                                                                                                 |     |

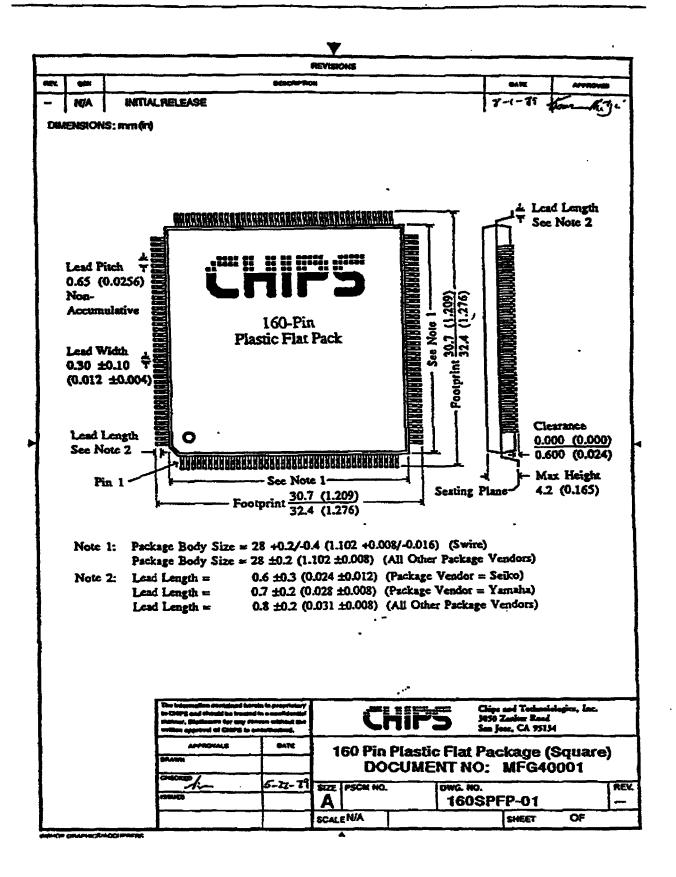

|            | 82C614 160 Pin Physical Dimensions                                                                                                |     |

### 1.0. Overview

The 82C614 is a chip for the MicroChannel Architecture that provides bus master capabilities to peripherals which would normally use the system board DMA controller. The advantage of doing this is greatly increased bandwidth (at least double for any given system) which means more time is available on the MicroChannel for other tasks. It also allows 4 concurrently operating DMA devices to share the same MicroChannel arbitration level.

Some of the possible applications for the 82C614 are as follows:

- SCSI Host Adapters

- High Performance Hard Disk Controllers

- Multiple high speed serial adapters

- High Performance LAN adapters

- Graphics adapters

- Modem and FAX adapters

- High Speed Printer Controllers

- ISDN adapters

The goal of this chip is to make it easy and cost effective enough that board designers will make almost every high-level function MicroChannel adapter a bus master instead of a DMA slave.

The 82C614 is a single 160 pin device which requires an absolute minimum of external logic to interface to both the MicroChannel and the local "Adapter Side." The 82C614 provides the following 3 major functions for a peripheral board:

- Complete interface between the MicroChannel and peripheral devices or memory. This includes converting the MicroChannel signals to read and write strobes which are more easily used by peripheral chips, adding programmed wait states, providing chip selects, and interrupt routing. The 82C614 also contains the data buffers between the MicroChannel and the peripheral devices.

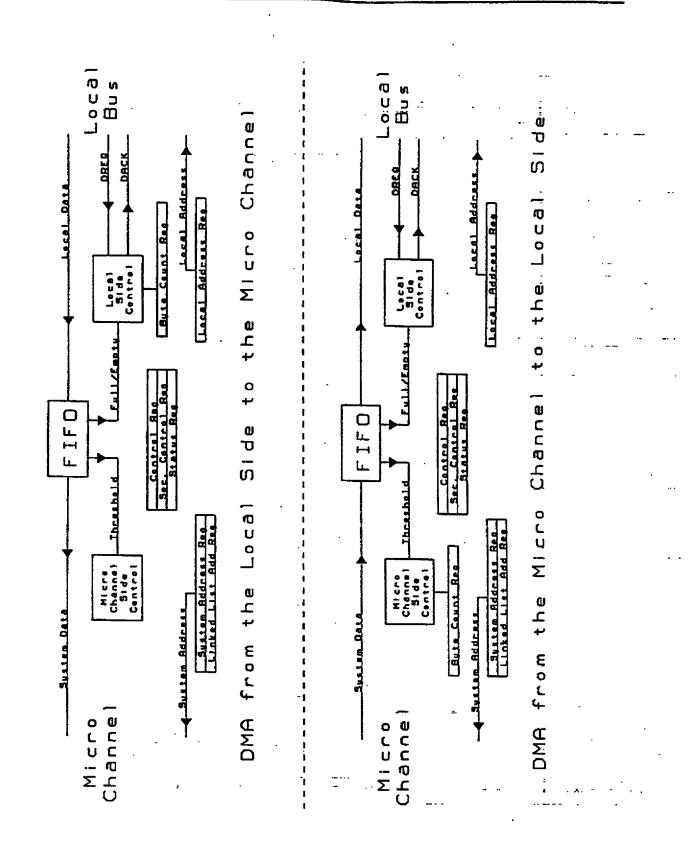

- Four DMA controllers with internal FIFO buffers. The FIFOs allow the data to be read from or written to the MicroChannel in blocks using burst mode and streaming data cycles (if supported by the system), while being written to or read from the local peripheral at what ever rate it requires. This reduces the amount of MicroChannel bandwidth required by the peripheral. On the local side, DMA REQuest and DMA ACKnowledge signals are provided to interface directly to the peripheral devices. In addition, a DMA address may be provided on the local side to DMA to or from I/O ports and memory areas. On the MicroChannel side the 82C614 performs the DMA transfers as a bus master.

| Page 4 |

|--------|

|--------|

The 82C614 contains all of the POS registers for the adapter card. It decodes the memory and/or I/O ranges used by the local peripherals and provides POS relocation for these decodes, allowing multiple boards  $(u_i = 0.8)$  of identical design to appear in the same system.

### 1.1 MicroChannel Interface

The 82C614 contains a complete interface to the MicroChannel that requires only one external TTL buffer. It arbitrates for use of the bus, and when granted the bus it generates and drives all of the necessary bus signals. The 82C614 supports a 32 bit address bus and a 16 bit data bus. The data bus has support for parity checking and generation.

The 82C614 supports fairness and burst transfer modes. It also contains a preempt timer that will transfer as much data as possible before relinquishing the bus.

The 82C614 also supports 100 ns streaming data transfers, thus allowing a maximum peak transfer rate of 20 megabytes per second. This compares favorably with the maximum transfer rate of 5 megabytes per second using the system board DMA controller in today's MicroChannel machines. Even without streaming data transfers, the 82C614 can transfer data at 10 megabytes per second - double the current DMA bandwidth.

For normal operation (as opposed to setup and configuration), the 82C614 is intended to be programmed from the MicroChannel Host Processor.

The 82C614 can cause an interrupt on the MicroChannel in response to a number of programmed conditions, or in response to a local interrupt input. It can also cause -CHCK to be asserted in response to a serious error. This can be due to internally detected conditions or in response to the local error input.

### **1.2 Local Interface**

The goal of the local interface is to provide a set of signals that look as much like the AT bus as possible, allowing the designer to easily convert existing designs. This also works out well for most peripheral chips. In addition to the standard signals, a group of Multifunction Pins allows further "customizing" of the local bus interface as required by an individual adapter card design.

The local bus interface supports a full 16 bit data path. In addition, 16 local address lines are available, multiplexed with the data lines.

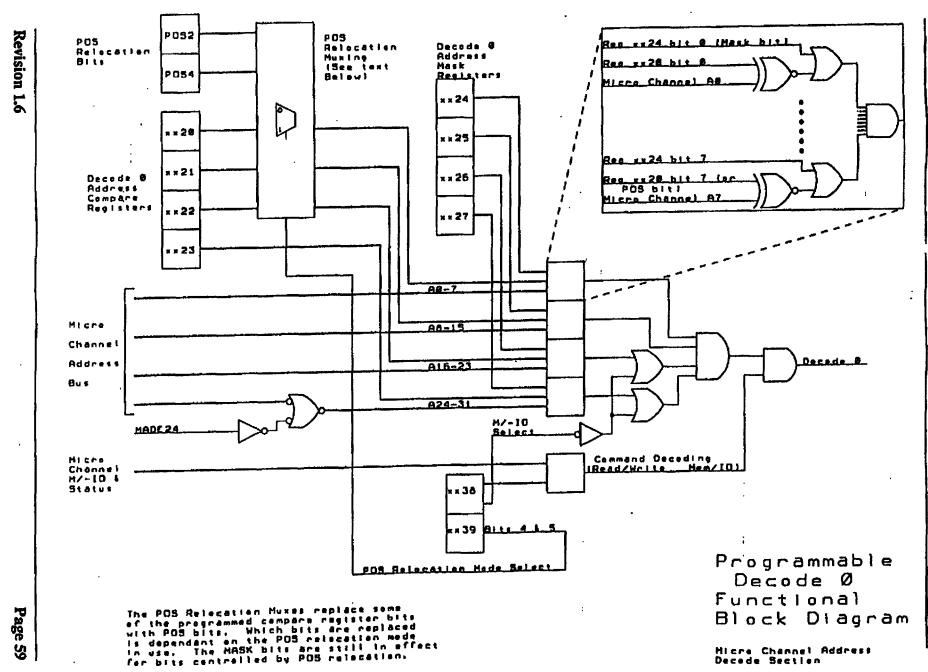

The 82C614 contains four programmable decodes which allow any type of MicroChannel access to produce a local side peripheral chip select. These programmable decodes have relocation control structures that are optimized for I/O, memory, and BIOS ROM spaces. Relocation can be controlled with the POS bits. Each decode can be programmed to respond to I/O cycles from the MicroChannel. One of the decodes may be programmed to respond to a memory range anywhere in the 32 bit address space, another may respond to a memory range in the bottom 1M only. They can be programmed to respond to Read cycles, Write cycles, or both. Each address bit may be compared to a 0, 1, or masked for a "don't care" condition. The number of wait states and the data size of the peripheral may also be programmed.

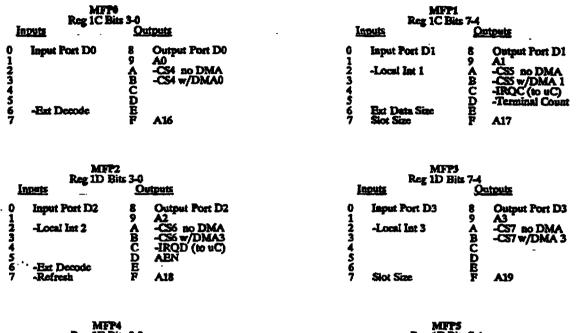

The 82C614 also contains 8 Multifunction Pins or MFPs. The board designer can customize the interface to fit the peripheral chips or functions being used with these pins. Some of the functions

which may be programmed include AEN, DMA Terminal Count, POS bits, local CPU interface, etc.

### **1.3 DMA Channels**

The 82C614 contains 4 independent DMA channels, but uses only one ARB level on the bus. This allows multiple devices to be resident on the same adapter card. It also allows "full duplex" DMA where one channel is dedicated to the "receive" function and another to the "transmit" function. This greatly reduces the software overhead on the host CPU and allows for greater system throughput since data can flow in both directions at the same time. This is only possible with a bus master implementation.

Each DMA channel has a DREQ and DACK line to interface to the peripheral chip. A local address may be provided for the peripheral access.

The 82C614 also supports linked list array chaining. This allows a series of commands to be placed in memory for the DMA Channel to execute. Once the list of commands is set up, all the host processor needs to do is issue a "start" command and the 82C614 will execute the entire sequence without any further processor intervention. Each entry of the linked list table provides the source and destination addresses, byte count, direction of transfer, and a pointer to the next linked list entry. The linked list entries are read from MicroChannel memory.

### 1.4 FIFO Buffers

In order to minimize the time spent on the bus, the 82C614 contains 80 bytes of FIFO buffer. This buffer may be allocated to the DMA channels in several ways to optimize for the application. All DMA transfers between the local devices and the MicroChannel go through the FIFO.

To minimize the time on the bus and prevent extra arbitration cycles from occurring, transfers on the MicroChannel side of the buffer may be non-contiguous. This means that if there is data waiting to be transferred for more than one DMA channel, all the data may be transferred in one burst even though the addresses are non-contiguous.

The buffer has programmable threshold levels to select the amount of space left in the FIFO before initiating a transfer on the MicroChannel. When transferring from the local side to the MicroChannel side, the buffer also has programmable "Flush" timers so that if the threshold has not been reached in a certain time, the transfer will be initiated anyway. This prevents data from being stuck in the buffer if the peripheral does not send data very often.

### **1.5 Initialization ROM**

Since the 82C614 requires more configuration bits than are supported by the POS mechanism, a facility is provided to download these bits from a small PROM located on the board. If the adapter board contains a BIOS ROM, the Initialization data may be contained in a section of it.

The board designer programs the INIT ROM to customize the 82C614 to the application. The INIT ROM provides the POS ID bytes, the I/O address for the 82C614's registers, the addresses (memory and/or I/O) for the local peripherals, and other configuration information.

Page 6

🔳 2098116 0009506 8T7 🔳

### 2.0 REGISTERS

The 82C614 registers occupy a block of 256 addresses in the MicroChannel I/O space. The 82C614 registers may be located anywhere in the I/O space, on a 256 port boundary. The I/O port range is determined by the INIT ROM and POS bits. A8-12 are set by the INIT ROM. POS register 2 defines A13-15 of the I/O address. This provides 8 different I/O locations, allowing up to 8 boards of identical design (same INIT ROM) to reside in the same system. In order to comply with the Assignable I/O Address mechanism, the INIT ROM should program A8-9 as 0s and A10-12 as 1s. The value written by the INIT ROM may be overwritten by an Extended POS access.

Within the 256 port block, there are 5 address ranges which are not used by the 82C614 and may be used by the local peripherals connected to the 82C614. There is one block of 32 ports and 4 blocks of 8 ports each available. The "Fixed Decodes" provide chip selects for these areas, and are available through the multifunction pins. When a peripheral uses a Fixed Decode, its I/O is addressed as if it were 82C614 registers. The 82C614 will respond to accesses to the entire 256 port range regardless of whether the fixed decodes are used.

### 2.1 Register Summary

RW = Read/Write RO = Read Only WO = Write Only

| I/O<br>Address | RW/<br>RO/WO | INIT<br>ROM<br>Load | Function                                                             |

|----------------|--------------|---------------------|----------------------------------------------------------------------|

| xx00           | RO           | N                   | Revision code of chip.                                               |

| <b>xx0</b> 1   | RO           | N                   | Features supported by chip.                                          |

| xx02           | RW           | N<br>Y              | Revision code of board.                                              |

| <b>xx</b> 03   | RW           | Ŷ                   | Features supported by board.                                         |

| xx04           | RW           | Y                   | MicroChannel side Configuration Register.                            |

| xx05           | RW           | Ŷ                   | Local Bus Configuration Register.                                    |

| xx06           | RW           | Ŷ                   | L/O address of 82C614 register set.                                  |

| xx07           | RŴ           | Ŷ                   | I/O address of 82C614 register set.<br>CDSLFBK, Card Size Indicator. |

|                | <b>D</b> 117 | 37                  |                                                                      |

| xx08           | RW           | Y                   | Fixed Decode Configuration.                                          |

| xx09           | RW           | Y                   | DMA Implicit I/O wait states.                                        |

| XX0A           | RW           | Y                   | CHCK Interrupt Enable Register.                                      |

| xx0B           | RW           | Y                   | CHCK status Register.                                                |

| xx0C           | RW           | Y                   | Internut Enable Register.                                            |

| xx0D           | RW           | Ŷ                   | Interrupt Enable Register.<br>Interrupt status Register.             |

| xx0E           | RW           | Ŷ                   | Reserved.                                                            |

| xx0F           | RW           | Ŷ                   | Multifunction pin I/O Port.                                          |

| ANUL           | IV 44        | •                   |                                                                      |

### 2.1 Register Summary (continued)

| I/O<br>Address | RW/<br>RO/WO | INIT<br>ROM<br>Load | Function                                                           |

|----------------|--------------|---------------------|--------------------------------------------------------------------|

| xx10-xx17      | •            | -                   | Reserved for future 82C614 Registers requiring INIT ROM setup.     |

| xx18           | RW           | Y                   | POS 0 alternate addressing (for loading by INIT ROM).              |

| xx19           | RW           | Y                   | POS 1 alternate addressing (for loading by INIT ROM).              |

| xx1A-xx1B      | -            | -                   | Reserved for future 82C614 Registers requiring INIT ROM setup.     |

| x1C-x1F        | RW           | Y                   | Multifunction Pin assignment.                                      |

| xx20-xx23      | RW           | Ŷ                   | Decode 0 Address Registers.                                        |

| xx24-xx27      | RW           | Ŷ                   | Decode 0 Mask Registers.                                           |

| xx28-xx2B      | RW           | Ŷ                   | Decode 1 Address Registers.                                        |

|                | IX VV        | 1                   | Decoue I Autiess Registers.                                        |

| xx2C-xx2F      | RW           | Y                   | Decode 1 Mask Registers.                                           |

| xx30-xx31      | RW           | Ŷ                   | Decode 2 Address Registers.                                        |

| xx32-xx33      | RW           | Ŷ                   | Decode 2 Mask Registers.                                           |

| xx34-xx35      | RW           | Ŷ                   | Decode 3 Address Registers.                                        |

| xx36-xx37      | RW           | Y                   | Decode 3 Mask Registers.                                           |

| xx38-xx3F      | RW           | Y                   | Decode 0-3 control                                                 |

| <b>xx</b> 40   | RW           | Ν                   | Buffer Testing Control Register.                                   |

| xx41           | RW           | N                   | Buffer Testing Data Register.                                      |

| xx42-xx47      | RW           | N                   | POS2-7 Alternate locations.                                        |

| xx48-xx4F      | -            | N                   | Reserved.                                                          |

| xx50-xx5F      | -            | N                   | Reserved for future 82C614 registers not requiring INIT ROM setup. |

| xx60-xx7F      | RW           | N                   | Decode #8 I/O space. Mapped to the local side.                     |

| xx80-xx97      | RW           | N                   | DMA Controller 0 Registers (some regs are RO or<br>WO).            |

| xx98-xx9F      | RW           | N                   | Decode #4 I/O space. Mapped to the local side.                     |

| xxA0-xxB7      | RW           | Ň                   | DMA Controller 1 Registers.                                        |

|                |              | ••                  | - 1.7 F AARWARAL V CARMENTS                                        |

| xxB8-xxBF      | RW           | N                   | Decode #5 I/O space. Mapped to the local side.                     |

| xxC0-xxD7      | RW           | N                   | DMA Controller 2 Registers.                                        |

| xD8-xDF        |              | N                   | Decode #6 I/O space. Mapped to the local side.                     |

| xxE0-xxF7      | RW           | Ň                   | DMA Controller 3 Registers.                                        |

| xxF8-xxFF      | RŴ           | Ň                   | Decode #7 I/O space. Mapped to the local side.                     |

.

### 2.2 POS Registers

These registers are accessed when in Card Setup Mode. They may also be accessed by I/O locations in the 82C614's normal I/O space when not in Card Setup Mode.

| Register   | Bit | Function                                                                                                                                                                                         |

|------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POS0, POS1 |     | Adapter ID Bytes.<br>Defined by the board designer. Loaded by the INIT<br>ROM.                                                                                                                   |

|            |     | XX at RESET. RO from System processor.<br>System processor reads 00 until the INIT ROM is fully<br>loaded. These registers may be read and written by the<br>system using I/O ports xx18 & xx19. |

| POS2       |     | Card Enable & I/O Select.<br>00 at RESET. RW. Also accessible through I/O address<br>xx42.                                                                                                       |

|            | 0   | Card Enable. 1=enable. Default at reset is 0.                                                                                                                                                    |

|            | 1-3 | I/O address selection. Used for bits 13-15 of system I/O address decode for 82C614 registers. Set to 0 at reset.                                                                                 |

|            | 4-7 | Programmable Decode Relocation. These bits specify<br>address bits A16-13 of any programmable decode<br>configured for 8K relocation. Used mainly for ROM BIOS<br>relocation.                    |

\_

\_\_\_\_

- ----

-----

| Register | Bit | Function                                                                                                                                                                                                                                                                                                  |

|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POS3     |     | Extended POS Register if POS7 not = 00. Extended POS is used for POS access of 82C614 register set and some local bus I/O.                                                                                                                                                                                |

|          |     | Standard POS Register if POS7 = 00.                                                                                                                                                                                                                                                                       |

|          |     | Arbitration Level, Parity, SFDBKRTN Check, &<br>Streaming Data Enable.<br>90 at RESET. RW. Also accessible through I/O address<br>xx43.                                                                                                                                                                   |

|          | 0-3 | Arbitration level which the 82C614 will use.                                                                                                                                                                                                                                                              |

|          | 4   | Fairness bit. When set to 1, fairness algorithm must be used.                                                                                                                                                                                                                                             |

|          | 5   | Parity check<br>0= no parity generated or checked. 1= Generate and<br>check MicroChannel Data Parity.                                                                                                                                                                                                     |

|          | 6   | Check SFDBKRTN. 1 enables checking SFDBKRTN<br>when a bus master, 0 disables. Register xx07 bit 4 must<br>also be a 1 for SFDBKRTN to be checked. Lack of<br>SFDBKRTN when checking is enabled will be indicated in<br>the appropriate DMA status register, and that DMA<br>channel will optionally halt. |

|          | 7   | Streaming Data cycle select.<br>0= allow streaming cycles,                                                                                                                                                                                                                                                |

|          |     | 1 = don't allow streaming cycles.                                                                                                                                                                                                                                                                         |

| POS4     |     | Extended POS Register if POS7 not = 00. Extended POS is used for POS access of 82C614 register set and some local bus I/O.                                                                                                                                                                                |

|          |     | Standard POS Register if POS7 = 00.<br>00 at RESET. RW. Also accessible through I/O address<br>xx44.                                                                                                                                                                                                      |

|          | 0-7 | Programmable Decode relocation bits. These can work multiple ways. See text.                                                                                                                                                                                                                              |

-----

- -

----

•

| Register | Bit  | Function                                                                                                                                                                                                                                       |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POS5     |      | Interrupt Select, MFP Outputs, Channel Check.<br>C0 at RESET. RW. Also accessible through I/O address<br>xx45.                                                                                                                                 |

|          | 0-1  | Interrupt Level used.                                                                                                                                                                                                                          |

|          |      | $\frac{10}{00} = IRQA (a dedicated pin).$<br>01 = IRQB (a dedicated pin).<br>10 = IRQC (a multifunction pin).<br>11 = IRQD (a multifunction pin).                                                                                              |

|          | 2-3  | Not used. Reserved.                                                                                                                                                                                                                            |

|          | 4-5  | Not used.                                                                                                                                                                                                                                      |

|          | 6    | Set to 0 when CHCK is asserted by the 82C614 to indicate that POS6 contains CHCK status. This bit is always the same as bit 7, and is read only.                                                                                               |

|          | 7    | Set to 0 when CHCK is asserted by the 82C614. Writing a 1 to this bit sets this bit and bit 6 to a 1, and clears all of the CHCK sources.                                                                                                      |

| POS6     |      | Extended POS Address Low & CHCK Status.<br>When POS5 bits 7-6 = 00, contains CHCK status and is<br>Read only. Otherwise, treated as extended POS address<br>register and is R/W. 00 at RESET. RW. Also accessible<br>through I/O address xx46. |

|          | 0    | CHCK status:<br>1 = Data parity error when written to as a slave.                                                                                                                                                                              |

|          | 1    | 1 = -CHCKIN input from local side active during<br>MicroChannel access to local device.                                                                                                                                                        |

|          | 2-7  | Always 0.                                                                                                                                                                                                                                      |

| POS7     | 8-15 | Extended POS Address.<br>00 at RESET. RW. Also accessible through I/O address<br>xx47.                                                                                                                                                         |

•

### 82C614 Data Sheet

### 2.3 I/O Port Registers

----

- --- -

| I/O Address | Bit | Function                                                                                                                                          |

|-------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|

| xx00        |     | Revision Code of the \$2C614.<br>RO (hardwired by chip design).<br>The INIT ROM will not overwrite the hardwired value.<br>00 = Initial revision. |

|             | 0-3 | For minor revision.                                                                                                                               |

|             | 4-7 | For major revision.                                                                                                                               |

| xx01        |     | Features supported by this Rev of the 82C614. 1=<br>Supported.                                                                                    |

|             |     | The INIT ROM will not overwrite the hardwired value.<br>RO (hardwired by chip design).                                                            |

|             | 0-7 | Reserved. Read as 0.                                                                                                                              |

| xx02        |     | Revision Code of Board.<br>These bits are defined by the designer of the adapter card.                                                            |

|             | 0-3 | It is suggested that these bits are used for minor Revisions.                                                                                     |

|             | 4-7 | It is suggested that these bits are used for major Revisions.                                                                                     |

|             |     | XX at reset. Set by INIT ROM. RW.                                                                                                                 |

| жк03        |     | Features supported by board.                                                                                                                      |

|             |     | 1 = Supported. These bits are defined by the designer of the adapter card.                                                                        |

|             |     | XX at RESET. Set by INIT ROM. RW.                                                                                                                 |

|             |     | 0-7 User defined.                                                                                                                                 |

Page 12

.

..

| I/O Address | Bit | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| xx04        |     | MicroChannel Side Configuration Register /Buffer<br>Allocation.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |     | XX at RESET. Set by INIT ROM. RW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | 0   | Arbitration method of the MicroChannel side of the DMA controllers. $0=$ rotating arbitration. $1=$ fixed arbitration (channel 0 is highest priority).                                                                                                                                                                                                                                                                                                                                                         |

|             | 1   | Halt DMA controllers on Channel Check. If a 1, all four<br>DMA controllers will halt if -CHCK goes low on the<br>MicroChannel (even if the 82C614 is not involved in the<br>operation). If 0 they will not halt.                                                                                                                                                                                                                                                                                               |

|             | 2   | Extended POS support. 0 disables extended support, 1 allows POS (register 3 and register 4) to become windows into extended POS.                                                                                                                                                                                                                                                                                                                                                                               |

| •.          | 3   | 128 byte relocation mode for Programmable Decodes.<br>0 = mode 0, 1 = mode 1.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | 4   | -PREEMPT Release. 0 = Conservative, 1 = Aggressive.<br>When programmed as Aggressive, the release time after -<br>PREEMPT will be extended (approximately doubled) by<br>the 82C614.                                                                                                                                                                                                                                                                                                                           |

| · .         | 5   | -CMD Active during Streaming Data. 0 = conservative, 1<br>= Aggressive. When programmed as Aggressive, the<br>-CMD active period is extended (approximately doubled)<br>by the 82C614.                                                                                                                                                                                                                                                                                                                         |

|             | 6-7 | Buffer configuration. These bits program how the 80 bytes<br>of FIFO buffer are divided amoung the 4 DMA channels.<br>The table below lists the number of bytes for each channel<br>for the 4 combinations of these bits. The buffer<br>configuration should be selected such that each device on<br>the local bus using DMA has enough FIFO space to<br>prevent overrun and underrun conditions. Performance<br>considerations should also be taken into account when<br>selecting the buffer configurations. |

|             |     | 76 CH0 CH1 CH2 CH3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             |     | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |     | 10 32 32 16 0 (channel 3 local to local<br>only)                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             |     | 11 64 16 0 0 (channels 2 & 3 local to local only)                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

**Revision 1.6**

Page 13

-

\_

| I/O Address | Bit | Function                                                                                                                                                                                                                                                                                                |

|-------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| xx05        |     | Local Bus Configuration Register.<br>XX at RESET. Set by INIT ROM.                                                                                                                                                                                                                                      |

|             | 0   | Arbitration method of local side of the DMA controllers.<br>0 = rotating arbitration. $1 = $ fixed arbitration.                                                                                                                                                                                         |

|             | 1   | Fixed priority order for the local side. $0 = priority$ order is 0-1-2-3. $1 = priority$ order is 3-2-1-0. Also affects direction for rotating priority.                                                                                                                                                |

|             | 2   | Local side arbitration time-out enable. Prevents a DMA channel from holding on to the local bus too long when other DMAs are pending. If a channel has had the bus for more than 4uS, it will not start a new bus cycle if a DMA from another channel is pending. $0=$ time-out disabled, $1=$ enabled. |

|             | 3   | Local side compressed timing. $0=$ normal timing (default) $1=$ compressed.                                                                                                                                                                                                                             |

|             | 4   | 8 bit data mode. When set to 8 bit data mode, AD8-15 are address only lines, and do not need a latch. The data path on the local side is only 8 bits wide. $1=8$ bit mode. $0=$ normal 16 bit mode.                                                                                                     |

|             | 5   | Address select for 8 bit data mode. Selects which address lines appear on AD8-15 when in 8 bit data mode. $0=A8-15$ . $1=A0-7$ . This bit has no effect when bit 4 is a 0. If bits 4 & 5 are both 1s, A8-15 are not available on the local side at all.                                                 |

|             | 6   | DREQ polarity. $0=$ active low, $1=$ active high. Active high is most common.                                                                                                                                                                                                                           |

|             | 7   | DACK polarity. 0=active low, 1=active high. Active low is most common.                                                                                                                                                                                                                                  |

| xx06        |     | I/O Address of 82C614 Register Set.<br>XX at reset. Set by INIT ROM. RW (with extreme<br>caution). INIT ROM should normally program a 1C at<br>this location to comply with the Assignable I/O Address<br>mechanism.                                                                                    |

|             | 0-4 | Selects address bits 8-12 for I/O accesses to the 82C614 register set. (Bits 13-15 are supplied by POS2 bits 1-3).                                                                                                                                                                                      |

|             | 5-7 | Not used.                                                                                                                                                                                                                                                                                               |

---- - - -

- - - **-**

\_

---

----

---

-

..

\_\_\_\_

\_

| I/O Address | Bit | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| xx07        |     | MicroChannel Side Card Size Indicator & wait states.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|             |     | XX at RESET. Bits 0-5 are RW, 6-7 are RO. Only bits 0-<br>5 are loaded by the INIT ROM.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | 0-1 | Bus Master timing. These bits adjust the timing parameters used to generate MicroChannel bus cycles when the 82C614 is a Bus Master.                                                                                                                                                                                                                                                                                                                                                                                                 |

|             | 0   | 0=Default cycle is 200nS. 1=default cycle is 300nS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | 1   | Reserved for future timing selections for MicroChannel<br>Master operation. Write as a 0.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             | 2-3 | Slave wait states. Determines the number of wait states<br>the 82C614 adds to register accesses when it is a slave.                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | 2   | 0=0 wait states, 1=1 wait state (additional 100nS - A<br>Synchronous Extended cycle).                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             | 3   | Reserved for future timing selections for MicroChannel slave operation. Write as a 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             | 4   | 1=Sample -SFDBKRTN when a bus master. 0=ignore.<br>Normally programmed the same as bit 5 since the<br>-SFDBKRTN signal is on the 32 bit extension. The DMA<br>registers specify the result of -SFDBKRTN being sampled<br>inactive.                                                                                                                                                                                                                                                                                                   |

|             | 5   | Card size bit. Tells the 82C614 what card size to assume.<br>Software will generally copy bit 7 of this register here. $0 = 16$ bit card size, $1 = 32$ bit card size. Only applies to the size of the address bus (24 or 32 bit) for the current rev of the 82C614. If the DMA controller attempts to do an access over 16M while programmed for a 16 bit slot, an error condition will occur which will be indicated in the particular DMA channel's status registers. The INIT ROM should generally program as a 1 (32 bit mode). |

|             | 6   | 1=bit 7 is valid. 0=bit 7 is always a 0.<br>This bit will be a 1 if either Multifunction Pin #1, #3, or<br>#7 is programmed to be the Card Size Indicator pin, and a<br>0 if none are programmed for this function.                                                                                                                                                                                                                                                                                                                  |

|             | 7   | Card Slot size. Indicates whether the adapter card<br>occupies a 16 bit or 32 bit card slot. Either Multifunction<br>Pin #1, #3, or #7 may be used for this. $1=32$ bit slot,<br>0=16 bit slot. This bit will read the inverted version of the<br>Multifunction pin. Always indicates 0 if the board has not<br>implemented this (the multifunction pin is used for<br>something else).                                                                                                                                              |

**Revision 1.6**

.

-

🖿 2098116 0009515 AOT 🖿

\_

\_

Page 15

| I/O Address | Bit | Function                                                                                                                                                                                                              |

|-------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| xx08        |     | Fixed Decode Configuration.                                                                                                                                                                                           |

|             | 0-1 | XX at RESET. RW.<br>Wait states added on the local bus when any fixed decode<br>is active.                                                                                                                            |

|             |     | $\frac{10}{00} = 0 \text{ wait states.}$<br>01 = 1  wait state (100nS added).<br>10 = 2  wait states (200nS added).<br>11 = 3  wait states (300nS added).                                                             |

|             | 2   | Data size for fixed decodes 4-7. $0=8$ bit, $1=16$ bit.                                                                                                                                                               |

|             | 3   | Data size for fixed decode 8. $0=8$ bit, $1=16$ bit.                                                                                                                                                                  |

|             | 4   | Buffered write enable when fixed decodes are active. $1 =$ enabled.                                                                                                                                                   |

|             | 5   | Data size when the External MicroChannel decode is<br>active. $1 = 16$ bit. $0 = 8$ bit. If Multifunction pin #1 is<br>programmed to provide the data size, that pin is inverted,<br>and ORed with this register bit. |

|             | 6-7 | Local Bus Minimum wait states. Sets the minimum<br>number of wait states for ALL local bus cycles. Same<br>encoding as bits 0-1 above.                                                                                |

| xx09        |     | DMA Implicit I/O wait states.<br>This register supplies the number of wait states added for<br>Implicit I/O cycles on the local bus for each DMA<br>channel. The encoding for each pair of bits is as follows:        |

|             |     | 00 = 0 wait states.<br>01 = 1 wait state (100nS added).<br>10 = 2 wait states (200nS added).<br>11 = 3 wait states (300nS added).                                                                                     |

|             |     | XX at reset. RW.                                                                                                                                                                                                      |

|             | 0-1 | DMA channel 0.                                                                                                                                                                                                        |

|             | 2-3 | DMA channel 1.                                                                                                                                                                                                        |

|             | 4-5 | DMA channel 2.                                                                                                                                                                                                        |

|             | 6-7 | DMA channel 3.                                                                                                                                                                                                        |

**2098116 0009516 746 🎟**

**Revision 1.6**

•

| I/O Address | Bit                                  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| xx0A        |                                      | CHCK Enable Register. Enables :e individual sources<br>for the CHCK interrupt. 1=interrupt enabled.<br>XX at RESET. Set by INIT ROM. RW.                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | 0                                    | Data parity error when written to as a slave.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             | 1                                    | -CHCKIN pin input local side during MicroChannel access to a local device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             | 2-7                                  | Not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| xx0B        |                                      | CHCK status Register. Gives the status of each source of<br>the CHCK interrupt. 1=device interrupting. Bits will be<br>active even if the interrupt is not enabled. When the<br>82C614 has issued a CHCK, POS6 contains a copy of this<br>register ANDed with the enable register (Reg 0Å).<br>Writing a 1 to the bit position will clear the interrupt.<br>Writing a 0 will leave it unchanged. Write a 1 to POS5 bit<br>7 will clear all bits in this register.<br>00 at RESET. RW. The INIT ROM should contain a 00,<br>which will have no effect on the register. |

|             | 0                                    | Data parity error when written to as a slave.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             | 1                                    | -CHCKIN input from local side during MicroChannel access to a local device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | 2-7                                  | Not used. Read as 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| жос         |                                      | Interrupt Enable Register. Enables the individual sources<br>for the standard interrupt. 1=interrupt enabled.<br>Register 0E bit 2 decides whether or not the interrupt goes<br>to the MicroChannel. If the destination is the<br>MicroChannel, POS5 bits 1-2 decide which IRQ pin is<br>used.                                                                                                                                                                                                                                                                        |

|             |                                      | XX at RESET. RW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|             | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | DMA Channel 0 interrupt enable.<br>DMA Channel 1 interrupt enable.<br>DMA Channel 2 interrupt enable.<br>DMA Channel 3 interrupt enable.<br>External Interrupt 0 input enable.<br>External Interrupt 1 input enable.<br>External Interrupt 2 input enable.<br>External Interrupt 3 input enable.                                                                                                                                                                                                                                                                      |

\_\_\_\_\_

Page 17

- ---- ----

•

•

### PRELIMINARY

-

### 82C614 Data Sheet

------

| I/O Address | Bit                                  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| xx0D        | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | Interrupt status Register. Gives the status of each source<br>of the standard interrupt. 1=device interrupting 0=device<br>not interrupting. Bits will be active even if interrupt not<br>enabled. Writing a 1 to bits 0-3 will clear the interrupt.<br>Writing a 0 will leave it unchanged. Bits 4-7 are straight<br>from the interrupt pins, and must be cleared by clearing<br>the external source. If an external interrupt is not<br>provided for by the multifunction pins, that bit position will<br>read as a 0.<br>X0 at RESET. RW INIT ROM should set to 00.<br>DMA 0 End of operation.<br>DMA 1 End of operation.<br>DMA 3 End of operation.<br>External Interrupt 0 (dedicated pin).<br>External Interrupt 1 (Multifunction pin).<br>External Interrupt 2 (Multifunction pin). |

| xx0E        | 7                                    | External Interrupt 3 (Multifunction pin).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| XXUE        |                                      | -INITROM pin configuration. Bit 7 is for the -INITROM<br>pin. 01 at RESET. The INIT ROM should program a 001<br>into the first 3 bits for future compatibility.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             | 0                                    | Program as 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | 1                                    | Program as 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | 2                                    | Program as 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | 3-6                                  | Not used. Read as 0s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|             | 7                                    | -INITROM status after init ROM load. 0=high,<br>1=tristated. See INIT ROM description for further<br>explanation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| xx0F        |                                      | Multifunction Pin Data Port. Each multifunction pin may<br>be programmed as an input port bit or an output port bit.<br>This register is the data register for the pins programmed<br>for this. A read of this register returns the value of all 8<br>Multifunction Pins regardless of how they are being used.<br>A write to this register writes to an internal latch. The<br>individual bits of the latch are sent to the corresponding<br>Multifunction Pin only if it is programmed as an Output<br>Port bit. XX at RESET. RW.                                                                                                                                                                                                                                                        |