# NEW IN THE 2001 EDITION:

ANALOG DEVICES

ADSP-219X

TIGERSHARC

MOTOROLA

DSP56800E

STARCORE SC140/

MOTOROLA MSC8101

Texas Instruments TMS320C55xx TMS320C64xx

IN INDEPENDENT EVALUATION OF THE MOST POPULAR PROCESSORS USED IN DSP

INCLUDES RESULTS FROM THE UPDATED AND EXPANDED VERSION OF THE **BDTI** BENCHMARKS™

#### © 2001 BERKELEY DESIGN TECHNOLOGY, INC. ALL RIGHTS RESERVED.

No part of this work may be reproduced in any form, stored in a retrieval system or transmitted by any means, electrical, mechanical, photographic, or otherwise, without the express written permission of Berkeley Design Technology, Inc., 2107 Dwight Way, Second Floor, Berkeley, CA 94704 USA.

#### RESTRICTED RIGHTS LEGEND

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

BERKELEY DESIGN TECHNOLOGY, INC. 2107 Dwight Way, Second Floor Berkeley, CA 94704

Unpublished — rights reserved under the copyright laws of the United States.

While every reasonable precaution has been taken in the preparation of this work to ensure accuracy of the information contained herein, Berkeley Design Technology, Inc., and its agents by necessity assume no responsibility for accuracy, errors or omissions, or for the uses made of any information and/or material contained herein or the decisions based on such use. NO WARRANTIES ARE MADE, EXPRESS OR IMPLIED, WITH REGARD TO THE CONTENTS OF THIS WORK, ITS MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE. BERKELEY DESIGN TECHNOLOGY, INC., AND ITS AGENTS SHALL NOT BE RESPONSIBLE FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES ARISING OUT OF THE USE AND/OR RELIANCE ON THE CONTENTS OF THIS WORK.

| Buyer's Guide to DSP Processors                                                      |    |           |               |             |    |

|--------------------------------------------------------------------------------------|----|-----------|---------------|-------------|----|

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

| Throughout this report, trademark name occurrence, we hereby state that we intention |    | the names | only in an ed |             |    |

|                                                                                      | or |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           | ř             |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      | 4  |           |               |             |    |

| ·                                                                                    |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             | V, |

|                                                                                      |    | •         |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               |             |    |

|                                                                                      |    |           |               | eley Design |    |

# Tired of borrowing Buyer's Guide to DSP Processors?

Get your own copy!

If your company has already purchased a copy of Buyer's Guide to DSP Processors, 2001 Edition you are eligible for a substantial discount! Contact BDTI for details.

> Berkeley Design Technology, Inc. 2107 Dwight Way, Second Floor Berkeley, CA 94704 USA

Telephone: +1 (510) 665-1600 Fax: +1 (510) 665-1680 E-mail: info@BDTI.com WWW: http://www.BDTI.com

Please, don't break the law. This publication may not be photocopied or reproduced without the express permission of Berkeley Design Technology, Inc.

# Support

For questions or comments regarding this report and information on updates and related reports and services, contact:

Berkeley Design Technology, Inc. 2107 Dwight Way, Second Floor Berkeley, CA 94704 USA

Telephone: +1 (510) 665-1600 Fax: +1 (510) 665-1680 Email: info@BDTl.com WWW: http://www.BDTl.com

Please complete and return a photocopy of the registration form on the following page to ensure that you receive timely information regarding updates to this report.

# **Excerpt Policy**

No part of this work may be reproduced in any form without the express written permission of Berkeley Design Technology, Inc.

Please contact us for information about our established policy regarding the use of excerpts from this work.

# **Registration Form**

To ensure that you receive timely information regarding updates to this report, please photocopy, complete, and return this form by mail or fax to:

# Berkeley Design Technology, Inc. 2107 Dwight Way, Second Floor Berkeley, CA 94704 USA

Fax: +1 (510) 665-1680

| Your Name                         |                                        |

|-----------------------------------|----------------------------------------|

| Title                             |                                        |

| Company Name                      |                                        |

| Mail Stop                         |                                        |

| Street Address                    |                                        |

| City/State/Postal Code            |                                        |

| Country                           |                                        |

| Telephone                         |                                        |

| Fax                               |                                        |

| Email Address                     |                                        |

| DSP<br>Application(s)             |                                        |

| DSP Processors Used<br>(If Any)   |                                        |

| How did you learn of this report? |                                        |

| Comments                          |                                        |

| Report Title                      | Buyer's Guide to DSP Processors (0101) |

#### **Table of Contents**

#### 1. Introduction 1

Scope and Purpose 1

Changes in the 2001 Edition 1

Organization 2

Related Resources 3

# 2. About the Authors 5

Primary Authors 6 Contributors 7 Acknowledgments 7

# 3. Digital Signal Processing and DSP Systems 9

Advantages of DSP 9

Characteristics of DSP Systems 10

Execution-Time Predictability 14

Classes of DSP Applications 17

# 4. Processor Architectures and Performance 21

Architectural Features for DSP 21 Classes of Processors for DSP 23 Hybrid Processors 29 Processor Embodiments 30 Performance Issues 35

# 5. Processors Not Covered in This Report 39

General-Purpose Processors and Hybrids 39 DSP Cores 39 Other DSP Processors 40

# 6. Choosing a Processor 41

The "Best" Processor 41

Selection Methodology 41

Performance Measures 42

#### 6.1 Application Profiling 43

Profiling Approaches 43

Limitations of Profiling Techniques 44

Benchmarks and Profiling Data 45

Application Profiling Examples 45

#### 6.2 Function-Level Profiling 47

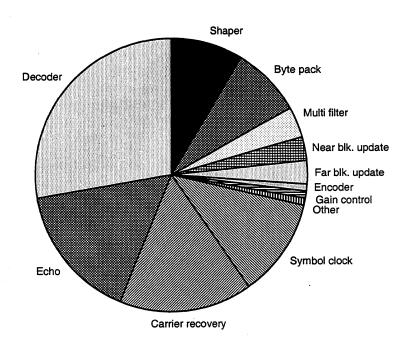

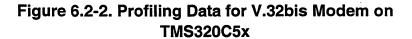

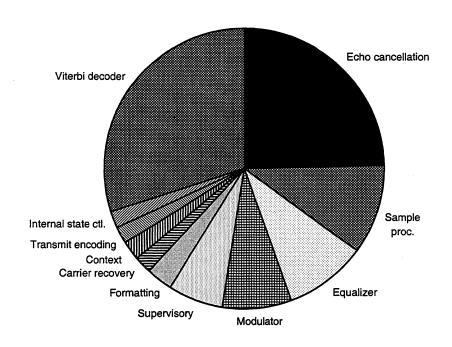

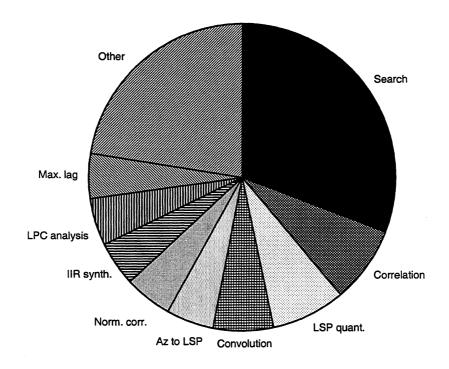

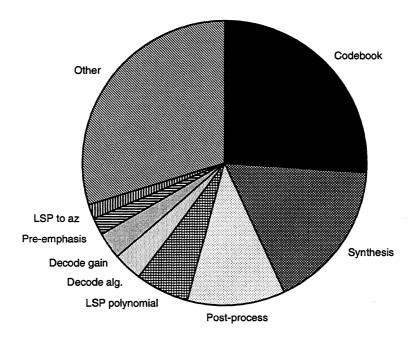

V.32bis Modem 49

V.17 Modem Receiver 55

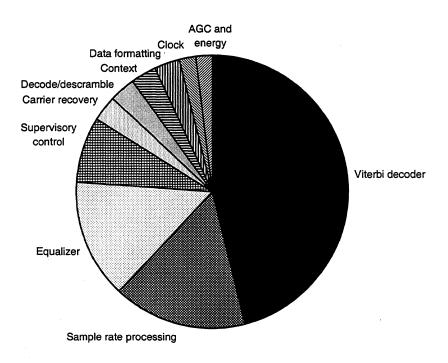

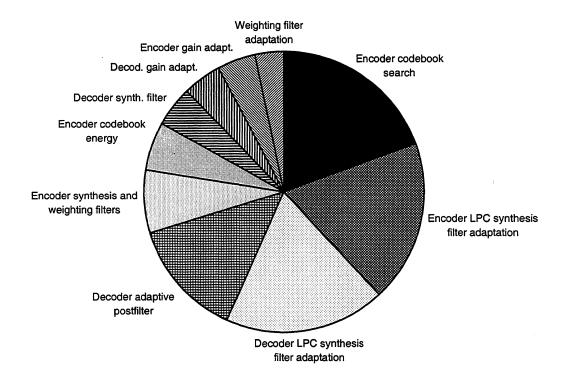

G.728 Speech Encoder 59

G.728 Speech Encoder and Decoder 63

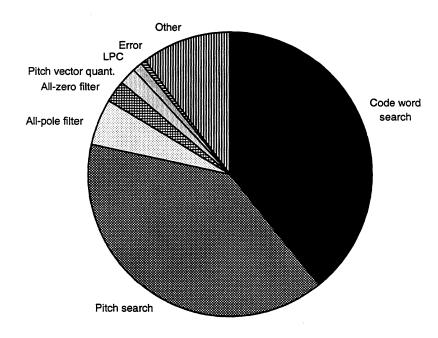

USFS 1016 CELP Speech Encoder 67

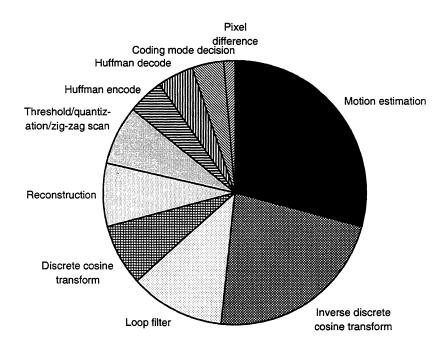

H.261 Video Encoder and Decoder 71

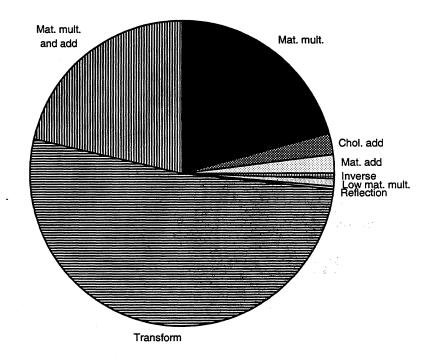

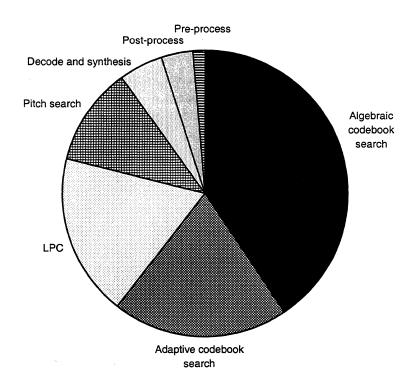

Adaptive Beamformer 75 GSM Speech Coder 79

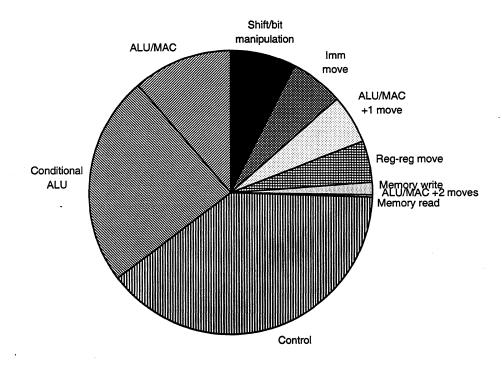

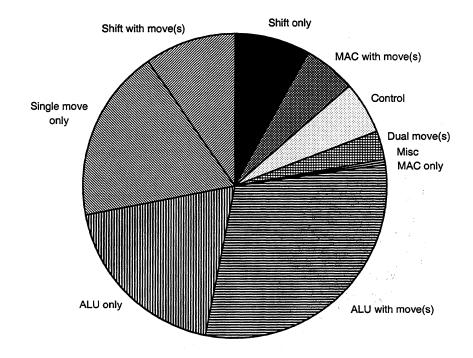

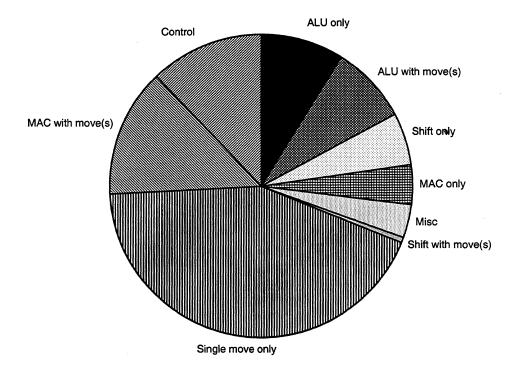

#### 6.3 Instruction-Level Profiling 87

**GSM Channel Coder 89**

**GSM Digital Receiver 93**

**GSM Speech Coder 97**

ADPCM Speech Coder 105

# 7. Processor Analyses 111

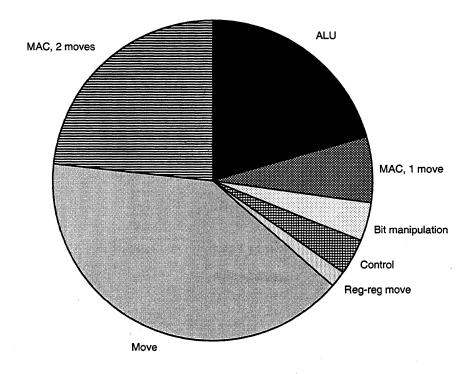

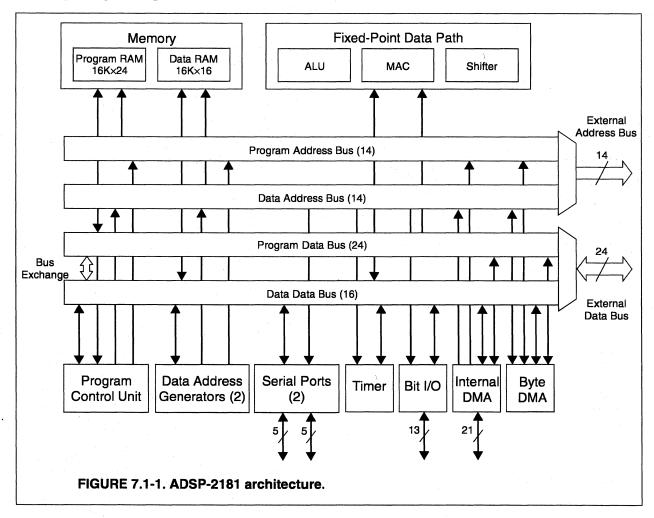

# 7.1 Analog Devices ADSP-21xx Family 115

Introduction 115

Architecture 115

Instruction Set 123

Execution Control 126

Peripherals 129

On-Chip Debugging Support 131

Power Consumption and Management 131

Benchmark Performance 132

Cost 135

Fabrication Details 135

Development Tools 135

Applications Support 138

Advantages 141

Disadvantages 142

#### 7.2 Analog Devices ADSP-219x Family 143

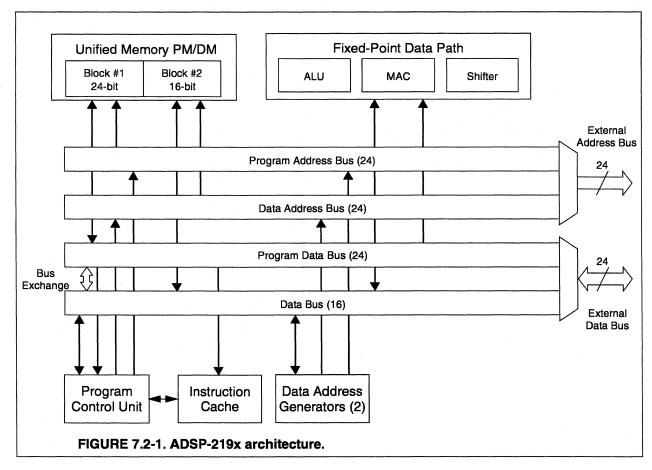

Introduction 143

Architecture 143

Instruction Set 148

Execution Control 152

Benchmark Performance 155

Development Tools 158

Applications Support 158

Advantages 158

Disadvantages 159

#### 7.3 Analog Devices ADSP-2106x Family 16

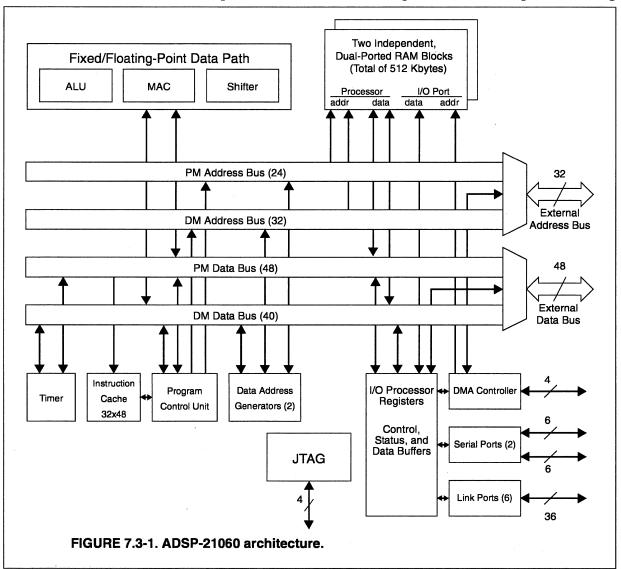

Introduction 161

Architecture 162

Instruction Set 170

**Execution Control** 174

Peripherals 176

On-Chip Debugging Support 179

Power Consumption and Management 180

Benchmark Performance 180

Cost 184

Fabrication Details 184

Development Tools 184

Applications Support 186

Advantages 186

Disadvantages 187

#### 7.4 Analog Devices ADSP-2116x Family 189

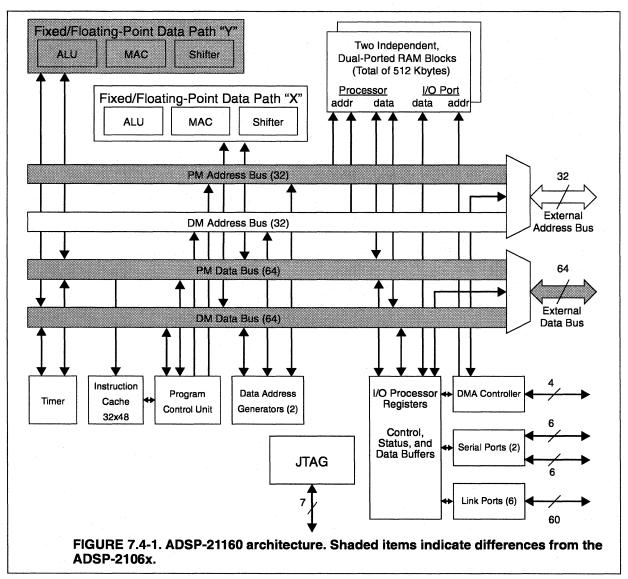

Introduction 189

Architecture 190

Instruction Set 195

Execution Control 196

Peripherals 197

On-Chip Debugging Support 197

Power Consumption and Management 198

Benchmark Performance 198

Cost 201

Fabrication Details 202

Development Tools 202

Applications Support 202

Advantages 202

Disadvantages 203

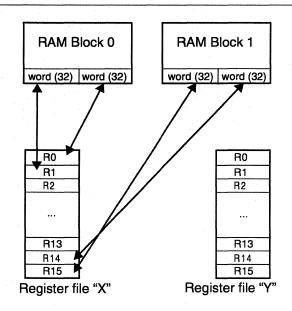

#### 7.5 Analog Devices ADSP-TS0xx Family 205

Introduction 205

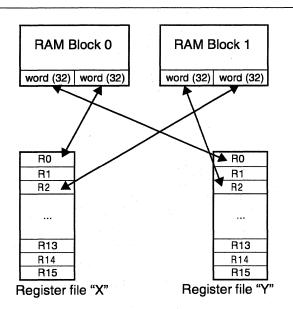

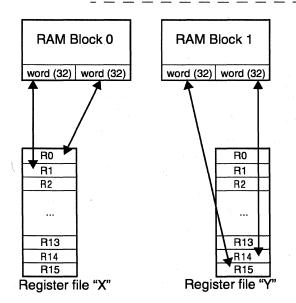

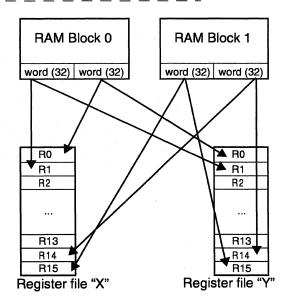

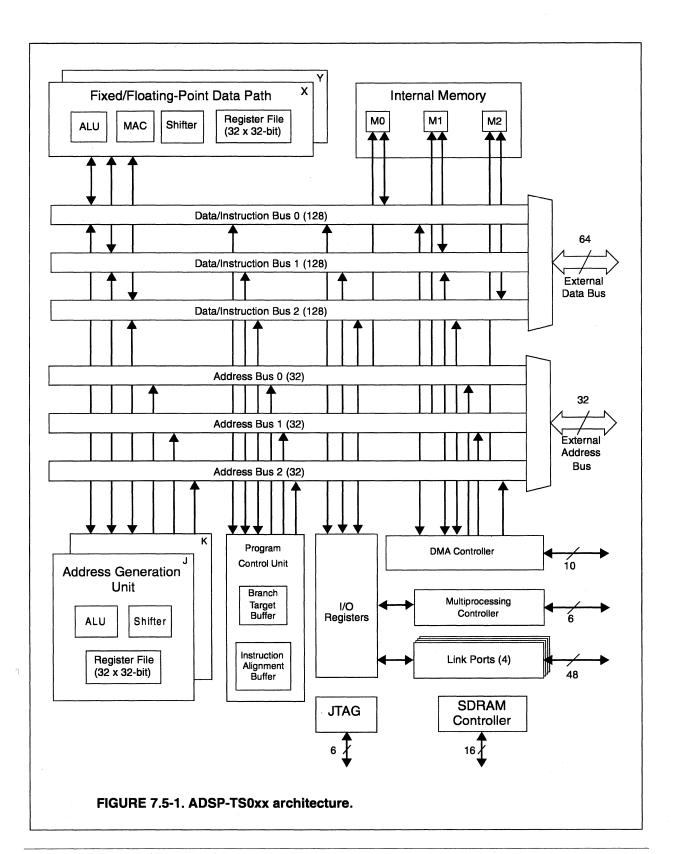

Architecture 206

Instruction Set 220

Execution Control 226

Peripherals 228

On-Chip Debugging Support 231

Power Consumption and Management 231

Benchmark Performance 231

Cost 232

Fabrication Details 232

Development Tools 232

Applications Support 233

Advantages 233

Disadvantages 234

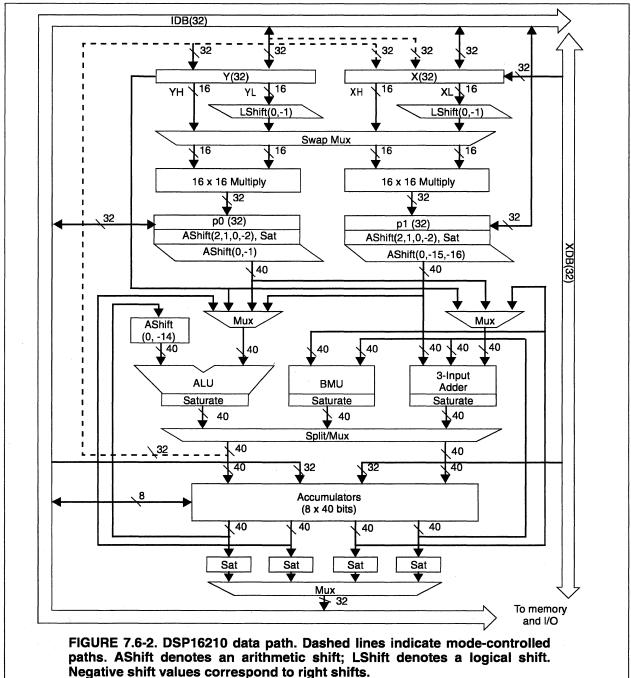

# 7.6 Lucent Technologies DSP16xxx Family 235

Introduction 235

Architecture 235

Instruction Set 245

Execution Control 250

Peripherals 253

On-Chip Debugging Support 255

Power Consumption and Management 256

Benchmark Performance 257

Cost 260

Fabrication Details 260

Development Tools 260

Applications Support 262

Advantages 262

Disadvantages 263

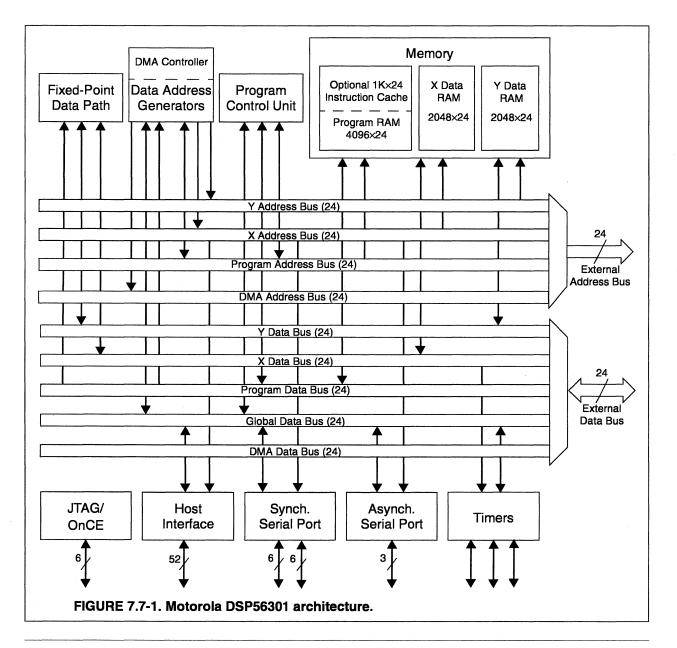

#### 7.7 Motorola DSP563xx Family 265

Introduction 265

Architecture 266

Instruction Set 274

Execution Control 278

Peripherals 280

On-Chip Debugging Support 284

Power Consumption and Management 285

Benchmark Performance 285

Cost 288

Fabrication Details 288

Development Tools 289

Applications Support 290

Advantages 290

Disadvantages 291

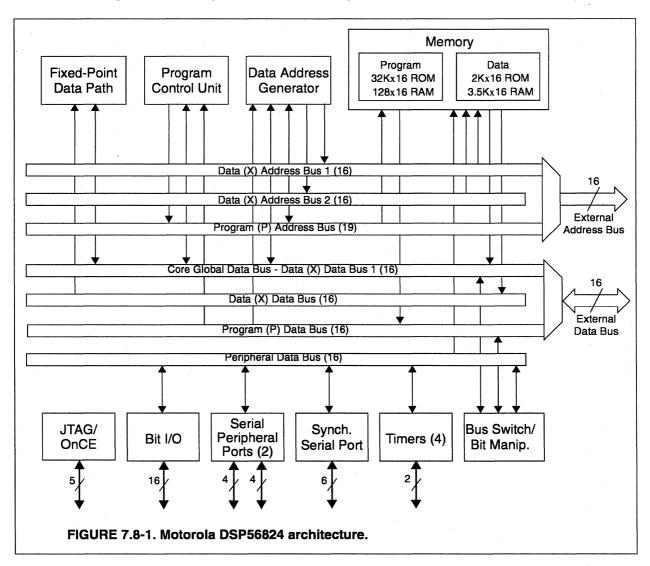

#### 7.8 Motorola DSP568xx Family 293

Introduction 293

Architecture 294

Instruction Set 299

Execution Control 302

Peripherals 305

On-Chip Debugging Support 309

Power Consumption and Management 309

Benchmark Performance 309

Cost 313

Fabrication Details 313

Development Tools 313

Applications Support 314

Advantages 315

Disadvantages 315

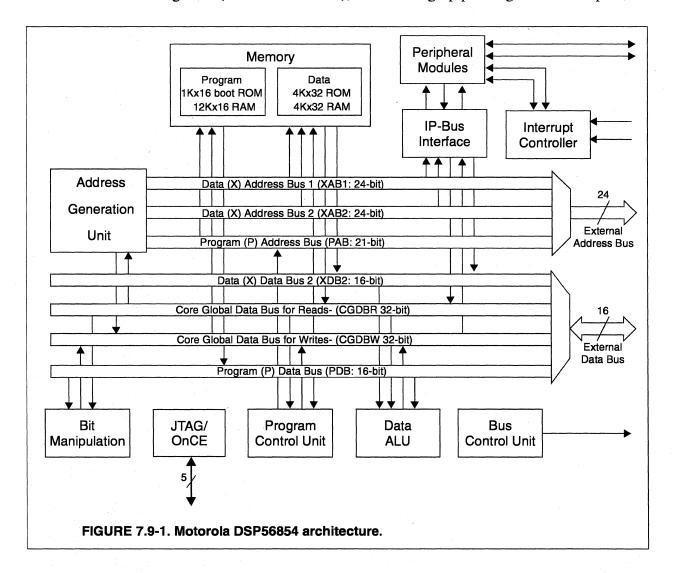

# 7.9 Motorola DSP5685x Family 317

Introduction 317

Architecture 318

Instruction Set 326

Execution Control 331

Peripherals 334

On-Chip Debugging Support 335

Power Consumption and Management 335

Benchmark Performance 336

Cost 340

Fabrication Details 340

Development Tools 340

Applications Support 341

Advantages 341

Disadvantages 342

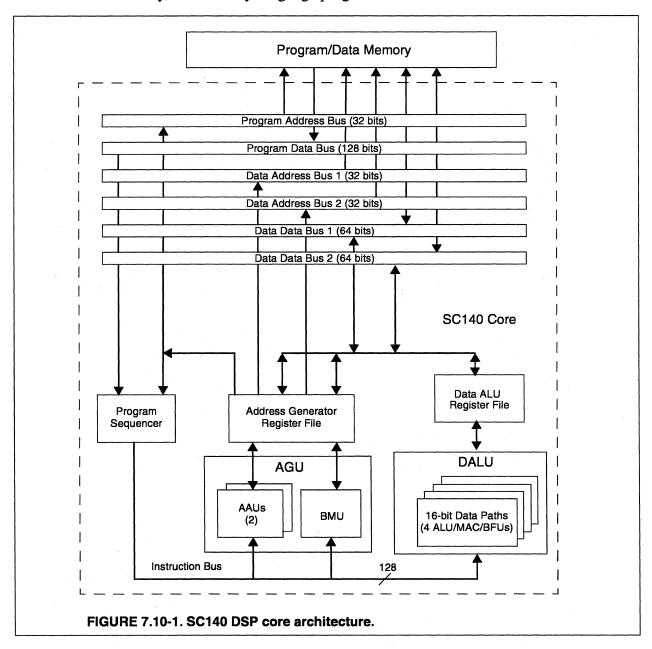

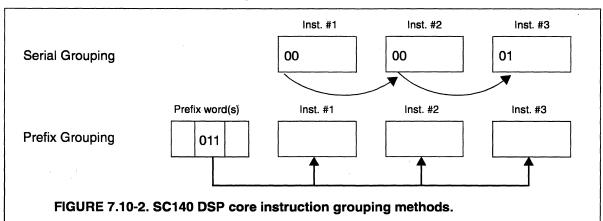

#### 7.10 StarCore SC140 Core, Motorola MSC8101 343

Introduction 343

Architecture 344

Instruction Set 352

Execution Control 358

Peripherals 361

On-Chip Debugging Support 362

Power Consumption and Management 363

Benchmark Performance 364

Cost 373

Fabrication Details 373

Development Tools 373

Applications Support 374

Advantages 374

Disadvantages 375

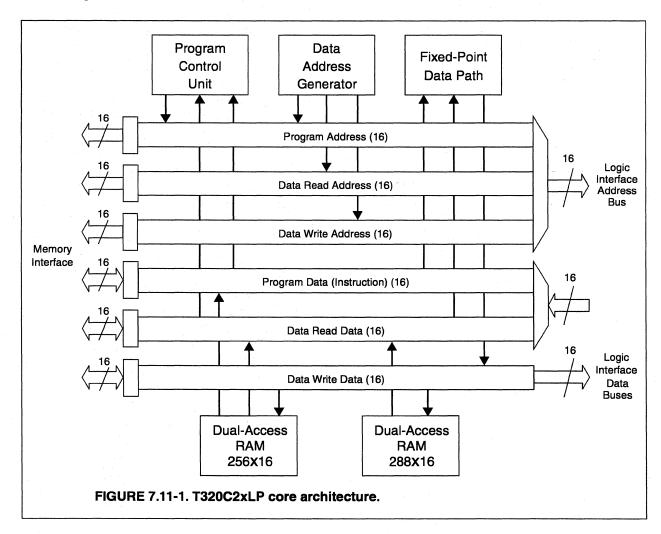

# 7.11 Texas Instruments TMS320C2xxx Family and T320C2xLP Core 377

Introduction 377

Architecture 380

Instruction Set 387

Execution Control 391

Peripherals 394

On-Chip Debugging Support 397

Power Consumption and Management 397

Benchmark Performance 398

Cost 400

Fabrication Details 400

Development Tools 400

Applications Support 402

Advantages 402

Disadvantages 403

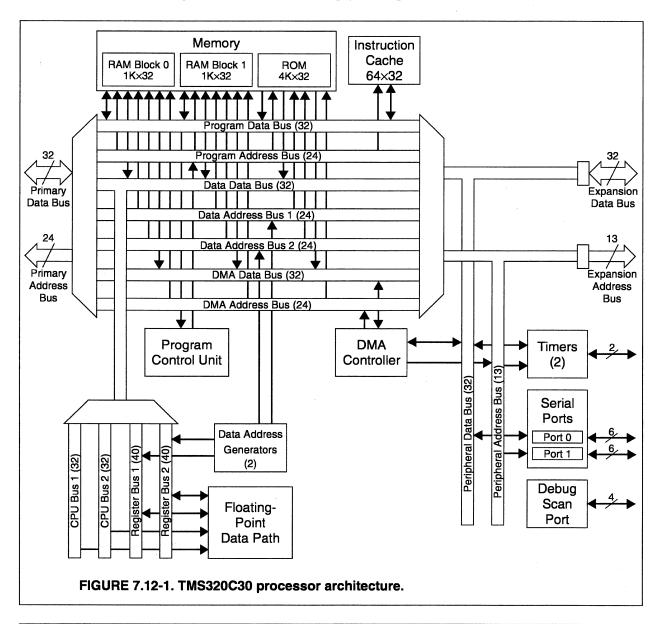

#### 7.12 Texas Instruments TMS320C3x Family 405

Introduction 405

Architecture 406

Instruction Set 413

Execution Control 416

Peripherals 418

On-Chip Debugging Support 419

Power Consumption and Management 419

Benchmark Performance 420

Cost 422

Fabrication Details 422

Development Tools 423

Applications Support 424

Advantages 424

Disadvantages 425

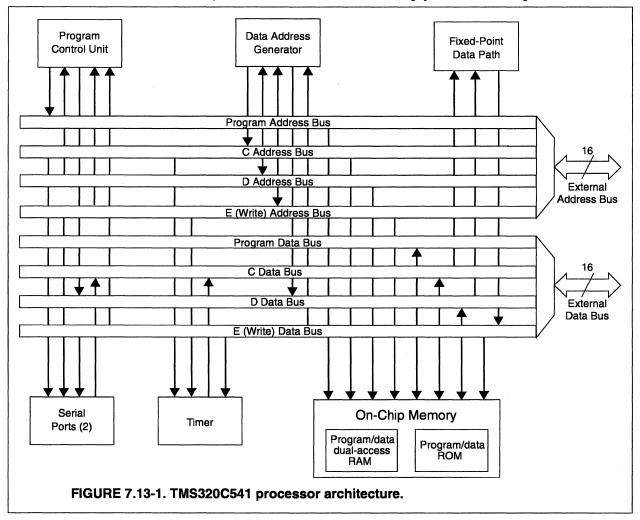

# 7.13 Texas Instruments TMS320C54xx Family 427

Introduction 427

Architecture 427

Instruction Set 437

Execution Control 441

Peripherals 444

On-Chip Debugging Support 448

Power Consumption and Management 448

Benchmark Performance 448

Cost 452

Fabrication Details 452

Development Tools 454

Applications Support 454

Advantages 455 Disadvantages 455

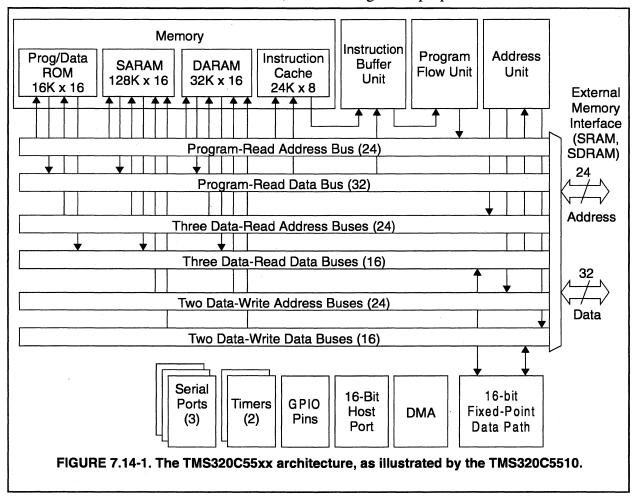

#### 7.14 Texas Instruments TMS320C55xx Family 457

Introduction 457

Architecture 458

Instruction Set 471

Execution Control 477

Peripherals 481

On-Chip Debugging Support 484

Power Consumption and Management 485

Benchmark Performance 485

Cost 492

Fabrication Details 493

Development Tools 493

Applications Support 494

Advantages 494

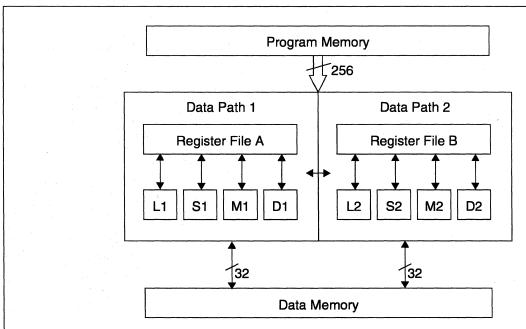

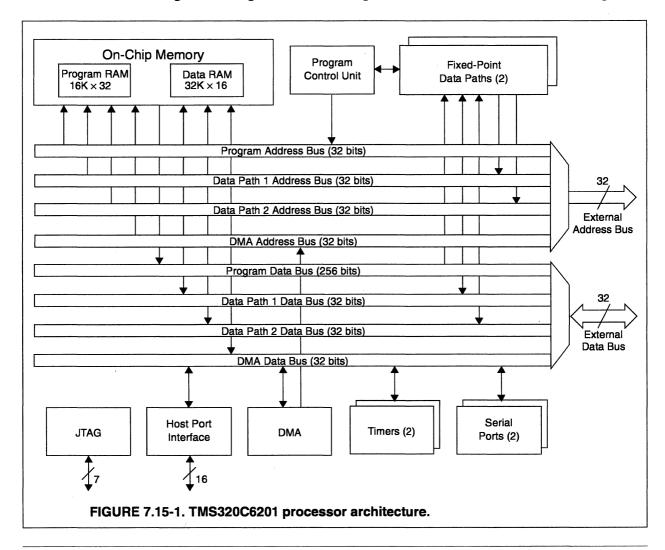

#### 7.15 Texas Instruments TMS320C62xx Family 497

Introduction 497

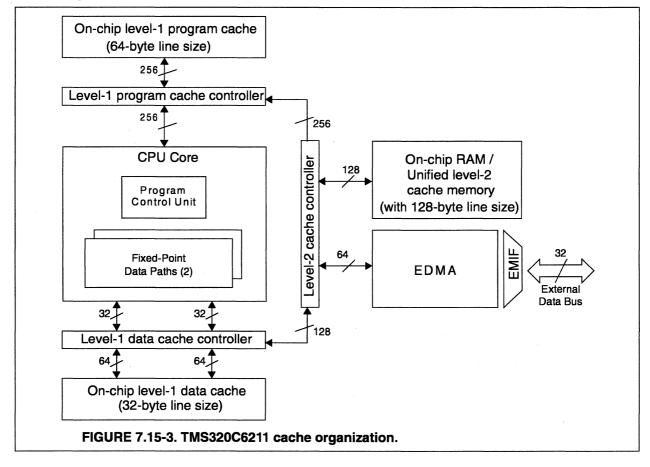

Architecture 500

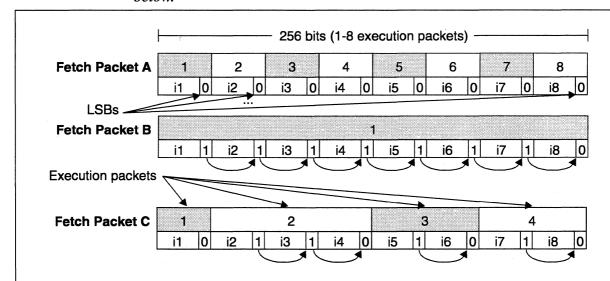

Instruction Set 516

Execution Control 520

Disadvantages 495

Peripherals 523

On-Chip Debugging Support 528

Power Consumption and Management 529

Benchmark Performance 530

Cost 537

Fabrication Details 537

Development Tools 537

Applications Support 543

Advantages 543

Disadvantages 544

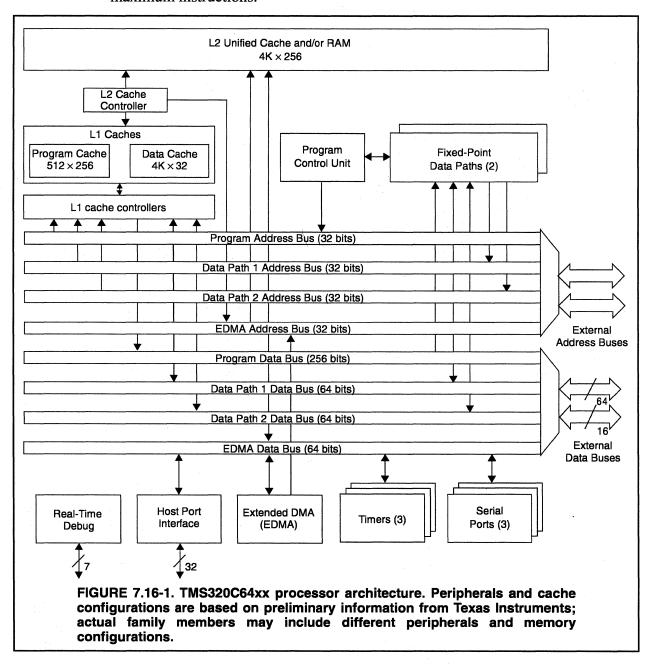

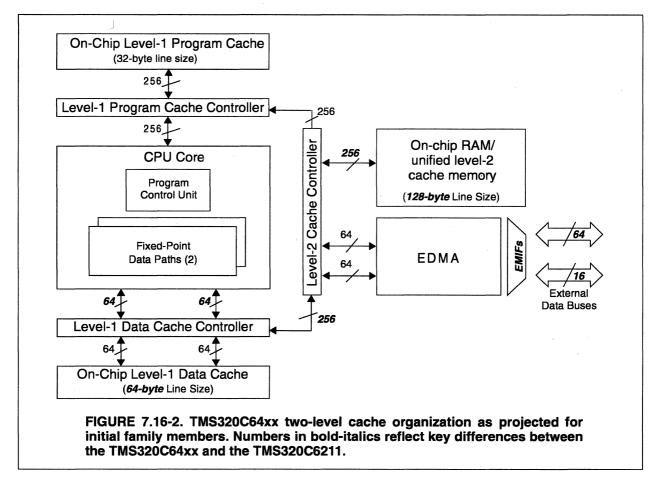

#### 7.16 Texas Instruments TMS320C64xx Family 545

Introduction 545

Architecture 547

Execution Control 568

Peripherals 570

On-Chip Debugging Support 571

Power Consumption and Management 571

Benchmark Performance 571

Memory Usage 576

Cost 578

Fabrication Details 579

Development Tools 579

Applications Support 579

Advantages 580

Disadvantages 580

#### 7.17 Texas Instruments TMS320C67xx Family 581

Introduction 581

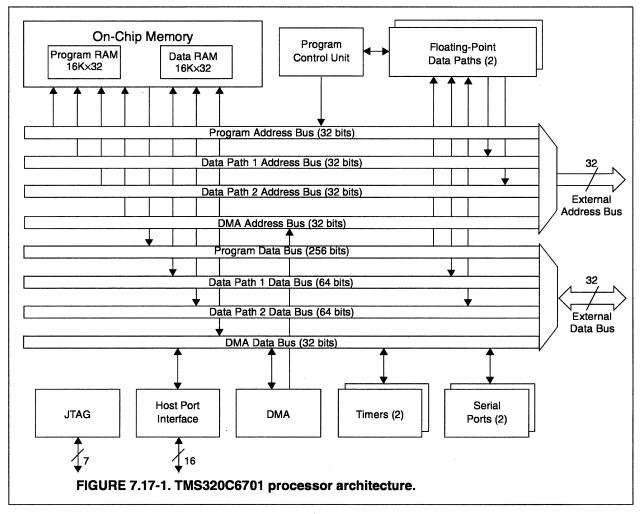

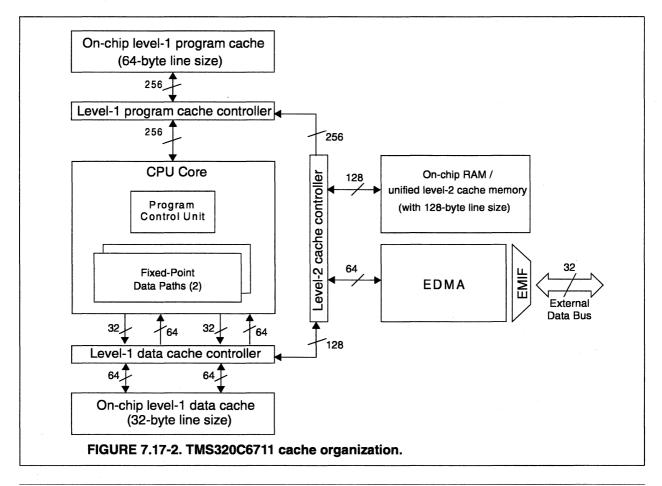

Architecture 583

Instruction Set 590

Execution Control 592

Peripherals 593

On-Chip Debugging Support 593

Power Consumption and Management 594

Benchmark Performance 594

Cost 601

Fabrication Details 602

Development Tools 602

Applications Support 603

Advantages 603

Disadvantages 604

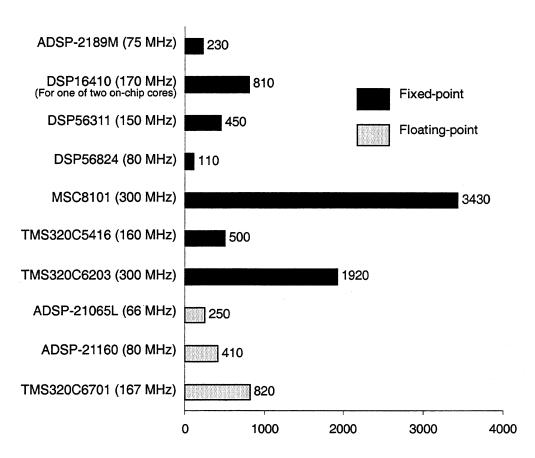

#### 8. BDTI Benchmark™ Results 605

The Need for Benchmarks 605

Benchmarking Approaches 606

Benchmarking Limitations 609

Processors Benchmarked 610

Organization of Benchmarking Results 612

Benchmark Specification and Methodology 613

| Notation 6 | 122 |

|------------|-----|

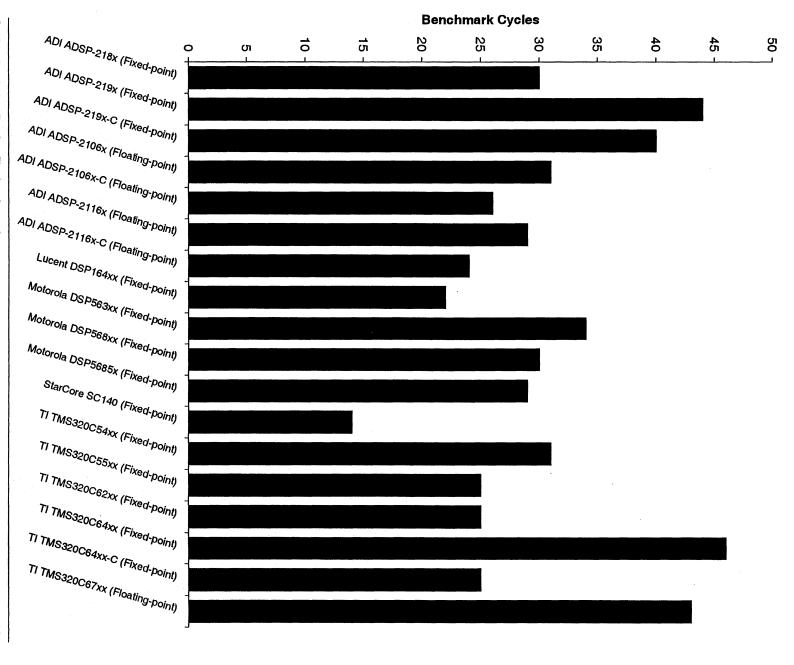

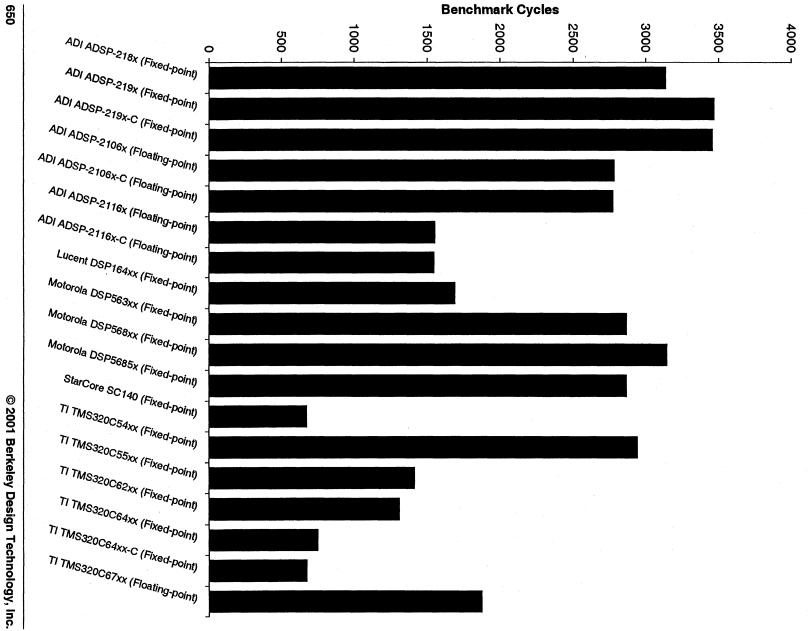

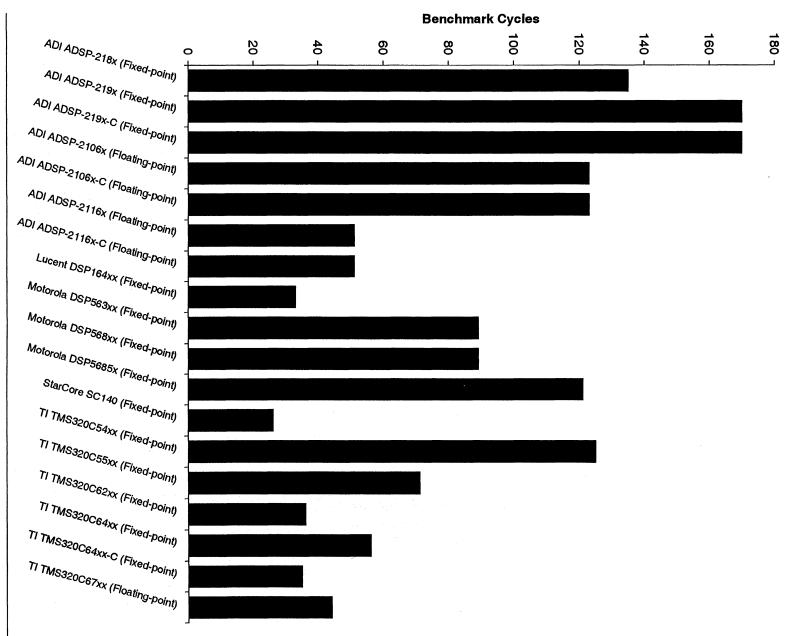

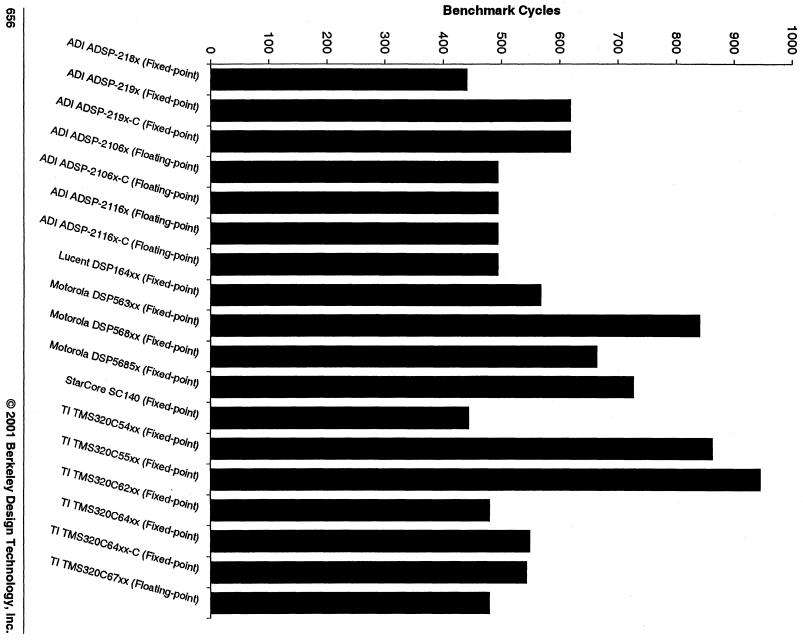

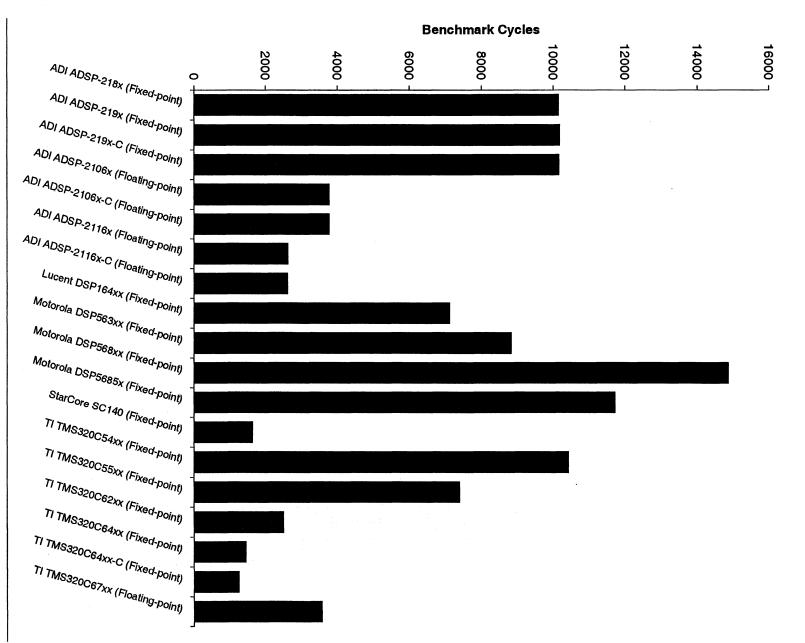

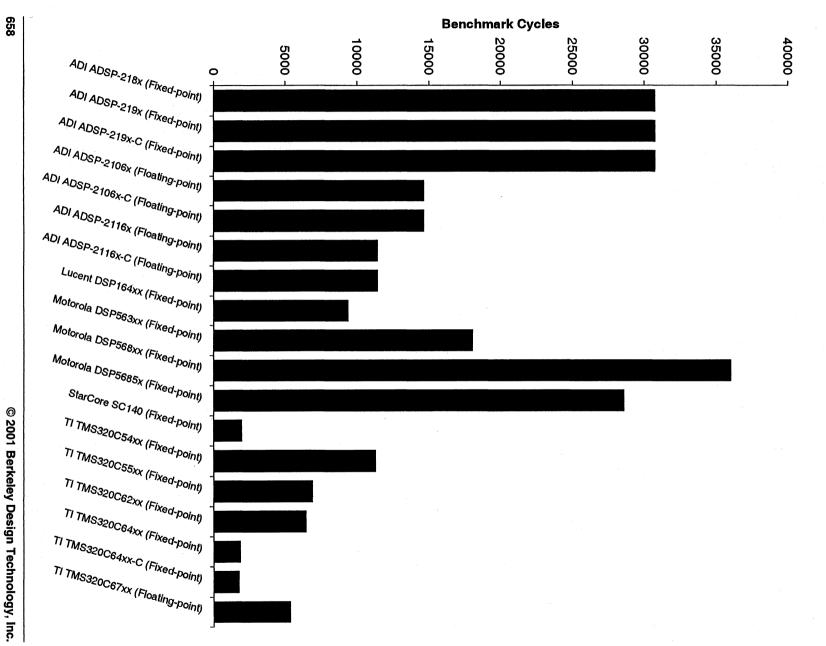

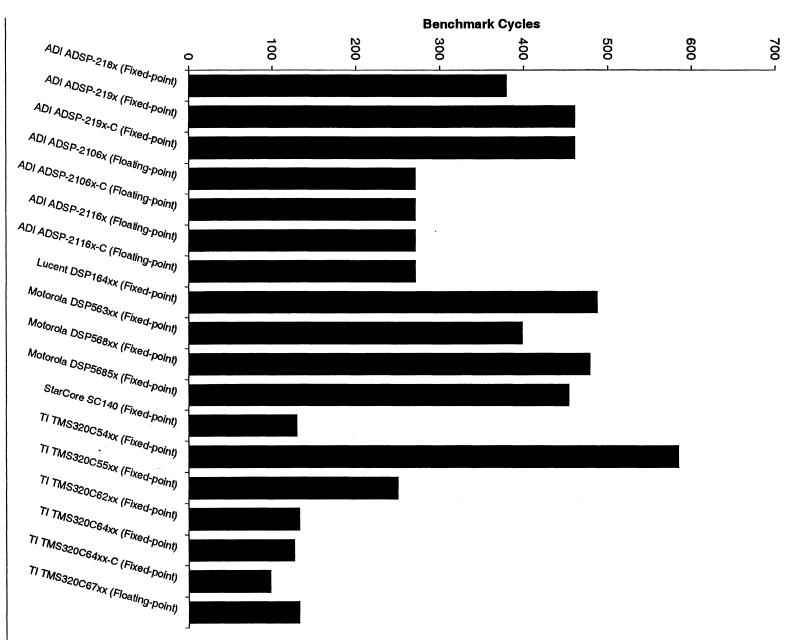

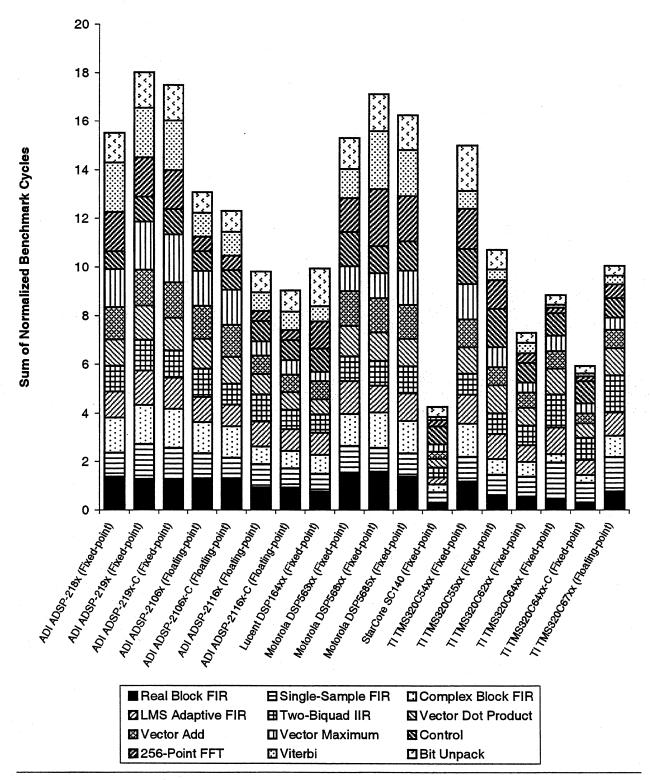

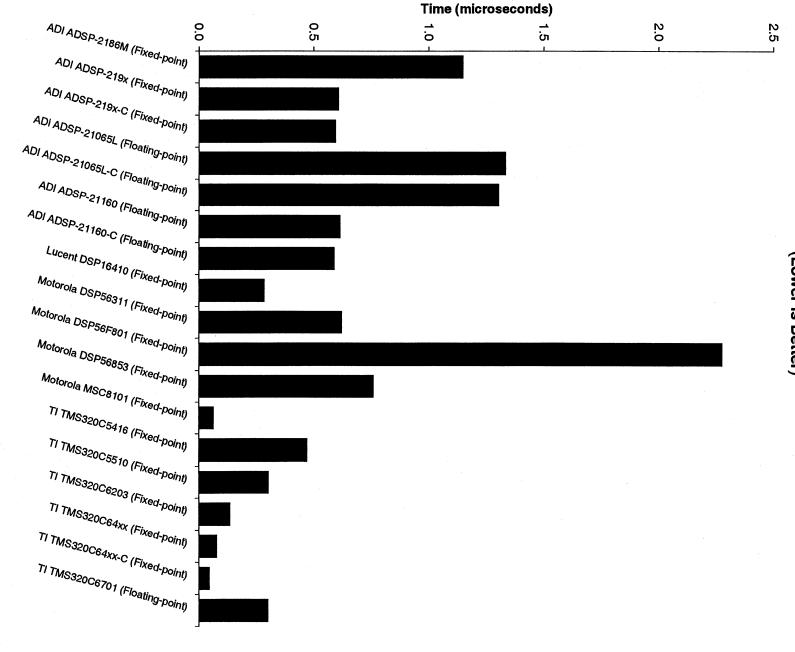

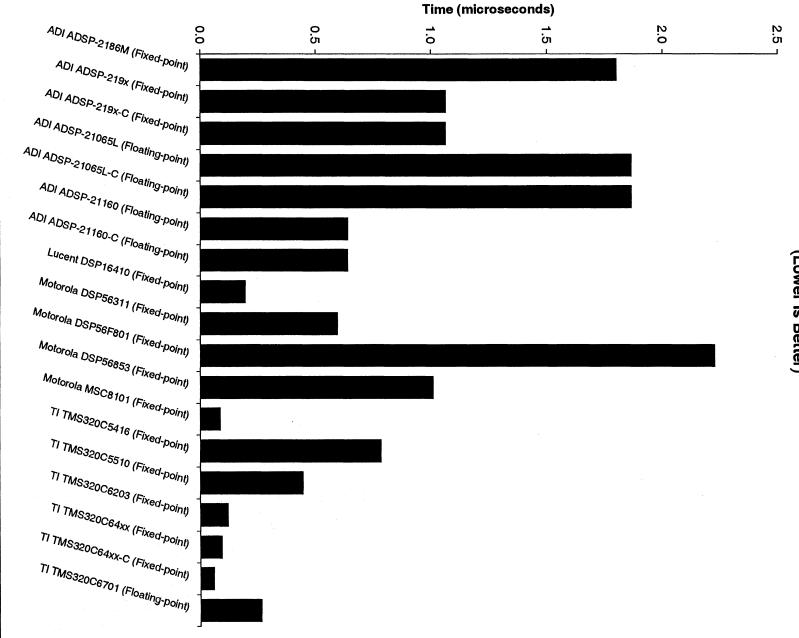

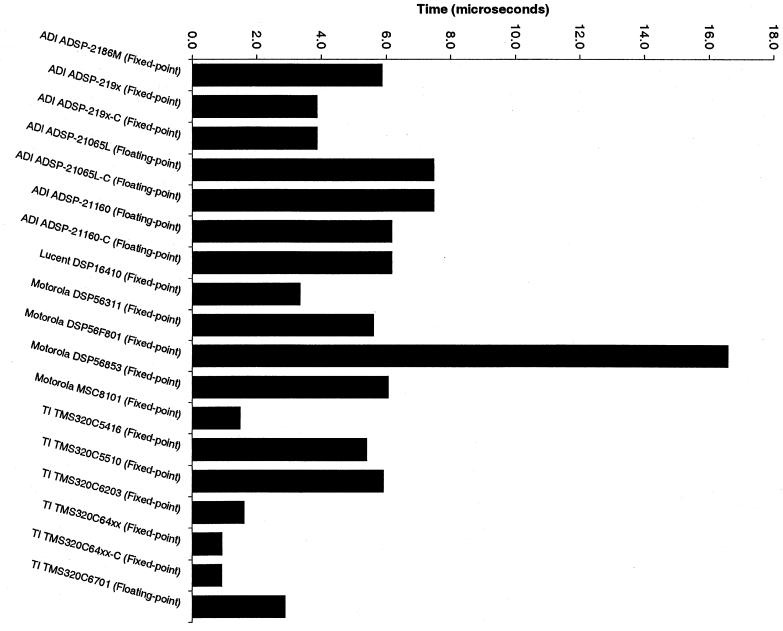

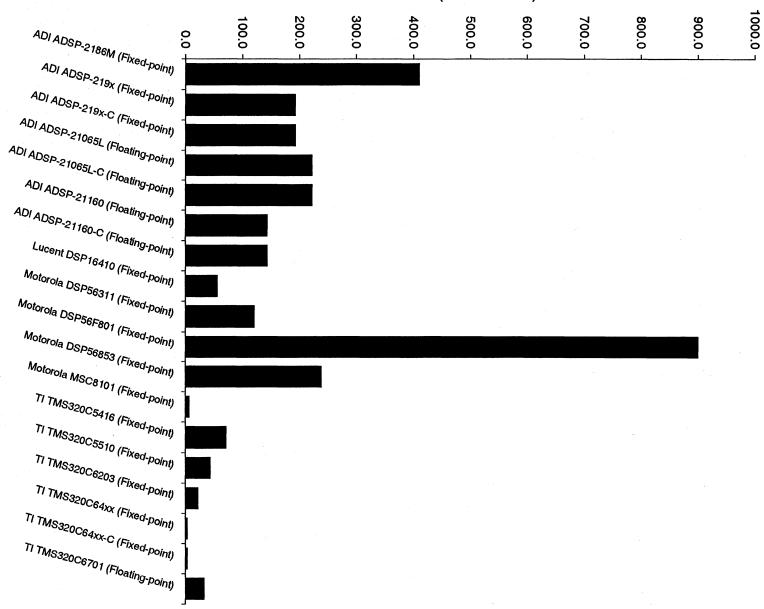

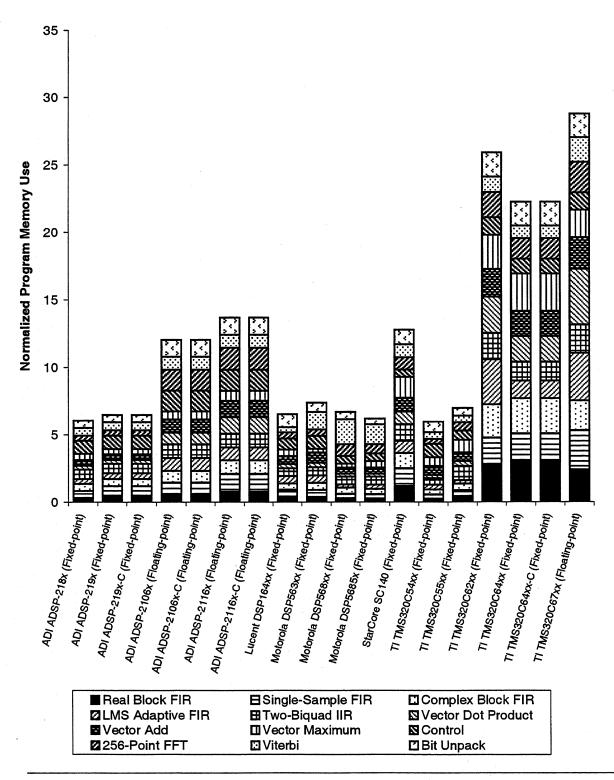

- 8.1 Instruction Cycle Counts 625 Analysis of Results 626

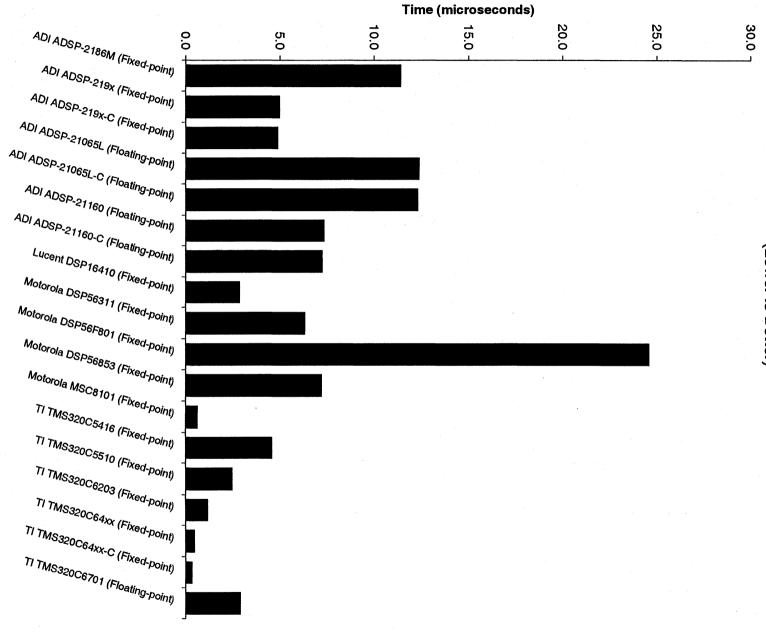

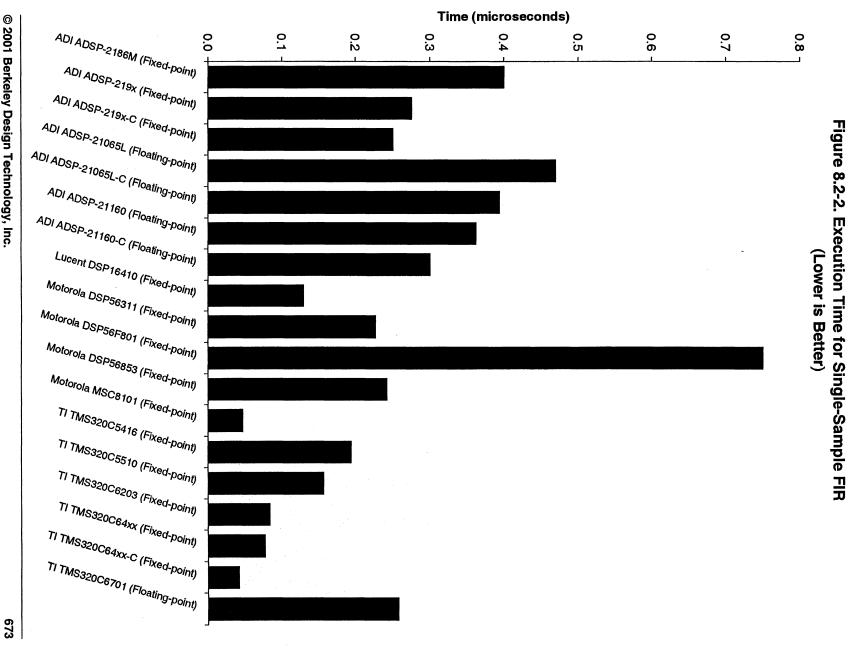

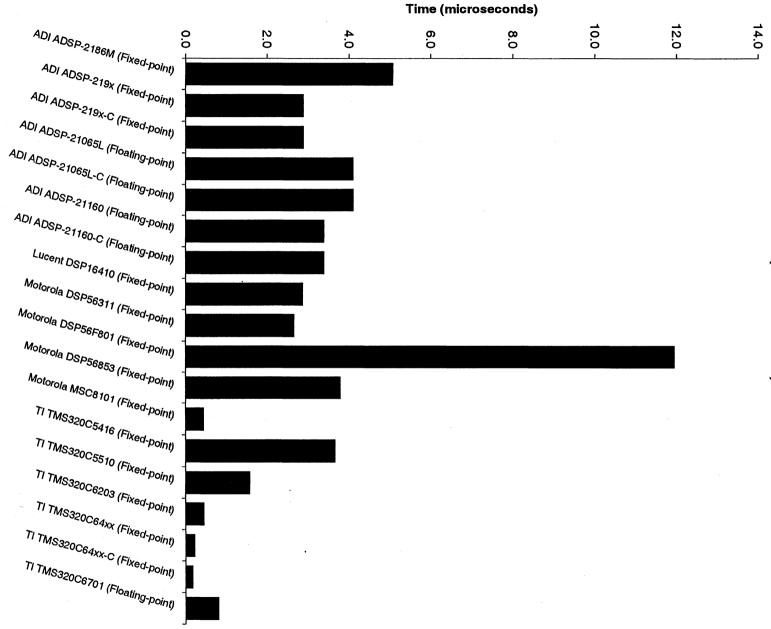

- 8.2 Execution Times 661

Analysis of Results 663

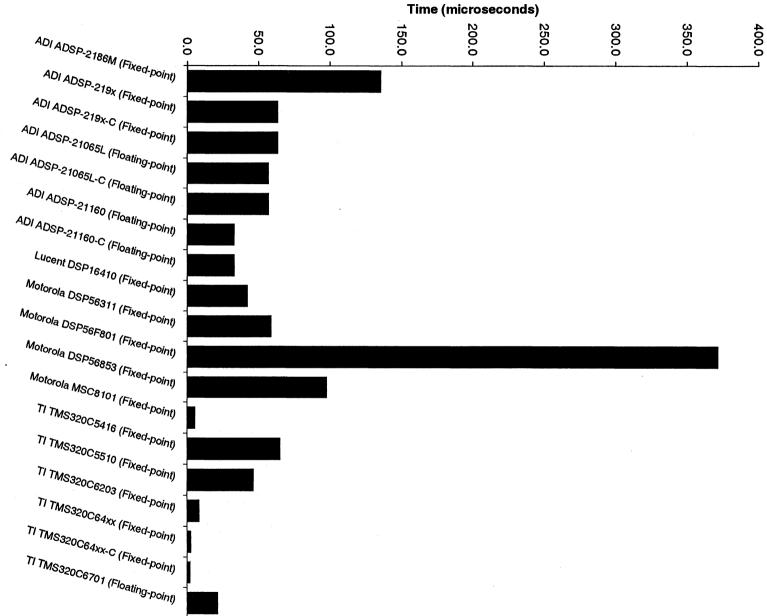

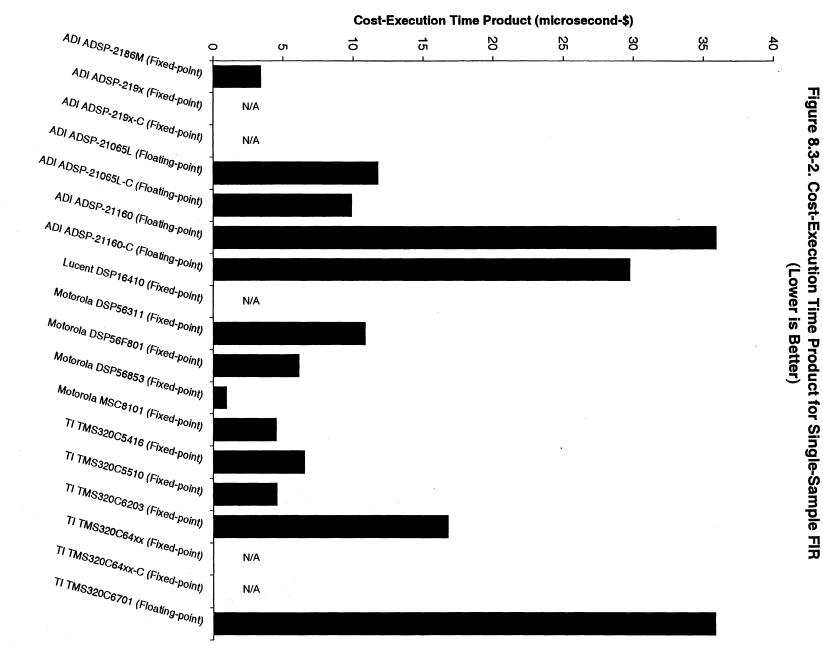

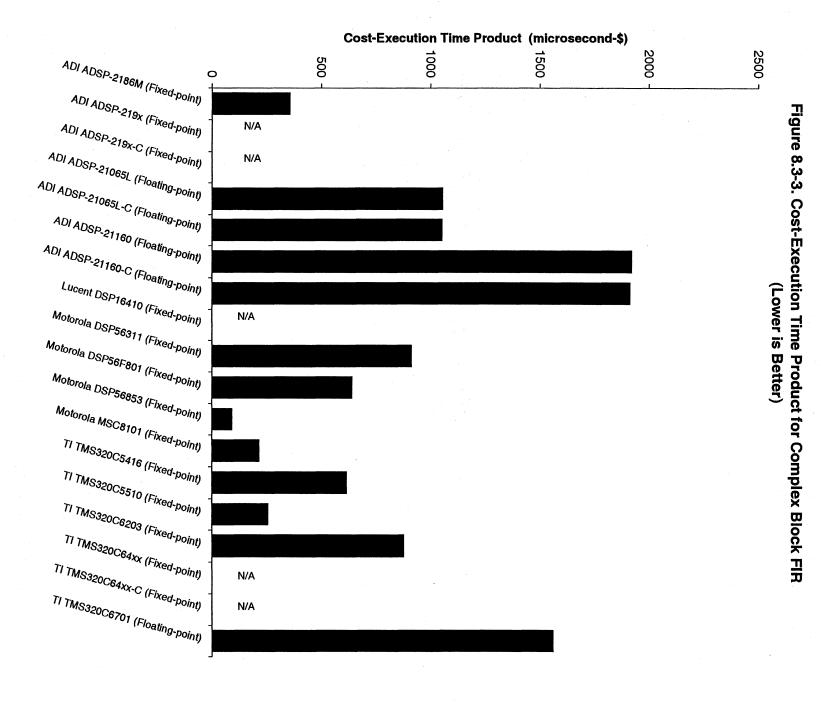

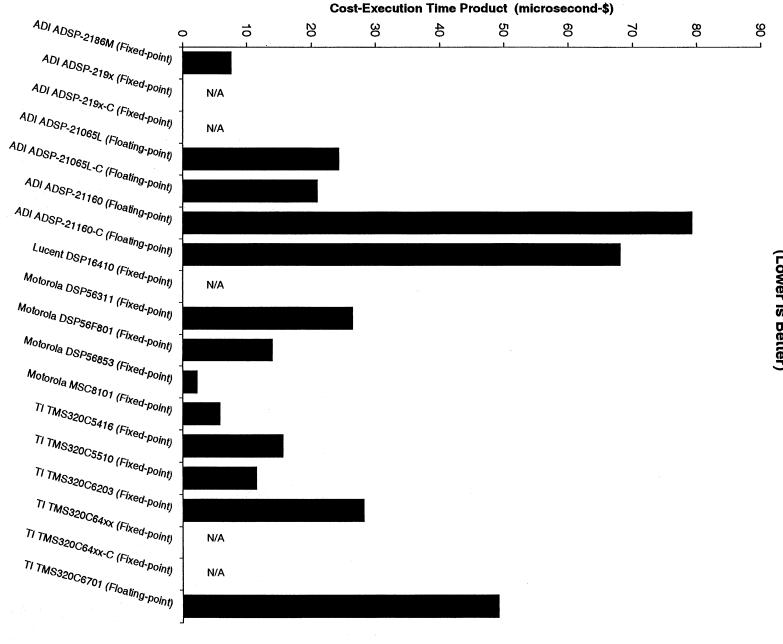

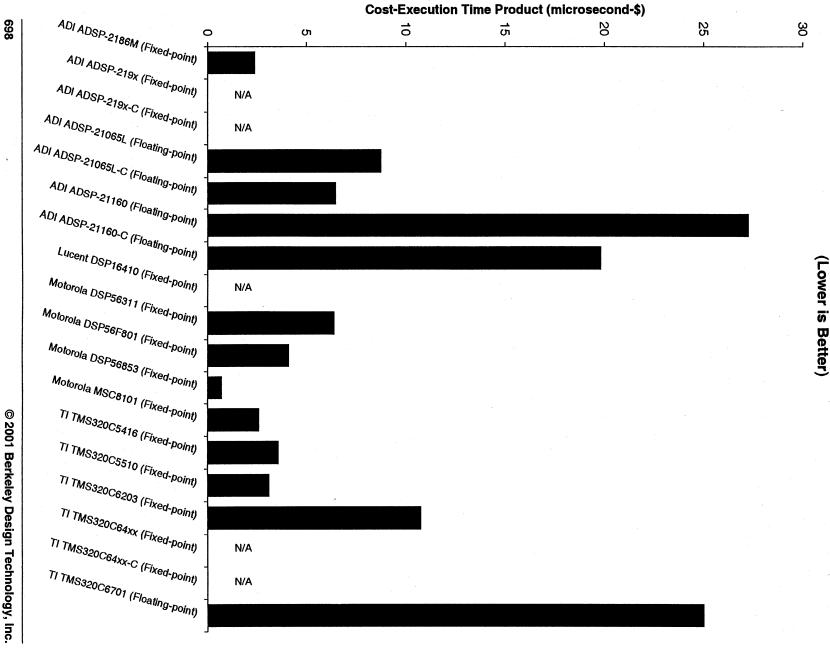

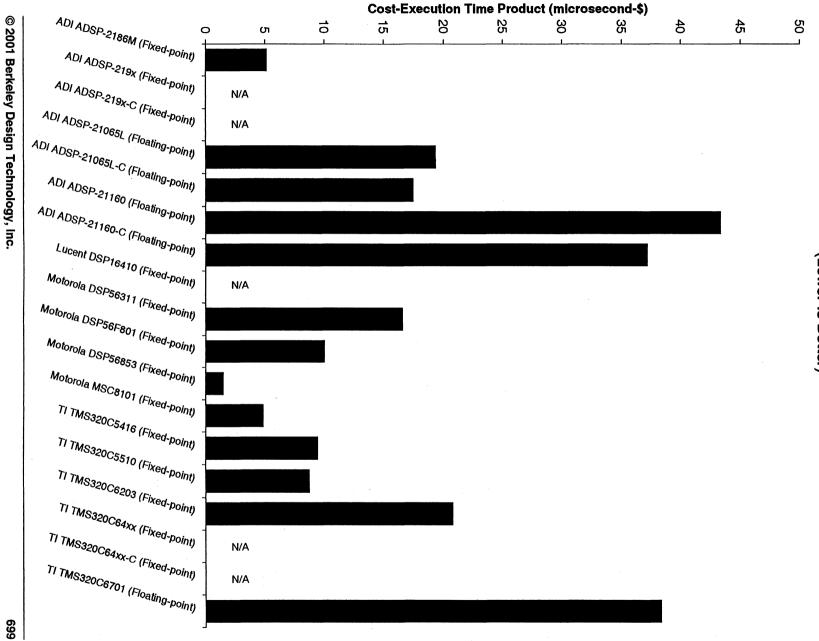

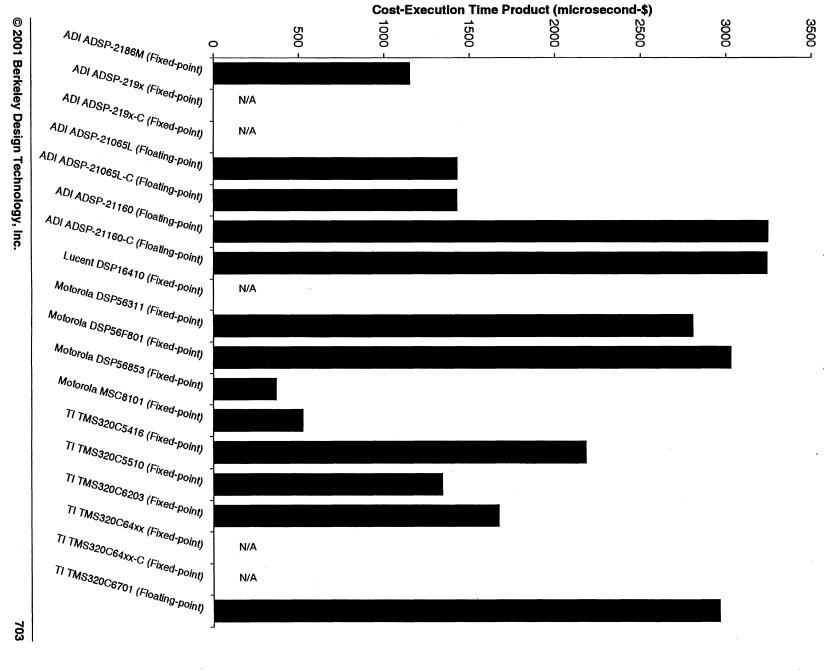

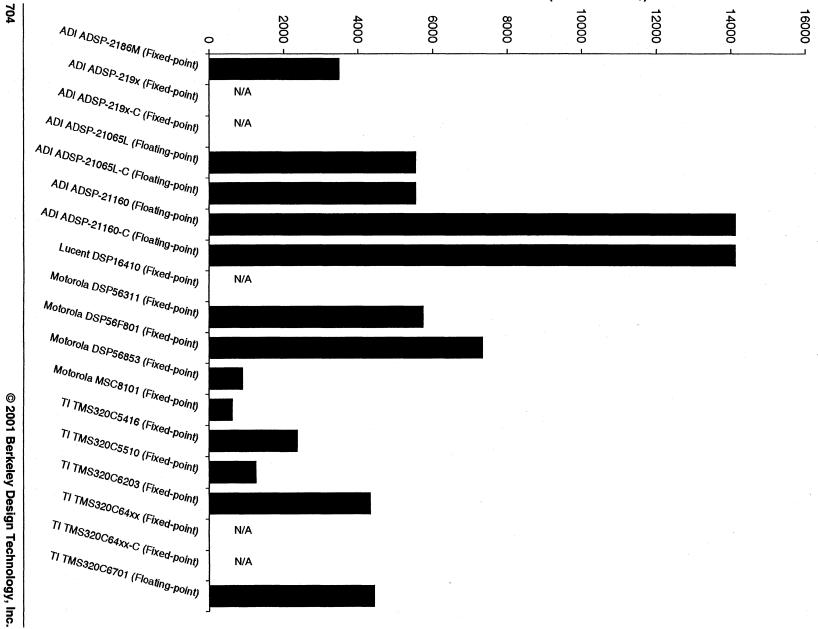

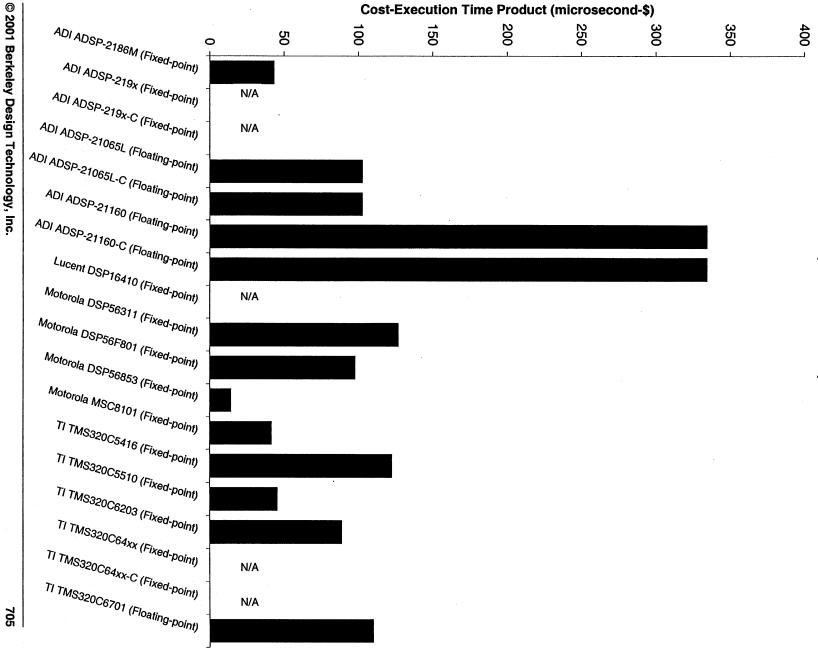

- 8.3 Cost-Execution Time Product 687

Analysis of Results 688

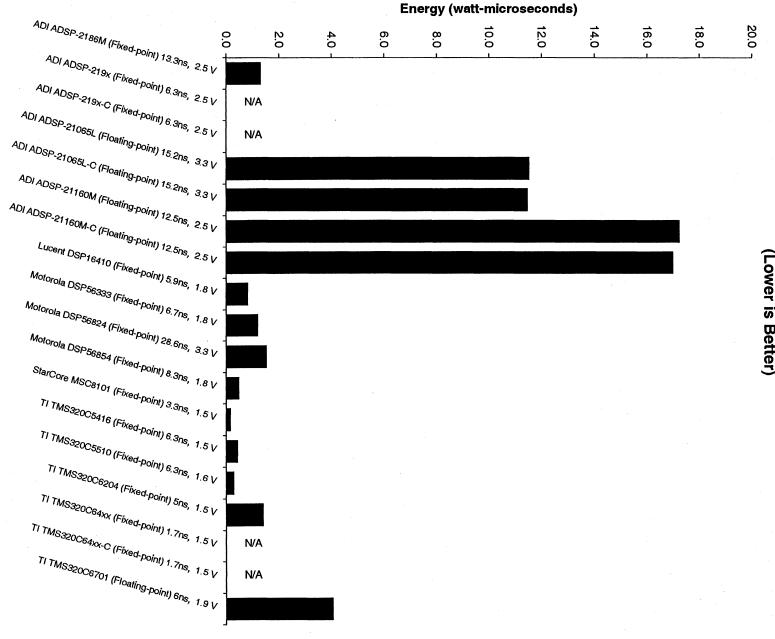

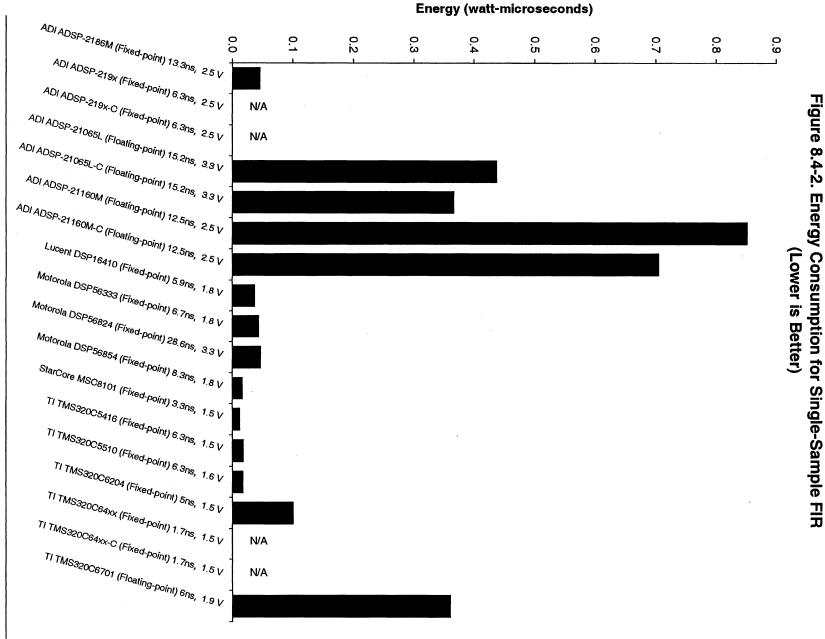

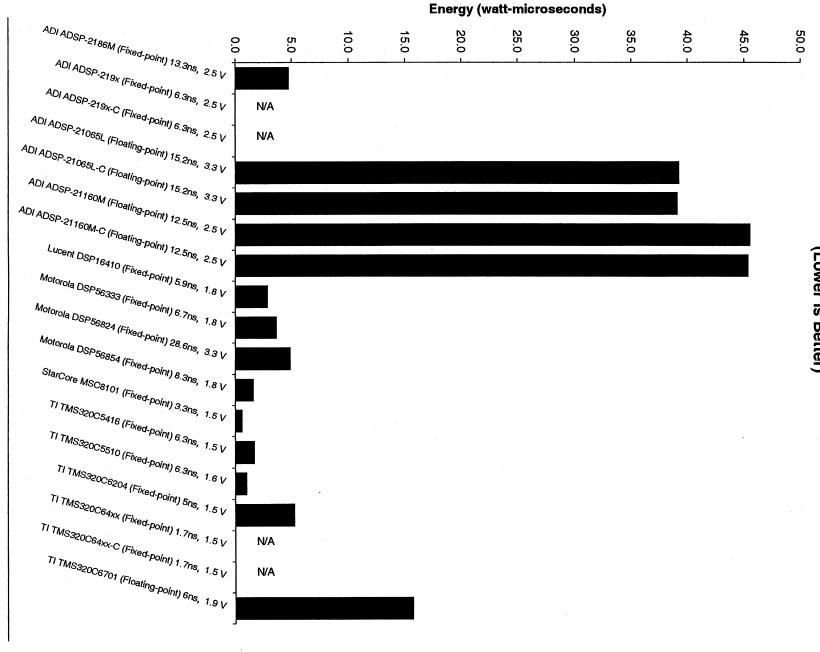

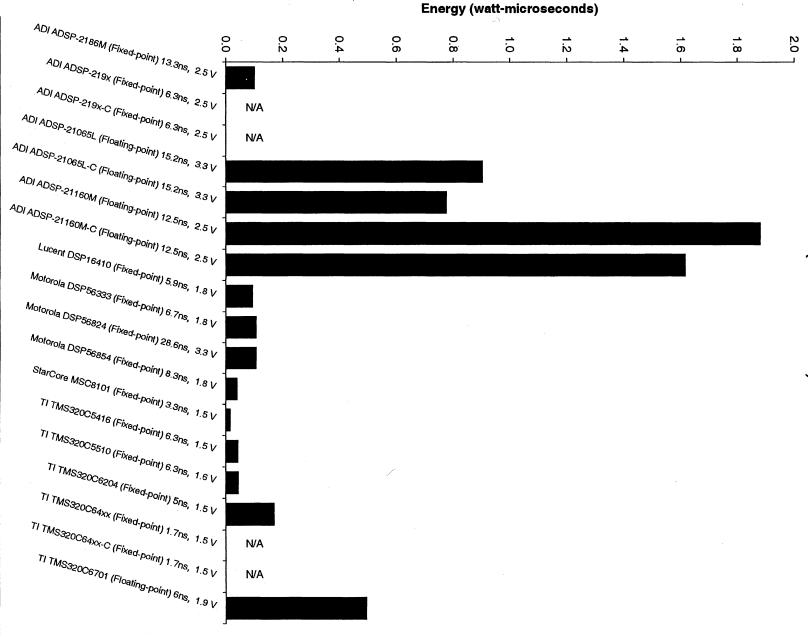

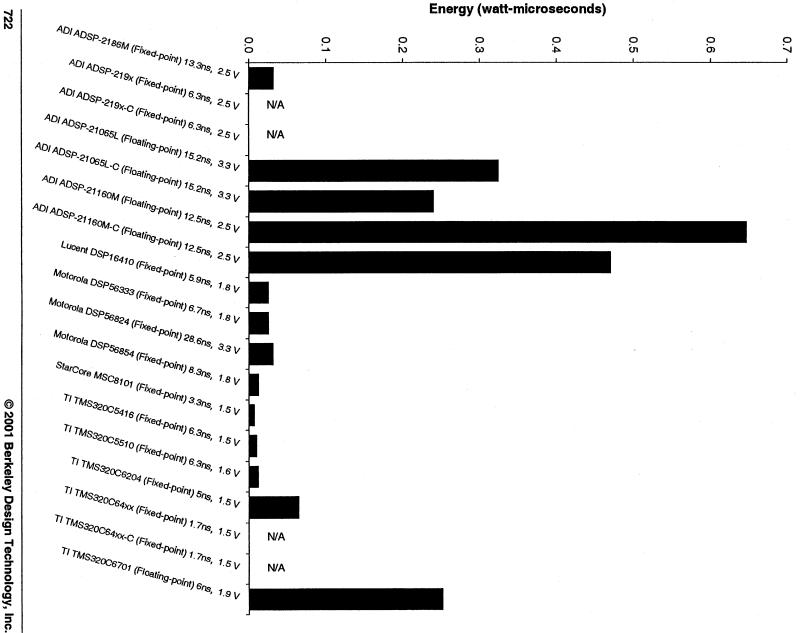

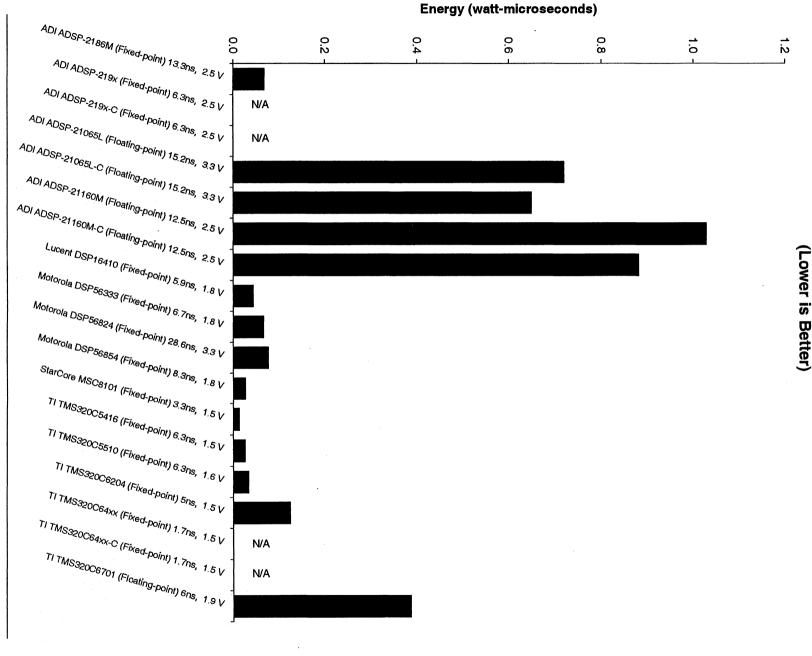

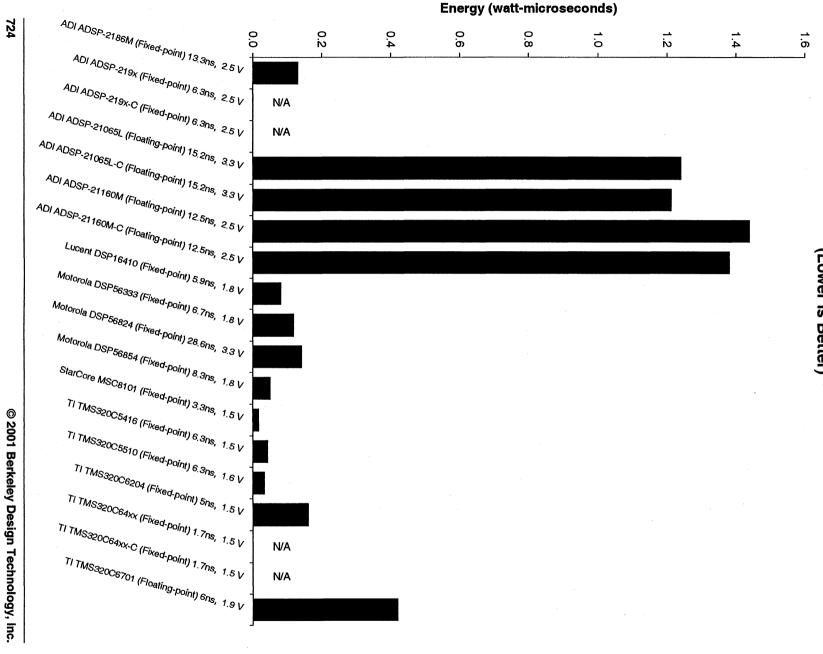

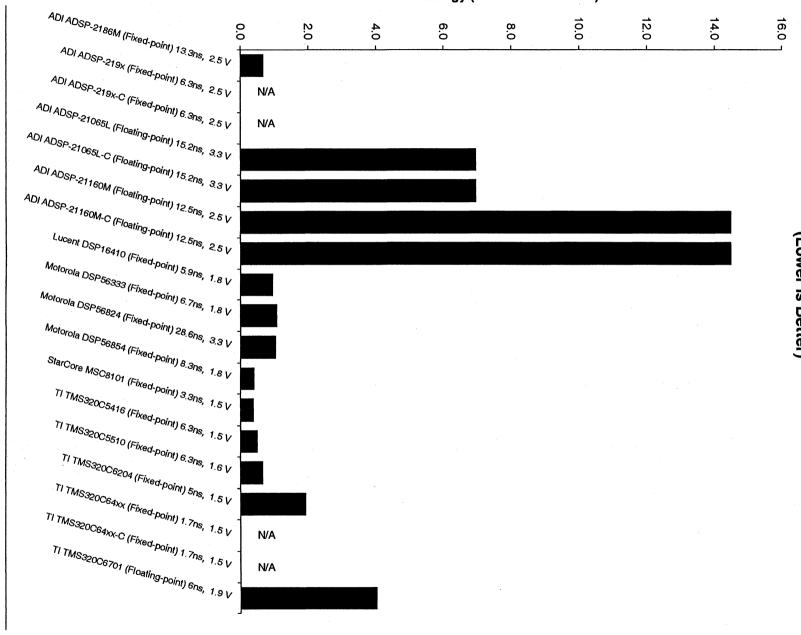

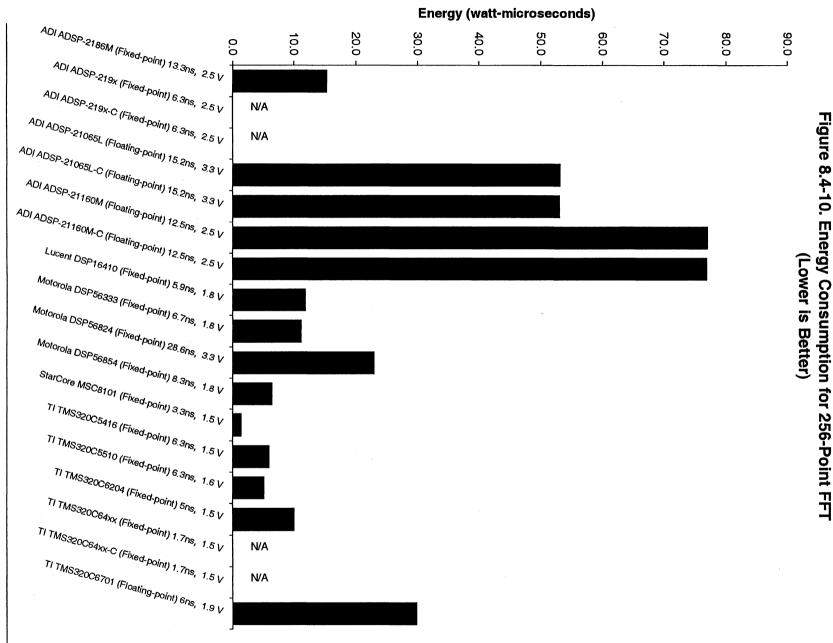

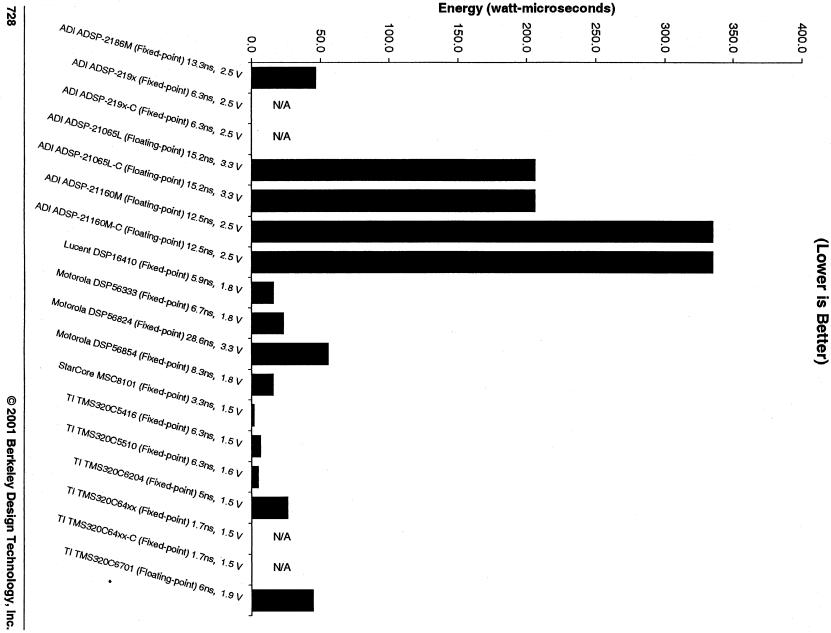

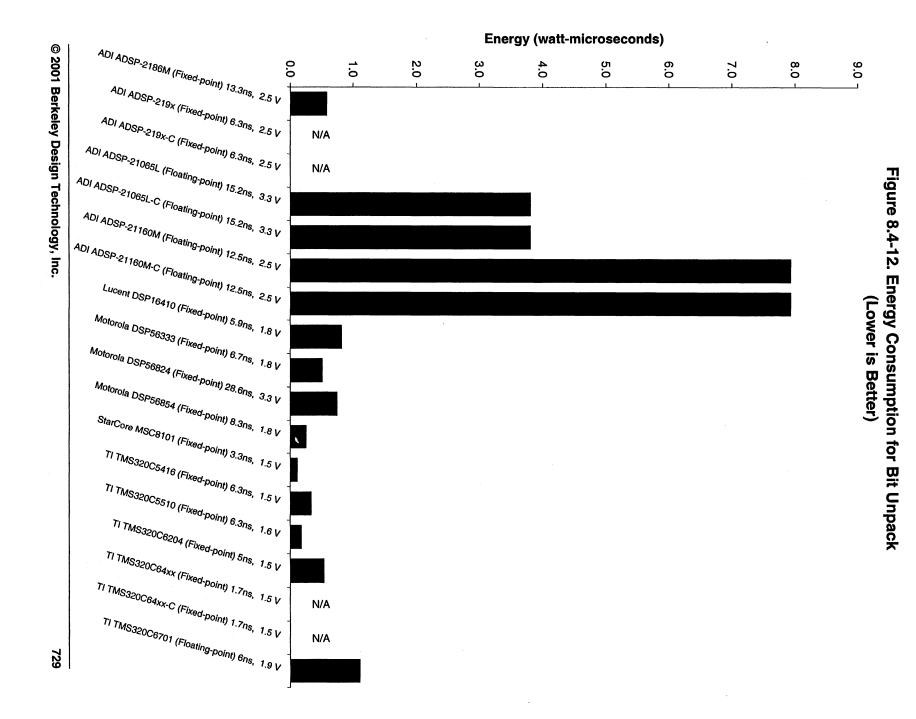

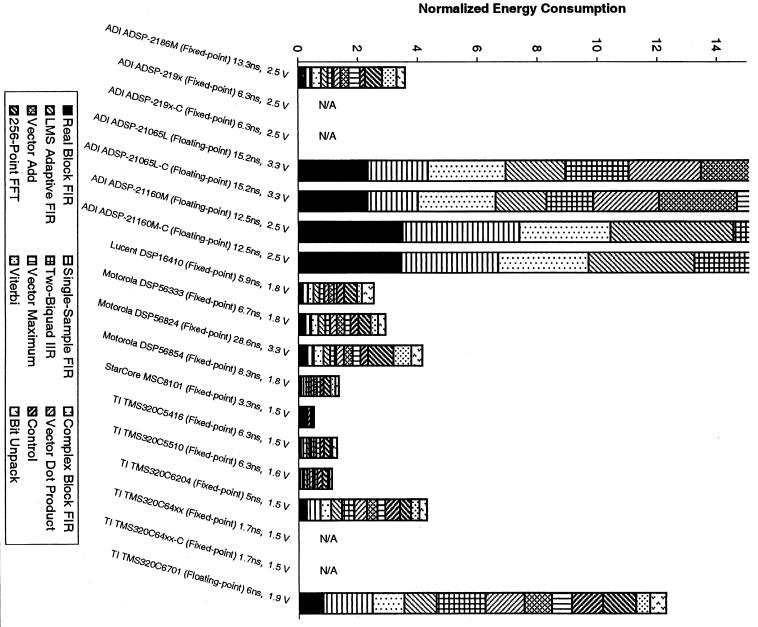

- 8.4 Energy Consumption 707

Analysis of Results 709

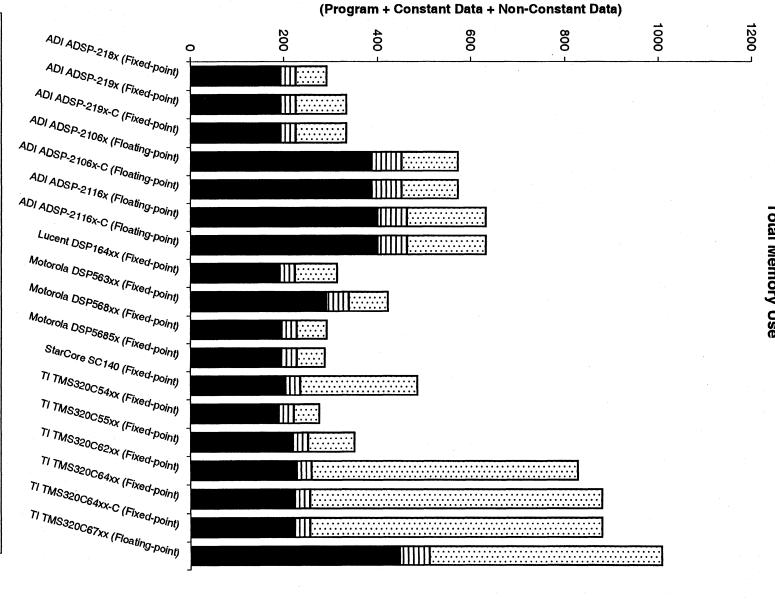

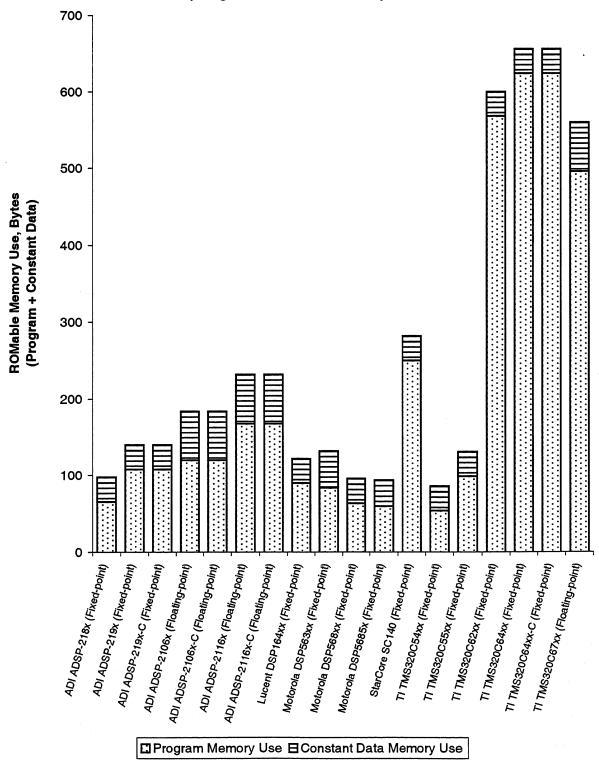

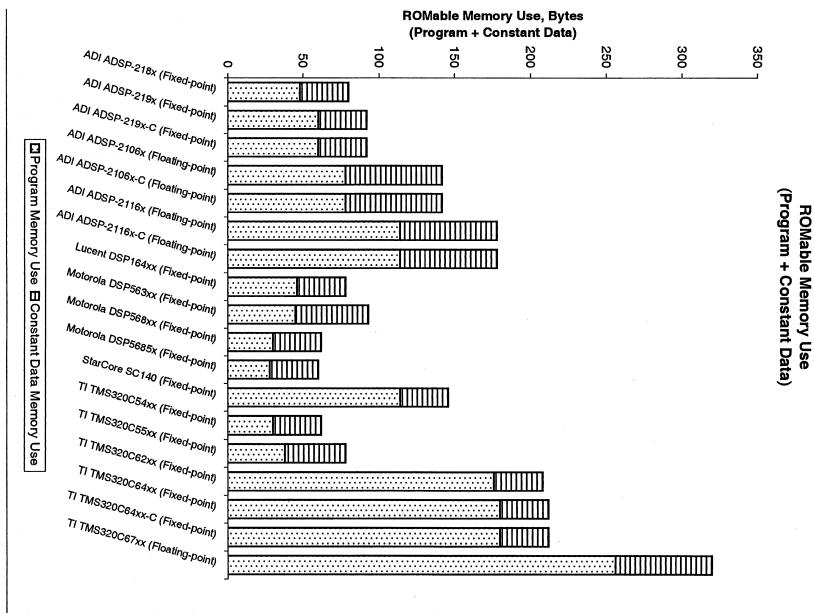

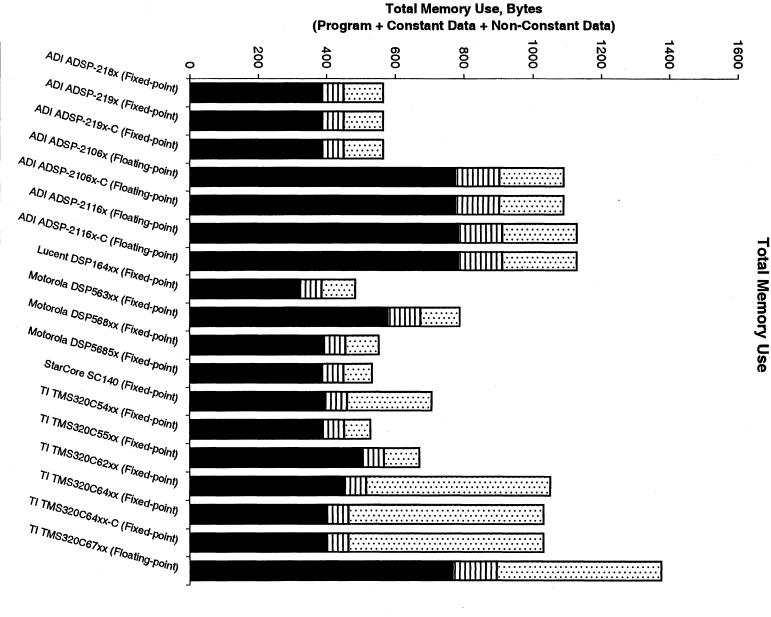

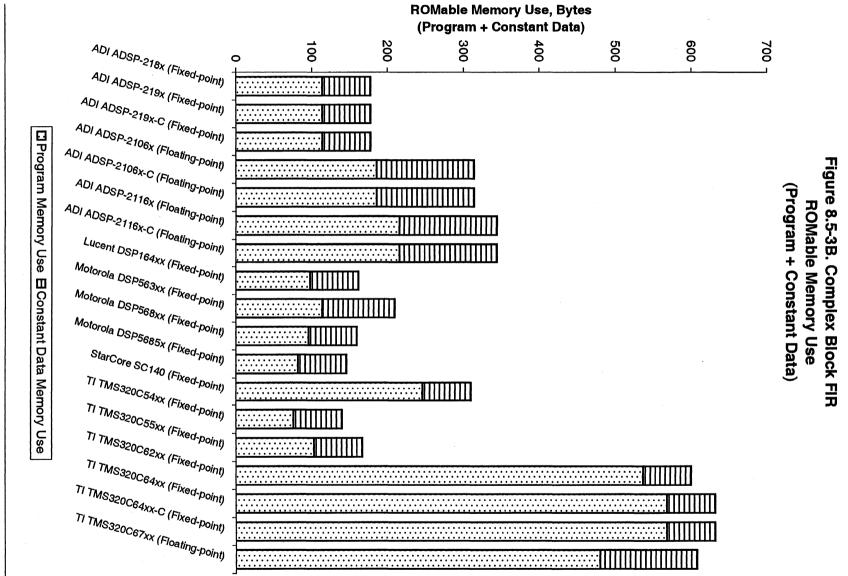

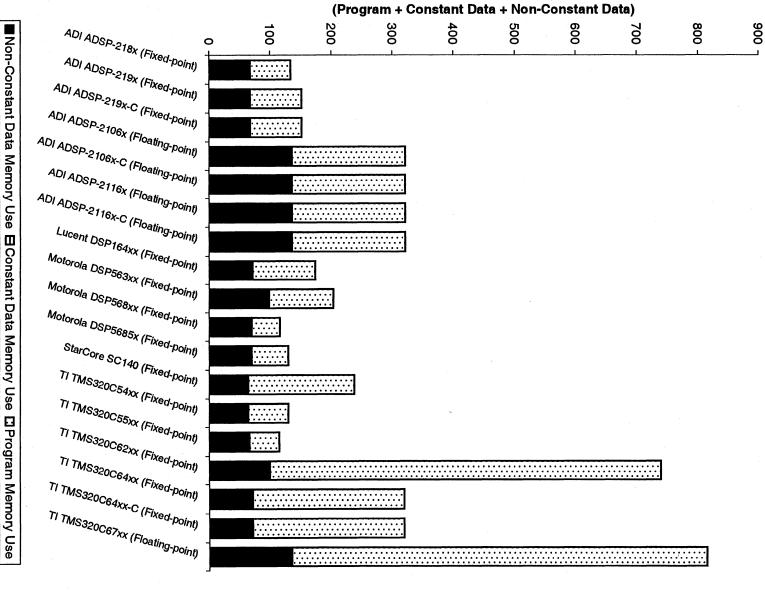

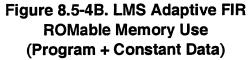

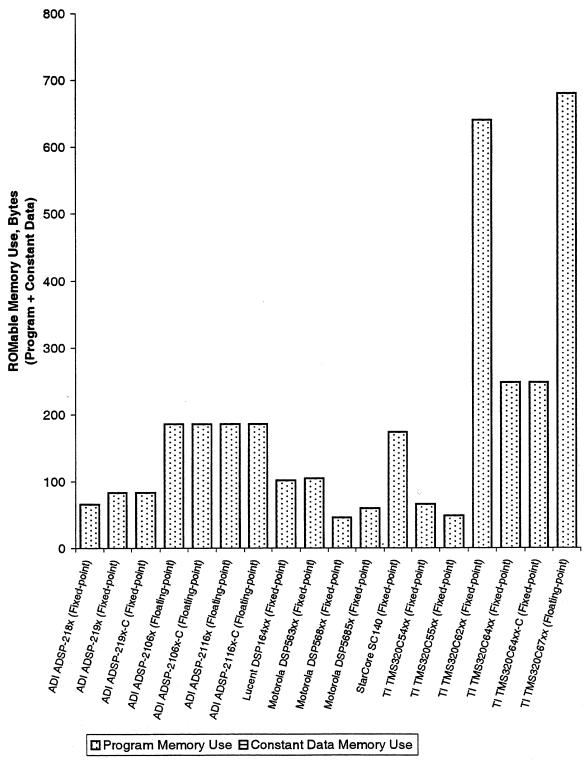

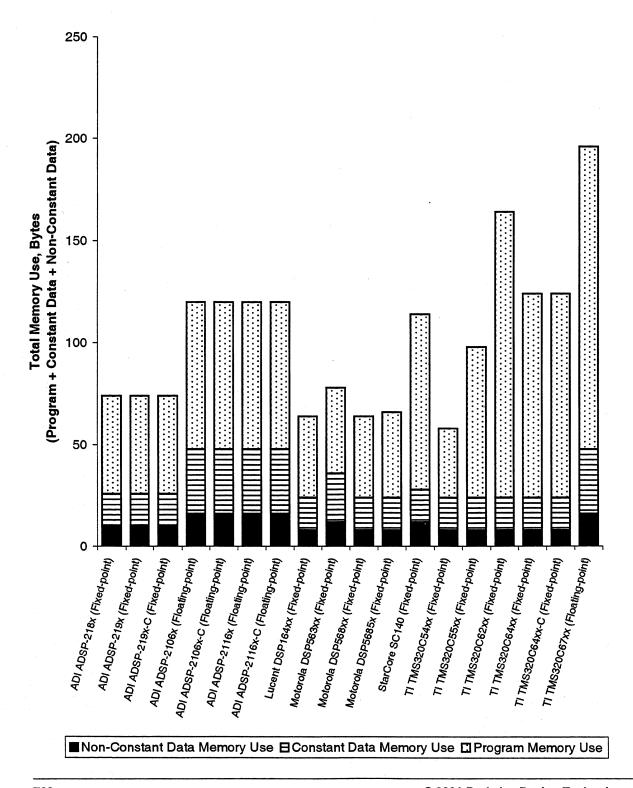

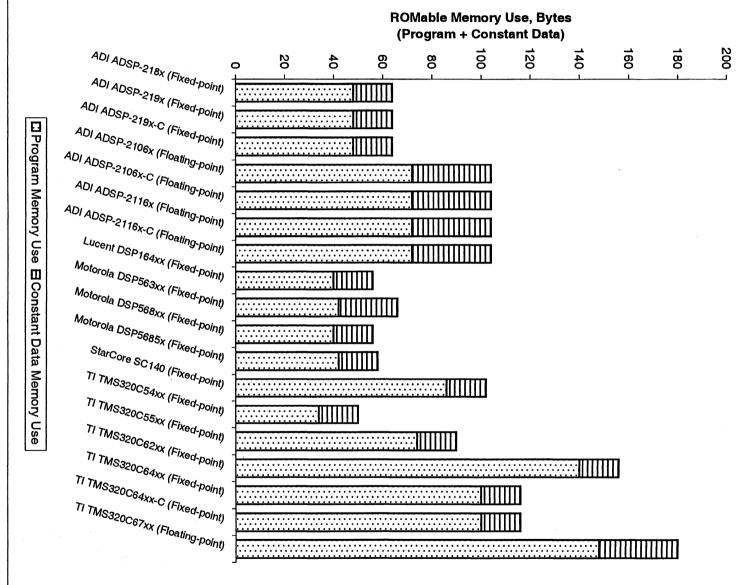

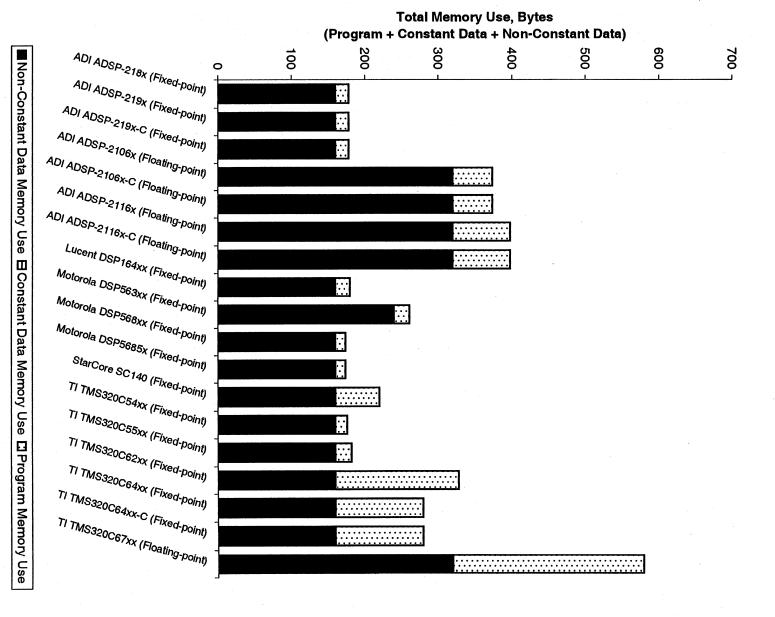

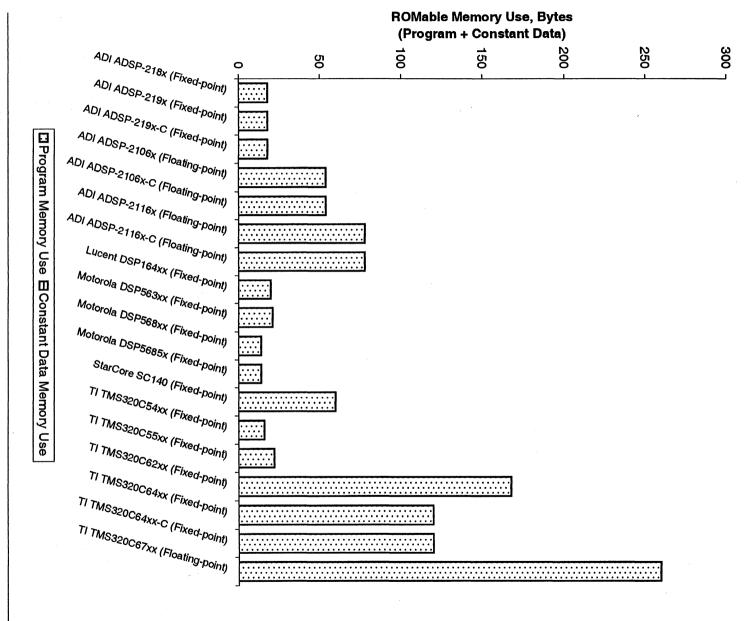

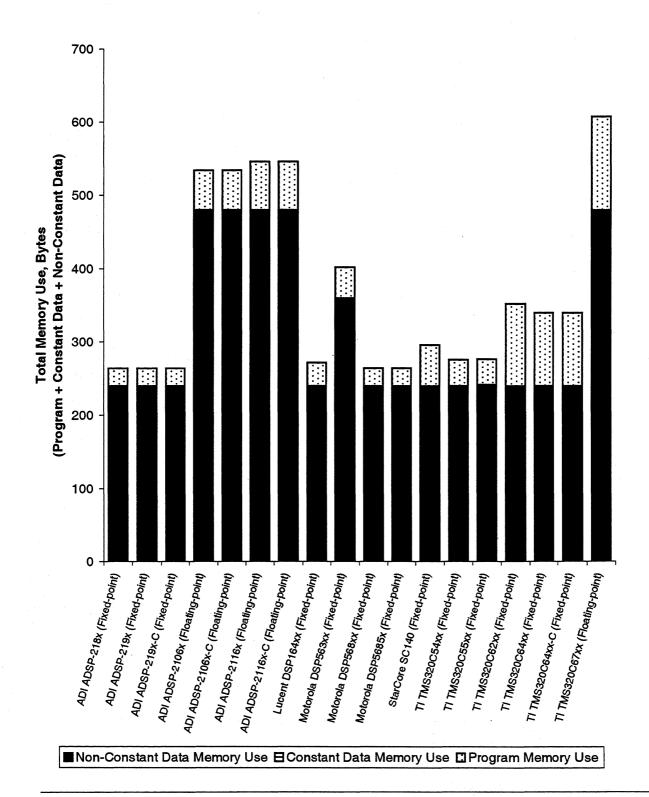

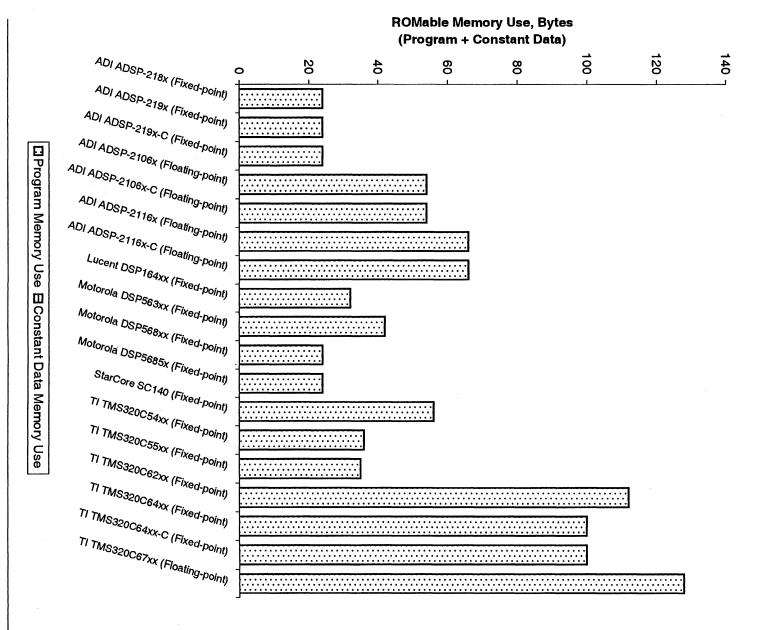

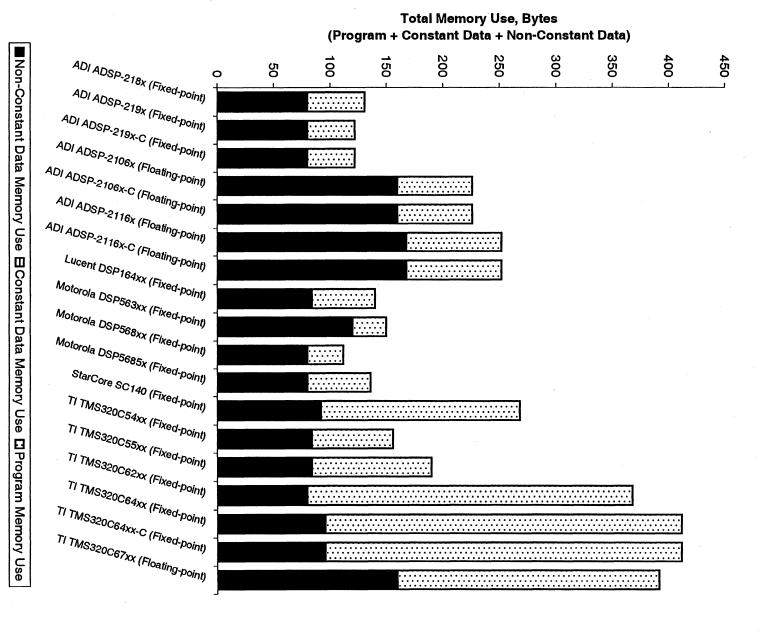

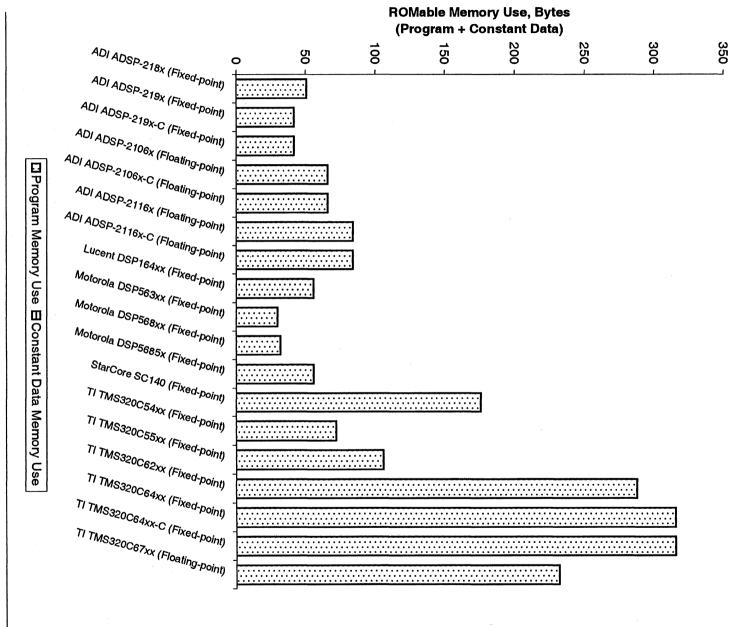

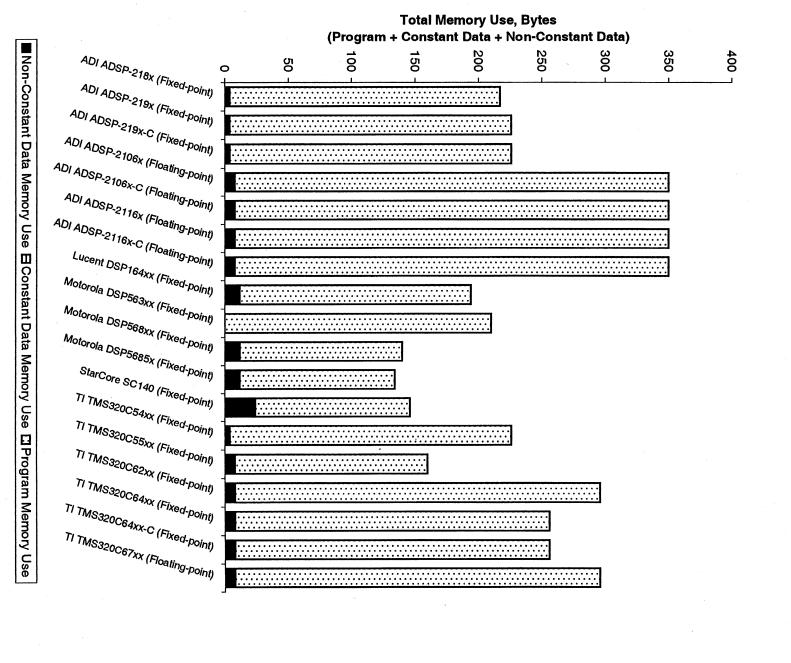

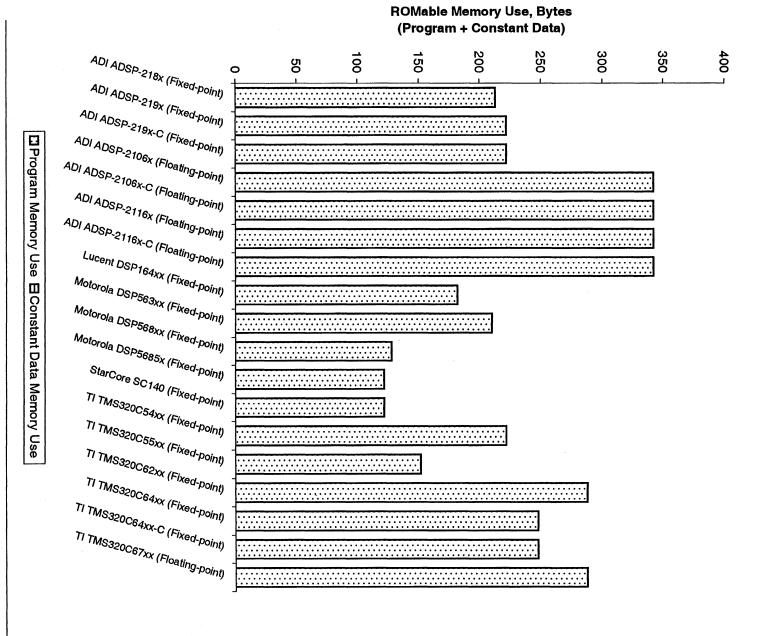

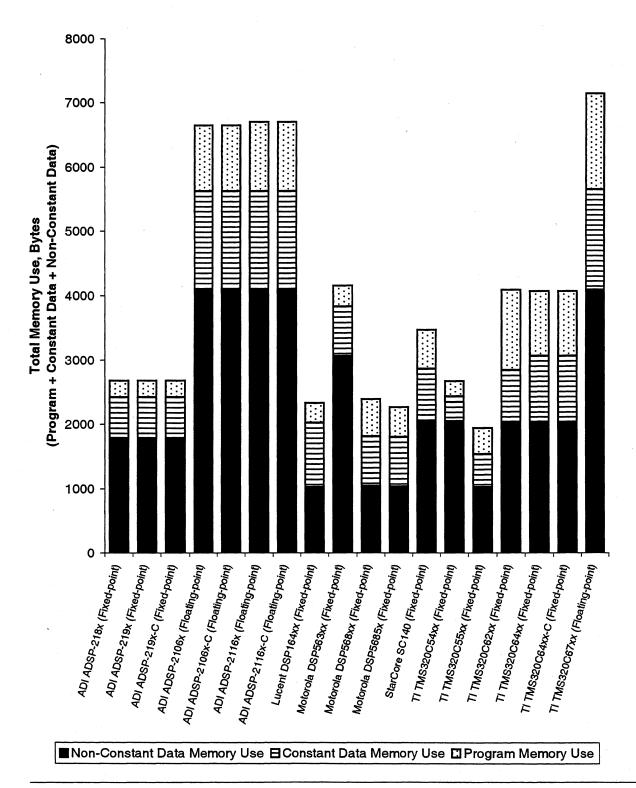

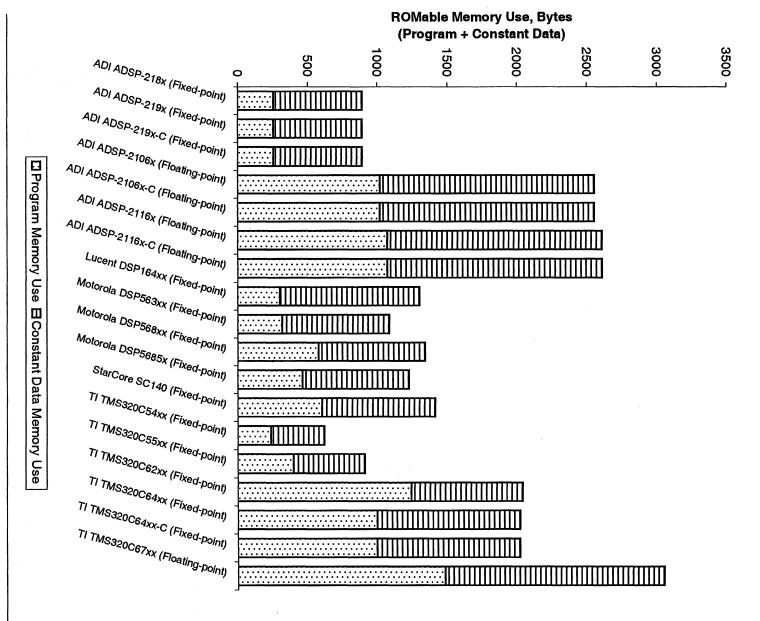

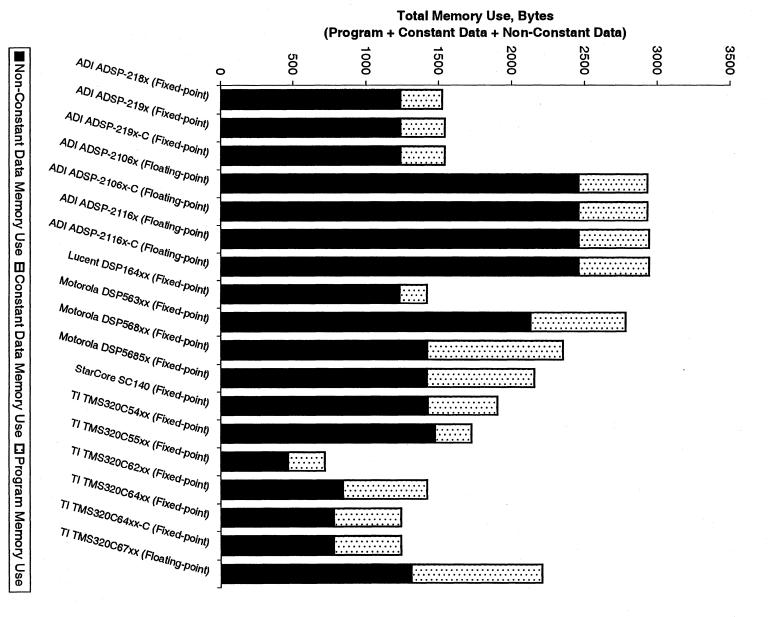

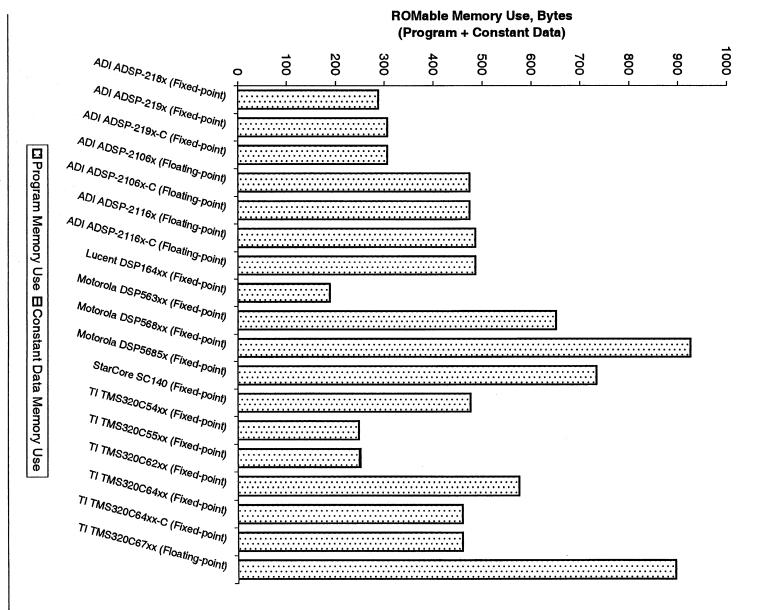

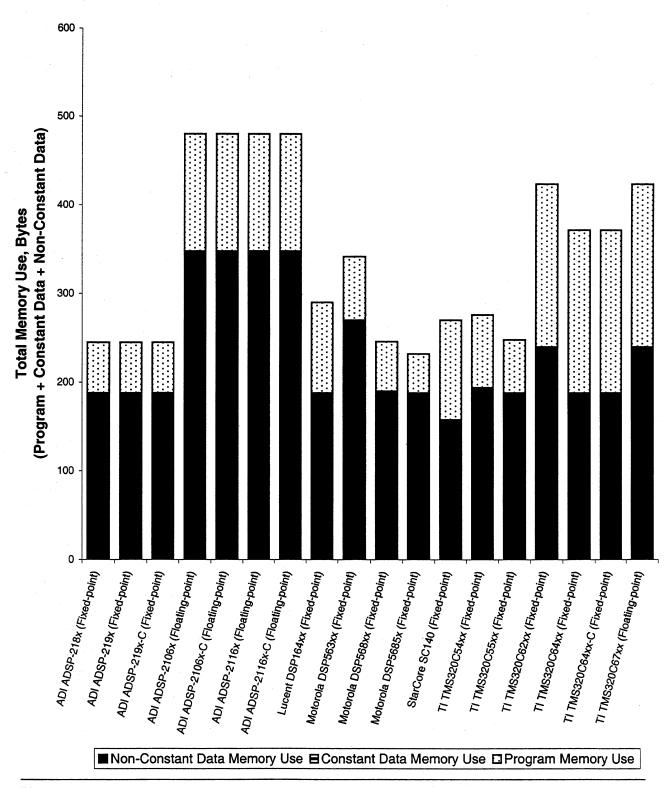

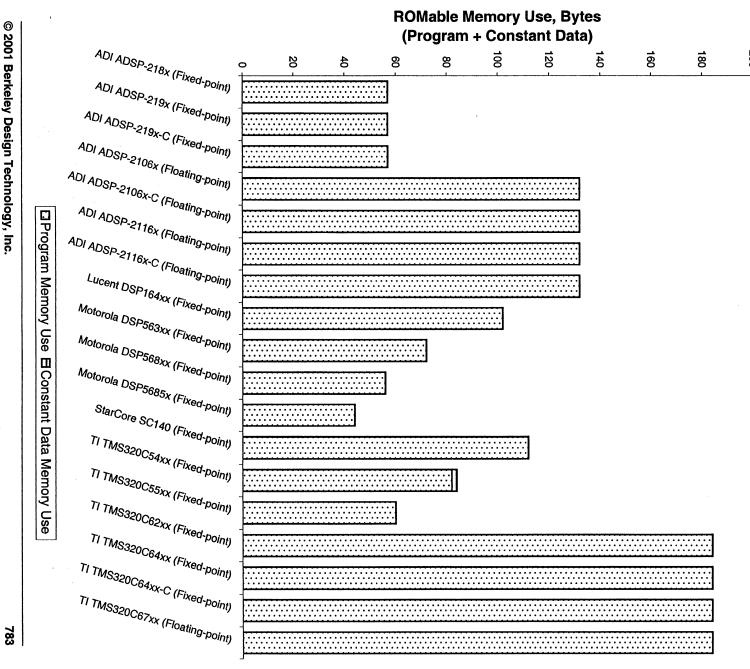

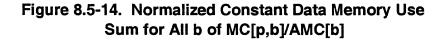

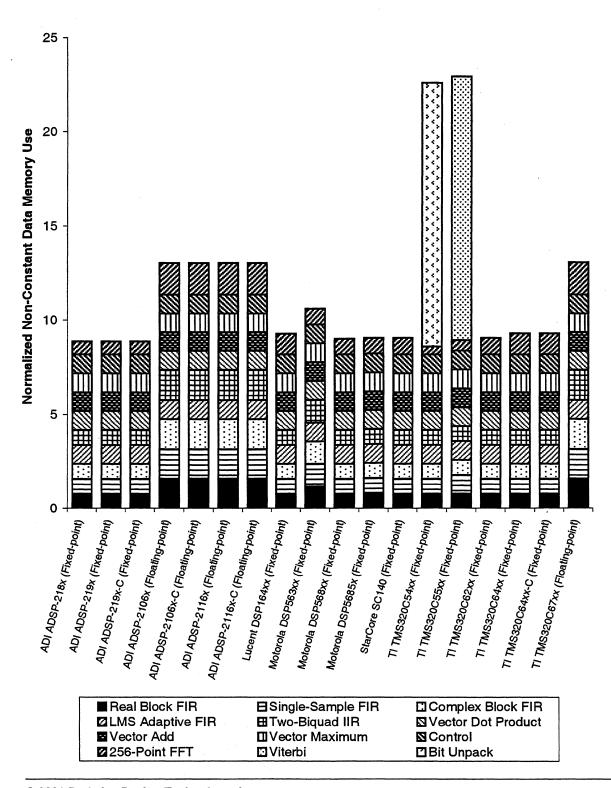

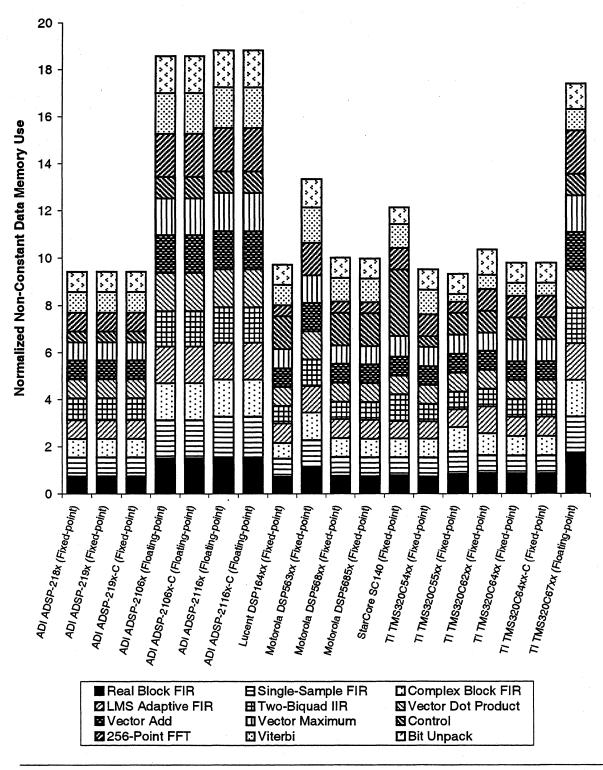

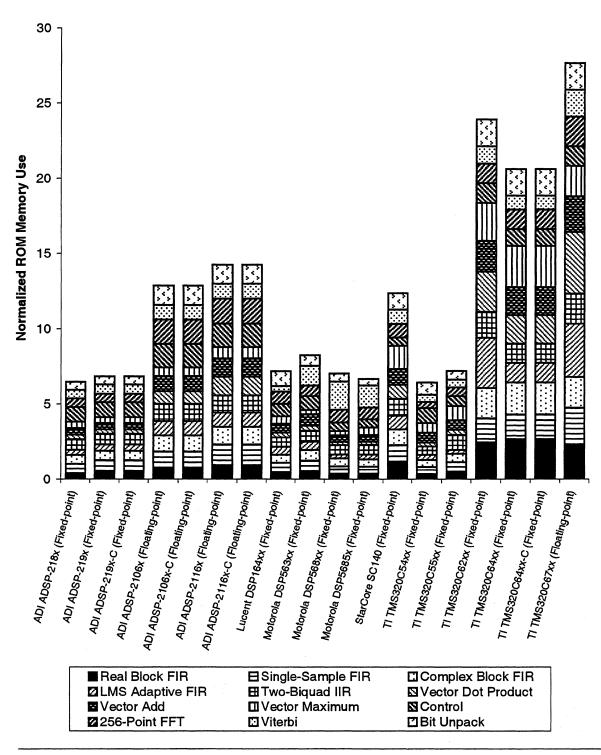

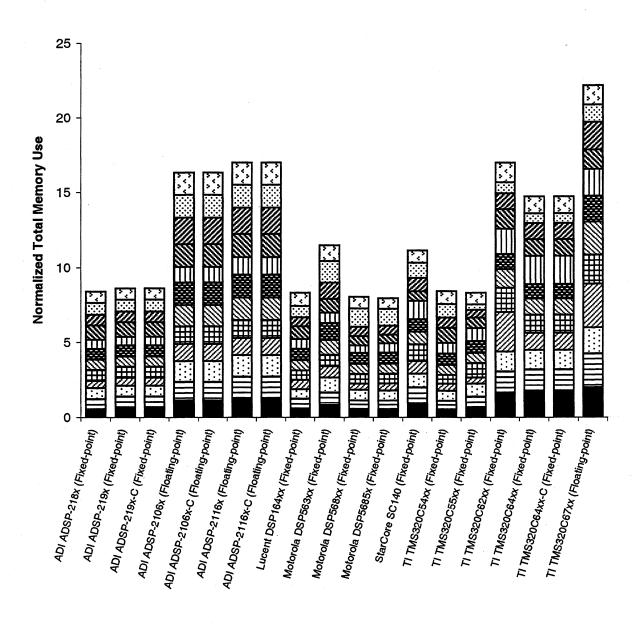

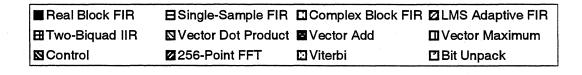

- 8.5 Memory Usage Benchmarking 733

Control Benchmark Memory Use 733

ROMable Memory Use 734

Total Memory Use 736

Organization of Results 736

Analysis of Results 739

#### 9. Conclusions 789

- 9.1 Comparing Processors 789

- 9.2 DSP Processors Trends and Challenges 790

- 9.3 Business and Infrastructure Trends and Challenges 794

- 9.4 Conclusions 799

**Vendor Contact Information 801**

References 805

Bibliography 807

Glossary 809

Index 843

#### 1. Introduction

This report is a comprehensive technical guide to programmable digital signal processors. Programmable digital signal processors (often called DSPs, PDSPs, or DSP processors) are microprocessors that are specialized to perform well in digital signal processing-intensive applications. Since the introduction of the first commercially successful DSP processors in the early 1980s, dozens of new processors have been developed, offering system designers a vast array of choices. According to the market research firm Forward Concepts, sales of user-programmable DSPs will total roughly US \$4.4 billion in 2001, with a projected annual growth rate of 40% [Stra98]. With semiconductor manufacturers vying for bigger shares of this booming market, designers' choices will broaden even further in the next few years.

# **Scope and Purpose**

This report is intended for anyone who is evaluating or comparing DSP processors. Our emphasis is on completeness, in-depth analysis, objectivity, and consistency. We present each of the key elements of DSP processor technology and examine current product offerings with a critical eye. We expect that this report will be especially useful for electronic systems designers, processor developers, engineering managers, product planners, and marketing managers. It will aid in choosing or designing the DSP processor or processors that are best suited to a given application and in developing an understanding of how the capabilities of DSP processors can be used to meet the needs of the application.

# Changes in the 2001 Edition

This is the 2001 Edition of *Buyer's Guide to DSP Processors*. The most significant changes from the 1999 edition include:

#### New Processors

We have added analysis and benchmark results for five new DSP processor families: the Texas Instruments TMS320C55xx, Texas Instruments TMS320C64xx, Analog Devices ADSP-219x, Motorola DSP5685x, and the StarCore SC140. We have also added an extensive qualitative analysis of Analog Devices' Tiger-SHARC architecture (benchmark results were not available at the time this report was published).

#### New Benchmarks

This is the first edition of *Buyer's Guide to DSP Processors* to use the new version of the BDTI Benchmarks<sup>TM</sup>, released in 1999. The new edition of the benchmark suite adds three new benchmarks (Viterbi Decoder, Control, and Bit Unpack), eliminates two benchmarks (Convolutional Encoder and FSM), and revises the specifications for several of the original BDTI Benchmarks, such as the Two-Biquad IIR and 256-Point FFT benchmarks.

#### BDTImark2000<sup>TM</sup> Scores

With the introduction of the new version of the BDTI Benchmarks, a new version of the BDTImark has also been created: the BDTImark2000. Like the original BDTImark, the BDTImark2000 provides a convenient estimate of processor's DSP speed and is much more realistic that traditional simplified metrics like MIPS and MFLOPS.

#### • Revised Analyses for Previously Evaluated Processors

We have expanded and updated our analysis for previously evaluated processor families with new insights and new family members, as well as updates on prices, package options, speeds, operating voltages, tools, and many other critical details. We have implemented the latest version of the BDTI Benchmarks for older processors that are included in the benchmark analysis in this report.

#### Coverage of Older or Highly Specialized Processors

For some older processors we have either eliminated coverage entirely or limited coverage to a description of the architecture without including detailed benchmark results. Additionally, we have discontinued coverage of processors that are highly specialized for niche applications. Excluding these processors allowed us to focus our evaluation on processors of the most interest to the largest number of users.

#### Scope of Coverage of DSP Processor Architectural Concepts

In this edition of *Buyer's Guide*, we have eliminated the detailed introduction to DSP processor architectures. This introduction can be found in BDTI's textbook, *DSP Processor Fundamentals* [BDTI96].

#### Organization

This report is organized as follows:

#### Authors

Chapter 2 provides brief background information on the authors of this report.

#### Digital Signal Processing and DSP Systems

Chapter 3 provides a high-level overview of digital signal processing, including DSP system features and applications.

#### • DSP Processor Embodiments and Alternatives

Chapter 4 provides a brief introduction to DSP processors and then discusses the different forms that DSP processors take, including chips, multi-chip modules, and SoC cores. In this chapter we also briefly touch on alternatives to DSP processors, such as fixed-function DSP integrated circuits and general-purpose processors.

#### Guidance for Choosing a Processor

In Chapter 6 we present detailed run-time profiling data to illustrate the kinds of demands that typical applications make on DSP processors.

#### Information on Other Processors

In Chapter 5 we provide information on where to find analyses on processors that are not covered in this report.

#### • In-Depth Processor Analyses

In Chapter 7 we provide in-depth analyses of seventeen DSP processors and processor families, highlighting the distinctive features, strengths, and weaknesses of each, including factors such as the quality of development tools and applications engineering support.

#### Benchmark Results

To provide a basis for fair comparisons of DSP processor performance, we have developed the BDTI Benchmarks<sup>TM</sup>. Chapter 8 presents benchmark results for fourteen processors and processor families, and examines the number of cycles required to execute the benchmarks, execution speed, cost-performance, energy efficiency, and memory usage.

#### Conclusions

In Chapter 9 we present our conclusions on strategies for comparing processors, the current state-of-the-art in DSP processors, and likely future developments in DSP processor technology.

#### • Vendor Contact Information

This appendix contains contact information for companies that sell DSP processors and related products and services covered in this report.

#### References, Bibliography, Glossary, and Index

A glossary of DSP processor-related terms provides definitions of technical terminology used in this report. The bibliography lists useful sources of information for those interested in delving more deeply into the topics covered here. The References section lists related publications referenced in this document. References are denoted with square brackets, as in [BDTI97]. To help you quickly find the information you need, an extensive index is included at the end of this report.

#### **Related Resources**

BDTI offers a number of products and services related to this report.

- BDTI publishes technical evaluations which provide in-depth analyses of specific processors. These reports provide detailed benchmark results, along with comparisons to competing processors from other vendors. Technical evaluations published to date include *Inside the StarCore SC140*, *Inside the Infineon Carmel, Inside the Siemens TriCore*, and *Inside the Lucent DSP16000*.

- BDTI offers the Benchmark Analysis Tool (BAT), a software complement to Buyer's Guide to DSP Processors. The BAT simplifies processor selection and competitive analysis by allowing easy customization of BDTI's detailed DSP benchmark analyses to study specific scenarios.

- BDTI licenses the BDTI Benchmark specification and methodology to processor developers and users to facilitate in-house benchmarking.

- BDTI provides a variety of training and consulting services which are further described in Chapter 2.

- BDTI's website, www.BDTI.com, offers a variety of information about DSP, including the comp.dsp newsgroup FAQ, summary descriptions of nearly all currently available DSP processors and cores, a pocket guide to DSP processors, and articles by BDTI authors.

#### 2. About the Authors

Berkeley Design Technology, Inc. (BDTI) was founded in 1991 to assist companies in creating, selecting, and using DSP technology. The technical staff of BDTI has extensive experience in the development of DSP-intensive software and hardware for commercial applications. In addition, each of the founders of BDTI has been a key contributor to pioneering research in the field of DSP design tools and methodologies at the University of California at Berkeley.

Berkeley Design Technology, Inc. offers a variety of services, including:

- Published reports on DSP technology. BDTI publishes a variety of unique technical reports and books. *Buyer's Guide to DSP Processors* is BDTI's comprehensive technical analysis of programmable digital signal processors. Nearly 900 pages in length, *Buyer's Guide* contains in-depth evaluations of the architecture, instruction set, peripherals, development tools, and applications support of every major commercial DSP processor. The evaluations are quantified with processors' scores on the BDTI Benchmarks<sup>TM</sup>, a suite of critical DSP algorithms that have become the industry-standard measure of DSP performance. Every benchmark implementation is coded in assembly language and painstakingly optimized to reveal each processor's true performance potential.

- BDTI also publishes a series of smaller, more focused reports that cover single processors. These reports include *Inside the StarCore SC140*, *Inside the Infineon Carmel, Inside the Siemens TriCore*, and *Inside the Lucent DSP16000*. New reports are added to the series regularly; contact BDTI for information.

- **Development of DSP software.** BDTI applies its unique expertise in processor architectures and DSP applications to provide DSP software development services. BDTI develops highly optimized DSP software for component libraries, modules, and complete applications, especially for audio and telecommunications applications. BDTI has experience programming a wide variety of target processors.

- Consulting and processor evaluation services. BDTI provides consulting services to leading companies that develop and use DSP technology. BDTI's consulting expertise is in the evaluation and specification of processor architectures, DSP design tools, DSP algorithms, and other DSP technology. BDTI's processor evaluation methodology, which features the BDTI Benchmark specification, is available for license to processor developers and users.

- Training. BDTI offers courses to help engineers, marketers, and managers develop their knowledge of DSP technology. Courses are available for on-site delivery or in electronic format. Course descriptions are posted on BDTI's website at www.BDTI.com. BDTI also develops custom courses for customers' specific needs.

BDTI's customers include major semiconductor, consumer electronics, telecommunications, and software companies who are leaders in the development and application of DSP technology.

The authors welcome your comments. Please forward your corrections and suggestions to the authors in care of BDTI.

BDTI can be reached by telephone at +1 (510) 665-1600, by fax at +1 (510) 665-1680, by electronic mail at info@BDTI.com, and on the World Wide Web at www.BDTI.com.

# **Primary Authors**

**Jeff Bier** is a founder and General Manager of BDTI. Mr. Bier is the author of numerous industry reports on DSP technology and is a member of the IEEE Design and Implementation of Signal Processing Systems and Industry DSP technical committees. Mr. Bier received his B.S. and M.S. degrees from Princeton University and U.C. Berkeley, respectively.

Laurent Bonetto is a DSP Engineer with BDTI, where he works on evaluating processors and on developing DSP software. Mr. Bonetto received his M.E. degree from the Georgia Institute of Technology, where he worked on Synthetic Aperture Radars with Prof. James McClellan. Mr. Bonetto also holds degrees in Mathematics and in Engineering from the Electrical and Computer Engineering School, Supelec, France, where his principal focus was DSP theory.

**Brian Cavagnolo** is a DSP Engineer with BDTI, where he is involved in processor evaluation and DSP software development. He holds a B.S. degree in electrical engineering from the U.C. Berkeley.

**Jennifer Eyre** is BDTI's Manager of Analysis and Publications. She is responsible for overseeing BDTI's analyses of processor architectures. Ms. Eyre holds an MSEE from UCLA and is author or co-author of numerous reports and articles on DSP processor technology.

**Bjorn Hori** is a DSP Engineer with BDTI, where he focuses primarily on digital audio applications and analysis of DSP processors. Mr. Hori received his B.S. degree in electrical engineering and computer science from U.C. Berkeley.

**Phil Lapsley** is a co-founder of BDTI. Mr. Lapsley is an expert on real-time DSP techniques and has extensive experience in the analysis of DSP processors, tools, and related technology. Mr. Lapsley received his B.S. and M.S. degrees from U.C. Berkeley.

Adam Lins is BDTI's Engineering Manager. Mr. Lins oversees BDTI's software development activities, and contributes to BDTI's processor analysis activities. Mr. Lins holds an M.S. degree in electrical engineering from the University of Canterbury, New Zealand, where his principal focus was digital communication systems.

**Frantz Lohier** is a DSP Engineer with BDTI, where he focuses primarily on evaluating processors and developing DSP software. Mr. Lohier holds M.S. and Ph.D. degrees from the Pierre et Marie Curie University, France. His Ph.D. thesis was on DSP Architectures and Programming Methodologies. Mr. Lohier also holds a French Computer Engineering Diploma.

Amit Shoham is a Senior DSP Engineer with BDTI, where he focuses primarily on benchmarking DSP processor performance and evaluating DSP design tools. His technical interests include digital audio and music synthesis. Prior to joining BDTI, Mr. Shoham developed factory diagnostics for digital audio hardware at Silicon Graphics. He holds a B.S. degree in computer systems engineering and an M.S. degree in electrical engineering, both from Stanford University.

#### **Contributors**

**Daniel** Ash, of Ashcan Engineering, contributed to the analysis of the TMS320C54xx and TMS320C55xx.

*Cynthia Keller*, BDTI's Office Manager, managed project administration and contributed to research and document production.

**John Strawn**, of S Systems, Inc., contributed to the analysis of the ADSP-TS0xx, DSP563xx, DSP568xx, and DSP5685x.

# **Acknowledgments**

This report would not have been possible without the help of many people.

We wish to especially acknowledge the assistance of those outside BDTI who assisted with benchmark coding, processor evaluations, and project administration: Maria Tagliaferro and David Starr of Analog Devices; Andy Soukup, Henry Wiechman, David Hoyle, Jim Larimer, and Martin Burgos of Texas Instruments; Yuval Ronen and Joe Gergen of Motorola; Diana Yannes and John Sweeney of Lucent Technologies. All gave generously of their time and expertise.

# 3. Digital Signal Processing and DSP Systems

For the purposes of this report, we define a DSP system to be any electronic system making use of digital signal processing. Our informal definition of digital signal processing is the application of mathematical operations to digitally represented signals. Signals are represented digitally as sequences of *samples*. Often, these samples are obtained from physical signals (for example, audio signals) through the use of *transducers* (such as microphones) and *analog-to-digital converters*. After mathematical processing, digital signals may be converted back to physical signals via *digital-to-analog converters* and transducers (such as speakers).

In some systems, the use of DSP is central to the operation of the system. For example, modems and digital cellular telephones rely very heavily on DSP technology. In other products, the use of DSP is less central, but often offers important competitive advantages in terms of features, performance, and cost. For example, manufacturers of analog consumer electronics devices such as audio amplifiers widely employ DSP technology to add features such as simulation of concert hall acoustics.

This chapter presents a high-level overview of digital signal processing. We first discuss the advantages of DSP over analog systems. We then describe some salient features and characteristics of DSP systems in general. We conclude with a brief look at some important classes of DSP applications.

This chapter is not intended to be a tutorial on DSP theory. For a general introduction to DSP theory, we recommend one of the many textbooks available on DSP, such as *Discrete-Time Signal Processing* by Oppenheim and Schafer [Oppe89] or *Understanding Digital Signal Processing* by Richard G. Lyons [Lyon97].

# **Advantages of DSP**

Digital signal processing enjoys several advantages over analog signal processing. The most significant of these is that DSP systems are able to accomplish tasks inexpensively that would be difficult or even impossible using analog electronics. Examples of such applications include speech synthesis, speech recognition, and high-speed data communication using error-correction coding. All of these tasks involve a combination of signal processing and control (e.g., making decisions regarding received bits or operating conditions) that is extremely difficult to implement using analog techniques.

DSP systems also enjoy two additional advantages over analog systems:

- Insensitivity to environment. Digital systems, by their very nature, are considerably less sensitive to environmental conditions than analog systems. For example, an analog circuit's behavior depends on its temperature. In contrast, barring catastrophic failures, a DSP system's operation does not depend on its environment. Whether in the snow or the desert, a DSP system delivers the same response.

- **Insensitivity to component tolerances.** Analog components are manufactured to particular tolerances—a resistor, for example, might be guaranteed to have a resis-

tance within one percent of its nominal value. The overall behavior of an analog system depends on the actual values of all of the analog components used. As a result, two analog systems of exactly the same design will have slightly different behaviors due to slight variations in their components. In contrast, barring a malfunction, two identical digital systems will always produce the same outputs given the same inputs.

These two advantages combine synergistically to give DSP systems an additional advantage over analog systems:

• **Predictable, repeatable behavior.** Because a DSP system's output does not vary due to environmental factors or component variations, it is possible to design systems having exact, known responses that do not vary.

Finally, some DSP systems have two other advantages over analog systems:

- **Reprogrammability.** If a DSP system is based on a programmable processor or other programmable device, it can be reprogrammed—even in the field—to perform other tasks. In contrast, analog systems usually require physically different components to perform different tasks.

- Size. The size of analog components varies with their values; for example, a 100-microfarad capacitor used in an analog filter is physically larger than a 10-picofarad capacitor used in a different analog filter. In contrast, DSP implementations of both filters might well be the same size—indeed, might even use the same hardware, differing only in their filter coefficients—and might be smaller than either of the two analog implementations.

These advantages, coupled with the fact that DSP can take advantage of the rapidly increasing densities and speeds enabled by more advanced digital IC manufacturing processes, make DSP the solution of choice for an expanding range of signal processing applications.

# **Characteristics of DSP Systems**

In this section we describe a number of characteristics common to all DSP systems, including algorithms, sample rate, clock rate, and arithmetic types.

#### **Algorithms**

DSP systems are often characterized by the *algorithms* used. The algorithms specify the arithmetic operations to be performed but do not specify how those operations are to be implemented. They might be implemented in software on an ordinary microprocessor or programmable signal processor, or they might be implemented in custom integrated circuits. The selection of an implementation technology is determined in part by the required processing speed and arithmetic precision. Table 3.0-1 lists some common types of DSP algorithms and some applications in which they are typically used.

| Classes of<br>DSP Algorithms              | System Application                                                                                                                                                                                                                                    |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Speech coding and decoding                | Digital cellular telephones, voice-over-Internet, digital cordless telephones, multimedia computers, secure communications, tapeless answering machines                                                                                               |

| Speech encryption and decryption          | Digital cellular telephones, personal communications systems, secure communications                                                                                                                                                                   |

| Speech recognition                        | Advanced user interfaces, multimedia computers, robotics, automotive applications, cellular telephones, personal communications systems, voice response systems                                                                                       |

| Speech synthesis                          | Advanced user interfaces, robotics, voice response systems                                                                                                                                                                                            |

| Speaker identification                    | Security, multimedia computers, advanced user interfaces                                                                                                                                                                                              |

| High-fidelity audio encoding and decoding | Consumer audio, consumer video, digital audio broadcast, professional audio, multimedia computers, Internet audio                                                                                                                                     |

| Modem algorithms                          | Digital cellular telephones, personal communications systems, digital cordless telephones, digital audio broadcast, digital signaling on cable TV, multimedia computers, wireless computing, navigation, data/facsimile modems, secure communications |

| Noise cancellation                        | Professional audio, advanced vehicular audio, industrial applications                                                                                                                                                                                 |

| Audio equalization                        | Consumer audio, professional audio, advanced vehicular audio, music, hearing aids                                                                                                                                                                     |

| Ambient acoustics emulation               | Consumer audio, professional audio, advanced vehicular audio, music, games                                                                                                                                                                            |

| Audio mixing and editing                  | Professional audio, music, multimedia computers                                                                                                                                                                                                       |

| Sound synthesis                           | Professional audio, music, multimedia computers, advanced user interfaces, games                                                                                                                                                                      |

| Vision                                    | Security, manufacturing, advanced user interfaces, instrumentation, robotics, navigation                                                                                                                                                              |

| Image compression and decompression       | Digital photography, digital video, multimedia computers, videoconferencing, consumer video                                                                                                                                                           |

| Image compositing                         | Multimedia computers, consumer video, advanced user interfaces, navigation                                                                                                                                                                            |

| Beamforming                               | Navigation, medical imaging, radar, sonar, signals intelligence, cellular base stations                                                                                                                                                               |

| Echo cancellation                         | Speakerphones, hands-free cellular telephones                                                                                                                                                                                                         |

| Spectral estimation                       | Signals intelligence, radar, sonar, professional audio, music                                                                                                                                                                                         |

TABLE 3.0-1. Common DSP algorithms and typical applications.

#### Sample Rates

A key characteristic of a DSP system is its *sample rate*: the rate at which samples are consumed, processed, or produced. Combined with the complexity of the algorithms used in the system, the sample rate determines the required speed of the implementation technology. A familiar example is the digital audio compact disc (CD) player, which produces samples at a rate of 44.1 kHz on two channels.

Of course, a DSP system may use more than one sample rate; such systems are said to be *multirate DSP systems*. An example is a converter from the CD sample rate of 44.1 kHz to the digital audio tape (DAT) rate of 48 kHz. Because of the awkward ratio between these sample rates, the conversion is usually done in stages, typically with at least two intermediate sample rates. Another example of a multirate algorithm is a filter bank, used in applications such as speech, audio, and video encoding and some signal analysis algorithms. Filter banks typically consist of stages that divide a signal into high- and low-frequency portions. These new signals are then downsampled (i.e., their sample rate is lowered by periodically discarding samples) and divided again. In multirate applications, the ratio between the highest and the lowest sample rates in the system can become quite large, sometimes exceeding 100,000 to 1.

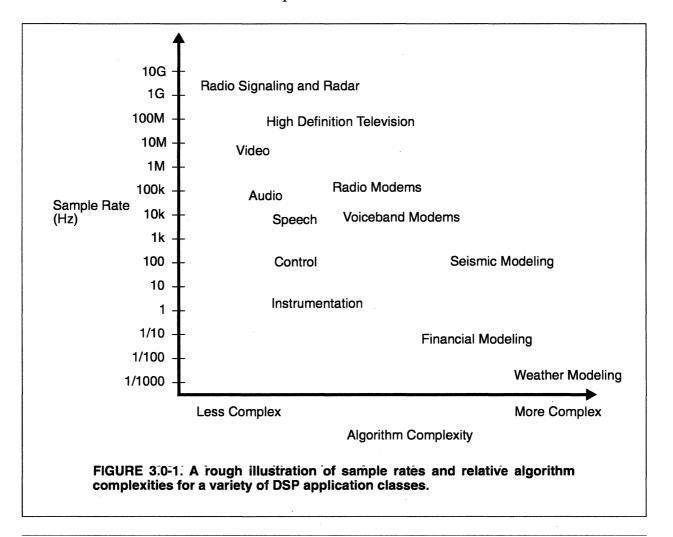

The range of sample rates encountered in signal processing systems is huge. In Figure 3.0-1 we show the rough positioning of a few classes of applications with respect to algorithm complexity and sample rate. Sample rates for applications range over 12 orders of magnitude! Only at the very top of that range is digital implementation rare. This is because the cost and difficulty of implementing a given algorithm digitally increases with the sample rate. For this same reason, DSP applications that use at higher sample rates tend to use less complex algorithms than those using lower sample rates.

#### **Clock Rates**

Digital electronic systems are often characterized by their *clock rates*. The clock rate usually refers to the rate at which a system or sub-system performs its most basic unit of work. Often, systems use different clock rates for different purposes. Within a single chip, clock rates of 500 MHz and higher are becoming common in mass-produced, commercial products. Between chips, clock rates of up to 100 MHz are common, with faster rates found in some high-performance products. For DSP systems, the ratio of clock rate to sample rate is one of the most important characteristics used to determine how the system will be implemented. The relationship between the clock rate and the sample rate in a system or component partially determines the amount of hardware needed to implement a given algorithm in real-time. As the ratio of sample rate to clock rate increases, so does the amount and complexity of hardware required to implement the algorithm.

#### **Numeric Representations**

Arithmetic operations such as addition and multiplication are at the heart of DSP algorithms and systems, and signal fidelity (i.e., range and precision) is usually a key per-

formance metric. As a result, the numeric representations and type of arithmetic used can have a profound influence on the behavior and performance of a DSP system. The most important choice for the designer is between *fixed-point* and *floating-point* arithmetic. Fixed-point arithmetic represents numbers in a fixed range (e.g., -1.0 to +1.0) with a finite number of bits of precision (called the *word width*). For example, an eight-bit fixed-point number provides a resolution of 1/256 of the range over which the number is allowed to vary. Numbers outside of the specified range cannot be represented; arithmetic operations that would result in a number outside this range either *saturate* (that is, are limited to the largest positive or negative representable value) or *overflow* (that is, the extra bits resulting from the arithmetic operation are discarded).

Floating-point arithmetic greatly expands the representable range of values. Floating-point arithmetic represents every number in two parts: a mantissa and an exponent. The mantissa is, in effect, forced to lie between -1.0 and 1.0, while the exponent keeps track of the amount by which the mantissa must be scaled (in terms of powers of two) in order to create the actual value represented. That is:

# $value = mantissa \times 2^{exponent}$

Floating-point arithmetic provides much greater dynamic range (that is, the ratio between the largest and smallest values that can be represented) than fixed-point arithmetic using the same number of bits. Because it reduces the probability of overflow and the necessity of scaling, floating-point arithmetic can considerably simplify algorithm and software design. Unfortunately, processors that use floating-point arithmetic are generally slower and more expensive than processors that use fixed-point arithmetic, because floating-point arithmetic is more complicated to implement in hardware.

Arithmetic and numeric formats are discussed in more detail in BDTI's textbook, DSP Processor Fundamentals.

#### **Execution-Time Predictability**

Many DSP systems are subject to *hard real-time constraints*, meaning that the system must process or respond to inputs within a specified amount of time in every instance. In such systems, failure to meet real-time deadlines may cause malfunctions ranging from a reduction in signal quality to a loss of data to failure of a communications link. This type of performance constraint differs from, for example, performance requirements of personal computers. In a personal computer, the system is expected to respond to inputs within a reasonable amount of time on average, but exceeding the maximum desired response time is generally not considered a failure.

To ensure that hard real-time constraints are met, the programmer must be able to predict how much time is required to execute time-critical sections of the application software. Hence, a processor's *execution-time predictability* is often a significant consideration in real-time DSP applications.

In many cases, programmers writing real-time DSP applications can execute their software on a development board and measure the execution time. Unfortunately, measuring execution time does not guarantee that the worst-case scenario is known; in some architectures, the execution timing of a specific segment of software may change depending on the instructions that preceded it, or depending on the locations of the instructions and associated data in memory. Execution timing may also be data dependent. Hence, measuring the execution time on hardware often does not solve the problem.

Even in the absence of hard real-time constraints execution-time predictability can be important, because it plays a role in software optimization. If it is difficult to predict how long a given section of software will take to execute, it can be difficult to determine the effect of changes to the software—will the modified software require more, less, or the same amount of time as the original software?

Of course, all processors are fundamentally deterministic; that is, given enough information about the processor's architecture and state, it is possible to predict the exact number of clock cycles required to execute a specific segment of software. However, the ease with which execution times can be predicted varies widely. Most DSP processors

have relatively straightforward architectures and are supported by tools to help the programmer predict execution times, such as software simulators that accurately report elapsed instruction cycles. In contrast, most high-performance general-purpose processors have very complex architectures and lack tool support to aid programmers in predicting execution times. These factors may make it extremely difficult to predict how long a section of DSP software will take to execute, thus complicating DSP software development and optimization on high-performance CPUs.

The complexity of DSP algorithms coupled with high data rates means that in many DSP applications, programmers develop (or optimize) software in assembly language in order to squeeze the maximum performance out of the processor. In such cases the application programmer must understand the intricacies of the processor's architecture (including execution timing) in order to effectively select a processor, predict performance, and optimize software. Where performance is not critical, developers sometimes make use of high-level language compilers to quickly generate application software. However, poor execution-time predictability is often a challenge for the compiler as well as the assembly-language programmer; if the rules governing the execution time of a small block of software are complicated, it may be difficult for the compiler to generate optimized software.

A few of the latest architectures targeting DSP applications have begun to incorporate dynamic features traditionally found only in high-end general-purpose processors, in an effort to boost performance. For this reason, we include a brief discussion of some of the dynamic features and their impact on execution-time predictability.

#### Caches

High-performance DSP processors often use on-chip instruction caches, and in a few cases have recently also begun to incorporate data caches. When the required instructions and data are contained in the on-chip caches, the processor executes at full speed. Otherwise, the processor may be stalled while instructions and data are loaded into the caches from main memory. In real-time applications, caches can be problematic because they complicate the task of predicting software execution times. For this reason, many DSP processors allow programmers to manually control cache segments, thereby ensuring that critical instructions and data are present in the caches when needed. The cost of this control is that of degraded performance in other sections of the program.

#### **Dynamic Memory**

To reduce costs, some systems rely on dynamic RAM (DRAM) for their main memory. Depending on the type of DRAM devices chosen and the details of the system design, accesses to DRAM-based main memory may degrade execution-time predictability because the DRAM may temporarily be unavailable while data is refreshed, and because DRAM requires variable access times, for example access times increase when crossing memory page boundaries.

#### **Branch Prediction**

Program branches can be very costly in terms of execution time, because instructions following the branch that have already entered the processor's pipeline must be flushed, and the pipeline must be reloaded. (See BDTI's textbook, DSP Processor Fundamentals, for a discussion of pipelines.) One approach to decreasing this execution-time penalty is to provide hardware in the processor that attempts to predict the outcome of upcoming branches. The processor then fetches instructions based on the outcome of this prediction, in an attempt to avoid fetching unneeded instructions and flushing the pipeline. Branch prediction schemes on high-performance general-purpose processors are often quite complicated. For example, they often feature sophisticated branch prediction mechanisms that keep a record of branch statistics and attempt to detect patterns of taken and not-taken branches. This can be a very effective tool for increasing performance; however, complicated branch prediction schemes adversely affect execution-time predictability. Among processors for DSP, the Analog Devices TigerSHARC and the Infineon TriCore are examples of processors that include branch prediction. Their branch predictability.

#### **Dynamic Instruction Scheduling**

Processors designed for DSP rely heavily on parallelism to achieve strong performance. Many DSP processors achieve parallelism by encoding several operations in a single instruction. Some processors achieve high parallelism by employing a *superscalar* architecture, in which several instructions are issued and executed in parallel. Superscalar processors dynamically select sequential instructions for parallel execution, depending on the available execution units and on dependencies between instructions. Run-time scheduling of instructions in superscalar processors can be quite a complex process, making execution timing difficult to predict.

Some superscalar processors, such as the Motorola PowerPC 604e and the Intel Pentium II and Pentium III processors, use *out-of-order* execution. When one of these processors fetches instructions from memory, the instructions are stored temporarily in a buffer in the processor and are not issued to their respective execution units until their operands become available. The processors can buffer dozens of instructions waiting to be issued. Since operands for the instructions may become available in a different order than the order in which the instructions occur in memory, the instructions may be issued to their respective execution units in a different order than they were fetched. Processors that employ out-of-order execution contain hardware that is responsible for committing results to registers and memory so that the processors appear to execute the instructions in the same order in which they occur in the program.

Some processors, such as the Texas Instruments TMS320C6xxx families, achieve high parallelism by employing a *VLIW* (very long instruction word) architecture. VLIW architectures are similar to superscalar architectures; several instructions are issued and executed in parallel. These instructions are fetched as part of one long super-instruction.

In a VLIW architecture, however, the programmer (or software-generation tool) explicitly specifies which instructions will be executed in parallel; this determination takes place before the program is executed, and does not affect the execution-time predictability of the processor.

#### **Tools**

Strong software and hardware development tools are essential for efficient application development in general, but are especially important for development of performance-critical, real-time applications. In such applications, developers need to be able to analyze and predict performance in detail, to perform real-time debugging, and to thoroughly optimize critical sections of software.

DSP processor tools generally include clock-cycle-accurate instruction-set simulators. Such simulators allow programmers to observe, cycle by cycle, software execution on the target processor for purposes of performance analysis, optimization, and debugging. For processors with difficult-to-predict execution times, the availability of a cycle-accurate simulator is an essential tool for software development and optimization. Development tools are discussed further in BDTI's textbook, *DSP Processor Fundamentals*.

# **Classes of DSP Applications**

Digital signal processing is used in an extremely diverse range of applications, from radar systems to consumer electronics. Naturally, no one processor can meet the needs of all or even most applications. Therefore, the first task for the designer selecting a processor is to weigh the relative importance of performance, cost, integration, ease of development, power consumption, and other factors for the application at hand. Here we briefly touch on the needs of just a few categories of DSP applications. Table 3.0-2 summarizes these categories.

| Category                              | Example Applications                                                                                                 |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Low-Cost Embedded<br>Systems          | Modems, radar detectors, pagers, cellular telephones, cordless telephones, disk drives, automotive real-time control |

| High-Performance Applications         | Radar, sonar, seismic imaging, speaker identification                                                                |

| Personal Computer-Based<br>Multimedia | Modems, voice mail, music synthesis, speech synthesis; speech, audio, and video compression and decompression        |

TABLE 3.0-2. Example DSP processor application types.

#### Low-Cost Embedded Systems

The largest applications (in terms of dollar volume) for digital signal processing are inexpensive, high-volume embedded systems, such as cellular telephones, disk drives (where DSPs are used for servo control), and modems. In these applications, cost and integration considerations are paramount. For portable, battery-powered products, power consumption is also critical. In these high-volume, embedded applications, performance and ease of development considerations are often given less weight, even though these applications usually involve development of custom software to run on the processor and custom hardware that interfaces with the processor. These products often must conform to published interface standards, such as the ITU-T V.90 modem standard.

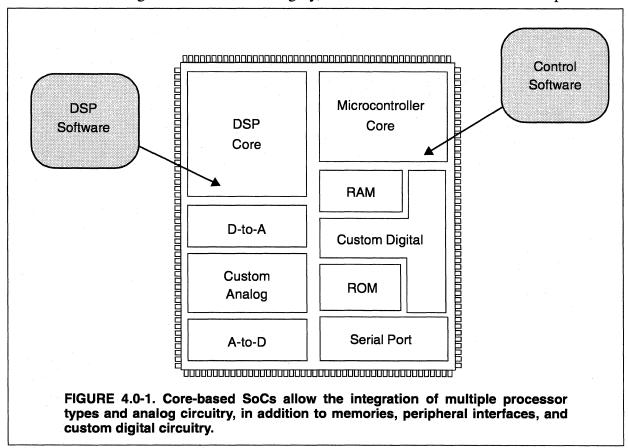

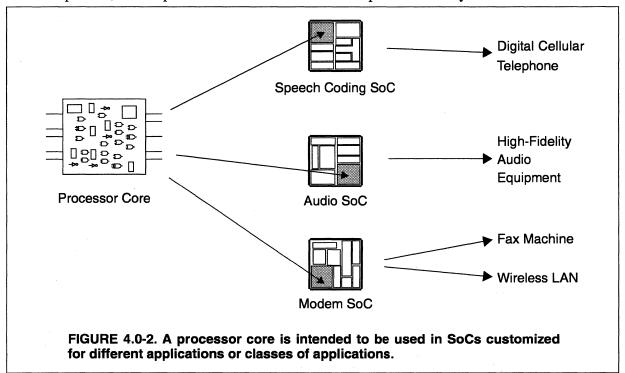

Low-cost general-purpose processors and microcontrollers are very common in embedded applications. In some of these applications, such as modems and digital cellular telephones, it is common to find a microcontroller and a DSP processor working together, sometimes integrated in the same chip. Typically, the microcontroller handles overall control, user interface, and some top-level protocol processing, while the DSP handles the computationally intensive signal processing tasks. Many microcontroller vendors, recognizing the benefits of a single-processor solution, offer DSP-enhanced versions of their microcontroller architectures. These hybrid DSP/microcontroller architectures typically include some (or many) of the architectural features common among DSP processors.

# **High-Performance Applications**

Another important class of applications involves processing large volumes of data with complex algorithms for specialized needs. This includes uses like sonar and seismic exploration, where production volumes are lower, algorithms more demanding, and product designs larger and more complex. As a result, designers favor processors with maximum performance, ease of use, and support for multiprocessor configurations. In some cases, rather than designing their own hardware and software from scratch, designers of these systems use off-the-shelf boards and ease their software development tasks by using existing software libraries.

High-performance floating-point DSP processors are common in these applications, as are high-performance general-purpose processors. Often, multiple processors are employed. It is common for a personal computer or workstation to be part of such systems, providing the user interface, access to mass storage, and other functions. Since personal computers and workstations are based on general-purpose processors, these processors have a foothold in such applications.

#### Personal Computer-Based Telecommunications and Multimedia

An important class of DSP applications is personal computer- and workstation-based telecommunications and multimedia functions. Increasingly, PCs are incorporating such capabilities as telephony, voice mail, data and facsimile modems, music and speech synthesis, and image compression. As with other high-volume, embedded applica-

tions, PC multimedia demands low cost and high integration. Unlike some other embedded applications, PC multimedia also demands high performance, since a multimedia PC may be called on to perform multiple functions simultaneously. Furthermore, the multitasking nature of such applications means that in addition to performing each function efficiently, the processor must have the ability to efficiently switch between functions. Memory capacity may also be an issue in these applications because many multimedia applications manipulate large amounts of data.

The first implementations of these integrated applications used separate DSP processors to handle real-time signal processing tasks. For example, in the late 1980s, NeXT workstations incorporated a Motorola DSP560xx processor. Later, some Apple Macintosh models incorporated the now obsolete Lucent Technologies DSP32xx. These approaches were innovative in that they replaced the multiple, fixed-function, ROM-programmed DSPs that would normally be found in a modem, a sound card, etc., with a single reprogrammable DSP.

In 1994, Intel announced an initiative called "Native Signal Processing," or "NSP," through which they planned to facilitate the implementation of real-time DSP functions on existing Intel processors in PCs. Intel's original NSP initiative was based entirely on software, including a version of Texas Instruments' SPOX real-time operating system and software libraries provided by Intel. This original software-only initiative had no significant impact on the marketplace, partly due to Microsoft's reluctance to allow SPOX to become a central component of the Windows PC software environment, but it did serve to raise awareness of the concept of using computer system host processors for signal processing. With Intel's addition of DSP hardware support to their processors via the MMX and SSE architecture extensions, products are beginning to emerge that employ NSP. In the meantime, other vendors of PC and workstation host processors have begun, with varying degrees of commitment, their own efforts in this direction. AMD, for example, offers its K6 processor, which is compatible with Intel's MMX extensions, and more recently added 3DNow! instructions to its processors. Other vendors have announced similar instruction set extensions; for example, Motorola offers the AltiVec instruction set extensions in its G4 PowerPC processor.

General-purpose processors are present in all PCs and workstations, and are among the highest-value components in these systems. Thus it is natural for manufacturers of these chips to take steps to defend their positions by minimizing the need for a second processor to implement telecommunications and media functions in computer systems.

# 4. Processor Architectures and Performance

Chapter 3, *Digital Signal Processing and DSP Systems*, described digital signal processing in general terms, focusing on DSP fundamentals, systems, and application areas. In this chapter we begin to examine specific characteristics of processors intended for use in DSP applications, starting with a high-level description of the features common to virtually all DSP processors. We then describe classes of architectures for DSP, including those used in dedicated DSP processors and those used in general-purpose processors. BDTI's textbook, *DSP Processor Fundamentals*, provides a more detailed treatment of DSP processor architectures and features.

#### **Architectural Features for DSP**

Most DSP applications require high performance in repetitive computation- and data-intensive tasks. The most important processor architecture features that support these kinds of tasks are introduced briefly here and summarized in Table 4.0-1.

#### Fast Multiply-Accumulate

The most often-cited feature of DSP processors is the ability to perform a *multi-ply-accumulate* operation (often called a *MAC*) in a single instruction cycle. The multiply-accumulate operation is useful in algorithms that use vector dot products, such as digital filters, correlation, and Fourier transforms. To achieve this functionality, DSP processors include one or more multipliers and accumulators integrated into the main arithmetic processing unit (called the *data path*) of the processor. In addition, to allow a series

| Feature                                          | Use                                                                                                                                                                                                          |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fast Multiply-<br>Accumulate                     | Most DSP algorithms, including filtering and transforms, are multiplication-intensive.                                                                                                                       |

| Multiple-Access<br>Memory<br>Architecture        | Many data-intensive DSP operations can be accelerated by reading a program instruction and multiple data items during each instruction cycle.                                                                |

| Specialized Addressing Modes                     | Efficient handling of data arrays and other common data types in DSP applications.                                                                                                                           |

| Specialized Program Control                      | Efficient control of loops is important for many iterative DSP algorithms. Fast interrupt handling is important for applications with frequent I/O operations.                                               |

| On-Chip Peripherals and Input/ Output Interfaces | On-chip peripherals, like analog-to-digital converters, allow for small, low-cost system designs. Similarly, I/O interfaces tailored for common peripherals allow simple interfaces to off-chip I/O devices. |

TABLE 4.0-1. Basic features common to virtually all DSP processors.

of multiply-accumulate operations to proceed without the possibility of arithmetic overflow, DSP processors generally provide extra bits in their accumulator registers to accommodate growth of the accumulated result. These bits are often referred to as "guard bits." Multiply-accumulate features are discussed in detail in BDTI's textbook, *DSP Processor* Fundamentals.

## Multiple-Access Memory Architecture

A second feature shared by most DSP processors is the ability to complete several accesses to memory in a single instruction cycle. This allows the processor to fetch an instruction while simultaneously fetching operands for a previously fetched instruction or storing the result of a previous instruction to memory. High bandwidth between the processor and memory is essential for good performance if repetitive data-intensive operations are required in an algorithm, as is common in many DSP applications.

In many DSPs, parallel memory accesses are subject to restrictions. Typically, all but one of the memory locations accessed must reside on-chip, and multiple memory accesses can take place only with certain instructions. To support simultaneous accesses of multiple memory locations, DSP processors provide multiple on-chip buses, multi-ported on-chip memories, and in some cases multiple independent memory banks. DSP processor memory structures are often quite distinct from those of general-purpose processors.

## **Specialized Addressing Modes**

To allow arithmetic processing to proceed at maximum speed while accessing common DSP data structures, DSP processors incorporate dedicated address generation units. Once the appropriate addressing registers have been configured, the address generation units operate in parallel with the processor's data path, forming the addresses required for operand accesses in parallel with the execution of arithmetic instructions. Address generation units typically support a selection of addressing modes tailored to DSP applications. The most common of these is register-indirect addressing with post-increment, which is useful in algorithms where a repetitive computation is performed on a series of data stored sequentially in memory. Special addressing modes called *circular* or *modulo* addressing are often supported to simplify the use of data buffers. Some processors support *bit-reversed* addressing, which eases the task of implementing the fast Fourier transform (FFT) algorithms.

#### **Specialized Execution Control**

Because many DSP algorithms involve repetitive computations in small loops, most DSP processors provide special support for efficient looping. Often, a special loop or repeat instruction is provided that allows the programmer to implement a *for-next* loop without expending any instruction cycles for updating and testing the loop counter or for jumping back to the top of the loop.

Some DSP processors provide other execution control features to improve performance, such as fast context switching and low-latency/low-overhead interrupts for fast input/output data handling.

## Peripherals and Input/Output Interfaces

To allow low-cost, high-performance input and output (I/O), most DSP processors incorporate one or more serial or parallel I/O interfaces, and specialized I/O handling mechanisms such as direct memory access (DMA). DSP processor peripheral interfaces are often designed to interface directly with common peripheral devices like analog-to-digital and digital-to-analog converters.

As integrated circuit manufacturing techniques have improved in terms of density and flexibility, DSP processor vendors have begun to include not just peripheral interfaces, but complete peripheral devices on-chip. Examples of this include chips designed for digital answering machine applications, several of which incorporate a digital-to-analog and analog-to-digital converter on-chip.

### **Classes of Processors for DSP**

Most DSP processors include the features outlined in the previous sections, enabling them to perform well on DSP algorithms. These features can be implemented within different architectural styles, and as the demand for DSP-capable processors has grown, the variety of styles of DSP processor architectures has widened. In addition, there are a growing number of processors that while not, strictly speaking, "DSP processors" are nonetheless capable of strong DSP performance. In the following sections, we provide an overview of the classes of processors commonly used to implement DSP. These processors can be grouped as follows:

- Conventional DSP processors

- Enhanced conventional DSP processors

- VLIW processors

- Superscalar processors

- General-purpose processors

- Hybrid processors

Note that these processor classes are not all mutually exclusive; for example, general-purpose processors are often superscalar.

#### Conventional DSP Processors

The first commercially successful programmable DSP processors were introduced in the early 1980's. For over a decade, virtually all subsequent DSP processors were based on the same style of architecture as the earliest DSPs, albeit with higher instruction execution rates, more powerful execution units, and larger address spaces. We refer to processors with this type of architecture as *conventional DSP processors*.