ADSP-1401 Program Sequencer

ADSP-1410 Address Generator

## Word-Slice User's Manual

ADSP-1401 Program Sequencer

ADSP-1410 Address

Generator

### Word-Slice<sup>TM</sup> User's Manual

©1987 Analog Devices, Inc. ALL RIGHTS RESERVED

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under the patent rights of Analog Devices.

Word-Slice is a trademark of Analog Devices.

Printed in USA.

### CHAPTER 1 INTRODUCTION

| 1.1 | System Overview     |       |

|-----|---------------------|-------|

| 1.2 | ADSP-1401 Overview  | . 1-2 |

| 1.3 | ADSP-1410 Overview  | 1 – 3 |

| 1.4 | Third-Party Support | 1 – 4 |

| 1.5 | Manual Organization | 1 – 5 |

### ADSP-1401: CHAPTERS 2 - 6

#### CHAPTER 2 INTERNAL ARCHITECTURE

| 2.1  | Introduction                         | 2 – 1  |

|------|--------------------------------------|--------|

| 2.2  | Instruction Port                     | 2 – 3  |

| 2.3  | Bidirectional Data Port              | 2 – 3  |

| 2.4  | Program Counter                      | 2-4    |

| 2.5  | Adder and Width Control              | 2 – 5  |

| 2.6  | Internal RAM and Stack Pointers      | 2 – 6  |

| 2.7  | Interrupts and Interrupt Vector File | 2-7    |

| 2.8  | Event Counters                       | 2 – 9  |

| 2.9  | Flag                                 | 2 – 9  |

| 2.10 | Trap/Tristate/Reset                  | 2 - 10 |

| 2.11 | Address Multiplexer and Address Port | 2 – 12 |

| 2.12 | Status Register                      | 2 – 12 |

#### CHAPTER 3 JUMPS

| 3.1 | Introdu | uction     | <br> | 3 – 1 |

|-----|---------|------------|------|-------|

| 3.2 | Condi   | tions      |      | 3 – 3 |

|     | 3.2.1   | Flag Input |      | 3 – 3 |

|     | 3.2.2   | Counters   |      | 3 – 4 |

| 3.3 | Address Sources           | 3 - 7  |

|-----|---------------------------|--------|

|     | 3.3.1 Direct Addressing   | 3 – 7  |

|     | 3.3.2 Indirect Addressing | 3 – 7  |

|     | 3.3.3 Register Stack      | 3 – 8  |

| 3.4 | Subroutines               | 3 – 10 |

#### CHAPTER 4 INTERRUPT PROCESSING

| 4.1 | Introduction                           | 4 - 1  |

|-----|----------------------------------------|--------|

| 4.2 | Masking and Enabling                   | 4 – 1  |

| 4.3 | Interrupt Service Routines             | 4 – 2  |

| 4.4 | Counter Underflow Interrupt            | 4-6    |

|     | Stack Overflow and Underflow Interrupt | 4 – 6  |

|     | 4.5.1 Stack Limit Register             | 4 – 8  |

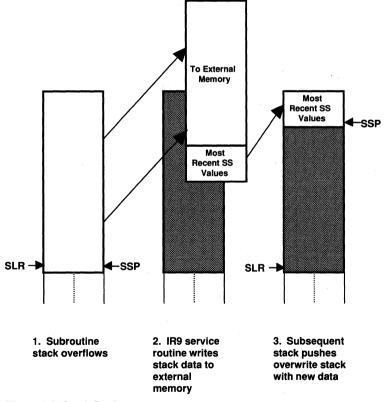

|     | 4.5.2 Stack Paging                     | 4 – 10 |

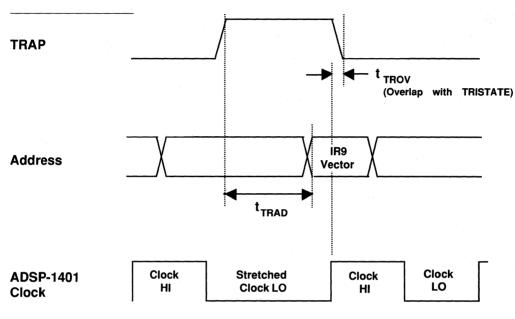

| 4.6 | Trap                                   | 4 – 11 |

|     |                                        |        |

#### CHAPTER 5 SYSTEM INTERFACE

| 5.1 | Introduction             |            | 5 – 1 |

|-----|--------------------------|------------|-------|

| 5.2 | Look-Ahead Pipeline      |            | 5 – 1 |

| 5.3 | Data Input and Output    |            | 5 – 1 |

| 5.4 | Instruction Hold Control | · · ·      | 5 – 3 |

| 5.5 | Tristate Outputs         |            | 5 – 4 |

| 5.6 | Writeable Control Store  |            | 5 – 5 |

| 5.7 | Reset                    | ۰.<br>مدین | 5 – 9 |

#### CHAPTER 6 INSTRUCTION SET

| 6.1 | Introd | uction     |                                  | 6 – 1 |

|-----|--------|------------|----------------------------------|-------|

| 6.2 |        | ction Refe |                                  | 6 – 2 |

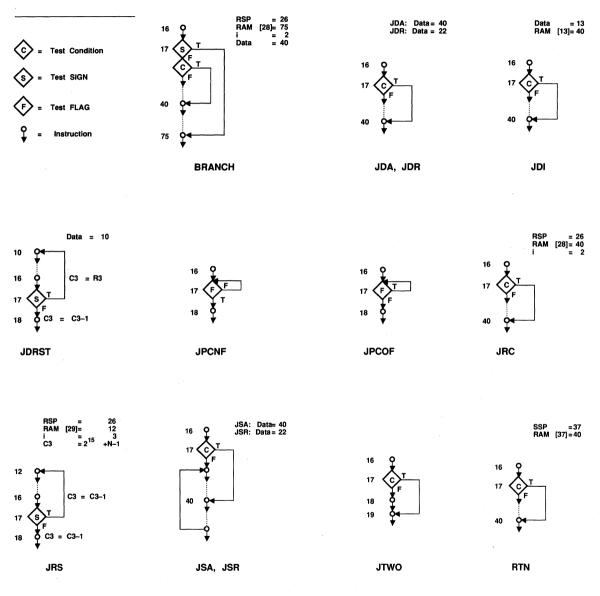

|     | 6.2.1  | Conditio   | nal Jump and Branch Instructions | 6 – 3 |

|     |        |            | BRANCH                           | 6-5   |

|     |        | 6.2.1.2    | JDA                              | 6 – 6 |

|     |        | 6.2.1.3    | JDI                              | 6 – 7 |

|     |        | 6.2.1.4    | JDR                              | 6 – 8 |

|     |        | 6.2.1.5    | JDRST                            | 6-9   |

|       | 6.2.1.6            | JPCNF                 | 6 – 10           |

|-------|--------------------|-----------------------|------------------|

|       | 6.2.1.7            | JPCOF                 | 6 – 11           |

|       | 6.2.1.8            | JRC                   | 6 – 12           |

|       | 6.2.1.9            | JRS                   | 6 – 13           |

|       | 6.2.1.10           | JSA                   | 6 – 14           |

|       | 6.2.1.11           | JSR                   | 6 – 15           |

|       | 6.2.1.12           | JTWO                  |                  |

|       | 6.2.1.13           |                       | 6 – 17           |

| 6.2.2 | Interrupt          | Control Instructions  | 6 – 18           |

|       | 6.2.2.1            | CAIR                  | 6 – 19           |

|       | 6.2.2.2            | CCIR                  | 6 – 20           |

|       | 6.2.2.3            | DISIR                 | 6 – 21           |

|       | 6.2.2.4            | ENAIR                 | 6 - 22           |

|       | 6.2.2.5            | IRMBC                 | 6 – 23           |

|       | 6.2.2.6            | IRMBS                 | 6 – 24           |

|       | 6.2.2.7            | RDIV                  | 6 – 25           |

|       | 6.2.2.8            | RTNIR                 | 6 – 26           |

|       | 6.2.2.9            | SLIR                  | 6 – 27           |

|       | 6.2.2.10           | SLRIVP                | 6 - 28           |

|       | 6.2.2.11           | STIR                  | 6 – 29           |

|       | 6.2.2.12           | WRIV                  | 6 – 30           |

| 6.2.3 |                    | ne Stack Instructions |                  |

|       | 6.2.3.1            | DSSP                  | 6 – 32           |

|       | 6.2.3.2            | PPSSD                 | 6 – 33           |

|       | 6.2.3.3            | PSDSS                 |                  |

|       | 6.2.3.4            | RDSSP                 | 6 – 35           |

|       | 6.2.3.5            | WRSSP                 | 6 – 36           |

| 6.2.4 |                    | Stack Instructions    |                  |

|       | 6.2.4.1            |                       | 6 - 38           |

|       | 6.2.4.2            |                       | 6 – 39           |

|       | 6.2.4.3            | PPRSD                 |                  |

|       | 6.2.4.4            | PSDRS                 | 6 – 41           |

|       | 6.2.4.5            | PSGSP                 | 6 - 42           |

|       | 6.2.4.6            | PSPC                  |                  |

|       | 6.2.4.7<br>6.2.4.8 | RDRSP<br>S1RSP        | 6 – 44<br>6 – 45 |

|       | 6.2.4.8<br>6.2.4.9 |                       |                  |

|       | 6.2.4.9            | S4RSP<br>SGSP         | 6 – 46<br>6 – 47 |

|       | 6.2.4.10           | SLSP                  | 6 - 48           |

|       | 6.2.4.12           |                       | 6 – 49           |

|       | V.L. T. LL         |                       | 5 45             |

v

| 6.2.5 | Counter Instructions                    | 6 - 50 |

|-------|-----------------------------------------|--------|

|       | 6.2.5.1 CLRS                            | 6 – 51 |

|       | 6.2.5.2 DCCNTR                          | 6 – 52 |

|       | 6.2.5.3 IFCDEC                          | 6 - 53 |

|       | 6.2.5.4 PPCNTR                          | 6 – 54 |

|       | 6.2.5.5 PSCNTR                          | 6 – 55 |

|       | 6.2.5.6 SETS                            | 6 - 56 |

|       | 6.2.5.7 WRCNTR                          | 6 – 57 |

| 6.2.6 | Status Register Instructions            | 6 – 58 |

|       | 6.2.6.1 PPSR                            | 6 – 59 |

|       | 6.2.6.2 PSSR                            | 6 - 60 |

|       | 6.2.6.3 RDSR                            | 6 – 61 |

|       | 6.2.6.4 WRSR                            | 6 - 62 |

| 6.2.7 | Relative Jump Offset Width Instructions | 6 – 63 |

|       | 6.2.7.1 REL16                           | 6 – 64 |

|       | 6.2.7.2 REL12                           | 6 – 65 |

|       | 6.2.7.3 REL8                            | 6 – 66 |

| 6.2.8 | Miscellaneous Instructions              | 6 – 67 |

|       | 6.2.8.1 CONT                            | 6 - 68 |

|       | 6.2.8.2 IDLE                            | 6 - 69 |

|       | 6.2.8.3 IHC                             | 6 – 70 |

|       | 6.2.8.4 WCS                             | 6 – 72 |

| Mnem  | onic and Opcode Summary                 | 6 - 74 |

### ADSP-1410: CHAPTERS 7 - 11

6.3

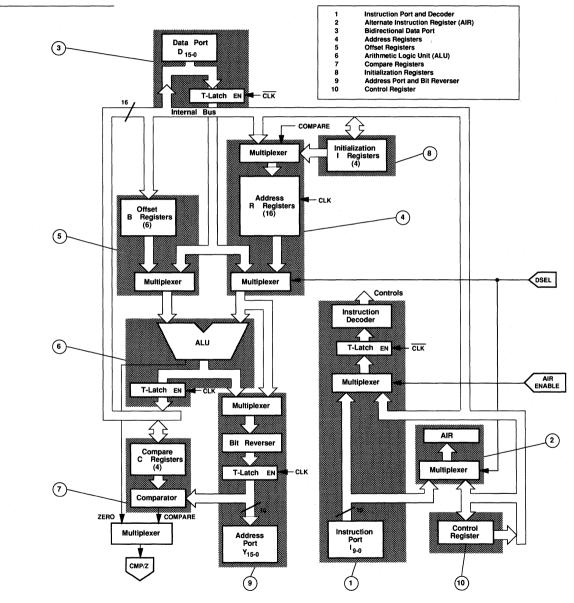

#### CHAPTER 7 INTERNAL ARCHITECTURE

| 7.1  | Introduction                                   | 7 – 1 |

|------|------------------------------------------------|-------|

| 7.2  | Instruction Port                               | 7 – 3 |

| 7.3  | Alternate Instruction Register (AIR)           | 7 – 3 |

| 7.4  | Bidirectional Data Port                        | 7 – 4 |

| 7.5  | Address Registers                              | 7 – 5 |

| 7.6  | Offset Registers                               | 7 – 5 |

| 7.7  | Arithmetic Logic Unit (ALU) and Shifter        | 7 – 7 |

| 7.8  | Compare Registers and Initialization Registers | 7 – 7 |

| 7.9  | Address Port and Bit Reverser                  | 7 – 9 |

| 7.10 | Control Register                               | 7 – 9 |

|      | -                                              |       |

### CHAPTER 8 ADDRESSING OPERATIONS

| 8.1 | Introduction                   | 8 – 1 |

|-----|--------------------------------|-------|

| 8.2 | Update Modes                   | 8 – 1 |

| 8.3 | Looping Instructions           | 8 – 2 |

| 8.4 | Data Selection Using DSEL      | 8 – 6 |

| 8.5 | Alternate Instruction Register | 8 – 7 |

#### CHAPTER 9 PRECISION MODES

| 9.1 | Introduction                   | 9 – 1 |

|-----|--------------------------------|-------|

| 9.2 | One-Chip/Single-Precision Mode | 9 – 1 |

| 9.3 | One-Chip/Double-Precision Mode | 9 – 2 |

| 9.4 | Two-Chip/Double-Precision Mode | 9 – 3 |

### CHAPTER 10 SYSTEM INTERFACE

| 10.1 | Introduction          | 10 – 1 |

|------|-----------------------|--------|

| 10.2 | Look-Ahead Pipeline   | 10 – 1 |

| 10.3 | Data Transfers        | 10 – 2 |

| 10.4 | Address Output Modes  | 10 – 3 |

| 10.5 | Sliding Window Timing | 10 – 3 |

| 10.6 | Compare/Zero          | 10 – 5 |

| 10.7 | Bit Reversal          | 10 – 5 |

| 10.8 | Reset                 | 10 – 9 |

|      |                       |        |

### CHAPTER 11 INSTRUCTION SET

| 11.1 | Introduction      |       | 11 – 1 |

|------|-------------------|-------|--------|

| 11.2 | Instruction Refer | ence  | 11 – 1 |

|      | 11.2.1 Looping    |       | 11 – 3 |

|      | 11.2.1.1          | YADD  | 11 – 4 |

|      | 11.2.1.2          | YDEC  | 11 – 6 |

|      | 11.2.1.3          | YINC  | 11 – 7 |

|      | 11.2.1.4          | YSUB_ | 11 – 8 |

|      | 11.2.2 | Register Transfer              | _ 11 – 9 |

|------|--------|--------------------------------|----------|

|      |        | 11.2.2.1 BTD                   | 11 – 11  |

|      |        | 11.2.2.2 BTR                   | 11 – 12  |

|      |        | 11.2.2.3 CTD                   | 11 – 13  |

|      |        | 11.2.2.4 DTI                   | 11 – 14  |

|      |        | 11.2.2.5 ITD                   | 11 – 15  |

|      |        | 11.2.2.6 ITR                   | 11 – 16  |

|      |        | 11.2.2.7 RTD                   | 11 – 17  |

|      |        | 11.2.2.8 YRTB                  | 11 – 18  |

|      |        | 11.2.2.9 YRTC                  | 11 – 19  |

|      |        | 11.2.2.10 YRTR                 | 11 – 20  |

|      | 11.2.3 | Logical and Shift              | 11 – 21  |

|      |        | 11.2.3.1 YAND                  | 11 – 22  |

|      |        | 11.2.3.2 YASR                  | 11 – 23  |

|      |        | 11.2.3.3 YLSL                  | 11 – 24  |

|      |        | 11.2.3.4 YOR                   | 11 – 25  |

|      |        | 11.2.3.5 YXOR                  | 11 – 26  |

|      | 11.2.4 | Control Register               | 11 – 27  |

|      |        | 11.2.4.1 CRTD                  | 11 – 28  |

|      |        | 11.2.4.2 DTCR                  | 11 – 29  |

|      |        | 11.2.4.3 RST                   | 11 – 30  |

|      |        | 11.2.4.4 SELB                  | 11 – 31  |

|      |        | 11.2.4.5 SELR                  | 11 – 32  |

|      |        | 11.2.4.6 SETA                  | 11 – 33  |

|      |        | 11.2.4.7 SETI                  | 11 – 34  |

|      |        | 11.2.4.8 SETP                  | 11 – 35  |

|      |        | 11.2.4.9 SETU                  | 11 – 36  |

|      |        | 11.2.4.10 SETY                 | 11 – 37  |

|      | 11.2.5 | Alternate Instruction Register | 11 – 38  |

|      |        | 11.2.5.1 LDA                   | 11 – 39  |

|      |        | 11.2.5.2 RDA                   | 11 – 40  |

|      |        | 11.2.5.3 WRA                   | 11 – 41  |

|      | 11.2.6 | Miscellaneous                  | 11 – 42  |

|      |        | 11.2.6.1 NOP                   | 11 – 43  |

|      |        | 11.2.6.2 YDTY                  | 11 – 44  |

|      |        | 11.2.6.3 YREV                  | 11 – 45  |

| 11.3 | Mnem   | onic and Opcode Summary        | 11 – 46  |

### LIST OF FIGURES

| 1.1  | Typical Word-Slice System                               | 1 – 1  |

|------|---------------------------------------------------------|--------|

| 2.1  | ADSP-1401 Block Diagram                                 | 2 – 2  |

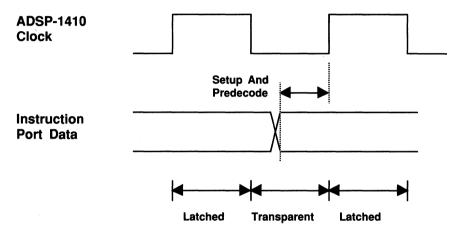

| 2.2  | Instruction Port Latching                               | 2 – 3  |

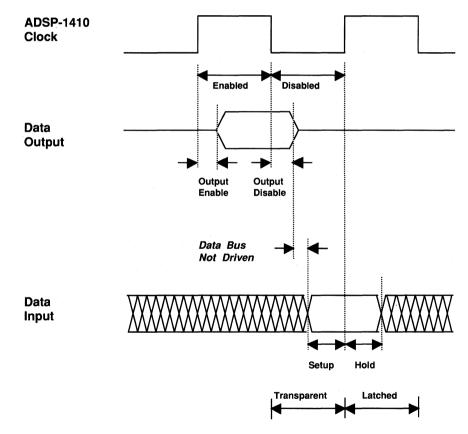

| 2.3  | Data Output Followed By Data Input                      | 2 - 4  |

| 2.4  | Sign Extension                                          | 2 – 5  |

| 2.5  | Typical Internal RAM Organization                       | 2 – 7  |

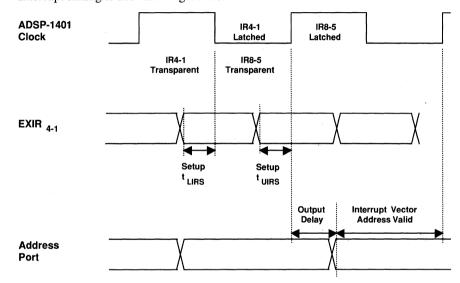

| 2.6  | External Interrupt Latching                             | 2 - 8  |

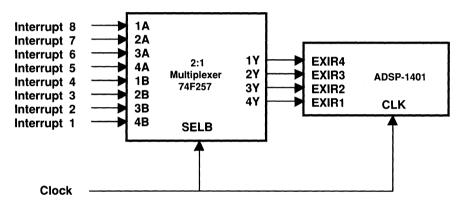

| 2.7  | Supporting Five to Eight External Interrupts            | 2 – 9  |

| 2.8  | Timing For Trap, Tristate, and Reset                    | 2 – 11 |

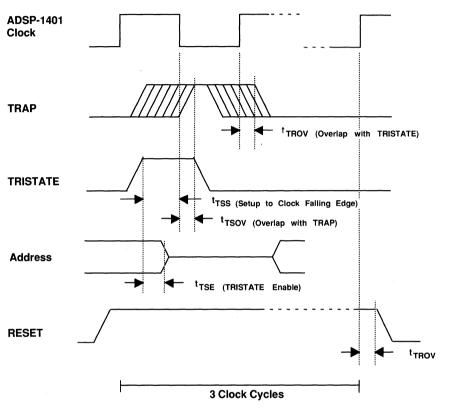

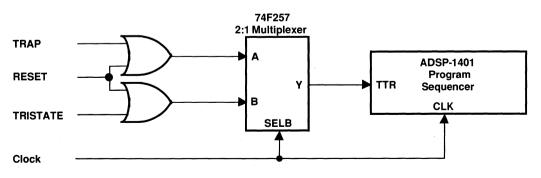

| 2.9  | TTR Multiplexing Circuit                                | 2 - 11 |

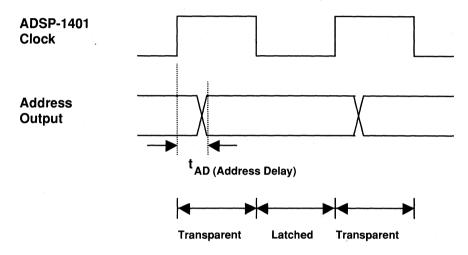

| 2.10 | Address Output                                          | 2 – 12 |

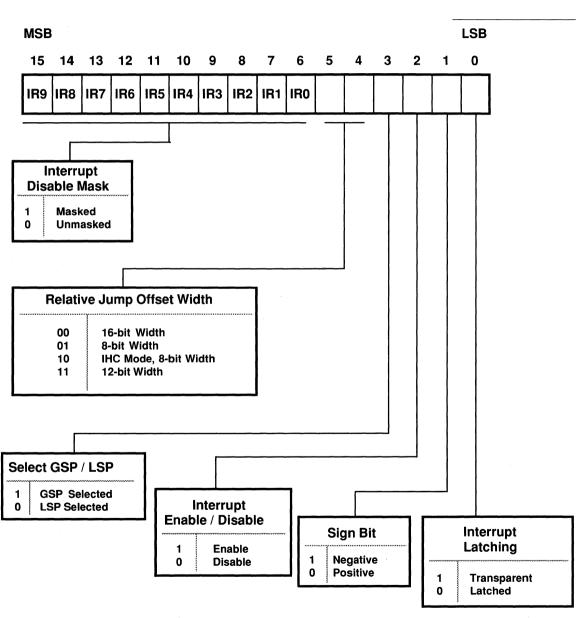

| 2.11 | Status Register                                         | 2 – 13 |

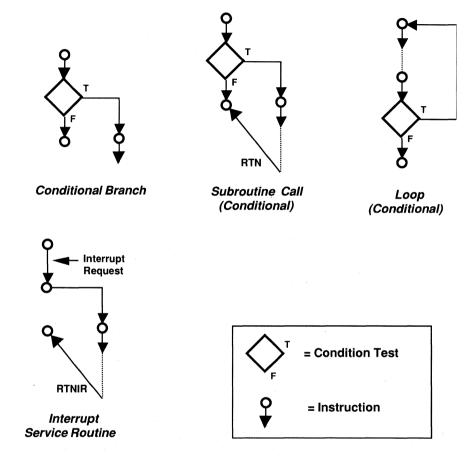

| 3.1  | Branches, Subroutines, and Loops                        | 3 – 2  |

| 3.2  | Loops Using Flag Input                                  | 3 – 4  |

| 3.3  | Flag Setup Time With and Without IR <sub>0</sub> Masked | 3 – 5  |

| 3.4  | Loop Until Sign Bit = 1                                 | 3 - 6  |

| 3.5  | Loop While Sign Bit = 1                                 | 3 – 6  |

| 3.6  | Positive and Negative Offsets                           | 3 – 8  |

| 3.7  | Local Stack After Three Subroutine Calls                |        |

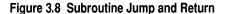

| 3.8  | Subroutine Jump and Return                              | 3 – 10 |

| 3.9  | Restoring Registers and Counters                        | 3 – 11 |

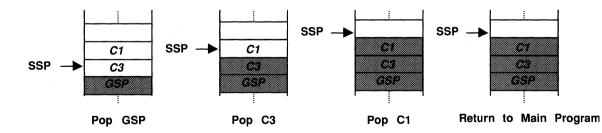

| 3.10 | Internal RAM With Three Levels of Nesting               | 3 – 13 |

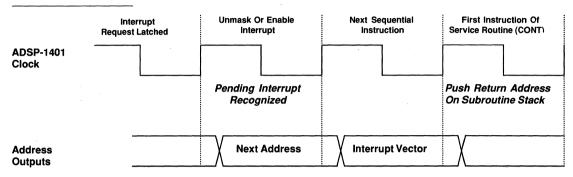

| 4.1  | One-Cycle Latency After Enabling Interrupts             | 4 – 2  |

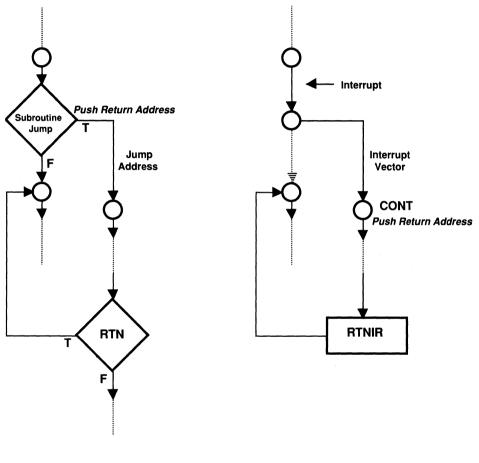

| 4.2  | Execution of Service Routines and Subroutines           | 4 – 3  |

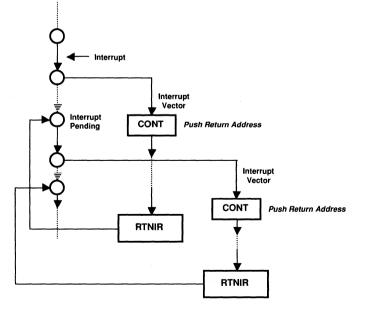

| 4.3  | Interrupting a Service Routine                          | 4-4    |

| 4.4  | Pending Interrupt on Return From Service Routine        |        |

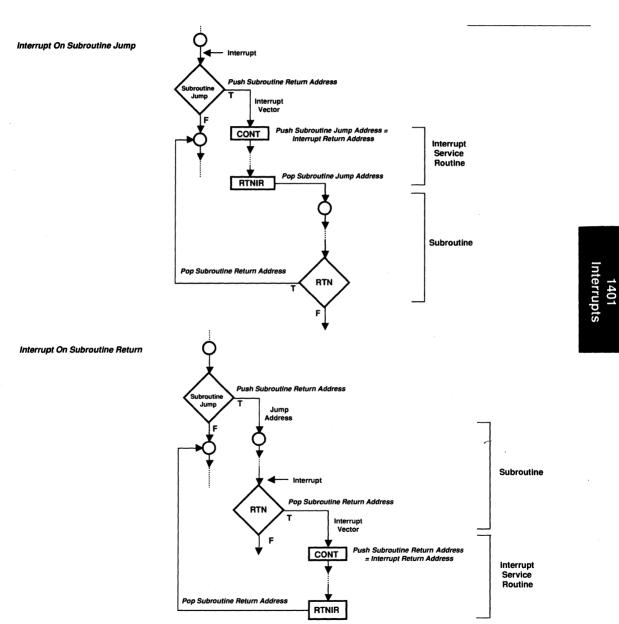

| 4.5  | Interrupt on Subroutine Jump or Return                  | 4 – 7  |

| 4.6  | Stack Underflow and Overflow                            |        |

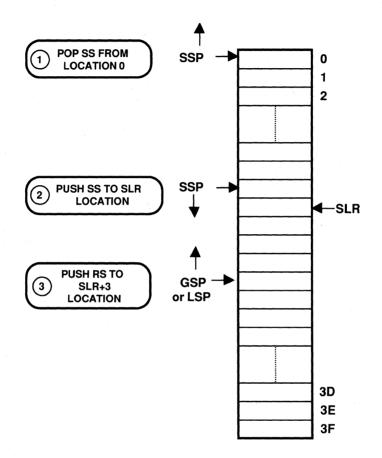

| 4.7  | Three Pushes on Stack Overflow                          | 4 – 9  |

| 4.8  | Stack Paging                                            | 4 – 10 |

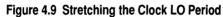

| 4.9  | Stretching the Clock LO Period                          |        |

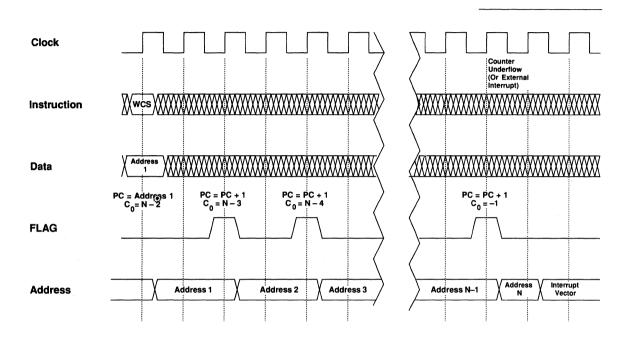

| 5.1  | Look-Ahead Pipeline Timing                              | 5 – 2  |

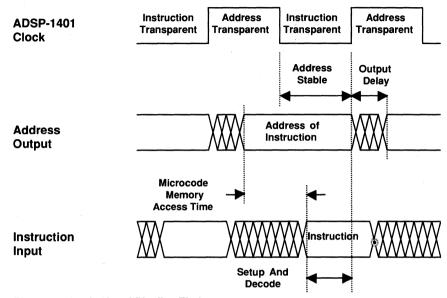

| 5.2  | Instruction Hold Control Using IR <sub>1</sub>          | 5 – 4  |

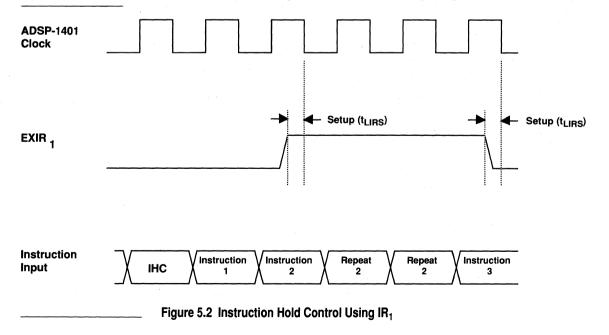

| 5.3  | Download From Host to Writeable Control Store           |        |

| 5.4  | WCS Timing                                              | 5 – 7  |

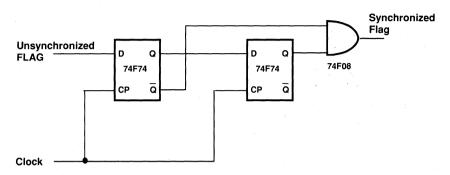

| 5.5  | Flag Synchronization For WCS                            | 5 – 8  |

| 6.1  | Jump Instruction Flow Charts                            | 6-4    |

ix

| ADSP-1410 Block Diagram                              | 7 <sup>′</sup> –2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction Latch Timing                             | 7 – 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Data Port Timing                                     | 7 – 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

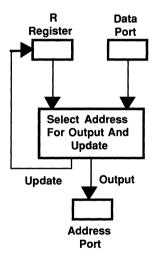

| Address Output and Update Paths                      | 7 – 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

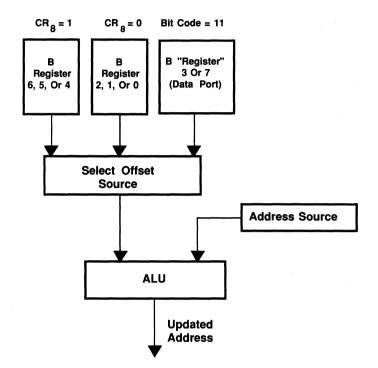

| Offset Paths                                         | 7 – 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Comparison and Reinitialization                      | 7 – 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

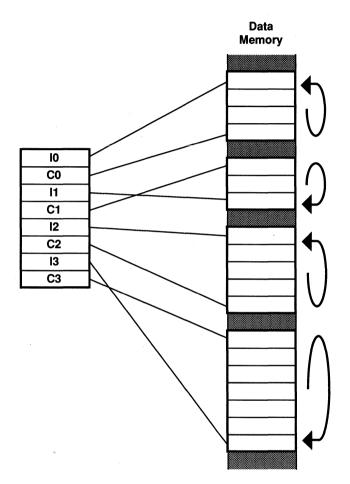

| Bit Reversal                                         | 7-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

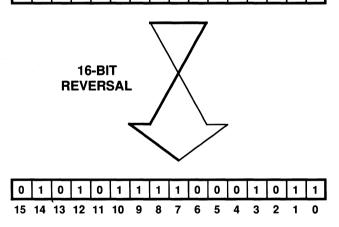

| Control Register                                     | 7 – 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

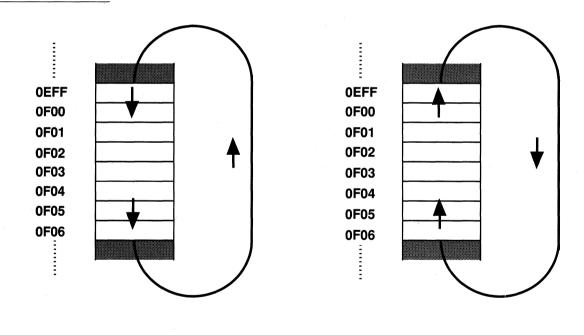

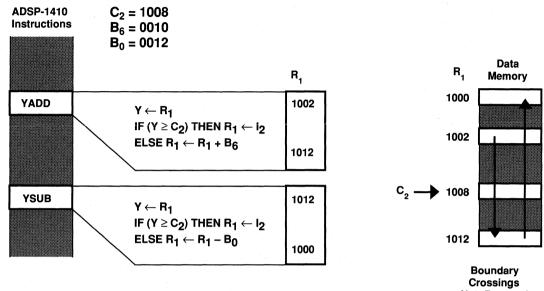

| Looping Address Sequences                            | 8 – 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

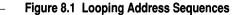

| Reinitialization to Form Circular Buffer             | 8-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

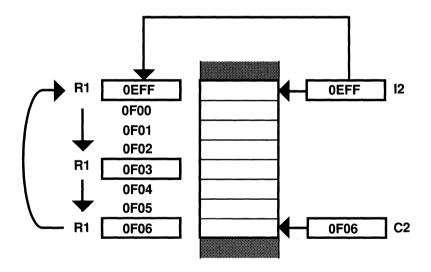

| Reinitialization in Pre-Update and Post-Update Modes | 8 – 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Address Increase Followed By Decrease                | 8 – 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

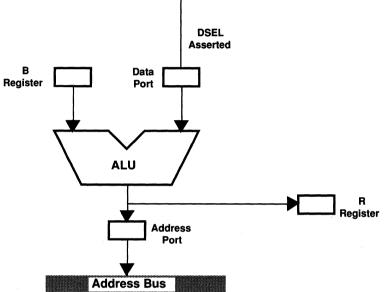

| DSEL for Single-Cycle Input, Update, and Output      | 8-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

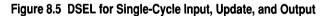

| Modulo Addressing                                    | 8 – 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

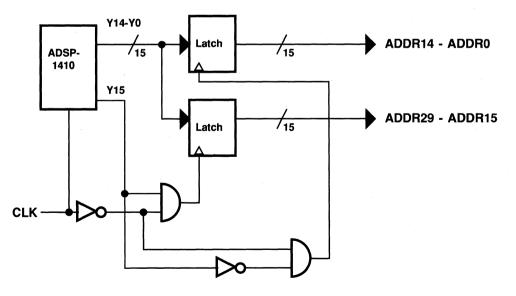

| Single-Chip Connections to 30-Bit Address Bus        | 9 – 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

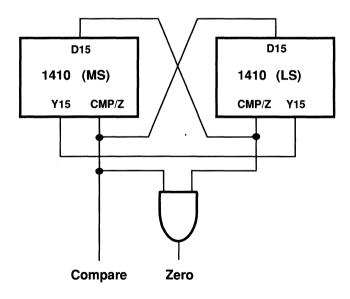

| Two-Chip Cascade Connections                         | 9 - 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Minimum Clock Period, Two-Chip/Double Precision      | 9 – 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

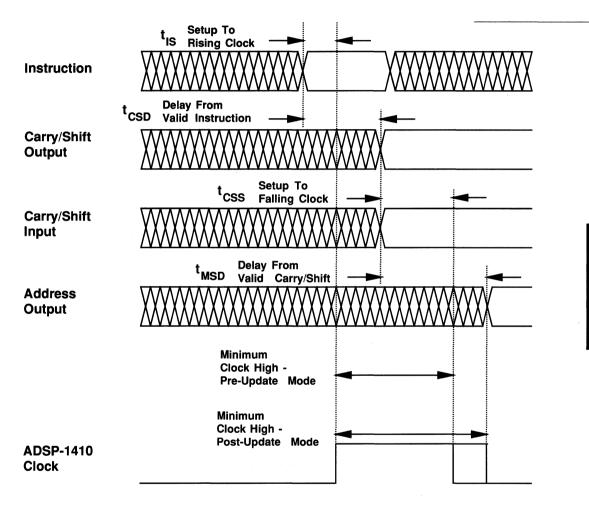

| Look-Ahead Pipeline Timing                           | 10 – 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

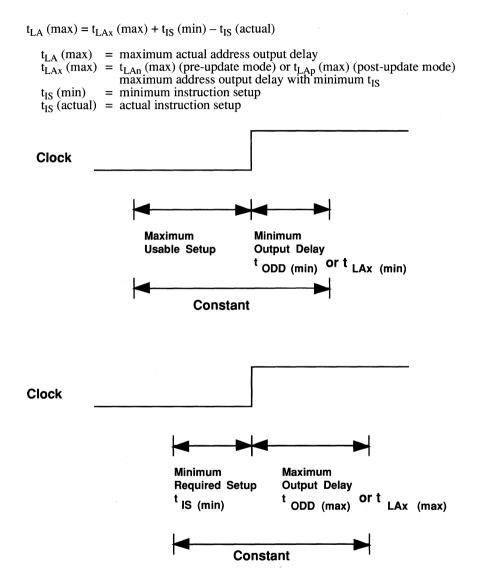

| Sliding Window Timing                                | 10 – 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Output Addresses From FFT                            | 10 – 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

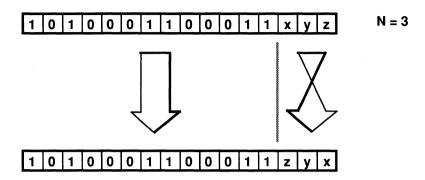

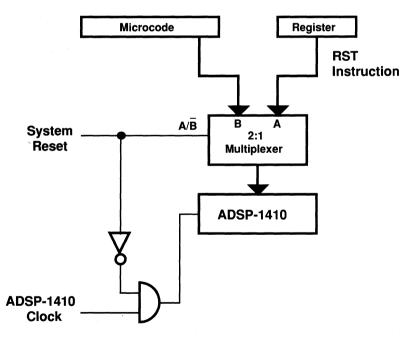

| Three-Bit-Wide Address Reversal                      | 10 – 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

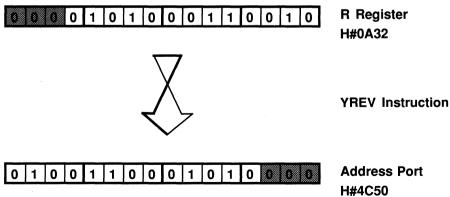

| First Bit-Reversed Address                           | 10 – 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Second Bit-Reversed Address                          | 10 – 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

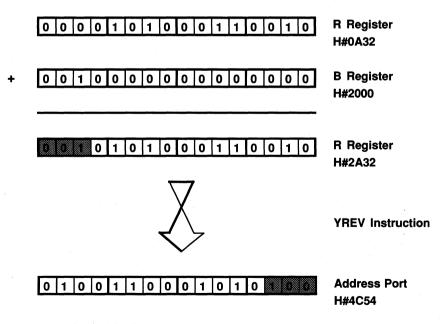

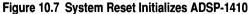

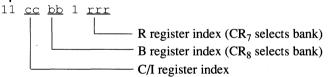

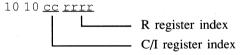

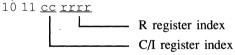

| System Reset Initializes ADSP-1410                   | 10 – 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

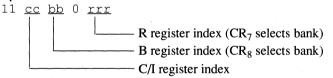

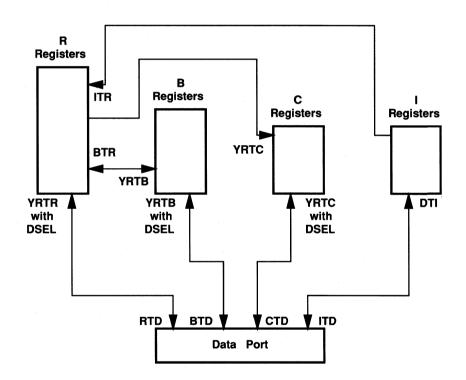

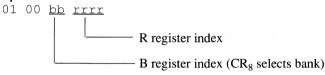

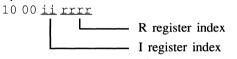

| Data Transfer Paths                                  | _ 11 – 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                      | Data Port Timing<br>Address Output and Update Paths<br>Offset Paths<br>Comparison and Reinitialization<br>Bit Reversal<br>Control Register<br>Looping Address Sequences<br>Reinitialization to Form Circular Buffer<br>Reinitialization in Pre-Update and Post-Update Modes<br>Address Increase Followed By Decrease<br>DSEL for Single-Cycle Input, Update, and Output<br>Modulo Addressing<br>Single-Chip Connections to 30-Bit Address Bus<br>Two-Chip Cascade Connections<br>Minimum Clock Period, Two-Chip/Double Precision<br>Look-Ahead Pipeline Timing<br>Sliding Window Timing<br>Output Addresses From FFT<br>Three-Bit-Wide Address Reversal<br>First Bit-Reversed Address<br>Second Bit-Reversed Address<br>System Reset Initializes ADSP-1410 |

#### LIST OF TABLES

| 2.1  | ADSP-1401 Pin Definitions            | 2 – 1   |

|------|--------------------------------------|---------|

| 2.2  | Status Register Bit Definition       | 2 – 14  |

| 5.1  | Relative Jump Offset Width Selection | 5 – 3   |

| 5.2  | Status After Reset Operation         | 5 – 9   |

| 7.1  | ADSP-1410 Pin Definitions            | 7 – 1   |

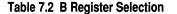

| 7.2  | B Register Selection                 | 7 – 6   |

| 7.3  | Control Register Bit Description     | 7 – 11  |

| 10.1 | Effect of RST Instruction            | 10 – 10 |

| 11.1 | Notation Terms                       | 11 – 2  |

|      |                                      |         |

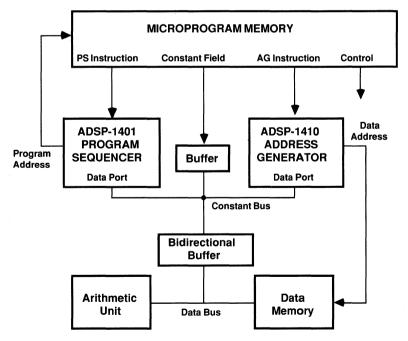

### 1.1 SYSTEM OVERVIEW

The ADSP-1401 Program Sequencer and the ADSP-1410 Address Generator form the Word-Slice<sup>TM</sup> chipset for implementing microcoded designs. A typical Word-Slice system is shown in Figure 1.1. The ADSP-1401 addresses the microcode memory, which provides instructions for all of the system components. Arithmetic processing can be provided by one or more computational devices, such as Analog Devices' fixed-point or floating-point ALUs and multipliers. Data transfers between the processing units and the data/coefficient memory are facilitated through addressing generated by one or more ADSP-1410s. Note that both the ADSP-1401 and the ADSP-1410 latch instructions internally, whereas the arithmetic processing units use external instruction latches.

Figure 1.1 Typical Word-Slice System

1

#### 1.2 ADSP-1401 OVERVIEW

The ADSP-1401 Program Sequencer provides the addresses needed to sequence a microcoded system through the instructions stored in microcode memory. It can output 16-bit addresses at a high speed because its internal Look-Ahead<sup>™</sup> pipeline coordinates the timing of its instruction input and address output, which are both latched on-chip. Because of this timing, the ADSP-1401 never incurs a delay performing a jump; the jump instruction is decoded *before* the next address is output.

ADSP-1401 instructions are only seven bits wide to minimize its instruction space in microcode. At the same time, these instructions are powerful, reducing the programming requirements for complex operations. Besides basic straight-line execution of code, the ADSP-1401 supports conditional and unconditional jumps, including subroutine and interrupt service routine jumps and returns. Four decrementing counters store twos-complement values whose sign bits can be used as conditions for jump execution. An external Flag input provides another jump condition. The ADSP-1401 can read an address or offset at its data port for absolute, relative, or indirect addressing.

On-chip RAM stores return addresses, jump addresses, registers values, and local variables. The RAM capacity is 64 words, large enough to accommodate many levels of subroutine nesting. The RAM consists of three sections: the subroutine stack, the register stack, and the indirect jump address space. The relative sizes of the three sections are user-configurable.

The ADSP-1401 provides complete interrupt processing on-chip. It stores vectors for eight external and two internal interrupts. The dedicated internal interrupts indicate stack limit violations and counter underflow. Interrupts can be individually masked, or disabled and enabled as a group. Interrupts are latched to ensure recognition even if the interrupt source removes the signal. This latching can be disabled (transparent) if not needed or desired. The ADSP-1401 handles an interrupt by outputting the corresponding vector and saving the return address.

The ADSP-1401 can be placed in a Writeable Control Store mode in which it provides sequential addressing to download instructions into microcode from an external source (without executing the downloaded instructions). In this mode, the ADSP-1401 conforms to download timing requirements through a handshake signal.

#### 1.3 ADSP-1410 OVERVIEW

The ADSP-1410 Address Generator produces the data memory addresses needed to implement digital signal processing and array processing algorithms quickly and efficiently. It can simultaneously output an address from one of its 16 address registers and calculate the address of the next data access in a single instruction cycle. The ADSP-1410 can also determine whether an address exceeds a user-defined limit and then reset the address value accordingly. This feature allows it to generate looping address sequences without overhead penalty.

The ADSP-1410 has an internal ALU that can update an existing address register through following operations:

- Increment

- Decrement

- Add offset value

- · Subtract offset value

- OR with preloaded value

- AND with preloaded value

- XOR with preloaded value

- Shift one bit left

- Shift one bit right

The ADSP-1410 can also bit-reverse addresses upon output.

A single ADSP-1410 provides 16-bit addresses; you can expand the addressing capability to 30 bits by either cascading two ADSP-1410 devices or executing two cycles for each address. A 16-bit bidirectional data port lets you transfer data to and from other devices. You can also transfer data between internal registers using dedicated instructions.

The internal Look-Ahead<sup>™</sup> pipeline latches the instruction input port and address output port in opposite phases of the clock cycle. This timing allows the ADSP-1410 to begin decoding the next instruction while maintaining the address of the current cycle. Predecoding instructions provides the fastest possible address output, for the maximum possible memory access time. If memory access time is not critical, however, you can forego predecoding and reduce the instruction setup time requirement.

The Alternate Instruction Register (AIR) of the ADSP-1410 provides a singleinstruction cache that can reduce microcode memory requirements for many applications. For example, if an instruction must be repeated, it would occupy several locations in microcode. You can store it in the AIR instead and enable the AIR the number of times needed. The AIR can also be used to supersede the instruction in microcode conditionally (to exit a loop, for example). Modulo addressing, which is described in Chapter 8, is accomplished using conditional AIR execution.

#### 1.4 THIRD-PARTY SUPPORT

A number of third-party vendors produce development tools for Word-Slice components. At the time of this publication, these tools include the following:

- METASTEP is a meta-assembler package from STEP Engineering that eases the task of writing microcode programs for Word-Slice components. This software runs on a variety of host computers, including the IBM PC and the VAX. STEP Engineering also sells its own development systems.

- Microtec Research supports Word-Slice components with two metaassemblers. Their META29R Relocatable Macro Meta-Assembler System consists of a definition program, an assembler, linker, and PROM formatter. META29R is Microtec's version of AMDASM. Their mcASM, a secondgeneration meta-assembler, can use files created by AMDASM and META29R but provides a high-level approach. Definition files for Word-Slice components are included with both meta-assemblers.

- HILEVEL Technology's HALE (HILEVEL Assembly Language Environment) supports both Word-Slice components and Analog Devices' floating-point components. HILEVEL also has two control store boxes: the DS370 Emulyzer and the DS3700 Emulyzer.

- The Hewlett-Packard (HP 64276) Microprogram Development Subsystem in conjunction with their HP 64320S Logic State/Software Analyzer provides control store emulation. The HP 64276 includes a meta-assembler which is not capable of storing permanent definition files. All of these tools require an HP 64110A development workstation as a host.

- Logic Automation's SmartModels are software behavioral models of various devices, including the Word-Slice components. Several simulation programs generate board-level simulations using these models. Prototyping time is thereby greatly reduced.

For more information, contact the vendors directly at the following addresses:

STEP Engineering P.O. Box 61166 Sunnyvale, CA 94088 800-538-1750

HILEVEL Technology 18902 Bardeen Way Irvine, CA 92715 800-HILEVEL

Hewlett-Packard (Contact a local sales office) Microtec Research P.O. Box 60337 Sunnyvale, CA 94088 408-733-2919

Logic Automation P.O. Box 310 Beaverton, OR 97075 503-690-6900

1 - 4

### 1.5 MANUAL ORGANIZATION

This manual is organized into two main sections, indicated by two banks of tabs that mark the chapters. The first section (Chapters 2 through 6) is devoted to the ADSP-1401; the second(Chapters 7 through 11) to the ADSP-1410. The chapters contain the following information:

- Chapter 1 describes the general features of the ADSP-1401 and the ADSP-1410 as well as the organization of this manual.

- Chapter 2 describes the internal architecture of the ADSP-1401. The function of each area of the device is explained, as well as the interrelationships between various areas.

- Chapter 3 describes how to implement program jumps, including loops and subroutines. Jump conditioning and addressing options are explained.

- Chapter 4 describes the interrupt processing capabilities of the ADSP-1401. The ADSP-1401 can handle up to eight external interrupts plus two interrupts generated internally.

- Chapter 5 describes the system interface of the ADSP-1401. Connections to and from the device are explained.

- Chapter 6 describes the instruction set of the ADSP-1401. The mnemonic, opcode, and description for each instruction are listed. Short examples are given for each instruction. A summary section provides the mnemonic, opcode, and a short description for each instruction.

- Chapter 7 describes the internal architecture of the ADSP-1410. The function of each area of the device is explained, as well as the interrelationships between various areas.

- Chapter 8 describes various addressing operations performed by the ADSP-1410, including how it selects the address to output and how it updates the address to anticipate the next access.

- Chapter 9 describes the precision modes of the ADSP-1410. Precision modes determine the width of the generated addresses.

- Chapter 10 describes the system interface of the ADSP-1410. Connections to and from the device are explained.

- Chapter 11 describes the instruction set of the ADSP-1410. The reference section of this chapter describes the instructions in detail and gives short examples. A summary section provides the mnemonic, opcode, and a short description for each instruction.

ADSP-1401

ADSP-1410

#### 2.1 INTRODUCTION

The ADSP-1401 is a 48-pin CMOS device. Pin names and definitions are listed in Table 2.1.

#### PIN NAME DEFINITION

| I <sub>6-0</sub>    | Instruction input, seven bits                                     |

|---------------------|-------------------------------------------------------------------|

| Y <sub>15-0</sub>   | Address output, 16 bits                                           |

| D <sub>15-0</sub>   | Data I/O, 16 bits                                                 |

| EXIR <sub>4-1</sub> | External interrupts, four inputs that are time-multiplexed to     |

|                     | generate eight internal signals (IR <sub>8-1</sub> )              |

| FLAG                | Condition input                                                   |

| TTR                 | Three-function control input that is time-multiplexed to generate |

|                     | internal Trap, Tristate, and Reset signals                        |

| CLK                 | Clock input                                                       |

| V <sub>DD</sub>     | +5 Volt supply                                                    |

| GND                 | Ground                                                            |

#### Table 2.1 Pin Definitions

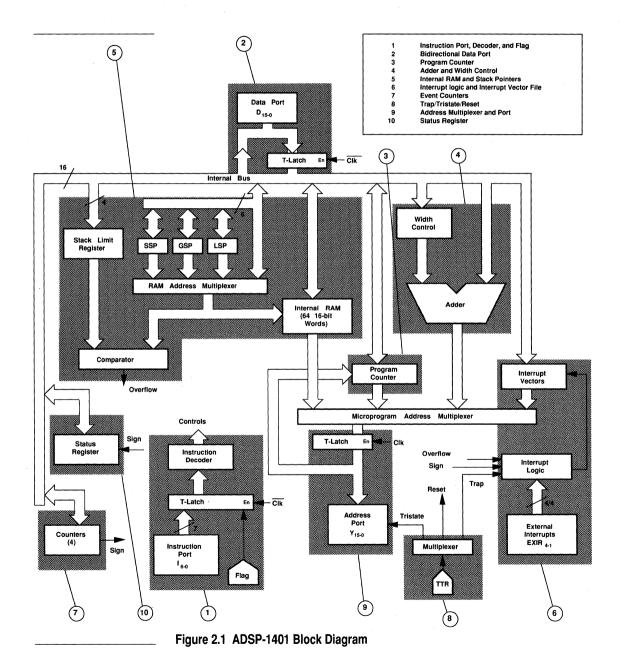

Figure 2.1 shows a block diagram of the ADSP-1401. The device consists of the following major areas, which are described in the sections of this chapter:

- Instruction Port and Instruction Decoder

- Bidirectional Data Port

- Program Counter

- Adder and Width Control

- Internal RAM and Stack Pointers

- Interrupt Logic and Interrupt Vector File

- Event Counters

- Flag

- Trap/Tristate/Reset

- Address Multiplexer and Address Port

- Status Register

2 - 2

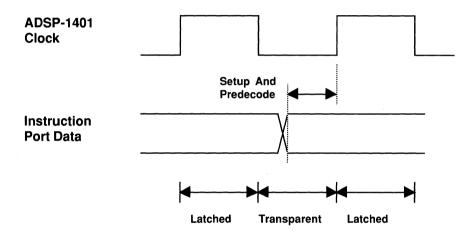

### 2.2 INSTRUCTION PORT

The ADSP-1401 receives instructions through its instruction port, which consists of seven pins  $(I_{6-0})$ . The ADSP-1401 latches an instruction during clock HI. The instruction port is transparent during clock LO to allow predecoding of the next instruction, as shown in Figure 2.2.

You can program the ADSP-1401 to repeat an instruction rather than latch in a new instruction. See *Instruction Hold Control* in Chapter 5 for more information.

Figure 2.2 Instruction Port Latching

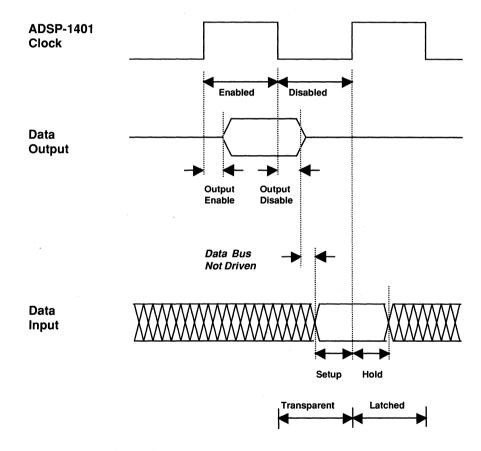

#### 2.3 BIDIRECTIONAL DATA PORT

The bidirectional data port consists of 16 I/O pins ( $D_{15-0}$ ) through which the ADSP-1401 loads values for direct or indirect addressing and transfers register values. Data input is latched during clock HI. Data output is enabled during clock HI and disabled during clock LO. This timing accommodates a data output followed by a data input in the next cycle, as shown in Figure 2.3. To prevent contention on the data bus, the ADSP-1401 disables data output in time to allow the data input to meet the required setup to the rising clock edge.

### 2.4 PROGRAM COUNTER

The program counter provides addressing for sequential program execution. The ADSP-1401 increments its 16-bit program counter at the end of every instruction cycle, unless the instruction specifically inhibits the increment. Jump instructions load the program counter with the jump address, so that sequential execution can continue after the jump.

Figure 2.3 Data Output Followed by Data Input

### 2.5 ADDER AND WIDTH CONTROL

The adder allows the ADSP-1401 to calculate relative jump addresses by adding offset values to the program counter. When the ADSP-1401 is executing a relative jump instruction, it has already incremented the program counter; therefore, the number of instructions from the address of the relative jump instruction to the jump address is the offset value plus one.

The ADSP-1401 reads offsets at the data port. You can program the ADSP-1401 to read the least significant 8 bits or 12 bits, or all 16 bits. Offsets fewer than 16 bits wide are automatically sign-extended before being added to the program counter address. Sign extension repeats the most significant bit to extend the value to 16 bits, as shown in Figure 2.4.

Data Port

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| х  | X  | x  | x  | x  | x  | X | x | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 |

Positive Offset, 8-bit Width Sign Extension Х Х Х Х Negative Offset, 12-bit Width Sign Extension

Figure 2.4 Sign Extension

#### 2.6 INTERNAL RAM AND STACK POINTERS

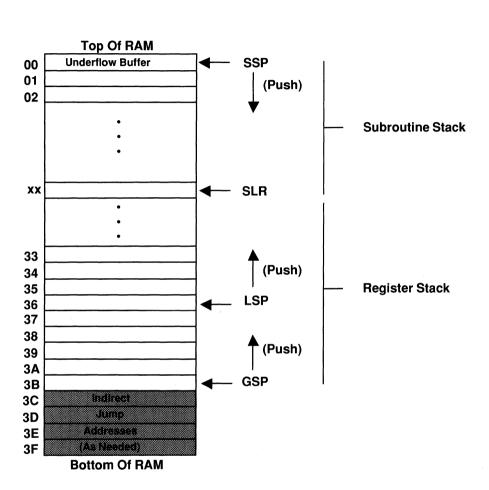

The internal RAM of the ADSP-1401 consists of 64 16-bit words. A typical RAM configuration is shown in Figure 2.5. The RAM can be divided into the following spaces:

- Subroutine Stack: The subroutine stack stores the return address needed to return from a subroutine or interrupt service routine automatically. You can also save counter, register, status and pointer values on the subroutine stack. The subroutine stack pointer (SSP) is a 6-bit register that contains the address of the most recently written stack location (the next stack location to be read). The subroutine stack grows in the direction of higher memory addresses. A subroutine stack push first increments the SSP, then writes the stack location. A pop reads the stack location (without erasing it), then decrements the SSP.

- *Register Stack:* The register stack comprises two other stacks: the local stack and the global stack. The local stack registers store jump addresses for each level of subroutine nesting, whereas the global stack registers store jump addresses accessible from any point in the program. The local stack pointer (LSP) contains the 6-bit address of the most recently written local register (the next register to be read), and the global stack pointer (GSP) contains the 6-bit address of the most recently written global register. Jump instructions that access the addresses stored on the register stack include two bits of opcode that select one of the top four registers. Both the local and global stacks grow in the direction of lower memory addresses. A register stack push first decrements the pointer (LSP or GSP), then writes the stack location. A pop reads the stack location (without erasing it), then increments the pointer.

- *Indirect Address Space:* The indirect address space stores jump addresses that are accessed by their location in the internal RAM. In indirect jump instructions, the RAM is addressed by the six least significant bits of the data port (D<sub>5-0</sub>).

The reset operation automatically initializes the SSP to location 0. You must initialize the GSP and LSP explicitly. Normally, the LSP is set to a lower address than the GSP, because the local stack must grow to accommodate several levels of nested subroutines, whereas the global stack can often be fixed at the outset of the program. Indirect addresses reside in high RAM (addresses greater than the global stack addresses).

Because the subroutine stack grows toward higher memory and the register stack grows toward lower memory, there is a potential for a stack collision. The Stack Limit Register (SLR) is a 4-bit register that defines the boundary between the two stacks. The ADSP-1401 generates an internal interrupt when it detects the overflow of either the subroutine stack or register stack. See *Stack Overflow and Underflow Interrupt* in Chapter 4 for more information.

Figure 2.5 Typical Internal RAM Organization

### 2.7 INTERRUPTS AND INTERRUPT VECTOR FILE

The ADSP-1401 processes up to eight interrupts from external sources plus two interrupts generated internally. The interrupt vector file stores ten 16-bit vectors (jump addresses). Each vector is the starting address of an interrupt service routine for one of the ten interrupts. The ADSP-1401 outputs the vector on the address port in the cycle following the recognition of the interrupt.

The ADSP-1401 receives external interrupts through four level-sensitive inputs  $(EXIR_{4-1})$  which are time-multiplexed to generate eight internal interrupt signals. Interrupts  $IR_{8-5}$  are normally latched on the  $EXIR_{4-1}$  pins during clock HI, and interrupts  $IR_{4-1}$  are normally latched on the  $EXIR_{4-1}$  pins during clock LO. Interrupt timing is shown in Figure 2.6.

#### Figure 2.6 External Interrupt Latching

You can enable or disable the processing of all interrupts, or mask interrupts individually. The ADSP-1401 still latches an interrupt while it is disabled or masked; if you re-enable or unmask the latched interrupt, the ADSP-1401 will process it.

The interrupt vector file is loaded from the data port; you can also read interrupt vectors at the data port. The Interrupt Vector Pointer (IVP) is a 4-bit register that contains the location of the next interrupt vector to be loaded or read. You load or read a specific vector by moving the IVP to the vector file location and performing the appropriate instruction.

An interrupting device can remove the interrupt signal after the interrupt has been latched. An interrupt remains latched until cleared by one of several instructions, usually in the interrupt service routine. You can also operate interrupts in a transparent mode, in which the latches are bypassed. In this mode, the interrupting device must maintain the interrupt signal until the interrupt is recognized. The transparent mode makes it possible to cancel an interrupt signal before the next clock edge to prevent interrupt servicing. The latching mode is determined by a bit in the status register; see *Status Register*, below.

Support of more than four interrupts requires an external two-to-one multiplexer, shown in Figure 2.7, to input the interrupt signals to the ADSP-1401 at the correct times. One to four interrupt sources can be connected directly to the EXIR<sub>4-1</sub> pins. These interrupts should conform to the timing for IR<sub>8-5</sub>, the higher priority interrupts, and you must also mask interrupts IR<sub>4-1</sub>. Any unused interrupt inputs (external multiplexer inputs or EXIR<sub>4-1</sub>) should be masked and preferably grounded as well, to prevent them from being activated.

#### Figure 2.7 Supporting Five to Eight External Interrupts

The internally generated interrupt signals are  $IR_9$ , which indicates a stack overflow or underflow, and  $IR_0$ , which indicates a counter underflow. These interrupts are described in Chapter 4, *Interrupt Processing*.

#### 2.8 EVENT COUNTERS

The four counters of the ADSP-1401 ( $C_{3-0}$ ) store 16-bit twos-complement values. These decrement-only counters keep track of events and implement programming loops. Several instructions use the sign bit (most significant bit) of a counter as a condition for executing a particular operation.

The ADSP-1401 always stores the sign bit of the most recently decremented counter (the value *before* decrement) in the status register; see *Status Register*, below. You can condition certain instructions on this stored sign bit. The sign bit of a counter can also generate the internal  $IR_0$  interrupt; this interrupt is provided primarily to end a download operation (see *Writeable Control Store* in Chapter 5). See *Counters* in Chapter 3 for more information on how to use counters to implement loops.

### 2.9 FLAG

The ADSP-1401 latches the Flag input during clock HI. Several instructions use the Flag input (or its complement) as a condition for executing a particular operation. See *Flag* in Chapter 3 for more information.

#### 2.10 TRAP/TRISTATE/RESET

The Trap/Tristate/Reset (TTR) input performs three functions:

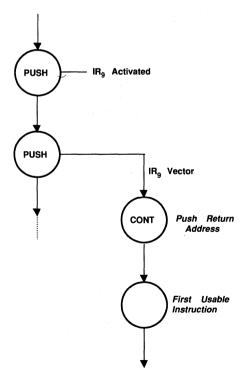

- *Trap:* The Trap signal is an asynchronous, nonmaskable interrupt. It usually indicates a system emergency, such as a power failure; you can also use it to implement a cache (see *Trap* in Chapter 4). If the TTR input is asserted (HI) during clock LO and deasserted (LO) during clock HI, a Trap signal is generated. The Trap interrupt is serviced by the same routine as IR<sub>9</sub>; the IR<sub>9</sub> vector is output a specified time after the assertion of the Trap signal. Therefore, if the Trap signal is used, the routine must determine whether the interrupt source is the internal IR<sub>9</sub> interrupt or the Trap signal.

- *Tristate*: The Tristate signal places the address port in the high-impedance state a specified time after its assertion. This signal allows another device to address the microcode memory without otherwise affecting the ADSP-1401 operation. If the TTR input is HI during clock HI and LO during clock LO (follows the clock signal), the address port is placed in the high impedance state, regardless of the executed instruction.

- *Reset:* The Reset signal initiates a reset operation, which places the ADSP-1401 in a known state. If the TTR input is asserted (HI) during both clock HI and clock LO, the ADSP-1401 initiates a reset operation. The TTR input must remain HI for two more cycles for the reset operation to complete.

The timing of the three signals is compared in Figure 2.8.

The Tristate signal can be active during clock LO only a maximum time of  $t_{TSOV}$  from the falling clock edge; otherwise, the Trap signal is activated. Similiarly, the Trap signal can be active during clock HI only a maximum time of  $t_{TROV}$  from the rising clock edge without activating Tristate. Figure 2.9 shows a time-multiplexing circuit that coordinates the Trap, Tristate and Reset signals to the TTR input. This circuit ensures that the Trap and Tristate signals are distinct. If both the Trap and Tristate signals are used, they cannot be asserted in the same cycle, because the ADSP-1401 recognizes this combination as a Reset signal.

#### 2.11 ADDRESS MULTIPLEXER AND ADDRESS PORT

The ADSP-1401 outputs the address of the next microcode instruction on its 16bit address port (pins  $Y_{15-0}$ ). Addresses are output during clock HI and latched for the duration of clock LO, as shown in Figure 2.10. No external latches are needed between the address port and the microcode address inputs.

#### Figure 2.10 Address Output

The address multiplexer selects the address from one of four sources in response to the given instruction:

- Program Counter: For sequential addresses

- Adder: For absolute or relative jump addresses

- Interrupt Vector File: For interrupt service routine addresses

- *Internal RAM:* For indirect jump addresses, local and global jump addresses, and subroutine return addresses

The tristate drivers of the address port are always active unless placed in the highimpedance state through either software (the IDLE instruction) or hardware (the TTR pin) control. For multitasking and context-switching applications, in which other devices must access microcode memory, placing the address drivers of the ADSP-1401 in the high-impedance state effectively removes the device from the address bus.

#### 2.12 STATUS REGISTER

The status register, shown in Figure 2.11, contains 16 bits  $(SR_{15.0})$  that control various operating modes of the ADSP-1401 according to Table 2.2. You can set

and clear all bits at once or individually, using dedicated instructions. The ADSP-1401 also writes the  $SR_1$  bit during the execution of instructions that decrement counters. You can load or read the entire status register from the data port. You can also save and restore the status register to and from the subroutine stack. The reset operation clears the entire status register.

#### SR BIT DESCRIPTION

- 0 Transparent Interrupt Selection: This bit, if set, disables the latching of external interrupts ( $IR_{8-1}$ ). Transparent interrupts require the interrupt source to maintain the interrupt signal until the service routine acknowledges the recognition of the interrupt. If this bit is cleared,  $IR_{8-5}$  are latched during clock HI and  $IR_{4-1}$  are latched during clock LO.

- 1 *Sign Bit:* This bit normally contains the value of the sign bit of the most recently decremented counter (value *before* decrement). It can also be set and cleared using dedicated instructions.

- 2 *Interrupt Enable:* This bit, if set, enables the processing of all unmasked interrupts. If this bit is cleared, processing of all interrupts, masked and unmasked, is disabled. External interrupts are still latched, unless  $SR_0$  is set.

- 3 *Register Stack Pointer Selection:* If this bit is set, all register stack instructions affect the global stack. If this bit is cleared, all register stack instructions affect the local stack.

- 5-4 *Relative Jump Offset Width and Instruction Hold Control Mode Selection:* These bits select the width of jump address offsets input at the data port and may also place the ADSP-1401 in the Instruction Hold Control mode, in which the instruction in the instruction latch is repeated under control of the IR<sub>1</sub> interrupt input.

- 15 6 *Interrupt Disable Mask:* These ten mask bits correspond to the ten interrupts. ( $SR_{15}$  is paired with  $IR_9$ ,  $SR_{14}$  with  $IR_8$ , and so forth.) If the mask bit is set, processing of the corresponding interrupt is disabled, although the interrupt signal is still latched. If the mask bit is cleared, the interrupt is enabled and disabled by the  $SR_2$  bit.

#### Table 2.2 Status Register Bit Definition

# Jumps 🗖 3

#### 3.1 INTRODUCTION

Normally, the ADSP-1401 provides sequential execution of microcode by incrementing the current address in the program counter. A jump is a deviation from sequential execution. A jump instruction outputs an address that is different from the next sequential address and reloads the program counter with this new address.

Jumps are used for several purposes, including:

- *Conditional Branches:* A conditional jump creates a branch in the program flow based on a specified condition (the ADSP-1401 provides four conditions). If the condition is true, the ADSP-1401 skips to another section of the program; if the condition is false, the ADSP-1401 continues to execute instructions sequentially. The ADSP-1401 also provides for a three-way branch, in which two conditions are tested instead of one.

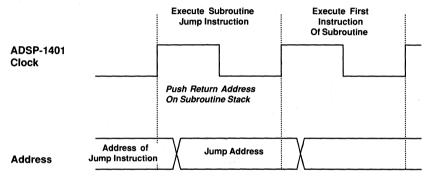

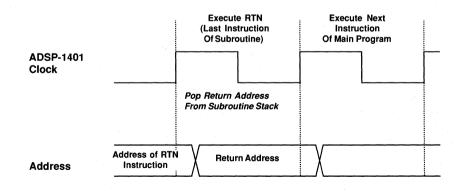

- Subroutine Calls: A jump to a subroutine executes a block of instructions in one section of the program and then resumes sequential execution. Before the ADSP-1401 performs a subroutine jump, it pushes the address of the next sequential instruction on the subroutine stack. When the subroutine execution completes, the ADSP-1401 pops the subroutine stack and program execution continues from the return address.

- *Loops:* A jump to a previously executed instruction repeats the execution of one or more instructions. The ADSP-1401 includes four event counters that you can use to set the number of loop iterations.

- *Interrupt Servicing:* A jump to an interrupt service routine is similar to a subroutine call in that the ADSP-1401 stores the next sequential address for the return jump. However, the jump is initiated by an interrupt signal rather than a software instruction. Interrupts are explained fully in Chapter 4, *Interrupt Processing*.

These operations are illustrated in Figure 3.1. Chapter 6 provides complete information on the specific instructions that perform these operations.

#### Figure 3.1 Branches, Subroutines, Loops, and Service Routines

The ADSP-1401 obtains jump addresses from several sources:

- *Data Port:* The jump address is usually given in a data field supplied with the jump instruction in microcode. The ADSP-1401 reads the address on its data port and can output this address unchanged (absolute addressing) or add it to the program counter value first (relative addressing).

- *Indirect Address Space:* An external source, usually microcode, provides an address on the six least significant bits of the data port. This 6-bit address selects a location in the indirect address space that contains a preloaded jump address.

- *Interrupt Vector File:* On the cycle following the detection of an interrupt, the ADSP-1401 outputs the appropriate interrupt vector on the address port.

- *Register Stack:* Several jump instructions access an address stored in the local stack or global stack. The stack location is specified relative to the location of the LSP or GSP.

- Subroutine Stack: Subroutines and interrupt service routines require jumps to return to their calling routine. To execute a return from a subroutine or interrupt service routine, the ADSP-1401 pops the return address from the subroutine stack.

#### 3.2 CONDITIONS

Conditional jump instructions contain two bits of opcode that are used to select one of four jump conditions. These conditions are often used to control loop iteration and subroutine execution, as well as conditional branching.

- FLAG Execute jump if Flag input is HI.

- NOT FLAG Execute jump if Flag input is LO.

- SIGN Execute jump if sign bit of specified counter is HI.

- UNCONDITIONAL Execute jump always

#### 3.2.1 Flag Input

The Flag input signal or its complement (Not Flag) can be selected as a jump condition. Through the Flag input, an external condition can control the execution of a jump instruction.

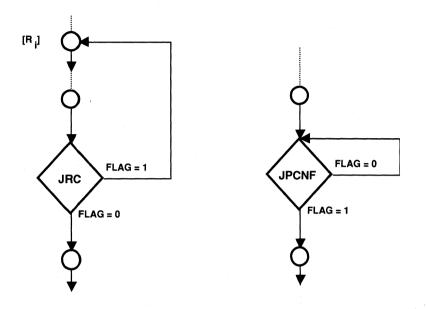

Figure 3.2 shows two kinds of Flag-controlled loops. In the first example, the jump to the top of the loop (JRC instruction to the address in  $R_i$ ) is conditioned on the Flag signal, and the loop repeats as long as the external device asserts the Flag input. In the second example, the JPCNF instruction creates a one-instruction loop that repeats the same microcode instruction for as long as the Flag input is inactive. (The JPCOF performs the same function for as long as the Flag input is active.) The Flag input can thus be used by an external device to control the repetition of an instruction. This type of loop is useful for reconciling timing differences.

Loop While Flag = 1

#### Figure 3.2 Loops Using the Flag Input

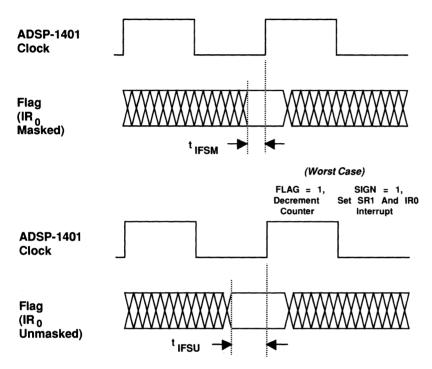

When  $IR_0$  (counter underflow interrupt) is not masked, the Flag input setup time is greater than for when  $IR_0$  is masked, as shown in Figure 3.3. In the worst-case timing, a Flag input leads to a counter underflow, and extra time is needed to process the  $IR_0$  interrupt after the underflow is detected. See the current ADSP-1401 Data Sheet for timing requirements. The  $IR_0$  interrupt is described in *Counter Underflow Interrupt*, in Chapter 4.

#### 3.2.2 Counters

The ADSP-1401 has four decrement-only event counters ( $C_{3-0}$ ), which store 16bit twos-complement values. The sign bit of any counter can be selected as a condition for several jump instructions; a negative sign bit (HI) represents a true Sign condition. Jump instructions conditioned on a counter sign bit can control the iteration of program loops. The sign bit of a counter (value before decrement) determines whether the loop repeats or ends. If the loop repeats, the counter is decremented.

Before it decrements a counter, the ADSP-1401 writes the counter's sign bit to  $SR_1$ . Thus,  $SR_1$  always contains the sign bit (before decrement) of the most recently decremented counter. The Sign condition is tested in one of two ways, depending on the type of instruction. If the instruction decrements a specific

#### Figure 3.3 Flag Setup Time With and Without IR<sub>0</sub> Masked

counter (conditionally or unconditionally), the sign bit of that counter (before decrement) is tested. If the instruction does not affect a counter, the  $SR_1$  bit is tested. The exception is the IFCDEC instruction; if the Sign condition is selected for this instruction,  $SR_1$  is tested even though the instruction decrements  $C_0$ . This instruction incurs a delay when used with the counter underflow interrupt,  $IR_0$ ; see *Counter Underflow Interrupt* in Chapter 4.

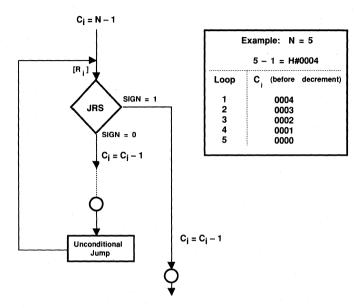

You can load counters from the data port. You can also save them to and restore them from the subroutine stack. The value you must load into a counter to execute a loop depends on the action performed by the instruction and the location of the conditional jump instruction within the loop (top or bottom). For example, in Figure 3.4 the Sign condition is tested at the top of the loop. If the condition is

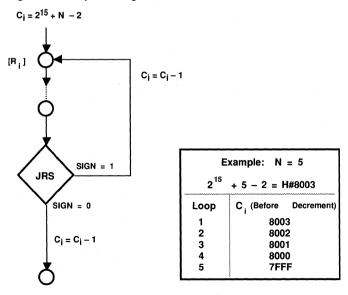

Figure 3.5 shows another way to construct a loop. The Sign condition is tested at the bottom of the loop. If the condition is true, the JRS instruction executes a jump to the top of the loop (address stored in  $R_i$ ). Otherwise, the instruction that follows the JRS instruction is executed, ending the loop. In either case,  $C_i$  is decremented. To iterate this loop N times, the counter must be loaded with a value  $2^{15}+N-2$ , a negative value, to perform the jump *while* the Sign condition is true.

Figure 3.4 Loop Until Sign Bit = 1

Figure 3.5 Loop While Sign Bit = 1

3 - 6

Examples using other instructions to create loops and count events are described in Using the Counters of the ADSP-1401 Program Sequencer for Loop and Event Counting. The use of the counter underflow interrupt (IR<sub>0</sub>) is explained in this application note, as well as in Chapter 4, Interrupt Processing.

## 3.3 ADDRESS SOURCES

The ADSP-1401 supports both direct and indirect addressing in its jump instructions. A direct address points to a microcode memory location. An indirect address points to a location in the indirect address space in the internal RAM of the ADSP-1401; this location in turn contains an address that points to a microcode memory location. The register stack is a third source of jump addresses. These addresses are accessed through either the GSP or LSP.

### 3.3.1 Direct Addressing

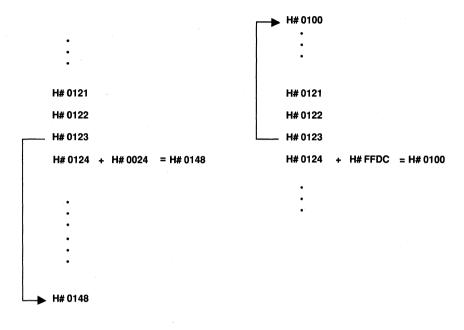

Direct addressing requires input from the data port. The ADSP-1401 can perform two types of direct jumps: an absolute jump, which interprets the given data value as the jump address, and a relative jump, which interprets the given data value as an offset from the program counter address. To perform an absolute jump, the ADSP-1401 passes the data port value through the width control block and adder to the address port unchanged. For a relative jump, the ADSP-1401 adds the data port value to the program counter value, and outputs the sum on the address port. Because the program counter contains the address of the next instruction, the jump distance from the relative jump instruction is one instruction more than the offset value. If the twos-complement offset is negative, however, the jump distance is one less than the offset value. In Figure 3.6, an offset of H#0024 results in a jump from address H#0123 to H#0148, whereas an offset of H#FFDC (the twos complement of H#0024) results in a jump from H#0123 to H#0100.

The ADSP-1401 recognizes three offset widths: 16, 12, and 8 bits. This feature conserves data bits in microcode for applications that do not require relative jump offset values larger than the selected data width can represent. Two status register bits select the offset width. The ADSP-1401 ignores the unused data bits when reading an offset from the data port.

### 3.3.2 Indirect Addressing

Indirect jump addresses are stored in the indirect address space (in the internal RAM). A 6-bit address provided at the data port with an indirect jump instruction specifies the RAM location. In principle, an indirect jump address can be stored in any RAM location. In practice, however, the indirect address space is usually located in the highest memory to eliminate the possibility of an indirect jump address being overwritten by a stack operation.

Positive Offset

Negative Offset

#### Figure 3.6 Positive and Negative Offsets

#### 3.3.3 Register Stack

The register stack consists of two stacks: the local stack and the global stack. Both of these stacks provide storage for jump addresses. The subroutine stack can be used for this purpose, but the SSP must be tracked so that subroutine nesting levels are not lost. The register stack does not have this constraint. The register stack pointers (LSP and GSP) can be moved as needed to access stack contents.

The local stack stores jump addresses used by particular subroutines. The global stack stores jump addresses that can be accessed from any subroutine, as well as the main program. For example, the global stack might contain a jump address used by several interrupt service routines. Sharing jump addresses on the global stack avoids the duplication of jump addresses in the local stack and conserves the code required to push the jump addresses on the local stack.

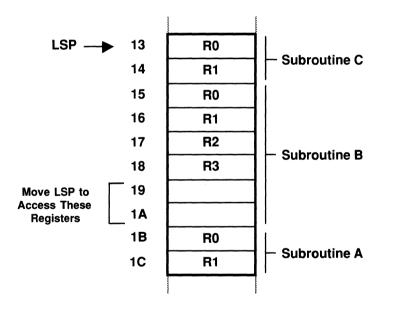

A single set of register stack instructions applies to both the local stack and the global stack. A status register bit determines which stack a register stack instruction affects. Certain jump instructions can access four registers of the selected stack as jump addresses. These registers are referenced by their location relative to the LSP or GSP; for example,  $R_2$  is the register at the location that is

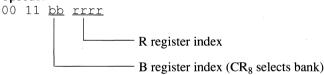

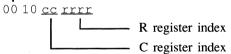

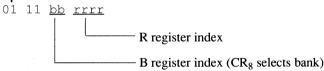

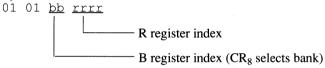

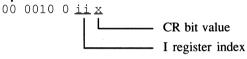

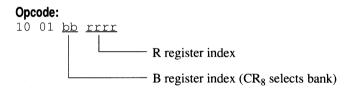

two greater than the LSP or GSP location. To access four other registers, you simply move the stack pointer.