# Am29PL141 Fuse Programmable Controller

Handbook

3

# コ

# **Advanced Micro Devices**

# Am29PL141 Fuse Programmable Controller

# Handbook

#### © 1986 Advanced Micro Devices

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This manual neither states nor implies any warranty of any kind, including but not limited to implied warranties of merchantability or fitness for a particular application. AMD assumes no responsibility for the use of any circuitry other than the circuitry embodied in an AMD product.

The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. AMD assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the information included herein. Additionally, AMD assumes no responsibility for the functioning of undescribed features or parameters.

Contributors to the Am29PL141 Fuse Programmable Controller Handbook:

Rajesh Tanna, Headquarters Applications, Sunnyvale, CA (Chapters 1 and 4) MS 151 Om Agrawal, Product Planning (Chapters 1, 2, and 3) William Chen, Product Planning (Chapters 2 and 3) Arthur Khu, Product Planning (Chapter 1) Rick Purvis, FAE, Austin, TX (Chapters 5 and 6) David Stoenner, FAE, Newport Beach, CA (Chapters 7 and 8) Robert O'Hara, FAE, Dorsey, MD (Chapter 9) Stephen L. Belechak-Becraft, former AMD FAE (Chapter 9) Dan Overman, Dibec, Inc. (Chapter 9) Frank Hudziak, Jr., FAE, Itasca, II (Chapter 10) Philip Freiden, Product Planning Manager

**Technical Writer:**

Erland Kyllonen, Senior Technical Writer, Headquarters, MS71

**Copyright Notices**

DEC, PDP, Q-Bus, and Unibus are trademarks of the Digital Equipment Company. IBM PC is a trademark of IBM SSR is a trademark of Advanced Micro Devices PAL is a registered Trademark of and used under license from Monolithic Memories, INC.

#### TABLE OF CONTENTS

| 1. | Fuse | e Proc | rammable Controller Ove     | rview   |          |         | ••• |     | 1-1        |

|----|------|--------|-----------------------------|---------|----------|---------|-----|-----|------------|

|    |      |        |                             |         |          |         |     |     | 1-1        |

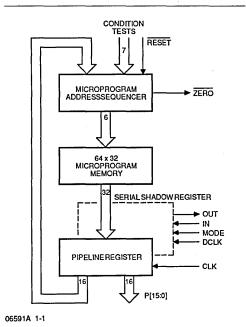

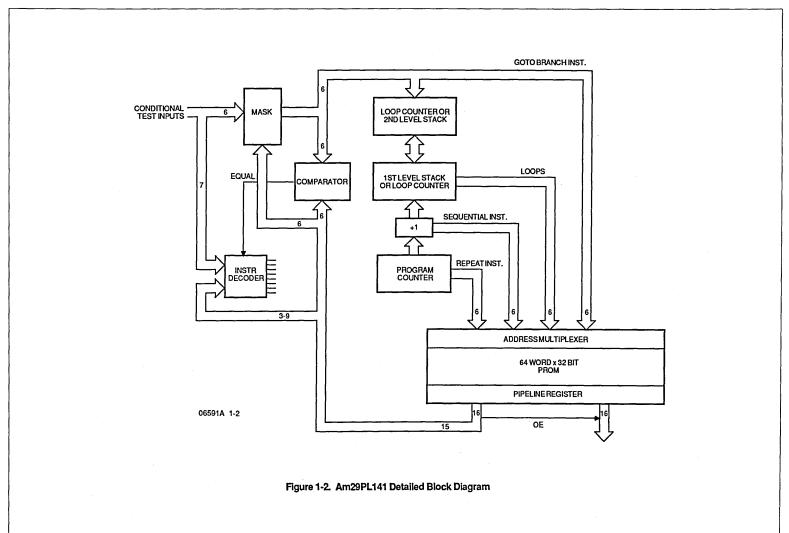

|    |      |        | PL141 Architecture Overv    |         | •••      |         | ••• |     | 1-1        |

|    |      |        | Address Sequencer           |         |          |         |     |     | 1-2        |

|    |      |        | Branch Control/Condition C  | ode Loa | ic       |         |     |     | 1-2        |

|    |      |        |                             |         |          |         |     |     | 1-2        |

|    |      |        | Microprogram Memory and     |         | Register |         | ••• |     | 1-4        |

|    |      | Micro  |                             |         |          | •••     |     |     | 1-4        |

|    |      |        | Microinstruction Format     | •••     |          |         |     |     | 1-4        |

|    |      |        | Microinstructions           | •••     | •••      | •••     | ••• |     | 1-4        |

|    |      | 1.0.2  | Looping                     | •••     | •••      | •••     | ••• | ••• | 1-4        |

|    |      |        | Conditional                 | •••     | •••      | •••     | ••• | ••• | 1-4        |

|    |      |        | Unconditional               | •••     | •••      | •••     | ••• | ••• | 1-4        |

|    |      | 100    |                             | •••     | •••      | •••     | ••• | ••• | 1-4        |

|    |      |        | SSR Diagnostics             | •••     | •••      | •••     | ••• | ••• |            |

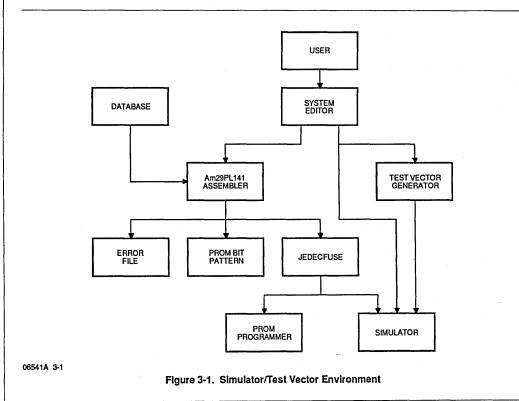

|    | 1.4  |        | PL141 Software Support      |         | •••      | •••     | ••• | ••• | 1-5        |

|    |      |        | Am29PL141 Assembler         |         | •••      | ••••    | ••• | ••• | 1-5        |

|    |      |        | Am29PL141 Test Vector G     |         | •••      | •••     | ••• | ••• | 1-6        |

|    |      |        | Am29PL141 Simulator         |         | •••      |         | ••• | ••• | 1-6        |

|    | 1.5  | An O   | verview of this Technical I | Manual  |          | •••     | ••• | ••• | 1-6        |

| _  |      |        |                             |         |          |         |     |     |            |

| 2. |      |        | 41 Assembler                | •••     |          | •••     | ••• | ••• | 2-1        |

|    | 2.1  |        | duction to the Am29PL141    | 1 Assem | bler     | •••     | ••• | ••• | 2-1        |

|    |      | 2.1.1  | Assembler Features          | •••     |          | •••     | ••• | ••• | 2-1        |

|    |      | 2.1.2  | Error Detection and Diagno  | osis    |          |         | ••• | ••• | 2-1        |

|    |      | 2.1.3  | System Requirements         |         |          |         | ••• |     | 2-2        |

|    |      | 2.1.4  | Making Backups              | •••     | •••      | •••     | ••• |     | 2-2        |

|    | 2.2  | User'  | s Guide                     |         |          | •••     | ··· |     | 2-2        |

|    |      | 2.2.1  | Notation                    |         |          |         |     | ••• | 2-2        |

|    |      | 2.2.2  | Running the Assembler       |         |          |         |     |     | 2-2        |

|    |      |        | Assembler Output            |         |          |         |     |     | 2-3        |

|    |      |        | JEDEC Standard Fuse         | Мар     |          | · • • • |     |     | 2-3        |

|    |      |        | PROM Bit Pattern            |         |          |         |     |     | 2-3        |

|    | 2.3  | Lang   | uage Reference              |         |          |         |     |     | 2-3        |

|    |      |        | Language Elements           |         |          |         |     |     | 2-3        |

|    |      |        | Keywords                    |         |          |         | ••• |     | 2-4        |

|    |      |        | Identifiers                 |         |          |         |     |     | 2-4        |

|    |      | 2.3.2  | Assembler Program Struct    |         |          |         |     |     | 2-4        |

|    |      |        | DEVICE Section              |         |          |         |     |     | 2-4        |

|    |      |        | SSR Section                 |         |          |         |     |     | 2-4        |

|    |      |        | DEFAULT Section             |         |          |         |     |     | 2-4        |

|    |      |        | DEFINE Section              |         | •••      |         |     |     | 2-4        |

|    |      |        | DEFAULT OUTPUT S            |         |          |         |     |     | 2-4        |

|    |      |        | TEST CONDITION              | conorr  | •••      |         | ••• |     | 2-5        |

|    |      |        | Main Body                   | •••     | •••      | •••     | ••• | ••• | 2-5        |

|    |      |        |                             | •••     | •••      | •••     | ••• | ••• | 2-5        |

|    |      | 2.3.3  | Statement Elements          | •••     | •••      | •••     | ••• | ••• | 2-5        |

|    |      |        | Labels                      | •••     | •••      | •••     | ••• | ••• | 2-5        |

|    |      |        | Control Output              | •••     | •••      | •••     | ••• | ••• | 2-6<br>2-6 |

|    |      | 0 0 4  | Logic Operators             | •••     | •••      | •••     | ••• | ••• | 2-0<br>2-6 |

|    |      |        | Statement Format            |         |          | •••     | ••• | ••• | 2-6<br>2-7 |

|    |      |        | Statements Available for th | ie Am29 | PL141    | •••     | ••• | ••• | 2-7        |

|    | •    |        | QUICK Reference Guide       |         | •••      | •••     | ••• | ••• |            |

|    | 2.4  | Desiç  | yn Example                  | •••     | •••      | •••     | ••• | ••• | 2-7        |

|    |      |        |                             |         |          |         |     |     |            |

|                                                                                             |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |     |         | and the second |

|---------------------------------------------------------------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|---------|------------------------------------------------------------------------------------------------------------------|

|                                                                                             |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |     |         |                                                                                                                  |

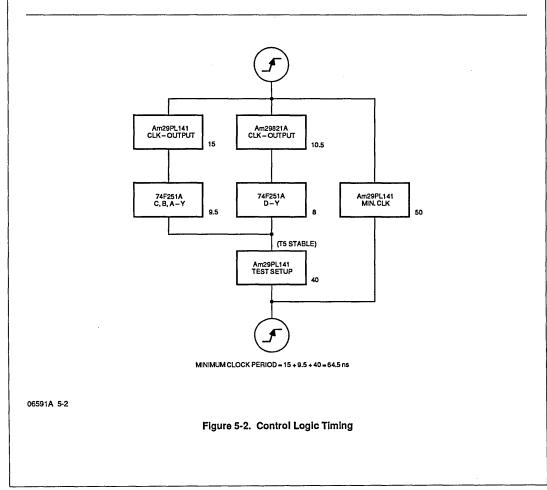

| 5-3 Microword Organization                                                                  | •••           | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |     | •••     | 5-4                                                                                                              |

| 5-4 Unibus Controller Source Program Lis                                                    | sting         | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •••     | ••• | •••     | 5-6                                                                                                              |

| 5-5 FPC PROM Contents                                                                       | •••           | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •••     | ••• | •••     | 5-8                                                                                                              |

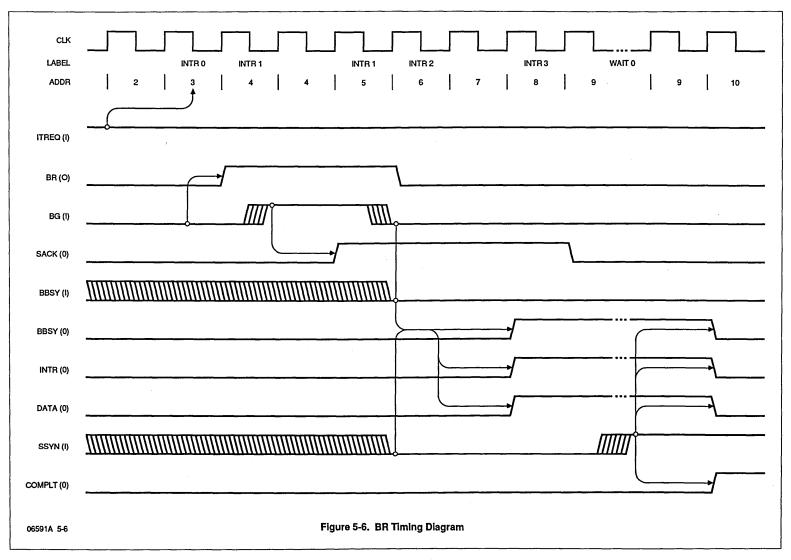

| 5-6 BR Timing Diagram                                                                       |               | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •••     | ••• | •••     | 5-9                                                                                                              |

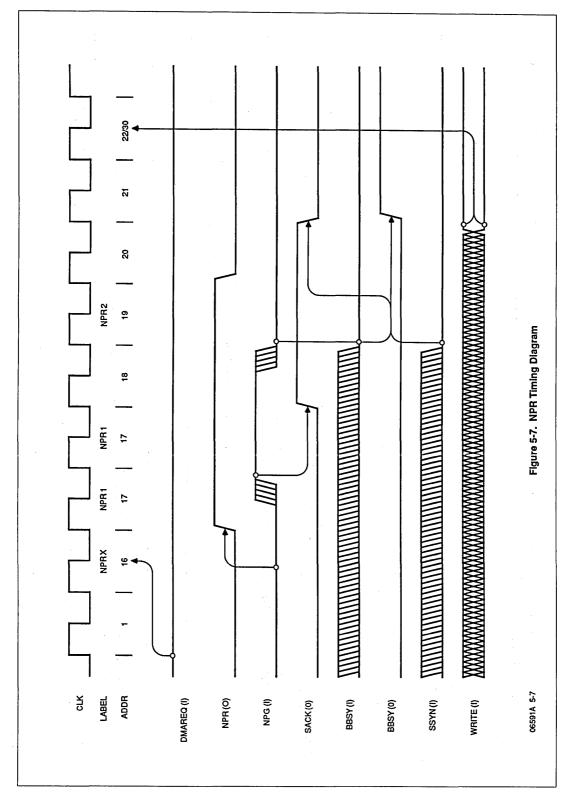

| 5-7 NPR Timing Diagram                                                                      |               | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •••     | ••• | •••     | 5-10                                                                                                             |

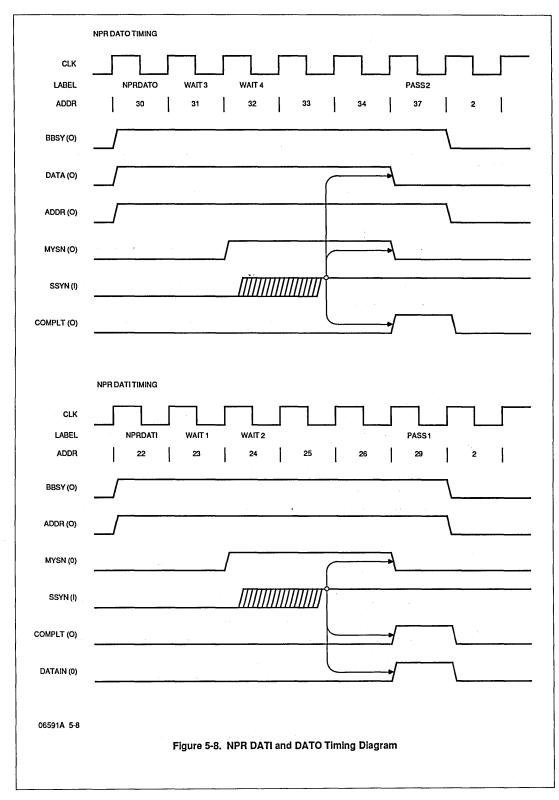

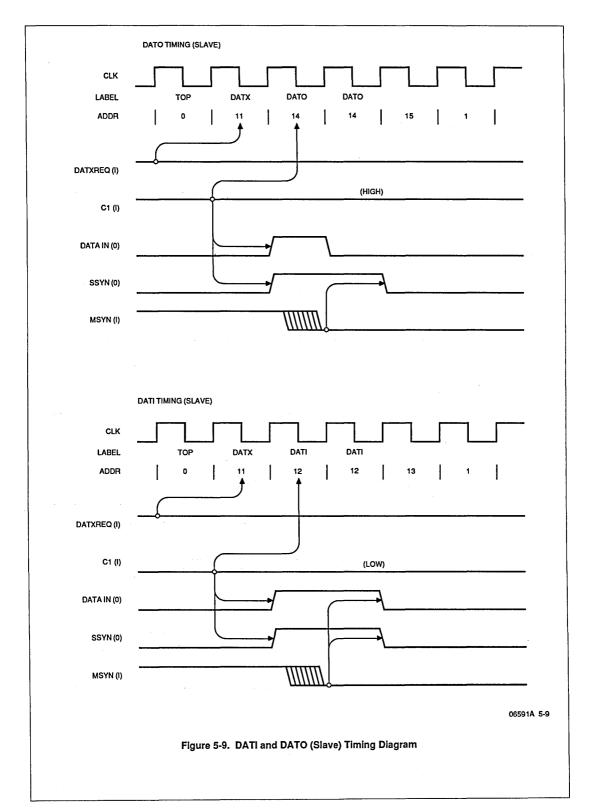

| 5-8 NPR DATI and DATO Timing Diagram                                                        |               | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •••     | ••• | •••     |                                                                                                                  |

| 5-9 DATI and DATO (Slave) Timing Diagr                                                      | am            | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •••     | ••• | •••     | 5-12                                                                                                             |

| C.1. O Bue Controller Block Discrem                                                         |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |     |         | <u> </u>                                                                                                         |

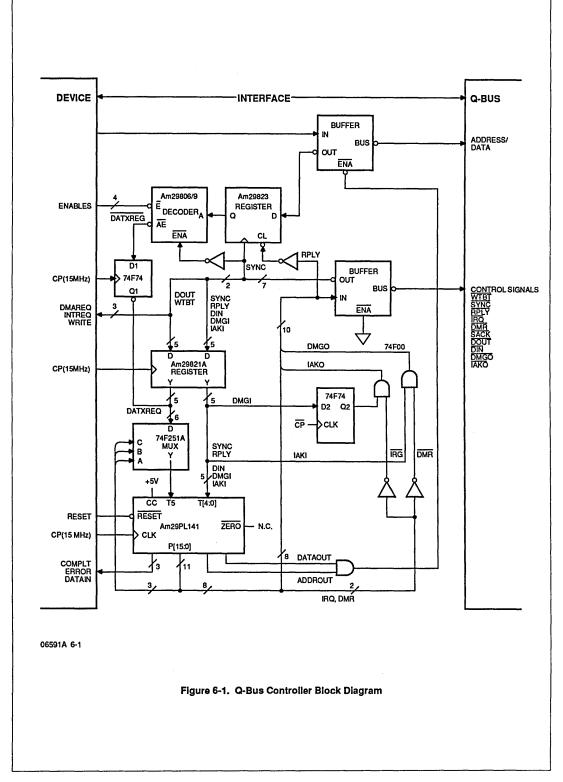

| 6-1 Q-Bus Controller Block Diagram                                                          | •••           | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •••     | ••• | •••     | 6-3                                                                                                              |

| 6-2 Q-Bus Controller Microword Format                                                       | •••           | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •••     | ••• | •••     | 6-4                                                                                                              |

| 6-3 Q-Bus Controller Source Program Lis                                                     | ting          | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •••     | ••• | •••     | 6-5                                                                                                              |

| 6-4 FPC PROM Program Listing                                                                | •••           | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •••     | ••• | •••     | 6-8                                                                                                              |

|                                                                                             |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |     |         |                                                                                                                  |

| 7-1 Starlan DMA Controller Block Diagram                                                    | n             | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •••     | ••• | •••     | 7-2                                                                                                              |

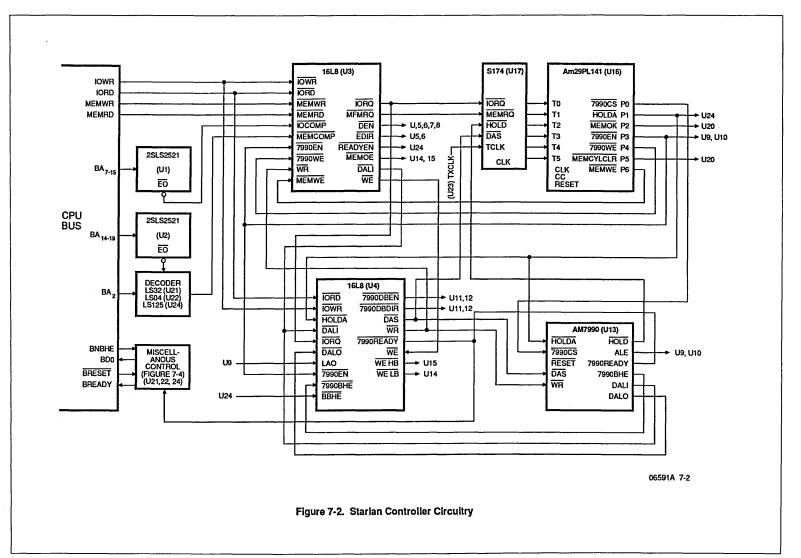

| 7-2 Starlan Controller Circuitry                                                            | •••           | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •••     | ••• | •••     | 7-3                                                                                                              |

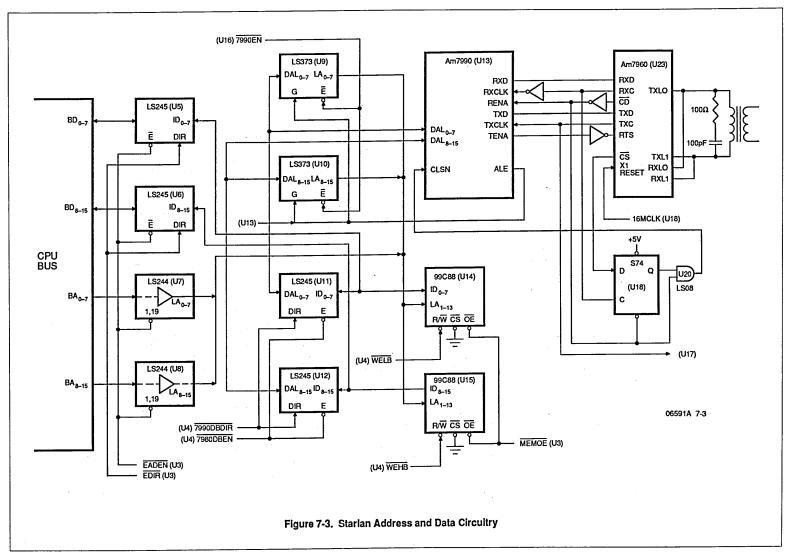

| 7-3 Starlan Address and Data Circuitry                                                      | •••           | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |     | •••     | 7-4                                                                                                              |

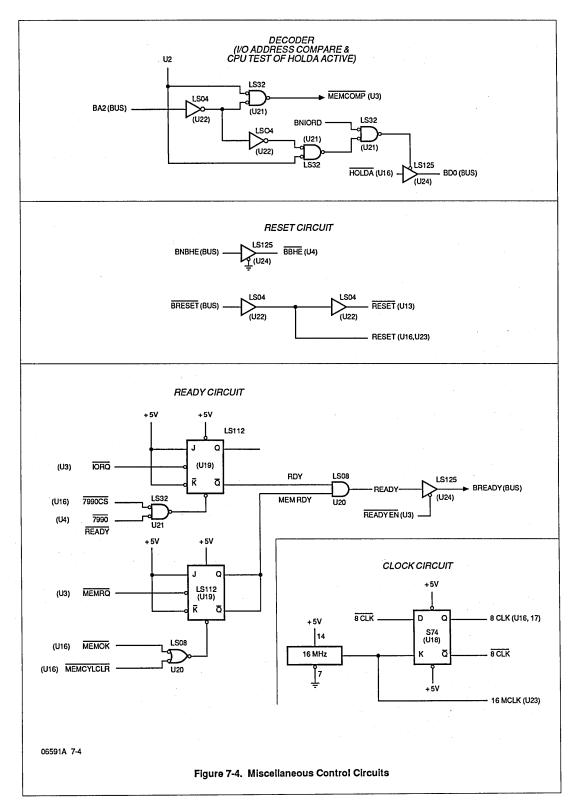

| 7-4 Miscellaneous Control Circuits                                                          |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         | ••• |         | 7-5                                                                                                              |

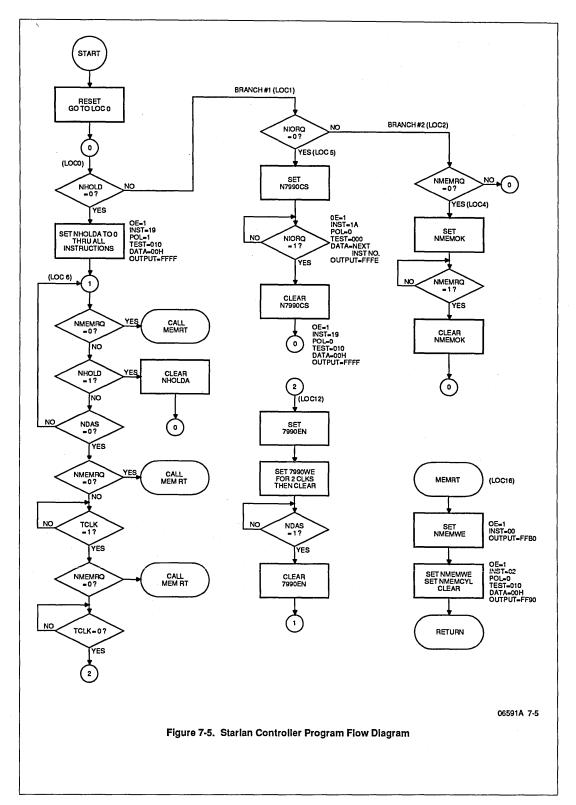

| 7-5 Starlan Controller Program Flow Diag                                                    |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |     |         | 7-8                                                                                                              |

| 7-6 Starlan Controller Source Program Li                                                    | sting         | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |     |         | 7-9                                                                                                              |

|                                                                                             |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |     |         |                                                                                                                  |

| 8-1 SSR Controller Block Diagram                                                            |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |     |         | 8-3                                                                                                              |

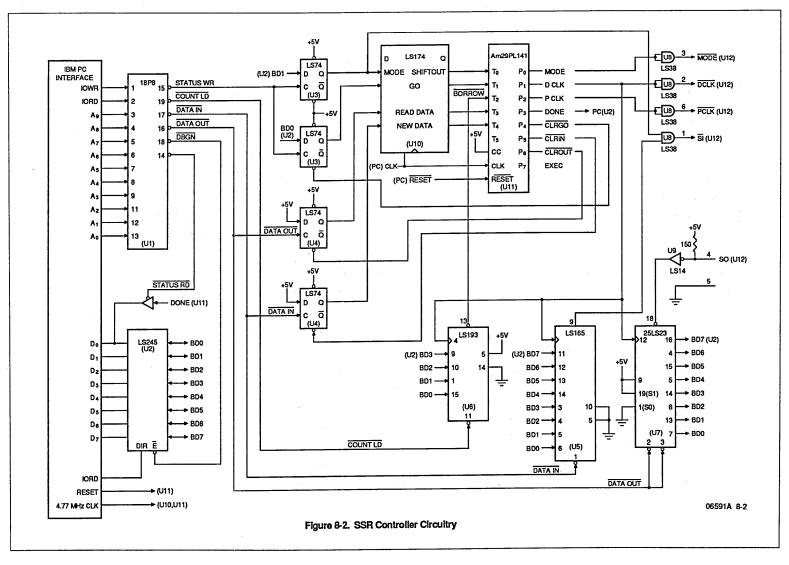

| 8-2 SSR Controller Circuitry                                                                |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |     |         | 8-4                                                                                                              |

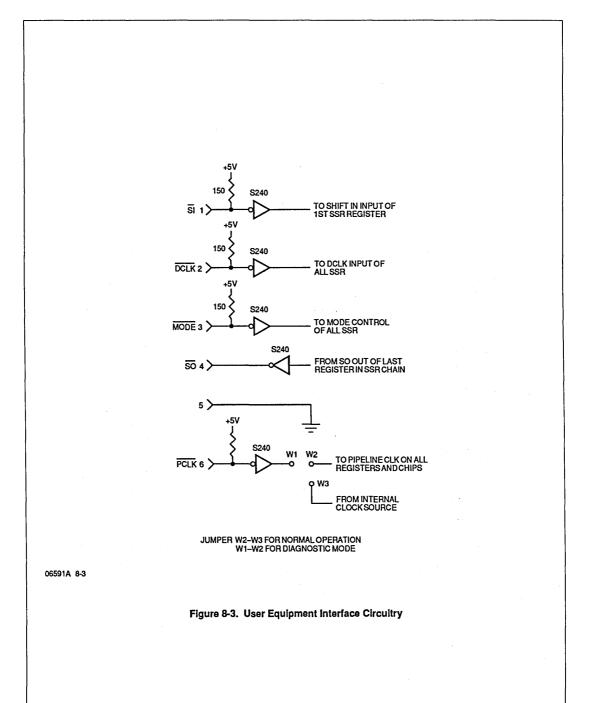

| 8-3 User Equipment Interface Circuitry                                                      |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |     |         | 8-5                                                                                                              |

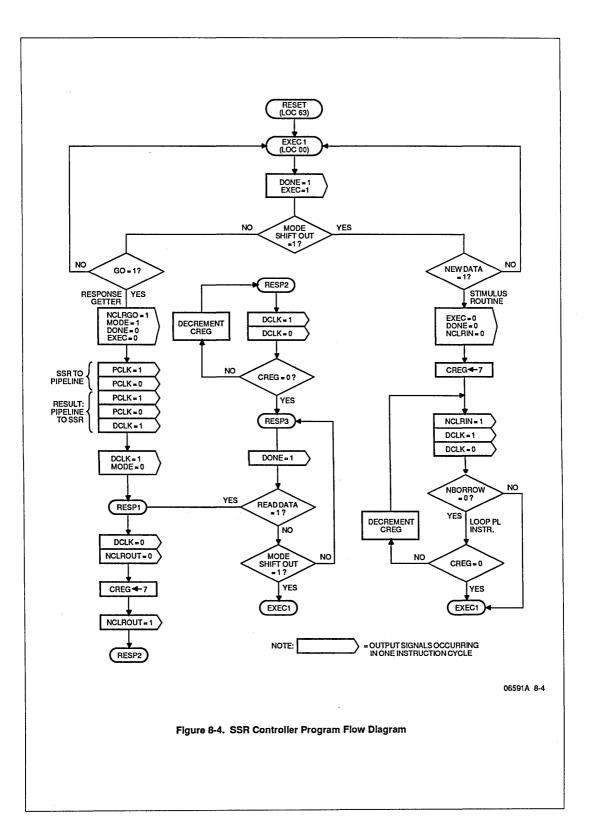

| 8-4 SSR Controller Program Flow Diagra                                                      | m             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |     |         | 8-6                                                                                                              |

| 8-5 SSR Controller Source Program Listin                                                    |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |     |         | 8-7                                                                                                              |

|                                                                                             | -             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |     |         |                                                                                                                  |

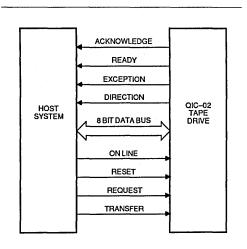

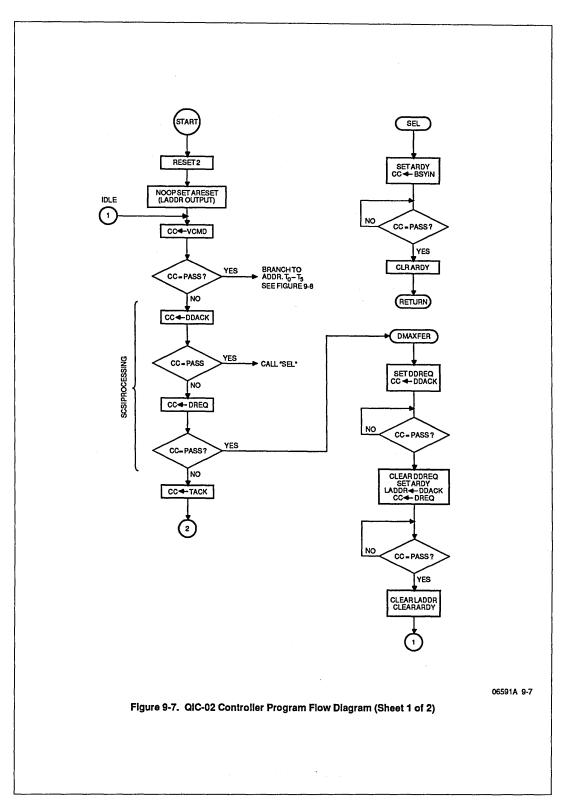

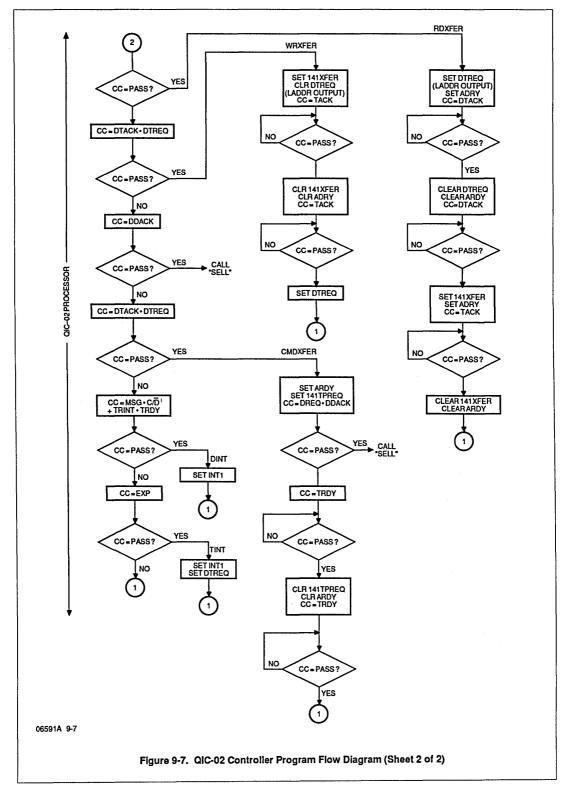

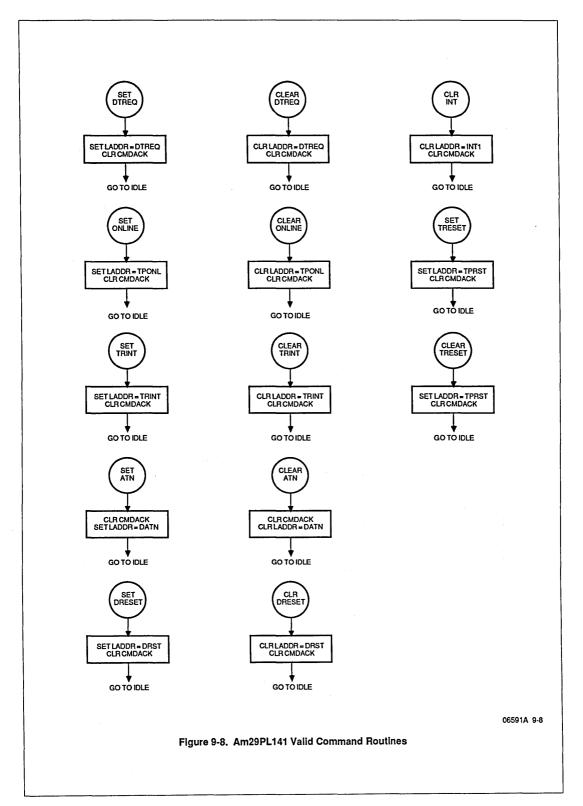

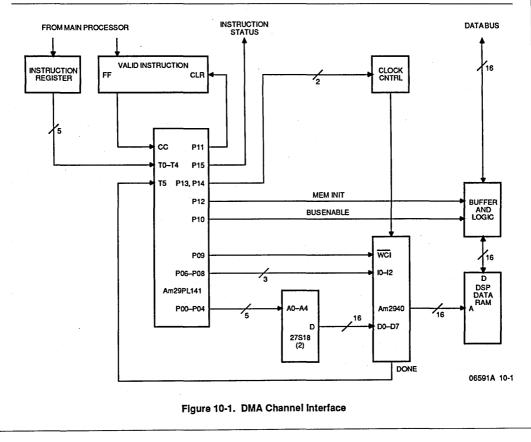

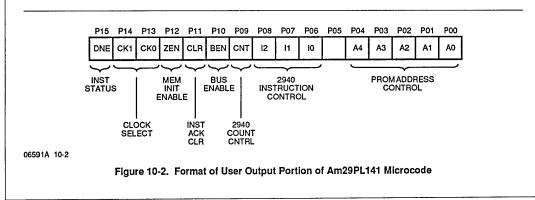

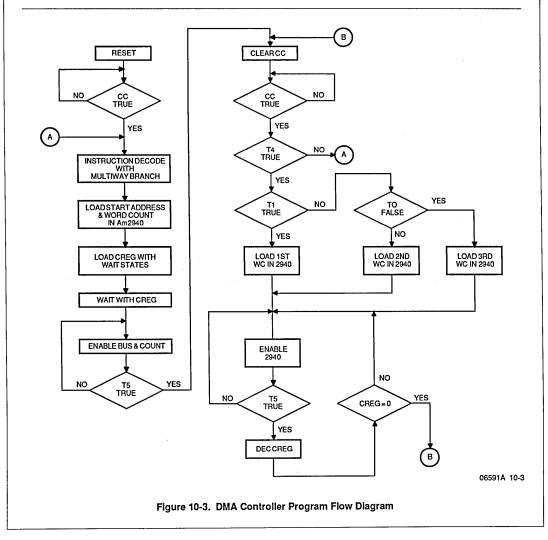

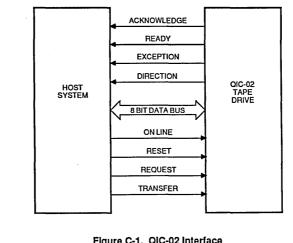

| 9-1 QIC-02 Interface                                                                        |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |     |         | 9-1                                                                                                              |

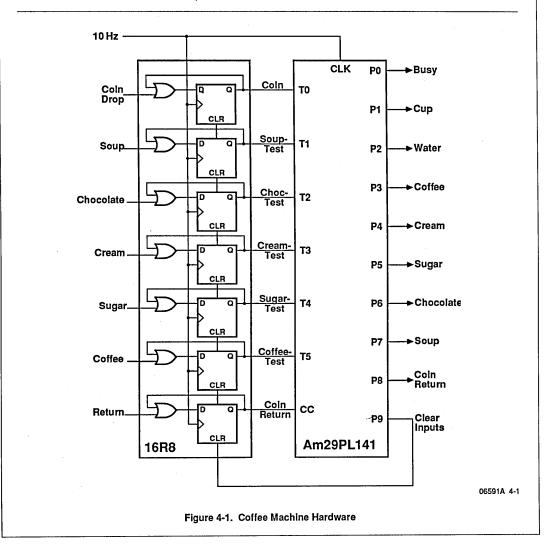

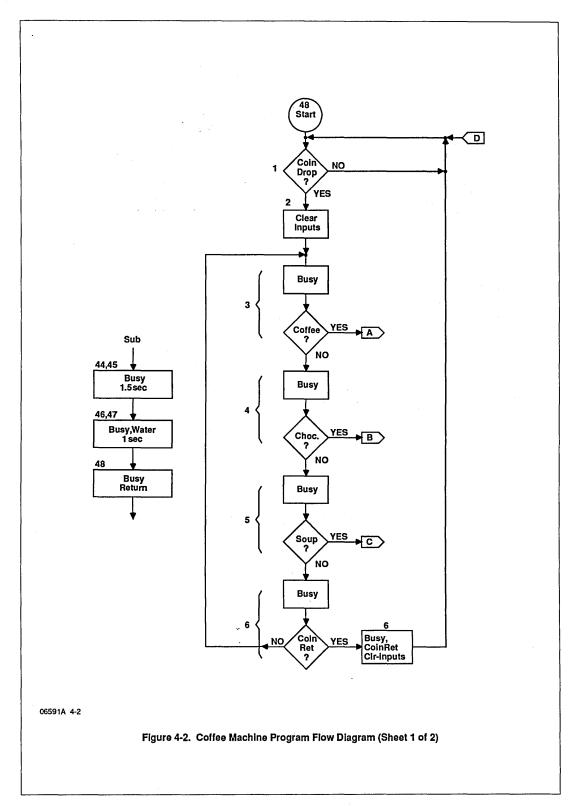

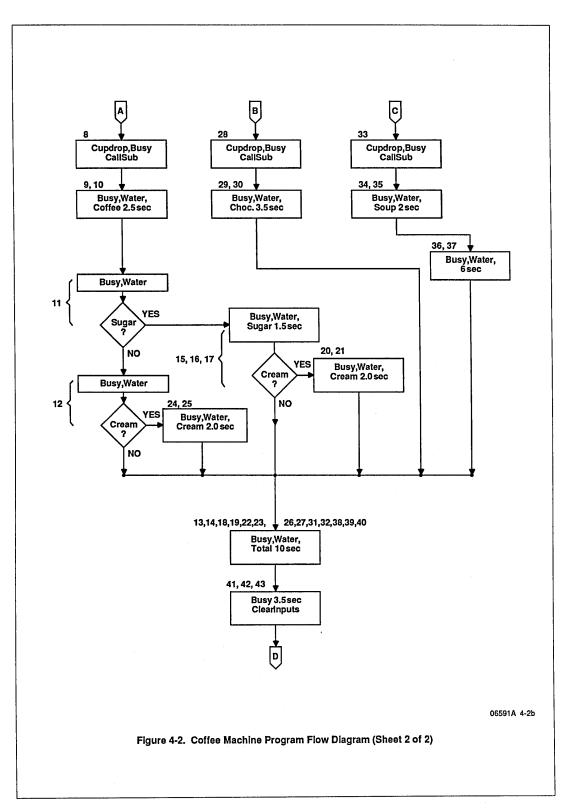

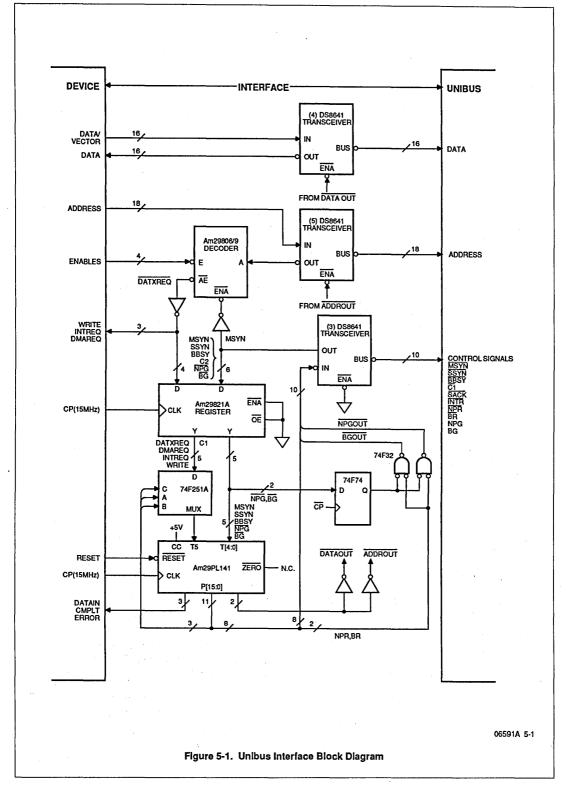

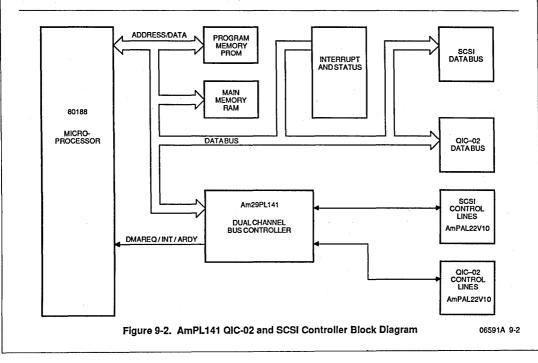

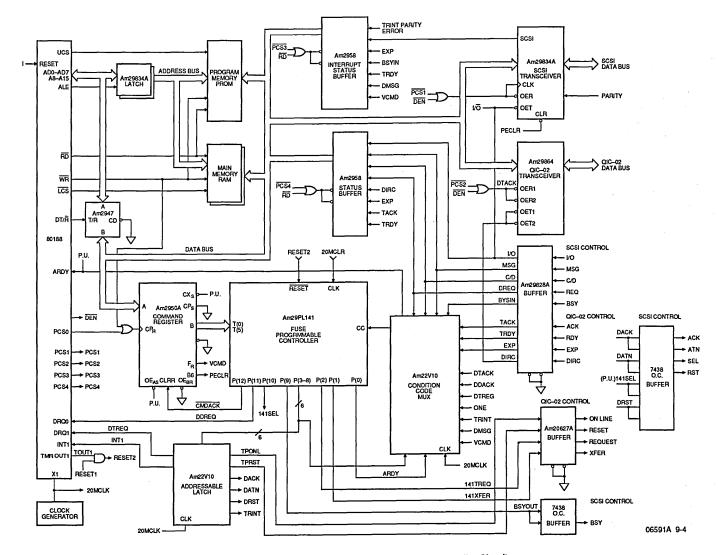

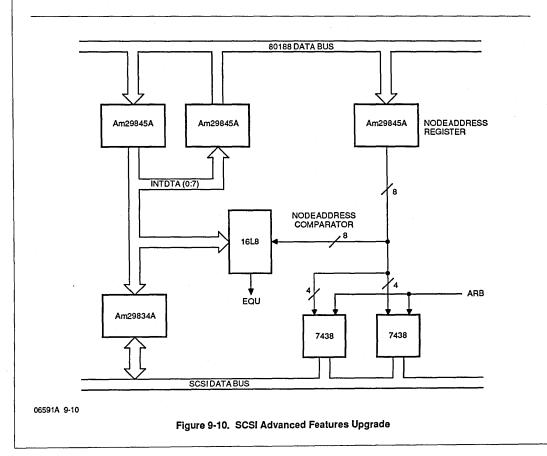

| 9-2 Am29PL141 QIC-02 and SCSI Control                                                       | oller Block   | Contraction Contractic Contr | m       |     |         | 9-2                                                                                                              |