Am29300 Demonstration System

### Application Note

Sequencer Floating Point Processor Bounds Checker

Advanced Micro Devices

## **Advanced Micro Devices**

# Am29300 Demonstration System

## **Application Note**

By Mark McClain

#### © 1988 Advanced Micro Devices

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This publication neither states nor implies any warranty of any kind, including but not limited to implied warranties of merchantability or fitness for a particular application. AMD assumes no responsibility for the use of any circuitry other than the circuitry embodied in an AMD product.

The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. AMD assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the information included herein. Additionally, AMD assumes no responsibility for the functioning of undescribed features or parameters.

901 Thompson Place, P.O. Box 3453, Sunnyvale, California 94088 (408) 732-2400 TWX: 910-339-9280 TELEX: 34-6306

## Preface

This application note describes the design of a high-performance microprogrammed 32-bit processor using the Am29300 family of 32-bit building blocks. Basic design philosophy for a microprogrammed processor is discussed as the design choices made for this system are explained. Support circuitry used with the Am29300 family components is also covered in detail. This circuitry includes: Writable Control Store, Serial Shadow Register diagnostics, and Programmable Array Logic. This edition of the application note is a reprint of the 1987 version with no changes. *However, some assumptions have been made for specifications on various data-sheet parameters that were applicable at the time of the writing in 1986, and have since been improved.* These improvements are reflected in the following table.

CMOS versions of the 29300-family devices, discussed in this application note, have recently been introduced. The table summarizes worst-case delay times for both the bipolar and CMOS versions. Also projected values for product speeds in early 1989 are indicated. In cases other than microprogrammable products, some new and faster devices, or devices of different architecture, may also affect the design.

CMOS processes have dramatically improved the power dissipation and, in many cases, the maximum specified delay. As advanced processes provide shorter gate lengths and smaller geometries, new products will feature reduced delay times.

The fastest cycle times are dependent on the architecture. Some designers are now using cycles of 50-55 ns for implementation in early 1989. The architectural flexibility and single-cycle execution of the powerful instruction set is the key to the Am29300 system performance.

#### SUPPORT TOOLS

There are other sources of information that may be useful to you. The most important design tool is the comprehensive Am29300/29C300 data book.

An Am29300 evaluation board is also available for device evaluation. It is a single-board computer that has a host 80188 microprocessor, 4K writable control store and one of each CMOS device in the Am29C300 family. There are RS232 ports for connection to a PC as well as a utility program for downloading microcode into resident EPROM.

With available design models and simulators running system timing and interconnections, your design and debugging time is reduced. Hardware tools and emulators with writable control store and logic analysis allow for interactive assembly. Sophisticated software support with a new friendly meta assembler helps software engineers write compact and efficient microcode in high-level language constructs and user-defined symbolics. All of this support speeds your product to market.

AMD applications and field sales engineers are just a phone call away and will update you on how to make designing an Am29300 system as easy as possible.

#### Am29300/29C300 LITERATURE

Contact your local sales office for copies.

|                           | Order # |

|---------------------------|---------|

| Am29300/29C300 Data Book  | 09372   |

| Am29C300 Family Brochure  | 07171   |

| Am29C325 Product Brochure | 09746   |

| Am29332 User's Manual     | 09287   |

| Am29C327 User's Manual    | 10028   |

| Device                                | Symbol               | Delay Assumed<br>In App Note<br>Value | Current<br>Bipolar<br>Specification | Current<br>CMOS<br>Specification | Expected<br>1Q89 Value |

|---------------------------------------|----------------------|---------------------------------------|-------------------------------------|----------------------------------|------------------------|

| REGISTER FILE Am29334/29C334          |                      |                                       |                                     |                                  |                        |

| Data Output                           | ACCESS               | 24                                    | 24                                  | 20                               | 16                     |

| OE to Output Valid                    | TURN-ON              | 20                                    | 20                                  | 16                               | 13                     |

| OE to Output 3 State                  | TURN-OFF             | 16                                    | 16                                  | 15                               | 13                     |

| Data Set-up                           | t <sub>DS</sub>      | 9                                     | 9                                   | 11                               | 9                      |

| ALU Am29332/29C332                    |                      |                                       |                                     |                                  |                        |

| Data A or B to Y Parity               | DA, DB to PY         | 42                                    | 42                                  | 48                               | 36                     |

| Instruction to Y Parity               | I to PY              | 53                                    | 53                                  | 60                               | 45                     |

| Width to Y Parity                     | W to PY              | 40                                    | 40                                  | 43                               | 34                     |

| Position to Y Parity                  | P to PY              | 48                                    | 48                                  | 51                               | 41                     |

| SEQUENCER Am29331/29C331              |                      |                                       |                                     |                                  |                        |

| Instruction to Y Output               | I to Y               | 25                                    | 25                                  | 17                               | 15                     |

| Instruction to D Output               | I to D               | 31                                    | 31                                  | 19                               | 16                     |

| Force Continue to Y Output            | FC to Y              | 21                                    | 21                                  | 15                               | 14                     |

| Interrupt Request to Interrupt Ack.   | INTR to INTA         | 11                                    | 11                                  | 11                               | 10                     |

| OE <sub>D</sub> to D Valid            | OE <sub>D</sub> to D | 25                                    | 25                                  | 16                               | 14                     |

| PARALLEL MULTIPLIER Am29C323          |                      |                                       |                                     |                                  |                        |

| Unclocked Multiply X or Y to P Parity | t <sub>MUC</sub>     | 150                                   | N/A                                 | 65                               | 60                     |

| Clocked Multiply Cycle Time           | t <sub>MC</sub>      | 125                                   | N/A                                 | 50                               | 45                     |

| Clocked Multiply Data to Clock Set-up | t <sub>sxy</sub>     | 20                                    | N/A                                 | 18                               | 17                     |

| Clocked Multiply Clock to Output      | t <sub>PDPP</sub>    | 40                                    | N/A                                 | 25                               | 22                     |

| FLOATING POINT PROCESSORS Am29        | 325/29C325           |                                       |                                     |                                  |                        |

| Unclocked Multiply                    | t <sub>MUC</sub>     | 125                                   | 105                                 | 125                              | 100                    |

| Clocked Multiply                      | t <sub>MC</sub>      | 100                                   | 70                                  | 97                               | 65                     |

| Data to Clock Set-up Clocked Multiply | t <sub>SD1</sub>     | 13                                    | 9                                   | 16                               | 9                      |

| Data to Clock Set-up                  | t <sub>SD2</sub>     | 104                                   | 80                                  | 118                              | 80                     |

#### WORST-CASE DELAY IN NANOSECONDS, OVER COMMERCIAL OPERATING RANGE

## **Table of Contents**

| SECTION 1 | Overview                                             | 1-1        |

|-----------|------------------------------------------------------|------------|

|           | SYSTEM LAYOUT                                        | 1-2        |

|           | DATA FLOW                                            | 1-2        |

|           | Memory and I/O Sections                              | 1-2        |

|           | Data Section                                         | 1-2        |

|           | Control Section                                      | 1-3        |

| SECTION 2 | Nomenclature                                         | 2-1        |

| SECTION 3 | Data Section Description                             | 3-1        |

|           | REGISTER FILE                                        | 3-1        |

|           | ARITHMETIC LOGIC UNIT                                | 3-1        |

|           | Am29332                                              | 3-1        |

|           | Macro Status Register                                | 3-1        |

|           | FLOATING POINT PROCESSOR                             | 3-4        |

| •         | Am29325                                              | 3-4        |

|           | FPP External Status Register                         | 3-6        |

|           | Seed Look-Up Table                                   | 3-6        |

|           | PARALLEL MULTIPLIER                                  | 3-8        |

| SECTION 4 | Memory and External System Interface                 | 4-1        |

|           | EXTERNAL BUS INTERFACE CONTROL                       | 4-2        |

|           | Host Access Definition                               | 4-2        |

|           | Host Interface Block Diagram                         | 4-3        |

|           | Event Signals<br>Memory Enable                       | 4-4<br>4-5 |

|           | AmPAL22V10 Support Logic                             | 4-5        |

|           | SSR Diagnostics                                      | 4-5        |

|           | Controller Description                               | 4-7        |

|           | MEMORY                                               | 4-10       |

| •         | Memory Components                                    | 4-10       |

|           | Addressing Scheme                                    | 4-10       |

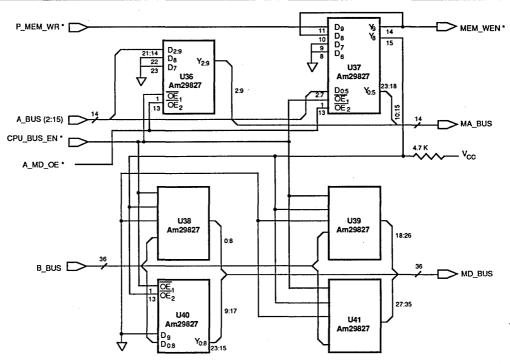

|           | CPU - Memory Buffers                                 | 4-12       |

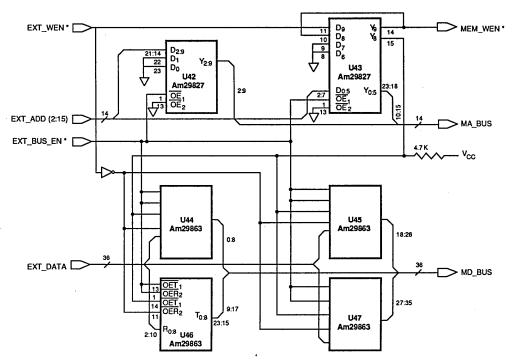

|           | External System Buffers                              | 4-13       |

| SECTION 5 | Control Section Description                          | 5-1        |

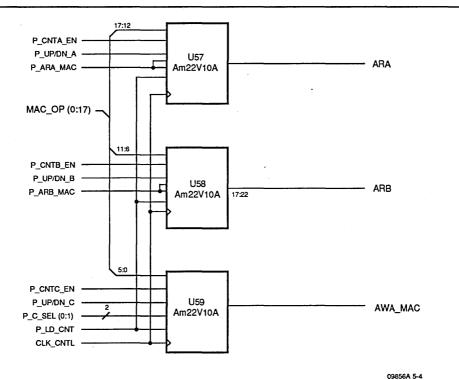

|           | MACRO OPCODE SUPPORT                                 | 5-1        |

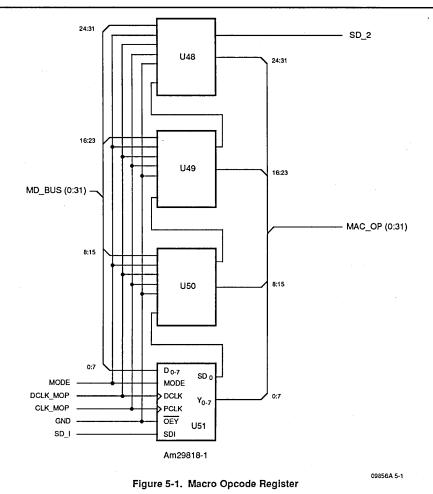

|           | Macro Opcode Register                                | 5-1        |

|           | Macro Opcode Format Restrictions                     | 5-2        |

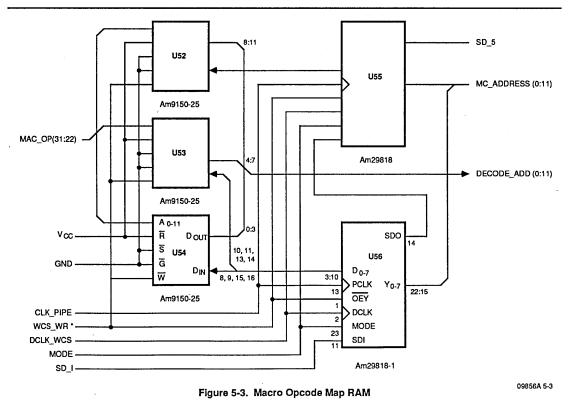

|           | Macro Opcode Decoding Method<br>Macro Opcode Map RAM | 5-3<br>5-3 |

|           | WCS Port                                             | 5-5<br>5-4 |

|           | Macro Operand Address Counters                       | 5-4        |

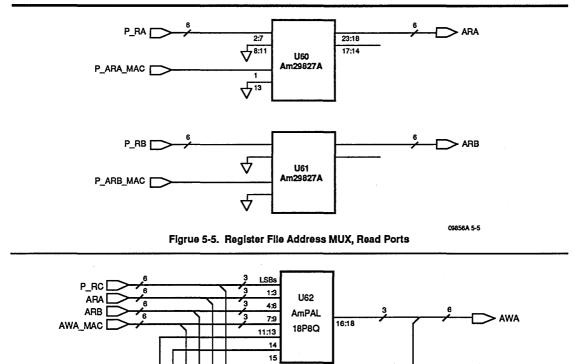

|           | REGISTER FILE ADDRESS MULTIPLEXER                    | 5-6        |

|           | Read Ports A and B                                   | 5-6        |

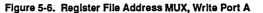

|           | Write Port A                                         | 5-7        |

|           | Write Port B                                         | 5-8        |

.

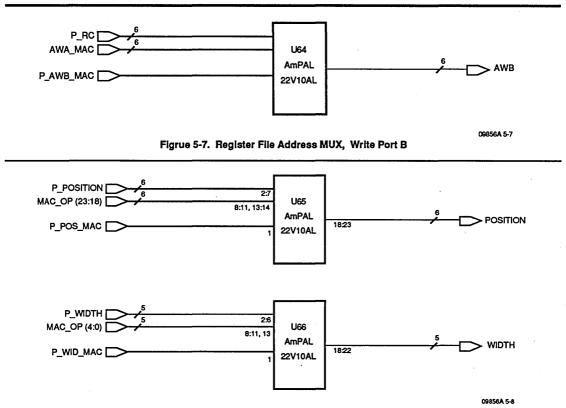

|                  | POSITION AND WIDTH MULTIPLEXERS                                               | 5-8          |

|------------------|-------------------------------------------------------------------------------|--------------|

|                  | SEQUENCER                                                                     | 5-9          |

|                  | D BUS TRANSCEIVER                                                             | 5-12         |

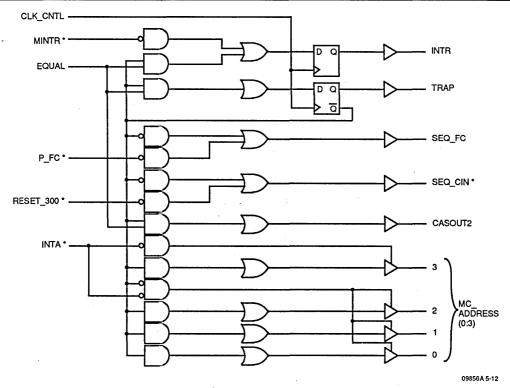

|                  | INTERRUPT CONTROL                                                             | 5-12         |

|                  |                                                                               | 5-12         |

|                  | Interrupt and Trap Philosophy<br>Interrupt Operation                          | 5-12         |

|                  | Trap Operation                                                                | 5-15         |

|                  |                                                                               | 0.0          |

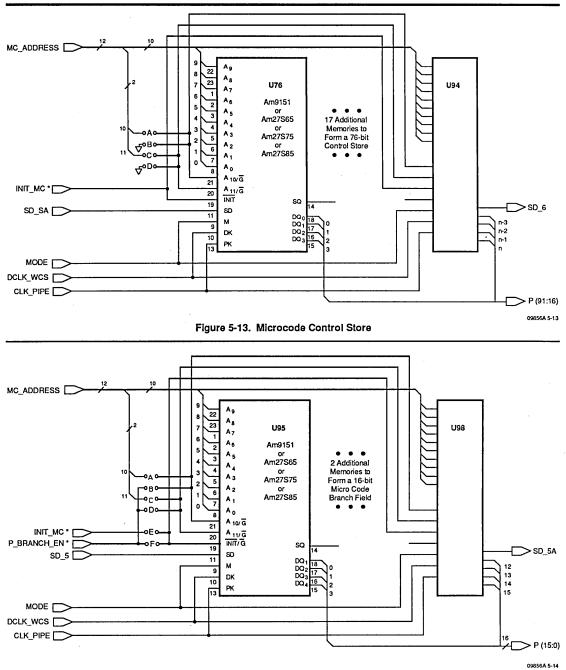

|                  | MICROCODE CONTROL STORE AND CONTROL PIPELINE<br>REGISTER                      | 5-16         |

|                  | Control Store Function                                                        | 5-16         |

| ŕ                | Pipeline Register Function                                                    | 5-16         |

|                  | Control Store Implementation                                                  | 5-16         |

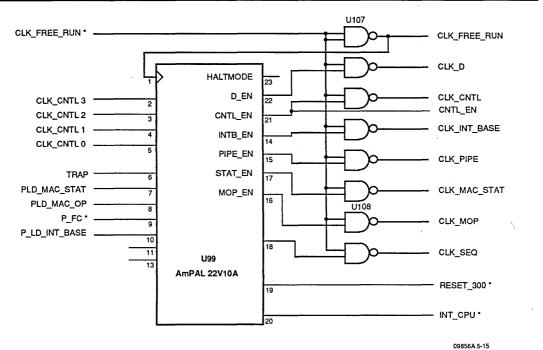

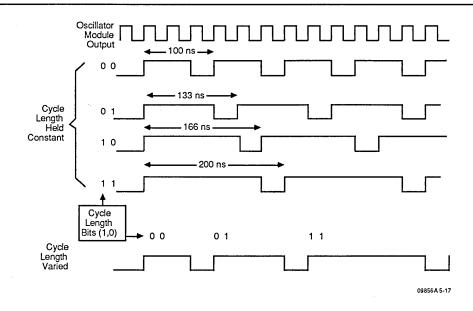

|                  | CLOCK CONTROL                                                                 | 5-18         |

|                  | Clock Qualification Circuit                                                   | 5-18         |

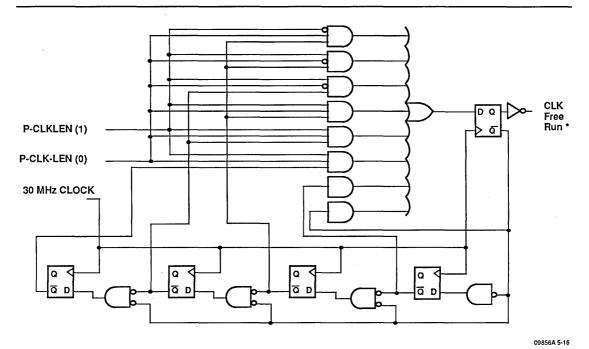

|                  | Clock Generator                                                               | 5-20         |

|                  |                                                                               |              |

|                  | MICROCODE WORD                                                                | 5-22         |

|                  | Control Philosophy                                                            | 5-22         |

|                  | Microcode Word Field Descriptions                                             | 5-22<br>5-28 |

|                  | Alternate Arrangements                                                        |              |

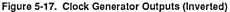

|                  | CONTROL DECODE                                                                | 5-30         |

|                  | What Is It Good For?                                                          | 5-30         |

|                  | Control Logic Description                                                     | 5-30         |

| <b>SECTION 6</b> | System Timing and Critical Path Analysis                                      | 6-1          |

|                  | DEFINITIONS                                                                   | 6-1          |

|                  | CONTROL AND DATA PATHS                                                        | 6-1          |

|                  | WORST CASE PATHS                                                              | 6-2          |

|                  | Case Definitions                                                              | 6-2          |

|                  | FINAL RESULTS                                                                 | 6-4          |

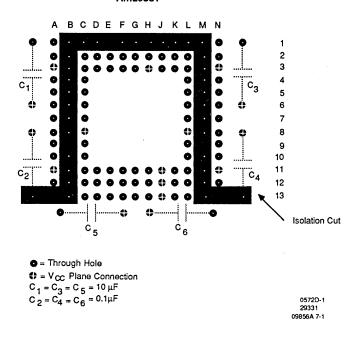

| SECTION 7        | Physical Issues                                                               | 7-1          |

|                  | ELECTRICAL LAYOUT ISSUES FOR POWER SUPPLY                                     | 7-1          |

|                  | DECOUPLING CAPACITORS                                                         | 7-1          |

|                  | SOCKETS                                                                       | 7-1          |

| SECTION 8        | Conclusion                                                                    | 8-1          |

| SECTION          | Conclusion                                                                    | 0-1          |

| APPENDIX A       | Related Reference Material                                                    | A-1          |

| В                | Signal to Figure Cross Reference                                              | B-1          |

| C                | FPP Status PAL Definition                                                     | C-1          |

| D                | Host Interface Glue PAL Definition                                            | D-1          |

| E<br>F           | Host Interface Am29PL141 Definition                                           | E-1          |

| г<br>G           | Memory Address Counter PAL Definition<br>Macro Operand Counter PAL Definition | F-1<br>G-1   |

| н                | Write Port A Multiplexer PAL Definition                                       | H-1          |

| 1                | Write Port B Multiplexer PAL Definition                                       | I-1          |

| J                | Trap Logic PAL Definition                                                     | J-1          |

| к                | Clock Qualification PAL Definition                                            | K-1          |

| L                | Clock Generator PAL Definition                                                | L-1          |

| М                | Control Decode PALs Definitions                                               | M-1          |

| N                | Components List                                                               | N-1          |

| 0                | Goals                                                                         | 0-1          |

|                  | Disclaimer                                                                    | 0-1          |

v

# SECTION 1 Overview

This application note describes the design of a high performance microprogrammed 32-bit processor using the Am29300 family of 32-bit building blocks.

Basic design philosophy for a microprogrammed processor is discussed as the design choices made for this system are explained. Issues of microprogram sequence control, interrupt handling, microprogram memory options, microword layout, macroprogramming, high speed multiply, and clock control are covered.

Support circuitry used with the Am29300 family components is also covered in detail. This circuitry includes: Writable Control Store, Serial Shadow Register diagnostics, and Programable Array Logic.

The use of the following Advanced Micro Devices components is illustrated in extensively documented examples:

| Am29331            | - 16-bit Address Sequencer,                                                 |

|--------------------|-----------------------------------------------------------------------------|

| Am29332            | - 32-bit Arithmetic Logic Unit,                                             |

| Am29334            | - 64 x 18-bit Four Port Register File,                                      |

| Am29C323           | <ul> <li>- 32-bit Parallel (Integer) Multiplier<br/>Accumulator,</li> </ul> |

| Am29325            | - 32-bit Floating Point Unit,                                               |

| Am29114            | - Interrupt Controller,                                                     |

| Am29800            | <ul> <li>Family of Interface and Diagnostics<br/>Logic Devices,</li> </ul>  |

| Am29PL141          | - Fuse Programmable State Machine,                                          |

| AmPAL18P8          | - Programmable Output 20-pin Combi-<br>natorial PAL,                        |

| AmPAL22V10         | - Output Macrocell 24-pin PAL,                                              |

| Am9151<br>Am99C165 | - Registered RAM with SSR™,<br>-16K x 4-bit CMOS high speed<br>RAM.         |

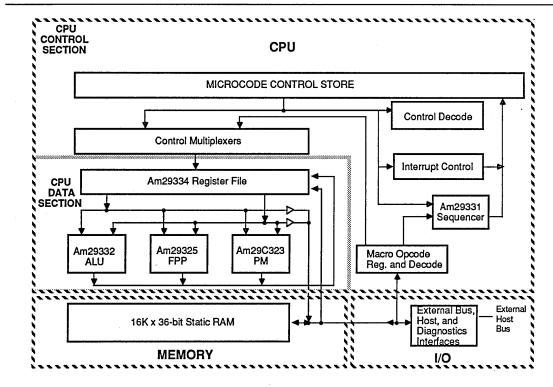

Figure 1-1. System Components

09856A 1-1

#### SYSTEM LAYOUT

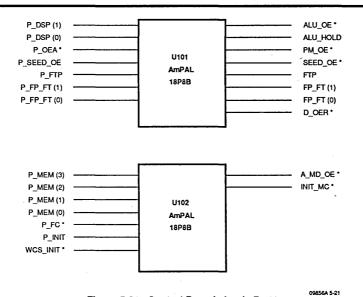

As with all processors, this system contains three main portions: Central Processing Unit (CPU), memory, and input/output (I/O) (see Figure 1-1).

The CPU consists of a control section and a data section:

The data section manipulates data via operations such as addition, subtraction, shifting, merging, multiplication, and division. These functions are implemented with the Am29332 Arithmetic Logic Unit (ALU), Am29325 Floating Point Processor (FPP), and Am29C323 Parallel Multiplier (PM). The data section also stores operands and intermediate results in Am29334 register files.

The control section directs the operations performed by the data section and determines the order in which the operations are performed. This section contains the Am29331 Microprogram Sequencer, macro opcode register & decode, interrupt control logic, microcode control store, control decoding logic, and control multiplexers for the register file and ALU.

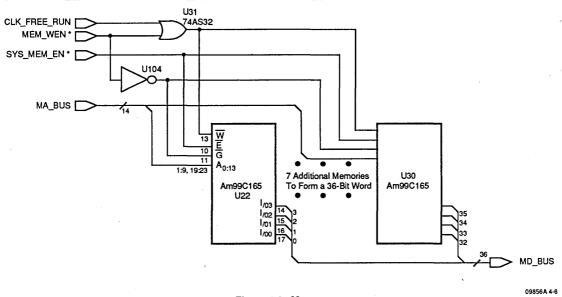

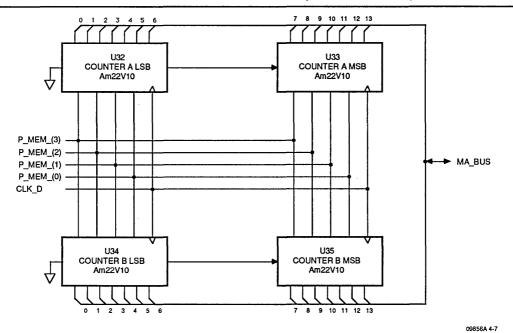

The memory contains a 16K word by 36-bit static RAM. Included as part of the memory block are two address registers/counters, which may be used to speed up sequential reads and writes made by the CPU.

The I/O portion is a simple connection to a host system's address and data bus. It is assumed that the Am29300 demonstration system operates as a peripheral processor to a larger host system, as might be the case with an array or digital signal co-processor. Information to be processed by the demonstration system is loaded into the memory portion via Direct Memory Access (DMA). When processing of the data is complete, the host system unloads the memory portion via DMA.

A diagnostics port is also provided as part of the I/O section. This port allows control over the demonstration system clock for single stepping, and it allows for serial diagnostics to display and control the state of the system.

Throughout the remainder of this application note, it is assumed that the reader has some previous experience with microprogrammed processor design and is familiar with the Am29300 family data sheets. For those readers not familiar with microprogrammed design, some reference material is listed in Appendix A.

#### DATA FLOW

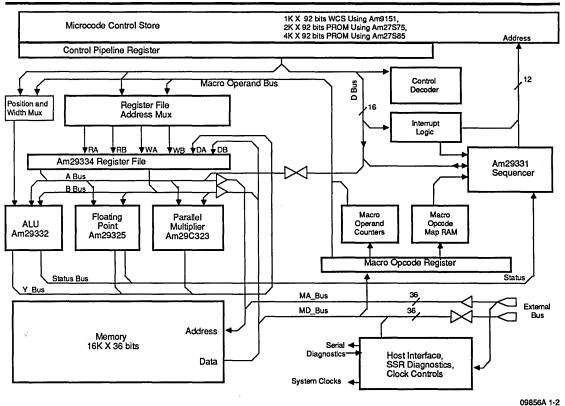

The system data paths are illustrated in the block diagram of Figure 1-2.

#### Memory and I/O Sections

Information processed by the Am29300 system is exchanged between the host system and the memory via the external bus interface. The information may be both data and macroinstructions.

From the external bus, the host system is able to address the memory via the bus driver connected to the memory address bus. Data is moved over the memory data bus. The host system's only access to the Am29300 system is via these buses to the memory. Therefore, all data to the system flows through the memory via DMA accesses by the host system.

Diagnostic control and information flows through the external bus interface via the host interface controller. It controls the clocking and single stepping of the system while loading and reading serial diagnostics via Serial Shadow Registers (SSR) that are placed in key locations throughout the system.

(SSR is a trademark of Advanced Micro Devices, Inc.)

#### **Data Section**

Data must be moved from the memory to the register file to be available to the ALU and multipliers for processing.

The register file has four access ports, two ports for writing data into the file and two ports for reading data out to the ALU and multipliers. This arrangement allows two operands to be read from the file in the same cycle as two operands are being written. The two read operands are used either as A and B operands for the ALU, FPP, or PM, or as address and data inputs to the memory.

To move data from the memory to the register file, an address to the memory is selected from the register file on the A read port. This address selects a word from the memory that is transferred on the memory data bus to the B write port of the register file.

Once data is loaded into the register file, it can then be selected for use on either the A or B read ports for input to the ALU, FPP, or PM.

Data processing results from the ALU, FPP, or PM are then placed on the Y bus for return to the register file A write port.

Finally, processed data is moved back to the memory via the B read port of the register file, while the location to be written in the memory is addressed by the value on the A read port of the register file.

#### SECTION 1 Overview

Figure 1-2. Am29300 Demonstration System

(NOTE: The advantage of using both write ports on the register file is that it is possible to perform calculations and write the results via the A write port at the same time that new data is being moved into the register file from the memory via the B write port. This will be illustrated in more detail later in this document.)

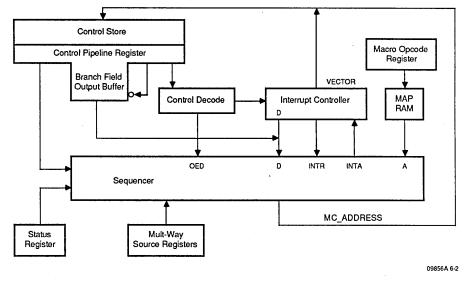

#### **Control Section**

#### D Bus

The D bus is a highway for information flow between the microcode control store, interrupt control sequencer, and data section of the CPU.

Branch addresses or constants from the microcode can pass to the sequencer via the D bus. The interrupt controller's interrupt vector base address register may also be loaded via the D bus.

Constants from the microcode can pass to the data section for use in calculations via the D bus to A bus transceiver. Microcode constants can also be used as

addresses to the memory, via a D bus to A bus to memory address bus connection.

Variable data can be passed from the register file to the sequencer. The sequencer can also return data to the register file, via the A bus to ALU Y bus to A write port path. The D bus path to the sequencer is valuable for storing and retrieving the state information in the sequencer when interrupts, traps, or context switches occur.

#### **Control Decode**

This section of logic expands encoded microcode fields into individual control lines used throughout the system.

#### Interrupt Logic

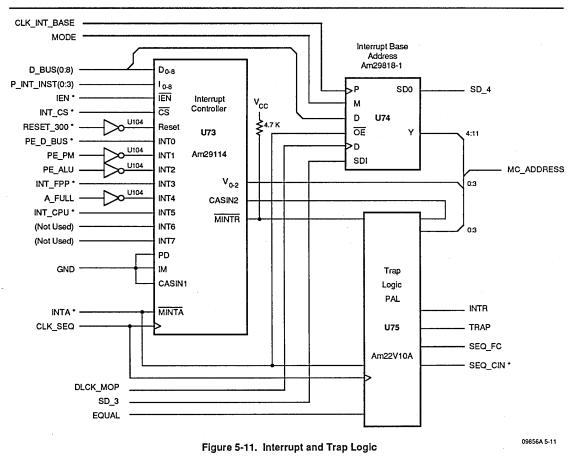

This circuit monitors interrupt and trap conditions such as parity errors and breakpoints. When an interrupt condition is detected, an interrupt request to the sequencer is made and an interrupt address vector generated.

#### Sequencer

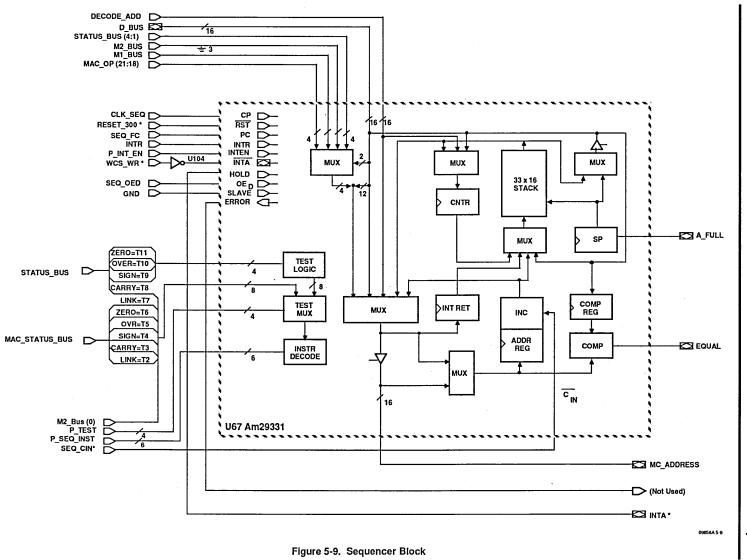

The sequencer is an address multiplexer with an on-chip address incrementer and stack. It selects the address for each microinstruction word read from the control store. The address selected depends on the instruction to the sequencer and on the state of test conditions. The sequencer can select addresses from the branch field of the control pipeline register, the macro opcode map, the internal stack, the increment of the last microinstruction address, or one of four status condition driven multi-way branch inputs.

#### Macro Opcode Support

Macro vs. Micro Programs: A microprogram is the definition for the state of the primary system control signals during each system clock cycle. Each word of microcode usually has a large number of bits so that many parallel operations may be controlled simultaneously. Each microcode word must deal with the intricate details of system operation. The writing of microcode is a slow tedious process that must take into account every facet of system operation in order to provide the most efficient use of system resources.

The advantage of microcode is that, very often, different system operations can be overlapped (done in parallel) since there is parallel control over all the system resources.

A "macroprogram" is a series of microcode subroutine calls. Each macroinstruction has an opcode field that is simply a value that can be translated into the starting address of a microcode subroutine within the system microprogram. The macroinstruction may include parameters that are passed to the microprogram. These parameters might be register addresses, loop counter values, immediate data, or memory addresses.

The advantage of a macroprogram is that the instructions are very simple and require relatively few bits to define as compared to a microcode word. The macroinstructions are simpler because all the details of system operation are specified by the underlying microcode instructions. The simpler instructions allow macroprograms to be written much more quickly than microprograms. Therefore, once a set of microcode subroutines are developed to perform the most often needed system operations, a wide variety of macroprogram applications can be quickly written. Macroinstructions remove the system programmer's concern over every detail of system operation.

The disadvantage of a macroprogram is that each instruction must be fetched from memory and decoded (translated to a microcode subroutine address) before each microcode subroutine is executed. When each subroutine execution is long compared to the overhead of fetching and decoding the macroinstruction, the macroprogram will run nearly as fast as an equivalent microprogram with the advantage being a much easier programming task. When the microcode subroutines are short compared to the macroinstruction overhead, the system speed can drop significantly.

So, if macroprogramming concepts are used carefully, a macroprogrammed approach to system design can yield a significant improvement in the ease of system use without a large decline in system performance.

For that reason, the Am29300 demonstration system includes the features described below, which allow a macroprogrammed approach. These features are intended to show how basic macroprogramming can be implemented.

Macro Opcode Register: When macro-instructions are executed, the instructions are addressed in the memory via the A read port of the register file in the same way as described earlier for data. The selected instruction is read from the memory via the memory data bus and written into the macro opcode register. The instruction can also be written into the register file via the B write port in the same cycle (which may be useful for instructions that contain immediate operands that would be used by the data section).

Macro Opcode Map RAM: The macro opcode map RAM is made of three Am9150 high speed SRAMs. The opcode portion of the macro opcode register addresses a microcode entry point table in the map RAM. This entry point is then used by the Am29331 sequencer as a branch address to the microcode routine that performs the function required by the macroinstruction.

Macro Operands: The operand portion of the macro opcode register is loaded into the macro operand counters. The macroinstruction operands allow the direct specification of register file addresses, ALU shift values, or ALU field masks to be used by the microcode routines.

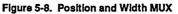

**Register File Address, Position, and Width Multiplexers:** Register file addresses are passed to the register file via the register file address multiplexer. Position and width information for shift values and field masks are passed to the ALU via the position and width multiplexers. These multiplexers allow either the microcode or the macroinstructions to control the register file and ALU.

# SECTION 2 Nomenclature

Throughout the remaining figures in this application note, some naming and drawing conventions are used as noted below.

All signal names are written as single word identifiers with underlines used to provide visual space between sections of a multi-word identifier.

Signals that are active low have names that end with an asterisk. In some of this document's programmable logic definition files, this convention is not allowed. In those situations, the active low signal names will begin with an exclamation point or end with an underline character.

Clock and qualified clock signals have names that begin with  $\mbox{CLK}\_.$

Groups of signals that form buses are shown as single lines with an associated number that indicates how many lines are involved. Bus lines are drawn with 45 degree turns and intersections instead of the usual right angle turns and intersections used with individual signal lines, in order to highlight buses visually. Major data highways such as the A BUS, B BUS, and Y BUS have signal names that end in BUS. The lines of a bus are numbered from least significant to most significant with the least significant identified as line zero (0). Where a subset of the lines in a bus is shown, the bus signal name will be followed by parentheses containing numbers that show the range of lines in use. The numbers of a continuous range are separated by a colon (:), non-contiguously numbered lines are separated by a comma (,). Where lines of a bus are split out to show the specific connection of bus lines in a circuit, a small number that indicates the line number within the bus will be shown near each line that is split off.

Four major buses in the system share a common structure. The A\_BUS, B\_BUS, Y\_BUS, and MD\_BUS all have the same layout. Each bus carries a 36-bit data word, which is arranged as four 8-bit bytes, each byte having its own parity bit. Byte zero (least significant) is located in bits 0:7; bit 32 is the parity bit for byte zero. Byte one is in bits 8:15 with its parity in bit 33. Byte two is in bits 16:23 with parity in bit 34. Byte three is in bits 24:31 with parity in bit 35.

Signals that come directly from the microcode memory pipeline register have signal names that begin with "P\_".

Ground symbols (zero volt points) are drawn as downward pointing triangles, or the signal name GND is used.

Points tied to +5 volts are labeled with the signal name  $V_{CC}$ .

Components are shown with pin numbers immediately outside the rectangle that defines the component. Component-specific signal names related to component pins may be shown immediately inside the component rectangle. Where there are several components shown on a page with very similar connections, only one of the components will have pin numbers and signal names shown. The remaining components on the page are wired in the same manner.

Each component is assigned and labeled with a "U number" that uniquely identifies the component. This helps identify specific components for discussion and separates identical type devices in the system component list.

Because this demonstration system is complex by nature, it must be illustrated with many figures, each focusing on a different portion of the overall system. In order to show the signal interconnections between all parts of the system, each signal that leaves or enters a figure is given a name. Often the names are abbreviations in order to save space in the figures. Each name shows a relationship to the signal's use. Wherever the same signal name appears in different figures, a connection between the figures is defined. To help in identifying all the figures to which a signal travels, there is a signal-to-figure cross reference listing in Appendix B.

-

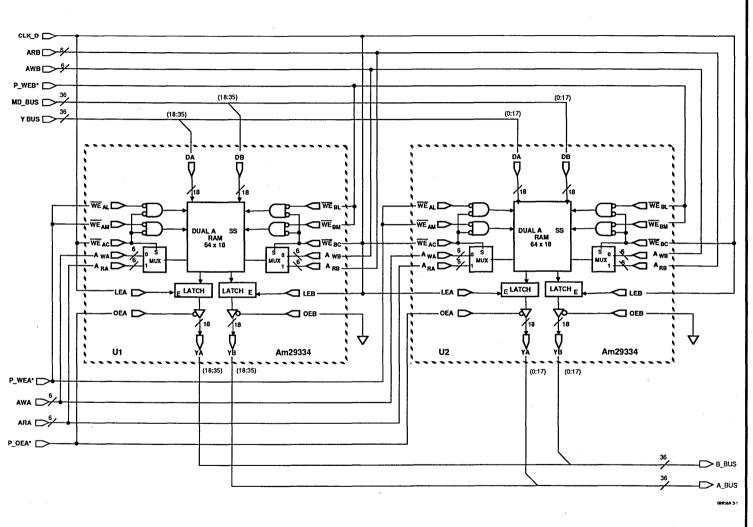

#### **REGISTER FILE**

Two Am29334 register files are used in tandem to provide a 64-register by 36-bit wide file. This allows the storage of 32-bit data plus parity (1 parity bit/byte). Each Am29334 contains 64 registers that are 18 bits wide; see Figure 3-1.

An Am29334 register file can both read and write data in the same cycle, but it does not perform the read and write simultaneously. The read must be performed during part of the system cycle and the write during another part of the cycle. Since read data is needed by the ALU and multipliers as early in the cycle as possible and, since data values to be written are only available later in the cycle, the reading of data is done in the first half of the cycle and the writing done in the second half of the cycle. A convenient way to separate the two parts of the cycle is to use the system clock signal to control the internal address mux and write enable.

As connected in Figure 3-1, the read port latch enables (LEA and LEB) and write port common enables (WEAC\* and WEBC\*) are tied to the data section clock line (CLK\_D). This causes read data to be accessed while CLK\_D is high and read data to be latched when CLK\_D is low. Data is written when CLK\_D is low if the port write enables are active (WEAL\* and WEAH\*, or WEBL\* and WEBH\*). The high and low byte write enables for each port are tied together since only full 36-bit word writes will be done in this system.

The various read and write addresses are provided from the register file address multiplexers, which will be covered later.

The output enable (P\_OEA\*) and write enables (P\_WEA\* and P\_WEB\*) come directly from the microc-ode pipeline register.

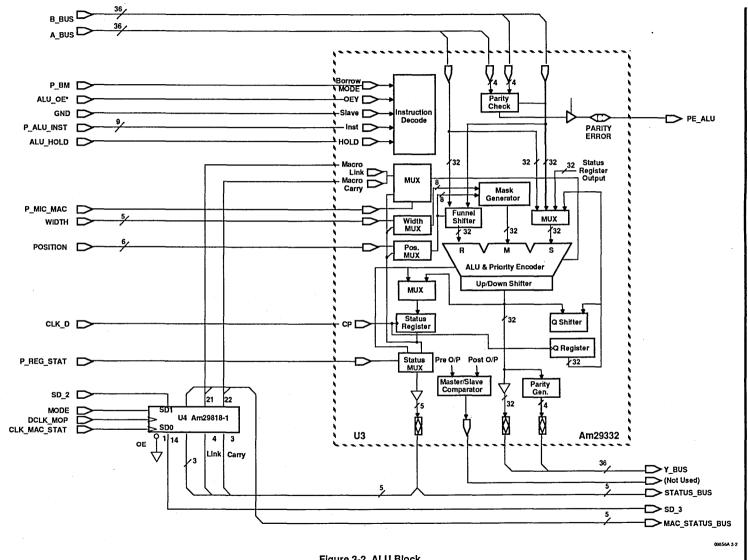

#### **ARITHMETIC LOGIC UNIT**

#### Am29332

The Am29332 provides a 64-bit funnel (barrel) shifter, 32-bit mask generator, and 32-bit ALU. The ALU can perform binary and BCD add or subtract, multi-cycle multiply or divide, and logical operations. This single, highly-integrated chip provides the complete function of the ALU block in this system. The only added component is an external register used to maintain status bits for the macroprogram separate from status information used by the micro program. The ALU is shown in Figure 3-2. Most of the control lines come directly from the microcode control pipeline register.

The ALU output enable (ALU\_OE\*) is decoded from the control pipeline register.

The POSITION and WIDTH signals come from the position and width multiplexers. These multiplexers select the position and width values from either the microcode pipeline or the macroinstruction in the macro opcode register.

The slave mode input is tied to ground since there will be no use of the slave mode comparisons in this system.

The HOLD input is used as an enable control over the clocking of the internal micro status register and Q register during times the ALU is not in use. Because the ALU, FPP, and PM share the same data source and destination buses (A\_BUS, B\_BUS, and Y\_BUS), they generally cannot be used simultaneously due to bus contention. In recognition of this, the control fields for the ALU, FPP, and PM have been overlapped in the microcode to minimize the required width of each microcode word. This means that at certain times the control lines to the ALU will be meaningless to the ALU because the values on the lines are determined by the needs of the FPP or PM. Therefore, unless the hold input is used to prevent clocking of the status and Q register duing these times, the ALU status could be lost whenever the FPP or  $\gamma$ PM are in use.

Note, however, that the hold input is not used as the general means to prevent clocking of the ALU registers when the whole system is halted (e.g., during single step mode). The data clock (CLK\_D) that is distributed throughout the data section of the CPU is a qualified clock and will be used to control the state change of all registers in the data section, including those in the ALU at times when the whole system is halted.

#### **Macro Status Register**

There are two levels of status information that the programmer of a microprogrammed system must track if that system executes macroinstructions. These are referred to as the micro and macro status. The micro status of the system is updated at the end of each microcode step and is part of the system state. The macro status is part of the macroprogram state as reflected at the end of each macro step. Since many microinstructions may be executed to perform the function defined by a given macroinstruction, the macro status reflects the machine state

Figure 3-1 Register File

3-2

Figure 3-2 ALU Block

မ-အ

from the macroprogram viewpoint. The macro status may be carried across many microinstruction cycles without change. This requires a separate register to contain the macro status independent of the micro status. The Am29332 does not have an internal macro status register so one must be provided externally. The loading of the macro status register and the use of the macro status information by the microprogram must be controlled by microcode. The Am29332 does provide an onboard multiplexer to select between the micro and macro status inputs. Only the carry and link values are used directly by the Am29332 since these are the only status values normally used to modify data values. The macro stat us for the zero, sign, and overflow flags can be used by the sequencer as test conditions for branch instructions.

The register used for holding macro status is an Am29818-1. The register is loaded (clocked) by a qualified clock called CLK\_MAC\_STAT. This clock is qualified by the load macro status bit in the control pipeline register. The Am29818-1 is also used to provide a diagnostic ability to read and load the macro status register through the use of an internal serial shadow register (SSR).

#### FLOATING POINT PROCESSOR

#### Am29325

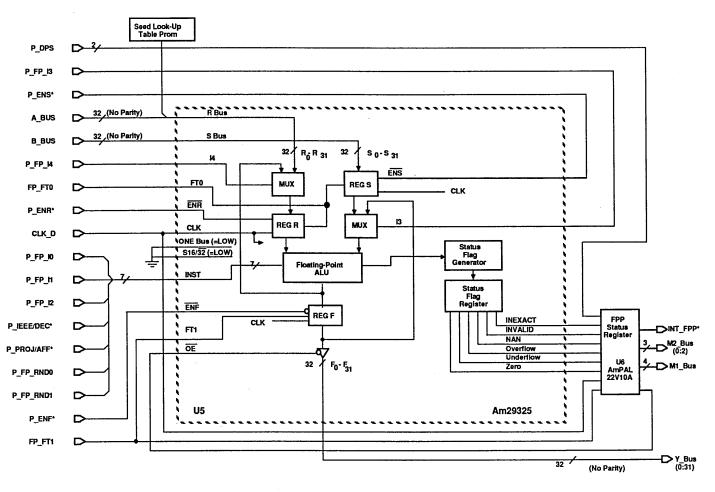

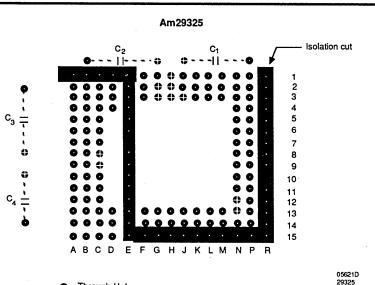

The Am29325 Floating Point Processor (FPP) performs 32-bit floating point multiplication, addition, or subtraction in a single cycle. Floating point division can be done in seven cycles using the Newton-Raphson method. The FPP is shown in Figure 3-3.

All the control lines for the FPP are driven directly by the microcode pipeline register with the exception of the FPP output enable and the register flow-through enables. Those signals are decoded from the data path select field of the microcode pipeline register. The output enable decode is done by the AmPAL22V10 in Figure 3-3. The register flow through enable decode is done by the control decode logic which is described later.

It should be noted that the Am29325 is not a full fledged member of the Am29300 family. It is different from the other Am29300 members with regard to three key characteristics: it is slower, does no data bus parity checking or generation, and has no slave mode capability.

The Am29325 flow through calculation time is 100 to 125 ns rather than the 42 or 70 ns for the ALU or PM (the current PM is at 120 ns, but the fastest version will be at 70 ns). This requires that whenever the FPP is used, the system clock cycle must be extended to allow for the slower propagation time. This extended clock timing is covered later in more detail.

The lack of parity checking is not much of a problem for the rest of the system since it only affects the data integrity of information going through the FPP. The lack of parity generation isn't a problem as long as only the FPP is working on the data. The problem starts when floating point data is moved back to memory or is converted to integer values for use by the ALU.

If data from the FPP is read by the ALU or PM, parity errors will be detected and a system interrupt may result. That problem can be avoided if the system has kept track of which data resulted from FPP calculations and if the parity errors are ignored when that data is read. But if FPP data results are moved directly to the memory and then on to the host system, the parity errors will eventually be found.

So some means of adding parity generation to the FPP should be provided. One way is to add four 8-bit parity generator chips to the FPP output bus. This consumes power and boardspace while providing a benefit only when FPP data is moved directly through the register file to the memory. A better way is to use the parity generators already available in the Am29332 by requiring that FPP data be passed through the ALU before being moved to the memory. Even though the data may not be modified by the ALU, correct parity will be generated on the ALU output.

With the use of a little trick, there is a way to provide parity checking on the FPP data inputs. To do this, one of the data path select codes is used to control the output enables of both the ALU and FPP. This code (P DSP = 11) causes the FPP outputs to be disabled and the ALU outputs enabled, even though the data path selected is the FPP. By turning on the ALU outputs, the ALU parity error output will also be enabled and any parity error on the A BUS or B BUS will be reported. At the same time, the control microcode for the FPP is still valid and may be used to load registers with the data present on the A BUS and B BUS. Of course the register file should not be loaded from the Y BUS in the cycle where this scheme is used because the ALU is driving nonsense information onto the Y\_BUS. Enabling the ALU outputs is only a trick used to make the ALU parity checker results available for this scheme. Note that the ALU hold input remains active even though the ALU output enable is active. This prevents any state change in the ALU when the FPP is the data path actually in use.

Finally, the issue of no slave error checking is unimportant, since the slave mode is not used in this system.

Figure 3-3 Floating Point Block

09856A 3-3

SECTION 3 Data Section Description

ა 5

#### **FPP External Status Register**

#### Status Pipeline Issue

The FPP status flags appear at the status outputs along with data at the Y outputs. If the FPP "F" register is made transparent, the status flag register is also transparent. If the F register is clocked, so is the status register. In this demonstration system this presents a problem.

Normally, status conditions from the data section are registered before being used by the control section. This maintains the pipelined, parallel operation of the control and data sections. The control section bases its testing on registered status from the last data section cycle rather than being forced to wait for status results of the current execution cycle before determining the next microinstruction to execute.

To provide the same system for the FPP requires an external status register for cycles in which the F register is transparent to allow results to pass directly to the register file. In that situation the status flags are not registered by the FPP and thus, without an external register, there is no place to pipeline the status for the control section.

#### Multiple Status Flag Test Issue

Several of the FPP status flags signal events of equal importance such that it would be a convenience to be able to test multiple flags in a single cycle rather than basing branches on only one flag at a time.

A simple way to test multiple conditions at one time is to execute a multi-way branch based on the bits being tested. In the case of the FPP there are six flags, too many for a single multi-way branch which can be based on only four bits. A solution is to OR some of the flags together as one of the multi-way branch bits and use the remaining bits directly as part of the multi-way branch address. In that way, one multi-way branch can test all six flags.

When testing the status, if no flags are active, no abnormal condition exists, and the zero value destination of the multi-way branch continues. If one or more of the direct flags is active, the multi-way branch goes straight to a routine to handle the problem. If one of the ORed flags is active, the multi-way branch destination instruction can either ignore the flags or take a second multi-way branch that is based on direct inputs of the flags that were ORed in the first multi-way branch (an advantage of having more than one source for multi-way branch conditions). The second multi-way branch determines which of the ORed flags was active in the first multi-way branch.

#### FPP Status Register Implementation

An AmPAL22V10 Programmable Array Logic device is used to register the FPP status flags and perform the OR of some of the flags.

This external status register loads new status only as the result of cycles in which the FPP is the selected data path during an instruction execution. When the FPP "F" register is in transparent mode, the external status register is loaded with the flags at the end of an FPP cycle. This results in a one level deep pipeline on status in the same way that ALU status is pipelined one level internal to the ALU. When the F register is in clocked mode, the external status register will load in the cycle following an FPP cycle. This will capture the data that is loaded into the FPP on chip status register at the end of the FPP cycle. This causes the status to be double pipelined for cycles in which the F register is clocked.

The multi-way branch outputs for the first level branch are the following flags: Overflow, Underflow, Invalid, and the OR of the Inexact, OR, NAN, and Zero flags. The multiway branch outputs for the second level branch are: Inexact, NAN, Zero, and Ground.

These groups of four bits are substituted for the least significant four bits of a branch address to act as a multi-way branch.

In addition to the multi-way branch test for flags, an added output of the status PAL ORs together the Overflow, Underflow, and Invalid flags for use as an interrupt signal to the system interrupt controller, thus giving one additional way to monitor the FPP error flags. Using the interrupt approach eliminates the need to follow floating point operations with multi-way branches in order to test for error conditions. Execution of instructions can proceed, assuming no major problems exist in an FPP cycle. If one of the above mentioned error flags is active, the resulting interrupt will deal with the error.

One last element of the status PAL is that it acts as part of the system control decode by decoding the data path select bits of the control pipeline to enable the FPP output when the FPP is the selected data path.

The logic definition file for the status PAL is listed in Appendix C.

#### Seed Look-Up Table

The Newton-Raphson division algorithm does a division of A by B by finding the inverse of B (i.e., 1/B) and performing a multiply against A. This scheme works with the Am29325 since finding the inverse of B requires only

a series of multiplies and subtracts which the Am29325 can do in single cycles. But, these multiplies and subtracts are performed only to refine the accuracy of a precalculated seed value (a rough approximation of the inverse of B). So a table of seed values must be available to support division with the Am29325.

This seed table is stored in PROM memory external to the FPP. The B variable is used to address the seed table, and the resulting seed value is fed into the FPP to be refined.

Placing the seed table in the path to one of the FPP inputs normally requires a 32-bit multiplexer to select between the PROM and the direct input bus for loading normal operands in multiply, add, and subtract operations. Building this multiplexer would require at least six hex-2-to-1 multiplexer chips. The PROM and multiplexer would also increase the propagation time needed to load the FPP, thereby requiring the cycle timing to be extended even more than is already required by the FPP.

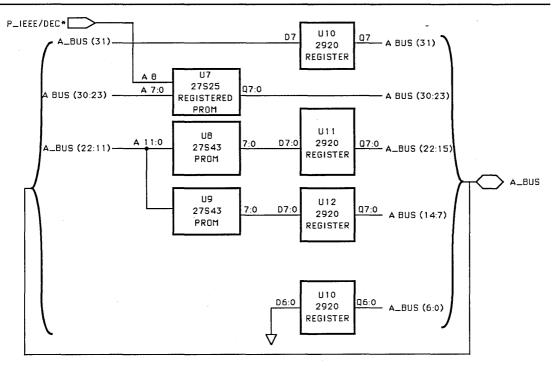

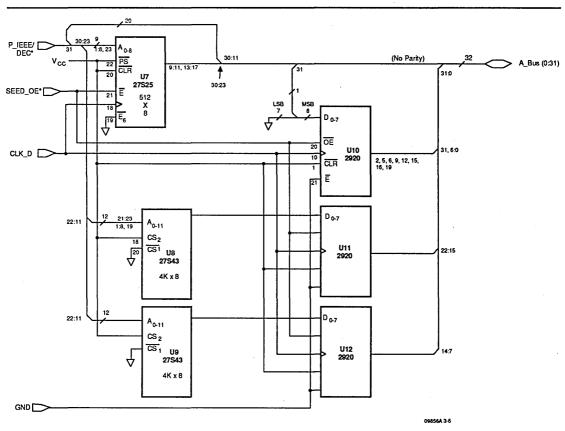

The implementation of the seed table in this system has been modified to save chips and cycle length. Instead of placing the seed table between the A BUS and the FPP, it is placed to the side as an appendage of the A BUS (see Figure 3-3). The inputs and outputs of the table are tied together and to the A BUS. The internal structure of the table is shown in Figure 3-4. It contains three PROMs, each of which is followed by a three-state output register (the Am27S25 has an internal register). In this arrangement the PROMs can be accessed by the value present on the A BUS in one cycle and the resulting seed loaded into the registers. In the following cycle the registers can drive the A BUS with the seed value. This scheme requires three fewer chips and no extension to the FPP cycle time. It is true that two cycles are now required to load the seed value but the cycle used to access the seed table can be combined with the operation of checking for a zero divisor. This operation is generally done during the setup for a divide.

09856A 3-4

#### Figure 3-4. Floating Point Block Seed Look-Up Table -- Data Flow Diagram

The detailed connections of the seed table are shown in Figure 3-5. The Am27S25 contains the seed values for the exponent and the two Am27S43s contain the seed for the fraction. The seed table output enable (SEED\_OE\*) signal is a decoded output of the microcode control pipeline register. The output register of the seed look-up table is clocked by the data section clock.

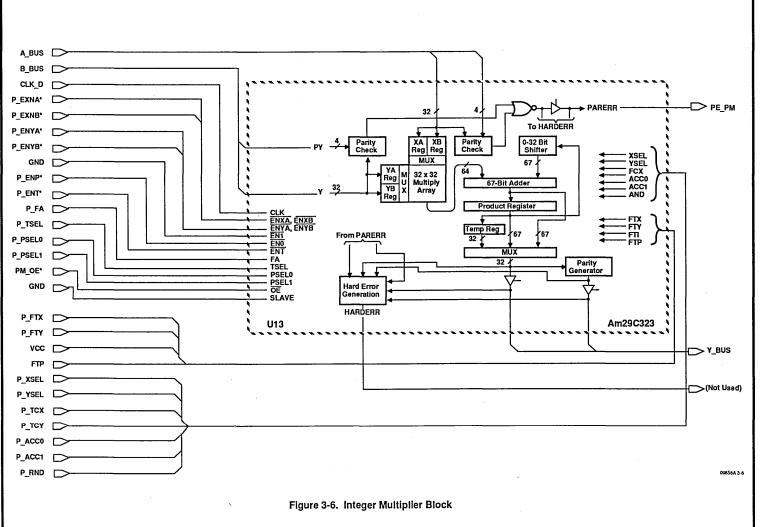

#### PARALLEL MULTIPLIER

The entire Parallel Multiplier (PM) block's function is provided by the single chip Am29C323 Parallel Multiplier. This chip performs 32-bit, 64-bit, 96-bit, and 128-bit integer multiplies. It also can perform multiply accumulate using an internal 67-bit accumulator. The PM is shown in Figure 3-6. Most of the control signals come directly from the control pipeline register. The Parallel Multiplier output enable (PM\_OE\*) is decoded from the data path select field of the microcode pipeline register. The enable and flow through controls for the instruction register (ENI\* and FTI) are tied respectively to GND and VCC to allow instructions to flow directly from the microcode pipeline register to the multiplier, since the microcode pipeline register already provides the one level of pipeline required in the system. The flow through enable on the product register is enabled only when the PM data path is selected via the control decode logic.

Figure 3-5. Floating Point Block Seed Look-Up Table -- Implementation

з-9

SECTION 3 Data Section Description · · · · ·

# Memory and External System Interface

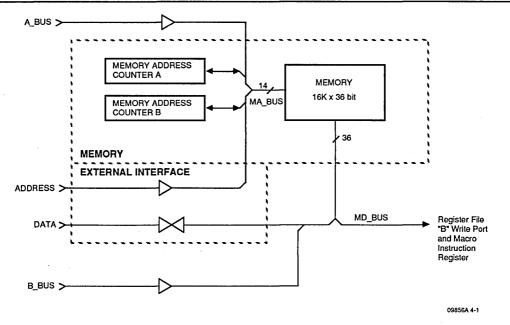

The memory block and external system interface are discussed together in this chapter because of the tight interconnection between these areas. It is helpful to view the two blocks together in order to understand the shared use these blocks make of the memory address bus (MA\_BUS) and the memory data bus (MD\_BUS). Figure 4-1 shows a block diagram of the data and address paths used in these sections.

One thing to note is that both the memory and the external interface are not elaborate in design. Essentially the external I/O section of this system is just a second port on the system memory. This system does little more than provide a simple arbitration scheme on access to the memory that allows an externally supplied DMA device to load and retrieve data from the memory. Event

or interrupt signaling between the CPU and host system is limited to a single pair of interrupt signals, one from host to CPU, one from CPU to host. Memory itself is only a simple bank of static RAM with two address counters on the input that help speed up array calculation.

The reason for this simple approach is that the design to the CPU using the Am29300 family of building blocks is the focus of this application note. Every reader who may find the information in this application note useful will have different memory and I/O requirements to handle and will very likely design individual approachs to memory and I/O. Therefore, only this simple approach is covered here so that more time can be spent discussing the CPU design.

Figure 4-1. Memory and External Interface Address and Data Paths

#### EXTERNAL BUS INTERFACE CONTROL

#### Host Access Definition

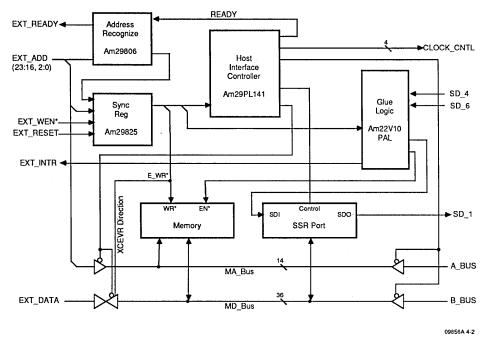

A block diagram of the host interface controller and its connection to the MA\_BUS and MD\_BUS buffers is shown in Figure 4-2.

The Am29300 demonstration system is treated as a coprocessor to some host system. It ultimately gets all of its instructions, data, and control from the external host system. To provide communication with the host using a minimum of design effort and special hardware, only two portals into the Am29300 system are allowed.

One portal is the Am29300 memory, which is treated as a dual port memory with all words directly mapped into the host bus address space. With this, the host has complete access to macroinstructions and data going into and out of the system.

The second port is a serial diagnostics shift chain that runs through key control registers of the system. This serial pathway gives access to loading and reading the microcode writable control store, to the control pipeline register, to loading and reading the macro opcode map RAM, to the macro opcode register, to the macro status register, and to the interrupt base address register. Through this serial port, the microinstructions are loaded by the host before program execution begins. Also, the system clocks can be controlled by the host to allow diagnostics and code debugging via single stepping and breakpoints.

These portals are controlled by a state machine that is separate from the Am29300 system. The state machine is referred to as the host interface controller. It constantly monitors the external host address bus. When the host presents an address that matches a preset address on the Am29300 system board, the host interface controller is selected to perform one of several interface functions.

Any function requested by the host takes priority over anything that the Am29300 CPU is doing. The host always gains control of the memory address and data buses as soon as the CPU clocks can be stopped and the CPU to memory bus buffers disabled.

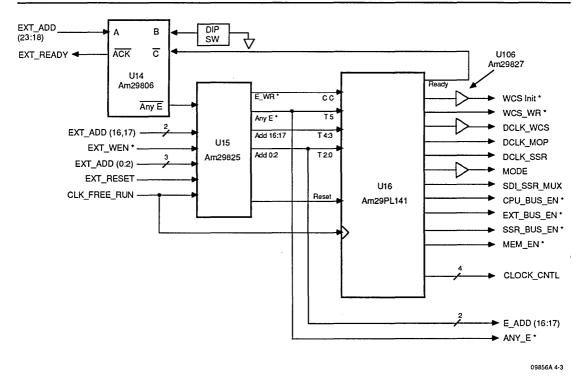

The function performed is dependent on the address used, thus the commands from the host to the interface controller are memory mapped. A 24-bit address from the host is assumed for this design. The 6 most significant bits (23:18) of the address are matched to the Am29300 system board address to select the host interface controller. The next two most significant bits (17:16) are used to select a command mode. The 3 least significant bits (2:0)

Figure 4-2. Host Interface Block Diagram

are used to select a specific command function within two of the command modes.

#### Host Interface Block Diagram

The 6 most significant bits of the host address are checked by the address recognition block: if the address matches the board address, then the match signal is fed into the input of a synchronizing register. Also fed into this register are: the external bus write enable line (EXT\_WEN\*); the external address bits 17, 16, 2:0 [EXT\_ADD(17,16,2:0)]; and the host system reset line.

The synchronizing register is clocked by a free-running version of the Am29300 system clock. The register used has special meta-stable hardened circuitry that prevents the outputs from oscillating, regardless of the timing relationship of input data to clock. This register allows the entire Am29300 system to run asynchronously with regard to the host system clock. All the interaction between the host system and the Am29300 system is synchronized to the Am29300 system clock by the register. Each command to the host interface controller is thus presented at the output of this register in synchronization with the host interface controller clock.

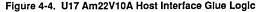

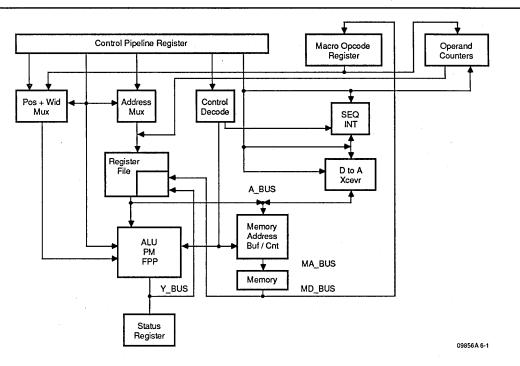

The heart of the host interface is an Am29PL141 Fuse Programmable Controller. It is a microprogrammed sequencer with on-chip microcode memory and pipeline register. This sequencer implements the state machine functions needed to control the interaction between the host and the Am29300 system. Used with the Am29PL141 is an Am22V10 PAL. This PAL collects together some glue logic functions: an interrupt signal latch, a multiplexer, and some encoding logic, all of which are described later.

The Am29PL141 provides control signals to the clock gating and distribution section of the Am29300 system. It also controls the enabling of all the buffers and transceivers that connect with the MA\_BUS and MD\_BUS. The controller acts as a "traffic cop" that allows only one driver on those buses at a time to prevent contention. The controller also manages the loading, reading, and shifting of the Serial Shadow Register diagnostic chain.

The Serial Shadow Register (SSR) diagnostics port is a 32-bit-wide parallel read and write register that also functions as a shift register. Data to be read or written to the SSR diagnostic chain is loaded or read via this port. The port is connected to the host via the MD\_BUS. The

Figure 4-3. Host Interface Controller

port is built from four Am29818-1 SSR diagnostic pipeline registers. These registers, like all the registers in the diagnostics chain in this system, contain one normal parallel input and output pipeline register that is backedup or "shadowed" by a second parallel input and output register that also acts as a serial shift register. The pipeline register can be loaded from the shadow register and the shadow register can be loaded from the outputs of the pipeline register. This gives the ability to move data into or out of the pipeline register via the shadow register. Data in the shadow register can be serially shifted to other similar registers in the system. By connecting all the diagnostic serial shadow registers together in a serial chain, data can be moved serially through a large number of key registers in the system using very few wires.

The SSR diagnostics port is just an extra section of the diagnostics chain that runs throughout the Am29300 system. This extra section is connected to the MD\_BUS to serve as a parallel input and output port that gives access to the serial shadow register chain.

A slightly more detailed view of the Host Interface Controller is shown in Figures 4-3 and 4-4.

#### **Event Signals**

The host and the Am29300 system need to be able to signal each other when important events occur, such as the transfer of ownership over sections of the dual port memory. To allow this, a simple interrupt setting and clearing scheme is provided.

The host interrupts the Am29300 system with a command to the host interface controller. The controller in turn sets an interrupt flag in the Am29300 system interrupt controller. The interrupt is cleared when the Am29300 services its interrupt controller.

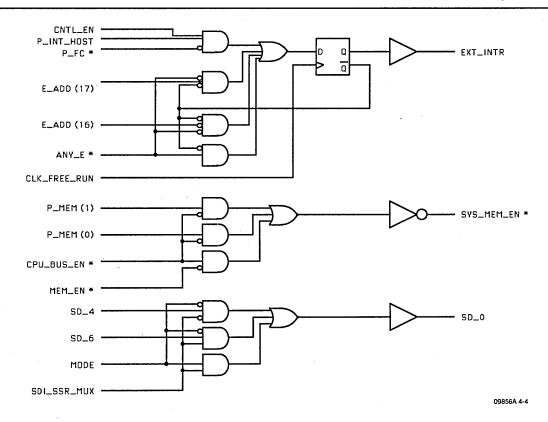

The Am29300 interrupts the host by using a microcode bit to set a latch that drives an interrupt line on the external bus. The interrupt is cleared whenever the host does an operation on the SSR port. The interrupt latch is implemented in the AmPAL22V10, as shown in Figure 4-4.

#### **Memory Enable**

The Am29300 system memory can be enabled by either the Am29300 microcode or by the host interface controller. A simple multiplexer is needed to direct the correct control signal to the memory enable input. This logic is also implemented in the AmPAL22V10 shown in Figure 4-4.

#### AmPAL22V10 Support Logic

Figure 4-4 shows the logic for the AmPAL22V10 that integrates the interrupt signal latch, SDI multiplexer, and memory enable logic. The logic equation definition file for this PAL is listed in Appendix D.

#### **SSR Diagnostics**

#### SSR Shift Path

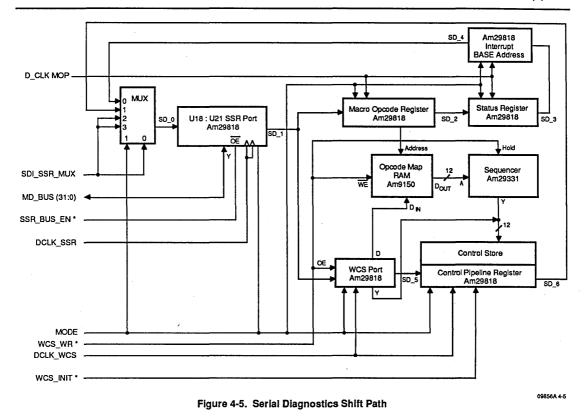

Figure 4-5 shows a block diagram of how the serial shadow registers in the system are linked together and how they relate to the macro opcode map RAM, se-

quencer, and microcode control store. Most of these registers are also depicted in other Figures throughout this application note in their rôles as parallel input and output pipeline registers. Figure 4-5 emphasizes the serial in and out and control connections of the shadow registers also contained in these registers.

The SSR diagnostics port is shown as the starting and ending point for the entire shift chain (or loop as seen here). Data to be loaded into the SSR loop is parallel loaded into this register from the MD\_BUS via the bidirectional outputs of the registers in this port (note: the shadow register in the Am29818-1 gets its input from the output pins of the Am29818-1 pipeline register).

Data loaded into this shadow register is then shifted into one of two branches of the SSR loop. One branch flows through the Writable Control Store (WCS) port and the microcode control store pipeline shadow registers. The WCS port is used to address the microcode control store or to receive (load) data from (to) the macro opcode map RAM. The microcode control store shadow register is used to write data into the microcode writable control store or to read the contents of the control pipeline

register. The second branch flows through the macro opcode, macro status, and the interrupt base address registers. The macro opcode register is used in part to address the macro opcode map RAM.

These branches are separate because it helps to shorten the shift chain length by using branches and because the shift chain clock to the writable control store and WCS port must be separate from the shift clocks to the rest of the diagnostics chain. The shift clocks must be separate because of the way the writable control store is loaded.

The data outputs of the control store are connected to the inputs of the pipeline register as required for normal use in the system. To write the memory, the inputs must be driven with the data to be written, turning the input pins into outputs. In the Writable Control Store (WCS) pipeline register this is fine, since the memory outputs are disabled during the write.

If other diagnostic registers in the system were tied to the same shift clock and mode control lines as the WCS pipeline, there could be a problem every time the WCS is written. The other diagnostic registers not involved in the WCS write would see the same control signals as the WCS registers and would drive their input pins. Depending on what the other registers were connected to, this situation could cause serious contention problems through the system.

For this reason, the SSR used to load WCS is treated separately from other SSR registers in the system. It is worth noting that the only control signal that need be separate is the shift clock. The mode and serial path may be shared with all SSR in the system. Putting the SSR into WCS loading mode, requires the shift clock to load an internal mode flip flop. If the shift clock is active only to the SSR used for WCS when the MODE and Serial Data In (SDI) signals are set high, only the WCS SSR will go into the input pin driving mode.

The end of each branch in the SSR loop returns to a multiplexer at the serial data input (SDI) of the SSR diagnostics port. This multiplexer allows the selection of the shifted branch into the port when the SSR loop is being read rather than written. It also allows the SDI value to be forced when the MODE signal is high. When the MODE signal is high, all the SSRs in the system pass

their SDI directly to their Serial Data Output (SDO). This causes the SDI value forced at the input of the SSR port to be passed directly to all SSRs in the system (note: significant propagation time from SDI to SDO for each SSR is involved). In this way the forced value of SDI becomes an additional control signal to all the SSRs in the system. The function of this multiplexer is integrated into the AmPAL22V10 as shown in Figure 4-4.

#### SSR Reading and Writing

To read the contents of the pipeline registers in the Am29300 system, the host must first send a command to load the SSR throughout the system from the pipeline registers. Then the host must shift the contents of the SSR into the SSR port register (up to 32 bits at a time). The host then performs a read of the SSR port. The host then repeats the shifting-and-reading process until the entire SSR chain has been read.

To write the system pipeline registers, the host reverses the above procedure. Data is first written into the SSR port. Then the SSR chain is shifted to move data into position. The SSR port loading and SSR chain shifting go on until the section of the SSR chain desired is filled. Finally a pipeline load command is issued by the host to load the contents of the SSR into the pipeline registers.

To write the macro opcode map RAM and the microcode writable control store (note: these are treated as a single WCS and must be written together), an address for the map RAM is first loaded into the macro opcode pipeline register via the method described above. Then the address for the microcode WCS is loaded into the WCS port pipeline register. Next, the data to be written into the map RAM and into the microcode WCS is shifted into the WCS port SR and WCS SSR. A load WCS command is then given which performs the actual write of data into the WCS port is enabled and the Am29331 sequencer output is disabled (via its HOLD pin).

The only trick involved in the SSR Reading and Writing is knowing how much to shift the SSR during each read or write. The problem is that the SSR chain length in this system (and in nearly every real system) is not an even multiple of the SSR port size. During the first (or last) shift operation of either the read or the write of pipeline registers, it will be necessary to shift fewer than the full 32 bits of the SSR port. The number of bits to be shifted depends on the chain length. One thing to note is that the chain length will be in a multiple of 4 bits because diagnostic pipeline registers are currently available only in 4-bit and 8-bit devices. So, when a shift operation is commanded by the host, the number of nibbles (4-bit shifts) to be shifted must be indicated.

A final note: during the shifting of the WCS SSR, the Am29300 system clocks must be halted. This is due to the fact that pipeline clock and shift clock to the Am9151 may not occur within 65 ns of each other. Since these clocks would occur within the above window in this system, the pipeline clock must not be active.

#### **Controller Description**

#### Function/Command Descriptions

The following is a list of the address values for functions that the host interface will perform when addressed by the host:

Memory Access: Reading and writing of the Am29300 system memory is done by selecting the address for the Am29300 system with address bits 16 and 17 equal to zero. The address for the specific word in memory is contained in address bits 0:15. The host interface controller, upon recognizing the host access, will stop the clocks to the Am29300 system and disable the CPU to MA\_BUS and MD\_BUS buffers. At the same time the external bus to MA\_BUS and MD\_BUS transceivers are enabled. This suspends the operation of the Am29300 system and gives memory access to the external host. The write enable line on the external bus determines whether a read or write occurs.

Note that by suspending the Am29300 system operation, the memory access is transparent to (or hidden from) the CPU. There is no action required on the part of the Am29300 microcode or interrupt control.

Serial Diagnostics Port Access: This access is very similar to that of a memory access. The difference is that the SSR port register is being read or written instead of memory.

| 1     | ADDR | ESS | BITS | 6 | FUNCTION                        |

|-------|------|-----|------|---|---------------------------------|

| 17    | 16   | 2   | 1    | 0 |                                 |

| <br>0 | 0    | х   | x    | x | Am29300 Memory Access           |

| 0     | 1    | х   | x    | x | Serial Diagnostics Port Access  |

| 1     | 0    | 0   | 0    | 0 | lllegal code                    |

| 1     | 0    | 0   | 0    | 1 | Halt CPU                        |

| 1     | 0    | 0   | 1    | 0 | Run CPU                         |

| 1     | 0    | 0   | 1    | 1 | Single Step CPU                 |

| 1     | 0    | 1   | 0    | 0 | Single Step CPU Control Section |

| 1     | 0    | 1   | 0    | 1 | Single Step CPU Data Section    |

| 1     | 0    | 1   | 1    | 0 | Interrupt CPU                   |

| 1     | 0    | 1   | 1    | 1 | Reset CPU                       |

| 1     | 1    | 0   | 0    | 0 | lllegal code                    |

| 1     | 1    | 0   | 0    | 1 | Load Pipeline Register          |

| 1     | 1    | 0   | 1    | 0 | Load Macro Opcode Register      |

| . 1   | 1    | 0   | 1    | 1 | Load Writable Control Store     |

| 1     | 1    | 1   | 0    | 0 | Load Initialization Register    |

| 1     | 1    | 1   | 0    | 1 | Load Serial Shadow Register     |

| 1     | 1    | 1   | 1    | 0 | Shift WCS SSR Chain             |

| · 1   | 1    | 1   | 1    | 1 | Shift Macro Opcode SSR chain    |

Halt CPU: This command throws the Am29300 system clocks in to a continuous stop condition until the mode is cleared by the RUN CPU command or temporarily overriden by one of the single step commands.

Run CPU: This command starts the Am29300 system clocks running.

Single Step CPU: When the CPU is halted, this command will cause all the system clocks to cycle once to advance the state of the CPU one step. Note that gated clocks will be active during this cycle only if their enables are active (i.e., gated clocks operate as they would during a normal clock cycle; they are not forced to operate).

This mode is useful during diagnostic operations to single step the machine between serial load and unload of the SSR diagnostics.

Single Step CPU Control Section: This will step only the clocks in the control section of the CPU. The control pipeline, macro opcode, macro operand, status, sequencer, and interrupt registers may be affected.

This is useful for forcing the control section into a new state under the control of diagnostics, such as a forced branch to a new location in the microcode. This is done by first loading the control pipeline with an instruction to branch via the SSR diagnostics chain. The control section would then be single stepped to execute the branch. Note that during these operations, the data section is not affected and no data is modified.

Single Step CPU Data Section: This operation single steps the clocks only in the data section of the CPU. This may be useful for repetitive diagnostic operations involving only the data section.

Interrupt CPU: This command causes the host interface controller to set an interrupt input to the Am29300 system interrupt controller. The interrupt controller in turn prioritizes the interrupt and causes an interrupt to the CPU when that type of interrupt is enabled.

**Reset CPU:** This will make the reset line to the Am29300 system active and step all the ungated system clocks. The clocking is required by some parts of the system to affect reset state changes.

Load Pipeline Register: This command will step only the clock to the control pipeline and WCS port for one cycle while forcing the pipeline registers to load data from the SSR chain. This is used to control the state of the pipeline through serial diagnostics. Load Macro Opcode Register: This steps only the clock to the macro opcode, macro operand, status, and interrupt base address pipeline registers while forcing the registers to load from the SSR chain.

Load Writable Control Store: This command initiates a series of clock cycles that cause data in the SSR chain to be loaded into the writable microcode control store and the macro opcode map RAM from the SSR chain. The address loaded is also specified in the SSR chain.

Load Initialization Register: Like the previous command, this operation loads the writable microcode store. The difference is that only the WCS (Am9151) initialize registers are loaded from the SSR chain.

Load Serial Shadow Register: This causes the contents of all diagnostic pipeline registers to be copied into the related SSR chain elements. This is used to read the Am29300 system state into the SSR chain so that it can be shifted out to the host.

Shift WCS SSR Chain: This command shifts the contents of the SSR port register into the SSR diagnostics chain used for the writable control store. It also brings the bits at the end of the WCS SSR chain into the SSR port register. This is the serial read and write operation of the WCS SSR chain (or loop).

Shift Macro Opcode SSR Chain: This is the same as the previous command but it affects the SSR chain associated with the macro opcode, status, and interrupt base address registers.

**Illegal Code:** Due to the way the host interface controller algorithm was implemented, this command (address combination) is illegal. If it is used, it will lock up the host interface controller in an infinite loop.

#### Access Timing

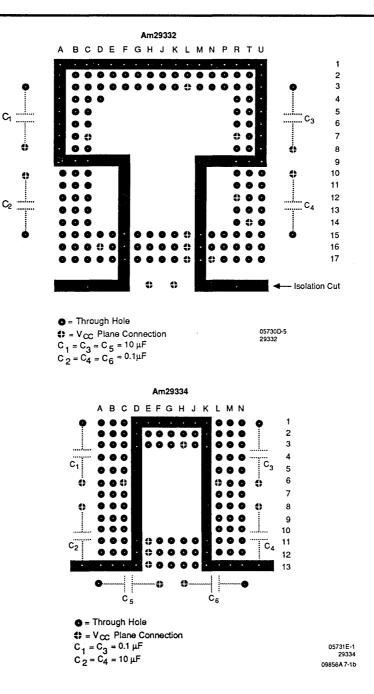

The speed of interaction between the host and the Am29300 system is regulated by both the host and the host interface controller.