Handbook

Array Processing and Digital Signal Processing

ADVANCED MICRO DEVICES

1

# Advanced Micro Devices

### Array Processing and Digital Signal Processing Handbook

The International Standard of Guality guarantees a 0.05% AQL on all electrical parameters, AC and DC, over the entire operating range.

# INT-STD-500

© 1986 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics. The performance characteristics listed in this data book are guaranteed by specific tests, correlated testing, guard banding, design and other practices common to the industry. For specific testing details contact your local AMD sales representative. The company assumes no responsibility for the use of any circuits described herein.

901 Thompson Place, P.O. Box 3453, Sunnyvale, California 94088 (408) 732-2400 TWX: 910-339-9280 TELEX: 34-6306

#### Table of Contents

| 1. INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                 |                                           |                                 |                                        | 1                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------------|----------------------------------------|-----------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                 |                                           |                                 |                                        |                                                                             |

| 2. NUMBER SYSTEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                 |                                           |                                 | •••                                    | 3                                                                           |

| 2.1 Fixed Point Numbers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                 |                                           |                                 |                                        | 3                                                                           |

| 2.1.1 Fixed Point Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •••                                                                                                                                                             |                                           |                                 |                                        | 4                                                                           |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                 |                                           |                                 |                                        |                                                                             |

| 2.2 Floating Point Numbers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | •••                                                                                                                                                             | •••                                       | •••                             | •••                                    | 7                                                                           |

| 2.2.1 When to use Floating Po                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | int                                                                                                                                                             |                                           | •••                             | •••                                    | 8                                                                           |

| 2.2.2 Floating Point Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                 |                                           |                                 |                                        | 8                                                                           |

| 3. ARRAY PROCESSING ALGORI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | гнмз                                                                                                                                                            |                                           |                                 |                                        | 9                                                                           |

| 3.1 Digital Filters in the Time D<br>3.2 Filtering in the Frequency I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                 |                                           |                                 |                                        | 9                                                                           |

| the Fourier Transform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                 |                                           |                                 |                                        | 14                                                                          |

| 3.2.1 Algorithm for Decimation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                 |                                           |                                 |                                        | 14                                                                          |

| 3.2.2 Algorithm for Decimation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                 | •••                                       |                                 | •••                                    | 14                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                 |                                           | •••                             | •••                                    |                                                                             |

| 3.2.3 Comparison of FFT and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                 | •••                                       | •••                             |                                        | 18                                                                          |

| 3.2.4 Inverse Fourier Transfor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | m                                                                                                                                                               | •••                                       | •••                             |                                        | 18                                                                          |

| 3.2.5 Radix 4 FFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                 |                                           | •••                             |                                        | 18                                                                          |

| 3.2.6 Real-Valued Input Fourie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | er Transforms                                                                                                                                                   |                                           |                                 |                                        | 20                                                                          |

| 3.3 Magnitude Calculations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                 |                                           |                                 |                                        | 22                                                                          |

| 4. SYSTEM DESIGN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                 |                                           |                                 | ••••                                   | 25                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                 |                                           |                                 |                                        |                                                                             |

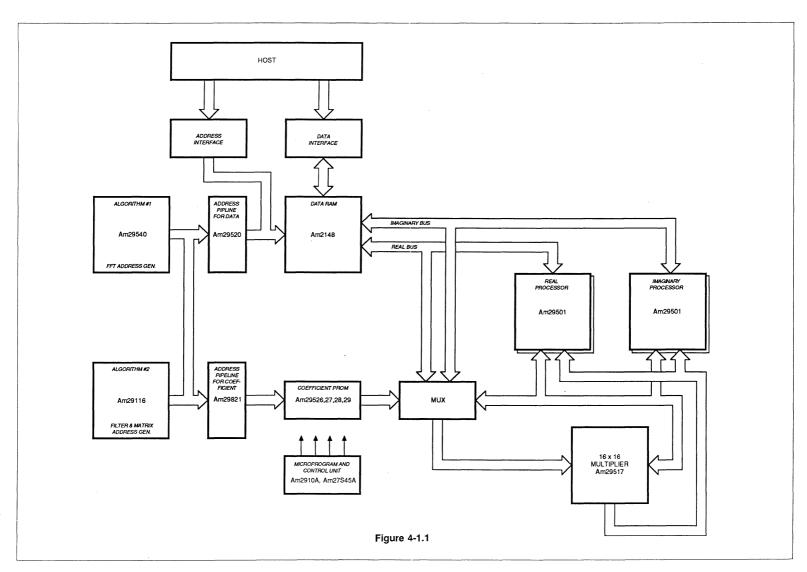

| 4.1 Array Processor Design ba                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | sed on Am295                                                                                                                                                    | 00 Family                                 | ,                               |                                        | 25                                                                          |

| 4.1 Array Processor Design ba                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                 |                                           |                                 |                                        | 25<br>26                                                                    |

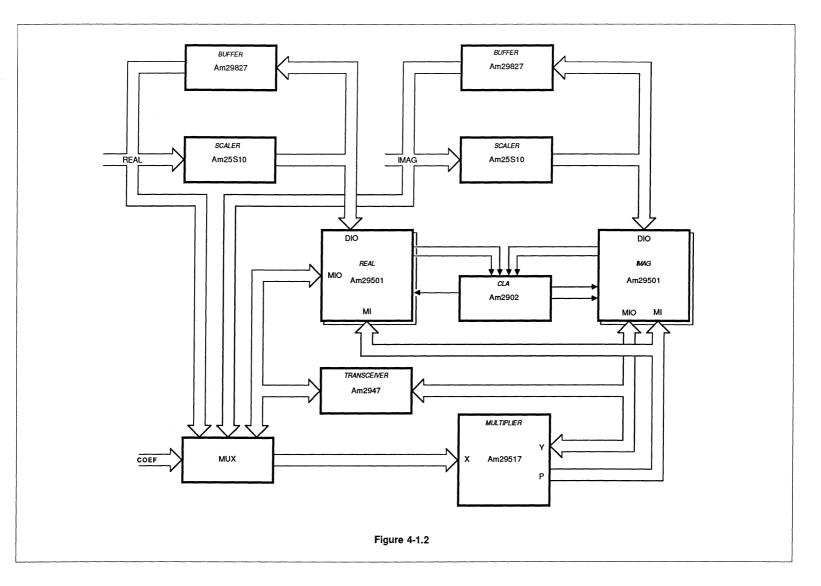

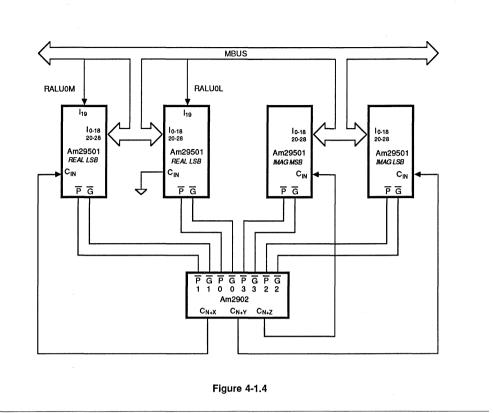

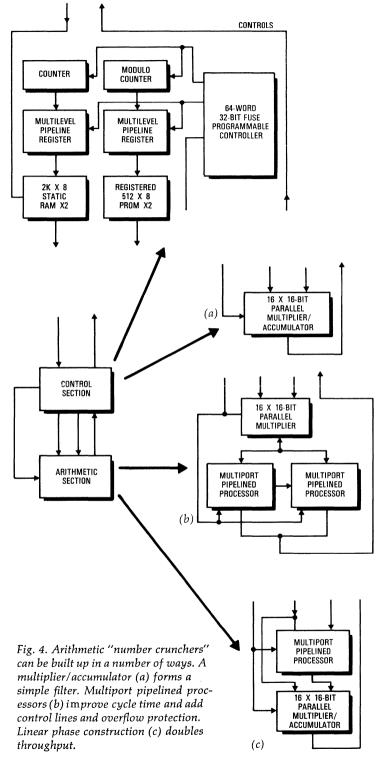

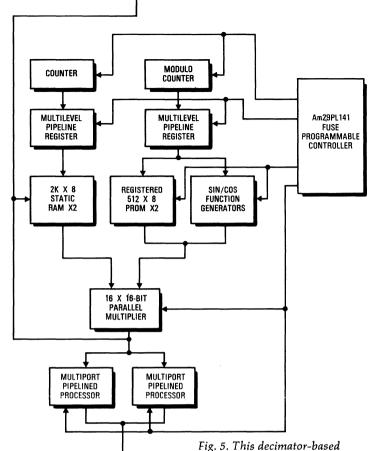

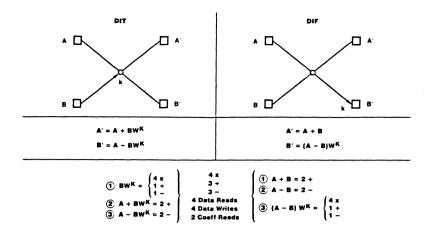

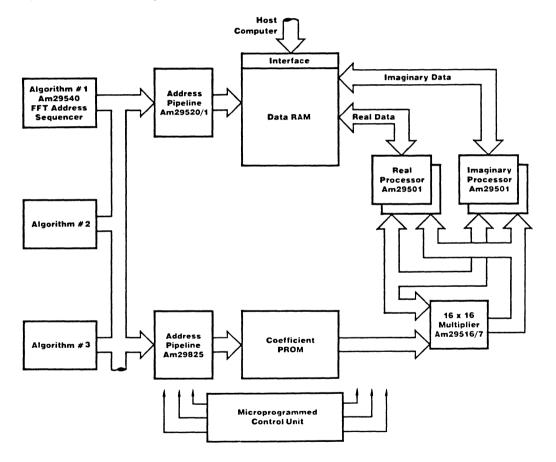

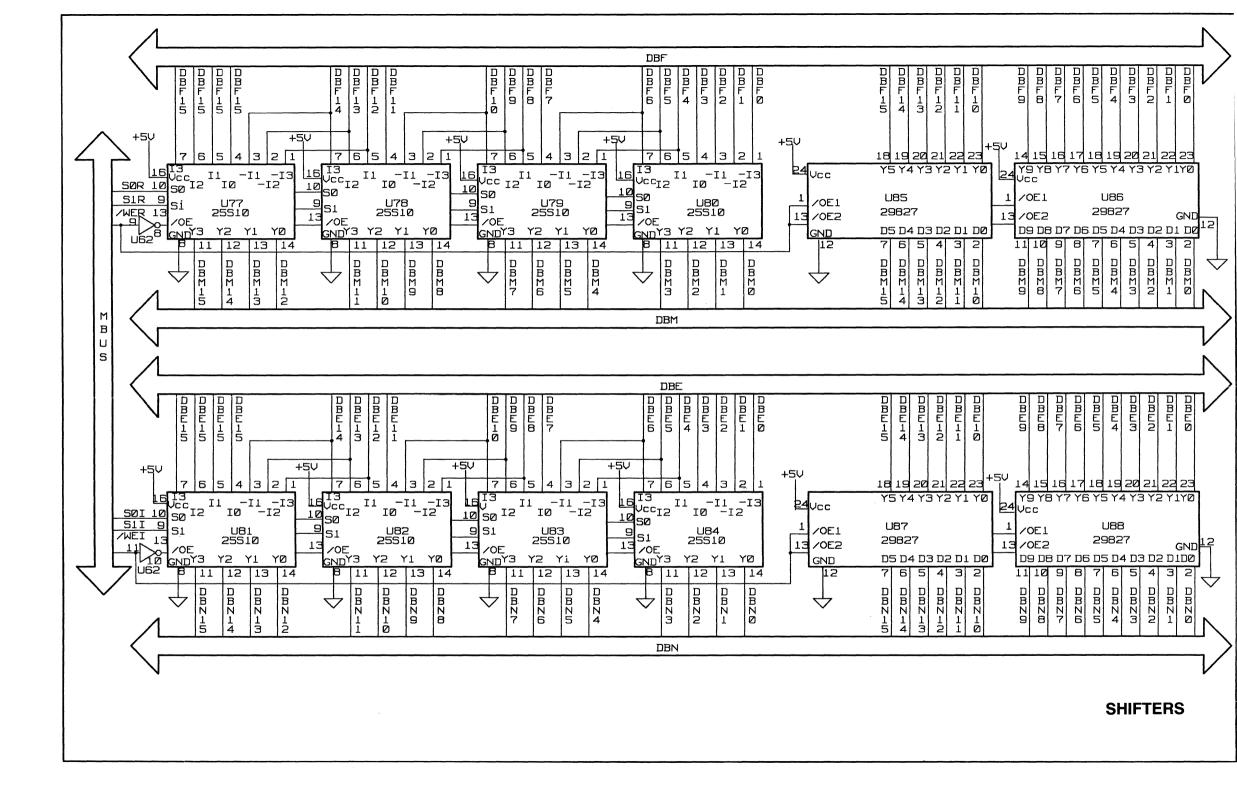

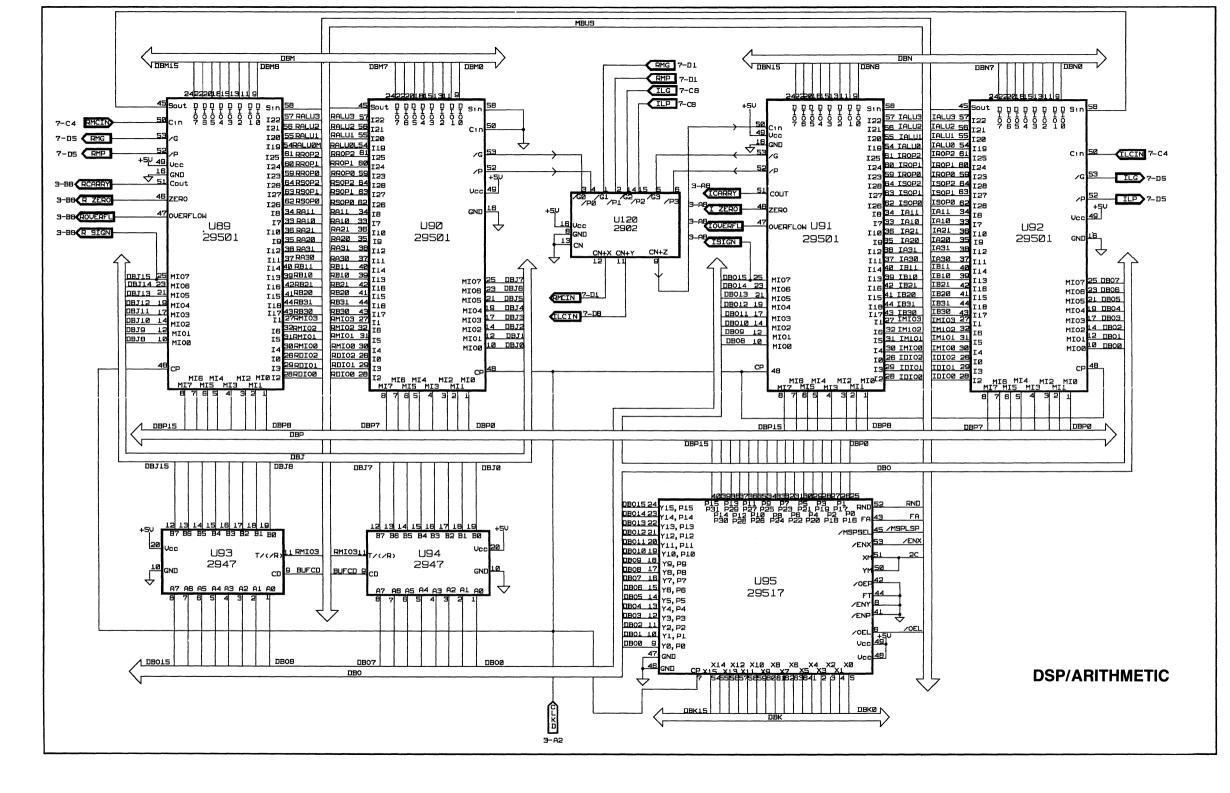

| 4.1.1 Arithmetic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                 |                                           |                                 |                                        | 26                                                                          |

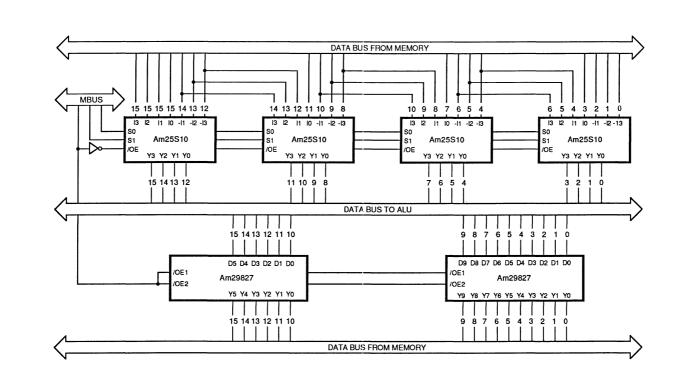

| 4.1.1 Arithmetic<br>4.1.2 Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <br>                                                                                                                                                            | <br>                                      | ····<br>···                     | <br>                                   | 26<br>30                                                                    |

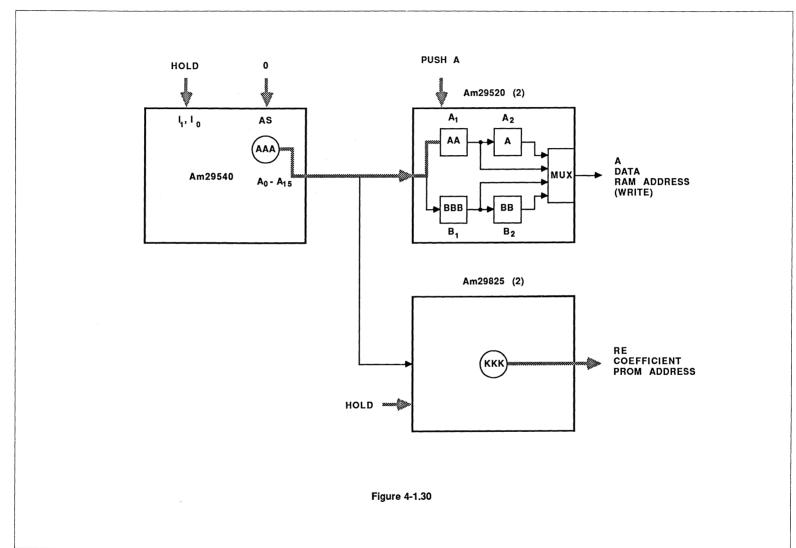

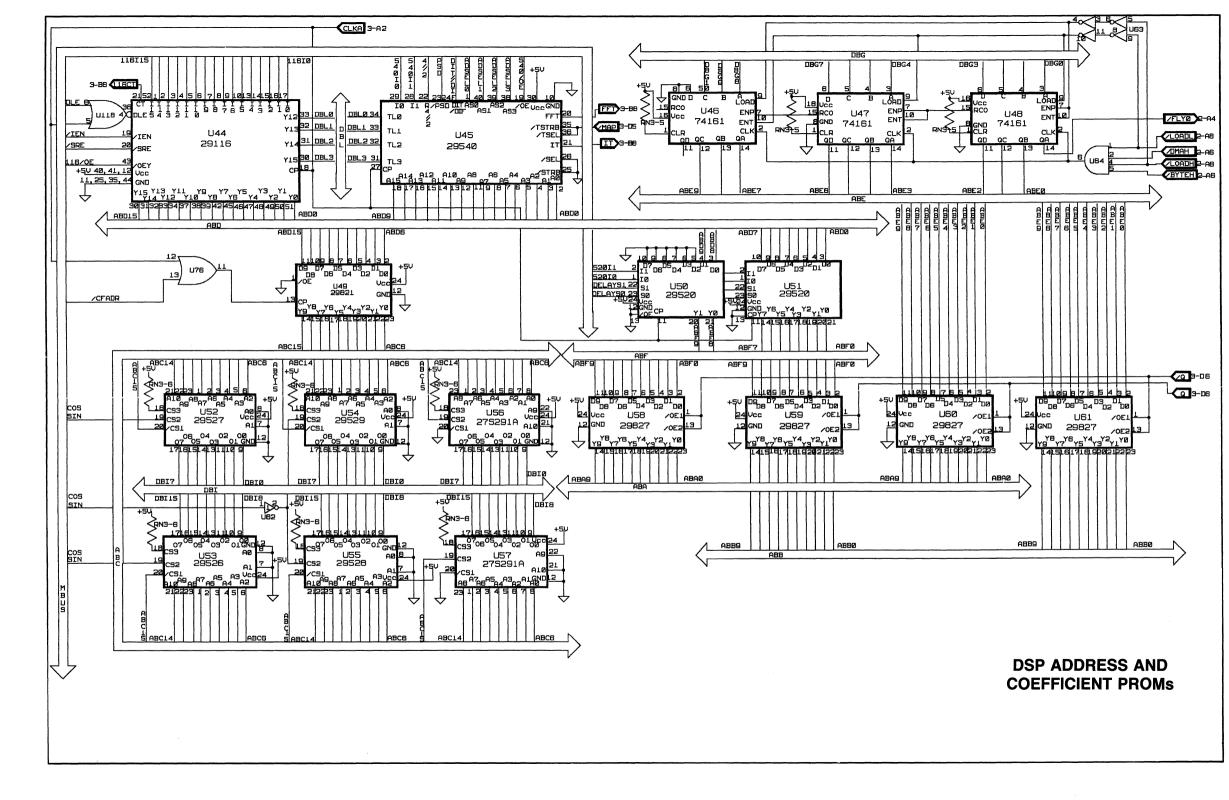

| 4.1.1 Arithmetic<br>4.1.2 Memory<br>4.1.3 Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                 |                                           |                                 | ····<br>···                            | 26<br>30<br>31                                                              |

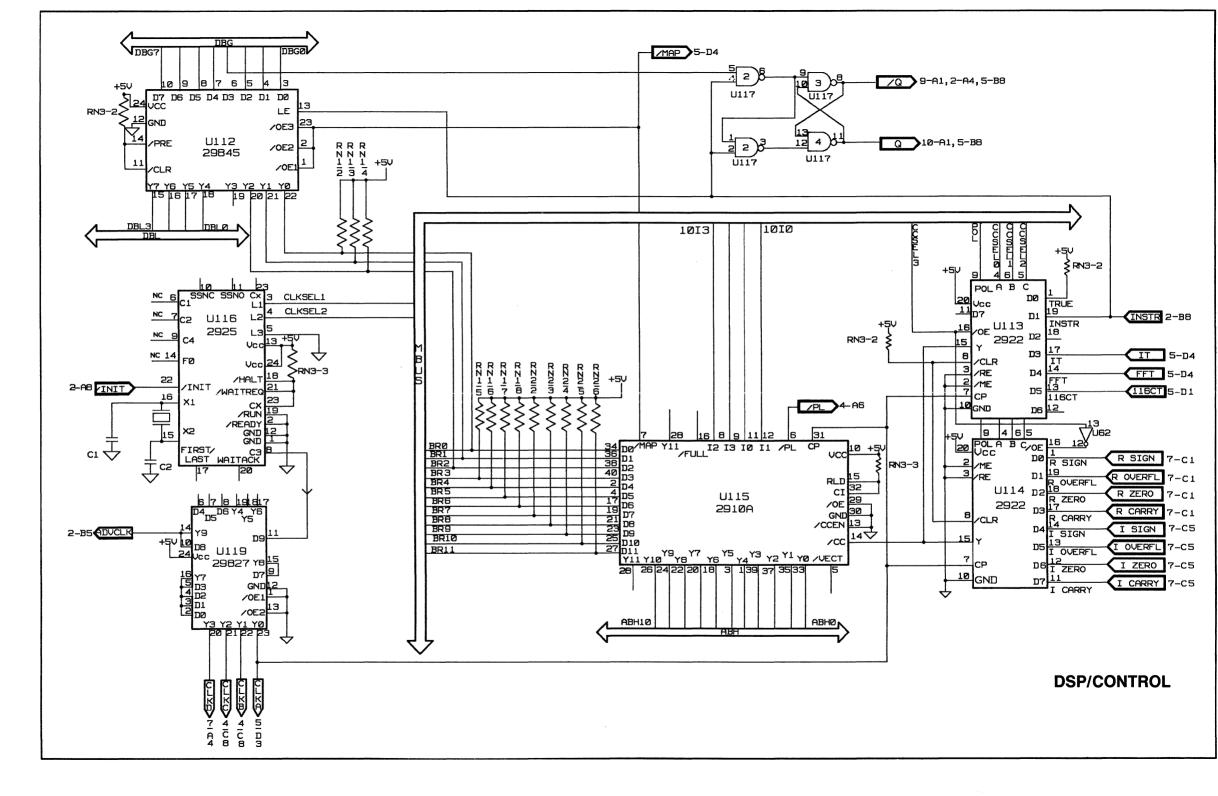

| 4.1.1 Arithmetic<br>4.1.2 Memory<br>4.1.3 Addressing<br>4.1.4 Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <br><br>                                                                                                                                                        | <br><br>                                  | ····<br>····                    | ····<br>····<br>···                    | 26<br>30<br>31<br>34                                                        |

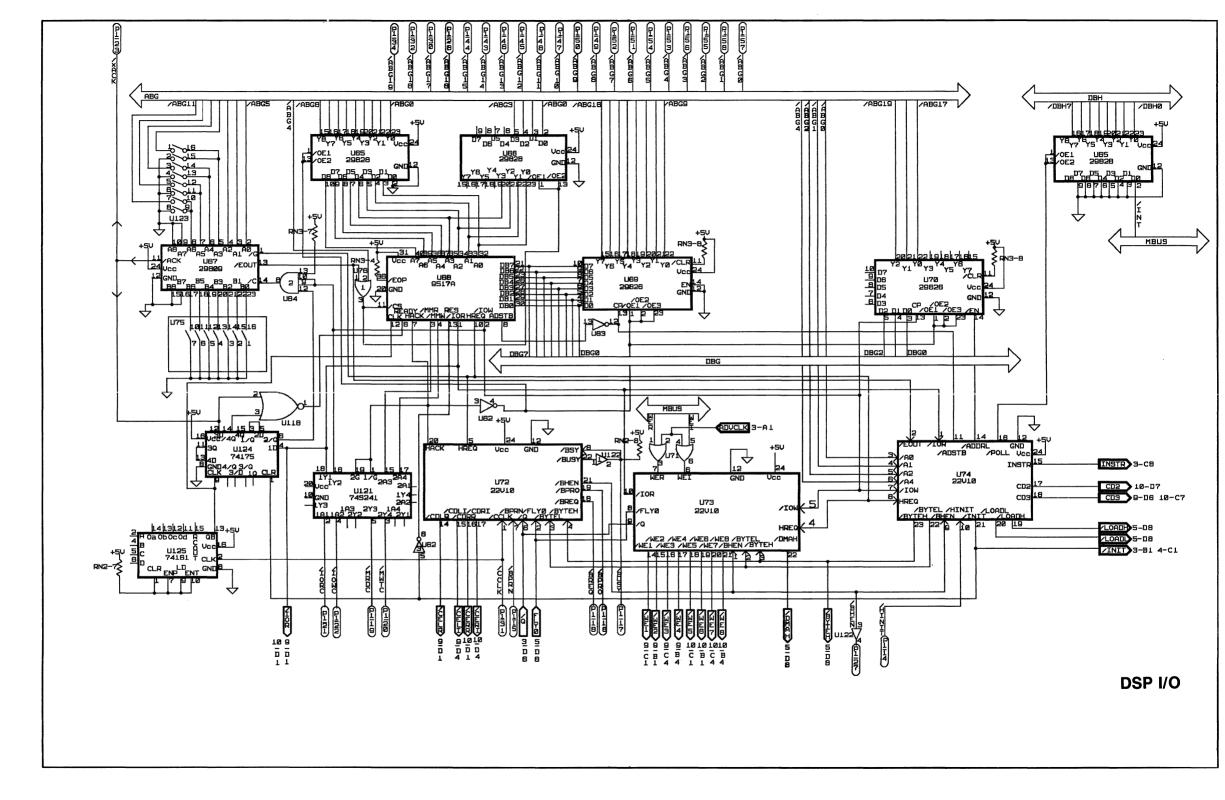

| 4.1.1       Arithmetic          4.1.2       Memory          4.1.3       Addressing          4.1.4       Control          4.1.5       Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <br><br><br>                                                                                                                                                    | <br>                                      | ····<br>···                     | ····<br>···                            | 26<br>30<br>31<br>34<br>35                                                  |

| 4.1.1       Arithmetic          4.1.2       Memory          4.1.3       Addressing          4.1.4       Control          4.1.5       Input/Output          4.1.6       Timing Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <br><br><br>                                                                                                                                                    | ····<br>···<br>···<br>···                 | ····<br>····<br>···             | ····<br>····<br>···                    | 26<br>30<br>31<br>34<br>35<br>38                                            |

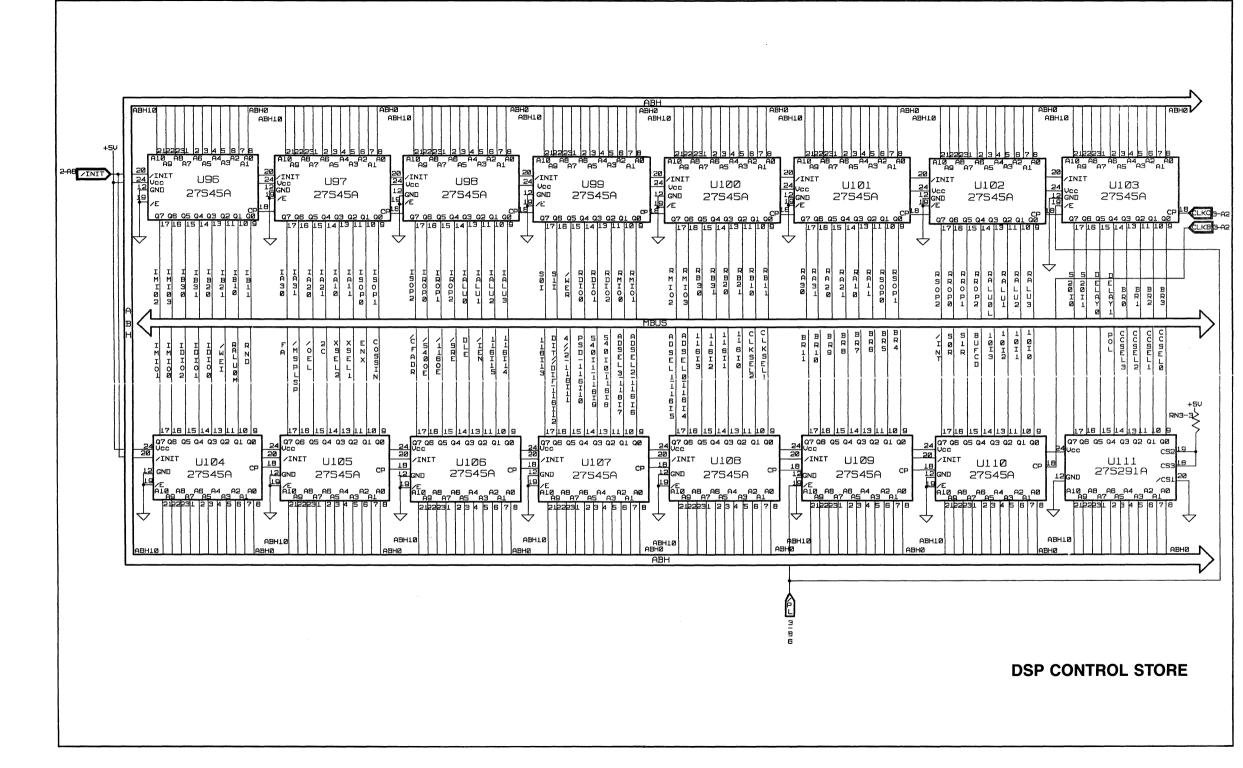

| 4.1.1 Arithmetic          4.1.2 Memory          4.1.3 Addressing          4.1.4 Control          4.1.5 Input/Output          4.1.6 Timing Considerations          4.1.7 Microcode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ···<br>···<br>···<br>···                                                                                                                                        | <br><br>                                  | ····<br>···<br>···<br>···       | ····<br>···<br>···<br>···              | 26<br>30<br>31<br>34<br>35<br>38<br>38                                      |

| 4.1.1       Arithmetic          4.1.2       Memory          4.1.3       Addressing          4.1.4       Control          4.1.5       Input/Output          4.1.6       Timing Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ···<br>···<br>···<br>···                                                                                                                                        | ····<br>···<br>···<br>···                 | ····<br>····<br>···             | ····<br>····<br>···                    | 26<br>30<br>31<br>34<br>35<br>38                                            |

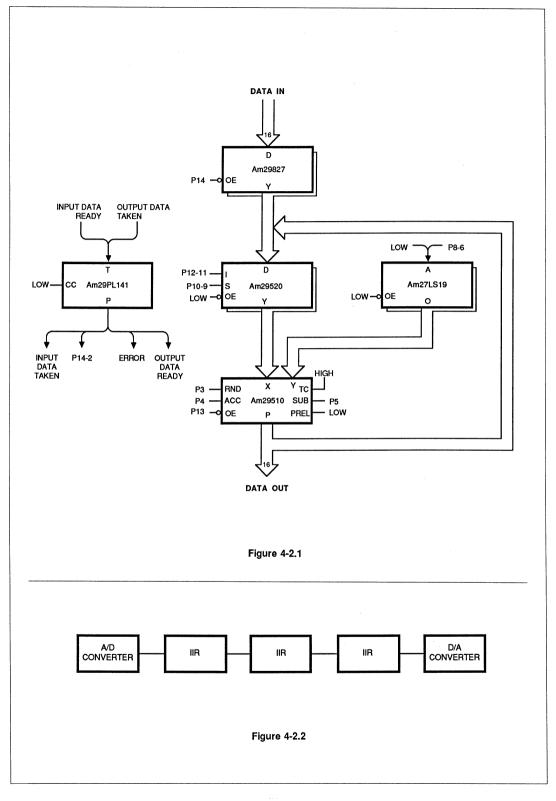

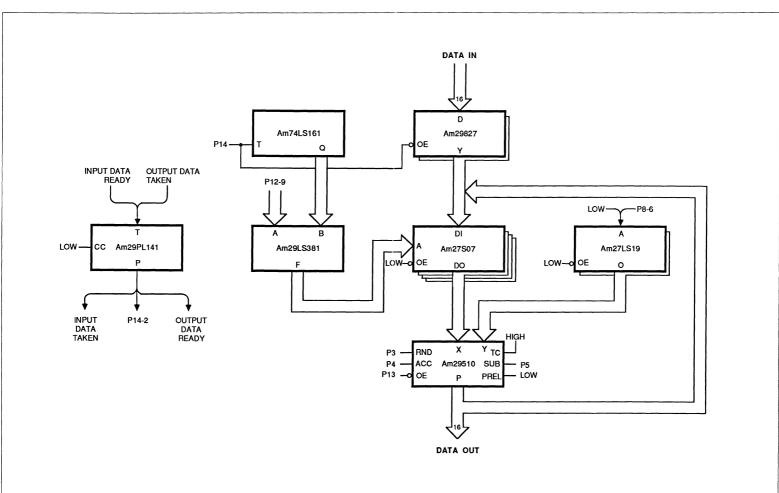

| 4.1.1 Arithmetic<br>4.1.2 Memory<br>4.1.3 Addressing<br>4.1.4 Control<br>4.1.5 Input/Output<br>4.1.6 Timing Considerations<br>4.1.7 Microcode<br>4.2 Digital Filter using Multiply-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <br><br><br><br>Accumulator                                                                                                                                     |                                           |                                 | ····<br>···<br>···<br>···              | 26<br>30<br>31<br>34<br>35<br>38<br>38<br>74                                |

| 4.1.1 Arithmetic          4.1.2 Memory          4.1.3 Addressing          4.1.4 Control          4.1.5 Input/Output          4.1.6 Timing Considerations          4.1.7 Microcode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ···<br>···<br>···<br>···                                                                                                                                        | ····<br>···<br>···<br>···                 | ····<br>···<br>···<br>···       | ····<br>···<br>···<br>···              | 26<br>30<br>31<br>34<br>35<br>38<br>38                                      |

| 4.1.1 Arithmetic<br>4.1.2 Memory<br>4.1.3 Addressing<br>4.1.4 Control<br>4.1.5 Input/Output<br>4.1.6 Timing Considerations<br>4.1.7 Microcode<br>4.2 Digital Filter using Multiply<br>5. ARTICLES<br>Record Signal-Processing Rates S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <br><br><br>Accumulator<br><br>pring from                                                                                                                       |                                           |                                 | ····<br>···<br>···<br>···              | 26<br>30<br>31<br>34<br>35<br>38<br>38<br>74<br>79                          |

| 4.1.1 Arithmetic<br>4.1.2 Memory<br>4.1.3 Addressing<br>4.1.4 Control<br>4.1.5 Input/Output<br>4.1.6 Timing Considerations<br>4.1.7 Microcode<br>4.2 Digital Filter using Multiply<br>5. ARTICLES<br>Record Signal-Processing Rates S<br>Chip Refinements, Electronics                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Accumulator                                                                                                                                                     |                                           |                                 | ····<br>···<br>···<br>···              | 26<br>30<br>31<br>34<br>35<br>38<br>38<br>74                                |

| 4.1.1 Arithmetic<br>4.1.2 Memory<br>4.1.3 Addressing<br>4.1.4 Control<br>4.1.5 Input/Output<br>4.1.6 Timing Considerations<br>4.1.7 Microcode<br>4.2 Digital Filter using Multiply-<br>5. ARTICLES<br>Record Signal-Processing Rates S<br>Chip Refinements, Electronics<br>One-Chip Sequencer Shapes up A                                                                                                                                                                                                                                                                                                                                                                                                                             | Accumulator<br><br>pring from<br>ddressing for                                                                                                                  | ····<br>···<br>···<br>···                 |                                 | ····<br>···<br>···<br>···              | 26<br>30<br>31<br>34<br>35<br>38<br>38<br>74<br>79<br>79                    |

| 4.1.1 Arithmetic<br>4.1.2 Memory<br>4.1.3 Addressing<br>4.1.4 Control<br>4.1.5 Input/Output<br>4.1.6 Timing Considerations<br>4.1.7 Microcode<br>4.2 Digital Filter using Multiply<br>5. ARTICLES<br>Record Signal-Processing Rates S<br>Chip Refinements, Electronics                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Accumulator<br><br>pring from<br>ddressing for                                                                                                                  | ····<br>···<br>···<br>···                 |                                 | ····<br>···<br>···<br>···              | 26<br>30<br>31<br>34<br>35<br>38<br>38<br>74<br>79                          |

| 4.1.1 Arithmetic<br>4.1.2 Memory<br>4.1.3 Addressing<br>4.1.4 Control<br>4.1.5 Input/Output<br>4.1.6 Timing Considerations<br>4.1.7 Microcode<br>4.2 Digital Filter using Multiply.<br>5. ARTICLES<br>Record Signal-Processing Rates S<br>Chip Refinements, Electronics<br>One-Chip Sequencer Shapes up A<br>Large FFT's, Electronic Design                                                                                                                                                                                                                                                                                                                                                                                           | Accumulator<br><br>pring from<br>ddressing for<br>                                                                                                              | ····<br>···<br>···<br>···                 |                                 | ····<br>···<br>···<br>···<br>···       | 26<br>30<br>31<br>34<br>35<br>38<br>38<br>74<br>79<br>79                    |

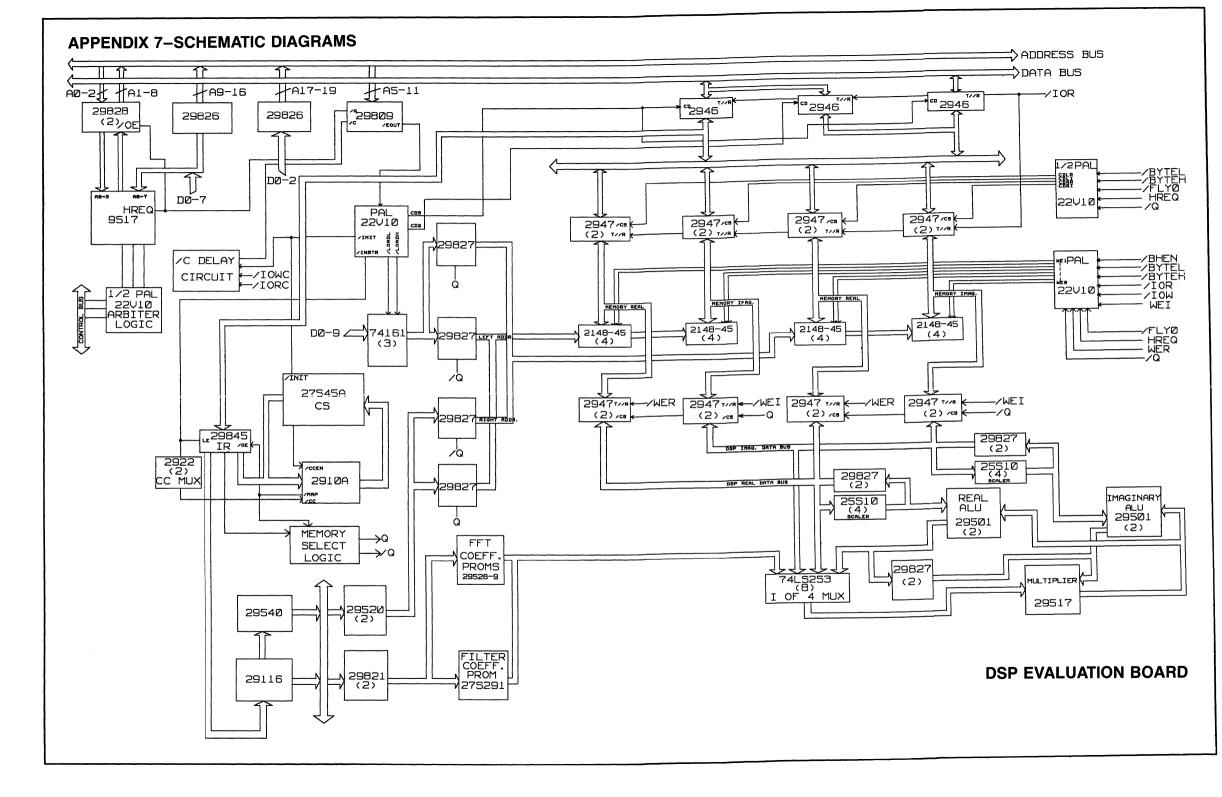

| 4.1.1 Arithmetic<br>4.1.2 Memory<br>4.1.3 Addressing<br>4.1.4 Control<br>4.1.5 Input/Output<br>4.1.6 Timing Considerations<br>4.1.7 Microcode<br>4.2 Digital Filter using Multiply<br>5. ARTICLES<br>Record Signal-Processing Rates S<br>Chip Refinements, Electronics<br>One-Chip Sequencer Shapes up A<br>Large FFT's, Electronic Design<br>500-kHz Single-Board FFT System                                                                                                                                                                                                                                                                                                                                                         | Accumulator<br><br>pring from<br>ddressing for<br>                                                                                                              | ····<br>···<br>···<br>···                 |                                 | ····<br>···<br>···<br>···<br>···       | 26<br>30<br>31<br>34<br>35<br>38<br>38<br>74<br>79<br>79                    |

| 4.1.1 Arithmetic<br>4.1.2 Memory<br>4.1.3 Addressing<br>4.1.4 Control<br>4.1.5 Input/Output<br>4.1.6 Timing Considerations<br>4.1.7 Microcode<br>4.2 Digital Filter using Multiply<br>5. ARTICLES<br>Record Signal-Processing Rates S<br>Chip Refinements, Electronics<br>One-Chip Sequencer Shapes up A<br>Large FFT's, Electronic Design<br>500-kHz Single-Board FFT System<br>DSP-Optimized Chips, EDN.                                                                                                                                                                                                                                                                                                                            | Accumulator<br><br>pring from<br>ddressing for<br>n<br>h<br>n                                                                                                   | ····<br>···<br>···<br>···                 |                                 | ····                                   | 26<br>30<br>31<br>34<br>35<br>38<br>38<br>74<br>79<br>79<br><b>83</b>       |

| 4.1.1 Arithmetic<br>4.1.2 Memory<br>4.1.3 Addressing<br>4.1.4 Control<br>4.1.5 Input/Output<br>4.1.6 Timing Considerations<br>4.1.7 Microcode<br>4.2 Digital Filter using Multiply<br>5. ARTICLES<br>Record Signal-Processing Rates S<br>Chip Refinements, Electronics<br>One-Chip Sequencer Shapes up A<br>Large FFT's, Electronic Design<br>500-KHz Single-Board FFT System<br>DSP-Optimized Chips, EDN.<br>Trim DSP Overhead by Changing S                                                                                                                                                                                                                                                                                         | Accumulator<br>Accumulator<br>pring from<br>ddressing for<br>n<br>hncorporates<br>                                                                              | ····<br>···<br>···<br>···                 |                                 | ······································ | 26<br>30<br>31<br>34<br>35<br>38<br>78<br>79<br>79<br><b>83</b><br>91       |

| 4.1.1 Arithmetic<br>4.1.2 Memory<br>4.1.3 Addressing<br>4.1.4 Control<br>4.1.5 Input/Output<br>4.1.6 Timing Considerations<br>4.1.7 Microcode<br>4.2 Digital Filter using Multiply<br>5. ARTICLES<br>Record Signal-Processing Rates S<br>Chip Refinements, Electronics<br>One-Chip Sequencer Shapes up A<br>Large FFT's, Electronic Desig<br>500-kHz Single-Board FFT System<br>DSP-Optimized Chips, EDN.<br>Trim DSP Overhead by Changing y<br>Sampling Rate, Integrated Circ                                                                                                                                                                                                                                                        | Accumulator<br>Accumulator<br>pring from<br>ddressing for<br>n<br>hncorporates<br>rour<br>cuits                                                                 | ····<br>···<br>···<br>···<br>···          |                                 | ····                                   | 26<br>30<br>31<br>34<br>35<br>38<br>38<br>74<br>79<br>79<br><b>83</b>       |

| 4.1.1 Arithmetic<br>4.1.2 Memory<br>4.1.3 Addressing<br>4.1.4 Control<br>4.1.5 Input/Output<br>4.1.6 Timing Considerations<br>4.1.7 Microcode<br>4.2 Digital Filter using Multiply<br>5. ARTICLES<br>Record Signal-Processing Rates S<br>Chip Refinements, Electronics<br>One-Chip Sequencer Shapes up A<br>Large FFT's, Electronic Desig<br>500-kHz Single-Board FFT System<br>DSP-Optimized Chips, EDN.<br>Trim DSP Overhead by Changing J<br>Sampling Rate, Integrated Cirr<br>DSP Building Blocks Allow Resourd                                                                                                                                                                                                                   | Accumulator<br>Accumulator<br>pring from<br>ddressing for<br>n<br>n Incorporates<br>your<br>cuits<br>co Optimization.                                           | <br><br><br><br><br>This manu             | <br><br><br><br><br><br>        |                                        | 26<br>30<br>31<br>34<br>35<br>38<br>74<br>79<br>79<br>83<br>91<br>99        |

| 4.1.1 Arithmetic<br>4.1.2 Memory<br>4.1.3 Addressing<br>4.1.4 Control<br>4.1.5 Input/Output<br>4.1.6 Timing Considerations<br>4.1.7 Microcode<br>4.2 Digital Filter using Multiply<br>5. ARTICLES<br>Record Signal-Processing Rates S<br>Chip Refinements, Electronics<br>One-Chip Sequencer Shapes up A<br>Large FFT's, Electronic Desig<br>500-kHz Single-Board FFT System<br>DSP-Optimized Chips, EDN.<br>Trim DSP Overhead by Changing y<br>Sampling Rate, Integrated Cir<br>DSP Building Blocks Allow Resourd<br>was originally prepared for and                                                                                                                                                                                 | Accumulator<br><br><br><br>Accumulator<br><br><br>ddressing for<br><br><br>ddressing for<br><br><br>n Incorporates<br><br><br>prover<br>cuits<br>presented at W | <br><br><br><br><br>This manu<br>ZESCON/8 | <br><br><br><br><br><br>        | ······································ | 26<br>30<br>31<br>34<br>35<br>38<br>74<br>79<br>79<br>83<br>91<br>99<br>109 |

| <ul> <li>4.1.1 Arithmetic</li> <li>4.1.2 Memory</li> <li>4.1.3 Addressing</li> <li>4.1.4 Control</li> <li>4.1.5 Input/Output</li> <li>4.1.6 Timing Considerations</li> <li>4.1.6 Timing Considerations</li> <li>4.1.7 Microcode</li> <li>4.1.2 Digital Filter using Multiply</li> <li>5. ARTICLES</li> <li>Record Signal-Processing Rates S<br/>Chip Refinements, Electronics</li> <li>One-Chip Sequencer Shapes up A<br/>Large FFT's, Electronic Desig</li> <li>500-kHz Single-Board FFT System<br/>DSP-Optimized Chips, EDN.</li> <li>Trim DSP Overhead by Changing y<br/>Sampling Rate, Integrated Cim<br/>DSP Building Blocks Allow Resourd<br/>was originally prepared for and<br/>A New Approach to Floating Point I</li> </ul> | Accumulator<br><br><br>pring from<br>ddressing for<br>1<br>n Incorporates<br>your<br>cuits<br>presented at W<br>DSP, 1984 IEEE                                  | <br><br><br><br><br>This manu<br>Press.   | <br><br><br><br><br><br>uscript |                                        | 26<br>30<br>31<br>34<br>35<br>38<br>74<br>79<br>79<br>83<br>91<br>99        |

| 4.1.1 Arithmetic<br>4.1.2 Memory<br>4.1.3 Addressing<br>4.1.4 Control<br>4.1.5 Input/Output<br>4.1.6 Timing Considerations<br>4.1.7 Microcode<br>4.2 Digital Filter using Multiply<br>5. ARTICLES<br>Record Signal-Processing Rates S<br>Chip Refinements, Electronics<br>One-Chip Sequencer Shapes up A<br>Large FFT's, Electronic Desig<br>500-kHz Single-Board FFT System<br>DSP-Optimized Chips, EDN.<br>Trim DSP Overhead by Changing y<br>Sampling Rate, Integrated Cir<br>DSP Building Blocks Allow Resourd<br>was originally prepared for and                                                                                                                                                                                 | Accumulator<br><br><br>pring from<br>ddressing for<br>1<br>n Incorporates<br>your<br>cuits<br>presented at W<br>DSP, 1984 IEEE                                  | <br><br><br><br><br>This manu<br>Press.   | <br><br><br><br><br><br>uscript |                                        | 26<br>30<br>31<br>34<br>35<br>38<br>74<br>79<br>79<br>83<br>91<br>99<br>109 |

| 6. PRODUCT SPECIF        |     | ONS |     | <br> |     |     |

|--------------------------|-----|-----|-----|------|-----|-----|

|                          |     |     |     |      |     |     |

| Am29501A                 | ••• |     |     | <br> |     | 129 |

| Am29509                  | ••• |     |     | <br> |     | 130 |

| Am29510/L510             | ••• |     |     | <br> |     | 131 |

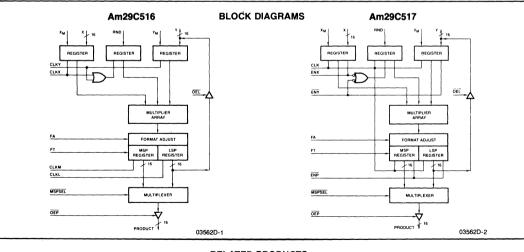

| Am29C516 Family          | ••• |     |     | <br> |     | 132 |

| Am29C517 Family          | ••• |     |     | <br> |     | 132 |

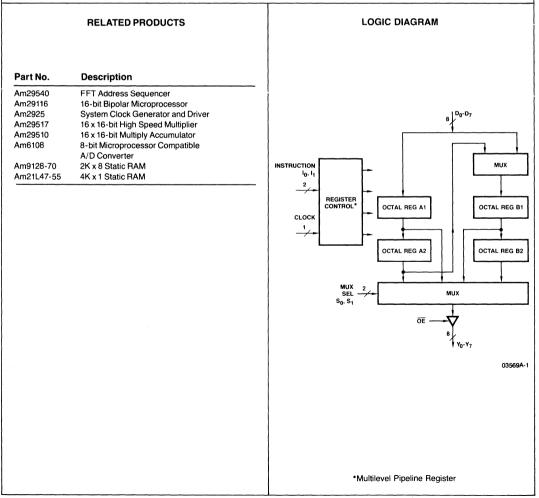

| Am29520/521              |     |     |     | <br> |     | 133 |

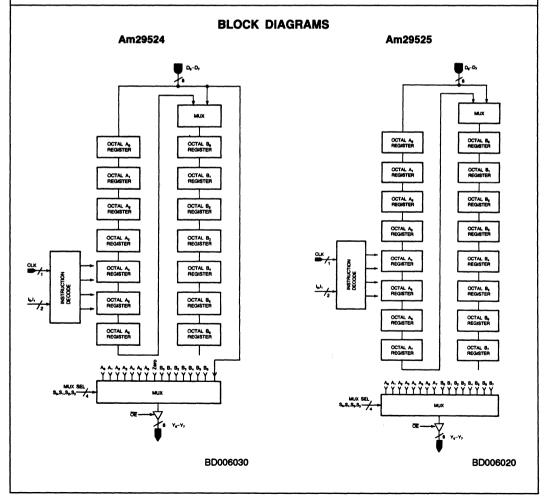

| Am29524/525              | ••• |     |     | <br> |     | 134 |

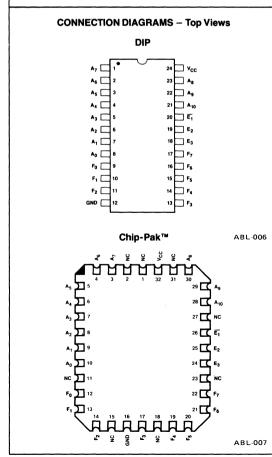

| Am29526/27/28/29         | ••• |     |     | <br> | ••• | 135 |

| Am29540                  | ••• |     |     | <br> |     | 136 |

| Am29323                  | ••• |     |     | <br> | ••• | 137 |

| Am29325                  | ••• |     |     | <br> |     | 138 |

| Am29331                  | ••• |     |     | <br> | ••• | 139 |

| Am29332                  | ••• |     |     | <br> |     | 140 |

| Am29334                  | ••• |     |     | <br> |     | 141 |

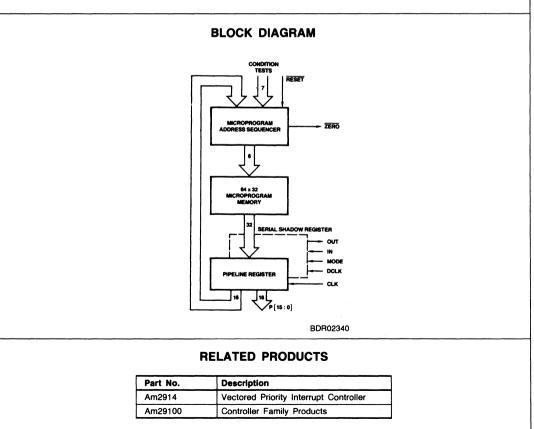

| Am2910A                  |     |     |     | <br> |     | 142 |

| Am29C10A                 |     |     |     | <br> | ••• | 143 |

| Am29112                  | ••• |     |     | <br> |     | 144 |

| Am29C116                 |     |     |     | <br> | ••• | 145 |

| Am29PL141                |     |     |     | <br> |     | 146 |

| 7. APPENDIXES            |     |     |     | <br> |     |     |

| Appendix 1               |     |     |     |      |     | 1-1 |

| Appendix 2               |     | ••• | ••• | <br> | ••• | 2-1 |

| Appendix 2<br>Appendix 3 | ••• |     |     | <br> | ••• |     |

| Appendix 3<br>Appendix 4 | ••• | ••• |     | <br> |     | 3-1 |

|                          | ••• |     | ••• | <br> | ••• | 4-1 |

| Appendix 5               | ••• | ••• |     | <br> | ••• | 5-1 |

| Appendix 6               |     |     |     | <br> | ••• | 6-1 |

| Appendix 7               | ••• | ••• |     | <br> | ••• | 7-1 |

#### CHAPTER 1 INTRODUCTION

#### What Is an Array Processor?

In recent years, Array Processing has become an increasingly significant aspect of computing. What once was a mysterious art, is now becoming common practice. Array processing is a form of computing that uses specialized hardware for special results—the array processor. This machine is characterized by its ability to handle many arithmetic computations at high speed. In other words, it is a "number cruncher." However, the specialization goes beyond a powerful hardware arithmetic unit. The machine invariably performs best when the data it is processing is structured in an array, such as a matrix or vector. Hence the name, Array Processor.

#### How Do Array Processors and General-Purpose Computers Differ?

Array processors and general purpose computers differ in a number of important aspects. The general purpose computer is usually of the classical Von Neumann architecture that was implemented by Mauchley and Eckert in the ENIAC machine, which became the first electronic Stored Program General Purpose Digital Computer. This machine had a memory area that allowed instructions and data to be intermixed. Conversely, array processors have separate memories for instructions and data (Harvard architecture). There may in fact be separate data memories for coefficients and variable data. The machines tend to be highly parallel, to allow for simultaneous multiplying and adding in the arithmetic section, while also performing address calculations for retrieving and storing the required data values.

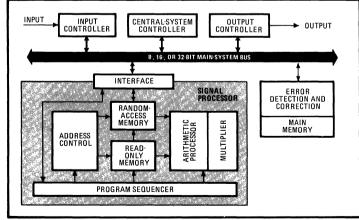

## What Is the Usual Architecture of Array Processors?

While there is no one standard architecture for all array processors, there are a number of characteristics that make the machine recognizable as an array processor. In addition to the above mentioned feature of separate data and instruction memories, pipelining is a common architectural attribute. This technique consists of placing intermediate registers in the data path, breaking up long combinatorial delay paths into shorter paths terminating in registers. The rate at which these registers can be clocked determines how fast the system runs. The register clock rate is obviously dependent upon the delay time of the operation preceding it. Pipelined systems have 'latency', which is the number of clock cycles that passes before the first valid result appears, but this value will generally be low compared to the large number of calculations performed.

Array processors also have dedicated hardware multipliers as part of their powerful arithmetic sections. Hardware floating point arithmetic may also be available, whereas some machines may have shifters to accomodate block floating point, and others may be dedicated to integer operation only. The basic operations that consume most of the processing time in matrix operations are multiplication and addition, as well as accessing the actual data values. Thus the architecture tends to be optimized for these operations.

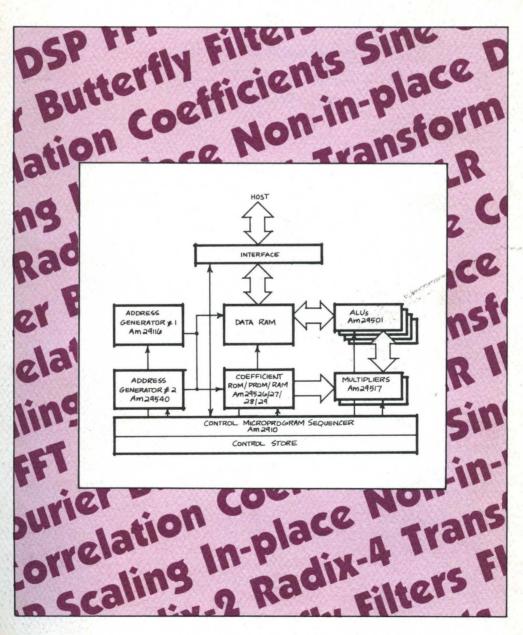

Microprogrammed architectures tend to be popular in array processing machines. This is the familiar AMD 2900 family "bit-slice" structure that allows a machine to be constructed from "building blocks" of ALU, sequencer, memory access and other required functions, without any predetermined instruction set or architectural constraints that might be imposed by fixed-instruction devices. Microprogramming is the technique of giving a machine its instruction set by means of microinstructions stored in a high speed memory and accessed by a special sequencer. These microinstructions operate at the primitive level of register, bus, and ALU function control. Since the control store is a memory, machine behavior may be modified by changing one or more of the microinstruction bits or words. The technique leads to an extremely flexible, often very high speed, implementation.

#### Where Are Array Processors Used?

If array processors are indeed so powerful, then one might reasonably ask why they don't replace general purpose machines. While array processors do an excellent job of handling their specialized type of problem, they are rather clumsy when confronted with problems that require a lot of branching within the program, which is where the general purpose computer performs so well. So rather than replacing the general purpose computer with an array processor, the tendency is to create an enhanced machine by using an array processor as a peripheral, as an 'accelerator' to the arithmetic-intensive portions of problems.

Array processors have traditionally been implemented in peripheral fashion and as specialized Super Computers that had array processing type architectures. This latter class of machine tended to be extremely expensive, but very powerful. The peripheral array processor was such a desirable approach that a number of companies make their entire livelihood from offering such devices. These peripheral array processors, or accelerators, generally attach to the bus or I/O structure of a scientific minicomputer. Now a tendency is evolving to offer array processors as options on engineering work stations, or even as option boards for personal computers.

Various types of problems lend themselves to array processing solutions, and so they are considered here. We wish to distinguish array processing by the type of hardware solution required, rather than the end application. Thus, robotics controllers, radar and sonar processors, flight simulators, graphics terminals, communications processors, medical analyzers, intelligent vision systems, and speech recognizers are all of interest here. If the problem is solved using multiply-and-add intensive algorithms, and the data and coefficients are structured in arrays, then we have an arrav processing application.

#### **Digital Signal Processing**

Digital signal processing is treated here as a subset of array processing because of the similarities that exist in the hardware and algorithms. The DSP engine tends to be more specific in its design and is generally imbedded in other hardware. DSP also tends to start out with a "live" analog signal, which is A/D converted, processed, and may or may not be converted back to analog. One could put an A/D converter in front of an array processor board and solve DSP problems.

#### What Is in this Book

We have attempted to collect in this book background and applications material that will motivate and guide the independent study of Array Processing. This book does not attempt to be a comprehensive text on the subject, but tends to emphasize the practical aspects of building array processor boards, implementing FFT's and FIR/IIR filters, selecting appropriate hardware, and writing microcode.

Finally, note that the devices whose data sheet summaries are included here are not only suitable for array processing applications. For example, for a fast eight-bit ALU with multiple I/O ports, the Am29501 is ideal. The part certainly won't be aware of what type of problem it is solving, so this should not limit the innovative spirit of the design engineer. For more information on the devices and systems described herein, contact your local AMD sales office, or AMD Headquarter Applications Department (408) 982-6266.

#### CHAPTER 2 NUMBER SYSTEMS

#### 2.1 Fixed Point Numbers

A binary number is an ordered set of binary digits (bits), each of which has a value 0 or 1. Each bit,  $b_i$ , is assigned a binary weight,  $2^i$ , and the value of the number is the sum of the weighted digits.

$$V = \sum_{i} b_{i} * 2^{i}$$

The simplest form of binary number is the unsigned integer. In an N-bit unsigned integer the index, i, ranges from 0 to N-1. The value is given by:

N...1

$$V_{integer} = \sum_{i=0}^{N} b_i * 2^i$$

The range of V is from 0 to  $2^{N}-1$ . This type of number has two obvious limitations; it cannot represent quantities which are negative or fractional. There are many ways to represent negative numbers. The simplest method is to use an unsigned number to represent the magnitude, and a flag to indicate the sign. Not suprisingly this scheme is known as signed-magnitude. In an N-bit representation, the most significant bit,  $b_{N-1}$ , is taken for the flag, with a 0 signifying positive, and a 1 negative. This leaves N-1 bits for the magnitude, giving a range from  $-2^{(N-1)+1}$  to  $+2^{(N-1)-1}$ . The value is given by:

$$V_{sign magnitude} = (-1)^{b} N-1 * \sum_{i=0}^{N-2} b_{i} * 2^{i}$$

An idiosyncrasy of signed-magnitude numbers is that there are two representations for zero, positive and negative. A similar scheme, which shares this characteristic, is one's complement. In one's complement, negative numbers are represented by inverting all bits of an unsigned number representing the magnitude. In order to distinguish positive and negative numbers, the magnitude range is restricted such that it can be expressed in N-1 bits. Thus the most significant bit is 0 for a positive number, and 1 for a negative number. One's complement numbers differ from signed-magnitude numbers only in that the magnitude bits are inverted in negative numbers.

Obviously, the range of numbers represented by a

one's complement number must be the same as for signed-magnitude numbers. The value of a one's complement word may most easily be determined by treating it as an unsigned word, after having inverted all bits if the most significant bit is 1, in which case the value is negative. Alternatively, the value of the magnitude bits may be calculated, and if the most significant bit is 1,  $2^{(N-1)-1}$  subtracted from this value.

V1's complement = -b<sub>N-1</sub> \* 2<sup>N-1</sup> - 1 +

$$\sum_{i=0}^{N-2}$$

b<sub>i</sub> \* 2<sup>i</sup>

A simple technique by which negative numbers may be represented without double representation of zero, is to add to the desired value the magnitude of the most negative representable number. This gives a positive number which may be represented in the unsigned format. The value of the number may be obtained by simply reversing this process. This scheme is known as offset binary, or excess-M, where M is the number added. The number M is often, but not always a power of two.

$$V_{\text{excess }M} = -M + \sum_{i=0}^{N-1} b_i * 2^i$$

The special case, where  $M = 2^{(N-1)}$ , has the property that all negative numbers have a most significant bit which is 0, while zero and all postive numbers have a 1. Inverting this most significant bit leads to a scheme known as two's complement, which may be interpreted in several ways. The most significant bit is often treated as a sign flag, as it is in signed-magnitude. If the sign bit is 1, the number is negative and the following serial process is applied to convert it to an unsigned number representing its magnitude. Starting at the least significant bit, the bits are inspected in turn until the first 1 is encountered. This and all lesser significant bits are left unchanged. All more significant bits are inverted. This process operates in both directions, converting a negative number to a positive number of the same magnitude, and vice versa. It may be viewed as inverting the number (one's complement) and incrementing, or as subtracting the number from  $2^{(N-1)}$ .

$$V_{2's \text{ complement}} = - (b_{N-1} * 2^{N-1} - \sum_{i=0}^{N-1} b_i * 2^i)$$

$$= -b_{N-1} * 2^{N-1} + \sum_{i=0}^{N-2} b_i * 2^i$$

Inspection of this formula shows that the magnitude of the sign bit's weighting is consistent with its position if the number were unsigned, but that the weighting is negative. This is an important conclusion, and leads to the most useful interpretation of two's complement numbers; they are identical to unsigned numbers except the most significant bit is weighted negatively. The range of values which can be represented by an N-bit two's complement number is -2(N-1) to +2(N-1)-1.

Any of the above schemes may also be used to represent fractional numbers. This is achieved simply by adopting a convention that the weighting of the least significant bit is  $2^{(-P)}$  rather than 20, and adjusting the other weights accordingly. Conceptually, this locates the binary point P bits from the least significant end. Because such a convention must be chosen in advance, and adhered to for all numbers, this is known as a fixed point number scheme. Other schemes, where the number contains a parameter locating the binary point, are known as floating point.

#### 2.1.1 Fixed Point Operations

Three basic operators are described here: addition, subtraction and multiplication. Only unsigned and two's complement formats are described in detail. They are the two formats most commonly used in fixed point operation. Signedmagnitude and offset binary are commonly used in floating point (see below), and are usually treated in fixed point by converting them to unsigned or two's complement, performing the operation and reconverting. One's complement is not in general usage.

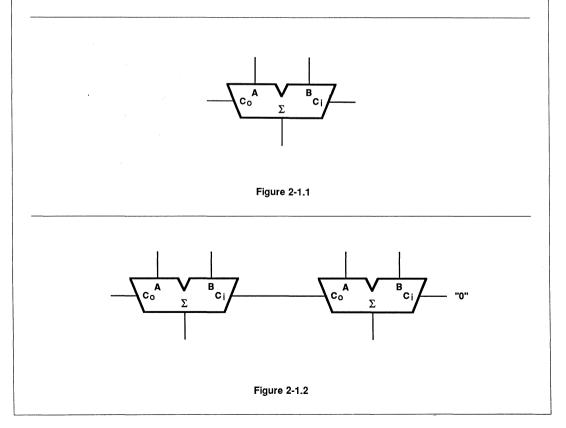

Addition of unsigned numbers is most easily performed by an iterative process known as ripple carry. The iterative block is shown in Figure 2-1.1. This has three inputs, which are equally weighted. Two of these are for operand bits,  $A_i$  and  $B_i$ , and the third is a carry input,  $C_{i-1}$ . The two outputs may be considered as a 2-bit word, representing the number of 1's present at the inputs. The unit weighted bit is the sum output,  $S_i$ , and the bit with weight two is the carry output,  $C_i$ . In cascade, the carry output of one cell becomes the carry input to the next more significant cell, maintaining the equal weighting in that cell, Figure 2-1.2.

The carry input to the least significant cell,  $C_{-1}$ , is assumed to be 0. For the complete multi-bit adder, for each pair of input bits  $A_i$  and  $B_i$ , there is one output bit,  $S_i$ . This new number is the sum. The characteristic that each carry out must be generated in turn before higher bits can be determined leads to the name "ripple carry."

It is also possible to generate the carry inputs to each cell without waiting for the ripple. Each cell is capable of creating a carry into the next cell in two ways; it can generate a carry if both  $A_i$  and  $B_i$  are 1s or it can propagate a carry if either  $A_i$  or  $B_i$  is a 1 and the carry input  $C_{i-1}$  is a 1. This is called "lookahead carry" and can be expressed by the equation:

$$C_i = A_i * B_i + (A_i + B_i) * C_{i-1}$$

$C_{i-1}$  can be expanded so that the equation for a carry lookahead of two cells is:

$C_i = A_i * B_i + (A_i + B_i) * (A_{i-1} * B_{i-1} + (A_{i-1} + B_{i-1}) * C_{i-2})$

This expansion can continue until the carry is expressed entirely in terms of the inputs and each cell can produce its output without waiting for output from any other cell.

As noted above, the range of an N-bit number is limited, and it is possible to overflow this range when adding two numbers. This may be overcome by making the adder one bit longer, thus doubling the range of the output. In order to provide the additional inputs, the operands are zeroextended. Inspection of the above formulae will show that the value of the unsigned words are not affected by leading 0's. Zero-extension is also used when adding numbers of dissimilar length. This is performed in an adder long enough to handle the larger input, the other being zeroextended. When the operand inputs to a cell are both 0, as in extension to prevent overflow, the sum output is equal to the carry input, and the carry output is identically 0. This fact may be exploited to save hardware, the carry line being used directly as the extra sum.

As the magnitude bits of a two's complement number are weighted the same as in an unsigned number, the same adder scheme may be used. In the most significant cell, the bits all have the same magnitude weighting, but while the carry remains positive, the operand inputs become negative. The cell is required to output a 2-bit two's complement number, that again represents the number of 1's present at the input, but taking into account their sign. As in the unsigned case, the carry would represent the sign-bit of a one bit longer word, which allows for overflow. Appropriately, the sum bit of this cell would be positively weighted as a magnitude-bit of the new word.

Adding two's complement numbers of dissimilar length raises a question. The value of a two's complement number is not affected by adding leading 0's if the existing weights, remain unchanged. However, this gives a number with a negatively weighted bit other than in the most significant position, which does not agree with the definition. This problem is overcome by using signextension, rather than zero-extension.

In sign-extension, additional bits are added which match the sign-bit. It must be stressed, however, that these are not extra sign-bits. A two's complement word can, by definition, only have one sign-bit; the negatively weighted most significant bit. When a new sign-bit is added, the old sign-bit reverts to a magnitude bit. If the number is positive, both old and new sign bits are 0, and the value cannot be changed by altering the weighting of 0's.

If the number is negative, the reversion of the old sign-bit to a magnitude bit changes the value positively by twice its weight (from  $-2^{N-1}$  to  $2^{N-1}$ ). This exactly cancels the contribution to the value from the new, more significant sign-bit, thus leaving the value unchanged. This proceedure may be repeated, making the number as long as necessary.

This process is reversible. If the most significant magnitude bit matches the sign-bit, then the number may be reduced in length by eliminating the sign-bit, the new most significant bit becoming the sign-bit. This fact is exploited to simplify the logic in the adder. If it is known that the sum cannot overflow into the N+1th bit, the sum output of the sign-bit adder cell can be taken as the sign-bit of the N-bit word. This is logically equivalent to the sum output of an unsigned adder cell, which may be used in place of the special cell. The carries, however, are not equivalent. If overflow is possible, it may be protected against by sign-additional adder cell to give the N+1-bit output.

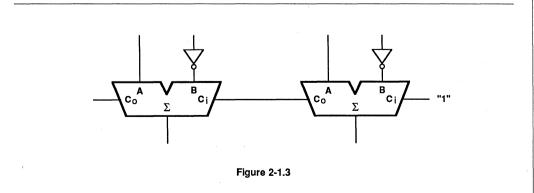

Two's complement subtraction is often described by modifying the adder, and re-interpreting the carry to become a borrow-not (analogous to decimal subtraction). This is confusing. A more straightforward explanation is that the number to be subtracted has its sign changed by being two's complemented, and the result added to the other operand, using the adder as an adder. As described above, two's complementing a number involves one's complementing it and then incrementing it. The one's complement can be performed with inverters, and the incrementation effected by entering an extra 1 in the unused least significant carry input, Figure 2-1.3. If exclusive ORs are used in place of inverters to allow controlled inversion, and the least significant carry also controlled, an adder/subtractor is obtained.

Unsigned subtraction does not really exist. The unsigned operands are converted to two's complement by adding 0 (positive) sign-bits. These are subtracted as above, giving a signed result. If this is positive, the 0 sign-bit can be dropped, reverting to an unsigned format. If it is known in advance that this is case, then it is not necessary to calculate the redundant sign-bit. This is what is sometimes referred to as an unsigned subtractor.

When adding two unsigned numbers with the result expressed in the same number of bits as the inputs, overflow is signified by a carry out of the most significant bit. In unsigned subtraction, a negative result is signalled by the absence of a carry out. In all two's complement operations, overflow is signalled by the carry out of the sign-bit being different from the carry into it. This may be detected with an exclusive OR (XOR).

Unsigned multiplication consists of addition of the partial products formed by weighting the multiplicand by each bit of the multiplier. Weighting by a multiplier bit which is 0 results in a partial product that is zero and weighting by a bit which is a 1 is a left shift of the multiplicand by a number of places equal to the bit position of the multiplier bit. A simple algorithm to perform multiplication is a shift and add procedure in which the multiplicand is shifted one bit position at a time and added to the product based on the corresponding multiplier bit and using the rules for adding operands of unequal lengths as stated in the discussion of addition above. Multiplication of two's complement numbers is the same when the rules for two's complement are applied, i.e., when the partial products are sign-extended instead of zero-extended for the shifted addition and the partial product from the multiplier sign bit is weighted by  $-b_{N-1}*2^{N-1}$  instead of  $+b_{N-1}*2^{N-1}$ .

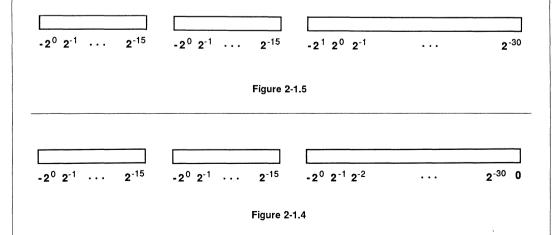

Multiplication of unsigned fractions is identical to multiplication of unsigned integers. Placement of the binary point is a matter of interpretation and does not require alteration of the algorithm, However, multiplication of two's complement fractions results in a product with different bit weights than the operands as shown in Figure 2-1.4. To obtain the same bit weights in the product as the operands it is necessary to shift the product left one position as shown in Figure 2-1.5. A product which has the same format as the operands is obtained when the less significant product is truncated or causes rounding of the more significant part. One problem with this shift is the possibility of overflow when both multiplier and multiplicand are equal to -1.0. The product is +1.0 which cannot be represented in two's complement fractional notation.

A common technique used to speed up multiplication is the Booth algorithm which examines consecutive bits of the multiplier. Whenever the consecutive multiplier bits change from a 1 to a 0, the multiplicand is added to the product with the proper bit weighting. When the bits change from a 0 to a 1, the multiplicand is subtracted; no operation is necessary when the bits are the same. This algorithm is based on the identities 3 = 2+1 = 4-1, 7 = 4+2+1 = 8-1, etc. which allow two operations (one addition and one subtraction) to replace a potentially larger number of operations (two additions, three additions, etc.). The worst case is a multiplier with alternating 1s and 0s for which there is the same number of operations as the add and shift algorithm when the multiplier is all 1s, i.e., one operation per multiplier

bit. A modification to the algorithm examines pairs of multiplier bits as shown in Figure 2-1.6 This modification is usually done to modularize hardware into a cell which can be repeated for each pair of multiplier bits.

#### 2.2 What Is A Floating-Point Number?

The numbers one encounters everyday, such as 12, 34.56, 0.0789, etc., are known as fixed-point numbers, because the decimal point is in a fixed position. Such numbers are fairly closely matched in magnitude and within about ten orders of magnitude from unity. Examples of such numbers are found in bank accounts, unit prices of store items and paychecks.

In scientific notation applications, the numbers encountered can be very large. Avogadro's number expressed in fixed-point notation is approximately

602,250,000,000,000,000,000,000.

A scientist may also use Planck's constant which would be approximately

#### 0.0000000000000000000000006626196

erg.sec. in fixed-point notation. These examples demonstrate the undesirability of writing fixed-point notation to represent numbers such as Avogadro's number and Planck's constant.

When a scientist writes the value of Avogadro's number, he writes 6.0225 x  $10^{23}$ . Similarly, he would express Planck's constant as 6.626196 x  $10^{-27}$  erg.sec.

The number 6.0225 x  $10^{23}$  is thus observed to consist of four parts:

**Sign.** The sign of the number (+ or –). The plus sign is usually assumed when no sign is shown.

Mantissa. Sometimes also known as the fraction. The mantissa describes the actual number. In the example, the mantissa is 6.0225.

**Exponent.** Sometimes also known as the characteristic. The exponent describes the order of magnitude of the number. In the example, the exponent is 23.

**Base.** Sometimes also known as the radix. The base is the number base in which the exponent is raised. In the example, the base is 10.

The parts of a floating-point number can then be represented by the following equation:

$$F = (-1)^{S} \cdot M \cdot B^{E}$$