Am29300 Family Handbook

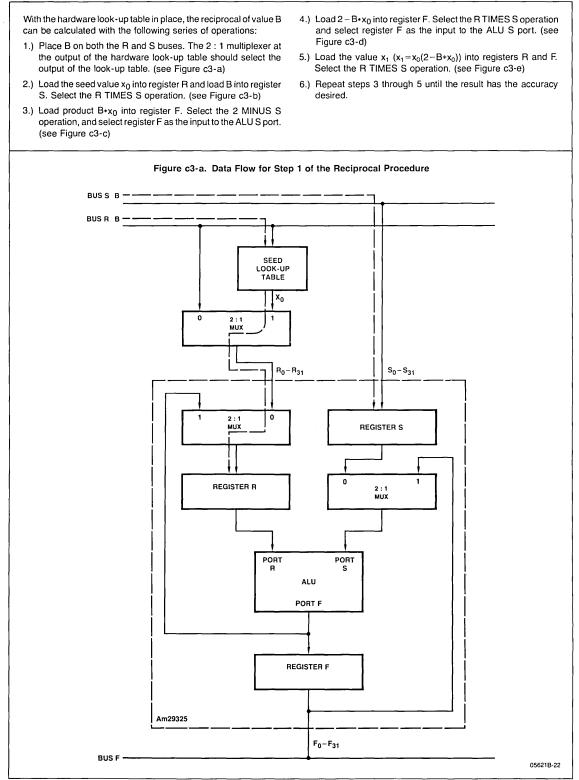

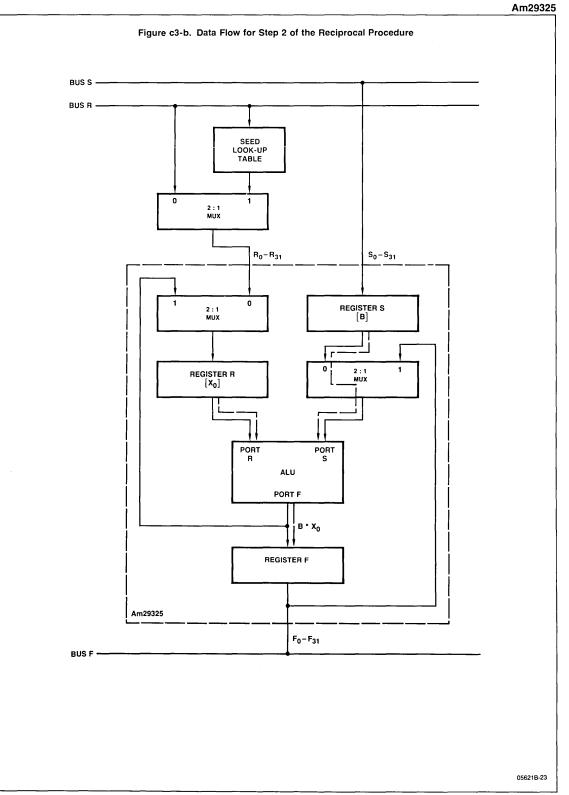

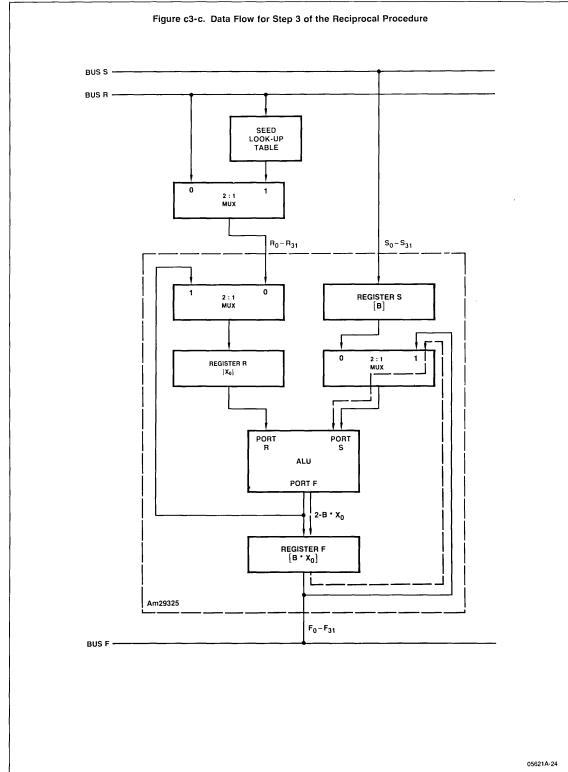

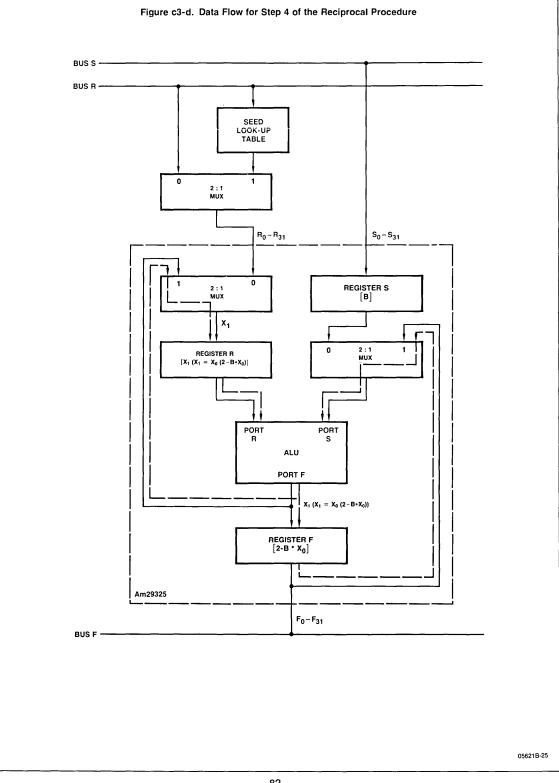

High Performance 32-Bit Building Blocks

April 1985

2

-

# TABLE OF CONTENTS

| I.   | Am29300 FAMILY OVERVIEW5                                                                                                                      |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| II.  | ARTICLES       (i) "32-Bit Bipolar Building Blocks Debut at AMD," Integrated Circuits                                                         |

| III. | BIBLIOGRAPHY43                                                                                                                                |

| IV.  | PRODUCT SPECIFICATIONS       45         • Am29325       51         • Am29331       99         • Am29332       113         • Am29334       123 |

•

# Am29300 Family Overview

Advanced Micro Devices has developed a new VLSI family to support very high performance applications in general purpose computation, intelligent peripheral controllers and array and digital signal processing—the Am29300 family.

The family features high performance, greatly increased functionality relative to earlier approaches, and a high degree of architectural flexibility.

# 32-BIT VLSI

Historically, the Am2901 made a radical departure from conventional MSI functions by integrating several elements of a CPU into a vertical 4-bit slice. The combination of memory and ALU logic in a single package offered the user added functionality, reduced package count and data-path width flexibility.

The Am29300 family reverses the trend of vertical slice partitioning by integrating *complete 32-bit functions* into single VLSI devices.

There are several reasons for the choice of a wider data path. First, cycle time is improved significantly if carry lookahead is contained entirely on the the chip. Second, certain powerful on-chip functions, such as the funnel shifter, priority encoder and mask generator are extremely difficult to expand when using vertical slices. Third, a higher level of integration leads to a more cost-effective system solution. The wider data path also affords greater I/O bandwidth, higher precision and increased memory addressability. These and other advantages contributed to the decision to make a family of *complete 32-bit functions* rather than slices.

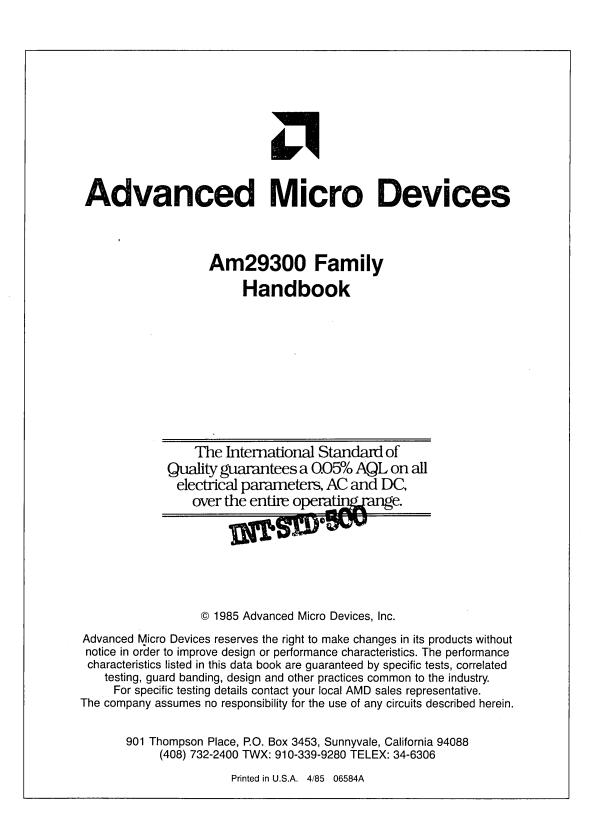

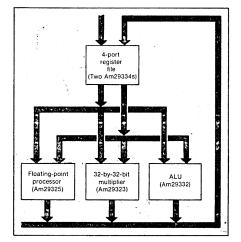

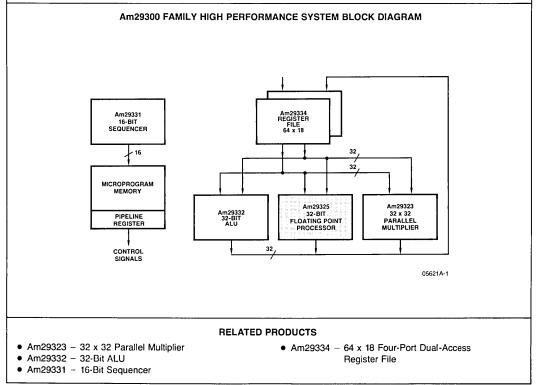

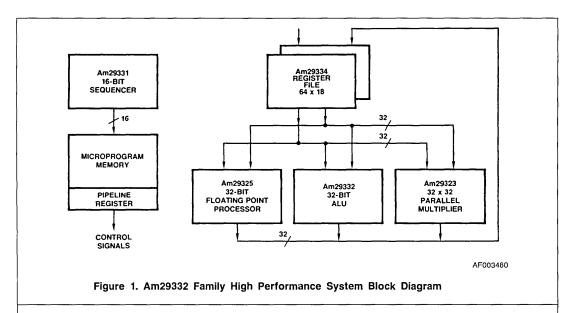

The Am29300 family currently consists of five members:

- Am29332 32-Bit ALU

- Am29331 16-Bit Microinterruptible Sequencer

- Am29334 62×18 Dual-Access Four-Port Register File

- Am29325 32-Bit Floating Point Processor

- Am29323 32×32 Parallel Multiplier

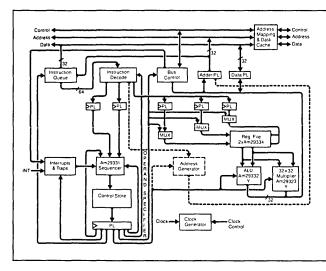

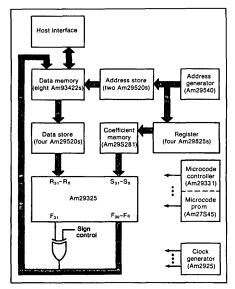

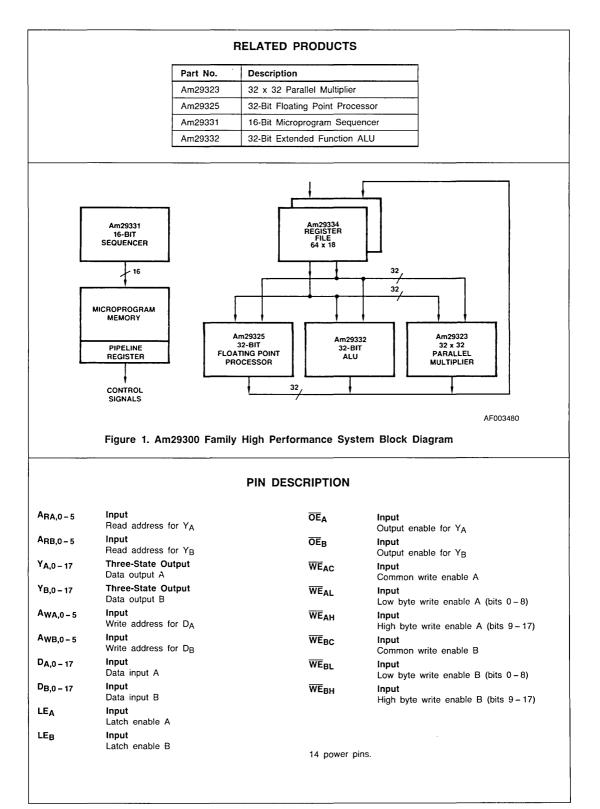

Figure 1. Am29300 Family High Performance System Block Diagram

# FUNCTIONAL PARTITIONING MORE EFFICIENT

The Am29300 family departs from vertically partitioned bit-slice functions because it is divided into larger, horizontally partitioned building blocks. The ALU no longer contains a register file. Instead, there is a more flexible stand-alone register file, the Am29334, making expansion and regular addressing much easier.

The new partitioning results in a number of benefits. The user gets a powerful processor with two uncommitted input buses and gains the flexibility of adding storage elements to these buses. The overall organization is more structured. Also, a larger power budget is available for the register file thus making it faster and bigger than if it had been in the processor chip. Functional partitioning results in an open system, giving the designer the ability to easily connect external components, e.g. memory components or arithmetic accelerators. Also, each of the Am29300 components, while designed to work together in a system, can be used as a standalone functional block.

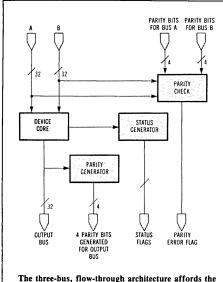

# THREE-BUS FLOW-THROUGH ARCHITECTURE

The Am29300 family features a three-bus flow-through architecture. The Am29332 ALU, Am29325 Floating Point Processor and Am29323 Multiplier all have two input buses and one output bus. This contributes to high throughput by eliminating bus bottlenecks caused by turnaround delays. It provides unlimited register file expansion and regular addressability. Moreover, the unlimited bus accessibility gives the designer the ability to configure the optimal micro-architecture for the application. If the design objectives change, the microarchitecture can be easily reconfigured. The three-bus configuration also supports concurrent processing and pipelined architectures.

# BALANCED TIMING

In previous generations of microprogrammed systems, the control path containing the sequencer has been the bottleneck because the sequencer was usually slower than the associated data path. Not so in the Am29300 family. The Am29331 sequencer has been designed so that the entire system timing is balanced between the control path and the data path leading to higher overall throughput.

# **POWERFUL INSTRUCTION SETS**

Each device in the family executes its instructions in a single cycle.

The Am29332's instruction set is symmetric and orthogonal. Symmetric means that an operation that can be executed on port A can also be executed on port B and vice versa. Orthogonal means that all operations are independent of the data type. The Am29332 can operate both on multibyte data and on variable-width field data. This regularity of the Am29332's instruction set makes it easy to create "clean" interfaces to compilers for high level language support.

The Am29331's instruction set is comprised of instructions that resemble *high level language constructs*. This makes it possible to write *structured* microprograms.

# COMPLETE INTERLOCKING FAULT DETECTION

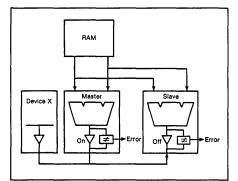

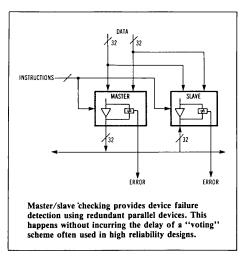

The family supports both master/slave fault detection and data path parity to enhance system reliability by ensuring data integrity and correct hardware operation.

The system features byte parity checking on the inputs and byte parity generation on the outputs of the Am29332 ALU and the Am29323 Multiplier. Also, the organization of the Am29334  $64 \times 18$  register file accommodates parity bits for each byte. The parity mechanism assures data path integrity.

Major functional blocks—the Am29332 ALU, Am29331 Sequencer and Am29323 Multiplier—also have master/slave fault detection to ensure correct device operation without having to carry parity through complex internal logic and without having to pay the resulting delay penalties. In master/slave mode, two functional units are connected in parallel with one unit performing the actual operation and the other checking the result, on a cycle-by-cycle, bit-by-bit basis.

The master is used in the normal data path. In the slave, however, all outputs become inputs, and the slave compares the outputs of the master with its own internally generated result. If the two don't match, an error signal is generated, which can trigger an interrupt at the microinstruction level. No specialized software is required. Also, the designer can choose to impose redundancy at the component or board level.

The parity and the master/slave provisions comprise a complete interlocking fault detection mechanism. Using costeffective hardware rather than expensive software, they provide a comprehensive solution for fault tolerant systems.

# PERFORMANCE/FLEXIBILITY/INTEGRATION

The Am29300 family achieves high performance and high integration but avoids architectural or pipelining restrictions. These become especially important in high performance parallel architectures or in emulations where the system is being optimized for particular instructions or processes.

The ECL-internal, TTL I/O Am29300 family minimizes the requirement for external components and achieves a *system* cycle time of well under 100 nsec.

# 32-bit bipolar building blocks debut at AMD

Alex Mendelsohn Editor-in-Chief he last six months have seen a procession of advanced microprocessors and peripheral support chips making the leap from NMOS fabrication technologies to CMOS. Although systems designers can now implement circuits with fast-running machines that dissipate less power than their NMOS forbears, true speed-demons still opt for bipolar devices.

Witness the success of the Advanced Micro Devices Type Am-29116, a microprogrammable 16bit bipolar microprocessor whose 100 nanosecond microcycle bit slice speed has been an attractive calling card in recent years for designers seeking maximum system throughput. Most designers using the 29116 haven't felt compromised by power dissipation and supply requirements the tradeoff has been a fair one.

AMD is now at it again, but in addition to bipolar speed, AMD's latest chip set features an open 32-bit wide "building block" register file/ALU architecture that lends itself to unique general purpose implementations, freeing you from cast-insilicon approaches.

Targeting designers looking for blazing speed for projects like

parity-equipped fault tolerant processors, advanced graphics systems, image processors, large register file based RISC machines, and high-throughput simulators, AMD has just announced a "superset" of the flexibility of the venerable 29116. This first ECL-internal/TTL-I/O 32-bit architecture is the 29300 Family.

Partitioned for performance into five individual bipolar devices, the 29300 offers a one-chip ALU with access to three 32-bit buses. You, as a designer, can thus arrange your own unique system as you see fit. The 29300 busing provides a "flow through" architecture and virtually unlimited bus accessibility and register file expansion. No bidirectional busing is used, and apparently AMD chip designers were not concerned with conserving package pins.

An all-important orthogonal instruction set facilitates structured micrprogramming, permitting the machine to execute a number of functions on each microcycle in a regular symmetric way. Pins are available to tell whether an operation is byte width or a 16-, 24-, or 32-bit operation. No coding changes are required to perform at the byte or at the 32-bit level. The compiler is therefore very easy to generate, without exception handling complexities; a high level language interface is thus a "clean" one.

All instructions execute in single machine cycles. During one such cycle a 29300 system can do as much as it would take six or seven cycles to perform in one of today's MOS machines. For example, a shift and rotate could

INTEGRATED CIRCUITS MAGAZINE

NOVEMBER 1984

Reprinted with permission from Hearst Business Communications, Inc., November 1984, Integrated Circuits, all rights reserved.

be combined with logical-ORs, something a 68020, even with its on-chip cache, would need multiple cycles to perform.

Functionally, the 29300-family is horizontally partitioned to provide faster processing than previous vertically partitioned bit-slice approaches. Five bipolar VLSI circuits are to be introduced between now and next summer. AMD has already seen first silicon on one of the elements, a 32bit math processor.

The five ICs are: a 32-bit arithmetic logic unit, dubbed the Am-29332; a four-port dual-access 64-by-18 register file—the Am-29334; the aforementioned high speed floating point processor, the Am29325; a Type Am29323 32-bit parallel multiplier with two Read and two Write ports; and lastly, a Type Am29331 16bit microprogram sequencer. Let's take a look at each. The 29332 arithmetic logic unit (ALU) is a 32-bit wide nonslice three bus IC that allows integration of functions that normally don't slice. Examples of these include shifters, priority encoders, and mask generators. Instructions are tailored to take advantage of these internal blocks (offering field logical operations or concatenation across word boundaries).

#### The Heart of the System

Cycle time for all 29332 ALU instructions are equal. Pipelined registers are avoided so that individual designers can build-in pipelining or not, according to their own schemes, paying no penalties for branching. The three bus architecture also allows ready design of parallel and reconfigurable architectures. The off-chip register file ensures unlimited expansion and regular addressability. The 29332 also includes a unique 64-bit in/32-bit out funnel shifter block. It allows n-bit shift-up/down as well as a 32bit barrel shifts (see *Integrated Circuits Magazine*, Jan./Feb. '84, page 34). The funnel shifter also permits 32-bit field extraction in conjunction with the mask generator. These unique functions can be combined with all logical instructions within the same cycle and with no increases in cycle time.

Shift control for the above functions can come from an external source or from the internal status register (generated on a previous instruction)—a useful feature for logical operations between non-aligned variablelength fields. It can also be used for floating point normalization.

Use of internal position and width status register fields can save eleven bits of microcode width. As mentioned previously,

#### INTEGRATED CIRCUITS MAGAZINE

### A LOOK AT COMPETITIVE ALUS

In evaluating the new AMD 29300-family architecture, it may pay to look at some of the competitive devices recently introduced by other IC vendors. For example, Texas Instruments has been expanding their low-voltage high speed small-transistor advanced Schottky (AS) bipolar line to include a 20 MHz 8-bit slice.

Their 74AS888 features a parallel 8-bit ALU with expansion inputs and outputs, a 16 x 8 register file, and handles bit, byte, and word length operations. When used with their new 25 nanosecond 74AS890 microinstruction sequencer, architectures can be built without limit (i.e. 64-bits wide).

The 74AS890 controller has an address width of 14-bits, and can thus address up to 16,384 words of microcode. These ICs are designed to implement systems with narrow microcode word widths and very high throughput, and as such, should compete favorably.

Also in the realm of ALUs, but in MOS technologies, Analog Devices (Norwood, Massachusetts) has recently announced their 16-bit Type ADSP-1201. This device, as the name suggests, is targeted at digital signal processor (DSP) designers. Similarly, Weitek, of Santa Clara, California, introduced an NMOS two chip set early this year; their 32-bit data path Type WTL1032 multiplier and WTL1033 ALU.

Both Weitek's and Analog Devices' ICs, while excellent for DSP applications, are somewhat limited for non-DSP circuits because of their extensive pipelining. Both include registered inputs and outputs, thus they both require more than one cycle to get results "off" the chip. Operands are entered, and the results taken, from the Weitek chip in about 125 nanoseconds, for example.

The ADSP-1201 also includes a single port 8-word register file in each data path, however this precludes expandability. The chip does include a barrel shifter, but use of the shifter and the ALU combinatorially in the same cycle isn't possible.

In contrast, 29332 ALU designers avoided the use of pipelining. There are no builtin penalties for branching. The simplicity of the three-bus ALU should also allow very easy implementation of parallel or reconfigurable architectures. Another consideration in the comparison: the 29332's offchip register file allows unlimited and regular addressability. In contrast, the ADSP-1201 has a single port eight-word register file in each input data path. These are not expandable.

The 29332 supports one-, two-, three-, and four-byte data for arithmetic and logic functions as well as multiprecision arithmetic and multiplebit shift operations. Neither Analog Devices' nor Weitek's ALUs support all data types for arithmetic operations. Neither can they support field logical operations as used in graphics.

P.

DR

$\mathsf{D}_\mathsf{A}$

P۸

INTEGRATED CIRCUITS MAGAZINE

The vanguard of the 29300 family is the 29325 floating point processor. Here's a photomicrograph of first silicon.

the 29332 also supports one-, two-, three-, or four-byte data as well as multiprecision arithmetic and multiple bit shift operations.

For logical operations, the 29332 can accommodate variable length fields up to 32-bits. When fewer than four bytes are selected, the unselected bits are passed to the destination without modification. Support of all data types is highly important for arithmetic operations; field logical operations are very necessary for applications such as graphics.

Support is also provided for two-bit at a time modified Booth's algorithm multiplication and one-bit at a time divide with both signed and unsigned integers. Parity checking on data inputs and generation on outputs, plus master/slave fault detection enhances applicability in fault tolerant systems.

# Separate Register File

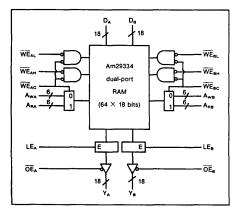

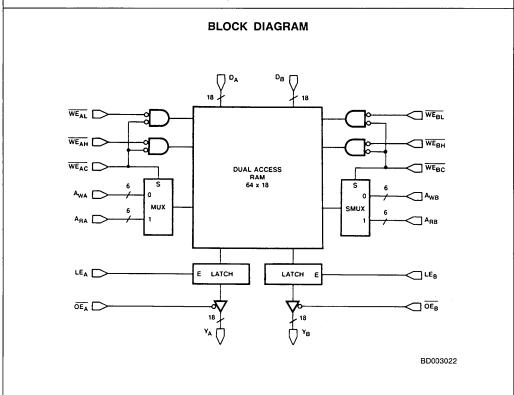

The Type 29334, the 20 nanosecond access time RAM register file chip, supports these parity equipped designs. A byte parity storage feature, with a width of 18-bits, provides consistency with the ALU for parity check and generation. No other multiport register file presently on the market offers this parity storage.

The 29334, with its two Read and two Write ports, can read and write simultaneously on both. It is cascadable to support wider word widths or to form deeper register files, or both. You can use multiple 29334's in an interleaved configuration, or you can build one file as high and as wide as you like. Write enable timing and multiplexer selection are derived from a single-phase clock; the MUX eliminates one "layer" of I/O delay. Also, individual byte write enables allow choice of either an 8- or 16-bit data interface.

#### Math Chip Here and Now

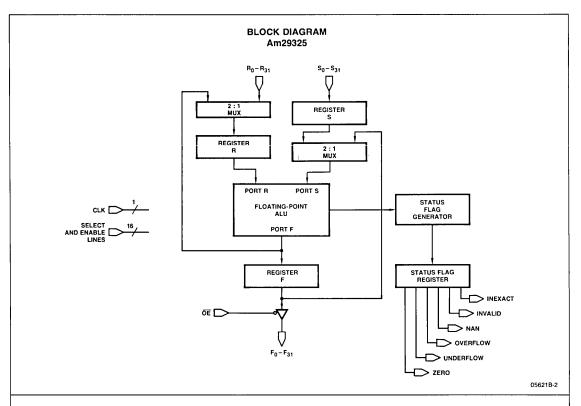

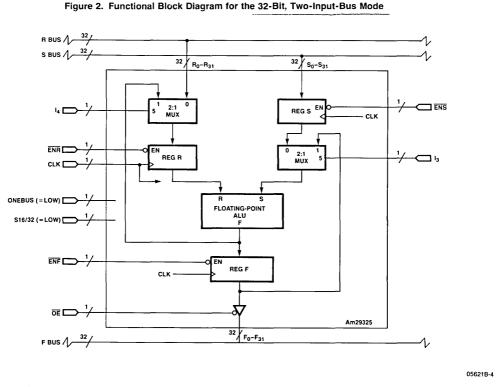

The single-chip 144-pin Type 29325 floating point processor the first VLSI family member to emerge from fab—performs very fast 32-bit single precision addition, subtraction, and multiplication. It conforms to the proposed IEEE P754 standard and also to Digital Equipment Corporation's (DEC) format.

Options for conversion between the 32-bit integer format and floating point are available, as are operations for converting between IEEE and DEC. Executing all instructions in a single cycle, the 29325's throughput equates to 8 MHz, regardless of the algorithm.

The 29325 features three 32bit wide non-multiplexed buses for high I/O bandwidth. The use of two 32-bit operand feedforward data paths on-chip support accumulation operations, including sum-of-products and Newton-Raphson division. All buses are registered and each has a clock enable. Registers can be independently transparent to eliminate unwanted pipelining if desired. Software synchronization of pipelining is not needed because there are no multi-stage pipeline structures.

#### Go Forth and Multiply

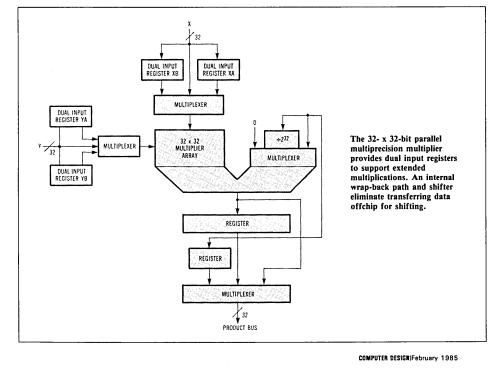

Although the Type 29323 multiplier chip is still in the design stage, and no working silicon has yet been seen, AMD chip designers are confident that the device will be able to perform a 32 by 32 multiply in only two cycles. They're hoping to achieve an 80 nanosecond clock-to-clock multiply time.

With two 32-bit input and one 32-bit output ports, there is no need to multiplex operands. The chip will be controlled by only one clock with individual register enables, thus leading to simple timing requirements. Dual input port registers will enable multiprecision multiplication (a 32-bit multiply will occur in one cycle; a 64-bit in four).

Like the floating point chip, the 29323 multiplier's registers can be made independently transparent tc eliminate unwanted pipeline delays in non-pipelined systems. A master/slave mode allows two 29323's to operate in parallel. A parity check/ generate feature will catch interdevice errors.

#### **Advanced Program Control**

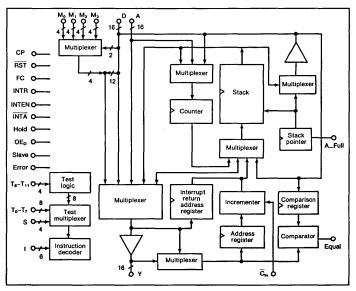

The remaining chip in the 29300-family will be the dual bus 29331 microprogram sequencer. Controlling the sequence of microinstructions stored in microprogram memory, the 29331 aids structured microprogramming, handling sequential execution, branches, subroutines, and loops. It can access up to 64 Kwords of microcode, and integrates otherwise external critical-path conditional

#### INTEGRATED CIRCUITS MAGAZINE

test logic into internal high speed gates to improve microcycle time. There is no branching penalty.

The 29331 generates inequality evaluation branch conditions from four ALU status bits. It features an eight external-test-condition multiplexer plus parity control. An address comparator allows breakpoint in the microcode for debug or for gathering run-time statistics. This latter feature is something AMD has identified that most systems builders want but, so far, no vendor has implemented in silicon.

Other 29331 features include four sets of 4-bit multiway inputs to implement table look-up or to use external conditions as part of a branch address, master/ slave error checking for parallel sequencer operation, real-time interrupt support, trap handling at any microinstruction boundary, and a 32-level stack. The latter provides the ability to support interrupts and loops as well as subroutine nesting. The stack can be read to support diagnostics or to run multi-tasking at the micro-architecture level. The chip's instruction set is designed to resemble high level language constructs.

# **Development Support**

AMD expects most customers will use Tektronix, Hewlett-Packard, or AMD development systems for microcode development, and AMD is introducing "M29" software that will run on VAX-size mini.

M29 uses a description language that can describe a variety of architectures. It consists of three programs: a microinstruction definition program, an assembler, and a relocation linker.

The definition program creates a file that describes each micro-

instruction field by field, defining its name and length, its fields and variations in format, and allowable values for each field. The file allows the assembler to be retargeted to support many different instruction formats.

The assembler allows you to create microcode in several styles depending on the amount of effort invested in the design of macros. The linker for the assembler is used to relocate assembly modules and link them together. Its output can be loaded into a writable control store or burned into PROMs.

For more details call AMD at 408-732-2400, or use the Reader Service card.

INTEGRATED CIRCUITS MAGAZINE

# 32-Bit ICs Enhance Array Processor Performance

by Dave Wilson, Executive Editor

uture high performance processors/controllers require faster processing rates, higher machine densities, and greater system reliability. The need for virtual memory support, increased memory bandwidth and improved precision means a growing demand for 32-bit performance. Advanced Micro Devices' (Sunnyvale, CA) Am-29300 family has been developed to address these needs in general purpose computation, intelligent peripheral control, and array and digital signal processing applications.

The Am29300 family evolved from the industry standard Am2900 bit-sliced family. A great number of the functional enhancements are the result of user feedback from existing Am2900-based designs. On the other hand, the Am29300 family has been designed from the ground up for higher performance and architectural flexibility. The Am29300 devices have internal ECL circuitry for speed, yet maintain TTL compatible inputs/outputs for ease of interface. A 32-bit Am29300 microprogrammed system has a system microcycle time of 70 to 80 nsec. In addition, the devices have regular and orthogonal instruction sets and contain built-in primitives to tackle crucial system issues such as fault tolerance/ detection.

AMD offers several support chips for Am29300-based designs. For instance, systems requiring a 32-bit data path can be configured with the following devices: the Am29332 Integer Processor, a 32-bit arithmetic/logic and shift unit with builtin support for variable byte and bit field Photomicrograph of AMD's 29325 floating point processor.

data; the Am29334 Register File, a true dual-ported register file which allows simultaneous read and write accesses, organized as 64 words by 18 bits; the Am29323 Parallel Multiplier, a 32 × 32 parallel multiplier capable of multiple cycle expansion to  $64 \times 64$  and  $128 \times 128$ without the use of external logic; and the Am29325 Floating Point Processor, which performs single cycle addition, subtraction, multiplication and conversions, using either the single precision IEEE or DEC format. Each of the above devices can be used in conjunction with or independent of the others. These devices can be configured in a variety of ways to tailor them to a specific application. All of the data path elements have single cycle instructions. The microinstructions are typically supplied by the control path. The key control path element is the Am29331 Microprogram Sequencer which supplies the next address to the control memory. The 16-bit Am29331 is also capable of handling interrupts or traps at the microinstruction level

Historically, the Am2900 devices have been partitioned vertically, combining register file and ALU in a single package. The Am29300 devices, however, are partitioned horizontally, so that the register file is separated from the rest of the data path elements. The functional partitioning has two advantages. First, it allows for an easily expandable register file space. Second, it also enables arithmetic accelerators to add to the data path.

A major disadvantage of a bit-sliced architecture is the time lost in transmitting carries from one chip to another. To avoid this, the Am29300 family arithmetic elements are constructed with full internal 32-bit data paths. Although the ALU has limited carry capability for cascading, it will normally perform multi-precision expansion through multiple cycle opera-

DIGITAL DESIGN & DECEMBER 1984

Reprinted with permission from Digital Design, Vol. 14, No. 11; copyright Morgan-Grampian Publishing Company, November 1984.

tions. The other data path elements use this scheme exclusively.

A second benefit of the full 32-bit data path elements is that they can include functions not easily sliced. Two classic examples of this are shift arrays and multipliers. Both of these require an unacceptable amount of information to be transferred between slices. Other functions, such as prioritization and mask generation for byte and word operation, while feasible, expand clumsily. All these functions are provided in the Am29300 family, either in the ALU, or in the 32-bit multiplier.

#### Three-Bus Flow Through Architecture

In order to fully exploit the 32-bit data path devices, it is necessary to provide adequate data transfer bandwidth. In the Am29300 family this is achieved through the use of a three-bus architecture. The Am29334 Register File is a true twoported file, allowing simultaneous access from each port. Output latches are provided to allow read and write operation within a single clock cycle. Each of the data path elements has two 32-bit operand input buses which can be sourced from the register file. The data path elements also have a 32-bit result bus which can return data to one input of the register file. With this organization, a three-address register to register operation may be completed within a single clock cycle.

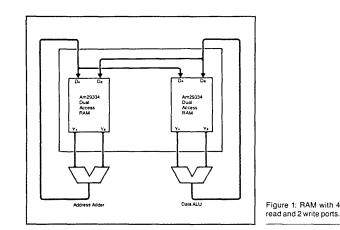

Two-register files may be used to achieve still higher bandwidth. Connecting the input ports in parallel, and writing duplicate data into the two files, allows four operands to be sourced simultaneously from a single database. Two results may also be written into the file simultaneously. This provides adequate data transfer for two groups of arithmetic elements to operate concurrently (Figure I). The flexibility of this three-bus architecture also allows the use of these parts in other configurations. In a signal or array processing application, the multiplier and ALU may be placed in series rather than parallel. This provides a "free operand," allowing the three-operand summation of products operation to proceed at maximum speed.

The cycle time of a microprogrammed system is dependent on both the control path (i.e., sequencer and microprogram memory) and the data path (i.e., register file and ALU). Traditionally, the system bottleneck has been the control path, especially the timing paths associated with conditional branching. The 16-bit Am29331 Microprogram Sequencer has been optimized for speed, so that the data path and control path timing are balanced. The previously external condition code multiplexer, test logic generator and polarity control logic (usually the system critical path), have been integrated on chip. Moreover, the Am29331 has several built-in features which enable it to respond to external stimuli with minimum latency. The sequencer can perform a 16-way branch, dependent on the simultaneous occurances of four external test conditions. The Am29331 Microprogram Sequencer can also handle interrupts or traps at the micro-level.

The system ARM concept (Availability, Reliability and Maintainability) is becoming increasingly important. The Am29300 addresses the problem of fault detection at the device level by a combination of two techniques – parity and master/slave. Parity at the byte level is generated on the 32-bit result bus of the data path elements, stored in the Am29334 Register File, and checked again going into

any of the operand buses of the data path elements. Thus any interconnection failure in the data bus can be detected. The choice of even parity scheme also allows detection of an open TTL bus which defaults to high impedance all "ones" state, an error condition. For functional verification, a master/slave mode of operation permits two units to be connected in parallel, with one unit actually performing the computation and the other checking the results on a cycle by cycle basis. The slave unit therefore verifies correct operation of the master. In addition, the master unit checks its internal result with the data on the output bus to ensure that no other device is driving the external bus when it is not supposed to be. Any fault detected can trigger an interrupt at the microinstruction level. Unlike previous redundant schemes, no specialized software is required. No system degradation results from the communication between the redundant functional units. This combination of parity checking and master/ slave operation, which uses cost-effective hardware, rather than expensive software. is the key to future redundant system design.

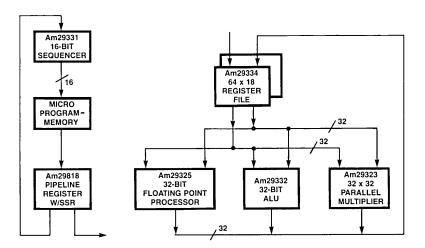

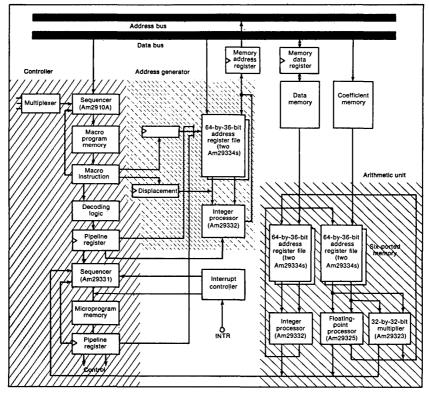

The functional and performance requirements of a general purpose superminicomputer and a digital signal processor are vastly different. Yet with functional partitioning and a simple three-bus architecture, the Am29300 devices are suited to address the needs of a diverse spectrum of applications. Figure 2 depicts an example of a microprogrammed supermini built out of Am29300 components. The data path consists of the Am29332 Integer Processor, the Am29323 Parallel Multiplier as an accelerator, and the Am29334 Register File. In this configuration, address calculation and data computation are performed in series. Alternatively, the Am29334 can be paralleled to yield effectively a six-ported register file, allowing four read accesses and two write accesses per microcycle. Another Am29332 can be dedicated to perform address computation concurrent with the normal ALU execution, sharing the register space. With a 70 to 80 nsec microcycle time, a processor/controller subsystem capable of several times the performance of a typical supermini can be built with the Am29300 parts, occupying far less board space and dissipating significantly less power.

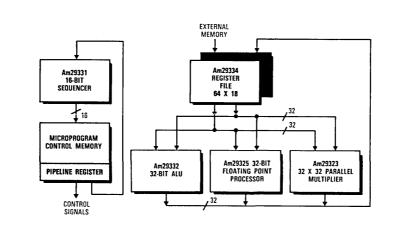

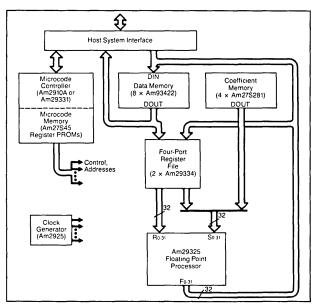

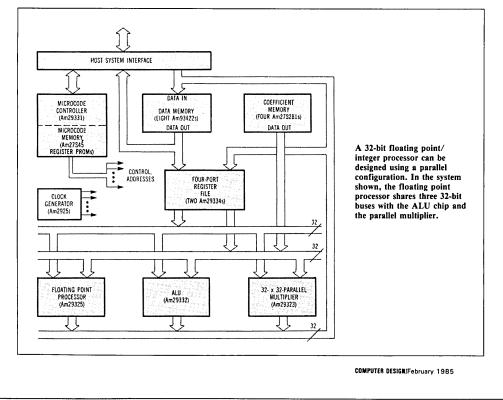

Figure 3 is a block diagram of a small array processor using the Am29325. A high-speed multi-port memory is used to provide storage for operands such that they may be accessed in simultaneous pairs. These operands may originate in the data memory, or may be intermediate results

DECEMBER 1984 S DIGITAL DESIGN

from the processor. One of these operands may be replaced with a value drawn from a non-volatile coefficient store.

The array processor is microprogram controlled, with memory addresses being derived directly from the microcode. This is probably inefficient for large programs, and some form of microprogrammed address generator would need to be added. The interface to the host processor is deliberately undefined, as this is user dependent.

As a benchmark, this processor can perform FFT butterflies in the canonical time of 10 cycles. At a 100 nsec cycle time, this permits one butterfly every 1  $\mu$ sec, or a 1024-pt complex transform in 5.12 msec. A simple modification to the architecture allows a second Am29325 to be incorporated to give a complex arithmetic processor. This doubles the throughput for the FFT, reducing the computation for the 1024-pt transform to 2.56 msec.

While the Am29325 only provides single-precision floating point operation, the Am29300 family also provides buscompatible devices which may be used to enhance the capabilities of the array processor described. The Am29332 Integer Processor offers a wide range of arithmetic, logic and shift facilities. This device may be operated with a reduced width data path, allowing words of 1 to 4 bytes. The internal architecture is designed for efficient programming of floating point operations, and may therefore be used to support the Am29325 with double-precision operations. To assist in double-precision floating point multiplication, or for integer multiplication, the Am29323 32-bit Multiplier provides  $32 \times 32$ -bit multiplication in a single cycle, and has internal facilities for multi-cycle expansion to  $128 \times 128$ .

These additional arithmetic elements have the same 32-bit, three-bus architecture as the Am29325. This allows them to be added in parallel. The routing of operands to the appropriate arithmetic element is a simple microcode task.

The horizontal partitioning of this new family of parts has resulted in a number Figure 2: Am29300-based supermini emulation.

of benefits. First, the user gains the flexibility of adding storage elements to two uncommitted output buses from the processor. Second, more power budget is available for the register file making it faster and bigger than if it had been in the processor chip. The family addresses a number of crucial system issues such as fault detection, support of high-level languages in systems programming and large register file-based architectures like RISC.

### **References:**

32-Bit Building Blocks for High Performance Processor/Controller, Paul Chu, Advanced Micro Devices, Sunnyvale, CA

A Very High Speed Floating Point Processor, B.J. New. Advanced Micro Devices, Sunnyvale, CA.

Figure 3: Am29300-based array processor.

DECEMBER 1984 I DIGITAL DESIGN

# Microprogrammable chips blend top performance with 32-bit structures

Broken down into 32-bit functional blocks instead of being sliced into multiple-bit sections, five VLSI bipolar chips match a supermini's speed.

esigners of systems and subsystems for high-speed computation, intelligent peripheral control, and array and digital signal processing typically need higher performance than standard microcomputer parts can deliver. The required precision, speed, and virtual memory support has to some degree been supplied by dedicated VLSI components that are customized for particular applications. Yet an overwhelming need still remains for a set of building blocks that can bring extremely high performance to a large assortment of applications.

A new approach extends the bit-slice concept to 32 bits and also satisfies system designs that require cycle times of less than 100 ns. With a family of five VLSI chips, designers of microprogrammed systems can count on cycle times of 70 to 80 ns, using merely a handful of com-

# Paul Chu and Bernard J. New Advanced Micro Devices Inc.

Paul Chu is now department manager of programmable processors in the product planning division of Advanced Micro Devices in Sunnyvale, Calif. He holds several patents for microprogrammable devices and has a BSEE and an MSEE from Stanford University.

As product planning manager for array processors at AMD, Bernard J. New is responsible for conceiving and defining arithmetic computing devices. The holder of a BSc (Hons) in electronic engineering from England's University of Birmingham, New has two patents on Am29500 products. ponents. The building blocks for 32-bit systems functionally partition the chips and separate the register file from the rest of the data path.

The following two articles first explore the key members of the Am29300 family and then focus on a floating-point processor, which is the first chip scheduled for sampling. Details are given on how to use the chip and other devices in the series to build a fast Fourier transform computer, as well as more general-purpose digital signal-processing circuits.

The Am29300 family addresses the problem of fault detection through an interlocking checking scheme—parity and master-slave. Byte parity is generated, stored, and then checked on all data-path elements as a means of detecting interconnection failures. Moreover, to verify certain functions, the master-slave operating mode permits two units to be connected in parallel, with one unit actually handling the computation and the other checking the result cycle by cycle.

Detecting a fault triggers an interrupt at the microinstruction level. Unlike previous redundant schemes, no specialized software is required. Furthermore, communication among the redundant functional units causes no system degradation.

The five chips form a strong foundation for any system designer's work. For instance, a 16-bit sequencer can handle interrupts and traps at the microinstruction level. There is

Electronic Design · November 15, 1984

Reprinted with permission from Electronic Design, Vol. 32, No. 22; copyright Hayden Publishing Co., Inc., 1984.

### Microprogrammable 32-bit chips

also a combined ALU and shifter that internally supports variable byte and bit fields. Together with the ALU-shifter chip, a true dualport register file, organized as 64 words by 18 bits, can build a basic system. The register file, designed for simultaneous read and write accesses, is separated from the data-path elements, thereby avoiding the problem of addressing an internal register file differently from external memory. The benefits of that separation are uniform register addressing and unlimited depth expansion.

Two accelerator chips — a floating-point processor and a parallel multiplier — can be added to the basic system to raise the number of functions and cut processing time. The 32-by-32-bit parallel multiplier can, on successive cycles, expand to 64 by 64 or 128 by 128 bits, without help from external logic. For its part, the math chip can tackle single-cycle addition, multiplication, subtraction, and conversions—all in single-precision IEEE or DEC formats.

Because of functional partitioning, a threebus flow-through architecture was chosen as the data path. For maximum bus accessibility, all data-path elements—the integer processor and the parallel multiplier, for example—share two operand and one result bus. The flowthrough architecture not only transfers data extremely quickly but also avoids the complex timing control needed to turn around bidirectional buses. Above all, the simplicity of the three-bus architecture allows these components to be configured in a variety of ways to optimize micro-architectures for different jobs.

# Bipolar building blocks deliver supermini speed to microcoded systems

s CMOS processes start to encroach on the performance of bipolar circuits, bipolar technology is taking the next step to keep itself in the lead for the highest speed systems. A family of five bipolar VLSI computational circuits—fabricated with a scaled,

#### Dhaval Ajmera, Øle Moller, and David Sorensen Advanced Micro Devices Inc.

Since the beginning of last year, Dhaval Ajmera has been a design engineer in product planning at Advanced Micro Devices in Sunnyvale, Calif. He holds an MSEE from the University of Florida.

Øle Moller is also a design engineer in AMD's product planning operation. He holds an MSEE from the Technical University of Denmark.

Another engineer in product planning, David Sorensen specializes in programmable processors. He holds a BSEE from Arizona State University. ion-implanted, oxide-isolated process and three levels of metal interconnections for high density—provides a set of functionally partitioned microprogrammable VLSI building blocks for systems such as superminicomputers, digital signal processors, high-speed controllers, and many others. The modularity of the system functions ensures that the chips can meet the performance requirements of a generalpurpose superminicomputer, as well as those of an image processor, which are radically different from each other.

Included in the family are three parts that form the core of a general-purpose microprogrammed system: a 32-bit arithmetic and logic unit (ALU), a 16-bit microprogram sequencer, and a 64-by-18 four-port, dualaccess RAM. And, for systems that do a large number of multiplications or floating-point

operations, two performance accelerators—a 32-by-32-bit multiplier and a 32-bit floatingpoint processor will be available to tie onto the buses (see Design Entry, p. 246).

The chips offer high performance, a flexible architecture, and microprogrammability, and even address the problem of fault detection for data integrity. These circuits can thus support an extremely fast microcycle—about 80 ns (projected). That high speed is the result of several design considerations: Each part is designed internally with emitter-coupled logic but has TTL-compatible inputs and outputs. Second, more power was allocated to the logic circuits used in the critical paths than for logic in the noncritical paths on each chip, to maximize the speed. Third, by integrating highly specialized logic on chip it is possible to execute very complex operations in a single cycle.

The microprogrammability of this chip set offers several benefits to the system designer. It provides a structured and systematic approach for implementing the control mechanism of the system, and like the bit slices, it allows the instruction set to be customized to suit the designer's application (see "Architectural Limitations of Bit Slices," opposite). And several versions of the initial design can be tested, or current designs can be enhanced simply by changing the microcode.

Thus, the functionally partitioned Am29300 family overcomes all of the performance penalties of bit-slice structures, while maintaining its ability to form a wide variety of architectures. Even though the chips are designed to work together as a family, each can also be used independently in an application that requires its unique capabilities.

# **Pipelines are out**

The flexibility of the Am29300 family is largely due to a decision not to place pipeline stages within the functional blocks. Not including the pipeline registers inside incurs some off-chip delays. This is a small price to pay to allow system designers to optimize the pipeline structure for their individual needs. Moving the register file out of the functional block for the ALU also slows things down. At the same time it does not force a fixed register size on the user, enabling systems to be created with dedicated registers, register windows, or register banks all with neither fixed depth nor width.

Additionally, the high level of integration helps eliminate the propagation delays often encountered when signals must go from chip to chip. The use of VLSI also results in fewer parts at the system level, which, in turn, conserves power (usually many watts in the case of bipolar systems) and board space. Lastly, a complete 32-bit solution is provided for applications that require increased precision for arithmetic operations, high memory bandwidth, and a

#### Architectural limitations of bit slices

The limited performance of bit-slice circuits can be improved by increasing the width of the slices. That higher level of integration results in higher performance by reducing the number of off-chip delays while preserving the flexibility that has made bit-slice systems so attractive. However, as higher levels of integration become possible, two inherent problems with bit-slice architectures will limit their ultimate speed. The first involves the off-chip delays inherent in cascading. For example, the carry chain is usually the slowest path of an ALU. Breaking this chain between slices introduces off-chip delays into the critical path.

The second problem is that the functional needs of many systems do not slice well. Barrel shifters and prioritizers are especially difficult to cascade. Unfortunately, the ability to perform N-bit shifts and locate the position of leading 1s are of greatest importance in applications that require heavy number crunching and manipulation of data fields, such as image processing, graphics, database management, and controllers. These are precisely the applications whose need for speed forces the use of bit-slice devices. The system performance is compromised not only because these operations must be done bit by bit, but also because many high speed algorithms cannot be efficiently implemented.

### Microprogrammable 32-bit chips

large addressing capability (4 billion bytes) to support virtual memory systems (Fig. 1).

The performance of a system depends, not just on its raw computing speed, but on its ability to respond to events such as interrupts and traps. For example, the Am29331 sequencer responds to both interrupts and traps at the microprogram level very quickly, and its response is completely transparent to the interrupted microroutine. Also, the Am29332 ALU indirectly supports the handling of these events by allowing its internal state to be saved or restored.

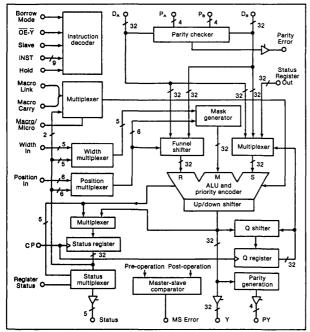

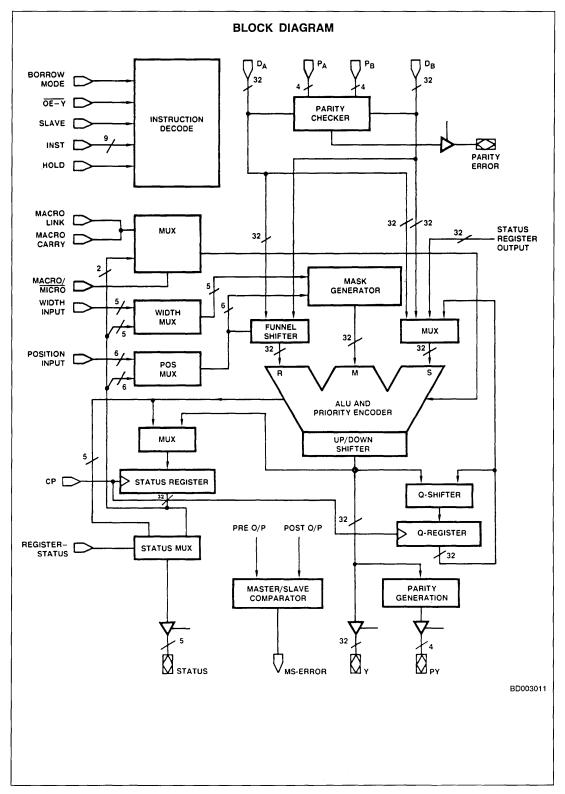

The Am29332, a noncascadable 32-bit-wide, ALU, provides fast number crunching, high data transfer rates, and powerful bit-manipulation capabilities. Intended to be used with the Am29334 dual-ported RAM, which serves as an external register file, the ALU has two 32-bit input buses (DA and DB) and one 32-bit output bus (Y).

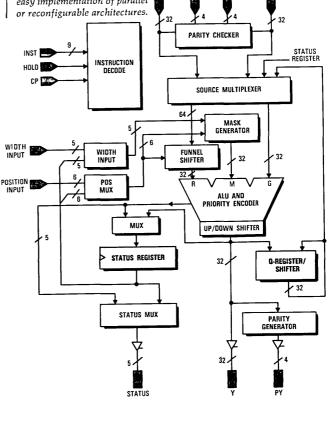

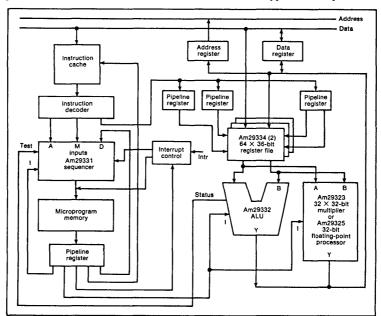

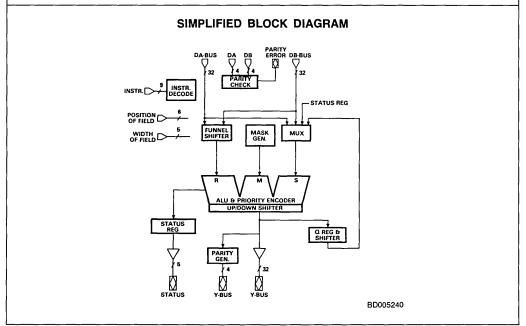

Internally, the device has a 32-bit data path that interconnects its various functional blocks. These blocks include various shifters and multiplexers, a mask generator, a funnel shifter, the ALU proper, a priority encoder, a parity generator and checker, a master-slave comparator, and the status and Q registers (Fig. 2). The ALU proper has three 32-bit inputs: R, S and M. The R input comes from the funnel shifter, the M input from the mask generator, and the S input from a variety of sources —the DA or DB buses, status register, or the Q register.

The power and flexibility of the Am29332 comes partly from its ability to perform operations on various data types. It can operate on

1. A conventional CPU, built with Am29300 building blocks, forms the focal point of an extremely compact system that cycles as fast as 80 ns.

variable bytes, variable-length bit fields, or single bits. This is made possible by the internal mask generator, which creates a 32-bit mask for each instruction (with no time overhead). The mask is used as an additional operand in each instruction to allow the operation on only selected data widths.

The type of mask generated depends on the type of instruction. For instructions that operate on variable bytes (1, 2, 3 or 4 bytes) the mask is a fence of 1s (bit 0 aligned) for all low-order selected bytes with a fence of 0s for all highorder unselected bytes. Instructions that operate on variable-length bit fields require a mask that is a string of contiguous 1s for all selected bit positions and 0s for all unselected bit positions. In cases where the field exceeds the 32-bit boundary, the mask does not wrap around, thus allowing operation on a contiguous field across a word boundary. For instructions that operate on a single bit, the mask is a 1 for the selected bit position and 0s for the other unselected bits.

For most single-operand instructions, the unselected bit positions pass the corresponding bits of the operand unmodified. For most twooperand instructions, the unselected bit positions pass the corresponding bits of the operand unmodified on the DB input. Thus, for twooperand instructions the mask allows the merging of two operands in a single cycle. In addition to being used internally, the mask can be sent out over the Y bus, permitting the generator to be used as a pattern generator for testing purposes.

To speed various mathematical and logical operations, many circuits have started to in-

2. To connect its various internal functional blocks, the Am29332 ALU employs a 32-bit bus. Among the chip's major features are a 64-bit funnel shifter, parity checking and generation, and a basic 32-bit ALU that has three input ports. The processor also has three 32-bit ports through which it transfers data into and out of the chip.

### Microprogrammable 32-bit chips

clude a barrel shifter, which has an N-bit input and an N-bit output. The barrel shifter would be used to shift or rotate the operand either up or down from 0 to N bits in a single cycle. Such high-speed shifting is very useful in operations such as the normalization of a mantissa for floating-point arithmetic or in applications in which the packing and unpacking of data are frequent operations.

However, a more useful circuit is a funnel shifter, which can be thought of as having two N-bit inputs and one N-bit output. Just such a circuit (with 32-bit-wide ports) was included on the 29332. The circuit can perform all the operations of a barrel shifter with capabilities extended to two operands instead of one. In addition, it can extract a 32-bit contiguous field across its two operands, a function very useful in several graphics applications. And any of its operations can be followed by a logical operation, with both completed in a single cycle.

#### Setting the priorities

Prioritization, useful to control N-way branches, perform normalizations, and in graphic operations such as polygon fills, can readily be handled by the ALU chip. The builtin priority encoder sends out a 5-bit binary weighted code that signifies the relative position of the most-significant 1 from the mostsignificant bit position of the byte width selected. That allows prioritization on either 8-, 16-,24-, or 32-bit operands. The priority encoder output can be passed on to the Y bus or stored in the status register.

If, for example, prioritization is used to normalize a mantissa during a floating-point arithmetic operation, it requires two cycles. In the first, the mantissa is prioritized to determine the number of leading 0s that need to be stripped off. In the next cycle, the mantissa is shifted up by the amount specified by the priority encoder output.

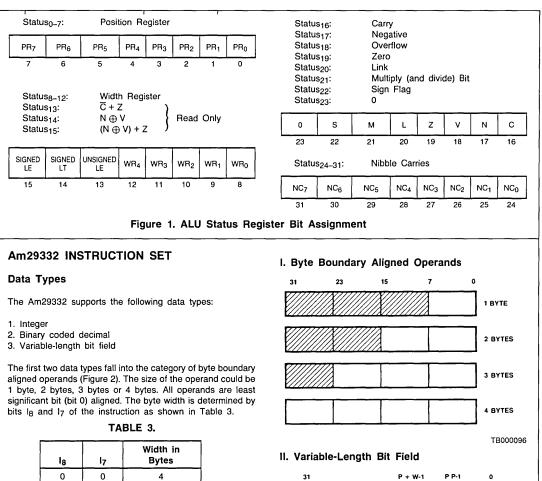

Relevant information for each operation performed by the chip is stored in the 32-bit status register after each microcycle. Each byte of the status word holds different information. The least-significant byte holds the position specifier. The next most-significant byte holds the width specifier and three other bits that are used to test the comparison of unsigned and signed operands. The next byte contains the Carry, Negative, Overflow, Link, Zero, M and S flags. The M flag stores the multiplier bit for multiply or the sign compare bit for signed division, and the S flag stores the sign of the partial remainder for unsigned division. The most significant byte stores the nibble carries for BCD operations.

The states of the Carry, Negative, Overflow, Link and Zero flags are available on the status pins, and the status multiplexer allows the user to select either the status of the previous instruction (register status) or the status of the current instruction (raw status) to appear on the status pins. The raw status could be used to update an external macro status register. This also allows branching at either the micro- or macro-level.

The Q shifter and Q register are primarily used to assemble the partial product or partial quotient in multiplication and division operations. Variable bytes of the status and Q register can either be loaded via the DA and DB inputs or can be read over the Y bus. Thus saving and restoring of the registers allows efficient interrupt handling after any microcycle. It is also possible to inhibit the update of both these registers by asserting the Hold pin.

#### Powerful and orthogonal instructions

The power of the ALU chip's instruction set comes directly from the integration of several functional blocks mentioned earlier. The commands are symmetrical as well as orthogonal, to make it easier for a compiler to generate efficient code. Thus, any operation on the DA input is also possible on the DB input, and each instruction is completely independent of its data type.

Three-fourths of the instruction set consists of variable byte-width (one, two, three or four) operand instructions. The byte-width is selected by two bits in the instruction. For these operands, the instruction set supports all conventional arithmetic, logical and shift operations. Arithmetic operations can be performed on both signed and unsigned binary integers.

Additionally, the instruction set supports multiprecision arithmetic such as addition with carrying and subtraction with carrying or

# Microprogrammable 32-bit chips

borrowing. For all subtract operations it provides the convenience of using borrowing instead of carrying by asserting the borrow pin. In this mode the carry flag is updated with the true Borrow. To allow efficient execution of macroinstructions the chip contains a Macro mode pin. When the chip asserts this pin, it allows the external Macro-Carry and Macro-Link bits instead of their microcounterparts to participate in the operation.

Instructions that execute algorithms for the multiplication and division of signed and unsigned integers are multiple cycles are also provided. For multiplication, the circuit supports the modified Booth algorithm, yielding two product bits in one cycle. Both single-precision and multiprecision division of signed and unsigned integers are supported at the rate of one quotient bit in every cycle.

Besides binary integers the instruction set provides basic arithmetic operations for binary-coded decimal (BCD) numbers. By operating directly on the decimal numbers created

3. To help ensure system integrity, two Am29332 processors can be set for master and slave operation. Both chips perform the same operation in parallel, and any difference in their results is flagged as an error. The master also checks its internal result against the data on the output bus to make sure that no other device (such as device X) is turned on at the same time.

in most business applications, significant processing time is saved by eliminating the need to convert from binary to BCD and vice versa. Also, the round-off errors involved in converting from one base to the other are eliminated.

The last group of instructions was created to support variable-length bit fields (1 to 32) and single-bit operands. The position and width of the field can be specified by either the position and width inputs or by fields in the status register, thereby saving bits in the microcode. Most of the time, the position and width are determined dynamically. It is therefore difficult to supply them via the microinstructions. For single bit operations only the position specifier is needed.

Bit-manipulation instructions include setting, resetting, or extracting a single bit of the operand or the status register. Logical operations on either aligned or nonaligned fields in the two operands include OR, AND, NOT and XOR. In the case of nonaligned fields it is assumed that at least one of the fields is aligned to bit position 0. It is also possible to extract a field from one operand and insert it into another operand or extract a field across two operands.

#### Enhancing system integrity

The growing need for data integrity has been addressed at both the system and the chip level by including hardware for fault detection. During calculations, byte-wide even parity is generated for the data result by the ALU and stored with the data in the external RAM. Byte-wide even parity is also checked at the ALU inputs and any error is flagged.

Even parity is specifically used to check for a floating TTL bus. Thus, all interchip connections are checked out. In addition, hardware for functional verification is also provided on the sequencer and the ALU functional verification can be implemented by using two similar devices in the master and slave mode (Fig. 3). In that setup, both chips perform the same operation, with any difference in their outputs being flagged as an error. The slave-mode chip's bidirectional buses operate in their input mode, allowing the master to compare its own internal result with that of the slave on every cycle. Additionally, the master checks the output bus to

# Microprogrammable 32-bit chips

make sure that no other device is turned on at the same time.

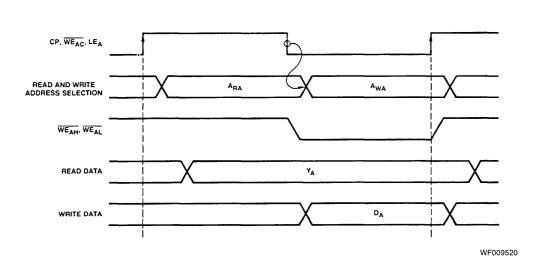

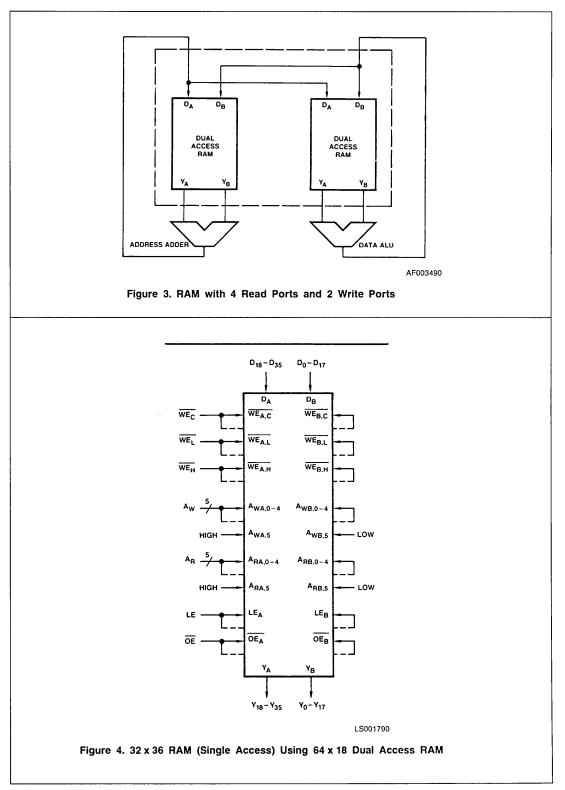

As mentioned earlier, the ALU architecture was designed to use an external register file. Keeping the file external to the chip permits the user to expand it to meet any system need. The Am29334, a high-speed 64-word-by-18-bit dualaccess RAM, provides two independent data input ports and two independent data output ports (Fig. 4). Each port can be read from or written to using the separate inputs and outputs. The two accesses are independent except for the case when simultaneous write operations are done to the same word—in which case the result is undefined. The read address inputs and the write address inputs of each side are se-

4. The dual-access RAM serves as an external register file for the arithmetic processor chip. The Am29334 holds 64 words, each 18 bits long. Two chips are often connected to build a RAM block with four data outputs, two data inputs, and six address lines. Each port of the RAM can be independently accessed to read or write.

parate in order to save the cost and time delay of external multiplexing between a read address and a write address.

The word width of 18 bits allows the RAM to store two bytes plus a parity bit for each. Each side has separate write enable for the lower and upper nine-bit bytes and a common write enable that also switches the address multiplexer. The actual write is delayed internally to allow the write address to set up internally before writing starts.

It is possible to build a RAM with four data outputs, two data inputs and six addresses by using two dual-access RAMs and on each side connecting the data input, write address and write enables of one RAM in parallel with the corresponding inputs of the other RAM. This expanded RAM may be used in concurrent processing applications in which an ALU and an adder (which generates the address) do their computations—this yields a result and an address in parallel. The two values can then be fed simultaneously to the multiport memory.

#### The sequencer controls the show

The cycle time of the microprogrammed system is dependent on both the control path (i.e., sequencer and microprogram memory) and the data path (i.e., register file and ALU). Traditionally, the system bottleneck has been the control path, especially the ciritical paths associated with conditional branching. Special care has been taken in the design of the Am29300 family to balance control and data-path timing.

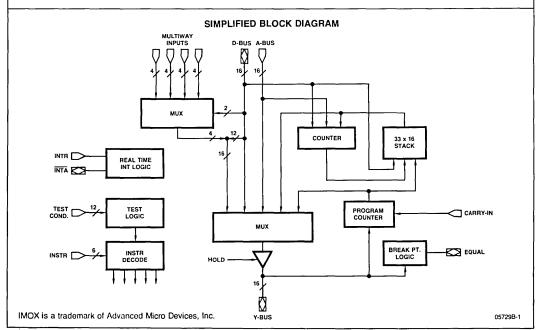

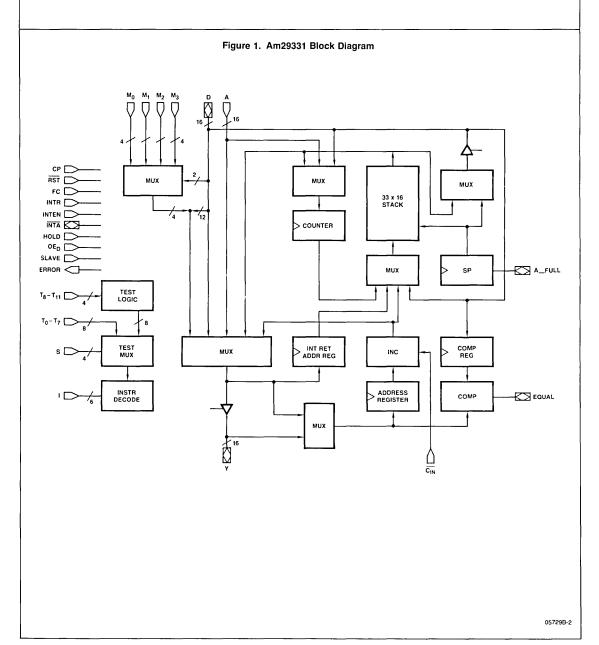

A key device contributing to the improved control-path timing is the Am29331 16-bit microprogram sequencer. It is designed for high speed, and that speed has been attained by the elimination of functions that would slow down the microaddress selection and by including the test logic and the test multiplexer in the sequencer (Fig. 5). As in most previous generation sequencers, the address register, the incrementer, the address multiplexer, the stack, and the counter are standard functions. The sequencer has multiway branch instructions that allow 1 of 16 consecutive addresses to be selected as the branch target in a single cycle.

The address register in most other sequencers is called a program counter, but this name is not correct if a strict definition is applied. In

# Microprogrammable 32-bit chips

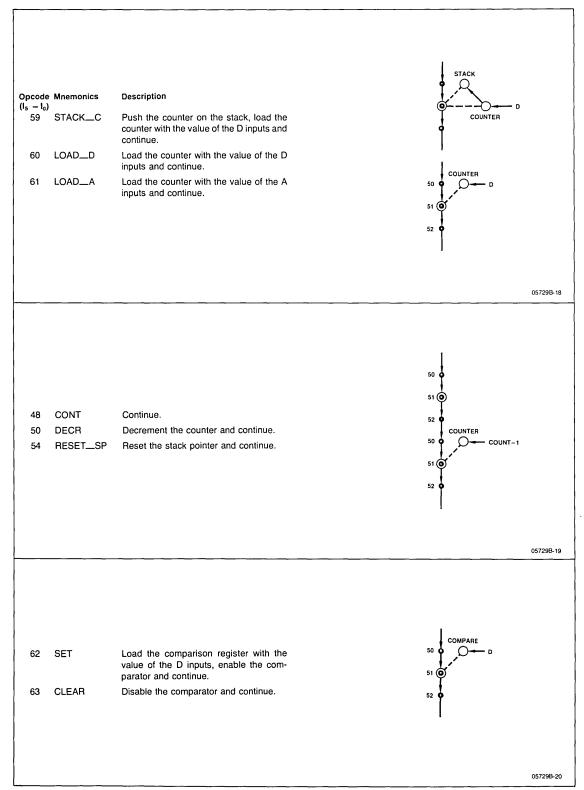

the Am29331, the incrementing counter is placed after the address register, which thus allows for the handling of traps. The stack stores return addresses, loop addresses and loop counts. It has 33 levels to permit the deep nesting of subroutines, loops and interrupts. An output, Almost Full (A-Full), indicates when 28 or more of the levels are in use.

Available for use in iterative loops, the counter can be loaded with an iteration count at the beginning of a loop, and the count is tested and then decremented at the end of the loop. The loop is terminated if the count is equal to one; otherwise a jump to the beginning of the loop is executed.

There are three buses that carry microaddresses. The bidirectional D bus can be connected to the pipeline register, providing branch addresses or loop counts, or used for two-way communication with the data processing part of the system. The A bus, called an alternate bus, can be connected to a mapping PROM to provide starting microaddresses for instructions in a computer. The Y bus sends out

5. To aid in handling trap operations, the incrementer is placed after the address register in the Am29331 microsequencer. Additionally, the chip has a 16-bit address bus, which enables it to access up to 64 kwords of control memory and handle interrupts and multiple-path branches.

#### Microprogrammable 32-bit chips

selected microaddresses to the microprogram memory and accepts interrupt or trap addresses if interrupt or trap is employed.

Four sets of 4-bit multiway inputs provide a simultaneous test capability of up to 4 bits. And, one way to use those inputs would be to decode mode bits in changing positions in macroinstructions. The four select lines select 1 of 16 tests to be used in conditional instructions. There are twelve test inputs. Four of these may be used for C (Carry), N (Negative), V (Overflow) and Z (Zero), generating internally the tests C+Z, C+Z, N XOR V, and N XOR V+Z, which are used for comparison of signed and unsigned numbers.

Relative addressing was the only somewhat useful function that was removed in order to maximize speed. The sequencer supports interrupts and traps with single-level pipelining, but may also be used with two levels of pipelining in the control path. It has a 16-bit-wide address path and cannot be cascaded, which thus limits the addressable memory depth to 64 kwords of microcode. That, however, is sufficient for the vast majority of applications — a typical computer, for instance, that has a microprogrammed instruction set, might use only about 1 to 2 kwords. However, for systems in which the microprogram is the sole program level, its size is generally larger.

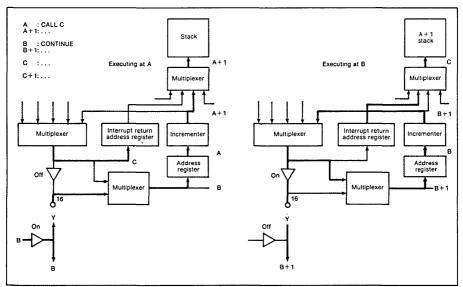

#### Microprogram interrupts supported

The Am29331 sequencer supports interrupts at the microprogram level. Like polling, interrupts handle asynchronous events. However, polling requires explicit tests in the microprogram for events, thus leading to long response times, lower throughput, and larger microprograms. Interrupts, on the other hand, have a response time equal to the cycle time of the system (approximately 80 ns), measured from the Interrupt Request input (INTR). The sequencer accepts interrupts at every microinstruction boundary when the Interrupt Enable input (INTEN) is asserted.

An actual interrupt turns off the Y bus driver and asserts the Interrupt Acknowledge output (INTA), which should be used to enable an external interrupt address onto the Y bus, thus driving the microprogram memory. The interrupt also causes the interrupt return address to be saved on the stack; this permits nested interrupts to be handled (Fig. 6).

The Am29331 is also the first sequencer that can handle traps. A trap is an unexpected situation caused by the current microinstruction, which must be handled before the microinstruction completes and changes the state of the system. An attempt to read a word from memory across a word boundary in a single cycle is an example of such a situation. When a trap occurs, the current microinstruction must be aborted and re-executed after the execution of a trap routine, which will take corrective measures.

Execution of a trap requires that the sequencer ignore the current microinstruction and push the trap return address—the address of the ignored microinstruction—on the stack. The trap address must be transferred onto the Y bus at the same time. All this can be accomplished by disabling the carry-in to the incrementer ( $\overline{C}_{in}$ ) and asserting the Force Continue input (FC) and the Interrupt Request input (INTR).

Also built into the sequencer is an address comparator, which allows detection of breakpoint in the microprogram. An output signal from the comparator indicates when the content of the comparator register is equal to the address on the Y bus. There is an instruction that loads the comparator register from the D bus and enables the comparator, which may later be disabled by another instruction.

Parallel microprocesses are useful when the system must deal with peripheral devices that are controlled at the microcode level. Normally only one processor is present and it must be time multiplexed between the concurrent operations that must be performed. When a process is suspended its private state must be saved, so that it can be restored when the process resumes execution. That, in turn, requires that the state of the sequencer be saved and restored, or each process must have its own sequencer that is active when the associated process is active. The first approach is the least expensive, but the second offers the advantage of shorter response time, because no time is spent on saving and restoring the state.

The Am29331 supports the first approach with its bidirectional D bus, through which the

# Microprogrammable 32-bit chips

entire state, with the exception of the comparator register, can be saved and restored. The sequencer also supports the multiple sequencer arrangement, in which the three-state Y buses from the sequencers are tied together driving a single microprogram memory. One of the sequencers is active, while the remaining sequencers are put on hold by asserting their Hold inputs. The Hold input disables most outputs (the D bus synchronously), disables the incrementer, and enables an internal Force Continue. This effectively detaches the sequencer from the system and preserves its state.

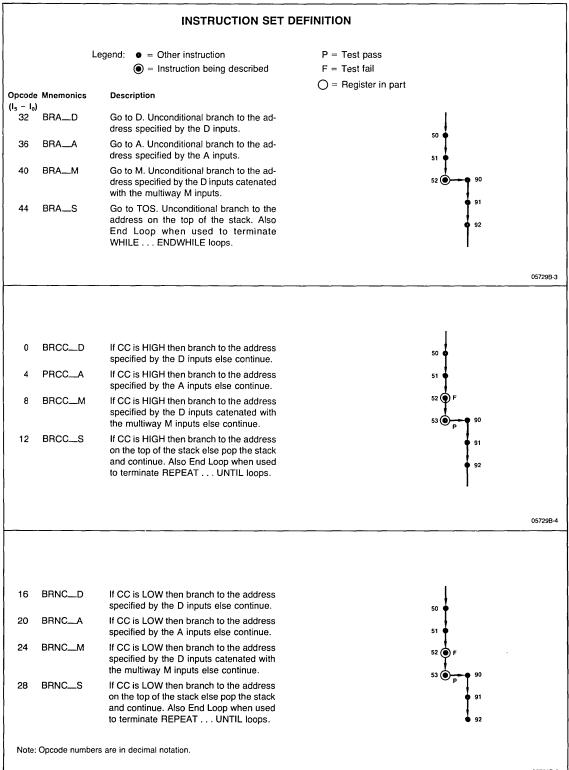

The sequencer has a 6-bit instruction input that is internally decoded to yield a set of 64 instructions. There are 16 basic branch instructions, each in an unconditional version, a conditional version, and a conditional version with complemented test. In addition there are 16 special instructions like Continue and Push C (push counter on stack). The branching instructions handle jumps, subroutines, various kinds of loops and exits out of loops, and FC actually overrides the instruction inputs with a continue

6. Because it can accept interrupts at any microinstruction boundary, the sequencer responds faster than most other microprogrammed systems. For example, while the instruction at point A in memory is being executed, the sequencer is directed to point B. The only restriction on the programmer is that the first instruction of the interrupt routine cannot use the stack, since the interrupt return address is pushed onto it at the start of the procedure.

# Microprogrammable 32-bit chips

instruction. FC is useful in field sharing and support for writable microprogram memory.

The Am29331 is one of the few sequencers where the stack is accessible from outside through the bidirectional D bus. This indirectly allows access to the whole state of the sequencer except the comparator register. This is useful when testing the device, and during system debugging, in which, for example, the contents of the counter and the stack may be examined and altered. By including the troubleshooting instructions in the microcode, the sequencer may aid in debugging itself and the rest of the system. The access to the state is also useful for changing context or extending the stack outside.

# Single-chip accelerators speed floating-point and binary computations

omplex multiplication or floating-point mathematical operations are frequently needed in most computer systems, but in many cases, not often enough to warrant the added cost of dedicating CPU hardware to the computational job. To speed up the calculations, many systems, though, allow for accelerator boards or boxes that can perform such operations at several megahertz speeds or more.

Already, many silicon designers have developed chips to simplify the design of such subsystems—16-bit parallel multipliers fabricated in bipolar, CMOS or NMOS processes, and single-chip or multichip floating-point processors made with CMOS or NMOS have been

#### David Quong and Robert Perlman Advanced Micro Devices Inc.

David Quong is a product planning engineer with the digital signal processing and array processing group at Advanced Micro Devices in Sunnyvale, Calif. He received a BSEE from California State University in Sacramento.

Robert Perlman is a senior product planning engineer with the digital signal processing and array processing group. He obtained a BSEE from the Rensselaer Polytechnic Institute and an MSEE from the Johns Hopkins University, and has previously done design work in airborne digital signal processing at Westinghouse. available for some time. However, they are lowperformance solutions to the problem, or in some cases, have limited application since they are intended for highly pipelined systems.

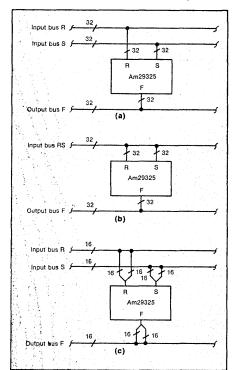

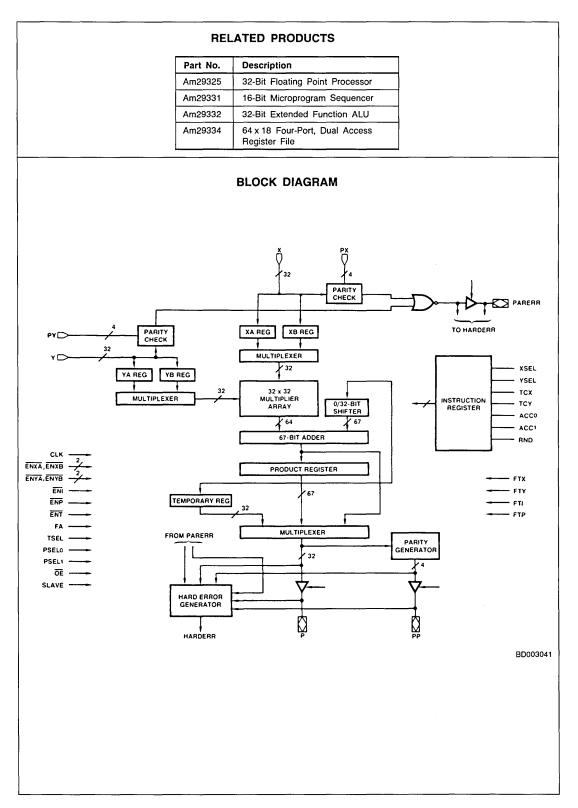

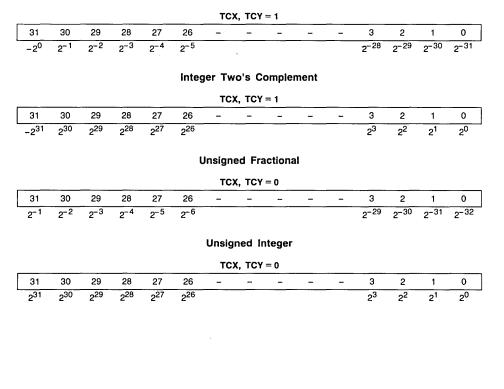

Now, the ability to handle 32-bit binary multiplication or 32-bit floating-point multiplication, addition or subtraction can be added to a system with just a single chip. The Am29323 is 32-bit parallel multiplier that accepts two 32-bit inputs and can deliver a 64-bit product in a single clock cycle of 80 ns. Alternatively, performing floating-point operations, the Am29325 accepts two 32-bit inputs and delivers a 32-bit result in less than 125 ns. It can operate with numbers represented in either the IEEE (P754) or Digital Equipment Corp. floatingpoint formats and can convert numbers from one format into the other.

Both chips are part of the just unveiled Am29300 series of 32-bit computational elements (Design Entry, p. 230). The multiplier is ideal for computer systems that do floatingpoint operations only infrequently but must often perform high-speed integer calculations such as those required in image manipulation. The floating-point processor enhances systems used for fast Fourier transform and scientific calculations. Systems could even contain both accelerators if a high-performance, general-

purpose system were built (Fig. 1).

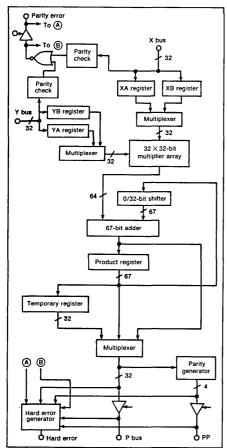

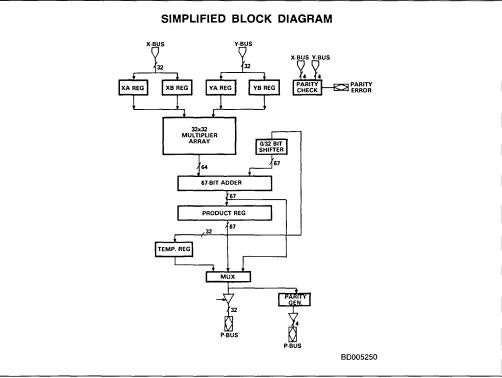

To speed the flow of data into and out of the chips, both circuits were designed with two 32-bit-wide input ports and one 32-bit output port. But the similarities end there, since the chips perform vastly different operations on the data. A fairly straightforward design, the multiplier uses a full Booth-encoded array to deliver a 64-bit product to the output register (Fig. 2). The output register feeds a multiplexer that sends the result, 32 bits at a time, to the output port.

Double-precision operations can be done thanks to dual 32-bit input registers that are multiplexed into the multiplier array. A 67-bit partial-product adder allows new products to be summed with the contents of the output register. During this operation, the contents of the output register may be scaled by 32 bits, if necessary. Four partial products are formed and summed, and a temporary register assists in the scheduling of output transfers. The effective pipelining throughput in the doubleprecision mode is one 64-bit multiplication every four cycles. The accumulator can also support 96- and 128-bit multiplications. However, for such operations, input data must be repeatedly applied.

The input and output registers of the multiplier have independent control signals so that they can be optimally timed in pipelined systems. However, in unpipelined systems, the registers can independently be made "transparent" so that data encounters no delays when entering or leaving the chip. Like the other chips in the Am29300 family, the multiplier has parity checking and generating circuits to ensure system data integrity. And, the circuit offers a slave mode in addition to its normal mode—if two chips are tied together to operate in parallel with one set to operate in the slave mode, the circuits will generate an error flag if unequal results are obtained.

In the world of floating-point computations, several single-chip units, designed to be general-purpose math coprocessors for microprocessor systems have achieved close to microsecond operating speeds. However, to achieve higher throughput rates, several recently announced two-chip sets have cut that speed by a factor of 10, achieving data throughput rates of 10 MHz for pipelined operations. But, if operated in nonpipelined systems, these chips lose considerable speed—often by a factor or two or three—since data must ripple through the stages of pipeline registers.

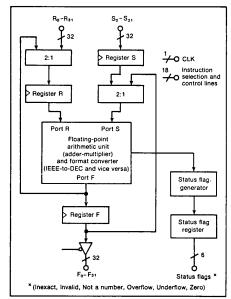

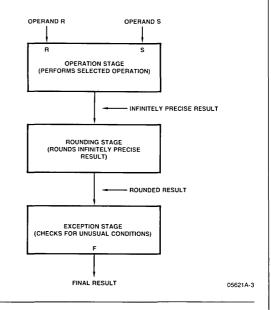

To cut the data delays, the Am29325 took a direct approach and eliminated all the pipelining. It is the first floating-point processor to contain a 32-bit floating-point adder/subtractor, multiplier, and flexible 32-bit wide data path on a single chip (Fig. 3). Additionally, support for division operations is included on the chip as well as a status flag generator.

Fabricated with the IMOX-S bipolar process and three levels of metal interconnections and

The 32-bit multiplier and the 32-bit floating-point processor can be used together in a system. Either chip also functions without the other if just one of the capabilities is needed.

# 32-bit math accelerators

housed in a 144-lead pin-grid-array package, the Am29325 can replace one to two boards of SSI and MSI logic typically used in generalpurpose computers, array processors and graphics engines, to provide high-speed floating-point math capability. When used in con-

Surrounding the 32-by-32-bit multiplier array on the Am29323 are multipliers for the two 32-bit input buses, which permit 64-bit multiplications to be done in just four cycles. The multiplier checks parity on the input data and generates parity bits for the output result.

cert, the on-chip functions will meet the computational and data-routing needs of these and many other applications.

Integrating these functions into a single device greatly reduces data routing problems and minimizes processing overhead that would otherwise be incurred when shuffling data on and off the chip. The internal data path is ideally suited for multiplication and accumulation, Newton-Raphson division, polynomial evaluation, and other often-used arithmetic sequences. Placing the data path on chip also dramatically reduces the number of ICs needed to interface the device to the rest of the system.

The three-port floating-point arithmetic unit at the chip's core can perform any of eight instructions in a single clock cycle. The absence of pipeline delay in the arithmetic unit means that the result of an operation is available for use as an input operand in the very next operation, a crucial feature when performing algorithms with tight feedback loops. Instructions and other operating modes are selected with dedicated input signals, an approach ideally suited to microprogrammed environments. The device easily interfaces with a variety of 16- and 32-bit systems using one of three programmable bus modes.

#### Delving into the operation

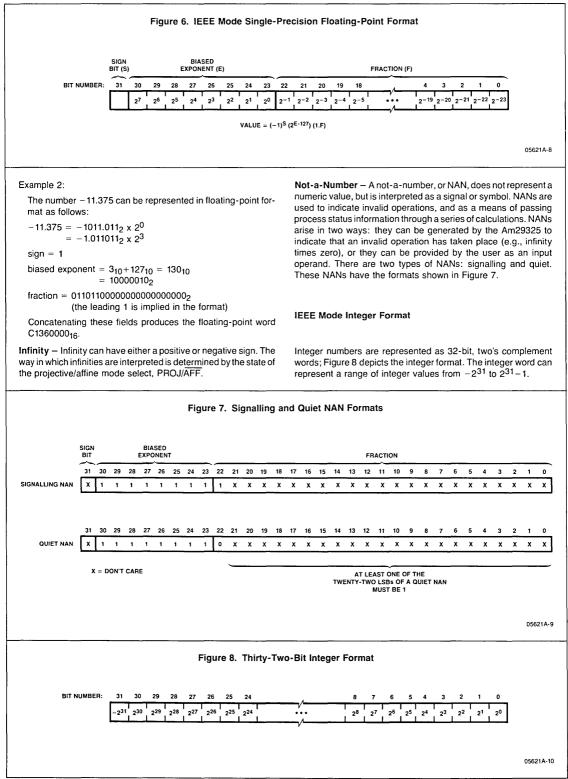

At the heart of the arithmetic unit are a highspeed adder-subtracter, a 24-by-24-bit multiplier, an exponent processor, and other logic needed to implement the floating-point operations. Two input ports, R and S, provide operands for the instruction to be performed; the result appears on port F. One of eight instructions is selected by placing a 3-bit code on lines  $I_0$ ,  $I_1$ , and  $I_2$ . The first three instructions— R + S, R - S, and  $R \times S$ —operate on both input operands; the remaining instructions need only one input operand.

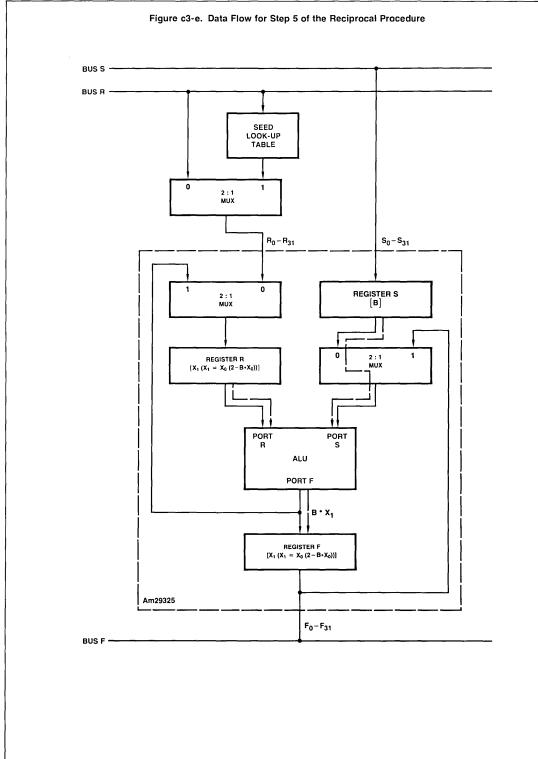

The fourth instruction, 2 - S, forms the core of the Newton-Raphson division algorithm, in which the quotient A/B is calculated by first evaluating 1/B, then postmultiplying by A. The reciprocal value 1/B is derived by using an external lookup table to provide an approximation of 1/B; this approximation is refined using the iterative equation:

$$x_n = x_{n-1} (2 - B x_{n-1}),$$

### 32-bit math accelerators

where  $x_n$  is the nth approximation of 1/B.

Once B and the approximation of 1/B are loaded into the Am29325, the approximation is refined using a sequence of  $R \times S$  and 2 - S instructions; no additional I/O operations are needed for reciprocal refinement. The remaining four instructions perform data format conversions. Instruction INT to FP converts a 32-bit, two's complement integer to floatingpoint form, useful when processing data initial-

3. Also using separate 32-bit buses for the inputs and output, the AM29325 floating-point processor handles either IEEE or DEC formatted data and can translate between formats, if necessary.

Electronic Design • November 15, 1984

ly generated in fixed-point format; conversion from floating point to integer format is handled by instruction FP to INT. Two other instructions convert between IEEE and DEC floatingpoint formats.

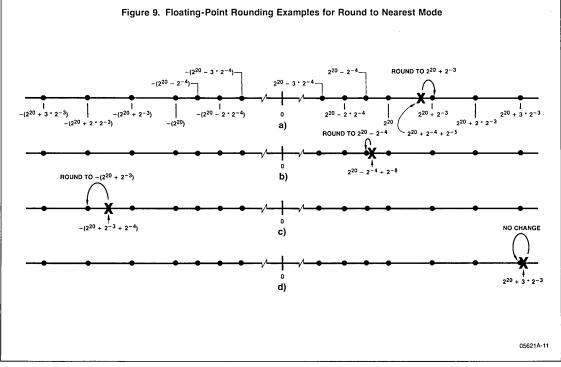

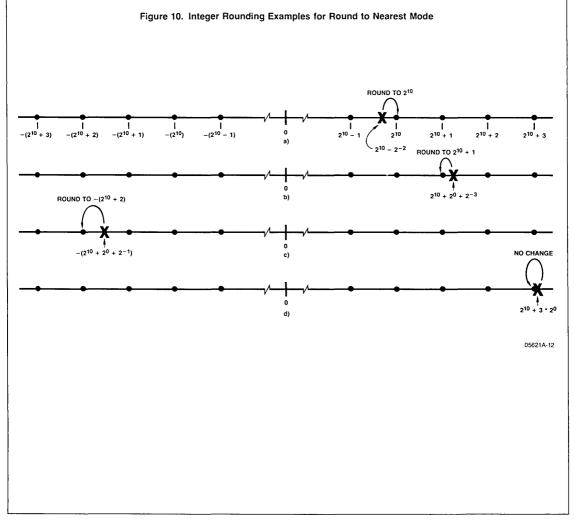

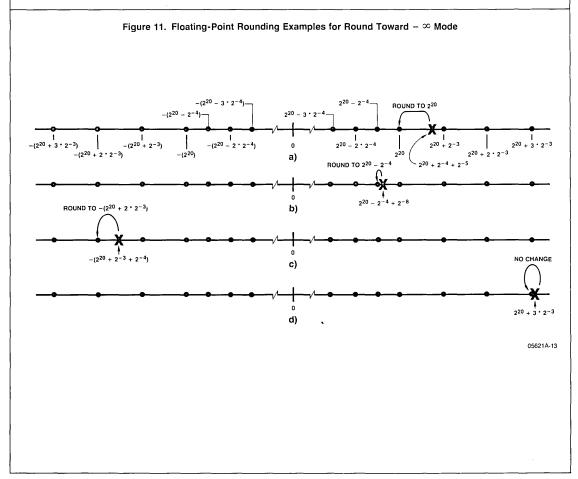

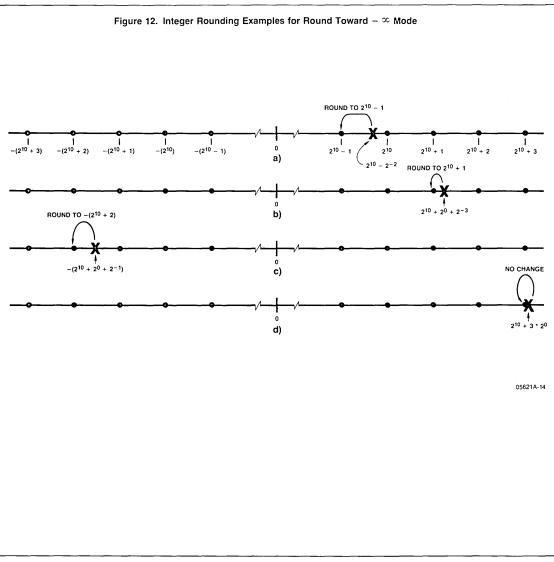

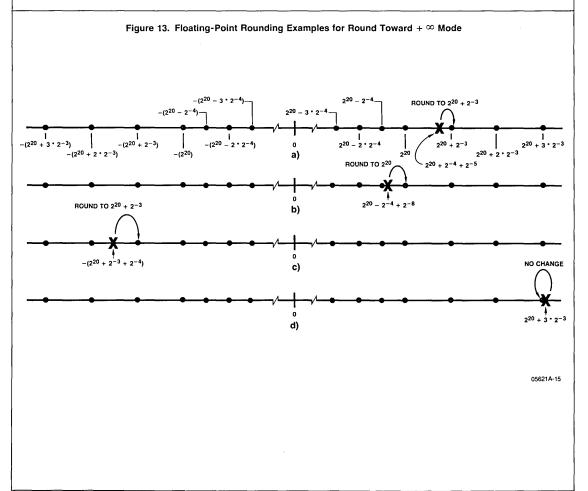

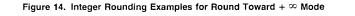

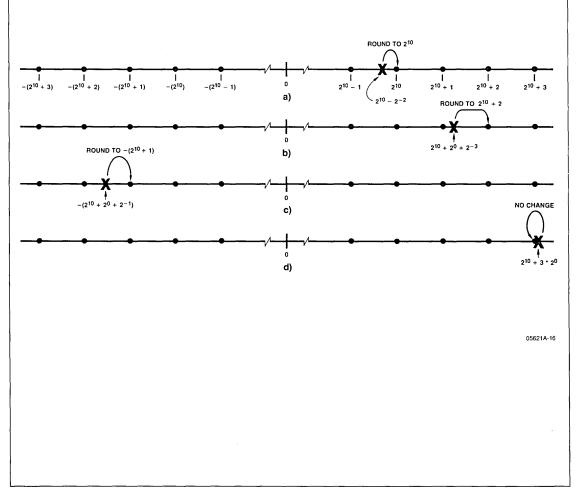

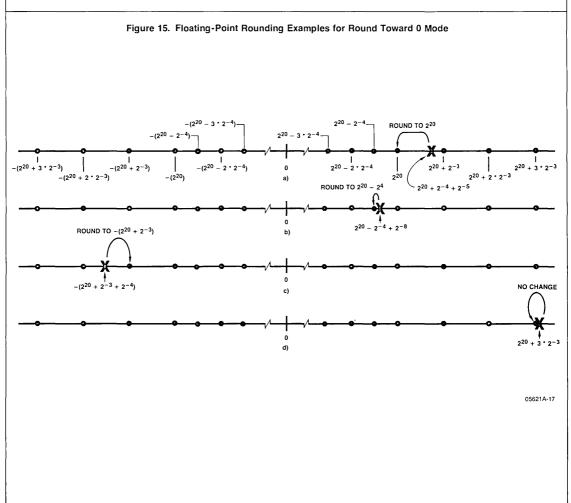

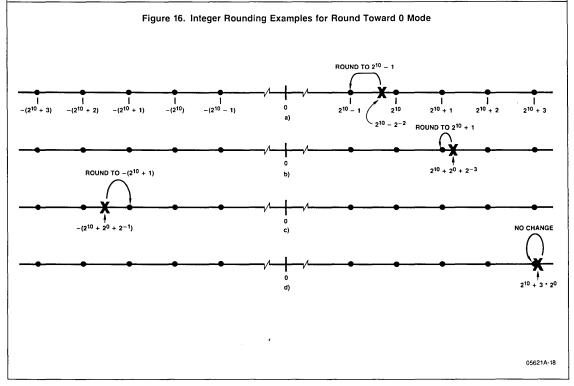

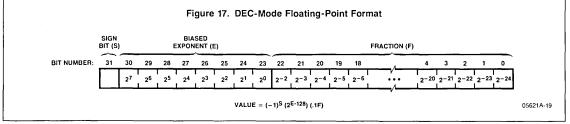

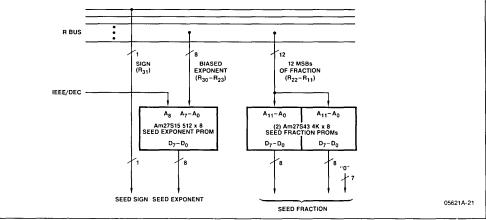

The arithmetic unit recognizes two singleprecision floating-point formats—the IEEE format as specified in proposed standard P754, draft 10.0, or the DEC format used in VAX minicomputers. The eight instructions can be performed using either format; the desired format is selected with the IEEE/DEC pin on the processor chip. The formats are broadly similar—each has an 8-bit biased exponent, a 24-bit significand comprising a 23-bit mantissa appended to an implied or "hidden" mostsignificant bit (MSB), and a sign bit.