# Quad Pixel Dataflow Manager (QPDM) Am95C60

Technical Manual Revision B

# **Advanced Micro Devices**

# Quad Pixel Dataflow Manager (QPDM) Am95C60

# Technical Manual REVISION B

© 1987 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics. The performance characteristics listed in this technical manual are guaranteed by specific tests, correlated testing, guard banding, design and other practices common to the industry. For specific testing details contact your local AMD sales representative. The company assumes no responsibility for the use of any circuits described herein.

> 901 Thompson Place, P.O. Box 3453, Sunnyvale, California 94088 (408) 732-2400 TWX: 910-339-9280 TELEX: 34-6306

Written by: Edited by: Tom Crawford Senior Applications Engineer Sue Louie Thilking Technical Editor

### **Please Register for Product Updates**

The Am95C60 QPDM Technical Manual is a "Preliminary Release". It is an accurate description of the device as originally designed and built. However, we anticipate some changes in the device as data is collected from the many systems now being designed with it. To be kept up-to-date on the status of the Am95C60 QPDM, and to receive new issues of the documentation as it becomes available, we ask that you submit your name and address to:

Advanced Micro Devices, Inc. Mr. Steve Crane (MS-30) QPDM Updates P. O. Box 3453 Sunnyvale, CA 94088-3453

Last minute additions for this manual: Page 3-5, VBLKI Interrupt: Change last sentence to: The condition is true for one VIDCLK period at the beginning of Vertical Blank.

Page 14-58, Point: Add sentence to Performance: The time for intermediate points (neither the first nor the last) in a list is 62 SYSCLK cyles.

Page 14-77, Set Scale Factor: Add sentence to Comments: The ratio of the scale factors must not exceed 16 to 1 (either way).

Page B-1, LS: This is a 1-bit field, not 2-bit as stated.

# TABLE OF CONTENTS

| 1. | INTI       | RODUCTION                           |           |              |     |      |     |     | 1-1        |

|----|------------|-------------------------------------|-----------|--------------|-----|------|-----|-----|------------|

|    |            |                                     |           |              |     |      |     |     |            |

|    | 1.1        | Overview                            | •••       |              | ••• | •••  | ••• | ••• | 1-1        |

|    | 1.2        | Description                         | •••       | •••          | ••• |      | ••• | ••• | 1-2        |

|    | 1.3        | Am95C60 Functions                   |           | •••          | ••• | •••  | ••• | ••• | 1-2        |

|    |            | 1.3.1 Display Refresh               |           | •••          | ••• |      | ••• | ••• | 1-2        |

|    |            | 1.3.2 Display Memory                |           | •••          | ••• | •••  | ••• | ••• | 1-2<br>1-2 |

|    | 1.4        | 1.3.3 Dynamic VRAM<br>Am95C60 Speed | •         | •••          | ••• | •••  | ••• | ••• | 1-2        |

|    | 1.4        | Am95C60 Speed<br>Am95C60 Windows    |           | •••          | ••• | •••  | ••• | ••• | 1-2        |

|    | 1.6        | Am95C60 Display Me                  |           | <br>nort     | ••• | ···· | ••• | ••• | 1-4        |

|    | 1.7        | Up to 64 Am95C60s C                 |           |              |     |      |     | ••• | 1-4        |

|    | 1.8        | Am95C60 Scaling                     |           |              |     |      |     |     | 1-4        |

|    |            | / interest of the ing               | •••       |              | ••• | •••  | ••• | ••• | •••        |

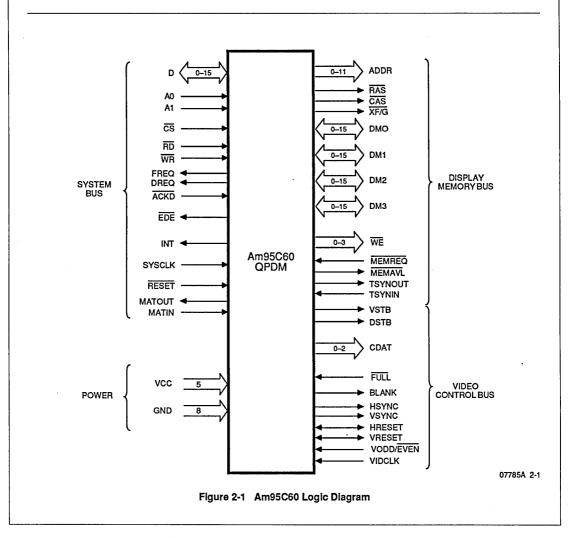

| 2. | HAF        | RDWARE INTERFA                      | CE        | •••          |     |      |     | ••• | 2-1        |

|    | 2.1        | Interface Buses                     | •••       |              | ••• |      |     |     | 2-1        |

|    |            | 2.1.1 System Bus                    |           |              |     |      |     | ••• | 2-1        |

|    |            | System Bus Pin                      |           |              | ••• | •••  | ••• |     | 2-1        |

|    |            | 2.1.2 Display Memory                |           |              |     |      |     |     | 2-4        |

|    |            | Display Memory                      | Bus Pinc  | outs         |     |      |     |     | 2-4        |

|    |            | 2.1.3 Video Control B               |           |              |     |      |     |     | 2-5        |

|    |            | Video Control B                     | us Pinout | Ś            |     |      |     | ••• | 2-5        |

|    |            | 2.1.4 Power Bus                     | •••       | •••          | ••• |      | ••• | ••• | 2-6        |

| 3. | ноя        | ST-Am95C60 COMI                     | MUNICA    | ATIONS       | i   |      |     | ••• | 3-1        |

|    | 3.1        | Reset Function                      |           |              |     |      |     |     | 3-1        |

|    | 3.2        | I/O Ports                           | •••       |              |     |      |     | ••• | 3-1        |

|    |            | 3.2.1 Write Instruction             |           | •••          | ••• |      |     | ••• | 3-1        |

|    |            | 3.2.2 Read Status Re                | gister    |              | ••• |      |     | ••• | 3-1        |

|    |            | 3.2.3 Write Block In F              | IFO (BIF) |              | ••• |      | ••• | ••• | 3-2        |

|    |            | 3.2.4 Read Block Out                |           | OF)          | ••• |      | ••• | ••• | 3-2        |

|    |            | 3.2.5 Write Address F               |           | •••          | ••• | •••  | ••• | ••• | 3-2        |

|    |            | 3.2.6 Read Address F                | 0         | •••          | ••• | •••  | ••• | ••• | 3-2        |

|    |            |                                     | •••       | •••          | ••• | •••  | ••• | ••• | 3-2        |

|    | ~ ~        | 3.2.8 Read Register                 |           | •••          | ••• | •••  | ••• | ••• | 3-2        |

|    | 3.3        | DMA Facilities.                     | •••       | •••          | ••• |      | ••• | ••• | 3-3        |

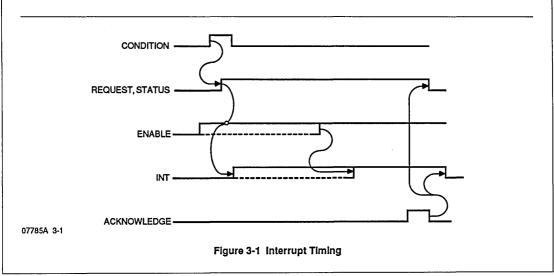

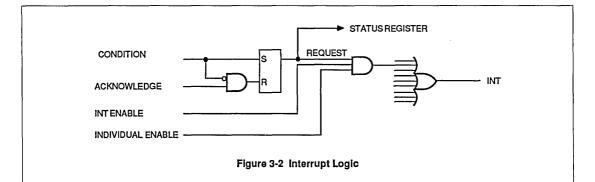

|    | 3.4<br>3.5 | Interrupt Facilities                |           | <br>into Amr |     | •••  | ••• | ••• | 3-3        |

|    | 3.5<br>3.6 | Considerations Involu               | -         | -            |     | •••  | ••• | ••• | 3-4        |

|    | 3.0        | Eight-Bit Interface                 | •••       | •••          | ••• | •••  | ••• | ••• | 3-4        |

| 4. | REC        | GISTER SET                          |           | •••          |     |      |     | •   | 4-1        |

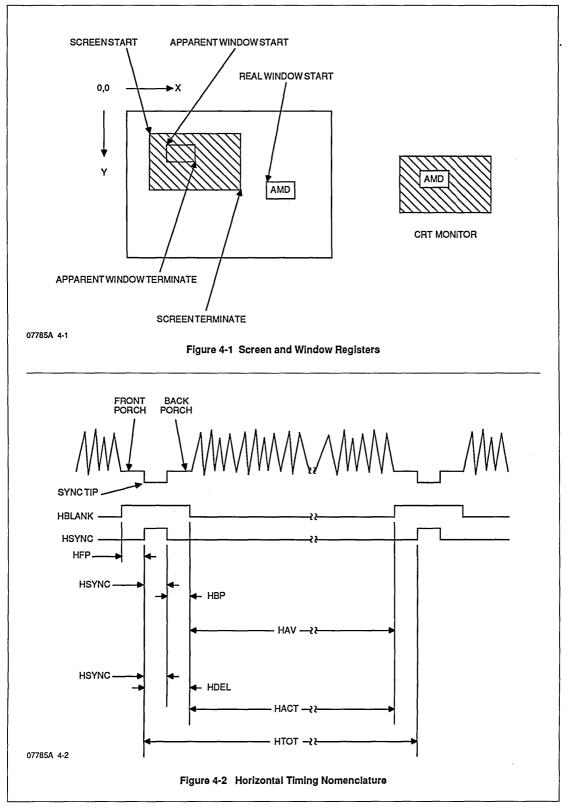

|    | 4.1        | Visible Screen Coord                | inate Red | gisters      |     |      |     |     | 4-1        |

|    | 4.2        | Window Control Regi                 |           |              |     |      |     |     | 4-1        |

|    | 4.3        | Video Timing Control                |           |              |     |      |     | ••• | 4-2        |

|    |            | 4.3.1 Horizontal Timin              |           |              |     |      |     | ••• | 4-2        |

|    |            | 4.3.2 Vertical Timing I             |           |              | ••• |      |     | ••• | 4-2        |

|    | 4.4        | Video Control Registe               |           |              | ••• |      | ••• | ••• | 4-4        |

|    |            | 4.4.1 Video Mode Reg                |           |              | ••• |      |     | ••• | 4-4        |

|    |            | 4.4.2 Video Timing Er               |           | ister        | ••• |      |     | ••• | 4-4        |

|    |            | 4.4.3 Video Refresh E               | Enable    |              |     | •••  | ••• | ••• | 4-4        |

|    | 4.5          | Displa      | ay RAM C  | Control Regi                          | sters       |          | ••           |          | •••     |     | 4-4 |

|----|--------------|-------------|-----------|---------------------------------------|-------------|----------|--------------|----------|---------|-----|-----|

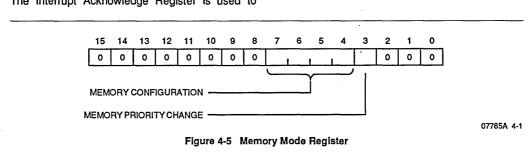

|    |              |             |           | Mode Regist                           |             |          | ••           | •••      |         | ••• | 4-5 |

|    |              | 4.5.2       | Dynamic   | Memory Ref                            | iresh F     | Rate Reg | gister       |          | •••     | ••• | 4-6 |

|    | 4.6          | Host-/      | Am95C60   | ) Communic                            | ations      | s Regist | ers          |          |         |     | 4-6 |

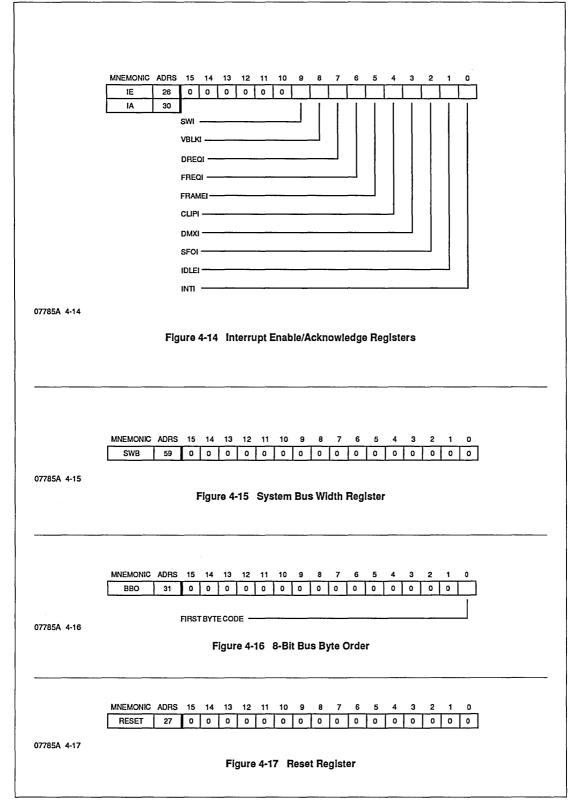

|    |              | 4.6.1       | Interrupt | Enable Regi                           | ster        |          | ••           | •••      |         | ••• | 4-6 |

|    |              |             |           | Acknowledge                           |             |          | ••           |          | •••     | ••• | 4-6 |

|    |              |             |           | Bus Width Re                          |             |          | ••           |          | •••     |     | 4-6 |

|    |              | 4.6.4       | Eight-Bit | Bus Byte Or                           | der         |          | ••           |          |         |     | 4-6 |

|    |              |             |           | egister                               |             |          |              |          |         |     | 4-6 |

|    | 4.7          |             |           | esentation of                         |             |          | S            |          | •••     |     | 4-6 |

|    |              |             | •         |                                       |             | -        |              |          |         |     |     |

| 5. | ADD          | DRES        | SING M    | ODES AN                               | D SC        | ALING    | i            | •••      | •••     | ••• | 5-1 |

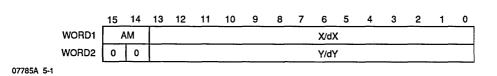

|    | 5.1          | Stand       | ard Oper  | and Addres                            | s Pair      |          |              |          |         | ••• | 5-1 |

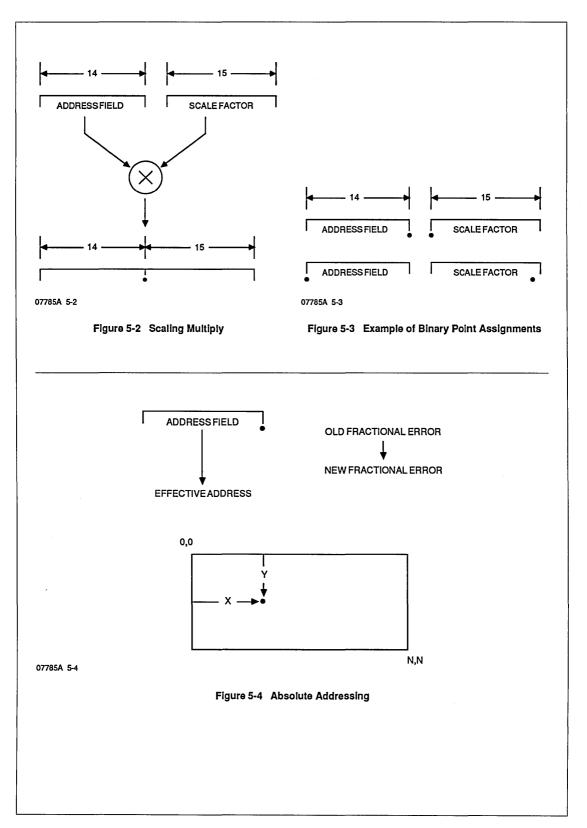

|    | 5.2          |             |           | slation                               |             |          | ••           |          |         | ••• | 5-1 |

|    |              |             |           | Addressing                            | Mode        |          |              |          |         | ••• | 5-2 |

|    |              |             |           | Addressing                            |             |          |              |          |         | ••• | 5-2 |

|    |              |             |           | Addressing N                          |             |          |              |          |         |     | 5-2 |

|    |              |             |           | Addressing N                          |             |          |              |          |         |     | 5-2 |

|    |              |             | Round-o   |                                       |             |          |              | •••      |         |     | 5-2 |

|    |              | 0.2.0       | nounu-o   | LIUIS                                 |             | • •      | •••          | •••      | •••     | ••• | 0-2 |

| 6. |              | - TEV       | TURE .    |                                       |             |          |              |          |         |     | 6 1 |

| 0. | LINI         |             | IUNE .    | •• •••                                |             | •        | •••          | •••      | •••     | ••• | 6-1 |

|    |              |             |           |                                       |             |          |              |          |         |     |     |

|    | 6.1          |             |           |                                       |             |          |              | •••      | •••     | ••• | 6-1 |

|    |              |             |           | ne Styles                             |             |          | •••          | •••      | •••     | ••• | 6-1 |

|    |              |             |           | Line Styles                           |             |          | •••          | •••      | •••     | ••• | 6-2 |

|    |              |             |           | les with Diag                         |             |          | •••          | •••      | •••     | ••• | 6-3 |

|    |              |             |           | les with Scali                        | ng          | •        |              |          | •••     | ••• | 6-3 |

|    | 6.2          | End-p       | oint Opt  | ions                                  |             |          | •••          | •••      | •••     | ••• | 6-3 |

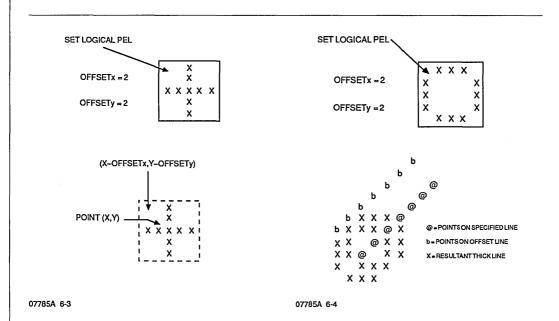

|    | 6.3          | Logic       | al PEL .  |                                       |             | •        | •••          |          |         | ••• | 6-3 |

|    |              | 6.3.1       | Using th  | e Logical PE                          | L for P     | oints    | •••          |          | •••     |     | 6-4 |

|    |              | 6.3.2       | Using th  | e Logical PE                          | L for L     | ines     | •••          |          |         |     | 6-4 |

|    |              | 6.3.3       | Using th  | e Logical PE                          | L for A     | rcs and  | Circles      |          |         |     | 6-5 |

|    |              |             | •         | -                                     |             |          |              |          |         |     |     |

| 7. | CLI          | <b>PPIN</b> | G AND I   | PICKING                               |             |          |              |          |         |     | 7-1 |

|    |              |             |           |                                       |             |          |              |          |         |     |     |

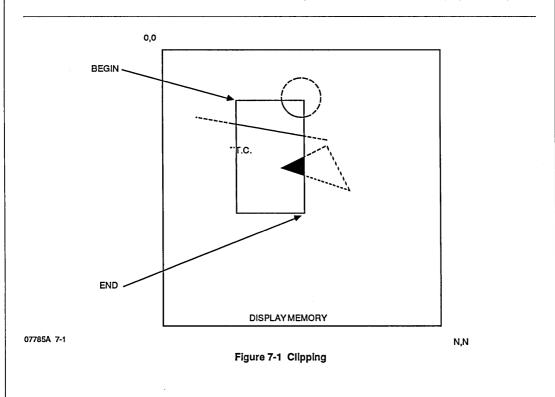

|    | 7.1          | Clippi      | ina .     |                                       |             |          |              |          |         | ••• | 7-1 |

|    | 7.2          | Pickir      |           | •••                                   |             | -        | •••          |          | •••     |     | 7-2 |

|    |              |             |           | of Picking                            |             |          |              |          | •••     |     | 7-2 |

|    |              |             |           | ,                                     |             | •        |              |          |         |     |     |

| 8. | GR/          |             | CAL OP    | ERATION                               | S           |          | •••          |          |         |     | 8-1 |

| •  | <b>C</b> 111 |             |           |                                       | •           | •        | •••          | •••      | •••     | ••• | ••• |

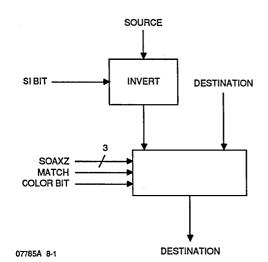

|    | 8.1          | SOAN        | (Z Field  |                                       |             |          |              |          |         |     | 8-1 |

|    | 0.1          |             |           | <br>Field in Instru                   | <br>uotiona |          | <br>na a Soi |          | <br>and | ••• | 8-1 |

|    |              | 0.1.1       |           |                                       |             |          | •            | •        |         | ••• | 8-1 |

|    |              |             |           | Logical SET                           |             |          | •••          | •••      |         | ••• |     |

|    |              |             |           | Logical OR                            | 、 …         | •        | •••          | •••      | •••     | ••• | 8-1 |

|    |              |             |           | Logical AND                           |             |          | •••          | •••      | •••     | ••• | 8-1 |

|    |              |             | 8.1.1.4   | · · · · · · · · · · · · · · · · · · · | -           | ••       | •••          | •••      | •••     | ••• | 8-1 |

|    |              |             | 8.1.1.5   | Logical ZER                           |             | ••       | •••          | •••      | •••     | ••• | 8-1 |

|    |              |             | 8.1.1.6   | Graphical S                           |             |          | •••          | •••      | •••     | ••• | 8-1 |

|    |              |             | 8.1.1.7   | Graphical O                           |             | ••       | •••          | •••      | •••     | ••• | 8-3 |

|    |              | _           | 8.1.1.8   | Graphical X                           |             |          | •••          |          |         | ••• | 8-3 |

|    |              | 8.1.2       |           | Field in Instru                       |             | Not Inv  | olving a     | Source C | Operand |     | 8-3 |

|    |              |             | 8.1.2.1   | Logical SET                           | •           |          |              | •••      | •••     | ••• | 8-3 |

|    |              |             | 8.1.2.2   | Logical OR                            |             |          | •••          |          |         |     | 8-3 |

|    |              |             | 8.1.2.3   | Logical AND                           | )           |          | •••          | •••      |         | ••• | 8-3 |

|    |              |             | 8.1.2.4   | Logical XOF                           | ٦. R        |          | •••          | •••      |         | ••• | 8-3 |

|    |              |             | 8.1.2.5   | Logical ZER                           |             |          | •••          |          |         |     | 8-3 |

|    |              |             | 8.1.2.6   |                                       |             |          | •••          | •••      | •••     |     | 8-5 |

|    |              |             |           | •                                     |             |          |              |          |         |     |     |

|                                                                      | 8.1.2.7                                                                                                                                                                                                          | Graphica                                                                                                                                                                                          | I OR                                                                                                                                          |                                                           |                                 |                                  |                                    |                                       | 8-5                                                                  |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------|----------------------------------|------------------------------------|---------------------------------------|----------------------------------------------------------------------|

| •                                                                    |                                                                                                                                                                                                                  | Graphica                                                                                                                                                                                          |                                                                                                                                               |                                                           |                                 |                                  |                                    |                                       | 8-5                                                                  |

|                                                                      |                                                                                                                                                                                                                  |                                                                                                                                                                                                   |                                                                                                                                               | •••                                                       | •••                             | •••                              | •••                                | •••                                   |                                                                      |

|                                                                      | .1.3 Color S                                                                                                                                                                                                     | trategy .                                                                                                                                                                                         | ••                                                                                                                                            | •••                                                       | •••                             | •••                              | •••                                | •••                                   | 8-5                                                                  |

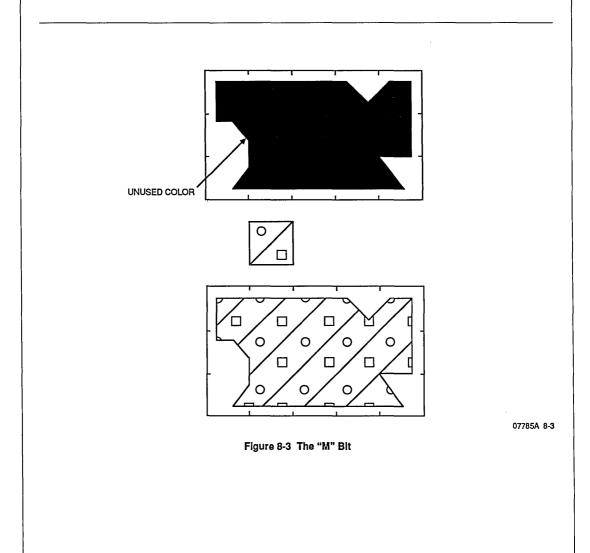

|                                                                      | he M Bit                                                                                                                                                                                                         |                                                                                                                                                                                                   | ••                                                                                                                                            | •••                                                       |                                 | •••                              | •••                                | •••                                   | 8-5                                                                  |

| 8.3 T                                                                | he SI Bit                                                                                                                                                                                                        |                                                                                                                                                                                                   |                                                                                                                                               |                                                           |                                 |                                  |                                    | •••                                   | 8-5                                                                  |

| 8.4 T                                                                | he SP Bit                                                                                                                                                                                                        |                                                                                                                                                                                                   |                                                                                                                                               |                                                           |                                 |                                  |                                    |                                       | 8-5                                                                  |

| •••••                                                                |                                                                                                                                                                                                                  |                                                                                                                                                                                                   |                                                                                                                                               |                                                           |                                 |                                  |                                    | •••                                   |                                                                      |

|                                                                      | ALIASING                                                                                                                                                                                                         |                                                                                                                                                                                                   |                                                                                                                                               |                                                           |                                 |                                  |                                    |                                       | o 4                                                                  |

| 9. ANTI-                                                             | ALIASING                                                                                                                                                                                                         | ••••                                                                                                                                                                                              | ••                                                                                                                                            | •••                                                       | •••                             | •••                              | •••                                | •••                                   | 9-1                                                                  |

|                                                                      |                                                                                                                                                                                                                  |                                                                                                                                                                                                   |                                                                                                                                               |                                                           |                                 |                                  |                                    | <i>'</i>                              |                                                                      |

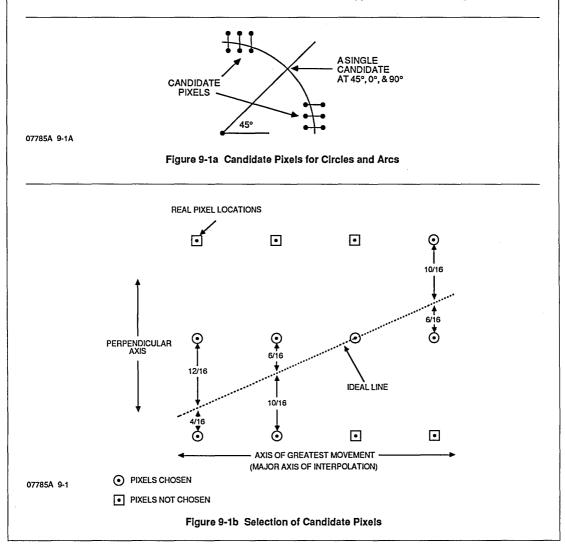

| 9.1 S                                                                | election of C                                                                                                                                                                                                    | Candidate                                                                                                                                                                                         | Pixels                                                                                                                                        |                                                           |                                 |                                  |                                    |                                       | 9-1                                                                  |

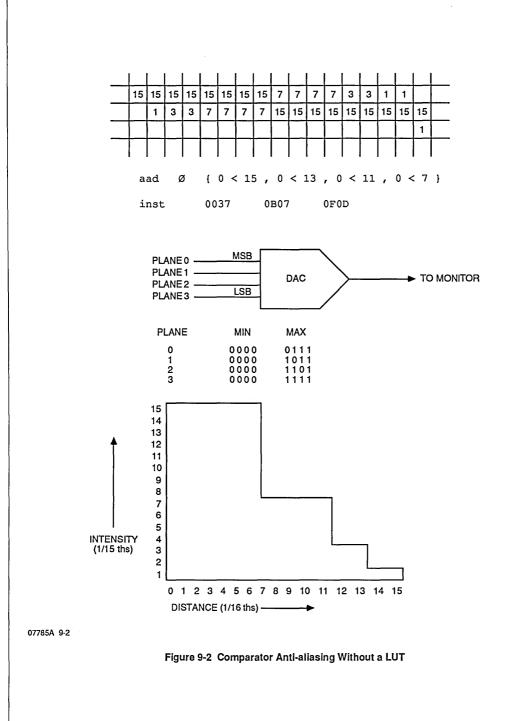

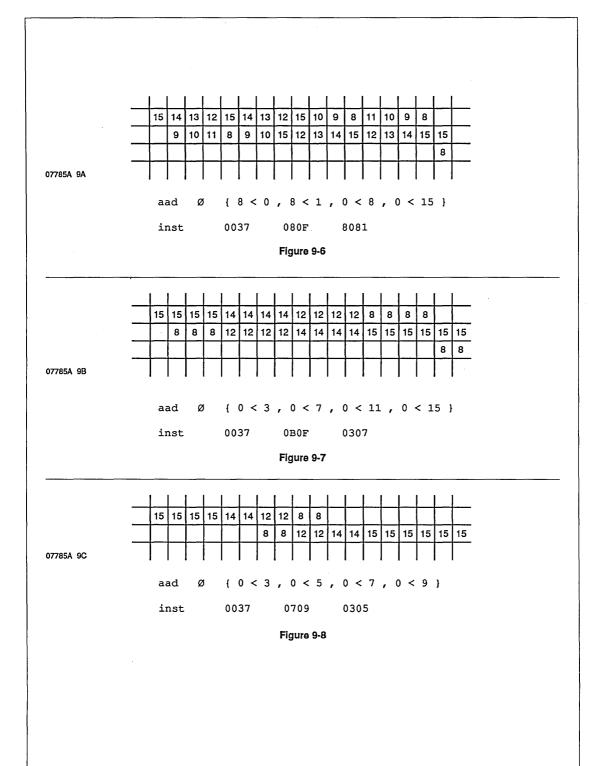

| 9.2 C                                                                | comparator A                                                                                                                                                                                                     | Anti-aliasi                                                                                                                                                                                       | na                                                                                                                                            |                                                           |                                 |                                  |                                    |                                       | 9-2                                                                  |

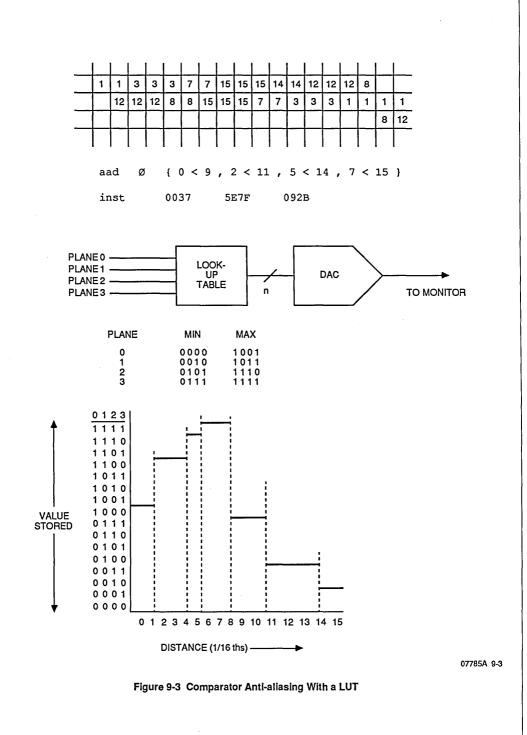

|                                                                      | .2.1 Compa                                                                                                                                                                                                       |                                                                                                                                                                                                   |                                                                                                                                               |                                                           |                                 | Tabla                            |                                    |                                       | 9-2                                                                  |

|                                                                      |                                                                                                                                                                                                                  |                                                                                                                                                                                                   |                                                                                                                                               |                                                           |                                 |                                  | •••                                | •••                                   | -                                                                    |

|                                                                      | .2.2 Compa                                                                                                                                                                                                       |                                                                                                                                                                                                   |                                                                                                                                               |                                                           | -                               | loie                             | •••                                | •••                                   | 9-2                                                                  |

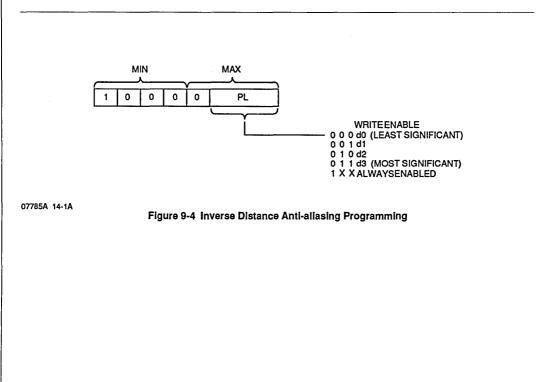

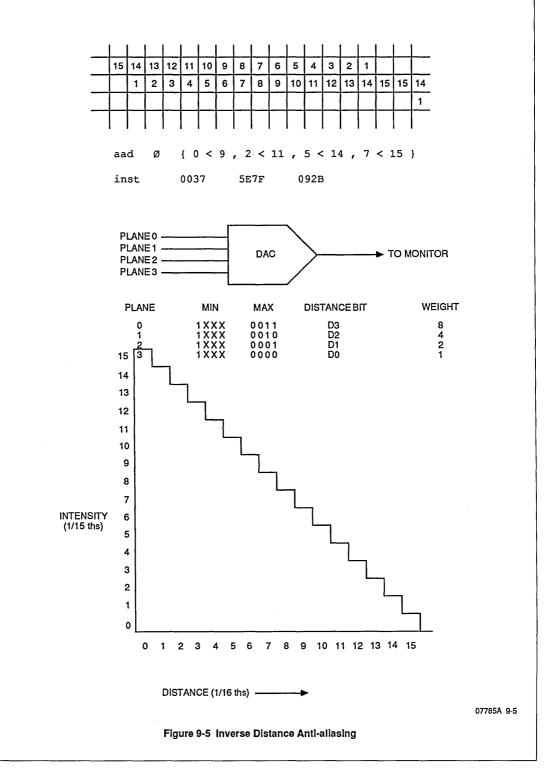

|                                                                      | verse Dista                                                                                                                                                                                                      |                                                                                                                                                                                                   |                                                                                                                                               |                                                           | •••                             | •••                              | •••                                | •••                                   | 9-5                                                                  |

| 9.4 A                                                                | Inti-aliasing                                                                                                                                                                                                    | in a Coloi                                                                                                                                                                                        | : Systen                                                                                                                                      | 1                                                         | ••••                            | •••                              | •••                                | •••                                   | 9-5                                                                  |

|                                                                      |                                                                                                                                                                                                                  |                                                                                                                                                                                                   |                                                                                                                                               |                                                           |                                 |                                  |                                    |                                       |                                                                      |

| 10. STR                                                              | ING OPER                                                                                                                                                                                                         | ATIONS                                                                                                                                                                                            | i                                                                                                                                             |                                                           |                                 |                                  |                                    |                                       | 10-1                                                                 |

|                                                                      |                                                                                                                                                                                                                  |                                                                                                                                                                                                   |                                                                                                                                               |                                                           | •••                             |                                  |                                    | •••                                   |                                                                      |

| 10.4                                                                 | Oversiever                                                                                                                                                                                                       |                                                                                                                                                                                                   | menette                                                                                                                                       |                                                           |                                 |                                  |                                    |                                       | 40.4                                                                 |

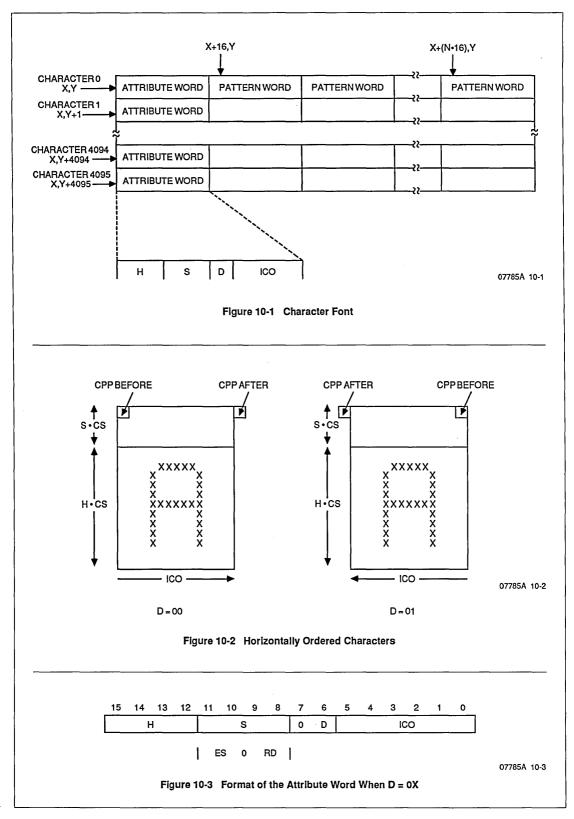

| 10.1                                                                 | Overview o                                                                                                                                                                                                       |                                                                                                                                                                                                   |                                                                                                                                               | ns                                                        | •••                             | •••                              | •••                                | •••                                   | 10-1                                                                 |

| 10.2                                                                 | The Charac                                                                                                                                                                                                       |                                                                                                                                                                                                   |                                                                                                                                               | •••                                                       | •••                             | •••                              | •••                                | •••                                   | 10-1                                                                 |

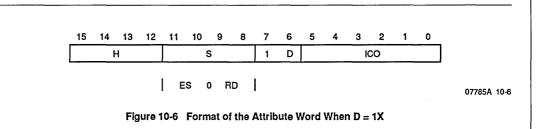

|                                                                      | 10.2.1 The                                                                                                                                                                                                       | Attribute \                                                                                                                                                                                       | Nord                                                                                                                                          |                                                           |                                 |                                  |                                    | •••                                   | 10-1                                                                 |

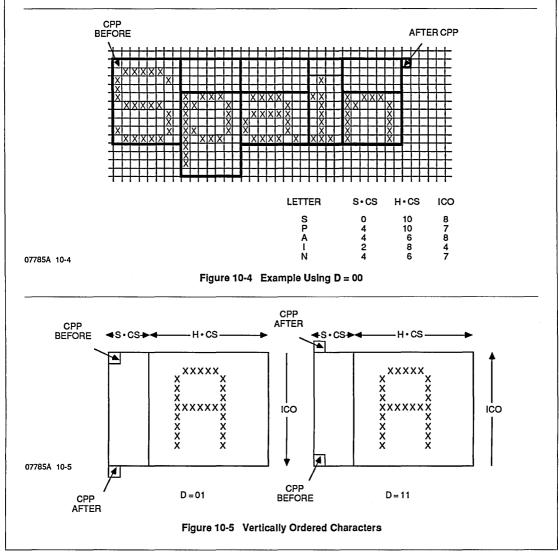

|                                                                      |                                                                                                                                                                                                                  | .1.1 Horiz                                                                                                                                                                                        |                                                                                                                                               | Ordered (                                                 | Character                       | rs                               |                                    |                                       | 10-1                                                                 |

|                                                                      |                                                                                                                                                                                                                  | .1.2 Verti                                                                                                                                                                                        |                                                                                                                                               |                                                           |                                 |                                  |                                    |                                       | 10-3                                                                 |

| 10.0                                                                 |                                                                                                                                                                                                                  |                                                                                                                                                                                                   |                                                                                                                                               |                                                           | aracters                        |                                  | •••                                | •••                                   |                                                                      |

| 10.3                                                                 | Establishin                                                                                                                                                                                                      |                                                                                                                                                                                                   |                                                                                                                                               |                                                           |                                 | •••                              | •••                                | •••                                   | 10-4                                                                 |

| 10.4                                                                 | Moving Cha                                                                                                                                                                                                       |                                                                                                                                                                                                   |                                                                                                                                               | Charac                                                    | ter                             |                                  |                                    |                                       |                                                                      |

|                                                                      | Font (String                                                                                                                                                                                                     |                                                                                                                                                                                                   |                                                                                                                                               | •••                                                       | •••                             | •••                              | •••                                | •••                                   | 10-5                                                                 |

| 10.5                                                                 | Nonprinting                                                                                                                                                                                                      | g Charact                                                                                                                                                                                         | ers                                                                                                                                           | •••                                                       |                                 |                                  |                                    | •••                                   | 10-5                                                                 |

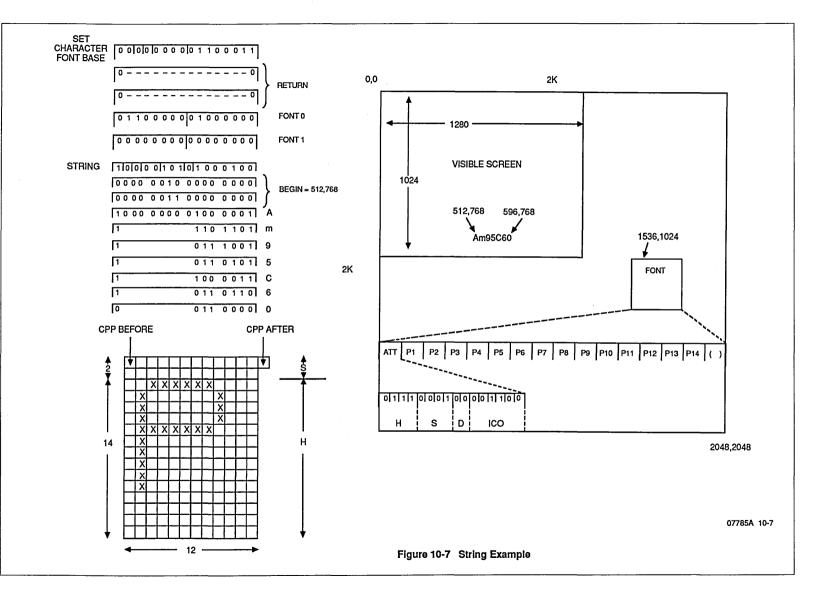

| 10.6                                                                 | An Example                                                                                                                                                                                                       | ė.                                                                                                                                                                                                |                                                                                                                                               |                                                           |                                 | •••                              |                                    | •••                                   | 10-6                                                                 |

|                                                                      | 10.6.1 Set                                                                                                                                                                                                       |                                                                                                                                                                                                   |                                                                                                                                               |                                                           |                                 |                                  |                                    |                                       | 10-6                                                                 |

|                                                                      |                                                                                                                                                                                                                  |                                                                                                                                                                                                   |                                                                                                                                               |                                                           | Clion                           | •••                              | •••                                |                                       | 10-6                                                                 |

|                                                                      | 10.6.2 Strin                                                                                                                                                                                                     |                                                                                                                                                                                                   |                                                                                                                                               | •••                                                       | •••                             | •••                              | •••                                | •••                                   |                                                                      |

|                                                                      | 10.6.3 Cha                                                                                                                                                                                                       |                                                                                                                                                                                                   |                                                                                                                                               |                                                           | •••                             | •••                              | •••                                | •••                                   | 10-6                                                                 |

| 10.7                                                                 | Building an                                                                                                                                                                                                      | id Using \                                                                                                                                                                                        | /ery Lar                                                                                                                                      | ge Fonts                                                  | 5                               | •••                              | •••                                | •••                                   | 10-6                                                                 |

| 10.8                                                                 | Text with C                                                                                                                                                                                                      | olored Ba                                                                                                                                                                                         | ickgrou                                                                                                                                       | nd                                                        |                                 |                                  |                                    | ••••                                  | 10-8                                                                 |

| 10.9                                                                 | Optimizing                                                                                                                                                                                                       | String Pe                                                                                                                                                                                         | rformar                                                                                                                                       | ICE                                                       |                                 |                                  |                                    |                                       | 10-8                                                                 |

|                                                                      |                                                                                                                                                                                                                  | •                                                                                                                                                                                                 |                                                                                                                                               |                                                           |                                 |                                  |                                    |                                       |                                                                      |

|                                                                      |                                                                                                                                                                                                                  |                                                                                                                                                                                                   |                                                                                                                                               |                                                           |                                 |                                  |                                    |                                       |                                                                      |

| 11. WIN                                                              | DOWE                                                                                                                                                                                                             |                                                                                                                                                                                                   |                                                                                                                                               |                                                           |                                 |                                  |                                    |                                       | 44.4                                                                 |

|                                                                      | 0000                                                                                                                                                                                                             | •••                                                                                                                                                                                               | •••                                                                                                                                           | •••                                                       | •••                             | •••                              | •••                                | •••                                   | 11-1                                                                 |

|                                                                      |                                                                                                                                                                                                                  |                                                                                                                                                                                                   |                                                                                                                                               |                                                           |                                 |                                  |                                    |                                       |                                                                      |

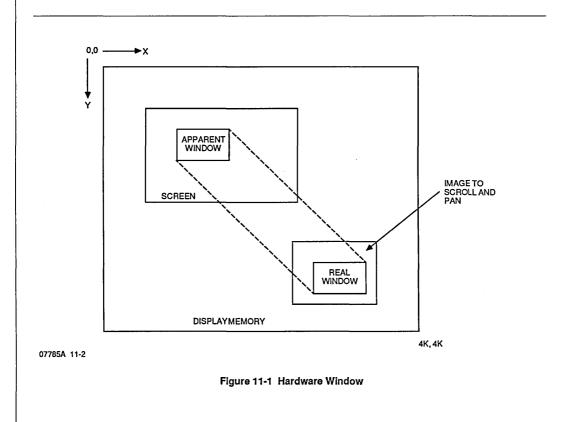

|                                                                      | Hardware F                                                                                                                                                                                                       |                                                                                                                                                                                                   |                                                                                                                                               |                                                           |                                 |                                  |                                    |                                       |                                                                      |

| 11.1                                                                 | i la                                                                                                                                                                         | Requireme                                                                                                                                                                                         | ents                                                                                                                                          |                                                           |                                 |                                  |                                    |                                       | 11-1                                                                 |

| 11.1                                                                 |                                                                                                                                                                                                                  |                                                                                                                                                                                                   |                                                                                                                                               |                                                           |                                 |                                  |                                    |                                       | 11-1                                                                 |

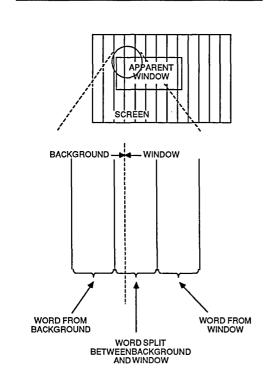

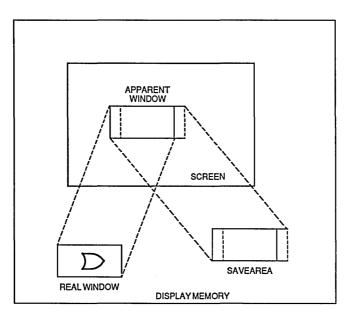

|                                                                      | How Does t                                                                                                                                                                                                       | the Hardv                                                                                                                                                                                         | vare Wir                                                                                                                                      | ndow Ap                                                   | pear                            |                                  |                                    |                                       |                                                                      |

| 11.2                                                                 | How Does t<br>to the User                                                                                                                                                                                        | the Hardv<br>?                                                                                                                                                                                    | vare Wir<br>                                                                                                                                  | ndow Ap<br>                                               | pear<br>                        |                                  |                                    |                                       | 11-2                                                                 |

| 11.2<br>11.3                                                         | How Does to<br>to the User<br>Window Co                                                                                                                                                                          | the Hardw<br>?<br>ontrol Reg                                                                                                                                                                      | vare Wir<br><br>Jisters                                                                                                                       | ndow Ap<br>                                               | pear<br>                        |                                  | <br>                               |                                       | 11-2<br>11-2                                                         |

| 11.2                                                                 | How Does t<br>to the User<br>Window Co<br>Tutorial on                                                                                                                                                            | the Hardw<br>?<br>ontrol Reg<br>How to U                                                                                                                                                          | vare Wir<br><br>Jisters<br>Ise the \                                                                                                          | ndow Ap<br><br><br>Window                                 | pear<br><br>                    | <br>                             |                                    | <br>                                  | 11-2<br>11-2<br>11-3                                                 |

| 11.2<br>11.3                                                         | How Does to<br>to the User<br>Window Co<br>Tutorial on<br>11.4.1 Drag                                                                                                                                            | the Hardw<br>?<br>ontrol Reg<br>How to U<br>gging an C                                                                                                                                            | vare Wir<br><br>Jisters<br>Jse the N<br>Object                                                                                                | ndow Ap<br>                                               | pear<br>                        |                                  | <br>                               |                                       | 11-2<br>11-2<br>11-3<br>11-3                                         |

| 11.2<br>11.3                                                         | How Does to<br>to the User<br>Window Co<br>Tutorial on<br>11.4.1 Drag<br>11.4.2 Pop                                                                                                                              | the Hardw<br>?<br>ontrol Reg<br>How to U<br>gging an C<br>-up Menu                                                                                                                                | vare Wir<br><br>j <b>isters</b><br>l <b>se the \</b><br>Object<br>s                                                                           | ndow Ap<br><br><br>Window<br>                             | pear<br><br>                    | <br>                             | <br>                               | <br>                                  | 11-2<br>11-2<br>11-3<br>11-3<br>11-3                                 |

| 11.2<br>11.3                                                         | How Does to<br>to the User<br>Window Co<br>Tutorial on<br>11.4.1 Drag                                                                                                                                            | the Hardw<br>?<br>ontrol Reg<br>How to U<br>gging an C<br>-up Menu                                                                                                                                | vare Wir<br><br>j <b>isters</b><br>l <b>se the \</b><br>Object<br>s                                                                           | ndow Ap<br><br><br>Window<br>                             | pear<br><br>                    | <br>                             | •••                                | <br><br>                              | 11-2<br>11-2<br>11-3<br>11-3                                         |

| 11.2<br>11.3<br>11.4                                                 | How Does to<br>to the User<br>Window Co<br>Tutorial on<br>11.4.1 Drag<br>11.4.2 Pop                                                                                                                              | the Hardw<br>?<br>ontrol Reg<br>How to U<br>gging an C<br>oup Menu<br>olling in a                                                                                                                 | vare Wir<br>Jisters<br>Ise the V<br>Object<br>S<br>Window                                                                                     | ndow Ap<br><br><br>Window<br>                             | pear<br><br><br>                | <br><br>                         | <br>                               | ····<br>···<br>···                    | 11-2<br>11-2<br>11-3<br>11-3<br>11-3                                 |

| 11.2<br>11.3<br>11.4                                                 | How Does to<br>to the User<br>Window Co<br>Tutorial on<br>11.4.1 Drag<br>11.4.2 Pop<br>11.4.3 Scru                                                                                                               | the Hardw<br>?<br>ontrol Reg<br>How to U<br>gging an C<br>oup Menu<br>olling in a                                                                                                                 | vare Wir<br>Jisters<br>Ise the V<br>Object<br>S<br>Window                                                                                     | ndow Ap<br><br><br>Window<br>                             | pear<br><br><br>                | ····<br>····<br>···              | <br><br>                           | <br><br>                              | 11-2<br>11-2<br>11-3<br>11-3<br>11-3<br>11-3                         |

| 11.2<br>11.3<br>11.4<br>11.5                                         | How Does t<br>to the User<br>Window Co<br>Tutorial on<br>11.4.1 Drag<br>11.4.2 Pop<br>11.4.3 Scro<br>Software W                                                                                                  | the Hardw<br>?<br>ontrol Reg<br>How to U<br>gging an C<br>-up Menu<br>olling in a<br>/indows                                                                                                      | vare Wir<br>Jisters<br>Ise the V<br>Object<br>S<br>Window                                                                                     | ndow Ap<br><br>Window<br><br>                             | pear<br><br><br><br>            | ····<br>····<br>···              | ····<br>···<br>···                 | ····<br>···<br>···<br>···             | 11-2<br>11-2<br>11-3<br>11-3<br>11-3<br>11-3<br>11-3                 |

| 11.2<br>11.3<br>11.4<br>11.5                                         | How Does to<br>to the User<br>Window Co<br>Tutorial on<br>11.4.1 Drag<br>11.4.2 Pop<br>11.4.3 Scru                                                                                                               | the Hardw<br>?<br>ontrol Reg<br>How to U<br>gging an C<br>-up Menu<br>olling in a<br>/indows                                                                                                      | vare Wir<br>Jisters<br>Ise the V<br>Object<br>S<br>Window                                                                                     | ndow Ap<br><br>Window<br><br>                             | pear<br><br><br><br>            | ····<br>····<br>···              | <br><br>                           | ····<br>···<br>···                    | 11-2<br>11-2<br>11-3<br>11-3<br>11-3<br>11-3                         |

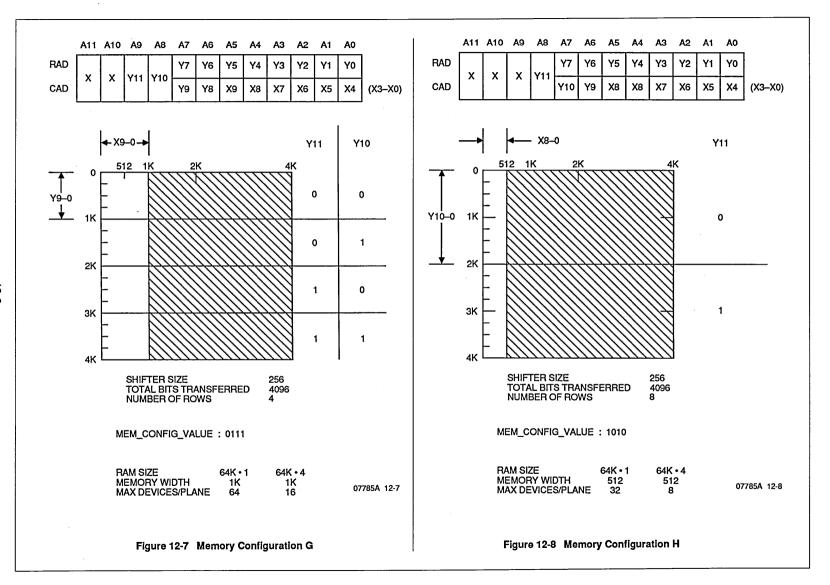

| 11.2<br>11.3<br>11.4<br>11.5<br>12. DISF                             | How Does to<br>to the User<br>Window Co<br>Tutorial on<br>11.4.1 Drag<br>11.4.2 Pop<br>11.4.3 Scro<br>Software W<br>PLAY MEM                                                                                     | the Hardw<br>?<br>pontrol Reg<br>How to U<br>gging an C<br>-up Menu<br>olling in a<br>/indows                                                                                                     | vare Wir<br>listers<br>lse the V<br>Dbject<br>s<br>Window<br><br>DNFIGI                                                                       | ndow Ap<br><br>Window<br><br>                             | pear<br><br><br><br>            | ····<br>····<br>···              | ····<br>···<br>···                 | ····<br>···<br>···<br>···             | 11-2<br>11-2<br>11-3<br>11-3<br>11-3<br>11-3<br>11-3<br>12-1         |

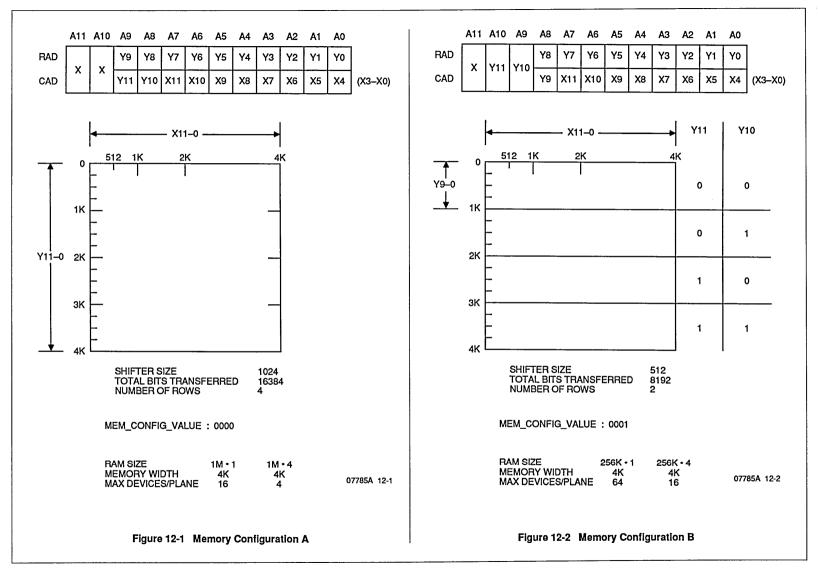

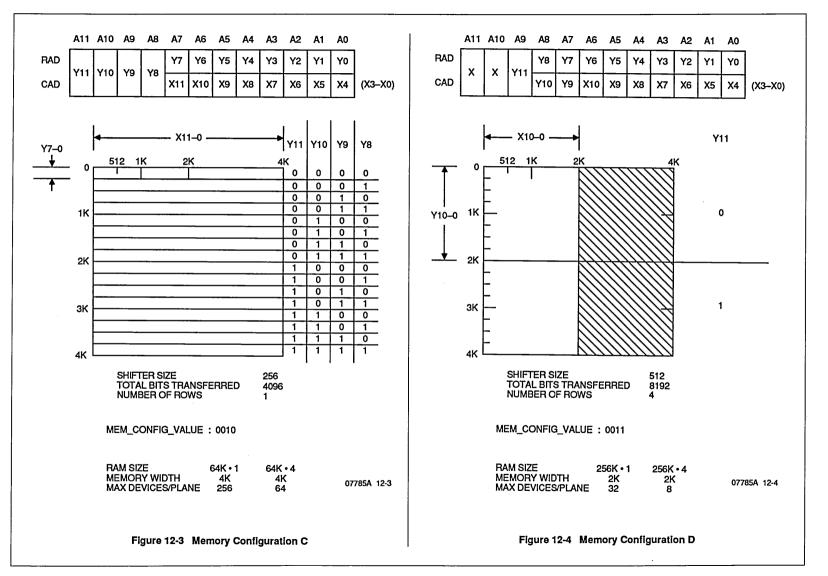

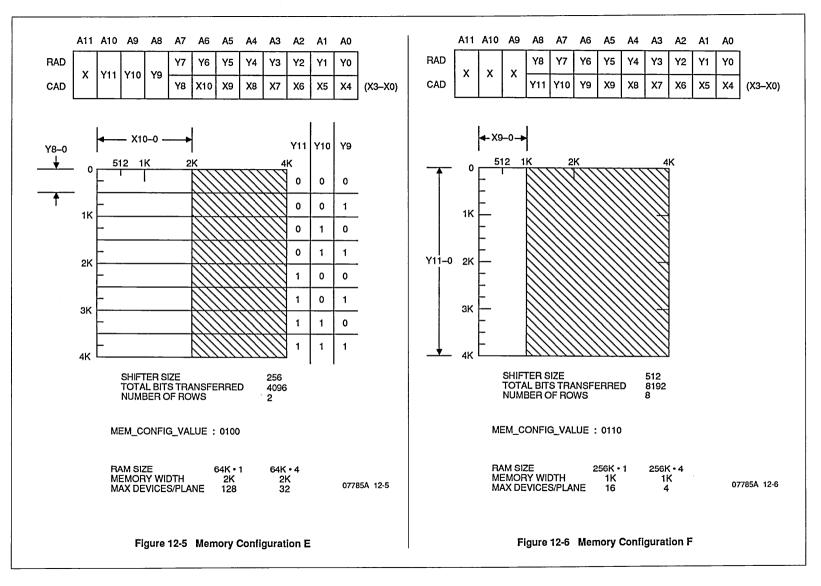

| 11.2<br>11.3<br>11.4<br>11.5<br>12. DISF<br>12.1                     | How Does to<br>to the User<br>Window Co<br>Tutorial on<br>11.4.1 Drag<br>11.4.2 Pop<br>11.4.3 Scro<br>Software W<br>PLAY MEM<br>Overview o                                                                       | the Hardw<br>?<br>pontrol Reg<br>How to U<br>gging an C<br>-up Menu:<br>billing in a<br>/indows<br>IORY CC<br>of Diagran                                                                          | vare Wir<br><br>Jisters<br>Ise the V<br>Object<br>S<br>Window<br><br>ONFIGI                                                                   | ndow Ap<br><br>Window<br><br><br>URATIC<br>               | pear<br><br><br><br>            | ····<br>····<br>···              | ····<br>···<br>···                 | ····<br>···<br>···<br>···             | 11-2<br>11-2<br>11-3<br>11-3<br>11-3<br>11-3<br>11-3<br>12-1<br>12-1 |

| 11.2<br>11.3<br>11.4<br>11.5<br>12. DISE                             | How Does to<br>to the User<br>Window Co<br>Tutorial on<br>11.4.1 Drag<br>11.4.2 Pop<br>11.4.3 Scro<br>Software W<br>PLAY MEM                                                                                     | the Hardw<br>?<br>pontrol Reg<br>How to U<br>gging an C<br>-up Menu:<br>billing in a<br>/indows<br>IORY CC<br>of Diagran                                                                          | vare Wir<br><br>Jisters<br>Ise the V<br>Object<br>S<br>Window<br><br>ONFIGI                                                                   | ndow Ap<br><br>Window<br><br><br>URATIC<br>               | pear<br><br><br><br><br><br>DNS | ····<br>···<br>···<br>···        | <br><br><br>                       | ····<br>···<br>···                    | 11-2<br>11-2<br>11-3<br>11-3<br>11-3<br>11-3<br>11-3<br>12-1         |

| 11.2<br>11.3<br>11.4<br>11.5<br>12. DISF<br>12.1<br>12.2             | How Does to<br>to the User<br>Window Co<br>Tutorial on<br>11.4.1 Drag<br>11.4.2 Pop<br>11.4.3 Scro<br>Software W<br>PLAY MEM<br>Overview o<br>Summary o                                                          | the Hardw<br>?<br>Dontrol Reg<br>How to U<br>gging an C<br>-up Menu<br>obling in a<br>/indows<br>IORY CC<br>of Diagran                                                                            | vare Wir<br><br>Jisters<br>Ise the V<br>Object<br>S<br>Window<br><br>ONFIGI                                                                   | ndow Ap<br><br>Window<br><br><br>URATIC<br>               | pear<br><br><br><br><br>DNS     | ····<br>···<br>···<br>···<br>··· | ····<br>···<br>···<br>···          | ····<br>···<br>···<br>···             | 11-2<br>11-2<br>11-3<br>11-3<br>11-3<br>11-3<br>11-3<br>12-1<br>12-1 |

| 11.2<br>11.3<br>11.4<br>11.5<br>12. DISF<br>12.1<br>12.2             | How Does to<br>to the User<br>Window Co<br>Tutorial on<br>11.4.1 Drag<br>11.4.2 Pop<br>11.4.3 Scro<br>Software W<br>PLAY MEM<br>Overview o                                                                       | the Hardw<br>?<br>Dontrol Reg<br>How to U<br>gging an C<br>-up Menu<br>obling in a<br>/indows<br>IORY CC<br>of Diagran                                                                            | vare Wir<br><br>Jisters<br>Ise the V<br>Object<br>S<br>Window<br><br>ONFIGI                                                                   | ndow Ap<br><br>Window<br><br><br>URATIC<br>               | pear<br><br><br><br><br>DNS     | ····<br>···<br>···<br>···<br>··· | ····<br>···<br>···<br>···          | ····<br>···<br>···<br>···             | 11-2<br>11-2<br>11-3<br>11-3<br>11-3<br>11-3<br>11-3<br>12-1<br>12-1 |

| 11.2<br>11.3<br>11.4<br>11.5<br>12. DISF<br>12.1<br>12.2             | How Does to<br>to the User<br>Window Co<br>Tutorial on<br>11.4.1 Drag<br>11.4.2 Pop<br>11.4.3 Scro<br>Software W<br>PLAY MEM<br>Overview o<br>Summary o                                                          | the Hardw<br>?<br>Dontrol Reg<br>How to U<br>gging an C<br>-up Menu<br>obling in a<br>/indows<br>IORY CC<br>of Diagran                                                                            | vare Wir<br><br>Jisters<br>Ise the V<br>Object<br>S<br>Window<br><br>ONFIGI                                                                   | ndow Ap<br><br>Window<br><br><br>URATIC<br>               | pear<br><br><br><br><br>DNS     | ····<br>···<br>···<br>···<br>··· | ····<br>···<br>···<br>···          | · · · · · · · · · · · · · · · · · · · | 11-2<br>11-2<br>11-3<br>11-3<br>11-3<br>11-3<br>11-3<br>12-1<br>12-1 |

| 11.2<br>11.3<br>11.4<br>11.5<br>12. DISF<br>12.1<br>12.2<br>13. MISC | How Does to<br>to the User<br>Window Co<br>Tutorial on<br>11.4.1 Drag<br>11.4.2 Pop<br>11.4.3 Scro<br>Software W<br>PLAY MEM<br>Overview o<br>Summary of<br>CELLANEA                                             | the Hardw<br>?<br>Dontrol Reg<br>How to U<br>gging an C<br>-up Menu-<br>obling in a<br>/indows<br>IORY CC<br>of Diagram<br>of Configu                                                             | vare Wir<br>Isters<br>Ise the V<br>Object<br>S<br>Window<br>Window<br>ONFIGI<br>Is<br>Irations<br>                                            | ndow Ap<br><br>Window<br><br><br>URATIC<br><br>           | pear<br><br><br><br><br>DNS     | ····<br>···<br>···<br>···<br>··· | ····<br>····<br>····               | · · · · · · · · · · · · · · · · · · · | 11-2<br>11-2<br>11-3<br>11-3<br>11-3<br>11-3<br>11-3<br>12-1<br>12-1 |