## The Am8052 CRT Controller

# **Advanced Micro Devices**

# Am8052 Alphanumeric CRT Controller

# **Technical Manual**

© 1984 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics. The company assumes no responsibility for the use of any circuits described herein.

901 Thompson Place, P.O. Box 3453, Sunnyvale, California 94088 (408) 732-2400 TWX: 910-339-9280 TELEX: 34-6306

Printed in U.S.A. CD-B-2.5M-11/84-1

## TABLE OF CONTENTS

| 1. | Introduction                                                                                                                                                                                                                               |                                        |  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|

| 2. | AM8052 Architecture                                                                                                                                                                                                                        |                                        |  |

|    | 2.1 Overview<br>2.1.1 Introduction<br>2.1.1 General Description<br>2.1.3 Basic Operation                                                                                                                                                   | 5<br>5<br>5<br>7                       |  |

|    | <ul> <li>2.2 Interface Signals</li> <li>2.3 Register Description <ul> <li>2.3.1 Introduction</li> <li>2.3.2 Register Addressing</li> <li>2.2.2 Register Description</li> <li>2.3.4 Video Timing Programming Example</li> </ul> </li> </ul> | 11<br>17<br>17<br>17<br>19<br>35       |  |

|    | 2.4 DMA Operation<br>2.4.1 DMA Signals and Protocol<br>2.4.2 Buffering BRQ<br>2.4.3 DMA Transfer Operation<br>2.4.4 DMA Burst Control                                                                                                      | 33<br>39<br>39<br>41<br>41<br>44       |  |

|    | 2.5Row Management Unit Operation2.5.1Introduction2.5.2Data Structure2.5.3Background Information Management2.5.4Window Information Management                                                                                               | 45<br>45<br>46<br>47<br>59             |  |

|    | 2.6 Attributes<br>2.6.1 Character Attributes<br>2.6.2 Field Attributes<br>2.6.3 Row Attributes<br>2.6.4 Frame Attributes<br>2.6.5 Cursor Display<br>2.6.6 The Fill Code<br>2.7 Interrupt Operation                                         | 63<br>63<br>66<br>67<br>68<br>69<br>71 |  |

|    | 2.8 Soft-Scroll Mechanism<br>2.9 Synchronization<br>2.10 RFI and Interface Video                                                                                                                                                           | 73<br>79<br>81                         |  |

| 3. | Am8052 Software Cookbook                                                                                                                                                                                                                   |                                        |  |

| 4. | Interfacing                                                                                                                                                                                                                                |                                        |  |

- in incentaeting

- 5. Application

- 6. Product Specifications

NOTE: Chapters 1, 3, 4, 5, 6 to be added at a later date.

## Acknowledgements:

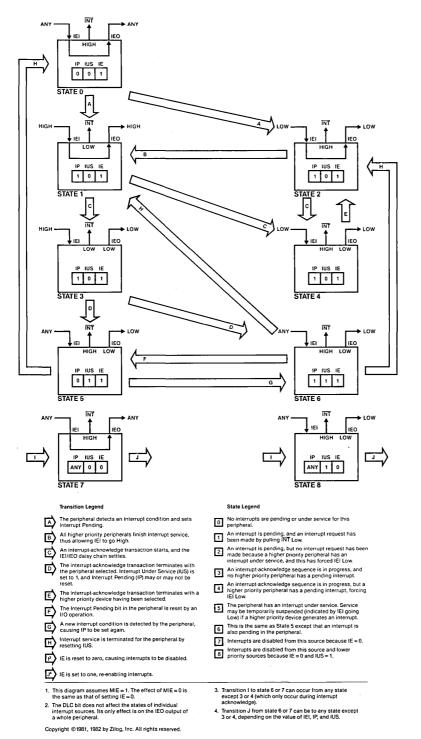

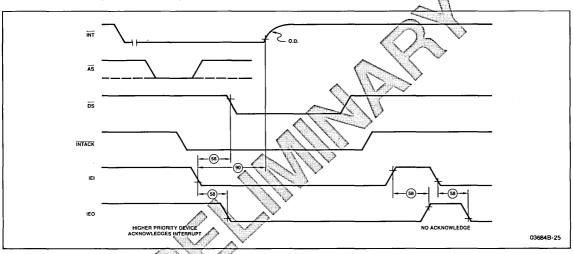

The bus request/acknowledge and the interrupt daisy-chain mechanisms used in this CRTC are based on the Z8000 structures originated by Zilog, Inc. Figure 2.44 is reprinted with their permission. Despite this conceptual heritage, the Am8052 interfaces very easily to other 16-bit microprocessors.

#### Copyright Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics. The company assumes no responsibility for the use of any circuits described herein.

> 901 Thompson Place, P.O.Box 3453, Sunnyvale, CA 94088 (408) 732-2400, TWX: 910-339-9280, TELEX: 34-6306

## 2.1 OVERVIEW

## 2.1.1 Introduction

The Am8052 CRTC is a general-purpose controller for raster scan CRT displays. It embodies all of the fundamental functions presently provided by various competing monolithic products. In addition, it contains many advanced, nextgeneration features not presently offered by the competition. A wide variety of systems will be able to take advantage of its features, turning them into powerful display controllers with a minimum chip count.

The Am8052 link-oriented data manipulation provides sophisticated text display without imposing undue overhead on the host CPU.

The versatility of the chip allows it to cover a wide range of applications from medium performance up to very-high performance displays.

## 2.1.2 General Description

A typical system diagram incorporating the Am8052 CRTC is shown in Figure 2.1.

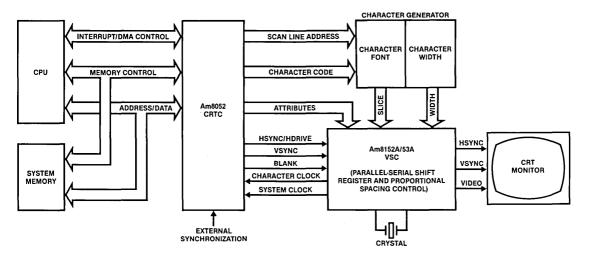

The circuit can be used together with the Am8152 or Am8153 video display controllers, specially designed to complement the Am8052 and enhance its displaying capabilities.

The Am8052, after initialization by the host processor, acts as a stand-alone device:

It fetches the data to be displayed from the main memory through its internal DMA controller.

It generates the displayable character codes along with their attributes.

It provides all the timing signals to synchronize the beamscanning with the character-pixel stream.

It configures the screen with useful features such as size programmable windows and vertical soft-scroll.

Due to the sophistication of the Am8052, we will first explain the general operation of the part, splitting it into functional blocks; each block will be described in more detail later.

Figure 2.1. CRT Controller System Diagram

03901A-02

The Am8052 is a real time raster scan display controller, which means that it keeps track of updating the display screen on a character-row basis by toggling its internal row-buffers, one being displayed by the display control block, while another is loaded through the DMA interface under control of the row management unit.

All the above operations are synchronized by the video timing control block and intialized by the host processor through the bus interface logic.

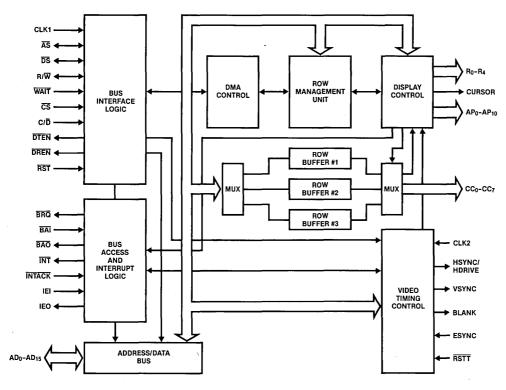

The block diagram of the Am8052 (Figure 2.2) shows the functional blocks, and how they interface with each other.

## 2.1.3 Basic Operation

Following reset, the Am8052 remains in slave mode and waits for the host processor to initialize its timing and control registers, as well as one address pointer to the start of the display data location in the host memory.

While in the idle state, the chip holds both HSYNC and VSYNC signals inactive (LOW), to prevent undefined synchronization to the CRT which might damage high bandwidth tubes, and it also holds the blank signal active to inhibit the CRT beam.

Once the part has been initialized, and upon a command from the CPU, the DMA enters into the bus request sequence to update its three internal row buffers whenever possible. A row buffer cannot be loaded at the same time that it is displayed.

The row management unit governs the loading of the characters to be displayed, as well as their attributes (whenever they are invoked) into the row buffers. This logic is also in charge of updating the display control registers (not accessible to the user), on a row by row basis, as specified by the row definition blocks located in main memory.

Before going further in the description of the internal functionality of the chip, let us see how it handles the data to be displayed and the screen organization.

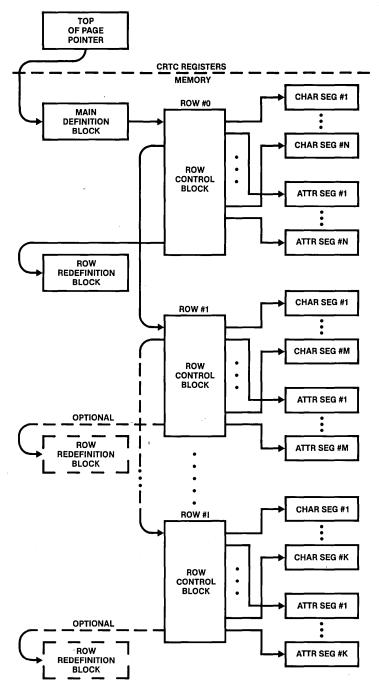

All the display information (characters, attributes, row structure) reside in main memory in a linked-block structure. Figure 2.3 shows how this structure is implemented with the Am8052.

Before the beginning of each frame display, the CRTC fetches the main definition block from main memory. This block tells it how to set-up the screen-dependent attributes such as softscroll rate, character and cursor blink rates and dutycycles, screen relative cursor coordinates, fill character code, etc.

03901A-03

An Am8052 internal register points to the Main Definition Block and links to the first Row Control Block in main memory.

Each Row Control Block links to the next Row Control Block, and contains the pointers to the character and attribute segments to be displayed, both located in main memory. This block also contains the visible and hidden character quantities for each character segment.

Each Row Control Block may optionally invoke a Row Redefinition Block. This Row Redefinition Block allows the user to redefine the row's attributes for the current and succeeding character rows.

The user-defined Row Attributes are contained in a 10-bit code which appears on the attribute bus during the horizontal retrace of the CRT; this is an extra feature which allows the user to define his own row attributes (e.g., invisible row, blinking row, highlight row).

The principal advantages of this linked-list architecture is to decrease the CPU overhead when editing text in system memory. Pointers are manipulated instead of executing CPU intensive data-block moves. Pages are switched on the display by changing a unique pointer (top of page pointer) inside the Am8052. Lines are deleted or inserted by modifying a few pointers in the linked-list structure.

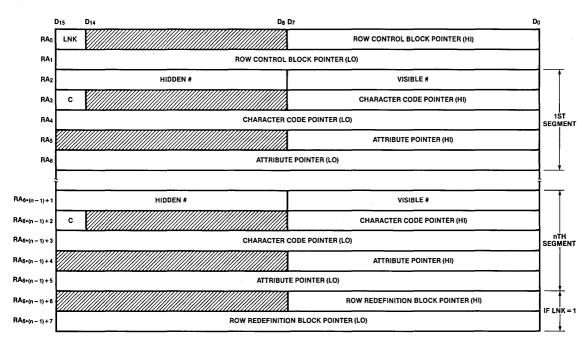

The "display control unit" combines the character stream from one of the three row buffers with the row or character dependent display characteristics of these characters. As a result, the display control block outputs the number of the line being scanned in the current row on RO-R4, and outputs the character-codes contained in this row on CCO-CC7. These two codes form the address sent to the character generator. The character code (most significant bits in the address) points to the matrix of pixels synthesizing the character on the screen, while the line-number (LSB) indicates which line of the matrix is to be displayed on the screen. The resultant line of pixels is output from the character generator and later processed by the various attributes and sent on the video output.

03901A-04

## 2.2 INTERFACE SIGNALS

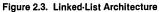

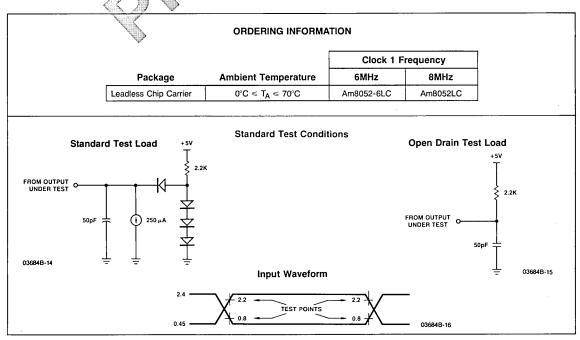

With the exception of CLK1 and CLK2 inputs, all inputs and outputs of the CRTC are TTL compatible. Figure 2.4 shows the device pin-out.

VSS1, VSS2 (Ground)

## VCC1, VCC2 (+5V Power Supply)

+/- 5% tolerance for commercial temperature devices. +/- 10% tolerance for military temperature devices.

#### CLK1 (System Clock, Input)

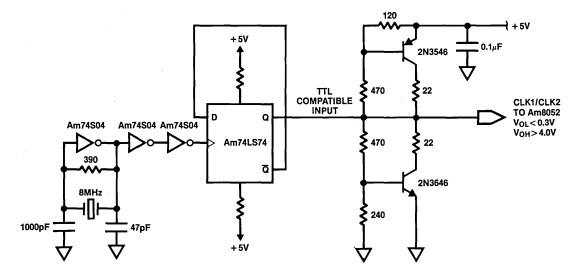

The Clock1 signal controls the DMA and peripheral portion of the CRTC, and times all memory accesses. It requires a timing duty cycle of 50% (+/- 5%) at its highest frequency and is driven by an external timing source, usually the CPU clock. In proportional spacing applications, where CLK2 is variable, CLK1 should be used to time the horizontal and vertical sync rates. CLK1 is not TTL compatible. Figure 2.5 shows a CLK1/CLK2 driver generating a clock signal with the required High and Low levels.

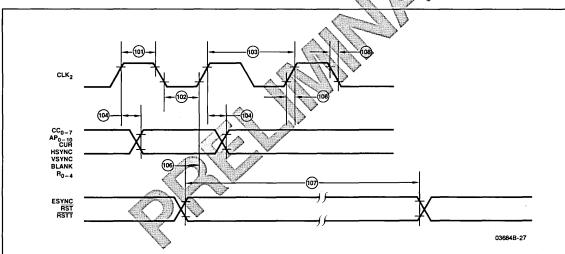

#### CLK2 (Character Clock, Input)

The Clock2 signal is used to time character accesses from the CRTC row buffers. In applications which do not use proportional spacing CLK2 is fixed in frequency and can, therefore, be used to time the horizontal and vertical sync rates, allowing CLK1, the system clock, to be unrelated and asynchronous to the display timing. CLK2 is not TTL compatible.

#### ADO-AD15 (Address/Data Bus, Input/Output)

The Address/Data Bus is a time-multiplexed, bidirectional, High-true, three-state bus. The presence of addresses is defined by the  $\overline{AS}$  signal and the presence of data is defined by the  $\overline{DS}$  signal. When the CRTC is in control of the system bus via its internal DMA capability, it dominates the AD Bus. When the CRTC is idle, the CPU or other external devices control the AD Bus and may use it to access the internal registers of the CRTC. The high-order 8-bit address is output on the ADØ-7 lines. Interrupt Vector information is also output on the ADØ-7 lines.

## AS (Address Strobe, Input/Output)

Address Strobe is a bidirectional, active Low, three-state signal. In slave mode this input controls the internal transparent latches at the C/D and  $\overline{CS}$  inputs:

In multiplexed address/data bus systems  $\overline{\text{AS}}$  High latches C/ $\overline{\text{D}}$  and CS.

In demultiplexed address/data bus systems  $\overline{\text{AS}}$  may be held Low to enable the above-mentioned latches.

When the CRTC is the bus master,  $\overline{AS}$  is an output indicating a valid address output on the AD-bus. The address may be latched with the rising edge of  $\overline{AS}$ . During page address update cycles  $\overline{AS}$  and R/W are both driven Low.

#### DS (Data Strobe, Input/Output)

Data Strobe is a bidirectional, active Low, three-state signal. When the CRTC is in the slave mode and the external system is transfering information to or from it,  $\overline{\text{DS}}$  is a timing input used by the CRTC to move data to or from the AD-bus. During a DMA operation when the CRTC is in control of the system,  $\overline{\text{DS}}$  is an output generated by the CRTC and used by the system to move data to or from the AD-bus. For slave mode the  $\overline{\text{DS}}$  signal may be asynchronous to CLK1.

## CS (Chip Select, Input)

The  $\overline{CS}$  input is an active Low signal used by the host processor to access the CRTC's internal registers. The  $\overline{CS}$  input is internally latched through an internal transparent latch controlled by the  $\overline{AS}$  input.

## WAIT (Wait, Input)

The  $\overline{WAIT}$  input is an active Low signal used to stretch the  $\overline{DS}$  strobe whenever the CRTC has access to the host's bus for data transfer. The status of the  $\overline{WAIT}$  signal is sampled only on the falling edge of time T2 of CLK1. WAIT is ignored during any non-memory read CRTC cycles.

## **R**/₩ (Read/Write, Input/Output)

Read/Write is a bidirectional, three-state signal. Read polarity is High and write polarity is Low. R/W indicates the data direction for the bus transaction under way, and remains stable for the length of the bus cycle. When CS input is active, Read (High) indicates that the system is requesting data from the CRTC and Write (Low) indicates that the system is presenting data to the CRTC. During a DMA operation when the CRTC is in control of the system, R/W is an output generated by the CRTC, with Read indicating that data is being requested by the CRTC from the addressed memory location, and Write to indicate that the CRTC outputs a high-order address to an external latch. During a dummy DMA cycle, R/W is driven High.

## $C/\overline{D}$ (Command/Data, Input)

$C/\overline{D}$  is used by the CRTC when in slave mode, to determine if an I/O transaction with the host CPU is transferring a command ( $C/\overline{D}$ =High) or data ( $C/\overline{D}$ =Low). When the CRTC is not involved in an I/O transaction with the host,  $C/\overline{D}$  is disregarded.  $C/\overline{D}$  flows through a transparent latch controlled by AS. A rising edge of AS latches  $C/\overline{D}$ .

## DTEN, DREN (Data Transmit Enable, Data Receive Enable, Open Drain Output)

Data Transmit Enable and Data Receive Enable are used to control bus transceivers external to the CRTC, should they be required. When DTEN is Low the transceivers should be driven out from the CRTC onto the bus. When DREN is Low, the transceivers should be driven from the bus into the CRTC. DTEN and DREN are never Low simultaneously.

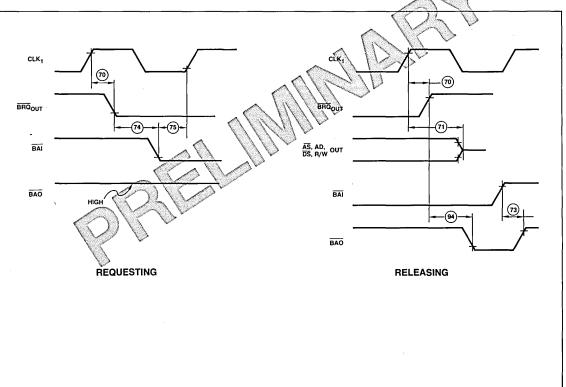

#### BRQ (Bus Request, Input/Output, Open Drain)

When the CRTC requires use of the bus for DMA activity, the BRQ line is driven Low. It remains Low until it has ceased using the bus. This pin is also an input pin which allows the CRTC to sense the BRQ line.

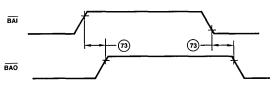

#### BAI (Bus Acknowledge In, Input)

Bus Acknowledge In is an active Low input. When the CRTC requires host bus access and has successfully pulled its  $\overline{\text{BRQ}}$  pin Low, a  $\overline{\text{BAI}}$  Low input signifies that the CRTC has obtained bus mastership.  $\overline{\text{BAI}}$  is internally synchronized for two periods of CLK1 to alleviate metastable problems. When the CRTC does not require host bus access, the  $\overline{\text{BAI}}$  input ripples to the  $\overline{\text{BAO}}$  output.

When  $\overline{\text{BAI}}$  is removed during a DMA burst, the CRTC finishes the current DMA cycle and then releases  $\overline{\text{BRQ}}$ . If the DMA burst is not completed and no other device requests the bus ( $\overline{\text{BRQ}}$  is High), the CRTC asserts  $\overline{\text{BRQ}}$  again. The CRTC releases the bus for a minimum of three system clock (CLK1) cycles.

#### BAO (Bus Acknowledge Out, Output)

BAO output is forced active high when the CRTC has obtained bus mastership, otherwise the BAI input ripples out of the CRTC via the BAO output.

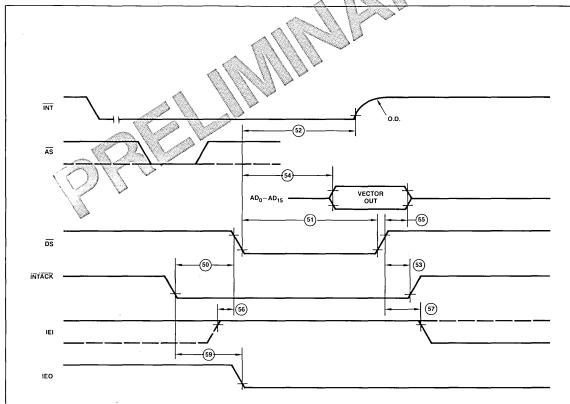

#### **INT** (Interrupt Request, Output, Open Drain)

This line is used to indicate an interrupt request to the host processor. It is driven Low by the CRTC until an interrupt acknowledge is received on the INTACK pin.

## **INTACK** (Interrupt Acknowledge, Input)

When this line is driven Low, the CRTC examines its IEI line to determine if it has been granted an acknowledge by the CPU. INTACK must be High for normal operation.

#### IEI (Interrupt Enable-In, Input)

A Low on IEI during Interrupt Acknowledge signifies that a higher priority interrupt on the daisy chain is being acknowledged.

#### IEO (Interrupt Enable Out, Output)

IEO follows IEI during Interrupt Acknowledge if the CRTC has not made an interrupt request. IEO Low disables lower priority devices from making interrupt requests. See the section on Interrupt protocol for a full discussion.

#### HSYNC (Horizontal Sync, Output)

HSYNC is an active High output which controls the horizontal retrace of the CRT's electron beam. This output is held inactive (Low) when the CRTC is reset to prevent unknown synchronization of the CRT which might cause damage to high bandwidth tubes. Note that this pin can also be initialized as Horizontal Drive.

#### VSYNC (Vertical Sync, Output)

VSYNC is an active High output which controls the vertical retrace of the CRT's electron beam. This output is held Low when the CRTC is reset to prevent damage to the CRT.

#### BLANK (Blank Video, Output)

BLANK is an active High output. It serves to blank out inactive display areas of the CRT. It is a composite of horizontal and vertical blank. This output is held active High when the CRTC is reset.

#### ESYNC (External Sync, Input)

This pin is the external synchronization input and should be used exclusively for power line synchronization. The ESYNC input cannot synchronize two video systems since HSYNC is not altered by this signal. This input is enabled by setting the ES bit in Mode Register 1. For further details on ESYNC operation, refer to Section 2.9.

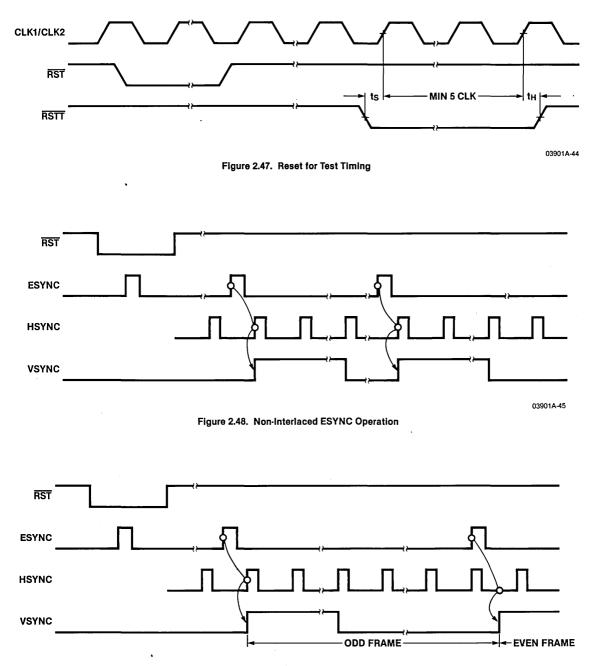

#### RSTT (Test Reset, Input)

This pin is used for test purposes. It may, however also be used to synchronize two Am8052 parts for some specific application. Whenever  $\overrightarrow{\text{RSTT}}$  input is lowered, the following will take effect:

HSYNC is held Low VSYNC is held Low Blank is held High Mode Register 2 bit 0 through bit 8 are reset Horizontal counter is reset Vertical counter is reset

For synchronizing two CRTCs, RSTT should be driven synchronously to the video timing clocks (CLK1 or CLK2).

## **RST** (Reset, Input)

A Low on this input for at least 5 clock cycles is interpreted by the CRTC as a reset signal. The effect of reset is to drive all CRTC bus signals into the high-impedance state and initialize Mode Registers 1 and 2. Additionally, the CRTC will go into Slave mode within the defined reset widths.

#### CCØ-7 (Character Code Outputs)

CCØ-7 outputs are active High. This character port outputs eight bits of data stored in the character code section of the row buffer currently being displayed. The character code output can be delayed by one or two clock periods (CLK2) in order to allow the attribute bits associated with the particular character code to be masked and decoded and to generate suitable synchronized attribute control.

#### RØ-4 (Scan Line Control, Outputs)

$R\emptyset-4$  outputs are active High. These outputs carry the binary address of the character slice being displayed. These outputs form the least significant address portion of a character ROM. The outputs are held High for the scan lines that do not carry active video.

#### APØ-AP1Ø, (Attribute Port, Outputs)

These eleven lines output the attribute information associated with the characters. During HSYNC the row attribute word contained in the Row Redefinition Block is output on APØ-AP4 and AP6-AP1Ø. This word can be stored externally by the falling edge of HSYNC.

## CURSOR (Cursor, Output)

This pin is the cursor output indicator. See character attributes section for further information.

15

POINTER ADDRESS (AD4-AD0)

|     |      | (           |                               |

|-----|------|-------------|-------------------------------|

| HEX | TYPE | ACTIVE BITS | REGISTER NAME                 |

| ØØ  | R/W  | 16          | MODE 1                        |

| Øl  | R/W  | 16          | MODE 2                        |

| Ø2  | W    | 12          | ATTRIBUTE ENABLE              |

| Ø3  | W    | 5           | ATTRIBUTE REDEFINITION        |

| Ø4  | R/W  | 8           | TOP OF PAGE SOFT (HI-ORDER)   |

| Ø5  | R/W  | 16          | TOP OF PAGE SOFT (LO-ORDER)   |

| Ø6  | R/W  | 8           | TOP OF WINDOW SOFT (HI-ORDER) |

| Ø7  | R/W  | 16          | TOP OF WINDOW SOFT (LO-ORDER) |

| Ø8  | W    | 16          | ATTRIBUTE FLAG                |

| Ø9  | R/W  | 8           | TOP OF PAGE HARD (HI)         |

| ØA  | R/W  | 16          | TOP OF PAGE HARD (LO)         |

| ØB  | R/W  | 8           | TOP OF WINDOW HARD (HI)       |

| ØC  | R/W  | 16          | TOP OF WINDOW HARD (LO)       |

| 1Ø  | W    | 16          | DMA BURST                     |

| 11  | W    | 12          | * VSYNC WIDTH/SCAN DELAY      |

| 12  | W    | 12          | * VERTICAL ACTIVE LINES       |

| 13  | W    | 12          | * VERTICAL TOTAL LINES        |

| 14  | W    | 16          | * HSYNC/VERTINT               |

| 15  | W    | 9           | * HDRIVE                      |

| 16  | W    | 9           | * H SCAN DELAY                |

| 17  | W    | 10          | * H TOTAL COUNT               |

| 18  | W    | 10          | * H TOTAL DISPLAY             |

|     |      |             |                               |

Table 1: Am8052 Registers

\* These registers should only be accessed when display enable ("DE" bit in Mode Register 1) is reset, since they control the video timing signals.

## 2.3 REGISTER DESCRIPTION

## 2.3.1 Introduction

This chapter provides a brief description of the command, status, and screen configuration registers contained in the CRTC. Each description includes the register address, the operation of the individual register fields and the state of the register after a reset (hardware or software).

Table 1 is a summary of the CRTC's 22 registers. The registers are addressed by an internal pointer which is five bits wide. The pointer is loaded via ADO-AD4 on the external AD-bus with a slave mode write and  $C/\overline{D}$  input High.

For details of the addressing schemes see in Section 2.3.2.

To set up the registers: 1) clear the DE bit of Mode Register 1 by hardware reset or by loading the register, 2) initialize all registers except Mode Register 1 with the appropriate values, 3) load Mode Register 1 with the DE-bit set to enable the display, and 4) load Mode Register 2.

Addressing the CRTC with non-specified pointers ( $\emptyset$ Ø-OF, 19-1F) will cause no problems. The registers can be loaded using a simple software loop starting at 00 and ending at 1F.

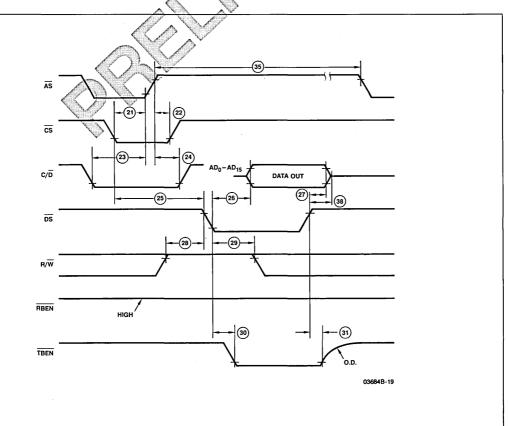

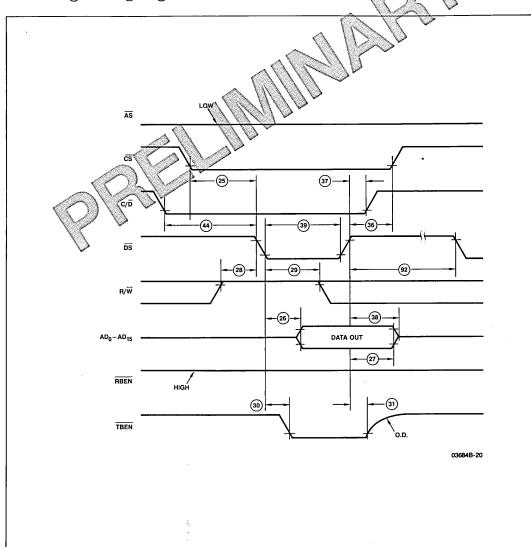

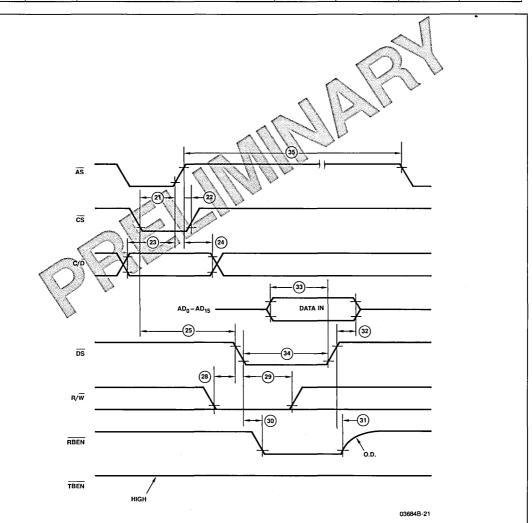

## 2.3.2 Register Addressing

The registers can be accessed only when the CRTC is in the slave mode. They are addressed in a two-step sequence:

- 1. Pull  $\overline{CS}$  Low and  $C/\overline{D}$  High to indicate a command type cycle, and strobe the register address present on ADØ-AD4 with an active Low pulse on  $\overline{DS}$ ; this clocks the register address into an internal pointer register. The pointer value remains valid until changed.

- 2. Reaccess the CRTC with  $\overline{CS}$  Low and  $C/\overline{D}$  Low to read or write the register pointed by the internal pointer. The data is strobed in or out by the  $\overline{DS}$  signal.

The CRTC is in slave mode if it has not been granted control of the bus. Even if the CRTC has asserted  $\overline{BRQ}$ , it is still in slave mode until it receives an acknowledge and takes over bus control. The CPU can access the CRTC registers any time, i.e. the CRTC places no restrictions on slave accesses.

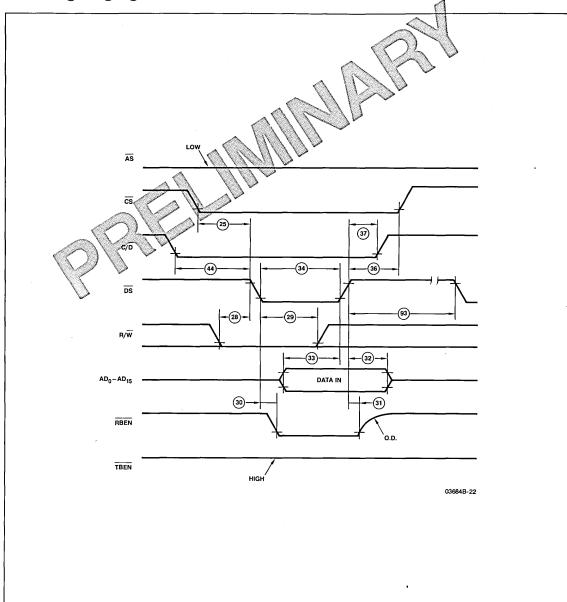

## CRTC SLAVE TRANSFERS:

All slave transfers with the CRTC can be carried out asynchronously with respect to the CRTC CLK1 input. Only  $\overline{AS}$ and  $\overline{DS}$  are used to time the information transfer. All transfers require two separate bus transactions. First, a pointer value must be written into the CRTC. The pointer value is written by carrying out a slave write transaction

.

03901A-06

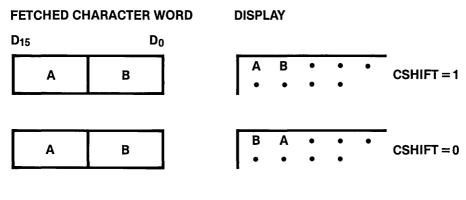

Figure 2.7. Character Positioning on the Display as a Function of CSHIFT

with C/D pulled High. Following the setting of the pointer, the data transfer can take place between the bus master and the CRTC internal register designated by the pointer.

The slave transaction typically commences with a pointer write, although repetitive accesses to the same CRTC register can be made without any intervening pointer modification. The transaction is timed off the  $\overline{\text{DS}}$  signal, since  $\overline{\text{AS}}$  may not be present in certain systems. The read transaction commences from the leading edge of DS. The write transaction takes place on the trailing edge of  $\overline{\text{DS}}$ . The  $\overline{\text{AS}}$  input is used to drive a transparent latch on the CRTC, which is used to capture C/D and  $\overline{\text{CS}}$  in a multiplexed address/data system. If the system is demultiplexed, then  $\overline{\text{AS}}$  should be driven Low when the CRTC is in the slave mode. This will drive the latch permanently transparent, allowing the demultiplexed  $\overline{\text{CS}}$  and  $\text{C}/\overline{\text{D}}$ to pass into the CRTC. When the  $\overline{\text{DS}}$  goes Low and a read transaction is in progress, the CR<u>TC</u> drives the read data onto its ADØ-15 lines and also drives DTEN Low. This enables any off-chip bus transceivers, allowing the data to be transmitted to the bus master. When the bus master captures the data, it drives the  $\overline{\text{DS}}$  signal High. This causes the CRTC to cease driving its ADØ-AD15 lines and also causes  $\overline{\text{DTEN}}$  to return High, switching off the bus transceivers.

#### 2.3.3 Register Description

#### MODE REGISTER 1:

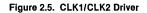

The Mode Register 1 contains display and DMA control bits (Figure 2.6). When the device is reset, all Mode Register 1 bits are cleared.

#### VIDEO TIMING CLOCK--CLK1/2 (D15)

This bit indicates which of CLK1 and CLK2 inputs will be used to time HSYNC (or HDRIVE), VSYNC and VIDEO-BLANK outputs. In proportional spacing applications CLK1 usually times the sync signal, since the frequency of CLK2 is modulated by the character width.

CLK1/2=0: CLK2 will be selected for clocking the sync counters CLK1/2=1: CLK1 will be selected for clocking the sync counters

#### CHARACTER SHIFT--CSHFT (D14)

This bit allows the CRTC to interpret a two-byte word fetched from main memory, in either of two ways, according to the system's 16-bit word organization. This applies only to characters since they are the only byte-data the CRTC has to interrupt (Figure 2.7). Hence, 16-bit word data such as addresses, attributes, etc., remain unaffected by CSHFT.

#### INVISIBLE ATTRIBUTE FLAG--IAF (D13)

- IAF=Ø: The character that invoked an attribute is loaded into the row buffer, and subsequently displayed. The character is affected by the attribute word.

- IAF=1: The character that invoked an attribute is not loaded into the line buffer, and is not displayed.

#### SCREEN WIDTH LIMIT--SLIM (D12)

The SLIM bit controls the number of characters loaded in each row buffer to either 132 or 96. This can reduce bus overhead when the CRTC row length is 96 characters or less.

SLIM=0: The row buffer size is set to 132 characters. SLIM=1: The row buffer size is set to 96 characters.

#### LINEAR/SEGMENTED MODE--L/S (D11)

This bit indicates whether the system/display memory access is accomplished by addressing it in a linear or segmented mode.

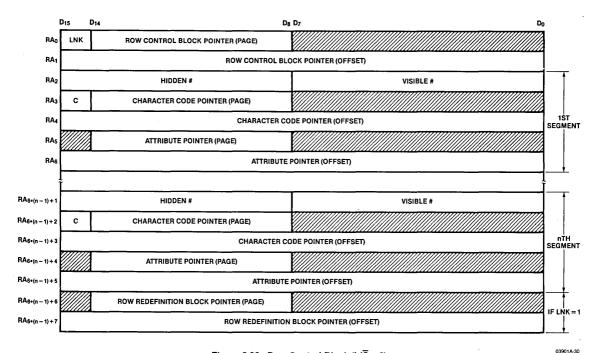

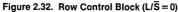

- L/S=0: The CRTC is set for segmented addressing. The linked-list address pointers are two words long. Seven bits (8:14) of the first word define the segment address. The second 16-bit word is the offset address within the segment. Any overflow of the 16-bit offset address does not carry into the upper 7-bit segment address.

- L/ $\overline{S}$ =1: The CRTC is set up for a linear addressing scheme. The most significant byte of the 24-bit linear address is stored in the lower half of the first word ( $\emptyset$ :7). The second word holds the remaining 16 bits.

During page update cycles the CRTC puts out the upper part of the 23/24-bit address on ADØ-AD7. The user may latch the 7/8-bit address.

#### VIDEO BLANK--VB (D1Ø)

This bit allows the user to blank the screen while making changes in the displayed text or when switching the context. The linked list must, however, be valid before VB is reset.

VB=Ø: Normal Operation

VB=1: The horizontal and vertical sync circuitry and outputs operate normally and the blank output is forced active High. DMA operation is suspended normal operation resumes when VB=Ø and the next vertical blanking period occurs.

## CHARACTER PERIOD SKEW--SK1, SKØ (D9, D8)

The skew bits are useful when implementing custom video systems which involve a significant amount of external character processing preceeding their display. In such systems the processed character may be logically delayed with respect to the VSYNC, HSYNC and BLANK signals. The skew bits program various delays in number of character clock cycles applied to the VSYNC, HSYNC and BLANK signals with respect to character code output. The attributes and cursor outputs can also be selectively delayed by SKØ and SK1. The following combinations are programmable:

| BIT SETTINGS                        | SIGNAL SKI                                    | EW (# OF CLK2                       | CYCLES)                               |

|-------------------------------------|-----------------------------------------------|-------------------------------------|---------------------------------------|

| <u>SK1 SKØ</u><br>0 1<br>1 0<br>1 1 | HSYNC, VSYNC<br>AND BLANK<br>0<br>1<br>2<br>1 | APO-10<br>AND CURSOR<br>0<br>1<br>1 | CCO-7<br>AND RO-4<br>0<br>0<br>0<br>0 |

#### HORIZONTAL OUTPUT SELECT--HOS (D7)

HOS=0: The HSYNC/HDRIVE output pin outputs the horizontal sync timing as programmed in the HSYNC register.

HOS=1: The HSYNC/HDRIVE output pin outputs the horizontal drive timing as programmed in the HDRIVE register.

#### WAIT STATE--WS1, WSØ (D6, D5)

These bits indicate the number of Wait states inserted for each DMA cycle. These Wait states are in addition to any externally applied wait states. When the CRTC is in Slave Mode, these bits are ignored.

| WS1 | WSØ | WAIT STATE                 |

|-----|-----|----------------------------|

| 0   | 0   | No Wait State              |

| 0   | 1   | DS stretched by one clock  |

| 1   | 0   | DS stretched by two clocks |

| 1   | 1   | Reserved                   |

#### DISPLAY HIDDEN---DH (D4)

Applies only to characters associated with Ignore Attribute: DH=Ø: Those characters are not loaded into the row-buffer. DH=1: Those characters are treated as displayable information. (See section 2.6.1, Ignore attribute.)

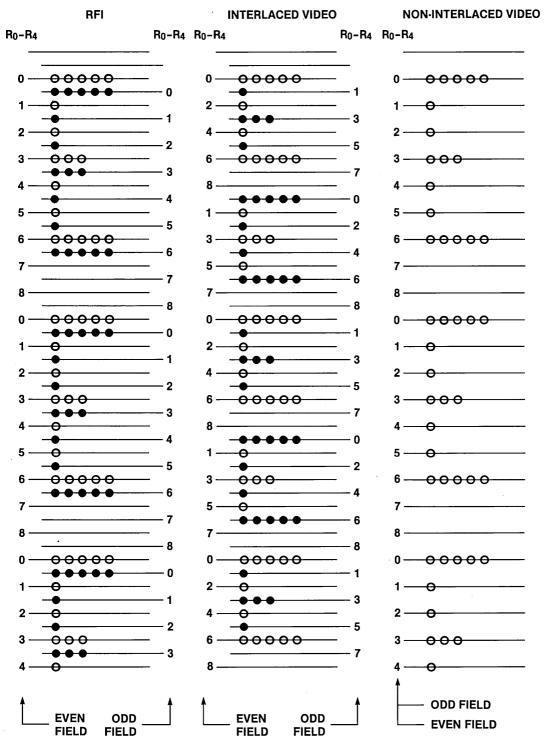

## INTERLACE--I1, IØ (D3, D2)

Control the timing of non-interlaced, interlaced, repeat field interface video to support different CRTs (see Section 2.10).

| 11 | IØ | MODE OF OPERATION            |

|----|----|------------------------------|

| 0  | 0  | Non-Interlaced Video         |

| 0  | 1  | Reserved                     |

| 1  | 0  | Repeat Field Interlace (RFI) |

| 1  | 1  | Interlaced Video             |

#### EXTERNAL SYNC ENABLE--ES (D1)

Enables the ESYNC input for power line synchronization.

- ES=Ø: ESYNC input is ignored

- ES=1: A rising edge at the ESYNC input during a vertical-retrace active period (even frame only in interlaced mode) causes the HSYNC/DRIVE output to go (or remain) active for a full horizontal retrace period. The VSYNC active period is stretched, even when register timing signifies an end to vertical retrace, until an ESYNC falling edge occurs.

DISPLAY ENABLE--DE (DO)

DE=Ø: VSYNC, HSYNC/HDRIVE outputs are inactive and the BLANK output is held active. DMA operation is disabled. The DE bit is reset by the the host processor command or by chip reset (RST=Low). DE=Øsets all scroll logic to the non-scrolling state.

> Resetting DE bit is equivalent to pulling the RST pin LOW causing the CRTC to enter the reset procedure.

DE=1: CRTC display operation enabled. DE is set by a host processor command. Setting the DE=1 causes the VSYNC, HSYNC, and BLANK outputs to become active and the DMA controller on board the CRTC eventually requests access to the system bus.

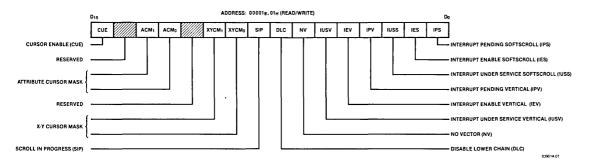

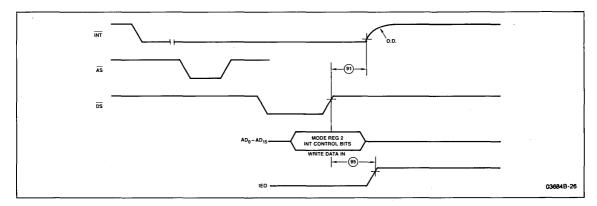

#### MODE REGISTER 2:

The Mode Register 2 contains the primary control bits for the interrupt control logic, and cursor definition (Figure 2.8).

Upon reset, all Mode Register 2 bits are reset to zero.

## CURSOR ENABLE--CUE (D15)

- CUE=Ø: The CRTC does not output any XY cursor information.

- CUE=1: The cursor X and Y register is enabled. CRTC outputs cursor at the character position defined by the XY cursor register (see Main Definiton Block).

## ATTRIBUTE CURSOR MASK - ACM1, ACMØ, (D13, D12)

XY CURSOR MASK - XYCM1, XYCMØ (D1Ø, D9) The cursor mask field (D13, D12, D10, D9) defines the type of cursor that will be generated when a cursor is required. This

field is divided into two parts:

- D13 D12 CURSOR ATTRIBUTE DEFINITION

- 0 0 Cursor Pin Whole

- 0 1 Cursor Pin Part

- 1 O Underline

- 1 1 Reverse

## D10 D9 XY CURSOR DEFINITION

- 0 0 Cursor Pin Whole

- 0 1 Cursor Pin Part

- 1 O Underline

- 1 1 Reverse

"Cursor Pin Whole" means that the cursor will be output on the cursor pin for every scan line of that character position (TSCC). CURS and CURE of the Row Definition Block are ignored.

"Cursor Pin Part" means that the cursor will be output on the cursor pin for those scan lines specified in the Row Redefinition Block (CURS and CURE).

"Underline" (BLOB) means that the cursor is output on the underline pin (AP1) for the scan lines specified in the Row Redefinition Block (CURS and CURE).

"Reverse" (part) means that the cursor is output on the reverse pin (AP5) for the scan lines specified in the Row Redefinition Block (CURS and CURE).

#### SCROLL IN PROGRESS--SIP (D8)

SIP is a status bit that is set/reset by the CRTC smooth scroll control logic.

SIP=0: The CRTC is not currently scrolling.

SIP=1: The CRTC is scrolling either window or background.

#### DISABLE LOWER CHAIN--DLC (D7)

- DLC=Ø: IEO operates normally.

- DLC=1: The Interrupt Enable Out (IEO) output of the device is forced Low, disabling interrupts from all lower priority devices on the daisy-chain.

## NO VECTOR--NV (D6)

- NV=Ø: The CRTC outputs the interrupt vector programmed in the Main Definition Block (See the section on Main Definition Block and Interrupt.)

- NV=1: The device is inhibited from outputting an interrupt vector during an interrupt acknowledge cycle. The vector can, therefore, be provided by external hardware if necessary. It has no effect on the setting of the Interrupt Under Service bits.

#### INTERRUPT UNDER SERVICE VERTICAL EVENT--IUSV (D5)

This status bit is automatically set if IPV (Interrupt Pending Vertical Event) is the highest priority interrupt request pending when an Interrupt Acknowledge sequence takes place. It can also be set or cleared directly by CPU command. While the IUSV is set, internal and external daisy-chains prevent the same and lower priority sources of interrupt from requesting interrupts. The IUSV can be cleared to "Ø" only by CPU command. For details of interrupt operation see Section 2.7.

#### INTERRUPT ENABLE VERTICAL EVENT--IEV (D4)

This bit enables or disables the vertical event interrupt logic.

IEV=Ø: The Vertical Interrupt is disabled. The CRTC does not request an interrupt at vertical event nor responds to an interrupt acknowledge.

#### \_1. The Vertical Interrupt is enabled.

Interrupt Enable (IEV) does not affect the normal operation of Interrupt Pending (IPV) and Interrupt Under Service (IUVS). If IEV disables the interrupt ( $IEV=\emptyset$ ), then setting the Interrupt Pending Bit (IPV) does not activate the Interrupt Request Line. If IEV=/, then a "1" in IUSV will affect the interrupt daisy chain; all lower priority devices are disabled.

### INTERRUPT PENDING VERTICAL EVENT--IPV (D3)

IPV is a status bit which, when set to "1", indicates that a vertical event has occurred and needs CPU notification. A vertical event occurs when the CRTC internal load row counter matches the VERTINT value loaded in the HSYNC/VERTINT register. This interrupt provides real time positional information. This is the lowest priority IP bit inside the CRTC. The IPV can be cleared only by a CPU command.

## INTERRUPT UNDER SERVICE SOFT-SCROLL--IUSS (D2)

Same as vertical event but applies for soft-scroll event.

## INTERRUPT ENABLE SOFT-SCROLL--IES (D1)

This bit enables or disables the soft-scroll's interrupt logic. Same as vertical event.

#### INTERRUPT PENDING SOFT-SCROLL--IPS (DO)

IPS is a status bit which when set, indicates that a softscroll event requires CPU intervention. This is the highest priority IP bit.

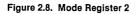

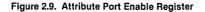

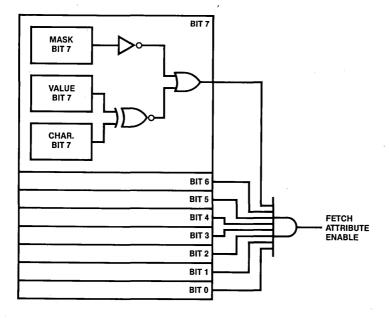

## ATTRIBUTE PORT ENABLE REGISTER:

Bits DØ through D1Ø in the Attribute Port Enable Register allow the corresponding attribute information to be output on the matching attribute pin (Figure 2.9). When reset, the corresponding attribute pin will be driven Low. When set, the corresponding pin will output attribute information. Bits D3 and D4 of this word affect the subscript and superscript attribute pin operation. If these bits are enabled for subscript or superscript, the corresponding pins will be active. These attributes are independent of the RØ-R4 outputs. The user can thus address a separate character font ROM for subscript or superscript display. The CURSOR PIN ENABLE (CPE, D13) bit of this register enables/disables only the cursor pin. When disabled, neither the X-Y cursor nor the attribute cursor is output through the cursor pin (CURSOR=Low).

#### ATTRIBUTE CURSOR ENABLE (ACE, D14)

The Attribute Cursor Enable Register enables/disables the path between attribute cursor in formation and cursor pin output.

03901A-10

Figure 2.11. Top of Page and Top of Window Pointer Formats with  $L/\overline{S} = 1$

03901A-11

Figure 2.12. Top of Page and Top of Window Pointer Formats with  $L/\overline{S} = 0$

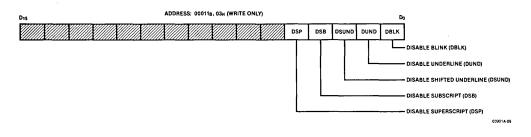

## ATTRIBUTE REDEFINITION REGISTER:

The Attribute Redefinition Register allows the user to redefine some of the internally processed attributes, which can, therefore, be treated as user definables (Figure 2.10). A "Ø" keeps normal attribute operation, a "1" directly outputs the attribute state to its corresponding pin without any internal processing of the attributes.

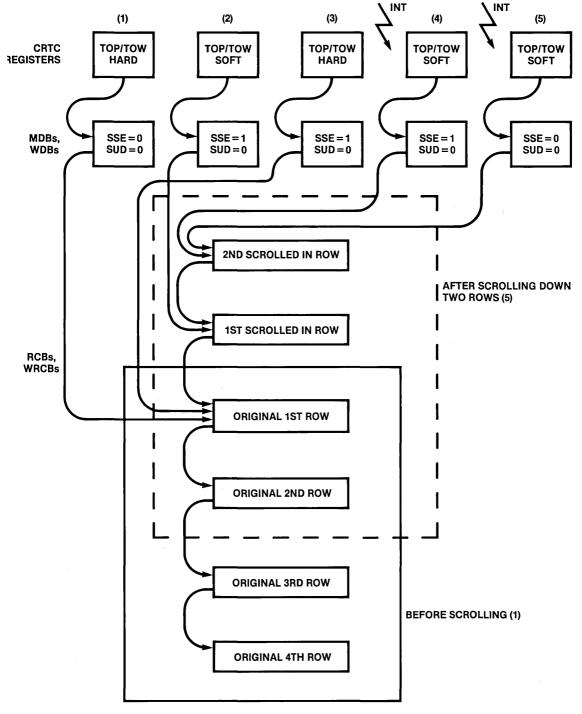

### TOP OF PAGE/TOP OF WINDOW REGISTERS:

Figures 2.11 and 2.12 show the format of these registers.

| REGISTER               | # OF ACTIV | <u>E BITS</u> | ADDRES | <u>S <u>TYPE</u></u> |

|------------------------|------------|---------------|--------|----------------------|

|                        | LINEAR     | SEG.          | BINARY | HEX                  |

| TOP OF PAGE SOFT (HI)  | 8          | 7             | 00100  | Ø4 R/W               |

| TOP OF PAGE SOFT (LO)  | 16         | 16            | 00101  | Ø5 R/₩               |

| TOP OF WINDOW SOFT (HI | ) 8        | 7             | 00110  | Ø6 R/₩               |

| TOP OF WINDOW SOFT (LO | ) 16       | 16            | 00111  | Ø7 R/W               |

| TOP OF PAGE HARD (HI)  | 8          | 7             | 01001  | Ø9 R/₩               |

| TOP OF PAGE HARD (LO)  | 16         | 16            | 01010  | ØA R∕₩               |

| TOP OF WINDOW HARD (HI | ) 8        | 7             | 01011  | ØB R∕₩               |

| TOP OF WINDOW HARD (LO | ) 16       | 16            | 01100  | ØC R/₩               |

The Top Of Page and Top Of Window Registers point to the Main Definition Block and Window Definition Block respectively; these blocks contain the primary information concerning the background display and the window display.

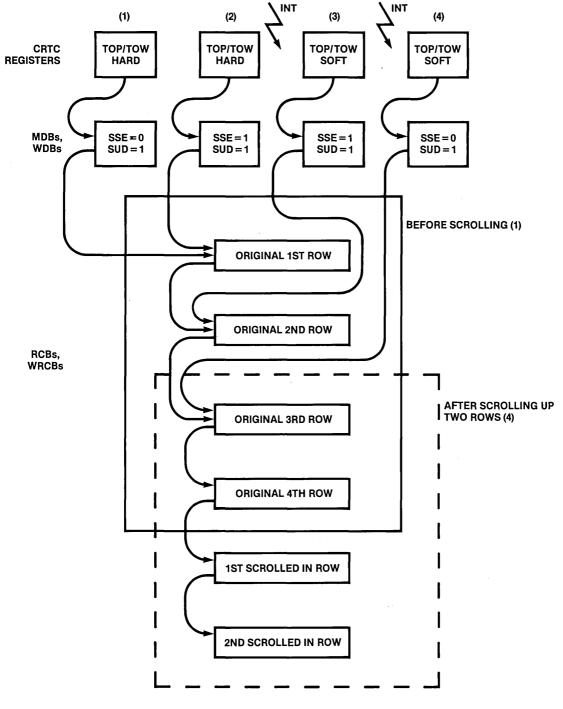

Two different forms of top of page/window register writes are available, hard and soft. Top of page/window soft is used to trigger the soft-scroll and to interact with the soft-scroll controller (see section on soft-scroll). Top of page/window hard has no effect on the soft-scroll procedure, and should be used for link manipulations that do not involve soft scroll. If the Top of Window Register contains "Ø", no window is displayed on the screen.

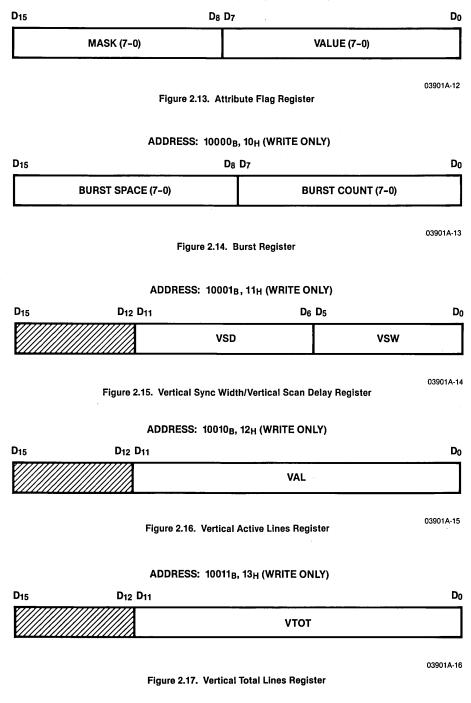

#### ATTRIBUTE FLAG REGISTER:

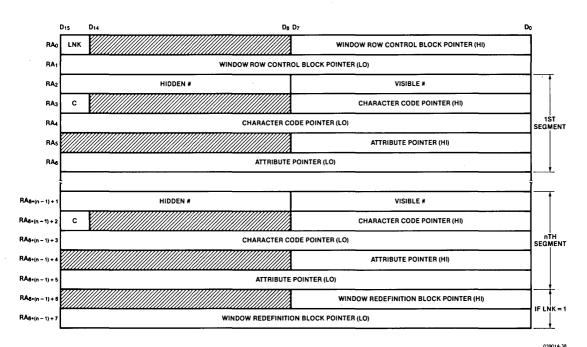

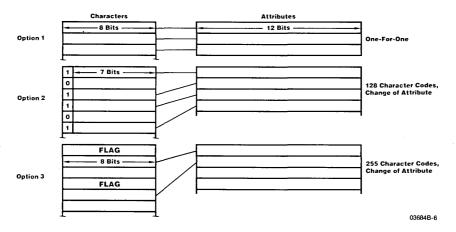

The attribute flag register defines the bit pattern that will invoke an attribute word from the attribute segment (Figure 2.13).

This 16-bit register is devided into two sections MASK and VALUE.

D15-D8 MASK (7-Ø) D7-DØ VALUE (7-Ø)

#### ADDRESS: 01000B, 08H (WRITE ONLY)

#### MASK (7-Ø) (D15-D8)

The mask register defines which bits of the 8-bit character field will be compared against the value register to determine if the character invokes an attribute word. A  $\emptyset$  in bit position N of the mask indicates that character bit N is a "don't care" in the value comparison. A "1" in bit position N of the mask indicates that character bit N should be compared against value bit N.

#### VALUE $(7-\emptyset)$ $(D7-D\emptyset)$

The value register holds up to 8 bits of information for comparison with the fetched character, to determine if an attribute is invoked. Note that only those bits of the value register which have the corresponding bits of the mask register set to "1" are compared against the character.

Example 1: We want all the control characters (characters between  $\emptyset\emptyset_H$  and  $1F_H$ ) to invoke an attribute. These characters are of the form:

|                   | ØØOXXXXX (XISDUN'I CAR | E) |

|-------------------|------------------------|----|

| THE MASK WILL BE  | 11100000               |    |

| THE VALUE WILL BE | 0 0 0 X X X X X        |    |

|                   |                        |    |

so the attribute flag register contents are:

$1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 (EØØØ_{H})$

Example 2: We want one specific flag  $(7F_{H})$  to invoke an attribute:

In this case we want to compare all the bits of the character to the value, so the mask is: 111111111 and the value is: 01111111 (7F<sub>u</sub>)

Hence the attribute register contains

111111110111111(FF7F<sub>H</sub>)

If the user wishes to disable the attribute fetch mechanism a practical approach is: Set all bits in the MASK register and load VALUE with an unused character code.

#### BURST REGISTER:

The Burst Register (Figure 2.14) specifies the bus occupancy of the CRTC DMA unit. BURST COUNT determines the maximum burst length. BURST SPACE determines the minimum release time between two bursts. This guarantees realtime responses of the CPU or other peripherals. BURST COUNT and BURST SPACE must be programmed with values allowing the CRTC to fetch all data needed for a flicker-free screen.

D15-D8 BURST SPACE (BS7-Ø) D7-DØ BURST COUNT (BC7-Ø)

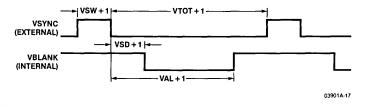

Figure 2.18. Non-Interlaced Video Vertical Sync Timing

#### BURST SPACE--BS7-Ø (D15-D8)

This 8-bit count specifies the number of 15 system clock cycle (CLK1) periods before another bus request will be issued. This count is triggered at the end of a DMA activity. If the count is set to "0" the CRTC occupies the bus as long as necessary to accomplish its DMA activity.

#### BURST COUNT---BC7-Ø (D8-DØ)

This 8-bit count specifies the number of word data transfers during DMA operation. Each count is equivalent to one DMA transfer cycle. If  $BS(7-\emptyset)$  is set to " $\emptyset$ ", no DMA activity will occur.

#### **VIDEO TIMING REGISTERS:**

These registers are initialized before setting the DE bit in Mode Register 1. They hold the parameters needed to generate vertical and horizontal sync and blank (VSYNC, HSYNC, and BLANK). These signals are put out on the like-named pins of the CRTC and are used by the Am8152A/53A. BLANK is a composite of horizontal and vertical blank (HBLANK and VBLANK).

Horizontal timing parameters are expressed in number of system or character clock cycles (CLK1/2 bit of Mode Register 1). Vertical timing parameters are expressed in number of scan lines.

HSYNC (8 bit counter) and HDRIVE (9 bit counter) represent two ways of specifying the signal waveform on the HSYNC output pin. HDRIVE usually determines a signal of 50% duty cycle because some monitors require a close to 50% duty cycle for the horizontal frequency.

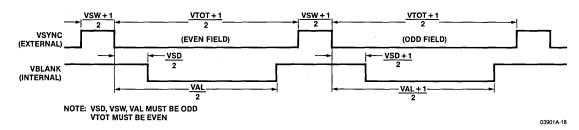

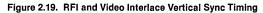

In the following discussion a frame consists of one field in non-interlaced mode and two fields (even and odd) in RFI and video interlace modes. Figures 2.18 and 2.19 show the vertical timing.

#### VERTICAL SYNC WIDTH/VERTICAL SCAN DELAY REGISTER:

Figure 2.15 shows the register format.

D15-D12 NOT USED D11-D6 VERTICAL SCAN DELAY (VSD) D5-DØ VERTICAL SYNC WIDTH (VSW)

#### VERTICAL SCAN DELAY--VSD (D11-D6)

The vertical scan delay field specifies the vertical blank time after the falling edge of VSYNC, thus defining the top border width, or vertical back porch of the screen. VSD is expressed in scan-line units. When in non-interlaced mode, the actual vertical scan delay is equal to VSD + 1 scan lines. When in video interlace mode or RFI (Repeat Field Interlace) mode, the actual vertical scan delay is equal to (VSD + 1)/2 lines. In this case VSD must be odd.

#### VERTICAL SYNC WIDTH--VSW (D5-D0)

The vertical sync width determines the width of the active High pulse signal which is sent through VSYNC output to the CRT monitor in order to synchronize it vertically.

VSW is expressed in scan line units. In non-interlaced mode, the actual vertical sync width is equal to VSW + 1 scan lines.

In interlaced and RFI mode, the actual vertical sync width is equal to (VSW + 1)/2 lines. In this case VSW must be odd.

#### VERTICAL ACTIVE LINES REGISTER:

D15-D12 NOT USED D11-DØ VERTICAL ACTIVE LINES (VAL)

This 12-bit field defines the number of scan lines between the end of a vertical sync pulse and the start of vertical blanking (Figure 2.16).

When in non-interlaced mode, the actual scan-line number between the falling edge of VSYNC and the rising edge of VBLANK is equal to VAL + 1. The active video area height on the screen is then (VAL + 1) - (VSD + 1)=VAL - VSD scan lines.

When in video interlace or RFI mode, the actual scan-line number between VSYNC and VBLANK is equal to (VAL + 1)/2. In this case VAL must be odd. The active video area height on the screen is then given by (VAL + 1)/2 - (VSD + 1)/2 = (VAL - VSD)/2 scan lines. This is true for the odd and even field.

## VERTICAL TOTAL LINES REGISTER:

D15-D12 NOT USED D11-DØ VERTICAL TOTAL LINES (VTOT)

The vertical total lines register defines the total number of scan lines per field minus the vertical sync width (Figure 2.17).

In non-interlaced mode, the actual scan line number between VSYNC and next VSYNC is (VTOT + 1).

In interlaced or RFI mode, this timing is (VTOT + 1)/2, and VTOT must be even (half scan line between even and odd fields).

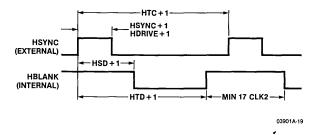

Figure 2.20 shows the horizontal timing.

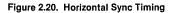

## HORIZONTAL SYNC AND VERTICAL INTERRUPT ROW REGISTER:

Figure 2.21 shows the register format.

D15-D8 VERTICAL INTERRUPT ROW (VERTINT)

D7-DØ HORIZONTAL SYNC WIDTH (HSYNC)

## VERTICAL INTERRUPT ROW--VERTINT (D8-D15)

This field determines the row number which, after being completely loaded by DMA, causes an interrupt.

## HORIZONTAL SYNC WIDTH--HSYNC (DØ-D7)

This field determines the width of the horizontal sync (active High) pulse in terms of video clock units (CLK1 or CLK2 depending upon CLK1/2 bit in Mode Register 1), provided that HSYNC is selected (HOS=Ø in Mode Register 1). These pulses are output on the HSYNC pin. The actual width of the signal is HSYNC + 1 clock periods.

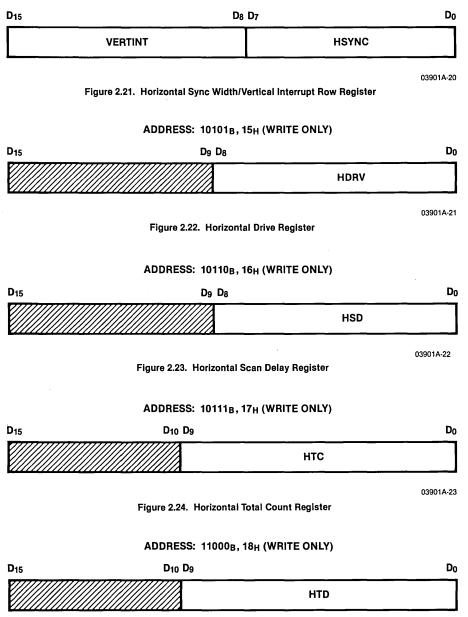

#### HORIZONTAL DRIVE REGISTER:

D15-D9 NOT USED D8-DØ HORIZONTAL DRIVE (HDRV)

This register determines the interval from HSYNC to HSYNC if horizontal drive is selected (HOS=1 in Mode Register 1). The interval is HDRV + 1 clock periods. This is also an output on the HSYNC pin. (See Figure 2.22).

#### HORIZONTAL SCAN DELAY REGISTER:

D15-D9 NOT USED D8-DØ HORIZONTAL SCAN DELAY (HSD)

The horizontal scan delay register determines the interval from rising edge of HSYNC to the falling edge of HBLANK, which defines the left border on the screen. The actual interval value is (HSD + 1) clock periods (See Figure 2.23).

#### HORIZONTAL TOTAL COUNT REGISTER:

D15-D1Ø NOT USED D9-DØ HORIZONTAL TOTAL COUNT (HTC)

This register determines the period of the HSYNC waveform. The period is (HTC + 1) clock periods (See Figure 2.24).

#### HORIZONTAL TOTAL DISPLAY REGISTER:

D15-D10 NOT USED D9-D0 HORIZONTAL TOTAL DISPLAY (HTD)

This register determines the interval from the rising edge of HSYNC to the rising edge of HBLANK. HTD must be odd in interlaced mode. The actual interval value is (HTD+1) clock periods (See Figure 2.25).

## ADDRESS: 10100B, 14H (WRITE ONLY)

03901A-24

Figure 2.25. Horizontal Total Display Register

#### 2.3.4 Video Timing Programming Example

We want to build a 30 row by 80 character display, each character embedded in a 8 x 17 (HxV) matrix, with a refresh rate of 50 Hz in non-interlaced mode using a CRT monitor with the following characteristics:

| Pixel Resolution:        | 1280 pixels horizontal |

|--------------------------|------------------------|

|                          | 1024 pixels vertical   |

| Scanning frequency:      | 28 - 36 kHz horizontal |

| <b>3 1 0</b>             | 45 - 65 Hz vertical    |

| Horizontal retrace time: | 6 microseconds         |

| Vertical retrace time:   | 600 microseconds       |

| Horzontal SYNC width:    | 3 microseconds         |

|                          |                        |

- - - -

. . . .

#### Solution:

The appropriate character clock and the timing parameters for the video timing register have to be calculated.

The active display size is given by: Horizontal: 80 characters x 8 pixels/char=640 pixels 30 rows x 17 scan lines/row=510 scan lines Vertical:

Assuming a 20% blank border vertically, the 510 scan lines occupy 80% of frame time. At a frame rate of 50Hz, the horizontal frequency can be calculated as: Total Scan Lines/frame: 510 scan lines/0.80=637 scan lines

637 x 50 Hz=31.85 kHz Horizontal Frequency:

Assuming a 20% blank horizontally, the 80 characters occupy 80% of row time. Character clock is therefore 100 times the horizontal frequency. Each character occupies 1/100 of the row.

Let us use a more convenient frequency, 3.00 MHz, as character clock and re-calculate the parameters:

| Character clock      | 3.00 MHz                    |

|----------------------|-----------------------------|

| Horizontal frequency | 30kHz                       |

| Scan line time       | 33.3 microseconds           |

| Frame time           | 637x33.3 microsec = 21.2 ms |

| Frame rate           | 47 Hz                       |

Now the registers' contents can be calculated:

Mode Register 1:

The character clock is 3 MHz; the CLK1/2 bit is set to "Ø" to select CLK2 for the frame timing generation.

With only 80 characters/row, we select "SLIM=1" which reduces the row buffer length to 96 characters.

The monitor accepts an HSYNC signal: "HOS=Ø"

Non-interlaced mode yields in: "Il= $\emptyset$ ", "IO= $\emptyset$ ".

External Sync EnableØ since we do not need to be synchronized to another signals.

Display Enable should be set to "1", once the other registers are set to the proper values.

## Vertical Active Line register:

This value is the total scan line number of the screen minus the number of scan lines contained in the bottom border area (10% of the screen height):

VAL + 1=0.9 x (VTOT+1) - 0.9x619 - 557 scan lines VAL = 556<sub>10</sub> = 22C<sub>H</sub>

ADDRESS:  $10010_{\rm R}$  (12<sub>H</sub>) VAL =  $022C_{\rm H}$

Vertical Total Line register:

VTOT + 1 = 637 - (VSW+1) - 619VTOT =  $618_{10} = 26A_{H}$ ADDRESS:  $10011_{P} (13_{H})$  VTOT =  $026A_{H}$

Vertical sync width/vertical scan delay register:

```

Vertical sync width:

VSW + 1 = 600 usec

VSW+1 = 600/33.3 = 18 scan lines

VSW = 17_{10} = 11_{H}

Vertical scan delay: (the top border width of the screen)

VSD + 1 = (VAL + 1) - 510

VSD = 46_{10} = 2E_{H}

VSD shifted 6 bits left to fit the field in the register.

VSD shift = B80_{H}

ADDRESS: 10001_{B} (11_{H})

WSD/VSW = 0B91_{H}

```

Horizontal sync and vertical interrupt row register:

We will set VERTINT to 0 in this example. HSYNC + 1 = 3 usec = 3 x 3 = 9 character-clocks. HSYNC =  $8_{10} = 8_{H}$ ADDRESS: 10100<sub>B</sub> (14<sub>H</sub>) VERTINT/HSYNC = 0008<sub>H</sub>

## Horizontal drive register:

Is don't care since HOS = 0. (HSYNC selected)

## Horizontal scan delay register:

(the left border area of the screen) HSD + 1 = (100-9-80)/2+9 = 15 character clocks HSD = 14 =  $0E_{H}$

ADDRESS:  $10110_{B} (15_{H})$  HSD =  $000E_{H}$

Horizontal total count register:

HTC + 1 = 100 character clocks HTC =  $99_{10} = 63_{H}$ ADDRESS: 10111<sub>B</sub> (17<sub>H</sub>) HTC = 0063<sub>H</sub>

Horizontal total display register:

HTD + 1=80+15 HTD =  $94_{10} = 5E_H$ ADDRESS: 11000<sub>R</sub> (18<sub>H</sub>) HTD =  $005E_H$

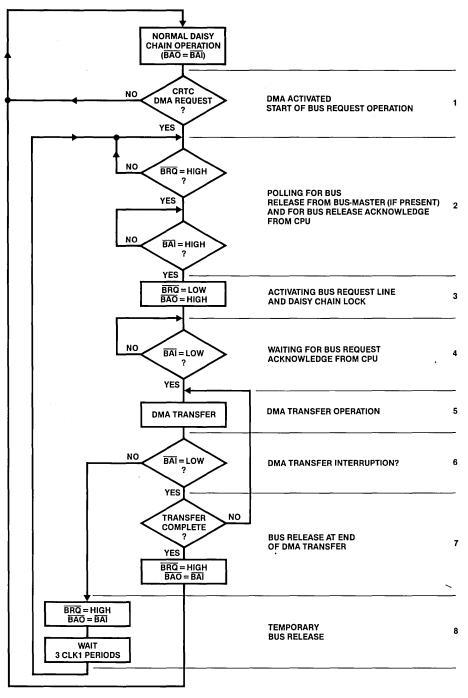

Figure 2.26. DMA Bus Request Flow Chart

### 2.4 DMA OPERATION

Once the CRTC has been initialized, and the various registers have been programmed to meet the application's needs, the CRTC is responsible for initiating system bus requests in order to fetch control data and display data from memory, and transfer them into its on-board-registers and row buffers respectively. The CRTC tries to get the bus after the DE bit in Mode Register 1 has been set to a "1".

## 2.4.1 DMA Signals And Protocol:

Before the CRTC can perform a DMA operation, it must gain control of the system bus. The  $\overline{BRQ}$ ,  $\overline{BAI}$  and  $\overline{BAO}$  interface pins constitute the basic interface between the CRTC and other devices capable of bus preemption (DMA devices, microprocessors, etc.) to arbitrate which device has control over the system bus. Whenever the CRTC wants to gain bus control, the operation is executed according to the flowchart in Figure 2.26.

#### DMA SEQUENCE DESCRIPTION:

- 1. If the CRTC needs to perform a DMA access, it triggers the bus request operation.

- First it checks whether the bus is mastered by another peripheral device by polling the BRQ line until it is High. Then it waits for the acknowledgement of bus release from the CPU through the daisy-chain (BAI = High).

- 3. At that time the bus is under control of the CPU, and the CRTC can issue its request by pulling BRQ Low. It also inhibits Bus Acknowledge to ripple toward lower priority devices (in the lower part of the daisy-chain) by pulling BAO High; this avoids bus preemption from a lower priority device which issued the BRQ at the same time the CRTC did.

- 4. Before initiating any DMA transfer, the CRTC waits for bus request acknowledge from the CPU by polling its BAI input.

- 5. DMA transfers are processed here, the CRTC now acts as the bus master.

- 6. The CRTC DMA transfer can be interrupted by removing Bus Acknowledge In (BAI = High).

- 7. The CRTC terminates transfer when it has filled the internal row buffers or when the burst count is timed out. The bus is released ( $\overline{BRQ}$  = High) and Bus Acknowledge ripples through ( $\overline{BAO}$  =  $\overline{BAI}$ ). Then either the CPU or a lower priority device on the daisy chain can gain control over the bus. The lower priority device might have pulled BRQ Low concurrently to the CRTC and is waiting for  $\overline{BAI}$  = Low to start its activity.

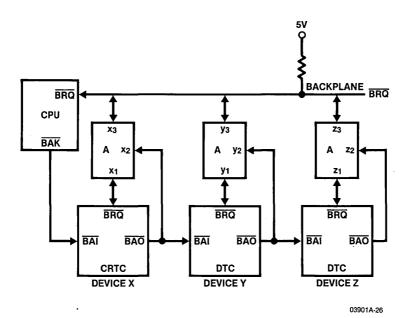

Figure 2.27. System with Multiple DMA Devices

•

8. The CRTC DMA transfer is interrupted by removing  $\overline{BAI}$ . The CRTC finishes the current bus cycle and releases the bus for three system clocks ( $\overline{BRQ}$  = High,  $\overline{BAO}$  =  $\overline{BAI}$ ). Then it tries to resume DMA activity and continues DMA operations and burst count from where it was interrupted.

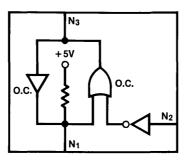

# 2.4.2 Buffering BRQ

When  $\overline{\text{BRQ}}$  needs to be buffered, e.g. to drive a system backplane, then a specific bidirectional interface buffer must be used. Such an interface and its implementation is described below:

Detail "A" in Figure 2.27 shows the  $\overline{BRQ}$  buffer logic. Note that the "buffer" and the "OR gate" are both open collector (0.C.) devices. When a High is on the backplane  $\overline{BRQ}$ , and no DMA device requested the bus, then all  $\overline{BAI}$ 's and  $\overline{BAO}$ 's are High, hence X3 and X2 are High and X1 is driven High.

If device X requests the bus, it will lock  $\overline{BAO}$  High and pull X1 Low to initiate a bus request, which will in turn pull X3 Low since X2 is High ( $\overline{BAO}$  High). The detail "A" logic is then locked into this state through the open collector buffer, as long as X2 remains High. The request is also transmitted to the CPU and the other detail "A" interfaces on the bus. All these interfaces will be locked the same way as the requesting one. A few cycles later, the CPU acknowledges the bus request by pulling BUSAK Low, the CRTC (device X) will then execute its transfers. When the CRTC finishes its transfers, it releases  $\overline{BRQ}$  and relinks its  $\overline{BAT}$  input to  $\overline{BAO}$  output, hence driving  $\overline{BAO}$  Low. The Low will propagate through the daisy chain, and as long as one of the  $\overline{BAO}$  is High, the backplane  $\overline{BRQ}$  line and the devices  $\overline{BRQ}$  signals will be held Low due to detail "A" logic structure.

Once all the  $\overline{BAO}$ 's have gone High, the backplane  $\overline{BRQ}$  goes High, and the CPU gains control over the bus.

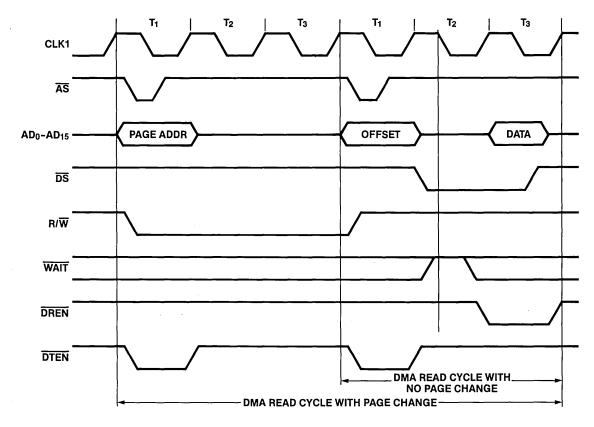

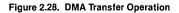

# 2.4.3 DMA Transfer Operation

The DMA transfer itself consists of data moves from memory into the CRTC, controlled by the CRTC's DMA unit.

If a control block is fetched, the words loaded will be steered toward the internal control registers. If display data (characters or attributes) is fetched from memory, it will be steered toward an internal row buffer.

In both cases the CRTC will have to:

- 1. Output the address of the data location

- 2. Sample the  $\overline{WAIT}$  input and stretch the read cycle if needed.  $\overline{WAIT}$  is sampled only at the falling edge of the system clock in T2.

- 3. Read the data and transfer it to the proper destination (buffer or internal register)

Since the Am8052 can address up to 16 Mbytes addressed as 256 pages of 64Kbytes each, there are two different methods for fetching data:

- 1. There is a page change between the previous fetch cycle and the current one, or this is the first fetch of a new frame. In either case, succeeding read cycles will be preceeded by a single write cycle to latch the new page address. (See Figure 2.28.)

- 2. There is no page change since the previous fetch cycle and it is not the first fetch of a new frame. In this case the succeeding fetches will not be preceeded by a page address write cycle. A new burst does not necessarily begin with a page address update.

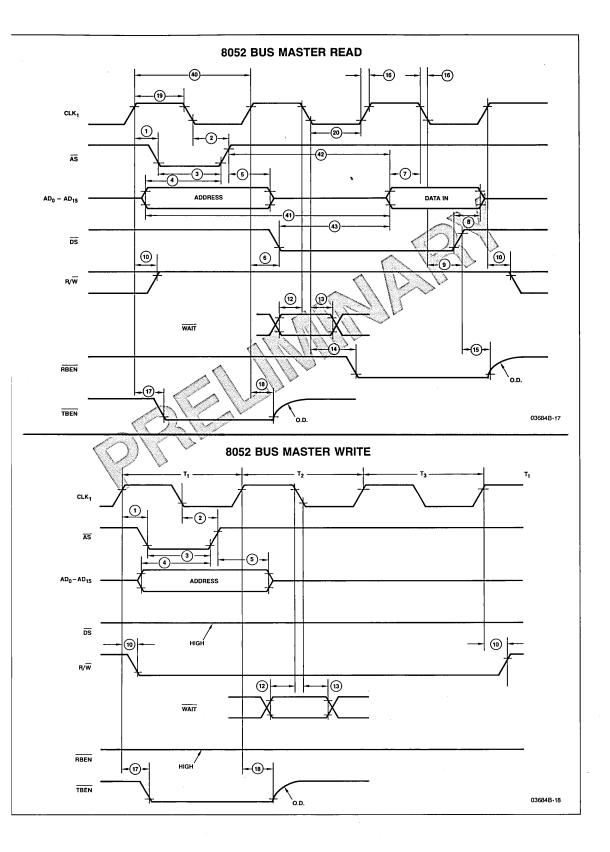

## DMA READ AND WRITE OPERATIONS:

The start of a DMA cycle is initiated by  $\overline{AS}$  being driven Low, which indicates a valid address on the ADØ-AD15 address-data lines. At that time  $\overline{DTEN}$  is also driven Low and allows the valid address to be buffered on the system bus through external buffers. The valid address may be latched on the system bus on the rising edge of  $\overline{AS}$ .

During the first portion of a DMA read cycle with page change,  $R/\overline{W}$  is pulled Low by the CRTC for three complete clock cycles, and the address present on the ADØ-AD7 bus during T1 is the updated page address which should be latched externally on the rising edge of  $\overline{AS}$ . The CRTC never outputs an active  $\overline{DS}$  during a write cycle. The next three clock cycles represent a normal DMA read cycle.

During T2 of these 3 clock cycles, the CRTC ceases driving the ADØ-AD15 bus with the address information, and  $\overline{\text{DTEN}}$  goes High. DS is driven Low as an indication to the memory system that it may drive the bus with the read data. Half of a clock cycle later,  $\overline{\text{DREN}}$  is driven Low to enable the receiving buffers local to the CRTC.

Data is captured by the CRTC on the falling edge of the T3 clock cycle; then both DS and DREN return High.

#### WAIT OPERATION:

During T2 of the read cycle, the WAIT signal is sampled by the falling edge of CLK1. If Low, the cycle will be stretched by one CLK1 cycle.

The CTRC also has a software Wait state capability: 0, 1 or 2 Wait states can be specified in Mode Register 1 and are automatically inserted in each read cycle independently of the WAIT input line. When both hardware and software Wait states are requested, they occur consecutively and not concurrently: The hardware Wait states is honored first, immediately followed by software Wait states if so programmed.

#### DUMMY DMA CYCLES:

A dummy DMA cycle takes place when a window row is filled with the fill code. At that time, the DMA keeps the bus mastership, although it does not fetch any character on this bus since the fill code is stored internally. Dummy DMA cycles are also executed under some circumstances when doing internal processing. Each dummy DMA cycles takes three system clock (CLK1) cycles to execute.

#### 2.4.4 DMA Burst Control

During DMA action, the CPU is denied access to the bus and therefore cannot execute programs. This situation can lead to problems in the interrupt response time of the CPU, since the CPU can only recognize and service an interrupt request while in control of the bus. Note that at the beginning of every frame, immediately after the vertical blanking interval goes active, the CRTC tries to request the bus.

To allow the CPU control of the bus within certain limits, a burst register is provided inside the CRTC and is programmable by the CPU. This burst register specifies a time slot during which the CRTC is allowed to request the bus. Both the time slot duration and its cycle time are programmable. For further information refer to the register section.

# 2.5 ROW MANAGEMENT UNIT OPERATION

## 2.5.1 Introduction

The Row Management Unit is in charge of the system for fetching, interpretation and steering the information contained in memory, to load the three row-buffers with displayable information and to update internal registers to redefine some of the screen characteristics.

Listed below is the information that the Row Management Unit may steer for updating.

### Steer into the row-buffers:

- characters

- attributes

### Steer into the internal registers:

- 1. alterable on a frame basis:

- absolute cursor coordinates (CUX, CUY)

- fill character code

- blink control and parameters (for cursors and characters)

- scroll control and parameters

- interrupt vectors (for vertical event and softscroll event)

2. alterable on a row basis:

- total scan line count per row (TSLC)

- normal character start and end line numbers (NCS, NCE)

- superscript character start and end scan-line numbers (SPCS, SPCE)

- subscript character start and end scan-line numbers (SBCS, SBCE)

- cursor pattern start and end scan-line numbers (CURS, CURE)

- underline position (UND)

- shifted underline position (SUND)

The information to be fetched by the Row Management Unit is addressed by linked-list pointers, and the Row Management Unit keeps track of the addresses of the information present in memory.

The Row Management Unit also interprets window information when it is present.

The final task performed by the Row Management Unit is the selection of displayable characters (which are the only ones loaded into the row buffers) depending upon the "ignore" and "invisible attribute flag" bits settings.

## 2.5.2 Data Structure

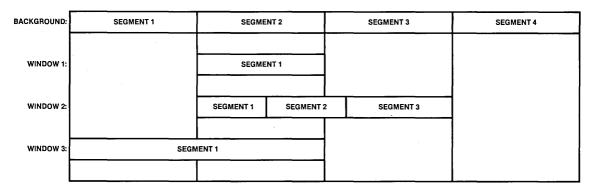

The CRTC is capable of controlling and displaying a text file on the screen (known as background) concurrently with other text files embedded in rectangles (known as windows) positioned anywhere inside the active display area of the screen. With conventional CRT controllers, this feature can only be implemented if the CPU is aware of the position and size of the window, with all the inconvenience and software complexity this implies. One of the important features of the Am8052 CRTC is that it allows the CPU to process a background file and a window file independently without continuously being concerned with size and position of the window.

The CRTC holds two pointer registers; each containing the starting address of a linked-list residing in memory: one pointer corresponds to the background information, while the other corresponds to the first window's information. The first window is the first one encountered when scanning the screen from top to bottom. Note that the user is able to define an arbitrary number of windows on the screen, as long as two background character rows (three for interlaced video) separate the windows vertically. Virtual windows, however, may occur side by side (horizontal split screen).

Each window links to the following one (ranging from top to bottom of the screen) with a link pointer. There are no more windows when the link pointer of the last window contains zero.

So far, we have explained that the CRTC is aware of two main lists in memory:

- 1. The background list pointed to by top of page (TOP) register, containing the parameters of the background display.

- The window(s) list pointed to by top of window (TOW) register, containing the parameters of the window(s) display.

Depending upon the memory addressing scheme, the user can choose either of two addressing modes: segmented more or linear mode:

#### SEGMENTED MODE:

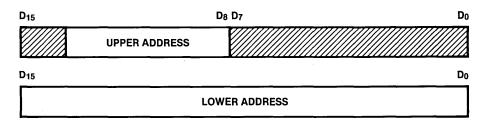

The segmented mode divides the memory into pages containing 64K bytes each. The CRTC can address 128 pages. In this case, the pointer is 23 bits wide arranged in two 16-bit words with the following configuration:

- 7 bits pointing to one page among the 128 addressable pages. These 7 bits are right justified in the most significant byte of first 16-bit word.

- 16 bits pointing to the address within the selected page. These 16 bits constitute the second word.

When operating in the segmented mode, crossing a page boundary does not increment the page number. It results in wrap-around operation within the same page.

#### LINEAR MODE:

In the linear mode the CRTC addresses memory as one 16 megaword block, with a 24-bit wide pointer arranged in two 16-bit words with the following configurations:

- 8 bits representing the most significant part of the address embedded in the least significant byte of the first word.

- 16 bits representing the least significant part of the address in the second word.

In this mode, when the second word crosses a 64K boundary, the first word is incremented by one.

The selection between these two modes is accomplished through the  $L/\overline{S}$  bit in Mode Register 1:

| L/S = Ø | segmented mode enabled |

|---------|------------------------|

| L/S = 1 | linear mode enabled    |

Consistent with the byte addressing method used by all 16-bit microprocessors, ADØ will always output a "Ø" at address time. This means that the CRTC actually addresses 32K 16-bit words instead of 64K bytes. This applies for both linear and segmented addressing modes.

Let us see now how background and window information is organized. We will first focus on the background list.

#### 2.5.3 Background Information Management

The "TOP" register points to the first data word of a block called "Main Definition Block". This block is unique for each background list, and the information it contains will be fetched on a frame basis and stored into the applicable internal registers of the CRTC.

## MAIN DEFINITION BLOCK (MDB) OVERVIEW:

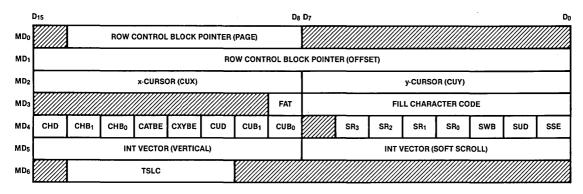

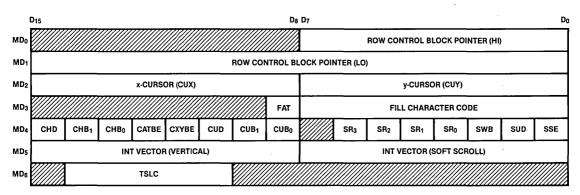

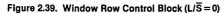

The Main Definition Block contains seven data words (MØ-6) defined as follows (Figure 2.29 and 2.30):

| MDØ,MD1 | - | "Row Control Block" pointer      |            |

|---------|---|----------------------------------|------------|

| MD2     | - | Absolute cursor coordinates ("X" | coordinate |

|         |   | byte and "Y" coordinate byte)    |            |

MD3 - Fill character code (1 flag bit + 1 byte code) MD4 - Blink control/scroll control MD5 - Interrupt vectors: vertical event/scroll event MD6 - Total scan line count per row

#### MDB DETAILED DESCRIPTION:

- MDØ,MD1 The Row Control Block pointer points to the block defining the first row's control information.

- MD2 The absolute cursor coordinates indicates the row number and the character position within this row where the absolute cursor is displayed. The topmost row is row "Ø" the leftmost character position is "Ø".

- MD3 -The fill character code is a user-defined 8-bit code. This is used as a filler in the row buffer if all the characters for that row have been loaded and did not fill the programmed buffer size. Seaments with a character code pointer of "0" are also filled with the fill code. The number of visible characters (visible #) specifies the length of these segments. Windows, where the window segments do not fill up the window size, are filled by the fill code The flag bit (flag attribute), when set, too. causes the CRTC to load an extra attribute word from the attribute list and use it as a latched attribute (immediately active) for the fill character. The extra attribute word must invoke a latched attribute.

- MD4 -

- The blink control/scroll control is composed of 15 bits.

**Soft Scroll Enable** (SSE) enables the soft-scroll operation for either the background or a window.

Ø Soft-scroll disabled

1 Soft-scroll enabled

Scroll Up/Down (SUD) indicates the direction of the scroll.

Ø Soft-scroll down

1 Soft-scroll up

Scroll Window/Background (SWB) indicates whether the background or a window will be scrolled.

Ø Soft-scroll background

1 Soft-scroll window

**Scroll Rate** (SR3-Ø) is a 4-bit word specifying the soft-scroll rate according to the following table:

| <u>SR3</u> | <u>SR2</u> | <u>SR1</u> | <u>SRO</u> | Scroll Rate                        |

|------------|------------|------------|------------|------------------------------------|

| 0          | 0          | 0          | 0          | l Scan Line Per Frame              |

| 0          | 0          | 0          | 1          | 2 Scan Lines Per Frame             |

| 0          | 0          | 1          | 0          | 3 Scan Lines Per Frame             |

| 0          | 0          | 1          | 1          | 4 Scan Lines Per Frame             |

| 0          | 1          | 0          | 0          | 5 Scan Lines Per Frame             |

| 0          | 1          | 0          | 1          | 6 Scan Lines Per Frame             |

| 0          | 1          | 1          | 0          | 7 Scan Lines Per Frame             |

| 0          | 1          | 1          | 1          | 8 Scan Lines Per Frame (fastest)   |

| 1          | 0          | 0          | 0          | l Scan Line Per l Frame            |

| 1          | 0          | 0          | 1          | l Scan Line Per 2 Frames           |

| 1          | 0          | 1          | 0          | l Scan Line Per 3 Frames           |

| 1          | 0          | 1          | 1          | l Scan Line Per 4 Frames           |

| 1          | 1          | 0          | 0          | l Scan Line Per 5 Frames           |

| 1          | 1          | 0          | ן י        | l Scan Line Per 6 Frames           |

| 1          | 1          | 1          | 0          | l Scan Line Per 7 Frames           |

| 1          | 1          | 1          | 1          | l Scan Line Per 8 Frames (slowest) |

.

**Cursor Blink Rate** (CUB1, CUBØ) defines the blinking rate for both attribute and absolute cursors:

| CUB 1 | CUBØ | Blink Period | Blink Frequency      |

|-------|------|--------------|----------------------|

|       |      |              | (at 60Hz Frame Rate) |

| 0     | 0    | 16 Frames    | 3.75 Hz              |

| 0     | 1    | 32 Frames    | 1.85 Hz              |

| 1     | 0    | 64 Frames    | 0.93 Hz              |

| 1     | 1    | 128 Frames   | 0.46 Hz              |

Cursor blink Duty cycle (CUD):

ſ

| CUD | Cursor Blink Duty Cycle               |

|-----|---------------------------------------|

| Ø   | Blink Output 75% Inactive, 25% Active |

| 1   | Blink Output 50% Inactive, 50% Active |

Character blink Duty cycle (CHD):

| CUD | Character Blink Duty Cycle |            |

|-----|----------------------------|------------|

| ø   | Blink Output 75% Inactive, | 25% Active |

| 1   | Blink Output 50% Inactive, | 50% Active |

| Absolute | cursor | Blink | <pre>Enable (CXYBE):</pre> |

|----------|--------|-------|----------------------------|

| ø        | Cursor | Blink | Disable                    |

| 1        | Cursor | Blink | Enable                     |

#### Attribute Cursor Blink Enable (CATBE):

Ø Cursor Blink Disable

1 Cursor Blink Enable

Character Blink Rate (CHB 1,0):

| CHB1 | CHBO | Blink Period | Blink Frequency      |

|------|------|--------------|----------------------|

|      |      | ,            | (at 60Hz Frame Rate) |

| 0    | 0    | 16 Frames    | 3.75 Hz              |

| 0    | 1    | 32 Frames    | 1.85 Hz              |

| 1    | 0    | 64 Frames    | 0.93 Hz              |

| 1    | 1    | 128 Frames   | 0.46 Hz              |

Note that the character and the cursor can have different blink rates and different duty cycles.

MD5 -

- The interrupt vector register contains the soft-scroll and vertical event interrupt vectors. When one of these interrupts is activated, the corresponding 8-bit vector is output on AD7-ADØ at interrupt acknowledge time, if the NV-bit in Mode Register 2 is reset.

The vertical event interrupt vector is totally user-programmable.

The soft-scroll interrupt vector is partially user-programmable: Bits  $\emptyset$ , 2-7 are user-definable while bit 1 reflects the state of the SIP (Scroll Interrupt Pending) bit. This feature allows the user to steer the soft-scroll interrupts into two different routines.

- SIP = 1 The CRT is informing the CPU to execute a relink during scrolling operation.

- SIP = Ø The CRT does not need CPU intervention but signals the CPU that the scroll operation is completed.

- MD6 TSLC is a 5-bit value defining the number of total scan lines per row minus one. This value is reprogrammable on a row basis via the Row Redefinition Block.

This TSLC must be equal to the TSLC of the first row in the linked-list.

In video interlace or RFI mode, the TSLCs of all rows displayed must be even or the TSLCs of all rows must be odd. In non-interlaced video, rows with odd and even TSLCs may be mixed. However, this is restricted when displaying windows (refer to Section 2.5.4). Figure 2.31 shows the values of the total number of scan lines for all video modes.

# TOTAL NUMBER OF SCAN LINES

| TSLC    | NON-INTERLACED<br>MODE | INTERLACE OR RFI<br>MODE |

|---------|------------------------|--------------------------|

| 00000   | 1                      | 1+1 = 2                  |

| 00000   |                        |                          |

| 00001   | 2                      | 1+2 = 3                  |

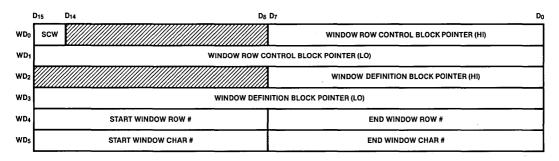

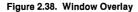

| 00010   | 3                      | 2+2 = 4                  |