ISDN

ISDN 1989/90 Data Book Advanced Micro Devices

Advanced Micro Devices

# ISDN Data Book

#### © 1989 Advanced Micro Devices

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics. The performance characteristics listed in this document are guaranteed by specific tests, correlated testing, guard banding, design and other practices common to the industry. For specific testing details, contact your local AMD sales representative. The company assumes no responsibility for the use of any circuits described herein.

> 901 Thompson Place, P.O. Box 3453, Sunnyvale, California 94088-3000 (408)732-2400 TWX: 910-339-9280 TELEX: 34-6306

AmLink, AmLink3, Digital Subscriber Controller, DSLAC, IDPC, Integrated Data Protocol Controller, ITCB, ISDN Terminal Coprocessor Board, SLAC, and World Network are trademarks of Advanced Micro Devices, Inc.

PAL is a registered trademark of Advanced Micro Devices, Inc.

٠

pROBE and pSOS are trademarks of Software Components, Inc.

IBM is a registered trademark of International Business Machines, Corp.

PC-AT and PC-XT are trademarks of International Business Machines, Corp.

ARCOFI, EPIC, HSCC, HSCX, IBC, IDC, IDEC, IDPC, IEC, IEC-Q, IOM, ISAC-P, ISAC-S, ITAC, ITCB, QEPC, SBC, and SBCX are trademarks of Siemens AG.

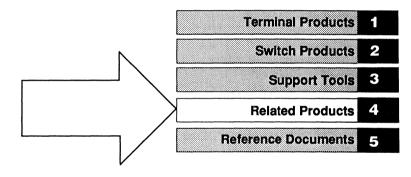

## **Table of Contents**

| Introduction                        | iv                  |

|-------------------------------------|---------------------|

| Chapter 1                           | Terminal Products   |

| Am79C30A/32A Data Sheet             |                     |

|                                     |                     |

| Am2085 Data Sheet                   |                     |

| Am2085 Data Sheet Amendment         |                     |

| Am2110 Data Sheet                   |                     |

| Am2160 Data Sheet                   |                     |

|                                     |                     |

|                                     |                     |

| Am82525 Data Sheet (see Chapter 2)  |                     |

| Z85C30 Data Sheet                   |                     |

| Chapter 2                           | Switch Products     |

| Am2055 Data Sheet                   |                     |

| Am2075 Data Sheet                   |                     |

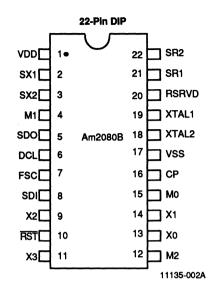

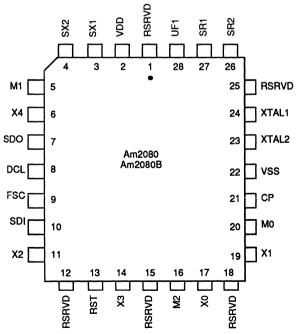

| Am2080/B Data Sheet                 |                     |

| Am2080/B Data Sheet Amendment       |                     |

| Am2081 Data Sheet                   |                     |

| Am2091 Data Sheet                   |                     |

| Am2095 Data Sheet                   |                     |

|                                     |                     |

|                                     |                     |

| Am79C401 Data Sheet (see Chapter 1) |                     |

| Am82520 Data Sheet (see Chapter 1)  |                     |

| Am82525 Data Sheet                  |                     |

| Chapter 3                           | Support Tools       |

| AmLink Interface Reference Guide    |                     |

|                                     | 3-30                |

| Am79B320 Technical Manual           |                     |

| Am79C30A LLD Reference Guide        |                     |

|                                     |                     |

| Chapter IV                          | Related Products    |

| •                                   |                     |

|                                     |                     |

|                                     |                     |

|                                     | Reference Documents |

|                                     |                     |

|                                     |                     |

|                                     |                     |

|                                     |                     |

| Giussaly                            |                     |

## Introduction

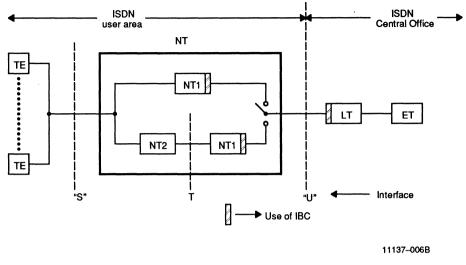

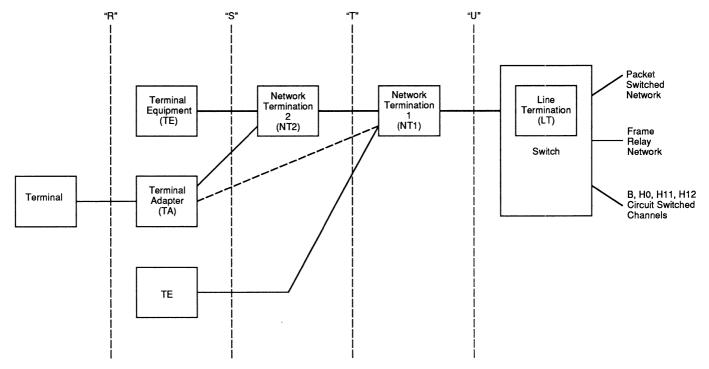

ISDN, the Integrated Services Digital Network, is the major component of an evolving World Network™ that is linking telephones and computers around the globe. This development is molding an intricate infrastructure of the world's telephones as well as the multitudes of existing computers and data networks.

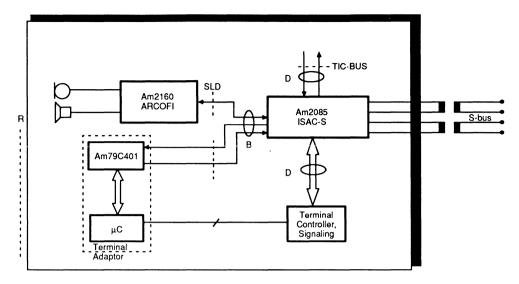

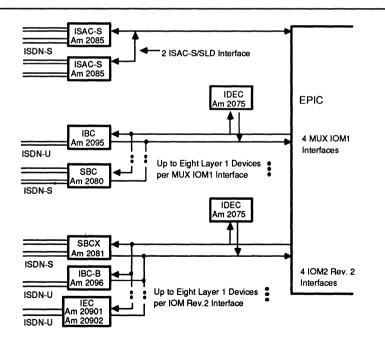

Advanced Micro Devices' family of ISDN devices provides comprehensive solutions for the new services that offer simultaneous transmission and reception of voice and data over a common network. AMD is a leading participant in the development and advancement of ISDN as a major worldwide technology.

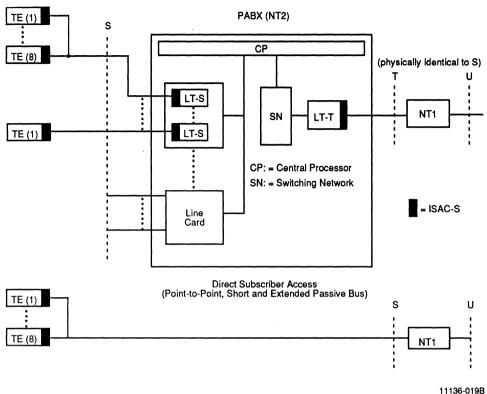

This Data Book is your comprehensive guide to Advanced Micro Devices' extensive line of ISDN products. Whether your application is terminal equipment, network terminators, line terminators, PABXs, concentrators or central office line cards, our products provide a cost-effective, complete solution with both highly integrated silicon and high-performance software that is compliant with the CCITT standards.

Advanced Micro Devices' commitment in 1982 to becoming a leader in ISDN is a reality today. We continue to apply substantial resources to maintain that leadership position—now and for the future. AMD's technical staff excels at offering support at every level. Our trained field applications engineers, specialists in communications, are backed by system experts in the factory. Call your local AMD sales office or the authorized representative listed in the back of this publication for further information about ISDN.

Gary Ashcraft Vice President Communication Products Division

# **Table of Contents**

## Chapter 1

#### **Terminal Products**

| Am79C30A/32A Data Sheet            | 1-1   |

|------------------------------------|-------|

| Am79C401 Data Sheet                | 1-71  |

| Am2085 Data Sheet                  |       |

| Am2085 Data Sheet Amendment        | 1-210 |

| Am2110 Data Sheet                  |       |

| Am2160 Data Sheet                  | 1-263 |

| Am82520 Data Sheet                 | 1-266 |

| Am82520 Data Sheet Amendment       | 1-281 |

| Am82525 Data Sheet (see Chapter 2) |       |

| Z85C30 Data Sheet                  | 1-283 |

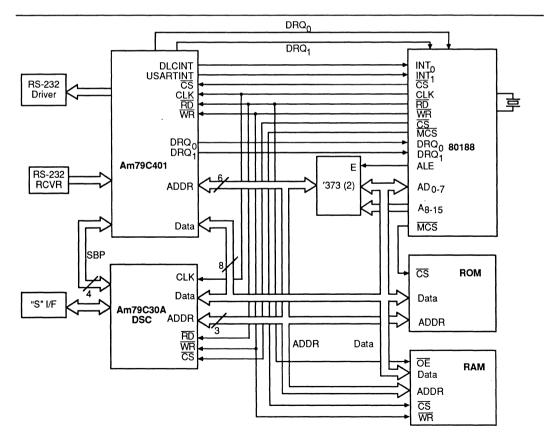

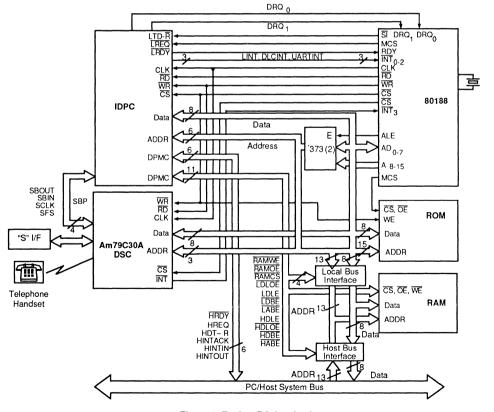

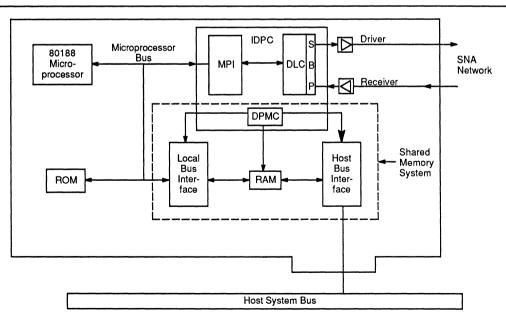

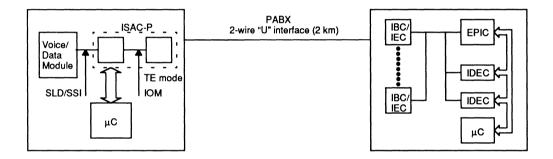

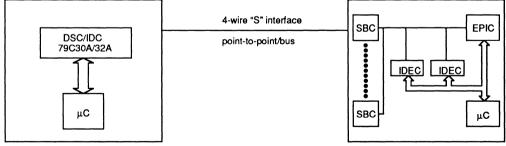

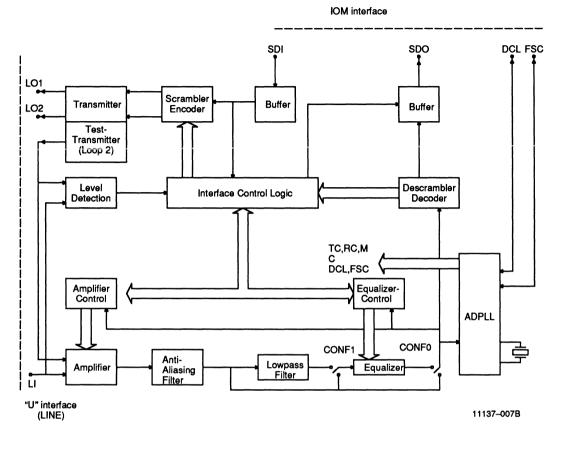

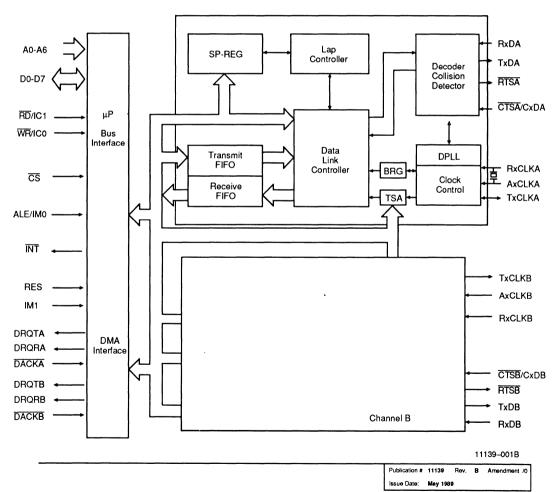

## **Am79C30A/32A** Digital Subscriber Controller (DSC) ISDN Data Controller (IDC)

## **DISTINCTIVE CHARACTERISTICS**

- Combines CCITT I.430 S/T Interface transcelver, D-channel LAPD processor, and audio processor (DSC only) in a single chip

- Interrupt-driven microprocessor interface

- CMOS technology, TTL compatible

- 'S' or 'T' Interface Transceiver

Level 1 Physical Layer Controller Supports point-to-point, short or extended passive bus configurations Multiframe support

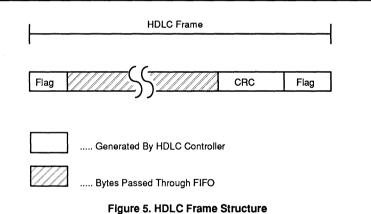

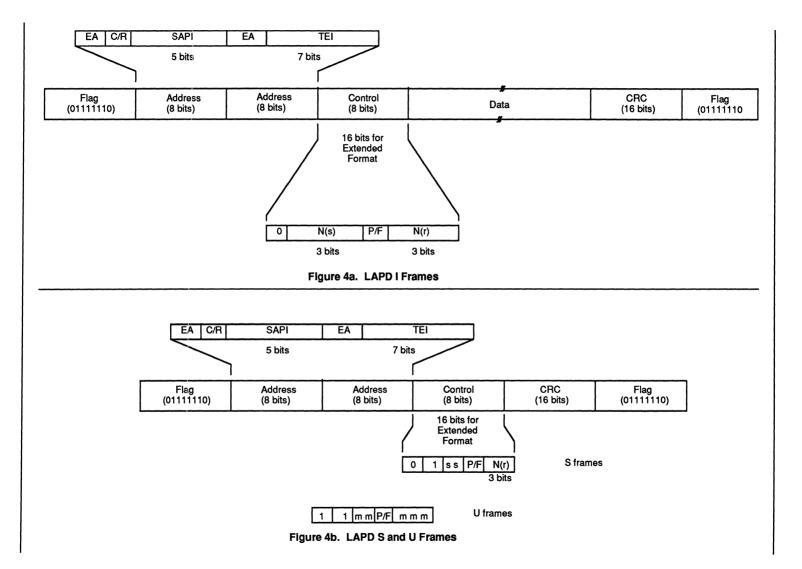

D-channel Processing Capability Flag generation/detection

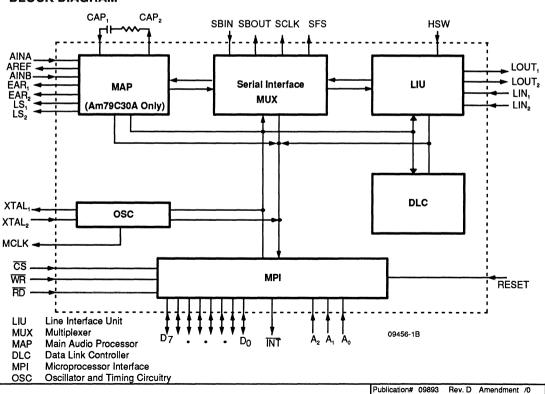

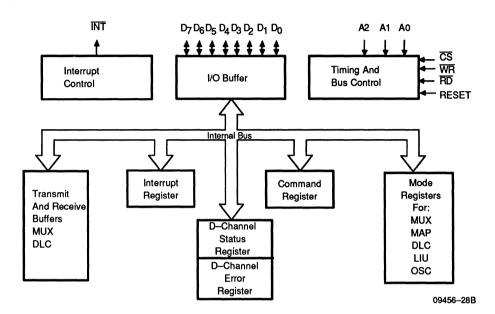

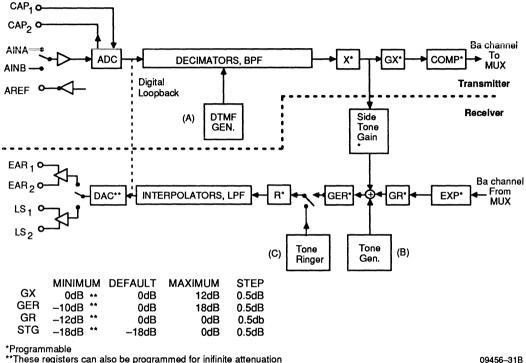

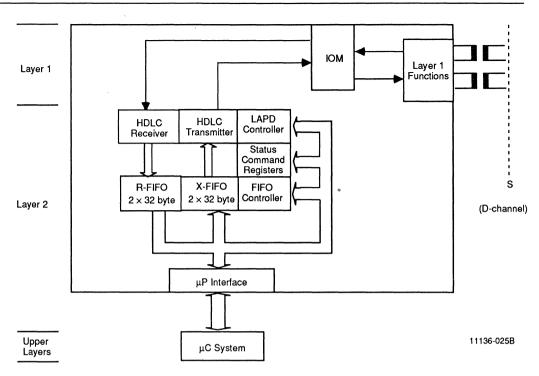

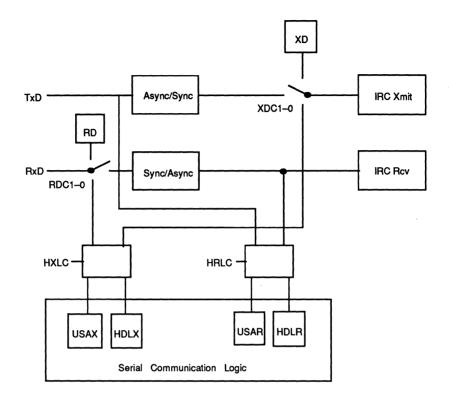

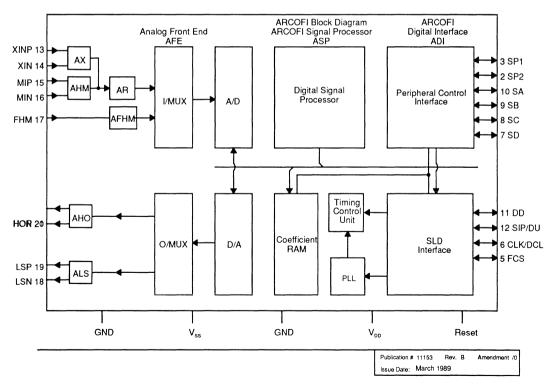

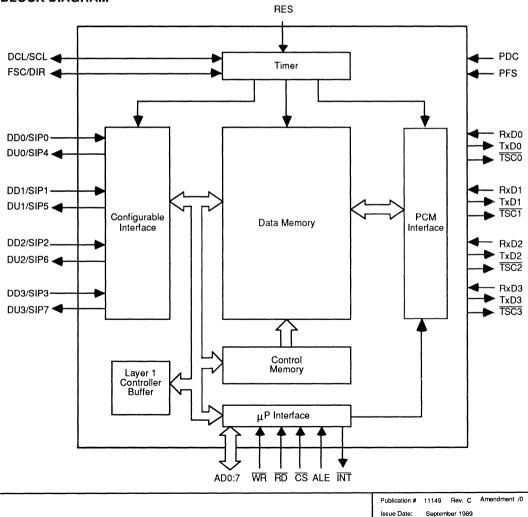

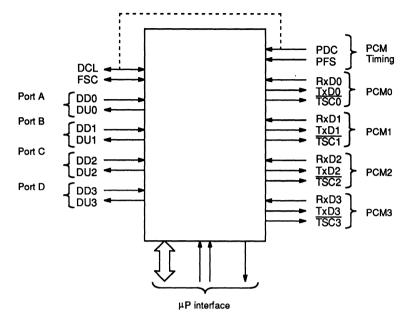

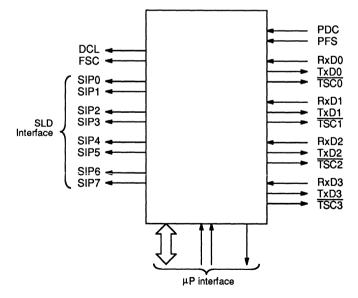

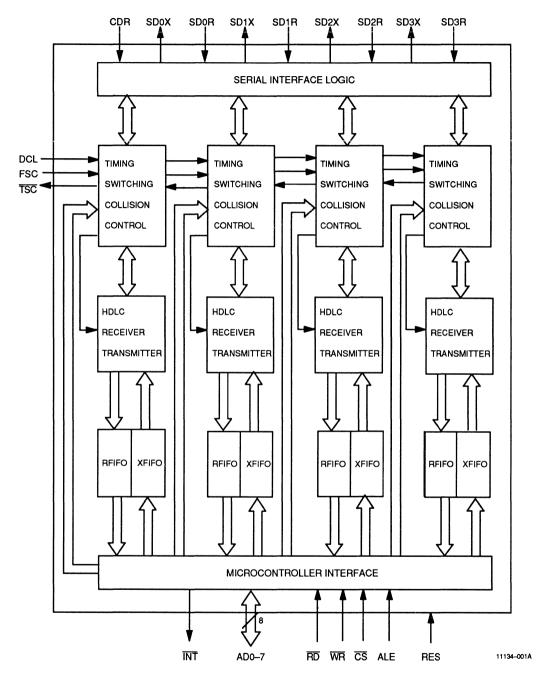

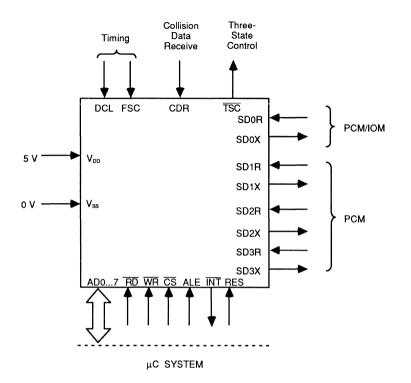

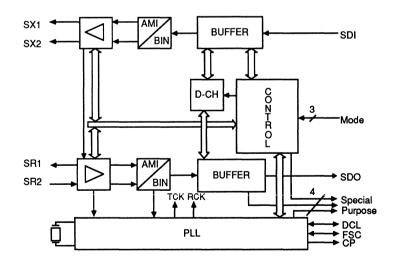

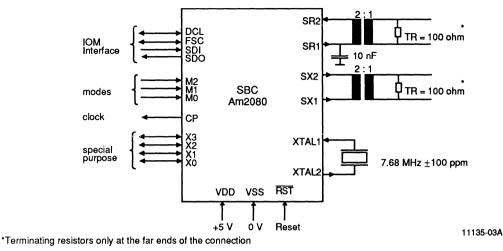

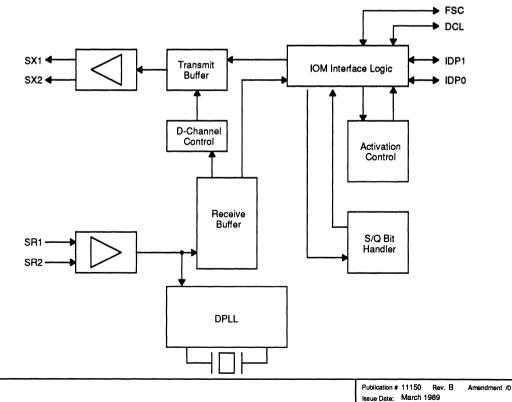

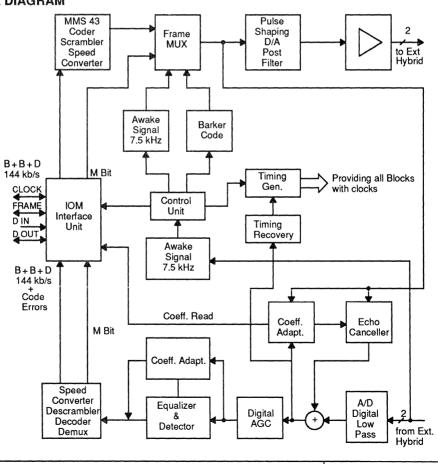

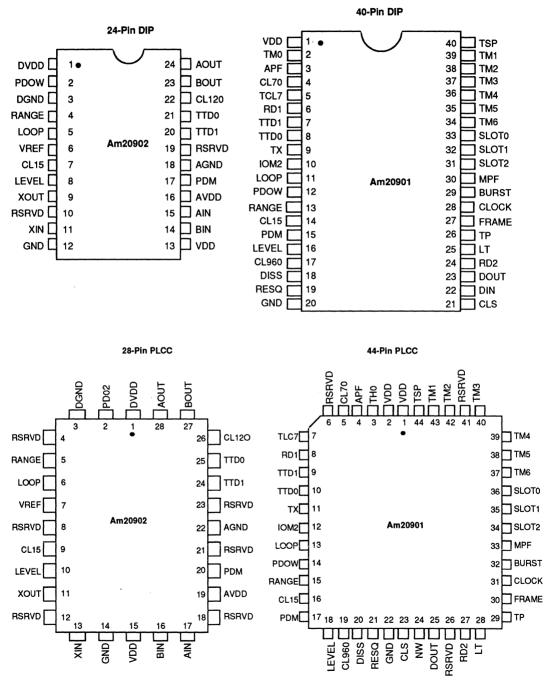

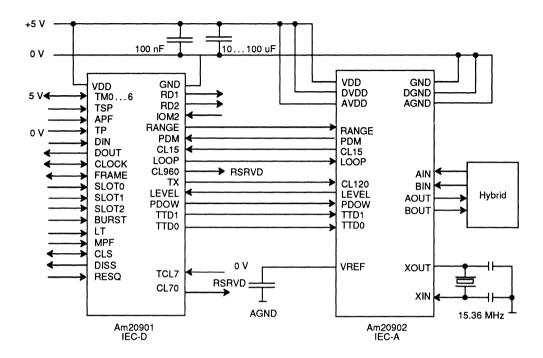

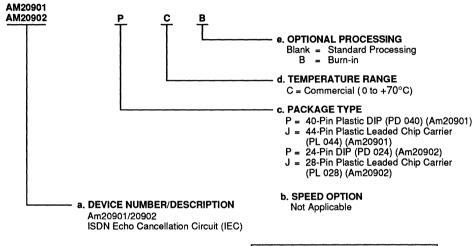

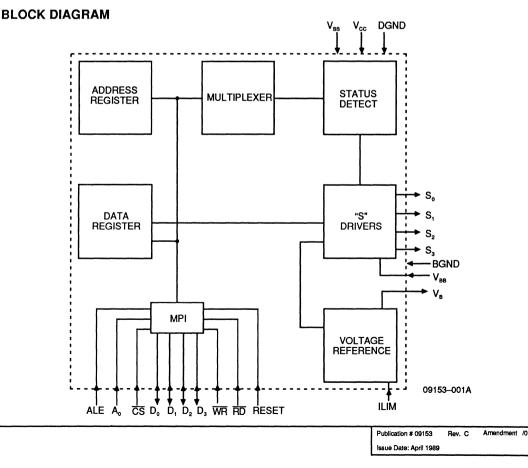

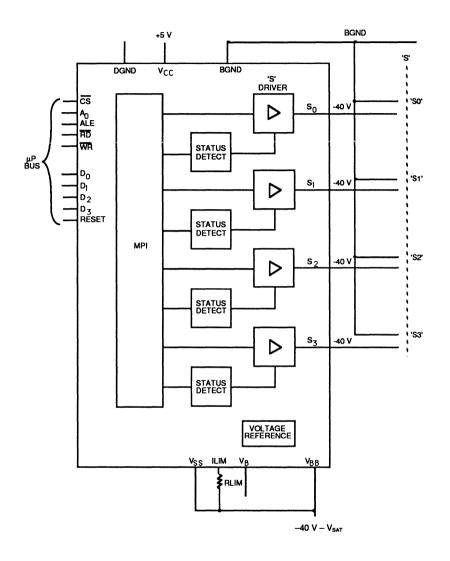

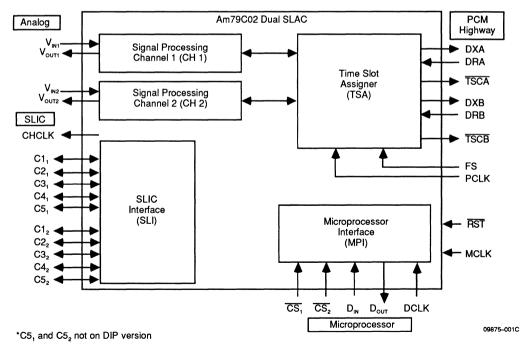

#### **BLOCK DIAGRAM**

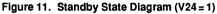

CRC generation/checking Zero insertion/deletion Four 2-byte address detectors Random number generation 8-byte transmit and receive FIFOs

Audio Processing Capability (DSC only)

Dual audio inputs Earpiece and loudspeaker drivers Filter/codec with A/mu selection Programmable gain and equalization filters Programmable sidetone level Programmable DTMF, single tone, and ringer tone generation

Publication# 09893 Rev. D Amendment /0 Issue Date: March 1989

## **GENERAL DESCRIPTION**

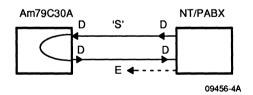

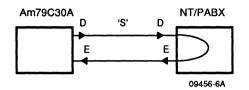

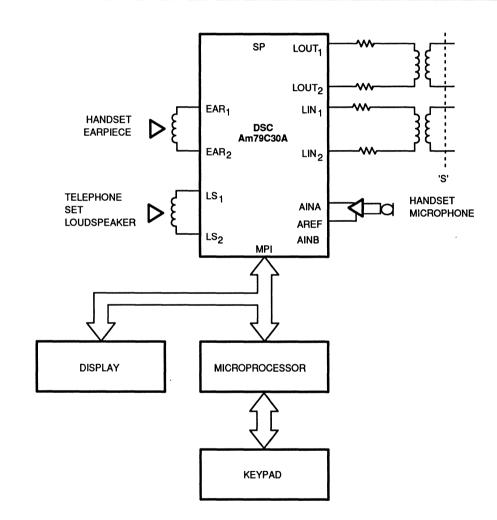

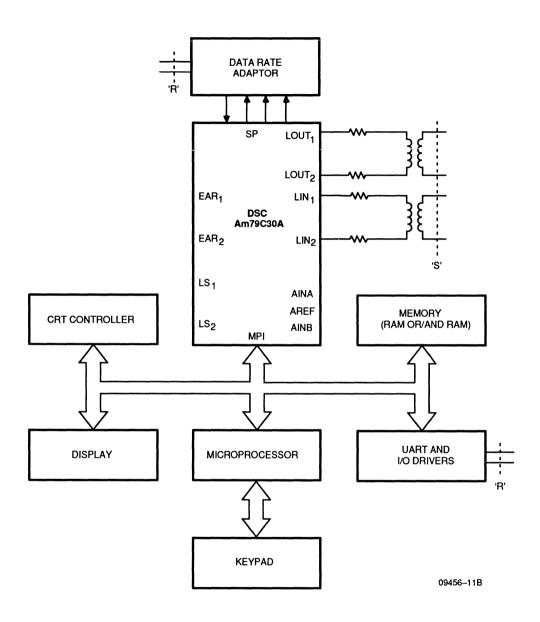

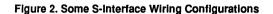

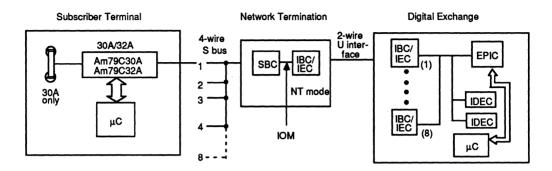

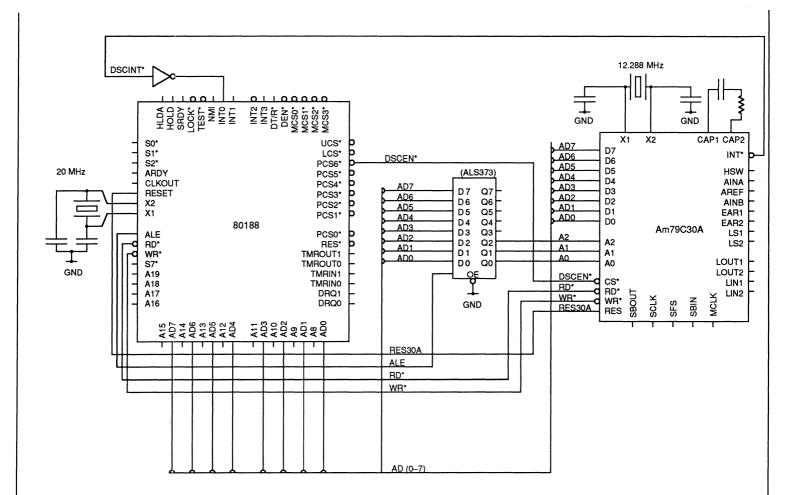

The Am79C30A Digital Subscriber Controller (DSC) and Am79C32A ISDN Data Controller (IDC), shown in the block diagram, provide the Terminal Equipment access to the ISDN. The Am79C30A/32A is compatible with the CCITT I-Series recommendations at the 'S' reference point allowing the user of the device to design TEs which conform to the international ISDN standards.

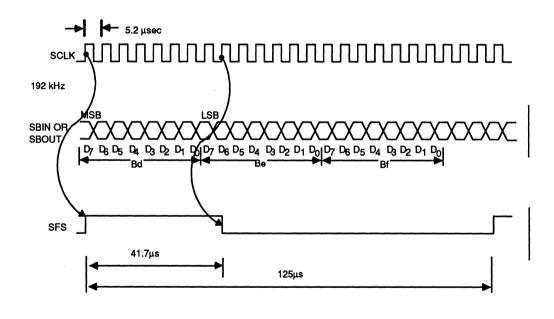

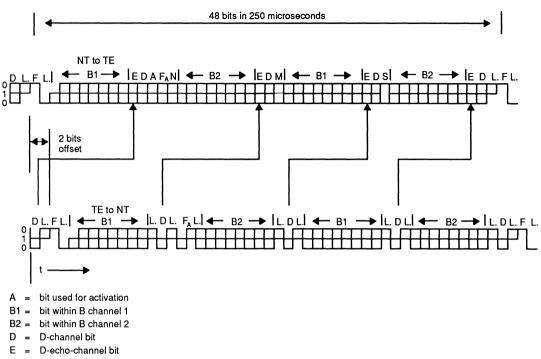

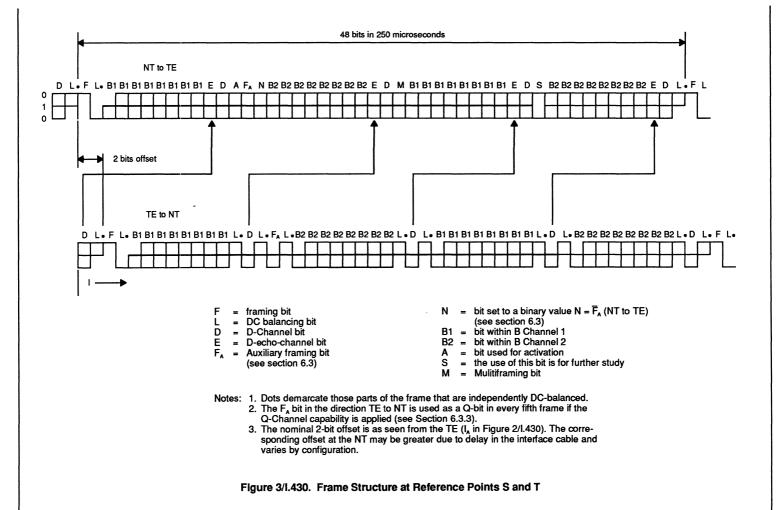

The Am79C30A/32A provides a 192 kbps full duplex digital path between the TE located in the subscriber's premises and the NT or PABX line card over 4-wires. The Am79C30A/32A separates the bit stream into the B1- (64 kbps), B2- (64 kbps) and D- (16 kbps) channels. The B-channels are routed to different sections of the Am79C30A under user control. The D-channel is partially processed in the Am79C30A/32A and passed to the microprocessor for further processing.

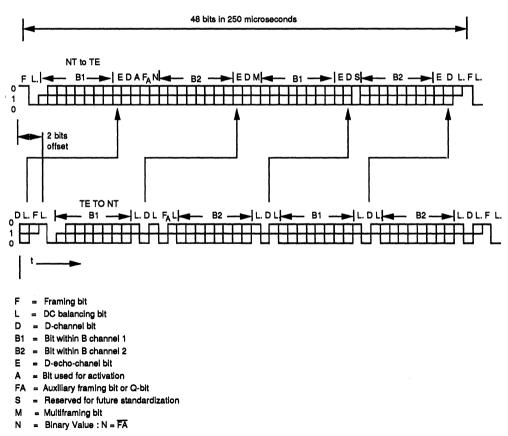

The transmission rate of 192 kbps provides a 48-bit frame every 250  $\mu$ s for framing and maintenance. The frame structure provides for frame synchronization and multiple terminal contention resolution as described in the CCITT I-series recommendations. Both point-to-point and point-to-multipoint connections are supported.

The Am79C30A can be used as a voice telephone, a digital data terminal, or a voice and data terminal. The Am79C32A can be used as a digital data terminal.

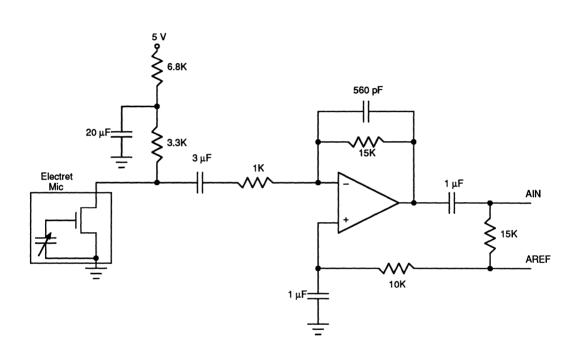

The audio processor in the Am79C30A, shown in the block diagram, uses Digital Signal Processing (DSP) to implement the codec and filter functions. The audio processor interfaces to a speaker, an earpiece, and two separate audio inputs. In the receive and transmit paths the user may program gain or alter the frequency response. The audio processor is not available in the Am79C32A.

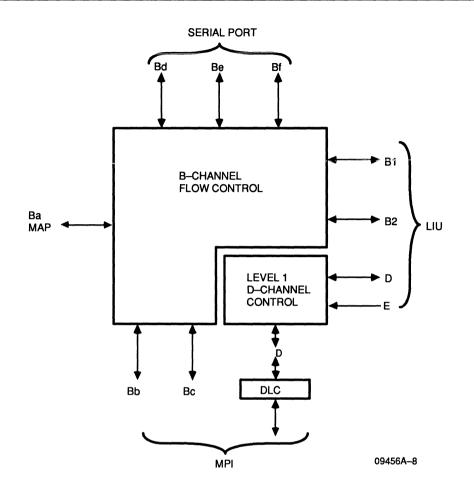

A serial port gives the user access to the B-channels of the Am79C30A/32A multiplexer. This serial port may be used by data terminals and provides, with additional circuitry, access to the CCITT 'R' reference point.

The Am79C30A/32A is controlled via an interrupt driven microprocessor bus interface by an external microprocessor. Using this interface, the microprocessor processes the D-channel information and programs the Am79C30A/32A accordingly. This includes programming a multiplexer within the Am79C30A/32A to route the B-channels as specified by the D-channel control information. The microprocessor can interrogate and program the Am79C30A/32A via its mode, status, and error registers.

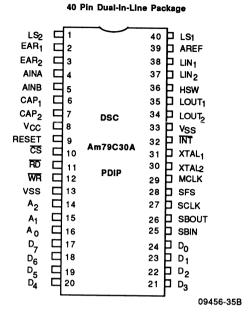

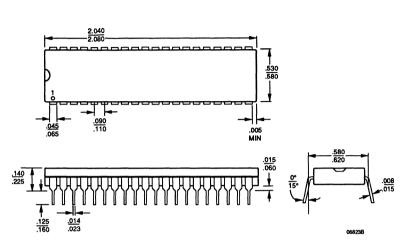

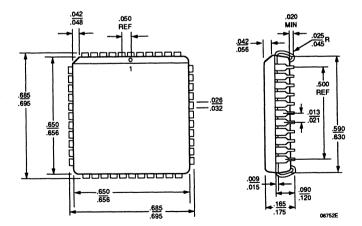

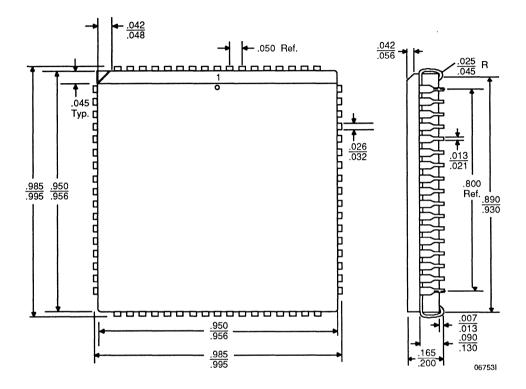

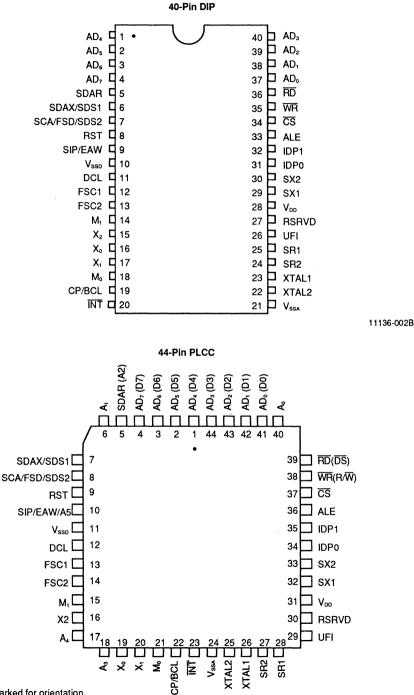

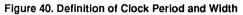

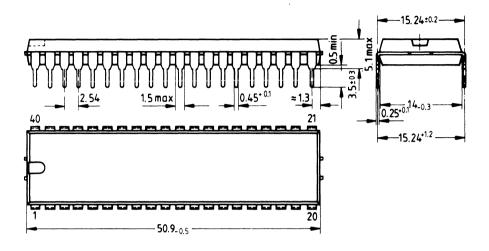

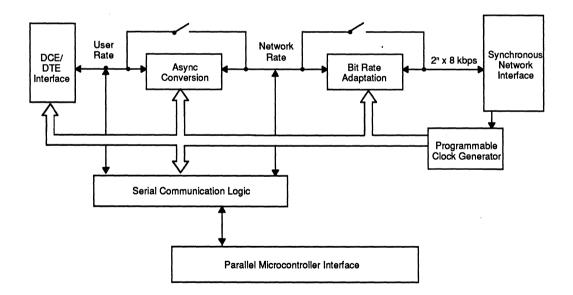

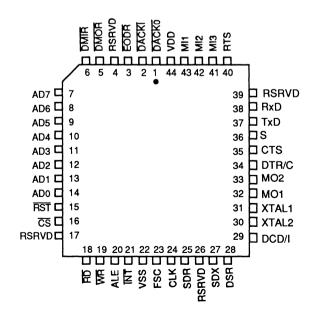

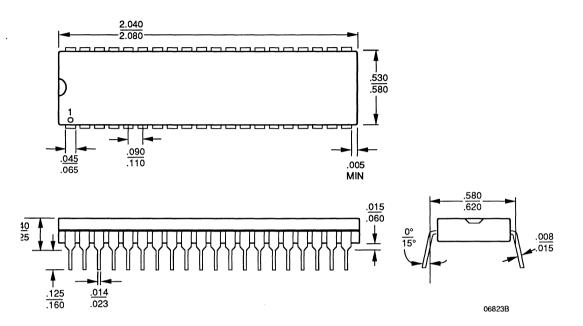

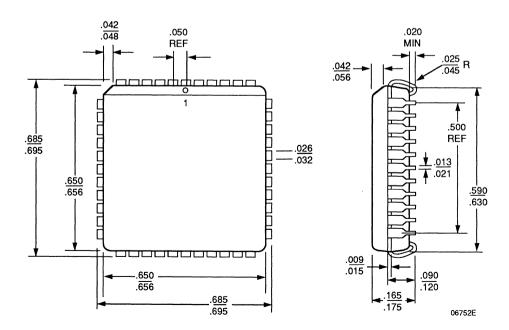

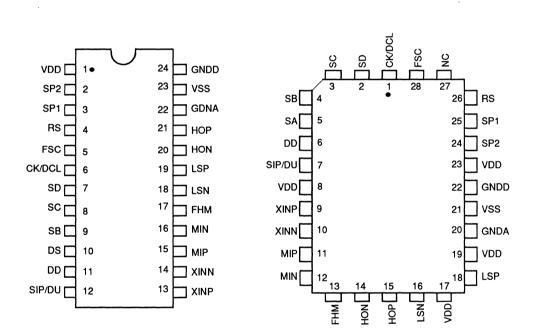

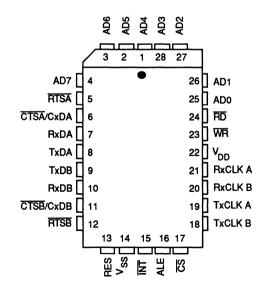

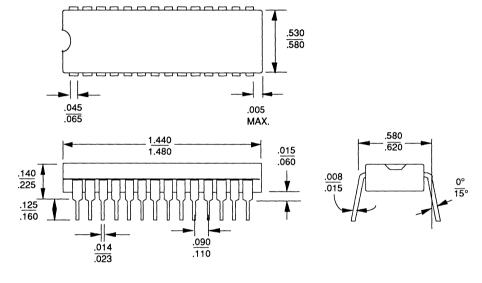

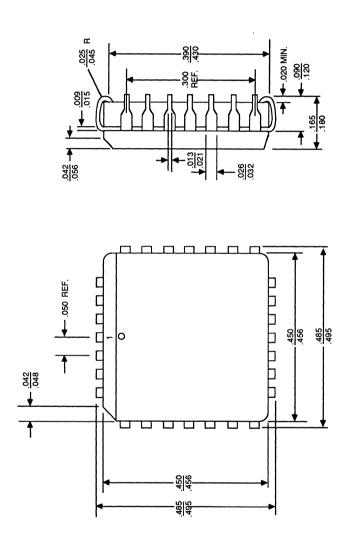

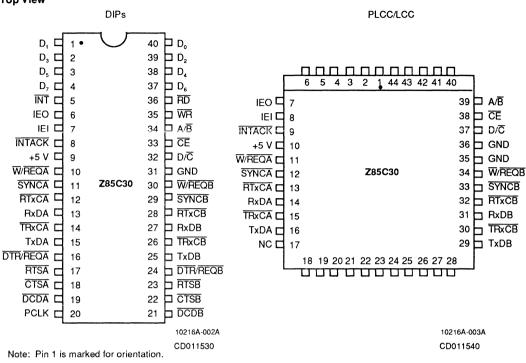

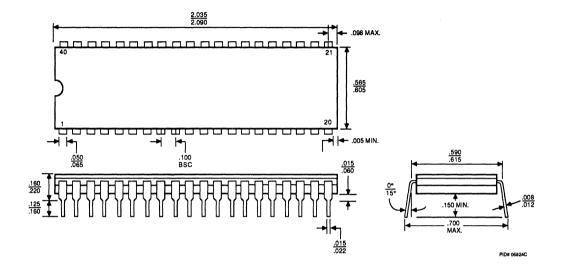

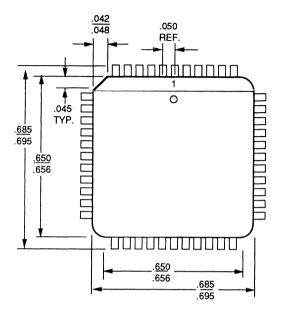

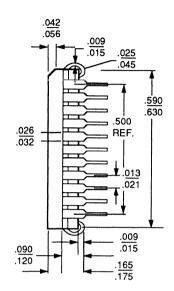

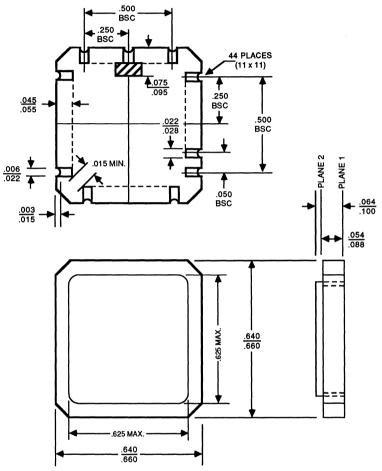

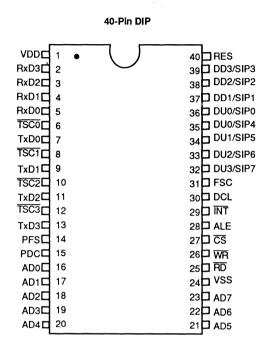

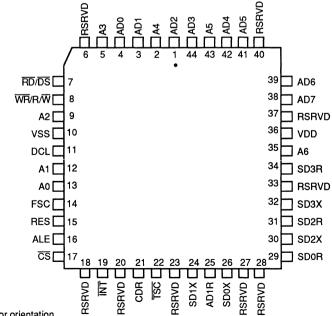

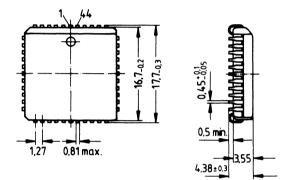

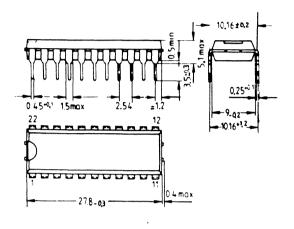

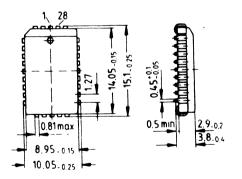

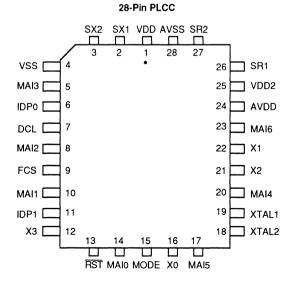

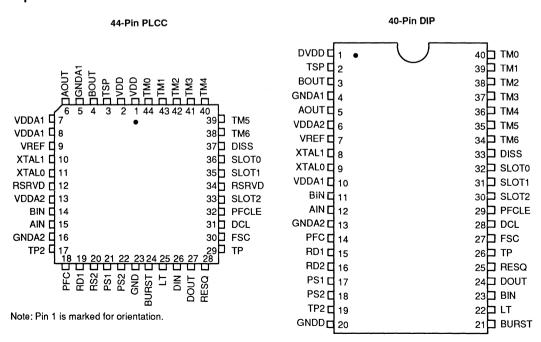

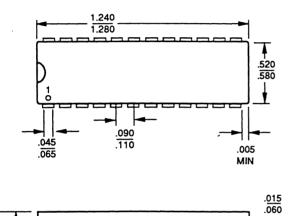

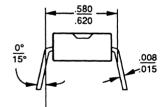

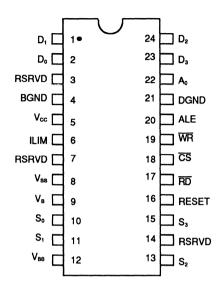

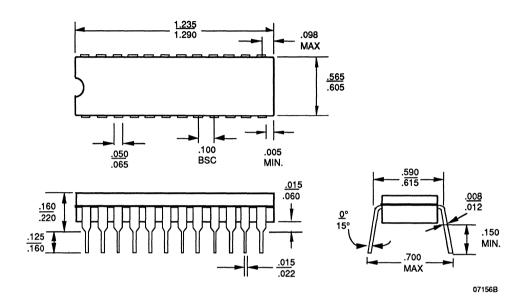

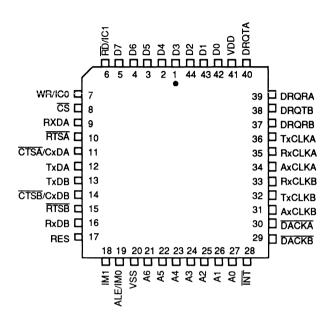

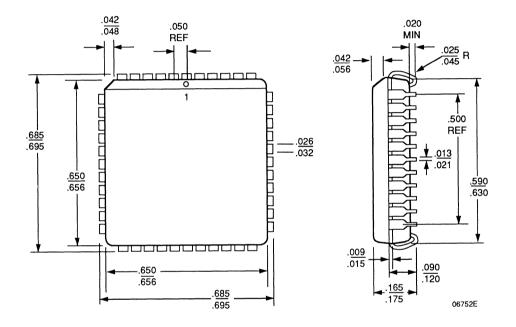

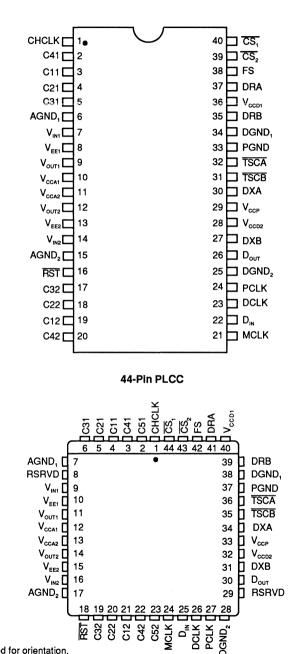

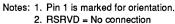

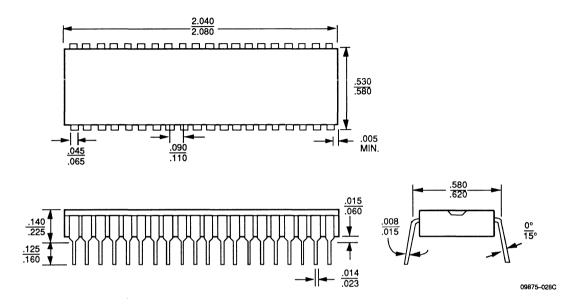

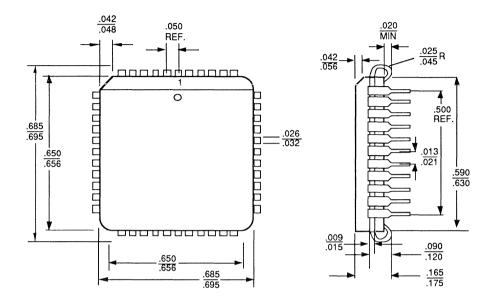

# CONNECTION DIAGRAMS Top View

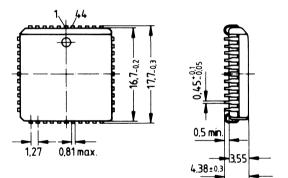

44 Pin Plastic Leaded Chip Carrier (PLCC)

#### Figure 2. Am79C30A DSC Connection Diagrams

#### 1

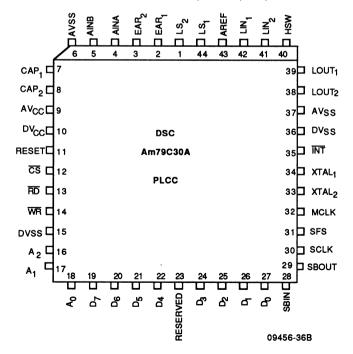

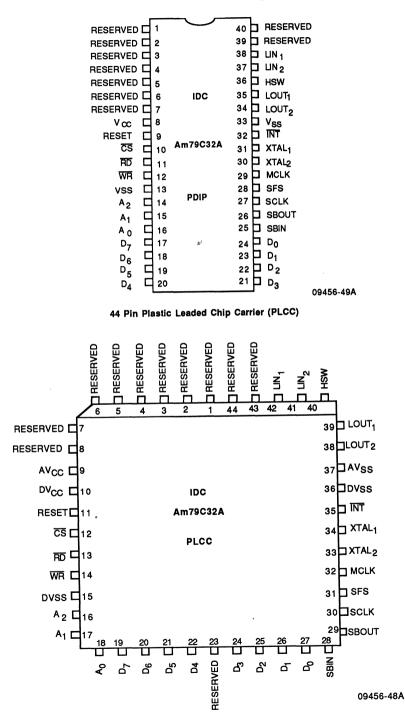

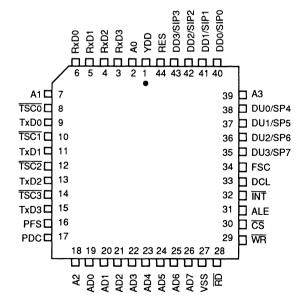

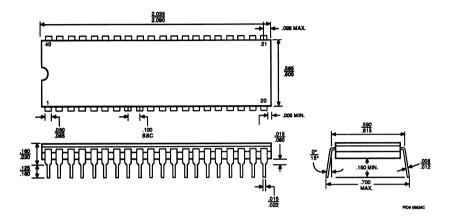

# CONNECTION DIAGRAMS Top View

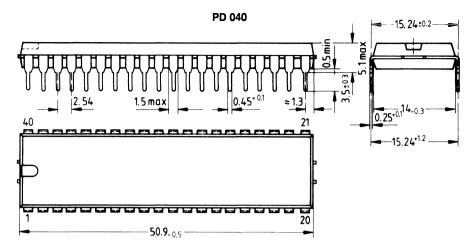

40 Pin Dual-In-Line Package

Figure 3. Am79C32A IDC Connection Diagrams

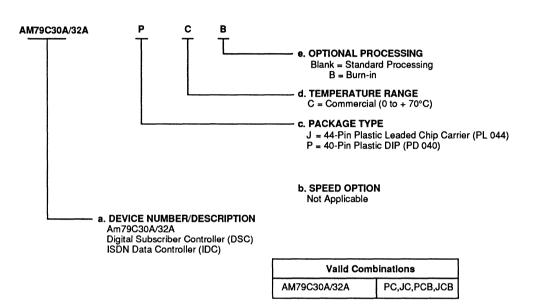

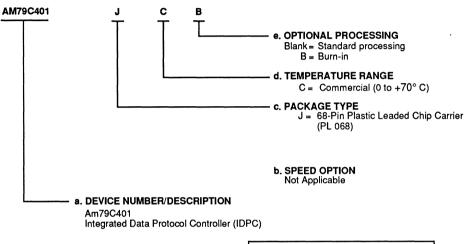

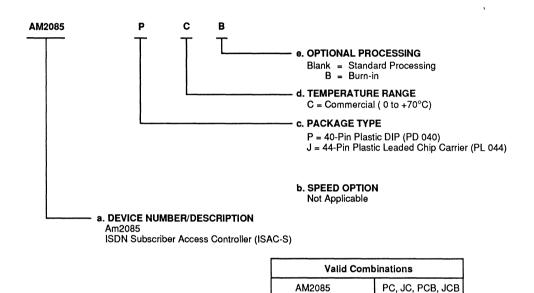

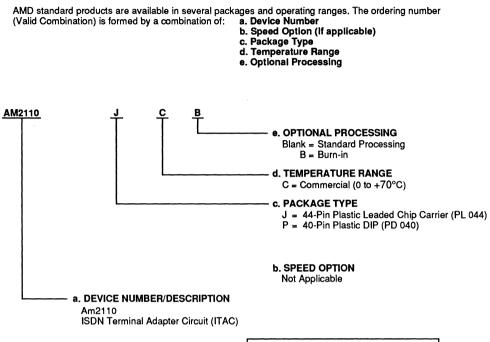

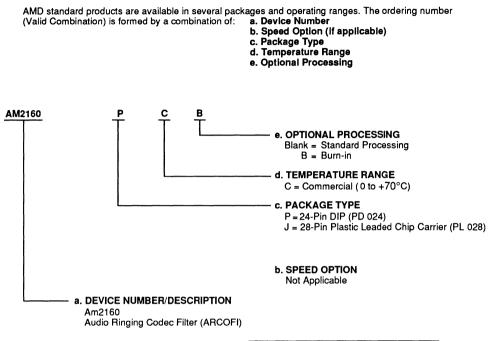

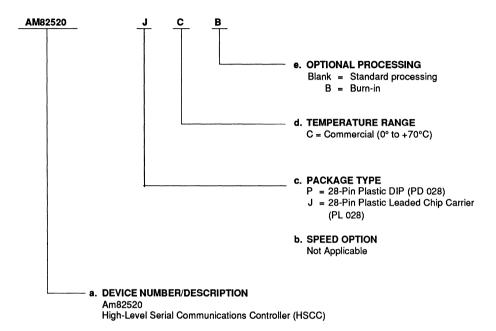

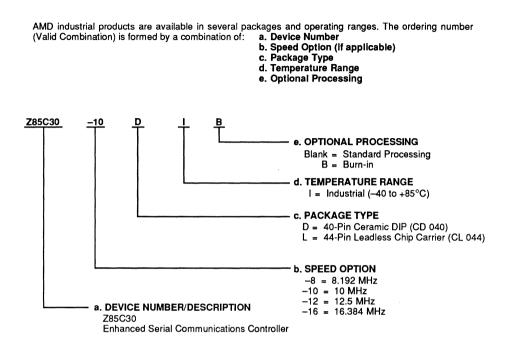

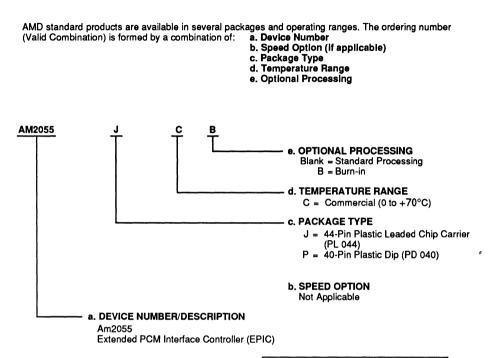

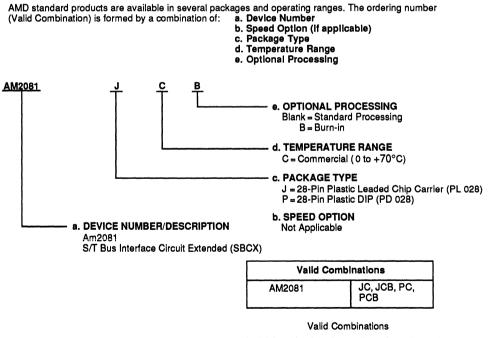

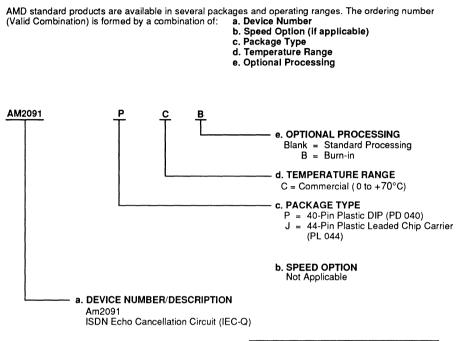

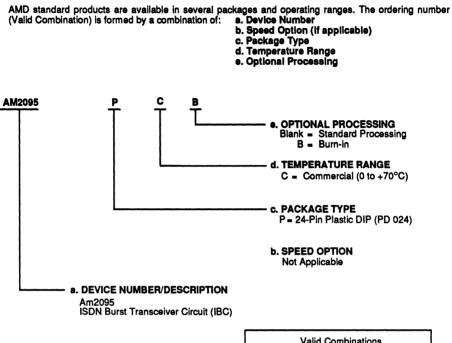

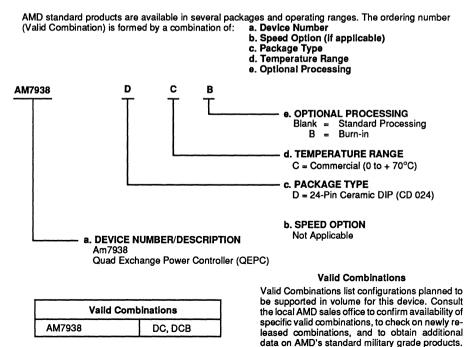

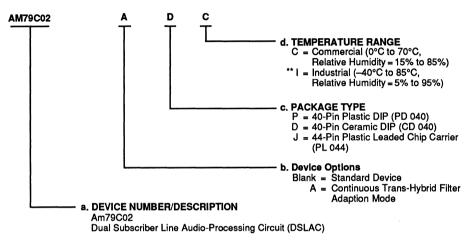

## ORDERING INFORMATION Standard Products

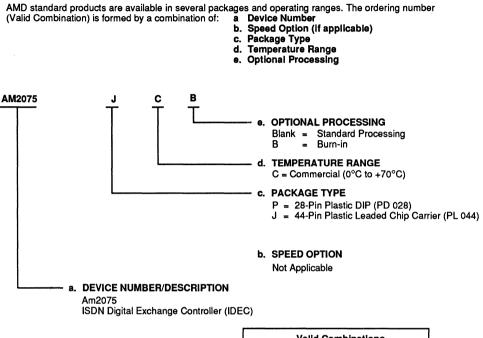

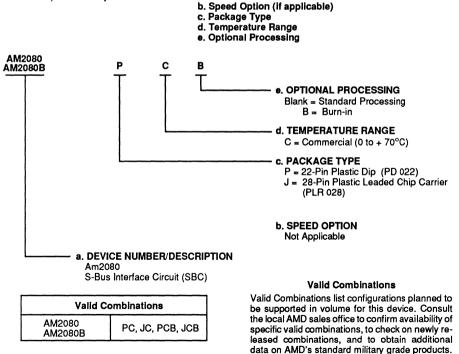

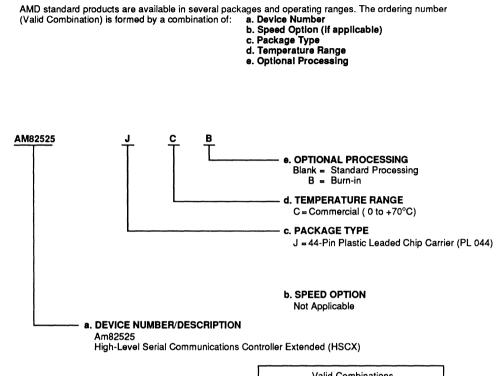

AMD standard products are available in several packages and operating ranges. The ordering number a. Device Number b. Speed Option (if applicable) (Valid Combination) is formed by a combination of:

- - c. Package Type

- d. Temperature Range

- e. Optional Processing

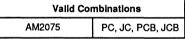

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

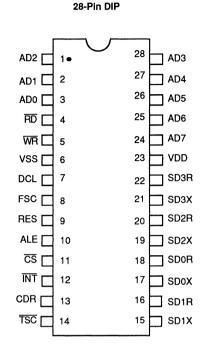

## **PIN DESCRIPTION**

All signal levels are TTL compatible unless otherwise stated.

## Line Interface Unit (LIU)

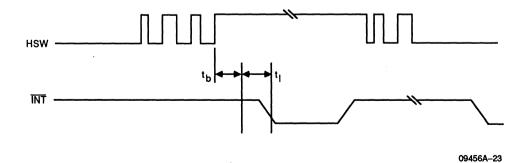

#### HSW

#### Hook-Switch (Input)

The HSW signal indicates if the hookswitch is on or off hook. This signal may be generated with a mechanical switch wired to ground with a pull-up resistor to Vcc. Any change in the HSW state causes an interrupt.

#### LIN1, LIN2 Subscriber Line Input (Differential Inputs)

The LIN1 and LIN2 inputs interface to the subscriber ('S' reference point) via an isolation transformer. LIN2 is the positive input, LIN1 is the negative input. These pins are not TTL compatible.

## LOUT1, LOUT2

## Subscriber Line Output (Differential Outputs)

The LOUT1 and LOUT2 line driver output signals interface to the subscriber line at the 'S' reference point via an isolation transformer and resistors. LOUT2 is the positive 'S' interface driver (that is, sources current during a high mark) and LOUT1 is the negative 'S' interface driver (that is, sources current during low mark). For multipoint applications, all TE's must maintain the same polarity on the 'S' interface. These pins are not TTL compatible.

## Multiplexer (MUX)

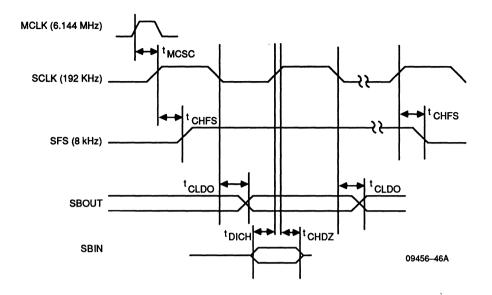

#### SBIN

#### Serial Channel (Input)

The data rate on SBIN is 192 kbps. SBIN consists of three 64 kbps serial channels. Data bytes are received MSB first.

#### SBOUT Serial Channel (Output)

The data rate on SBOUT is 192 kbps. SBOUT consists of three 64 kbps serial channels. Data bytes are transmitted MSB first.

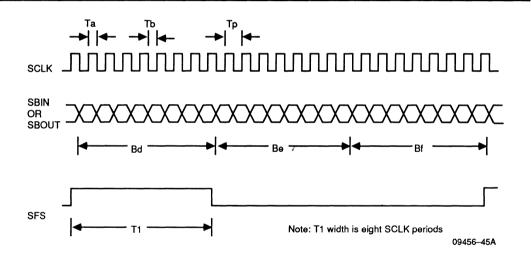

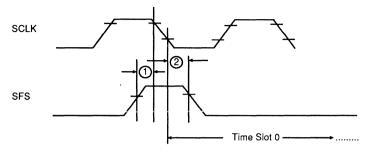

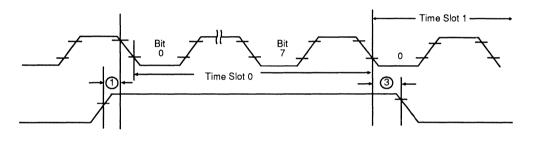

## SCLK

#### Serial Clock (Output)

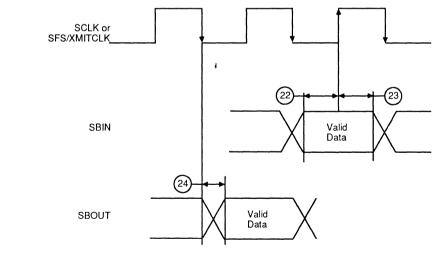

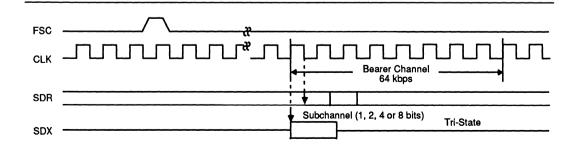

SCLK is a 192 kbps synchronization clock which defines the position of the serial bits in the SBOUT and SBIN channels. Data at the SBIN input must be valid on the rising edge of SCLK. The data on the SBOUT pin changes on the falling edge of SCLK. SCLK powers up tri-stated, and is enabled when a MUX connection is programmed.

#### SFS

## Serial Channel Frame Sync. (Output)

SFS is an 8 kHz signal which identifies the beginning of each frame by a low to high transition. The 192 kbps data stream on SBIN and SBOUT is referenced to SFS. SFS

powers up tri-stated, and is enabled when a MUX connection is programmed.

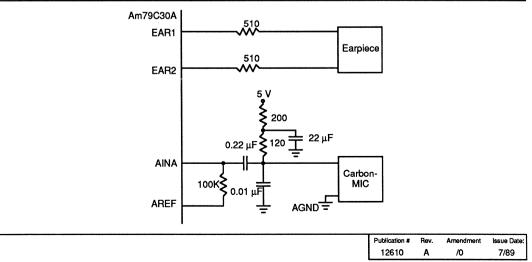

## Main Audio Processor (MAP)

All MAP pins are analog, and hence not TTL compatible.

#### AINA, AINB Analog (Inputs)

These analog inputs allow for two separate analog (audio) inputs to the transmit path of the codec/ filter. Input signals on either of these pins must be referenced to AREF.

## AREF

## Analog Reference (Output)

This is a nominal 2.4 V reference voltage output for biasing the analog inputs. Note that AREF is only available when the MAP is active.

#### CAP1, CAP2

#### Capacitor/Resistor (CAP1, Input; CAP2, Output)

An external resistor and capacitor are connected in series between these pins. These components are needed for the integrator in the Analog to Digital Converter (ADC).

#### EAR1, EAR2

#### Earpiece Interface (Differential Outputs)

EAR1 and EAR2 are the outputs from the receive path of the filter codec. These differential outputs can directly drive 600 ohms.

#### LS1, LS2

#### Loudspeaker Interface (Differential Outputs)

LS1 and LS2 are push-pull outputs which can directly drive a 50 ohm loudspeaker.

## **Microprocessor Interface (MPI)**

## A2-A0

#### Address Line (Inputs)

A2, A1, and A0 signals select source and destination registers for read and write operations on the data bus.

## CS

## Chip Select (Input)

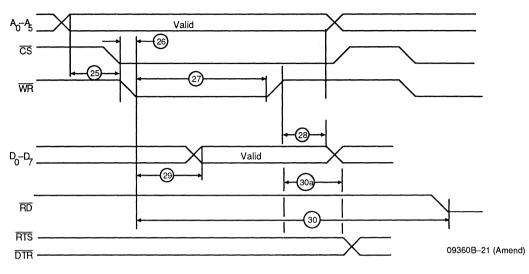

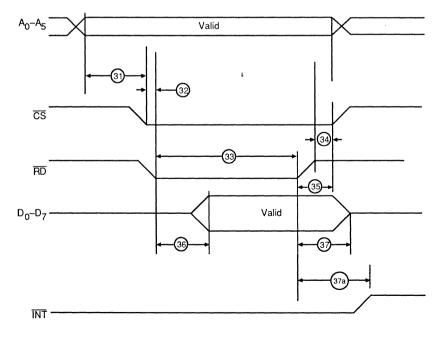

CS must be low to read or write to the Am79C30A/32A. Data transfer occurs over the bidirectional data lines (D7-D0).

#### D7-D0

#### Data Bus (Bidirectional with High Impedance State)

The eight bidirectional data bus lines are used to exchange information with the microprocessor. D0 is the least significant bit (LSB) and D7 is the most significant bit (MSB). A high on the data bus line corresponds to a logic '1' and low corresponds to a logic '0'. These lines act as inputs when both  $\overline{WR}$  and  $\overline{CS}$  are active and as outputs when both  $\overline{RD}$  and  $\overline{CS}$  are active. When  $\overline{CS}$  is inactive or both  $\overline{RD}$  and  $\overline{WR}$  are inactive, the D0-D7 pins are in a high impedance state.

## INT

## Interrupt (Output)

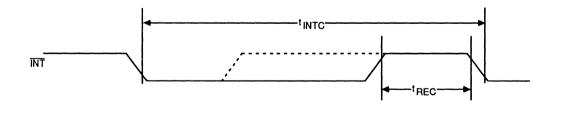

An active low output on the  $\overline{\text{INT}}$  pin informs the external microprocessor that the Am79C30A/32A needs interrupt service.  $\overline{\text{INT}}$  is updated once every 125 µs. The  $\overline{\text{INT}}$  pin remains active until the Interrupt Register (IR) is read or the Am79C30A/32A is reset.

## RESET

#### Reset (Input)

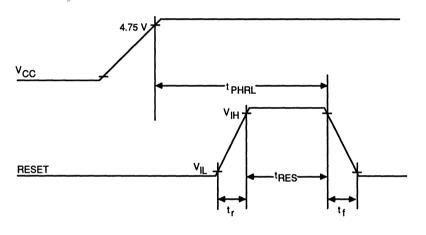

Reset is an active high signal which causes the Am79C30A/32A to immediately terminate its present activity and initialize to the reset condition. When reset returns low, the Am79C30A/32A enters the idle mode.

#### RD

#### Read (Input)

The active low read signal is conditioned by  $\overline{CS}$  and indicates that internal information is to be transferred onto the data bus. A number of internal registers are user accessible. The contents of the accessed register are transferred onto the data bus after the high to low transition of the  $\overline{RD}$  input.

#### WR

#### Write (Input)

The active low write signal is conditioned by  $\overline{CS}$  and indicates that external information on the data bus is to be transferred to an internal register. The contents of the data bus are loaded on the low to high transition of the WR input.

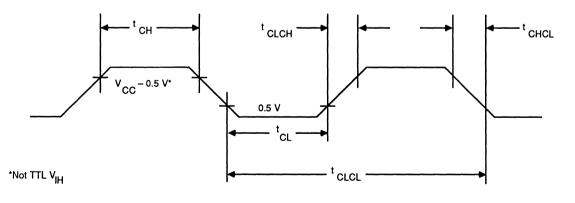

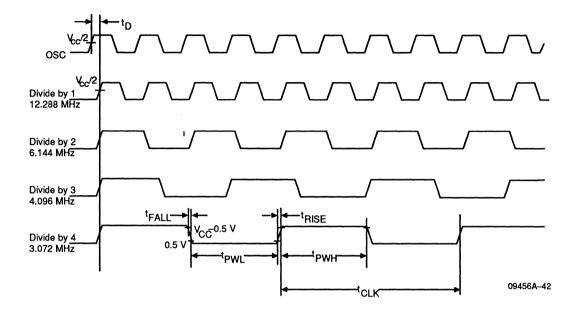

## **Oscillator (OSC)**

## MCLK

## Master Clock (Output)

The MCLK output is available for use as the system clock for the microprocessor. It is derived from the 12.288 MHz crystal via a programmable divider in the Am79C30A/32A which provides the following MCLK output frequencies: 12.288, 6.144, 4.096, and 3.072 MHz.

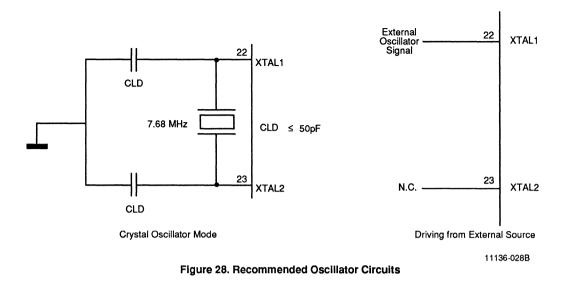

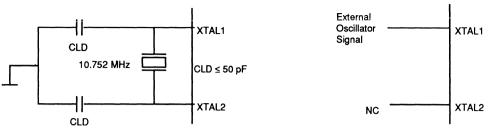

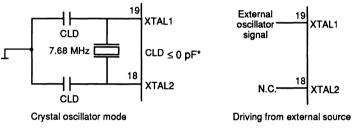

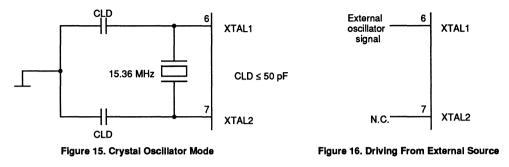

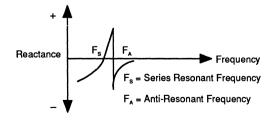

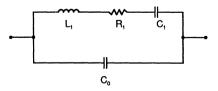

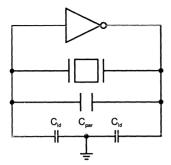

#### XTAL1, XTAL2 External Crystal (Output/Input)

XTAL1 and XTAL2 are connected to an external parallel resonant crystal for the on-chip oscillator. XTAL2 can also be connected to an external source instead of a crystal, in which case XTAL1 should be left disconnected. The frequency must be 12.288 MHz, ± 80 ppm.

## **Power Supply Pins**

#### PLCC Packages

- AVcc +5V analog power supply  $\pm 5\%$  (PLCC only)

- AVss Analog ground (PLCC only)

- DVss Digital ground (PLCC only)

- DVcc +5V digital power supply, ±5% (PLCC only)

#### **DIP Packages**

- Vcc +5V power supply, ±5% (DIP only)

- Vss Ground (DIP only)

Note: For best performance, decoupling capacitors should be installed between Vcc and Vss as close to the chip as possible. Do not use separate supplies for analog and digital power and ground connections.

## **OPERATIONAL DESCRIPTION**

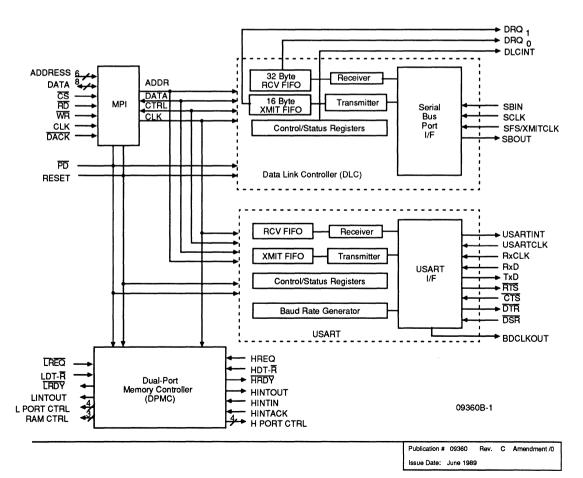

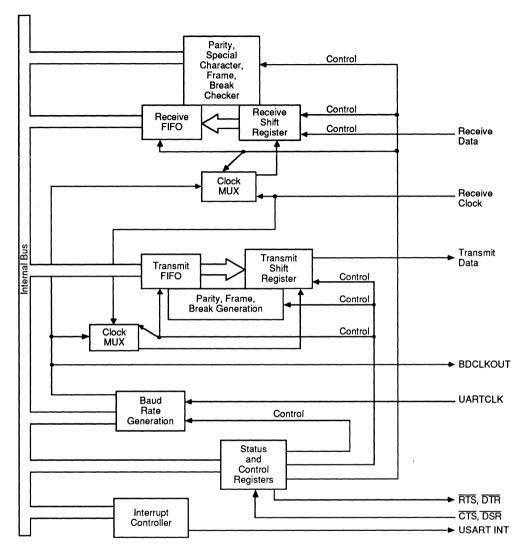

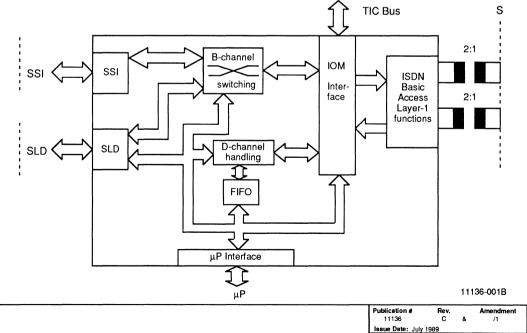

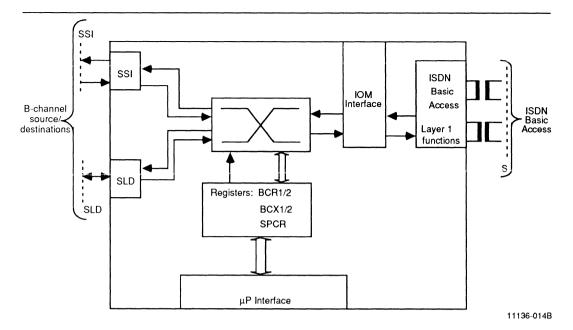

In order to specify the functions of the Am79C30A/32A, the device has been divided into blocks as shown in the block diagram. Each of the blocks listed below is defined separately in the Functional Description.

LIU Line Interface Unit

- MUX Multiplexer

- MAP Main Audio Processor (Am79C30A only)

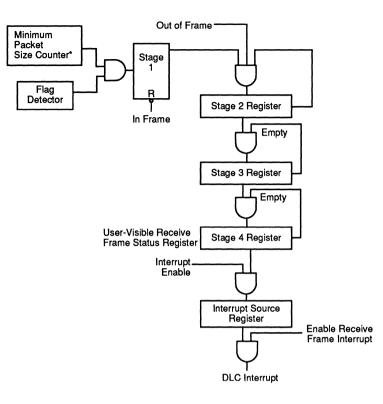

- DLC Data Link Controller

MPI Microprocessor Interface

OSC Oscillator and Timing Circuitry

#### User Accessible Registers/Buffers

The microprocessor interface is used to program and control the operation of the Am79C30A/32A. The following registers/buffers are user accessible in each of the blocks listed above and are described in the respective Functional Description Sections.

| Registers                                                                       | No. | Mnemonic    |

|---------------------------------------------------------------------------------|-----|-------------|

| Line Interface Unit (LIU)                                                       |     |             |

| LIU Status Register                                                             | 1   | LSR         |

| LIU Priority Register                                                           | 1   | LPR         |

| LIU Mode Registers                                                              | 2   | LMR         |

| Multiframe Register                                                             | 1   | MF          |

| Multiframe S-Bit/Status Buffer                                                  | 1   | MFSB        |

| Multiframe Q-Bit Buffer                                                         | 1   | MFQB        |

| Multiplexer (MUX)                                                               |     |             |

| MUX Control Registers                                                           | 4   | MCR         |

| Main Audio Processor (MAP)<br>(Am79C30A only)                                   |     |             |

| X Filter Coefficient Registers                                                  | 16  | ×           |

| R Filter Coefficient Registers                                                  | 16  | Ř           |

| GX Gain Coefficient Registers                                                   | 2   | H<br>GX     |

| GR Gain Coefficient Registers                                                   | 2   | GR          |

| GR Gain Coefficient Registers                                                   | 2   | GR          |

| Sidetone Gain Coefficient Registers                                             | 2   | STGR        |

| Frequency Tone Generator Registers                                              | 2   | FTGR        |

| Amplitude Tone Generator Registers                                              | 2   |             |

| MAP Mode Registers                                                              | 2   | ATGR<br>MMR |

| Data Link Controller (DLC)                                                      |     |             |

| . ,                                                                             |     | 5040        |

| First Received Byte Address Registers                                           | 4   | FRAR        |

| Second Received Byte Address Registers                                          | 4   | SRAR        |

| Transmit Address Register (16 bit)                                              | 1   | TAR         |

| D-channel Receive Byte Limit Register (16 bit)                                  | 1   | DRLR        |

| D-channel Receive Byte Count Register (16 bit) (2 byte FIFO)                    | 1   | DRCR        |

| D-channel Transmit Byte Count Register (16 bit)                                 | 1   | DTCR        |

| Random Number Generator Registers                                               | 2   | RNGR        |

| D-channel Mode Registers                                                        | 4   | DMR         |

| D-channel Status Registers                                                      | 2   | DSR         |

| Address Status Register (2 byte FIFO)<br>D-channel Error Register (2 byte FIFO) | 1   | ASR<br>DER  |

|                                                                                 | •   | DER         |

| Microprocessor Interface (MPI)                                                  |     |             |

| Initialization Register                                                         | 1   | INIT        |

| Command Register                                                                | 1   | CR          |

| Interrupt Register                                                              | 1   | IR          |

| Data Register                                                                   | 1   | DR          |

| D-channel Transmit Buffer (8 byte FIFO)                                         | 1   | DCTB        |

| D-channel Receive Buffer (8 byte FIFO)                                          | 1   | DCRB        |

| Bb Transmit Buffer                                                              | 1   | BBTB        |

| Bb Receive Buffer                                                               | 1   | BBRB        |

| Bc Transmit Buffer                                                              | 1   | BCTB        |

| Bc Receive Buffer                                                               | 1   | BCRB        |

| Note: See the Microprocessor Interface section for register add                 | !   |             |

Note: See the Microprocessor Interface section for register addressing.

#### Initialization

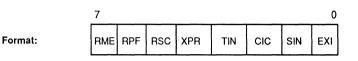

The initialization procedure is controlled via the Initialization Register (INIT) which is accessed by the microprocessor as defined in the Microprocessor Interface Initialization Register (INIT), Read/Write section. This Initialization Register (INIT) has the following format:

| Bit #      |   |   |   |   |   |   |   |                         |                             |

|------------|---|---|---|---|---|---|---|-------------------------|-----------------------------|

| <u>7 6</u> | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Control                 | Function                    |

| <b>x</b> > | x | х | х | х | х | 0 | 0 | Power Mode Selection    | Idle Mode (default)         |

| х >        | x | х | Х | Х | Х | 0 | 1 |                         | Active Mode (voice & data)  |

| х >        | x | х | Х | х | х | 1 | 0 |                         | Active Mode (Data only)     |

| х          | x | х | х | х | х | 1 | 1 |                         | Reserved                    |

| х )        | x | x | x | x | 0 | х | x | Interrupt Selection     | Enable INT pin (default)    |

| x          | x | X | X | X | 1 | x | X |                         | Disable INT pin             |

|            |   |   |   |   |   |   |   |                         |                             |

|            |   | 0 | 0 | 0 |   | X |   |                         | Divide by 2 (default)       |

|            |   | 0 | 0 | 1 | X | Х |   | Clock Divider Selection | Divide by 1                 |

|            |   | 0 | 1 | 0 | Х |   |   |                         | Divide by 4                 |

| X)         | X | 0 | 1 | 1 | Х | х | х |                         | Divide by 2                 |

| X >        | X | 1 | 0 | 0 | Х | Х | х |                         | Divide by 3                 |

| x )        | X | 1 | 0 | 1 | Х | Х | х |                         | Divide by 2                 |

| x )        | X | 1 | 1 | 0 | Х | Х | х |                         | Divide by 2                 |

| X          | x | 1 | 1 | 1 | Х | Х | х |                         | Divide by 2                 |

| X 1        | 1 | х | х | x | x | х | x | Abort Selection         | Receive abort               |

| XC         | Ď | X | X | X | X | X | X |                         | No Receive abort (default)  |

| 1 )        | x | X | X | x | X | X | X |                         | Transmit abort              |

| 0 3        |   |   |   |   | X | x | X |                         | No Transmit abort (default) |

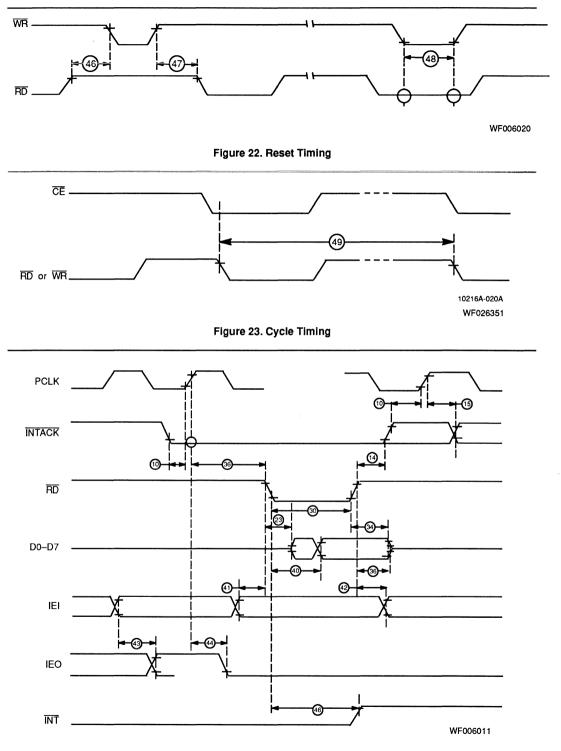

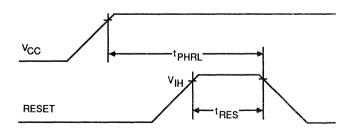

## Reset

The Am79C30A/32A can be reset by driving the reset pin high. When power is first supplied to the Am79C30A/32A, a reset must be asserted. This

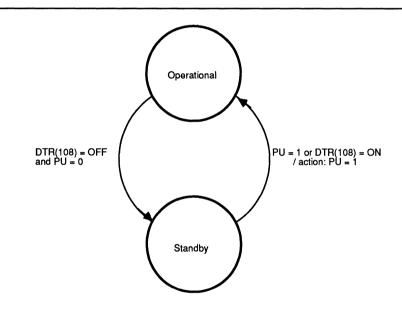

## **Idle Mode Operation**

To conserve power the Am79C30A/32A can be placed in the idle mode. This can be done by either asserting the RESET signal or by clearing bits 0 and 1 in the INIT initializes the Am79C30A/32A to its default values as defined in the subsequent sections. After reset, the Am79C30A/32A enters the idle mode.

register. When the Am79C30A/32A is in the idle mode, and there is no activity on any of the external interfaces, the state of the output pins are:

| Pin Name  | State following RESET | Idle Mode<br>High impedance                          |  |  |  |

|-----------|-----------------------|------------------------------------------------------|--|--|--|

| D7-D0     | High impedance        |                                                      |  |  |  |

| MCLK      | 6.144 MHz             | As programmed (see Initialization section)           |  |  |  |

| INT       | Logical '1'           | Logical '1' can be driven low by internal conditions |  |  |  |

|           |                       | explained below                                      |  |  |  |

| SBOUT     | High impedance        | High impedance                                       |  |  |  |

| SFS       | High impedance        | 8 kHz                                                |  |  |  |

| SCLK      | High impedance        | 192 kHz period                                       |  |  |  |

| LS1, LS2, |                       |                                                      |  |  |  |

| EAR1,     | High impedance        | High impedance                                       |  |  |  |

| EAR2,     |                       |                                                      |  |  |  |

| AREF      |                       |                                                      |  |  |  |

| LOUT1,    | High impedance        | High impedance                                       |  |  |  |

| LOUT2     |                       |                                                      |  |  |  |

SFS and SCLK will be high impedance after a reset, and will become active upon the first write to any MCR registers.

The minimum idle mode power consumption is met if bits 3 and 5 of the INIT register are set to a logical '0' and bit 4 is set to a logical '1', thus ensuring that the MCLK output is 3.072 MHz.

In the idle mode the MAP, SBP, MUX and DLC blocks are disabled and the OSC, MPI and LIU blocks are active. The programmed state of the Am79C30A/32A is maintained (hence the programmable registers retain their data) and the Am79C30A/32A can be programmed while in the idle mode. The DLC read only registers are reset. The microprocessor can access any of the Am79C30A/32A registers but the idle mode power consumption specification does not apply when the microprocessor is accessing the Am79C30A/32A.

If the receiver is enabled, the LIU responds automatically to activity when the Am79C30A/32A is in the idle mode. Thus, if the receiver is enabled and the LIU either detects activity on the 'S' interface or receives an activation request from the microprocessor, the LIU follows the CCITT activation procedure and interrupts the microprocessor when activation has been achieved. The default value of LIU Mode Register 1 bit 6 disables the receiver. The Am79C30A/32A idle mode can be terminated in the following three ways:

- When the LIU achieves activation on the 'S' interface, the Am79C30A/32A interrupts the microprocessor (depending on the programmed state of the Am79C30A/32A's LIU Mode Register 1). This interrupt "wakes up" the microprocessor if it is in its idle mode. The microprocessor then programs the Am79C30A/32A to the proper mode via bits 0 and 1 in the INIT register. (See LIU section.)

- 2) The Am79C30A/32A has a hookswitch (HSW) detector with debounce circuitry to accommodate the requirements of a mechanical switch. When the HSW changes state, an interrupt is generated to the microprocessor if the HSW interrupt is enabled. The microprocessor can then read the status of the

HSW via the LIU Status Register and power-up the Am79C30A/32A as required.

At any time, the microprocessor can terminate the idle mode by writing to bit 0 and bit 1 of the INIT Register.

## **MCLK Options**

Upon reset the Am79C30A/32A crystal frequency of 12.288 MHz is divided by two and output as the MCLK. The microprocessor can alter this output frequency through the INIT register as per its timing requirements. It should be noted that the MCLK is never stopped. The frequencies available at the MCLK output pin are:

- 1) 12.288 MHz (divide by 1)

- 2) 6.144 MHz (divide by 2)

- 3) 4.096 MHz (divide by 3)

- 4) 3.072 MHz (divide by 4)

#### **Receive and Transmit Abort Commands**

The microprocessor has the option via INIT register bits 6 and 7 to abort the receive and transmit D-channel packets. When the microprocessor sets one of these bits, the Am79C30A/32A aborts the respective operation. The frame abort sequence is defined in greater detail later. (See Data Link Controller section.)

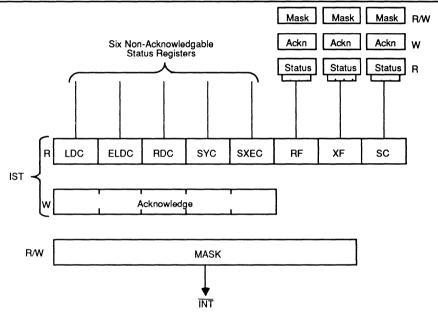

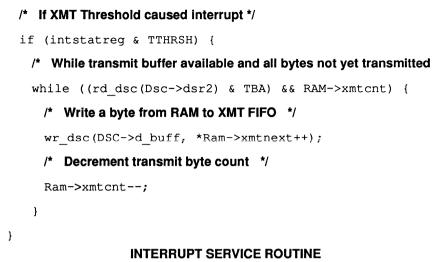

#### **Interrupt Handling**

The Am79C30A/32A generates either no interrupt or only one interrupt every 125  $\mu$ sec. Once asserted, INT remains active until the microprocessor responds by interrogating the Am79C30A/32A's Interrupt Register. Reading the Interrupt Register in response to an activated INT pin deactivates the INT pin, and clears the interrupt register.

If an interrupt causing event occurs while the Interrupt Register (IR) is being read by the microprocessor, the effect of the event is held until the microprocessor has completed it's read cycle. A reset clears all interrupt causing conditions.

The INT pin remains active until the Interrupt Register is read or reset is driven active. The Interrupt Register is cleared by reading the Interrupt Register, or by reset.

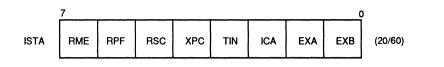

## Interrupt Register (IR), Read Only

The Interrupt Register has the following format:

| Bit | Interrupt ge    | nerated/action required                                            | Interrupt Mask |

|-----|-----------------|--------------------------------------------------------------------|----------------|

| 0   | D-channel trar  | DMR1 bit 0                                                         |                |

| 1   | D-channel rec   | eive threshold interrupt/read D-channel Receive Buffer             | DMR1 bit 1     |

| 2   | D-channel sta   | tus interrupt/read DSR1                                            |                |

|     | Source          | Cause                                                              |                |

|     | DSR1 bit 0      | Valid Address (VA) or End of Address (EOA)                         | DMR3 bit 0     |

|     | DSR1 bit 1      | When a closing flag is received or a receive error occurs          | DMR1 bit 3     |

|     | DSR1 bit 6      | When a closing flag is transmitted                                 | DMR3 bit 1     |

| 3   | D-channel erro  | or interrupt/read DER and DSR2 bit 2                               |                |

|     | Source          | Cause                                                              |                |

|     | DER bit 0       | Current received packet has been aborted                           | DMR2 bit 0     |

|     | DER bit 1       | Non-integral number of bytes received                              | DMR2 bit 1     |

|     | DER bit 2       | Collision abort detected                                           | DMR2 bit 2     |

|     | DER bit 3       | FCS error                                                          | DMR2 bit 3     |

|     | DER bit 4       | Overflow error                                                     | DMR2 bit 4     |

|     | DER bit 5       | Underflow error                                                    | DMR2 bit 5     |

|     | DER bit 6       | Overrun error                                                      | DMR2 bit 6     |

|     | DER bit 7       | Underrun error                                                     | DMR2 bit 7     |

|     | DSR2 bit 2      | Receive packet lost                                                | DMR3 bit 6     |

| 4   | Bb or Bc byte   | available or buffer empty interrupt/read or write Bb or Bc buffers | MCR4 bit 3     |

| 5   | LIU status inte | errupt/read LSR                                                    |                |

|     | Source          | Cause                                                              |                |

|     | LSR bit 3       | Change of state to F3                                              | LMR2 bit 3     |

|     | LSR bit 4       | Change of state from/to F7                                         | LMR2 bit 6     |

|     | LSR bit 5       | Change of state from/to F8                                         | LMR2 bit 4     |

|     | LSR bit 7       | HSW change of state                                                | LMR2 bit 5     |

| 6   | D-Channel sta   | tus interrupt/read DSR2                                            |                |

|     | Source          | Cause                                                              |                |

|     | DSR2 bit 0      | Last byte of received packet                                       | DMR3 bit 2     |

|     | DSR2 bit 1      | Receive byte available                                             | DMR3 bit 3     |

|     | DSR2 bit 3      | Last byte transmitted                                              | DMR3 bit 4     |

|     | DSR2 bit 4      | Transmit buffer available                                          | DMR3 bit 5     |

| 7   | Multiframe inte | errupt/read MFSB                                                   |                |

|     | Source          | Cause                                                              |                |

|     | MFSB bit 5      | S-data available                                                   | MF bit 1       |

|     | MFSB bit 6      | Q-bit buffer empty                                                 | MF bit 2       |

|     | MFSB bit 7      | Multiframe change of state (In/Out of sync.)                       | MF bit 3       |

Bits 0, 1 and 4 of the IR, if set, advise the microprocessor that the respective buffer is ready for reading or writing. If bit 0 is set due to an empty buffer, the D-Channel Transmit Buffer must be serviced within 375 us. If bit 1 is set and the D-Channel Receive Buffer is full, the buffer must be serviced within 425 µs. This is to prevent erroneous data transfers causing transmitter underrun and receiver overrun errors. If bit 4 is set then the Bb or Bc buffers must be accessed within 122.4 µs. This is to prevent erroneous data transfers. Only one interrupt is used to signal accessibility for both B-channels of the 'S' interface. Since the data transfer must occur synchronously to the 'S' interface, any data access to either Bb or Bc or both must be made within the 122.4 µs limit. Note: even though only a single interrupt is issued, either or both 'S' interface B-channels must be serviced.

IR bits 2, 3, 5, 6, and 7, if set, indicate that a bit has been set in the associated status or error register. All of the interrupts generated by the Am79C30A/32A can be individually disabled.

DMR1, DMR2, DMR3, LMR2, MCR4, and MF control the mask conditions which affect the INT pin. The INT pin is activated only by interrupts which are not disabled and the Interrupt Register reflects the status of enabled interrupts. The INT pin can be disabled by setting INIT register bit 2 to a logical '1'.

The Am79C30A/32A has facilities that allow the microprocessor to read the status registers (status update is inhibited during status read) or the IR at any time during functional operation.

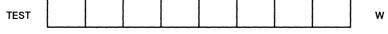

#### **Test Facilities**

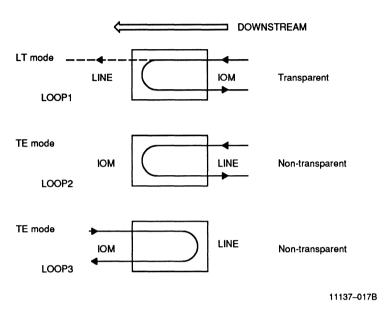

The Am79C30A/32A provides three types of test facilities:

- The ability to suppress the framing signals from the Am79C30A/32A to the network termination. This simulates a loss of synchronization and is programmed into LMR1 bits 2 and 3.

- 2) Three types of D-channel loopbacks, two on the 'S' interface for maintenance purposes and one on the microprocessor interface for local testing. Normally, the Am79C30A/32A compares its transmitted Dchannel bits to its received E-channel bits. Any difference is interpreted as an error condition which halts transmission. However, in these loopbacks, the Am79C30A/32A ignores any such difference,

thereby allowing transmission to proceed. These loopback test modes are selected via LMR2 bits 0,1 and 2. See LIU Registers section for more details.

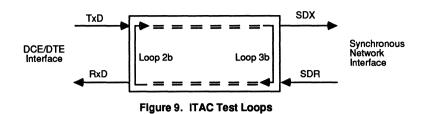

3) Two MAP loopbacks, one analog and one digital. The analog loopback enables an analog signal to be sent in on AINA or AINB and out on EAR1/EAR2 or LS1/LS2. This loopback is selected by connecting Ba to Ba in the multiplexer. The digital loopback tests the digital portion of the MAP by routing the data from the MUX through to the interpolator and then feeding it into the decimator. The ADC and DAC are disconnected from the loopback path. This loopback is selected by setting bit 7 of MMR1 to a logical '1' (See Figure 9).

## FUNCTIONAL DESCRIPTION

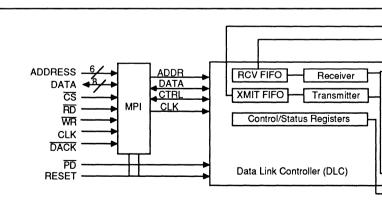

## **Microprocessor Interface (MPI)**

The Am79C30A/32A can be connected to any general purpose 8-bit microprocessor via the MPI. The MCLK from the Am79C30A/32A can be used as the clock for the microprocessor. The MPI is an interrupt driven interface containing all the circuitry necessary for access to the internal programmable registers, status registers, coefficient RAM, and transmit/receive buffers.

## **MPI External Interface**

The MPI has the following external connections:

| Name         | Direction     | Function       |

|--------------|---------------|----------------|

| D7-D0        | Bidirectional | Data Bus       |

| A2, A1, & A0 | Inputs        | Address Line   |

| RD           | Input         | Read enable    |

| WR           | Input         | Write enable   |

| CS           | Input         | Chip Select    |

| RESET        | Input         | Initialization |

| INT          | Output        | Interrupt      |

## **Register Selection**

#### **Directly Accessed Registers/Buffers**

| Register                                                                                                                                                                                                                                                                                                                                | Mnemonic |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Command Register<br>Interrupt Register<br>Data Register<br>D-channel Status Register 1<br>D-channel Error Register (2 byte FIFO)<br>D-channel Transmit Buffer (8 byte FIFO<br>D-channel Receive Buffer (8 byte FIFO<br>Bb Transmit Buffer<br>Bb Receive Buffer<br>Bc Receive Buffer<br>Bc Receive Buffer<br>D-channel Status Register 2 | ) DCTB   |

|                                                                                                                                                                                                                                                                                                                                         |          |

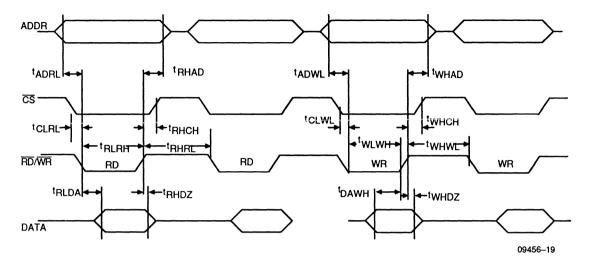

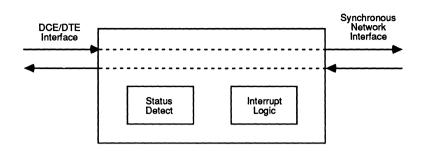

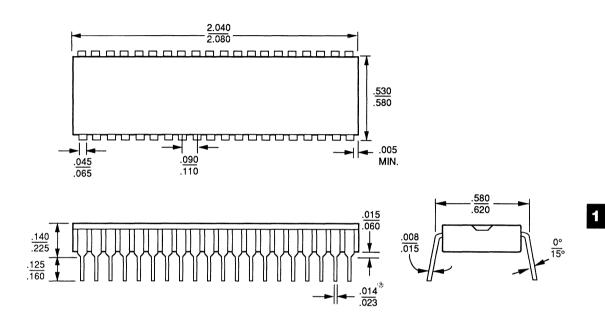

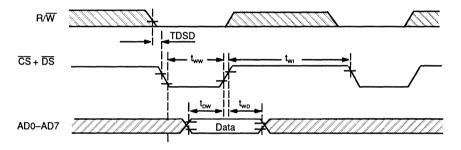

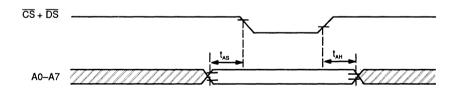

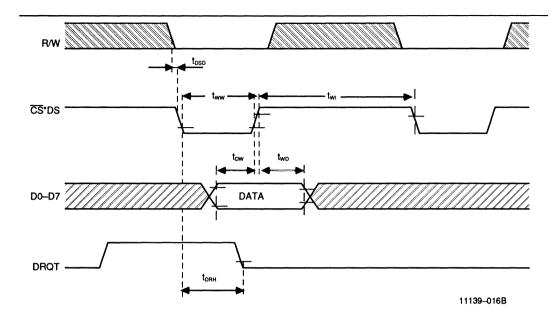

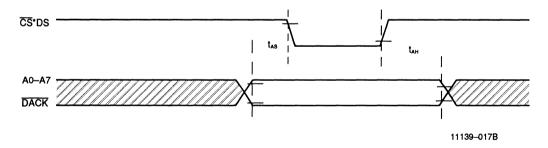

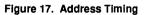

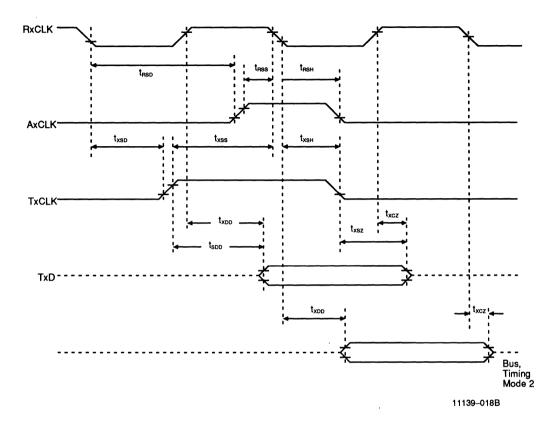

The 8-bit bidirectional data bus (D7-D0) is used to communicate with these registers. The selection of which register(s) is (are) accessed is controlled by the  $\overline{CS}$ ,  $\overline{RD}$ ,  $\overline{WR}$ , A2, A1, and A0 signals from the microprocessor to the Am79C30A/32A in the following manner (see Figure 4):

| CS | RD | WR | A2 | A1 | A0 | Register(s) Accessed                                       |

|----|----|----|----|----|----|------------------------------------------------------------|

| 0  | 1  | 0  | 0  | 0  | 0  | Command Register (CR), write only                          |

| 0  | 0  | 1  | 0  | 0  | 0  | Interrupt Register (IR), read only                         |

| 0  | 1  | 0  | 0  | 0  | 1  | Data Register (DR), write only                             |

| 0  | 0  | 1  | 0  | 0  | 1  | Data Register (DR), read only                              |

| 0  | 0  | 1  | 0  | 1  | 0  | D-channel Status Register 1 (DSR1), read only              |

| 0  | 0  | 1  | 0  | 1  | 1  | D-channel Error Register (DER), read only (2 byte FIFO)    |

| 0  | 1  | 0  | 1  | 0  | 0  | D-channel Transmit Buffer (DCTB), write only (8 byte FIFO) |

| 0  | 0  | 1  | 1  | 0  | 0  | D-channel Receive Buffer (DCRB), read only (8 byte FIFO)   |

| 0  | 1  | 0  | 1  | 0  | 1  | Bb channel Transmit Buffer (BBTB) write only               |

| 0  | 0  | 1  | 1  | 0  | 1  | Bb channel Receive Buffer (BBRB), read only                |

| 0  | 1  | 0  | 1  | 1  | 0  | Bc channel Transmit Buffer (BCTB), write only              |

| 0  | 0  | 1  | 1  | 1  | 0  | Bc channel Receive Buffer (BCRB), read only                |

| 0  | 0  | 1  | 1  | 1  | 1  | D-channel Status Register 2 (DSR2), read only              |

| 1  | х  | х  | х  | х  | х  | No access (X = logical '0' or '1')                         |

Note: The RD and WR signals must never both be low under normal operating conditions.

#### Indirectly Accessed Registers

To read from or write to any of the indirect data registers a command is first written to the Command Register (CR). Depending on the command, one (or more) data byte(s) is then transferred to or from the selected register(s) as follows:

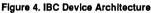

Figure 4. MPI Block Diagram

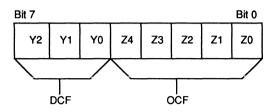

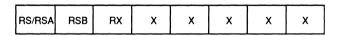

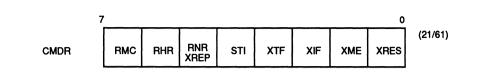

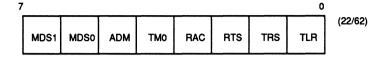

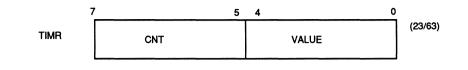

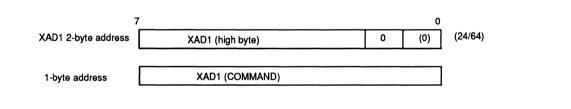

#### Command Register (CR), Write only

The Command Register (CR) is used to hold the index for the indirectly accessed registers. The CR is one byte wide and divided into two fields, the destination code field (DCF) and the operational code field (OCF):

The 'Y' bits in the DCF determine to which block the OCF is related. The 'Y' bits are defined below:

| Am79C30A/32A block  | Y2 | Y1 | YO |  |

|---------------------|----|----|----|--|

| RESERVED            | 0  | 0  | 0  |  |

| INIT                | 0  | 0  | 1  |  |

| MUX                 | 0  | 1  | 0  |  |

| MAP (Am79C30A only) | 0  | 1  | 1  |  |

| DLC                 | 1  | 0  | 0  |  |

| LIU                 | 1  | 0  | 1  |  |

| RESERVED            | 1  | 1  | 0  |  |

| RESERVED            | 1  | 1  | 1  |  |

The 'Z' bits of the OCF contain the operation code used to address a specific register within a DCF block. For each DCF there is a different set of OCFs. Each of the OCFs and their associated data registers are defined in the following sections. When the OCF indicates a read or write operation is possible, then the appropriate access is achieved by asserting either the read or write signals to the Am79C30A/32A.

Registers within certain groups can be quickly accessed by using internal circuitry which automatically increments the indirect address (index value) contained in the OCF. The CR is first loaded with the index value, then the data bytes are transferred in sequence between the Am79C30A/32A and the microprocessor via the DR. For example, operation number 5 in the MPI-LIU definition allows operations 2 to 4 to be performed sequentially without reloading the CR. Whenever the CR register is loaded, any previous commands are automatically terminated.

In the following tables the "bytes transferred" numbers next to the OCFs are the number of bytes which are read or written to the DR after the CR has been loaded.

#### **MPI-INIT** Definition

The INIT register is used by the microprocessor to select the MCLK output frequency and the power-up/idle

states of the Am79C30A/32A. This register is accessed via the 'Z' bits in the CR as follows:

| •                             |    |    | oc | F         |           |                      |

|-------------------------------|----|----|----|-----------|-----------|----------------------|

| INIT OPERATION<br>(DCF = 001) | Z4 | Z3 | Z2 | <b>Z1</b> | <b>Z0</b> | Bytes<br>Transferred |

| R/W INIT register             | 0  | 0  | 0  | 0         | 1         | 1                    |

#### **MPI-LIU Definition**

The LIU contains the following registers:

| LIU Registers           | No. | Mnemonic   |

|-------------------------|-----|------------|

| LIU Status Register     | 1   | LSR        |

| LIU Priority            | 1   | LPR        |

| LIU Mode Registers      | 2   | LMR1, LMR2 |

| Multiframe Register     | 1   | MF         |

| Multiframe S-bit Buffer | 1   | MFSB       |

| Multiframe Q-bit Buffer | 1   | MFQB       |

These registers are accessed via the 'Z' bits in the CR as follows:

|                              |           |    | oci | F          |           |                      |

|------------------------------|-----------|----|-----|------------|-----------|----------------------|

| LIU OPERATION<br>(DCF = 101) | <b>Z4</b> | Z3 | Z2  | <b>Z</b> 1 | <b>Z0</b> | Bytes<br>Transferred |

| 1. Read LSR                  | 0         | 0  | 0   | 0          | 1         | 1                    |

| 2. R/W LPR                   | 0         | 0  | 0   | 1          | 0         | 1                    |

| 3. R/W LMR1                  | 0         | 0  | 0   | 1          | 1         | 1                    |

| 4. R/W LMR2                  | 0         | 0  | 1   | 0          | 0         | 1                    |

| 5. Perform<br>Operations 2-4 | 0         | 0  | 1   | 0          | 1         | 3                    |

| 6. Read/Write MF             | 0         | 0  | 1   | 1          | 0         | 1                    |

| <ol><li>Read MFSB</li></ol>  | 0         | 0  | 1   | 1          | 1         | 1                    |

| 8. Write MFQB                | 0         | 1  | 0   | 0          | 0         | 1                    |

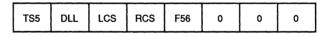

#### **MPI-MUX** Definition

The MUX contains four microprocessor read/write control registers MCR1, MCR2, MCR3, and MCR4. These registers are accessed via the 'Z' bits in the CR as follows:

|                              |    |    | oc | F  |           |                      |

|------------------------------|----|----|----|----|-----------|----------------------|

| MUX OPERATION<br>(DCF = 010) | Z4 | Z3 | Z2 | Z1 | <b>Z0</b> | Bytes<br>Transferred |

| 1. R/W MCR1                  | 0  | 0  | 0  | 0  | 1         | 1                    |

| 2. R/W MCR2                  | 0  | 0  | 0  | 1  | 0         | 1                    |

| 3. R/W MCR3                  | 0  | 0  | 0  | 1  | 1         | 1                    |

| 4. R/W MCR4                  | 0  | 0  | 1  | 0  | 0         | 1                    |

| 5. Perform<br>Operations 1-4 | 0  | 0  | 1  | 0  | 1         | 4                    |

When more than one byte is being transferred due to OCF command 5, MCR1 is always accessed first, followed by MCR2, then MCR3, and finally MCR4.

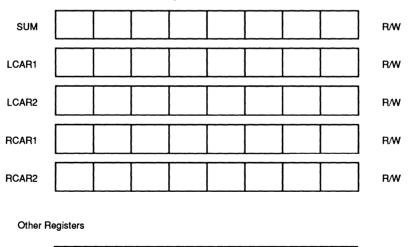

## MPI-MAP Definition (Am79C30A only)

The MAP registers are:

| MAP Registers                       | No. | Mnemonic |  |

|-------------------------------------|-----|----------|--|

| X Filter Coefficient Registers      | 16  | X        |  |

| R Filter Coefficient Registers      | 16  | R        |  |

| GX Gain Coefficient Registers       | 2   | GX       |  |

| GR Gain Coefficient Registers       | 2   | GR       |  |

| GER Gain Coefficient Registers      | 2   | GER      |  |

| Sidetone Gain Coefficient Registers | 2   | STGR     |  |

| Frequency Tone Generator Registers  | 2   | FTGR     |  |

| Amplitude Tone Generator Registers  | 2   | ATGR     |  |

| MAP Mode Registers                  | 2   | MMR      |  |

These registers are accessed via the OCF 'Z' bits in the CR.

|                                           |    |    | OCF |           |            | Bytes       |

|-------------------------------------------|----|----|-----|-----------|------------|-------------|

| MAP OPERATION (DCF = 011)                 | Z4 | Z3 | Z2  | <b>Z1</b> | <b>Z</b> 0 | Transferred |

| 1. R/W X Filter Coefficients              | 0  | 0  | 0   | 0         | 1          | 16          |

| 2. R/W R Filter Coefficients              | 0  | 0  | 0   | 1         | 0          | 16          |

| 3. R/W GX Gain Coefficients               | 0  | 0  | 0   | 1         | 1          | 2           |

| 4. R/W GR Gain Coefficients               | 0  | 0  | 1   | 0         | 0          | 2           |

| 5. R/W GER Gain Coefficients              | 0  | 0  | 1   | 0         | 1          | 2           |

| <ol><li>R/W STG Coefficients</li></ol>    | 0  | 0  | 1   | 1         | 0          | 2           |

| 7. R/W FTGR1 & FTGR2                      | 0  | 0  | 1   | 1         | 1          | 2           |

| <ol> <li>B/W ATGR1 &amp; ATGR2</li> </ol> | 0  | 1  | 0   | 0         | 0          | 2           |

| 9. R/W MMR1                               | 0  | 1  | 0   | 0         | 1          | 1           |

| 10. R/W MMR2                              | 0  | 1  | 0   | 1         | 0          | 1           |

| 11. Perform Operations 1-10               | 0  | 1  | 0   | 1         | 1          | 46          |

## **MPI-DLC Definition**

The indirectly accessible DLC registers are:

| Registers                                                    | No. | Mnemonic |

|--------------------------------------------------------------|-----|----------|

| First Received Byte Address Registers                        | 4   | FBAR     |

| Second Received Byte Address Registers                       | 4   | SRAR     |

| Transmit Address Register (16 bit)                           | 1   | TAR      |

| D-channel Receive Byte Limit Register (16 bit)               | 1   | DRLR     |

| D-channel Receive Byte Count Register (16 bit) (2 word FIFO) | 1   | DRCR     |

| D-channel Transmit Byte Count Register (16 bit)              | 1   | DTCR     |

| Random Number Generator Registers                            | 2   | RNGR     |

| D-channel Mode Registers                                     | 4   | DMR      |

| Address Status Register (2 byte FIFO)                        | 1   | ASR      |

v

| DLC OPERATION (DCF = 100)    | <b>Z</b> 4 | <b>Z</b> 3 | OCF<br>Z2 | Z1 | <b>Z</b> 0 | Bytes<br>Transferred |

|------------------------------|------------|------------|-----------|----|------------|----------------------|

| 1. R/W FRAR1, 2 & 3          | 0          | 0          | 0         | 0  | 1          | 3                    |

| 2. R/W SRAR1, 2 & 3          | 0          | 0          | 0         | 1  | 0          | 3                    |

| 3. R/W TAR                   | 0          | 0          | 0         | 1  | 1          | 2                    |

| 4. R/W DRLR                  | 0          | 0          | 1         | 0  | 0          | 2                    |

| 5. R/W DTCR                  | 0          | 0          | 1         | 0  | 1          | 2                    |

| 6. R/W DMR1                  | 0          | 0          | 1         | 1  | 0          | 1                    |

| 7. R/W DMR2                  | 0          | 0          | 1         | 1  | 1          | 1                    |

| 8. Perform Operations 1-7    | 0          | 1          | 0         | 0  | 0          | 14                   |

| 9. Read DRCR                 | 0          | 1          | 0         | 0  | 1          | 2                    |

| 10. R/W RNGR1                | 0          | 1          | 0         | 1  | 0          | 1                    |

| 11. R/W RNGR2                | 0          | 1          | 0         | 1  | 1          | 1                    |

| 12. R/W FRAR4                | 0          | 1          | 1         | 0  | 0          | 1                    |

| 13. R/W SRAR4                | 0          | 1          | 1         | 0  | 1          | 1                    |

| 14. R/W DMR3                 | 0          | 1          | 1         | 1  | 0          | 1                    |

| 15. R/W DMR4                 | 0          | 1          | 1         | 1  | 1          | 1                    |

| 16. Perform Operations 12-15 | 1          | 0          | 0         | 0  | 0          | 4                    |

| 17. Read ASR                 | 1          | 0          | 0         | 0  | 1          | 1                    |

| Block<br>Accessed | Opera-<br>tion# | Register<br>Name | Y & Z HEX<br>Coding | Byte<br>Sequence         |

|-------------------|-----------------|------------------|---------------------|--------------------------|

| MPI-INIT          | 1               | INIT             | 21                  | One byte transferred     |

| MPI-LIU           | 1               | LSR              | A1                  | One byte transferred     |

|                   | 2               | LPR              | A2                  | One byte transferred     |

|                   | 3               | LMR1             | A3                  | One byte transferred     |

|                   | 4               | LMR2             | A4                  | One byte transferred     |

|                   | 5               | Perform 2-4      | A5                  | LPR, LMR1, LMR2          |

|                   | 6               | MF               | A6                  | One byte transferred     |

|                   | 7               | MFSB             | A7                  | One byte transferred     |

|                   | 8               | MFQB             | A8                  | One byte transferred     |

| MPI-MUX           | 1               | MCR1             | 41                  | One byte transferred     |

|                   | 2               | MCR2             | 42                  | One byte transferred     |

|                   | 3               | MCR3             | 43                  | One byte transferred     |

|                   | 4               | MCR4             | 44                  | One byte transferred     |

|                   | 5               | Perform 1-4      | 45                  | MCR1, MCR2, MCR3, MCR4   |

| MPI-MAP           | 1               | X Coeff.         | 61                  | h0 LSB,h0 MSBh7 MSB      |

| (see Fig. 9)      | 2               | R Coeff.         | 62                  | h0 LSB,h0 MSBh7 MSB      |

|                   | 3               | GX Coeff.        | 63                  | LSB, MSB                 |

|                   | 4               | GR Coeff.        | 64                  | LSB, MSB                 |

|                   | 5               | GER Coeff.       | 65                  | LSB, MSB                 |

|                   | 6               | STG Coeff.       | 66                  | LSB, MSB                 |

|                   | 7               | FTGR1, FTGR2     | 67                  | FTRG1, FTGR2             |

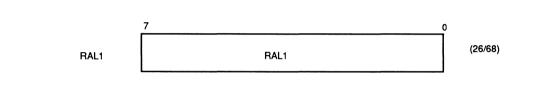

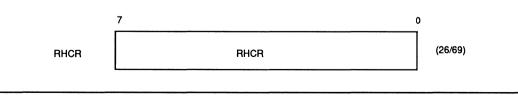

|                   | 8               | ATGR1, ATGR2     | 68                  | ATGR1, ATGR2             |

| *                 | 9               | MMR1             | 69                  | One byte transferred     |

|                   | 10              | MMR2             | 6A                  | One byte transferred     |

|                   | 11              | Perform 1-10     | 6B                  | 46 bytes loaded 1-10     |

| MPI-DLC           | 1               | FRAR1, 2 & 3     | 81                  | FRAR1, FRAR2, FRAR3      |

|                   | 2               | SRAR1, 2 & 3     | 82                  | SRAR1, SRAR2, SRAR3      |

|                   | 3               | TAR              | 83                  | LSB, MSB                 |

|                   | 4               | DRLR             | 84                  | LSB, MSB                 |

|                   | 5               | DTCR             | 85                  | LSB, MSB                 |

|                   | 6               | DMR1             | 86                  | One byte transferred     |

|                   | 7               | DMR2             | 87                  | One byte transferred     |

|                   | 8               | Perform 1-7      | 88                  | 14 bytes loaded 1-7      |

|                   | 9               | DRCR             | 89                  | LSB, MSB                 |

|                   | 10              | RNGR1 (LSB)      | 8A                  | One byte transferred     |

|                   | 11              | RNGR2 (MSB)      | 8B                  | One byte transferred     |

|                   | 12              | FRAR4            | 8C                  | One byte transferred     |

|                   | 13              | SRAR4            | 8D                  | One byte transferred     |

|                   | 14              | DMR3             | 8E                  | One byte transferred     |

|                   | 15              | DMR4             | 8F                  | One byte transferred     |

|                   | 16              | Perform 12-15    | 90                  | FRAR4, SRAR4, DMR3, DMR4 |

|                   | 10              | ASR              | 91                  | One byte transferred     |

## **Microprocessor Access Guide for Indirect Registers**

\*Note: LSB=Least Significant Byte; MSB=Most Significant Byte

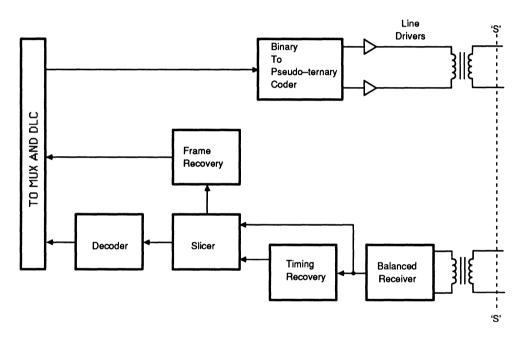

## Line Interface Unit (LIU)

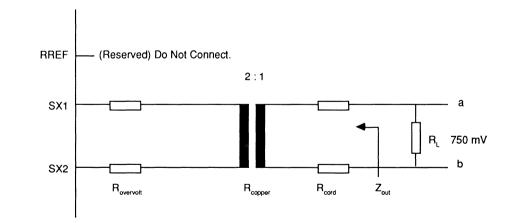

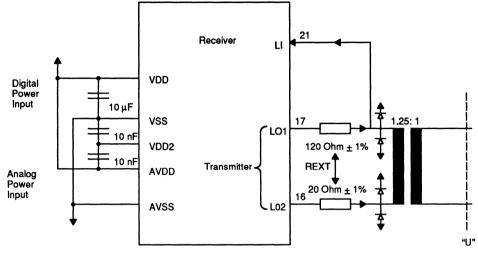

The LIU connects to the four wire 'S' interface through a pair of isolation transformers, one for the transmit and one for the receive direction, as shown in Figure 5.

The receiver section of the LIU consists of a differential receiver, circuitry for bit timing recovery, circuitry for detecting high marks and low marks, and a frame recovery circuit for frame synchronization. The receiver converts the received pseudo-ternary coded signals to binary before delivering them to the other blocks of the Am79C30A/32A. It also performs collision detection (E

and D bit comparison) per the CCITT recommendations so that several TEs can be connected to the same 'S' interface.

The transmitter consists of a binary to pseudo-ternary encoder and a differential line driver which meets the CCITT recommendations for the 'S' interface.

The Am79C30A/32A can establish multiframe synchronization, receive S-bits, and transmit Q-bits synchronized to the received frame.

09456A--3

Figure 5. LIU Block Diagram

## **External Interface**

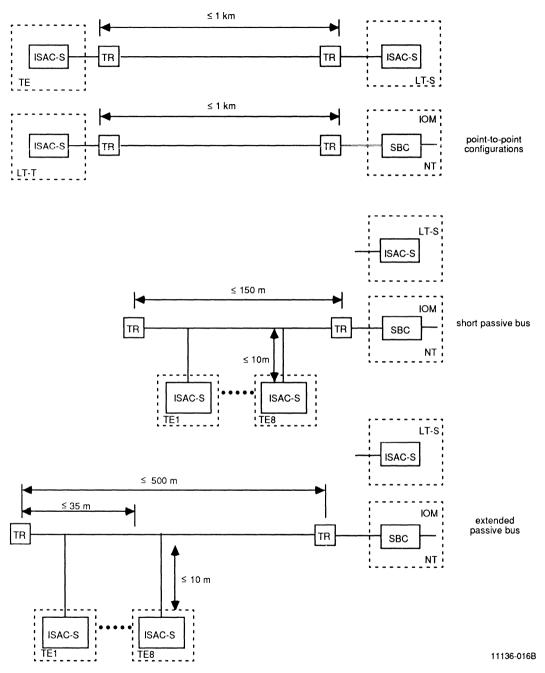

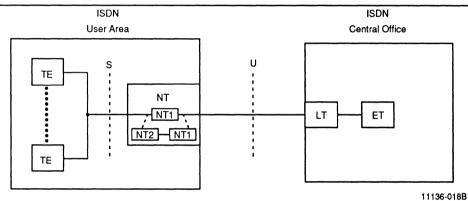

The LIU can be connected to both point-to-point and point-to-multipoint configurations at the CCITT 'S' reference point. The point-to-point configuration consists of one TE connected to the NT or PABX line card. The point-to-multipoint configuration can have multiple TEs connected to one NT.

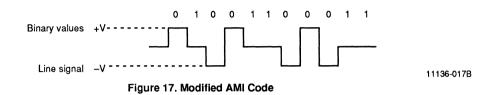

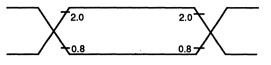

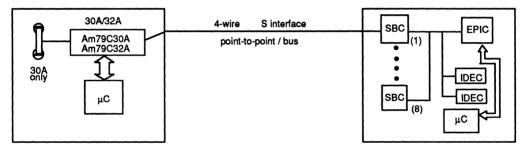

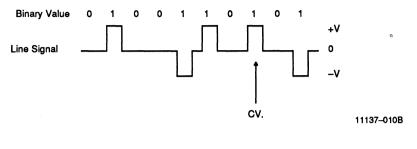

## Line Code

Pseudo-ternary coding is used for both transmitting and receiving over the 'S' interface. In this type of coding, a binary '1' is represented by a space (zero voltage) and a binary '0' is represented by a high mark or a low mark. Two consecutive binary '0's are represented by alternate marks to reduce DC offset on the line. A mark followed, either immediately or separated by spaces, by a mark of the same polarity, is defined as a code violation. Code violations are used to identify the boundaries of the frame.

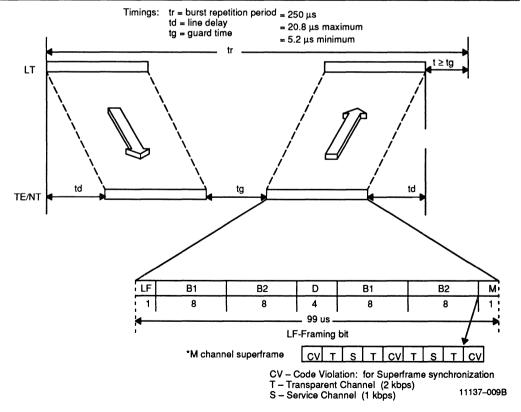

## Frame Structures

In both transmit and receive directions, the bits are grouped into frames of 48 bits each. The frame structure is identical for both point-to-point and point-to-multipoint configurations. Each frame transmitted, at 4 kHz, consists of several groups of bits.

## Multiframing

If multiframing is enabled, the Am79C30A/32A recognizes and establishes multiframe synchronization based on the monitoring of the FA- (Q-bit control) and M- (M-bit control) bits. The Am79C30A/32A also receives and compiles S-bits, and transmits Q-bits synchronized to the received frame.

# Establishment of Multiframe Synchronization

When the 'enable multiframe synchronization' bit (bit 0 of the Multiframe Register) is set and the LIU is in state F7, the LIU monitors the FA- (Q-bit control) and M- (M-bit control) bits. When three consecutive multiframes with the M-bits and FA bits set as defined in Figure 2.4 are received, the 'multiframe synchronized' bit (bit 7 of the Multiframe Register) and 'multiframe change of state' bit (bit 7 of the Multiframe S-bit/Status Buffer) are set. Note that S-bit data is received, compiled and transferred to the user after attaining synchronization at the start of the next multiframe.

## S-bit Reception

After multiframe synchronization has been requested and established, the microprocessor can read the Multiframe S-bit/Status Buffer (MFSB) once the 'S-data available' bit (bit 5 of MFSB) is set. The 'S-data available' bit is set to a logical '1' when the Am79C30A/32A has received five S-bits (one S-bit per 'S' interface frame) synchronized to the setting of the FA-bit to a logical '1' and transferred them into the MFSB. Once the 'Sbit available' bit is set, the MFSB must be accessed within 1.25 ms or succeeding S-data will be lost.

## **Transmission of Q-bits**

The microprocessor can load the Multiframe Q-bit Buffer (MFQB) once the 'Q-bit buffer empty' bit (bit 6 of the Multiframe S-bit/Status Buffer) is set. The 'Q-bit buffer empty' bit is set to a logical '1' at reset or when data that has been written to the Multiframe Q-bit Buffer is transferred to the LIU. The 'Q-bit buffer empty' bit is cleared to a logical '0' when the Multiframe S-bit/Status Buffer is read. After multiframing has been requested and established, the Am79C30A/32A transfers the data written into the Q-bit Register to the LIU synchronized to the multiframe irrespective of the receipt of valid Q-control bits. If the microprocessor does not reload the Q-bit Register for retransmission, the Q-bit pattern is repeated in the next multiframe.

If multiframing is enabled but multiframe synchronization is not established, the LIU transmits the value loaded in MFQB bit 4 in all Q-bits. The default value of MFQB bit 4 is a logical '0' which satisfies the CCITT recommendations. When synchronization is achieved, the contents of MFQB bits 3 to 0 are transmitted according to Figure 6.

## Loss of Multiframe Synchronization

The Am79C30A/32A continuously monitors the FA- (Qbit control) and the M-bits to assure multiframe synchronization. Once multiframe synchronization is established, multiframe synchronization is lost if three consecutive invalid multiframes are received or the LIU exits state F7 or multiframing is disabled. When loss of multiframe synchronization occurs, bit 7 of the Multiframe Register is set to a logical '0' and bit 7 of the Multiframe S-bit/Status Buffer is set to a logical '1'. The Am79C30A/32A also terminates the reception of S-bits and transmission of Q-bits until multiframing synchronization is re-established.

## **LIU Registers**

The LIU contains the following registers:

| Registers                        | No. | Mnemonic   |

|----------------------------------|-----|------------|

| LIU Status Register              | 1   | LSR        |

| LIU Priority Register            | 1   | LPR        |

| LIU Mode Registers               | 2   | LMR1, LMR2 |

| Multiframe Register              | 1   | MF         |

| Multiframe S-Bit/Status Register | 1   | MFSB       |

| Multiframe Q-Bit Buffer          | 1   | MFQB       |

## LIU Status Register (LSR), Read Only

The LSR has the following format:

| Bit   | Logical '1'                                                                                                                        | Generates Interrupt |

|-------|------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 2,1,0 | Binary values 000 through 110 represent the LIU activation circuitry's<br>current state (F2 through F8 respectively) Bit 2 is MSB. | No                  |

| 3     | Change of state to F3                                                                                                              | If LMR2 bit 3 = 1   |

| 4     | Change of state from/to F7                                                                                                         | If LMR2 bit 6 = 1   |

| 5     | Change of state from/to F8                                                                                                         | If LMR2 bit 4 = 1   |

| 6     | HSW state                                                                                                                          | No                  |

| 7     | HSW change of state                                                                                                                | If LMR2 bit 5 = 1   |

When the microprocessor reads the LSR bits 3, 4, 5, and 7 are cleared. The other bits retain the current status of the LIU. Bits 0 to 2 are defined such that state F2 (see CCITT I.430 state matrix tables) is coded as 0, F3 as 1, F4 as 2, and so on, where bit 0 is the LSB. The LIU interrupts the microprocessor via bit 4 of the LSR when activation has been achieved (that is, when the LIU moves to state F7 upon receipt of INFO 4). During reset the LSR is zero. Subsequent to removing the reset, the Am79C30A/32A goes to state F2 and reflects the condition of the HSW as well as the condition of 'S' interface after the receiver has been enabled.

#### LIU D-channel Priority Register (LPR), Read/Write

The LPR contains the priority level for D-channel access. Its default value after reset is zero.

The D-channel access procedure of the Am79C30A/32A uses the priority level programmed in the LPR. The priority mechanism defined by the CCITT I-series recommendations is fully implemented if the LPR is programmed via the microprocessor to conform to the priority class of the layer 2 frame to be transmitted.

The LPR has 16 possible programmable priority levels. The priority levels are numbered from 0 to 15. Priority level 0 corresponds to counting 8 ones in the echo channel, priority level 1 corresponds to counting 10 ones in the echo channel, and priority level 2 corresponds to counting 12 ones, etc. The DSC automatically handles transitions between the programmed priority level "n" and the associated odd value n + 1. The priority is incremented following a successfully transmitted packet, and decremented when the higher count has been satisfied.

The LPR has the following format:

| Bits    | Description                                       |

|---------|---------------------------------------------------|

| 3,2,1,0 | D-Channel access priority level.<br>Bit 0 is LSB. |

| 7,6,5,4 | Not used, read logical '0'                        |

## LIU Mode Register (LMR1), Read/Write

LMR1 is defined as follows:

| Bit | Logical '1'                  | Logical '0' (default value)  |  |

|-----|------------------------------|------------------------------|--|

| 0   | Enable B1 transmit           | Disable B1 transmit          |  |

| 1   | Enable B2 transmit           | Disable B2 transmit          |  |

| 2   | Disable F transmit           | Enable F transmit            |  |

| 3   | Disable FA transmit          | Enable FA transmit           |  |

| 4   | Activation request           | No activation request        |  |

| 5   | Go from F8 to F3             | No transition                |  |

| 6   | Enable receiver/transmitter  | Disable receiver/transmitter |  |

| 7   | Not used, reads logical '0 ' | Not used, reads logical '0'  |  |

The F and FA bits in LMR1 (bits 2 and 3) should be enabled during the activation procedure so that the Am79C30A/32A can respond with INFO 3.

LMR1 bit 4 is used to transfer the signals 'PH-AR' and 'Expiry of Timer' from the microprocessor to the LIU (see CCITT I.430 state diagram — activation request). 'PH-AR' is defined as bit 4 being a logical '1' and 'Expiry of Time' is defined as the transition of bit 4 from a logical

## LIU Mode Register 2 (LMR2), Read/Write

LMR2 is used to select the following operations:

'1' to a logical '0'. This bit must not be set until the LIU, as reflected in the LSR, is in state F3, F6 or F7 and the receiver has been enabled for a minimum of 250  $\mu$ s.

LMR1 bit 6 is primarily used to disable the receiver when the terminal does not require access to the 'S' interface signals. This bit is cleared by reset and must be written to logical '1' in order to receive activation from the 'S' interface, or to request activation.

| Bit | Logical '1'                               | Logical '0' (default value)                |

|-----|-------------------------------------------|--------------------------------------------|

| 0   | D-channel loopback at Am79C30A/32A enable | D-channel loopback at Am79C30A/32A disable |

| 1   | D-channel loopback at LIU enable          | D-channel loopback at LIU disable          |

| 2   | D-channel back-off disable                | D-channel back-off enable                  |

| 3   | F3 change of state interrupt enable       | F3 change of state interrupt disable       |

| 4   | F8 change of state interrupt enable       | F8 change of state interrupt disable       |

| 5   | HSW interrupt enable                      | HSW interrupt disable                      |

| 6   | F7 change of state interrupt enable       | F7 change of state interrupt disable       |

| 7   | Not used, reads logical '0'               | Not used, reads logical '0'                |

The three D-channel loopback controls defined in LMR2 bits 0,1, and 2 are explained below:

Bit 0, D-channel loopback at Am79C30A/32A enable:

This remote loopback is provided for maintenance purposes from the NT's perspective. The NT transmits Dchannel bits to the Am79C30A/32A where they are internally looped (with the Data Link Controller) and transmitted back to the NT. The incoming D-channel data can be accessed by the microprocessor; however, the microprocessor cannot send data on the outgoing D-channel.

Any difference between the transmitted D-channel bits and the received E-channel bits to/from the Am79C30A/32A (normally detected as an error which halts the transmission) is ignored thereby allowing the transmission to continue.

Bit 1, D-channel loopback at LIU enable:

This local loopback is provided for local testing. Data on the incoming D-channel is ignored. The data from the microprocessor is processed by the DLC and then looped back to the microprocessor in addition to being output to the 'S' interface. The looped back data stream is processed by the DLC.

Bit 2, D-channel back off disable:

This loopback is provided for maintenance purposes from the TE's perspective. The Am79C30A/32A transmits D-channel bits to the NT where they are looped and transmitted back to the Am79C30A/32A in the E-channel. The operation is normal except differences between the D- and E-channels do not halt the transmission.

#### Multiframe Register (MF), Read/Write

| Bit   | Logical '1'                                   | Logical '0' (Default value)             |

|-------|-----------------------------------------------|-----------------------------------------|

| 0     | Enable multiframe synchronization             | Disable multiframe synchronization      |

| 1     | Enable 'S-data available' interrupt           | Disable interrupt                       |

| 2     | Enable 'Q-bit buffer empty' interrupt         | Disable interrupt                       |

| 3     | Enable 'Multiframe change of state' interrupt | Disable interrupt                       |

| 6,5,4 | Not used, read logical '0'                    | Not used, read logical '0'              |

| 7     | Multiframe synchronized (read only )          | Multiframe not synchronized (read only) |

#### Multiframe S-bit/Status Buffer (MFSB), Read Only

| Bit | Description                | Generates Interrupt |  |

|-----|----------------------------|---------------------|--|

| 0   | S1                         | No                  |  |

| 1   | S2                         | No                  |  |

| 2   | S3                         | No                  |  |

| 3   | S4                         | No                  |  |

| 4   | S5                         | No                  |  |

| 5   | S-data available           | If MF bit 1 = 1     |  |

| 6   | Q-bit buffer empty         | If MF bit 2 = 1     |  |

| 7   | Multiframe change of state | If MF bit 3 = 1     |  |

The MFSB is cleared when read or upon reset.

#### Multiframe Q-bit Buffer (MFQB), Write Only

| Bit   | Description                                                                          |

|-------|--------------------------------------------------------------------------------------|

| 0     | Q1 (default = 1)                                                                     |

| 1     | Q2 (default = 1)                                                                     |

| 2     | Q3 (default = 1)                                                                     |

| 3     | Q4 (default = 1)                                                                     |

| 4     | Q-bit value when multiframing enabled but synchronization not achieved (default = 0) |

| 5,6,7 | Not used                                                                             |

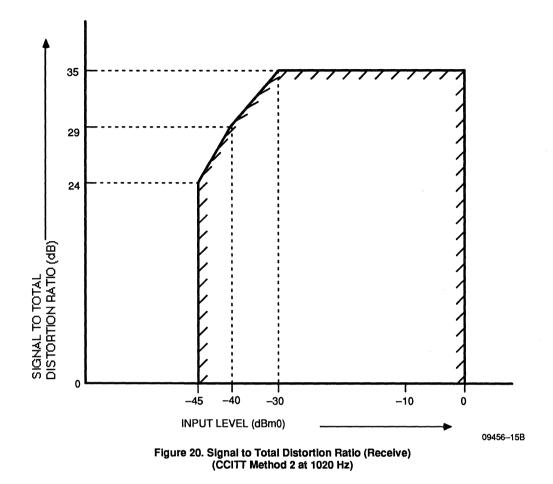

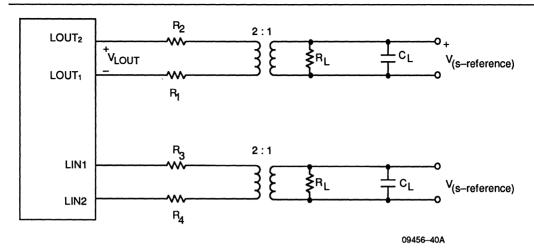

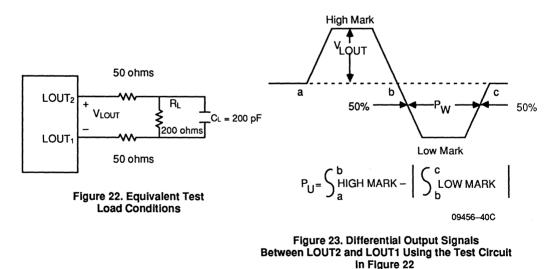

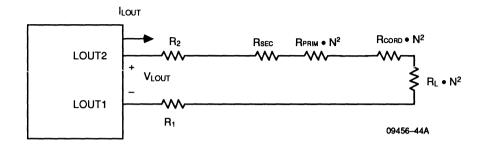

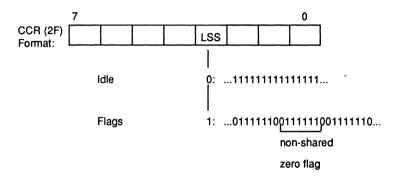

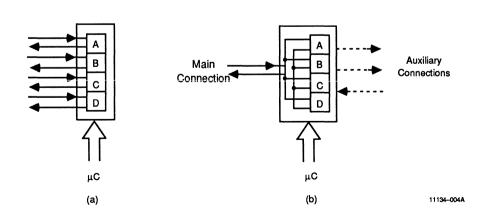

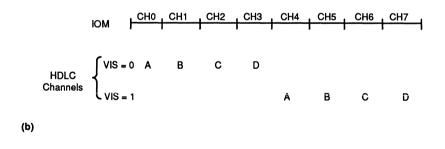

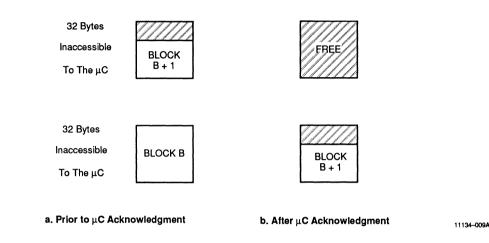

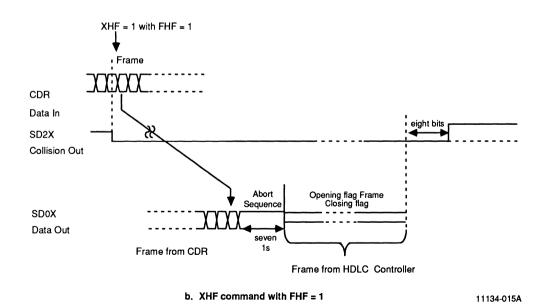

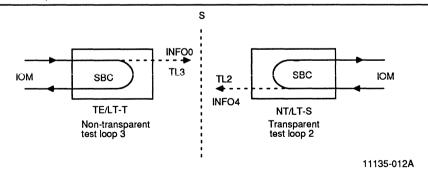

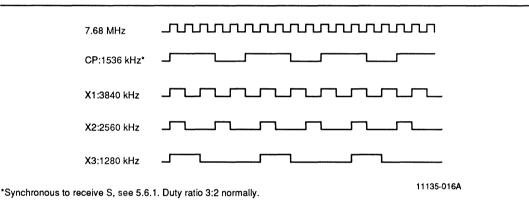

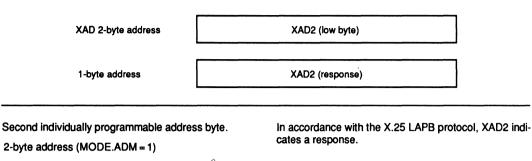

## S-Bit Channel Structure