# 29K Family

1990 Data Book

Advanced Micro Devices

Advanced Micro Devices

# 29K Family Data Book

#### © 1989 Advanced Micro Devices

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics. The performance characteristics listed in this document are guaranteed by specific tests, correlated testing, guard banding, design and other practices common to the industry. For specific testing details, contact your local AMD sales representative. The company assumes no responsibility for the use of any circuits described herein.

> 901 Thompson Place, P.O. Box 3453, Sunnyvale, California 94088-3000 (408)732-2400 TWX: 910-339-9280 TELEX: 34-6306

Am29000, Am29027, Am29041, 29K, ADAPT29K, ASM29K, BTC, Branch Target Cache, Fusion29K, HighC29K, MON29K, PCEB29K, and XRAY29K are trademarks of Advanced Micro Devices, Inc.

CROSSTALK is a registered trademark of Digital Communications Associates, Inc.

DEC is a registered trademark of Digital Equipment Corporation.

Hewlett-Packard is a registered trademark of Hewlett-Packard, Inc.

IBM and PC-AT are registered trademarks of International Business Machines Corporation.

MetaWare is a trademark of MetaWare, Inc.

Motorola and MC68000 are registered trademarks of Motorola, Inc.

PAL is a registered trademark of Advanced Micro Devices, Inc.

Sun Workstation is a registered trademark of Sun Microsystems, Inc.

Sun and Sun-3 are trademarks of Sun Microsystems, Inc.

Tektronix is a registered trademark of Tektronix, Inc.

UniSite is a trademark of Data I/O Corporation.

UNIX is a registered trademark of American Telephone and Telegraph Company.

VAX is a registered trademark of Digital Equipment Corporation.

# INTRODUCTION

The RISC-based Am29000 Streamlined Instruction Processor from Advanced Micro Devices is the highperformance solution for your general-purpose embedded systems needs. As the heart of the 29K Family, this 32bit CMOS microprocessor delivers outstanding performance, yet offers flexible cost-effective solutions that can guickly move your product to market.

This data book is your comprehensive guide to AMD's 29K Family of microprocessors and development tools. These products have helped current developers create applications that fully exploit the power of the Am29000 microprocessor: laser printers of all types, real-time graphics systems, networks and bridges, and a host of other peripheral and communication devices.

To provide a total system solution for you, AMD has taken the 29K Family's advantages of 17-MIPS performance, flexible memory-configuration requirements, and outstanding development tools and coupled them with our Fusion29K<sup>™</sup> program. This program provides you with AMD and industry-standard third-party solutions, including the application-specific solutions you need for successful system integration that can substantially shorten the time-to-market factor of your design.

AMD is committed to the 29K Family, and will continue to apply substantial resources to ensure that the present levels of high performance, cost and design flexibility, and rapid design cycles are maintained and further enhanced. Qualified support is readily available for our customers—our highly trained field applications engineers are backed by experts in the factory. For further details on how the 29K Family can be the solution to your design needs, call your local AMD sales office or the authorized representative listed in the back of this publication.

Geoff Tate Senior Vice President Microprocessors & Peripherals Group

# PREFACE

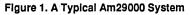

Advanced Micro Devices' 29K<sup>™</sup> Family is a new generation of high-performance CMOS microprocessor components and associated software tools. The heart of the 29K Family is the RISC-based Am29000<sup>™</sup> microprocessor. The Am29000 Streamlined Instruction Processor is a high-performance, general-purpose, 32-bit microprocessor that supports a variety of applications, by virtue of a flexible architecture and rapid execution of simple instructions which are common to a wide range of tasks. The 29K Family's microprocessors are fully described in Chapter 1.

The Am29000 Streamlined Instruction Processor efficiently performs operations common to all systems, while deferring most decisions on system policies to the system architect. It is well suited for applications in high-performance workstations, general-purpose super minicomputers, high-performance real-time controllers, laser printer controllers, network protocol converters, and many other applications where high performance, flexibility, and the ability to program using standard software tools is important.

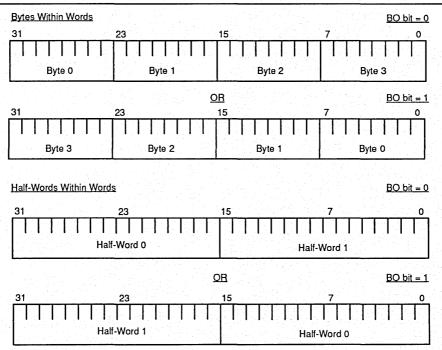

The Am29000 microprocessor has been enhanced to support byte and half-word loads and stores. This feature is provided as an option, requiring that an external device or memory be able to write individual bytes and/or half-words of a word. The Am29000 microprocessor can perform all necessary padding, sign extension, and alignment within the word. Furthermore, this feature is defined to be compatible with existing 29K Family software.

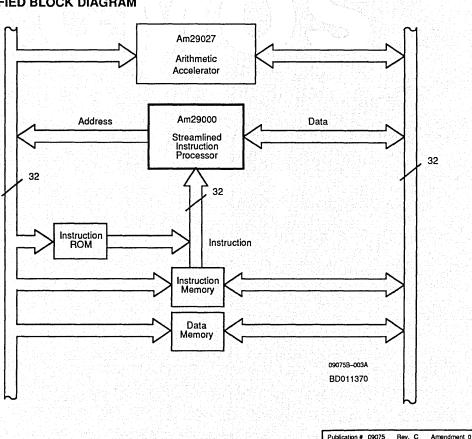

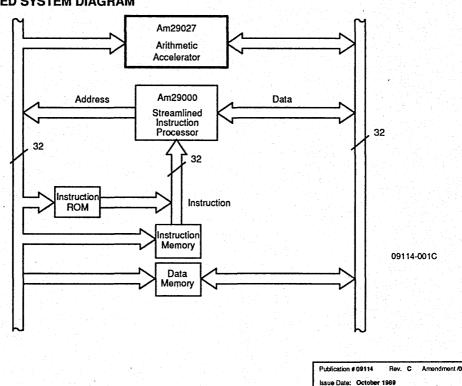

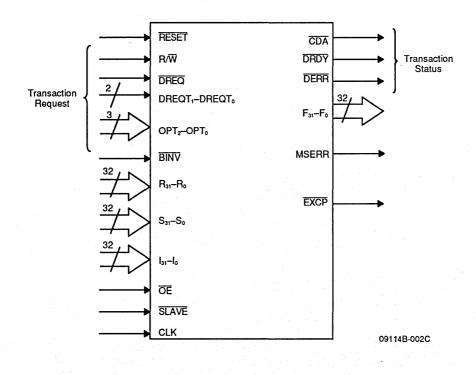

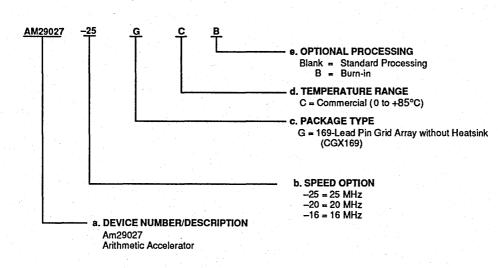

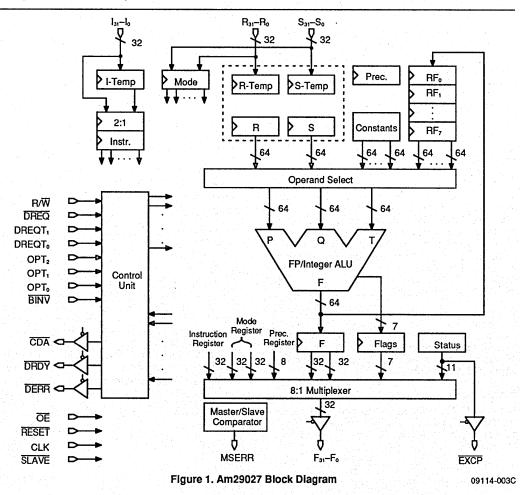

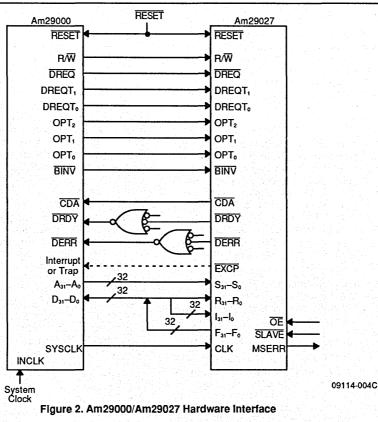

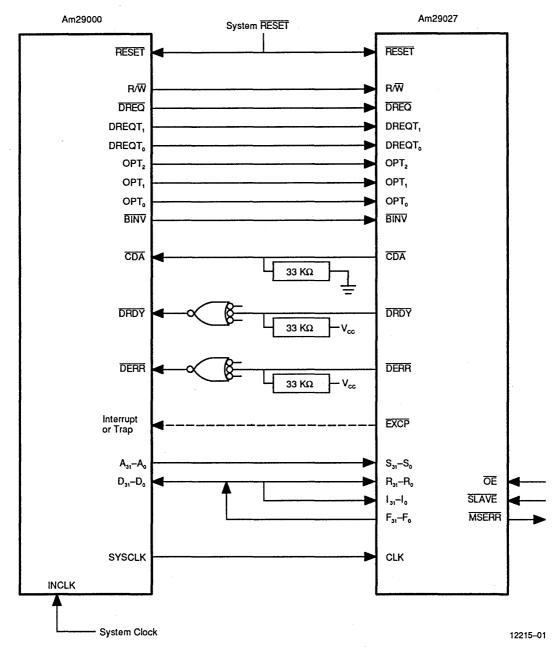

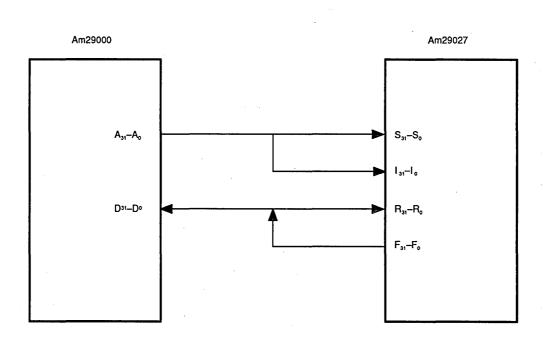

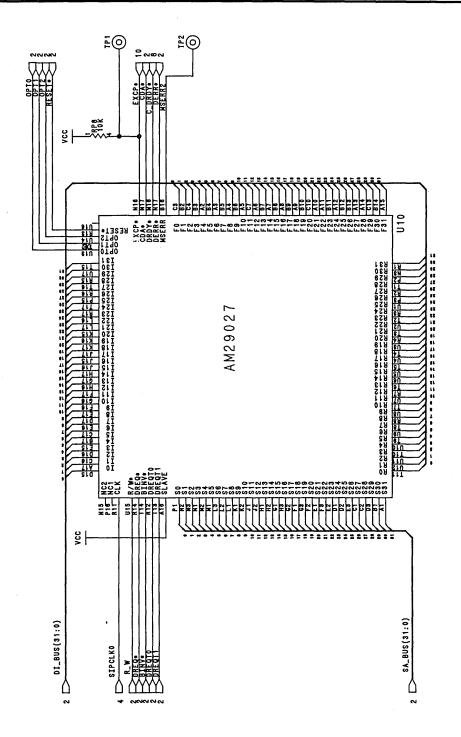

The Am29027<sup>™</sup> Arithmetic Accelerator is a high-computational unit intended for use with the Am29000 Streamlined Instruction Processor. It connects directly to the Am29000 microprocessor's system buses, and requires no additional interface circuitry. When added to an Am29000 microprocessor-based system, the Am29027 coprocessor can improve floating-point performance by an order of magnitude or more. The Am29027 coprocessor implements an extensive floating-point and integer instruction set, and can perform operations on single-, double-, or mixed-precision operands.

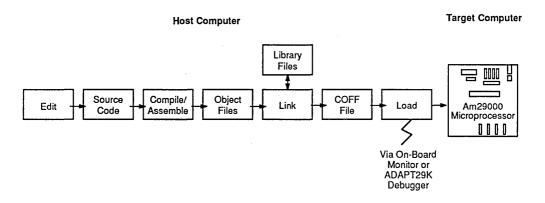

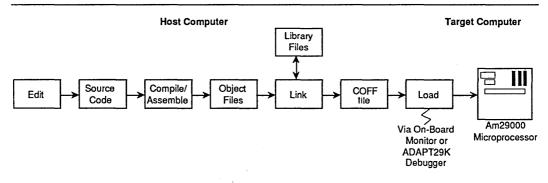

But the superior performance of the 29K Family of microprocessors is only part of the story: AMD also provides a comprehensive set of software and hardware development tools, as shown in Chapter 2. These tools, coupled with the growing number of development products from established third-party vendors, can drastically reduce the time-to-market factor of designs.

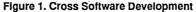

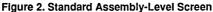

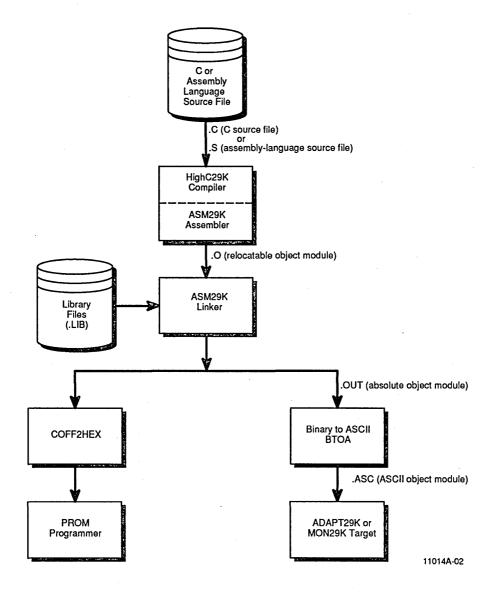

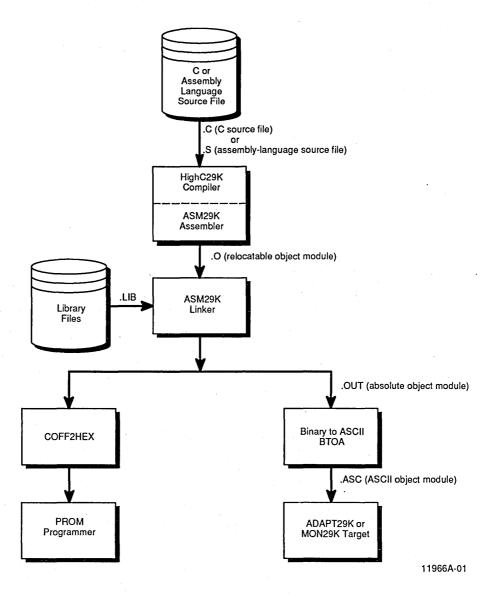

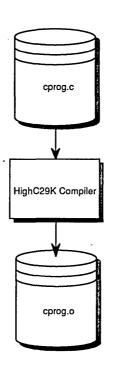

For software development, AMD offers the globally optimizing HighC29K<sup>™</sup> Cross-Development Toolkit, complete with high-performance math libraries. The HighC29K compiler is packaged with the ASM29K<sup>™</sup> Cross-Development Toolkit, which includes a relocatable macro assembler, linker/loader, librarian, and a full architectural simulator of the Am29000 microprocessor.

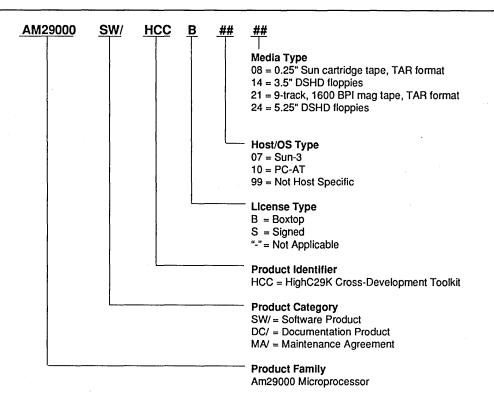

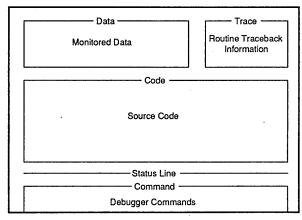

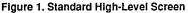

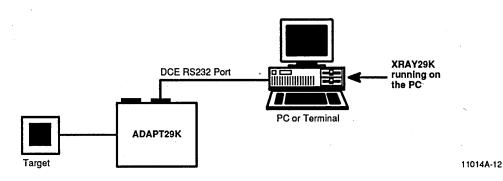

Several debugging tools are available, including the XRAY29K<sup>™</sup>, a source-level debugger for high-level and assembly-level debugging and the software-based MON29K<sup>™</sup> target-resident debugger/monitor. All tools work at the Am29000 processor's clock rate to allow debugging while operating at full microprocessor speed.

The application notes in Chapter 3 make development with the 29K Family of silicon and tools a simpler task. Within these documents, AMD engineers explore solutions of common problems that stand as roadblocks in your development path. So whether you need general information on programming standalone Am29000 microprocessor-based systems or detailed specifics on how to make your product HIF compatible, these application notes can provide the answers. And with new notes constantly being written and released, this wealth of knowledge will continue to be integral to your development process.

**Table of Contents**

v

# 29K FAMILY DATA BOOK TABLE OF CONTENTS

| Chapter 1        | 29K Family CMOS Devices  |       |

|------------------|--------------------------|-------|

| 29000 Data Sheet |                          |       |

| 29027 Data Sheet |                          | 1-111 |

|                  |                          |       |

| Chapter 2        | 29K Family Support Tools |       |

###

#### Chapter 3

### 29K Family Application Notes

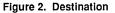

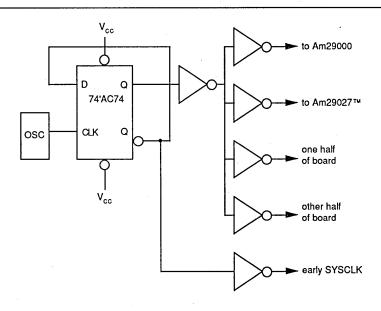

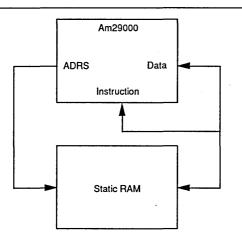

| Am29000 SYSCLK Driving        |                               | 3-3 |

|-------------------------------|-------------------------------|-----|

|                               | on/Data Buses                 |     |

| Byte-Writable Memories for th | e Am29000                     |     |

| Am29027 Hardware Interface    |                               |     |

| When is Interleaved Memory    | with the Am29000 Unnecessary? |     |

| Implementation of an Am2900   | 0 Stack Cache                 |     |

| Introduction to the Am29000 I | Development Tools             |     |

| Preparing PROMs Using the     | Am29000 Development Tools     |     |

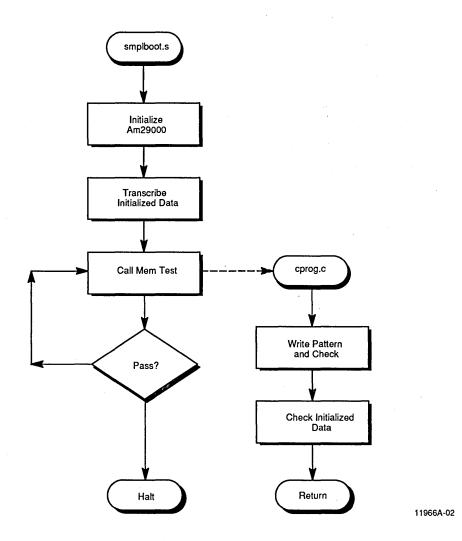

| Programming Standalone Am     | 29000 Systems                 |     |

| Host Interface (HIF) v1.0 Spe | cification                    |     |

| · · ·                         |                               |     |

## Chapter 4

## **General Information**

| Related Literature | .4-3 |

|--------------------|------|

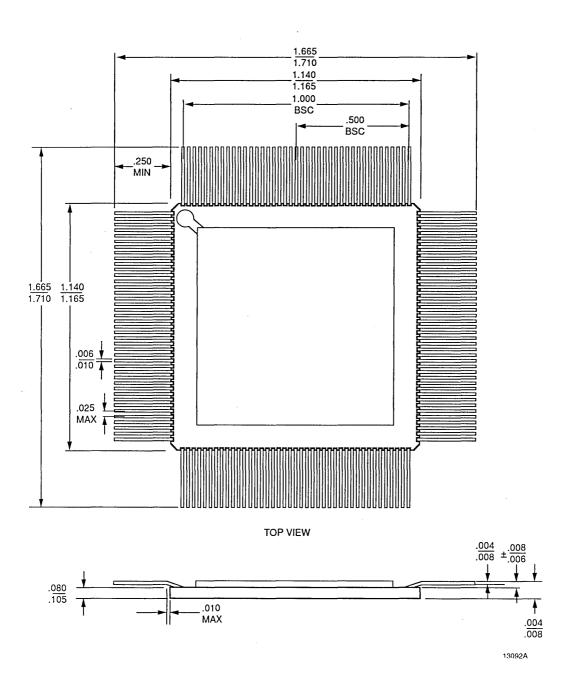

| Package Outlines   | 4-4  |

# CHAPTER 1 29K Family CMOS Devices

| Am29000 Data Sheet | 1-3   |

|--------------------|-------|

| Am29027 Data Sheet | 1-111 |

• •

Am29000

Advanced Micro

Devices

# Preliminary

# Am29000

# **Streamlined Instruction Processor**

# **DISTINCTIVE CHARACTERISTICS**

- Full 32-bit, three-bus architecture

- 23 million instructions per second (MIPS) sustained at 33 MHz

- 33-, 25-, 20-, and 16-MHz operating frequency

- Efficient execution of high-level language programs

- CMOS technology

- 4-gigabyte virtual address space with demand paging

- Concurrent instruction and data accesses

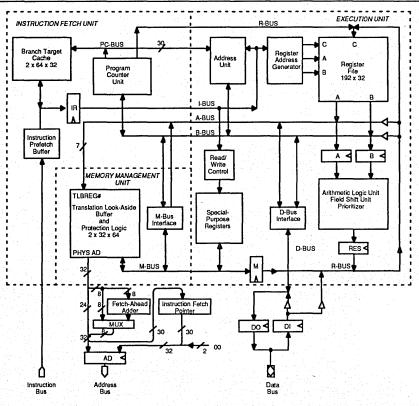

# SIMPLIFIED BLOCK DIAGRAM

Burst-mode access support

- 192 general-purpose registers

- 512-byte Branch Target Cache™

- 64-entry Memory-Management Unit

- Demultiplexed, pipelined address, instruction, and data buses

- Three-address instruction architecture

- On-chip byte-alignment support allows optional byte/half-word accesses

Issue Date: November 1989

# TABLE OF CONTENTS

| DISTINCTIVE CHARACTERISTICS                                                                                                                                                                                                                                 | . 1-3                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| SIMPLIFIED BLOCK DIAGRAM                                                                                                                                                                                                                                    |                                                              |

| GENERAL DESCRIPTION                                                                                                                                                                                                                                         | . 1-7                                                        |

| RELATED AMD PRODUCTS                                                                                                                                                                                                                                        |                                                              |

|                                                                                                                                                                                                                                                             | . 1-8                                                        |

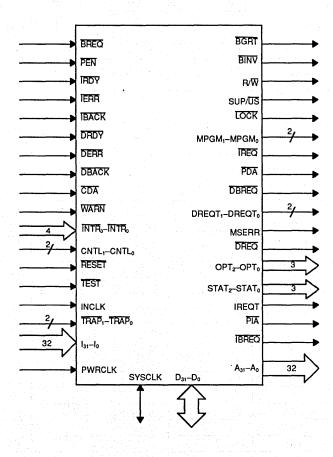

| PIN DESIGNATION                                                                                                                                                                                                                                             | 1-10                                                         |

| LOGIC SYMBOL                                                                                                                                                                                                                                                | 1-14                                                         |

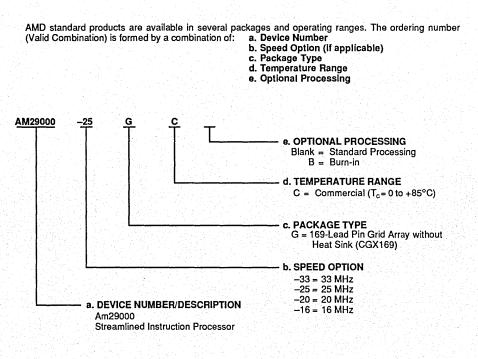

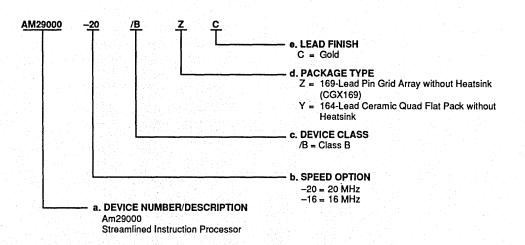

| ORDERING INFORMATION                                                                                                                                                                                                                                        | 1-15                                                         |

| PIN DESCRIPTION                                                                                                                                                                                                                                             |                                                              |

| FUNCTIONAL DESCRIPTION<br>Product Overview .<br>Cycle Time .<br>Four-Stage Pipeline<br>System Interface .<br>Register File<br>Instruction Execution<br>Branch Target Cache                                                                                  | 1-21<br>1-21<br>1-21<br>1-21<br>1-21<br>1-22<br>1-22         |

| Branching<br>Loads and Stores<br>Memory Management<br>Interrupts and Traps<br>Floating-Point Arithmetic Unit                                                                                                                                                | 1-22<br>1-23<br>1-23<br>1-23                                 |

| ARCHITECTURE HIGHLIGHTS<br>Architecture Overview<br>Program Modes<br>Visible Registers<br>Instruction Set Overview<br>Data Formats and Handling<br>Interrupts and Traps<br>Memory Management<br>Coprocessor Programming<br>Timer Facility<br>Trace Facility | 1-24<br>1-24<br>1-26<br>1-29<br>1-30<br>1-31<br>1-31<br>1-31 |

| FUNCTIONAL OPERATION<br>Four-Stage Pipeline<br>Function Organization<br>Instruction Fetch Unit<br>Execution Unit<br>Memory Management Unit<br>Processor Modes<br>System Interface                                                                           | 1-32<br>1-32<br>1-32<br>1-32<br>1-33<br>1-34                 |

# TABLE OF CONTENTS (continued)

| Channel                                                        | 1-34 |

|----------------------------------------------------------------|------|

| Test/Development Interface                                     | 1-35 |

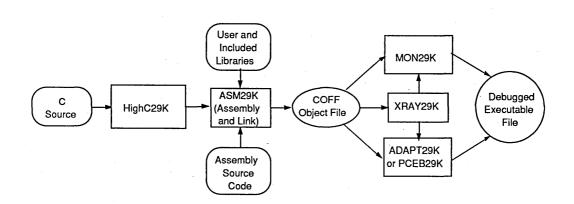

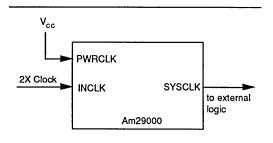

| Clocks                                                         | 1-35 |

| Master/Slave Operation                                         | 1-35 |

| Coprocessor Attachment                                         |      |

| Program Modes                                                  |      |

| Supervisor Mode                                                |      |

| User Mode                                                      |      |

|                                                                |      |

|                                                                | 1-37 |

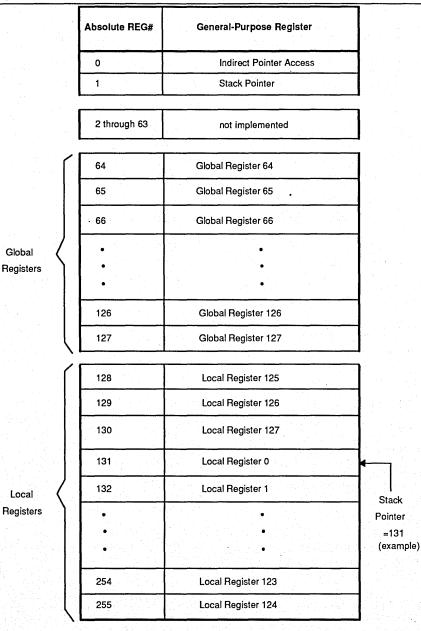

| General-Purpose Registers                                      |      |

|                                                                |      |

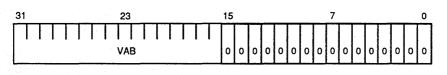

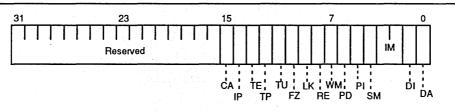

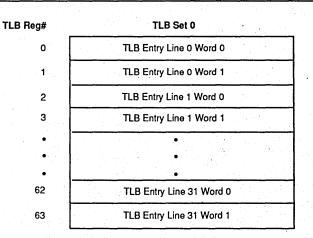

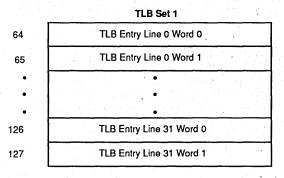

| TLB Registers                                                  | 1-54 |

| INSTRUCTION SET                                                | 4 57 |

|                                                                |      |

|                                                                |      |

| Compare                                                        |      |

| Logical                                                        |      |

| Shift                                                          |      |

| Data Movement                                                  | 1-57 |

| Constant                                                       | 1-57 |

| Floating-Point                                                 | 1-57 |

| Branch                                                         | 1-57 |

| Miscellaneous                                                  | 1-57 |

| Reserved Instructions                                          |      |

|                                                                |      |

| DATA FORMATS AND HANDLING                                      | 1-64 |

| Integer Data Types                                             |      |

| Floating-Point Data Types                                      |      |

| Special Floating-Point Values                                  |      |

| External Data Accesses                                         |      |

| Addressing and Alignment                                       |      |

|                                                                |      |

| Byte and Half-Word Accesses                                    |      |

| INTERRUPTS AND TRAPS                                           | 4 76 |

|                                                                |      |

| Interrupts                                                     |      |

| Traps                                                          |      |

| Wait Mode                                                      |      |

| Vector Area                                                    |      |

| Interrupt and Trap Handling                                    |      |

| WARN Trap                                                      |      |

| Sequencing of Interrupts and Traps                             | 1-80 |

| Exception Reporting and Restarting                             | 1-80 |

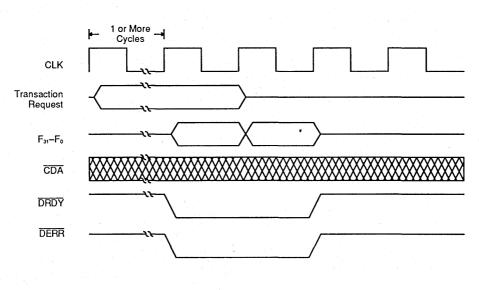

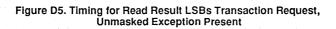

| Arithmetic Exceptions                                          | 1-82 |

| Exceptions During Interrupt and Trap Handling                  | 1-83 |

| 그는 것 같아요. 그는 것 같아요. 말을 알 때 아내는 것 같아요. 그는 것 같아요. 그는 것 같아요. 말했다. |      |

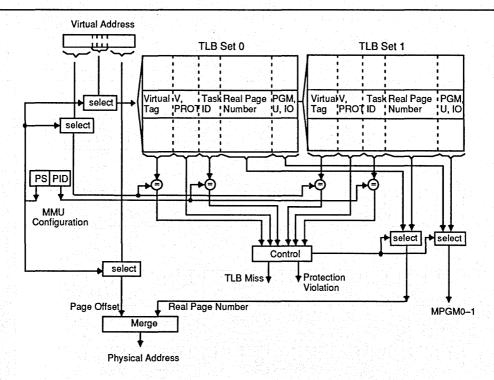

| MEMORY MANAGEMENT                                              | 1-84 |

| Translation Look-Aside Buffer                                  |      |

| Address Translation                                            |      |

| Reload                                                         |      |

| Entry Invalidation                                             |      |

| Protection                                                     |      |

|                                                                |      |

# 29K Family CMOS Devices TABLE OF CONTENTS (continued)

| CHANNEL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1-89    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| User-Defined Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1-89    |

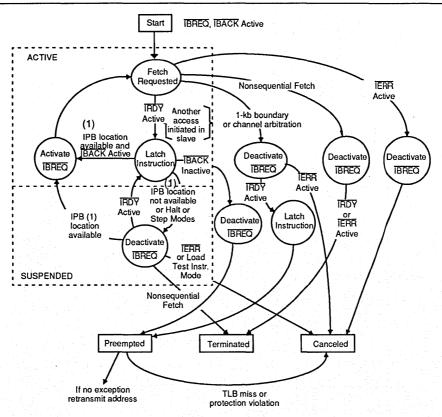

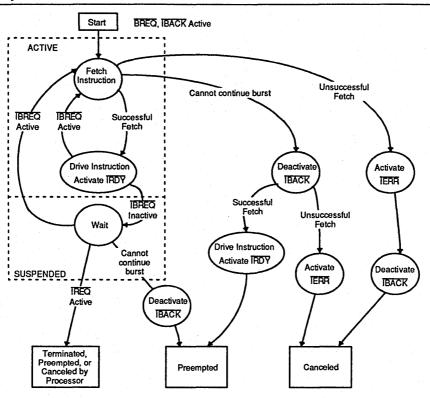

| Instruction Accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |

| Data Accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-89    |

| Reporting Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |

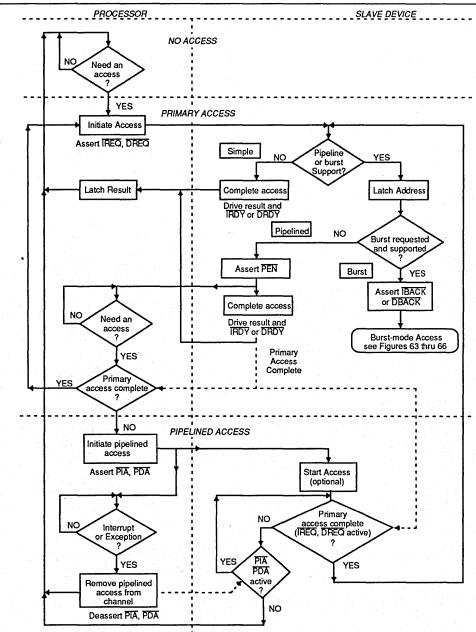

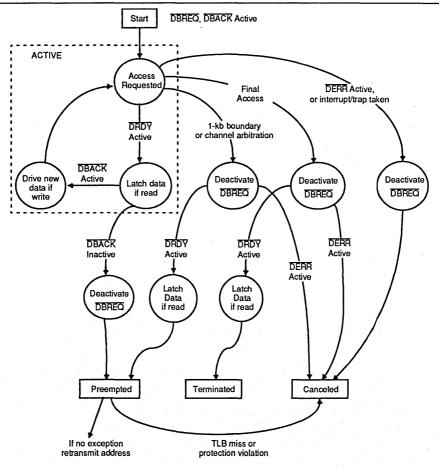

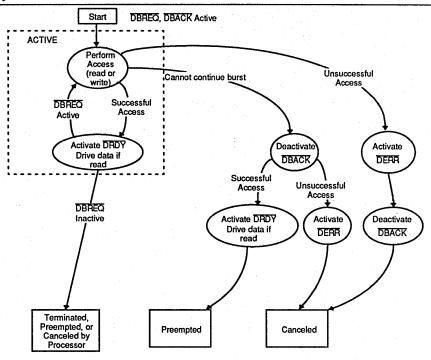

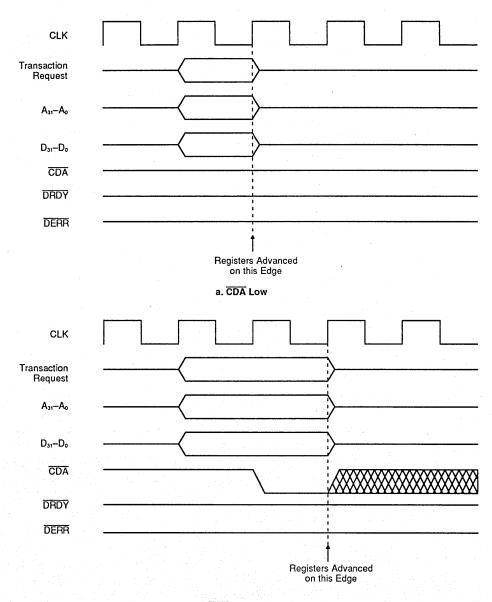

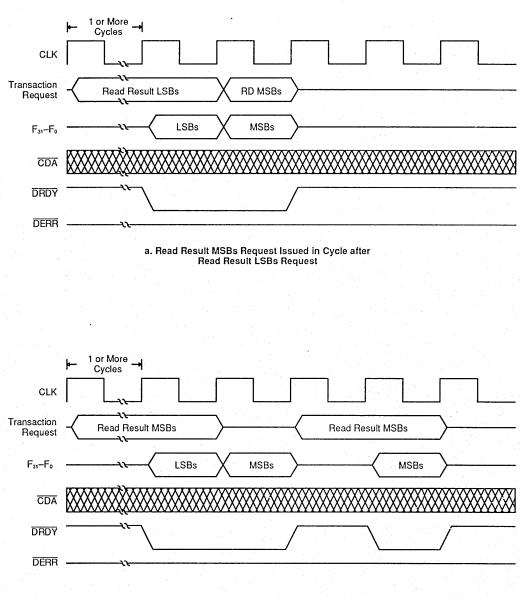

| Access Protocols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-90    |

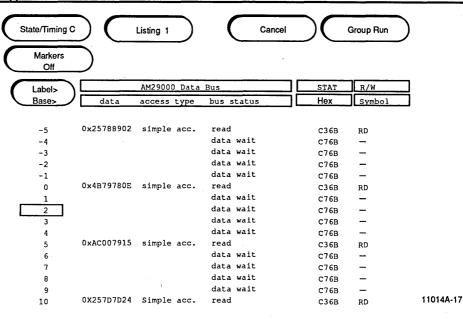

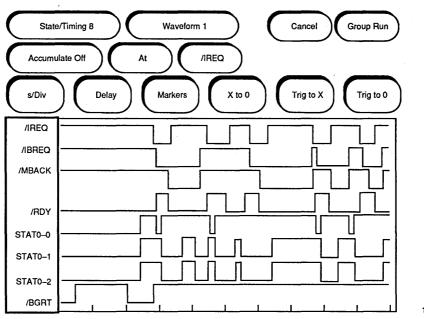

| Simple Accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |

| Pipelined Accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1-90    |

| Burst-Mode Accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |

| Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1-97    |

| Use of BINV to Cancel an Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-98    |

| Bus Sharing—Electrical Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |

| Channel Behavior for Interrupts and Traps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-99    |

| Effect of the LOCK Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-99    |

| Initialization and Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |

| ABSOLUTE MAXIMUM RATINGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 1-101 |

| <u>그는 것은 것이 있는 것이 있는 것이 있는 것이 없는 것이 없는 것이 없다. 이 가</u> 지 않는 것이 없는 것이 없는 것이 없는 것이 없는 것이 없는 것이 없다. 이 가지 않는 것이 있는 것이 없는 것이 있는 것이 없는 것이 없는 것이 없다. 이 가지 않는 것이 없는 것이 없다. 이 가지 않는 것이 없는 것이 없다. 이 가지 않는 것이 없는 것이 없다. 것이 없는 것이 없 않이 않이 않이 않는 것이 없는 것이 않이 않이 않이 않이 않이 않이 않는 것이 없는 것이 없이 않이 |         |

| OPERATING RANGES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 1-101 |

| DC CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |

| DC CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 1-101 |

| CAPACITANCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1 101   |

| CAPACITANCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 1-101 |

| SWITCHING CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-102   |

| ション・ション ション ないしょう うたかし ション かれた 見たい 一般的 かたいかかた おうしょうかい                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |

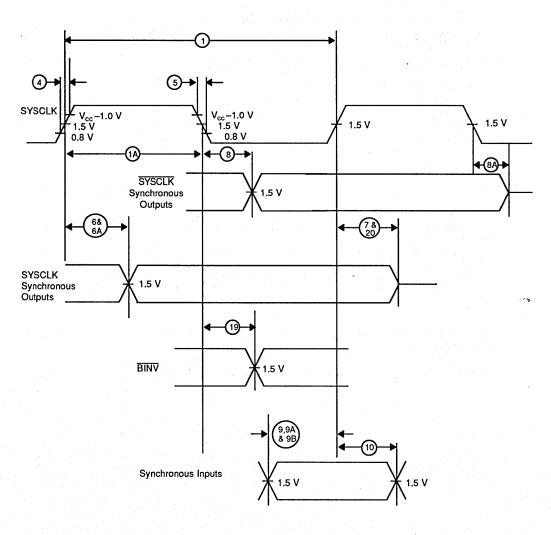

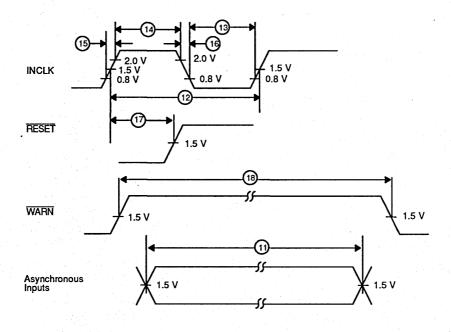

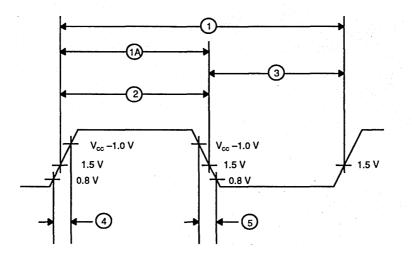

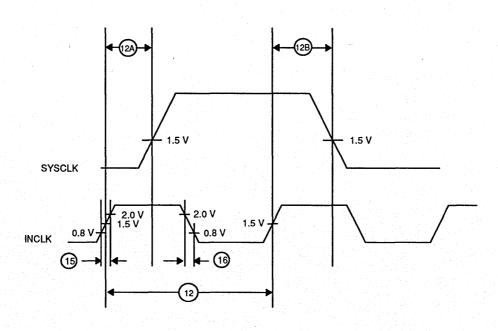

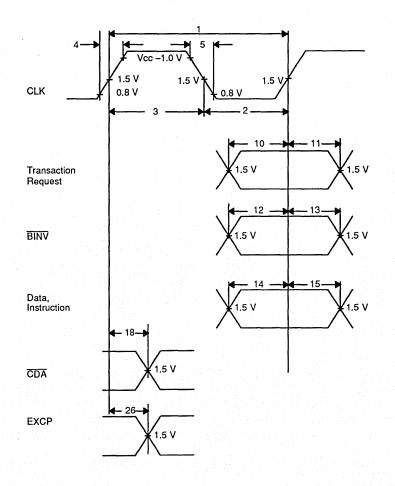

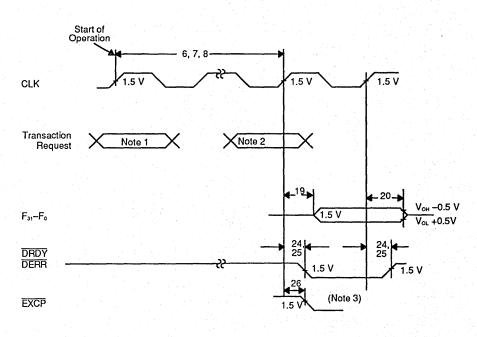

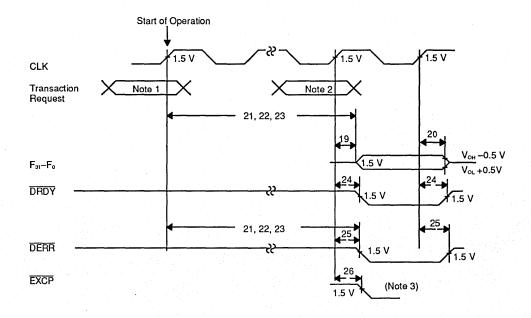

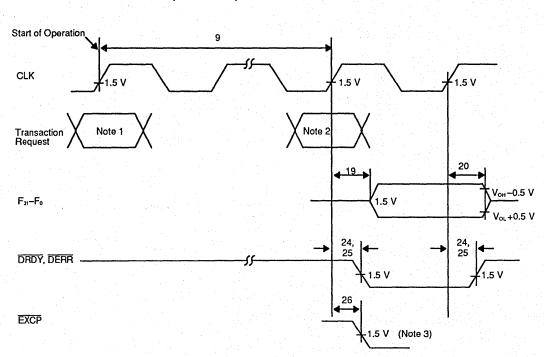

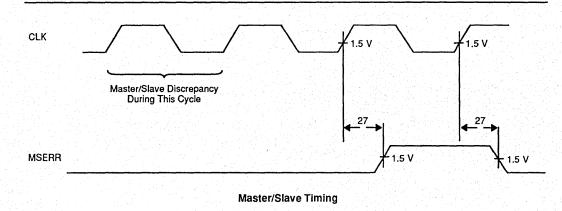

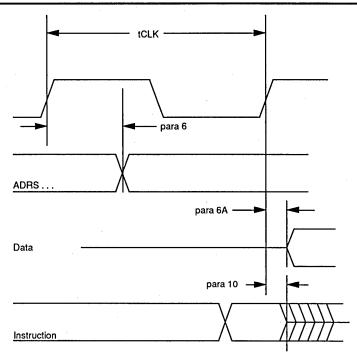

| SWITCHING WAVEFORMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 1-106 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |

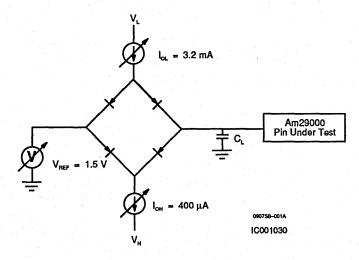

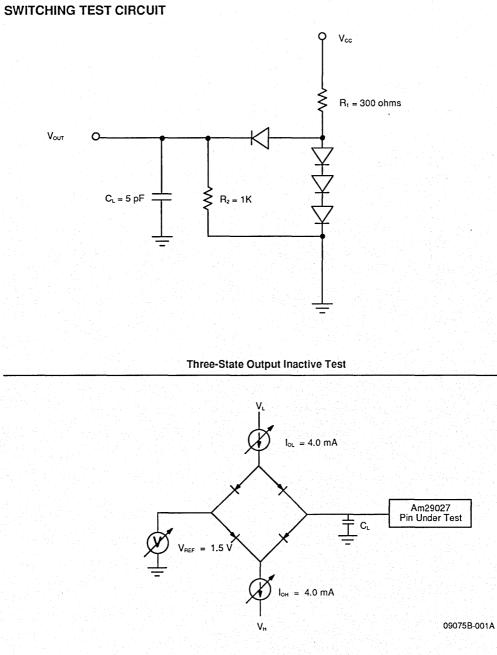

| SWITCHING TEST CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 1-109 |

# **GENERAL DESCRIPTION**

The Am29000™ Streamlined Instruction Processor is a high-performance, general-purpose, 32-bit microprocessor implemented in CMOS technology. It supports a variety of applications by virtue of a flexible architecture and rapid execution of simple instructions that are common to a wide range of tasks.

The Am29000 efficiently performs operations common to all systems, while deferring most decisions on system policies to the system architect. It is well-suited for application in high-performance workstations, generalpurpose super-minicomputers, high-performance realtime controllers, laser printer controllers, network protocol converters, and many other applications where high performance, flexibility, and the ability to program using standard software tools is important. The Am29000 instruction set has been influenced by the results of high-level language, optimizing compiler research. It is appropriate for a variety of languages because it efficiently executes operations that are common to all languages. Consequently, the Am29000 is an ideal target for high-level languages such as C, FORTRAN, Pascal, Ada, and COBOL.

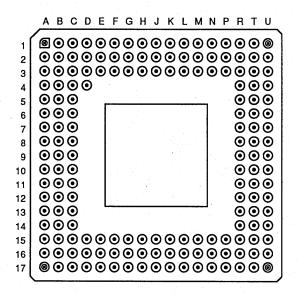

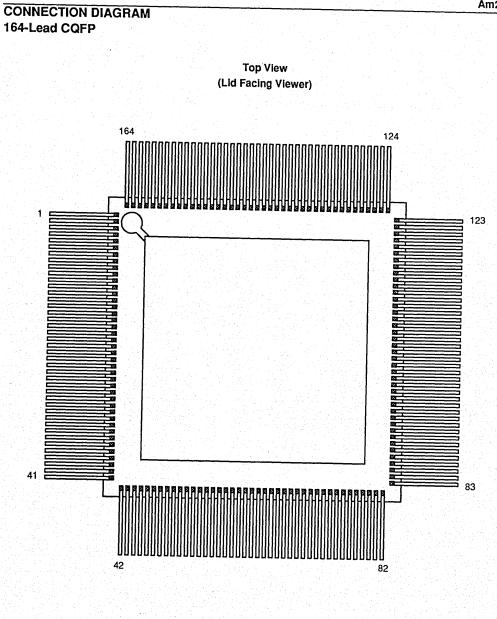

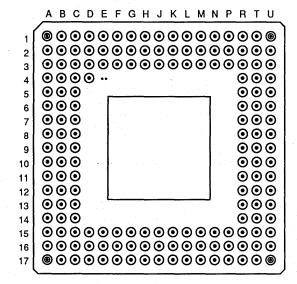

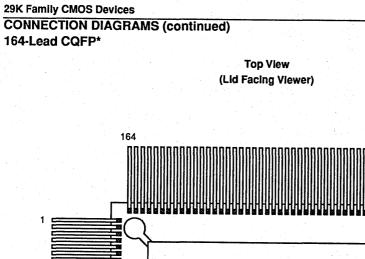

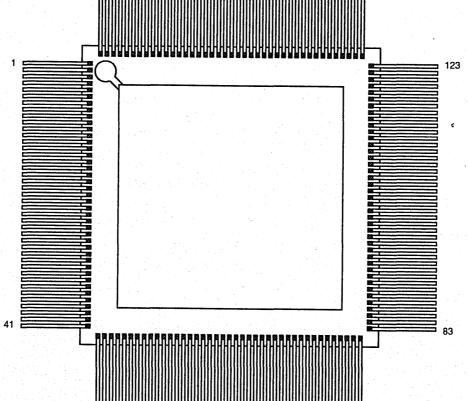

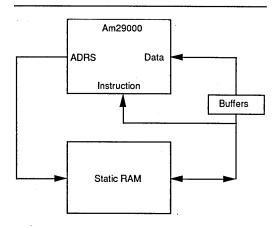

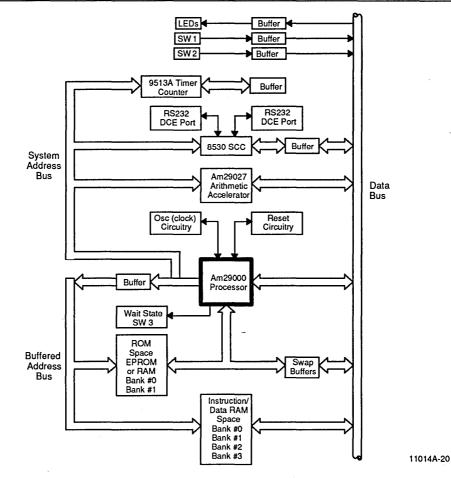

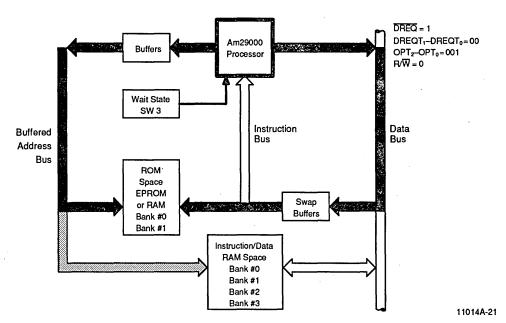

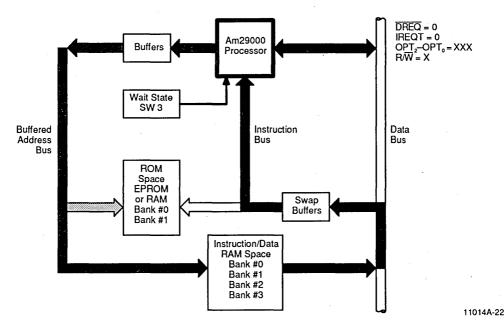

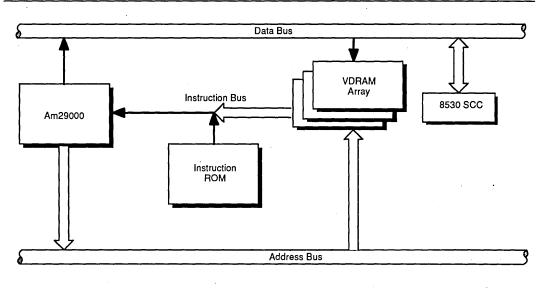

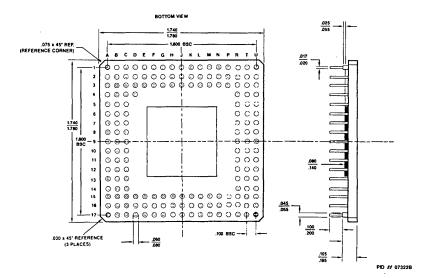

The processor is available in two packaging options: a 169-lead pin-grid-array (PGA) package, and a 164-lead Ceramic Quad Flat Pack (CQFP) package for the military. The PGA has 141 signal pins, 27 power and ground pins, and 1 alignment pin. The CQFP has 141 signal pins and 23 power and ground pins. A representative system diagram is shown on page 1.

# 29K<sup>™</sup> Family Development Support Products

Contact your local AMD representative for information on the complete set of development support tools.

Software development products on several hosts:

- Optimizing compilers for common high-level languages

- Assembler and utility packages

- Source- and assembly-level software debuggers

- Target-resident development monitors

- Simulators

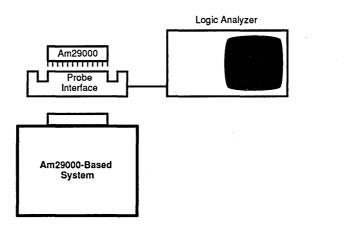

Hardware Development:

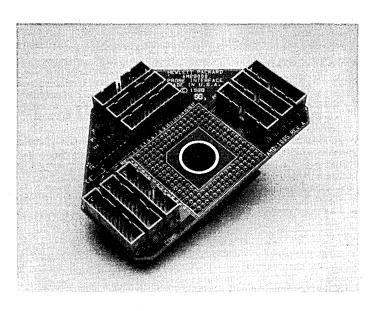

■ ADAPT29K<sup>™</sup> Advanced Development and Prototyping Tool

# **RELATED AMD PRODUCTS**

# Am29000 Peripheral Devices

| Part No. | Description            |  |

|----------|------------------------|--|

| Am29027™ | Arithmetic Accelerator |  |

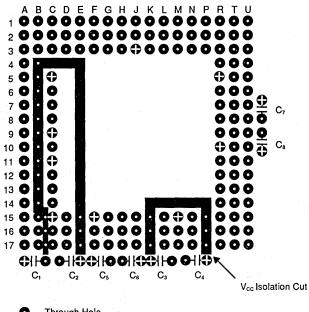

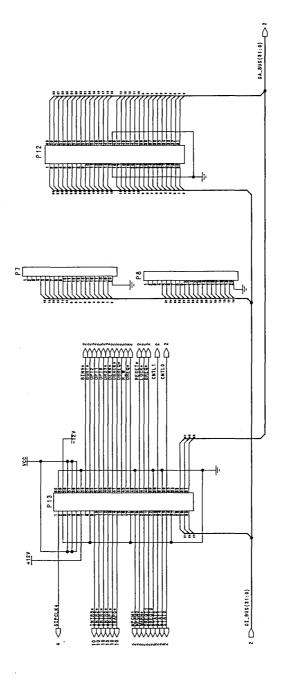

CONNECTION DIAGRAM 169-Lead PGA\*

**Bottom View**

\* Pinout observed from pin side of package.

Am29000

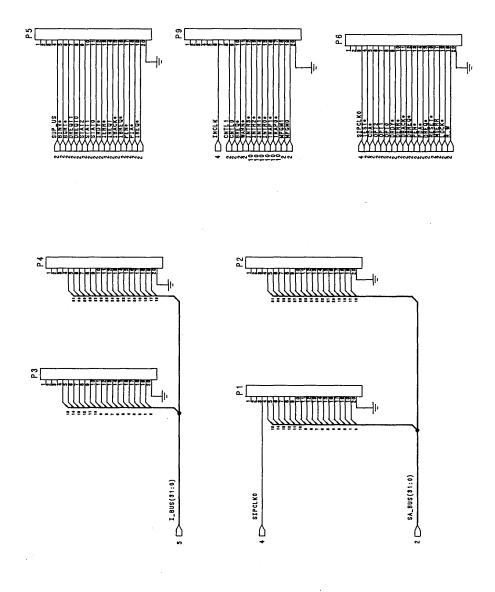

PGA PIN DESIGNATION (Sorted by Pin No.)

| Pin No.    | Pin Name   | Pin No.     | Pin Name                                                                                                         | Pin No.      | Pin Name                                                                                                        | Pin No. | Pin Name                 |

|------------|------------|-------------|------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------|---------|--------------------------|

| A-1        | GND        | C-10        | GND                                                                                                              | J-16         | A16                                                                                                             | R-12    | STAT <sub>2</sub>        |

| A-2        | 11         | C-11        | GND                                                                                                              | J-17         | A14                                                                                                             | R-13    | GND                      |

| A-3        | lo         | C-12        | D22                                                                                                              | K-1          | 126                                                                                                             | R-14    | <b>OPT</b> <sub>0</sub>  |

| ۹-4        | D2         | C-13        | D26                                                                                                              | K-2          | 125                                                                                                             | R-15    | A2                       |

| A-5        | D4         | C-14        | Vcc                                                                                                              | K-3          | GND                                                                                                             | R-16    | A6                       |

| A-6        | De         | C-15        | D30                                                                                                              | K-15         | Vcc                                                                                                             | R-17    | A7                       |

| A-7        | De         | C-16        | D31                                                                                                              | K-16         | A12                                                                                                             | T-1     | INCLK                    |

| <b>A-8</b> | D11        | C-17        | A29                                                                                                              | K-17         | A13                                                                                                             | T-2     | BREQ                     |

| A-9        | D12        | D-1         | el <b>h</b> national                                                                                             | L-1          | 127                                                                                                             | T-3     | DERR                     |

| A-10       | D14        | D-2         | 110                                                                                                              | L-2          | 128                                                                                                             | T-4     | IRDY                     |

| A-11       | D16        | D-3         | i <b>1</b> 7 <sup>- 1</sup> - 1                                                                                  | L-3          | Vcc                                                                                                             | T-5     | WARN                     |

| A-12       | D18        | D-4         | PIN169                                                                                                           | L-15         | Vcc                                                                                                             | T-6     | <b>INTR</b> <sub>2</sub> |

| A-13       | D20        | D-15        | A31                                                                                                              | L-16         | A10                                                                                                             | T-7     | <b>INTR</b> ₀            |

| A-14       | D21        | D-16        | A28                                                                                                              | L-17         | A11                                                                                                             | T-8     | BINV                     |

| A-15       | D25        | D-17        | A26                                                                                                              | M-1          | 129                                                                                                             | Т-9     | BGRT                     |

| A-16       | D27        | E-1         | l13                                                                                                              | M-2          | 130                                                                                                             | T-10    | DREQ                     |

| A-17       | GND        | E-2         | l12                                                                                                              | M-3          | GND                                                                                                             | T-11    | LOCK                     |

| B-1        | 16         | E-3         | Vcc                                                                                                              | M-15         | GND                                                                                                             | T-12    | MSERR                    |

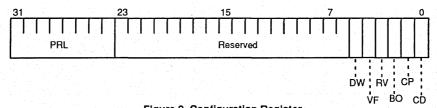

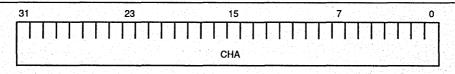

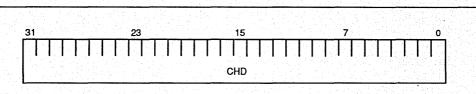

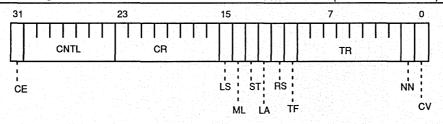

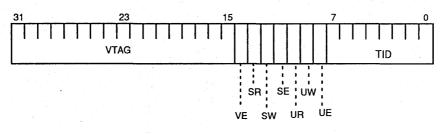

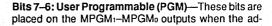

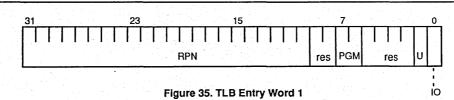

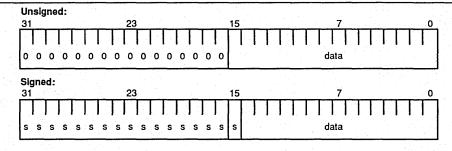

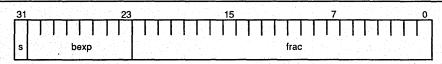

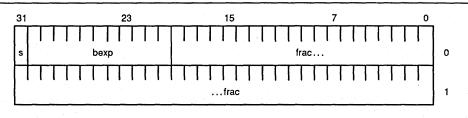

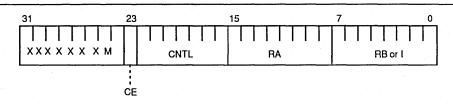

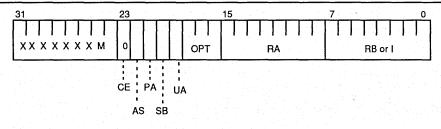

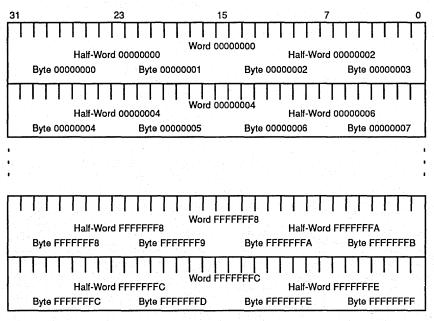

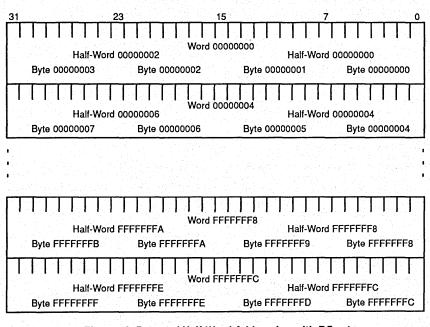

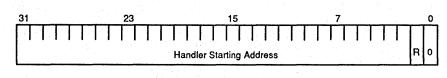

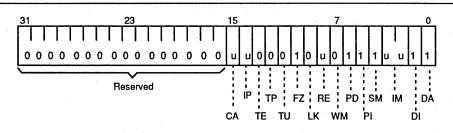

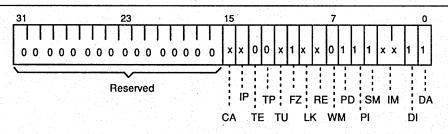

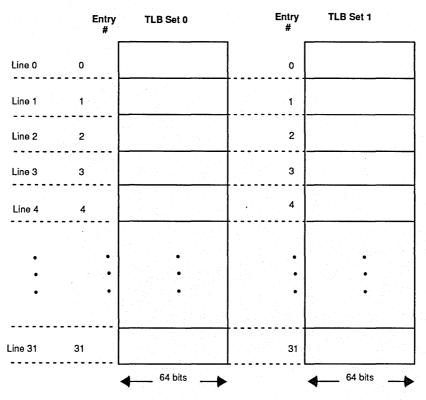

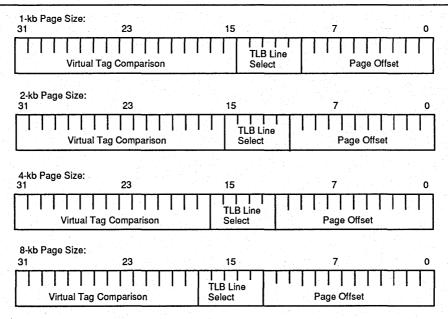

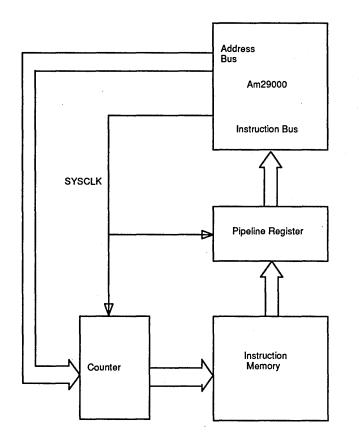

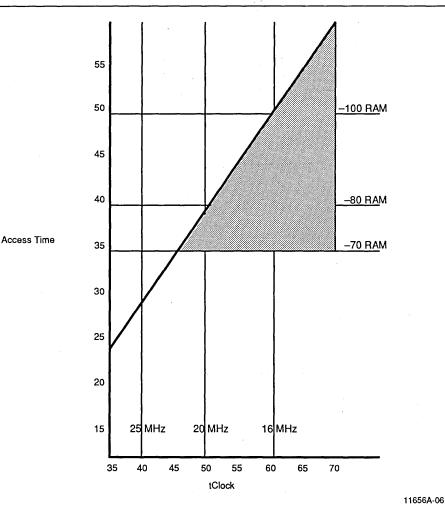

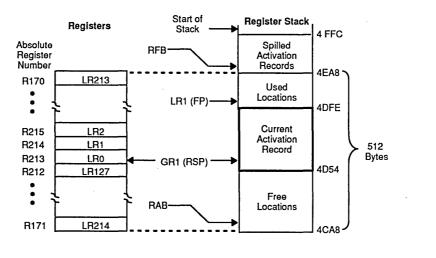

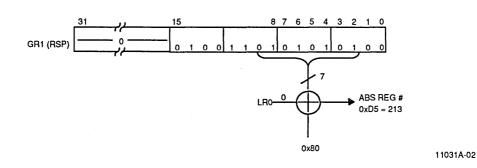

| 3-2        | 15         | E-15        | GND                                                                                                              | M-16         | Ao                                                                                                              | T-13    | STAT <sub>0</sub>        |